### US007334108B1

### (12) United States Patent

### Case et al.

# (10) Patent No.: US 7,334,108 B1 (45) Date of Patent: \*Feb. 19, 2008

# 5 902 605 A

# (54) MULTI-CLIENT VIRTUAL ADDRESS TRANSLATION SYSTEM WITH TRANSLATION UNITS OF VARIABLE-RANGE SIZE

(75) Inventors: Colyn S. Case, Grass Valley, CA (US); Dmitry Vyshetsky, Cupertino, CA

(US); Sean J. Treichler, Mountain

View, CA (US)

(73) Assignee: **NVIDIA Corporation**, Santa Clara, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 296 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 10/769,388

- (22) Filed: Jan. 30, 2004

- (51) Int. Cl. G06F 12/10 (2006.01)

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,677,546 | $\mathbf{A}$ | 6/1987    | Freeman et al.  |

|-----------|--------------|-----------|-----------------|

| 4,835,734 | $\mathbf{A}$ | 5/1989    | Kodaira et al.  |

| 4,992,936 | $\mathbf{A}$ | 2/1991    | Katada et al.   |

| 5,058,003 | $\mathbf{A}$ | 10/1991   | White           |

| 5,375,214 | $\mathbf{A}$ | 12/1994   | Mirza et al.    |

| 5,394,537 | $\mathbf{A}$ | 2/1995    | Courts et al.   |

| 5,446,854 | $\mathbf{A}$ | 8/1995    | Khalidi et al.  |

| 5,465,337 | A            | * 11/1995 | Kong 711/207    |

| 5,479,627 | A            | 12/1995   | Khalidi et al.  |

| 5,555,387 | A            | 9/1996    | Branstad        |

| 5,784,707 | $\mathbf{A}$ | 7/1998    | Khalidi et al.  |

| 5,796,978 | A            | 8/1998    | Yoshioka et al. |

| 5,802,605 | A            |   | 9/1998  | Alpert et al.        |    |

|-----------|--------------|---|---------|----------------------|----|

| 5,822,749 | $\mathbf{A}$ |   | 10/1998 | Agarwal              |    |

| 5,860,146 | $\mathbf{A}$ | * | 1/1999  | Vishin et al 711/20  | )7 |

| 5,928,352 | $\mathbf{A}$ |   | 7/1999  | Gochman et al.       |    |

| 5,930,832 | A            | * | 7/1999  | Heaslip et al 711/20 | )7 |

| 5,956,756 | A            |   | 9/1999  | Khalidi et al.       |    |

| 5,963,984 | A            |   | 10/1999 | Garibay, Jr. et al.  |    |

|           |              |   |         |                      |    |

### (Continued)

### OTHER PUBLICATIONS

Case et al., U.S. Appl. No. 10/769,357 for "Virtual Address Translation System With Caching of Variable-Range Translation Clusters," filed Jan. 30, 2004.

### (Continued)

Primary Examiner—Donald Sparks

Assistant Examiner—Jared I Rutz

(74) Attorney, Agent, or Firm—Townsend and Townsend and Crew LLP

### (57) ABSTRACT

A virtual address translation table and an on-chip address cache are usable for translating virtual addresses to physical addresses. Address translation information is provided using a cluster that is associated with some range of virtual addresses and that can be used to translate any virtual address in its range to a physical address, where the sizes of the ranges mapped by different clusters may be different. Clusters are stored in an address translation table that is indexed by virtual address so that, starting from any valid virtual address, the appropriate cluster for translating that address can be retrieved from the translation table. Recently retrieved clusters are stored in an on-chip cache, and a cached cluster can be used to translate any virtual address in its range without accessing the address translation table again.

### 26 Claims, 23 Drawing Sheets

# US 7,334,108 B1 Page 2

| U.S. PATENT           | DOCUMENTS             | 6,560,688 B1                 |            | Strogin et al.                    |

|-----------------------|-----------------------|------------------------------|------------|-----------------------------------|

| 6,003,123 A * 12/1999 | Carter et al 711/207  | 6,618,770 B2<br>6,628,294 B1 |            | Nayyar et al.<br>Sadowsky et al.  |

| 6,075,938 A * 6/2000  | Bugnion et al 703/27  | 6,728,858 B2*                |            | Willis et al 711/206              |

| 6,104,417 A * 8/2000  | Nielsen et al 345/542 | 6,766,434 B2*                |            | Gaertner et al 711/207            |

| 6,112,285 A 8/2000    | Ganapathy et al.      | , ,                          |            | Gurumoorthy et al.                |

| 6,205,530 B1 3/2001   | Kang                  | , ,                          |            | Kalyanasundharam                  |

| 6,205,531 B1 3/2001   | Hussain               | 2004/0117594 A1              |            | Vanderspek                        |

| 6,260,131 B1* 7/2001  | Kikuta et al 711/210  | 2005/0044340 A1*             |            | Sheets et al 711/206              |

| 6,272,597 B1 8/2001   | Fu et al.             | 2005/0055510 A1*             | 3/2005     | Hass et al 711/133                |

| 6,349,355 B1 2/2002   | Draves et al.         |                              |            | D.T. T.C. I.M.T.C. T.C.           |

| 6,356,991 B1 3/2002   | Bauman et al.         | OTF                          | HER PU     | BLICATIONS                        |

| 6,374,341 B1 4/2002   | Nijhawan et al.       | Case et al IIS Ann           | 1 No 1     | 0/769,326 for "In-Memory Table    |

| 6,418,522 B1 7/2002   | Gaertner et al.       | , 11                         |            | anslation System With Translation |

| 6,418,523 B2 7/2002   | Porterfield           | Units of Variable Rang       |            |                                   |

| 6,457,068 B1 9/2002   | Nayyar et al.         | Onits of variable Rang       | ,C 51ZC, . | inca jan. 50, 2004.               |

| 6,477,612 B1 11/2002  | Wang                  | * cited by examiner          |            |                                   |

FIG. 3

450 460(1) 460(5) 460(3) 460(7) 452 454 BLOCK BLOCK BLOCK **BLOCK BLOCK** BLOCK PTR 7 **BLOCK** BLOCK **BASE** SIZE PAD FMT PTR 2 PTR 0 PTR 1 PTR 6 PTR 3 PTR 5 PTR 4 460(0) 460(4) 460(2) 460(6) 458 470

FIG. 4B

Feb. 19, 2008

FIG. 5A

FIG. 5B

FIG. 6

FIG. 7

FIG. 10

FIG. 13

Feb. 19, 2008

FIG. 15

FIG. 16

Feb. 19, 2008

FIG. 17

FIG. 19

FIG. 21

FIG. 23

FIG. 24

### MULTI-CLIENT VIRTUAL ADDRESS TRANSLATION SYSTEM WITH TRANSLATION UNITS OF VARIABLE-RANGE SIZE

# CROSS-REFERENCES TO RELATED APPLICATIONS

The present disclosure is related to the following commonly-assigned co-pending U.S. patent application Ser. No. 10 10/769,357, filed on the same date as the present application, entitled "VIRTUAL ADDRESS TRANSLATION SYSTEM WITH CACHING OF VARIABLE-RANGE TRANSLATION CLUSTERS"; and Ser. No. 10/769,326, filed on the same date as the present application, entitled "IN-MEMORY 15 TABLE STRUCTURE FOR VIRTUAL ADDRESS TRANSLATION SYSTEM WITH TRANSLATION UNITS OF VARIABLE RANGE SIZE." The respective disclosures of these applications are incorporated herein by reference for all purposes.

### BACKGROUND OF THE INVENTION

The present invention relates in general to memory management systems and in particular to an address translation 25 system with caching of variable-range translation clusters.

Most modern computer systems generally implement some form of virtual memory, in which processes reference system memory locations using a "virtual" address rather than an address of a specific location in the memory. When 30 a process makes a memory request using a virtual address, the system uses a page table to translate the virtual address to a specific location and accesses that location. The page table is typically implemented in a block of memory that includes an entry for each page (e.g., 4 kilobytes) of the 35 virtual address space; the entry stores a physical address of a corresponding page of a physical address space. Page tables can also be structured hierarchically, so that only a portion of the page table needs to be resident in system memory at all times; the portion held in system memory can 40 be used to locate other portions that may have been swapped out.

Virtual memory has a number of common uses. For example, general-purpose computer systems generally cannot guarantee that a process will receive memory resources in any particular arrangement or at any particular location. Virtual addressing enables processes to treat the memory as if it were arranged in a convenient manner, regardless of how it is actually arranged. As another example, systems that support parallel execution of multiple processes can provide a different virtual memory space for each process. This helps to avoid address conflicts between processes. Virtual addressing can also be used to map storage other than system memory, thereby enabling the system to swap data in and out of the system memory, address data in storage 55 devices other than memory storage (e.g., image files resident on a system disk), and so on.

Within graphics processing subsystems, use of virtual memory has been relatively uncommon. Typically, a graphics processing subsystem is implemented on a plug-in 60 printed circuit card that connects to a system bus, such as a PCI (Peripheral Component Interconnect) or AGP (Accelerated Graphics Port) bus. The card usually includes a graphics processing unit (GPU) that implements graphics functionality (e.g., rasterization, texture blending, etc.) and 65 dedicated graphics memory. This memory is generally managed by the GPU or by a graphics driver program executing

2

on the system central processing unit. The GPU can address graphics memory using either physical addresses or offset values that can be converted to physical addresses by the addition of a constant base address. The GPU (or graphics driver program) can also control the arrangement of physical memory allocations. For instance, a pixel buffer that is to be scanned out to a display device can be arranged to occupy a contiguous block of the graphics memory address space. Elements of graphics processing subsystems, including scanout control logic (or display drivers), graphics driver programs, GPUs, and the like are generally designed to use physical addressing and to rely on particular arrangements and allocations of memory.

As the amount of data (e.g., texture data) needed for graphics processing increases, graphics processing subsystems are beginning to rely on system memory for at least some storage of data (and in some instances command lists, etc.). Such subsystems generally use virtual addressing for system memory, with the required address translation being performed by a component external to the graphics processing subsystem. For instance, the AGP bus includes a Graphics Address Relocation Table (GART) implemented in the host-side chipset. Emerging high-speed bus technologies, such as PCI Express (PCI-E), do not provide GART or any other address translation functionality. As a result, graphics cards configured for such protocols will need to implement their own address translation systems if they are to access system memory.

An alternative to the graphics card is an integrated graphics processor (IGP). An IGP is a graphics processor that is integrated with one or more other system bus components, such as a conventional "north bridge" chip that manages the bus connecting the CPU and the system memory. IGPs are appealing as an inexpensive alternative to graphics cards. Unlike conventional graphics cards, an IGP system usually does not include much (or in some cases any) dedicated graphics memory; instead the IGP relies on system memory, which the IGP can generally access at high speed. The IGP, however, generally does not control the physical arrangement or address mapping of the system memory allocated to it. For example, it is not guaranteed that the pixel buffer will occupy a single contiguous block in the physical address space. Thus, designers of IGPs are faced with the choice of redesigning the co-processor and the associated driver programs to use physical addresses provided by the system or relying on virtual addressing.

Given the level of complexity and sophistication of modern graphics processing, redesigning around (unpredictable) physical addresses is a daunting task, which makes a virtual addressing solution desirable. Unfortunately, in many computer systems, virtual addressing can introduce a significant degree of memory overhead, making this option too slow or resource intensive for graphics processing components such as display systems. For example, a typical display system provides a screen's worth of pixel data (e.g., 1280×1024) pixels at four bytes per pixel, for a total of over 5 MB per screen) from the pixel buffer to a display device at a constant screen refresh rate of about 70 Hz. Virtual address translation for this much data would introduce an additional latency that is potentially long and may be highly variable. Such long or variable delays in receiving pixel data from memory could result in incorrect (or black) pixels, or other undesirable artifacts. In addition, if address translation for scanout or other purposes requires a large number of page table accesses, performance of other system components may be adversely affected (e.g., due to congestion on the bus or in the system memory). Conventional address caching and

translation lookaside buffer techniques do not alleviate the problem because it is difficult and expensive to provide an on-chip cache large enough to hold all the page addresses needed for scanout.

Another solution is to maintain a complete page table on 5 the graphics chip, thereby allowing faster access times and/or less variability in latency. This solution, however, becomes impractical for large page table sizes. Still another solution divides the virtual address space into "large" and "small" sections, depending on whether the section is 10 mapped to blocks of contiguous physical addresses that exceed a "large size" threshold of e.g., 32 or 64 KB. Pointers to the physical address blocks for "large" sections are stored on chip, while for "small" sections, a lookup in the complete page table is required to complete the translation. In some 15 cases, the result of the most recent page table lookup for each of some number of translation clients can be stored and re-used until the client requests a virtual address on a different page. Such systems can reduce the number of page table accesses in some situations, but the ability to store only 20 one result per client and the inability to share results can still lead to a large number of page table accesses.

Thus, an improved virtual memory system that reduces the number of page table accesses required to translate a group of virtual addresses would be desirable.

### BRIEF SUMMARY OF THE INVENTION

Embodiments of the present invention provide systems and methods for implementing a virtual address translation 30 table and an on-chip address cache that can substantially reduce the number of page table accesses needed to translate a given range of virtual addresses to physical addresses. Address translation information is provided using a translation data structure, referred to herein as a "cluster," that is 35 associated with some range of virtual addresses; the cluster can be used to translate any virtual address in its range to a physical address. The sizes of the ranges mapped by different clusters may be different, and the size of the cluster data structure may be independent of its range size. Clusters may 40 be stored in an address translation table that is indexed by virtual address so that, starting from any valid virtual address, the appropriate cluster for translating that address can be retrieved from the translation table. Recently retrieved clusters can be stored in an on-chip cache in such 45 a manner that a cached cluster can be used to translate any virtual address in its range without accessing the in-memory translation table again.

According to one aspect of the present invention, a translation lookaside buffer system for translating virtual 50 addresses to physical addresses includes an input arbitration module, a primary cluster store, a primary lookup logic circuit, and a translation module. The input arbitration module is configured to receive translation requests from a number of clients, each translation request including a target 55 virtual address, and is further configured to select one of the translation requests for processing. The primary cluster store has a number of locations, each location configured to store a cluster. Each cluster provides a mapping to a respective physical address for each virtual address in a range of virtual 60 address space; the respective ranges of different ones of the clusters have different sizes. The primary lookup logic circuit is coupled to receive the selected translation request from the input arbitration circuit and configured to associate one of the locations in the primary cluster store with the 65 selected translation request, thereby designating the associated location for storing a cluster whose range includes the

4

target virtual address. The translation module is configured to translate the target virtual address of the selected translation request to a physical address based at least in part on the mapping provided by the cluster stored in the primary cluster store location associated with the selected translation request.

In some embodiments, the system also includes a primary tag store coupled to the primary lookup logic circuit and configured to store a tag corresponding to each location in the primary cluster store, where each tag encodes the range of the virtual address space mapped by the cluster in the corresponding primary cluster store location. The primary lookup logic circuit may be further configured to detect a primary cluster hit in the event that the target virtual address of the selected translation request matches one of the tags in the primary tag store and to detect a primary cache miss otherwise. The primary lookup logic circuit may be further configured to respond to a primary cache hit by associating the location in the primary cluster store that corresponds to the matched tag with the selected translation request. The primary lookup logic circuit may also be configured to store a new primary tag for the current target address in the primary tag store in the event of a primary cache miss, thereby designating a location in the primary cluster cache 25 for storing a new cluster corresponding to the new primary tag, where the new primary tag encodes a minimum-size range of the virtual address space. Upon storing the new cluster in the primary cluster cache, the new primary tag may be updated to reflect the range of virtual addresses for which the new cluster provides a mapping.

In some embodiments, the primary lookup logic circuit is further configured to process a selected translation request before the cluster for a previously selected translation request is present in the primary cluster store location associated with the previously selected translation request.

In some embodiments that include a primary tag store, each of the clients is allocated a non-overlapping portion of the primary tag store. In other embodiments, one of the clients may generate translation requests for a number of address streams, and the portion of the primary tag store allocated to that client may be subdivided among the address streams.

According to another aspect of the invention, a method for translating virtual addresses to physical addresses is provided. A number of clusters are defined, wherein each cluster provides a mapping to a respective physical address for each virtual address in a range of virtual address space, and wherein respective sizes of the ranges mapped by different ones of the clusters are different. A first translation request is received from a client, the first translation request including a first target virtual address. A first tag is stored in a tag store, with the first tag encoding a minimum size range of the virtual address space that includes the first target virtual address, and with the first tag further identifying a first location in a primary cluster store. The first request is associated with the first location in the primary cluster store. A first cluster that maps a range of the virtual address space that includes the first target virtual address is fetched into the first location in the primary cluster store. The first target virtual address to a physical address based at least in part on the mapping provided by the first cluster. In some embodiments, subsequently to storing the first tag, the first tag is modified to encode the range of the virtual address space mapped by the first cluster.

In some embodiments, subsequently to receiving the first translation request, a second translation request is received from the client, the second translation request including a

second target virtual address. It is determined whether the second target virtual address matches the first tag. In the event that the second target virtual address matches the first tag, the second request is associated with the first location in the primary cluster store; the first cluster is retrieved from 5 the first location in the primary cluster store; and the second target virtual address is translated to a physical address based at least in part on the mapping provided by the first cluster.

The following detailed description together with the 10 accompanying drawings will provide a better understanding of the nature and advantages of the present invention.

### BRIEF DESCRIPTION OF THE DRAWINGS

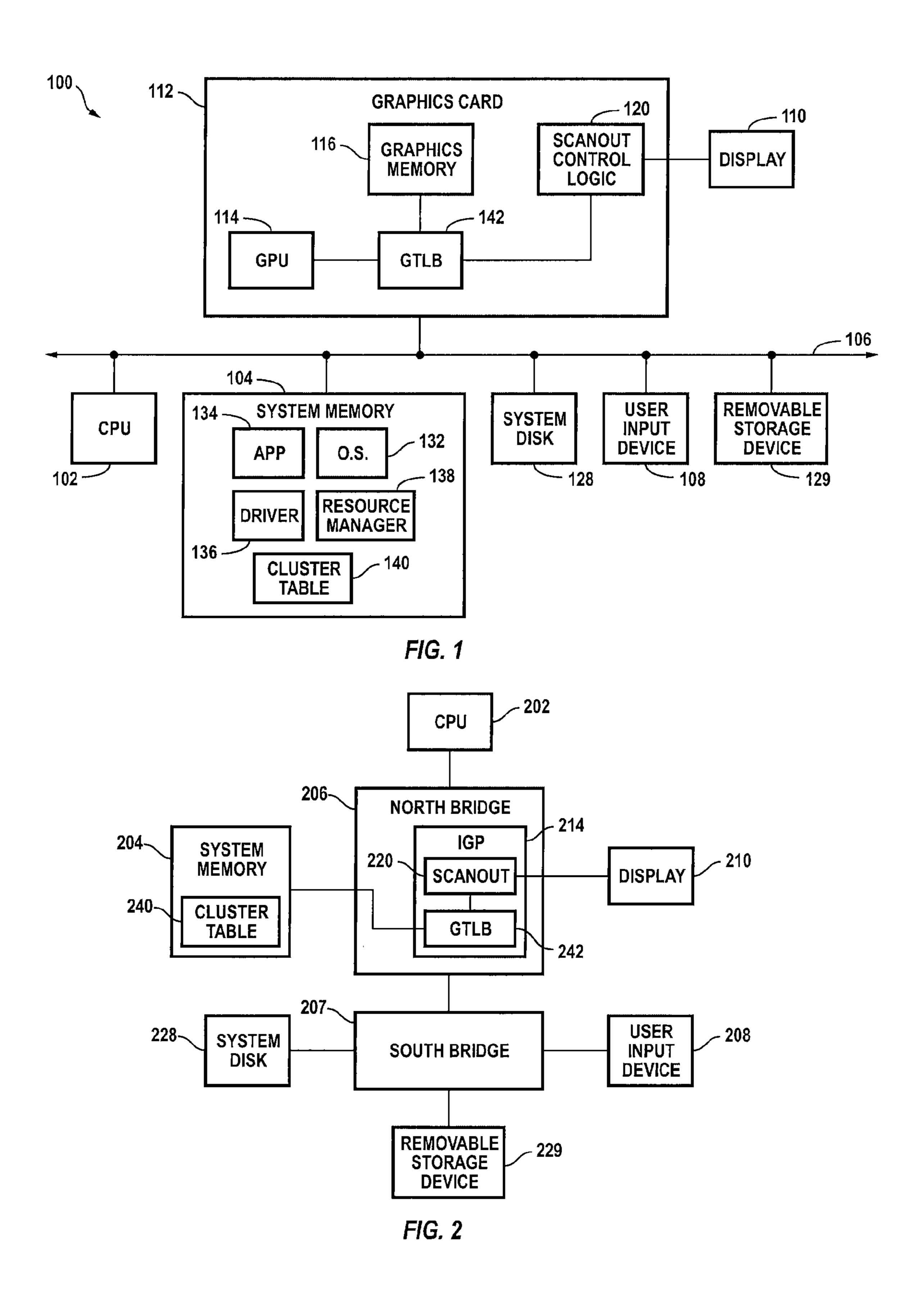

- FIG. 1 is a block diagram of a computer system according to an embodiment of the present invention;

- FIG. 2 is a block diagram of a computer system according to another embodiment of the present invention;

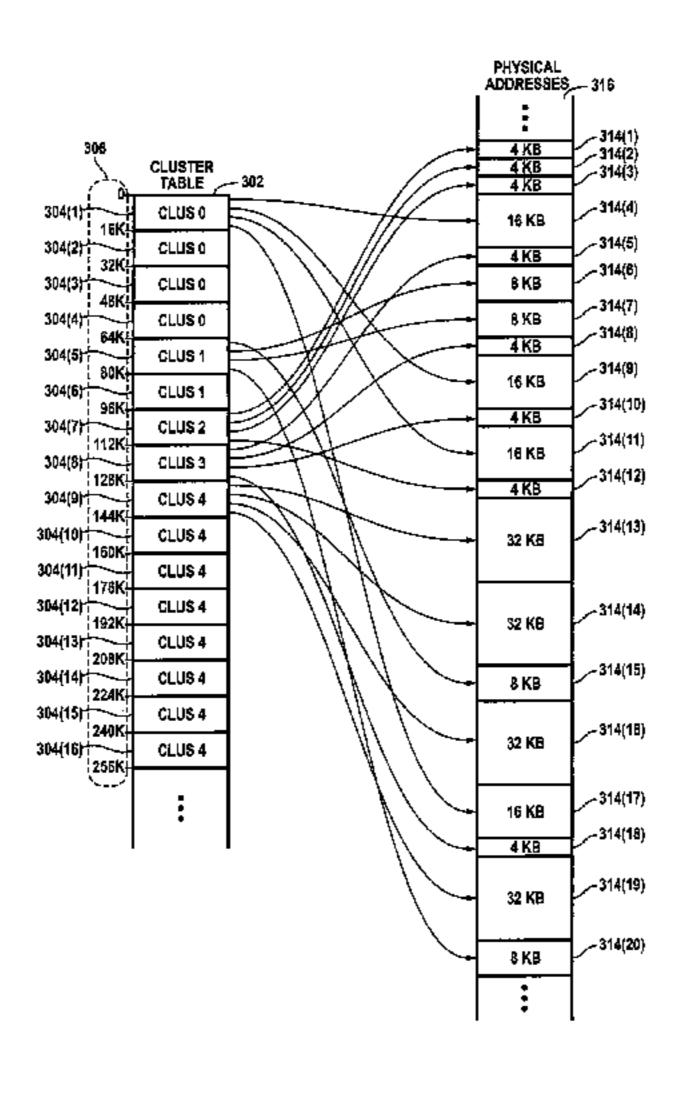

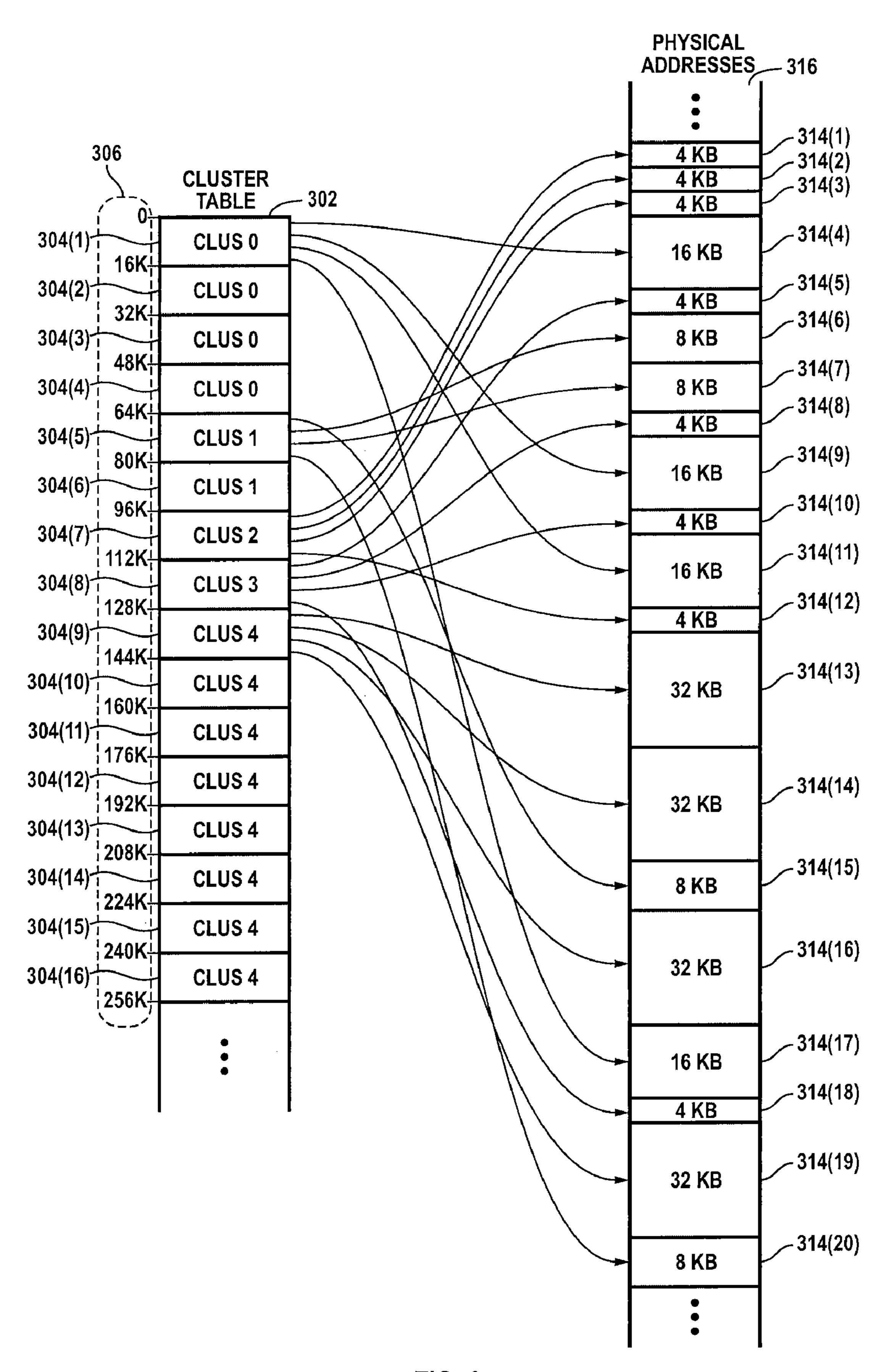

- FIG. 3 illustrates a mapping from a cluster table to 20 physical addresses according to an embodiment of the present invention;

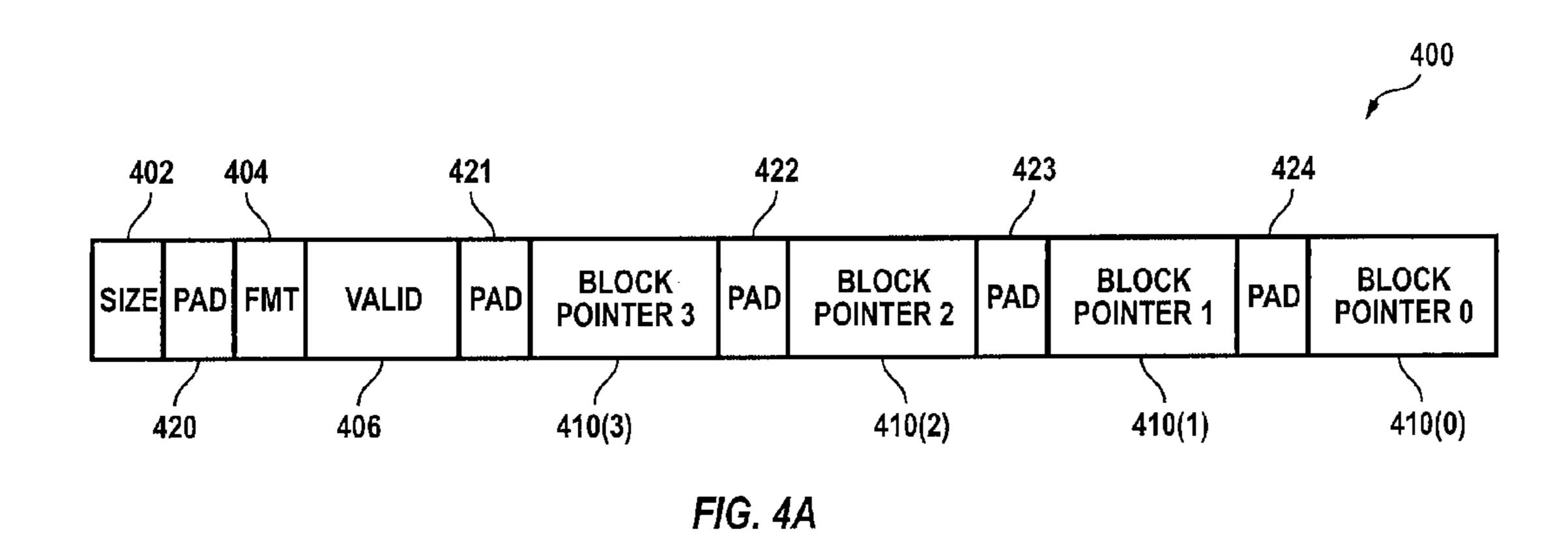

- FIGS. 4A-B are bit-field representations of two cluster data structures according to embodiments of the present invention;

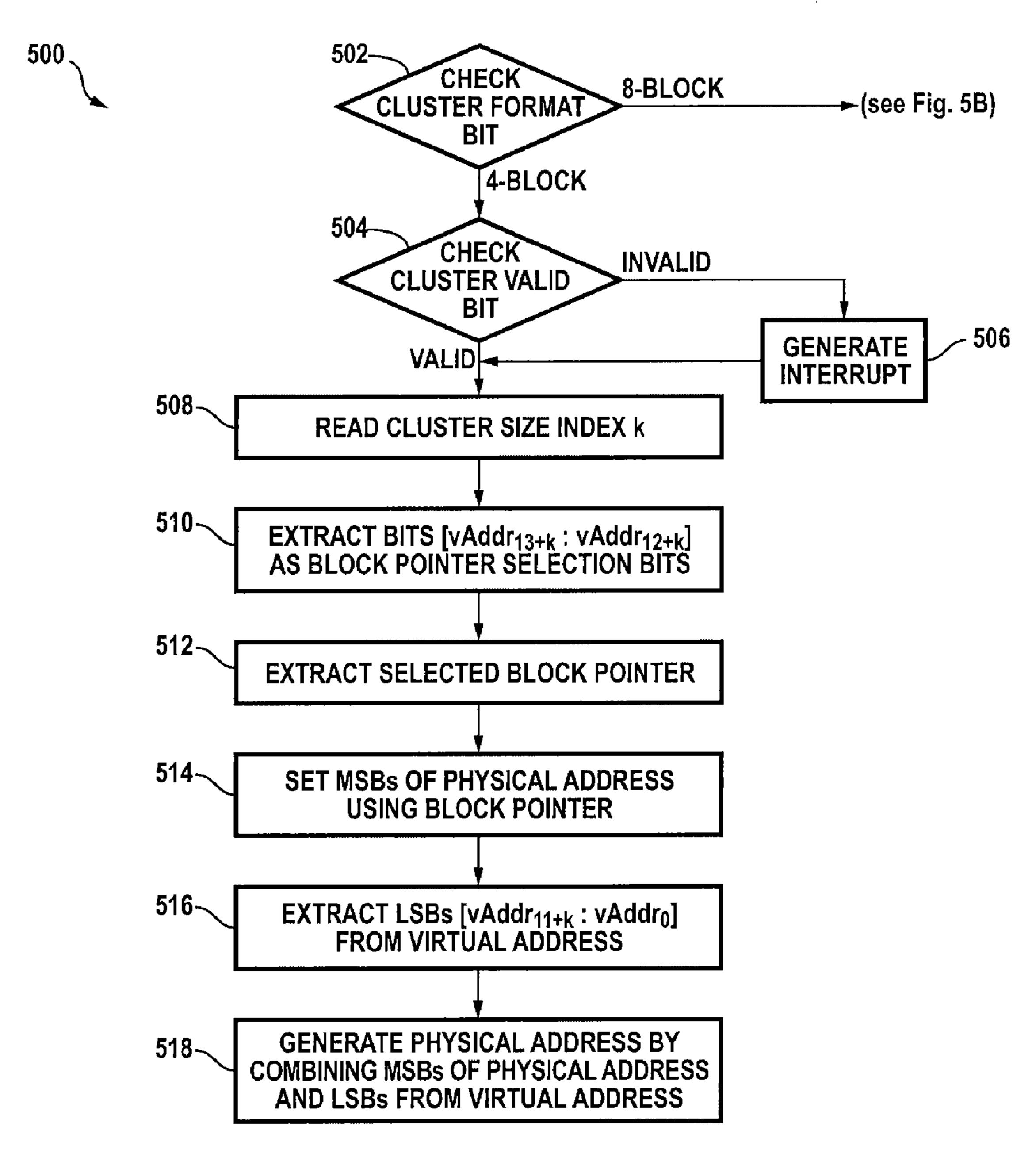

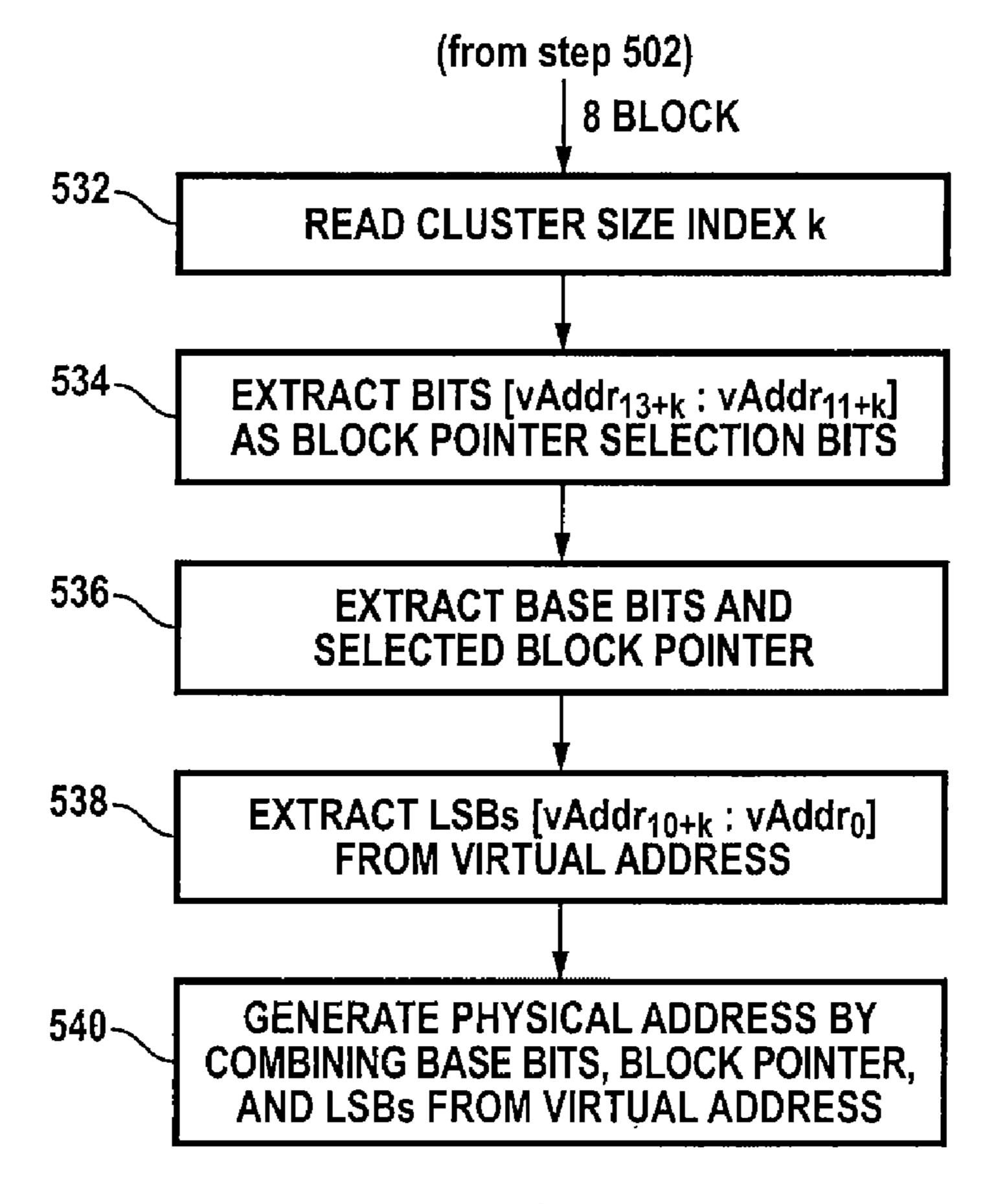

- FIGS. **5**A-B are flow diagrams of a process for translating a virtual address given a corresponding cluster according to an embodiment of the present invention;

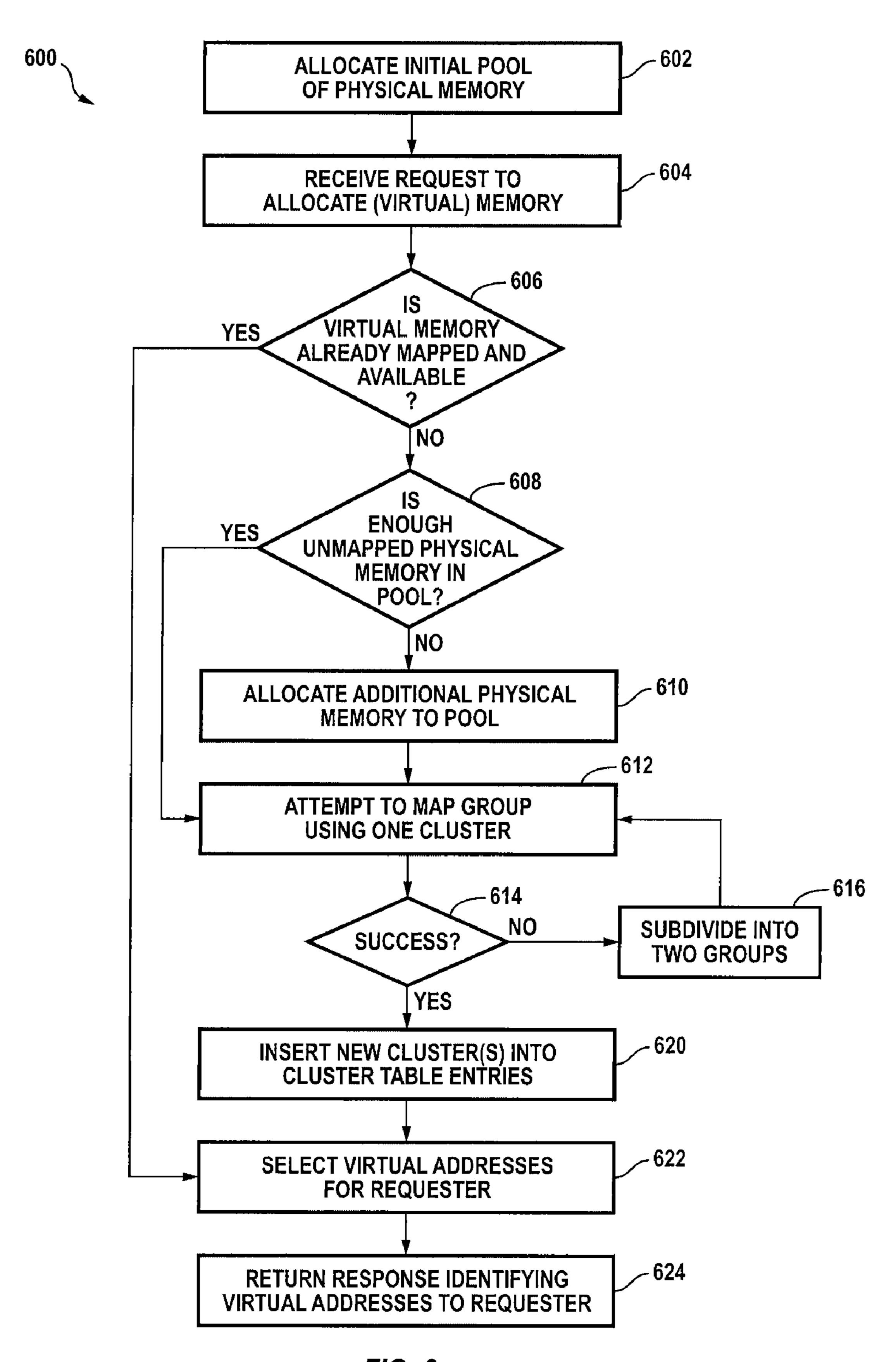

- FIG. 6 is a flow diagram of a process for managing a virtual address space according to an embodiment of the 30 present invention;

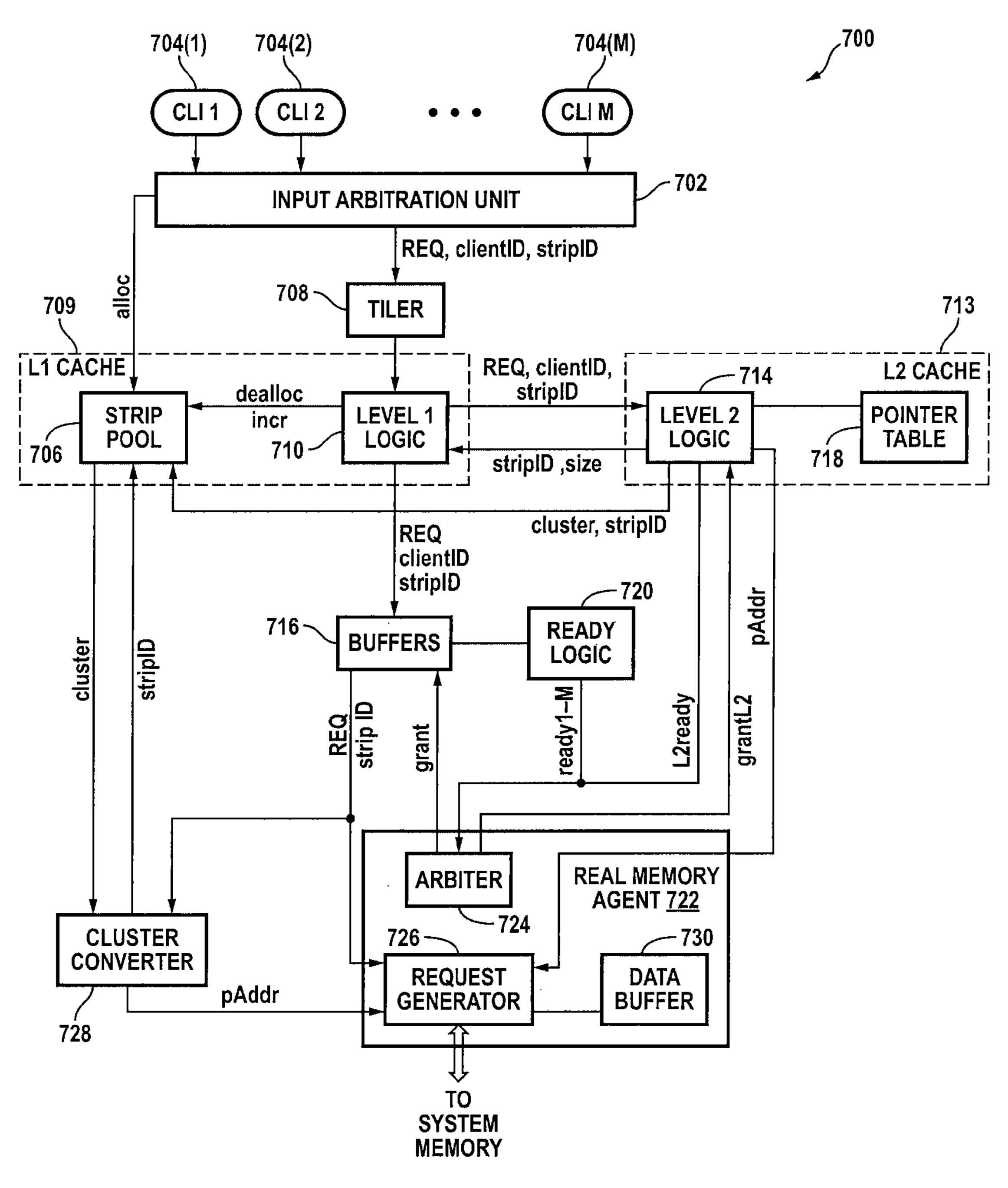

- FIG. 7 is a high-level block diagram of a translation lookaside buffer (TLB) system with a two level cache according to an embodiment of the present invention;

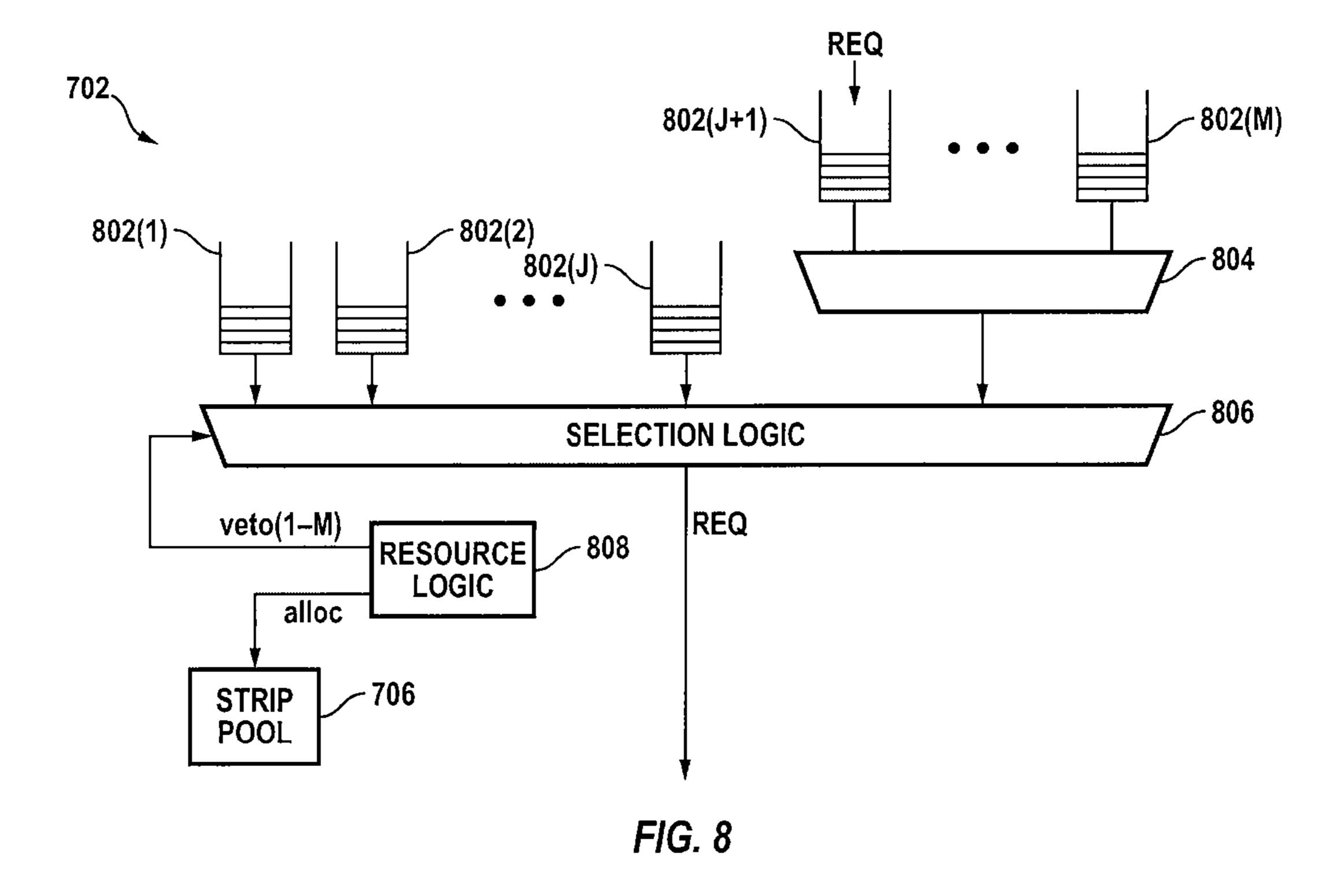

- a multi-client TLB system according to an embodiment of the present invention;

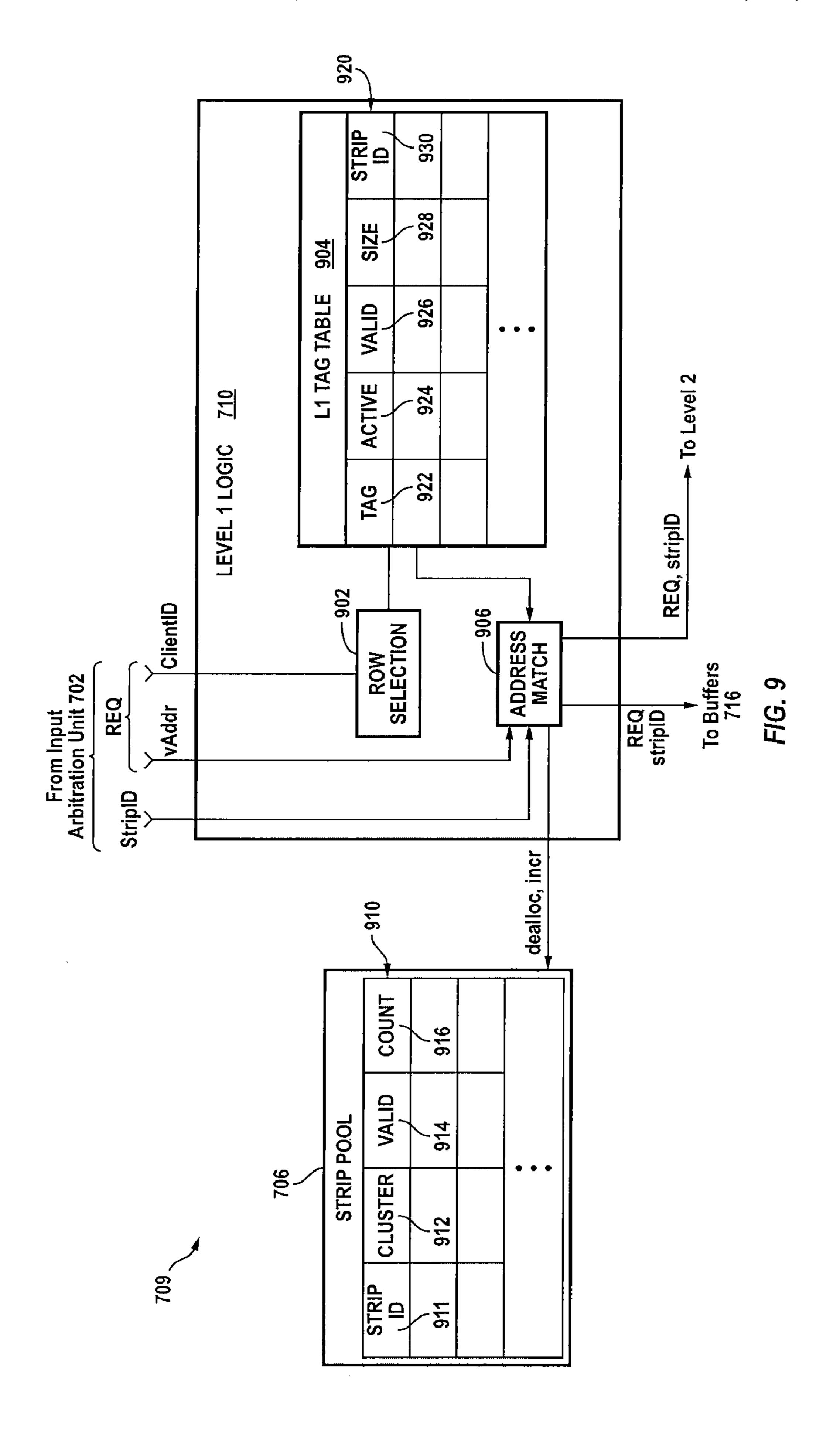

- FIG. 9 is a block diagram of a Level 1 lookup logic block and cluster cache according to an embodiment of the present invention;

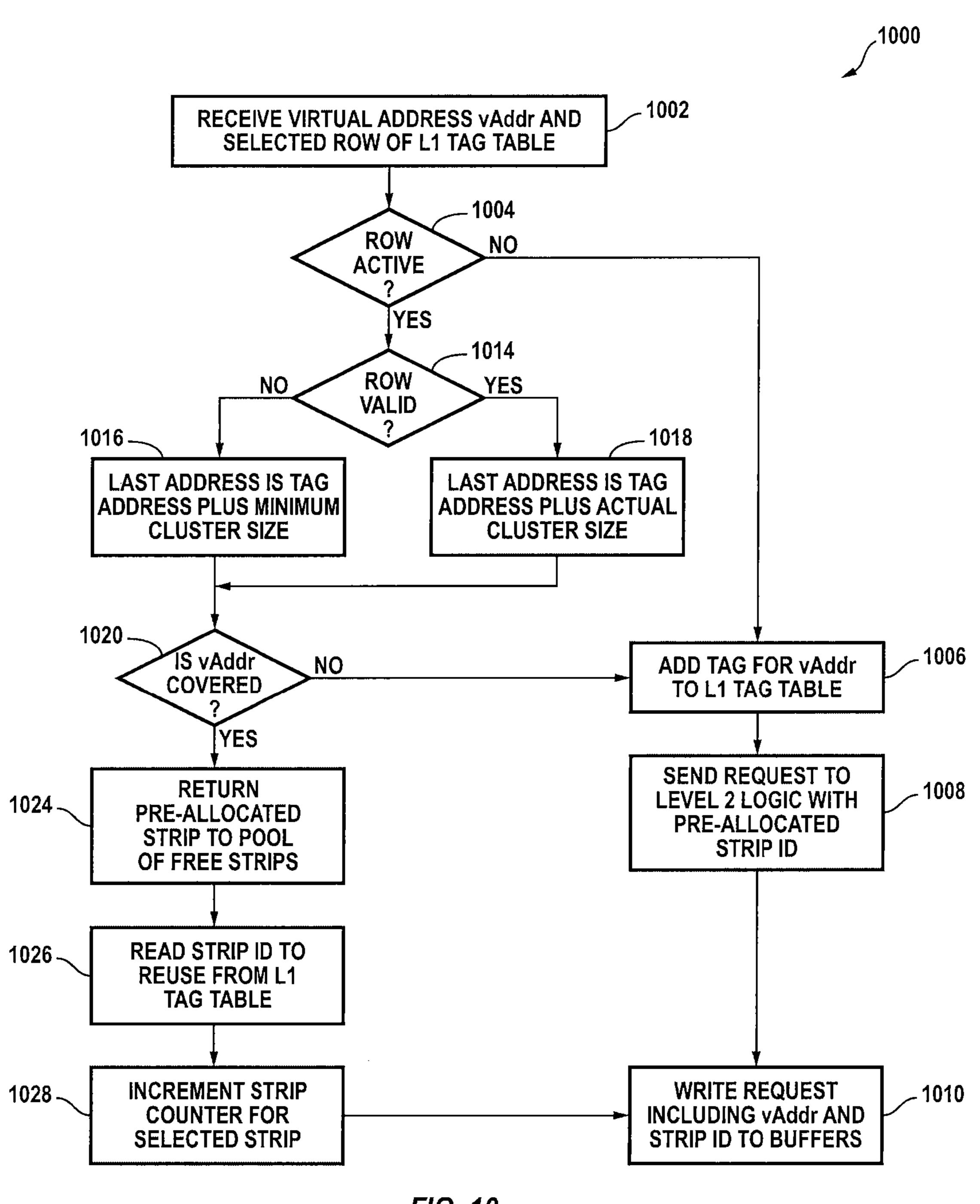

- FIG. 10 is a flow diagram of a Level 1 lookup process for determining whether a requested virtual address is mapped by a cached cluster according to an embodiment of the present invention;

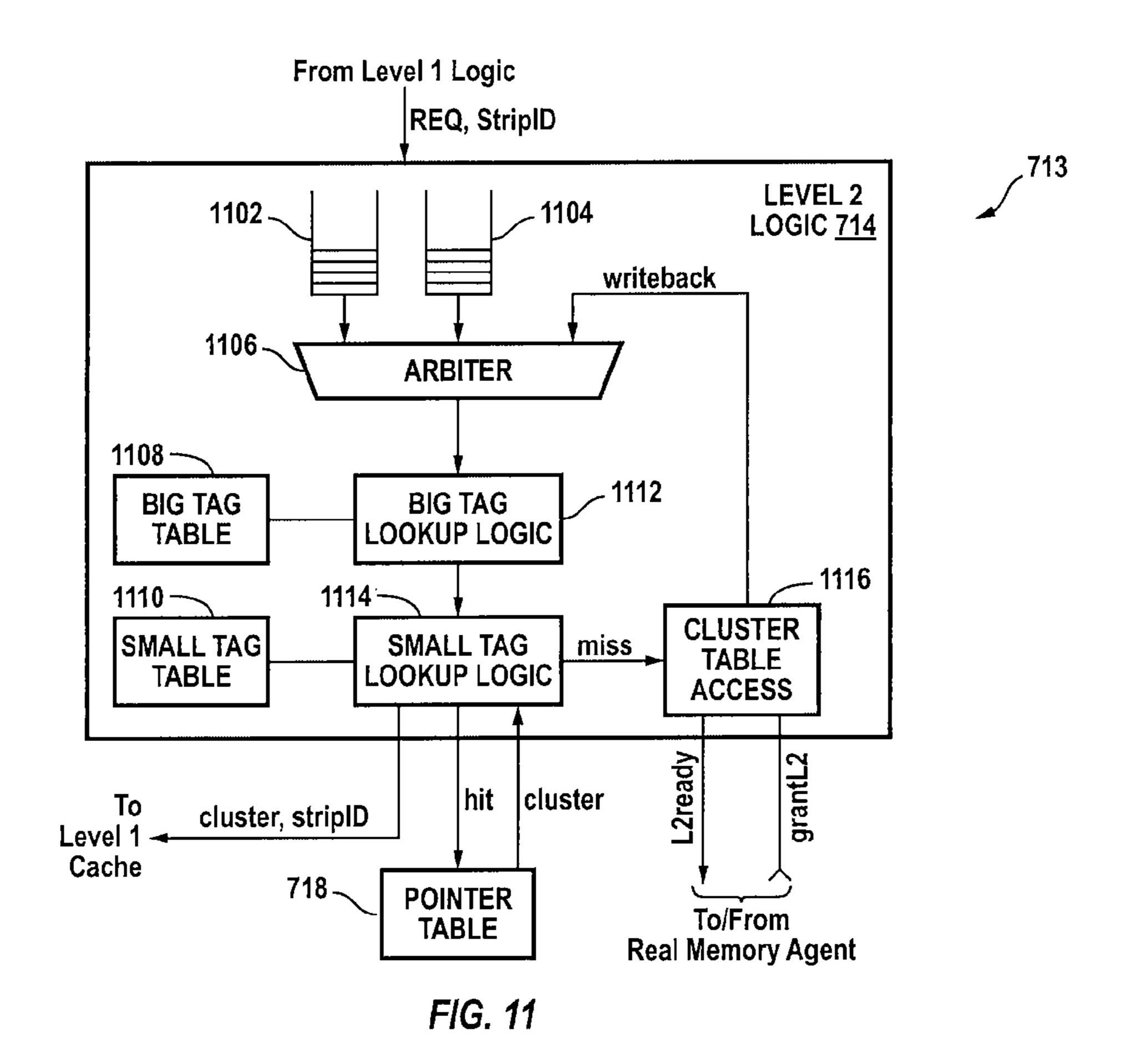

- FIG. 11 is a block diagram of a Level 2 lookup logic block 45 and cluster cache according to an embodiment of the present invention;

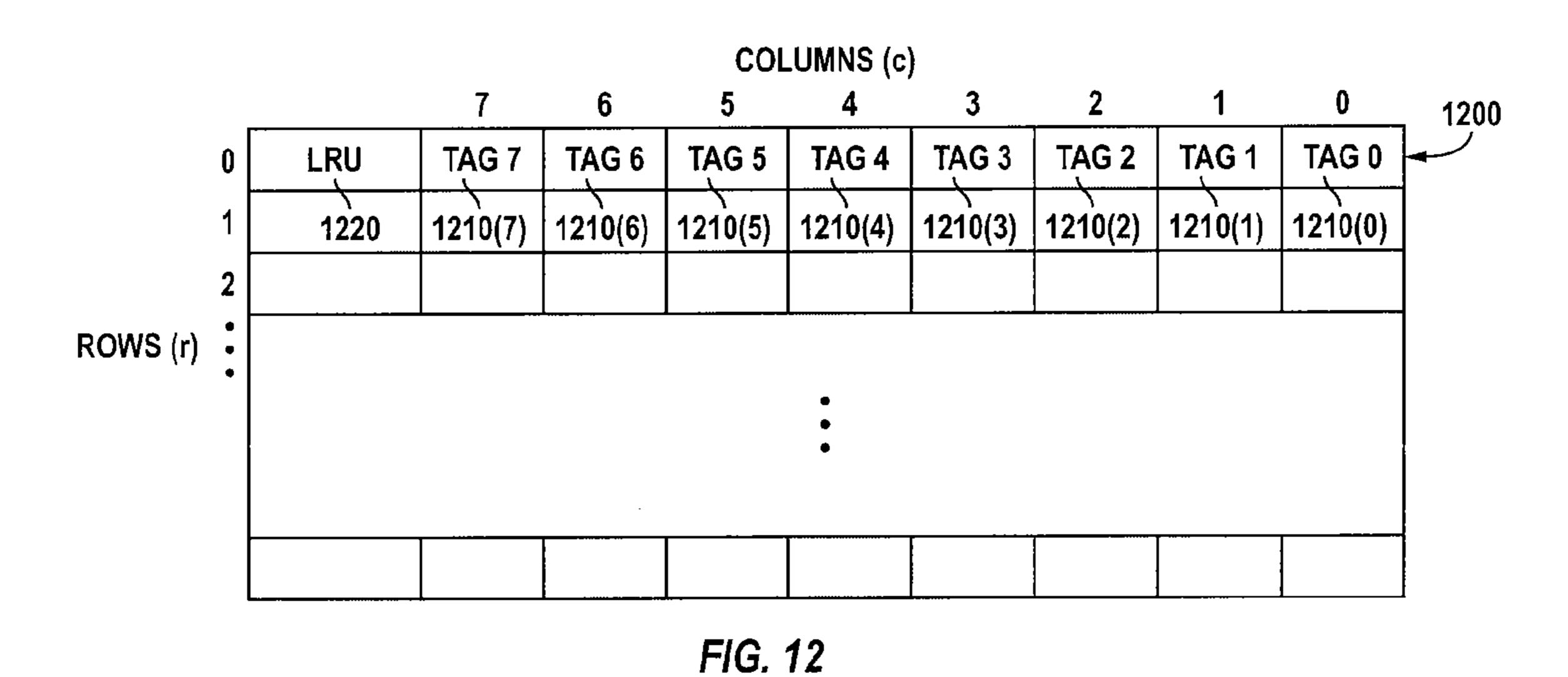

- FIG. 12 illustrates a structure of a Level 2 tag table according to an embodiment of the present invention;

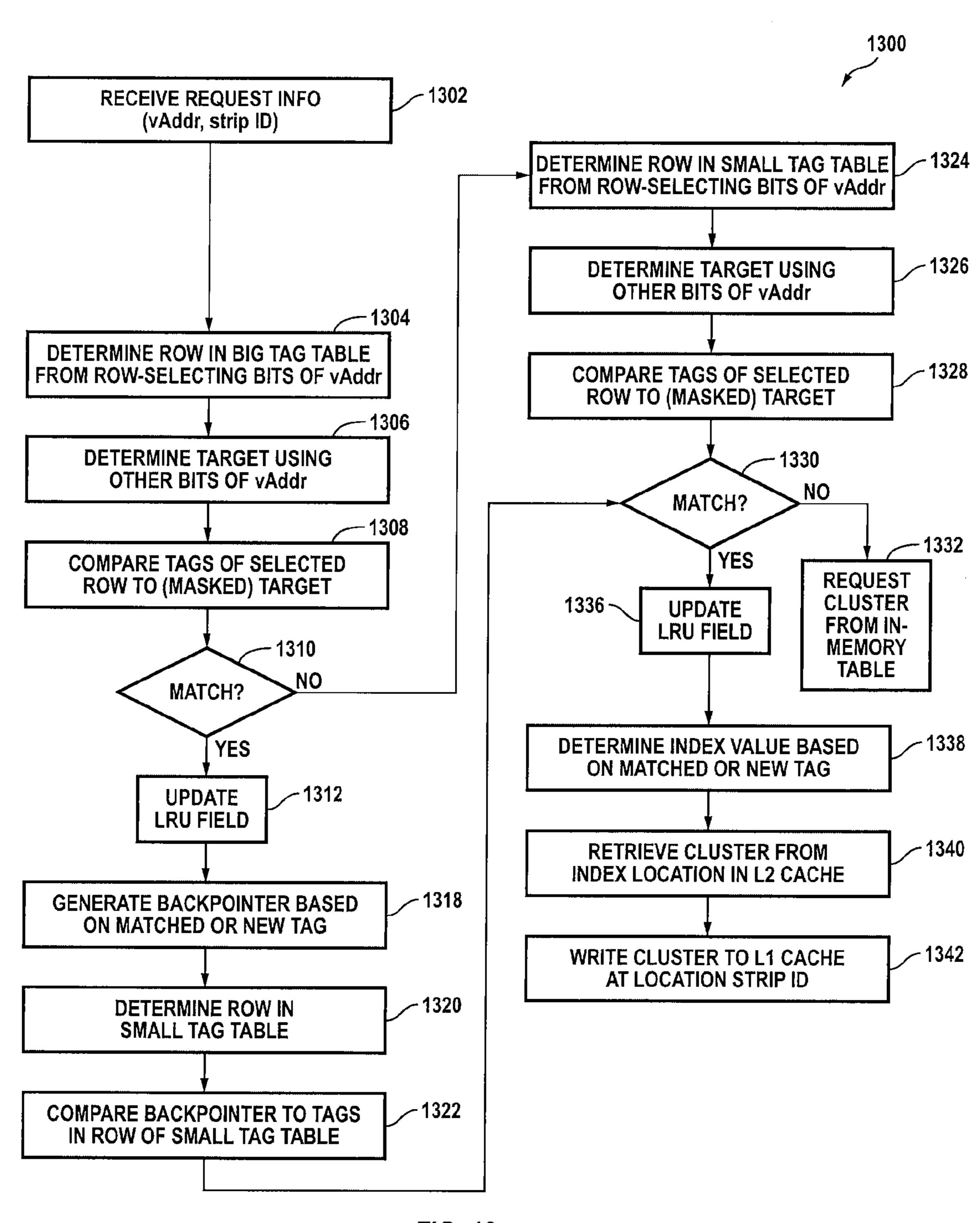

- FIG. 13 is a flow diagram of a Level 2 lookup process for 50 determining whether a requested virtual address is mapped by a cached cluster according to an embodiment of the present invention;

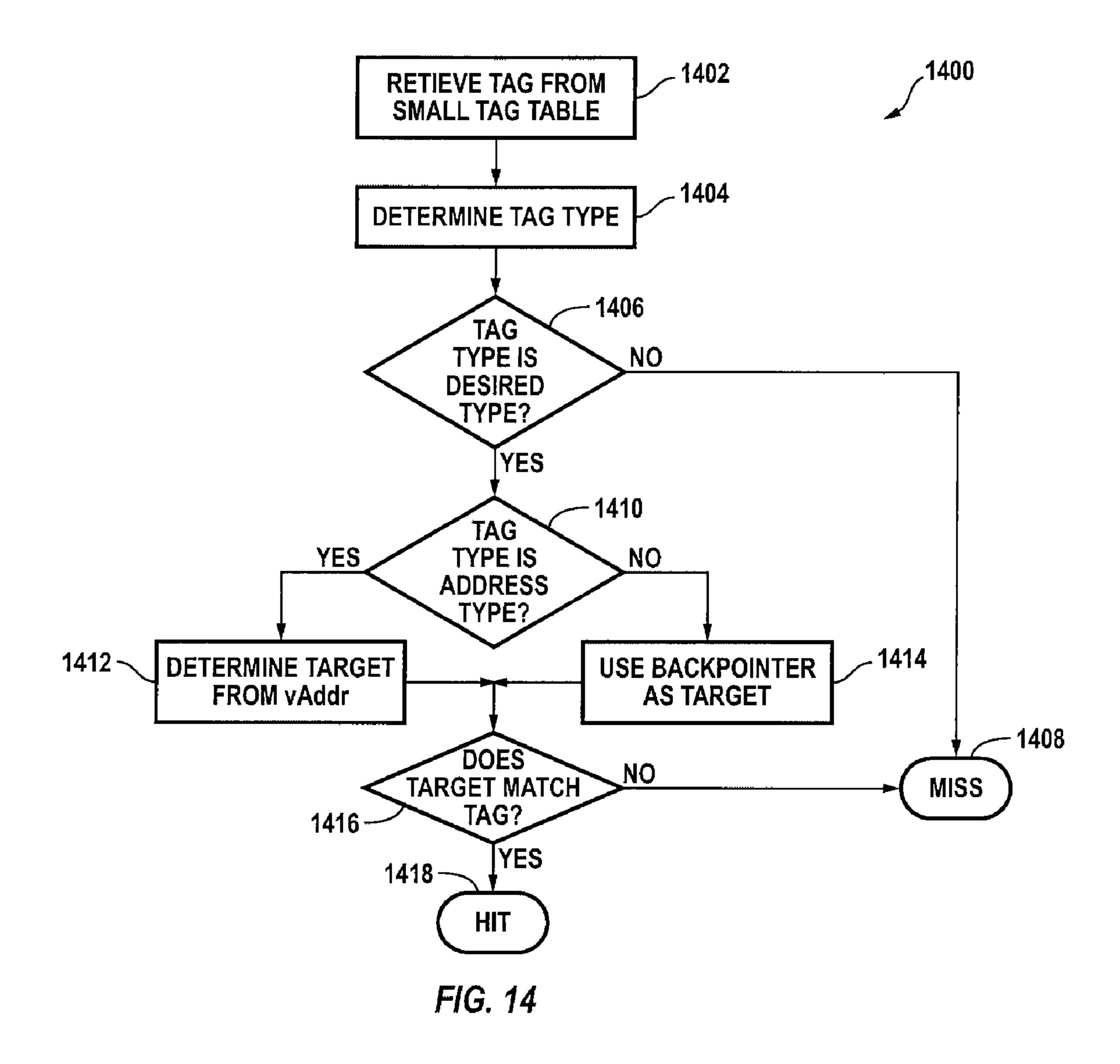

- FIG. 14 is a flow diagram of a comparison step for the lookup process of FIG. 13 according to an embodiment of 55 the present invention;

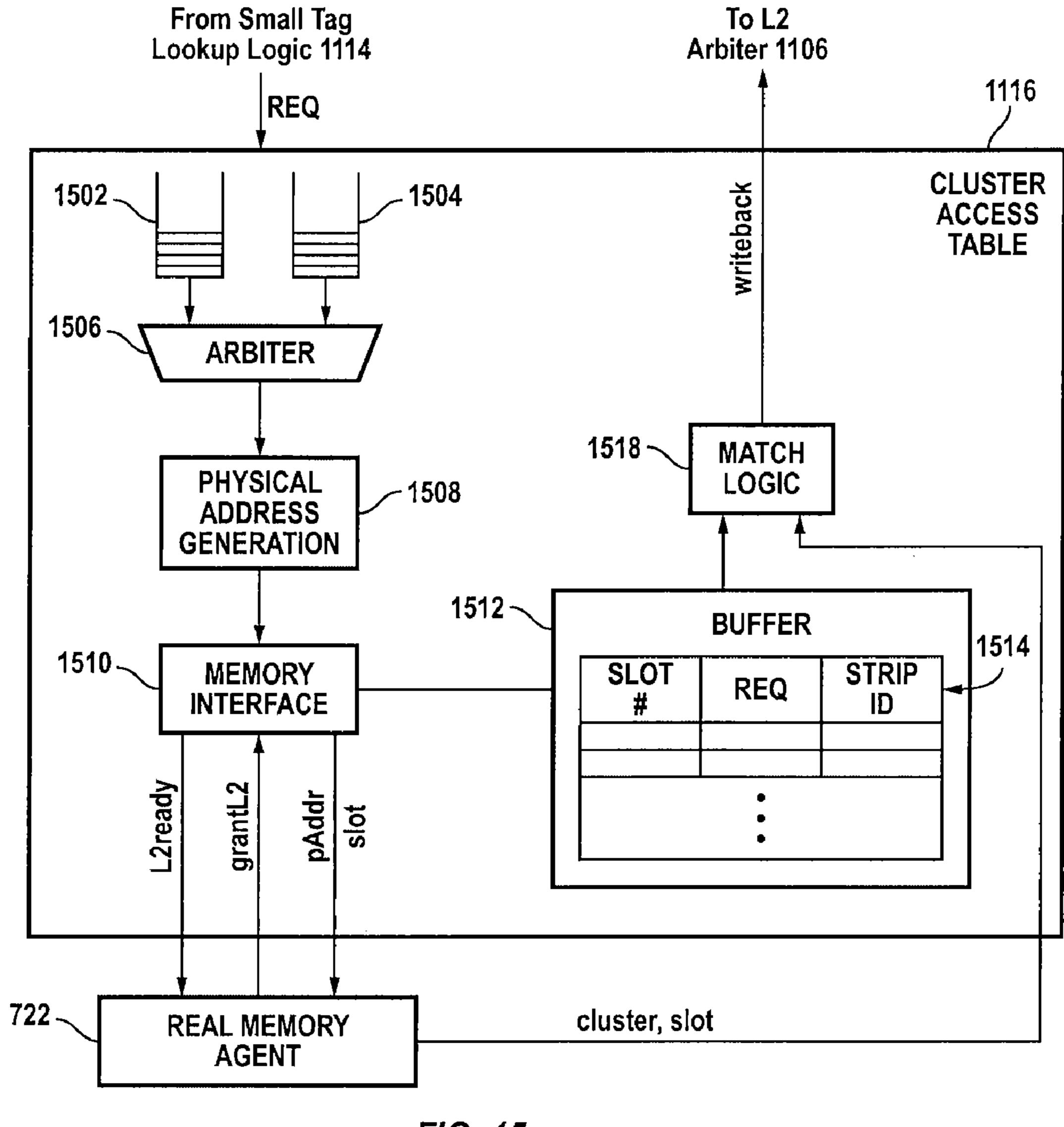

- FIG. 15 is a block diagram of a circuit for requesting cluster data from an in-memory cluster table according to an embodiment of the present invention;

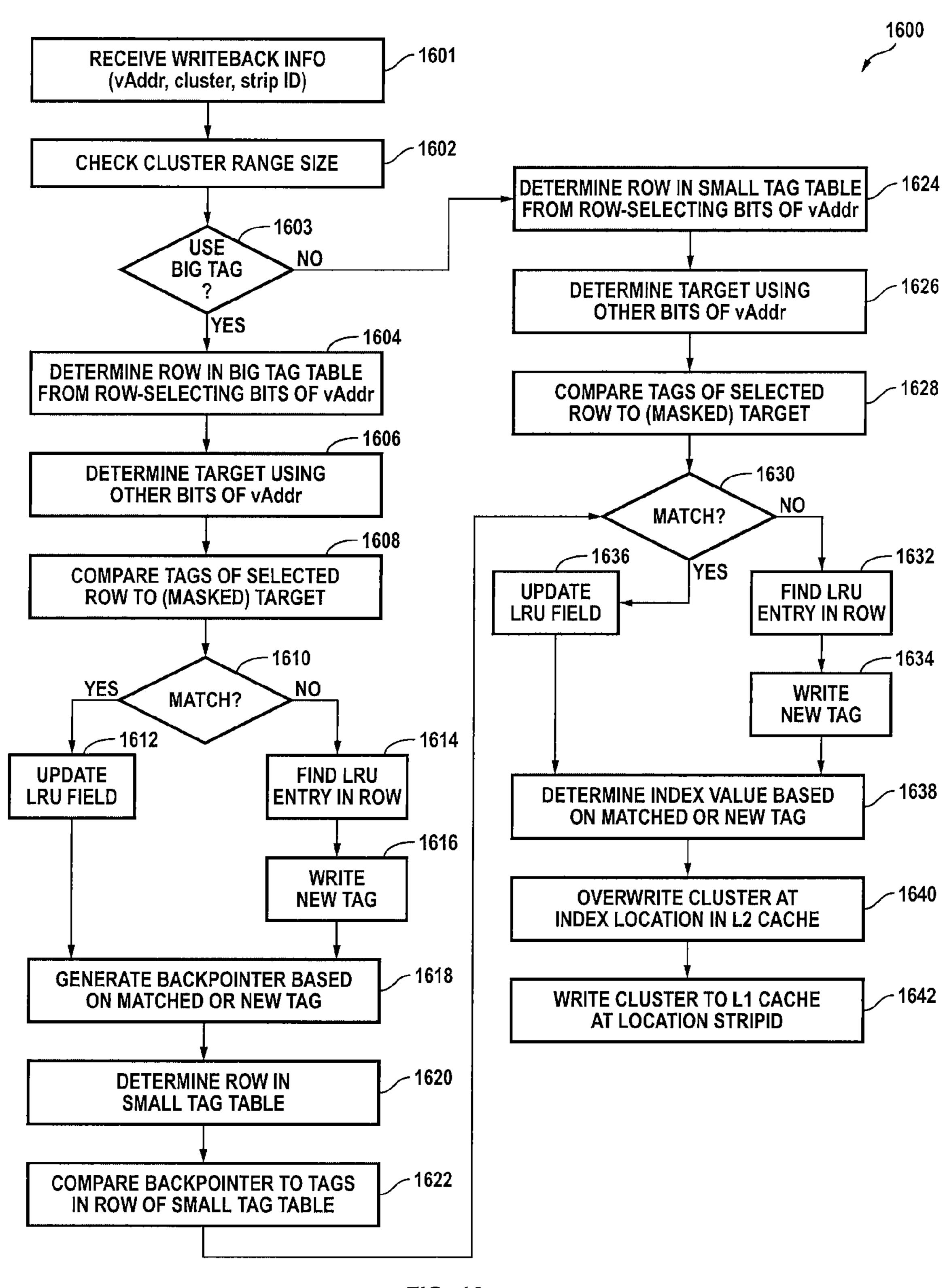

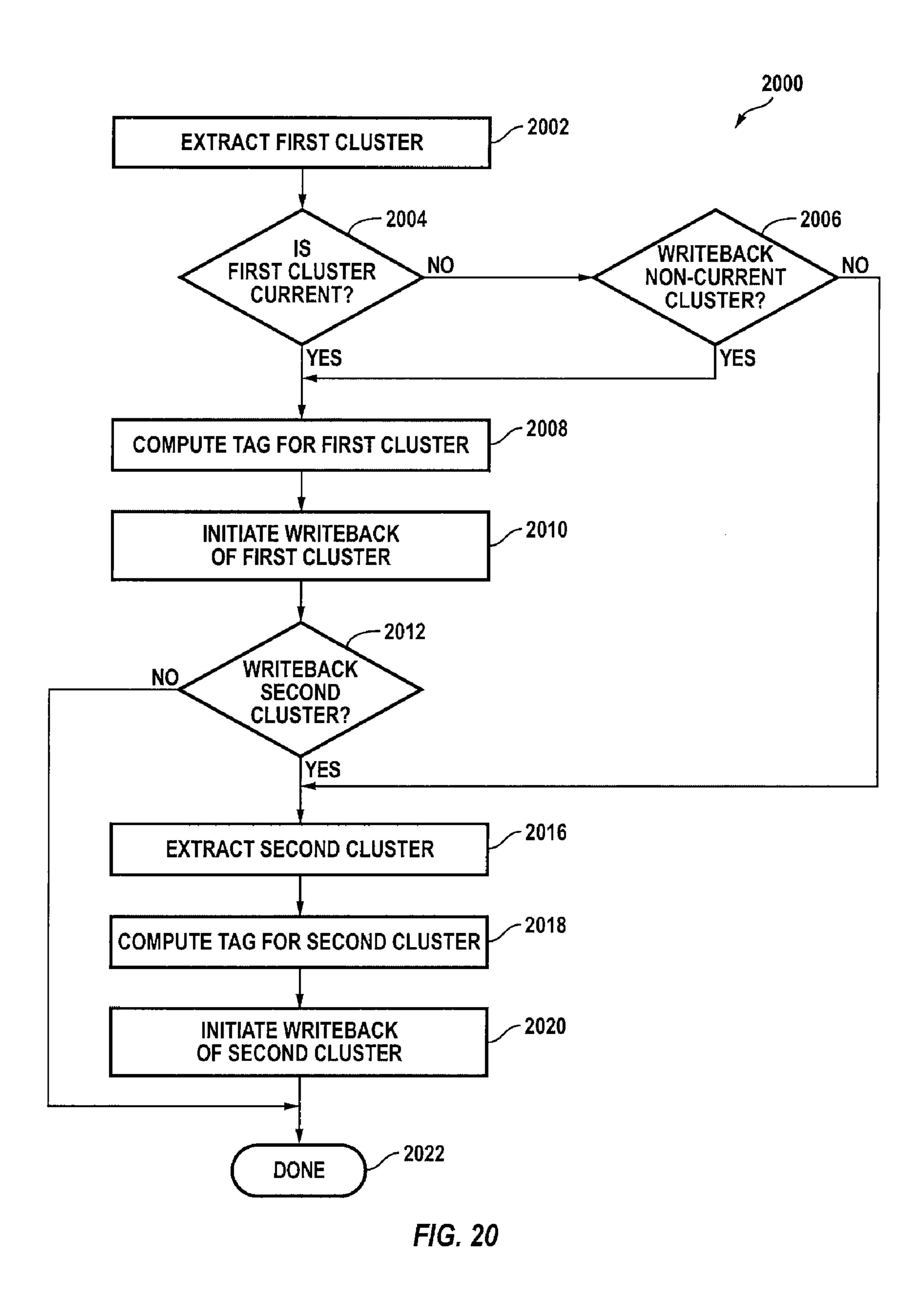

- FIG. **16** is a flow diagram of a cluster writeback process 60 according to an embodiment of the present invention;

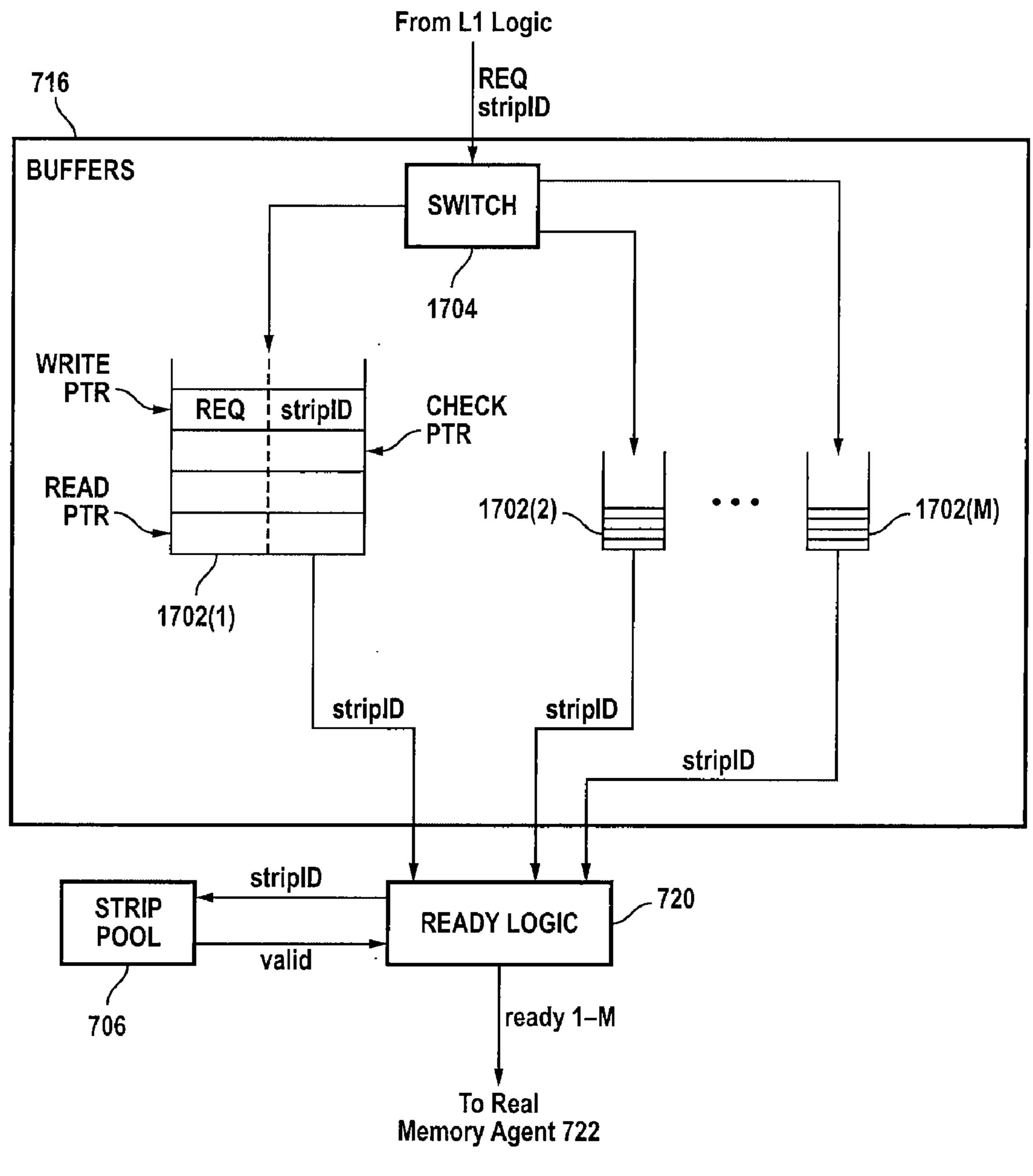

- FIG. 17 is a block diagram showing buffering and ready logic for a TLB system according to an embodiment of the present invention;

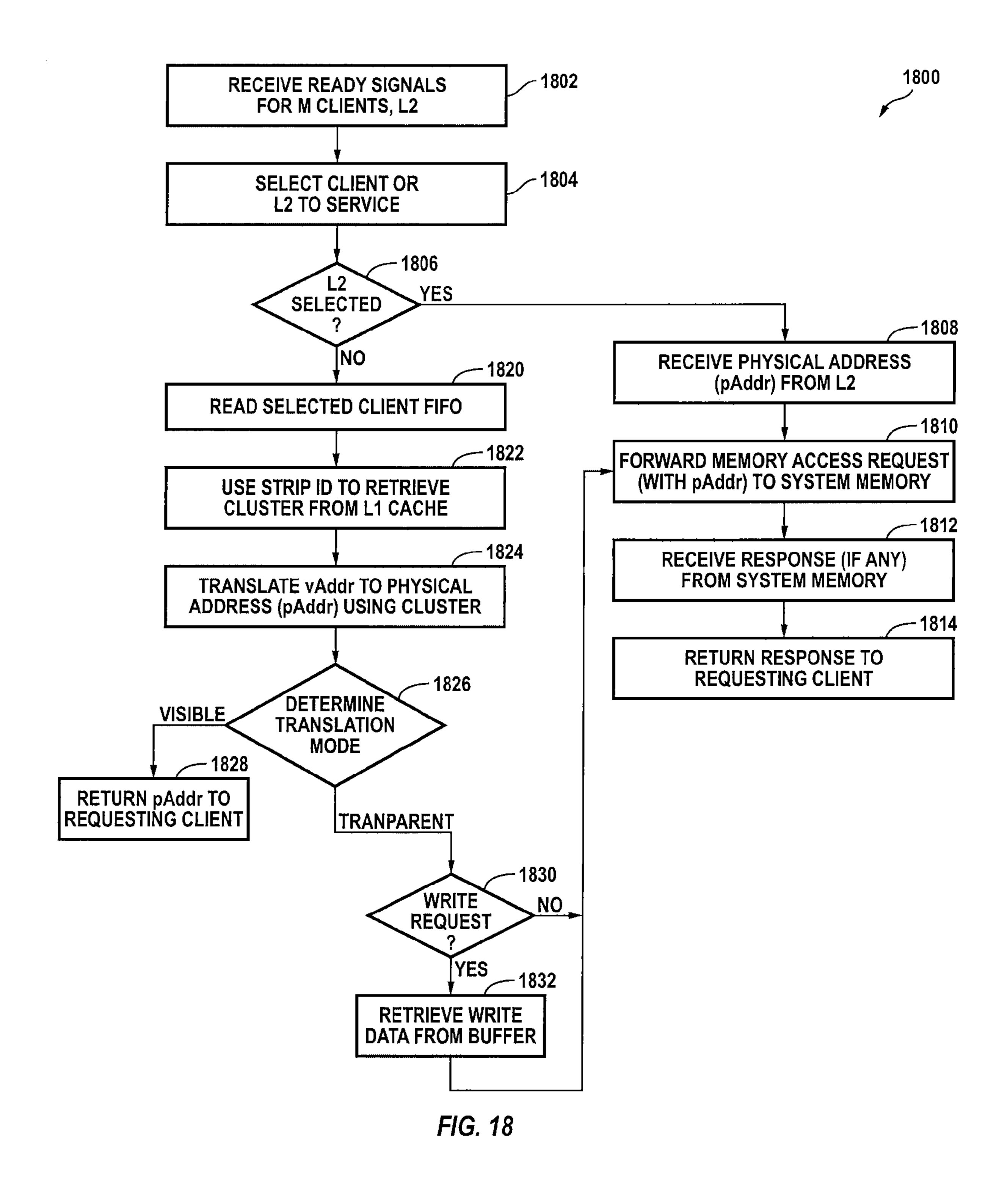

- FIG. 18 is a flow diagram of processing operations in a 65 real memory agent according to an embodiment of the present invention;

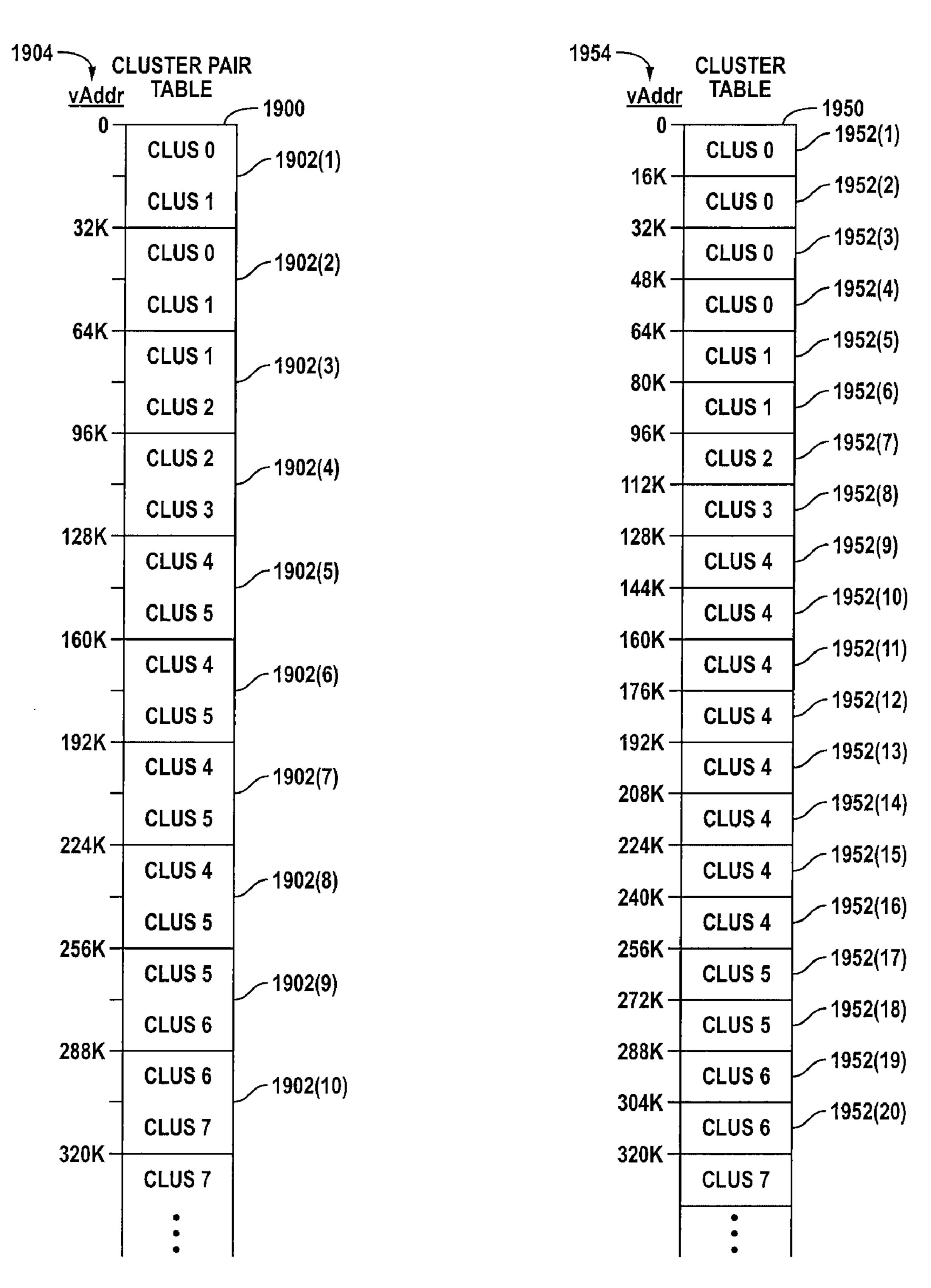

- FIG. 19 illustrates cluster data stored in a cluster table according to an embodiment of the invention that stores cluster pairs;

- FIG. 20 is a flow diagram of a writeback control process according to a cluster pair embodiment of the present invention;

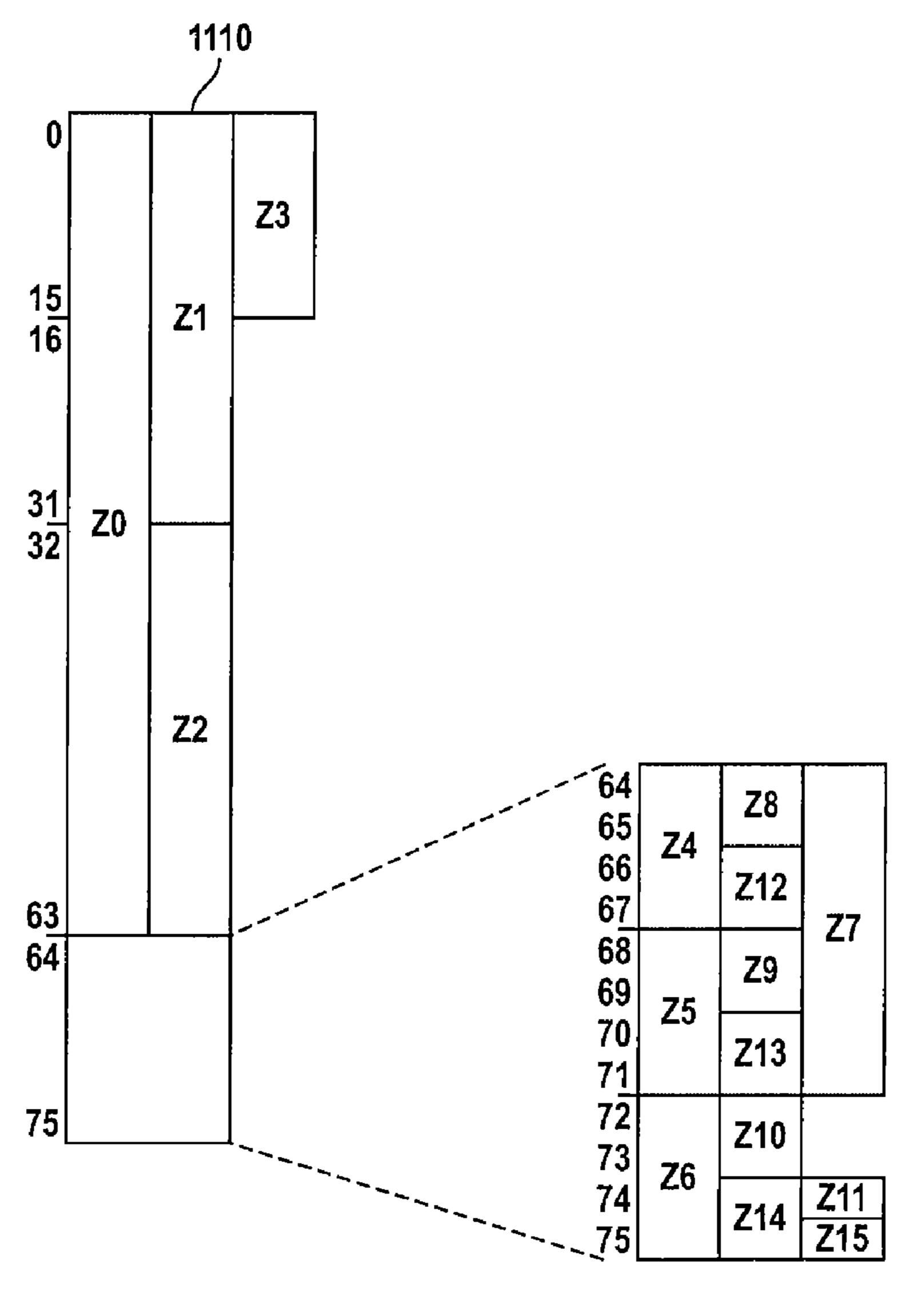

- FIG. 21 illustrates an allocation of zones in a tag table among multiple clients according to an embodiment of the present invention;

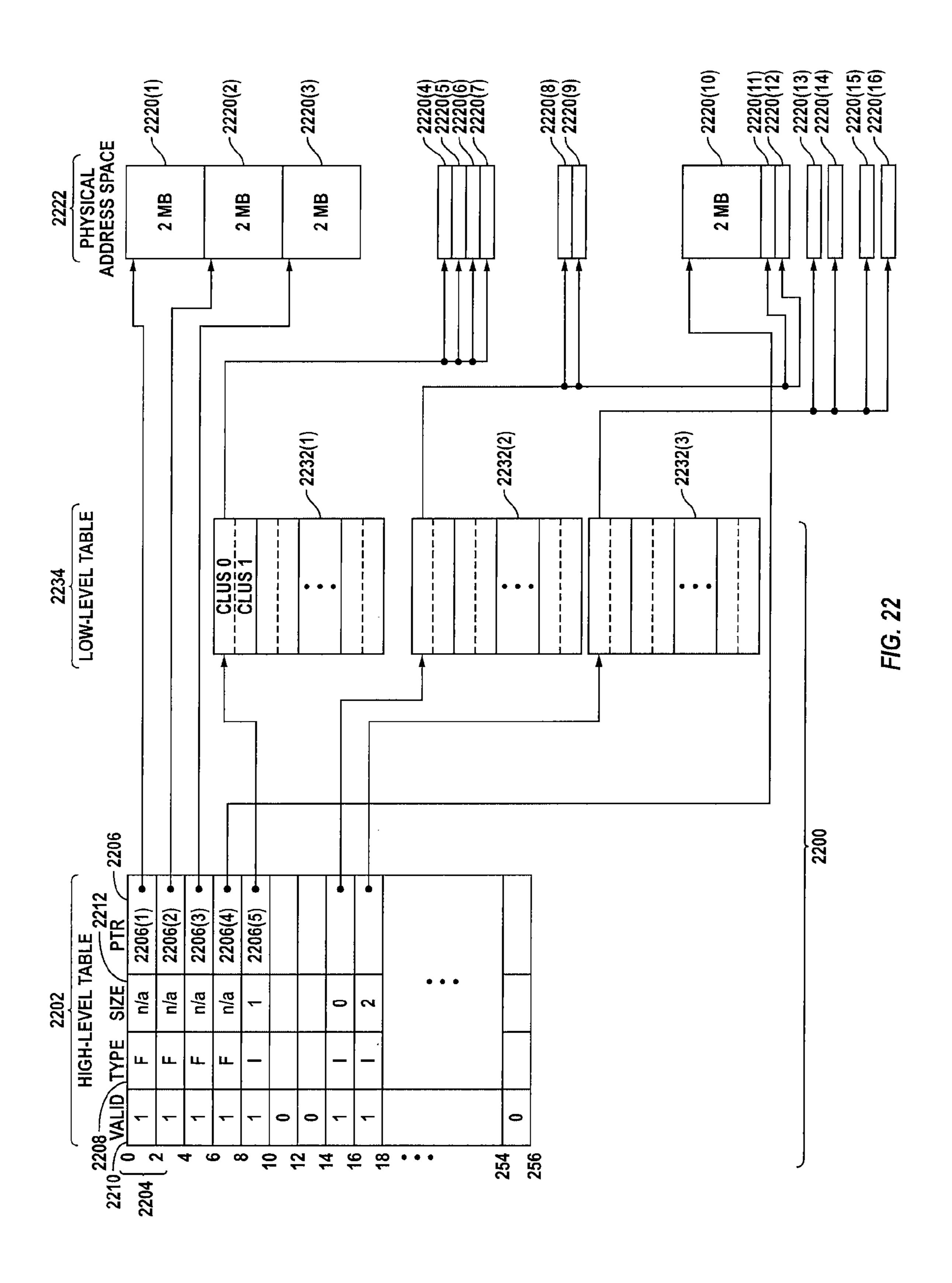

- FIG. 22 illustrates translation data stored in a hierarchical translation table according to an embodiment of the present invention;

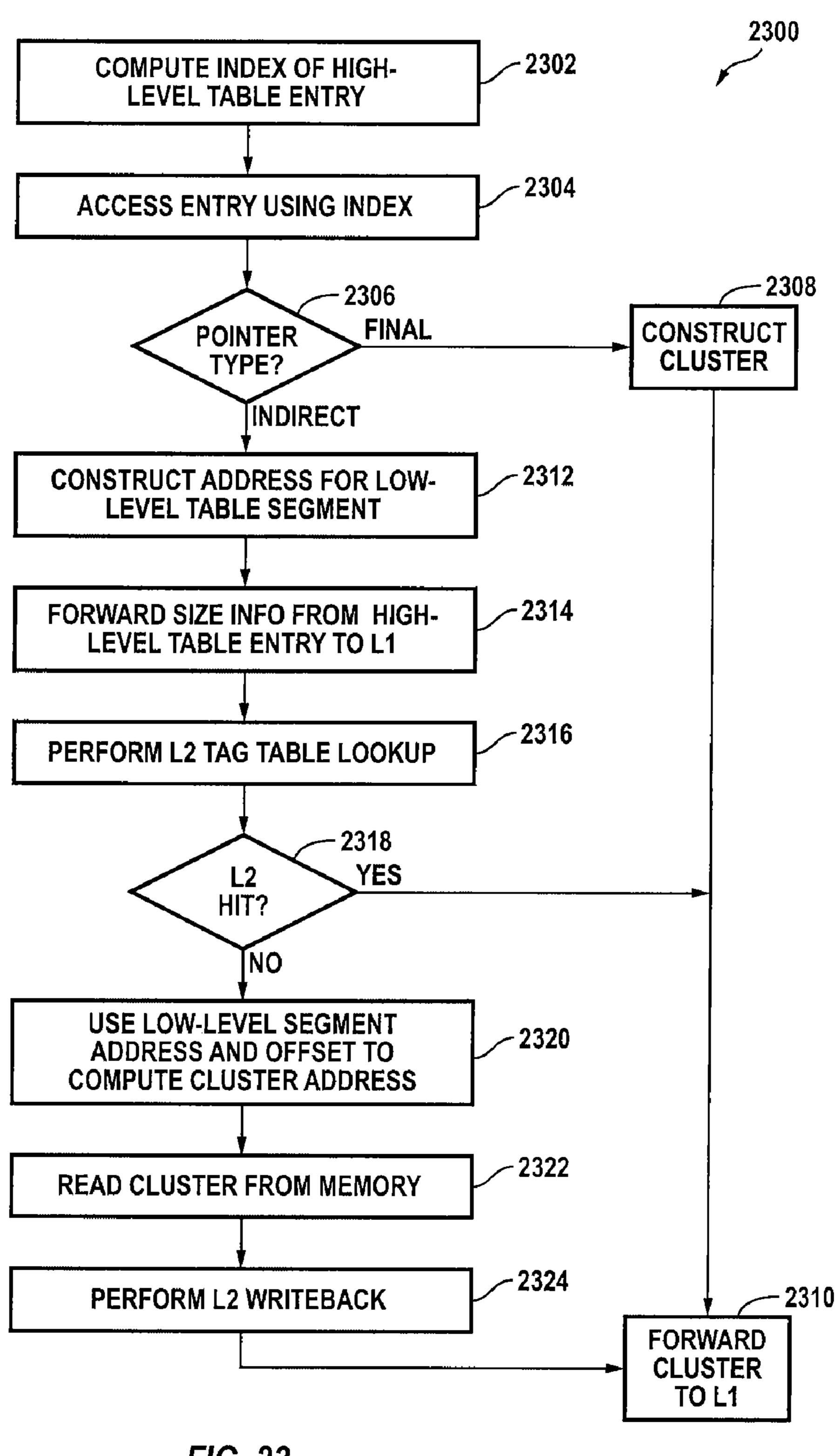

- FIG. 23 is a flow diagram of a Level 2 lookup process that uses the hierarchical translation table of FIG. 22; and

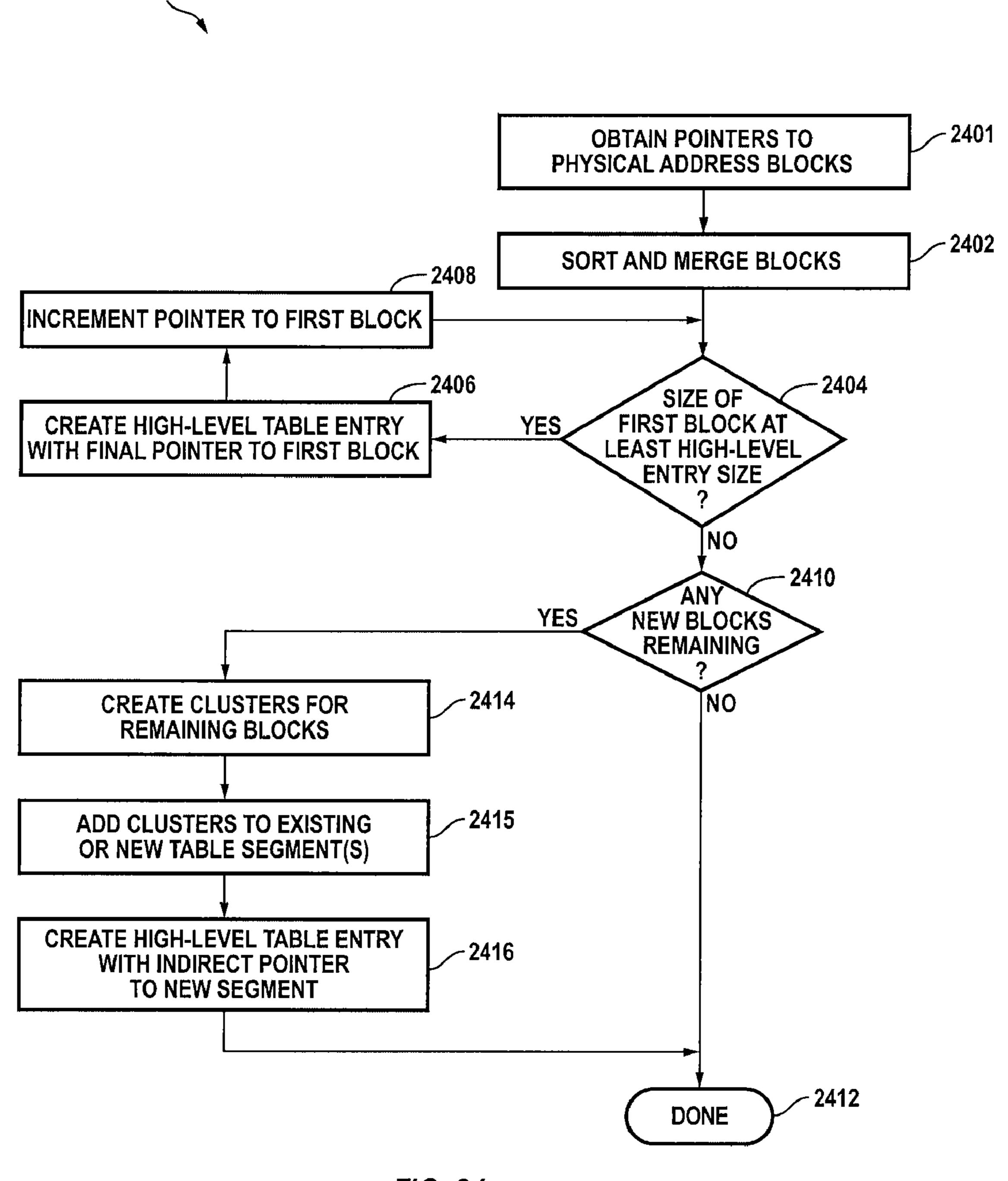

- FIG. **24** is a flow diagram of a process for creating entries in the hierarchical translation table of FIG. 22.

### DETAILED DESCRIPTION OF THE INVENTION

Embodiments of the present invention provide systems and methods for implementing a virtual address translation table and an on-chip address cache that can substantially reduce the number of page table accesses needed to translate 25 a given range of virtual addresses to physical addresses. Address translation information is provided using a translation data structure, referred to herein as a "cluster," that is associated with some range of virtual addresses; the cluster can be used to translate any virtual address in its range to a physical address. The sizes of the ranges covered by (or mapped by) different clusters may be different, and in some embodiments, the size of the cluster data structure is independent of its range size. For example, in one embodiment, each cluster is 16 bytes and can map anywhere from 4 to 512 FIG. 8 is a block diagram of an input arbitration unit for 35 pages of the virtual address space. Clusters may be stored in an address translation table (e.g., in system memory) that is indexed by virtual address so that, starting from any valid virtual address, the appropriate cluster for translating that address can be retrieved from the translation table. Recently 40 retrieved clusters can be stored in an on-chip cache in such a manner that a cached cluster can be used to translate any virtual address in its range without accessing the address translation table again. One embodiment of the invention provides an address translation lookaside buffer (TLB) system that can handle requests from multiple clients in a pipelined fashion and can make the translation process transparent or not to individual clients as desired. Thus, the TLB system can be integrated with existing graphics processor designs.

> The present description is organized as follows: Section I describes examples of computer systems according to embodiments of the present invention; Section II describes a cluster table implementation of an address translation table according to one embodiment of the present invention; Section III describes a TLB system according to an embodiment of the present invention; and Section IV describes further embodiments of the invention, including a "cluster pair" embodiment and additional features related to managing requests from multiple clients. It is to be understood that all embodiments described herein are illustrative and not limiting of the scope of the invention.

### I. COMPUTER SYSTEM OVERVIEW

FIG. 1 is a block diagram of a computer system 100 according to an embodiment of the present invention. Computer system 100 includes a central processing unit (CPU)

102 and a system memory 104 communicating via a bus 106. User input is received from one or more user input devices 108 (e.g., keyboard, mouse) coupled to bus 106. Visual output is provided on a pixel based display device 110 (e.g., a conventional CRT or LCD based monitor) operating under control of a graphics card 112 coupled to system bus 106. A system disk 128 and other components, such as one or more removable storage devices 129 (e.g., floppy disk drive, compact disk (CD) drive, and/or DVD drive), may also be coupled to system bus 106. System bus 106 may be 10 implemented using one or more of various bus protocols including PCI (Peripheral Component Interconnect), AGP (Accelerated Graphics Port) and/or PCI Express (PCI-E); appropriate "bridge" chips such as a north bridge and south bridge (not shown) may be provided to interconnect various 15 components and/or buses.

Graphics card 112 includes a graphics processing unit (GPU) 114, a graphics memory 116, a graphics translation lookaside buffer (GTLB) 142, and scanout control logic 120, which may be implemented, e.g., using one or more integrated circuit devices (including programmable processors and/or application specific integrated circuits (ASICs)). GPU 114 may be configured with one or more processing cores to perform various tasks, including generating pixel data from graphics data supplied via system bus 106, interacting with graphics memory 116 to store and update pixel data, and the like. Such elements of GPU 114 may be of generally conventional design, and a detailed description is omitted. Communication with graphics memory 116 is managed by GTLB 142 as described below.

Scanout control logic 120 reads pixel data from graphics memory 116 (or, in some embodiments, system memory 104) via GTLB 142 and transfers the data to display device 110 to be displayed. In one embodiment, scanout occurs at a constant refresh rate (e.g., 80 Hz); the refresh rate can be 35 a user selectable parameter. Scanout control logic 120 may also perform other operations such as adjusting color values for particular display hardware; generating composite screen images by combining the pixel data with data for a video or cursor overlay image or the like obtained, e.g., from graphics memory 116, system memory 104, or another data source (not shown); converting digital pixel data to analog signals for the display device; and so on. It will be appreciated that the particular configuration of graphics card 112 or its components is not critical to the present invention.

During operation of system 100, CPU 102 executes various programs that are (temporarily) resident in system memory 104. In one embodiment, these programs include one or more operating system (OS) programs 132, one or more application programs 134, one or more driver pro- 50 grams 136 for graphics card 112, and a resource manager program 138 that provides various support services to driver program 136. It is to be understood that, although these programs are shown as residing in system memory 104, the invention is not limited to any particular mechanism for 55 supplying program instructions for execution by CPU 102. For instance, at any given time some or all of the program instructions for any of these programs may be present within CPU 102 (e.g., in an on-chip instruction cache and/or various buffers and registers), in a page file or memory 60 mapped file on system disk 128, and/or in other storage space.

Operating system programs 132 and/or application programs 134 may be of conventional design. An application program 134 may be, for instance, a video game program 65 that generates graphics data and invokes appropriate rendering functions of GPU 114 to transform the graphics data

8

to pixel data. Another application program 134 may generate pixel data and provide the pixel data to graphics card 112 for display. It is to be understood that any number of application programs that generate pixel and/or graphics data may be executing concurrently on CPU 102. Operating system programs 132 (e.g., the Graphical Device Interface (GDI) component of the Microsoft Windows operating system) may also generate pixel and/or graphics data to be processed by graphics card 112.

Driver program **136** enables communication with graphics card 112. Driver program 136 advantageously implements one or more standard application program interfaces (APIs), such as Open GL, Microsoft DirectX, or D3D for communication with graphics card 112; any number or combination of APIs may be supported, and in some embodiments separate driver programs 136 are provided to implement different APIs. By invoking appropriate API function calls, operating system programs 132 and/or application programs 134 are able to instruct driver program 136 to transfer graphics data or pixel data to graphics card 112 via system bus 106, to invoke various rendering functions of GPU 114, and so on. The specific commands and/or data transmitted to graphics card 112 by driver program 136 in response to an API function call may vary depending on the implementation of GPU **114**, and driver program **136** may also transmit commands and/or data implementing additional functionality (e.g., special visual effects) not controlled by operating system programs 132 or application programs 134.

Resource manager 138 is advantageously provided to support interactions of driver program 136 with system hardware components such as system memory 104. Resource manager 138 implements low-level hardware- and operating-system-specific functionality that is used by driver program 136 in processing requests from operating system programs 132 and/or application programs 134. For example, resource manager 138 may handle tasks such as allocation and deallocation of system memory for driver program 136 and/or GPU 114. Providing resource manager 138 enables program code for driver program 136 to be written at a level of abstraction that hides details of the hardware and/or operating system on which driver program 136 is executed; thus, the same driver code can be adapted to different hardware configurations by providing a different 45 implementation of resource manager **138**. It will be appreciated that the functionality of resource manager 138 might also be implemented in driver program 136.

In system 100, GPU 114 can access system memory 104 by reference to virtual addresses, which are translated to physical addresses in order to fulfill the memory access request. An address translation table 140, shown as being resident in system memory 102, stores translation information that can be used to convert a given virtual address to the corresponding physical address. In accordance with an embodiment of the present invention, the translation information is advantageously stored in one or more clusters, where a cluster is a data structure that provides the translation information for a variable-size range of the virtual address space. Embodiments of cluster data structures and cluster tables that implement address translation table 140 are described in Section II below. Although address translation table 140 is shown as being resident in system memory 104, it may also be stored elsewhere, e.g., in graphics memory 116 or in GPU 114.

GTLB **142** receives memory requests from various "clients" executing in a processing core (not shown) of GPU **114** and/or from scanout control logic **120** and performs address

translations in the course of responding to these requests. In response to a memory request that includes a virtual address (or in response to an address translation request that does not include a memory access request), GTLB 142 retrieves a cluster from address translation table 140 or from its own 5 cache of recently used clusters and converts the virtual address to a physical address based on data contained in the cluster. GTLB **142** is advantageously implemented such that address translation can be made invisible to some or all clients; that is, a client can simply issue a memory access 10 command referencing a virtual address and receive a response (including the data, in the case of a read command) from the appropriate physical memory system, without the client needing to be aware that any translation has occurred. Thus, existing driver programs and/or GPU-implemented 15 algorithms can be used regardless of whether the memory being used is dedicated graphics memory 116 or system memory 104. In this embodiment, GTLB 142 also manages access by components of graphics processing subsystem 112 to system memory 104, graphics memory 116, and any other 20 physical memory resource of system 100 that is accessible to graphics processing components. For each such resource, GTLB **142** performs the appropriate address translation; in some instances (e.g., for graphics memory 116), no translation may be required. In other embodiments, GTLB **142** 25 manages only accesses to system memory 104; access to graphics memory 116 may be provided via an alternative path.

In the course of its operations, GTLB 142 may store copies of some or all of the clusters retrieved from address 30 translation table 140 in its own cache (not shown), thereby facilitating the handling of subsequent requests for similar addresses. Cluster caching and other features of GTLB 142 may be implemented in various ways, examples of which are described in Section III below. GTLB 142 can be implemented in hardware resident on graphics card 112 (optionally integrated with GPU 114), in software executing on GPU 114 and/or CPU 102, or any combination thereof.

FIG. 2 is a block diagram of another computer system 200 according to another embodiment of the present invention. 40 Computer system 200 includes a CPU 202 and system memory 204 communicating via a "north bridge" chip 206. North bridge chip 206 advantageously implements one or more high-speed bus protocols (these may be conventional protocols) that facilitate rapid communication between CPU 45 202 and system memory 204. North bridge chip 206 also communicates with a "south bridge" chip 207 that implements one or more bus protocols (which may be the same as or different from protocols used by north bridge chip 206) for connecting various peripheral devices, such as a user 50 input device 208, a system disk 228, and a removable storage device 229. South bridge chip 207 and any peripheral devices may be of generally conventional design.

North bridge chip 206 includes an integrated graphics processor (IGP) 214 that implements graphics functionality 55 similar to that of GPU 114 of system 100 (FIG. 1). For example, IGP 214 includes scanout control logic 220 that provides pixel data to a display device 210. (Scanout control logic 220 may be generally similar to scanout control logic 120 of FIG. 1.) IGP 214 also includes a GTLB 242 that 60 manages access to system memory 204 for IGP 214 and its components, including scanout control logic 220.

Operation of system 200 is generally similar to operation of system 100 described above. For example, a graphics driver program, a resource manager program, application 65 programs, and operating system programs (not shown) may be executed by CPU 202. In system 200, IGP 214 might not

10

have access to a dedicated graphics memory area at all, although some embodiments may include at least a small amount of dedicated graphics memory. If IGP 214 does not have dedicated graphics memory, or if additional memory beyond the dedicated graphics memory is required, IGP 214 accesses system memory 204 by reference to virtual addresses that are translated to corresponding physical addresses. An address translation table 240 is provided for storing address translation data (e.g., clusters), and GTLB 242 performs the address translations. Address translation table 240 and GTLB 242 may be generally similar in design and operation to address translation table 140 and GTLB 142 of FIG. 1.

It will be appreciated that systems 100 and 200 are illustrative and that variations and modifications are possible. Arrangement of system components may be varied; for instance, in some embodiments, communication with system memory may be routed through the CPU. Some components may be duplicated or absent as desired. A graphics card may be implemented with any amount of on-card memory or with no dedicated graphics memory at all, and a GPU can use a combination of on-card memory and system memory in any manner desired. Where a graphics card has no on-card memory, the GPU may use system memory exclusively. An IGP can be provided with dedicated memory if desired and can use a combination of dedicated memory and system memory in any manner desired. A single computer system may include multiple graphics processors implemented using any combination of IGPs and/or GPUs. For example, a graphics card based on the AGP or PCI-E bus standard can be connected to north bridge chip 206 or south bridge chip 207 of FIG. 2, as is known in the art, and various control technologies can be provided for controlling operations of the multiple graphics processors. One or more graphics processors may also be implemented as a separate chip that mounts onto the motherboard of a computer system. In view of the present disclosure, persons of ordinary skill in the art will recognize that the present invention can be embodied in a wide variety of system configurations.

It will also be appreciated that, although the address translation techniques described herein are introduced in the context of graphics processing subsystems, these techniques may also be adapted for other computer system components that use virtual addressing. For example, an address translation table in accordance with an embodiment of the present invention may be implemented for other peripheral devices (e.g., disk drives), for virtual memory management by a CPU, and so on. Accordingly, where the following description refers to a "client," it is to be understood that the client may be any component of a computer system that accesses any memory resource by reference to a virtual address or that requests a translation of a virtual address.

In embodiments described herein, the physical memory resource is of generally conventional design. Physical memory is byte-addressable and is allocated by the operating system in fixed-size units (e.g., 4 KB) of physically adjacent memory locations; the fixed-size unit is a "page" in the physical address space. The physical address of a byte of memory is specified by a page address and a byte offset within the page. It is to be understood that a physical address may be expressed in various ways, including as a "linear address" that may be further converted to a hardware-dependent identifier of a particular storage location (e.g., row and column addresses for a memory cell array).

The number of bits in a physical address or page address is implementation dependent and may vary, e.g., according

to the size of the physical address space for a particular system. By way of illustration, some examples herein refer to a 36-bit physical address space in which the 24 most significant bits (MSBs) of an address determine the page address and the 12 least significant bits (LSBs) correspond to the byte offset within a 4 KB page. Bit ranges within addresses are sometimes represented herein as a range of bits, e.g., [Addr<sub>35</sub>:Addr<sub>12</sub>] for the page address, and [Addr<sub>11</sub>: Addr<sub>0</sub>] for the byte offset. Those of ordinary skill in the art will recognize that other embodiments adapted to different memory implementations of physical memory (e.g., different page sizes, different sizes and organizations of physical address space, addressability in units other than bytes) and that the present invention is not limited to any particular memory system or physical address space.

### II. CLUSTER TABLE

A cluster table that implements an address translation table according to an embodiment of the present invention 20 will now be described. This cluster table, which can be resident in the main system memory (e.g., cluster table 140 of FIG. 1 or 240 of FIG. 2) or elsewhere in the system, provides data that can be used to translate virtual addresses to physical addresses. Like a conventional page table, an 25 entry in the cluster table is accessed by reference to a virtual address. Unlike a conventional page table, the cluster table entry does not directly provide the address for the corresponding page of physical memory. Instead, each cluster table entry stores a data structure (called a cluster) that maps 30 some range of the virtual address space to physical addresses. As will become apparent, the size of the range mapped by a cluster can vary, depending on how the physical memory is allocated; a single cluster can map an arbitrarily large range of virtual address space.

### A. Cluster Table Structure

FIG. 3 is a conceptual illustration of a mapping from a cluster table to physical addresses according to an embodiment of the present invention. At the left is a cluster table 302, which contains a number of entries 304. (Herein, 40 multiple instances of like objects are denoted with reference numbers identifying the object and parenthetical numbers identifying the instance where needed.) An entry 304 in cluster table 302 is accessed by reference to the virtual address index 306 shown at left; index 306 may be obtained 45 for any given virtual address, e.g., by aligning that virtual address at a 16K boundary. For example, a virtual address of 86K would align to an index 306 value of 80K, which corresponds to entry 304(6). In some embodiments, determining the virtual address index from a virtual address 50 includes additional manipulations, such as dividing by 1024, so that the index can be used as an offset relative to a base address of the cluster table in system memory. Such manipulations are known in the art.

Each entry **304** stores a cluster (represented as CLUS n, 55 where n=0, 1, 2, . . . ), and the same cluster can be stored in multiple entries (e.g., CLUS **0** is stored in each of entries **304(1)-304(4)**). In this embodiment, each cluster is a fixed-size data structure (e.g., 16 bytes) that can map a variable range of the virtual address space to corresponding physical addresses; it is to be understood that in other embodiments, different clusters may have different sizes. The mapping is provided by address translation data in the cluster. The address translation data generally includes a starting address for a block of contiguous addresses (e.g., page addresses) in 65 the physical address space, and sequential virtual addresses in the cluster's range are mapped to sequential physical

12

addresses in the block. In some embodiments, clusters may include starting addresses for more than one block; sequential virtual addresses can be mapped to sequential physical addresses in the first block until the first block is exhausted, then to sequential physical addresses in the second block, and so on for any number of blocks.

FIG. 3 also illustrates how clusters CLUS 0-CLUS 4 of cluster table 302 might map to a physical address space 316. Physical address space 316 includes a number of blocks 314, where each block 314 is a contiguous range of physical addresses and is mapped to a contiguous range of virtual addresses. Each block is also labeled with its size (in KB). In this example, each cluster CLUS n provides mappings via pointers to four blocks 314. (Examples of encoding such 15 pointers into a cluster data structure are described below.) The four blocks **314** pointed to by a particular cluster CLUS n are all the same size (e.g., CLUS 0 points to four blocks 314(4), 314(9), 314(11), 314(17) that are 16 KB each), but there is no necessary relationship between the locations of the four blocks. In addition, blocks pointed to by different clusters may be of different sizes (e.g., CLUS 0 points to 16-KB blocks 314(4), 314(9), 314(11), 314(17) while CLUS 1 points to 8-KB blocks 314(6), 314(7), 314(15), 314(20)). The block size for each cluster is determined when that cluster is created, as described in Section II.D below. In general, block size is affected by the degree of fragmentation present in the physical memory. In other embodiments, one cluster may point to blocks of different sizes; in still other embodiments, some relationship (e.g., locality) between the addresses of blocks pointed to by a cluster may be required.

Each entry 304 in cluster table 302 may be regarded as a "virtual block" in the virtual address space. All virtual addresses within the address range of a virtual block are guaranteed to be mapped to physical addresses by the cluster stored in that entry; e.g., all addresses in the 80-96 KB range corresponding to entry 304(6) are mapped by CLUS 1. It is to be understood that the virtual block size need not correspond to a physical page size of the physical address space; e.g., each virtual block (i.e., entry) in cluster table 302 covers four 4-KB physical pages. It should also be noted that some clusters might map virtual addresses for more than one virtual block; e.g., CLUS 1 is also stored in entry 304(5) and therefore also maps virtual addresses in the 64-80 KB virtual block. Thus, the "range" of a cluster (i.e., the set of all virtual addresses mapped by that cluster) may include any number of virtual blocks.

To the extent that an entry 304 may be regarded as a virtual block, the index 306 used to find the cluster for that entry may be regarded as a virtual block address. For instance, in cluster table 302, a virtual address (e.g., vAddr=86 KB) can be translated by first identifying the virtual block to which it belongs, i.e., the corresponding index 306 (e.g., 80 KB, or in some embodiments 80). Using the index 306, a cluster (e.g., CLUS 1) for the virtual block (e.g., entry 304(6)) is obtained from cluster table 302, and a translation operation is performed on the cluster to obtain the physical address, which in this example would be in one of physical blocks 314(6), 314(7), 314(15), 314(20). It should be noted that in this embodiment, prior knowledge of the size of the virtual address range mapped by a cluster is not required to obtain the correct cluster. Thus, no more than one access to cluster table 302 is required to translate any virtual address.

Given a cluster, the translation operation for a virtual address mapped by that cluster depends on the particular cluster structure used in a given embodiment. Examples of cluster structures and associated translation operations will now be described; it will be appreciated that these structures and operations are illustrative and not restrictive of the scope of the invention.

### B. Cluster Structure Examples

FIGS. 4A-B are bit-field representations of two cluster data structures according to embodiments of the present invention. FIG. 4A shows bit fields of a four-block cluster 400 (which may be stored as clusters CLUS n in cluster table 302 of FIG. 3), and FIG. 4B shows bit fields of an eight-block cluster 450 that may be stored in the same cluster table with four-block clusters 400 of FIG. 4A.

Turning first to FIG. 4A, four-block cluster 400 is a 16-byte (128-bit) data structure for mapping part of a 36-bit physical address space. Cluster 400 provides physical addresses for the respective starting locations of each of four blocks, which may be located anywhere in the physical address space. Blocks of varying sizes can be mapped by cluster 400, although each of the four mapped blocks has the same size.

In this embodiment, cluster 400 includes a 3-bit size index 402. Size index 402 encodes the size of each of the four blocks mapped by the cluster. Eight block sizes are supported, from a minimum size of 4 KB (one page) up to a maximum size of 512 KB (128 pages). Since the total amount of memory mapped by cluster 400 (referred to herein as the "range size") is four times the block size, size index 402 also encodes the range size, which varies from 16 KB (four one-page blocks) to 2048 KB (four 128-page blocks). Block sizes and range sizes corresponding to each value of size index 402 for cluster 400 are summarized in Table 1. It will be appreciated that other block or range sizes, including larger sizes, could be supported if desired, e.g., by expanding size index 402 to a larger number of bits.

TABLE 1

| Size index | Block Size (KB) | Range Size (KB) |

|------------|-----------------|-----------------|

| 0          | 4               | 16              |

| 1          | 8               | 32              |

| 2          | 16              | 64              |

| 3          | 32              | 128             |

| 4          | 64              | 256             |

| 5          | 128             | 512             |

| 6          | 256             | 1024            |

| 7          | 512             | 2048            |

Format field **404** comprises one bit. In this embodiment, the bit is set to "0" for a four-block cluster. As will be seen below, format field **404** allows four-block clusters **400** and eight-block clusters **450** to co-exist in the same cluster table. In other embodiments, more than two formats can be supported, and format field **404** may contain additional bits so that each format has a unique identifier. In still other embodiments, only one cluster format is supported, and format field **404** may be omitted.

Valid field **406** also comprises one bit, which is set to "1" (or logical True) if the cluster contains valid block addresses and to "0" (or logical False) otherwise. For example, when the system is initialized, before any memory is mapped to virtual addresses, the cluster table would be filled with 60 clusters with a valid bit of "0." As memory is mapped, the valid bit is changed for the appropriate clusters. When a cluster is accessed, its valid bit can be checked and any requests that return invalid clusters can be flagged.

Cluster 400 also includes four 24-bit "block pointer" 65 fields 410. Each block pointer field 410 stores the page address (e.g., physical address or pointer) of the first page in

**14**

one of the four blocks of physical address space mapped by cluster 400. Each page address is advantageously stored as a page index (e.g., without the 12 LSBs that correspond to byte offset within a page). The block pointers are advantageously arranged so that the lowest virtual addresses mapped by cluster 400 correspond to block pointer 410(0), the next virtual addresses correspond to block pointer 410 (1), and so on. Accordingly, if a requested virtual address is in the first quarter of the range mapped by cluster 400, block pointer 410(0) is used to obtain the physical address; if the requested virtual address is in the second quarter, then block pointer 410(1) is used; and so on. It should be noted that the block pointers need not be arranged in order of physical address.

As an example, in cluster table 302 of FIG. 3, entry 304(1) stores a cluster CLUS 0, which may be an instance of cluster 400. In this example, block pointer 410(0) would store the starting address for block 314(4), block pointer 410(1) would store the starting address for block 314(9), block pointer 410(2) would store the starting address for block 314(11), and block pointer 410(3) would store the starting address for block 314(17).

For an invalid cluster, valid field **406** is set to logical false, and each block pointer field **410** is advantageously set to reference a "bit bucket" page in the system memory. As is known in the art, a bit bucket is an area of system memory that is guaranteed not to be used for storing meaningful data and therefore is a safe target for invalid (or null) pointers. When block pointer fields **410** of invalid clusters are set to reference a bit bucket page, any memory access operations that reference (by virtual address) an invalid cluster can be processed normally without affecting any data.

The remaining pad fields **420-424** include a total of 27 bits, bringing the size of cluster **400** to 16 bytes. Any number of pad fields can be arranged as desired within cluster **400**. In this embodiment, pad fields **420-424** are not used to share cluster information, but other embodiments may use some or all of these bits (e.g., if more than 24 bits are needed for each block pointer **410**).

Turning now to FIG. 4B, eight-block cluster 450 is also a 16-byte (128-bit) data structure for mapping part of a 36-bit physical address space. Cluster 450 provides physical addresses for the respective starting locations of each of eight blocks. The eight-block cluster allows a larger number of mappings (eight rather than four) to be stored in a single cluster although, as will be seen, the physical addresses of each of the eight blocks are required to have some number of MSBs in common. (Where this is not the case, two four-block clusters 400 can be used instead.)

In this embodiment, cluster 450 includes a three-bit size index 452. Like size index 402 of cluster 400, size index 452 encodes the size of each of the blocks mapped by the cluster 450, as well as the range size (which in the case of an eight-block cluster is eight times the block size). Block sizes and range sizes for size index 452 are summarized in Table 2. It will be appreciated that other block sizes or range sizes, including larger sizes, could also be supported, and that size index 452 may be modified to include the appropriate number of bits.

TABLE 2

| Size field | Block Size (KB) | Range Size (KB) |

|------------|-----------------|-----------------|

| 1          | 4               | 32              |

| 2          | 8               | 64              |

| 3          | 16              | 128             |

TABLE 2-continued

| Size field | Block Size (KB) | Range Size (KB) |

|------------|-----------------|-----------------|

| 4          | 32              | 256             |

| 5          | 64              | 512             |

| 6          | 128             | 1024            |

| 7          | 256             | 2048            |

Comparing Table 2 with Table 1, it will be apparent that size indices 402 and 452 are defined such that a given value of size index 402 or 452 corresponds to the same range size, regardless of whether the cluster is a four-block cluster 400 or an eight-block cluster 450. (Thus, for eight-block clusters, a size index value of zero is not used.) In embodiments 15 where four-block clusters 400 and eight-block clusters 450 co-exist, this size-index definition allows the range size of a cluster to be readily determined without knowing whether the cluster is a four-block or eight-block cluster. Other definitions may also be used, and a particular size index 20 value in eight-block cluster 450 need not correspond to any particular size index value in four-block cluster 400.

In eight-block cluster **450**, format field **454** comprises one bit, which is set to "1" to distinguish eight-block cluster **450** from four-block cluster **400**. Thus, a cluster table can store 25 any combination of four-block and eight-block clusters, and the format field (advantageously placed at the same bit position for both cluster types) can be used to determine whether a particular cluster is a four-block or eight-block cluster.

Unlike four-block cluster 400, eight-block cluster 450 does not include a valid field, and eight-block clusters 450 are presumed valid. Eight-block cluster 450 may be invalidated by setting format field 454 to "0", making it a four-block cluster 400 whose valid bit 406 can then be set to 35 "0". (Bit bucket references are advantageously entered in block pointers 410 as described above.)

Cluster 450 also includes a ten-bit base field 458 and eight fourteen-bit block pointer fields **460**. These fields encode the respective physical addresses of the first page in each of 40 eight blocks of memory. In one embodiment, base field 458 holds ten MSBs common to the physical addresses of all eight blocks, and each block pointer field 460 holds the next fourteen bits for one of the blocks, so that the starting physical address for a block can be formed by concatenating 45 one of the block pointer fields 460 with base pointer field **458**. In some embodiments, blocks may share fewer than ten MSBs; examples will be described below. Block pointers **460** are advantageously arranged so that the lowest virtual addresses mapped by cluster 450 correspond to block 50 vAddr $_{12+k}$ ]. pointer 460(0), the next virtual addresses correspond to block pointer 460(1), and so on. Accordingly, if a requested virtual address is in the first eighth of the range mapped by cluster 450, block pointer 460(0) is used to obtain the physical address; if the requested virtual address is in the 55 second eighth, then block pointer 460(1) is used; and so on. It should be noted that the block pointers are not necessarily arranged in order of physical address.

The remaining pad field 470 includes two bits, bringing the size of cluster 450 to 16 bytes. These pad bits may be 60 disposed as desired within cluster 450. In this embodiment, pad field 470 is not used to store cluster content, although other embodiments might use these bits.

It will be appreciated that the cluster formats described herein are illustrative and that variations and modifications 65 are possible. Cluster data structures may be adapted to provide translation data for various ranges of virtual address **16**

space, and clusters translating different-sized ranges in the virtual address space may co-exist in a cluster table. Cluster data may be structured in any manner desired, and the content or format of a cluster may vary from the embodiments described herein. Clusters are advantageously constructed such that the size of the cluster data structure is constant, regardless of the size of the address range mapped.

C. Address Translation Using Clusters

Embodiments of processes for using clusters to translate virtual addresses to physical addresses will now be described, with reference to the four-block clusters 400 and eight-block clusters 450 of FIGS. 4A-B. It is to be understood that similar processes may be implemented for other cluster formats.

FIG. 5A illustrates a process 500 for translating a virtual address (vAddr) given a corresponding cluster, where the cluster may have either of the formats shown in FIGS. 4A-B. The corresponding cluster may be obtained, e.g., from an in-memory cluster table by using an index derived from the virtual address vAddr, as described above with reference to FIG. 3.

At step 502, the cluster format field is checked to determine whether the cluster is a four-block cluster 400 or an eight-block cluster 450. Processing steps for an eight-block cluster 450 are described below with reference to FIG. 5B. For a four-block cluster 400, the valid bit is checked at step 504. An invalid cluster may cause an "invalid page request" or other appropriate interrupt to be generated at step 506 without otherwise affecting processing. At step 508, a size index k (in this embodiment 0≤k≤7) is determined by reading size field 402 of cluster 400.

At step 510, two block pointer selection bits are extracted from the virtual address vAddr for use in selecting one of the four block pointers 410 in the cluster 400. Because block size is variable, which bits are used depends on the size index k. As described above, block pointer 410(0) should be used if the virtual address vAddr is in the first quarter of the range mapped by cluster 400 and so on. Accordingly, the two block pointer selection bits are those bits of vAddr that correspond to dividing the range of virtual addresses mapped by the cluster into quarters. For example, if the size index k is 0 (4 KB blocks), each block is one page (4 KB), and the block pointer is selected by bits in vAddr corresponding to page-size units (e.g., [vAddr<sub>13</sub>:vAddr<sub>12</sub>]). If the size index k is 1 (8 KB blocks), each block is two pages, and the block pointer is selected by bits in vAddr that correspond to two-page units (e.g., [vAddr<sub>14</sub>:vAddr<sub>13</sub>]). More generally, in this embodiment, the block pointer selection bits for a cluster 400 having size index k are given by  $[vAddr_{13+k}]$ :

At step **512**, the block pointer selection bits are interpreted as a number from 0 to 3 to select the corresponding 24-bit block pointer **410(0)**, **410(1)**, **410(2)**, or **410(3)**. At step **514**, the selected block pointer is used to generate the 24 MSBs of a base physical address (pAddr). In one embodiment, the 24 bits [pAddr<sub>35</sub>:pAddr<sub>12</sub>] are set equal to the corresponding bits of the selected block pointer **410**, and the remaining bits of pAddr [pAddr<sub>11</sub>:pAddr<sub>0</sub>] are initialized to zero. At step **516**, the 12+k LSBs of the virtual address vAddr, corresponding to an offset within the block of size index k, are extracted.

At step **518**, the physical address is generated by combining the MSBs of the physical address generated at step **514** with the LSBs [vAddr<sub>11+k</sub>:vAddr<sub>0</sub>] of the virtual address. For example, in one embodiment, blocks are naturally aligned in the system physical address space (i.e., blocks of size 4 KB start at 4 KB boundaries of the address

space, blocks of size 8 KB start at 8 KB boundaries, and so on). In this embodiment, for a cluster of size index k, only the 24–k MSBs of the block pointer are of interest, since the rest would be zero by the alignment rules. Accordingly, the physical address can be generated by setting bits [pAddr<sub>35</sub>: 5 pAddr<sub>12+k</sub>] to the corresponding number of MSBs of the block pointer and setting bits [pAddr<sub>11+k</sub>:pAddr<sub>0</sub>] to the corresponding number of LSBs of the virtual address. In another embodiment, the LSBs [vAddr<sub>11+k</sub>:vAddr<sub>0</sub>] of the virtual address are added to the physical address generated 10 at step **514**. Other techniques for generating the physical address may also be used.

Returning to step 502, if the cluster is an eight-block cluster 450, the processing is shown in FIG. 5B. At step 532, a size index k (in this embodiment  $1 \le k \le 7$ ) is determined by 15 reading size field 452 of cluster 450. At step 534, three block pointer selection bits are extracted from the virtual address vAddr for use in selecting one of the eight block pointers 460. As with four-block clusters, because block size is variable, which bits are extracted depends on the size index 20 k. As described above, block pointer 460(0) should be used if the virtual address vAddr is in the first eighth of the range mapped by cluster 450 and so on. Accordingly, the three block pointer selection bits are those bits of vAddr that correspond to dividing the region of virtual address space 25 mapped by the cluster into eighths. For instance, if the size index 452 is 1 (4 KB blocks), each block is one page (4 KB), and the block pointer is selected by bits in vAddr that correspond to one-page units (e.g., [vAddr<sub>14</sub>:vAddr<sub>12</sub>]). If the size index 452 is 2 (8 KB blocks), each block is two 30 pages, and the block pointer is selected by bits in vAddr that correspond to two-page units (e.g., [vAddr<sub>15</sub>:vAddr<sub>13</sub>]). More generally, in this embodiment, the block pointer selection bits for an eight-block cluster 450 having size index k are given by  $[vAddr_{13+k}:vAddr_{11+k}]$ .

At step 536, the block pointer selection bits are used to select one of the eight fourteen-bit block pointers 460, and the ten-bit base pointer 458 is also extracted. At step 538, the 11+k least significant bits of virtual address vAddr, corresponding to an offset within the block of size index k, are 40 extracted. At step 540, a physical address is generated by combining the base pointer (Base), the block pointer (Block), and the LSBs of the virtual address. This combination can be made in various ways.

For example, in one embodiment, the physical address is 45 obtained by: (1) dropping the k-1 LSBs of the base address; (2) using the remaining bits of the base address [Base<sub>9</sub>: Base<sub>k-1</sub>] as the MSBs of the physical address [pAddr<sub>35</sub>: pAddr<sub>25+k</sub>]; (3) concatenating the fourteen block pointer bits [Block<sub>13</sub>:Block<sub>0</sub>] as bits [pAddr<sub>24+k</sub>:pAddr<sub>11+k</sub>]; and (4) 50 concatenating the 11+k LSBs of the virtual address [vAddr<sub>10+k</sub>:vAddr<sub>0</sub>] as bits [pAddr<sub>10+k</sub>:pAddr<sub>0</sub>].

In another embodiment, the physical address is obtained by: (1) using the ten bits of the base address as the MSBs of a block starting address; (2) using the fourteen bits of the 55 base pointer as the remaining bits of the block starting address; and (3) adding the 11+k LSBs of the virtual address as an offset to the block starting address.

In yet another embodiment, the physical address is obtained by a shifting procedure that includes: (1) aligning 60 the ten bits of the base pointer [Base<sub>9</sub>:Base<sub>0</sub>] at the ten MSBs of a first 24-bit field (BF1) [BF1<sub>28</sub>:BF1<sub>14</sub>]; (2) shifting the block pointer left by k–1 bits in a second 24-bit field (BF2) so that the block pointer occupies [BF2<sub>12+k</sub>: BF2<sub>k-1</sub>] and the other bits of field BF2 are zero; (3) adding 65 the bit fields BF1 and BF2 to obtain the 24 MSBs of the starting physical address; and (4) adding the 11+k LSBs of

**18**

the virtual address as an offset. In a variation of this embodiment, a shift limit (M) is imposed. In this variation, the block pointer is shifted left by k-1 bits only if  $k-1 \le M$ . If k-1 exceeds M, then the block pointer is shifted left by M bits.

More generally, any suitable combination of drop, shift, concatenation, and arithmetic operations may be performed on the base address, block pointer and virtual address bits to obtain the translation. In some embodiments, selection of a translation operation may depend on size index k.

It is to be understood that the address translation processes described herein are illustrative and that variations and modifications are possible. Steps described as sequential may be executed in parallel, order of steps may be varied, and steps may be modified or combined. While specific translation operations have been described in connection with particular cluster formats, those skilled in the art will recognize that a variety of other translation operations adapted to other cluster formats may also be implemented within the scope of the invention.

### D. Creation of Clusters

Specific processes for creating clusters and updating cluster table 302 will now be described. As described above, a cluster stored in a cluster table entry provides data (e.g., address bits) for translating virtual addresses to physical addresses, and the range of virtual address space mapped by a particular cluster (referred to herein as "range size") is variable. FIG. 3 illustrates that the same cluster (e.g., CLUS 0) may be stored in multiple cluster table entries (e.g., entries 304(1)-304(4)) of cluster table 302. This arrangement allows each cluster to be obtained from cluster table 302 by reference to any virtual address mapped by that cluster; thus, the correct cluster for a particular translation can be obtained with one table access operation without advance knowledge of range sizes or boundaries.

Range sizes are established as clusters are created and added to the cluster table. In one embodiment for a graphics processing system, virtual address management and cluster creation are handled by a resource manager program (or graphics driver program) that manages a pool of physical memory. During system initialization, the resource manager requests an initial memory allocation (e.g., 8 to 64 MB) from system memory and places it into the pool. The resource manager then receives memory allocation requests from its clients (e.g., graphics driver programs) and allocates the requested memory from its pool, returning corresponding virtual addresses to the requesting client. If the amount of free memory in the pool is insufficient, the resource manager may request an additional increment of physical memory for the pool. Creation of clusters, which define mappings of virtual addresses to physical addresses, can occur when memory is added to the pool or as allocation requests are received.

More specifically, FIG. 6 is a flow diagram of a process 600 that the resource manager may use to manage a virtual frame buffer, where the virtual frame buffer includes a physical memory pool and a corresponding virtual address space. At step 602, a pool of physical memory is created by requesting an initial memory allocation from an operating system, e.g., during system startup. This initial allocation may be large, e.g., 8-64 MB; a specific value may be selected based on anticipated demand for memory resources by clients of the resource manager. This physical memory may become unavailable to the rest of the system, although it is not yet usable by clients of the resource manager. In some embodiments, clusters that define mappings between some or all of this memory and the virtual address space may be

created in anticipation of allocation requests; any such cluster creation may be done in accordance with steps 612, 614, 616 described below.

At step **604**, the resource manager receives a memory allocation request from a requester, e.g., a driver or application process. The requester may be unaware that the frame buffer is implemented as a virtual frame buffer, so that from the requester's perspective, the request and response may be indistinguishable from the case of a non-virtual frame buffer.

At step 606, the resource manager determines whether a sufficiently large block of virtual memory is already mapped and available (i.e., not already allocated to a previous requester). If not, then at step 608, the resource manager determines whether a sufficient amount of unmapped physical memory is available in its pool. If, at step 608, sufficient physical memory is not available, the resource manager allocates an additional increment of physical memory at step 610. In one embodiment, this increment is at least large enough to fulfill the current request and may be larger (e.g., a 2 MB minimum).

At step **612**, once a sufficiently large amount of unmapped physical memory has been allocated, the resource manager attempts to represent all of the unmapped physical addresses using a single four-block or eight-block cluster. That is, it attempts to divide the physical addresses into four or eight 25 blocks of the same size, where each block consists of a contiguous range of physical addresses. Different blocks in the cluster might or might not occupy contiguous physical addresses (see, e.g., CLUS 1 of FIG. 3, where blocks 314(5) and **314(6)** are contiguous but blocks **314(15)** and **314(20)** 30 are not). At step 614, if the attempt is unsuccessful, the resource manager subdivides the unmapped physical addresses into two groups at step 616 and returns to step 612 to attempt to represent each of these smaller groups using a single cluster. Division into groups is advantageously based 35 on physical addresses, and the two groups need not contain equal amounts of memory. Iteration of steps 612, 614, and 616 may continue until all of the unmapped physical addresses have been placed into clusters, or until a collection of new clusters large enough to fulfill the current request has 40 been generated.

At step 620, the new clusters are inserted into entries of the cluster table. For example, in an embodiment where each cluster maps at least 16 KB of virtual address space, each cluster is inserted at a 16 KB virtual address boundary. Each 45 cluster is inserted at one or more entries corresponding to the virtual addresses that it maps, as shown in FIG. 3. It will be appreciated that the number of entries containing a particular cluster is determined by the range size of the cluster; for instance, a cluster of FIG. 4A (or FIG. 4B) that has size 50 index k would be inserted at  $2^k$  entries. For example, in cluster table 302, a cluster with a range size of more than 16 KB (e.g., CLUS 0) is inserted at the entry corresponding to the first address it maps and every following entry within its range. Note that the position of the cluster in the table 55 determines which virtual addresses are mapped to the physical addresses referenced by the cluster; accordingly, newly created clusters can be placed in the cluster table at any convenient position. For example, in some embodiments, clusters may be aligned at natural virtual address boundaries 60 corresponding to the range size of the cluster (e.g., the first address mapped by a 16 KB cluster is aligned at a 16 KB boundary, the first address mapped by a 32 KB cluster is aligned at a 32 KB boundary, and so on). When a group of clusters is created, the clusters may be re-ordered to comply 65 with such a rule, or with any other alignment rules that may be implemented.

**20**

At step 622, once clusters have been defined for a sufficient amount of the virtual address space, a range of virtual addresses to be allocated to the requester is selected. The resource manager may simply select the next unused virtual addresses, or it may select virtual addresses based on the client and/or intended use of the allocated space (e.g., the first 2 MB of virtual address space could be reserved for a pixel buffer). It should be noted that the range of virtual addresses selected at step 622 need not align with cluster boundaries or with block boundaries within a cluster. Various techniques for selecting addresses to satisfy a memory allocation request are known in the art and may be employed at step 622.

At step **624**, a response is returned to the requester. The response may include an identifier of the starting virtual address for the allocated range. This identifier is advantageously provided in a form that can be used in a conventional fashion; the requester may be unaware of clusters or other details of the virtual frame buffer implementation.

To facilitate management of the virtual address space, the resource manager may also maintain an allocation table that tracks whether a given virtual address has a cluster, whether it is allocated or available, and the like. Memory allocation tables of generally conventional design may be adapted for use in this context. Where the resource manager is able to define mappings for the virtual address space (i.e., create clusters) at a different time and with a different granularity than its allocations of virtual memory to clients, the likelihood of creating large clusters increases.