#### US007303962B2

# (12) United States Patent

# Chou et al.

# (10) Patent No.: US 7,303,962 B2 (45) Date of Patent: Dec. 4, 2007

# (54) FABRICATING METHOD OF CMOS AND MOS DEVICE

(75) Inventors: Pei-Tu Chou, Taipei County (TW);

Min-Chieh Yang, Kaohsiung (TW);

Wen-Han Hung, Kaohsiung (TW)

(73) Assignee: United Microelectronics Corp.,

Hsinchu (TW)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 11/164,274

(22) Filed: Nov. 16, 2005

# (65) Prior Publication Data

US 2007/0111452 A1 May 17, 2007

(51) Int. Cl. H01L 21/8234 (2006.01)

### (56) References Cited

#### U.S. PATENT DOCUMENTS

2003/0181005 A1\* 9/2003 Hachimine et al. ...... 438/231 2006/0172481 A1\* 8/2006 Tsui et al. ...... 438/199

#### OTHER PUBLICATIONS

Wolf et al., Silicon Processing for the VLSI Era, vol. 1: Process Technology, 1986 by Lattice Press, pp. 429-431 and 434-437.\* Wolf et al., Silicon Processing for the VLSI Era, vol. 1" Process Technology, 1986 by Lattice Press, pp. 429-431 and 434-437.\*

\* cited by examiner

Primary Examiner—George Fourson Assistant Examiner—Julio J. Maldonado (74) Attorney, Agent, or Firm—Jianq Chyun IP Office

## (57) ABSTRACT

A complementary metal-oxide-semiconductor (CMOS) device comprising a substrate, a first type of metal-oxidesemiconductor (MOS) transistor, a second type of MOS transistor, an etching stop layer, a first stress layer and a second stress layer is provided. The substrate has a first and a second active region. The first active region is isolated from the second active region through an isolation structure. The first type of MOS transistor is disposed in the first active region of the substrate and the second type of MOS transistor is disposed in the second active region of the substrate. The etching stop layer covers conformably the first type of MOS transistor, the second type of MOS transistor and the isolation structure. The first stress layer is disposed on the etching stop layer in the first active region and the second stress layer is disposed on the etching stop layer in the second active region.

### 7 Claims, 5 Drawing Sheets

FIG. 1A

FIG. 1B

FIG. 2A

Dec. 4, 2007

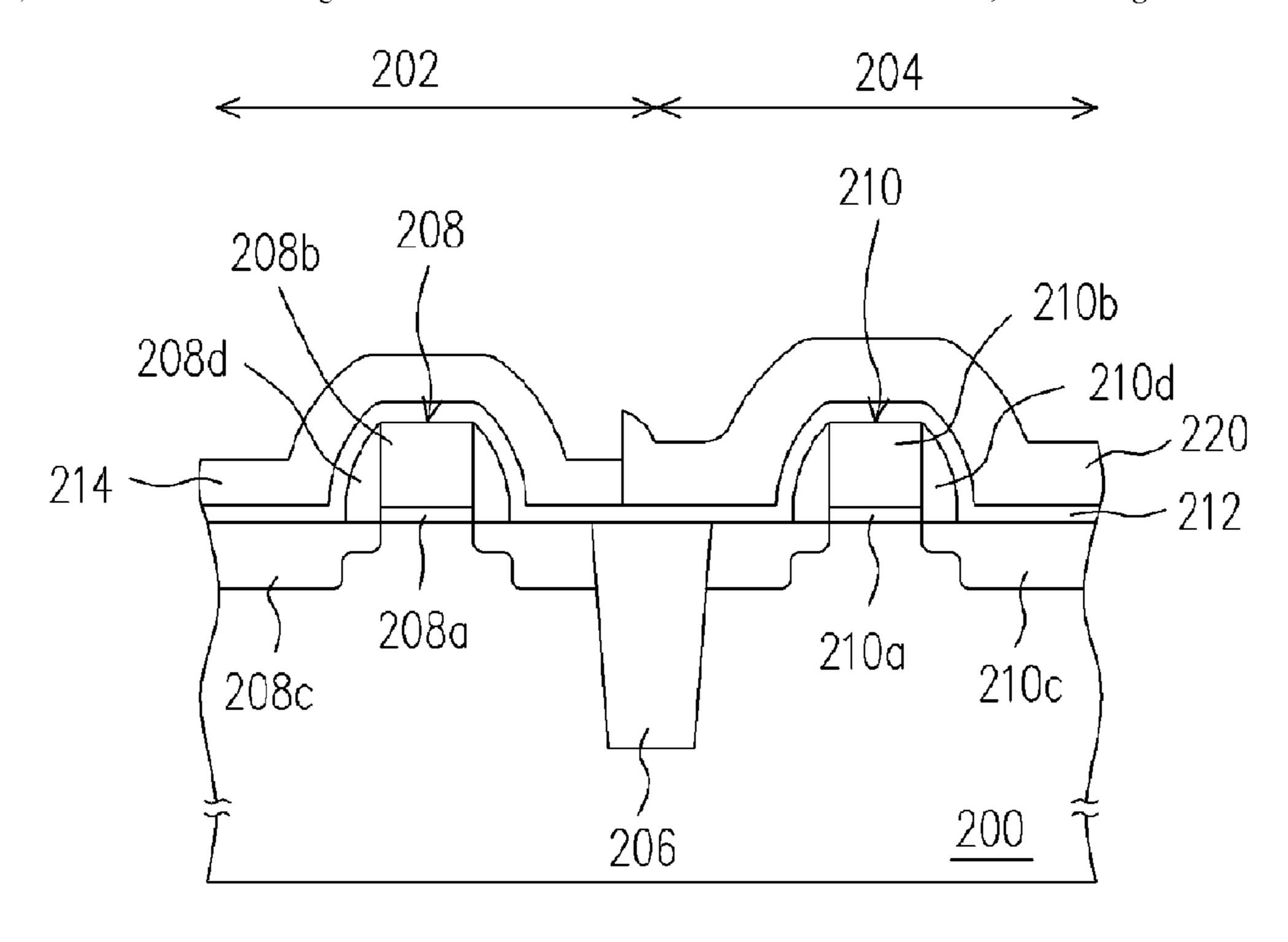

202 204 208 210 210b 208b 210d 216 208d 208a 210a 210c 208c 206

FIG. 20

FIG. 2E

1

# FABRICATING METHOD OF CMOS AND MOS DEVICE

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a semiconductor device and fabricating method thereof. More particularly, the present invention relates to a complementary metal-oxide-semiconductor (CMOS) device and a metal-oxide-semiconductor (MOS) device and their fabricating methods therefore.

#### 2. Description of the Related Art

In the development of integrated circuit devices, higher operating speed and a lower power consumption is often achieved by reducing the size of each device. However, further reduction in the dimension of each device is subjected to factors including the bottleneck in the fabricating technique and the expense in the production. Consequently, other types of techniques different from the technique of miniaturizing devices have been developed to improve the driving current of devices. With this background, somebody has proposed the utilization of the stress in the channel region of a transistor to combat the limits in device miniaturization. The method uses stress to change the pitch of silicon crystal grid so that the mobility of electrons and holes is increased and lead to a higher device performance.

One of the conventional method of utilizing stress to increase device performance includes using the stress in a silicon nitride layer that serves as a contact etching stop 30 layer to influence the driving current of the device. Although the driving current in the n-channel region will increase when the tensile stress of the silicon nitride layer is increased, the driving current in the p-channel region will drop. Conversely, although the driving current in the p-channel will increase when the compressive stress of the silicon nitride layer is increased, the driving current of the n-channel region will drop. In other words, the method of using the stress in a silicon nitride layer to improve the performance of the transistor can be used only for increasing the driving 40 current of a N-type metal-oxide-semiconductor (NMOS) transistor or the driving current of a P-type metal-oxidesemiconductor (PMOS) transistor. There is no way to increase the driving current of both the NMOS transistor and the PMOS transistor at the same time.

To increase the driving current of NMOS transistor and PMOS transistor simultaneously, a method for forming a semiconductor device with the following steps is proposed. First, an NMOS transistor and a PMOS transistor are formed on a substrate such that a shallow trench isolation (STI) 50 structure is also formed between the two transistors. Hence, the NMOS transistor and the PMOS transistor are electrically isolated. Thereafter, a silicon nitride layer with tensile stress is deposited to cover up the entire substrate. After that, a patterned photoresist layer is formed over the silicon 55 nitride layer with tensile stress to expose the silicon nitride layer above the PMOS transistor. Using the patterned photoresist layer as a mask, an etching process is performed to remove the exposed silicon nitride layer while retaining the silicon nitride layer on the NMOS transistor. Then, the 60 patterned photoresist layer is removed. Afterwards, using a similar method, another silicon nitride layer with compressive stress is deposited over the entire substrate. Then, the silicon nitride layer above the NMOS transistor is removed while retaining the silicon nitride layer with compressive 65 stress over the PMOS transistor. Consequently, a silicon nitride layer with tensile stress is formed over the NMOS

2

transistor while another silicon nitride layer with compressive stress is formed over the PMOS transistor. In other words, the driving current of both the NMOS transistor and the PMOS transistor is increased simultaneously.

Although the aforesaid method can increase the driving current of both the NMOS transistor and the PMOS transistor, a few problems that may affect the driving current and performance of the transistors are not tackled. For example, in areas where the pitch between devices is small, the silicon nitride layer at different stress levels may merge together and doubling the thickness of the silicon nitride layer there. Therefore, the silicon nitride layer needs to be over-etched in an etching operation in order to ensure the silicon nitride layer not covered by the photoresist is completely removed. However, this extended etching may damage the film layers and elements such as the spacers and silicone dioxide layer and nickel-silicide of STI structure in the no-transistor region underneath the silicon nitride layer. Ultimately, there will be some adverse effects on the performance of the device.

#### SUMMARY OF THE INVENTION

Accordingly, at least one objective of the present invention is to provide a method of forming a complementary metal-oxide-semiconductor (CMOS) device that can prevent possible damages to film layers and increase the performance of the device.

At least another objective of the present invention is to provide a complementary metal-oxide-semiconductor (CMOS) device that can avoid the problem of having damages in the film layers and provide a higher device performance.

At least another objective of the present invention is to provide a method of forming a metal-oxide-semiconductor (MOS) device that can prevent possible damages to film layers and increase the performance of the device.

At least another objective of the present invention is to provide a metal-oxide-semiconductor (MOS) device that can avoid the problem of having damages in the film layers and provide a higher device performance.

To achieve these and other advantages and in accordance with the purpose of the invention, as embodied and broadly described herein, the invention provides a method of form-45 ing a complementary metal-oxide-semiconductor (CMOS) device comprising the following steps. First, a substrate is provided. The substrate has a first active region and a second active region. The first active region is isolated from the second active region through an isolation structure. Then, a first type of metal-oxide-semiconductor (MOS) transistor and a second type of MOS transistor are formed on the first active region and the second active region of the substrate respectively. Thereafter, a first etching stop layer is formed on the substrate to cover conformably the first type of MOS transistor, the second type of MOS transistor and the isolation structure. Then, a first stress layer and a second etching stop layer are formed in sequence over the first etching stop layer. After that, a first photoresist layer is formed on the second etching stop layer in the first active region. Using the first photoresist layer as a mask, a portion of the second etching stop layer and a portion of the first stress layer is removed to expose the first etching stop layer. Thereafter, the first photoresist layer is removed. A second stress layer is formed over the substrate to cover the first etching stop layer and the second etching stop layer. Then, a second photoresist layer is formed on the second stress layer in the second active region. Using the second photoresist layer as

3

a mask, a portion of the second stress layer is removed to expose the second etching stop layer. Afterwards, the second photoresist layer and the second etching stop layer are removed.

According to the embodiment of the present invention, a 5 curing process may be carried out after forming the first stress layer. And a curing process may be carried out after forming the second stress layer.

According to the embodiment of the present invention, the first etching stop layer is fabricated using silicon oxide, 10 silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride and has a thickness between about 50 Å~200 Å, for example. Similarly, the second etching stop layer is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride 15 and has a thickness between about 50 Å~200 Å, for example.

According to the embodiment of the present invention, the first stress layer is fabricated using silicon nitride, for example. Similarly, the second stress layer is fabricated 20 using silicon nitride, for example.

According to the embodiment of the present invention, if the first type of MOS transistor is an N-type metal-oxide-semiconductor (NMOS) transistor and the second type of MOS transistor is a P-type metal-oxide-semiconductor 25 (PMOS) transistor, then the first stress layer is a tensile stress layer and the second stress layer is a compressive stress layer. On the other hand, if the first type of MOS transistor is a P-type metal-oxide-semiconductor (PMOS) transistor and the second type of MOS transistor is an N-type metal-oxide-semiconductor (NMOS) transistor, then the first stress layer is a compressive stress layer and the second stress layer is a tensile stress layer.

The present invention also provides a complementary metal-oxide-semiconductor (CMOS) device. The CMOS 35 device comprises a substrate, a first type of metal-oxidesemiconductor (MOS) device, a second type of MOS device, an etching stop layer, a first stress layer and a second stress layer. The substrate has a first active region and a second active region. The first active region and the second active 40 region are isolated from each other through an isolation structure. The first type of MOS transistor is disposed in the first active region of the substrate and the second type of MOS transistor is disposed in the second active region of the substrate. The etching stop layer is covered conformably the 45 first type of MOS transistor, the second type of MOS transistor and the isolation structure. The first stress layer is disposed above the etching stop layer in the first active region and the second stress layer is disposed above the etching stop layer in the second active region.

According to the embodiment of the present invention, the etching stop layer is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride and has a thickness between about 50 Å~200 Å, for example.

According to the embodiment of the present invention, the first stress layer is fabricated using silicon nitride, for example. Similarly, the second stress layer is fabricated using silicon nitride, for example.

According to the embodiment of the present invention, if 60 the first type of MOS transistor is an N-type metal-oxide-semiconductor (NMOS) transistor and the second type of MOS transistor is a P-type metal-oxide-semiconductor (PMOS) transistor, then the first stress layer is a tensile stress layer and the second stress layer is a compressive stress 65 layer. On the other hand, if the first type of MOS transistor is a P-type metal-oxide-semiconductor (PMOS) transistor

4

and the second type of MOS transistor is an N-type metal-oxide-semiconductor (NMOS) transistor, then the first stress layer is a compressive stress layer and the second stress layer is a tensile stress layer.

The present invention also provides a method of forming a metal-oxide-semiconductor (MOS) device. The method includes the following steps. First, a conductive type MOS transistor is formed on a substrate. Then, an etching stop layer is formed over the substrate to cover conformably the conductive type MOS transistor. Thereafter, a stress layer is formed over the etching stop layer.

According to the embodiment of the present invention, a curing process may be carried out after forming the stress layer.

According to the embodiment of the present invention, the etching stop layer is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride and has a thickness between about 50 Å~200 Å, for example.

According to the embodiment of the present invention, the stress layer is fabricated using silicon nitride, for example. Furthermore, if the conductive type MOS transistor is an N-type MOS transistor (NMOS), then the stress layer is a tensile stress layer. On the other hand, if the conductive type MOS transistor is a P-type MOS transistor (PMOS), then the stress layer is a compressive stress layer.

The present invention also provides a metal-oxide-semiconductor (MOS) transistor. The MOS transistor comprises a conductive type MOS transistor, an etching stop layer and a stress layer. The conductive MOS transistor is disposed on a substrate. The etching stop layer is covered conformably the conductive type MOS transistor. Furthermore, the stress layer is disposed on the etching stop layer.

According to the embodiment of the present invention, the etching stop layer is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride and has a thickness between about 50 Å~200 Å, for example.

According to the embodiment of the present invention, the stress layer is fabricated using silicon nitride, for example. Furthermore, if the conductive type MOS transistor is an N-type MOS transistor (NMOS), then the stress layer is a tensile stress layer. On the other hand, if the conductive type MOS transistor is a P-type MOS transistor (PMOS), then the stress layer is a compressive stress layer.

In the present invention, an etching stop layer is formed between the stress layer and the transistor. Hence, the problem of damaging the spacers and silicone dioxide layer and nickel-silicide of STI structure in the no-transistor region as in a conventional method can be avoided. Furthermore, the presence of the etching stop layer in the present invention will not affect the properties of the stress layer and hence degrade the stress layer.

It is to be understood that both the foregoing general description and the following detailed description are exemplary, and are intended to provide further explanation of the invention as claimed.

### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings are included to provide a further understanding of the invention, and are incorporated in and constitute a part of this specification. The drawings illustrate embodiments of the invention and, together with the description, serve to explain the principles of the invention.

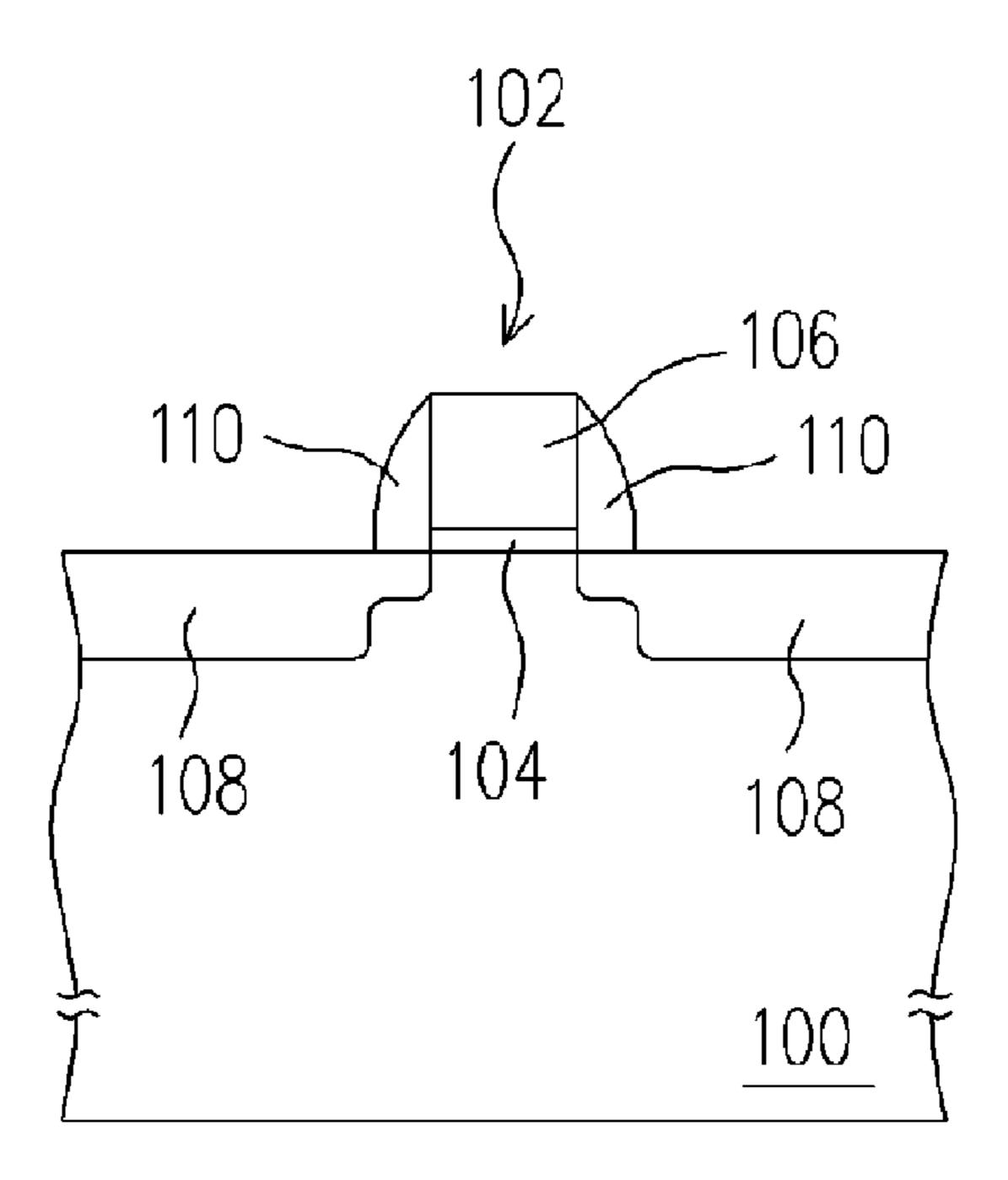

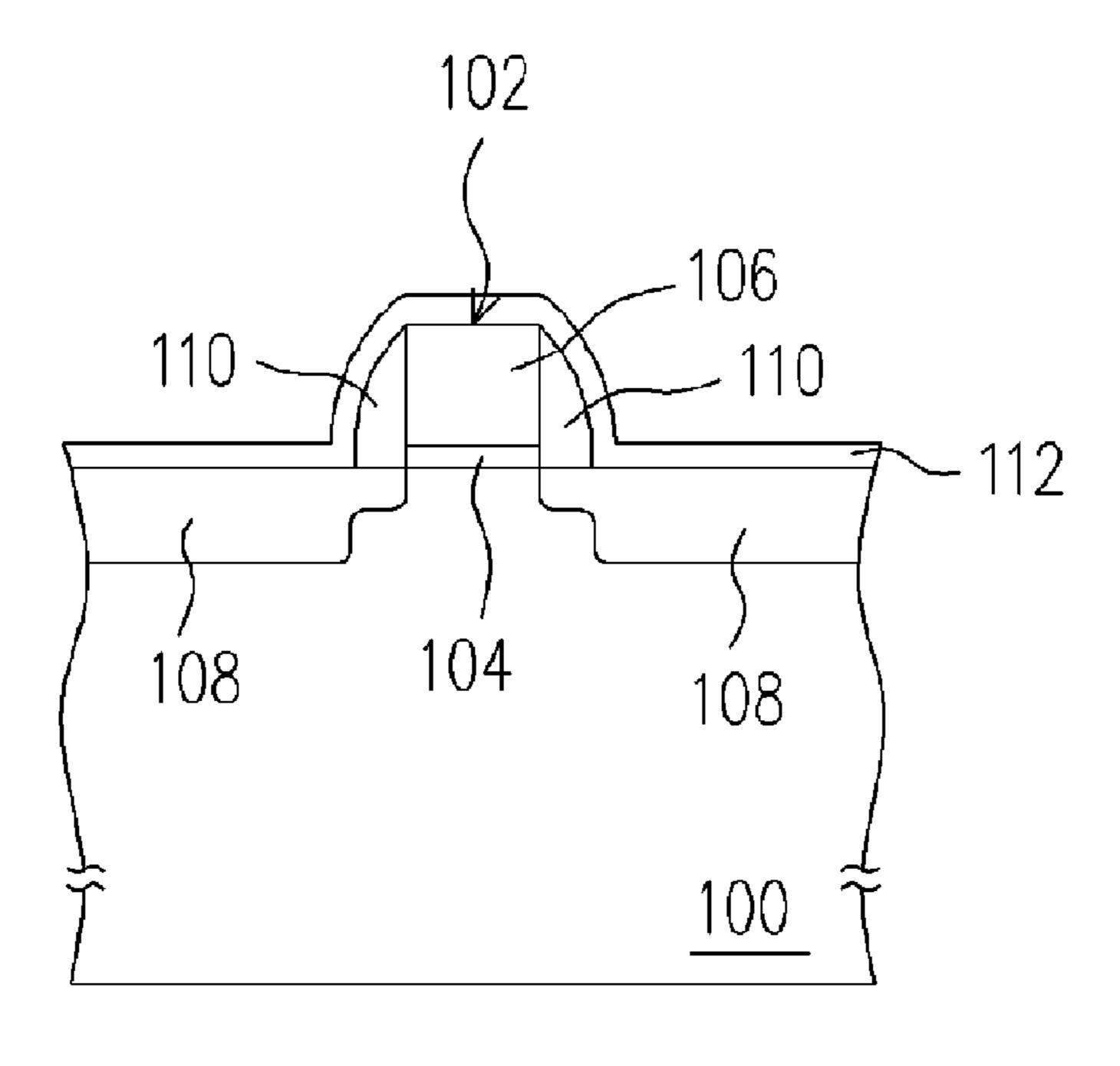

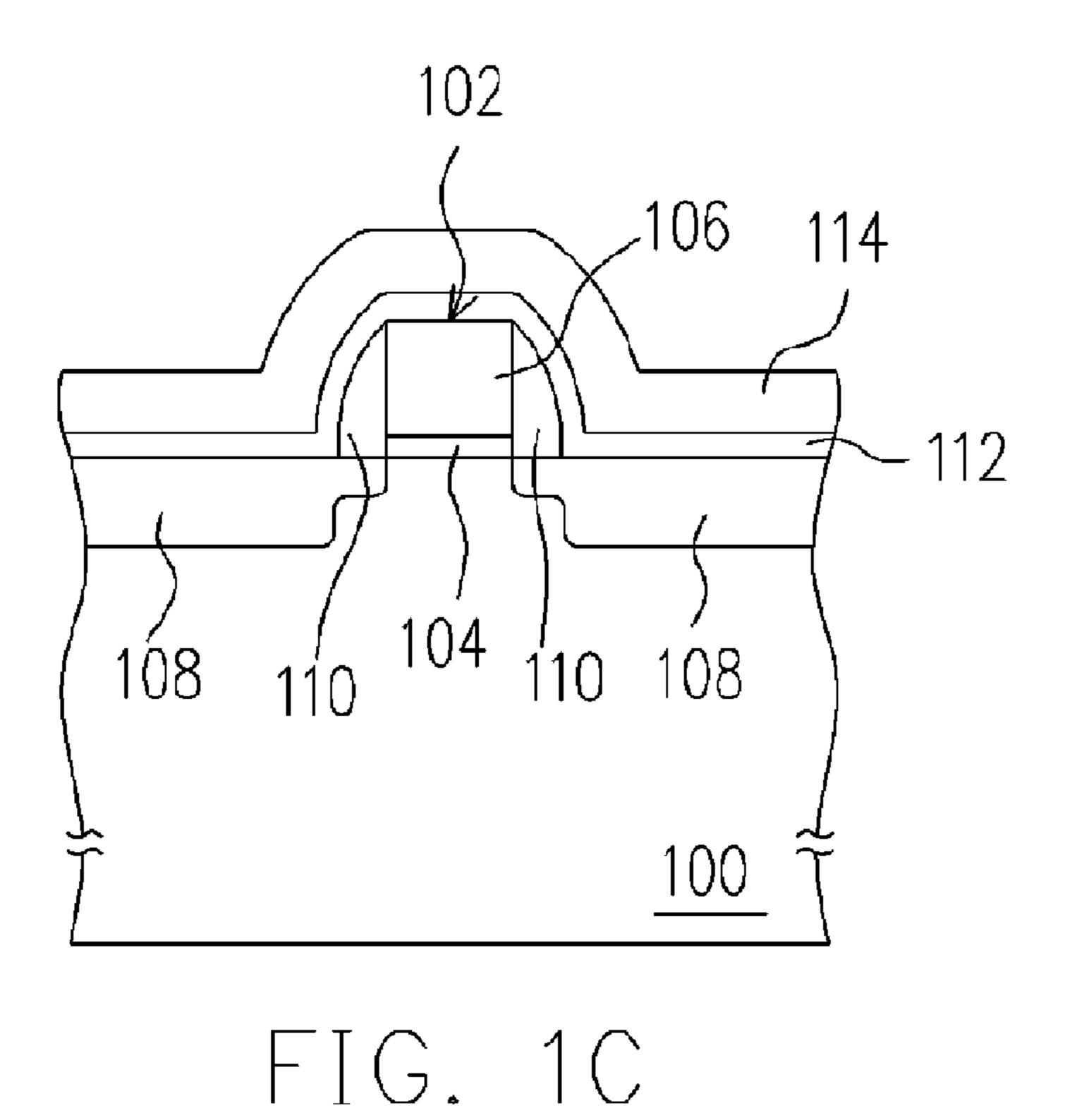

FIGS. 1A through 1C are schematic cross-sectional views showing the steps for forming a MOS device according to one embodiment of the present invention.

FIGS. 2A through 2G are schematic cross-sectional views showing the steps for forming a CMOS device according to 5 one embodiment of the present invention.

### DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Reference will now be made in detail to the present preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers are used in the drawings and the description to refer to the same or like parts.

FIGS. 1A through 1C are schematic cross-sectional views showing the steps for forming a MOS device according to one embodiment of the present invention. First, referring to FIG. 1A, a conductive type metal-oxide-semiconductor (MOS) transistor 102 is formed on a substrate 100. In the 20 present embodiment, the conductive type MOS transistor **102** is an N-type MOS transistor, for example. The conductive type MOS transistor 102 comprises a gate dielectric layer 104, a gate 106, a pair of source/drain regions 108 and a pair of spacers 110. In one embodiment, a metal silicide 25 layer (not shown) may also be formed on the gate 106 and the source/drain regions 108 to lower the resistance. The metal silicide layer is fabricated using nickel silicide, tungsten silicide or cobalt silicide, for example. Since the elements of the conductive type MOS transistor 102, the 30 layer. materials constituting the elements and the method of fabricating the conductive type MOS transistor 102 should be familiar to those knowledgeable in this field, a detailed description is omitted.

over the substrate 100 to cover conformably the conductive type MOS transistor 102. The etching stop layer 112 has a thickness smaller than 500 Å, preferably between 50 Å~200 A. The etching stop layer 112 is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate 40 or silicon-carbon nitride, for example. The etching stop layer 112 is formed, for example, by performing a chemical vapor deposition process or other suitable process.

Referring to FIG. 1C, a stress layer 114 is formed over the etching stop layer 112. The stress layer 114 is a silicon 45 nitride layer having a thickness between 600 Å~1500 Å, for example. Because the conductive type MOS transistor 102 in the present embodiment is an NMOS transistor, the stress layer 114 is a tensile stress layer.

In one embodiment, a curing process may be carried out 50 after forming the stress layer 114 for increasing the tensile stress in the stress layer 114. The aforesaid curing process is an ultraviolet curing process, for example.

Obviously, subsequent processes of forming interconnects can be carried out after forming the stress layer 114. The interconnect fabrication process includes, for example, forming a dielectric layer (not shown) over the stress layer 114 and forming a contact opening (not shown) in the dielectric layer, the stress layer 114 and the etching stop layer 112. Thereafter, a conductive layer (not shown) is 60 type of MOS transistor 208 and second type of MOS formed in the contact opening to serve as a contact so that corresponding devices are electrically connected together.

Obviously, the conductive type MOS transistor 102 in the foregoing embodiment is illustrated using a NMOS transistor. In another embodiment, the conductive type MOS 65 transistor 102 can be a PMOS transistor. In that case, the stress layer 114 is a compressive stress layer.

In the aforementioned embodiment, the formation of a stress layer on the conductive type MOS transistor can affect the driving current of the device and improve the performance of the device. In addition, the etching stop layer between the conductive type MOS transistor and the stress layer can be fabricated using a material having an etching selectivity ratio different from the silicon nitride layer, for example. Hence, the etching stop layer can prevent possible damage to the spacers and silicone dioxide layer and nickelsilicide of STI structure in the no-transistor region.

In the following, a MOS device fabricated using the aforementioned method is described. Referring to FIG. 1C, a metal-oxide-semiconductor (MOS) device comprising a conductive type MOS transistor 102, an etching stop layer 112 and a stress layer 114 is provided. The conductive type MOS transistor 102 is disposed on a substrate 100. The etching stop layer 112 is covered conformably the conductive type MOS transistor 102. The etching stop layer 112 has a thickness smaller than 500 Å, and preferably between 50 Å~200 Å. The etching stop layer 112 is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride, for example. Furthermore, the stress layer 114 is disposed on the etching stop layer 112 and has a thickness between 600 Å~1500 Å, for example. If the conductive type MOS transistor 102 is an N-type MOS (an NMOS) transistor, then the stress layer 114 is a tensile stress layer. On the other hand, if the conductive type MOS transistor 102 is a P-type MOS (a PMOS) transistor, then the stress layer 114 is a compressive stress

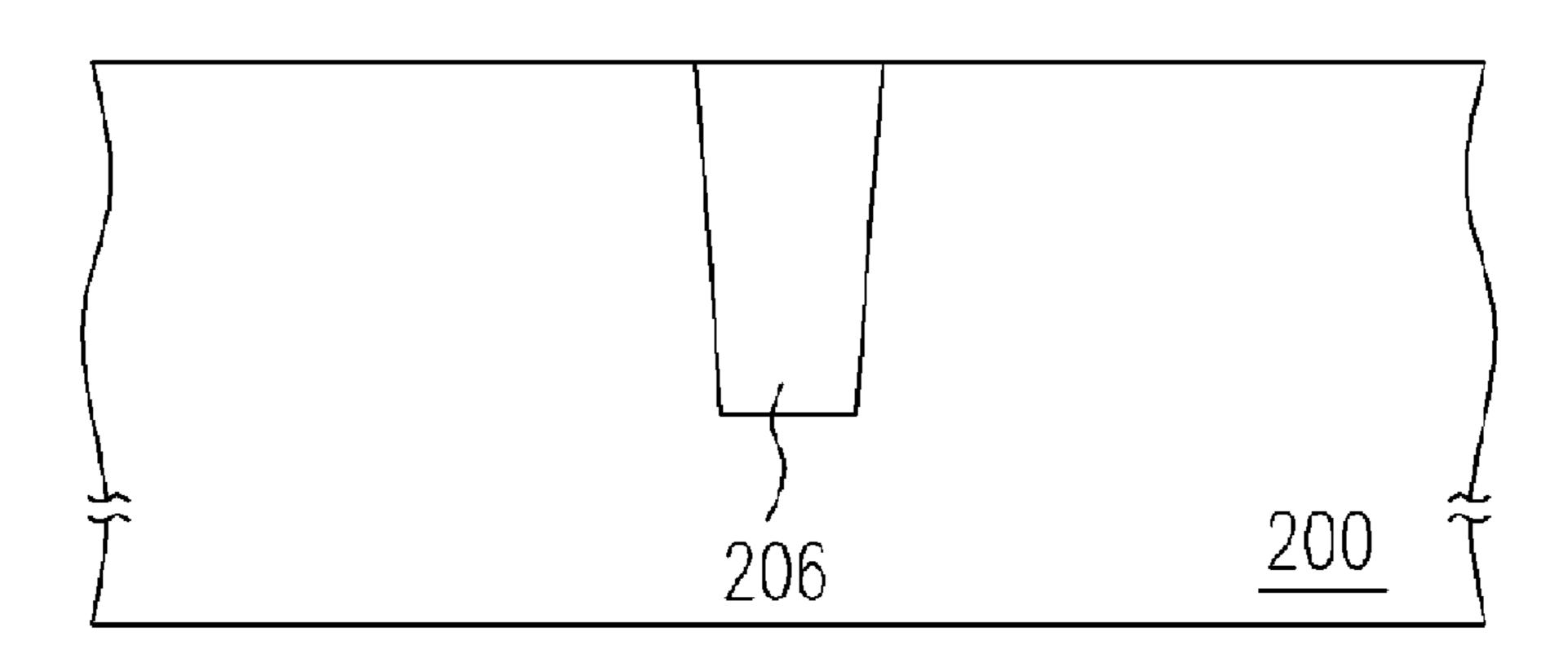

Aside from the aforementioned embodiment, the present invention can also be implemented in another configuration. FIGS. 2A through 2G are schematic cross-sectional views showing the steps for forming a CMOS device according to Referring to FIG. 1B, an etching stop layer 112 is formed 35 one embodiment of the present invention. First, referring to FIG. 2A, a substrate 200 is provided. The substrate 200 has a active region 202 and a active region 204. The active regions 202 and 204 are isolated from each other through an isolation structure 206. The isolation structure 206 can be a shallow trench isolation (STI) structure or other suitable types of isolation structures, for example.

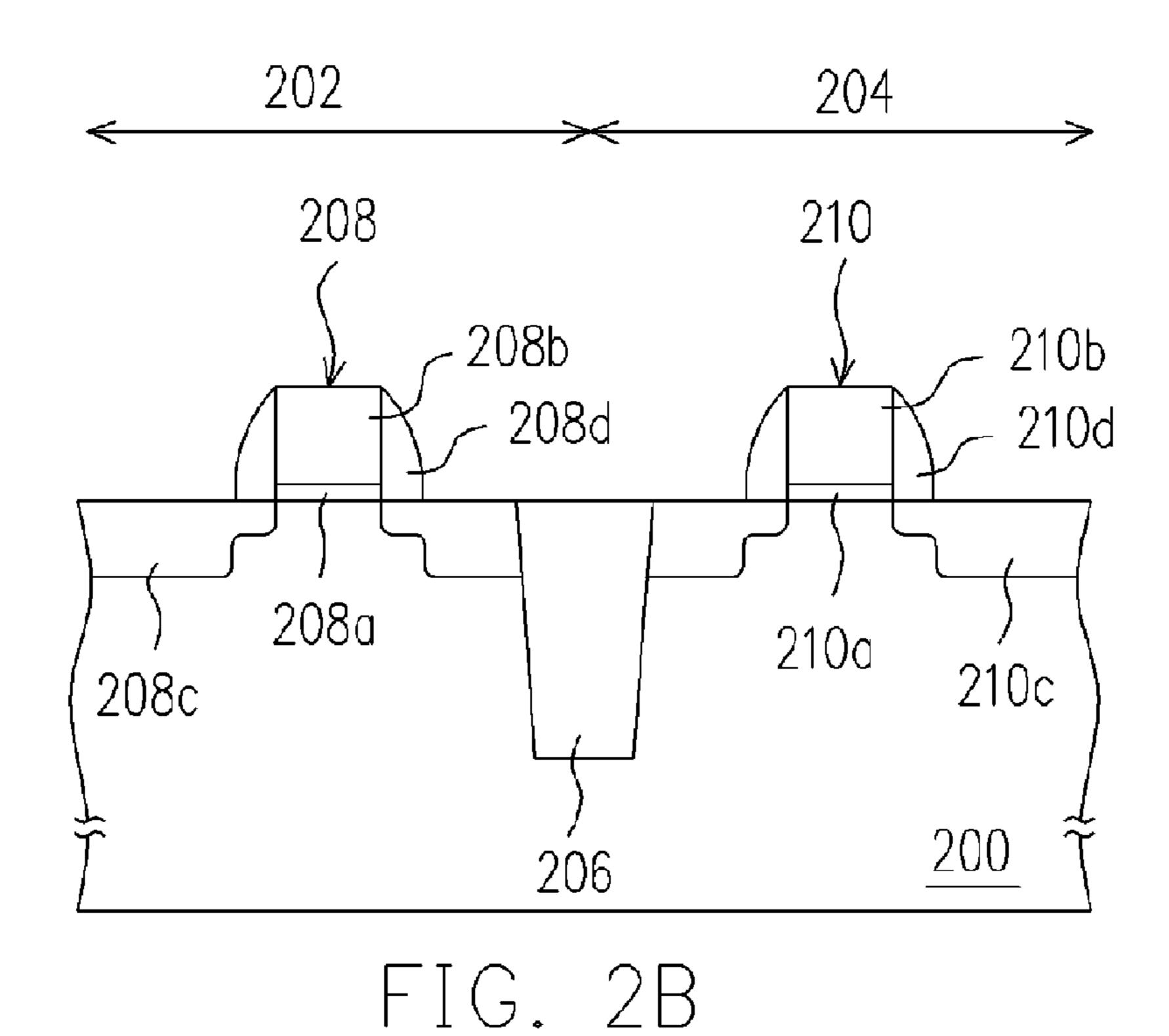

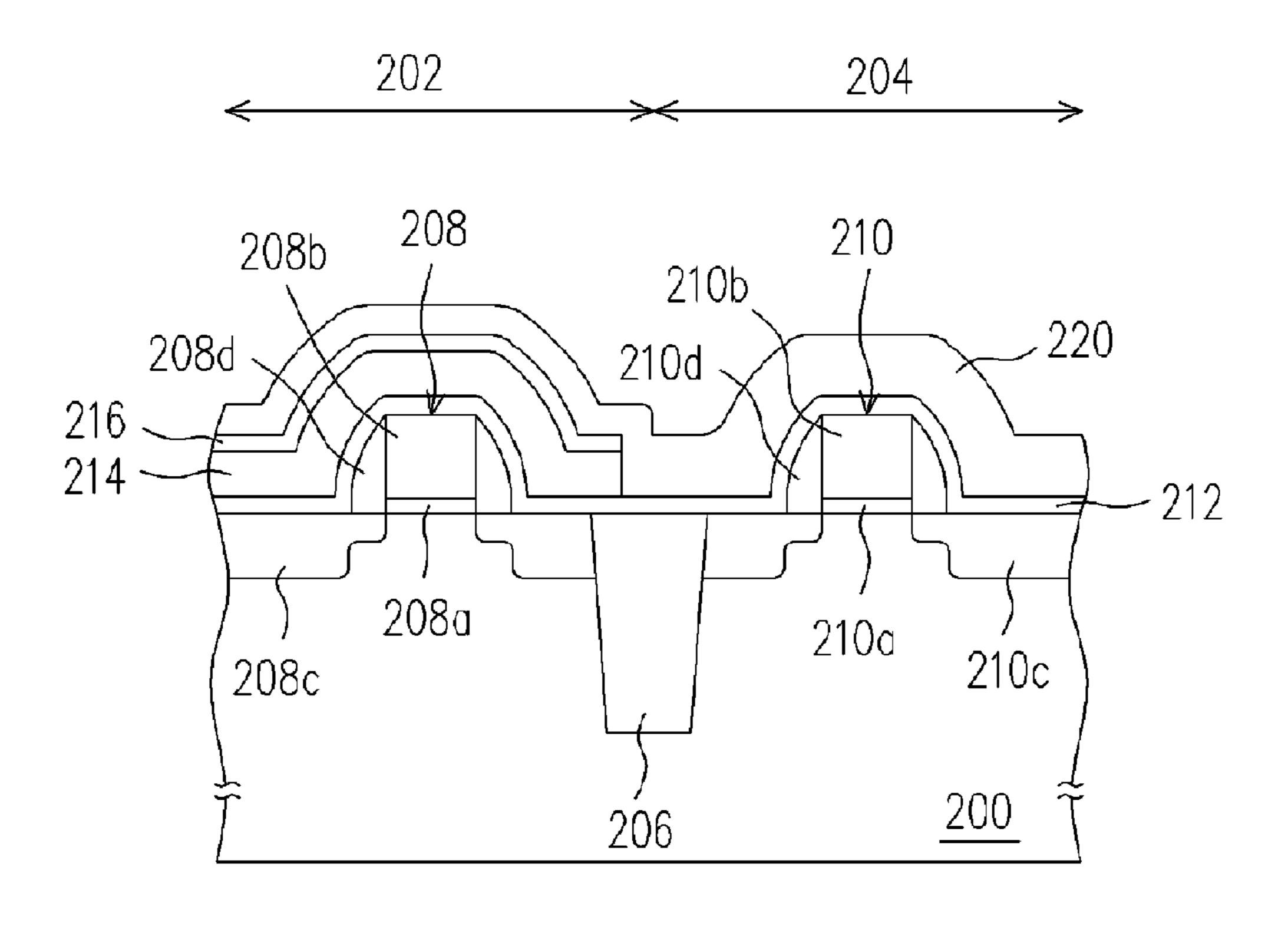

Referring to FIG. 2B, a first type of MOS transistor 208 and a second type of MOS transistor 210 are formed in the first active region 202 and the second active region 204 of the substrate 200 respectively. In the present embodiment, the first type of MOS transistor 208 and the second type of MOS transistor 210 are NMOS transistor and PMOS transistor respectively. The first type MOS transistor 208 comprises a gate dielectric layer 208a, a gate 208b, a pair of source/drain region 208c and a pair of spacers 208d. The second type MOS transistor 210 comprises a gate dielectric layer 210a, a gate 210b, a pair of source/drain region 210cand a pair of spacers 210d. In one embodiment, a metal silicide layer (not shown) can be formed on the gate 208b and the source/drain regions 208c and the gate 210b and the source/drain regions 210c to lower the resistance there. The metal silicide layer is fabricated using nickel silicide, tungsten silicide or cobalt silicide, for example. Since the various elements and materials constituting the aforementioned first transistor 210 and method of fabricating the same should be familiar to those persons knowledgeable in this technological field, a detailed description is omitted.

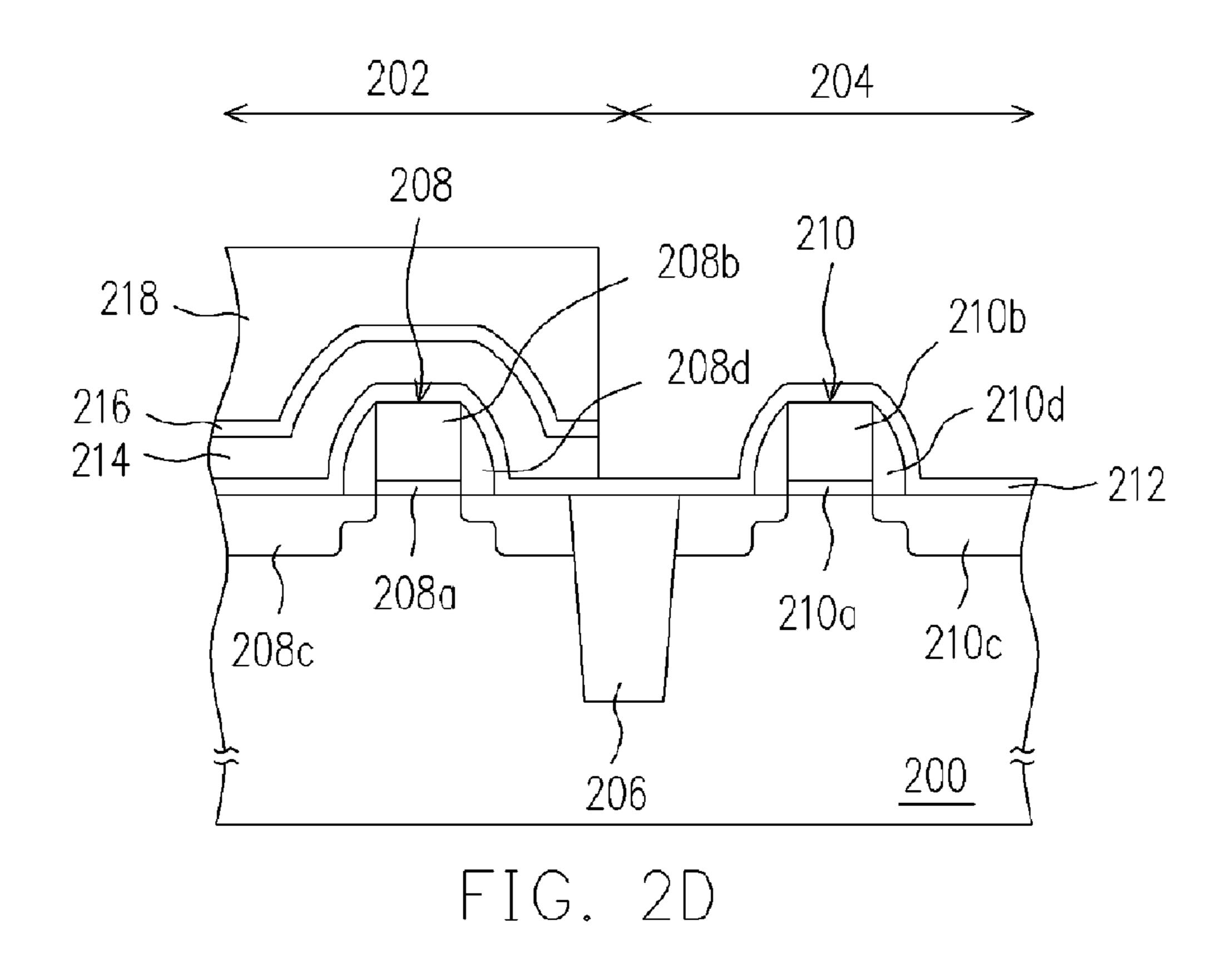

Referring to FIG. 2C, an etching stop layer 212 is formed over the substrate 200 to cover conformably the first type of MOS transistor 208, the second type of MOS transistor 210 and the isolation structure 206. The etching stop layer 212

has a thickness, for example, smaller than 500 Å, and preferably between 50 Å~200 Å. The etching stop layer 212 is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride, for example. The etching stop layer 212 is formed, for example, 5 by performing a chemical vapor deposition process or other suitable process.

Thereafter, a stress layer **214** and an etching stop layer 216 are formed in sequence over the etching stop layer 212. In the present embodiment, the stress layer **214** is fabricated 10 using silicon nitride, for example. The stress layer 214 serves as a tensile stress layer and has a thickness between about 600 Å~1500 Å. In addition, the etching stop layer 216 has a thickness, for example, smaller than 500 Å, and preferably between 50 Å~200 Å. The etching stop layer 216 15 is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride, for example. The etching stop layer 216 is formed, for example, by performing a chemical vapor deposition process or other suitable process. In one embodiment, a curing process may 20 be carried out after forming the stress layer **214** so that the tensile stress in the stress layer **214** is further increased. The aforesaid curing process can be an ultraviolet curing process, for example.

In the embodiment of the present invention, the etching <sup>25</sup> stop layers 212 and 216 can be fabricated using the same material or different materials. Furthermore, the thickness of the etching stop layers 212 and 216 can be the same or can be different. There are no particular limitations in the present invention.

Referring to FIG. 2D, a photoresist layer 218 is formed on the etching stop layer 216 in the active region 202. Then, using the photoresist layer 218 as a mask, a portion of the etching stop layer 216 and a portion of the stress layer 214 method of removing the etching stop layer 216 and the stress layer 214 includes performing an etching process, for example.

Referring to FIG. 2E, the photoresist layer 218 is removed. Then, another stress layer 220 is formed over the substrate 200 to cover the etching stop layer 212 and the etching stop layer **216**. In the present embodiment, the stress layer 220 is a silicon nitride layer, for example. The stress layer 220 is a compressive stress layer having a thickness between about 600 Å~1500 Å, for example.

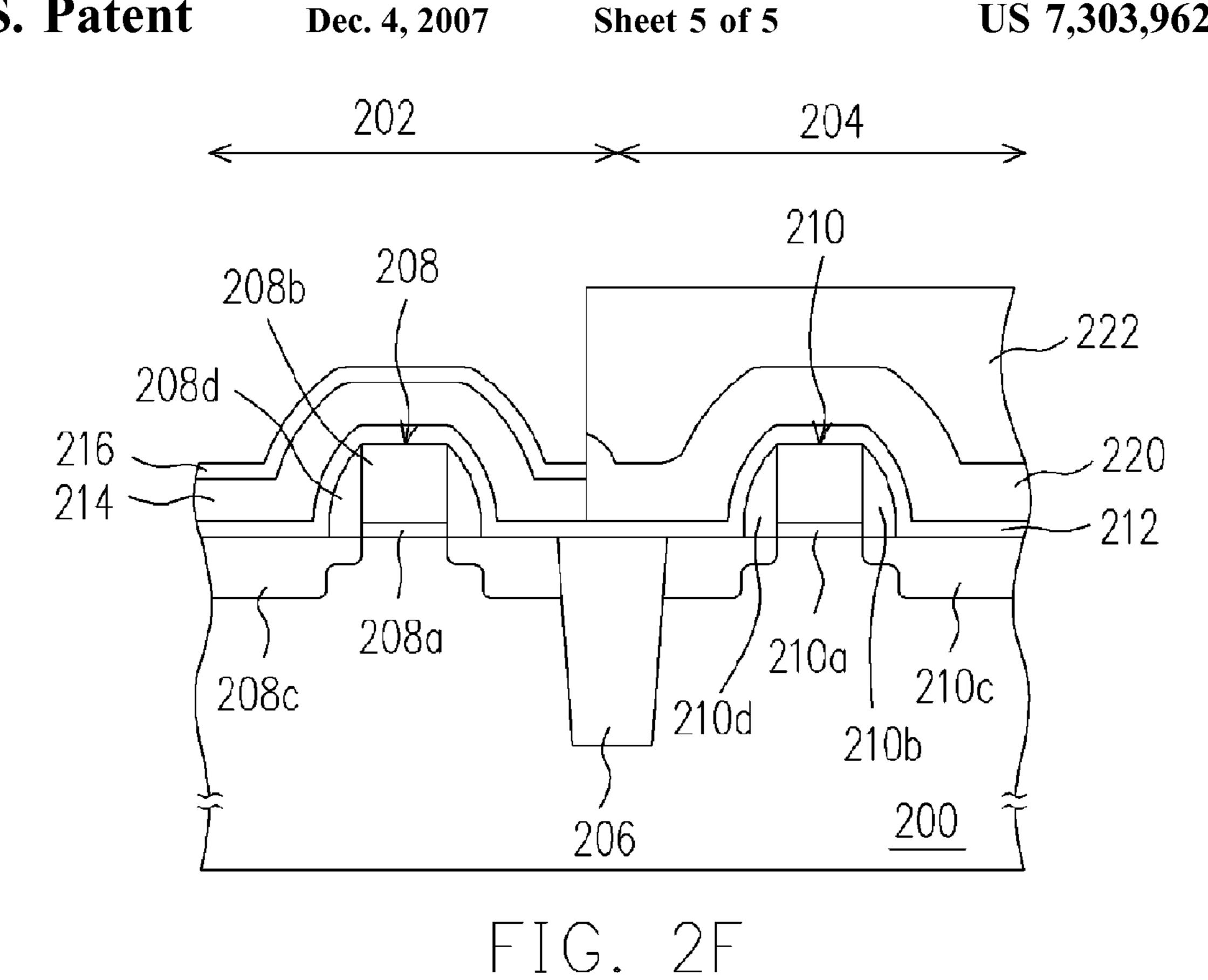

Referring to FIG. 2F, a photoresist layer 222 is formed on the stress layer 220 in the active region 204. Then, using the photoresist layer 222 as a mask, a portion of the stress layer **220** is removed to expose the etching stop layer **216**. The  $_{50}$ method of removing the stress layer 216 includes performing an etching operation, for example. In one embodiment, a curing process may be carried out after forming the stress layer 220. The aforesaid curing process can be an ultraviolet curing process, for example.

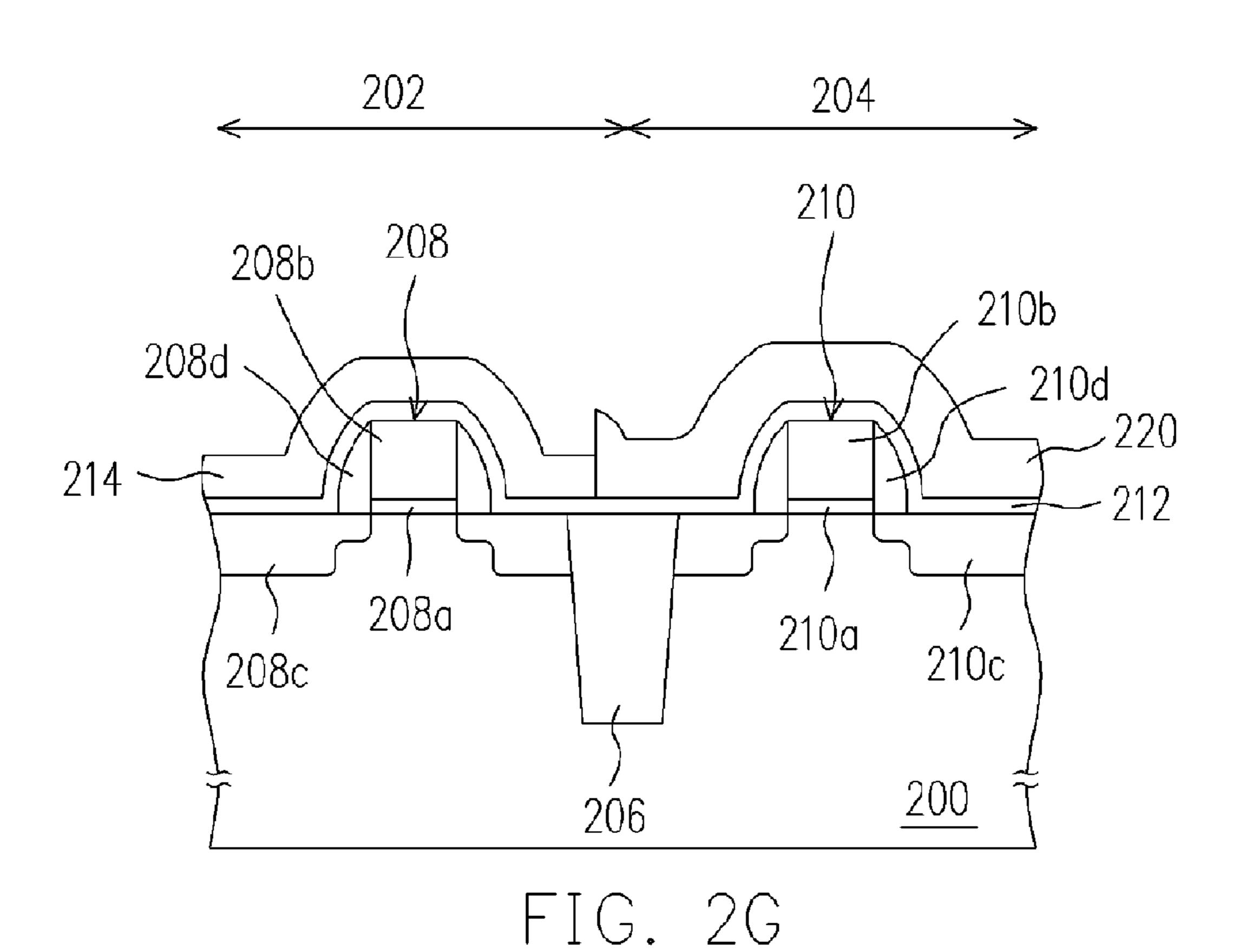

Referring to FIG. 2G, the photoresist layer 222 is removed. Then, the etching stop layer 216 is removed. The method of removing the etching stop layer 216 includes performing a wet cleaning process, for example.

Obviously, subsequent processes for forming intercon- 60 tests are listed in Table 1 below. nects can be performed after forming the stress layers 214 and 220. In the process of fabricating interconnects, a dielectric layer (not shown) is formed over the substrate 200 to cover the stress layers 214 and 220. Then, a contact opening (not shown) is formed in the dielectric layer, the 65 stress layers 214 and 220, and the etching stop layer 212. Thereafter, a conductive layer (not shown) is formed inside

the contact opening to serve as a contact for electrically connecting corresponding devices together.

In one embodiment, after removing the photoresist layer 222, the step of removing the etching stop layer 216 can't be performed and subsequent processes for forming interconnects can be performed. In the step of forming a contact opening of interconnects, an etching process is performed simultaneously on the etching stop layer 216 while a dielectric layer covered the stress layers 214 and 220 is etched.

In the following, a complementary metal-oxide-semiconductor (CMOS) device fabricated using the aforesaid method is described. As shown in FIG. 2G, the CMOS device comprises a substrate 200, a first type of MOS transistor 208, a second type of MOS transistor 210, an etching stop layer 212, a first stress layer 214 and a second stress layer 220. The substrate 200 has a active region 202 and a active region 204. The first active region 202 and the second active region 204 are isolated from each other through an isolation structure 206. The first type of MOS transistor 208 is disposed in the first active region 202 of the substrate 200 and the second type of MOS transistor 210 is disposed in the second active region 204 of the substrate **200**. The etching stop layer **212** is covered conformably the first type of MOS transistor 208, the second type of MOS transistor 210 and the isolation structure 206. The etching stop layer 212 has a thickness smaller than 500 Å, and preferably between 50 Å~200 Å, for example. The etching stop layer 212 is fabricated using silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-30 carbon nitride, for example. Furthermore, the stress layer 212 is disposed on the etching stop layer 212 in the first active region 202 and the stress layer 220 is disposed on the etching stop layer 214 in the second active region 204. The stress layers 214 and 220 are fabricated using silicon nitride, are removed to expose the etching stop layer 212. The 35 for example. The stress layer 214 is a tensile stress layer while the stress layer 220 is a compressive stress layer. Furthermore, the stress layers 214 and 220 have a thickness between about 600 Å~1500 Å, for example.

In another embodiment, the first type of MOS transistor 208 is a PMOS transistor and the second type of MOS transistor 210 is an NMOS transistor. In this case, the stress layer 214 is a compressive stress layer and the stress layer 220 is a tensile stress layer.

It should be noted that a tensile stress layer is formed on 45 an NMOS transistor and a compressive stress layer is formed on a PMOS transistor to affect the driving current of the device and increase the performance of the CMOS device at the same time. In addition, the etching stop layer in the embodiment can prevent possible damage to the spacers and silicone dioxide layer and nickel-silicide of STI structure in the no-transistor region so that the reliability of the process is improved.

In particular, the etching stop layer in the embodiment of the present invention protects the spacers and silicone diox-55 ide layer and nickel-silicide of STI structure in the notransistor region against possible damage without causing any adverse effect on the stress-related properties of the stress layer. The effect of the etching stop layer to the stress layer can be determined from a few tests. The results of the

TABLE 1

|               | Ion gain | Ion gain (%) |

|---------------|----------|--------------|

| Experiment #1 | 1        | O            |

| Experiment #2 | 1.0968   | 9.68         |

|               | Ion gain | Ion gain (%) |  |

|---------------|----------|--------------|--|

| Experiment #3 | 1.1019   | 10.19        |  |

| Experiment #4 | 1.0968   | 9.86         |  |

In Table 1, four different wafers are tested. In experiment 10 #1, a tensile stress layer is formed on a substrate with devices thereon and an electrical test is performed thereafter. In experiment #2, a curing process is carried out after forming the stress layer and an electrical test is performed thereafter. In experiment #3, an etching stop layer with a 15 thickness of about 100 Å and a tensile stress layer are formed in sequence over a substrate with devices thereon. The substrate is cured and then an electrical test is performed. In experiment #4, an etching stop layer with a thickness of about 150 Å and a tensile stress layer are 20 formed in sequence over a substrate with devices thereon. The substrate is cured and then an electrical test is performed. In all the aforesaid experiments #1~4, the tensile stress layer has a thickness of about 1000 Å.

According to Table 1, the electrical test value, the ion 25 gain, obtained in experiment #1 is used as a reference. The resulting electrical test values (ion gains) in experiment #2~4 are 1.0968 (9.68%), 1.1019 (10.19%) and 1.0968 (9.68%) respectively. The foregoing results show that the electrical test values obtained from the experiment #3, 4 and 30 the experiment #2 are very similar. In other words, the etching stop layer in the present invention has very little effect on the stress-related properties of the tensile stress layer and the degradation of the tensile stress layer is minimal.

Although the tests in Table 1 is performed to determine the effects to a tensile stress layer, the etching stop layer of the present invention similarly will not affect the stressrelated properties of a compressive stress layer leading to a degradation of the compressive stress layer.

In summary, major advantages of the present invention includes at least:

- 1. The stress layer on the MOS transistor can affect the driving current of the device and improve device performance. Additionally, the present invention can increase the 45 performance the NMOS device and the PMOS device at the same time.

- 2. The etching stop layer can avoid the problem of having any damage to the spacers and silicone dioxide layer and nickel-silicide of STI structure in the no-transistor region. 50

- 3. The etching stop layer formed between the MOS transistor and the stress layer in the present invention is able to protect the spacers and silicone dioxide layer and nickel-silicide of STI structure in the no-transistor region against possible damage without causing change in stress-related 55 properties such as releasing the stress in the stress layer. In other words, the degradation of the stress layer is minimal.

It will be apparent to those skilled in the art that various modifications and variations can be made to the structure of the present invention without departing from the scope or spirit of the invention. In view of the foregoing, it is intended that the present invention cover modifications and variations of this invention provided they fall within the scope of the following claims and their equivalents.

What is claimed is:

1. A method of forming a complementary metal-oxidesemiconductor (CMOS) device, comprising: **10**

providing a substrate having a first active region and a second active region, wherein the first active region and die second active region are isolated from each other through an isolation structure;

forming a first type of metal-oxide-semiconductor (MOS) transistor and a second type of MOS transistor on the first active region and die second active region of the substrate respectively;

forming a first etching stop layer over the substrate to cover conformably the first type of MOS transistor, the second type of MOS transistor and the isolation structure;

forming a first stress layer over the first etching stop layer; performing a first curing process to the first stress layer; forming a second etching stop layer over the first stress layer;

forming a first photoresist layer over the second etching stop layer in the first active region after the first curing process;

removing a portion of the second etching stop layer and a portion of the first stress layer using the first photoresist layer as a mask to expose the first etching stop layer;

removing the first photoresist layer;

forming a second stress layer over the substrate to cover the first etchings stop layer and the second etching stop layer;

performing a second curing process to the second stress layer;

forming a second photoresist layer over the second stress layer in the second active region after the second curing process;

removing a portion of the second stress layer using the second photoresist layer as a mask to expose the second etching stop layer; and

removing the second photoresist layer and the second etching stop layer.

- 2. The method of forming the CMOS device of claim 1, wherein the material constituting the first etching stop layer and the second etching stop layer comprise silicon oxide, silicon oxynitride, silicon carbide, silicon carbonate or silicon-carbon nitride.

- 3. The method of forming the CMOS device of claim 1, wherein each of the first etching stop layer and the second etching stop layer has a thickness between 50 Å~200 Å.

- 4. The method of forming the CMOS device of claim 1, wherein the material constituting the first stress layer and the second stress layer comprises silicon nitride.

- 5. The method of forming die CMOS device of claim 1, wherein the first type of MOS transistor is an N-type MOS (NMOS) transistor and the second type of MOS transistor is a P-type MOS (PMOS) transistor, then the first stress layer is a tensile stress layer and the second stress layer is a compressive stress layer.

- 6. The method of forming the CMOS device of claim 1, wherein the first type of MOS transistor is a P-type MOS (PMOS) transistor and the second type of MOS transistor is an N-type MOS (NMOS) transistor, ten the first stress layer is a compressive stress layer and the second stress layer is a tensile stress layer.

- 7. The method of forming the CMOS device of claim 1, wherein the first and second curing processes are a UV curing process, respectively.

\* \* \* \*