US007244996B2

## (12) United States Patent Hirashita et al.

# (54) STRUCTURE OF A FIELD EFFECT TRANSISTOR HAVING METALLIC SILICIDE AND MANUFACTURING METHOD THEREOF

(75) Inventors: Norio Hirashita, Tokyo (JP); Takashi

Ichimori, Tokyo (JP)

(73) Assignee: Oki Electric Industry Co., Ltd., Tokyo

(JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 718 days.

(21) Appl. No.: **09/825,973**

(22) Filed: Apr. 5, 2001

(65) Prior Publication Data

US 2001/0028087 A1 Oct. 11, 2001

#### (30) Foreign Application Priority Data

(51) Int. Cl. H01L 29/76 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,968,644 A \* 11/1990 Gallagher et al. ....... 438/680

#### (10) Patent No.: US 7,244,996 B2

#### (45) **Date of Patent:** Jul. 17, 2007

| 5,728,625 | A *  | 3/1998  | Tung 4           | 438/586 |

|-----------|------|---------|------------------|---------|

| 5,807,770 | A *  | 9/1998  | Mineji 4         | 438/151 |

| 5,915,197 | A *  | 6/1999  | Yamanaka et al 4 | 438/586 |

| 6,323,130 | B1 * | 11/2001 | Brodsky et al 4  | 438/682 |

| 6,344,675 | B1 * | 2/2002  | Imai 2           | 257/347 |

#### OTHER PUBLICATIONS

Deep sub-0.1 um MOSFET's with Very Thin SOL Layer for Ultra-Low Power Applicants, Information and Communication Engineers C-II vol. J81-C-II No. 3, pp. 313-319, Aug. 1998. Optimization of Series Resistance in Sub-0.2 um SOI MOSFET's, IEEE Electron Device letters, vol. 15, No. 9, Sep. 1994, p. 363-365. Optimization of series resistance in Sub-0.2 um SOI MOSFET's, 1993 IEEE, pp. IEDM93-723-726-IEDM 93.

#### \* cited by examiner

Primary Examiner—George Fourson Assistant Examiner—Julio J. Maldonado (74) Attorney, Agent, or Firm—Volentine & Whitt, P.L.L.C.

#### (57) ABSTRACT

A field effect transistor having metallic silicide layers is formed in a semiconductor layer on an insulating layer of an SOI substrate. The metallic silicide layers are composed of refractory metal and silicon. The metallic silicide layers extend to bottom surfaces of a source and a drain regions. A ratio of the metal to the silicon in the metallic silicide layers is X to Y. A ratio of the metal to the silicon of metallic silicide having the lowest resistance among stoichiometaric metallic silicides is X0 to Y0. X, Y, X0 and Y0 satisfy the following inequity: (X/Y)>(X0/Y0).

#### 14 Claims, 5 Drawing Sheets

Fig. 2

F-7-4

Tig-5 (a)

Fig. 5(b)

[ ] (c)

Fig - 6

#### STRUCTURE OF A FIELD EFFECT TRANSISTOR HAVING METALLIC SILICIDE AND MANUFACTURING METHOD THEREOF

The present application claims priority under 35 U.S.C. 119 to Japanese Application No. 2000-104733 filed on Apr, 6, 2000, which is hereby incorporated by reference in its entirety for all purposes.

#### BACKGROUND OF THE INVENTION

#### (1). Field of the Invention

The present invention relates to a field effect transistor (FET) which is formed in a silicon layer located on an insulating film, or a silicon on insulator (SOI) substrate. The SOI substrate has an insulating film and a thin silicon layer formed over a conductive substrate used as the conventional substrate to form the FET. The present invention also relates to a method of manufacturing such a field effect transistor.

#### (2). Description of the Related Art

Recently, a field effect transistor is formed on an SOI substrate (SOI-FET) in stead of a conventional bulk semiconductor substrate. The SOI-FET is formed in a thin silicon 25 film (SOI layer) formed on an insulating film. As a junction capacitance is reduced, the SOI-FET can operate with a high-speed. Particularly, a fully depleted SOI-FET formed in the SOI layer is known as a low-power device which has a small parasitic capacitance and a subthreshold swing smaller than that of the conventional bulk semiconductor substrate. The fully depleted transistor has a depletion layer, which expands to the bottom surfaces of a source region and a drain region, when a voltage is supplied to a gate electrode thereof. As an expansion of depletion layers of the fully 35 depleted SOI-FET is defined by a thickness of the SOI layer, a short channel effect can be restrained. Thus, for achieving the fully depleted operation of the SOI-FET, it is necessary to reduce the thickness of the SOI layer, as a device becomes microscopic.

The low-power device is shown in The article magazine of Institute of Electronics, Information and Communication Engineers C-II Vol. J81-C-II No. 3, pp. 313–319, "Deep Sub-0.1 µm MOSFET's with Very Thin SOI Layer for Ultra-Low Power Applications", published in March 1998 45 (hereinafter a first thesis). The shorter the gate length of the SOI-FET, the thinner the thickness of the SOI layer is. In the case where the gate length is 0.1 µm, the thickness of the SOI layer should be set 20 nm or below. Therefore, it is necessary to reduce the thickness of the SOI layer, if the SOI-FET 50 becomes smaller. The thickness of the SOI layer becomes thinner, the deterioration of the drive current occurs since the enlargement of the parasitic resistance in the source and drain regions becomes remarkable. Nowadays, a silicide technology using titanium (Ti) or cobalt (Co) is adopted to 55 depleted SOI-FET,; restrain the deterioration of the drive current. A metallic silicide layer is comprised of refractory metal and silicon. Titanium disilicide (TiSi<sub>2</sub>) and Cobalt disilicide (CoSi<sub>2</sub>) are widely used for their low resistivity.

However, when the specific contact resistivity between a metallic silicide layer and a silicon layer exceeds  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup>, and the thickness of the SOI layer located under the metallic silicide layer is less than 10 nm, the parasitic resistance would be increased so as to increase a resistance of a diffusion layer. As a result, the drive current of the SOI-FET might be reducing. This relationship is shown in IEEE ELECTRON DEVICE LETTERS, VOL. 15 No. 9,

2

and pp. 363–365, "Optimization of Series Resistance in Sub-0.2  $\mu$ m SOI MOSFET's", published in September 1998 (hereinafter a second thesis).

Currently, no metallic materials which have a specific contact resistivity less than 1×10<sup>-7</sup> Ω-cm² have been known. Hence, it is required that the SOI-FET layer be comprised of a silicide layer and a non-silicide layer over 10 nm in a diffusion layer. However, when a gate length becomes smaller, the thickness of the SOI layer become too thin to form such silicide and silicon multi-layered structure.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to provide a field effect transistor, having a satisfied drive current thereof for adapting microscopic devices.

In order to achive the above object, in a field effect transistor having metallic silicide layers composed of refractory metal and silicon, the bottom surfaces of the metallic silicide layers respectively extend to the bottom surfaces of a semiconductor layer, wherein a ratio of the metal to the silicon in the metallic silicide layers is X to Y, a ratio of the metal to the silicon of metallic silicide having the lowest resistance among stoichiometric metallic silicides is X0 to Y0, and X, Y, X0 and Y0 satisfy the following inequality: (X/Y)>(X0/Y0).

According to the present invention, the field effect transistor is capable of restraining the reduction of the drive current thereof. The transistor of the present invention can be formed in a microscopic size.

Typical ones of various inventions of the present application have been shown in brief. However, the various inventions of the present application and specific configurations of these inventions will be understood from the following description.

#### BRIEF DESCRIPTION OF THE DRAWINGS

While the specification concludes with claims particularly pointing out and distinctly claiming the subject matter which is regarded as the invention, it is believed that the invention, the objects and features of the invention and further objects, features and advantages thereof will be better understood from the following description taken in connection with the accompanying drawings in which:

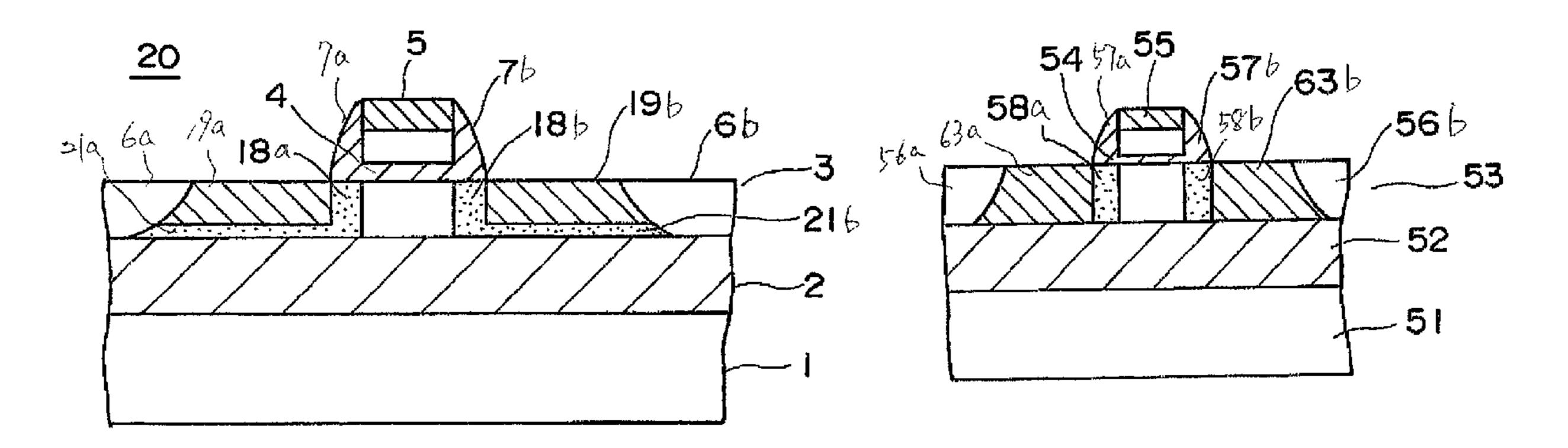

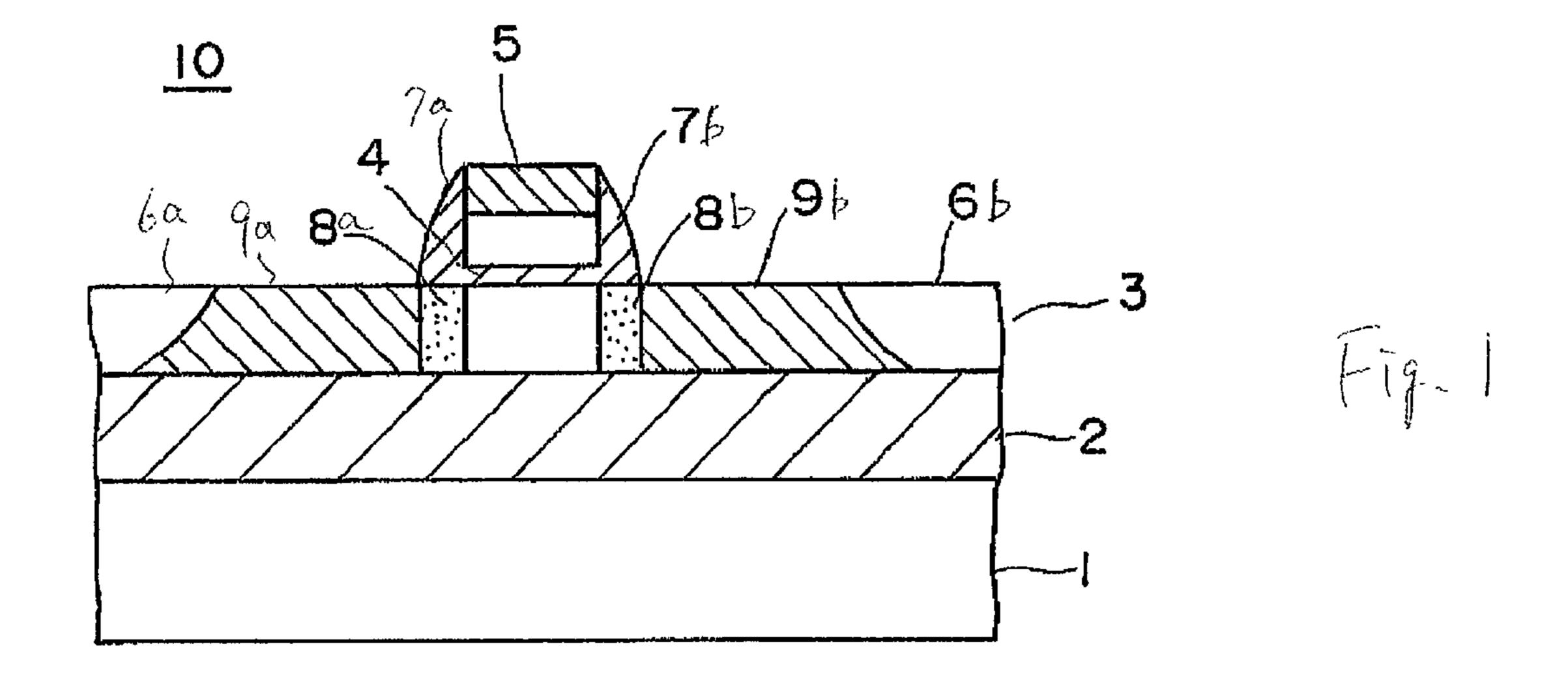

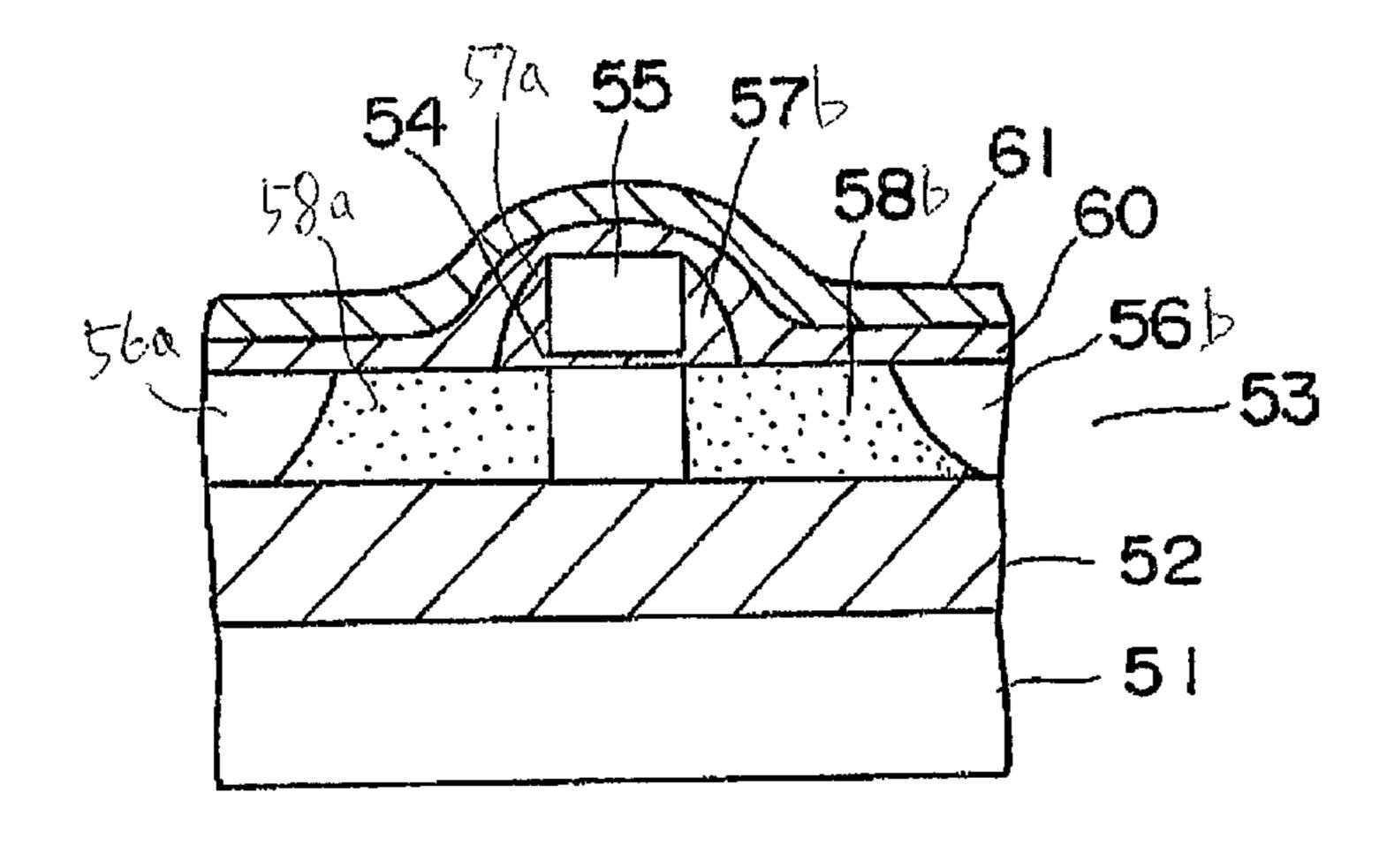

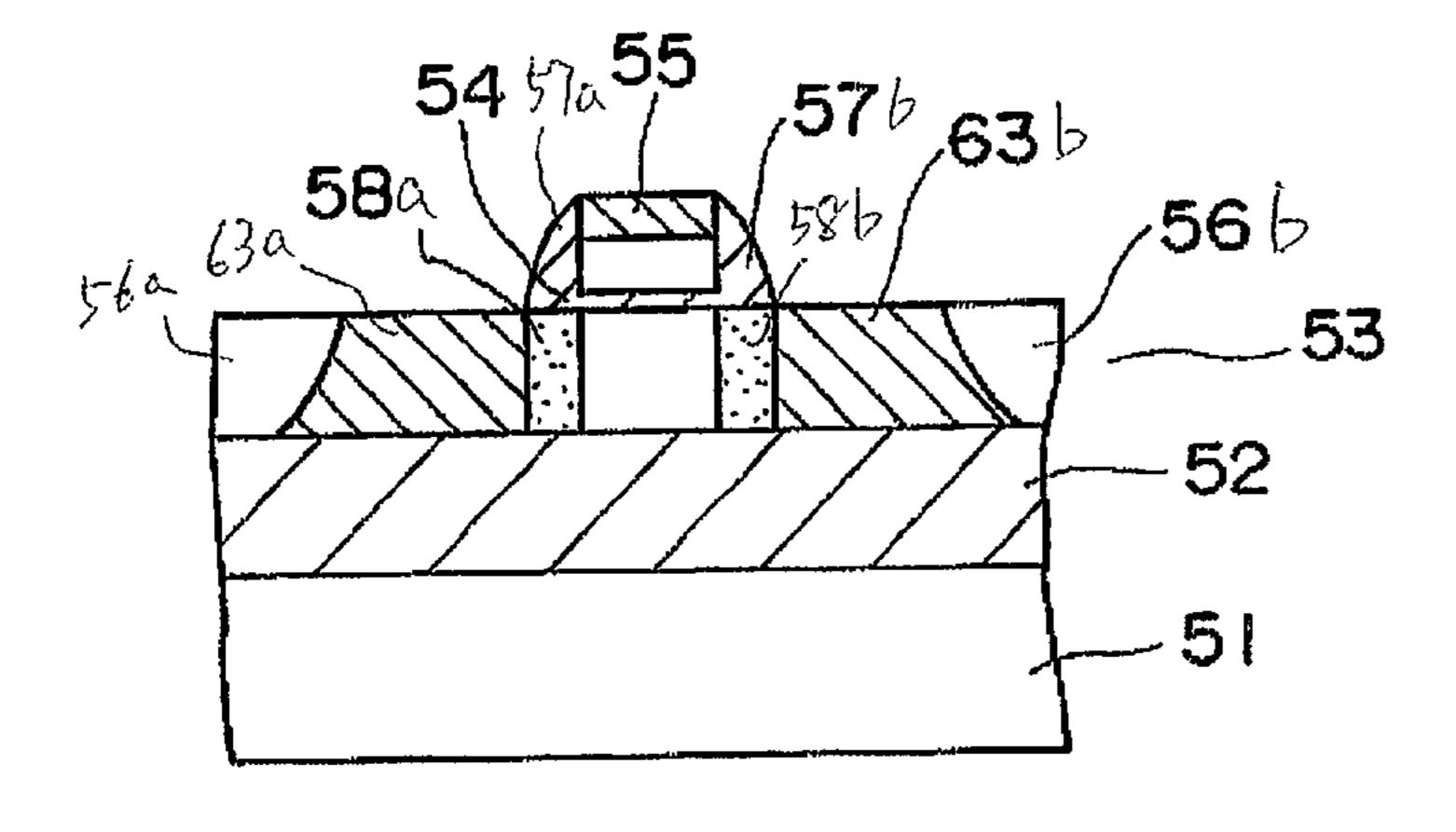

FIG. 1 is a cross-sectional view describing a field effect transistor according to a first preferred embodiment,;

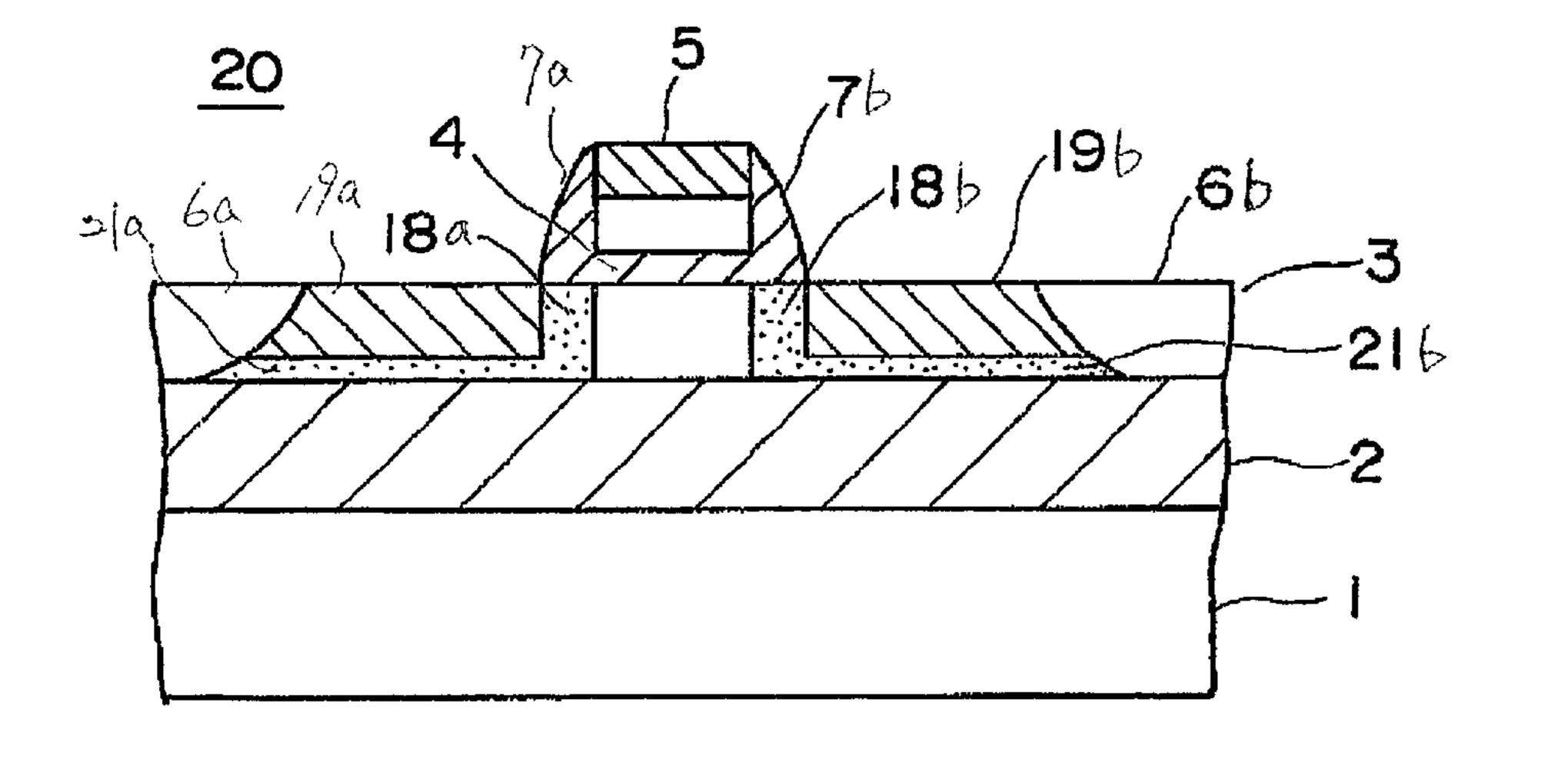

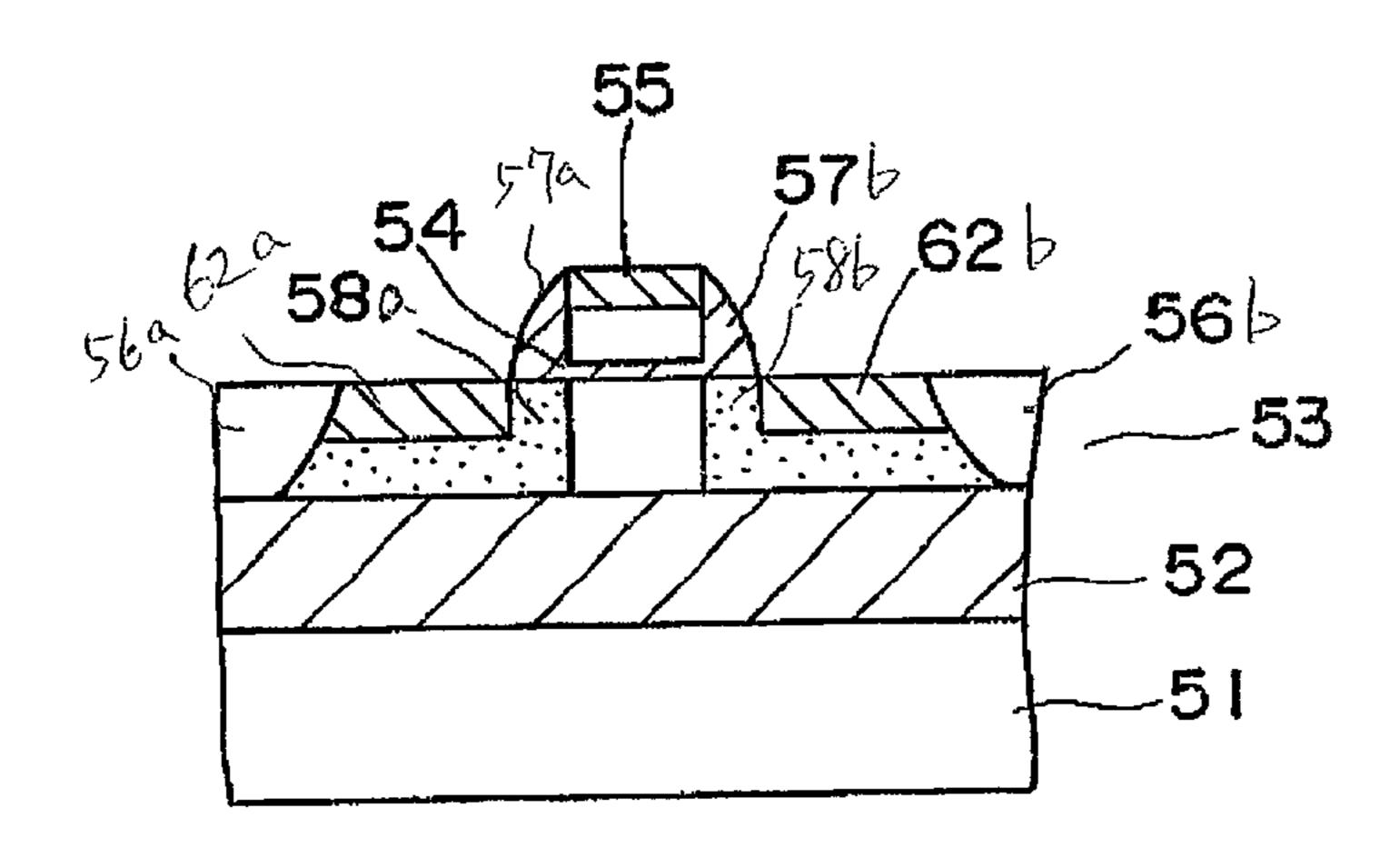

FIG. 2 is a cross-sectional view describing a field effect transistor according to a second preferred embodiment,;

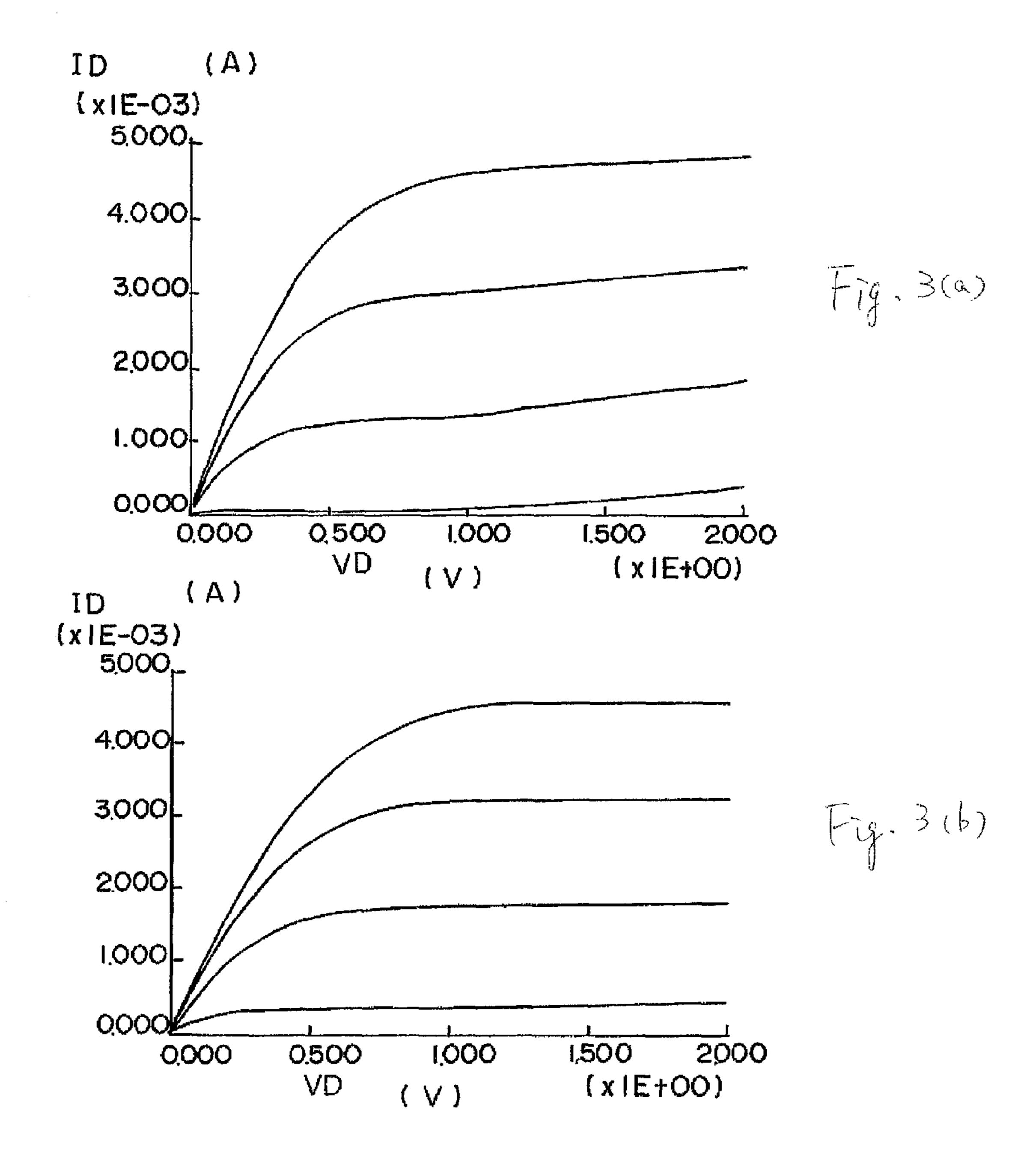

FIG. 3(a)–FIG. 3(b) are explanation diagrams describing relationship between the drain current and drain voltage characteristics of the fully depleted SOI-FET,;

FIG. 4 is an explanation diagram showing the drain voltage dependence of a threshold voltage for the fully depleted SOI-FET,;

FIG. 5(a)–FIG. 5(c) are cross-sectional views describing a method of fabricating a field effect transistor according to a third preferred embodiment,; and

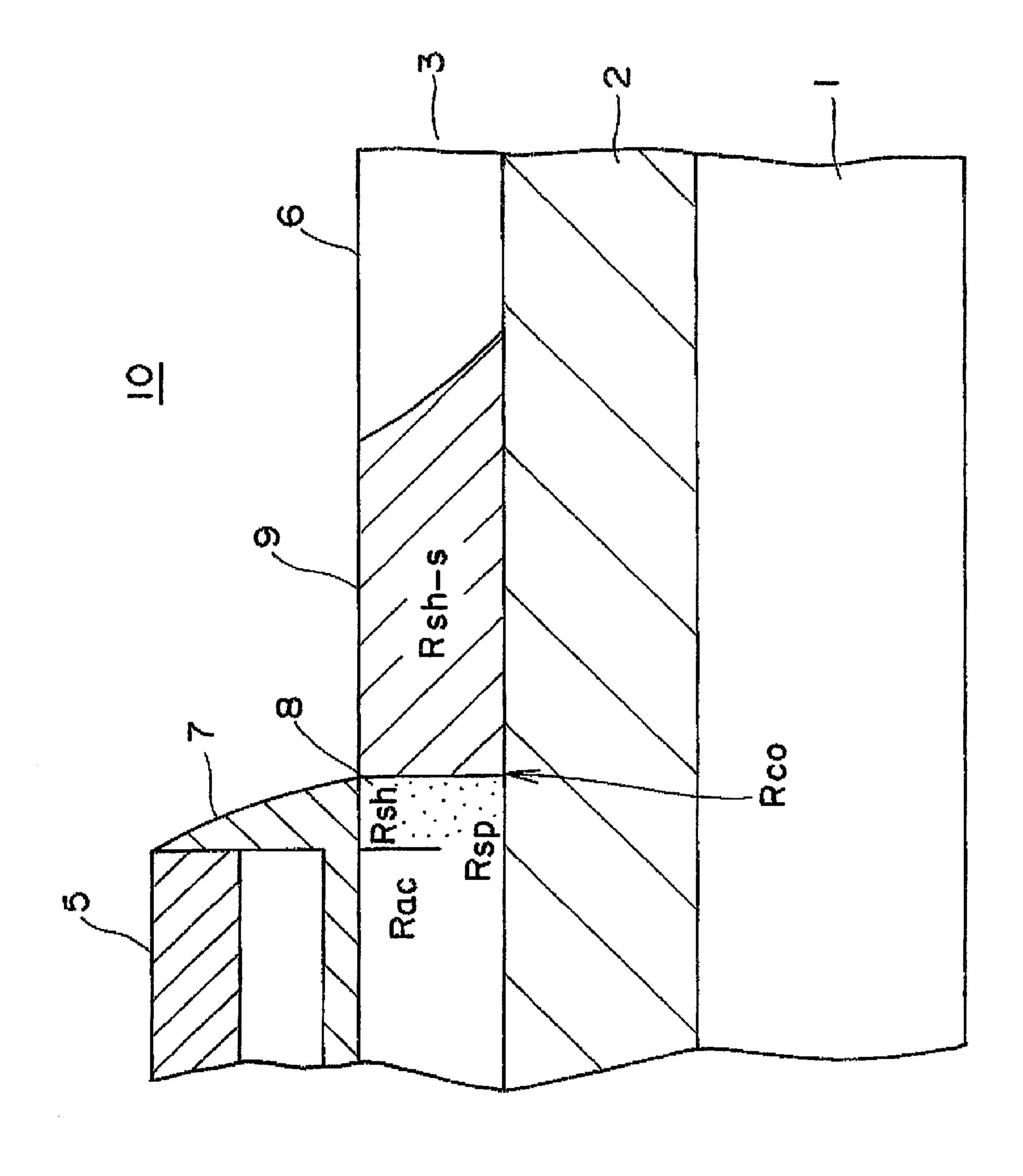

FIG. **6** is an enlarged cross-sectional view illustrating the first preferred embodiment.

### DESCRIPTION OF THE PREFERRED EMBODIMENTS

Preferred embodiments of the present invention will hereinafter be described in detail with reference to the accompanying drawings. The drawings used for this description

typically illustrate major characteristic parts in order that the present invention will be easily understood. In this description, one embodiment is shown in which the present invention is applied to a field effect transistor having metallic silicide layers.

First Embodiment

FIG. 1 is a cross-sectional view describing a field effect transistor according to a first preferred embodiment, showing in detail a fully depleted SOI-FET formed on an SOI substrate. The SOI-FET is formed in a thin silicon film (SOI 10 a thickness of 4.5 nm. The drain current substrate.

An SOI-FET 10 is formed on an SOI substrate which is comprised of a silicon substrate 1, an insulating layer 2 formed on the silicon substrate 1, and a thin silicon layer 15 (SOI layer) 3 formed on the insulating layer 2. The SOI-FET 10 is formed in an active area surrounded by field oxide films 6a and 6b, and includes a gate electrode 5 of the SOI-FET is formed on a gate oxide film 4 which is formed on the SOI layer 3. A pair of highly doped silicon layers 8a and 8b is formed in a source region and a drain region under sidewalls 7a and 7b, respectively. A channel region is defined between the pair of highly doped silicon layers 8a and 8b.

The source and the drain regions excepting the highly- 25 doped silicon impurity layers 8a and 8b are comprised of metallic silicide layers 9a and 9b. The metallic silicide layers 9a and 9b are composed of refractory metal and silicon. An amount of refractory metal contained in the metallic silicide layers 9a and 9b is more than that of silicon. In the first preferred embodiment, the metallic silicide layers 9a and 9b are comprised of a CoSiz layer in which a ratio of cobalt to silicon is one to z (1<z<2). In other words, a ratio of metal to silicon in the metallic silicide layer is X to Y, a ratio of metal to silicon of metallic silicide having the lowest 35 resistance among stoichiometric metallic silicides is X0 to Y0, and X, Y, X0 and Y0 satisfy the following inequality: (X/Y)>(X0/Y0). The CoSiz layers 9a and 9b are formed by a conventional silicide process, for more detail, all of the source region and the drain region except under the side- 40 walls la and 7b are changed into the cobalt silicide layers 9a and 9b. That is, bottom surfaces of the cobalt silicide layers 9a and 9b extend to bottom surfaces of the SOI layer 3. An electrical connection between the CoSiz layers 9a and 9b and the SOI layer 3 is performed between the highly doped 45 silicon layers 8a and 8b and the CoSiz layers 9a and 9b only.

According to the second thesis as described above, in the case where the contact specific resistance between refractory metal and silicon becomes less than  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup>, the parasitic resistance of the transistor does not increase and the 50 drive current of the transistor does not reduce. Inventors of the present invention found that the metallic silicide layers 9a and 9b are able to cause the contact specific resistance between refractory metal and silicon to be less than  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup>. A result of verification will be shown as follows.

FIG. 3(a)—FIG. 3(b) are explanation diagrams describing relationship between the drain current and the drain voltage characteristic of the fully depleted SOI-FET. In the first preferred embodiment, the SOI-FET 10 is an N type MOS transistor. A characteristic between a drain current and a 60 drain voltage of a conventional SOI-FET is shown in FIG. 3(a). The conventional SOI-FET is comprised of an SOI layer having a thickness of 50 nm and a pair of impurity layers having a thickness of more than 10 nm under CoSi<sub>2</sub> layers. A characteristic between the drain current and the 65 drain voltage of the first preferred embodiment is shown in FIG. 3(b). The SOI-FET 10 is comprised of an SOI layer 3

4

having a thickness of 20 nm, sidewalls 7a and 7b having a width of 0.1  $\mu$ m, a pair of highly doped silicon layers 8a and 8b, and the CoSiz layers 9a and 9b formed by a silicide process. The CoSiz layers 9a, 9b are composed that all of the source region and the drain region except under sidewalls 7a and 7b are changed into the cobalt silicide layers 9a and 9b. Both of the conventional FET and the SOI-FET of the first preferred of the invention are comprised of a gate length of 0.18  $\mu$ m, a gate width of 10  $\mu$ m and a gate oxide film having a thickness of 4.5 nm

The drain current shown in FIG. 3(a) is similar to the current shown in FIG. 3(b). Wherefore, it is easily understood that the drive current of SOI-FET structure in the first preferred embodiment becomes stable. In other words, the drain current of both structures becomes stable when the drain voltage thereof exceeds a predetermined voltage. Additionally, it has been already identified that the drive current of a P type MOS SOI-FET is as stable as that of the N type MOS SOI-FET comprised of the N type MOS transistor. A range of the total series parasitic resistance of the SOI-FETs of the present embodiment is obtained as follows. The total series parasitic resistance of the N type MOS transistor is about  $400 \ \Omega$ - $\mu$ m. That of the P type MOS transistor is about  $1 \ K \ \Omega$ - $\mu$ m.

An estimated total series parasitic resistance of the SOI-FET of the first preferred embodiment will next be described. FIG. 6 is an enlarged partial cross-sectional view of the SOI-FET described in FIG. 1. Incidentally, the same reference numbers identifies the same elements of structure as the SOI-FET shown in FIG. 1 and the description of certain common elements will therefore be omitted.

The total series parasitic resistance Rtot of the SOI-FET 10 is derived from a following formula.

$Rtot=2\times(Rac+Rsp+Rsh+Rsh-s+Rco)$

Wherein:

Rac represents an accumulation resistance of the highly doped silicon layer 8.

Rsp represents a spreading resistance of the highly doped silicon layer 8.

Rsh represents a diffusion layer resistance of the highly doped silicon layer 8 under a sidewall 7.

Rsh-s represents a sheet resistance of the CoSiz layer 9. Rco represents a contact resistance between the highly doped silicon layer 8 and the CoSiz layer 9.

As the accumulation resistance Rac, the spreading resistance Rsp, and the sheet resistance Rsh-s are negligible small, they are out of consideration in the above formula.

If the impurity of 1×10<sup>21</sup>/cm<sup>3</sup> is distributed in an N type drain region, the diffusion layer resistance of the N type MOS transistor becomes 80 Ω/sq. Also, if the impurity of 1×10<sup>20</sup>/cm<sup>3</sup> is distributed in a P type drain region, the diffusion layer resistance of the P tape MOS transistor is 500 Ω/sq. The diffusion layer resistances Rsh of the N type MOS and the P type MOS transistors each having a channel width of 1 μm are 192 Ω-μm and 450 Ω-μm, respectively. The contact specific resistances between the N<sup>+</sup> and P<sup>+</sup> type drain regions and the CoSiz 9 is about 4×10<sup>-8</sup> Ω-cm<sup>2</sup> and 9×10<sup>-8</sup> Ω-cm<sup>2</sup>, respectively.

In fact, it will be expected that the contact specific resistance would be further reduced, by considering the accumulation resistance Rac, the spreading resistance Rsp and the sheet resistance Rsh-s in the above formula. The contact specific resistance between the cobalt silicide (Co-Six) and the silicon of the first preferred embodiment is far smaller than  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup> introduced in the above second thesis.

FIG. 4 is an explanation diagram showing the drain voltage dependence of a threshold voltage for the fully depleted SOI-FET. In FIG. 4, the SOI-FET is the N type MOS transistor, as well as FIG. 3(a) and FIG. 3(b). The drain voltage of the conventional SOI-FET is shown as a 5 mark of "X" and that of the first preferred embodiment is shown as a mark of "•". When a substrate floating effect, such as a parasitic bipolar effect occurs in the fully depleted SOI-FET, the drain voltage will rise up. FIG. 4 shows that a reduction of a threshold voltage of the conventional 10 SOI-FET is remarkable, as a drain voltage rises up. However, the reduction of the threshold voltage of the SOI-FET of the first preferred embodiment is minimal. In other words, a leakage current of the SOI-FET can be cut down.

According to the first preferred embodiment of the present 15 invention, a field effect transistor capable of restraining the reduction of the drive current of the SOI-FET is provided. Further, the SOI-FET of the first preferred embodiment enables formation of microscopic devices. Additionally, since the SOI-FET of the first preferred embodiment can 20 precisely reduce the leakage current, the SOI-FET is useful as a low-power transistor.

Second Embodiment

FIG. 2 is a cross-sectional view describing a field effect transistor (FET) according to a second preferred embodi- 25 ment. Particularly, the FET is a fully depleted SOI-FET formed on an SOI substrate. Incidentally, the same reference numbers identifies the same elements of structure as those shown in FIG. 1.

An SOI-FET 20 is formed on an SOI substrate which 30 comprises a silicon substrate 1, an insulating layer 2 formed on the silicon substrate 1, and a thin silicon layer (SOI layer) 3 formed on the insulating layer 2. The SOI-FET 20 is formed in an active area surrounded by field oxide film 6a gate oxide film 4 located on the SOI layer 3. A pair of highly doped silicon layers 18a and 18b is formed in a source region and a drain region. A channel region is defined between to the pair of highly doped silicon layers 18a and **18**b.

The source and the drain regions include the highly doped silicon layers 18a and 18b and metallic silicide layers 19aand 19b, respectively. The metallic silicide layers 19a and 19b are composed of refractory metal and silicon. An amount of refractory metal contained in the metallic silicide 45 layers 19a and 19b is more than that of silicon. In the second embodiment as well as the first embodiment, the metallic silicide layers 19a and 19b are comprised of a CoSiz layer having a ratio of cobalt to silicon that is one to z (1<z<2). The CoSiz layers 19a and 19b are formed by the conventional silicide process. In more detail, the source region and the drain region except under the sidewalls 7a and 7b are changed into the cobalt silicide layers 19a and 19b.

The CoSiz layers 19a and 19b respectively have a thickness which is equal to or more than 80% thickness of from 55 top surfaces of the CoSiz layers 19a and 19b to bottom surfaces of the SOI layer 3. In other words, portions 21a and 21b of the highly doped silicon layers 18a and 18b respectively extend between bottom surfaces of the CoSiz layers 19a and 19b and a top surface of the insulating layer 2.

If a conventional CoSi<sub>2</sub> layer is used as the metallic silicide layer, the conventional CoSi<sub>2</sub> layer would be formed so as to have a thickness of the CoSi<sub>2</sub> layer less than 80% thickness of from top surfaces of the CoSi<sub>2</sub> to bottom surfaces of the SOI layer.

On the other hand, 1993 IEEE, pp. IEDM 93-723~726-IEDM 93, "OPTIMIZATION OF SERIES RESISTANCE

IN SUB-0.2 m SOI MOSFETs" (hereinafter a third thesis), reports the following concerning a conventional CoSi, layer:

- 1) A void would be generated at an interface between a metallic silicide layer and a silicon layer.

- 2) A parasitic resistance, which increases traceable to increase a sheet resistance of the metallic silicide layer. The void and the parasitic resistance influence a characteristic of a semiconductor device.

According to the second preferred embodiment of the present invention, since the metallic silicide layers are comprised of the CoSiz layer in which a ratio of cobalt to silicon is one to z (1 < z < 2), a field effect transistor can be formed by the CoSiz layer having a thickness which occupies equal to or more than 80% thickness of from a top surface of the CoSiz layer to bottom surfaces of the SOI layer. In fact, the degradation of a device characteristic traceable to above 1) and 2) can be perfected.

According to the second preferred embodiment of the present invention, as a small amount of silicon remains under the metallic silicide layers, a field effect transistor having a low resistance and a stable metallic silicide layer can be provided.

Third Embodiment

A method of manufacturing the field effect transistor described in the third preferred embodiment, will be shown hereinafter referring to FIG. 5(a)-FIG. 5(c). In FIG. 5(a), the SOI-FET is formed on an SOI substrate, which comprises a silicon substrate **51**, an insulating film **52**, and an SOI layer 53. Field oxide films 56a and 56b and heavily doped impurity layers 58a and 58b are formed in the SOI layer 53by using a conventional process. A channel region is defined between the pair of highly doped silicon layers 58a and 58b. A gate electrode 55 is formed on a gate oxide film 54 and located on the channel region. Cobalt (Co) film 60 is formed and 6b. the SOI-FET 20 has a gate electrode 5 formed on a 35 on the gate electrode 55 and highly doped silicon layers 58a and 58b. The cobalt film 60 is a refractory metal film for forming a metallic silicide layer. A titanium (Ti) film 61 or a titanium nitride (TiN) film 61 are formed on the cobalt film 60 as an antioxidant film 61 when a following heat treat-40 ment.

Then, a first heat treatment is carried out. The first heat treatment is conducted at a temperature within a range of 400° C.~600° C. with a lamp. Thereby, the cobalt silicide layers are formed on top surfaces of the gate electrode 55 and the highly doped silicon layers **58***a* and **58***b*. The cobalt silicide layers 62a and 62b are comprised of CoSi which has a composition ratio of cobalt to silicon that is 1:1, and Co<sub>2</sub>Si that includes more cobalt than silicon. In the third preferred embodiment, the cobalt silicide layers 62a and 62b formed by the first heat treatment, are comprised of CozSi (z>=1) as stated previously.

After the first heat treatment, the antioxidant film **61** and the cobalt film 60 remaining on the field oxide film 56 and the sidewalls 57a and 57b, are selectively removed by a conventional etching agent, such as aqueous sulfuric or aqueous ammonia, as shown in FIG. 5(b). Thereby, the cobalt layer remaining on the gate electrode 55 and the highly doped silicide layers 58a, 58b are removed.

Then, a dielectric interlayer is formed over the SOI substrate including the cobalt silicide layer 62a and 62b. Contact holes are formed in the dielectric interlayer, by a conventional process. In the third preferred embodiment, an illustration and a description of the conventional process are omitted.

Then, a second heat treatment is carried out. The second heat treatment is conducted at a temperature equal to or more than 700° C. with a lamp. Thereby, cobalt silicide layers 63a

and 63b are formed on top surfaces of the gate electrode 55 and all of the highly doped silicon layers 58a and 58b expect under sidewalls 57a and 57b, as shown in FIG. 5(c). The resistance of the cobalt silicide layers 63a and 63b are smaller than that of the CozSi layers 62a and 62b. In the 5 third preferred embodiment, the cobalt silicide layers 63a and 63b formed by the second heat treatment, are comprised of a CoSiz in which a composition ratio of cobalt to silicon is one to z (1 < z < 2).

The third preferred embodiment could be applied to 10 manufacture the SOI-FET explained in the second preferred embodiment, as well as the first preferred embodiment.

According to the present invention, a field effect transistor capable of restraining the reduction of the current drive capacity of the transistor is provided. Also, the transistor as provided enables formation of microscopic devices including the SOI-FET described above. Since the transistor of the present invention can precisely reduce the leakage current, a low-power transistor can be provided. Additionally, as a small amount of silicon remains under the metallic silicide layers, a field effect transistor having a low resistance and a stable metallic silicide layer can be provided.

What is claimed is:

1. A field effect transistor including a gate electrode and 25 a channel region defined by a source region and a drain region, comprising:

an insulating layer;

- a semiconductor layer formed on the insulating layer, wherein the semiconductor layer includes the channel <sup>30</sup> region therein;

- a pair of impurity layers respectively formed in the source region and the drain region, and which are in contact with the channel region; and

- a pair of metallic silicide layers respectively formed in the source region and the drain region, wherein the pair of metallic silicide layers are respectively in contact with the pair of impurity layers, wherein bottom surfaces of the pair of metallic silicide layers extend to bottom surfaces of the semiconductor layer,

- wherein the cobalt silicide layers are composed of cobalt and silicon, wherein a ration of cobalt to silicon is one to  $\alpha(1<\alpha<2)$ .

- 2. The field effect transistor according to claim 1, wherein said field effect transistor has a depletion layer which expands to bottom surfaces of the source region and the drain region when a voltage is supplied to the gate electrode thereof.

- 3. The field effect transistor according to claim 1, wherein a contact specific resistance between the cobalt silicide layers and the impurity layers is less than  $1\times10^{-7} \Omega$ -cm<sup>2</sup>.

- 4. A field effect transistor including a gate electrode and a channel region defined by a source region and a drain region, comprising:

an insulating layer;

- a semiconductor layer formed on the insulating layer, wherein the semiconductor layer includes the channel region therein;

- a pair of impurity layers respectively formed in the source 60 region and the drain region, and which are in contact with the channel region; and

- a pair of cobalt silicide layers respectively formed in the source region and the drain region, wherein the pair of cobalt silicide layers are respectively in contact with 65 the pair of impurity layers, wherein the pair of cobalt silicide layers have a thickness which is equal to or

8

more than 80% thickness of from an upper surface of the cobalt silicide layers to a bottom surface of the semiconductor layer;

- wherein the cobalt silicide layers are composed of cobalt and silicon, wherein a ratio of cobalt to silicon is one to  $\alpha(1<\alpha<2)$ .

- 5. The field effect transistor according to claim 4, wherein said field effect transistor has a depletion layer which expands to bottom surfaces of the source region and the drain region when a voltage is supplied to the gate electrode thereof.

- 6. The field effect transistor according to claim 4, wherein a contact specific resistance between the cobalt silicide layers and the impurity layers is less than  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup>.

- 7. The field effect transistor according to claim 4, wherein the pair of impurity layers respectively extend between the pair of cobalt silicide layers and the bottom surface of the semiconductor layer.

- 8. A field effect transistor formed in a semiconductor layer located on an insulating layer, the field effect transistor having a source region and a drain region formed in the semiconductor layer, comprising:

- the source region including a first impurity layer and a first cobalt silicide layer, wherein the first impurity layer and the first cobalt silicide layer are formed so as to reach the insulating layer through the semiconductor layer; and

- the drain region including a second impurity layer and a second cobalt silicide layer, wherein the second impurity layer and the second cobalt silicide layer are formed so as to reach the insulating layer through the semiconductor layer;

- wherein the first impurity layer is located so as to face to the second impurity layer,

- wherein a channel between the source region and the drain region is between the first impurity layer and the second impurity layer, and

- wherein the first cobalt silicide layer and the second cobalt silicide layer are composed of cobalt and silicon, wherein a ratio of cobalt to silicon is one to  $\alpha(1<\alpha<2)$ .

- 9. The field effect transistor according to claim 8, wherein said field effect transistor has a depletion layer which expands to bottom surfaces of the source region and the drain region when a voltage is supplied to the gate electrode thereof.

- 10. The field effect transistor according to claim 8, wherein a first contact specific resistance between the first cobalt silicide layer and the first impurity layer, and a second contact specific resistance between the second cobalt silicide layer and the second impurity layer, are less than  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup>.

- 11. A field effect transistor formed in a semiconductor layer located on an insulating layer, the field effect transistor having a source region and a drain region formed in the semiconductor layer, comprising:

- the source region including a first impurity layer and a first cobalt silicide layer, wherein the first cobalt silicide layer has a thickness which is equal to or more than 80% thickness of from an upper surface of the first cobalt silicide layer to a bottom surface of the semiconductor layer; and

- the drain region including a second impurity layer and a second cobalt silicide layer, wherein the second cobalt silicide layer has a thickness which is equal to or more than 80% thickness of from an upper surface of the second cobalt silicide layer to a bottom surface of the semiconductor layer;

- wherein the first impurity layer is located so as to face to the second impurity layer,

- wherein a channel between the source region and the drain region is between the first impurity layer and the second impurity layer, and

- wherein the first cobalt silicide layer and the second cobalt silicide layer are composed of cobalt and silicon, wherein a ratio of cobalt to silicon is one to  $\alpha(1<\alpha<2)$ .

- 12. The field effect transistor according to claim 11, wherein said field effect transistor has a depletion layer which expands to bottom surfaces of the source region and the drain region when a voltage is supplied to a gate electrode thereof.

**10**

- 13. The field effect transistor according to claim 11, wherein a first contact specific resistance between the first cobalt silicide layer and the first impurity layer, and a second contact specific resistance between the second cobalt silicide layer and the second impurity layer, are less than  $1\times10^{-7}$   $\Omega$ -cm<sup>2</sup>.

- 14. The field effect transistor according to claim 11, wherein the first impurity layer extends between the first cobalt silicide layer and the bottom surface of the semiconductor layer, and wherein the second impurity layer extends between the second cobalt silicide layer and the bottom surface of the semiconductor layer.

\* \* \* \* \*