#### US006686861B1

## (12) United States Patent

Kobayashi et al.

## (10) Patent No.: US 6,686,861 B1

(45) **Date of Patent:** Feb. 3, 2004

# (54) SLICE CIRCUIT CAPABLE OF ACCURATE CONVERSION OF AN ANALOG SIGNAL TO A DIGITAL SIGNAL

(75) Inventors: **Keiji Kobayashi**, Hyogo (JP); **Hisayasu Satoh**, Hyogo (JP)

(73) Assignee: Renesas Technology Corp., Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 10/351,483

(22) Filed: Jan. 27, 2003

### (30) Foreign Application Priority Data

(51) Int. Cl.<sup>7</sup> ...... H03M 1/12

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,412,692 A | 5/1995    | Uchida           |         |

|-------------|-----------|------------------|---------|

| 5,978,422 A | * 11/1999 | Weber et al      | 375/317 |

| 6,104,238 A | 8/2000    | Mattisson et al. |         |

| 6,349,121    | <b>B</b> 1 | * 2/2002  | Anderson          |

|--------------|------------|-----------|-------------------|

| 6,445,246    | <b>B</b> 1 | 9/2002    | Yoshida           |

| 6,633,752    | <b>B</b> 1 | * 10/2003 | Hashigaya 455/296 |

| 2001/0001616 |            |           |                   |

| 2002/0001354 | <b>A</b> 1 | 1/2002    | McNally           |

#### FOREIGN PATENT DOCUMENTS

JP 2002124857 4/2002

Primary Examiner—Howard L. Williams (74) Attorney, Agent, or Firm—Leydig, Voit & Mayer, Ltd.

#### (57) ABSTRACT

A slice circuit includes a DC component adjusting circuit, an integrator, a low pass filter, and a comparator. The DC component adjusting circuit adjusts only a DC component in an input signal sent from an input terminal to produce a DC component having a uniform voltage level. The integrator amplifies only a high frequency component of or above a predetermined frequency in the input signal received from the DC component adjusting circuit. The low pass filter detects an average voltage of the input signal received from the DC component adjusting circuit. The comparator compares a voltage of the output signal sent from the integrator with a voltage of an output signal sent from the low pass filter, and provides a digital signal having a logical level corresponding to results of the comparison to an output terminal.

#### 18 Claims, 53 Drawing Sheets

<sup>\*</sup> cited by examiner

FIG. 2

FIG.3

FIG.4

FIG.5

FIG.7

FIG.8

FIG.9

FIG. 12

FIG.13

Feb. 3, 2004

FIG. 16

FIG.17

FIG.18

Feb. 3, 2004

FIG.21

FIG.22

FIG.23

-IG.25

FIG. 26

FIG.27

FIG. 29

FIG. 30

FIG.31

976

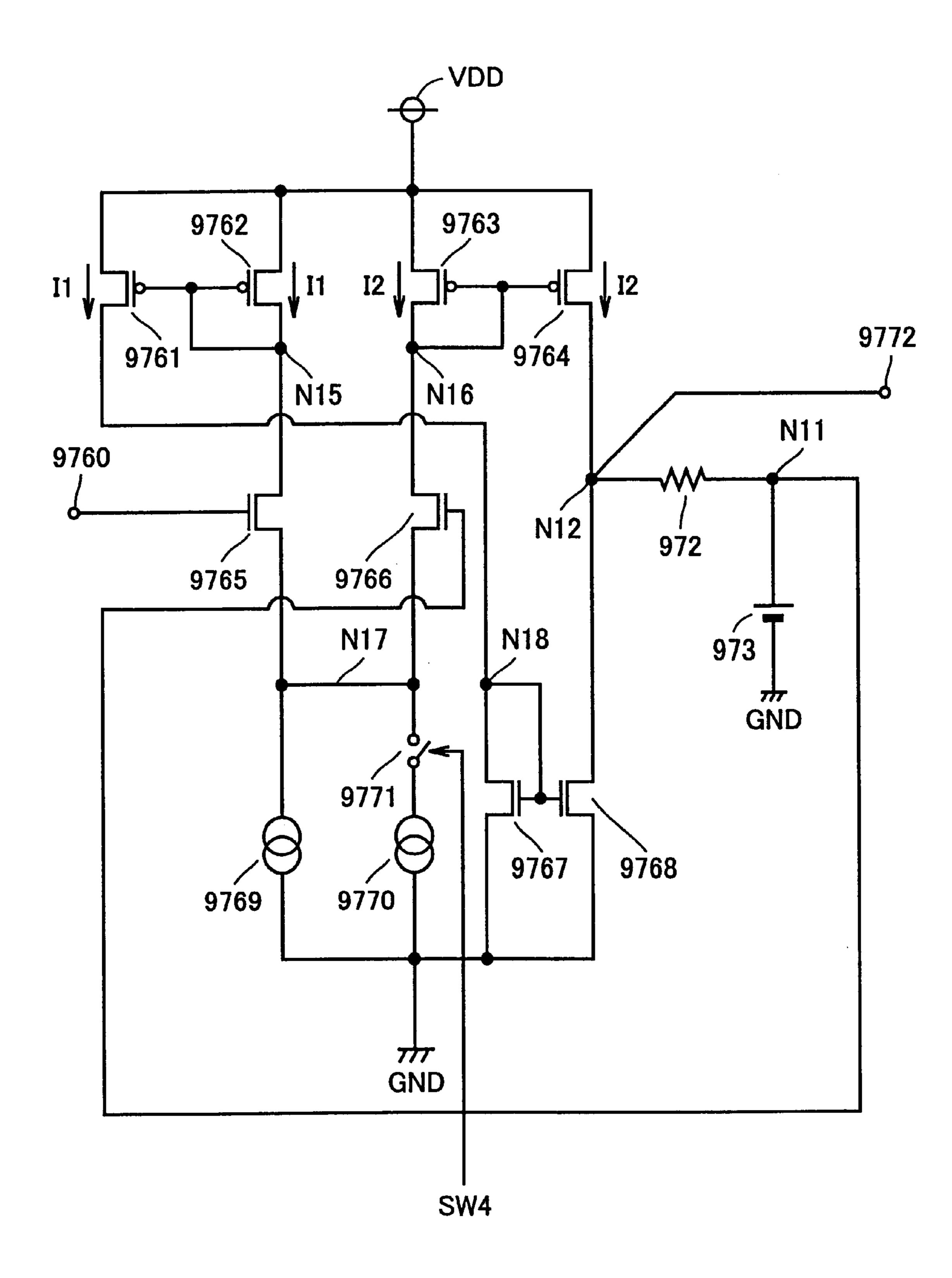

FIG.32

US 6,686,861 B1

-1G.34

-IG.35

-IG.37

FIG. 38

-IG.40

FIG.41

-IG.45

FIG. 47

FIG. 48

FIG.49

Feb. 3, 2004

IG.52 PRIOR A

FIG.53 PRIOR ART

# SLICE CIRCUIT CAPABLE OF ACCURATE **CONVERSION OF AN ANALOG SIGNAL TO** A DIGITAL SIGNAL

#### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to a slice circuit, and particularly to a slice circuit converting an FM demodulation 10 output analog signal to a digital signal in an FSK (Frequency Shift Keying) demodulator of an FSK receiver.

2. Description of the Background Art

For various applications such as DECT (Digital European Cordless Telephone) and Bluetooth, an FSK demodulator <sup>15</sup> uses a slice circuit as shown in FIG. 52.

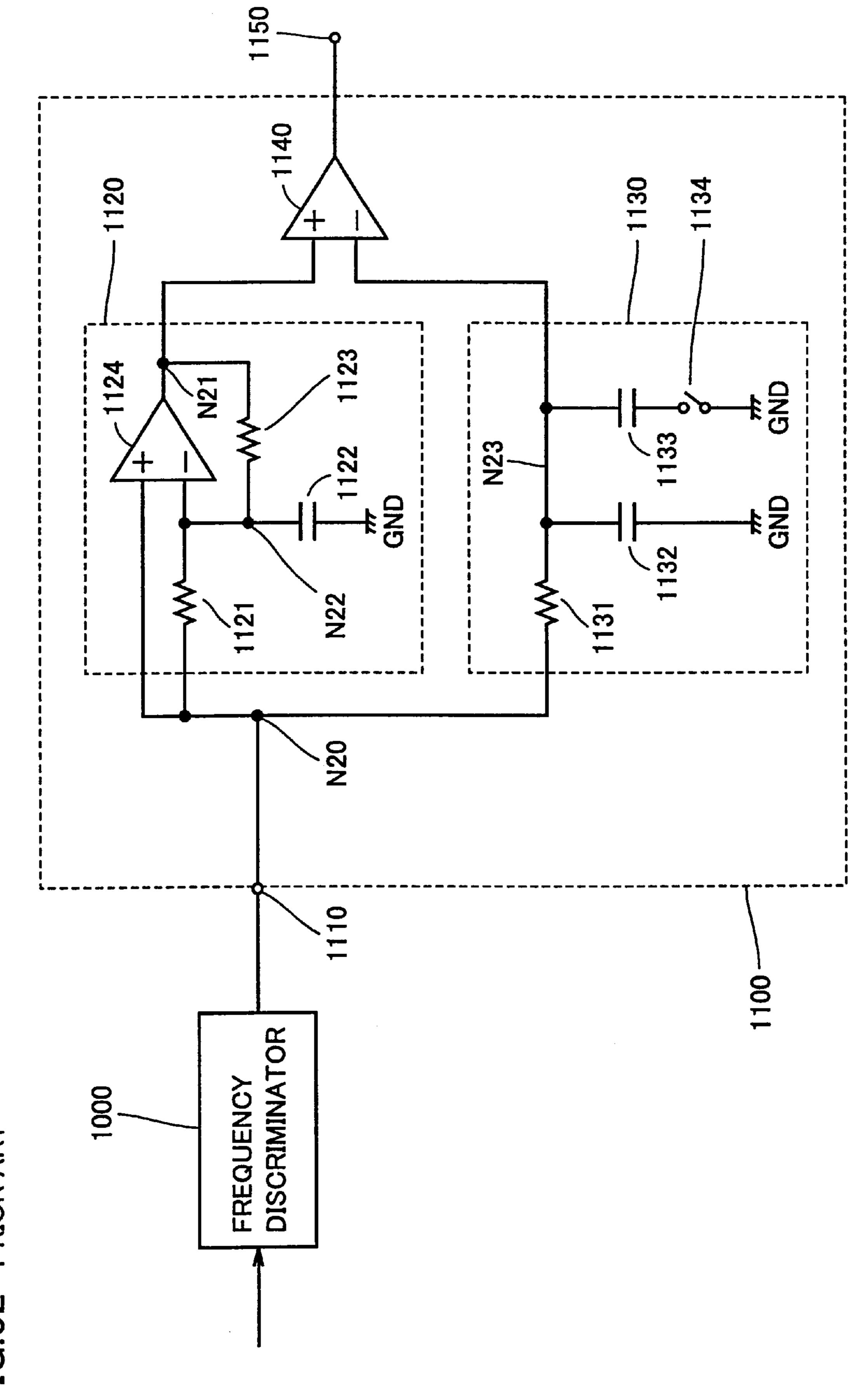

Referring to FIG. 52, a conventional slice circuit 1100 includes an integrator 1120, a LPF (Low Pass Filter) 1130 and a comparator 1140.

Integrator 1120 includes resistances 1121 and 1123, a capacitor 1122 and an operational amplifier 1124. One end of resistance 1121 is connected to a node N20 and the other end is connected to an inverting input terminal of operational amplifier 1124, respectively. Capacitor 1122 is connected between a node N22 and a ground node GND. Resistance 1123 is connected between nodes N21 and N22.

Operational amplifier 1124 receives on its noninverting input terminal a signal carried on node N20, and receives on its inverting input terminal a signal carried on node N22. The 30 signal on node N22 is equal to a signal produced by integrating an input signal by a low pass filter formed of resistance 1121 and capacitor 1122.

Accordingly, operational amplifier 1124 amplifies only high frequency components of or above a predetermined 35 frequency in the input signal by a gain determined by resistances 1121 and 1123, and provides or passes components lower than the predetermined frequency as they are.

Low pass filter 1130 includes a resistance 1131, capacitors 1132 and 1133, and a switch 1134. Resistance 1131 is 40 connected between nodes N20 and N23. Capacitor 1132 is connected between node N23 and ground node GND. Capacitor 1133 and switch 1134 are connected in series between node N23 and ground node GND. Capacitor 1132 is connected in parallel to capacitor 1133 and switch 1134.

When switch 1134 is off, low pass filter 1130 detects an average voltage of voltages forming the signal on node N20 by resistance 1131 and capacitor 1132. When switch 1134 is on, low pass filter 1130 detects an average voltage of voltages forming the signal on node N20 by resistance 1131 and capacitors 1132 and 1133.

Thus, low pass filter 1130 detects the average voltage of voltages forming the signal on node N20 while changing a low pass filter 1130 has a larger time constant when switch **1134** is on.

Slice circuit 1100 receives an input signal subjected to FM demodulation by a frequency discriminator 1000, and converts the received input signal from an analog signal to a 60 digital signal.

Therefore, integrator 1120 receives the input signal from frequency discriminator 1000 via an input terminal 1110, and amplifies only high frequency components, which have frequencies equal to or higher than a predetermined 65 frequency, in the received input signal for providing it to the noninverting input terminal of comparator 1140.

Low pass filter 1130 receives the input signal from frequency discriminator 1000 via input terminal 1110, and detects the average voltage of voltages forming the received input signal. Low pass filter 1130 provides the detected average voltage to an inverting input terminal of comparator **1140**.

Comparator 1140 receives on its noninverting input terminal the input signal amplified by integrator 1120, and receives the average voltage of the input signal on its inverting input terminal. Comparator 1140 compares the voltage of the input signal with the average voltage, and provides a signal at an H (logical high) level to an output terminal 1150 when the voltage of the input signal is higher than the average voltage. When the voltage of the input signal is equal to or lower than the average voltage, comparator 1140 provides a signal at an L (logical low) level to output terminal 1150.

As described above, slice circuit 1100 amplifies only high frequency components in the input signal subjected to the FM demodulation by frequency discriminator 1000, and converts the signal from the analog signal to the digital signal.

However, the conventional slice circuit suffers from the following problems.

- (1) When the input signal demodulated by the frequency discriminator is accompanied by drift of DC offset changing fast, the slice circuit cannot follow such changes, and the input signal cannot be accurately converted from the analog signal to the digital signal.

- (2) According to modulation conditions, when "1" or "0" continues, the input signal sent from the frequency discriminator keeps a uniform voltage value for a certain duration. When the slice circuit receives this input signal, comparator 1140 receives from integrator 1120 the voltage at substantially the same level as the voltage received from low pass filter 1130 so that the comparing operation in comparator 1140 cannot be performed accurately.

- (3) When noise components of high frequencies are input, these noise components are erroneously detected as intended signal components.

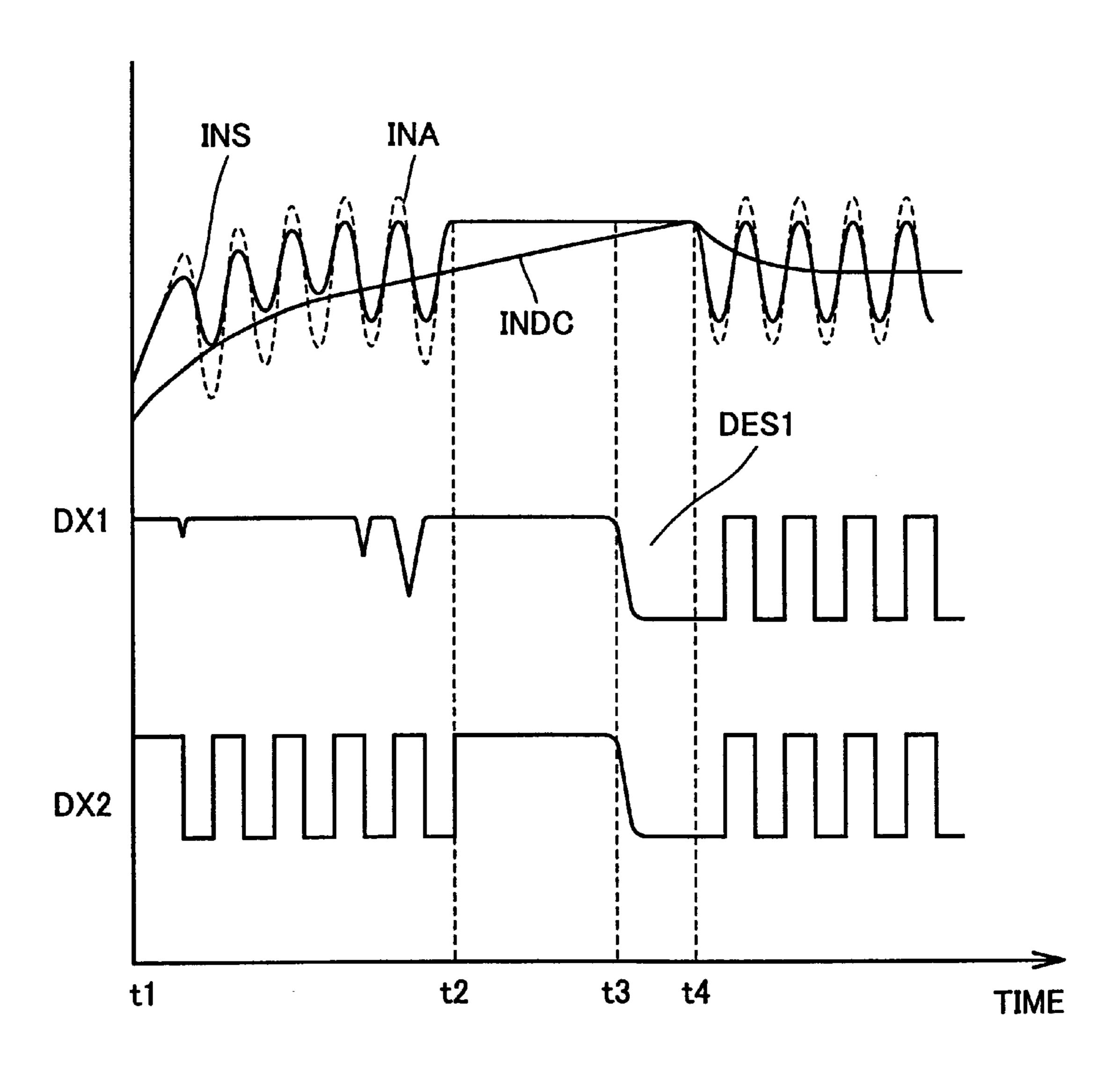

Referring to FIG. 53, the foregoing problems (1)–(3) will now be described in greater detail. When an input signal INS accompanied by fast drift of DC offset, low pass filter 1130 of slice circuit 1100 cannot follow such fast changes, and provides a signal INDC indicating the average voltage of voltages forming input signal INS to the inverting input terminal of comparator 1140.

Thereby, the voltage level of signal INDC hardly crosses the voltage level of input signal INS for a period from timing 50 t1 to timing t2, and comparator 1140 can hardly compare the voltage level of input signal INS with the voltage level of signal INDC. Consequently, comparator 1140 provides a signal DX1. Thus, slice circuit 1100 cannot accurately convert the input signal from the analog signal to the digital capacitance by turning on and off switch 1134. Therefore, 55 signal when the input signal is accompanied by the fast drift of DC offset.

> When slice circuit 1100 receives components corresponding to components including a succession of "1" or "0" according to the FSK modulation at or after timing t2, the voltage level of signal INDC approaches the voltage level of input signal INS, and the voltage level of input signal INS cannot be discriminated from the voltage level of signal INDC during a period from timing t3 to timing t4. Consequently, comparator 1140 cannot accurately compare the voltage level of input signal INS with the voltage level of signal INDC, and provides a signal DX1 including an error component DES1.

A gain of integrator 1120 may be increased for overcoming the problem of the above item (1). In this case, however, integrator 1120 provides an amplified signal INA having a larger amplitude than input signal INS. Thereby, the voltage level of signal INDC crosses the voltage level of amplified 5 signal INA during the period between timing t1 and timing t2, and comparator 1140 provides a signal DX2. As described above, the problem of the foregoing item (1) can be overcome by increasing the gain of integrator 1120. However, if input signal INS contains noise components 10 having the same frequency as the high frequency components to be amplified in integrator 1120, amplified signal INS contains amplified noise components, resulting in the problem of the foregoing item (3).

The conventional slice circuit **1100** is configured to overcome the problems of the above items (1) and (2) by turning off switch **1134** of low pass filter **1130** to reduce the time constant during an initial period of reception of the input signal, and by turning on switch **1134** to increase the time constant during a latter period of reception of the input signal. This is because the drift of DC offset is generally fast during the initial period of reception of the input signal, and the drift of DC offset is generally slow during the latter period of reception of the input signal.

Accordingly, by controlling the time constant of the low pass filter as described above, it is attempted to cope with the fast drift of DC offset during the initial reception period, and to delay the timing, at which the voltage level of signal INDC approaches the voltage level of input signal INS, during the latter reception period as far as possible.

However, even if the measures are attempted by increasing the time constant of low pass filter 1130 and delaying the approach of the output voltage of low pass filter 1130 to the output voltage of integrator 1120 as far as possible, these measures do not fundamentally overcome an erroneous inverting operation of comparator 1140. Thus, conventional slice circuit 1100 cannot overcome both the problems in the items (1) and (2) at the same time.

For removing the noise components contained in the input signal as far as possible, the gain in integrator 1120 may be reduced. In this case, however, the voltage level of signal INDC cannot cross the voltage level of input signal INS when the input signal is accompanied by the fast drift of DC offset as described above. Therefore, comparator 1140 cannot accurately provide the digital signal. Thus, conventional slice circuit 1100 cannot overcome both the problems in the items (1) and (3) at the same time.

# SUMMARY OF THE INVENTION

Accordingly, an object of the invention is to provide a slice circuit, which can accurately convert an input signal from an analog signal to a digital signal even when the input signal contains fast drift of DC offset.

Another object of the invention is to provide a slice 55 circuit, which can accurately convert an input signal from an analog signal to a digital signal by removing noises even when the input signal contains fast drift of DC offset.

According to the invention, a slice circuit receiving an input signal prepared by demodulating a receive signal 60 subjected to frequency modulation in a predetermined manner and having a voltage level corresponding to the frequency modulation, and converting the received input signal from an analog signal to a digital signal, includes a signal processing circuit and a comparator.

The signal processing circuit produces, based on the input signal, one of a first processing signal formed of a first main

4

signal and a first reference signal, a second processing signal formed of a second main signal and a second reference signal, and a third processing signal formed of the first main signal and the second reference signal.

The comparator compares the voltage level of the first main signal with the voltage level of the first reference signal to provide a digital signal having a voltage level corresponding to results of the comparison when receiving the first processing signal. The comparator compares the voltage level of the second main signal with the voltage level of the second reference signal to provide a digital signal having a voltage level corresponding to results of the comparison when receiving the second processing signal. Further, the comparator compares the voltage level of the first main signal with the voltage level of the second reference signal to provide a digital signal having a voltage level corresponding to results of the comparison when receiving the third processing signal.

The first main signal is a signal having an amplified high frequency component of or above a predetermined frequency and a DC component formed of a predetermined voltage level, or is a signal having the high frequency component and a DC component at a voltage level changing in accordance with the DC component in the input signal. The second main signal is a signal having the high frequency component and a DC component being the same as the DC component in the input signal. Further, the first reference signal is a signal having an average voltage obtained by smoothing the input signal as it is. The second reference signal is a signal at a voltage level lower than the average voltage.

According to the invention, therefore, the slice circuit can achieve all or some of the following three effects.

- (a) Even when an input signal Vin contains the drift of DC offset, the drift of DC offset can be removed, and input signal Vin can be accurately followed and converted from an analog signal to a digital signal.

- (b) Even when the input signal contains components formed of a succession of uniform voltage levels, the input signal can be accurately converted from an analog signal to a digital signal.

- (c) Even when the input signal contains noise components, erroneous detection of noise components can be prevented.

The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

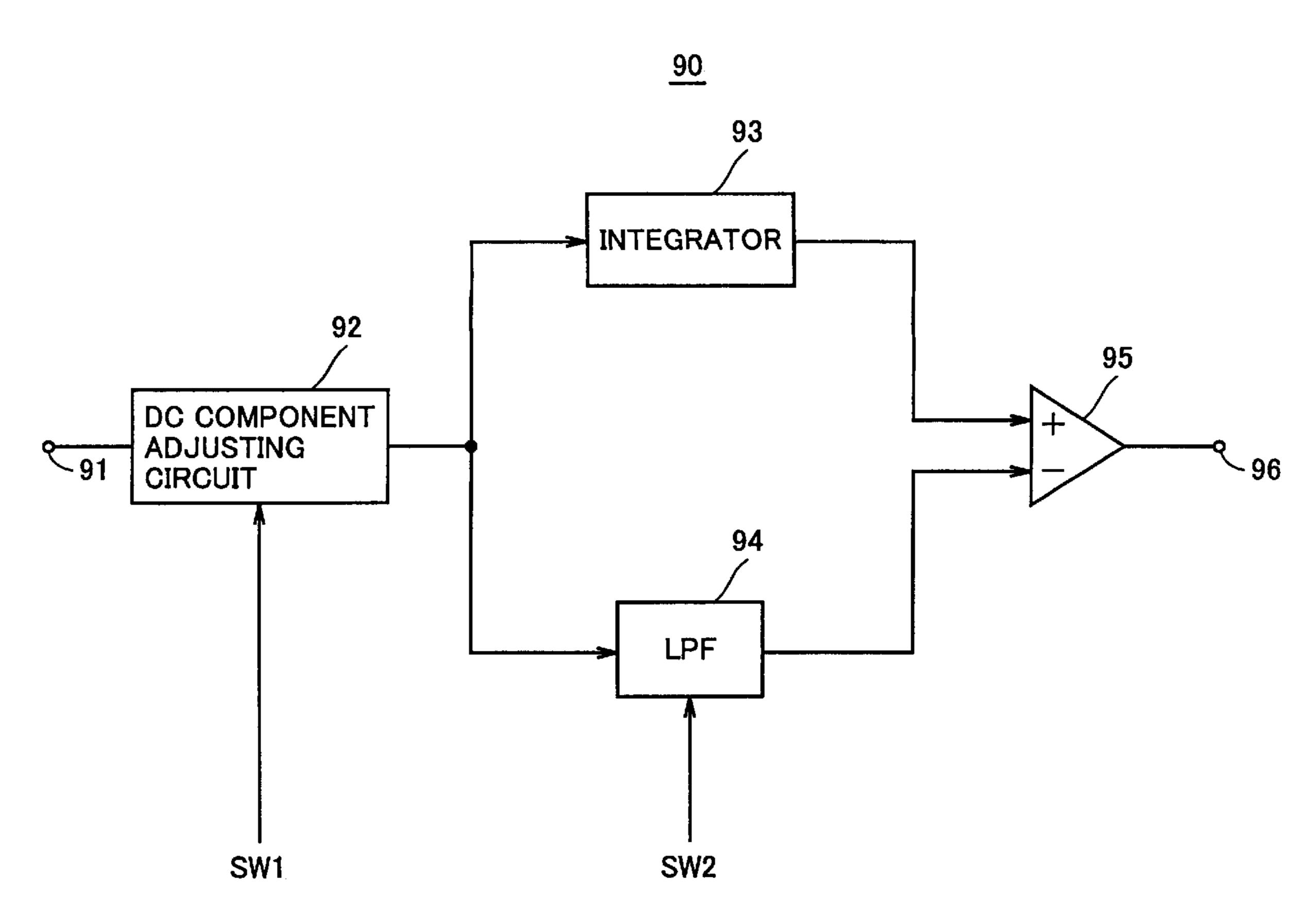

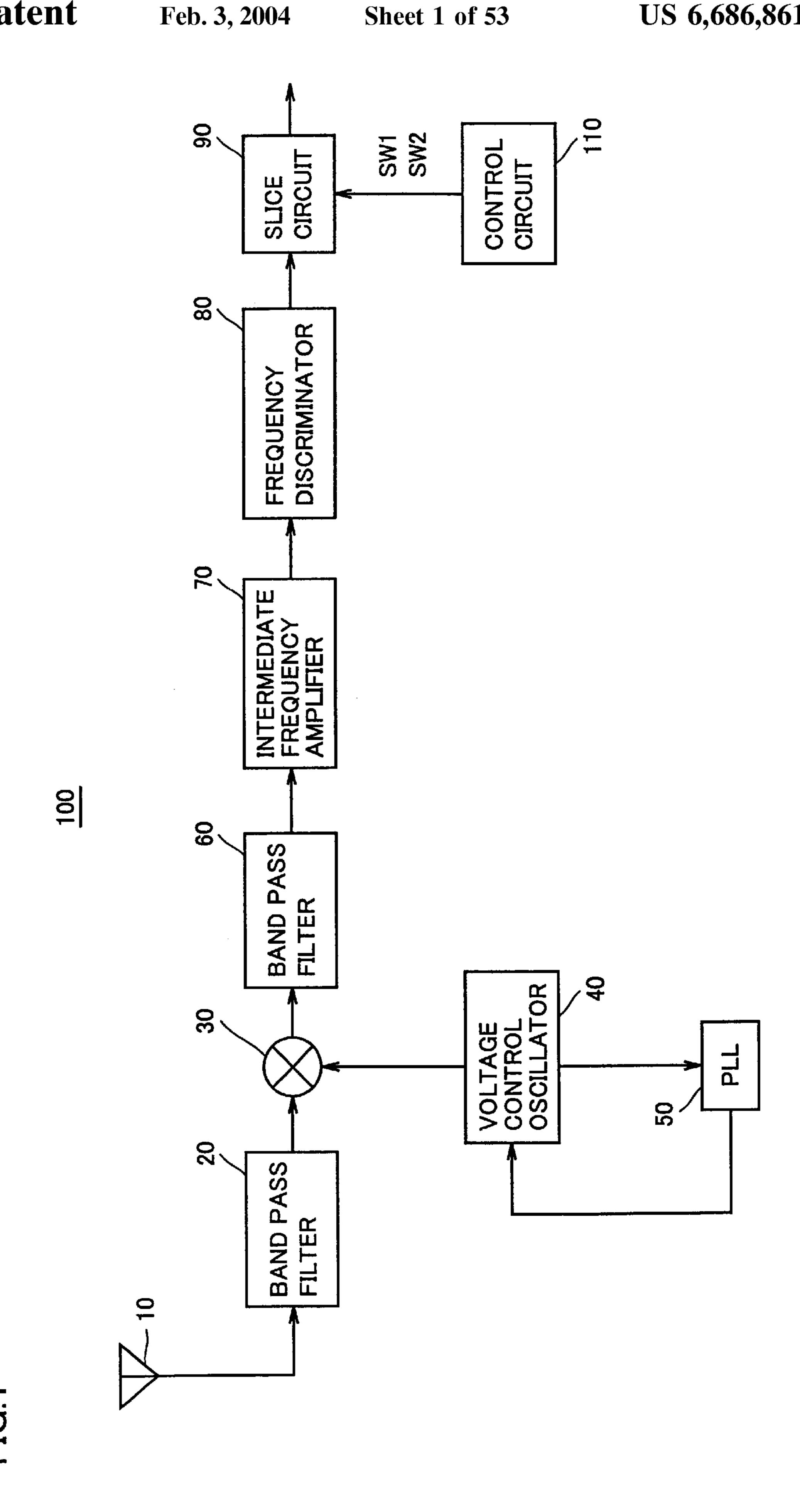

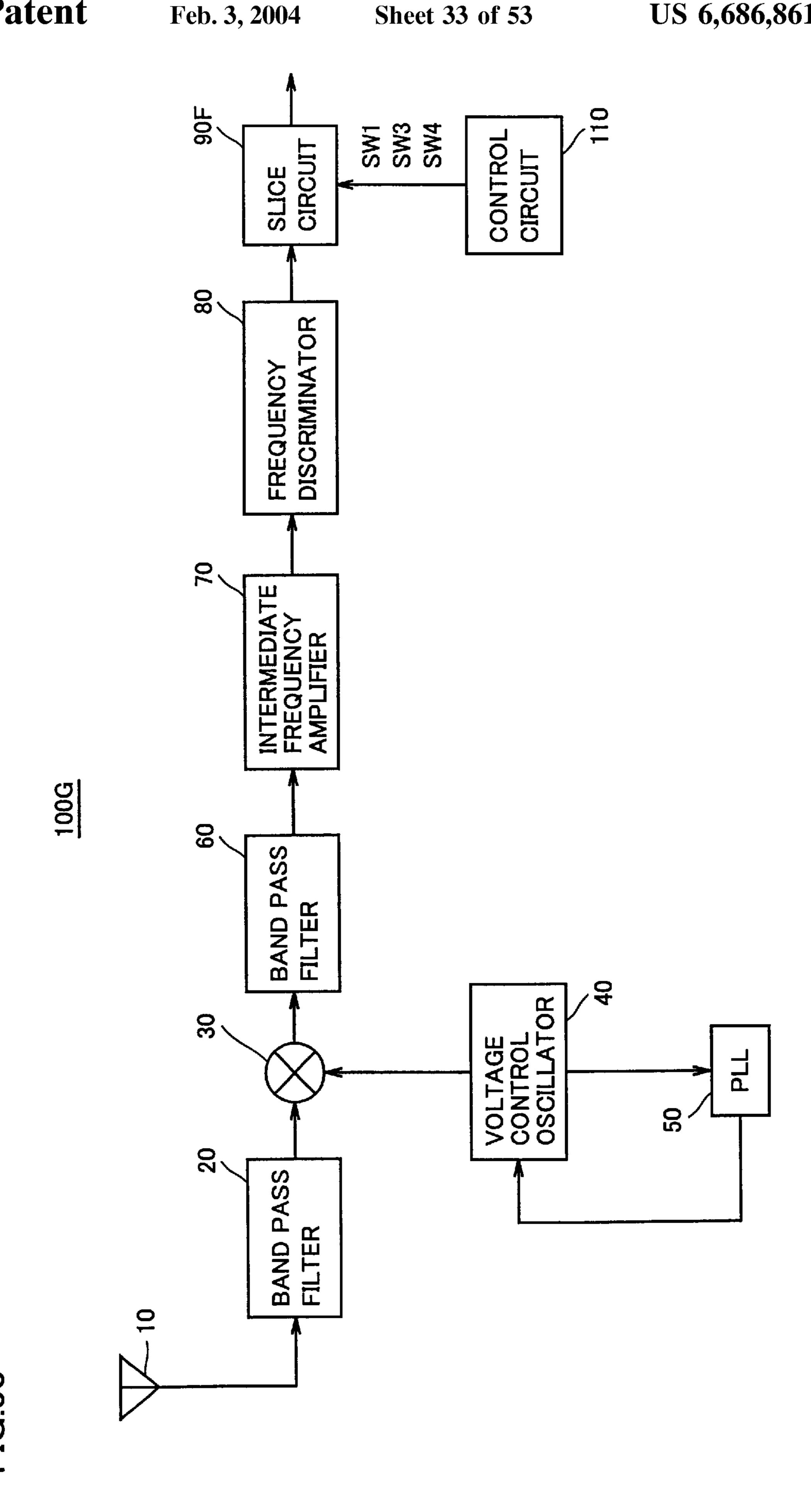

FIG. 1 is a schematic block diagram of a receiver of a first embodiment;

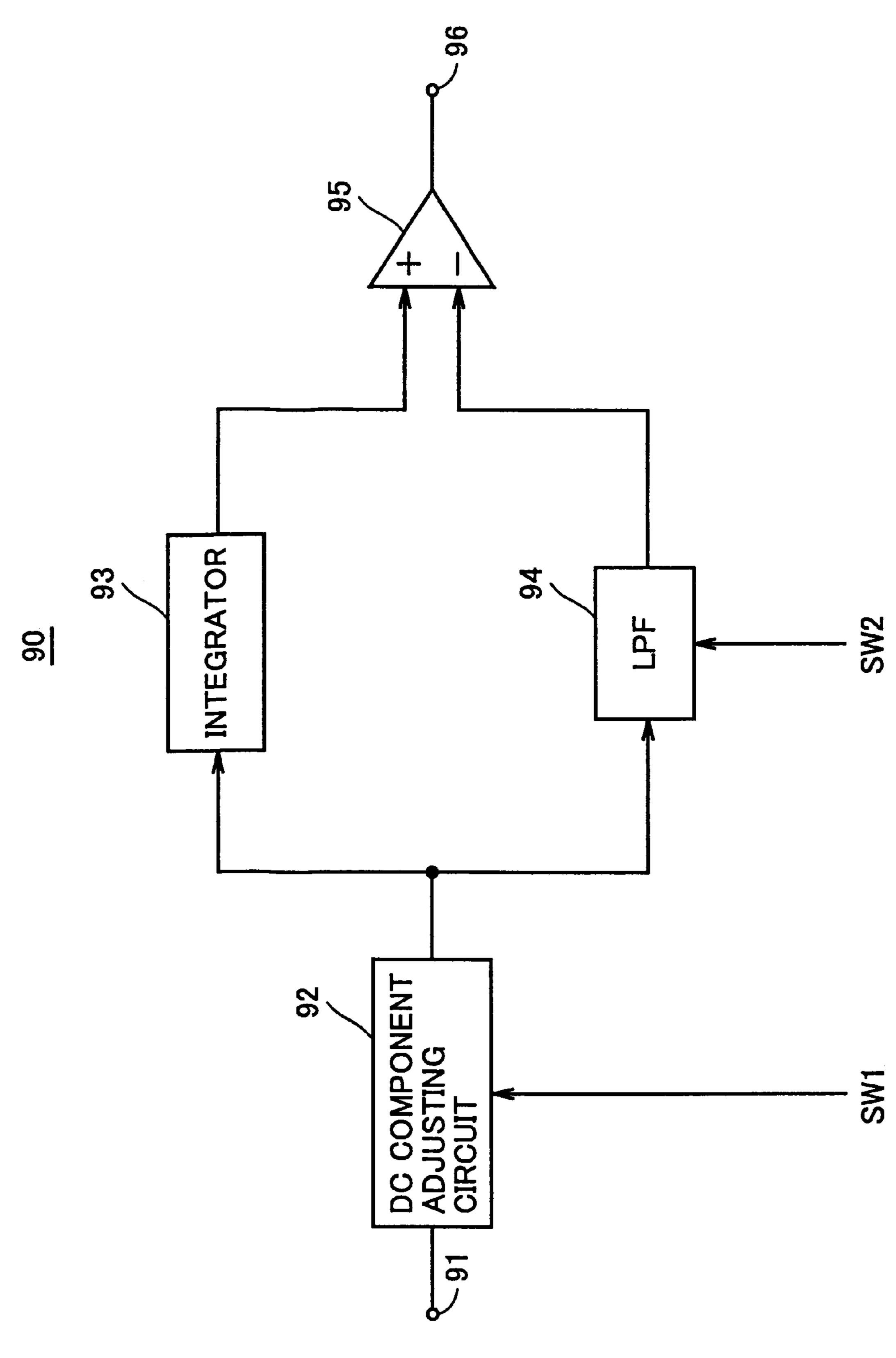

FIG. 2 is a block diagram of a slice circuit shown in FIG. 1:

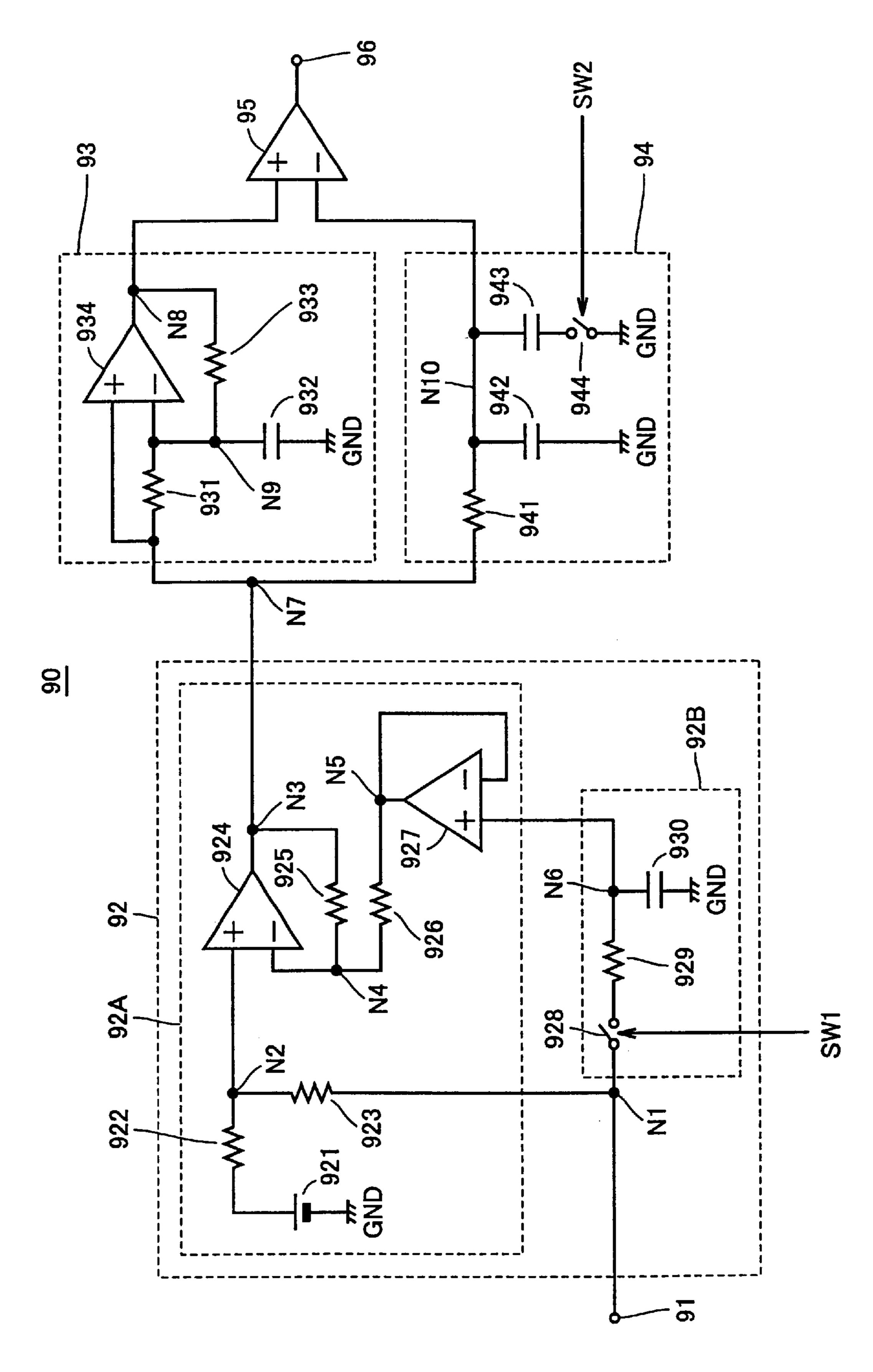

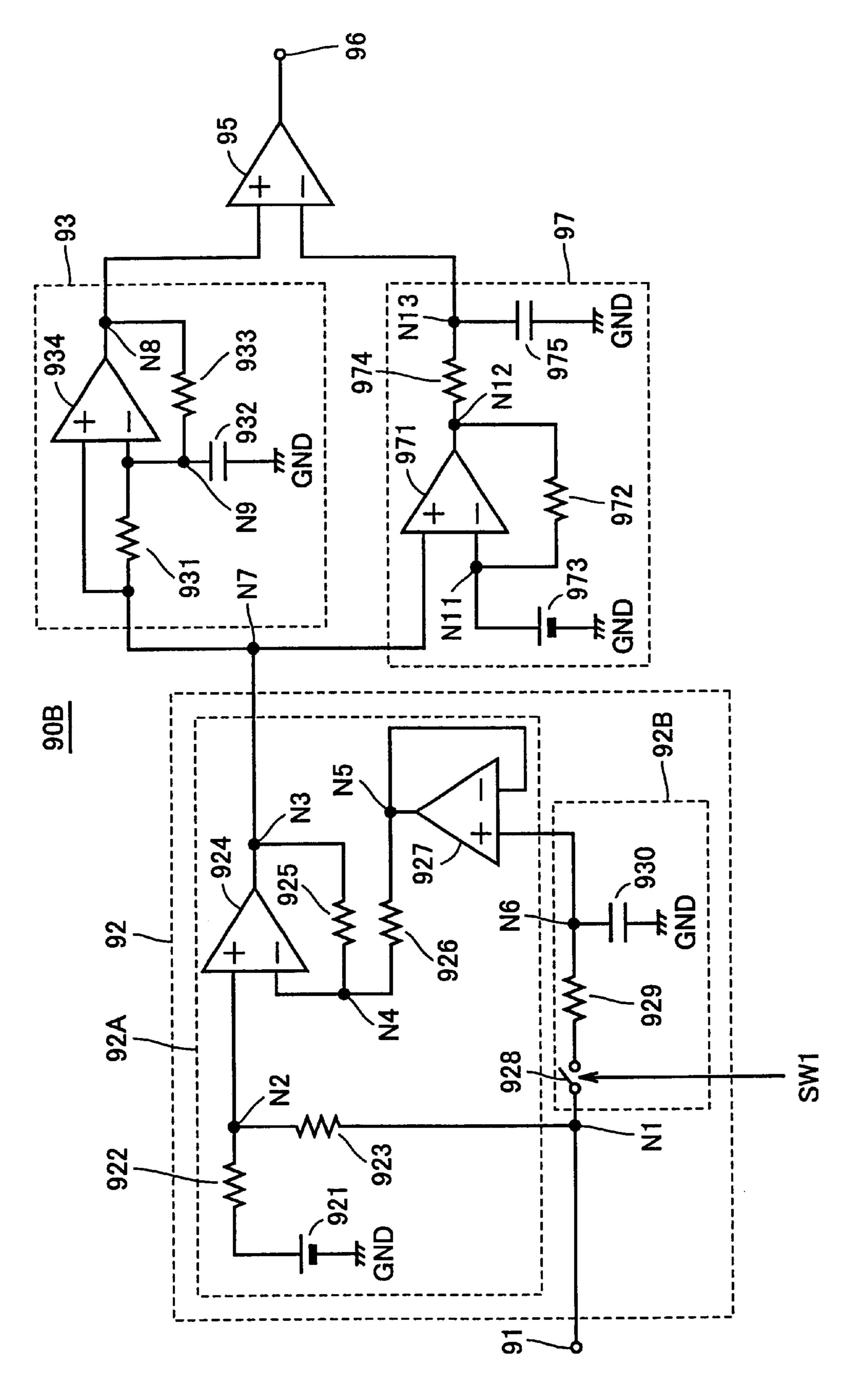

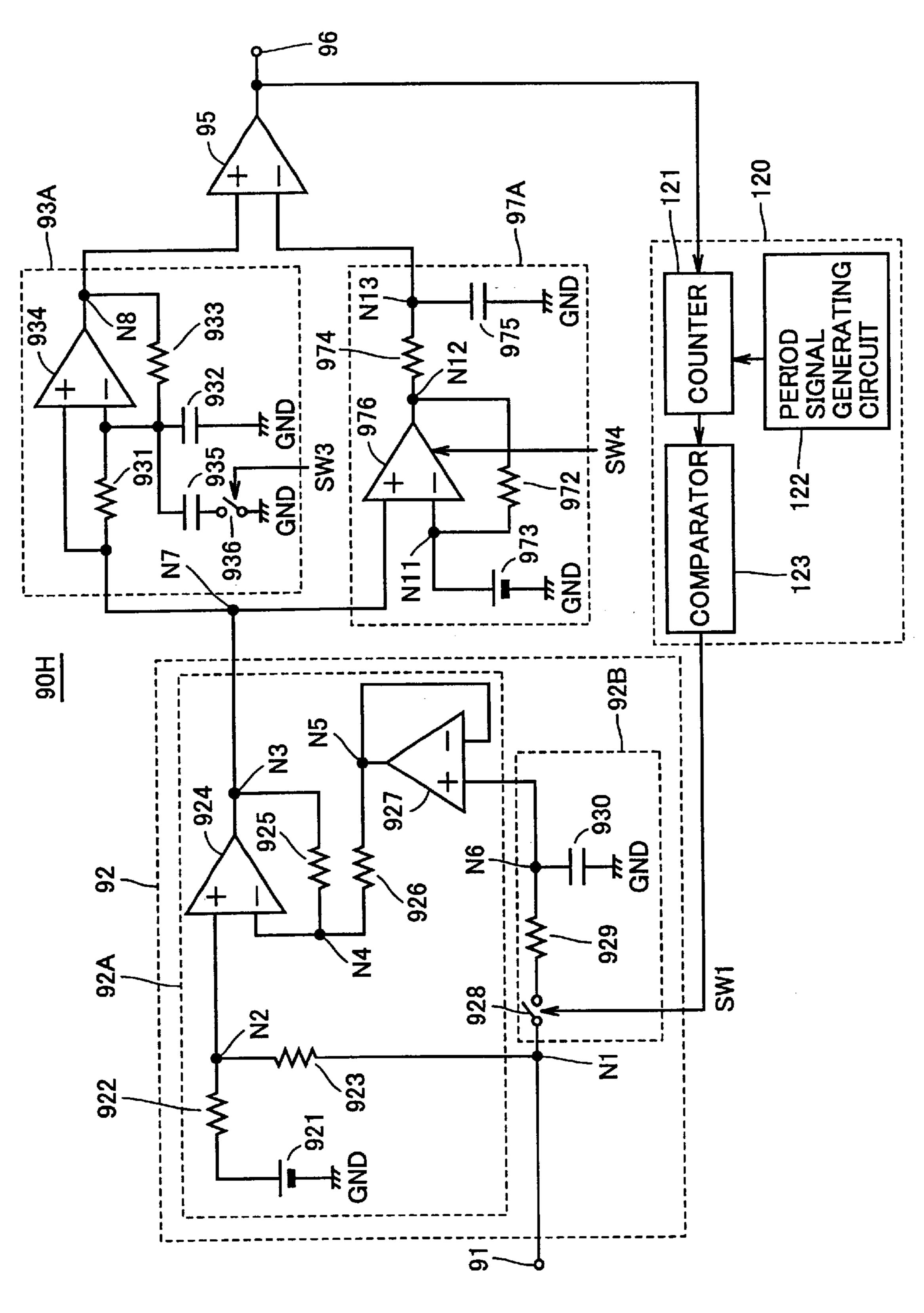

FIG. 3 is a circuit diagram of a DC component adjusting circuit, an integrator, a comparator and a low pass filter;

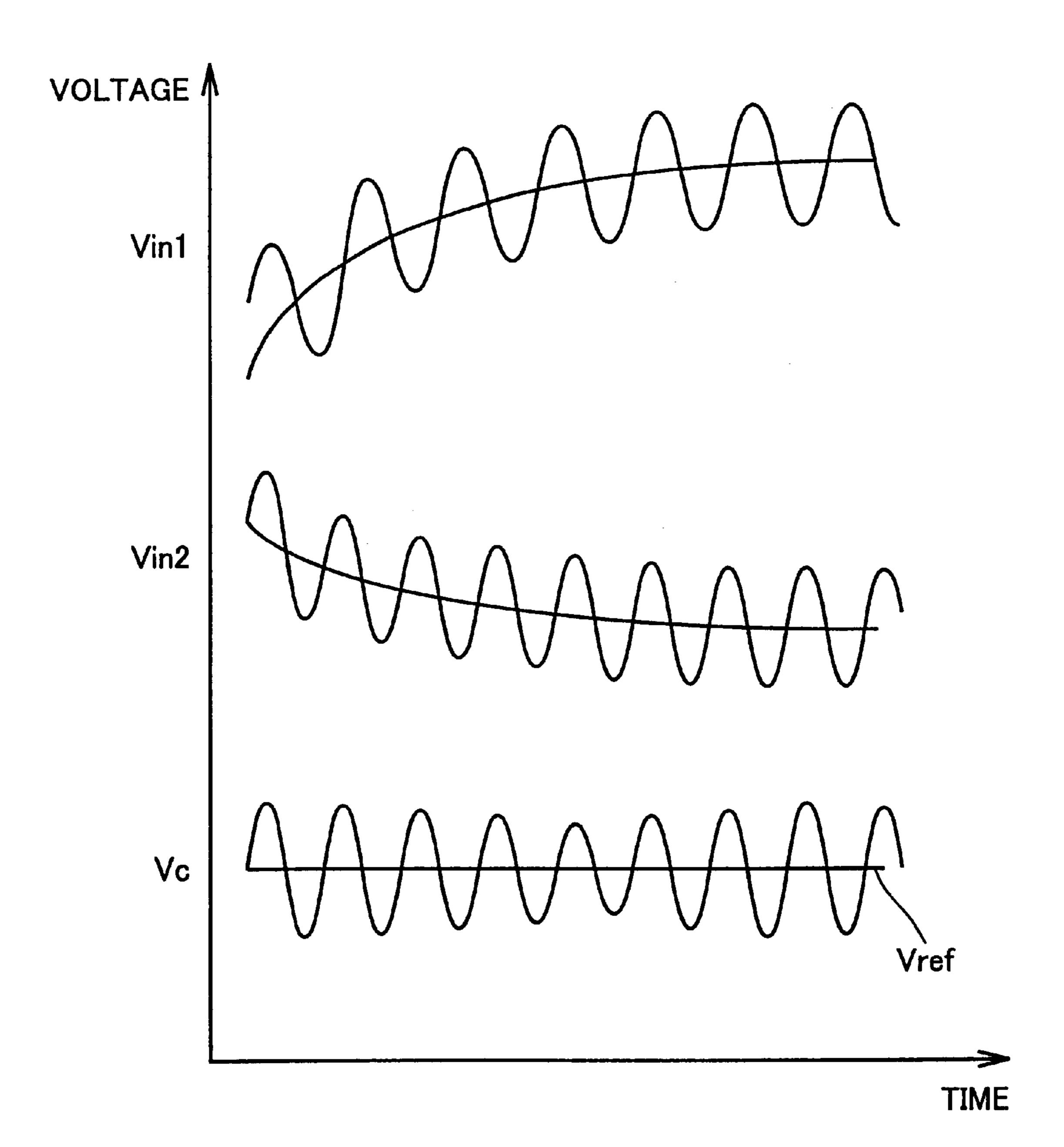

FIG. 4 is a timing chart of signals for illustrating a function of the DC component adjusting circuit shown in FIG. 2;

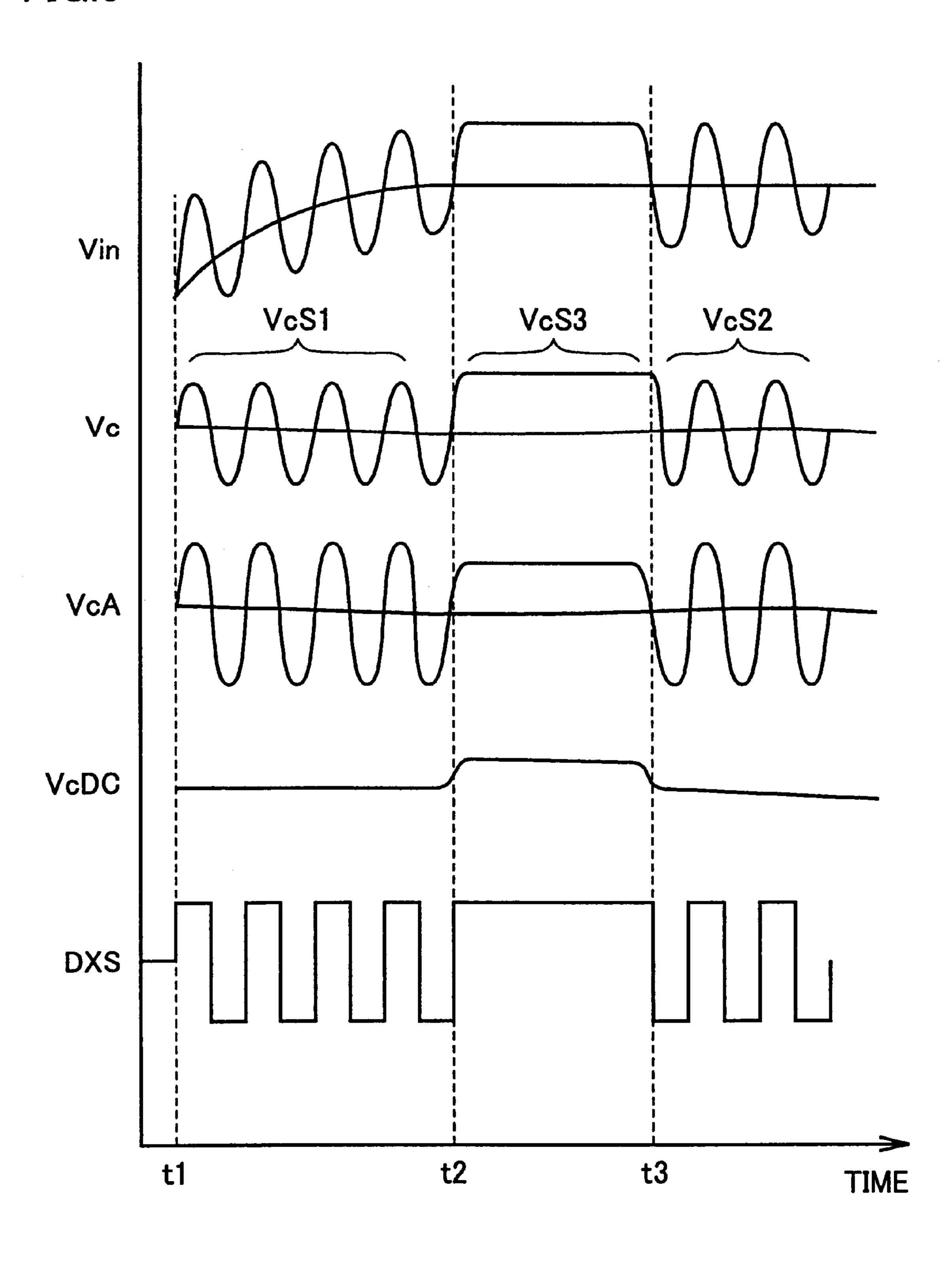

FIG. 5 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 1;

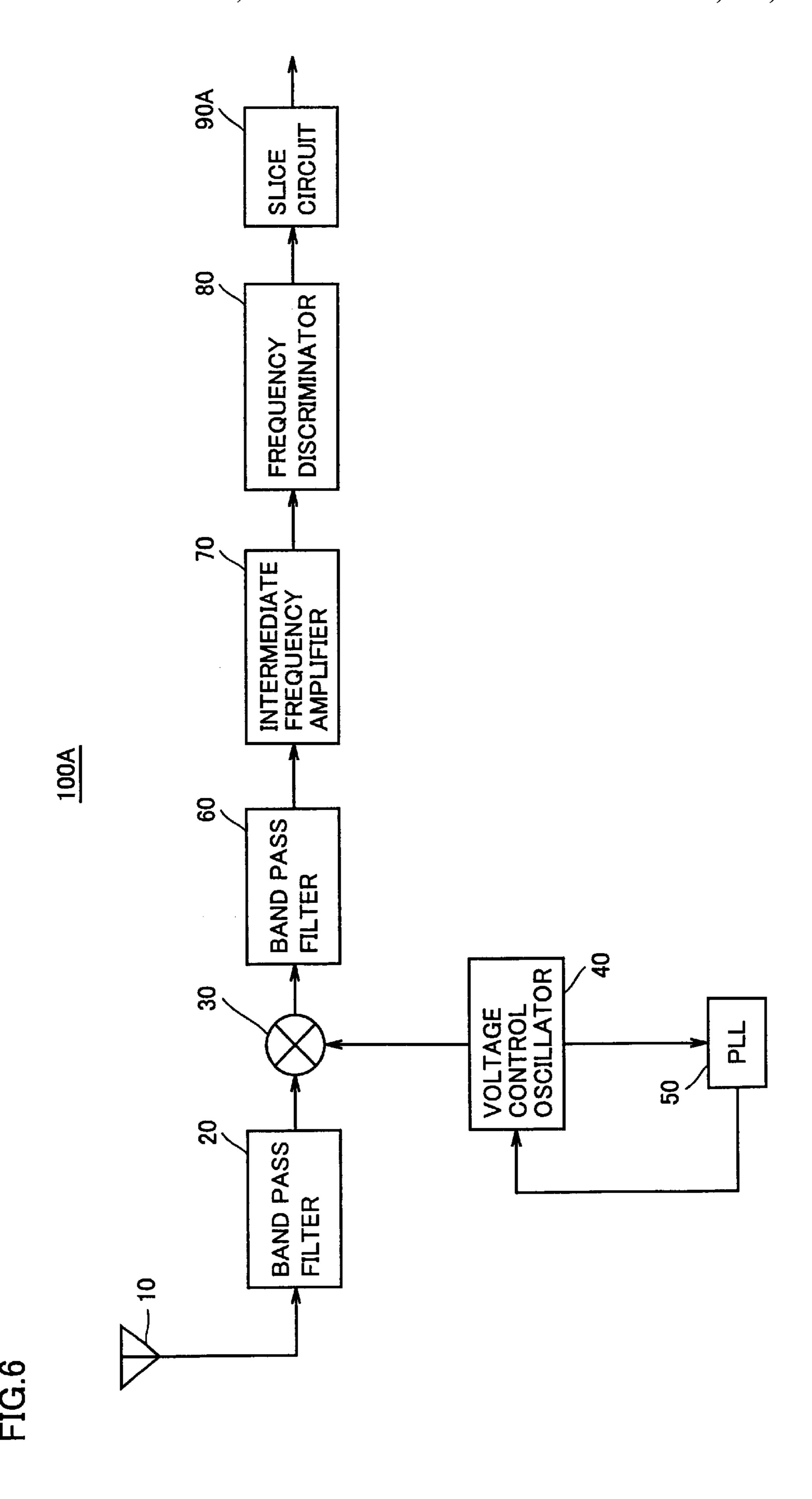

FIG. 6 is a schematic block diagram of a receiver of a second embodiment;

FIG. 7 is a block diagram of the slice circuit shown in FIG. 6;

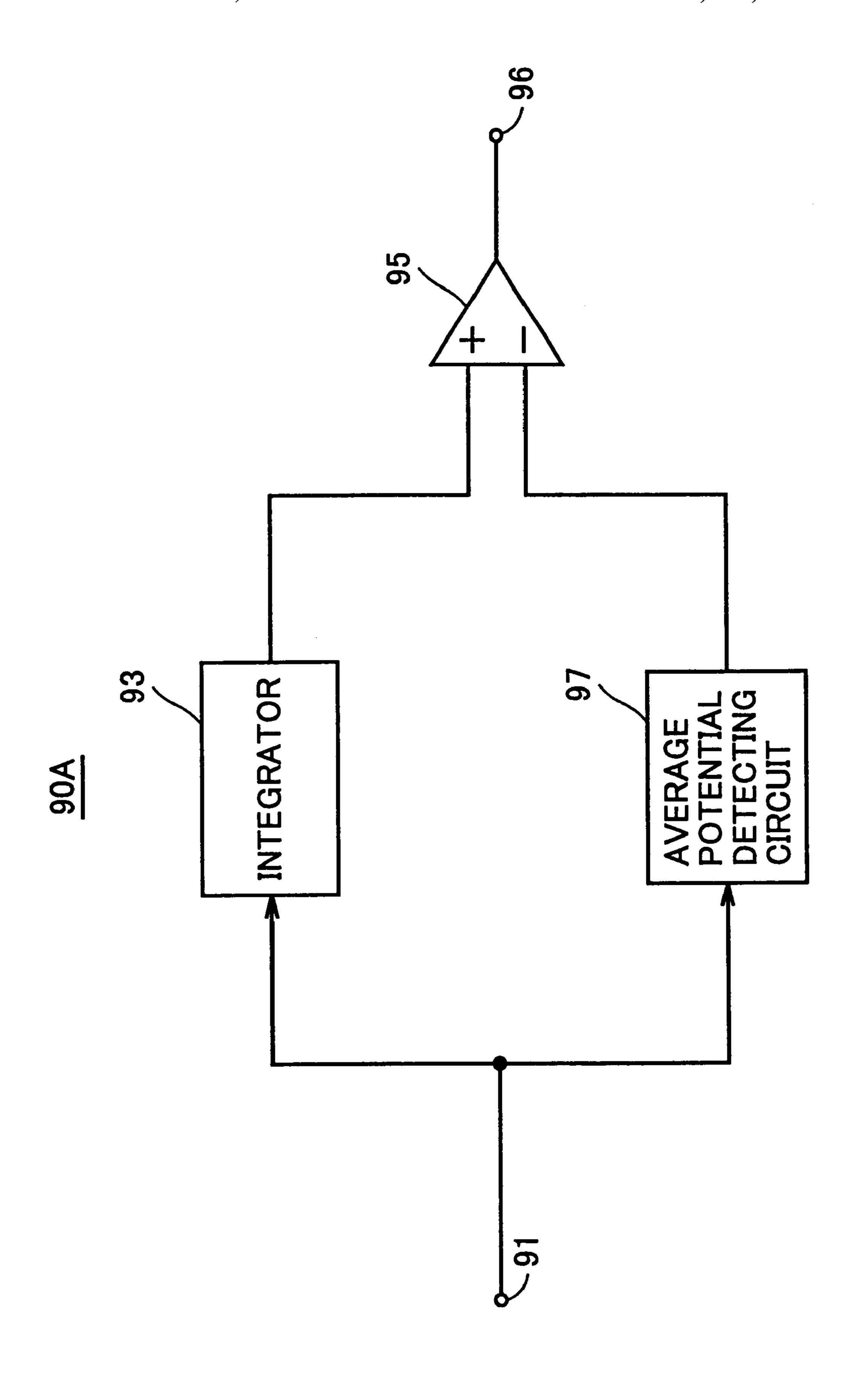

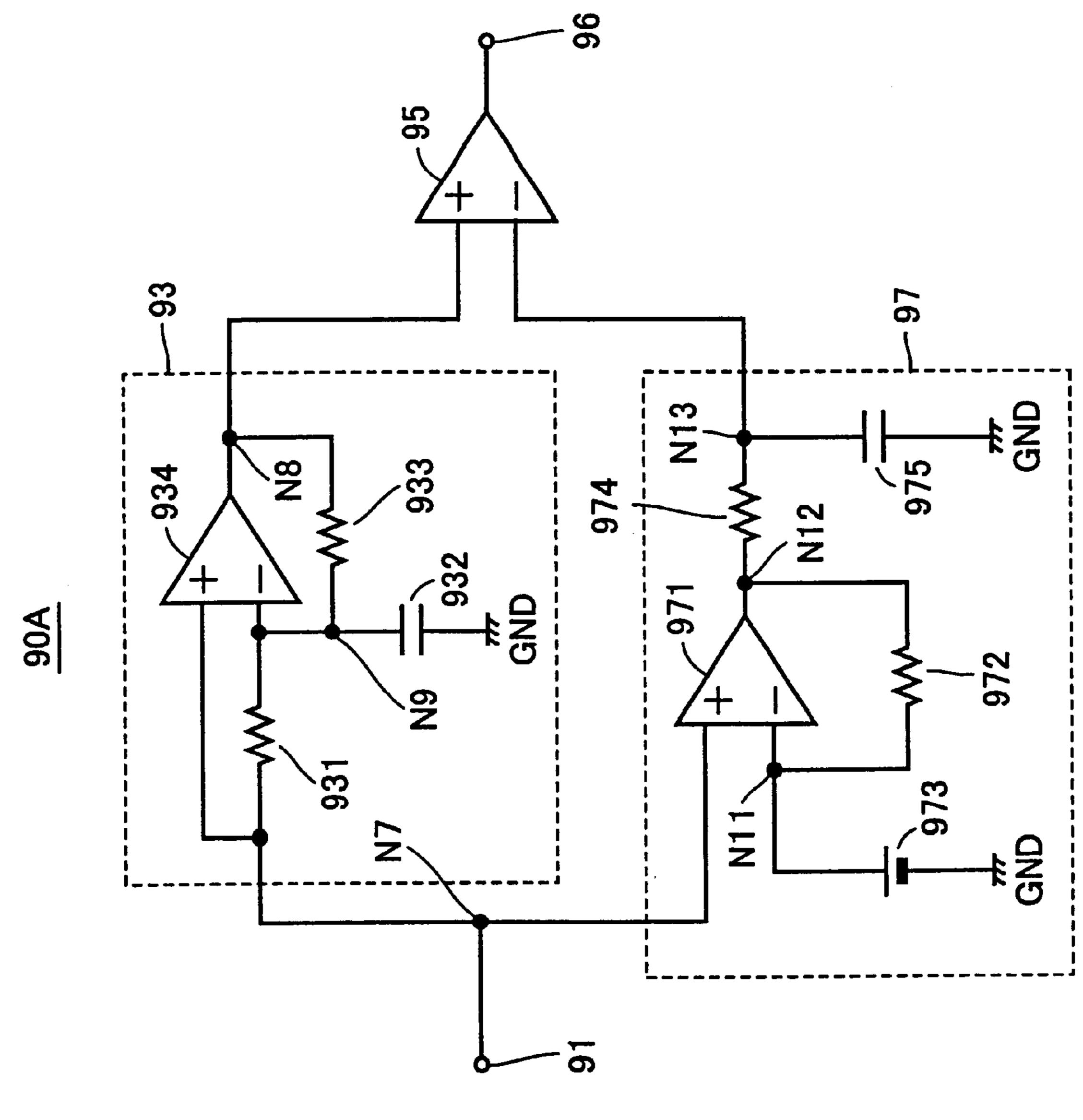

- FIG. 8 is a circuit diagram of an integrator, a comparator and an average potential detecting circuit shown in FIG. 7;

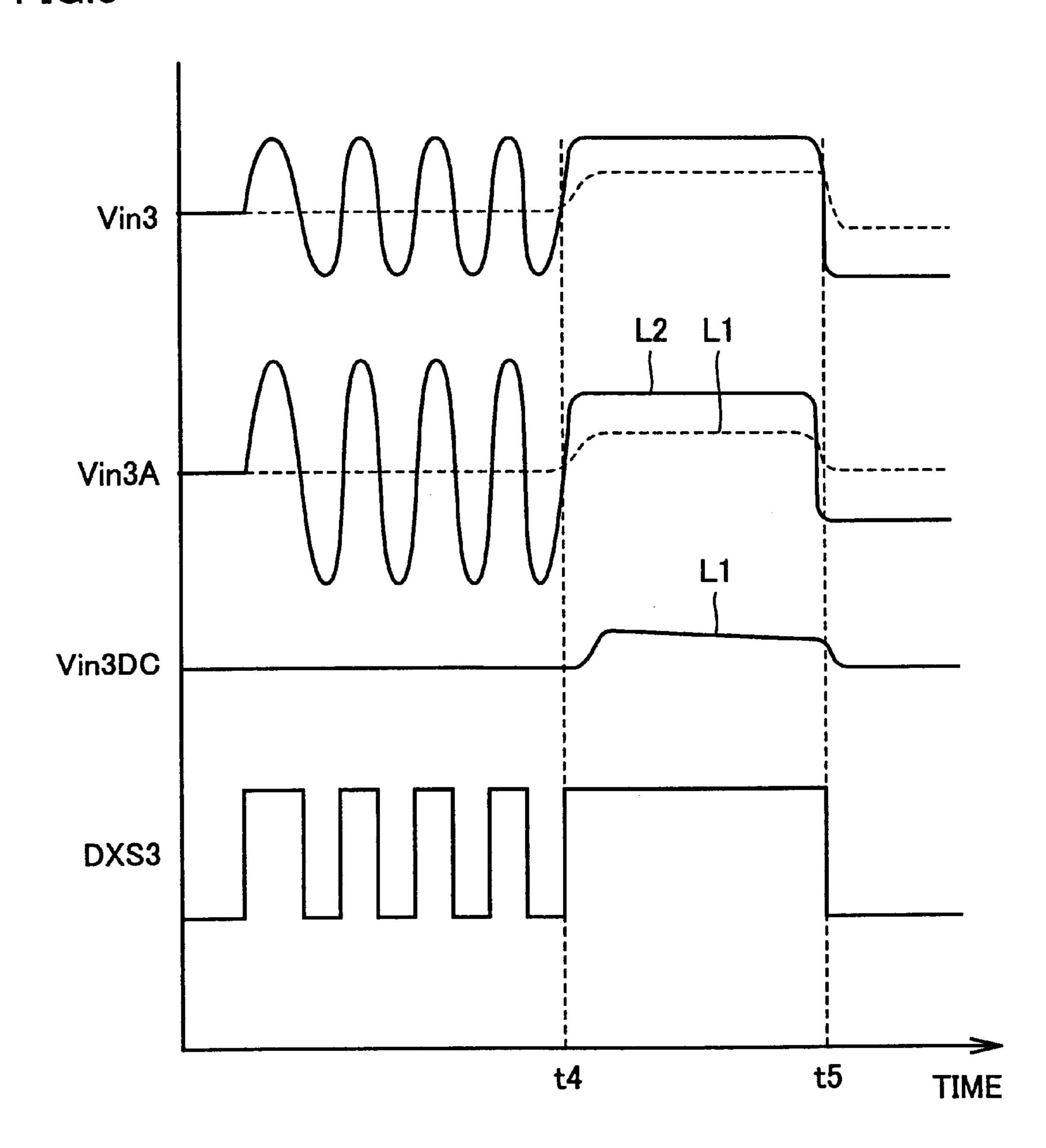

- FIG. 9 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 6;

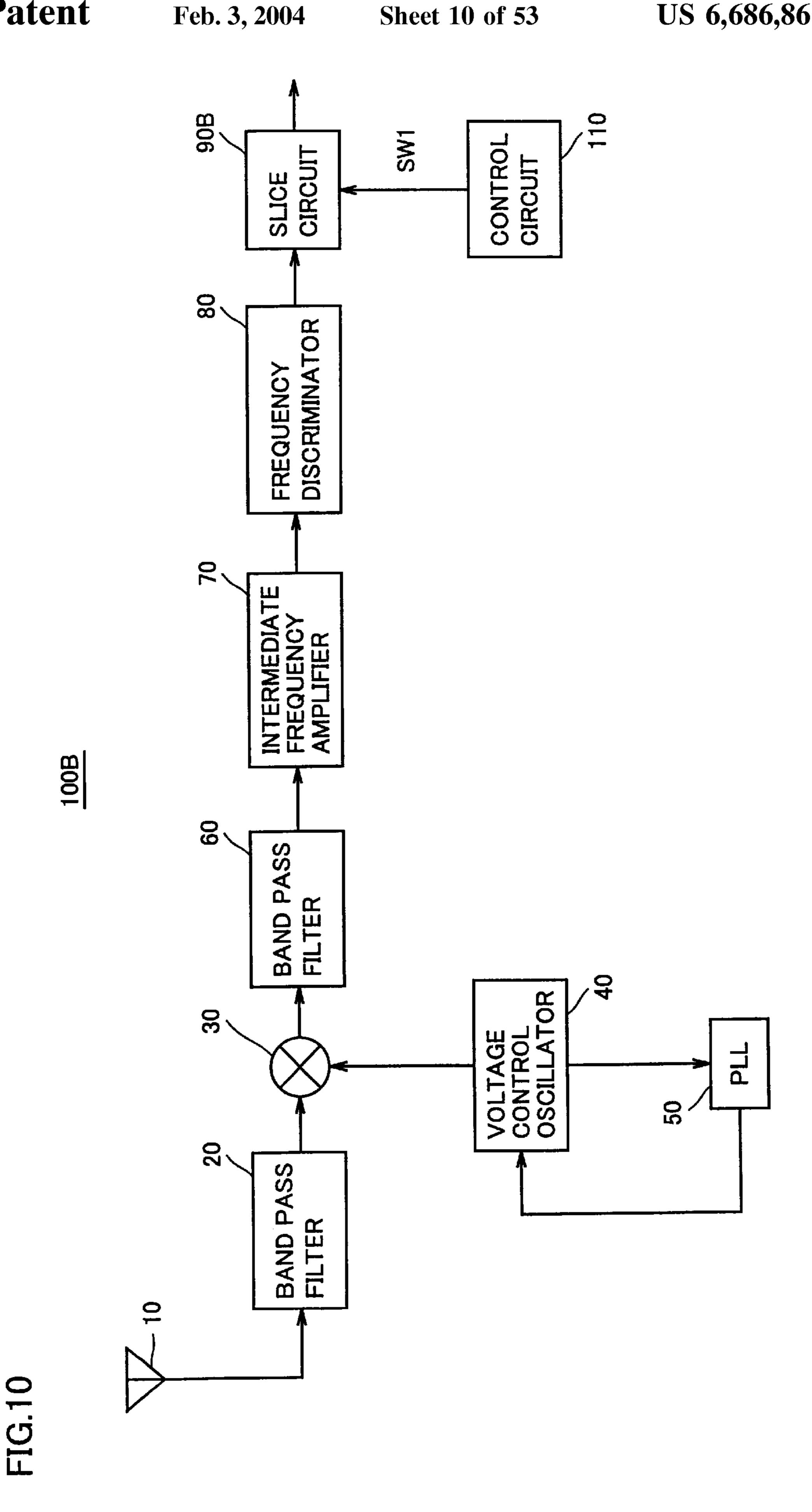

- FIG. 10 is a schematic block diagram of a receiver according to third and fourth embodiments of the invention;

- FIG. 11 is a block diagram of a slice circuit shown in FIG. **10**;

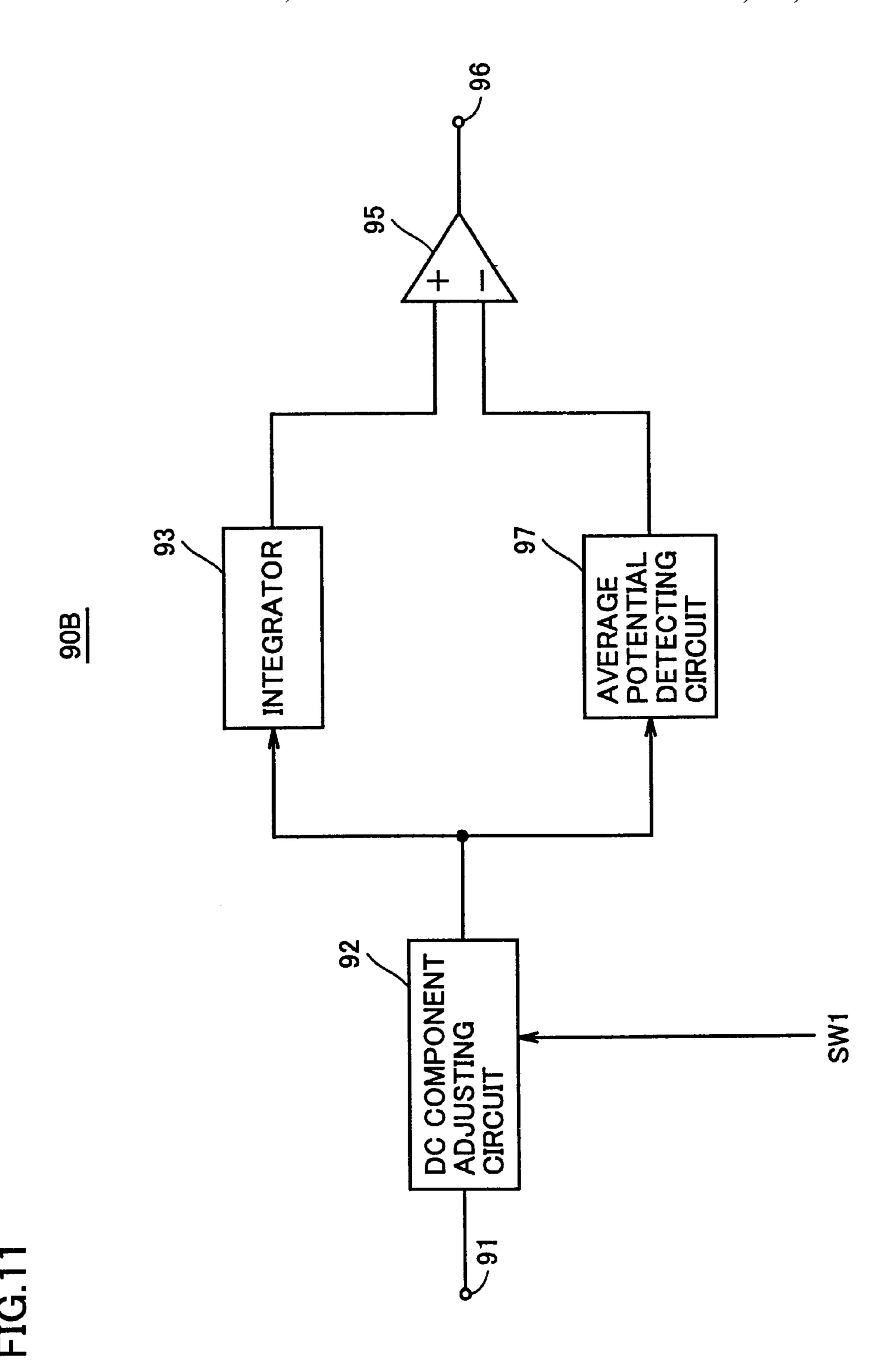

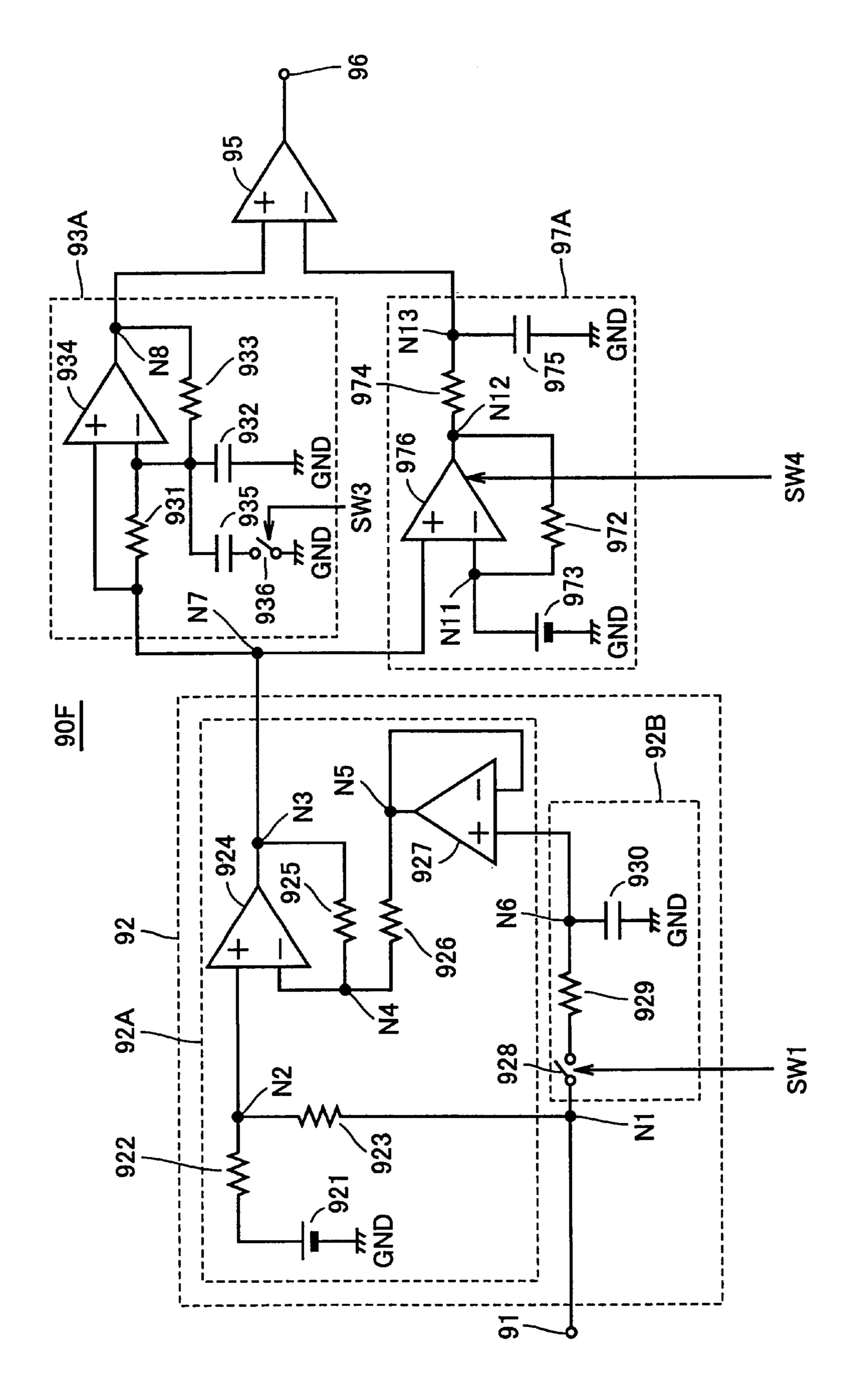

- FIG. 12 is a circuit diagram of a DC component adjusting 10 circuit, an integrator, a comparator and an average potential detecting circuit shown in FIG. 11;

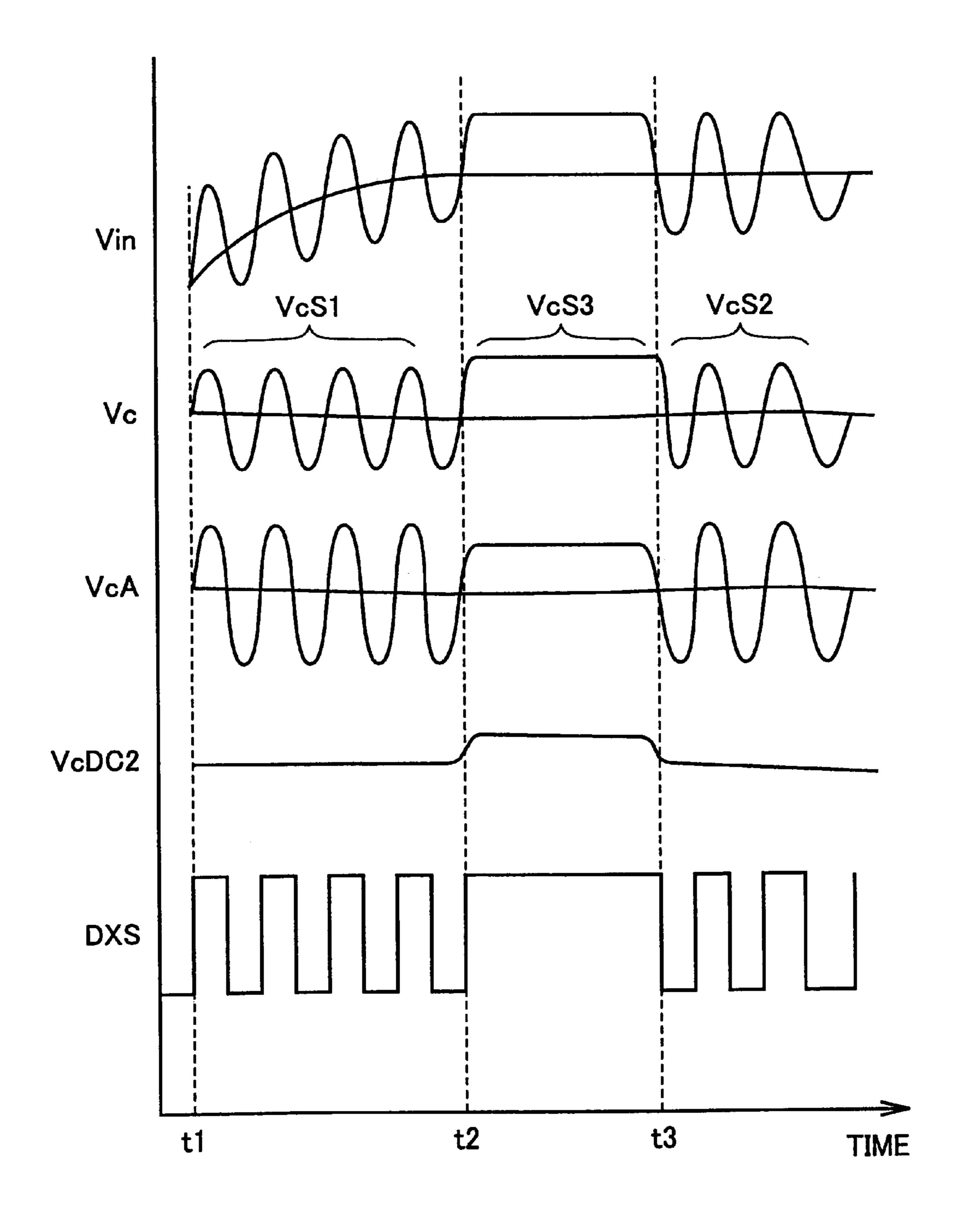

- FIG. 13 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 10;

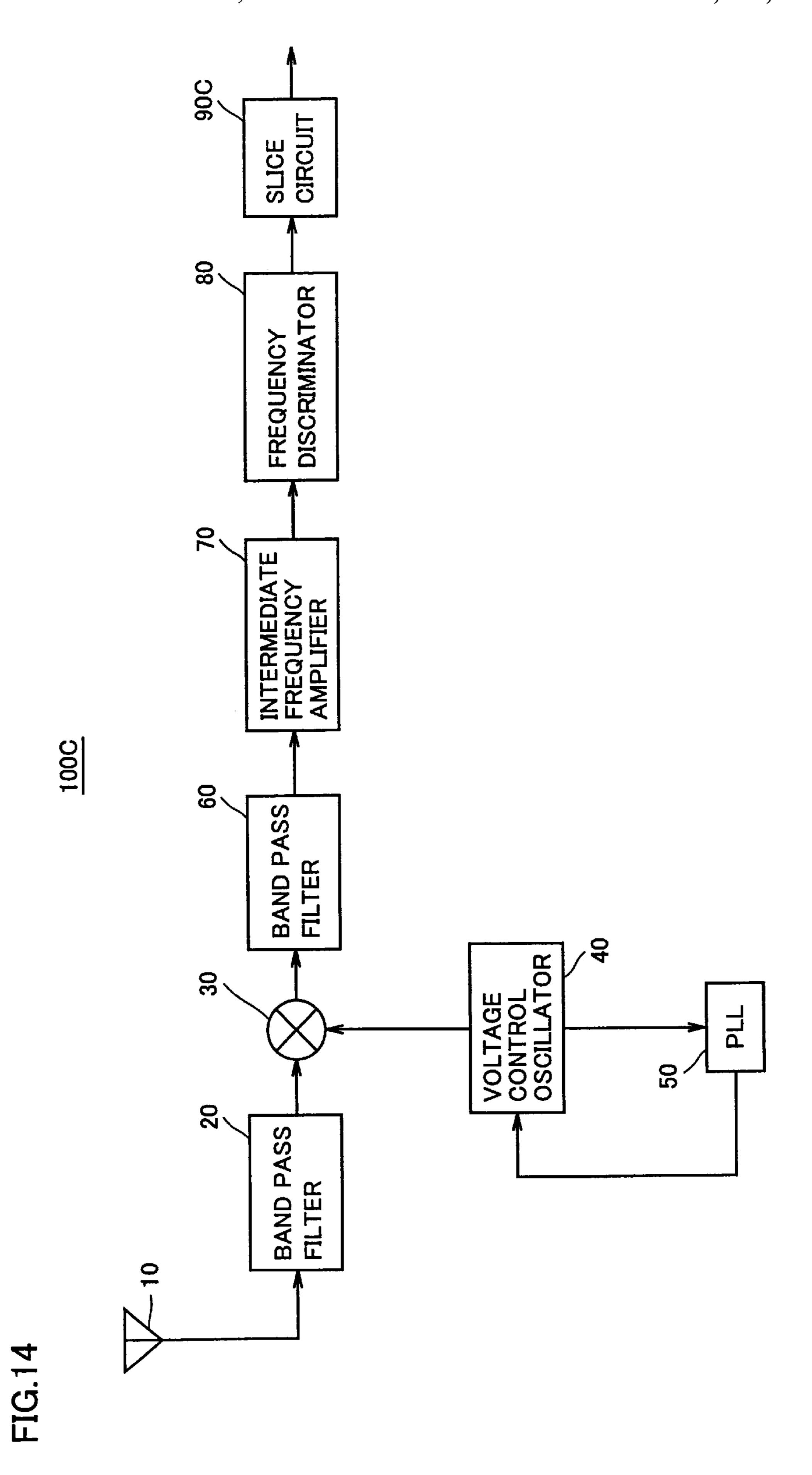

- FIG. 14 is a schematic block diagram of a receiver <sup>15</sup> according to a fifth embodiment;

- FIG. 15 is a block diagram of a slice circuit shown in FIG. 14;

- FIG. 16 is a circuit diagram of a DC component adjusting 20 circuit, an integrator, a comparator, an average potential detecting circuit and a voltage difference detecting circuit shown in FIG. 15;

- FIG. 17 is a timing chart of signals for illustrating an operation of the voltage difference detecting circuit shown in 25 FIGS. 15 and 16;

- FIG. 18 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 14;

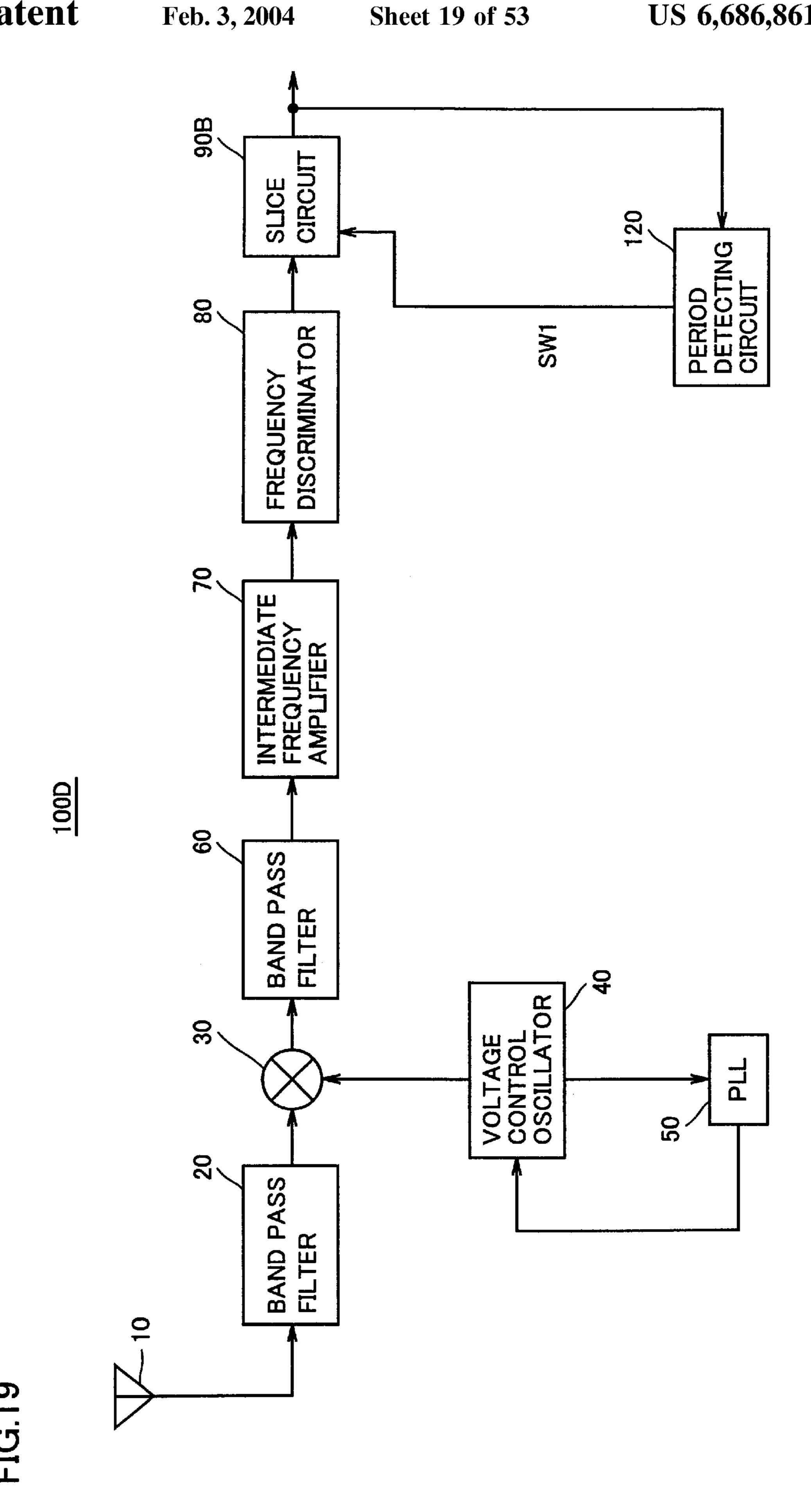

- FIG. 19 is a schematic block diagram of a receiver according to a sixth embodiment;

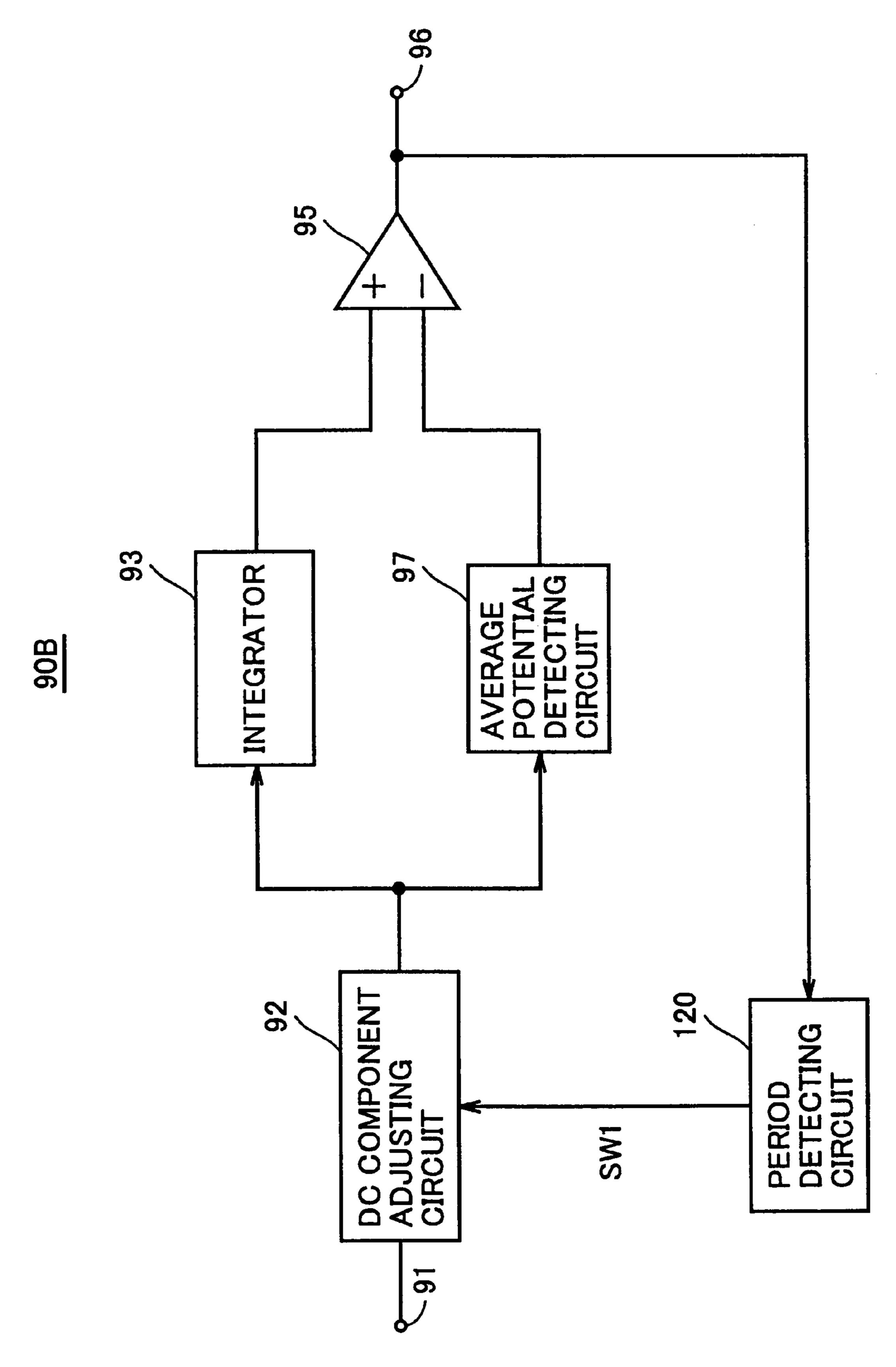

- FIG. 20 is a block diagram of a slice circuit shown in FIG. 19;

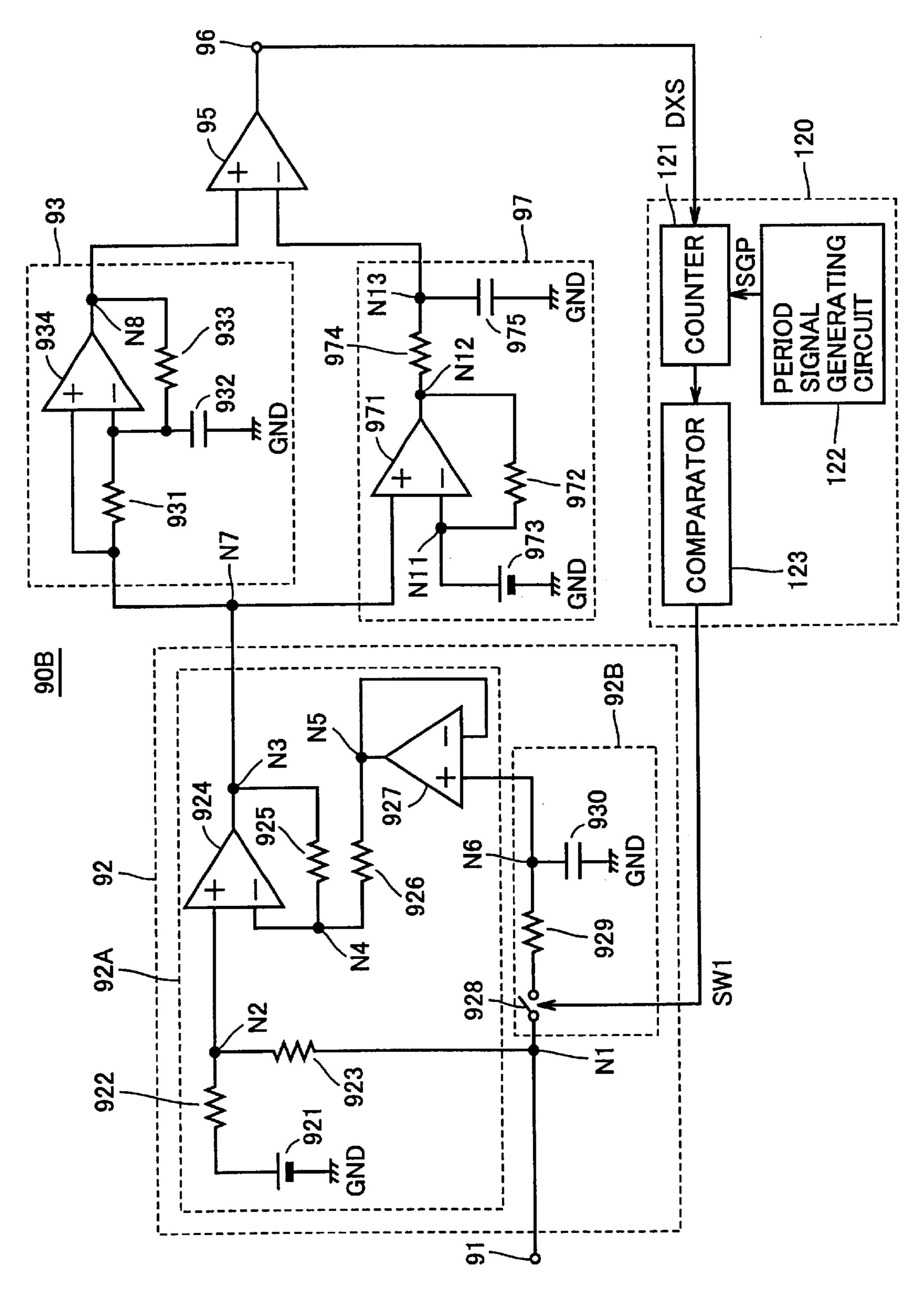

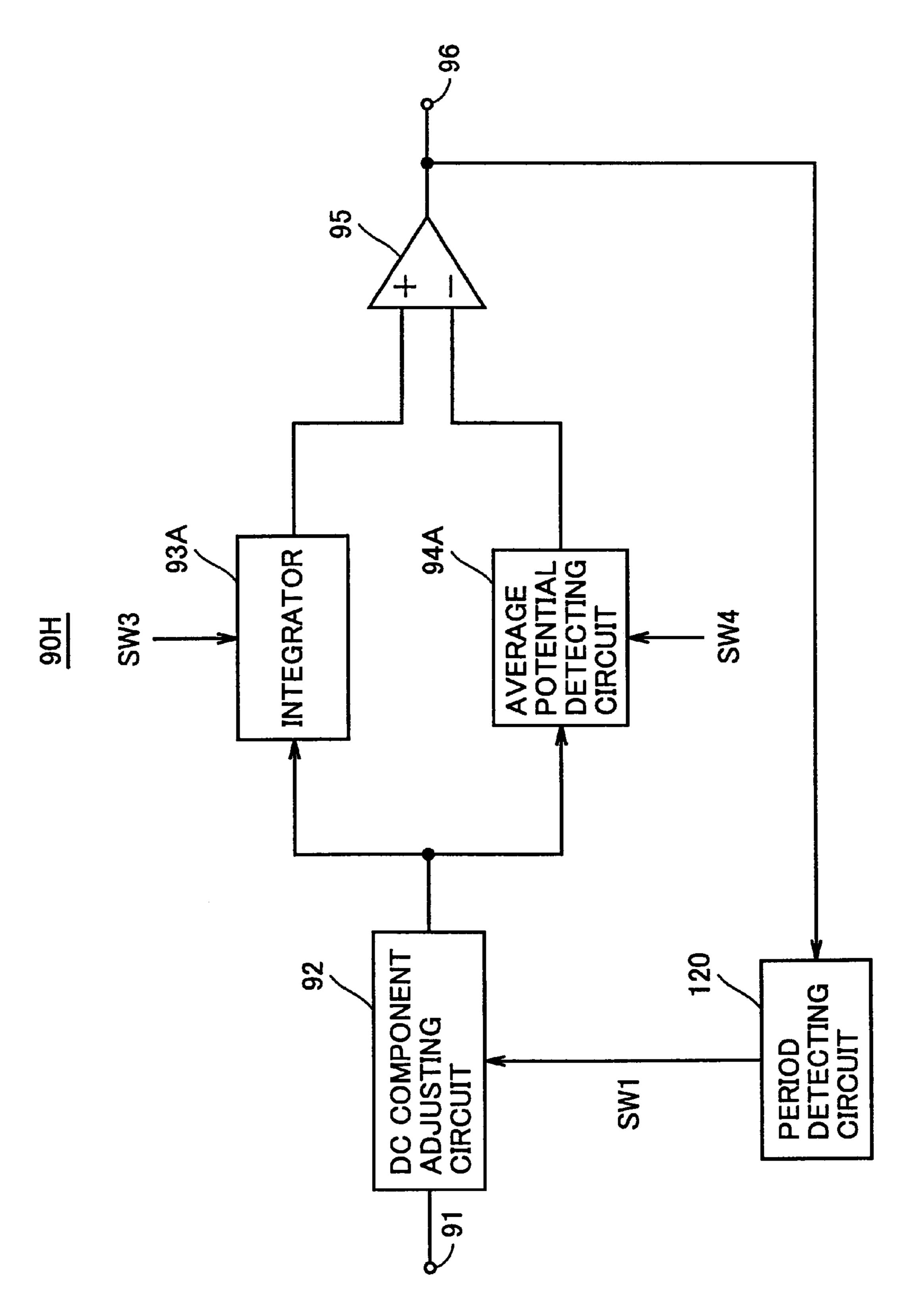

- FIG. 21 is a circuit diagram showing a DC component adjusting circuit, an integrator, a comparator and an average 35 potential detecting circuit shown in FIG. 20, and also shows a period detecting circuit in a block from;

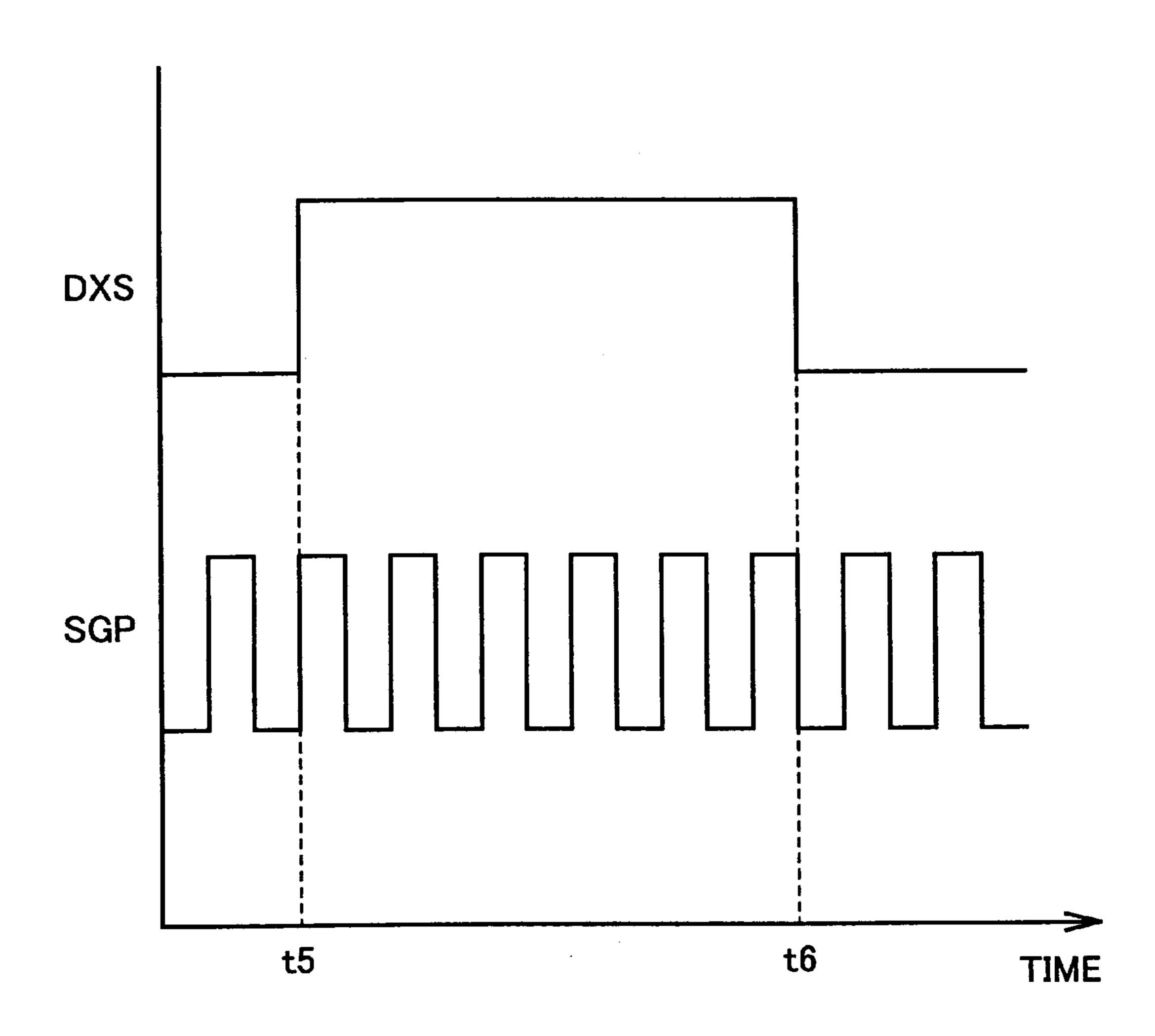

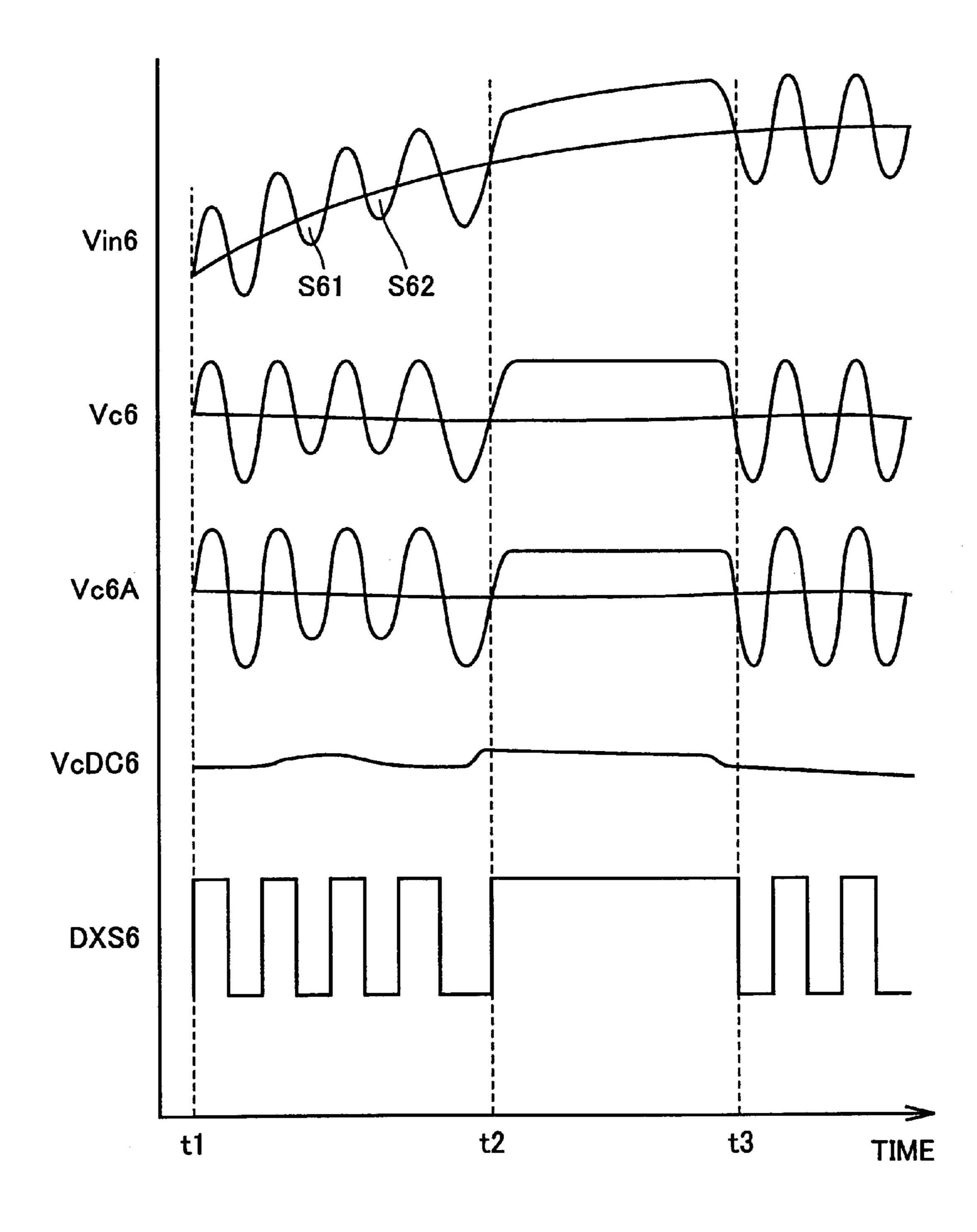

- FIG. 22 is a timing chart of signals for illustrating a function of the period detecting circuit shown in FIGS. 20 and **21**;

- FIG. 23 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 19;

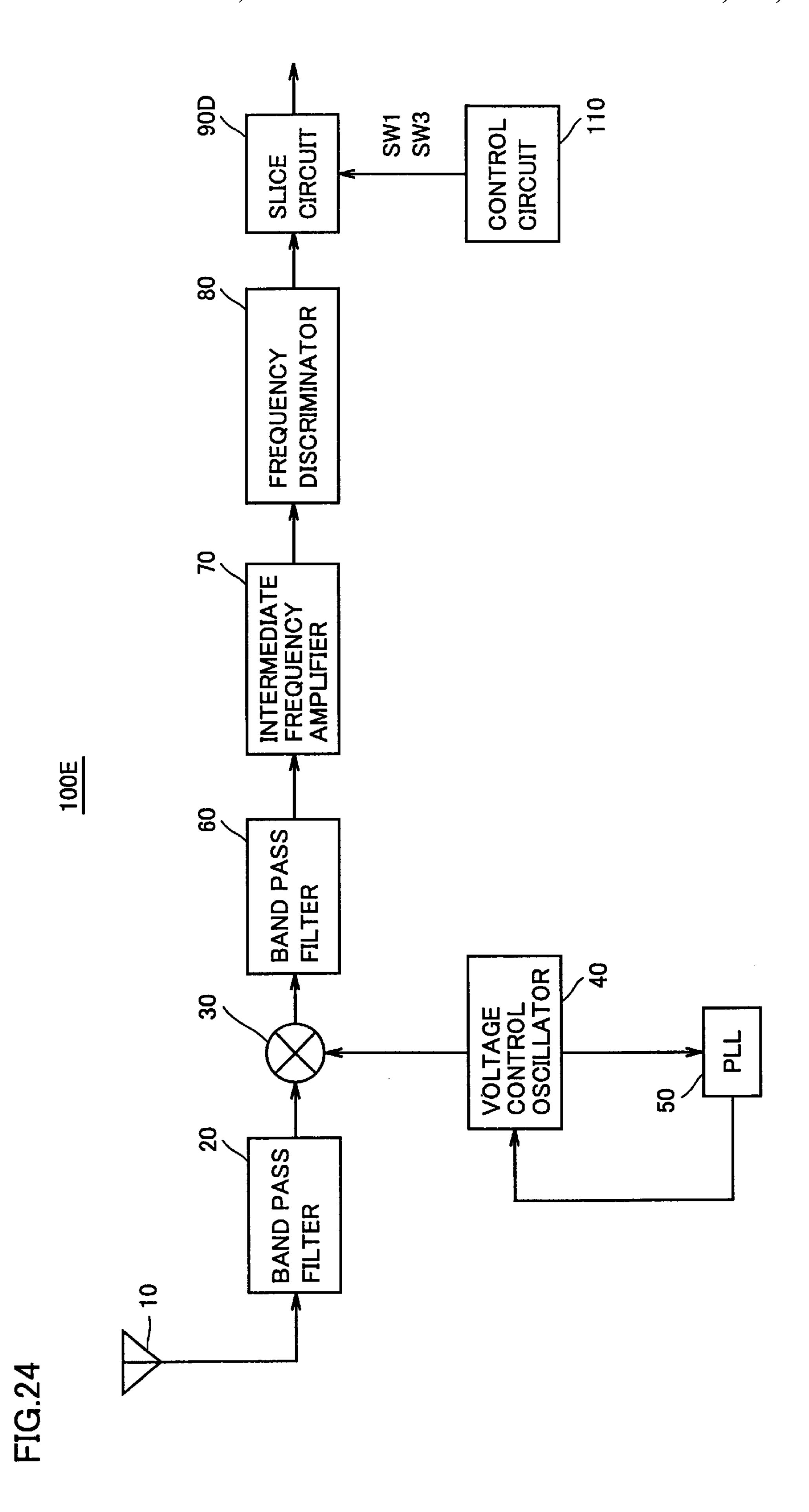

- FIG. 24 is a schematic block diagram of a receiver according to a seventh embodiment;

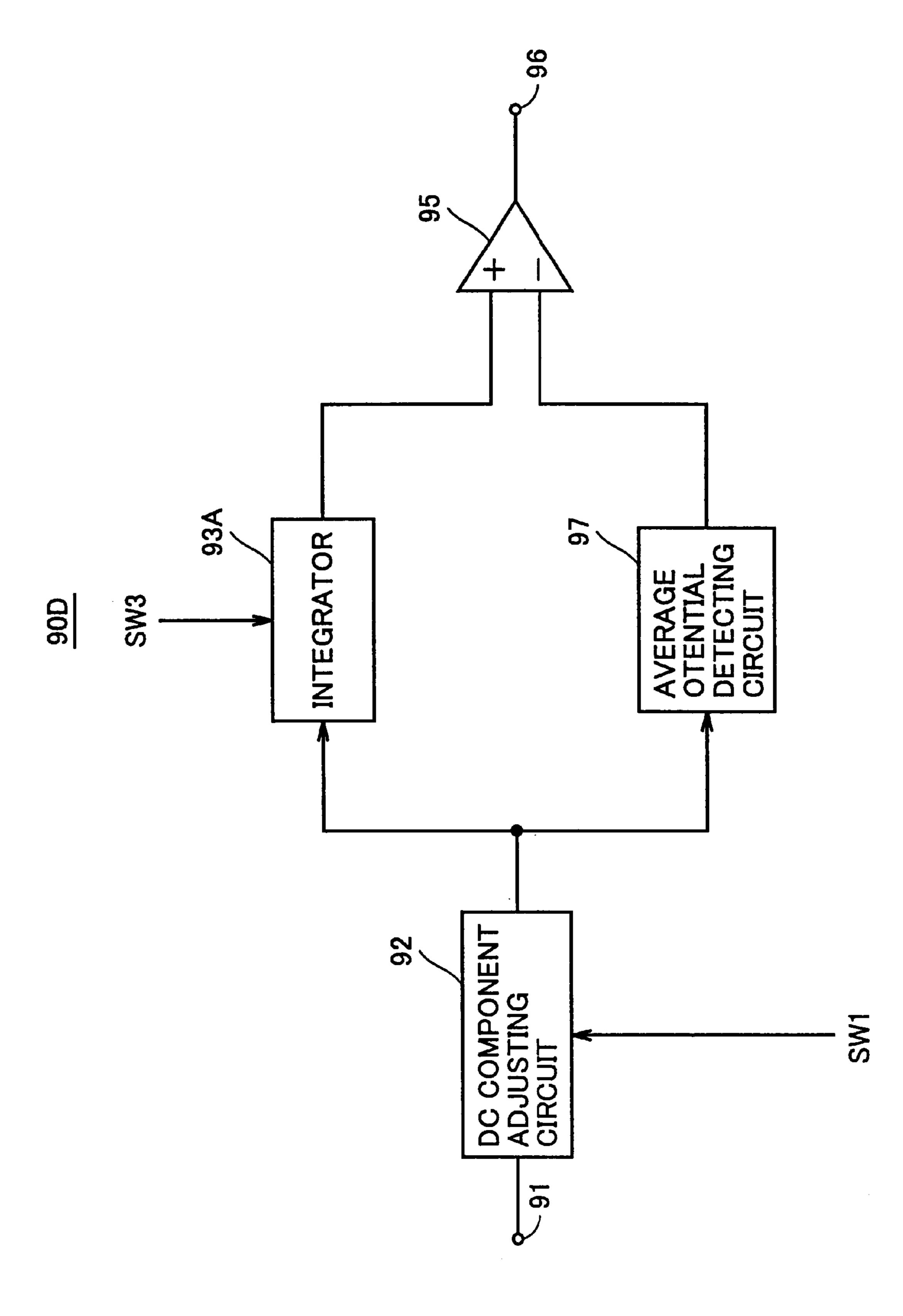

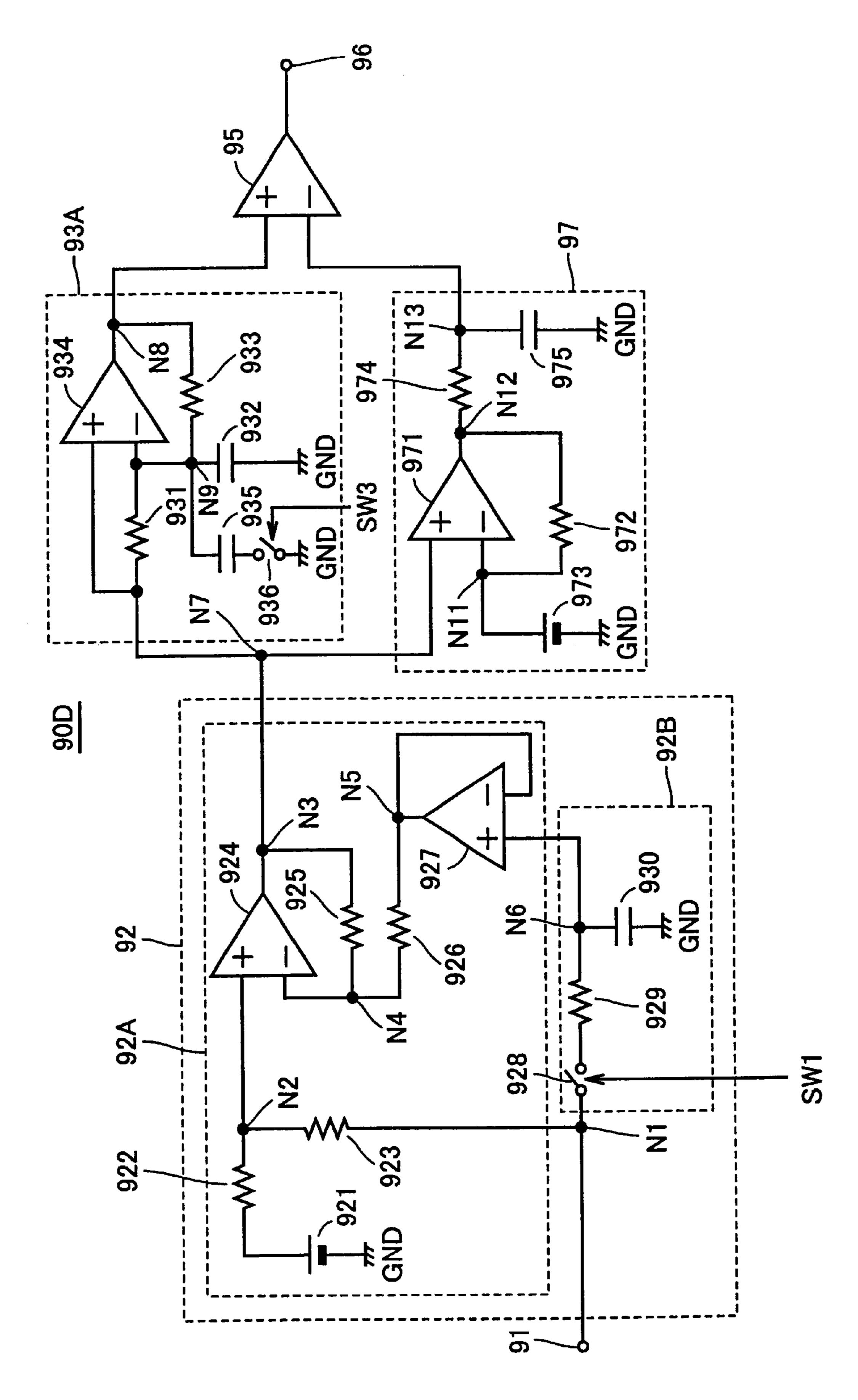

- FIG. 25 is a block diagram of a slice circuit shown in FIG. 24;

- FIG. 26 is a circuit diagram showing a DC component adjusting circuit, an integrator, a comparator and an average potential detecting circuit shown in FIG. 25;

- FIG. 27 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 24;

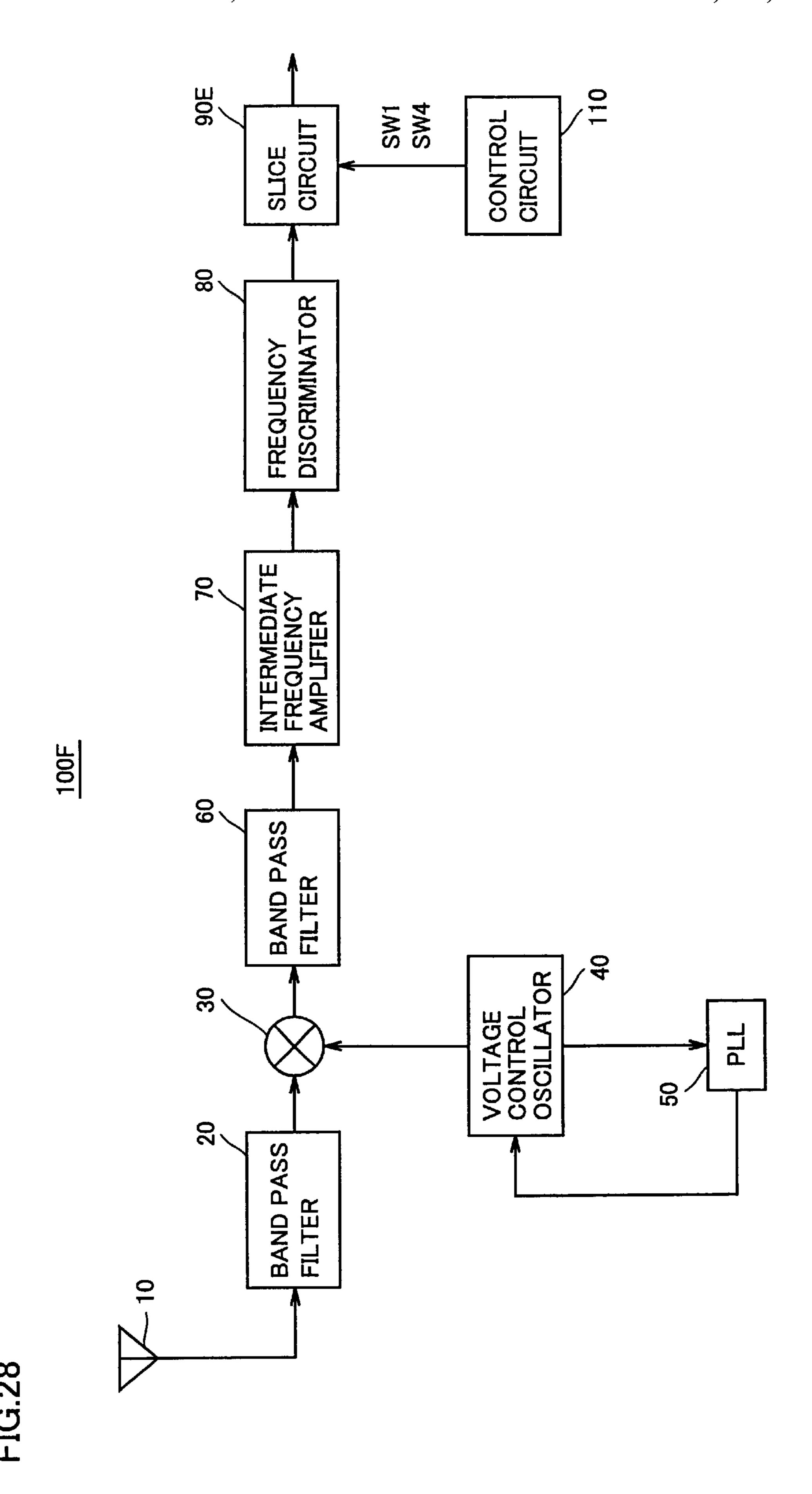

- FIG. 28 is a schematic block diagram of a receiver according to an eighth embodiment;

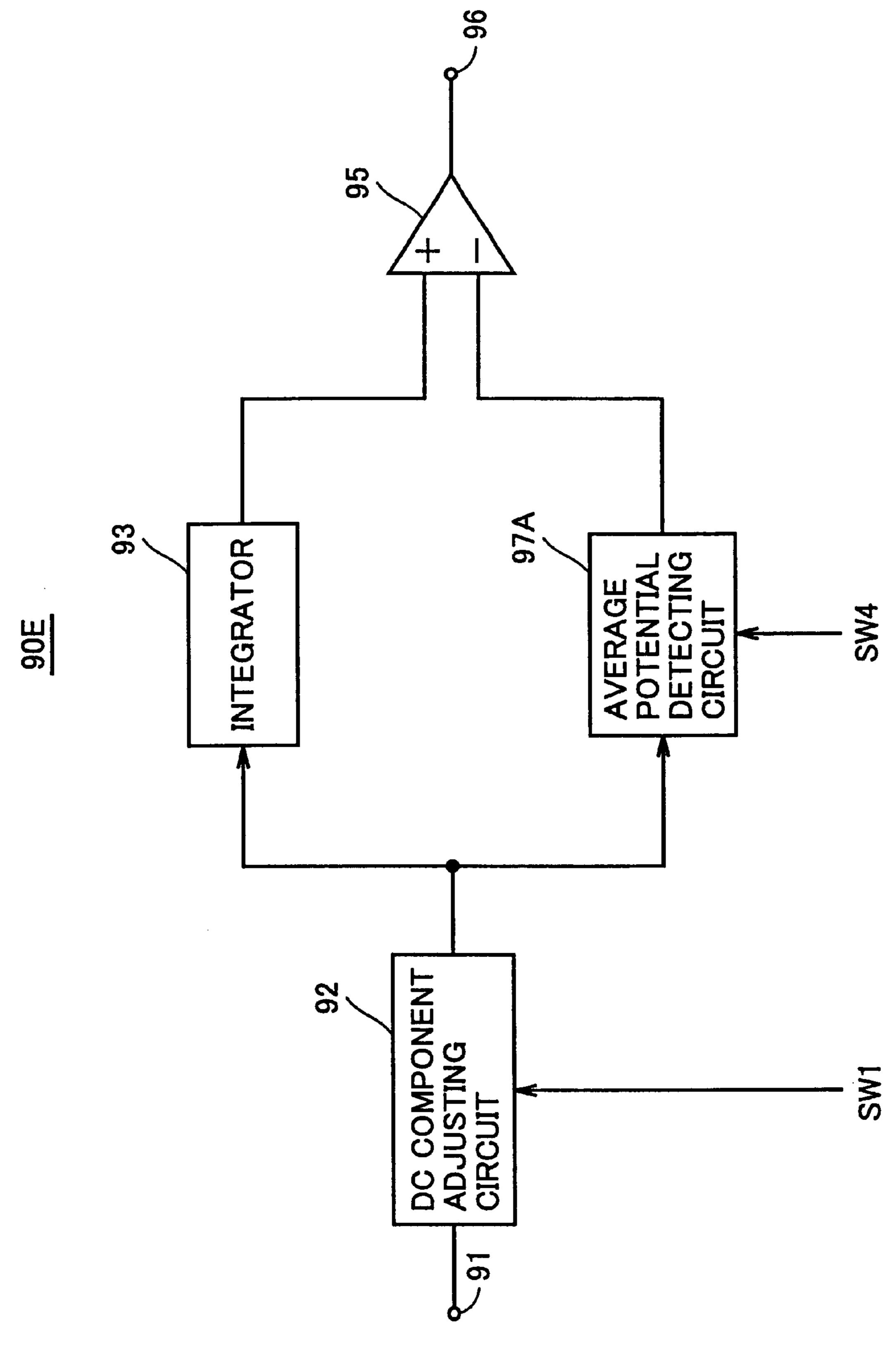

- FIG. 29 is a block diagram of a slice circuit shown in FIG. 55 28;

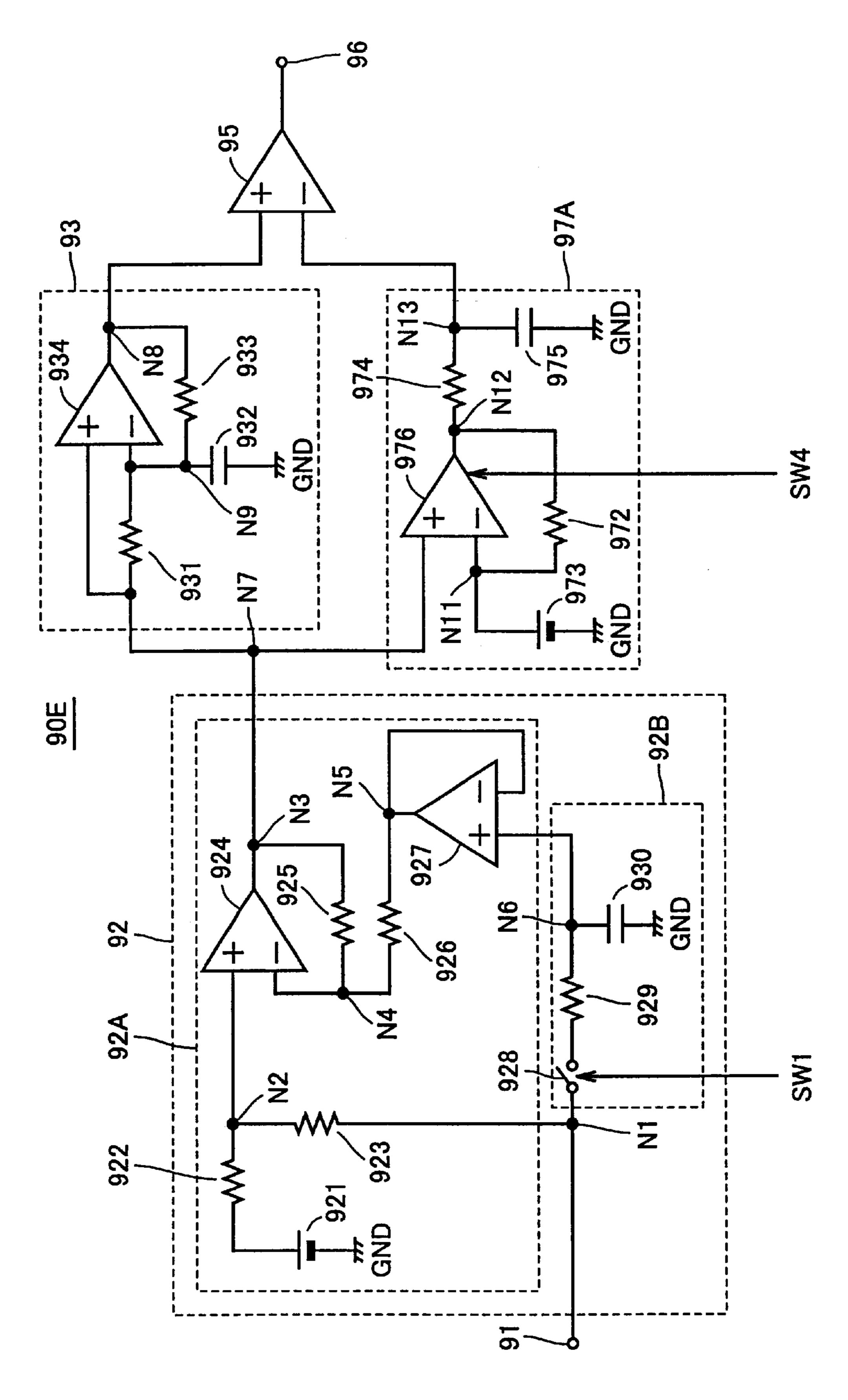

- FIG. 30 is a circuit diagram showing a DC component adjusting circuit, an integrator, a comparator and an average potential detecting circuit shown in FIG. 29;

- FIG. 31 is a circuit diagram of an operational amplifier included in an average potential detecting circuit shown in FIG. **30**;

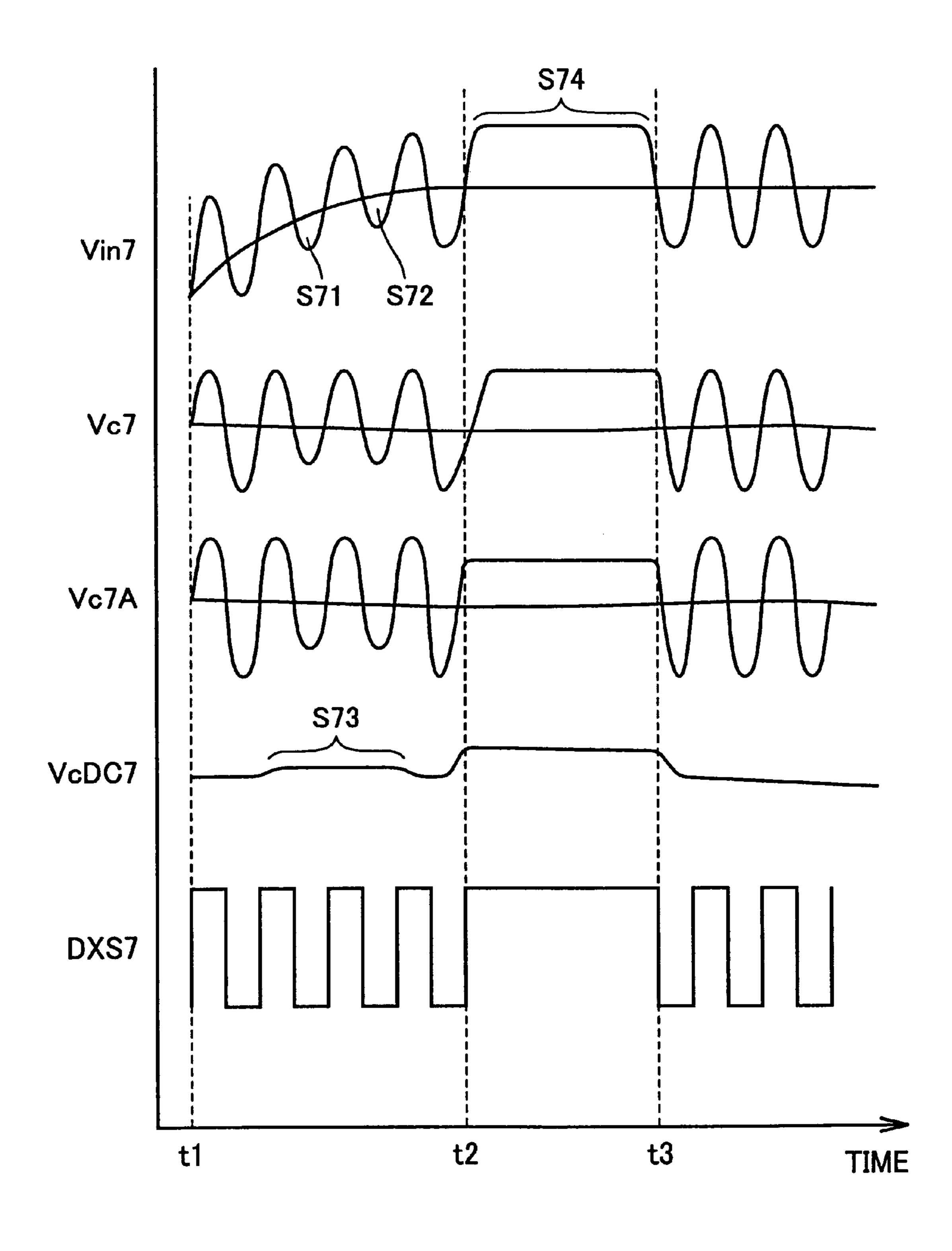

- FIG. 32 is a timing chart of signals for illustrating an operation of the slice circuit shown in FIG. 28;

- FIG. 33 is a schematic block diagram of a receiver according to a ninth embodiment;

- FIG. 34 is a block diagram of a slice circuit shown in FIG. 33;

- FIG. 35 is a circuit diagram showing a DC component adjusting circuit, an integrator, a comparator and an average potential detecting circuit shown in FIG. 34;

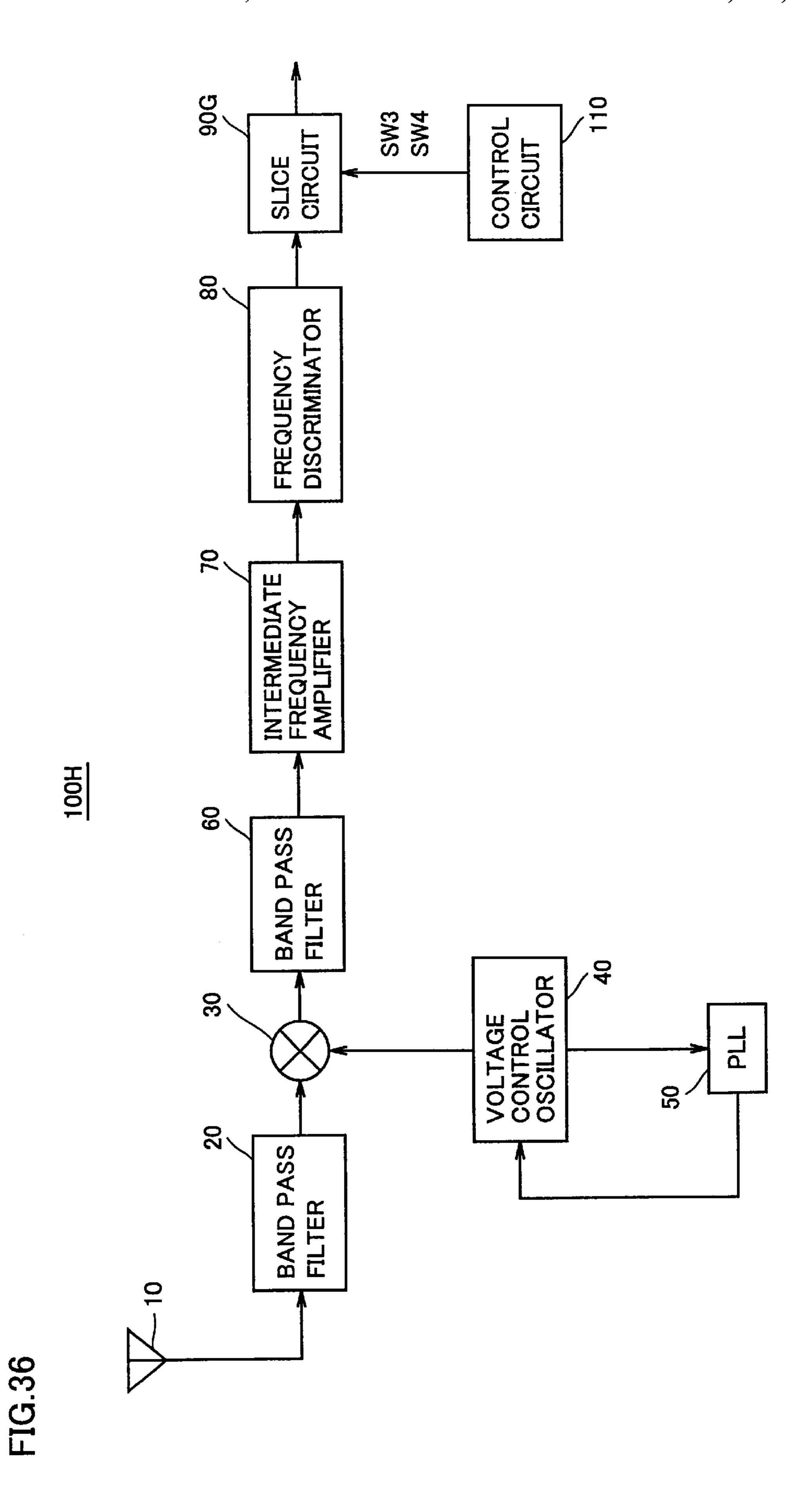

- FIG. 36 is a schematic block diagram of a receiver according to a tenth embodiment;

- FIG. 37 is a block diagram of a slice circuit shown in FIG. 36;

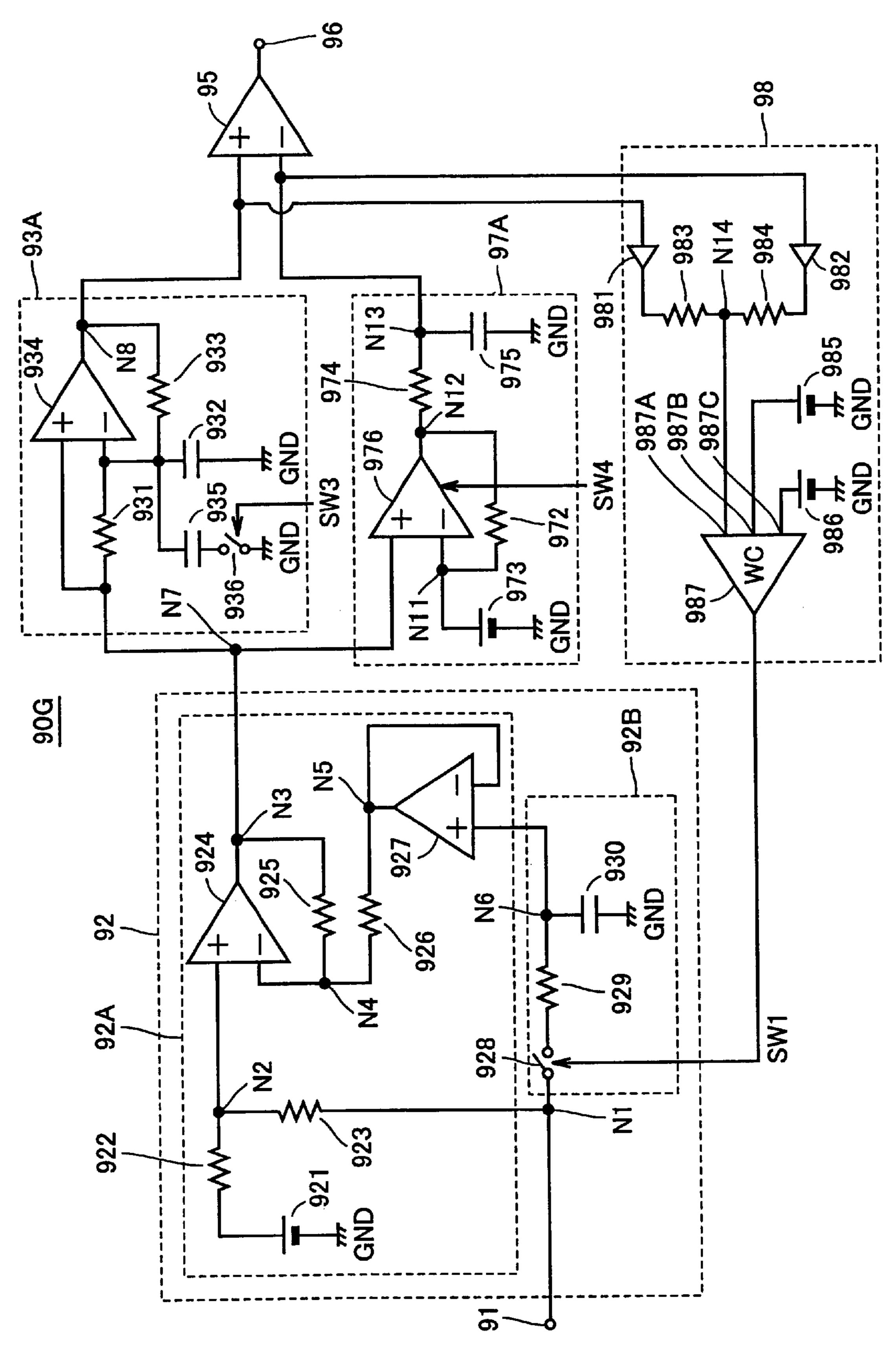

- FIG. 38 is a circuit diagram showing a DC component adjusting circuit, an integrator, a comparator, an average potential detecting circuit and a voltage difference detecting circuit shown in FIG. 37;

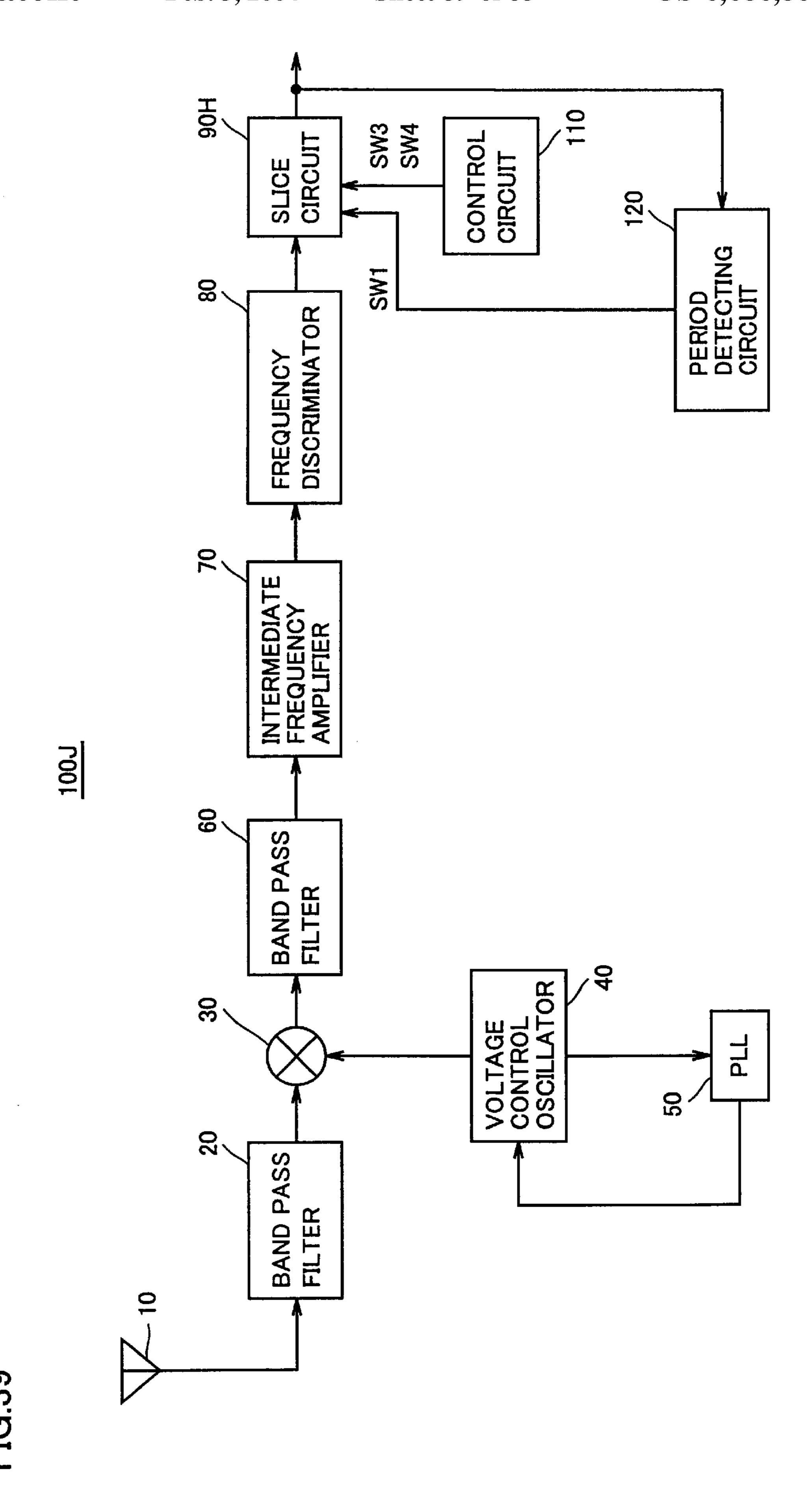

- FIG. 39 is a schematic block diagram of a receiver according to an eleventh embodiment;

- FIG. 40 is a block diagram of a slice circuit shown in FIG. 39;

- FIG. 41 is a circuit diagram showing a DC component adjusting circuit, an integrator, a comparator, an average potential detecting circuit and a period detecting circuit shown in FIG. 40;

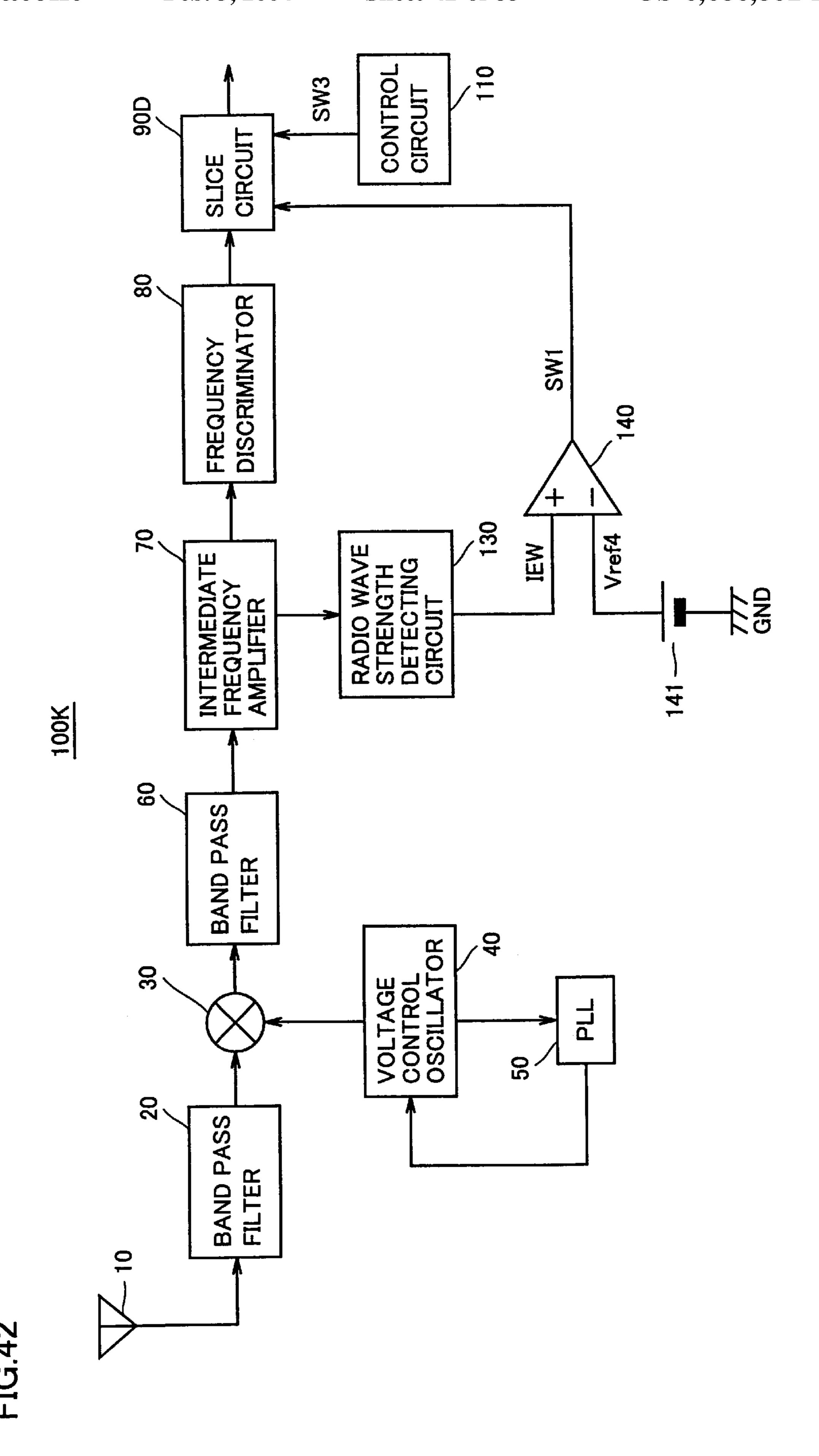

- FIG. 42 is a schematic block diagram of a receiver according to a twelfth embodiment;

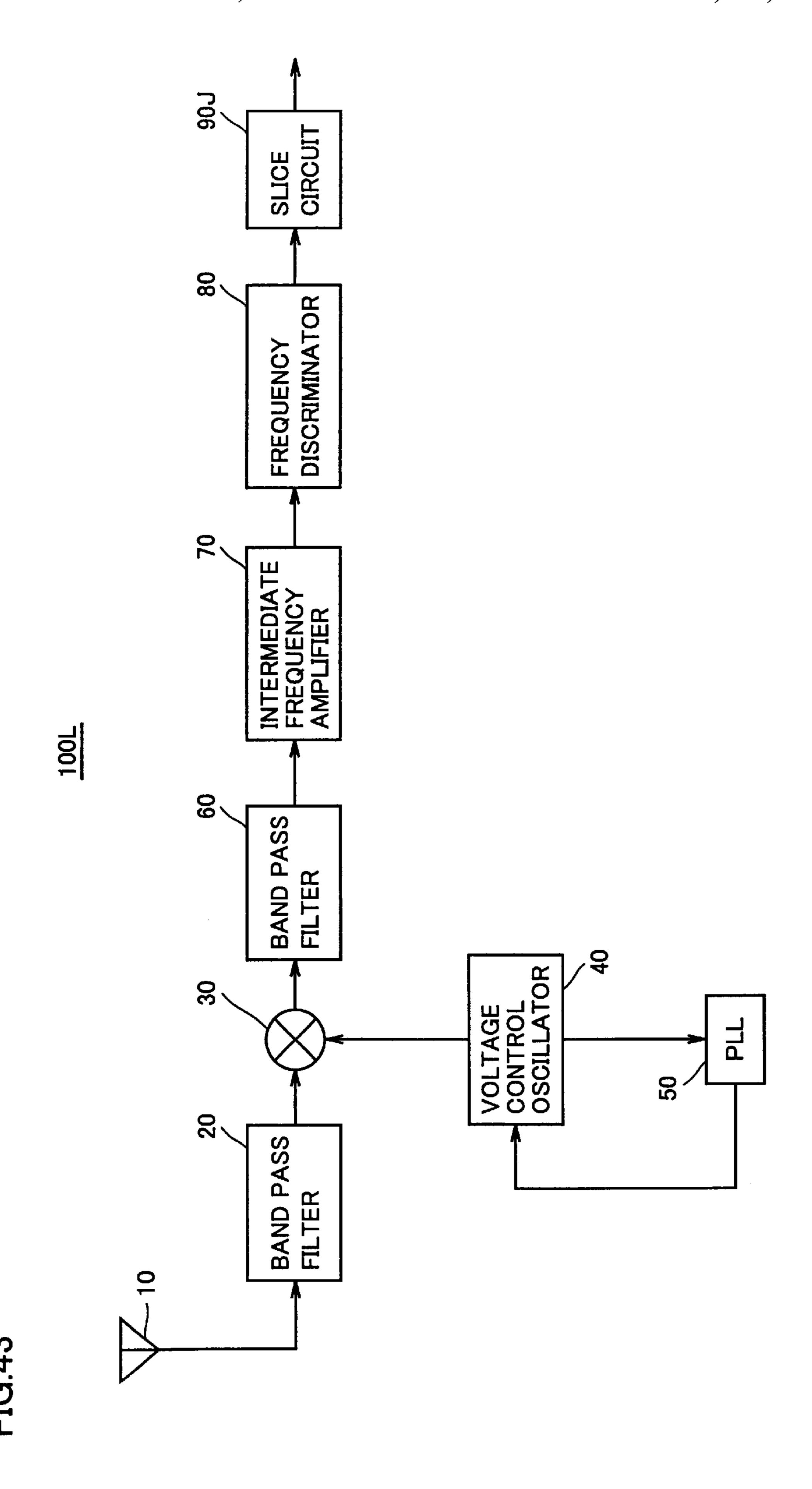

- FIG. 43 is a schematic block diagram of a receiver according to a thirteenth embodiment;

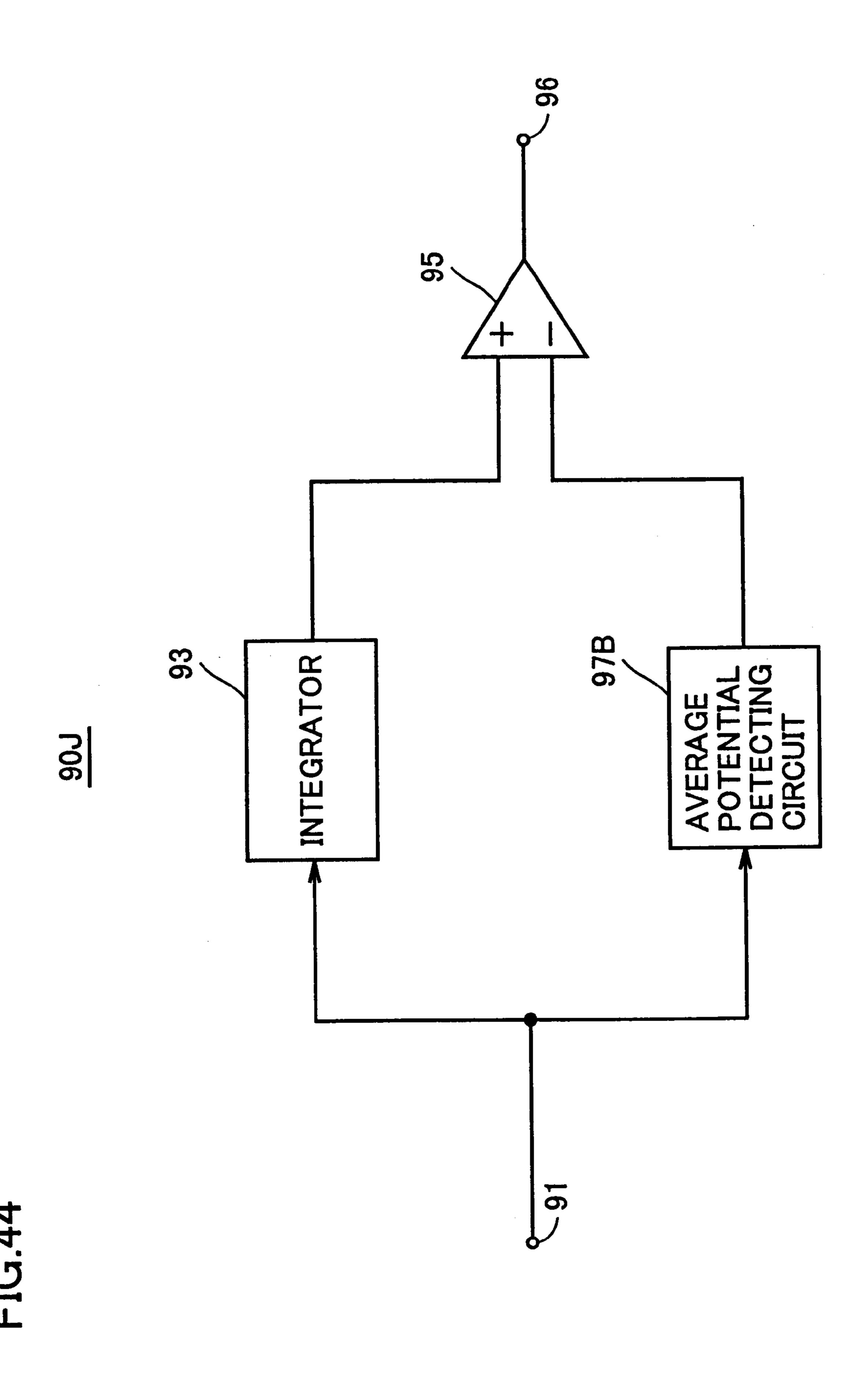

- FIG. 44 is a block diagram of a slice circuit shown in FIG. 43;

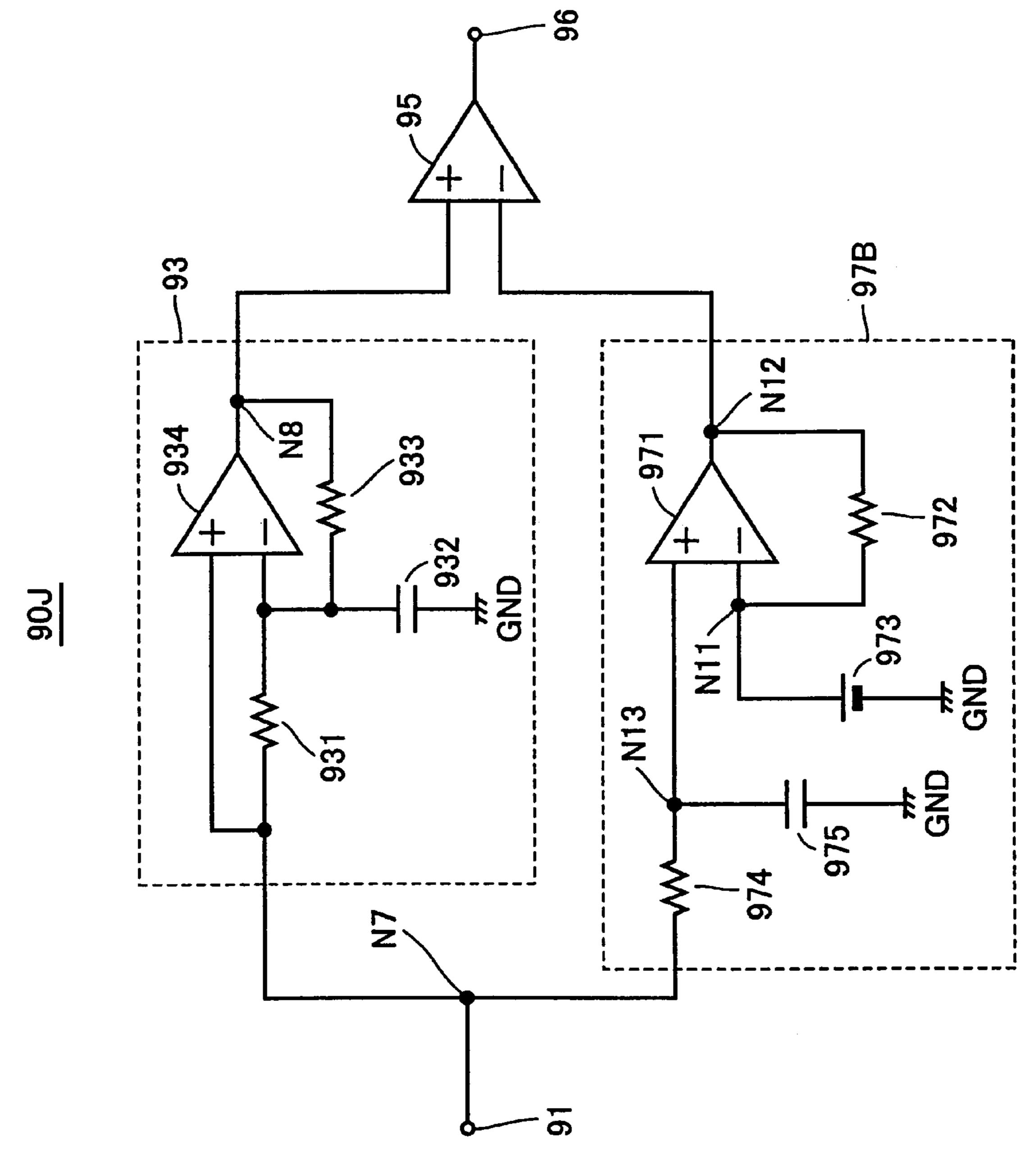

- FIG. 45 is a circuit diagram showing an integrator, a comparator and an average potential detecting circuit shown in FIG. 44;

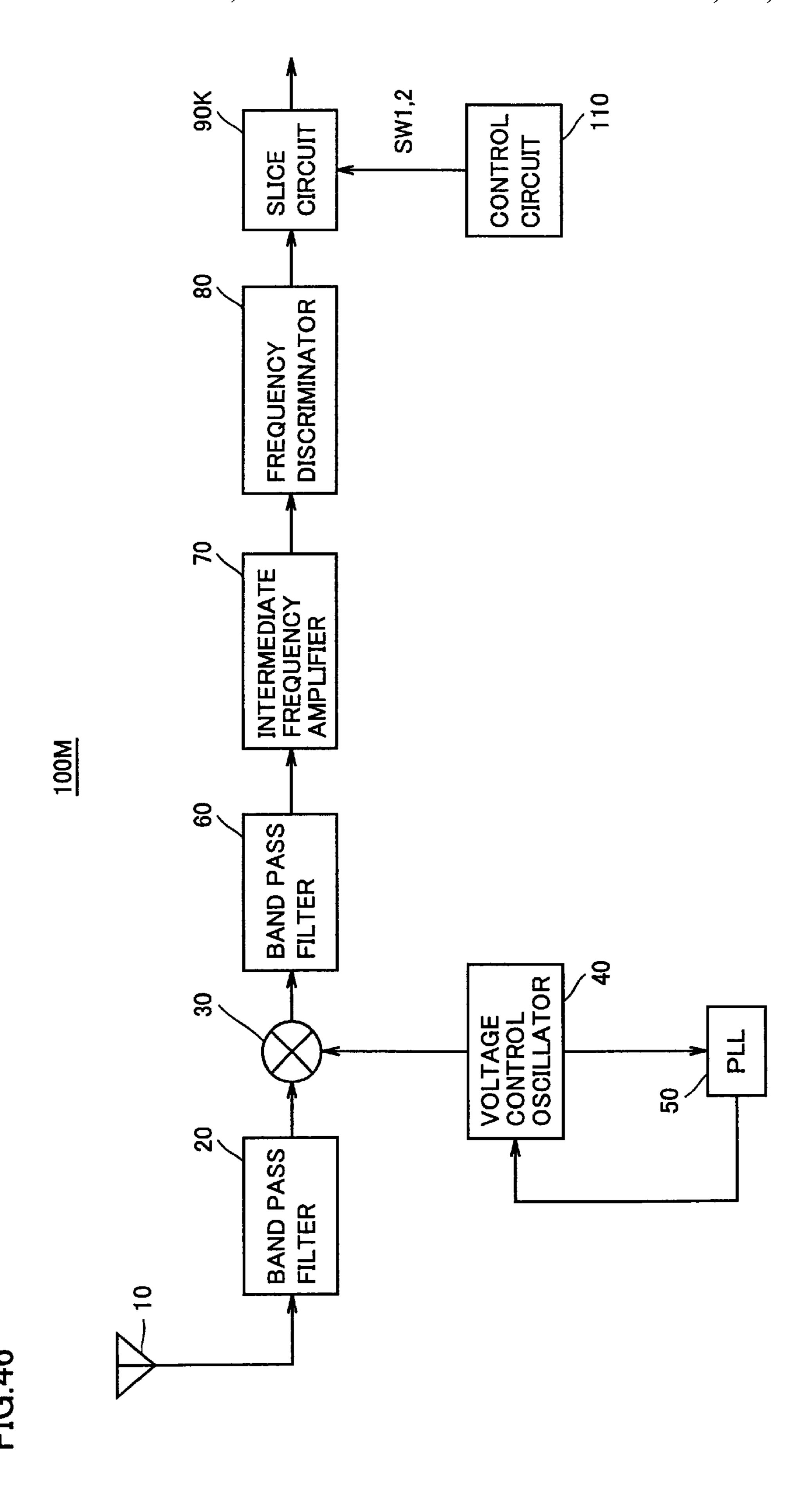

- FIG. 46 is a schematic block diagram of a receiver according to a fourteenth embodiment;

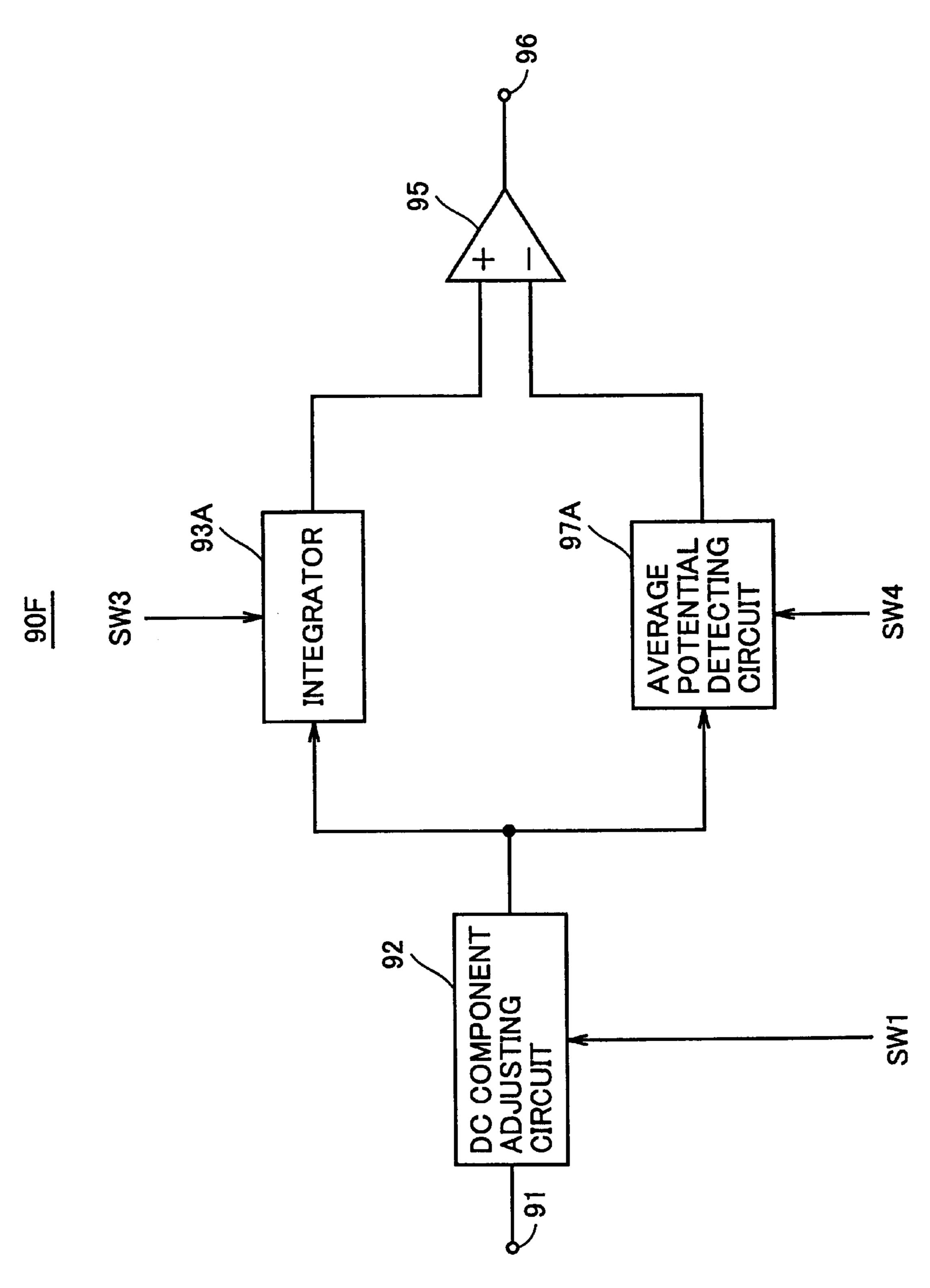

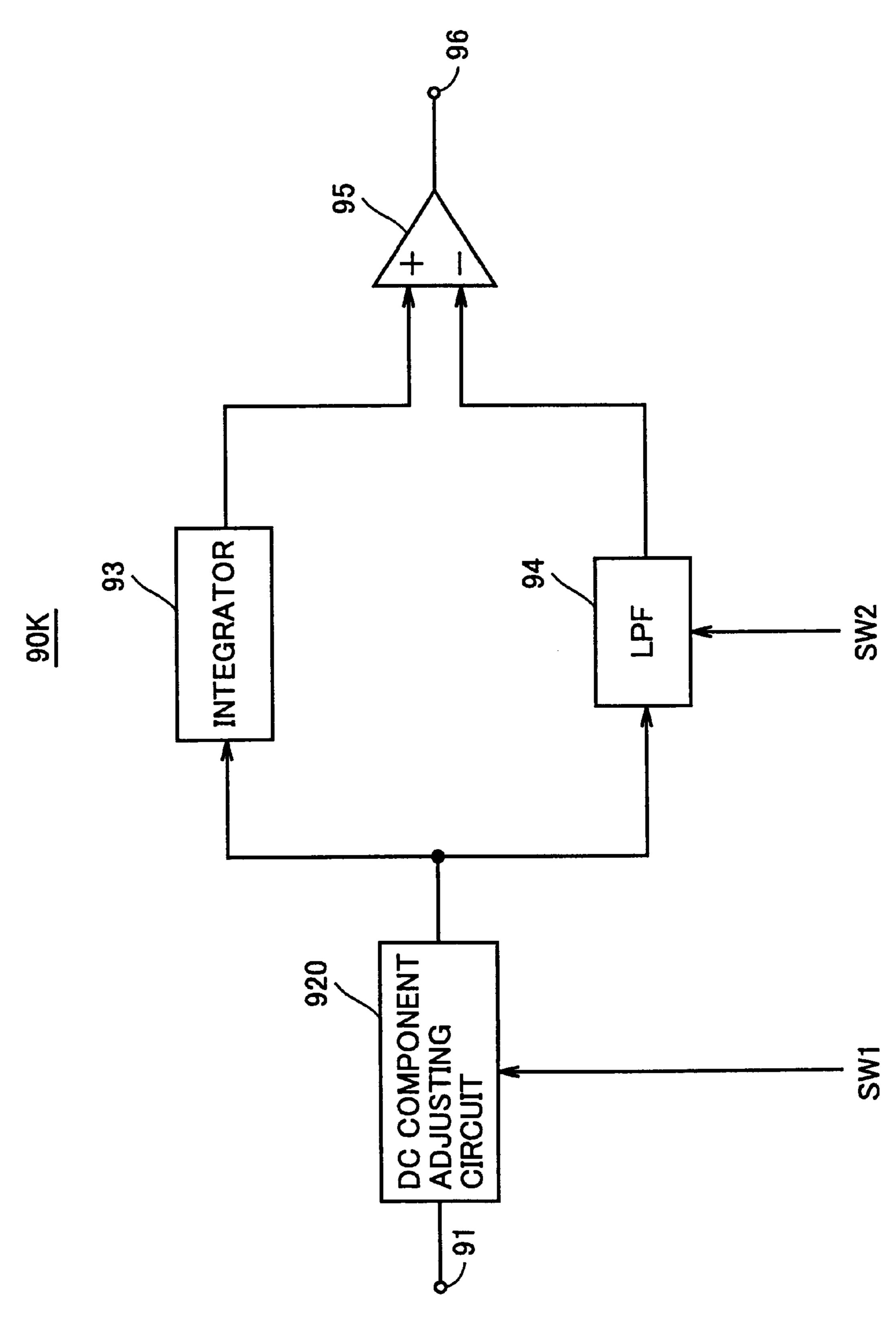

- FIG. 47 is a block diagram of a slice circuit shown in FIG. 46;

- FIG. 48 is a circuit diagram showing a DC component adjusting circuit, an integrator, a low pass filter and a 40 comparator shown in FIG. 47;

- FIG. 49 is a timing chart of signals for illustrating a function of the DC component adjusting circuit shown in FIGS. 47 and 48;

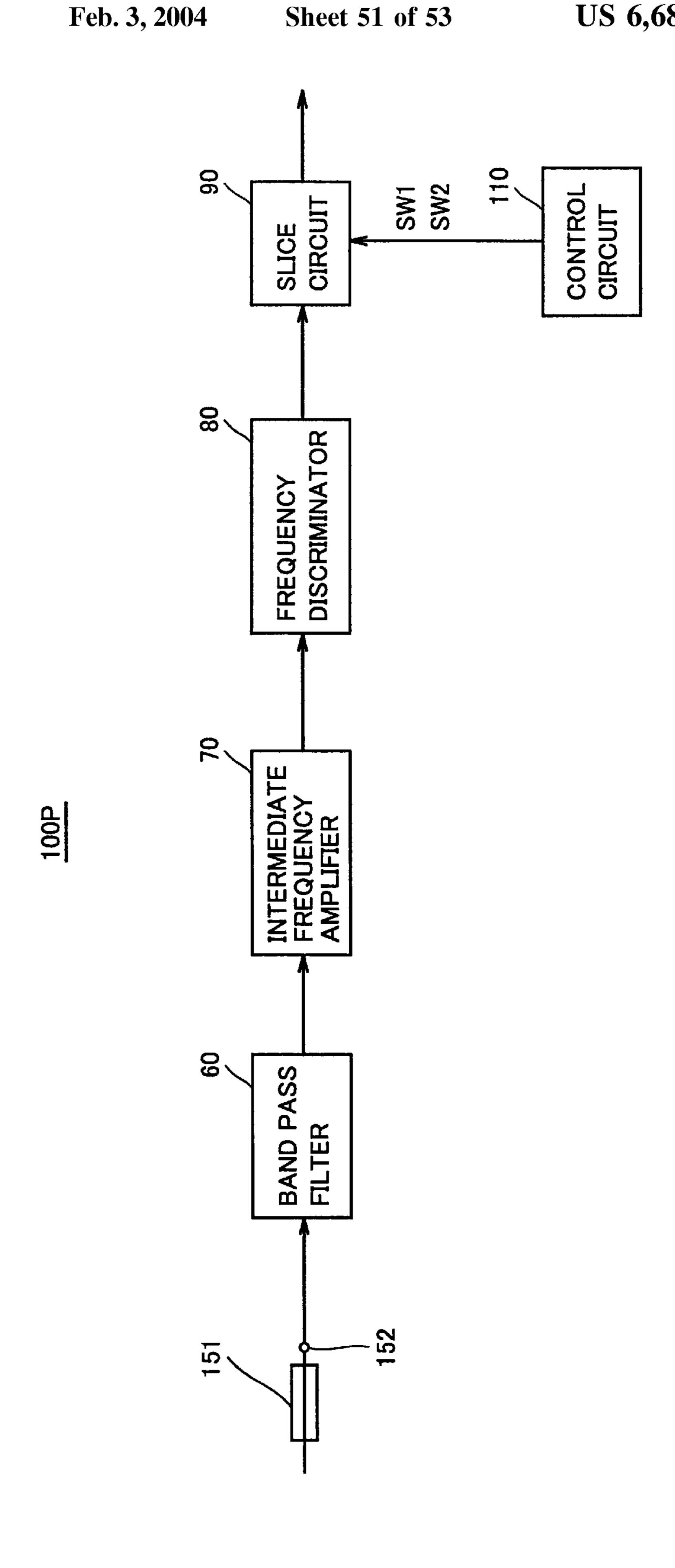

- FIG. 50 is a schematic block diagram of another receiver according to the invention;

- FIG. 51 is a schematic block diagram of still another receiver according to the invention; and

- FIG. **52** is a circuit diagram of a conventional slice circuit; and

- FIG. 53 is a timing chart of signals for illustrating problems of the conventional slice circuit.

# DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Embodiments of the invention will now be described with reference to the drawings. In the figures, the same or corresponding portions bear the same reference numbers, and description thereof is not repeated.

# First Embodiment

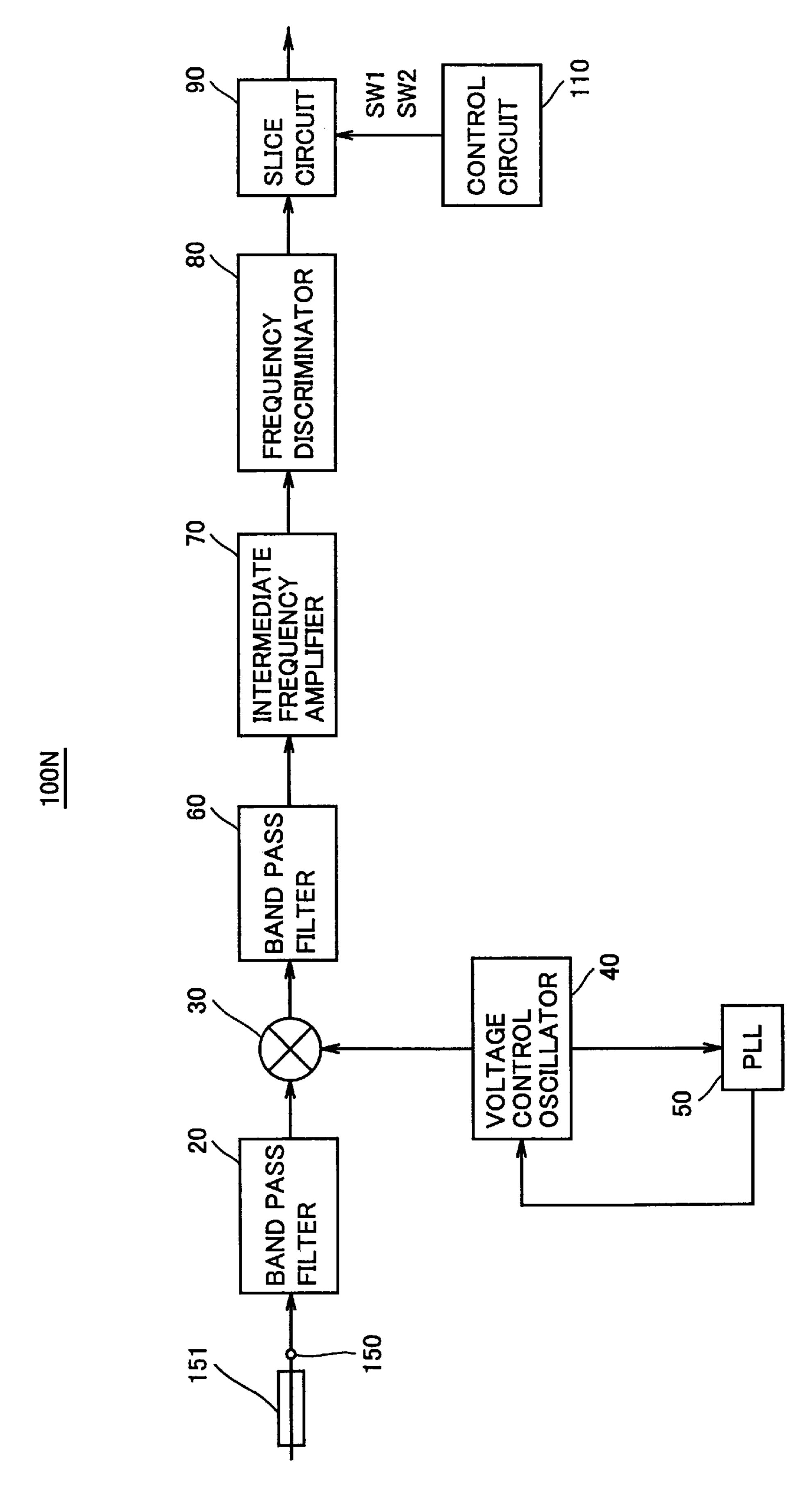

Referring to FIG. 1, a receiver 100 according to a first embodiment of the invention includes an antenna 10, band pass filters 20 and 60, a mixer 30, a voltage control oscillator 65 40, a PLL (Phase Locked Loop) 50, an intermediate frequency amplifier 70, a frequency discriminator 80, a slice circuit 90 and a control circuit 110.

Antenna 10 receives a receive signal subjected to FSK modulation, and provides the receive signal to band pass filter 20. Band pass filter 20 extracts a signal, which has a frequency in an intended frequency band, from the signal received from antenna 10, and provides the extracted signal to mixer 30.

Mixer 30 mixes the signal sent from band pass filter 20 with the signal sent from voltage control oscillator 40, and provides the mixed signals to band pass filter 60. It is assumed that band pass filter 20 provides a signal having a predetermined frequency width and a central frequency of fc, and voltage control oscillator 40 provides a signal of a frequency of f0. In this case, mixer 30 provides a signal of a frequency of (fc+f0) and a signal of a frequency of (fc-f0) to band pass filter 60.

Voltage control oscillator 40 divides the frequency of a period signal sent from PLL 50 to provide a signal of a predetermined frequency (e.g., of f0) to mixer 30 and PLL **50**. PLL **50** provides a period signal, which is synchronized with the signal of the predetermined frequency sent from voltage control oscillator 40, to voltage control oscillator 40.

Band pass filter 60 extracts a signal having an intended frequency of (fc-f0) from the signal, which is sent from mixer 30 and has frequencies of (fc+f0) and (fc-f0), and provides the extracted signal to intermediate frequency amplifier 70.

Intermediate frequency amplifier 70 amplifies the signal of the frequency of (fc-f0) until it has a substantially constant amplitude. Frequency discriminator 80 converts the frequency-modulated signal to an amplitude-modulated signal. Thus, frequency discriminator 80 converts the frequency-modulated signal to a signal performing indication by means of differences in voltage level (which means that the FM demodulation is performed).

Slice circuit 90 converts the input signal sent from frequency discriminator 80 from the analog signal to the digital signal in a manner to be described later. Control circuit 110 provides signals SW1 and SW2 to slice circuit 90.

Referring to FIG. 2, slice circuit 90 includes a DC component adjusting circuit 92, an integrator 93, a low pass 40 filter 94 and a comparator 95. DC component adjusting circuit 92 receives an input signal subjected to the FM demodulation from frequency discriminator 80 via an input terminal 91. DC component adjusting circuit 92 adjusts only the DC components in the received input signal to provide 45 DC components formed of a uniform voltage level, and sends an input signal having the DC components thus adjusted to integrator 93 and a low pass filter 94. A manner of adjusting the DC components in the input signal will be described later.

Integrator 93 amplifies only components, which have high frequencies equal to or higher than a predetermined frequency, in the input signal sent from DC component adjusting circuit 92. Low pass filter 94 detects an average voltage of the input signal received from DC component 55 adjusting circuit 92.

Comparator 95 receives the output signal of integrator 93 on its noninverting input terminal, and receives the output signal of low pass filter 94 on its inverting input terminal. Comparator 95 compares the voltage of the input signal, in 60 which only high frequency components of or above the predetermined frequency are amplified, with the average voltage of the input signal, and provides a digital signal having theological level corresponding to results of this comparison to an output terminal 96.

Thus, comparator 95 provides a signal at H-level to output terminal 96 when the voltage of the input signal, in which 8

only the high frequency components are amplified, is higher than the average voltage of the input signal, and provides a signal at L-level to output terminal 96 when the voltage of the input signal, in which only the high frequency components are amplified, is equal to or lower than the average voltage of the input signal.

DC component adjusting circuit 92, integrator 93 and low pass filter 94 form a signal processing circuit.

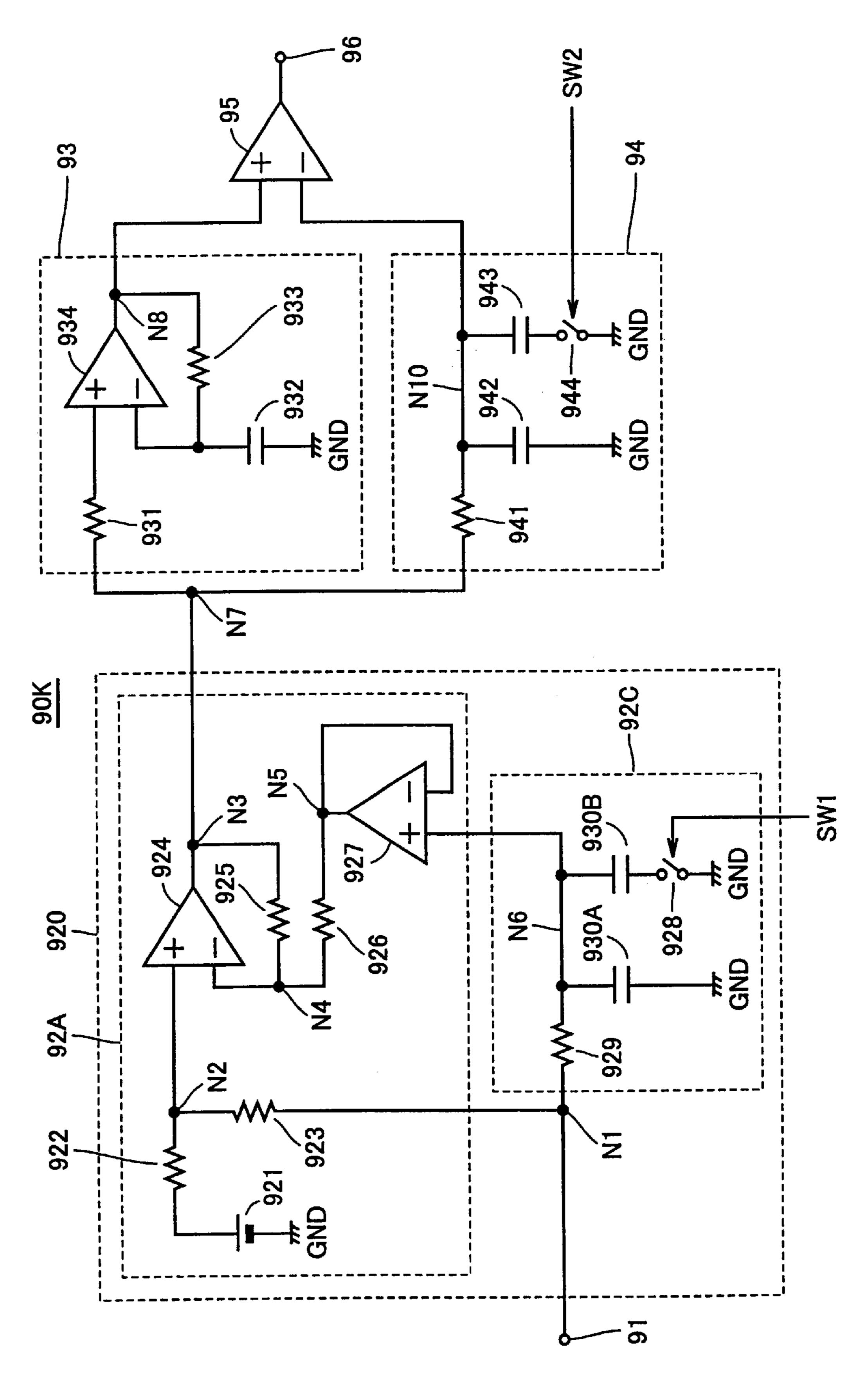

FIG. 3 is a circuit diagram of DC component adjusting circuit 92, integrator 93, low pass filter 94 and comparator 95 shown in FIG. 2. Referring to FIG. 3, DC component adjusting circuit 92 includes a DC level converting circuit 92A and a sample hold circuit 92B.

DC level converting circuit 92A includes a voltage supply 921, resistances 922, 923, 925 and 926, and operational amplifiers 924 and 927.

Voltage supply 921 and resistance 922 are connected in series between node N2 and ground node GND. Resistance 922 is connected to node N2, and resistance 923 is connected between nodes N1 and N2.

Operational amplifier 927 has a noninverting input terminal receiving an output signal of sample hold circuit 92B, and also has an inverting input terminal connected to its output terminal. Thus, operational amplifier 927 forms a buffer, and sends the output signal of sample hold circuit 92B to a node N5 as it is.

Resistance 925 is connected between nodes N3 and N4. Resistance 926 is connected between nodes N4 and N5. 30 Operational amplifier 924 receives on its noninverting input terminal a signal carried on node N2, and also receives on its inverting input terminal a signal carried on node N4. Operational amplifier 924 receives its output signal (i.e., signal on node N3) on its inverting input terminal via resistance 925, and also receives on its inverting input terminal an output signal of operational amplifier 927 (i.e., signal on node N5) via resistance 926.

Sample hold circuit 92B includes a switch 928, a resistance 929 and a capacitor 930. Switch 928 and resistance 929 are connected in series between nodes N1 and N6. Switch 928 is connected to node N1, and resistance 929 is connected to node N6. Capacitor 930 is connected between node N6 and ground node GND.

Switch 928 receives a signal SW1 from control circuit 110. Switch 928 is turned on by signal SW1 at H-level, and is turned off by signal SW1 at L-level. Resistance 929 and capacitor 930 form a low pass filter.

The input signal subjected to FM demodulation by frequency discriminator 80 is sent to node N1 through input terminal 91. This signal is supplied from node N1 to DC level converting circuit 92A and sample hold circuit 92B. Assuming that Vin represents this input signal, Vb represents a signal on node N6, input signal Vin has a frequency of f, resistance 929 has a resistance value of R1 and capacitor 930 has a capacitance of C, the following equation is established when switch 928 is on.:

$$Vb = Vin/(1 + j\omega CR1) \tag{1}$$

where  $\omega$  is equal to  $2\pi f$

65

Accordingly, the low pass filter formed of resistance 929 and capacitor 930 has frequency characteristics, in which cut-off frequency fc is determined by the following equation:

$$fc=1/(2\pi CR1) \tag{2}$$

When signal SW1 turns on switch 928, the voltage of input signal Vin is transmitted via node N1 to resistance 929

and capacitor 930 so that capacitor 930 accumulates electric charges. The voltage on node N6 becomes equal to Vb expressed by the equation (1). When signal SW1 turns off switch 928, the charges accumulated in capacitor 930 will be gradually discharged. In this case, the voltage on node N6 maintains the level, which was kept immediately before turn-off of switch 928, for a predetermined time, and then will gradually lower.

A time required for discharging the charges accumulated in capacitor 930 depends on the self-discharging of capacitor 10 930 and an input resistance to the noninverting input terminal of operational amplifier 927. By employing operational amplifier 927 having a high input resistance, the noninverting input terminal of operational amplifier 927 takes in only a minute current, and capacitor 930 substantially holds the 15 accumulated charges.

Accordingly, when signal SW1 turns on switch 928, sample hold circuit 92B detects an average voltage of input signal Vin, and provides signal Vb formed of the average voltage expressed by the equation (1). When signal SW1 20 turns off switch 928, sample hold circuit 92B holds the detected average voltage, and provides the average voltage thus held.

Sample hold circuit 92B receives signal SW1 at H-level from control circuit 110 during an initial period of reception 25 of the input signal, and receives signal SW1 at L-level from control circuit 110 during a latter period of reception of the input signal. In the invention, the "initial period of reception" represents a period, during which an access code is primarily sent, and the "latter period of reception" represents 30 a period, during which data is primarily sent.

During the initial period of reception of the input signal, therefore, switch 928 is turned on, and sample hold circuit 92B detects the average voltage of input signal Vin to provide it to the noninverting input terminal of operational 35 amplifier 927. During the latter period of reception of the input signal, switch 928 is turned off, and sample hold circuit 92B provides the hold value of the detected average voltage to the noninverting input terminal of operational amplifier 927.

Input signal Vin sent to node N1 is supplied to node N2 via resistance 923. Assuming that voltage supply 921 provides output voltage Vref, signal Va is present on node N2, resistances 922, 923, 925 and 926 have resistance values R2, R3, R4 and R5, respectively, signal Vc is the output signal of operational amplifier 924 and thus is present on node N3, signal Vp is present on node N4, and signal Vd is the output signal of operational amplifier 927 and thus is present on node N5, the following equations (3) and (4) are established:

$$Va=Vin+(R3/(R2+R3))(Vref-Vin)$$

(3)

$$Vp = (R4Vd + R5Vc)/(R4 + R5)$$

$$(4)$$

In operational amplifier 924, a relationship of Va=Vp is established as a result of imaginary short, and signal Vc can be expressed as followed by substituting Va for Vp:

$$Vc = ((R4+R5)/R5)Va - (R4/R5)Vd$$

(5)

Operational amplifier 924 receives signal Va expressed by the equation (3) on its noninverting input terminal, and more 60 specifically receives signal Va prepared by dividing a voltage difference between output voltage Vref (which may also be referred to as a "reference voltage") of voltage supply 921 and the voltage of input signal Vin in accordance with resistance values R2 and R3 of resistances 922 and 923, and 65 adding the voltage of input signal Vin to the divided voltage produced by the above division. Operational amplifier 924

10

forms a noninverting amplifier circuit together with resistances 925 and 926, and receives output signal Vd of operational amplifier 927 on its bias terminal.

In an ordinary noninverting amplifier circuit, one terminal of resistance 926 determining the gain thereof, i.e., node N5 is grounded. According to the invention, however, one end of resistance 926 receives output signal Vd of operational amplifier 927. Thus, the bias terminal of the noninverting amplifier circuit formed of operational amplifier 924 and resistances 925 and 926 is floated by the voltage forming output signal Vd.

According to the invention, a ratio between resistance values R2 and R3 of resistances 922 and 923 is set to 1:1. Therefore, the equation (3) can be changed as follows:

$$Va=Vin+(Vref-Vin)/2$$

(6)

In the invention, a ratio between resistance values R4 and R5 of resistances 925 and 926 is set to 1:1. Therefore, the equation (5) can be changed as follows:

$$Vc=2Va-Vd \tag{7}$$

Since operational amplifier 927 provides signal Vd, which is received on its noninverting input terminal, as it is, Vd is equal to Vb. Therefore, signal Vc can be expressed as follows from the equations (6) and (7) as well as the relationship of Vd=Vb.

$$Vc = Vin + Vref - Vb$$

(8)

When switch 928 is turned on, Vin is equal to Vb so that a relationship of (Vc=Vref) is obtained from the equation (8). Since signal Vb is formed of an average voltage of input signal Vin, the relationship of (Vc=Vref) is established by the DC components of output signal Vc, and the AC components of output signal Vc are the same as the AC components in input signal Vin according to the equation (8).

Accordingly, when switch 928 of sample hold circuit 92B is turned on, DC level converting circuit 92A converts the DC components in input signal Vin to DC components formed of a uniform voltage level (Vref), and provides the AC components in input signal Vin as they are.

When switch 928 of sample hold circuit 92B is turned off, a relationship of (Vin=Vb) is not established, and the average voltage of input signal Vin, which was attained immediately before the turn-off of switch 928, is held in signal Vb. In this case, therefore, operational amplifier 924 provides output signal Vc expressed by the equation (8). The DC components in input signal Vin are not changed to DC components formed of a uniform voltage level, and output signal Vc of which DC offset changes in accordance with input signal Vin is provided.

As described above, when switch 928 is turned on, DC component adjusting circuit 92 maintains the AC components in input signal Vin received through input terminal 91 as they are, and provides an output signal produced by converting the DC components to DC components formed of a uniform voltage level (Vref). When switch 928 is turned off, it provides the output signal, in which DC offset changes in accordance with input signal Vin.

During the initial period of reception of input signal Vin, slice circuit 90 receives input signals Vin1 and Vin2, in which DC offset drifts to a large extent as shown in FIG. 4. When switch 928 is turned on, DC component adjusting circuit 92 provides the output signal, in which the AC components in input signal Vin are maintained as they are, and the DC components are changed to DC components

formed of a uniform voltage level, as described above. Therefore, even when input signals Vin1 and Vin2, in which the DC offset drifts to a large extent, is received, DC component adjusting circuit 92 provides output signal Vc, in which the DC components are changed to the DC components formed of the uniform voltage level (Vref).

By using DC component adjusting circuit 92, input signals Vin1 and Vin2, which have drifting DC components, can be changed to input signal Vc having uniform DC offset.

Referring to FIG. 3 again, integrator 93 includes resistances 931 and 933, a capacitor 932 and an operational amplifier 934. Resistance 931 is connected between nodes N7 and N9. Resistance 933 is connected between node N8 and N9. Capacitor 932 is connected between node N9 and ground node GND. Operational amplifier 934 receives an 15 input signal sent from DC component adjusting circuit 92 on its noninverting input terminal via node N7, receives the input signal sent from DC component adjusting circuit 92 on its inverting input terminal via a low pass filter formed of resistance 931 and capacitor 932, and receives an output 20 signal, i.e., a signal on node N8 on its inverting input terminal via resistance 933.

Accordingly, integrator 93 amplifies only high frequency components, which have frequencies equal to or higher than a predetermined frequency, in the input signal, and sends 25 them to comparator 95. The high frequency components of or above the predetermined frequency are components, of which inversion from "1" to "0" or from "0" to "1" by the FSK modulation occurs within a period shorter than a predetermined period.

LPF 94 includes a resistance 941, capacitors 942 and 943, and a switch 944. Resistance 941 is connected between nodes N7 and N10. Capacitor 942 is connected between node N10 and ground node GND. Capacitor 943 and switch 944 are connected in series between node N10 and ground 35 node GND. Switch 944 is turned on by a signal SW2 at H-level sent from control circuit 110, and is turned off by signal SW2 at L-level sent from control circuit 110.

Low pass filter 94 receives the input signal sent from DC component adjusting circuit 92 via node N7, and detects the 40 average voltage of the received input signal. Low pass filter 94 provides the detected average voltage to an inverting input terminal of comparator 95. Switch 944 in low pass filter 94 is employed for changing a time constant. When switch 944 is on, the capacitance of low pass filter 94 is equal to a sum of the capacitances of capacitors 942 and 943 so that the time constant is large. When switch 944 is off, the capacitance of low pass filter 94 is equal to the capacitance of capacitor 942 so that the time constant is small. As described above, the time constant can be adjusted in low 50 pass filter 94.

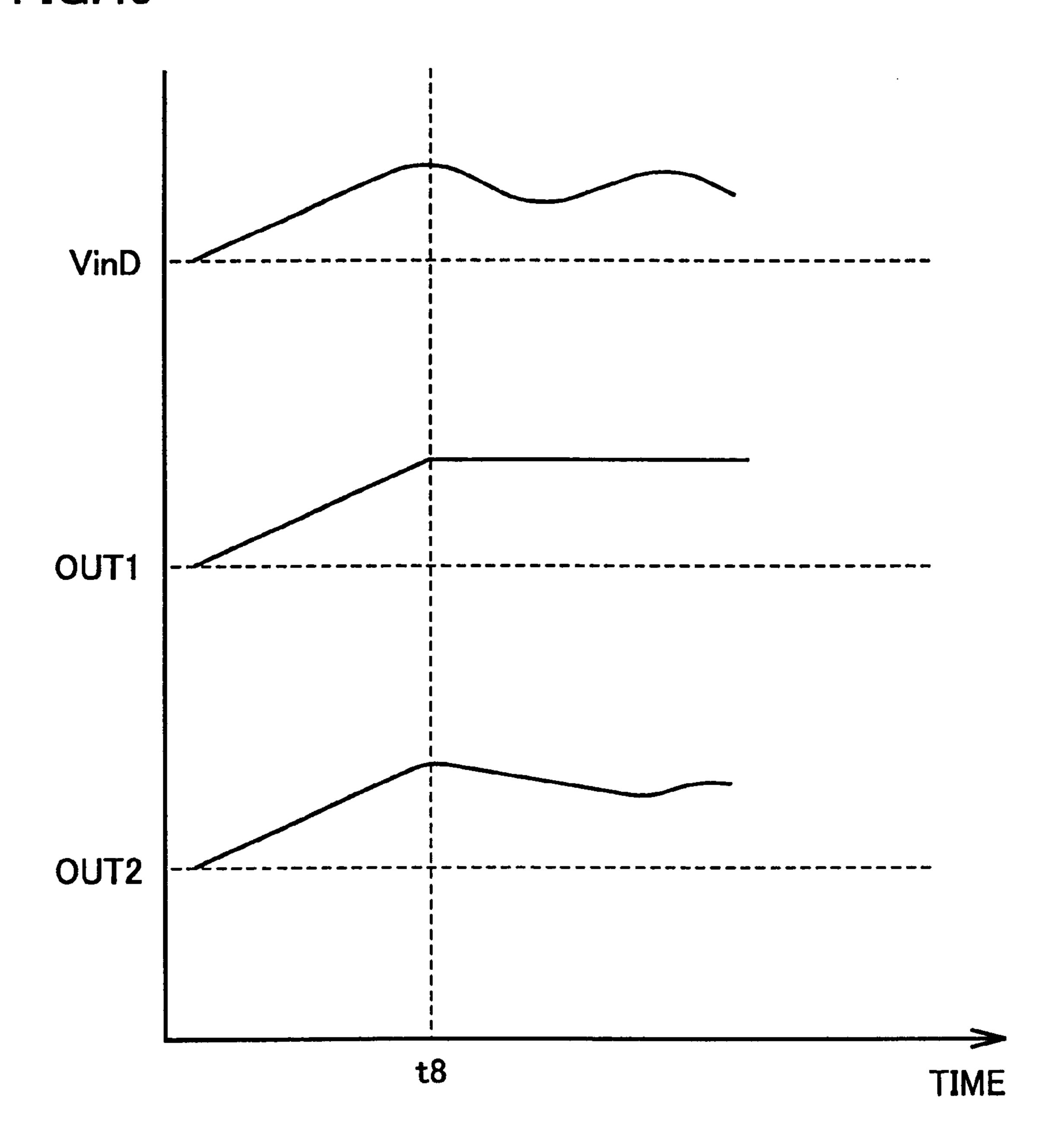

Referring to FIG. 5, an operation of slice circuit 90 will now be described. In FIG. 5, switch 928 in sample hold circuit 92B is on during a period from timing t1 to timing t2, and switch 928 is off after timing t2. Switch 944 in low pass 55 filter 94 is off.

When slice circuit 90 receives input signal Vin via input terminal 91, DC component adjusting circuit 92 maintains the AC components in input signal Vin during the period from ting t1 to timing t2 as they are, changes the DC 60 components to the DC components formed of the uniform voltage level during the above period, and provides signal Vc, in which DC offset changes in accordance with the DC offset in input signal Vin after timing t2, as already described. After timing t2, the DC offset in input signal Vin 65 hardly drifts so that the DC offset in signal Vc provided after timing t2 is equal to the DC components (DC offset) formed

12

of the uniform voltage level changed by the DC component adjusting circuit 92 during the period from timing t1 to timing t2.

Integrator 93 receives signal Vc provided from DC component adjusting circuit 92 via node N7, and amplifies only high frequency components of or above a predetermined frequency in the received signal Vc to provide a signal VcA to the noninverting input terminal of comparator 95. Low pass filter 94 receives signal Vc sent from DC component adjusting circuit 92 via node N7, detects the average voltage of received signal Vc, and provides a signal VcDC formed of the detected average voltage to the inverting input terminal of comparator 95.

Thereby, comparator 95 compares the voltage of signal VcA sent from integrator 93 with the voltage of signal VcDC sent from low pass filter 94, and provides a digital signal DXS corresponding to results of the comparison to output terminal 96.

As described above, even when input signal Vin contains the drift of DC offset, slice circuit 90 removes the drift of DC offset, and provides signal Vc formed of the uniform voltage level (signal Vc during the period from timing t1 to timing t2). Integrator 93 provides the signal by amplifying components VcS1 forming signal Vc during the period from timing t1 to timing t2 and components VcS2 forming signal Vc after timing t3, and provides the signal without amplifying components VcS3 forming signal Vc during a period from timing t2 to timing t3.

As a result, even if input signal Vin contains fast drift of the DC offset, input signal Vin can be followed and converted from the analog signal to the digital signal. Since low pass filter 94 has a small time constant, low pass filter 94 can follows signal Vc sent from DC component adjusting circuit 92, and the voltage of output signal VcDC of low pass filter 94 does not approach the voltage of output signal VcA. Therefore, even when slice circuit 90 receives the components corresponding to a signal including a succession of "1" or "0" produced by FSK modulation, input signal Vin can be accurately converted from an analog signal to a digital signal.

Referring to FIG. 1 again, an operation of receivier 100 will now be described. Antenna 10 receives a signal, and provides the received signal to band pass filter 20. Band pass filter 20 extracts only a signal in an intended frequency band from the signal received from antenna 10, and provides the extracted signal to mixer 30. Voltage control oscillator 40 provides a signal of a predetermined frequency to mixer 30. Mixer 30 mixes the signal sent from band pass filter 20 with the signal sent from voltage control oscillator 40, and provides a signal produced by the mixture to band pass filter 60.

Thereby, band pass filter 60 extracts a signal having an intended frequency from the signal sent from mixer 30, and provides it to intermediate frequency amplifier 70. Intermediate frequency amplifier 70 amplifies the signal sent from band pass filter 60 to attain a uniform amplitude. Frequency discriminator 80 effects FM demodulation on the signal sent from intermediate frequency amplifier 70, and provides the demodulated input signal to slice circuit 90.

Control circuit 110 provides signal SW1 at H-level to slice circuit 90 during a period from start (timing t1) of the signal reception to timing t2, provides signal SW1 at L-level to slice circuit 90 after timing t2, and provides signal SW2 at L-level to slice circuit 90 regardless of the period.

Thereby, slice circuit 90 accurately converts input signal Vin from the analog signal to the digital signal by removing the drift of DC offset in input signal Vin during the initial

period (from timing t1 to timing t2) of reception of input signal Vin. Also, even if input signal Vin contains components formed of a succession of uniform voltage levels during the latter period (after timing t2) of reception of input signal Vin, slice circuit 90 accurately converts input signal 5 Vin from the analog signal to the digital signal. Receiver 100 provides the input signal, which is converted from the analog signal to the digital signal, to a bas band portion. Thereby, the operation in receiver 100 ends.

**13**

According to the first embodiment, the slice circuit used 10 in the receiver includes the DC component adjusting circuit, which maintains the AC components in the input signal as they are, and converts the DC components to the DC components formed of the uniform voltage level, as well as the low pass filter, of which gain can be set small. Therefore, 15 even if the input signal contains the fast drift of DC offset, the input signal can be accurately converted from the analog signal to the digital signal. Even when the input signal contains the components corresponding to the signal formed of a succession of "1" or "0" produced by the FSK 20 modulation, the input signal can be accurately converted from the analog signal to the digital signal.

# Second Embodiment

Referring to FIG. 6, a receiver 100A according to a second 25 embodiment is the same as receiver 100 except for that control circuit 100 in receiver 100 is removed, and slice circuit 90 in receiver 100 is replaced with a slice circuit 90A.

Referring to FIG. 7, slice circuit 90A includes integrator 93, comparator 95 and an average potential detecting circuit 97. Integrator 93 and comparator 95 are substantially the same as those in the first embodiment. In slice circuit 90A, however, integrator 93 and average potential detecting circuit 97 receive the input signals via input terminal 91.

Average potential detecting circuit 97 attenuates input signal Vin received via input terminal 91, and detects the average voltage of the input signal thus attenuated. Average potential detecting circuit 97 provides the detected average voltage to the inverting input terminal of comparator 95.

Integrator 93 and average potential detecting circuit 97 form a signal processing circuit.

FIG. 8 is a circuit diagram showing integrator 93, comparator 95 and average potential detecting circuit 97 shown in FIG. 7. The circuit structures of integrator 93 and comparator 95 are already described.

Referring to FIG. 8, average potential detecting circuit 97 includes an operational amplifier 971, resistances 972 and 974, a voltage supply 973 and a capacitor 975. Voltage supply 973 is connected between a node N11 and ground node GND, and provides a uniform voltage Vref1. Resistance 972 is connected between nodes N11 and N12. Operational amplifier 971 receives on its noninverting input terminal the input signal carried on node N7, and receives on its inverting input terminal the signal carried on node N11. Assuming that resistance 972 has a resistance value of Rc, operational amplifier 971 serves as a differential amplifier circuit, which uses uniform voltage Vref1 and resistance Rc as a reference and a load, respectively, and has a gain below one.

Resistance 974 is connected between nodes N12 and N13. Capacitor 975 is connected between node N13 and ground node GND. Resistance 974 and capacitor 975 form a low pass filter.

Uniform voltage Vref1 provided by voltage supply 973 65 depends on the power supply voltage of slice circuit 90A, and is set to maximize the input/output dynamic range of

slice circuit 90A. For example, uniform voltage Vref1 is set to half the power supply voltage of slice circuit 90A.

14

Operational amplifier 971 receives the input signal on node N7 and uniform voltage Vref1 on node N11, and differentially amplifies the input signal based on uniform voltage Vref1 for providing the amplified signal to node N12. In this case, the gain of operational amplifier 971 is smaller than "1" so that operational amplifier 971 attenuates the input signal and provides it to node N12.

The low pass filter formed of resistance 974 and capacitor 975 smoothes the signal on node N12, and thus detects the average voltage of the signal on node N12 for providing the average voltage thus detected to the inverting input terminal of comparator 95. The low pass filter formed of resistance 974 and capacitor 975 does not smooth the original input signal, but smoothes the input signal attenuated by operational amplifier 971. Therefore, even if the input signal contains the components corresponding to the signal formed of a succession of "1" or "0" produced by the FSK modulation, the output average voltage is lower than the voltage of the output signal of integrator 93.

As described above, average potential detecting circuit 97 detects the average voltage of the input signal in the attenuated form.

Referring to FIG. 9, an operation of slice circuit 90A will now be described. When slice circuit 90A receives an input signal Vin3 subjected to the FM demodulation, integrator 93 amplifies only the high frequency components of frequencies equal to or higher than the predetermined frequency, and provides a signal Vin3A produced by this amplification to the noninverting input terminal of comparator 95.

Average potential detecting circuit 97 attenuates the amplitude of input signal Vin3 on node N7, detects the average voltage of the input signal having the attenuated amplitude, and provides a signal Vin3DC formed of the detected average voltage to the inverting input terminal of comparator 95. Comparator 95 compares the voltage of output signal Vin3A sent from integrator 93 with the voltage of output signal Vin3DC sent from average potential detecting circuit 97, and provides a digital signal DXS3 having the logical level corresponding to results of the comparison to output terminal 96. Thereby, the operation in slice circuit 90A ends.

As described above, average potential detecting circuit 97 of slice circuit 90A attenuates the amplitude of input signal Vin3 by operational amplifier 971, and detects the average voltage of the input signal thus attenuated. Accordingly, the voltage of signal Vin3DC is lower than the voltage of signal Vin3A during a period from timing t4 to timing t5. As a result, even if input signal Vin3 contains components corresponding to the signal formed of a succession of "1" or "0" produced by the FSK modulation, a voltage level L1 of output signal Vin3DC of average potential detecting circuit 97 does not approach a voltage level L2 of output signal Vin3A of integrator 93 so that comparator 95 can accurately convert the input signal from the analog signal to the digital signal.

Owing to provision of average potential detecting circuit 97, comparator 95 can accurately convert input signal Vin3 from the analog signal to the digital signal without requiring setting of a large gain in operational amplifier 934 included in integrator 93, and therefore the amplification factor of integrator 93 can be small. As a result, even when input signal Vin3 contains noise components of the same frequencies as the high frequency components to be amplified by integrator 93, such an error can be prevented that the noise components are amplified and detected as an intended signal.

Operations of receiver 100A are the same as those of receiver 100 except for that the operation of slice circuit 90 is replaced with an operation of slice circuit 90A.

Structures and operations other than the above are the same as those in the first embodiment.

According to the second embodiment, the slice circuit includes the average potential detecting circuit attenuating the amplitude of the input signal, and detecting the average voltage of the attenuated input signal. Therefore, even if the input signal contains components corresponding to the signal formed of a succession of "1" or "0" produced by the FSK modulation, the input signal can be accurately converted from the analog signal to the digital signal, and such an error can be prevented that the noise components are detected as the intended signal.

### Third Embodiment

Referring to FIG. 10, a receiver 100B of a third embodiment is the same as receiver 100 except for that slice circuit 20 on receiver 100 is replaced with a slice circuit 90B.

Referring to FIG. 11, slice circuit 90B includes DC component adjusting circuit 92, integrator 93 and average potential detecting circuit 97.

As already described in connection with the first 25 embodiment, DC component adjusting circuit 92 receives the input signal via input terminal 91, maintains the AC components in the received input signal as they are, and converts the DC components to the DC components formed of a uniform voltage level. DC component adjusting circuit 30 92 provides the input signal, in which the voltage level of the DC components is changed, to integrator 93 and average potential detecting circuit 97.

Integrator 93 amplifies only the high frequency components of or above the predetermined frequency in the input signal sent from DC component adjusting circuit 92, and provides the amplified input signal to the noninverting input terminal of comparator 95, as already described in connection with the first embodiment.

Average potential detecting circuit 97 receives the input signal from DC component adjusting circuit 92, attenuates the amplitude of the received input signal, and detects the average voltage of the attenuated input signal. Average potential detecting circuit 97 provides the detected average voltage to the inverting input terminal of comparator 95.

Comparator 95 compares the voltage of the output signal of integrator 93 with the voltage of output signal of average potential detecting circuit 97, and provides the digital signal having the logical level corresponding to results of the comparison to output terminal 96.

DC component adjusting circuit 92, integrator 93 and average potential detecting circuit 97 form a signal processing circuit.

FIG. 12 is a circuit diagram showing DC component 55 adjusting circuit 92, integrator 93, comparator 95 and average potential detecting circuit 97. DC component adjusting circuit 92, integrator 93 and comparator 95 have the same structures as those shown in the circuit diagram of FIG. 3, and average potential detecting circuit 97 has the same 60 structure as that shown in the circuit diagram of FIG. 8. Therefore, the structures in FIG. 12 will now be described in greater detail.

Referring to FIG. 13, an operation of slice circuit 90B will now be described. When input signal Vin is received via 65 input terminal 91, DC component adjusting circuit 92 maintains the AC components in input signal Vin as they are, and

16

converts the DC components to DC components formed of a uniform voltage level to provide signal Vc to integrator 93 and average potential detecting circuit 97.

Integrator 93 amplifies only the high frequency components of or above the predetermined frequency in signal Vc sent from DC component adjusting circuit 92, and provides signal VcA to the noninverting input terminal of comparator 95. Average potential detecting circuit 97 attenuates the amplitude of signal Vc sent from DC component adjusting circuit 92, and detects the average voltage of the attenuated signal. Average potential detecting circuit 97 provides a signal VcDC2 formed of the detected average voltage to the inverting input terminal of comparator 95.

Thereby, comparator 95 compares the voltage of signal VcA sent from integrator 93 with the voltage of signal VcDC2 sent from average potential detecting circuit 97, and provides digital signal DXS, which has the logical level corresponding to results of the comparison, to the output terminal. Thereby, the operation in slice circuit 90B ends.

As described above, slice circuit 90B produces signal Vc by maintaining the AC components in input signal Vin as they are, and converting the DC components to the DC components formed of the uniform voltage level. Further, slice circuit 90B attenuates the amplitude of signal Vc, and detects the average value of the attenuated signal.

Accordingly, even if input signal Vin contains the drift of DC offset, slice circuit 90B removes the drift of DC offset so that input signal Vin can be accurately followed and converted from the analog signal to the digital signal.

Slice circuit 90B attenuates the amplitude of input signal Vin and detects the average voltage of input signal Vin, input signal Vin can be accurately converted from the analog signal to the digital signal even when input signal Vin contains components VcS3 corresponding to the signal formed of a succession of "1" or "0" produced by the FSK modulation.

Further, a small gain can be set in integrator 93 when slice circuit 90B amplifies only the high frequency components of or above the predetermined frequency in signal Vc sent from DC component adjusting circuit 92. Therefore, erroneous detection of noise components can be prevented.

The operations of receiver 100B are the same as those of receiver 100 except for that the operation of slice circuit 90 is replaced with the operation of slice circuit 90B.

Structures and operations other than the above are the same as those in the first embodiment.

According to the third embodiment, the slice circuit includes the DC component adjusting circuit, which maintains the AC components in the input signal as they are, and converts the DC components to the DC components formed of the uniform voltage level, and the average potential detecting circuit, which attenuates the amplitude of the input signal, and detects the average voltage of the attenuated input signal. Therefore, the following three effects can be achieved.

- (a) Even when input signal Vin contains the drift of DC offset, the drift of DC offset can be removed, and input signal Vin can be accurately followed and converted from the analog signal to the digital signal.

- (b) Even when the input signal contains components formed of a succession of uniform voltage levels, the input signal can be accurately converted from the analog signal to the digital signal.

- (c) Even when the input signal contains noise components, erroneous detection of noise components can be prevented.

#### Fourth Embodiment

A receiver according to a fourth embodiment is the same as receiver 100B of the third embodiment. In the fourth embodiment, control circuit 110 provides signal SW1 at H-level to switch 928 of slice circuit 90B during the initial period of reception of the receive signal, and provides signal SW1 at L-level to switch 928 during the latter period of reception of the receive signal.

During the initial period of reception of the receive signal, 10 DC component adjusting circuit 92 maintains the AC components in input signal Vin as they are, and converts the DC components to the DC components formed of a uniform voltage level in accordance with signal SW1 at H-level sent from control circuit 110. During the latter period of recep- 15 tion of the receive signal, DC component adjusting circuit 92 provides the output signal, in which the AC components in input signal Vin are maintained as they are, and the DC offset changes in accordance with input signal Vin, in accordance with signal SW1 at L-level sent from control 20 circuit 110.

Structures and operations other than the above are the same as those already described in connection with the third embodiment.

As described above, even if the DC components in input signal Vin drift during the initial period of reception of the receive signal, slice circuit 90B of the third embodiment changes input signal Vin to the signal, from which drift of the DC components is removed, during the above initial period. During the latter period of reception of the receive signal, slice circuit 90B changes input signal Vin to the signal, in which the DC components change in accordance with input signal Vin, and converts input signal Vin from the analog signal to the digital signal.

signal Vin occurs throughout the period of reception of the receive signal. In practice, however, the drift of DC components primarily occurs during the initial period of reception of the receive signal, and hardly occurs during the latter period of reception of the receive signal.

Accordingly, by controlling DC component adjusting circuit 92 as described above, input signal Vin can be accurately converted from the analog signal to the digital signal.

According to the fourth embodiment, the slice circuit remove the drift of DC components in input signal Vin during the initial period of reception of the receive signal. During the latter period of reception of the receive signal, the slice circuit changes input signal Vin to the signal, in 50 which the DC components change in accordance with input signal Vin, and converts input signal Vin from the analog signal to the digital signal. Therefore, the drift of DC components in the input signal can be efficiently removed.

# Fifth Embodiment

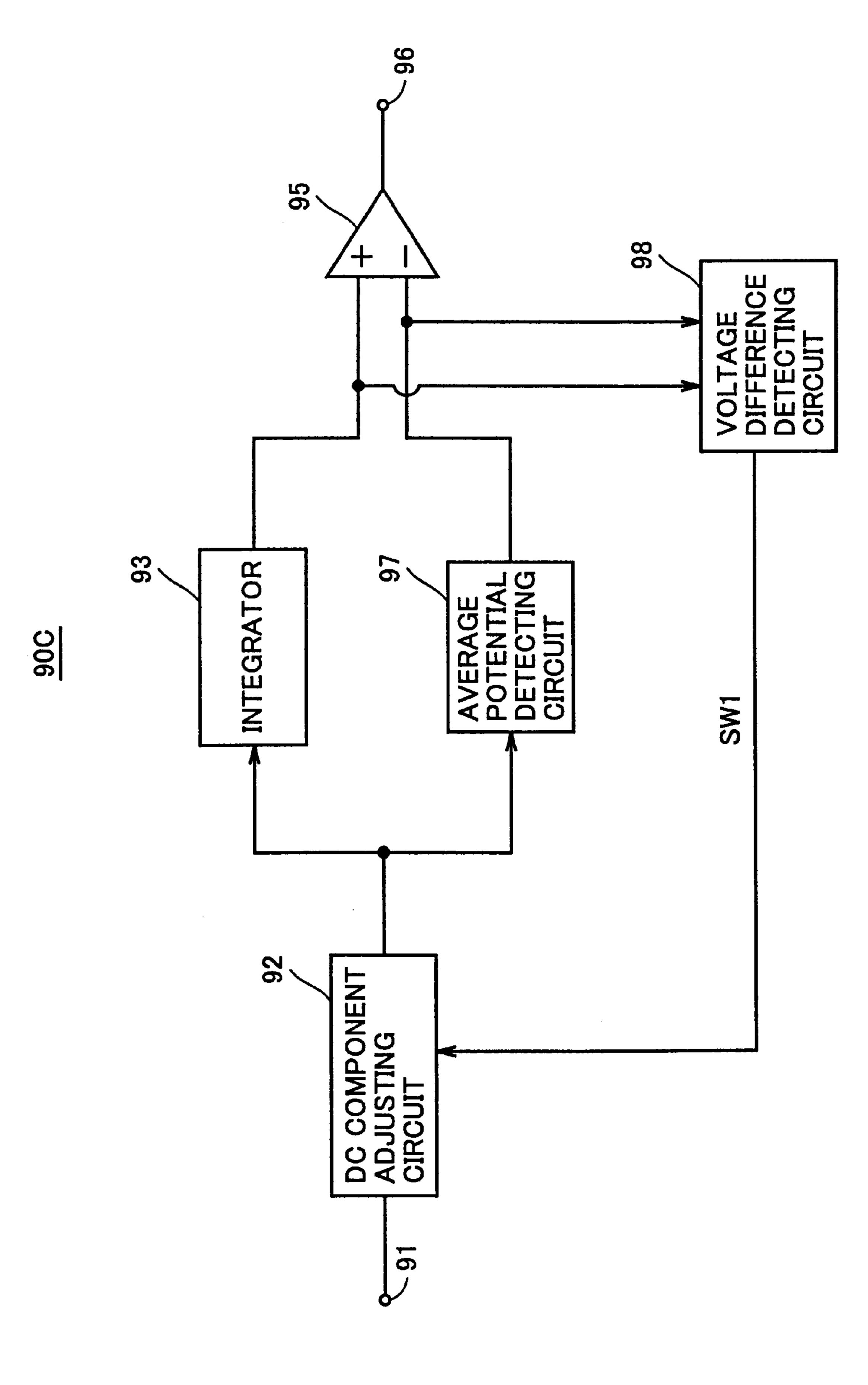

Referring to FIG. 14, a receiver 100C according to a fifth embodiment is the same as receiver 100 except for that control circuit 110 in receiver 100 is removed, and slice circuit 90 in receiver 100 is replaced with a slice circuit 90C. 60

Referring to FIG. 15, slice circuit 90C is the same as slice circuit 90B except for that a voltage difference detecting circuit 98 is additionally employed. Voltage difference detecting circuit 98 detects a voltage difference between two signals applied to comparator 95, and provides signal SW1 65 at H-level to DC component adjusting circuit 92 when the detected voltage difference falls within a predetermined

18

range. When the detected voltage difference falls outside the predetermined range, it provides signal SW1 at L-level to DC component adjusting circuit 92.

DC component adjusting circuit 92, integrator 93 and average potential detecting circuit 97 form a signal processing circuit.

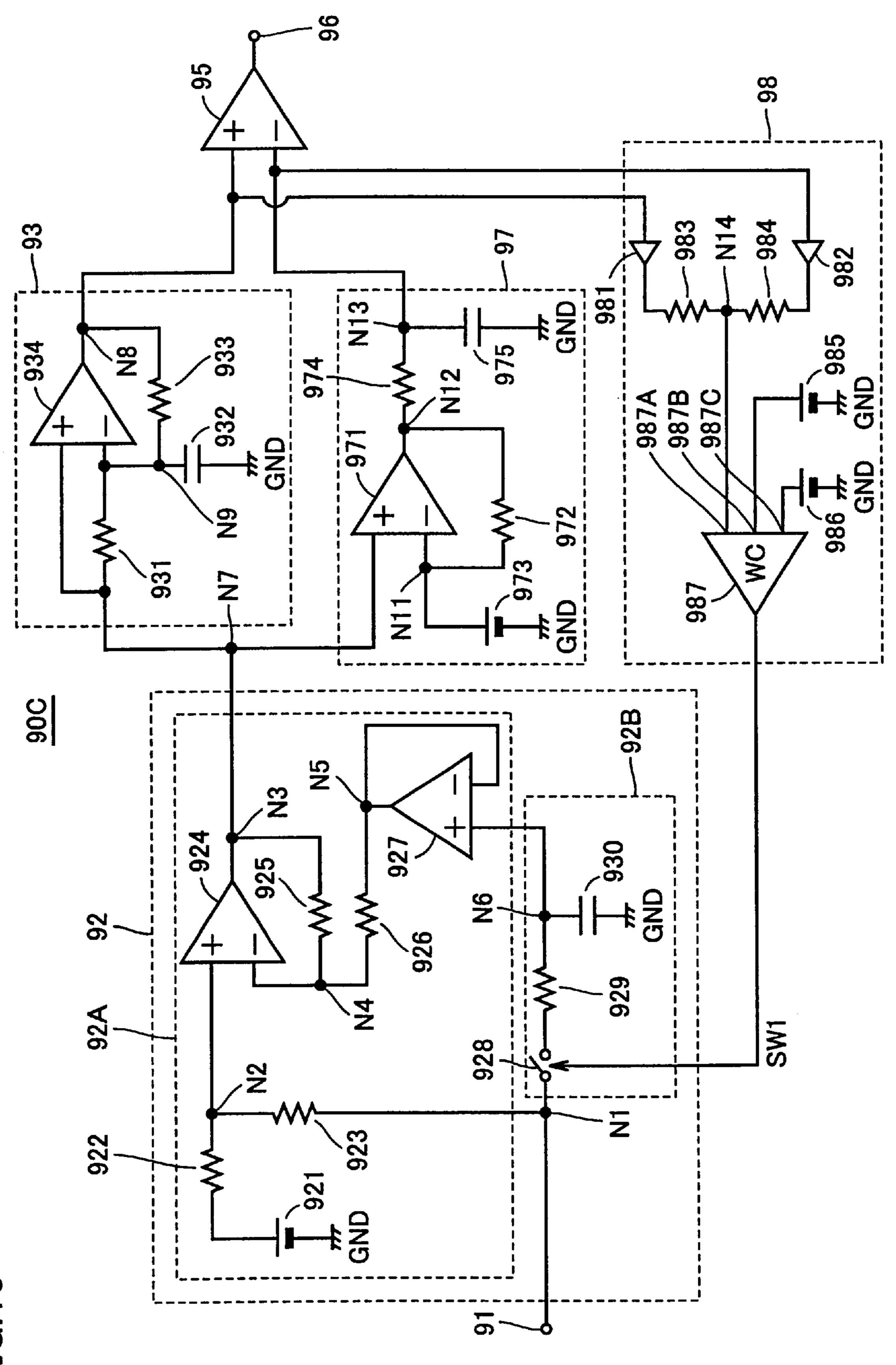

FIG. 16 is a circuit diagram showing DC component adjusting circuit 92, integrator 93, comparator 95, average potential detecting circuit 97 and voltage difference detecting circuit 98 shown in FIG. 15. DC component adjusting circuit 92, integrator 93, comparator 95 and average potential detecting circuit 97 are the same as those already described, and description thereof is not repeated.

Referring to FIG. 16, voltage difference detecting circuit 98 includes buffers 981 and 982, resistances 983 and 984, power supplies 985 and 986, and a window comparator 987. Buffer 981 is connected between node N8 and resistance 983. Buffer 981 provides the output signal of integrator 93 to resistance 983 as it is.

Buffer 982 is connected between node N13 and resistance 984. Buffer 982 sends the output signal of average potential detecting circuit 97 to resistance 984 as it is.

Resistances 983 and 984 are connected in series between buffers 981 and 982. A ratio between resistance values of resistances 983 and 984 is set to 1:1. Therefore, the voltage dividing circuit formed of resistances 983 and 984 detects the voltage difference between the output signal of integrator 93 and the output signal of average potential detecting circuit 97, and provides a divided voltage, which is produced by halving the detected voltage difference, from node N14.

A voltage supply 985 is connected between an input terminal 987B of window comparator 987 and ground node GND. Voltage supply 985 supplies a uniform voltage Vref2. It is preferable that the drift of DC components in input <sup>35</sup> A voltage supply 986 is connected between an input terminal 987C of window comparator 987 and ground node GND. Voltage supply 986 supplies a uniform voltage Vref3 lower than uniform voltage Vref2.

> Window comparator 987 receives on its input terminal 987A the voltage placed on node N14, receives uniform voltage Vref2 on its input terminal 987B and receives uniform voltage Vref3 on its input terminal 987C.

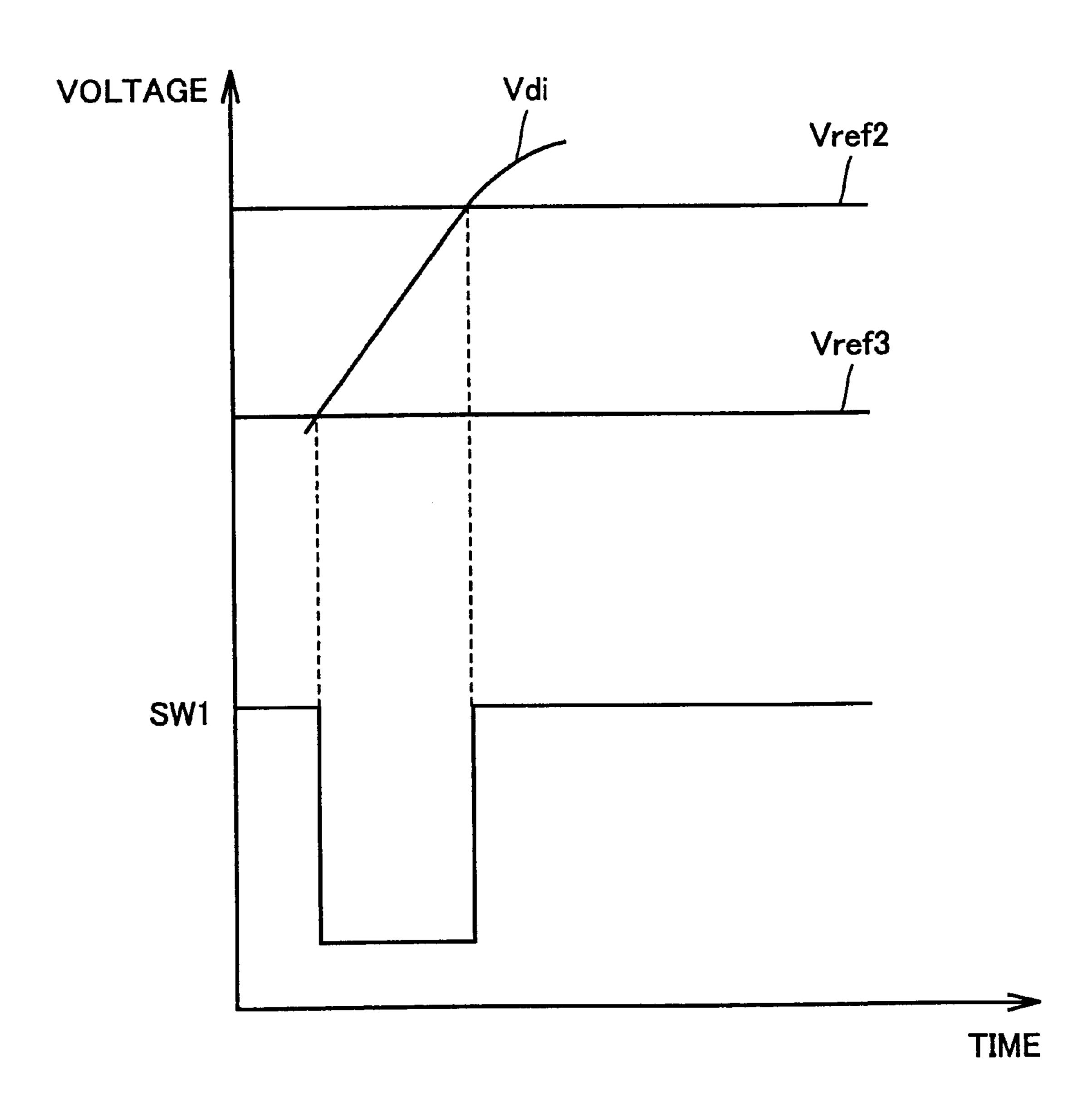

> Referring to FIG. 17, description will now be given on the operation of window comparator 987. Window comparator 987 compares a divided voltage Vdi received on input terminal 987A with uniform voltage Vref2 received on input terminal 987B and uniform voltage Vref3 received on input terminal 987C, and provides signal SW1 formed of the logical level corresponding to results of the comparison to switch 928. Divided voltage Vdi is produced by halving the voltage difference between the output signals of integrator 93 and average potential detecting circuit 97.

More specifically, window comparator 987 provides signal SW1 at L-level when divided voltage Vdi is equal to or higher than uniform voltage Vref3, and is equal to or lower than uniform voltage Vref2. When divided voltage Vdi is lower than uniform voltage Vref3, or is higher than uniform voltage Vref2, window comparator 987 provides signal SW1 at H-level. Thus, window comparator 987 provides signal SW1 at L-level when divided voltage Vdi falls within a predetermined range between uniform voltages Vref3 and Vref3, and provides signal SW1 at H-level when divided voltage Vdi falls outside the predetermined range.

As described above, voltage difference detecting circuit 98 provides signal SW1 at L-level to switch 928 of sample hold circuit 92B when the voltage difference between the

output signals of integrator 93 and average potential detecting circuit 97 falls within the predetermined range, and provides signal SW1 at H-level to switch 928 of sample hold circuit 92B when the voltage difference between the output signals of integrator 93 and average potential detecting 5 circuit 97 falls outside the predetermined range.

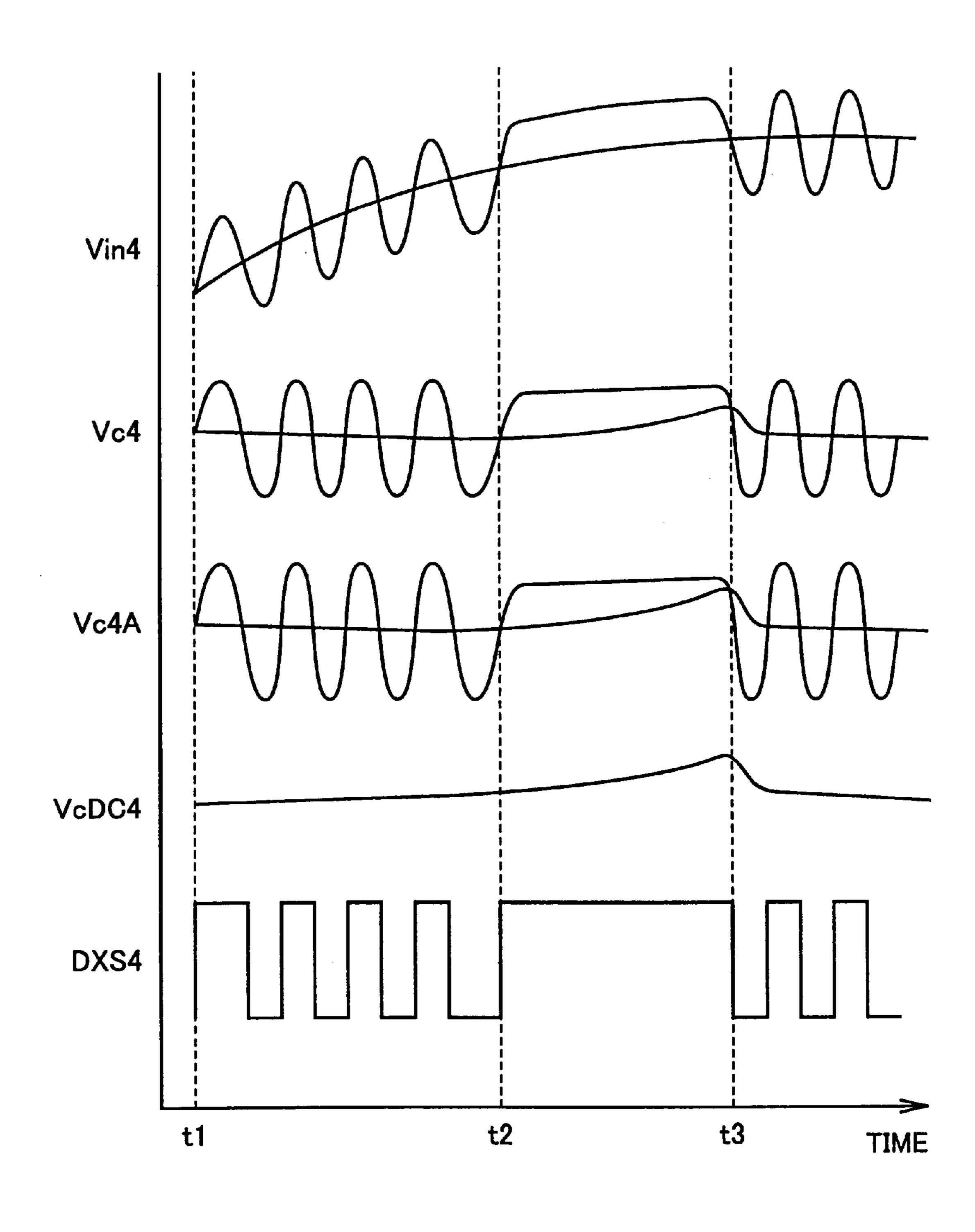

Referring to FIG. 18, description will now be given on the operation of slice circuit 90C. When an input signal Vin4 is applied to DC component adjusting circuit 92 via input terminal 91, DC component adjusting circuit 92 also 10 receives signal SW1 at H-level from voltage difference detecting circuit 98. During the initial period of reception of input signal Vin4, the voltage difference between the two signals supplied to comparator 95 is small (lower than uniform voltage Vref3) so that voltage difference detecting circuit 98 provides signal SW1 at H-level.

In accordance with signal SW1 at H-level, DC component adjusting circuit 92 produces an input signal Vc4, in which AC components in input signal Vin4 are maintained as they are, and DC components are converted to the DC components formed of the uniform voltage level, and provides it to node N7.

Integrator 93 receives input signal Vc4 from DC component adjusting circuit 92, amplifies only the high frequency components of or above the predetermined frequency in input signal Vc4, and provides a signal Vc4A thus produced to the noninverting input terminal of comparator 95 and voltage difference detecting circuit 98. Average potential detecting circuit 97 receives input signal Vc4 from DC component adjusting circuit 92, attenuates the amplitude of input signal Vc4 and detects the average voltage of the signal having the attenuated amplitude. Average potential detecting circuit 97 provides a signal VcDC4 formed of the detected average voltage to the inverting input terminal of comparator 95 and voltage difference detecting circuit 98.

At timing t2, the voltage difference between signal Vc4A sent from integrator 93 and signal VcDC4 sent from average potential detecting circuit 97 falls within the predetermined range so that voltage difference detecting circuit 98 provides signal SW1 at L-level to DC component adjusting circuit 92 40 in the manner already described. In accordance with signal SW1 at L-level, DC component adjusting circuit 92 produces input signal Vc4, in which the voltage level of DC components at timing t2 is maintained in accordance with signal SW1 at L-level, and the DC components change in 45 of the uniform voltage level, and the signal processing of accordance with the change in DC offset in input signal Vin4, and provides it to node N7.

During a period from timing t2 to timing t3, integrator 93 performs the foregoing operation, and provides signal Vc4A to the noninverting input terminal of comparator 95 and 50 voltage difference detecting circuit 98. Average potential detecting circuit 97 provides signal VcDC4 to the inverting input terminal of comparator 95 and voltage difference detecting circuit 98.

Immediately before timing t3, the voltage difference 55 between signal Vc4A sent from integrator 93 and signal VcDC4 sent from average potential detecting circuit 97 becomes lower than uniform voltage Vref3, and falls outside the predetermined range, so that voltage difference detecting circuit 98 provides signal SW1 at H-level to DC component 60 adjusting circuit 92.

At timing t3, DC component adjusting circuit 92 produces input signal Vc4, in which the AC components in input signal Vin4 are maintained, and the DC components are changed to the DC components formed of the uniform 65 voltage level, in accordance with signal SW1 at H-level, and provides it to node N7.

Thereafter, integrator 93 and average potential detecting circuit 97 perform the same operations as those already described. Thus, integrator 93 provides signal Vc4A to the noninverting input terminal of comparator 95 and voltage difference detecting circuit 98, and average potential detecting circuit 97 provides signal VcDC4 to the inverting input terminal of comparator 95 and voltage difference detecting circuit 98.

Thereby, comparator 95 accurately compares the voltage of signal Vc4A sent from integrator 93 with the voltage of signal VcDC4 sent from average potential detecting circuit 97 throughout the period, and provides a digital signal DXS4 having the logical level corresponding to results of the comparison to output terminal 96. Thereby, the operation of slice circuit 90C ends.

In slice circuit 90C, since voltage difference detecting circuit 98 provides signal SW1 to switch 928 of DC component adjusting circuit 92, it is not necessary to use control circuit 110, and switch 928 of sample hold circuit 92B can be automatically switched in accordance with the voltage difference between the two signals supplied to comparator

When the voltage difference between the two signals supplied to comparator 95 falls outside the predetermined range, the DC components in the input signal are changed to the DC components formed of the uniform voltage level. Based on the input signal, in which the DC components have the uniform voltage level, integrator 93 amplifies the high frequency components in the input signal, and average potential detecting circuit 97 detects the average voltage of the input signal. Therefore, comparator 95 can always compare the voltage of output signal of integrator 93 with the voltage of output signal of average potential detecting circuit 97, and can accurately convert the input signal from the analog signal to the digital signal.

The operation of receiver 100C is the same as that of receiver 100 except for that the operation of slice circuit 90 is replaced with the operation of slice circuit 90C.

Structures and operations other than the above are the same as those in the first and third embodiments.

According to the fifth embodiment, the slice circuit includes the DC component adjusting circuit for selectively performing the signal processing, in which the AC components in the input signal are maintained as they are, and the DC components are changed to the DC components formed providing the input signal, in which the DC components change in accordance with the DC offset in the input signal. Also, the slice circuit includes the average potential detecting circuit attenuating the amplitude of the input signal and detecting the average voltage of the attenuated input signal, and the voltage difference detecting circuit producing the signal, which switches the signal processing in the DC component adjusting circuit, in accordance with the voltage difference between the two signals supplied to the comparator. Therefore, the single slice circuit can achieve the following three effects.

- (a) Even when input signal Vin contains the drift of DC offset, the drift of DC offset can be removed, and input signal Vin can be accurately followed and converted from the analog signal to the digital signal.

- (b) Even when the input signal contains components formed of a succession of uniform voltage levels, the input signal can be accurately converted from the analog signal to the digital signal.

- (c) Even when the input signal contains noise components, erroneous detection of noise components can be prevented.

# Sixth Embodiment

Referring to FIG. 19, a receiver 100D according to a sixth embodiment is the same as receiver 100 except for that control circuit 110 in receiver 100 is removed, and slice circuit 90 in receiver 100 is replaced with slice circuit 90B.

Although a period detecting circuit 120 is shown in FIG. 19, period detecting circuit 120 is included in a base band portion arranged in a stage next to receiver 100D, and is not included in receiver 100D.

Period detecting circuit 120 detects a period, for which H-level continues in the digital signal issued from slice circuit 90B, or a period, for which L-level continues in the above digital signal, and provides signal SW1 at H-level to slice circuit 90B when the detected period falls outside a predetermined range. When the detected period falls within the predetermined range, period detecting circuit 120 provides signal SW1 at L-level to slice circuit 90B.

Referring to FIG. 20, slice circuit 90B includes DC component adjusting circuit 92, integrator 93, comparator 95 and average potential detecting circuit 97. DC component adjusting circuit 92, integrator 93, comparator 95 and average potential detecting circuit 97 perform the same functions as those already described in connection with the third embodiment.

DC component adjusting circuit 92 processes the input signal in accordance with the logical level of signal SW1 sent from period detecting circuit 120. In accordance with signal SW1 at H-level sent from period detecting circuit 120, DC component adjusting circuit 92 maintains the AC components in the input signal as they are, and changes the DC components to the DC components formed of the uniform voltage level. DC component adjusting circuit 92 provides the signal, in which the DC components change in accordance with the change in DC offset in the input signal, in accordance with signal SW1 at L-level sent from period detecting circuit 120.

FIG. 21 is a circuit diagram showing DC component adjusting circuit 92, integrator 93, comparator 95 and average potential detecting circuit 97, and also shows period detecting circuit 120 in a block form.

DC component adjusting circuit 92, integrator 93, comparator 95 and average potential detecting circuit 97 have the circuit structures already described.

Referring to FIG. 21, period detecting circuit 120 includes a counter 121, a period signal generating circuit 122 and a comparator 123. Counter 121 receives digital signal DXS from output terminal 96, and receives a period signal SGP from period signal generating circuit 122. Counter 121 counts period signal SGP during a period, for which H-level or L-level continues in digital signal DXS, and provides the count thus obtained to comparator 123.

Period signal generating circuit 122 generates period signal SGP having a uniform period, and provides period 55 signal SGP thus generated to counter 121. Comparator 123 compares the count provided by counter 121 with a reference value. Comparator 123 provides signal SW1 at H-level to DC component adjusting circuit 92 when the count is larger than the reference value, and provides signal SW1 at 60 L-level to DC component adjusting circuit 92 when the count is equal to or lower than, the reference value.

Referring to FIG. 22, an operation in period detecting circuit 120 will now be described. Counter 121 receives digital signal DXS from output terminal 96, and also 65 receives period signal SGP from period signal generating circuit 122. When digital signal DXS changes from L-level

22

to H-level at timing t5, counter 121 starts counting of the components included in period signal SGP, and provides the results to comparator 123.

Then, digital signal DXS changes from H-level to L-level at timing t6 so that counter 121 stops counting. In connection with FIG. 22, it has been described that the components included in period signal SGP are counted when digital signal DXS changes from L-level to H-level. However, counter 121 also starts counting of the components included in period signal SGP when digital signal DXS changes from H-level to L-level. Thus, counter 121 starts counting of the components included in period signal SGP whenever digital signal DXS changes its logical level, and will reset the count for recounting the components included in period signal SGP when a next change occurs in logical level of digital signal DXS.

Thereby, comparator 123 compares the count with the reference value every time it receives the count from counter 121, and provides signal SW1 at H-level to DC component adjusting circuit 92 when the count is larger than the reference value. When the count is equal to or smaller than the reference value, comparator 123 provides signal SW1 at L-level to DC component adjusting circuit 92.

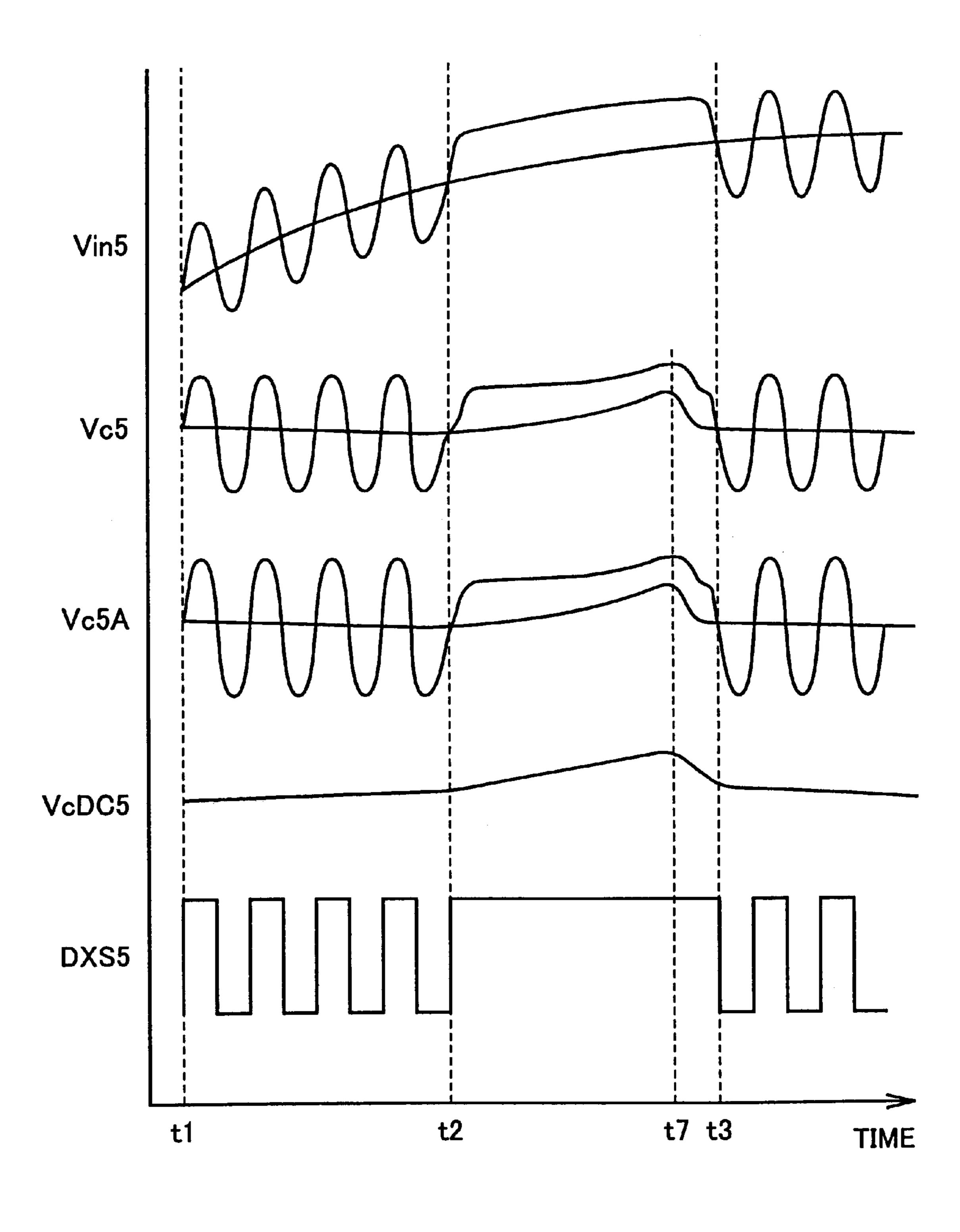

Referring to FIG. 23, the operation of slice circuit 90B in the sixth embodiment will now be described. When an input signal Vin5 is applied to DC component adjusting circuit 92 via input terminal 91, DC component adjusting circuit 92 receives signal SW1 at H-level from period detecting circuit 120. At the start of reception of input signal Vin5, the digital signal provided from slice circuit 90B includes a succession of L-levels so that period detecting circuit 120 provides signal SW1 at H-level.

DC component adjusting circuit 92 provides an input signal Vc5, in which the AC components in input signal Vin5 are maintained as they are, and the DC components are converted to the DC components formed of a uniform voltage level, to node N7 in accordance with signal SW1 at H-level.