US006639854B2

# (12) United States Patent

Hur et al.

(10) Patent No.: US 6,639,854 B2

(45) Date of Patent: Oct. 28, 2003

# (54) REDUNDANCY CIRCUIT OF SEMICONDUCTOR MEMORY DEVICE

(75) Inventors: Young Do Hur, Chungcheongbuk-do

(KR); Jong Chern Lee, Chungcheongbuk-do (KR)

(73) Assignee: Hynix Semiconductor Inc.,

Kyoungki-do (KR)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 37 days.

(21) Appl. No.: 10/020,168

(22) Filed: Dec. 18, 2001

(65) Prior Publication Data

US 2002/0176287 A1 Nov. 28, 2002

(30) Foreign Application Priority Data

May 25, 2001 (KR) ...... 2001-29101

(51) Int. Cl.<sup>7</sup> ...... G11C 7/00

# (56) References Cited

### U.S. PATENT DOCUMENTS

5,561,636 A \* 10/1996 Kirihata et al. ....................... 365/201

\* cited by examiner

Primary Examiner—David Lam

(74) Attorney, Agent, or Firm—Birch, Stewart, Kolasch & Birch, LLD

Birch, LLP.

### (57) ABSTRACT

A semiconductor memory device having a redundancy circuit, includes a normal memory cell array unit, a redundancy memory cell array unit for recovering defective cells of the normal memory cell array unit, and a memory driving unit for operating the normal memory cell adjacent to the redundancy memory cell array unit immediately after a word line move time 'tcycle' is elasped by using address data.

## 32 Claims, 21 Drawing Sheets

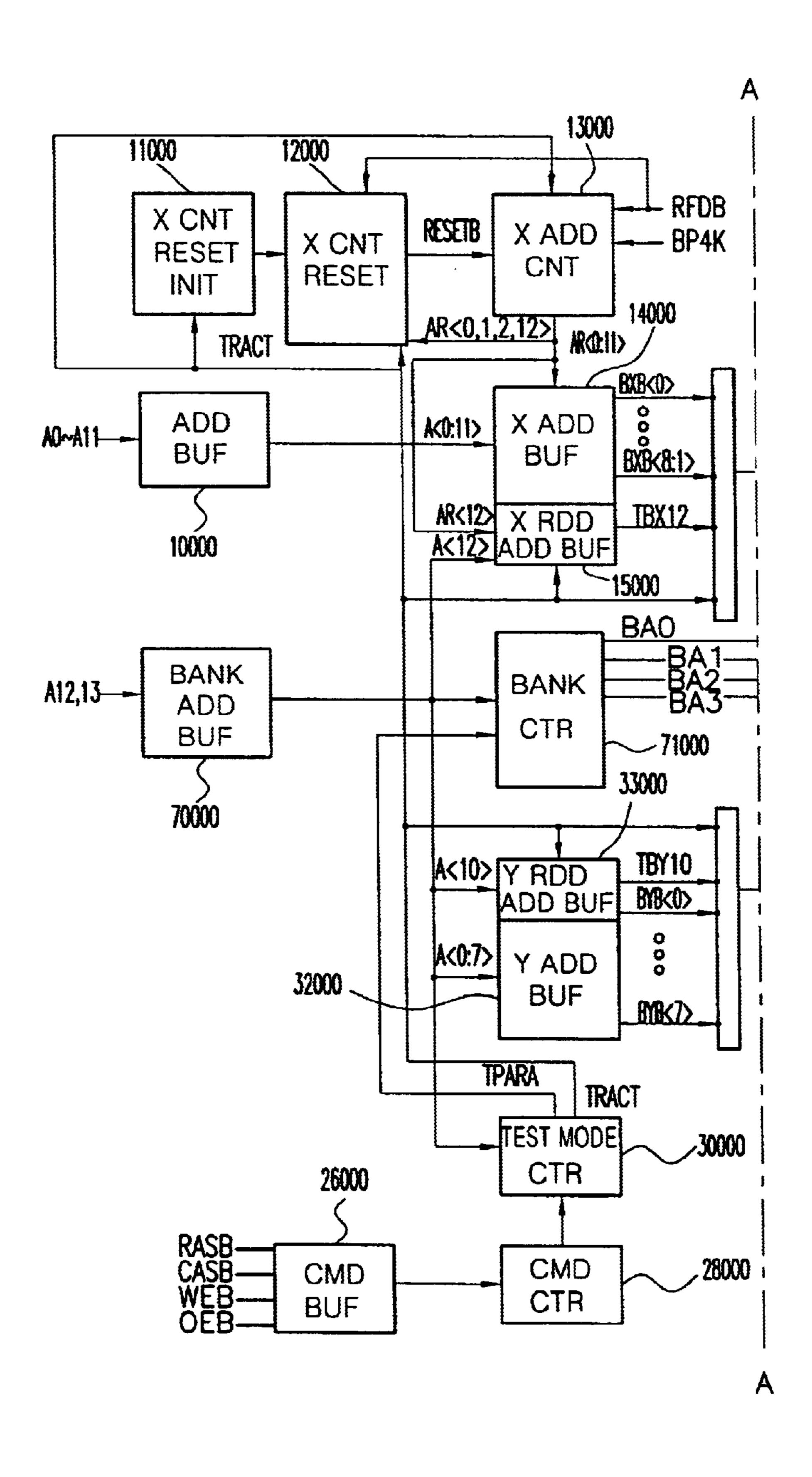

FIG.1

(PRIOR ART)

FIG.2

FIG.3

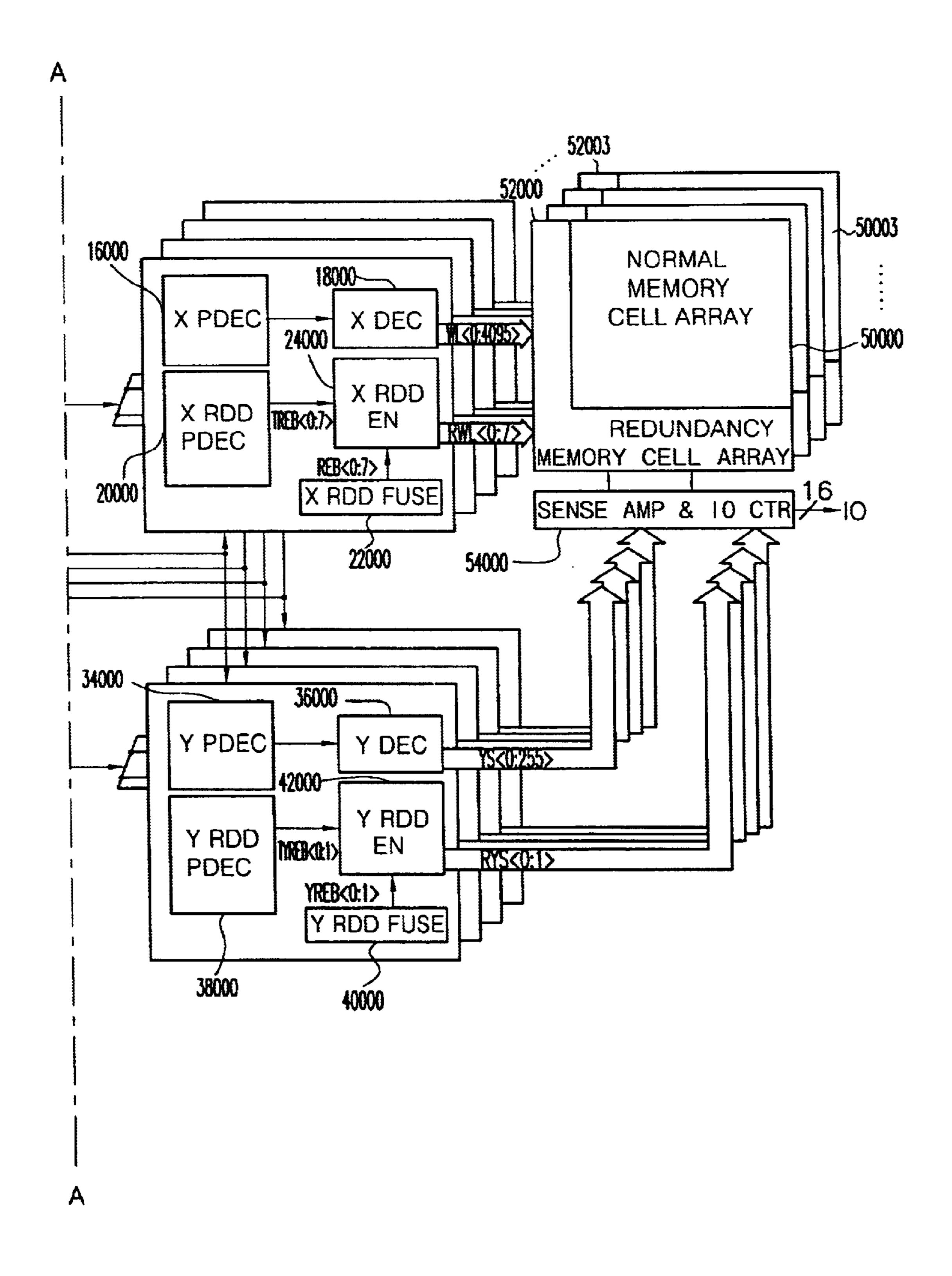

(PRIOR ART)

FIG.4

(PRIOR ART)

FIG.5

(PRIOR ART)

FIG.6

(PRIOR ART)

FIG.7

(PRIOR ART)

FIG.8

(PRIOR ART)

FIG.9 CTR ∞ಶ AMP SENSE 2300 15/0255 88 **#**<(15191) FUSE DEC Y RDD  $\times$ 景 000 \**equiv** 22 喜~  $\times \underline{a}$  $\times$ RFDB BP4K **88 IBX12 TBY10** BB<7> 。。 **\$ BB**<0> **BXB**<0> 000 **A**R<0:15 MODE CMD X RDE ADD BU TEST **35** AR (0,1 A<0:8> ¥0:10 €0:10 RESETB CMD BUF **3**900 88 1300 COUNTER RESET |

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG.20

FIG.21a

FIG.21b

## REDUNDANCY CIRCUIT OF SEMICONDUCTOR MEMORY DEVICE

#### **RELATED APPLICATION**

The present application claims the benefit of Korean Patent Application No. 2001-29101 filed on May 25, 2001, which is herein fully incorporated by reference.

## BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a semiconductor memory device and, more particularly, to a semiconductor memory device having a redundancy circuit capable of detecting <sup>15</sup> deterioration by interference of normal memory cell and redundancy memory cell while reducing detection time.

## 2. Description of the Related Art

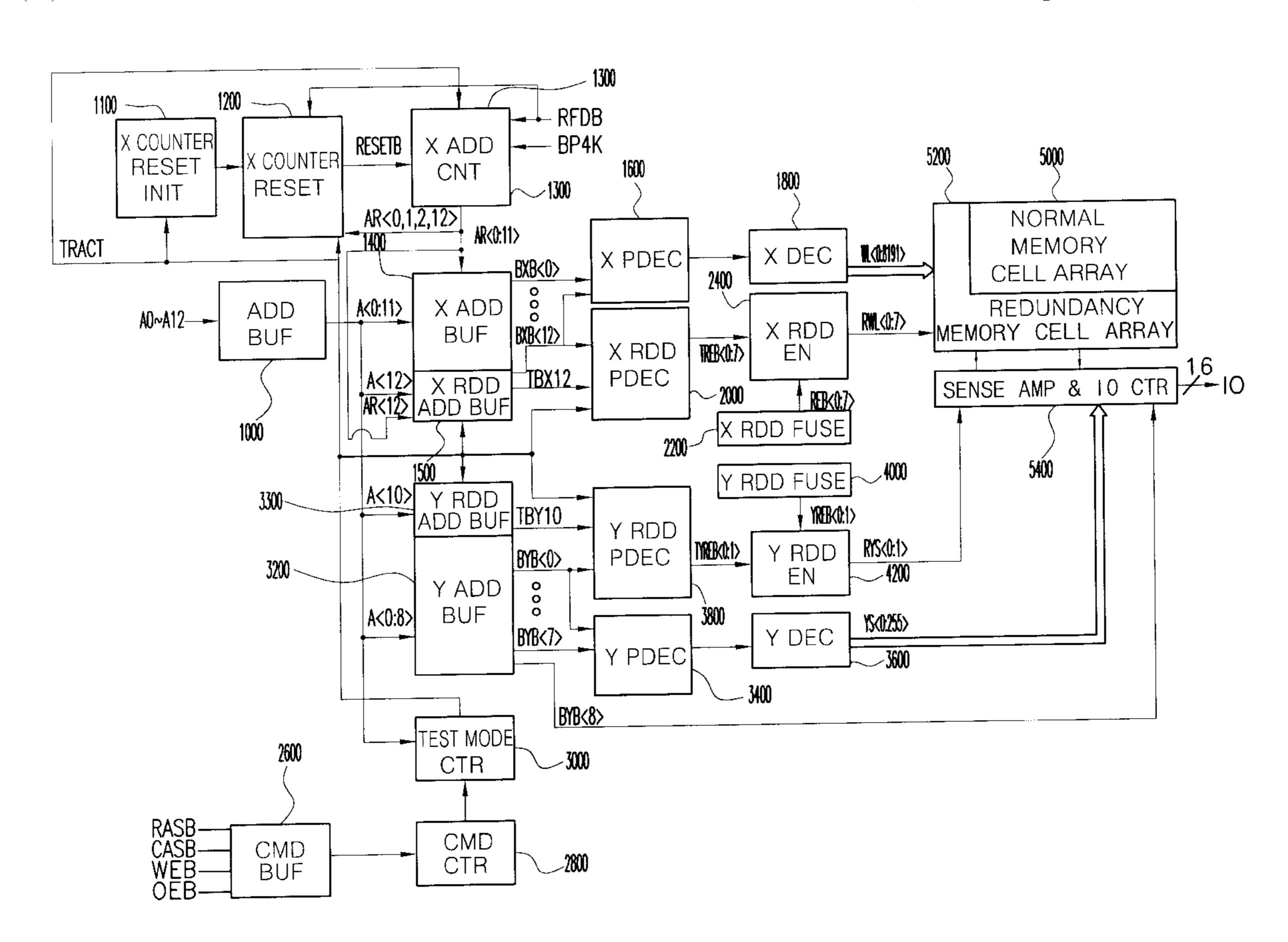

FIG. 1 shows a conventional semiconductor memory device having a redundancy circuit with 64M bit capacitance. Referring to FIG. 1, the conventional semiconductor memory device having the redundancy circuit comprises: a memory cell array unit 50 of 64M bit for storing a plurality of data; a redundancy memory cell array unit 52 of 1K for recovering defective cells of the memory cell array unit 50; and a sense amplification and I/O (input/output) control unit(s) 54 for sensing and amplifying read data received from the memory cell array unit 50 or from the redundancy memory cell array unit 52 and then outputting the amplified data to an I/O line or for sensing and amplifying write data received through the I/O line and then outputting the amplified data to the memory cell array unit 50 or to the redundancy memory cell array unit 52.

The conventional semiconductor memory device further comprises: an address buffer unit 10 for receiving address signals A0~A12 from an external source; a row address counter unit 12 for generating row address counter signals AR<0:12>; a row address buffer unit 14 for receiving the address signals A<0:12> from the address buffer unit 10 and the row address counter signals AR<0:12> from the row address counter unit 12 and generating row address data signals BXB<0:12>; a row predecoder unit 16 for receiving the row address data signals BXB<0:12> from the row address buffer unit 14 and generating decoded signals; and a row decoder unit 18 for decoding signals received from the row predecoder unit 16 and generating signals WL<0:8191> to select word lines of the memory cell array unit 50.

The conventional semiconductor memory device further comprises: a command buffer unit 26 for receiving command signals i.e., row address strobe bar signal RASB, column address strobe bar signal CASB, write enable bar signal WEB, output enable bar signal OEB from external source(s); a command control unit 28 for receiving signals from the command buffer unit 26; and a test mode control unit 28 and the address signals from the command control unit 28 and the address signals A<0:12> from the address buffer unit 10 and generating test mode signals TRATX, TRATY to detect deterioration in word lines and bit lines of the redundancy memory cell array unit 52.

The conventional semiconductor memory device further comprises: a row redundancy predecoder unit 20 for receiving row address data signals BXB<0:2> from the address buffer unit 14 and the test mode signals TRATX from the test mode control unit 30 and generating decoded signals 65 TREB<0:7>; a row redundancy fuse unit 22 for generating signals REB<0:7> by programming row redundancy data;

2

and a row redundancy enable signal generating unit 24 for receiving the decoded signals TREB<0:7> from the row redundancy predecoder unit 20 and the signals REB<0:7> from the row redundancy fuse unit 22 and generating signals RWL<0:7> to select word lines of the redundancy memory cell array unit 52.

The conventional semiconductor memory device further comprises: a column address buffer unit 32 for receiving address signals A<0:8> from the address buffer unit 10 and generating column address data signals BYB<0:8>; a column predecoder unit 34 for receiving column address data signals BYB<0:7> from the column address buffer unit 32 and generating decoded signals; and a column decoder unit 36 for receiving the decoded signals from the column predecoder unit 34, generating signals YS<0:255> to select bit lines of the memory cell array unit 50 and outputting the signals YS<0:255> to the sense amplification and I/O control unit 54.

The conventional semiconductor memory device still further comprises: a column redundancy predecoder unit 38 for receiving a column address data signal BYB<0> from the column address buffer unit 32 and the test mode signals TRATY from the test mode control unit 30 and generating decoded signals TYREB<0:1>; a column redundancy fuse unit 40 for generating signals YREB<0:1> by programming column redundancy data; and a column redundancy enable generating unit 42 for receiving the decoded signals TYREB<0:1> from the column redundancy predecoder unit 38 and the signals YREB<0:1> from the column redundancy fuse unit 40, generating signals RYS<0:1> to select bit lines of the redundancy memory cell array unit 52, and outputting the signals RYS<0:1> to the sense amplification and I/O control unit 54.

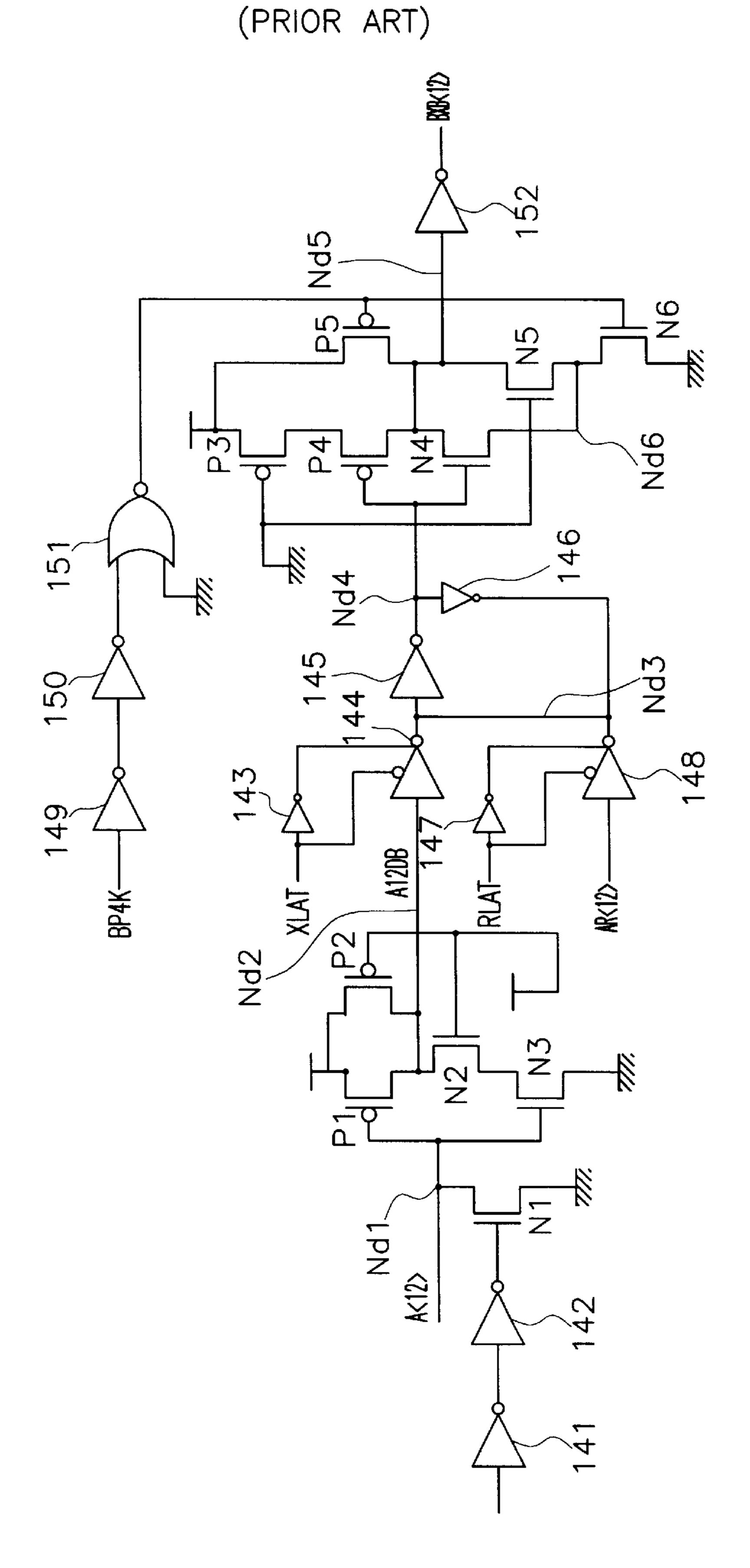

FIG. 2 is a circuit diagram of a part of the conventional row address buffer unit 14 for receiving the highest row address A<12> in FIG. 1. As shown in FIG. 2, the row address buffer unit 14 comprises: an inverter 141 for receiving signals BP4K outputted from a command decoder (not shown) in a refresh operation; an inverter 142 for inverting signals received from the inverter 141; an NMOS transistor Ni for discharging electric potential of a node Nd1 that receives the highest row address signal AK<12> from the address buffer unit 10 according to the signals received from the inverter 142 to the ground voltage Vss; a PMOS transistor P1 for transmitting a source voltage Vcc to a node Nd2 when the signal of the node Nd1 is at a low level; a PMOS transistor P2 connected to the PMOS transistor P1 in a row for applying the source voltage Vcc to its gate; NMOS transistors N2, N3 connected between the node Nd2 and the ground voltage Vss and their operation being controlled by signals of the source voltage Vcc and the node Nd1; an inverter 143 for inverting control signals XLAT; a clock inverter 144 for receiving signals of the node Nd2 according to the control signals XLAT being active at a high level in all operations except for refresh and outputting the inverted signals to a node Nd3; an inverter 145 for receiving signals of the node Nd3 and outputting the inverted signals to a node Nd4; an inverter 146 for receiving signals of the node Nd4 and outputting the inverted signals to the node Nd3; a clock 60 inverter 148 for outputting the highest row address signal AR<12> received from the row address counter unit 12 to the node Nd3 according to control signal RLAT being active at a high level in a refresh operation; PMOS transistors P3, P4 connected between the source voltage Vcc and a node Nd5 in series and their operation being controlled by the ground voltage Vss and the node Nd4; an NMOS transistor N4 connected between the node Nd5 and a node Nd6 and its

operation being controlled by signals of the node Nd4; an inverter 149 for receiving signals BP4K outputted from a command decoder (not shown) in a refresh operation and outputting the inverted signals; an inverter 150 for inverting and outputting signals received from the inverter 149; a 5 NOR gate 151 for receiving signals received from the inverter 150 and the ground voltage Vss and outputting signals according to its NOR logic operation; a PMOS transistor P5 connected between the source voltage Vcc and the node Nd5 and for applying output signals of the NOR 10 gate 151 to the gate; NMOS transistors N5, N6 connected between the node Nd5 and the ground voltage Vss in series and their operation being controlled by the ground voltage Vss and the output signals of the NOR gate 151; and an inverter 152 for inverting signals received from the node 15 Nd5 and outputting them as the row address data signal BXB<12>.

In the highest row address buffer having the above-mentioned structure, the signal BP4K outputted from the command decoder is at a low level, the control signal RLAT is at a low level and the control signal XLAT is at a high level in a normal operation, thereby latching the highest row address signal A<12> received from the address buffer unit 10 and outputting the latched signal as the highest row address data signal BXB<12>.

On the other hand, in a 4K refresh operation, the signal BP4K outputted from the command decoder is at a high level, the control signal RLAT is at a high level and the control signal XLAT is at a low level. Therefore, in the 4K refresh operation, the highest row address buffer is not used since the electric potential of the node Nd1 for receiving the highest row address signal A<12> from the address buffer unit 10 is discharged to the ground Vss by the NMOS transistor N1, and the NMOS transistor N6 connected to the output terminal is turned off by the output signal of the NOR gate 151. At this time, the output signal BXB<12> of the highest row address buffer is at a low level.

In a 8K refresh operation, the signal BP4K outputted from the command decoder is at a low level, the control signal RLAT is at a high level and the control signal XLAT is at a low level. The highest row address signal AR<12> received from the row address counter unit 12 is transmitted to the node Nd3 through the clock inverter 148 operated by the high control signal RLAT. The highest row address signal AR<12> received from the row address counter unit 12 and transmitted to the node Nd3 is latched by the inverters 145, 146 and the latched highest row address signal AR<12> received from the row address counter unit 12 is outputted as the highest row address data signal BXB<12> through the output terminal.

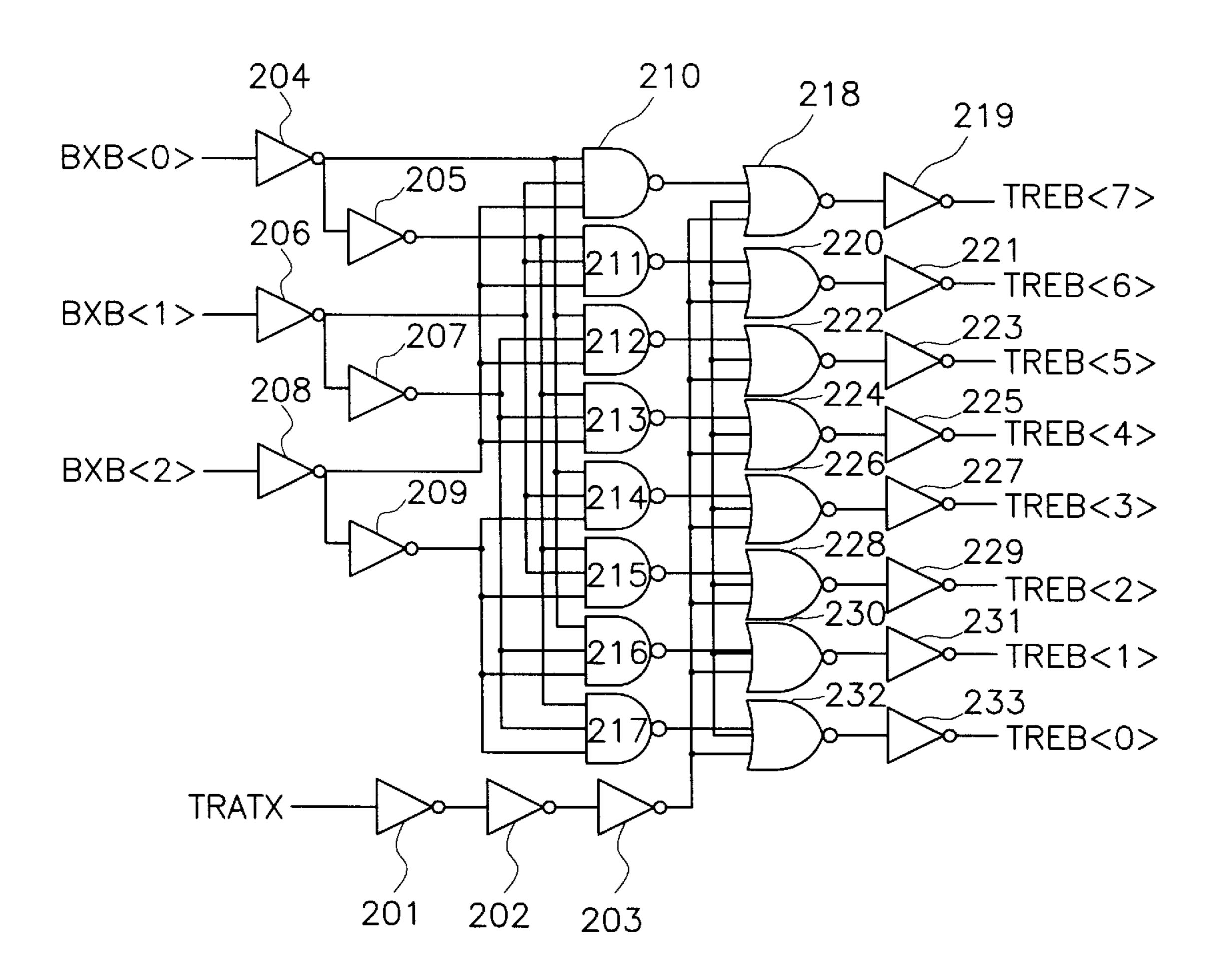

FIG. 3 is a circuit diagram of the conventional row redundancy predecoder unit **20** in FIG. 1. As shown in FIG. 3, the row redundancy predecoder unit 20 includes: an inverter 204 for receiving a row address data signal BXB<0> received from the row address buffer unit 14 and outputting 55 the inverted signal; an inverter 205 for inverting and outputting signals received from the inverter 204; an inverter 206 for receiving a row address data signal BXB<1> received from the row address buffer unit 14 and outputting the inverted signal; an inverter 207 for inverting and out- 60 putting the signal received from the inverter 206; an inverter 208 for receiving a row address data signal BXB<2> received from the row address buffer unit 14 and outputting the inverted signal; an inverter 209 for inverting and outputting the signal received from the inverter 208; a NAND 65 gate 210 for receiving signals from the inverters 204, 206, 208 and outputting signals generated according to its NAND

4

logic operation; a NAND gate 211 for receiving signals from the inverters 205, 206, 208 and outputting signals generated according to its NAND logic operation; a NAND gate 212 for receiving signals from the inverters 204, 207, 208 and outputting signals generated according to its NAND logic operation; a NAND gate 213 for receiving signals from the inverters 205, 207, 208 and outputting signals generated according to its NAND logic operation; a NAND gate 214 for receiving signals from the inverters 204, 206, 209 and outputting signals generated according to its NAND logic operation; a NAND gate 215 for receiving signals from the inverters 205, 206, 209 and outputting signals generated according to its NAND logic operation; a NAND gate 216 for receiving signals from the inverters 204, 207, 209 and outputting signals generated according to its NAND logic operation; a NAND gate 217 for receiving signals from the inverters 205, 207, 209 and outputting signals generated according to its NAND logic operation; an inverter 201 for receiving the test mode signal TRATX from the test mode control unit 30 and outputting the inverted signal; an inverter 202 for receiving the inverted signal from the inverter 201 and outputting the twice-inverted signal; and an inverter 203 for receiving and inverting the twice-inverted signal from the inverter 202 and outputting the three-times inverted signal.

The conventional row redundancy predecoder unit 20 further includes: a NOR gate 218 for receiving output signals from the NAND gate 210 and from the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 219 for receiving and inverting an output signal from the NOR gate 218 and outputting the inverted signal TREB<7>; a NOR gate 220 for receiving output signals from the NAND gate 211 and the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 221 for receiving and inverting an output signal from the NOR gate 220 and outputting the inverted signal TREB<6>; a NOR gate 222 for receiving output signals from the NAND gate 212 and from the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 223 for receiving and inverting an output signal from the NOR gate 222 and outputting the inverted signal TREB<5>; a NOR gate 224 for receiving output signals from the NAND gate 213 and from the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 225 for receiving and inverting an output signal from the NOR gate 224 and outputting the inverted signal TREB<4>; a NOR gate 226 for receiving output signals from the NAND gate 214 and from the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 227 50 for receiving and inverting an output signal from the NOR gate 226 and outputting the inverted signal TREB<3>; a NOR gate 228 for receiving output signals from the NAND gate 215 and the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 229 for receiving and inverting an output signal from the NOR gate 228 and outputting the inverted signal TREB<2>; a NOR gate 230 for receiving output signals from the NAND gate 216 and from the inverter 203 and outputting signals generated according to its NOR logic operation; an inverter 231 for receiving and inverting an output signal from the NOR gate 230 and outputting the inverted signal TREB<1>; a NOR gate 232 for receiving output signals from the NAND gate 217 and from the inverter 203 and outputting signals generated according to its NOR logic operation; and an inverter 233 for receiving and inverting an output signal from the NOR gate 232 and outputting the inverted signal TREB<**0**>.

In the conventional row redundancy predecoder unit 20 having the above-mentioned structure, when the test mode signal TRATX generated at the test mode control unit 30 is active, one of output signals TREB<0:7> is selected at a low level by the row address data signals BXB<0:2> received from the row address buffer unit 14.

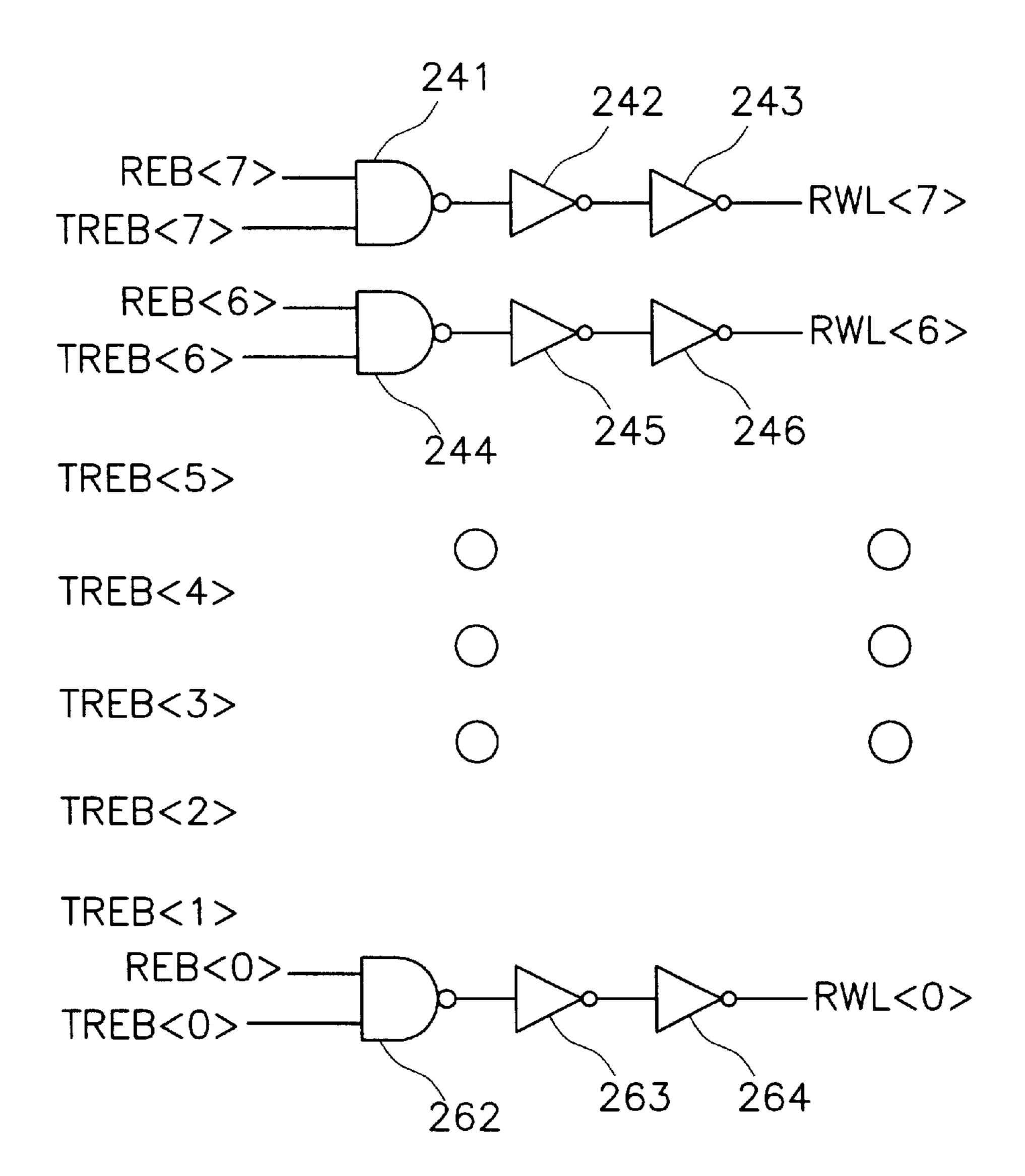

FIG. 4 is a circuit diagram of the conventional row redundancy enable signal generating unit 24 in FIG. 1. As shown in FIG. 4, the conventional row redundancy enable signal generating unit 24 includes: a NAND gate 241 for 10 receiving the signal REB<7> from the row redundancy fuse unit 22 and the signal TREB<7> from the row redundancy predecoder unit 20; an inverter 242 for receiving and inverting an output signal from the NAND gate 241 and outputting the inverted signal; an inverter 243 for receiving and inverting an output signal from the inverter 242 and outputting an inverted signal RWL<7>; a NAND gate 244 for receiving the signal REB<6> from the row redundancy fuse unit 22 and the signal TREB<6> from the row redundancy predecoder unit 20; an inverter 245 for receiving and inverting an 20 output signal from the NAND gate 244 and outputting the inverted signal; and an inverter 246 for receiving and inverting an output signal from the inverter 245 and outputting an inverted signal RWL<6>. In the same manner, the other signals TREB<5>...TREB<0> and the other signals 25 REB<5> . . . REB<0> are processed by the corresponding NAND gate and two inventers to output signals RWL<5>... RWL<0>. For instance, a NAND gate 262 receives the signal REB<0> from the row redundancy fuse unit 22 and the signal TREB<0> from the row redundancy predecoder 30 unit 20. An inverter 263 receives and inverts an output signal from the NAND gate 262 and outputs the inverted signal. Then an inverter 264 receives and inverts an output signal from the inverter 263 and outputs the inverted signal RWL<**0**>.

The signals REB<0:7> received from the row redundancy fuse unit 22 become 'low' when the row address signal applied externally is a row address signal necessary for redundancy and corresponds to data programming in the fuse. In a test mode, however, all of the signals REB<0:7> 40 become 'high'.

FIG. 5 is a circuit diagram of a part of the conventional column address buffer unit 32 in FIG. 1 for particularly illustrating a column address buffer that receives a column address signal A<8> from the address buffer unit 10. 45 Although not shown, the column address buffer unit 32 further includes multiple buffers each having the same structure as shown in FIG. 5 and receiving and processing other column address signals A<0:7>.

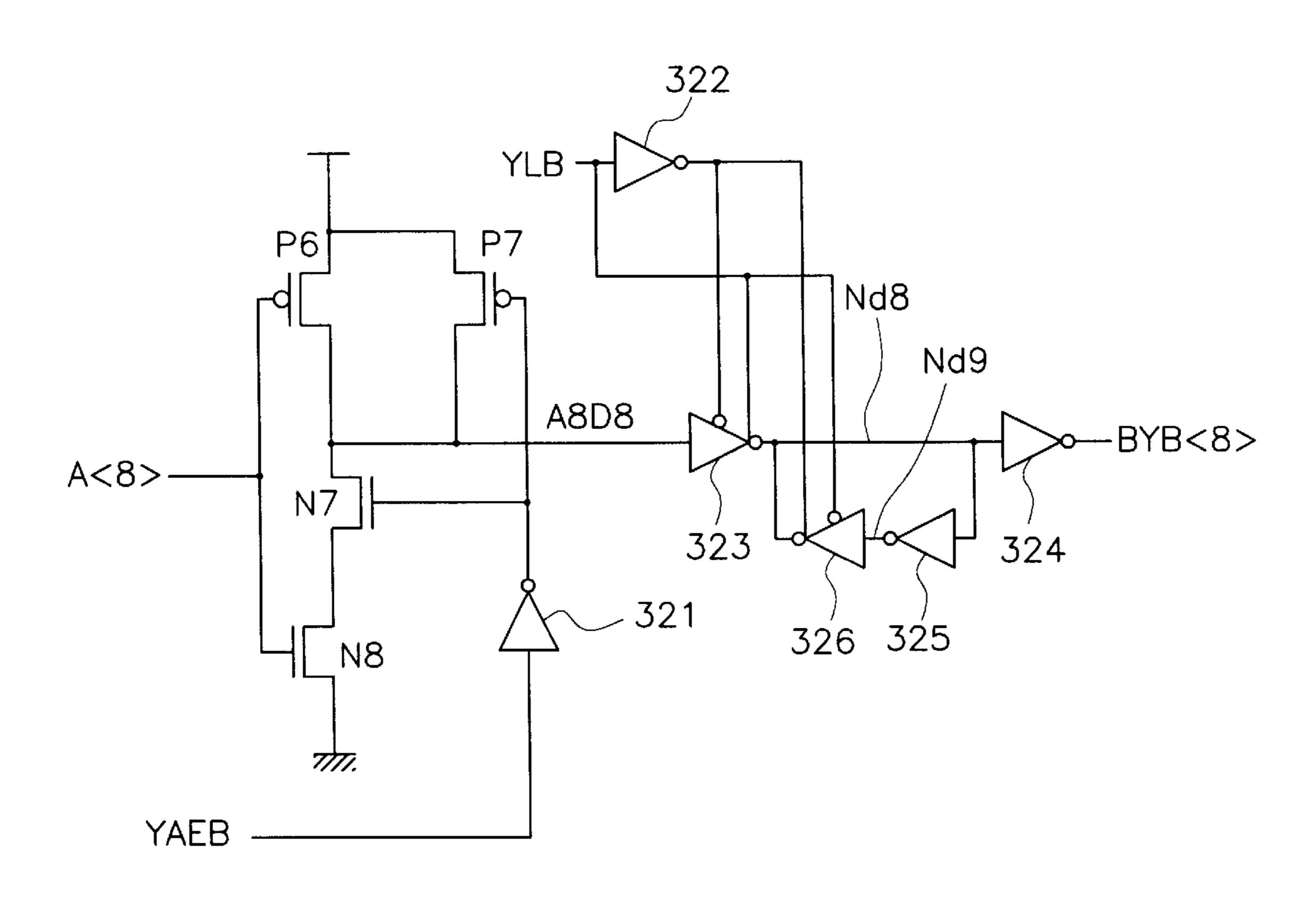

Referring to FIG. 5, the conventional column address 50 buffer unit 32 comprises: a PMOS transistor P6 for transmitting a source voltage Vcc to a node Nd7 by a column address signal A<8> received from the address buffer unit 10; an inverter 321 for receiving and inverting a control signal YAEB and outputting the inverted signal; a PMOS 55 transistor P7 for transmitting the source voltage Vcc to the node Nd7 by the signal received from the inverter 321; NMOS transistors N7, N8 connected between the node Nd7 and the ground voltage Vss in series and their operation being controlled by the output signal of the inverter 321 and 60 the signal A<8> received from the address buffer unit 10; an inverter 322 for inverting a control signal YLB; a clock inverter 323 for transmitting the signal of the node Nd7 to a node Nd8 by a control signal YLB; an inverter 325 for receiving and inverting the signal of the node Nd8 and 65 outputting the inverted signal to node Nd9; a clock inverter 326 for transmitting the signal of the node Nd9 to the node

6

Nd8 by the control signal YLB; and an inverter 324 for receiving and inverting the signal of the node Nd8 and outputting the inverted signal BYB<8>.

The control signal YAEB is a signal for controlling receipt of the column address signal A<8> from the address buffer unit 10. The control signal YLB becomes 'low' in a column operation, thereby transmitting to the node Nd8 and latching the column address signal A<8> transmitted to the node Nd7.

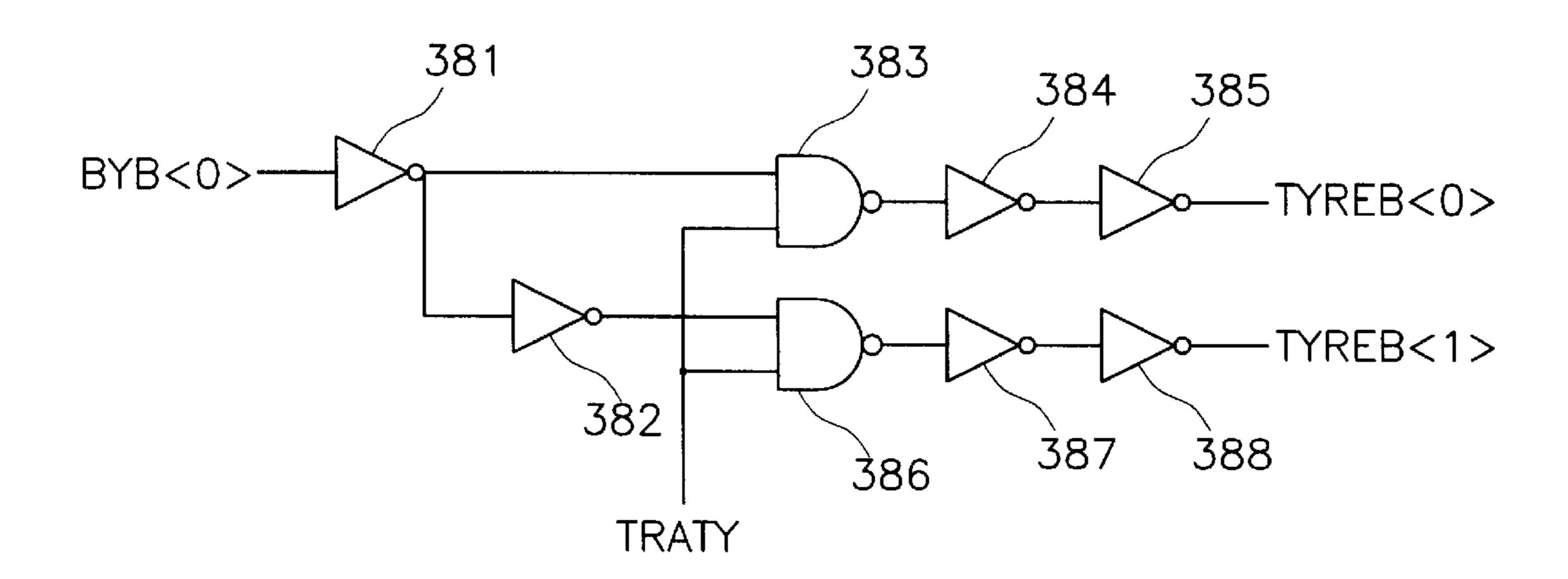

FIG. 6 is a circuit diagram of the conventional column redundancy predecoder unit 38 in FIG. 1. As shown in FIG. 6, the column redundancy predecoder unit 38 comprises: an inverter 381 for receiving and inverting a signal BYB<0> from the column address buffer unit 32 and outputting the inverted signal; a NAND gate 383 for receiving signals from the inverter **381** and the test mode signal TRATY from the test mode control unit 30 and outputting signals generated according to its NAND logic operation; an inverter 384 for receiving and inverting an output signal from the NAND gate 383 and outputting the inverted signal; an inverter 385 for receiving and inverting a signal from the inverter **384** and outputting an inverted signal TYREB<0>; an inverter 382 for receiving and inverting an output signal from the inverter **381** and outputting the inverted signal; a NAND gate **386** for receiving an output signal from the inverter 382 and the test mode signal TRATY from the test mode control unit 30 and outputting signals generated according to its NAND logic operation; an inverter 387 for receiving and inverting an output signal from the NAND gate 386 and outputting the inverted signal; and an inverter 388 for receiving and inverting an output signal from the inverter 387 and outputting the inverted signal TYREB<1>. When the test mode signal TRATY from the test mode control unit 30 is active, one of the outputted signals TYREB<0:1> becomes 'low' according to the signal BYB<0> received from the column address buffer unit 32.

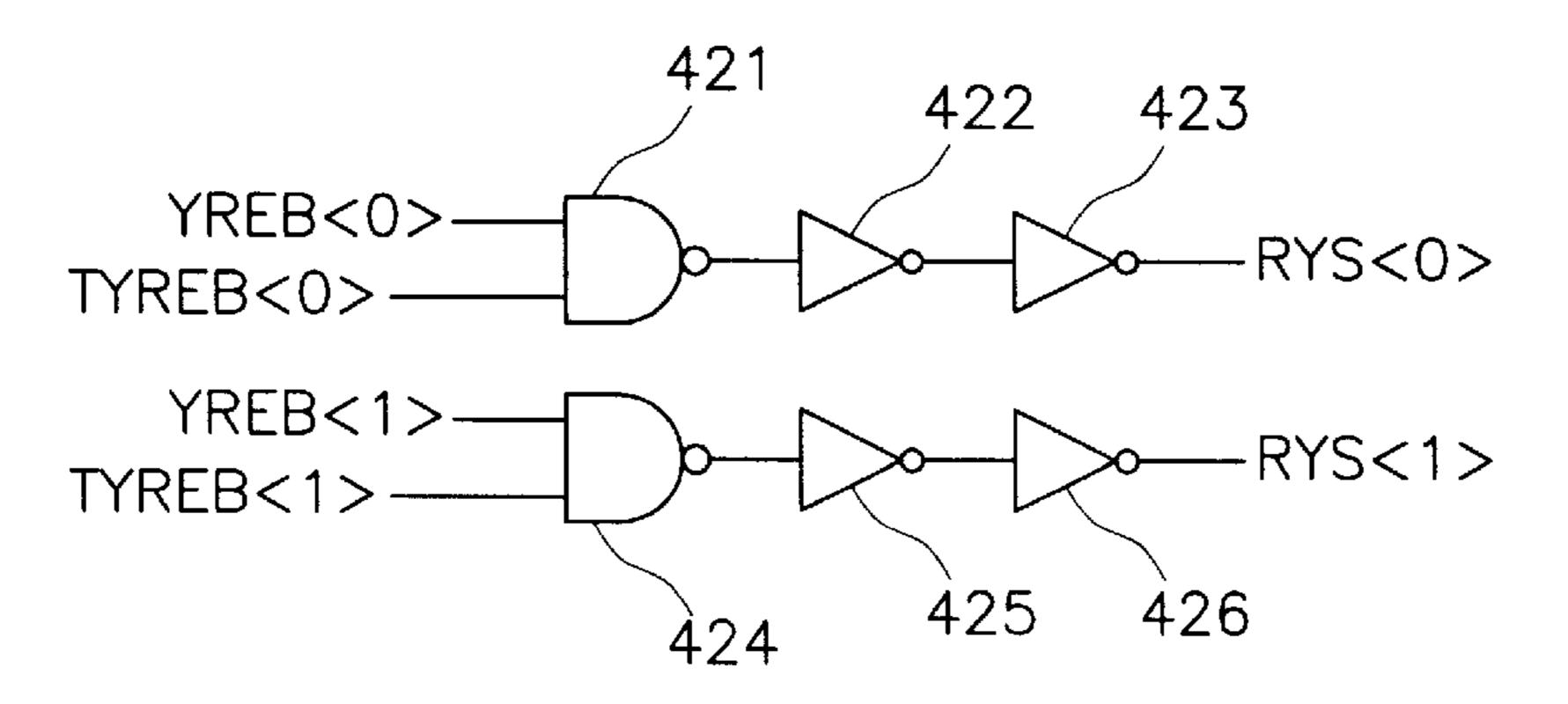

FIG. 7 is a circuit diagram of the conventional column redundancy enable signal generating unit 42 in FIG. 1. As shown in FIG. 7, the column redundancy enable signal generation unit 42 comprises: a NAND gate 421 for receiving the signal YREB<0> from the column redundancy fuse unit 40 and the signal TYREB<0> from the column redundancy predecoder unit 38; an inverter 422 for receiving and inverting an output signal from the NAND gate 421 and outputting the inverted signal; an inverter 423 for receiving and inverting an output signal from the inverter 422 and outputting the inverted signal RYS<0>; a NAND gate 424 for receiving the signal YREB<1> from the column redundancy fuse unit 40 and the signal TYREB<1> from the column redundancy predecoder unit 38; an inverter 425 for receiving and inverting an output signal from the NAND gate 424 and outputting the inverted signal; and an inverter 426 for receiving and inverting an output signal from the inverter 425 and outputting the inverted signal RYS<1>.

The signals YREB<0:1> received from the column redundancy fuse unit 40 become 'low' by data programming in fuse. Here, the signals YREB<0:1> become 'low' when the column address signal applied externally is a column address signal necessary for redundancy and corresponds to data programming in the fuse. In a test mode, however, all of the signals YREB<0:1> become 'high'.

The operation of the conventional semiconductor memory device having the above-mentioned structure will be described in more detail as follows.

In order to use redundancy memory cells provided in a redundancy region of the memory device, it is first required

to detect deterioration of redundancy memory cells. If there is no deterioration or damage to the redundancy memory cells, the redundancy memory cells will replace defective memory cells. The test operation to detect any deterioration in the redundancy memory cells starts when a test mode 5 signal TRATX becomes active and involves detection of any deterioration of word lines in the redundancy memory cell array unit 52.

The test mode signal TRATX is generated by a combination of the address signals A<0:8> received from the address buffer unit 10 and the signal received from the command control unit 28 in the test mode control unit 30, and is applied to the row redundancy predecoder unit 20.

The row redundancy predecoder unit 20 outputs one of 8 output signals TREB<0:7> as a 'low' level signal based on the test mode signal TRATX received from the test mode control unit 30 and the row address data signals BXB<0:2> received from the row address buffer unit 14. Here, the operation that a 'low' signal is generated from the row redundancy predecoder unit 20 corresponds to the operation that redundancy cells are selected instead of the defective cells in a normal operation mode. And, the defects of word lines are detected by accessing the redundancy cell array. In a normal operation, a signal for selecting redundancy memory cells by fuse data is one of signals REB<0:7> outputted from the row redundancy fuse unit 22 that becomes 'low'.

The test operation to detect a deterioration of bit lines of the redundancy cell array unit 52 is performed by applying the test mode signal TRATY to the column redundancy predecoder unit 38.

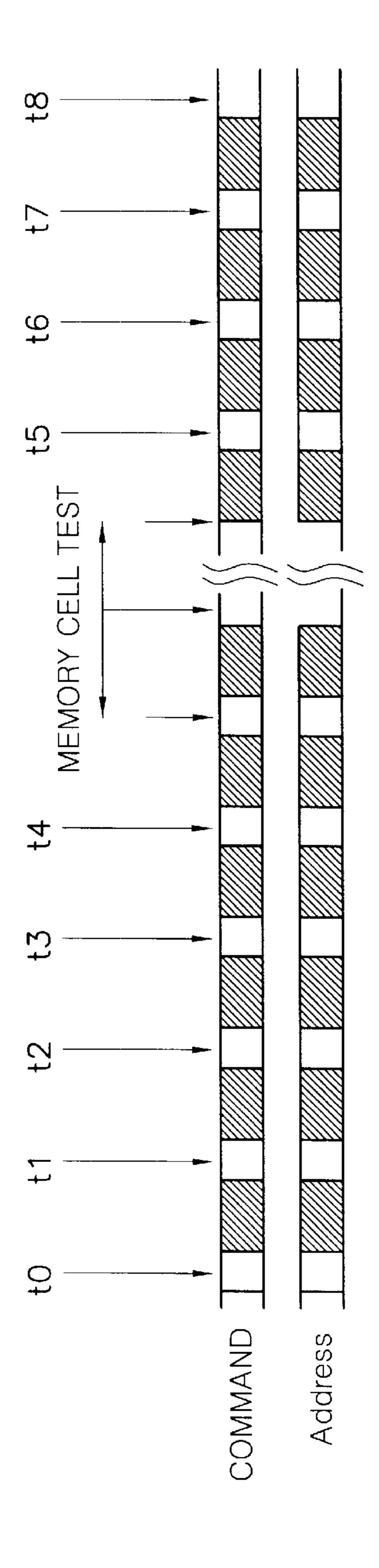

FIG. 8 is an operation timing for detecting deterioration of redundancy memory cells by using the conventional semiconductor memory device having the redundancy circuit as 35 discussed above. In FIG. 8, to represents a time when a normal operation is performed, t1 represents a time for precharging all memory cells, t2 represents a time for entering into the test mode by application of particular commands and addresses, t3 represents a time for activating 40 the test mode signal TRATX or TRATY for redundancy memory cell test, t4 represents a time for testing deterioration of redundancy memory cells, t5 represents a time for exiting the test mode, t6 represents a time for precharging all memory cells, t7 represents a time for applying a particular 45 command for a normal operation, and t8 represents a time for performing a normal operation instead of the test mode operation.

However, the conventional semiconductor memory device having the redundancy circuit has at least several <sup>50</sup> drawbacks. First, a word line disturb test mode is a mode for testing the interference effect of all word line operations by fixing all bit lines (bit line addresses) and is essential to detecting deterioration of memory cells. The necessary time for the word line disturb test mode will be represented in <sup>55</sup> EQUATION 1.

tWRITE+tDISTURB+tSCAN+tREAD=(tcycle×Nred\_memory)+(trefresh×Nword)+(tcycle×Nword2)+(tcycle×Nred\_memory) capable of [EQUATION 1] 60 invention.

In EQUATION 1 above, "tWRITE" is a time necessary for a write operation, and "tcycle" is a time necessary for turning off the word lines, after driving the word lines of memory cells and performing one read or write operation. "tcycle" is also referred to hereinafter as "word line move 65 time". Generally, the word line move time is 100 ns. "Nred\_memory" is the number of redundancy memory cells

8

and "tDISTURB" is a time necessary for being influenced by all the word lines "Nword" including tested word lines of the memory cells, corresponding to continuous on/off time during a refresh time "trefresh" (generally 64 msec) to all word lines. "tSACN" is an operation signal for refreshing all the word lines in order to maintain data of the memory cells connected to unselected word lines. The refresh operation is expressed by "Nword2". The "tREAD" is a time necessary for performing a read operation.

The test time T of normal memory cell regions is represented in EQUATION 2. In this equation, "Nmemory" indicates the entire normal memory cell area.

T=(tcycle×Nmemory)+(trefresh×Nword)+(tcycle×Nword2)+(tcycle×Nmemory)

[EQUATION 2]

As an example, when a redundancy memory cell having 8 word lines and 2 column lines is connected to a normal memory cell of 64M bit having 8192 word lines, and 4 bit lines are connected to 1 column line comprising 16 I/O lines, Nred\_memory is 1024 bit. Here, the Nred\_memory having 1024 bit needs the test time of approximately 531 sec. according to EQUATION 1 above. The time for testing normal memory cells is also determined to be 537.7 sec. and EQUATIONs 1 and 2 have an approximate value by a multiplication 'trefresh×Nword'. This is because word lines having redundancy memory cells connected thereto correspond to the number of word lines of normal memory cells and therefore, a disturb operation time is necessary for all word lines. That is, there is a problem in that the test time for redundancy memory cells is similar to that for normal memory cells although the number of redundancy memory cells is smaller than the number of normal memory cells.

Second, there is still a problem in that there remains deterioration that is not detected by testing of the redundancy memory cells. That is, in the conventional test mode for detecting redundancy memory cells, redundancy memory cell blocks are detected by performing a test mode after detecting the normal memory cells and therefore, any deterioration generated at the interface of redundancy memory cells adjacent to the normal memory cells is not tested due to the time lapse of several msec. Therefore, certain defective memory cells are substituted with those redundancy memory cells having deteriorations. This causes a problem of recovery failures and deterioration in device performance.

# SUMMARY OF THE INVENTION

Accordingly, the present invention has been made to solve the above-mentioned problems and other problems associated with conventional art.

An object of the invention is to provide a redundancy method for semiconductor memory device, capable of detecting deterioration by interference of memory cells adjacent to a normal memory cell with a redundancy memory cell while reducing the detection time.

Another object of the present invention is to provide a semiconductor memory device having a redundancy circuit capable of realizing a redundancy method of the present invention

In order to achieve the above and other objects, a semiconductor memory device according to an embodiment of the present invention comprises a normal memory cell array unit, a redundancy memory cell array unit for recovering defective cells of the normal memory cell array unit, and a memory driving unit for operating the redundancy memory cell array unit and the adjacent normal memory cell imme-

diately after a word line move time 'tcycle' in the normal memory cell array unit by using address data.

The memory driving unit according to an embodiment of the present invention comprises: a test mode signal generating unit for generating a test mode signal to indicate a test 5 operation; a row address counter unit for receiving the test mode signal, a first signal enabled in a refresh mode and a second signal toggling in the refresh mode and for generating a row address counter signal; a row counter reset unit for receiving the test mode signal, the second signal and a 10 part of the row address counter signal and for generating a reset signal to reset the row address counter unit; a row counter reset initializing unit for receiving the test mode signal and for generating an initialization signal to initialize the row counter reset unit; a row address buffer unit for 15 receiving the row address counter signal and a row address signal from an external source and for generating a row address data signal; a row predecoder and a decoder unit for receiving the row address data signal and for generating a signal to select word lines of the normal memory cell array 20 unit; a row redundancy address buffer unit for receiving the highest row address signal received from an outside source, the test mode signal and the row address counter signal and for generating a row redundancy address signal; a row redundancy predecoder and decoder unit for receiving the 25 row address data signal, the test mode signal and the row redundancy address signal and for generating a signal to select word lines of the redundancy memory cell array unit; a column address buffer unit for receiving a column address signal from an external source and for generating a column 30 address data signal; a column predecoder and decoder unit for receiving the column address data signal and for generating a signal to select word lines of the normal memory cell array unit; a column redundancy address buffer unit for receiving the highest column address signal received from 35 an external source and the test mode signal and for generating a column redundancy address signal; and a column redundancy predecoder and decoder unit for receiving the column address data signal, the test mode signal and the column redundancy address signal and for generating a 40 signal to select redundancy word lines of the redundancy memory cell array unit.

A semiconductor memory device according to another embodiment of the present invention comprises: a normal memory cell array unit comprising N memory banks for 45 storing a plurality of data; a redundancy memory cell array unit comprising N memory banks for recovering defective cells of the normal memory cell array unit; a test mode signal generating unit for generating a test mode signal to indicate a test operation; a row address counter unit for 50 receiving the test mode signal, a first signal enabled in a refresh mode and a second signal toggling in the refresh mode and for generating a row address counter signal; a row counter reset unit for receiving the test mode signal, the second signal and a part of the row address counter signal 55 and for generating a reset signal to reset the row address counter unit; a row counter reset initializing unit for receiving the test mode signal and for generating an initialization signal to initialize the row counter reset unit; a row address buffer unit for receiving the row address counter signal and 60 a row address signal from an outside source and for generating a row address data signal; N row predecoder and decoder units for receiving the row address data signal and for generating a signal to select word lines of the normal memory cell array unit; a row redundancy address buffer 65 unit for receiving the highest row address signal, the test mode signal and the row address counter signal and for

10

generating a row redundancy address signal; N row redundancy predecoder and decoder units for receiving the row address data signal, the test mode signal and the row redundancy address signal and for generating a signal to select redundancy word lines of the redundancy memory cell array unit; a column address buffer unit for receiving a column address signal from an external source and for generating a column address data signal; N column predecoder and decoder units for receiving the column address data signal and for generating a signal to select word lines of the normal memory cell array unit; a column redundancy address buffer unit for receiving the highest column address signal received from an external source and the test mode signal and for generating a column redundancy address signal; N column redundancy predecoder and decoder units for receiving the column address data signal, the test mode signal and the column redundancy address signal and for generating a signal to select redundancy word lines of the redundancy memory cell array unit; a band address buffer unit for receiving an address signal having address data of a memory bank; and a bank control units for selectively controlling operations of the N row predecoder and decoder unit, the N row redundancy predecoder and decoder units, the N column predecoder and decoder units, and the N column redundancy predecoder and decoder units by decoding address signals received from the bank address buffer unit in the test mode.

These and other objects of the present application will become more readily apparent from the detailed description given hereinafter. However, it should be understood that the detailed description and specific examples, while indicating preferred embodiments of the invention, are given by way of illustration only, since various changes and modifications within the spirit and scope of the invention will become apparent to those skilled in the art from this detailed description.

## BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will become more fully understood from the detailed description given hereinbelow and the accompanying drawings which are given by way of illustration only, and thus are not limitative of the present invention and wherein:

FIG. 1 is a block diagram for showing a semiconductor memory device having a conventional redundancy circuit.

FIG. 2 is a circuit diagram of a conventional row address buffer unit receiving the highest row address signal illustrated in FIG. 1.

FIG. 3 is a circuit diagram of a conventional row redundancy predecoder unit illustrated in FIG. 1.

FIG. 4 is a circuit diagram of a conventional row redundancy enable signal generating unit illustrated in FIG. 1.

FIG. 5 is a circuit diagram of a conventional column address buffer unit illustrated in FIG. 1.

FIG. 6 is a circuit diagram of a conventional column redundancy predecoder unit illustrated in FIG. 1.

FIG. 7 is a circuit diagram of a conventional column redundancy enable signal generating unit illustrated in FIG. 1

FIG. 8 is an operation timing for detecting defects of redundancy memory cells in a semiconductor memory device having a conventional redundancy circuit.

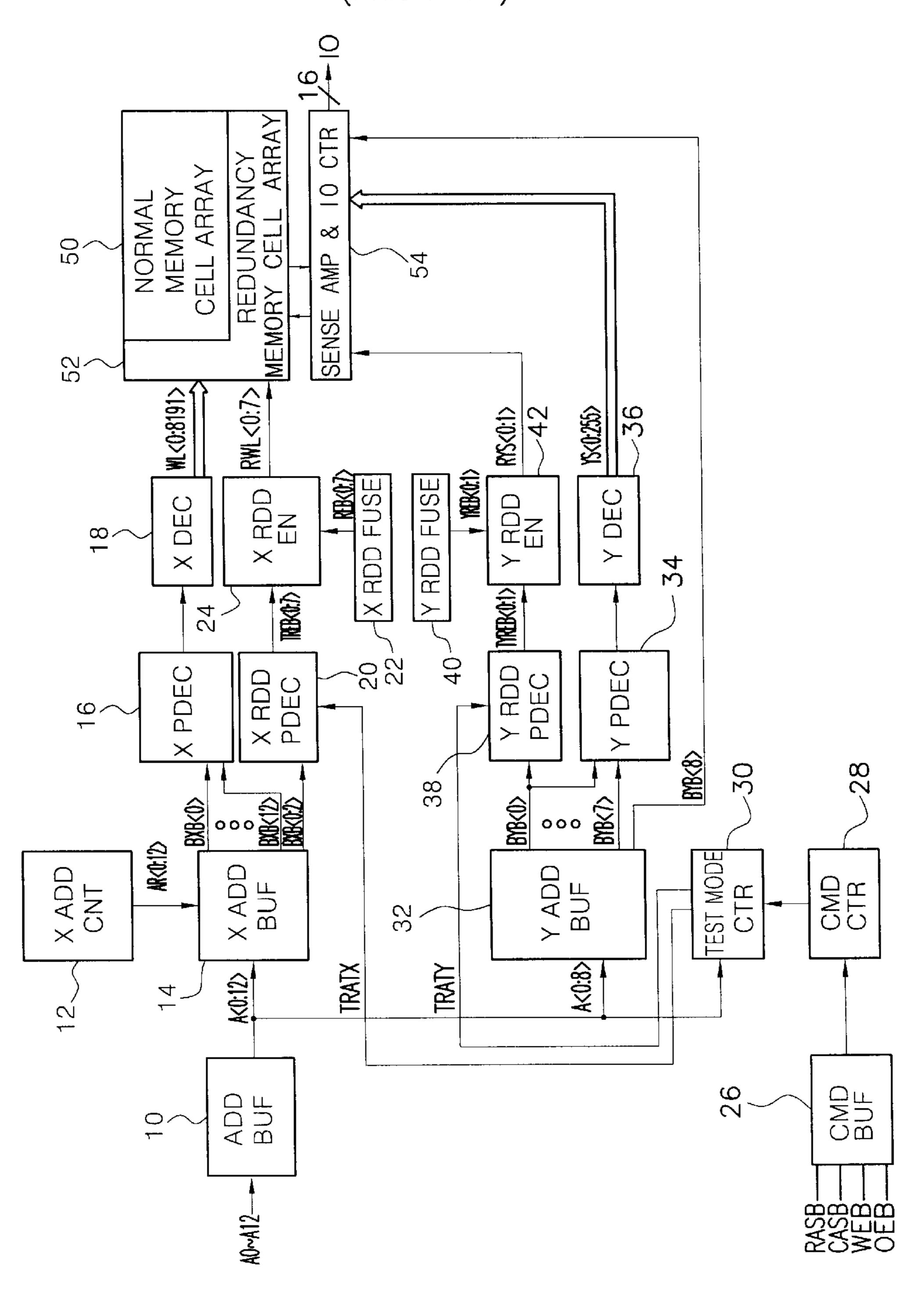

FIG. 9 is a block diagram of a semiconductor memory device having a redundancy circuit according to a first embodiment of the present invention.

FIG. 10 is a circuit diagram of a row redundancy address buffer unit for receiving the row redundancy highest address signal in the device of FIG. 9 according to an embodiment of the present invention.

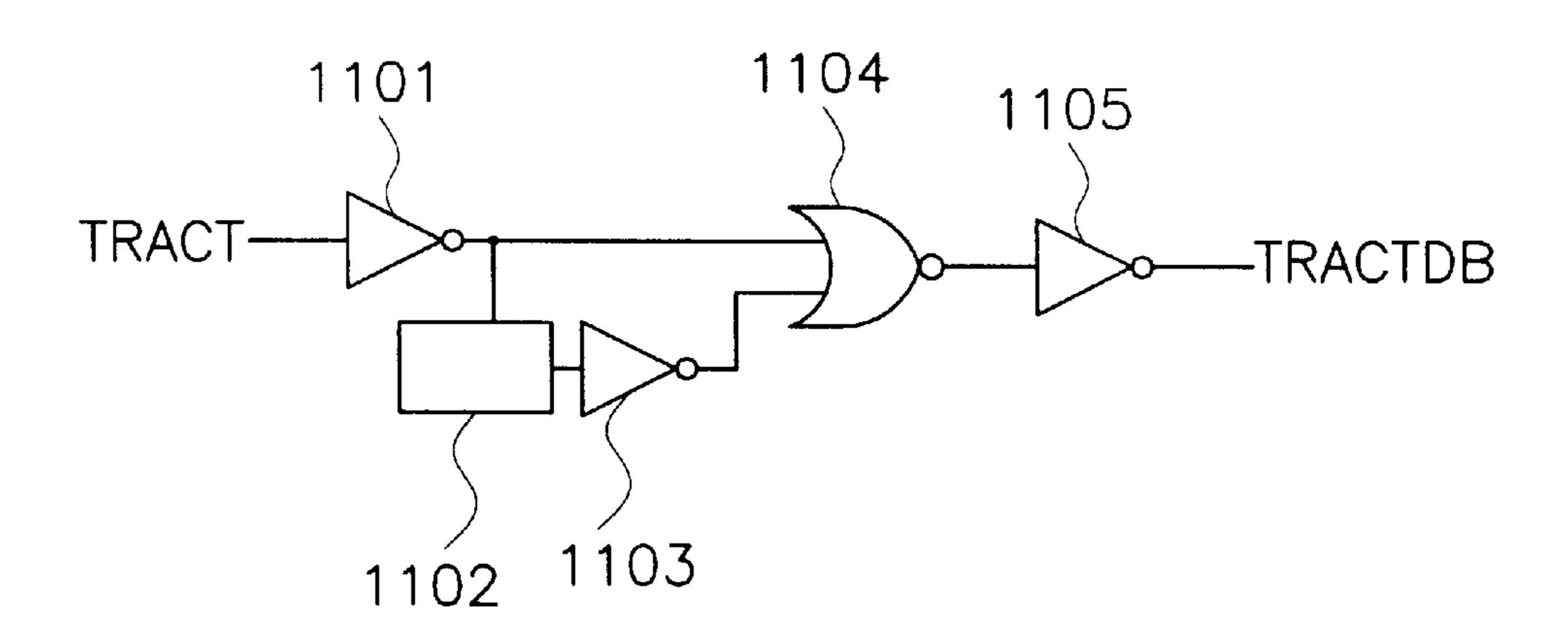

FIG. 11 is a circuit diagram of a column redundancy address buffer unit of the device illustrated in FIG. 9 according to an embodiment of the present invention.

FIG. 12 is a circuit diagram of a row redundancy predecoder unit of the device illustrated in FIG. 9 according to an embodiment of the present invention.

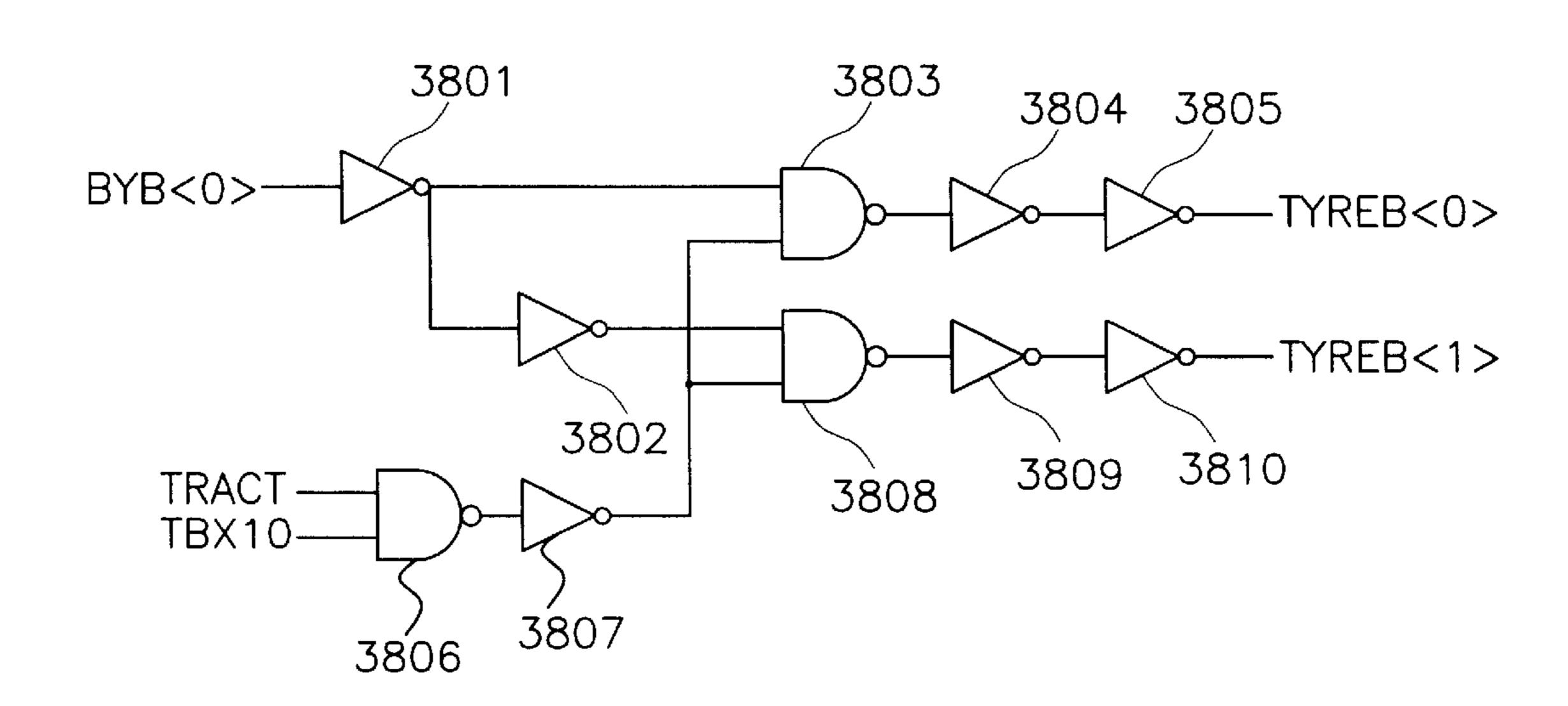

FIG. 13 is a circuit diagram of a column redundancy predecoder unit of the device illustrated in FIG. 9 according to an embodiment of the present invention.

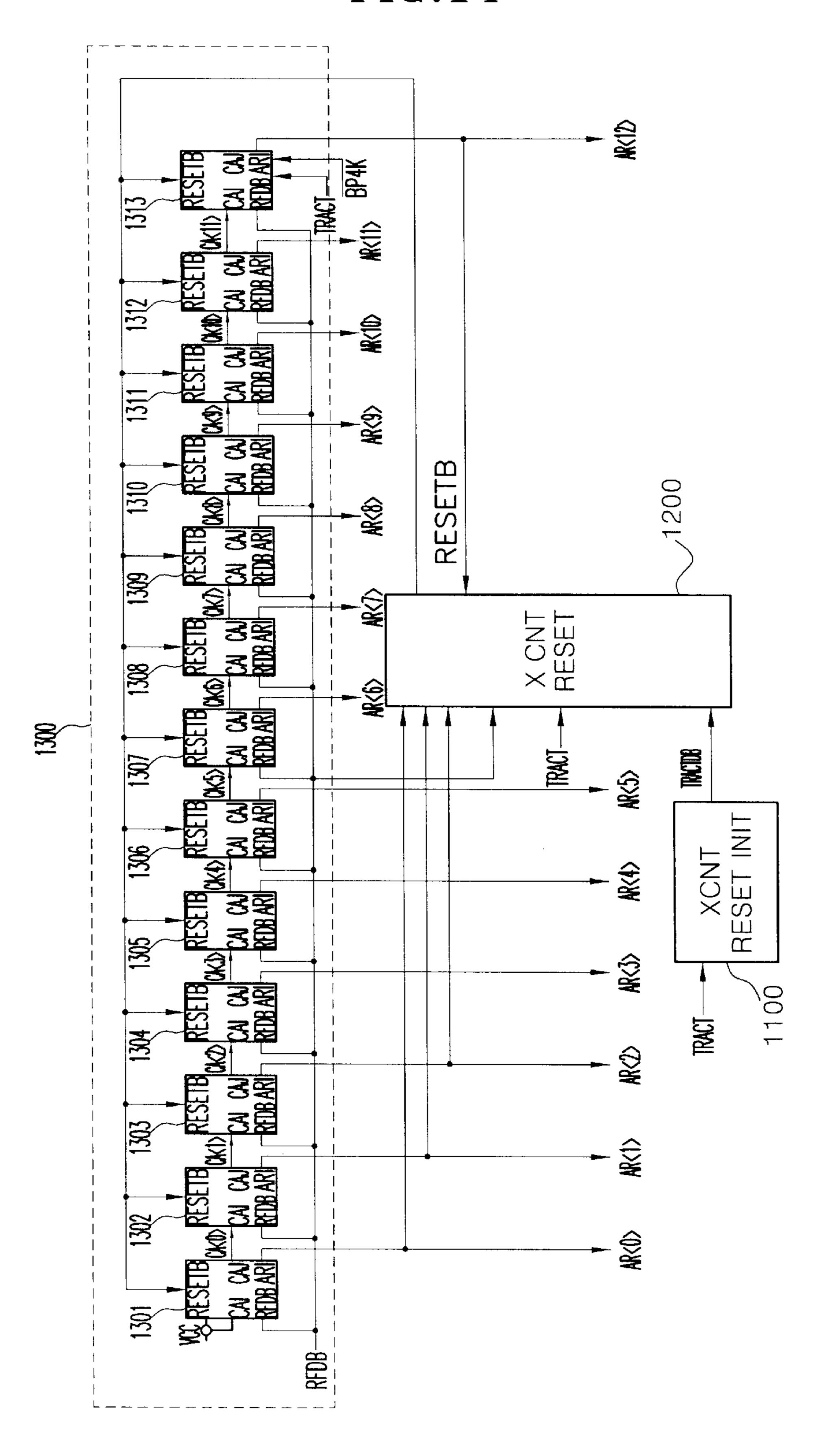

FIG. 14 is a diagram of a row counter reset initialization unit, a row counter reset unit and a row address counter unit of the device illustrated in FIG. 9 according to an embodiment of the present invention.

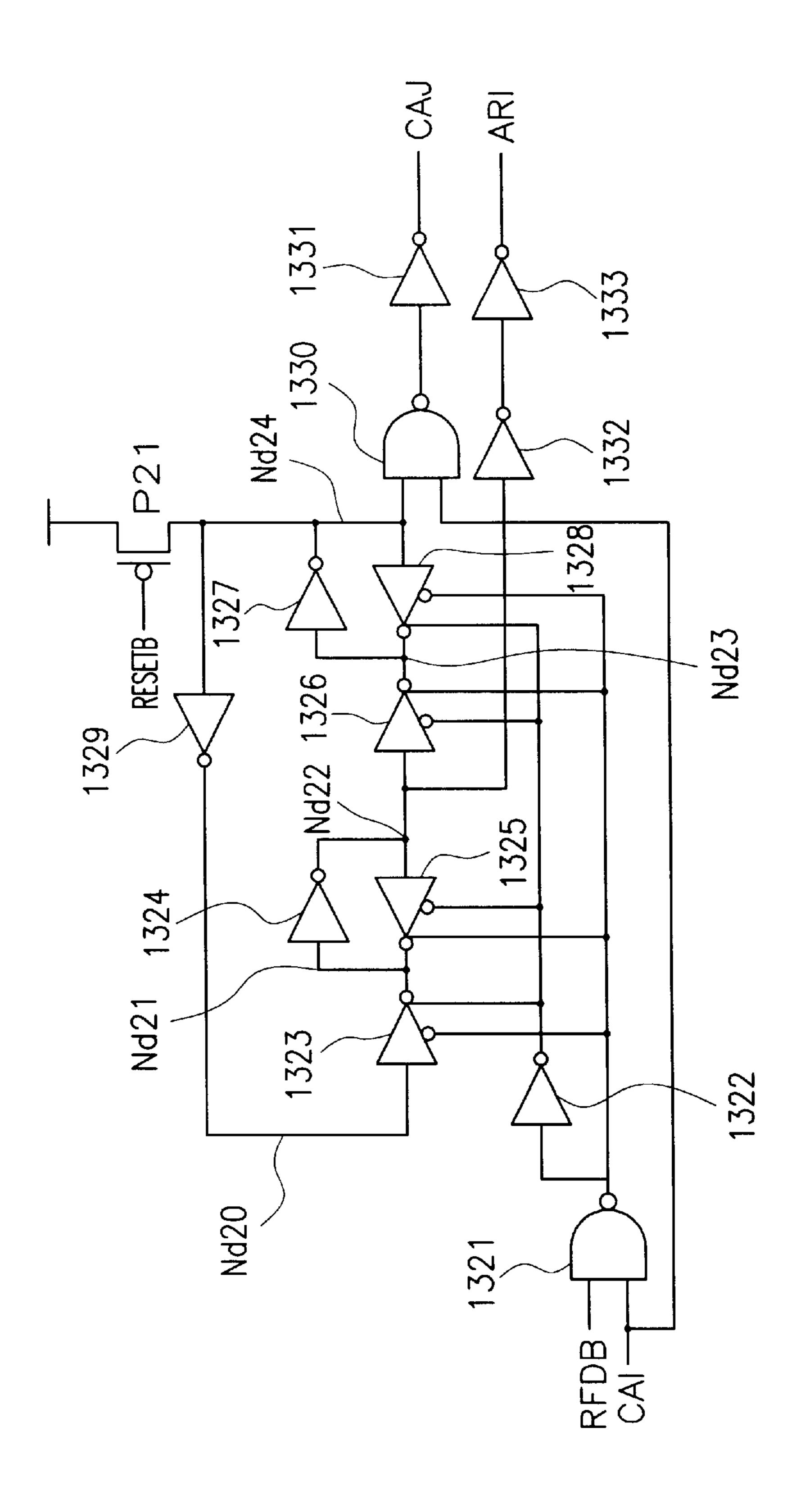

FIG. 15 is a circuit diagram of first to twelfth row counter register units of the row address counter unit illustrated in 20 FIG. 14 according to an embodiment of the present invention.

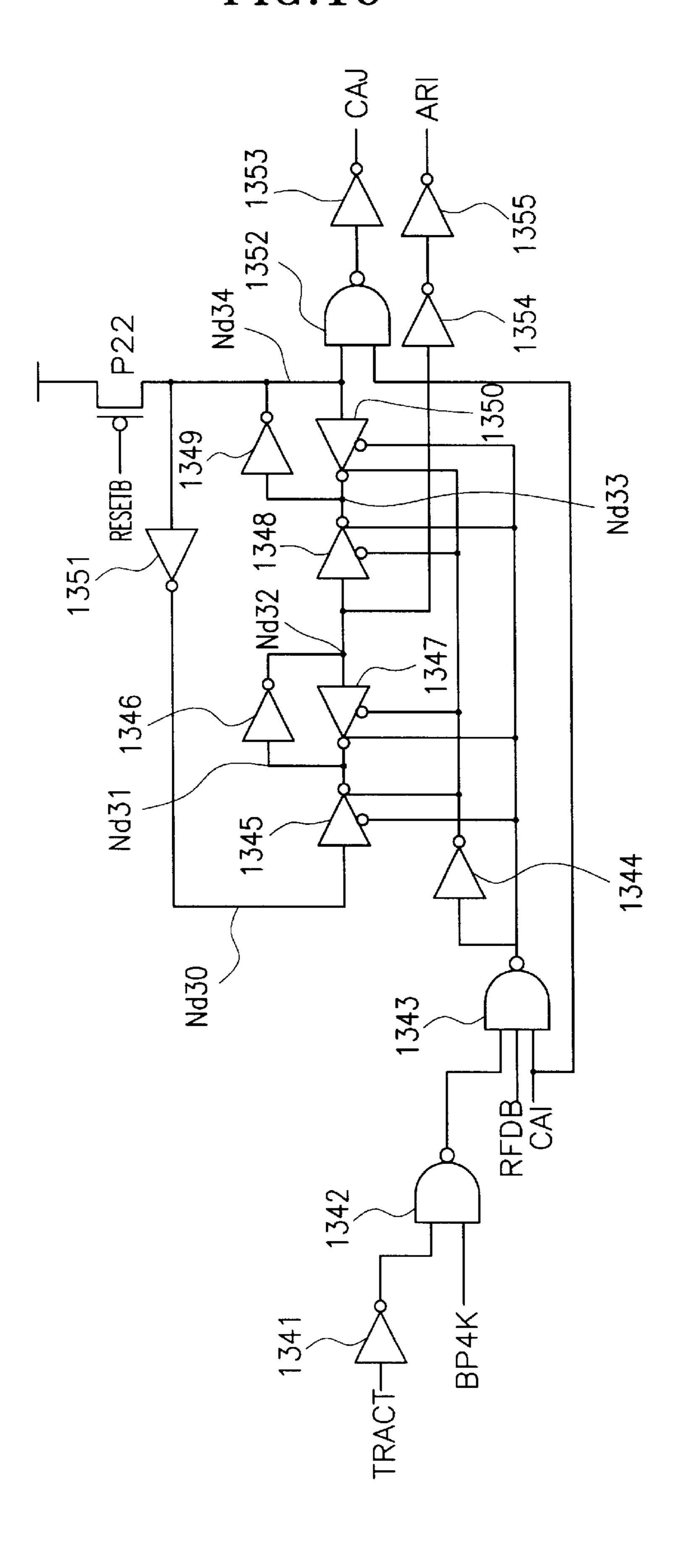

FIG. 16 is a circuit diagram of a thirteenth row counter register unit of the row address counter unit in FIG. 14 according to an embodiment of the present invention.

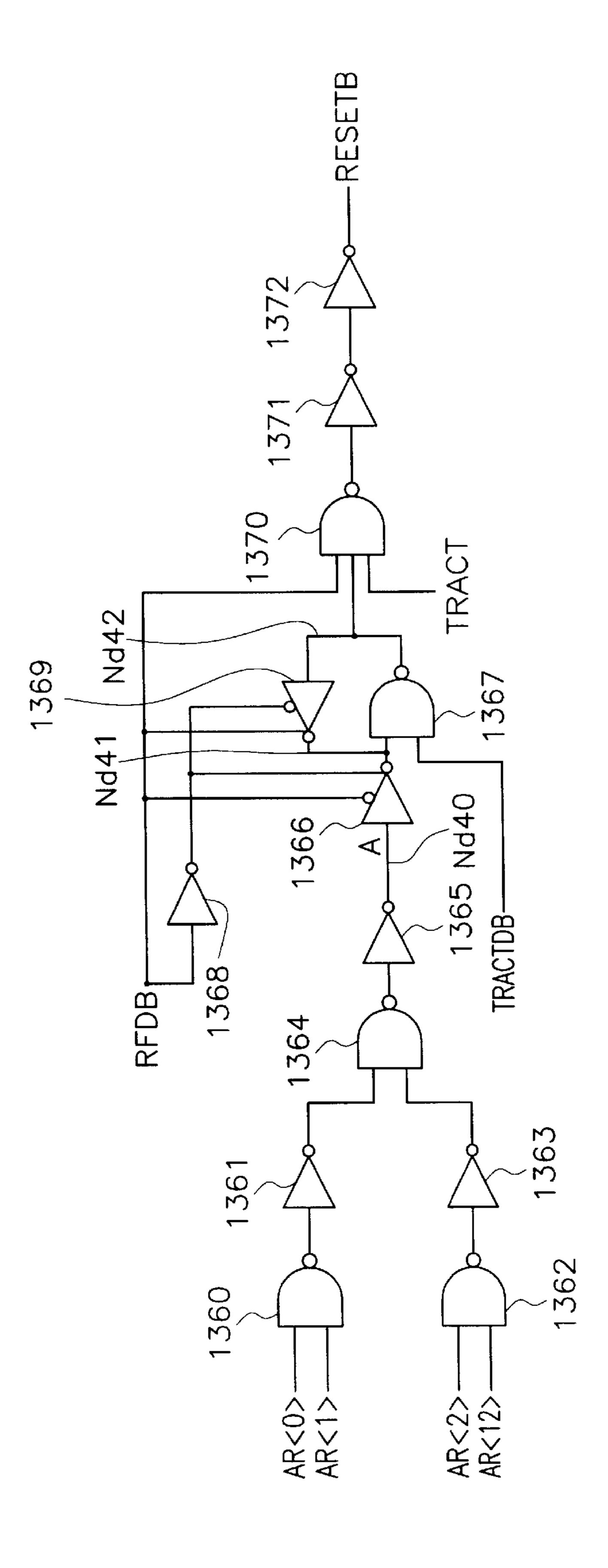

FIG. 17 is a circuit diagram of the row counter reset unit illustrated in FIG. 14 according to an embodiment of the present invention.

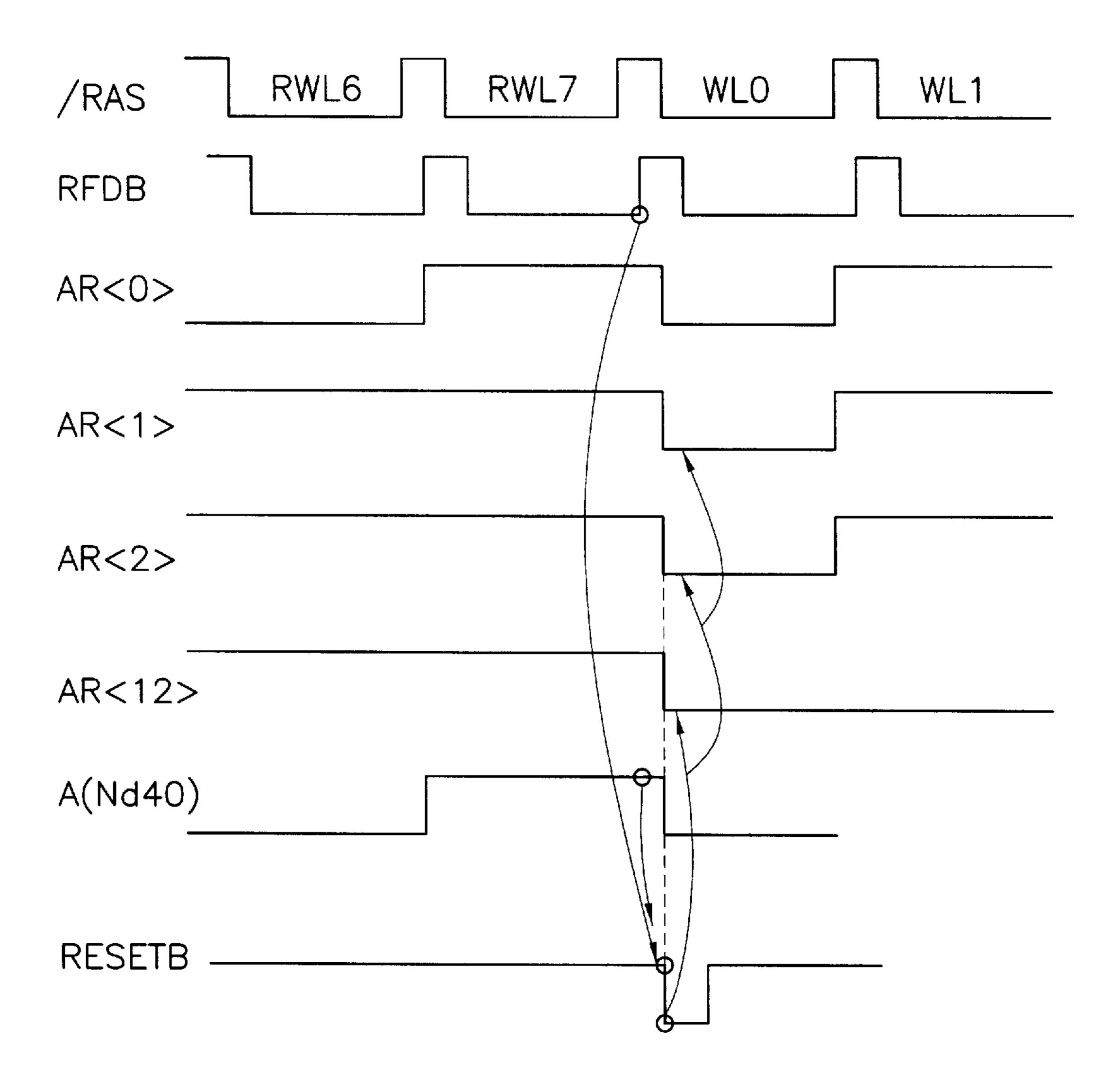

FIG. 18 is a diagram for showing the operation of the row counter reset unit illustrated in FIG. 17 according to an embodiment of the present invention.

FIG. 19 is a circuit diagram of the row counter reset initialization unit illustrated in FIG. 14 according to an embodiment of the present invention.

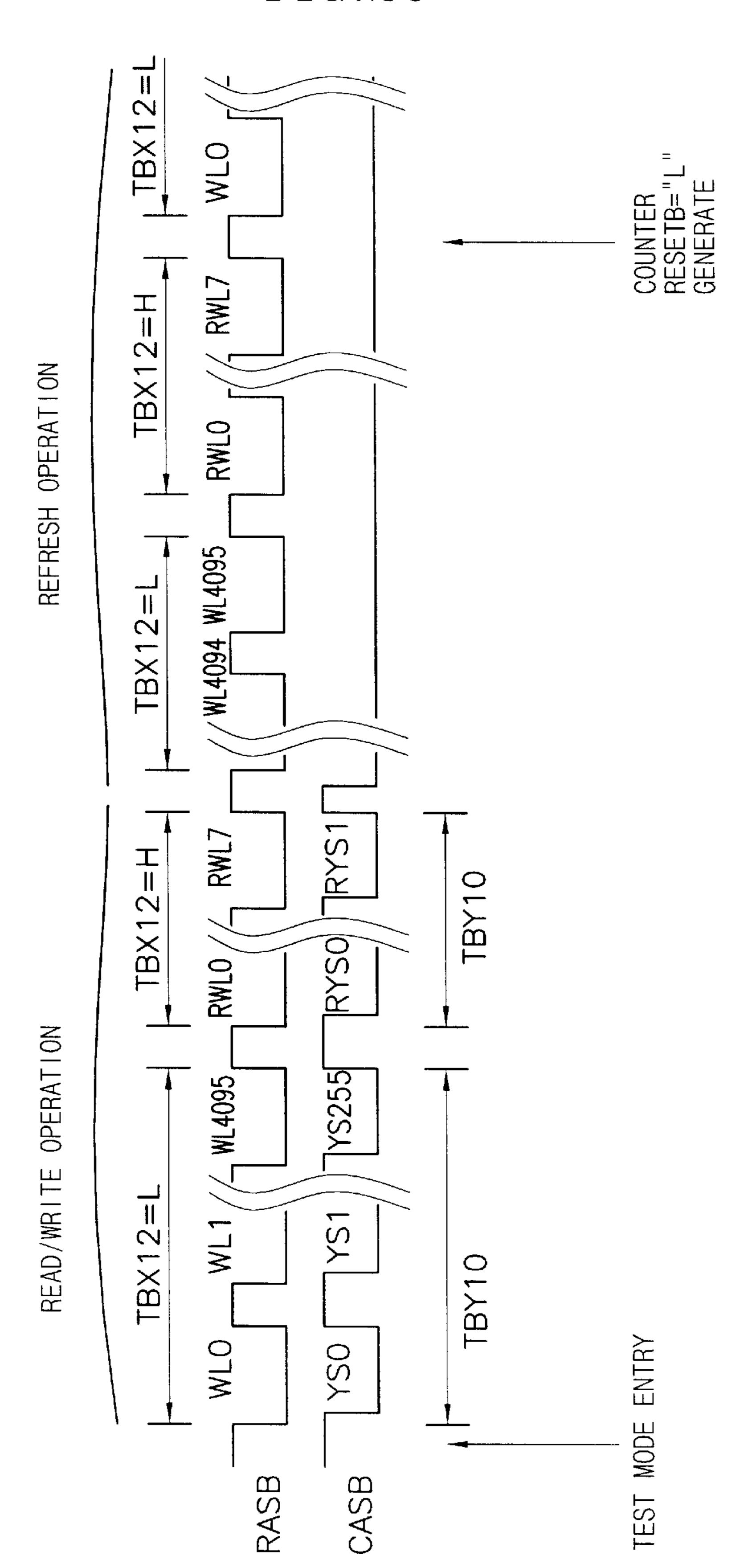

FIG. 20 is a diagram for showing the operation of a test mode signal outputted from the test mode control unit illustrated in FIG. 9 according to an embodiment of the present invention.

FIG. 21 is a block diagram of a semiconductor memory device having a redundancy circuit according to a second embodiment of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The embodiments of the present invention will be described in detail with reference to accompanying drawings. In the drawings, a part having the same function will be represented by the same reference numerals and there will be no repeated description of the same parts. In addition, all the elements shown in the drawings in connection with the present invention are operatively coupled.

FIG. 9 is a block diagram of a semiconductor memory device having a redundancy circuit according to a first 55 embodiment of the present invention. In this example, the memory device is a memory having 64M bit.

Referring to FIG. 9, the semiconductor memory device having the redundancy circuit of the present invention comprises: a normal memory cell array unit 5000 of 64M bit 60 for storing a plurality of data and information; a redundancy memory cell array unit 5200 of 1K bit for recovering defective cells in the normal memory cell array unit 5000; and a sense amplification unit and I/O control unit 5400 for sensing and amplifying read data received from the normal 65 memory cell array unit 5000 or the redundancy memory cell array unit 5200 and outputting the data to an I/O line or for

12

sensing and amplifying write data received through the I/O line and outputting the data to the memory cell array unit **5000** or to the redundancy memory cell array unit **5200**.

The semiconductor memory device further comprises: an address buffer unit 1000 for receiving address signals A0~A12 from an external source; a command buffer unit 2600 for receiving command signals i.e., row address strobe bar signal RASB, column address strobe signal CASB, write enable bar signal WEB, output enable bar signal OEB from an external source; a command control unit 2800 for receiving output signals from the command buffer unit 2600; and a test mode control unit 3000 for receiving signals from the command control unit 2800 and the address signals A<0:12> from the address buffer unit 1000 and for generating a test mode signal TRACT to detect deterioration of word lines and bit lines in the redundancy memory cell array unit 5200.

The semiconductor memory device further comprises: a row address counter unit 1300 for receiving the test mode signal TRACT from the test mode control unit 3000, a delayed refresh enable bar signal RFDB motivated by the RASB command and toggling once from a 'high' to a 'low' level in the refresh operation to one word line, and a bonding pad 4K refresh enable signal BP4K generated at a command decoder (not shown) in the refresh operation and for gen-25 erating row address counter signals AR<0:12>; a row counter reset unit 1200 for receiving the refresh delay bar signal RFDB and the TRACT signal from the test mode control unit 3000 and row address counter signals AR<0,1, 2,12> from the row address counter unit 1300 and for 30 generating a reset signal RESETB to the row address counter unit 1300; and a row counter reset initializing unit 1100 for receiving the test mode signal TRACT from the test mode control unit 3000 and for generating an initialization signal TRACTDB to the row counter reset unit 1200.

The semiconductor memory device further comprises: a row address buffer unit 1400 for receiving address signals A<0:12> from the address buffer unit 1000 and row address counter signals AR<0:11> from the row address counter unit 1300 and for generating row address data signals BXB<0:12>; a row predecoder unit 1600 for receiving the row address data signals BXBK<0:12> from the row address buffer unit 1400 and for generating decoded signals; and a row decoder unit 1800 for decoding signals received from the row predecoder unit 1600 and for generating signals WL<0:8191> to select word lines of the normal memory cell array unit 5000.

The semiconductor memory device further comprises: a row redundancy address buffer unit 1500 for receiving the highest row address signal A<12> from the address buffer unit 1000, the test mode signal TRACT from the test mode control unit 3000 and the row address counter signal AR<12> from the row address counter unit 1300 and for generating a row redundancy address signal TBX12; a row redundancy predecoder unit 2000 for receiving the row address data signals BXB<0:12> from the row address buffer unit 1400, the test mode signal TRACT from the test mode control unit 3000 and the row redundancy address signal TBX12 from the row redundancy address buffer unit 1500 and for generating decoded signals TREB<0:7>; a row redundancy fuse unit **2200** for generating programming row redundancy data signals REB<0:7>; and a row redundancy enable signal generating unit **2400** for receiving the decoded signals TREB<0:7> from the row redundancy predecoder unit 2000 and the programming row redundancy data signals REB<0:7> from the row redundancy fuse unit 2200 and for generating signals RWL<0:7> to select word lines of the redundancy memory cell array unit **5200**.

The semiconductor memory device further comprises: a column address buffer unit 3200 for receiving address signals A<0:8> from the address buffer unit 1000 and for generating column address data signals BYB<0:8>; a column predecoder unit 3400 for receiving the column address 5 data signals BYB<0:7> from the column address buffer unit 3200 and for generating a decoded signal; and a column decoder unit 3600 for receiving the decoded signal from the column predecoder unit 3400 and for generating and outputting signals YS<0:255> used to select bit lines of the 10 normal memory cell array unit 5000 to the amplification and I/O control unit **54**.

The semiconductor memory device further comprises: a column redundancy address buffer unit 3300 for receiving the row address signal A<10> from the address buffer unit  $_{15}$ 1000 and the test mode signal TRACT from the test mode control unit 3000 and for generating a column redundancy address signal TBY10; a predecoder unit 3800 for receiving column address data signals BYB<0:7> from the column address buffer unit **3200**, the test mode signal TRACT from <sub>20</sub> the test mode control unit 3000 and the column redundancy address signal TBY10 from the column redundancy address buffer unit 3300 and for generating decoded signals TYREB<0:1>; a fuse unit 4000 for generating programming redundancy enable signal generating unit 4200 for receiving the decoded signals TYREB<0:1> from the column redundancy predecoder unit 3800 and the programming column redundancy data signals YREB<0:1> from the column redundancy fuse unit 4000 and for generating and outputting signals RYS<0:1> used to select bit lines of the redundancy memory cell array unit 5200 to the sense amplification and I/O control unit(s) 5400.

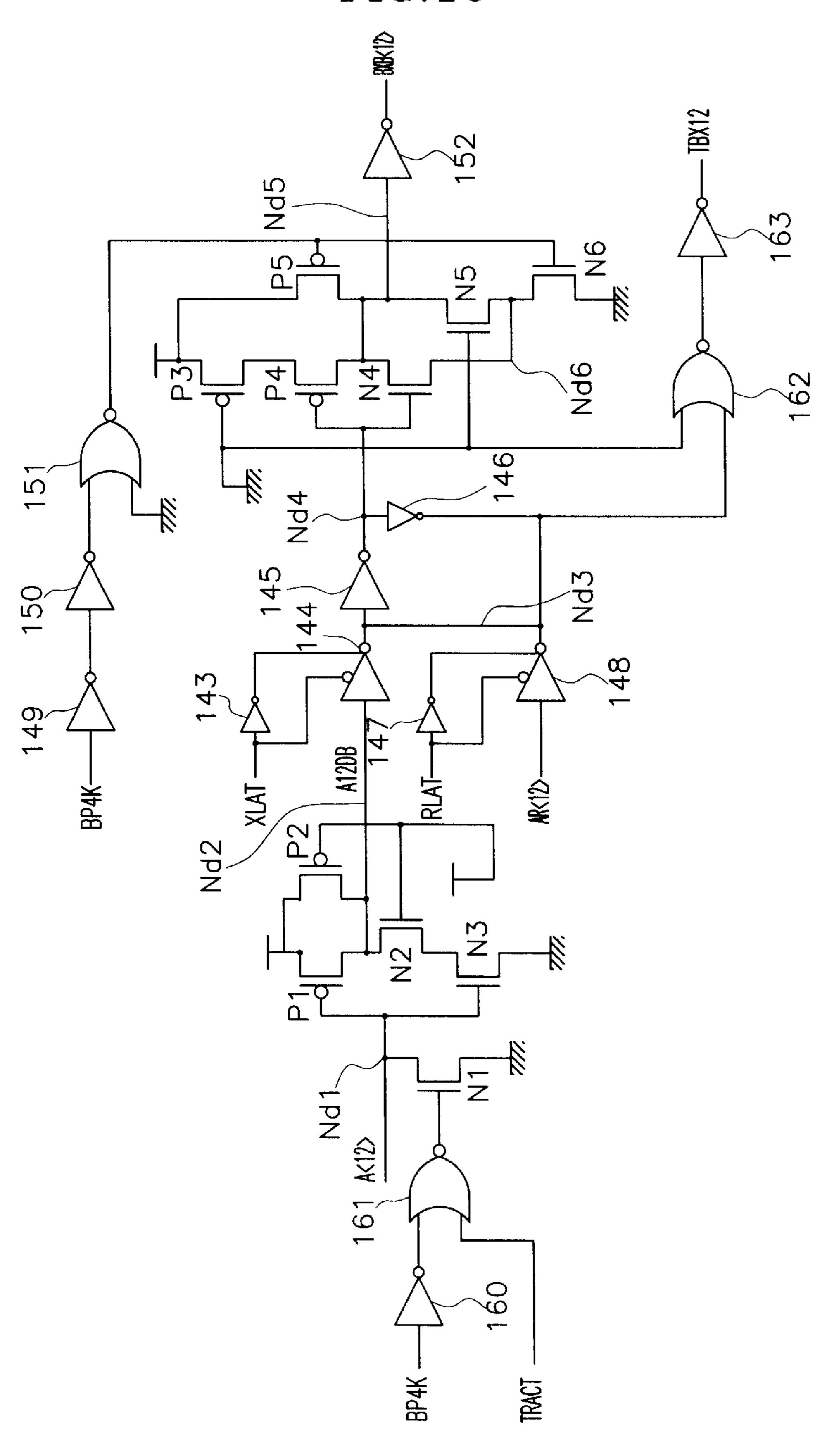

FIG. 10 is a circuit diagram of the row redundancy redundancy address buffer unit 1500 comprises: an inverter 160 for receiving a BP4K signal outputted from a command decoder (not shown) in a refresh operation; a NOR gate 161 for receiving an output signal from the inverter 160 and the test mode signal TRACT from the test mode control unit 40 **3300** and for generating a signal according to its NOR logic operation; an NMOS transistor N1 for discharging the electric potential of the node Nd1 that receives the highest row address signal A<12> from the address buffer unit 1000 by the operation of the output signal from the NOR gate 161, 45 to a ground voltage Vss; a PMOS transistor P1 for transmitting a source voltage Vcc to the node Nd2 when the signal of the node Nd1 is 'low'; a PMOS transistor P2 connected to the PMOS transistor P1 in a row, for receiving the source voltage Vcc at its gate; and NMOS transistors N2, 50 N3 connected between the node Nd2 and the ground voltage Vss, and their operation being controlled by the source voltage Vcc and the signal of node Nd1.

The semiconductor memory device further comprises: a clock inverter 144 for receiving a signal of the node Nd2 under control of a control signal XLAT activated as 'high' in operation except for a refresh and for outputting the inverted signal to a node Nd3; an inverter 145 for receiving and inverting a signal of the node Nd3 and for outputting the inverted signal to a node Nd4; an inverter 146 for receiving 60 and inverting a signal of the node Nd4 and for outputting the inverted signal to the node Nd3; a clock inverter 148 for outputting the highest row address signal AR<12> received from the row address counter unit 1300 to the node Nd3 by a control signal RLAT activated as 'high' in the refresh 65 operation; a NOR gate 162 for receiving a signal of the node Nd3 and the ground voltage Vss and for outputting a signal

14

generated according to its NOR logic operation; an inverter 163 for receiving and inverting an output signal from the NOR gate 162 and for outputting an inverted signal TBX12; PMOS transistors P3, P4 connected between the source voltage Vcc and a node Nd5 in series, and their operation being controlled by the ground voltage Vss and the signal of node Nd4; and a NMOS transistor N4 connected between the node Nd5 and the node Nd6 and its operation being controlled by the signal of the node Nd4.

The semiconductor memory device further comprises: an inverter 149 for receiving and inverting the signal BP4K outputted from a command decoder (not shown) in the refresh operation and for outputting the inverted signal; an inverter 150 for inverting and outputting a signal received from the inverter 149; a NOR gate 151 for receiving a signal output from the inverter 150 and the ground voltage Vss and for outputting a signal generated according to its NOR logic operation; a PMOS transistor P5 connected between the source voltage Vcc and the node Nd5 an receiving an output signal of the NOR gate 151 at its gate; NMOS transistors N5, N6 connected between the node Nd5 and the ground voltage Vss in series, their operation being controlled by the ground voltage Vss and the output signal of the NOR gate 151; and an inverter 152 for inverting a signal received from the node column redundancy data signal YREB<0:1>; and a column 25 Nd5 and thereby outputting to the row address data signal BXB<12>.

First, read/write operations in a normal operation will be described. In this section, BP4K generated from the command decoder in a refresh operation is 'low' and TRACT generated from the test mode control unit 3000 is 'low'. And, the control signal RLAT is 'high' and the control signal XLAT is 'low'. Therefore, the row redundancy address buffer unit 1500 performs 8K refresh operation and the highest row address signal A<12> from the address buffer address buffer unit 1500 in FIG. 9. As shown, the row 35 unit 1000 is transmitted to the node Nd2. The highest row address signal A<12> transmitted to the node Nd12 is transmitted through the clock inverter 144 controlled by the control signal XLAT and then, decoded by the inner decoder circuit in the next terminal to finally generate a row address data signal BXB<12>. Here, the row address data signal BXB<12> is changed according to the state of the highest row address signal A<12>. The row redundancy address signal TBX12 is also changed according to the highest row address signal A<12>, however, it is not affected by the highest row address signal A<12> in the subsequently following operation since the test mode signal TRACT is 'low'. Therefore, the row redundancy address buffer unit 1500 is not affected by the highest row address signal A<12> in the subsequently following operation since the test mode signal TRACT is 'low' in a normal operation, not in a test mode.

> Next, read/write operations in a test mode will be described. In a test mode, the BP4K is 'high' since the 8K refresh operation is converted into a 4K refresh operation and performed and the test mode signal TRACT is 'high'. The control signal RLAT is 'high' and the control signal XLAT is 'low'. The highest row address data signal BXB<12> generated at the row redundancy address buffer unit 1500 is continuously maintained at 'low' level and therefore, the highest row address data signal BXB<12> significant in the 8K refresh operation is operated. And, the row redundancy address signal TBX12 is generated by the highest row address signal A<12> generated at the row address buffer unit 1000. Here, when the row redundancy address signal TBX12 is 'low', the normal memory cell array unit 5000 is selected and when it is 'high', the redundancy memory cell array unit 5200 is selected.

Next, a refresh operation will be described when the device is not in a test mode. In this section, BP4K generated from the command decoder unit in a refresh operation is 'low' and TRACT generated from the test mode control unit 3000 is 'low'. And, the control signal RLAT is 'high' and the control signal XLAT is 'low'. Therefore, the row redundancy address buffer unit 1500 performs a 8K refresh operation and generates a row address data signal BXB<12> by the highest row address counter signal AR<12> generated at the row address counter unit 1300. Here, the row address  $_{10}$ data signal BXB<12> is changed according to the highest row address counter signal AR<12>. And, the row redundancy address signal TBX12 is also changed according to the highest row address counter signal AR<12>, however, is not affected by the highest row address counter signal 15 AR<12> in the subsequently following operation since the test mode signal TRACT is 'low'.

Next, a refresh operation in a test mode will be described. In a test mode, a 8K refresh operation is converted into a 4K refresh operation and is performed similar to read/write 20 operations in the test mode. Therefore, the BP4K is 'high' and the test mode signal TRACT is 'high' in a test mode. And, the control signal RLAT is 'high' and the control signal XLAT is 'low'. The highest row address data signal unit 1500 is continuously maintained at 'low' level and therefore, the highest row address data signal BXB<12> significant in the 8K refresh operation is operated. And, a row redundancy address signal TBX12 is generated by the highest row address counter signal AR<12> generated at the  $_{30}$ row address counter unit 1300. Here, when the row redundancy address signal TBX12 is 'low', the normal memory cell array unit 5000 is selected and when it is 'high', the redundancy memory cell array unit **5200** is selected.

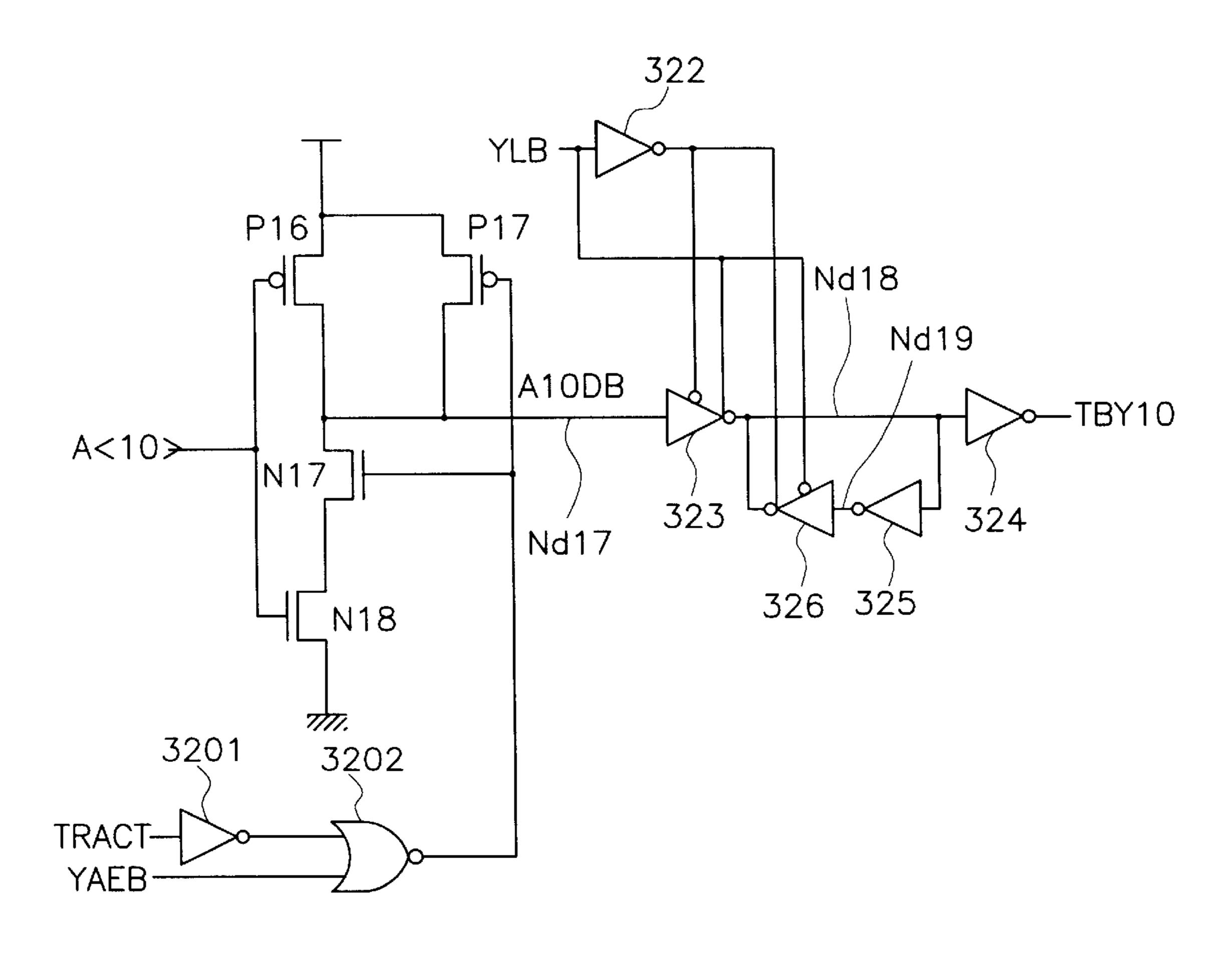

FIG. 11 is a circuit diagram of the column redundancy address buffer unit 3300 of the present invention illustrated in FIG. 9, which comprises: a PMOS transistor P16 for transmitting a source voltage Vcc to a node Nd17 by a column address signal A<10> received from the address buffer unit 1000; an inverter 3201 for receiving and inverting the test mode signal TRACT from the test mode control unit 3000 and for outputting the inverted signal; a NOR gate 3202 for receiving a signal from the inverter 3201 and control signal YAEB and for outputting a signal generated according to the NOR logic operation; a PMOS transistor 45 P17 for transmitting the source voltage Vcc to the node Nd17 by a signal received from the NOR gate 3202; NMOS transistors N17, N18 connected between the node Nd17 and ground voltage Vss in series, the operation being controlled by an output signal of the NOR gate 3202 and the signal 50 A<10> received from the address buffer unit 1000; a clock inverter 323 for transmitting the node signal Nd17 to a node Nd18 under control of a control signal YLB; an inverter 325 for receiving the signal of the node Nd18 and for outputting the inverted signal to a node Nd19; a clock inverter 326 for 55 transmitting the signal of the node Nd19 to the node Nd18 under control of the control signal YLB; and an inverter 324 for receiving and inverting the signal of the node Nd18 and for outputting the inverted signal TBY<10>. The control signal YAEB is a signal controlling to receive a column 60 address signal A<10> from the address buffer unit 1000 and the control signal YLB becomes 'low' in column operation to transmit and latch the column address signal A<10> transmitted to the node Nd17 to the node Nd18.

First, read/write operations in a normal operation will be 65 described. The row address signal is applied by the RASB and after a predetermined time, the control signal YAEB

**16**

becomes 'low' under control of the column address strobe signal CASB and then the control signal YLB becomes 'low'. At this time, the highest column address signal A<10> received from the address buffer unit 1000 is blocked and not transmitted to the inside since the test mode signal TRACT is 'low'. Therefore, at this point, the column redundancy address buffer unit 3300 does not generate a column redundancy address signal TBY10.

Next, a column redundancy address signal TBY10 is generated based on the highest column address signal A<10> received from the address buffer unit 1000 since the test mode signal TRACT is 'high' in the read/write operation of the test mode. Here, when the column redundancy address signal TBY10 is 'low', the normal memory cell array unit 5000 is selected and when it is 'high', the redundancy memory cell array unit **5200** is selected.

Next, the test mode signal TRACT turns 'low' in a refresh operation when the device is not in a test mode. Therefore, the highest column address signal A<10> received from the address buffer unit 1000 is blocked and not transmitted to the inside. As a result, the column redundancy address buffer unit 3300 does not generate the column redundancy address signal TBY10 at this time.

Next, in a test mode, the test mode signal TRACT is 'high' BXB<12> generated at the row redundancy address buffer 25 in a refresh operation and therefore, a column redundancy address signal TBY10 is generated by the highest column address signal A<10> received from the address buffer unit 1000. When the column redundancy address signal TBY10 is 'low', the normal memory cell array unit **5000** is selected and when it is 'high', the redundancy memory cell array unit **5200** is selected.

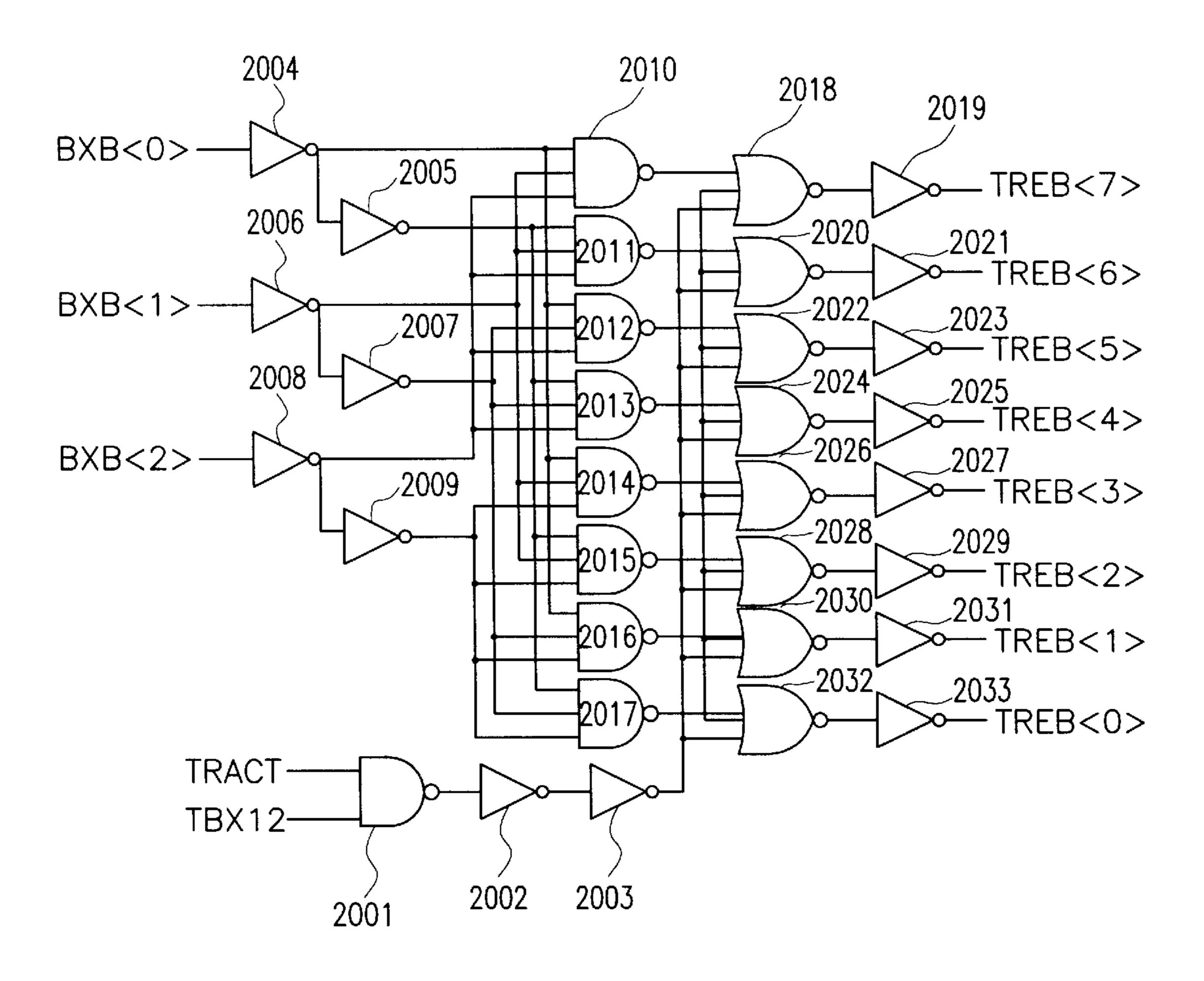

FIG. 12 is a circuit diagram of the row redundancy predecoder unit 2000 of the present invention illustrated in FIG. 9. The row redundancy predecoder unit 2000 comprises: an inverter 2004 for receiving and inverting a row address data signal BXB<0> received from the row address buffer unit 1400 and for outputting the inverted signal; an inverter 2005 for inverting a signal output from the inverter 2004 and outputting the inverted signal; an inverter 2006 for receiving and inverting a row address data signal BXB<1> received from the row address buffer unit 1400 and for outputting the inverted signal; an inverter 2007 for inverting a signal output from the inverter 2006 and outputting the inverted signal; an inverter 2008 for receiving and inverting a row address data signal BXB<2> received from the row address buffer unit 1400 and for outputting the inverted signal; an inverter 2009 for inverting a signal output from the inverter 2008 and outputting the inverted signal; a NAND gate 2010 for receiving signals from the inverters 2004,2006,2008 and for outputting signals generated according to the NAND logic operation; a NAND gate 2011 for receiving signals from the inverters 2005,2006,2008 and for outputting signals generated according to the NAND logic operation; a NAND gate 2012 for receiving signals form the inverters 2004,2007,2008 and for outputting signals generated according to the NAND logic operation; a NAND gate 2013 for receiving signals from the inverters 2005,2007,2008 and for outputting signals generated according to the NAND logic operation; a NAND gate 2014 for receiving signals from the inverters 2004,2006,2009 and for outputting signals generated according to the NAND logic operation; a NAND gate 2015 for receiving signals from the inverters 2005,2006,2009 and for outputting signals generated according to the NAND logic operation; a NAND gate 2016 for receiving signals from the inverters 2004,2007,2009 and for outputting signals generated according to the NAND logic operation; and a NAND gate

2017 for receiving signals from the inverters 2005,2007, 2009 and for outputting signals generated according to the NAND logic operation.

The row redundancy predecorder unit 2000 further comprises: a NAND gate 2001 for receiving the test mode signal TRACT from the test mode control unit 3000 and the row redundancy address signal TBX12 from the row redundancy address buffer unit 1500 and for outputting signals generated according to the NAND logic operation; an inverter 2002 for receiving and inverting a signal from the NAND gate 2001 10 and for outputting the inverted signal; an inverter 2003 for receiving and inverting a signal from the inverter 2002 and for outputting the inverted signal; a NOR gate 2018 for receiving the output signal from the NAND gate 2010 and the output signal from the inverter 2003 and for outputting 15 a signal generated according to the NOR logic operation; an inverter 2019 for receiving and inverting a signal from the NOR gate 2018 and for outputting the inverted signal TREB<7>; a NOR gate 2020 for receiving the signal output from the NAND gate 2011 and the signal output from the 20 inverter 2003 and for outputting a signal generated according to the NOR logic operation; an inverter 2021 for receiving and inverting the signal output from the NOR gate **2020** and for outputting the inverted signal TREB<6>; a NOR gate 2022 for receiving the signal output from the 25 NAND gate 2012 and the signal output from the inverter 2003 and for outputting a signal generated according to the NOR logic operation; an inverter 2023 for receiving and inverting the signal output from the NOR gate 2022 and for outputting the inverted signal TREB<5>; a NOR gate 2024 30 for receiving the signal output from the NAND gate 2013 and the signal output from the inverter 2003 and for outputting a signal generated according to the NOR logic operation; an inverter 2025 for receiving and inverting the signal output from the NOR gate 2024 and for outputting the 35 inverted signal TREB<4>; a NOR gate 2026 for receiving the signal output from the NAND gate 2014 and the signal output from the inverter 2003 and for outputting a signal generated according to the NOR logic operation; an inverter 2027 for receiving and inverting the signal output from the 40 NOR gate 2026 and for outputting the inverted signal TREB<3>; a NOR gate 2028 for receiving the signal output from the NAND gate 2015 and the signal output from the inverter 2003 and for outputting a signal generated according to the NOR logic operation; an inverter 2029 for 45 receiving and inverting the signal output from the NOR gate **2028** and for outputting the inverted signal TREB<2>; a NOR gate 2030 for receiving the signal output from the NAND gate 2016 and the signal output from the inverter **2003** and for outputting a signal generated according to the 50 NOR logic operation; an inverter 2031 for receiving and inverting the signal output from the NOR gate 2030 and for outputting the inverted signal TREB<1>; a NOR gate 2032 for receiving the signal output from the NAND gate 2017 and the signal output from the inverter 2003 and for out- 55 putting a signal generated according to the NOR logic operation; and an inverter 2033 for receiving and inverting the signal from the NOR gate 2032 and for outputting the inverted signal TREB<0>.

When the test mode signal TRACT generated at the test 60 mode control unit 3000 is activated to be at 'high' level, one of the row redundancy predecoder signals TREB<0:7> is generated to be at 'low' level by the row address data signals BXB<0:2> received from the row address buffer unit 1400. Here, the row redundancy enable signal generating unit 65 2400 is operated based on the row redundancy predecoder signals TREB<0:7> having 'low' signals, thereby generating

18

signals to drive the redundancy word lines of the redundancy memory cell array unit **5200**. When the test mode signal TRACT generated at the test mode control unit **3000** is 'low', all of the row redundancy predecoder signals TREB<0:7> become 'high', thereby not driving the redundancy word lines of the redundancy memory cell array unit **5200**.

FIG. 13 is a circuit diagram of the column redundancy predecoder unit 3800 of the present invention illustrated in FIG. 9. The column redundancy predecoder unit 3800 comprises: a NAND gate 3806 for receiving test mode signal TRACT from the test mode control unit 3000 and the column redundancy address signal TBY10 from the column address buffer unit 3300 and for outputting a signal generated according to the NAND logic operation; an inverter **3807** for receiving and inverting the signal output from the NAND gate 3806 and for outputting the inverted signal; an inverter 3801 for receiving and inverting a signal BYB<0> from the column address buffer unit 3200 and for outputting the inverted signal; a NAND gate 3803 for receiving the signal output from the inverter 3801 and the signal output from the inverter 3807 and for outputting a signal generated according to the NAND logic operation; an inverter 3804 for receiving and inverting the signal output from the NAND gate 3803 and for outputting the inverted signal; and an inverter 3805 for receiving and inverting the signal output from the inverter **3804** and for outputting the inverted signal TYREB<**0**>.

The column redundancy predecoder unit 3800 further comprises: an inverter 3802 for receiving and inverting the signal output from the inverter 3801 and for outputting the inverted signal; a NAND gate 3808 for receiving the signal output from the inverter 3802 and the signal output from the inverter 3807 and for outputting a signal generated according to the NAND logic operation; an inverter 3809 for receiving and inverting the signal output from the NAND gate 3808 and for outputting the inverted signal; and an inverter 3810 for receiving and inverting the signal output from the inverter 3809 and for outputting the inverted signal TYREB<1>.

When the test mode signal TRACT from the test mode control unit 3000 is activated to be at a 'high' level, one of the column redundancy predecoder signals TYREB<0:1> becomes 'low' according to the BYB<0> signal received from the column address buffer unit 3200. Here, the column redundancy enable signal generating unit 4200 is operated based on the column redundancy predecoder signals TYREB<0:1> having 'low' levels, thereby generating signals to drive the redundancy column line of the redundancy memory cell array unit 5200. When the test mode signal TRACT generated at the test mode control unit 3000 is at a 'low' level, all of the column redundancy predecoder signals TYREB<0:1> become 'high', thereby not driving the redundancy column line of the redundancy memory cell array unit 5200.

FIG. 14 is a block diagram of the row counter reset initialization unit 1100, the row counter reset unit 1200 and the row address counter unit 1300 of the present invention illustrate in FIG. 9.

Referring to FIG. 14, the row counter reset initialization unit 1100 receives the test mode signal TRACT from the test mode control unit 3000 and generates an initialization signal TRACTDB to initialize the row counter reset unit 1200.

The row counter reset unit 1200 is motivated by the test mode signal TRACT from the test mode control unit 3000 and RASB, and thereby receives a signal RFDB toggling

from 'high' to 'low' once in a refresh operation to one word line and row address counter signals AR<0,1,2,12> to generate a reset signal RESETB to the row address counter unit **1300**.

The row address counter unit **1300** receives the test mode 5 signal TRACT from the test mode control unit 3000, RFDB motivated by the RASB signal and toggling from 'high' to 'low' once in the refresh operation to one word line, BP4K outputted from the command decoder (not shown) in the refresh mode, and the reset signal RESETB from the row 10 counter reset unit 1200, thereby generating row address counter signals AR<0:12>.

The row address counter unit 1300 comprises: a first counter register 1301 for receiving the source voltage Vcc as a carry signal CAi, RFDB as a toggle signal and the reset 15 signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<0> and a carry signal CA<0>; a second counter register 1302 for receiving the carry signal CA<0> generated at the first counter register 1301 as a carry signal 20 CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<1> and a carry signal CA<1>; a third counter register 1303 for receiving the carry signal CA<1> generated at the 25 second counter register 1302 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<2> and a carry signal CA<2>; a fourth counter register 1304 for 30 receiving the carry signal CA<2> generated at the third counter register 1303 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<3>; and a 35 carry signal CA<3>; a fifth counter register 1305 for receiving the carry signal CA<3> as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<4> and a 40 carry signal CA<4>; a sixth counter register 1306 for receiving the carry signal CA<4> generated at the fifth counter register 1305 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and 45 for generating a row address counter signal AR<5> and a carry signal CA<5>; a seventh counter register 1307 for receiving the carry signal CA<5> generated at the sixth counter register 1306 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row 50 counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<6> and a carry signal CA<6>; and an eighth counter register 1308 for receiving the carry signal CA<6> generated at the seventh counter register 1307 as a carry signal CAi, RFDB as a 55 toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<7> and a carry signal CA<7>.

ninth counter register 1309 for receiving the carry signal CA<7> generated at the eighth counter register 1308 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address 65 counter signal AR<8> and a carry signal CA<8>; a tenth counter register 1310 for receiving the carry signal CA<8>

generated at the ninth counter register 1309 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<9> and a carry signal CA<9>; an eleventh counter register 1311 for receiving the carry signal CA<9> generated at the tenth counter register 1310 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<10> and a carry signal CA<10>; a twelfth counter register 1312 for receiving the carry signal CA<10> generated at the eleventh counter register 1311 as a carry signal CAi, RFDB as a toggle signal and the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB and for generating a row address counter signal AR<11> and a carry signal CA<11>; and a thirteenth counter register 1313 for receiving the carry signal CA<11> generated at the twelfth counter register 1312 as a carry signal CAi, RFDB as a toggle signal, the reset signal RESETB from the row counter reset unit 1200 as a reset input signal REESTB, and BP4K outputted from the command decoder by the test mode signal TRACT and the refresh mode and turning 'high' in the 4K refresh mode as a control signal and for generating a row address counter signal AR<12>.

For the refresh operation of the redundancy memory cell in a test mode TRACT='high', when the row address counter signal AR<12> is 'low', the refresh operation is performed to a normal memory cell section and when the row address counter signal AR<12> is 'high', the refresh operation is performed to a redundancy memory cell section. That is, the memory operation having a 8K refresh cycle becomes a refresh operation of 8 redundancy word lines to 4K normal word line in a test mode and the row address signal A<12> is employed after being changed into the separation function of a normal memory cell area and a redundancy memory cell area.

FIG. 15 is a circuit diagram of each of the first to twelfth row counter registers 1301 to 1312 of the row address counter unit 1300 of the present invention illustrated in FIG. 14. Each of the counter registers 1301 to 1312 comprises: a NAND gate 1321 for receiving the signal RFDB and the carry signal CAI and for generating a signal generated according to the NAND logic operation; an inverter 1322 for receiving and inverting the signal output from the NAND gate 1321 and for outputting the inverted signal; a clock inverter 1323 for transmitting the signal of a node Nd20 to a node Nd21 under control of the output signal of the inverter 1322 and an output signal of the NAND gate 1321; an inverter 1324 for receiving and inverting the signal output from the node Nd21 and for outputting the inverted signal to a node Nd22; a clock inverter 1325 for receiving and inverting the signal of the node Nd22 under control of the signals output from the inverter 1322 and the NAND gate 1321 and for outputting the inverted signal to the node Nd21; a clock inverter 1326 for receiving and inverting the signal of the node Nd22 under control of the signal from the inverter 1322 and signal from the NAND gate 1321 and for outputting the inverted signal to the node Nd23; an inverter The row address counter unit 1300 further comprises: a 60 1327 for receiving and inverting the signal output from the node Nd23 and for outputting the inverted signal to a node Nd24; a clock inverter 1328 for receiving and inverting the signal of the node Nd24 under control of the signal output from the inverter 1322 and the signal output from the NAND gate 1321 and for outputting the inverted signal to the node Nd23; a NAND gate 1330 for receiving the signal from the node Nd24 and the carry signal CAI and for outputting a

signal generated according to the NAND logic operation; an inverter 1331 for receiving and inverting the signal output from the NAND gate 1330 and for outputting the inverted signal CAJ; an inverter 1332 for receiving and inverting the signal from the node Nd22 and for outputting the inverted signal; an inverter 1333 for receiving and inverting the signal output from the inverter 1332 and for outputting the inverted signal ARI; an inverter 1329 for receiving and inverting the signal output from the node Nd24 and for outputting the inverted signal to the node Nd24 and for outputting the inverted signal to the node Nd20; and a PMOS transistor P21 for transmitting the source voltage Vcc to the node Nd24 according to the reset signal RESETB output from the row counter reset unit 1200.

The first to the twelfth row counter registers 1301 to 1312 of the row address counter unit 1300 further comprise the reset signal RESETB supplied typically to conventional row counter registers.

FIG. 16 is a circuit diagram of the thirteenth row counter register 1313 of the row address counter unit 1300 of the present invention illustrated in FIG. 14, which comprises: an 20 inverter 1341 for receiving and inverting the test mode signal TRACT from the test mode control unit 3000 and for outputting the inverted signal; a NAND gate 1342 for receiving the signal output from the inverter 1341 and BP4K outputted from the command decoder by the refresh mode 25 and having a 'high' level in the 4K refresh mode and for outputting a signal generated according to the NAND logic operation; a NAND gate 1343 for receiving the signal output from the NAND gate 1342, RFDB and the carry signal CAI and for outputting a signal generated according to the 30 NAND logic operation; an inverter 1344 for receiving and inverting the signal output from the NAND gate 1343 and for outputting the inverted signal; a clock inverter 1345 for transmitting the signal of a node Nd30 to a node Nd31 based on the output signal of the inverter 1344 and the output 35 signal of the NAND gate 1343; and an inverter 1346 for receiving and inverting the signal output from the node Nd31 and for outputting the inverted signal to a node Nd32.