#### US006576527B2

### (12) United States Patent

#### Nakamura

### (10) Patent No.: US 6,576,527 B2

### (45) Date of Patent: \*Jun. 10, 2003

## (54) SEMICONDUCTOR DEVICE AND METHOD FOR FABRICATING THE SAME

- (75) Inventor: Shunji Nakamura, Kawasaki (JP)

- (73) Assignee: Fujitsu Limited, Kawasaki (JP)

- (\*) Notice: This patent issued on a continued prosecution application filed under 37 CFR

1.53(d), and is subject to the twenty year patent term provisions of 35 U.S.C.

154(a)(2).

Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

- (21) Appl. No.: **08/965,010**

- (22) Filed: Nov. 5, 1997

- (65) Prior Publication Data

US 2001/0044181 A1 Nov. 22, 2001

#### (30) Foreign Application Priority Data

| (51) Int. Cl. <sup>7</sup> |      | •••••• | H011 | L <b>21/20</b> |

|----------------------------|------|--------|------|----------------|

| Jul. 10, 1997              | (JP) | •••••  | 9    | -185263        |

| Nov. 6, 1996               | (JP) |        | 8    | -293593        |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,401,681 A  | * | 3/1995  | Dennison                |

|--------------|---|---------|-------------------------|

| 5,408,114 A  | * |         | Kinoshita et al 257/296 |

| 5,539,230 A  | * | 7/1996  | Cronin 257/306          |

| 5,668,412 A  | * | 9/1997  | Kim 257/773             |

| 5,739,068 A  | * | 4/1998  | Jost et al 438/637      |

| 5,773,314 A  | * | 6/1998  | Jiang et al 438/3       |

| 5,792,681 A  | * | 8/1998  | Chang et al 438/210     |

| 5,828,092 A  | * | 10/1998 | Tempel                  |

| 5,828,097 A  | * | 10/1998 | Tanigawa                |

| 5,895,947 A  | * | 4/1999  | Lee et al 257/303       |

| 6,144,056 A  | * | 11/2000 | Manning                 |

| 6,214,727 B1 | * | 4/2001  | Parekh 438/618          |

| 6,232,169 B1 | * | 5/2001  | Widemann et al 438/243  |

<sup>\*</sup> cited by examiner

Primary Examiner—Amir Zarabian Assistant Examiner—Jeff Vockrodt

(74) Attorney, Agent, or Firm—Armstrong, Westerman & Hattori, LLP

#### (57) ABSTRACT

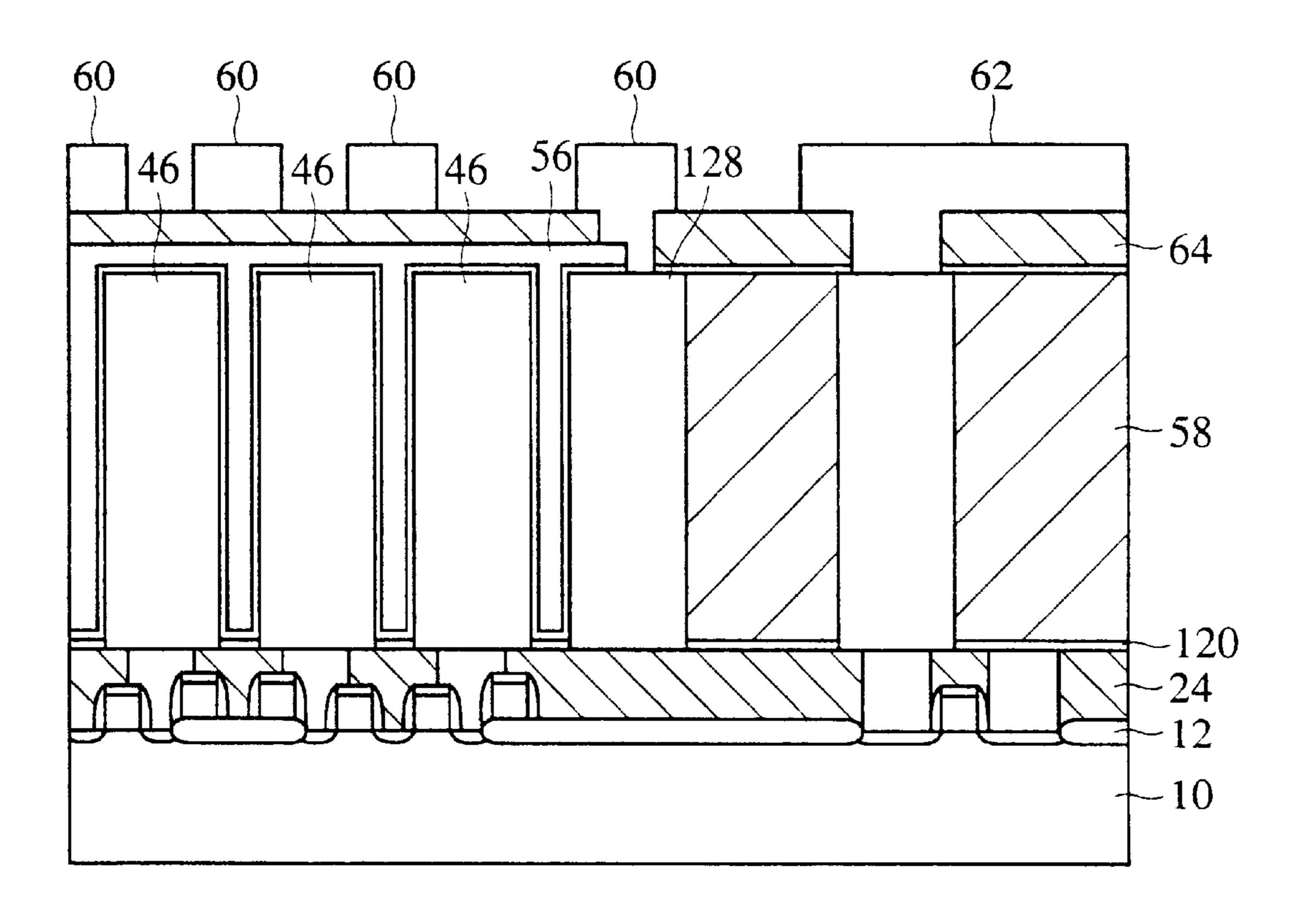

The semiconductor device including a memory cell region and a peripheral circuit region on a semiconductor substrate 10 comprises a transfer transistor formed in the memory cell region, a capacitor constituted by a storage electrode 46 connected to one of diffused layers 20 of the transfer transistor and formed of a first conducting layer, a dielectric film 52 covering a sidewall of the storage electrode 46, and an opposed electrode 56 formed on the dielectric film 52; a conducting plug formed of the first conducting layer and connected to the peripheral circuit region of the semiconductor substrate 10; and a first interconnection 62 electrically connected to the conducting plug 48.

#### 34 Claims, 53 Drawing Sheets

FIG. 2B

FIG. 2C

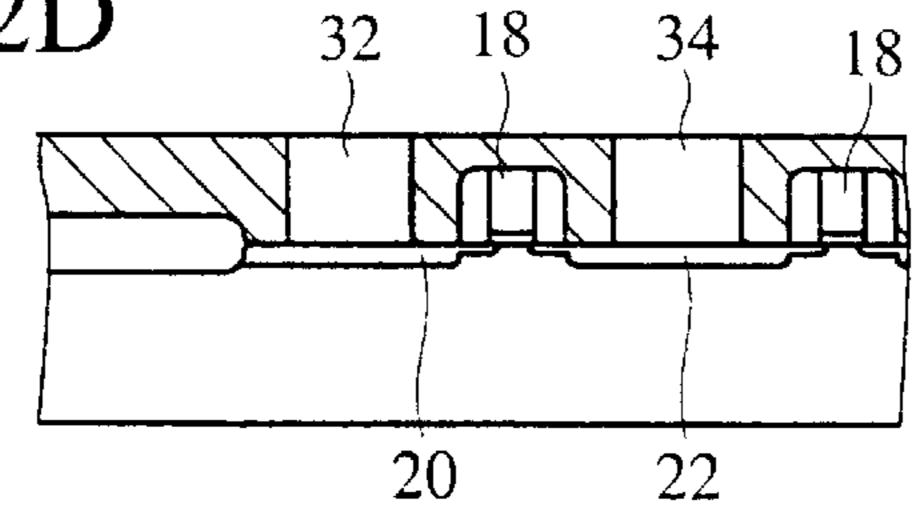

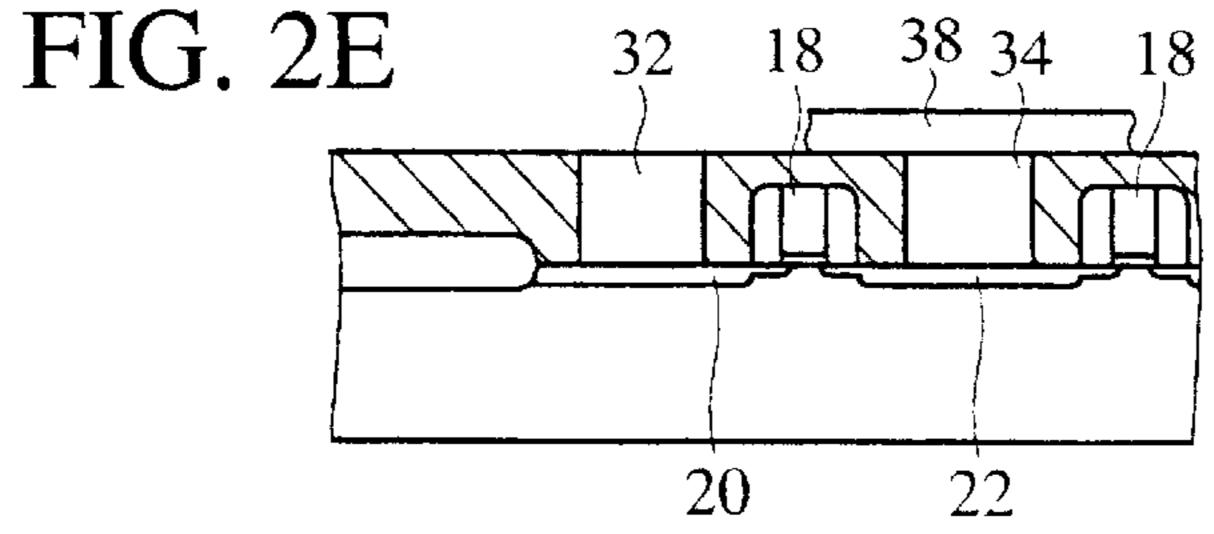

FIG. 2D

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7

FIG. 8A

FIG. 8B

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 10C

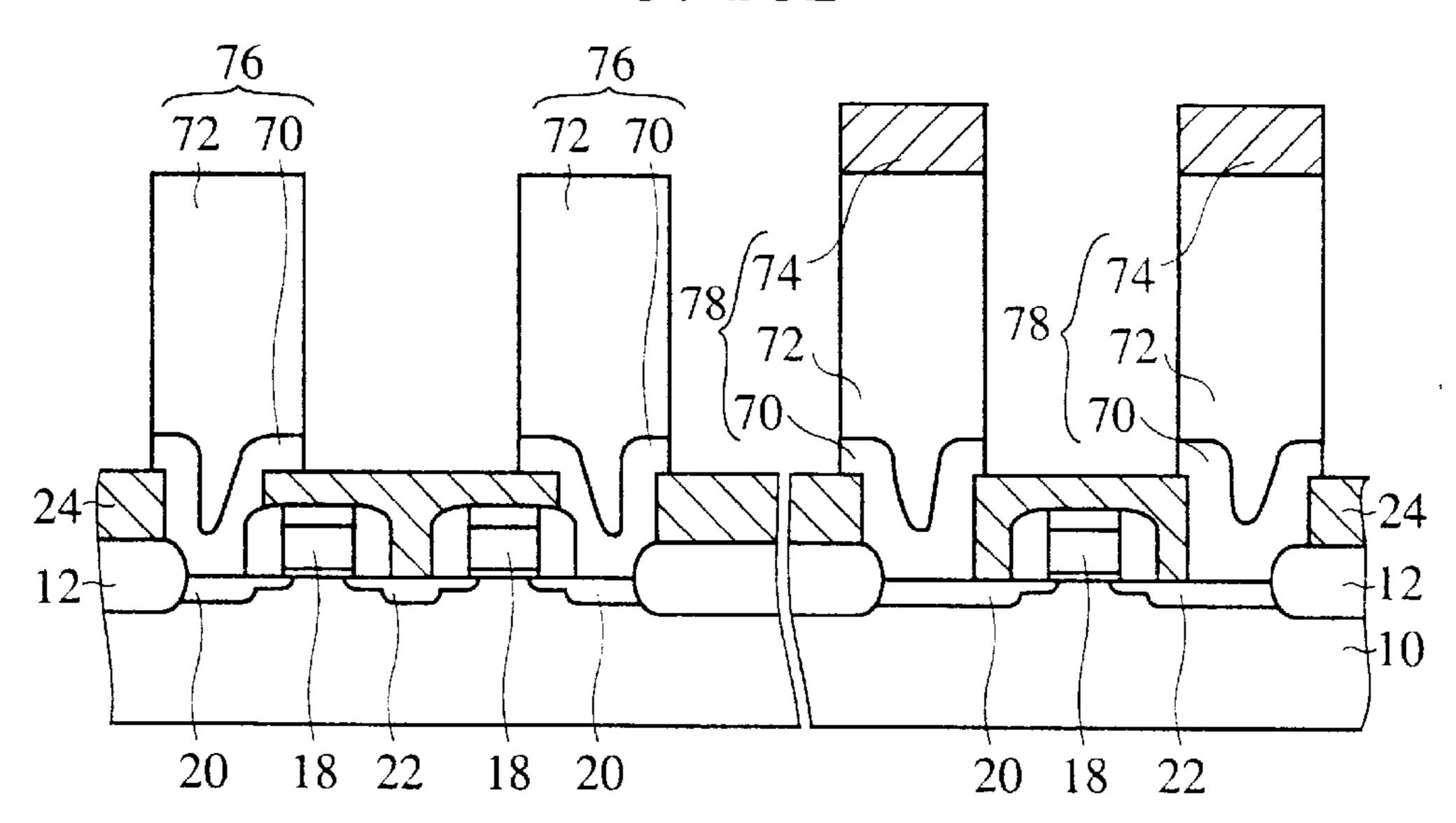

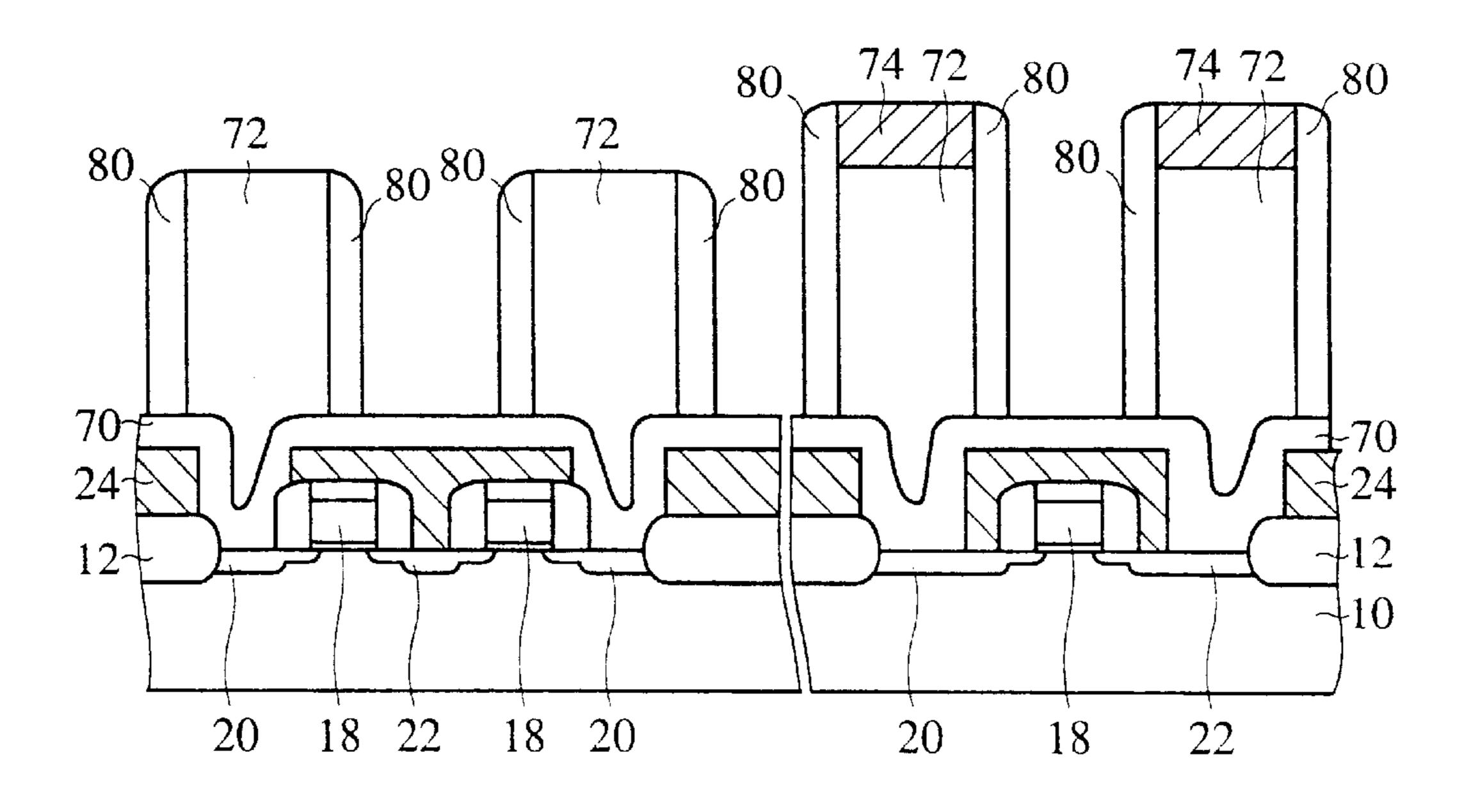

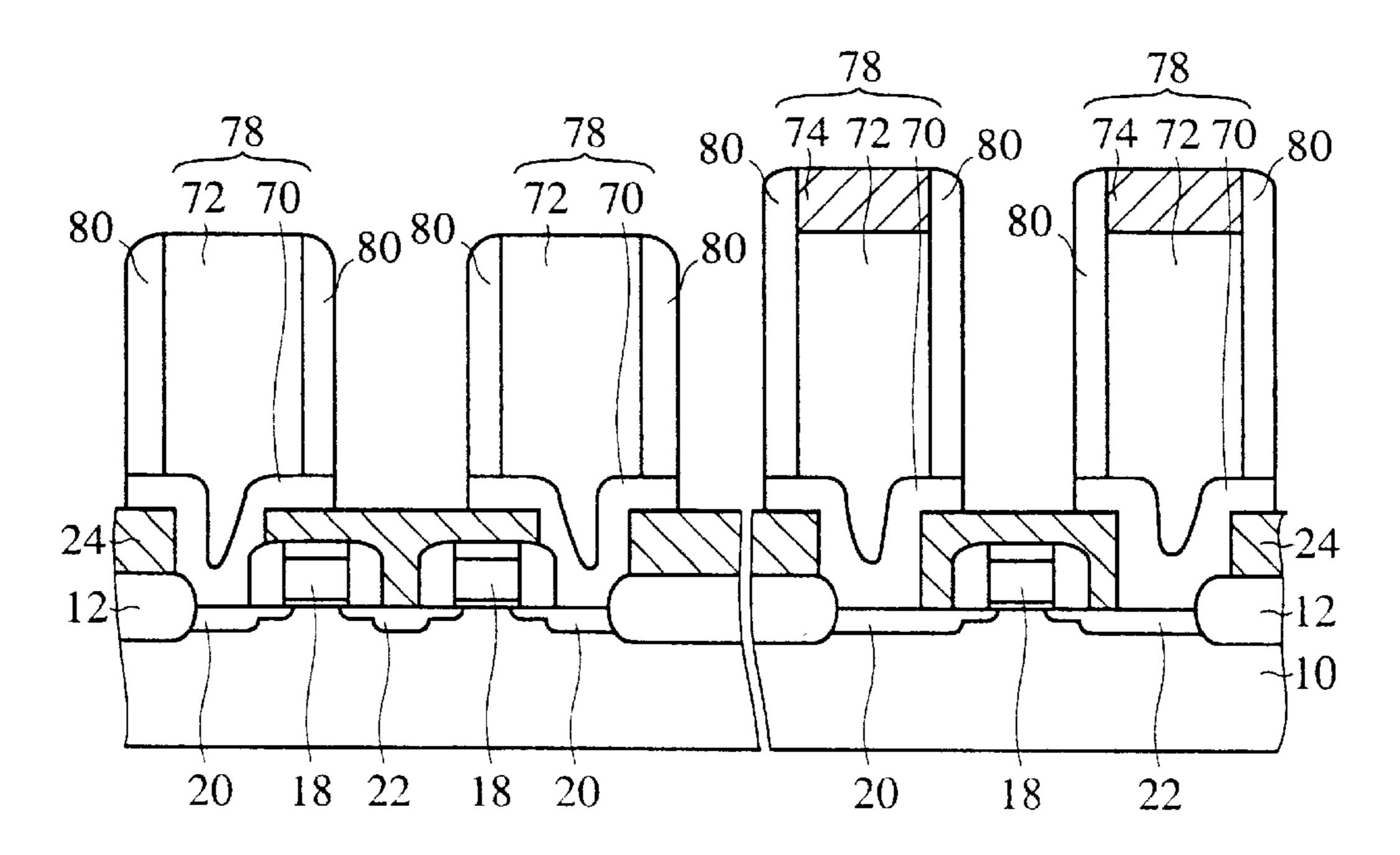

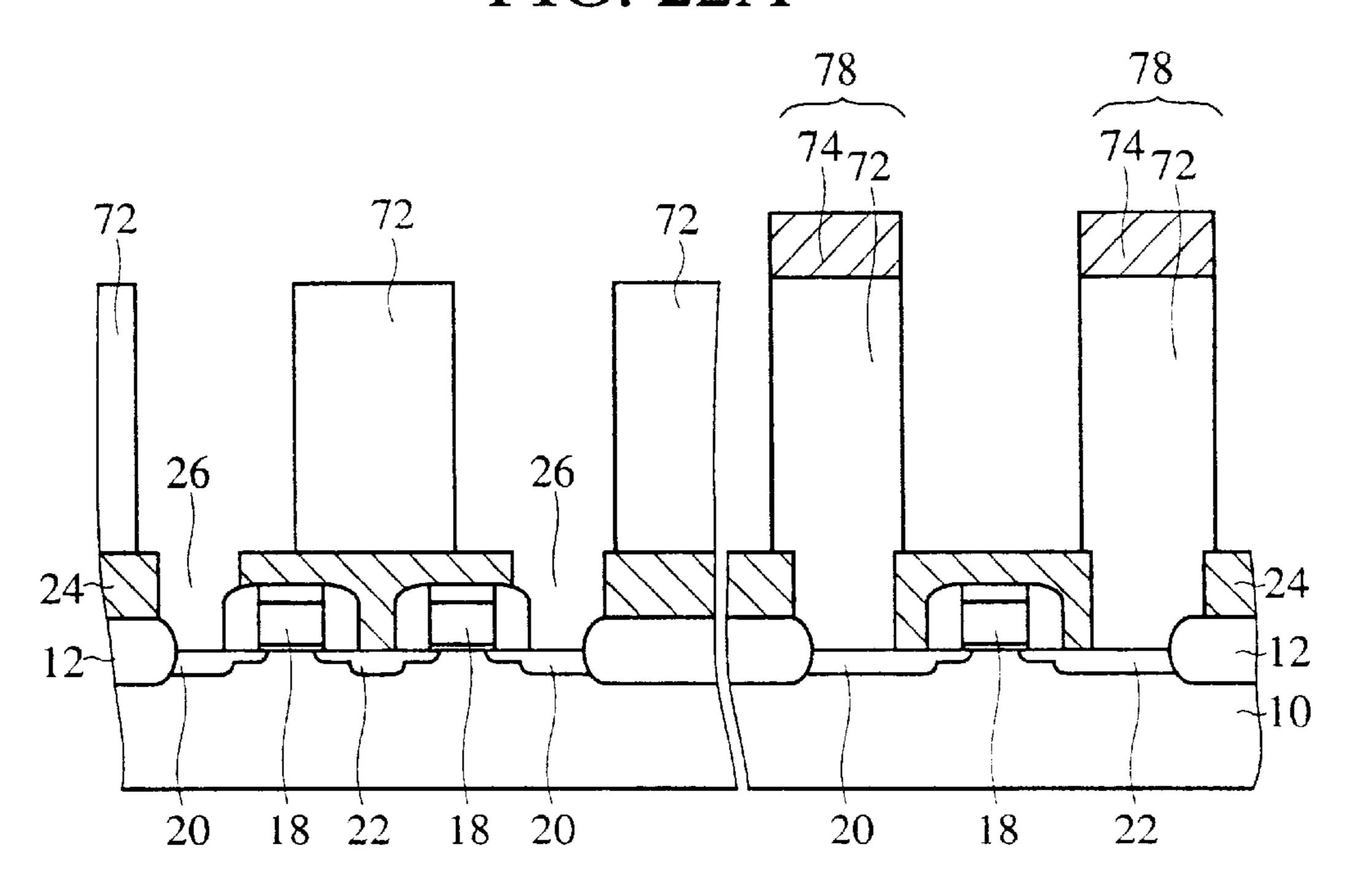

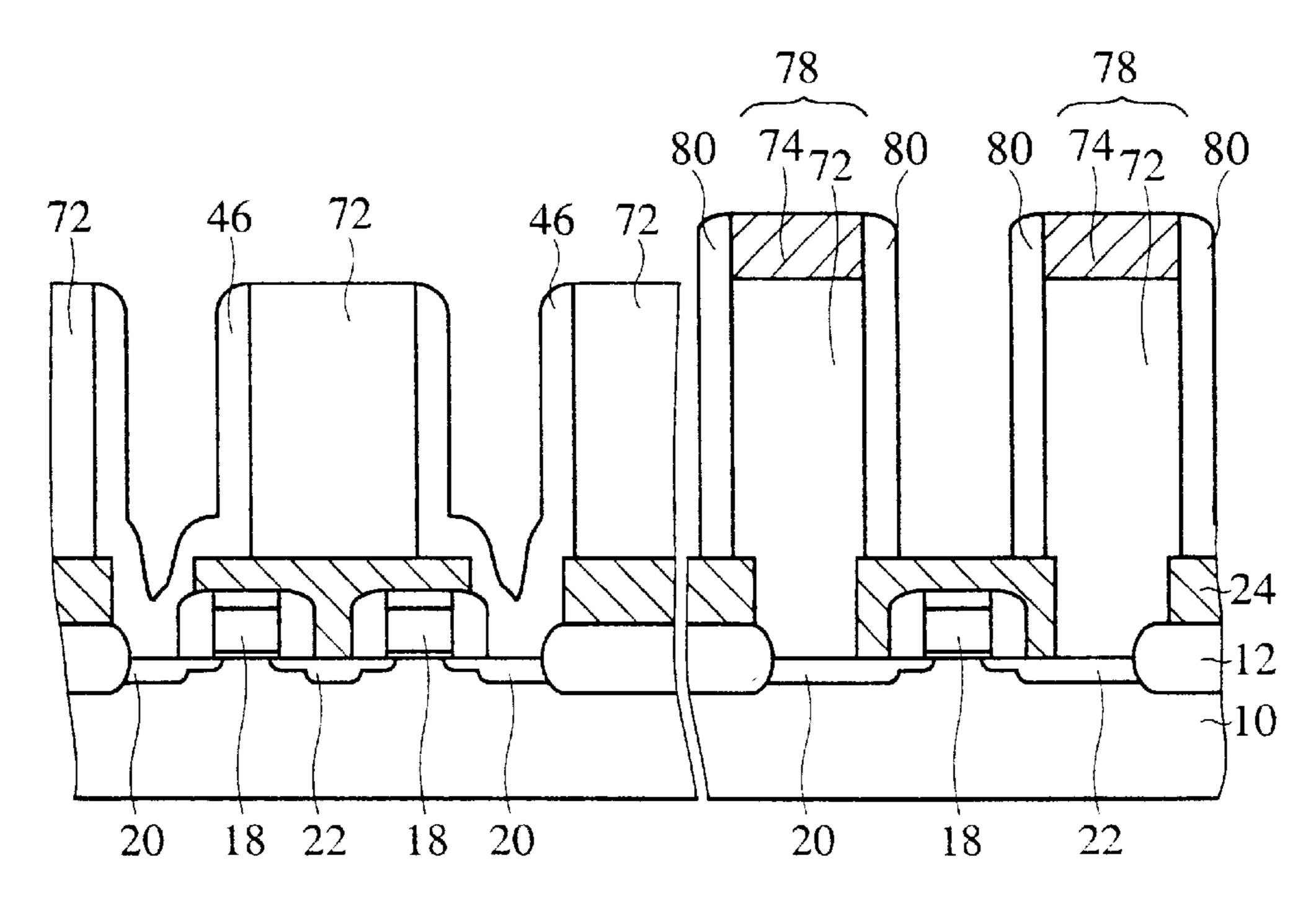

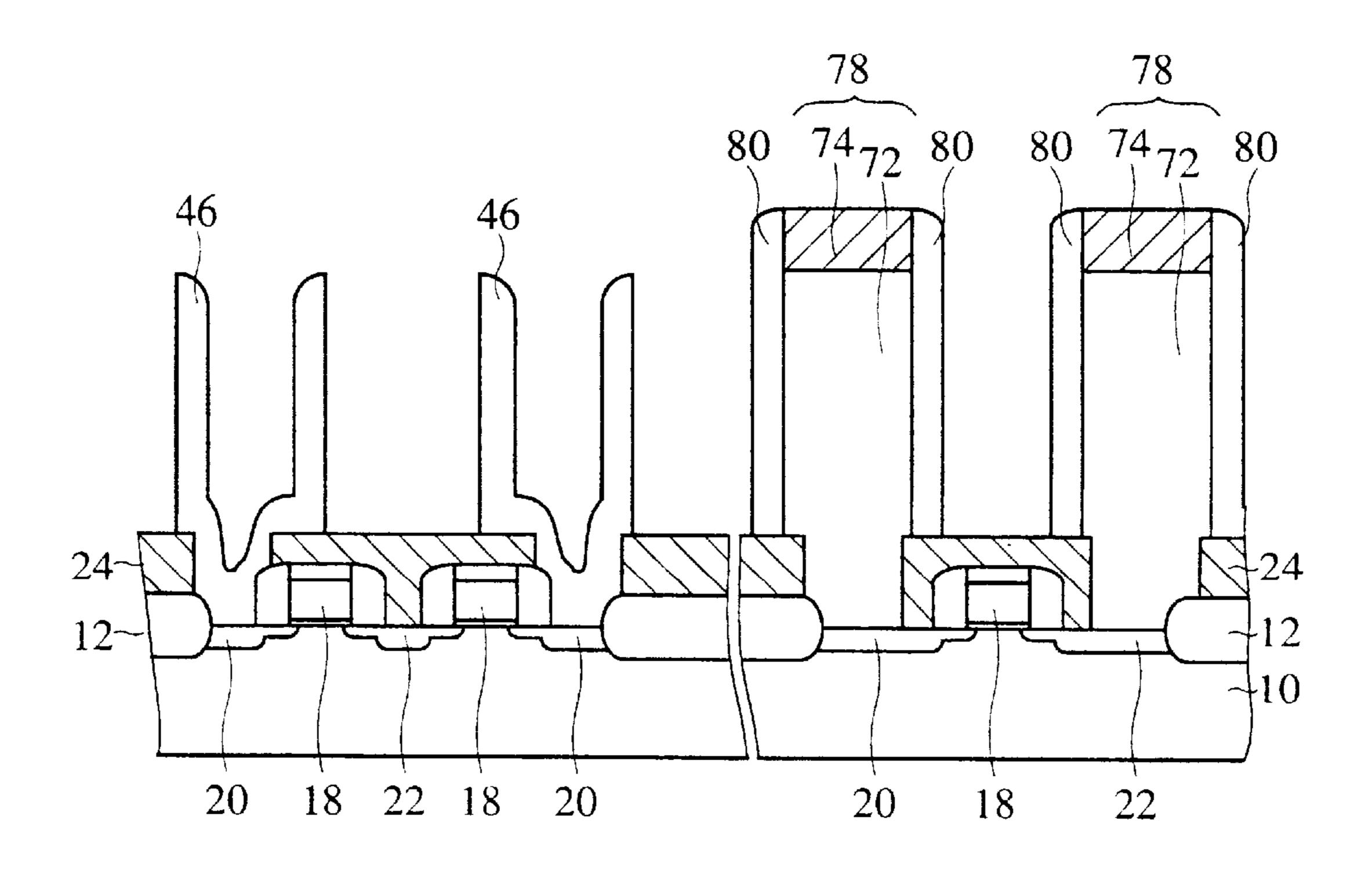

## FIG. 11A

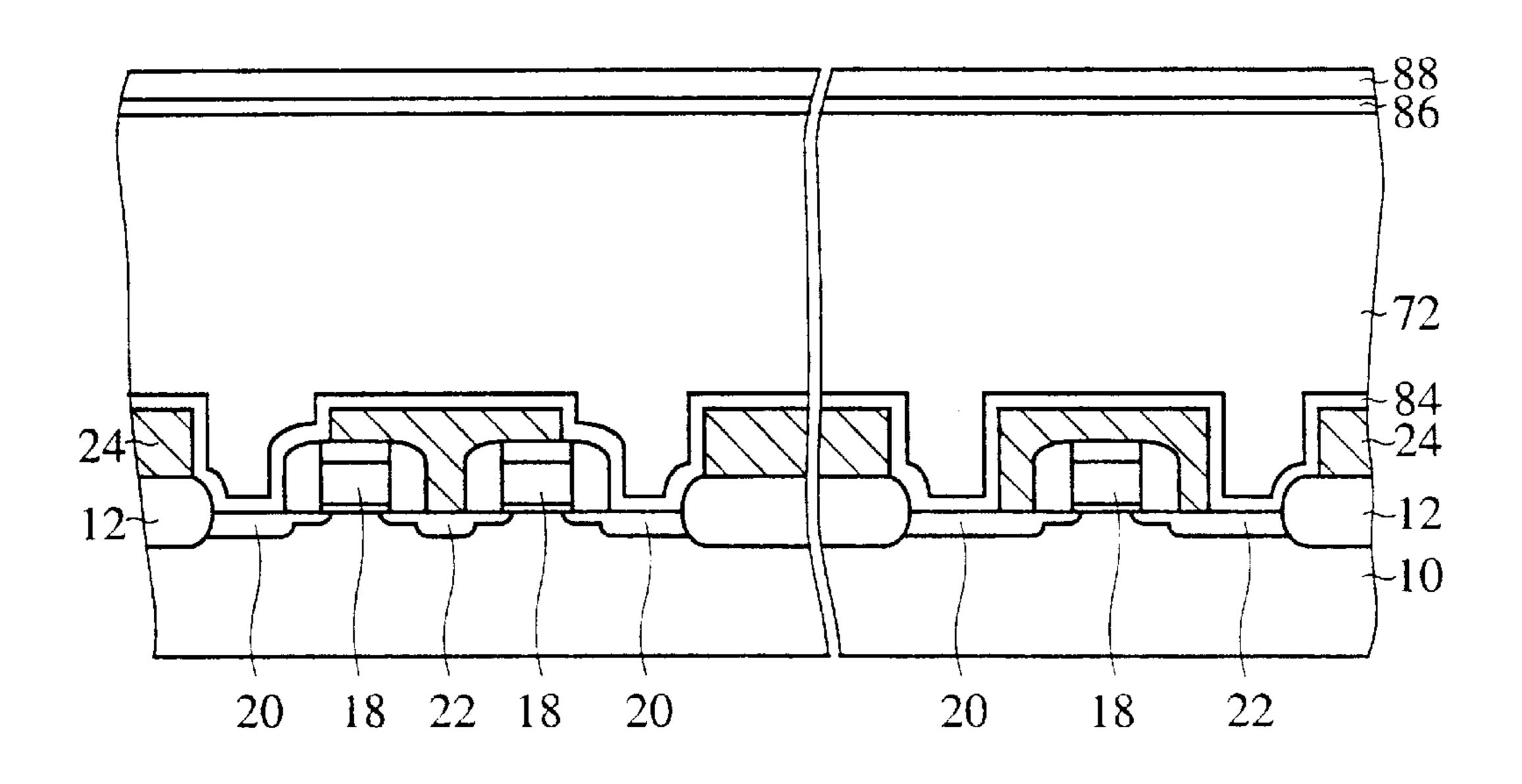

FIG. 11B

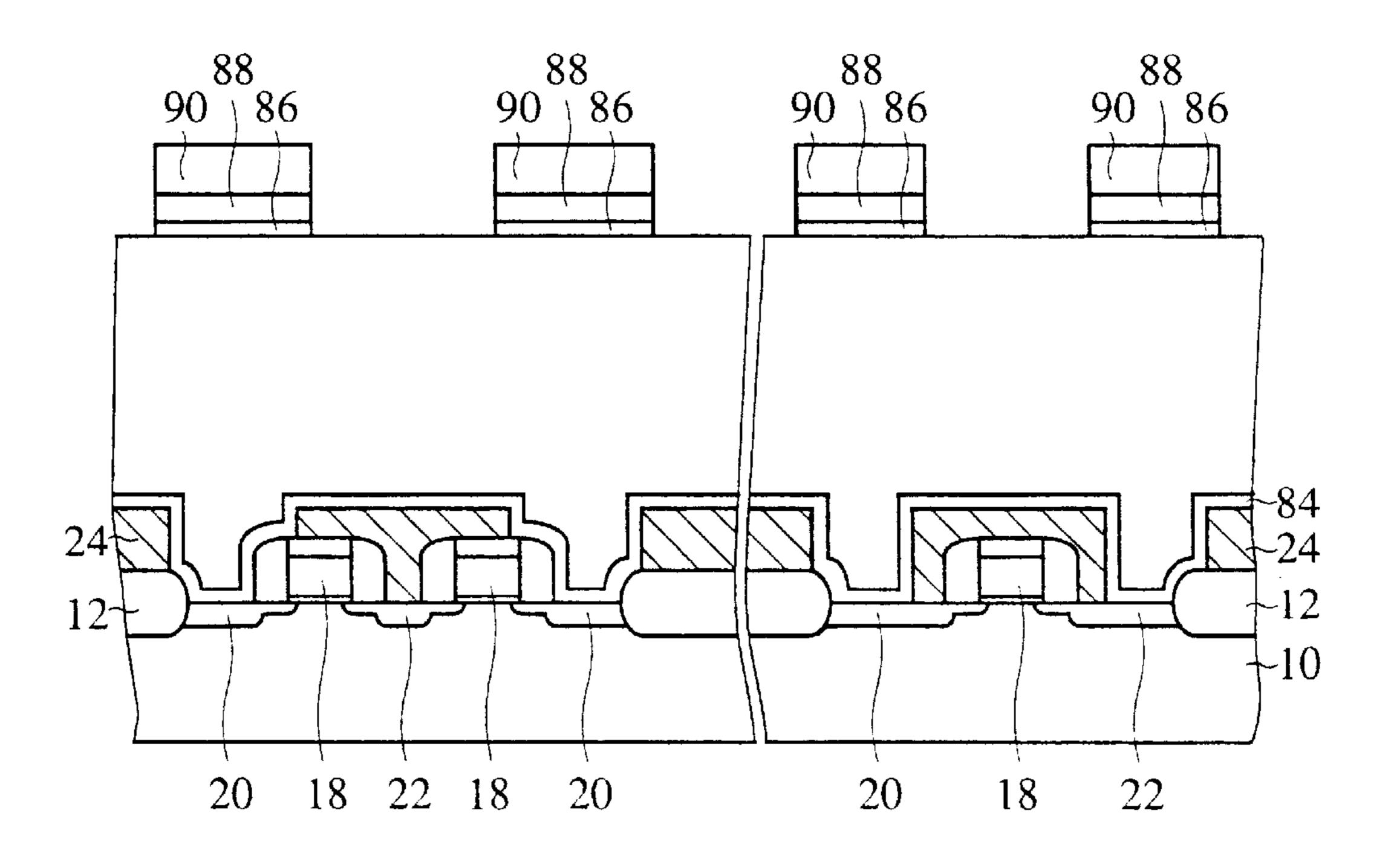

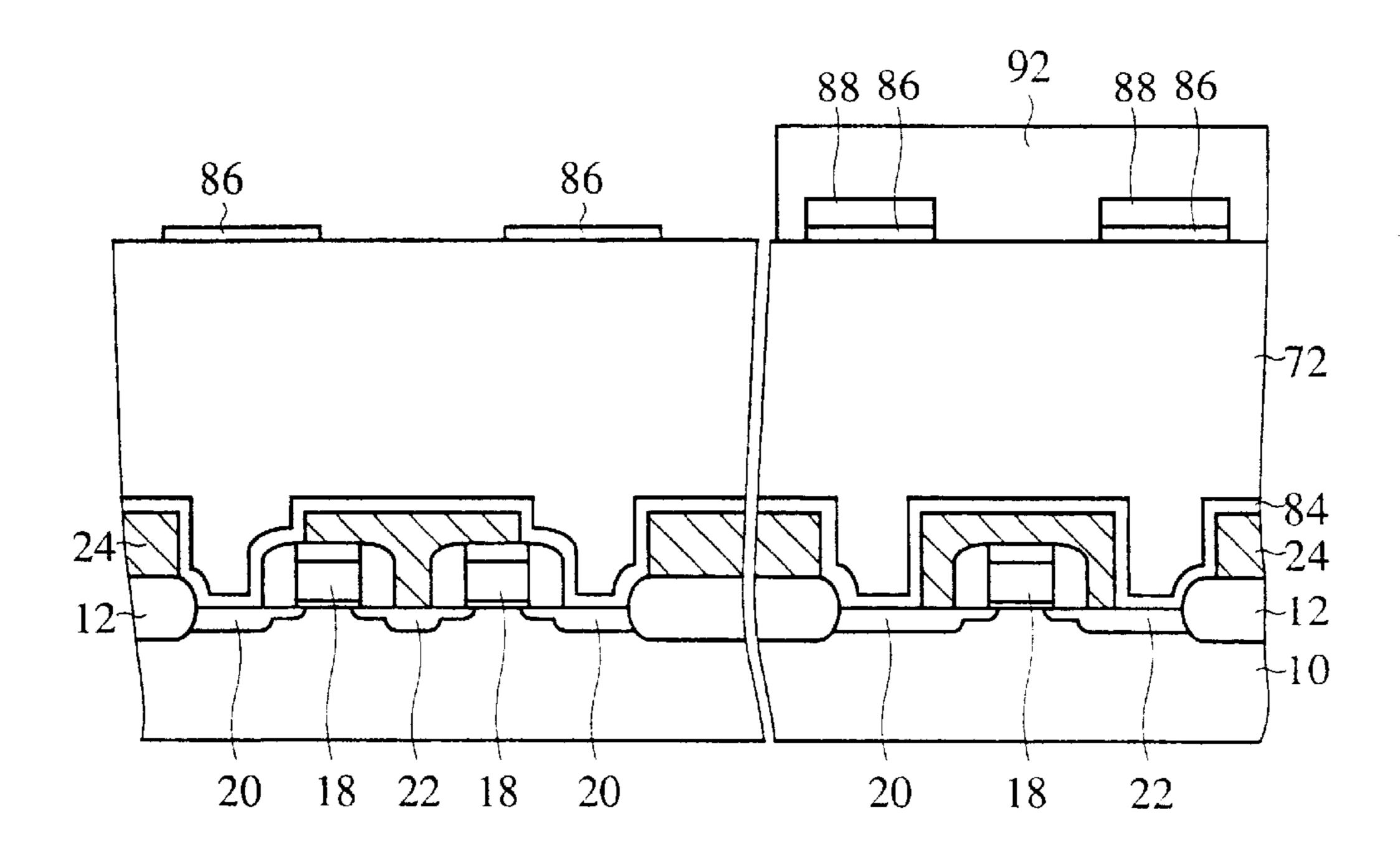

FIG. 11C

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16B

FIG. 16C

76

76

76

76

77

80

78

74

72

70

80

80

80

80

80

80

24

12

12

10

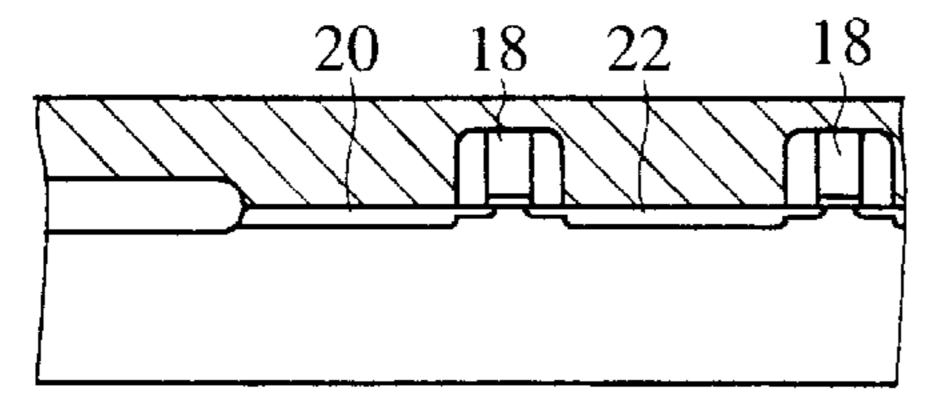

20

18

22

18

20

20

18

22

FIG. 17A

FIG. 17B

FIG. 18A

FIG. 18B

FIG. 19

# FIG. 20A

FIG. 20B

FIG. 21A

FIG. 21B

FIG. 22A

FIG. 22B

FIG. 23

FIG. 24A

FIG. 24B

FIG. 25A

FIG. 25B

FIG. 26A

FIG. 26B

FIG. 27

FIG. 28A

FIG. 28B

FIG. 29

FIG. 30A

FIG. 30B

FIG. 31A

FIG. 31B

56 52 46 46 58

60

58

56

24

24

12

10

FIG. 32A

FIG. 32B

FIG. 33A

FIG. 33B

FIG. 34

FIG. 35A

FIG. 35B

FIG. 35C

FIG. 36

FIG. 37A

FIG. 37B

FIG. 37C

FIG. 38

FIG. 39A

FIG. 39B

FIG. 40

### FIG. 41A

# FIG. 41B

### FIG. 41C

# FIG. 41D

FIG. 42A

FIG. 42B

FIG. 42C

FIG. 43A

FIG. 43B

FIG. 44A

FIG. 44B

FIG. 45A

FIG. 45B

FIG. 46A

FIG. 46B

FIG. 47A

FIG. 47B

# FIG. 48A

FIG. 48B

FIG. 49

FIG. 50A

FIG. 50B

FIG. 51

FIG. 52

PRIOR ART

FIG. 53

PRIOR ART

# SEMICONDUCTOR DEVICE AND METHOD FOR FABRICATING THE SAME

#### BACKGROUND OF THE INVENTION

The present invention relates to a fabrication technology of a semiconductor device, more specifically to a semiconductor device having a DRAM-type memory device and a method for fabricating the same.

A DRAM is a semiconductor memory device which can be formed by one transistor and one capacitor. Various structures for DRAMs of higher density and higher integration, and methods for fabricating DRAMs of such structures have been conventionally studied.

Recently in the field of the fabrication of the DRAM-type semiconductor device the competition among makers has become severe, and it is an important subject how to fabricate DRAM-type semiconductor devices of higher integration and higher achievement at low costs.

To this end, the capacitor requires a simpler structure. Structures which are simple and can secure sufficient capacities are studied. One of such structures of the capacitor uses a pillar-shaped conductor as the storage electrode.

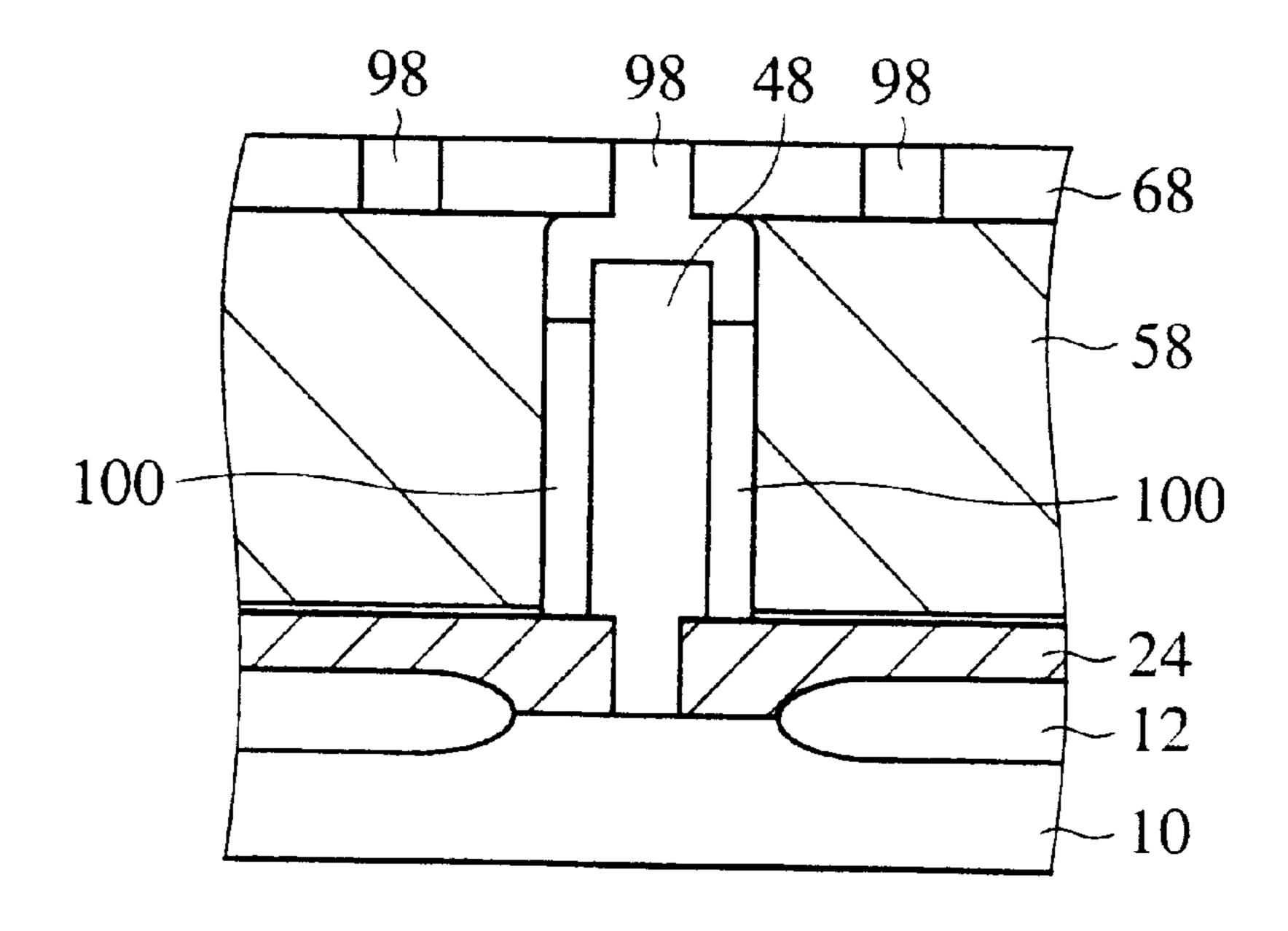

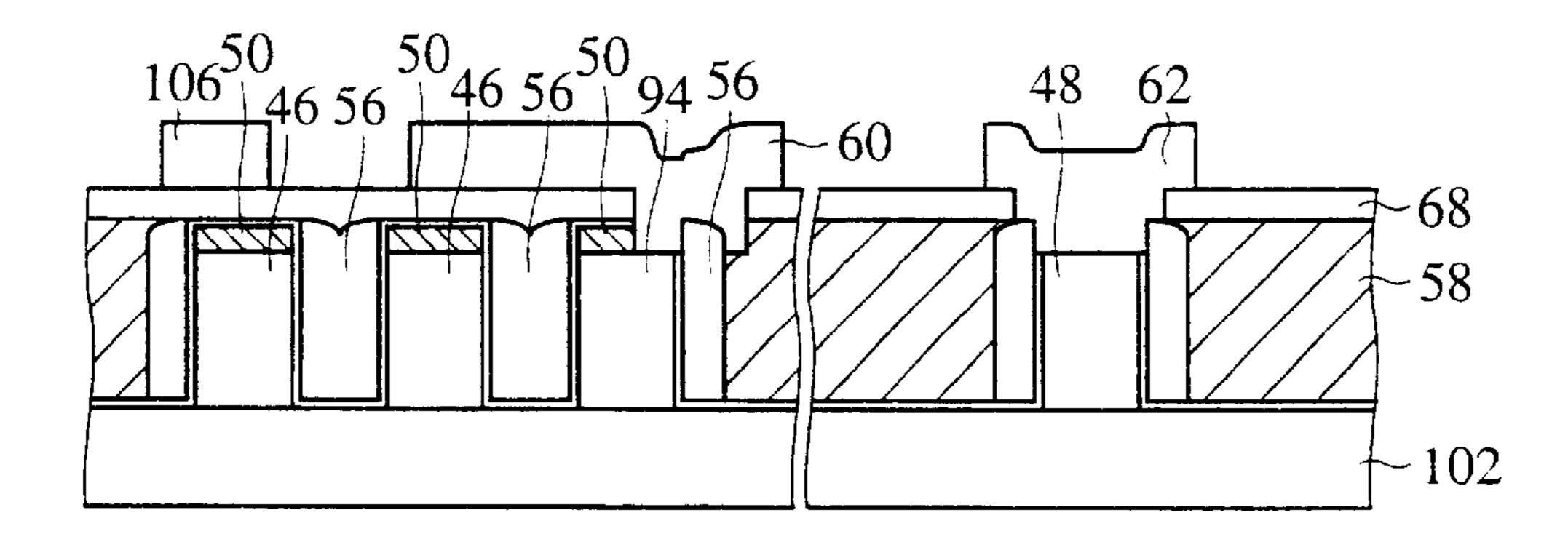

A semiconductor device using the pillar-shaped conductor 25 as the storage electrode will be explained with reference to FIG. 52.

On a semiconductor substrate 10 there are formed source/drain diffused layers independent of each other. A gate electrode 18 is formed on the semiconductor substrate 10 <sup>30</sup> between the source/drain diffused layers 20, 22 through a gate oxide film. Thus a memory cell transistor comprising a gate electrode 18, the source/drain diffused layers 20, 22 is formed.

An inter-layer insulation film 24 with a through-hole formed in above the source/drain diffused layer 20 is formed on the semiconductor substrate 10 with the memory cell transistor formed on.

In the through-hole a storage electrode 46 is formed with the bottom connected to the source/drain diffused layer 20 and protruded onto the inter-layer insulation film 24. An opposed electrode 56 is formed on the upper surface and the sidewalls of the storage electrode 46 through a dielectric film 52, and the storage electrode 46, the dielectric film 52 and the opposed electrode 56 constitute a capacitor.

On the semiconductor substrate 10 with the memory cell transistor and the capacitor interconnections 60, 62 are formed trough an inter-layer insulation film 68. The interconnection 60 is connected to the opposed electrode 56, and the interconnection 62 is connected to the semiconductor substrate 10 in a peripheral circuit region.

Thus a DRAM comprising one transistor and 1 capacitor is formed.

As described above, the conventional semiconductor 55 device shown in FIG. **52** has the storage electrode **46** constituting the capacitor in the simple pillar-shaped structure, which can be easily formed by one film forming step and one patterning step. Thus the capacitor forming step can be drastically simplified, and the forming costs can be 60 accordingly lower.

However, in the conventional semiconductor device using the pillar-shaped storage electrode 46 the memory cell region is higher than the peripheral circuit region by a height of the storage electrode 46, which makes it difficult to open 65 a contact hole for connecting the interconnection 62 to a peripheral circuit.

2

That is, usually a contact hole for connecting the interconnection to the peripheral circuit is formed through the inter-layer insulation film 48 formed on the storage electrode 46 (FIG. 52). However because of a large height difference of the inter-layer insulation film 68 between the memory cell region and the peripheral region, in simultaneously forming the contact hole to be opened on the opposed electrode 56 and the contact hole to be opened in the peripheral region, a sufficient depth of focus cannot be obtained in the contact hole opening step and the metallization step, which required micronized processing precision. Neither of the two contact holes cannot be correctly formed.

To ensure a sufficient depth of focus, the inter-layer insulation film 68 is planarized by, e.g., CMP (chemical mechanical polishing) method. However, the contact hole in the peripheral circuit region has a very high aspect ration, which makes it difficult to open the contact hole. It also makes it difficult to bury the interconnection in the contact-hole (FIG. 53).

To the semiconductor device fabrication process it is important for lower fabrication costs how to decrease lithography steps, and semiconductor structures and methods for fabricating the same which can decrease lithography steps are needed.

Each lithography step needs a pattern layout which considers a alignment allowance. For micronization of the devices, new means which enables the pattern layout to be conducted without considering the alignment allowance is needed.

### SUMMARY OF THE INVENTION

An object of the present invention is to provide a semiconductor device and a method for fabricating the same which can form a memory cell in a simple structure and by a simple fabrication process, and which are superior in alignment with a process for forming a contact hole in a peripheral circuit region.

The above-descried object is achieved by a semiconductor device including a memory cell region and a peripheral circuit region of a semiconductor substrate, comprising: a transfer transistor formed in the memory cell region; a capacitor connected to one of diffused layers of the transfer transistor and including a storage electrode formed of a first conducting layer, a dielectric film covering a sidewall of the storage electrode and an opposed electrode formed on the dielectric film; a first conducting plug formed of the first conducting layer and connected to the peripheral circuit region of the semiconductor substrate; and a first interconnection electrically connected to the first conducting plug. This structure of the semiconductor device allows the region interconnecting the first interconnection and the semiconductor substrate to be raised by the first conducting plug, which makes it unnecessary to open the contact hole deep enough to reach the semiconductor substrate so as to bury the first interconnection, with the result that the etching step and the interconnection forming step can be simple. Also in forming the interconnection connected to the opposed electrode simultaneously with the first interconnection, because the opposed electrode and the first conducting plug are substantially on the same level, the contact hole and the interconnection can be patterned irrespective of depth of focus. Because the first conducting plug can be formed of the same conducting layer as the storage electrode, the first conducting plug can be formed without making fabrication process complicated.

In the above-described semiconductor device, it is preferable that the storage electrode includes a second conduct-

ing layer on a surface thereof contacting the dielectric film. This structure of the semiconductor device makes it possible to maintain an operational speed of the semiconductor device without degrading characteristics of the capacitor. That is, it is preferred that the first conducting plug inter- 5 connecting the first interconnection and the semiconductor substrate has smaller resistance value because a resistance value of the first conducting plug influences the operational speed of the semiconductor device. On the other hand, it is required that a storage electrode have good compatibility with a dielectric film, and to this end, because the dielectric film and the first conducting plug are formed of the same material, a material thereof must be selected based on both conditions. However, this structure makes it possible to select a material low resistance as a material of the first conducting plug without considering a material of the stor- 15 age electrode. Thus, without degrading characteristics of the capacitor, the semiconductor device can retain an operational speed.

In the above-described semiconductor device, it is preferable that a plurality of the storage electrodes are provided, <sup>20</sup> and the opposed electrode is buried between said a plurality of the storage electrodes. This structure of the semiconductor device makes it possible to form the opposed electrode by self-alignment with the storage electrode. A lithography step for patterning the opposed electrode is not necessary.

In the above-described semiconductor device, it is preferable that the semiconductor device further comprises, on a sidewall of the first conducting plug, a first insulation film formed of the same insulation layer as the dielectric film, and a sidewall film formed of the same conducting layer as the opposed electrode.

In the above-described semiconductor device, it is preferable that the first conducting plug is crown-shaped.

In the above-described semiconductor device, it is preferable that a second conducting layer is buried in the crown-shaped first conducting plug.

In the above-described semiconductor device, it is preferable that the semiconductor device further comprises a dummy electrode formed of the first conducting layer and 40 insulated from the semiconductor substrate; and a second interconnection connected to the opposed electrode, wherein the opposed electrode is extended on a sidewall of the dummy electrode or on the dummy electrode, and the second region where the dummy electrode is provided. This structure of the semiconductor device facilitates connection of the second interconnection to the opposed electrode without short-circuiting with the storage electrode.

In the above-described semiconductor device, it is pref- 50 erable that the first interconnection is a buried interconnection buried in a second insulation film formed on the first conducting plug. The first interconnection can be a buried interconnection.

In the above-described semiconductor device, it is pref- 55 erable that a cavity is formed in a peripheral part of the first conducting plug. This structure of the semiconductor device makes it possible to reduce parasitic capacitance between the interconnections.

In the above-described semiconductor device, it is preferable that the semiconductor device further comprises: a second conducting plug connected to the other diffused layer of the transfer transistor and formed of the first conducting layer; and a bit line electrically connected to the second conducting plug. This structure allows the second conduct- 65 ing plug to be used for the connection between the second conducting plug and the transfer transistor.

In the above-described semiconductor device, it is preferable that the semiconductor device further comprises: an annular dummy electrode provided around the memory cell region and surrounding the same.

In the above-described semiconductor device, it is preferable that the annular dummy electrode is formed of the first conducting layer.

In the above-described semiconductor device, it is preferable that the semiconductor device further comprises: a third insulation film selectively covering a surface of the opposed electrode; and a third interconnection arranged on the capacitor, the third interconnection being insulated from the opposed electrode by the third insulation film. This structure of the semiconductor device keeps the interconnection of the capacitor from connecting to the opposed electrode, which permits the interconnection for connecting to the peripheral circuit region can be extended on the memory cell region. Thus, the layout of the interconnection of a peripheral circuit can have high freedom degree, and accordingly the semiconductor device can have improved integration.

The above-described object can be also achieved by a method for fabricating a semiconductor device comprising: a storage electrode forming step of forming a plurality of storage electrodes on a base substrate; a dielectric film forming step of forming a dielectric film covering said a plurality of storage electrodes; and an opposed electrode forming step of depositing and etching back a first conducting film on the base substrate with the dielectric film formed on to form an opposed electrode filled between said a plurality of storage electrodes covered with the dielectric film and formed of the first conducting film. This fabrication of the semiconductor device makes it possible to form the opposed electrode by self-alignment with the storage electrode, which allows a lithography step required to form an opposed electrode by the conventional semiconductor device fabrication method to be omitted.

The above-described object can be also achieved by a method for fabricating a semiconductor device comprising: a storage electrode forming step of forming a plurality of storage electrodes in a first region of a base substrate and forming a first pillar-shaped conductor formed of the same conducting layer as the storage electrodes in a second region interconnection is connected to the opposed electrode at a 45 of the base substrate; a dielectric film forming step of forming a dielectric film covering said a plurality of storage electrodes; an opposed electrode forming step of depositing and etching back a first conducting film on the base substrate with the dielectric film formed on to form an opposed electrode filled between said a plurality of storage electrodes covered with the dielectric film and formed of the first conducting film; and an interconnection forming step of forming a first interconnection on the first pillar-shaped conductor and connected to the base substrate in the second region through the first pillar-shaped conductor. This fabrication of the semiconductor device allows the region interconnecting the first interconnection and the semiconductor substrate to be raised by the first pillar-shaped conductor. Because the pillar-shaped conductor can be formed of the same conducting layer as the storage electrode, the pillarshaped conductor can be formed without making fabrication process complicated. Because the opposed electrode can be formed by self-alignment with the storage electrode, a lithography step for patterning the opposed electrode is not necessary.

> In the above-described method for fabricating a semiconductor device, it is preferable that in the opposed electrode

forming step, a sidewall film formed of the first conducting film and formed on a sidewall of the first pillar-shaped conductor is further formed.

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprises after the opposed electrode forming step: a first insulation film forming step of depositing a first insulation film; and a first insulation film removing step of removing the first insulation film until top surfaces of the storage electrodes and of the pillar-shaped conductor are exposed. This fabrication of the semiconductor device exposes by self-alignment the first pillar-shaped conductor on the surface of the first insulation film, which makes it unnecessary to open by lithography a new contact hole which reaches the first pillar-shaped conductor, and makes it possible to form the interconnection connected to the base substrate without disalignment.

In the above-described method for fabricating a semiconductor device, it is preferable that in the storage electrode forming step, the storage electrodes and the first pillar-shaped conductor having the top surfaces covered with a cap film are formed; and in the first insulation film removing step, the first insulation film is removed until a top surface of the cap film is exposed. This fabrication exposes self-alignment the opposed electrode on the surface of the first insulation film, which makes it possible to for the interconnection connected to the base substrate without forming a new contact hole.

In the method for fabricating a semiconductor device, it is preferable that the method further comprises after the first insulation film removing step: a cap film removing step of removing the cap film on the first pillar-shaped conductor to expose the first pillar-shaped conductor. This fabrication of the semiconductor device makes it possible to form by self-alignment the contact hole exposing the first pillar-shaped conductor. The cap film is formed of an insulating material, and the cap film in the memory cell-region is selectively left on, whereby the opposed electrode alone can be exposed in the memory cell region. Thus, the interconnection formed in the memory cell region can be connected only to the opposed electrode without interposing the interlayer insulation film.

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprises after the first insulation film removing step: a second insulation film forming step of depositing a second insulation film; and an opening forming step of forming a first opening opened on the first pillar-shaped conductor in the second insulation film. This fabrication of the semiconductor device makes it also possible that the first interconnection is connected to the first pillar-shaped conductor through the first opening formed in the second insulation film.

In the above-described method for fabricating a semiconductor device, it is preferable that in the storage electrode 55 forming step, a second pillar-shaped conductor which is not electrically connected to the base substrate and spaced from the storage electrodes by a prescribed interval, and are formed of the same conducting layer as the first pillar-shaped conductor is formed in a third region adjacent to the 60 first region; and in the opening forming step, a second opening formed in the second insulation film on the opposed electrode near the second pillar-shaped conductor. This fabrication of the semiconductor device can prevents the second opening formed in the second insulation film from 65 extending on the storage electrode. Thus, the lithography step for forming the second opening can be simplified.

6

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprises after the first insulation film removing step: a second insulation film forming step of depositing a second insulation film; and an opening forming step of forming a second opening opened on the opposed electrodes in the second insulation film.

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprises after the first insulation film removing step: a second insulation film forming step of chemically or thermally treating a surface of the opposed electrode to form a second insulation film on the surface of the opposed electrode. This fabrication of the semiconductor device makes it possible the interconnection can be formed on the memory cell region, insulated from the opposed electrode.

In the method for fabricating a semiconductor device, it is preferable that in the storage electrode forming step, a second pillar-shaped conductor formed of the same conducting layer as the first pillar-shaped conductor, and spaced from the storage electrodes at a prescribed interval and not connected electrically to the base substrate is further formed in a third region adjacent to the first region; and which further comprises after the second insulation film forming step, an opening forming step of forming a second opening formed in the second insulation film on the opposed electrode near the second pillar-shaped conductor. This fabrication of the semiconductor device can prevent the second opening for forming the insulation film from extending on the storage electrode. Thus, the lithography step for forming the second opening can be made simple.

In the method for fabricating the semiconductor device, it is preferable that the first opening is an interconnection groove for burying an interconnection in the insulation film. The first interconnection is a buried interconnection buried in the second insulation film.

In the method for fabricating the semiconductor device, it is preferable that the method further comprises after the storage electrode forming step: a conducting film forming step of forming a second conducting film on sidewalls of the storage electrodes. Because by providing the second conducting film on the sidewalls of the storage electrode, a material of the storage electrode does not influence characteristics of the dielectric film, the storage electrode can be formed of a material having a desirable low resistance which is suitable for the first pillar-shaped conductor.

The above-described object can be also achieved by a method for fabricating a semiconductor device comprising: a pillar-shaped conductor forming step of forming a pillarshaped body formed in a first region of a base substrate and formed of a first conducting layer and a second conducting layer laid the latter on the former, and forming a first pillar-shaped conductor connected to a second region of the base substrate and formed of a first conducting layer and a second conducting layer laid the latter on the former; a sidewall film forming step of forming a sidewall film formed of a third conducting film on a sidewall of the pillar-shaped body and the first pillar-shaped conductor; a storage electrode forming step of selectively removing the second conducting film forming the pillar-shaped body and forming a crown-shaped storage electrode of the first conducting film and the sidewall in the first region; a dielectric film forming step of forming a dielectric film for covering the storage electrodes; an opposed electrode forming step of depositing and patterning a fourth conducting film on the base substrate with the dielectric film formed on and forming an opposed

electrode covering the storage electrodes through the dielectric film; and an interconnection forming step of forming a first interconnection on the first pillar-shaped conductor and connected to the base substrate in the second region through the first pillar-shaped conductor. This fabrication of the 5 semiconductor device can raise the region interconnecting the first interconnection and the base substrate by the first pillar-shaped conductor, which makes it unnecessary to make the contact hole deep enough to reach the semiconductor substrate to bury the first interconnection. Accordingly the etching step and the interconnection forming step can be simplified. The crown-shaped storage electrode can be formed simultaneously with the formation of the first pillar-shaped conductor, which makes it possible to form the pillar-shaped conductor without complicating fabrication 15 process. By using the crown-shaped capacitor, a height of the storage electrode and the first pillar-shaped conductor can be reduced to about a half, and accordingly the first pillar-shaped conductor can have reduced electric resistance.

The above-described object can be also achieved by a 20 method for fabricating a semiconductor device comprising: a pillar-shaped conductor forming step of depositing and patterning a first conducting film on a base substrate and forming the first conducting film having an opening on a first region of the base substrate and having a first pillar-shaped 25 conductor on a second region of the base substrate; a second conducting film forming step of forming a second conducting film on the first conducting film and the base substrate; a second conducting film removing step of removing the second conducting film, leaving the second conducting film 30 on a inside wall and a bottom surface of the opening and on a sidewall of the first pillar-shaped conductor, and forming a storage electrode extended from the bottom surface of the opening to the inside wall of the opening, and a sidewall film formed on the sidewall of the first pillar-shaped conductor; 35 a first conducting film removing step of removing the first conducting film except the first conducting film formed in the second region; a dielectric film forming step of forming a dielectric film covering a surface of the storage electrode; an opposed electrode forming step of depositing and pat- 40 terning a fourth conducting film on the base substrate with the dielectric film formed on, and forming an opposed electrode covering the storage electrode through the dielectric film; and an interconnection forming step of forming a first interconnection formed on the first pillar-shaped 45 conductor, and connected to the base substrate in the second region through the first pillar-shaped conductor. This fabrication of the semiconductor device can raise the region interconnecting the first interconnection and the base substrate by the first pillar-shaped conductor, which makes it 50 unnecessary to make the contact hole deep enough to reach the semiconductor substrate to bury the first interconnection. Accordingly the etching step and the interconnection forming step can be simplified. The crown-shaped storage electrode can be formed simultaneously with the formation of 55 the first pillar-shaped conductor, which makes it possible to form the pillar-shaped conductor without complicating fabrication process. By using the crown-shaped capacitor, a height of the storage electrode and the first pillar-shaped conductor can be reduced to about a half, and accordingly 60 the first pillar-shaped conductor can have reduced electric resistance.

In the above-described method for fabricating a semiconductor device, it is preferable in which in the pillar-shaped conductor forming step, the first pillar-shaped conductor 65 having a top surface covered with a cap film is formed; and the method further comprises after the opposed electrode

8

forming step: a first insulation film forming step of depositing a first insulation film; a fist insulation film removing step of removing the first insulation film until a top surface of the cap film is exposed; and a cap film removing step of removing the cap film on the first pillar-shaped conductor to expose the first pillar-shaped conductor. This fabrication of the semiconductor device makes it possible to form by self-alignment the contact hole for exposing the first pillar-shaped conductor.

In the above-described method for fabricating a semiconductor device, it is preferable that in the pillar-shaped conductor forming step, the cap film is formed of a fifth conducting film having substantially the same etching characteristics as the first conducting film, and a mask film to be a mask for processing the second conducting film formed on the fifth conducting film; and in the cap film removing step, the mask film is removed to expose the fifth conducting film on the first pillar-shaped conductor. This fabrication of the semiconductor device makes it possible that even in a case that the second conducting film is formed of a material which is difficult to have a selective ratio with respect to the resist film, the second conducting film can be processed stably to form the storage electrode and the first pillarshaped conductor. Because the fifth conducting film is formed of a film having substantially the same etching characteristics as the first conducting film, the storage electrode and the first conducting film forming the first pillarshaped conductor can be processed simultaneously with the removal of the fifth conducting film ont eh storage electrode.

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprises after the first insulation film removing step: a second insulation film forming step of depositing a second insulation film; and an opening forming step of forming in the second insulation film a first opening formed on the first pillar-shaped conductor, in the cap film removing step, the cap film exposed in the first opening is removed. This fabrication of the semiconductor device makes it possible to connect the first interconnection to the first pillar-shaped conductor through the second insulation film.

In the above-described method for fabricating a semiconductor device, it is preferable that in the pillar-shaped conductor forming step, a second pillar-shaped conductor formed of the same conducting layer as the first pillar-shaped conductor, and spaced from the storage electrode by a prescribed interval and not connected electrically to the base substrate is formed in a third region adjacent to the first region; and in the opening forming step, a second opening opened on the opposed electrode near the second pillar-shaped conductor is formed in the second insulation film. This fabrication of the semiconductor device makes it possible that the second opening for connecting the interconnection to the opposed electrode is opened easily and simultaneously with the first opening.

In the method for fabricating a semiconductor device, it is preferable that the formation of the first opening and the second opening in the opening forming step and the removal of the cap film in the cap film removing step are conducted with one resist pattern as a mask. This fabrication of the semiconductor device makes it possible that the formation of the first opening and the second opening, and the removal of the cap film can be conducted with one resist pattern as a mask. Accordingly the contact hole for exposing the opposed electrode and the first pillar-shaped conductor can be formed without complicating fabrication process.

In the above-described method for fabricating a semiconductor device, it is preferable that in the interconnection

forming step, a second interconnection connected to the opposed electrode is further formed.

The above-described object can be also achieved by a method for fabricating a semiconductor device comprising: an insulation film forming step of forming an insulation film on a base substrate; a storage electrode forming step of forming a storage electrode buried in the insulation film and buried in a first opening formed in a first region, and a first pillar-shaped conductor buried in the insulation film and buried in a second opening formed in a second region; an insulation film removing step of selectively removing the insulation film in the first region to expose a sidewall of the storage electrode; a dielectric film forming step of forming a dielectric film for covering a surface of the storage electrode; a opposed electrode forming step of forming an opposed electrode on the surface of the storage electrode through the dielectric film; and an interconnection forming step of forming a first interconnection disposed on the first pillar-shaped conductor and connected to the base substrate in the second region through the first pillar-shaped conductor. The storage electrode and the first pillar-shaped conductor are formed by forming openings in the insulation film having good global flatness and burying the conducting film in the opening, so that the surface flatness of the insulation film can be more improved than in the case that the storage electrode and the first pillar-shaped conductor are formed before forming the insulation film.

In the above-described method for fabricating a semiconductor device, it is preferable that in the storage electrode forming step, an annular dummy electrode disposed around the first region and surrounding the same, and buried in a third opening formed in the insulation film is further formed; and in the insulation film removing step, the insulation film in the first region is selectively removed with the annular dummy electrode as a stopper. As in the case that the insulation film is formed prior to the formation of the storage electrode and the pillar-shaped conductor, a space for burying the opposed electrode can be selectively formed in the insulation film, because the annular dummy electrode is disposed around the first region and surrounding the same.

In the above-described method for fabricating a semiconductor device, it is preferable that in the storage electrode forming step, the first opening, the second opening and the third opening are concurrently formed, and the storage electrode, the first pillar-shaped conductor and the annular dummy electrode are formed of the same conducting layer. The storage electrode, first pillar-shaped conductor and annular dummy electrode can be formed simultaneously so that the fabrication process can be rationalized.

In the above-described method for fabricating a semiconductor device, it is preferable that in the storage electrode forming step, the first opening, the second opening and the third opening are formed at different times, and the storage electrode, the first pillar-shaped conductor and the annular dummy electrode are formed of conducting layers different form each other, whereby the storage electrode and the first pillar-shaped conductor can be formed by different materials each other.

In the above-described method for fabricating a semiconductor device, it is preferable that in the insulation film 60 removing step, the insulation film is removed with a mask member, as a mask, for exposing at least a partial region of the insulation film in the first region, whereby the alignment precision of the lithography step can made rough. Thus, the lithography step can be simplified.

In the above-described method for fabricating a semiconductor device, it is preferable that in the insulation film

10

removing step, the insulation film is removed by wet etching, in which etching isotropically advances, whereby all the insulation film in the first region can be selectively etched by using the mask for exposing at least a partial region of the insulation film in the first region.

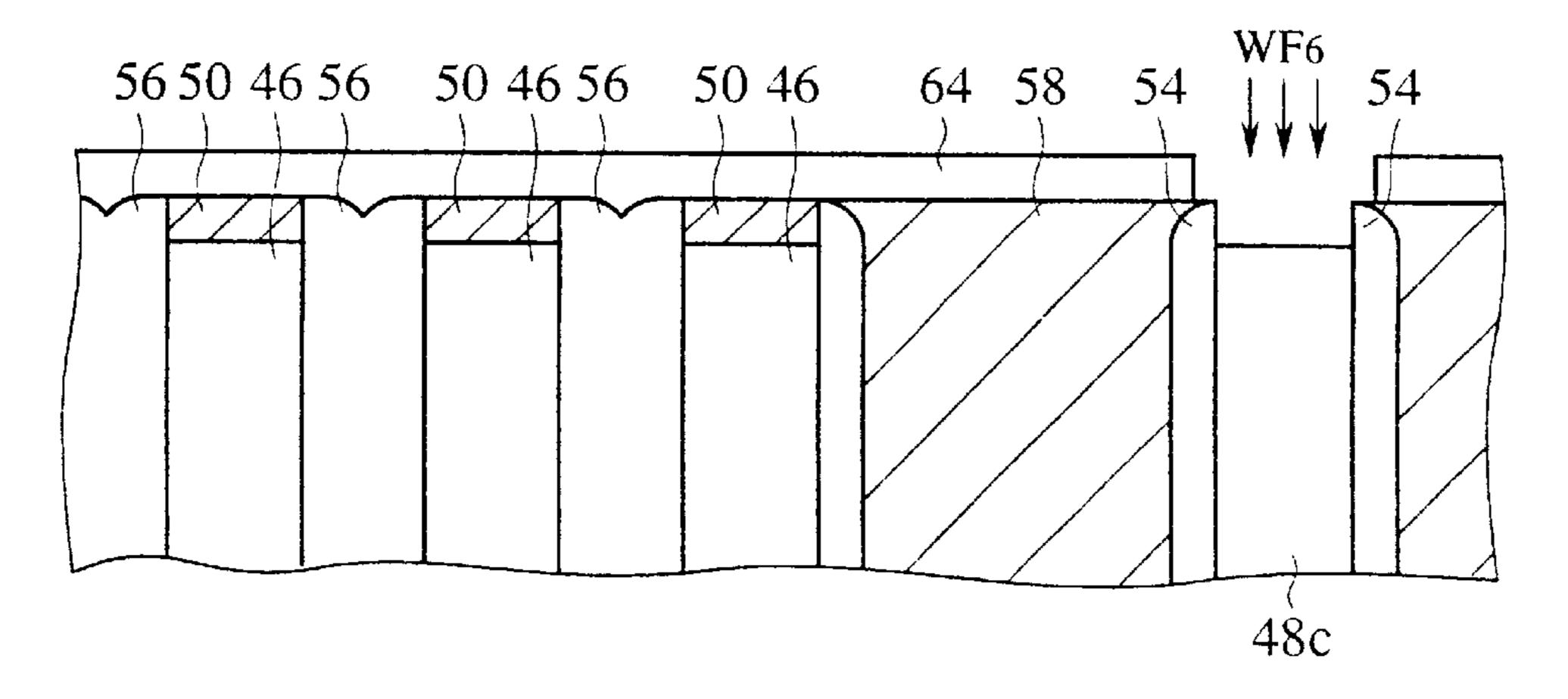

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprising after the storage electrode forming step: a first conducting film replacing step of replacing the first conducting film forming the first pillar-shaped conductor by a third conducting film of lower resistance value by the time when the processing arrives at the interconnection forming step. This fabrication of the semiconductor device makes it possible that the first pillar-shaped conductor is selectively replaced by a low-resistance material in a later step even in a case that the storage electrode and the first pillar-shaped conductor are formed of a high-resistance material having good compatibility with the dielectric film.

In the above-described method for fabricating a semiconductor device, it is preferable that in the first conducting film replacing step, the first conducting film of polycrystalline silicon film is exposed to  $WF_6$  gas to replace the first conducting film with a third conducting film formed of tungsten film.

In the above-described method for fabricating a semiconductor device, it is preferable that in the interconnection forming step, the second interconnection connected to the opposed electrode is further formed. This fabrication of the semiconductor device makes it possible that the second interconnection connected to the opposed electrode is formed simultaneously with the first interconnection connected to the first pillar-shaped conductor.

In the above-described method for fabricating a semiconductor device, it is preferable that the first opening is an interconnection groove for burying the interconnection in the second insulation film. This fabrication of the semiconductor device makes it possible that the first interconnection is a buried interconnection buried in the second insulation film.

In the above-described method for fabricating a semiconductor device, it is preferable that the method further comprises after the first insulation film forming step: a sidewall film removing step of removing the sidewall film and forming a cavity between the first insulation film and the first pillar-shaped conductor. This fabrication of the semiconductor device makes it possible that the cavity is formed in a peripheral part of the first pillar-shaped conductor. This reduce parasitic capacitance between the interconnections.

### BRIEF DESCRIPTION OF THE DRAWINGS

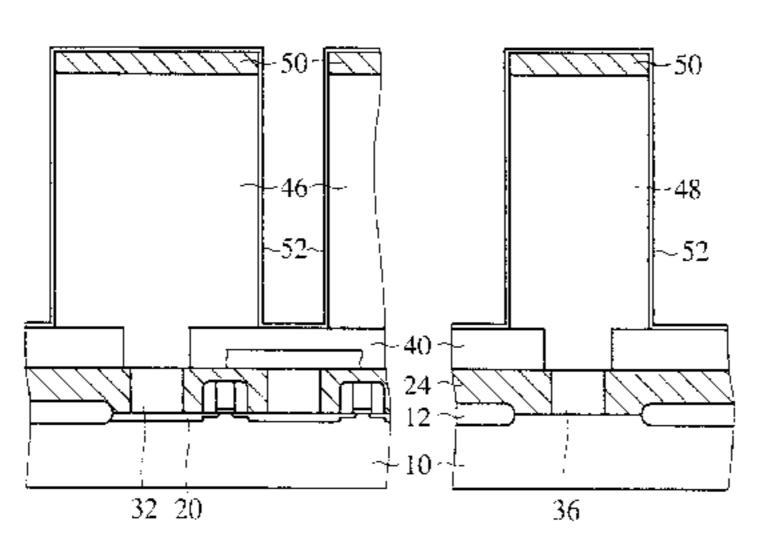

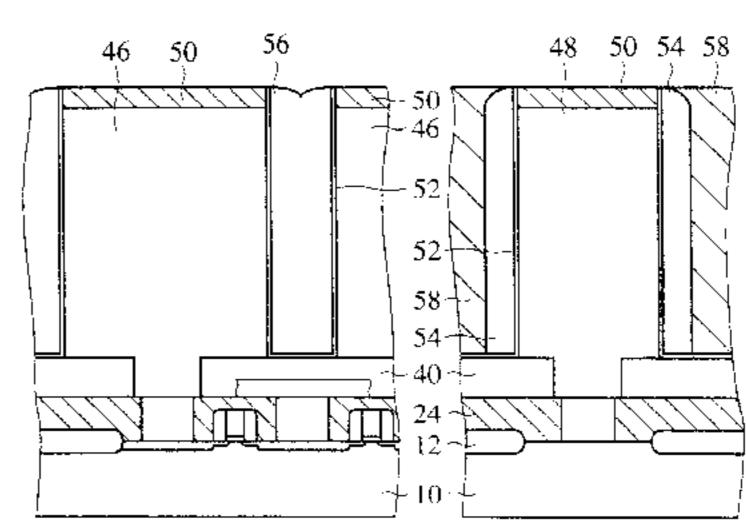

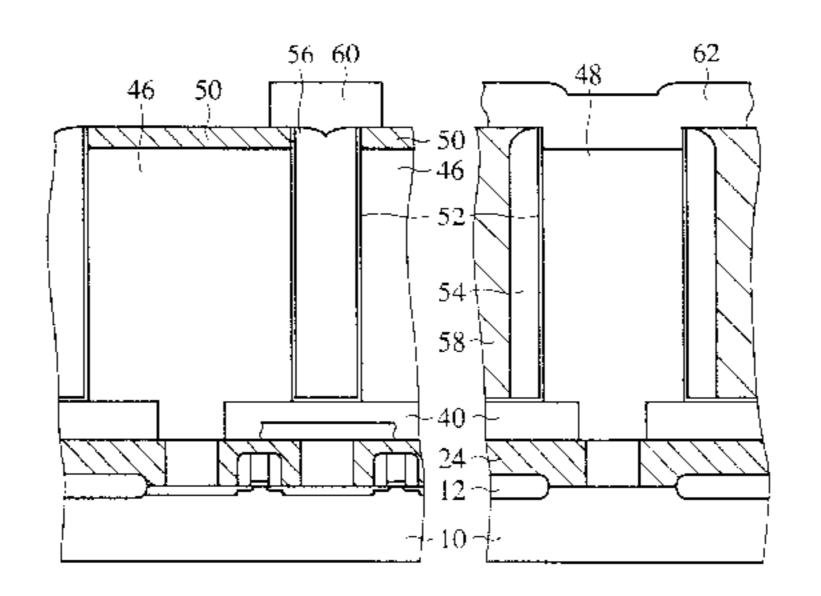

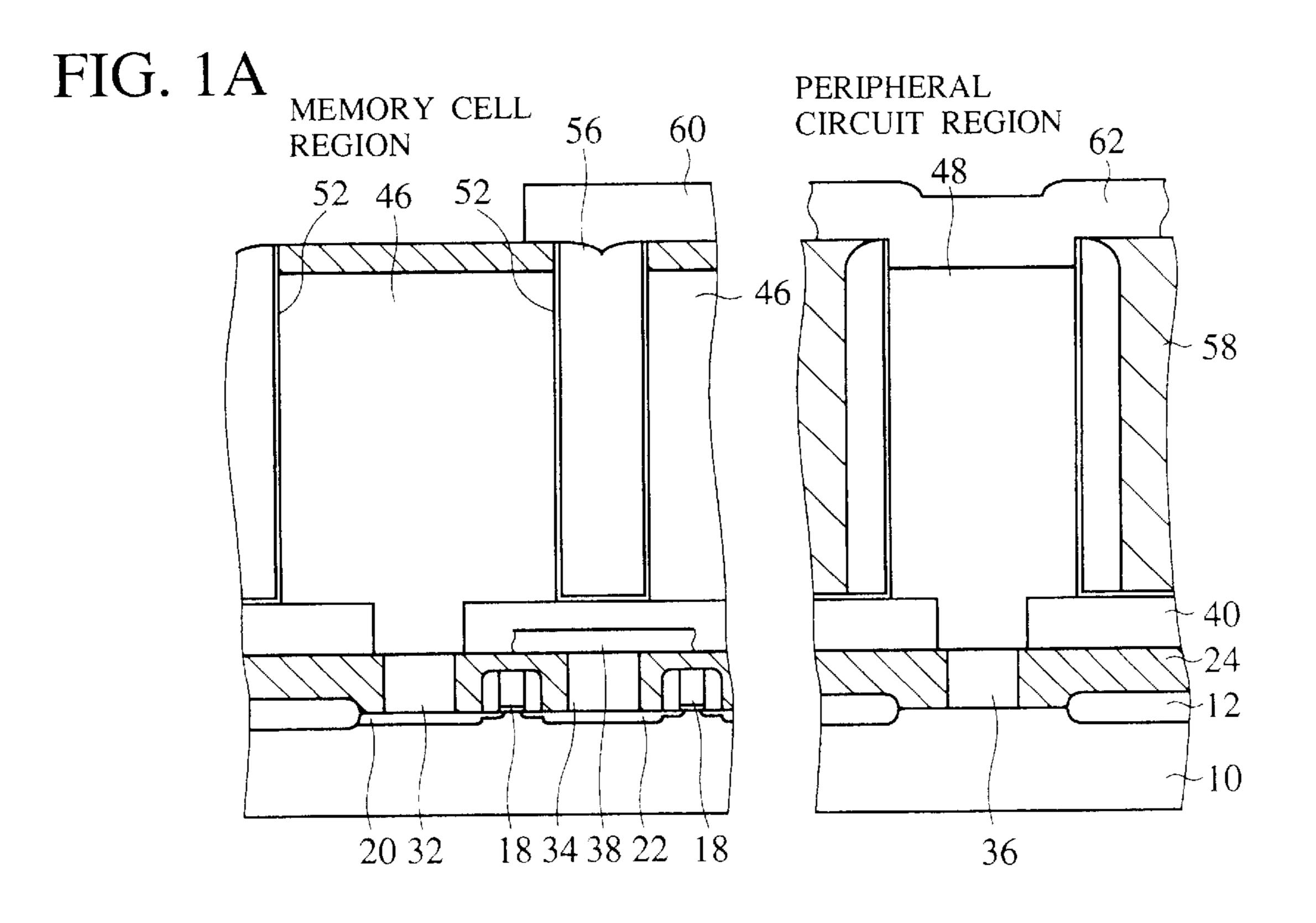

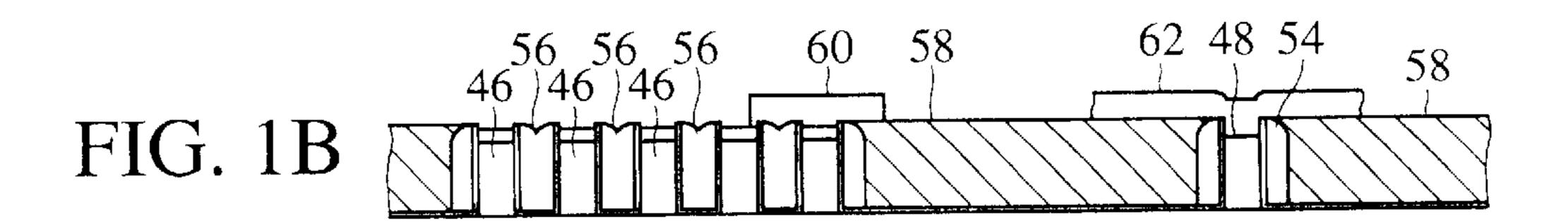

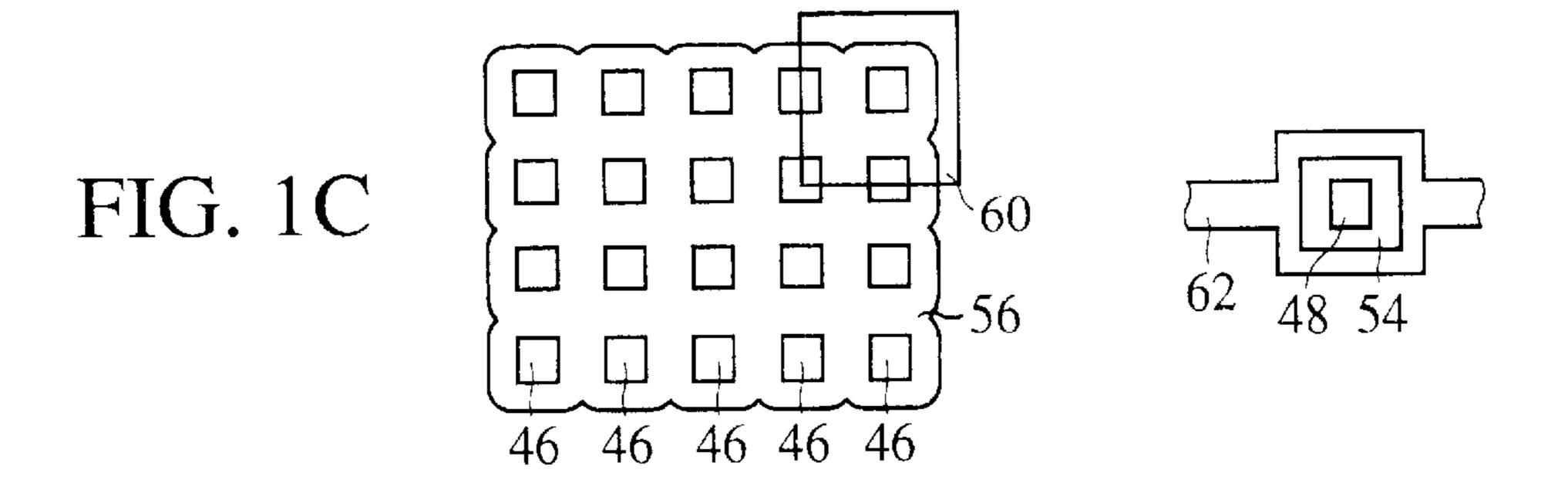

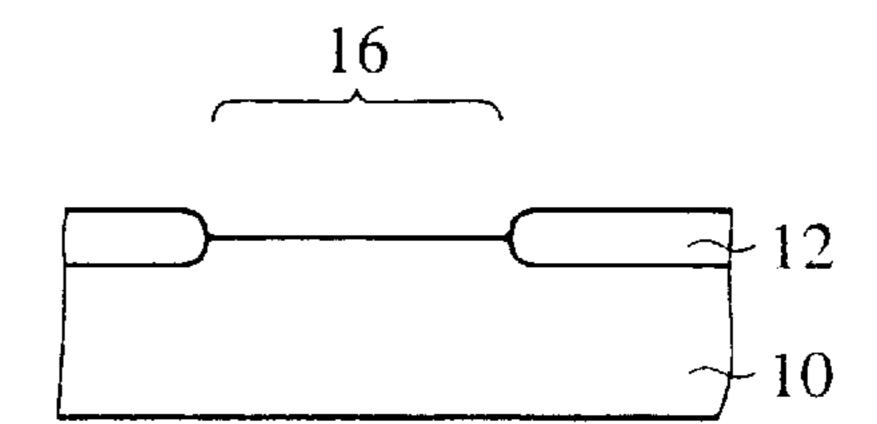

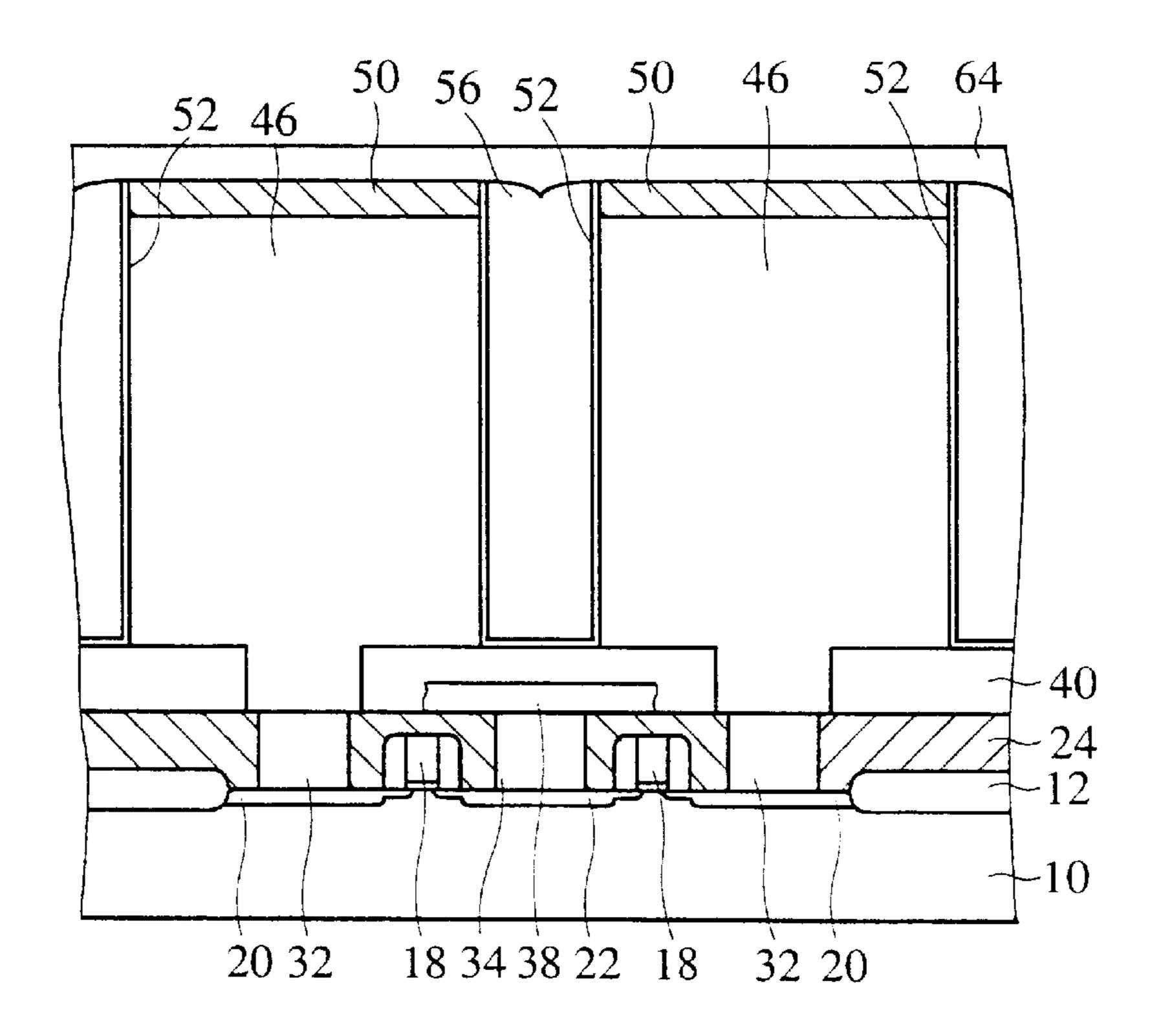

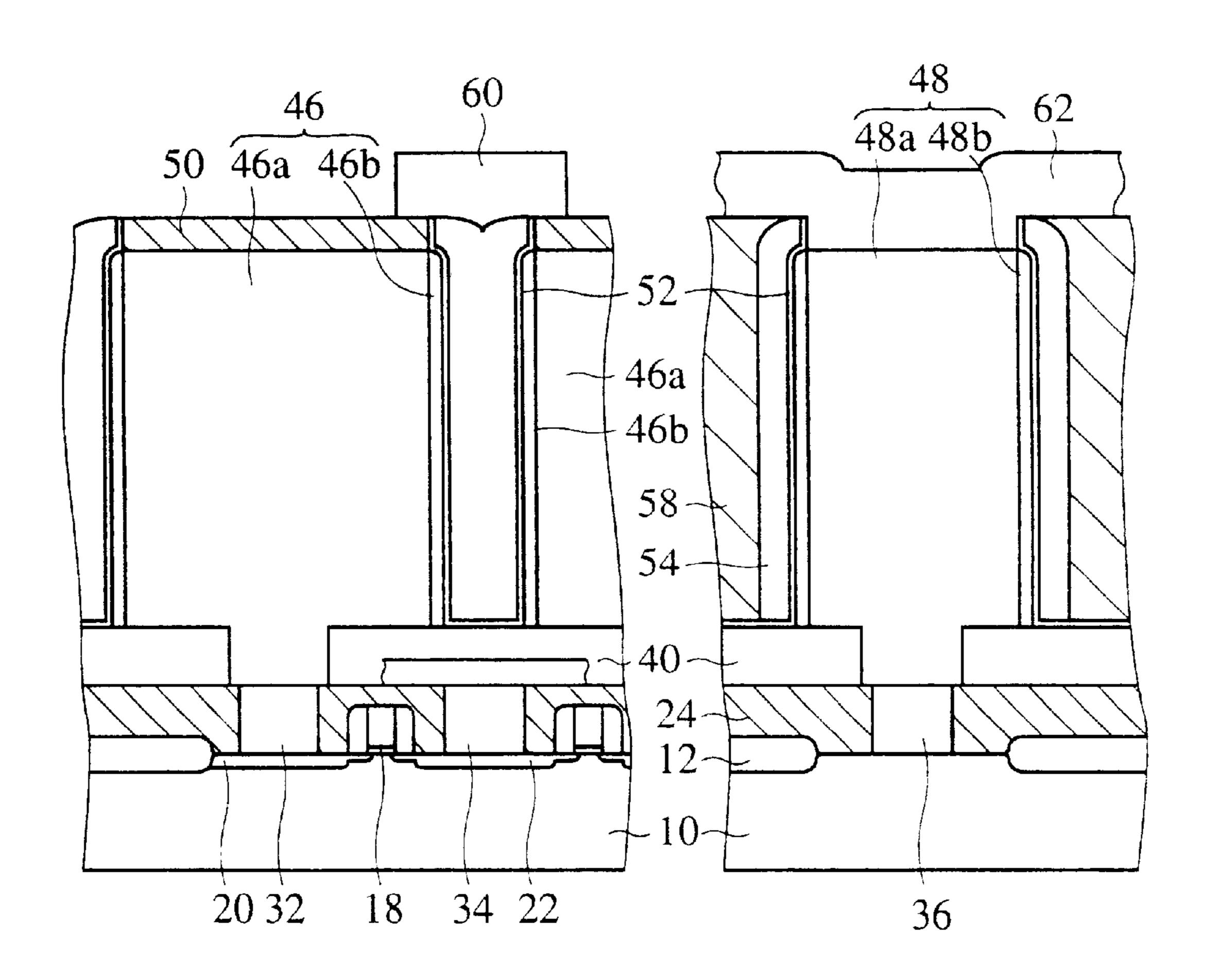

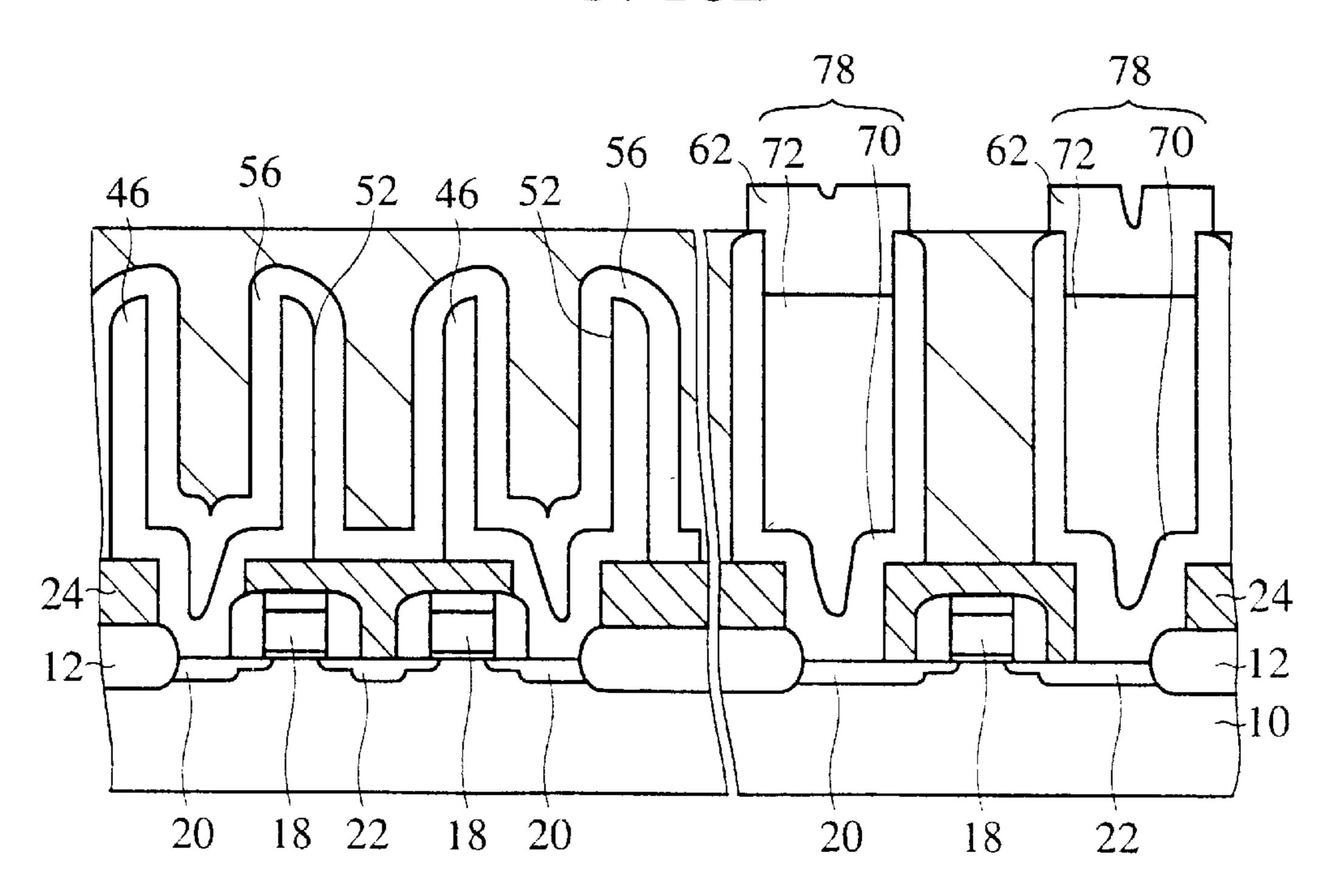

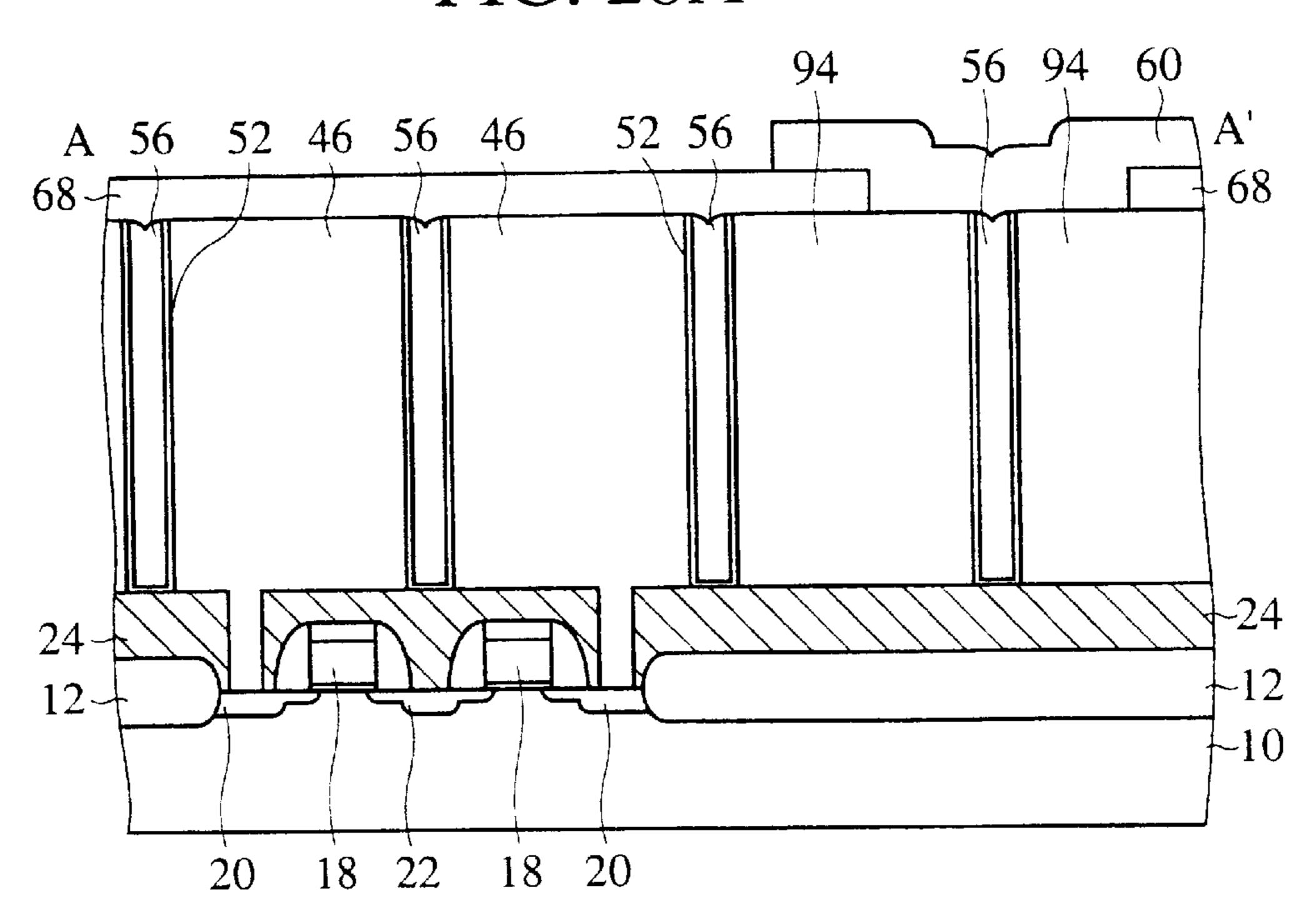

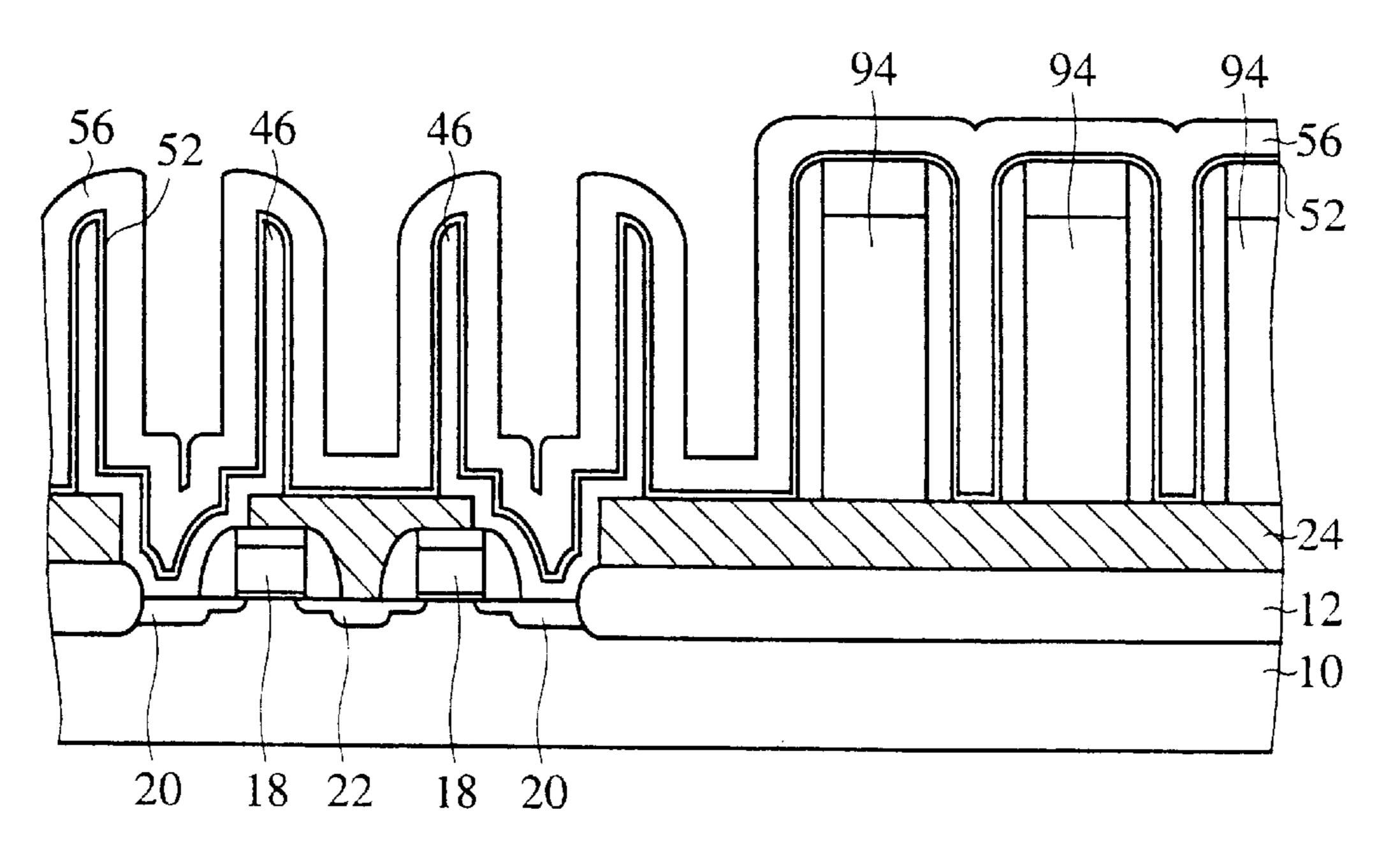

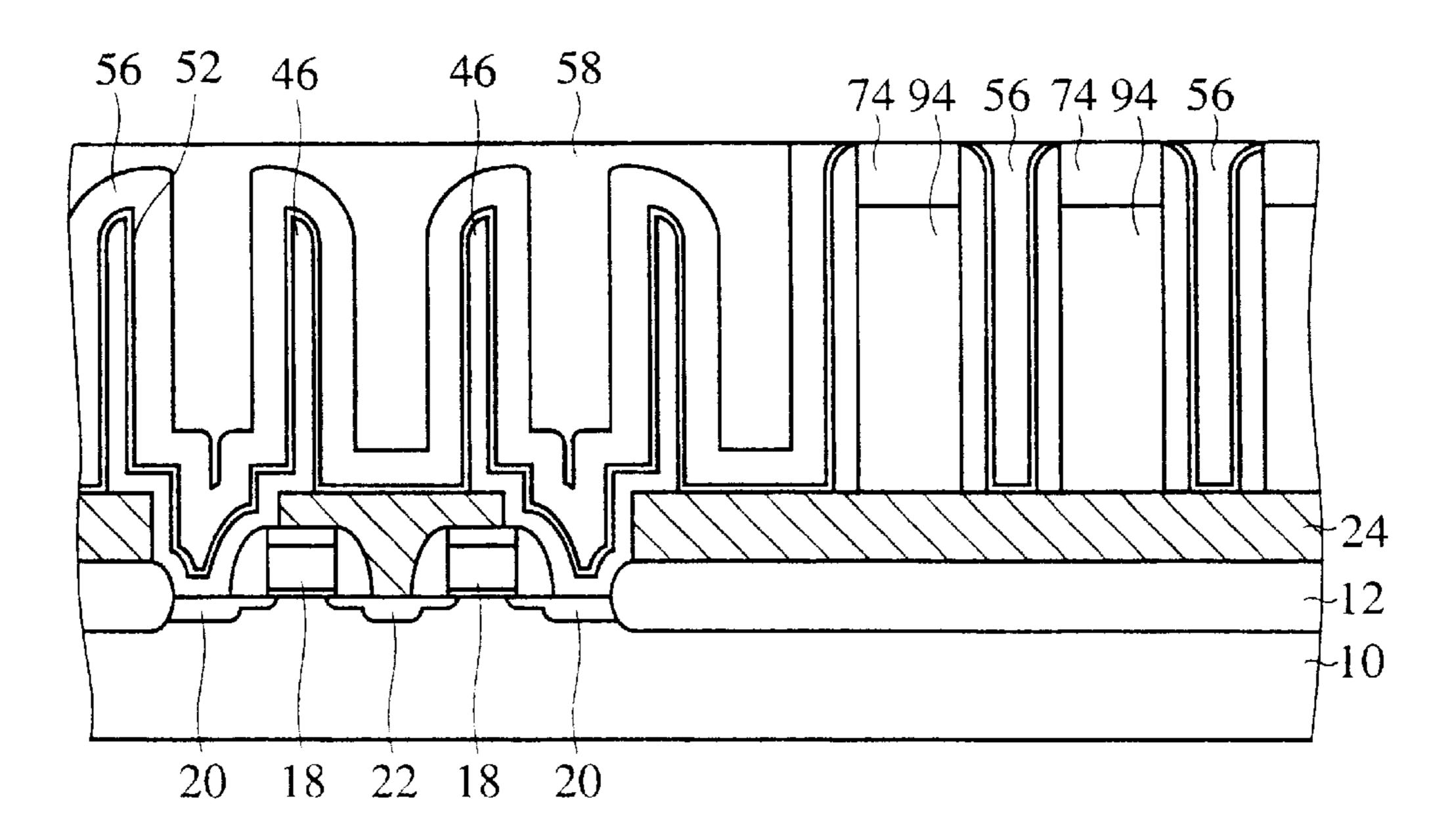

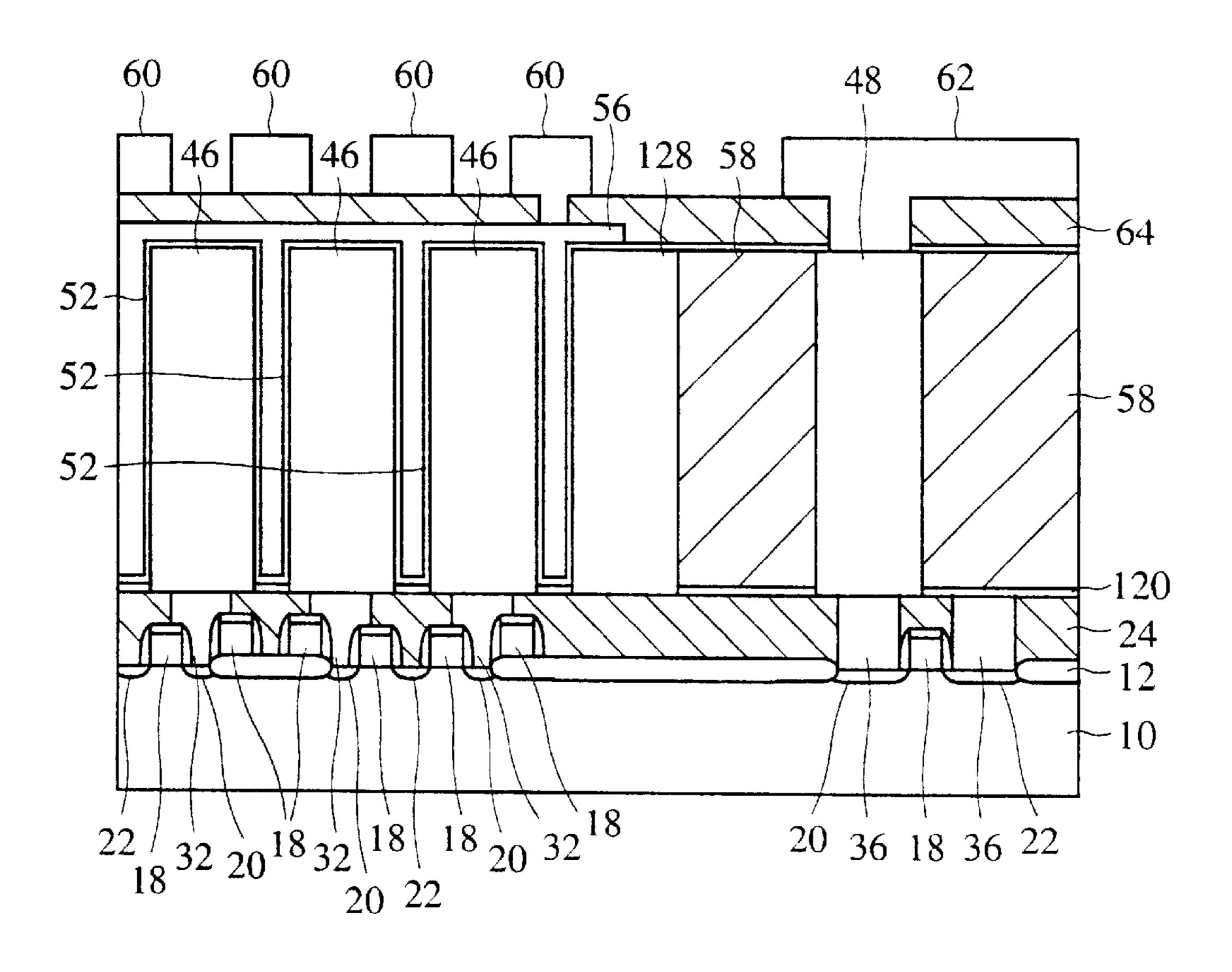

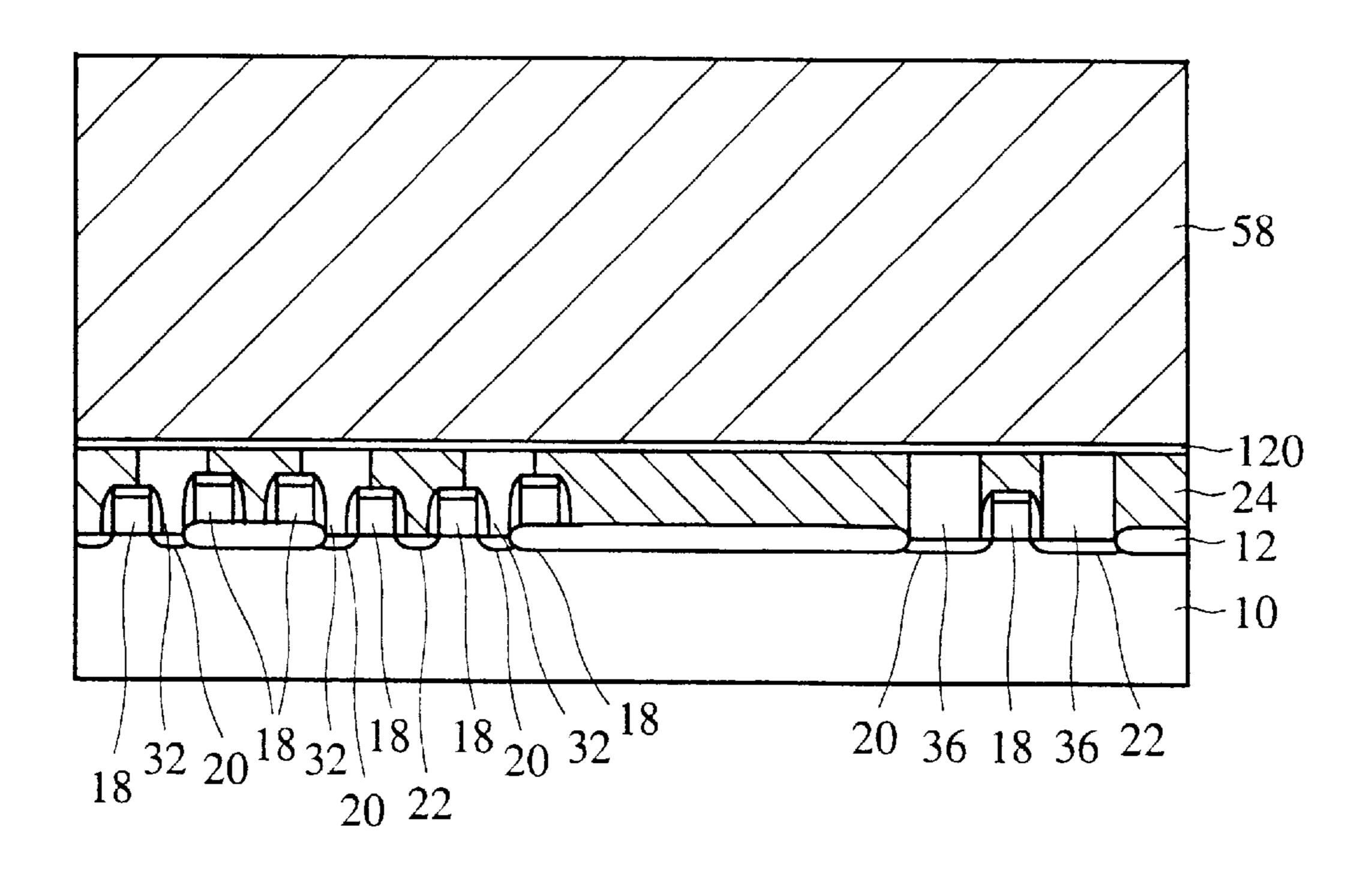

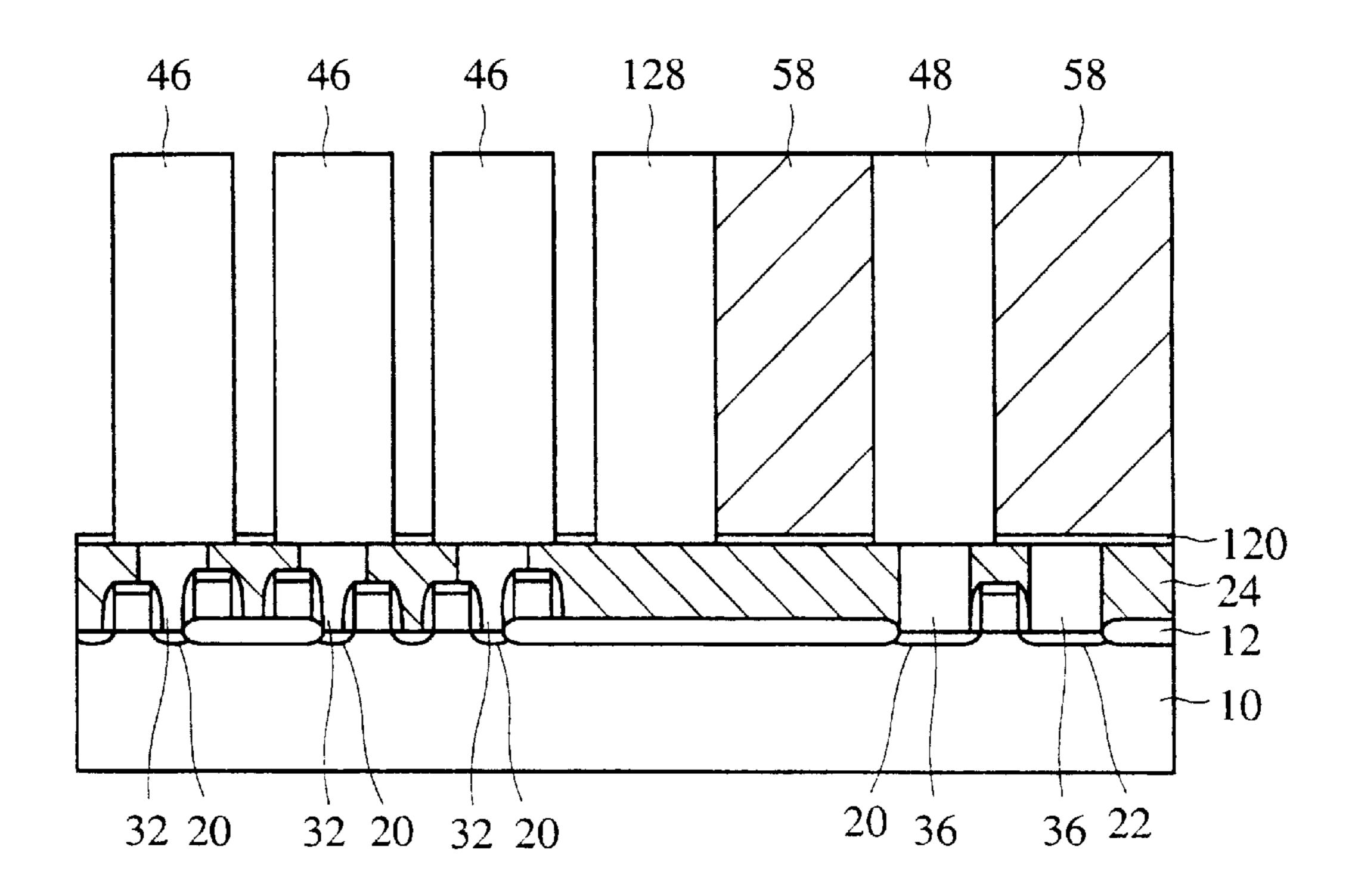

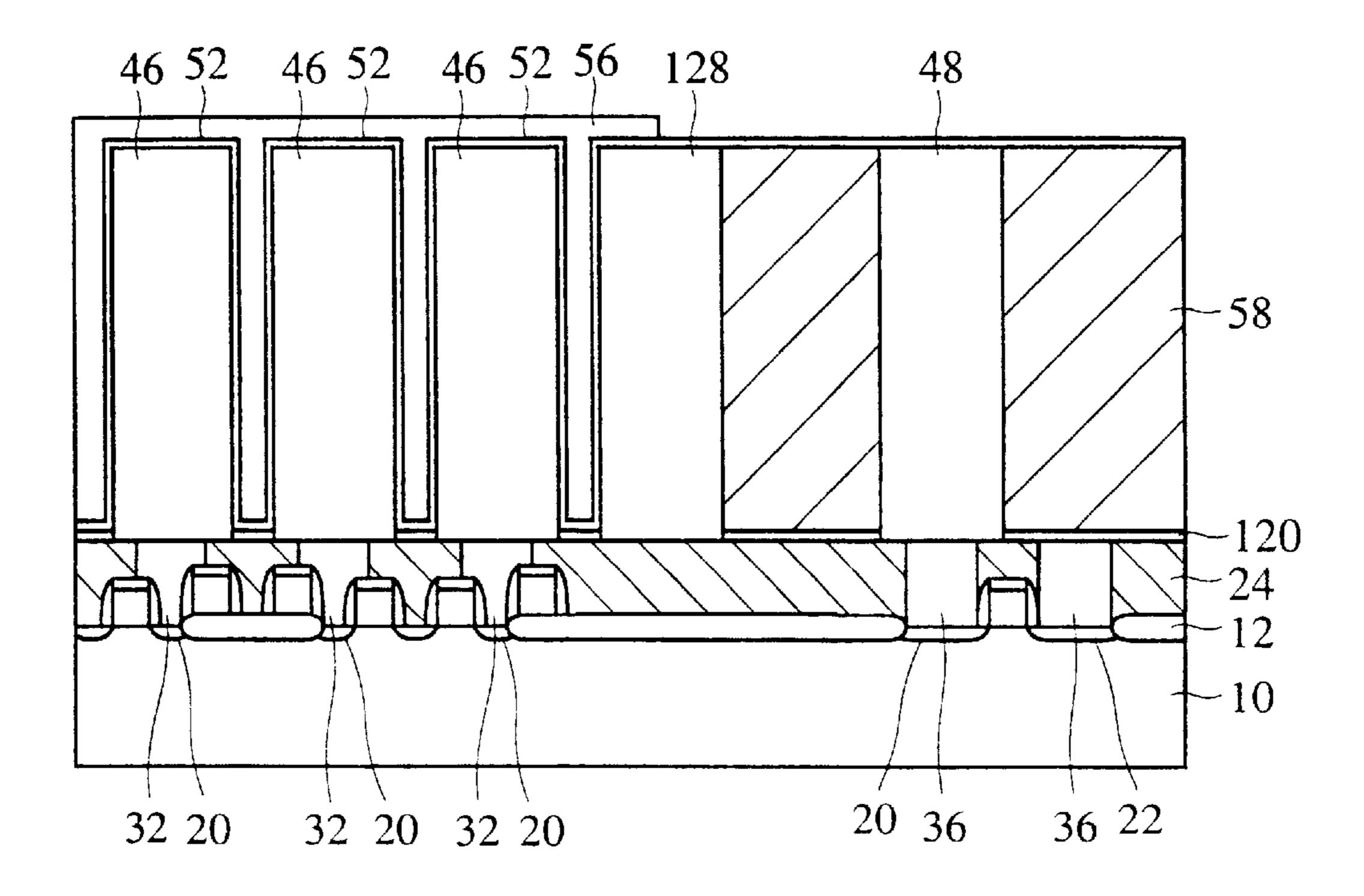

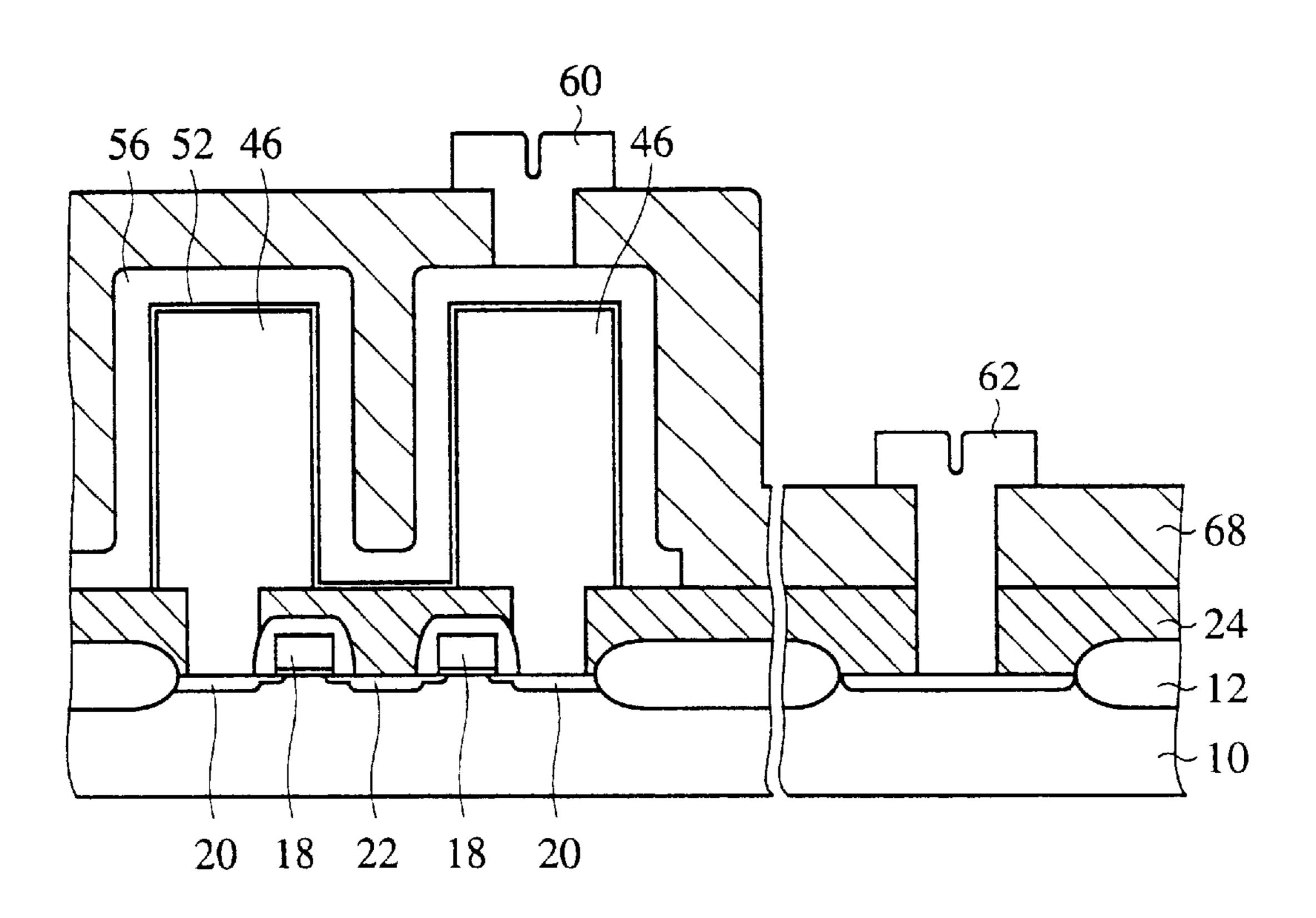

FIGS. 1A and 1B are sectional views of the semiconductor device according to a first embodiment of the present invention, which show a structure of the semiconductor device.

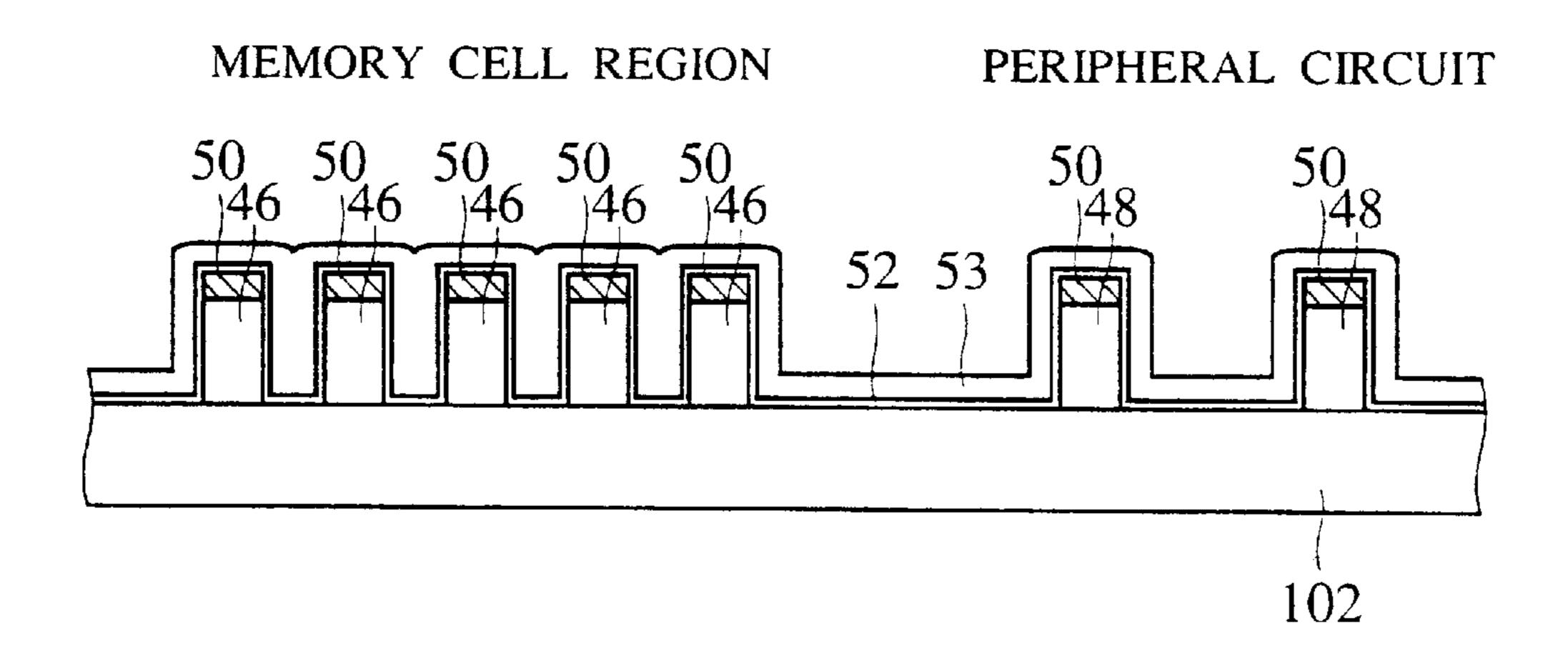

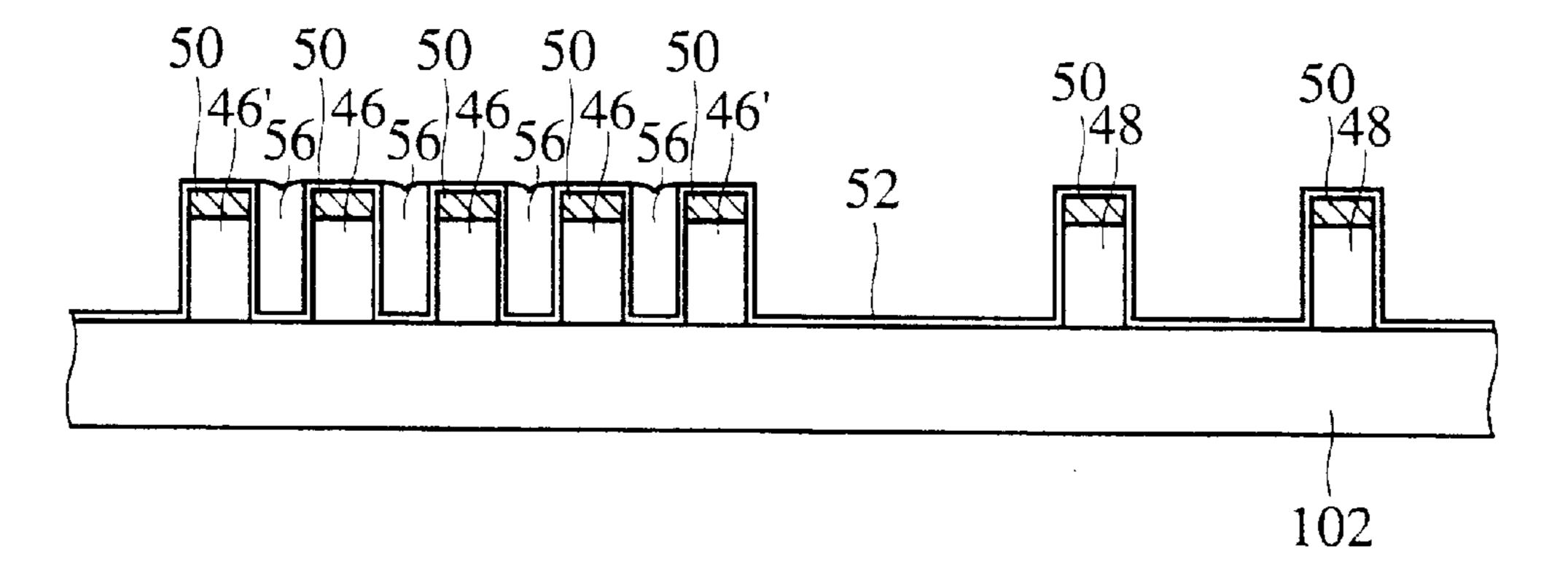

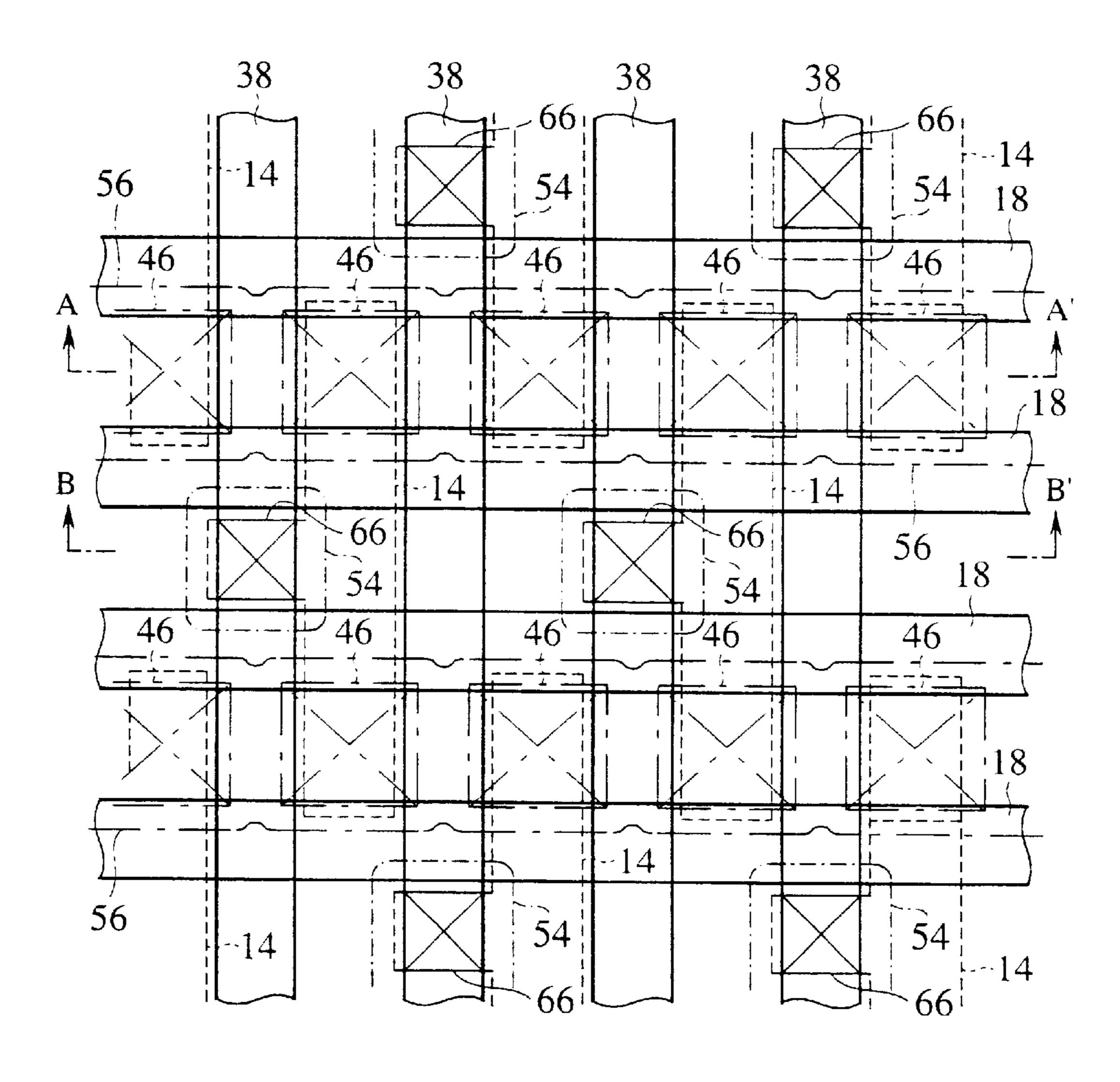

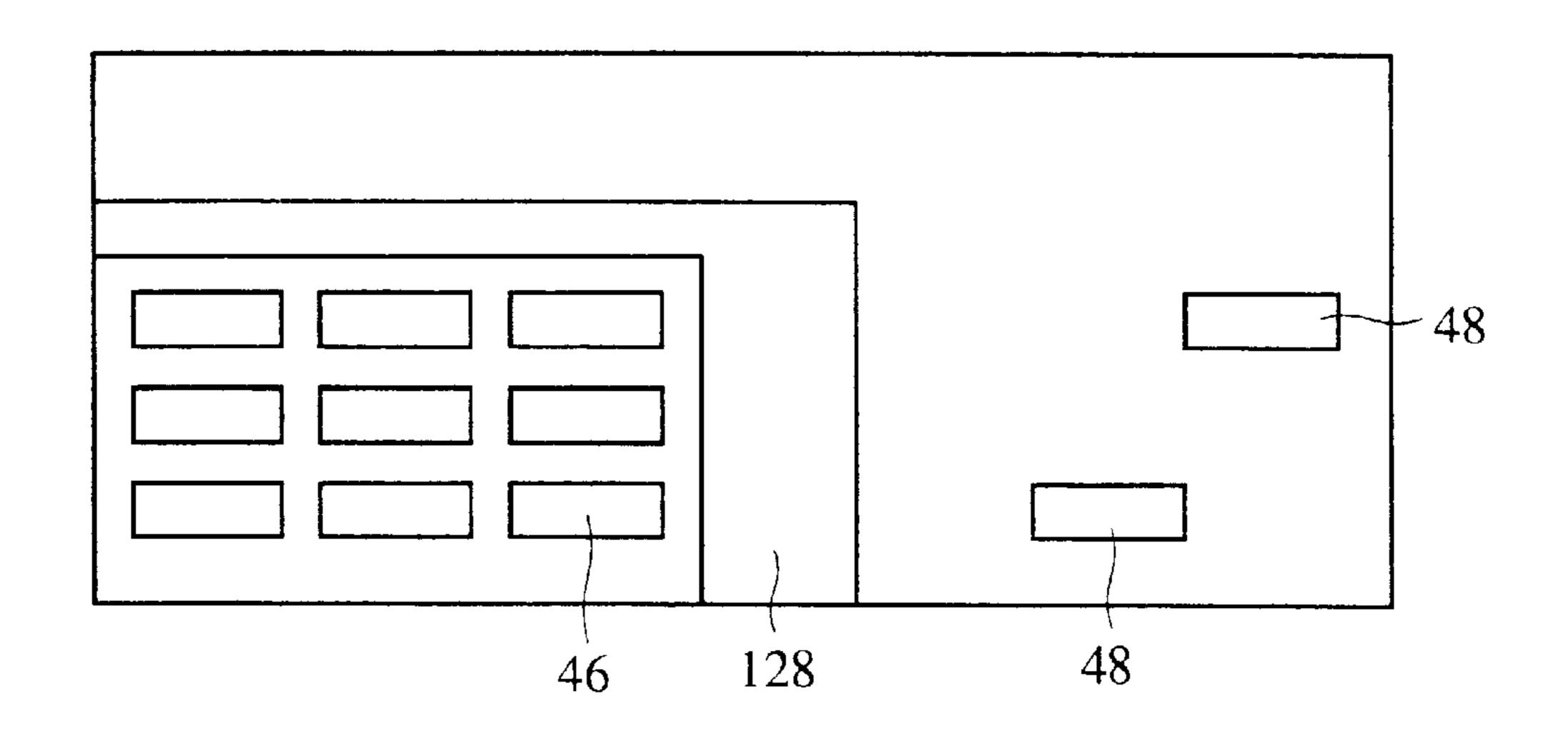

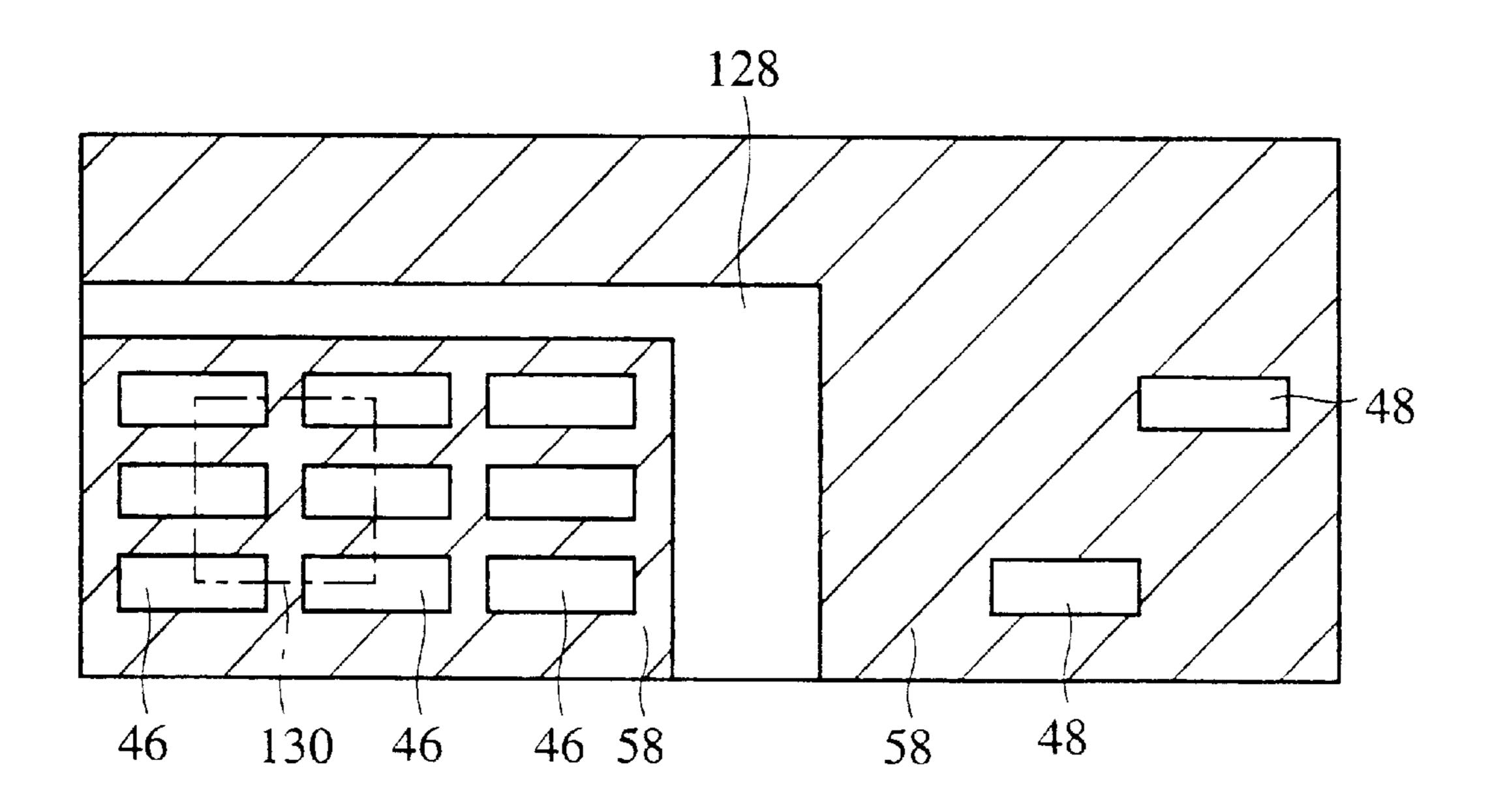

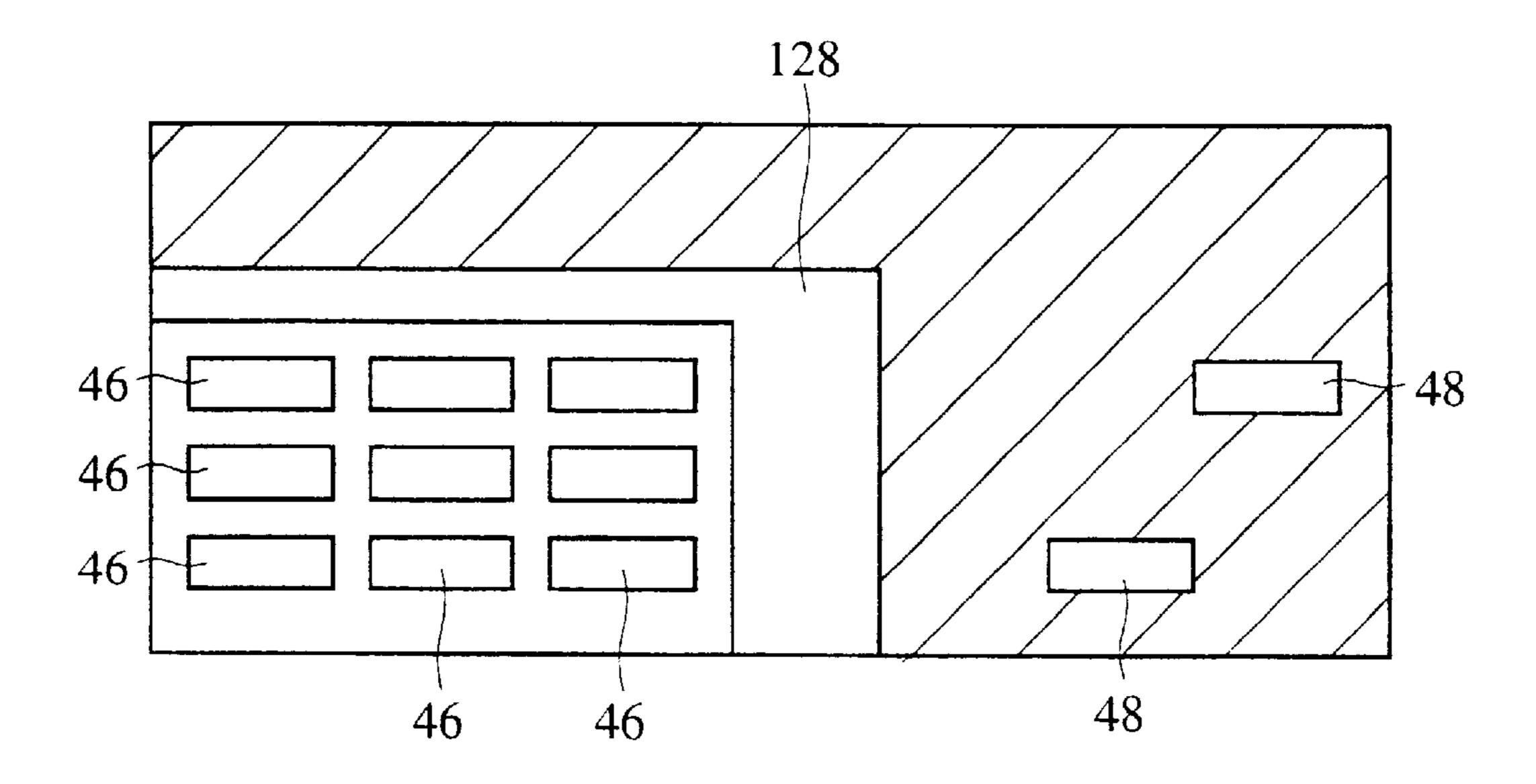

FIG. 1C is a plan view of the semiconductor device according to a first embodiment of the present invention, which show a structure of the semiconductor device.

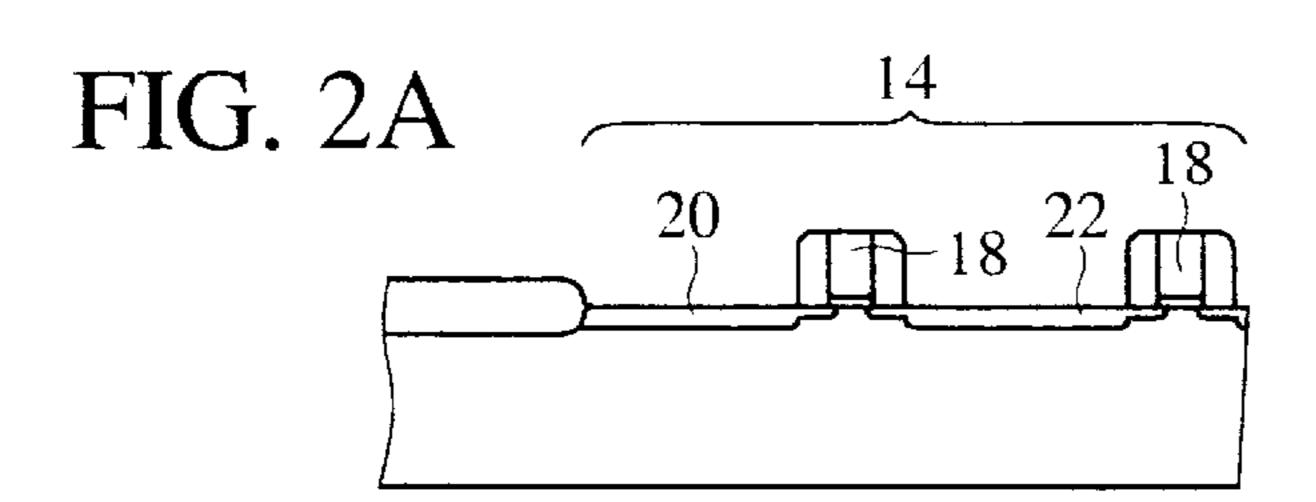

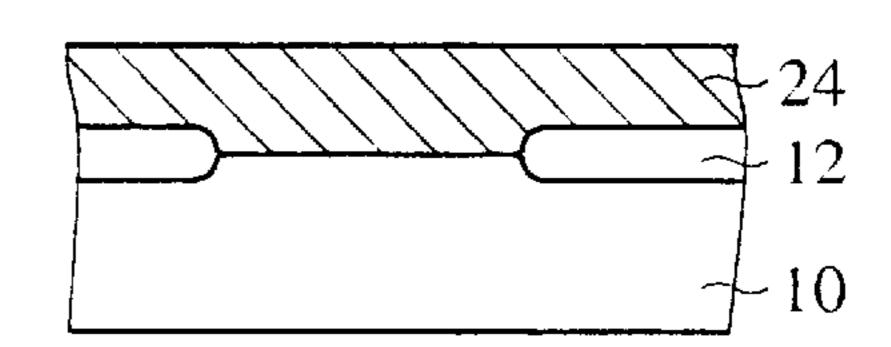

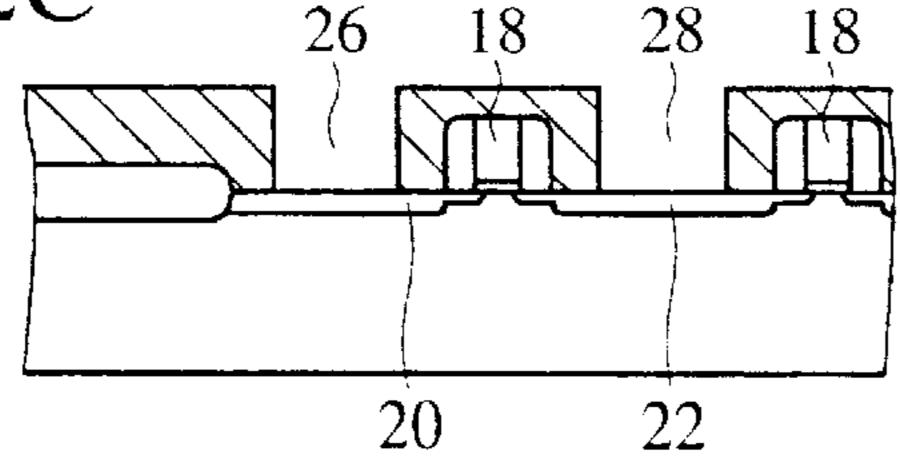

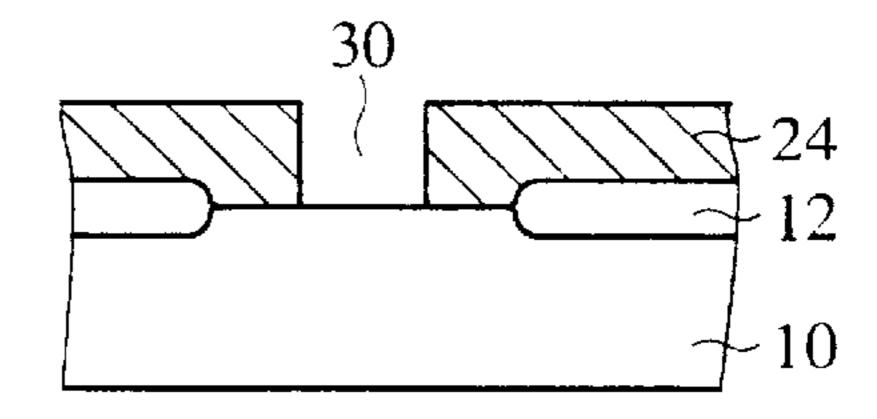

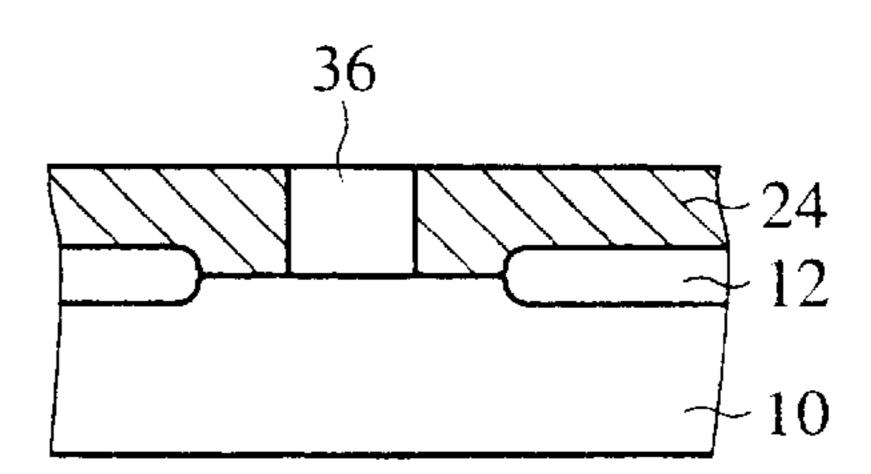

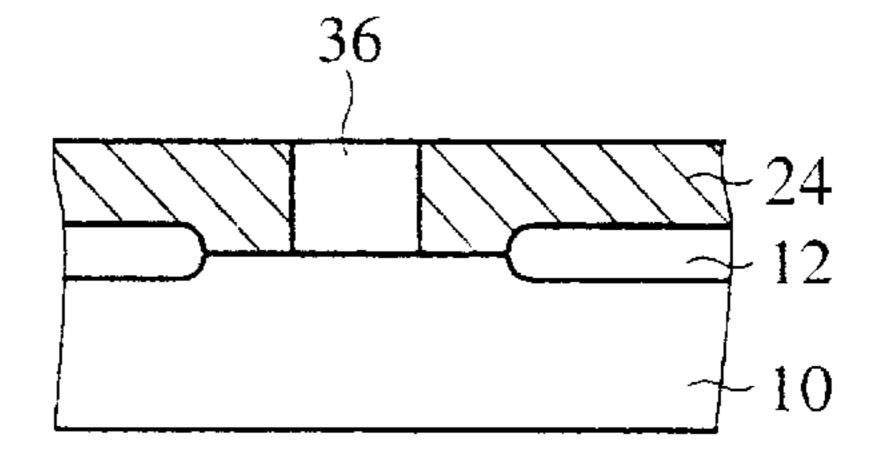

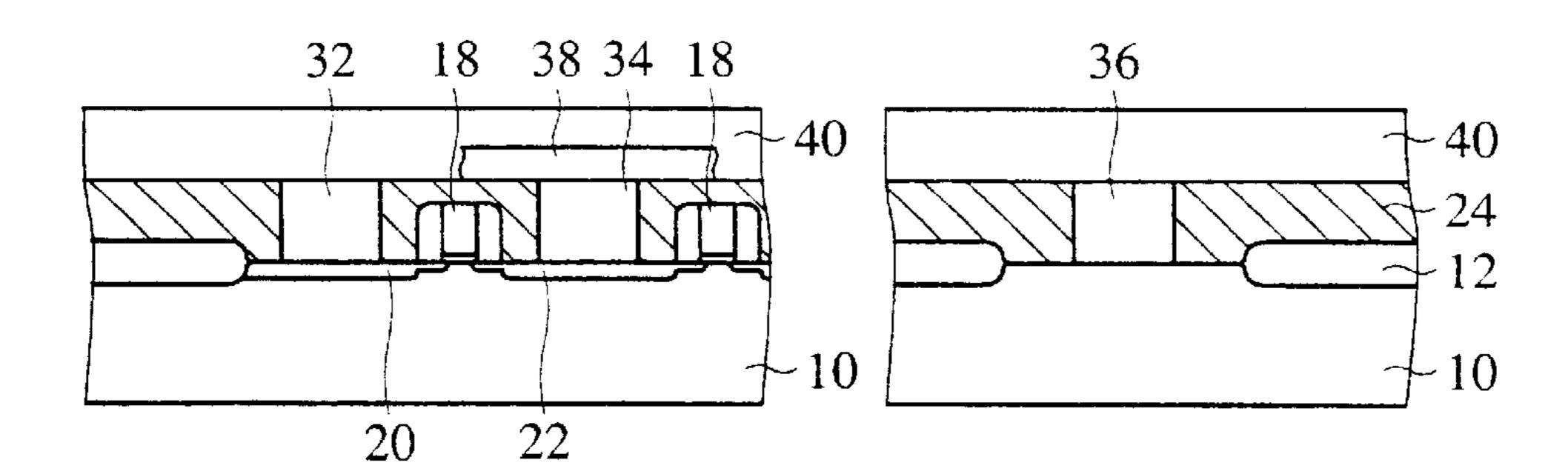

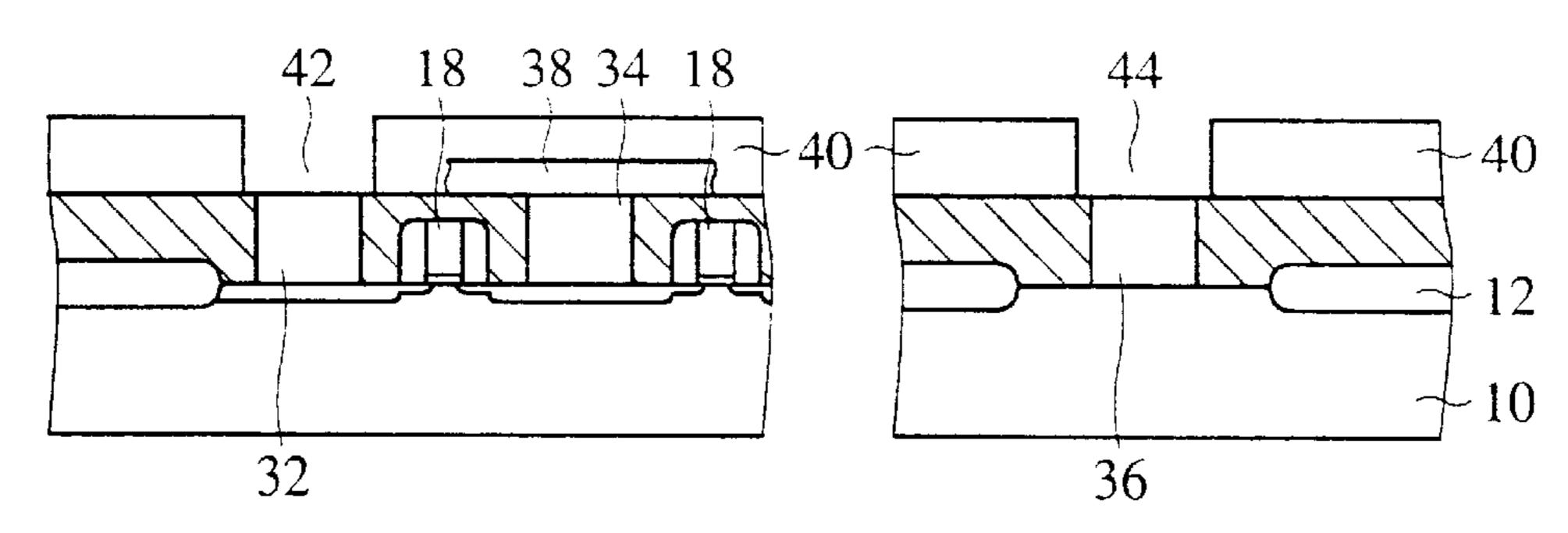

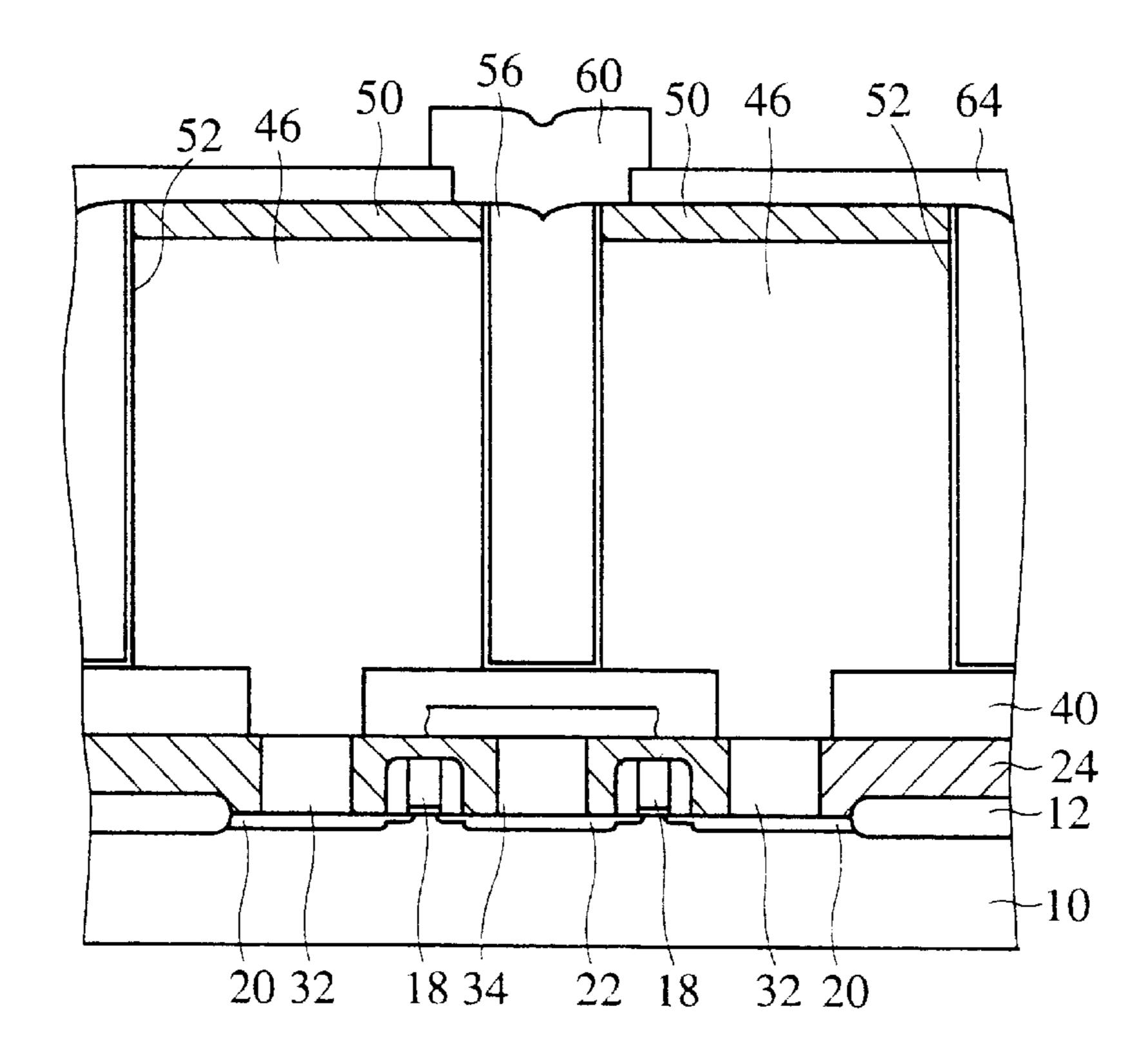

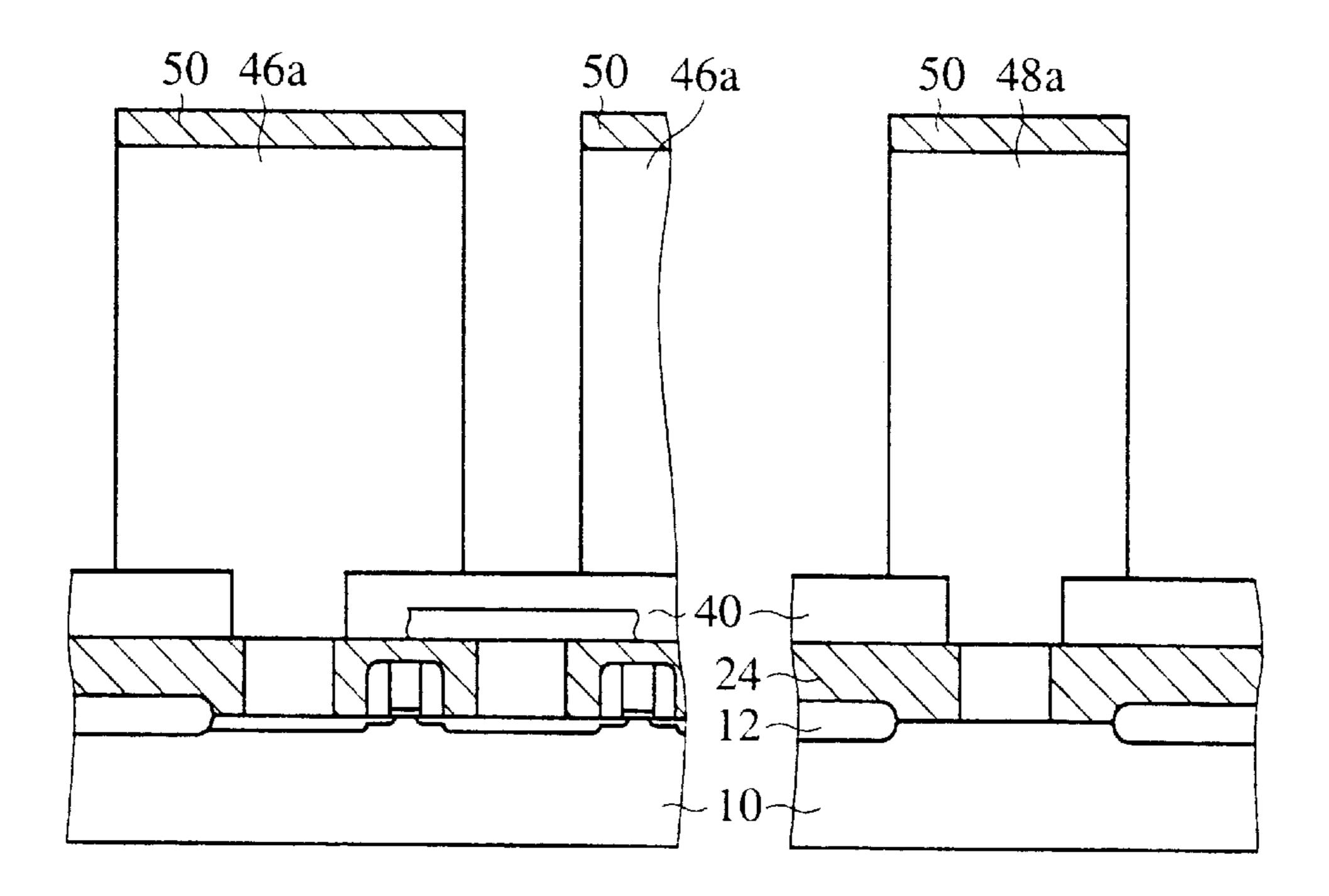

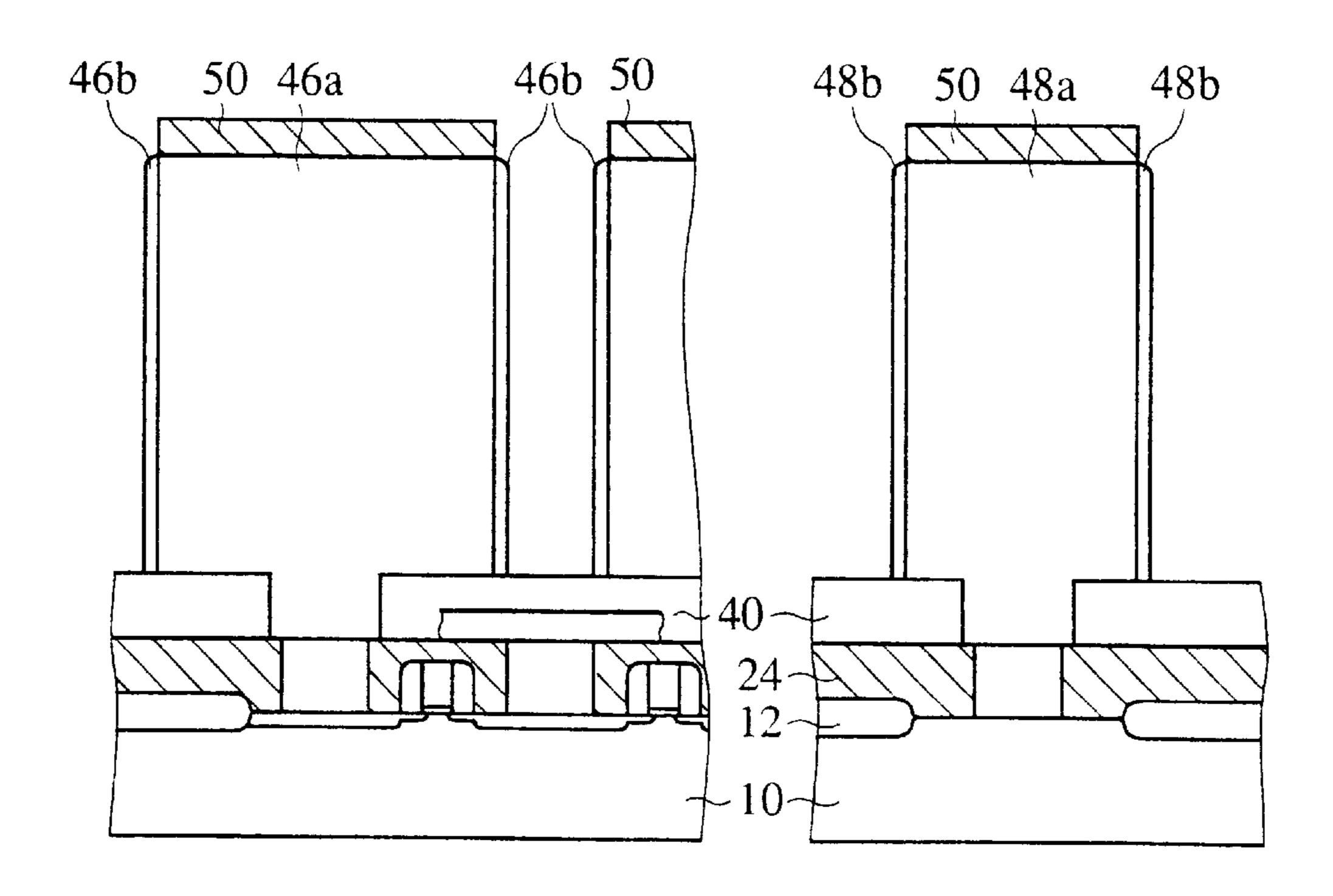

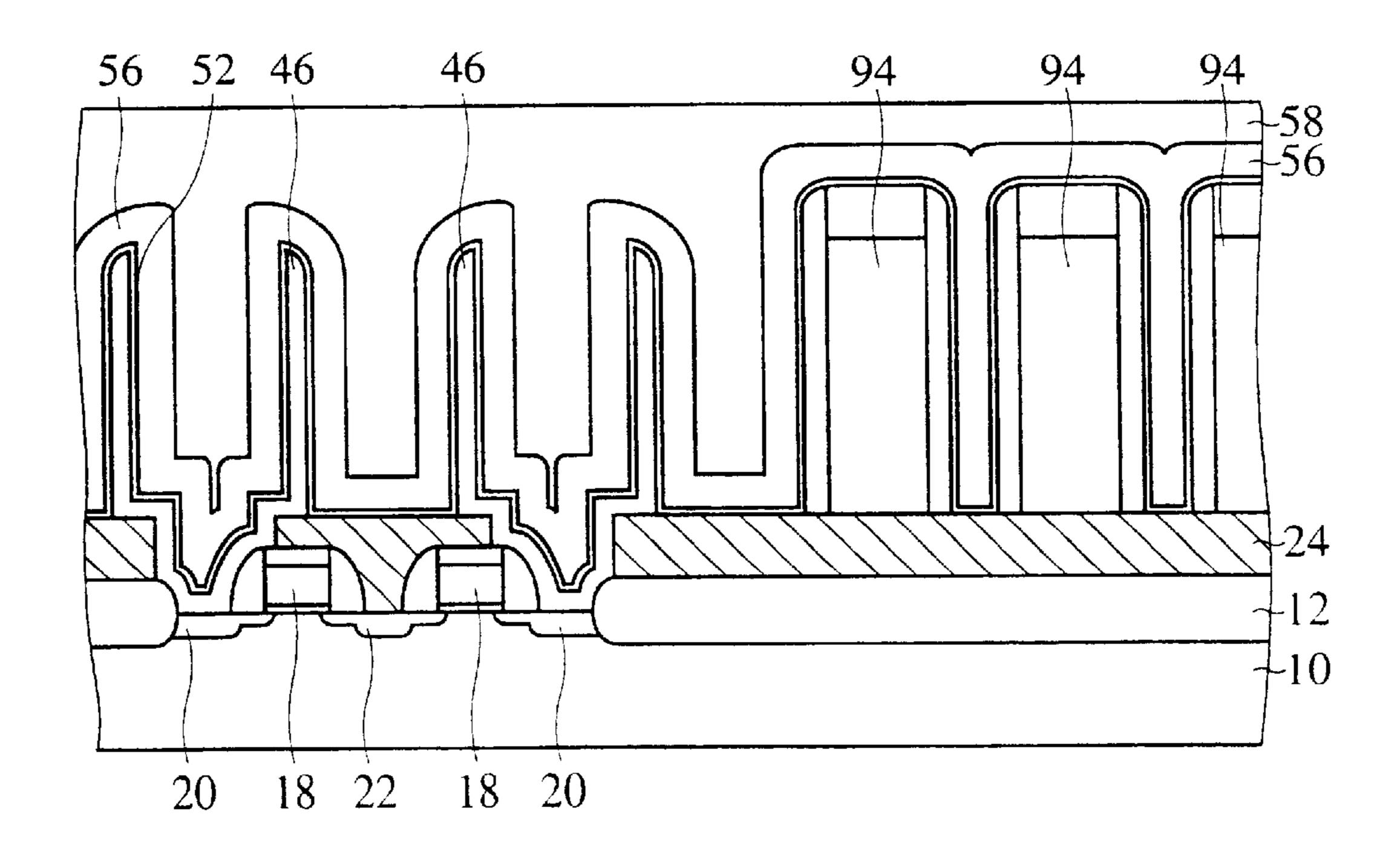

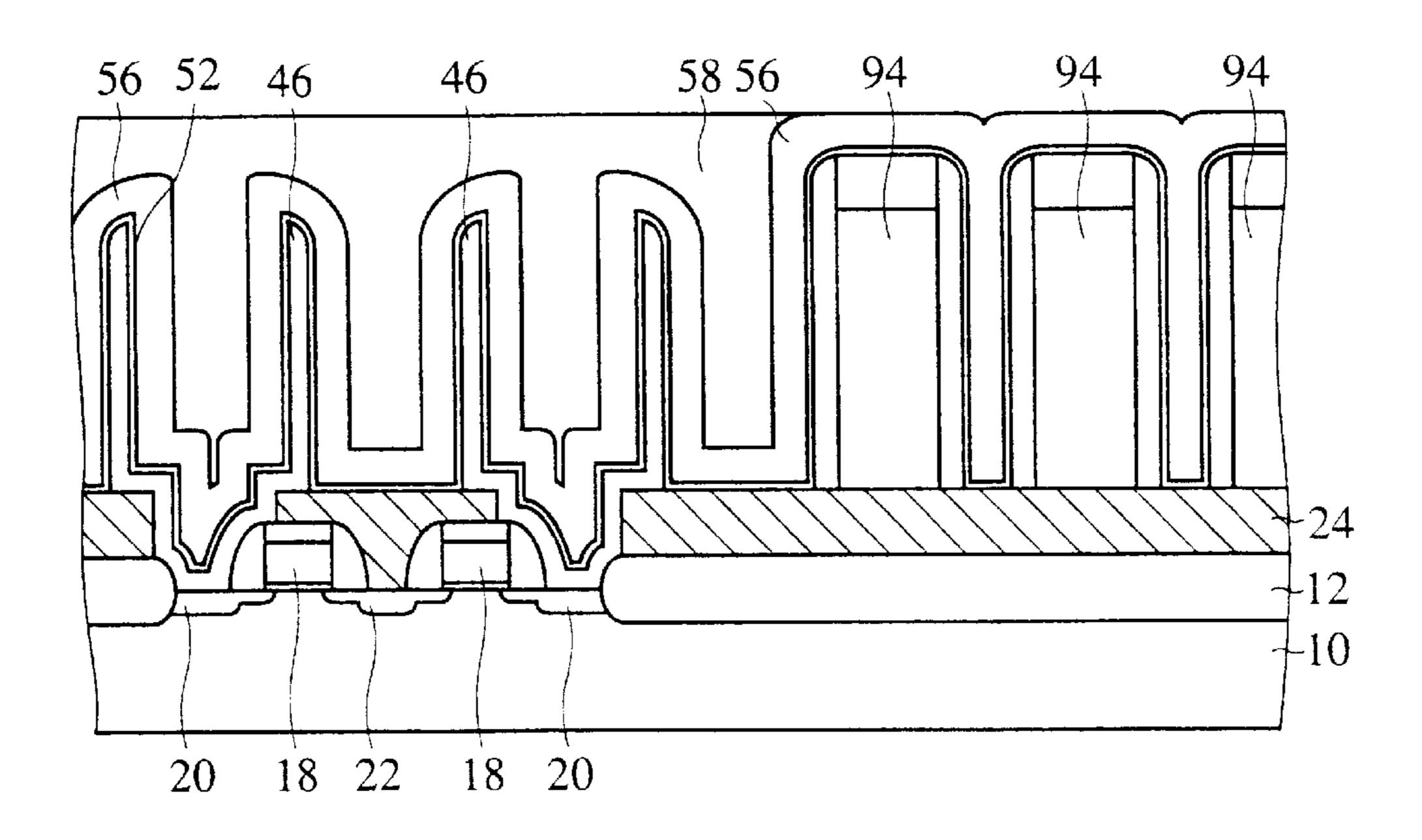

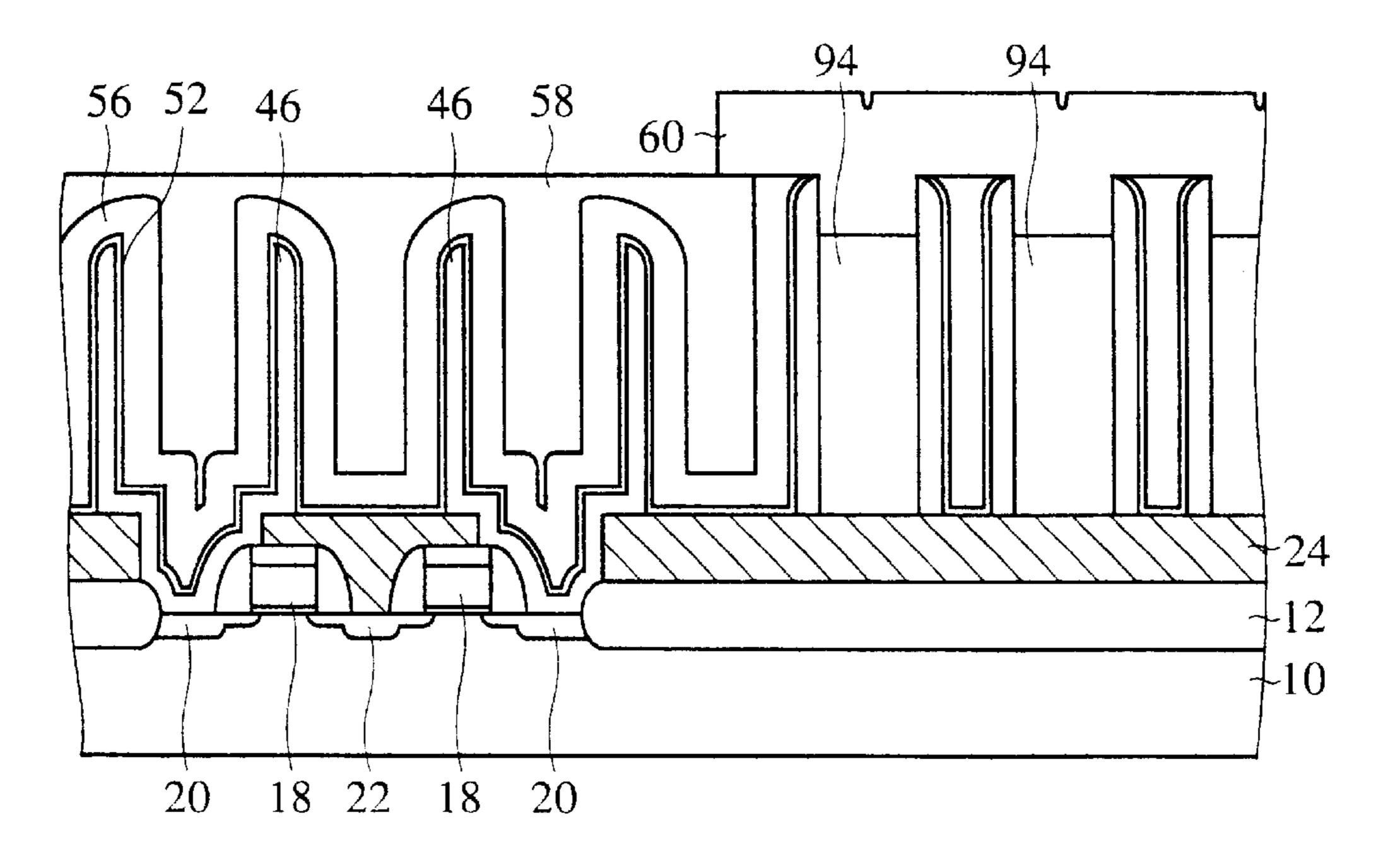

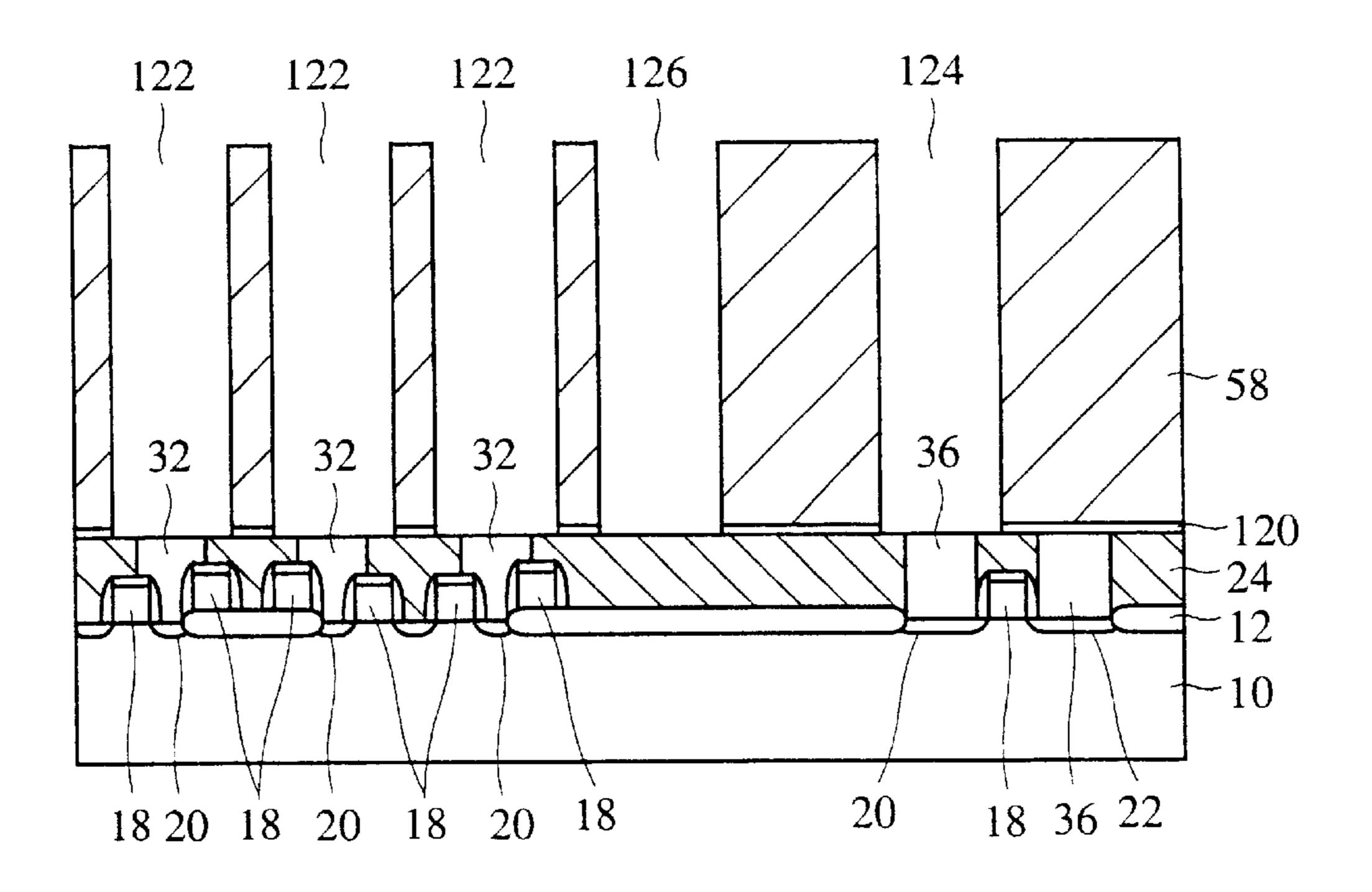

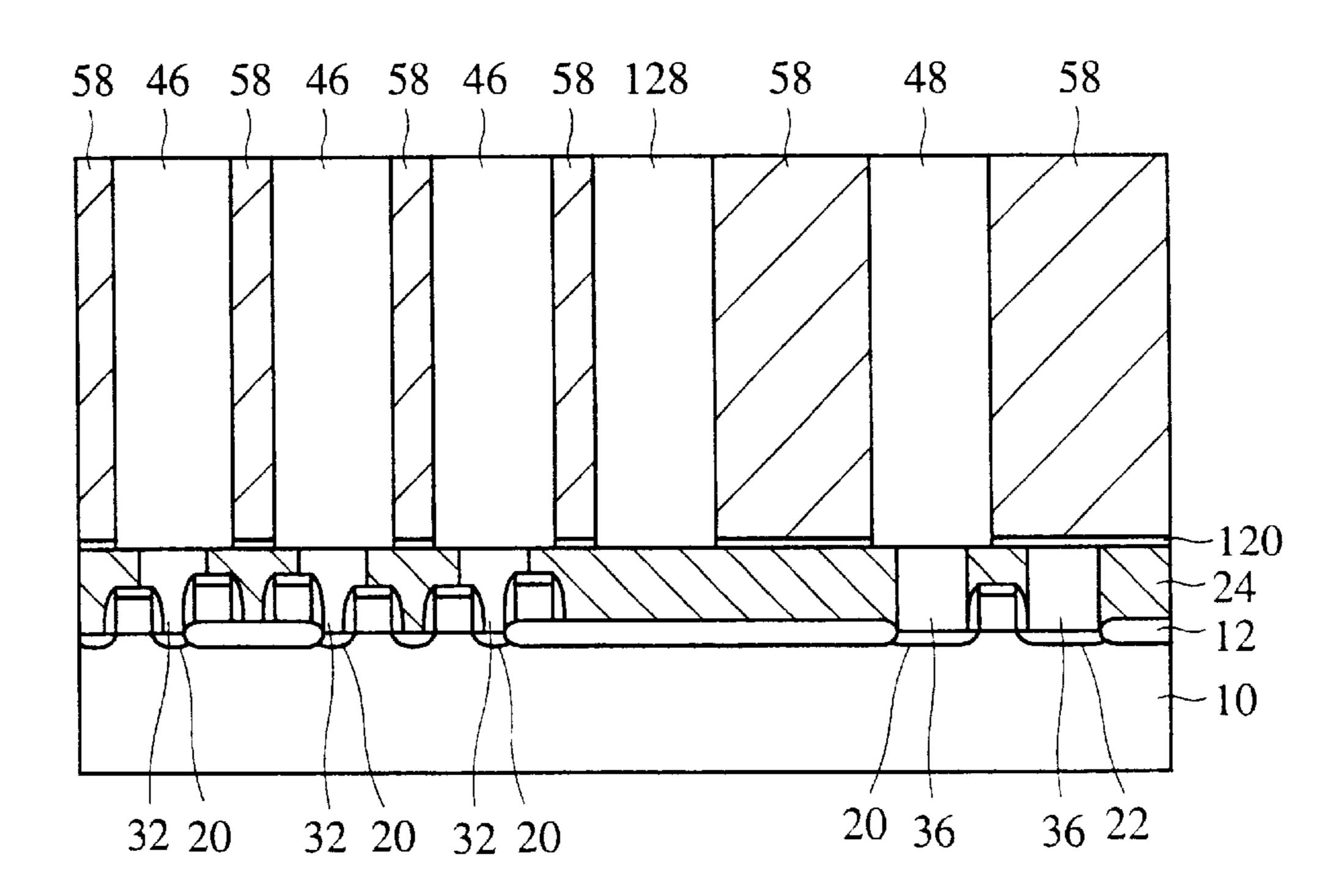

FIGS. 2A–2E, 3A–3C and 4A–4B are sectional views of the semiconductor device according to the first embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 5A-5B and 6A-6B are sectional views of the semiconductor device according to a modification of the first embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIG. 7 is a diagrammatic sectional view of the semiconductor device according to a second embodiment of the present invention.

FIGS. 8A–8B and 9 are sectional views of the semiconductor device according to the second embodiment of the 5 present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 10A–10C are sectional views of the semiconductor device according to a third embodiment of the present invention in the steps of the method for fabricating the same, 10 which explain the method.

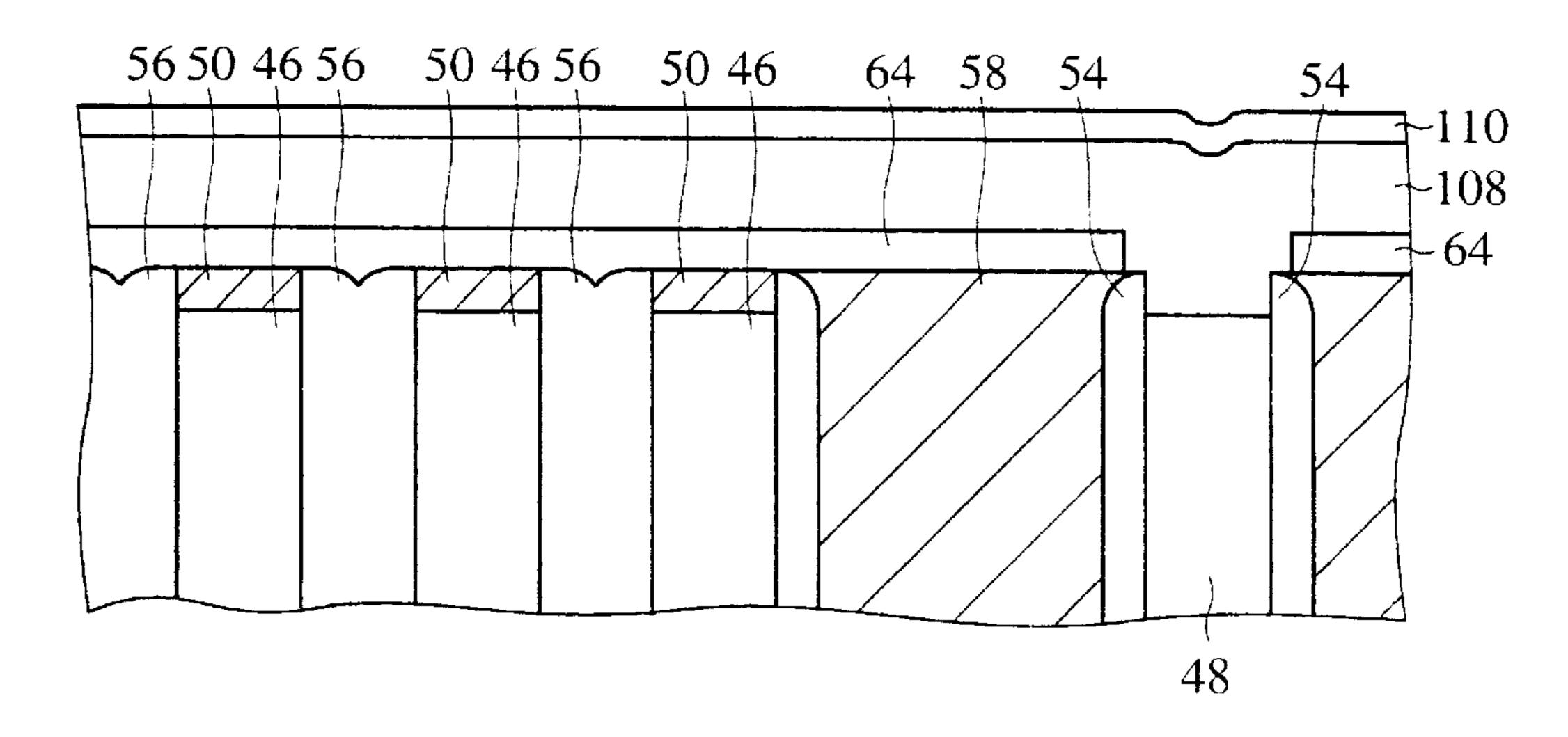

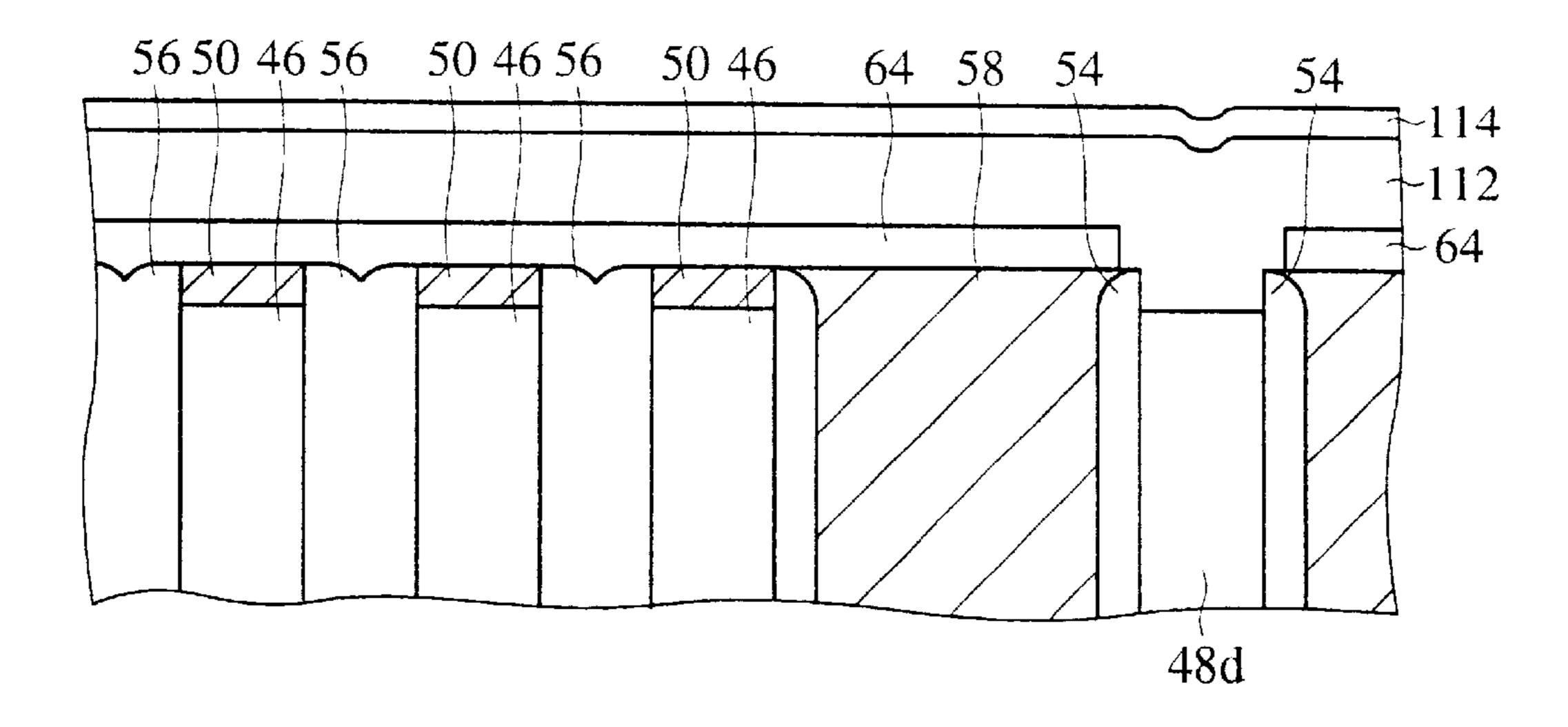

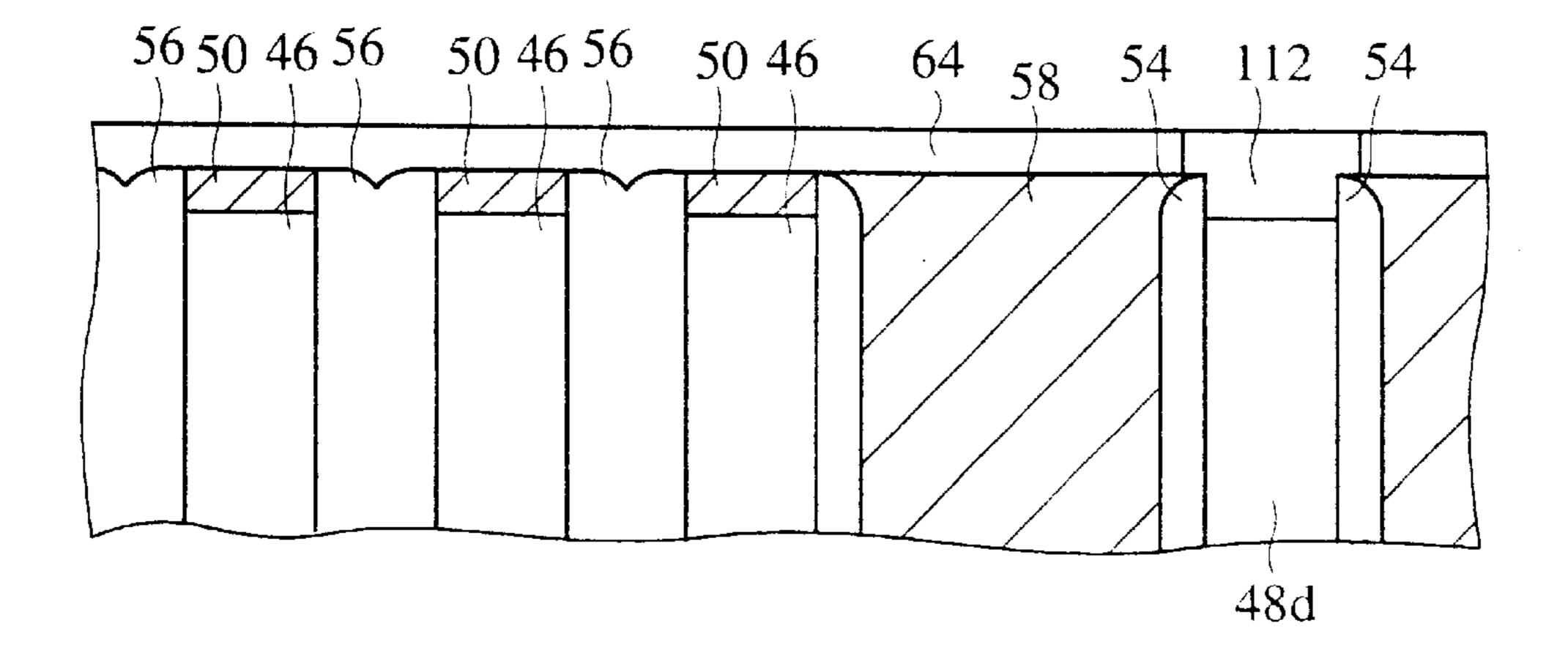

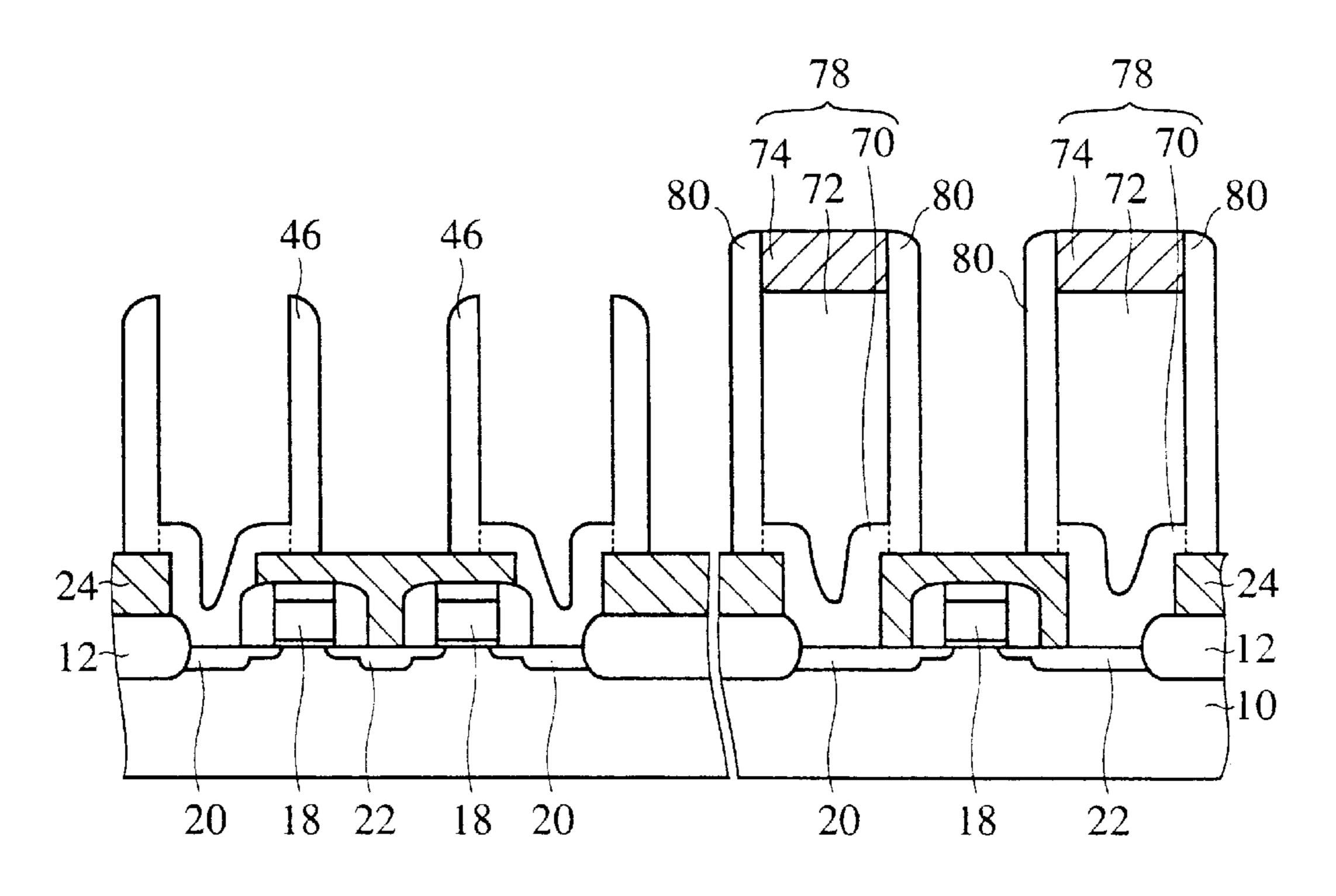

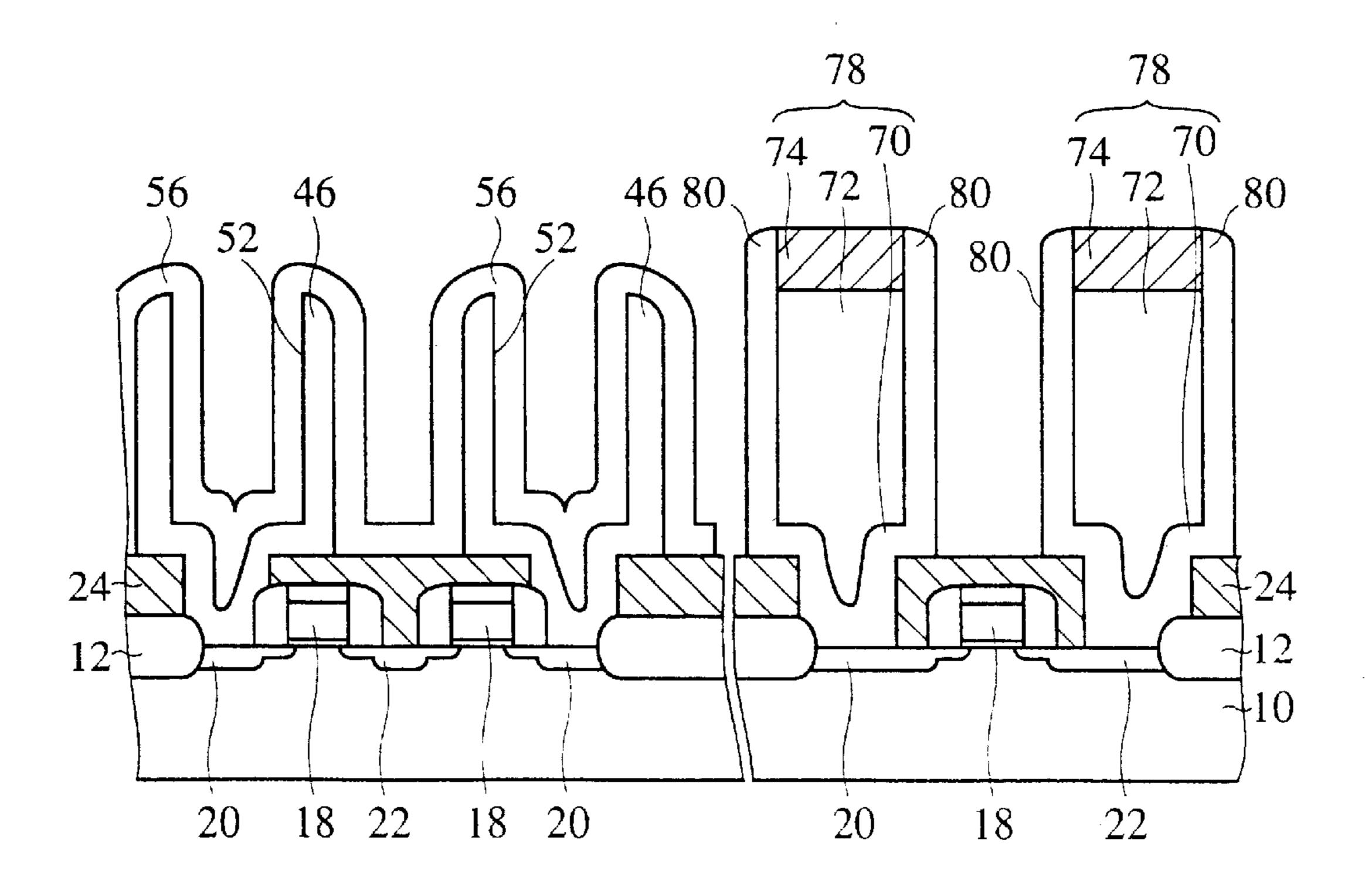

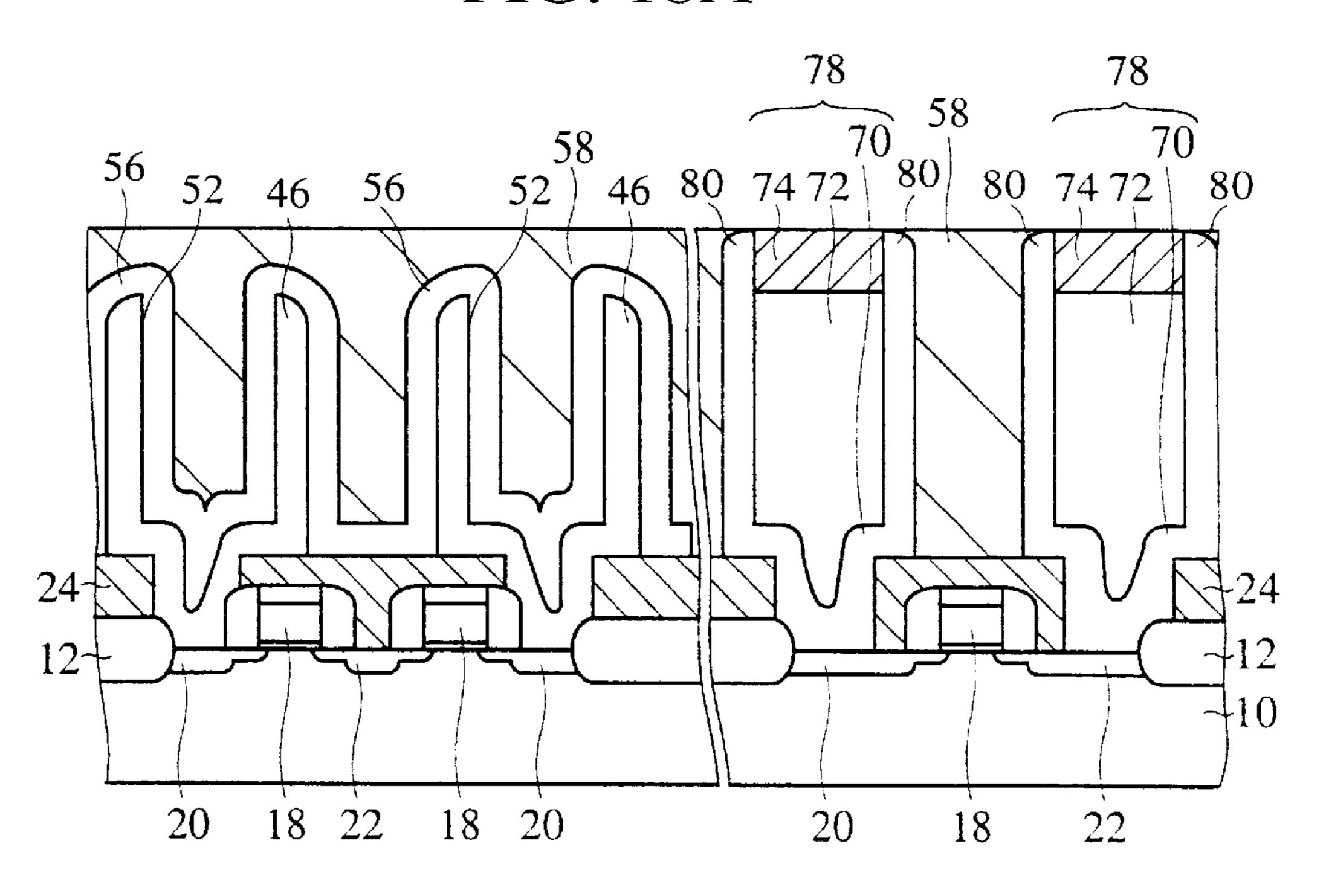

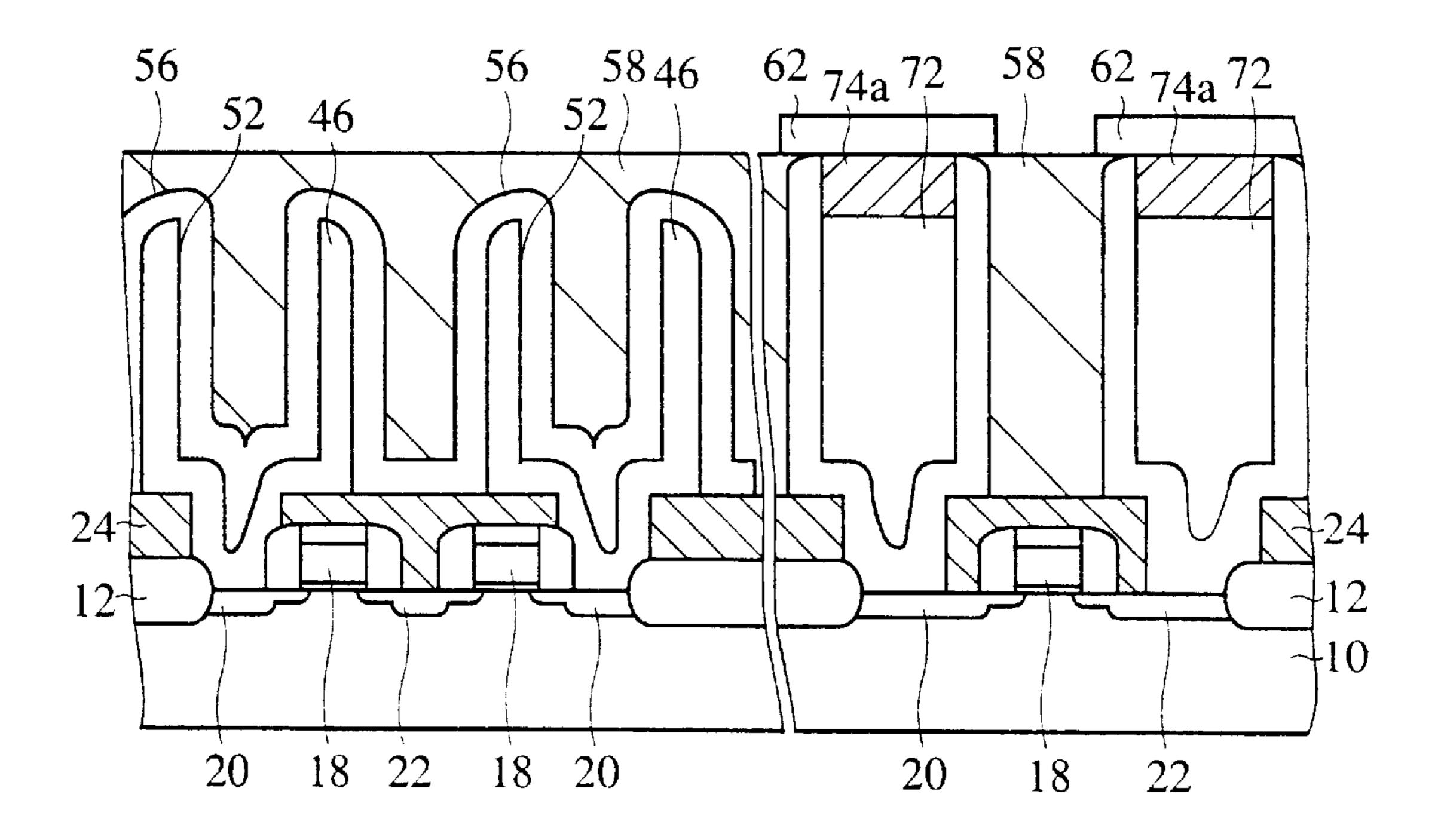

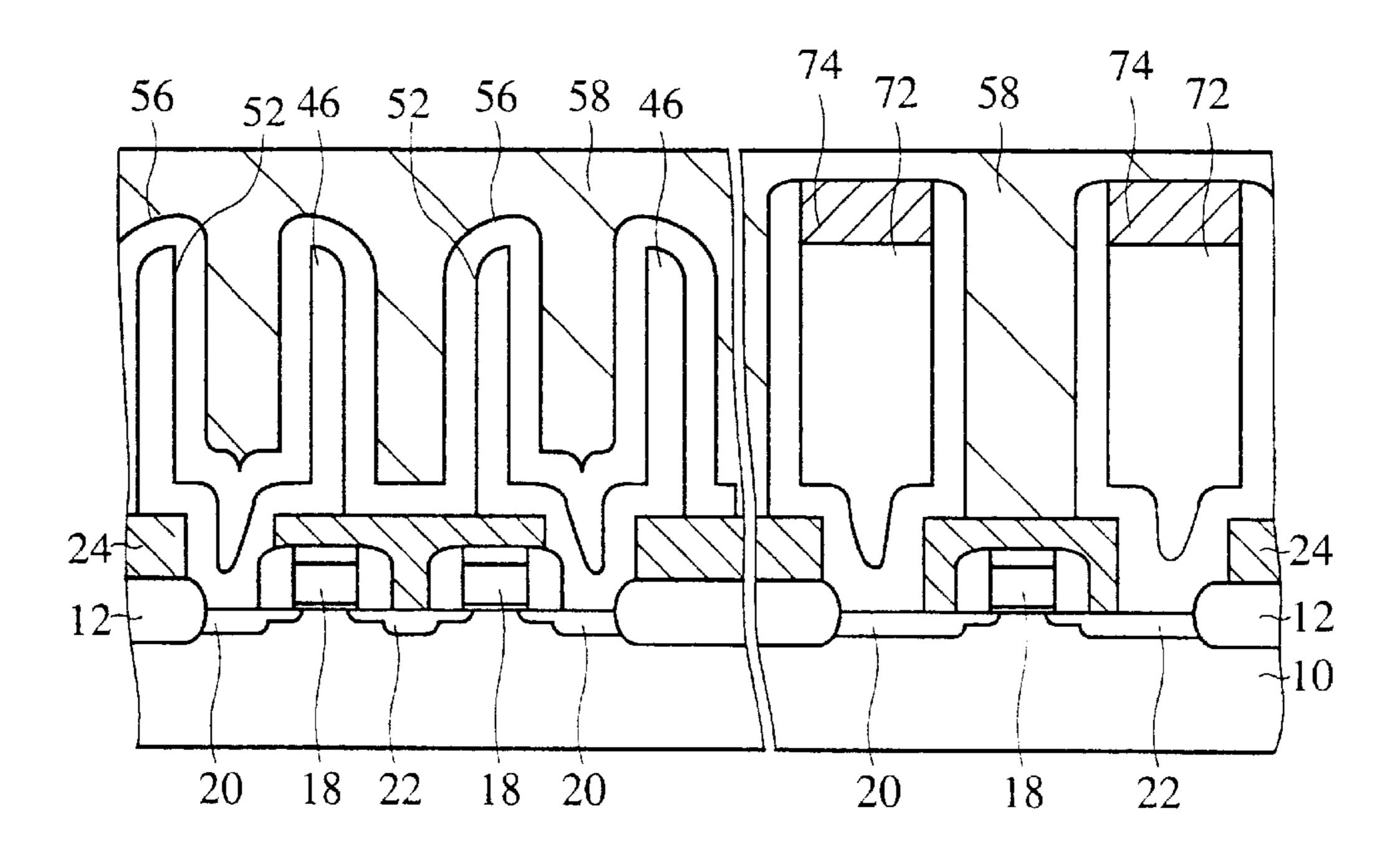

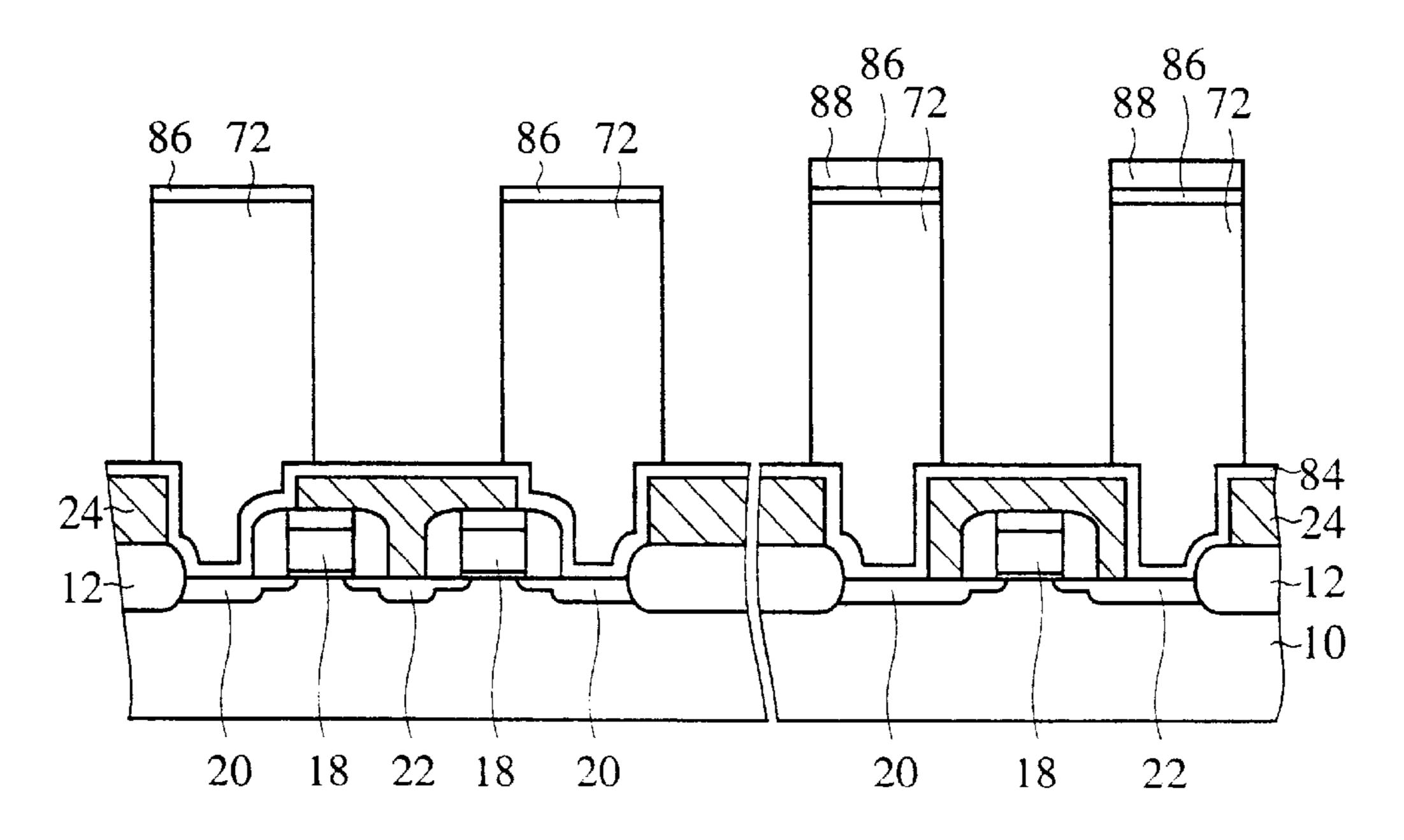

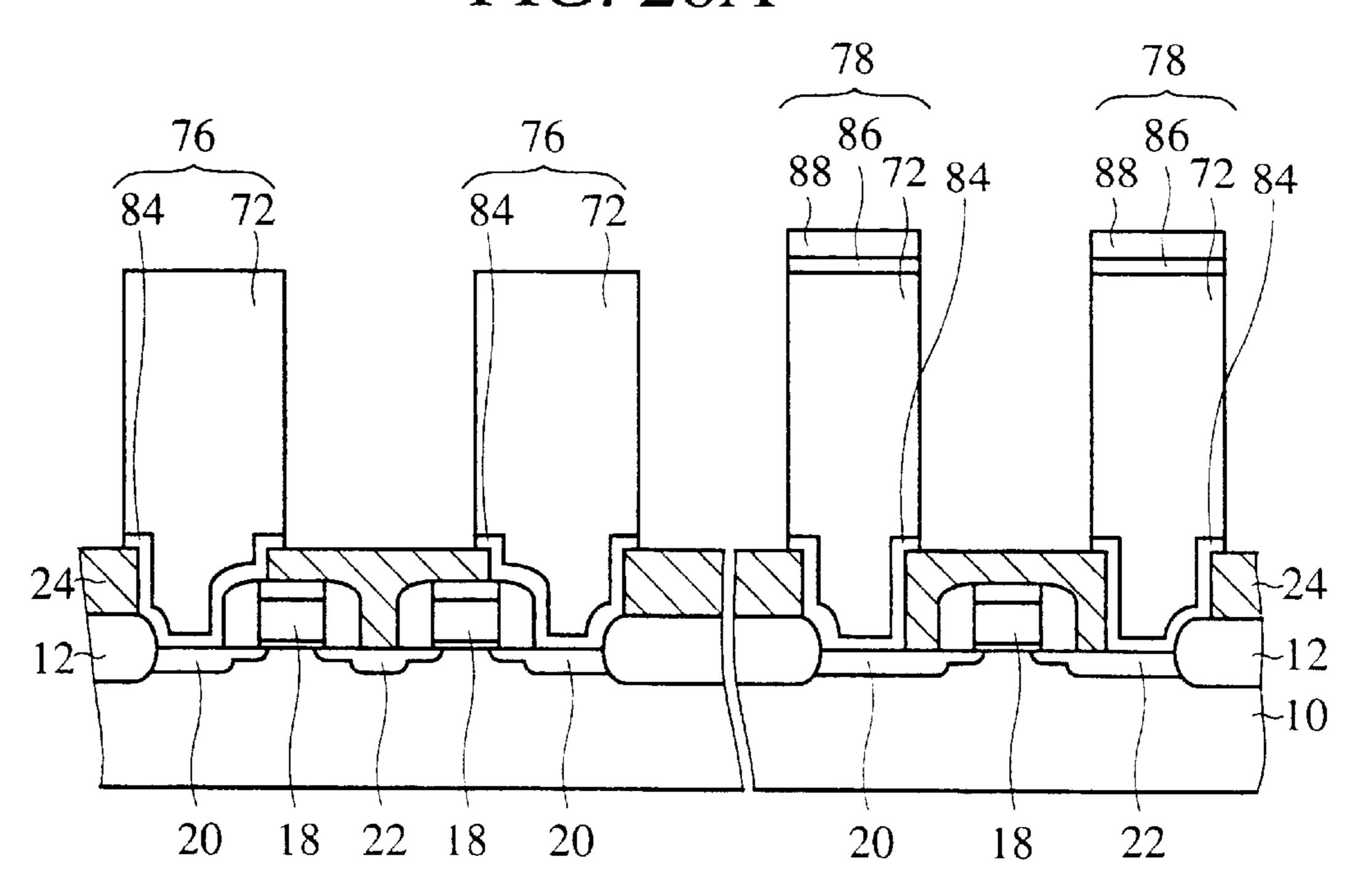

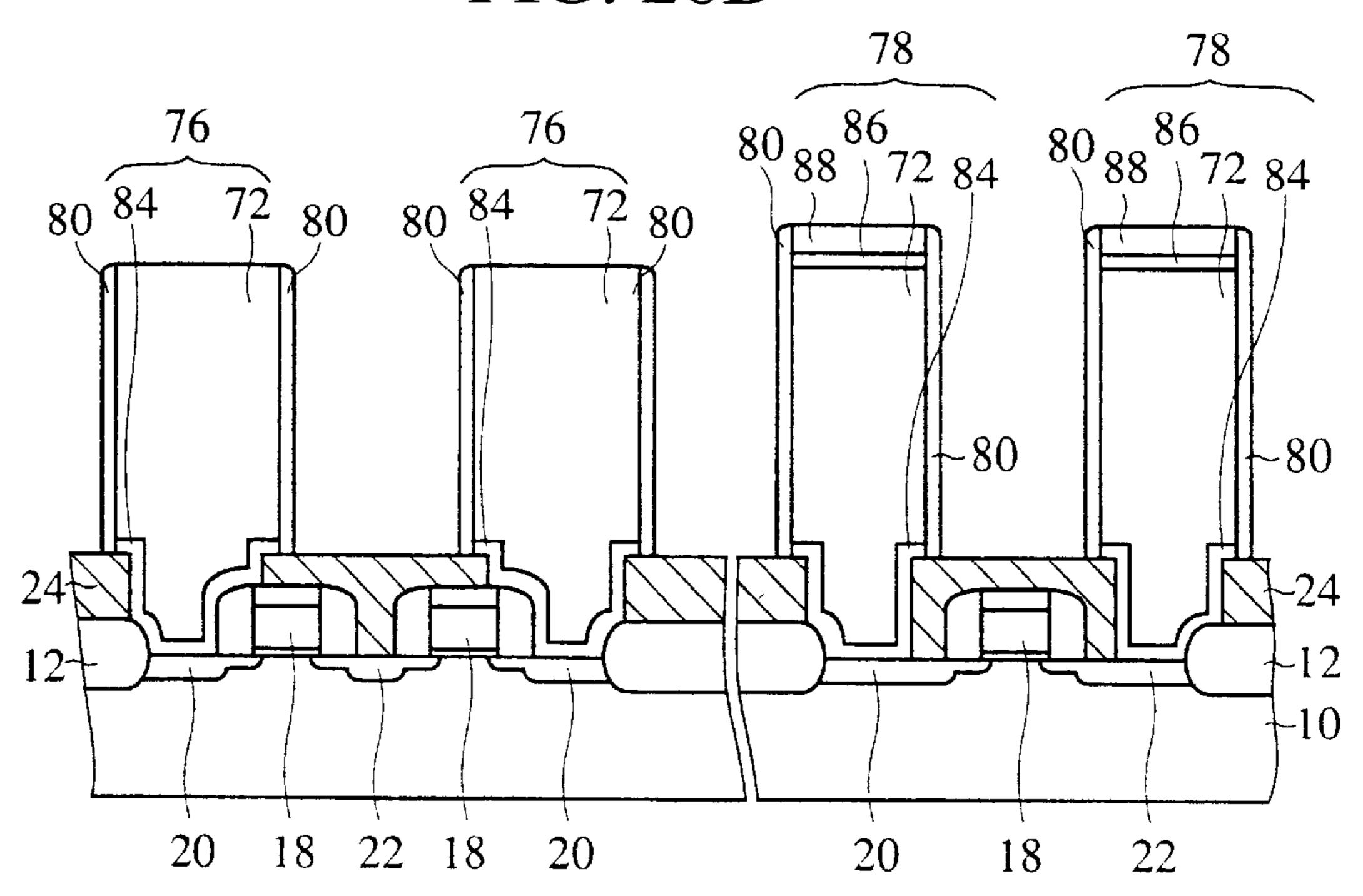

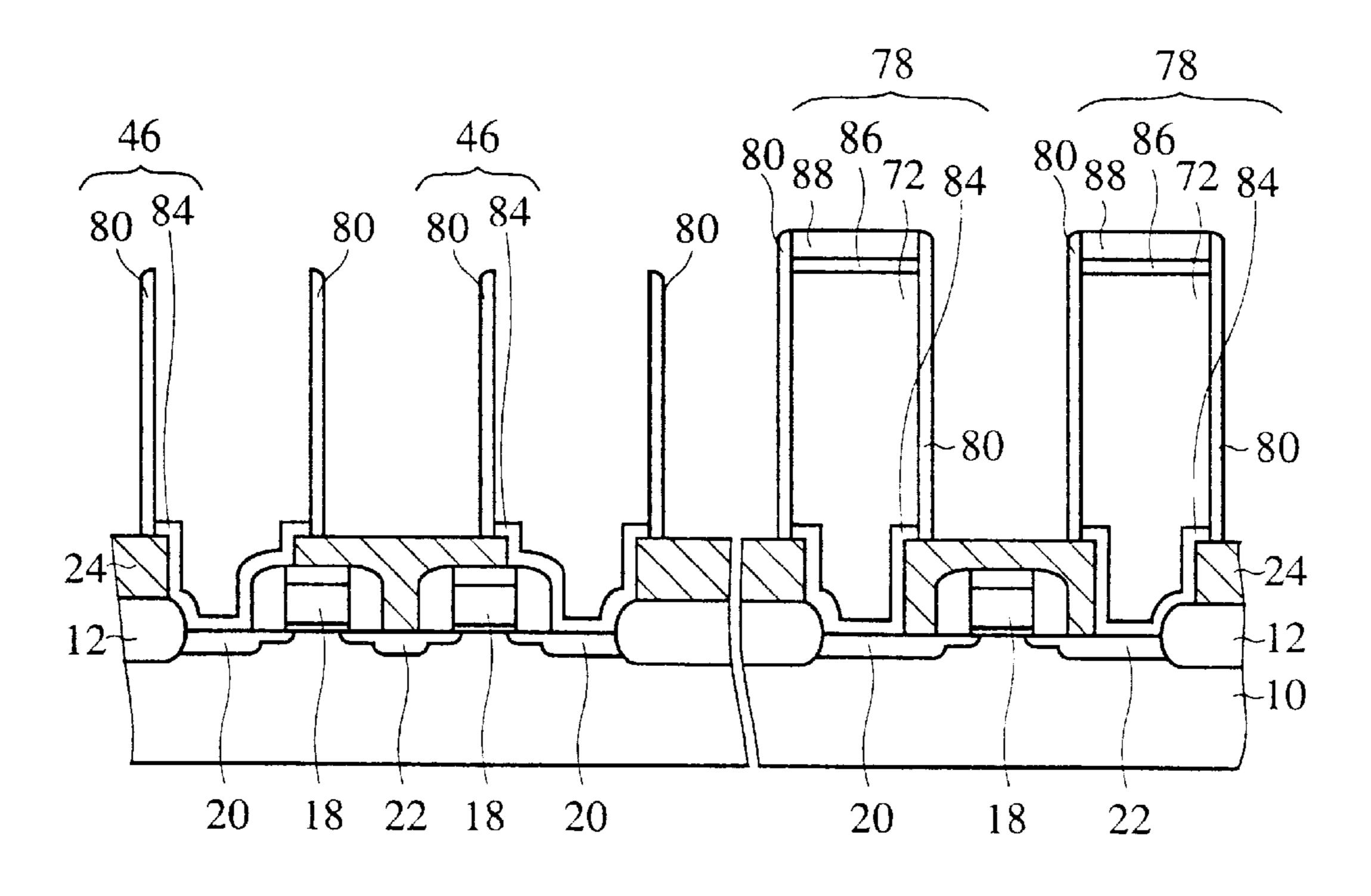

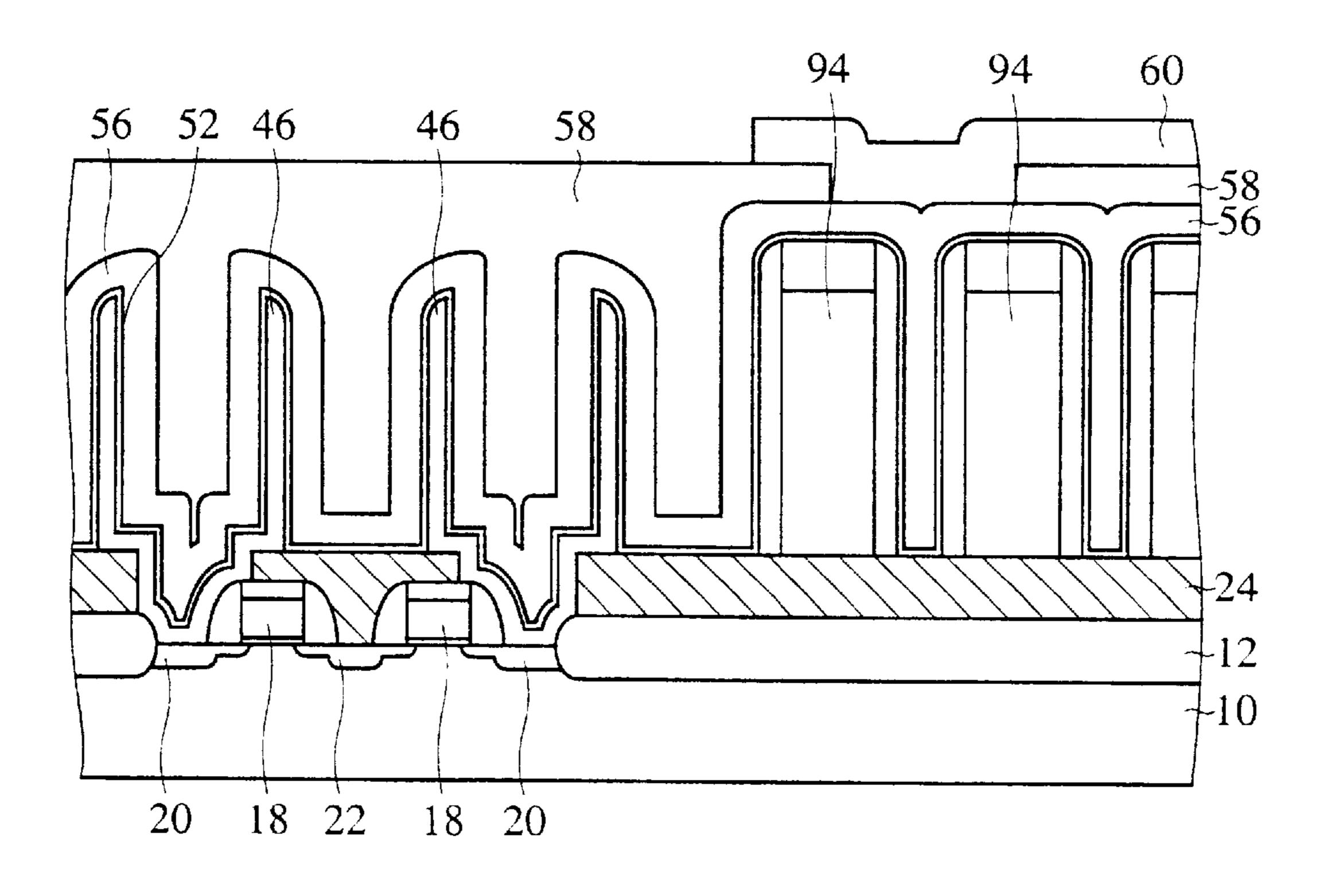

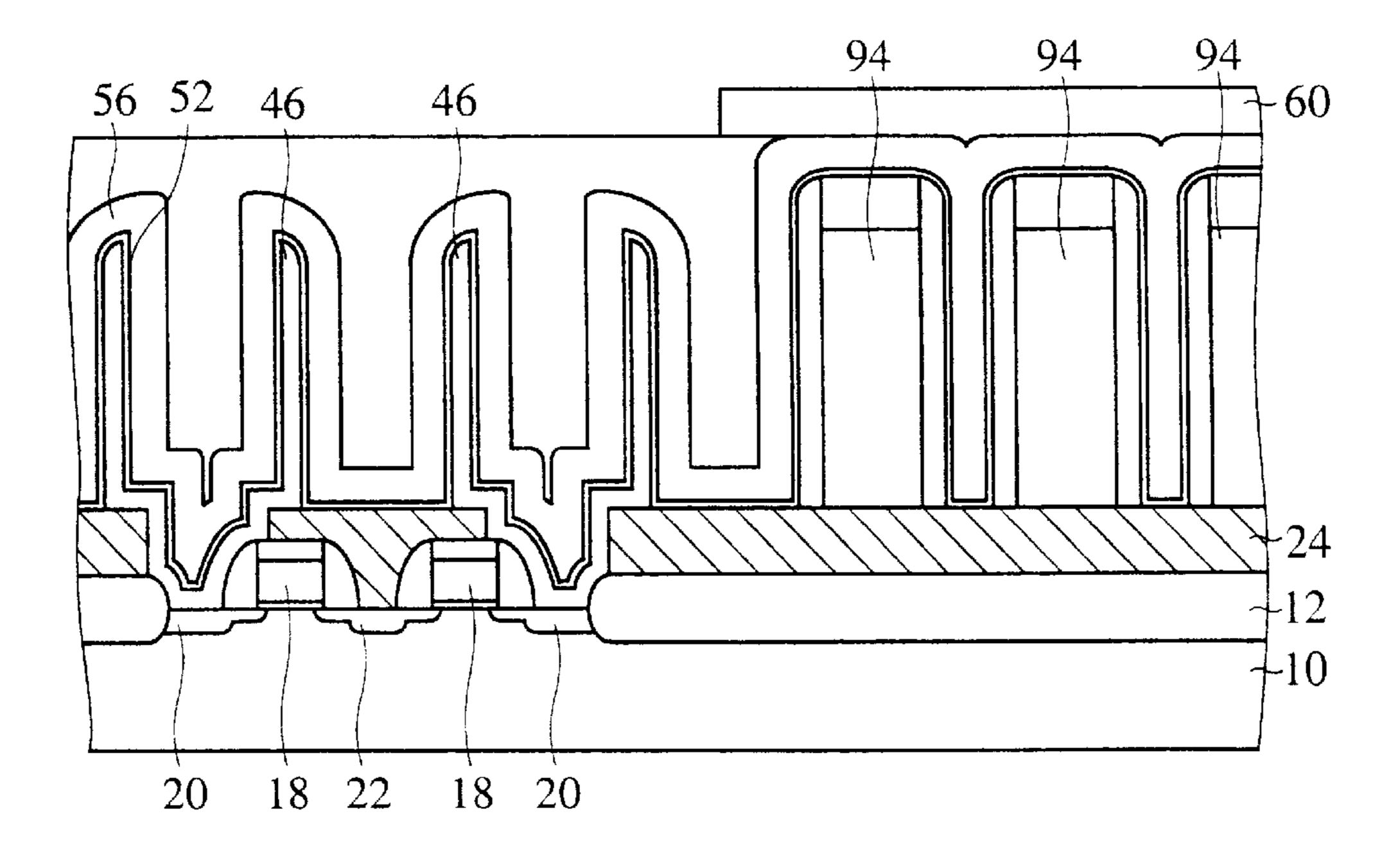

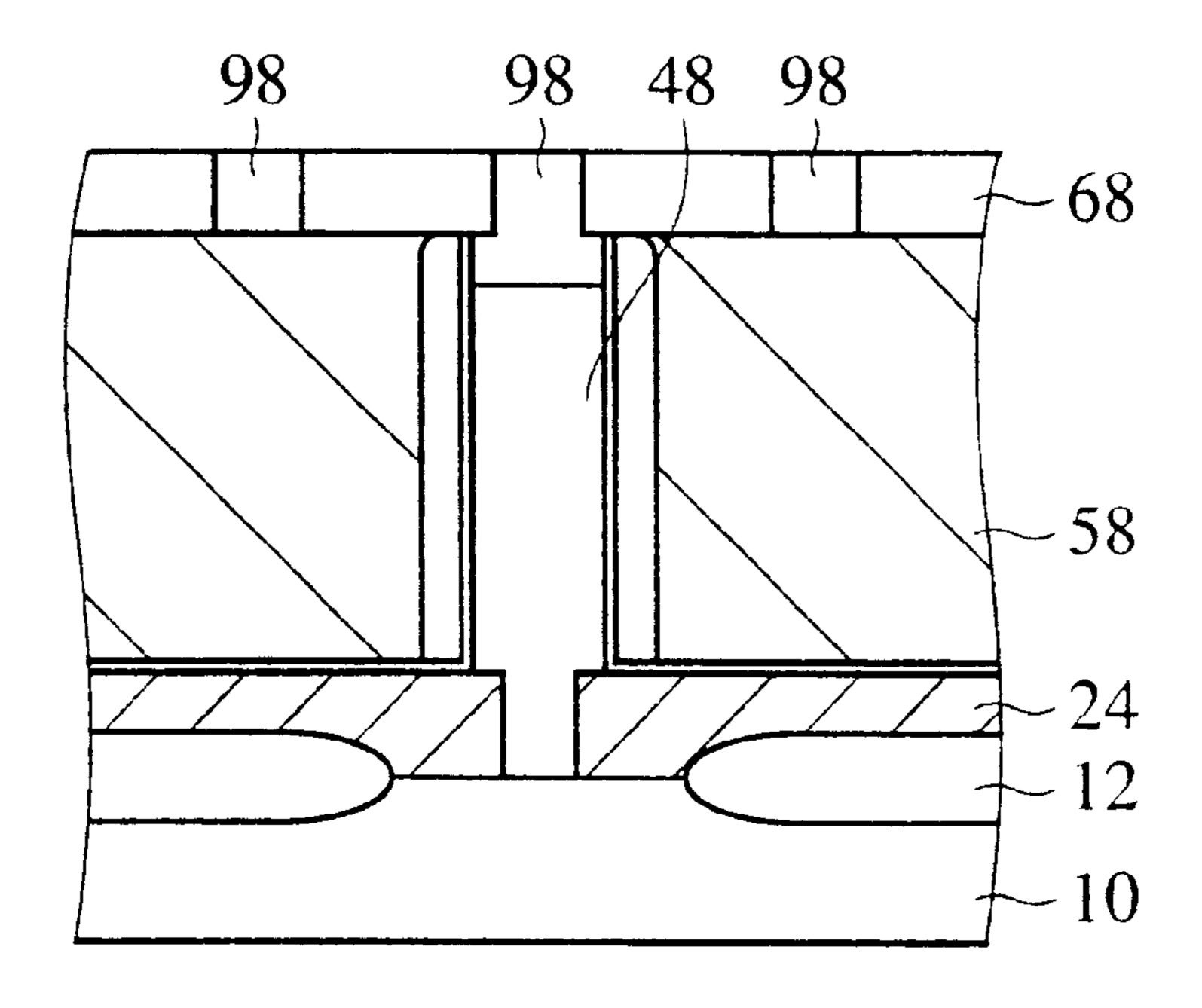

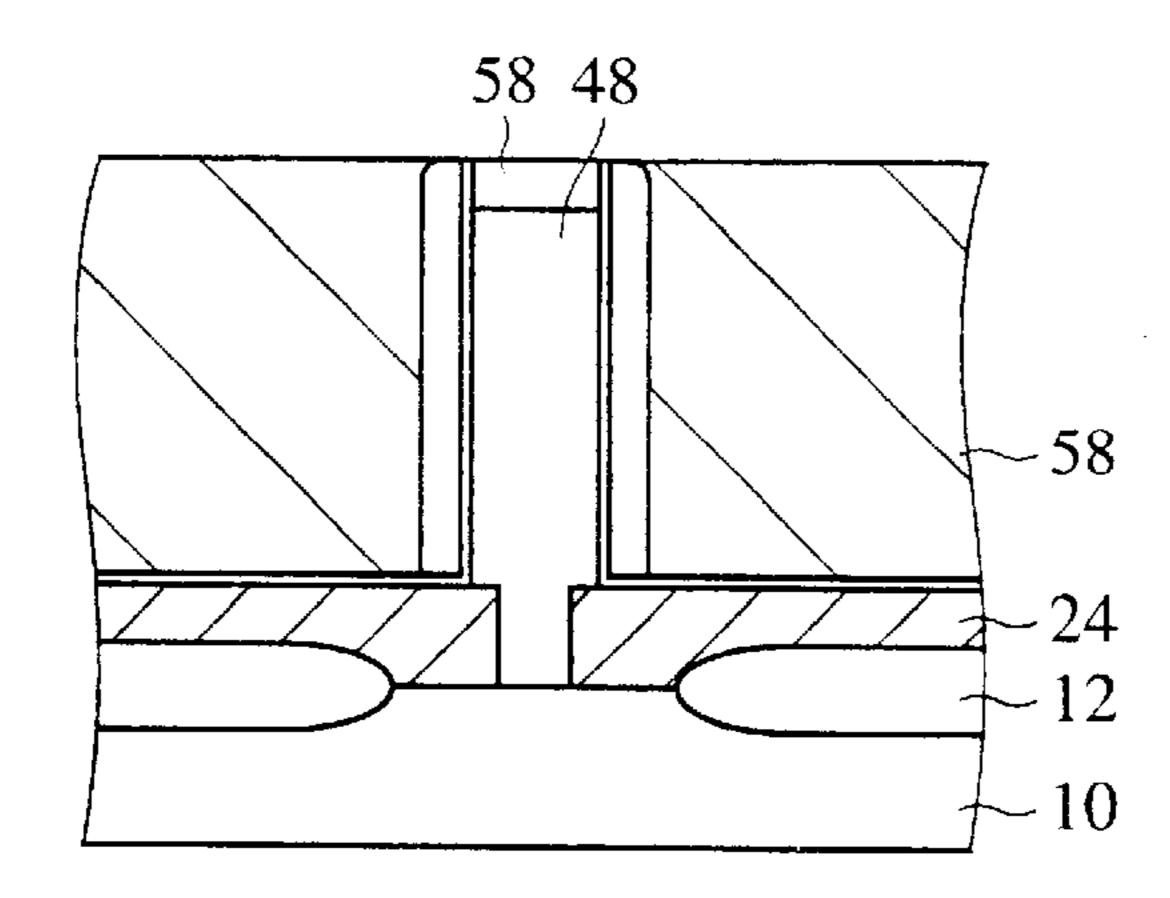

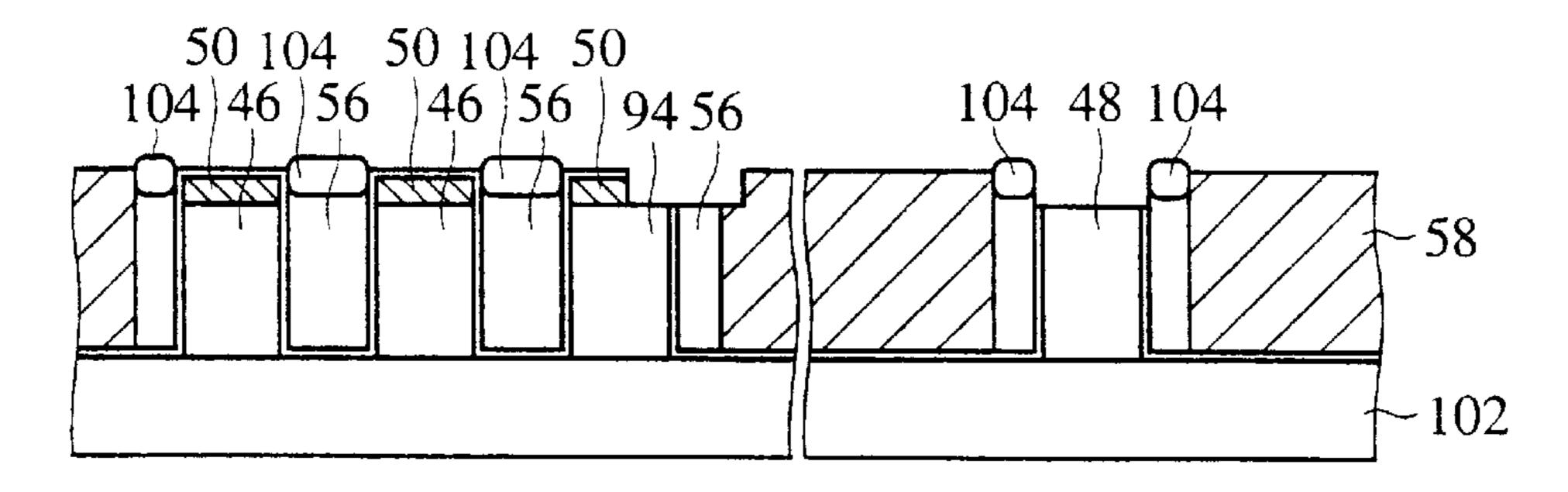

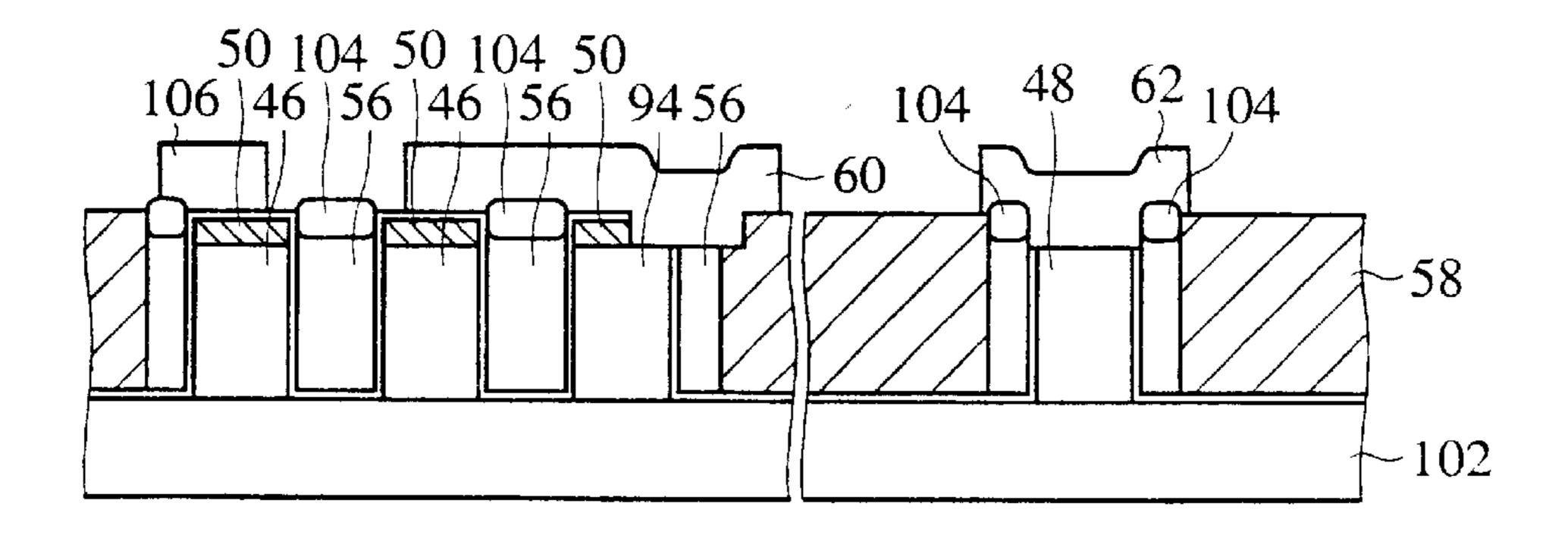

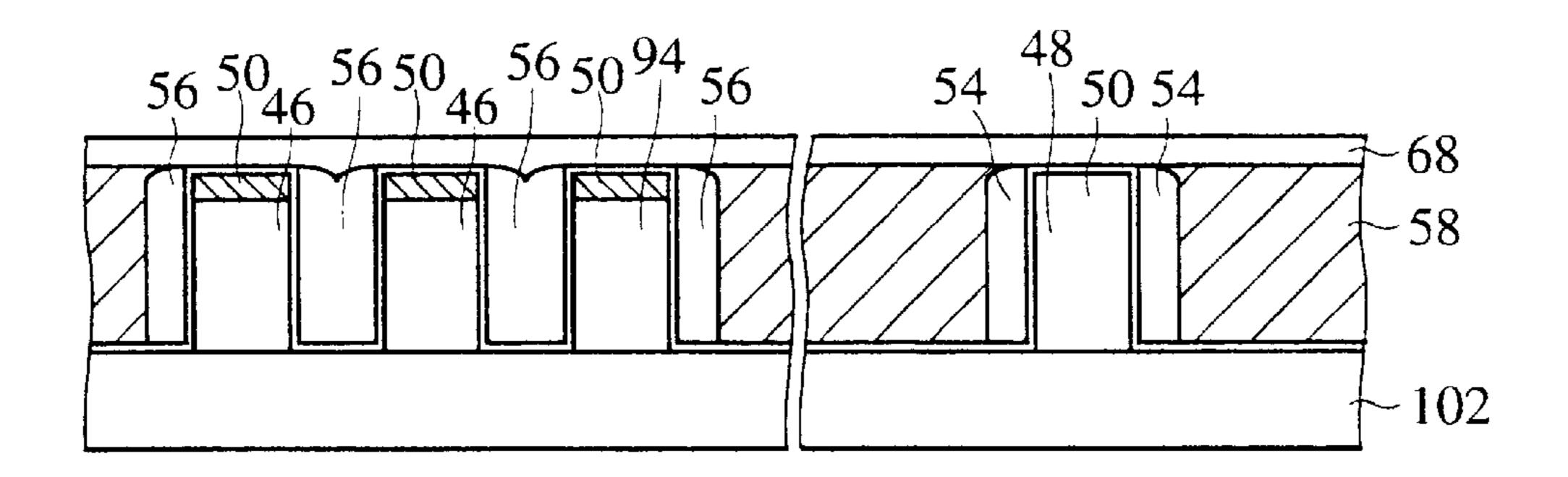

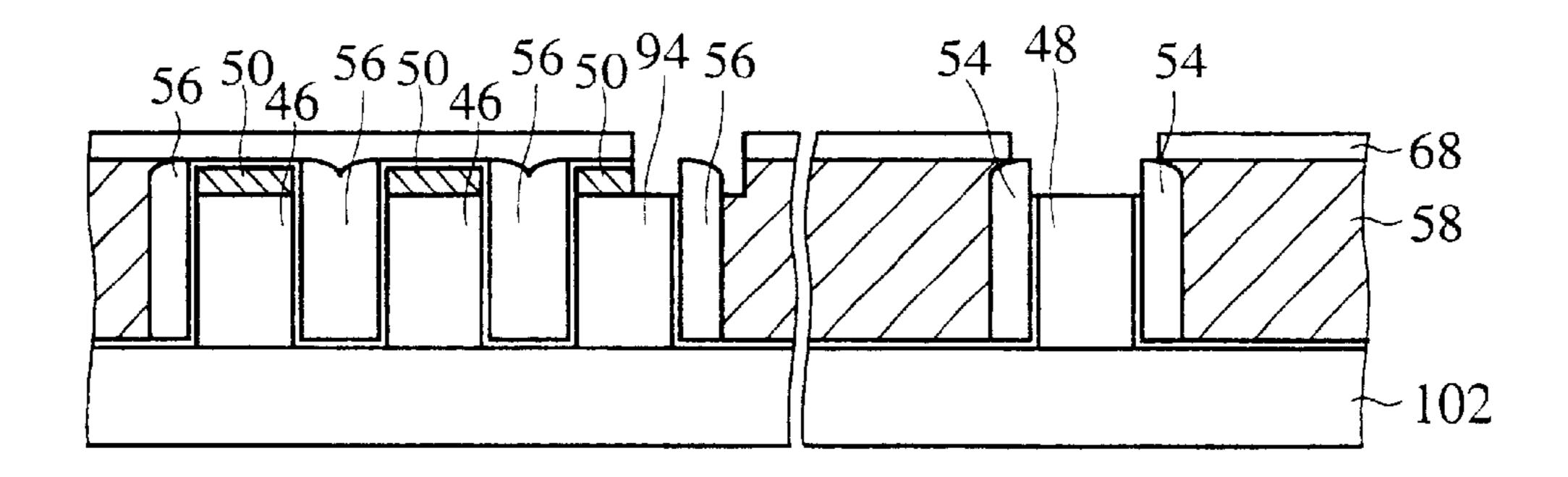

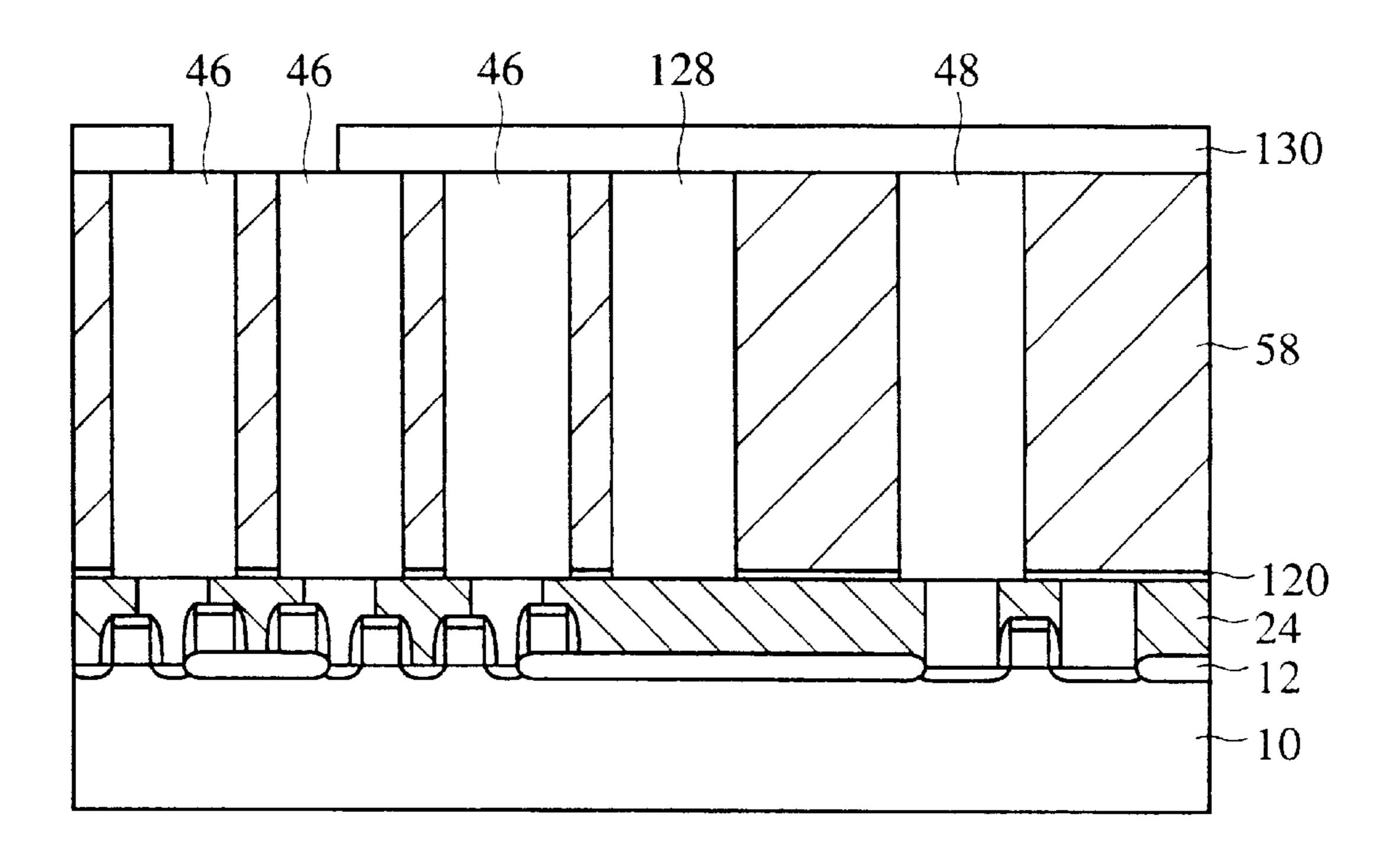

FIGS. 11A–11C are sectional views of the semiconductor device according to a fourth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

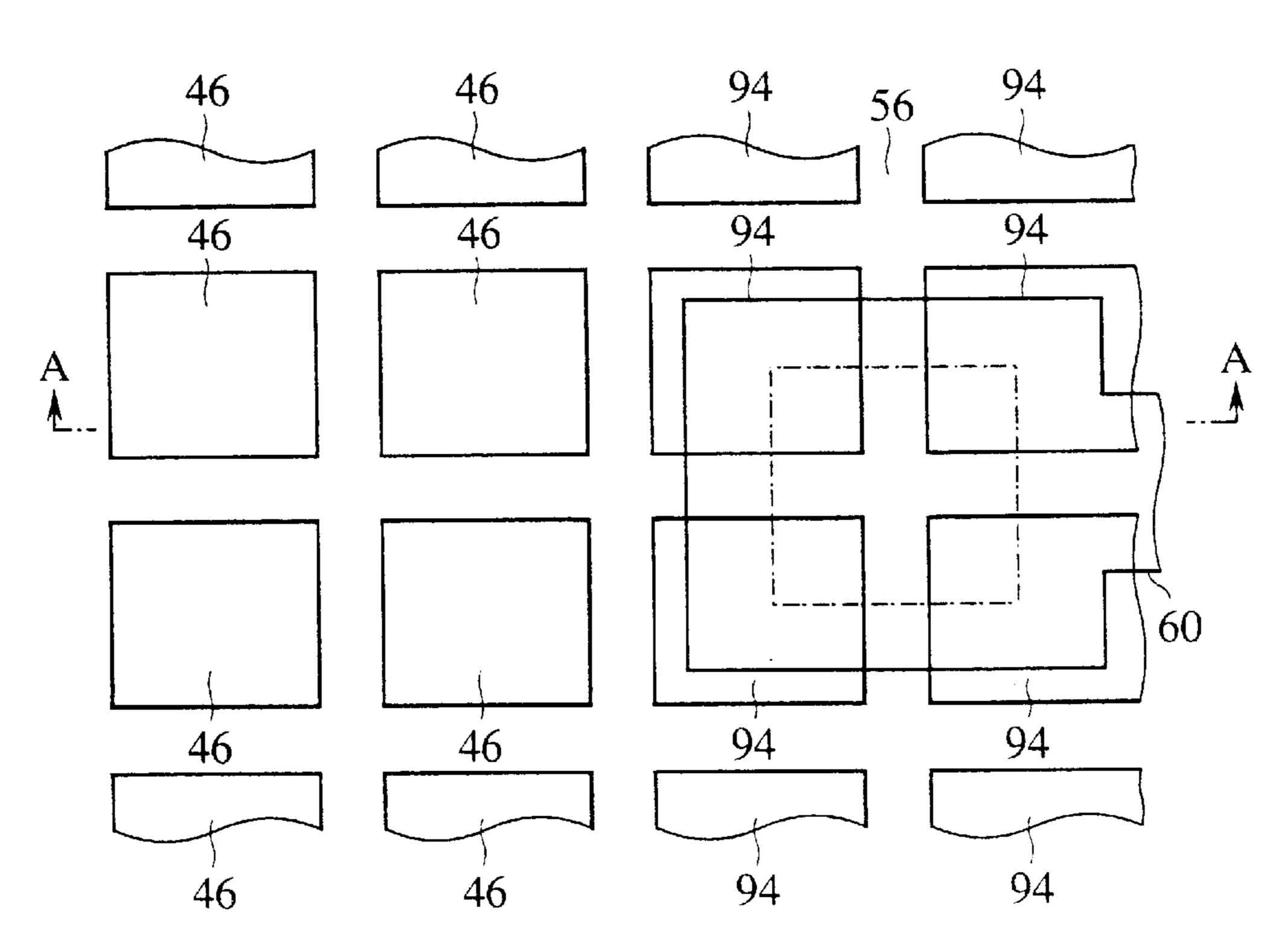

FIG. 12 is a plan view of the semiconductor device according to a fifth embodiment of the present invention, which shows a structure thereof.

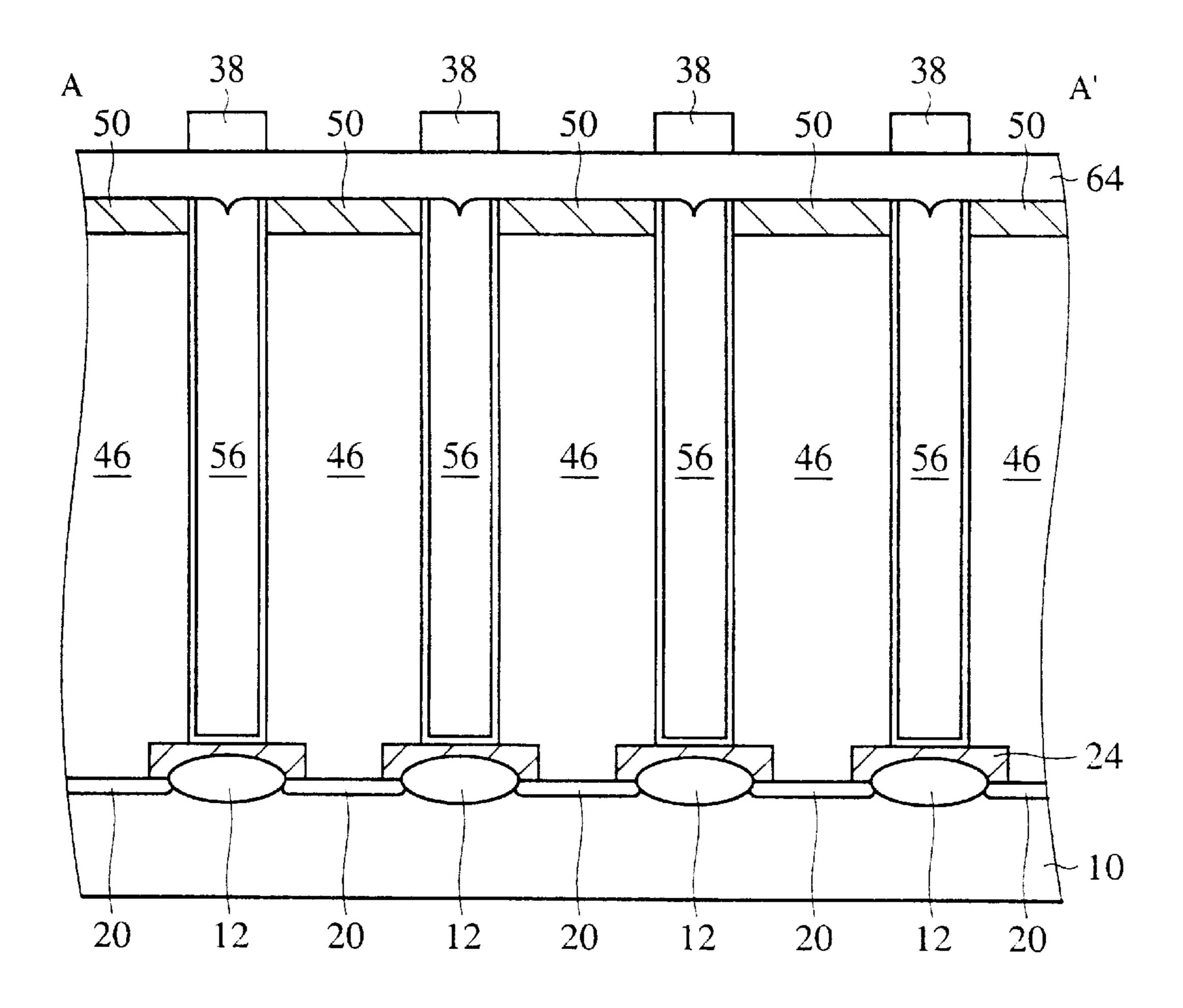

FIG. 13 is a sectional view of the semiconductor device of FIG. 12 along the line A-A'.

FIG. 14 is a sectional view of the semiconductor device of FIG. 12 along the line B–B'.

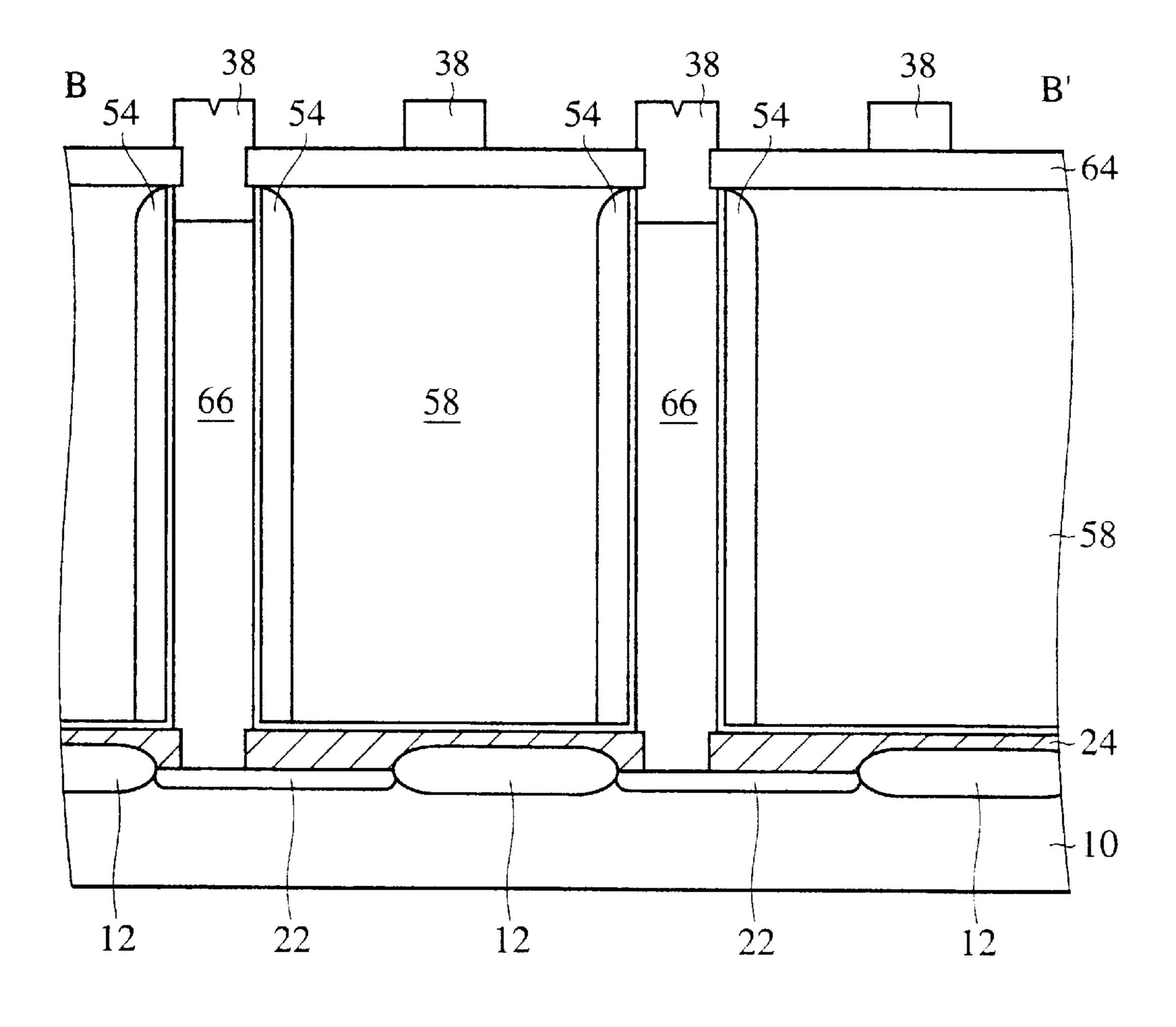

FIG. 15 is a diagrammatic sectional view of the semiconductor device according to a sixth embodiment of the present invention, which shows a structure thereof.

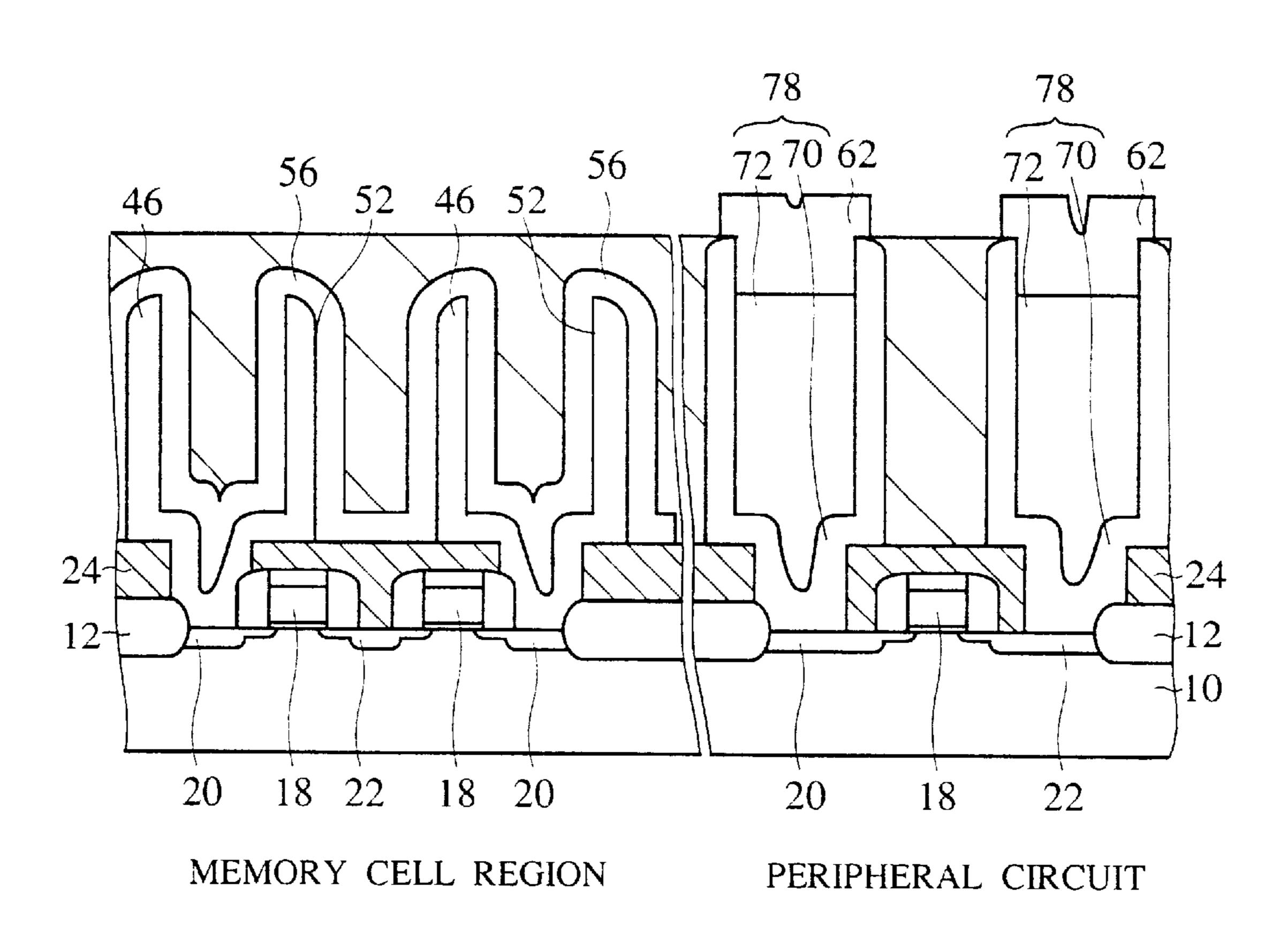

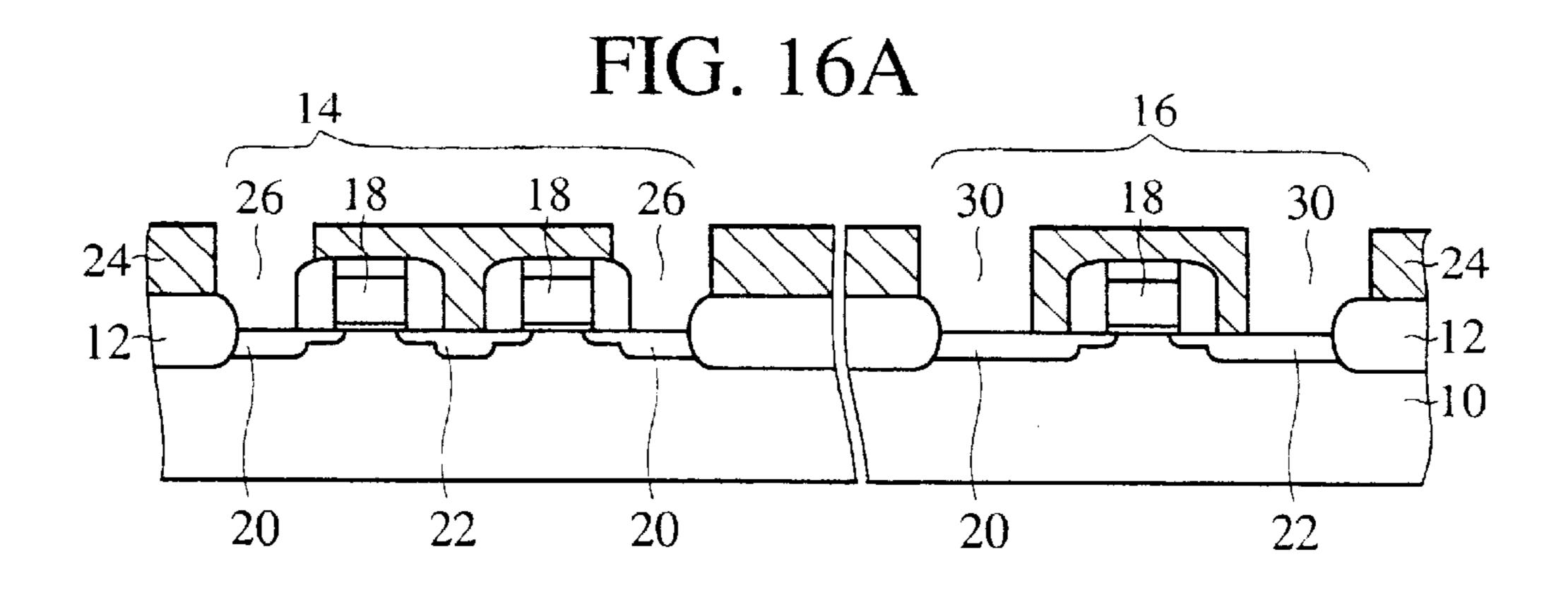

FIGS. 16A–16C, 17A–17B and 18A–18B are sectional views of the semiconductor device according to the sixth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIG. 19 is a diagrammatic sectional view of the semiconductor device according to a modification of the sixth embodiment of the present invention, which shows a structure thereof.

FIGS. 20A–20B and 21A–21B are sectional views of the semiconductor device according to the modification of the sixth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 22A–22B and 23 are sectional views of the semiconductor device according to a seventh embodiment of the present invention in the steps of the method for fabricating 40 the same, which explain the method.

FIGS. 24A–24B, 25A–25B, 26A–26B and 27 are sectional views of the semiconductor device according to an eighth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIG. 28A is a sectional view of the semiconductor device according to a ninth embodiment of the present invention, which show a structure thereof.

FIG. 28B is a plan view of the semiconductor device according to a ninth embodiment of the present invention, which show a structure thereof.

FIG. 29 is a diagrammatic sectional view of the semiconductor device according to a tenth embodiment of the present invention, which shows a structure thereof.

FIGS. 30A–30B and 31A–31B are sectional views of the semiconductor device according to the tenth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 32A–32B and 33A–33B are sectional views of the semiconductor device according to a modification of the tenth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIG. 34 is a diagrammatic sectional view of the semicon- 65 ductor device according to an eleventh embodiment of the present invention, which shows a structure thereof.

FIGS. 35A–35C are sectional views of the semiconductor device according to the eleventh embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIG. 36 is a diagrammatic sectional view of the semiconductor device according to a twelfth embodiment of the present invention, which shows a structure thereof.

FIGS. 37A–37C are sectional views of the semiconductor device according to the twelfth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIG. 38 is a diagrammatic sectional view of the semiconductor device according to a modification of the twelfth embodiment of the present invention, which shows a structure thereof.

FIGS. 39A and 39B are sectional views of the semiconductor device according to the modification of the twelfth embodiment of the present invention in the steps of the method for fabricating the same, which explain a structure thereof and the method.

FIG. 40 is a diagrammatic sectional view of the semiconductor device according to a thirteenth embodiment of the 25 present invention, which shows a structure thereof.

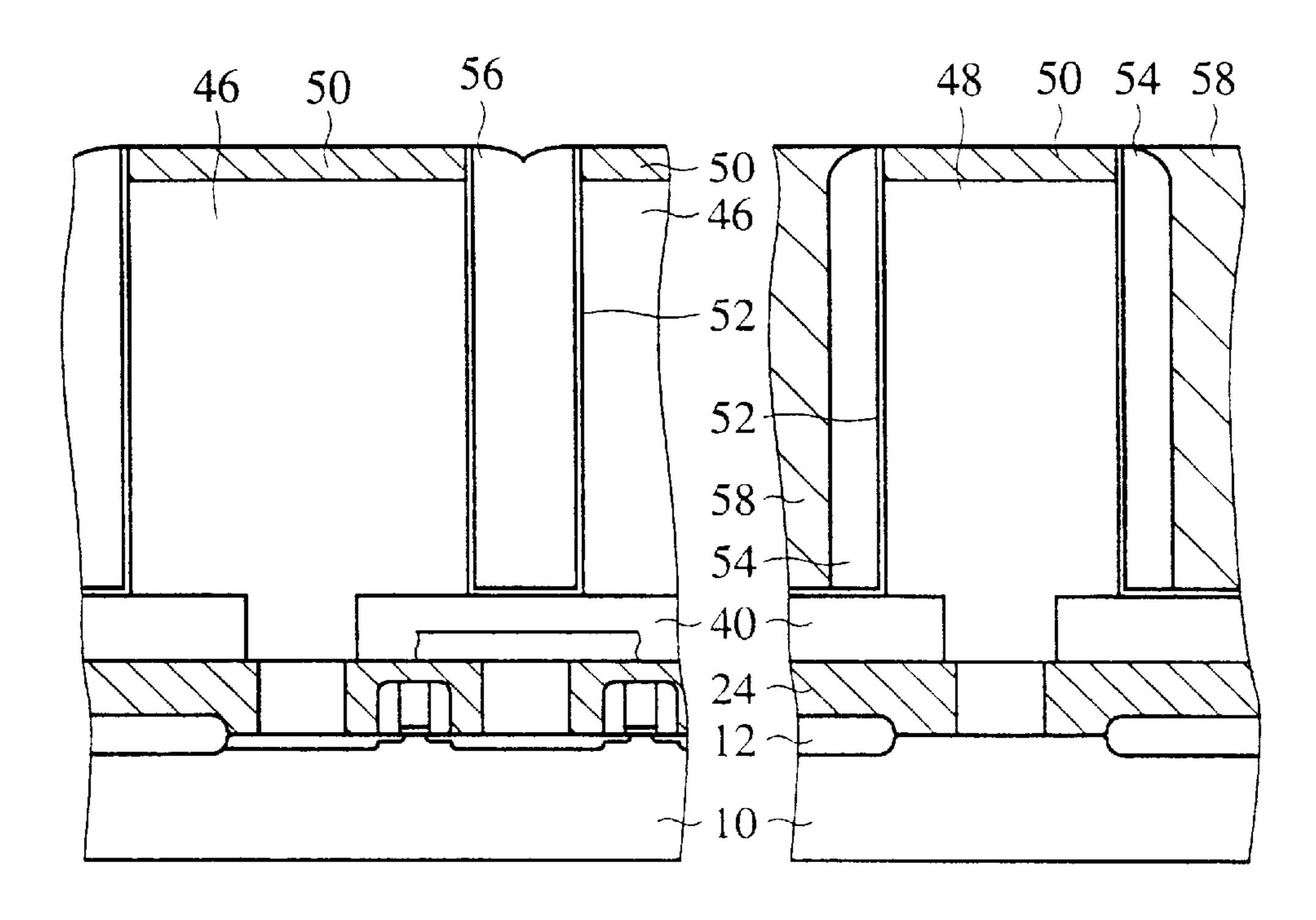

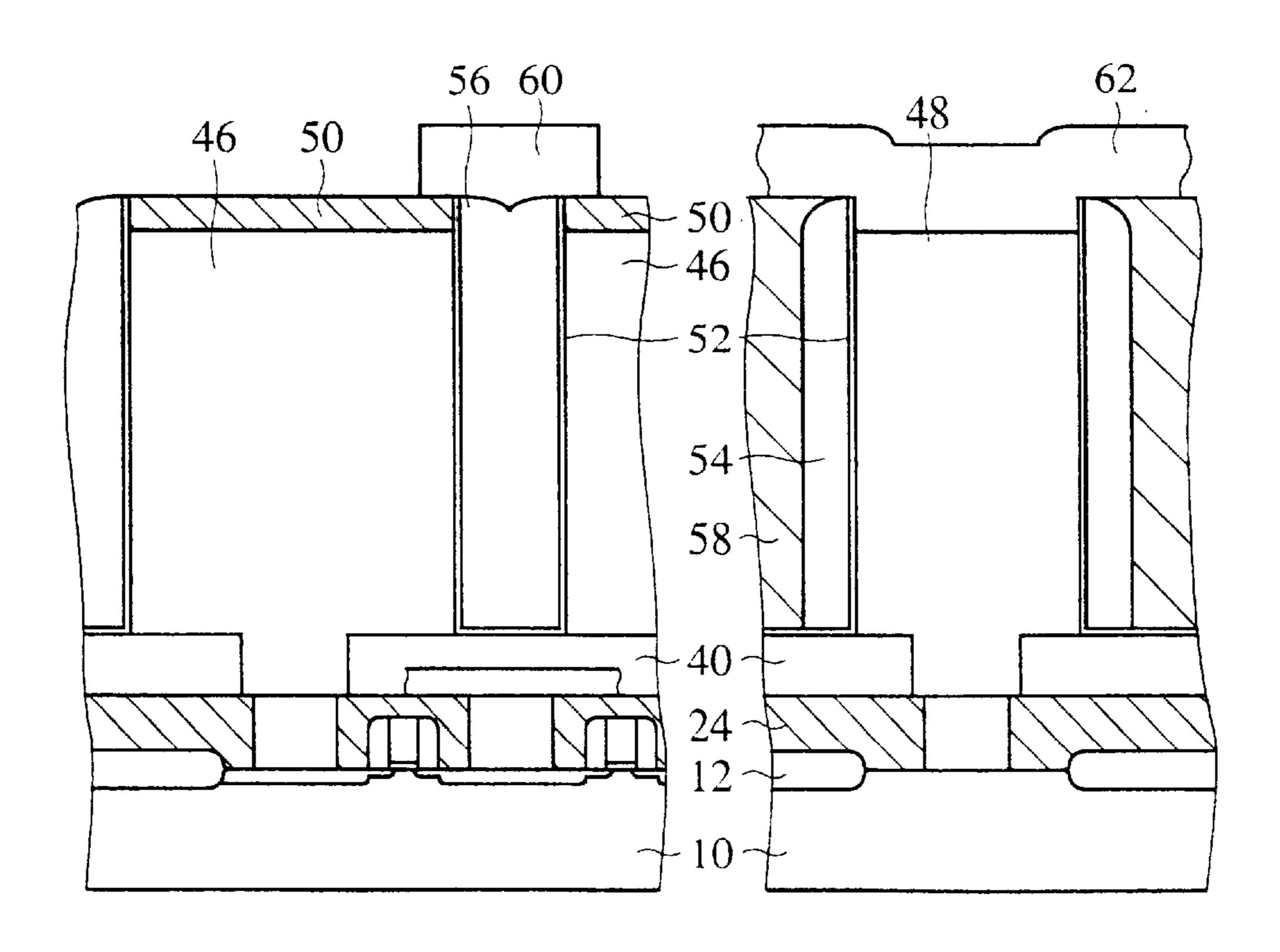

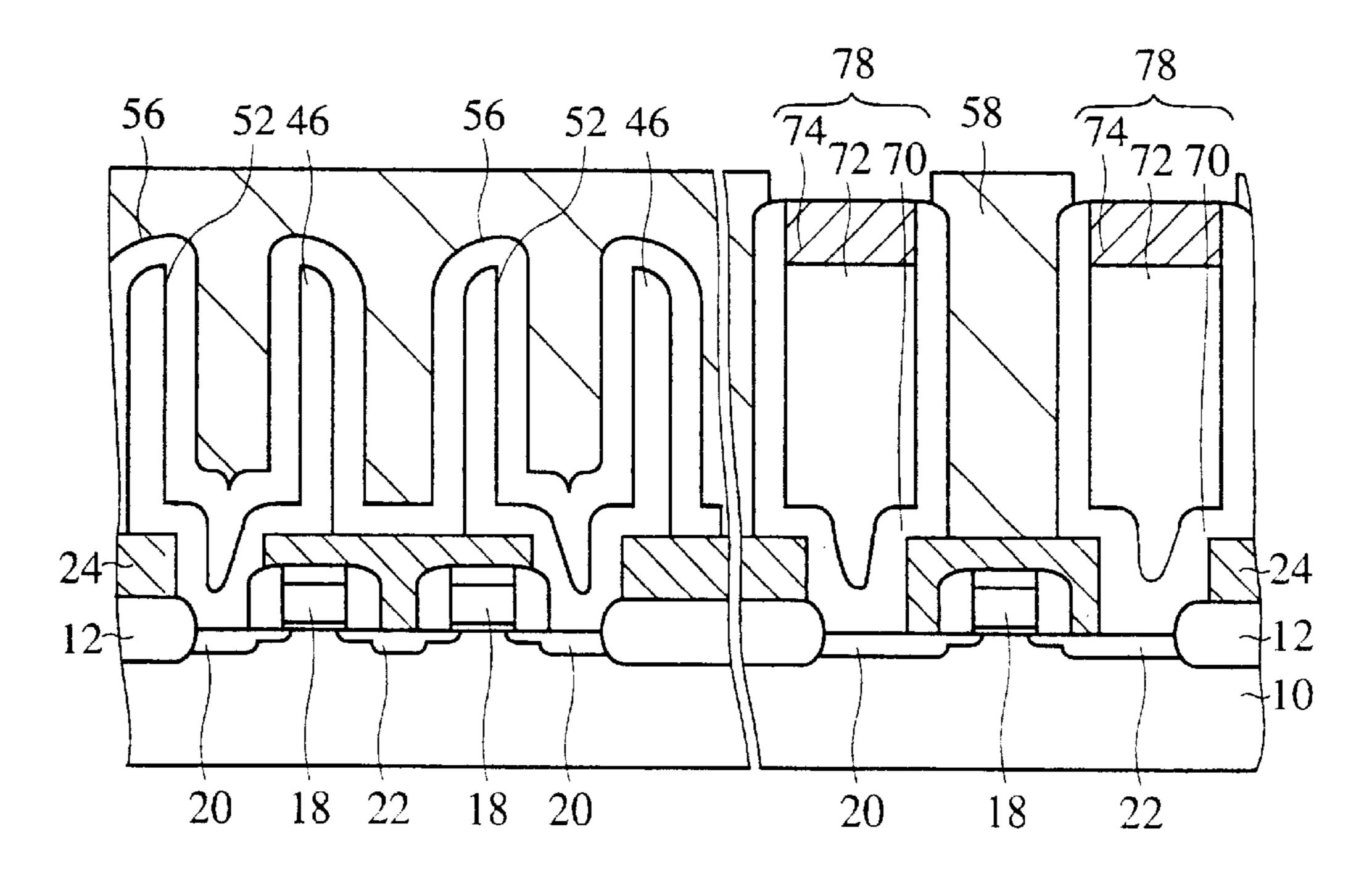

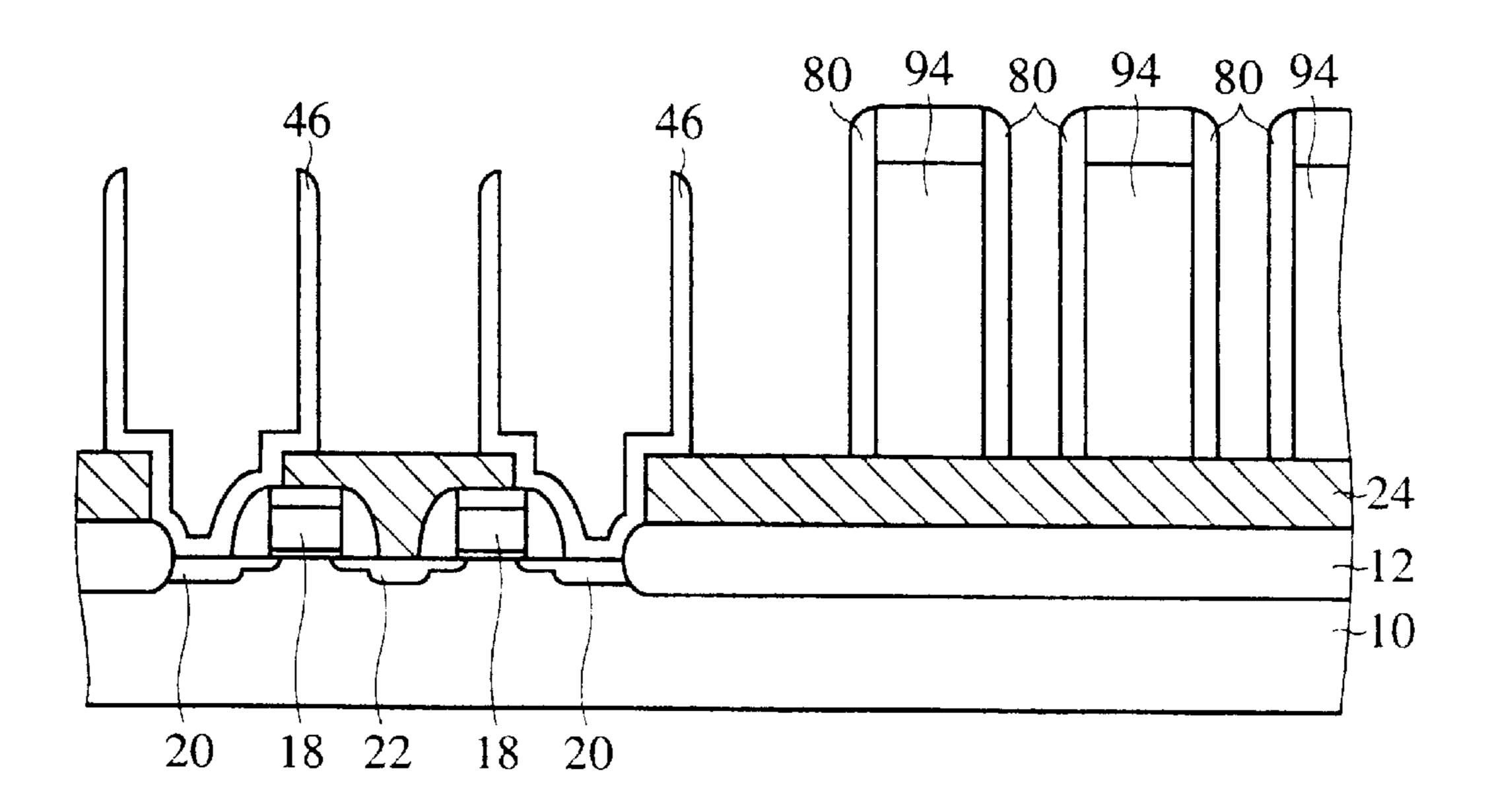

FIGS. 41A–41D are sectional views of the semiconductor device according to the thirteenth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 42A–42C are sectional views of the semiconductor device according to a modification of the thirteenth embodiment of the present invention in the steps of the method for fabricating the same, which explain a structure thereof and the method.

FIG. 43A is a plan view of the semiconductor device according to a fourteenth embodiment of the present invention, which shows a structure thereof.

FIG. 43B is a sectional view of the semiconductor device according to a fourteenth embodiment of the present invention, which shows a structure thereof.

FIGS. 44A–44B, 45A–45B, 46A, 47A, 48A–48B and 49 are sectional views of the semiconductor device according to the fourteenth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 46B and 47B are plan views of the semiconductor device according to the fourteenth embodiment of the present invention in the steps of the method for fabricating the same, which explain the method.

FIGS. 50A and 50B are sectional views of the semiconductor device according to a modification of the fourteenth embodiment of the present invention, in the steps of the method for fabricating the same, which explain the method.

FIG. 51 is a diagrammatic sectional view of the semiconductor device according to the modification of the fourteenth embodiment of the present invention, which shows a structure thereof.

FIG. 52 is a diagrammatic sectional view of a conventional semiconductor device, which shows a structure thereof (Part 1).

FIG. 53 is a diagrammatic sectional view of a conventional semiconductor device, which shows a structure thereof (Part 2).

**12**

### DETAILED DESCRIPTION OF THE INVENTION

[A First Embodiment]

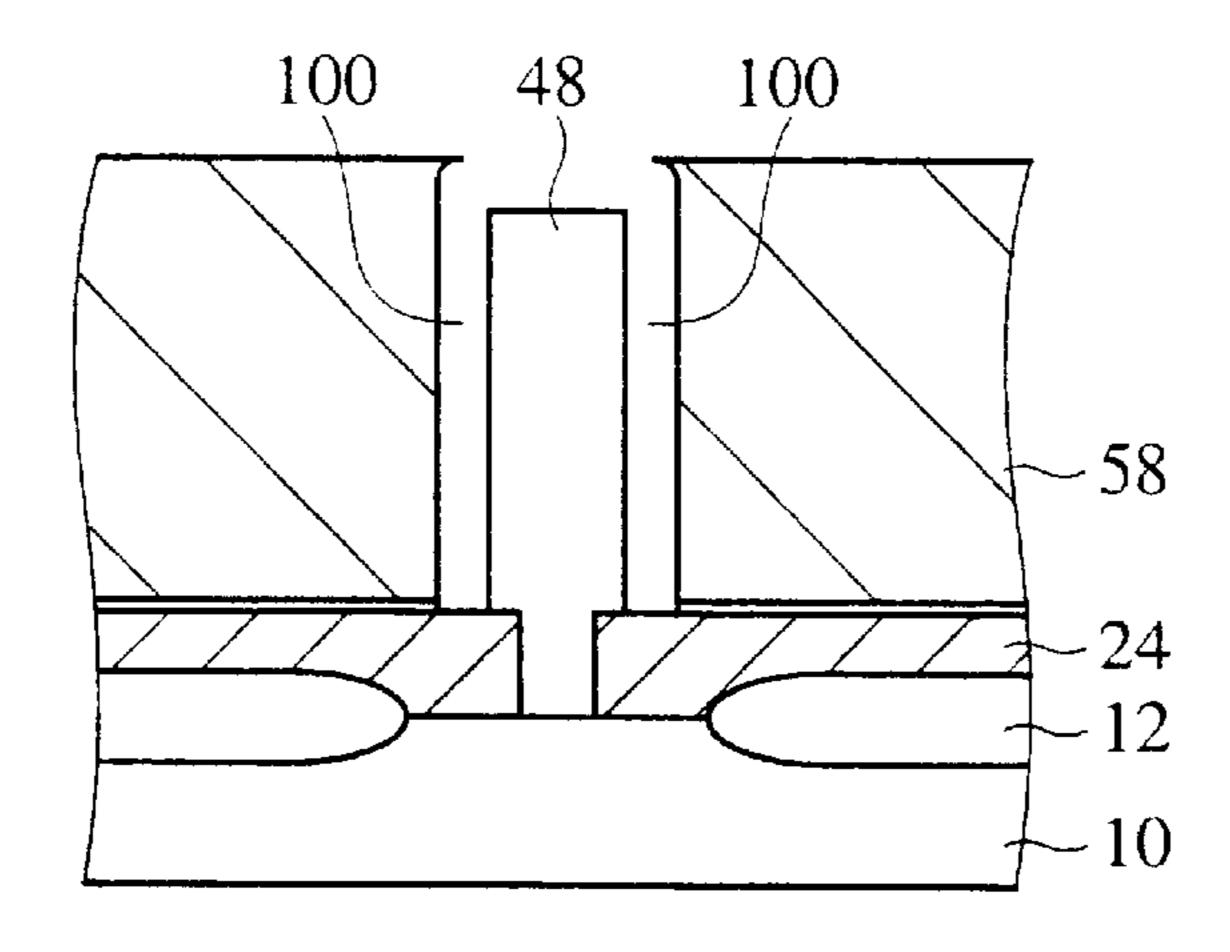

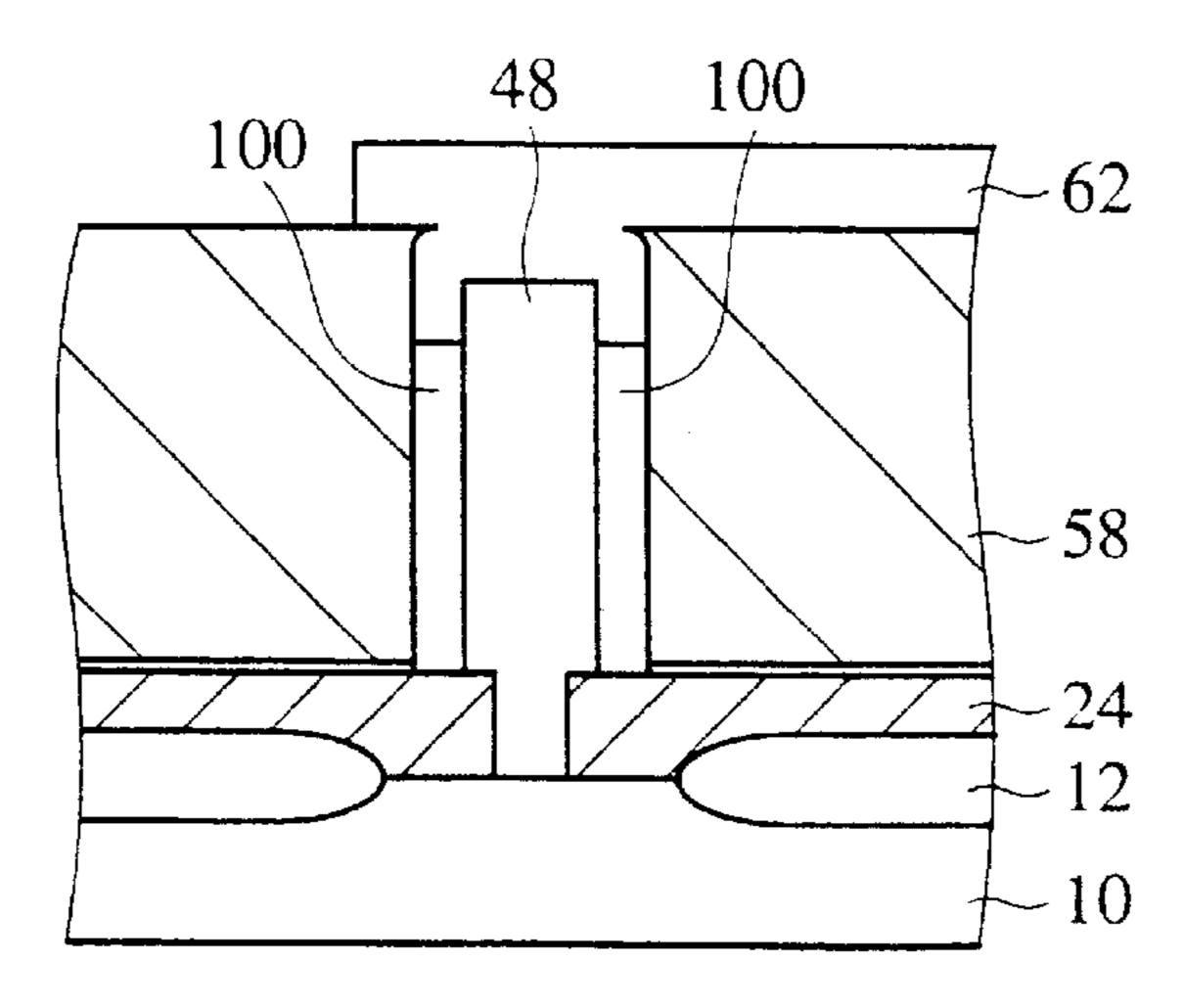

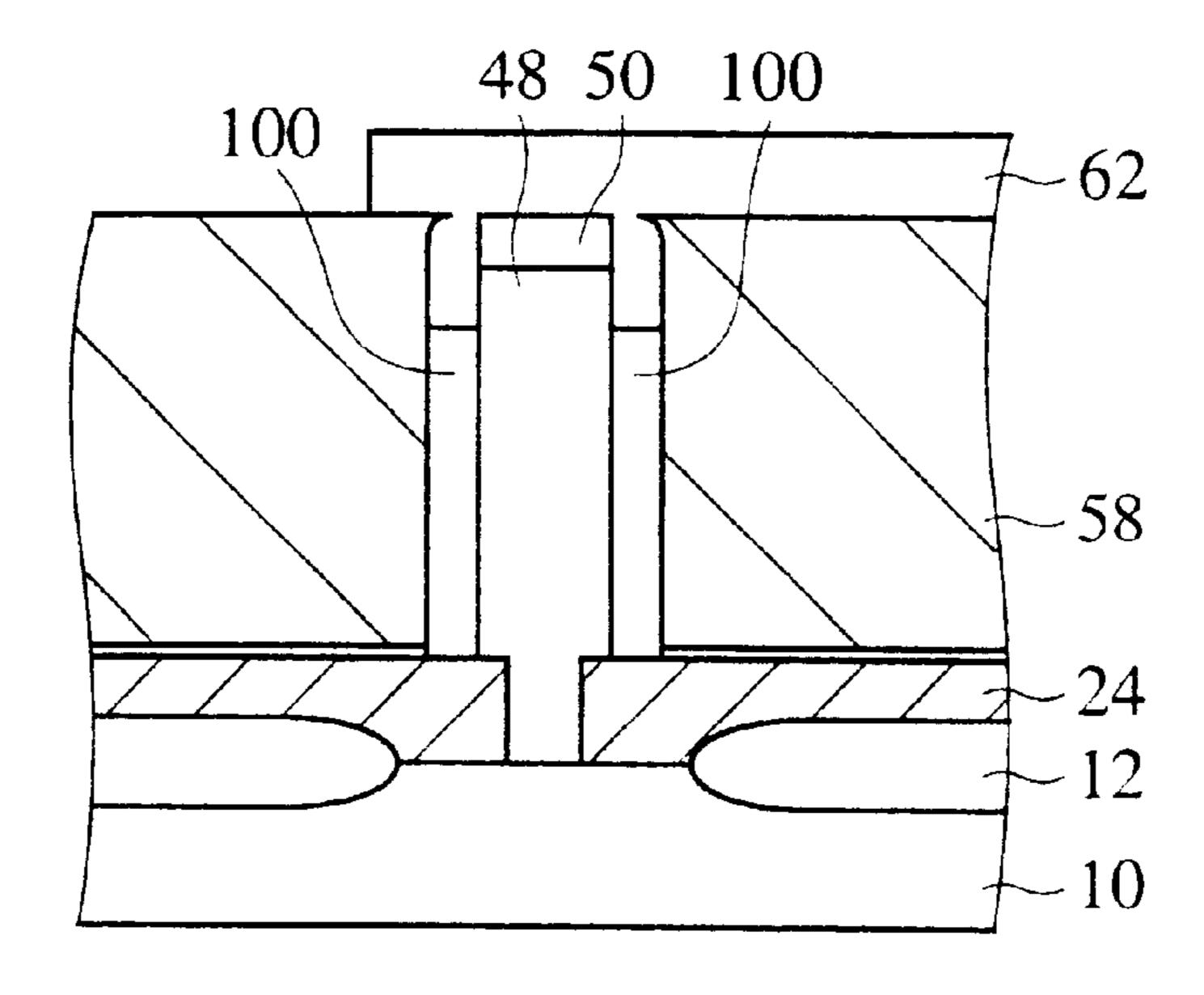

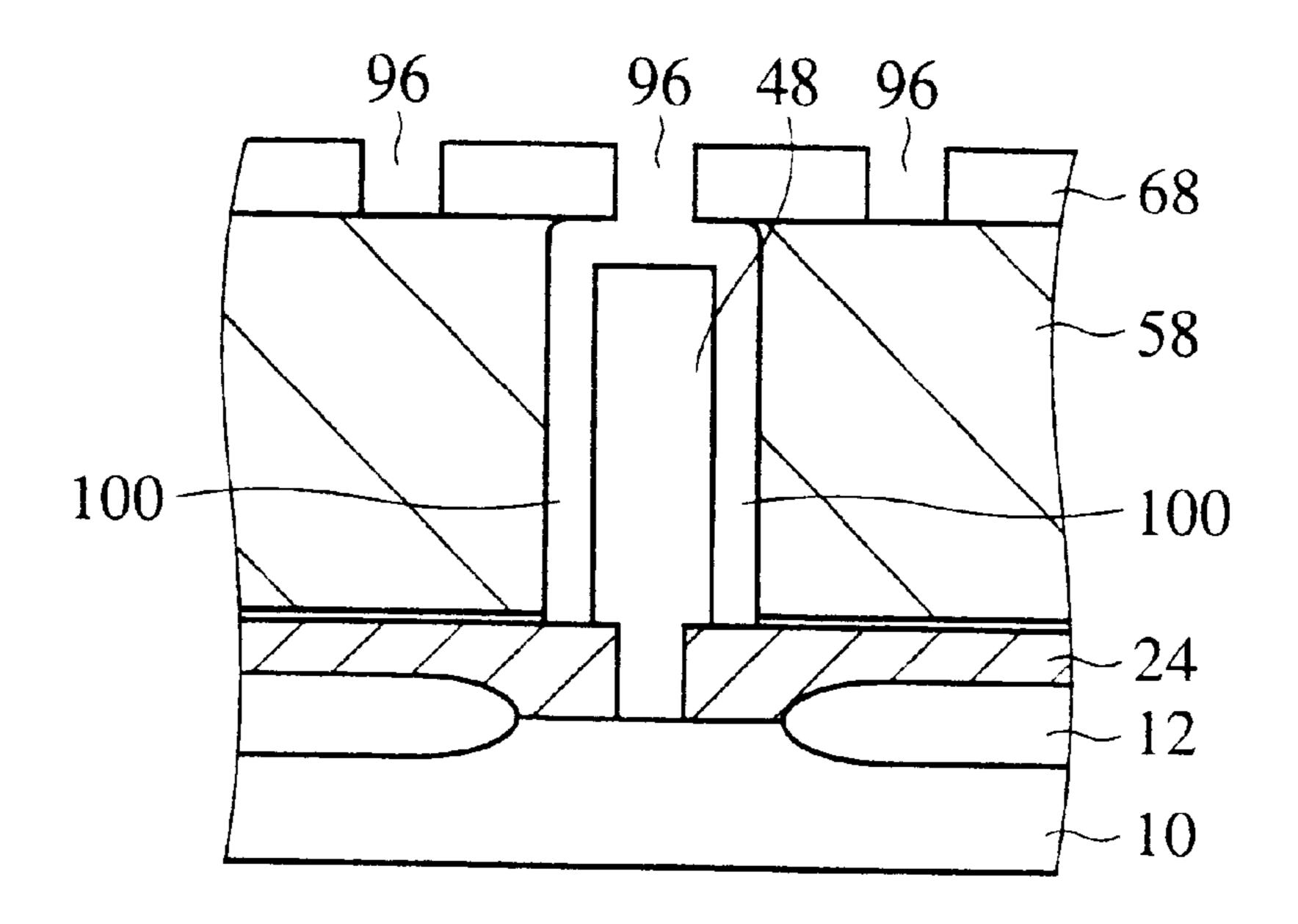

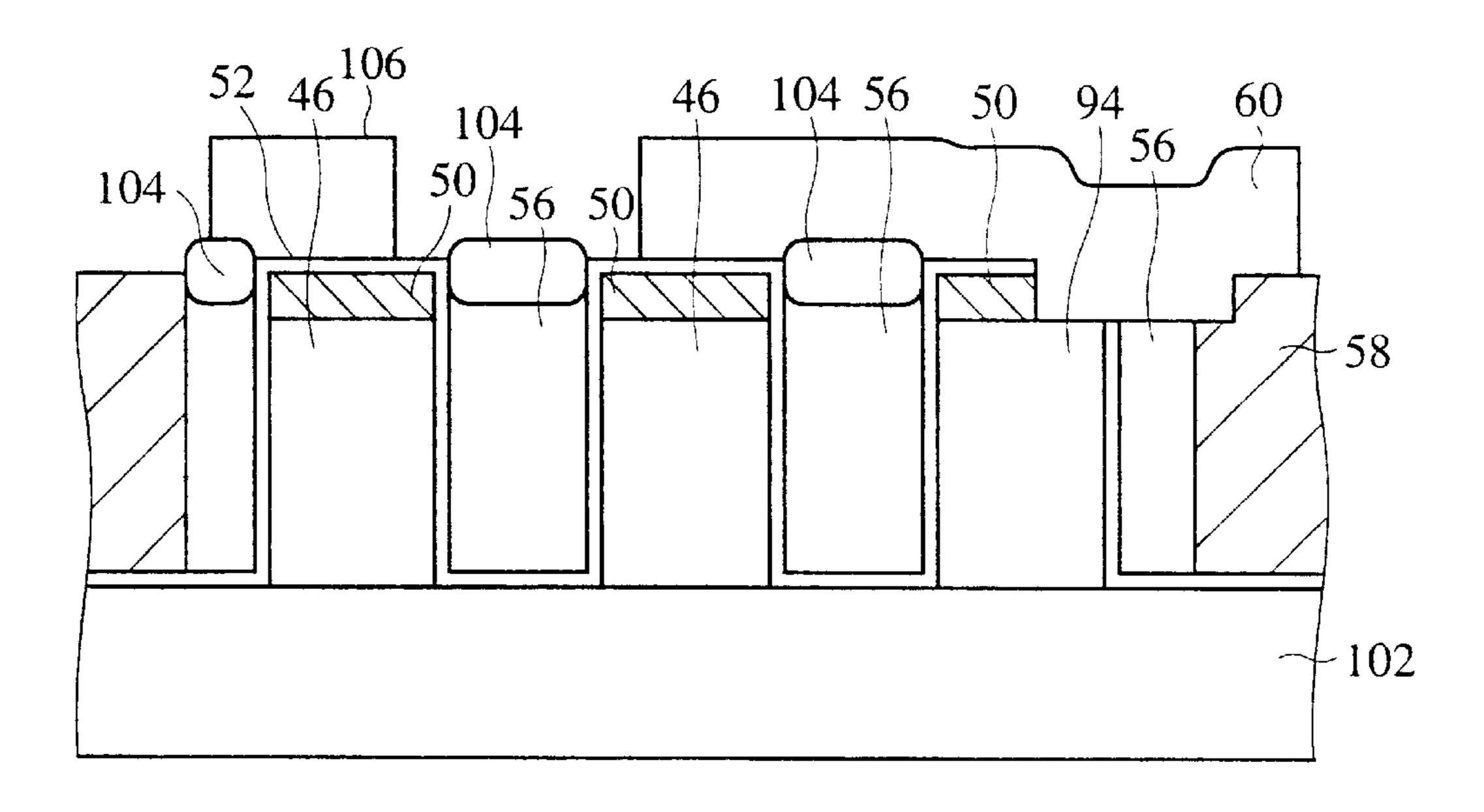

The semiconductor device according to a first embodiment and the method for fabricating the same will be explained with reference to FIGS. 1A–1C, 2A–2E, 3A–3C and 4A–4B.

FIGS. 1A–1C show a plan view and sectional views of the semiconductor device according to the present embodiment, which explain a structure thereof. FIGS. 2A–2E, 3A–3C and 4A–4B are sectional views of the semiconductor device according to the present embodiment at the steps of the method for fabricating the semiconductor device, which explain the method.

First, the structure of the semiconductor memory device according to the present embodiment will be explained with reference to FIGS. 1A–1C. FIG. 1A is an enlarged sectional view of the semiconductor device according to the present embodiment, which shows the structure thereof. FIG. 1B is a sectional view of the semiconductor device according to the present embodiment over a large area. FIG. 1C is a plan 20 view of the semiconductor device according to the present embodiment, which shows the structure thereof.

Source/drain diffused layers 20, 22 are formed independent of each other in set regions on a semiconductor substrate 10 defined by a device isolation film 12. A gate 25 electrode 18 is formed on the semiconductor substrate 10 through a gate oxide film between the source/drain diffused layers 20, 22. Thus a memory cell transistor comprising the gate electrode 18 and the source/drain diffused layers 20, 22 is formed. The gate electrode 18 is arranged in a direction 30 normal to the device region and functions as a word line which functions as the gate electrodes of the memory cell transistors of the rest plural memory cells.

On the semiconductor substrate 10 on which the memory cell transistor is formed on an inter-layer insulation film 24 35 with a plug 32 buried in on the source/drain diffused layer 20 and a plug 34 buried in on the source/drain diffused layer 22.

In the actual device structure, however, the plug 32 and the plug 34 sometimes are not present on one section cleaved 40 in plane, but for the convenience of explanation, in the specification the plugs are shown in one sectional view.

A bit line 38 is formed on the plug 34 and is connected to the source/drain diffused layer 22 through the plug 34. In FIG. 1A only the contact portion of the bit line 38 is shown, 45 but in a prescribed region perpendicular to the sheet is extended in the direction of intersection with the gate electrode (word line) 18.

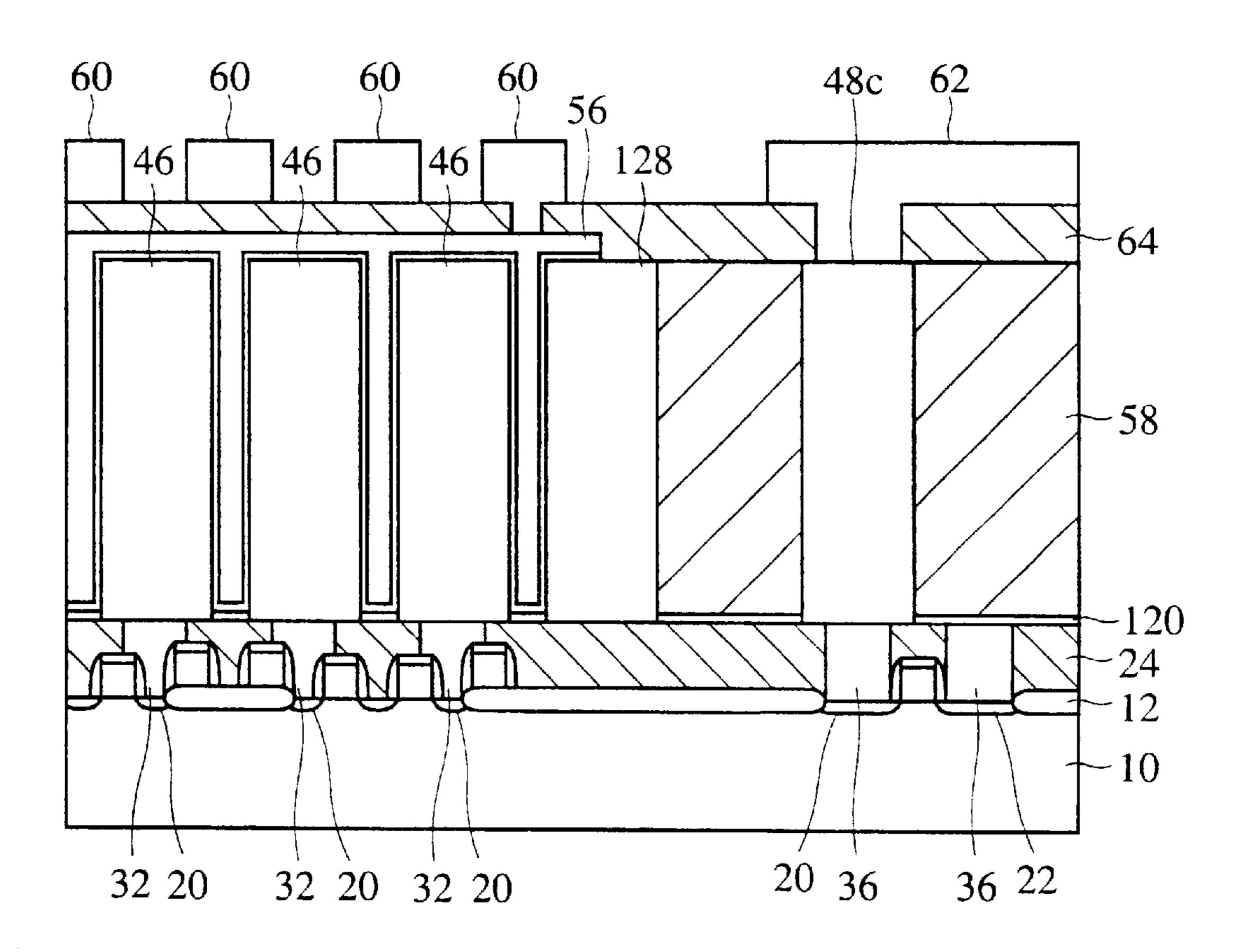

An inter-layer insulation film 40 is formed on the semiconductor substrate 10 with the bit line 38 formed on. On the 50 inter-layer insulation film 40 a pillar-shaped storage electrode 46 which is connected to the plug 32 through the inter-layer insulation film 40 and is protruded onto the inter-layer insulation film 40 is formed. An opposed electrode 56 is formed on the sidewalls of the storage electrode 55 46 through a dielectric film 52. The opposed electrodes 56 bury gaps between adjacent storage electrodes 46. Thus a capacitor comprising the storage electrode 46, the dielectric film 52 and the opposed electrode 56 is formed.

An interconnection 60 connected to the opposed electrode 60 60 is formed on the opposed electrode 56. Thus a DRAM comprising one transistor and one capacitor is formed.

This unit cells are provided adjacent to each other in a memory cell region (FIG. 1B). The opposed electrodes 56 forms a mesh structure enclosing the storage electrodes 46 65 (FIG. 1C). To simplify the drawing, FIG. 1B shows only the structure upper of the storage electrode 46.

14

On the other hand, in a peripheral circuit region adjacent to the memory cell region, a pillar-shaped conductor 48 connected to the semiconductor substrate 10 through the plug 36 is formed on the inter-layer insulation film 40 to function to electrically connect an interconnection 62 formed on the pillar-shaped conductor 48 to the semiconductor substrate 10. The pillar-shaped conductor 48 is formed of the same conductor layer as the storage electrode 46.

Next, the method for fabricating the semiconductor device according to the present embodiment will be explained with reference to FIGS. 2A–2E, 3A–3C and 4A–4B.

First, the device isolation film 12 is formed on the primary surface of the semiconductor substrate 10 by, e.g., the usual LOCOS (LOCal Oxidation of Silicon) method to define the device regions 14, 16. Here the device region 14 indicates the memory cell region where the memory cells are formed, and the device region 16 indicates the peripheral circuit region where a peripheral circuit is formed.

Then, the memory cell transistors are formed in the device region 14 by, e.g., the usual MOS transistor forming method. The gate electrodes 18 of the memory cell transistors function as word lines connected to the gate electrodes of the adjacent memory cell transistors (not shown) (FIG. 2A).

In FIG. 2, no devices, such as transistors, are formed in the device region 16, but the present embodiment is applicable to a case that devices are formed in the device region 16. The device regions 14, 16 may be provided in wells formed in the semiconductor substrate 10, and the source/drain diffused layers 20, 22 do not have essentially the shown LDD structure.

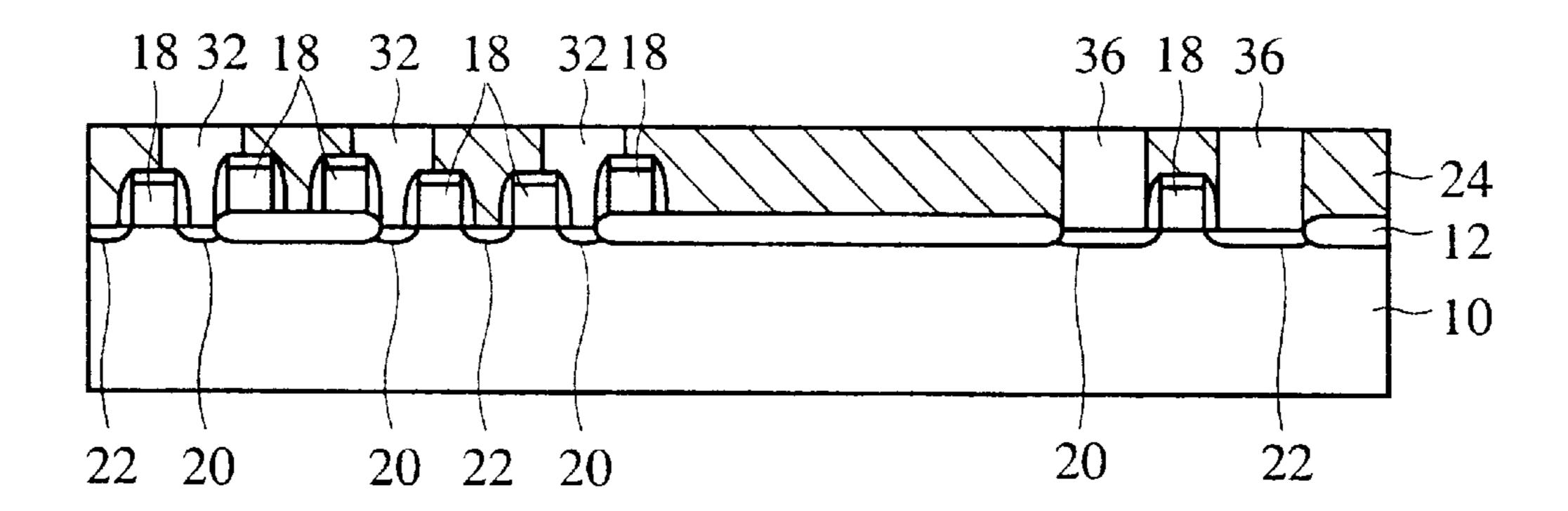

Subsequently, an about 300 nm-thick silicon oxide film is deposited by, e.g., CVD (Chemical Vapor Deposition) method, and the surface of the silicon oxide film is polished by CMP method. Thus the inter-layer insulation film 24 having the surface planarized is formed (FIG. 2B). The inter-layer insulation film 24 may be deposited by other methods. The surface of the inter-layer insulation film 24 may be planarized by the use of SOG film, reflow or other means.

Then, the through-holes 26, 28 opened on the source/drain diffused layers 20, 22, and the through-hole 30 on the device region 16 are formed by the usual lithography and etching (FIG. 2C).

Then, the plugs 32, 34, 36 are buried respectively in the through-holes 26, 28, 30 opened in the inter-layer insulation film 24 (FIG. 2D). For example, polycrystalline silicon film is deposited by CVD method and etched back to leave the polycrystalline silicon only in the through-holes 26, 28, 30, and then the polycrystalline silicon film is doped by ion implantation to lower the resistance. Thus the plugs 32, 34, 36 are formed. The plugs 32, 34, 36 are not essentially formed, and are formed as required by a device structure or processing conditions.

Etching-back is generally a technique for etching the entire surface of a deposited film to planarize the surface of the film or bury a conducting film. In the specification of the present application etching-back is inclusive of even means for removing the entire surface to thereby produce the same effect. That is, the etching-back in the present specification includes the technique for dry-etching the entire surface, the technique for polishing the entire surface by CMP or others, and other techniques.

Then, the bit line 38 connected to the source/drain diffused layer 22 through the plug 34 is formed on the inter-layer insulation film 24 (FIG. 2E). FIG. 2E shows the

contact portion of the bit line 38 connected to the source/drain diffused layer 22, but in a prescribed region perpendicular to the sheet the bit line 38 is extended in the direction of intersection with the word line.

Then, an about 300 nm-thick silicon oxide film is deposited by, e.g., CVD method, and the surface of the silicon oxide film is polished by CMP method. Thus the inter-layer insulation film 40 having the surface planarized is formed (FIG. 3A). The inter-layer insulation film 40 may be deposited by other means. The surface of the inter-layer insulation film 40 may be planarized by SOG film, reflow or other means.

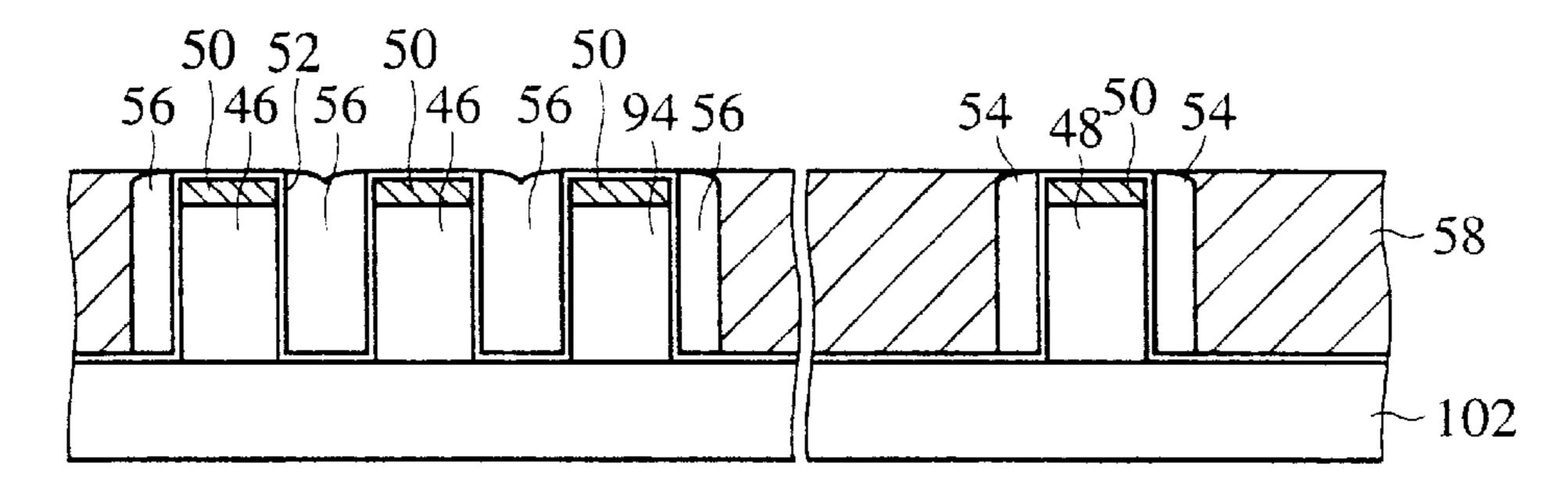

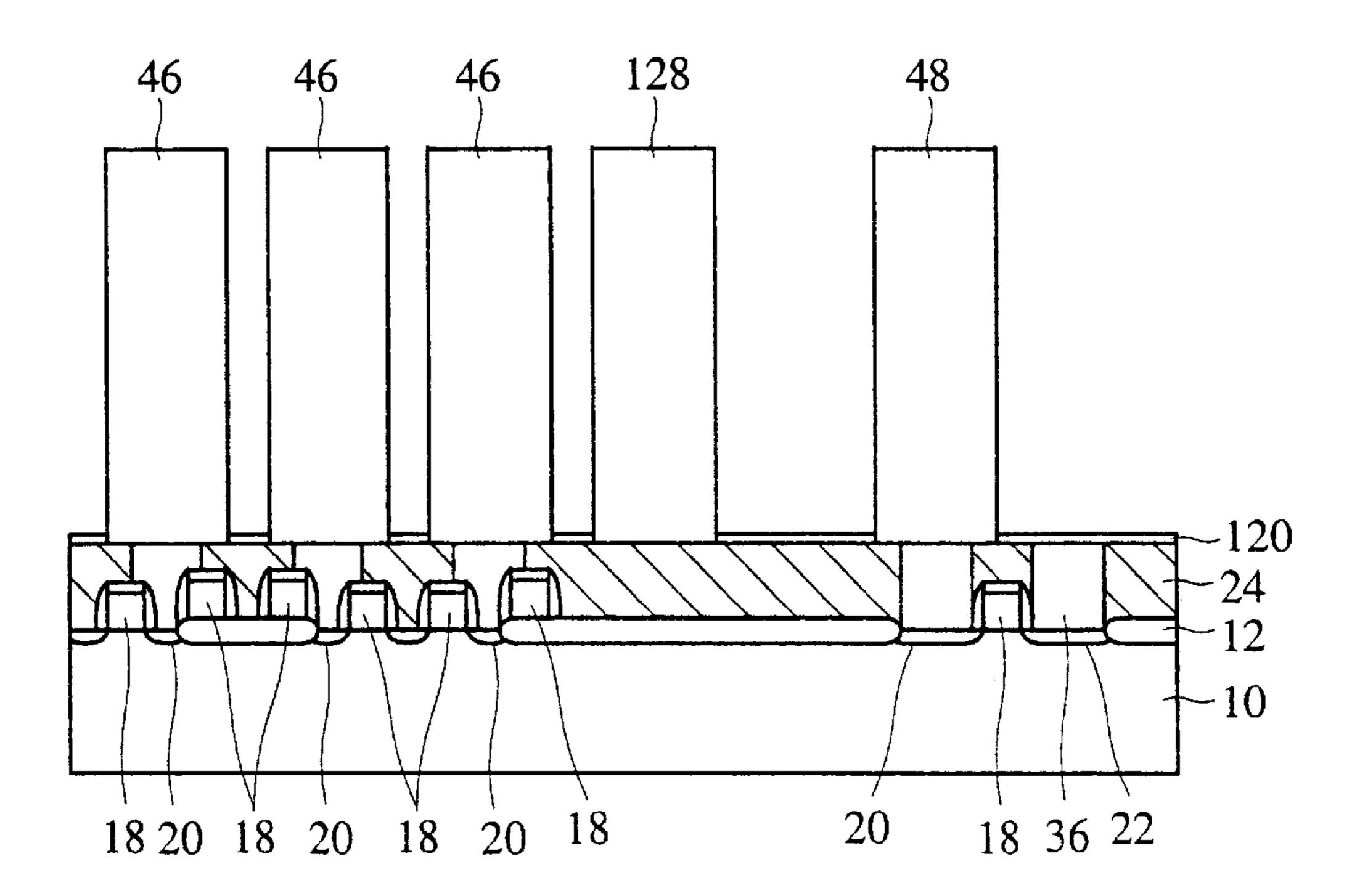

Then, the through-hole 42 opened on the plug 32 and the through-hole 44 opened on the plug 36 are formed by the usual lithography and etching (FIG. 3B).

In the present embodiment, the plugs 32, 36 are in <sup>15</sup> advance buried in the through-holes 26, 30, but the interlayer insulation film 24 may be etched concurrently with opening the through-holes 42, 44. That is, the inter-layer insulation film 40 and the inter-layer insulation film 24 are continuously etched to open the through-hole 42 down to the <sup>20</sup> source/drain diffused layer 20 and the through-hole 44 down to the device region 16.

Then, an about 1.5  $\mu$ m-thick doped polycrystalline silicon film is deposited by, e.g., CVD method. The polycrystalline silicon film is to patterned in a later step to be the storage 25 electrode. It is preferable that an thickness of the polycrystalline silicon film is adjusted suitably corresponding to a required capacitance of the capacitor.

A silicon nitride film is deposited on the polycrystalline silicon film by, e.g., CVD method.

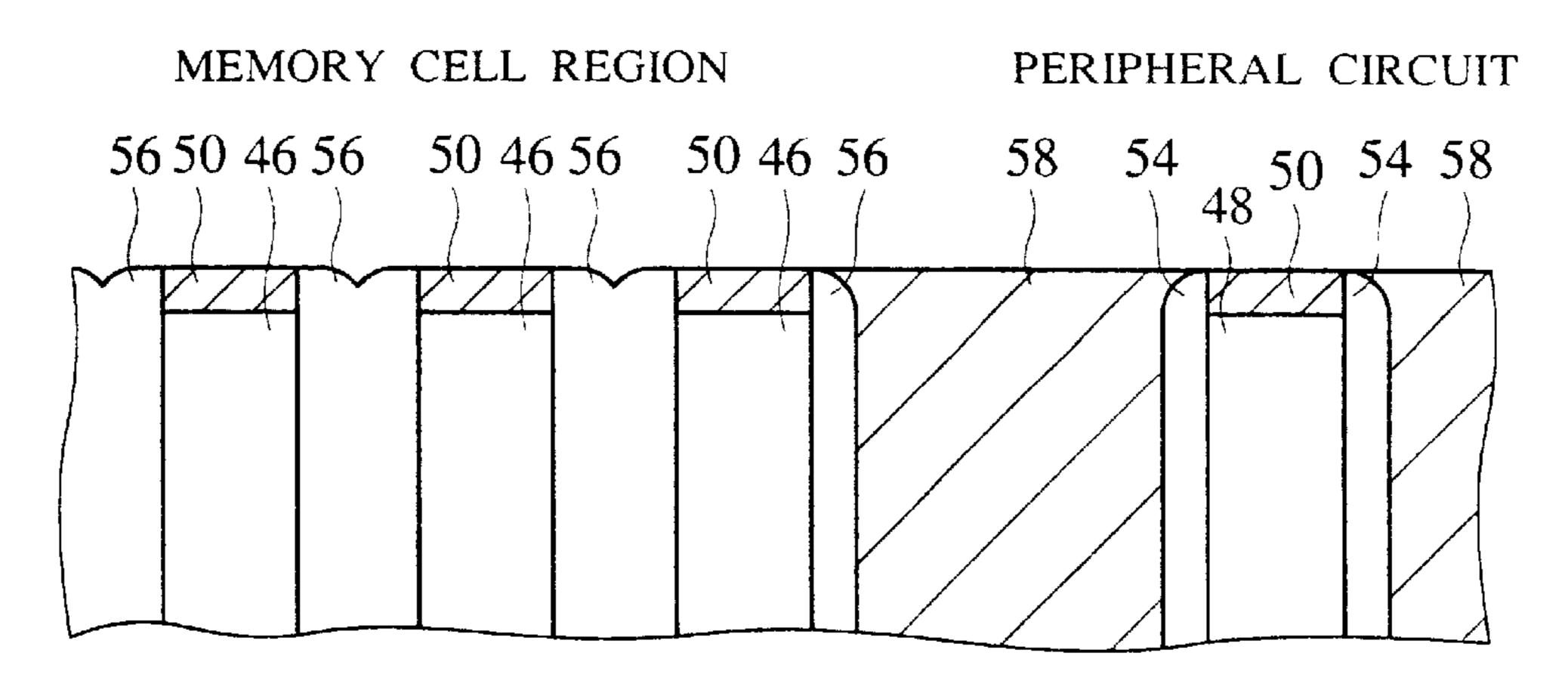

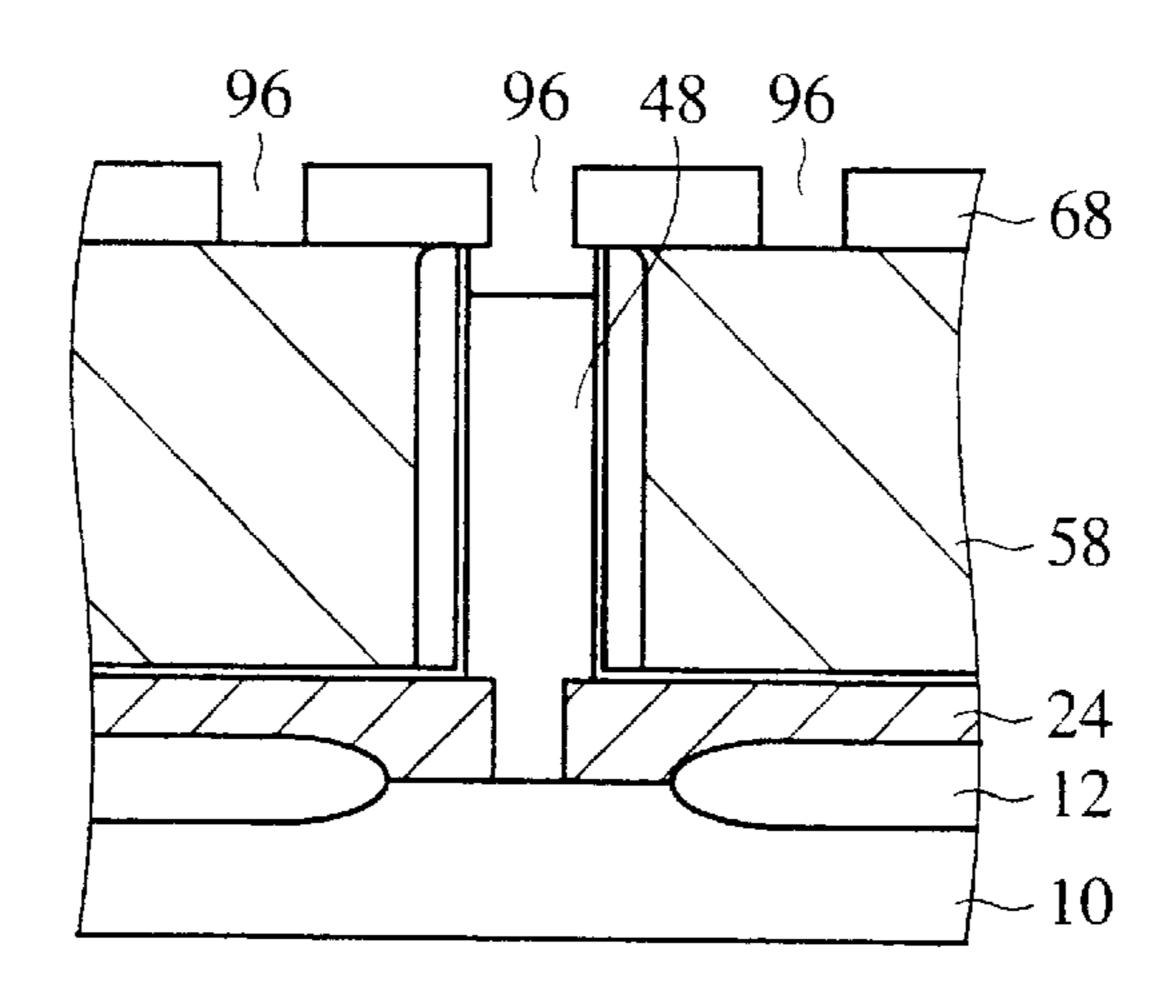

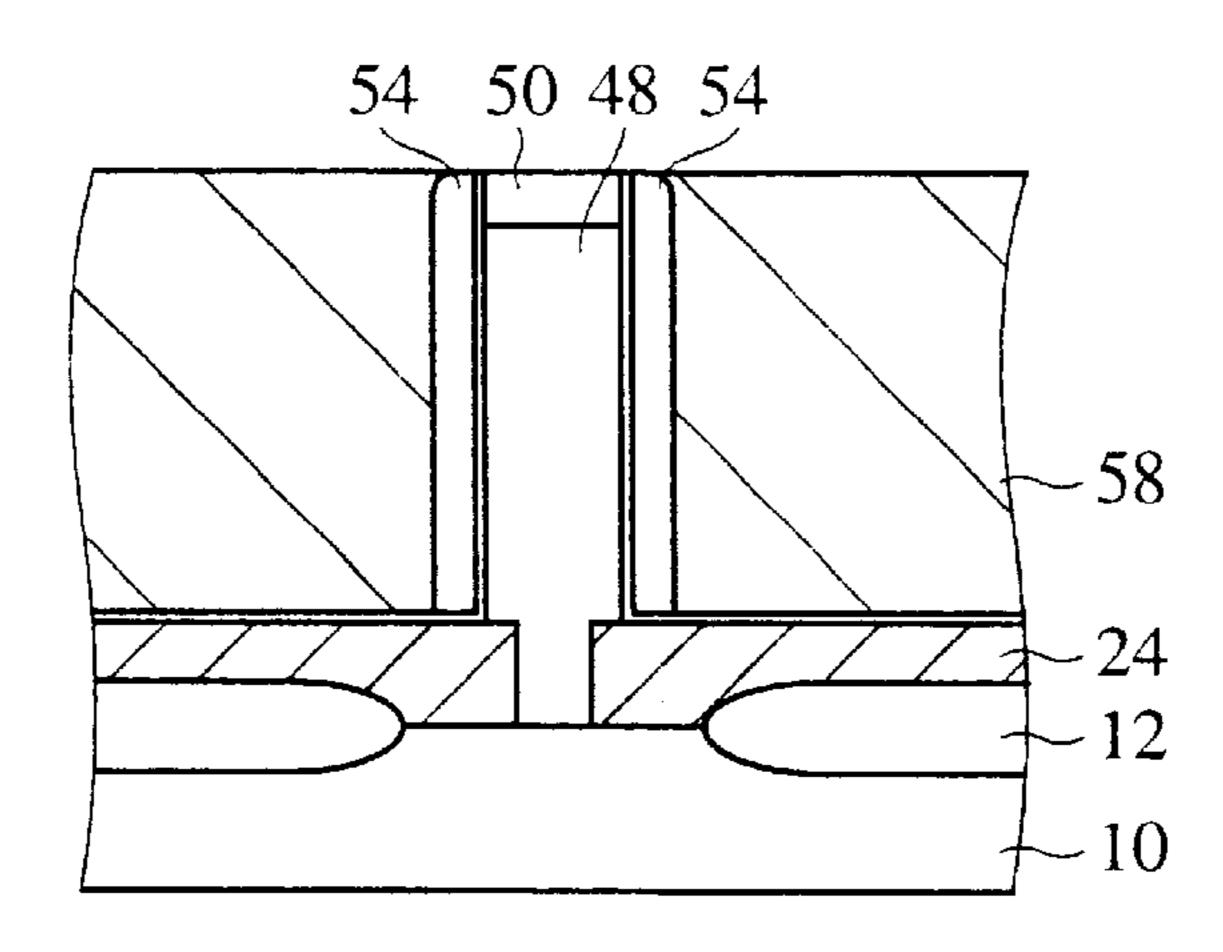

The silicon nitride film and the polycrystalline silicon film are processed in the same pattern by the usual lithography and etching to form the pillar-shaped storage electrode 46 connected to the plug 32 and the pillar-shaped conductor 48 connected to the plug 36. The tops of the thus-formed 35 storage electrode 46 and of the pillar-shaped conductor 48 are covered with a cap film 50 of the silicon nitride film. A gap between the storage electrodes 46 is, e.g.,  $0.15 \mu m$ , and a gap of, e.g., above  $0.3 \mu m$  is ensured between the pillar-shaped conductors 48.

Next, a silicon nitride film is formed by, e.g., CVD method, and the surface of the silicon nitride film is oxidized in a pyrogenic atmosphere to form the dielectric film 52 in, e.g., an about 0.1–4 nm-thick converted to an oxide film. The storage electrodes 46 and the pillar-shaped conductors 48 45 are covered with the dielectric film 52.

In the present embodiment, the dielectric film 52 is the silicon oxynitride film but may be other dielectric films. Especially by using a film having a higher dielectric constant than the silicon oxynitride film, a larger capacitance per a 50 unit area is obtained, which makes it possible to reduce a height of the storage electrode 46. This facilitates patterning of the storage electrode 46. A height of the pillar-shaped conductor 48 is reduced, which can reduce resistance of the interconnection in the peripheral circuit region.

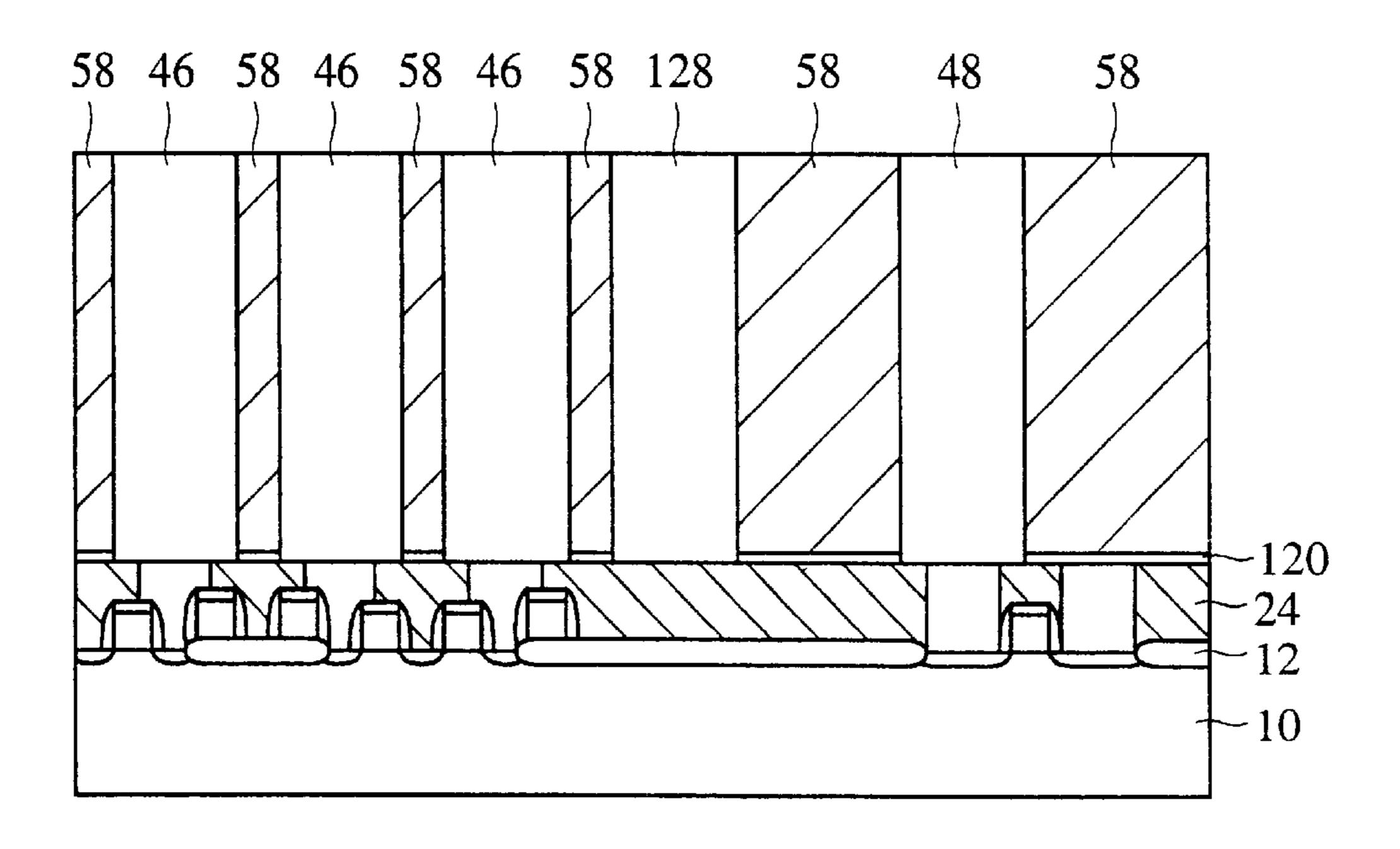

Then, an about 100 nm-thick doped polycrystalline silicon film is deposited by, e.g., CVD method and is anisotropically etched to form the sidewall films 54 of the polycrystalline silicon film on the sidewalls of the storage electrode 46 and the pillar-shaped conductor 48.

In the memory cell region where a gap between the storage electrodes 46 is as small as about  $0.15 \mu m$ , the sidewall films 54 formed between the adjacent storage electrodes 46 are connected to each other, whereby the conductor buried in the storage electrodes 46 in a mesh 65 structure is formed. Thus the opposed electrodes 56 of the mesh structure are formed (see FIG. 1C).

**16**

Thus, the sidewall films 54 are left only on the sidewalls of the structures of the storage electrode 46, the pillar-shaped conductor 48, etc., and accordingly the sidewall films 54 are absent in regions remote from the structures by a distance larger than a width of the sidewall films. Accordingly it is not necessary to separately pattern the opposed electrode 56 after the formation of the sidewall films 54. That is, the opposed electrode 56 can be formed in such a manner as self-alignment with respect to the storage electrode 46 without a lithography step for patterning the opposed electrode 56. No lithography with a large depth of focus for a high aspect ratio is unnecessary.

To thus form the opposed electrode **56** by self-alignment, it is preferable to adjust a gap of the storage electrodes **46** and a film thickness of the polycrystalline silicon film so that the sidewall films **54** are completely buried in the gaps between the adjacent storage electrodes **46**.

On the other hand, in the peripheral circuit region, the pillar-shaped conductors 48 are arranged at a gap larger than a width of the sidewall films 54, so that the sidewall films 54 are formed, surrounding the pillar-shaped conductors 48, but the sidewall films 54 surrounding each pillar-shaped conductor 48 are not connected to the sidewall films (not shown) of its adjacent pillar-shaped conductor 48.

In the present embodiment, the pillar-shaped conductors 48 are arranged, spaced from each other by a prescribed gap because there is a risk that the sidewall films 54 buried between the adjacent pillar-shaped conductors 48 may cause capacitance-coupling between the pillar-shaped conductors 48 through the dielectric films 52 and the sidewall films 54 and cause adverse influences, such as interconnection delay, etc.

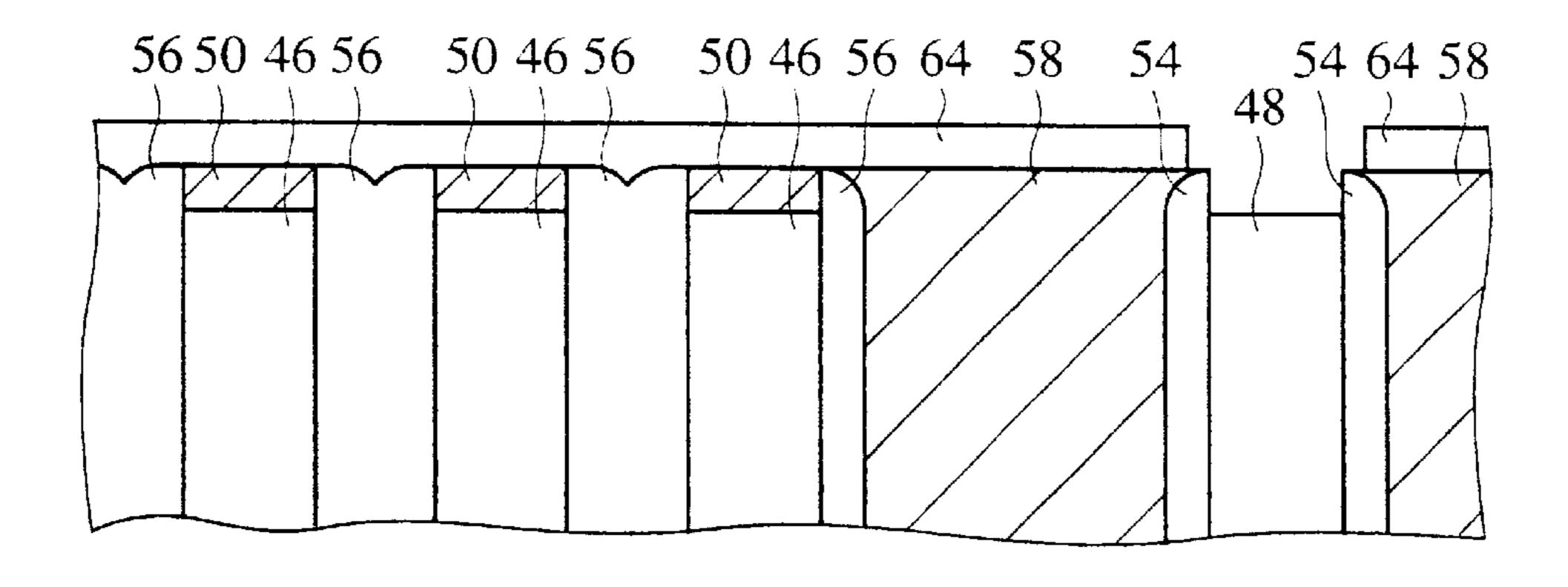

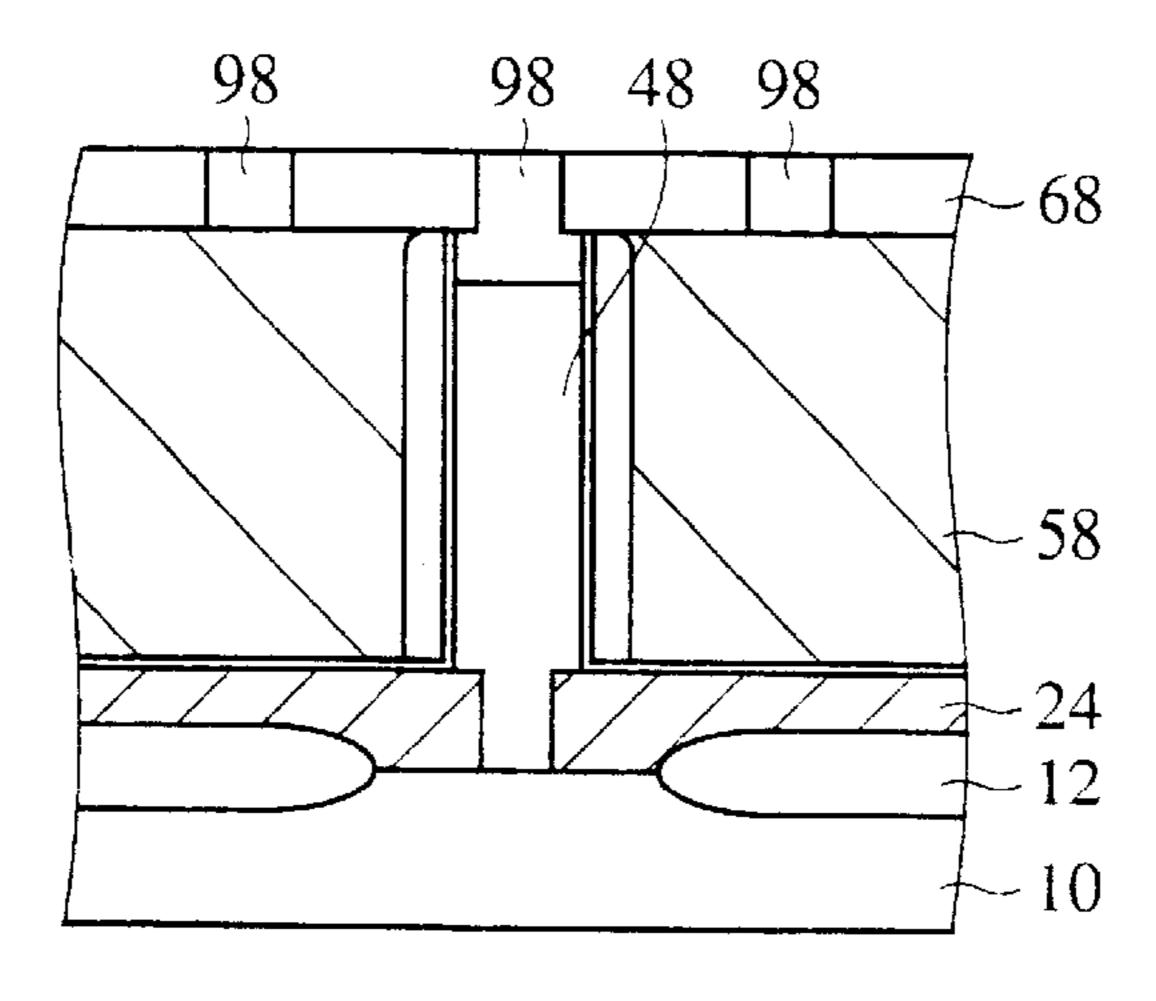

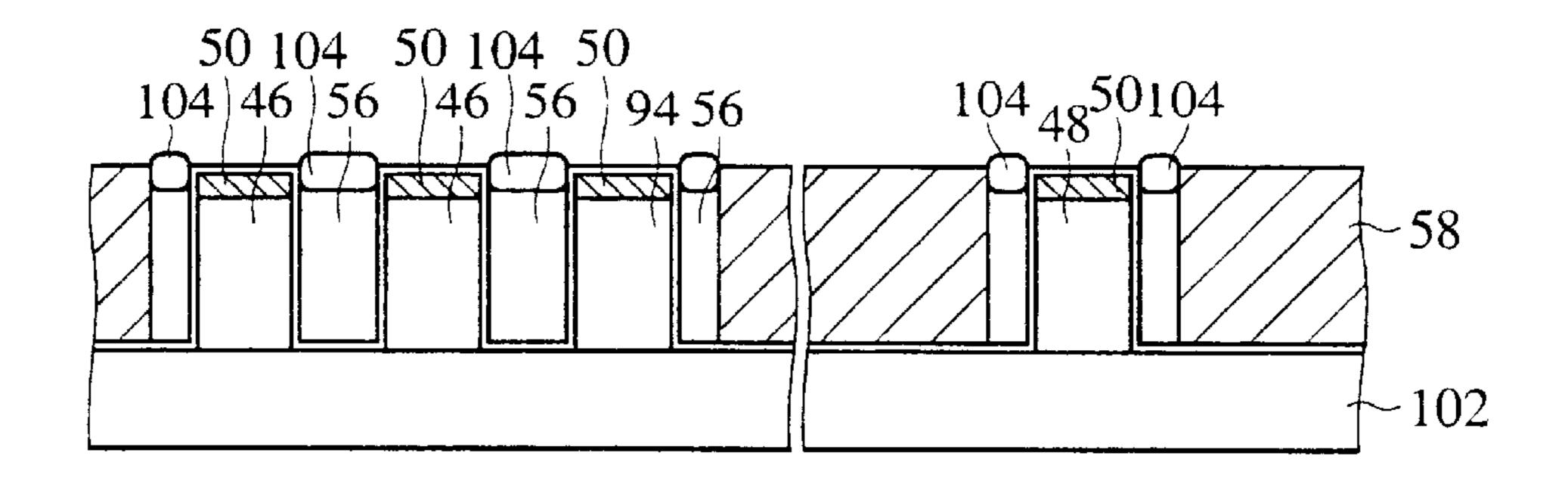

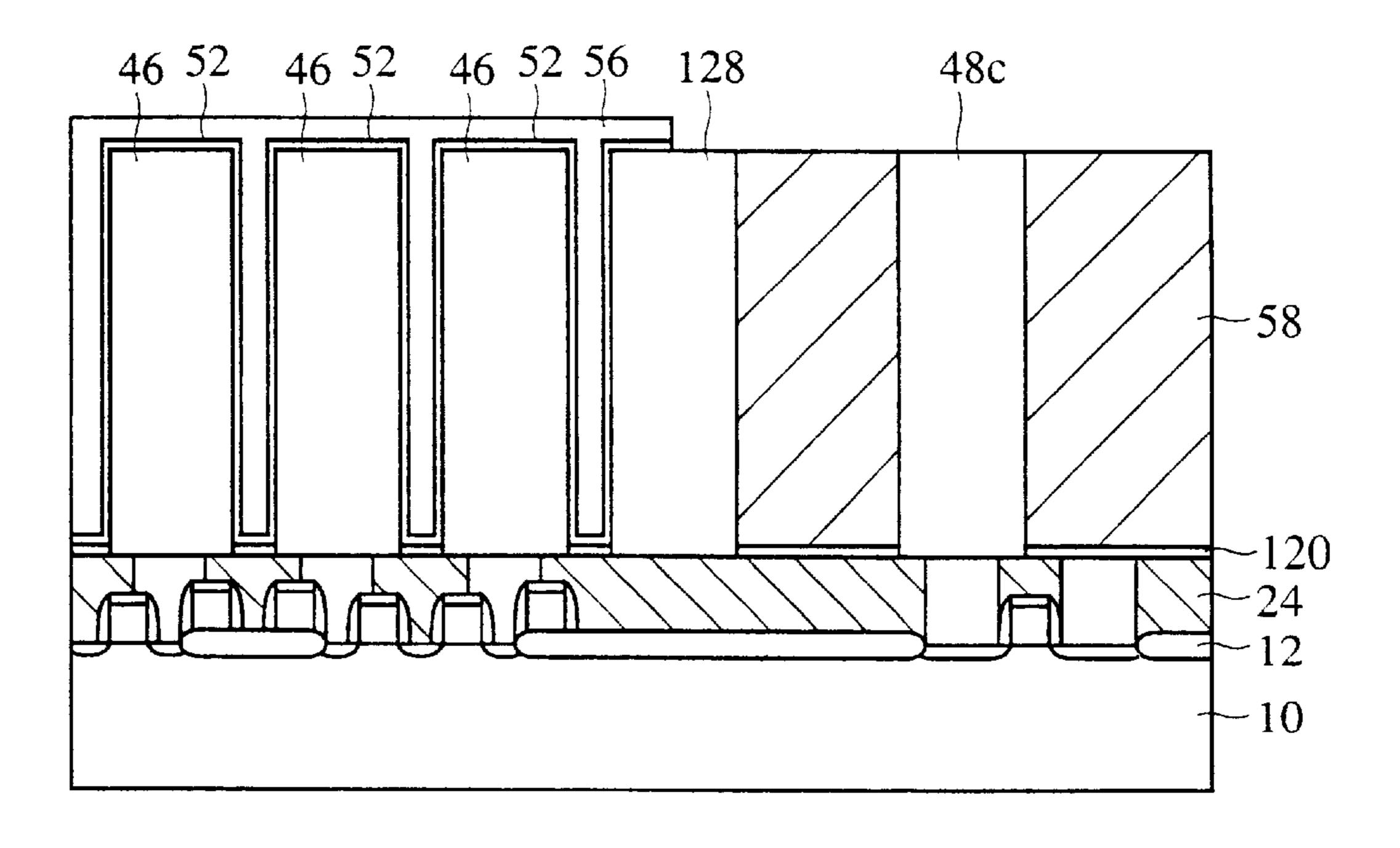

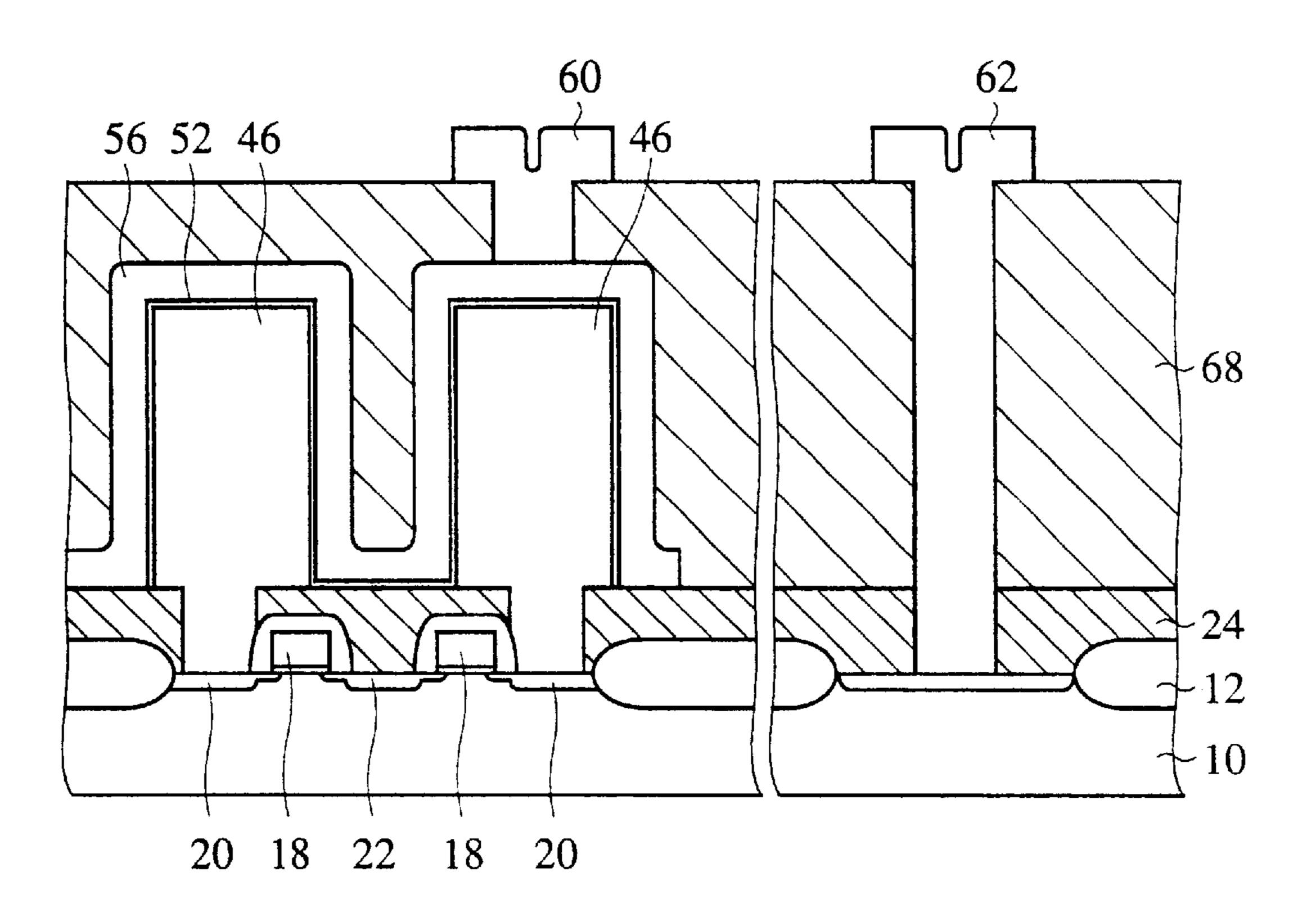

Then an about 0.2 µm-thick silicon oxide film is deposited by, e.g., CVD method, and the surface of the silicon oxide film is polished by CMP method. Thus the inter-layer insulation film 58 having the surface planarized is formed (FIG. 4A). The cap film 50 of the silicon nitride film formed on the storage electrode 46 and the pillar-shaped conductor 48 is used as the etching stopper for the etching to finish the polishing with good controllability.

The cap film 50 on the pillar-shaped conductor 48 is selectively removed by the usual lithography and etching, and the opposed electrode 56 and the pillar-shaped conductor 48 are exposed on the surface of the substrate. The cap film 50 of silicon nitride film is immersed in, e.g., boiled phosphoric acid to be etched.

In etching using phosphoric acid, a resist film used as a mask is sometimes solved together. In such case, thin silicon oxide film is deposited directly below the resist film and is processed in the same pattern as the resist film, whereby the cap film 50 can be etched with the silicon oxide film as a mask.

In the conventional fabrication method for semiconductor devices, the contact hole in the peripheral circuit region is opened in alignment with the planarized surface by the polishing. However, the planarized surface by the polishing makes it difficult to read alignment marks of a ground pattern. Accordingly contact holes cannot be opened with good precision with respect to the ground pattern.

However, in the method for fabricating the semiconductor device according to the present embodiment, a rough alignment of covering the entire memory cell region with a resist is sufficient, which allows the resist to be patterned even on the planarized surface without difficulty.

In the method for fabricating the semiconductor device according to the present embodiment, the cap film 50 is simply etched to thereby open the contact holes by self-

alignment with respect to the ground pattern. In the conventional semiconductor device shown in FIG. 43, it is difficult due to the depth of focus problem that the contact holes in the memory cell region and the contact hole in the peripheral region are concurrently opened. However, the semiconductor device according to the present embodiment has no step between the memory cell region and the peripheral circuit region, and is free from the depth of focus problem. In addition, the contact hole in the peripheral circuit region can be opened without lithography step, and the fabrication process can be much simplified.

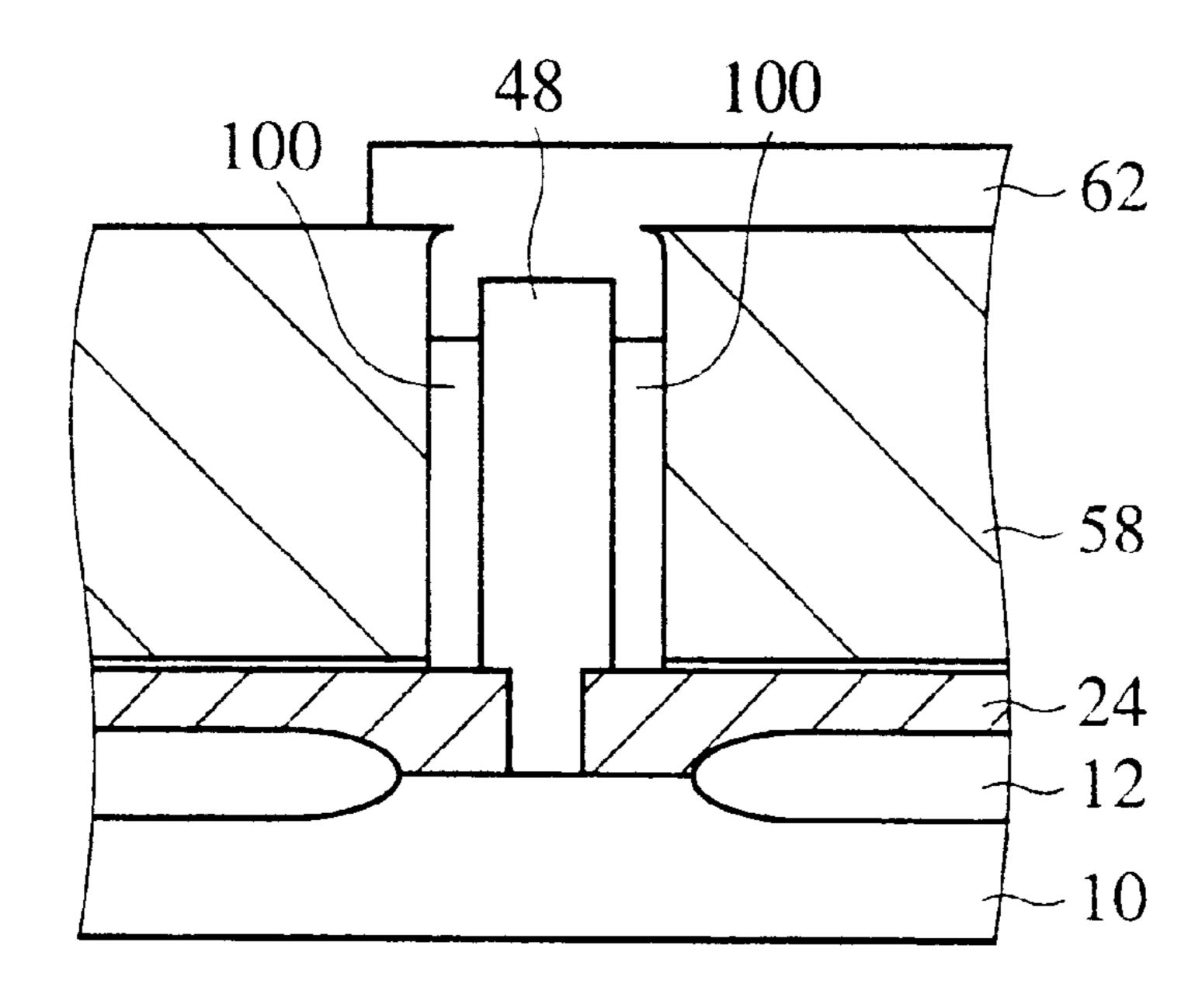

Subsequently, a conducting film of a metal is deposited on the thus-formed base substrate, and the interconnection connected to the opposed electrode 56 and the interconnection 62 connected to the peripheral circuit are formed (FIG. 4B).

Thus a DRAM comprising one transistor and one capacitor can be fabricated.

As described above, according to the present embodiment, the storage electrode 46 and the contact plug (the pillar-shaped conductor 48) connected to the peripheral 20 circuit are formed of one and the same conducting layer by one and the same processing step, whereby the interconnection 60 connected to the memory cell region and the interconnection 62 connected to the peripheral circuit region can be formed without making the contact holes deep, whereby 25 the fabrication process for the semiconductor device can be much simplified.

The opposed electrode **56** is formed by self-alignment with the storage electrode **46**, whereby it is unnecessary to pattern the opposed electrode **56**. Lithography steps, which 30 much affect TAT, can be reduced.

In the present embodiment, the inter-layer insulation film 58 is planarized with the cap film 50 as the etching stopper, and the interconnection 60 is formed on the opposed electrode 56 exposed on the surface, but it is possible that after 35 the inter-layer insulation film 58 is planarized, the inter-layer insulation film 64 of, eg., silicon oxide film, is deposited (FIG. 5A), and the interconnection 60 is connected through an opening formed in the inter-layer insulation film 64 (FIG. 5B).

Owing to this, as etching conditions for opening the opening for connecting the interconnection **60**, conditions which make the silicon oxide film vulnerable and the silicon nitride film invulnerable to the etching are selected, whereby the cap film **50** of the silicon nitride film functions as the 45 etching stopper. Even when the opening in the inter-layer insulation film **64** is rough, the contact for the opposed electrode **54** can be accurately formed. The top of the storage electrode **46** is protected by the cap film **50**, whereby short-circuit between the storage electrode **46** and the inter- 50 connection **60** does not take place.

In the present embodiment, the sidewall film 54 formed on the sidewall of the pillar-shaped conductor 48 remains to the end but may be removed in the fabrication process. For example, after the opposed electrode 56 and the sidewall 55 film 54 are formed, the sidewall film 54 can be removed by isotropical etching, as of wet etching or others, with a memory cell region alone covered with a resist film or others.

Such removal of the sidewall film **54** adds to a number of 60 the fabrication steps, but without the sidewall film **54** on the sidewall of the pillar-shaped conductor **48**, a gap between the pillar-shaped conductors **48** can be the more reduced. This more improves integration around the contact than the semiconductor device shown in FIGS. **1A–1C**.

In the present embodiment, the etching for forming the opposed electrode 56 is anisotropic, but the opposed elec-

18

trode 56 may be formed by isotropic etching, such as wet etching or others.

That is, the polycrystalline silicon film 53 to be the opposed electrode 56 is deposited (FIG. 6A) after the step of FIG. 3B), and a required amount of the polycrystalline silicon film is etched by isotropic etching, such as wet etching or others, whereby the opposed electrodes 56 are left in the mesh structure in the memory cell region, but no sidewall film is formed on the pillar-shaped conductor 48 in the peripheral circuit region (FIG. 6B).

Accordingly, even in a case that a plurality of the pillar-shaped conductors 48 are formed adjacent to each other, the pillar-shaped conductors 48 do not short-circuit with each other through the sidewall films 54. This improves integration around the contact than in the semiconductor device shown in FIGS. 1A–1C.

In the present embodiment, the cap film **50** covering the storage electrode **46** and the pillar-shaped conductor **48** is silicon nitride film, but other insulation films, as of Al<sub>2</sub>O<sub>3</sub>, etc., may be used. The cap film is not essential. Conducting films, such as polycrystalline silicon film, chrome (Cr) film, etc., may be used in place of silicon nitride film. This enables the contact of the peripheral circuit region to be exposed without removing the cap film **50**.

In this case, the cap film 50 connected to the storage electrode 46, and the opposed electrode 56 are exposed on the memory cell region, which makes it difficult to form the interconnection 60 connected to the opposed electrode 56, electrically isolated from the storage electrode 46. However, by the use of the method for fabricating the semiconductor device according to, e.g., a ninth embodiment of the present invention which will be described later, the interconnection 60 can be connected to the opposed electrode 56.

In the present embodiment, the storage electrode 46, the pillar-shaped conductor 48, the sidewall films 54 and the opposed electrode 56 are formed of doped polycrystalline silicon film but may be formed of other materials, e.g., metal materials, such as amorphous silicon, tungsten (W), titanium (Ti), aluminum (Al), ruthenium (Ru), palladium (Pd), cobalt 40 (Co), copper (Cu), silver (Ag), chrome (Cr), platinum (Pt), nickel (Ni), molybdenum (Mo) and iridium (Ir); metal nitrides, such as WN, TiN, etc., metal oxides, such as RuO<sub>2</sub>, etc.; metal silicides, such as Wsi, CoSi, TiSi, etc.; composite metal materials, such as W/TiN/Ti, Ru/TiN/Ti, etc. Preferably these materials are selected in consideration of their compatibility with an insulation material used as the dielectric film **52** and their resistance values. It is also preferable that these materials are selected in consideration of a heat treatment amount required by the process.

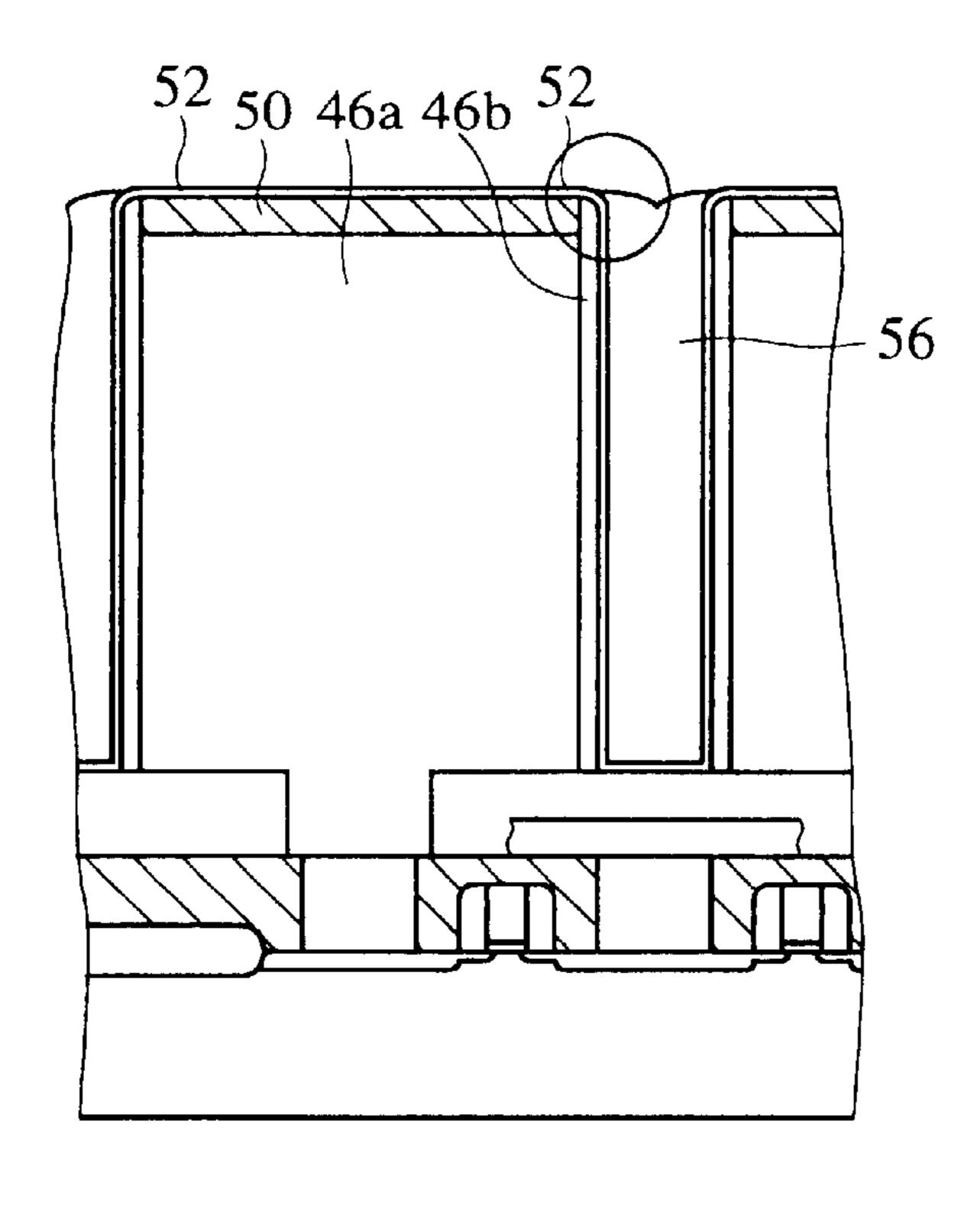

### [A Second Embodiment]

The semiconductor device according to a second embodiment of the present invention and a method for fabricating the semiconductor device will be explained with reference to FIGS. 7, 8A–8B and 9. The same members of the semiconductor device according to the present embodiment as those of the semiconductor device according to the first embodiment are represented by the same reference numerals not to repeat or simplify their explanation.

FIG. 7 is a diagrammatic sectional view of the semiconductor device according to the present embodiment, which shows a structure thereof. FIGS. 8A–8B and 9 are sectional views of the semiconductor device according to the present embodiment in the steps of the method for fabricating the same, which explain the method.

In the semiconductor device according to the first embodiment the pillar-shaped conductor 48 is formed of polycrystalline silicon film. However, because polycrystalline silicon

film has a resistance value about two orders larger than metal materials, it is preferable to operate the peripheral circuit at high speed that polycrystalline silicon film is replaced by a low resistance material, e.g., tungsten film. In this case, because the pillar-shaped conductor 48 is formed of the same material as the storage electrode 46, when the material of the pillar-shaped conductor is replaced by tungsten film, the storage electrode 46 is formed of the pillar-shaped conductor 48 as well is formed of the tungsten film.

However, silicon oxynitride film widely used as the dielectric film **52** has poor compatibility with certain materials, such as tungsten film, etc., and a film of good quality cannot be sometimes formed on the surface of tungsten film depending on film forming conditions and conditions, such as processing temperatures, etc. Other materials having high dielectric constant, e.g., Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, (Ba<sub>x</sub>Sr<sub>1-x</sub>)TiO<sub>3</sub>, PZT, etc. have compatibility with electrode materials, and it is necessary to select an electrode material corresponding to a dielectric film.

In place of forming the dielectric film on the surface of the storage electrode, the dielectric film may be formed by 20 oxidizing or nitridizing the storage electrode itself. For example, the surface of the storage electrode formed of tantalum (Ta) is oxidized to form Ta<sub>2</sub>O<sub>5</sub> film.

The present embodiment shows the semiconductor device and the method for fabricating the same can make the 25 contact plug for the peripheral circuit less resistance, and form an electrode having good compatibility with a dielectric film of a capacitor.

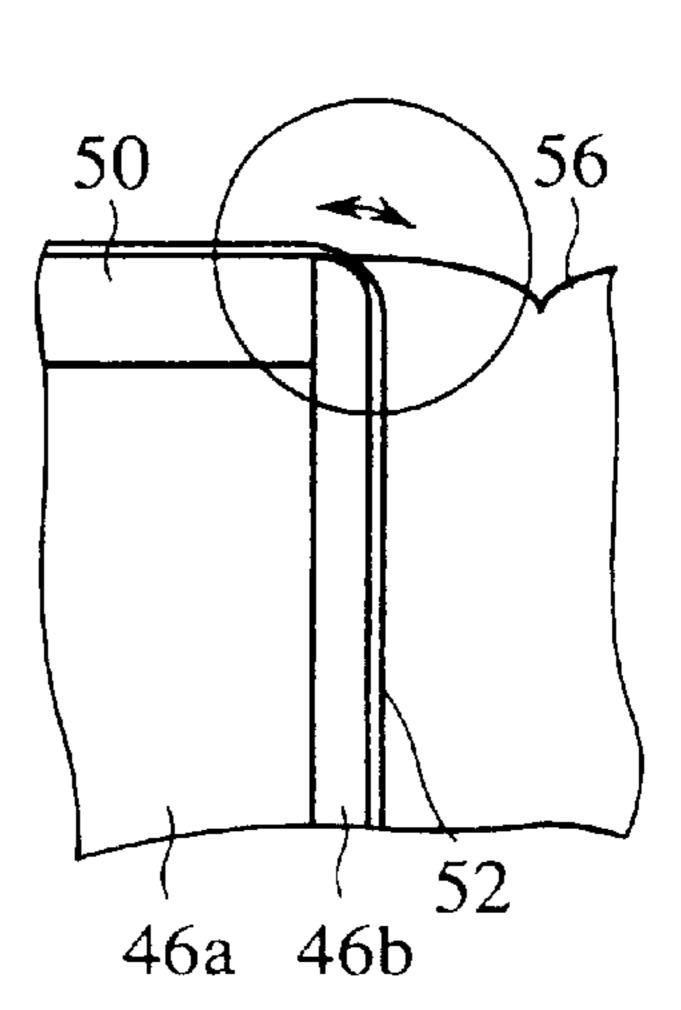

The semiconductor device according to the present embodiment is characterized in that a storage electrode 46 30 comprises a pillar-shaped conductor 46a of tungsten film, and a conducting film 46b formed on the sidewall of the pillar-shaped conductor 46a and having good compatibility with the dielectric film 52, and a pillar-shaped conductor 48 comprises a pillar-shaped conductor 48a of tungsten film 35 and a conductor film 48b formed on the sidewall of the pillar-shaped conductor 48a.

This structure of the semiconductor device can make the contact plug for the peripheral circuit less resistance and can form the capacitor without degrading characteristics of the 40 dielectric film 52.

Then, the method for fabricating the semiconductor device according to the present embodiment will be explained with reference to FIGS. 8A-8B and 9.

First, the pillar-shaped conductor 46a connected to the plug 32 and the pillar-shaped conductor 48a connected to the plug 36 are formed in the same way as in, e.g., the method for fabricating the semiconductor device according to the first embodiment shown in FIGS. 2A to 3C. In the present embodiment, tungsten film is used in place of polycrystal-so line silicon film to form the pillar-shaped conductors 46a, 48a of tungsten (FIG. 8A). The pillar-shaped conductor 46a corresponds to the storage electrode 46 of the first embodiment.

Then, polycrystalline silicon film is selectively grown by CVD method on regions of the sidewalls of the pillar-shaped conductors **46***a*, **48***a* where the tungsten is exposed. The technique for selectively growing polycrystalline silicon film on tungsten is already established, and polycrystalline silicon film can be easily selectively grown under the conventionally known growth conditions. Thus, the conducting films **46***b*, **48***b* covering the sidewalls of the pillar-shaped conductors **46***a*, **48***a* are formed (FIG. **8B**). The pillar-shaped conductor **46***a* and the conducting film **46***b* form the conduction film.

In the present **46***a*, **48***a* are formed of the pillar-shaped conductor **48***a* and the conducting film **48***b* constitute the pillar-shaped conductor **48***a* and the conducting film **48***b* constitute the pillar-shaped conductor **48***a* and the conducting film **48***b* constitute the pillar-shaped conductor **48***a* and the conducting film **48***b* constitute the other low-resist of the pillar-shaped conductor **48***a* are formed of the pillar-shaped film.

20

In the present embodiment, the conducting films 46b, 48b are formed only on the sidewalls of the pillar-shaped conductors 46a, 48a and is not formed on the sidewall of the cap film 50. This is because the dielectric film 52 is sometimes abraded on the corners by the etching in burying the opposed electrode 56, and in a case that the conducting films 46b, 48b are provided even on the sidewall of the cap film 50, there is a risk that leak current may flow between the opposed electrode 56 and the conducting film 46b (see FIG. 9).

Accordingly, in a case that the etching for burying the opposed electrode **56** is conducted with a selective ratio sufficient not to abrade the dielectric film **52**, the conducting films **46***a*. **48***b* may be extended onto the sidewall of cap film **50**.

Even when the dielectric film 52 is abraded, the surface is a little oxidized to decrease leak current.

Then, the dielectric film 52 and the opposed electrode 56, etc. are formed in the same way as in, e.g., the method for fabricating the semiconductor device according to the first embodiment shown in FIGS. 3C to 4B, whereby a DRAM can be fabricated, making the contact plug for the peripheral circuit less resistance.

As described above, according to the present embodiment, the contact plug for the peripheral circuit is provided by the pillar-shaped conductor 48a having low resistance value, and the surface of the pillar-shaped conductor 46a is covered with the conducting film 46b having good compatibility with the dielectric film 52, whereby the dielectric film 52 of the capacitor can be formed stable.

In the present embodiment, the selective growth of the polycrystalline silicon film on tungsten is used to form the conducting films 46b, 48b but can be formed by the following method.

First, polycrystalline silicon film is deposited by, e.g., CVD method and is heat-treated at about 800–850° C. This heat-treatment causes silicidation reaction in a region where the polycrystalline silicon film and the pillar-shaped conductors 46a, 48a contact each other, and the conducting films 46b, 48b of tungsten silicide film are formed.

Subsequently the polycrystalline silicon film which has not contributed to the silicidation reaction is selectively removed. Thus, the conducting films 46b, 48b are formed selectively only on the sidewalls of the pillar-shaped conductors 46a, 48a.

The polycrystalline silicon film which has not reacted is etched off, or the polycrystalline silicon film alone is selectively replaced by the oxide film by the use of a difference in oxidation rate between the tungsten silicide film and the polycrystalline silicon film.

Thus, the conducting films 46b, 48b can be selectively left only on the sidewalls of the pillar-shaped conductors 46a, 48a.

It is also possible that as shown in FIG. 8A, the pillar-shaped conductors 46a, 48a are formed and are subjected to heat-treatment of, e.g., 600–850° C. in a nitrogen atmosphere or an ammonium atmosphere to nitridize the surfaces of the pillar-shaped conductors 46a, 48a into thin tungsten nitride (WN) films. The tungsten nitride film is selectively formed only on the sidewalls of the tungsten film and, in addition, has conductivity, and can be used as the conducting films 46b, 48b.

It is possible that the pillar-shaped conductors 46a, 48a are formed of titanium and have the surfaces nitridized to form the conductor films 46b, 48b of titanium nitride (TiN) film.

In the present embodiment, the pillar-shaped conductors **46***a*, **48***a* are formed of tungsten film but may be formed of other low-resistance materials.

The conductor films 46b, 48b covering the sidewalls of the pillar-shaped conductors 46a, 48b can be formed of any material that functions as the electrodes of a required dielectric film. For example, doped polycrystalline silicon film, metal silicide films, such as tungsten silicide film, 5 titanium silicide film, metal nitride films, such as TiN film, WN film, etc., may be used.

[A Third Embodiment]