US006462285B2

# (12) United States Patent

Enroth et al.

# (10) Patent No.: US 6,462,285 B2

(45) **Date of Patent:** Oct. 8, 2002

# (54) WAVE SOLDER APPLICATION FOR BALL GRID ARRAY MODULES WITH PLUGGED VIAS

(75) Inventors: Wesley M. Enroth, Mooresville, NC (US); George D. Oxx, Jr., Concord, NC (US); Jenny B. Porter, Charlotte,

NC (US)

(73) Assignee: International Business Machines Corporation, Armonk, NY (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: **09/827,111**

(22) Filed: Apr. 5, 2001

(65) Prior Publication Data

US 2001/0011608 A1 Aug. 9, 2001

#### Related U.S. Application Data

| (63) | Continuation of application No. 09/211,976, filed on Dec. |

|------|-----------------------------------------------------------|

|      | 15, 1998, now Pat. No. 6,248,961.                         |

- (51) Int. Cl.<sup>7</sup> ...... H01R 9/09; H01R 1/16

# (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,628,409 A | * 12/1986 | Thompson et al 361/760 |

|-------------|-----------|------------------------|

| 4,700,473 A | * 10/1987 | Freyman et al 29/846   |

| 4,739,919 A | 4/1988    | Van Den Brekel et al.  |

| 5,326,937 A | 7/1994    | Watanabe               |

| 5,402,314 | A          |   | 3/1995  | Amago et al.           |

|-----------|------------|---|---------|------------------------|

| 5,434,365 | A          |   | 7/1995  | Mori et al.            |

| 5,511,306 | A          |   | 4/1996  | Denton et al.          |

| 5,656,798 | A          | * | 8/1997  | Kubo et al             |

| 5,796,163 | A          | * | 8/1998  | Glenn et al 257/698    |

| 5,834,705 | A          | * | 11/1998 | Jonaidi                |

| 5,883,335 | A          | * | 3/1999  | Mizumoto et al 174/266 |

| 5,973,396 | A          | * | 10/1999 | Farnworth              |

| 6,087,597 | A          | * | 7/2000  | Shimada et al 174/263  |

| 6.199.273 | <b>B</b> 1 | * | 3/2001  | Kubo et al 29/843      |

<sup>\*</sup> cited by examiner

Primary Examiner—Kammand Cuneo (74) Attorney, Agent, or Firm—Schmeiser, Olsen & Watts; Lawrence R. Fraley

## (57) ABSTRACT

A method and product for fabricating a printed circuit board assembly comprising a via, wherein the method inhibits the flow of molten solder into the via during a wave soldering step, thereby preventing heat transfer that might otherwise degrade a solder joint at a top pad that is thermally coupled to the via. The method comprises the steps of: (1) fastening a bottom component to the bottom surface of the circuit board by a screening and reflow of solder paste that also generates a solder plug in the via; (2) fastening top components to the top surface of the circuit board by a screening and reflow of solder paste, wherein the top components comprise ball grid arrays and other surface mount devices that are to be affixed to pads which are connected to vias; and (3) wave soldering the bottom surface to affix additional components onto the circuit board, such as pin-in-hole components placed on the top surface. The solder plug formed in the via during the first step prevents molten solder from flowing into the via during the subsequent wave soldering step, thereby inhibiting heat transfer from the molten solder to the solder joint at the top pad.

#### 11 Claims, 9 Drawing Sheets

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 7

# WAVE SOLDER APPLICATION FOR BALL GRID ARRAY MODULES WITH PLUGGED **VIAS**

This application is a continuation of Ser. No. 09/211,976 filed on Dec. 15, 1988 now U.S. Pat. No. 6,248,961.

#### BACKGROUND OF THE INVENTION

#### 1. Technical Field

The present invention relates to a printed circuit board and more particularly to a technique and product for fabricating a printed circuit board so as to prevent the flow of molten solder into a via during the process of wave soldering the bottom surface of the circuit board.

The following paragraph replaces the paragraph beginning on page 1, line 19:

After BGA modules are installed on the top surface of a circuit board, pin-in-hole components such as connectors, single in-line packages (SIPS), and dual in-line packages 20 (DIPS) are placed on the top surface of the circuit board and are affixed by wave soldering the bottom surface of the circuit board. During the wave soldering of the bottom surface, the circuit board is transported over a molten bath of solder, wherein upward movement of solder through a 25 chimney causes a fountain of solder to be drawn into pin holes so as to encase leads of pin-in-hole components. Unfortunately, the molten solder also travels up the vias. The hot solder within a via transfers substantial heat to its associated top pad because of a large thermal conductance 30 between the via and the pad. Accordingly, the solder joint at the top pad is susceptible to reflow (liquidization and redistribution) from the applied heat, which may cause an open circuit. Alternatively, the heat and consequent reflow the solder joint susceptible to fracture from stress during subsequent usage of the circuit board.

## 2. Related Art

A printed circuit board typically accommodates a surface mount device such as a ball grid array (BGA) module. A 40 BGA module comprises an array of solder balls located on the underside of the BGA module. The top surface of a printed circuit board contains a landing area comprising a corresponding array of top pads. When a BGA module is installed on the landing area of the top surface, each solder 45 ball rests on a top pad and is affixed to the top pad by means of a solder joint. Each such top pad is electrically connected to a via. The via is a cylindrical hole extending through the thickness of the circuit board and is lined with a material, such as copper, that acts as both an electrical and a thermal 50 conductor. The via provides a path of electrical conduction between the BGA module and electrical circuit patterns located within internal layers of the circuit board.

After BGA modules are installed on the top surface of a circuit board, pin-in-hole components such as connectors, 55 SIPS, and DIPS are placed on the top surface of the circuit board and are affixed by wave soldering the bottom surface of the circuit board. During the wave soldering of the bottom surface, the circuit board is transported over a molten bath of solder, wherein upward movement of solder through a 60 chimney causes a fountain of solder to be drawn into pin holes so as to encase leads of pin-in-hole components. Unfortunately, the molten solder also travels up the vias. The hot solder within a via transfers substantial heat to its associated top pad because of a large thermal conductance 65 between the via and the pad. Accordingly, the solder joint at the top pad is susceptible to reflow (liquidization and

redistribution) from the applied heat, which may cause an open circuit. Alternatively, the heat and consequent reflow may degrade the integrity of the solder joint, thereby making the solder joint susceptible to fracture from stress during subsequent usage of the circuit board.

In order to avoid the expense and time delay associated with rework and repair due to impaired solder joints resulting from wave soldering, it is necessary to block the transfer of heat from the molten solder to the top pads. The prevailing method of inhibiting such heat transfer is to cover the via opening at the bottom surface of the circuit board with insulating material such as KAPTON® (a trademark of DuPont for a polyimide) tape. See U.S. Pat. No. 5,511,306 (Denton et al., Apr. 4 1994) which is hereby incorporated by reference. The technique of covering the via opening has the disadvantages of adding steps to the board-fabrication process and incurring the cost of materials such as the [KAPTON] KAPTON® tape.

Thus, there is a need for an efficient and inexpensive method of preventing hot molten solder from flowing up through a via during the wave soldering process in order to inhibit heat transfer from the molten solder to a top pad.

#### SUMMARY OF THE INVENTION

The present invention provides a method and product of inhibiting the transfer of heat, during a wave soldering of the bottom surface of a printed circuit board, from the molten solder to a solder joint at a top pad on the top surface. The present invention creates a mechanical plug in the via prior to the wave soldering in order to obstruct the bottomside flow of molten solder into the interior of the via. By preventing the molten solder from transferring heat to the conductive lining of the via, the plug shields the top pad may degrade the integrity of the solder joint, thereby making 35 from heat that might otherwise cause degradation of the solder joint at the top pad.

> Affixation of Surface Mount Technology (SMT) components onto the bottom surface of the printed circuit board is accomplished by screening solder paste onto bottomside pads, dispensing adhesive onto the bottom surface in the vicinity of the solder paste, placing each component on the bottom surface by placing the component body on the adhesive and the component lead on the solder paste, and reflowing the solder paste and adhesive. This provides a mechanical and electrical connection between the bottomside components and the bottom surface. The present invention enables the plug to be formed as a part of this screening and reflow step. This is accomplished by having the screen comprise apertures corresponding to both the bottom pads and the vias. In this manner, solder paste is screened into the vias at the same time that solder paste is screened onto the bottom pads. The reflow step creates plugs of solder in the vias by redistributing the solder paste within the vias at the same time that the solder paste on the bottom pads are reflowed to form solder joints.

> After completion of the bottomside process, BGA modules and other components may be affixed to the top surface of the circuit board by use of another screening and reflow process which creates solder joints at the pad-component interfaces on the top surface of the circuit board. Next, pin-in-hole components on the top surface, as well as additional components previously mounted on the bottom surface, may be affixed to the circuit board by wave soldering. During the wave soldering of the bottom surface, the solder joints on top pads attached to vias are adequately protected from thermal degradation by the insulating effect of the plugged vias.

3

A solder plug in a via is effective for the present invention because the plug prevents molten solder from entering the via and the plug has a high thermal resistance to the conductive transport of heat. Nevertheless, because the solder plug is a good electrical conductor, the plug may serve as an electrical contact point for placing probes and the like during a testing phase after the circuit board assembly is completed. The plug provides the additional advantage of preventing oxidation within the via lining. This is especially valuable, because the material that lines the via, typically 10 copper, is subject to oxidation and an oxidized via lining is ineffective for conducting electricity to an applied instrumental probe. Although the via lining is typically coated with a material that inhibits oxidation, this protective coating can be burned off during the heating phases (e.g., during 15 reflow) of circuit board assembly. The consequent oxidation of the via lining after loss of the protective coating places an upper limit on circuit board assembly time. The solder plug of the present invention circumvents these problems by inhibiting oxidation of the via lining and providing an 20 accessible electrical contact surface for an applied probe.

Thus, the present invention has several advantages. The present invention provides a low cost, time-efficient method of preventing thermal degradation of solder joints at top pads that are connected to vias. The present invention also 25 eliminates the extra step inherent in the prior art method of taping the via opening. Additionally, the present invention inhibits oxidation of the via lining, thereby providing electrical contact surfaces for probing the printed circuit board at the vias during testing of the circuit board following 30 assembly.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 depicts a top perspective view of a simplified circuit board assembly in accordance with the preferred 35 embodiment of the present invention.

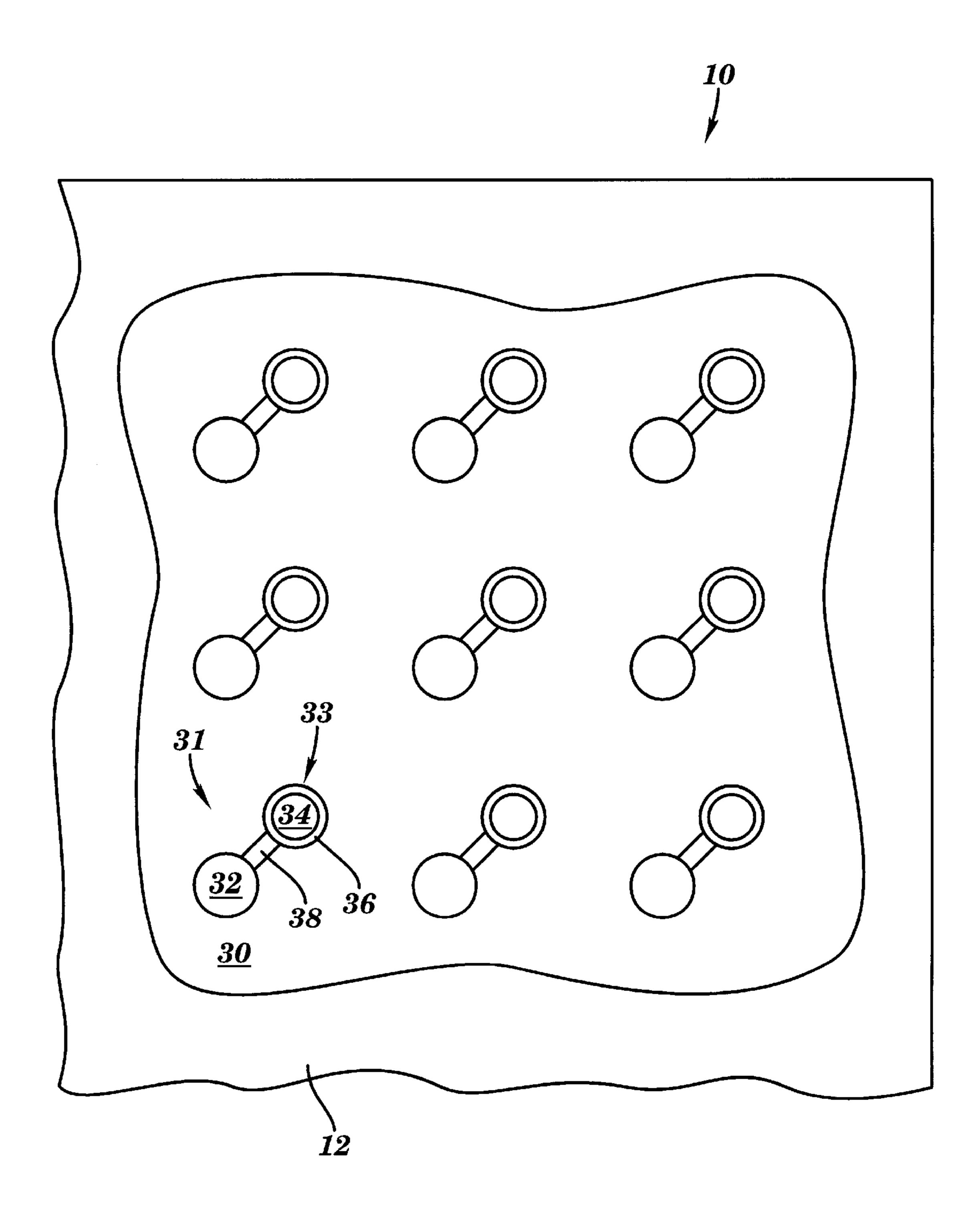

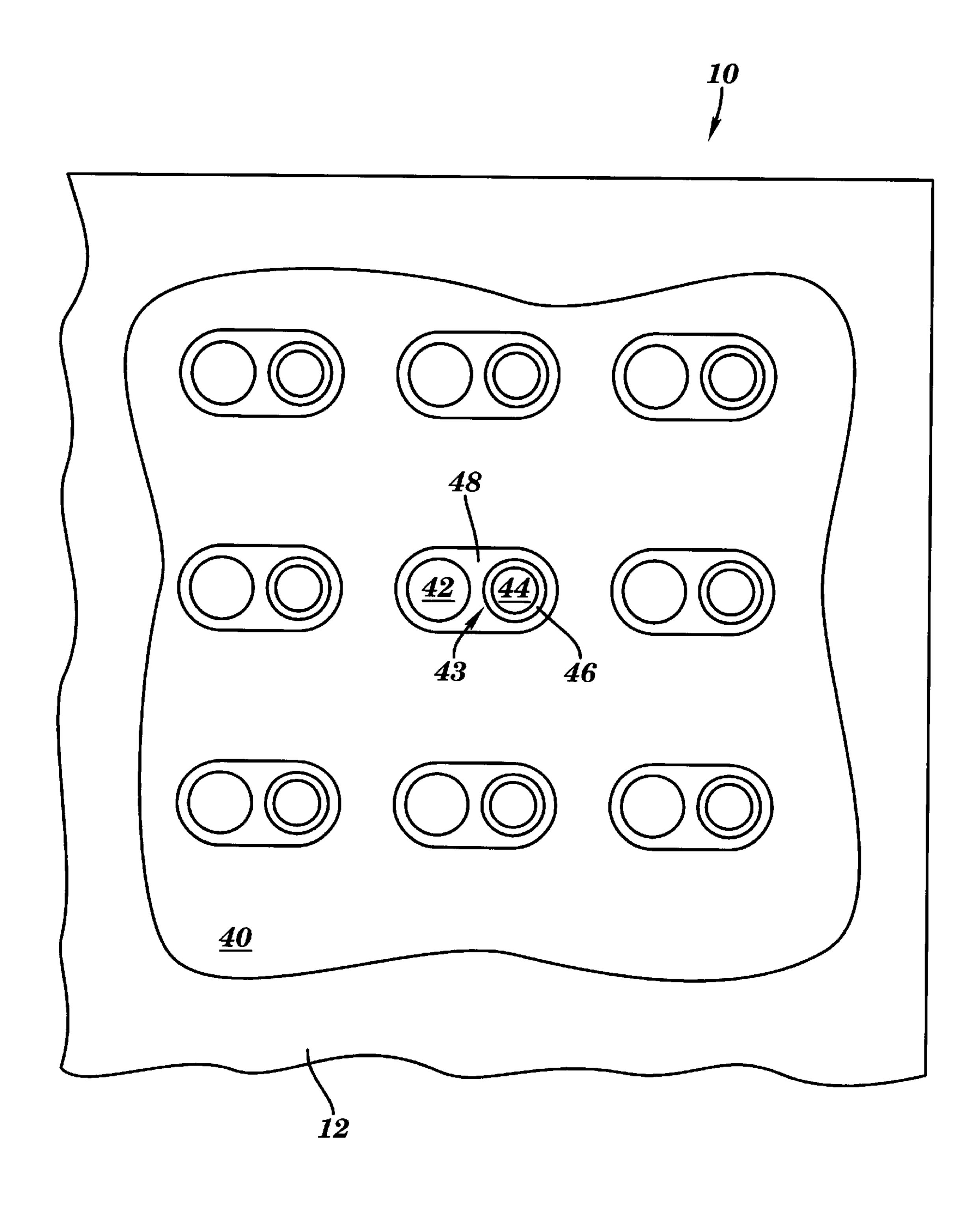

FIG. 2 depicts a top view of the top surface of FIG. 1, illustrating a ball grid array landing area with a dog bone pattern.

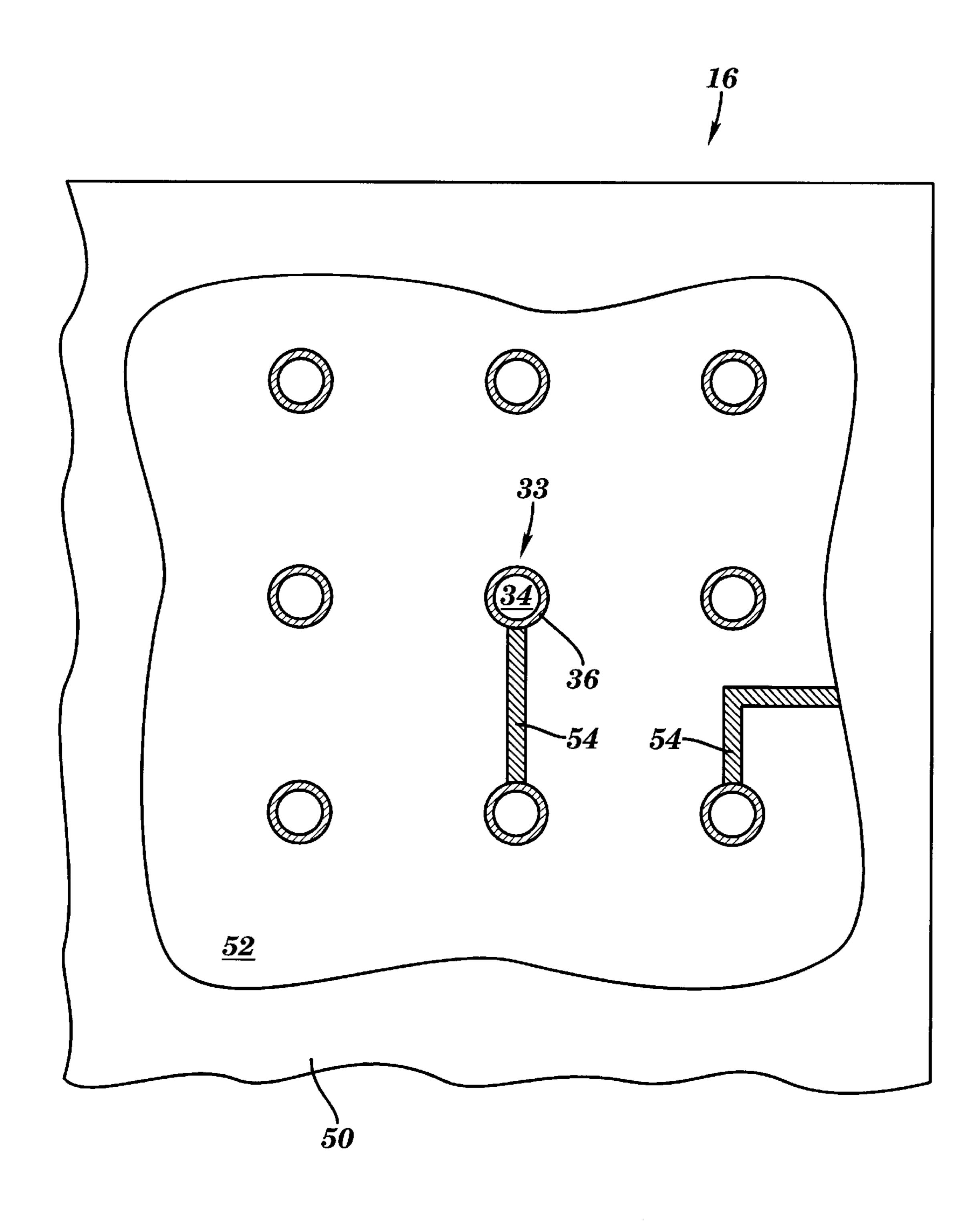

FIG. 3 depicts a cross-sectional view of the middle layer of FIG. 1, illustrating a via coupled to a conductive circuit trace.

FIG. 4 depicts a top view of the top surface of FIG. 1, illustrating a ball grid array landing area with a connecting plate pattern.

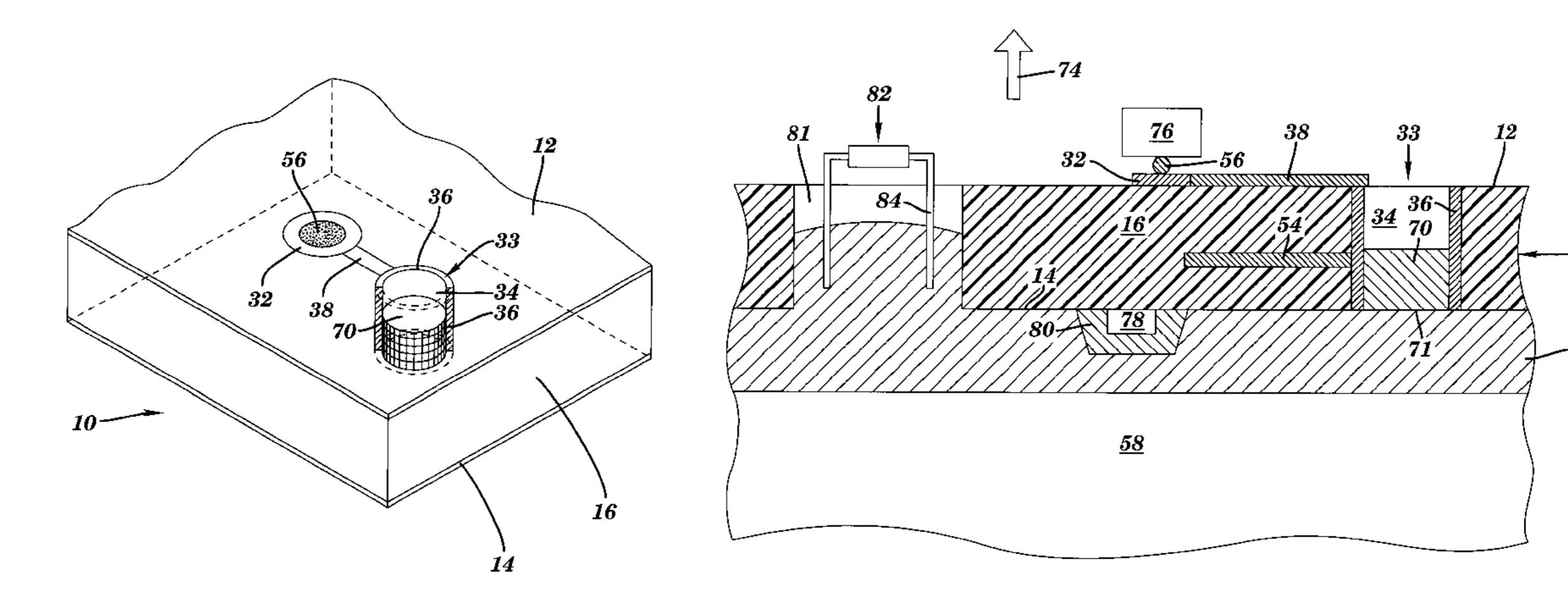

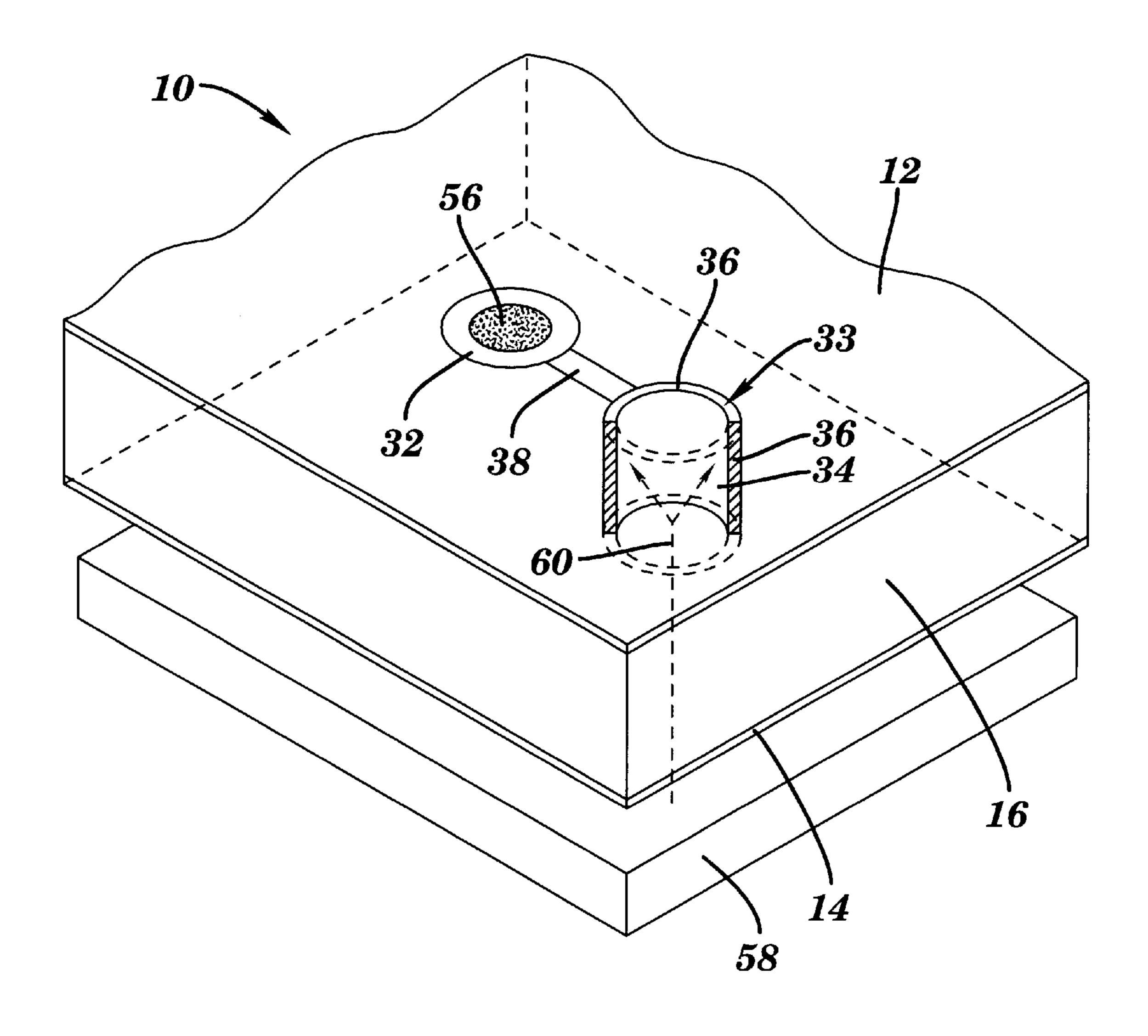

FIG. 5 depicts a top perspective view of the via in FIG. 2, illustrating the electrical connections and further illustrating the flow of hot molten solder into a via through the bottom face, wherein the via is shown in its entirety in a partially cut-away configuration.

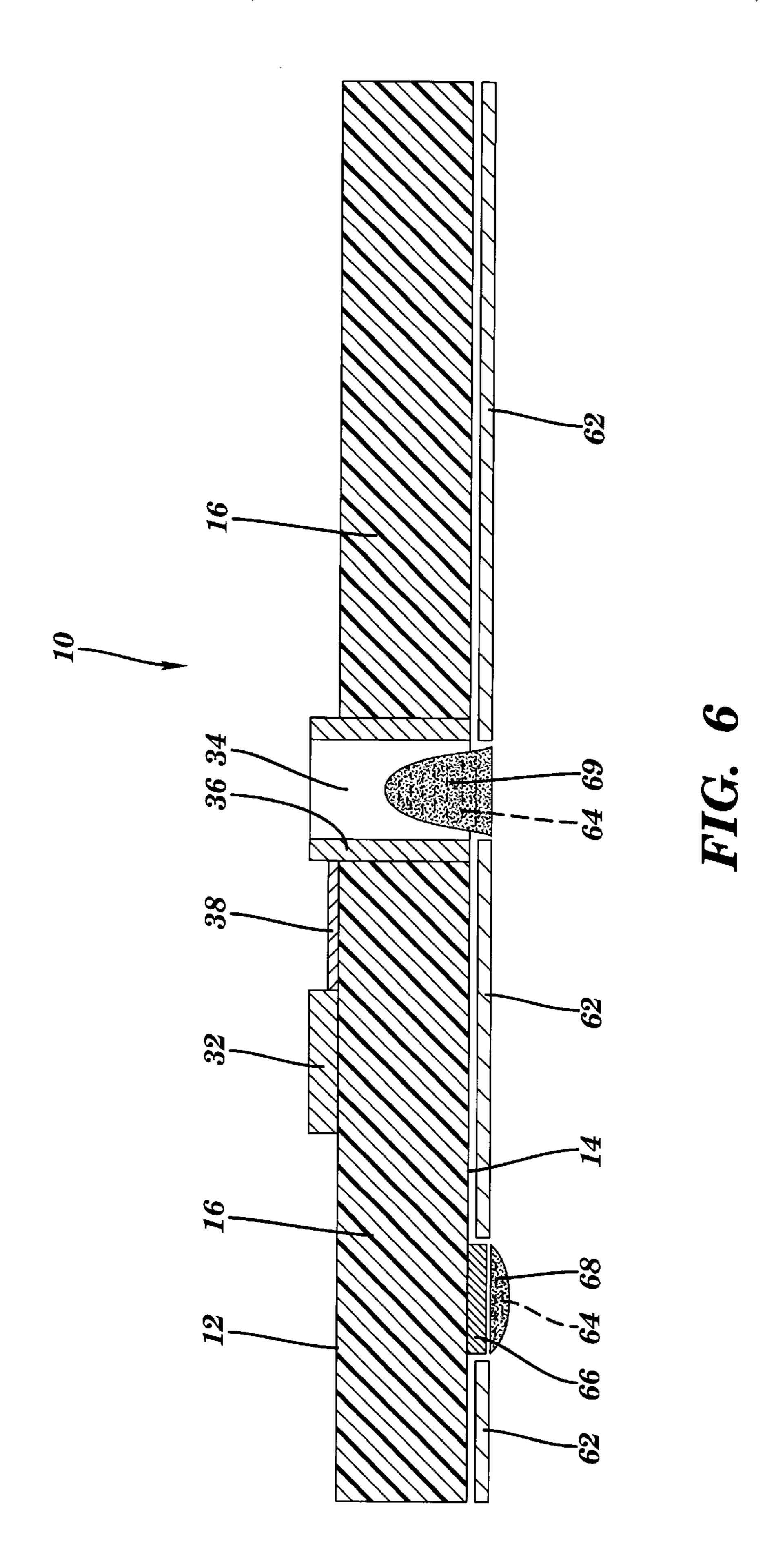

FIG. 6 depicts a cross-sectional view of the printed circuit board, illustrating the screening of solder paste onto a bottom pad and into a via in accordance with the preferred embodiment of the present invention.

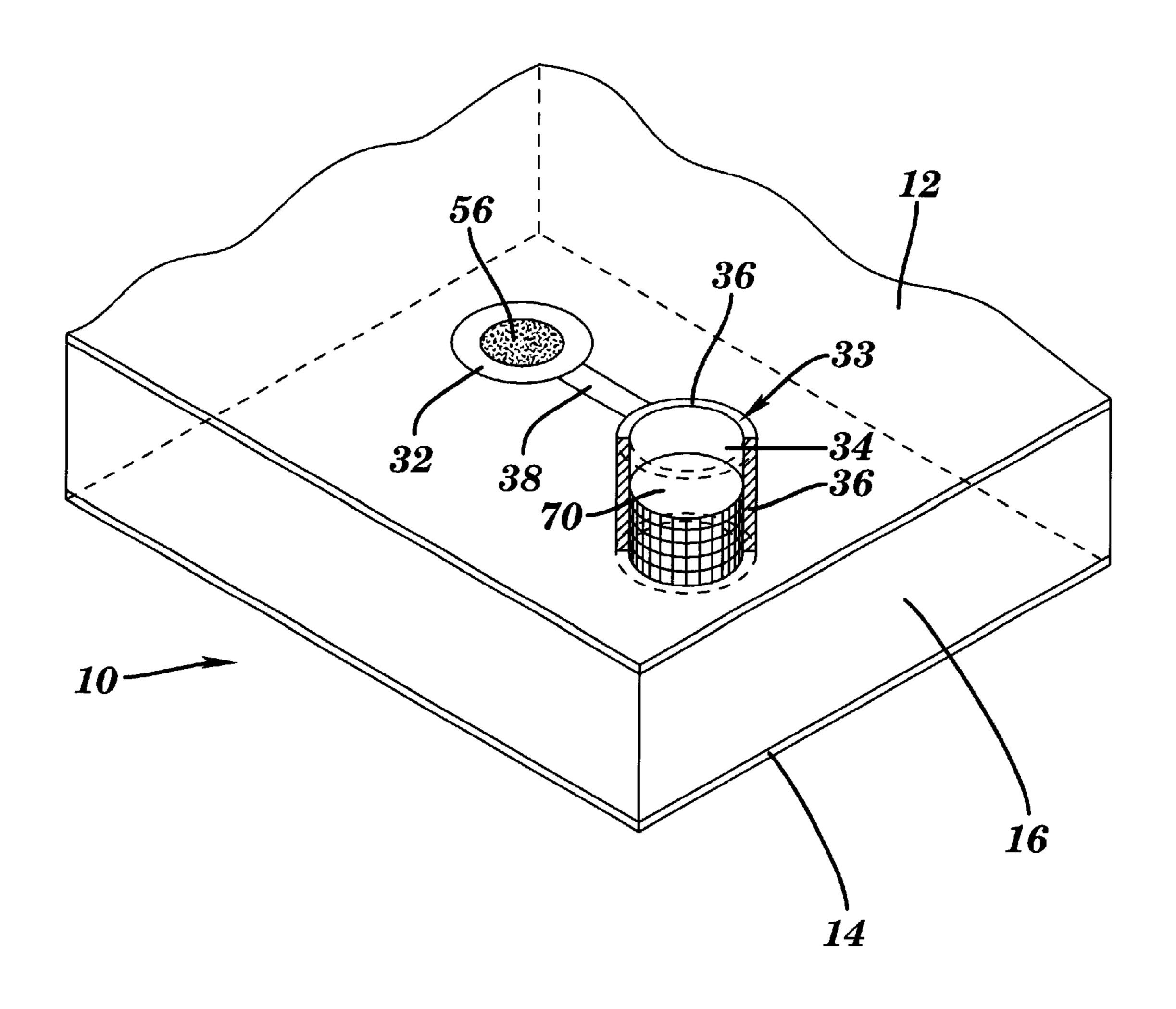

FIG. 7 depicts a top perspective view of the via in FIG. 2, illustrating a solder plug in the via, wherein the via is show in its entirety in a partially cut-away configuration, in accordance with the preferred embodiment of the present invention.

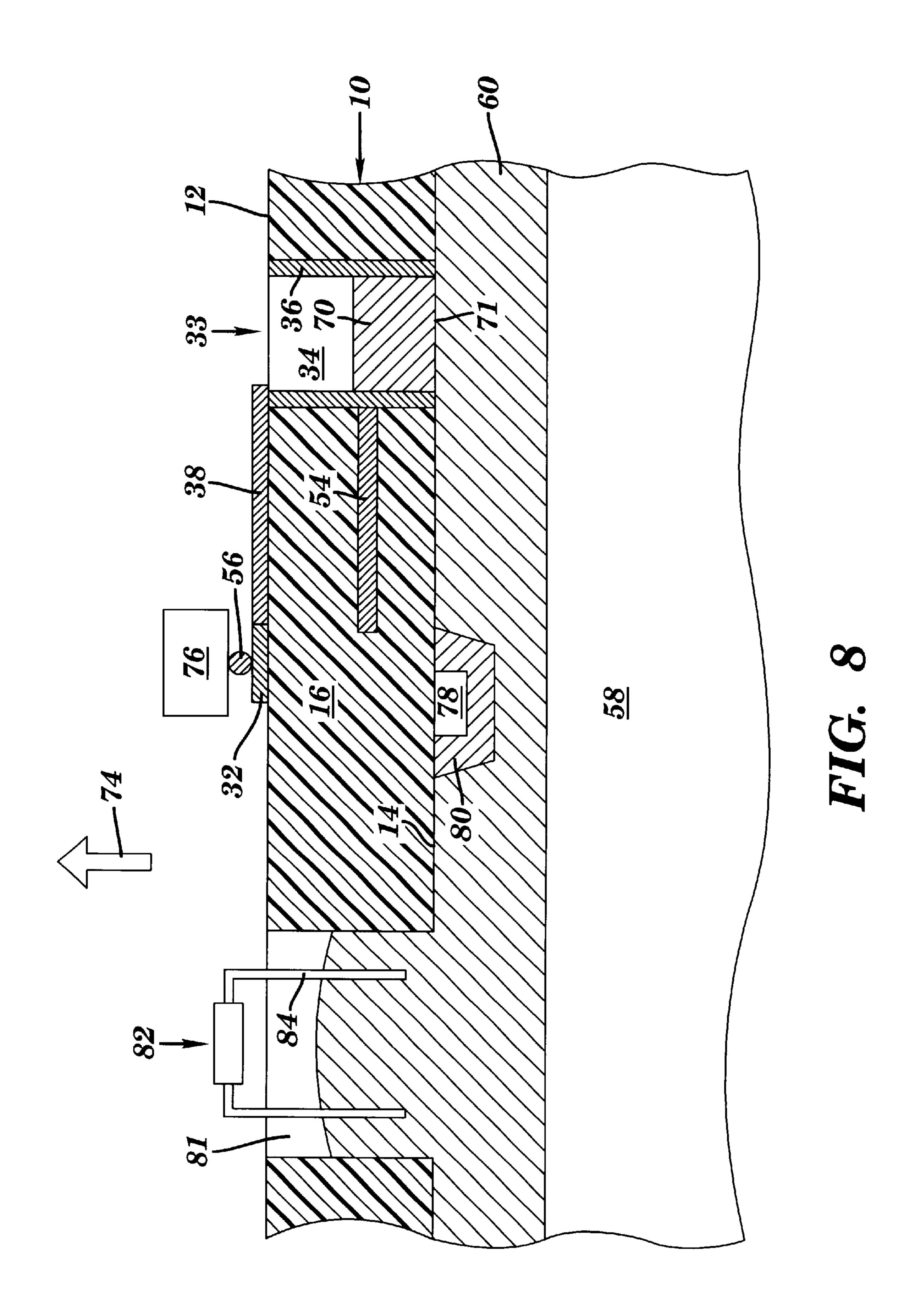

FIG. 8 depicts a front cross-sectional view of the printed circuit board of FIG. 7 being wave soldered with molten solder in contact with the bottom surface of the printed circuit board.

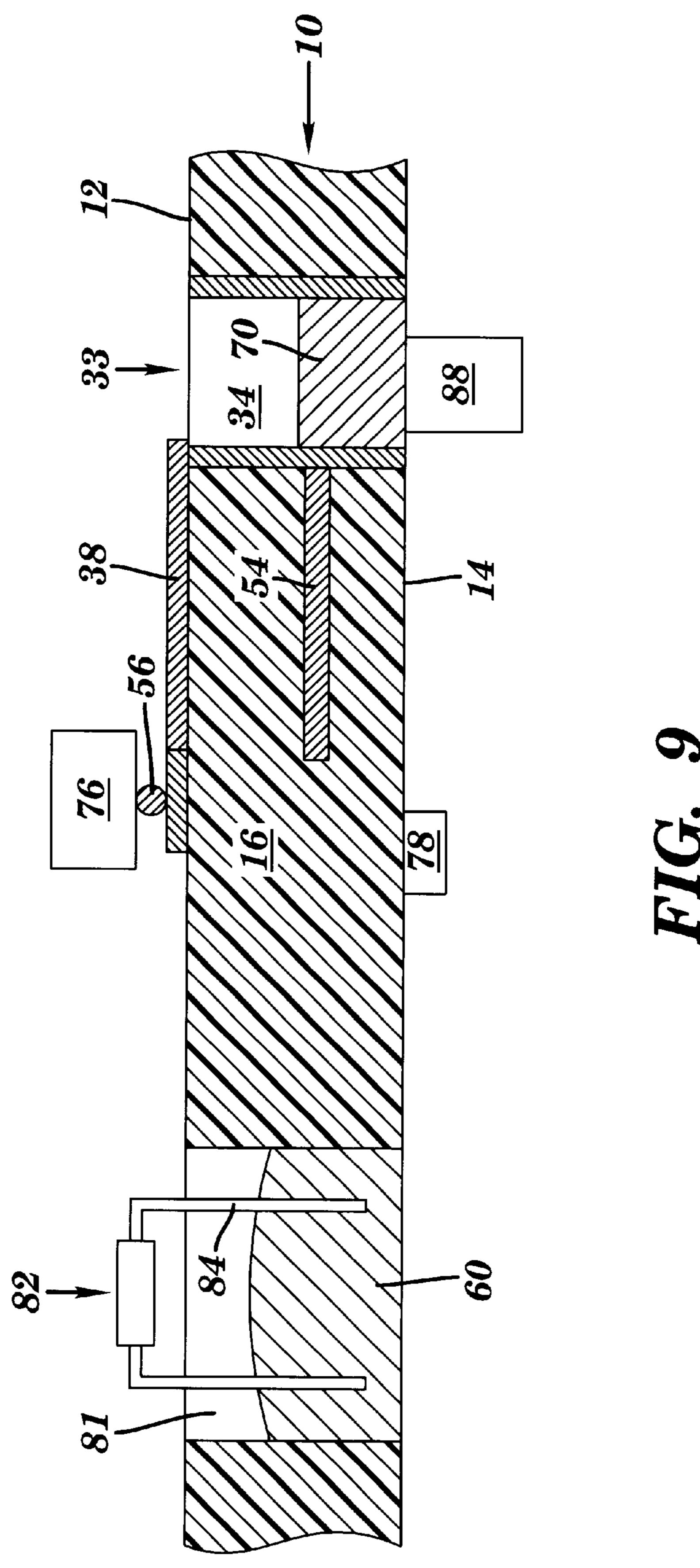

FIG. 9 depicts the printed circuit board of FIG. 8, fol- 65 lowing the wave soldering, with an added instrumental probe.

4

FIG. 1 illustrates a top perspective view of a simplified circuit board 10 having a top surface 12, a bottom surface 14, and one or more middle layers. Assembly of BGA component 18 and other components to the top surface 12, and assembly of bottom components to the bottom surface 14, of the printed circuit board 10 may be accomplished in the following steps: (1) installing bottom components to the bottom surface 14, typically by the screening and reflow of solder paste; (2) installing the BGA component 18 and other components to the top surface 12, typically by the screening and reflow of solder paste; and (3) wave soldering the bottom surface 14 to affix pin-in-hole component surface 12 (e.g., connectors, SIPS, DIPS) as well as additional components previously mounted on the bottom surface 14. During the wave soldering, components affixed to the bottom surface in a prior step may be shielded from the wave soldering by use of a mask such as that described in U.S. Pat. No. 4,739,919 (Van Den Becked et al., Jun. 15, 1987) which is hereby incorporated by reference. Note that the first two steps, installing of components to the bottom surface 14 and top surface 12, are interchangeable for the purpose of the present invention.

FIG. 2 shows the top surface 12 with a BGA landing area 30 for receiving the BGA component 18 (component 18 is shown in FIG. 1). The landing area 30 comprises an ordered array of "dogbones" 31. Each dogbone 31 comprises a conductive top pad 32, a via 33, and a conductive connecting strip 38 that connects the top pad 32 to the via 33. The via 33 comprises a cylindrical void 34 within a conductive lining 36 through the circuit board 10 from the top surface 12 to the bottom surface 14. Each via 33 is electrically coupled to other vias and to other electrical components by electrical circuit traces 54 in the middle layer 16, as illustrated in a middle-layer cross sectional view in FIG. 3. It should be noted that a landing area for a BGA middle-layer cross sectional view in FIG. 3. It should be noted that a landing area for a BGA component need not be based on a dogbone pattern. Any conductive pattern that connects a top pad to a via will suffice. FIG. 4, for example, illustrates a top surface 12 with a BGA landing area 40 in which a conductive connecting plate 48 electrically couples a top pad 42 to a via 43, wherein the via 43 comprises a void 44 within a conductive lining 46.

FIG. 5, which depicts a top perspective view of a via 33 connected to a top pad 32, illustrates the electrical connections of the present invention. The BGA component 18 (component 18 is shown in FIG. 1) contains an ordered array of solder balls 56 and each solder ball 56 is to be affixed to a corresponding top pad 32. The path of electrical conduction is from the solder ball 56 to the circuit trace 54: solder ball 56 to top pad 32 to connecting strip 38 to via lining 36 to circuit trace 54 (circuit trace 54 is shown in FIG. 3).

FIG. 5 also illustrates how, absent the present invention, heat would be transferred from molten solder 60 to the top pad 32 during the wave soldering of the bottom surface 14. The molten solder 60 from the wave soldering source 58 is drawn into the via void 34, where it contacts the via lining 36 and passes heat to the via lining. Heat is then conducted along the via lining 36 into the connecting strip 38 (or into the connecting plate 48 for the configuration of FIG. 4) and finally into the solder pad 32 where it may reflow the solder joint and cause an open circuit or degrade the integrity of the solder joint.

FIGS. 6 and 7 illustrate how the present invention prevents heat from the molten solder from being transferred to the top pad 32. Referring to FIG. 6, which depicts a cross-sectional view of the printed circuit board 10 with a

5

screen 62 mounted to the bottom surface 14, heat is prevented from being transferred from the molten solder 60 to the top pad 32 by modifying the step of screening and reflowing of solder paste during installation of bottom components to the bottom surface 14. During the screening 5 of the bottom surface 14, solder paste 64 is applied through the screen 62 to a bottom pad 66 to form a solder layer 68 (for subsequent mounting of a bottom component) and into the via void 34 to form a solder mass 69. After the screen 62 is removed and the bottom component is attached to the solder layer 68, the solder layer 68 and the solder mass 69 are reflowed causing affixation of the bottom component to the bottom surface 14 and redistribution of the solder mass 69 to form a plug.

The plug 70, which is shown in FIG. 7, is capable of <sup>15</sup> inhibiting the flow of molten solder into the via void 34 in the subsequent wave soldering step, which effectively inhibits heat transfer from molten solder to the top pad 32. Generation of the plug 70 in the preceding screening and reflow step is essentially free of cost inasmuch as the <sup>20</sup> screening and reflow is performed during the step of affixing the bottom component to the bottom surface 14. For embodiments not requiring screening and reflow to affix a bottom component, a screening and reflow step could nevertheless be added to prevent heat transfer from molten solder to a top <sup>25</sup> pad 32.

FIG. 8 illustrates a front cross-sectional view of the printed circuit board 10 of FIG. 7 being wave soldered with the molten solder 60 (see FIG. 5; page 7, lines 12-15) in contact with the bottom surface 14 of the printed circuit 30 board 10 and also in contact with an end 71 of the conductive plug 70. The molten solder 60 is moving in a direction 74 from the wave soldering source 58 (see FIG. 5) toward the bottom surface 14. The plug 70 obstructs a flow of the molten solder 60 into the via 33. Accordingly, the plug 70 35 inhibits heat transfer from the molten solder 60 to the conductive lining 36, and thus to the top pad 32. Consequently, heat from the molten solder 60 cannot cause degradation at the solder ball 56 interface between the top pad 32 and a component 76 (e.g., a BGA). Note that a component 78 at the bottom surface 14 is shielded from the molten solder 60 by a mask 80. Conductive leads 84 of a pin-in-hole component 82 in a via 81 is contacted by the molten solder 60. The via 33 is in electrically conductive contact with the electrical circuit trace 54 (see FIG. 3) within the middle layer 16.

FIG. 9 illustrates the printed circuit board 10 of FIG. 8 following the wave soldering. An instrumental probe 88 is in electrically conductive contact with the plug 70. The instrumental probe 88 is used for testing the printed circuit board 10. Note that the solder 60 in FIG. 9 is not molten as it was in FIG. 8, because the configuration of FIG. 9 exists after the wave soldering and not during the wave soldering.

Although the preferred embodiment of the present invention utilizes a screening and reflow process for generating a plug 70 in the via void 34, any method for generating a volumetric plug within the via void 34, that would effectively prevent heat transfer from molten solder to a top pad 32, is within the scope of the present invention. Likewise, 60 the plug material need not be solder and the plug may comprise any material capable of thermally insulating the via from the molten solder.

The present invention encompasses any embodiment that creates a plug in a via void even in the absence of a wave 65 soldering step, since the plug may be useful for purposes other than inhibiting heat transfer. By its contact with the

6

exposed surface of the via lining, for example, the plug may beneficially retard oxidation of the via lining. Additionally, an electrically conductive plug may facilitate the testing of a circuit board assembly by serving as an electrical contact surface for an instrumental probe.

Thermal degradation of a solder joint at the interface between a component and a pad is a potential problem whenever a top pad is electrically and thermally coupled to a via. Accordingly, the potential problem is not specific to a BGA configuration. Thus, while the preferred embodiment involves a via associated with a BGA configuration, the present invention encompasses any surface mount component affixed to a pad that is electrically coupled to a via, including a component having a lead.

Although the preceding description of the preferred embodiment depicts a printed circuit board as having a top and a bottom surface, any orientation of the circuit board with respect to the horizontal plane is within the scope of the present invention.

While preferred and particular embodiments of the present invention have been described herein for purposes of illustration, many modifications and changes will become apparent to those skilled in the art. Accordingly, the appended claims are intended to encompass all such modifications and changes as fall within the true spirit and scope of this invention.

What is claimed is:

- 1. A structure, comprising:

- a printed circuit board having a top surface, a bottom surface, and a middle layer between the top surface and the bottom surface;

- a conductive pad on the top surface;

- a via extending through the printed circuit board from the top surface to the bottom surface, wherein a conductive lining on an interior wall of the via is conductively coupled to the pad;

- a solid plug within the via, wherein the plug comprises a solder material, and wherein a portion of the plug is within a bottom portion of the via; and

- molten solder in contact with an end of the plug, where in the end of is at the bottom surface, and wherein the plug obstructs flow of the molten solder into the via through the bottom portion of the via.

- 2. The structure of claim 1, wherein the plug inhibits heat transfer from the molten solder to the conductive lining.

- 3. The structure of claim 1, wherein the plug inhibits heat transfer from the molten solder to the conductive pad.

- 4. The structure of claim 1, further comprising a component coupled to the conductive pad by a solder joint, wherein heat from the molten solder does not cause degradation of the solder joint.

- 5. The structure of claim 4, wherein the component includes a BGA component.

- 6. The structure of claim 1, further comprising a component affixed to the bottom surface and a mask that shields the component from the molten solder.

- 7. The structure of claim 1, further comprising a pin-in-hole component, wherein the molten solder is in contact with the pin-in-hole component.

- 8. The structure of claim 1, wherein the solder material is distributed throughout the plug.

- 9. A structure, comprising:

- a printed circuit board having a top surface, a bottom surface, and a middle layer between the top surface and the bottom surface;

- a conductive pad on the top surface;

7

- a via extending through the printed circuit board from the top surface to the bottom surface, wherein a conductive lining on an interior wall of the via is conductively coupled to the pad;

- a solid plug within the via, wherein a portion of the plug is within a bottom portion of the via; and

- molten solder in motion from a wave soldering source and moving toward the bottom portion of the via such that the moving molten solder contacts an end of the plug, wherein the end of the plug is at the bottom surface,

8

wherein the plug obstructs flow of the molten solder into the via through the bottom portion to the via, and wherein the molten solder is made by the wave soldering source.

- 10. The structure of claim 9, wherein the plug comprises a solder material.

- 11. The structure of claim 10, wherein solder material is distributed throughout the plug.

\* \* \* \* \*