US006438569B1

# (12) United States Patent Abbott

### (10) Patent No.: US 6,438,569 B1

(45) Date of Patent: Aug. 20, 2002

#### (54) SUMS OF PRODUCTION DATAPATH

(75) Inventor: Curtis Abbott, Menlo Park, CA (US)

(73) Assignee: PMC-Sierra, Inc., Burnaby (CA)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/399,981

(22) Filed: Sep. 20, 1999

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3,980,992 A | 9/1976  | Levy et al 340/172.5    |

|-------------|---------|-------------------------|

| 4,558,411 A | 12/1985 | Faber et al 364/200     |

| 4,791,602 A | 12/1988 | Resnick 364/900         |

| 4,791,603 A | 12/1988 | Henry 364/900           |

| 4,821,183 A | 4/1989  | Hauris 364/200          |

| 4,823,286 A | 4/1989  | Lumelsky et al 364/521  |

| 4,992,680 A | 2/1991  | Benedetti et al 307/465 |

| 5,055,712 A | 10/1991 | Hawley et al 307/465    |

| 5,175,862 A | 12/1992 | Phelps et al 395/800    |

| 5,185,706 A | 2/1993  | Agrawal et al 364/489   |

#### OTHER PUBLICATIONS

International Search Report, Int'l Appln PCT/US98/11889, mailed Oct. 23, 1998, 5 pgs.

C.S. Wallace, "A Suggestion for a Fast Multiplier," IEEE Transaction son Electronic Computers, Feb. 1964, pp. 14–17.

Charles R. Baugh and Bruce A. Wooley, "A Two's Complement Parallel Array Multiplication Algorithm," IEEE Transactions on Computers, vol. C–22, No. 12, Dec. 1973, pp. 1045–1047.

Earl E. Swartzlander, Jr. "Merged Arithmetic," IEEE Transactions on Computers, vol. C–5, No. 10, Oct. 1980, pp. 946–950.

Michael Bolotski, Andre DeHon, and Thomas F. Knight, Jr., Transit Note #95 *Unifying FPGAs and SIMD Arrays*, Mit Transit Project, Sep. 1993, 14 pps.

(List continued on next page.)

Primary Examiner—David H. Malzahn (74) Attorney, Agent, or Firm—Blakely, Sokoloff, Taylor & Zafman LLP

#### (57) ABSTRACT

A method and apparatus for a sums of products datapath. According to one embodiment of the invention, an apparatus has a number of inputs and a number generation units. Each of the generation units is coupled to the inputs. Each of the generation units includes a separate selection circuit coupled to each one of the inputs to selectively pass the signal provided on that input. In addition, each of the generation units includes a number of reduction circuits having inputs coupled to mutually exclusive pluralities of the selection circuits and each having an output. The apparatus also includes a first and second summation circuit coupled to the output of the plurality of reduction circuits in mutually exclusive pluralities of generation units. Additionally, the apparatus includes a subtraction circuit coupled to an output of the first and second summation circuit.

#### 46 Claims, 19 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 5,220,213 A  | 6/1993  | Chan et al 307/465       |

|--------------|---------|--------------------------|

| 5,231,588 A  | 7/1993  | Agrawal et al 364/489    |

| 5,321,845 A  | 6/1994  | Sawase et al 395/800.37  |

| 5,446,651 A  | 8/1995  | Moyse et al 364/760      |

| 5,619,668 A  | 4/1997  | Zaidi 395/376            |

| 5,751,619 A  | 5/1998  | Agrawal et al 364/736.02 |

| 5,930,160 A  | 7/1999  | Mahant-Shetti 708/603    |

| 5,974,435 A  | 10/1999 | Abbott 708/553           |

| 6,085,213 A  | 7/2000  | Oberman et al 708/603    |

| 6,212,618 B1 | 4/2001  | Roussel 708/603          |

| 6,247,036 B1 | 6/2001  | Landers et al 708/603    |

#### OTHER PUBLICATIONS

Debabrata Ghosh, et al., "Architectural Synthesis of Performance–Driven Multipliers with accumulator Interleaving", 30th ACM/IEEE Design Automation Comference, (1993) pp. 303–307.

Andre DeHon, Transit Note #118 Notes on Coupling Processors with Reconfigurable Logic, MIT, pp. 1–40.

Andre DeHon, Reconfigurable Architectures for General-Purpose Computing, 258 pps.

PCT Written Opinion, Int'l Appln PCT/US98/11889, mailed Jun. 01, 1999, 6 pps.

**FIG. 1**

Aug. 20, 2002

FIG. 5C

FIG. 6

Aug. 20, 2002

Aug. 20, 2002

#### SUMS OF PRODUCTION DATAPATH

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application contains subject matter related to: non-provisional application Ser. No. 08/953,766, filed Oct. 17, 1997, now U.S. Pat. No. 5,974,435, entitled "A RECONFIGURABLE ARITHMETIC DATAPATH," to Curtis Abbott, which is a continuation of provisional application No. 60/057,156, filed Aug. 28, 1997; non-provisional application Ser. No. 09/346,556, filed Jun. 30, 1999, now U.S. Pat. No. 6,150,836, entitled "A MULTILEVEL LOGIC FIELD PROGRAMMABLE DEVICE," to Curtis Abbott, which is a continuation-in-part of non-provisional application Ser. No. 08/874,817, filed Jun. 13, 1997, now U.S. Pat. No. 6,006,321 entitled "PROGRAMMABLE LOGIC DATAPATH THAT MAY BE USED IN A FIELD PROGRAMMABLE DEVICE," to Curtis Abbott.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The invention relates to the field of logic devices. More specifically, the invention relates to the field of programmable logic devices.

#### 2. Background Information

Fast multiplication and addition are key arithmetic operations in digital signal processing (DSP), as well as other forms of computer data processing. In DSP especially, it is often necessary to multiply several pairs of numbers and accumulate the results by addition into a single number. Mathematically, this operation is called a "dot product" or "sum of products." It can be written  $a_1*b_1+a_2*b_2+\ldots+a_n*b_n$ , where the  $a_i$  and  $b_i$  sequences are paired up, and each corresponding element is multiplied, with the results accumulated. In a typical digital filter, the first sequence may be a fixed sequence of filter coefficients, while the second sequence may be a contiguous set of data samples from a longer input sequence.

Some application-specific examples of constant coefficient sums of products over low resolution data include: multi-tap constant coefficient FIR filters such as pulse shaping filters, especially over low precision data; fixed-pattern correlators (matched filters), despreaders, etc. Other applications that involve higher precision data include: fast block transforms, such as DCT, FFT, wavelets, etc.; IP checksums (reduction of 64 bits/cycle in the main body of an IP packet), etc.

The precision requirements for these multiplication and addition operations can vary tremendously, as can the 50 desired representations of the numbers involved. For example, in some applications it is desired to use floating point number representations; in others, the fixed point representation is sufficient and is more cost effective. Among fixed point representations, the number of integral and 55 fractional digits can vary, as can the total number of digits. Additionally, the numbers may be signed or unsigned. Beyond the data representations themselves, certain details of the processing operations are important. For example, multiplication and addition operations produce outputs with 60 a greater number of digits than their inputs. Thus, when such operations are composed, the number of digits in the results can grow dramatically. Commonly, the exact results include digits that do not represent useful information, so some digits are discarded using truncation and rounding. The art 65 of discarding digits that are not useful is both important and complex.

2

The precision requirements for the multiplication and addition operations are generally related to: the precision of the input data; the precision of the coefficients; the type of processing algorithm; and certain parameters of that algorithm such as how truncation and rounding are performed. The analysis of these requirements is sufficiently complex that a whole branch of mathematics, known as Numerical Analysis, has been developed for them.

In response to the widespread need for fast multiplication and addition with a variety of precisions and data representations, an extensive literature has been created and many hardware and software implementations have been developed. For most implementations, the complexity increases roughly as N\*M where N and M are the number of bits of the two input operands. Thus, for N by N multiplication, the complexity increases as N². Algorithms are known that reduce this complexity for very large operands, but for most applications, the operand sizes are not large enough to make these algorithms practically useful. On the other hand, many ideas have been developed that do effectively exploit properties of hardware technologies and multiplication algorithms to speed up implementations having a particular precision and numerical representation.

The straightforward approach to multiplication is adding up a set of appropriately shifted partial products, each generated by multiplying the multiplicand by one of the digits of the multiplier. The only difficulty about addition is carries between digits, since the carry out from a particular digit depends on the carry into that digit, so that the carry propagation aspect of addition is inherently sequential. Since it is possible that a carry may propagate across all the digits of a sum, the number of sequential steps required for the addition is equal to the number of digits being added. Many techniques are known for reducing the maximum number of sequential steps requires for the addition; however these techniques generally require more hardware.

Many hardware designs for fast multiplication embody an extended version of the straightforward multiplication algorithm, consisting of a first part that generates partial products, a second part that sums the partial products to two numbers (referred to as "carry" or "C" and "save" or "S") whose sum is the correct answer, and a third part that adds together C and S to produce the answer. The partial product generation may include any form of multiplicand preprocessing, such as Booth encoding. The numbers C and S are developed in such a way that carry propagation is largely or completely avoided during the second part. The apparatus implementing the second part is generally known as a "Carry Save Adder," sometimes abbreviated "CSA." Carry propagation is unavoidable during the third part of the multiplication algorithm, but only two numbers are then involved, and any of the known techniques can be used to speed up the addition. The third part of this multiplication algorithm is also called the "Carry Propagate Adder," sometimes abbreviated "CPA".

The variations among hardware multiplier designs of this type generally involve one or more of the following: the method for generating partial products, the method for reducing them to numbers C and S, the method for performing the final addition of numbers C and S, and the method for modifying the partial products and/or carry save adder to accommodate signed number representations.

More generally, systems applications may use several of the DSP algorithms that were just briefly described, and may use other algorithms involving multiplications and additions as well. Depending on the total throughput required by the

application, it may be necessary to provide dedicated hardware multiplication and addition circuits for each operation through which data flows in fixed connection patterns, or on the other hand, it may be possible to reuse one or more hardware multiplication and addition circuits with data flows 5 directed by a control element.

When designing dedicated hardware for performing sums of products, the hardware designer will exploit certain simplifications resulting from zero bits in the (constant) coefficients. A designer/architect will use other techniques to minimize the number of non-zero bits in the coefficients. For example, with 1-bit data interpreted as 1 and -1, an FIR filter reduces to adding and subtracting the coefficients according to the state of each data bit. The result is that multiplications involving constant coefficients are much more efficient in dedicated hardware as opposed to "general purpose" multiplication hardware. However, programmable CPU and DSP hardware typically provides only general purpose multiplies.

In particular, CPU and DSP circuits usually implement complex numerical algorithms by the sequential composition of simpler operations into and out of register files that store intermediate results, coefficients, and so on. For example, a sum of squares of differences algorithm may be implemented by a first operation that takes the difference of two numbers, a second operation that squares the result, and a third operation that accumulates the result of the second operation into a running sum. In case each operation takes a single cycle, the algorithm would then be completed in 3 cycles.

However, since the inherent complexity of multiplication is higher than that of addition or subtraction, hardware designers often optimize the clock speed of their designs by pipelining the multiplication operation, so that it completes after more than one cycle. For example, a particular design might complete in 3 cycles but allow a new multiply operation to be started on every cycle. In such a case, the sum of squares of differences algorithm discussed earlier might complete in 5 cycles. Depending on certain details of the hardware design, it might be possible to overlap the calculation for the next pair of vector elements so that on average, each pair of elements would be subtracted, squared, and summed in 3 cycles.

While many design variations are possible that involve more or less parallel hardware, it is generally desirable for designs to require as few cycles as possible to complete an algorithm; this is especially important for the most widely used algorithms, including those mentioned in the foregoing. If a first design uses K cycles while a second uses L>K, then the first design is also more cost-effective if it uses less than L/K as much hardware. Implementers of systems applications are generally desirous of designs that are fast, cost-effective, and reconfigurable.

#### SUMMARY OF THE INVENTION

A method and apparatus for a sums of products datapath is described. According to one embodiment of the invention, an apparatus has a number of inputs and a number generation units. Each of the generation units is coupled to the inputs. Each of the generation units includes a separate 60 selection circuit coupled to each one of the inputs to selectively pass the signal provided on that input. In addition, each of the generation units includes a number of reduction circuits having inputs coupled to mutually exclusive pluralities of the selection circuits and each having an output. 65 The apparatus also includes a first and second summation circuit coupled to the output of the plurality of reduction

4

circuits in mutually exclusive pluralities of generation units. Additionally, the apparatus includes a subtraction circuit coupled to an output of the first and second summation circuit.

#### BRIEF DESCRIPTION OF THE DRAWINGS

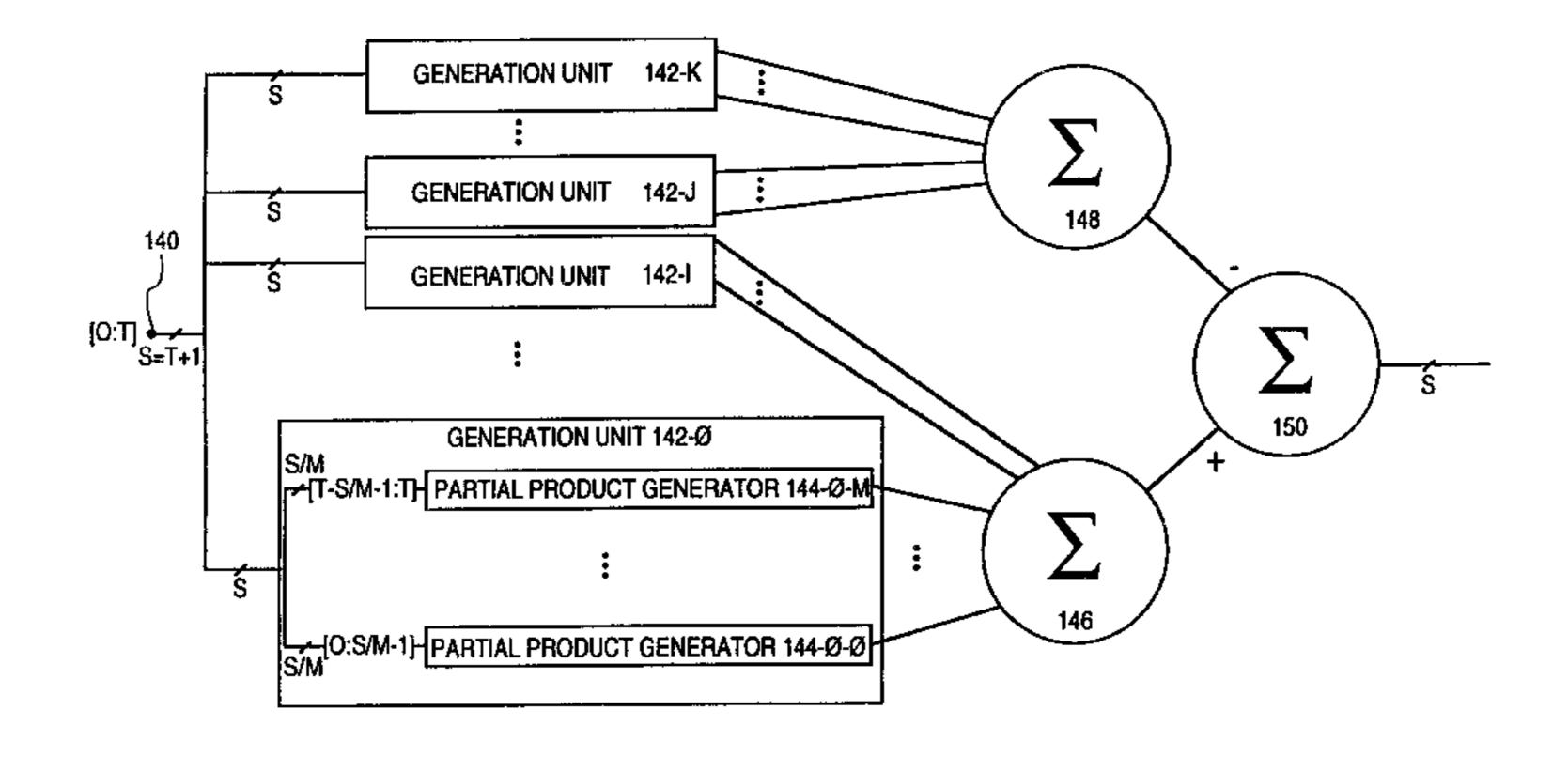

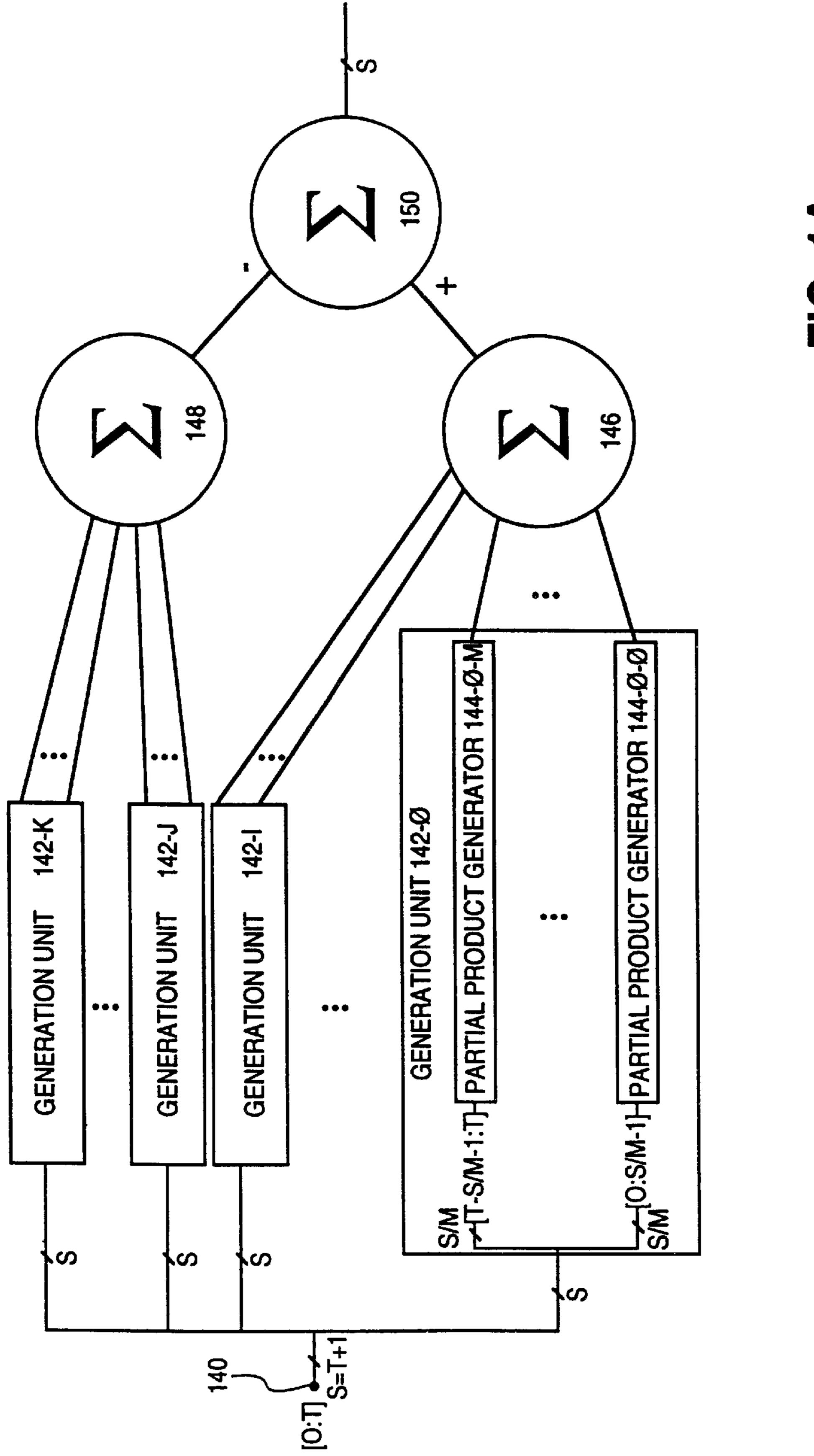

FIG. 1A is a block diagram illustrating a sums of products datapath according to one embodiment of the invention;

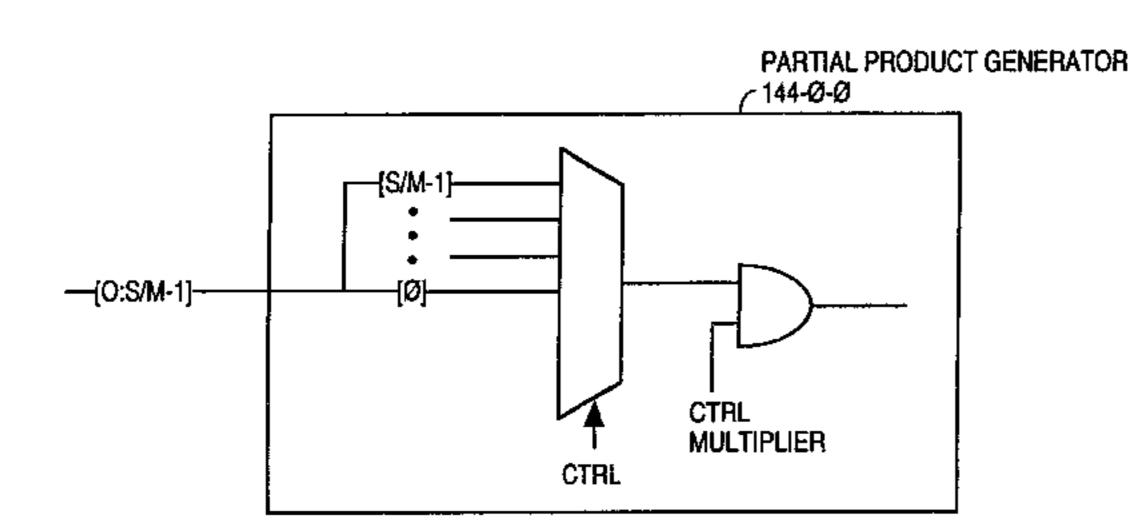

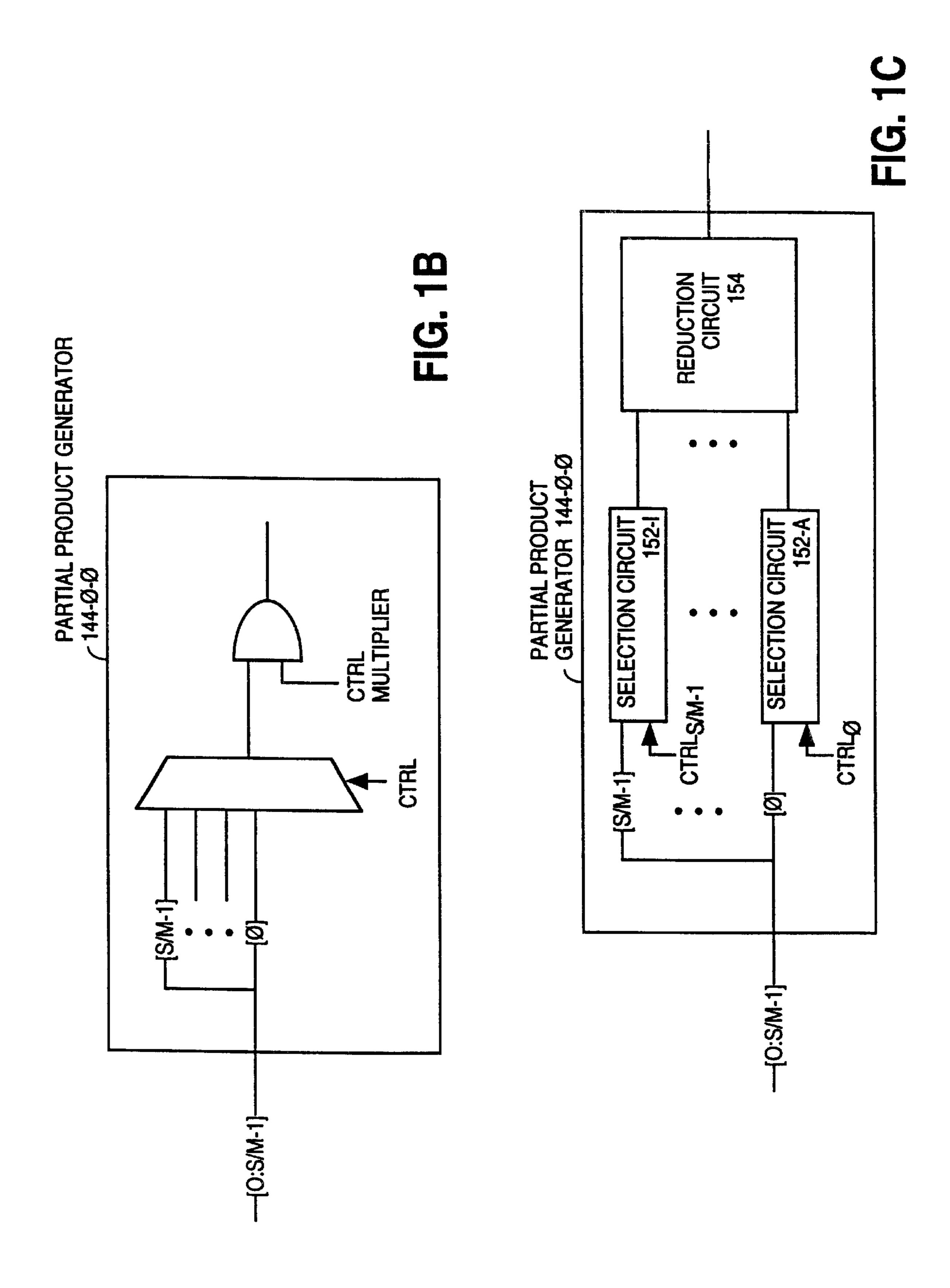

FIG. 1B is a block diagram illustrating a partial product generator from the sums of products datapath of FIG. 1A according to one embodiment of the invention;

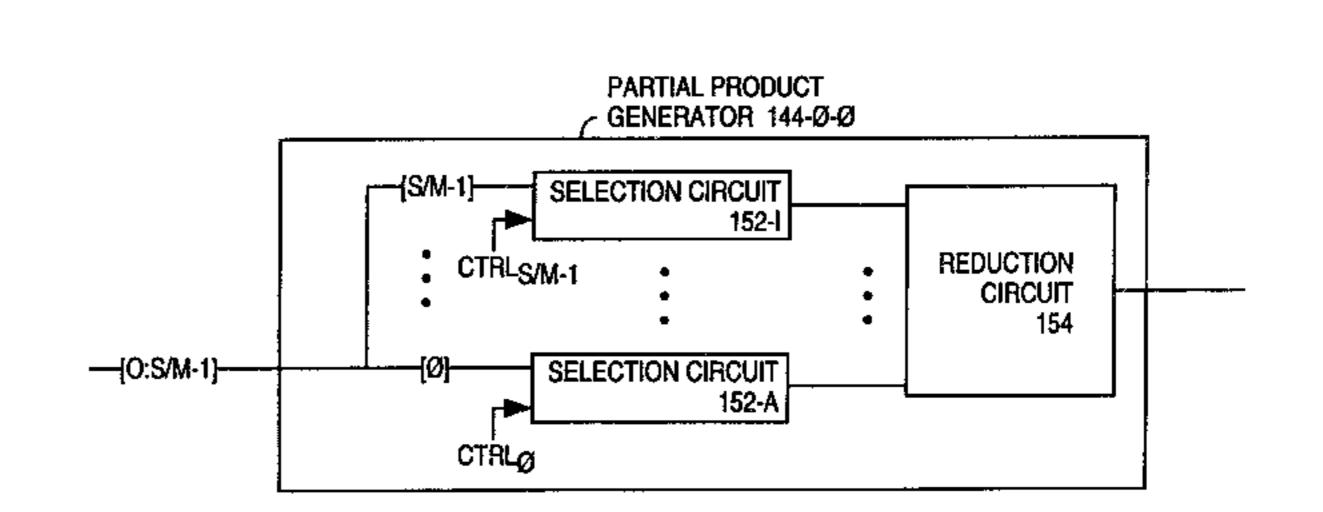

FIG. 1C is a block diagram illustrating a partial product generator from the sums of products datapath of FIG. 1A according to another embodiment of the invention;

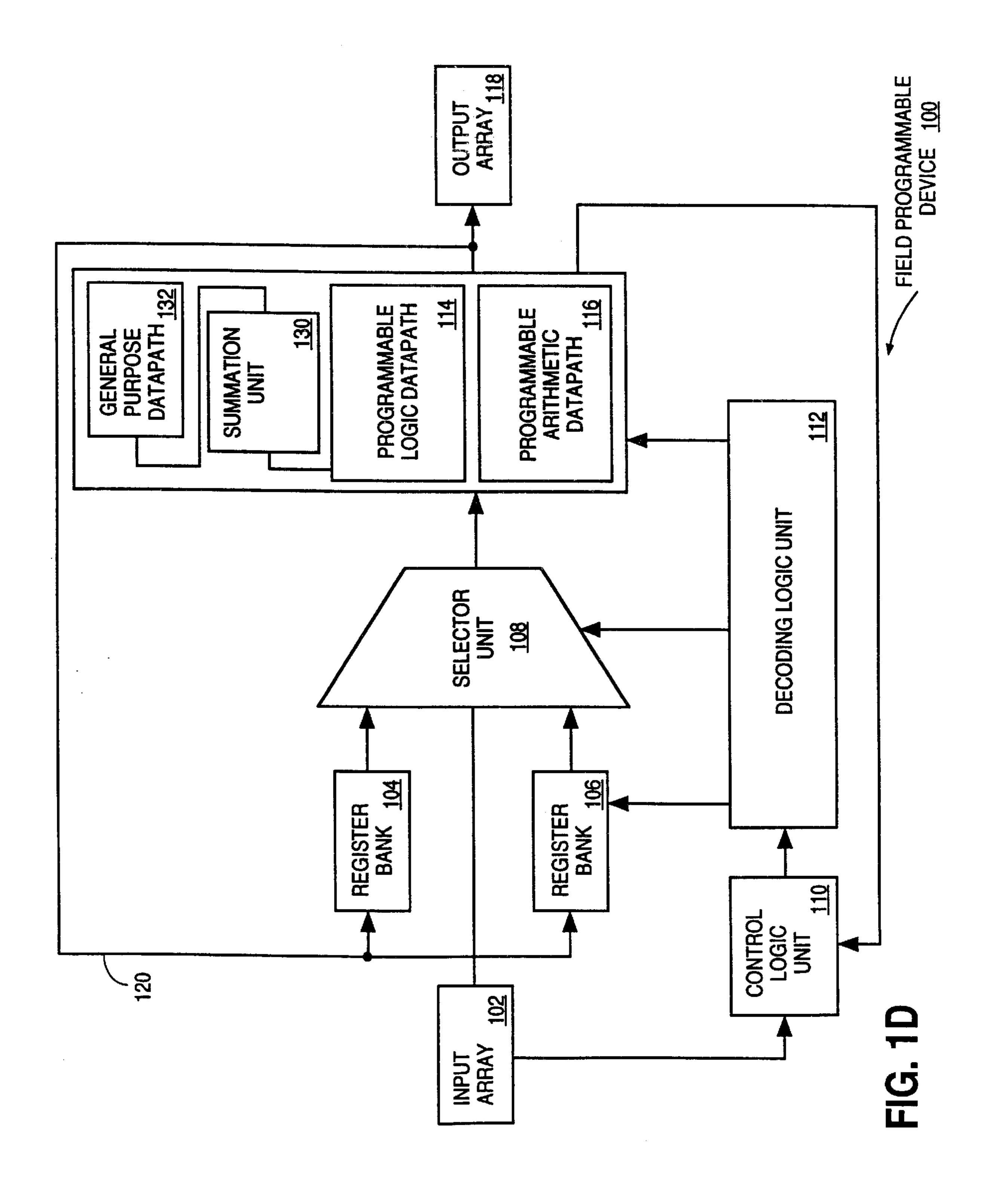

FIG. 1D is a block diagram illustrating a field programmable device according to one embodiment of the invention;

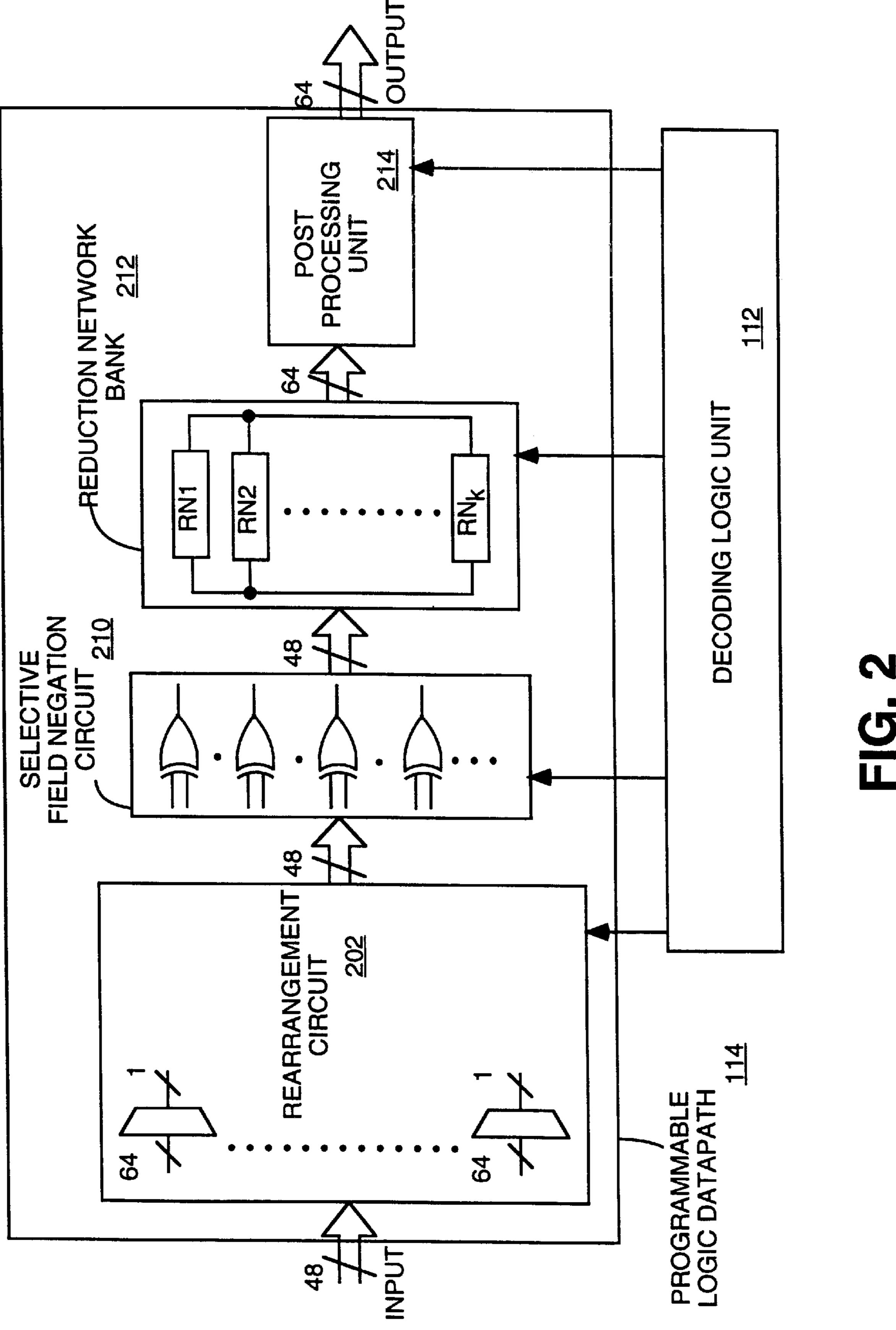

FIG. 2 is a more detailed block diagram of the programmable logic datapath and the sums of products datapath of the field programmable device according to one embodiment of the invention;

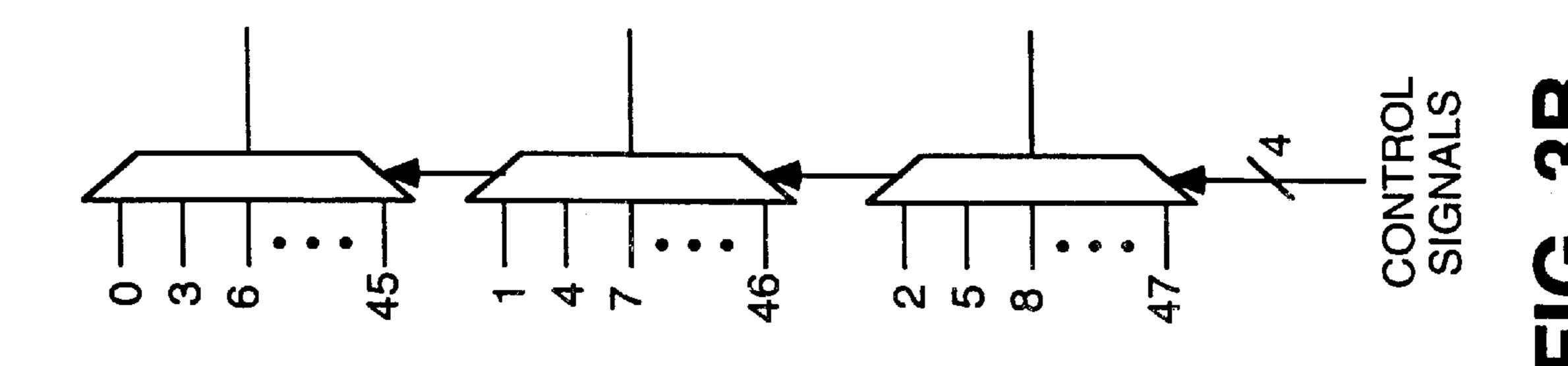

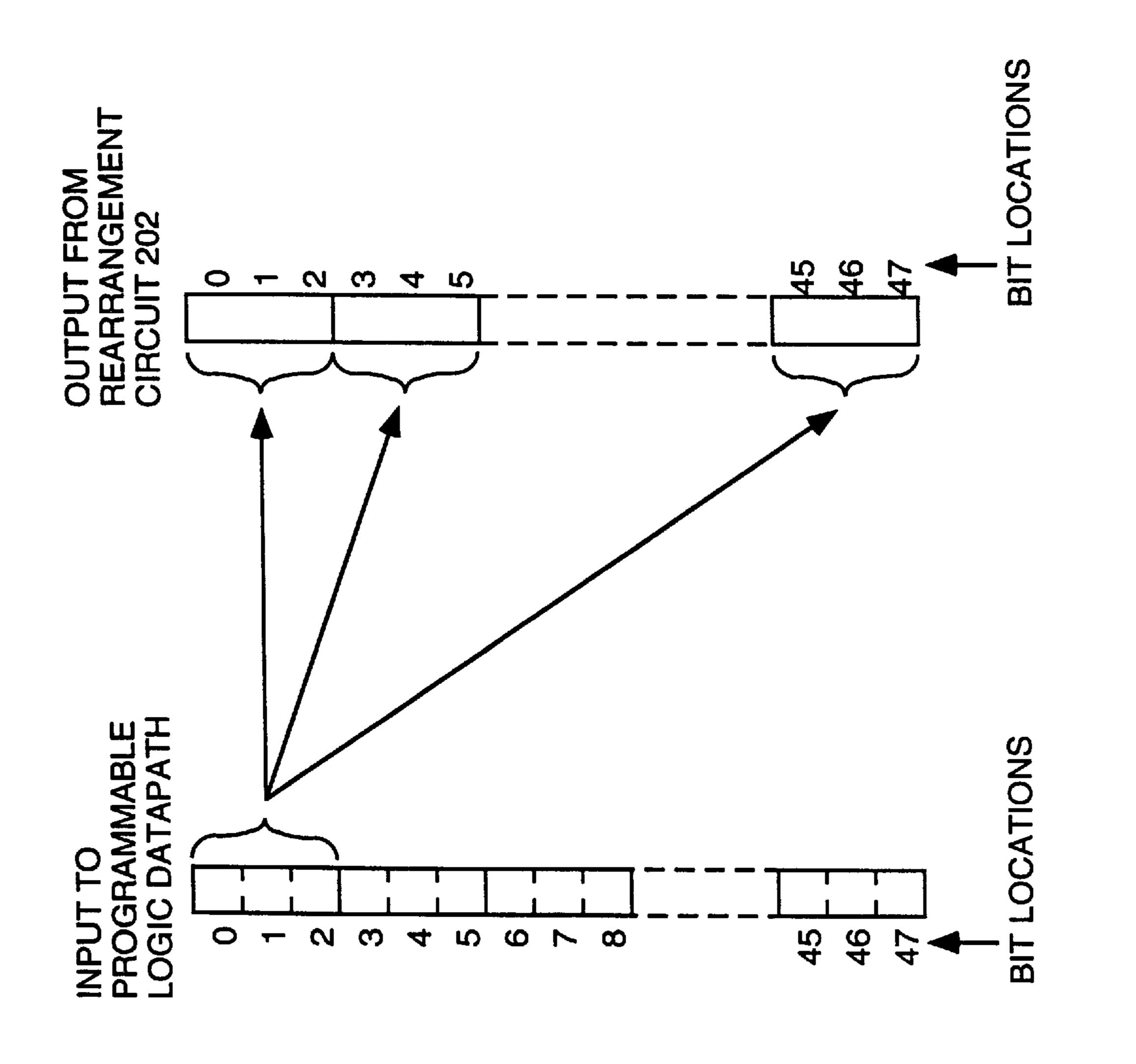

FIG. 3A is a block diagram illustrating the rearrangements of three bit fields according to one embodiment of the invention;

FIG. 3B is a block diagram illustrating one group of three multiplexers that selectively provides one of the three bit fields according to one embodiment of the invention;

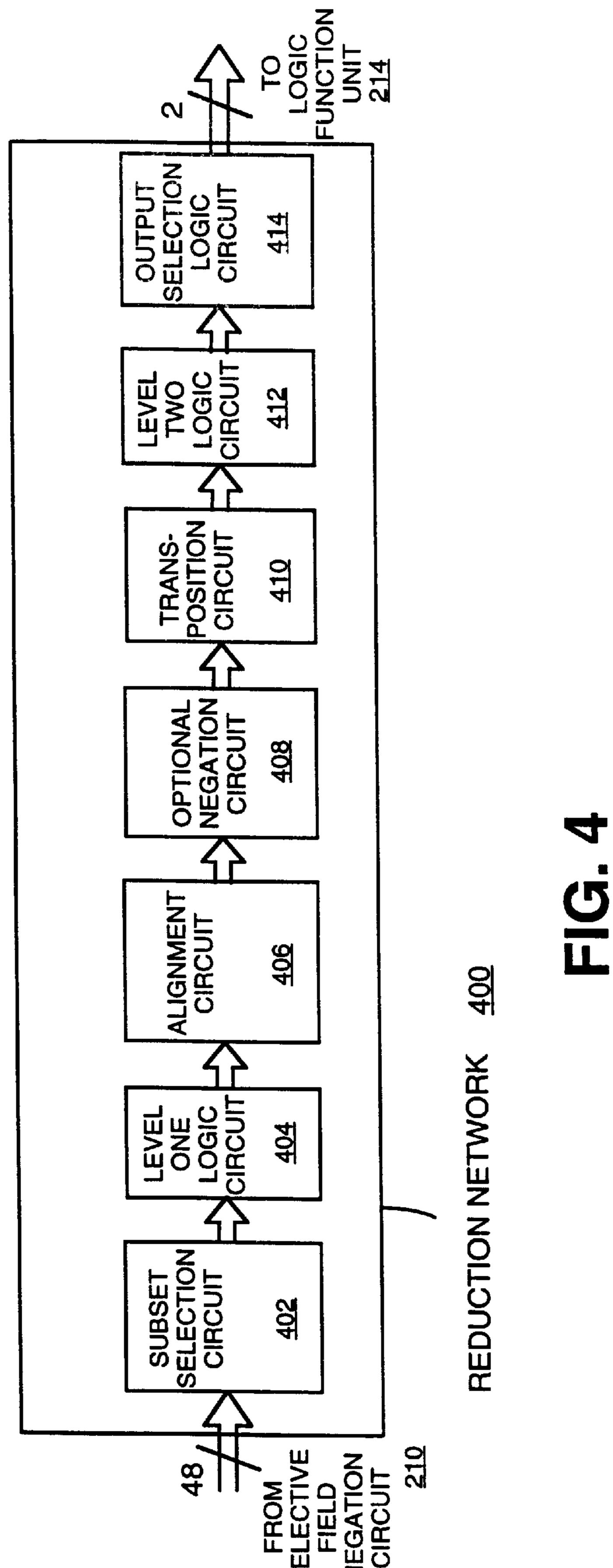

FIG. 4 is a block diagram illustrating a reduction network in the programmable logic datapath according to one embodiment of the invention;

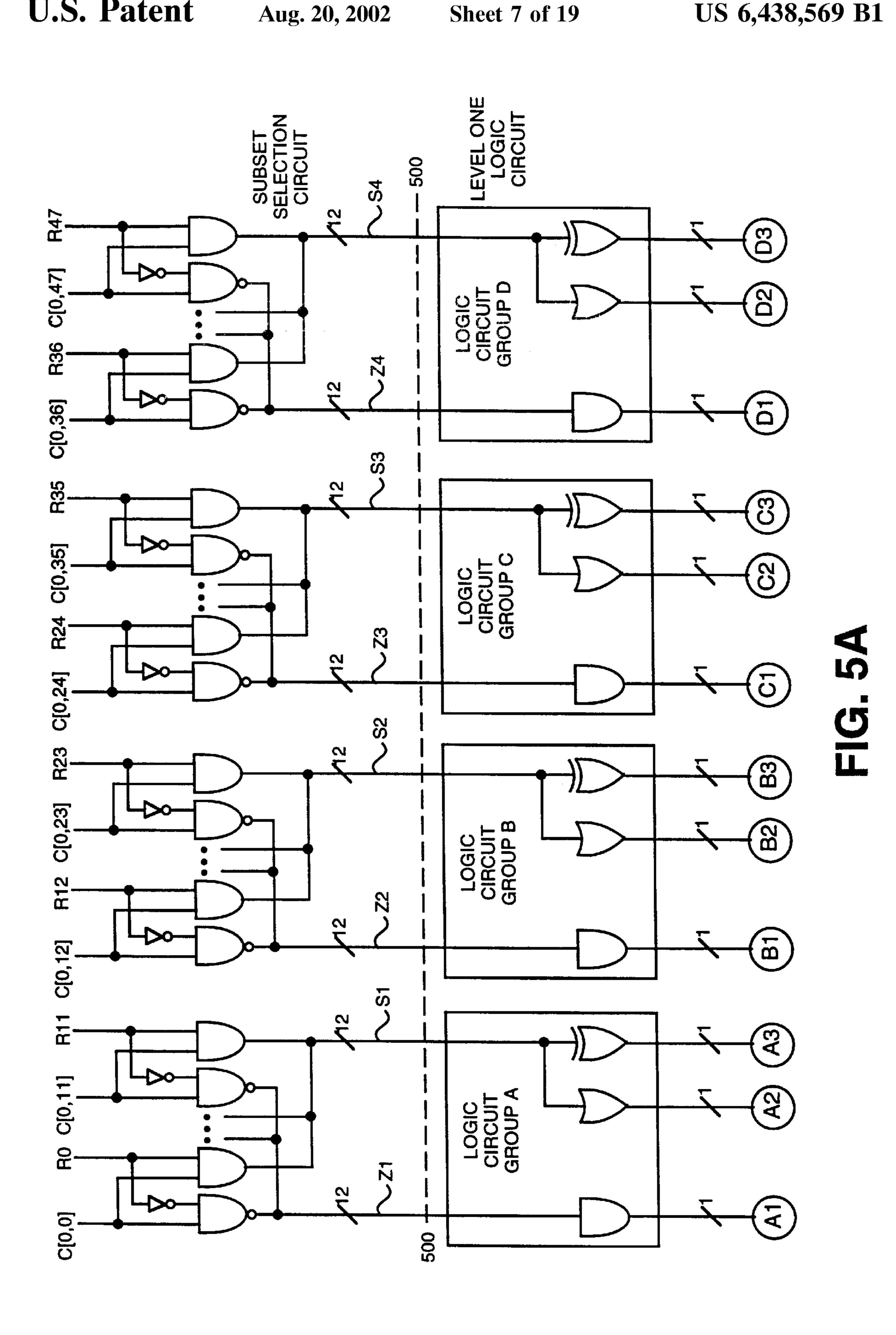

FIG. 5A is a schematic diagram illustrating the subset selection circuit 402 and the level one logic circuit 404 of FIG. 4 according to one embodiment of the invention;

FIG. 5B is a schematic diagram illustrating an accumulator-based bit generation circuit 40 located in the alignment circuit 406 of FIG. 4 according to one embodiment of the invention;

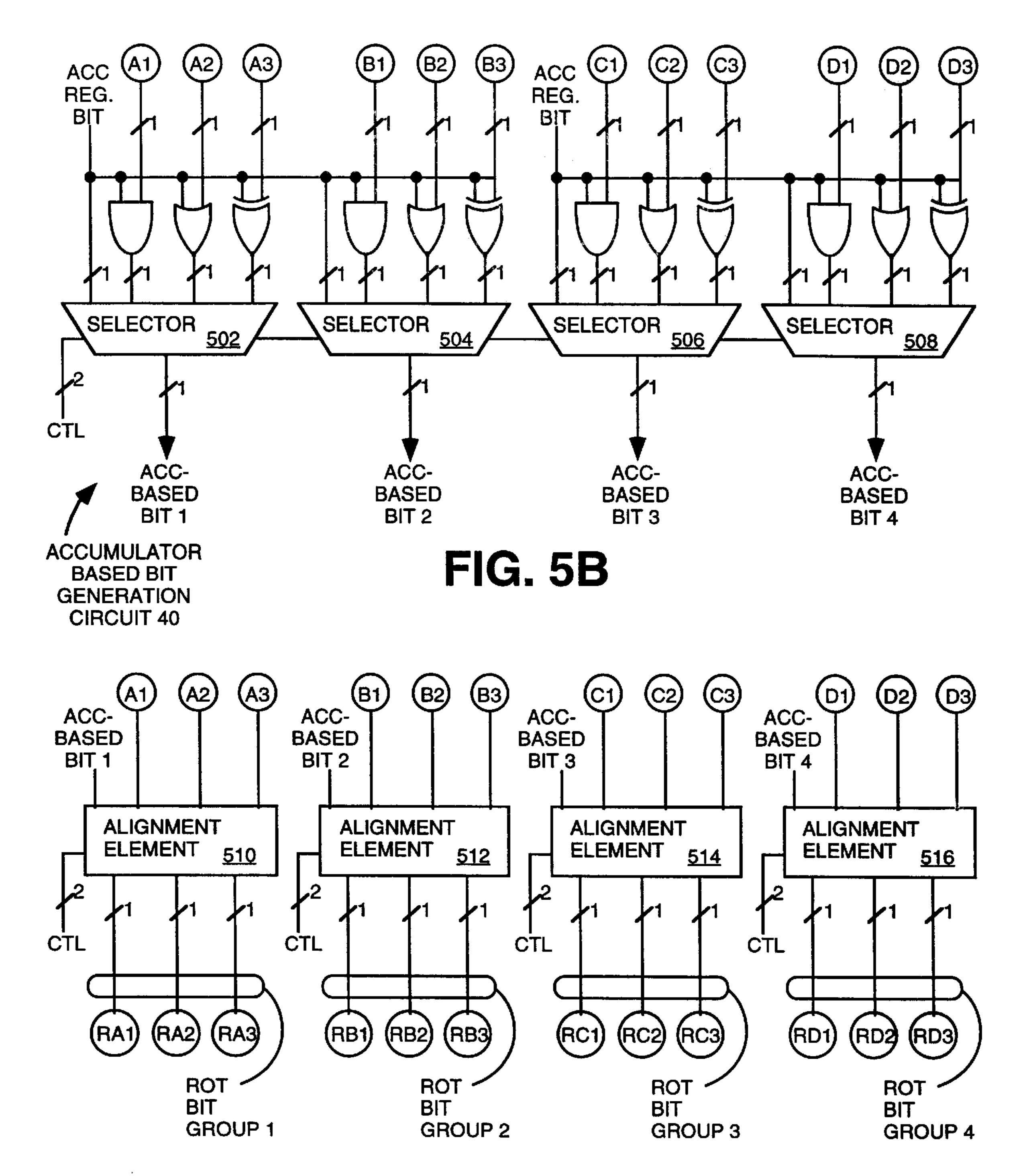

FIG. 5C is a schematic diagram illustrating the remainder of the alignment circuit 406 of FIG. 4 according to one embodiment of the invention;

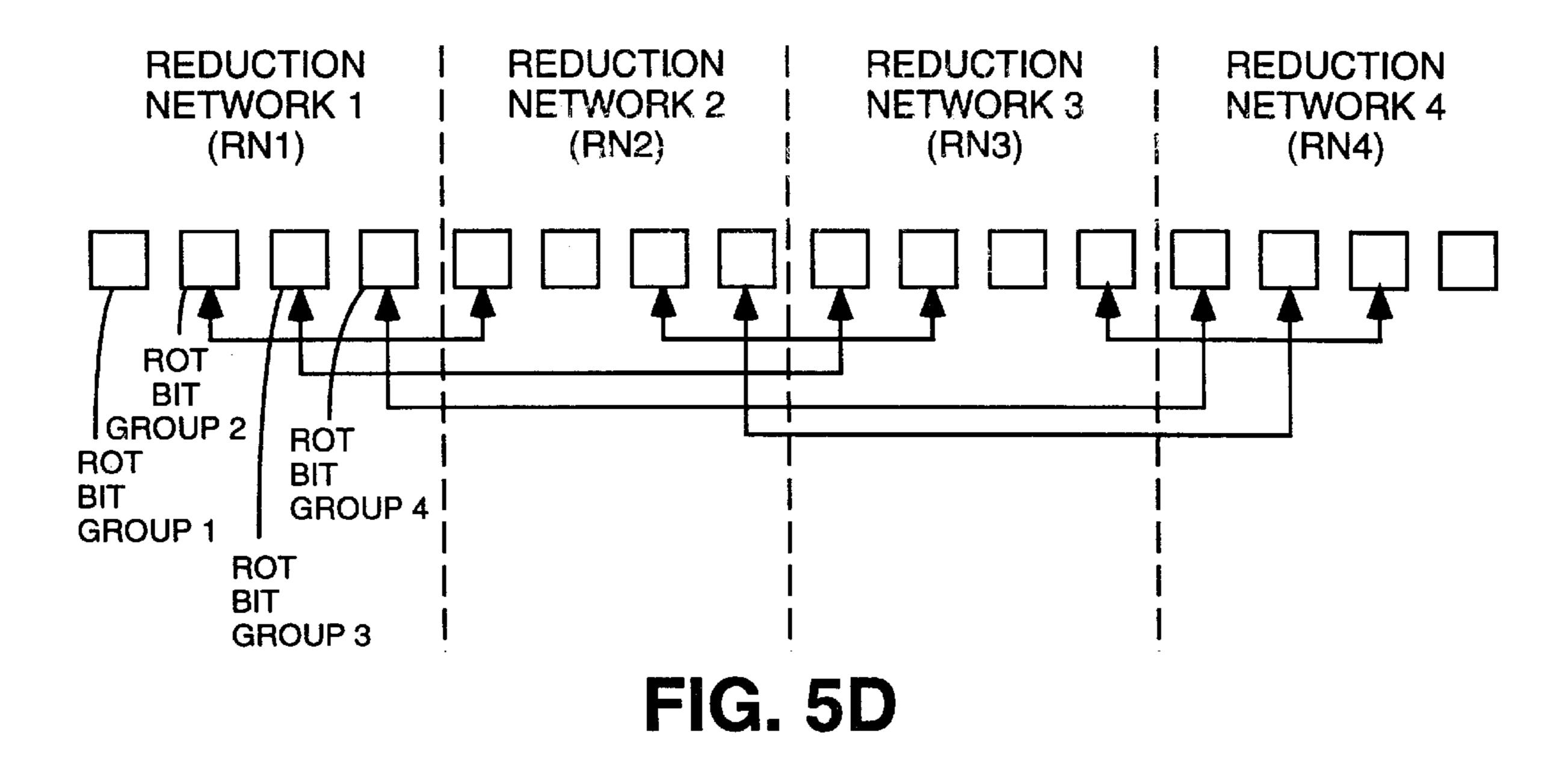

FIG. **5**D is a data flow diagram illustrating a 4×4 matrix transposition of operands between four adjacent reduction networks according to one embodiment of the invention;

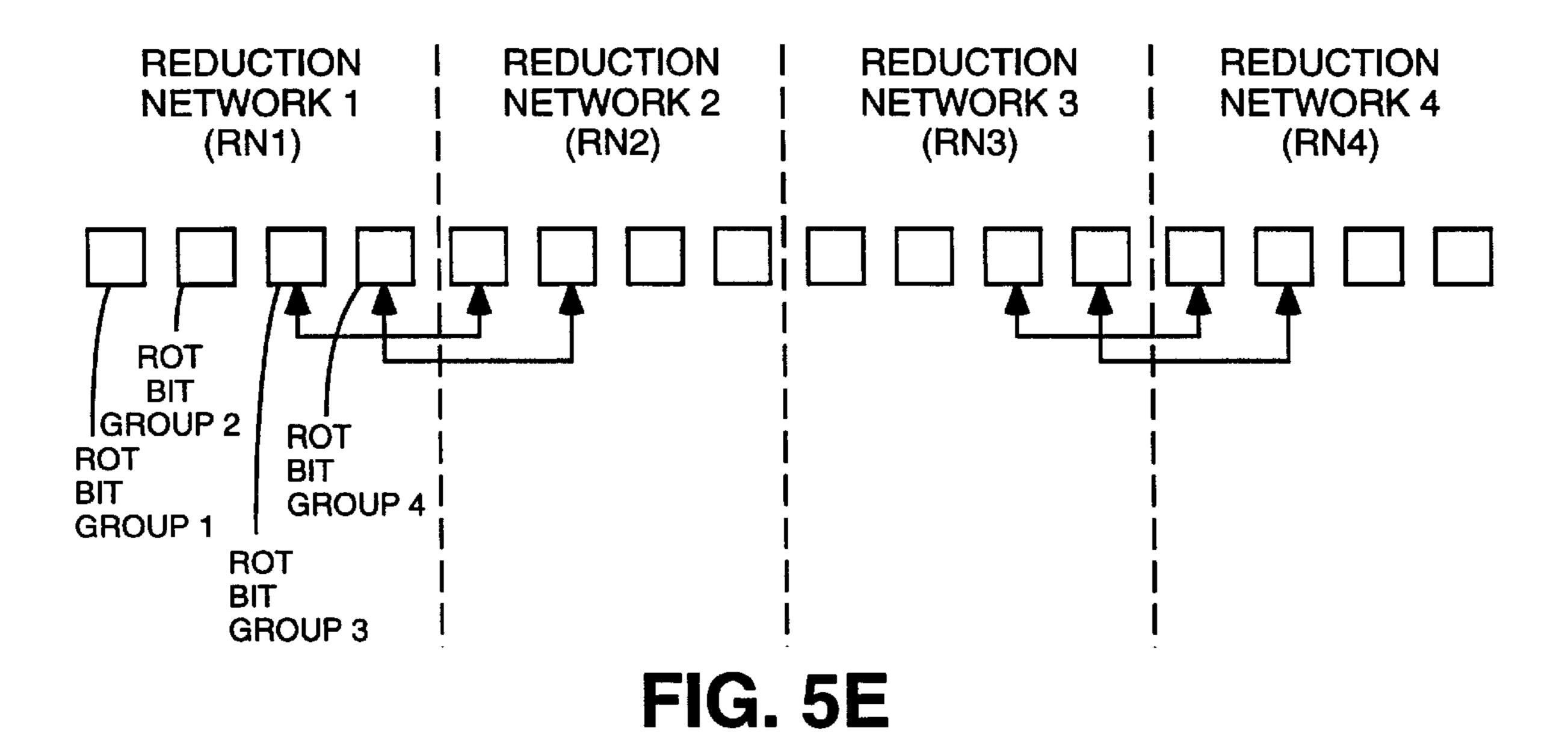

FIG. **5**E is a data flow diagram illustrating a 2×2 matrix transposition of operands between four adjacent reduction networks according to one embodiment of the invention;

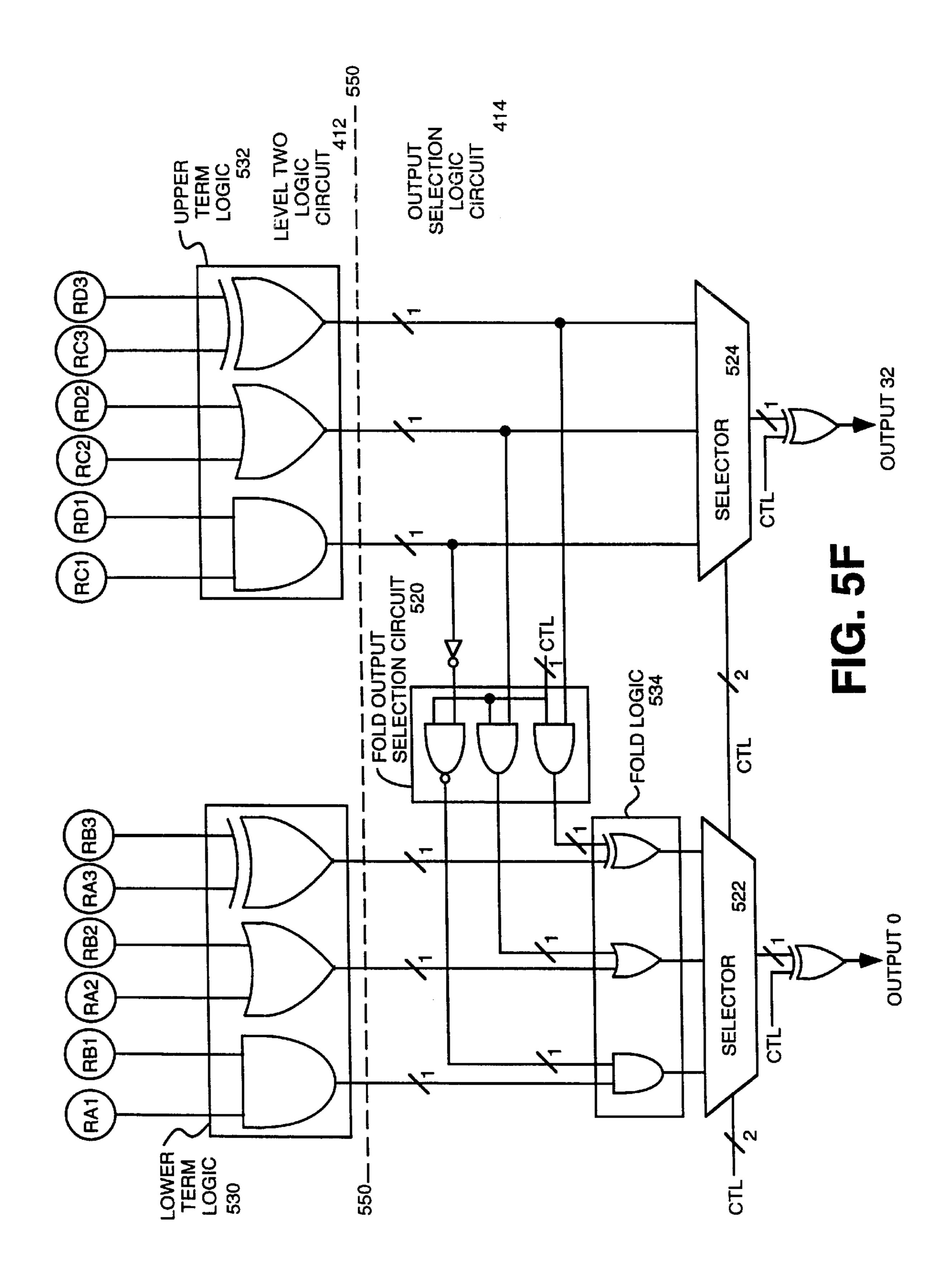

FIG. 5F is a schematic diagram illustrating the level two logic circuit 412 and the output selection circuit 414 of FIG. 4 according to one embodiment of the invention;

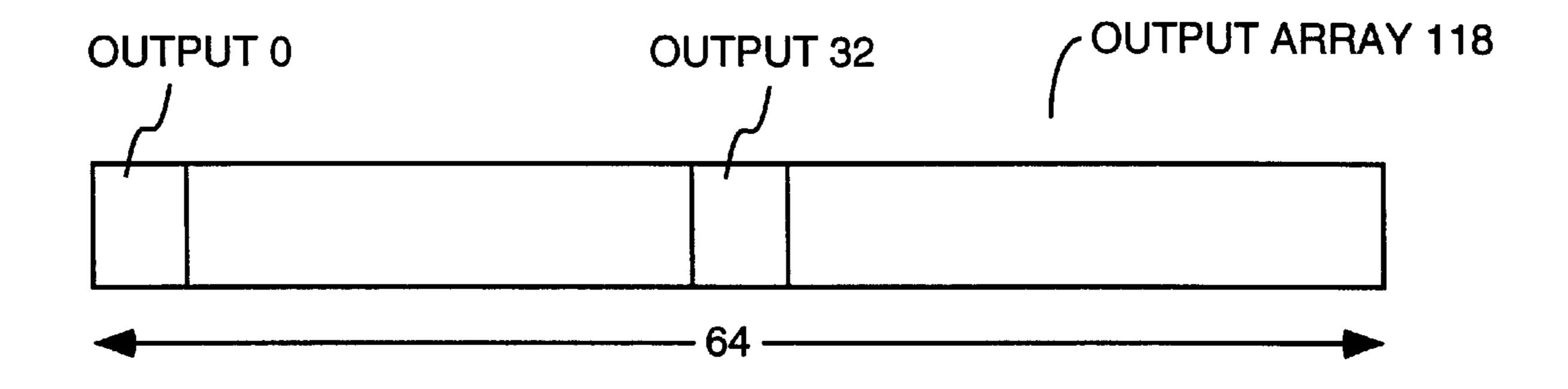

FIG. 6 is a diagram illustrating an output array according to one embodiment of the invention;

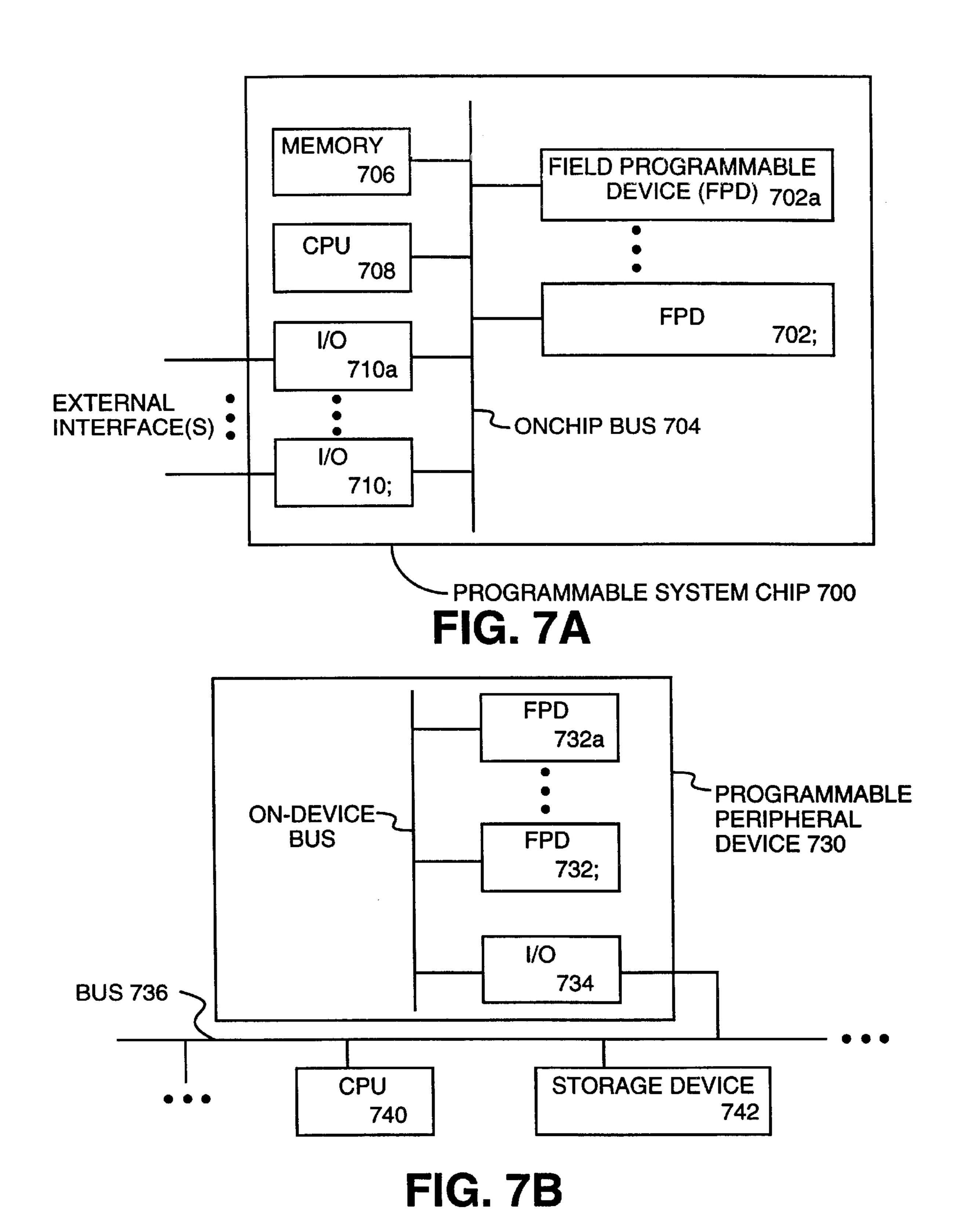

FIG. 7A is a block diagram illustrating an exemplary programmable system chip 700 according to one embodiment of the invention;

FIG. 7B is a block diagram illustrating an exemplary computer system including a programmable peripheral device 730 according to one embodiment of the invention;

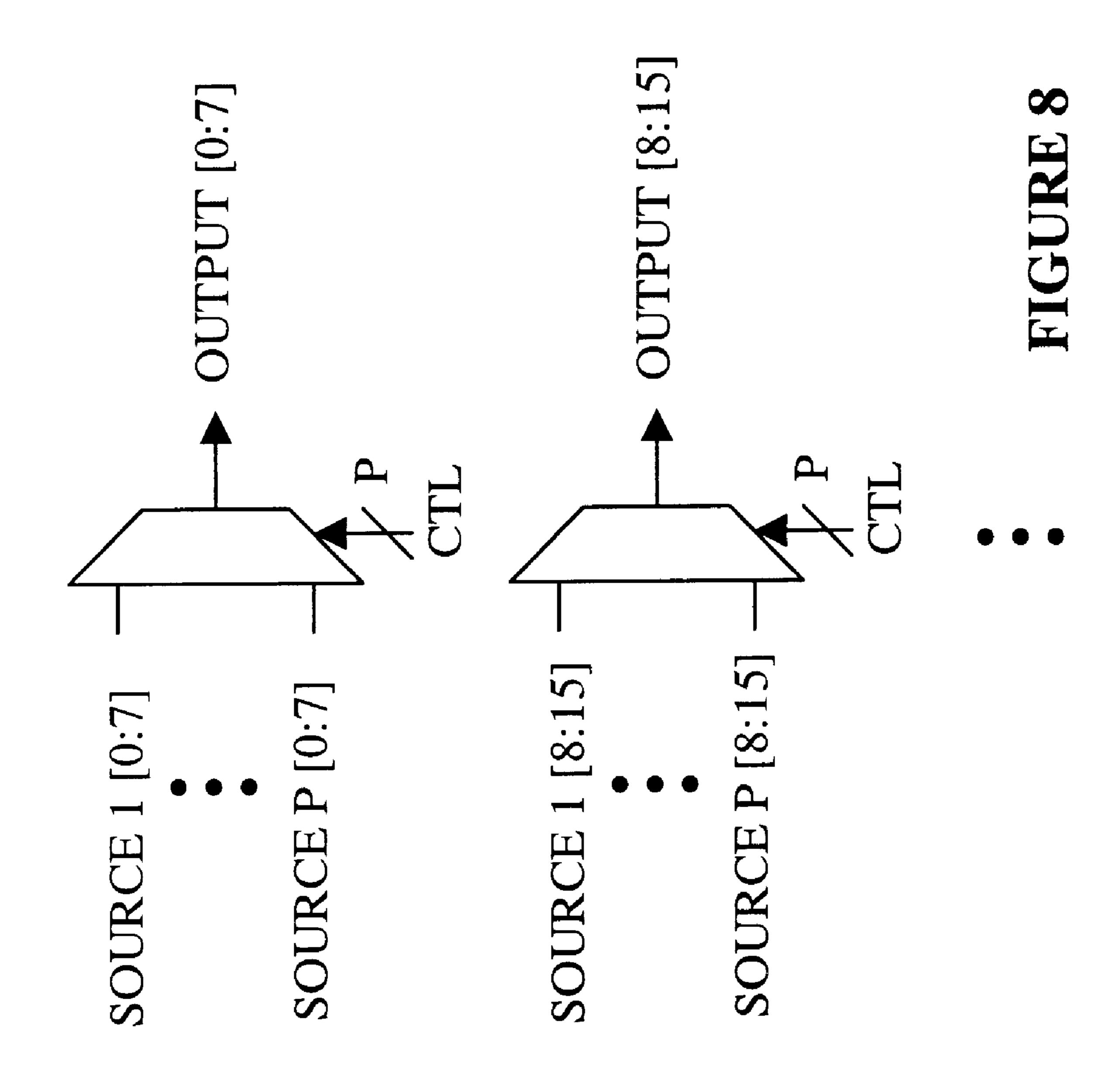

FIG. 8 illustrates the selector unit of FIG. 1D according to one embodiment of the invention;

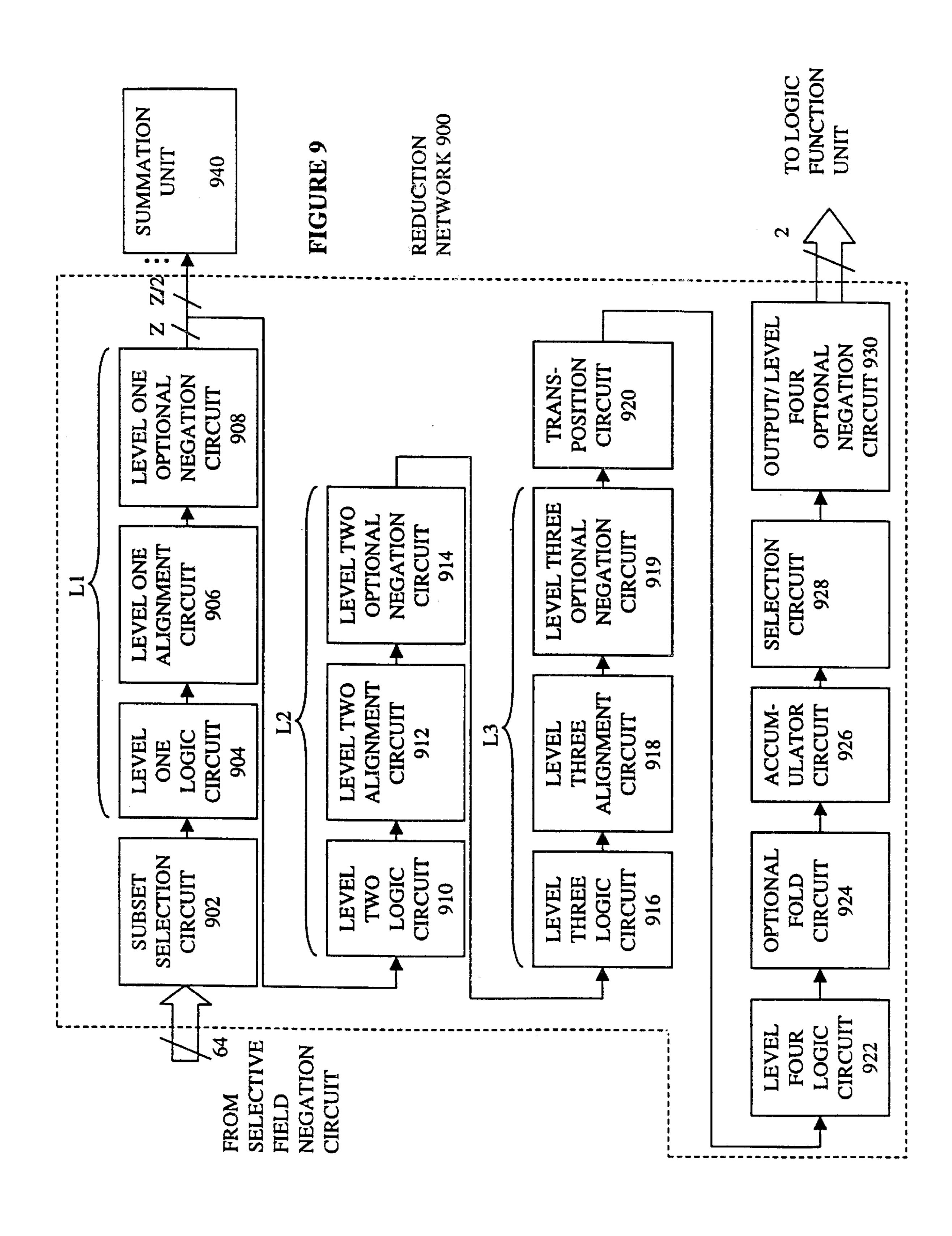

FIG. 9 is a block diagram illustrating one reduction network 900 in the reduction network bank according to an alternative embodiment of the invention;

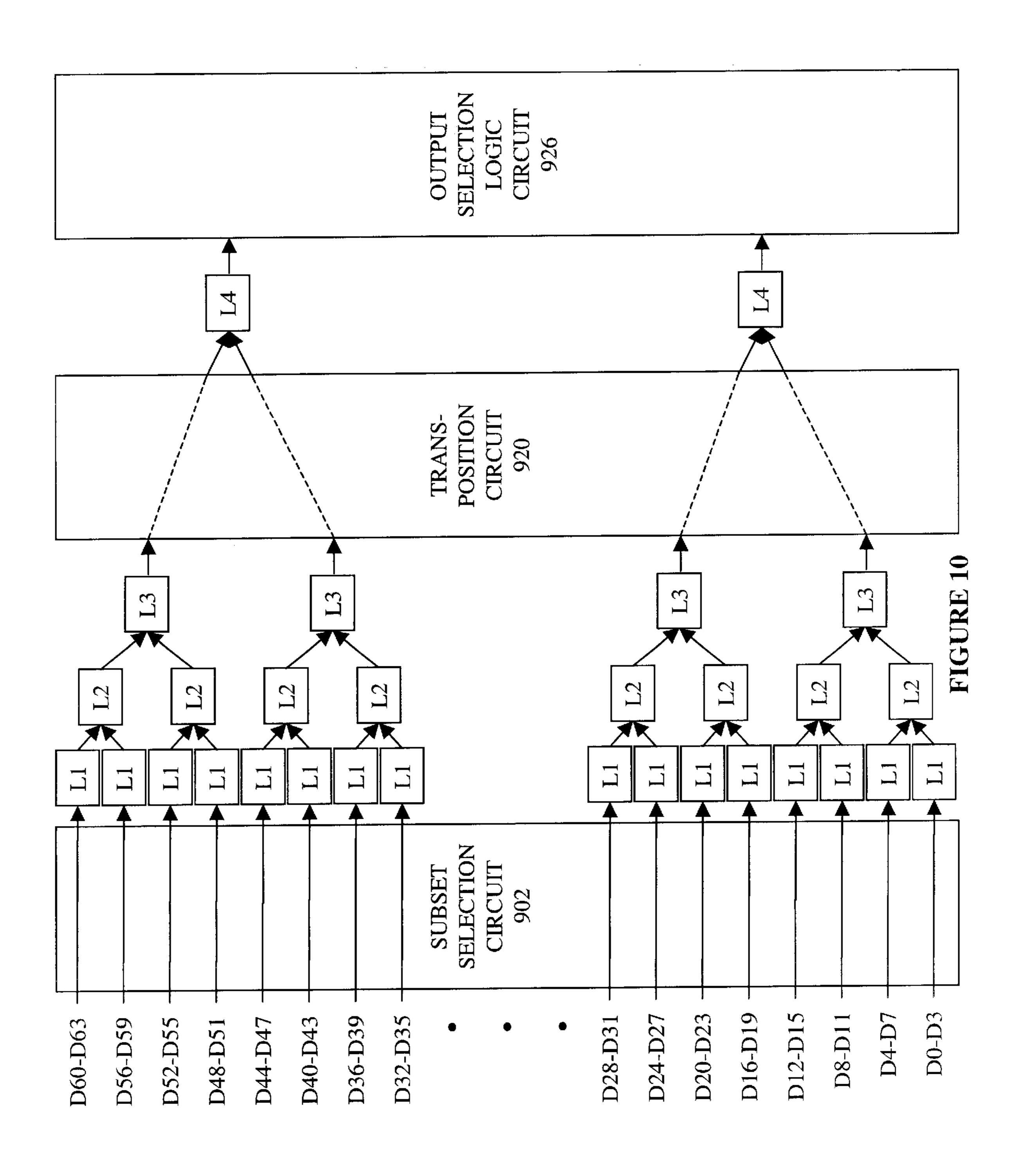

FIG. 10 is a block diagram illustrating a different representation of the reduction network of FIG. 9 according to one embodiment of the invention;

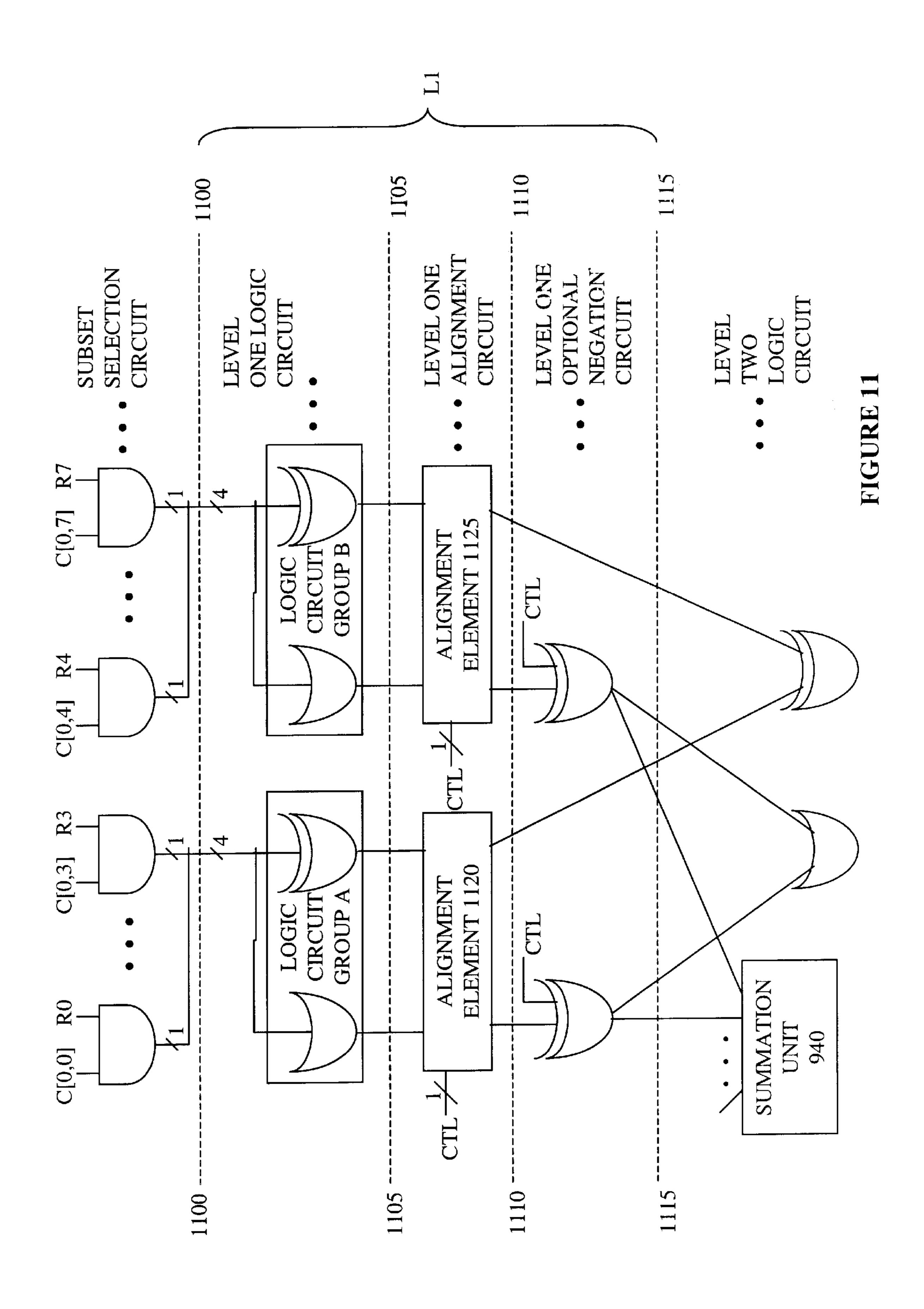

FIG. 11 is a schematic diagram illustrating parts of the subset selection circuit 902, the L1 logic level, and the level two logic circuit 910 of FIG. 9 according to one embodiment of the invention;

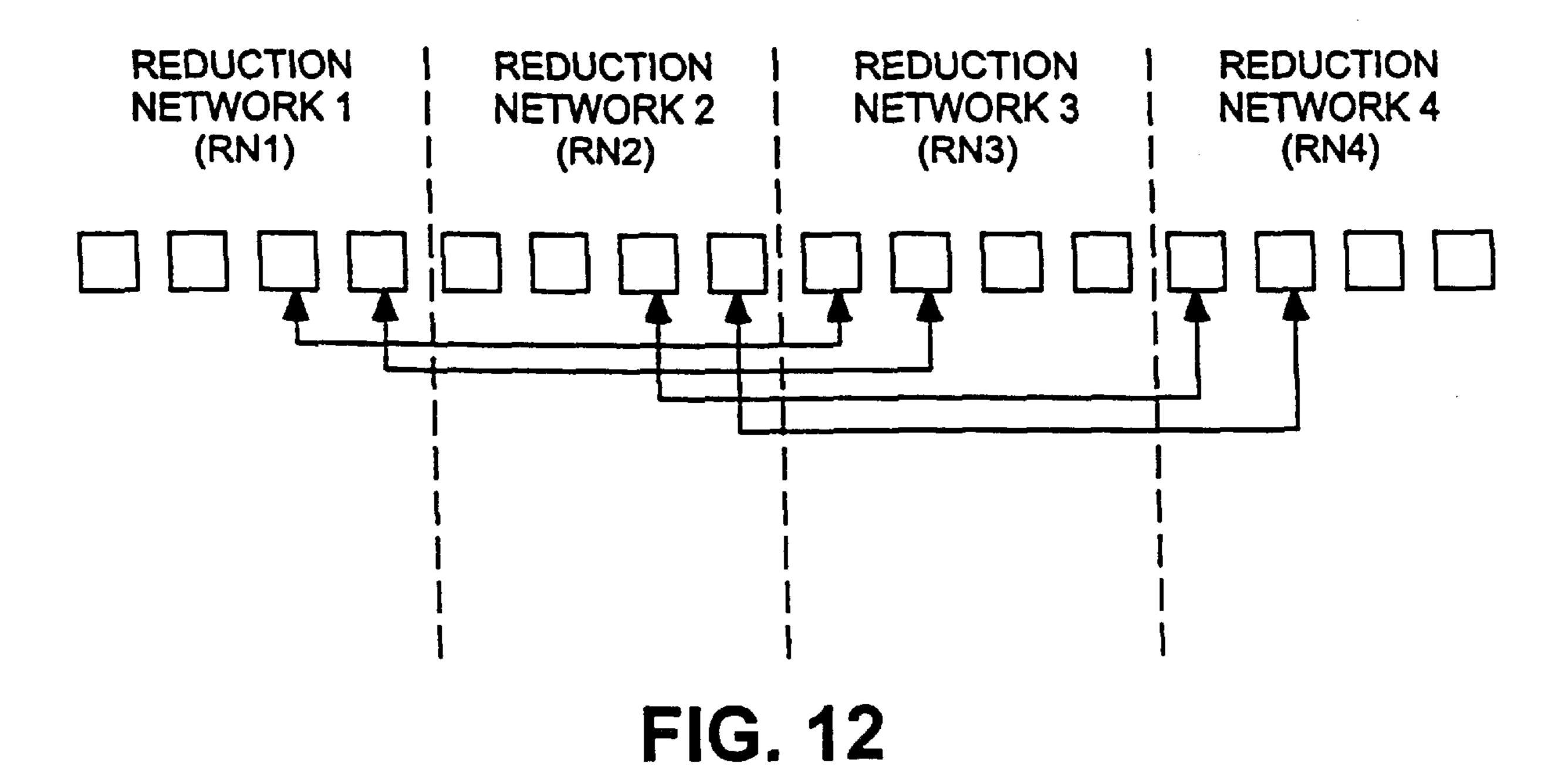

FIG. 12 illustrates another exemplary transposition option;

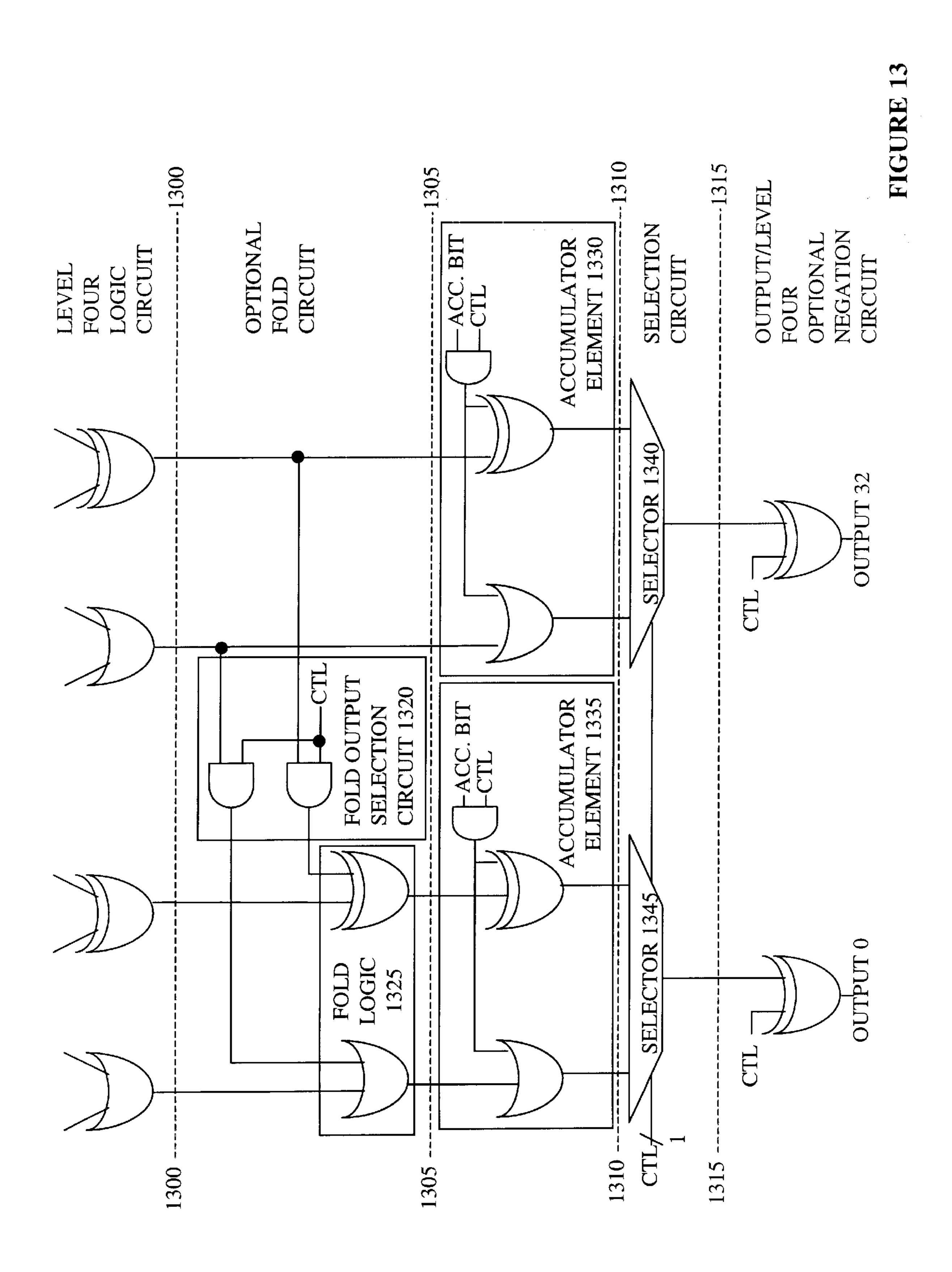

FIG. 13 is a schematic diagram illustrating parts of the L4 logic level and the output selection logic circuit of FIG. 9 according to one embodiment of the invention; and

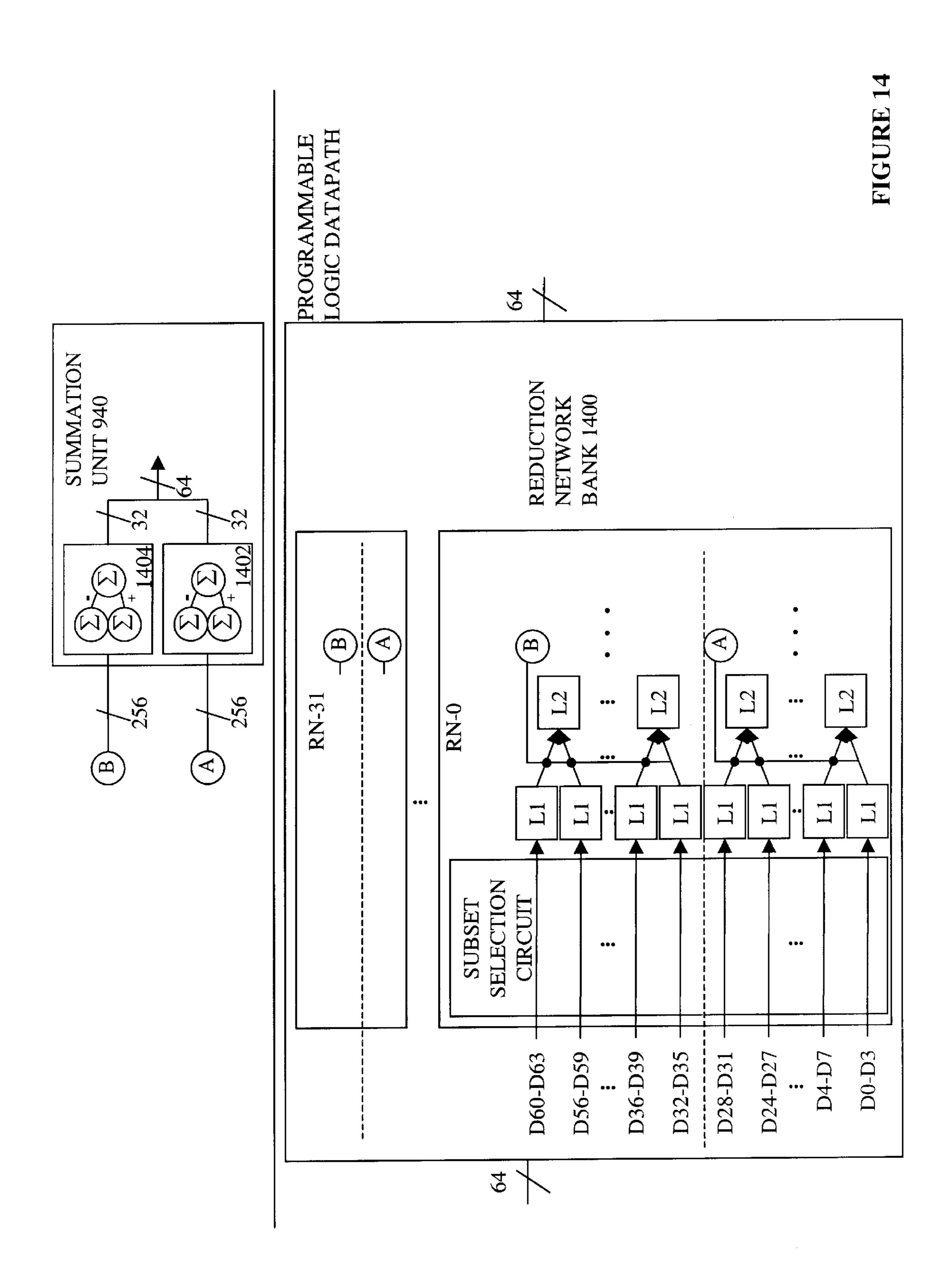

FIG. 14 is a block diagram illustrating a different representation of the coupling of the summation unit of a sums of products datapath to the reduction network bank of the programmable logic datapath of FIGS. 9–13 according to one embodiment of the invention.

#### DETAILED DESCRIPTION

In the following description, numerous specific details are set forth to provide a thorough understanding of the invention. However, it is understood that the invention may be practiced without these specific details. In other instances, well-known circuits, structures and techniques have not been shown in detail to avoid obscuring the invention.

#### Sums of Products Datapath

FIG. 1A is a block diagram illustrating a sums of products datapath according to one embodiment of the invention. FIG. 1A shows data having bit positions [0:T] are provided at a set of S inputs 140 (where S=T-1). In addition, FIG. 1A shows a number of generation units 142-0 through 142-K. Each of the generation units 142 is coupled to the inputs 140. Thus, the data on the inputs 140 is duplicated for each of the generation units 142.

Each of the generation units 142 includes M partial product generators 144. For instance, the generation unit 142-0 includes the partial product generators 144-0-0 through 144-0-M. Within each generation unit, the inputs 140 are divided into mutually exclusive input groups (e.g. [0:S/M-1], ..., {T-S/M-1:T]), one input group coupled to each of the partial product generators 144. Thus, the inputs 140 are divided into M mutually exclusive input groups, each including S/M inputs.

To provide an example, assuming that the inputs 140 are made up of 32 inputs (S=32), data bits [0:31] would be provided at the inputs 140. Each of the generation units 142 would receive the same 32 data inputs. Also assuming that each generation unit includes 8 partial product generators (M=8), the 32 data bits are divided into 8 mutually exclusive input groups, each input group including 4 inputs (S/M=32/8=4).

Data representing separate multiplicands are simultaneously provided at the inputs 140. Each of the multiplicands is to be multiplied by a separate corresponding multiplier. Although the data representing the multiplicands provided at the inputs 140 can have a number of different sarrangements, it is contemplated that the data provided on a given input group may include bits from different multiplicands. In other words, certain of the partial product generators 144 may receive bits from different multiplicands. The partial product generators 144 are controlled to provide the partial products for the multiplication of the input multiplicands by the separate corresponding multipliers (thus, a given partial product generator which is not necessary for a given operation will not be delivering a partial product for that operation).

For a given partial product generator that is providing a partial product for the current operation, the partial product

6

generator: 1) selects from the data provided on the input group which bit(s) from which multiplicand(s) is used by the partial product generator; and 2) selectively passes the selected bit(s) of the chosen multiplicand(s) based on a control input which is a function of the corresponding multiplier(s) for the chosen multiplicand(s). For instance, assume that a partial product generator receives data containing bits from both a first and second multiplicand and that the operation requires that the partial product generator provides a partial product for the multiplication of the first multiplicand by its corresponding multiplier. As such, the partial product generator would: 1) inhibit all of the data in its input group except the bit from the first multiplicand; and 2) selectively pass the bit from the first multiplicand based on a corresponding bit of the first multiplicand's corresponding multiplier. In this manner, the partial products for the multiplication of the provided multiplicands and multipliers are generated.

It should therefore be understood that the duplication of the input data to all of the generation units (and thus, the duplication of the input data to the partial product generators in each of the generation units) requires that different ones of the partial product generators be controlled to operate on different multiplicand/multiplier pairs. As such, the partial product generators that are to provide the partial products for a given multiplicand/multiplier pair must be controlled to select from the data the multiplicand they are to consider and operate on that multiplicand with the appropriate multiplier data to produce the partial products for that multiplicand/ multiplier pair.

To continue this description, it should be understood that the circuit of FIG. 1 relies on the concept that  $2^{n-1}+2^{n-2}+2^{n-3}=2^n-2^{n-3}$ . For example, 7=4+2+1=8-1. This technique can be generalized to longer strings of consecutive 1 bits, and can be used to transform any string of consecutive 1 bits in the binary representation of a number into a pair of 1 bits, one of which is negated. When there are 3 or more consecutive 1 bits, this transformation reduces the total number of 1 bits.

This recoding technique replaces a string of positive bits with one positive and one negative bit, thereby creating negative bits. Signed coefficients and/or data also create the need for bits that are interpreted as negative. For example, an N-bit representation of a signed number in 2's complement form is as follows:  $-b_{N-1}2^{N-1}+\Sigma b_i2^i$ , where i ranges from 0 to to N-2. In other words, the uppermost bit is negative; the others are positive. This recoding technique is not limited to, but is particularly useful for, the representation of constant coefficients. As such, in one embodiment of the invention the multiplier's used in the circuit of FIG. 1A are constants.

Based on the above recoding technique, the circuit of FIG. 1A includes a set of summation circuits 146, 148, and 150. The partial product generators 144 in mutually exclusive groups of the generation units 142 are coupled to the summation circuits 146 and 148 according to a predefined pattern as described later herein (e.g., in FIG. 1A the generation units 142-0 through 142-I are coupled to the summation circuit 146, while the generation units 142-J through 142-K are coupled to the summation circuit 148). The output of the summation circuits 146 and 148 are coupled to the summation circuit 150. In particular, the output of the summation circuits 146 and 148 are respectively treated as a positive and negative sum when provided 65 to the summation circuit 150 (in other words, the summation circuit 150 acts as a subtraction circuit). The output of the summation circuit 150 is S bits representing the sum of the

products for the multiplicands provided at the inputs 140 and their corresponding multipliers.

While a number of different predefined patterns could be used for coupling the generation units to the summation circuits **146** and **148**, the following Table 1 illustrates the predefined pattern according to one embodiment of the invention. In particular, Table 1 defines the significance assigned to each of the partial product generators **144** in each of the generation units **142**. Table 1 assumes that there are 32 inputs, 32 generation units, and 8 partial product generators per generation unit; therefore there are 4 inputs to each partial product generator.

8

with unsigned parts of the numbers produce rows of negative bits that are shifted up in significance. The intended way to support low precision data with this approach is to map the problem so that the answer comes out shifted up by 9 bits (or more) and then to shift the result as necessary. While the embodiment described with reference to Table 1 is intended to handle the requirements of the types of problems identified earlier (sums of products over low to moderate precision data), it is understood that this is a design choice and that alternative embodiments of the invention can handle higher precision data.

TABLE 1

| Signif.         | Positive sources [Generation Unit 142-X], [Partial Product Generators 144-X-Y] | Positive<br>Depth | Negative Sources [Generation Unit 142-X], [Partial Product Generators 144-X-Y] | Negative<br>Depth |

|-----------------|--------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------|-------------------|

| 2°              | 0, 0–3                                                                         | 4                 |                                                                                |                   |

| 2 <sup>1</sup>  | 0, 4–7                                                                         | 4                 |                                                                                |                   |

| $2^{2}$         | 1, 0–3                                                                         | 4                 |                                                                                |                   |

| $2^{3}$         | 1, 4–7                                                                         | 4                 |                                                                                |                   |

| 24              | 2, 0–3                                                                         | 4                 |                                                                                |                   |

| 2 <sup>5</sup>  | 2, 4–7                                                                         | 4                 |                                                                                |                   |

| 2 <sup>6</sup>  | 3, 0-7                                                                         | 8                 |                                                                                |                   |

| 27              | 4, 0-7                                                                         | 8                 |                                                                                |                   |

| 2 <sup>8</sup>  | 5, 0-7                                                                         | 8                 |                                                                                |                   |

| 2°              | 6, 0-7                                                                         | 8                 | 25, 0–1                                                                        | 2                 |

| 2 <sup>10</sup> | 7, 0–7                                                                         | 8                 | 25, 2–3                                                                        | 2                 |

| 2 <sup>11</sup> | 8, 0-7                                                                         | 8                 | 25, 4–5                                                                        | 2                 |

| $2^{12}$        | 9, 0-7                                                                         | 8                 | 25, 6–7                                                                        | 2                 |

| 2 <sup>13</sup> | 10, 0-7                                                                        | 8                 | 26, 0–1                                                                        | 2                 |

| 214             | 11, 0–7                                                                        | 8                 | 26, 2–4                                                                        | 3                 |

| 2 <sup>15</sup> | 12, 0-7                                                                        | 8                 | 26, 5–7                                                                        | 3                 |

| 2 <sup>16</sup> | 13, 0-7                                                                        | 8                 | 27, 0–2                                                                        | 3                 |

| 2 <sup>17</sup> | 14, 0-7                                                                        | 8                 | 27, 3–5                                                                        | 3                 |

| 2 <sup>18</sup> | 15, 0-7                                                                        | 8                 | 27, 6–7 & 28, 0–1                                                              | 4                 |

| 2 <sup>19</sup> | 16, 0-7                                                                        | 8                 | 28, 2–4                                                                        | 3                 |

| $2^{20}$        | 17, 0–7                                                                        | 8                 | 28, 5–7                                                                        | 3                 |

| $2^{21}$        | 18, 0-7                                                                        | 8                 | 29, 0–2                                                                        | 3                 |

| $2^{22}$        | 19, 0–7                                                                        | 8                 | 29, 3–5                                                                        | 3                 |

| $2^{23}$        | 20, 0-7                                                                        | 8                 | 29, 6-7 & 30, 0-1                                                              | 4                 |

| $2^{24}$        | 21, 0-7                                                                        | 8                 | 30, 2–4                                                                        | 3                 |

| $2^{25}$        | 22, 0-7                                                                        | 8                 | 30, 5–7                                                                        | 3                 |

| $2^{26}$        | 23, 0–3                                                                        | 4                 | 31, 0–1                                                                        | 2                 |

| $2^{27}$        | 23, 4–7                                                                        | 4                 | 31, 2–3                                                                        | 2                 |

| $2^{28}$        | 24, 0–3                                                                        | 4                 | 31, 4–5                                                                        | 2                 |

| $2^{29}$        | 24, 4–7                                                                        | 4                 | 31, 6–7                                                                        | 2.                |

The arrangement of positive and negative sources is intended to cover the requirements of the types of problems identified earlier: sums of products over low to moderate precision data. Negative bits are found starting at 2<sup>9</sup> because with moderate precision data, the cross product of sign bits

By way of example, consider the following problem:  $x_0k_0+x_1k_1+x_2k_2+x_3k_3+x_4k_4$ , where  $x_i$ , is a 6 bit unsigned number and  $k_i$  is a 12 bit signed number where  $k_0=9$ ,  $k_1=-15$ ,  $k_2=40$ ,  $k_3=892$ ,  $k_4=2047$ . Table 2 shows the binary form of the coefficients before and after recoding:

TABLE 2

| Coefficient                                                | Binary                                                                                                                                                                                | Recoded                                                                    | Pos<br>bits                   | Neg<br>bits    |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|----------------|

| $egin{array}{c} k_0 \ k_1 \ k_2 \ k_3 \ k_4 \ \end{array}$ | 0, 0, 0, 0, 0, 0, 0, 0, 1, 0, 0, 1<br>-1, 1, 1, 1, 1, 1, 1, 1, 0, 0, 0, 1<br>0, 0, 0, 0, 0, 0, 1, 0, 1, 0, 0, 0<br>0, 0, 1, 1, 0, 1, 1, 1, 1, 1, 0, 0<br>0, 1, 1, 1, 1, 1, 1, 1, 1, 1 | 0, 0, 0, 0, 0, 0, 0, 0, 1, 0, 0, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, | 0, 3<br>0<br>3, 5<br>10<br>11 | 4<br>2, 7<br>0 |

With reference to Table 2, the bits in the same bit positions for the recoded coefficients are referred to as columns. The columns are referred to starting with zero for the rightmost column and counting up. Thus, there are a total of 2 positive bits in column 0; none in columns 1 and 2; 2 in column 3; 5 none in column 4; and 1 each in columns 5, 10, and 11. Also, there is one negative bit each in columns 0, 2, 4, and 7. To map this problem in the pattern shown in Table 1, the result is shifted up at least 9 positions, since the least significant negative bit available is in column 9. However, to simplify mapping, the result is shifted up by 11 in this example. (again, it is understood that the predefined pattern in Table 1 is a design choice; thus, predefined patterns different from the one in Table 1 are contemplated and these different predefined patterns may provide/necessitate different mapping(s)).

Since the data in this exemplary problem are 6 bit values, each non-zero coefficient position leads to 6 places where a data bit is admitted into the summation circuits. A non-zero coefficient at significance  $2^i$  leads to data bits at  $2^i$ ,  $2^{i+1}$ , ...,  $2^{1+5}$ . If we number the data bits of  $x_i$   $x_{i0}$  through  $x_{i5}$ , Table 3 shows the summation requirements.

TABLE 3

| Column | Positive                                 | Negative                 |

|--------|------------------------------------------|--------------------------|

| 11     | $X_{00}, X_{10}$                         | X <sub>40</sub>          |

| 12     | $X_{01}, X_{11}$                         | $X_{41}$                 |

| 13     | $x_{02}, x_{12},$                        | $X_{42}, X_{30}$         |

| 14     | $X_{03}, X_{13}, X_{00}, X_{20}$         | $X_{43}, X_{31}$         |

| 15     | $X_{04}, X_{14}, X_{01}, X_{21}$         | $x_{44}, x_{32}, x_{30}$ |

| 16     | $X_{05}, X_{15}, X_{02}, X_{22}, X_{20}$ | $X_{45}, X_{33}, X_{11}$ |

| 17     | $x_{03}, x_{23}, x_{21}$                 | $x_{34}, x_{12}$         |

| 18     | $x_{04}, x_{24}, x_{22}$                 | $X_{35}, X_{13}, X_{30}$ |

| 19     | $x_{05}, x_{25}, x_{23}$                 | $X_{14}, X_{31}$         |

| 20     | <b>X</b> <sub>24</sub>                   | $x_{15}, x_{32}$         |

| 21     | $x_{25}, x_{30}$                         | X <sub>33</sub>          |

| 22     | $X_{31}, X_{40}$                         | X <sub>34</sub>          |

| 23     | $x_{32}, x_{41}$                         | X <sub>35</sub>          |

| 24     | $X_{33}, X_{42}$                         |                          |

| 25     | $X_{34}, X_{43}$                         |                          |

| 26     | $X_{35}, X_{44}$                         |                          |

| 27     | X <sub>45</sub>                          |                          |

In each column, the depth of the positive and negative sources fits within the available depths for that column (as defined in Table 1). Therefore, the problem can be mapped in this way as long as the data bits can be applied to the right 45 ones of the inputs 40.

It should be noted that there will be many possible mappings of multiplicands (data) and corresponding multiplier (e.g., coefficient) bits for any given problem, and that finding any of the possible mappings can be performed by an 50 automated tool.

FIGS. 1B and 1C are block diagrams illustrating partial product generators for the sums of products datapath of FIG. 1A according to alternative embodiments of the invention. In particular, FIG. 1B illustrates an embodiment of the 55 partial product generator 144-0-0. As previously described, the partial product generator 144-0-0 is coupled to inputs [0:S/M-1] of the inputs 140. Each of these inputs is coupled as the input to a multiplexer. This multiplexer is controlled to select one of the data bits provided on the inputs [0:S/ 60] M-1]. The output of this multiplexer is coupled as one of the inputs to an AND gate. The other input to the AND gate is a bit of the selected multiplicand's corresponding multiplier (it should be noted, that if this partial product generator is not needed for the current operation, the input to this AND 65 gate is controlled such that the output of the AND gate will not affect the operation—e.g. the AND gate outputs a zero

10

signal). While particular circuits are shown in FIG. 1B (e.g., an AND gate), alternative embodiments could be implemented using different circuitry that provides a similar output).

In FIG. 1C, an embodiment of the partial product generator 144-0-0 for an alternative embodiment of the invention is illustrated. As in FIG. 1B, the partial product generator 144-0-0 of FIG. 1C is coupled to inputs [0:S/M-1] of the inputs 140. However, in FIG. 1C each of the inputs [0:S/M-1] is coupled to a selection circuit 152-0 through 152-1. Each of the selection circuits 152 also receive an independent control signal that controls whether the data input to that selection circuit is provided at its output. While such operation can be performed by a number of different circuit, in one embodiment of the invention each of the selection circuits is an AND gate.

The outputs of the selection circuits 152 are coupled to a reduction circuit 154 which reduces the data to a single bit. Thus, the selection circuits 152 of the partial product generator 144-0-0 act to inhibit the passing of data bits upon which the partial product generator is not to consider in the generation of its partial product, while the other selection circuit(s) 152 of the partial product generator are controlled by bits of the corresponding multiplier(s). The reduction circuit 154 then combines the outputs of the selection circuits to provide a single bit that is the partial product. While the operation of the reduction circuit 154 can be performed by a number of different circuits, in one embodiment the reduction circuit 154 is an OR gate.

Alternative embodiments of the invention can implement the partial product generators 144 in any number of other ways (e.g., a one hot multiplexer, etc.). Furthermore, while one embodiment is described in which the partial product generators of a given generation unit are all provided to the 35 same summation circuit, in alternative embodiments of the invention: 1) not all of the partial product generators need be coupled to a summation circuit; 2) different partial product generators in a given generation unit can be coupled to different summation circuits; 3) a given partial product generator can be coupled to both summation circuits; etc. Furthermore, while one embodiment is implemented to use the described recoding technique, alternative embodiments of the invention could use a more straightforward approach (e.g., no recoding) and/or a different recoding technique. Such alternative embodiments would have a different configuration of summation circuit(s). In particular, the recoding technique of Table 2 is particularly useful for constant coefficients. Thus, an alternative embodiment designed to operate on more dynamic data may avoid the use of this recoding technique.

The circuit described in FIG. 1A could be used in any number of different systems. By way of example, the circuit of FIG. 1A could be implemented in a field programmable device as described later herein. In addition, it is understood that the circuit of FIG. 1A could be used with different combinations of the items described with reference to the field programmable device herein.

#### Field Programmable Device

FIG. 1D is a block diagram illustrating a field programmable device according to one embodiment of the invention. In FIG. 1D, a field programmable device 100 is shown which includes an input array 102 and an output array 118. The input array 102 represents one or more bits that are input to the field programmable device 100. Similarly, the output array 118 represents one or more bits that are output by the field programmable device 100. In one embodiment, the

input array 102 and/or the output array 118 may represent registered/latched input and output bits, respectively.

The input array 102, a register bank 104, and a register bank 106 are shown coupled to a selector unit 108. The register banks 104 and 106 each represents a set of one or more registers/latches for storing data (or a subset thereof): 1) input into the input array 102; and/or 2) output by the datapath(s) provided via a feedback path 120. Thus, the register bank 104 and/or 106 may represent or include an accumulator, as will become further apparent from the 10 description that follows. In one embodiment, the register banks 104 and 106 are 32-bits wide and 2048 bits deep, and are dual ported for read and write operations. In alternative embodiments, more or fewer register banks may be used having various port and storage capacity configurations. For 15 example, one embodiment has no register banks, but stores inputs and/or results needed for subsequent datapath operations in registers contained in the datapath. Another embodiment does not include any mechanism (e.g., register banks) to store inputs and/or outputs for use in subsequent datapath operations.

The selector unit 108 is shown coupled to provide input from the register bank 104, the register bank 106, and/or the input array 102 to a programmable logic datapath 114, a programmable arithmetic datapath 116, and a general purpose datapath 132. The programmable logic datapath 114, the programmable arithmetic datapath 116, and the general purpose datapath are each coupled to provide output data to the output array 118. The programmable logic datapath 114 and the programmable arithmetic datapath 116 are configured to perform (Boolean) logic operations and arithmetic (e.g., add, multiply, divide, etc.) operations, respectively.

A sums of products datapath is provided by a combination of part of the programmable logic datapath and a summation unit 130. The summation unit 130 is coupled to receive intermediate data results generated by the programmable logic datapath 114. Thus, the summation unit 130 can be conceptualized as a second stage of the programmable logic datapath 114. With reference to the sum of products datapath previously described, circuitry in the programmable logic datapath 114 is used to provide the generation units 142, while the summation unit 130 provides the summation circuits. As described later herein, the sums of products datapath maybe designed to provide one or more sum of products results simultaneously.

The location within the programmable logic datapath 114 that is coupled to the summation unit 130 is a design choice. While various such locations are described herein, it is understood that this design choice is based on the design of the programmable logic datapath and other considerations. As such, various alternative embodiments are contemplated for the coupling of these two datapaths. The output of the summation unit 130 is coupled as an input of the general purpose datapath 132 for purposes described later herein.

The general purpose datapath 132 is configured to perform various general purpose operations (e.g. shifting, packing, relatively simple logic and arithmetic operations). In one particular embodiment, the sums of products datapath can generate two separate sums of products (e.g., two sets of summations circuits are provided) at a time, and the summation unit 130 provides two 32-bit outputs accordingly. The general purpose datapath 132 can shift these two 32-bit outputs by arbitrary amounts and then pack them into a pair of 16-bit numbers.

While one embodiment is described herein in which the sums of products datapath is incorporated as illustrated in

12

FIG. 1D, alternative embodiments can use a number of different approaches. For example, the sums of products datapath could be a separate datapath that receives inputs directly from the selector unit, as opposed to intermediate results from the programmable logic datapath. In such a design, additional logic would need to be included to provide for the generation units of the sums of products datapath. As another example, rather than having a separate summation unit providing separate summation circuits, the summation circuits for the sums of products datapath could be provided by summation circuits in the programmable arithmetic datapath (the intermediate results from the programmable logic datapath 114 would be provided to summation circuits in the programmable arithmetic datapath 116). As yet another example, separate generation units for the sums of products datapath could be included; the results of such generation units being provided to the summation circuits of the programmable arithmetic datapath 116. As another example, the operations described later herein performed by the general purpose datapath 132 for the summation unit 130 could be implemented in dedicated circuitry for the sums of products datapath.

It should be noted that the sums of products datapath described with reference to the field programmable device is designed to operate using corresponding variable multiplicands provided as data through the selector unit and constant coefficients (the multipliers). However, alternative embodiments of the invention could be designed such that both the multiplicands and multipliers are variable data. It should be noted that while the term constant coefficient is used herein, the constant coefficients need not be entirely unprogrammable. For instance, with respect to the field programmable device described herein, control signals representing the constant coefficient multipliers are preprogrammed in a 35 ROM and/or RAM (described later herein) prior to the more dynamic data (the multiplicands) being provided by the selector unit 108. With particular respect to the sums of products datapath, the memory of the decoding logic unit 112 is preprogrammed with data representing the multipliers (e.g. constant coefficients). These control signals are applied to the programmable logic datapath 114 such that part of it acts as the generation units from FIG. 1A as described later herein. In this sense, the multipliers can be changed by selecting different vectors from the memory and/or reprogramming these vectors (if necessary and some form of reprogrammable storage is provided, such as a RAM, and EEPROM, etc.).

It should be noted that one embodiment of the field programmable device is designed so that the sums of products of ucts datapath provides good support for constant coefficient sums of products over low precision data, and reasonable support for higher precision data (e.g. up to about 14 bits). One reason for this design choice is that the programmable arithmetic datapath 116 is designed to provide good support for higher precision data (e.g. 16 and 32 bits).

In FIG. 1D, the input array 102 is further coupled to a control logic unit 110, which in turn is coupled to a decoding logic unit 112. In one embodiment, the control logic unit 110 provides an indirect control vector (ICV) to the decoding logic unit 112. While any number of ICVs may be stored in the control logic unit 110, in one embodiment of the invention the control logic unit 110 stores 128 ICVs, each 102 bits in length and consisting of several sub-fields of differing lengths. Some of these sub-fields are used directly to control parts of the field programmable device 100, and are therefore called "direct ICV sub-fields". Other of these sub-fields are further decoded by the decoding logic unit 112, to select

other parts of a direct control vector (DCV) to program/configure various portions of the field programmable device 100. These sub-fields are called "indirect ICV sub-fields".

The DCV is selected from as many memories as there are indirect ICV sub-fields. Each memory is of an appropriate width to control those parts of the field programmable device 100 to which it is dedicated, and has a depth, or number of elements, equal to  $2^x$  where X is the length of the indirect ICV sub-field that addresses that memory. These DCV memories may be of any type, including one or more of DRAM, SRAM, ROM, etc. While one embodiment is described which uses subfields and separate memories, alternative embodiments could use most or all of the ICV to address a single memory.

In one embodiment, the decoding logic unit stores 32 DCVs for the subset selection portion (described later herein) of the programmable logic datapath 114 in a random access memory (RAM) (alternative embodiments can store more or less DCVs, as well as additionally or alternatively store DCVs in a ROM or other type storage media). The memory width needed to control this portion of the programmable logic datapath in this embodiment is 1536 bits, while the length of the indirect ICV sub-field that addresses this memory is 5 bits (in an alternative embodiment described later herein with respect to FIGS. 9-11, the memory width used to control the subset selection portion is 2048 bits). Other memories control other portions of the selected DCV, applying them as control signals to the selector unit 108, the register bank 106, the register bank 104, other parts of the programmable logic datapath 114, the programmable arithmetic datapath 116, the general purpose datapath 132 and the sums of products datapath.

In one embodiment, the indirect control vectors are selected by the control logic unit 110 from multiple conceptually distinct "threads" of control, using parallel hardware to perform the "thread switching" on a cycle-by-cycle basis. Distinct portions of the register bank 104 and/or the register bank 106 may be used by different threads to avoid thread switching overhead. In an alternative embodiment, the control logic unit 110 is not present and the decoding logic unit 112 is operatively coupled to receive the indirect control vectors from the input array 102 (e.g., an opcode contained in an instruction provided by a microprocessor that may be coupled to the field programmable device 100). In yet another alternative embodiment, rather than decoding, a serially programmable 1-deep memory is included to provide the control signals.

Thus, in one embodiment further described herein, by providing approximately 2,500 control bits concurrently with up to 64 operand bits to selecting, routing and combining circuitry, the programmable logic datapath of the invention can provide dynamic programmability on a cycle-by-cycle basis to perform a number of logic operations on inputs of various lengths and provide up to 64 outputs. In addition, the sums of products datapath can provide dynamic programmability on a cycle-by-cycle basis to perform a number of sums of products operations on multiplicands/multipliers of various lengths. While an embodiment is described with reference to a specific number of inputs, outputs and control bits, alternative embodiments can have more or fewer inputs, outputs and/or control bits.

## Programmable Logic Datapath and Sums of Products Datapath

FIG. 2 provides a more detailed block diagram of the programmable logic datapath and the sums of products

14

datapath of the field programmable device according to one embodiment of the invention. In FIG. 2, the programmable logic datapath 114 and summation unit 130 of FIG. 1D is shown coupled to the decoding logic unit 112. As described with reference to FIG. 1D, the decoding logic unit 112 provides control bits for the various circuits of the field programmable device 100.

Rearrangement

As shown in FIG. 2, the programmable logic datapath includes a rearrangement circuit 202 configured to allow for flexible rearrangement and duplication of the input data bits. While any number of input bits may be used, the embodiment shown receives 48 input bits, which are either the upper 48 or lower 48 of the 64 bits formed by the concatenation of two 32-bit register bank outputs. The set of input bits may include data bits for a current cycle of operation and/or accumulated bits (e.g., output bits from a previous cycle of a logic and/or arithmetic operation).

The number of bits output by the rearrangement circuit 202 is a design choice. Thus, while one embodiment is described that outputs the same number of bits as are input, alternative embodiments can output more or fewer bits than are input. (If more bits are output than input, by necessity some input bits will be duplicated in the output.)

In one embodiment that receives 48 input bits and provides 48 outputs, the rearrangement circuit **202** comprises a set of forty-eight 48-to-1 multiplexing circuits (each coupled to receive the 48 input bits) for selectively routing any of the 48 input bits to its output. To control the forty-eight multiplexing circuits, each multiplexing circuit receives a different set of six control/configuration bits from the decoding logic unit **112** (making a total of 288 control bits). Thus, the 48 multiplexing circuits operate to dynamically select and/or rearrange (i.e., modify relative bit positions) the input bits.

In alternative embodiments, the bits input to the rearrangement circuit 202 may be selectively routed to the outputs in fixed sized, non-overlapping fields of multiple, consecutive bits. For example, one such embodiment selectively routes 48 inputs to 48 outputs using 3-bit fields as shown in FIG. 3A. This embodiment can be implemented using forty-eight 16-to-1 multiplexers, where the forty-eight 16-to-1 multiplexers are grouped in sets of 3 to create 16 groups of 3 multiplexers. FIG. 3B is a block diagram illustrating one group of 3 multiplexers used to route one 3-bit field according to one embodiment of the invention. Each group of multiplexers receives a different set of 4 control bits provided by the decoding logic unit 112 (the multiplexers in each group each receive the same 4 control bits).

In general, given J input bits, L output bits, and a rearrangement field size of F bits (where J/F is an integer), the rearrangement circuit **202** can include L J/F-to-1 multiplexing circuits, each controlled by X control signals, where X is the least power of 2 greater than or equal to J/F, and such that consecutive groups of F multiplexing circuits are controlled by the same X control signals. To illustrate, in the embodiment described above that uses forty-eight 48-to-1 multiplexers, J=48, L=48, F=1, and X=6; while, in the embodiment described above that uses forty-eight 16-to-1 multiplexers, J=48, L=48, F=3, and X=4. While two embodiments of the rearrangement circuit **202** have been described, it should be understood that the rearrangement circuit **202** could be adapted for various input and rearrangement bit field widths.

65 Selective Field Negation

As shown in the embodiment illustrated in FIG. 2, the rearrangement circuit 202 is followed by a selective field

negation circuit 210. The selective field negation circuit 210 selectively negates certain bits output by the rearrangement circuit 202 based on control bits provided by the decoding logic unit 112. In one embodiment, the selective field negation circuit 210 includes one or more logic elements 5 that are configured to selectively negate alternating fields output by the rearrangement circuit 202. The field width used for the selective field negation circuit may be unrelated to that used by the rearrangement circuit. As shown in FIG. 2, the selective field negation circuit 210 includes a series of 10 exclusive-OR (XOR) gates positioned to accept some of the bits output by the rearrangement circuit 202. In one embodiment, the field width for the selective field negation circuit is 3, which means that alternating groups of 3 bits output by the rearrangement circuit 202 are either wired 15 straight through or input to an XOR gate. By supplying a control bit from the decoding logic unit to the other input of each of the XOR gates, the selective field negation circuit 210 provides for the selective negation of every other field output by the rearrangement circuit 202. The number of 20 distinct control bits may be varied according to the degree of general purpose control required. In one embodiment, a different control bit is used for each field of 3 XOR gates, so that the total number of control bits is 8 (since there are sixteen 3-bit fields from 48 bits and half of them are wired 25 straight through). In another embodiment, one bit fields are used wherein every other output of the rearrangement circuit is coupled as an input to an XOR gate, and there are a total of 24 control bits used.

By using a multi-input negation element (e.g., an XOR 30 gate) and by allowing input of an appropriate control input to the negation element, negation of (alternating) rearranged fields may be performed in a controlled/selective manner. As such, subsequent stages of the programmable logic datapath 114 described below can implement logic operations upon 35 mostly positive and/or negative terms, a relatively balanced combination of positive and negative terms, and/or via logical equivalencies as provided by DeMorgan's Law over mostly positive or negative terms.

While one embodiment has been described that selectively rearranges according to predetermined bit fields and selectively negates alternating bit fields, alternative embodiments of the invention may not rearrange input bits and/or not include a selective field negation circuit. Furthermore, in alternative embodiments, input bit field rearrangement and/ 45 or negation may be performed according to several methods other than the ones described above. For example, selective negation may be performed using logic elements other than XOR gates (e.g., inverters and multiplexers).

#### Reduction Network Bank

Referring again to FIG. 2, the negated and/or non-negated results of the rearrangement circuit 202 (having a total width of 48 bits in one embodiment) are provided to a reduction network bank 212. The reduction network bank 212 comprises a set of (k) reduction networks shown in FIG. 2 as the 55 elements RN<sub>1</sub> through RN<sub>k</sub>. The number of reduction networks is a design choice. In one embodiment, each of 32 reduction networks in the reduction network bank 212 receives the negated and/or non-negated outputs from the rearrangement circuit 202 and generates a two bit result. The 60 structure and operation of a reduction network according to one embodiment of the invention will be described in further detail below with reference to FIGS. 5A–5F.

Sums of Products Datapath

FIG. 2 also illustrates that intermediate results in the 65 reduction network bank 212 are provided to the summation unit 130. A further description of the relationship between

16

the programmable logic datapath 114 and the sums of product datapath is provided later herein.

Post Processing

The reduction network bank 212, upon performing various bit routing, bit selection, and/or logic operations, outputs 64 bits to a post processing unit 214. The post processing unit 214 may be configured to perform various functions upon the output of the reduction network bank 212. For example, in one embodiment, the post processing unit 214 may be configured to detect the number and/or positions of (e.g., zeros and/or ones) in various fields of the output bits of the reduction network bank 212. Several exemplary functions that may be performed by post processing unit 214 and/or the reduction network bank 212 are described below.

In alternative embodiments, the post processing unit 214 may not be included in the programmable logic datapath 114. For example, in one embodiment, a device (e.g., a processor) coupled to the programmable logic datapath of the present invention obtains the output/result generated by the programmable logic datapath and performs a "post processing" function. In another embodiment, post processing functions are not performed. In yet another alternative embodiment, the post processing functions are performed by the general purpose datapath 132. Thus, in this embodiment, the output of the reduction network bank 212 is provided to the general purpose datapath 132.

### Reduction Networks in the Reduction Network Bank

FIG. 4 is a block diagram illustrating one reduction network 400 in the reduction network bank 212 according to one embodiment of the invention. The reduction network 400 includes a subset selection circuit 402. In the embodiment in which the rearrangement circuit provides 48 outputs, the subset selection circuit 402 is configured to receive the 48 outputs from the rearrangement circuit 202 and/or the selective field negation circuit 210. The subset selection circuit 402 provides outputs to a level one logic circuit 404.

In addition, FIG. 4 shows the location within the reduction network 400 chosen for one particular design to be coupled to the summation unit 130. As described later herein, the partial product generators from FIG. 1A are provided by parts of the subset selection circuit 402 and the level one logic circuit 404 in this particular exemplary design.

Subset Selection

FIG. 5A is a schematic diagram illustrating the subset selection circuit 402 and the level one logic circuit 404 of FIG. 4 according to one embodiment of the invention. In FIG. 5A, the circuitry above and below the dashed line 500 is respectively part of the subset selection circuit 402 and the level one logic circuit 404.

In FIG. 5A, an embodiment of the subset selection circuit 402 that includes four groups of NAND and AND gates is shown, wherein each of the four groups includes twelve pairs of NAND and AND gates. Each AND gate is coupled to receive a control bit C[i,j] and an input bit R<sub>n</sub>, where i indicates one of the 32 reduction networks 0–31, j represents one of the 48 gate control bits 0–47, and Rn represents one of the bits 0–47 input to the reduction network. Each NAND gate receives the same inputs as the AND gate to which it is paired, except the Rn input to the NAND gate is negated.

By gating the 48 bits with a control bit, a subset of the input bits can be selected (e.g., when the control bit is a logical "1", the input bit will be contained in a subset). The result generated by the 48 NAND gates of the subset

selection circuit **402** is shown in FIG. **5**A as four twelve-bit output lines **Z1**–**Z4**. Similarly, the result of the 48 AND gates is shown as four twelve-bit output lines **S1**–**S4**. It should be understood, however, that each of the four lines **S1**–**S4** and **Z1**–**Z4** represents twelve logically/electrically distinct bits. 5

While one embodiment has been described wherein subset selection is implemented with a series of NAND and AND gate pairs, alternative embodiments may use several other types and/or combinations of logic elements (e.g., NAND gates, NOR gates, MUXes, etc.) to perform subset 10 selection. For example, commonly available logic synthesis tools, such as Design Compiler® from Synopsys®, Inc., might be applied to a design description of the subset selection to create the logically equivalent configuration of gate elements that is optimal for a given VLSI design 15 environment. Furthermore, alternative embodiments of the reduction network 400 may not include a subset selection circuit.

According to one embodiment of the invention, the AND gates of the subset selection circuits are used to provide the 20 selection circuits for the partial product generators 144 of FIGS. 1A and 1C.

Level One Logic

The result generated by the subset selection circuit 402, and in particular, the twelve-bit output lines **Z1–Z4** and 25 S1–S4, are shown coupled to four groups of logic circuits A–D, wherein each group includes an AND, OR, and XOR logic network. The four output lines Z1–Z4 are respectively coupled to the AND logic of logic groups A-D, while the four output lines S1–S4 are respectively coupled to both the 30 OR and XOR logic of logic groups A–D. Although each of the four groups of logic circuits A–D is conceptually shown to include three 12-input logic elements, in practice, it should be understood that such elements typically have fan-in limitations that may limit the number of inputs. 35 Accordingly, in one implementation, each group of the logic circuits A–D may contain twelve 2-input AND gates, twelve 2-input OR gates, and twelve 2-input XOR gates. However, it should be understood that several other combinations of input-type (e.g., 2-input, 4-input, 8-input) and/or logic type 40 (e.g., NAND, NOR, NOT, etc.) of logic elements may be utilized in alternative embodiments of the level one logic circuit 404. While one embodiment is shown having three different logic functions in each logic circuit group A-D, alternative embodiment may support more, less, and/or 45 different logic functions.

As shown in FIG. 5A, each of the four logic circuit groups A–D generates three one-bit outputs. For example, the logic circuit group A is shown to generate an AND output bit A1, an OR output bit A2, and an XOR output bit A3. Similarly, 50 the logic circuit groups B, C, and D are shown to generate three output bits B1–B3, C1–C3, and D1–D3, respectively.

While one embodiment is shown in which static logic is used in the logic levels, alternative embodiment replace certain or all of the static logic with logic blocks (e.g., 55 SRAMs).

With respect to the sums of products datapath, in one embodiment of the invention the output of the OR gates in the level one logic circuit provide for the reduction circuits of the partial product generators 144 of FIGS. 1A and 1C. 60 Thus, in an alternative embodiment of the invention, the output of these OR gates are coupled to the summation unit 130 to provide the intermediate results from the reduction networks. In contrast, in the embodiment shown in FIG. 4, one of the outputs from the optional negation circuits 408 for each logic circuit group is coupled to the summation unit to provide the intermediate results from the programmable

logic datapath. As such, through the use of the below described alignment elements, any of the logic operations provided by the logic circuit groups (as well as an accumulator input) can be selected for provision to the summation unit.

18

Alignment

Referring back to FIG. 4, the level one logic circuit 404 is shown further coupled to an alignment circuit 406. The alignment circuit 406, according to one embodiment of the invention, is described with reference to FIGS. 5B and 5C.

In one embodiment of the invention, the alignment circuit 406 is configured to receive the output bits A1–D3 of the level one logic circuit 404, as well as a set of accumulator-based bits, as shown in FIG. 5C. FIG. 5B will now be described to illustrate the generation of the accumulator-based bits, according to one embodiment of the invention. Accumulator

FIG. 5B is a schematic diagram illustrating an accumulator-based bit generation circuit 40 located in the alignment circuit 406 of FIG. 4 according to one embodiment of the invention. As shown in FIG. 5B, the accumulator-based bit generation circuit 40 includes a set of selectors 502, 504, 506, and 508. Each selector is coupled to receive an accumulator register bit, depicted as ACC REG BIT. The ACC REG BITs constitute an additional input to the programmable logic datapath component of the field programmable device, which may represent a stored result of one or more logic and/or arithmetic operations previously performed by the field programmable device 100 of FIG. 1D, or could alternatively be furnished as an additional output of selector unit 108. In one embodiment, there are 64 ACC REG BITs stored within the programmable logic datapath, two for each reduction network 400 of FIG. 4, with one bit associated with selectors 502 and 504 and the other associated with selectors 506 and 508. In addition to the appropriate ACC REG BIT, each selector receives the result of gating the ACC REG BIT with one of the output bits A1–D3 of level one logic circuit 404 (e.g., through an AND, OR, and XOR logic circuit, as depicted in FIG. 5B). In particular, since the output bit A1 was generated by an AND operation, the output bit A1 and the appropriate ACC REG BIT are provided as inputs to an AND gate. In this manner, the result of a previous operation (ACC REG BITs) can be logically combined with the current input.

While one embodiment is shown in which each of the selectors 502, 504, 506, and 508 receives the same two control bits, in an alternative embodiment of the invention each selector receives a different set of control bits. The control bits provided to each selector facilitates selection of one of the inputs of that selector, such as the ACC REG BIT or the gated result of the ACC REG BIT and another bit (e.g., one of the output bits A1–D3 of the level one logic circuit 404 described with reference to FIG. 5A). Accordingly, the selectors 502, 504, 506, and 508 output a selected one of an ACC-BASED BIT 1, ACC-BASED BIT 2, ACC-BASED BIT 3, and ACC-BASED BIT 4, respectively.

It should be appreciated that alternative embodiments may use several types and combinations of logic elements to gate the ACC REG BIT, or may not gate the ACC REG BIT. Furthermore, alternative embodiments of the invention may not include an accumulator-based bit generation circuit and/or utilize an accumulator result.

Alignment Elements

FIG. 5C is a schematic diagram illustrating the remainder of the alignment circuit 406 of FIG. 4 according to one embodiment of the invention. In FIG. 5C, a set of four

alignment elements **510**, **512**, **514**, and **516** are shown. Each of the alignment elements **510**, **512**, **514**, and **516** is coupled to receive an ACC-BASED BIT and three output bits of one of the logic circuit groups A–D described with reference to FIG. **5A**. For example, the alignment element **510** is shown receiving the ACC-BASED BIT **1**, and the bits A**1**–A**3**. Similarly, the alignment element **512** is configured to receive the ACC-BASED BIT **2**, and the bits B**1**–B**3**.

Each of the alignment elements 510, 512, 514, and 516 also receives two control bits. While in one embodiment the 10 alignment elements in each reduction network (e.g., the alignment elements 510, 512, 514, and 516) receive the same two control bits, the level of individual control of the alignment elements is a design choice. In one embodiment, the alignment elements 510, 512, 514, and 516 are each 15 configured to rotate their respective four inputs by either 0, 1, 2, or 3 positions, based on the two control bits, and generate three outputs, RA1-RA3, RB1-RB3, RC1-RC3, and RD1-RD3, which are grouped as ROT BIT GROUP 1, ROT BIT GROUP 2, ROT BIT GROUP 3, and ROT BIT 20 GROUP 4, respectively (ROT is an acronym for "rotated"). The three outputs of each of the alignment elements 510, 512, 514, and 516 represents the rotated/shifted result of three of the four inputs to that alignment element. Thus, in one embodiment, the output bit RA1 of the alignment 25 element 510, for example, may correspond to one of the ACC BASED BIT 1, A1, A2, or A3, depending on the rotation of input bits performed by the alignment element **510**.

The alignment elements **510**, **512**, **514**, and **516** are 30 utilized in one embodiment to route/align data bits as they propagate through levels of logic in a reduction network. For example, in the creation of AND-OR logic functions, the level one logic circuit **404** may perform AND operations and the alignment circuit **406** may be utilized to align the result 35 of the AND operations to OR logic elements (e.g., as may be contained in a level two logic circuit, as described below).

However, it should be understood that alternative embodiments of the invention may not include an alignment circuit. It should further be understood that there are several alternative embodiments of the alignment circuit 406 and the alignment elements 510, 512, 514, and 516. For example, shifters, multiplexers, and/or other devices may be utilized to implement the alignment elements 510, 512, 514, and 516. Furthermore, in alternative embodiments, each alignment element may be configured to receive/generate fewer or greater than the number of inputs, control signals, and/or outputs as described with reference to the exemplary embodiment of alignment elements illustrated in FIG. 5C. For example, in one embodiment, one or more alignment 50 elements of the alignment circuit 406 does not receive an ACC-BASED BIT.

#### Optional Negation

Referring back to FIG. 4, the alignment circuit 406 is further coupled to an optional negation circuit 408. In one 55 embodiment, the optional negation circuit selectively negates one or more of the outputs ROT BIT GROUP 1, ROT BIT GROUP 2, ROT BIT GROUP 3, and ROT BIT GROUP 4 generated by the alignment circuit 406. In one embodiment, the optional negation circuit contains a set of 60 controlled negation elements (e.g., XOR gates) to selectively negate the output bits RA1–RA3, RB1–RB3, RC1–RC3, and RD1–RD3 generated by the alignment circuit 406 based on a control bit. While one embodiment is described in which the output bits of the alignment circuit 406 are selectively negated as a single group, the level of individual control of the negation elements is a design

20

choice (i.e., additional control bits could be used to selective negate different sets of the bits output by the alignment circuit 406).

The optional negation circuit 408 may be utilized in an embodiment of the invention to facilitate certain logic functions, for example, through DeMorgan's law. It should be understood, however, that alternative embodiments of the reduction network 400 may not include the optional negation circuit 408.

#### Sums of Products Datapath

As previously described, one of the outputs for each logic circuit group from the optional negation circuit 408 is coupled to the summation unit to provide the intermediate results to the summation unit 130. It is again noted that the location within the reduction networks that are coupled to the summation unit is a design choice. With reference to FIGS. 4 and 5A, the groups of data inputs (R0:R11), [R12:R23], [R24:R35], and [R36:R47]) form the input groups to the partial product generators (with reference to FIG. 1A, the number of inputs S equals 48, the number of partial product generators equals 4, and each of these 4 partial product generators receives 12 bits). To operate the sums of products datapath, the appropriate multiplicand data must be mapped to the appropriate input groups such that the operation can be performed. In embodiments with a selector unit 108 and a rearrangement circuit 202, either one or both of these components can be utilized to achieve the appropriate mappings. For example, the rearrangement circuit can be used to spread out the multiplicand bits, one multiplicand bit per input group. Of course, alternative approaches to achieving the appropriate mapping can be used.