US006429675B2

# (12) United States Patent Bell

(10) Patent No.: US 6,429,675 B2

(45) Date of Patent: \*Aug. 6, 2002

# (54) STRUCTURE AND METHOD FOR PROBING WIRING BOND PADS

- (75) Inventor: Paul Davis Bell, Colchester, VT (US)

- (73) Assignee: International Business Machines Corporation, Armonk, NY (US)

- (\*) Notice: This patent issued on a continued pros-

ecution application filed under 37 CFR 1.53(d), and is subject to the twenty year patent term provisions of 35 U.S.C. 154(a)(2).

Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/293,449

- (22) Filed: Apr. 16, 1999

#### Related U.S. Application Data

- (62) Division of application No. 09/159,446, filed on Sep. 24, 1998.

# (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3 717 800 A                | 2/1973  | Thillays et al.     |

|----------------------------|---------|---------------------|

| 3,717,800 A<br>4,223,337 A | 9/1980  | Kojima et al 357/68 |

| 4,241,360 A                | 12/1980 | Hambor et al.       |

| 4,403,240 A                | 9/1983  | Seki et al.         |

| 4,447,857 A                | 5/1984  | Marks et al 361/395 |

| 4,990,996 A                | 2/1991  | Kumar et al 357/68  |

| 5,155,577 A                | 10/1992 | Chance et al.       |

| 5,442,241 A                | 8/1995  | Tane                |

| 5,455,460 A                | 10/1995 | Hongo et al.        |

| 5.473.196 A                | 12/1995 | De Givrv            |

| 5,517,127 A | 5/1996   | Bergeron et al 324/760 |

|-------------|----------|------------------------|

| 5,554,940 A | * 9/1996 | Hubacher               |

| 5,731,709 A | 3/1998   | Pasatore et al 324/760 |

| 5,783,868 A | 7/1998   | Galloway               |

| 5,854,513 A | 12/1998  | Kim 257/737            |

| 5,856,687 A | 1/1999   | Kimura 257/235         |

| 5,886,414 A | * 3/1999 | Galloway               |

| 5,923,047 A | * 7/1999 | Chia et al             |

| 6,025,733 A | * 2/2000 | Saitoh et al 324/765   |

#### FOREIGN PATENT DOCUMENTS

| JP | 56-124240 | 9/1981 |

|----|-----------|--------|

| JP | 57-122542 | 7/1982 |

| JP | 58-15251  | 1/1983 |

#### OTHER PUBLICATIONS

Gow et al., "Semiconductor Chip I/O Configuration for Plastic Flat Pack, Tape Automated Bonding, or Solder Ball–Joined Flip Chip Packages", IBM Technical Disclosure Bulletin, vol. 33, No. 10B, pp. 332–333, Mar. 1991. DeLuca et al., "Dynamic Burn–In of Integrated Circuit Chips at the Wafer Level", IBM Technical Disclosure Bulletin, vol. 29, No. 6, p. 2766, Nov. 1986. Bona et al., "Optical Networks for VLSI–Interconnects on

Flexible GaAs Substrate", IBM Technical Disclosure Bulletin, vol. 35, No. 2, pp. 26–27, Jul. 1992.

#### \* cited by examiner

Primary Examiner—N. Le Assistant Examiner—Wasseem H. Hamdan (74) Attorney, Agent, or Firm—Schmeiser, Olsen & Watts; Howard J. Walter, Jr.

## (57) ABSTRACT

An integrated circuit device structure having probe pad extensions in electrical communication with the wire bond pads and a method for performing failure analysis thereon. The invention provides an improved probing system for wire bond packages such that neither the wire nor the wire bond from the pads on the chip surface need be removed during testing procedures. Included in the integrated circuit device is a plurality of conductive pads having a first area for receiving a wire bond and a second area for receiving a probe, wherein the second area abuts, and is an electrical communication with the first area.

## 7 Claims, 5 Drawing Sheets

106

Aug. 6, 2002

Aug. 6, 2002

FIG. 11

FIG. 12

FIG. 14

1

# STRUCTURE AND METHOD FOR PROBING WIRING BOND PADS

This is a divisional application of co-pending application, Ser. No. 09/159,446, filed on Sep. 24, 1998, entitled INTEGRATED CIRCUIT HAVING WIREBOND PADS SUITABLE FOR PROBING.

#### TECHNICAL FIELD

The present invention generally relates to a structure and method for testing integrated circuit devices, and more particularly, to a structure and method for performing failure analysis on an integrated circuit.

#### **BACKGROUND ART**

The ability to perform failure analysis on integrated circuit (IC) divices is an important aspect of ensuring quality during the ongoing development life cycle of an IC. The process of analyzing faults may need to occur any where 20 from early design stages of an IC right through to a point where an end user discovers a failure. Once the reason for the failure is detected, the IC design can be modified in order to correct the problem.

The process of performing fault analysis on an IC typi- 25 cally requires the removal of at least a portion of the packaging that makes up the IC device in order to expose the necessary electrical components. One of the most common IC packages includes the use of a chip carrier or lead frame to hold the much smaller chip or die, which contains the <sup>30</sup> functional circuitry. Electrical connections between the chip and lead frame are typically accomplished with a wire bonding system where wires, typically formed of gold or aluminum, connect wire bond pads on the chip to metal pads on the lead frame. FIGS. 1 and 2 depict a chip 10 having pads 12 for receiving a wire 16. It can be seen that a first end of the wire 16 is formed into a ball or wire bond 14 that is bonded to pad 12. Once these connections have been made, the exposed area is encapsulated into a final product. In performing fault analysis on IC's using lead frame <sup>40</sup> packaging, the encapsulated area must be removed in order to expose the chip pads 12.

Once the chip pads 12 are exposed, probes can be set in contact with the pads 12 in order to determine the cause of the failure. Unfortunately, an initial polishing step must be performed in order to remove most of the wire 16 and wire bond 14 from the pad 12. Without this removal step, it is very difficult to position the required number of probes in place. Furthermore, if the wire 16 and wire bond 14 are left in place, the probe would not directly contact the pad 12, and therefore potentially cause a faulty test result. Accordingly, under previous fault isolation techniques, it has been necessary to remove the ball bonds before attempting to probe for failures.

Unfortunately, in addition to adding an extra step, the removal of the wires and wire bonds from the chip limits the type and extent of testing that can be performed. For example, connections on and between chip pads cannot be verified. Thus, without an improved structure and method for performing fault analysis, the deficiencies of the prior art will remain.

# SUMMARY OF THE INVENTION

The present invention overcomes the deficiencies of the 65 prior art by including a structure and method for providing chips with probe pad extensions in electrical communication

2

with the chip's pads. Accordingly, during a failure analysis process, probing can occur without removing the wire and/or wire bond from the pads on the chip surface. The invention therefore provides an integrated circuit comprising a plurality of conductive pads having a first area for receiving a wire bond and a second area for receiving a probe, wherein the second area abuts, and is in electrical communication with the first area.

In addition, a method for forming an integrated circuit device having wire bond pads that are easily probed is provided and comprises the steps of: (1) creating each wire bond pad within a single layer of the integrated circuit device during a fabrication process; and (2) forming each wire bond pad with a first area for receiving a wire bond and a second area for receiving a probe, wherein the first and second area are integrally formed substantially simultaneously, and wherein the first and second areas are in electrical communication with each other.

Finally, a method is provided for performing failure analysis on an integrated circuit after packaging is completed and a fault has been detected, wherein the integrated circuit comprises wire bond pads each having a pad extension formed adjacent to a portion of the pad having a wire bond, wherein the method comprises the steps of: (1) removing a portion of a lead frame packaging to expose the wire bond pads; and (2) probing the pad extension of at least one of the wire bond pads with the wire bond remaining affixed to the at least one wire bond pad.

It is therefore an advantage of the present invention to provide a system for more easily performing tests oil an integrated circuit device.

It is therefore a further advantage of the present invention to provide a system for performing more robust tests on an integrated circuit device.

It is therefore a further advantage of the present invention to provide a system for performing failure analysis tests without removing wires and wire bonds from the pads of a chip.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These and other features and advantages of this invention will be more readily understood from the following detailed description of the various aspects of the invention taken in conjunction with the accompanying drawings in which:

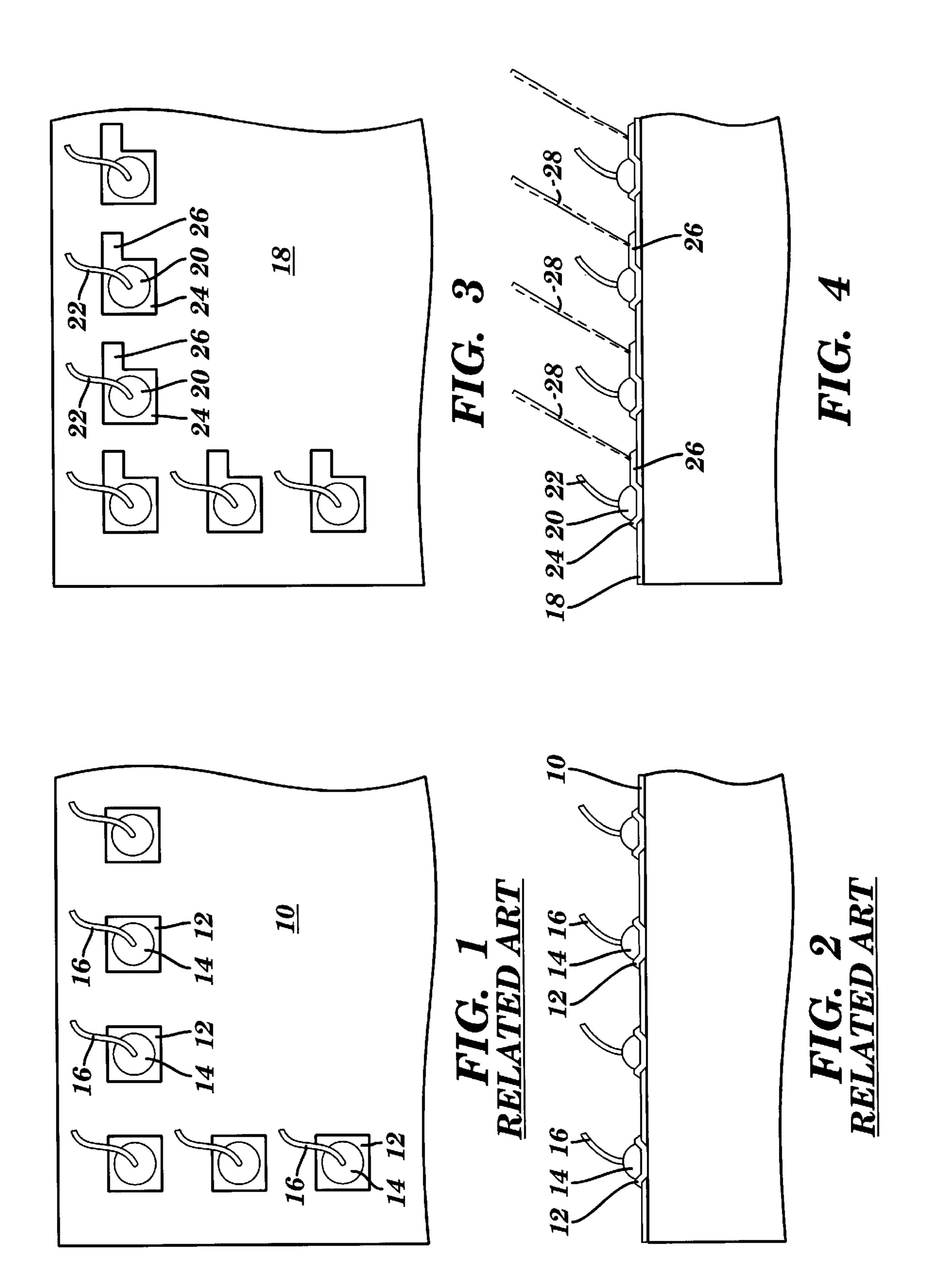

FIG. 1 depicts a top view of a chip with traditional wire bond pads;

FIG. 2 is a cross-sectional side view of FIG. 1;

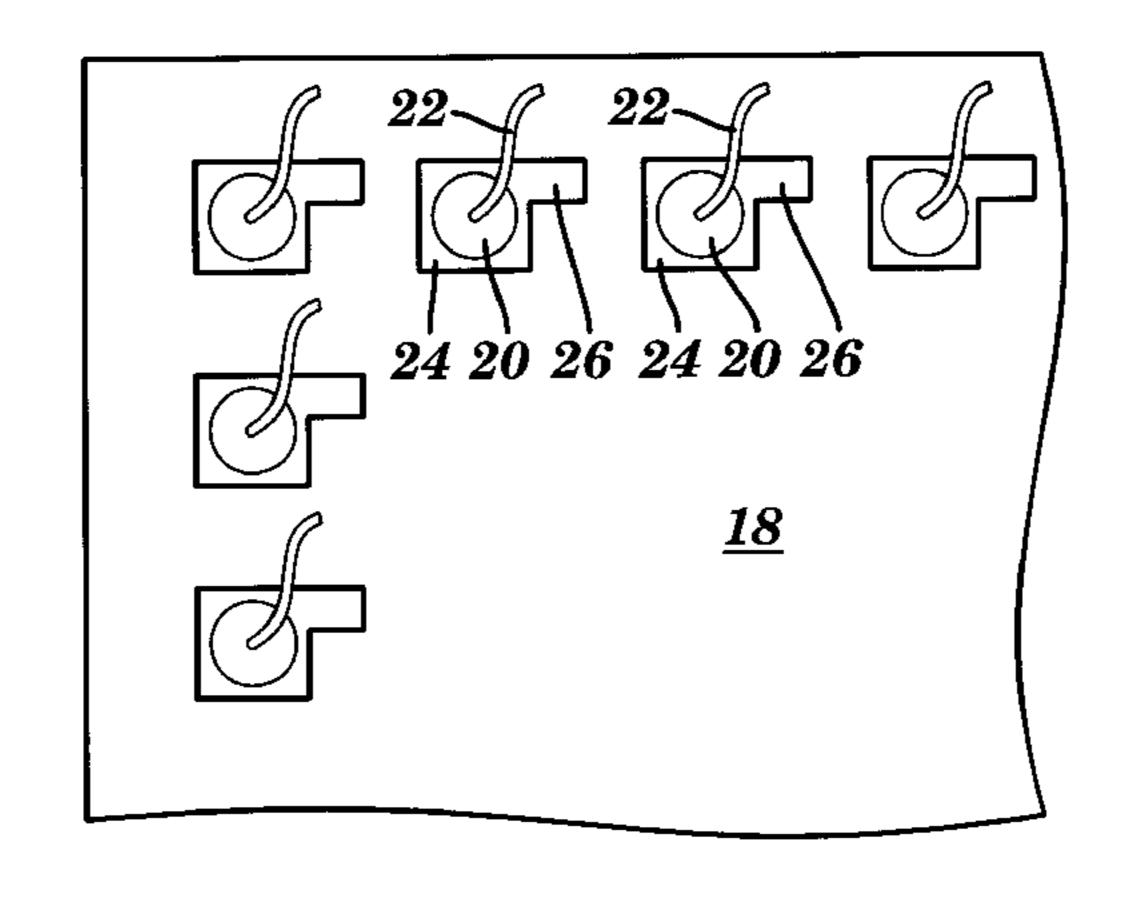

FIG. 3 is a top view of an integrated circuit chip having wire bond pads in accordance with an exemplary embodiment of the present invention;

FIG. 4 is a cross-sectional side view of FIG. 3;

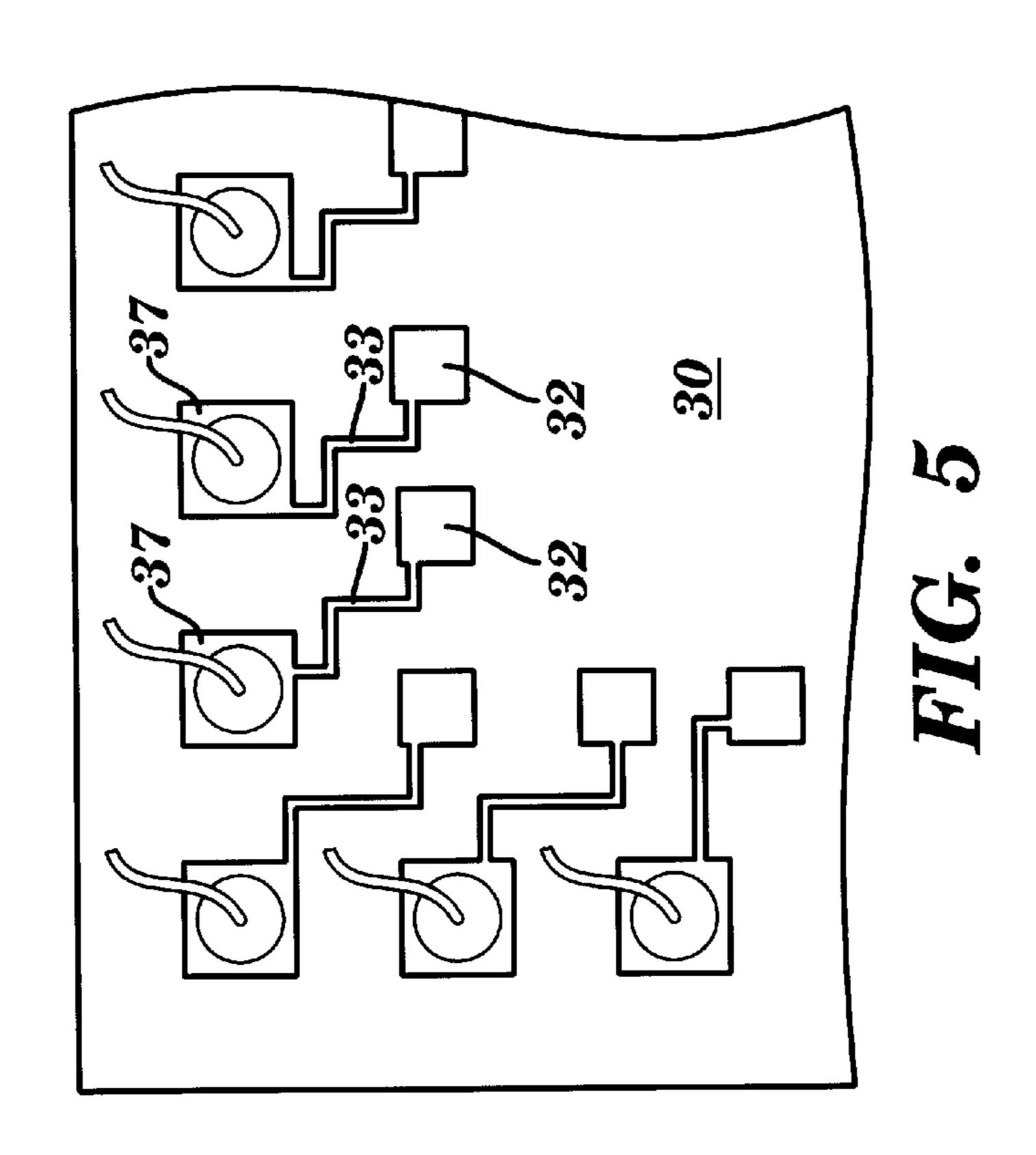

FIG. 5 is an alternate embodiment of the present invention;

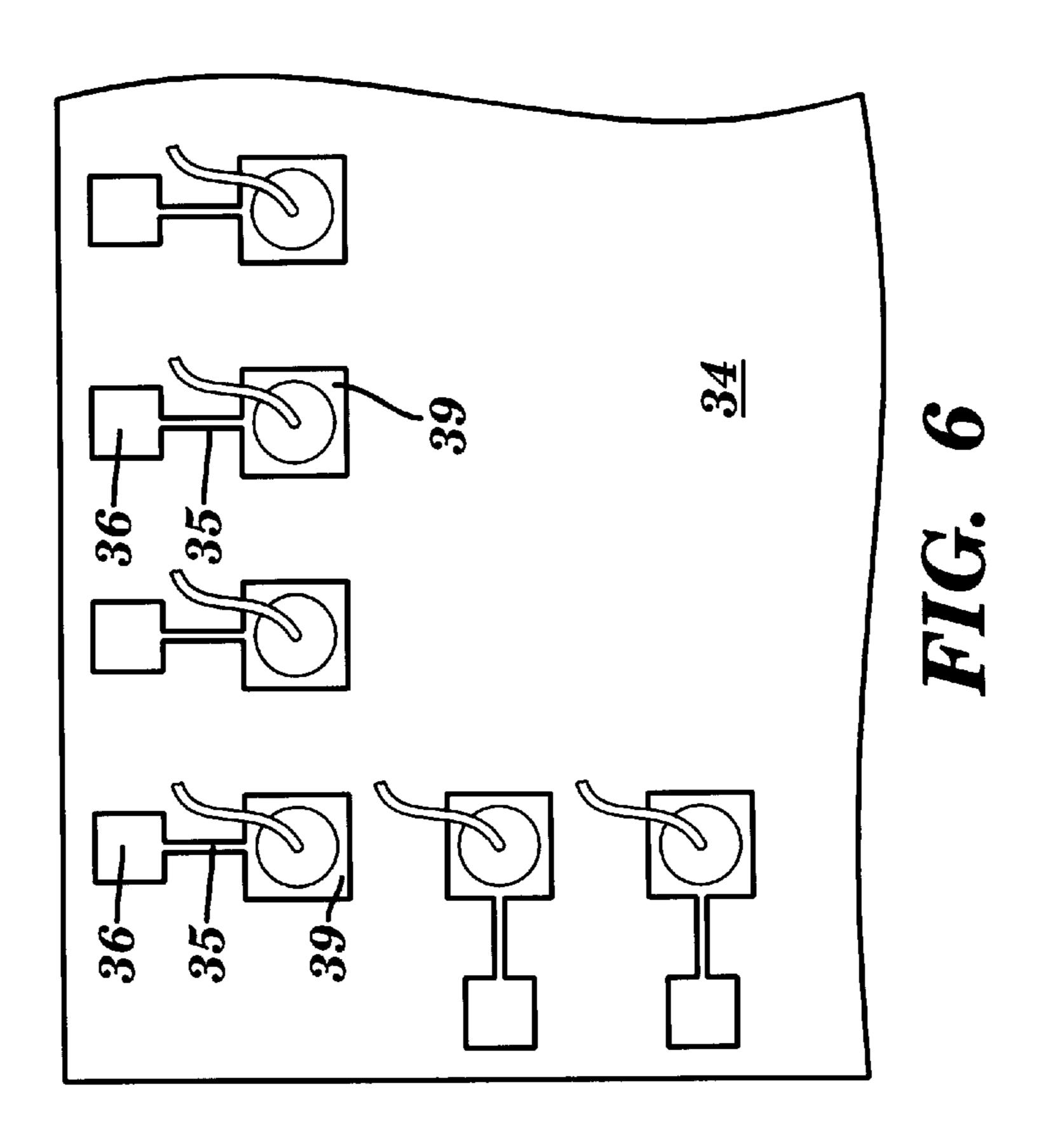

FIG. 6 is a second alternate embodiment of the present invention;

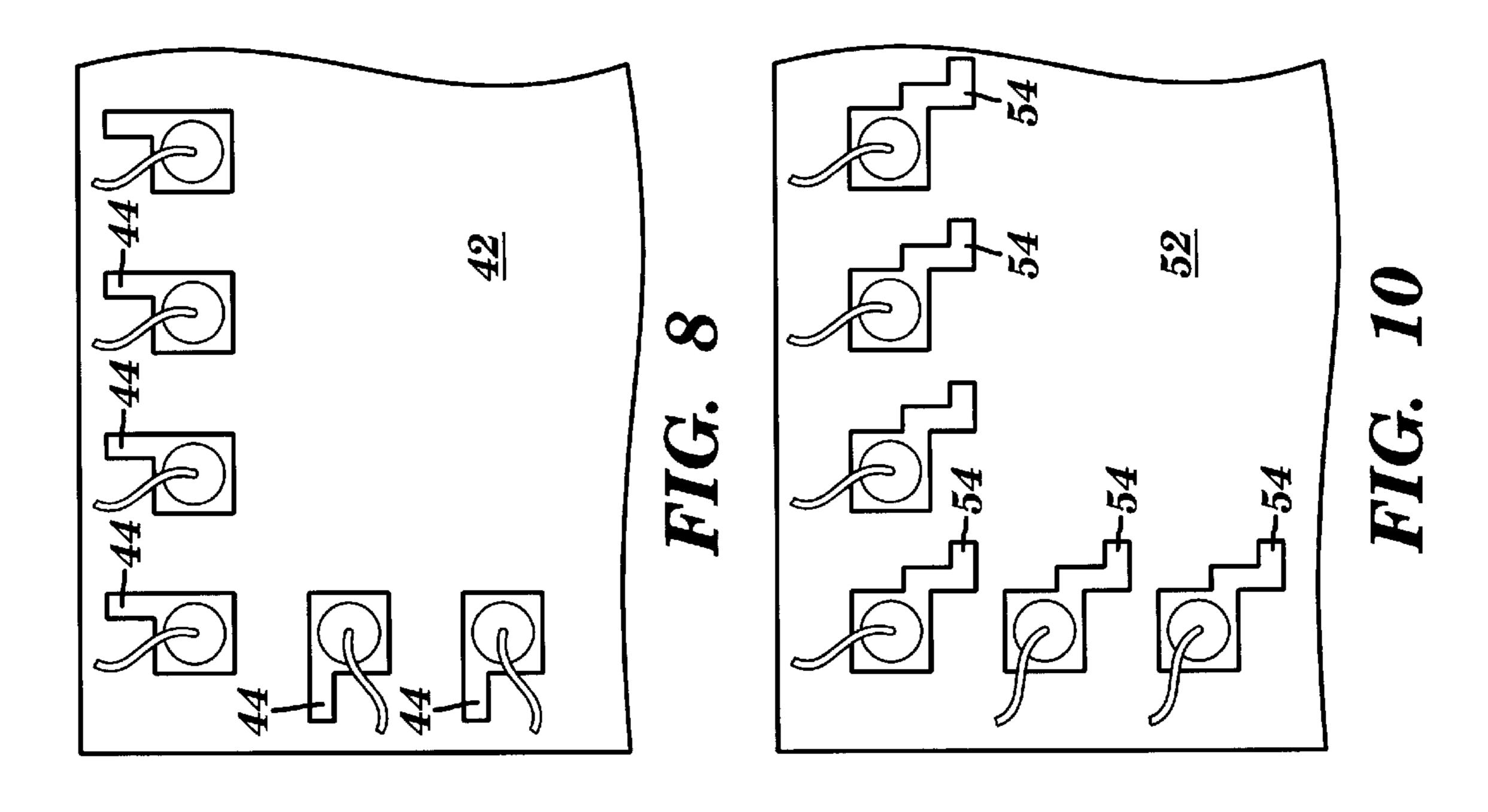

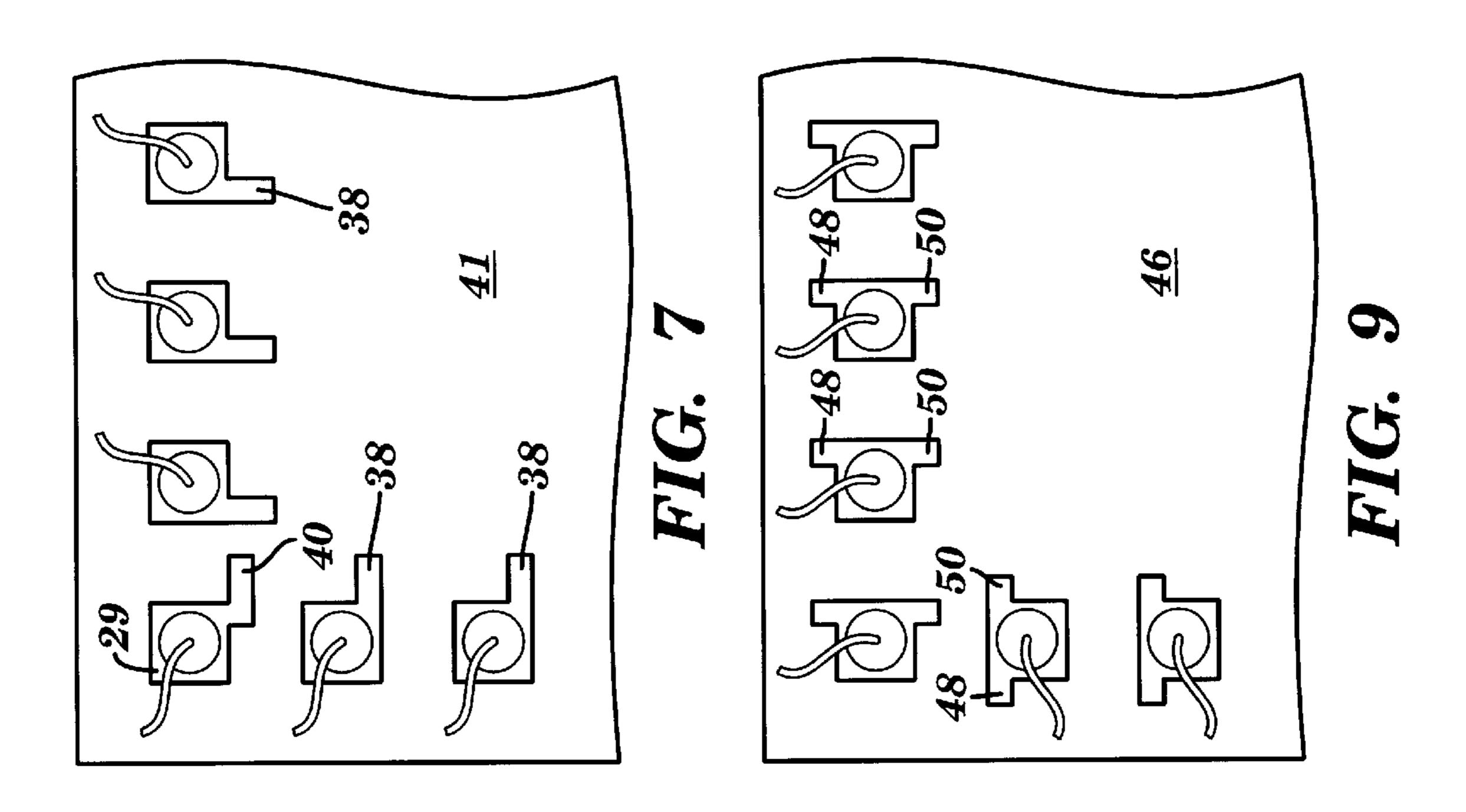

FIG. 7 is a third alternate embodiment of the present invention;

FIG. 8 is a fourth alternate embodiment of the present invention;

FIG. 9 is a fifth alternate embodiment of the present invention;

FIG. 10 is a sixth alternate embodiment of the present invention;

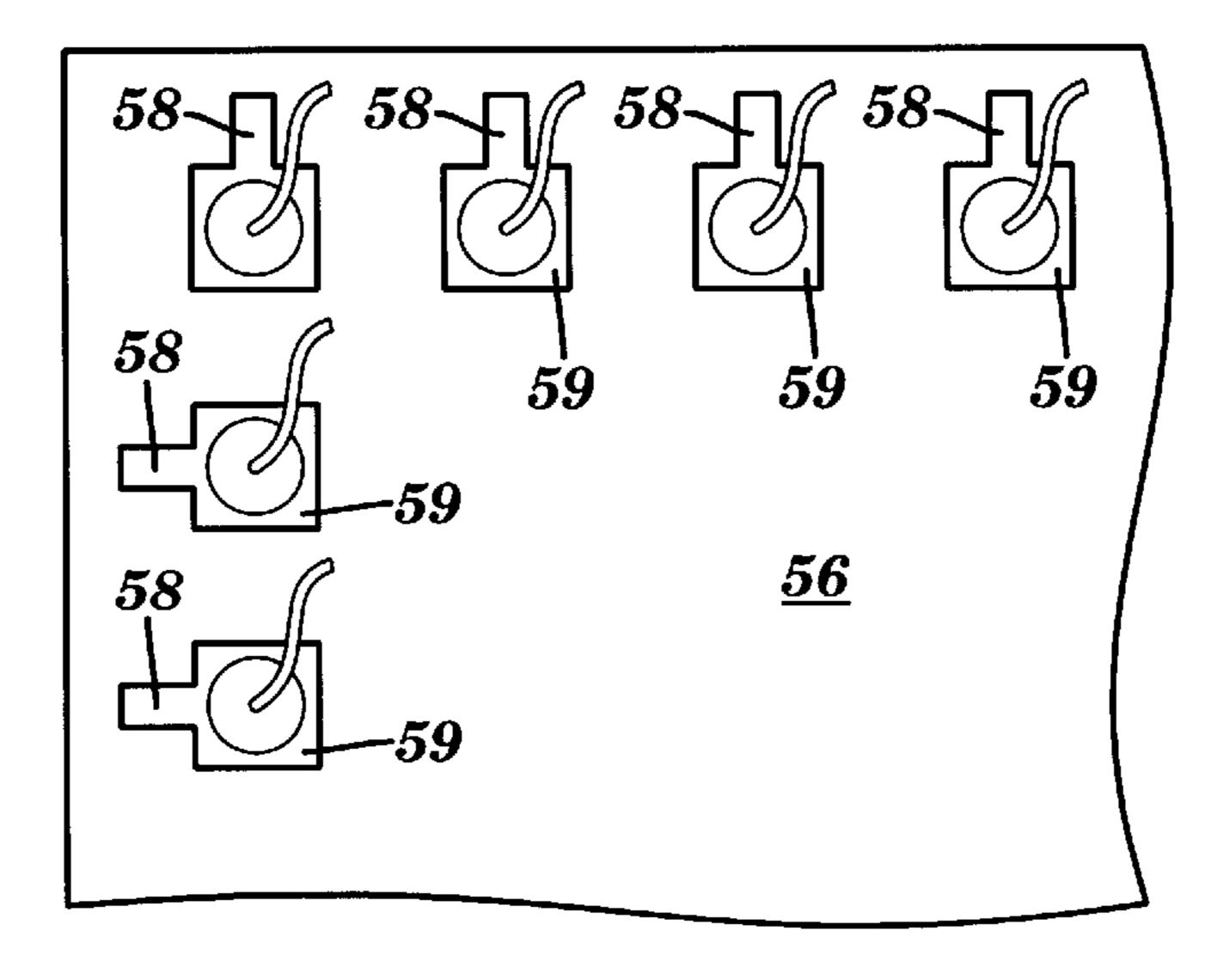

FIG. 11 is a seventh alternate embodiment of the present invention;

3

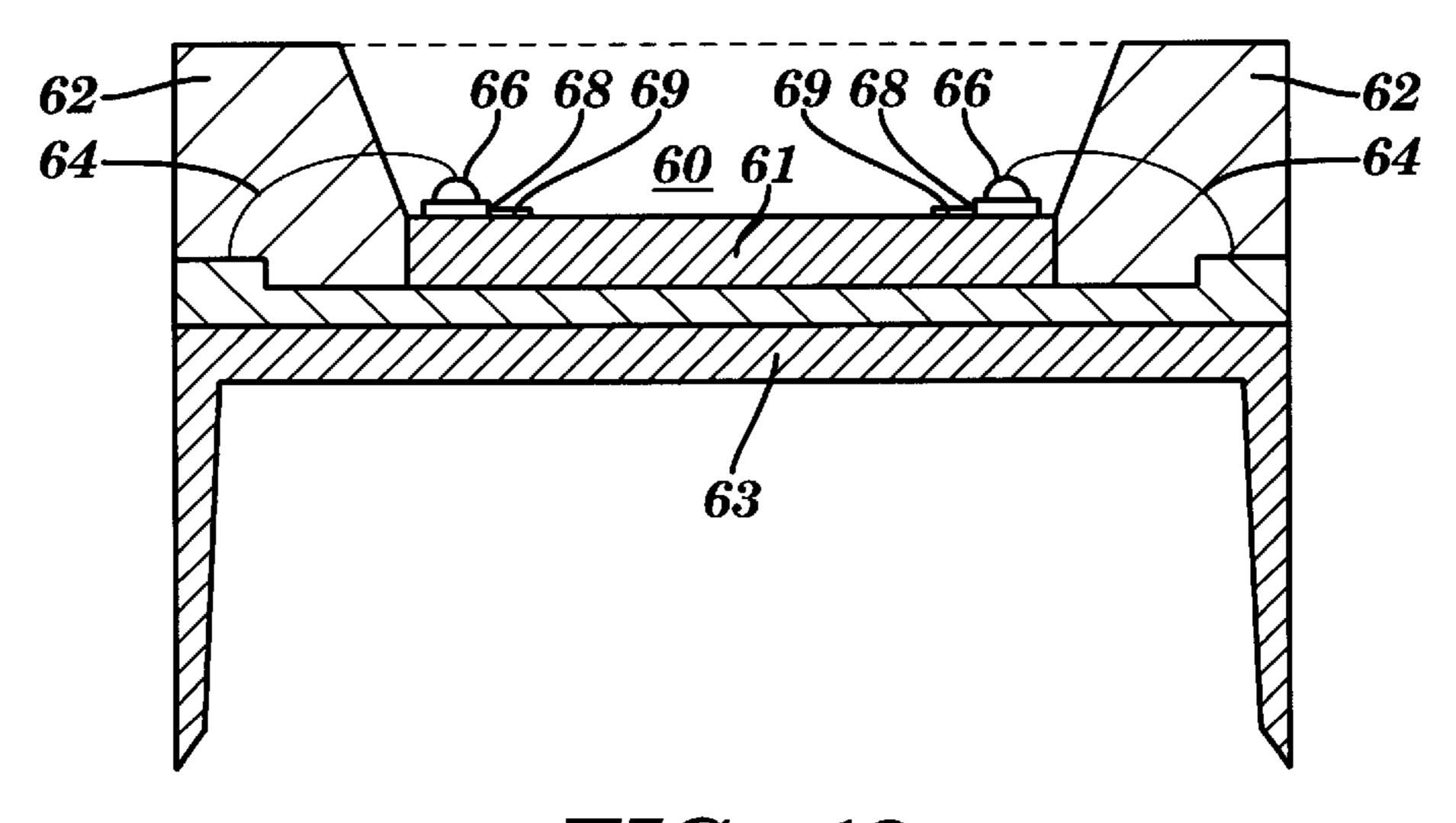

FIG. 12 is a cross-section side view of an integrated circuit device with a portion of the encapsulation removed in accordance with an exemplary embodiment of the present invention;

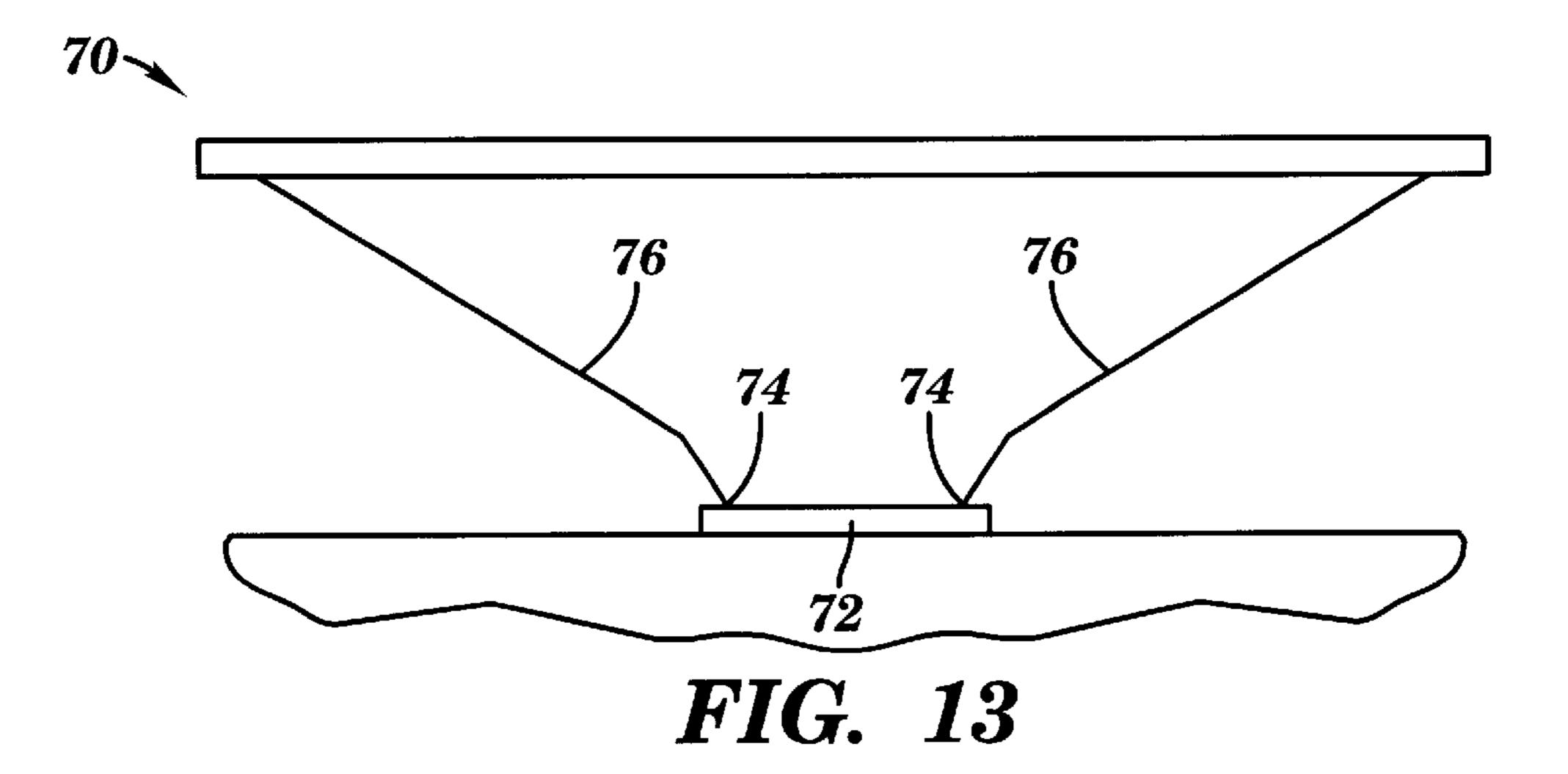

FIG. 13 is a side view of a probe ring in accordance with an exemplary embodiment of the present invention; and

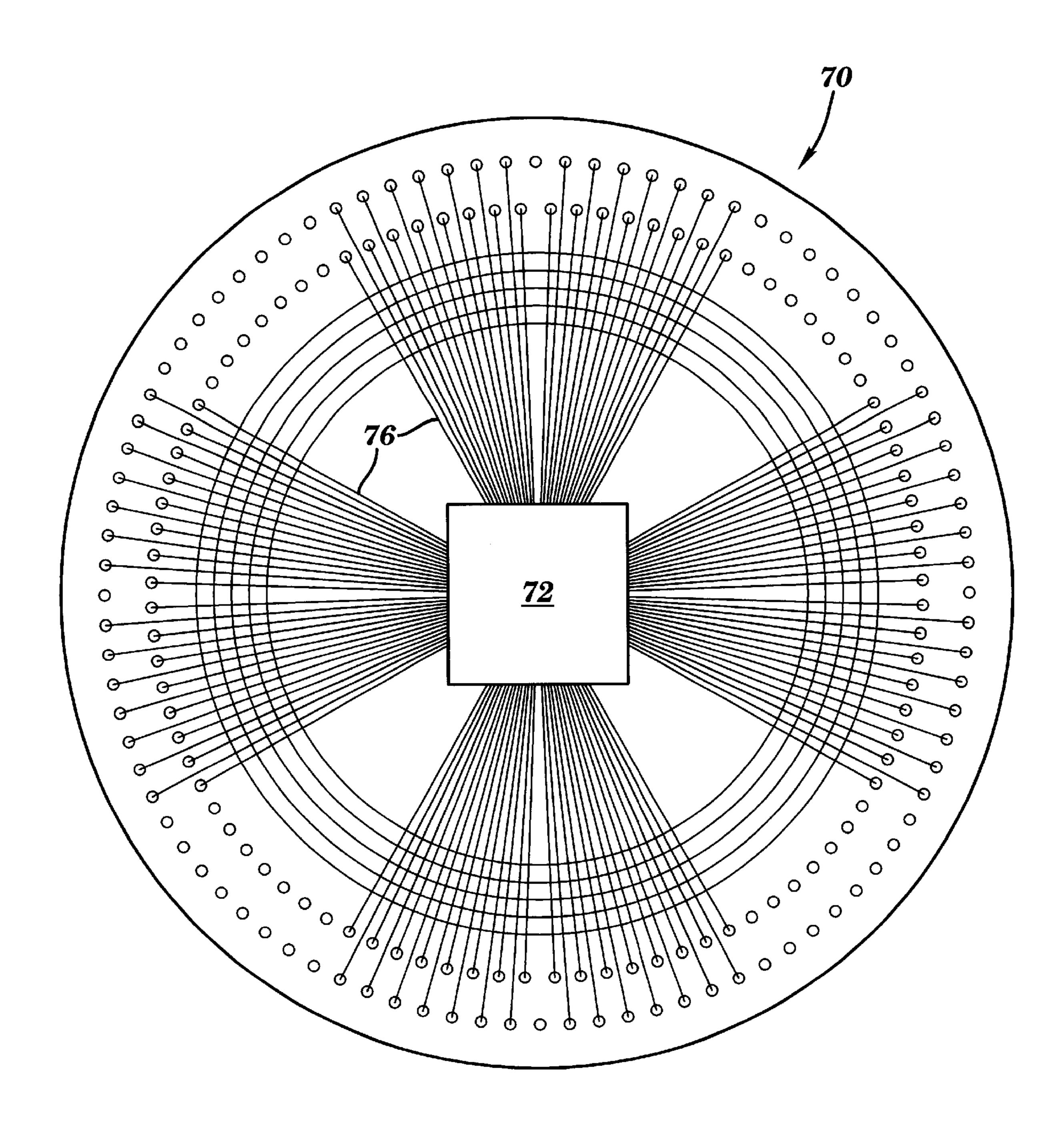

FIG. 14 is a top view of a probe ring in accordance with an exemplary embodiment of the present invention.

## DESCRIPTION OF THE EMBODIMENTS

Referring now to the drawings, FIGS. 1 and 2 depict a chip 10 with pads 12 designed in accordance with known techniques. Attached to each pad 12 is a wire bond 14 and wire 16 that electrically connects pad 12 to a lead frame or chip carrier (not shown). In the past, in order to probe pads 12, the wire bond 14 and wire 16 were required to be removed with a polishing mechanism or other technique in order to provide enough surface area to allow a probe to contact pad 12. As noted above, this requirement represents a limitation. In particular, by disconnecting wires 16 from pads 12, the package is no longer in a usable state and package defects can no longer be isolated from IC defects. Thus, under existing techniques, it was impossible to exercise the IC to full application specifications for diagnostics and fault localization.

Referring now to FIGS. 3 and 4, a novel pad 24 is depicted on chip 18 that provides a pad extension 26 that allows the pad 24 to be probed without first removing the wire 22 and/or wire bond 20. As can be seen in FIG. 4, a probe tip 28 can be placed in contact with the pad extension 26 in order to effectuate a test without removing wire bond 20 or wire 22. In this embodiment, the pad extensions 26 extend between the pads and are about  $\frac{1}{4}$  the size of the pad 24. Typical pads are 100 mm by 100 mm and include a pitch of 35 about 200 mm. Therefore, the extensions are approximately 50 mm by 50 mm. It is conceivable that the pad extensions 26 could be 10 mm by 10 mm, or smaller, so long as the probe tips could be manufactured to contact the pad extensions. Thus, the actual size of the pad and pad extensions 40 will generally be dictated by the need to maneuver between the wires extending from the balls as shown in FIG. 4.

Referring now to FIGS. 5 and 6, two alternate embodiments of the present invention are depicted on chip 30 and chip 34, respectively. FIG. 5 shows probe pads 32 arranged in a ring inside of the wire bond pads 37 and electrically connected by leads 33. FIG. 6 depicts probe pads 36 that are arranged in a ring outside of the wire bond pads 39 and connected by leads 35. Because the leads 33 and 35 need only be about 20mm wide, these arrangements present no additional chip size requirement. The embodiments depicted in FIGS. 5 and 6, which neatly organize the probe pads on the chip, are particularly suited for chips that require a large number of probes.

FIGS. 7–11 depict additional embodiments of the present 55 invention. For example, FIG. 7 depicts a chip 41 that includes pad extensions 38 extending towards an interior portion of the chip and include corner pads 29 with pad extensions 40 that are also offset towards the center of the chip 41. FIG. 8 depicts a chip 42 with pad extensions 44 that 60 extend towards an exterior portion of the chip 42. FIG. 9 depicts a chip 46 with pads that include two pad extensions 48 and 50 that extend both toward and away from the center of the chip 46. FIG. 10 depicts a chip 52 that includes pad extensions 54 that are bent to extend in two directions. FIG. 65 11 depicts a chip 56 having pad extensions 58 that extend from a center portion of a pad 59 toward an exterior portion

4

of the chip **56**. As is evident from these embodiments, any number of alternative designs are possible and arc considered to be within the scope of this invention. The placement of the pad extensions may be in part influenced by the type of probing system used to perform failure analysis. For example, probing may be performed with a group of single probes on a probe station or with a probe ring on a tester, voltage contrast tool, or any other analytical equipment. Certain configurations may be particularly suited for use with a probe ring, while others may be better suited for single probe usage.

In an exemplary emibodiment of the present invention the entire wire bond pad is created within a single layer of the integrated circuit device during the fabrication process. In this manner, no additional cost or processes are added to the manufacturing of the chip in order to add this additional functionality. Thus, the wire bond pad will be formed with a first area for receiving the wire bond, and a second area for receiving the probe, wherein the first and second area will be integrally formed substantially simultaneously during the fabrication process. The implementation of the pad extensioin is therefore accomplished during the same fabrication step as the pad itself. Accordingly, the only alteration necessary during the fabrication process may be modification to the mask used to define the pad configuration on the layer at which the pads reside. The remaining fabrication steps (e.g., applying photoresist, developing photoresist, and the etching process) need not be altered.

In addition, a novel method for performing failure analysis on the integrated circuit after packaging is completed and a fault has detected, is described. Referring to FIG. 12, an integrated circuit device is depicted that includes a chip 61 and lead frame 63. Chip 61 includes pads 68 each having a wire bond 66 and wire 64 that electrically connects chip 61 to lead frame 63. In accordance with this invention, pad extensions 69 are also included to facilitate in the testing process. During the packaging process, chip 61 and the associated electrical connections are encapsulated in an insulative material 60 and 62 that entirely surrounds the chip 61. During the failure analysis procedure, a first portion 60 of the encapsulation material is removed. The removal of the encapsulation may be done with any known method, including the use of nitric acid. As can be seen, a second portion 62 of the encapsulation material is left intact. Once the first portion 60 of the encapsulation material is removed, probing of the system, using probe extensions 69 can occur without removing wire bond 66 or wire 64 from the pad 68. In addition to the example depicted in FIG. 12, it is understood that this technique could be used for the testing of any wire bonded system, including the case where a chip is wire bonded directly to a circuit board. In addition to the failure analysis application described herein, it is understood that the testing or probing procedures may be performed on the chip after the wire bond has been formed but prior to the encapsulation process. Thus, the probe extensions could be used as a mechanism for testing the chip prior to final packaging.

Referring to FIGS. 13 and 14, a probe ring 70 is depicted. The probe ring includes a plurality of probes 76 that contact pad extensions 74 on the chip 72. In general, the probes arc configured in a circular fashion around and above the chip 72. Generally, each pad on the chip 72 will have a probe in contact therewith for isolating faults.

While invention has been described in detail herein in accordance with certain exemplary embodiments thereof, many modifications and changes therein may be affected by those skilled in the art. Accordingly, it is intended by the

30

4

appended claims to proper all such modifications and changes as fall within the true spirit and scope of the invention.

What is claimed is:

1. A metohod for forming an integrated circuit device 5 having wire bond pads that are easily probed, comprising the steps of:

providing a mounting surface and an integrated circuit chip thereon, said integrated circuit chip having a plurality of wire bond pads within a single layer of the <sup>10</sup> integrated circuit chip;

providing a plurality of pad extensions electrically connected to said wire bond pads, each said pad extension adapted to receive a probe; and

providing, a probe ring structure on the integrated circuit chip, wherein each wire bond pad has a first area for receiving a wire bond, wherein the first areas and pad extensions are integrally formed around a central chip location, and wherein the first areas and pad extensions are in substantially coplanar electrical communication with each other, and wherein the pad extension is connected to at least one corresponding probe ring pad of the probe ring structure via at least one probe.

2. The method of claim 1, comprising the further steps of: completing a packaging of the integrated circuit chip, including bonding the wire bond pads of the integrated circuit chip to a lead frame with lead wires;

testing the integrated circuit chip; and

upon the detection of a fault, performing the steps of: removing a portion of the packaging to expose at least one wire bond pad; and

placing the probe on said pad extension connected to the exposed wire bond pad to analyze the fault. 6

- 3. The method of claim 2, wherein the step of placing the probe is accomplished without removing the lead wires from the wire bond pads.

- 4. The method of claim 1, comprising the further step of: testing the integrated circuit by placing at least one probe on one of the wire bond pad's pad extension, prior to packaging.

- 5. The method of claim 1, wherein the pad extension is formed such that it extends towards a center region of the integrated circuit device.

- 6. The method of claim 1, wherein the pad extension is formed such that it extends towards a peripheral portion of the integrated circuit device.

- 7. A method for performing failure analysis on an integrated circuit after packaging is completed and a fault has been detected, wherein the integrated circuit comprises wire bond pads each having a pad extension formed substantially integrally and simultaneously with the pad, wherein said pad extensions are formed extending from a central chip location, and wherein said pad extensions are adjacent to a portion of the pad having a wire bond, said method comprising the steps of:

removing a portion of a lead frame packaging to expose the wire bond pads;

probing the pad extension of a first wire bond pad of the wire bond pads, with the wire bond remaining affixed to said first wire bond pad; and

providing a probe ring structure wherein the wire bond pads are electrically connected to at least one corresponding probe ring pad of the probe ring structure via at least one probe.

\* \* \* \*