US006333892B2

# (12) United States Patent

# Hamamoto et al.

# (10) Patent No.: US 6,333,892 B2

# (45) Date of Patent: Dec. 25, 2001

# (54) SYNCHRONOUS SEMICONDUCTOR MEMORY DEVICE CAPABLE OF SELECTING COLUMN AT HIGH SPEED

(75) Inventors: Takeshi Hamamoto; Zenya

Kawaguchi; Motoko Hara, all of

Hyogo (JP)

(73) Assignee: Mitsubishi Denki Kabushiki Kaisha,

Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/725,851

(22) Filed: Nov. 30, 2000

### Related U.S. Application Data

(62) Division of application No. 09/265,856, filed on Mar. 11, 1999.

# (30) Foreign Application Priority Data

| Jul. 29, 1998 | (JP) | ••••• | 10-213950 |

|---------------|------|-------|-----------|

|               |      |       |           |

(51) Int. Cl.<sup>7</sup> ...... G11C 8/00

365/230.08. 230.00

# (56) References Cited

### U.S. PATENT DOCUMENTS

5,467,315 11/1995 Kajimoto et al. .

| 5,568,445 | * | 10/1996 | Park et al    | 365/233 |

|-----------|---|---------|---------------|---------|

| 5,581,512 | * | 12/1996 | Kitamura      | 365/233 |

| 5,867,446 | * | 2/1999  | Konishi et al | 365/233 |

| 5,867,447 | * | 2/1999  | Koshikawa     | 365/233 |

| 5,892,730 |   | 4/1999  | Sato et al    |         |

| 5,953,267 |   | 9/1999  | Oh.           |         |

| 5,959,906 |   | 9/1999  | Song et al    |         |

#### FOREIGN PATENT DOCUMENTS

02-143444 6/1990 (JP).

Primary Examiner—Hoai V. Ho

(74) Attorney, Agent, or Firm—McDermott, Will & Emery

# (57) ABSTRACT

A command decoder receives an externally supplied command independently of an internal clock signal, decodes the command, generates a column access mode instruction signal, and activates a column address activation signal when the internal clock signal rises. An internal column address signal generating circuit generates an internal column address signal according to the column address activation signal. Accordingly, the internal column address is generated at an advanced timing to enable a following column selecting operation to be started at a faster timing. A synchronous semiconductor memory device capable of performing the column selecting operation at a high speed is thus provided.

# 7 Claims, 20 Drawing Sheets

<sup>\*</sup> cited by examiner

F I G. 2

FIG. 3

F I G. 4

F I G. 5

F I G. 6

F I G. 7

FIG. 8A

F I G. 8 B

F I G. 9

F I G. 10

F I G. 11

F I G. 12

F I G. 13

US 6,333,892 B2

F I G. 14

F I G. 15

F I G. 16

F I G. 17

F I G. 18

F I G. 19

F I G. 20

F I G. 21

F I G. 22

F I G. 23

F I G. 24

F I G. 25

F I G. 26

F I G. 27

F I G. 28A

F I G. 28B

F I G. 29

F I G. 30

FIG. 31A

F I G. 31B

F I G. 32

F I G. 33

F I G. 34

F I G. 35

F I G. 36

# F I G. 37

# F I G. 38

Dec. 25, 2001

:WITHOUT INTERCONNECTION LINE 108a WITH INTERCONNECTION LINE 108b

# F I G. 39

:WITH INTERCONNECTION LINE 108a WITHOUT INTERCONNECTION LINE 108b

F I G. 40A

FIG. 40B

F I G. 41A

F I G. 41B

# F I G. 42A

# F I G. 42B

F I G. 43A

F I G. 43B

FIG. 44 PRIOR ART

FIG. 45 PRIOR ART

FIG. 46 PRIOR ART

# SYNCHRONOUS SEMICONDUCTOR MEMORY DEVICE CAPABLE OF SELECTING COLUMN AT HIGH SPEED

This application Div. of Ser. No. 09/265,856, filed Mar. 11, 1999.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a synchronous semiconductor memory device, and particularly to a configuration of column-selection-related circuitry for achieving a high-speed column selecting operation. More specifically, the present invention relates to a configuration of circuitry related to internal column addresses in the synchronous semiconductor memory device.

# 2. Description of the Background Art

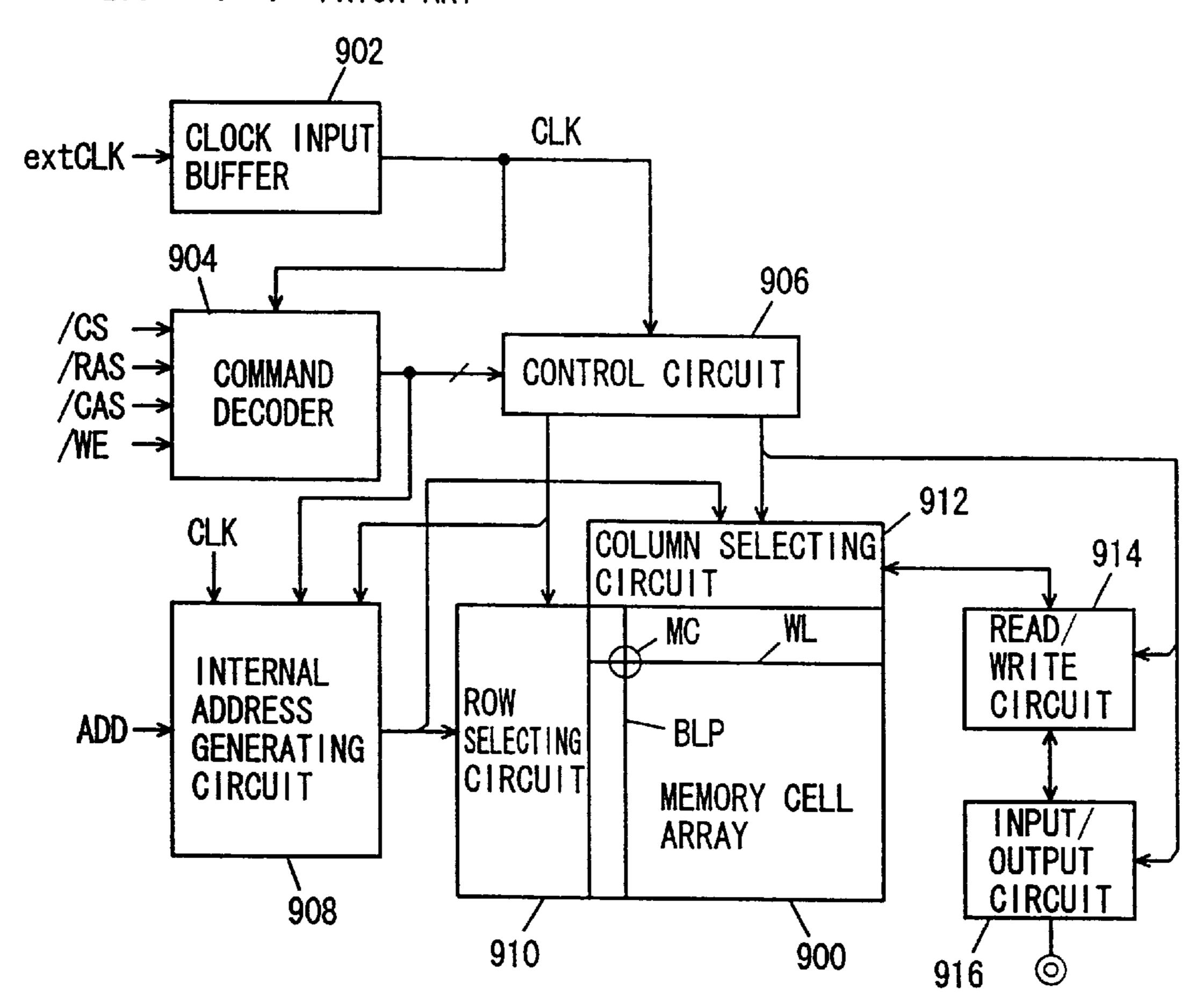

FIG. 44 is a schematic diagram showing an entire structure of a conventional synchronous semiconductor memory device. Referring to FIG. 44, the conventional synchronous semiconductor memory device includes a memory cell array 900 having a plurality of memory cells MCs arranged in rows and columns. In memory cell array 900, word lines WLs corresponding to respective rows of the memory cells and bit line pairs BLPs corresponding to respective columns of the memory cells are arranged.

The synchronous semiconductor memory device further includes: a clock input buffer 902 buffering an externally supplied clock signal extCLK to generate an internal clock 30 signal CLK; a command decoder 904 determining the states of control signals that are externally supplied synchronously with internal clock signal CLK, i.e., a chip select signal /CS, a row address strobe signal /RAS, a column address strobe signal /CAS, and a write enable signal /WE, and generating 35 an operation mode instruction signal indicating an operation mode according to the result of the determination; a control circuit 906 generating (activating) various control signals for performing the operation mode designated by the operation mode instruction signal from command decoder 904; an 40 internal address generating circuit 908 taking in an externally supplied address signal ADD in synchronization with internal clock signal CLK, passing the address signal according to a signal from command decoder 904, and latching the address signal under the control of control 45 circuit 906 to generate an internal row/column address signal; a row selecting circuit 910 for driving a word line corresponding to an addressed row of memory cell array 900 to a selected state according to the internal row address signal from internal address generating circuit 908 under the 50 control of control circuit 906; and a column selecting circuit 912 for selecting an addressed column of memory cell array 900 according to the internal column address signal from internal address generating circuit 908 under the control of control circuit 906.

Command decoder 904 detects the states of chip select signal /CS, row address strobe signal /RAS, column address strobe signal /CAS, and write enable signal /WE at rising of clock signal CLK and determines the designated operation mode based on the detected states. The combination of the 60 states of these control signals is referred to as "command". Command decoder 904 thus decodes a command to generate an operation mode instruction signal indicating the designated operation mode.

Row selecting circuit 910 includes a decode circuit decoding the internal row address signal from internal address generating circuit 908 to generate a row selection signal, and

2

a word line drive circuit driving a word line corresponding to a selected row to a selected state according to the row selection signal. Column selecting circuit 912 includes a column decode circuit (which may include a predecoder) decoding the internal column address signal from internal address generating circuit 908, and a column selection gate corresponding to each column of memory cell array 900 for selecting a corresponding column and coupling the column to an internal data bus according to a column selection signal from the column decode circuit.

The synchronous semiconductor memory device further includes a read/write circuit 914 supplying/receiving data to/from a selected memory cell via column selecting circuit 912 synchronously with internal clock signal CLK under the control of control circuit 906, and an input/output circuit 916 operating under control of control circuit 906 for communicating data between read/write circuit 914 and an external unit.

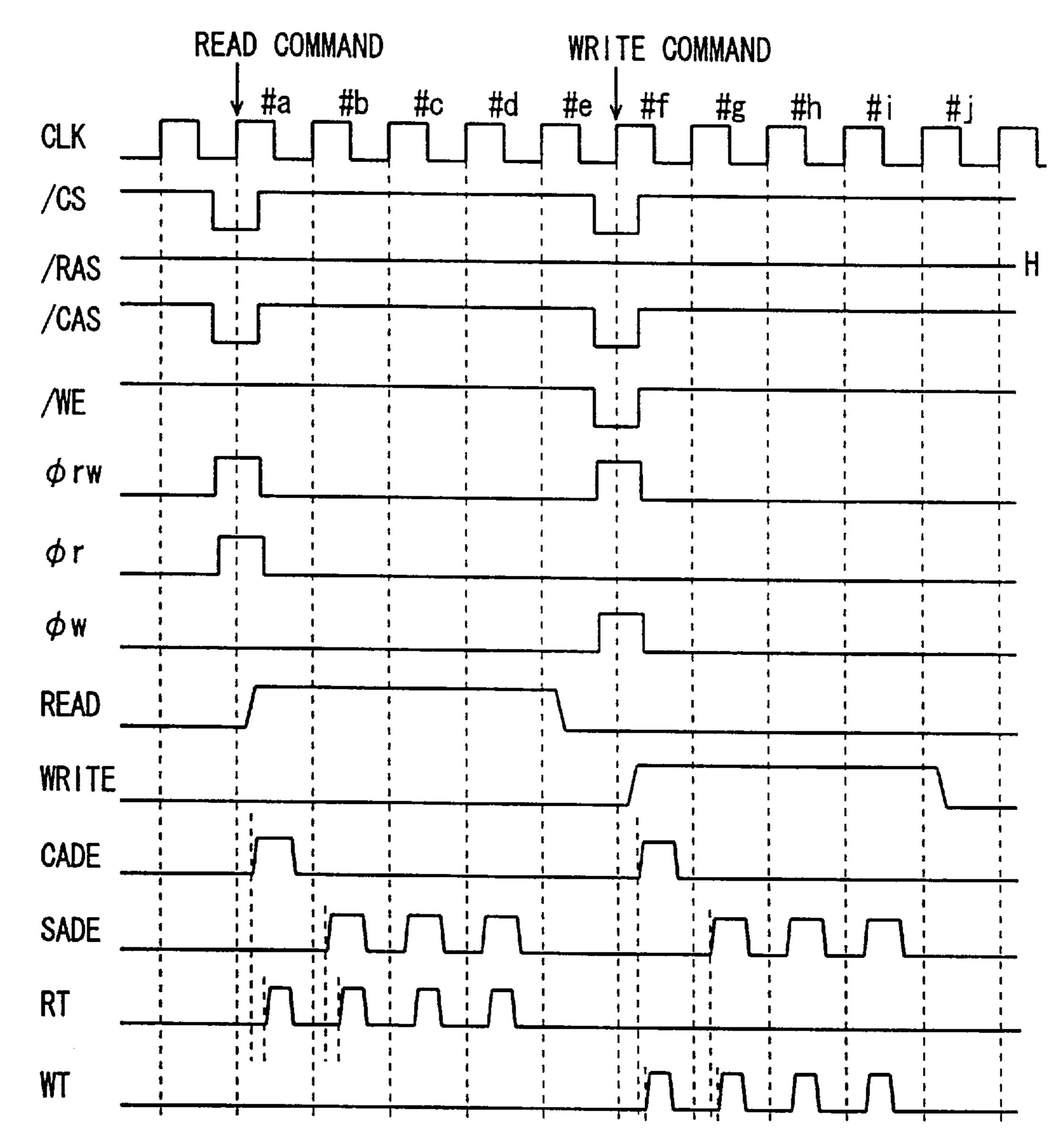

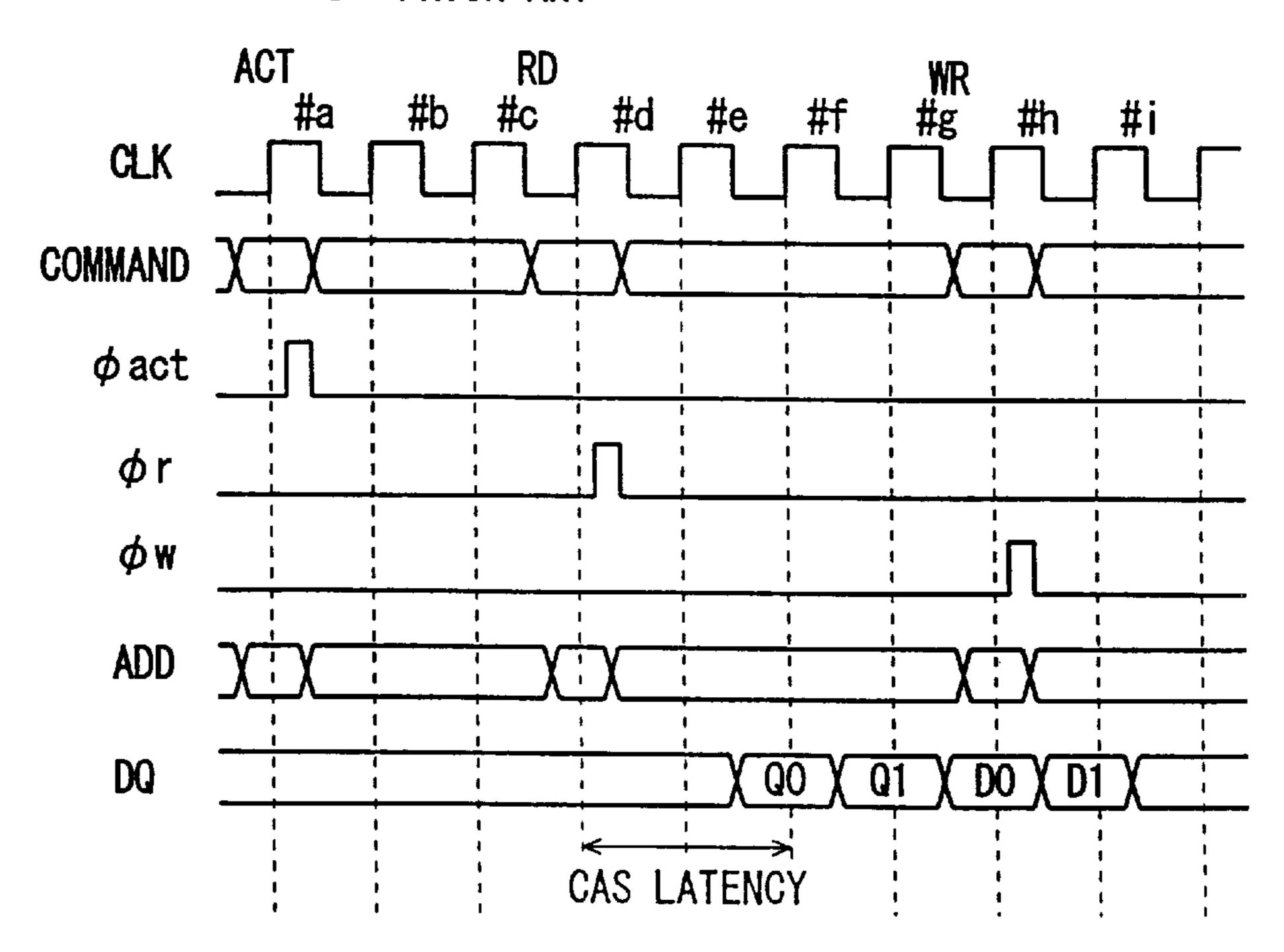

Referring to the timing chart illustrated in FIG. 45, an operation of the synchronous semiconductor memory device shown in FIG. 44 is briefly described.

An active command ACT is supplied in clock cycle #a. The active command is issued by setting chip select signal /CS and row address strobe signal /RAS to a logical low or L level, and setting column address strobe signal /CAS and write enable signal /WE to a logical high or H level. When active command ACT is supplied, command decoder 904 decodes the command, drives an array activation instruction signal pact into an active state, and supplies it to control circuit 906. Control circuit 906 activates row selecting circuit 910 according to array activation instruction signal pact, and causes internal address generating circuit 908 to generate an internal row address signal.

Internal address generating circuit 908 takes in external address signal ADD synchronously with rising of clock signal CLK, latches the external address signal according to array activation instruction signal tact from command decoder 904, and generates an internal row address signal under the control of control circuit 906. Row selecting circuit 910 then drives an addressed row of memory cell array 906 to a selected state according to the internal row address signal from internal address generating circuit 908. When row selecting circuit 910 operated, data of memory cells of one row connected to a selected row (selected word line) WL is amplified to be latched by a sense amplifier (not shown) under the control of control circuit 906.

In clock cycle #d, a read command RD is supplied. Read command RD is issued by setting chip select signal /CS and column address strobe signal /CAS to L level, and setting row address strobe signal /RAS and write enable signal /WE to H level. The read command instructs reading of data, and command decoder 904 accordingly supplies a reading operation instruction signal por to control circuit 906. Internal address generating circuit 908 takes in external address signal ADD synchronously with clock signal CLK, generates an internal column address signal from the received external address signal in response to the reading operation instruction signal from command decoder 904, and latches the generated internal address signal under the control of control circuit 906.

Column selecting circuit 912 performs the column selecting operation according to the column address signal from internal address generating circuit 908, and selects an addressed column in memory cell array 900. Data of a selected memory cell is read synchronously with clock signal CLK via read/write circuit 914 and input/output

circuit 916 under the control of control circuit 906. The period required from supply of read command RD to external output of valid data is referred to as CAS latency. FIG. 45 illustrates waveforms in data reading with the CAS latency of 2. The number of data that are consecutively read after one read command is supplied is referred to as a burst length. FIG. 45 illustrates a data reading operation with the burst length of 2. Accordingly, after two clock cycles from supply of read command RD, in two clock cycles #f and #g, data Q0 and Q1 are defined to be sampled by an external unit.

In clock cycle #h, a write command WR is supplied to designate writing of data. Write command WR is issued by setting chip select signal /CS, column address strobe signal /CAS, and write enable signal /WE all to L level, and setting row address strobe signal /RAS to H level. When write command WR is supplied, command decoder 904 activates a writing operation instruction signal  $\phi$ w and supplies it to control circuit 906. In response to activation of writing operation instruction signal \phi w from command decoder 904, 20 internal address generating circuit 908 generates an internal column address signal from address ADD taken synchronously with internal clock signal CLK, and latches it under the control of control circuit 906. Column selecting circuit 912 again performs the column selecting operation according to the internal column address signal, and data D0 which is supplied simultaneously with write command WR in the clock cycle is taken to be written into a selected memory cell. FIG. 45 illustrates the data writing operation with the burst length of 2. Data D0 and D1 supplied in clock cycles 30 #h and #i are written into selected memory cells synchronously with the clock signal according to a prescribed sequence.

When data for the burst length are read/written, a burst address counter included in internal address generating 35 circuit 908 operates to internally generate a column address signal in a prescribed sequence, and the column selecting operation is performed according to the column address signal from the burst address counter.

In the synchronous semiconductor memory device, externally supplied signals /CAS, /RAS, /CS /WE and address signal ADD are taken synchronously with clock signal CLK, and data are input/output synchronously with clock signal CLK. As to these external signals, it is enough to consider the skew of the external signals relative to clock signal CLK, and consideration of the skew between the external signals is unnecessary, so that an internal signal can be so generated at a high speed as to start an internal operation at an advanced tiling. Further, data are input/output synchronously with clock signal CLK and equivalently the burst 50 length data are input/output at the frequency of clock signal CLK, so that data are input/output at a high speed.

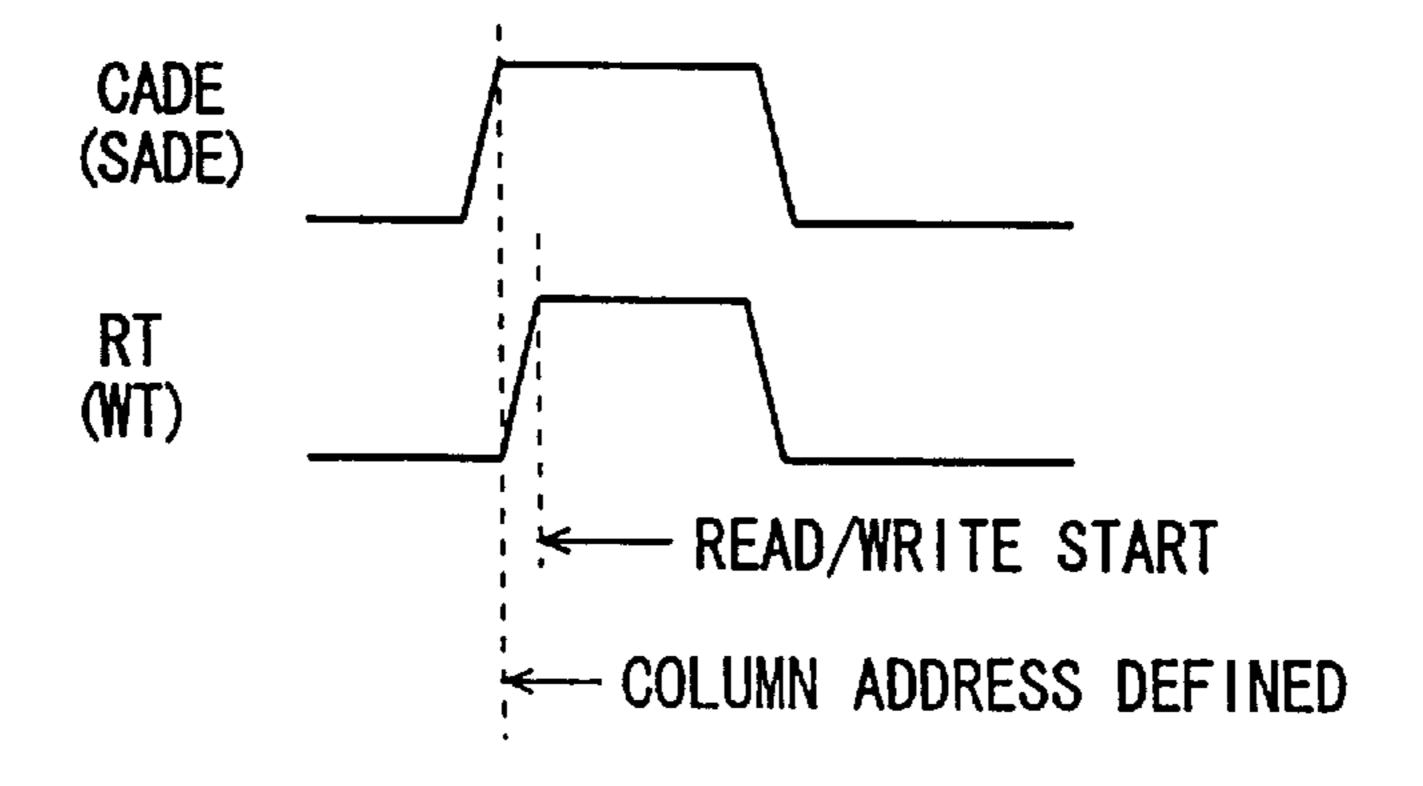

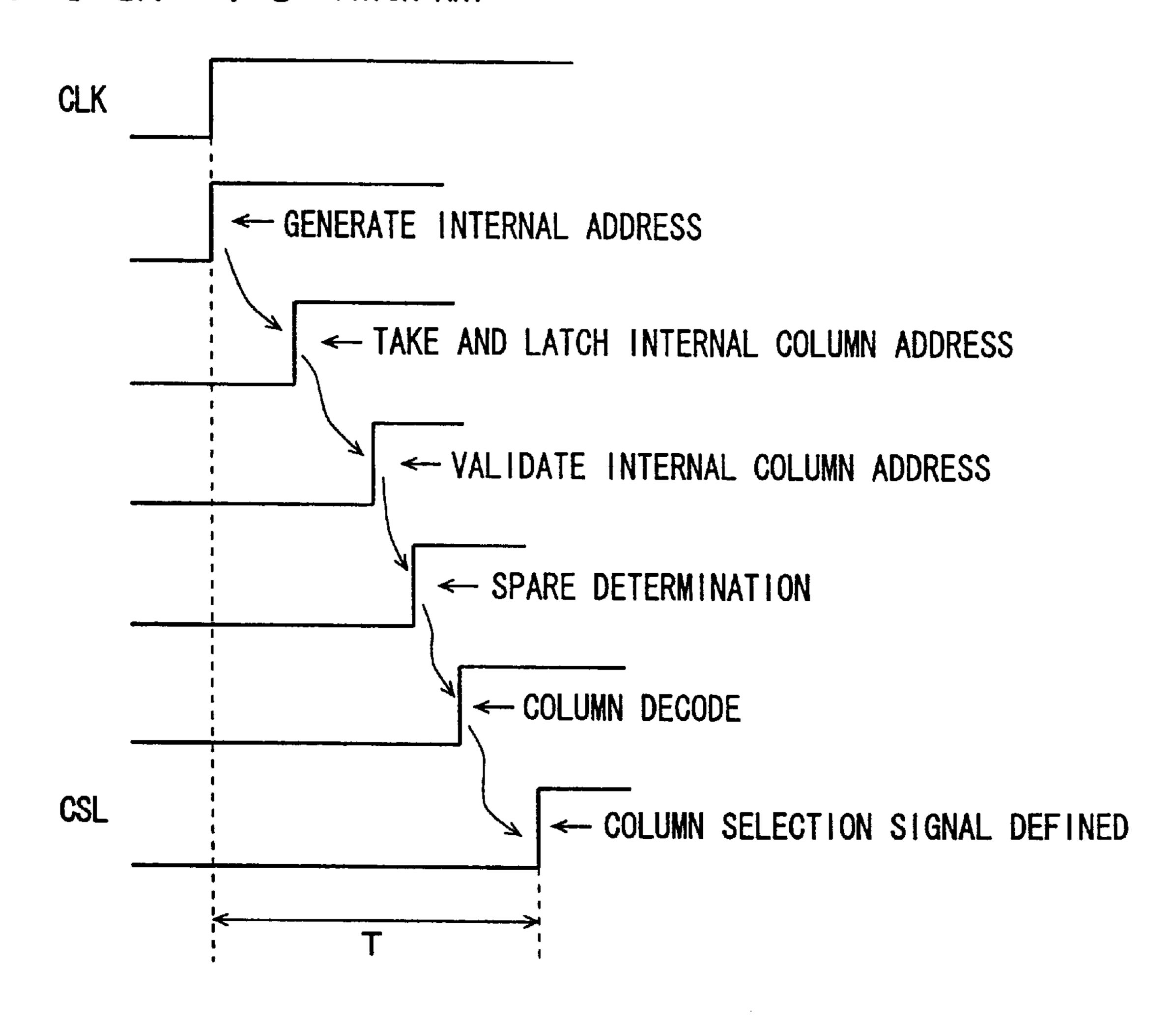

FIG. 46 schematically illustrates a sequence of a column selecting operation of the conventional synchronous semi-conductor memory device. An address buffer is commonly provided to a row address signal and a column address signal. In response to rising of internal clock signal CLK, the address buffer generates an internal address signal. The generated internal address signal is taken as a column address signal to be latched according to a read command or a write command (hereinafter referred to collectively as access command). The taken internal column address signal is output as a valid column address signal to be supplied to a predecoder/decoder. Spare determination for determining whether the valid internal column address signal designates a defective column or not is made. If a defective column is addressed, the defective column has to be replaced by a

4

redundant column. After the spare determination is done, a normal column decoding operation is performed when a normal column is selected, and a column selection line CSL is driven to a selected state. Accordingly, time period T is necessary from the time of rising of clock signal CLK to H level to start a clock cycle to the time at which a signal on column selection line CSL attains a definite state. Internal clock signal CLK is a clock signal which is synchronous with external clock signal extCLK. As the clock frequency becomes higher, the clock cycle becomes shorter. Therefore, time T should be made as short as possible for accessing to data of memory cells. In particular, in order to use the synchronous semiconductor memory device as a main memory for the recently employed processor that operates according to a high speed clock signal of 100 MHz or 200 MHz, the time required for internally selecting memory cells should be made as short as possible to minimize so called "column access time (CAS access time)". The CAS access time is a time period required from supply of a read command to an external actual reading of memory cell data. Various improvements in terms of the circuit or the layout are made in order to minimize time T which is necessary from rising of clock signal CLK to driving of an addressed column to a selected state. However, there still remains room for improvement in the approach for shortening time T.

#### SUMMARY OF THE INVENTION

An object of the present invention is to provide a synchronous semiconductor memory device in which the time required for column selection can be reduced sufficiently.

Another object of the present invention is to provide a synchronous semiconductor memory device capable of generating an internal column address signal in a definite state at a high speed from an external address signal.

Still another object of the present invention is to provide a synchronous semiconductor memory device capable of performing a column decode operation at a timing as fast as possible.

A synchronous semiconductor memory device according to a first aspect of the present invention includes a memory array having a plurality of memory cells arranged in rows and columns, an address input gate passing an externally supplied address signal in synchronization with a clock signal, an address generating circuit generating a complementary internal address signals according to the address signal from the address input gate, and a column selection signal generating circuit generating a column selection signal which designates a column of the memory array according to the complementary internal address signals from the address generating circuit.

A synchronous semiconductor memory device according to a second aspect includes an access command decode circuit receiving an externally supplied command independently of a clock signal to decode the command for activating a column access mode instruction signal when the command is an access command which designates column selection (column access), a first circuit taking and latching the column access mode instruction signal from the access command decoding circuit synchronously with the clock signal to generate a column address activation signal, and a first address generating circuit generating an internal column address signal from an externally supplied address signal according to the column address activation signal from the first circuit.

A synchronous semiconductor memory device according to a third aspect includes: an access command decode circuit

receiving and decoding an externally supplied command for generating a column access instruction signal synchronously with a clock signal when the command is an access command instructing column selection; a read command decode circuit generating a read trigger signal synchronously with 5 the clock signal when the received command instructs a data writing operation; a write command decode circuit generating a write trigger signal synchronously with the clock signal when the received command instructs a data writing operation; a circuit generating a column address activation 10 signal in response to the column access instruction signal; a counter taking an externally supplied address signal in response to activation of the column access instruction signal, and performing a counting operation synchronously with the clock signal according to a prescribed sequence 15 with the taken external address signal being an initial value; a circuit generating a counter address activation signal which makes an address of the counter valid in response to the clock signal in a cycle of the clock signal following a cycle in which the access command is supplied, when the 20 column access instruction signal is activated; a column address generating circuit generating an internal column address signal from the external address signal synchronously with the clock signal in response to activation of the column address activation signal, and generating an internal 25 column address signal from a count value of the counter when the counter address activation signal is activated; a column selection signal generating circuit generating a column selection signal for selecting a column of memory cells according to the internal column address signal from the 30 column address generating circuit when activated and a control circuit activating the column selection signal generating circuit according to activation of one of the read trigger signal and the write trigger signal, or activation of one of the column address activation signal and the counter address 35 activation signal. The control circuit includes means for alternatively validating a set of trigger signals and a set of address activation signals.

A circuit configuration of a column address input portion can be simplified by generating complementary address signals synchronously with a clock signal, and accordingly an address signal can be transmitted at a high speed to generate an internal address signal.

A logic gate is unnecessary for generating complementary column address signals according to the result of command decoding since complementary internal address signals are generated according to the clock signal, so that complementary internal column address signals can be generated at a high speed.

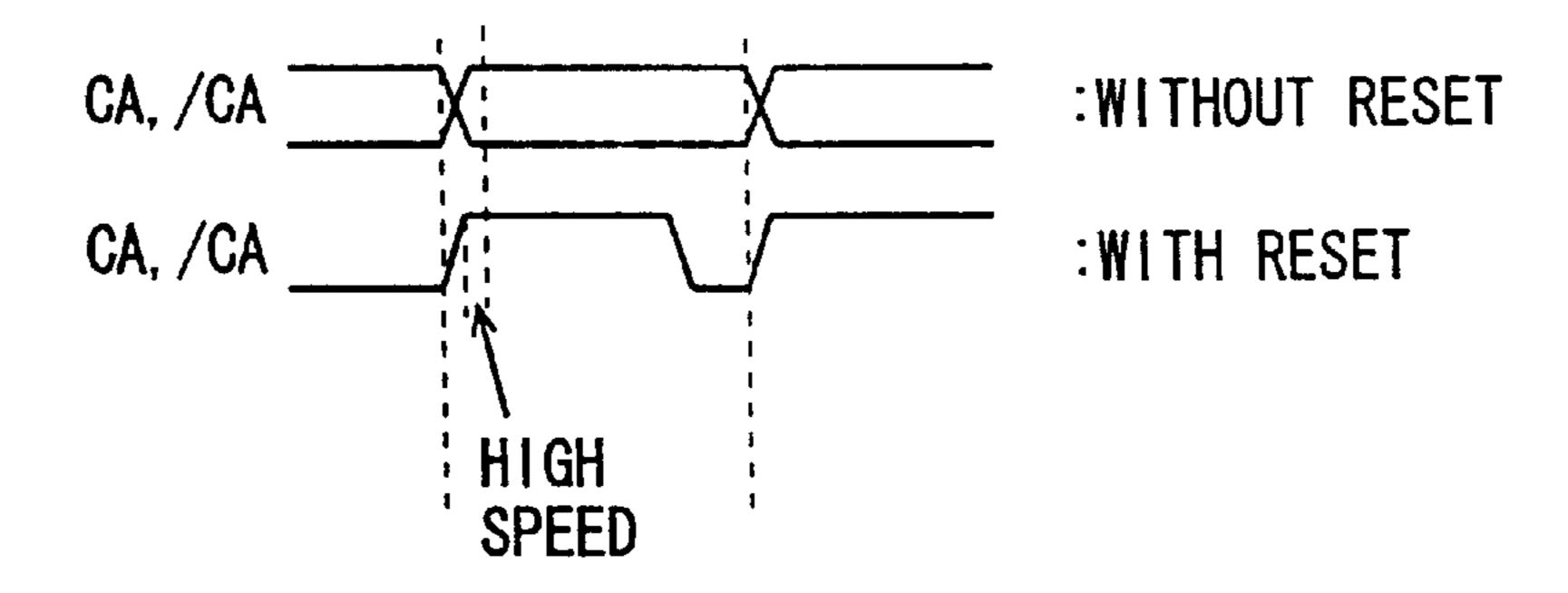

A column address signal is reset in each clock cycle so that the column address signal can be changed in each clock cycle without affection by an address signal in a preceding cycle. Accordingly, the column address signal can be set into a definite state at an advanced timing to achieve a high speed access.

A command is decoded independently of the clock signal so that decoding of the command can be started at advanced timing after rising of the clock signal. Accordingly, an operation mode instruction signal can be driven into the definite state at an advanced timing and thus, an internal column address signal can be defined at a best timing.

An internal column address signal is predecoded according to a column address activation signal so that generation and predecoding of the internal column address signal can 65 be done in one stage of logic gate, and a predecode signal can be generated at a higher speed compared with the

6

configuration in which the internal column address signal is generated and thereafter the internal column address signal is predecoded.

Further, in spare determination, a supplied address signal attains the definite state at a fast timing so that the spare determination can be made at a high speed and the column decoding operation can be started at an advance timing.

In addition, the determination circuit is configured to increase the speed of its determining operation and accordingly, a high speed determining operation is possible.

In the predecoder, an output of an inverter receiving a group specification bit is used as one operation power supply voltage of a circuit which decodes a column specifying address bit. Accordingly, an output load of the inverter of the group specifying bit is reduced and thus a high speed predecoding operation is possible.

A signal for activating a column decoder is activated by using one of a set of read trigger signal and a write trigger signal and a set of a column address activation signal and a counter address activation signal. Accordingly, a column decoding operation is performed at an optimum timing according to the frequency of the clock signal used, and a column selection signal can be driven into the definite state at a high speed.

The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

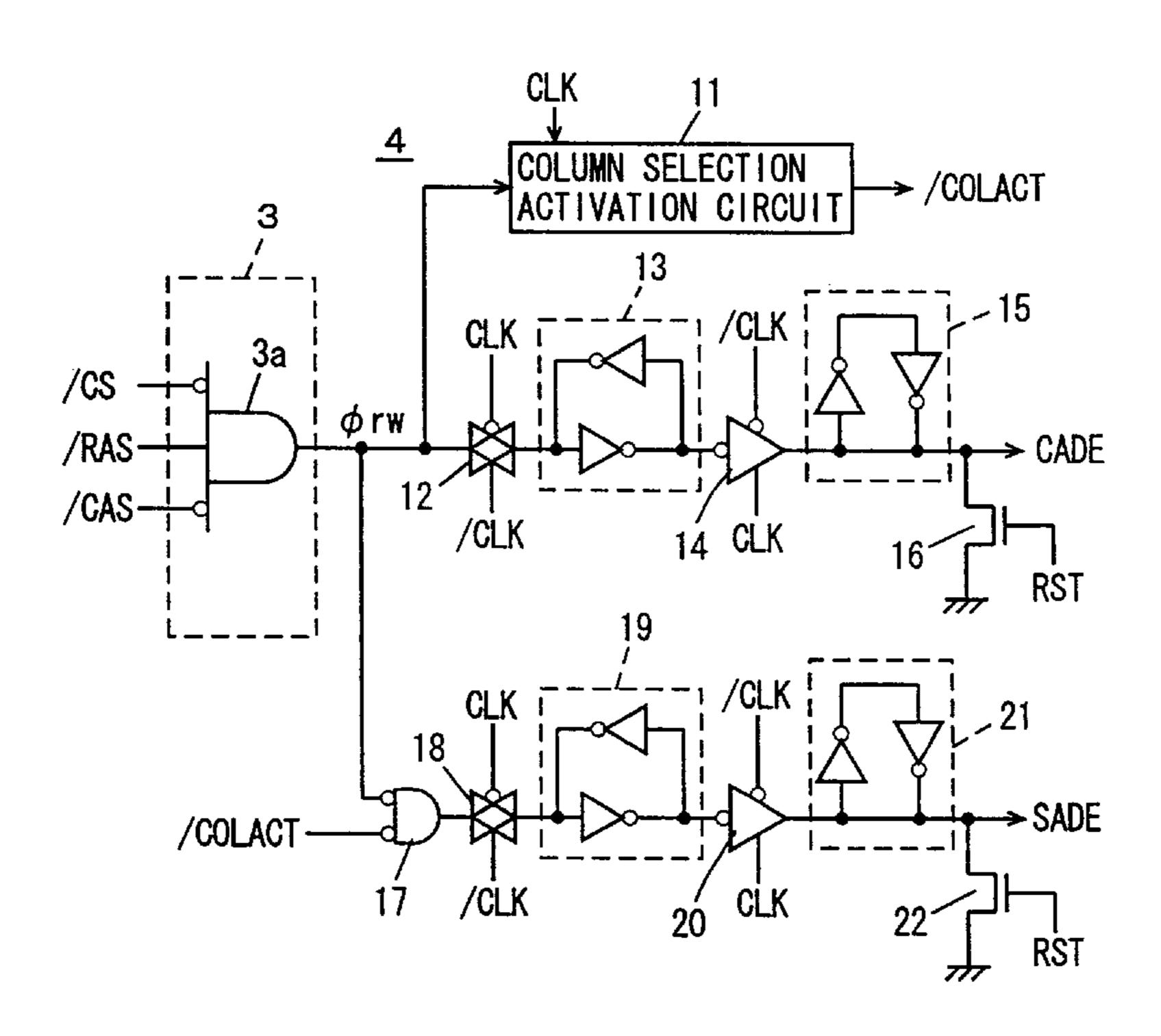

- FIG. 1 is a schematic diagram illustrating an entire structure of a synchronous semiconductor memory device according to the present invention.

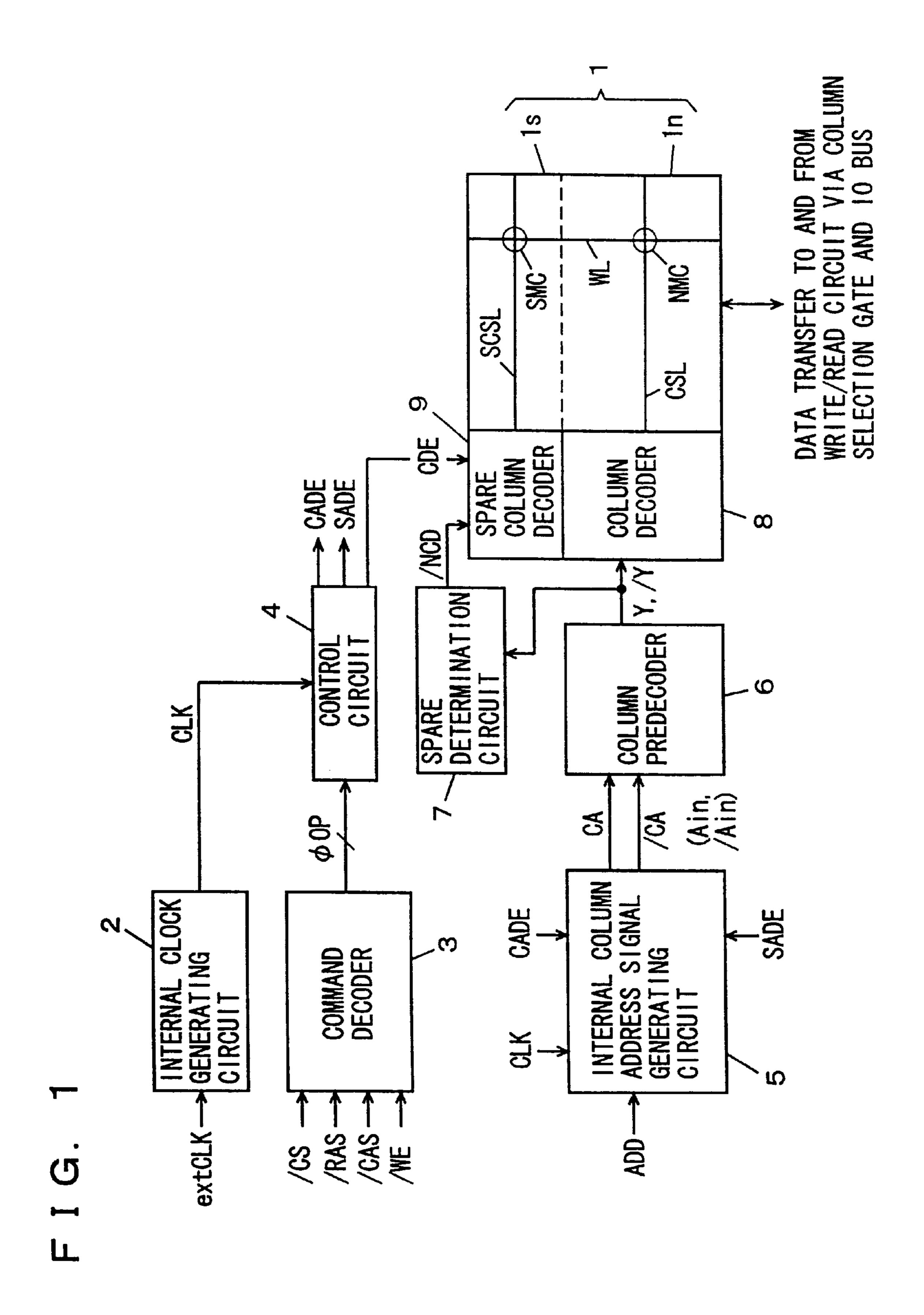

- FIG. 2 illustrates structures of a command decoder and a control circuit of the synchronous semiconductor memory device shown in FIG. 1.

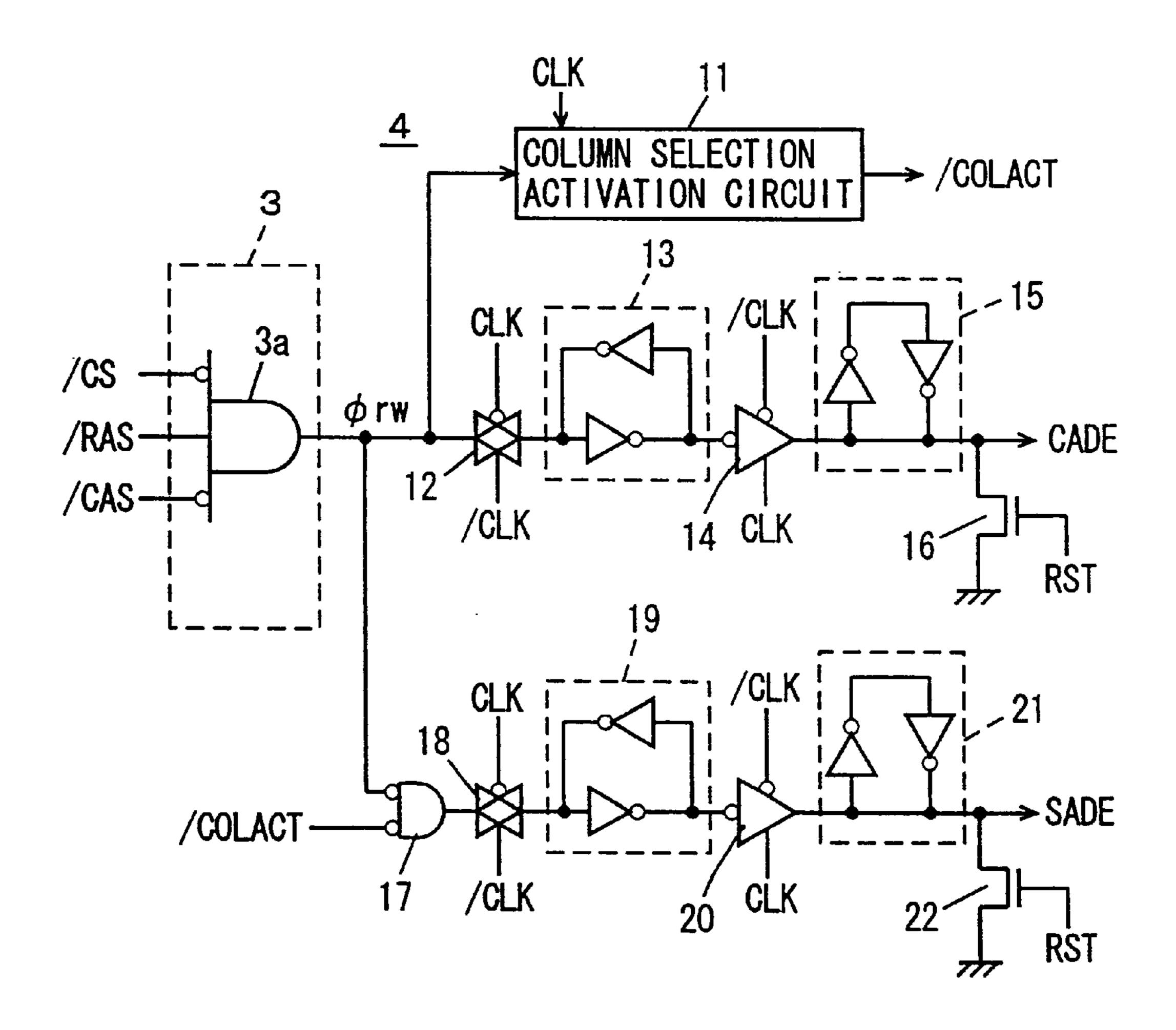

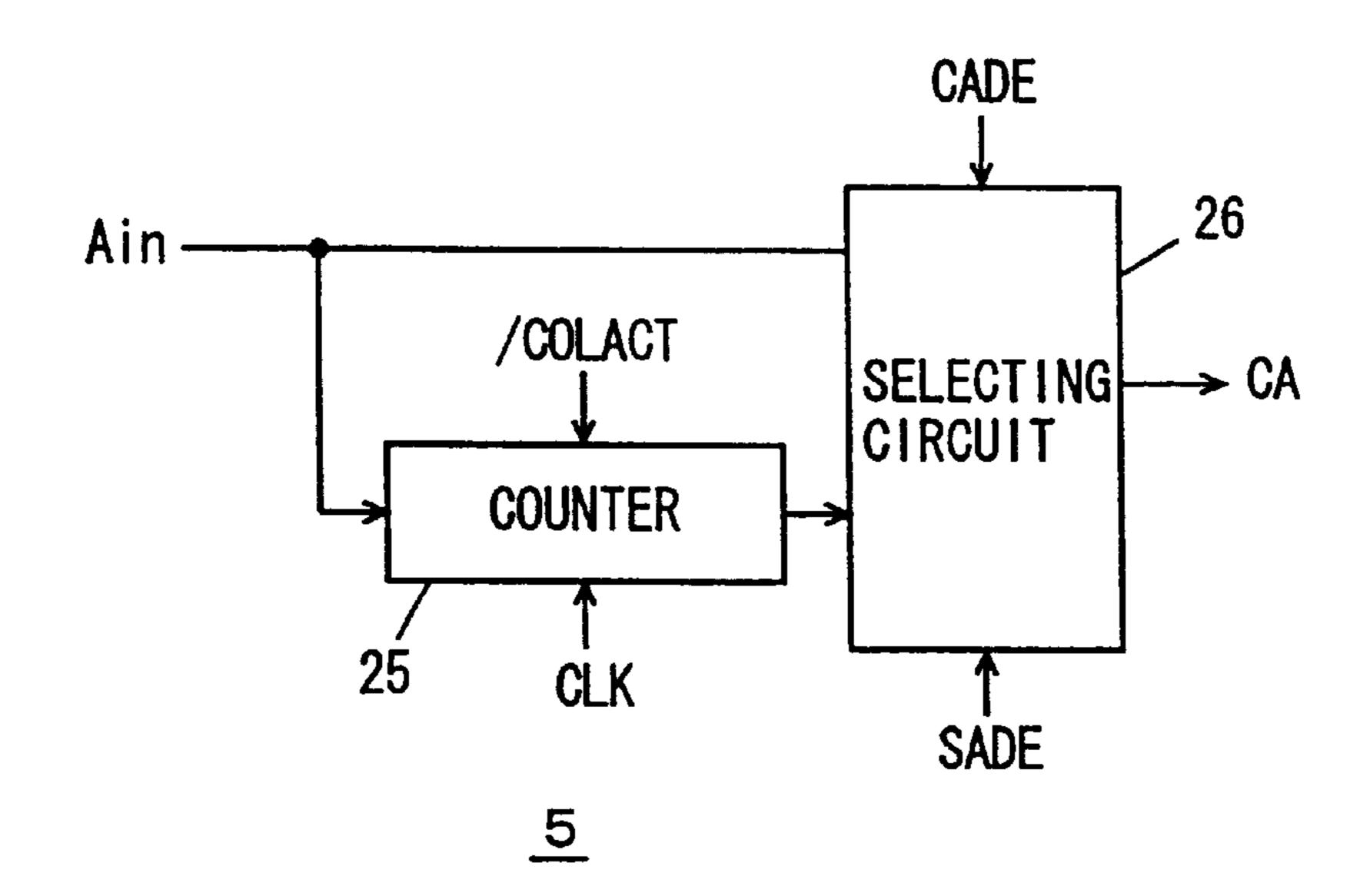

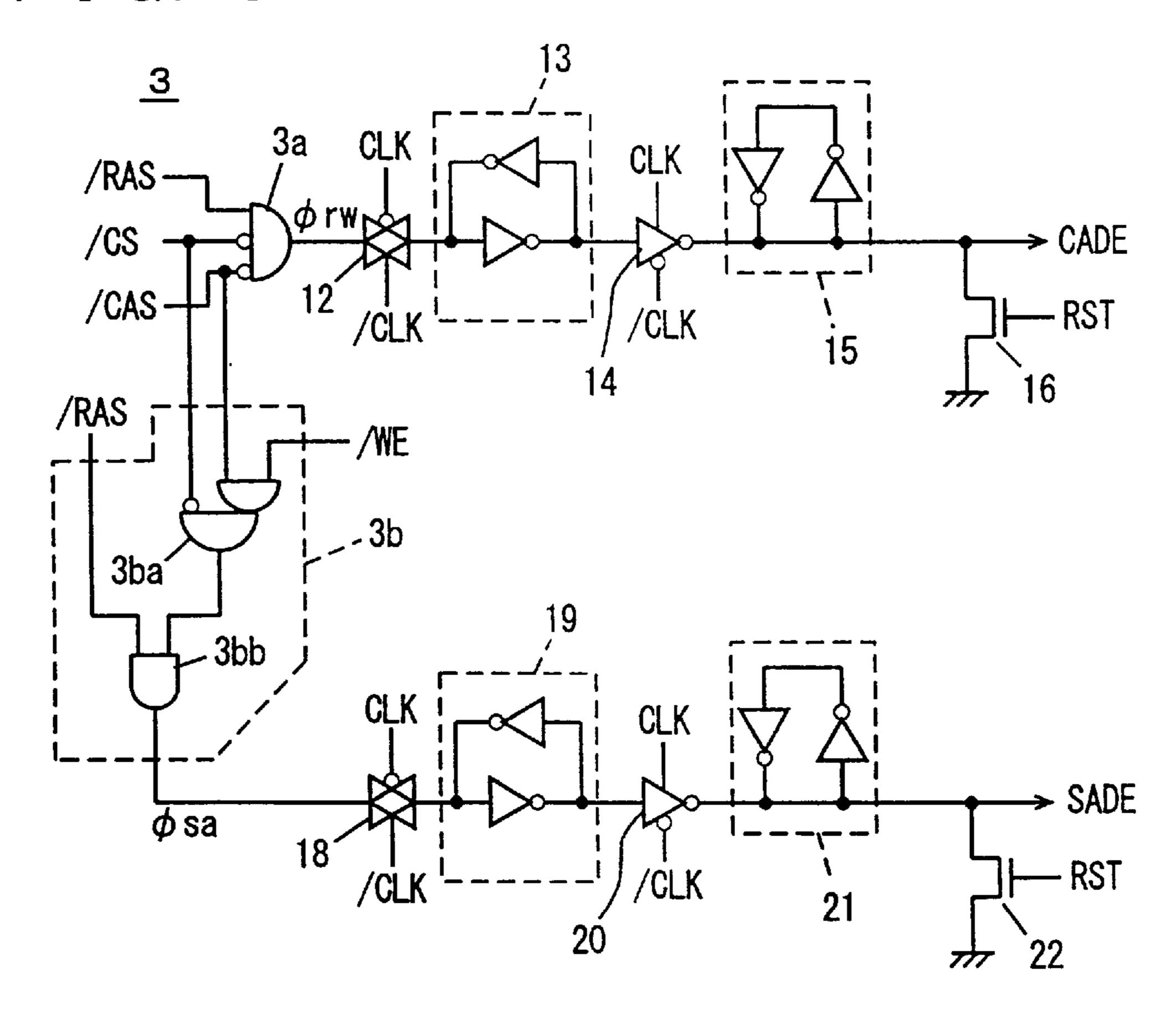

- FIG. 3 is a schematic diagram illustrating a structure of an internal column address signal generating circuit shown in FIG. 1.

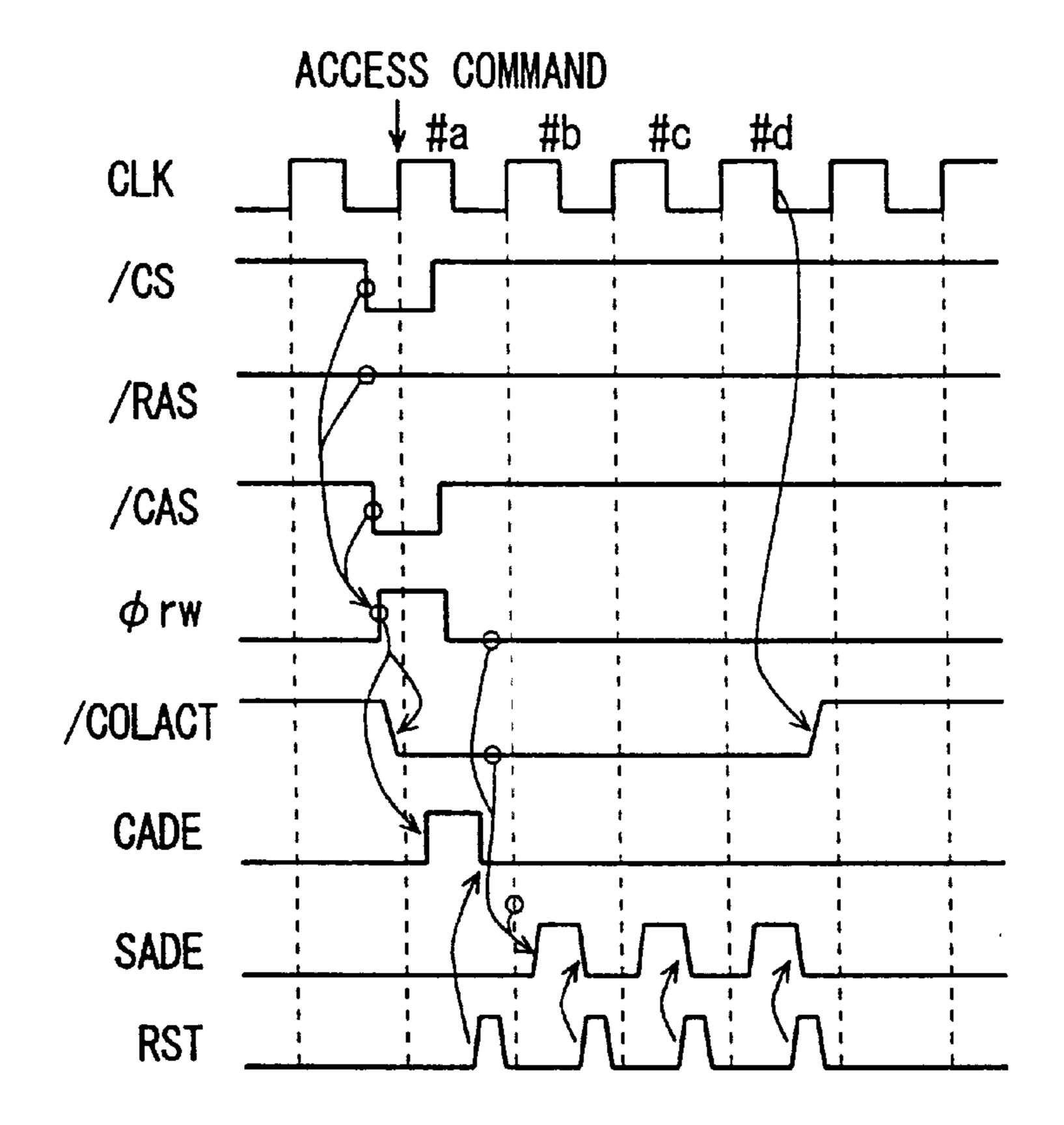

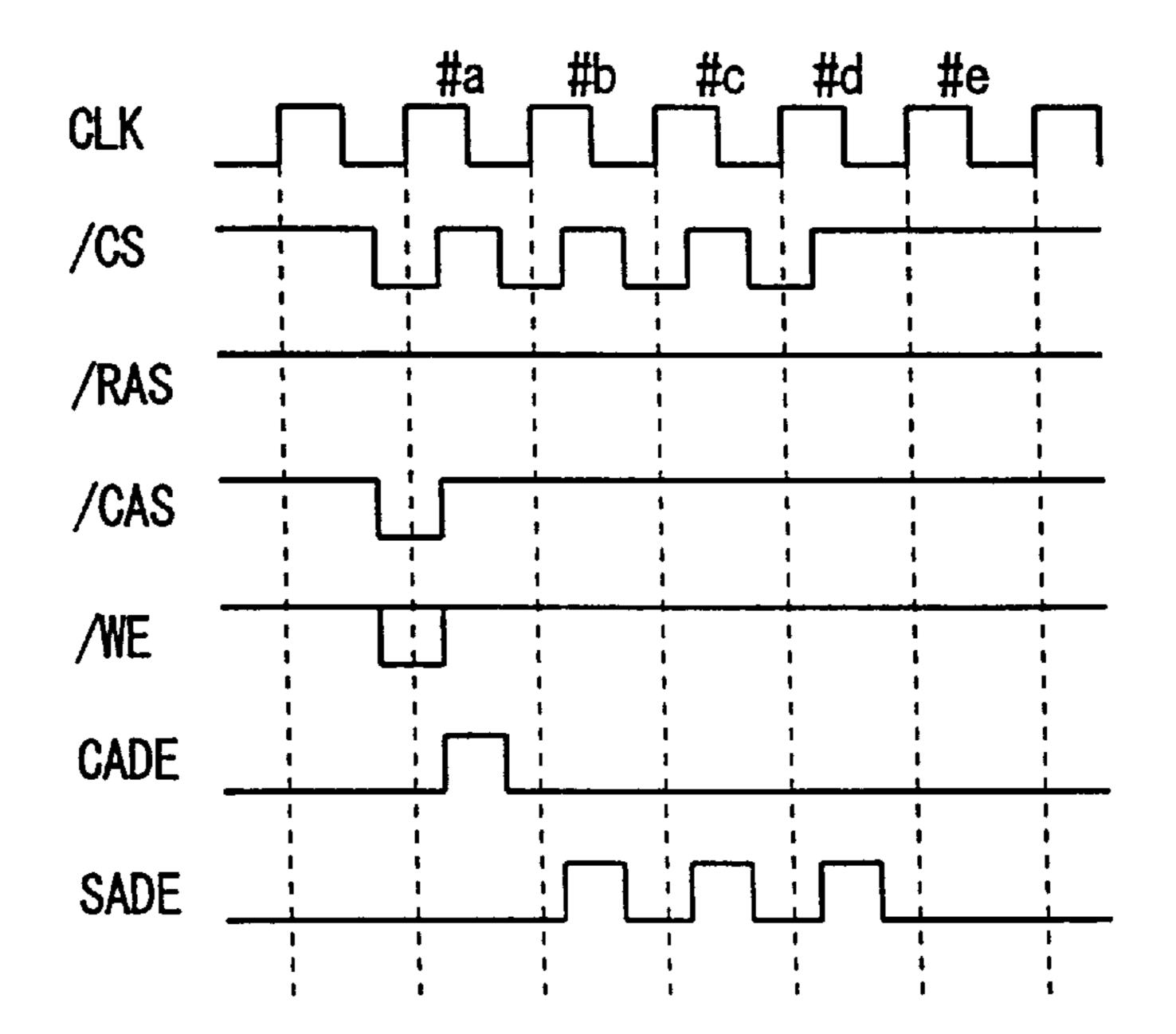

- FIG. 4 is a timing chart representing an operation of the circuits illustrated in FIGS. 2 and 3.

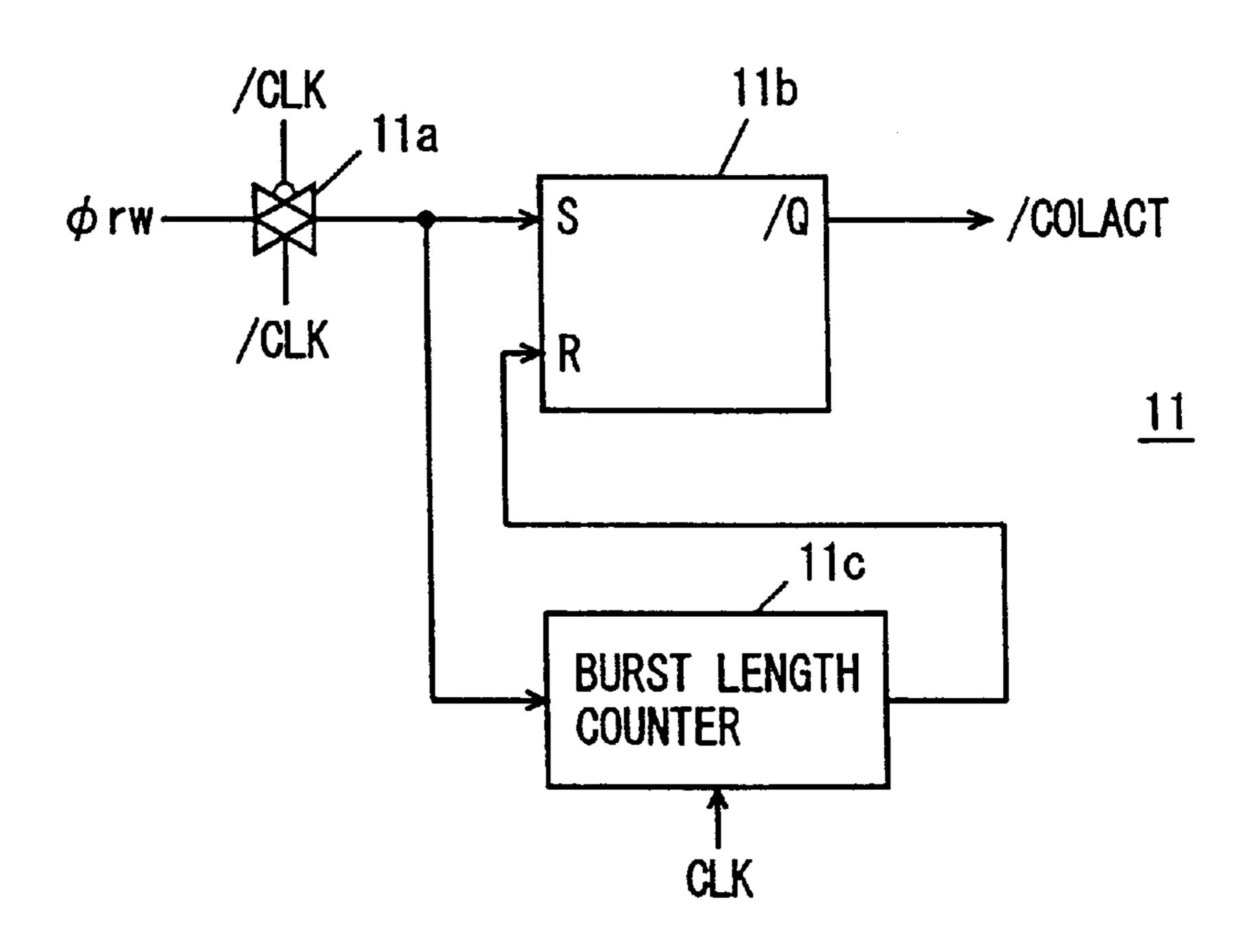

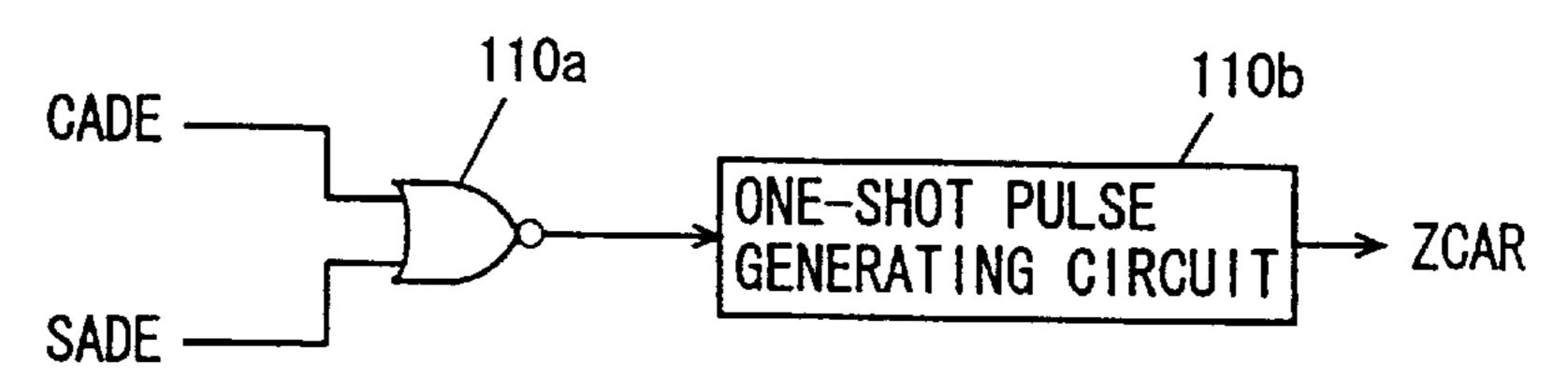

- FIG. 5 is a schematic diagram showing a structure of the portion for generating a column selecting operation activation signal shown in FIG. 2.

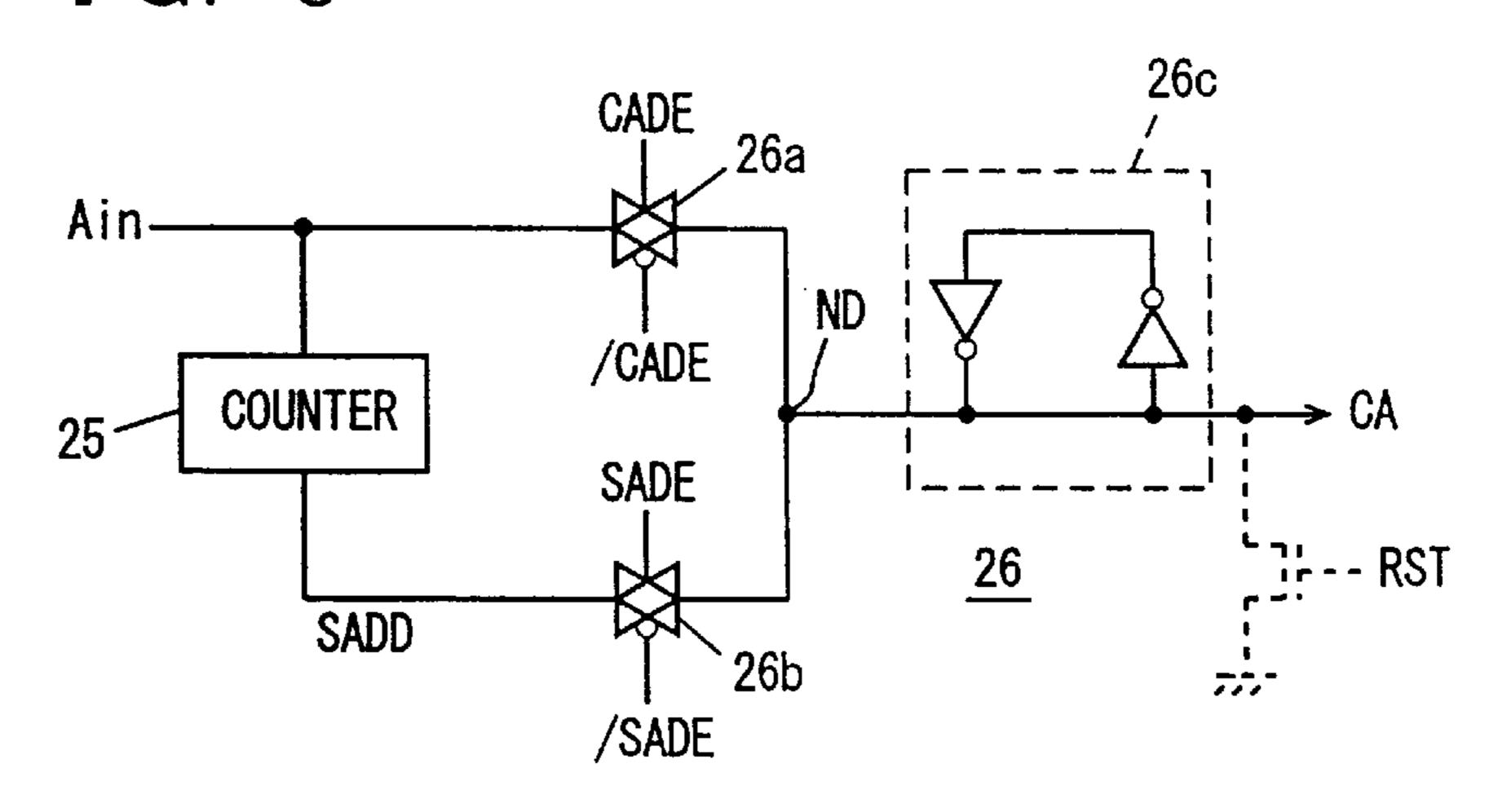

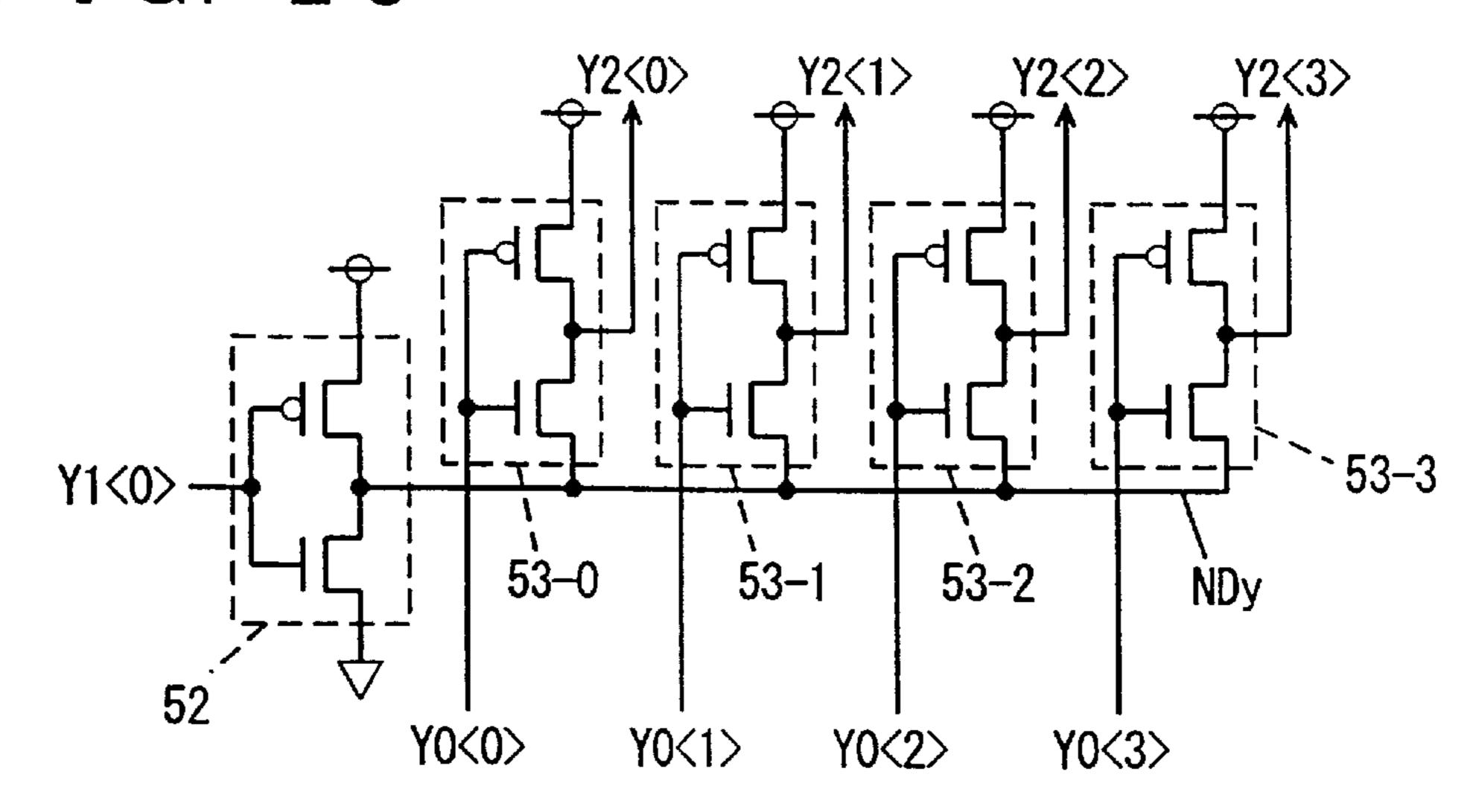

- FIG. 6 illustrates a structure of a selecting circuit shown in FIG. 3.

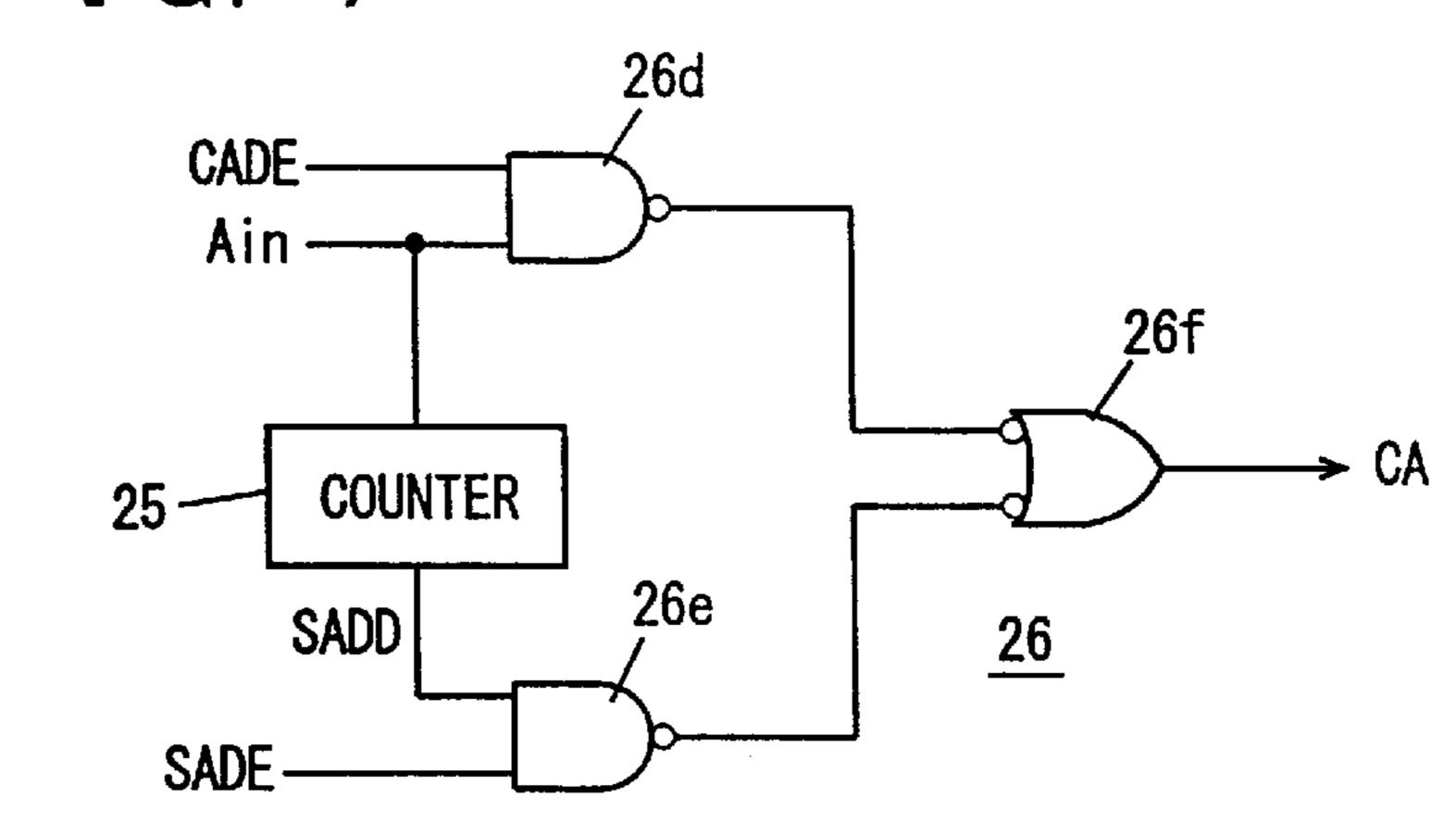

- FIG. 7 illustrates another structure of the selecting circuit shown in FIG. 3.

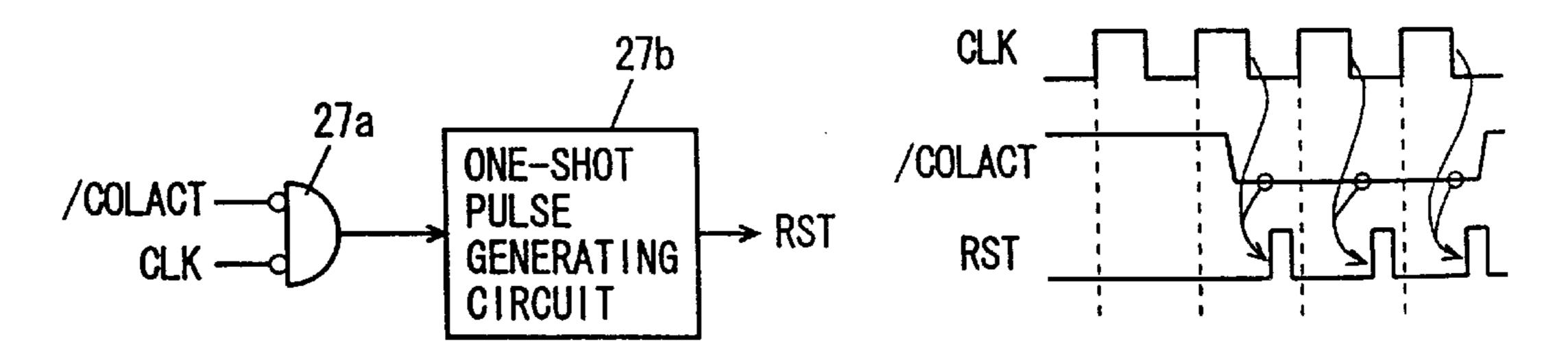

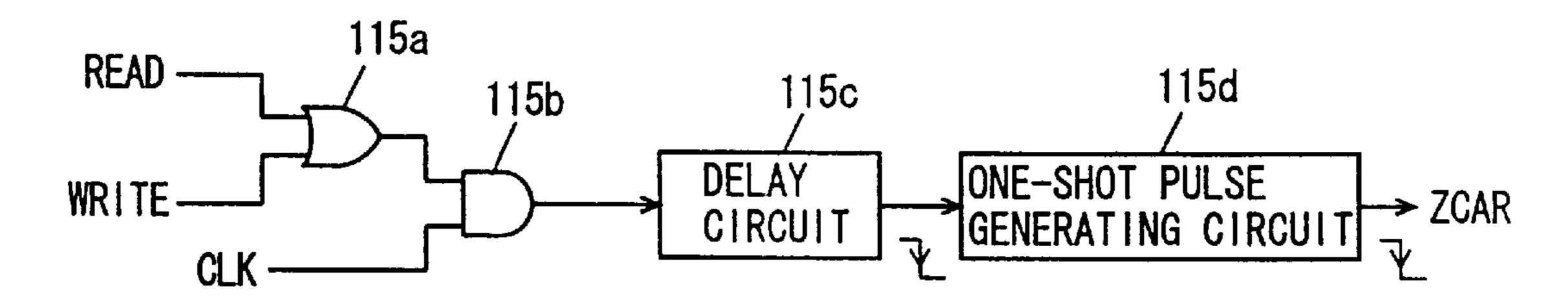

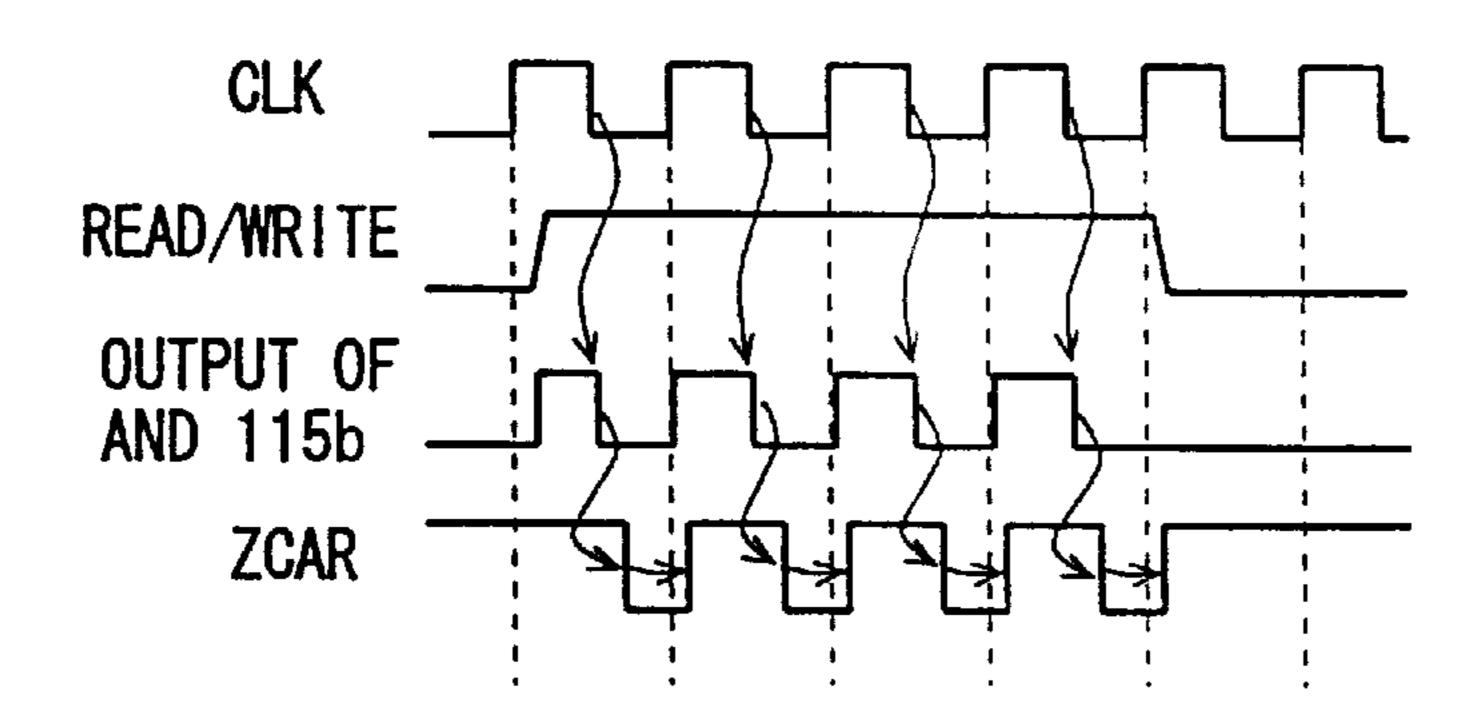

- FIG. 8A illustrates a structure of a circuit for generating a reset signal shown in FIG. 2, and FIG. 8B is a timing chart representing an operation of the circuit shown in FIG. 8A.

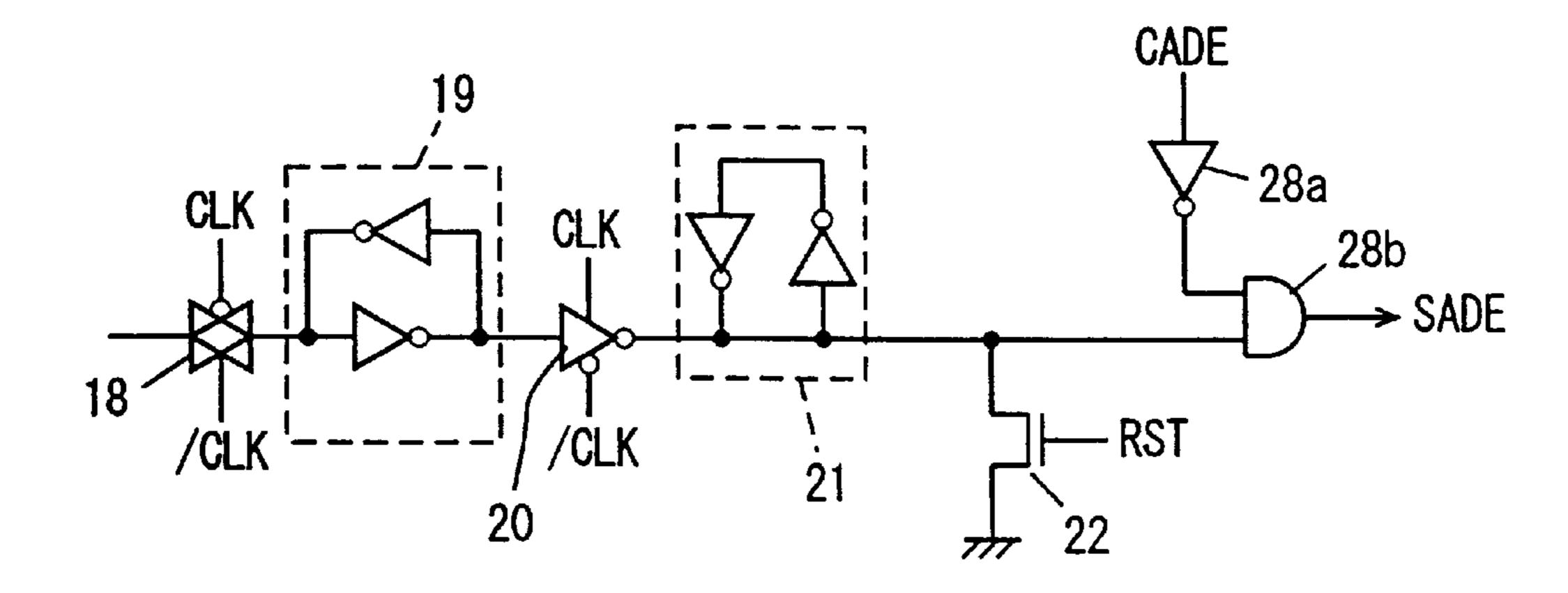

- FIG. 9 illustrates a modification of the circuit shown in FIG. 2.

- FIG. 10 is a timing chart representing an operation of the circuit shown in FIG. 9.

- FIG. 11 is a modification of the circuits shown in FIGS. 2 and 9.

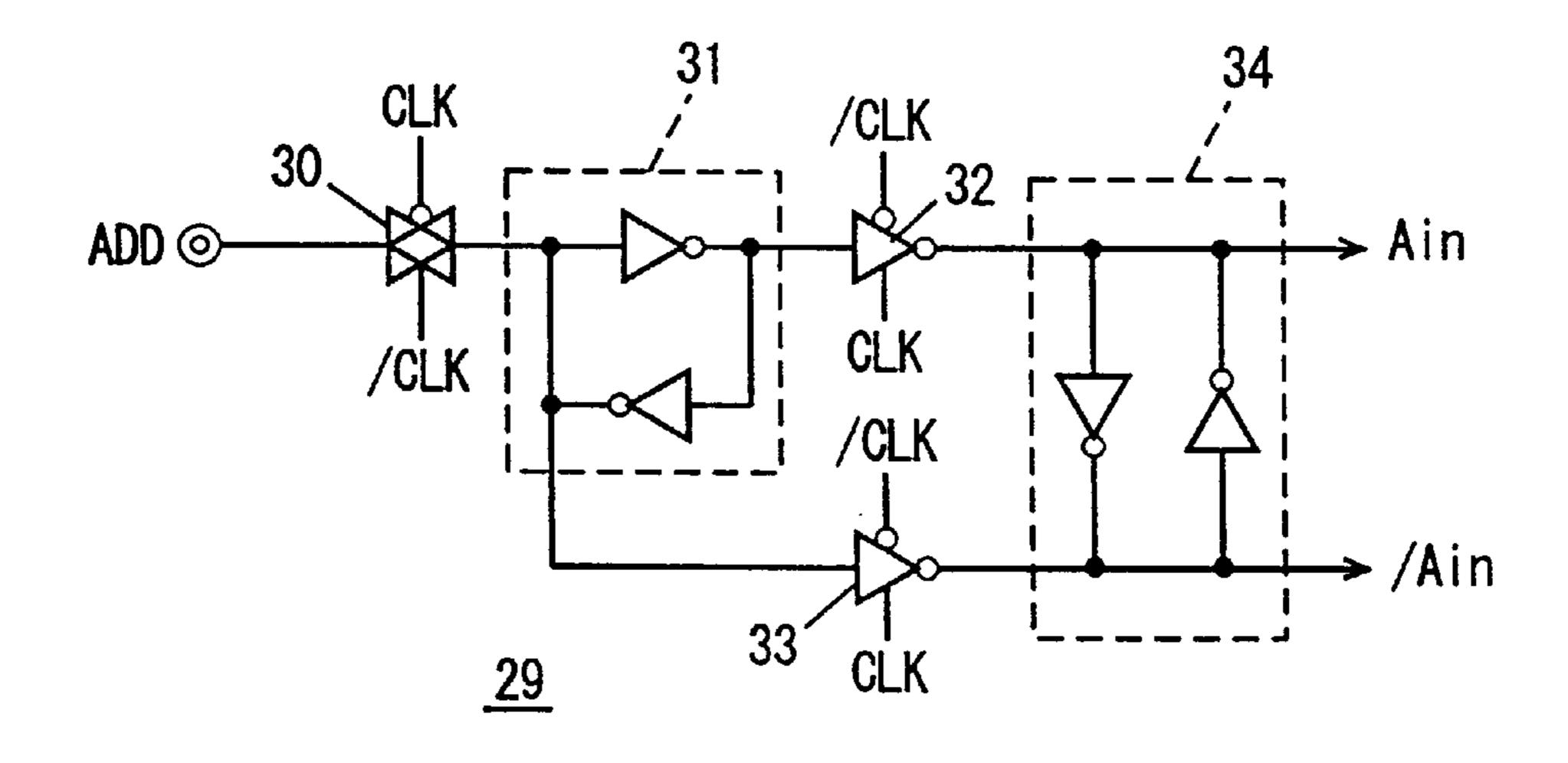

- FIG. 12 illustrates a structure of a portion for generating an internal address signal of the internal column address signal generating circuit shown in FIG. 1.

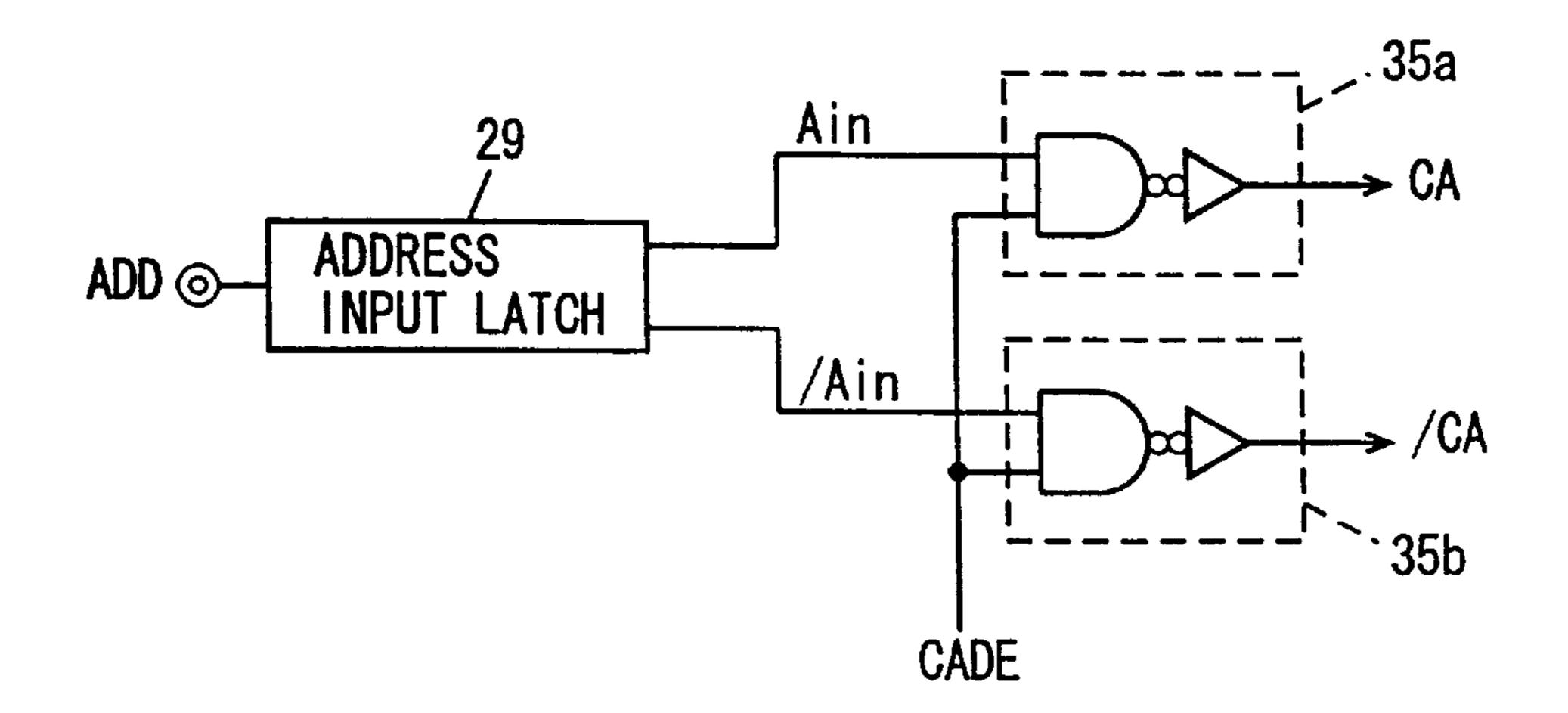

- FIG. 13 is a schematic diagram illustrating a structure of the internal column address signal generating circuit shown in FIG. 1.

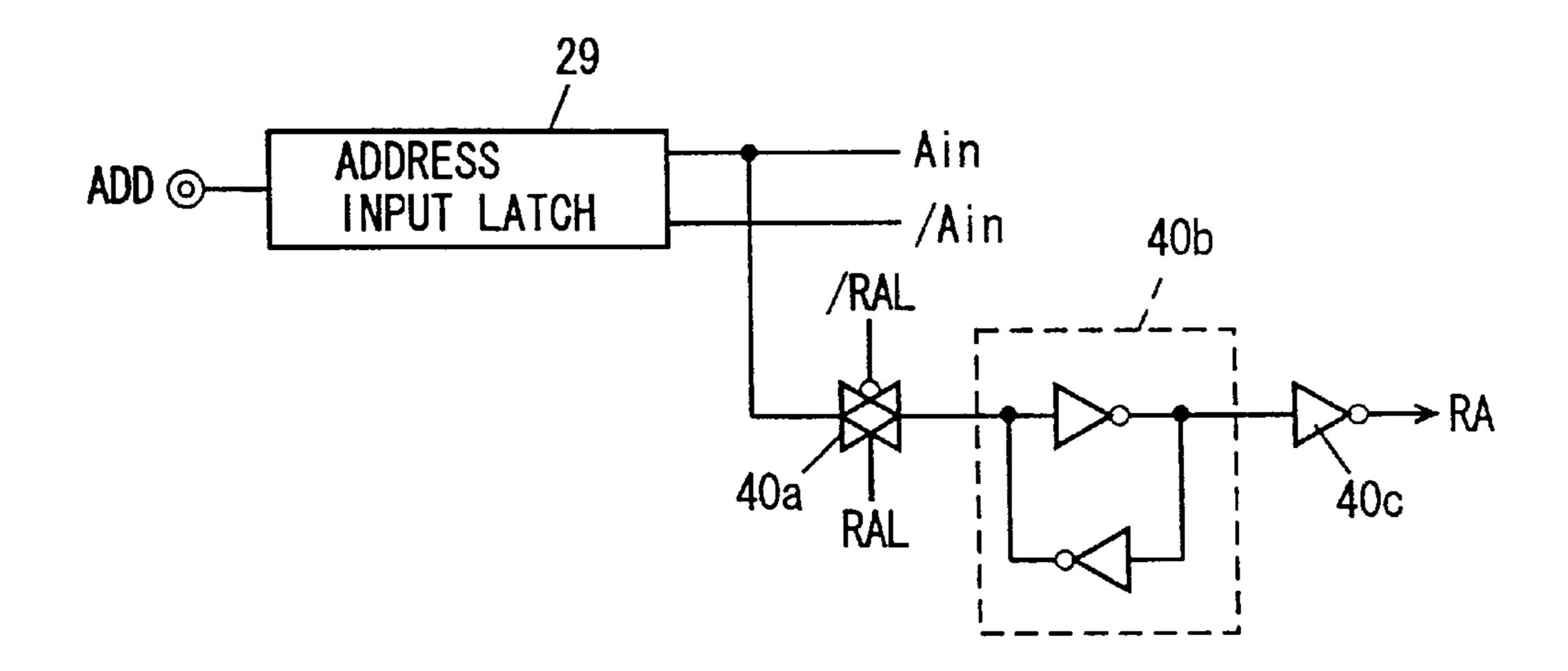

FIG. 14 shows a structure of an internal row address signal generating portion for illustrating an effect of the circuit shown in FIG. 13.

FIG. 15 shows signal waveforms illustrating an operation of the circuit shown in FIG. 13.

FIG. 16 is a modification of the internal address signal generating portion shown in FIG. 12.

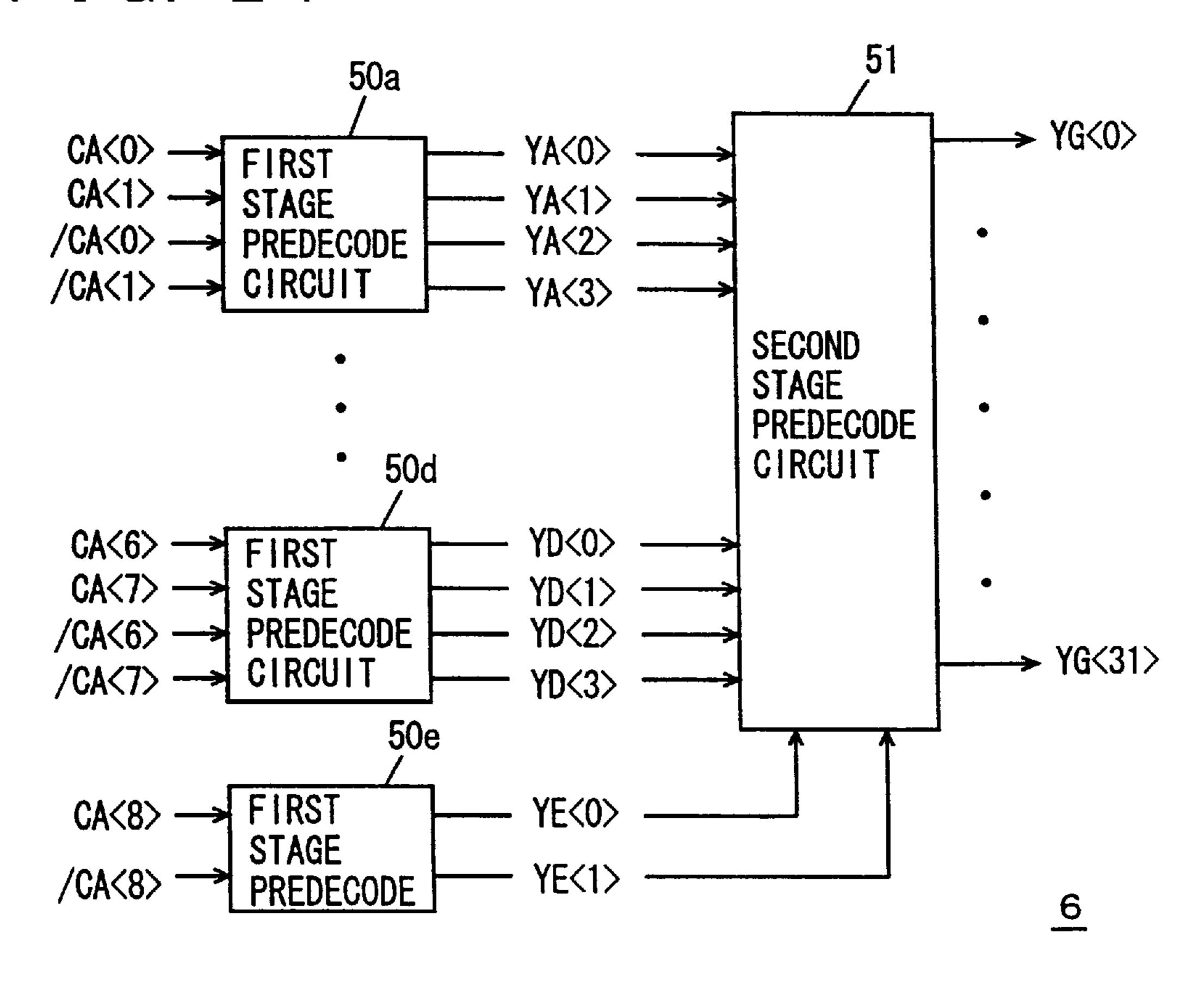

FIG. 17 is a schematic diagram illustrating a structure of a column predecoder shown in FIG. 1.

FIG. 18 specifically shows a structure of the predecoder 10 shown in FIG. 17.

FIG. 19 is a timing chart representing an operation of the predecoder shown in FIG. 17.

FIG. 20 is a schematic diagram of a modification of the predecoder shown in FIG. 17

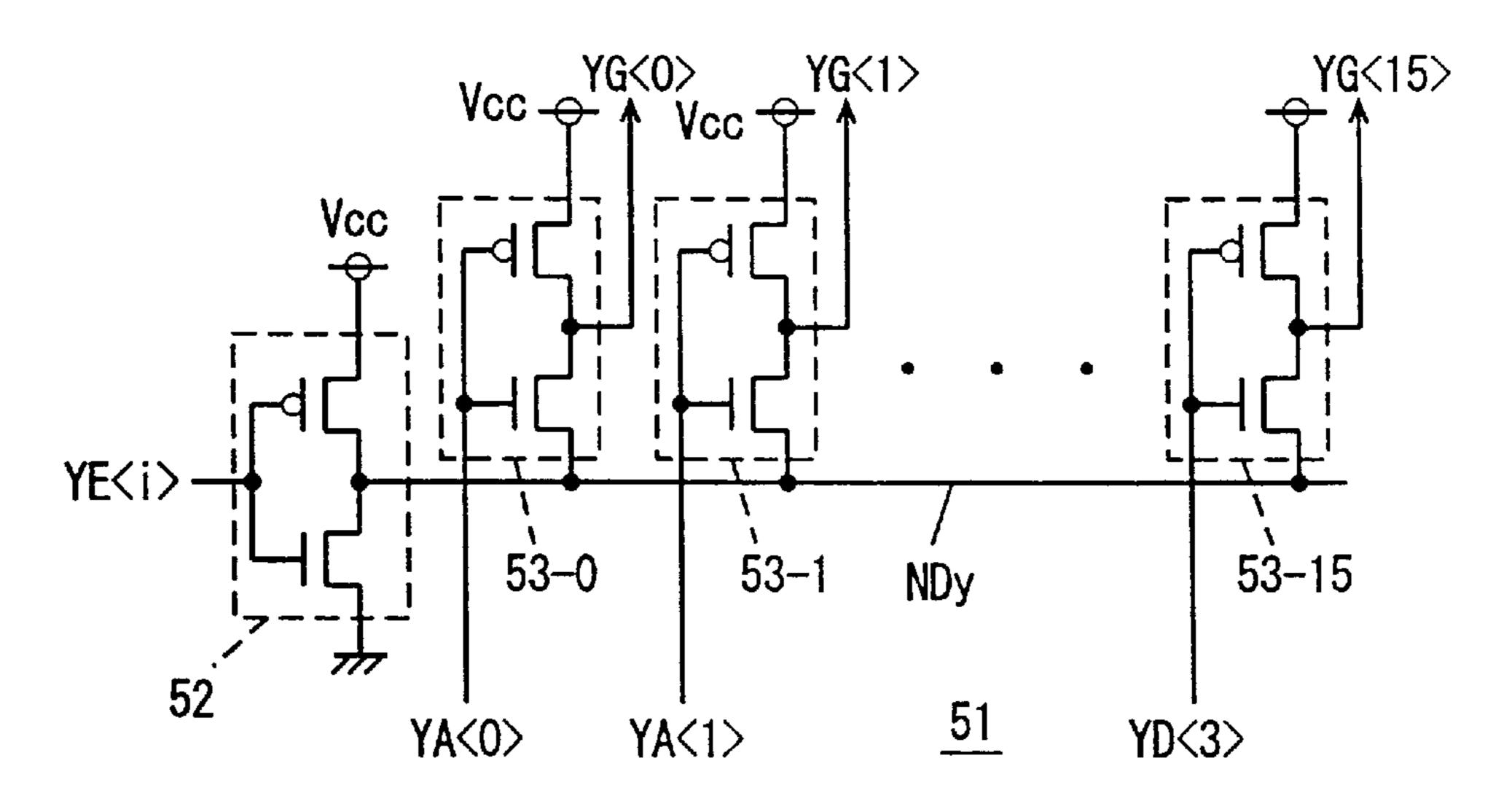

FIG. 21 is a modification of the predecoder shown in FIG. 1.

FIG. 22 shows a structure of a second stage predecode circuit shown in FIG. 21.

FIG. 23 shows signal waveforms representing an operation of the second stage predecode circuit shown in FIG. 22.

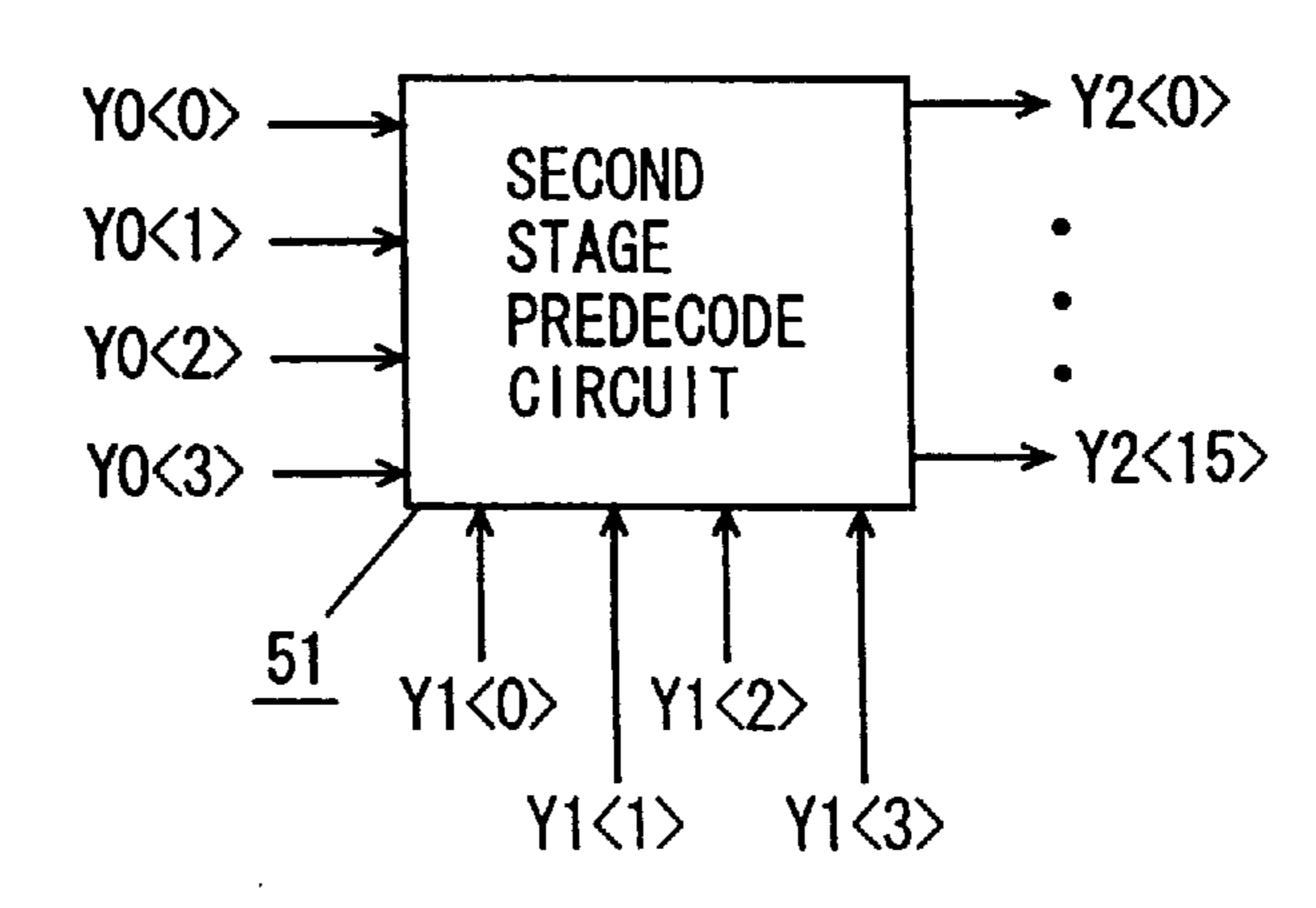

FIG. 24 is a modification of the second stage predecode circuit shown in FIG. 21.

FIG. 25 illustrates a structure of the second stage predecode circuit shown in FIG. 24.

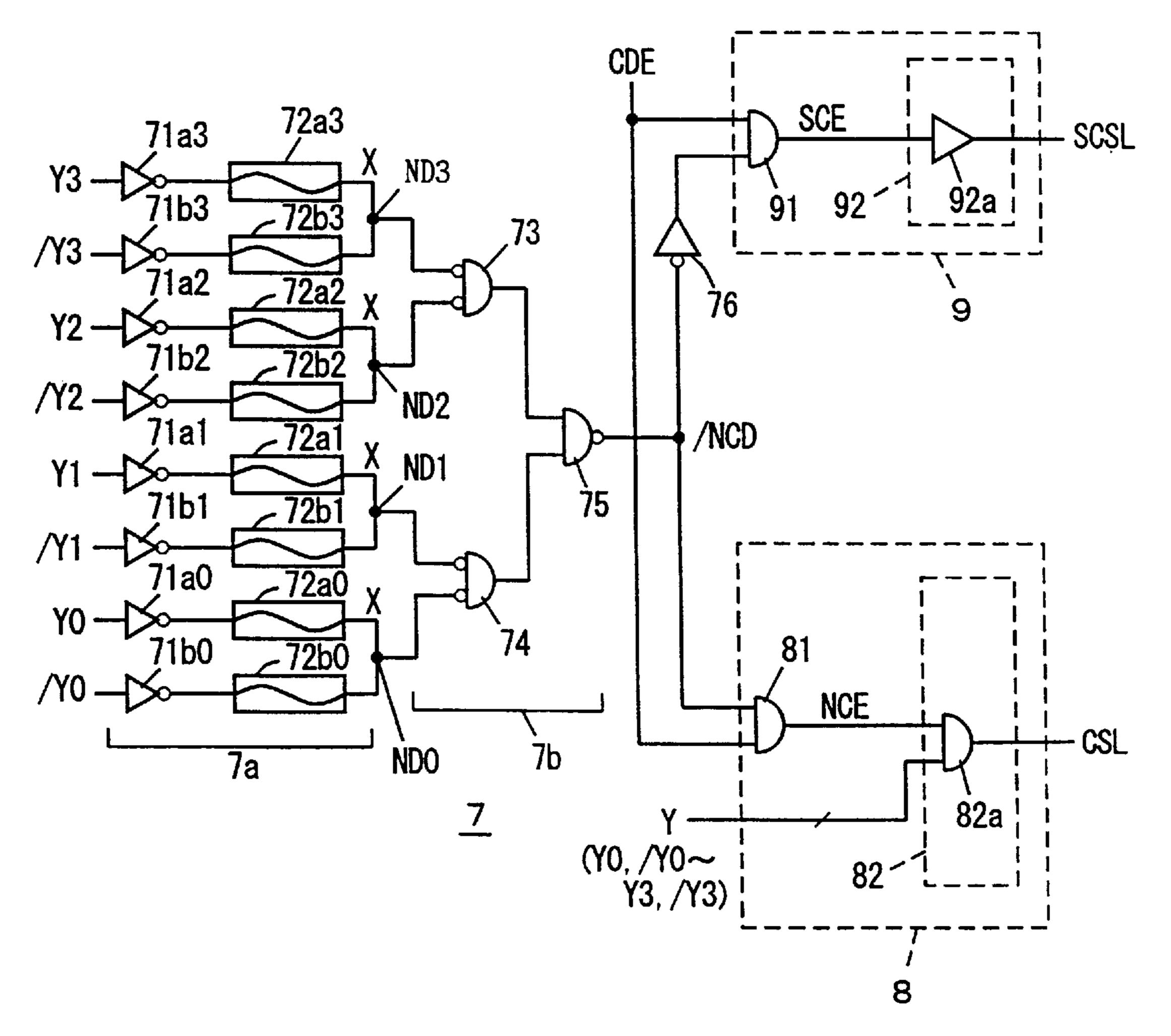

FIG. 26 is a schematic diagram illustrating structures of a spare determination circuit, a spare column decoder, and a column decoder shown in FIG. 1.

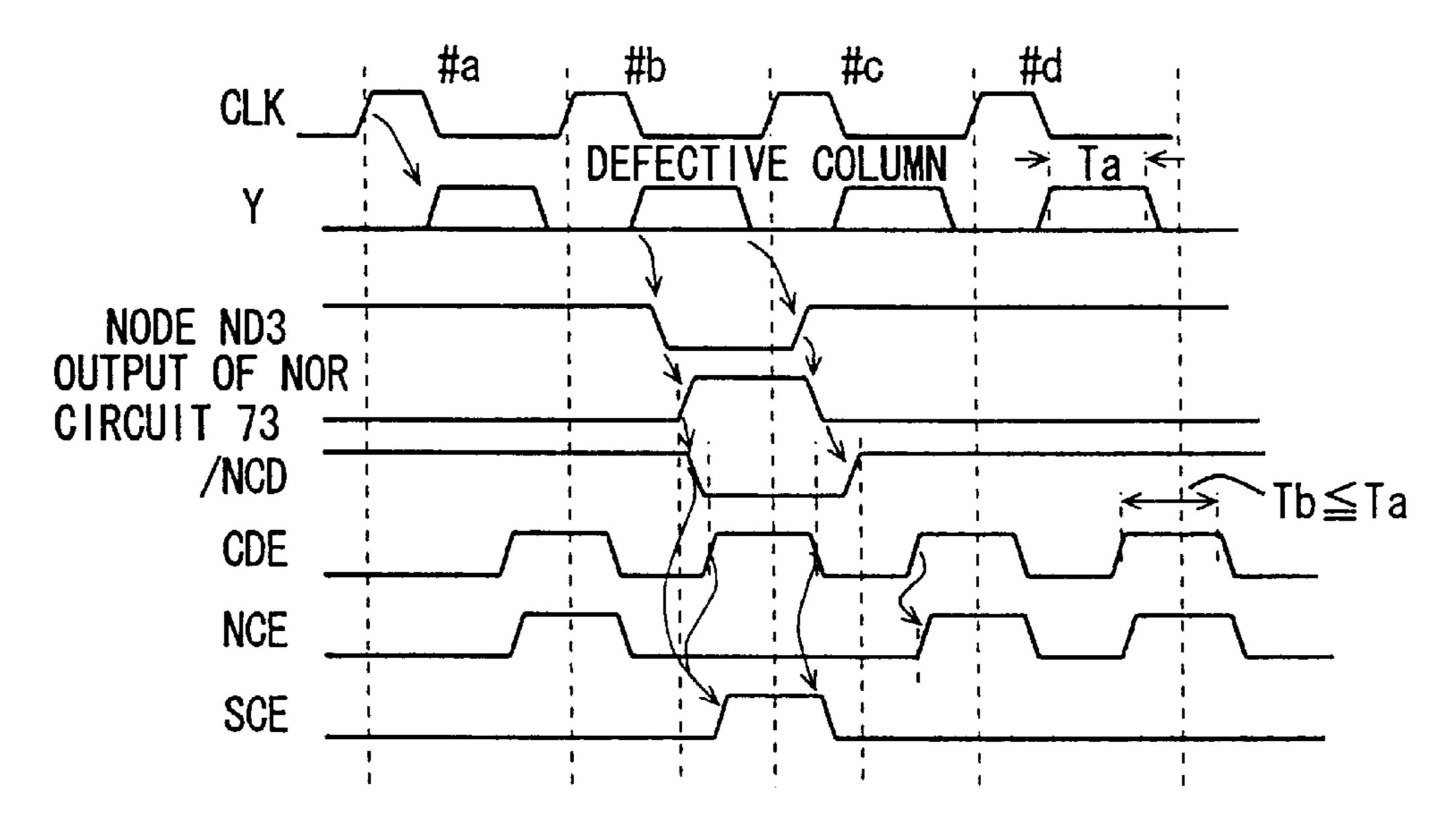

FIG. 27 illustrates signal waveforms representing an operation of the spare determination circuit shown in FIG. 26.

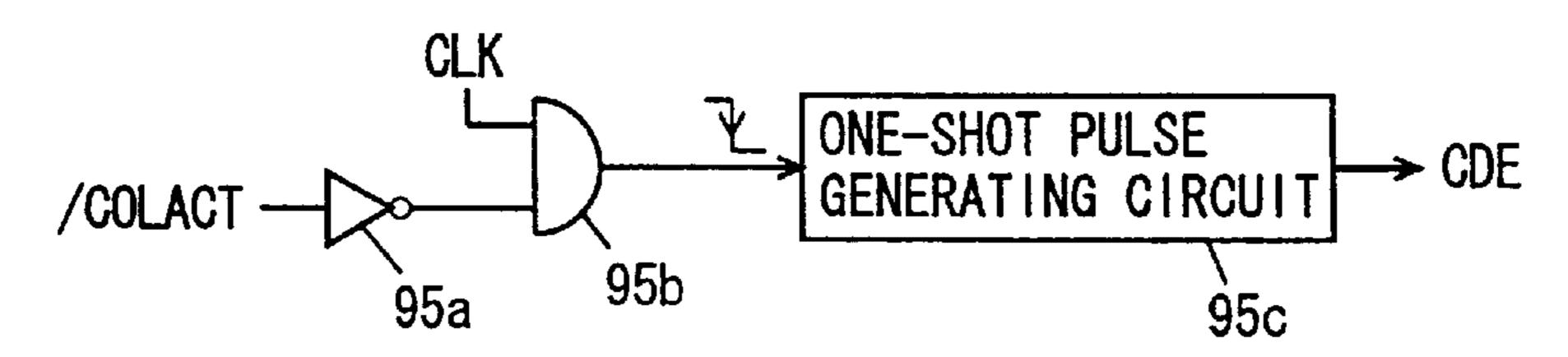

FIGS. 28A and 28B are schematic diagrams each illustrating a structure of a column decoder enable signal generating portion shown in FIG. 26.

FIG. 29 is a schematic diagram illustrating current driving capability of an elementary gate of the spare determination circuit shown in FIG. 26.

FIG. 30 illustrates signal waveforms representing an operation of the spare determination circuit shown in FIG. 40 29.

FIGS. 31A and 31B specifically show a structure of a gate circuit shown in FIG. 29.

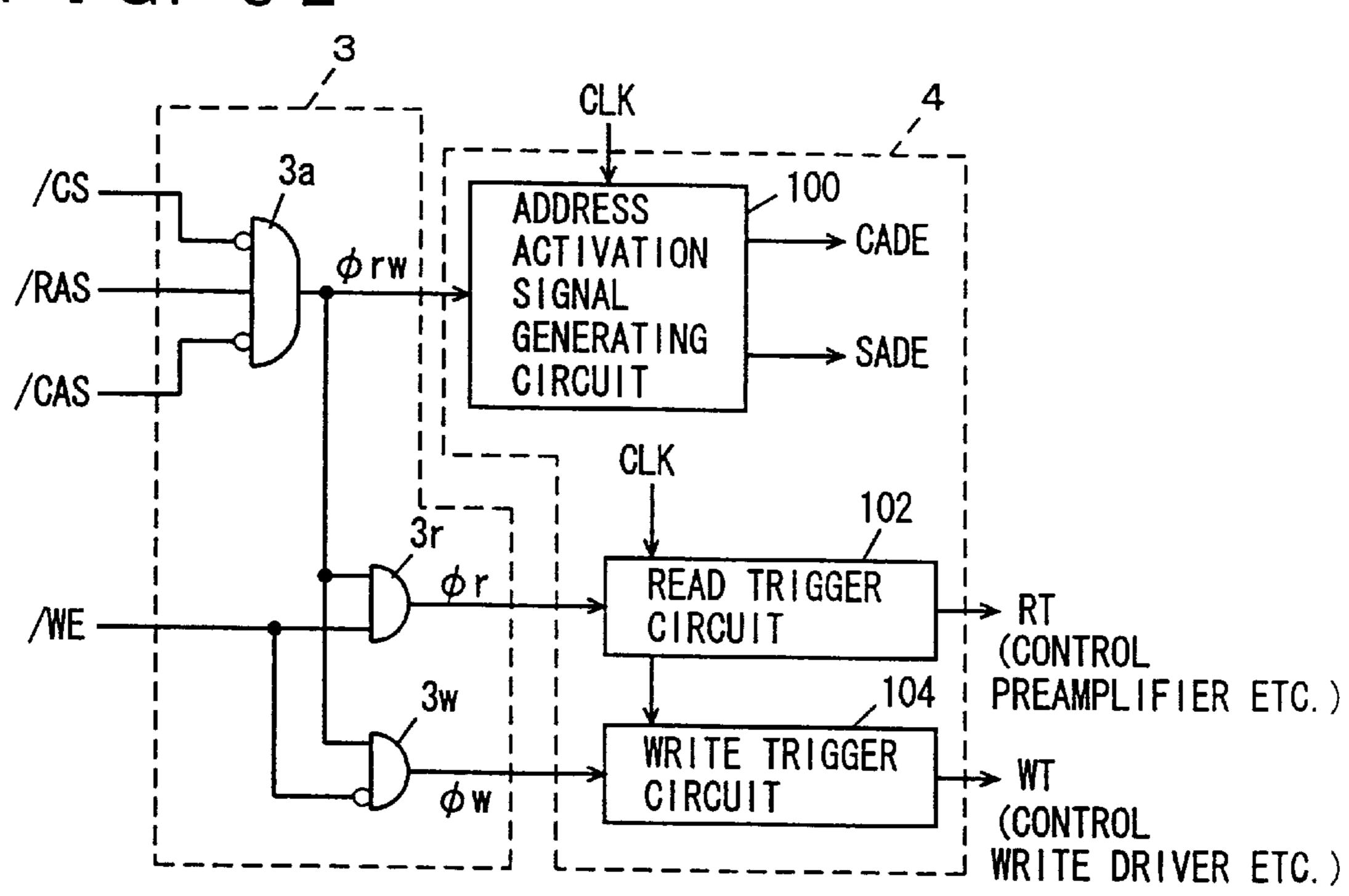

FIG. 32 is a schematic diagram illustrating structures of the command decoder and the control circuit shown in FIG. 1.

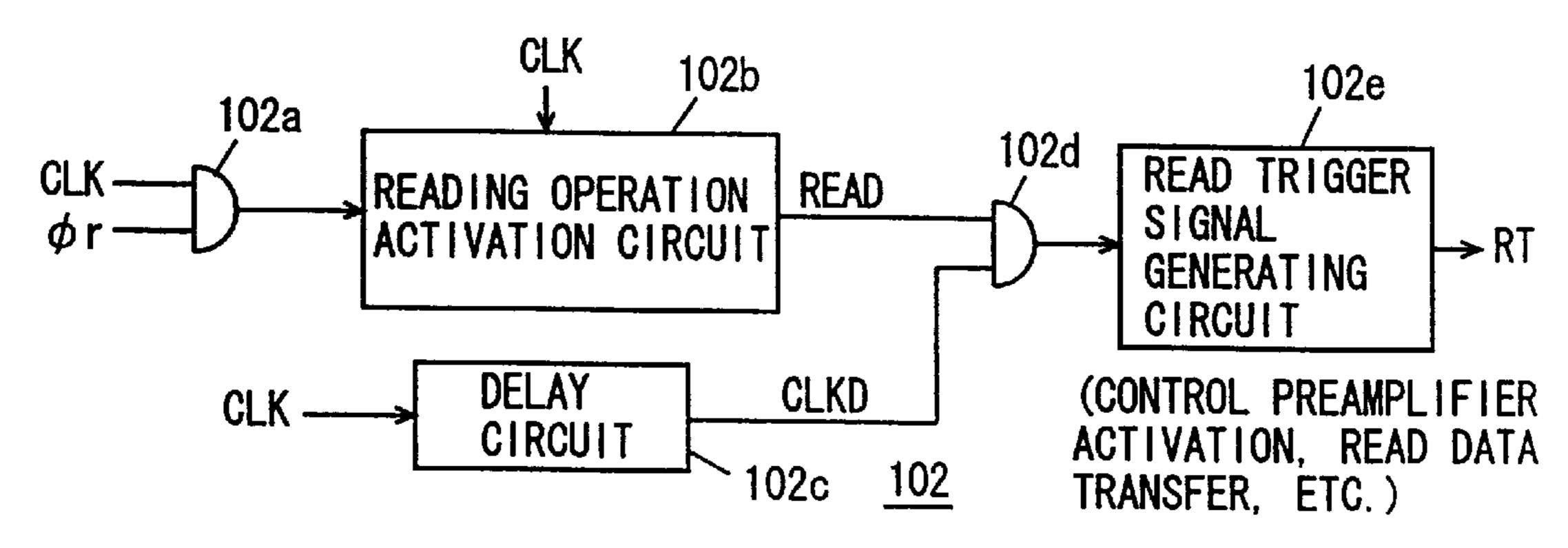

FIG. 33 is a schematic diagram illustrating a structure of a read trigger circuit shown in FIG. 32.

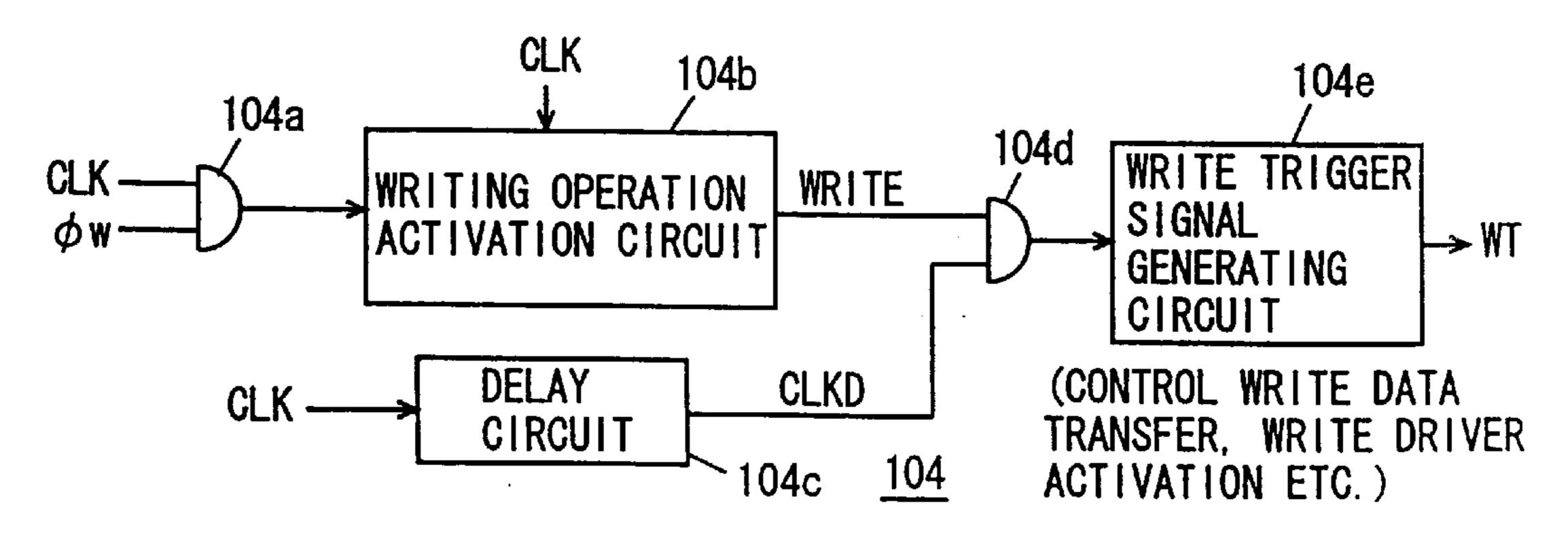

FIG. 34 is a schematic diagram illustrating a write trigger circuit shown in FIG. 32.

FIG. 35 is timing chart representing operations of those circuits shown in FIG. 32 to FIG. 34.

FIG. 36 illustrates specific operations performed by an address activation signal and a read/write trigger signal.

FIG. 37 illustrates a structure of a column decoder enable signal generating portion.

FIG. 38 is a timing chart representing an operation of the column decoder enable signal generating portion shown in FIG. 37.

FIG. 39 is a timing chart reprinting an operation of the column decoder enable signal generating portion shown in FIG. 37.

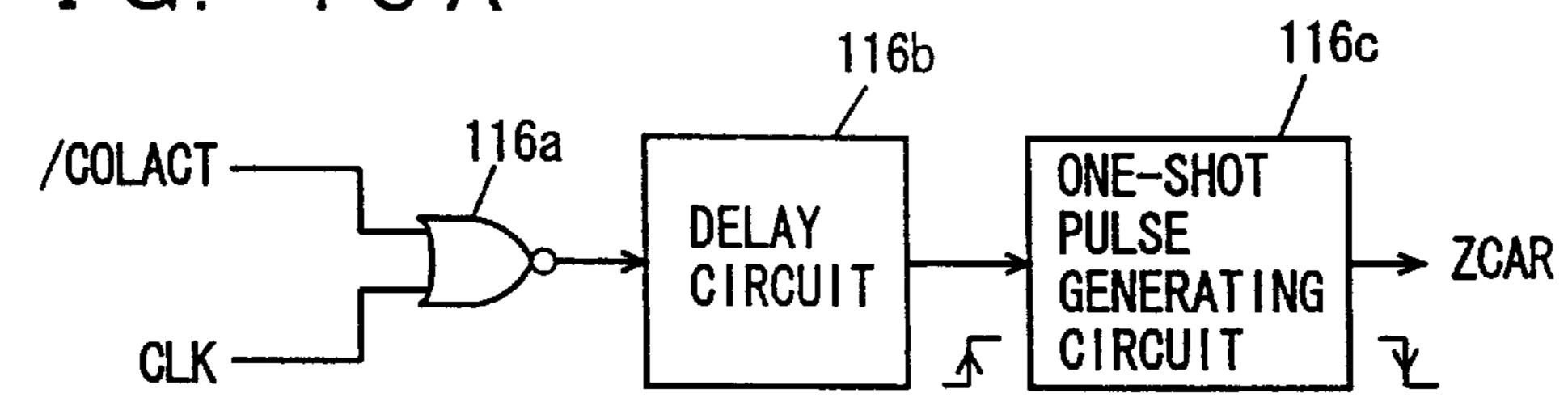

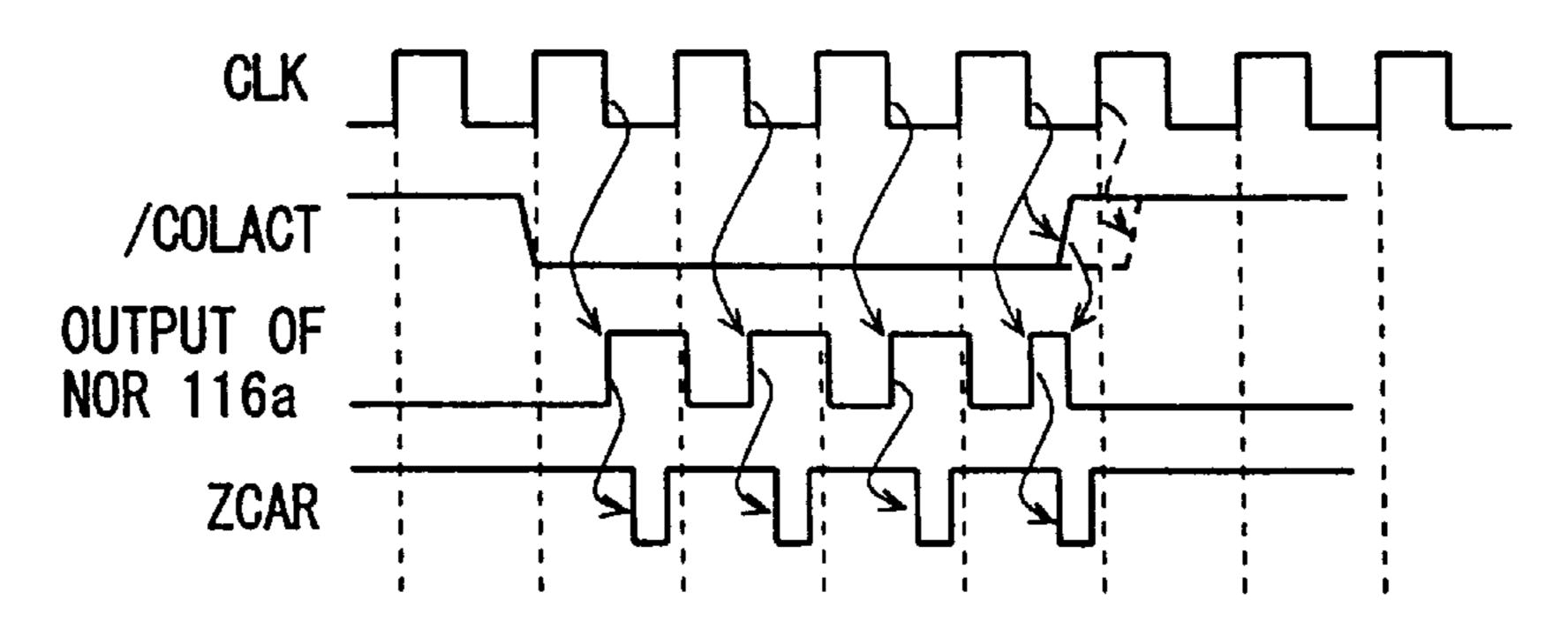

FIG. 40A illustrates a structure of a reset signal generating portion shown in FIG. 37, and FIG. 40B illustrates signal 65 waveforms representing a circuit operation shown in FIG. 40A.

8

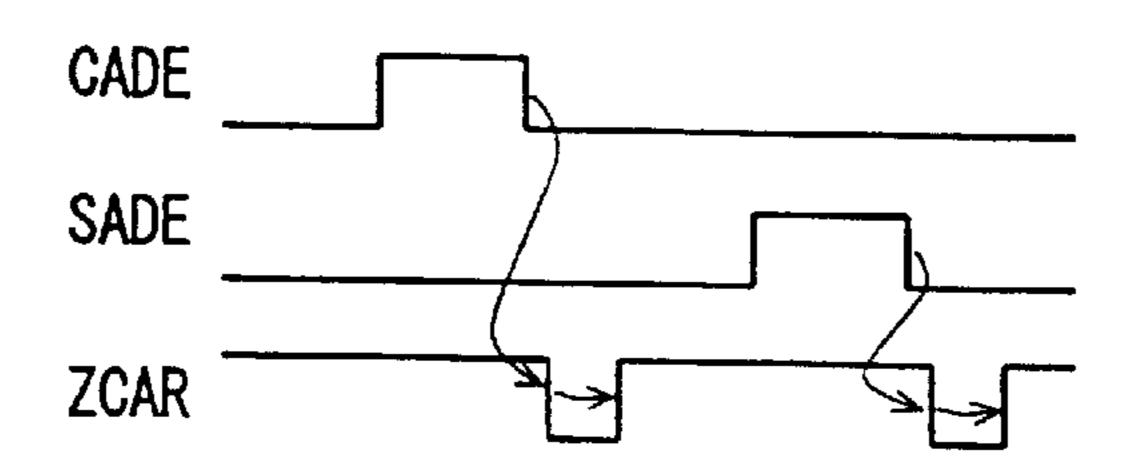

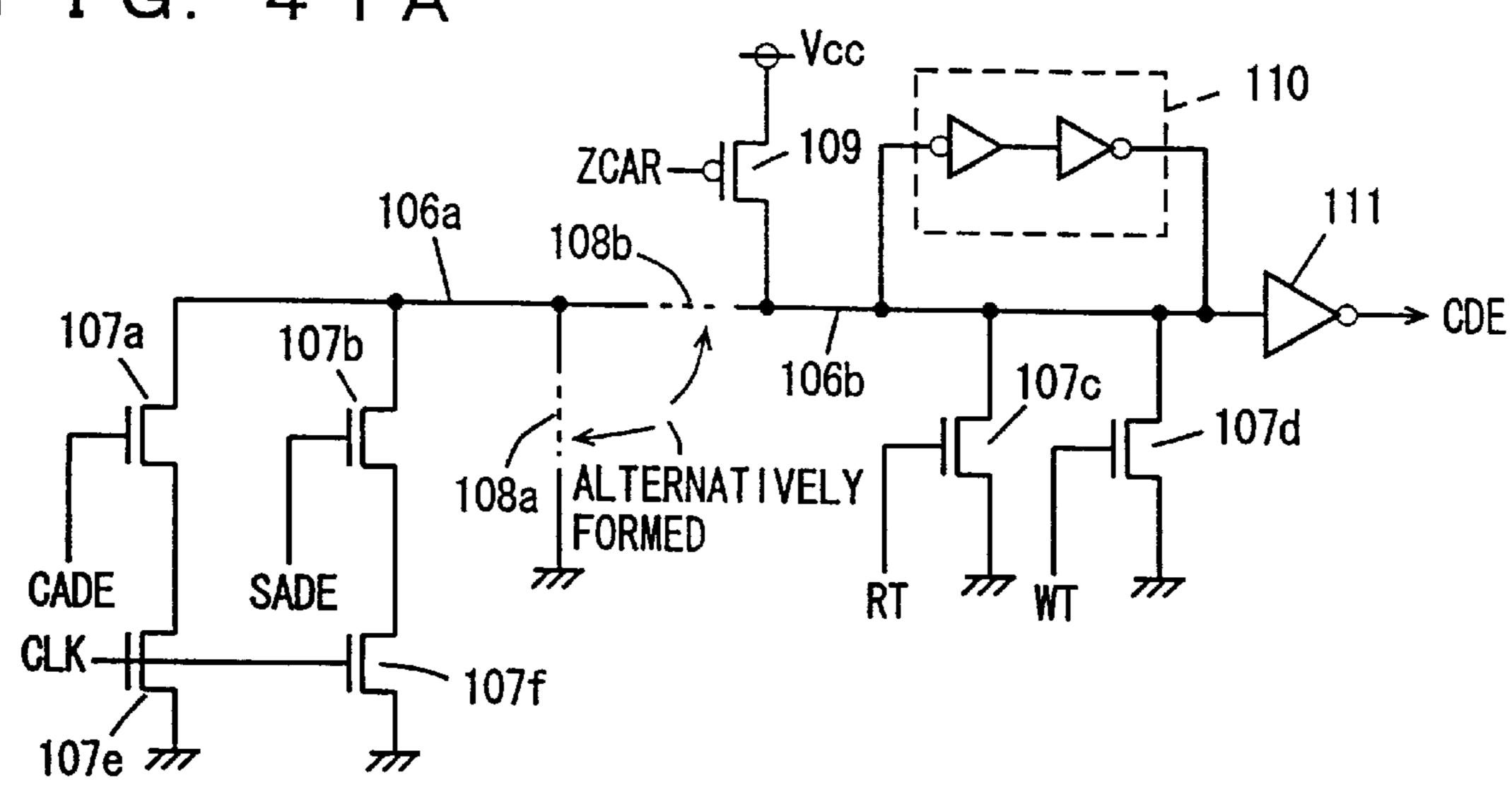

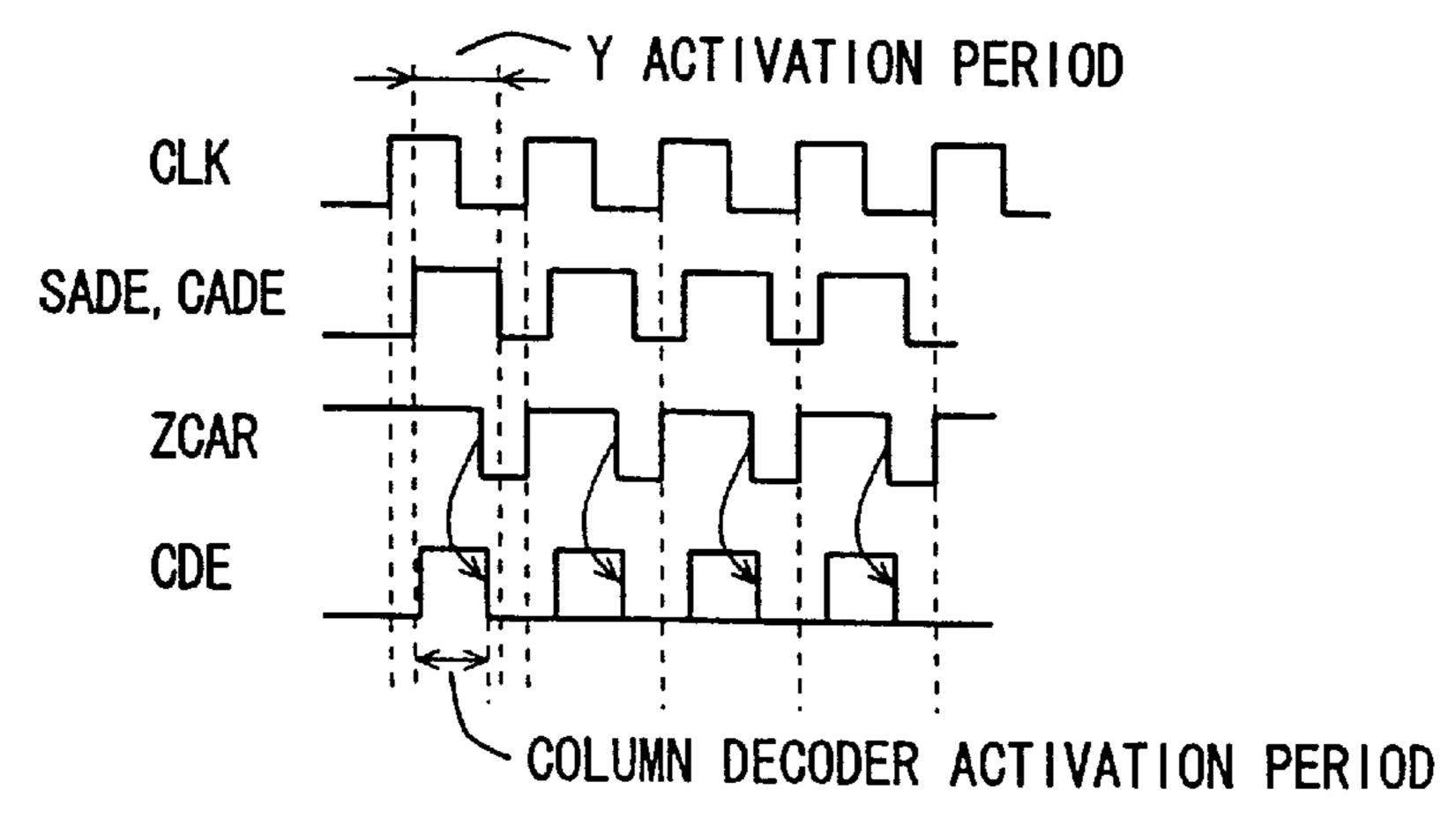

FIG. 41A illustrates a structure of a modification of the column decoder enable signal generating portion, and FIG. 41B is a timing chart representing a circuit operation shown in FIG. 41A.

FIG. 42A is a schematic view illustrating a reset signal generating portion shown in FIG. 41A, and FIG. 42B is a timing chart representing a circuit operatic shown in FIG. 42A.

FIG. 43A illustrates another structure of the reset signal generating portion shown in FIG. 41A, and FIG. 43B is a timing chart representing an operation of the circuit shown in FIG. 43A.

FIG. 44 is a schematic diagram illustrating an entire structure of a conventional synchronous semiconductor memory device.

FIG. 45 is a timing chart representing an operation of the synchronous semiconductor memory device shown in FIG. 44.

FIG. 46 illustrates a column selecting operation sequence in the synchronous semiconductor memory device.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

#### Overall Structure

FIG. 1 is a schematic diagram illustrating a structure of a portion related to column selection of a synchronous semiconductor memory device according to the present invention. Referring to FIG. 1, the synchronous semiconductor memory device according to the present invention includes a memory allay 1 having a plurality of memory cells arranged in rows and columns. Memory array 1 includes a normal memory array 1n having normal memory cells NMCs arranged in rows and columns, and a spare memory array 1s having spare memory cells SMCs arranged in rows and columns for repairing a defective column in normal memory array 1n. Although normal memory array 1n and spare memory array 1s are shown being arranged separately, spare memory cells SMCs in spare memory array 1s may be dispersed in normal memory array 1n. In other words, a configuration that normal memory allay in is divided into a plurality of column blocks and columns of the spare memory cells are arranged at each column block may be used.

The synchronous semiconductor memory device further includes: internal clock generating circuit 2 receiving an externally supplied clock signal extCLK to generate an internal clock signal CLK which is in synchronization with the external clock signal, a command decoder 3 receiving externally supplied control signals /CS, /RAS, /CAS, and 50 /WE independently of from internal clock signal CLK and decoding them to generate an operation mode instruction signal pop for instructing an operation mode designated by a command, and a control circuit 4 generating various operation mode activation signals synchronously with internal clock signal CLK from internal clock generating circuit 2 according to the operation mode instruction signal from command decoder 3.

Command decoder 3 receives an externally supplied command (externally supplied control signals /CS, ERAS, 60 /CAS and /WE) independently of internal clock signal CLK, and decodes the received command independently of internal clock signal CLK, so that an operation for decoding the command can be performed at a timing preceding the time at which internal clock signal CLK rises. As a result, internal operation mode instruction signal pop can be driven into a definite state at an advanced timing to start an internal operation at an advanced timing.

Internal clock generating circuit 2 may be configured by any of a buffer, a PLL (Phase Locked Loop), and DLL (Delayed Locked Loop).

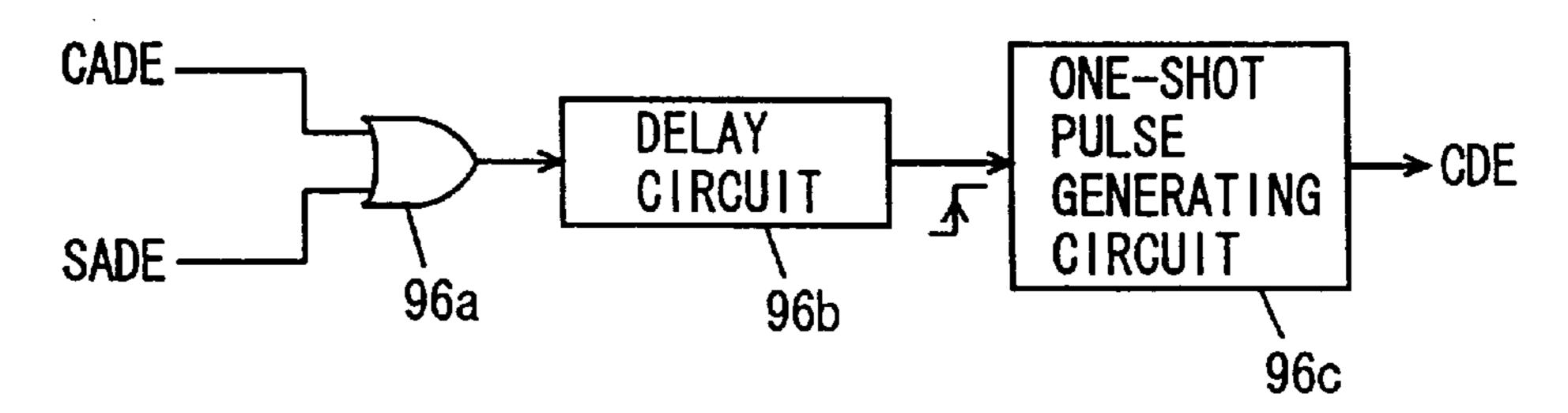

Control circuit 4 generates various control signals according to the operation mode instruction signal from command decoder 3. FIG. 1 representatively shows a column address activation signal CADE, a counter address activation signal (serial address activation signal) SADE, and a column decoder activation signal CDE supplied from control circuit 4.

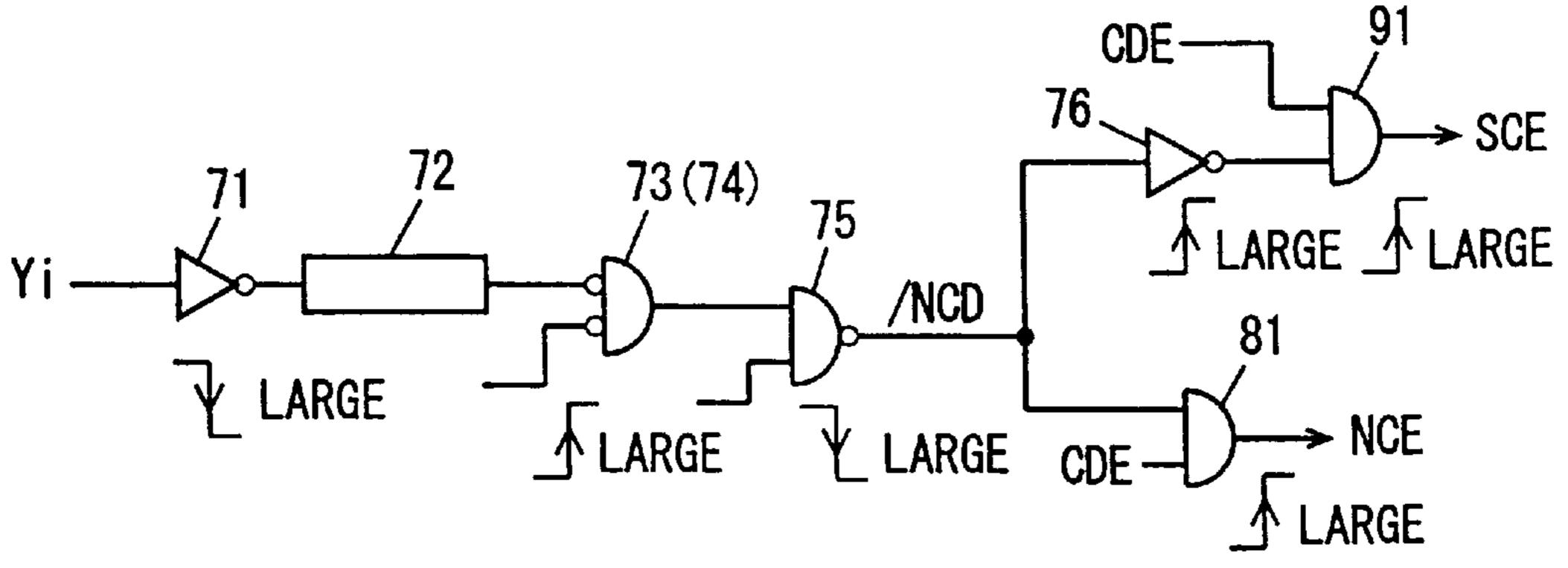

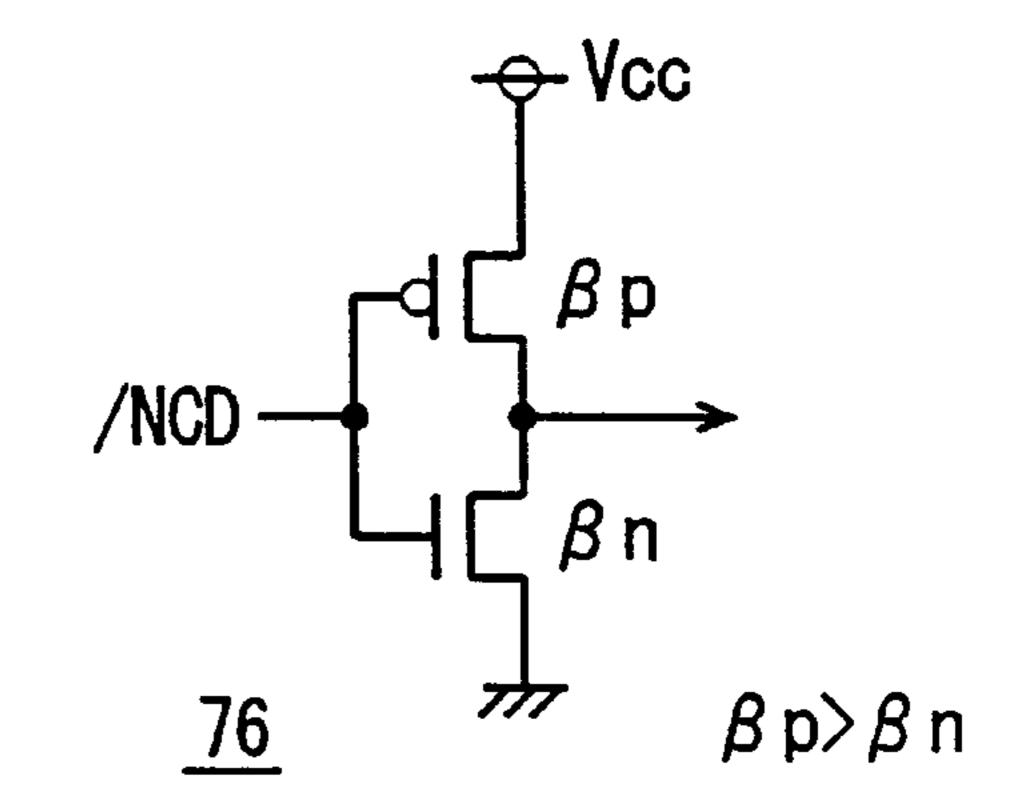

The synchronous semiconductor memory device further includes an internal column address signal generating circuit 5 generating complementary internal address signals from an external address signal ADD according to internal clock signal CLK, and generating complementary internal column <sup>15</sup> address signals CA and /CA according to column address activation signal CADE and counter address activation signal SADE, a column predecoder 6 predecoding internal column address signals CA and /CA from internal column address signal generating circuit 5, a spare determination <sup>20</sup> circuit 7 receiving predecode signals Y and /Y from column predecoder 6 to determine whether a defective column is designated or not, a column decoder 8 selectively activated according to a normal column decoder disable signal /NCD from spare determination circuit 7 and column decoder <sup>25</sup> activation signal CDE from control circuit 4, for decoding the predecode signal from column predecoder 6, to select a memory cell column in normal memory array 1n, and a spare column decoder 9 selectively activated according to normal column decoder disable signal /NCD from spare determination circuit 7 and column decoder activation signal CDE, for selecting a redundant column replacing the defective column in spare memory array 1s.

Spare determination circuit 7 includes a programming circuit storing a column address of a defective column therein, compares the predecode signal from column predecoder 6 with the stored defective column address, for activating one of the spare column decoder 9 and column decoder 8 according to the result of comparison. Column decoder 8 selects a column selection line CSL in the normal memory array according to the supplied predecode signal when activated while spare column decoder 9 selects a spare column selection line SCSL in spare memory array 1s when activated. Data of a selected memory cell on a memory cell column selected by spare column decoder 9 or column decoder 8, is coupled to a write/read circuit via a column selection gate and an IO bus (not shown) and accordingly, data is written/read.

Internal column address signal generating circuit 5 generates complementary column address signals CA and /CA from the external address signal according to internal clocksignal CLK. Consequently, an internal column address signal can be defined at an advanced timing. (This configuration will be described in detail below.)

Column predecoder 6 may be configured to predecode internal address signals Ain and /Ain from internal column address signal generating circuit 5 upon activation of the column address activation signal (This configuration will be described in detail later).

According to the present invention, a column selecting operation can be done at high speed by minimizing the propagation time of a signal from internal column address signal generating circuit 5 to column decoder 8 and spare column decoder 9.

Internal column address signal generating circuit 5 includes a burst address counter performing a counting

10

operation in each clock cycle with an externally supplied address signal used as a leading address, to generate an internal column address signal. Activation signal SADE for the address signal from the burst address counter and column address activation signal CADE for activating the externally supplied address signal are separately generated to allow the internal column address signal to be driven into an active state according to the externally supplied address signal at an advanced timing. In each clock cycle, the internal column address signal can be driven into the active state at the same timing as that of a leading internal column address signal according to a burst address. Consequently, it is unnecessary to consider a time lag in definition timing between the leading address (internal column address according to external address) and the burst address in each clock cycle, so that the column selecting operation can be done more speedily.

Column predecoder 6 directly receives the internal address signal from internal column address signal generating circuit 5, so that the predecode signal can be driven into the definite state at an advanced timing.

Spare determination circuit 7 is configured to perform its determining operation more quickly to enable the column selecting operation in each clock cycle to be done more speedily. The structure of each circuit portion is hereinafter described in detail.

#### First Embodiment

Generation of Address Activation Signal:

FIG. 2 illustrates the structures of command decoder 3 and control circuit 4 shown in FIG. 1. Referring to FIG. 2, command decoder 3 includes an access command decode circuit 3a which receives externally supplied command, i.e., chip select signal /CS, row address strobe signal /RAS and column address strobe signal /CAS. When chip select signal 35 /CS and column address strobe signal /CAS are at L level, and row address strobe signal /RAS is at H level, reading or writing is designated in accordance with the state of write enable signal /WE. In writing and reading data, the column selecting operation is performed. Therefore, whether or not the data access to a memory cell or the column selection is performed can be determined by signals /CS, /RAS and /CAS. The read command and the write command are collectively referred to as access command. Access command decode circuit 3a chives column selecting operation 45 instruction signal of the active state when a supplied command is the access command.

Control circuit 4 includes a column selection activation circuit 11 which takes column selecting operation instruction signal \$\phi\$rw from command decoder 3 synchronously with rising of internal clock signal CLK, and outputs a column selecting operation activation signal COLACT which is held at L level of the active state during a prescribed period (burst length). A circuit portion related to the column selection is activated according to column selecting operation activation signal COLACT.

Control circuit 4 further includes a CMOS transmission gate 12 which is rendered non-conductive in synchronization with rising of internal clock signal CLK and takes in the column selecting operation instruction signal, rw an inverter latch 13 which inverts and latches a signal supplied from CMOS transmission gate 12, a tristate inverter buffer 14 which is set into an operable state synchronously with rising of internal clock signal CLK, inverts the signal held by inverter latch 13 and outputs column address activation signal CADE, and an inverter latch 15 which holds column address activation signal CADE output from tristate inverter buffer 14.

Inverter latch 13 is constituted of inverters having their inputs and outputs cross-coupled to each other, and inverter latch 15 includes inverters connected to the output node of tristate inverter buffer 14 in a looped manner. Inverter latch 13 transmits a signal from CMOS transmission gate 12 and latches it with a relatively large latching capability. Inverter latch 15 has a configuration of so-called "half latch," and has a latching capability weakened to allow a reset transistor 16 to easily reset column address activation signal CADE.

Control circuit 4 further includes an NOR circuit 17 10 which receives column selecting operation instruction signal  $\phi$ rw from access command decode circuit 3a and column selecting operation activation signal /COLACT from column selection activation circuit 11, a CMOS transmission gate 18 which is rendered conductive when internal clock 15 signal CLK is at L level, to pass a signal output from NOR circuit 17, an inverter latch 19 which latches and inverts a signal output from CMOS transmission gate 18, a tristate inverter buffer 20 which is set into an operable state when internal clock signal CLK is at H level, to invert a signal 20 from inverter latch 19 for outputting counter address activation signal SADE, an inverter latch 21 which latches counter address activation signal SADE from tristate inverter buffer 20, and a reset transistor 22 which resets counter address activation signal SADE to L level in 25 response to reset signal RST.

Inverter latches 19 and 21 have configurations similar to those of inverter latches 13 and 15 respectively. NOR circuit 17 outputs a signal of L level in a clock cycle in which an access command is supplied and column selecting operation 30 instruction signal of was driven into the active state. Accordingly, in the cycle in which the access command is supplied, counter address activation signal SADE maintains an inactive state. From the following clock cycle, counter address activation signal SADE is driven into H level and 35 then reset to L level in each clock cycle during a period in which column selecting operation activation signal, COLACT is at L level of the active state. At this time, column address activation signal CADE is maintained at L level. Two address activation signals CADE and SADE are 40 generated. Reset signal RST is activated in each clock cycle during the burst length period.

FIG. 3 is a schematic diagram illustrating a main portion of internal column address signal generating circuit 5 shown in FIG. 1. Referring to FIG. 3, internal column address 45 RST. signal generating circuit 5 includes a counter 25 which takes internal address signal Ain in response to activation of column selecting operation activation signal, COLACT, to perform a counting operation synchronously with falling of internal clock signal CLK, and a selecting circuit **26** which 50 selects one of internal address signal Ain and an output count of counter 25 according to column address activation signal CADE and counter address activation signal SADE to output internal column address signal CA. Selecting circuit 26 selects internal address signal Ain when column address 55 activation signal CADE is in the active state, and selects an output count of counter 25 when counter address activation signal SADE is in the active state. The timing of generating the internal address signal is hereinbelow described in detail.

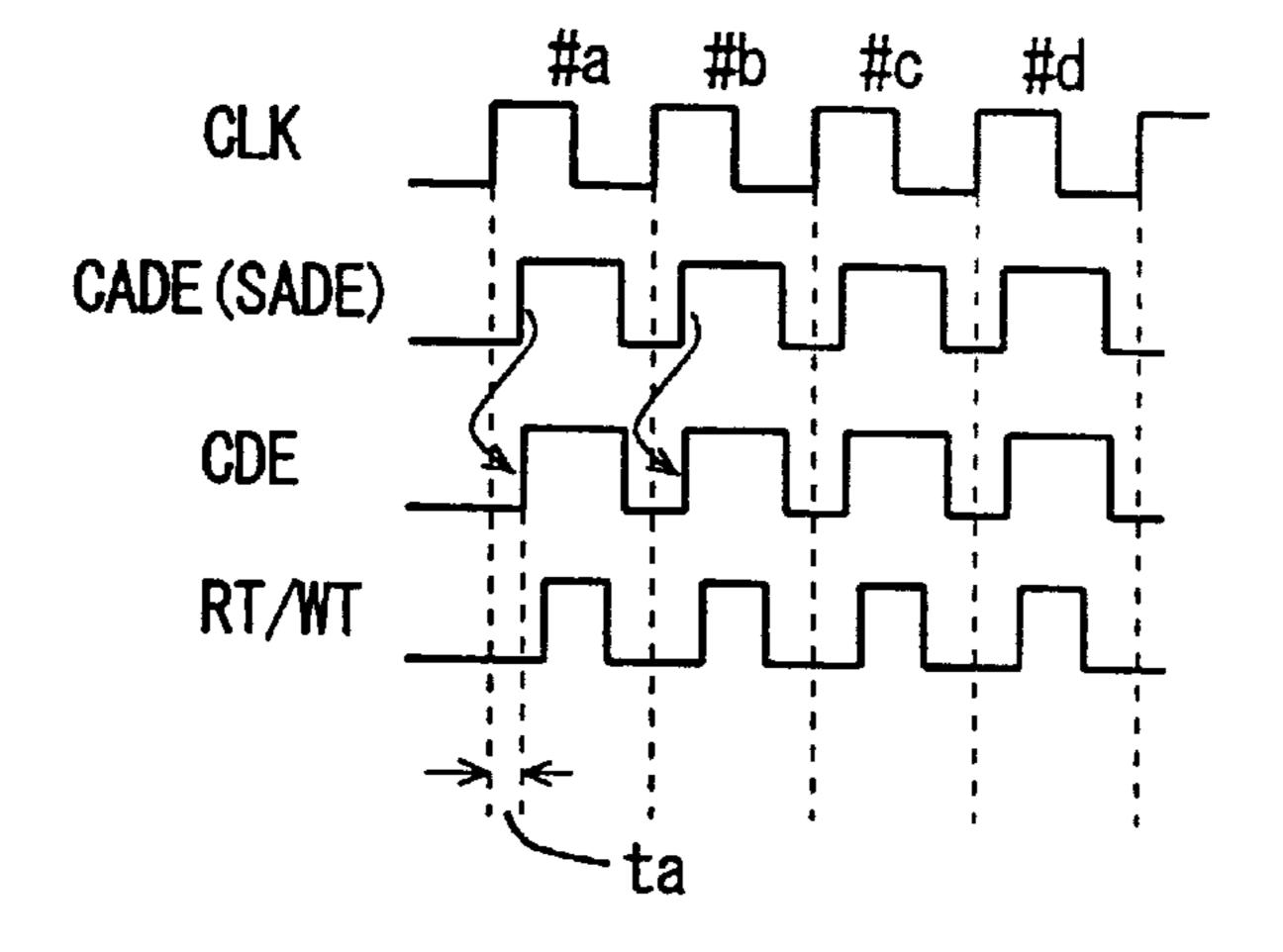

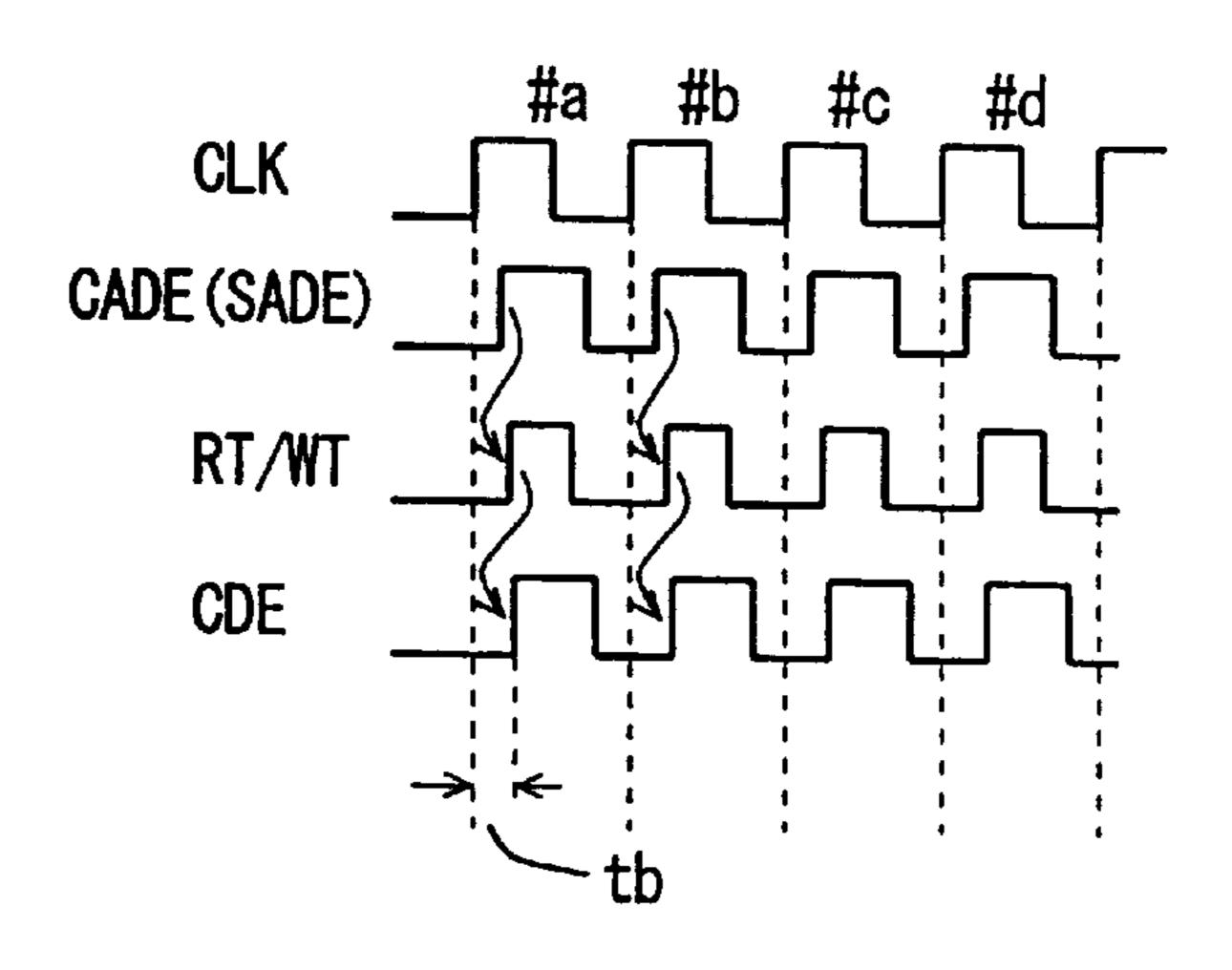

Operations of the circuits shown in FIGS. 2 and 3 are 60 described referring to the timing chart shown in FIG. 4.

In clock cycle #a, an access command is supplied. According to the access command, chip select signal /CS and column address strobe signal /CAS are set at L level and row address strobe signal /RAS is set at H level at a rising 65 edge of internal clock signal CLK. The command has a set up time for internal clock signal (external clock signal).

12

Therefore, chip select signal /CS and column address strobe signal /CAS are set at L level at a timing preceding the rising edge of internal clock signal CLK.

Under this condition, column selecting operation instruction signal  $\phi$ rw from access command decode circuit 3ashown in FIG. 2 is driven into the active state at the time when the access command is supplied independently of internal clock signal CLK. CMOS transmission gate 12 is in the conductive state when internal clock signal CLK is at L level, and accordingly passes column selecting operation instruction signal orw to supply it to inverter latch 13. When internal clock signal CLK attains H level and CMOS transmission gate 12 is set into the non-conductive state, column selecting operation instruction signal of win the active state has already been latched by inverter latch 13. When internal clock signal CLK attains H level, tristate inverter buffer 14 operates to invert the signal latched by inverter latch 13 and output an inverted version of the latched signal. Accordingly, after internal clock signal CLK rises, column address activation signal CADE is driven into H level at an advanced timing.

In the cycle preceding clock cycle #a, when CMOS transmission gate 18 is in the conductive state (internal clock signal CLK is at L level), column selecting operation instruction signal of which will be at H level and an output signal of NOR circuit 17 is at L level. When internal clock signal CLK attains H level and CMOS transmission gate 18 is set into the non-conductive state, inverter latch 19 latches a signal of H level and supplies it to tristate inverter buffer 20. Even if internal clock signal CLK rises, counter address activation signal SADE maintains the L level.

In clock cycle #a, selecting circuit 26 selects internal address signal Ain and generates internal column address signal CA.

Column selection activation circuit 11 takes column selecting operation instruction signal of w synchronously with rising of internal clock signal CLK, and maintains column selecting operation activation signal /COLACT at L level for a prescribed period. Consequently, column selecting operation activation signal /COLACT is maintained at L level in a prescribed period (burst length period) from clock cycle #a (FIG. 4 illustrates an operation for the burst length of 4). After the prescribed period passes, column address activation signal CADE is reset to L level by reset signal RST.

In clock cycle #b, chip select signal /CS is maintained at H level to process the supplied command as an NOP (No Operation) command. In this state, when CMOS transmission gate 12 is rendered conductive, column selecting operation instruction signal \( \phi \) w is at L level, and column address activation signal CADE maintains L level.

When signals orw and /COLACT are both at L level, NOR circuit 17 outputs a signal at H level. In clock cycle #b, when internal clock signal CLK rises to H level, a signal of L level is already transmitted to tristate inverter buffer 20 via CMOS transmission gate 18. When internal clock signal CLK rises to H level, tristate inverter buffer 20 operates to drive counter address activation signal SADE to H level according to the signal latched by inverter latch 19. Accordingly, in clock cycle #b, selecting circuit 26 selects a count value from counter 25 to generate internal column address signal CA.

Counter 25 takes internal address signal Ain as an initial value synchronously with rising of column selecting operation activation signal /COLACT or in response to activation of column selecting operation instruction signal \( \phi vw, \) and performs the counting operation synchronously with falling

of internal clock signal CLK during the period in which column selecting operation activation signal /COLACT is in the active state. The count value from counter 25 changes in a prescribed sequence in the burst length period. In the following clock cycles #c and #d, selecting circuit 26 selects 5 the count value from counter 25 to generate column address signal CA according to activation of counter address activation signal SADE.

After the burst length period passes, column selecting operation activation signal /COLACT from column selection activation circuit 11 rises to H level. Accordingly, an output signal of NOR circuit 17 falls to L level, and counter address activation signal SADE maintains L level even if internal clock signal CLK rises.

As shown in FIG. 2, a command is received to be decoded for generating an internal operation instruction signal independently of internal clock signal CLK, and the signal is latched synchronously with rising of the internal clock signal for generating the internal operation instruction signal or internal operation activation signal. Accordingly, column address activation signal CADE and counter address activation signal SADE can be driven into the active state at the advanced timing, compared with the configuration in which the decoding operation is started synchronously with rising of internal clock signal CLK. Consequently, internal address signal CA can be driven into a definite state at an advanced timing.

Further, column address activation signal CADE for selecting internal address signal Ain and counter address activation signal SADE for selecting an address signal from 30 counter 25 are separately generated. As a result, the column address signal can be made definite at an advanced timing, compared with the configuration in which internal address signal Ain is set in the counter and column address signal CA is generated through the counter.

FIG. 5 is a schematic diagram illustrating one example of the structure of column selection activation circuit 11 shown in FIG. 2. Referring to FIG. 5, column selection activation circuit 11 includes a CMOS transmission gate 11a which passes column selecting operation instruction signal prw 40 from access command decode circuit 3a when internal clock signal CLK is at L level, a set/reset flip-flop 11b which is set in response to rising of an output signal of CMOS transmission gate 11a, and a burst length counter 11c which is started up in response to rising of the output signal of CMOS 45 transmission gate 11a, to count the falling of internal clock signal CLK, and outputs a count up signal when the count value reaches a prescribed value to reset set/reset flip-flop 11b. Column selecting operation activation signal /COLACT is output from an output /Q of set/reset flip-flop 50 11b. Burst length counter 11c is constituted of a shift register which takes a supplied signal in response to rising of internal clock signal CLK, and outputs the taken signal in response to failing of internal clock signal CLK. Burst length counter 11c is constituted by serially connecting the shift registers 55 equal in number to the burst length.

Counter 25 shown in FIG. 3 is constituted of a counter which can be preset.

FIG. 6 illustrates one example of a structure of selecting circuit 26 shown in FIG. 3.

Referring to FIG. 6, selecting circuit 26 includes a CMOS transmission gate 26a which is rendered conductive when column address activation signal CADE is activated to pass internal address signal Ain, a CMOS transmission gate 26b which is rendered conductive when counter address activation signal SADE is activated to pass count value SADD from counter 25, and a latch circuit 26c which latches a

signal selected by CMOS transmission gates 26a and 26b. In the structure shown in FIG. 6, internal address signal Ain and count value SADD from counter 25 CA can be selected to generate internal column address signal with a simple circuit configuration, through the arrangement of connecting CMOS transmission gates 26a and 26b commonly to a node ND and generating internal column address signal CA from node ND. Internal column address signal CA is reset to L level by a resetting n channel MOS transistor which is rendered conductive in response to reset signal RST. One-shot pulsization of internal column address signal CA enables the column selecting operation to be performed at a high speed as described later.

14

FIG. 7 illustrates another structure of selecting circuit 26 shown in FIG. 3. Referring to FIG. 7, selecting circuit 26 includes an NAND circuit 26d which receives column address activation signal CADE and internal address signal Ain, an NAND circuit 26e which receives counter address activation signal SADE and output count SADD of counter 25, and an NAND circuit 26f which receives output signals of NAND circuits 26d and 26e for generating internal column address signal CA. Internal address signal Ain and output count SADD of counter 25 are both constituted of multiple bits, and these NAND circuits 26d, 26e and 26f are provided corresponding to respective bits.

When column address activation signal CADE is activated, counter address activation signal SADE is at L level of the inactive state. Accordingly, NAND circuit 26d operates as an inverter and NAND circuit 26e outputs a signal at H level regardless of the output count value of counter 25. NAND circuit 26f accordingly operates as an inverter to invert a signal output from NAND circuit 26d. When column address activation signal CADE is activated, internal column address signal CA is generated according to internal address signal Ain.

On the other hand, when column address activation signal CADE is at L level and counter address activation signal SADE is at H level of the active state, an output signal of NAND circuit 26d is fixed at H level, NAND circuits 26e and 26f operate as the inverters, and internal column address signal CA is generated according to count SADD from counter 25.

In the case of the structure shown in FIG. 7, when activation signals of CADE and SADE are at L level, an output signal of NAND circuit 26f or internal column address signal CA is set to L level, so that the internal column address signal can be reset into the standby state in each clock cycle and accordingly an extra reset circuit is not necessary.

FIG. 8A illustrates one example of a structure of the portion for generating reset signal RST shown in FIG. 2. Referring to FIG. 8A, a reset signal generating portion includes an NOR circuit 27a which receives column selecting operation activation signal /COLACT and internal clock signal CLK, and a one-shot pulse generating circuit 27b which generates a one shot-pulse signal in response to rising of an output signal of NOR circuit 27a. The one-shot pulse signal from one-shot pulse generating circuit 27b is used as reset signal RST. An operation of the reset signal generating portion shown in FIG. 8A is hereinbelow described with reference to the timing chart shown in FIG. 8B.

When column selecting operation activation signal /COLACT is at H level, the output signal of NOR circuit 27a is fixed at L level and reset signal RST from one-shot pulse generating circuit 27b is maintained at L level. When column selecting operation activation signal /COLACT is driven to the active state of L level, the output signal of NOR

circuit 27a attains H level in response to falling of internal clock signal CLK. One-shot pulse generating circuit 27b generates a one-shot pulse signal in response to rising of the output signal of NOR circuit 27a to activate reset signal RST. Accordingly, reset transistors 16 and 22 shown in FIG. 2 and the reset transistor indicated by the broken line in FIG. 6 are rendered conductive, and address activation signals CADE and SADE and column address signal CA shown in FIG. 6 are reset to L level of the initial state. During the period in which column selecting operation activation signal /COLACT is in the active state of L level, reset signal RST is activated in response to falling of internal clock signal CLK. In each clock cycle, address activation signals CADE and SADE and column address CA can be reset to L level, so that it is possible to prevent generation of an internal column address signal according to an unstable internal <sup>15</sup> address signal when internal address signal Ain or count SADE from counter 25 changes, and thus the internal column address can be stably generated.

#### Modification 1

FIG. 9 illustrates a structure of a modification of the first embodiment of the present invention. In the structure illustrated in FIG. 9, a command for generating an internal column address signal according to an externally supplied address signal and a command utilizing a count value from 25 the counter as a column address signal are separately provided. Therefore, a command decoder 3 includes an access command decode circuit 3a which generates a signal for instructing an access operation to write/read data and a counter address access command decode circuit 3b which  $_{30}$ outputs a signal  $\phi$ sa for instructing to utilize the count (counter address) of the counter as a column address. Access command decode circuit 3a which decodes a normal access command and the circuit portion which generates column address activation signal CADE according to column select- 35 ing operation instruction signal of w from access command decode circuit 3a are similar to those circuit portions illustrated in FIG. 2. Therefore, corresponding components have the same reference characters and description thereof is omitted.

Counter address access command decode circuit 3b includes a composite gate 3ba which receives chip select signal /CS, column address strobe signal /CAS and write enable signal /WE, and an AND circuit 3bb which receives an output signal of composite gate 3ba and row address 45 strobe signal /RAS. Composite gate 3ba is equivalent to a structure including an AND circuit which receives column address strobe signal /CAS and write enable signal /WE and a gate circuit which receives an output signal from the AND circuit and chip select signal /CS. The gate circuit sets the 50 output signal at H level when chip select signal /CS is at L level and the output signal of the AND circuit is at H level. Accordingly, composite gate 3ba outputs a signal of H level when chip select signal /CS is at L level and column address strobe signal /CAS and write enable signal /WE are both at 55 H level.

AND circuit 3bb drives a count address validation instruction signal \$\phi\$sa into the active state when an output signal of composite gate 3ba and row address strobe signal /RAS are both at H level. When chip select signal /CS is at L level and other signals /RAS, /CAS and AWE are all at H level, signal 0sa is driven into H level. Signal \$\phi\$sa is transmitted via CMOS transmission gate 18 which is set into the nonconductive state in synchronization with rising of internal clock signal CLK.

The circuit portion which generates counter address activation signal SADE according to signal \$\phi\$sa is similar to the

**16**

circuit portion which generates counter address activation signal SADE according to an output signal of NOR circuit 17. Therefore, corresponding components have the same reference characters and description thereof is omitted. An operation of the circuit illustrated in FIG. 9 is now described referring to the timing chart of FIG. 10.

Before internal clock signal CLK rises in clock cycle #a, chip select signal /CS, column address strobe signal /CAS are set at L level, and write enable signal /WE is set at H level or L level according to writing/reading mode of data. In this state, a normal read command or write command is supplied. When column selecting operation instruction signal  $\phi$ rw from access command decoder circuit 3a rises to H level, column address activation signal CADE from tristate inverter buffer 14 rises to H level in synchronization with rising of internal clock signal CLK. On the other hand, in counter access command decode circuit 3b, column address strobe signal /CAS is at L level and an output signal of composite gate 3b is at L level. Accordingly, signal  $\phi$ sa is at <sup>20</sup> L level and counter address activation signal SADE is also held at L level. Before internal clock signal CLK rises in clock cycle #b, chip select signal /CS is set at L level, and other signals /RAS, /CAS and /WE are set at H level. In this state, an output signal of composite gate 3ba rises to H level, and accordingly counter address validation instruction signal  $\phi$ sa from AND circuit 3bb attains H level. In response to rising of internal clock signal CLK, CMOS transmission gate 18 is set into the non-conductive state and tristate inverter buffer 20 operates to drive counter address activation signal SADE into the active state of H level. Therefore, chip select signal /CS is similarly driven to L level and the other signals /RAS, /CAS and /WE are maintained at H level similarly during the burst length period in which data reading is done. Consequently, count address validation instruction signal \phisa is produced and counter address activation signal SADE is activated in each of clock cycles #c and #d.

In clock cycle #e, chip select signal /CS is maintained at H level to set output signals  $\phi$ rw and  $\phi$ sa of command decode circuits 3a and 3b into L level and to maintain address activation signals CADE and SADE at L level.

As illustrated in FIG. 9, a command for validating a counter address and a command for instructing a normal access operation indicating reading/writing of data are separately provided to allow data of the necessary number in the burst length to be written/read.

In the structure illustrated in FIG. 9, reset signal RST is driven into the active state for a prescribed period in synchronization with falling of internal clock signal CLK when column selecting operation activation signal /COLACT from a control portion (not shown) is activated.

Although signals of wand of sa are driven into H level upon activation thereof, they may be driven into L level upon activation thereof. In other words, the polarity of illustrated signals may be reversed.

### Modification 2

FIG. 11 illustrates a structure of Modification 2 of the first embodiment of the present invention. FIG. 11 shows a structure of the portion which generates the counter address activation signal SADE. A trigger signal for generating counter address activation signal SADE may be generated according to any of the circuit structures illustrated in FIG. 9 or FIG. 2. In the structure shown in FIG. 11, in addition to the components illustrated in FIG. 2 or FIG. 9, an inverter 28a which receives column address activation signal CADE,

and an AND circuit 28b which receives an output signal of tristate inverter buffer 20 and an output signal of inverter 28a to generate counter address activation signal SADE are provided.

In the structure illustrated in FIG. 11, when column address activation signal CADE is activated, counter address activation signal SADE is forced to be reset to L level. Accordingly, when an access command is supplied and an externally supplied address signal is taken to generate an internal column address signal in the cycle in which the access command is supplied, collision of an externally supplied address signal and an erroneously simultaneously selected address signal from the counter can be prevented. In the second clock cycle and following cycles, column address activation signal CADE is set at L level, so that counter 15 address activation signal SADE is activated according to an output signal of tristate inverter buffer 20.

According to the first embodiment of the present invention, a command related to column selection is decoded at a timing preceding the internal clock signal and an internal operation activation signal is generated according to the internal clock signal. As a result, the internal operation activation signal (address activation signal) can be driven into the active state at a high speed to start an internal operation at an advanced timing.

Further, an address signal which is externally supplied and an address signal from the counter are selected according to separate control signals respectively to generate an internal column address signal. Therefore, in each clock cycle, an internal column address signal can be generated at the same timing and it is unnecessary to consider the margin of the timing at which the internal column address signal is made definite for the column address signal from the counter address and the externally supplied address signal. Accordingly, the column selecting operation can be started at an advanced timing.

# Second Embodiment

Structure of Column Address Signal Generating Circuit: FIG. 12 illustrates a structure of an address input portion included in internal column address signal generating circuit 5 shown in FIG. 1. Although the circuit structure shown in FIG. 12 is provided to each bit of a multi-bit address signal, a circuit portion corresponding to address signal ADD of one bit is shown. The address input portion latches a supplied address signal according to internal clock signal CLK to generate internal address signals Ain and /Ain.

Address input latch 29 includes a CMOS transmission gate 30 which passes address signal ADD supplied to an 50 address input terminal when internal clock signal CLK is at L level, an inverter latch 31 which inverts the address signal passing through CMOS transmission gate 30 and latches the inverted signal, a tristate inverter buffer 32 which is enabled when internal clock signal CLK is at H level, to invert an 55 output signal of inverter latch 31, a tristate inverter buffer 33 which is enabled when internal clock signal CLK is at H level, to invert an address signal from CMOS transmission gate 30, and an inverter latch 34 which latches the output signals from tristate inverter buffers 32 and 33. Internal 60 address signal Ain is output from tristate inverter buffer 32, and complemental internal address signal /Ain is output from tristate inverter buffer 33. Inverter latch 34 includes inverters that are connected in anti-parallel between the outputs of tristate inverter buffers 32 and 33.

In the structure of address input latch 29 illustrated in FIG. 12, when internal clock signal CLK is at L level,

18

CMOS transmission gate 30 passes the address signal provided to the address input node to supply it to inverter latch 31. When internal clock signal CLK rises to H level, CMOS transmission gate 30 is in the non-conductive state and the address input latch is in a latching state. In response to rising of internal clock signal CLK, tristate inverter buffers 32 and 33 are enabled to invert output and input signals of inverter latch 31 respectively to generate complementary internal address signals Ain and /Ain. These internal address signals Ain and /Ain are latched by inverter latch 34.

As illustrated in FIG. 12, the complementary internal address signals are generated to be latched in address input latch 29 with internal clock signal CLK used as trigger, so that the internal column address signal is defined at an earlier stage. Further, the circuit structure of the column address generating portion can be simplified.

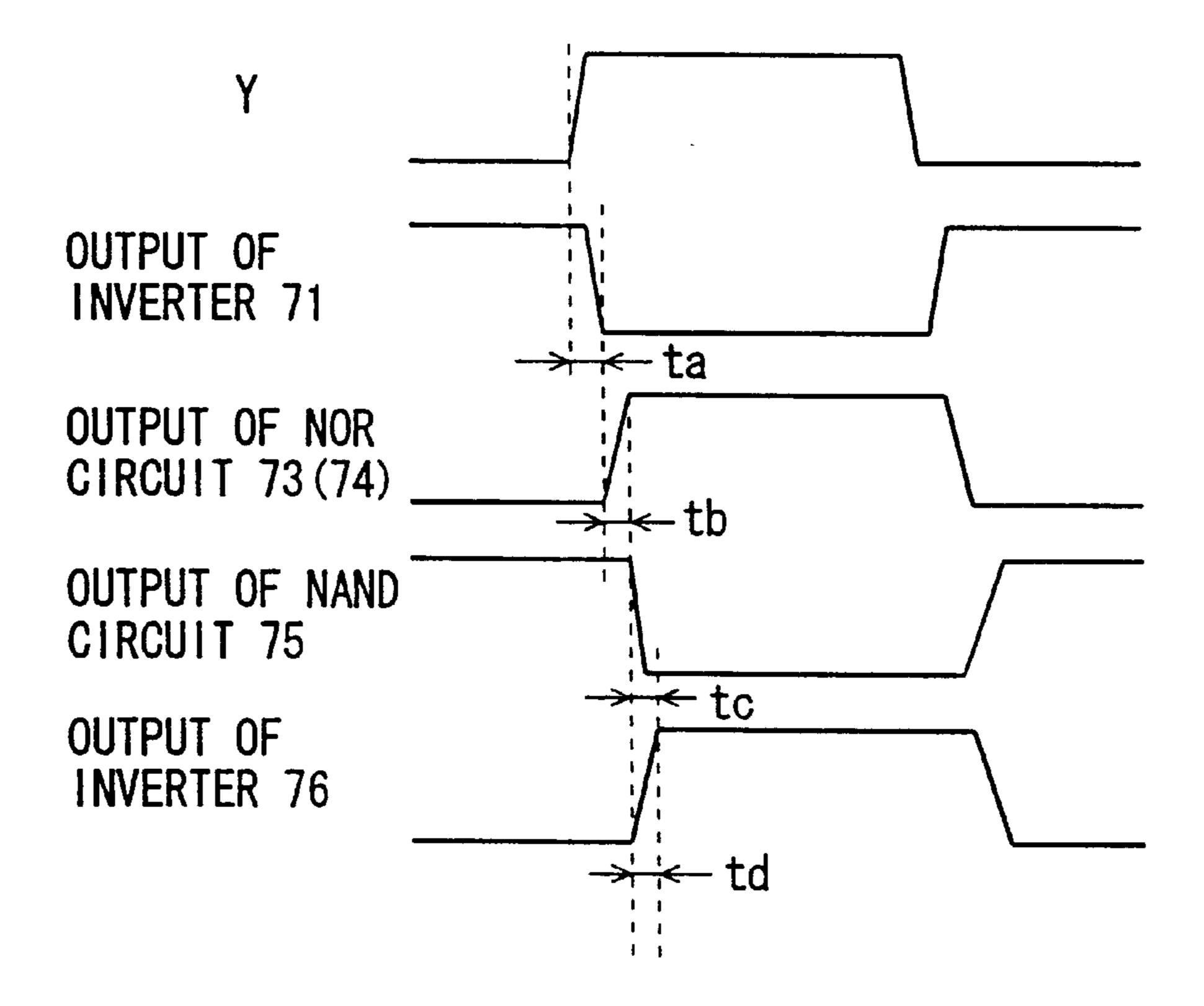

FIG. 13 illustrates a structure of the column address signal generating portion. Referring to FIG. 13, the column address signal generating portion includes an AND circuit 35a which passes internal address signal Ain from address input latch 29 in response to column address activation signal CADE, to generate internal column address signal CA, and an AND circuit 35b which passes complemental internal address signal /Ain from address input latch 29 when column address activation signal CADE is activated, to generate complementary internal column address signal /CA. According to column address activation signal CADE, complementary internal address signals Ain and /Ain from address input latch 29 are gated to generate internal column address signals CA and /CA. Accordingly, the structure of the internal column address signal generating portion can be simplified as that of the structure illustrated in FIG. 3, and the internal column address signals CA and /CA can be made definite at the same timing. AND circuits 35a and 35b are 35 simply provided in the arrangement of the internal column address signal generating portion shown in FIG. 13, and internal column address signals CA and /CA are not latched, offering advantages as discussed below.

FIG. 14 is a schematic diagram illustrating a structure of an internal row address signal generating portion. Referring to FIG. 14, the internal row address signal generating portion includes a CMOS transmission gate 40a which passes internal address signal Ain from address input latch 29 when row address latch enable signal RAL is activated, an inverter latch 40b which inverts and latches an output signal of CMOS transmission gate 40a, and an inverter 40c which inverts an output signal of inverter latch 40b. Complementary internal row address signals are generated from internal row address signal RA according to row address activation signal RADE.

In the structure of the row address signal generating portion illustrated for comparison in FIG. 14, internal row address signal RA is latched and is not reset. If the internal column address signal is also latched as the row address signal is done, the states of internal column address signals CA and /CA change from the states in the preceding cycle in synchronization with rising of internal clock signal CLK as shown in FIG. 15, and the latched state should be reversed, so that it takes much time for the signal states to be made definite. If the complementary internal column address signals are generated according to column address activation signal CADE merely using the AND circuits as illustrated in FIG. 13, the signal potential changes from the reset state and the latched state need not be reversed. It is only necessary to 65 consider the gate delay in AND circuits 35a and 35b, and accordingly internal column address signals CA and /CA can be driven into the definite state at a high speed as shown in

FIG. 15. As a result, the internal column address signal can be made definite at an advanced timing and the internal column selecting operation can be started at an advanced timing.

Further, the circuit for latching the column address signal is not required and the circuit structure of the internal column address signal generating portion can be simplified. It is also unnecessary to generate column address latch instruction signal CAL corresponding to row address latch instruction signal RAL for the row address signal, and 10 consequently the complementary internal address signals can be generated in synchronization with the internal clock signal and the internal column address signal can be generated by column address activation signal CADE. By activating column address activation signal CADE at a fast <sup>15</sup> timing after internal clock signal CLK rises, the internal column address signal can be set into the definite state at a fast timing (since the gate responsive to signal CAL is unnecessary).

Address input latch 29 may be configured to allow complementary signals Ain and /Ain to be reset using reset signal RST according to the first embodiment. As internal column address signals CA and /CA, one of the column address signals from AND circuits 35a and 35b and the counter address from the counter is alternatively selected in combination with counter address activation signal SADE for selecting an address from the counter according to the first embodiment. A selecting circuit which receives internal column address signals CA and /CA will be provided to the structure shown in FIG. 13.

# Modification

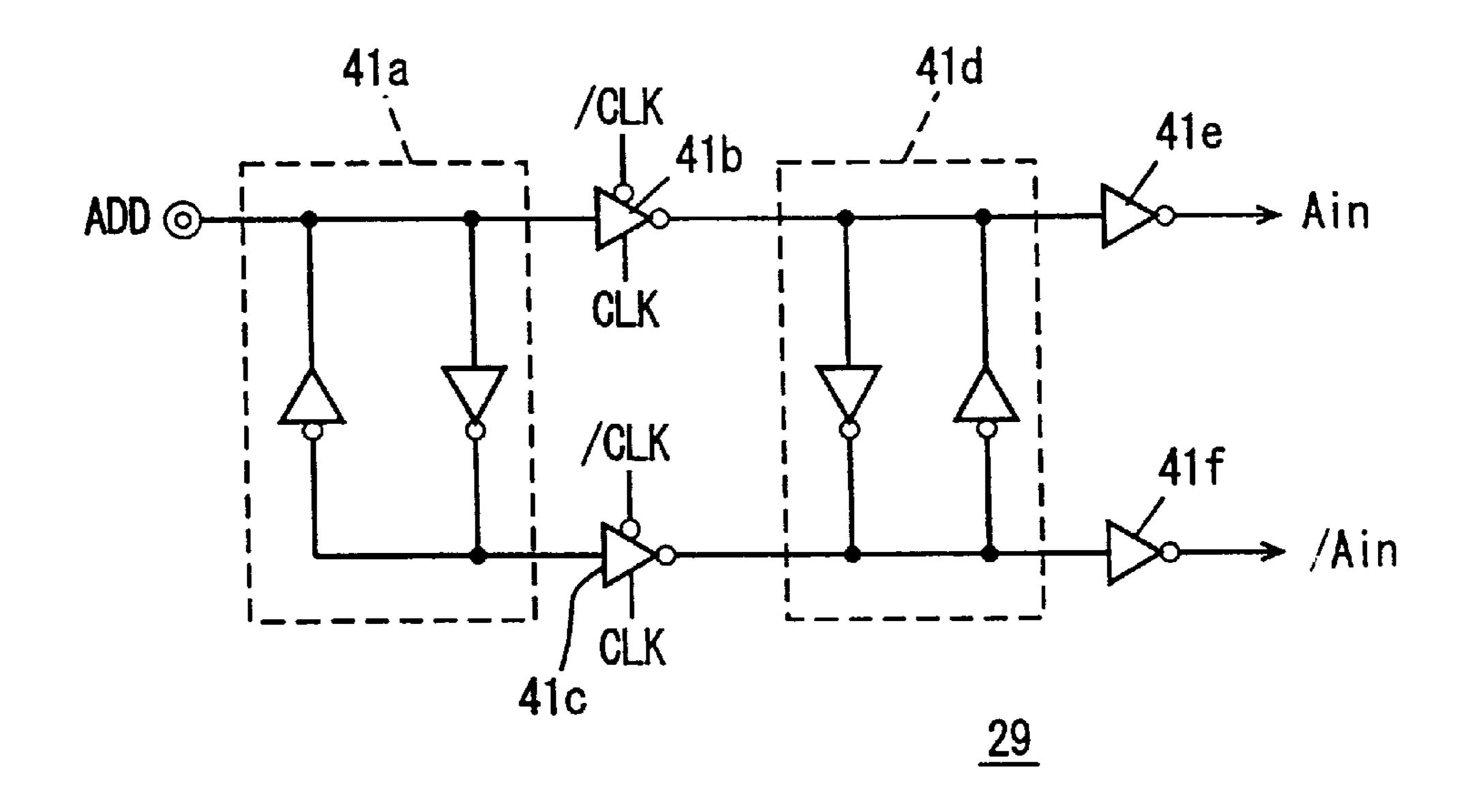

FIG. 16 illustrates a structure of a modification of the second embodiment of the present invention. Referring to FIG. 16, an address input latch 29 includes an inverter latch 41a which latches an address signal supplied to an address input node, a tristate inverter buffer 41b which operates when internal clock signal CLK attains H level, to invert address signal ADD provided to the address input node, a 40 tristate inverter buffer 41c which receives an inverted version of address signal ADD from inverter latch 41a, and operates when internal clock signal CLK attains H level to invert the inverted address signal from inverter latch 41a, an inverter buffers 41b and 41c, an inverter 41e which inverts an output signal of tristate inverter buffer 41b to generate internal address signal Ain, and an inverter 41f which inverts an output signal of tristate inverter buffer 41c to generate a complemental internal address signal /Ain. Inverter latch 41a includes inverters connected in anti-parallel to each other between the inputs of tristate inverter buffers 41b and 41c. Inverter latch 41d includes inverters connected in anti-parallel between the outputs of tristate inverter buffers **41***b* and **41***c*.

In the address input latch illustrated in FIG. 16, the delay times on the paths transmitting complementary internal address signals Ain and /Ain are the same with each other from the time at which internal clock signal CLK rises. Therefore, after internal clock signal CLK rises, address 60 signals Ain and /Ain can be set into the definite state at the same timing. Accordingly, the internal address signal can be set into the definite state at an advanced timing. The internal column address signal can be made definite at a fast timing.

According to the second embodiment, the external 65 address signal is latched in synchronization with the internal clock signal to generate the complementary internal address

signals. As a result, the structure of the address latch circuit can be simplified. Further, the internal column address signals are generated from the complementary internal address signals by the logical product with the column address activation signal, simplifying the circuit structure. Further, the internal column address signal can be set into the definite state at a fast timing.

The internal column address signal is reset to the initial state in each clock cycle, so that only one of complementary internal column address signals is charged in the clock cycle, accordingly the current flows only in one direction. The current flowing from the power supply to the ground is reduced compared with the state in which both signals change due to the influence of the address signal in the preceding cycle.

The signal changes in one direction from the voltage level at the same reset state without influence by the column address signal in the preceding clock cycle. Therefore, the internal column address signal can be driven into the definite state at the same timing without the influence of the voltage level of the column address signal in the preceding clock cycle, and accordingly the internal column address signal can be set into the definite state at a fast timing.

### Third Embodiment

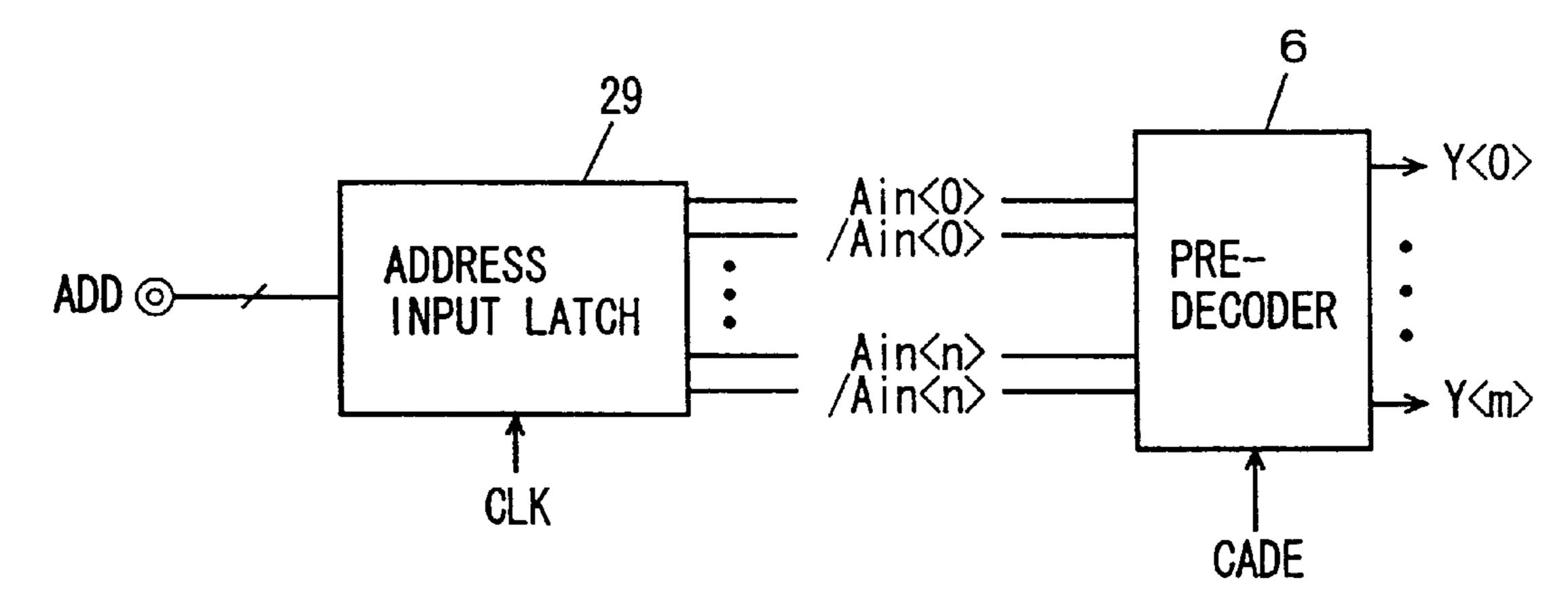

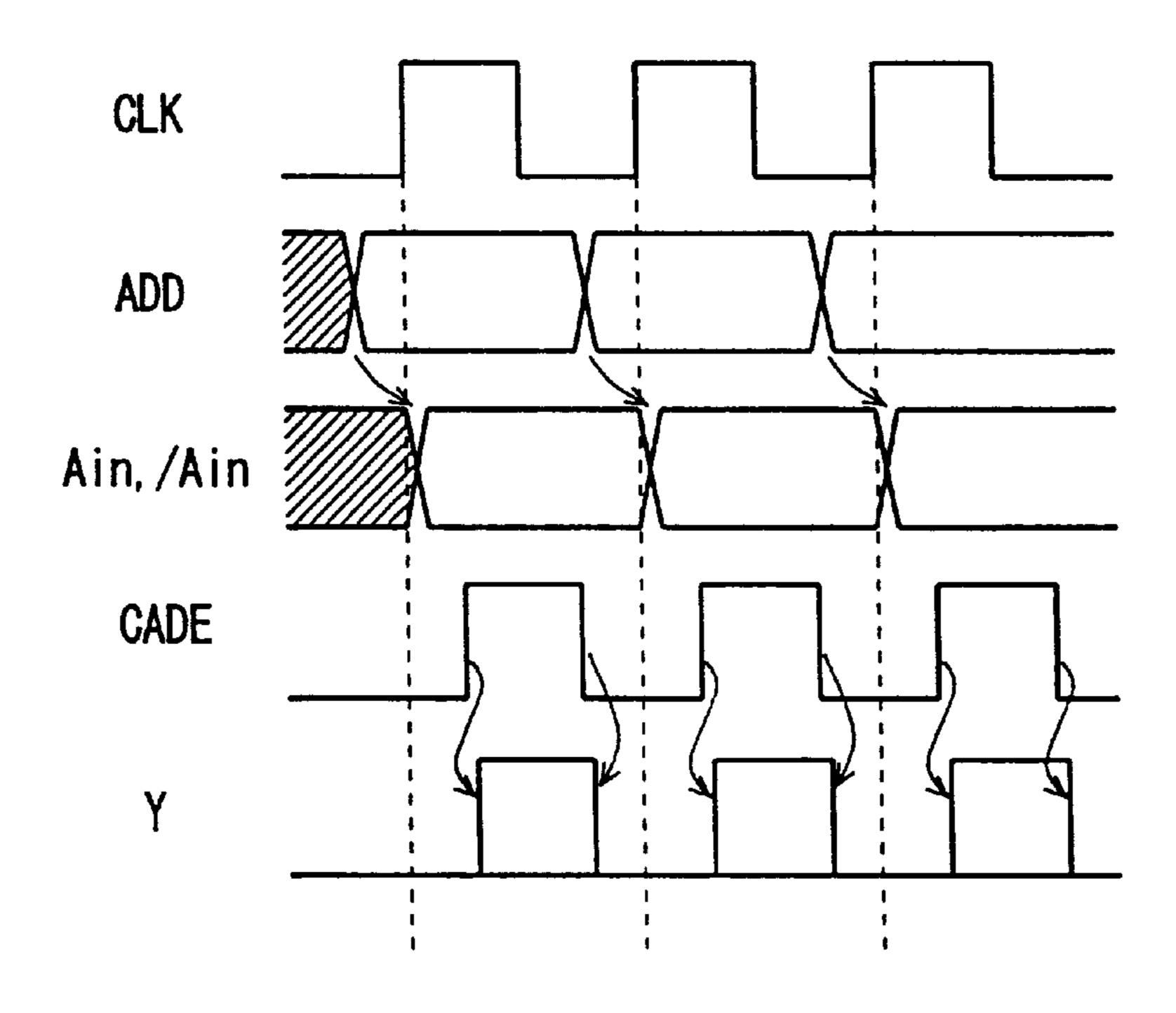

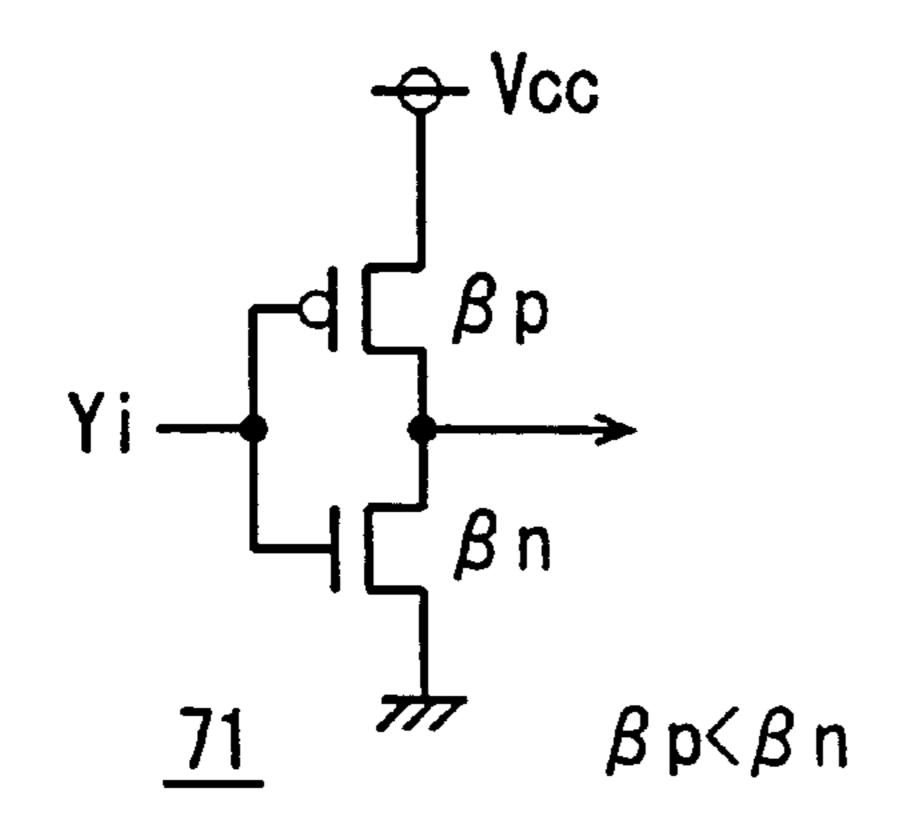

FIG. 17 illustrates a structure of a main portion of a semiconductor memory device according to the third embodiment of the present invention. Referring to FIG. 17, predecoder 6 shown in FIG. 1 is enabled in response to activation of column address activation signal CADE to predecode internal address signal bits Ain<0>, /Ain<0>-Ain<n>, and /Ain<n> and generate predecode signals Y<0>-Y<m>. Predecoder 6 performs the predecoding operation according to activation of column address activation signal CADE when complementary internal address signals are generated, and the predecoding operation is not performed after internal column address signals CA and ICA are made definite. When internal clock signal CLK rises, internal address signals Ain<0>, /Ain<0>-Ain<n>, and /Ain<n> from address input latch 29 are predecoded, so that predecode signals Y<0>Y<m> can be made definite at a fast timing.

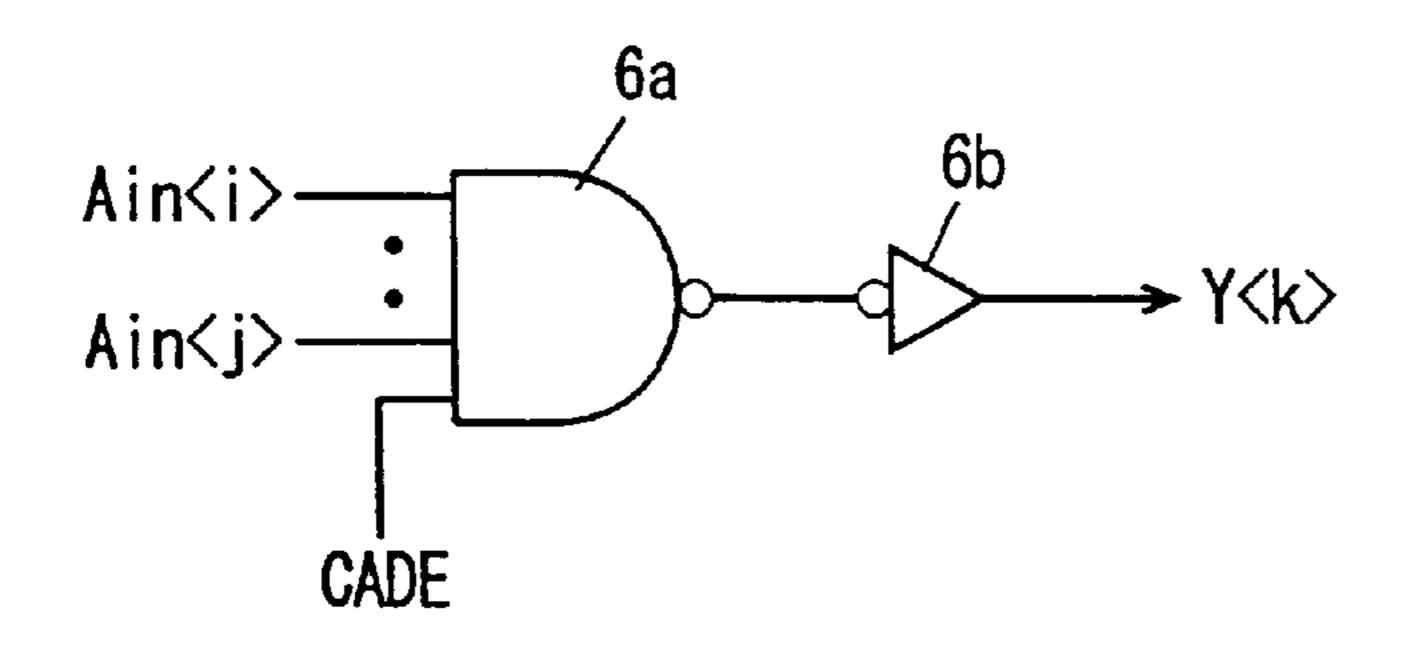

FIG. 18 illustrates a structure of a predecode circuit inverter latch 41d which latches output signals from tristate 45 included in predecoder 6 illustrated in FIG. 17. FIG. 18 show a predecode circuit for prededode signal Y<k>. The predecode circuit includes an NAND circuit 6a which receives a prescribed set of internal address signals, Ain<i>, . . . Ain<j> from address input latch 29, and column address activation signal CADE, and an inverter 6b which inverts an output signal of NAND circuit 6a to generate predecode signal Y<k>. Referring now to FIG. 19, an operation of predecoder 6 illustrated in FIGS. 17 and 18 is described.

> When column address activation signal CADE is at L 55 level of the inactive state, an output signal of NAND 6a is at H level and predecode signal Y<k> maintains a nonselected state of L level. When column address activation signal CADE is activated, an output signal of NAND circuit 6a is made definite by a combination of supplied internal address signals Ain<i>, . . . Ain<j> (including a complemental address signal), and the state of predecode signal Y<k> is made definite according to the combination. Address input latch 29 is commonly provided to a row address signal and a column address signal, and whether the address signal is a row address signal or a column address signal is determined according to column address activation signal CADE. The predecoding operation is done simulta-

neously with determination of the column address signal, so that the predecode signal can be set into the definite state at a faster timing to speedily perform the column selecting operation.

When column address activation signal CADE is inactivated, predecoder 6 is disabled and predecode signals Y<0>-Y<m> are reset to L level (initialized). Consequently, the valid period of the predecode signals is determined, and the predecode signals always change from L level, so that the predecode signals always change at the same timing to reach the definite state without influence by the state of the predecode signal in the preceding cycle. Therefore, the margin for the timing at which the predecode signal is made definite (margin determined by considering the speed of change from the predecode signal in the preceding cycle) 15 need not be considered and the predecode signal is set into the definite state at an advanced timing to perform the column selecting operation.

In the arrangement of address input latch 29 and predecoder 6 illustrated in FIG. 17, any of the structures of the address input latch according to the second embodiment may be employed as the structure of address input latch 29.

In each clock cycle, column address activation signal CADE is activated. However, if an address signal from a burst address counter is used, counter address activation signal SADE is used in place of column address activation signal CADE. In this case, a signal generated by ORing column address activation signal CADE and counter address activation signal SADE can be used for activating the predecoder. In this case, a structure for switching internal address signal Ain and counter address SAin from the counter is necessary.

# Modification

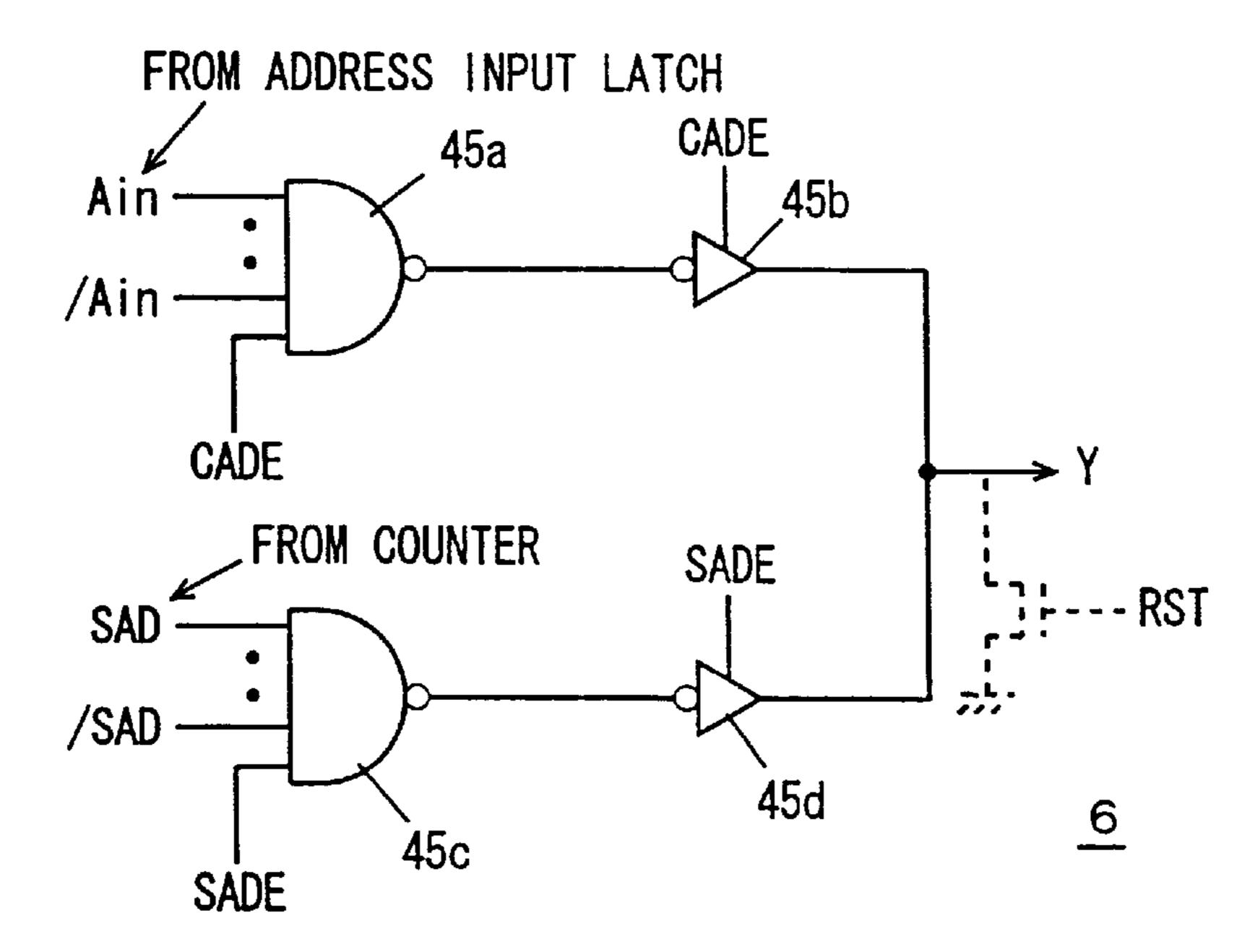

FIG. 20 illustrates a structure of a modification according to the third embodiment of the present invention. Referring to FIG. 20, a predecoder 6 includes an NAND type decode circuit 45a receiving complementary internal address signals Ain and /Ain supplied from an address input latch and predecoding supplied complementary internal address signals Ain and /Ain in response to activation of column address activation signal CADE, a tristate inverter buffer 45b set into an operable state in response to activation of column address activation signal CADE to invert an output signal of NAND type decode circuit 45a, an NAND type decode circuit 45c receiving count address signals SAD and /SAD from the counter, and predecoding counter addresses SAD and /SAD in response to activation of counter address activation signal SADE, and a tristate inverter buffer 45d set into an operable state in response to activation of counter address activation signal SADE, to invert an output signal of NAND type decode circuit 45c. The outputs of tristate inverter buffers 45b and 45d are commonly coupled to generate predecode signal Y.

Even with the structure of the predecoder illustrated in FIG. 20, addresses SAD and /SAD from the counter are predecoded simultaneously with activation of counter address activation signal SADE under a burst mode operation, so that predecode signal Y can be generated at a 60 fast timing. The illustrated structure needs a reset MOS transistor for resetting predecode signal Y in response to reset signal RST as shown by dotted lines.