US006313539B1

## (12) United States Patent

Yokoyama et al.

(10) Patent No.: US 6,313,539 B1

(45) Date of Patent: Nov. 6, 2001

| (54) | SEMICONDUCTOR MEMORY DEVICE AND |

|------|---------------------------------|

|      | PRODUCTION METHOD OF THE SAME   |

(75) Inventors: Seiichi Yokoyama, Kashiwa; Shun Mitarai, Nishinomiya; Masaya Nagata; Jun Kudo, both of Nara; Nobuhito Ogata, Tenri; Yasuyuki Itoh,

Hamamatsu, all of (JP)

(73) Assignee: Sharp Kabushiki Kaisha, Osaka (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/219,310

(58)

(22) Filed: **Dec. 23, 1998**

## (30) Foreign Application Priority Data

| Dec. 24, 1997 | (JP) | 9-354710  |

|---------------|------|-----------|

| Feb. 18, 1998 | (JP) | 10-035639 |

(51) Int. Cl.<sup>7</sup> ...... H01L 23/48

> > 609, 681, 686, 778, 396

(56) References Cited

### U.S. PATENT DOCUMENTS

| 5,335,138 * | 8/1994 | Sandhu et al | 257/306 |

|-------------|--------|--------------|---------|

|-------------|--------|--------------|---------|

| 5,554,866 | * | 9/1996  | Nishioka et al    | 257/295 |

|-----------|---|---------|-------------------|---------|

| 5,874,364 | * | 2/1999  | Nakabayashi et al | 438/738 |

| 5,965,942 | * | 10/1999 | Itoh et al        | 257/761 |

| 6,015,989 | * | 1/2000  | Horikawa et al    | 257/309 |

| 6,239,460 | * | 5/2001  | Kuroiwa et al     | 257/300 |

#### OTHER PUBLICATIONS

M. Nakabayashi et al, "Electrodes for Ferroelectric Materials"; The 43<sup>rd</sup> Spring Meeting of the Japanese Society of Applied Physics and the Related Societies, 28p–V–4, 1996, p. 499.

Primary Examiner—Stephen D. Meier Assistant Examiner—C. Johnson (74) Attorney, Agent, or Firm—Nixon & Vanderhye P.C.

## (57) ABSTRACT

A semiconductor memory device includes: a capacitor formed on a substrate and including a lower electrode, a dielectric film and an upper electrode; a selection transistor formed at the substrate; an electrically conductive plug for providing electrical connection between the selection transistor and the capacitor; and a diffusion barrier film provided between the electrically conductive plug and the lower electrode of the capacitor. The diffusion barrier film is a  $Ta_xSi_{1-x}N_y$  film or a  $Hf_xSi_{1-x}N_y$  film (where 0.2 < x < 1 and 0 < y < 1). The lower electrode includes an Ir film and an  $IrO_2$  film which are sequentially formed.

## 7 Claims, 24 Drawing Sheets

<sup>\*</sup> cited by examiner

FIG. 1

FIG.2

Ta composition x in  $Ta_x Si_{(1-x)} N_y$  film

FIG.3A

FIG.3B

FIG.3C

FIG. 4

FIG. 6

FIG. 8A

FIG.8B

FIG.8C

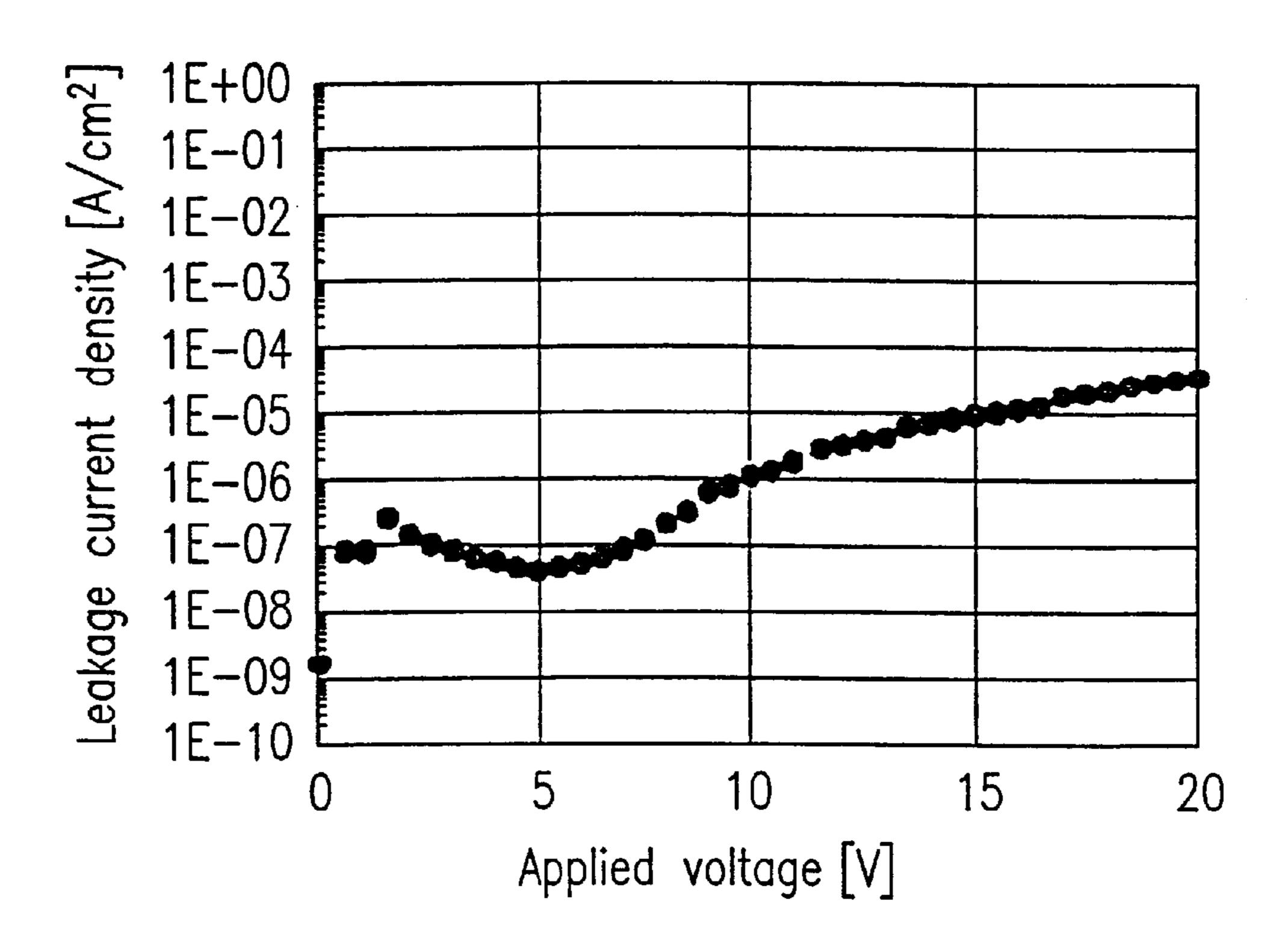

Applied voltage [V]

FIG. 10

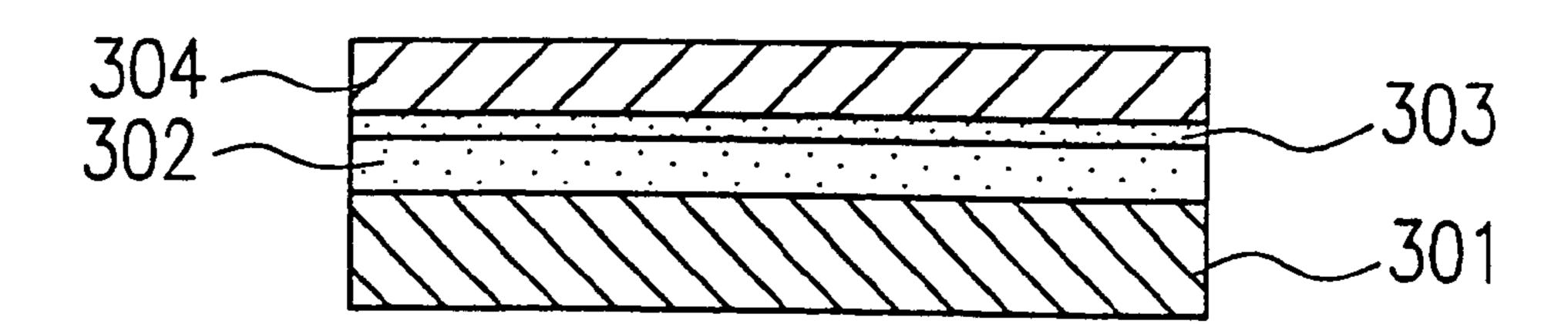

FIG. 12A

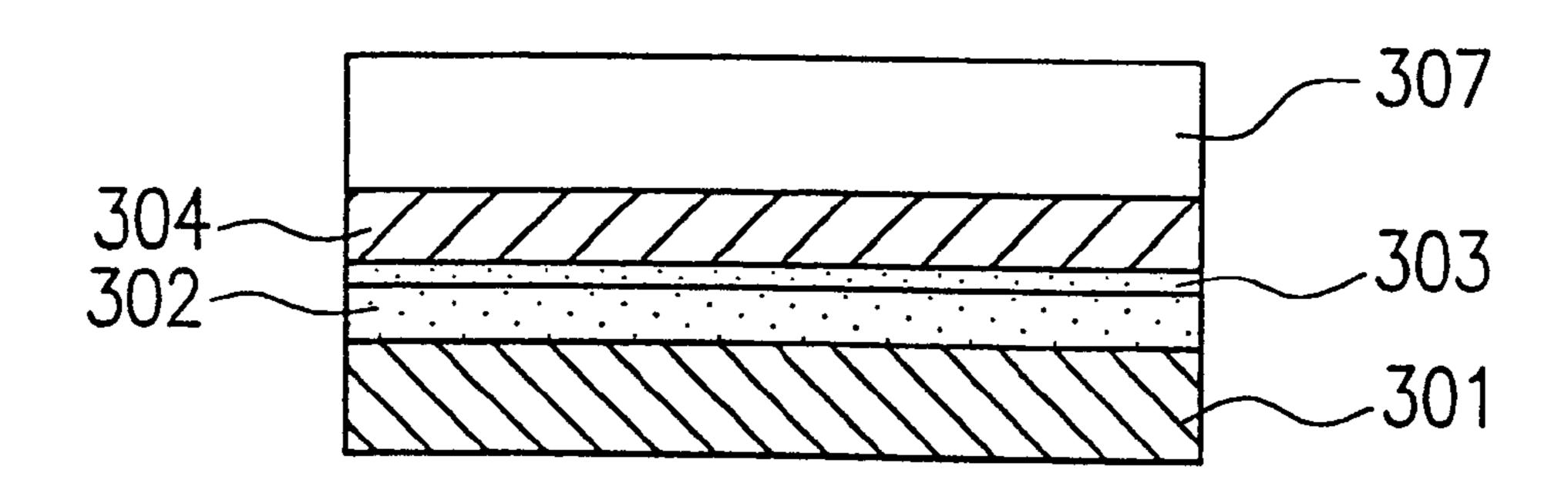

FIG. 12B

FIG. 14

FIG. 15

FIG. 17A

FIG. 17B

FIG. 17C

FIG. 19

FIG. 20

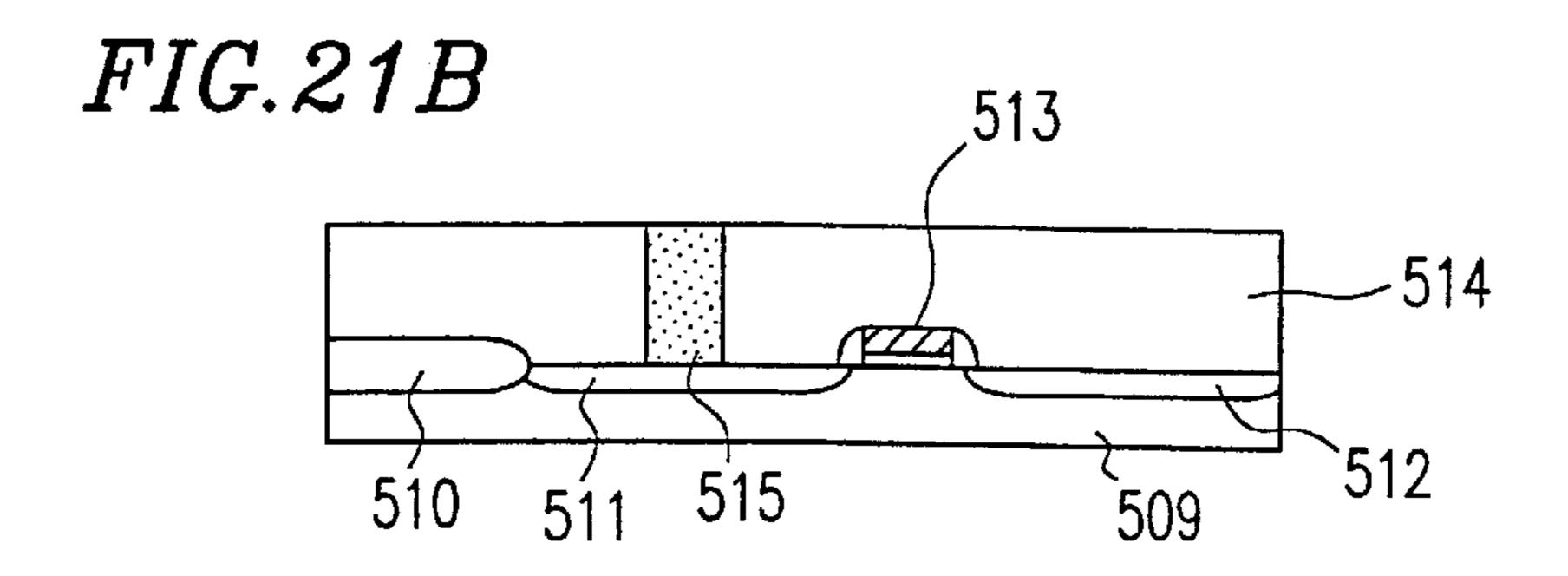

FIG.21A513 514

FIG. 21C

FIG.21D

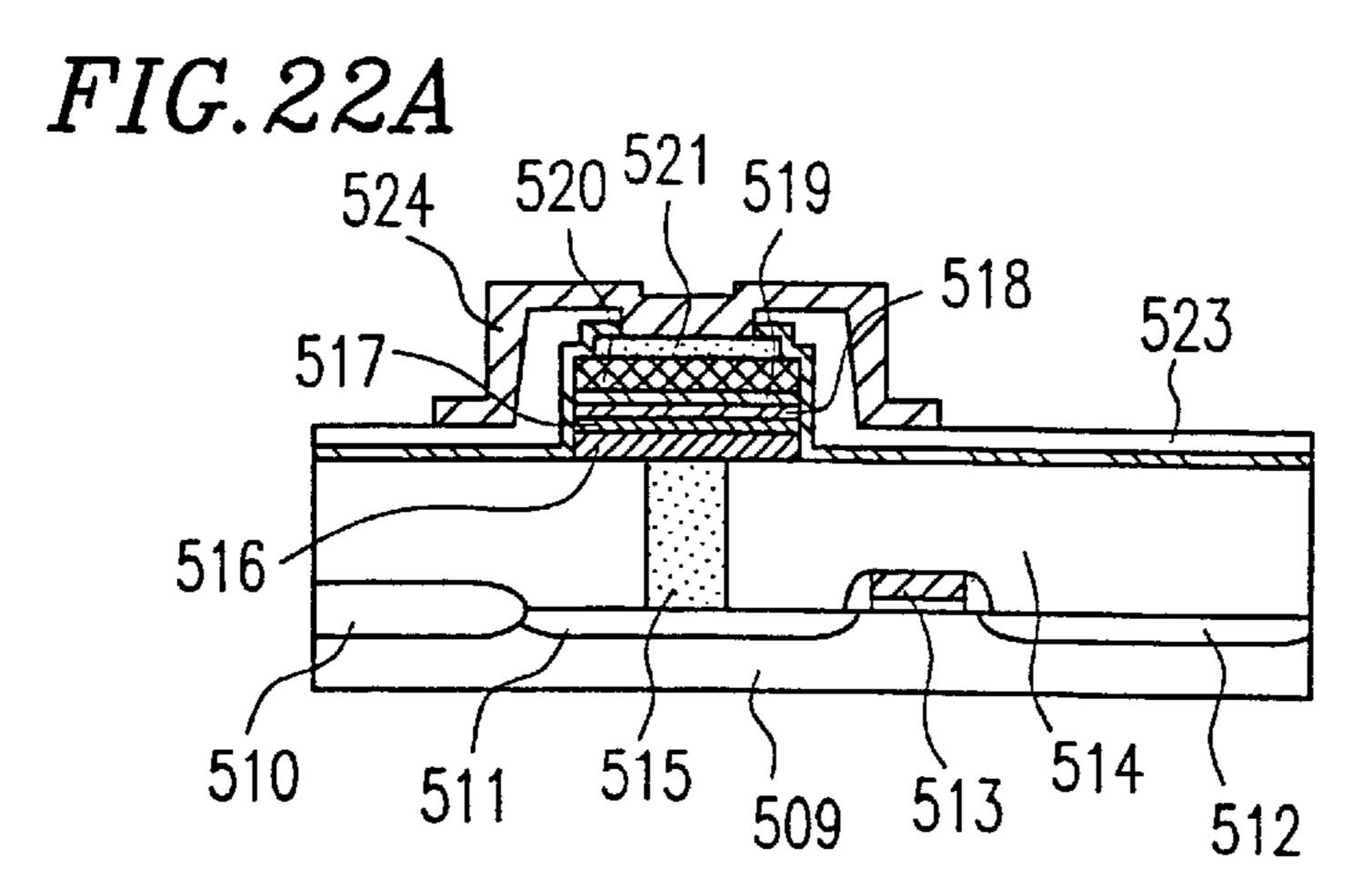

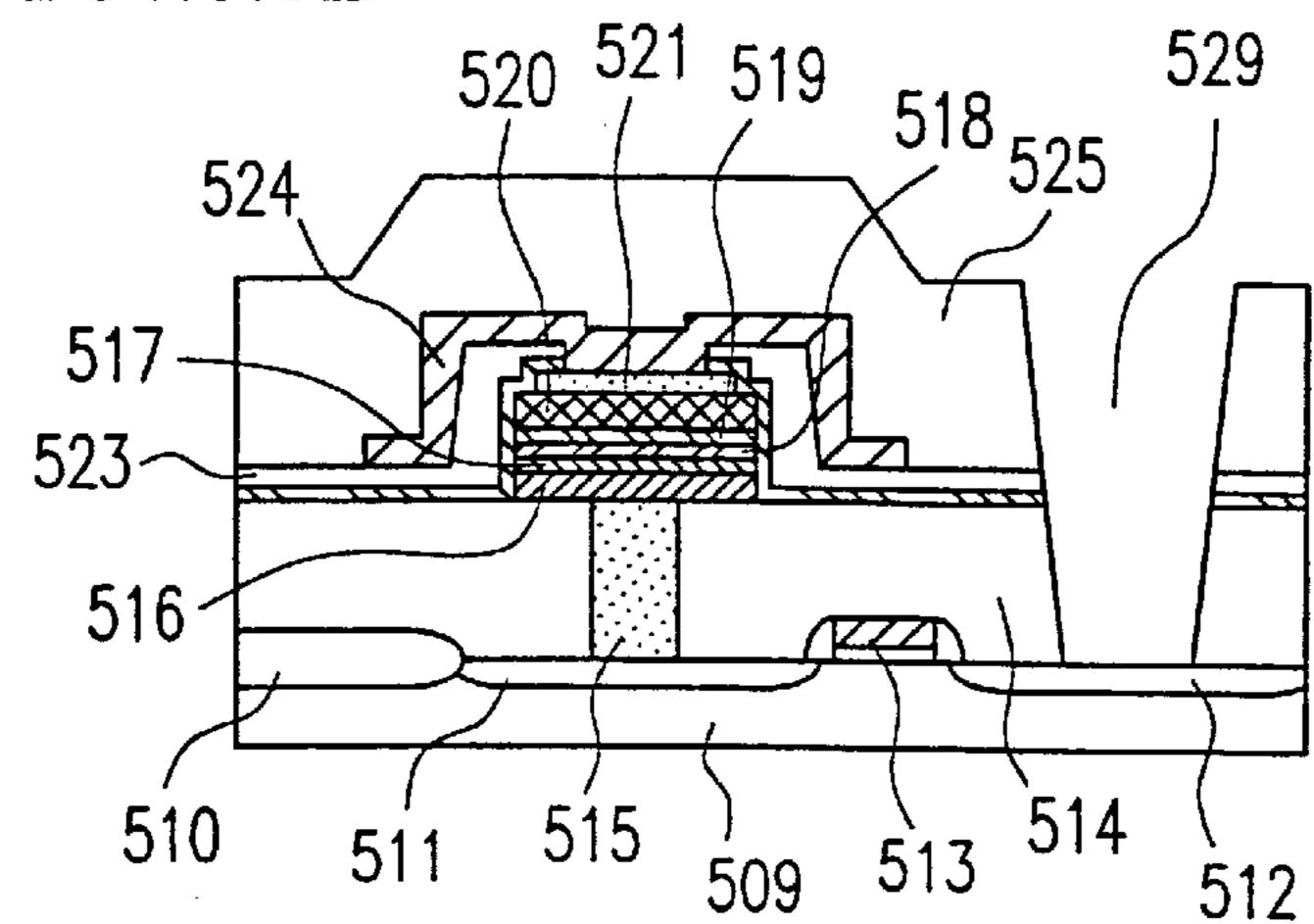

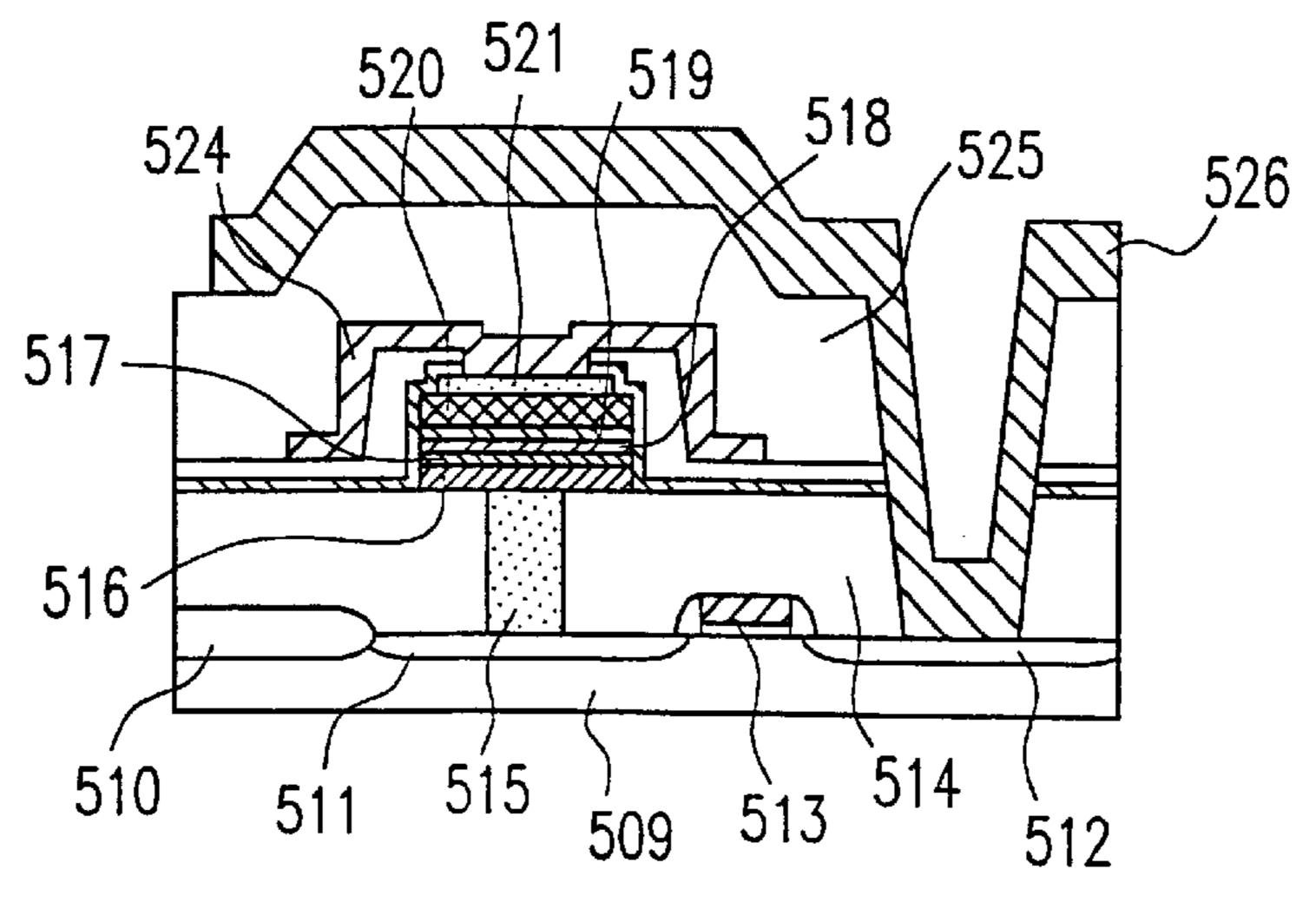

FIG.22B

FIG.22C

FIG. 23

FIG. 24

FIG. 25

## SEMICONDUCTOR MEMORY DEVICE AND PRODUCTION METHOD OF THE SAME

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a semiconductor memory device and a method for producing the same. In particular, the present invention relates to a semiconductor memory device incorporating a capacitor which includes a lower electrode, a dielectric film, and an upper electrode, the capacitor being electrically connected to a selection transistor via an electrically conductive plug and a diffusion barrier film, as well as a method for producing the same. The present invention further relates to a method for producing a capacitor for use in such a semiconductor memory device, the capacitor including a ferroelectric film (hereinafter, such a capacitor will also be referred to as a "ferroelectric capacitor"), as well as a method for producing a non-volatile semiconductor memory device incorporating such a ferroelectric capacitor.

### 2. Description of the Related Art

Ferroelectric materials have a large range of applications for various devices utilizing their functions including spontaneous polarization, high dielectric constant, electro-optical effects, piezoelectric effects, pyroelectric effects, and the like. For example, the pyroelectric properties of ferroelectric materials are utilized in infrared linear array sensor applications; their piezoelectric properties are utilized in ultrasonic wave sensor applications; their electro-optical effects are utilized in waveguide type optical modulator applications; their high dielectric properties are utilized in capacitors for use in DRAMs (Dynamic Random Access Memories) and MMICs (Monolithic Microwave Integrated Circuits), and so on.

Above all, non-volatile memories (FRAMs: ferroelectric non-volatile memories), which incorporate a ferroelectric film and are capable of high-density implementation and high-speed operation, have been a subject of intensive development, in response to the recent development in thin film formation technologies in combination with semiconductor memory art. FRAMs provide advantages such as high-speed writing/reading, low voltage operation, and high endurance through repetitive writing/reading. Therefore, research and development efforts have been made to implement FRAMs which can replace not only conventional 45 non-volatile memories but potentially SRAMs and/or DRAMs also.

Conventional non-volatile memories such as EPROMs, EEPROMs, and flash memories require a read time which is equivalent to that required for a DRAM. However, they 50 require a long write time, thereby hindering high-speed operation. On the other hand, FRAMs are capable of both reading and writing at a rate which is equivalent to-that of DRAMs. Thus, high-speed operation is expected of FRAMS. In a typical device structure of an FRAM, one cell 55 is constructed from one selection transistor and one ferroelectric capacitor; alternatively, one cell is constructed from two selection transistors and two ferroelectric capacitors.

Conventionally, oxide ferroelectric materials (PZT (lead zirconate titanate),  $SrBi_2Ta_2O_9$ ,  $Bi_4Ti_3O_{12}$ , etc.) have been 60 studied as ferroelectric materials for use in a ferroelectric capacitor. As a lower electrode of such a ferroelectric capacitor, electrodes formed of a precious metal material (e.g., Pt, Pt/Ta, Pt/Ti) or composite electrodes formed of precious metal material(s) and a closely contacting film have 65 been used for improved characteristics of the resultant thin ferroelectric film.

2

A ferroelectric film must be in the form of a crystallized film in order for its functions to be fully utilized. Therefore, a high-temperature heat treatment at about 600° C. to about 800° C. in an oxygen atmosphere is required as a crystallization process.

Furthermore, it is generally considered essential to employ a stacked structure in order to achieve a high density integration, e.g., 4 Mbits or above, by utilizing such a ferroelectric capacitor and manufacturing processes thereof. This in turn requires a structure in which a selection transistor is electrically coupled to a ferroelectric capacitor via an electrically conductive plug, e.g., polysilicon. In the case of a Pt/polysilicon structure, a diffusion barrier film (e.g., TiN) is required so as to prevent silicidation of a Pt lower electrode which may occur during a crystallization process of the ferroelectric material.

However, although a Pt film itself has sufficient anti-oxidation properties, the TiN layer in a Pt/TiN/Ti structure may be oxidized by oxygen gas which has moved along grain boundaries in the Pt film during the crystallization process of the ferroelectric material, as reported in the Extended Abstracts of the 43rd Spring Meeting (1996) of the Japanese Society of Applied Physics and the related Societies, 28p-V-6 (p. 500). Furthermore, as reported in the above publication as the article 28p-V-7, oxidation of TiN, if it occurs, may cause peeling at the Pt/TiN interface or hillocks in an upward direction within the Pt film so as to alleviate any variation in stress due to volume expansion resulting from the oxidation of TiN. This presents a considerable problem.

The aforementioned movement of oxide through the Pt film presents another problem in that, in the case where a closely contacting film is employed in a Pt/Ta/TiN/Ti structure or a Pt/Ti/TiN/Ti structure, an insulating material may be formed as a result of oxidation of the Ta or Ti immediately underlying the Pt, thereby disrupting the electrical connection. The lowermost Ti film is a requirement in these multi-layer structures to establish contact between the respective structure and polysilicon.

Thus, constructing an electrode only from a Pt film, or a combination of a Pt film and a closely contacting film can result in marked problems associated with hillocks and/or insufficient electrical contact due to the oxidation of a diffusion barrier film such as TiN. These problems make it difficult to realize stacked type structures.

On the other hand, the use of an oxide electrode material (e.g., IrO<sub>2</sub>, RuO<sub>2</sub>, RhO<sub>2</sub>, OSO<sub>2</sub>, and ReO<sub>2</sub>) for a lower electrode under the aforementioned oxide ferroelectric film has begun to be studied because they provide excellent barrier properties and excellent matching with an overlying oxide dielectric material.

Among others, the use of IrO<sub>2</sub> can greatly improve the fatigue characteristics of a layer of PZT formed upon an Ir/IrO<sub>2</sub>/polysilicon electrode or a Pt/IrO<sub>2</sub>/polysilicon electrode, as reported in Appl. Phys. Lett., vol. 65 (1994), pp. 1522–1524 and Jpn. J. Appl. Phys., vol. 33 (1994), pp. 5207–5210, which ascribes such improvement to the barrier properties of the IrO<sub>2</sub> film against the elements (e.g., Pb) composing the ferroelectric film. However, again such a structure is susceptible to the problem of insufficient electrical contact due to oxidation of the polysilicon at the IrO<sub>2</sub>/polysilicon interface, as well as silicidation of IrO<sub>2</sub> formed immediately above the polysilicon, during the IrO<sub>2</sub> film formation and the ferroelectric film formation.

An IrO<sub>2</sub>(1000Å)/Ir(500Å)/TiN/Ti lower electrode, incorporating a TiN film as a barrier metal for an oxide electrode

(IrO<sub>2</sub> electrode), has been reported in the Extended Abstracts of the 43rd Spring Meeting (1996) of the Japanese Society of Applied Physics and the related Societies, 28p-V-4 (p. 499) for solving the problem associated with the reaction between Ir or IrO<sub>2</sub> and polysilicon. In this reference, contact 5 characteristics between a silicon substrate having a reduced resistance due to ion implantation and a SrTiO<sub>3</sub> film serving as a high dielectric film was examined. As a result, it was confirmed that ohmic contact is established therebetween. More specifically, a leakage current density of about  $10^{-7}$  10 A/cm<sup>2</sup> and a dielectric constant of about 216 are reported to be obtained, both of these values being substantially equal to those obtainable for the Pt electrode. Such an IrO<sub>2</sub>/Ir/TiN/Ti structure prevents any degradation in electric characteristics of the capacitor which is associated with hillocks and 15 reduced flatness typically caused in the relatively lowtemperature process of about 200° C. to about 450° C. to be performed for forming a SrTiO<sub>3</sub> film as a high dielectric material film. Thus, the IrO<sub>2</sub>/Ir/TiN/Ti structure was confirmed to be a promising candidate for use in the stacked 20 type structure incorporating a high dielectric capacitor.

However, the ferroelectric material crystallization process requires the use of an oxygen atmosphere at a temperature of about 600° C. or higher even for forming a PZT film. Moreover, an oxygen atmosphere at about 800° C. or higher is often used for a SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> film. In the Pt/TiN/Ti structure, an insulating material may be formed at such a high temperature as a result of oxidation of the Ti which is a closely contacting film, thereby disrupting the electrical conduction. In addition, hillocks may be produced by the film stress due to oxidation of TiN. In the IrO<sub>2</sub>/Ir/TiN/Ti structure as well, hillocks may be produced by the film stress due to the crystallization process at a high temperature (i.e., >about 600° C.).

In view of the aforementioned problems, Ir and IrO<sub>2</sub> having excellent crystallinity are required to obtain improved anti-oxidation properties. However, when the IrO<sub>2</sub> film is formed directly on the Ir film at a high temperature, the IrO<sub>2</sub> film becomes non-uniform in quality, making it impossible to form a homogenous film at a high temperature. Moreover, hillocks or the like may be produced in a high-temperature atmosphere due to the poor anti-heat properties of the diffusion barrier film.

Thus, in order to practically produce the memories incorporating a ferroelectric film or high dielectric film in the stacked type structure, it is desirable to implement a lower electrode structure exhibiting no reaction with ferroelectric materials to be provided thereon and having anti-heat properties in an oxidation atmosphere at about 600° C. or higher; a flat, dense profile; and a resistivity which is equivalent to or better than that of the conventional Pt electrode.

SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> has been actively studied as a promising candidate of a ferroelectric material for use in the ferroelectric capacitor, because it has better fatigue characteristics and requires lower driving voltage as compared to the conventionally used PZT. Unlike the conventional ferroelectric materials such as PZT, SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> is crystallized through heat-treatment in a high-temperature oxidizing atmosphere of about 700° C. to about 800° C. in any of the formation methods including an MOD (Metal Organic Decomposition) method, a sol-gel method, an MOCVD (Metal Organic Chemical Vapor Deposition) method and a sputtering method, as disclosed in Japanese Laid-Open Publication Nos. 8-23073 and 9-36309.

It should be noted that such heat-treatment in the hightemperature oxidizing atmosphere does not cause a serious 4

problem in the case of a relatively poorly integrated ferroelectric capacitor with a flat structure. However, in the stacked type structure which is essential to achieve a highdensity integration of the ferroelectric memories, a polysilicon plug typically used to establish contact with a lower electrode and/or a diffusion barrier layer (barrier metal layer), e.g., TiN or TaSiN, for preventing diffusion between the plug and the lower platinum electrode, tend to be oxidized during the high-temperature process. Such oxidation of the polysilicon plug and/or diffusion barrier layer (barrier metal layer), if it occurs, may disrupt electrical conduction between the plug and the lower electrode, and/or may cause peeling due to expansion of the barrier metal.

#### SUMMARY OF THE INVENTION

A semiconductor memory device of the present invention includes: a capacitor formed on a substrate and including a lower electrode, a dielectric film and an upper electrode; a selection transistor formed at the substrate; an electrically conductive plug for providing electrical connection between the selection transistor and the capacitor; and a diffusion barrier film provided between the electrically conductive plug and the lower electrode of the capacitor. The diffusion barrier film is a  $Ta_xSi_{1-x}N_y$  film or a  $Hf_xSi_{1-x}N_y$  film (where 0.2<x<1 and 0<y<1), and the lower electrode includes an Ir film and an IrO<sub>2</sub> film which are sequentially formed.

The lower electrode may further include an electrically conductive film formed on the IrO<sub>2</sub> film, the electrically conductive film containing at least one of metal elements selected from the group consisting of Pt, Ir, Ru, Rh, Os and Re.

The diffusion barrier film may be a  $Ta_xSi_{1-x}N_y$  film or a  $Hf_xSi_{1-}N_y$  film (where 0.75<x<0.95 and 0.3<y<0.5).

A ratio of a thickness d1 of the  $IrO_2$  film to a thickness d2 of the Ir film may satisfy a relation of  $1 \le d1/d2 \le 3$ .

Another aspect of the present invention provides a method for producing a semiconductor memory device including a capacitor which includes a lower electrode, a dielectric electrode and an upper electrode. The capacitor is electrically connected to a selection transistor via an electrically conductive plug and a diffusion barrier film. The method includes the steps of: forming the diffusion barrier film at a prescribed position on a substrate; forming an Ir film on the diffusion barrier film; forming an initial film with a thickness of about 50 Å to about 300 Å on the Ir film at a temperature of about 300° C. to about 400° C., the initial film containing at least one of metal elements selected from the group consisting of Ir, Ru, Rh, Os and Re; forming an IrO<sub>2</sub> film on the initial film to obtain a layered structure of the lower electrode; forming the dielectric film on the lower electrode; and forming the upper electrode on the dielectric film.

The method may further include the step of forming an electrically conductive film on the IrO<sub>2</sub> film. The electrically conductive film contains at least one of metal elements selected from the group consisting of Pt, Ir, Ru, Rh, Os and Re.

The IrO<sub>2</sub> film may be formed at a temperature of about 450° C. to about 700° C.

A ratio of a thickness d1 of the  $IrO_2$  film to a thickness d2 of the Ir film may satisfy a relation of  $1 \le d1/d2 \le 3$ .

The initial film may be formed as an IrO<sub>2</sub> film.

The diffusion barrier film may be formed as a  $Ta_xSi_{1-x}N_y$  film or a  $Hf_xSi_{1-x}N_y$  film (where 0.2<x<1 and 0<y<1). Preferably, the diffusion barrier film is formed as a  $Ta_xSi_{1-x}N_y$  film or a  $Hf_xSi_{1-x}N_y$  film (where 0.75<x<0.95 and 0.3<y<0.5).

Still another aspect of the present invention provides a method for producing a semiconductor memory device including a capacitor which includes a lower electrode, a dielectric film and an upper electrode, in which the capacitor is electrically connected to a selection transistor via an 5 electrically conductive plug and a diffusion barrier film. The method includes the steps of: forming the diffusion barrier film at a prescribed position on a substrate; forming an Ir film on the diffusion barrier film; forming the dielectric film on the Ir film using a material which contains oxygen; and  $_{10}$ forming the upper electrode on the dielectric film.

The diffusion barrier film may be formed as a  $Ta_xSi_{1-x}N_y$ film or a  $Hf_xSi_{1-x}N_y$  film (where 0.2<x<1 and 0<y<1). Preferably, the diffusion barrier film is formed as a  $Ta_xSi_{1-x}N_x$  film or a  $Hf_xSi_{1-x}N_x$  film (where 0.75<x<0.95 and 0.3 < y < 0.5).

In the aforementioned production method of the present invention, the dielectric film may be a ferroelectric film, and the step of forming the ferroelectric film may include the step of crystallizing the ferroelectric film by conducting heat-treatment in an inert gas atmosphere.

In such a case, the method may further include the step of conducting heat-treatment for supplementing oxygen loss of the ferroelectric film, after the step of crystallizing the ferroelectric film, wherein the heat-treatment is conducted in an oxygen atmosphere at such a temperature that prevents an underlying layer of the lower electrode from being oxidized. The heat-treatment for supplementing the oxygen loss may be conducted after the formation of the upper electrode.

The step of forming the ferroelectric film may include the steps of: applying a constituent material of the ferroelectric film to a prescribed thickness by a film application method; drying the applied constituent material; and repeating the applying step and the drying step a prescribed number of times to form the ferroelectric film having a desired thickness.

Alternatively, the step of forming the ferroelectric film may include the steps of: forming a film of a constituent material of the ferroelectric film to a prescribed thickness; crystallizing the film of the constituent material by conducting heat-treatment in an inert gas atmosphere; and repeating the film forming step and the crystallizing step a prescribed number of times to form the ferroelectric film having a desired thickness. The film of the constituent material of the ferroelectric film may be formed by a film application method.

The ferroelectric film may be formed from a Bismuthlayer-structured-family compound. For example, the Bismuth-layer-structured-family compound may be SrBi<sub>2</sub>  $(Ta_{1-x}Nb_x)_2O_9$  (where 0<x<1).

The heat-treatment for crystallizing the ferroelectric film may be conducted at a temperature of about 650° C. to about 800° C.

The method may further include the steps of: forming the selection transistor at the substrate; forming an interlayer 55 insulation film on the selection transistor; and forming a contact hole in the interlayer insulation film and forming the electrically conductive plug in the contact hole, wherein the diffusion barrier film is formed on the electrically conductive plug in the semiconductor substrate so as to be electri- 60 cally connected to the electrically conductive plug.

Thus, the invention described herein makes possible the advantages of (1) providing a semiconductor memory device incorporating a ferroelectric capacitor which exhibits excellent ferroelectric characteristics, and (2) providing a method 65 for producing such a semiconductor memory device with high yield.

These and other advantages of the present invention will become apparent to those skilled in the art upon reading and understanding the following detailed description with reference to the accompanying figures.

#### BRIEF DESCRIPTION OF THE DRAWINGS

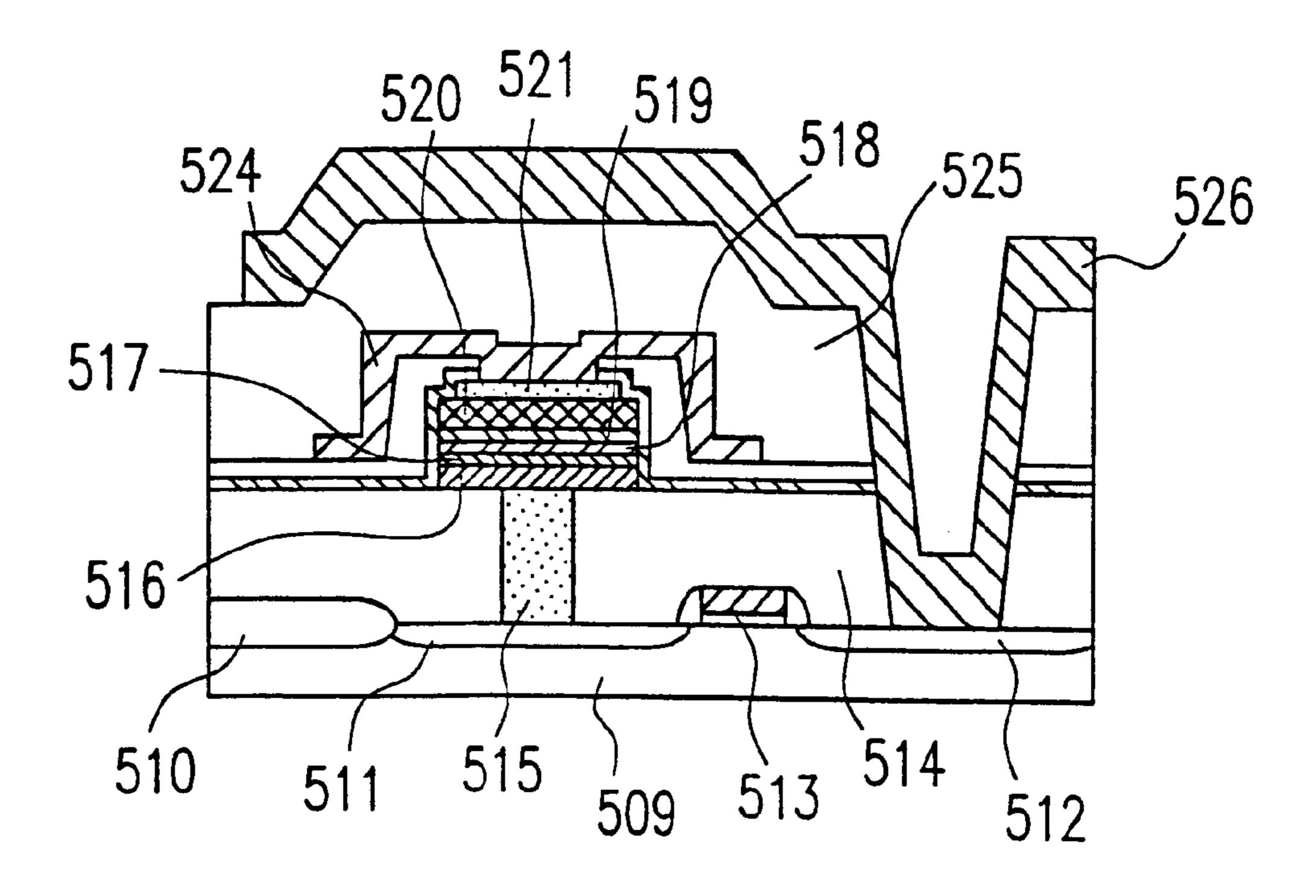

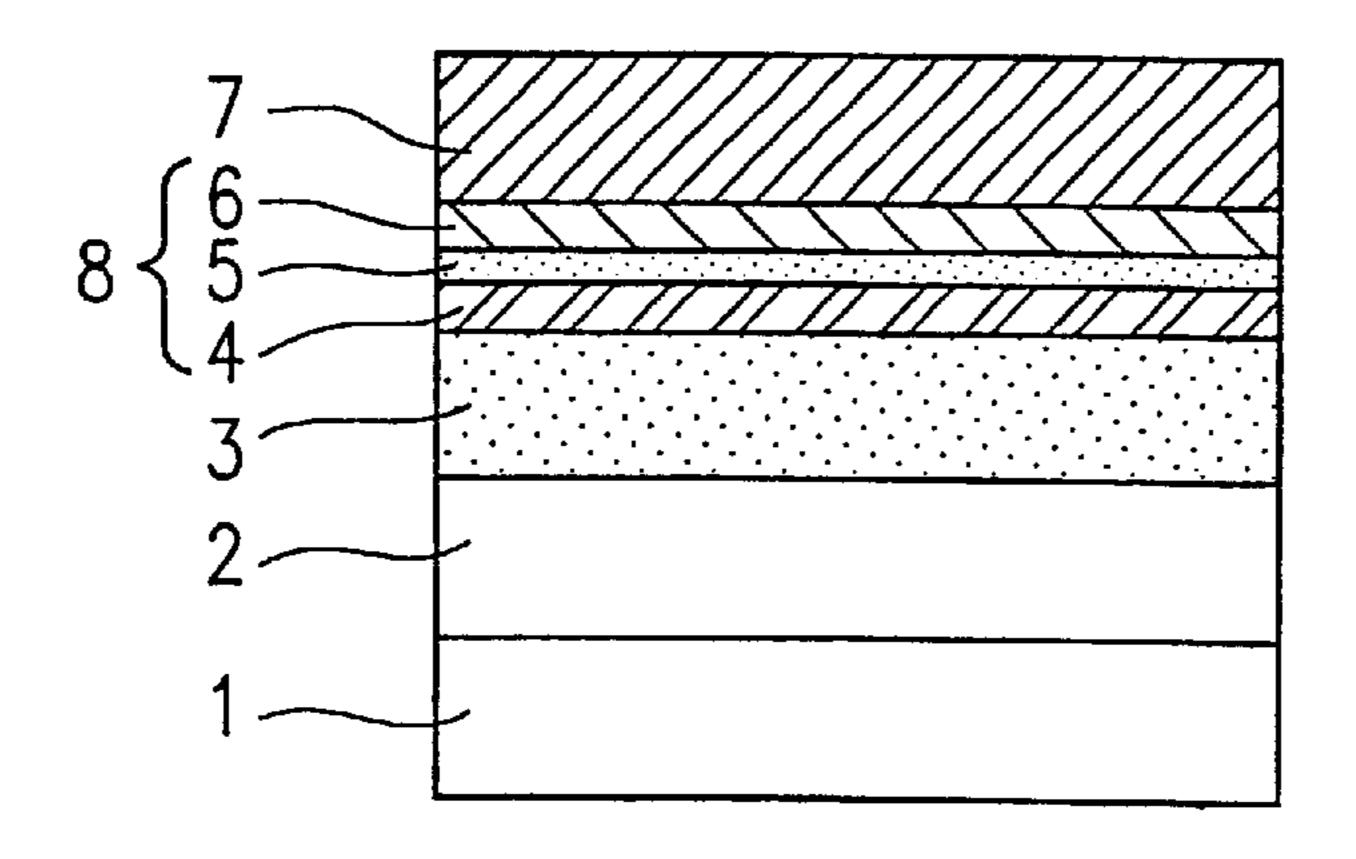

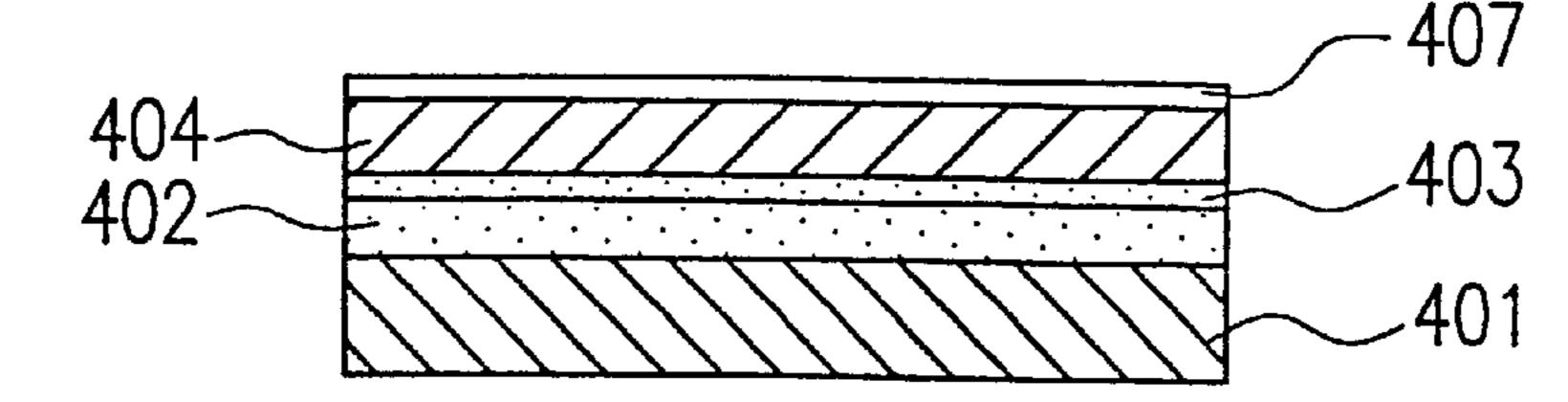

- FIG. 1 is a cross sectional view schematically showing a structure of a ferroelectric capacitor including a ferroelectric film formed on a lower electrode, according to Example 1 of the present invention;

- FIG. 2 is a diagram showing a variation in resistivity with different Ta compositions x in a  $Ta_xSi_{(1-x)}N_y$  film which is included in the structure of the ferroelectric capacitor of <sub>15</sub> FIG. 1;

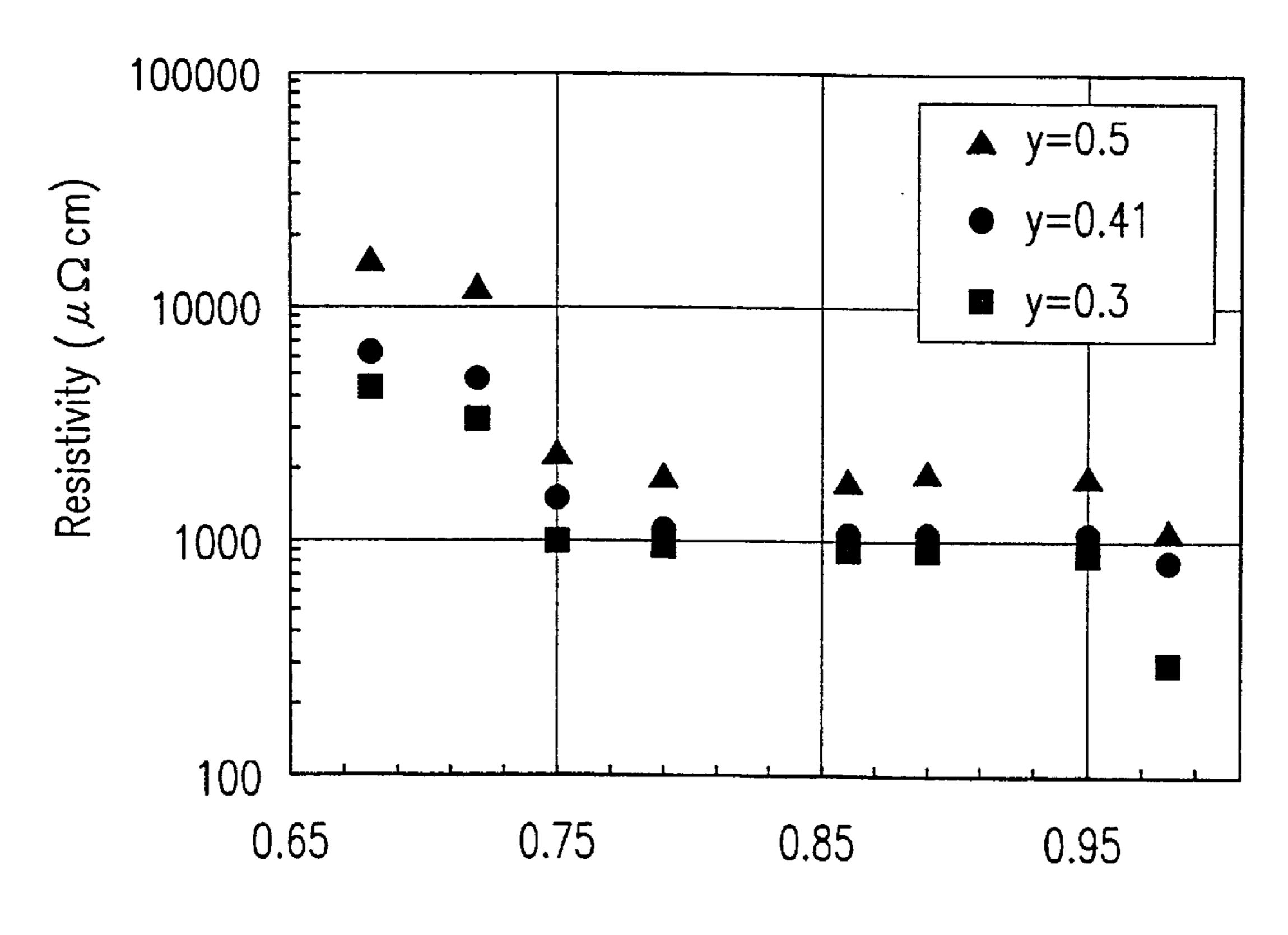

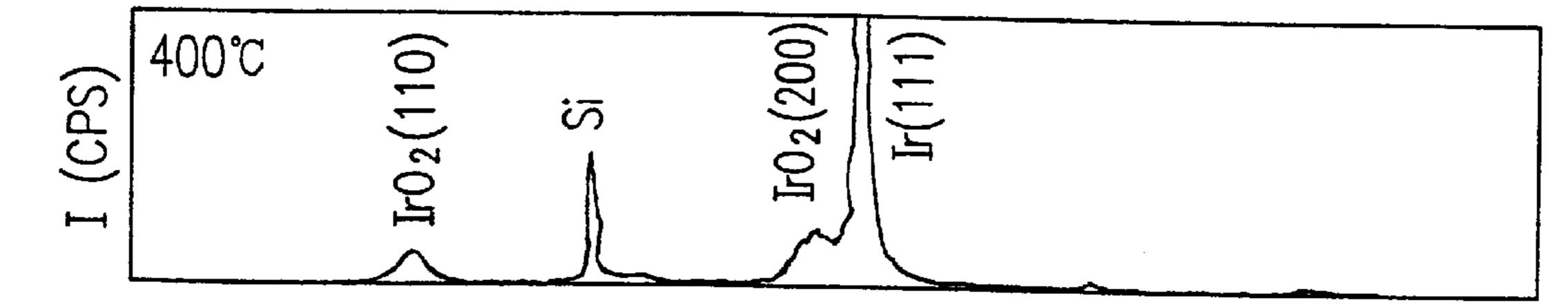

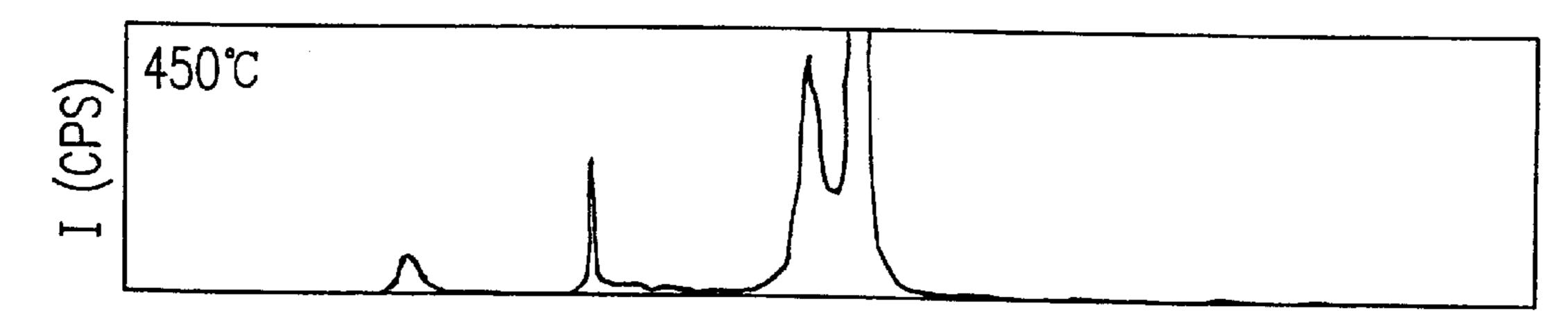

- FIGS. 3A to 3C are diagrams showing XRD chart characteristics of an IrO<sub>2</sub> film respectively formed at different temperatures;

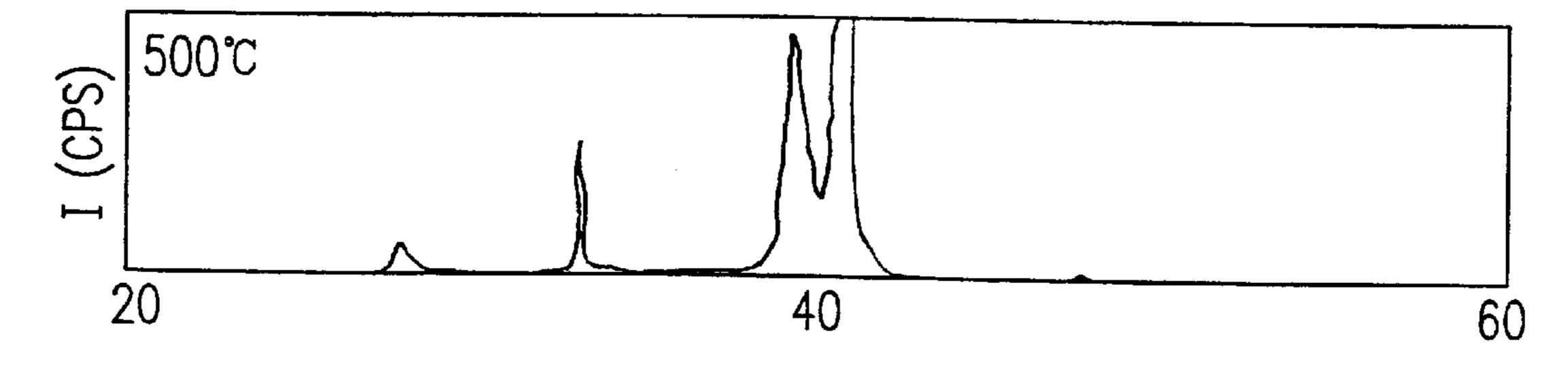

- FIG. 4 is a diagram showing a variation in resistivity of the IrO<sub>2</sub> film formed at different temperatures;

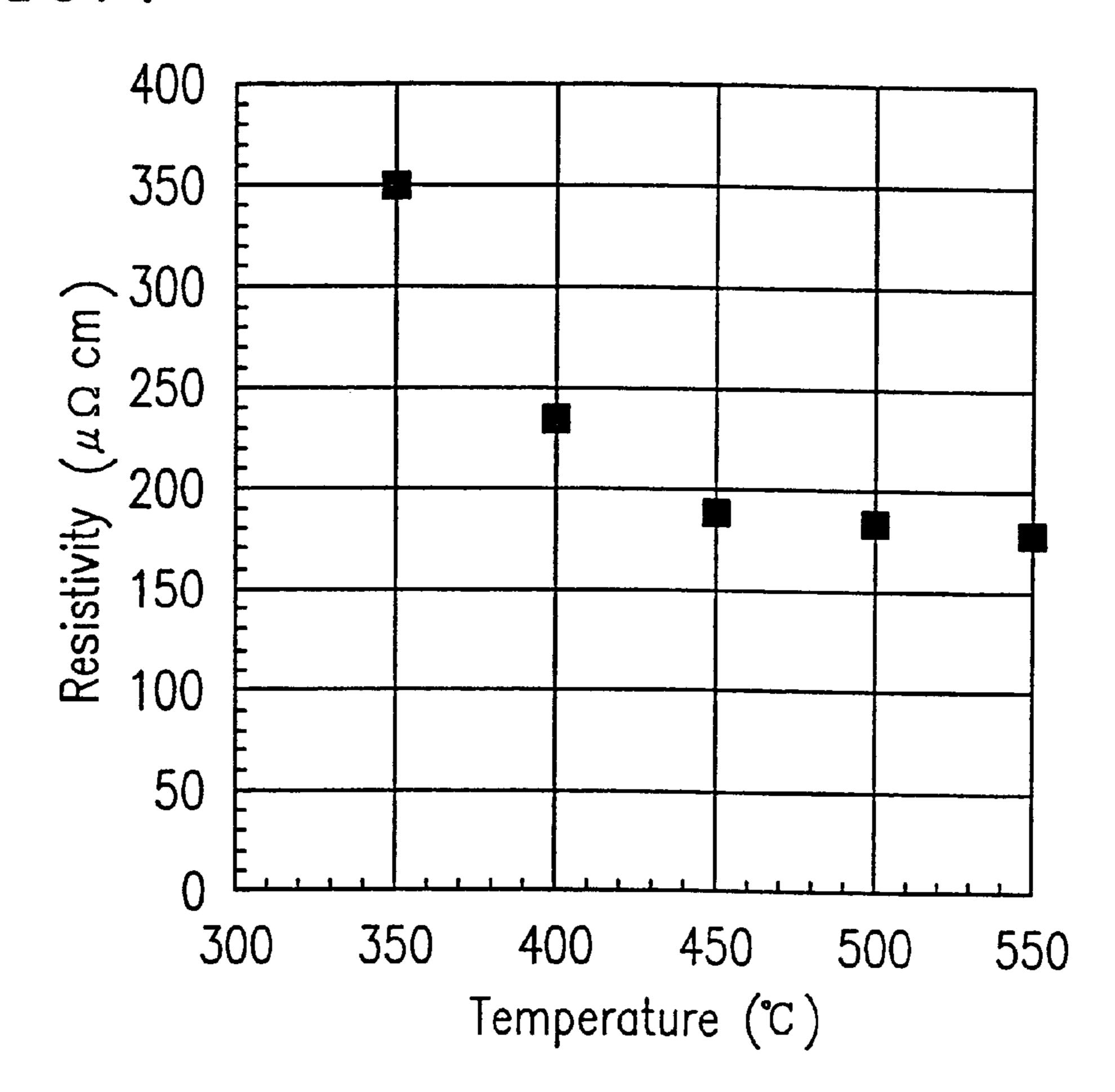

- FIG. 5 is a cross sectional view showing a structure of a semiconductor memory device of the present invention which incorporates the ferroelectric capacitor of FIG. 1;

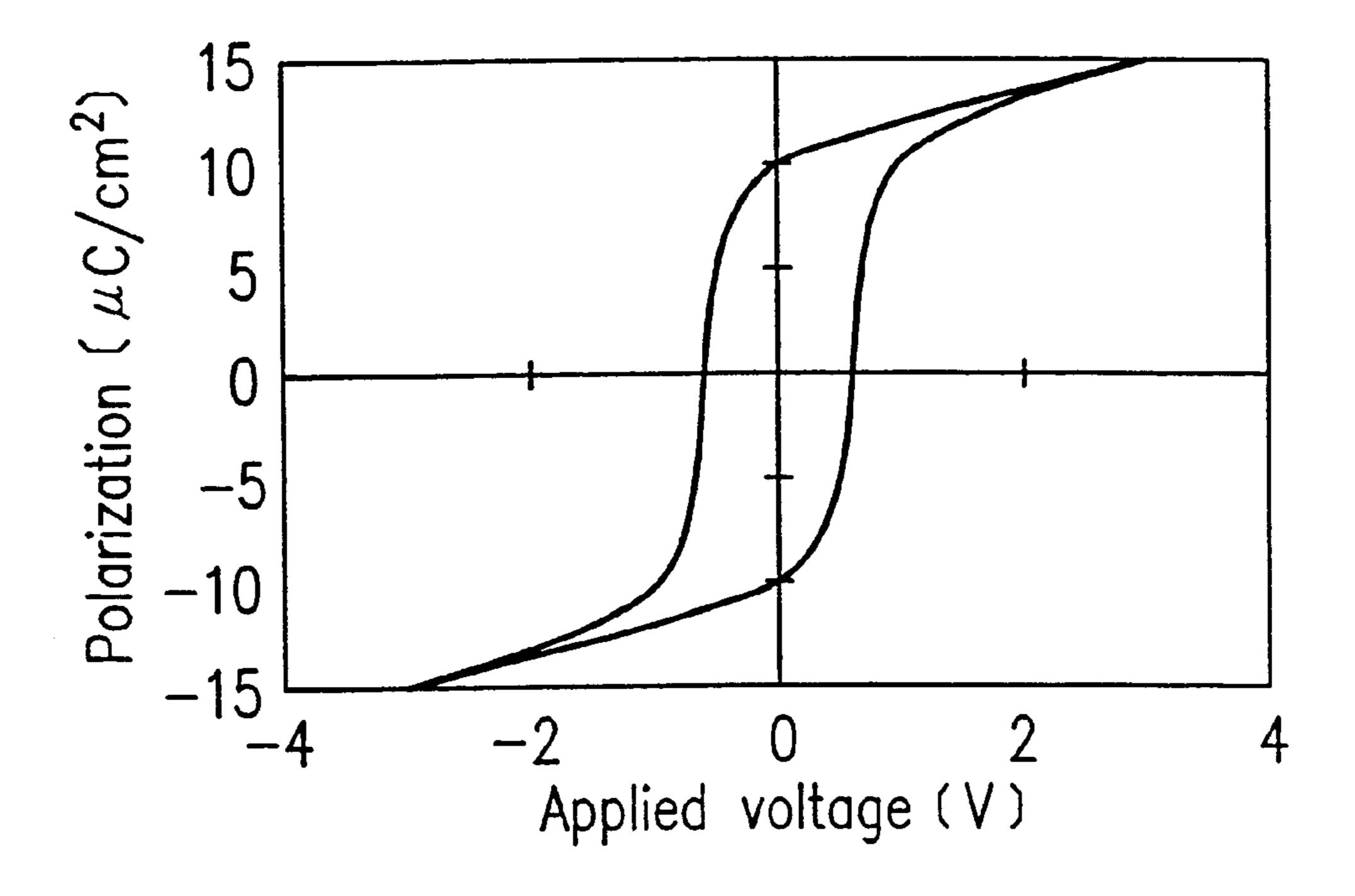

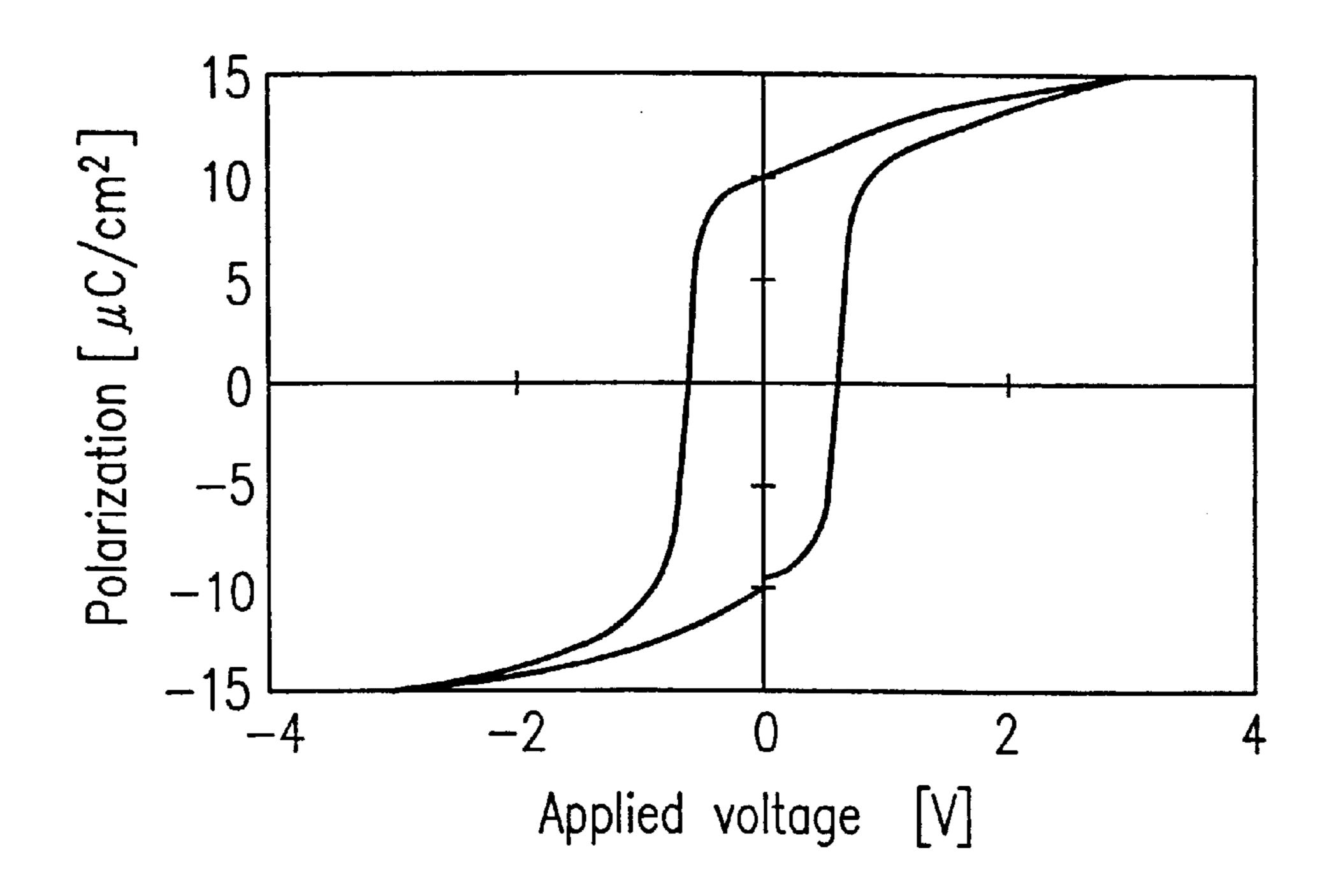

- FIG. 6 is a diagram showing a hysteresis loop obtained by the semiconductor memory device of FIG. 5;.

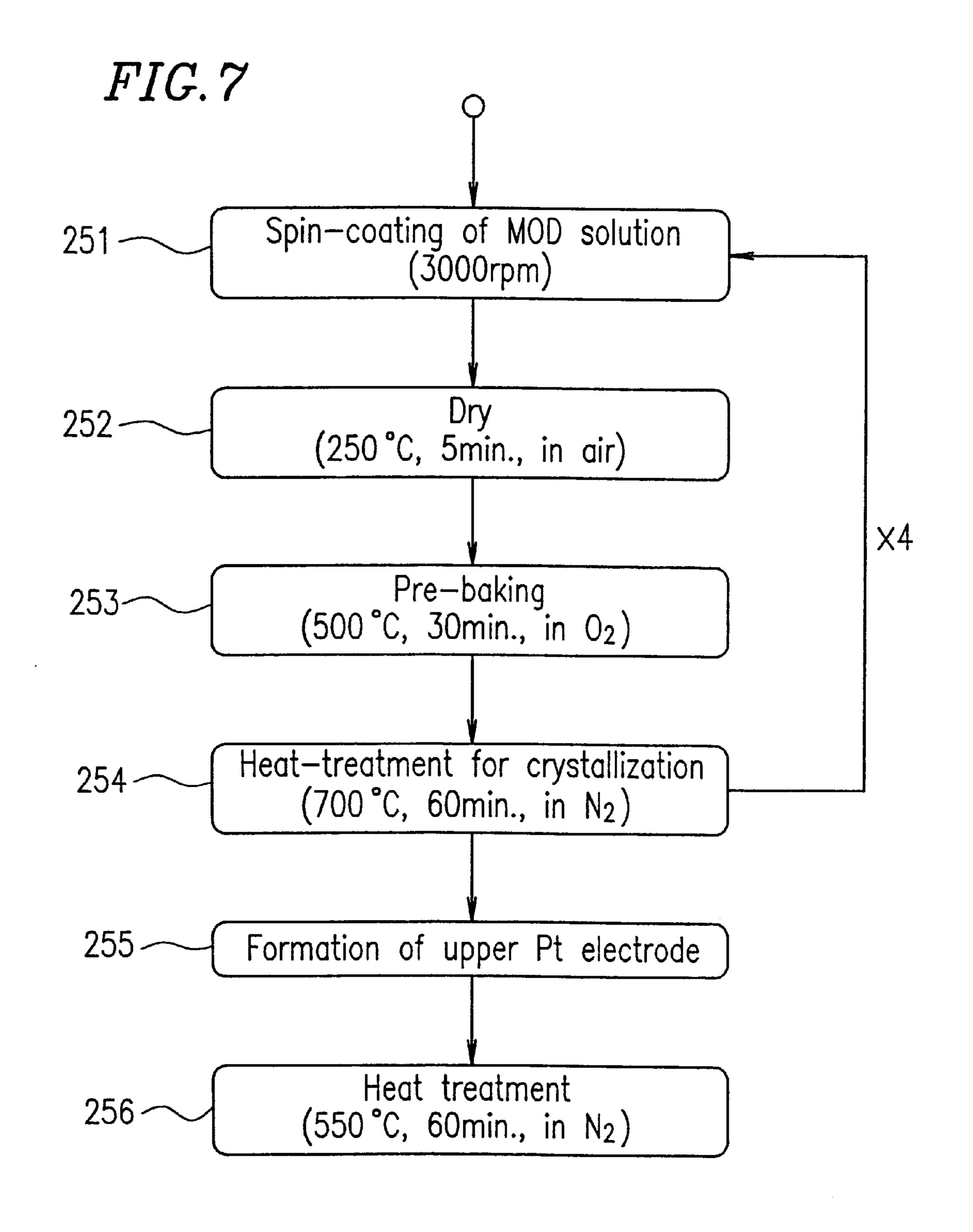

- FIG. 7 is a flow chart illustrating a process for producing a ferroelectric capacitor according to Example 2 of the present invention;

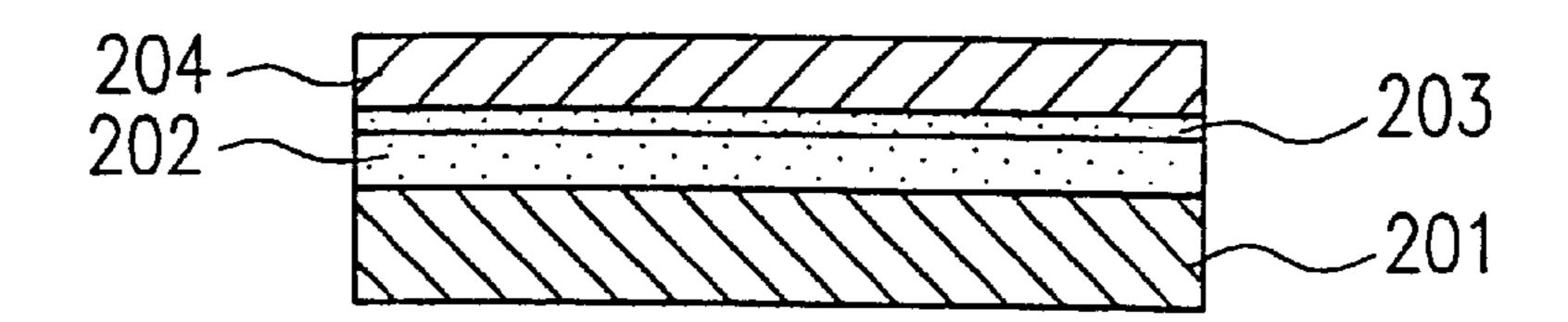

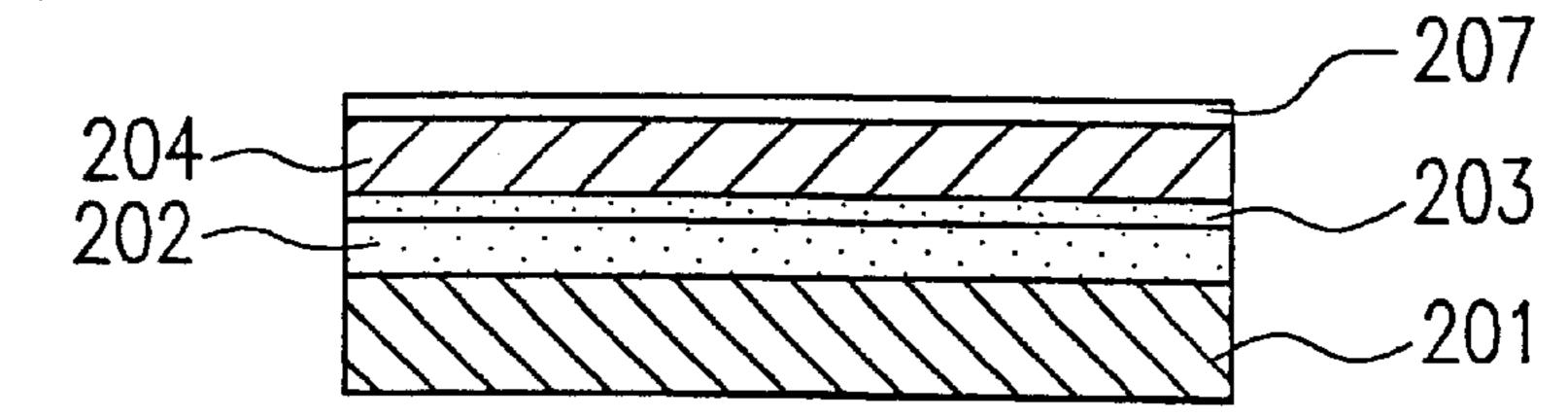

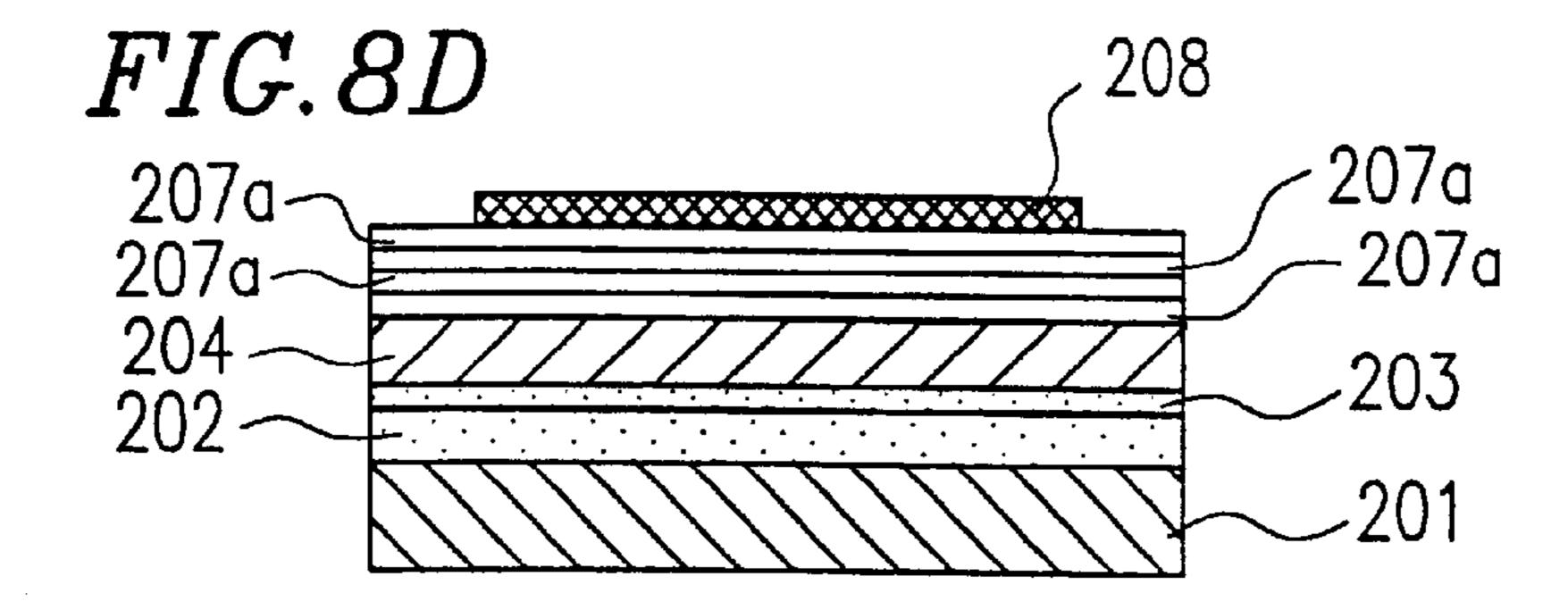

- FIGS. 8A to 8D are schematic cross sectional views illustrating the steps of the production process of Example 2;

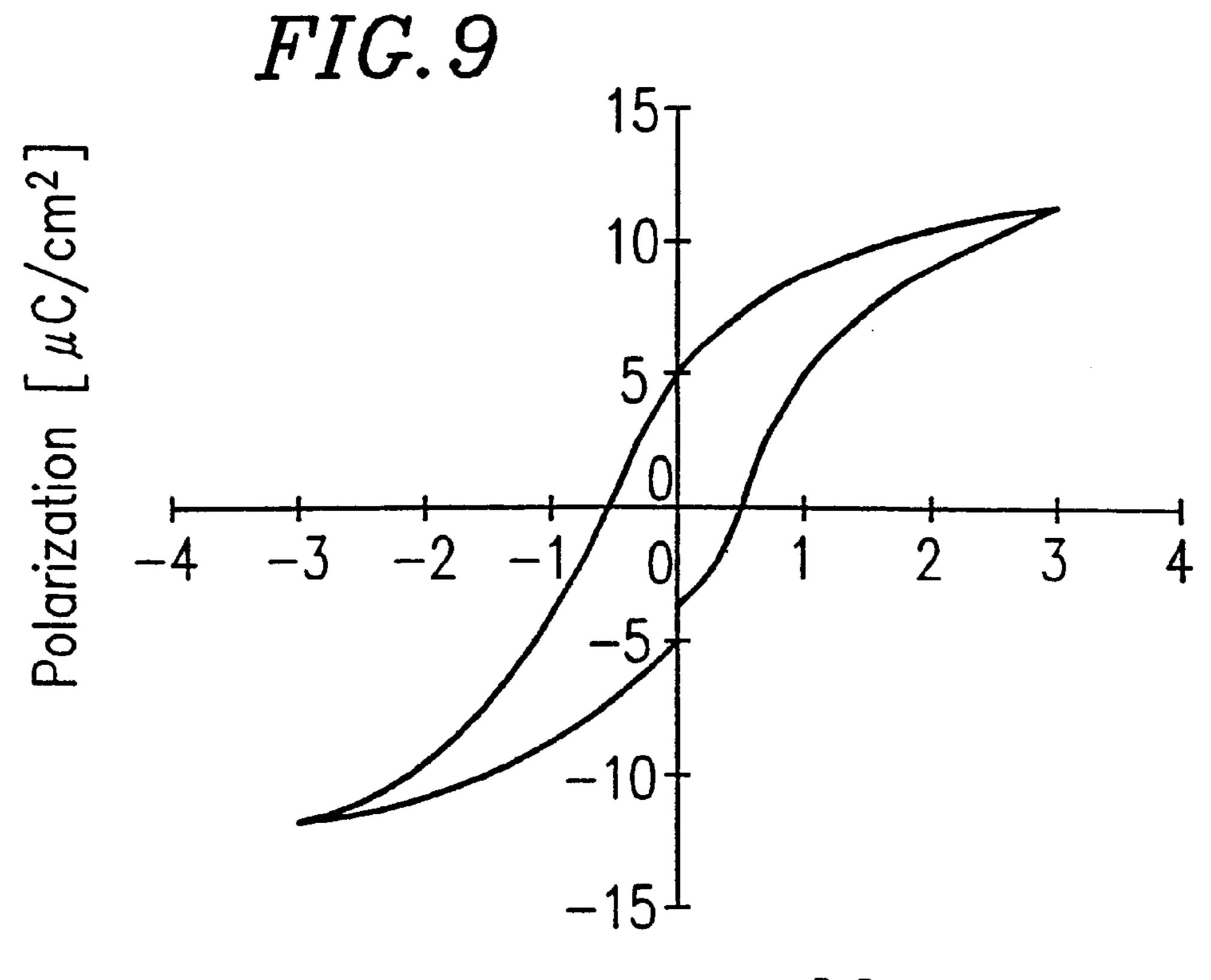

- FIG. 9 is a diagram showing hysteresis characteristics of the ferroelectric capacitor produced by the production process of Example 2;

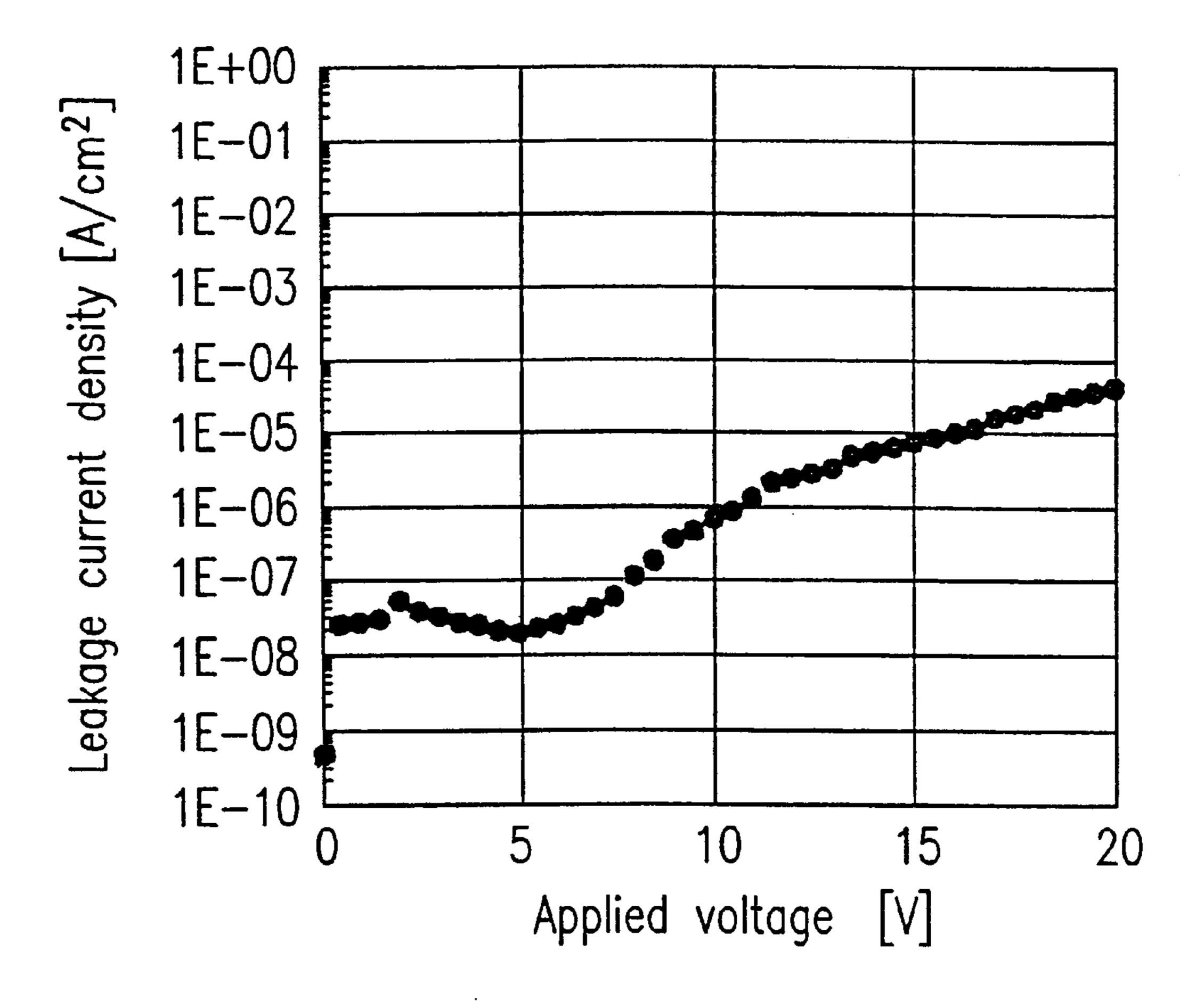

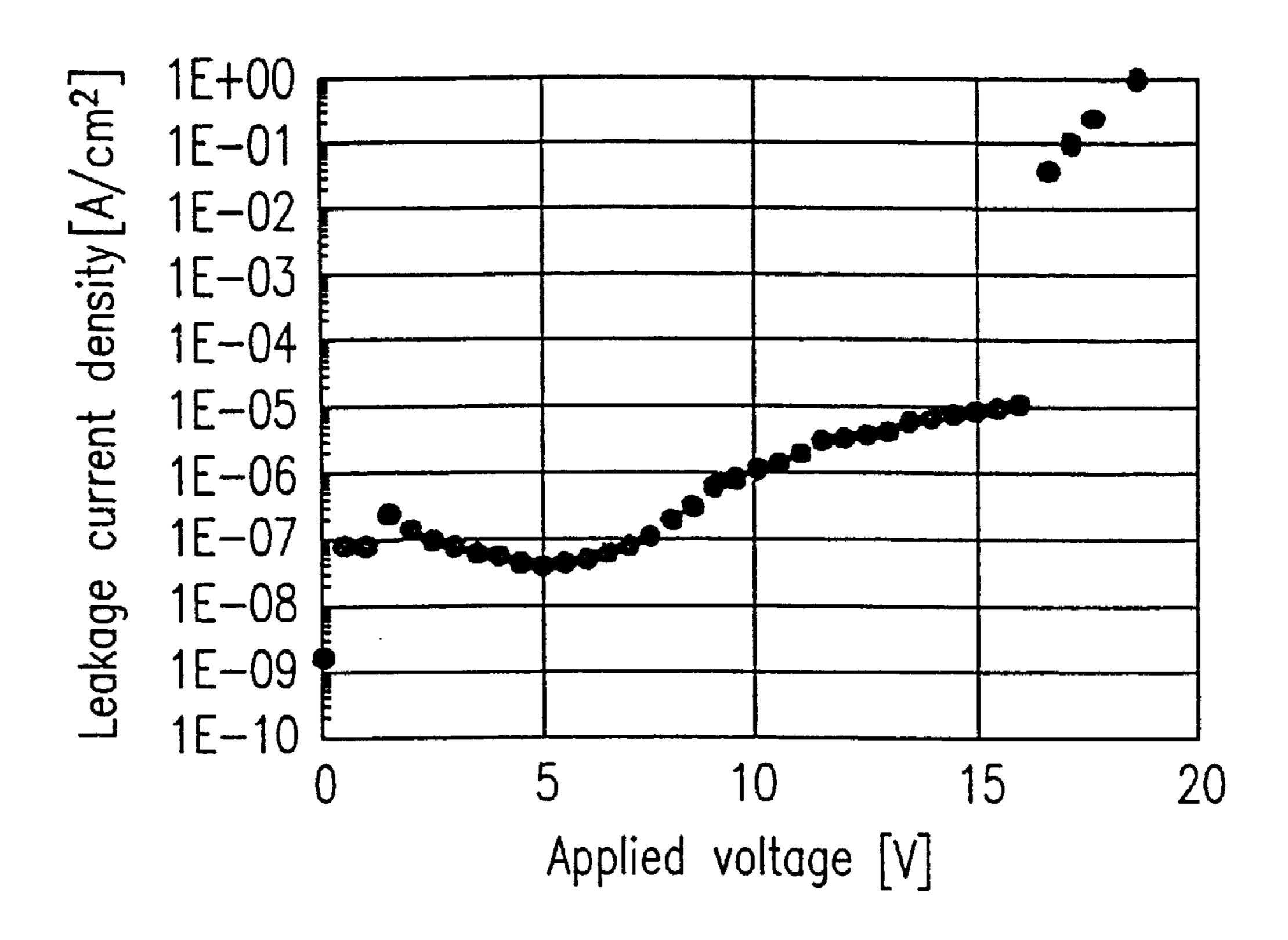

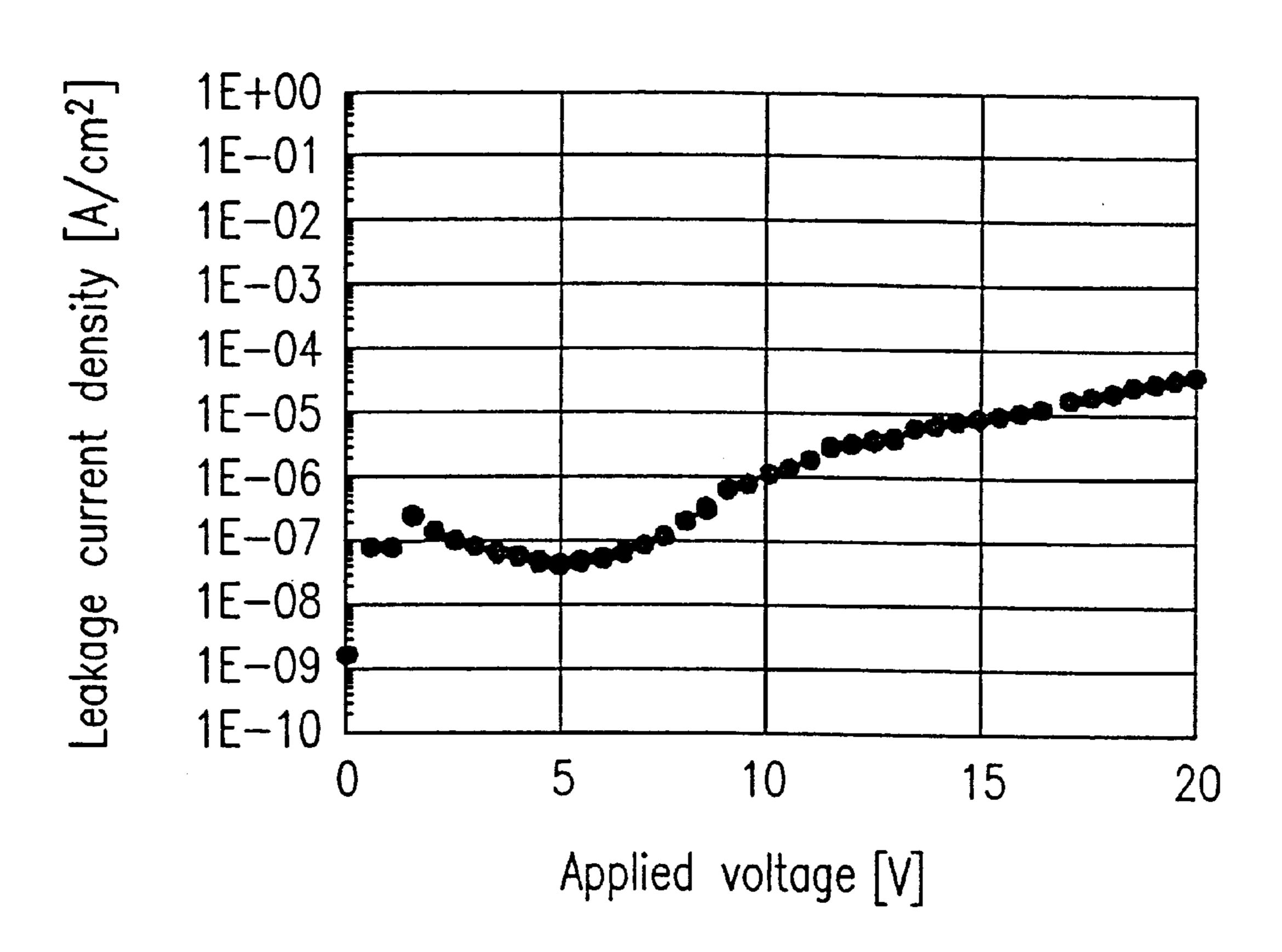

- FIG. 10 is a diagram showing leakage current characteristics of the ferroelectric capacitor produced by the production process of Example 2;

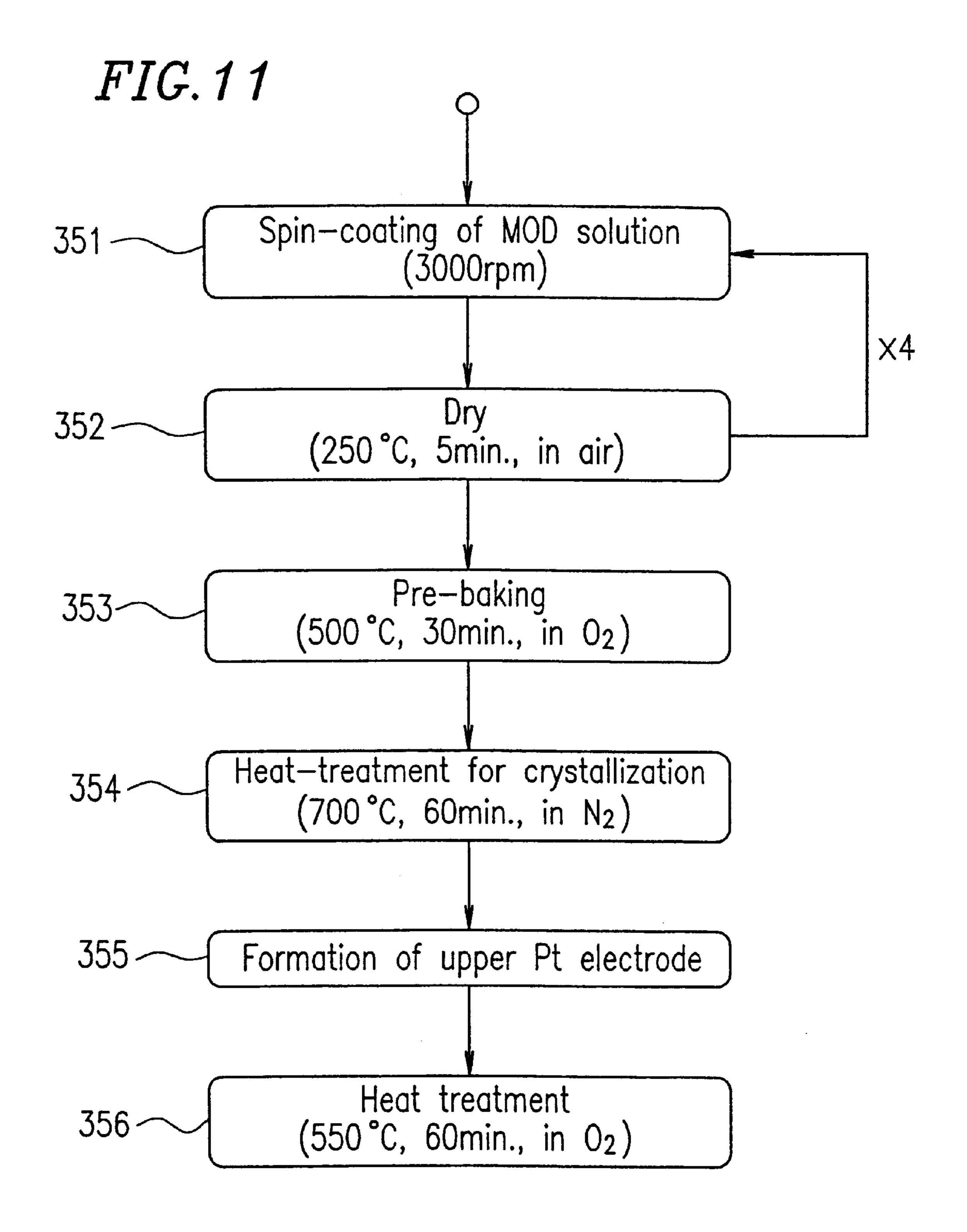

- FIG. 11 is a flow chart illustrating a process for producing a ferroelectric capacitor according to Example 3 of the present invention;

- FIGS. 12A to 12C are schematic cross sectional views illustrating the steps of the production process of Example 3;

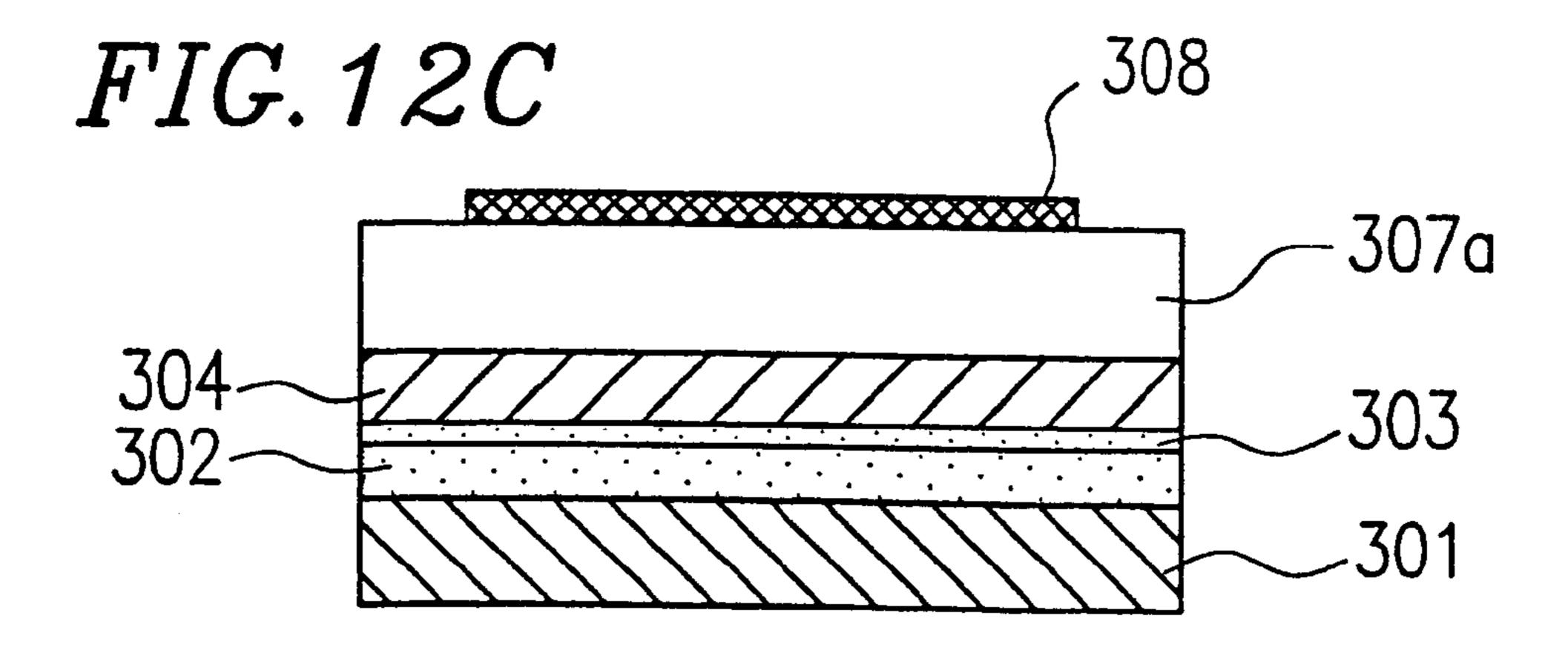

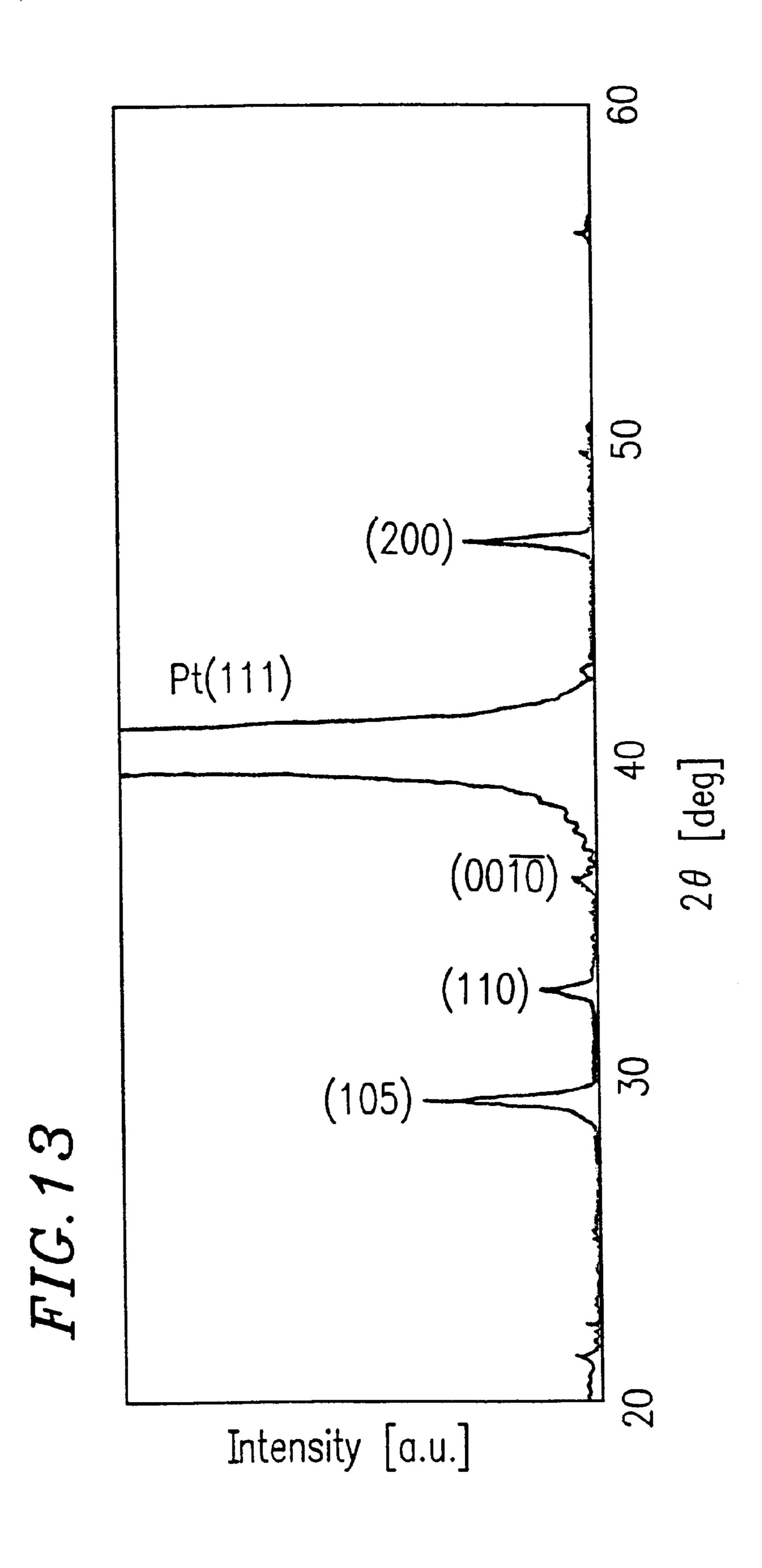

- FIG. 13 is a diagram showing an XRD pattern of a ferroelectric film formed by the production process of Example 3;

- FIG. 14 is a diagram showing hysteresis characteristics of the ferroelectric capacitor produced by the production process of Example 3;

- FIG. 15 is a diagram showing leakage current characteristics of the ferroelectric capacitor produced according to the production process of Example 3;

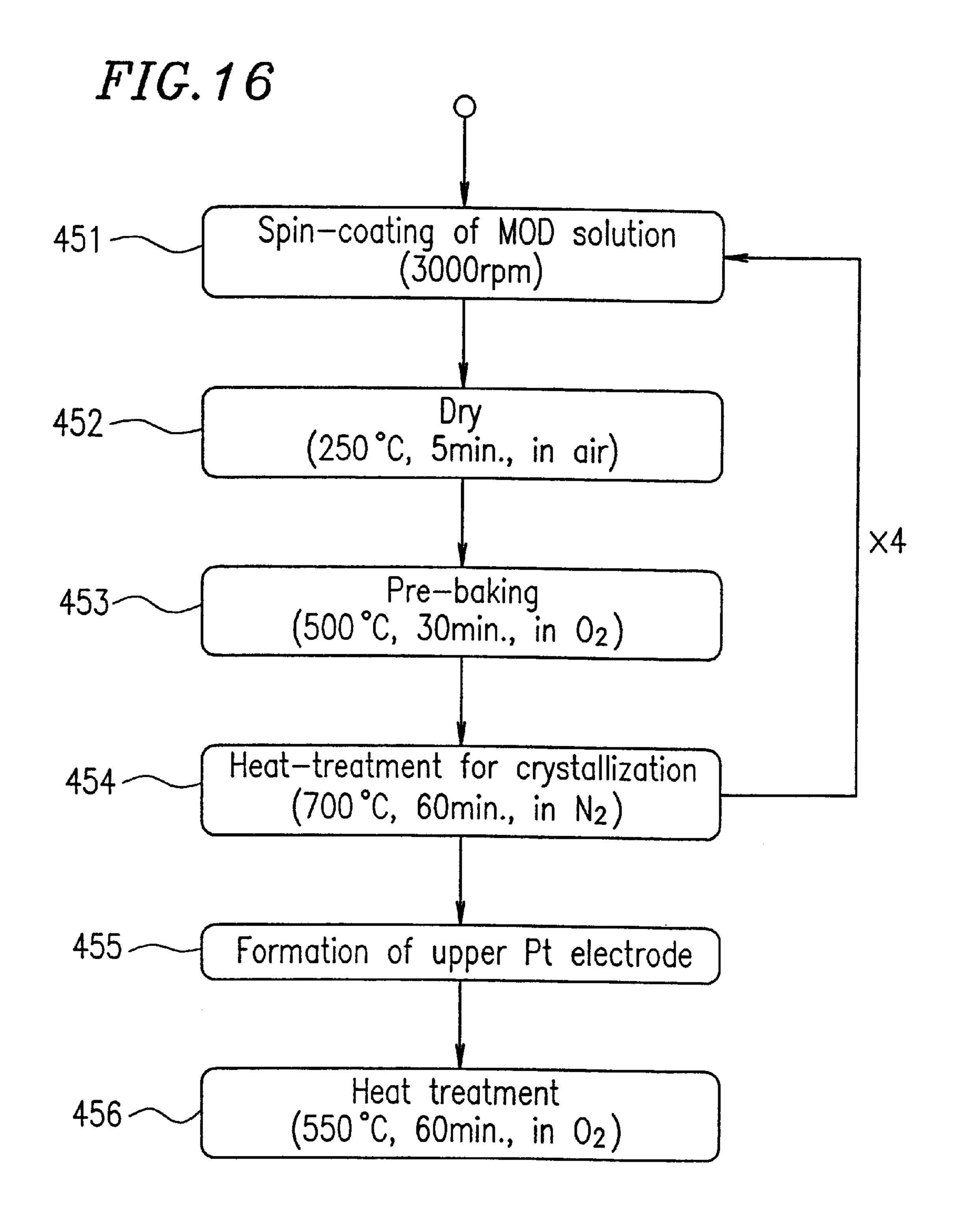

- FIG. 16 is a flow chart illustrating a process for producing a ferroelectric capacitor according to Example 4 of the present invention;

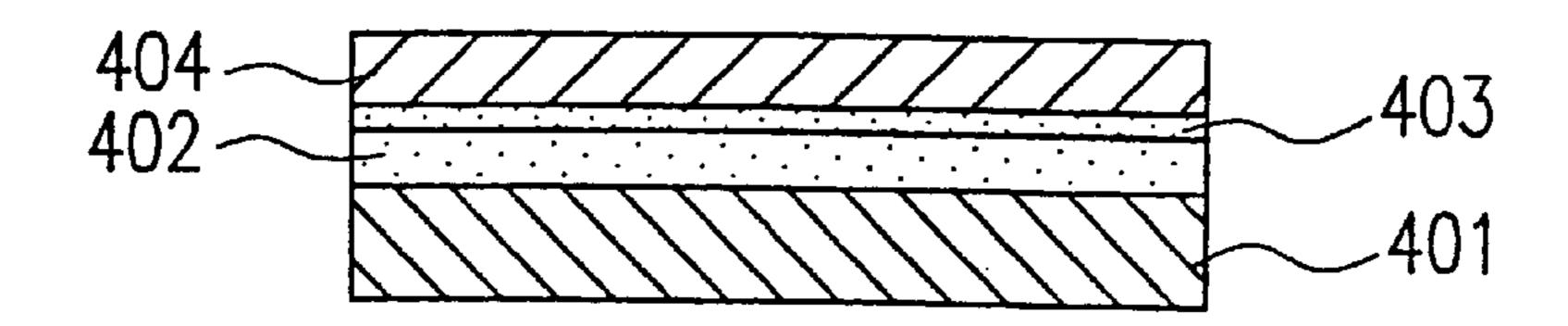

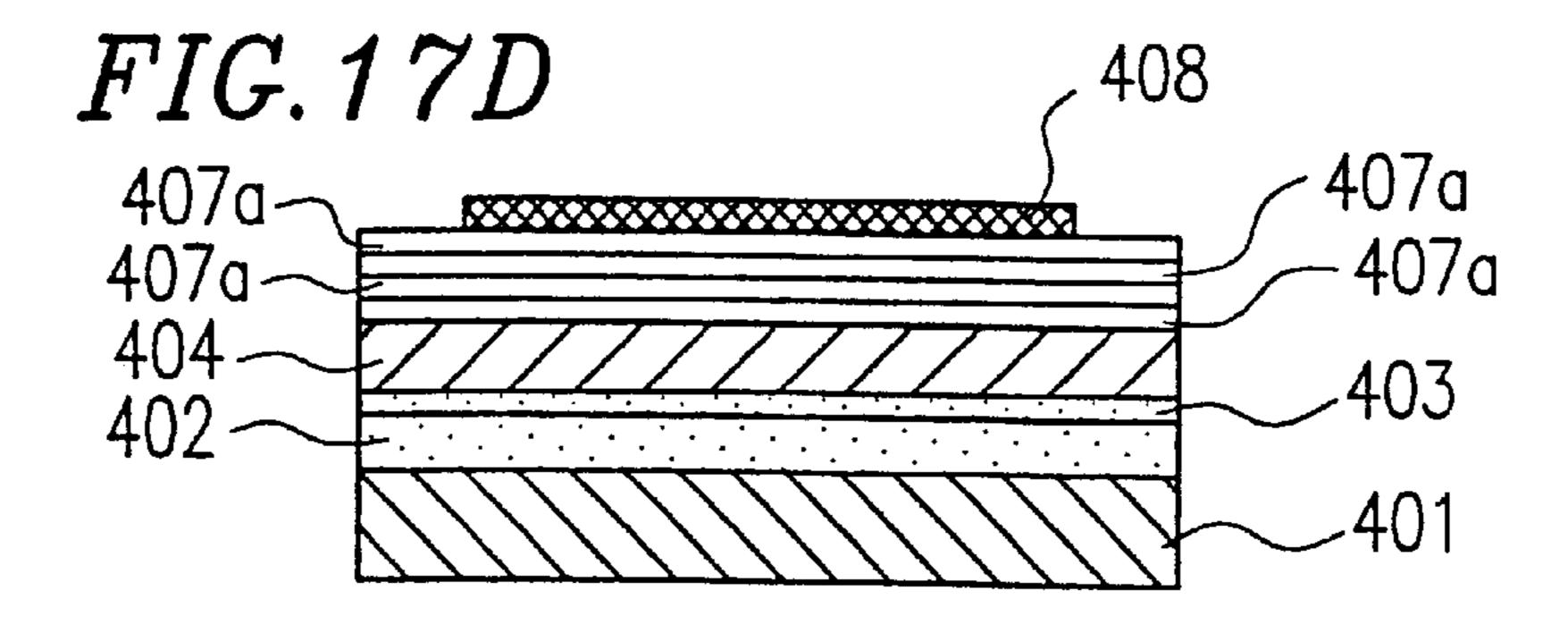

- FIGS. 17A to 17D are schematic cross sectional views illustrating the steps of the production process of Example 4;

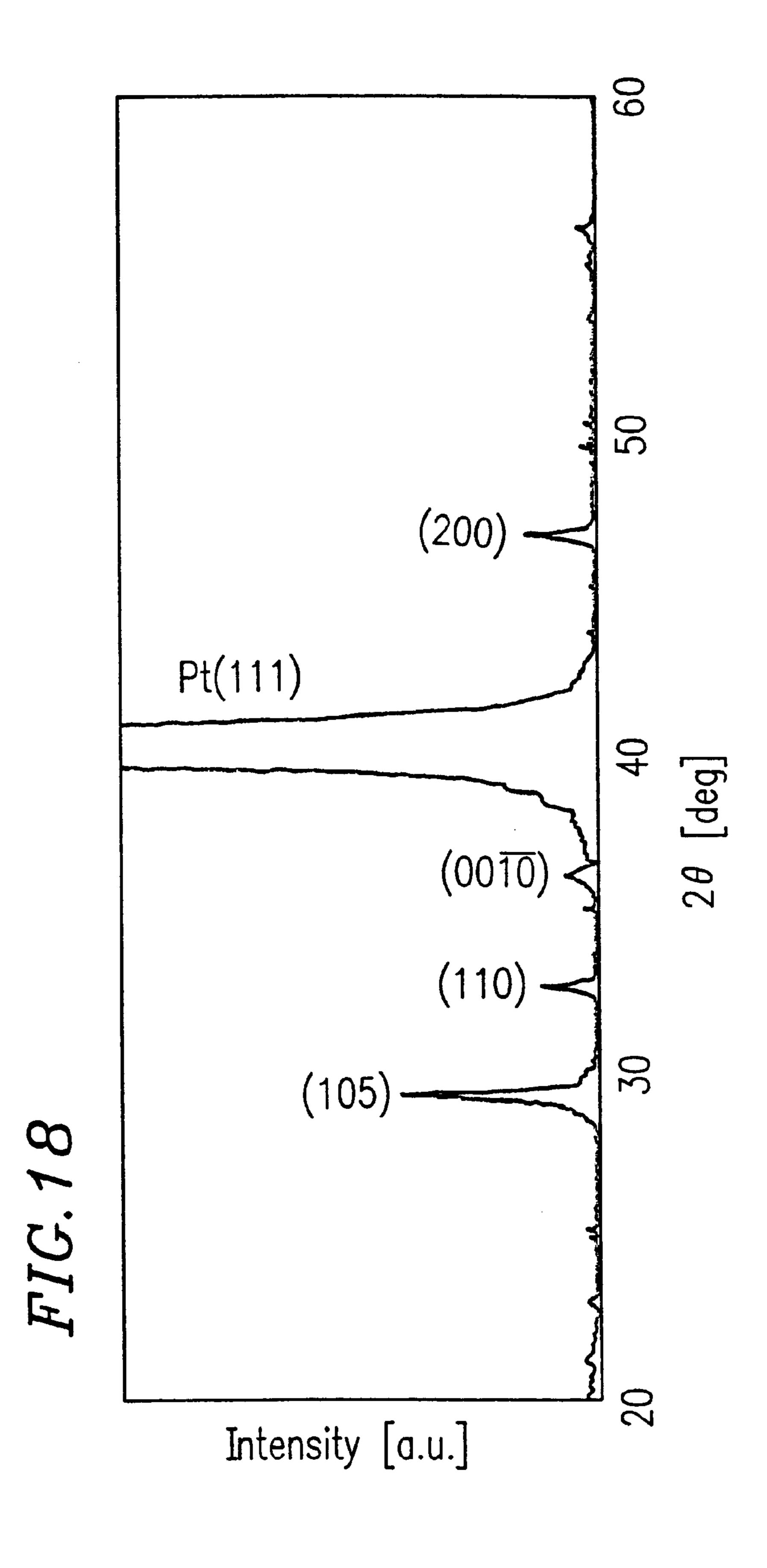

- FIG. 18 is a diagram showing an XRD pattern of a ferroelectric film formed by the production process of Example 4;

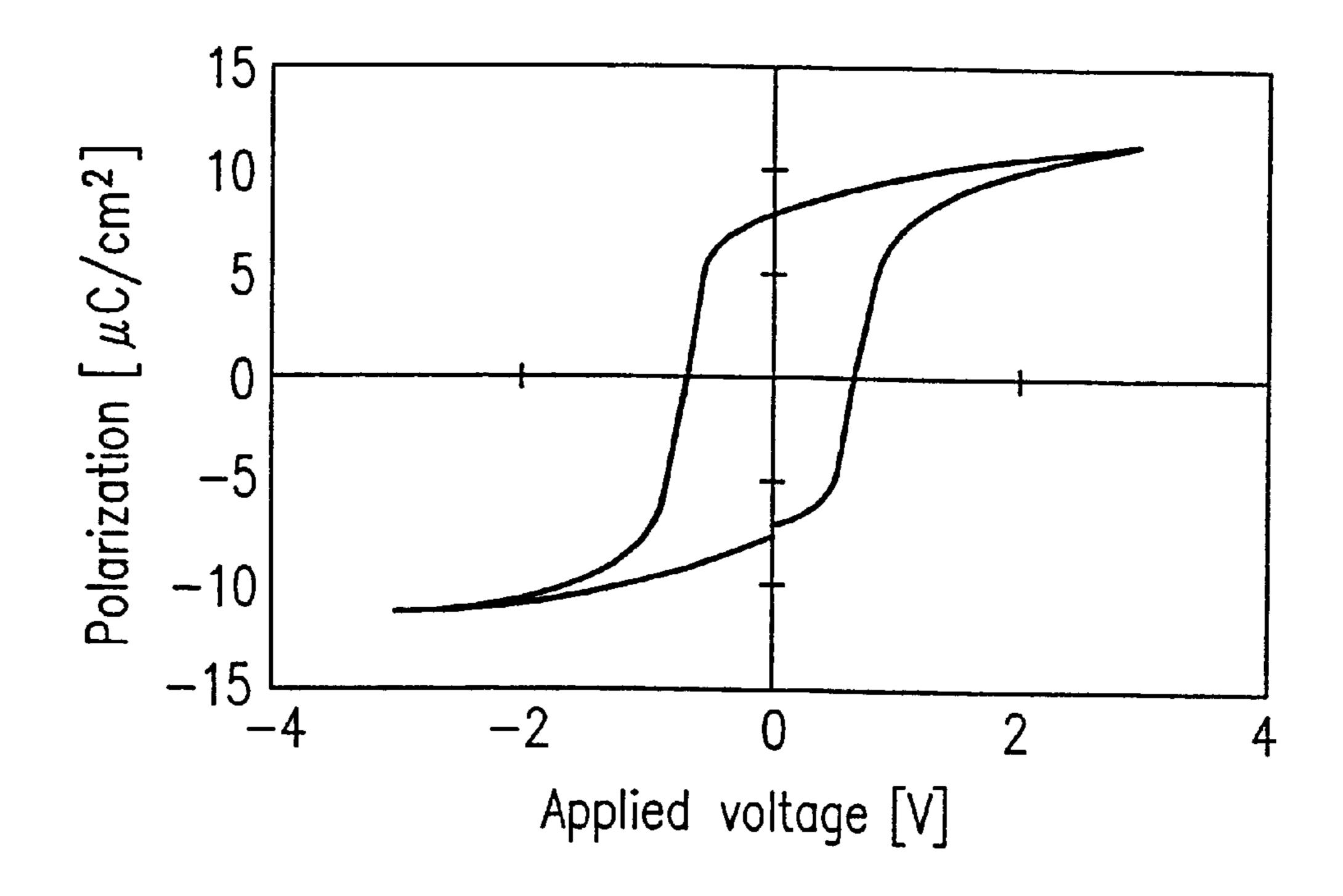

- FIG. 19 is a diagram showing hysteresis characteristics of the ferroelectric capacitor produced by the production process of Example 4;

- FIG. 20 is a diagram showing leakage current characteristics of the ferroelectric capacitor produced by the production process of Example 4;

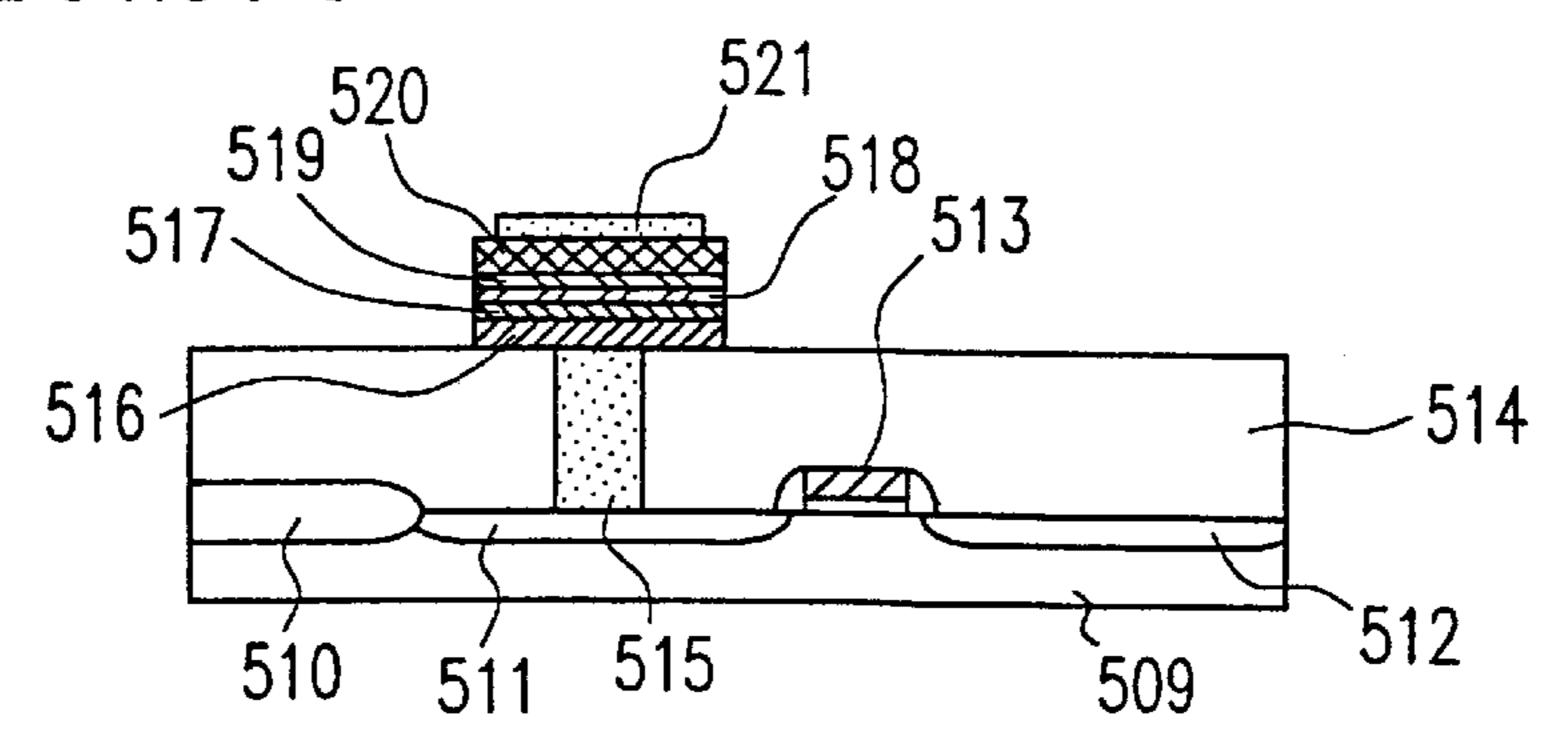

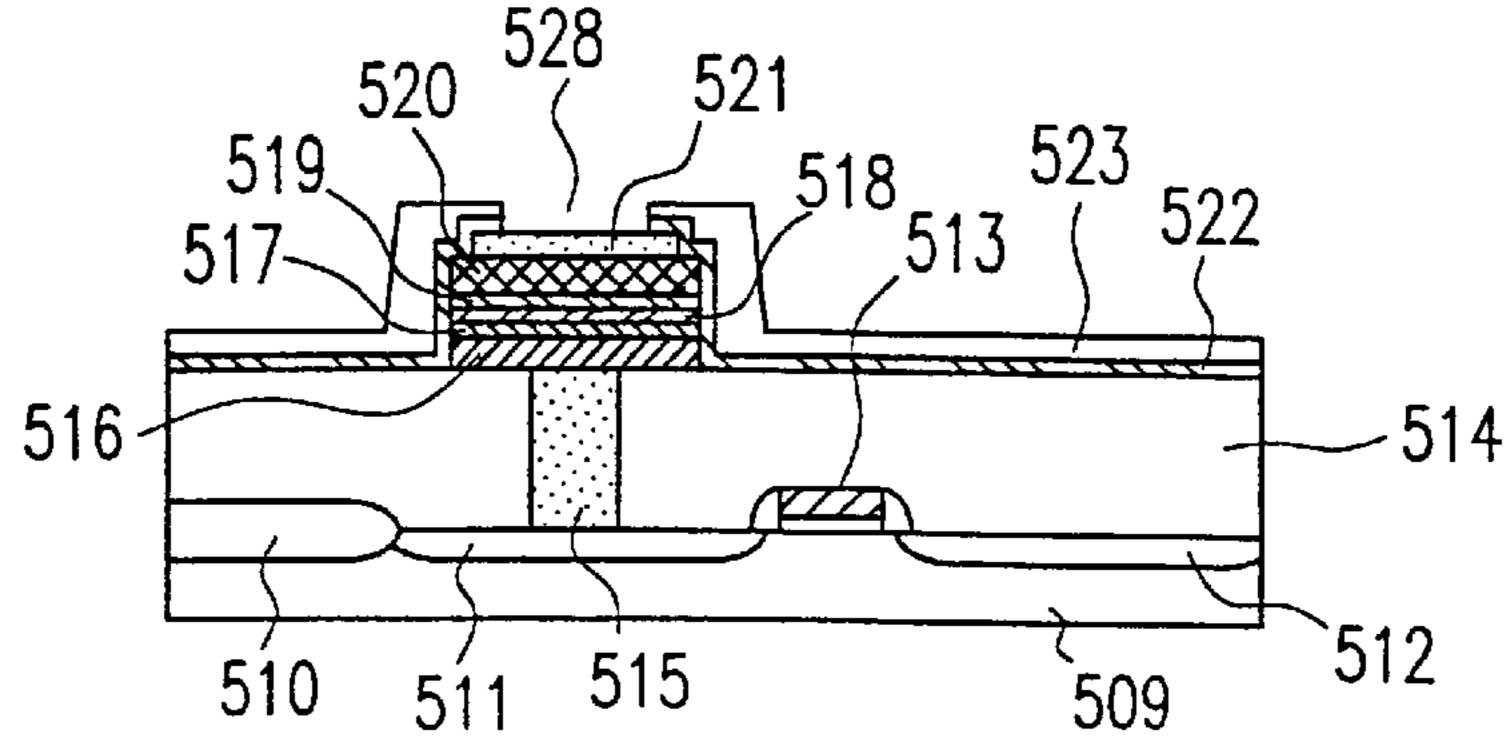

FIGS. 21A to 21D are schematic cross sectional views illustrating the first half of a process for producing a ferroelectric memory device according to Example 5 of the present invention;

FIGS. 22A to 22C are schematic cross sectional views <sup>5</sup> illustrating the latter half of the production process according to Example 5;

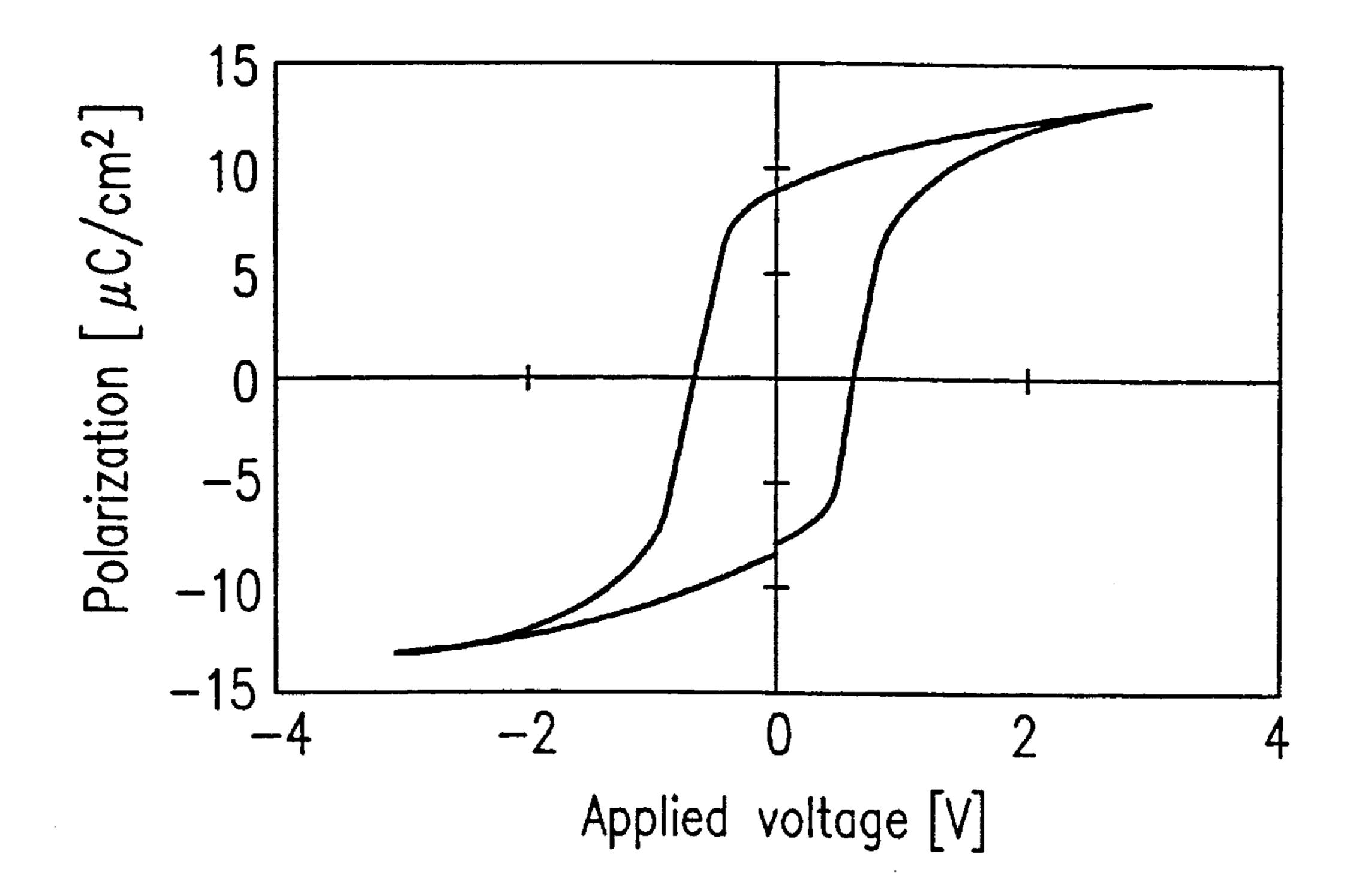

FIG. 23 is a diagram showing hysteresis characteristics of a ferroelectric capacitor incorporated in the ferroelectric memory device produced by the production process of Example 5;

FIG. 24 is a diagram showing leakage current characteristics of the ferroelectric capacitor incorporated in the ferroelectric memory device produced by the production process of Example 5; and

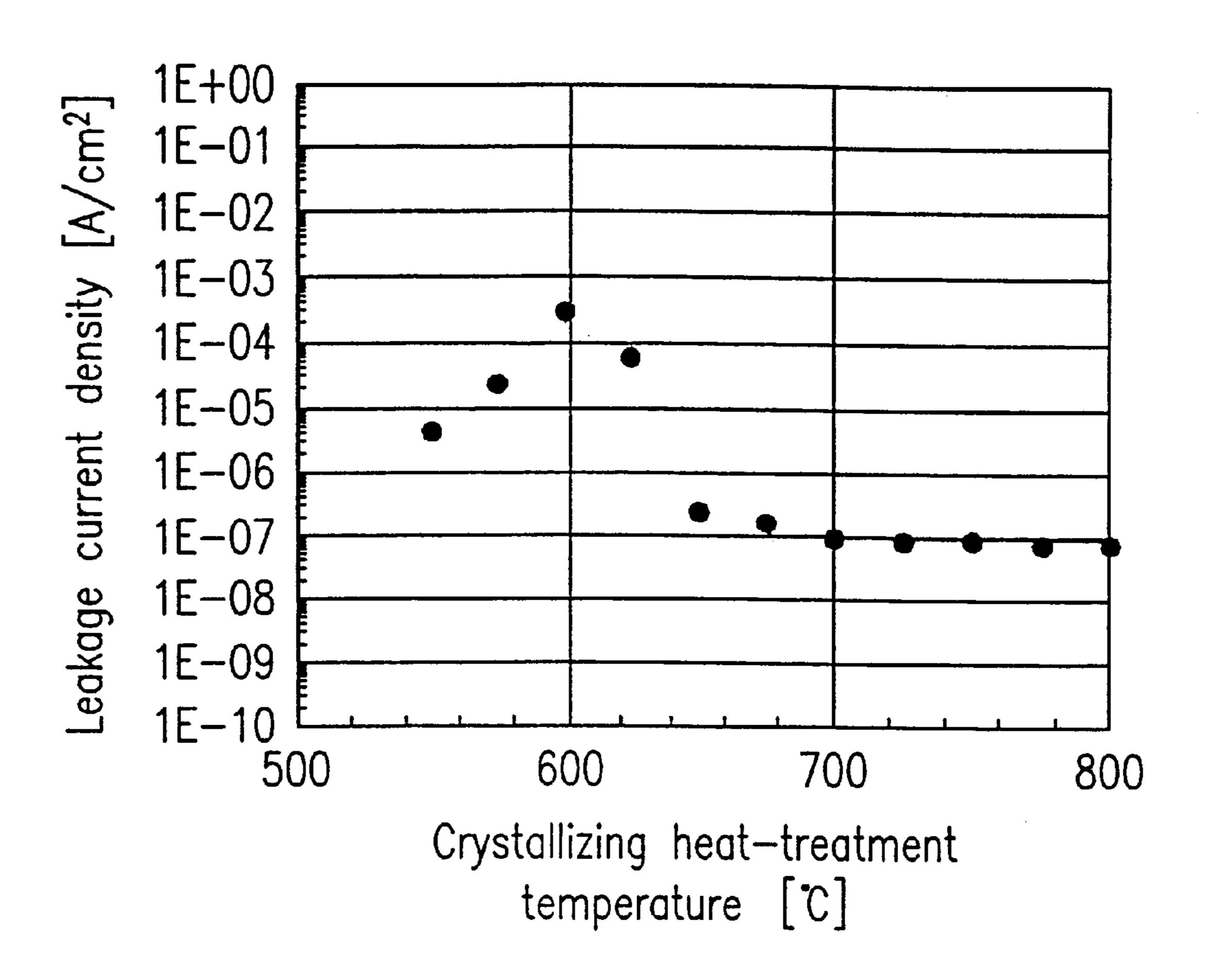

FIG. 25 is a diagram showing the relation between a heat-treatment temperature for crystallizing a ferroelectric film and a leakage current density.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

(Example 1)

FIG. 1 is a cross sectional view schematically showing a structure of a ferroelectric capacitor including a ferroelectric film formed on a lower electrode, according to Example 1 of 25 the present invention. FIG. 2 is a diagram showing a variation in resistivity with different Ta compositions x in a  $Ta_xSi_{(1-x)}N_v$  film (hereinafter, also referred to as a TaSiN film) which is included in the structure of the ferroelectric capacitor of FIG. 1; FIGS. 3A to 3C are diagrams showing 30 XRD chart characteristics of an IrO<sub>2</sub> film respectively formed at different temperatures; and FIG. 4 is a diagram showing a variation in resistivity of the IrO<sub>2</sub> film formed at different temperatures. Furthermore, FIG. 5 is a cross sectional view showing a structure of a semiconductor memory 35 device of the present invention which incorporates the ferroelectric capacitor of FIG. 1, and FIG. 6 is a diagram showing a hysteresis loop obtained by the semiconductor memory device of FIG. 5.

In FIGS. 1 and 5, reference numeral 1 denotes a silicon 40 substrate; 2 denotes a thermal oxide film; 3 denotes a TaSiN film; 4 denotes an Ir film; 5 denotes an initial film; 6 denotes an IrO<sub>2</sub> film; 7 denotes a ferroelectric film; 8 denotes a lower electrode; 9 denotes a LOCOS (LOCal Oxidation of Silicon) oxide film; 10 denotes a gate electrode; 11 denotes source/ 45 drain regions; 12 denotes a first silicon oxide film; 13 denotes a polysilicon plug; 18 denotes an upper electrode; 19 denotes a second silicon oxide film; 20 denotes a first aluminum extended electrode; and 21 denotes a second aluminum extended electrode.

The substrate 1 used in the semiconductor memory device incorporating the ferroelectric capacitor according to the present invention is not limited to a specific material, as long as the substrate 1 can be used for normal semiconductor devices, integrated circuits or the like. For example, the 55 substrate may be selected from a semiconductor substrate (e.g., silicon), a compound semiconductor substrate (e.g., GaAs), an oxide crystalline substrate (e.g., MgO) or a glass substrate, according to the types, applications or the like of the device to be formed. However, a silicon substrate is 60 preferable.

In the structure of FIG. 1, the lower electrode 8 is formed on such a substrate 1. The lower electrode 8 represents a part of a semiconductor memory device to be formed, that is, an electrode to be utilized as a capacitance material of the 65 capacitor. The lower electrode 8 is usually formed on the substrate 1. However, components such as an insulation

8

film, lower layer interconnection, a desired element and an interlayer insulation film may be provided alone or in combination on the substrate 1, so that the lower electrode 8 may be formed thereover.

Each of the films included in the structure of FIG. 1 is formed by, for example, a sputtering method. By inserting the initial film 5 between the IrO<sub>2</sub> film 6 and the Ir film 4, non-uniformity in quality (more specifically, crystallinity) of the IrO<sub>2</sub> film 6 can be prevented from being generated during its formation at a high temperature. The initial film 5 may be a thin film containing at least one of Ir, Ru, Rh, Os and Re. This allows for high-temperature formation of the films, thereby improving the crystallinity of the electrode material. As a result, the electrode structure having both 15 excellent anti-oxidation properties and excellent anti-heat properties is provided. Moreover, by optimizing the composition of the TaSiN film 3 to be combined with the lower electrode 8, the electrode structure having improved characteristics of resistance to a high-temperature oxygen atmo-20 sphere can be implemented.

According to the conventional production method, an electrode having an Ir/Iro<sub>2</sub>/Ir/Ti structure is formed by heat-treatment at about 600° C. for about 60 minutes in a diffusion furnace. During this heat-treatment, Ti is oxidized, thereby disrupting electrical conduction with underlying silicon. According to the present invention, however, the TaSiN film 3 serving as a diffusion barrier film is not oxidized even during the heat-treatment at about 700° C. for about 60 minutes. Therefore, the oxide electrode, having anti-heat properties as well as anti-oxidation properties at a temperature higher by at least 100° C. as compared with the conventional production method, can be realized.

The ferroelectric capacitor includes the electrode structure of the present invention as the lower electrode 8, and the ferroelectric film 7 formed thereon. The ferroelectric film 7 may be formed from a material such as an oxide ferroelectric material (e.g., PZT, SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> or Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>). The ferroelectric film 7 is not limited to a specific material as long as the ferroelectric film 7 is a Bi-type ferroelectric material having a laminar perovskite structure. However, the ferroelectric film 7 is preferably a ferroelectric material represented as  $Bi_2A_{m-1}B_mO_{3m+3}$  (where A is Na, K, Pb, Ca, Sr, Ba or Bi; and B is Fe, Ti, Nb, Ta, W or Mo), and more preferably, m is a natural number. More specifically, the ferroelectric film 7 may be Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>, SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, BaBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, BaBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, PbBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, PbBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, PbBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, SrBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, BaBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, Sr<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>, Ba<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>, Pb<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>,  $Na_{0.5}Bi_{4.5}Ti_4O_{15}$ ,  $K_{0.5}Bi_{4.5}Ti_4O_{15}$ ,  $Sr_2Bi_4Ti_4O_{18}$ , 50 Ba<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>, Pb<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub> or the like, wherein SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> is preferable.

Such a ferroelectric film 7 is formed by the methods such as a spin-on method, a reactive deposition method, an EB (electron beam) deposition method, a sputtering method and a laser ablation method. For example, according to the spin-on method, constituent elements of the abovementioned thin film are partially or entirely dispersed in a solvent and applied onto the substrate by a spin coating method. Then, the applied dispersion is dried, and a carbon component present in the resultant film is baked by sintering (pre-baking). Thereafter, the resultant material is baked in a gaseous phase containing oxygen or oxygen compound to obtain a crystal having a perovskite structure, whereby the ferroelectric film 7 is finally obtained.

The upper electrode 18 (see FIG. 5) is formed on the ferroelectric film 7. The upper electrode 18 may either have a single-layer structure of, for example, a Pt film, or a

multi-layer structure formed by using the same materials and the same method as those of the lower electrode 8. The ferroelectric capacitor is completed by forming interconnection, an insulation film and the like each having a desired shape on the upper electrode 18.

The semiconductor memory device of the present invention including the ferroelectric film 7 can be mounted on an integrated circuit wafer, thereby constituting an integrated circuit. In this case, the ferromagnetic element is utilized as a ferroelectric capacitor; alternatively, the ferroelectric element may be utilized as a ferroelectric device or a part of the semiconductor device. For example, when the ferroelectric element is applied as a capacitance portion of a non-volatile memory or as the gate electrode of the FET and further combined with a gate insulating film, source/drain regions and the like, the semiconductor memory device of the present invention can be used as MFMIS-FET, MFS-FET or the like.

Hereinafter, the production process of the semiconductor memory device of the present invention will be described particularly with respect to the steps of producing the 20 diffusion barrier film 3, the lower electrode 8 and the ferroelectric film 7 of the capacitor portion.

Referring to FIG. 1, the thermal oxide film 2 with a thickness of about 6000 Å is first formed on a surface of the silicon substrate 1. Then, the amorphous TaSiN film 3 25 serving as a diffusion barrier film is formed thereon with a thickness of about 1000 Å by a DC magnetron sputtering method. Thereafter, the resultant substrate is heat-treated in a nitrogen atmosphere so as to stabilize the TaSiN film 3. This heat-treatment may be omitted depending upon the 30 conditions for forming the TaSiN film 3.

The composition of the TaSiN film 3 thus formed is desirably  $Ta_xSi_{1-x}N_y$  (where 0.2<x<1 and 0<y<1), and more desirably, 0.75 < x < 0.95 and 0.3 < y 0.5.

the TaSiN film 3 is varied (for example, even when y=0.5, 0.41 and 0.3), the resistivity of the TaSiN diffusion barrier film 3 can be suppressed to about  $1000 \mu\Omega$ cm to about 2000 $\mu\Omega$ cm when the Ta composition x is in the range of 0.75 to 0.95. Moreover, from an Auger electron spectroscopy, it has 40 been confirmed that by setting the composition of the TaSiN diffusion barrier film 3 to the above-mentioned range, the reaction between the polysilicon plug 13 (see FIG. 5) provided for establishing electrical connection with the substrate 1 and the constituent components of the thin film formed on the TaSiN film 3 can be sufficiently suppressed. However, for 0.5<y or y<0.3, the TaSiN film 3 does not have sufficient barrier properties even when 0.75<x<0.95. In this case, the reaction between the underlying polysilicon plug 13 and the overlying thin film easily occurs at the sintering 50 temperature of about 600° C. or less. Therefore, 0.5<y and y<0.3 are not appropriate.

The amorphous TaSiN film 3 of Example 1 is formed by using an alloy target of Ta/Si=10/3 at a substrate temperature of about 500° C.; a sputtering power of about 2000 W; a 55 sputtering gas pressure of about 0.7 Pa; and a flow rate ratio of sputtering gases (i.e., an Ar flow rate/a N2 flow rate) of 3/2. Moreover, the amorphous TaSiN film 3 of Example 1 is subjected to a heat-treatment at about 600° C. for about one hour in a pure nitrogen atmosphere with a temperature rising 60 rate of about 5° C./min. The TaSiN film 3 formed under the aforementioned conditions was confirmed to have an amorphous structure by X-ray diffraction spectroscopy, and to have a composition of Ta<sub>0.85</sub>Si<sub>0.15</sub>N<sub>0.4</sub> according to the analysis by the Auger electron spectroscopy.

Thereafter, the lower electrode 8 is formed on the TaSiN film 3 by the DC magnetron sputtering method. The lower **10**

electrode 8 has an IrO<sub>2</sub>/Ir structure, wherein the Ir film 4 and the IrO<sub>2</sub> film 6 are sequentially formed in this order.

More specifically, the Ir film 4 having a thickness of about 1000 Å is first formed at a DC power of about 0.5 kW; a substrate temperature of about 500° C.; and a gas pressure of about 0.6 Pa. Only Ar gas is used as a sputtering gas. The Ir film 4 thus formed exhibits a dense, flat surface profile, regardless of the high temperature of about 500° C. This is because, by reducing the sputtering power, and hence, the sputtering rate, rapid grain growth is suppressed so that the flat film surface can be maintained. The surface profile of the electrode structure is observed by a SEM (Scanning Electron Microscope).

Thereafter, the initial film 5 for forming the IrO<sub>2</sub> film 6 at about 500° C. is formed on the Ir film 4. The initial film 5 is formed with a thickness of about 200 Å at a DC power of about 1 kW; a substrate temperature of about 350° C.; and a gas pressure of about 0.71 Pa. A flow rate ratio of sputtering gases (i.e., an Ar flow rate/an O<sub>2</sub> flow rate) is 1/9. Thus, the IrO<sub>2</sub> film 5 is formed as the initial film 5 by a reactive sputtering method using an Ir target.

The reason why the initial film 5 is formed at about 350° C. is as follows: the film is not uniformly formed on a metal such as the Ir film 4 when the film formation temperature is higher than about 400° C., while the film exhibits nonuniform crystallinity by the subsequent film formation at a high temperature when the film formation temperature is less than about 300° C.

Although the initial film 5 is shown to have a thickness of about 200 Å, the initial film 5 may have any thickness of about 300 Å or less as long as a uniform film is obtained. However, the initial film 5 must have a thickness of at least 50 Å. The initial film 5 with a thickness larger than about 300 Å would have a locally non-uniform anti-oxidation As shown in FIG. 2, even if the nitrogen composition y of 35 properties due to the non-uniform crystallinity resulting from the high-temperature process. As a result, hillocks are locally produced in the initial film 5.

> It should be noted that when a film is formed by the sputtering method, only an island-like film can be obtained if the thickness thereof is about 100 Å or less. Thus, a uniform IrO<sub>2</sub> film having any thickness can be formed on the surface of the Ir film 4 by exposure to oxygen plasma or ozone radiation onto the substrate surface. Therefore, when the initial film 5 having a thickness of about 100 Å or less is required, the IrO<sub>2</sub> film thus formed by the plasma exposure or the ozone radiation can be used as the initial film 5.

> Although the initial film 5 is shown to be the IrO<sub>2</sub> film, the initial film 5 may be any film containing at least one of the metal elements selected from the group consisting of Ir, Ru, Rh, Os and Re. However, in terms of improvement in the film characteristics as well as simplification of the process, it is desirable to form the initial film 5 from IrO<sub>2</sub> using a target of the same material as that used in the subsequent formation of the IrO<sub>2</sub> film **6**.

> Thereafter, the IrO<sub>2</sub> film 6 having a thickness of about 1300 Å is formed on the initial film 5 at a DC power of about 1 kW; a gas pressure of about 0.71 Pa; a flow rate ratio of sputtering gases (i.e., an Ar flow rate/an O<sub>2</sub> flow rate) of 1/9; and a temperature of about 500° C.

From the comparison between the XRD chart of the IrO<sub>2</sub> film 6 formed at about 400° C. (FIG. 3A) and the XRD charts of the IrO<sub>2</sub> film 6 formed at about 450° C. or higher (FIGS. 3B and 3C), it is apparent that the peak intensity of IrO<sub>2</sub> (200) of the IrO<sub>2</sub> film 6 formed at about 450° C. or 65 higher is at least four-times higher than that of the IrO<sub>2</sub> film 6 formed at about 400° C. It is also apparent that the IrO<sub>2</sub> films formed at about 450° C. and about 500° C. have

approximately the same XRD chart. Accordingly, it can be seen from the charts in FIGS. 3A to 3C that the crystallinity of the IrO<sub>2</sub> film 6 is varied at a film formation temperature between about 400° C. and about 450° C. so that IrO<sub>2</sub>(200) is dominantly aligned. The crystallinity of the IrO<sub>2</sub> film 6 is 5 not varied at the film formation temperature of about 450° C. or higher.

As shown in FIG. 4, for the film formation temperature up to about 450° C., the resistivity p of the resultant IrO<sub>2</sub> film 6 is reduced with the increase in the film formation 10 temperature, while being kept at a low, substantially constant value for the temperature higher than about 450° C.

From the foregoing, the temperature for forming the IrO<sub>2</sub> film 6 is preferably set to be equal to or higher than about 450° C.

Moreover, it has been experimentally confirmed that at the atmospheric temperature of about 700° C. or higher, the Ir film 4 is oxidized at the heated substrate surface by oxygen which is introduced into the chamber upon forming the IrO<sub>2</sub> film 6, whereby a dense IrO<sub>2</sub> aggregate is formed. 20 In order to avoid such a problem, the temperature for forming the IrO<sub>2</sub> film 6 must be about 700° C. or less.

Furthermore, in order to examine the anti-oxidation properties of the IrO<sub>2</sub> film 6, the IrO<sub>2</sub>/Ir/TaSiN multilayered electrodes (including the IrO<sub>2</sub> film 6) formed at various 25 temperatures were annealed in oxygen to determine the presence/absence of hillocks. For the IrO<sub>2</sub> film 6 formed at about 400° C. or less, hillocks were produced when the IrO<sub>2</sub> film 6 was annealed in oxygen at about 600° C. or higher, whereby sufficient anti-heat properties and anti-oxidation 30 properties were not obtained. However, for the IrO<sub>2</sub> film 6 formed at about 450° C. or higher, no hillocks were produced even when the IrO<sub>2</sub> film 6 was annealed in oxygen at a temperature up to about 800° C.

perature for forming the IrO<sub>2</sub> film 6 is advantageously set to about 450° C. or higher.

Thereafter, by using the spin-on method, the SBT film 7 (Sr/Bi/Ta=8/24/20) serving as the ferroelectric film 7 is formed on the lower electrode 8 formed as described above. 40

More specifically, constituent elements of the SBT film 7 are dispersed in a solvent to prepare a precursor solution. The precursor solution thus prepared is applied on the lower electrode 8 using a spinner operated at a rotational speed of about 3000 rpm. Then, the resultant substrate is dried in the 45 atmosphere at about 150° C. for about 10 minutes, pre-baked in the atmosphere at about 400° C. for about 30 minutes, and thereafter, crystallized at about 700° C. for about one hour. These steps are repeated three times to form the SBT film 7 having a thickness of about 2000 Å. After the SBT film 7 50 was formed, hillocks or the like were not recognized in the lower electrode 8, and through analysis of their cross section by the SEM and the Auger electron spectroscopy, it was confirmed that no reaction occurs between the lower electrode 8 and the SBT film 7.

It should be noted that similar effects can be obtained even by using a HfSiN film instead of the TaSiN film as the diffusion barrier film 3.

Moreover, even when a Pt film having a thickness of about 500 Å is formed on the lower electrode 8 to complete 60 the lower electrode structure, and the SBT film 7 is similarly formed on the lower electrode structure thus completed, neither hillocks nor the reaction between the lower electrode 8 and the SBT film 7 is observed. In this structure, a leakage current is also reduced by about one digit. More specifically, 65 the leakage current is about  $1.2 \times 10^{-6}$  A/cm<sup>2</sup> in the SBT/IrO<sub>2</sub> (including IrO<sub>2</sub> serving as the initial film 5)/Ir/TaSiN

structure, while being about  $9.8 \times 10^{-8}$  A/cm<sup>2</sup> in the SBT/Pt/ IrO<sub>2</sub> (including the IrO<sub>2</sub> initial film 5)/Ir/TaSiN structure.

It should be noted that similar effects can be obtained even by providing a thin film of Ir, Ru, Rh, Os, Re or alloy thereof (e.g., Pt-Rh) as an underlying film of the SBT film 7, instead of the Pt film.

As described above, in the lower electrode 8 including an electrically conductive oxide film such as IrO<sub>2</sub>, the initial film 5 is first formed on the Ir film 4, and the IrO<sub>2</sub> film 6 is then formed thereon, whereby the IrO<sub>2</sub> film 6 can be formed at a high temperature of about 450° C. or higher. Thus, the crystallinity of the IrO<sub>2</sub> film 6 is improved to prevent oxygen from passing through the IrO<sub>2</sub> film 6. Therefore, The TaSiN film 3 is not oxidized in a high-temperature oxygen atmo-15 sphere.

Thus, according to the present invention, the ferroelectric film 7 can be formed in a high-temperature oxygen atmosphere, whereby the lower electrode 8 having sufficient barrier properties required for realizing high-density FRAMs can be formed.

Hereinafter, the result of examining the respective thicknesses of the Ir film 4 and the IrO<sub>2</sub> film 6 which constitute the lower electrode 8 of the present invention will be discussed.

For examination, some samples were produced in a manner similar to the above-mentioned process as follows.

First, the thermal oxide film 2 having a thickness of about 6000 Å is formed on the silicon substrate 1, and the TaSiN film 3 is formed thereon. Thereafter, the lower electrode 8 having an IrO<sub>2</sub>/Ir structure is formed thereon by the DC magnetron sputtering method. The IrO<sub>2</sub>/Ir structure is formed by first forming the Ir film 4 and then forming the IrO<sub>2</sub> film 6 thereon. More specifically, the Ir film 4 is first formed with a thickness of about 1000 Å at a DC power of From these results, it has been confirmed that the tem- 35 about 0.5 kW; a substrate temperature of about 500° C.; and a gas pressure of about 0.6 Pa. Only Ar gas is used as a sputtering gas. Then, the initial film 5 of IrO<sub>2</sub> for forming the IrO<sub>2</sub> film 6 at about 500° C. is formed on the Ir film 4. More specifically, the initial film 5 is formed with a thickness of about 200 Å at a DC power of about 1 kW, a substrate temperature of about 350° C., a gas pressure of about 0.71 Pa, and a flow rate ratio of sputtering gases (an Ar flow rate/an O<sub>2</sub> flow rate) of 1/9. Subsequently, the IrO<sub>2</sub> film 6 is formed at about 500° C. on the initial film 5. More specifically, the IrO<sub>2</sub> film 6 is formed at a DC power of about 1 kW, a gas-pressure of about 0.71 Pa, and a flow rate ratio of sputtering gases (an Ar flow rate/an O<sub>2</sub> flow rate) of 1/9. Under these conditions, the thickness of the IrO<sub>2</sub> film 6 was varied in the range of about 500 Å to about 1800 Å.

> The relation between the thickness and the anti-heat properties of the IrO<sub>2</sub> film 6 is evaluated according to the presence/absence of hillocks which result from annealing in oxygen. It should be noted that "the thickness of the IrO<sub>2</sub> film 6" as used in the following description is intended to 55 include the thickness of the initial film 5 if the initial film 5 formed from the IrO<sub>2</sub> film is present between the Ir film 4 and the IrO<sub>2</sub> film **6**.

From the evaluation result, it was confirmed that hillocks are not produced in the IrO<sub>2</sub>/Ir/TaSiN multilayered electrode when  $1 \le (a \text{ thickness of the IrO}_2 \text{ film } 6)/(a \text{ thickness of the IrO}_2)$ Ir film **4**)<3.

When 1>(a thickness of the IrO<sub>2</sub> film 6)/(a thickness of the Ir film 4), the Iro<sub>2</sub> film 6 does not have the oxygen barrier properties, thereby allowing oxygen to pass therethrough. Accordingly, Ir is segregated on the IrO<sub>2</sub> film 6 to form single crystalline IrO<sub>2</sub>, resulting in a rough surface of the IrO<sub>2</sub> film 6. Moreover, when 3<(a thickness of the IrO<sub>2</sub> film

6)/(a thickness of the Ir film 4), the IrO<sub>2</sub> film 6 is thick, whereby a strong stress is generated in the transverse direction during the high-temperature process, producing small cracks. Oxygen is introduced through the cracks onto the Ir film 4. Moreover, since the thickness of the Ir film 4 5 in this condition does not provide sufficient resistance to oxygen, whereby the oxygen thus introduced reaches the TaSiN film 3. Accordingly, expansion of the TaSiN film 3 due to oxidation occurs, resulting in peeling between Ir and TaSiN.

When 1<(a thickness of the IrO<sub>2</sub> film 6)/(a thickness of the Ir film 4), the Iro<sub>2</sub> film 6 has sufficient anti-oxygen properties to prevent oxygen from passing therethrough. Therefore, such peeling does not occur. Moreover, when (a thickness of the IrO<sub>2</sub> film 6)/(a thickness of the Ir film 4) $\leq$ 3, 15 stress is alleviated, whereby hillocks are not produced.

It should be noted that in the exemplary structure described above with reference to FIG. 1, the thickness of the Ir film 6 is about 1000 Å, and the total thickness of the initial film 5 and the IrO<sub>2</sub> film 6 is about 1500 Å. Therefore, 20 (a thickness of the IrO<sub>2</sub> film 6)/(a thickness of the Ir film **4**)=1.5.

From the above result, generation of hillocks can be suppressed by controlling the respective thicknesses of the Ir film 4 and the IrO<sub>2</sub> film 6 which constitute the lower 25 electrode 8, thereby making it possible to form the electrode 8 having an excellent anti-heat (lower) electrode 8 for realizing high-density FRAMs.

Hereinafter, the result of examining the effects of the composition of the TaSiN film 3 serving as the diffusion 30 barrier film upon its anti-heat properties and anti-oxidation properties will be discussed.

For examination, some samples were produced in a manner similar to the above-mentioned process as follows.

thickness of about 6000 Å is first formed on the silicon substrate 1, and the TaSiN film 3 having the same composition as described above is formed thereon. Subsequently, by the DC magnetron sputtering method, the Ir film 4 having a thickness of about 1000 Å is formed thereon at a DC power 40 of about 0.5 kW, a substrate temperature of about 500° C., and a gas pressure of about 0.6 Pa. Only Ar gas is used as a sputtering gas. Then, the SBT film 7 is formed on the Ir film 4 by the spin-on method. In forming the SBT film 7, the baking step for crystallization is repeated three times, each 45 being at about 700° C. for about 1 hour, so that the baking process is conducted for about 3 hours in total.

After the SBT film 7 was formed by the above-mentioned method, no hillocks as well as no reaction between the SBT film 7 and other films was recognized by the SEM obser- 50 vation of their cross section. Moreover, as a result of the analysis by the Auger electron spectroscopy, a region having a thickness of about 100 Å in which the constituent elements are diffused with each other was observed at the interface between the SBT film 7 and the Ir film (electrode) 4, and 55 oxygen diffusion with the thickness of about 300 Å in the Ir film 4 was also observed.

The IrO<sub>2</sub> film 6 included in the structure of FIG. 1 is not formed on the Ir film 4 in the above examination. Also in this case, oxygen does not pass through the Ir film 4. The 60 principle thereof can be explained as follows.

Upon forming the SBT film 7, the surface of the Ir film 4 is oxidized, whereby an IrO<sub>2</sub> film having a thickness of about 100 Å to about 300 Å is formed. At the same time, an oxide film such as SBT or the like is formed on the Ir film 65 4. For example, in the spin-on method, this oxidation at the surface of the Ir film 4 is conducted by oxygen contained in

**14**

a solution. The oxide film thus formed has the same effects and oxygen barrier properties as those of another IrO<sub>2</sub> film 6 which is formed on the Ir film 4.

Accordingly, the lower electrode having the oxygen barrier properties can be formed even without conducting the step of forming the IrO<sub>2</sub> film 6 on the Ir film 4.

By setting the composition of the  $Ta_xSi_{1-x}N_y$  film 3 serving as the diffusion barrier film to 0.75<x<0.95 and 0.3<y<0.5, the  $Ta_xSi_{1-x}N_v$  film 3 having excellent oxygen 10 barrier properties can be formed by the high-temperature process of about 600° C. or higher.

Similar effects can be obtained even when the ferroelectric film 7 is formed by the sputtering method or MOCVD method instead of the spin-on method. Moreover, the respective thicknesses of the Ir film 4 and the TaSiN film 3 are not limited to the specific values described above, as long as the reaction does not occur at a desired temperature. Similar effects can be also obtained even when a HfSiN film instead of the TaSiN film is used as the diffusion barrier film 3. Furthermore, similar effects can be obtained even when a Pt, Ru or Os film instead of the Ir film is used as the electrode film 4 formed on the TaSiN film or HfSiN film serving as the diffusion film 3.

Thus, by setting the composition of the diffusion barrier film 3 to the above-mentioned range, the anti-heat properties and anti-oxidation properties thereof are improved, whereby the TaSiN film 3 is completely prevented from being oxidized in a high-temperature oxygen atmosphere. Therefore, the ferroelectric film 7 can be formed in a high-temperature oxygen atmosphere, making it possible to form the electrode structure having sufficient oxygen barrier properties required to implement high-density FRAMs.

Hereinafter, a production process of the semiconductor memory device incorporating the ferroelectric capacitor will More specifically, the thermal oxide film 2 having a 35 be described with reference to FIGS. 5 and 6, wherein the semiconductor memory device includes the lower electrode 8 which uses an oxide conductor having such a structure as described above.

> First, the LOCOS oxide film 9 having a thickness of about 5000 Å is formed at the surface of the substrate 1 to form an element isolation region. Then, the selection transistor including the gate electrode 10, the source/drain regions 11 and the like is formed, and the first silicon oxide film 12 having a thickness of about 5000 Å is formed as an interlayer insulation film by a CVD (Chemical Vapor Deposition) method. Thereafter, a contact hole having a diameter of about 0.5  $\mu$ m is formed therein. The contact hole is then filled with polysilicon by the CVD method, and a surface of the filled region is planarized, whereby the polysilicon plug 13 is formed.

> Then, as described above, the amorphous TaSiN film 3 serving as the diffusion barrier film is formed with a thickness of about 1000 Å on the polysilicon plug 13 by the DC magnetron sputtering method. The resultant substrate is subjected to heat-treatment in a nitrogen atmosphere so as to stabilize the TaSiN film 3. This heat-treatment may be omitted depending upon the conditions for forming the TaSiN film 3.

> The amorphous TaSiN film 3 of Example 1 is formed by using an alloy target of Ta/Si=10/3 at a substrate temperature of about 500° C.; a sputtering power of about 2000 W; a sputtering gas pressure of about 0.7 Pa; and a flow rate ratio of sputtering gases (i.e., an Ar flow rate/a N<sub>2</sub> flow rate) of 3/2. Moreover, the amorphous TaSiN film 3 of Example 1 is subjected to heat-treatment at about 600° C. for about one hour in a pure nitrogen atmosphere at a temperature rising rate of about 5° C./min. The TaSiN film 3 formed under the

aforementioned conditions was confirmed to have an amorphous structure by X-ray diffraction spectroscopy, and to have a composition of  $Ta_{0.85}Si_{0.15}N_{0.4}$  according to the analysis by the Auger electron spectroscopy.

Thereafter, the lower electrode 8 is formed on the TaSiN 5 film 3 by the DC magnetron sputtering method. The lower electrode 8 has a multi-layer electrode structure employing an oxide dielectric material.

More specifically, the Ir film 4 is first formed with a thickness of about 1000 Å at a DC power of about 0.5 kW; 10 a substrate temperature of about 500° C.; and a gas pressure of about 0.6 Pa. Only Ar gas is used as a sputtering gas. Thereafter, an IrO<sub>2</sub> film is formed on the Ir film 4 as an initial film for forming the IrO<sub>2</sub> film 6 at about 500° C. (not shown in FIG. 5; see FIG. 1). This IrO<sub>2</sub> film as the initial film is 15 formed with a thickness of about 200 Å at a DC power of about 1 kw; a substrate temperature of about 350° C; a gas pressure of about 0.71 Pa; and a flow rate ratio of sputtering gases (an Ar flow rate/an O<sub>2</sub> flow rate) of 1/9. Then, the IrO<sub>2</sub> film 6 is formed on the initial film. More specifically, it the 20 IrO<sub>2</sub> film 6 is formed with a thickness of about 1300 Å at a DC power of about 1 kW; a gas pressure of about 0.71 Pa; and a flow rate ratio of sputtering gases (an Ar flow rate/an  $O_2$  flow rate) of 1/9.

The lower electrode 8 is constituted as a layered structure 25 of the Ir film 4 and the IrO<sub>2</sub> film 6 (the IrO<sub>2</sub> film 6 includes the initial film if formed). As described above, a leakage current can further be reduced by additionally forming a Pt film having a thickness of about 500 Å on the IrO<sub>2</sub> film 6.

Thereafter, the ferroelectric film 7 is formed on the lower 30 electrode 8 by the process previously described. Then, the upper electrode 18 having a thickness of about 500 Å is formed on the ferroelectric film 7 by the DC magnetron sputtering method. The ferroelectric film 7 is patterned by a dry etching method using Ar and  $C_2F_6$ , whereas the upper 35 electrode 18 is patterned by a dry etching method using  $Cl_2$ , both the ferroelectric film 7 and the upper electrode 18 being patterned into a prescribed shape of, for example, a square of about 2.6  $\mu$ m by 2.6  $\mu$ m. Then, the lower electrode 8 having the aforementioned layered structure is patterned into 40 a prescribed shape by a dry etching method using, for example,  $Cl_2$  and  $C_2F_6$ , whereas the TaSiN film 3 is patterned into a prescribed shape by a dry etching method using  $C_2F_6$ .

Thereafter, the second silicon oxide film 19 is formed as an interlayer insulation film by the CVD method, and contact holes are formed at respective prescribed positions through the second silicon oxide film 19. Then, by the DC magnetron sputtering method, the aluminum extended electrode 20 from the upper electrode 18 of the ferroelectric 50 capacitor and the aluminum extended electrode 21 from the selection transistor are respectively formed in the contact holes thus formed, whereby the semiconductor memory device as shown in FIG. 5 is formed.

The semiconductor memory device of FIG. 5 produced according to the aforementioned process exhibits a hysteresis loop as shown in FIG. 6 when a triangular wave voltage is applied between the aluminum extended electrode 20 from the upper electrode 18 of the capacitor including the ferroelectric film and the aluminum extended electrode 21 60 from the silicon substrate 1 (from the selection transistor). The applied triangular wave voltage has such an intensity as to form an electric field having an intensity of about 150 kV/cm between the upper electrode 18 and the lower electrode 8. A frequency of the applied voltage is about 75 Hz. 65 It can be seen from FIG. 6 that sufficient ferroelectric characteristics as the ferroelectric capacitor have been

16

achieved. Moreover, the hysteresis loop maintains its symmetry, showing that sufficiently excellent contact has been established between the silicon substrate 1 and the Ir/IrO<sub>2</sub> lower electrode 8. This means that there is no reaction between the Ir film 4 included in the lower electrode 8 and the underlying polysilicon plug 13, and that there is no reaction between the diffusion barrier film 3 and the Ir/IrO<sub>2</sub> lower electrode 8.

Furthermore, no reaction between the films were recognized through observation of the cross-sectional structure by an electron microscope as well as analysis by the Auger electron spectroscopy.

In addition to a process for applying a film, such as an MOD method, other methods including a vacuum deposition method, a DC magnetron sputtering method and an MOCVD method may be used to form the ferroelectric film 7. Moreover, although the SBT film is shown to be used as the ferroelectric film 7, sufficient anti-oxidation properties can also be obtained by using other ferroelectric materials including SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>, BaBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, BaBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, PbBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, SrBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, SrBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, PbBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, Na<sub>0.5</sub>Bi<sub>4.5</sub>Ti<sub>4</sub>O<sub>15</sub>, K<sub>0.5</sub>Bi<sub>4.5</sub>Ti<sub>4</sub>O<sub>15</sub>, Sr<sub>2</sub>Bi<sub>4</sub>Ti<sub>4</sub>O<sub>18</sub>, Ba<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub> and Pb<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>, or high dielectric materials including (Ba<sub>x</sub>Sr<sub>1-x</sub>)TaO<sub>3</sub> and SrBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub> as the ferroelectric film 7.

Although the contact plug 13 is shown to be formed from polysilicon, similar effects can be obtained even when the contact plug 13 is formed from materials other than polysilicon (e.g., tungsten).

As specifically described above, according to the structure of the semiconductor memory device of the present invention, the diffusion barrier film 3 has an amorphous structure, and therefore, does not have any grain boundaries. As a result, the diffusion barrier film 3 has significant barrier properties against oxygen, platinum, bismuth or the like. Moreover, in forming the lower electrode 8 having the layered structure of Ir/IrO<sub>2</sub>, the IrO<sub>2</sub> film 6 is formed by a high-temperature process after the initial film 5 is formed on the Ir film 4. Therefore, oxygen can be completely prevented from passing through the IrO<sub>2</sub> film 6 even during the sintering process in a high-temperature oxygen atmosphere. Accordingly, the upper surface of the plug 13 formed from polysilicon, tungsten or the like, which is located under the lower electrode 8, is not oxidized, whereby excellent contact between the plug 13 and the lower electrode 8 is maintained.

By achieving such an electrode structure capable of enduring high-temperature annealing, the semiconductor memory device having excellent characteristics can be obtained.

Moreover, by forming the lower electrode 8 additionally including an electrically conductive film containing at least one of the metal elements selected from the group consisting of Pt, Ir, Ru, Rh, Os and Re on the layered structure of Ir/IrO<sub>2</sub>, a leakage current can further be reduced.

By setting the composition of the diffusion barrier film 3 to  $Ta_xSi_{1-x}N_y$  or  $Hf_xSi_{1-x}N_y$  (where 0.75<x<0.95 and 0.3<y<0.5), the oxygen barrier properties can further be improved.

Furthermore, by setting the thickness ratio of  $IrO_2$  film 6 to the Ir film 4 to  $1 \le (a \text{ thickness of the } IrO_2 \text{ film } 6)/(a \text{ thickness of the Ir film 4}) \le 3$ , generation of hillocks can be suppressed.

Moreover, by setting the temperature for forming the Iro<sub>2</sub> film 6 included in the layered structure of the lower electrode 8 to the range of about 450° C. to about 700° C., the resistivity of the IrO<sub>2</sub> film 6 to be formed can be reduced, as well as the formation of a dense IrO<sub>2</sub> aggregate resulting

from oxidation of the underlying Ir film 4 during formation of the IrO<sub>2</sub> film 6 can be suppressed.

Furthermore, by conducting the steps of forming the dielectric film 7 from a material including oxygen and forming the upper electrode 18 on the dielectric film 7, after 5 the step of forming the Ir film 4 on the diffusion barrier film 3, the lower electrode 8 having oxygen barrier properties can be obtained without separately conducting the step of forming the IrO<sub>2</sub> film 6. As a result, the number of process steps can be reduced.

Furthermore, by using, as the initial film 5, an IrO<sub>2</sub> film which can be formed by a target of the same material as that used for forming the IrO<sub>2</sub> film 6, film characteristics can be improved as well as the process can be simplified.

The following Examples relate to a method for forming a 15 ferroelectric capacitor which can be incorporated in the semiconductor memory device as described above as Example 1, and a method for producing a non-volatile semiconductor memory device incorporating this ferroelectric capacitor, and in particular, relate to a process of 20 annealing a ferroelectric film included in a capacitor portion.

The substrate to be used in the semiconductor memory device incorporating the ferroelectric capacitor according to the present invention is not limited to a specific material, as long as the substrate can be used for normal semiconductor 25 devices, integrated circuits or the like. For example, the substrate may be selected from a semiconductor substrate (e.g., silicon), a compound semiconductor substrate (e.g., GaAs), an oxide crystalline substrate (e.g., MgO) or a glass substrate, according to the types, applications or the like of 30 the device to be formed. However, a silicon substrate is desirable.

In the following description, the ferroelectric film may be formed from a Bismuth-layer-structured-family compound such as Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub>, SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, SrBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, 35  $SrBi_2(Ta_{1-x}Nb_x)_2O_9$ ,  $BaBi_2Nb_2O_9$ ,  $BaBi_2Ta_2O_9$ , PbBi<sub>2</sub>Nb<sub>2</sub>O<sub>9</sub>, PbBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>, PbBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, SrBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, BaBi<sub>4</sub>Ti<sub>4</sub>O<sub>15</sub>, Sr<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>, Ba<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>, Pb<sub>2</sub>Bi<sub>4</sub>Ti<sub>5</sub>O<sub>18</sub>,  $Na_{0.5}Bi_{4.5}Ti_4O_{15}$ ,  $K_{0.5}Bi_{4.5}Ti_4O_{15}$  or the like, wherein  $SrBi_2Ta_2O_9$  and  $SrBi_2(Ta_{1-x}Nb_x)_2O_9$  (where 0 < x < 1) are 40 preferable.

The ferroelectric film is formed on the above-mentioned substrate by any of the known methods in the art including: the methods for applying a film such a sol-gel method and an MOD method; an MOCVD method; or a sputtering 45 method.

In the film application method, a raw-material solution is prepared by mixing (i) an organic solvent including a salt of a part of the constituent elements of the ferroelectric film, metal alkoxide or the like, with (ii) an organic solvent 50 including a salt of the remaining elements, metal alkoxide or the like. Then, by using a spin-coating method or the like, the raw-material solution thus prepared is applied with a thickness of about 20 nm to about 100 nm per one application. Thereafter, the drying step is conducted at about 100° C. to about 300° C.

Hereinafter, one exemplary method for preparing a rawmaterial solution for use in the MOD method will be described.

2-ethylhexanoate (Bi(OCOC<sub>7</sub> $H_{15}$ )<sub>2</sub>) and strontium 2-ethylhexanoate  $(Sr(OCOC_7H_{15})_2)$  are used as starting raw-materials for preparing the solution. First, tantalum ethoxide is weighed to be dissolved in 2-Ethylhexanoic acid. Then, in order to facilitate the reaction, the resultant solution 65 is heated to about 100° C. to the maximum temperature of about 120° C. for 30 minutes with stirring. Then, ethanol and

18

water resulting from the aforementioned reaction at about 120° C. are removed. Strontium 2-ethylhexanoate dissolved in about 20 ml to about 30 ml of xylene is added at an appropriate amount to the resultant solution so as to achieve Sr/Ta=8/20. Then, the solution is heated to about 125° C. to the maximum temperature of about 140° C. for 30 minutes with stirring. Thereafter, bismuth 2-ethylhexanoate dissolved in about 10 ml of xylene is added at an appropriate amount to the resultant solution so as to obtain Sr/Bi/Ta=8/ 10 24/20. Then, the solution is heated to about 130° C. to the maximum temperature of about 150° C. for about 10 hours with stirring.

The resultant solution is then distilled at about 130° C. to about 150° C. for about 5 hours in order to remove alcohol having a low molecular weight, water, and xylene used as a solvent. Thereafter, the solution is adjusted to have a SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> concentration of about 0.1 mol/l. The solution thus prepared is used as a precursor solution.

It should be noted that the starting raw-materials are not limited to the above-mentioned materials as long as they are organic metals containing oxygen. Moreover, the solvent is not limited to the above-mentioned solvent as long as the starting materials are sufficiently dissolved therein.

According to the conventional method for applying a film, all of the subsequent processes including prebaking at about 500° C. to about 600° C.; a heat-treatment at about 650° C. to about 800° C. for crystallizing the ferroelectric film; a formation of the upper electrode; a subsequent heattreatment at about 500° C. to about 700° C. for suppressing a leakage current across the film in the post-process, are conducted in an oxidizing atmosphere.

On the other hand, in the following Examples of the present invention, heat-treatment for crystallization which requires heat-treatment at the highest temperature (hereinafter, such heat-treatment is also referred to as "crystallizing heat-treatment") is conducted in an inert atmosphere such as nitrogen or argon.

This crystallizing heat-treatment in the inert atmosphere is preferably conducted in the temperature range of about 650° C. to about 800° C., in view of the relation between crystallizing heat-treatment temperature and leakage current density as shown in FIG. 25. It should be noted that FIG. 25 shows the data which was obtained by the present inventors in the course leading to the present invention. Specifically, FIG. 25 shows the data obtained from the samples prepared by applying an MOD solution on a four-layered substrate of Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si; annealing the resultant substrate in a nitrogen atmosphere for about 60 minutes for crystallizing the film(s) at one time; forming the upper electrode; and conducting heat-treatment in an oxygen atmosphere at about 550° C. for about 60 minutes.

The crystallizing heat-treatment may be conducted either as batch-crystallization for collectively heat-treating the film deposited to a desired thickness by repeating the applying and drying steps several times, or as a crystallization process for heat-treating the films on a film-by-film basis after every applying and drying step. Moreover, the time for the heattreatment is not specifically limited. The heat-treatment may be conducted for several minutes to several hours in a Tantalum ethoxide  $(Ta(OC_2H_1)_5)$ , bismuth 60 diffusion furnace, or may be conducted for several tens of seconds to several minutes by RTA (Rapid Thermal Annealing). In short, the time for the heat-treatment is determined so that sufficient crystallization can be achieved in respective heat-treatment processes.

> In general, heat-treatment for crystallizing an oxide must be conducted in an oxygen atmosphere due to its requirement to supply a sufficient amount of oxygen. On the other

hand, in the methods such as a sol-gel method and an MOD method, a large amount of oxygen is contained in the raw materials such as metal alkoxide and salt. Therefore, crystallization can be conducted even in an inert atmosphere such as nitrogen or argon. However, in order to improve the ferroelectric characteristics and suppress a leakage current, it is preferable to conduct heat-treatment at about 400° C. to about 650° C. after the formation of the upper electrode.

According to the MOCVD method, the ferroelectric film is formed as follows: a film is deposited in an oxygen- 10 containing atmosphere at a relatively low substrate temperature of about 650° C., whereby an amorphous or insufficiently-crystallized film is obtained. The deposition conditions including types of a source material, a carrier gas flow rate, an oxygen concentration and a pressure are 15 determined so that a sufficient amount of oxygen can be introduced into the film to result in sufficient crystallization by the post-annealing process. The post-annealing process is then conducted in an inert atmosphere such as nitrogen or argon at about 650° C. to about 800° C., thereby crystalliz- 20 ing the ferroelectric film. Such film deposition and postannealing process may be conducted either by collectively performing the post-annealing process for the film deposited to a desired thickness, or by repeating the film deposition and the post-annealing process several times until a desired 25 film thickness is obtained. In either case, the upper electrode is formed after the post-annealing process, and heattreatment is then conducted at about 400° C. to about 650° C. in order to suppress a leakage current as well as supplement the oxygen loss.

According to the sputtering method, the ferroelectric film is formed as in the case of the MOCVD method as follows: a film is deposited in an oxygen-containing atmosphere at a relatively low substrate temperature of about 650° C., whereby an amorphous or insufficiently-crystallized film is 35 obtained. The deposition conditions including types of a source material, a carrier gas flow rate, an oxygen concentration and a pressure are determined so that a sufficient amount of oxygen can be introduced into the film to allow sufficient crystallization by the post-annealing process. Also 40 in this case, the post-annealing process is conducted thereafter in an inert atmosphere such as nitrogen or argon at about 650° C. to about 800° C., thereby crystallizing the ferroelectric film. Such film deposition and post-annealing process may be conducted either by collectively performing 45 the post-annealing process for the film deposited to a desired thickness, or by repeating the film deposition and the postannealing process several times until a desired thickness is obtained. In either case, the upper electrode is formed after the post-annealing process, and heat-treatment is then con- 50 formed. ducted at about 400° C. to about 650° C. in order to suppress a leakage current as well as supplement the oxygen loss.

By using the above-mentioned methods, the heattreatment for crystallizing the ferroelectric film, which generally requires the highest temperature, can be conducted in 55 an inert atmosphere such as nitrogen or argon, whereby damages to the stacked-type ferroelectric memory device due to oxidation in a high-temperature process can be sufficiently suppressed.

Hereinafter, some examples regarding a process for heat-treating the ferroelectric film according to the present invention will be described with reference to the accompanying drawings.

(Example 2)

A process of producing a ferroelectric memory device 65 according to Example 2 of the present invention will now be described with reference to FIGS. 7 and 8A to 8D.

20

First, a thermal oxide film (SiO<sub>2</sub> film) **202** having a thickness of about 200 nm is formed on a silicon substrate **201** by heat-treatment in an oxygen atmosphere containing vapor at about 1050° C. for about 20 minutes. Then, a Ti film having a thickness of about 20 nm is formed on the thermal oxide film **202** by sputtering Ti at a DC power of about 2 kW and a substrate temperature of about 400° C. A closely contacting TiO<sub>2</sub> film **203** having a thickness of about 40 nm is formed by thermally oxidizing the Ti film. Thereafter, a lower Pt electrode **204** having a thickness of about 200 nm is formed by sputtering Pt at a DC power of about 2 kW and a substrate Ad temperature of about 500° C. Thus, a Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si substrate as shown in FIG. **8**A is prepared.

Then, an MOD solution of ferroelectric material SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> (Sr/Bi/Ta=8/24/20) produced by the above-mentioned method for producing the raw-material solution is applied on the Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si substrate by a spin-coating method at a rotational speed of about 3000 rpm so that each layer has a thickness of about 50 nm (Step 251). The resultant substrate is dried in air at 250° C. for about 5 minutes (Step 252). Thereafter, the substrate is pre-baked in a normal-pressure oxygen atmosphere at a substrate temperature of about 500° C. for about 30 minutes (Step 253) so as to decompose a residual organic compound in the film. Then, heat-treatment is conducted in a normal-pressure nitrogen atmosphere at about 700° C. for about 60 minutes (Step 254), thereby crystallizing a SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> film 207 (See FIG. 8B).

The series of Steps 251 to 254 is repeated four times to form the SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> film 207 having a total thickness of about 200 nm (See FIG. 8C).