**Patent Number:**

US006157973A

6,157,973

## United States Patent [19]

Ohtani et al. [45] Date of Patent: Dec. 5, 2000

[11]

| [54] | MICROCOMPUTER HAVING MEMORY AND   |

|------|-----------------------------------|

|      | PROCESSOR FORMED ON THE SAME CHIP |

|      | TO INCREASE THE RATE OF           |

|      | INFORMATION TRANSFER              |

[75] Inventors: Jun Ohtani; Naoto Okumura; Akira

Yamazaki, all of Hyogo, Japan

[73] Assignee: Mitsubishi Denki Kabushiki Kaisha,

Tokyo, Japan

[21] Appl. No.: **09/226,195**

[22] Filed: Jan. 7, 1999

## [30] Foreign Application Priority Data

| Oct.                      | 24, 1996              | [WO] WIPO | •••••                                   | PCT/J      | P96/03103                |

|---------------------------|-----------------------|-----------|-----------------------------------------|------------|--------------------------|

| [51]                      | Int. Cl. <sup>7</sup> | •••••     | • • • • • • • • • • • • • • • • • • • • | <b>G</b> 0 | 6F 13/00                 |

| $\Gamma \subset \Delta I$ | TIO OI                |           | <b>=</b> 4.0/4.00                       | E4 0 /4 00 | <b>5</b> 40/4 <b>0</b> 0 |

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,296,469 | 10/1981 | Gunter 710/128 |

|-----------|---------|----------------|

| 5,264,746 | 11/1993 | Ohmae 714/700  |

| 5,287,527 | 2/1994  | Delp et al     |

| 5,321,845 | 6/1994  | Sawase         |

| 5,638,272 | 6/1997  | Minowa 701/114 |

| 5,774,684 | 6/1998  | Haines 710/126 |

| 5,784,637 | 7/1998  | Sawase         |

| 5,809,319 | 9/1998  | Kim            |

| 5,826,100 | 10/1998 | Bonet 712/221  |

|           |         |                |

#### FOREIGN PATENT DOCUMENTS

57-111733 7/1982 Japan.

# [45] Date of Fatent:

7/1982 57-11733 Japan . 3-135640 6/1991 Japan . 5-502125 4/1993 Japan. 6-267274 9/1994 Japan . 2/1995 7-040794 Japan . 2/1991 WO 91/02311 WIPO.

Primary Examiner—John A. Follansbee

Assistant Examiner—Stacy Whitmore

Attorney, Agent, or Firm—Burns, Doane, Swecker & Mathis, LLP

#### [57] ABSTRACT

A first memory of a large storage capacity is connected to a DQ pad for inputting and outputting an information signal through a bus interface unit. A first bidirectional transfer circuit and a second bidirectional transfer circuit for bidirectionally transmitting an information signal are provided between a high-speed memory and the memory of the large storage capacity. The first bidirectional transfer circuit is connected with the large storage capacity memory through a common bus, and the high-speed memory is interconnected with the second transfer circuit through a fifth bus. This second bidirectional transfer circuit is connected to an instruction register and a data register through a sixth bus. A processor is arranged in proximity to this instruction register and the data register, so that the processor processes an instruction from the instruction register and data from the data register and stores a processing result in the data register again. The bus interface unit is interconnected with the DQ pad through a first bus, and interconnected with the mass storage capacity memory through the second bus. The first and second bidirectional transfer circuits are interconnected with each other through a fourth bus. By arranging the respective buses independently of each other respectively, the processor can execute processing internally through an available bus during information signal transmission in an exterior.

19 Claims, 21 Drawing Sheets

261

FIG.1 PRIOR ART

FIG.2

BUS CPU 128 SBL

F16.

48 DR MRB DRB BUS DWB BUS DRB

F16. 4

FIG. 5

FIG. 8

FIG.9 lia IDA —T5 T6— # TRIa LATCH AMPLIFIER  $\phi$  TRIb (128 BITS AT A TIME) (128 BITS AT A TIME) ITG ⊹IV6 -ILAb -ILAa ILĆH - $\phi$  ISEL MUX lRi < \( \phi \) Ig

(32 BITS SELECTED) ISG-> IRBj:TO PROCESSOR 52 INSTRUCTION BUS LINE

FIG. 11

FIG.12

FIG.13

FIG. 14

**Sheet 12 of 21**

FIG. 15

FIG. 16

FIG. 18

FIG.21

34x 34y 210X 210y SBL E( BRTE SSAE CLOCK GENERATION CIRCUIT CMD 52

FIG.26

F1G. 27

FIG. 28

# MICROCOMPUTER HAVING MEMORY AND PROCESSOR FORMED ON THE SAME CHIP TO INCREASE THE RATE OF INFORMATION TRANSFER

This application claims priority under 35 U.S.C. §119 from International Application PCT/JP96/03103 with an international filing date of Oct. 24, 1996, now abandoned.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a microcomputer having a processor and a memory formed on the same chip, and more particularly, it relates to the layout of a processor and a memory as well as a transfer unit for performing data transfer between these processor and memory.

#### 2. Description of the Background Art

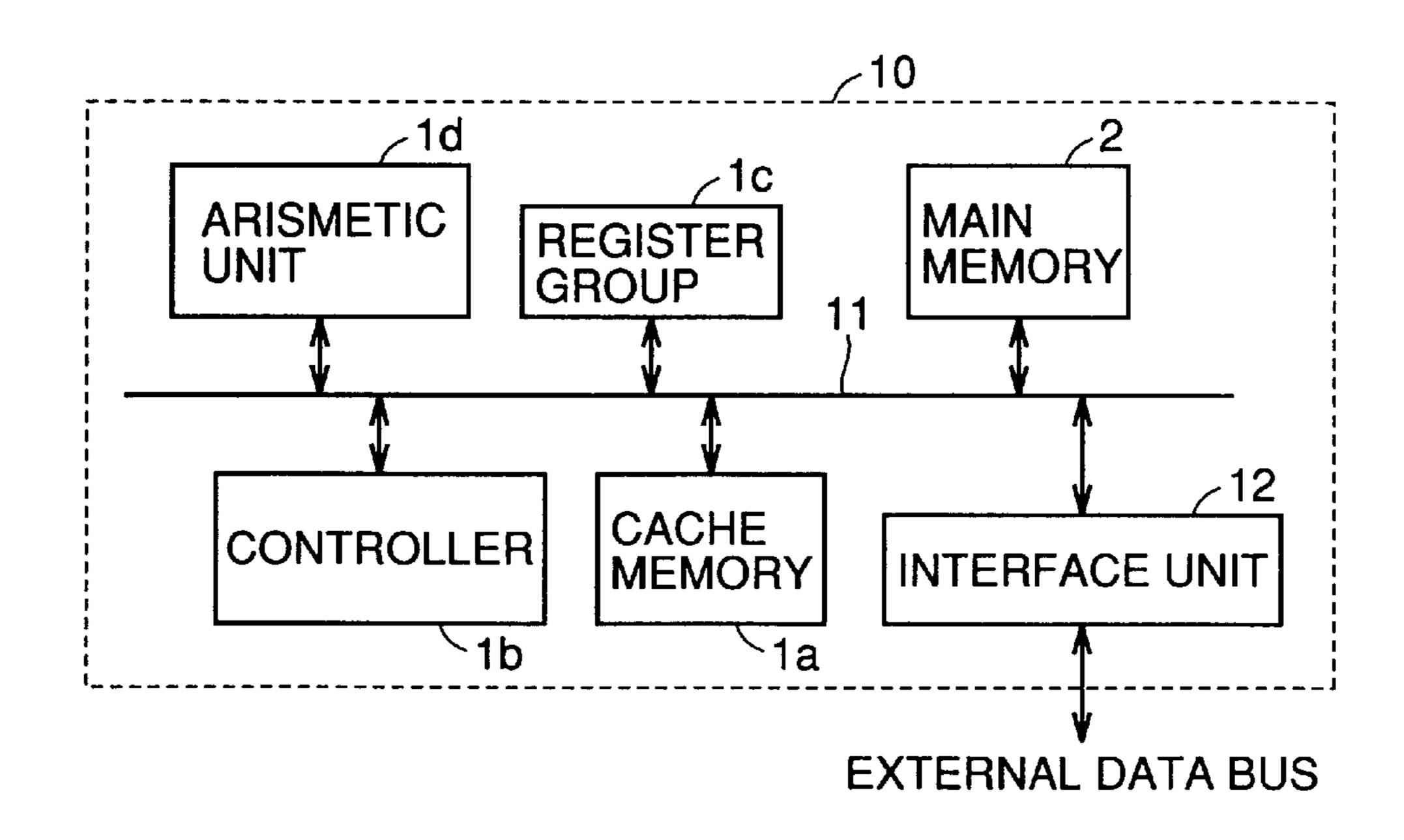

FIG. 1 is a diagram schematically showing an exemplary structure of a conventional processing system. Referring to FIG. 1, the processing system includes a processor 1 performing required arithmetic and logic processing operations, and a main memory 1 provided in the exterior of the processor 1 and serving as a main storage for this processor 1. The processor 1 is connected to the main memory 2 through an external data bus 3. This main memory 2 stores instructions and processed or pre-processed data (hereinafter both are referred to as information).

The processor 1 includes a cache memory 1a for storing information, a controller 1b forming various control signals in accordance with the information stored in this cache memory 1a, a register group 1c for temporarily storing data required for arithmetic and logic processing, and an arithmetic unit 1d performing required operations in accordance with the control signals from the controller 1d. The cache memory 1a, the controller 1b, the register group 1c and the arithmetic unit 1d are interconnected with each other through an internal data bus 1e. This internal data bus 1e is connected to the external data bus 3 through an interface 1f. The interface 1f manages data transfer between the main memory 2, the cache memory 1a and the controller 1b under control of this controller 1b.

When the controller 1b requires information which is not stored in the cache memory 1a in the structure of this processing system shown in FIG. 1, the information required by this controller 1b is transferred from the main memory 2 through the external data bus 3 and the interface 1f.

The main memory 2, which is formed by a DRAM (dynamic random access memory) of a large storage 50 capacity, for example, cannot operate at such a high speed as the processor 1. The speed of data transfer between the main memory 2 and the processor 1 is determined by the bus width (bit width) of the external data bus 3. The bus width of the external data bus 3 is determined by the number of data input/output terminals of the main memory 2. Thus, there arises such a problem that the data transfer between the main memory 2 and the processor 1 cannot be performed at a high speed, the processor I is entered into a wait state in the data transfer with this main memory 2, and the performance of the processing system reduces.

In order to solve the problem resulting from the low-speediness of the main memory 2 in this processing system shown in FIG. 1, it is conceivable to form the processor 1 and the main memory 2 on the same chip for widening the 65 bus width of the external data bus 3 to perform the data transfer at a high speed.

2

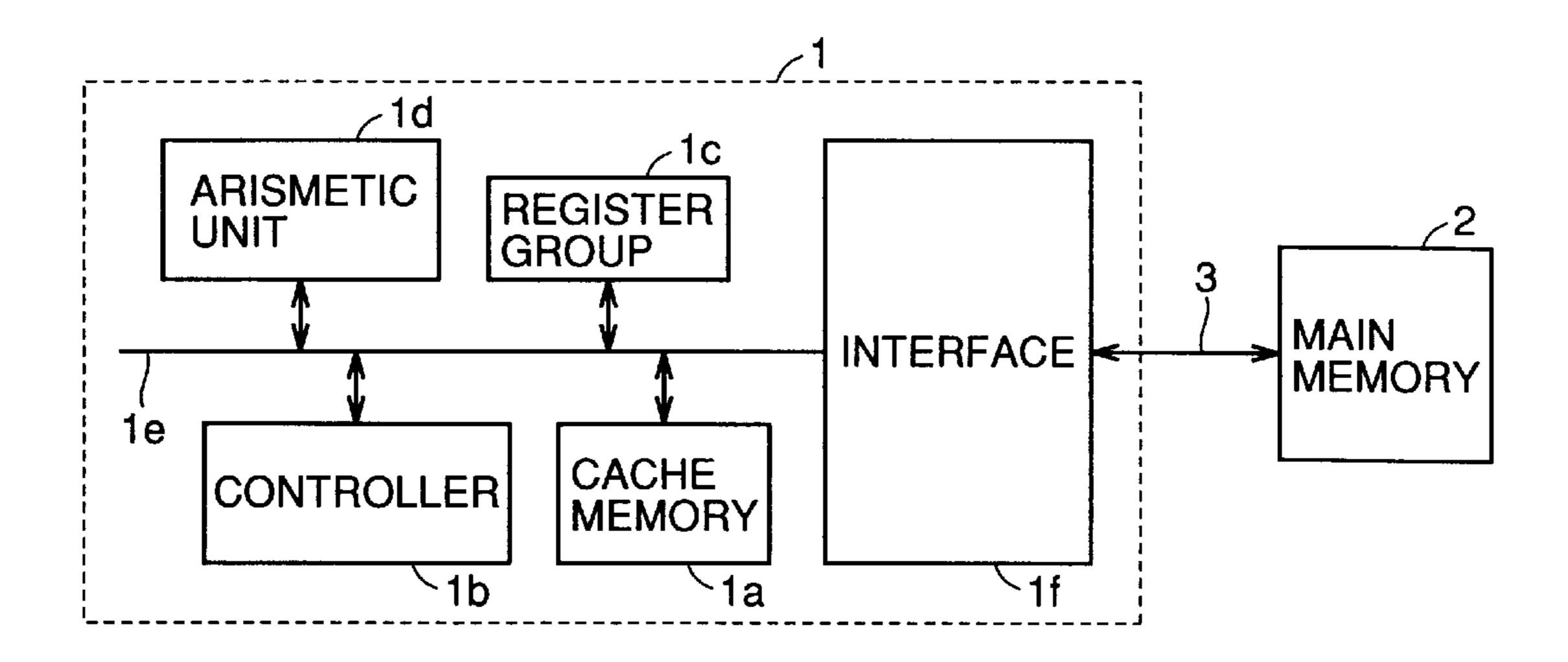

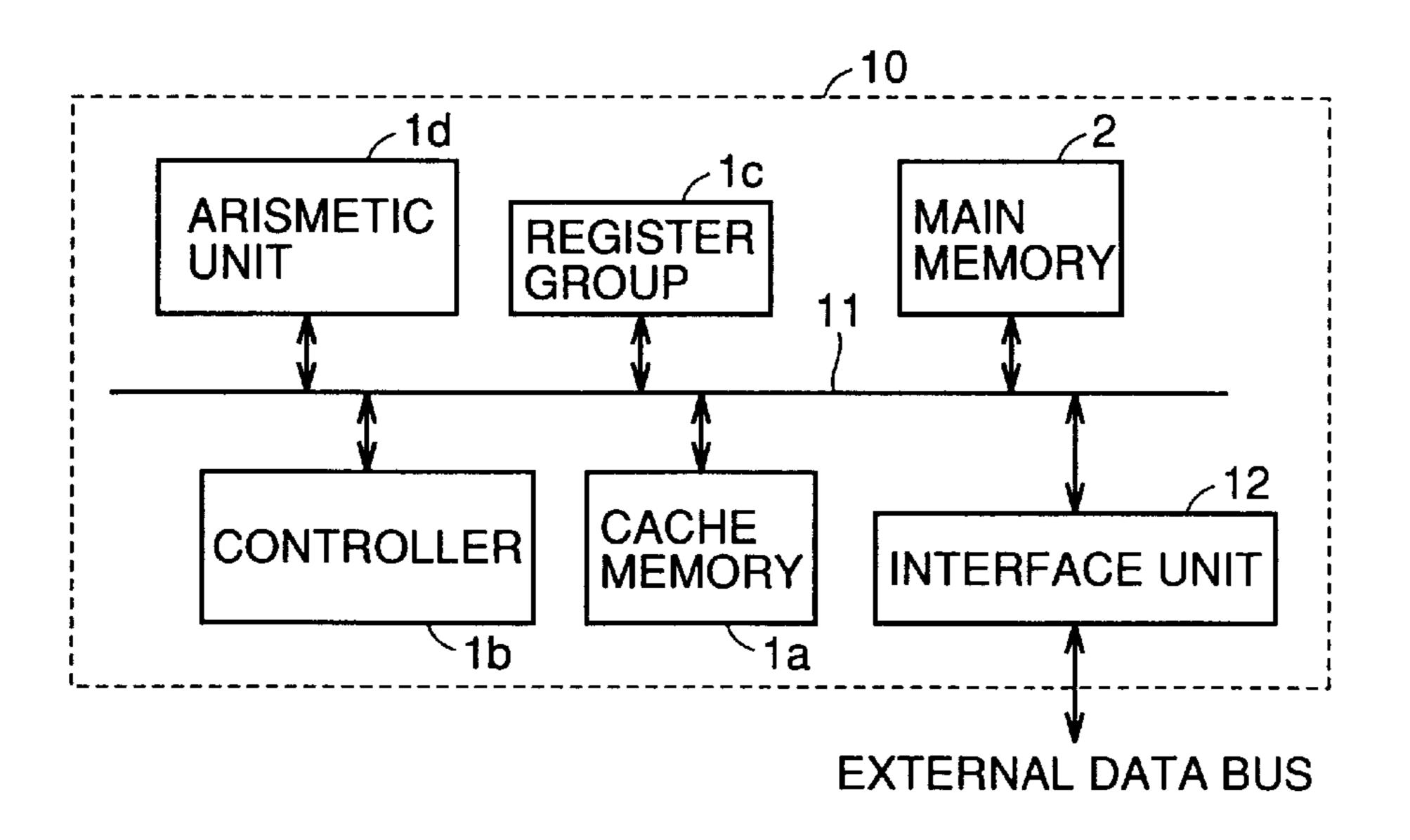

FIG. 2 is a diagram schematically showing an exemplary structure of such a microcomputer that a processor and a main memory are formed on the same chip. Referring to FIG. 2, the microcomputer 10 includes a cache memory 1a, a controller 1b, a register group 1c and an arithmetic unit 1d, similarly to the structure shown in FIG. 1. This microcomputer 10 further has a built-in main memory 2. The cache memory 1a, the controller 1b, the register group 1c, the arithmetic unit 1d and the main memory 2 are interconnected with each other through an internal data bus 11. This internal data bus 11 is connected to an external data bus through an interface unit 12 to perform transfer of information with an external unit.

By providing the main memory 2 in the microcomputer 10, information with the bus width (bit width) of this internal data bus 11 can be transferred without being subjected to restriction of the number of data input/output terminals of the main memory 2, dissimilarly to the structure shown in FIG. 1. Therefore, a large quantity of information can be simultaneously transferred and high-speed data transfer can be implemented by widening the bus width of this internal data bus 11. Further, the load capacitance of the internal data bus 11 is sufficiently small as compared with the load capacitance of the external data bus 3 which is an on-board wire shown in FIG. 1, and information transfer can be performed between the main memory 2, the cache memory 1a and the controller 1b at a higher speed. At this time, an output circuit of the main memory 2 is not required to drive a large load capacitance since the load capacitance of the internal data bus 11 is small, and current consumption of the processing system is reduced.

When performing transfer of information with the external unit in the structure of this microcomputer shown in FIG. 2, however, the interface unit 12 occupies the internal data bus 11. Thus, there arises such a problem that the controller 1b cannot utilize this internal data bus 11 during access to the main memory 2 by the interface unit 12, for example, arithmetic or logic operations stop during this period and the processing performance of the microcomputer reduces.

In such a microcomputer having a built-in memory, further, there is a sufficient room for further consideration as to what internal bus arrangement makes it possible to efficiently perform information transfer in the interior at a high speed.

There is also sufficient room for further consideration as to how to arrange the processor, the main memory and the interface unit to implement efficient information transfer in the interior of the microcomputer at a high speed and improving the processing performance.

#### SUMMARY OF THE INVENTION

An object of the present invention is to provide a microcomputer having a built-in memory which can perform information transfer efficiently at a high speed without reducing processing performance.

Another object of the present invention is to provide a microcomputer having a built-in memory whose processing performance does not reduce also in information transfer with the exterior of the microcomputer.

The microcomputer having a built-in memory according to the present invention includes a plurality of data input/output pads, bus interface circuitry which is connected to those plurality of data input/output pads through a first bus to provide an interface for information input/output through these data input/output pads, a first memory which is connected to the bus interface circuitry through a second bus for

performing transfer of information with the bus interface circuitry, first bidirectional transfer circuitry which is connected to the first memory through a third bus for bidirectionally transferring information with a selected memory cell of this first memory, and second bi-directional transfer circuitry which is connected to this first bidirectional transfer circuitry through a fourth bus for bidirectionally transferring information at least with this first bidirectional transfer circuitry. The first and second bidirectional transfer circuitries include means latching supplied information and 10 then transferring the latched information.

The microcomputer having a built-in memory according to the present invention further includes a second memory which is connected to the second bidirectional transfer circuitry on/through a fifth bus, a second memory for 15 performing transfer of information with this second bidirectional transfer circuitry, and a processing circuitry which is connected to the second bidirectional transfer circuitry through a sixth bus for performing transfer of information with the second bidirectional transfer circuitry, executing an 20 instruction included in this information, and transmitting data of a result of the execution to the sixth bus.

The bus interface circuitry for performing transfer of information with the exterior of the microcomputer is connected with the first memory through the second bus, and the first and second memories are connected through the first and second bidirectional transfer circuitries having latching and transferring functions. The second memory is connected with the second bidirectional transfer circuitry through the fifth bus, and this second bidirectional transfer circuitry is <sup>30</sup> connected with the processing circuitry through the sixth bus. In information transfer between the bus interface circuitry and the first memory or between the bus interface and the exterior of the microcomputer, therefore, the processing circuitry can perform a processing by accessing the second memory, and reduction of the processing performance in information transfer is prevented. By providing the first and second bidirectional transfer circuitries, further, the processing circuitry can still access the second memory through the second bidirectional transfer circuitry in information transfer from the first memory to the first bidirectional transfer means. Therefore, information transfer can be internally performed without reducing the processing performance.

The foregoing and other objects, features aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a diagram schematically showing the structure of a conventional processor and the structure of a memory system.

- FIG. 2 is a diagram schematically showing a structure in case of making the processing system shown in FIG. 1 on one chip.

- FIG. 3 is a diagram schematically showing the structure of the interior of a microcomputer according to an embodiment 1 of the present invention.

- FIG. 4 is a diagram showing the flow of information signals in bus arrangement shown in FIG. 3.

60

- FIG. 5 is a timing chart showing the flow of the information signals in information load request in the embodiment 1 of the present invention.

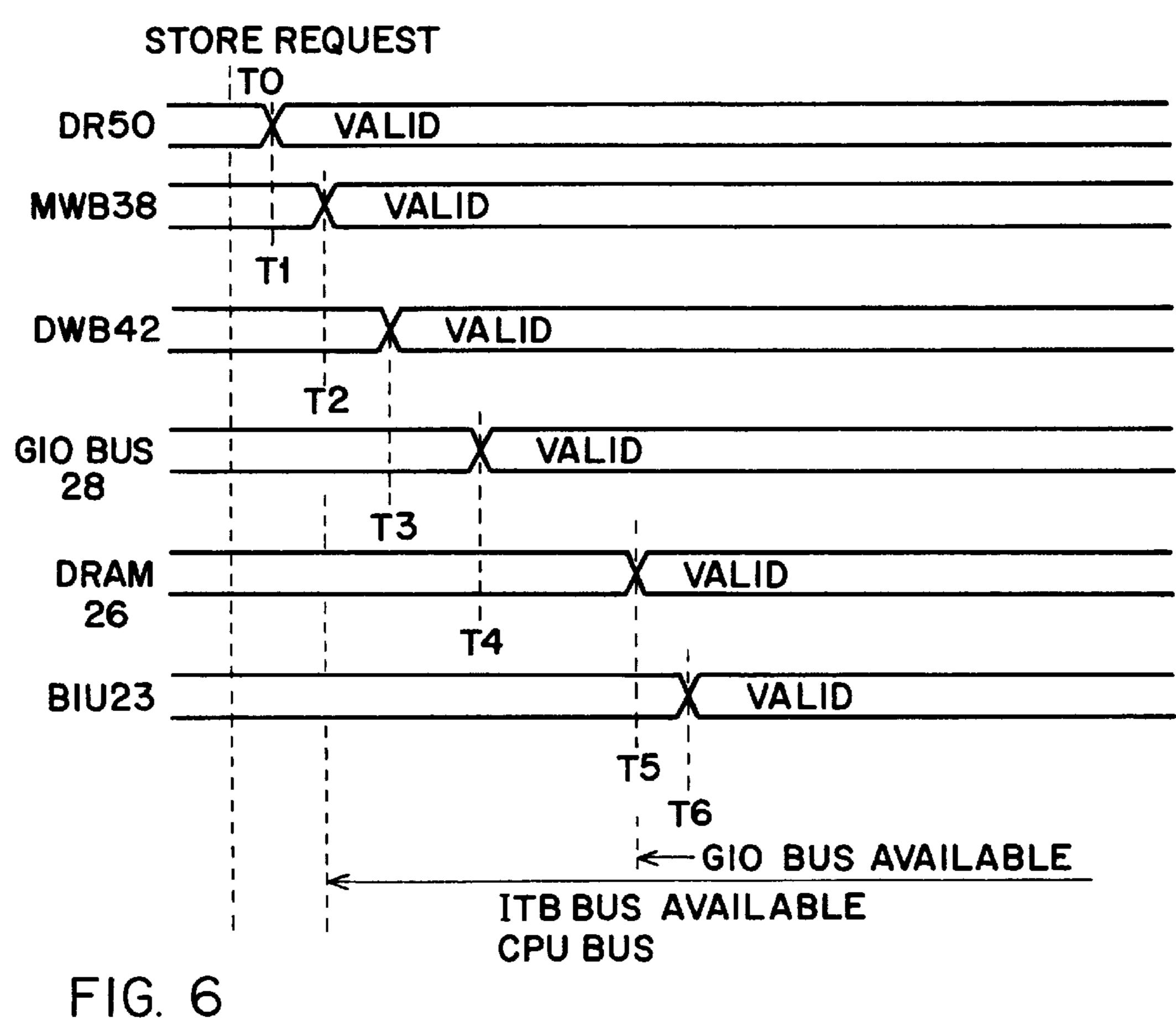

- FIG. 6 is a timing chart showing the flow of information signals in generation of information store request.

4

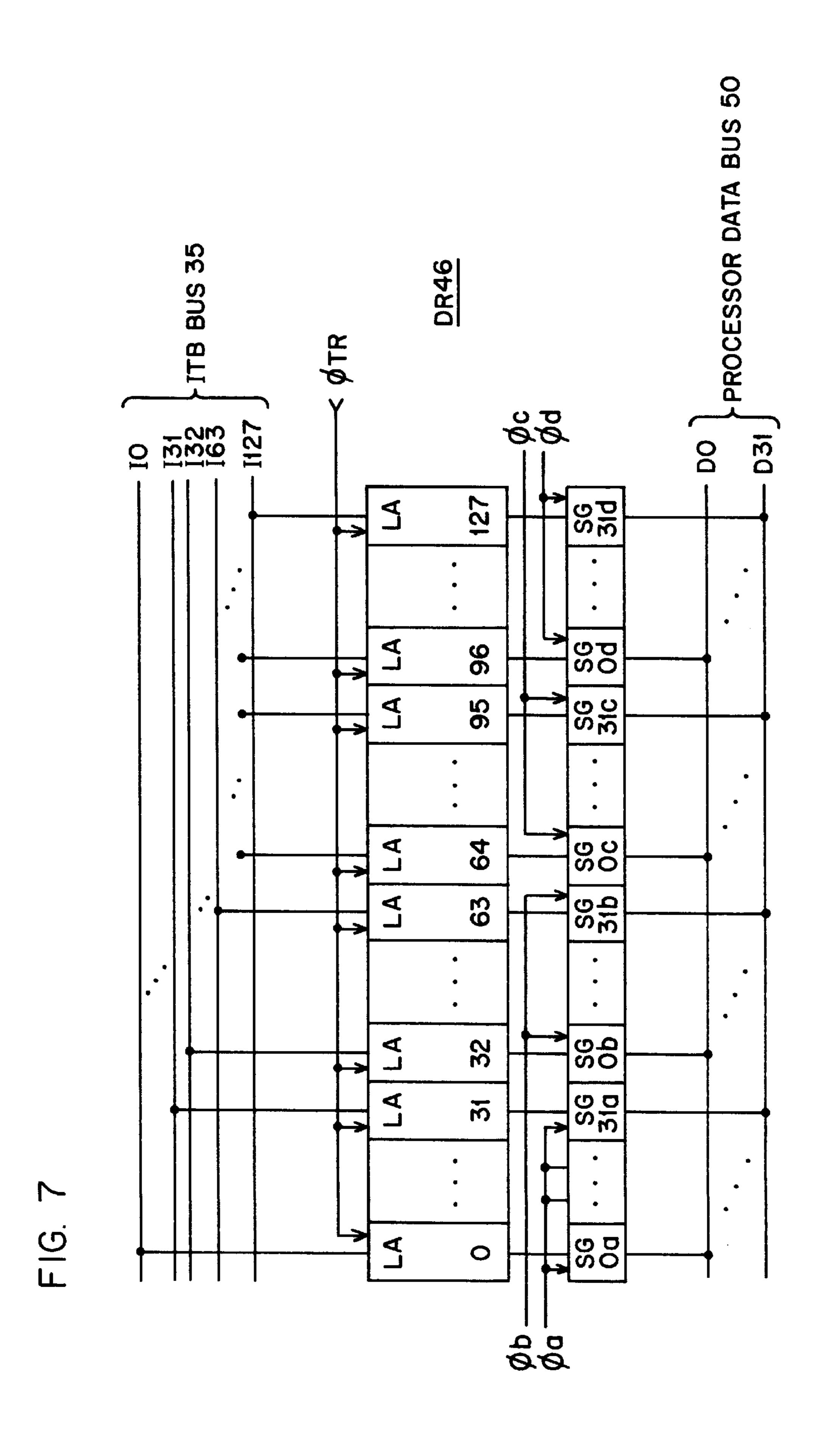

- FIG. 7 is a diagram schematically showing the overall structure of a data register (DR) shown in FIG. 3.

- FIG. 8 is a diagram showing the structure of a 1-bit part of an instruction register shown in FIG. 3.

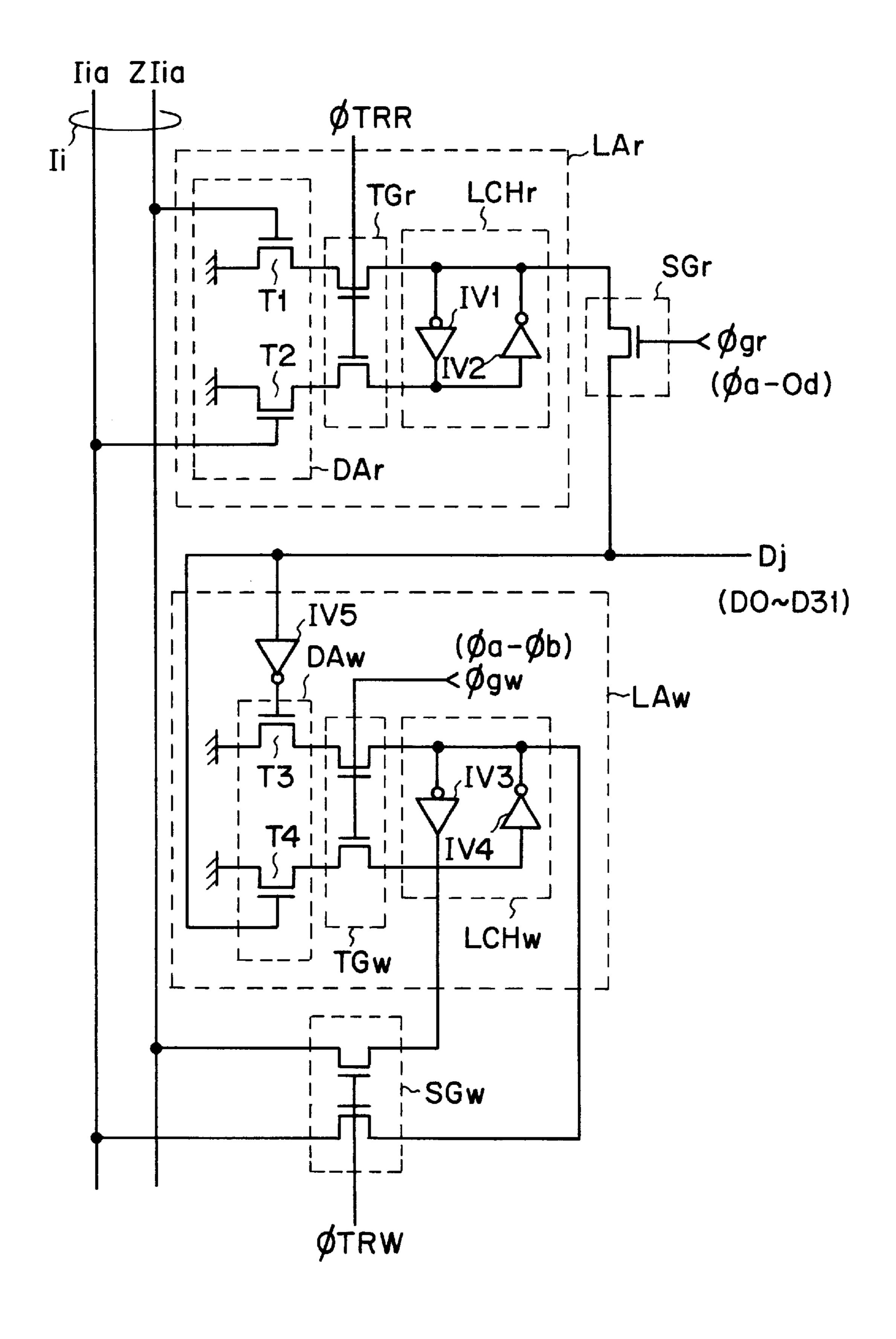

- FIG. 9 is a diagram showing the structure of a 1-bit part of the data register shown in FIG. 7.

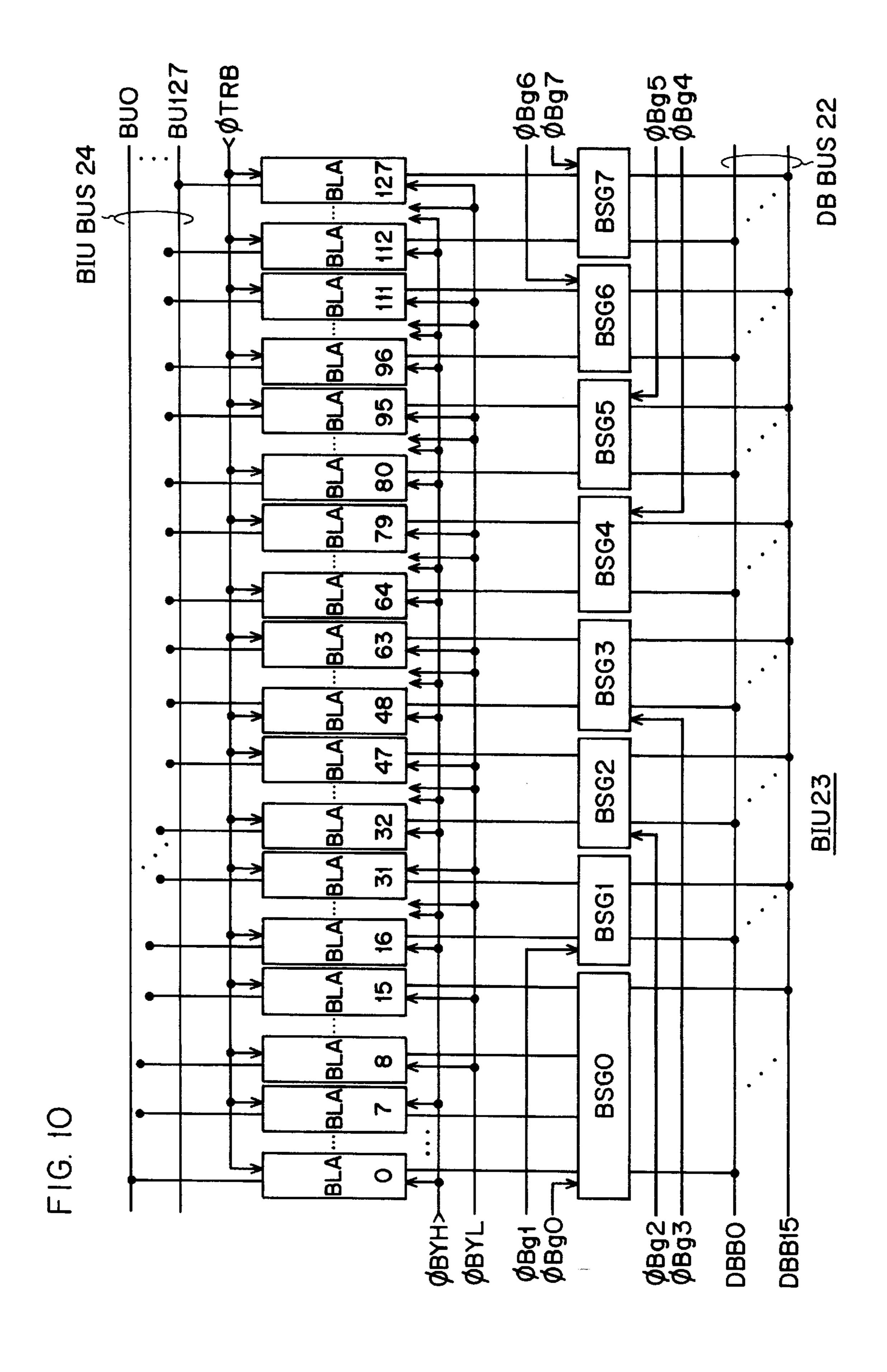

- FIG. 10 is a block diagram schematically showing the overall structure of a bus interface unit (BIU) shown in FIG. 3.

- FIG. 11 is a diagram showing the structure of a 1-bit part of the bus interface unit shown in FIG. 10.

- FIG. 12 is a diagram schematically showing the structure of a DRAM shown in FIG. 3.

- FIG. 13 is a diagram schematically showing the structure of a bidirectional transfer circuit part shown in FIG. 3.

- FIG. 14 is a diagram showing the structure of a 1-bit part of a DRAM read buffer shown in FIG. 13.

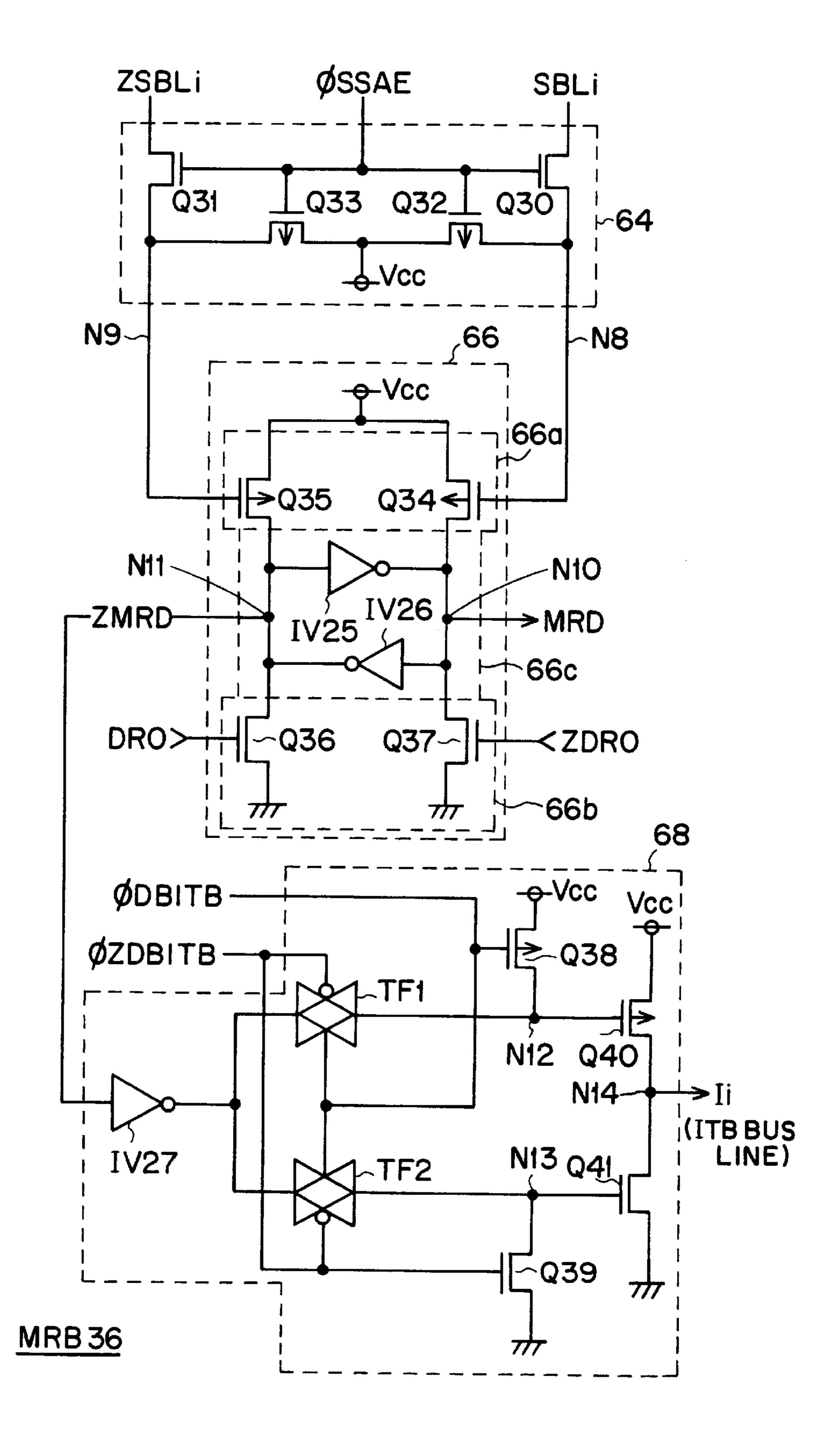

- FIG. 15 is a diagram showing the structure of a 1-bit part of a memory read buffer shown in FIG. 13.

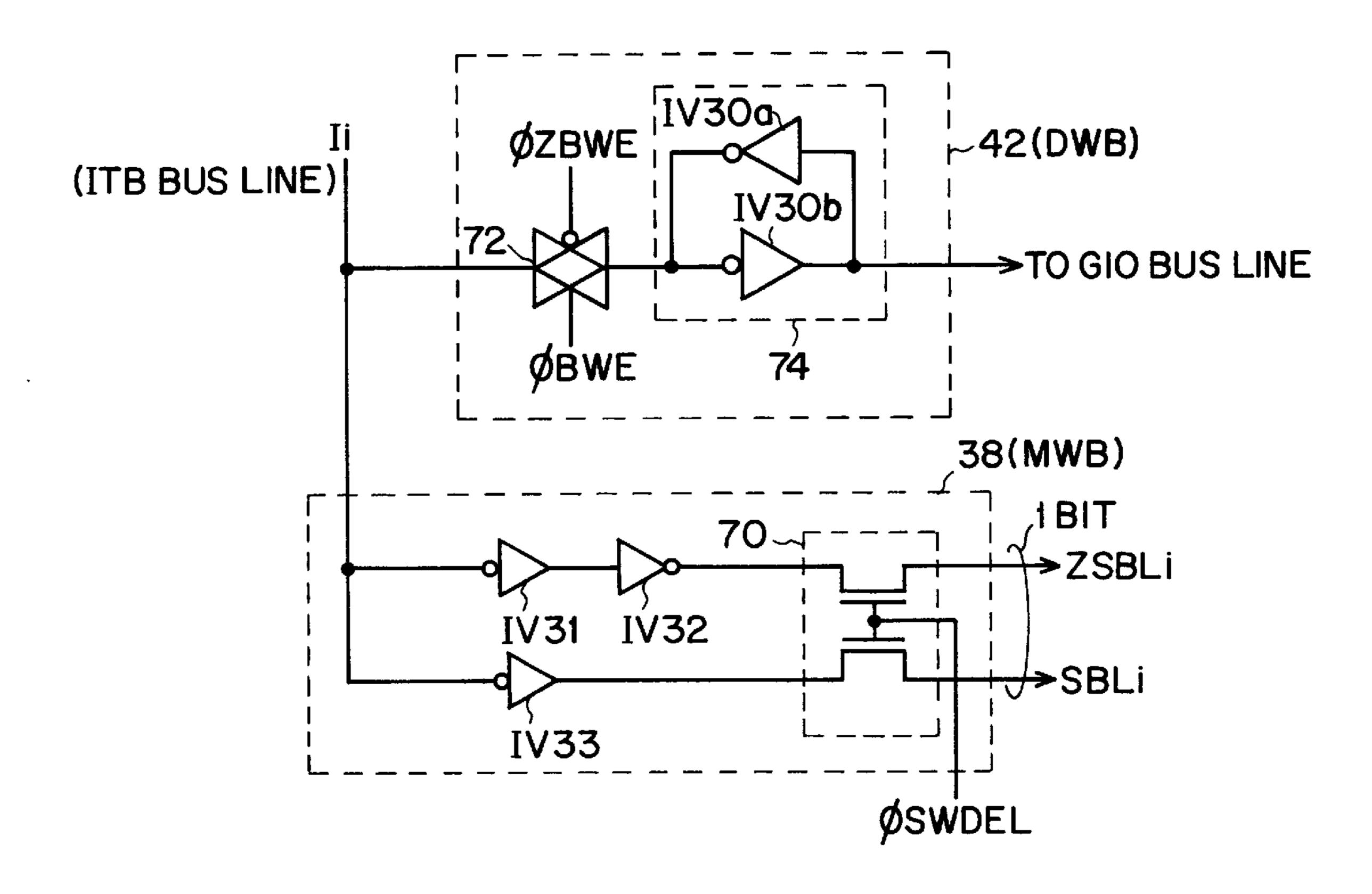

- FIG. 16 is a diagram showing the structures of 1-bit parts of a DRAM writer buffer and a memory write buffer shown in FIG. 3.

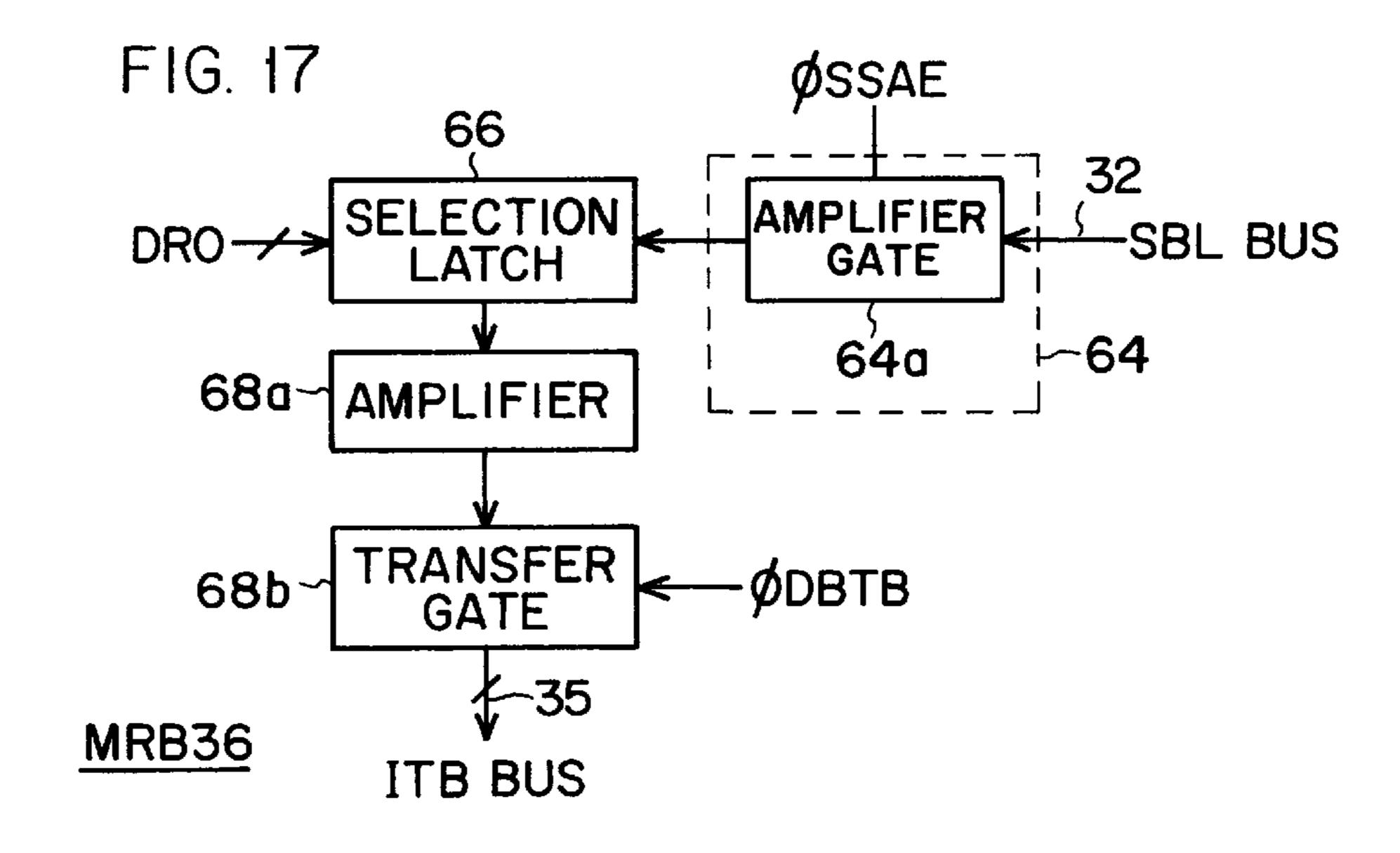

- FIG. 17 is a diagram showing the structure of a modification of the memory read buffer shown in FIG. 13.

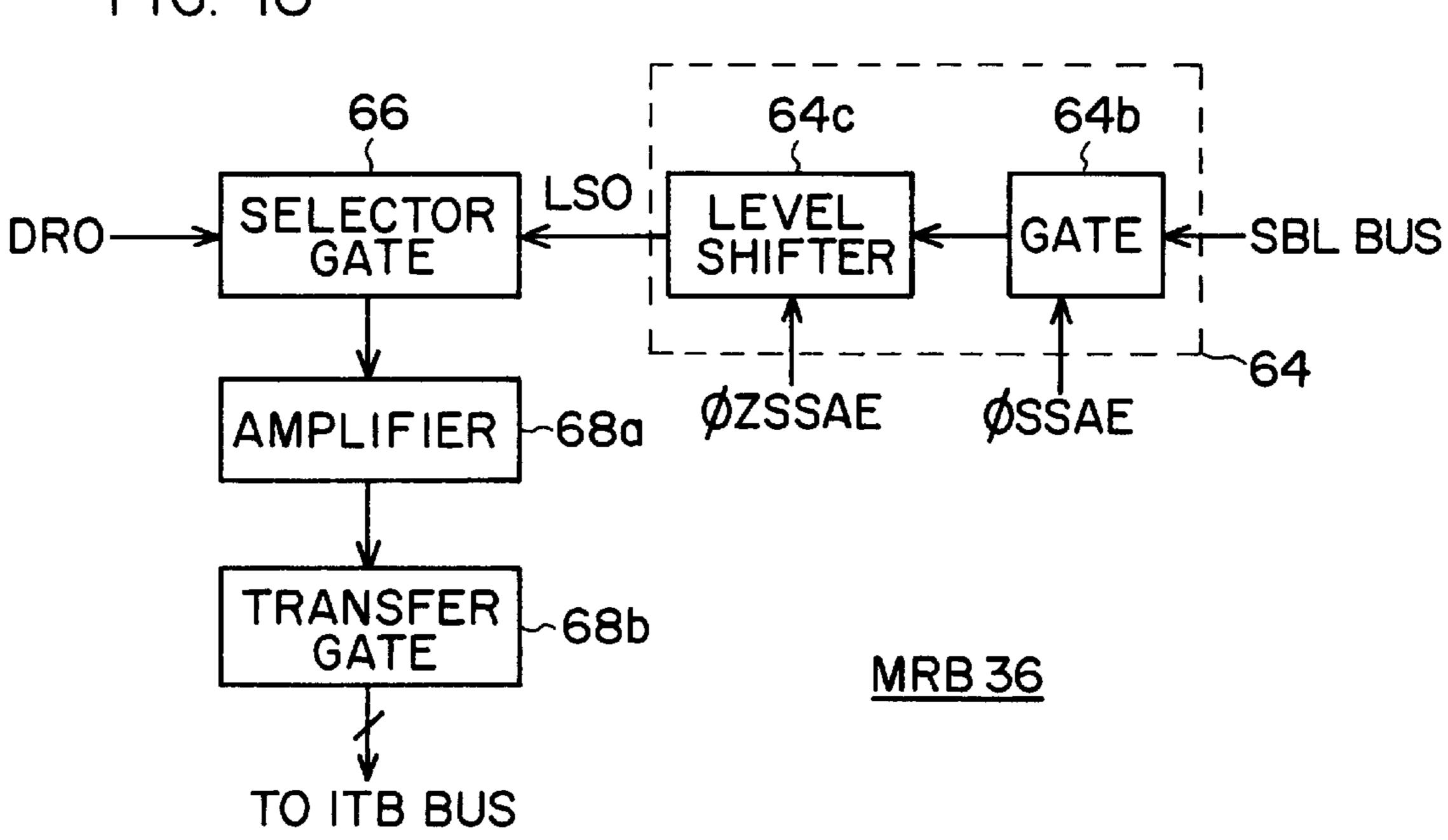

- FIG. 18 is a diagram schematically showing the structure of another modification of the memory read buffer shown in FIG. 13.

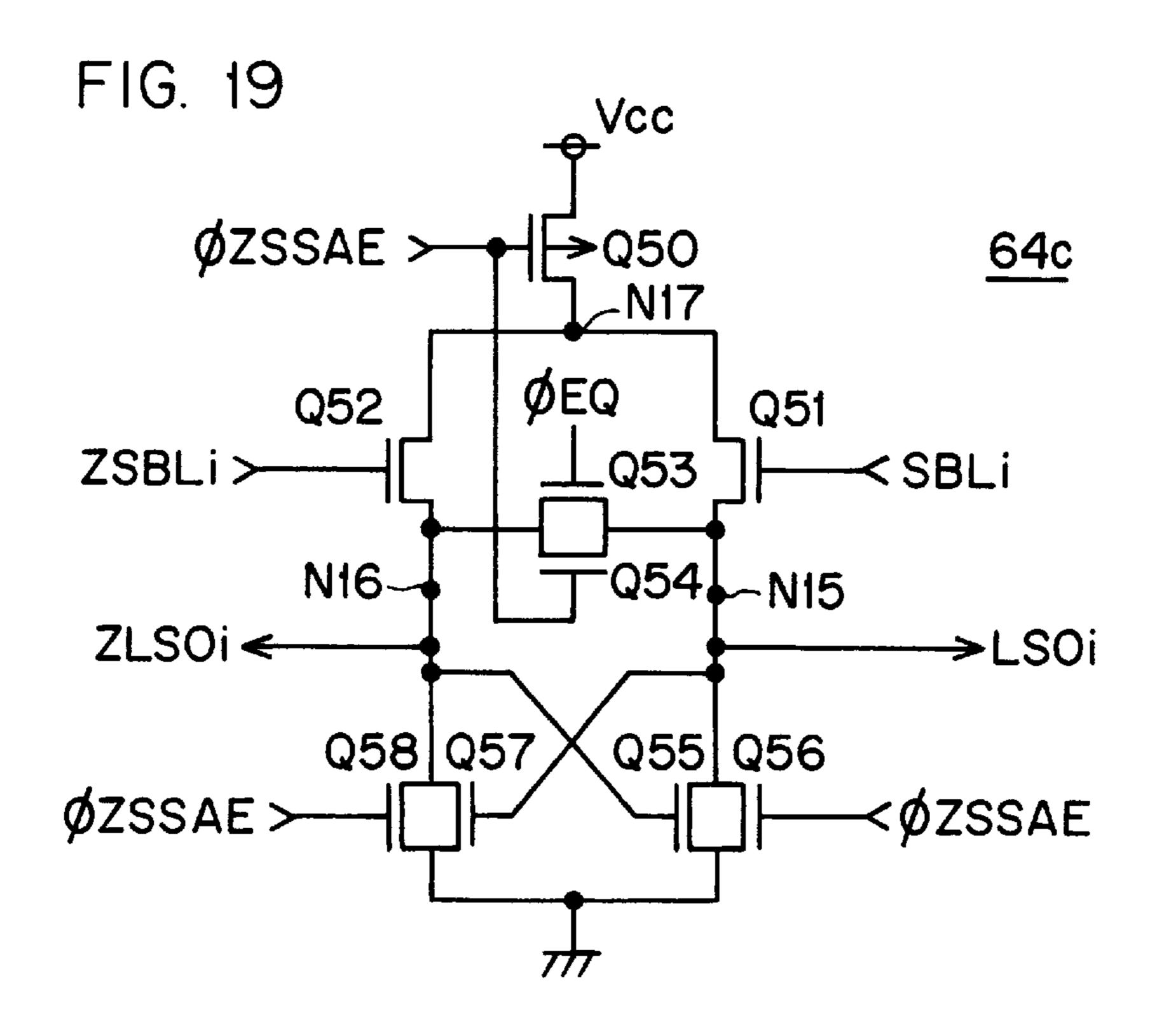

- FIG. 19 is a diagram showing the structure of a 1-bit part of a level shifter shown in FIG. 18.

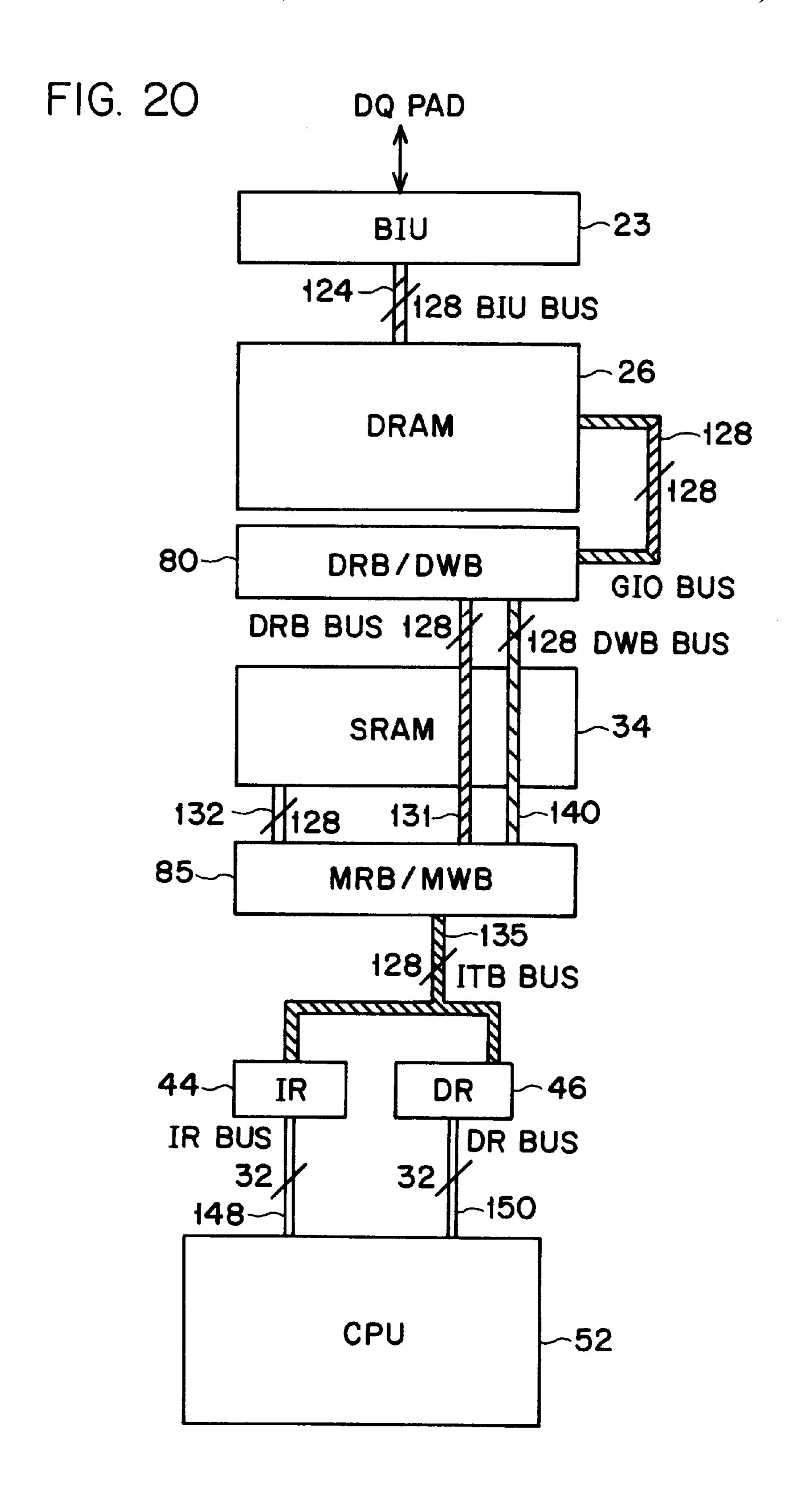

- FIG. 20 is a diagram schematically showing arrangement of bus lines of a microcomputer according to an embodiment 2 of the present invention.

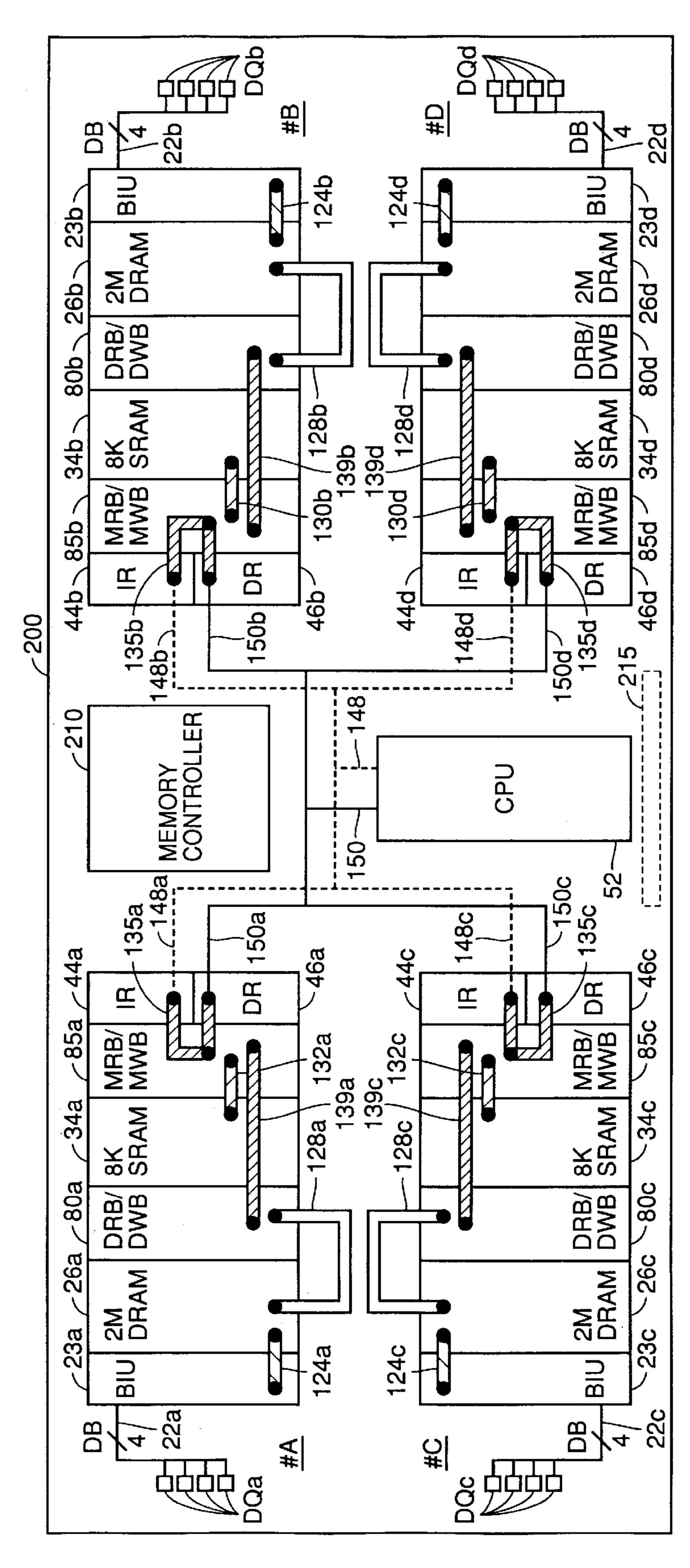

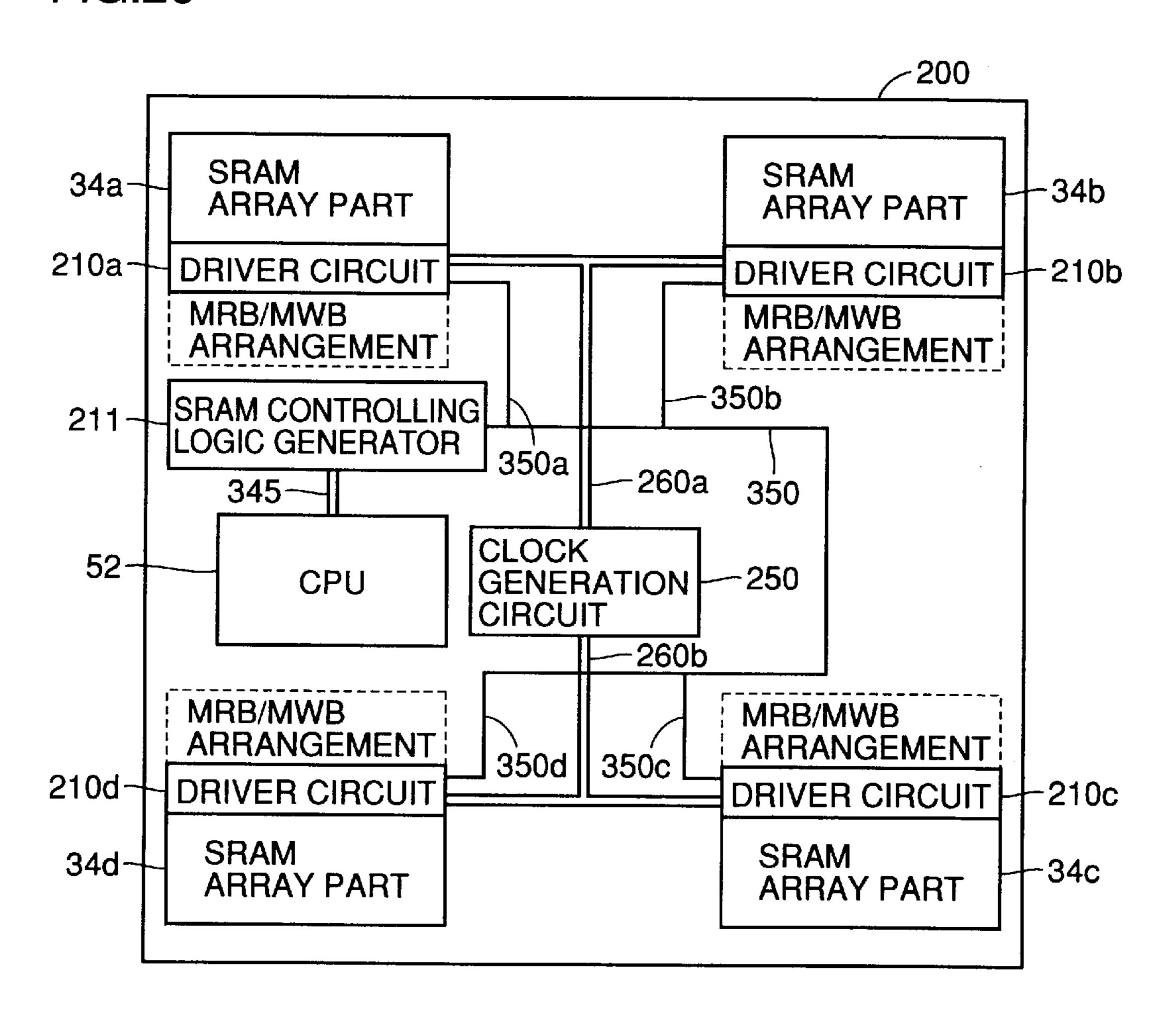

- FIG. 21 is a diagram schematically showing the on-chip layout of the microcomputer according to the embodiment 2 of the present invention.

- FIG. 22 is a diagram schematically showing the structure of a main part of a microcomputer according to an embodiment 3 of the present invention.

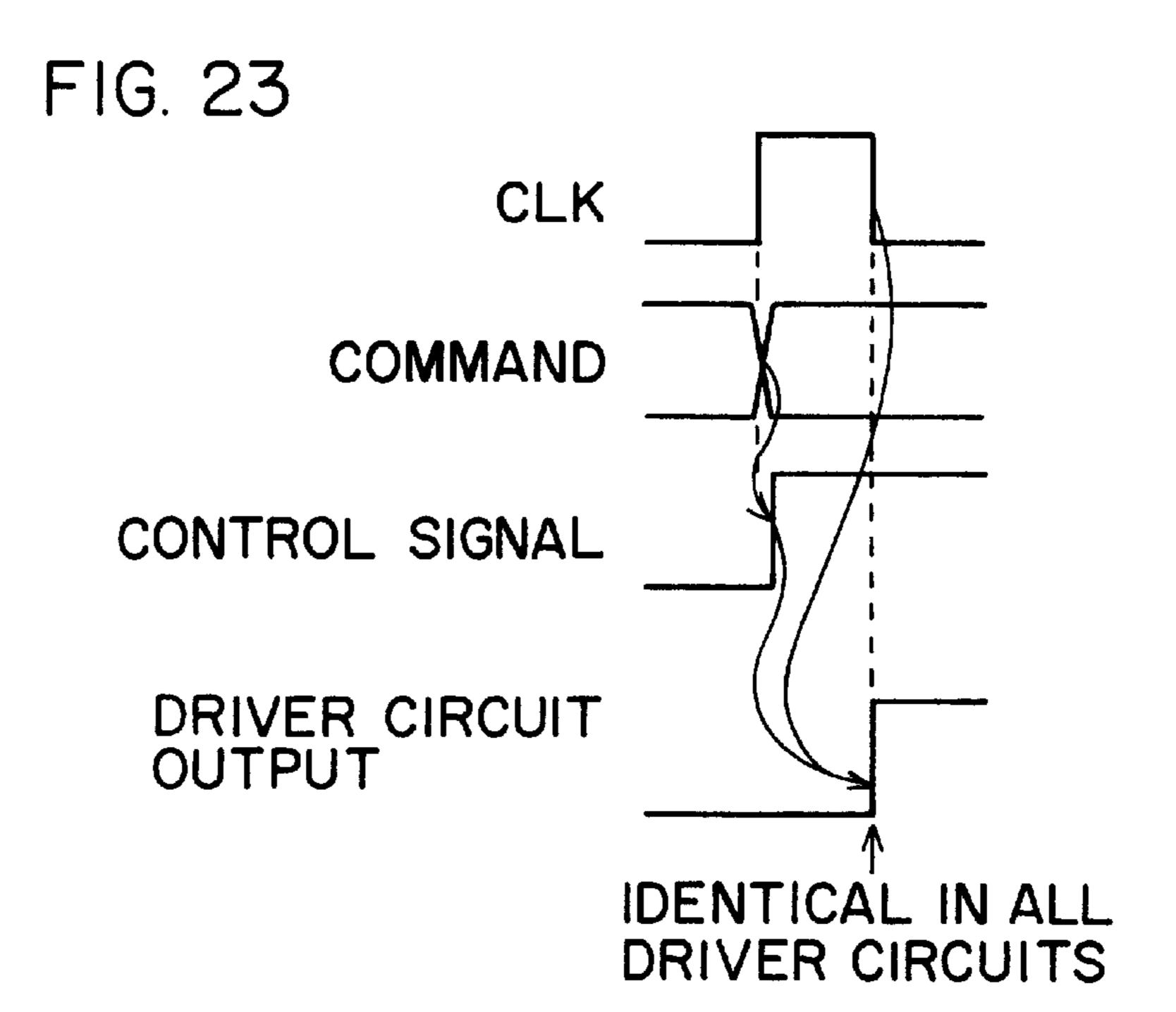

- FIG. 23 is a waveform diagram representing an operation of an SRAM control part shown in FIG. 22.

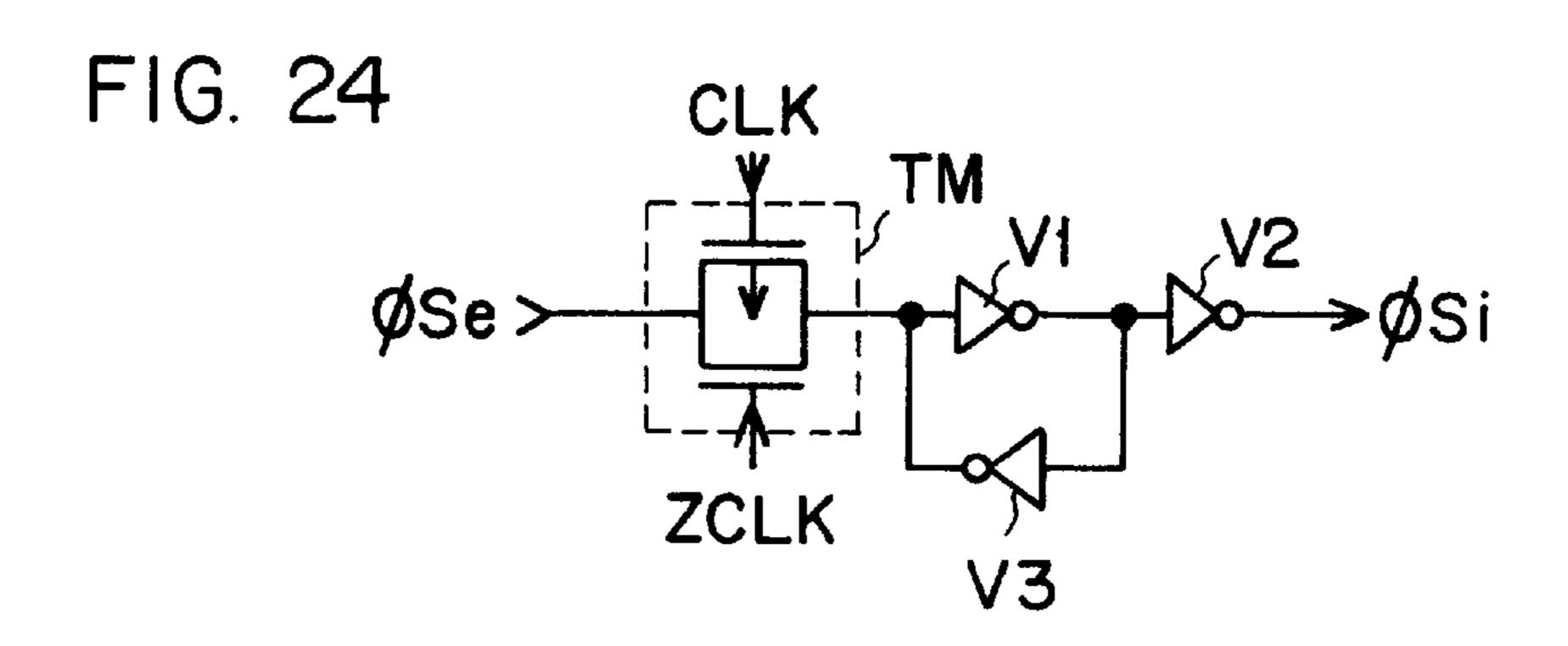

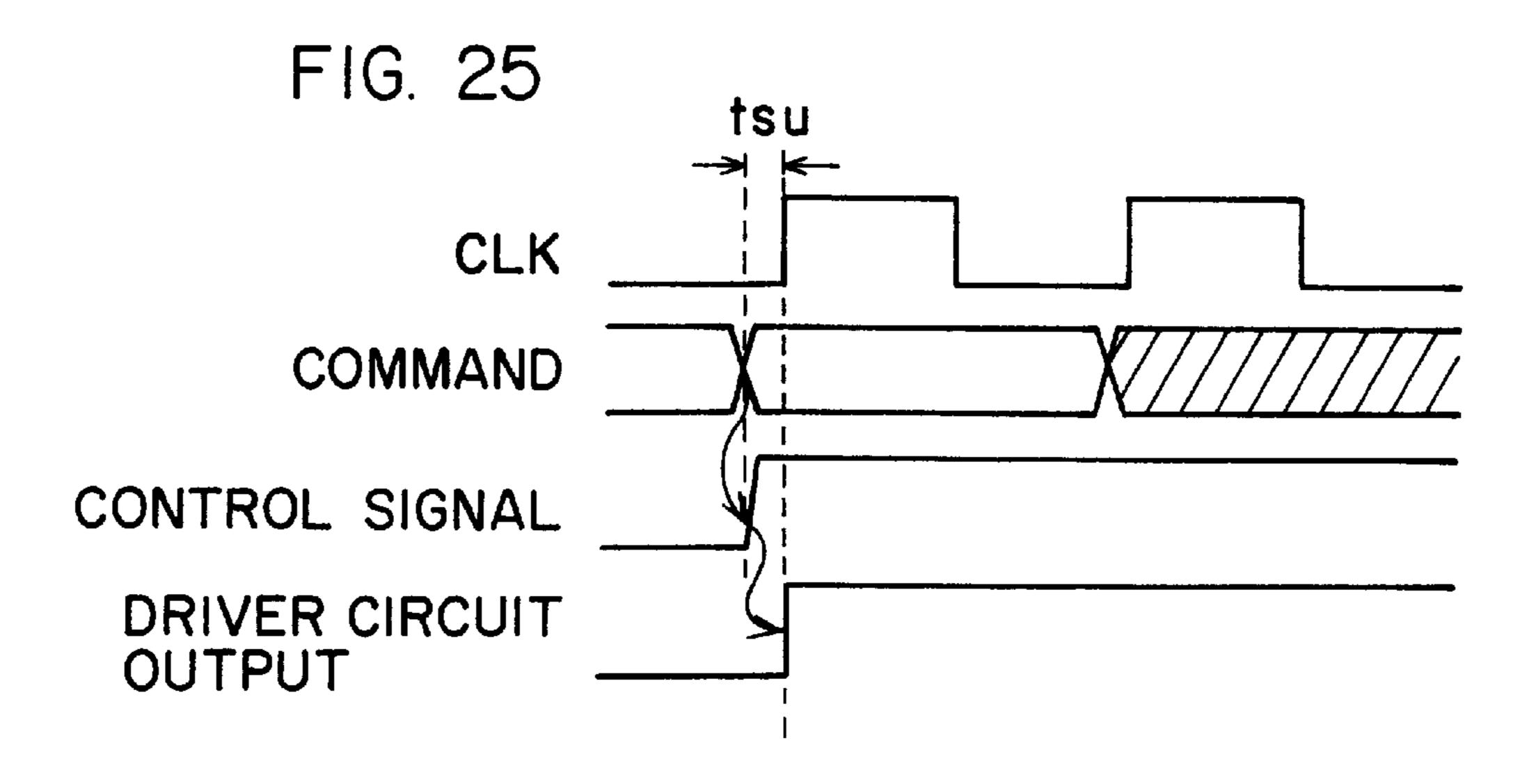

- FIG. 24 is a diagram showing an exemplary structure of an input first stage of a driver circuit shown in FIG. 22.

- FIG. 25 is a diagram showing another operation sequence of the SRAM control part shown in FIG. 22.

- FIG. 26 is a diagram schematically showing the on-chip layout of the microcomputer according to the embodiment 3 of the present invention.

- FIG. 27 is a diagram schematically showing the structure of a main part of a microcomputer according to an embodiment 4 of the present invention.

- FIG. 28 is a diagram schematically showing the structure of a modification of the embodiment 4 of the present invention.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 3 is a block diagram schematically showing the structure of a main part of a microcomputer having a built-in memory according to an embodiment 1 of the present invention. Referring to FIG. 3, the microcomputer 20 includes a DQ pad 21 connected to an external bus and inputting/outputting information, a bus interface unit (BIU) 23 connected to the DQ pad 21 through a DB bus 22 recited

as a first bus and managing and executing information transfer between an exterior and an interior of the microcomputer, and a dynamic random access memory (hereinafter referred to as a DRAM) 26 recited as a first memory connected to the bus interface unit BIU through a 5 BIU bus 24 and transferring stored information with the bus interface unit 23. DRAM 26 is connected to a GIO bus 28 recited as a third bus.

The bus width (bit width) of the DB bus 22 is 16 bits, while the bus width (bit width) of each of the BIU bus 24 and the GIO bus 28 is 128 bits, for example. The bus interface unit 23, the structure of which is described later in detail, includes 128 latches, and executes information transfer in units of 16 bits with an external device and information transfer in units of 128 bits in an internal unit device by selectively connecting these latches to the DB bus 22. Thus, speeding-up of the information transfer in the internal device is attained. The DRAM 26 is a dual port memory having a port connected to the BIU bus 24 and a port connected to the GIO bus 28, and this DRAM 26 can perform information transfer simultaneously with the BIU bus 24 and the GIO bus 28 unless competition of the memory takes place.

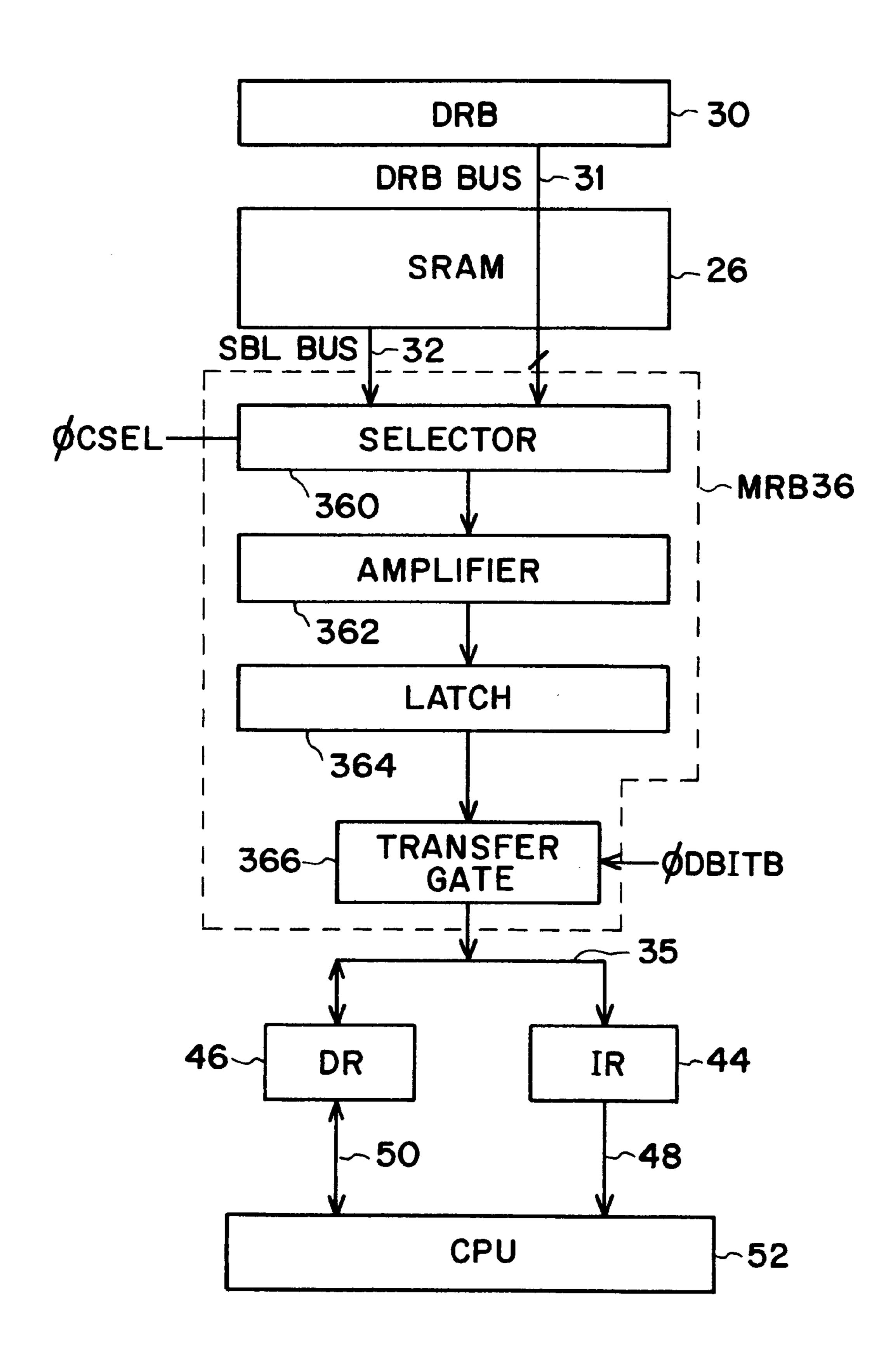

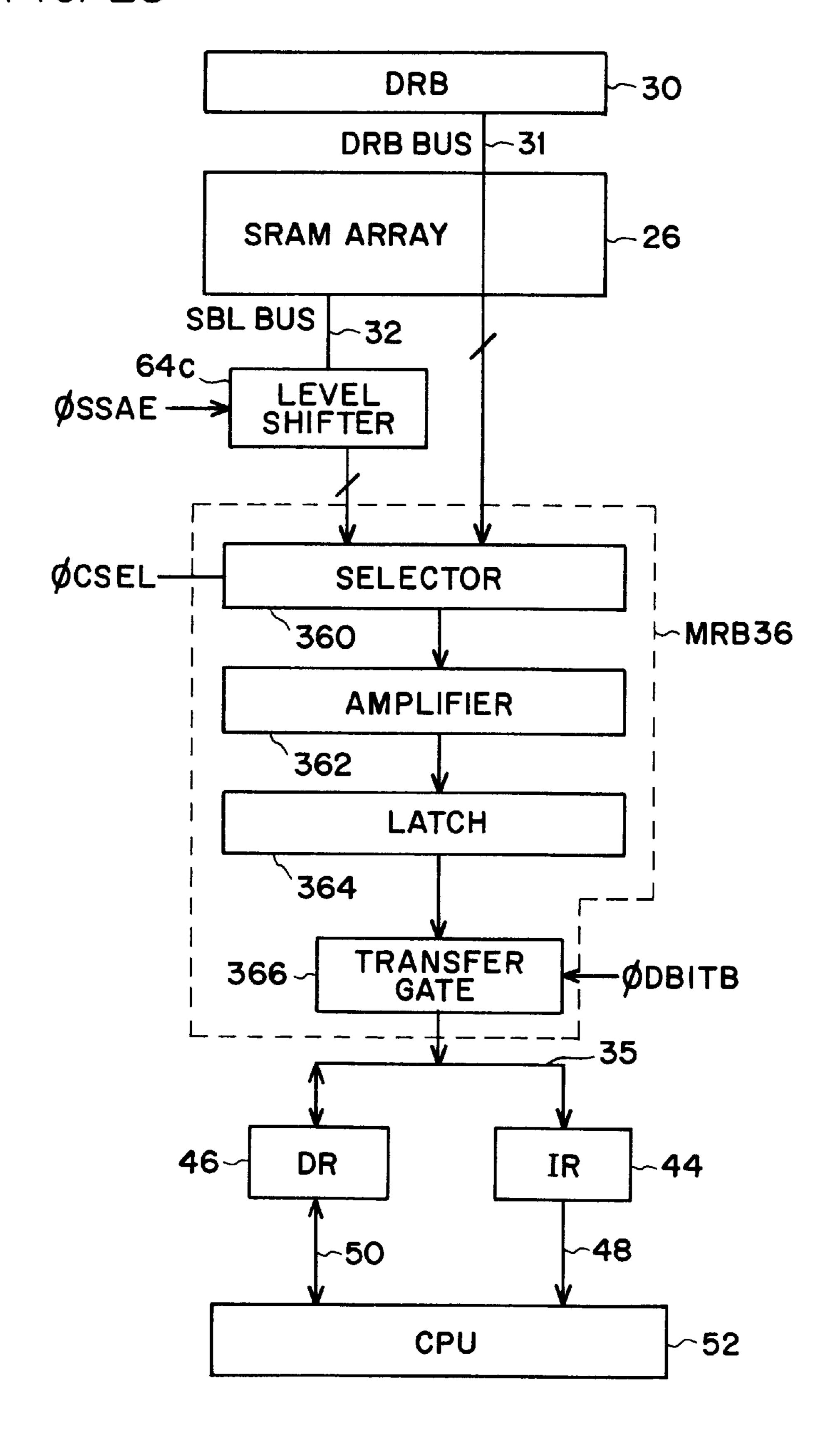

The microcomputer 20 further includes a DRAM read buffer (DRB) 30 for latching information read from the DRAM 26 through the GIO bus 28 for transference to a DRB bus 31, and a memory read buffer (MRB) 36 for latching the information supplied from the DRAM read buffer (DRB) 30 through the DRB bus 31 or information read from a static random access memory (hereinafter referred to as an SRAM) 34 through an SBL bus 32 and transferring the latched information to a memory write buffer (MWB) 38 through an ITB bus 35 or the SBL bus 32. This memory read buffer (MRB) 36 includes a circuit for amplifying the latched information. The bit width of each of the GIO bus 28, the DRB bus 31 and the ITB bus 35 is 128 bits, for example. The bus width of the SBL bus 32 is also 128 bits, and the SRAM 34 inputs/outputs information of 128 bits at once.

The memory write buffer (MWB) 38 latches the information supplied on the ITB bus 35 and the information supplied from the memory read buffer (MRB) 36 through the SBL bus 32 for transference to a DRAM write buffer (DWB) 42 through a DWB bus 40. This memory write buffer (MWB) 38 also has a function of transferring the information supplied through the ITB bus 35 to the SRAM 34 through the SBL bus 32.

The DRAM write buffer (DWB) 42 transfers the information supplied from the memory write buffer (MWB) 38 through the DWB bus 40 to the DRAM 26 through the GIO bus 28. The DWB bus 40 has a bus width of 128 bits. By providing the DRB bus 31 and the DWB bus 40 independently of each other, data transfer from the DRAM 26 to the SRAM 34 and data transfer from the SRAM 34 to the DRAM 26 can be executed in parallel.

The microcomputer 20 further includes an instruction register (IR) 44 storing instructions which are included in the information supplied from the memory read buffer (MRB) 36 through the ITB bus 35, and a data register (DR) 46 which is connected with the ITB bus 35 to bidirectionally perform data transfer for storing data. The instruction register 44 and the data register 46 are connected to a processor (CPU) 52 through an instruction bus 48 and a data bus 50 respectively.

The instruction register (IR) contains latches of the same 65 number as the bus width (bit width) of the ITB bus 35, and simultaneously selects 32 latches among these 128 latches

6

and supplies latch information (instruction) to the processor (CPU) 52 through the instruction bus 48. The data register (DR) also similarly includes 128 latches, and selectively connects 32 latches to the data bus 50 to transfer data with the processor (CPU).

The processor (CPU) 52 has an internal structure shown in FIG. 1, executes processing operations specified by instructions on data with the instructions supplied from the instruction register (IR) 44 and the data supplied from the data register (DR) 46, and stores results of the processing operations in the data register (DR) 46 again.

GIO bus 28 transfers the information at a rate of 30 MHz, for example. On the other hand, ITB bus 35 transfers the information at a rate of about 100 MHz, for example.

FIG. 4 is a diagram illustratively showing an information transfer path in the bus arrangement of FIG. 3. Referring to FIG. 4, arrows show the flow of information. Referring to FIG. 4, the bus interface unit (BIU) 23 bidirectionally transfers the information with the bus interface unit (BIU) 23 through the BIU bus 24. The DRAM 26 transfers the information of a selected memory cell to the DRAM read buffer (DRB) 30 through the GIO bus 28, and DRAM 26 writes the information supplied from the DRAM write buffer (DWB) through the GIO bus 28 in a selected memory cell. DRAM read buffer 30 transfers latched information to the memory read buffer (MRB) through DRB bus 31. On the other hand, DRAM write buffer (DWB) 42 latches the information supplied from the memory write buffer (MWB) 38 through the DWB bus 40, and then transfers the latching information to DRAM 26 through GIO bus 28.

The memory read buffer (MRB) 36 latches and amplifies one of the information supplied through the DRB bus 31 and the information read from the SRAM 34, for transference to the ITB bus 35 or to the memory write buffer (MWB) 38. By performing information transfer from this memory read buffer (MRB) 36 to the memory write buffer (MWB) 38, information transfer from SRAM 34 to DRAM 26 is enabled.

The memory write buffer (MWB) 38 transfers one of the data supplied from the data register (DR) 46 through the ITB bus 35 and the information supplied from the memory read buffer (MRB) 36 to SRAM 34 or DRAM write buffer (DWB) 42.

The instruction register (IR) 44 stores the instructions included in the information supplied to the ITB bus 35, and supplies the instructions to the processor (CPU) 52 through the instruction bus 48. The data register (DR) 46 stores the data included in the information supplied through the ITB bus 35 and supplies the same to the processor (CPU) 52, while storing the data supplied from this processor (CPU) 52 through the data bus 50 and transferring the same to the memory write buffer (MWB) 38 through the ITB bus 35.

A data transfer operation is now described.

(i) When the processor (CPU) **52** issues an information load request to an external device such as an external memory:

Information supplied from the external memory or the like through the DQ pad 21 and the DB bus 22 is stored in the bus interface unit (BIU) 23. The bus interface unit (BIU) 23 transfers externally loaded information through the BIU bus 24 for writing into the DRAM 26. The DRAM 26 transfers this loaded information to the DRAM read buffer (DRB) 30 through the GIO bus 28. The DRAM read buffer (DRB) 30 latches this information supplied from the DRAM 26 through the GIO bus 28, and then transfers the same to the memory read buffer (MRB) 36 through the DRB bus 31.

The memory read buffer (MRB) 36 amplifies this information transferred from the DRAM read buffer (DRB) 30 for transference to the instruction register (IR) 44 and the data register (DR) 46 through the ITB bus 35. This information transferred to the instruction register (IR) 44 and the data register (DR) 46 is transferred to the processor (CPU) 52 through the instruction bus 48 and the data bus 50 respectively.

The ITB bus 35 transfers the information in accordance with a high-speed clock signal of about 100 MHz, for <sup>10</sup> example, while the information is transferred on the GIO bus 28 in accordance with a low-speed clock signal of about 30 MHz, for example, since the information from the DRAM 26 which is a low-speed memory or the bus interface unit (BIU) 23 accessing the external device is transferred to the <sup>15</sup> GIO bus 28.

After the processor (CPU) 52 issues the information load request and before the required information reaches the processor (CPU) 52, therefore, a considerable cycle number of the clock signal driving this ITB bus 35 is required. In this case, the GIO bus 28 and the ITB bus 35 are isolated from each other, and hence the processor (CPU) 52 can utilize the instruction bus 48 and the data bus 50 as well as the ITB bus 35 until the required information reaches the ITB bus 35.

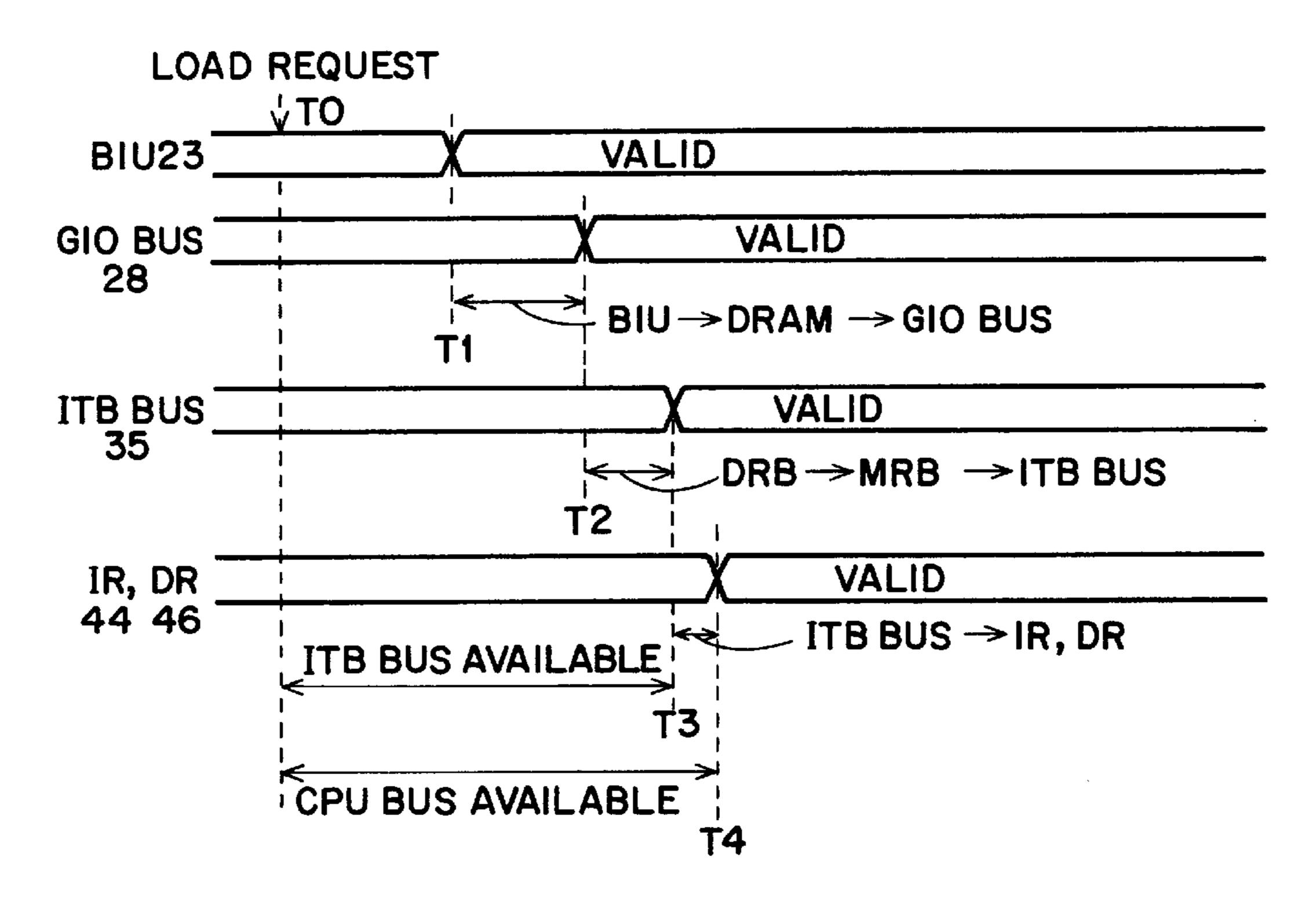

More specifically, when the processor (CPU) 52 generates a load request at a time T0 as shown in an information transfer sequence of FIG. 5, valid information is stored in the bus interface unit (BIU) 23 at a time T1. The information stored in the bus interface unit (BIU) 23 is transferred to the GIO bus 28 through the DRAM 26, and the valid information appears on the GIO bus 28 at a time T2. This valid information on the GIO bus 28 is transferred to the ITB bus 35 through the DRAM read buffer (DRB) and the memory read buffer (MRB), and the valid information is transferred onto the ITB bus 35 at a time T3. This valid information on the ITB bus 35 is transferred to the instruction register (IR) 44 and the data register (DR) 46 respectively, and the valid information requested by the processor (CPU) is stored in the instruction register (IR) 44 and the data register (DR) 46 at a time T4. After the time T4, the processor (CPU) can access the required load-requested information in the instruction register (IR) 44 and the data register (DR) 46.

When a load request to the external memory or the like is issued as shown in this FIG. 5, therefore, the processor (CPU) can access the SRAM 34 through this ITB bus 35 and can access the instruction register (IR) 44 and the data register (DR) 46 through a CPU bus (including both of the instruction bus 48 and the data bus 50) up to the time T3 when the valid information is transferred onto the ITB bus 35. Up to the time T4 when the valid information is stored in the instruction register (IR) 44 and the data register (DR) 46, further, the processor (CPU) can access the instruction register (IR) 44 and the data register (DR) 46 through the CPU bus (the instruction bus 48 and the data bus 50) to perform a processing.

By providing the GIO bus 28, the ITB bus 35 and the CPU bus (the instruction bus 48 and the data bus 50) independently of each other, therefore, the processor (CPU) can execute a processing through an available bus until the load-requested information arrives, and reduction in processing performance upon data transfer from the external device is suppressed.

(ii) When the processor issues a data store request for storing data in the external memory or the like:

An operation in data store request issuance is described also with reference to a timing chart shown in FIG. 6.

8

At a time T0, the processor (CPU) 52 generates a store request while storing data to be stored in the data register (DR) 50 through the data bus 50, and valid data is stored in the data register (DR) 50 at a time T1. The data stored in the data register (DR) 50 is transferred to the memory write buffer (MWB) 38 through the ITB bus 35 and stored therein. The data stored in the memory write buffer (MWB) 38 is transferred to the DRAM write buffer (DWB) 42 through the DWB bus 40 and latched therein. The memory write buffer (MWB) 38 has a latch function. After the data to be stored is stored in memory write buffer (MWB) 38, therefore, the processor (CPU) 52 can access the SRAM 34 and the instruction register (IR) 44 and the data register (DR) 46 through the ITB bus 35 and the CPU bus (the instruction bus 38 and the data bus 50) for executing a processing. This ITB bus 35 is a high-speed bus, and the processor (CPU) 52 can execute a required processing at a high speed after transferring the data to be stored to and storing them in the memory write buffer (MWB) 38 through the data register (DR) 50, and performance reduction of this microcomputer is suppressed.

The data (brought into a valid state at a time T3) latched in the DRAM write buffer (DWB) 42 is transferred to and stored in the DRAM 26 through the low-speed GIO bus 28. The GIO bus 28 is a low-speed bus and the valid data appears thereon at a time T4, and the valid data is stored in the DRAM 26 at a time T5. The DRAM 26 is a two-port memory, and the valid data can be stored from the DRAM 26 in the bus interface unit (BIU) 23 at a relatively fast timing by performing the writing and reading in the same cycle. Thus, the valid data in the bus interface unit 23 which is brought into the valid state is successively transferred to the exterior in units of 16 bits and stored in the external memory at a time T6. Also when the data store operation for the external memory is done in this microcomputer, therefore, the internal processor (CPU) 52 can access the SRAM 34 through the ITB bus 35 after the time T2, while the GIO bus 28 becomes available after the time T5 and reduction of the processing performance can be suppressed.

When only data transfer between the external memory and the DRAM 26 is performed, the processor (CPU) 52 can execute required processings by constantly utilizing the ITB bus 35, the instruction bus 48 and the data bus 50, as apparent from the timing chart diagrams shown in FIG. 5 and FIG. 6.

By connecting the bus interface unit (BIU) for performing data input/output with the external device only to the DRAM, isolating any buses (the ITB bus 35, the instruction bus 48 and the data bus 50) accessed by the processor (CPU) from the bus interface unit (BIU), providing the buffers (DRB, DWB, MRB and MWB) recited as bidirectional transfer means between the GIO bus 28 connected with the DRAM 26 and the ITB bus 35, and providing these with latch functions, as hereinabove described, the internal ITB bus can be brought into a free state so that the processor (CPU) can utilize the same also in information transfer of this microcomputer with an external device, and the processing performance can be improved due to no interruption of processing in external transfer of the information.

The DB bus 22 between the bus interface unit (BIU) and the DQ pad may be of such a structure that a bus for inputting formation and a bus for outputting information are provided independently of each other.

[Structures of Respective Parts]

(1) Structure of Data Register (DR) 46

FIG. 7 is a diagram schematically showing the overall structure of the data register (DR) 46 shown in FIG. 3 and

FIG. 4. Referring to FIG. 7, the data register (DR) 46 includes latch amplifiers LA0 to LA127 which are provided in correspondence to bus lines I0 to I127 of the ITB bus 35 respectively and connected with the corresponding bus lines in response to activation of a transfer instruction signal φTR. These latch amplifiers LA0 to LA127, the structure of which is described later in detail, include both of read buffers for transferring data from the ITB bus 35 to the processor (CPU) and write buffers for transferring data supplied from the processor (CPU) to the ITB bus 35. Each of these amplifies and latches supplied data when activated.

9

The data register (DR) 46 further includes selecting gates SG0a to SG31a which are provided in correspondence to the latch amplifiers LA0 to LA31 respectively and conduct in response to a group selection signal  $\phi$ a for connecting the latch amplifiers LA0 to LA31 to bus lines D0 to D31 of the processor data bus 50, selection gates SG0b to SG31b which are provided in correspondence to the latch amplifiers LA32 to LA63 respectively and conduct in response to a group selection signal  $\phi$ b for connecting the latch amplifiers LA32 to LA63 to the data bus lines D0 to D31 respectively, 20 selection gates SG0c to SG31c which are provided in correspondence to the latch amplifiers LA64 to LA95 respectively and conduct in response to a group selector signal  $\phi c$  for connecting the respective latch amplifiers LA64 to LA95 to the data bus lines D0 to D31, and selection 25 gates SG0d to SG31d which are provided in correspondence to the latch amplifiers LA96 to LA127 respectively and conduct in response to a group selection signal  $\phi d$  for connecting the latch amplifiers LA96 to LA127 to the data bus lines D0 to D31 respectively.

Transfer of information of different bit widths can be performed by making the bus widths of the ITB bus 35 and the processor data bus 50 different from each other, and there is no requirement to deteriorate the processing performance of the processor (CPU) 52. Further, the bus width of the data 35 bus 50 for the processor (CPU) 52 is small, and the layout area required for the bus in the vicinity of this processor (CPU) 52 can be reduced.

In this structure of the data register (DR) 46 shown in FIG. 7, the bus lines I0 to I127 of the ITB bus 35 and the latch 40 amplifiers LA0 to LA127 simultaneously transfer data of 128 bits in accordance with the transfer instruction signal φTR. Among these latch amplifiers LA0 to LA127 of 128 bits, latch amplifiers of 32 bits are selectively connected to the processor data bus 50 (the data bus lines D0 to D31) in 45 accordance with the group selection signals φa to φd.

FIG. 8 is a diagram showing exemplary a structure of one bit of each of the latch amplifiers and the selection gates shown in FIG. 7. Referring to FIG. 8, the structures of a latch amplifier and a selection gate provided for a bus line Ii and 50 a data bus line Dj of the ITB bus 35 are shown as an example. The ITB bus line Li includes complementary signal lines Iia and ZIia.

The latch amplifier includes a read latch amplifier LAr which is activated in response to a transfer instruction signal 55 φTRR for amplifying and latching complementary signals on the ITB bus line Ii, and a write latch amplifier LAw for amplifying and latching a signal on the data bus line Dj. The selection gate SG includes a read selection gate SGr which conducts in response to a group selection signal φgr for 60 transferring the latch data of the read latch amplifier LAr to the data bus line Dj, and a write selection gate SGw transferring the latch information of the write latch amplifier LAw to the ITB bus signal lines Iia and ZIia in response to a transfer instruction signal φTRW.

The transfer instruction signals  $\phi$ TRR and  $\phi$ TRW are supplied in common to the latch amplifiers LA0 to LA126

in both read transfer and write transfer. The group selection signals  $\phi$ gr and  $\phi$ gw are supplied only to a latch amplifier group of a selected group in both read transfer and write transfer.

**10**

The read latch amplifier LAr includes a differential amplifier DAr differentially amplifying signal potentials on the signal lines Iia and ZIia, a transfer gate TGr conducting in response to the read transfer instruction signal φTRR, and a latch circuit LCHr amplifying and latching data from the differential amplifier circuit DAr transmitted through the transfer gate TGr. The differential amplifier circuit DAr includes an n-channel MOS transistor (insulated gate field effect transistor) T1 connected between the transfer gate TGr and a ground potential with a gate thereof connected to the signal line ZIia, and an n-channel MOS transistor T2 connected between a ground node and the transfer gate TGr with a gate thereof connected to the signal line Iia. The latch circuit LCHr includes an invertor circuit IV1 having an input part connected to a drain node of the MOS transistor T1 through the transfer gate TGr, and an invertor circuit IV2 having an input part connected to a drain node of the MOS transistor T2 through the transfer gate TGr. The transfer gate TGr includes n-channel MOS transistors which are provided in correspondence to the MOS transistors T1 and T2 respectively. The read selection gate SGr includes a transfer gate which conducts in response to the group selection signal \( \phi \)gr for transmitting an output signal of the invertor IV2 to the data line Dj. While one n-channel MOS transistor is typically shown as the transfer gate included in this read selector 30 gate SGr, the transfer gate may be formed by a CMOS transmission gate. Further, this read selection gate SGr may be formed by a tri-state buffer.

The write latch amplifier LAw includes an invertor circuit IV5 inverting a signal on the data line Dj, a differential amplifier circuit DAw differentially amplifying an output signal of the invertor circuit IV5 and the signal of the data line Dj, a transfer gate TGw transmitting an output signal of this differential amplifier circuit DAw in response to the group selection signal  $\phi$ gw, and a latch circuit LCHw latching the output signal of the differential amplifier circuit DAw transmitted through the transfer gate TGw.

The differential amplifier circuit DAw includes an n-channel MOS transistor T3 connected between the transfer gate TGw and a ground node and receiving the output signal of the invertor circuit T5 at a gate thereof, and an n-channel MOS transistor T4 connected between a ground node and the transfer gate TGw with a gate thereof connected to the data line Dj. The transfer gate TGw includes transfer gate transistors provided in correspondence to the MOS transistors T3 and T4 respectively.

The latch circuit LCHw includes an invertor circuit IV3 having an input part connected to a drain node of the MOS transistor T3 through the transfer gate TGw, and an invertor circuit IV4 having an input part connected to a drain node of the MOS transistor T4 through the transfer gate TGw.

The write selection gate SGw includes a transfer gate transistor pair conducting in response to the write transfer instruction signal  $\phi$ TRW for transferring output signals of the invertor circuits IV3 and IV4 to the signal lines ZIia and Iia respectively. The operation is now briefly described.

It is assumed now that the signal on the signal line Iia is at a high level and the signal on the signal line ZIia is at a low level. In this state, the conductance of the MOS transistor T1 becomes smaller than the conductance of the MOS transistor T2 in the differential amplifier circuit DAr. When the read transfer instruction signal \$\phi TRR\$ enters an active state (high level), the transfer gate TGr is brought into a

conducting state, and the MOS transistors T1 and T2 of the differential amplifier circuit DAr are connected to the invertor circuits IV1 and IV2 respectively. The potential of an input node of the invertor circuit IV2 reduces since the conductance of the MOS transistor T2 is larger than the 5 conductance of the MOS transistor T1. This potential reduction of the input node of the invertor circuit IV2 is amplified and latched by the invertor circuit IV2 and the invertor circuit IV1. Thus, a small potential difference detected by the differential amplifier circuit DAr is amplified and latched 10 by the latch circuit LCHr. When the group selection signal \$\phi\$gr then enters an active state (high level), the read selection gate SGr conducts, and the output signal (high level) of the invertor circuit IV2 is transmitted to the data line Dj, and transmitted to the processor.

In data transfer from the processor to the ITB bus, the write latch amplifier circuit LAw is activated. When data of a high level is transferred onto the data line Dj, the output signal of the invertor circuit IV5 is at a low level. In this state, the conductance of the MOS transistor T3 becomes 20 smaller than that of the MOS transistor T4 in the differential amplifier circuit DAw. When the group selection signal φgw shifts to an active state (high level), the transfer gate TGw is brought into a conducting state, and the differential amplifier circuit DAw is connected to the latch circuit 25 LCHw. Due to the large conductance of the MOS transistor T4, the potential of the input node of the invertor circuit IV4 reduces. This potential reduction is amplified and latched by the invertor circuits IV4 and IV3 (the MOS transistor T3 is substantially in an OFF state). Then, the write transfer 30 instruction signal  $\phi$ TRW shifts to an active state (high level), and the selection gate SGw conducts. Thus, the signal of a low level outputted from the invertor circuit IV3 and the signal of a high level outputted from the invertor circuit IV4 are transmitted to the signal lines ZIia and Iia respectively. 35

The instruction register (IR) is merely required to transfer instructions to the processor (CPU) through the instruction bus. This instruction register (IR) also has a structure substantially identical to the data register (DR) 46 shown in 40 FIG. 7.

[Structure of Instruction Register (IR)]

FIG. 9 is a diagram schematically showing a structure of a 1-bit of the instruction register (IR). An instruction register IRi provided in correspondence to the ITB bus line Ii is shown in FIG. 9. Referring to FIG. 9, the instruction register 45 IRi includes two latch amplifiers ILAa and ILAb connected to the ITB bus line Ii in parallel with each other.

The latch amplifier ILAa is activated in response to a transfer instruction signal  $\phi$ TRIa, for amplifying and latching the complementary signals on the ITB bus line Ii. The 50 latch amplifier ILAb is activated in response to a transfer instruction signal  $\phi$ TRIb, for amplifying and latching the complementary signals on this ITB bus line Ii. FIG. 9 shows only the structure of the latch amplifier ILAa. The latch amplifier ILAb has a structure similar to the latch amplifier 55 ILAa.

The latch amplifier ILAa includes a differential amplifier circuit IDA differentially amplifying the signals on the signal lines Iia and ZIia of the bus line Ii, a transfer gate ITG conducting in response to the transfer instruction signal 60  $\phi$ TRIa for transmitting an output signal of the differential amplifier circuit IDA, and a latch circuit ILCH amplifying and latching the signal transmitted through the transfer gate ITG.

The differential amplifier IDA includes an n-channel 65 MOS transistor T5 thereof connected between a ground node and the transfer gate ITG with a gate thereof connected

nected between a ground node and the transfer node ITG with a gate thereof connected to the signal line ZIia.

The transfer gate ITG includes two MOS transistors (transfer gate transistors) provided in correspondence to the

to the signal line Iia, and an n-channel transistor T6 con-

The transfer gate ITG includes two MOS transistors (transfer gate transistors) provided in correspondence to the MOS transistors T5 and T6 respectively and conducting in activation of the transfer instruction signal φTRIa. This transfer gate ITB may be formed by a CMOS transmission gate.

The latch circuit ILCH includes an invertor circuit IV6, having an input part connected to a drain of the MOS transistor T6 through the transfer gate ITG, and an invertor circuit IV7 whose input part is connected to a drain of the MOS transistor T5 through the transfer gate ITG.

The instruction register IRi further includes a multiplexer MUX selecting an output signal of one of the latch amplifiers ILAa and ILAb in response to a selection signal φISEL, and a selection gate ISG conducting in response to a group selection signal φIg for transmitting the signal selected in the multiplexer MUX to an instruction bus line IRBj. While the selection gate ISG is shown being formed by one MOS transistor in FIG. 10, this selection gate ISG may be formed by a CMOS transmission gate or a tri-state buffer.

The transfer instruction signal  $\phi$ TRIa is supplied in common to the latch amplifier ILAa provided for each ITB bus line of the instruction register IR. The transfer instruction signal  $\phi$ TRIb is supplied in common to the latch amplifier ILAb in each register of the instruction register (IR). One of the transfer instruction signals  $\phi$ TRIa and  $\phi$ TRIb is brought into an active state. The group selection signal  $\phi$ Ig selects instruction registers of 32 bits.

Operations of the latch amplifiers ILAa and ILAb in activation thereof are identical to that of the data register (DR) (see FIG. 8), and the signals of the signal lines Iia and ZIia are differentially amplified by the differential amplifier circuit IDA, and an output signal of the differential amplifier circuit IDA is transferred to the latch circuit ILCH and further amplified and latched therein in conduction of the transfer gate ITG. Therefore, signals of the ITB bus lines IO to I127 of 128 bits are simultaneously latched by the latch amplifier ILAa or ILAB of 128 bits of the instruction register (IR). Then, one of the latch amplifiers ILAa and ILAb is selected in accordance with the selection signal  $\phi$ ISEL. Further, instructions of 32 bits are selected from these instructions of 128 bits in accordance with the group selection signal  $\phi$ Ig, transferred to the instruction bus line (IRB) 48 and supplied to the processor 52.

The latch amplifiers ILAa and ILAb are provided in each bit of the instruction register (IR). A next instruction is stored in a first latch amplifier while transmitting instruction information stored in a second latch amplifier. Thus, instructions can be successively transferred to the processor (CPU) 52 in a pipeline mode, and high-speed instruction transfer can be implemented.

By providing the instruction register (IR) and the data register (DR) independently of each other, further, instructions and data can be simultaneously transferred to the processor (CPU) 52, and a high-speed information transfer operation can be implemented.

(3) Bus Interface Unit (BIU)

FIG. 10 is a diagram schematically showing the overall structure of the bus interface unit (BIU) shown in FIG. 3 and FIG. 4. Referring to FIG. 10, the bus interface unit (BIU) 23 includes latch amplifiers BLA0 to BLA127 provided in correspondence to bus lines BU0 to BU127 of the BIU bus 24 respectively, activated in response to a transfer instruction signal φTRB to be connected with the corresponding bus lines BU0 to BU127.

Each of the latch amplifiers BLA0 to BLA127 includes a latch amplifier circuit for information transfer from the BIU bus 24 to the DB bus 22 and a latch amplifier circuit for information transfer from the DB bus 22 to the BIU bus 24. The latch amplifiers BLA0 to BLA127 are divided into 5 groups in a unit of eight latch amplifiers, and brought into operating states in response to byte control signals φBYH and φBYL. By employing these byte control signals φBYH and φBYL, it is possible to handle both of 16-bit information and 8-bit information.

The bus interface unit (BIU) 23 further includes selection circuits BSG0 to BSG7 for selecting 16 latch amplifiers from the 128 latch amplifiers BLA0 to BLA126 for connection to the bus lines DB0 to DB15 of the DB bus 22 respectively. The selector circuit BSG0 conducts in response 15 to a group selection signal  $\phi Bg 0$ , for connecting the latch amplifiers BLA0 to BLA15 to bus lines DBB0 to DBB15 of the DB bus 22 respectively. The selection circuit BSG1 conducts in response to a group selection signal  $\phi$ Bg1, for connecting the latch amplifiers BLA16 to BLA31 to the bus 20 lines DBB0 to DBB15 respectively. The selection circuit BSG2 conducts in response to a group selection signal φBg2, for connecting the respective latch amplifiers BLA32 to BLA47 to the bus lines DBB0 to DBB15. The selection circuit BSG3 conducts in response to a group selection 25 signal  $\phi$ Bg3, for connecting the respective latch amplifiers BLA48 to BLA63 to the bus lines DBB0 to DBB15.

The selection circuit BSG4 conducts in response to a group selection signal φBg3, for connecting the latch amplifiers BLA64 to BLA79 to the bus lines DBB0 to DBB15. 30 The selection circuit BSG5 conducts in response to a group selection signal φBg5, for connecting the latch amplifiers BLA80 to BLA95 to the bus lines DBB0 to DBB15. The selection circuit BSG6 conducts in response to a group selector signal φBg6, for connecting the latch amplifiers 35 BLA96 to BLA111 to the bus lines DBB0 to DBB15. The selection circuit BSG7 conducts in response to a group selection signal φBg7, for connecting the latch amplifiers BLA112 to BLA127 to the bus lines DBB0 to DBB15.

By employing the selection circuits BSG0 to BSG7, 40 transfer of information between the BIU bus 24 of the 128-bit width and the DB bus 22 of the 16-bit width can be efficiently performed. The DQ pads are connected to the respective bus lines DB0 to DB15 of the DB bus 22. Bus lines of 16 bits are merely connected to the external device, 45 it is not necessary to provide 128 input/output buffers for driving external bus lines, the number of these input/output buffers is reduced, and current consumption is also reduced.

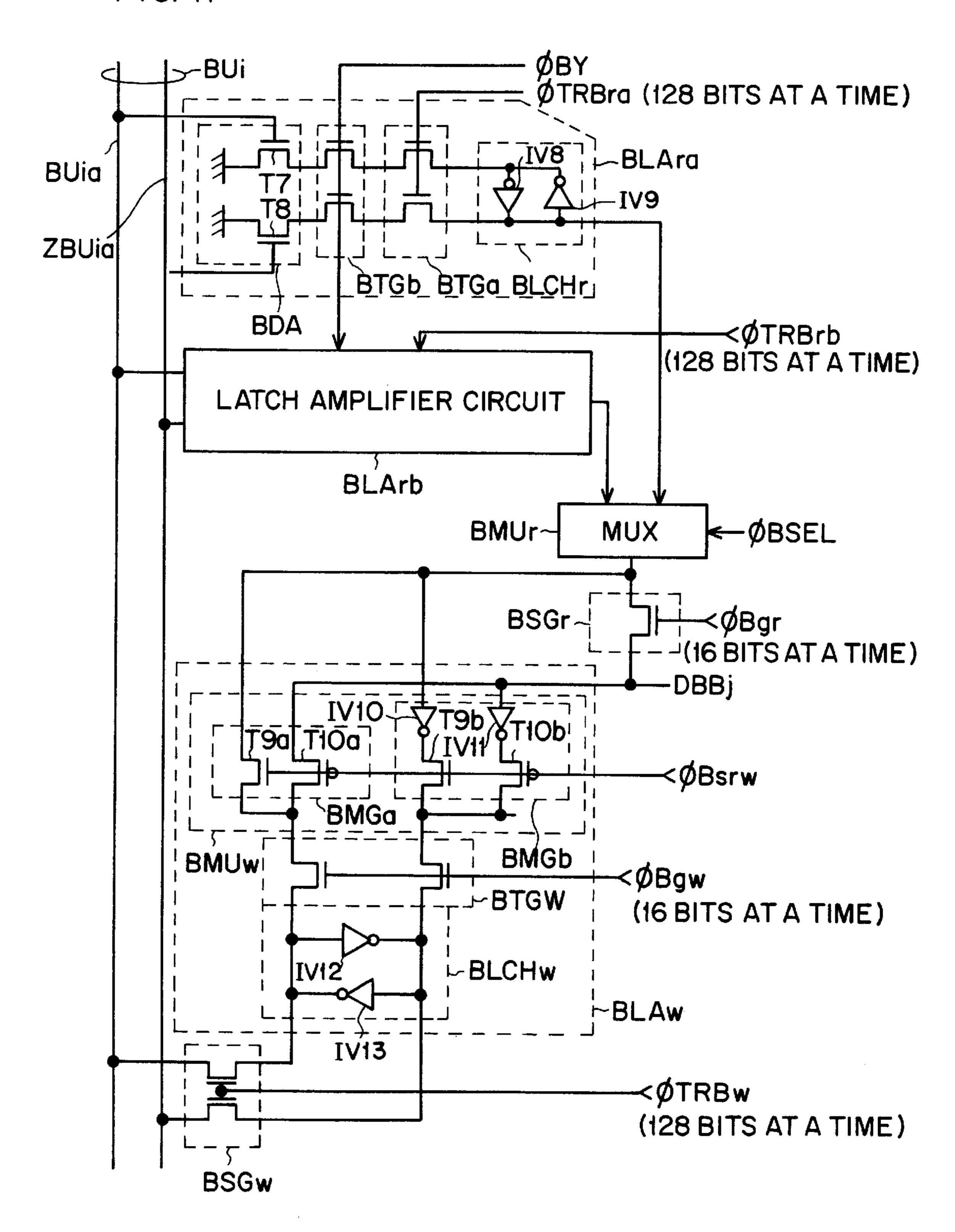

FIG. 11 is a diagram showing a structure of a one-bit portion of the bus interface unit shown in FIG. 10. The 50 structure of a bus interface unit circuit provided between a bus line BUi of the BIU bus 24 and a bus line DBBj of the DB bus 22 is shown in this FIG. 11. The bus line BUi includes complementary signal lines BUia and ZBUia.

Referring to FIG. 11, the bus interface unit circuit (1-bit 55 bus interface unit) includes a latch amplifier circuit BLAra which is brought into an operating state in response to a byte control signal \$\phi BY\$ and a transfer instruction signal \$\phi TRBra\$ for amplifying and latching signal potentials on the signal lines BUia and ZBUia, a latch amplifier circuit BLArb 60 which is brought into an operating state in response to the byte control signal \$\phi BY\$ and a transfer instruction signal \$\phi TRBrb\$ for amplifying and latching the signals on the signal lines BUia and ZBUia, a multiplexer (MUX) BMUr selecting one of latched signals of the latch amplifier circuits 65 BLAra and BLArb in response to a selection signal \$\phi BSEL\$, and a selection circuit BSGr which conducts in response to

a group selection signal  $\phi$ Bgr for transmitting an output signal of the multiplexer BMUr to the DBB bus line DBBj.

The byte control signal \$\phi BY\$ is one of the byte control signals \$\phi BYH\$ and \$\phi BYL\$. One of the 128 bit-batch transfer instruction signals \$\phi TRBra\$ and \$\phi TRBrb\$ is brought into an active state. In output of the latched signal from one of the latch amplifier circuits BLAra and BLArb, information signals of the signal lines BUia and ZBUia are stored in the other latch amplifier circuit. Thus, high-speed information transfer is implemented.

The latch amplifier circuits BLAra and BLArb have the same structure, and FIG. 11 specifically shows only the circuit structure of the latch amplifier circuit BLAra. The latch amplifier circuit BLAra includes a differential amplifier circuit BDA which differentially amplifies signal potentials on the signal lines BUia and ZBUia, a transfer gate BTGb which conducts in response to the byte control signal \$\phi BY\$ for transmitting an output signal of the differential amplifier circuit BDA, a transfer gate BTGa which conducts in response to the transfer instruction signal \$\phi TRBra\$ for further transmitting the signal transmitted from the transfer gate BTGb, and a latch circuit BLCHr which amplifies and latches the signal potential transferred from the transfer gate BTGa.

The differential amplifier circuit BDA includes an n-channel MOS transistor T7 provided between a ground node and the transfer gate BTGb with a gate thereof connected to the signal line BUia, and an n-channel MOS transistor T8 provided between a ground node and the transfer gate BTGb with a gate thereof connected to the signal line ZBUia.

The transfer gate BTGb includes a pair of transfer gate transistors provided in correspondence to the respective MOS transistors T7 and T8 and conducting in response to the byte control signal  $\phi$ BY. The transfer gate BTGa includes a transfer gate transistor pair provided for the respective transfer gate transistor pair of the transfer gate BTGb and conducting in response to the transfer instruction signal  $\phi$ TRBra. The transfer gate transistors of the transfer gates BTGa and BTGb may be formed by CMOS transmission gates.

The latch circuit BLCHr includes an invertor circuit IV8 having an input connected to a drain node of the MOS transistor T7 in conduction of the transfer gates BTGa and BTGb, and an invertor circuit IV9 having an input connected to a drain node of the MOS transistor T8 in conduction of the transfer gates BTGa and BTGb.

When the signal potential of the signal line BUia is at a high level, the conductance of the MOS transistor T7 becomes larger than that of the MOS transistor T8, and the drain potential of the MOS transistor T7 lowers below that of the MOS transistor T8. When the transfer gates BTGb and BTGa conduct in response to the signals \$\phi BY\$ and \$\phi TRBra\$, the drains of these MOS transistors T7 and T8 are connected to the latch circuit BLCHr. Since the potential of the drain node of the MOS transistor T7 is lower than the potential of the drain node of the MOS transistor T8, an output signal of the invertor circuit IV8 is driven to a high level, this output signal is fed back by the invertor circuit IV9, and the drain node potentials of these MOS transistors T7 and T8 are amplified and latched by the latch circuit BLCHr.

When the multiplexer BMUr selects this latch amplifier circuit BLAra in response to the selection signal \$\phi BSEL\$, the high-level output signal of the invertor circuit W8 is transmitted to the selection gate BSGr. When the group selection signal \$\phi Bgr\$ is brought into an active state, a high-level signal from the multiplexer BMUr is transmitted to the bus line DBBj through the selection gate BSGr.

The latch amplifier circuit BLAw latches the signal on the bus line DBBj and forms complementary signals for transmission to the signal lines BUia and ZBUia. The latch amplifier circuit BLAw includes a multiplexer BMUw selecting one of the output signal of the multiplexer BMUr 5 and the signal on the bus line DBBj, a transfer gate BTGw made conductive in response to a group selection signal \$\phi\$Bgw for transmitting an output signal of the multiplexer BMUw, a latch circuit BLCHw latching the signal transmitted from the transfer gate BTGw, and a selection gate BSGw 10 made conductive in response to transfer instruction signal \$\phi\$TRBw for transmitting the signal latched by the latch circuit BLCHw to the signal lines BUia and ZBUia.

The multiplexer BMUw includes a selection circuit BMGa selecting one of the output signal of the multiplexer 15 BMUr and the signal on the bus line DBBj, and a selection circuit BMGb inverting each of the output signal of the multiplexer BMUr and the signal of the data line DBBj and selecting one of the inverted signals. As an example, the selection circuit BMGa includes an n-channel MOS transis- 20 tor T9a transmitting the output signal of the multiplexer BMUr, and a p-channel MOS transistor T10a transmitting the signal on the bus line DBBj. A selection signal φBsrw is supplied to the gates of these MOS transistors T9a and T10a. The selection circuit BMGb includes an invertor circuit 25 IV10 inverting the output signal of the multiplexer BMUr, an invertor circuit IV11 inverting the signal on the bus line DBBj, an n-channel MOS transistor T9b transmitting an output signal of the invertor circuit IV10, and a p-channel MOS transistor T10b transmitting an output signal of the 30 invertor circuit IV11. The selection signal φBsrw is supplied to the gates of the MOS transistors T9b and T10b. The selection circuits BMGa and BMGb may include CMOS transmission gates or tri-state buffers in place of the MOS transistors. They may simply have a function of selecting 35 one of the signal from the multiplexer BMUr and the signal on the bus line DBBj in accordance with the selection signal φBsrw.

The transfer gate BTGw includes a transfer gate transistor pair provided for the respective selector circuits BMGa and 40 BMGb. The latch circuit BLCHw includes an invertor circuit IV12 having an input connected to an output node of the selection circuit BMGa through the transfer gate BTGw, and an invertor circuit IV13 having an input connected to an output node of the selection circuit BMGb through the 45 transfer gate BTGw.

The selection gate BSGw includes a transfer gate transistor pair which conduct in response to the transfer instruction signal  $\phi$ TRBw for transmitting output signals of the respective invertor circuits IV12 and IV13 to the signal lines 50 ZBUia and BUia. The operation is now briefly described.

In accordance with the selection signal \$\phi Bsrw\$, the multiplexer BMUw selects one of the signal outputted from the multiplexer BMUr and the bus line DBBj. Then, the group selection signal \$\phi Bgw\$ is brought into an active state, and an 55 output signal of the multiplexer BMUw is latched by the latch circuit BLCHw. This group selection signal \$\phi Bgw\$ is supplied in common to bus interface unit circuits of 16 bits, so that respective bits on DB bus of 16 bits are latched. Then, the transfer instruction signal \$\phi TRBw\$ is brought into an 60 active state, and selection gates BSGw of 128 bits are brought into conducting states in the bus interface unit (B1IU), so that latched signals of the corresponding latch circuits BLCHw are transmitted to the signal lines BUia and ZBUia.

When the signal of the bus line DBBj is selected and the signal of this bus line DBBj is at a high level, for example,

this high-level signal is latched by the latch circuit BLCHw through the multiplexer BMUw and the transfer gate BTGw. In this state, the output signal of the invertor circuit IV12 is at a low level, and the output signal of the invertor circuit IV13 is at a high level. When the selection gate BSGw conducts, therefore, the high-level signal is transmitted to the signal line BUia, and the low-level signal is transmitted to the signal line ZBUia.

The multiplexer BMUw is provided in order to implement a "copyback" operation for storing information temporarily read from the DRAM back in the DRAM again.

When DB bus includes separately provided signal output bus and signal input bus, the selection gate BSGr is connected to the output bus, and the latch amplifier circuit BLAw is connected to the signal input bus.

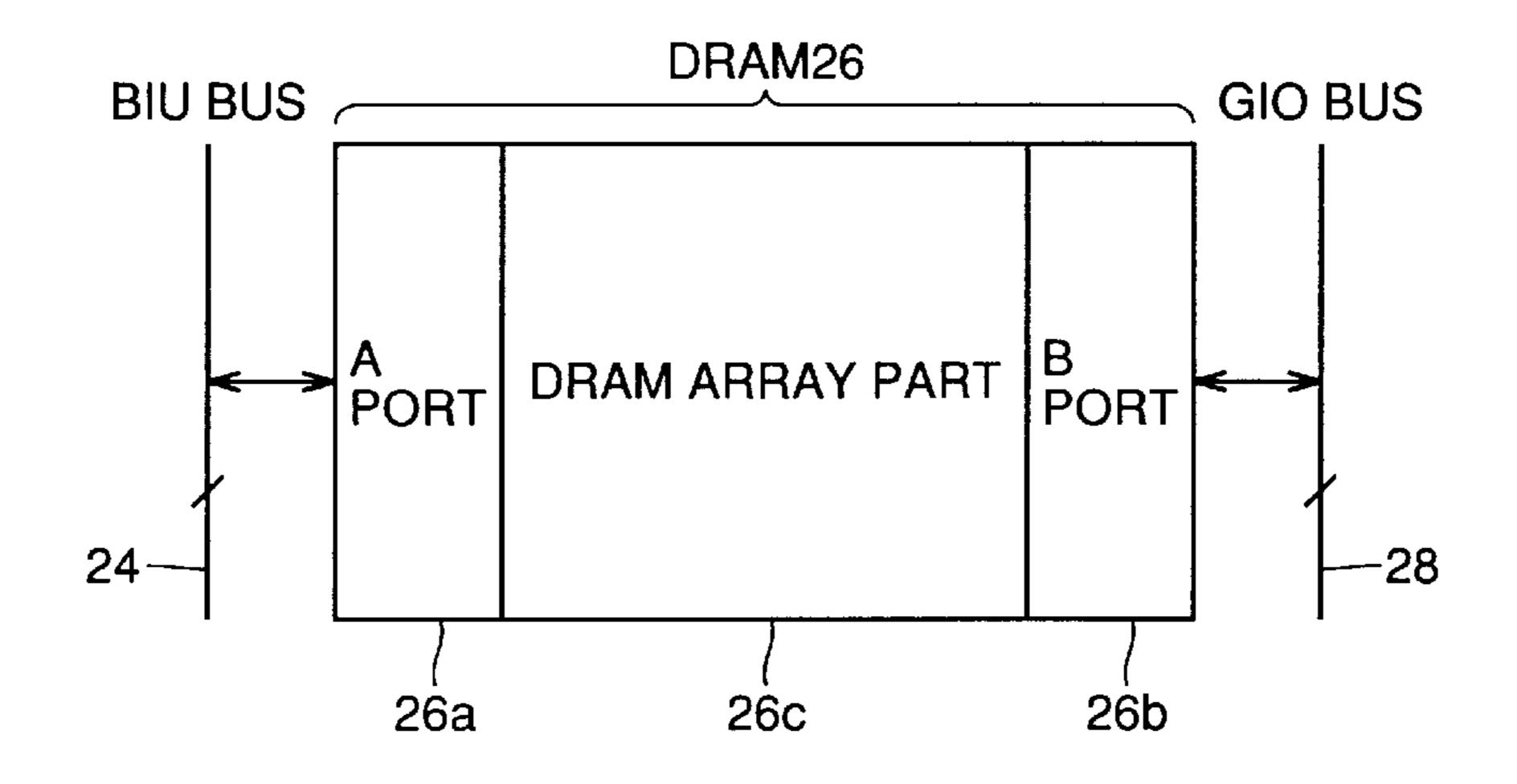

#### (4) Structure of DRAM 26

FIG. 12 is a diagram schematically showing the structure of the DRAM 26 shown in FIG. 3 and FIG. 4. Referring to FIG. 12, the DRAM 26 includes an A port 26a connected to the BIU bus 24, a B port 26b connected to the GIO bus 28, and a DRAM array part 26c accessible through the A port 26a and the B port 26b. The DRAM array part 26c includes dynamic memory cells arranged in a matrix form, a sense amplifier amplifying and latching information of a selected memory cell, a precharge circuit precharging each column (bit line pair) at a prescribed potential in a standby cycle, and others. Each of the A port 26a and the B port 26b includes a row decoder selecting a row of the DRAM array part, a column decoder selecting a column of the DRAM array part, and a peripheral control circuit generating a control signal driving the DRAM array part to a selected state.

The A port 26a and the B port 26b can be brought into an active state independently of each other (under control from a memory controller which is not shown). The structure of this DRAM 26 may be similar to the structure of a general two-port memory. Due to the structure of driving the A port **26***a* and the B port **26***b* independently of each other, information can be transferred between the BIU bus 24 and the GIO bus 28 while employing the DRAM array part 26c as a buffer. More specifically, the A port 26a and the B port 26b bring the same row and column of the DRAM array part 26c into selected states, and one operates in an information write mode while the other operates in an information read mode in accordance with a direction of the information transfer. An information store operation into the DRAM array part **26**c and information transfer between the BIU bus **24** and the GIO bus 28 can be simultaneously executed.

The SRAM 34 is identical to a general SRAM, and includes an address buffer, a row decoder, a column decoder and an SRAM cell matrix. Namely, this SRAM 34 has the same internal structure as an SRAM (chip) formed as a discrete device.

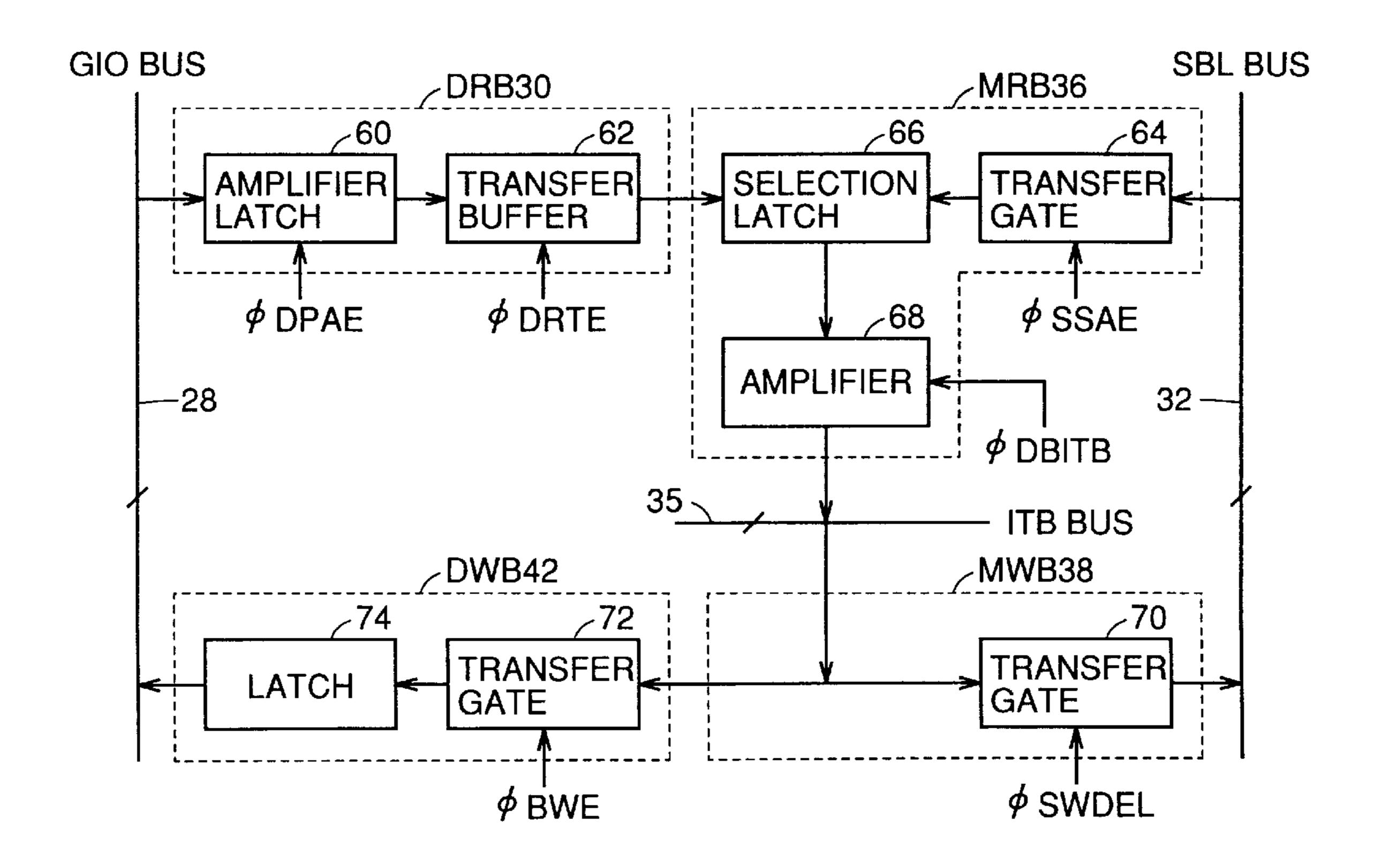

### (5) Structure of Bidirectional Transfer Gate

FIG. 13 is a block diagram schematically showing the structure of a transfer part for performing data transfer between the GIO bus 28, the SBL bus 32 and the ITB bus 35. Referring to FIG. 13, the DRAM read buffer (DRB) 30 transferring the information supplied through the GIO bus 28 includes an amplifier latch 60 activated in response to activation of a preamplifier activation signal φDPAE for amplifying and latching an information signal transmitted onto the GIO bus 28, and a transfer buffer 62 transferring the information latched by the amplifier latch 60 to the memory read buffer (MRB) 36 in response to activation of a transfer instruction signal φDRTE. This transfer buffer 62, which has a buffering function, may simply be a gate such as a CMOS transmission gate.

The memory read buffer (MRB) 36 includes a transfer gate 64 activated in response to activation of a transfer operation activation signal φSSAE for transferring the information transmitted from the SRAM onto the SBL bus 32, a selection latch 66 selectively latching information transferred from the DRAM read buffer (DRB) 30 and the transfer gate 64, and an amplifier 68 amplifying the information signal latched by the selection latch 66 for outputting to the ITB bus 35 and/or the memory write buffer (MWB) 38 in response to activation of a bus transfer enable signal 10 φDBITB.

Since only one of the transfer buffer 62 and the transfer gate 64 is brought into an active state at a time (which is described later), the selection latch 66 latches the information from this transfer buffer 62 or transfer gate 64 which is 15 in the active state. The output signals of the transfer buffer 62 and the transfer gate 64 are reset at prescribed potential levels in inactivation thereof.

The memory write buffer (MWB) 38 transfers the information supplied on the ITB bus 35 to the SBL bus 32 in 20 response to activation of a write decode enable signal \$\phi\sWDEL\$. This write decode enable signal \$\phi\sWDEL\$ starts an address decode operation of the SRAM. A bus line between this transfer gate 70 and the ITB bus 35 is utilized as a latch. This is because an input part of this transfer gate 25 70 is held in a determinant signal state by the output signal of the amplifier 68 or the data register (DR) in inactivation of the transfer gate 70.

The DRAM write buffer (DWB) 42 includes a transfer gate 72 brought into an active state in response to activation 30 of a buffer write enable signal \$\phi BWE\$ for transferring information supplied through the memory write buffer (MWB) 38, and a latch 74 latching the information transferred from the transfer gate 72 for transmission onto the GIO bus 28. The transfer gate 72 is directly connected to the 35 ITB bus 35 through a bus line.

By simply configuring a part implementing a latch function only by a bus line in the memory write buffer (MWB) 38, it is not necessary to further provide a transfer gate for performing transfer to the DRAM write buffer (DWB) 42 in addition to the transfer gate 70 transferring the information to the SBL bus 32 in this memory write buffer (MWB) 38, it is not necessary to provide a latch circuit, and the occupying area and power consumption of this memory write buffer (MWB) 38 are reduced.

As shown in FIG. 13, information can be transferred at a high speed with no collision of data and with no signal loss by providing the latch function and the amplifying function as well as the transfer gate with each transfer buffer.

In this FIG. 13, the signals φDRTE, φSSAE, φDBITB, 50 φBWE and φSWDEL excluding the preamplifier enable signal φDPAE are generated from the SRAM memory controller controlling access to the SRAM described later, on the basis of commands from the processor. The DRAM preamplifier enable signal φDPAE supplied to the amplifier 55 latch 60 of the DRAM read buffer (DRB) 30 is generated from a DRAM memory controller controlling the operations of the DRAM and the bus interface unit (BIU).

By generating these control signals (excluding the signal  $\phi$ DPAE) from the SRAM controller, information can be 60 transferred at a correct timing with no collision of the information.

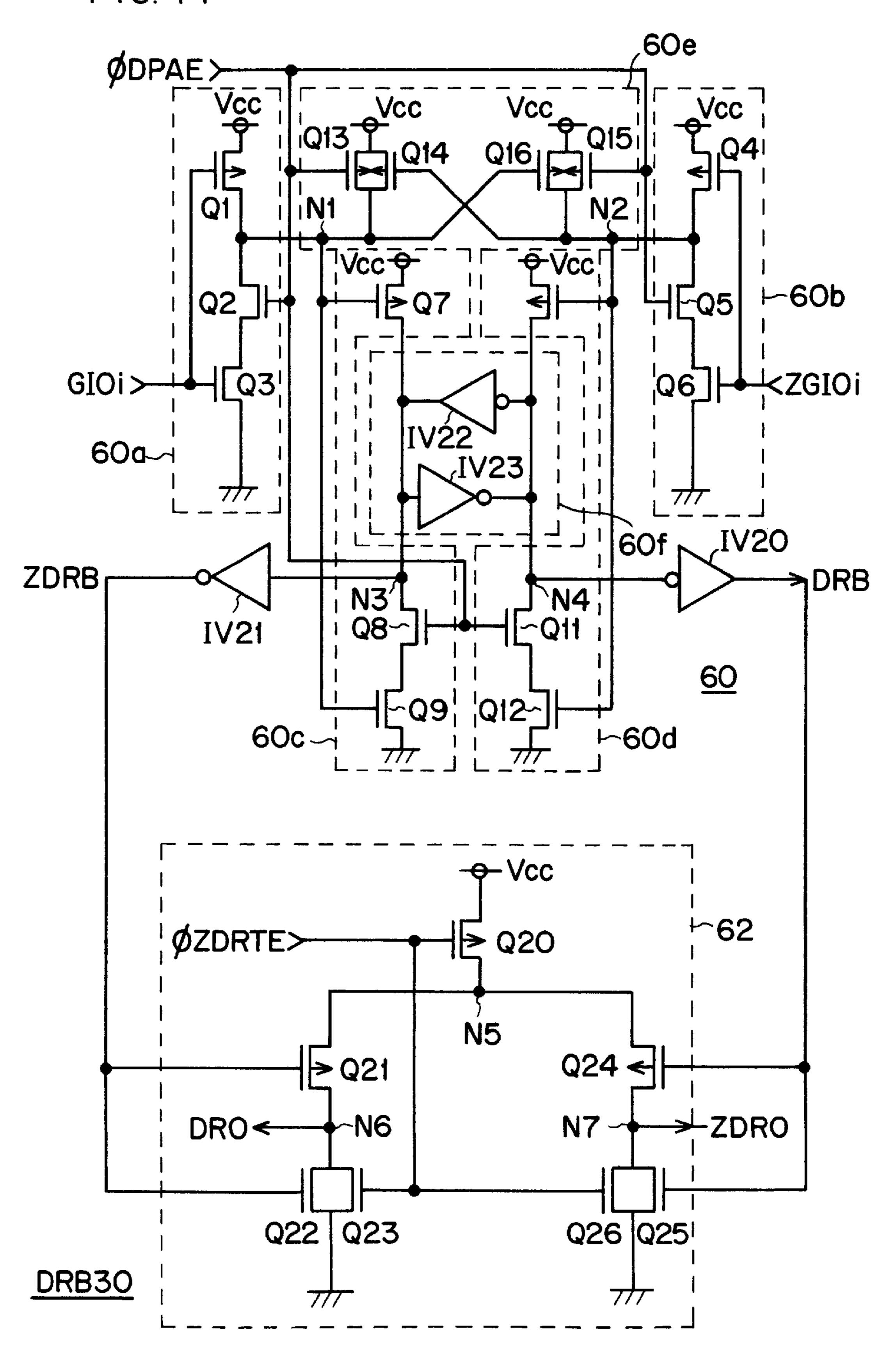

[Structure of DRAM Read Buffer (DRB) 30]

FIG. 14 is a diagram showing an exemplary structure of the DRAM read buffer (DRB) 30 shown in FIG. 13. The 65 structure of a 1-bit portion of DRAM read buffer is shown in FIG. 14.

18

Referring to FIG. 14, the amplifier latch 60 includes an invertor buffer 60a activated in response to activation of the preamplifier enable signal  $\phi$ DPAE for inverting and amplifying a signal on a GIO bus line GIOi, an invertor buffer **60**b activated in response to activation of the preamplifier enable signal  $\phi$ DPAE for inverting and amplifying a signal on a GIO bus line ZGIOi, an invertor buffer 60c activated in response to activation of the preamplifier enable signal φDPAE for further amplifying an output signal of the invertor buffer 60a, an invertor buffer 60d activated in response to activation of the preamplifier enable signal φDPAE for further amplifying an output signal of the invertor buffer 60b, a differential amplifier circuit 60e activated in response to activation of the preamplifier enable signal  $\phi$ DPAE for differentially amplifying and latching the output signals of the invertor buffers 60a and 60b, a latch circuit 60f latching the output signals of the invertor buffers 60a and 60b, and invertor circuits IV20 and IV21 inverting and outputting the latched signals of the latched circuit 60f respectively.

Complementary signals DRB and ZDRB from the invertor circuits IV20 and IV21 are supplied to the transfer buffer 62.

The GIO bus lines GIOi and ZGIOi are signal lines complementary to each other, and form a 1-bit bus line.

The invertor buffer 60a includes a p-channel MOS transistor Q1 connected between a power supply node Vcc and a node N1 with a gate thereof connected to the GIO bus line GIOi, and n-channel MOS transistors Q2 and Q3 serially connected between the node N1 and a ground node. The preamplifier enable signal  $\phi$ DPAE is supplied to the gate of the MOS transistor Q2. The gate of the MOS transistor Q3 is connected to the GIO bus line GIOi. The invertor buffer 60b includes a p-channel MOS transistor Q4 connected between a power supply node Vcc and a node N2 with a gate thereof connected to the GIO bus line ZGIOi, and n-channel MOS transistors Q5 and Q6 serially connected between the node N2 and a ground node. The preamplifier enable signal φDPAE is supplied to the gate of the MOS transistor Q5. The gate of the MOS transistor Q6 is connected to the GIO bus line GIOi.

The invertor buffer 60c includes a p-channel MOS transistor Q7 connected between a power supply node Vcc and a node N3 with a gate thereof connected to the node N1, and n-channel MOS transistors Q8 and Q9 connected between the node N3 and a ground node. The preamplifier enable signal \$\phi DPAE\$ is supplied to the gate of the MOS transistor Q8. The gate of the MOS transistor Q9 is connected to the node N1.

The invertor buffer 60d includes a p-channel MOS transistor Q10 connected between a power supply node Vcc and a node N4 with a gate thereof connected to the node N2, and n-channel MOS transistors Q11 and Q12 serially connected between the node N4 and a ground node. The preamplifier enable signal φDPAE is supplied to the gate of the MOS transistor Q11. The gate of the MOS transistor Q12 is connected to the node N2.

The latch circuit 60f includes an invertor circuit IV22 inverting a signal potential on the node N4 and transmitting the same to the node N3, and an invertor IV23 inverting a signal on the node N3 and transmitting the same to the node N4.

The differential amplifier circuit 60e includes a p-channel MOS transistor Q13 connected between a power supply node Vcc and the node N1 and receiving the preamplifier enable signal  $\phi$ DPAE on a gate thereof, a p-channel MOS transistor Q14 connected between a power supply node Vcc

and the node N1 with a gate thereof connected to the node N2, a p-channel MOS transistor Q15 connected between a power supply node Vcc and the node N2 and receiving the preamplifier enable signal  $\phi$ DPAE on a gate thereof, and a p-channel MOS transistor Q16 connected between a power 5 supply node Vcc and the node N2 with a gate thereof connected to the node N1. The MOS transistors Q14 and Q16 are cross-coupled with each other, and raise a high-level potential on the node N1 or N2 to a power supply potential Vcc (the node and the voltage are denoted by the same 10 symbol). The operation of this amplifier latch 60 is now described.

The GIO bus lines GIOi and ZGIOi are precharged at high levels in the standby cycle. When the preamplifier enable signal  $\phi$ DPAE is at a low level, the MOS transistors Q2 and 15 Q5 are in OFF states, and the invertor buffers 60a and 60b are in output high impedance states.

In the differential amplifier circuit 60e, the MOS transistors Q13 and Q15 are in ON states in accordance with the low-level preamplifier enable signal  $\phi$ DPAE, and the nodes 20 N1 and N2 are precharged at the power supply potential Vcc level. These nodes N1 and N2 are at high levels, and the MOS transistors Q7 and Q10 are both in OFF states. Further, the preamplifier enable signal  $\phi$ DPAE is at the low level, and the MOS transistors Q8 and Q11 are in OFF states. In this 25 state, the latch circuit 60f latches information in a precedent cycle, and signals in the precedent cycle are sustainingly outputted from the invertor circuits IV20 and IV21.

When the preamplifier enable signal  $\phi$ DPAE rises to a high level, the MOS transistors Q2 and Q5 enter ON states, 30 the invertor buffers 60a and 60b are brought into operating states, and the signals of the GIO bus lines GIOi and ZGIOi are inverted and amplified to be transmitted to the nodes N1 and N2 respectively. In the differential amplifier circuit 60e, the MOS transistors Q13 and Q14 are brought into OFF 35 states, and the signal potentials transmitted onto these nodes N1 and N2 are further differentially amplified by the MOS transistors Q14 and Q16. Now, consider such a case that a high-level signal is transmitted onto the GIO bus line GIOi and a low-level signal is transmitted to the GIO bus line 40 ZGIOi. In this state, the node N1 is at a low level, while the node N2 maintains a high level. The MOS transistor Q16 enters an ON state in accordance with the low level of the node N1, and maintains the node N2 at the power supply potential Vcc level. On the other hand, the MOS transistor 45 Q14 is brought into an OFF state, and the potential level of the node N1 lowers.

The conductance of the MOS transistor Q7 increases in accordance with this potential change of the nodes N1 and N2, while the MOS transistor Q10 maintains an OFF state. 50 Thus, a current is supplied from the power supply node Vcc toward the node N3 through the MOS transistor Q7. Further, the MOS transistors Q8 and Q11 enter ON states, and the node N4 is discharged through the MOS transistors Q11 and Q12 (the potential of the node N2 is at a high level). On the 55 other hand, the MOS transistor Q9 is in an OFF state, since the potential of the node N1 is at a low level. Thus, the output signals of the invertor buffers 60c and 60d change at a high speed, and the output signals of the invertor buffers 60c and 60d are latched by the latch circuit 60f.

In this state, the node N3 attains a high level, and the node N4 attains a low level. Signals on these nodes N3 and N4 are inverted and amplified by the invertor circuits IV21 and IV20 for transmission.

By utilizing these invertor buffers and the differential 65 amplifier circuit, small potential change of the GIO bus lines GIOi and ZGIOi is amplified at a high speed. By the invertor

circuits IV22 and IV23 of the latch circuit 60f, the potentials of the nodes N3 and N4 are changed and latched at a high speed, and information transfer at a high speed is enabled.

The transfer buffer 62 includes a p-channel MOS transistor Q20 connected between a power supply node Vcc and a node N5 and receiving the read transfer enable signal φDRTE on a gate thereof, a p-channel MOS transistor Q21 connected between the node N5 and a node N6 and receiving the output signal ZDRB of the amplifier latch 60, an n-channel MOS transistor Q22 connected between the node N6 and a ground node and receiving the signal ZDRB on a gate thereof, an n-channel MOS transistor Q23 connected between the node N6 and a ground node and receiving the read transfer enable signal  $\phi DRTE$  on a gate thereof, a p-channel MOS transistor Q24 connected between the node N5 and a node N7 and receiving the output signal DRB of the amplifier latch 60 on a gate thereof, an n-channel MOS transistor Q25 connected between the node N7 and a ground node and receiving the signal DRB on a gate thereof, and an n-channel MOS transistor Q26 connected between the node N7 and a ground node and receiving the read transfer enable signal  $\phi$ DRTE on a gate thereof.

Signals DRO and ZDRO complementary to each other are outputted from the nodes N6 and N7, and supplied to the selection latch 66 of the memory read buffer (MRB) 36. The operation is now briefly described.

When the read transfer enable signal  $\phi$ ZDRTE is at a high level of an inactive state, the MOS transistor Q20 is in an OFF state, and the MOS transistors Q23 and Q26 are in ON states. In this state, the nodes N6 and N7 are fixed at the ground potential level through the MOS transistors Q23 and Q26.

When the read transfer enable signal \$\psiZDRTE\$ is brought into an active state of a low level, the MOS transistors Q23 and Q26 enter OFF states, the MOS transistor Q20 enters an ON state, and the power supply potential Vcc is transmitted to the node N5. Thus, the MOS transistors Q21 and Q22 operate as a CMOS invertor, and invert the output signal ZDRB from the amplifier latch 60 to generate the signal DRO. Further, the MOS transistors Q24 and Q25 operate as a CMOS invertor, and invert the output signal DRB from the amplifier latch 60 to generate the signal ZDRO.

By implementing the two-stage latch and amplifier transfer structure with this amplifier latch 60 and the transfer buffer 62, amplified, latched and stabilized information is reliably transmitted to a circuit at a next stage. By providing the latch, further, information can be successively correctly transferred every clock cycle (transfer cycle).

[Structure of Memory Read Buffer (MRB)]

FIG. 15 is a diagram showing an exemplary structure of the memory read buffer (MRB) 36 shown in FIG. 13. The structure of a 1-bit part of the memory read buffer (MRB) 36 is shown in FIG. 15.

Referring to FIG. 15, the transfer gate 64 includes n-channel MOS transistors Q30 and Q31 which conduct in response to activation of the SRAM transfer enable signal φSSAE for transmitting signals on SBL bus lines SBLi and ZSBLi to the nodes N8 and N9 respectively, and p-channel MOS transistors Q32 and Q33 which conduct in inactivation of the SRAM transfer enable signal φSSAE for transmitting the power supply potential Vcc to the nodes N8 and N9. The bus lines SBLi and ZSBLi are complementary signal lines, and form a 1-bit SBL bus line.

The selection latch 66 includes a differential amplifier circuit 66a differentially amplifying the complementary signals transferred from this transfer gate 64 onto the nodes N8 and N9, a differential amplifier circuit 66b differentially

amplifying the complementary signals DRO and ZDRO transmitted from the transfer buffer 62 shown in FIG. 14, and a latch circuit 66c amplifying and latching an output signal from one of the differential amplifier circuits 66a and 66b.

The differential amplifier circuit 66a includes a p-channel MOS transistor Q34 connected between a power supply node Vcc and a node N10 with a gate thereof connected to the node N8, and a p-channel MOS transistor Q35 connected between a power supply node Vcc and a node N11 with a 10 gate thereof connected to the node N9. The differential amplifier circuit 66b includes an n-channel MOS transistor Q36 connected between the node N11 and a ground node and receiving the output signal DRO from the transfer buffer 62 on a gate thereof, and an n-channel MOS transistor Q37 15 connected between the node N10 and a ground node and receiving the output signal ZDRO from the transfer buffer 62 on a gate thereof.