#### US006114721A

6,114,721

### United States Patent [19]

### Ema [45] Date of Patent: Sep. 5, 2000

[11]

# [54] DYNAMIC RANDOM ACCESS MEMORY DEVICE AND METHOD FOR PRODUCING THE SAME

[75] Inventor: Taiji Ema, Kawasaki, Japan

[73] Assignee: Fujitsu Limited, Kawasaki, Japan

[21] Appl. No.: **09/385,964**

Nov. 25, 1987

[22] Filed: Aug. 30, 1999

#### Related U.S. Application Data

[60] Continuation of application No. 08/716,782, Sep. 24, 1996, Pat. No. 6,046,468, which is a division of application No. 08/291,581, Aug. 16, 1994, Pat. No. 5,572,053, which is a continuation of application No. 07/815,581, Dec. 30, 1991, abandoned, which is a division of application No. 07/536, 757, Jun. 12, 1990, Pat. No. 5,128,273, which is a division of application No. 07/462,290, Dec. 29, 1989, Pat. No. 4,953,126, which is a continuation of application No. 07/274,279, Nov. 22, 1988, abandoned.

#### [30] Foreign Application Priority Data

| Nov. | 30, 1987              | [JP]                                    | Japan   | 62-302464                            |

|------|-----------------------|-----------------------------------------|---------|--------------------------------------|

| [51] | Int. Cl. <sup>7</sup> |                                         |         | H01L 27/108                          |

| [52] | U.S. Cl.              | • • • • • • • • • • • • • • • • • • • • |         | . <b>257/306</b> ; 257/308; 257/309; |

|      |                       |                                         |         | 257/311; 438/253                     |

| [58] |                       |                                         |         |                                      |

|      | 2                     | 257/307                                 | 7, 308, | 309, 310, 311, 207; 438/253,         |

|      |                       |                                         |         | 396                                  |

Japan ...... 62-396669

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,493,056 | 1/1985  | Mao                  |

|-----------|---------|----------------------|

| 4,651,183 | 3/1987  | Lange et al          |

|           |         | Mimoto et al         |

| 4,742,018 | 5/1988  | Kimura et al 438/253 |

| 4,794,563 | 12/1988 | Maeda                |

| 4,800,525 | 1/1989  | Shah et al           |

| 4,974,040 | 11/1990 | Taguchi et al        |

#### FOREIGN PATENT DOCUMENTS

0 161 850 11/1985 European Pat. Off. .

0 191 612 8/1986 European Pat. Off. . 56-058254 5/1981 Japan .

Patent Number:

(List continued on next page.)

#### OTHER PUBLICATIONS

"LSI Handbook", The Institute of Electronics and Communications Engineers, 1984, p. 495.

M. Koyanagi et al., "A 5–V Only 16–kbit Stacked–Capacitor MOS RAM", IEEE Transaction on Electron Devices, vol. D–27, No. 8, pp. 1596–1601, 1980.

Koyanagi et al. "A 5–V Only 16–kbit Stacked–Capacitor MOS RAM," *IEEE Journal of Solid–State Circuits*, vol. SC–15, No. 4, Aug. 1980, pp. 661–666.

Shah et al., "A 4–Mbit DRAM with Trench–Transistor Cell," *IEEE Journal of Solid–State Circuits*, vol. SC–21, No. 5, Oct. 1986, pp. 618–624.

Patent Abstracts of Japan, vol. 9, No. 31 (E–295)(1754), Feb. 9, 1985 & JP–A–59 175153 (Nippon Kenki K.K.), Oct. 3, 1984.

Patent Abstracts of Japan, vol. 9, No. 106 (E–313)(1829), May 10, 1985 & JP–A–59 231851 (Nippon Deshin Denwa Kosha), Dec. 26, 1984.

Patent Abstracts of Japan, vol. 11, No. 376 (E–563)(2823), Dec. 8, 1987 & JP–A–62 145765 (Hitachi Ltd.), Jun. 19, 1987.

Primary Examiner—David Hardy

Assistant Examiner—George Eckert, II

Attorney, Agent, or Firm—Staas & Halsey LLP

#### [57] ABSTRACT

A DRAM device includes bit lines formed on an interlayer insulation film which covers gate electrodes on an insulation film on a semiconductor substrate. Each bit line is in contact with the corresponding source region formed in the substrate through an opening in the insulation films. Another insulation film is formed so as to cover the bit lines. A storage electrode is formed on the insulation film covering the bit line, and is in contact with a drain region in the substrate through another opening in the insulation films. The bit line has a vertical layer level lower than that of the storage electrode. The storage electrode is covered with a dielectric film, which is covered with an opposed electrode.

#### 10 Claims, 29 Drawing Sheets

FIG. IA PRIOR ART

FIG. 1B PRIOR ART

FIG. 2A

FIG.2B

FIG. 2C

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 5A

FIG. 5B

FIG. 5C

17(BL1)

FIG. 90

23

32)

五 の ら 可

Sep. 5, 2000

五四。四五

35 32 3 37 (BL4) 33

37(BL4)

(BL4) (BL4)

7(BL M 344.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 35.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4.45. 36.4 43 442 48 39 38

FIG. IIJ

46 45c

46 45c

37(BL4) 33 34D 37(BL4) 31

F 6 .

# FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13B

FIG. 13C

<u>5</u>

Sep. 5, 2000

FIG. 50

下 ( ) ( ) ( )

Sep. 5, 2000

6,114,721

# DYNAMIC RANDOM ACCESS MEMORY DEVICE AND METHOD FOR PRODUCING THE SAME

This application is a continuation of application Ser. No. 5 08/716,782, filed Sep. 24, 1996, now U.S. Pat. No. 6,046, 468, which is a divisional application of application Ser. No. 08/291,581 filed Aug. 16, 1994, now U.S. Pat. No. 5,572, 053, which is a continuation application of application Ser. No. 07/815,581, filed Dec. 30, 1991, now abandoned, which is a divisional application of application Ser. No. 07/536,757 filed Jun. 12, 1990, now U.S. Pat. No. 5,128,273, which is a divisional application of application Ser. No. 07/462,290 filed Dec. 29, 1989, now U.S. Pat. No. 4,953,126, which is a continuation of application Ser. No. 07/274,279 filed Nov. 15 22, 1988, now abandoned.

#### BACKGROUND OF THE INVENTION

The present invention generally relates to a dynamic random access memory device and a method for producing the same and, more particularly, to improvements in the layer structure of a dynamic random access memory device and a method for producing such an improved dynamic random access memory device.

A dynamic random access memory (hereinafter simply referred to as a DRAM device) has a number of memory cells. Each memory cell is composed of a memory cell capacitor and a transfer gate transistor. Currently, there has been considerable activity in reduction of the size of a 30 DRAM device. It is required particularly to reduce the size of a memory cell capacitor in order to reduce the size of DRAM devices. It is noted that the area of memory cell capacitors which occupies a semiconductor substrate decreases, capacitance of each memory cell capacitor decreases. The capacitance of the memory cell capacitor depends greatly on the size of a storage electrode of the memory cell, which is paired with an opposed electrode thereof. As the area of the storage capacitor which occupies the semiconductor substrate decreases, the capacitance of 40 the memory cell capacitor decreases considerably. The reduction of the size of the memory cell capacitor, particularly the reduction of the size of the storage electrode causes the following problems in addition to the decrease in capacitance of the memory cell capacitor. First, soft errors due to irradiation of α-particles increase with a decrease of the capacitance of the memory cell capacitor. Secondly, although it is known to make the storage electrode thick so as to increase the side wall area thereof and thereby increase the entire surface area of the storage electrode, it is difficult to obtain a fine pattern because the aspect ratio with respect to bit lines and contact holes increases. Thirdly, neighboring bit lines are located closer, or in other words, a separation distance between the neighboring bit lines decreases. The closer the neighboring bit lines are arranged, the greater the coupling capacitance therebetween.

#### SUMMARY OF THE INVENTION

It is therefore a general object of the present invention to provide a novel and useful random access memory device 60 and a method for producing the same in which the aforementioned disadvantages are eliminated.

A more specific object of the present invention is to provide a random access memory device having a storage electrode having an increased surface area. An increased 65 surface area of the storage electrode can provide various advantages.

2

Another object of the present invention is to provide a random access memory device in which neighboring bit lines are electrically shielded very well.

The above objects of the present invention can be achieved by a random access memory device which comprises a semiconductor substrate having a source region and a drain region, a first insulation film formed on a surface of the semiconductor substrate, a gate electrode formed on the first insulation film, a second insulation film formed so as to cover the gate electrode, a bit line formed on the second insulation film, the bit line being in contact with the source region through a first opening formed in the first and second insulation films, a third insulation film formed so as to cover the bit line, a storage electrode formed on the third insulation film and being in contact with the drain region through a second opening formed in the first, second and third insulation films, a dielectric film formed so as to surround the storage electrode, and an opposed electrode formed so as to cover the dielectric film.

Still another object of the present invention is to provide a method for producing the above-mentioned DRAM device.

The above another object of the present invention can be achieved by a method which comprises the steps of forming a gate electrode on a first insulation film formed on a semiconductor substrate and source and drain regions in the semiconductor substrate, forming a second insulation film so as to cover the gate electrode, forming a first opening in the first and second insulation films, forming a bit line being in contact with the drain region through the first opening and overlying the second insulation film, forming a third insulation film so as to cover the bit line, forming a second opening in the first, second and third insulation films, forming a storage electrode being in contact with the source region through the second opening and overlying the third insulation film, forming a dielectric film so as to surround the storage electrode; and forming an opposed electrode so as to cover the dielectric film.

A further object of the present invention is to provide a method for producing the aforementioned DRAM device in which a contact hole with respect to the drain region and the storage electrode is formed by a self-alignment process.

The further object of the present invention can be achieved by a method for producing the DRAM which comprises the steps of forming a gate electrode on a first insulation film formed on a semiconductor substrate and source and drain regions in the semiconductor substrate, forming a second insulation film so as to cover the gate electrode, forming a first opening in the first and second embodiment, forming a conductive film on the second insulation film, forming a third insulation film on the conductive film, patterning the conductive film and the third insulation film so as to shape a bit line on which the third insulation film remains, forming a fourth insulation film on the bit line and the second and third insulation films, forming a second opening in the first, second and fourth insulation films by a self-alignment process in which the bit line is used as a mask film so that the fourth insulation film remains so as to surround a side wall of the bit line, forming a storage electrode being in contact with the drain region and overlying the third and fourth insulation films, forming a dielectric film so as to surround the storage electrode, and forming an opposed electrode so as to cover the dielectric film.

Other objects, features and advantages of the present invention will become apparent from the following detailed description when read in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

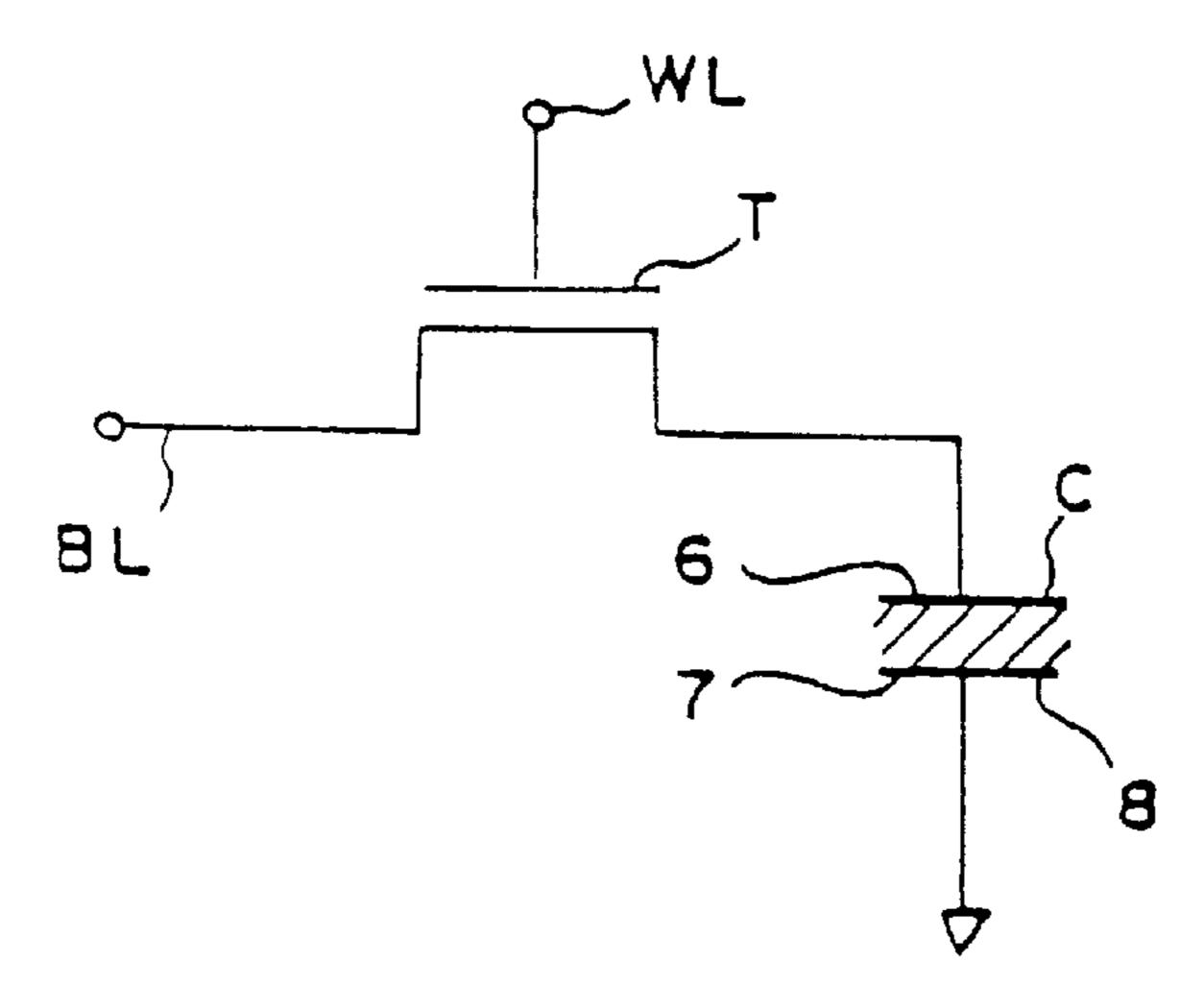

FIG. 1A is a circuit diagram of a memory cell of a DRAM device;

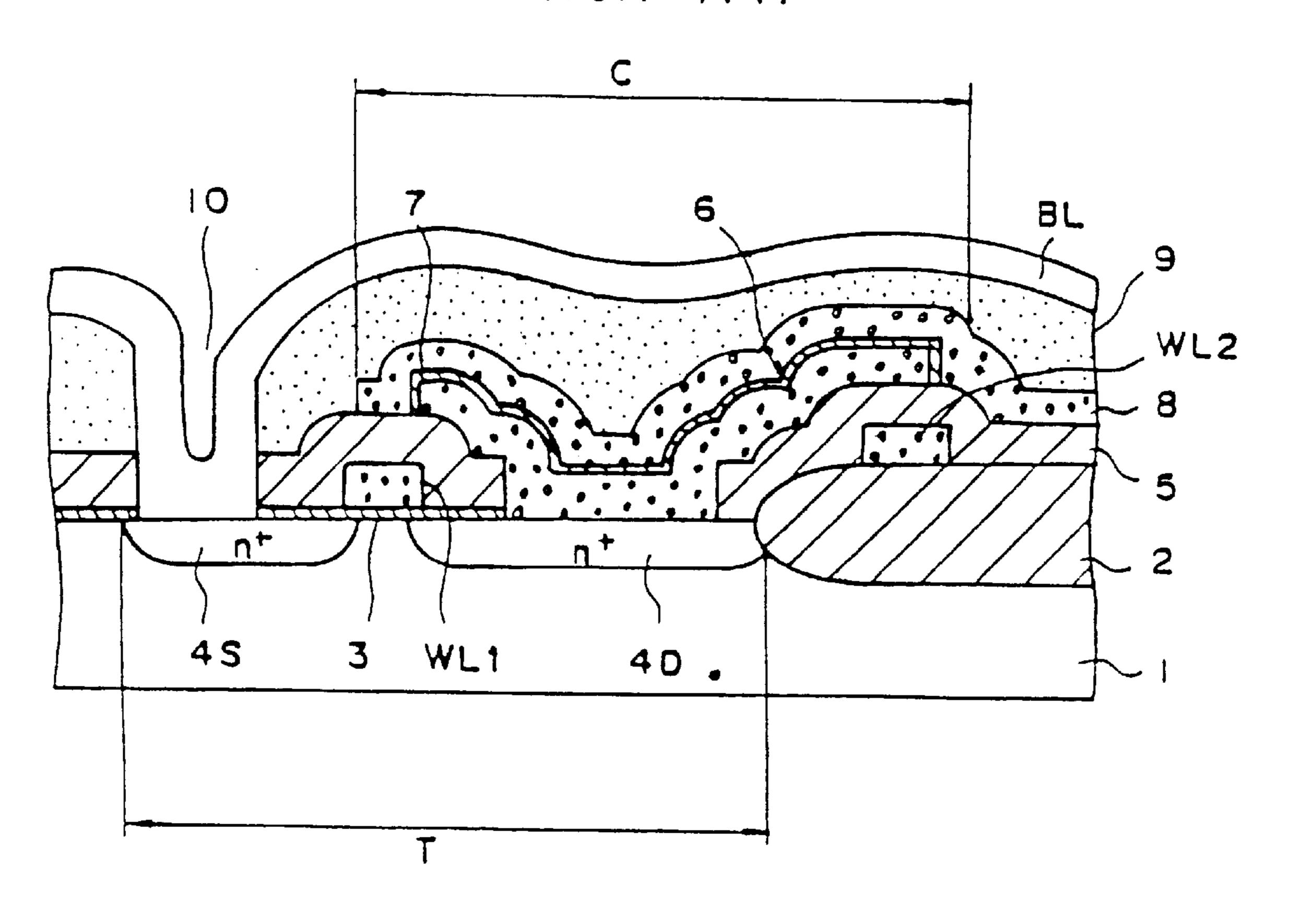

FIG. 1B is a cross sectional view of a layer structure of a memory cell for a conventional DRAM device;

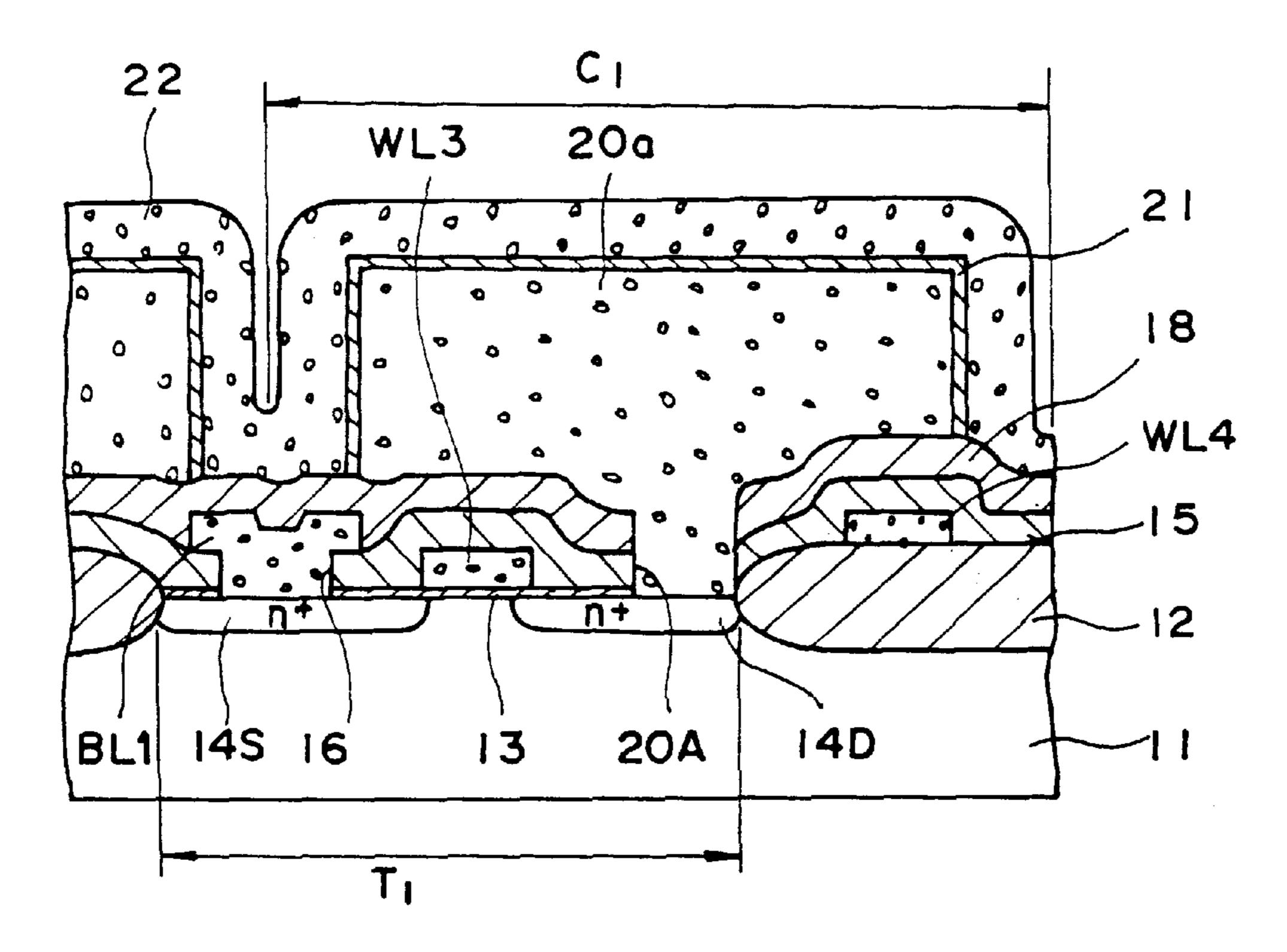

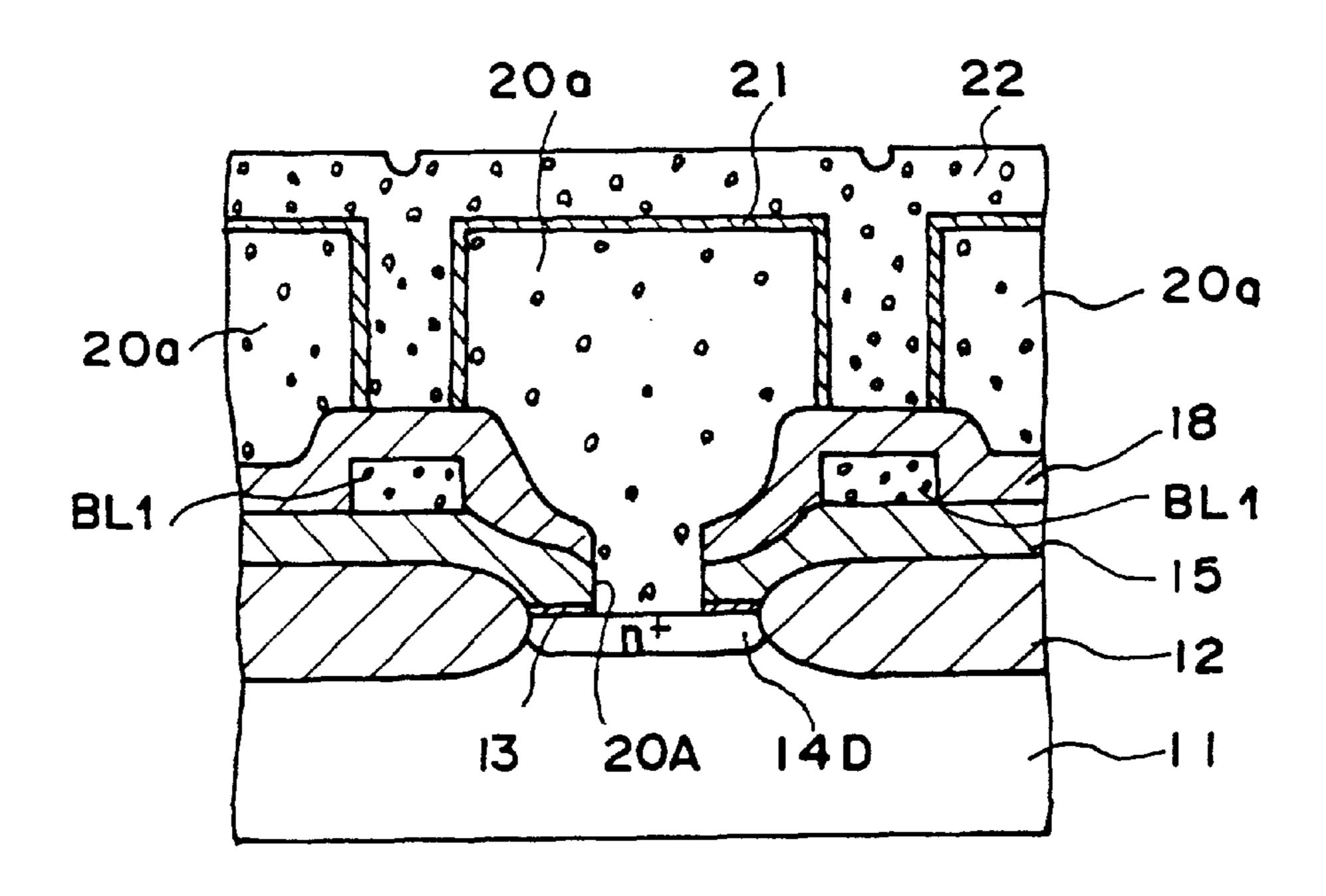

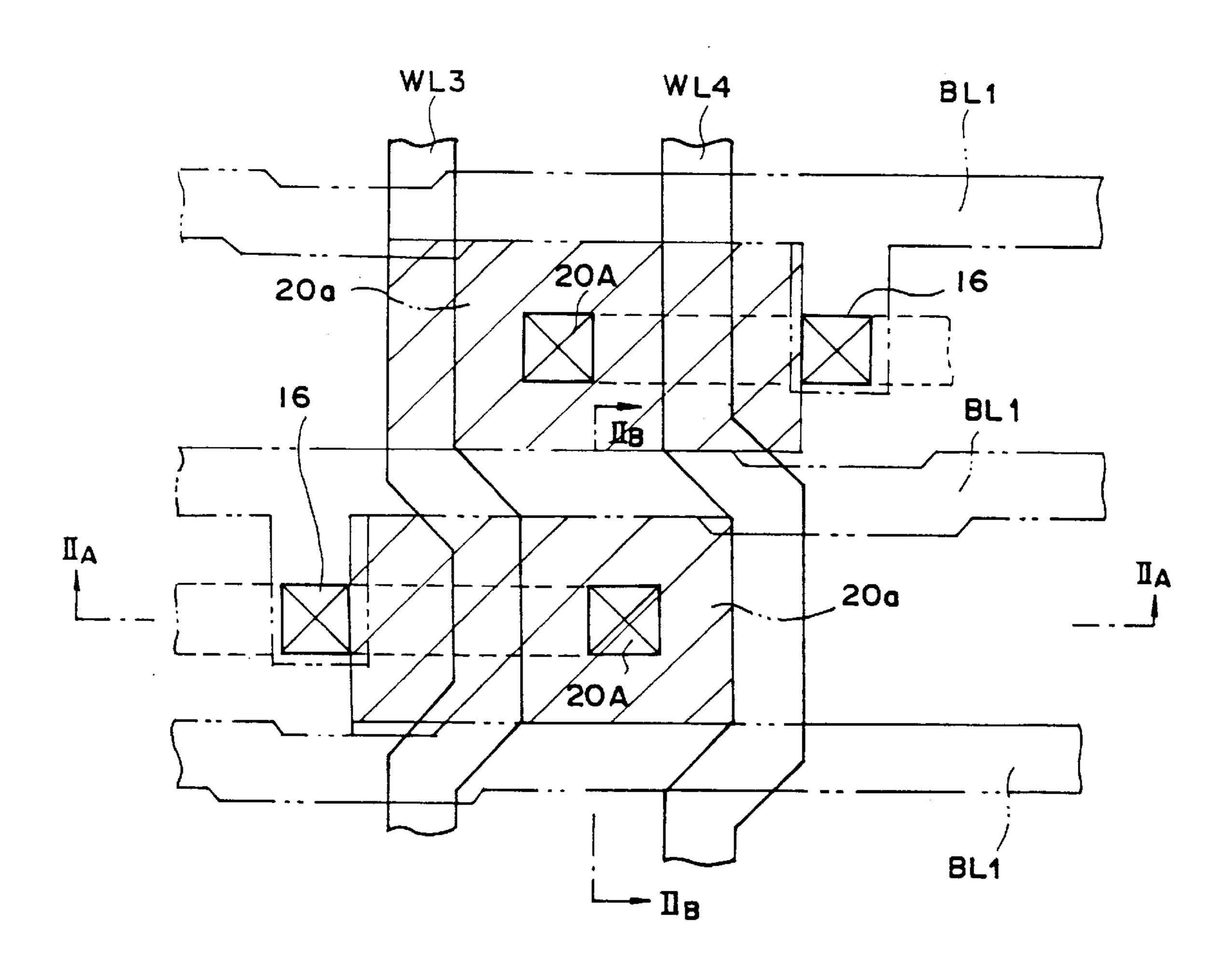

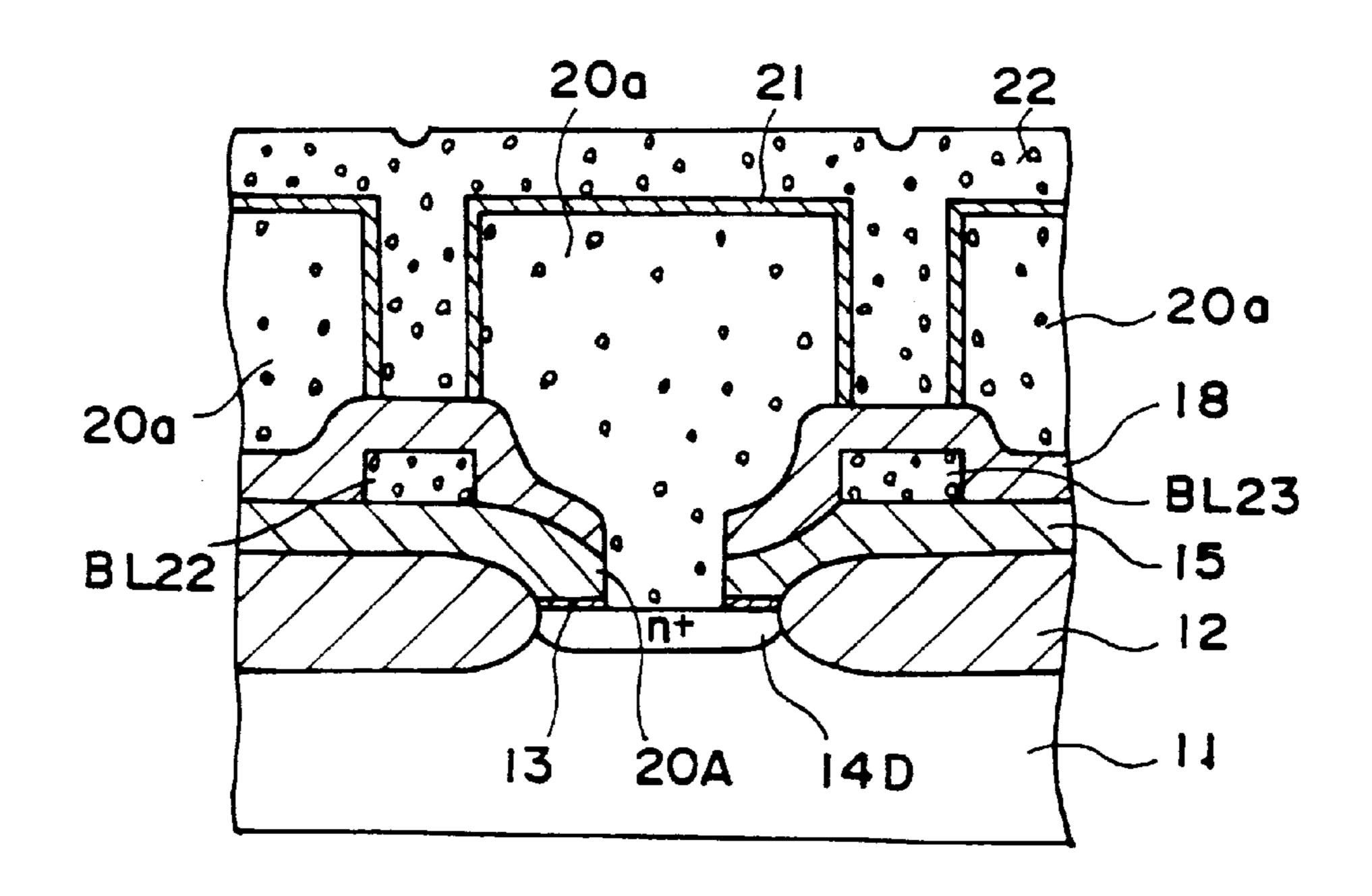

FIGS. 2A through 2C are views showing the first preferred embodiment of the present invention;

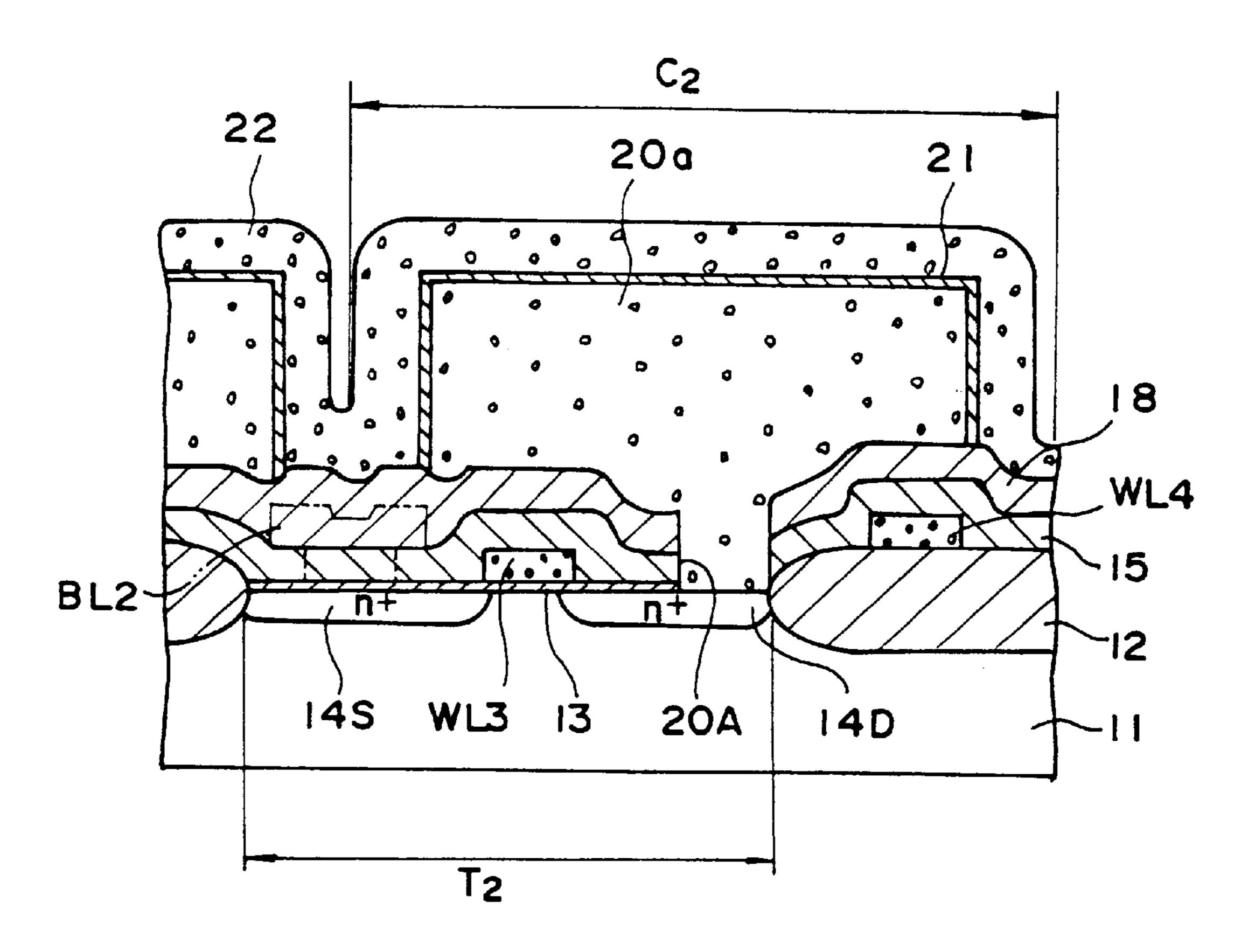

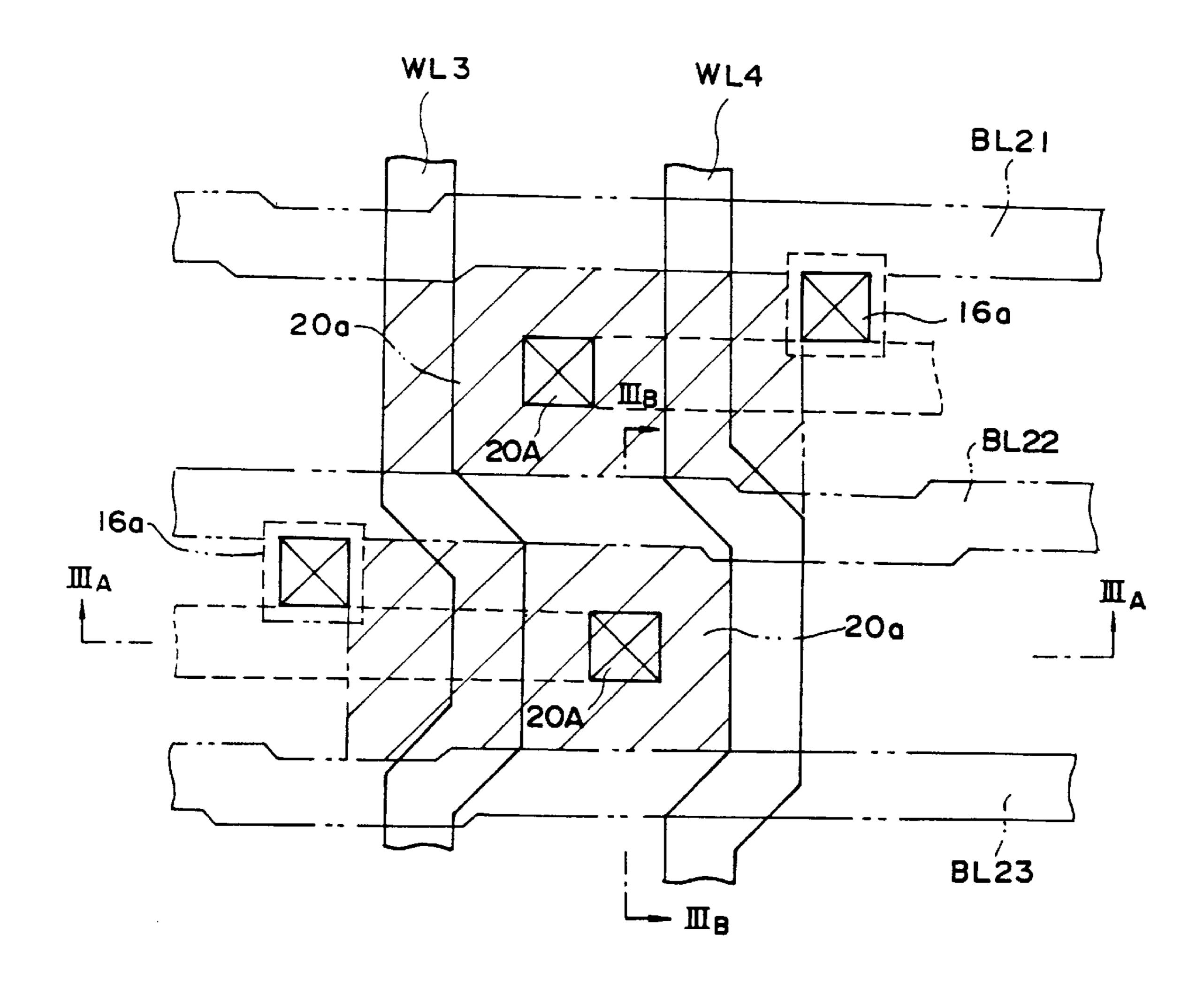

FIGS. 3A through 3C are views showing the second preferred embodiment of the present invention;

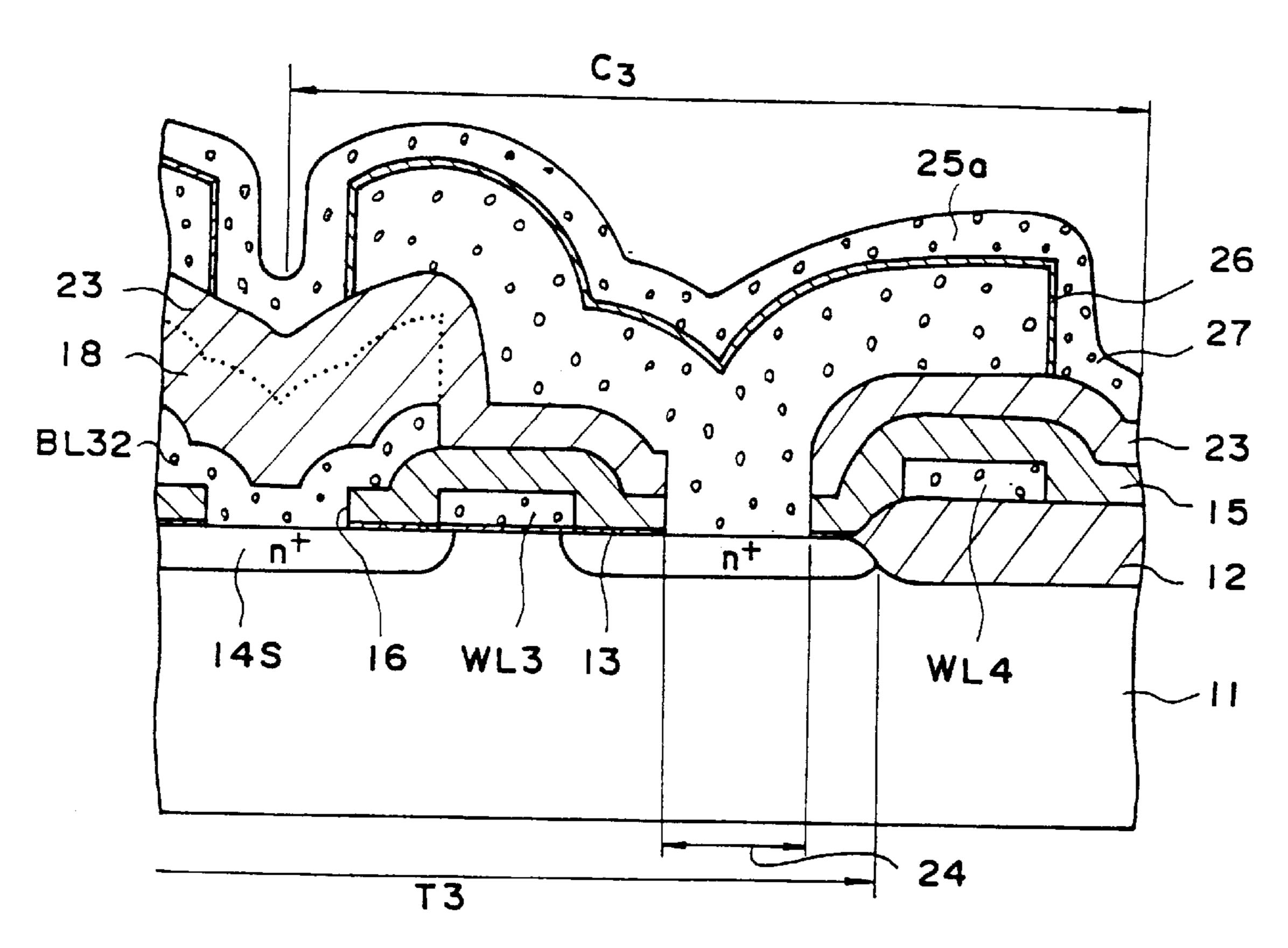

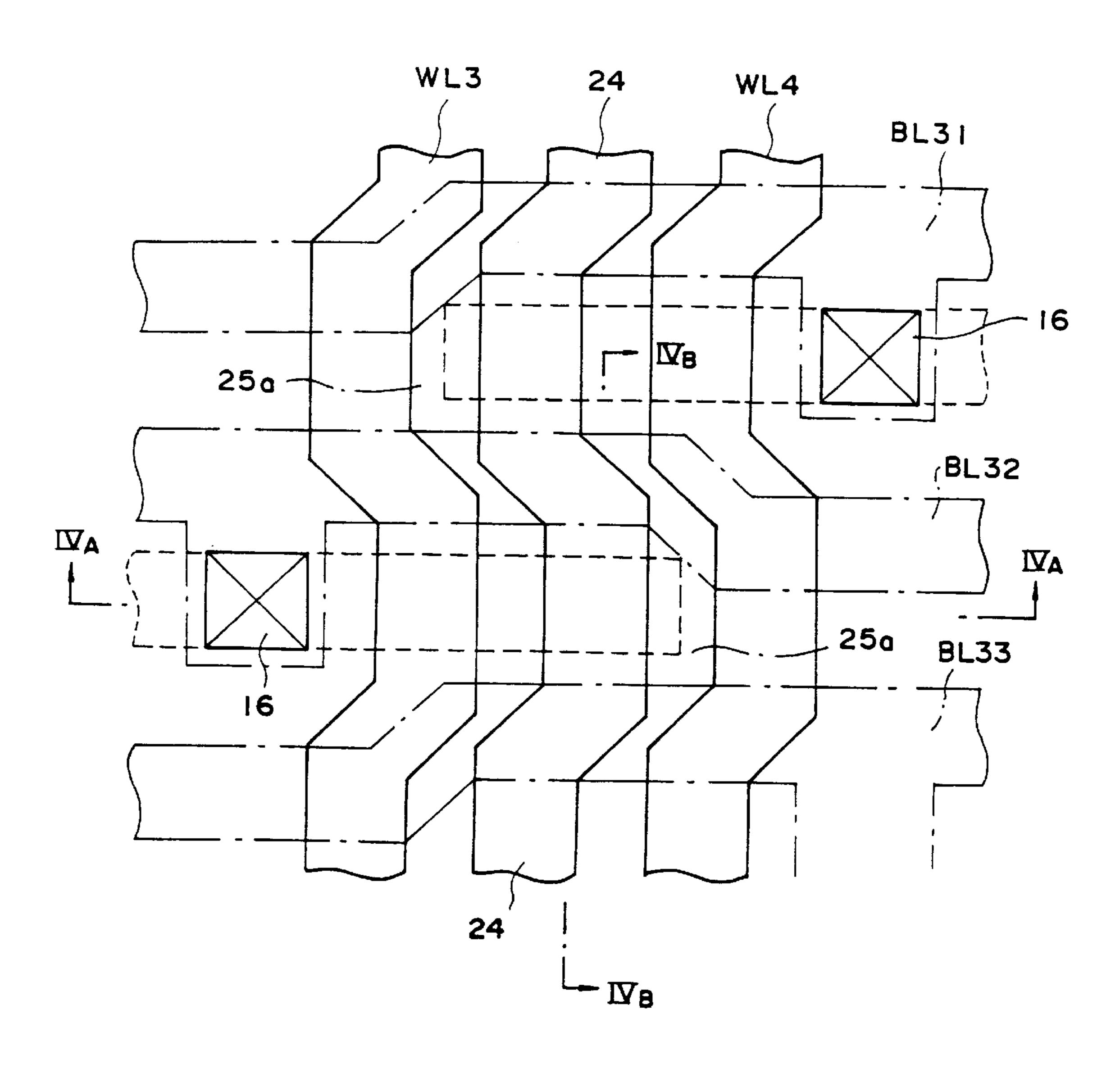

FIGS. 4A through 4C are views showing the third preferred embodiment of the present invention;

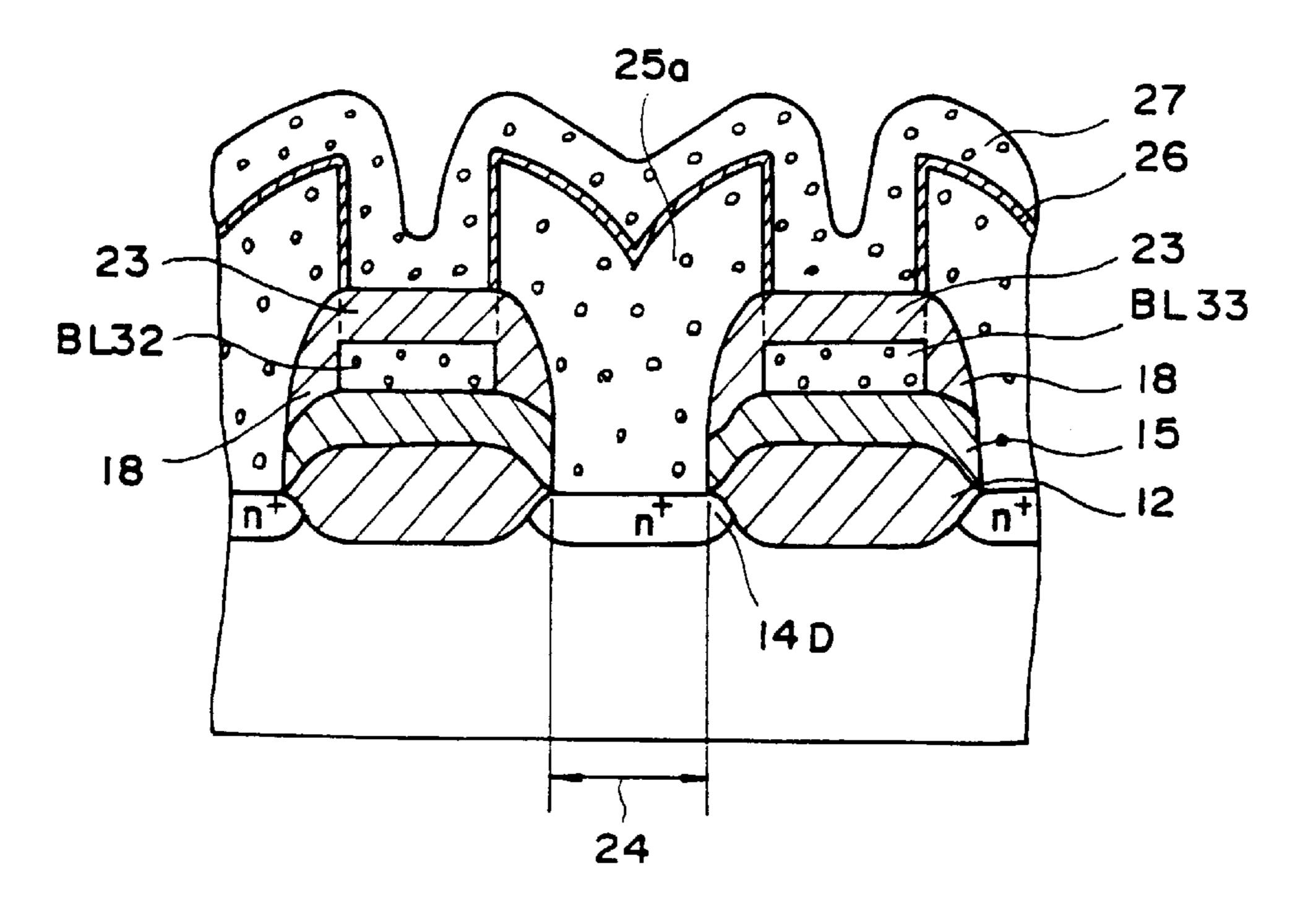

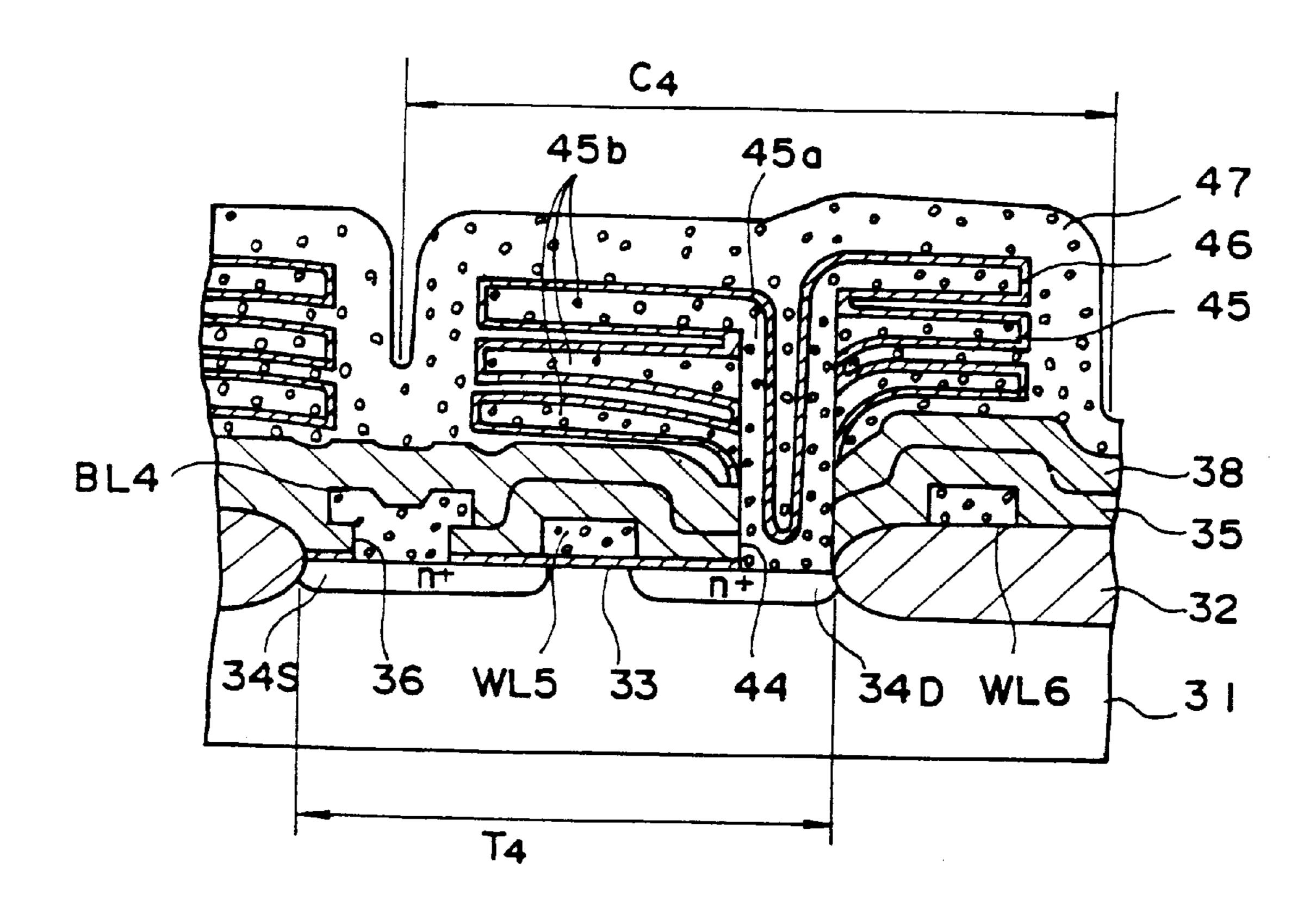

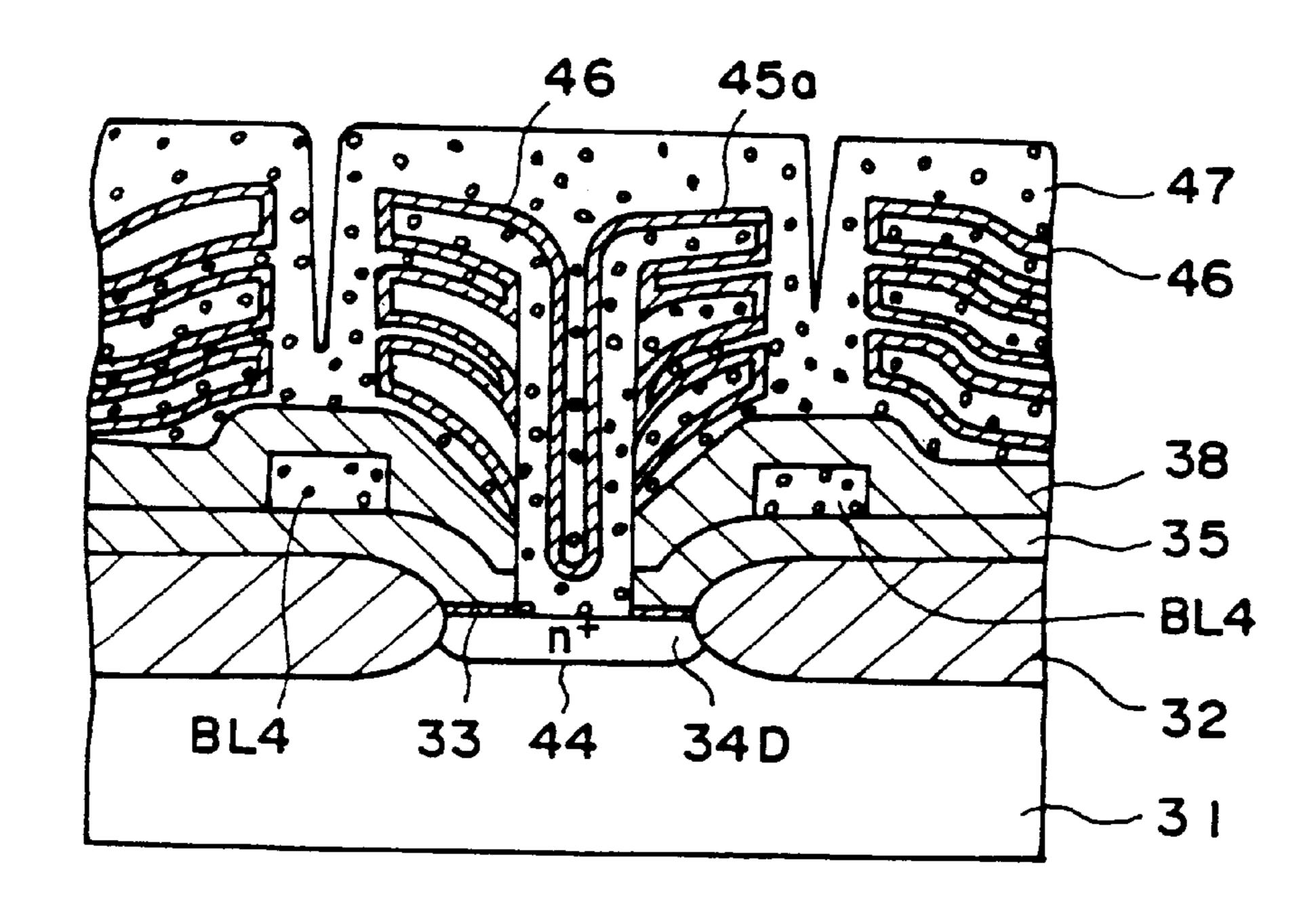

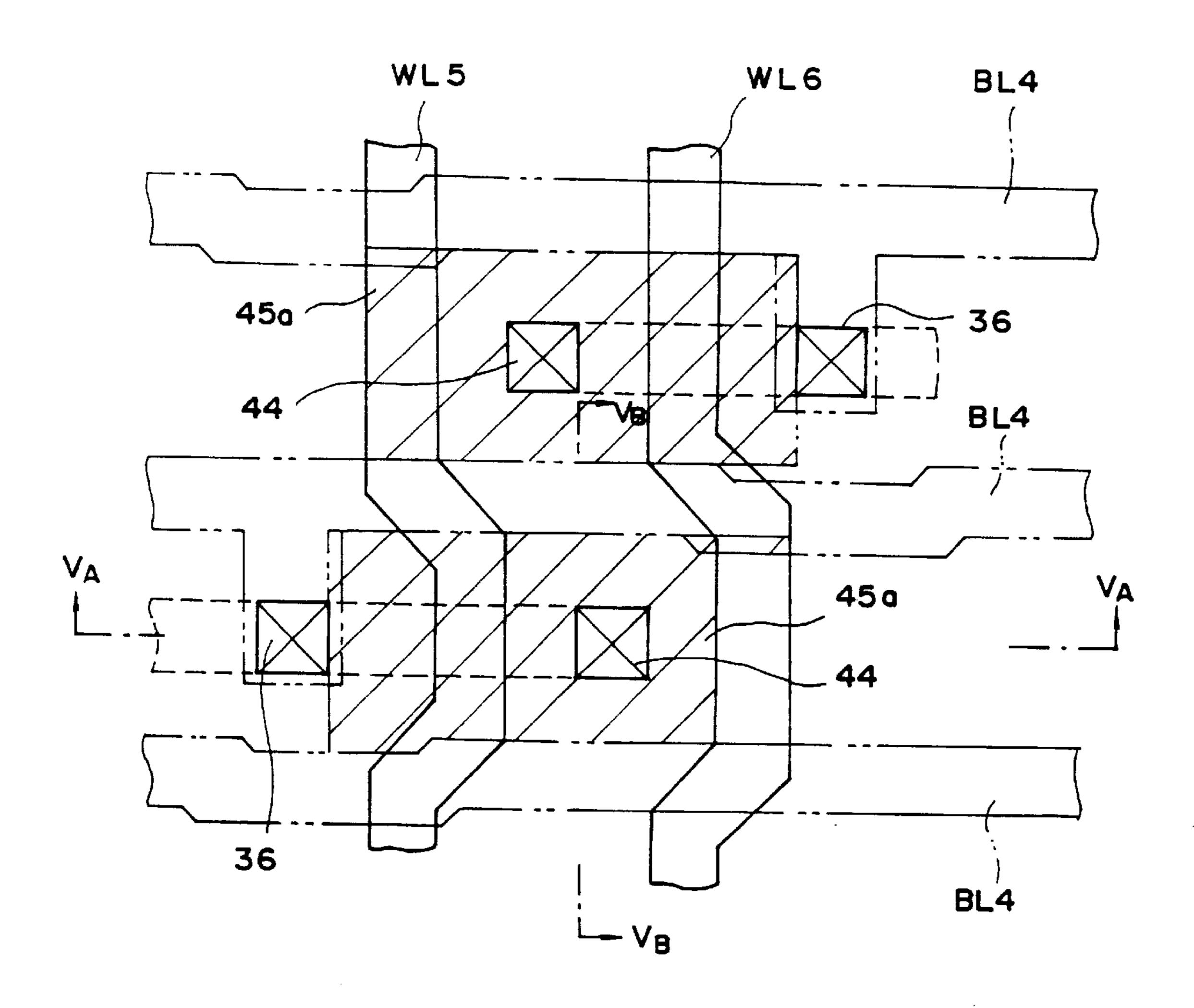

FIGS. 5A through 5C are views showing the fourth preferred embodiment of the present invention;

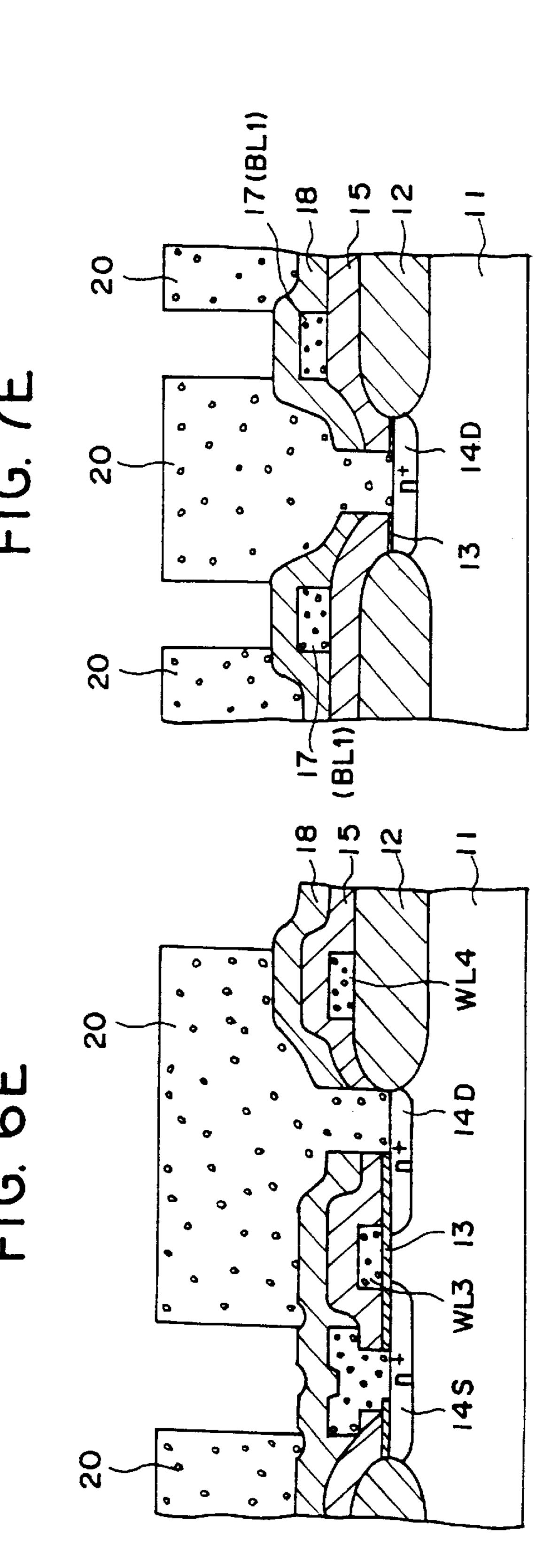

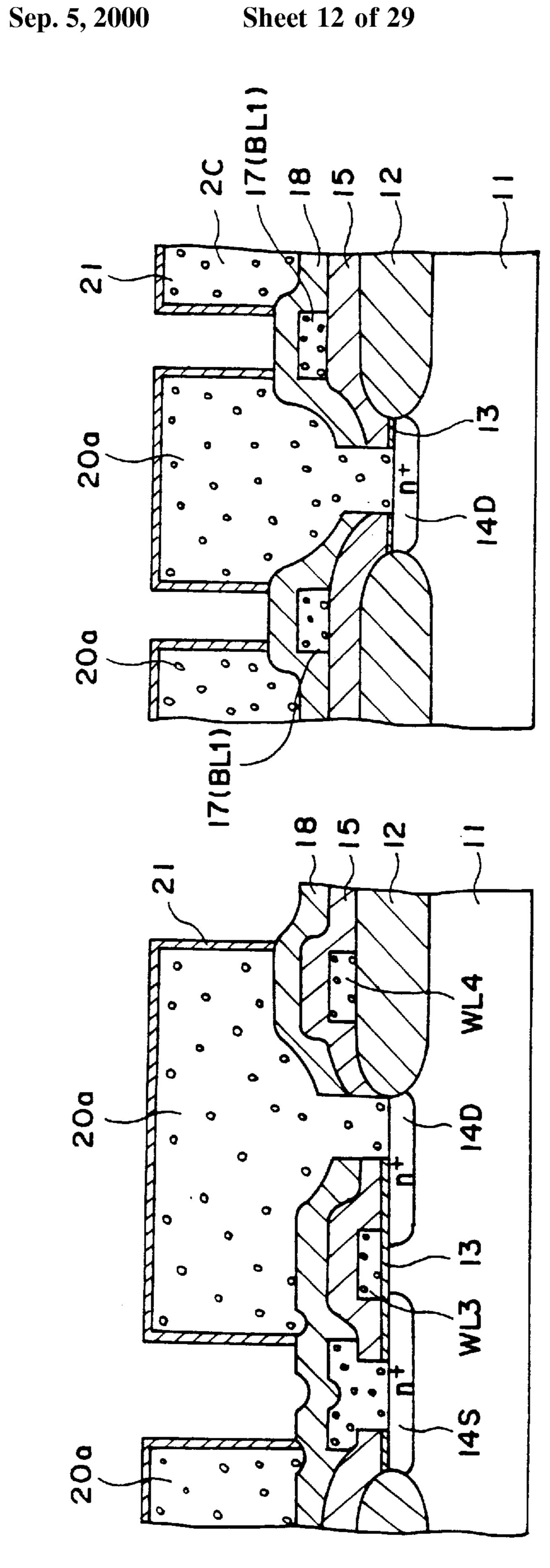

FIGS. 6A through 6F are cross sectional views taken along a line  $II_A$ — $II_A$  shown in FIG. 2C, which are observed in different manufacturing steps for the first embodiment;

FIGS. 7A through 7F are cross sectional views taken along a line  $II_B$ — $II_B$  shown in FIG. 2C, which are observed in different manufacturing steps for the first embodiment;

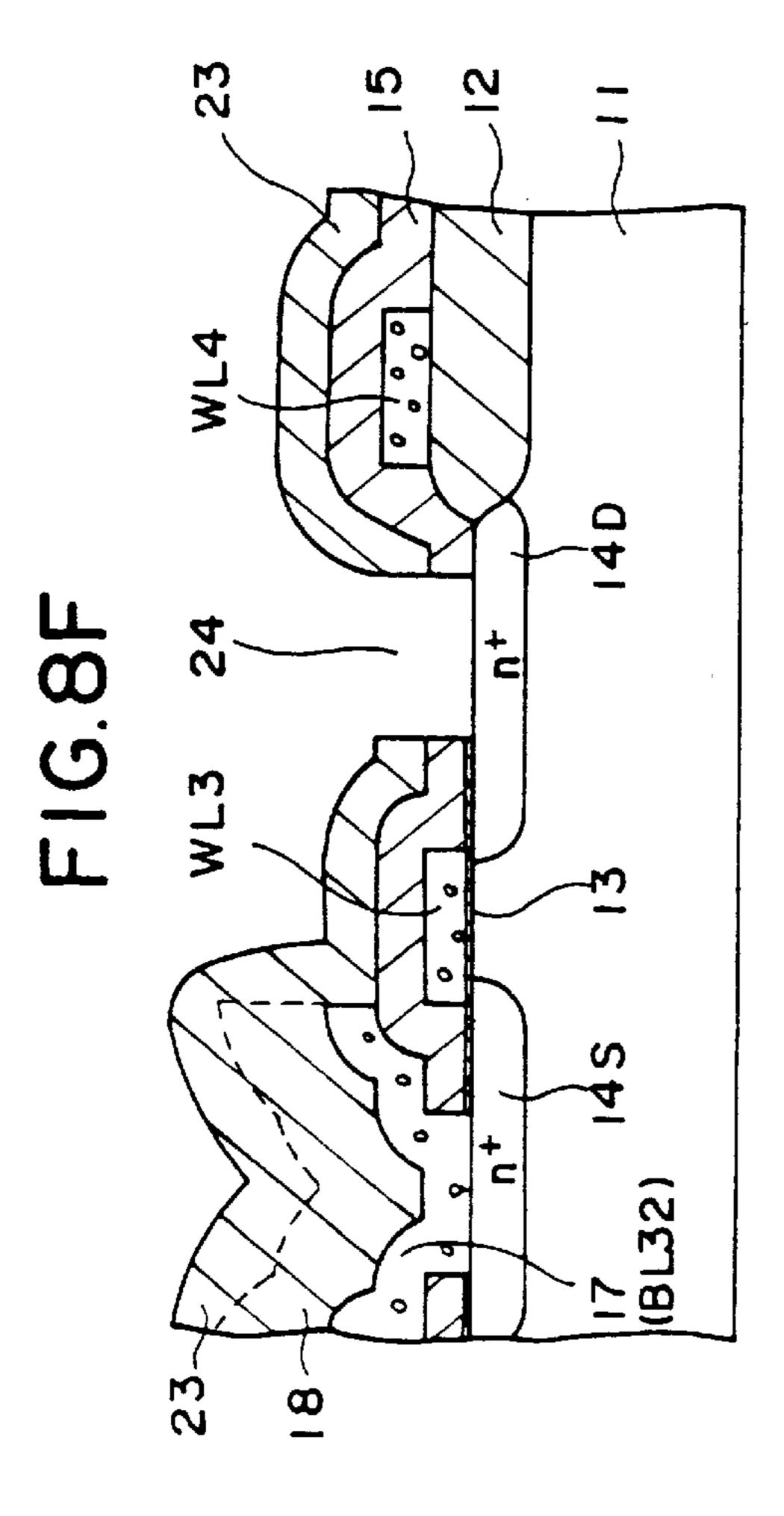

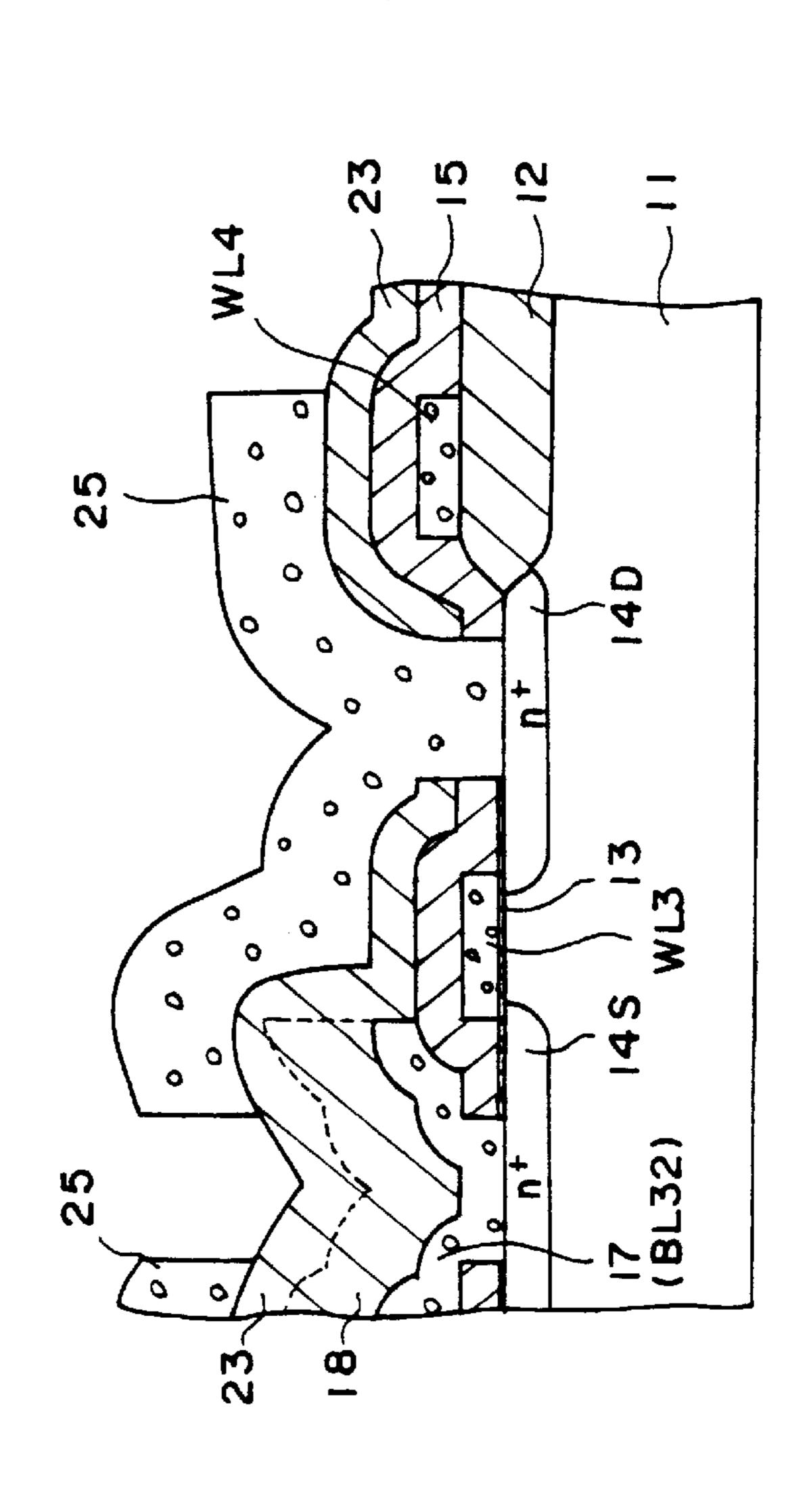

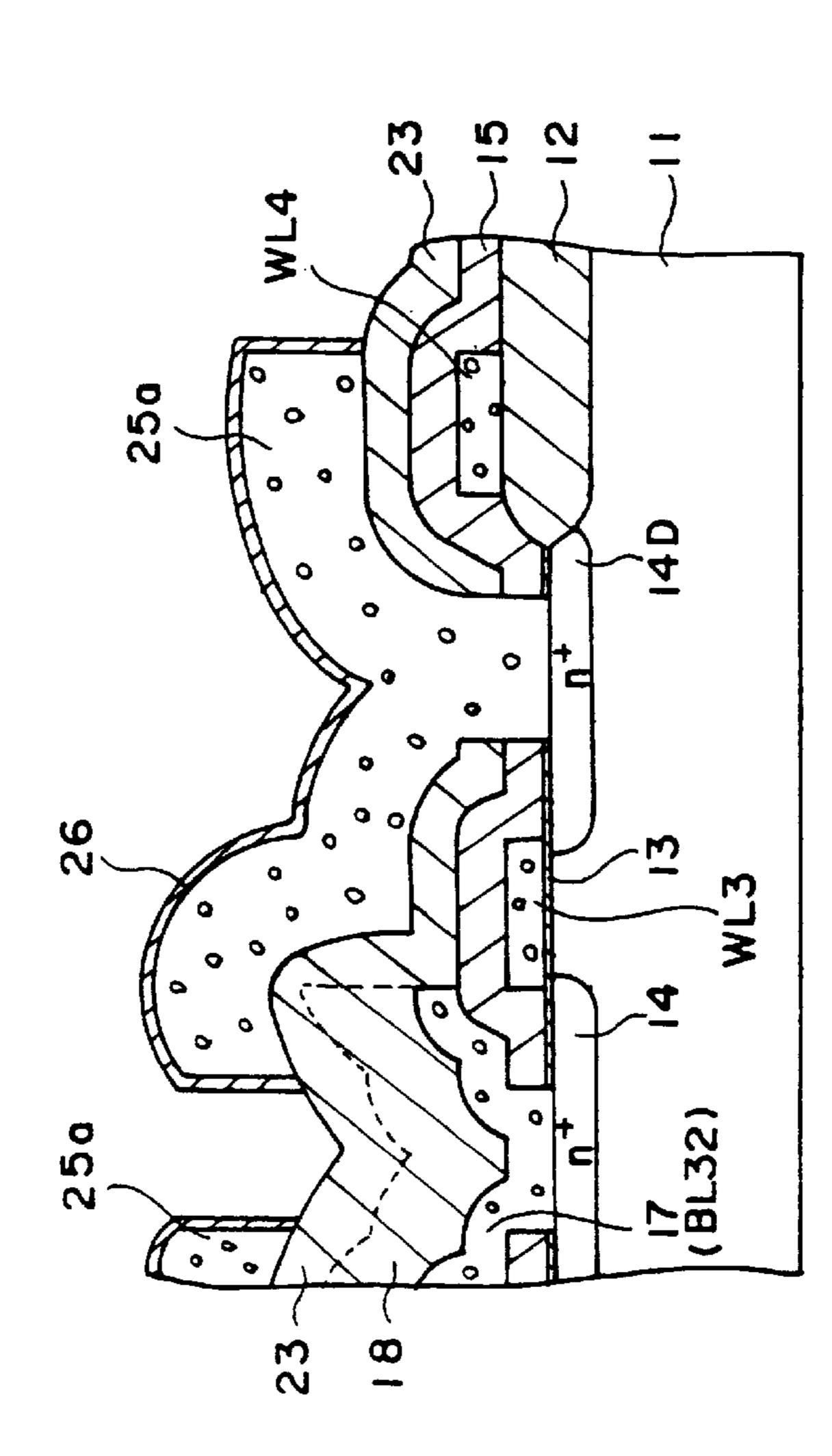

FIGS. 8A through 8H are cross sectional views taken along a line  $IV_A$ — $IV_A$  shown in FIG. 4C, which are observed in different manufacturing steps for the third embodiment;

FIGS. 9A through 9H are cross sectional views taken along a line  $IV_B$ — $IV_B$  shown in FIG. 4C, which are observed in different manufacturing steps for the third embodiment;

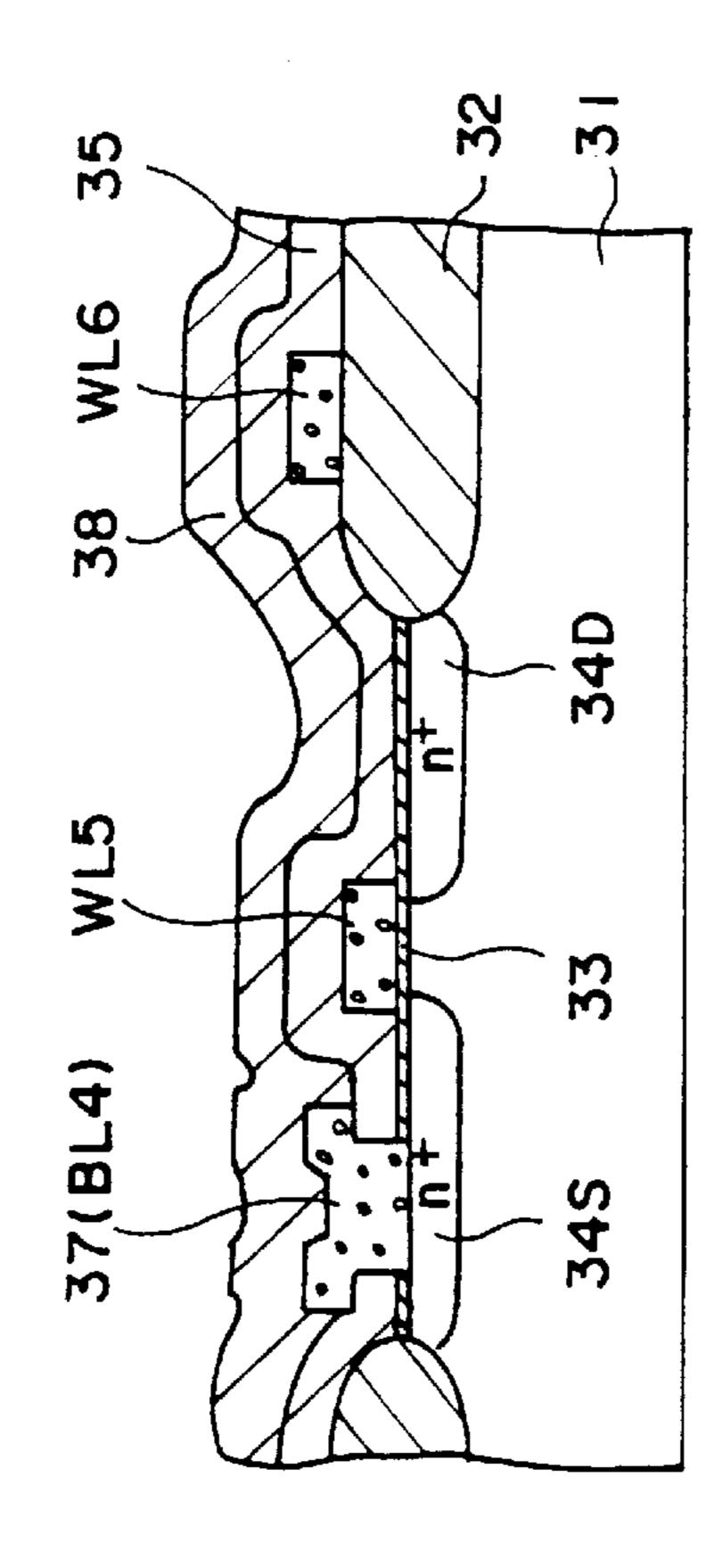

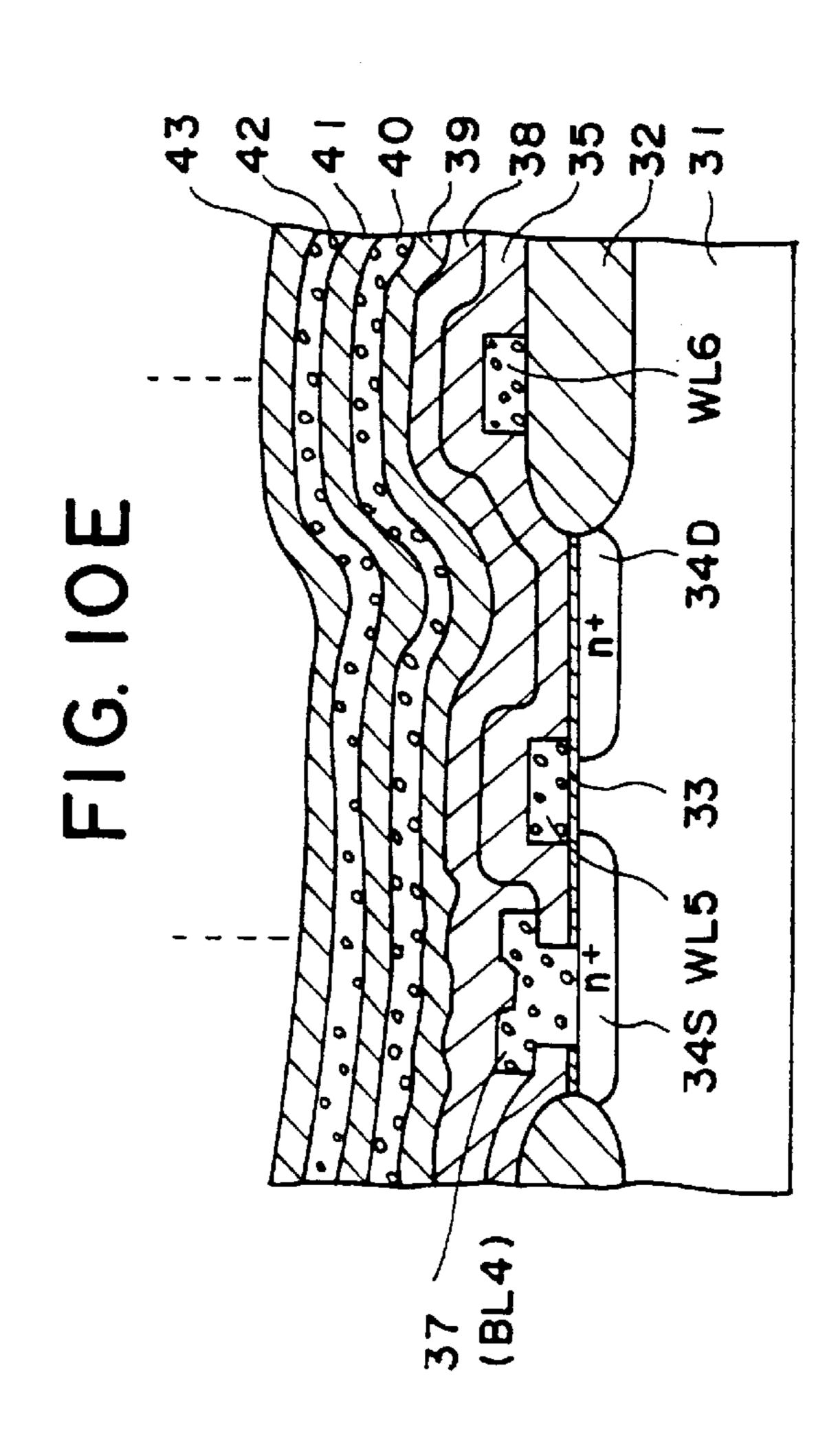

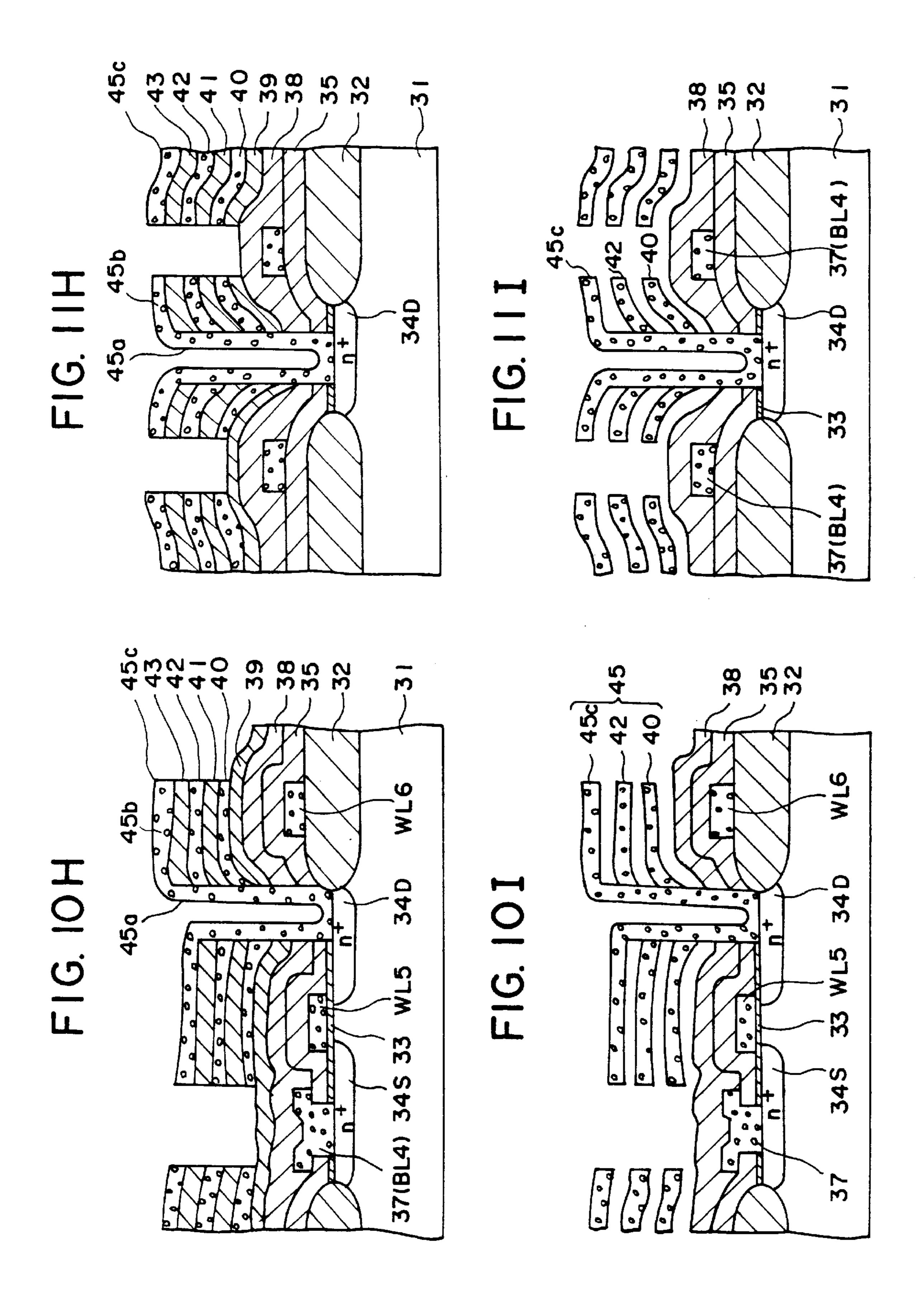

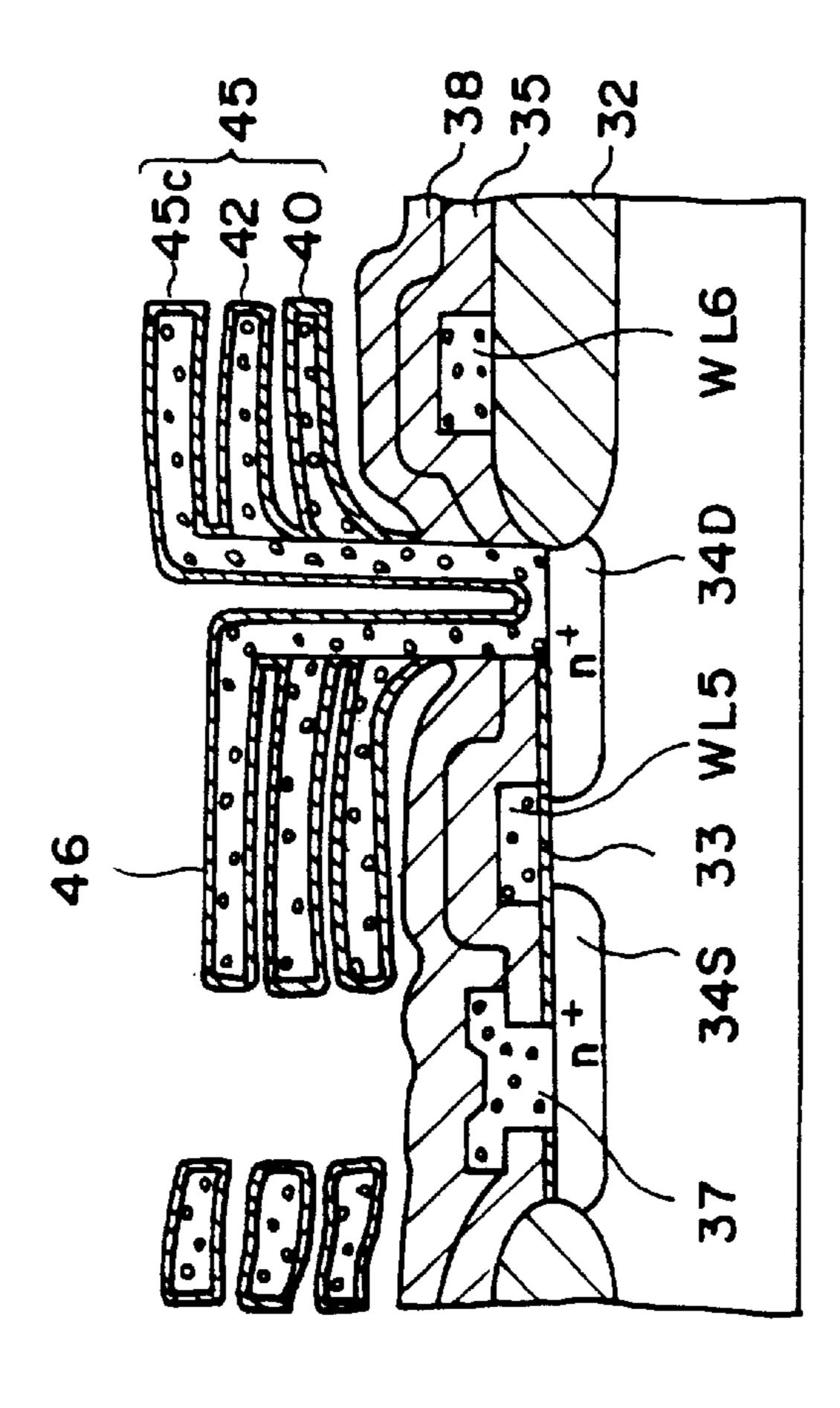

FIGS. 10A through 10J are cross sectional views taken 30 along the line  $V_A$ — $V_A$  shown in FIG. 5C, which are observed in different manufacturing steps for the fourth embodiment;

FIGS. 11A through 11J are cross sectional views taken along the line  $V_B$ — $V_B$  shown in FIG. 5C, which are observed in different manufacturing steps for the fourth embodiment;

FIGS. 12A and 12B are cross sectional views for describing some problems which may be encountered in the first embodiment;

FIGS. 13A through 13C are views showing a modification of the first embodiment;

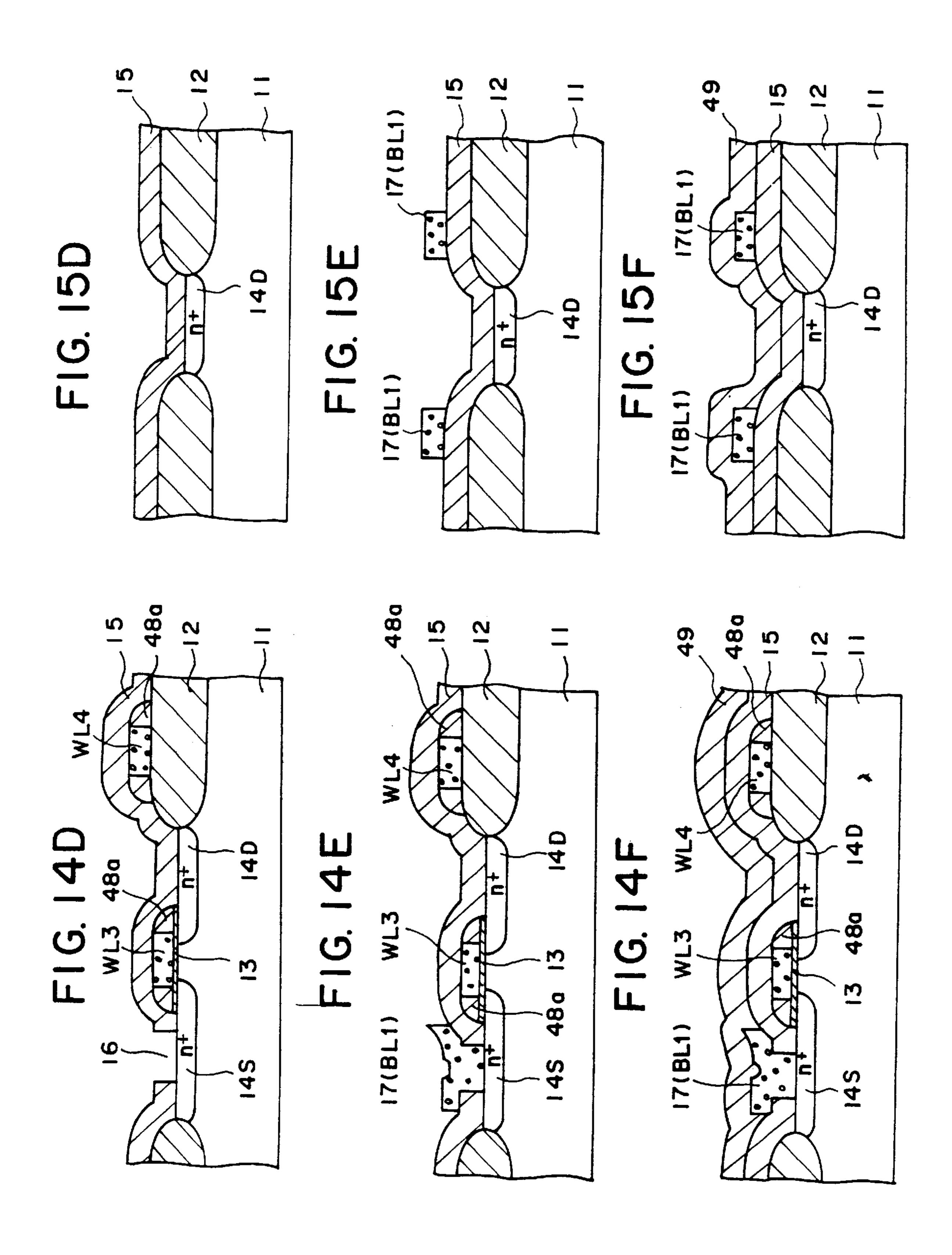

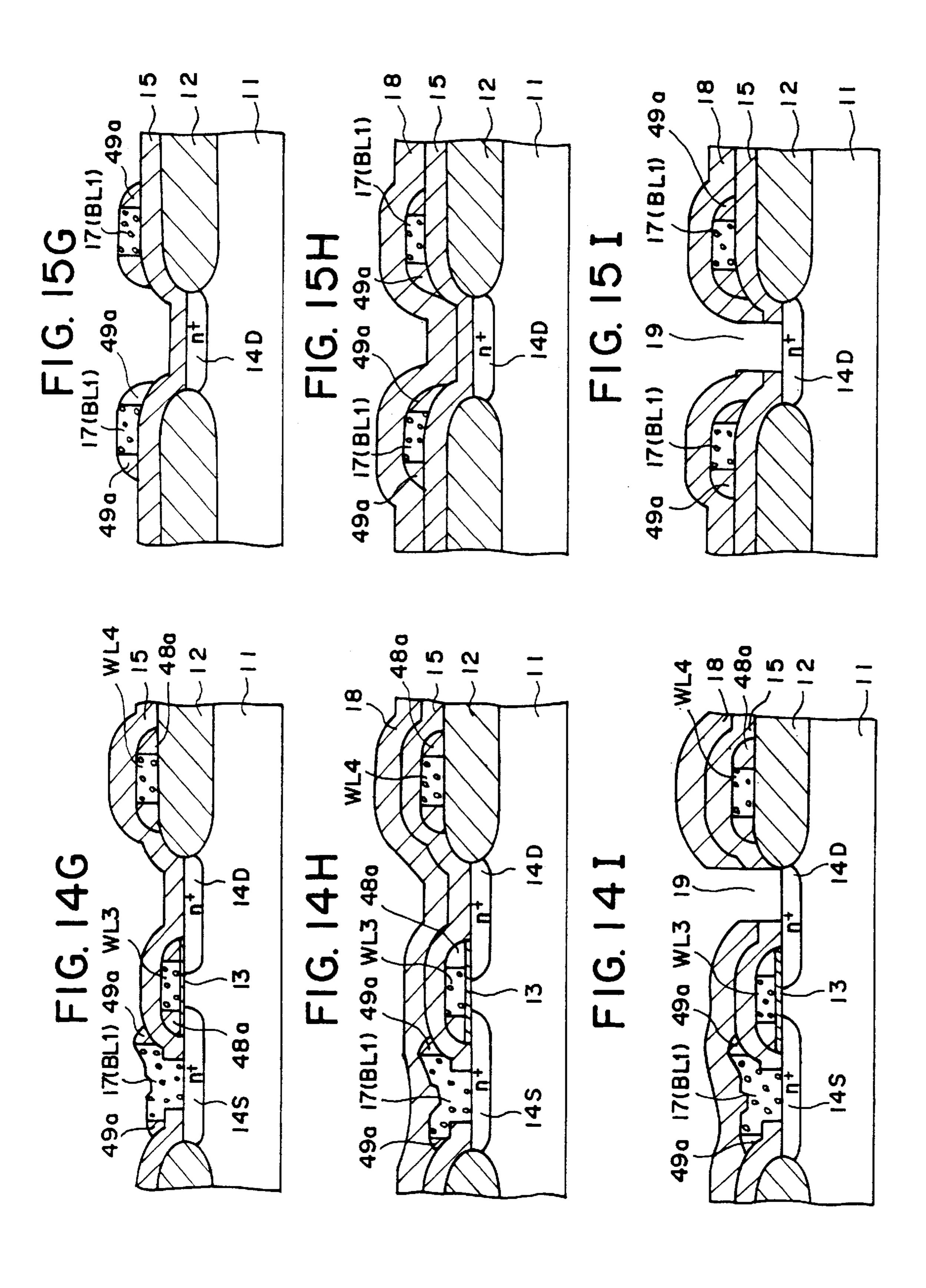

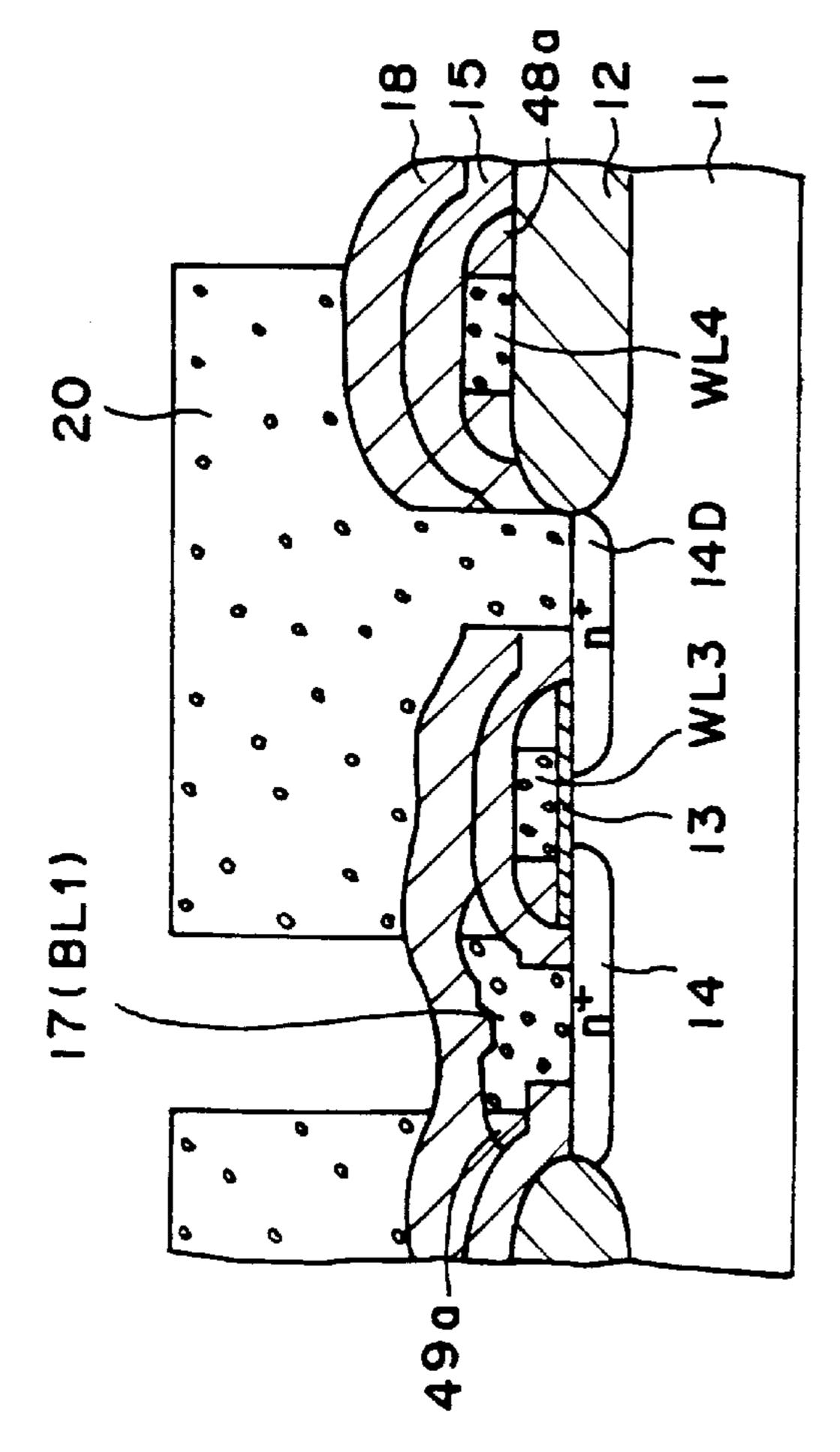

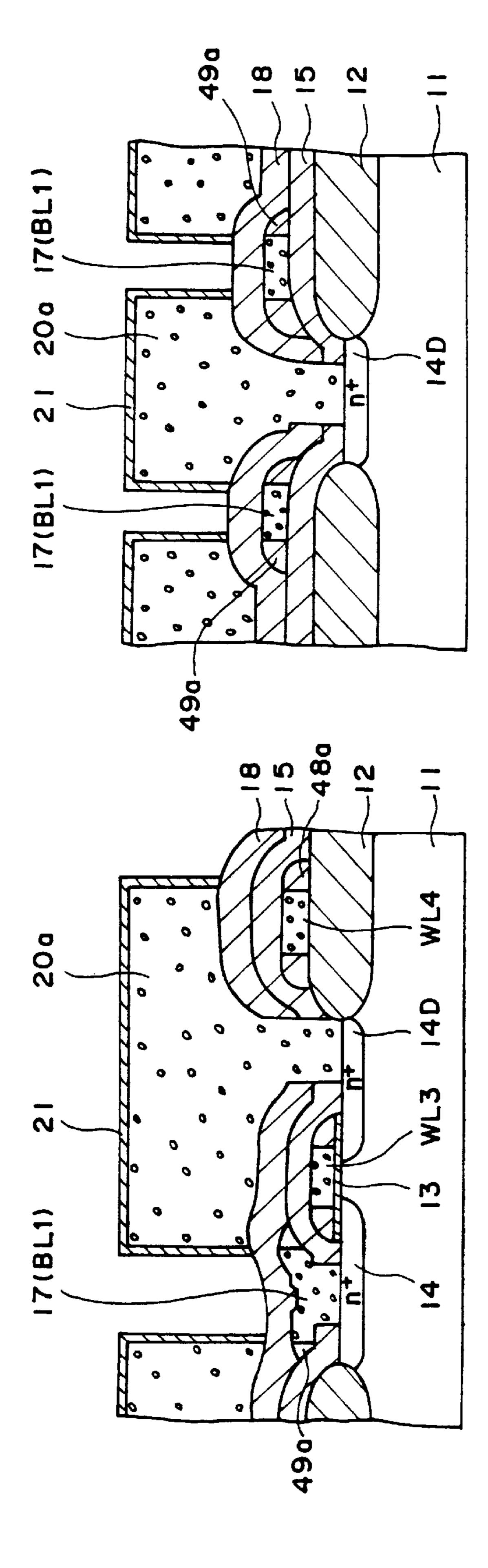

FIG. 14A through 14K are cross sectional views taken along a line XIII<sub>A</sub>—XIII<sub>A</sub> shown in FIG. 13C, which are observed at different manufacturing steps for the modification of FIGS. 13A through 13C; and

FIGS. 15A through 15K are cross sectional views taken along a line  $XIII_B$ — $XIII_B$  shown in FIG. 13C, which are observed at different manufacturing steps for the modification of FIGS. 13A through 13C.

#### DETAILED DESCRIPTION

Before describing the preferred embodiments of the present invention, a description is given of a memory cell for 55 a conventional DRAM device with reference to FIGS. 1A and 1B.

FIG. 1A is a circuit diagram of a memory cell for a DRAM device. As shown, a memory cell is composed of a transfer gate transistor T and a memory cell capacitor C. A 60 source of the transfer gate transistor T is connected to a corresponding bit line BL, and a drain thereof is connected to a storage electrode 6. A gate of the transfer gate transistor T is connected to a corresponding word line WL. An opposed electrode 8 is connected to a constant power source. 65 A dielectric film 7 is provided between the storage electrode 6 and the opposed electrode 8.

4

FIG. 1B shows a cross section of a conventional layer structure which provides the memory cell of FIG. 1A. The memory cell comprises a p-type silicon substrate 1, a field insulation film 2, a gate insulation film 3, a drain region 4D, a source region 4S, and a silicon dioxide film 5. The gate electrode WL1 is concerned with the transfer gate transistor T, and the gate electrode WL2 is concerned with another transfer gate transistor (not shown). Gate electrodes WL1 and WL2 of polysilicon are formed on the gate insulation film 3 and the silicon dioxide film 5, respectively. The storage electrode 6 is formed so as to be in contact with the drain region 4D. The dielectric film 7 is formed so as to surround the storage electrode 6. The dielectric film 7 is covered with the opposed electrode 8. A passivation film 9 of phosphosilicate glass (PSG) is formed on the entire surface of the silicon substrate 1. The bit line BL which overlies the passivation film 9 is in contact with the source region 4S. In the conventional layer structure of FIG. 1B, it is particularly noted that the bit line BL has a vertical layer level higher than that of the layer of the memory cell capacitor C composed of the storage electrode 6, the dielectric film 7 and the opposed electrode 8.

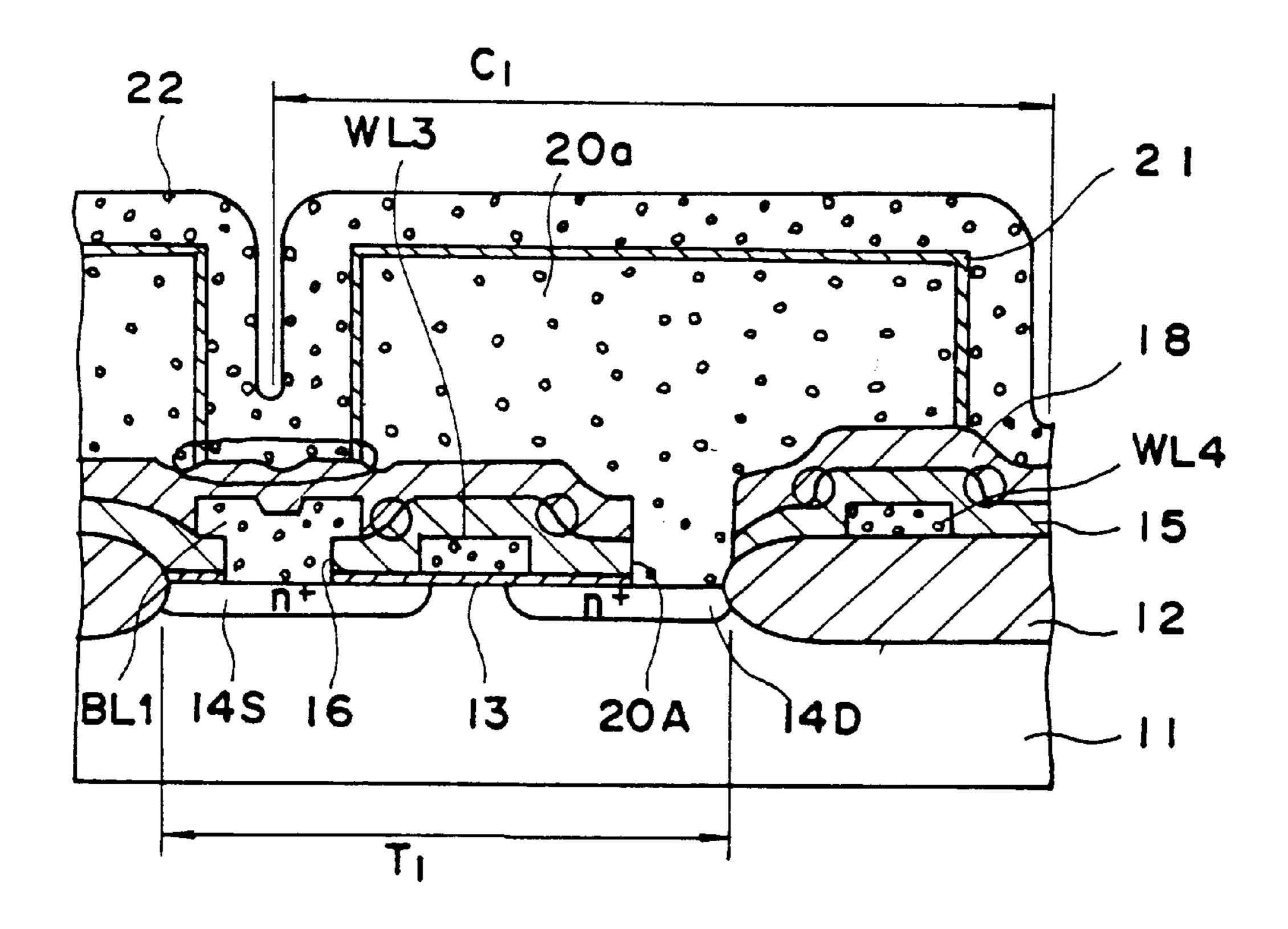

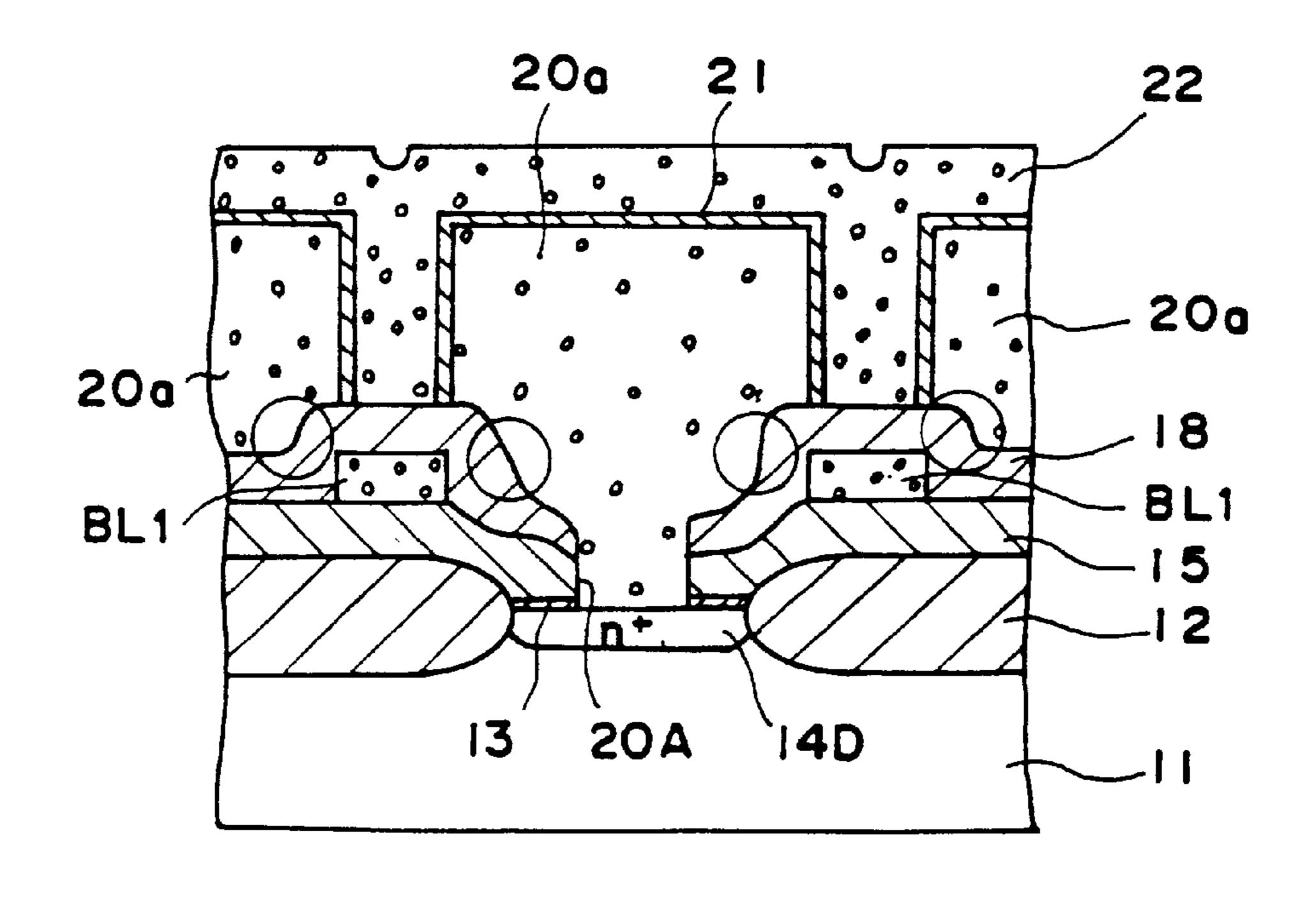

A description is given of the first preferred embodiment of the present invention with reference to FIGS. 2A through 2C.

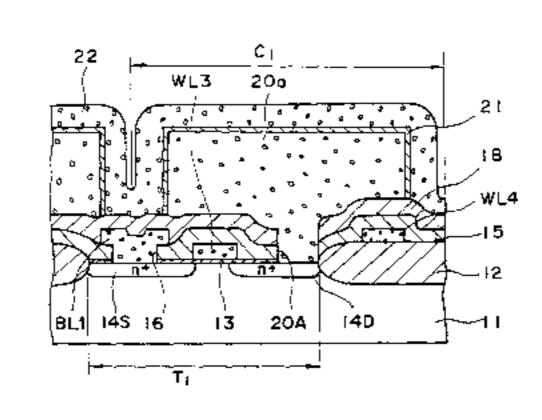

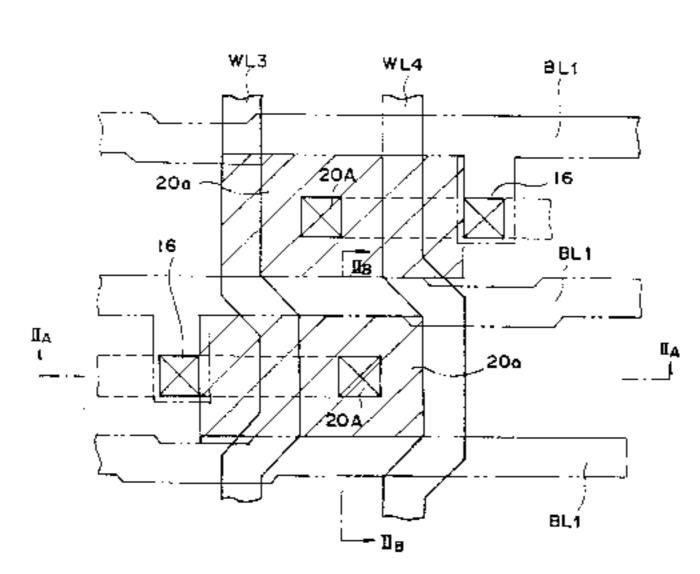

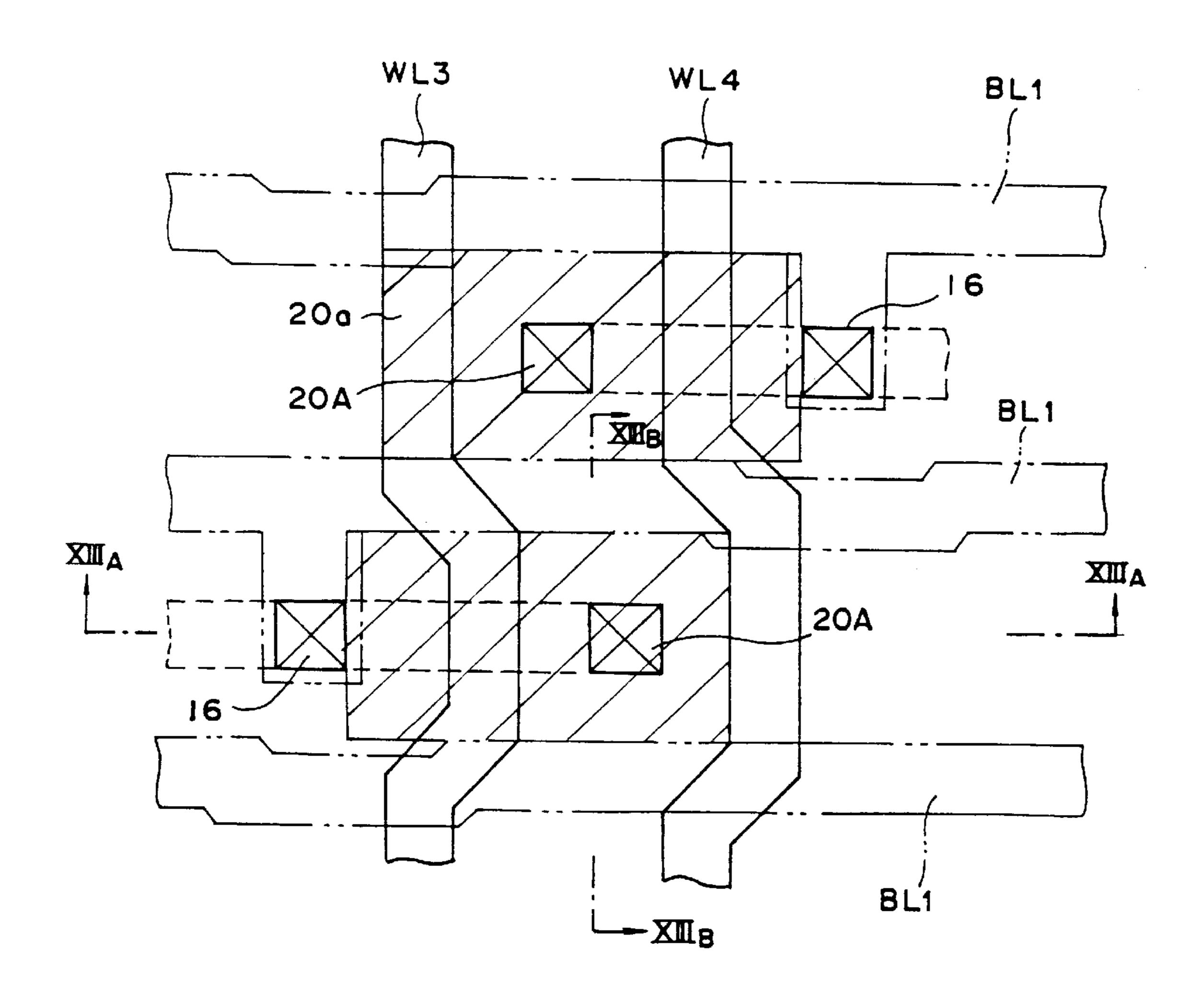

FIGS. 2A through 2C show the first preferred embodiment of the present invention. FIG. 2C is a plan view of the first embodiment. FIG. 2A is a cross sectional view taken along the line  $II_A$ — $II_A$  shown in FIG. 2C, and FIG. 2B is a cross sectional view taken along the line  $II_B$ — $II_B$ .

Referring to FIGS. 2A through 2C, a field insulation film 12 is formed on a main surface of a silicon substrate 11. A gate insulation layer 13 is formed on the surface of the silicon substrate 11. Gate electrodes WL3 and WL4 of polysilicon films are formed on the gate insulation films 13 and the field insulation film 12, respectively. The gate electrodes WL3 and WL4 function as word lines of the transfer gate transistor T1. Then, impurity diffusion layers 14S and 14D are formed by implanting arsenic ions (As<sup>+</sup>) into the silicon substrate 11, wherein the gate electrodes WL3 and WL4 are used as a mask. The impurity diffusion layers 14S and 14D function as the source and drain of a transfer gate transistor T1, respectively. An interlayer insulation film 15 of silicon dioxide (SiO<sub>2</sub>) is formed so as to cover the gate electrodes WL3 and WL4. Bit lines BL1 of polycide or polysilicon which contains n<sup>+</sup>-type impurity ions such as arsenic ions (As<sup>+</sup>) are formed so as to make contact with the source region 14S through a bit line contact hole 16, and overlie the interlayer insulation film 15. An insulation film 18 of silicon dioxide film is formed on the interlayer insulation film 15 so as to cover the bit lines BL1. The transfer gate transistor T1 is composed of the drain and source regions 14D and 14S, the gate electrode WL3 and the bit line BL1.

A storage electrode 20a is formed on the silicon dioxide film 18 and is in contact with the drain region 14D through a contact hole 20A. The storage electrode 20a is made of polysilicon, and is doped with n<sup>+</sup>-type impurity ions such as arsenic (As<sup>+</sup>). The storage electrode 20a is covered with a dielectric film 21 of silicon dioxide, which is formed by thermal oxidation with respect to the storage electrode 20a. An opposed electrode 22, which is paired with the storage electrode 20a, is formed so as to surround the dielectric film 21. The opposed electrode 22 is made of polysilicon containing n<sup>+</sup>-type impurity ions such as phosphorus. A memory cell capacitor or storage capacitor C1 is composed of the storage electrode 20a, the dielectric film 21 and the opposed electrode 22.

It is particularly noted that each bit line BL1 has a layer level lower than that of the storage electrode 20a. Therefore, it is unnecessary to form bit lines on an insulation film which covers the memory cell capacitor. Additionally, it becomes possible to increase the storage electrode 20a because there is no bit line contact hole in the insulation film which covers the memory cell capacitor. As a result, the storage electrode **20***a* thicker than the storage electrode **6** shown in FIG. 1B can be formed. It is noted that the thicker storage electrode 20a increases the capacitance of the memory cell capacitor. In the case where each bit line has a layer level higher than that of the storage electrode as in the case of the conventional DRAM device of FIG. 1B, there is a limit on the film thickness of the storage electrode 6. This is because the presence of a thick storage electrode in the conventional 15 layer structure makes it difficult to make contacts between the source regions 3S and the bit lines BL.

It is further noted that the adjacent bit lines BL1 of the first embodiment are electrically shielded by the storage electrode **20***a* and opposed electrode **22** interposed therebetween. Although the storage electrode **20***a* is normally in a floating state, there exists the strong capacitive coupling between the storage electrode **20***a* and the opposed electrode **22**. As a result, the storage electrode **20***a* can function as an electrical shield member with respect to the neighboring bit lines BL1. With the above structure, it becomes possible to reduce noise introduced on the bit lines BL1.

A description is given of the second preferred embodiment of the present invention with reference to FIGS. 3A through 3C. In FIGS. 3A through 3C, those parts which are 30 the same as those in the previous figures, are given the same reference numerals. FIGS. 3A and 3B are cross sectional views taken along the lines III<sub>A</sub>—III<sub>A</sub> and III<sub>B</sub>—III<sub>B</sub> of FIG. 3C, respectively.

The second embodiment of the present invention is com- 35 posed of a transfer gate transistor T2 and a memory cell capacitor C2, as in the case of the first embodiment. The second embodiment is different from the first embodiment in position of bit line contact holes. As shown in FIG. 2C, each bit line contact hole 16 and the corresponding storage 40 electrode contact hole 20A are aligned in the direction of extension of the bit lines BL1. Particularly, the bit line contact hole 16 is positioned in the center of a distance between the neighboring bit lines BL1. On the other hand, as shown in FIG. 3C, a bit line contact hole 16a with respect 45 to a bit line BL22 and the corresponding storage electrode contact hole 20A of the transfer gate transistor T2, are not arranged into a line. The bit line contact hole 16a of the bit line BL22 is positioned closer to the bit line BL22 than a bit line BL23. Similarly, the bit line contact hole 16a of a bit 50 line BL21 is positioned closer to the bit line BL21 than the bit line BL22. The cross section of the contact hole 16a of the bit line BL22 does not appear in the cross section of FIG. 3A. That is, the cross section of FIG. 3A differs from the cross section of FIG. 2A. With the aforementioned arrange- 55 ment of the bit line contact holes 16a, it becomes possible to improve insulation properties between the neighboring bit lines such as the bit lines BL21 and BL22 and to achieve easy patterning. The source region 14S is the same as the source region 14S of the first embodiment. Other portions of 60 the second embodiment are the same as those of the first embodiment.

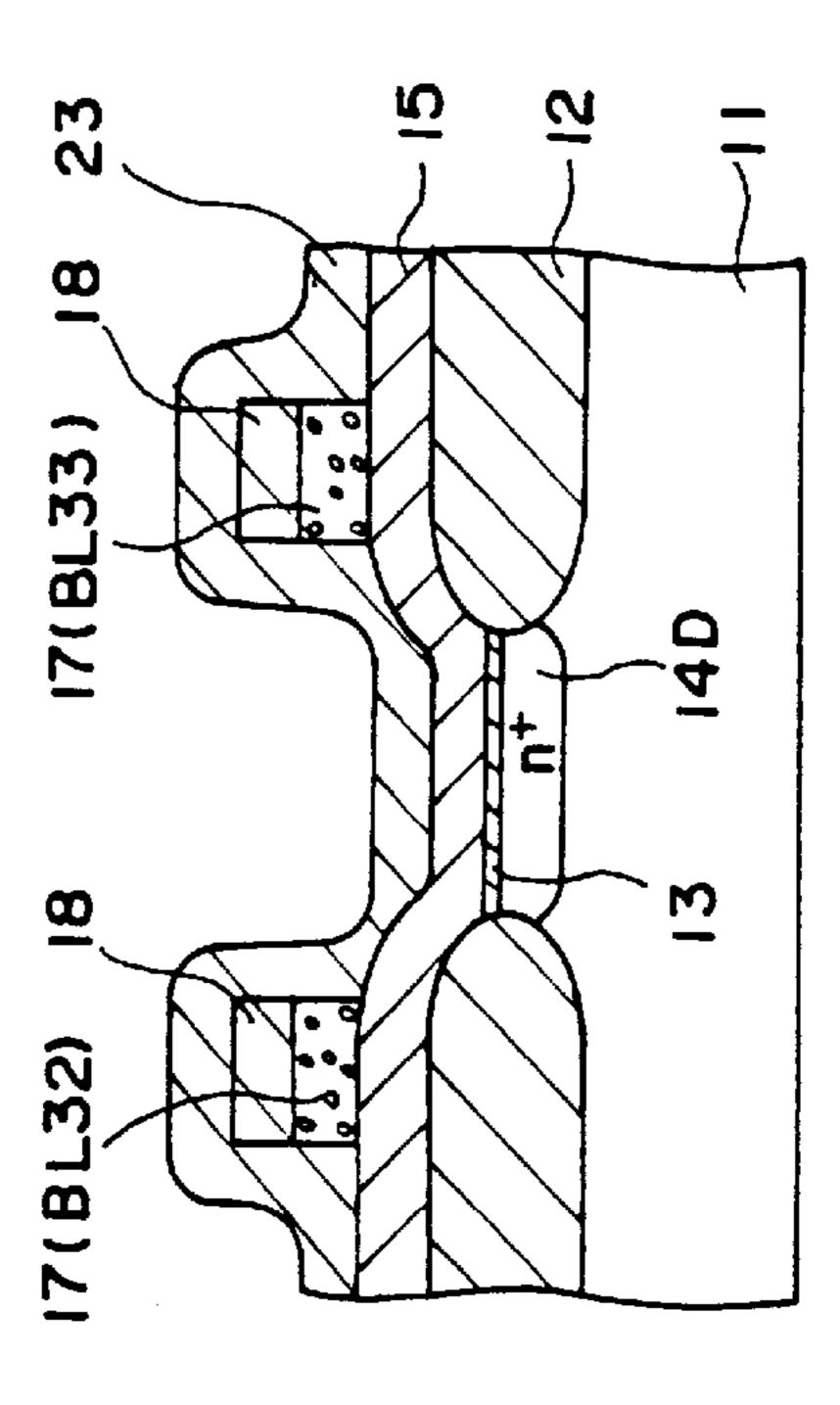

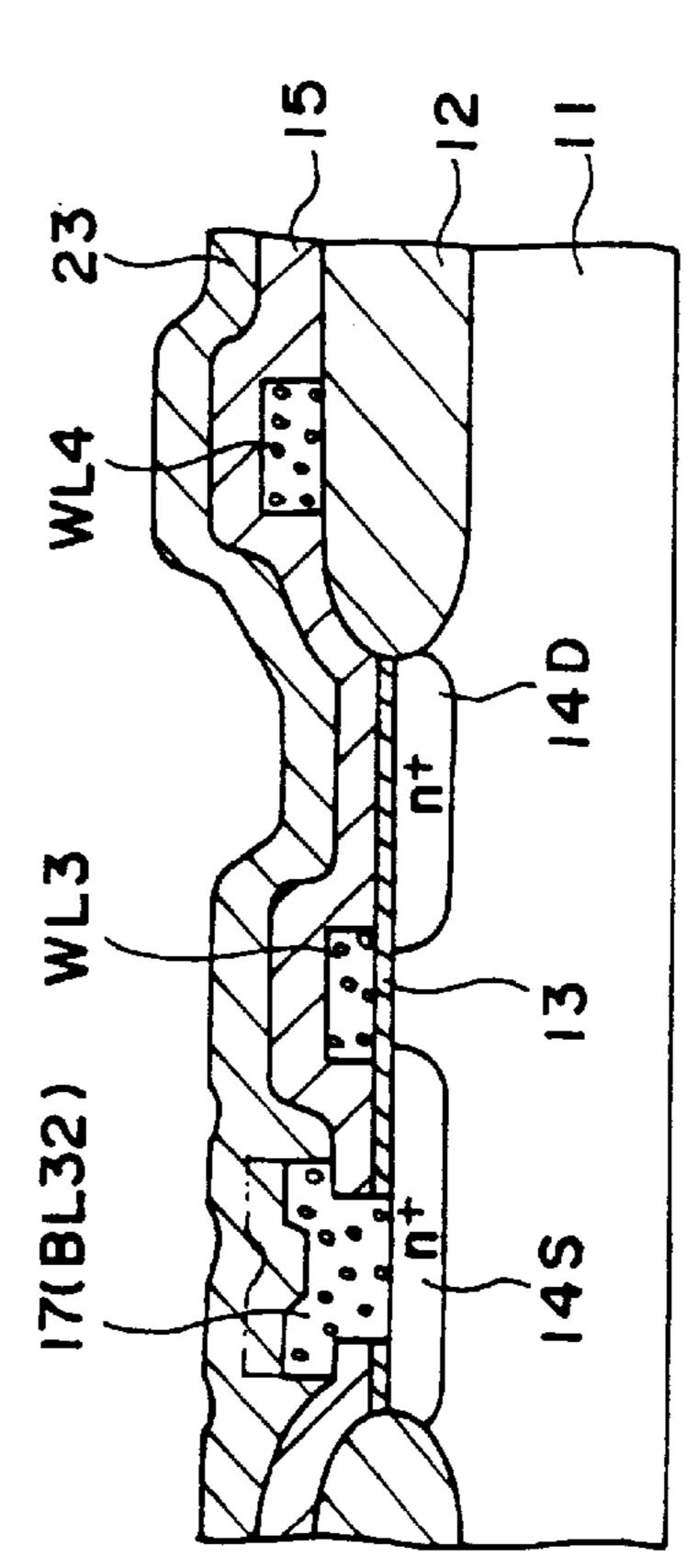

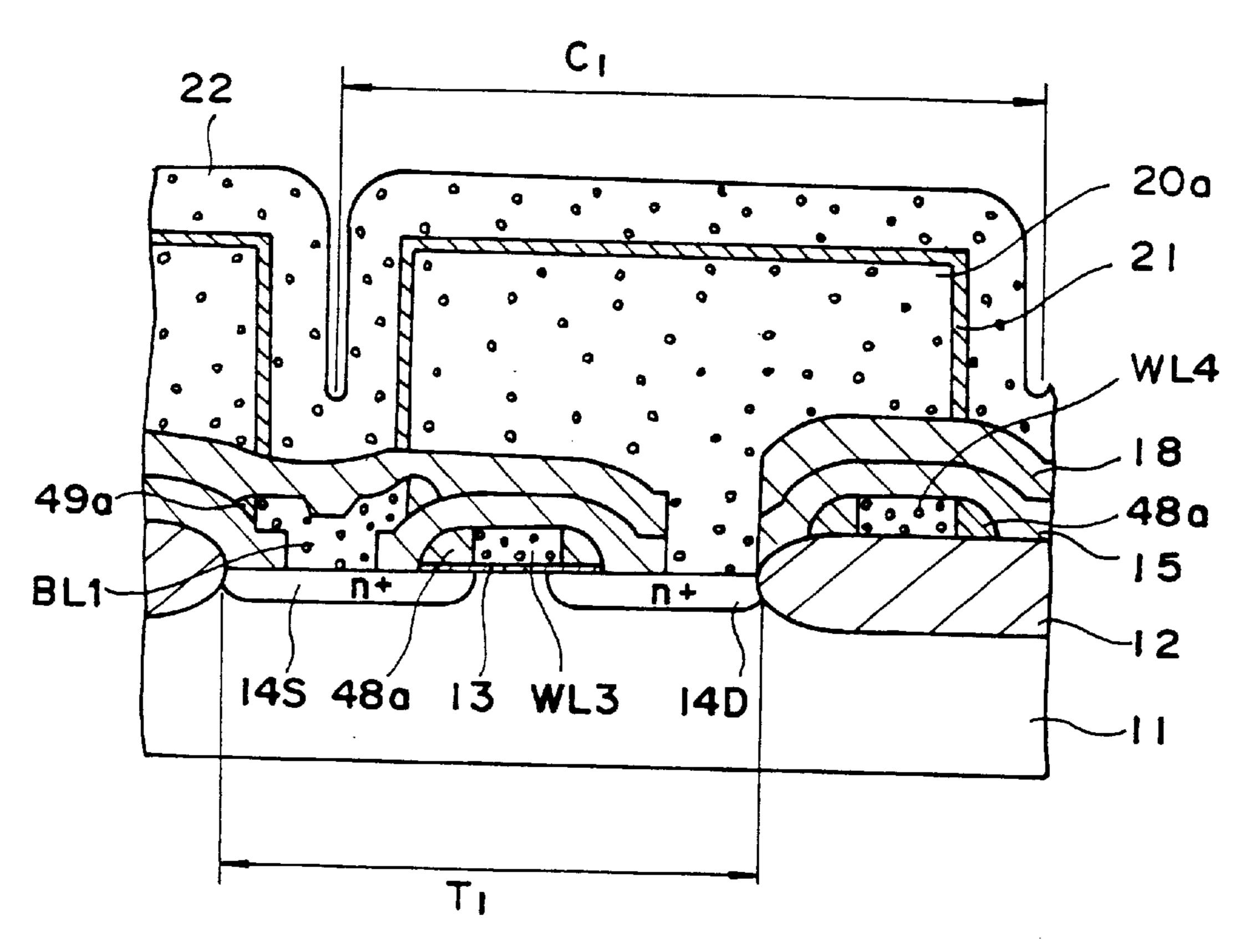

A description is given of the third embodiment of the present invention with reference to FIGS. 4A through 4C. FIGS. 4A and 4B are cross sectional views taken along the 65 lines  $IV_A$ — $IV_A$  and  $IV_B$ — $IV_B$  of FIG. 4C, respectively. The third embodiment is composed of a transfer gate transistor

T3 and a memory cell capacitor C3. The transfer gate transistor T3 comprises the source and drain regions 14S and 14D, the gate electrode 13 and a bit line BL32. The memory cell capacitor C3 comprises a storage electrode 25a of polysilicon, a dielectric film 26 of silicon dioxide, and an opposed electrode 27 of polysilicon. The storage electrode 25a and the opposed electrode 27 are doped with n<sup>+</sup>-type impurity such as arsenic (As) and phosphorus (P), respectively.

The third embodiment has an essential feature in which it has a storage electrode contact hole 24 which is formed in an insulation film by a self-alignment process in which bit lines BL31, BL32 and BL33 function as a resist mask film. As shown in FIG. 4C, the storage electrode contact hole 24 has a slit shape. By the self-alignment process, it is unnecessary to carry out a positioning operation with respect to the storage electrode contact holes 24. Additionally, a decreased area of the memory cell which occupies the silicon substrate 11, is obtainable.

A description is given of the fourth embodiment of the present invention with reference to FIGS. 5A through 5C. FIGS. 5A and 5B are cross sectional views taken along the lines  $V_A - V_A$  and  $V_B - V_B$  of FIG. 5C, respectively. Referring to FIGS. 5A through 5C, a field insulation film 32 is formed on a main surface of a p-type silicon substrate 31. A gate insulation film 33 is formed on the surface of the silicon substrate 31. Gate electrodes, or word lines WL5 and WL6 are formed on the gate insulation film 33 and the field insulation film 32, respectively. Then, source and drain regions 34S and 34D are formed in the silicon substrate 31. The source and drain regions 34S and 34D are n<sup>+</sup>-type impurity diffusion regions. The word lines WL5 and WL6 are covered with an interlayer insulation film 35 of silicon dioxide. Bit line contact holes 36 are formed in the interlayer insulation film 35 and the gate insulation film 33. Bit lines BL4 are formed on the interlayer insulation film 35, and are in contact with the respective source regions 34S through bit line contact holes 36. A silicon nitride film 38 is formed so as to cover the bit lines BL4. A transfer gate transistor T4 of the fourth embodiment is composed of the source and drain regions 34S and 34D, the word line WL5 and the bit line BL**4**.

Storage electrode contact holes 44 are formed so as to penetrate the silicon nitride film 38, the interlayer insulation film 35 and the gate insulation film 33. A memory cell capacitor C4 includes a storage electrode 45, a dielectric film 46 and an opposed electrode 47. The storage electrode 45 of polysilicon has a vertical portion 45a and three flange or wing portions 45b which are connected to the vertical portion 45a. The vertical portion 45a is in contact with the drain region 34D. The uppermost wing portion 45b is formed integrally with the vertical portion 45a. The wing portions 45b are separated from each other in the vertical direction. In other words, a gap is formed between the adjacent wing portions 45b. The above-mentioned structure enables an increase of the capacitance of the storage capacitor C4. The wing portions 45b extend above the gate electrodes WL5 and WL6. A surface of the storage electrode 45 is covered with the dielectric film 46 of silicon dioxide. The opposed electrode 47 of polysilicon are formed so as to cover the dielectric film 46. It is noted that the gap between the adjacent wing portions 45b is filled with polysilicon of the opposed electrode 47. The storage electrode 45 and the opposed electrode 47 are doped with n<sup>+</sup>-type impurity such as arsenic (As) and phosphorus (P), respectively.

As can be seen from FIGS. 5A through 5C, the surface area of the storage electrode 45 can be greatly increased. As

a result, the memory cell capacitor including the storage electrode 45 has a further increased capacitance value.

A description is given of a method for producing the first embodiment of the present invention with reference to FIGS. 6A through 6F, and FIGS. 7A through 7F. FIGS. 6A through 6F show cross sectional views along the line  $II_A$ — $II_A$  shown in FIG. 2C observed at different manufacturing steps, and FIGS. 7A through 7F show cross sectional views along the line  $II_B$ — $II_B$  shown in FIG. 2C observed at different manufacturing steps.

Referring to FIGS. 6A and 7A, the field insulation film 12 is formed by a selective thermal oxidation process such as the LOCOS process in which an oxidation-resistant mask film is used. After removing the oxidation-resistant mask film, the gate insulation film 13 is formed to a thickness of 15 about 200 Å by a thermal oxidation process. Then, a polysilicon film is deposited to a thickness of approximately 2000 Å by chemical vapor deposition (CVD). Thereafter, the polysilicon film is patterned so as to form the gate electrodes WL3 and WL4. The patterning process is carried out by <sup>20</sup> forming a resist mask film by the conventional photolithography technology, and then etching the polysilicon film by reactive ion etching (RIE) in which an etching gas of CCl<sub>4</sub>/O<sub>2</sub> is used. Thereafter, impurity ions such as arsenic ions (As<sup>+</sup>) are implanted into the silicon substrate 11 by self-alignment in which the gate electrodes WL3 and WL4 are used as a mask film. Thereby, the source and drain regions 14S and 14D are formed in the silicon substrate 11.

Referring to FIGS. 6B and 7B, the interlayer insulation film 15 of silicon dioxide is deposited to a thickness of approximately 1000 Å so as to cover the gate electrodes WL3 and WL4. Then the interlayer insulation film 15 is etched by an anisotropic etching process such as RIE so as to form the opening (bit line contact hole) 16. In the RIE process, an etching gas of CHF<sub>3</sub>+H<sub>2</sub> is used.

Referring to FIGS. 6C and 7C, an impurity-doped polysilicon film having a thickness of approximately 1000 Å is deposited on the entire surface of the silicon substrate 11 by low-pressure chemical vapor deposition. Then deposited polysilicon film is patterned by anisotropic etching such as RIE so as to form the bit lines (BL1) 17. A polycide film can be substituted with the polysilicon film. In this case, a polysilicon film is deposited, and then a tungsten silicide film is deposited on the polysilicon film. Thereafter, the polysilicon film and the tungsten silicide film are patterned by the conventional photolithography technology. The tungsten silicide film can be substituted with a refractory metal film of molybdenum silicide, tantalum silicide, or titanium silicide.

Referring to FIGS. 6D and 7D, the insulation film 18 of silicon dioxide or silicon nitride is deposited by chemical vapor deposition so as to cover the bit lines 17. After providing a mask film (not shown) on the insulation film 18, the insulation film 18 and 15 the gate insulation film 13 are etched so as to form an opening 19. The opening 19 functions as the storage electrode contact hole 20A.

Referring to FIGS. 6E and 7E, a polysilicon film 20 is deposited by chemical vapor deposition on the entire surface 60 of the silicon substrate 11, and is then patterned by anisotropic etching such as RIE so as to form the storage electrodes 20a. The polysilicon film 20 is approximately 4000 Å thick. An etching gas of CCl<sub>4</sub>/O<sub>2</sub> is used in the anisotropic etching process.

Referring to FIGS. 6F and 7F, the dielectric film 21 having a thickness of approximately 100 Å is formed by

8

thermal oxidation with respect to the storage electrodes 20a. Then, as shown in FIGS. 2A and 2B, the opposed electrodes 22 are deposited so as to cover the dielectric films 21.

The manufacturing process for the second embodiment is the same as that for the first embodiment except for the size of the source region 14S and the mask film used for forming the opening 16a in the gate insulation film 13 and the interlayer insulation film 15. Therefore, a description of the manufacturing process for the second embodiment is omitted.

A description is given of a method for producing the third embodiment of the present invention with reference to FIGS. 8A through 8H, and FIGS. 9A through 9H. The steps of FIGS. 8A and 9A, and FIGS. 8B and 9B are the same as those of FIGS. 6A and 7A, and FIGS. 6B and 7B. Therefore, a description of the steps of FIGS. 8A, 9A, 8B and 9B are omitted.

Referring to FIGS. 8C and 9C, a polycide film 17 and a silicon dioxide film 18 are grown by low-pressure chemical vapor deposition. The polycide film 17 can be substituted with a polysilicon film containing n<sup>+</sup>-type impurity ions.

Referring to FIGS. 8D and 9D, after providing a resist mask film (not shown), the polycide film 17 is patterned by anisotropic etching such as RIE so as to form the bit lines such as BL32 and BL33. At this step, it is preferable that portions of the silicon dioxide film 18 on the patterned polycide films 17 are left. The presence of the silicon dioxide film 18 on the patterned polycide film 17 is necessary to form the storage electrode contact holes 24 by self-alignment, as described later.

Referring to FIGS. 8E and 9E, the silicon dioxide film 23 having a thickness of approximately 1000 Å is deposited on the entire surface of the silicon substrate 11 by chemical vapor deposition.

Referring to FIGS. 8F and 9F, the opening or storage electrode contact hole 24 is formed by anisotropic etching such as RIE so as to penetrate the silicon dioxide film 23, the interlayer insulation film 15 and the gate insulation film 13. The opening 24 can be formed by self-alignment in which the bit lines BL32 and BL33 are used as a mask film. It is noted that as shown in FIG. 9F, the upper surface of each polycide film 17 is covered with the silicon dioxide film 18, and side walls of each polycide film 17 and side walls of each silicon dioxide film 18 are covered with the silicon dioxide film 23. The presence of the silicon dioxide film 18 on the upper surface of the polycide film 17 can prevent shorting between the polycide film 17 and a polysilicon film 25 deposited in the subsequent manufacturing step. In a case where the silicon dioxide film 18 is completely removed at the step of FIGS. 8D and 9D, the upper and/or side surfaces of the polycide film 17 may be partially exposed after the step of FIGS. 8F and 9F. For the sake of simplicity, a group of the insulation films covering the polycide film 17 is indicated by a reference numeral 23 in other figures.

It is noted that an alignment margin or tolerance is not needed at the time of forming the opening 24 by the self-alignment process. On the other hand, in the aforementioned method for producing the first embodiment, some alignment margin is necessary to prevent the bit lines BL1 from being exposed after the step of FIGS. 6D and 7D.

Referring to FIGS. 8G and 9G, the polysilicon film 25 is deposited on the entire surface of the silicon substrate 11 by low-pressure chemical vapor deposition. Thereafter, a resist mask film (not shown) is deposited, and then the polysilicon film 25 is patterned by anisotropic etching such as RIE. Each patterned polysilicon film 25 provides the storage electrodes 25a.

Then, as shown in FIGS. 8H and 9H, the dielectric film 26 of silicon dioxide is formed so as to cover the surface of each storage electrode 25. Finally, the polysilicon film 27 is deposited so as to cover the dielectric film 26 as shown in FIGS. 4A and 4B.

A description is given of a method for producing the fourth embodiment of the present invention with reference to FIGS. 10A through 10J, and FIGS. 11A through 11J.

Referring to FIGS. 10A and 11A, the field insulation film 32, the source and drain regions 34S and 34D, the gate insulation film 33, and the gate electrodes WL5 and WL6 are formed, as in the case of the manufacturing process for the first embodiment.

Referring to FIGS. 10B and 11B, the interlayer insulation film 35 of silicon dioxide is deposited on the entire surface of the silicon substrate 31. After depositing a resist mask film (now shown), the opening 36 is formed in the interlayer insulation film 35 and the gate insulation film 33 by anisotropic etching such as RIE in which an etching gas of CHF<sub>3</sub>+H<sub>2</sub> is used. The opening 36 functions as the bit line contact hole.

Referring to FIGS. **10**C and **11**C, an impurity-doped polysilicon film is deposited to a thickness of approximately 1000 Å by low-pressure chemical vapor deposition, and is then patterned by anisotropic etching such as RIE. The patterned polysilicon film **37** provides the bit lines such as BL4. The polysilicon film can be substituted with a polycide film.

Referring to FIGS. 10D and 11D, the insulation film 38 of 30 silicon nitride is formed on the entire surface of the silicon substrate 31. As shown, the patterned polysilicon film 37 is covered with the insulation film 38.

Referring to FIGS. **10**E and **11**E, a silicon dioxide film **39** having a thickness of approximately 1000 Å, and a polysilicon film **40** which contains impurity ions and has a thickness of approximately 1000Å, are sequentially deposited. Further, a silicon dioxide film **41** having the same thickness and a polysilicon **42** having the same thickness are sequentially deposited. In this manner, N+1 number of times of deposition of the silicon dioxide film, and N number of times of deposition of the polysilicon film are carried out as necessary.

Referring to FIGS. 10F and 11F, N+1 silicon dioxide films, N polysilicon films, the silicon nitride film 38, the interlayer insulation film 35 and the gate insulation film 33 are etched by anisotropic etching such as RIE so as to form the opening 44. In this etching process, an etching gas of CHF<sub>3</sub>+H<sub>2</sub> is used with respect to the silicon dioxide and silicon nitride films, and an etching gas of CCl<sub>4</sub>/O<sub>2</sub> is used with respect to the polysilicon films.

Referring to FIGS. 10G and 11G, a polysilicon film 45c is deposited on the entire surface of the silicon substrate 31 by low-pressure chemical vapor deposition. Thereby the top and side surfaces of a stacked layer composed of the silicon dioxide and polysilicon films are covered with the polysilicon film 45c.

Referring to FIGS. 10H and 11H, the polysilicon films 45c, 42 and 40, and the silicon dioxide films 43 and 41 are patterned by anisotropic etching such as RIE. The patterned polysilicon film 45c has the vertical portion 45a and the wing portion 45b. The patterned polysilicon films 42 and 40 correspond to the wing portions 45b shown in FIGS. 5A and 5B.

Referring to FIGS. 10I and 11I, the patterned silicon dioxide films 43, 41 and 39 are removed by an anisotropic

10

etching process in which an etching liquid of HF is used. It is noted that the polysilicon film 37 of the bit line BL4, and the silicon nitride film 38 covering the gate electrodes WL5 and WL6 are not etched with an HF etching liquid. As shown, the storage electrode 45 has a tree-shaped cross section.

Referring to FIGS. 10J and 11J, the dielectric film of silicon dioxide 46 is formed on the surface of the storage electrode 45 by thermal oxidation. Then, the opposed electrode 47 of polysilicon is formed so as to cover the dielectric film 46.

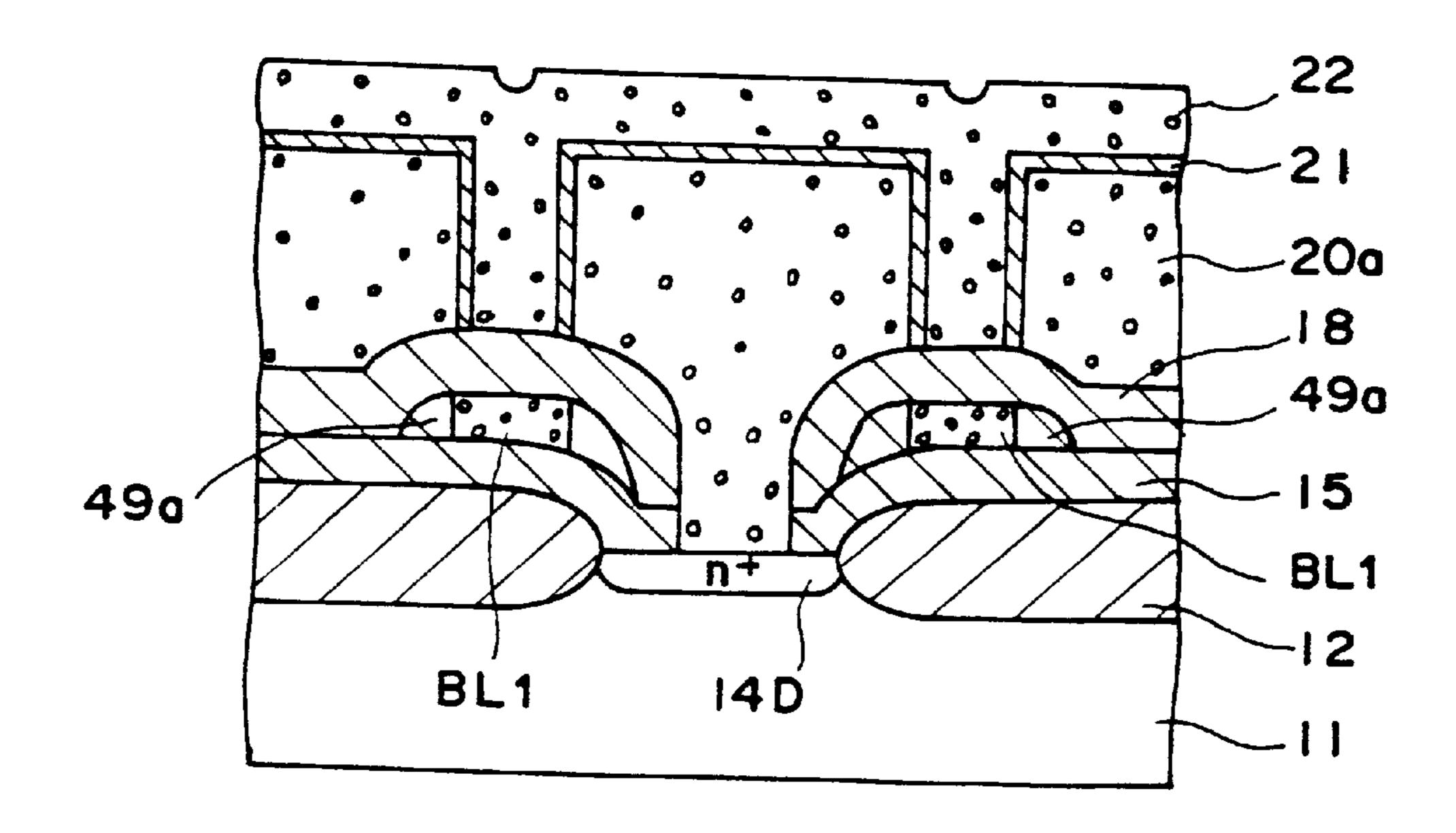

A description is given of a modification of the first embodiment with reference to FIGS. 13A through 13C. In FIGS. 13A through 13C, those parts which are the same as those in FIGS. 2A through 2C, are indicated by the same reference numerals.

The modification of the first embodiment has an essential feature in which side wall films are provided so as to surround side surfaces of the gate electrodes WL3 and WL4 and the bit lines BL1. In FIGS. 12A and 12B which show the cross section of the aforementioned first embodiment, film portions surrounded by circles are not flat, and have some differences in vertical layer level. In other words, the film portions surrounded by the circles are convex and recess portions. The presence of some convex and recess portions makes it difficult to suitably form a film thereon. Additionally, it is inevitable that the film formed on the convex and recess portions becomes thin. Additionally, a film portion under an overhang portion may remain without being etched. As a result, insulation properties of the film are degraded. The modification of the first embodiment can overcome the above disadvantages.

Referring to FIGS. 13A through 13C, side wall films 48a of silicon dioxide or silicon nitride are provided so as to surround vertical side walls of the gate electrodes WL3 and WL4. The cross section of each side wall film 48a has a slope which connects the upper surface of the word line WL3, WL4 and the upper surface of the field insulation film 12 or the gate insulation film 13. The side wall films 48a contribute to smoothing the upper surface of the insulation film 15, providing easy etching with respect to films formed on the insulation film 15, and improving the insulation properties of the insulation film 15.

Side wall films 49a of silicon dioxide or silicon nitride are provided so as to surround vertical side walls of the bit lines BL1. The cross section of each side wall film 49a has a slope which connects the upper surface of the bit line BL1 and the upper surface of the interlayer insulation film 15. The side wall films 49a contribute to improving the insulation properties of the interlayer insulation film 18, providing easy etching with respect to films on the insulation film 18, and smoothing the upper surface of the interlayer insulation film 18.

A description is given of a method for producing the modified device of FIGS. 13A through 13C with reference to FIGS. 14A through 14K, and FIGS. 15A through 14K.

The step of FIGS. 14A and 15A is the same as that shown in FIGS. 6A and 7A. Therefore, a description with respect to FIGS. 14A and 15A is omitted.

Referring to FIGS. 14B and 15B, an insulation film 48 of silicon dioxide is formed on the entire surface of the silicon substrate 11 by chemical vapor deposition. Thereafter, the insulation film 48 is dry-etched by anisotropic etching such as RIE. Thereby, as shown in FIGS. 14C and 15C, film portions around the side walls of the gate electrodes WL3 and WL4 remain without being removed. Such film portions

are the side wall films 48a. In the etching process of the silicon dioxide film 48, an etching gas of CHF<sub>3</sub>+H<sub>2</sub> is used.

Referring to FIGS. 14D and 15D, the interlayer insulation film 15 of silicon dioxide having a thickness of about 1000 Å is deposited on the entire surface of the silicon substrate 5 11. Then a resist mask film (not shown) is placed on the silicon substrate 11, and the insulation film 15 is etched by anisotropic etching such as RIE so as to form the opening 16 of the bit line contact hole.

Referring to FIGS. **14**E and **15**E, the polysilicon film containing n<sup>+</sup>-type impurity ions such as arsenic ions (As<sup>+</sup>) is deposited to a thickness of approximately 1000 Å by low-pressure chemical vapor deposition. Subsequently, a tungsten silicide film is deposited to a thickness of approximately 1000 Å by chemical vapor deposition. Then the polysilicon and tungsten silicide films are subjected to the patterning process based on RIE. Thereby, the patterned polysilicon and tungsten silicide films **17** of the bit lines BL1 are formed.

Referring to FIGS. 14F and 15F, a silicon dioxide film 49 is deposited to a thickness of about 2000 Å by chemical vapor deposition. Thereafter, the silicon dioxide film 49 is subjected to anisotropic etching such as RIE in which CHF<sub>3</sub>+H<sub>2</sub> is used. Thereby, as shown in FIGS. 14G and 15G, film portions 49a around the side walls of the bit line BL1 are left without being removed. Such film portions 49a are side wall films around the bit lines BL1.

Referring to FIGS. 14H and 15H, the insulation film 18 of silicon dioxide or silicon nitride is deposited on the entire 30 surface of the silicon substrate 11 by chemical vapor deposition. The insulation film 18 is approximately 1000 Å.

Referring to FIGS. 14I and 15I, by using a resist mask film (not shown), the insulation film 18 and the interlayer insulation film 15 are selectively etched so as to form the 35 opening 19 through which a surface of the drain region 14D is exposed. The opening 19 functions as the storage electrode contact hole.

Referring to FIGS. 14J and 15J, the polysilicon film 20 containing n<sup>+</sup>-type impurity ions is deposited, and is then 40 patterned by anisotropic etching such as RIE in which a resist mask film (not shown) is used. The patterned polysilicon film 20 provides storage electrodes 20a.

Referring to FIGS. 14K and 15K, the dielectric film 21 is formed by thermal oxidation so as to surround the surface of 45 each storage electrode 20a. Finally, the opposed electrode 22 is formed so as to cover the dielectric films 21.

According to the modification of the first embodiment, the electrical insulation between the gate electrodes WL3 and WL4 and the storage electrode 20a and between the bit lines BL1 and the storage electrode 20a, can be greatly improved. Additionally, upper surfaces of the insulation films such as the interlayer insulation film 15 and the insulation film 18 are made flat. As a result, easy etching for obtaining bit lines BL1 and storage electrodes 20a is obtainable.

The aforementioned side wall films are applicable to the second, third and fourth embodiments of the present invention.

The present invention is not limited to the aforementioned embodiments, and variations and modifications may be made without departing from the scope of the present invention.

What is claimed is:

- 1. A dynamic random access memory device, comprising: a plurality of memory cells;

- a plurality of bit lines disposed in a bit line layer;

12

- a plurality of word lines respectively associated with the plurality of memory cells and disposed in a word line layer; and

- each memory cell being located along a respectively associated said bit line and comprising:

- a storage capacitor,

- a transfer transistor which electrically connects the storage capacitor to the respectively associated bit line in response to a select signal applied thereto via the respectively associated word line,

- the storage capacitor comprising a storage electrode disposed in a storage electrode layer, the storage electrode layer being electrically conductive and thicker than each of the respective thicknesses of the word line and bit line layers, a dielectric film on the storage electrode, and an opposed electrode on the dielectric film, the bit line layer being lower than the storage electrode layer,

- said transfer transistor comprising first and second impurity diffused regions, the second impurity diffused region being electrically connected to said storage electrode,

- said respectively associated bit line having a portion making an electrical connection with the first impurity diffused region at a connecting position thereon, and

- said respectively associated word line crossing said respectively associated bit line and extending between the first and second impurity diffused regions;

- an associated bit line of one transfer transistor being paired with and spaced from an adjacent bit line respectively associated with an adjacent transfer transistor, the paired bit lines having corresponding portions making respective electrical connections with the corresponding first impurity diffused regions of the one and the adjacent transfer transistors at respective connecting positions thereon;

- the respective connecting positions of the one and the adjacent transfer transistors being spaced apart in a direction in which the paired bit lines commonly extend; and

- the one and the adjacent transfer transistors being located so that two word lines extend between the respective connecting positions thereof.

- 2. The dynamic random access memory device as claimed in claim 1, wherein the opposed electrode is formed so that it faces upper, side and lower surfaces of the storage electrode.

- 3. The dynamic random access memory device as claimed in claim 1, wherein the word lines have bent portions in areas in which the transfer transistors are formed.

- 4. The dynamic random access memory device as claimed in claim 1, wherein the storage electrode comprises electrically conductive portions which are spaced apart from each other in a vertical direction and which laterally extend.

- 5. The dynamic random access memory device as claimed in claim 1, further comprising a field insulating film on which the word lines are provided, wherein the storage electrode extends above and overlaps an adjacent word line.

- 6. A dynamic random access memory device, comprising: a plurality of memory cells;

- a plurality of bit lines disposed in a bit line layer;

- a plurality of word lines respectively associated with the plurality of memory cells and disposed in a word line layer; and

each memory cell being located along a respectively associated said bit line and comprising:

a storage capacitor,

a transfer transistor which electrically connects the storage capacitor to the respectively associated bit 5 line in response to a select signal applied thereto via the respectively associated word line,

the storage capacitor comprising a storage electrode disposed in a storage electrode layer, the storage electrode layer being electrically conductive and 10 thicker than each of the respective thicknesses of the word line and bit line layers, a dielectric film on the storage electrode, and an opposed electrode on the dielectric film, the bit line layer being lower than the storage electrode layer,

said transfer transistor comprising first and second impurity diffused regions, the second impurity diffused region being electrically connected to said storage electrode,

said respectively associated bit line having a portion 20 making an electrical connection with the first impurity diffused region at a first connecting position, and

said respectively associated word line crossing said respectively associated bit line and extending between the first and second impurity diffused 25 regions;

adjacent, first and second memory cells having respective, first and second transfer transistors with respectively associated, first and second bit lines in paired and spaced relationship, the first transfer transistor having a first impurity diffused region and the respectively associated, first bit line thereof having a portion making

an electrical connection with the first impurity diffused region thereof at a first connecting position thereon and the second transfer transistor having a first impurity diffused region and the respectively associated, second bit line thereof having a portion making an electrical connection with the first impurity diffused region thereof at a second connecting position thereon;

the first and second connecting positions being spaced apart in a direction in which said first and second associated bit lines commonly extend; and

the first transfer transistor relating to the first connecting position and the second transfer transistor relating to the second connecting position being located so that two word lines extend between the first and second connecting positions.

7. The dynamic random access memory device as claimed in claim 6, wherein the opposed electrode is formed so that it faces upper, side and lower surfaces of the storage electrode.

8. The dynamic random access memory device as claimed in claim 6, wherein the word lines have bent portions in areas in which the transfer transistors are formed.

9. The dynamic random access memory device as claimed in claim 6, wherein the storage electrode comprises electrically conductive portions which are spaced apart from each other in a vertical direction and which laterally extend.

10. The dynamic random access memory device as claimed in claim 6, further comprising a field insulating film on which the word lines are provided, wherein the storage electrode extends above and overlaps an adjacent word line.

\* \* \* \*

## UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO.

: 6,114,721

Page 1 of 1

DATED

: September 5, 2000

INVENTOR(S) : Taija Ema

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

Title page,

Item [30], Foreign Application Priority Data, change "62-396669" to -- 62-296669 ---

Item [56], References Cited, add the following foreign references:

| # ( D 0 ] , | ,       | •     |

|-------------|---------|-------|

| 56-58255    | 05/1981 | Japan |

| 59-198753   | 11/1984 | Japan |

| 59-231841   | 12/1984 | Japan |

| 61-219166   | 09/1986 | Japan |

| 62-128168   | 06/1987 | Japan |

| 57-120295   | 07/1982 | Japan |

| 61-258467   | 11/1986 | Japan |

| 62-086853   | 04/1987 | Japan |

| 62-286269   | 12/1987 | Japan |

| 63-287363   | 11/1988 | Japan |

| 59-231851   | 12/1984 | Japan |

| 59-175153   | 10/1984 | Japan |

| 62-145765   | 12/1987 | Japan |

| 57-120295   |         | Japan |

| 59-175153   | 10/1984 | Japan |

| 59-231851   | 12/1984 | Japan |

| 62-145765   | 06/1987 | Japan |

|             |         |       |

Signed and Sealed this

Twenty-third Day of October, 2001

Attest:

Nicholas P. Ebdici

NICHOLAS P. GODICI Acting Director of the United States Patent and Trademark Office

Attesting Officer