#### US006088404A

6,088,404

#### United States Patent [19]

#### Jekal [45] Date of Patent: Jul. 11, 2000

[11]

9836500

| [54] | METHOD AND APPARATUS FOR   |

|------|----------------------------|

|      | DECODING TRELLIS CODE DATA |

[75] Inventor: Heon Jekal, Seoul, Rep. of Korea

[73] Assignee: Daewoo Electronics Co., Ltd., Seoul,

Rep. of Korea

[21] Appl. No.: **09/064,931**

[22] Filed: Apr. 22, 1998

#### [30] Foreign Application Priority Data

| Apr. 30, 1997 | [KR] | Rep. of Korea | ••••• | 97-16788 |

|---------------|------|---------------|-------|----------|

|               |      |               |       |          |

714/796

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 5,717,471 | 2/1998  | Stewart  | 348/726 |

|-----------|---------|----------|---------|

| 5,838,729 | 11/1998 | Hu et al | 375/265 |

| 5,841,819 | 11/1998 | Hu et al | 375/341 |

#### FOREIGN PATENT DOCUMENTS

0677967 10/1995 European Pat. Off. .

0801501 10/1997 European Pat. Off. .

Patent Number:

0801501 10/1997 European 9319418 9/1993 WIPO.

8/1998

9602100 1/1996 WIPO.

Primary Examiner—Chi H. Pham

Assistant Examiner—Jean B. Corrielus

Attorney, Agent, or Firm—Andersson Kill & Olick, P.C.

WIPO.

#### [57] ABSTRACT

A method for decoding a trellis encoded stream  $d_k$  by the use of either an 8 state maximum likelihood response decoding mode through a Gaussian channel or a 16 state partial response decoding mode through a partial response channel is disclosed. In response to a mode selection signal FENA, after passing off the trellis encoded stream for the 8 state mode and removing the influence of a segment synchronization signal from the trellis encoded stream for the 16 state mode, all branch metrics with different values in parallel for either the 8 or the 16 state mode. After selecting a predetermined number of branch metrics required for each state among all the branch metrics of either the 8 or the 16 state mode determined based on the FENA and finding the predetermined number of candidate path metrics and determining a survivor metric and a determination vector thereof, a decoded symbol is determined by tracing back for a decoding depth in response to the FENA based on the determination vector of each state.

#### 49 Claims, 31 Drawing Sheets

# FIG.2(PRIOR ART)

FIGE ART)

6,088,404

FIG. 10

$\varphi$ CLEAR SYSENA C832

FIG. 12

$\mathbb{Z}$

FIG. 14

## FIG. 15A

FIG. 15B

FIG. 15C

FIG. 15E

FIG. 15F

FIG. 15H

FIG. 15I

FIG. 15J

FIG. 15K

FIG. 15L

FIG. 15M

FIG. 15N

FIG. 150

FIG. 15P

6,088,404

FIG. 16

6,088,404

# HIG. 21

-15) 10) 412 2 7 X1(168) 16 X1(108) X0(108) Ö

# FIG.23A

#### $420 - 1 \sim 420 - 14$

# FIG.23B

# FIG.24A

#### 440-1~440-9

# FIG.24B

1

### METHOD AND APPARATUS FOR DECODING TRELLIS CODE DATA

#### FIELD OF THE INVENTION

The present invention relates to a TCM decoder for 5 decoding signals encoded by a trellis-coded modulation (TCM) and, more particularly, to a method and an apparatus capable of decoding trellis code data in both 8 state Gaussian channel mode and 16 state partial response channel mode in a forward error correction decoder for HDTV.

#### DESCRIPTION OF THE PRIOR ART

Recently, there has been increasing interest in some types of combined modulation and coding schemes, called trelliscoded modulation(TCM), that achieve coding gain without any bandwidth expansion in a bandwidth-limited channel. The TCM includes a finite-state encoder and a non-binary modulator. Therefore, as compared with a conventional modulation, the TCM can achieve net coding gains of 3 to 6 dB, relative to uncoded case, in the presence of an additive white Gaussian noise(AWGN).

In a concatenated coding technique implementing a concatenated coding by connecting two different coders, e.g., an inner and an outer coders, so as to advance data reliability, a well known convolutional encoder or a TCM encoder is used as the inner coder and data encoded by the inner coder are decoded by a trellis decoder employing a Viterbi algorithm. A Reed-Solomon coder can be used as the outer coder. The outer coder corrects errors which have not been corrected at the inner coder to thereby minimize the rate of errors. This concatenated coding technique achieves more advanced implementation with less complex hardware than a coding technique having one coding method.

At a receiving end, the TCM data are decoded through the use of the trellis decoder. The trellis decoder is a maximum 35 likelihood decoder that provides a forward error correction. Trellis decoding is used in decoding a sequence of encoded symbols, such as a bit stream. The bit stream can represent encoded information in telecommunication transmission through various media with each set of bits representing a 40 symbol instant. In the decoding process, the trellis decoder works back through a sequence of possible bit sequences at each symbol instant to determine which bit sequence could most likely have been transmitted. The possible transitions from a bit at one symbol instant, or state, to a bit at a next, 45 subsequent, symbol instant or state are limited. Each possible transition from one state to a next state can be shown graphically and defined as a branch. A sequence of interconnected branches defines a path. Each state can transit only to a limited number of next states upon receiving a next 50 bit in the bit stream. Thus, some paths survive during the decoding process and the other paths do not. By eliminating those transition paths that are not permissible, computational efficiency can be improved in determining those paths most likely to survive. The trellis decoder typically defines and 55 calculates a branch metric associated with each branch and employs this branch metric to determine which paths will survive and which paths will not.

A branch metric is calculated at each symbol instant for each possible branch. Each path has an associated metric, an accumulated value, that is updated at each symbol instant. For each possible transition, the accumulated value for the next state is obtained by selecting the smallest of the sums of the branch metrics for different possible transitions and the path metrics from the previous states.

While several paths may survive at the transition from one symbol instant to a next symbol instant, there is only one

2

path accumulated with a minimum value. A sequence of symbol instants is referred to as a trace-back. The number of symbol instants tracing back through the trellis that extends a path with the minimum accumulated value defines the length, or decoding depth D, of a trace-back. The individual state in the trellis associated with the minimum accumulated value in a trace-back is translated into most likely bits that could have been transmitted in that symbol instant. The bits are referred to as a decoded symbol.

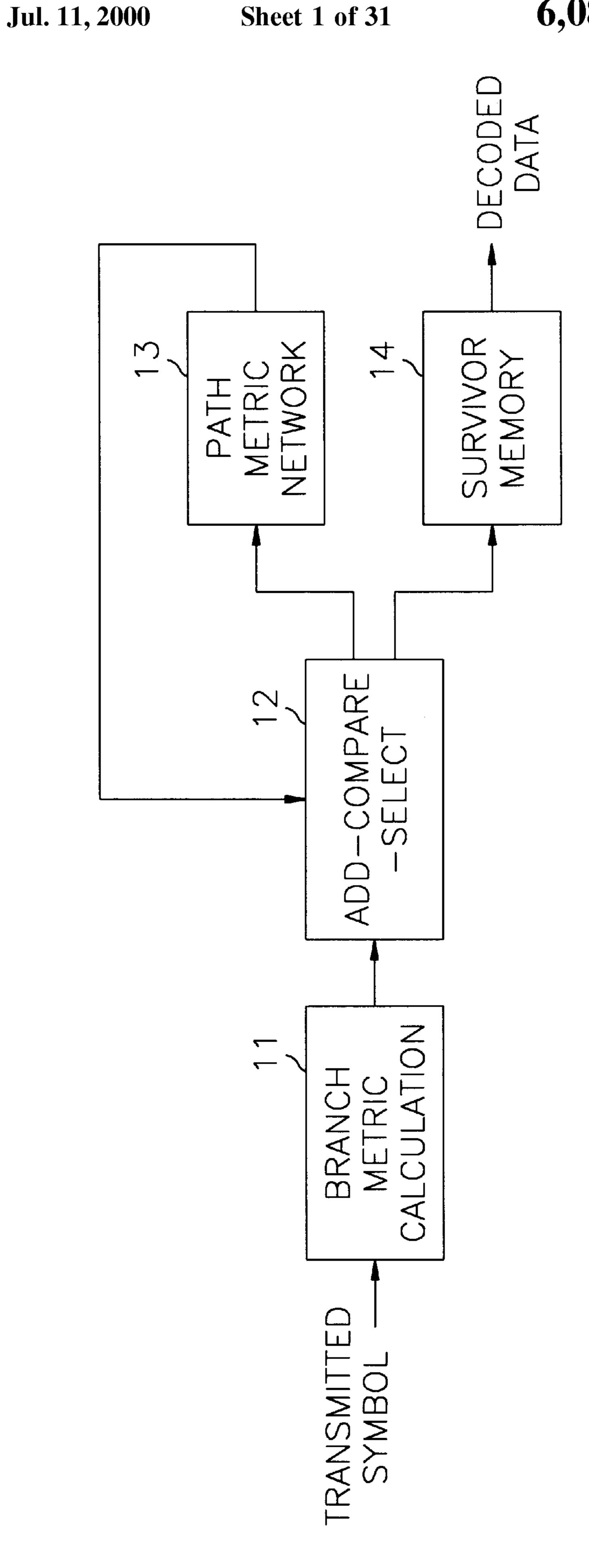

Referring to FIG. 1, there is shown a schematic block diagram of a conventional trellis decoder including a branch metric calculation unit(BMU) 11, an add-compare-select unit(ACS) 12, a path metric network(PMN) 13, and a survivor memory unit(SMU) 14.

The branch metric calculation unit 11 receives a sequence of transmitted symbols and calculates branch metrics, i.e., distances between branches associated with each state and the transmitted symbol. The branch metrics are provided to the add-compare-select unit 12. The add-compare-select unit 12 chooses a path having a minimum path metric among paths corresponding to each state. Specifically, the addcompare-select unit 12 adds the branch metrics provided from the branch metric calculation unit 11 to corresponding previous path metrics from the path metric network 13; and compares candidate path metrics, i.e., the sums of the branch metrics and the corresponding previous path metrics with one another to thereby choose a new path metric having a smallest value. The selected path metric is provided to the path metric network 13 as a new path metric for each state and information for tracing back on the selected path is coupled to the survivor memory unit 14. The survivor memory unit 14 stores the information from the addcompare-select unit 12 as the length of a survivor path, i.e., a decoding depth in order to decode the transmitted symbols and outputs decoded data by tracing back to the survivor path based on a trace-back algorithm.

One example of trellis decoders having the above structure is a decoder used in a GA HDTV receiving system proposed by a Grand Alliance(GA). The GA HDTV transmission system encodes data in an 8-level vestigial sideband modulation (VSB) mode and transmits the coded data on a frame-by-frame basis.

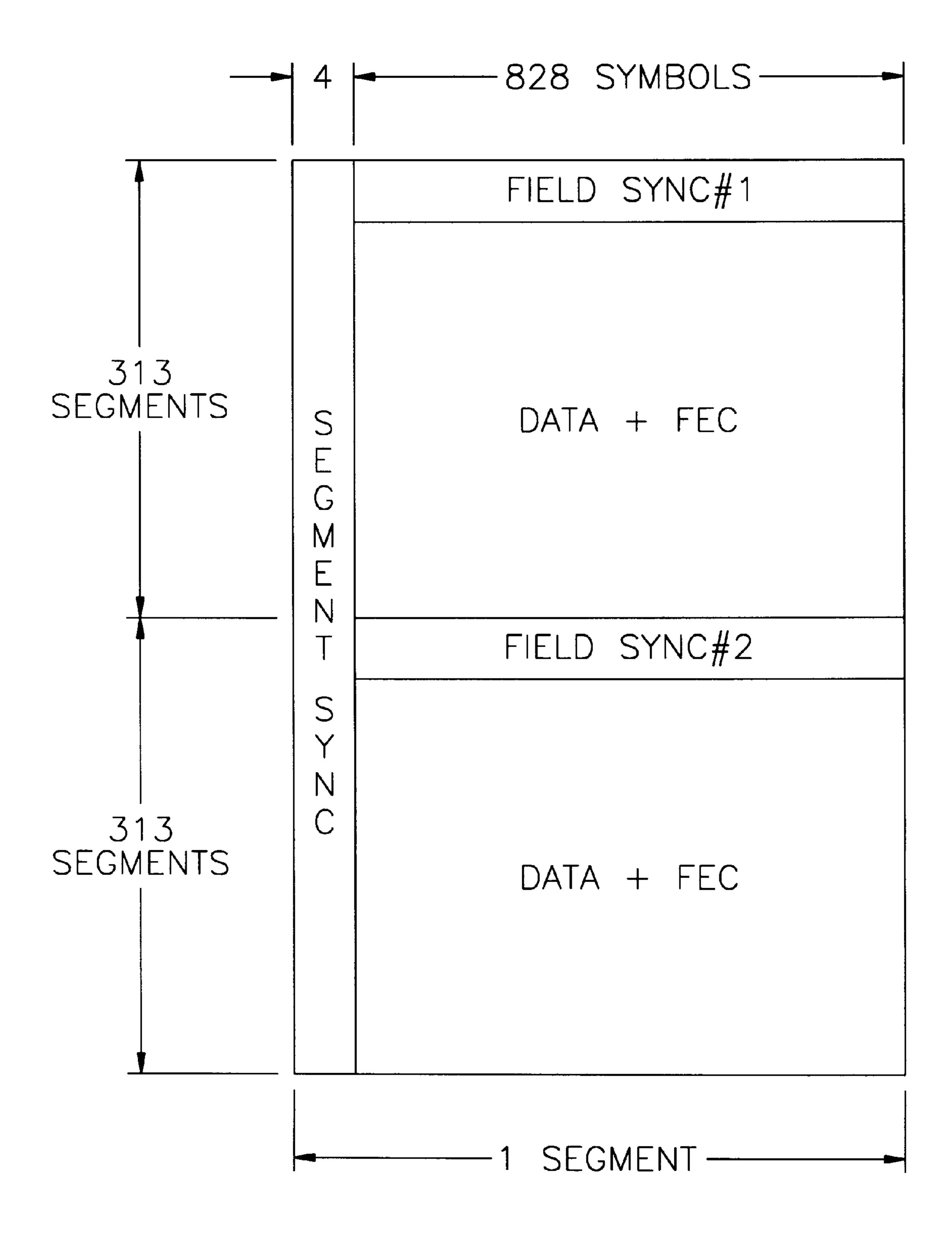

Referring to FIG. 2 representing a data frame structure used in the GA HDTV transmission system, a frame consists of two fields and each field is divided into 313 segments. Each segment includes a segment synchronization signal of 4 symbols and 828 (data+forward error correction symbol (FEC))'s and a first segment of each field is allotted to a field synchronization signal.

In order to produce a transmission signal, a randomized signal is coded by using Reed-Solomon coding; interleaved; and trellis-coded. The trellis coded signal is incorporated with the segment synchronization and the field synchronization signals and the incorporated signal is combined with a pilot signal. The combined signal is modulated through the VSB and transmitted by a carrier.

Referring to FIG. 3, there is provided a convolutional trellis coding block for 8-level VSB mode, which includes a pre-coder 30, a trellis encoder 32, and an 8-level symbol mapper 34.

A higher input bit X1 is exclusive-ORed with a 12 symbol delayed previous bit at the pre-coder 30 and, then, the exclusive-ORed signal is outputted as a middle output bit Y1. The middle output bit Y1 is directly inputted to the 8-level symbol mapper 34 as an input bit Z2 without being coded at the trellis encoder 32. A lower input bit X0 is

55

convolutionally encoded in a coding rate of 1/2 at the trellis encoder 32 so that two output bits Z1 and Z0 are generated and, then, the convolutionally encoded bits Z1 and Z0 are provided as input bits to the 8-level symbol mapper 34. The input bits **Z2**, **Z1** and **Z0** provided from the trellis encoder 5 32 of a coding rate 2/3 are converted to 8-level symbols(R: -7, -5, -3, -1, 1, 3, 5, 7) at the 8-level symbol mapper **34** so that an 8-level VSB modulation signal can be transmitted.

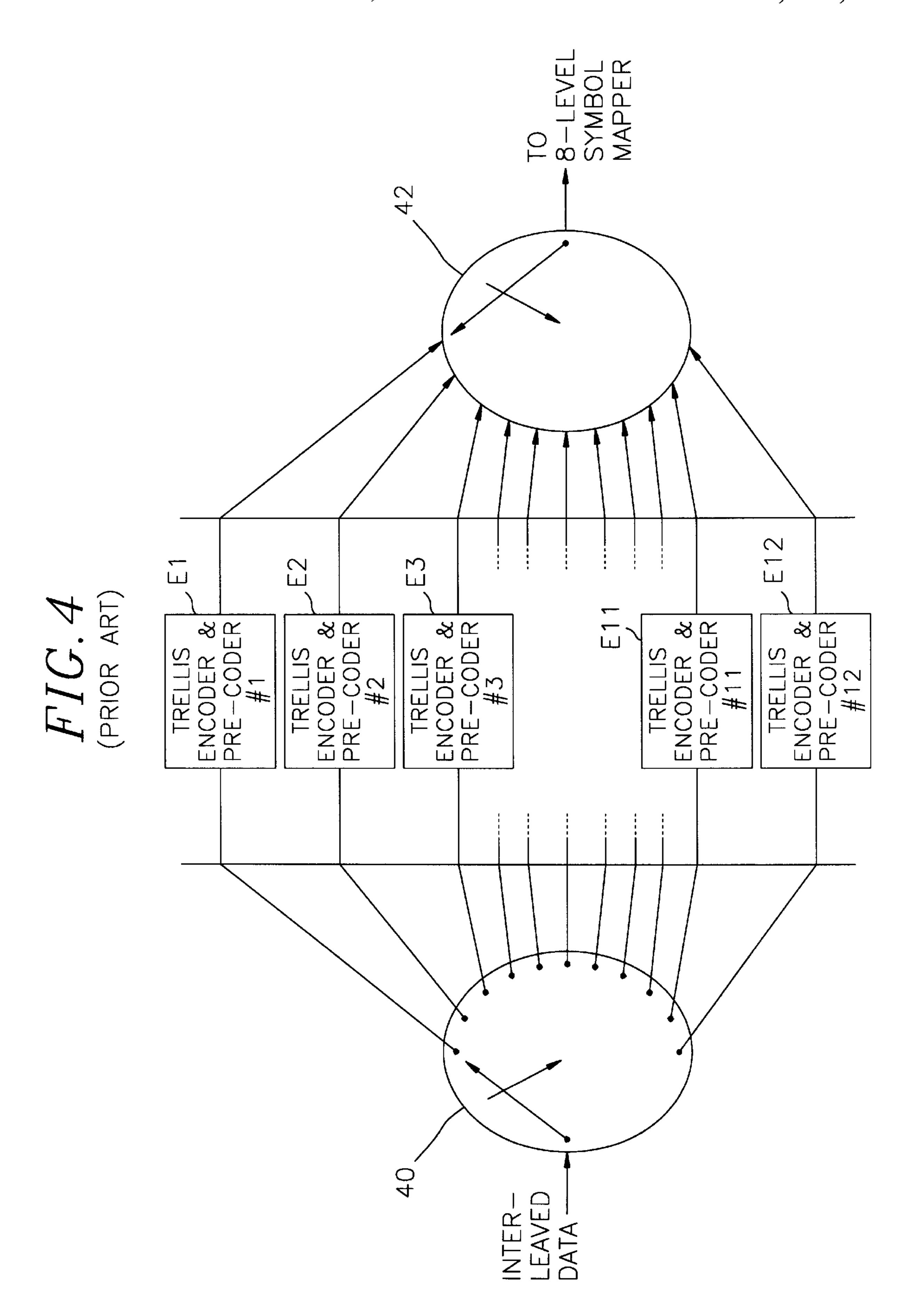

In the meantime, the trellis coding has a strong characteristic against the AWGN but a weak characteristic against 10 a group error and, therefore, input symbols may be sequentially inputted to 12 trellis coding blocks which are connected in parallel so that the input symbols may be 12 symbol intra-segment interleaved as can be shown in FIG. 4.

Referring to FIG. 4, a trellis code interleaver comprises an 15 input switch 40, 12 trellis encoders E1 to E12 and an output switch 42, wherein the input switch 40 converts interleaved data transmitted on a packet-by-packet basis to a symbolby-symbol basis, each symbol having two bits, i.e., X1 and X0; each trellis encoder containing the pre-coder 30 and the  $^{20}$ trellis encoder 32 as shown in FIG. 3 sequentially receives the interleaved symbols connected to each of the 12 outputs of the input switch 40; and the output switch 42 sequentially transfers the outputs of the trellis encoders E1 to E12 to the 8-level symbol mapper **34**. It is noted that the input switch <sup>25</sup> 40 and the output switch 42 are synchronized with each other.

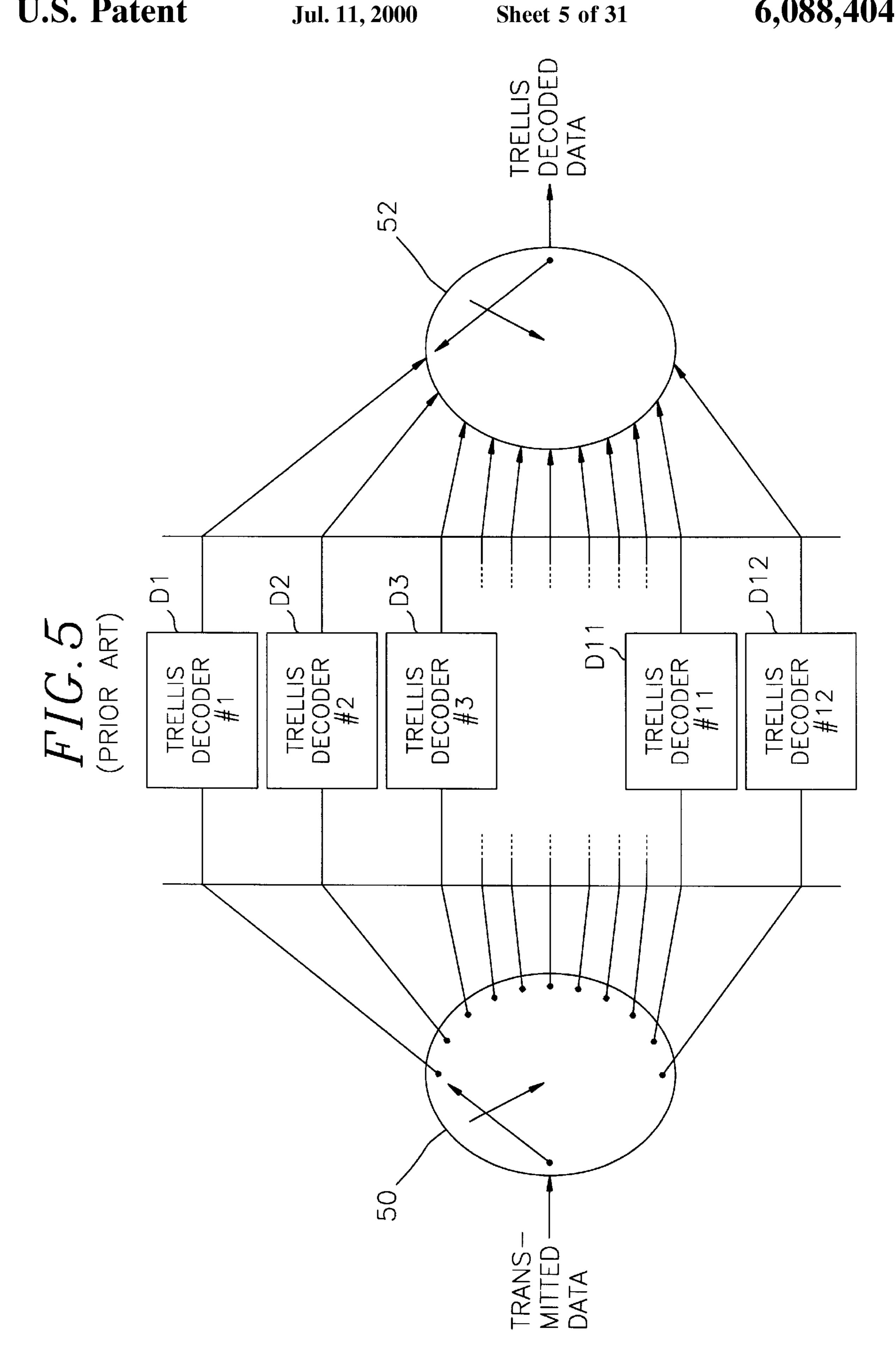

In FIG. 5, there is provided a block diagram of a trellis code deinterleaver in a GA HDTV receiving system. Since TCM codes have been interleaved by a unit of 12 symbols at the trellis code interleaver, the trellis code deinterleaver must involve 12 number of trellis decoders D1 to D12 connected in parallel in order to deinterleave transmitted data. Accordingly, each of the trellis decoders deinterleaves to decode every 12th symbol sequentially inputted.

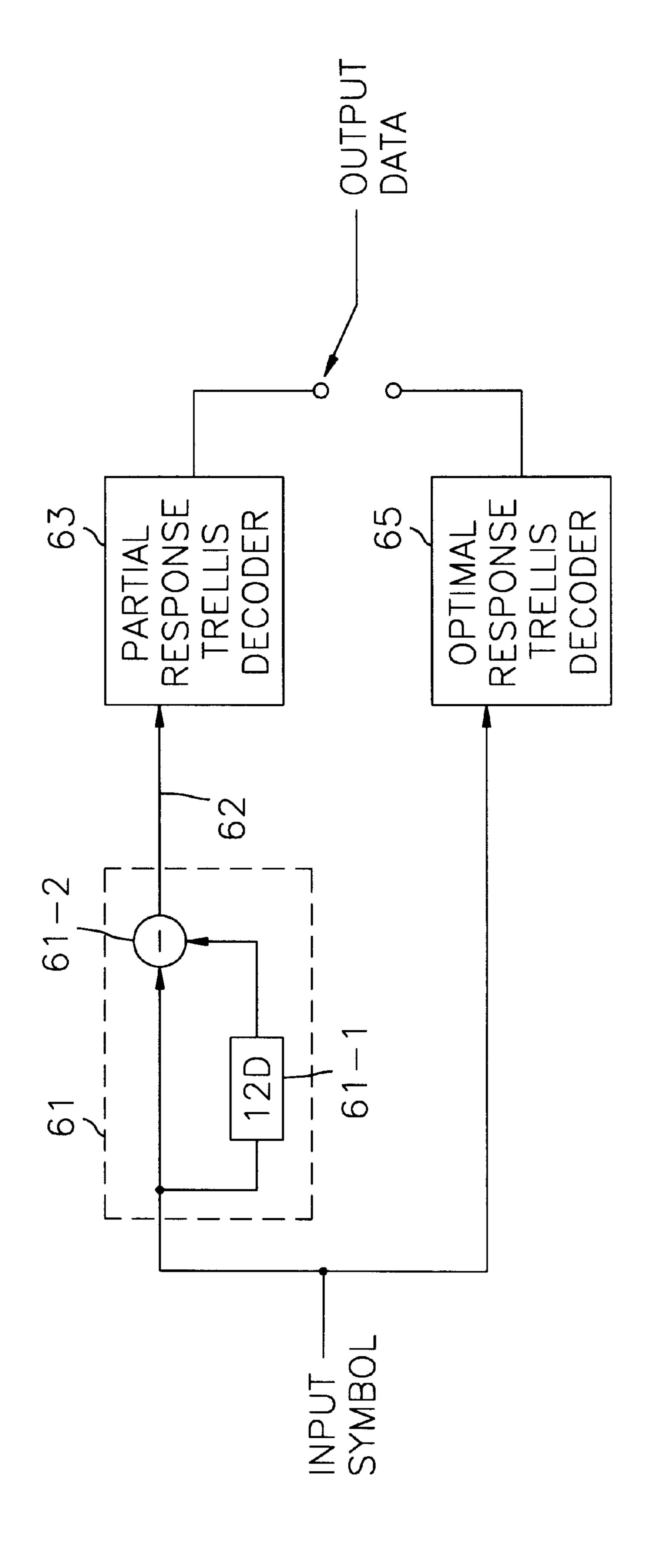

The TCM decoding path has two different paths depending on whether an NTSC interference rejection filter is used or not as shown in FIG. 6. Referring to FIG. 6, in case the NTSC interference rejection filter is not used, an optimal 40 response trellis decoder 65 which performs 8-state mode decoding for a real channel with the AWGN is only utilized in order to restore input symbols. On the other hand, in the event the NTSC interference rejection filter 61 is used, the output signals of the filter 61 is changed from 8 to 15 levels 45 according to the transfer function of the filter and, therefore, a partial response trellis decoder **63** which performs 16 state mode decoding should be utilized.

As can be seen above, the conventional trellis decoder contains either only the 8-state mode optimal trellis decoder 50 65 or both the 8-state mode optimal trellis decoder 65 and the 16-state mode partial response trellis decoder 63, depending on whether the NTSC interference rejection filter 61 is used or not. Therefore, there is a problem that an area occupied by a number of trellis decoders increases.

#### SUMMARY OF THE INVENTION

It is, therefore, a primary object of the present invention to provide an apparatus capable of decoding trellis code data in both 8 state mode and 16 state mode in a smallest area 60 with complexity of only 16 state mode.

In accordance with the present invention, there is provided a method for decoding a trellis encoded stream d<sub>k</sub> by the use of either an 8 state maximum likelihood response decoding mode, in short, an 8 state mode, through a Gaus- 65 sian channel or a 16 state partial response decoding mode, in short, a 16 state mode, through a partial response channel,

wherein the trellis encoded stream  $d_k$  is obtained by an M symbol intra-segment interleaving technique using M number of trellis encoders and an index k for identifying a trellis encoded stream generated from a kth trellis encoder among total M trellis encoders is equal to or greater than 1 and equal to or smaller than M, M being a positive integer representing the number of the trellis encoders, the method comprising the steps of:

- (a) in response to a mode selection signal FENA, passing off the trellis encoded stream for the 8 state mode and removing the influence of a segment synchronization signal from the trellis encoded stream for the 16 state mode;

- (b) calculating all branch metrics with different values in parallel for either the 8 or the 16 state mode determined based on the FENA;

- (c) selecting a predetermined number of branch metrics required for each state among all the branch metrics of either the 8 or the 16 state mode determined based on the FENA, thereby finding the predetermined number of candidate path metrics and determining a survivor metric and a determination vector thereof, wherein the survivor metric represents a candidate path metric with a maximum likelihood among all the candidate path metrics;

- (d) providing the survivor metric for said each state determined in step (c) as a previous path metric for a previous state;

- (e) tracing back for a decoding depth of the 8 or the 16 state mode in response to the FENA based on the determination vector of said each state determined in step (c), thereby finding a decoded symbol; and

- (f) intra-segment deinterleaving the decoded symbol and converting the intra-segment deinterleaved decoded symbol in the unit of a predetermined size of packet.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above and other objects and features of the present invention will become apparent from the following description of preferred embodiments given in conjunction with the accompanying drawings, in which:

FIG. 1 shows a block diagram of a conventional trellis decoder applied with a Viterbi algorithm;

FIG. 2 presents a data frame in a transmission system of Grand Alliance high definition television (GA HDTV);

FIG. 3 provides a block diagram of an 8-level vestigial sideband modulation (VSB) trellis coding block in a GA HDTV transmission system;

FIG. 4 depicts a block diagram of a trellis code interleaver for carrying out an intra-segment interleaving;

FIG. 5 represents a block diagram of a trellis code deinterleaver in a GA HDTV receiving system;

FIG. 6 illustrates a block diagram of a trellis decoder with and without a NTSC interference rejection filter;

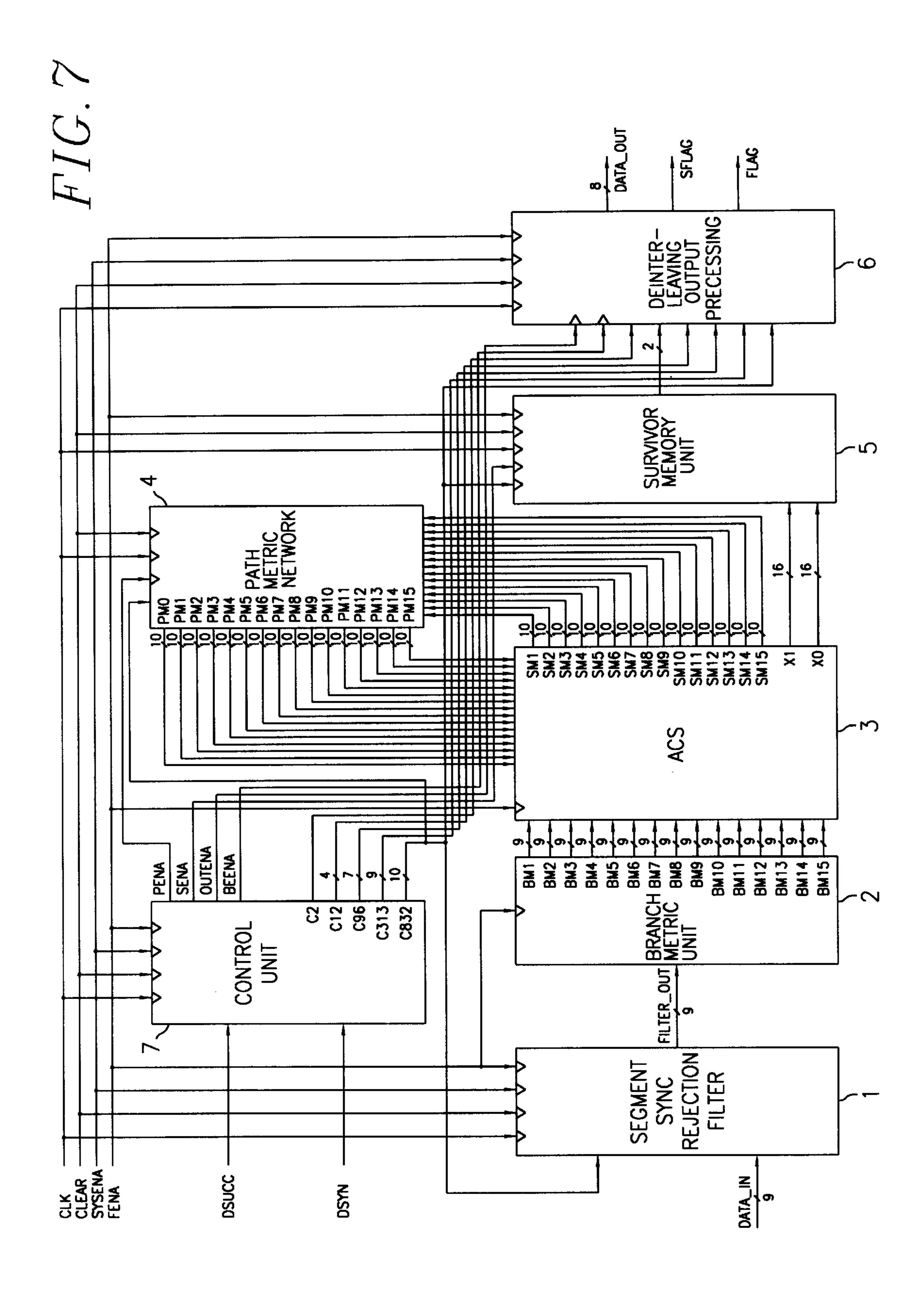

FIG. 7 describes a block diagram of a trellis decoder in accordance with the present invention;

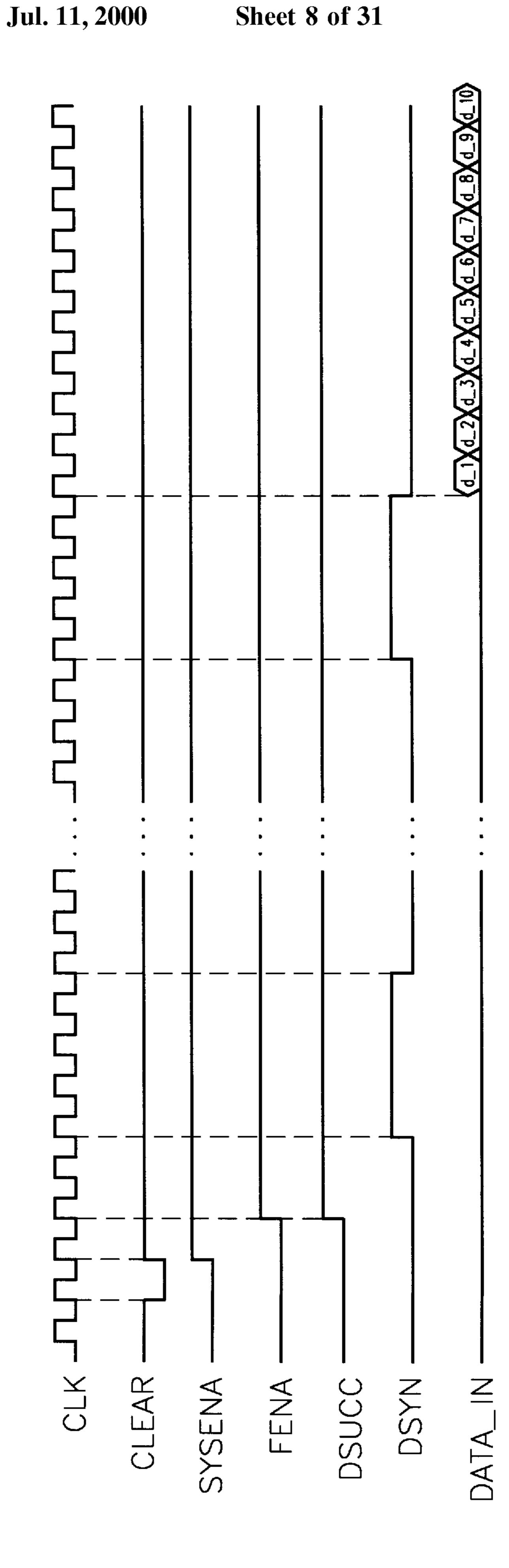

FIG. 8 portrays a timing diagram of input signals inputted into the trellis decoder shown in FIG. 7;

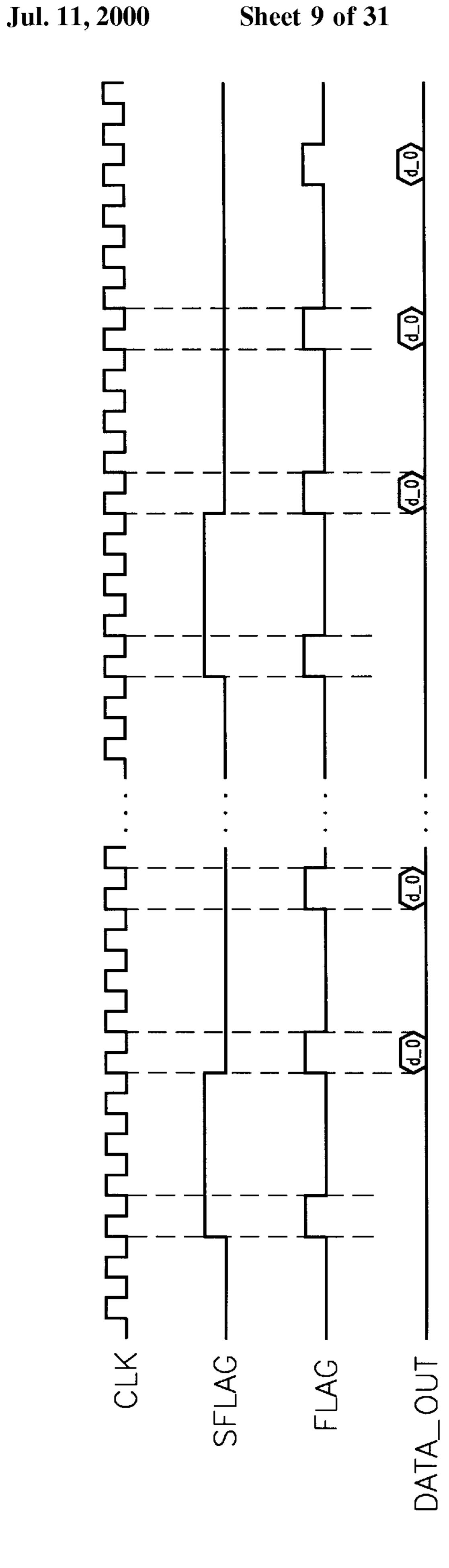

FIG. 9 delineates a timing diagram of output signals fed from the trellis decoder shown in FIG. 7;

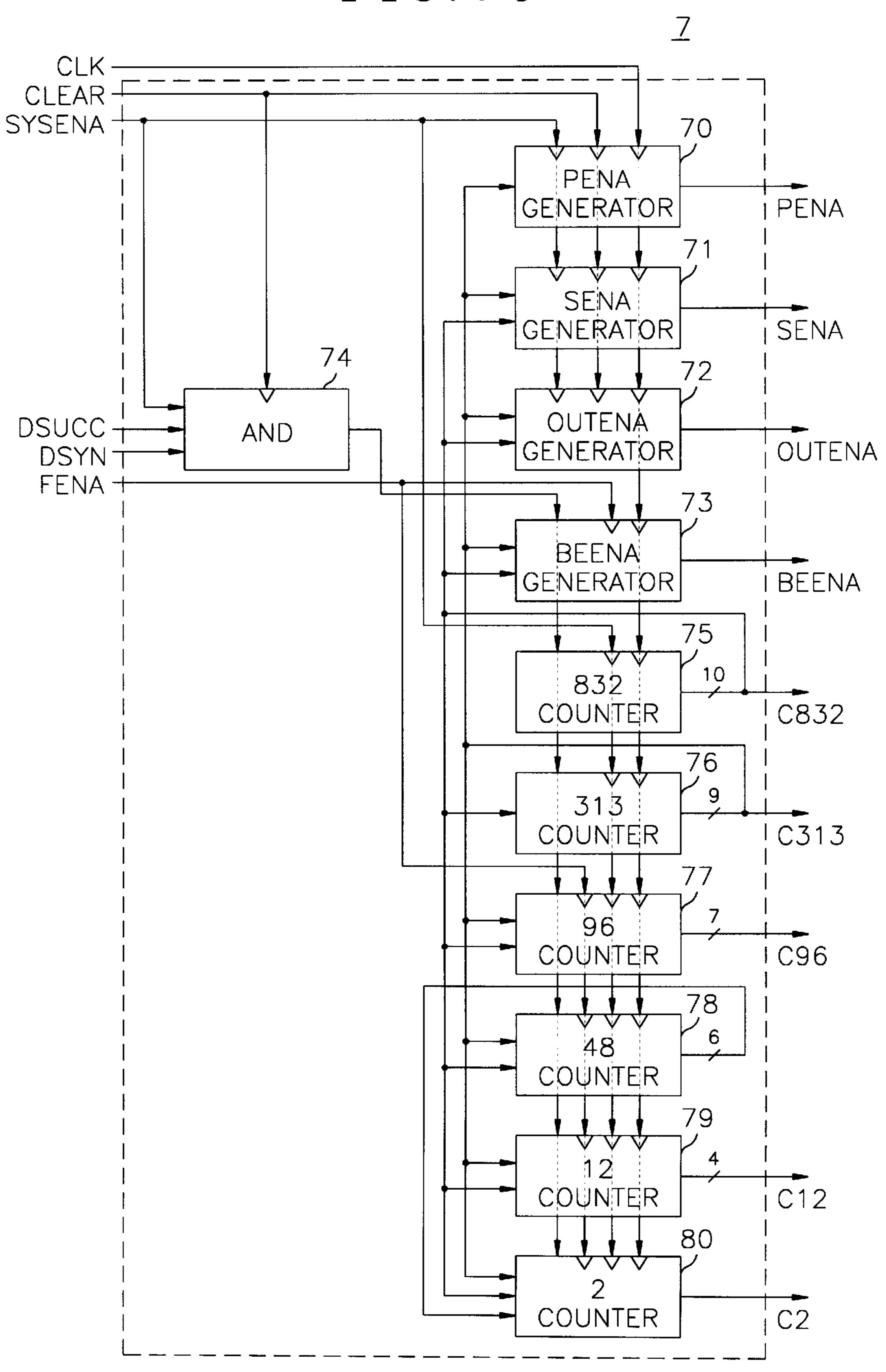

FIG. 10 pictures a detailed circuit of a control unit shown in FIG. **7**;

FIG. 11 shows a detailed circuit of a segment synchronization rejection filter shown in FIG. 7;

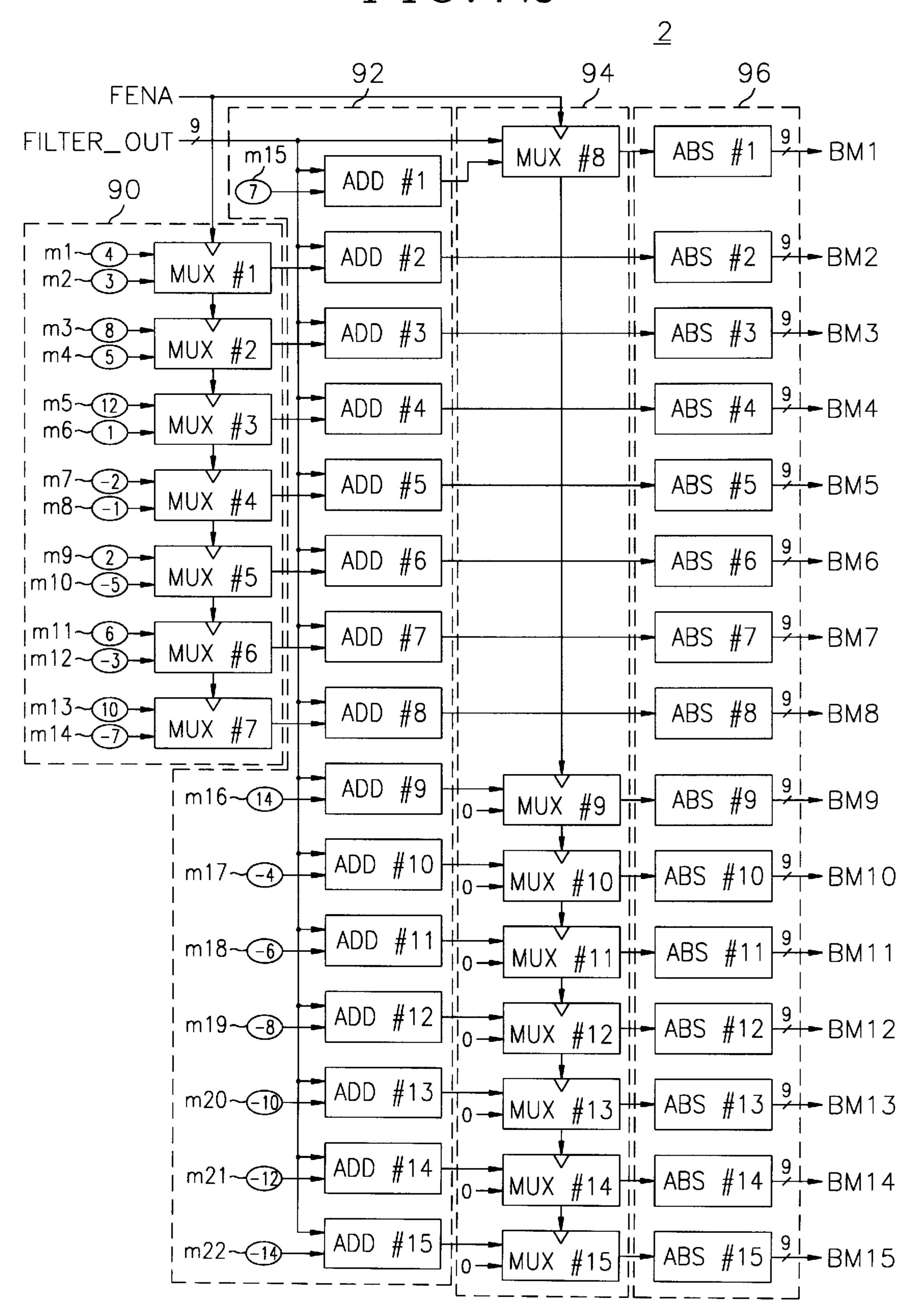

FIG. 12 presents a detailed circuit of a branch metric unit (BMU) shown in FIG. 7;

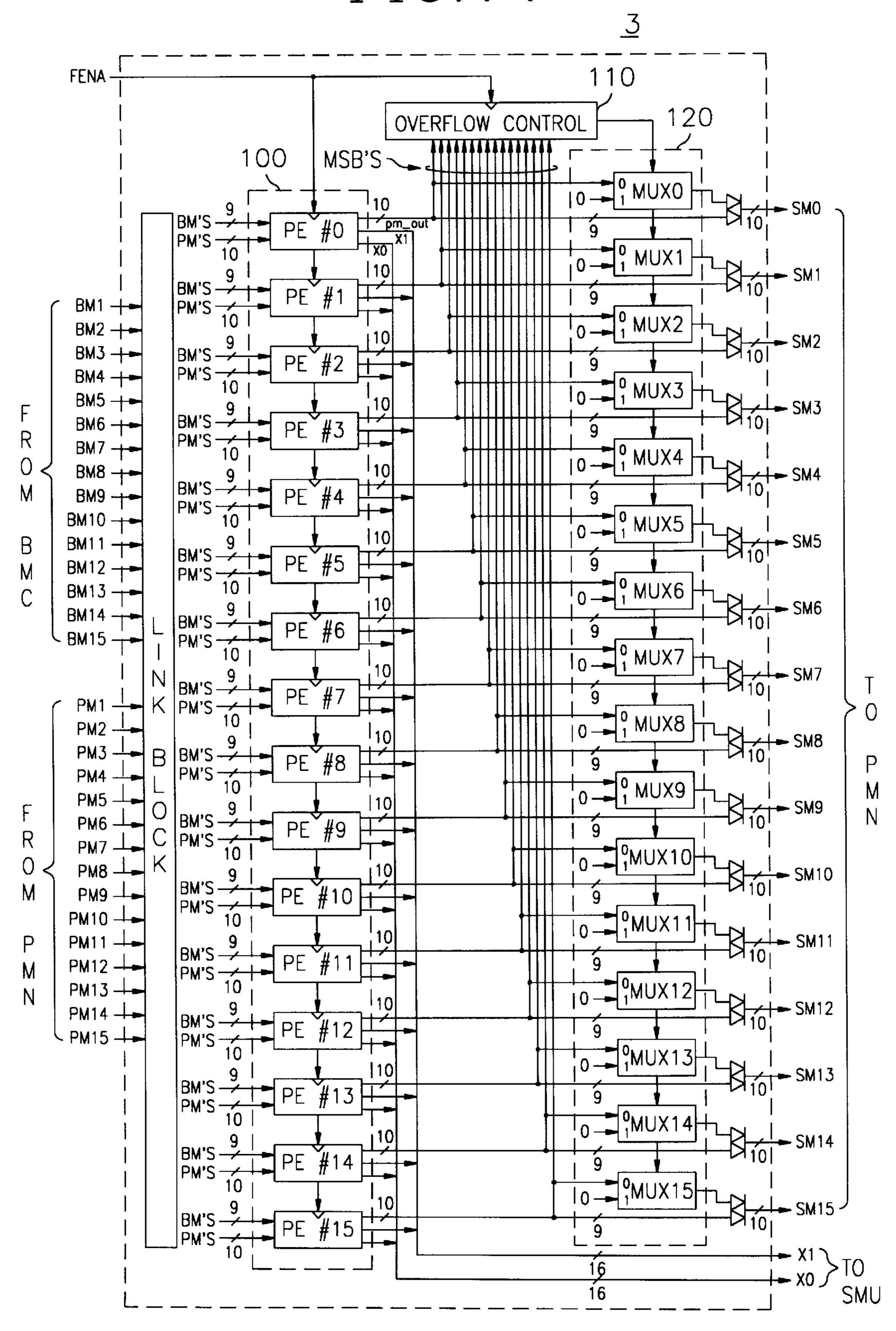

FIG. 13 provides a block diagram of an add-compareselect (ACS) shown in FIG. 7;

FIG. 14 depicts a exemplary circuit for the ACS shown in FIG. 13;

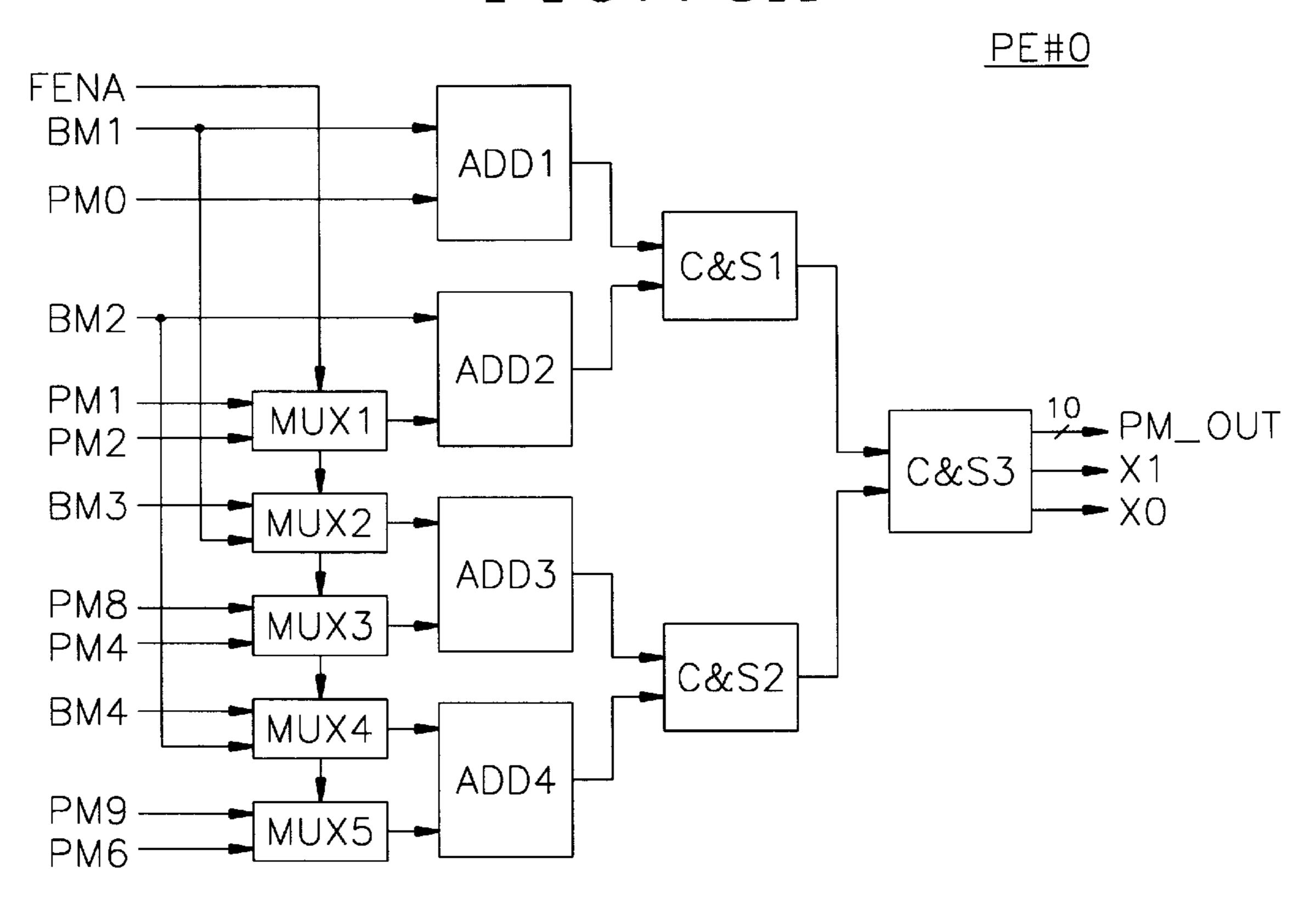

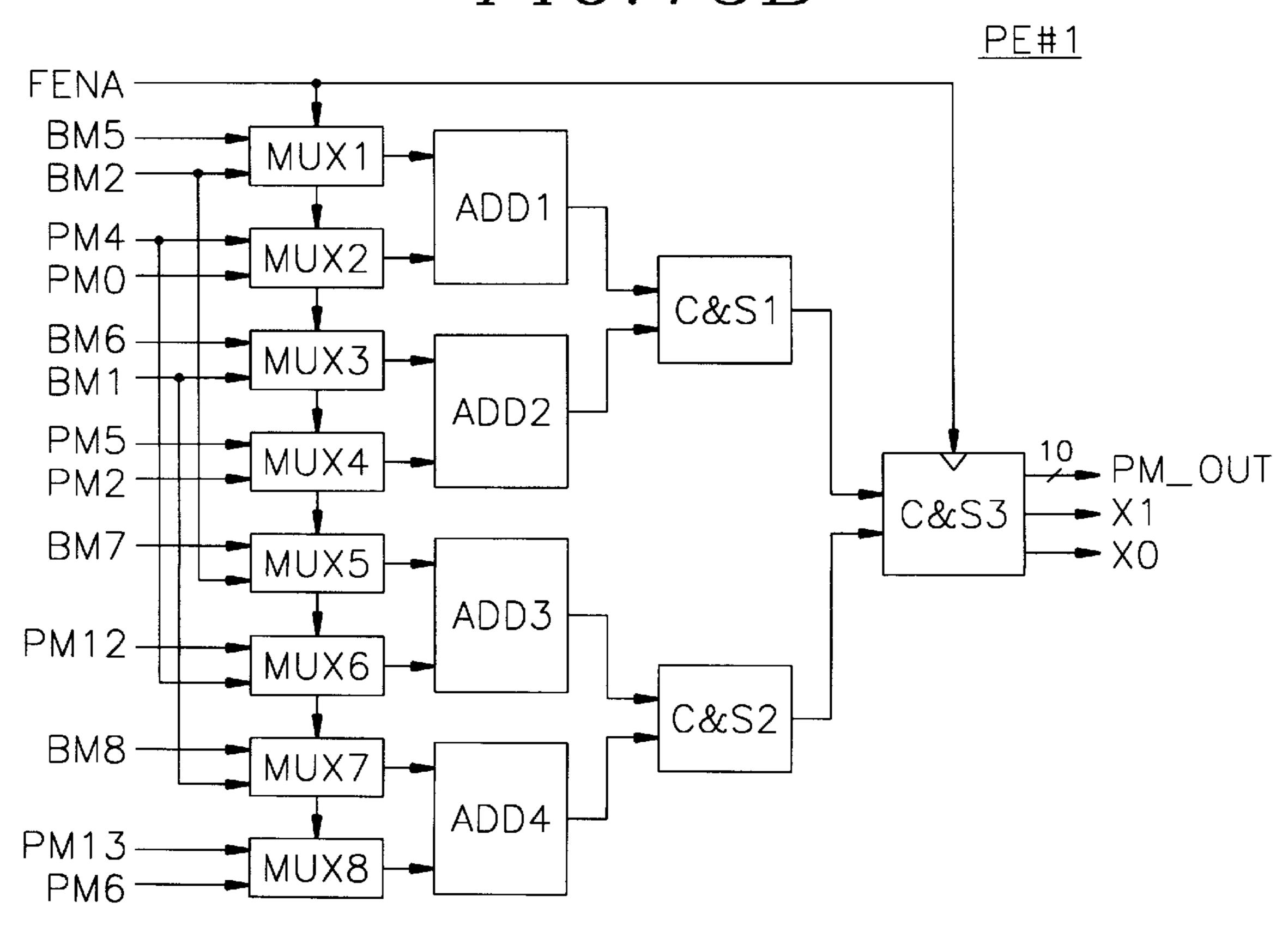

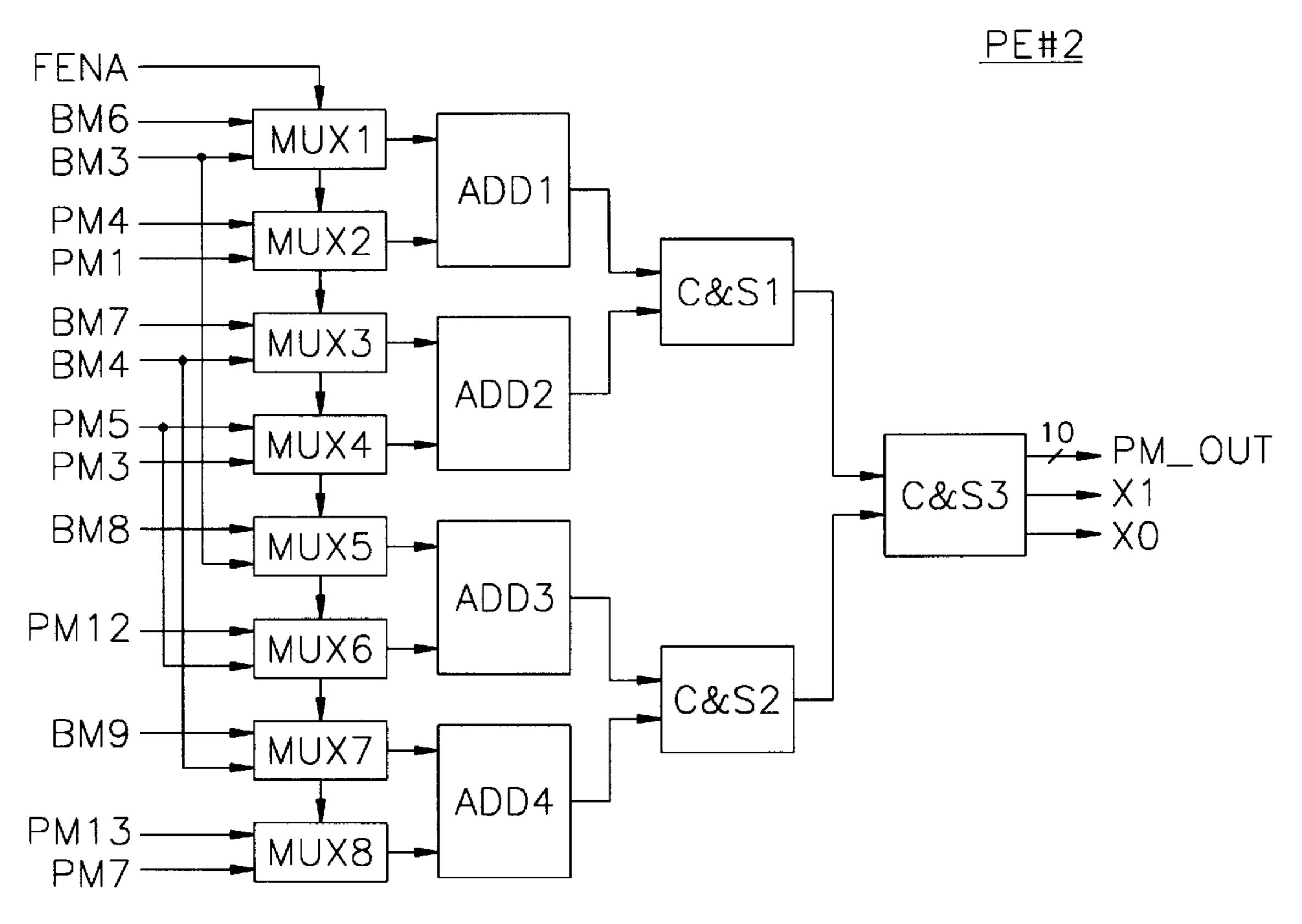

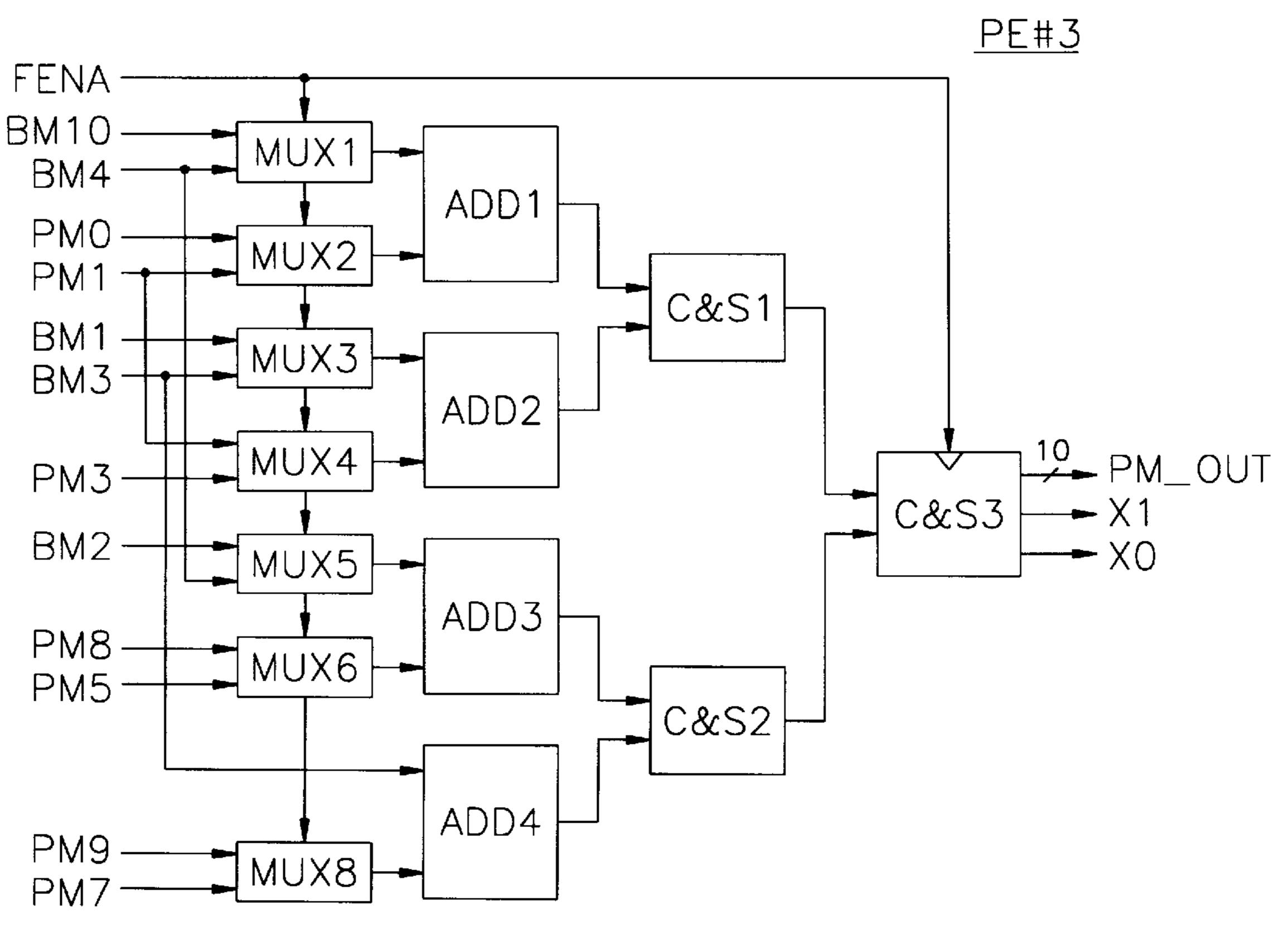

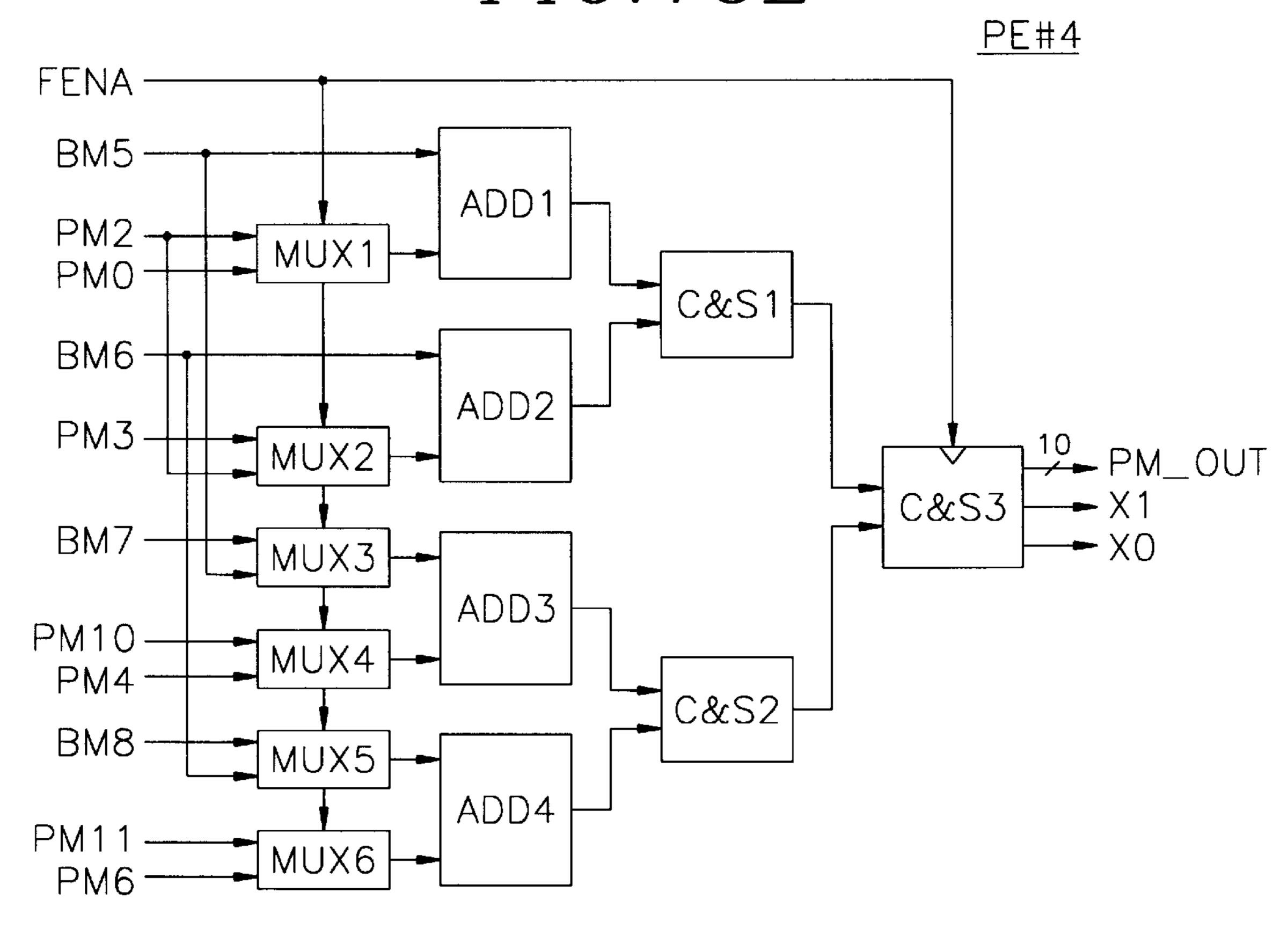

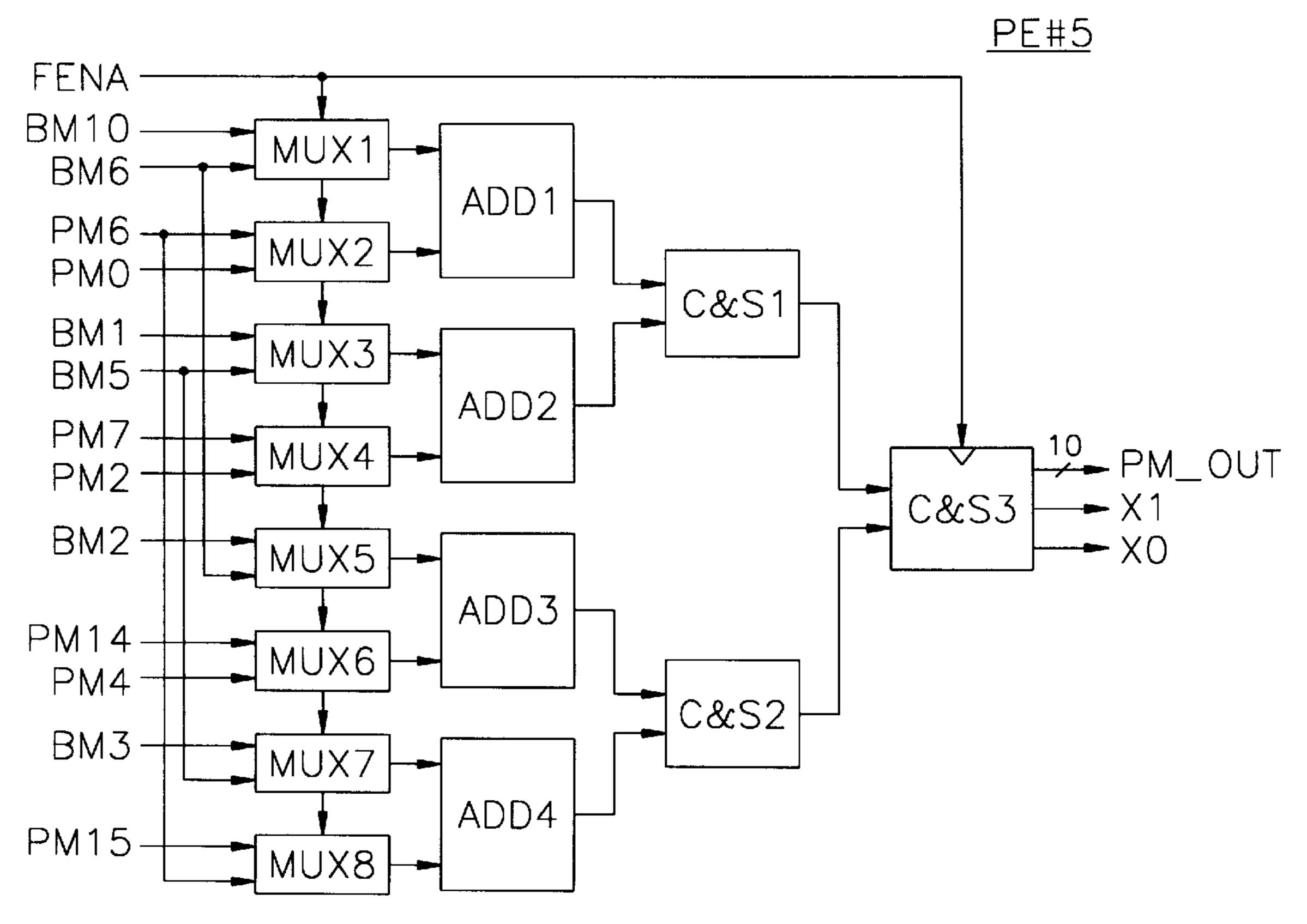

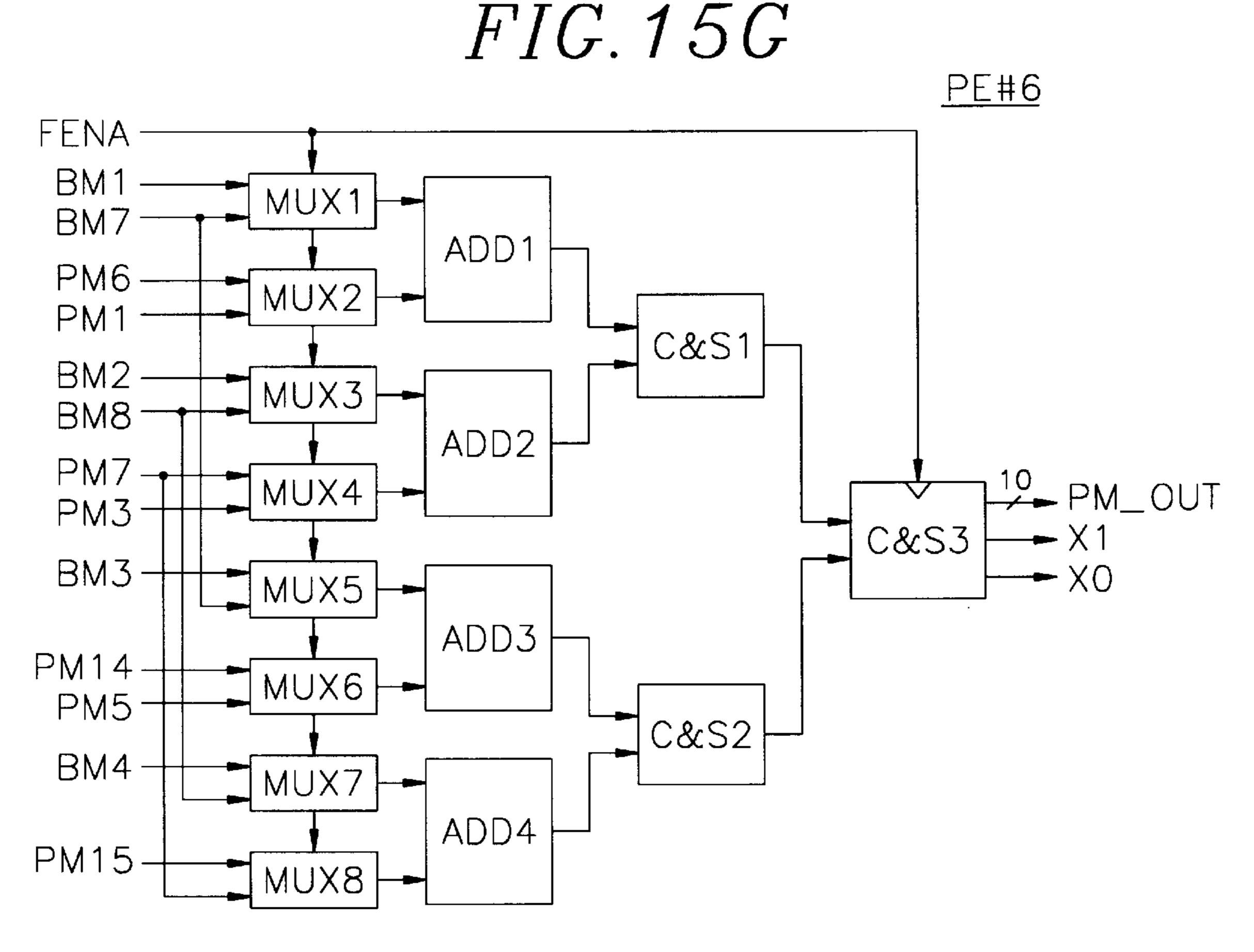

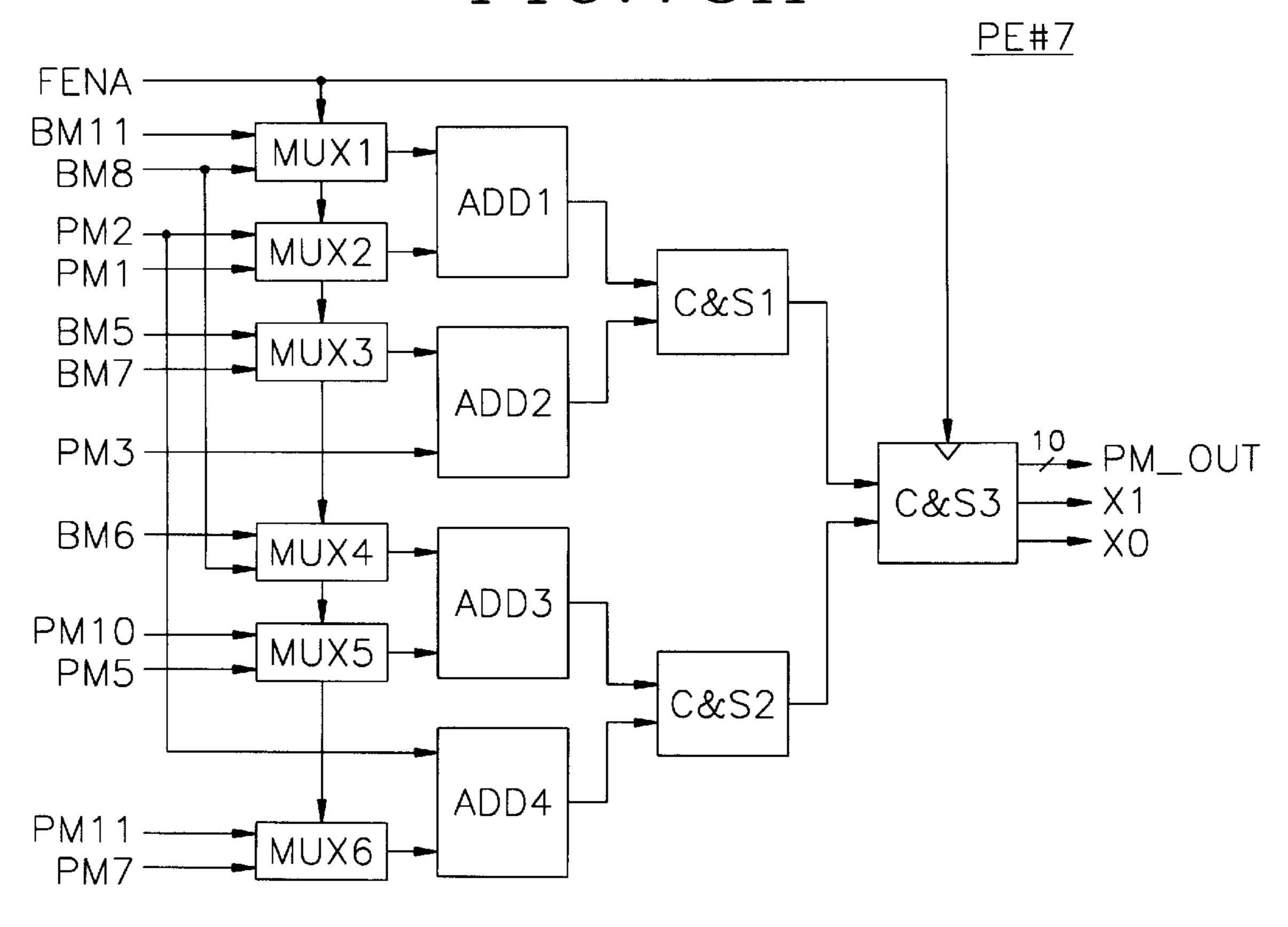

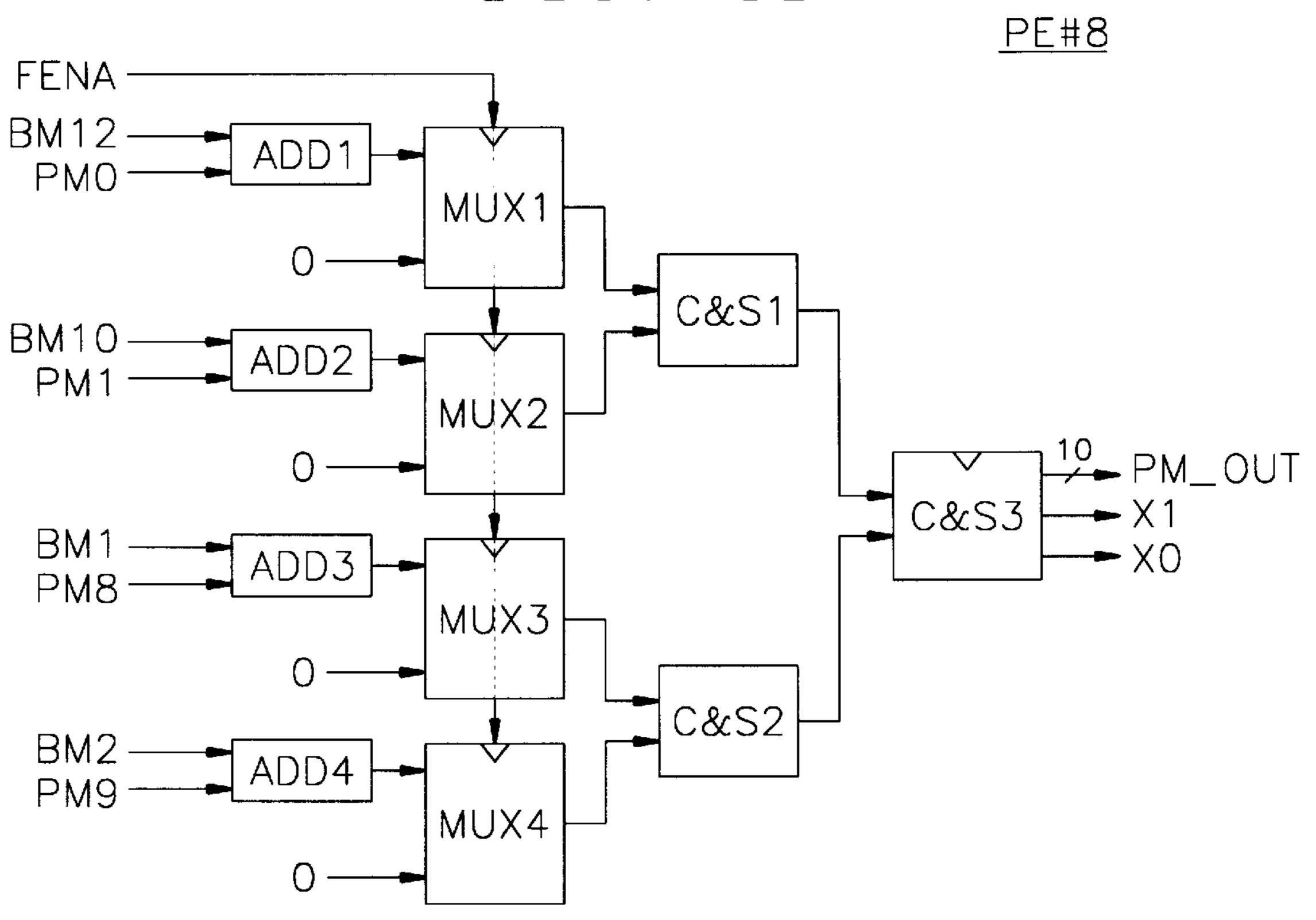

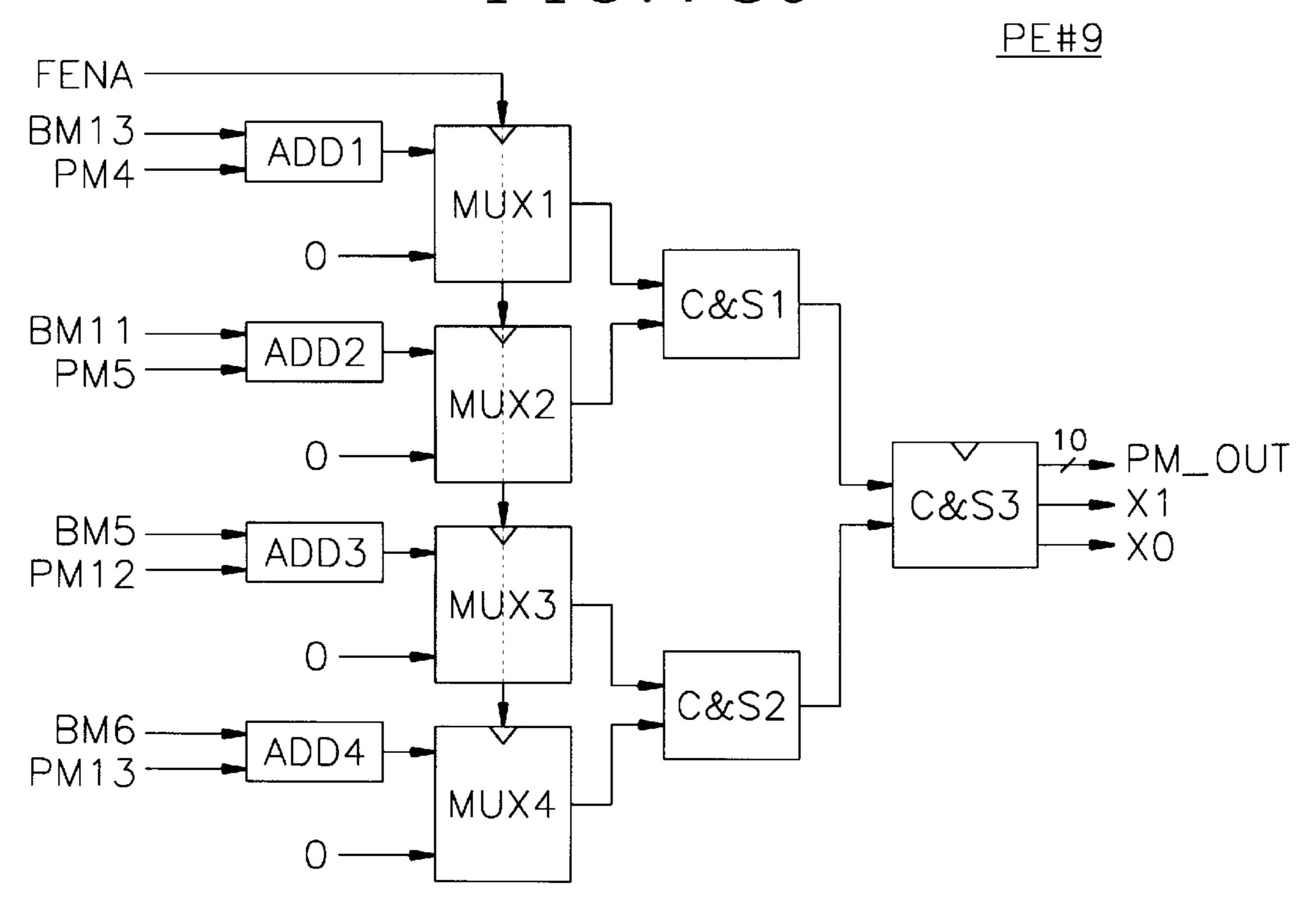

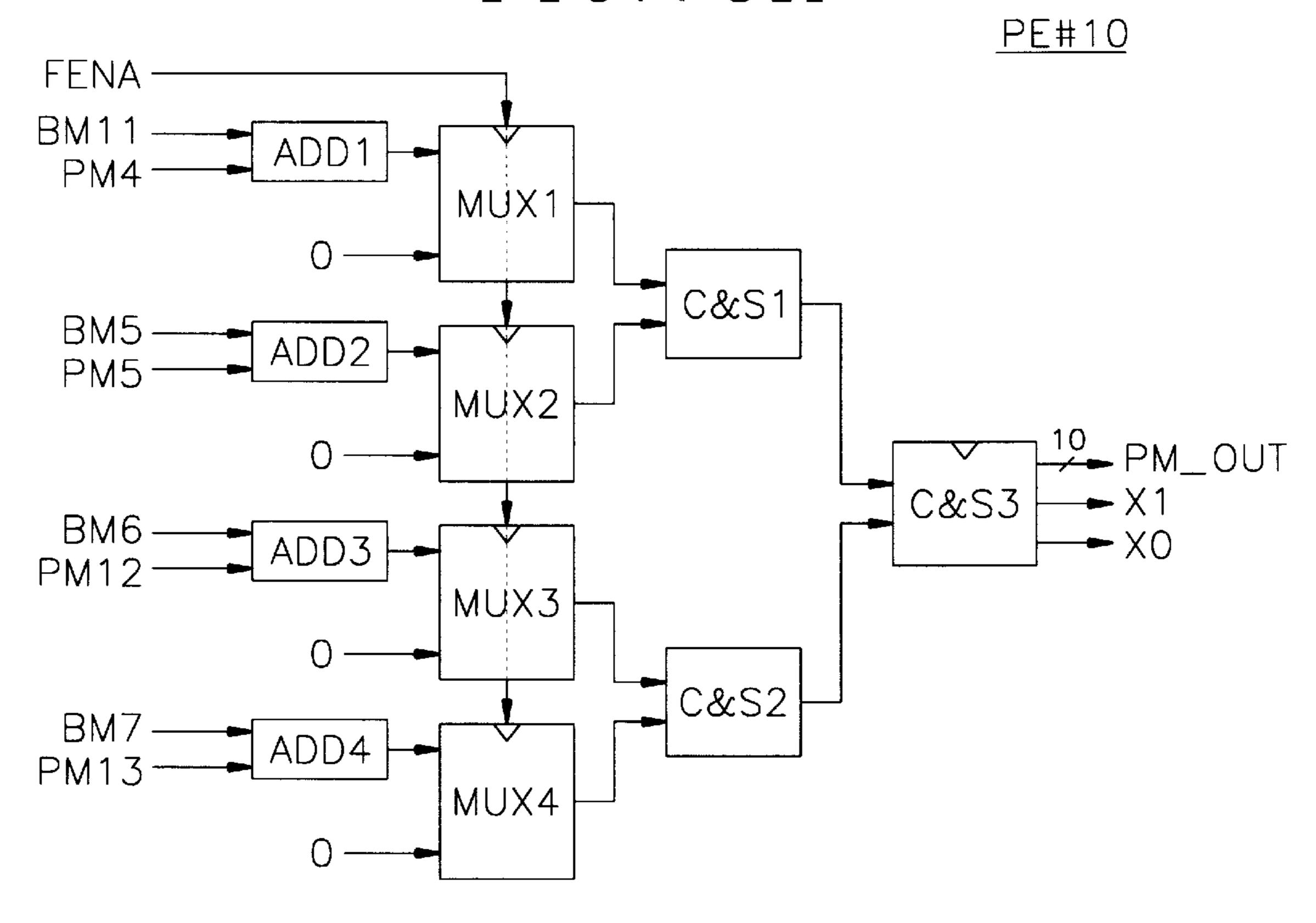

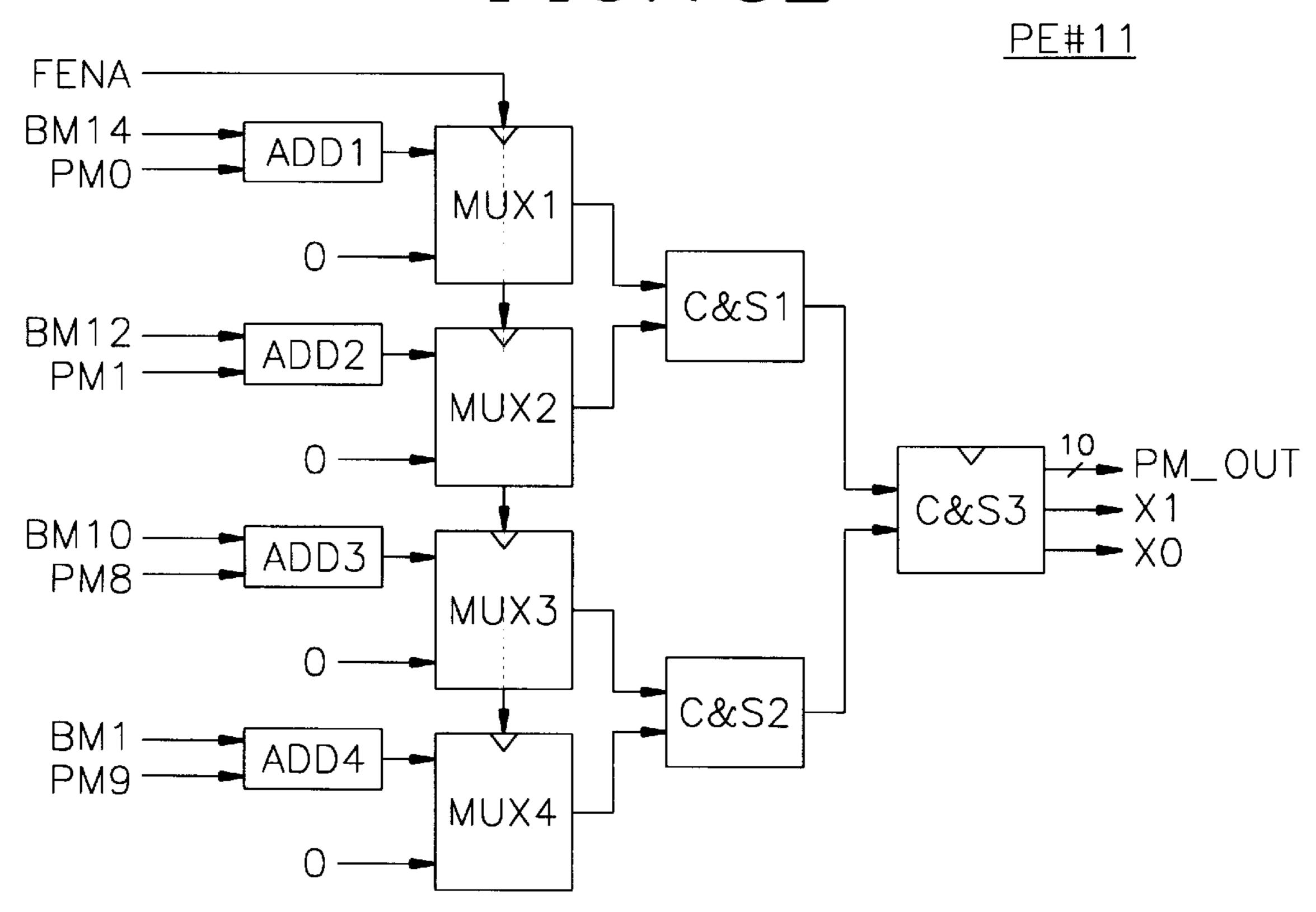

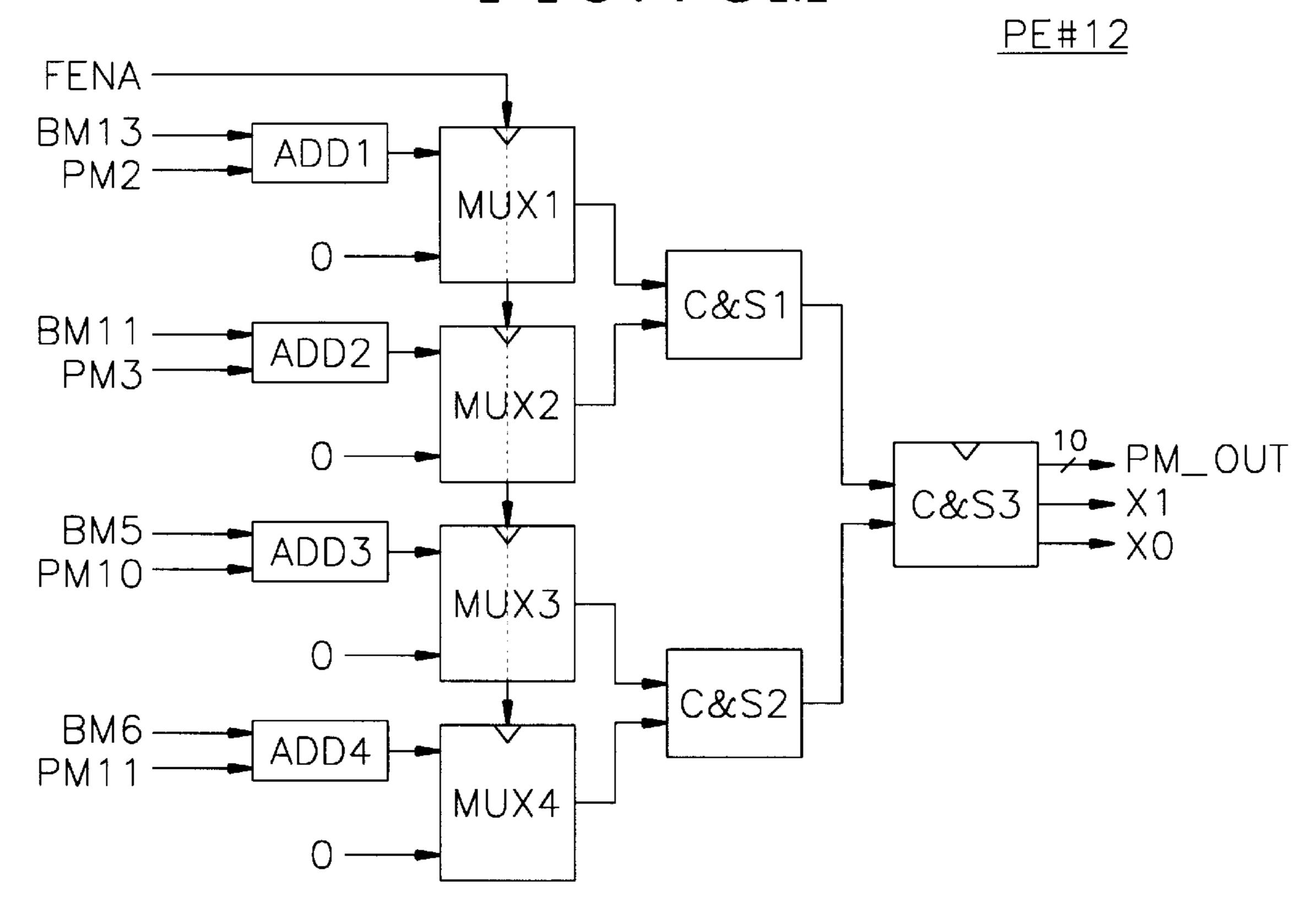

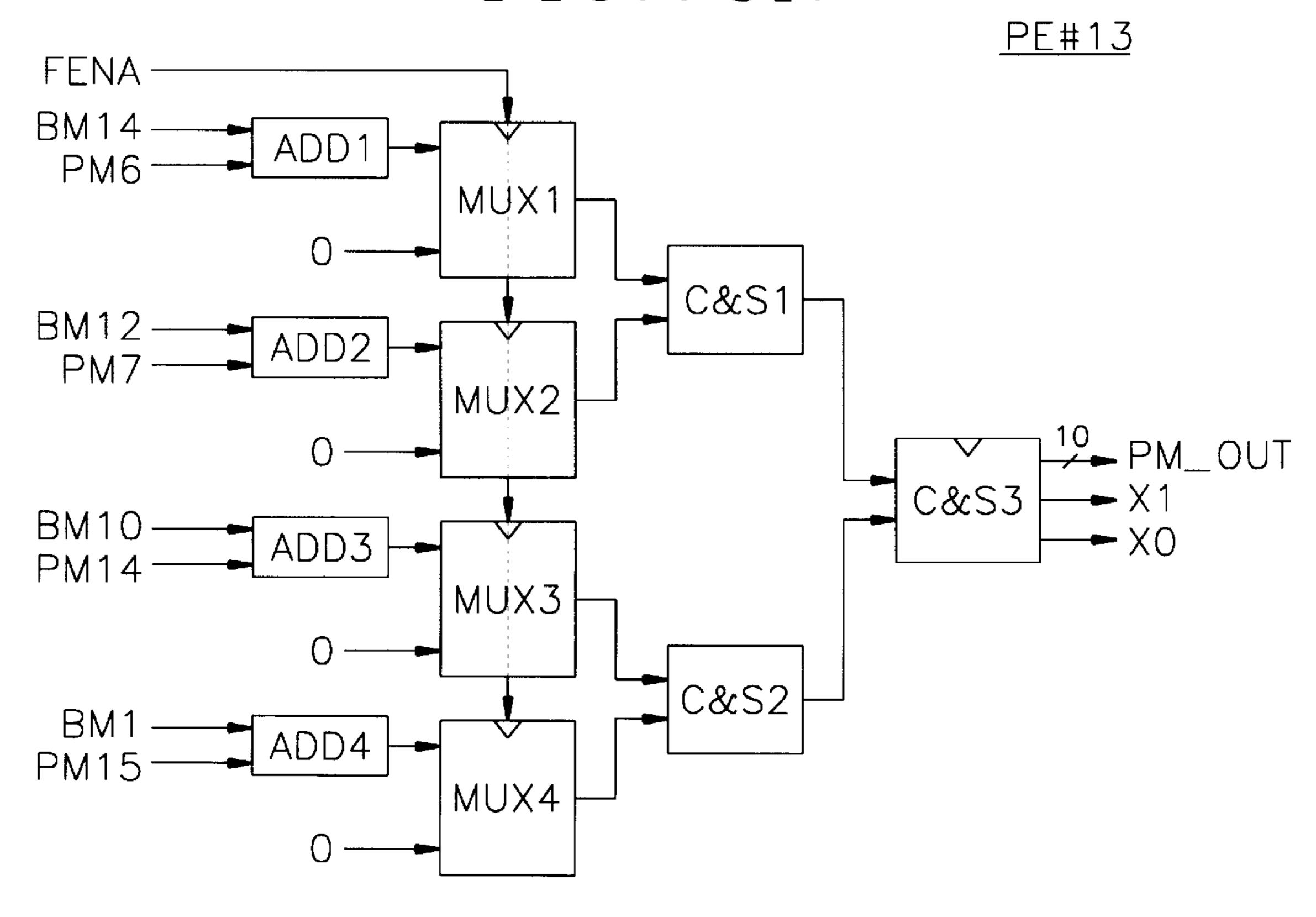

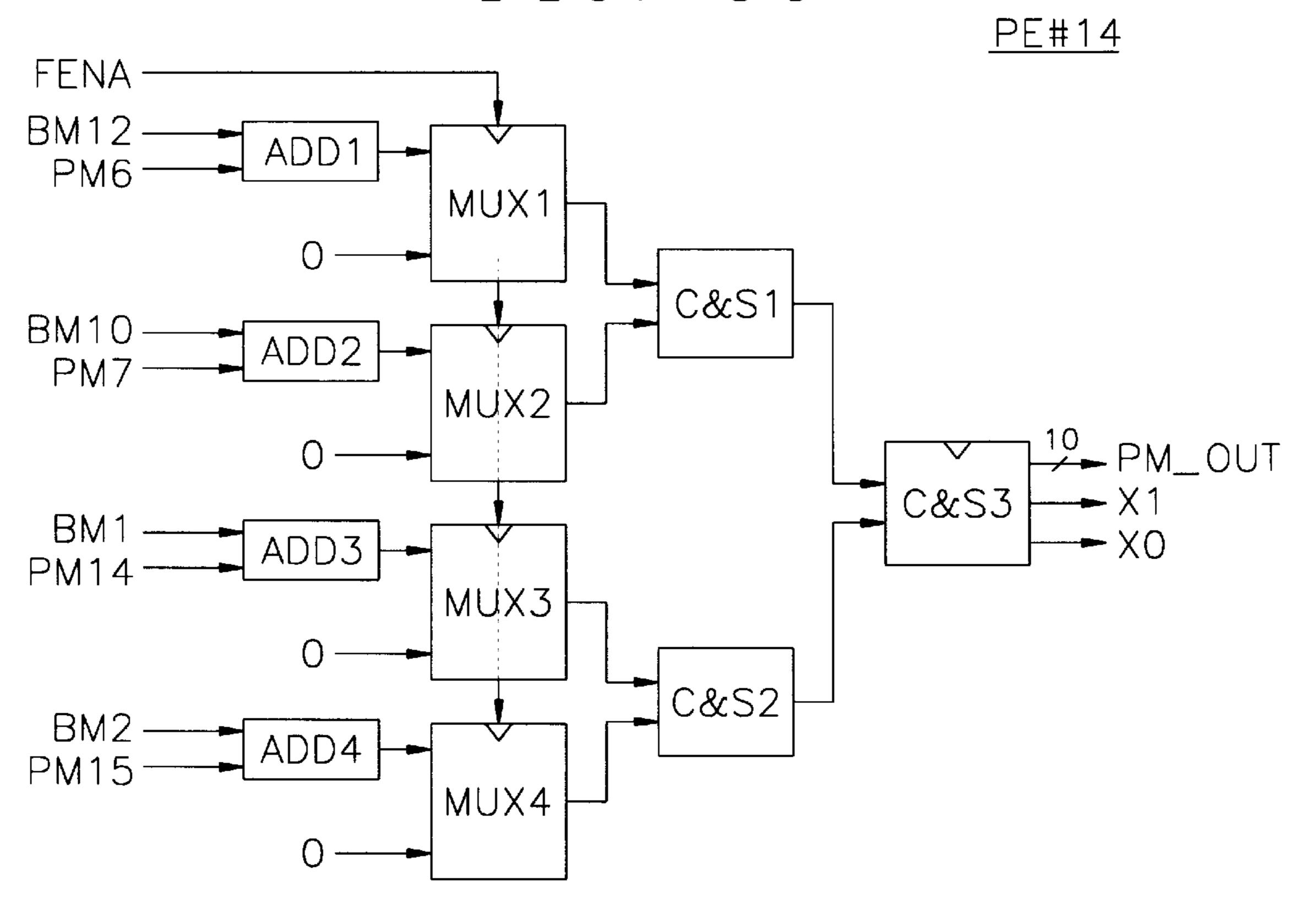

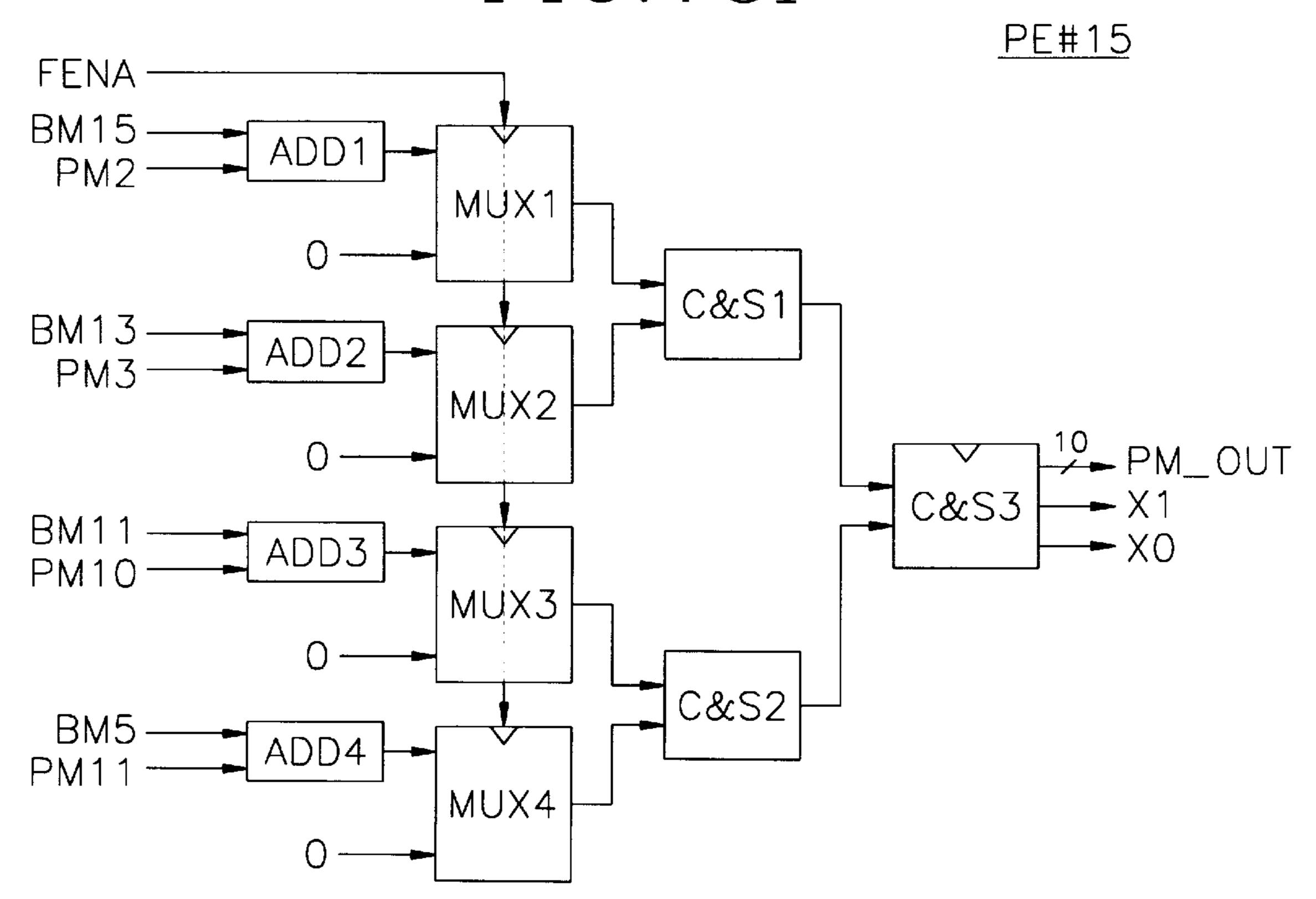

FIGS. 15A to 15P represent detailed circuits of processing elements shown in FIG. 14, respectively;

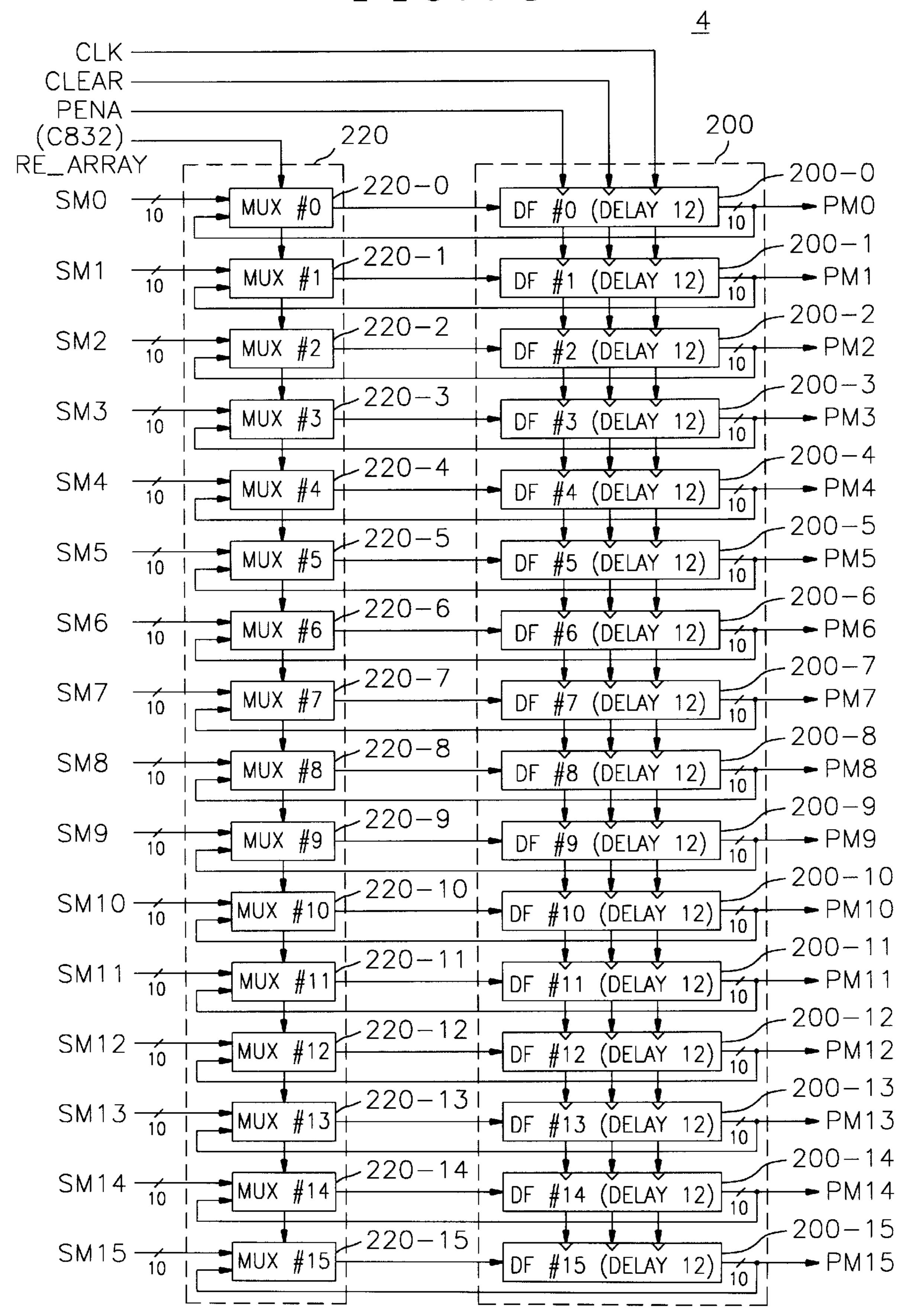

network (PMN) shown in FIG. 7;

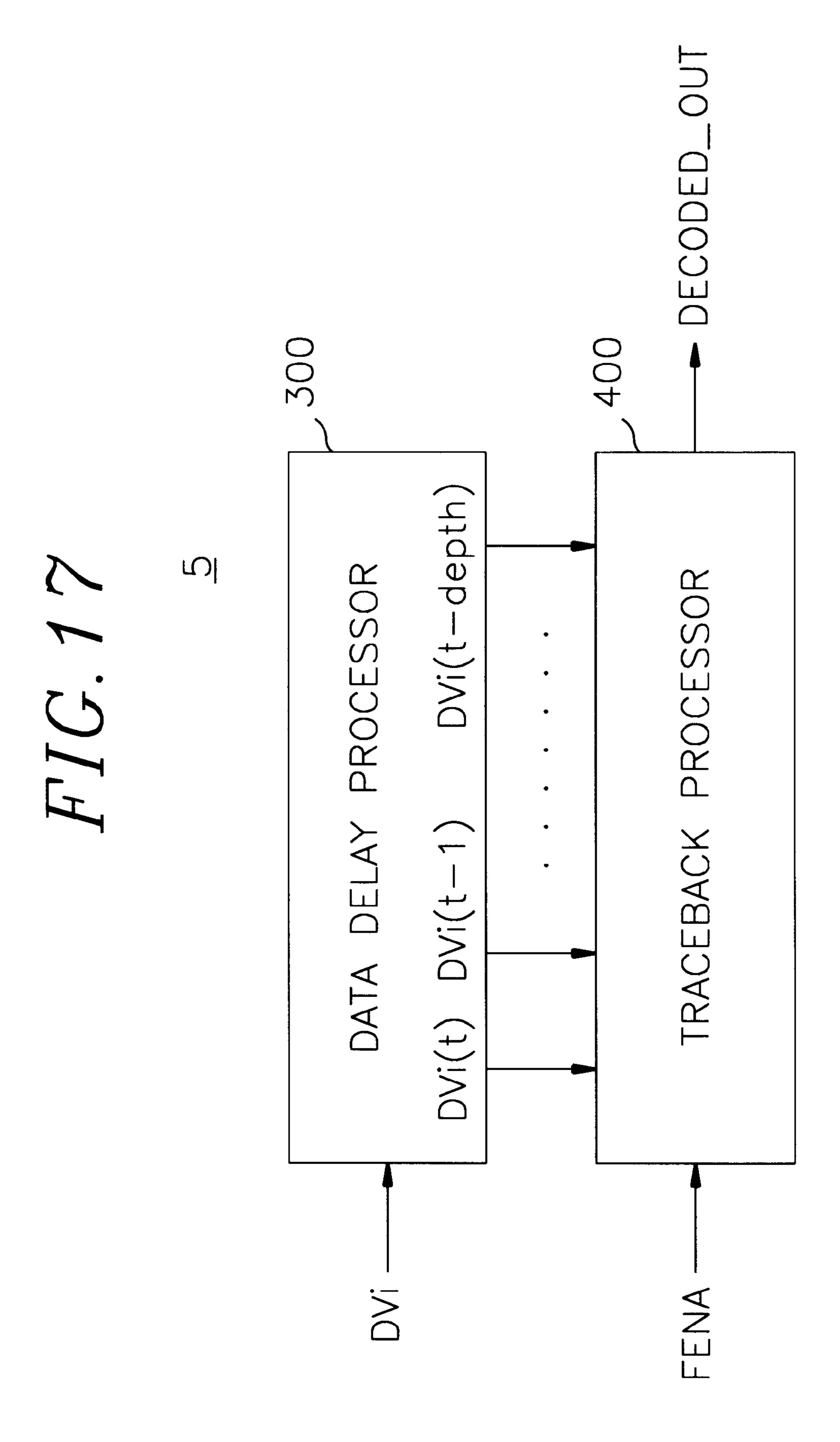

FIG. 17 describes a block diagram of a survivor memory unit (SMU) shown in FIG. 7;

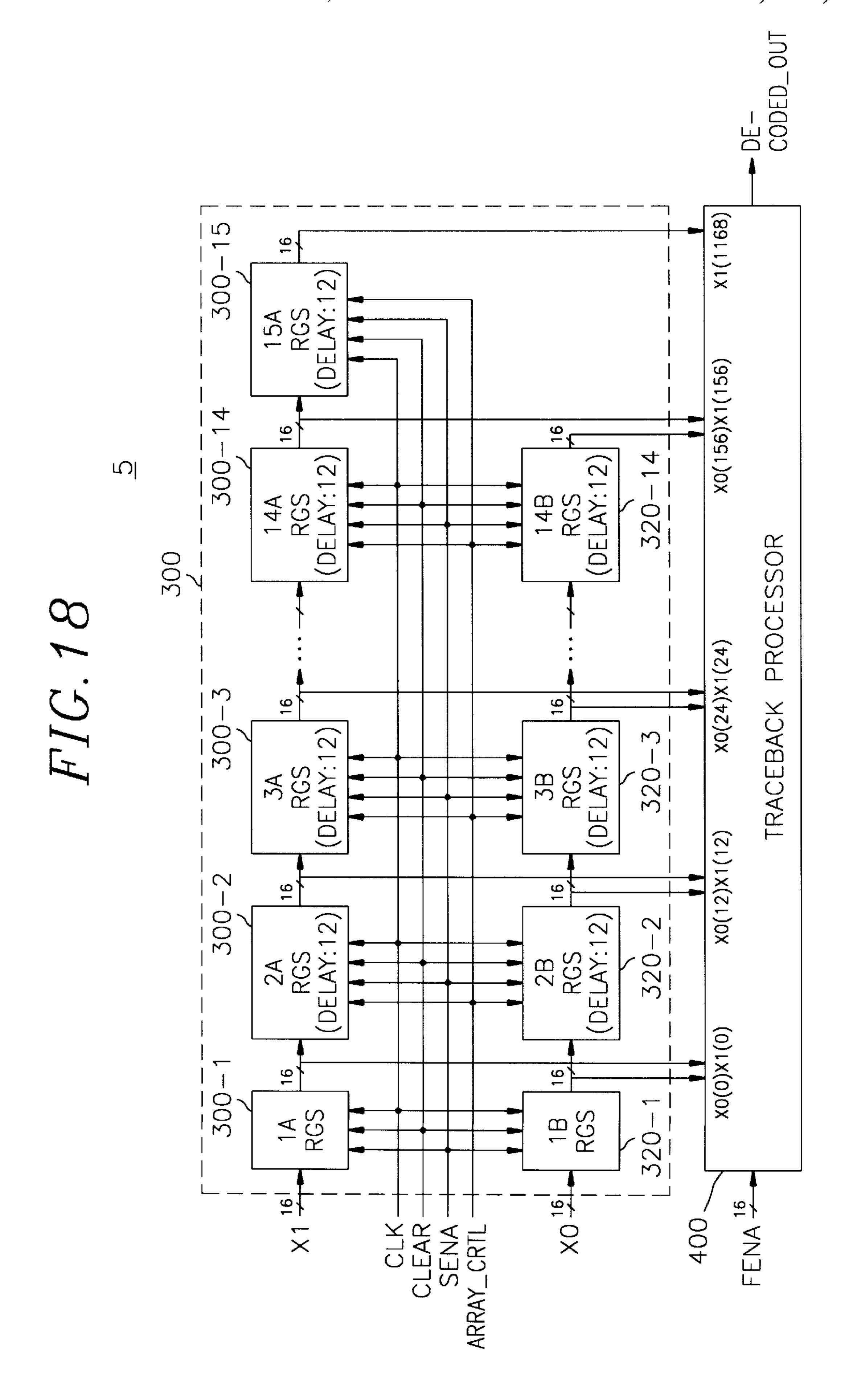

FIG. 18 portrays a data delay processor shown in FIG. 17;

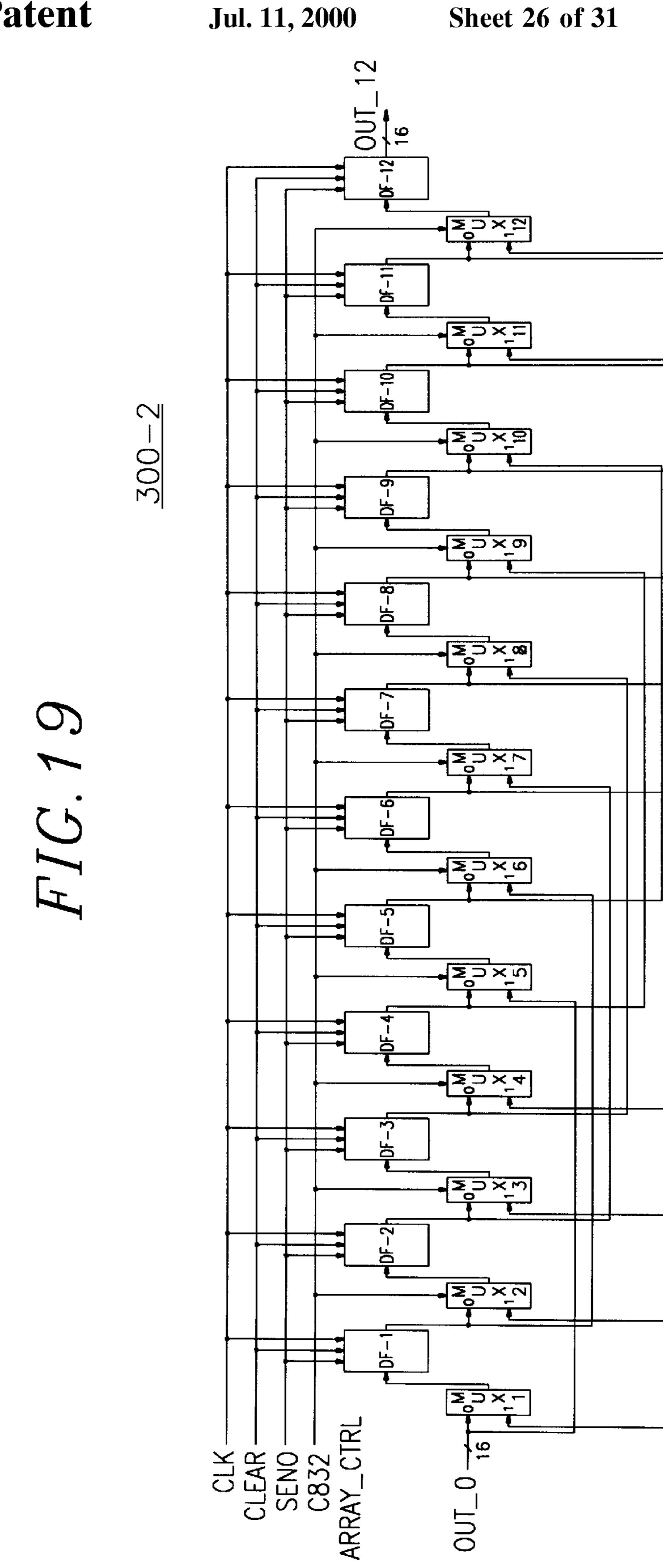

FIG. 19 delineates a detailed circuit of a 12-symbol delay register module shown in FIG. 18;

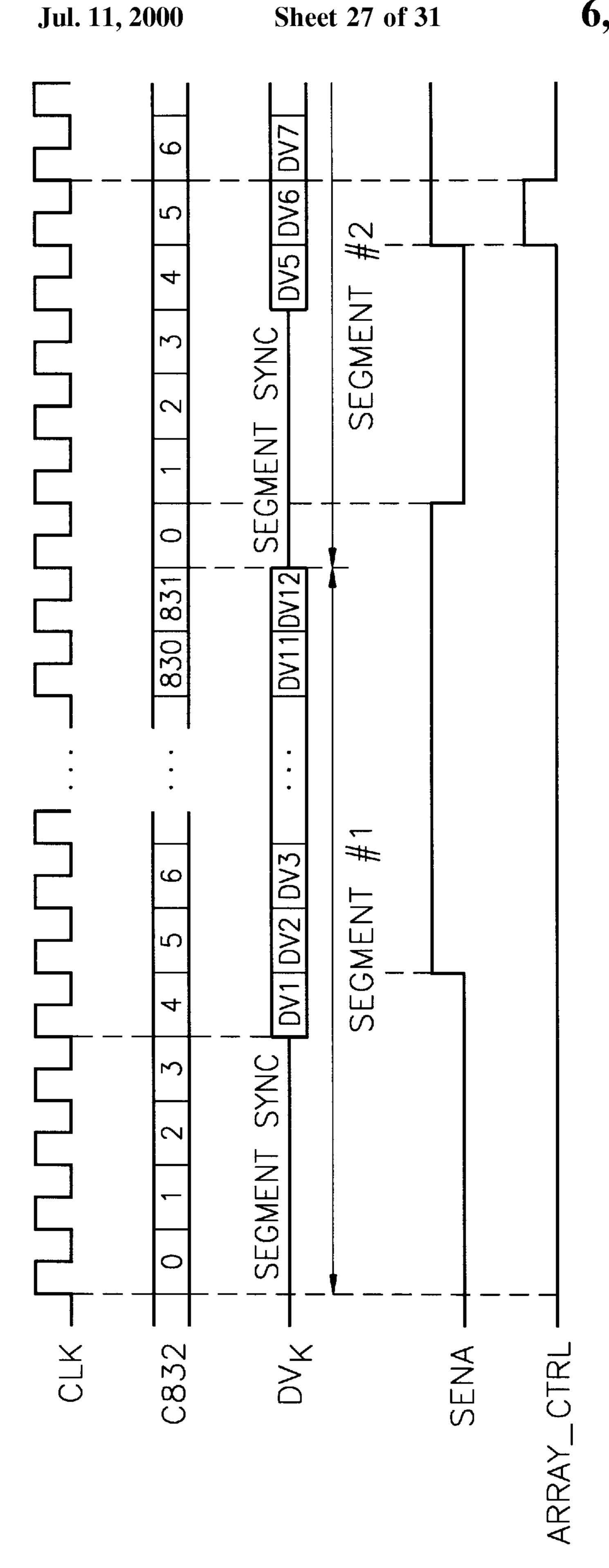

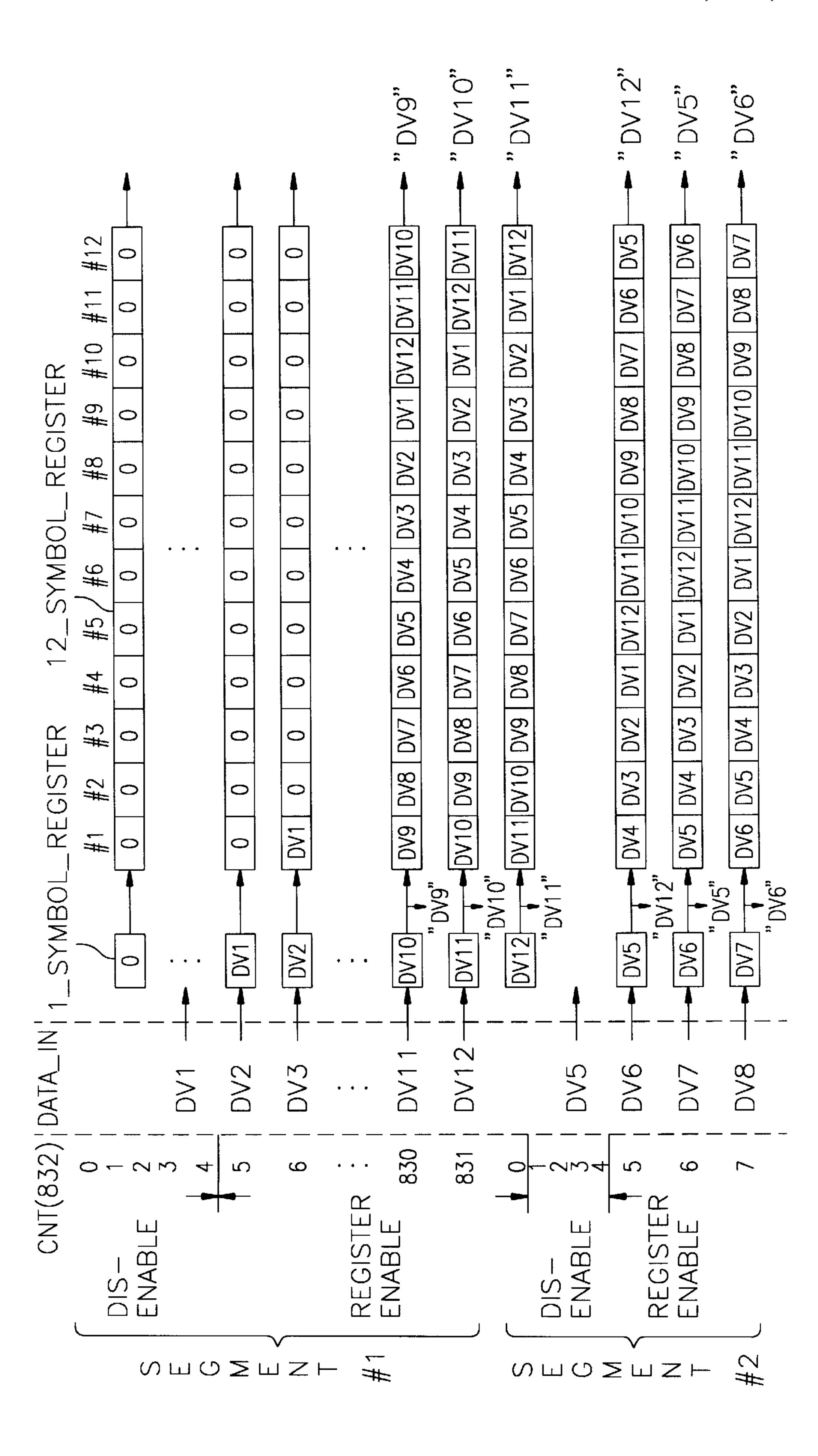

FIG. 20 pictures a timing diagram of several control signals for illustrating an operation of the delay register shown in FIG. 18;

FIG. 21 shows a state diagram of input signals, saved data and output signals of each 12-symbol delay register for illustrating an operation of the 12-symbol delay register shown in FIG. 19;

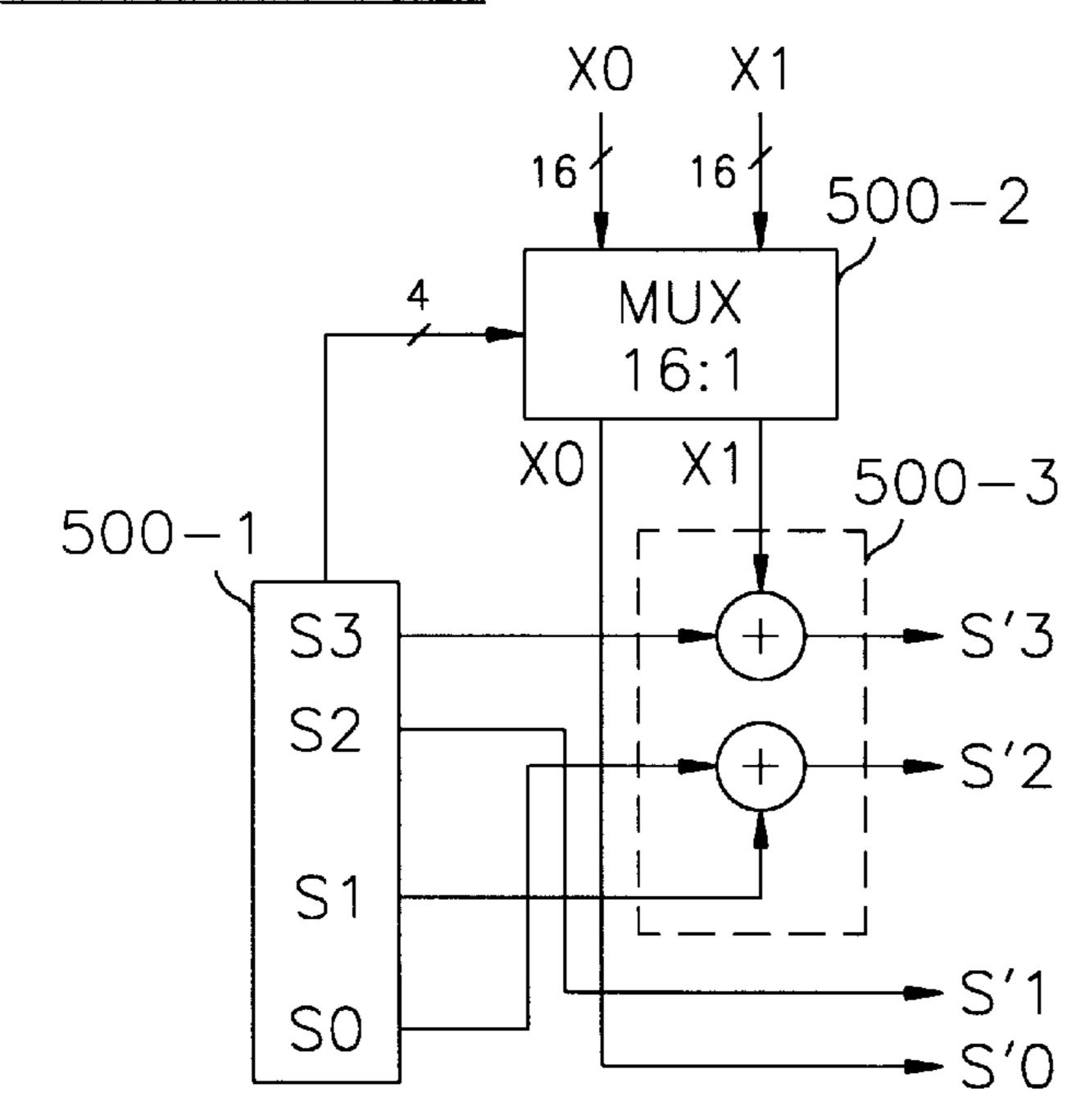

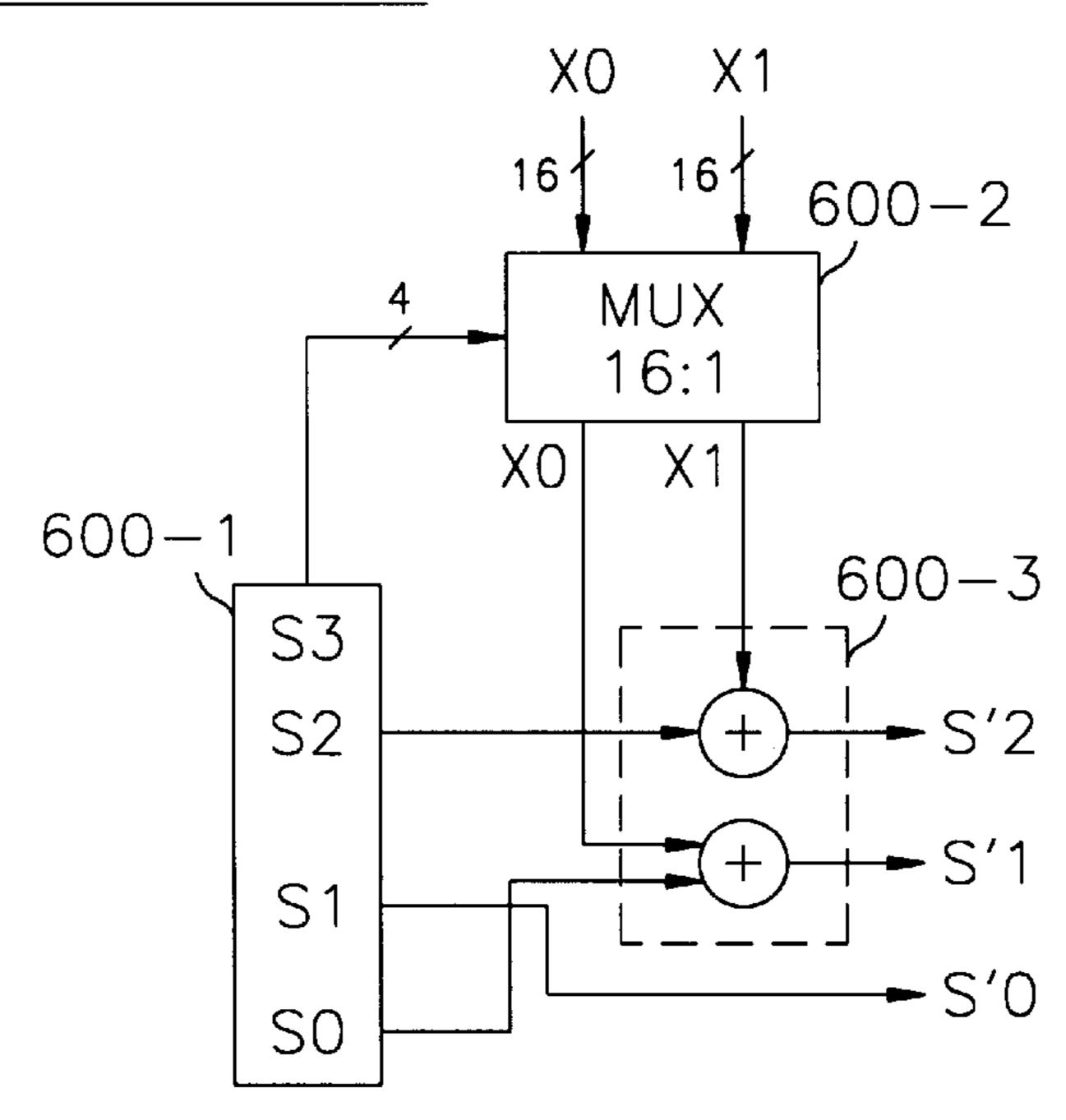

FIG. 22 presents a traceback processor shown in FIG. 18. 25 FIGS. 23A and 23B provide detailed circuits of the processing elements in the first operation module shown in FIG. **21**; and

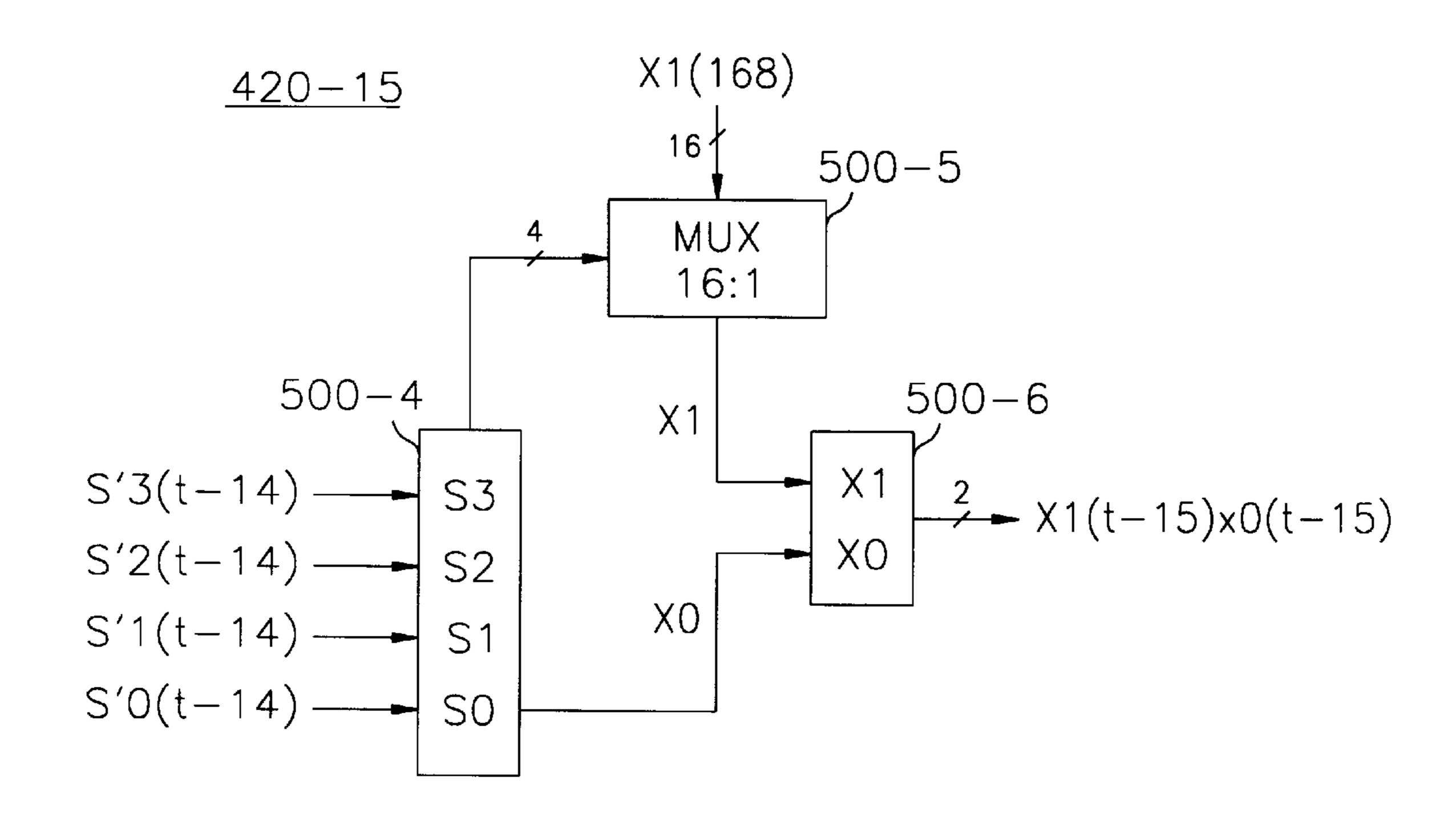

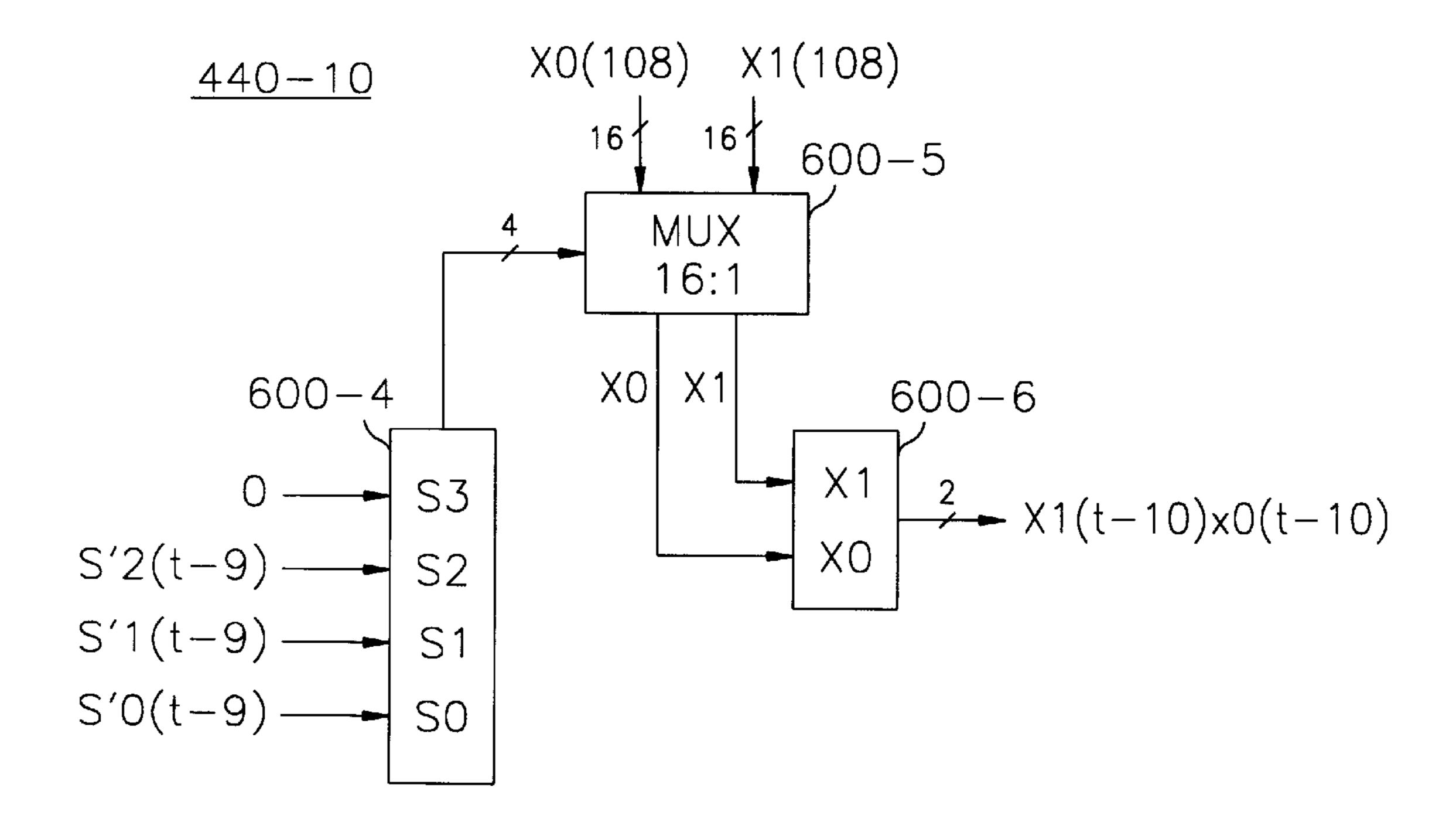

FIGS. 24A and 24B depict detailed circuit of the processing elements in the second operation module shown in FIG. 30 **21**.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

An embodiment of the present invention is illustrated to design a trellis decoder, which may decodes trellis code data encoded according to a transmission specification of the Grand Alliance high definition television (GA HDTV).

Referring to Table 1, there is illustrated coded streams in 40 the unit of a segment, wherein each coded stream is provided through a trellis code interleaver, shown in FIG. 4, employed in GA HDTV.

TABLE 1

| segmen   | t group 1               | group 2                 | group 69                |  |

|----------|-------------------------|-------------------------|-------------------------|--|

| #1<br>#2 | d1, d2 d12<br>d5, d6 d4 | d1, d2 d12<br>d5, d6 d4 | d1, d2 d12<br>d5, d6 d4 |  |

| #3       | d9, d10 d8              | d9, d10 d8              | d9, d10 d8              |  |

In Table 1, since each group is carried out by a 12 symbol intra-segment interleaving, it is classified in the unit of 12 symbols and an index attached to each data is identical to that of a corresponding trellis encoder shown in FIG. 4. That 55 is, d1 is data fed from a first trellis encoder(E1), d2 is data fed from a second trellis encoder(E2) and so on. The data stream fed from each trellis encoder is periodically repeated with a period of 3 segments. For example, the first segment #1 starts with the data d1 fed from the first trellis encoder 60 (E1) and includes d2, d3, d4, . . . and d12 in sequence; the second segment #2 starts with the data d5 fed from the 5th trellis encoder(E5) and includes d6, d7, d8, . . . and d4 in sequence; and the third segment #3 starts with the data d9 fed from the 9th trellis encoder(E9) and includes d9, d10, 65 d11, . . . and d8 in sequence. The above sequence results from a switching operation of the interleaver during the

receipt of 4 symbols of segment synchronization signal. Therefore, the data stream di with an index i shown in Table 1 should be applied to a trellis decoder Di with the same index i. That is, d1 is available to a first trellis decoder(D1), d2 is available to a second trellis decoder(D2) and so on.

Since a conventional GA HDTV receiver employs 12 trellis decoders as shown in FIG. 1 to perform 12 symbol intra-segment deinterleaving and decoding at the same time, only one decoder operates every 12th symbol and the FIG. 16 illustrates a block diagram of a path metric 10 remaining 11 decoders do not operate at all. That is, the whole 12 trellis decoders used in the receiver do not operate simultaneously for every data input so that it will be possible to use only one trellis decoder by performing a time-division multiplexing technique in the unit of 12 symbols. Although 15 12 trellis decoders may be simply designed by duplicating the same decoding unit, a much larger space will be needed. Meanwhile, one trellis decoder by the time-division multiplexing technique has a little complex design but requires a smaller space.

> The trellis decoder in the present invention is designed to include only one trellis decoder by employing the timedivision multiplexing technique so as to be used in two mode, i.e., 8 and 16 state mode according to the characteristics of channels. The specification for a trellis coded modulation(TCM) decoder in the present embodiment is defined as follows:

TABLE 2

|                | 16 state mode TCM | 8 state mode TCM |

|----------------|-------------------|------------------|

| decoding depth | 15                | 10               |

| branch metric  | 9 bits            | 8 bits           |

| path metric    | 10 bits           | 9 bits           |

| state          | 4 bits            | 3 bits           |

A larger bit number and a higher decoding depth are required in order to design the 16 state mode TCM as shown in Table 2. This means that much more registers are needed in the path metric network (PMN) and the survivor memory unit (SMU). The trellis decoder in accordance with the present invention does not include both the 8 state mode and the 16 state mode separately, but is designed basically with the specification of the 16 state mode which can also be used in the 8 state mode.

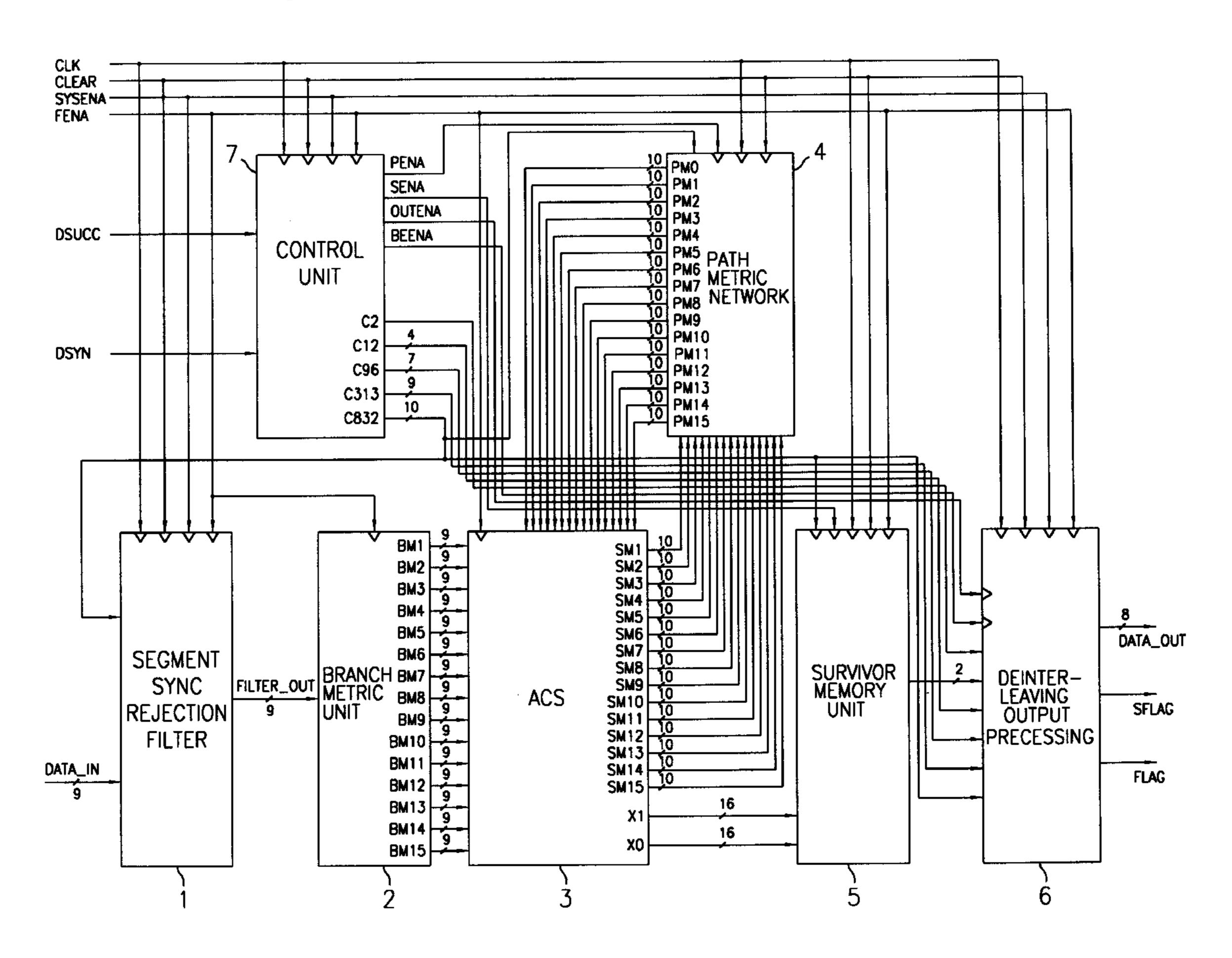

Referring to FIG. 7, there is a block diagram of a trellis decoder in accordance with the present invention, which comprises a segment synchronization rejection filter 1, a branch metric calculation unit (BMU) 2, an add-compareselect unit(ACS) 3, a path metric network(PMN) 4, a 50 survivor memory unit (SMU) 5, a deinterleaving and output processing unit (DOUT) 6 and a control unit 7.

As illustrated above, the trellis decoder basically comprises the BMU 2, the ACS 3 and the SMU 5. Further, the PMN 4 is required for providing previous path metrics in order to calculate new path metrics for each new state. Since input symbols in the 16 state mode should pass through an NTSC interference rejection filter, the segment synchronization rejection filter 1 precedes the BMU 2 in order to remove the influence of the segment synchronization signals. In order to carry out an intra-segment deinterleaving process in the unit of byte on decoded data, which is provided from the SMU 5 in the unit of symbol (2-bits), the DOUT 6 follows the SMU 5. The control unit 7 is added in order to generate control signals needed to control the respective elements.

If trellis code data received corresponds to the 8 state mode, the segment synchronization rejection filter 1 passes 7

the trellis code data based on a mode selection signal (FENA) and, otherwise, i.e., if the trellis code data corresponds to the 16 state mode, the segment synchronization rejection filter 1 removes the influence of the segment synchronization signal to generate a to-be-decoded symbol. 5 The BMU 2 receives the to-be-decoded symbol from the segment synchronization rejection filter 1 and calculates all branch metrics which can be generated for each of two modes based on the FENA as follows: 7 branch metrics BM1 to BM7 are generated in the 8 state mode, while 15 branch metrics BM1 to BM1 are calculated in the 16 state mode. The ACS 3 receives the FENA and all the branch metrics from the BMU 2; selects several branch metrics  $BM_{i,1}$  to  $BM_{i,4}$  required for each state  $S_i(t)$ , which can be generated in each of two state modes; accumulates the branch metrics for each state and previous path metrics  $PM_{i,1}$  to  $PM_{i,4}$ , fed from the PMN 4, for the previous states associated with the selected branch metrics to determine new candidate path metrics; and provides a most likely path metric as a survivor metric SM, for each state with a determination vector DV, for the survivor metric. The PMN 4 temporally stores the 20 survivor metric SM, for each state from the ACS 3 and provides the stored survivor metric SM; to the ACS 3 as a previous path metric PM, for a next state. The SMU 5 receives the determination vector  $DV_i=(X1, X0)$  for each state from the ACS 3 based on the FENA; and tracing back a previous state for each of the two modes as far as a decoding depth based on the determination vectors DV,'s by a traceback algorithm to generate a decoded symbol (decoded\_out) with 2 bits. The DOUT 6 carries out an intra-segment deinterleaving process for the decoded symbol fed from the SMU 5 based on the FENA and, then, converts the 2 bit decoded symbol into the unit of packet, i.e., 8 bits in order to be adapted to a next unit.

Referring to FIG. 8, a timing diagram of input signals into the TCM decoder and the function of the input signals will be described as follows:

- 1. CLK: a clock signal in which an ascending edge represents an enable state;

- 2. CLEAR: a clear signal to reset the system;

- 3. SYSENA: a system enable signal to make the entire system enable;

- 4. DSUCC: a demodulation success signal to indicate that VSB modulation signals at the front end of the TCM decoder are successfully decoded, wherein, if the VSB modulation signals are successfully decoded, the TCM decoder may be operated while the DSUCC remains 45 '1'.

- 5. DSYN: a signal to represent whether a segment synchronization signal is received or not, wherein the segment synchronization signal with 4 symbols may be received while the DSYN remains '1';

- 6. FSYN: a signal to show whether a field synchronization signal is received or not, wherein the field synchronization signal with 828 symbols is received while the FSYN remains '1';

- 7. FENA: a signal to indicate whether or not the NTSC 55 interference rejection filter is used according to the channel characteristics, wherein a FENA signal value '1' represents the TCM decoder is operated in the 16 state mode, while a FENA signal value '0' represents the TCM decoder is operated in the 8 state mode; and 60

- 8. DATA\_IN: an input of the trellis encoded data, wherein the trellis encoded data is received in the unit of symbol each clock.

Referring to FIG. 9, there is illustrated a timing diagram of output signals fed from the TCM decoder shown in FIG. 65 7 and the function of the output signals will be described as follows:

8

- 1. SFLAG: a signal to indicate whether the segment synchronization signal is provided or not, wherein the segment synchronization signal with 4 symbols may be generated while the SFLAG remains '1';

- 2. FLAG: a signal to show whether valid decoded data is generated or not, wherein the valid decoded data is provided while the FLAG remains '1'.

- 3. DATA\_OUT: an output of the decoded data from the TCM decoder, wherein the decoded data is provided in the unit of packet with 8 bits at every 4th clock.

While the field synchronization signal is received, the trellis decoded data must not be outputted and the FLAG signal remains '0'. Since both the FLAG signal and the SFLAG signal at the first clock of 4 clocks, during which the segment synchronization signal is outputted, remain '1', output data provided during the first clock must not be valid.

While, input data in the encoding process is transmitted in the unit of frame as described above, wherein each frame consists of 2 fields and each field consists of 313 segments. The first segment (segment #1) is for the field segment synchronization signal and the remaining 312 segments are for valid data. Each segment has 208 packets, i.e., 832 symbols (=208×4 symbols) so that each packet has 8 bits and the first packet, i.e., the first 4 symbols of each segment is for the segment synchronization signal. All data is received in the unit of packet so that one packet is received at every 4th clock.

Also, decoded data at every 4th clock may be provided in the decoding process. The decoded data has a size of a packet, i.e., 4 symbols and, only when the synchronization signals such as the segment synchronization signal and the field synchronization signal are received in the TCM decoder, no decoded data can be provided. If the FLAG remains '1', 4 symbols, each symbol having 2 bits, are packaged to be outputted in the unit of a packet.

Referring to FIG. 10, there is illustrated a detailed circuit of the control unit 7 shown in FIG. 7, wherein the control unit 7 includes a PENA generator 70, a SENA generator 71, an OUTENA generator 72, a BEENA generator 73, a logic 40 AND gate 74, an 832 counter 75, a 313 counter 76, a 96 counter 77, a 48 counter 78, a 12 counter 79 and a 2 counter 80.

The PENA generator 70 generates a PMN enable signal (PENA) that enables the PMN 4. The SENA generator 71 generates a SMU enable signal(SENA) that enables the SMU 5. The OUTENA generator 72 generates a DOUT enable signal(OUTENA) that enables the DOUT 6. The BEENA generator 73 generates a BEENA signal required to generate the FLAG signal, which is an indication signal to indicate that valid decoded data is outputted. The BEENA signal remains '0' until the first output from the TCM is provided and turns to be '1' after the first output.

The logic AND gate 74 generates a START UP signal by processing an AND operation on DSYN(segment synchronization signal), DSCUU(demodulation success signal), CLEAR, SYSENA(system enable signal), wherein the START UP signal tells whether the TCM decoder can be operated or not. When the START UP signal turns to be '1', the BEENA generator 73, the 832 counter 75, the 313 counter 76, the 96 counter 77, the 48 counter 78, the 12 counter 79 and the 2 counter 80 start to operate.

Since each segment has 832 symbols, the 832 counter 75 generates a c832 counting signal for identifying segments by counting the number of symbols and the c832 counting signal is provided to the SENA generator 71, the OUTENA generator 72, the BEENA generator 73, the 313 counter 76, the 96 counter 77, the 48 counter 78, the 12 counter 79 and

the 2 counter 80 within the control unit 7 and is also provided to the segment synchronization rejection filter 1, the PMN 4, the SMU 5 and the DOUT 6 for their respective controls.

Since each field has 313 segments, the 313 counter 76 generates a c313 counting signal for identifying fields by counting the number of segments and the c313 counting signal is provided to the PENA generator 70, the SENA generator 71, the OUTENA generator 72, the BEENA generator 73, the 96 counter 77, the 48 counter 78, the 12 10 counter 79 and the 2 counter 80 within the control unit 7 and is also provided to the DOUT 6.

The 96 counter 77, the 48 counter 78, the 12 counter 79 and the 2 counter 80 are used in order that the DOUT 6 carries out an intra-segment deinterleaving for decoded 15 symbols and converts the size of the intra-segment deinterleaved data so as to control the output timing of the decoded data.

If the first output is provided from the DOUT 6, the 96 counter for data output starts to count the byte number of 20 data so that it may output one byte of data at every 4th clock and, if necessary, stops to count during the output of the segment synchronization signal. According to the 48 counter 78, the 12 counter 79 and the 2 counter 80 for data input, each input data is assigned to an 8-bit register within one of 25 two register groups of the DOUT 6, each register group having 12 number of 8-bit registers.

That is, as soon as first 2 bit data from the SMU 5 is provided to the DOUT 6 to be stored therein, the 48 counter 78 starts to count, but is controlled in such a way that it does 30 not count during 4 clocks while the segment synchronization signal being received. If a register group is filled up with 48 symbol data, it is controlled for the 2 counter 80 to start to count.

The 2 counter **80** selects one of two register groups 35 alternatively, wherein one of the two register groups provides the data stored therein while the other register group receives another input data so that the receiving and providing the data can be carried out continuously by two register groups.

The 12 counter **79** determines which 8-bit register among 12 8-bit registers of the selected register group receives the input data; as soon as first data from the SMU **5** is provided to the DOUT **6** to be stored therein, the 12 counter **79** starts to count, but is controlled in such a way that it does not count 45 during 4 clocks while the segment synchronization signal being received. Data received in the unit of symbol at each clock is shifted to be stored in a next 8-bit register at each clock and in turn is stored in the same 8-bit register at every 12th clock.

Referring to FIG. 11, there is a detailed circuit for the segment synchronization rejection filter 1 shown in FIG. 7. In the 16 state mode, the segment synchronization rejection filter 1 eliminates the influence of the segment synchronization signal in input data DATA\_IN so that only valid data, 55 i.e., FILTER\_OUT can be provided to the next unit, i.e., the BMU 2. While, in the 8 state mode, the segment synchronization rejection filter 1 receives input data simply for providing to the next BMU 2.

As described above, if transmitted data shown in FIG. 5 60 passes through the NTSC interference rejection filter, a current input signal is subtracted from a previous signal delayed by as long as 12 symbols so that the 8 level symbol may be converted into a 15 level symbol. Table 3 represents the memory states of 12 symbol delay memories in a 65 conventional NTSC interference rejection filter, input signals and output signals. The input signals shown in Table 3

**10**

represent signals from the trellis encoders based on the second segment #2 shown in Table 1 and, therefore, correspond to the output of the NTSC interference rejection filter after the receipt of the 4 symbols of the segment synchronization signals S1 to S4.

TABLE 3

| clock | input .            | 12 s                 | ymbol dela           | y men | ıory          | output signal<br>_(=input signal - |

|-------|--------------------|----------------------|----------------------|-------|---------------|------------------------------------|

| CLK   | signal             | m1                   | m2                   |       | m12           | m12)                               |

| 1     | S1                 | d12 <sub>(t-1)</sub> | d11 <sub>(t-1)</sub> |       | $d1_{(t-1)}$  | S1-d1 <sub>(t-1)</sub>             |

| 2     | <b>S</b> 2         | S1                   | $d12_{(t-1)}$        |       | $d2_{(t-1)}$  | $S2-d2_{(t-1)}$                    |

| 3     | S3                 | S2                   | Sì                   |       | $d3_{(t-1)}$  | $S3-d3_{(t-1)}$                    |

| 4     | S4                 | S3                   | S2                   |       |               | $S4-d4_{(t-1)}$                    |

| 5     | $d5_{(t)}$         | S4                   | S3                   |       |               | $d5_{(t)}$ - $d5_{(t-1)}$          |

| 6     | $d6_{(t)}$         | $d5_{(t)}$           | S4                   |       | , ,           | $d6_{(t)}-d6_{(t-1)}$              |

| 7     | $d7_{(t)}$         | $d6_{(t)}$           | $d5_{(t)}$           |       |               | $d7_{(t)} - d7_{(t-1)}$            |

| 8     | $d8_{(t)}$         | $d7_{(t)}$           | $d6_{(t)}$           |       |               | $d8_{(t)} - d8_{(t-1)}$            |

| 9     | $d9_{(t)}$         | $d8_{(t)}$           | $d7_{(t)}$           |       | $d9_{(t-1)}$  | $d9_{(t)} - d9_{(t-1)}$            |

| 10    | $d10_{(t)}$        | $d9_{(t)}$           | $d8_{(t)}$           |       | $d10_{(t-1)}$ | $d10_{(t)}-d10_{(t-1)}$            |

| 11    | d11 <sub>(t)</sub> | $d10_{(t)}$          | $d9_{(t)}$           |       | $d11_{(t-1)}$ | $d11_{(t)}-d11_{(t-1)}$            |

| 12    | $d12_{(t)}$        | $d11_{(t)}$          | $d10_{(t)}$          |       | $d12_{(t-1)}$ | $d12_{(t)}$ - $d12_{(t-1)}$        |

| 13    | $d1_{(t)}$         | $d12_{(t)}$          | $d11_{(t)}$          |       | $\hat{S1}$    | $d1_{(t)}-S1$                      |

| 14    | $d2_{(t)}$         | $d1_{(t)}$           | $d12_{(t)}$          |       |               | $d2_{(t)}^{(s)}-S2$                |

| 15    | $d3_{(t)}$         | $d2_{(t)}$           | $d1_{(t)}$           |       | S3            | $d3_{(t)}^{(r)}$ -S3               |

| 16    | $d4_{(t)}^{(t)}$   | $d3_{(t)}$           | $d2_{(t)}^{(t)}$     |       | S4            | $d4_{(t)}^{(t)}$ -S4               |

| 17    | $d5_{(t+1)}$       | d4 <sub>(t)</sub>    | d3 <sub>(t)</sub>    |       | $d5_{(t)}$    | $d5_{(t+1)}^{(t)}$ - $d5_{(t)}$    |

As shown in Table 3, the NTSC interference rejection filter first receives 4 symbols of the segment synchronization signal and continues to receive trellis data, i.e., 12 symbol intra-segment interleaved data from 12 trellis encoders so that a difference signal between a current signal and a corresponding 12 symbol delayed previous signal is provided as an output signal. The difference signal corresponds to a difference between two data generated in the same encoder. The difference signals during CLK13 to CLK16, however, do not represent trellis coded data but are influenced by the segment synchronization signal.

In order to process 12 symbol intra-segment interleaved data by using only one decoder, therefore, the segment synchronization signal must be eliminated from the output signal during 4 clocks after the instance delayed by as long as 12 symbols clocks from the receipt of the segment synchronization signal.

To overcome the above drawback, the segment synchronization rejection filter 1 shown in FIG. 11 includes a 12 delay flip-flop 82 for delaying input data DATA\_IN, an adder 84 and a multiplexor MUX 86. The 12 delay flip-flop 82 enabled by the SYSENA and synchronized by the CLK receives the input data DATA\_IN in sequence and shifts it 50 by as much as 12 symbols so that the DATA\_IN delayed by as much as 12 symbols is provided to the adder 84 as delayed data. The adder 84 adds the DATA\_IN to the delayed data of the 12 delay flip-flop **82** to provide the adding result to the MUX 86 as an adder output. The MUX 86 receives the DATA\_IN at an input end '0' and the adder output of the adder 84 at another input end '1' and generates as a FILTER\_OUT either the DATA\_IN or the adder output based on the combination of the FENA and the c832 counting signal. Either the 16 state mode or the 8 state mode is determined based on the FENA, while a section at which the segment synchronization signal must be eliminated in the 16 state mode is determined based on the c832 counting signal for identifying each segment by counting the number of symbols (1 segment=832 symbols). That is, based on the combination of the FENA and the c832 counting signal, the MUX 86 selects the input end '1' within only 4 clocks after the instance delayed by as much as 12 clocks from the first

receipt of the segment synchronization signal Si while it selects the other input end '0' during the remaining time.

The Table 4 demonstrates the elimination of the segment synchronization signal by the use of the segment synchronization rejection filter 1 according to the above operation.

Referring back to FIG. 7, the BMU 2 receives the FILTER\_OUT from the segment synchronization rejection filter 1; calculates branch metrics BM's; and provides them to the ACS 3. If a branch from a previous state to a current state is built up through an accurate path, a branch metric '0'

TABLE 4

| clock    |                                                |                                  | mbol delay<br>lip-flop                                                                  | adder<br>output                                        | MUX output                                             |

|----------|------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| CLK      | DATA_IN                                        | m1                               | m12                                                                                     | (DATA_IN + m12)                                        | (FILTER_OUT)                                           |

| 1        | S1-d1 <sub>(t-1)</sub>                         | $d12_{(t-1)}$ - $d12_{(t-2)}$    | $d1_{(t-1)}$ - $d1_{(t-2)}$                                                             | S1-d1 <sub>(t-1)</sub>                                 | X                                                      |

| 2        | $S2-d2_{(t-1)}$                                | $S1-d1_{(t-1)}$                  | $d2_{(t-2)}$ $d2_{(t-1)}$ $d2_{(t-2)}$                                                  | $S2-d2_{(t-1)}$                                        | X                                                      |

| 3        | $S3-d3_{(t-1)}$                                | $S2-d2_{(t-1)}$                  | $d3_{(t-2)}$ $d3_{(t-1)}$ $d3_{(t-2)}$                                                  | $S3-d3_{(t-1)}$                                        | X                                                      |

| 4        | $S4-d4_{(t-1)}$                                | $S3-d3_{(t-1)}$                  | $d3_{(t-2)}$ $d4_{(t-1)}$ $d4_{(t-2)}$                                                  | $S4-d4_{(t-1)}$                                        | X                                                      |

| 5        | $d5_{(t)}$ - $d5_{(t-1)}$                      | $S4-d4_{(t-1)}$                  | $d5_{(t-2)}$ $d5_{(t-2)}$                                                               | $d5_{(t)}$ - $d5_{(t-2)}$                              | $d5_{(t)}$ - $d5_{(t-1)}$                              |

| 6        | $d6_{(t)}$ - $d6_{(t-1)}$                      | $d5_{(t)}$ - $d5_{(t-1)}$        | $d6_{(t-1)}$ -                                                                          | $d6_{(t)}$ - $d6_{(t-2)}$                              | $d6_{(t)}$ - $d6_{(t-1)}$                              |

| 7        | $d7_{(t)}$ - $d7_{(t-1)}$                      | $d6_{(t)}$ - $d6_{(t-1)}$        | $d6_{(t-2)}$ $d7_{(t-1)}$                                                               | $d7_{(t)}$ - $d7_{(t-2)}$                              | $d7_{(t)}$ - $d7_{(t-1)}$                              |

| 8        | $d8_{(t)}$ - $d8_{(t-1)}$                      | $d7_{(t)}$ - $d7_{(t-1)}$        | $d7_{(t-2)}$ $d8_{(t-1)}$                                                               | $d8_{(t)}$ - $d8_{(t-2)}$                              | $d8_{(t)}$ - $d8_{(t-1)}$                              |

| 9        | $d9_{(t)}$ - $d9_{(t-1)}$                      | $d8_{(t)}$ - $d8_{(t-1)}$        | $   \begin{array}{c}     d8_{(t-2)} \\     d9_{(t-1)} \\     d9_{(t-2)}   \end{array} $ | $d9_{(t)}$ - $d9_{(t-2)}$                              | $d9_{(t)}$ - $d9_{(t-1)}$                              |

| 10       | $d10_{(t)}$ - $d10_{(t-1)}$                    | $d9_{(t)}$ - $d9_{(t-1)}$        | $\dots d10_{(t-1)}$ -                                                                   | $d10_{(t)}$ - $d10_{(t-2)}$                            | $d10_{(t)}$ - $d10_{(t-1)}$                            |

| 11       | $d10_{(t-1)}$ $d11_{(t)}$ - $d11_{(t-1)}$      | $d10_{(t)}$ - $d10_{(t-1)}$      | $\dots d11_{(t-1)}$ -                                                                   | $d11_{(t)}$ -                                          | $d10_{(t-1)}$ $d11_{(t)}$ $d11_{(t-1)}$                |

| 12       | $d12_{(t)}$ -                                  | d11 <sub>(t)</sub> -             | $1d12_{(t-1)}$ -                                                                        | $d12_{(1)}$ -                                          | $d12_{(t)}$ -                                          |

| 13       | $d12_{(t-1)}$<br>$d1_{(t)}$ -S1                | $d11_{(t-1)}$ $d12_{(t)}$        | $d12_{(t-2)}$<br>$S1-d1_{(t-1)}$                                                        | $d12_{(t-2)}$<br>$d1_{(t)}$ - $d1_{(t-1)}$             | $d12_{(t-1)}$<br>$d1_{(t)}$ - $d1_{(t-1)}$             |

| 14<br>15 | $d2_{(t)}$ -S2                                 | $d12_{(t-1)}$ $d1_{(t)}$ -S1     | $S2-d2_{(t-1)}$<br>$S3-d3_{(t-1)}$                                                      | $d2_{(t)}-d2_{(t-1)}$                                  | $d2_{(t)}-d2_{(t-1)}$                                  |

|          | d3 <sub>(t)</sub> -S3<br>d4 <sub>(t)</sub> -S4 | $d2_{(t)}$ -S2<br>$d3_{(t)}$ -S3 | $ S4-d4_{(t-1)}$                                                                        | $d3_{(t)}$ - $d3_{(t-1)}$<br>$d4_{(t)}$ - $d4_{(t-1)}$ | $d3_{(t)}$ - $d3_{(t-1)}$<br>$d4_{(t)}$ - $d4_{(t-1)}$ |

| 17       | $d5_{(t+1)}^{(t)}$ - $d5_{(t)}^{(t)}$          | d4 <sub>(t)</sub> -S4            | $d5_{(t)}-d5_{(t-1)}$                                                                   | $d5_{(t+1)}^{(t)} - d5_{(t-1)}^{(t-1)}$                | $d5_{(t)}^{(t)} - d5_{(t-1)}^{(t-1)}$                  |

As shown in Table 4, the adder output from the adder 84 equals a sum of a current input data DATA\_IN, i.e., the output signal of the NTSC rejection filter and a 12 symbol delayed previous signal through the 12 symbol delay flipflop. Since the segment synchronization signal Si in the 45 DATA\_IN is, therefore, offset by the Si in the 12 symbol delayed previous signal during the time interval from CLK13 to CLK16, the adder output of the adder 84 naturally corresponds to a difference between two trellis coded data encoded at the same trellis encoder. As a result, the segment 50 synchronization signal(Si) generated within the time interval from CLK13 to CLK16 is eliminated by the use of the adder 84 and the eliminated result, i.e., the adder output selected by the MUX 86 is provided to the BMU 2. Any output of the MUX 86 will do within 4 clocks CLK1 to CLK4 from the initial instant of a segment, because the TCM decoder does not operate during 4 clocks CLK1 to CLK4.

As described above, the segment synchronization rejection filter 1 in the 8 state mode provides the input data DATA\_IN directly. In the meantime, the segment synchronization filter 1 in 16 the state mode selects the adder output of the adder 84 during the 4 clocks while the segment synchronization signal(Si) being included in the DATA\_IN, 65 but selects the DATA\_IN directly during the remaining clocks except the above 4 clocks.

is generated. Any noise may be included in a real signal transmitted through a real channel with the additive white Gaussian noise(AWGN), not an ideal communication environment with no noise. The AWGN, therefore, is really added to the trellis encoded data for transmitting and a TCM decoder of the receiver calculates a difference between the real data with noise and the reference value of each branch, wherein the difference is hardly equal to '0' and approximates to '0'. Each difference corresponds to a branch metric(BM).

Each transfer between two states in each mode and a corresponding input and output signals will be illustrated and, then, a rule for calculating a branch metric in each state mode will be described.

## (1) The 16 State Mode

In Table 5, input bits (X1,X0) are provided to the trellis coding block shown in FIG. 3; previous output (Z2', Z1', Z0') and current output (Z2, Z1, Z0) correspond to 8-level values to be provided to the 8-level symbol mapper 34 shown in FIG. 3. Each channel symbol is the difference between a current output(Z) and a previous output(Z') so that the channel symbol is really transmitted.

TABLE 5

| Previous   Previous   California   Cournet   State   California   Ca |       |         | 1.7  | ABLE 3  |     |       |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|------|---------|-----|-------|----|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | state | output  | bits | output  |     | state |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000  | 000( 7) | 00   | 000( 7) | 0   | 0000  | 00 |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | • /     |      | 000(-7) |     | 0000  |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ` ′     |      |         |     |       |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | • /     |      |         |     |       |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ` ′     |      | 010(-2) |     | 0001  |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ` ′     |      | 010(-3) |     | 0001  |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ` ′     |      |         |     |       |    |

| 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | • •     |      |         |     |       |    |

| 0101 011(-1) 006 00 1100 1101 1101 111(+7) 1014 111 1100 110(-3) 10 1014 111 1100 110(-3) 11 1014 111 1100 11000 100(-3) 01 0 000 000(-7) 00 001(-5) +4 0011 01 1000 1100(-3) 01 0 000(-7) 00 001(-5) +2 0100 00 000(-7) 00 001(-5) +2 0100 00 000(-7) 00 001(-5) +2 0100 00 0011 010(-3) 002 00 0110 110(+5) 106 10 1011 110(+5) 1010 110 110 110 110 110 110 110 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | • /     |      | 000(-7) |     | 0010  |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ` ′     |      | 000( 7) |     | 0010  |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | ` ′     |      |         |     |       |    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | • /     |      |         |     |       |    |