US006060383A

## United States Patent [19]

### Nogami et al.

### [11] Patent Number:

# 6,060,383

[45] Date of Patent:

May 9, 2000

| ני ין | COAXIAL INTERCONNECT STRUCTURE |                                                                                                                                                                                                             |  |

|-------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [76]  | Inventors:                     | Takeshi Nogami, 180 Elm Ct. #405,<br>Sunnyvale, Calif. 94086; Sergey<br>Lopatin, 1000 Kiely Blvd., #66, Santa<br>Clara, Calif. 95051; Shekhar<br>Pramanick, 1322 Steelhead Common,<br>Fremont, Calif. 94536 |  |

| [21]  | Appl. No.:                     | 09/131,919                                                                                                                                                                                                  |  |

| [22]  | Filed:                         | Aug. 10, 1998                                                                                                                                                                                               |  |

| [51]  |                                |                                                                                                                                                                                                             |  |

| [52]  | U.S. Cl                        |                                                                                                                                                                                                             |  |

438/620; 438/623; 438/667; 438/672; 438/675;

438/685; 257/758; 257/759; 257/760; 257/763;

257/768

438/643, 669, 672, 675

METHOD FOR MAKING MULTILAYERED

## [56] References Cited

[58]

| U.S. PATENT DOCUMENTS |         |                    |  |  |  |

|-----------------------|---------|--------------------|--|--|--|

| 4,933,743             | 6/1990  | Thomas et al       |  |  |  |

| 4,948,755             | 8/1990  | Mo                 |  |  |  |

| 5,262,353             | 11/1993 | Sun et al 438/400  |  |  |  |

| 5,286,674             | 2/1994  | Roth et al 438/624 |  |  |  |

| 5,436,412             | 7/1995  | Ahmad et al        |  |  |  |

| 5,453,154             | 9/1995  | Thomas et al       |  |  |  |

| 5,468,685             | 11/1995 | Orisaka et al      |  |  |  |

| 5,482,900             | 1/1996  | Yang 438/623       |  |  |  |

| 5,656,543             | 8/1997  | Chung              |  |  |  |

| 5,656,883             | 8/1997  | Christensen        |  |  |  |

| 5,666,007             | 9/1997  | Chung              |  |  |  |

| 5,679,982             |         | Gardner            |  |  |  |

| 5,682,062 |         | Gaul                           |

|-----------|---------|--------------------------------|

| 5,691,280 |         | Eckstein et al 505/329         |

| 5,691,572 | 11/1997 | Chung                          |

| 5,712,768 | 1/1998  | Werther                        |

| 5,811,352 | 9/1998  | Numata et al 438/622           |

| 5,817,572 | 10/1998 | Chiang et al 438/624           |

| 5,824,599 | 10/1998 | Schacham-Diamand et al 438/678 |

| 5,851,849 |         | Comizolli et al 438/38         |

| 5,858,869 | 1/1999  | Chen et al 438/597             |

| 5,863,832 | 1/1999  | Doyle et al 438/622            |

| 5,880,030 | 3/1999  | Fang et al 438/701             |

| 5,882,963 | 3/1999  | Kerber et al 438/195           |

| 5,919,531 | 7/1999  | Arkles et al 427/576           |

| 5,935,868 | 8/1999  | Fang et al 438/692             |

Primary Examiner—Tom Thomas

Assistant Examiner—Bernard E. Souw

Attorney, Agent, or Firm—Amin, Eschweiler & Turocy,

LLP

### [57] ABSTRACT

A method of forming a multi-layered interconnect structure is provided. A first conductive pattern is formed over an insulation layer. A first dielectric material is deposited over the first conductive pattern, and plugs are formed in the first dielectric material. A second conductive pattern is formed over the first dielectric material and plugs so as to form the multi-layered interconnect structure in part. Then, the first dielectric material is stripped away to leave the multilayered interconnect structure exposed to air. A thin layer of second dielectric material is deposited so as to coat at least a portion of the interconnect structure. Next, a thin layer of metal is deposited so as to coat the at least a portion of the interconnect structure coated with the thin layer of second dielectric material. A third dielectric material is deposited over the interconnect structure to replace the stripped away first dielectric material.

### 17 Claims, 11 Drawing Sheets

Prior Art Fig. 1

Fig. 3a

Fig. 3b

Fig. 5

Fig. 6

Fig. 7

Fig. 13

# METHOD FOR MAKING MULTILAYERED COAXIAL INTERCONNECT STRUCTURE

#### TECHNICAL FIELD

The present invention generally relates to a multi-layered coaxial interconnect structure and method for making the same.

#### BACKGROUND OF THE INVENTION

There is an increasing demand for miniaturization in the integrated circuits industry. This demand has led to an ever constant reduction in separation between conductive lines (e.g., metal lines) in order to reduce integrated circuit size and/or increase density. The reduced spacing between the conductive lines has the undesirable effect of increasing the capacitance of whatever material lies between the conductive lines. This phenomenon is known as capacitive crosstalk.

In the past, overall integrated circuit (IC) performance depended primarily on device properties, however, this is no longer the case. Parasitic resistance, capacitance and inductance associated with interconnections and contacts of an IC are beginning to become increasingly significant factors in IC performance. In current IC technology, the speed limiting factor is no longer device delay, but the resistive-capacitive (RC) delays associated with the conductive interconnections (e.g. metal lines) of the IC.

Conventional ICs typically employ an interconnect structure wherein a first conductive line is adjacent a second conductive line. If the crosstalk or capacitance between the first conductive line and the second conductive line is high, then the voltage on the first conductive line alters or affects the voltage on the second conductive line. This alteration in voltage may result in the IC being inoperable as a result of misinterpreting logic zeros, logic ones and voltage levels, and consequently incorrectly processing binary and/or analog information

In order to reduce capacitive coupling and therefore reduce capacitive crosstalk, low dielectric constant (low-K) 40 materials have been developed to replace conventional dielectric/insulation materials that lie between conductive lines in order to insulate one conductive line from the other. Conventional insulation materials such as silicon dioxide exhibit a dielectric constant of about 4.0. Newer materials 45 with lower dielectric constants have been developed. For example, polyimides generally exhibit a dielectric constant of about 2.4 to about 3.0; Teflon exhibits a dielectric constant of about 1.6 to 2.2; and aerogels typically exhibit a dielectric constant of about 2. However, the use of many 50 low-K dielectric/insulation materials is not practicable because equipment is not available to properly process the new dielectric/insulation materials in various ICs. Furthermore, the chemical or physical properties of many low-K dielectric/insulation materials are usually difficult to 55 make compatible or integrate into conventional IC processing. For example, as multiple layers of interconnects are formed, many low dielectric constant materials used to insulate conductive lines exhibit cracking.

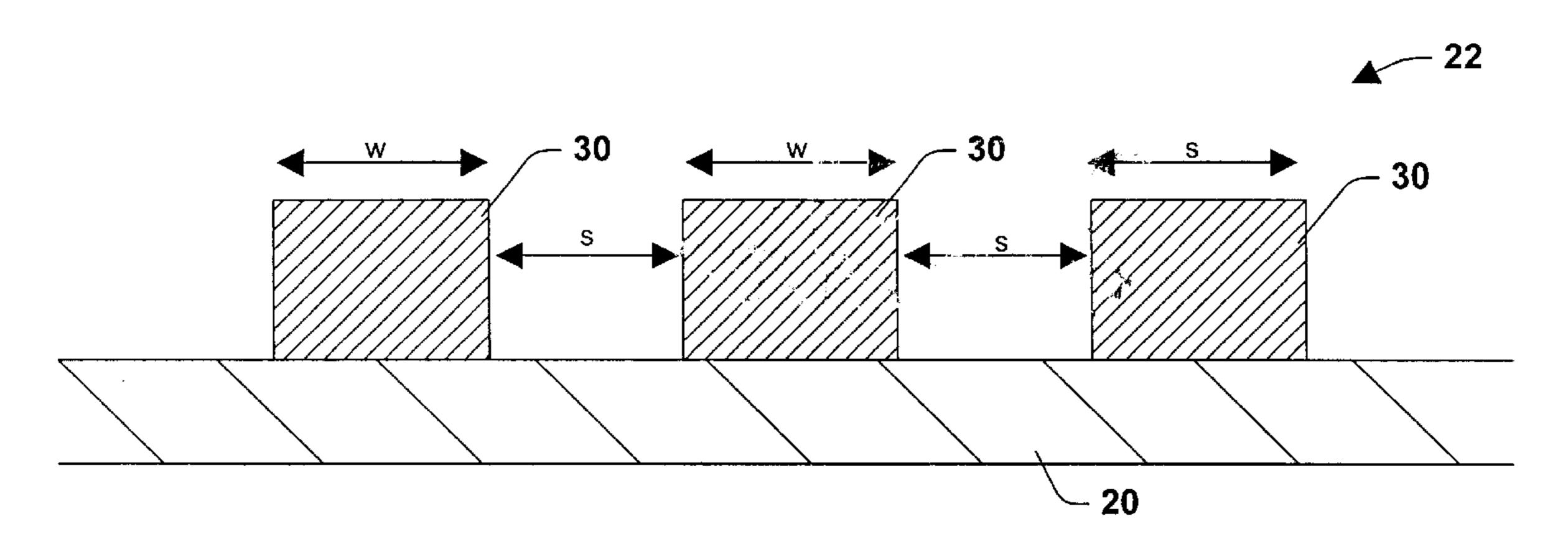

FIGS. 1 and 2 illustrate the relationship between closely spaced conductive lines and capacitive coupling. Conductive lines 30 are adjacent each other and provide necessary electrical connections between devices of an integrated circuit (not shown). Although only three conductive lines 30 are shown for ease of understanding, it is to be appreciated that many thousands or even millions more such conductive lines may exist in the integrated circuit. As noted above, the

2

increasing demand for miniaturization in the integrated circuits industry has led to an ever constant reduction in separation between the conductive lines 30 in order to reduce integrated circuit size. However, the reduced spacing between the conductive lines 30 has the undesirable effect of increasing the capacitance of whatever material lies between the conductive lines 30 to result in capacitive crosstalk between adjacent conductive lines.

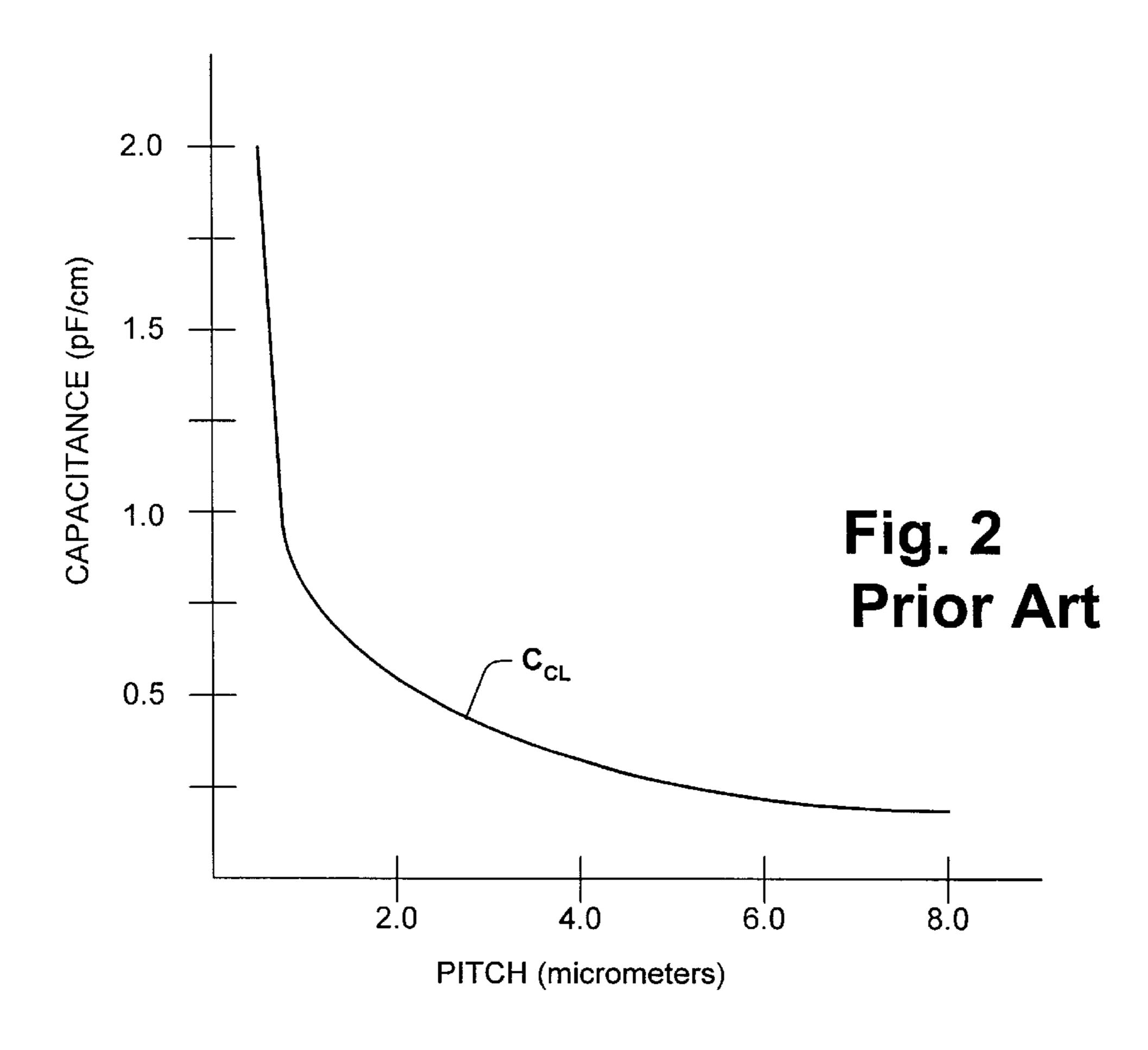

A quantity known as pitch (pitch=w+s) is often employed to characterize conductive capacitance crosstalk for adjacent conductive lines used in the integrated circuit industry, where "w" is the cross-sectional width of a conductive line and "s" is the distance of separation between adjacent conductive lines. FIG. 2 graphically illustrates the capacitance between the conductive lines 30 as a function of physical separation. A reduction in pitch is an ongoing activity in the integrated circuit industry in order to optimize substrate surface area utilization in integrated circuits. The capacitance between the conductive lines 30 labeled  $C_{CL}$  in FIG. 2 is shown to increase exponentially as pitch is reduced or as the conductive lines 30 are brought closer together. The increase in capacitive coupling resulting from the conductive lines 30 being brought closer together contributes to capacitive crosstalk between the adjacent conductive lines **30**, respectively.

Since market forces are driving the integrated circuitry towards bringing the conductive lines 30 closer together in order to maximize substrate surface utilization, insulation having low dielectric constant is required between the conductive lines 30 in order isolate the conductive lines 30 from one another and to lower capacitive coupling between the conductive lines 30, respectively, and in turn reduce capacitive crosstalk.

Conventional semiconductors such as for example those fabricated according to the aforementioned method do not provide for sufficient insulation between the conductive lines 30 suitable for overcoming capacitive crosstalk between closely spaced conductive lines, particularly at higher frequencies approaching the gigahertz range.

In view of the above, it would be desirable to have a semiconductor fabrication method which provides for an insulation material between conductive lines having a dielectric constant suitable for attaining higher IC control speed and meet increasing substrate surface utilization requirements. Furthermore, it would be desirable for such a method to also provide for formation of a coaxial interconnect structure so as to further enhance IC functionality.

### SUMMARY OF THE INVENTION

The present invention provides for a multi-layered interconnect structure which employs dielectric material having a dielectric constant suitable for overcoming capacitive cross-talk between conductive lines. Furthermore, at least some of the conductive lines of the multi-layered interconnect structure are coaxial in nature, wherein the coaxial conductive lines include a central conductive portion which is surrounded by a thin dielectric material and the thin dielectric material surrounded by a metal conductor. Thus, a coaxial conductive line of the present invention provides for a metal conductor circumferentially surrounding a signal carrying central conductor with an insulating material interposed there between. The central conductor is thus substantially shielded from passing noise and induced electromagnetic fields resulting from changing signals therein as well as the central conductor being substantially shielded from externally generated noise and electromagnetic fields.

In making the multi-layered interconnect structure of the present invention, metal lines are formed on a substrate. Then a first dielectric material (eg., SiO<sub>2</sub>) is deposited on the metal lines, and vias are formed in the first dielectric material thereafter. Then plugs are formed in the vias and subsequent interconnect layers are formed over this first interconnect layer accordingly. Once the base multi-level interconnect structure is formed, the first dielectric material is stripped leaving the multi-level interconnect structure (e.g., conductive lines and plugs) exposed to air. Then a first deposition step is performed to form a thin coat of second dielectric material on the multi-level interconnect structure. A second deposition step is performed thereafter to form a thin coat of metal over the coat of dielectric material so as to make those portions of the multi-layered interconnect 15 structure exposed to the ALD steps coaxial in nature. Next, a third dielectric material (having a dielectric constant suitable for mitigating capacitive cross-talk between adjacent conductive lines) is deposited on the interconnect structure to replace the first dielectric material which was stripped away.

The resulting multi-layered interconnect structure may exhibit superior performance as compared to those fabricated in accordance with conventional techniques. In particular, the present invention provides for employing a dielectric material of desirably low dielectric constant which could not be employed in conventional IC fabrication processes without exhibiting cracking. Furthermore, the present invention provides for at least some of the conductive lines and plugs of the multi-level interconnect structure to be coaxial in nature which affords for an increased scope of functionality as compared to conventionally fabricated multi-layered interconnect structures.

In accordance with one particular aspect of the invention, a method of forming a multi-layered interconnect structure includes the steps of: forming a first conductive pattern over an insulation layer; depositing a first dielectric material over the first conductive pattern; and forming plugs in the first dielectric material. The method further includes the steps of forming a second conductive pattern over the first dielectric material and plugs so as to form a multi-layered interconnect structure; stripping the first dielectric material; and depositing a second dielectric material over the interconnect structure to replace the stripped away first dielectric material.

Another aspect of the present invention relates to a method of forming an interconnect structure having at least a coaxial portion including the steps of: forming a first conductive pattern over an insulation layer; depositing a first dielectric material over the first conductive pattern; and 50 forming plugs in the first dielectric material. The method also includes the steps of: forming a second conductive pattern over the first dielectric material and plugs so as to form the interconnect structure; stripping the first dielectric material; depositing a thin layer of second dielectric material 55 so as to coat at least a portion of the interconnect structure; and depositing a thin layer of metal so as to coat the at least a portion of the interconnect structure coated with the thin layer of second dielectric material.

Yet another aspect of the present invention relates to a 60 semiconductor device including: a substrate; and an insulating layer formed on the substrate. The semiconductor device further includes an interconnect structure which comprises: a first conductive pattern formed on the insulating layer, the conductive pattern including at least two 65 conductive lines adjacent one another, a first dielectric material formed over the conductive pattern, the first dielec-

4

tric material filling a space between the at least two conductive lines; at least one plug formed in the first dielectric material; and a second conductive pattern formed over the first dielectric material and the at least one plug. At least a portion of the interconnect structure is coaxial in nature.

Still another aspect of the present invention relates to a method of forming an interconnect structure having at least a coaxial portion, including the steps of: forming a first conductive pattern over an insulation layer; depositing a first dielectric material over the first conductive pattern; and forming plugs in the first dielectric material. The method also includes the steps of forming a second conductive pattern over the first dielectric material and plugs so as to substantially form the interconnect structure; stripping the first dielectric material; depositing a thin layer of second dielectric material so as to coat at least a portion of the interconnect structure; depositing a thin layer of metal so as to coat the at least a portion of the interconnect structure coated with the thin layer of second dielectric material; and depositing a third dielectric material over the interconnect structure to replace the stripped away first dielectric material.

To the accomplishment of the foregoing and related ends, the invention, then, comprises the features hereinafter fully described and particularly pointed out in the claims. The following description and the annexed drawings set forth in detail certain illustrative embodiments of the invention. These embodiments are indicative, however, of but a few of the various ways in which the principles of the invention may be employed. Other objects, advantages and novel features of the invention will become apparent from the following detailed description of the invention when considered in conjunction with the drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

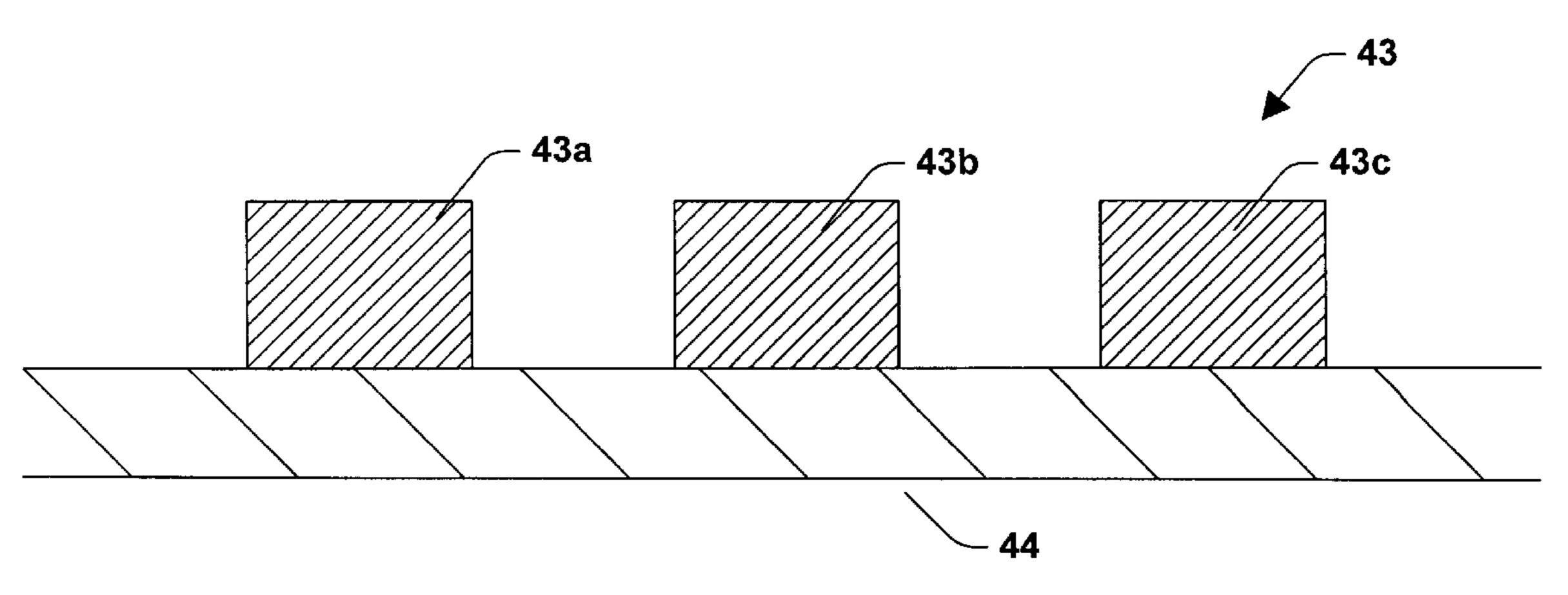

FIG. 1 is a schematic cross-sectional illustration of a portion of a prior art semiconductor device including a conductive pattern;

FIG. 2 is a graphical illustration of a relationship between conductive line pitch and capacitive coupling;

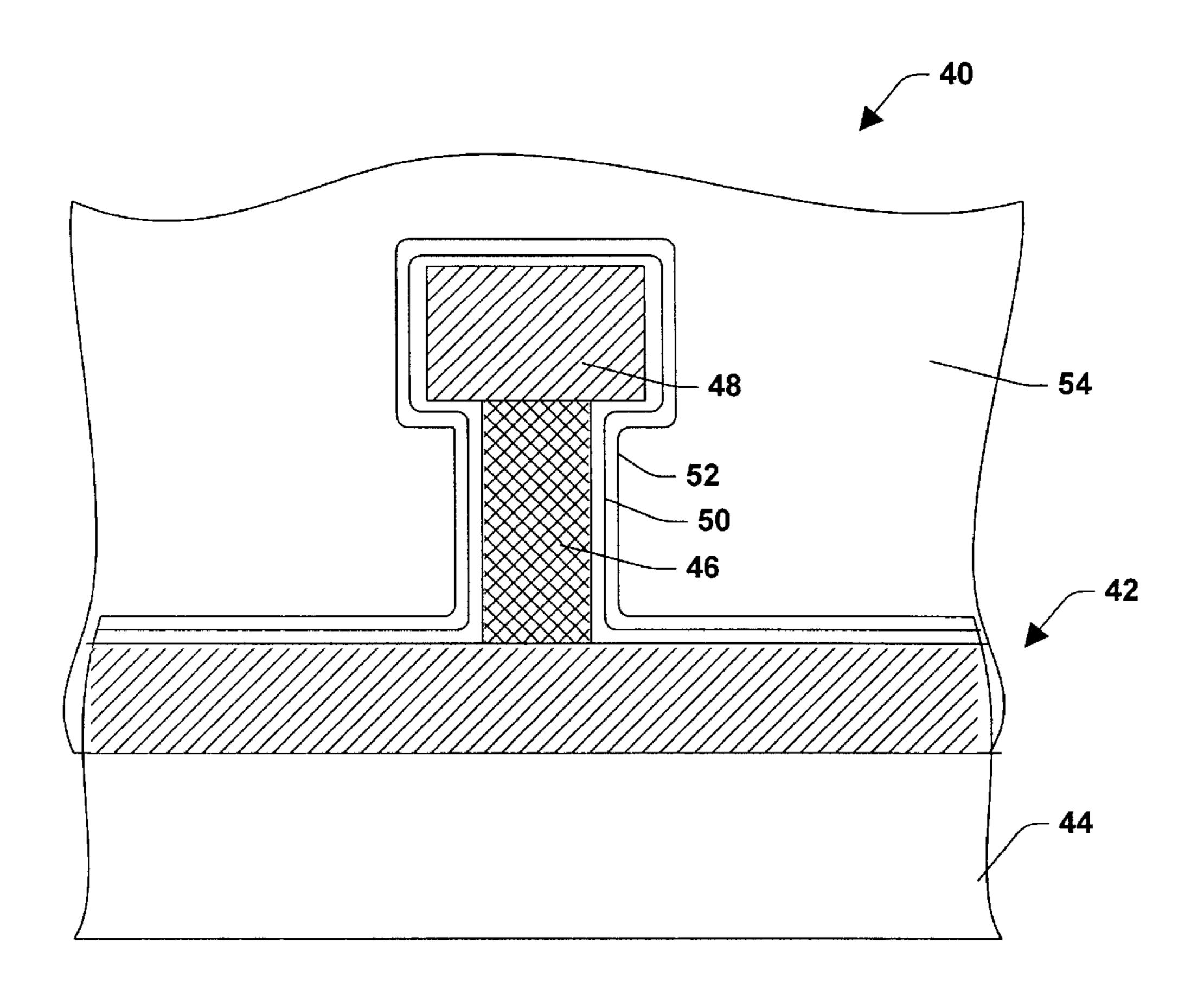

FIG. 3a is a partial schematic cross-sectional illustration of a mult-layered interconnect structure in accordance with the present invention;

FIG. 3b is a schematic cross-sectional illustration of a first layer of conductive lines being formed on a semiconductor substrate in accordance with the present invention;

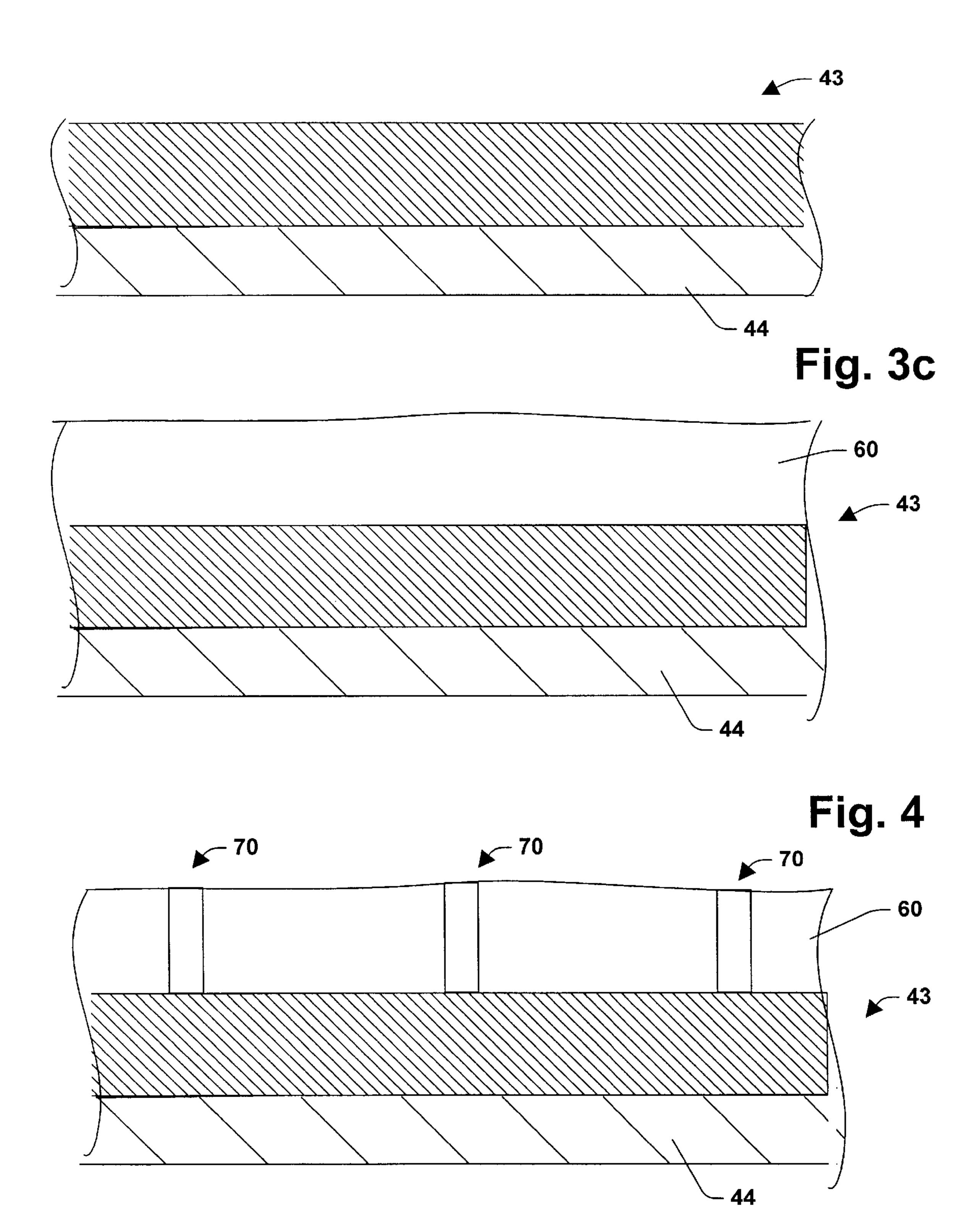

FIG. 3c is a schematic cross-sectional illustration of the first layer of conductive lines of FIG. 3b from a perpendicular view in accordance with the present invention;

FIG. 4 is a schematic cross-sectional illustration of dielectric material being deposited over the conductive lines of FIG. 3 in accordance with the present invention;

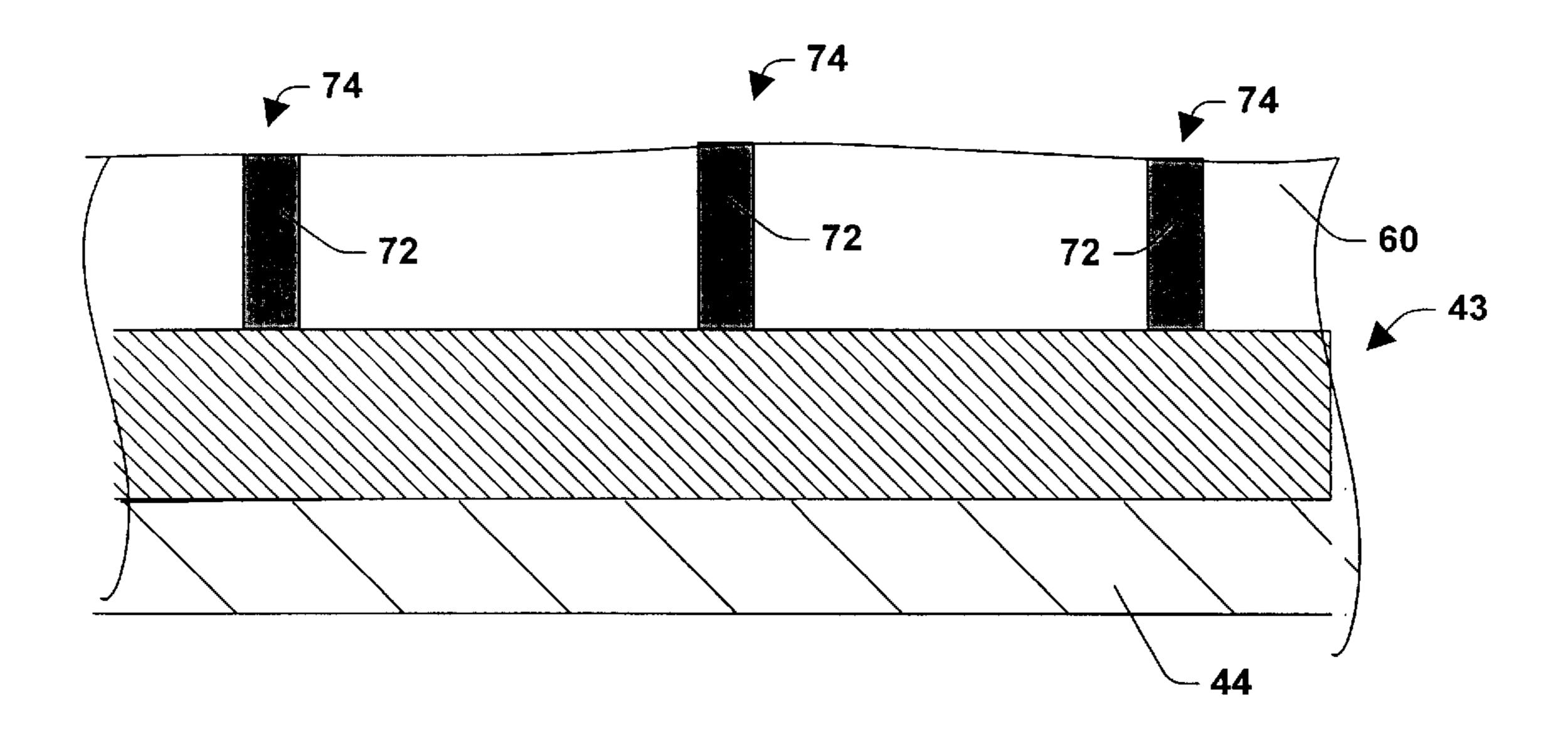

FIG. 5 is a schematic cross-sectional illustration of vias being formed in the dielectric material of FIG. 3 in accordance with the present invention;

FIG. 6 is a schematic cross-sectional illustration of the vias of FIG. 5 being filled to form plugs in accordance with the present invention;

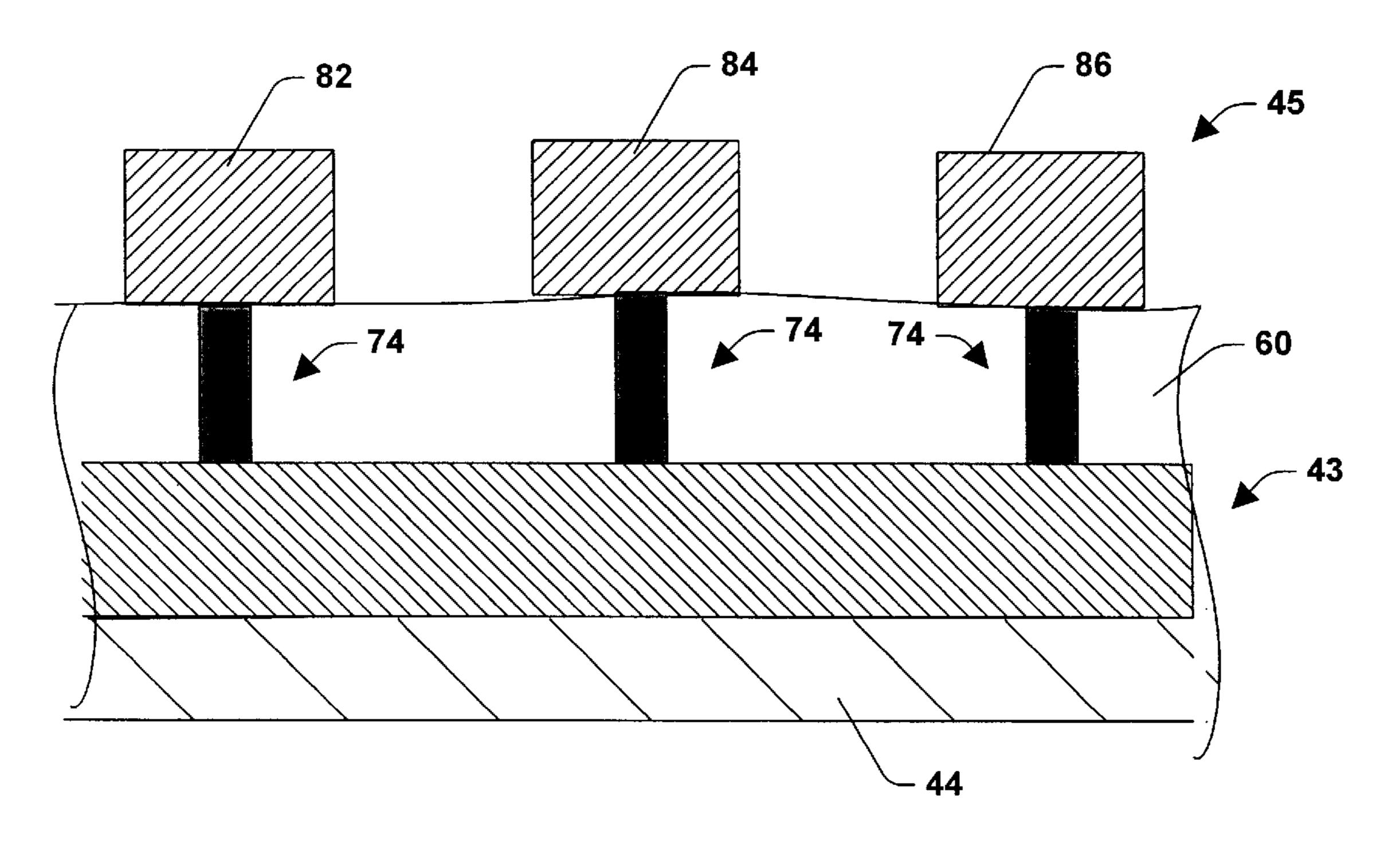

FIG. 7 is a schematic cross-sectional illustration of a second layer of conductive lines being formed over the plugs and dielectric layer of FIG. 6 in accordance with the present invention;

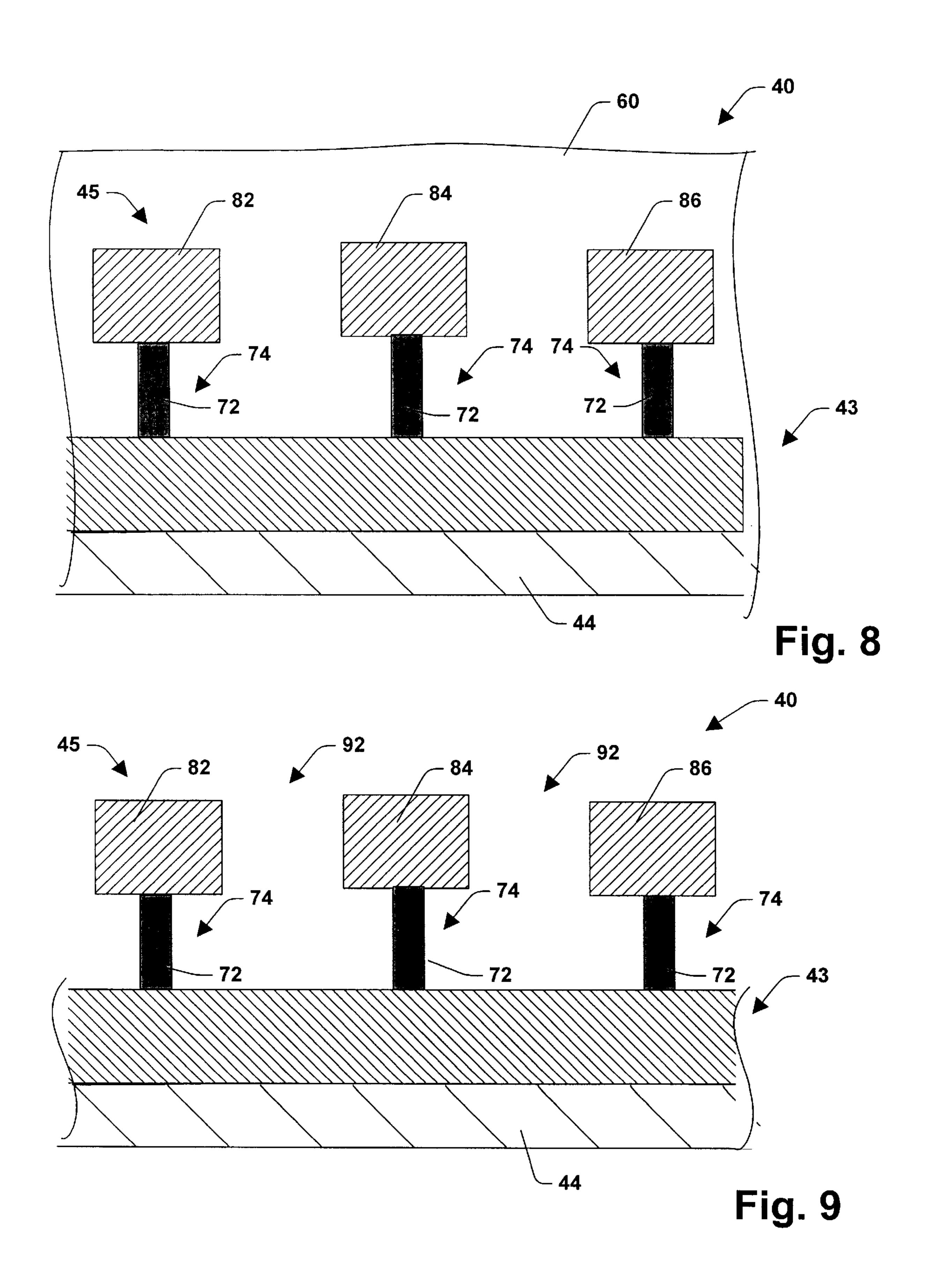

FIG. 8 is a schematic cross-sectional illustration of dielectric material being formed over the second layer of conductive lines of FIG. 7 in accordance with the present invention;

FIG. 9 is a schematic cross-sectional illustration of the interconnect structure of FIG. 7 after the dielectric material has been stripped away in accordance with the present invention;

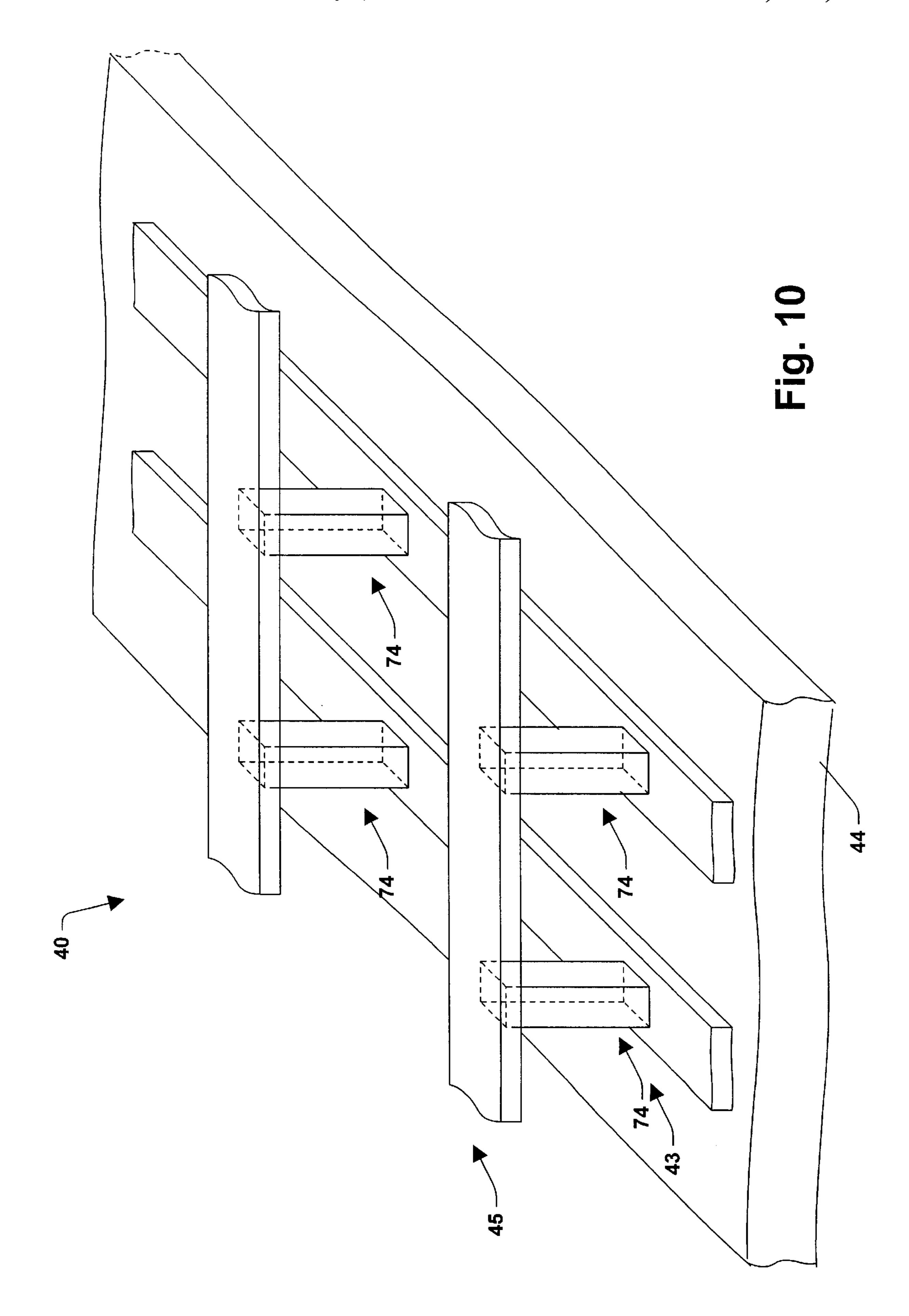

FIG. 10 is a schematic partial perspective illustration of 5 the interconnect structure of FIG. 9 in accordance with the present invention;

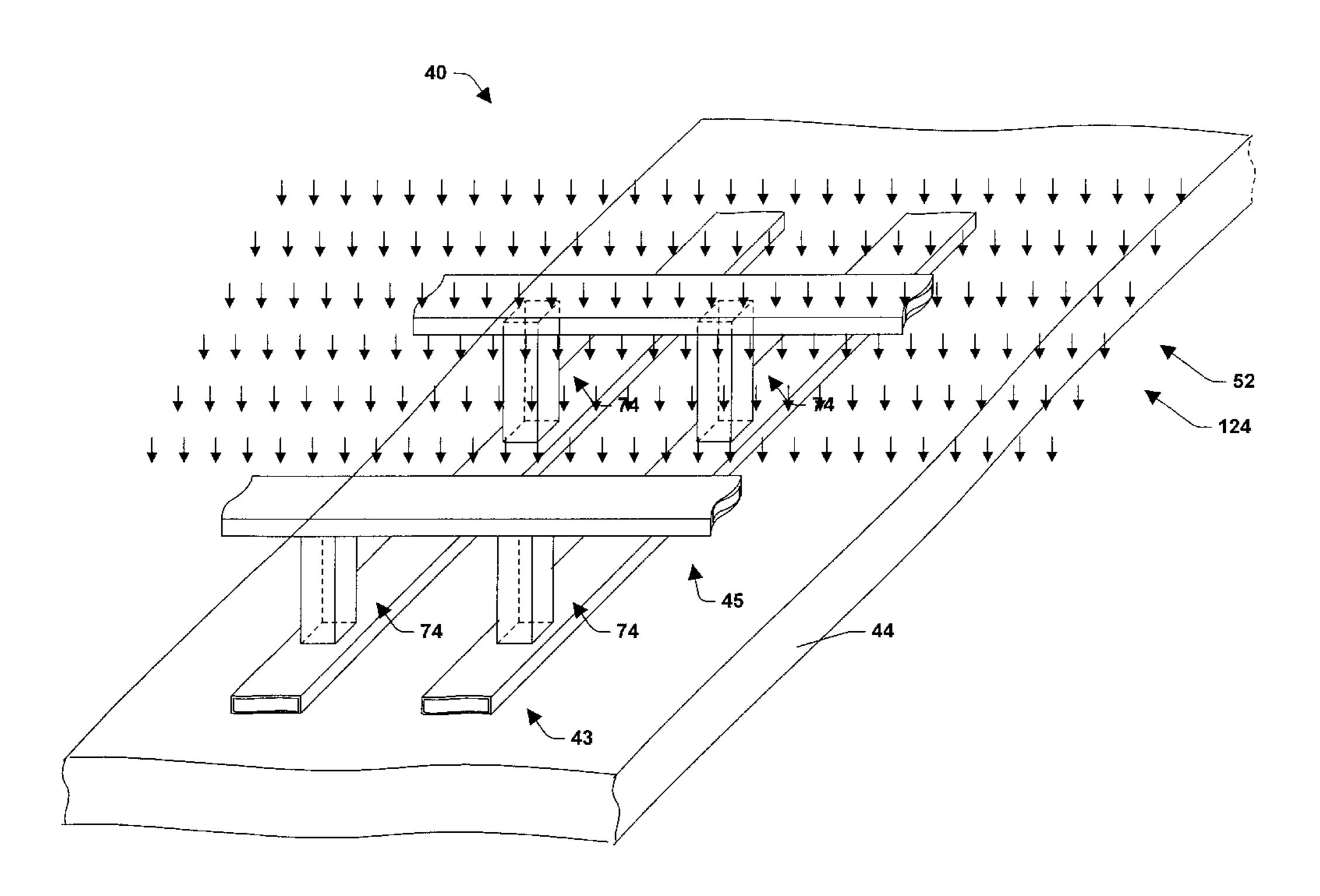

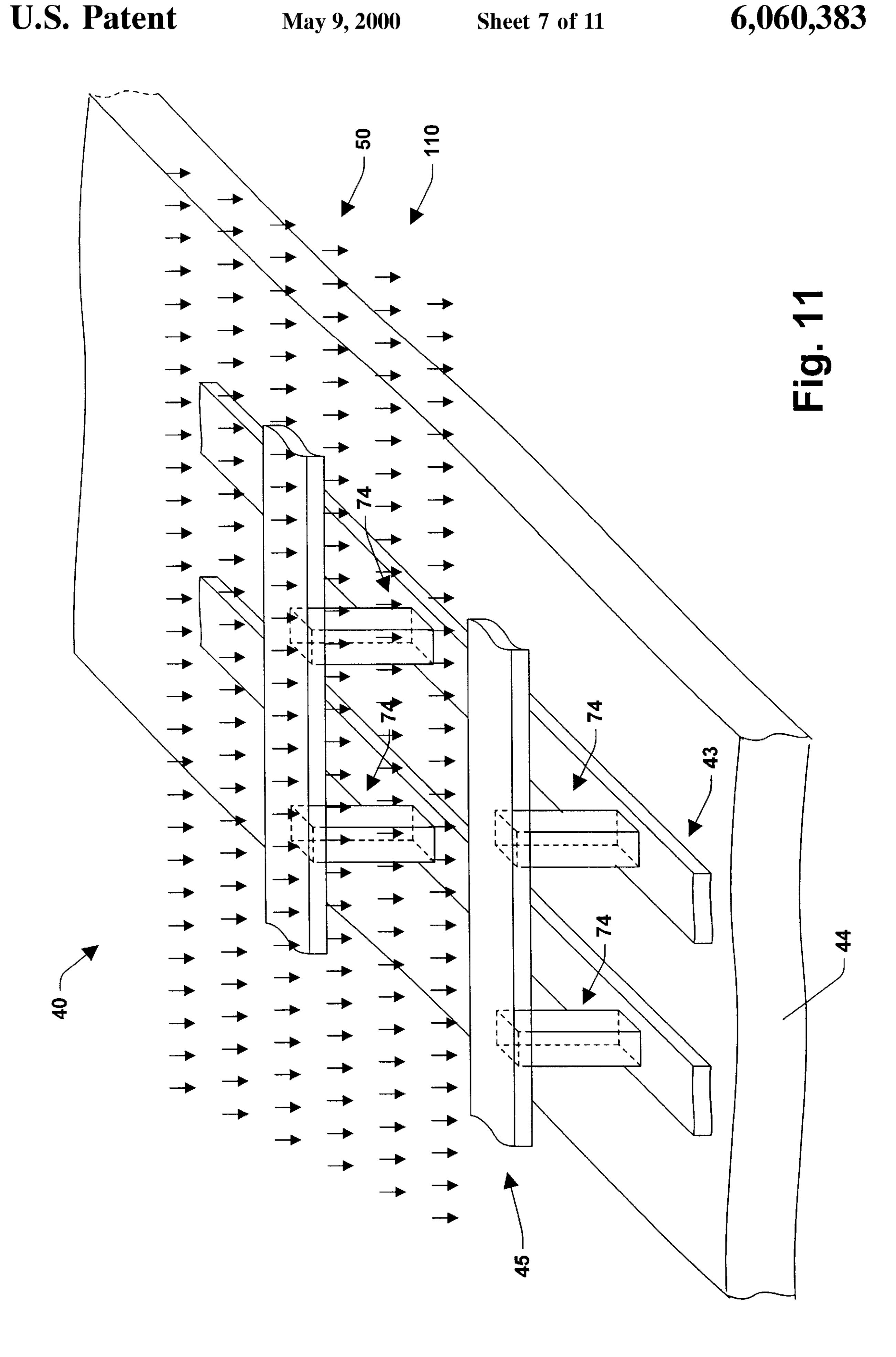

FIG. 11 is a schematic perspective illustration of the interconnect structure of FIG. 10 undergoing a first atomic layer deposition step in accordance with the present invention;

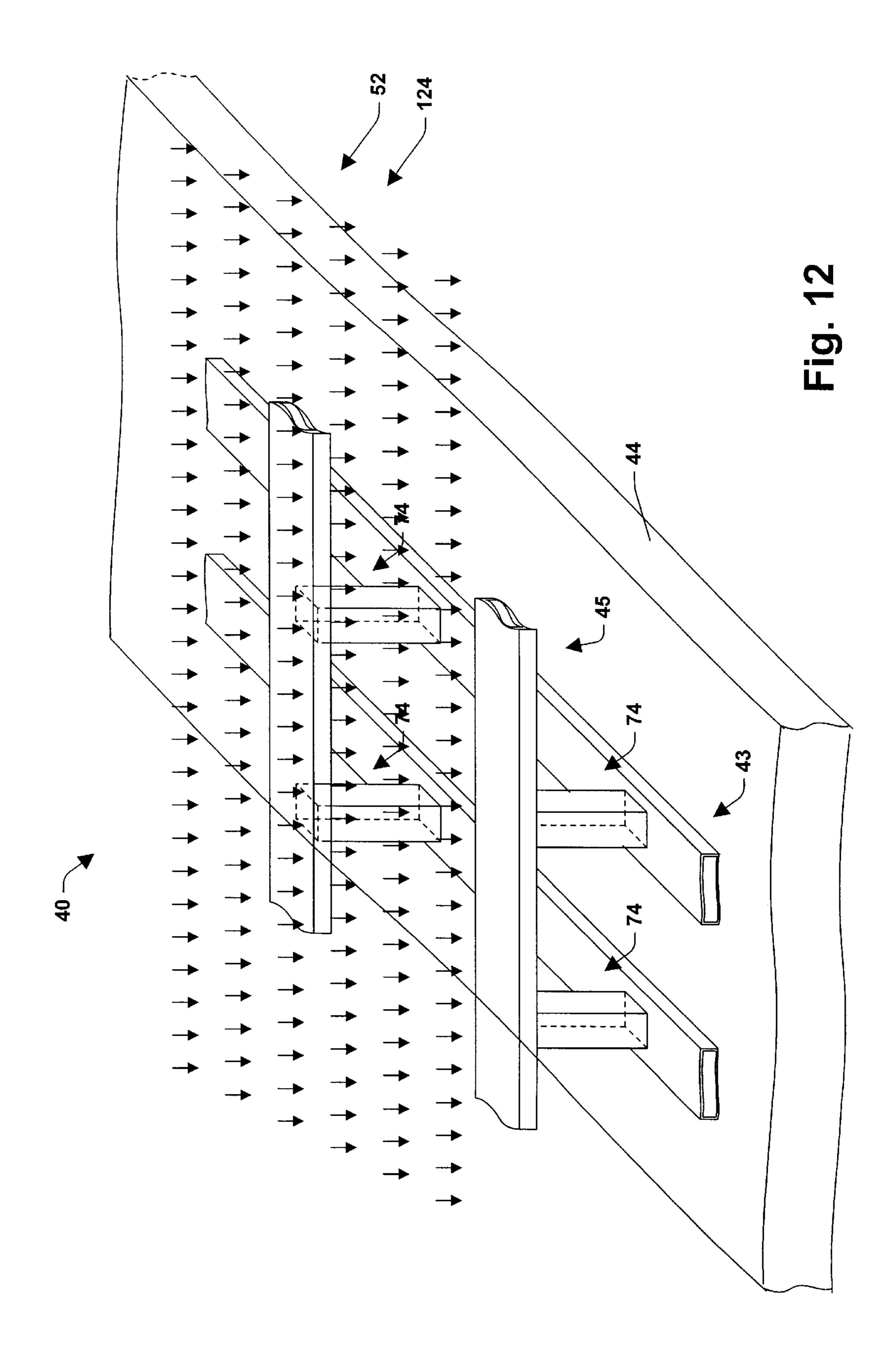

FIG. 12 is a schematic perspective illustration of the interconnect structure of FIG. 11 undergoing a second atomic layer deposition step in accordance with the present invention;

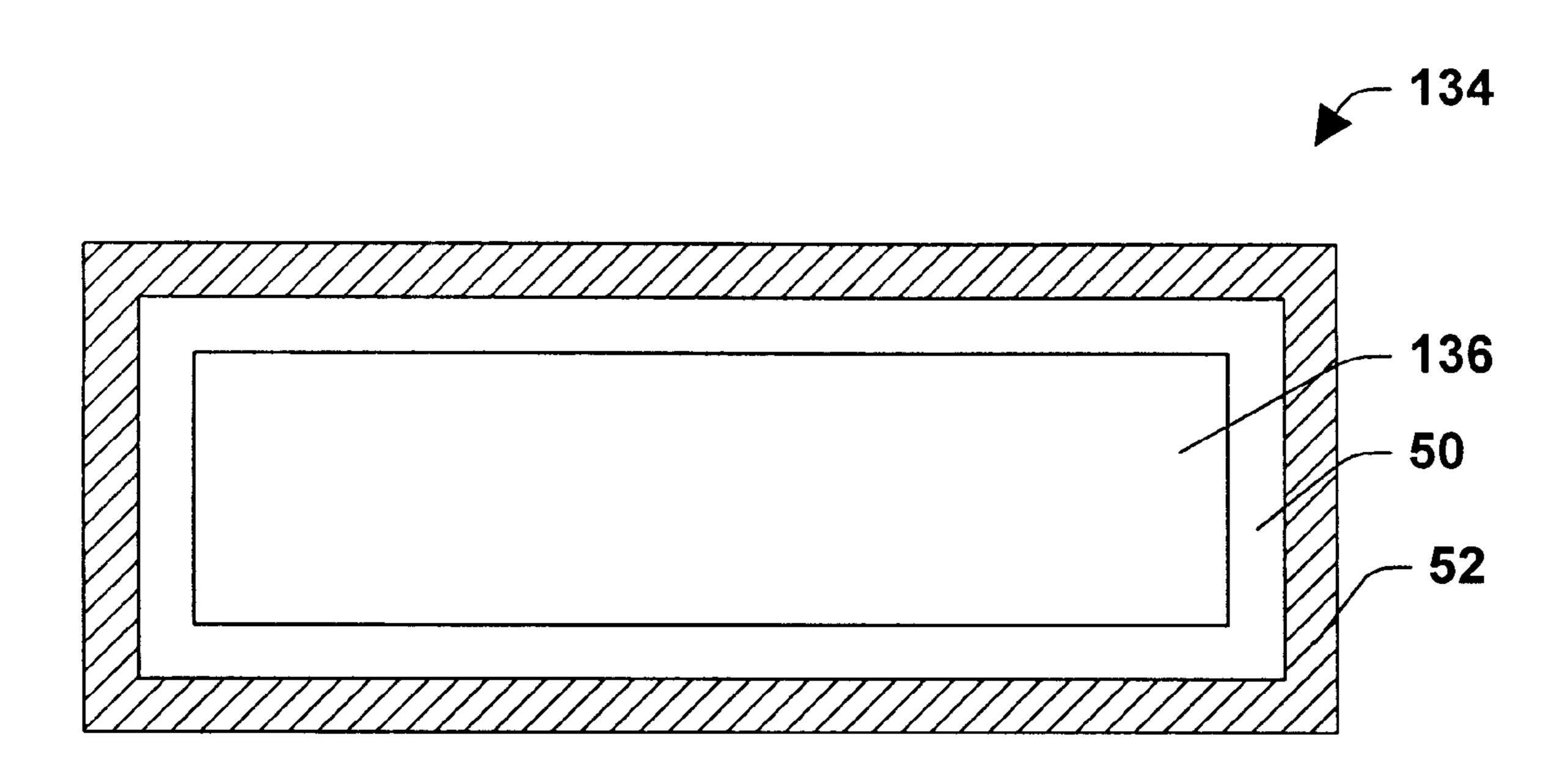

FIG. 13 is a schematic cross-sectional illustration of a coaxial interconnect line in accordance with the present invention;

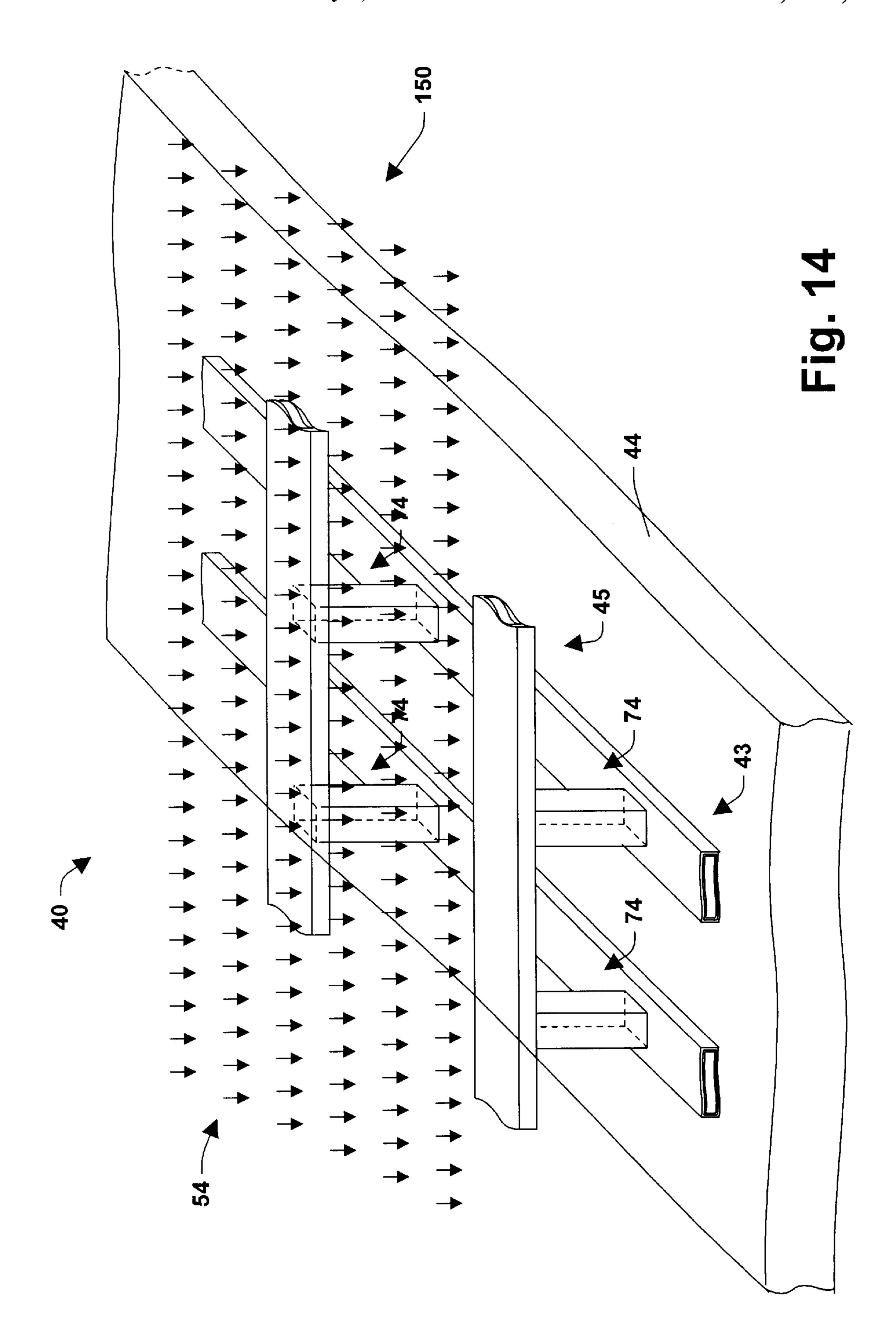

FIG. 14 is a schematic perspective illustration of the interconnect structure of FIG. 12 having a dielectric material of suitably low dielectric constant being deposited thereon; and

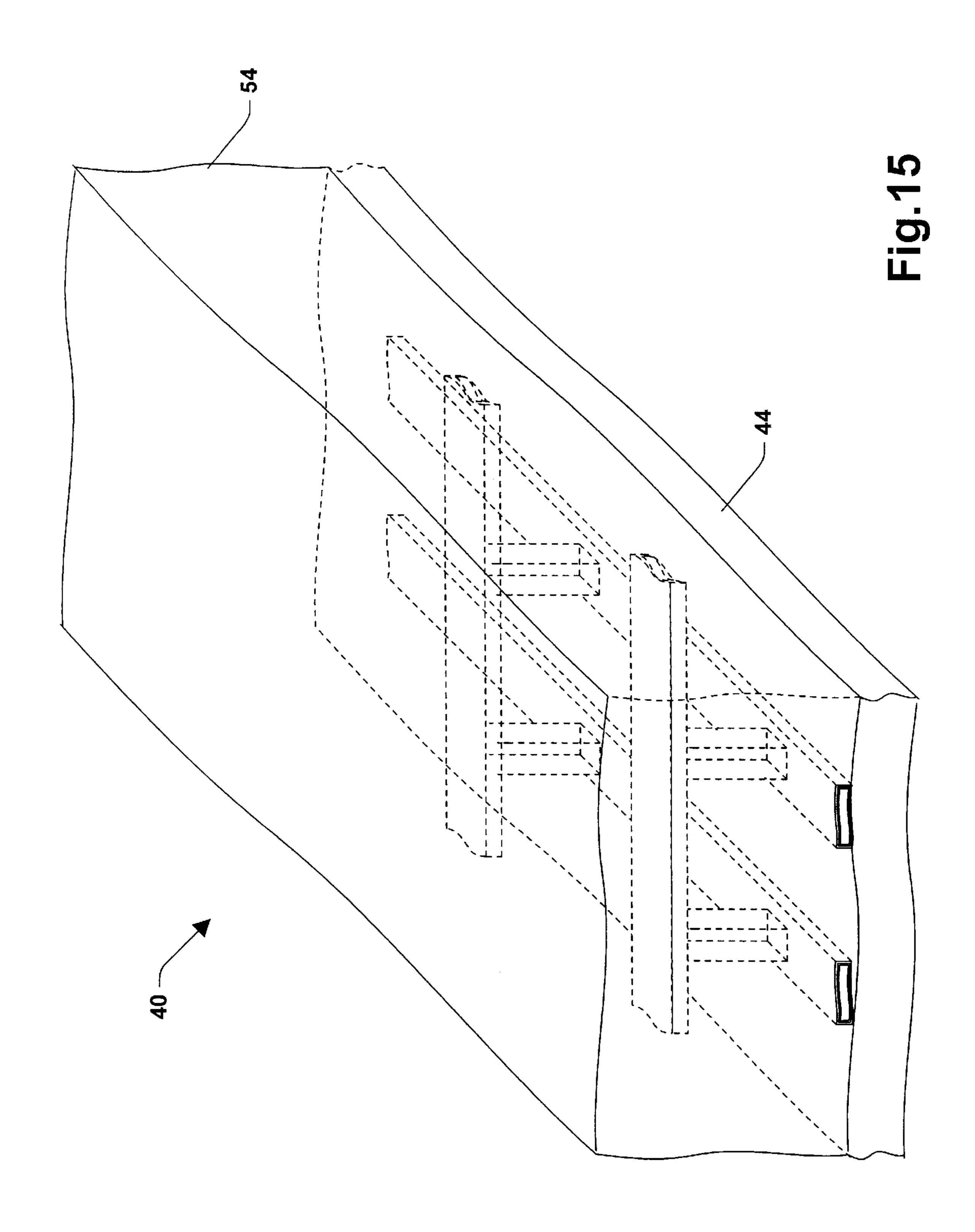

FIG. 15 is a schematic perspective illustration of the interconnect structure of FIG. 14 after the dielectric material 25 having suitably low dielectric constant has been deposited over the interconnect structure in accordance with the present invention.

# DETAILED DESCRIPTION OF THE INVENTION

The present invention will now be described with reference to the drawings, wherein like reference numerals are used to refer to like elements throughout. The method of the present invention will be described with reference to the 35 formation of a multi-layered interconnect structure having at least a coaxial portion, and utilizing a dielectric material having a dielectric constant suitable for mitigating capacitive coupling between closely spaced conductive lines of the multi-layered interconnect structure. The following detailed description is of the best modes presently contemplated by the inventors for practicing the invention. It should be understood that the description of these preferred embodiments are merely illustrative and that they should not be taken in a limiting sense.

Referring initially to FIG. 3a, a partial cross-sectional illustration is shown of a multi-layered interconnect structure 40 in accordance with the present invention. The multi-layered interconnect structure 40 includes a first conductive line 42 formed on an insulated substrate 44. The first 50 conductive line 42 is part of a first conductive pattern 43 (FIG. 3c) which lies atop the insulated substrate 44. The structure 40 includes a plug 46 for providing electrical connection between the first conductive line 42 and a second conductive line 46 (which is part of a second conductive 55 pattern 45 (FIG. 8)). At least a portion of the multi-layered interconnect structure 40 is coaxial in nature. As shown, the second conductive line 46 and the plug 46 are circumferentially surrounded by a thin insulating dielectric material **50**. Circumferentially surrounding the thin insulating dielec- 60 tric material 50 is a thin metal conductor 52, which may be grounded. Since the first conductive line 42 lies on top of the insulated substrate 44, the side of the first conductive line 42 facing the insulated substrate 44 will not be covered with the dielectric material **50** or the metal conductor **52**. The coaxial 65 portion of the structure 40 will enhance the functionality of the resulting IC employing the multi-layered interconnect

6

structure 40. The multi-layered interconnect structure 40 is covered with a dielectric material 54 suitable for facilitating the mitigation of capacitive crosstalk between adjacent conductive lines of the structure 40.

As will be discussed in greater detail below, the present invention employs a robust first dielectric material (e.g., SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>) during initial formation of the multi-layered interconnect structure 40 of the IC, and after the base multi-layered interconnect structure 40 is substantially complete deposition steps are performed on the multi-layered interconnect structure 40 to form at least some coaxial interconnect lines and/or plugs using the dielectric material 50 (second dielectric material). Thereafter, the dielectric material 54 (third dielectric material—e.g., polyimides, Teflon, aerogels) having a dielectric constant suitable for mitigating capacitive crosstalk between adjacent conductive lines is deposited over the multi-layered interconnect structure 40. As noted above, newer dielectric materials having low dielectric constant such as Teflon are not amendable to being used during fabrication of the multi-layered interconnect structure because the newer dielectric materials are relatively weak and tend to crack during the fabrication steps. However, because the newer dielectric material is applied after the multi-layered interconnect structure 40 is substantially complete the newer dielectric material may be employed without being exposed to the harsh fabrication steps that cause cracking thereof.

Referring now to FIG. 3b, an insulating layer is formed on the substrate 44 via a suitable deposition technique such as for example using chemical vapor deposition (CVD) or by a spinning technique. Both the insulating layer and substrate are illustrated in common for ease of understanding and are referenced by number 44. A conductive pattern 43 (e.g., including conductive lines 43a, 43b and 43c) is formed over the insulating/substrate layer 44. Preferably a metalization pattern is formed by depositing a metalization layer and patterning employing suitable photolithographic and etching techniques (e.g., anisotropic etching such as reactive ion etching). The conductive pattern 43 may be deposited by any of a variety of suitable deposition techniques, such as CVD processes including low pressure chemical vapor deposition (LPCVD) and plasma enhanced chemical vapor deposition (PECVD), melting or sputtering.

The conductive pattern 43 formed in the claimed invention may comprise any suitable conductive material employable for forming conductive patterns in the semiconductor industry. Preferably, the conductive material includes a member selected from the group consisting of refractory materials, such as titanium and titanium alloys, tungsten and tungsten alloys, aluminum and aluminum alloys, copper and copper alloys and polycrystalline silicon. The insulating material 44 employed in the present invention may comprise any suitable insulating material employable in the semiconductor industry for forming insulating layers. Preferably, the insulating material 44 comprises a member selected from the group consisting of nitrides, oxides, oxy-nitrides, polyimides and polymeric materials.

Turning now to FIG. 3c, a schematic cross section illustration is shown of a first layer (e.g., pattern) of the conductive lines 43 of FIG. 3b from a view perpendicular to the direction the conductive lines 43a, 43b and 43c are running. FIG. 4 is a schematic cross-sectional view of a first dielectric material 60 (e.g., SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>) being deposited over the conductive lines 43. The first dielectric material 60 in the exemplary embodiment is preferably silicon dioxide (SiO<sub>2</sub>), however, it will be appreciated that any suitable dielectric material may be employed to carry out the present invention and falls within the scope of the claims.

Any suitable technique for depositing the dielectric material 60 may be employed such as PECVD, or high density plasma chemical vapor deposition (HDPCVD) techniques such as electron cyclotron resonance (ECR), inductor coupled plasma (ICP), transformer coupled plasma (TCP) and helicon plasma The dielectric material 60 is deposited over the conductive pattern 43 so as to form a seal of dielectric material over the conductive lines 43a, 43b and 43c and the spaces between the conductive lines 43a, 43b and 43c.

Turning now to FIGS. 5 and 6, vias 70 are formed within the dielectric material 60 and the vias 70 are filled with a suitable material (e.g., tungsten, copper) to form plugs which provide conductive pathways through the dielectric layer 60 to connect interconnects of different conductor 15 layers. Although, the present invention is described with respect to forming only two conductive layers for ease of understanding, it is to be appreciated that many more conductive layers separated with the dielectric material 60 may be formed, and such structures are intended to fall <sup>20</sup> within the scope of the hereto appended claims. While different conductive materials are suitable to fill the vias 70, in this example tungsten forms conductive material 72. The tungsten filled vias 70 are referred to as tungsten plugs 74. Copper, aluminum or an aluminum alloy are exemplary of 25 other plug conductors. The plugs 74 may comprise any other suitable conductive material, which is chemical-vapor deposited with a flow rate sufficient to fill the vias 70 so as to have an aspect ratio less than, for example, 4:1. The plug material 72 is removed from the upper surfaces of dielectric 30 **60** using, for example, sacrificial etchback or CMP.

In an alternative embodiment, the conductive pattern 43 and/or plugs 74 may include copper (Cu). Since Cu easily diffuses into dielectric materials such as SiO<sub>2</sub>, a damascene process may be employed to create a barrier layer (e.g., Ta<sub>2</sub>N) between the Cu and the dielectric so as to mitigate diffusion of the Cu into the dielectric 60. Damascene techniques are known in the art, and therefore further discussion related thereto is omitted for sake of brevity. It is to be appreciated that the damascene technique may be performed to generate a barrier layer between any other suitable metal (e.g., tungsten) employed in the formation of the conductive pattern 43 and/or plugs 74.

FIG. 8 illustrates the second conductive layer 45 (including conductive lines 82, 84 and 86) being formed over the dielectric material 60 and the plugs 74. Thus, the plugs 74 provide for electrically connecting respective lines of the second conductive layer 45 to respective lines of the first conductive layer 43. The second conductive layer 45 is formed in a manner substantially similar to the manner of forming the first conductive layer 43, and therefore further discussion related thereto is omitted for sake of brevity. The first conductive layer 43, the plugs 74 and the second conductive layer 45 collectively form the multi-layered interconnect structure 40. Of course, the multi-layered interconnect structure 40 may include additional conductive layers and layers of plugs.

FIG. 8 is a cross-sectional illustration of the multi-layered interconnect structure 40 after additional first dielectric 60 material 60 is deposited thereon to cover the second conductive layer 45 and fill spaces 92 between lines of the second conductive layer 45.

Turning now to FIG. 9, the first dielectric material 60 is shown stripped away to leave the multi-layered interconnect 65 structure 40 exposed to air. In the preferred embodiment, hydrofluoric acid (HF) is employed to strip the first dielec-

8

tric 60 via an HF dip, however any suitable technique (e.g., wet etch) for stripping the first dielectric material may be employed. The HF dip affords for stripping the first dielectric material 60 (e.g., SiO<sub>2</sub>) without stripping the barrier layer (not shown) that may be coating the conductive patterns 43 and 45 and/or plugs 74. Although air is an ideal insulator (K≈1), the multi-layered interconnect structure 40 is substantially weak and maintaining integrity thereof without supportive materials would be difficult. Thus, as will be discussed in greater detail below, after the base interconnect structure 40 is complete the third dielectric material 54 (see FIG. 14) is deposited over the interconnect structure to replace the stripped away first dielectric material 60. The third dielectric material 54 provides support to the interconnect structure 40 and facilitates mitigating capacitive crosstalk between adjacent conductive lines of the interconnect structure 40. FIG. 10 is a schematic partial perspective view of the multi-layered interconnect structure 40 shown in FIG. 9.

FIG. 11 is a schematic illustration of the multi-layered interconnect structure 40 undergoing a first atomic layer deposition (ALD) step 110 wherein the thin layer of second dielectric material 50 (e.g., SiO<sub>2</sub>, silicon nitrides (Si<sub>x</sub>N<sub>z</sub>),  $Si_xO_vN_z$ —where "x", "y" and "z" are integers) is formed on at least a portion of the multi-layered interconnect structure 40. This thin layer of second dielectric material 50 will be an insulating material which is interposed between a central conductor and an outer conductor of a coaxial interconnect in accordance with the present invention. FIG. 12 illustrates the multi-layered interconnect structure 40 undergoing a second ALD step 124 wherein the thin layer of metal 52 (e.g., Ta<sub>2</sub>N) is formed over the portions of the multi-layered interconnect structure 40 selected to be coated with the second dielectric material 50 applied in the first ALD step 110. The thin layer of metal 52 will be the outer conductor of the coaxial interconnect. Thus, the first and second ALD steps provide for forming coaxial interconnects (e.g., conductive lines or plugs which are coaxial in nature).

Although, atomic layer deposition is a preferred technique for depositing the thin dielectric material layer and thin metal layer, it is to be appreciated that other techniques (e.g., vacuum evaporation, chemical vapor deposition, electrochemical deposition) may be employed. Any suitable deposition technique or other means for carrying out the present invention may be employed and is intended to fall within the scope of the present claims. ALD and the other aforementioned techniques are well known in the art, and thus based on the description herein one skilled in the art could readily carry out suitable deposition techniques to generate the coaxial portions of the present invention.

Referring now to FIG. 13, a schematic cross-sectional illustration of a coaxial interconnect 134 is shown. The coaxial interconnect includes a central conductor 136, the outer metal conductive material 52 and the dielectric material 50 interposed between the central conductor 136 and the outer conductive material 52. The coaxial interconnect 134 provides for the signal carrying central conductor 136 to be circumferentially surrounded by the outer metal conductor 52 which may be grounded and the insulating dielectric material 50 interposed there between. The central conductor 136 is thus substantially shielded from passing noise and induced electromagnetic fields resulting from changing signals therein as well as the central conductor 136 being substantially shielded from externally generated noise and electromagnetic fields.

Turning now to FIG. 14, the interconnect structure 40 is shown substantially complete, however, the interconnect

structure 40 is exposed to air. Thus, the interconnect structure 40 is in a form which may not be structurally sound enough to withstand prolonged exposure to vibrations, movement, etc. Therefore, a step of depositing the third dielectric material 54 over the interconnect structure 40 is 5 performed. The third dielectric material 54 is selected to have a dielectric constant suitable to facilitate mitigating capacitive crosstalk between conductive lines of the interconnect structure 40. Accordingly, the third dielectric material 54 preferably has a dielectric constant less than 3.0. Any suitable material (eg., polyimides, Teflon, aerogels) may be employed as the third dielectric material 54 and is intended to fall within the scope of the hereto appended claims.

The third dielectric material 54 is deposited over the interconnect structure 40 to replace the stripped away first 15 dielectric material 60. Any suitable technique for depositing the third dielectric material 54 may be employed. For example, any of the following deposition techniques may be employed: PECVD, or high density plasma chemical vapor deposition (HDPCVD) techniques such as electron cyclo- 20 tron resonance (ECR), inductor coupled plasma (ICP), transformer coupled plasma (TCP) and helicon plasma. The third dielectric material 54 is deposited over the interconnect structure 40 so as to form a seal of dielectric material over conductive lines of the various conductive patterns and fill 25 spaces between the conductive lines and the conductive patterns. Thus, the third dielectric material 54 provides for structurally supporting the interconnect structure 40 and also provides for facilitating the mitigation of capacitive crosstalk between adjacent conductive lines of the interconnect structure 40.

FIG. 15 is a schematic partial perspective illustration of the interconnect structure 40 complete in relevant part.

What has been described above are preferred embodiments of the present invention. It is, of course, not possible to describe every conceivable combination of components or methodologies for purposes of describing the present invention, but one of ordinary skill in the art will recognize that many further combinations and permutations of the present invention are possible. Accordingly, the present invention is intended to embrace all such alterations, modifications and variations that fall within the spirit and scope of the appended claims.

What is claimed is:

1. A method of forming a multi-layered interconnect structure, comprising the steps of:

forming a first conductive pattern over an insulation layer; depositing a first dielectric material over the first conductive pattern;

forming plugs in the first dielectric material;

forming a second conductive pattern over the first dielec- <sup>50</sup> tric material and plugs so as to form a multi-layered interconnect structure;

stripping the first dielectric material; and

- depositing a second dielectric material over the interconnect structure to replace the stripped away first dielectric material.

- 2. The method of claim 1 further including the step of having the second dielectric material be of lower dielectric constant than the first dielectric material.

- 3. The method of claim 1 further including the step of <sup>60</sup> using SiO<sub>2</sub> as the first dielectric material.

- 4. The method of claim 1 further including the step of using Si<sub>3</sub>N<sub>4</sub> as the first dielectric material.

- 5. The method of claim 1 further including the step of using polyimides as the second dielectric material.

- 6. The method of claim 1 further including the step of using Teflon as the second dielectric material.

10

- 7. The method of claim 1 further including the step of using an aerogel as the second dielectric material.

- 8. The method of claim 1 further including the step of using tungsten as material for the plug.

- 9. A method of forming an interconnect structure having at least a coaxial portion, comprising the steps of:

forming a first conductive pattern over an insulation layer; depositing a first dielectric material over the first conductive pattern;

forming plugs in the first dielectric material;

forming a second conductive pattern over the first dielectric material and plugs so as to form the interconnect structure;

stripping the first dielectric material;

depositing a thin layer of second dielectric material so as to coat at least a portion of the interconnect structure; and

depositing a thin layer of metal so as to coat the at least a portion of the interconnect structure coated with the thin layer of second dielectric material.

- 10. The method of claim 9 further including a step of depositing a third dielectric material over the interconnect structure so as to substantially replace the stripped away first dielectric material.

- 11. The method of claim 9 further including the step of using atomic layer deposition to apply at least one of the thin layer of second dielectric material and thin layer of metal.

- 12. The method of claim 9 further including the step of using at least one of: vacuum evaporation, chemical vapor deposition, and electrochemical deposition to apply at least one of the thin layer of second dielectric material and thin layer of metal.

- 13. The method of claim 9 further including the step of using one of SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and silicon oxynitride as the second dielectric material.

- 14. The method of claim 9 further including the step of using tantalum nitride (Ta<sub>2</sub>N) as the thin metal layer.

- 15. The method of claim 9 further including the step of using one of SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> as the first dielectric material.

- 16. A method of forming an interconnect structure having at least a coaxial portion, comprising the steps of:

forming a first conductive pattern over an insulation layer; depositing a first dielectric material over the first conductive pattern;

forming plugs in the first dielectric material;

forming a second conductive pattern over the first dielectric material and plugs so as to substantially form the interconnect structure;

stripping the first dielectric material;

depositing a thin layer of second dielectric material so as to coat at least a portion of the interconnect structure;

depositing a thin layer of metal so as to coat the at least a portion of the interconnect structure coated with the thin layer of second dielectric material; and

depositing a third dielectric material over the interconnect structure to replace the stripped away first dielectric material.

17. The method of claim 16 further including a step of creating a barrier layer via a damascene process so as to mitigate diffusion of metal from at least one of the first conductive pattern, plugs and the second conductive pattern into at least one of the first dielectric material and the third dielectric material.

\* \* \* \* \*