### US005930520A

Patent Number:

# United States Patent [19]

# Ando [45] Date of Patent: Jul. 27, 1999

[11]

# [54] PIPELINING DEVICE IN A PARALLEL PROCESSING APPARATUS AND AN INSTRUCTION SUPPLYING METHOD THEREFOR

[75] Inventor: **Hideki Ando**, Hyogo-ken, Japan

[73] Assignee: Mitsubishi Denki Kabushiki Kaisha,

Tokyo, Japan

[21] Appl. No.: 08/800,191

[22] Filed: Feb. 13, 1997

### Related U.S. Application Data

[62] Division of application No. 08/300,235, Sep. 6, 1994, Pat. No. 5,619,730, which is a continuation of application No. 07/779,176, Oct. 17, 1991.

# [30] Foreign Application Priority Data

| Oct. | 17, 1990              | [JP]                                    | Japan                                   | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | 2      | -279654 |

|------|-----------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|--------|---------|

| [51] | Int. Cl. <sup>6</sup> | •••••                                   | • • • • • • • • • • • • • • • • • • • • | G06                                     | F 15/00                                 | ); G06 | 6F 6/00 |

| [52] | U.S. Cl.              | • • • • • • • • • • • • • • • • • • • • | 3                                       | 395/800.2                               | <b>3</b> ; 395/.                        | 393; 3 | 395/388 |

| [58] | Field of              | Search                                  | •••••                                   | • • • • • • • • • • • • • • • • • • • • | 395/80                                  | 0.23,  | 800.24, |

|      |                       |                                         |                                         |                                         |                                         | 395/39 | 93, 388 |

# [56] References Cited

## U.S. PATENT DOCUMENTS

| 3,665,422 | 5/1972  | McCoy et al      |

|-----------|---------|------------------|

| 3,727,196 | 4/1973  | McKenny .        |

| 3,953,838 | 4/1976  | Gilberg et al    |

| 4,295,193 | 10/1981 | Pomerene         |

| 4,374,428 | 2/1983  | Barnes .         |

| 4,423,482 | 12/1983 | Hargrove et al   |

| 4,476,525 | 10/1984 | Ishii .          |

| 4,521,851 | 6/1985  | Trubisky et al   |

| 4,591,971 | 5/1986  | Darlington et al |

| 4,837,678 | 6/1989  | Culler et al     |

|           |         |                  |

(List continued on next page.)

#### OTHER PUBLICATIONS

5,930,520

Minagawa et al. "Predecoding Mechanism For SuperScaler Architecture" May 1991.

Grohoski, "Machine Organization of the IBM RISC System/6000 Processor", *IBM J. Res. Develop.*, vol. 34, No. 1, (Jan. 1990), pp. 37–58.

Groves et al, "An IBM Second Generation RISC Processor Architecture" Proceedings of the 35th Compcon, IEEE 1990, pp. 162–170.

S. McGeady, "The 1960CA SuperScalar Implementation of the 80960 Architecture", Proceedings of the 35th Compson, IEEE 1990, pp. 232–240.

Microsoft Press Computer Dictionary copyright 1994.

Primary Examiner—Larry D. Donaghue Attorney, Agent, or Firm—McDermott, Will & Emery

# [57] ABSTRACT

A parallel processing apparatus of a superscalar type includes an instruction decoding stage which decodes four instructions simultaneously fetched from an instruction memory and issues instructions which allows simultaneous execution to related function units. The instruction decoding stage includes an instruction decoder which decodes the instruction and issues the instructions allowing simultaneous execution to the function units, and a queue which queues and stores the instructions fetched from the instruction memory. This instruction decoding stage also includes a scope logic which forms a read queue address for reading the instructions of the queue in accordance with the number of issued instructions in the instruction decoder and whether a branch is generated by a branch instruction, and a queue top logic which forms a write address in the queue in accordance with a storage state of an unissued available instruction in the queue. Instructions are read from four successive addresses starting from the read address. Fetched instructions are stored in four addresses in the queue starting from the write address. Four instructions to be decoded are always supplied to the instruction decoder in accordance with an issue state of the instructions. Four instructions are always fetched from the instruction memory and queued. Therefore, the instructions can be efficiently supplied to the instruction decoder in accordance with the execution state of the instructions.

### 40 Claims, 27 Drawing Sheets

# **5,930,520**Page 2

|           | U.S. PA | TENT DOCUMENTS               | 5,150,468 | 9/1992  | Staplin et al 395/376   |

|-----------|---------|------------------------------|-----------|---------|-------------------------|

| 1 050 105 | 0/1000  | Varirona et al               | 5,185,868 | 2/1993  | Tran                    |

|           |         | Kuriyama et al<br>Ward et al | 5,202,967 | 4/1993  | Matsuzaki et al 395/376 |

| 4,907,198 |         |                              | 5,214,763 | 5/1993  | Blaner et al            |

| 4,924,376 | 5/1990  | Yasushi Ooi .                | 5,233,694 | 8/1993  | Hotta et al             |

| , ,       | -       | Shintani et al               | 5,251,306 | 10/1993 | Tran                    |

| , ,       |         | Ngai et al                   | 5,295,249 | 3/1994  | Blaner et al            |

| 5,036,434 | -       | Rau et al<br>Johnson .       | 5,303,356 | 4/1994  | Vassiliadis et al       |

Jul. 27, 1999

| FIG. 3 | PRIOR ART   |                        |

|--------|-------------|------------------------|

| CYCLE  | INSTRUCTION |                        |

| 1      | 1 2 3 4     | : ISSUANCE OF "1"      |

| 2      | 2 3 4       | ; ISSUANCE OF "2"&"3"  |

| 3      | 4           | ISSUANCE OF "4"        |

| 4      | 5 6 7 8     | ; ISSUANCE OF 5% 6     |

| 5      | 7 8         | ; ISSUANCE OF "7"& "8" |

| 6      |             |                        |

|        |             |                        |

FIG.4

| CYCLE   | INSTRUCTION                       |                              |

|---------|-----------------------------------|------------------------------|

| 1       | 1 2 3 4                           | ; 1 ISSUED                   |

| 2       | 2 3 4 5                           | ; ~2~&~3~ ISSUED             |

| 3       | 4 5 6 7                           | ; 48586 ISSUED               |

| 4       | 7 8 9 10                          | ; ~ 7 & ~ ISSUED             |

| 5       |                                   |                              |

| FIG.5   |                                   |                              |

| (1) 2 3 | 4 5 ; 2 <sup>*</sup> & "3" ISSUED |                              |

| (2) 4 5 | 一 ; SHIFT IN INSTRU               | CTION REGISTERS              |

| (3) 4 5 | 6 7 ; FETCH OF INSTRUCT           | CTIONS INTO<br>ION REGISTERS |

FIG. 6

FIG.7

FIG. 9

x:UNDETERMINED

FIG. 10

|                                                | BA | SIC | : B | EHA | VIC   | )R ( | OF ( | UE | UE, | que | eue_ | top, | scope   |

|------------------------------------------------|----|-----|-----|-----|-------|------|------|----|-----|-----|------|------|---------|

| QUEUE ADDRESS                                  | 0  | 1   | 2   | 3   | 4     | 5    | 6    | 7  | 8   | 9   | 10   | 11   |         |

| (1) INSTRUCTION  AVAIL. FLAG  que ue_top scope |    |     |     |     |       | X    |      |    |     |     | X    | X    | 1 CYCLE |

| (2) INSTRUCTION  AVAIL.FLAG  queue_top scope   |    |     |     |     |       |      |      |    |     |     | X    |      |         |

| (3) INSTRUCTION  AVAIL. FLAG  queue-top scope  | 0  | 1   | 2   | 3   | 4 1 1 | 5    | _    |    | X   |     | X    | X    |         |

| (4) INSTRUCTION  AVAIL. FLAG  queue_top  scope |    |     |     |     |       |      |      |    |     |     | 10   |      |         |

| (5) INSTRUCTION  AVAIL. FLAG  queue_top scope  |    |     |     |     |       |      |      |    |     |     | 10   |      |         |

| (6) INSTRUCTION  AVAIL. FLAG  queue_top  scope |    |     |     |     |       | 5    |      |    |     | 9   | 10   | 11   |         |

F16.1

| RANCH TAKES PLACE | 1 CYCLE                                        | WHERE INSTRUCTION 2 IS A BRANCH INSTRUCTION AND A BRANCH THEREBY IS GENERATED | ; BRANCH TARGET INSTRUCTION<br>1S INSTRUCTION 20 |

|-------------------|------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------|

| WHER<br>11        | 1                                              | <b>₽</b>                                                                      | <b>♂</b>                                         |

| 9<br>10           | 9                                              | <b>&amp;</b>                                                                  | ∞                                                |

| scop<br>9         | 7                                              |                                                                               |                                                  |

| ор,<br>8          | 9                                              | 9 -                                                                           | 9                                                |

| ıe_t<br>7         | 5                                              | လ                                                                             | 1                                                |

| que ue            | 7                                              | 7 0                                                                           | 1                                                |

| , LO              | €0 <del></del>                                 | m 0                                                                           | 7                                                |

| JEUE<br>4         | 7                                              | 7 0 -                                                                         | 1 - 1                                            |

| 3 OU              |                                                | <b></b>                                                                       | <del></del>                                      |

| 2<br>2            | 1                                              | 0                                                                             | 0 -                                              |

| 710F              |                                                | <b>—</b>                                                                      | <del></del>                                      |

| BEHAVIOR<br>0 1   | 10                                             | 2                                                                             | 2 _                                              |

| QUEUE ADDRESS     | (11) INSTRUCTION  AVAIL FLAG  queue_top  scope | 4 AVAIL FLAG  queue_top Scope                                                 | (13) INSTRUCTION  AVAIL FLAG  queue - top  Scope |

| JCT10N<br>OF                |               | 1 CACLE                                     | NO INSTRUCTION IS SUPPLIED FROM INSTRUCTION MEMORY | WAITING FOR INSTRUCTION SUPPLY              | INSTRUCTIONS<br>ARE SUPPLIED                         |

|-----------------------------|---------------|---------------------------------------------|----------------------------------------------------|---------------------------------------------|------------------------------------------------------|

| STR1<br>SOR                 | 11            |                                             |                                                    |                                             |                                                      |

| ES.                         | 10            | 9                                           | 9                                                  | 9 -                                         | 9 -                                                  |

| HH                          | 9             | S -                                         | <b>₽</b> ←                                         | <b>₩</b>                                    | <b>₩</b>                                             |

| ₹ O V                       | 8             | 4                                           | 7                                                  | 4                                           | <b>4</b>                                             |

| Pe<br>SNS                   | 7             | ري<br>ا                                     | m 0                                                | m 0                                         | 15                                                   |

| Scol<br>STC                 | 9             | 1                                           | 7                                                  | 7 0                                         | 17                                                   |

| 주<br>군<br>건<br>건            | 2             | -                                           | 0                                                  | - 0                                         | ₩<br>—                                               |

| P. to                       | 7             | 1                                           | 00-                                                | 0 0 -                                       | 12                                                   |

| Le u                        | က             |                                             |                                                    |                                             | <del></del>                                          |

| ٦<br>٦                      | 7             | 10                                          | 2 -                                                | 2 -                                         | 10                                                   |

| QUEUE<br>10T SUF<br>INSTRU( | -             | 6                                           | <b>σ</b> -                                         | <b>5</b> −                                  | <b>♂</b>                                             |

|                             | 0             | 1                                           | <b>∞</b> –                                         | - σ                                         | ω -                                                  |

| BEHAVIOR OF MEMORY CANI     | QUEUE ADDRESS | (21) INSTRUCTION AVAIL FLAG queue-top scope | (22) INSTRUCTION AVAIL FLAG queue_top scope        | (23) INSTRUCTION AVAIL FLAG queue-top scope | (24) INSTRUCTION<br>AVAIL FLAG<br>queue_top<br>scope |

F16.12

F16.15

| _     |                       | <del></del> | <del></del> |        |      |            | ·.,.          |        | ·           |             |               |             |               |

|-------|-----------------------|-------------|-------------|--------|------|------------|---------------|--------|-------------|-------------|---------------|-------------|---------------|

| queue | top – in              | 0           | queue_top_L | branch | inst | _entry(*1) | 1 queue_top_L | ( * 2) | queue_top_L | 1 dop-fob-t | ( <b>*</b> 2) | queue_top_L | I queue-top-L |

| duene | -avail                | ×           | ×           | ×      |      |            | ×             | -      | 0           | ×           | 1             | 0           | ×             |

| 10    | ready                 | ×           | ×           | ×      |      |            | 0             |        | 1           | 0           |               | •           | ×             |

| 10    | miss<br>L             | ×           | ×           | ×      |      |            | ×             | ×      | ×           | -           |               | _           | 0             |

| 10    | _fetch                | ×           | ×           | ×      |      |            | -             |        | 1           | ×           | X             | ×           | 0             |

| þ     | -taken                | ×           | ×           |        |      |            | 0             | 0      | 0           | 0           | 0             | 0           | 0             |

| queue | -init<br>-state<br>-L | ×           |             | 0      |      |            | 0             | 0      | 0           | 0           | 0             | 0           | 0             |

| reset |                       |             | ×           | 0      |      |            | 0             | 0      | 0           | 0           | 0             | 0           | 0             |

X: ARBITRARY

branch.inst.entry=QUEUE ADDRESS AT WHICH A BRANCH queue\_state= NORMAL (2ND STATE OF QUEUE) queue\_state = NORMAL

```

else queue_state=NORMA

```

# FIG.14

LOGIC OF SCOPE\_NEXT

- (1) reset : scope\_next = 0 ;

- (2) br\_taken: scope\_next = branch\_inst\_entry;

- (3) else: scope\_next = scope\_L+ NUMBER OF ISSUED INSTRUCTIONS

(issued\_inst\_count);

if (scope\_next > 11)

scope\_next = scope\_next - 12;

# FIG. 15

LOGIC OF IC\_FETCH

- (1) / reset and /IC\_busy; IC\_fetch = 1;

- (2) else.  $IC_fetch = 0$ ;

FIG.16

LOGIC OF OF IC\_MISS

| reset | br_taken | IC_tetch_L | 1C_ready | IC_miss   |

|-------|----------|------------|----------|-----------|

| 1     | X        | X          | X        | ,         |

| 0     | 1        | X          | X        | 0         |

| 0     | 0        | 1          | 0        |           |

| 0     | 0        | X          | 1        | 0         |

| 0     | 0        | 0          | 0        | IC_miss_L |

x: ARBITRARY

FIG.17A

# LOGIC OF QUEUE\_AVAIL

| reset | br_taken | queue_fu!! | queue - avail |   |

|-------|----------|------------|---------------|---|

| 1     | X        | X          | 1             |   |

| 0     | 1        | X          |               | 7 |

| 0     | 0        | 0          | 1             | 7 |

| 0     | 0        | 1          | 0             |   |

x: ARBITRARY

# FIG.17B

queue\_full

scope\_next : = SCOPE IN THE NEXT CYCLE queue\_top.in ;=QUEUE\_TOP IN THE NEXT CYCLE

(1) scope\_next < queue\_top\_in: if  $(scope_next + 12 - queue_top_in > = 4)$  FALSE; else TRUE: (2) scope\_next > queue\_top\_in; if ( scope\_next - queue\_top\_in> = 4 ) FALSE;

else TRUE; (3) scope\_next == queue\_top\_in ; if (queue\_state == NORMAL) FALSE else TRUE;

FIG.17C

FIG. 17D

FIG. 18A

<NORMAL STATE>

| QUEUE | INSTRUCTION | POINTER   |              |

|-------|-------------|-----------|--------------|

| 0     |             |           |              |

| 1     |             |           |              |

| 2     | X           | scope     |              |

| 3     | X           |           |              |

| 4     | X           |           |              |

| 5     | X           |           |              |

| 6     |             | queue_top |              |

| 7     |             |           |              |

| 8     |             |           | x: UN-ISSUED |

| 9     |             |           | INSTRUCTION  |

| 10    |             |           |              |

| 11    |             |           |              |

FIG.18B

FIG. 19A

| < REV | ERSE STATE > |           |              |             |

|-------|--------------|-----------|--------------|-------------|

| QUEUE | INSTRUCTION  | POINTER   |              |             |

| 0     | X            |           |              |             |

| 1     | X            |           |              |             |

| 2     |              | queue_top |              |             |

| 3     |              |           |              |             |

| 4     |              |           |              |             |

| 5     |              |           |              |             |

| 6     | X            | scope     |              |             |

| 7     | X            |           |              |             |

| 8     | X            |           |              |             |

| 9     | X            |           |              |             |

| 10    | X            |           | : <b>x</b> : | UN-ISSUED   |

| 1 1   | X            |           |              | INSTRUCTION |

FIG. 19B

<AT REVERSE STATE SCOPE\_NEXT = QUEUE\_TOP\_IN >

| QUEUE | INSTRUCTION | POINTER                        |

|-------|-------------|--------------------------------|

| 0     |             |                                |

| 1     | X           |                                |

| 2     | X           |                                |

| 3     | X           |                                |

| 4     | X           |                                |

| 5     | X           |                                |

| 6     | X           | scope_next<br>queue_top_in     |

| 7     | X           |                                |

| 8     | X           |                                |

| 9     | X           |                                |

| 10    | X           |                                |

| 11    | X           | : x : UN-ISSUED<br>INSTRUCTION |

FIG. 20

| (1) reset = 1 ; queue_state = NORMAL                                 |                          |

|----------------------------------------------------------------------|--------------------------|

| (2) queue _ top > 11 == 1  scope > 11 == 0 ; queue _ state = REVERSE | queue_top_in             |

| (3) scope > 11 == 1;  queue_state = NORMAL                           |                          |

| (4) br_taken =1 ; queue_state = NORM                                 | AL br — scope queue_ top |

FIG. 21

| reset | br_taken | IC_fetch_L | IC_miss_L | inst_avail_in |

|-------|----------|------------|-----------|---------------|

| 1     | X        | X          | X         |               |

| 0     | 1        | X          | X         | 0             |

| 0     | 0        | 1          | X         | IC_ready      |

| 0     | 0        | X          | 1         | IC_ready      |

| 0     | 0        | 0          | 0         | 0             |

x: ARBITRARY

FIG. 22

| reset | br<br>_taken | IC<br>_fetch_L | IC<br>_miss_L | IC<br>_ready | queue_init_state   |

|-------|--------------|----------------|---------------|--------------|--------------------|

| 1     | X            | X              | X             | <u> </u>     | 1                  |

| X     | 1            | X              | X             | X            | 1                  |

| 0     | 0            | 1              | X             | 1            | <u> </u>           |

| 0     | 0            | X              | 1             | 0            | <u> </u>           |

| 0     | 0            | X              | 1             | 1            |                    |

| 0     | 0            | 0              | 0             | X            | queue_init_state_L |

x : ARBITRARY

FIG. 24

- (a) CYCLE

- (b) IC\_fetch

- (c) iC\_ready

- (d) br\_taken

- (e) queue\_top

- (f) scope

- (g) queue\_init\_state

- (h) queue\_avail

- (i) inst\_avail in

FIG. 25

STEPS OF FIG.12; (21) (22) (23) (24)

- (b) IC\_fetch

- (c) IC\_miss

- (d) IC\_ready

- (e) IC\_busy

- (f) queue\_top

- (g) scope

- (h) queue\_init\_state

- (i) queue\_avail

- (j) inst\_avail\_in

FIG. 26

5,930,520

FIG. 27

| I        | 1 I I C C C C 1 2 3 4 31 31 31 |

|----------|--------------------------------|

| O-TH BIT | 31ST BIT                       |

FIG. 28

| P P P C C C 1 2 3 4 0 0 0 0 | P P P P C C C 1 2 3 4 31 31 31 31 |

|-----------------------------|-----------------------------------|

| O-TH BIT                    | 31ST BIT                          |

FIG. 29

| inst_<br>avail_<br>in_0 | avail_ | inst_avail_ | avai&_ |

|-------------------------|--------|-------------|--------|

|                         | 177 1  | in _ 2      | 1n_3   |

5,930,520

FIG. 30A

94 arō

31 95 vb(0X1X2X3)rb(0X1X2X3) (0X0X0X0) (0X0X0X0) \$ | ₹ | ₹

FIG. 33

FIG. 34

FIG. 35

FIG. 36

# PIPELINING DEVICE IN A PARALLEL PROCESSING APPARATUS AND AN INSTRUCTION SUPPLYING METHOD **THEREFOR**

This application is a division of U.S. application Ser. No. 08/300,235 filed Sep. 6, 1994, U.S. Pat. No. 5,619,730, which is a continuation of Ser. No. 07/779,176 filed Oct. 17, 1991.

### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a parallel processing apparatus, and particularly to an improvement for efficiently supplying instructions in processors of a superscalar type.

### 2. Description of the Background Art

In recent years, microprocessors have been remarkably advanced, and particularly their performance and operation speed have been increased. However, high speed of semi- 20 conductor memories has not been increased enough to follow the increased operation speed of the microprocessors, and thus the access of the semiconductor memories provides bottle neck against increasing the speed of the processors. Therefore, parallel processing has been employed for 25 improving the performance of the microprocessors.

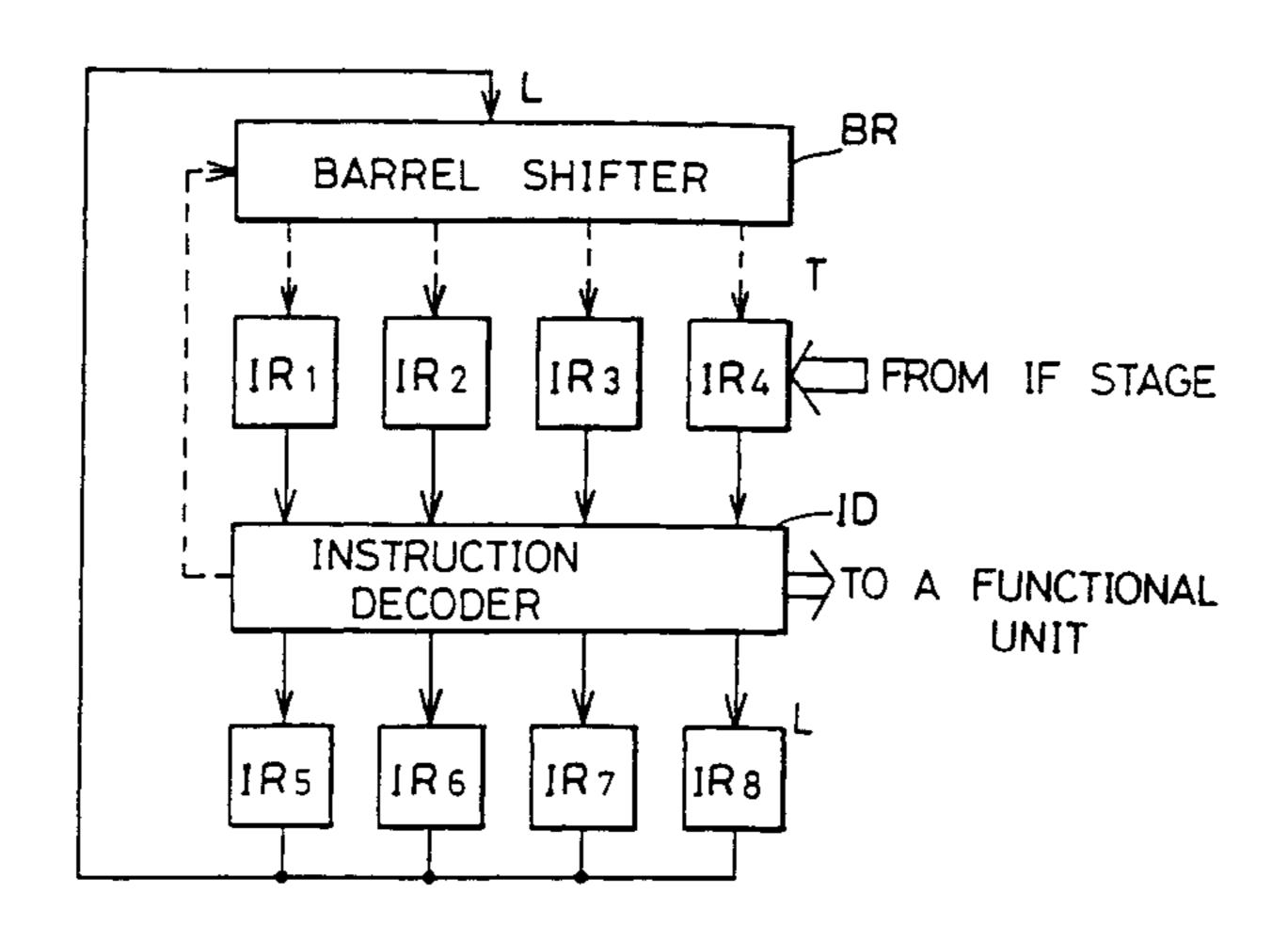

As a method for achieving the parallel processing, there is a processing method called as a superscalar. A processor of this superscalar type (will be called merely as a "superscalar") has a construction, as shown in FIG. 1, in 30 which a scheduler 200 in the superscalar detects parallelism in an instruction stream to supply instructions which can be processed in parallel to parallel pipelines P1, P2 and P3. That is; the superscalar is a processing device having following features.

- (1) It fetches simultaneously a plurality of instructions.

- (2) It has a plurality of function units (pipe lines) and can execute simultaneously a plurality of instructions.

- (3) It finds simultaneously executable instructions among 40 a plurality of fetched instructions, and simultaneously dispatches these simultaneously executable instructions to related function units (pipe lines).

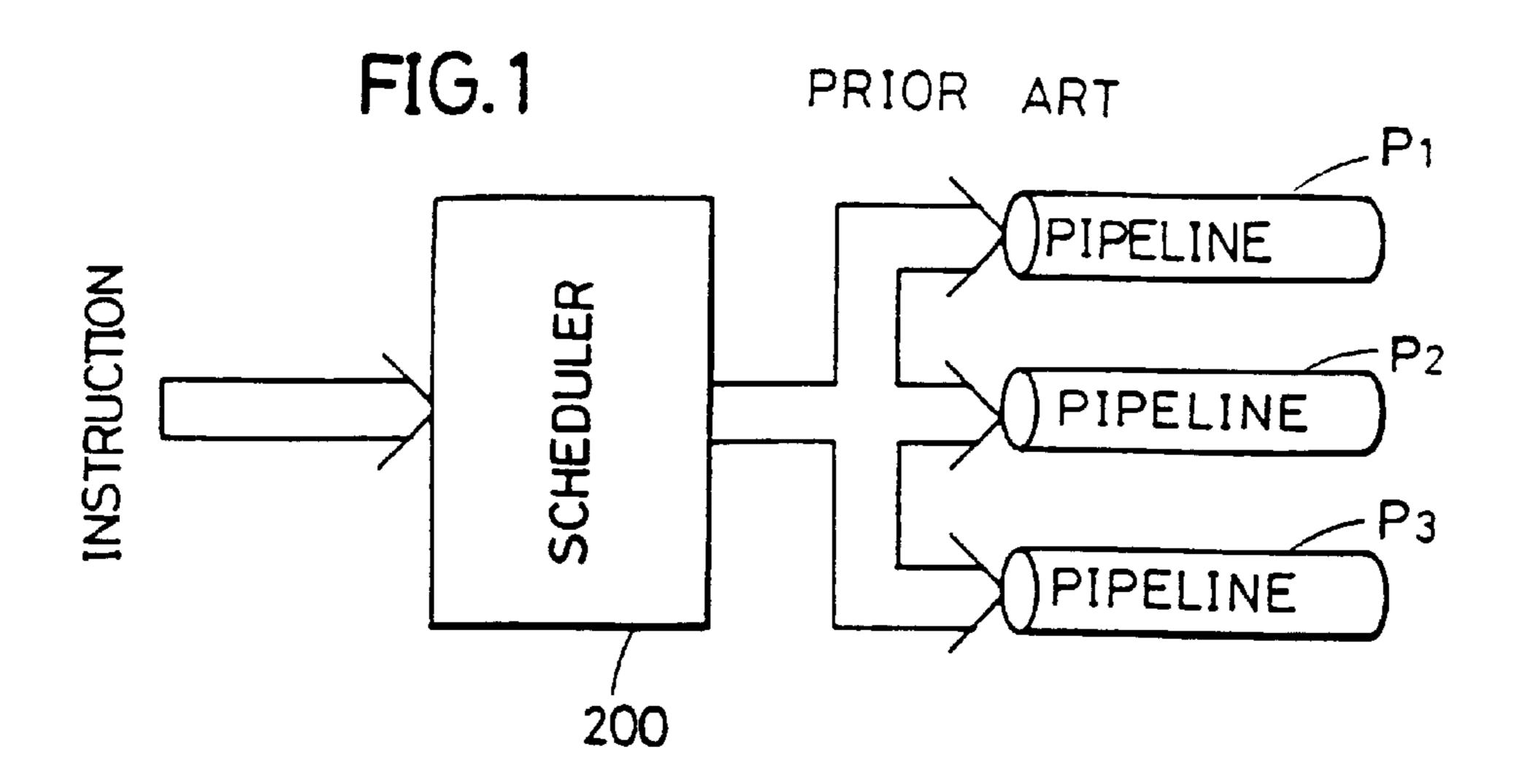

FIG. 2 shows a general construction of a superscalar. In FIG. 2, the superscalar includes a plurality of function units 45 4, 5, 6 and 7 which perform predetermined functions, respectively, as well as instruction memory 1 for storing instructions, an instruction fetching (IF) stage 2 for fetching simultaneously a plurality of instructions from the instrucwhich receives instructions fetched by the instruction fetching stage 2. The instruction decoding stage 3 finds simultaneously executable instructions among the instructions and dispatches them to corresponding function units. The superscalar further includes a data memory 8 for storing results of 55 processing and others. The instruction memory 1 includes a cache memory and an external memory, and can perform high-speed reading of the instructions in a case of cache hit, i.e., if required instructions exist in the cache memory.

The instruction fetching stage 2 supplies an instruction 60 pointer (IF\_PC) to the instruction memory 1 to fetch the instructions corresponding to this instruction pointer IF\_PC from the instruction memory 1.

The instruction decoding stage 3 includes an instruction decoder and a pipeline sequencer. The instruction decoder 65 receives the fetched instructions from the instruction fetching stage 2 and decodes them. The pipeline sequencer

(instruction scheduler) identifies, for example, machine types of the decoded instructions and dispatches simultaneously the instructions of different machine types to corresponding function units. The machine type is information 5 for representing a function unit by which a particular instruction is processed.

Each of the function units 4-7 has a pipeline configuration, and executes an applied instruction in response to clock signals. In an example shown in FIG. 2, 10 four function units are provided, and parallel processing of up to 4 instructions can be performed. The function units 4 and 5 are integer operational units for performing integer addition or others and include executing stages EX for executing the integer arithmetic and writing stages WB for writing results of executed processing into data registers.

The function unit 6 is provided for executing access (i.e., loading or storing of data) to the data memory 8, and includes an address forming stage (ADR), an access executing stage (MEM) for the data memory 8 and a writing stage (WB) for writing the data in a data register (not shown). In the writing stage (WB), loading of the data is performed.

A function unit 7 is provided for executing, e.g., a floating-point addition, and includes three executing stages (EX1, EX2 and EX3) and a writing stage (WB) for writing the execution result in data register. The floating-point number is a number expressed by an index and mantissa and having a point which is not fixed. The execution of the floating point arithmetic operation requires more cycles than the integer arithmetic and others.

In this parallel processing apparatus, each step has a pipeline configuration, and the operation periods for instructions fetching, instruction-decoding, instruction executing and data writing overlap each other. Therefore, an instruction fetched from the instruction memory will be decoded by the instruction decoding stage in a next cycle. An operation will be briefly described below.

The instruction decoding stage 3 supplies an instruction fetch request to the instruction fetching stage 2. The instruction fetching stage 2 supplies the instruction pointer IF\_PC to the instruction memory 1 in response to this instruction fetch request and fetches a plurality of instructions corresponding to the instruction pointer IF\_PC from the instruction memory 1. These fetched instructions are simultaneously supplied to the instruction decoding stage 3, which in turn simultaneously decodes these supplied instructions. Among the decoded instructions, the instruction decoding stage 3 detects instructions, which include non-competitive calculation resources and data registers and thus allows tion memory 1 and an instruction decoding (ID) stage 3 50 parallel processing, and issues or dispatches these instructions allowing parallel processing to the corresponding function units, respectively.

The function units supplied with the instructions execute the parallel processing in accordance with the instructions. The processing in the function units 4–7 are executed in a pipeline manner, and are executed sequentially in the respective stages shown in FIG. 2. Operations of the instruction fetching stage 2, instruction decoding stage 3 and instruction executing stage (function units 4–7) are performed in the pipeline manner, and overlap each other when predetermined operations are performed.

The operations of the respective stages in the pipeline manner and the parallel processing by the function units, which are described above, enable high-speed execution of the instructions.

Processors having parallel processing capability are disclosed, for example, in (1) "The i960CA Superscalar

Implementation of the 80960 Architecture", by S. McGeagy, Proceedings of 35th COPMCON, IEEE 1990, pp 232–240, and (2) "An IBM Second Generation RISC Processor Architecture", by R. D. Groves, Proceedings of 35th COMPCON, IEEE 1990, pp 162–170. The above prior art 5 (1) discloses a processor which simultaneously fetches four instructions, and can simultaneously execute three instructions by function units of REG, MEM and CTRL.

The prior art (2) discloses a RISC processor which simultaneously fetches four instructions. This RISC proces- 10 sor includes a floating-point processor, fixed point processor, branch processor and control unit, and can simultaneously execute the four instructions.

As described above, in the superscalar, a plurality of instructions are fetched, and a plurality of instructions are 15 simultaneously executed, so that the processing speed can be increased as compared with ordinary computers. For example, in the construction shown in FIG. 2, when the four instructions which are simultaneously fetched are executed in parallel by the four function units 4–7, the four instructions can be processed in 4 clock cycles (in a case that the pipelines of the function units 4, 5 and 6 are in a waiting condition until the termination of the processing of the function units 7).

Although the instruction scheduler (or the pipeline sequencer included in the instruction decoding stage) executes the scheduling of instructions for efficiently executing the parallel processing, the instructions which are simultaneously fetched may not be simultaneously executed. As an example, instructions having following data dependency will be reviewed.

- (1) add R1, R2, R3; R2+R3=R1

- (2) sub R4, R1, R5; R1\_R5=R4

register R3 to a content of the register R2 and to write a result of addition in the register R1. Here, the superscalar is one of RISCs, and has a register file. The operation is executed using a register of the register file. Access to a memory (data memory) is performed only by loading and 40 storing instructions.

The above instruction 2 serves to subtract a content in the register R5 from a content in the register R1, and write a result of the subtraction in the register R4. The operation by these instructions 1 and 2 correspond to the processing of, for example, (x+y\_z).

When the instructions 1 and 2 are simultaneously fetched, they commonly use the register R1 and the instruction 2 uses the result of the execution of the instructions 1, so that these instructions 1 and 2 cannot be simultaneously executed. If there is such data dependency between the instructions, conditions of issue of instructions (i.e., a form of issue of the instructions from the instruction decoding stage to the function units) can be as shown in FIG. 3.

FIG. 3 shows conditions in which only the instructions allowing simultaneous processing are issued. The simultaneously issued instructions are determined in an order from a smaller address to a larger address (from left to right in the Figure).

In FIG. 3, numerals encircled by squares represent instructions which can be issued without mutual data dependency.

In a cycle 1 shown in FIG. 3, the instructions 2, 3 and 4 have data dependency on each other or on the instruction 1. 65 Therefore, the instructions 2, 3 and 4 cannot be issued, and only the instruction 1 is issued.

In a cycle 2, the instruction 4 has the data dependency on the instruction (2) and/or (3) and the instructions 2 and 3 have not mutual data dependency, so that the instructions 2 and 3 are issued.

In a cycle 3, the remaining instruction 4 is issued.

In a cycle 4, four instructions 5–8 which are newly fetched are decoded, and the instructions 5 and 6 having no mutual data independency are issued.

In a cycle 5, the instructions 7 and 8 do not have the mutual data dependency, and thus are issued. In a scheme shown in FIG. 3, fetching of the instructions is delayed until the last instructions 1–4 which were simultaneously fetched are entirely issued, in which case it requires five cycles between the issue of all the first fetched instructions 1–4 and the issue of all the subsequently fetched instructions 5–8. Therefore, in such an instruction supplying and issuing method, emptiness is formed in the pipelines, and thus the high-speed processing efficiency of the parallel processing apparatus is impaired.

Even in this case, if there were no data dependency between the instruction 4 and the instructions 5 and 6 in FIG. 3, and a given number of instructions could be fetched from the instruction memory, an instruction issue scheme shown in FIG. 4 would be allowed. FIG. 4 shows instruction issue conditions in an improved issue scheme.

Referring to FIG. 4, the instruction 1 among the simultaneously fetched four instructions 1–4 is issued in the cycle

In the cycle 2, a new instruction 5 is supplied, and the instructions 2–5 are decoded. Among the four instructions 2–5, the instructions 2 and 3 having no dependency are issued.

In the cycle 3, new instructions 6 and 7 are supplied, and The above instruction (1) serves to add a content of the 35 the instructions 4–7 are decoded. In accordance with a result of decoding, instructions 4, 5 and 6 are issued.

> In the cycle 4, new instructions 8, 9 and 10 are supplied and the instructions 7–10 are decoded. In accordance with the result of this decoding, the instructions 7 and 8 are issued.

> In the instructions issuing scheme shown in FIG. 4, only four cycles are required for issuing the eight instructions 1-8, and high-speed processing can be executed as compared with the scheme shown in FIG. 3. As one of methods for achieving the instruction issue scheme shown in FIG. 4, a method shown in FIG. 5 can be contemplated. FIG. 5 shows procedures for supplying instructions, by which the instruction issue conditions shown in FIG. 4 can be achieved.

In a step (1) shown in FIG. 5, when instructions 2 and 3 among the instructions 2–5 held by an instruction register, which is employed for holding the instructions, are issued, emptiness is formed in the instruction register.

In a step (2), a content of the instruction register is shifted by a number corresponding to the number of the empty registers. That is; in the step (2) in FIG. 5, register positions of the instructions 4 and 5 are respectively shifted leftward by two.

In a step (3), subsequent instructions 6 and 7 are fetched into these empty instruction registers. The steps (1)–(3) shown in FIG. 5 must be executed in one cycle. A construction shown in FIG. 6 may be contemplated for performing the instruction shifting operation shown in FIG. 5.

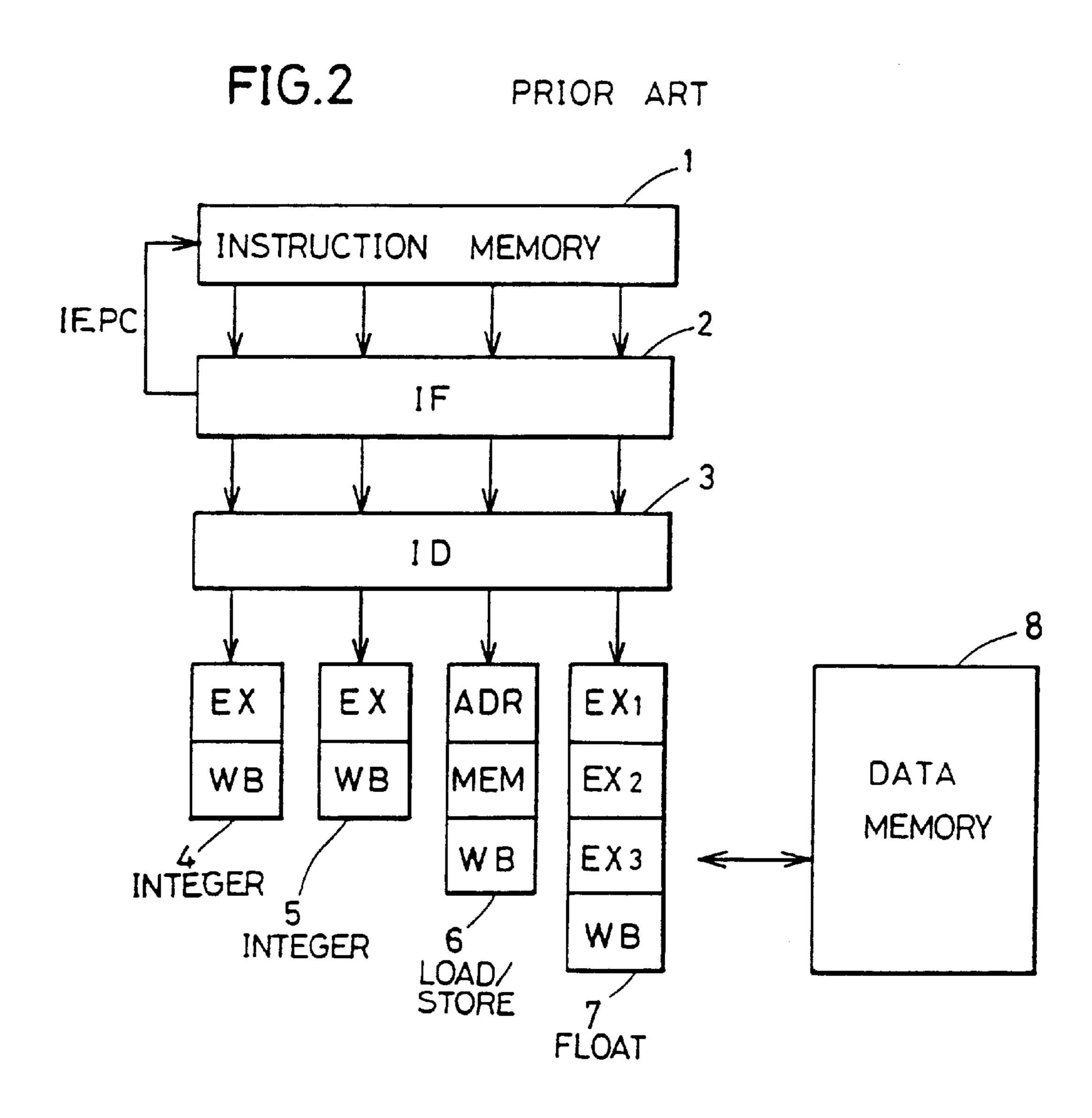

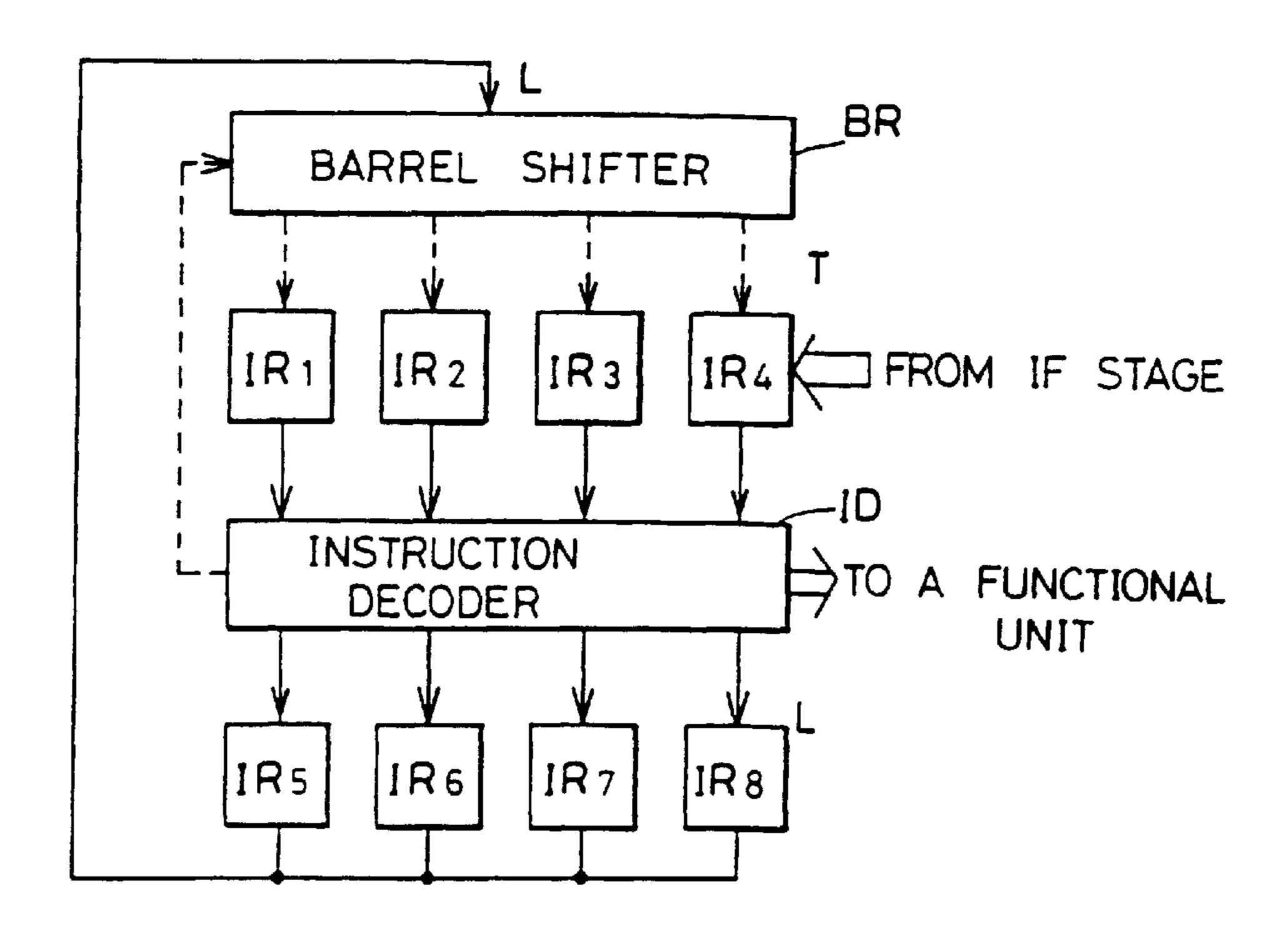

In FIG. 6, an instruction decoding stage includes instruction registers R1-R8 for storing the instructions, a barrel shifter BR for shifting the applied instructions and an

instruction decoder ID. The instruction registers IR1–IR4 store the instructions fetched by the instruction fetching stage 2 and the instructions shifted by the barrel shifter. The instruction registers IR5–IR8 accommodate the instructions applied to the instruction decoder ID without decoding. The barrel shift BR shifts the instructions from the instruction registers IR5–IR8 in accordance with information of issued instruction count from the instruction decoder ID.

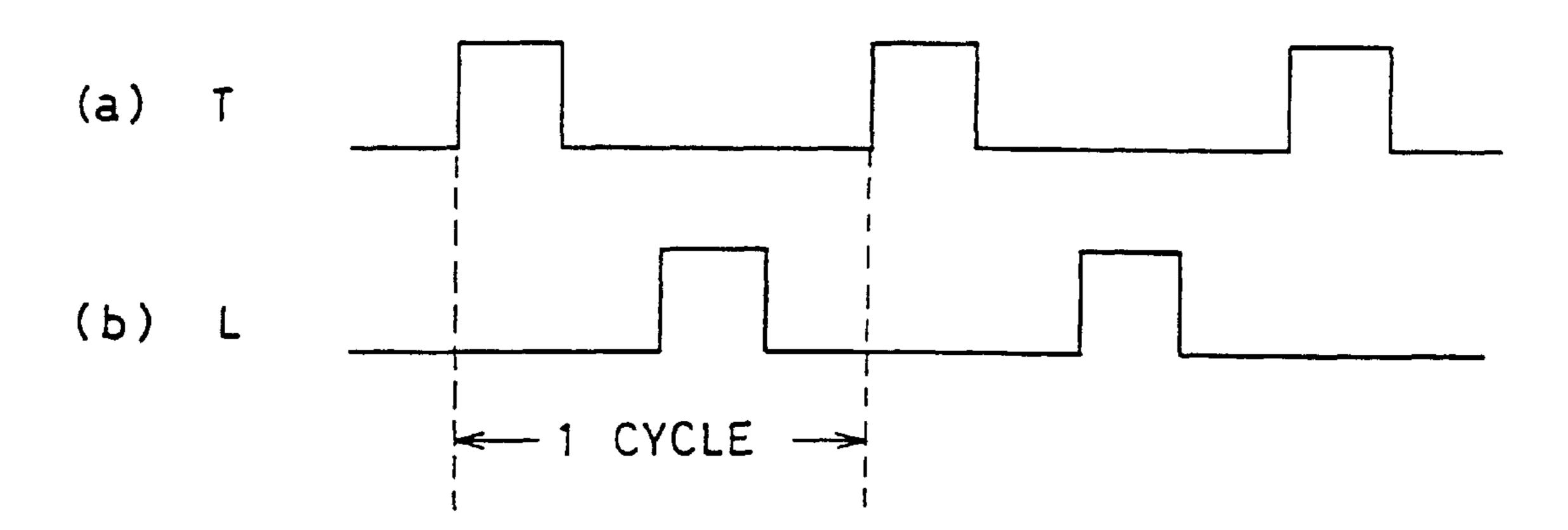

Usually, the parallel processing apparatus operates in accordance with clock signals T and L in two phases without 10 mutual overlapping. An operation will be briefly described below.

Instructions which were fetched in the last cycle are held in the instruction registers IR1–IR4 in response to the clock signal T. The holding instructions of the instruction registers 15 IR1–IR4 are applied to and decoded by the instruction decoder ID, and are issued to the instruction units in accordance with a decoded result.

The instruction registers IR5–IR8 are responsive to the clock signal to hold the instructions applied to the instruction decoder ID and apply the same to the barrel shifter BR. The barrel shift BR responds to the information of the issued instruction count from the instruction decoder ID by shifting the instructions applied from the instruction registers IR5-IR8. The contents of the barrel shifter BR are applied to and held by the instruction registers IR1–IR4 in response to the subsequent clock signal T.

In this case, the barrel shifter is required to complete the shifting operation for the instructions in a period between 30 the clock signal L and the subsequent clock signal T. In the barrel shifter BR, however, an instruction length is long (e.g., 32 bits; the instruction length is fixed in RISC), so that the instruction shifting operation cannot be performed at a high-speed and requires a long period of time. Therefore, it 35 for generating said write queue addresses and read queue is impossible to apply the instructions to the instruction registers IR1-IR4 to be held therein in response to the subsequent clock signal T, and thus it is impossible to supply the instructions to the instruction decoder ID at a high speed, which impairs the high-speed operability of the parallel 40 processing apparatus.

The instruction memory is required to obtain information of a number of the empty registers in the instruction registers IR1–IR4 and determine the instruction supply number and the instruction supply positions based on this information. 45 The information relating to the number of the existing empty registers in the instruction registers RI1–RI4 is obtained by the issued instruction count information from the instruction decoder ID. However, this issued instruction count information is issued after the decoding operation by the instruction decoder ID. Therefore, it requires a long time to determine the instruction supply number and instruction supply positions by the instruction memory, and a timing for starting the determining operation is delayed. Therefore, it requires a long period of time for fetching the desired 55 instructions, and increased period of the clock signals T and L is required for executing the instructions without disturbing the pipeline architecture, which impairs the high-speed operability of the parallel processing apparatus.

### SUMMARY OF THE INVENTION

Accordingly, an object of the invention is to provide a parallel processing apparatus capable of efficiently performing parallel processing.

Another object of the invention is to provide a parallel 65 processing apparatus provided with an instruction suppling device capable of efficiently performing parallel processing.

Still another object of the invention is to provide an instruction supplying device for improving a parallel processing performance of a processor of a superscalar type.

Yet another object of the invention is to provide an instruction supplying method for improving a parallel processing performance in a parallel processing apparatus.

Further another object of the invention is to provide an instruction supplying method for improving a parallel processing performance in a parallel processing apparatus of a superscalar type.

An instruction supplying device in a parallel processing apparatus according to the invention includes means for forming an availability flag indicating availability/ unavailability of an instruction in response to a signal which indicates whether the instruction is supplied from an instruction memory device or not, a reset signal and branch generation indicating information which indicates generation of branch; and memory means for simultaneously storing a plurality of instructions, which are simultaneously fetched from an instruction memory as well as addresses and availability flags of the simultaneously fetched instructions in said instruction memory. This memory means includes a plurality of entry storing regions, of which each entry is formed of one instruction, a corresponding address and a corresponding availability flag. This memory means further includes a plurality of input ports to which respectively different write entry contents are simultaneously transmitted, a plurality of output ports to which respectively different read entry contents are simultaneously transmitted, and means for coupling a plurality of write entries and a plurality of read entries to the input ports and the output ports in response to write queue addresses and read queue addresses, respectively.

This instruction supplying device further includes means addresses in response to issued instruction count information, a branch generation indicating signal and an instruction supply indication signal indicating a fact that an instruction is supplied, respectively.

Contents of the entries which are simultaneously read from the memory means are applied to the instruction decoding device.

The memory device includes the input ports and output ports which can be individually accessed. Through these output ports, a plurality of instructions which are simultaneously fetched from the instruction memory are stored together with the addresses and the availability flags in the different entry regions, respectively.

A plurality of entry regions are simultaneously selected from these entry storing regions in response to the read queue addresses and are connected to the different output ports, respectively, whereby a plurality of entry contents are simultaneously read. Since these input ports and output ports are individually accessible, writing and reading for the entries can be simultaneously executed. The write queue addresses and read queue addresses are selected in accordance with the conditions of issue of the instructions and the conditions of supply of the instructions from the instruction memory, and a constant number of instructions are always 60 applied to the instruction decoding device as issue target instructions. The availability flags determine whether the issue of the instructions are allowed.

In this manner, an appropriate number of instructions which compensates the issued instructions are always supplied simultaneously to the instruction decoding device, and thus the instruction supply can be efficiently conducted, which enables high-speed execution of the instructions.

The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 shows a conceptional construction of a parallel processing apparatus;

- FIG. 2 shows a general construction of a parallel processing apparatus;

- FIG. 3 shows an instruction supplying scheme in a prior art parallel processing apparatus;

- FIG. 4 shows an instruction supplying scheme intended 15 by the present invention;

- FIG. 5 shows an instruction supplying scheme which can be contemplated for achieving an instruction supplying scheme shown in FIG. 4;

- FIG. 6 shows an example of a construction for achieving an instruction supplying scheme in FIG. 5;

- FIG. 7 shows two-phase clocks used in an parallel processing apparatus;

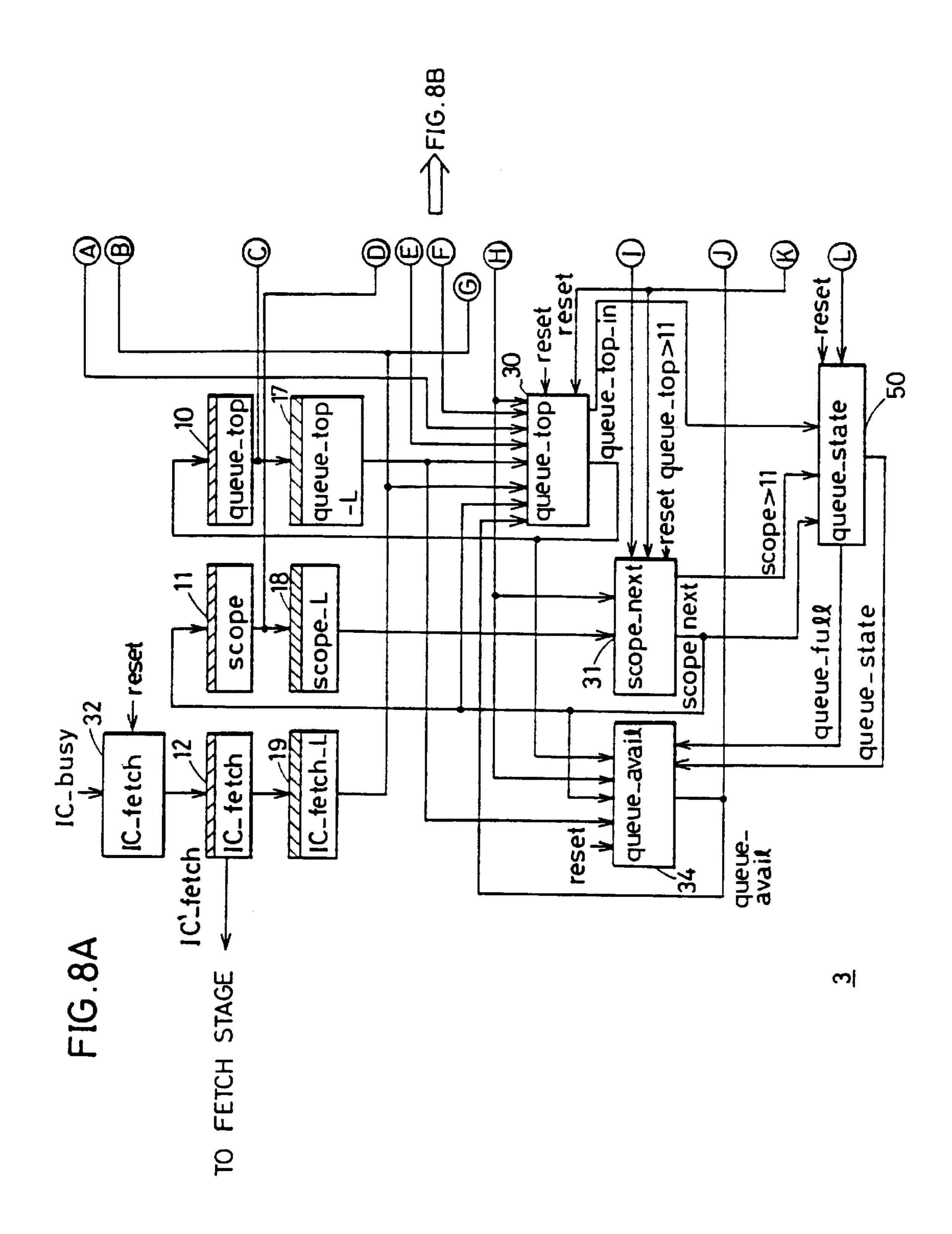

- FIGS. 8(A) and 8(B) show a construction of an instruction 25 supplying stage in a parallel processing apparatus of an embodiment of the invention;

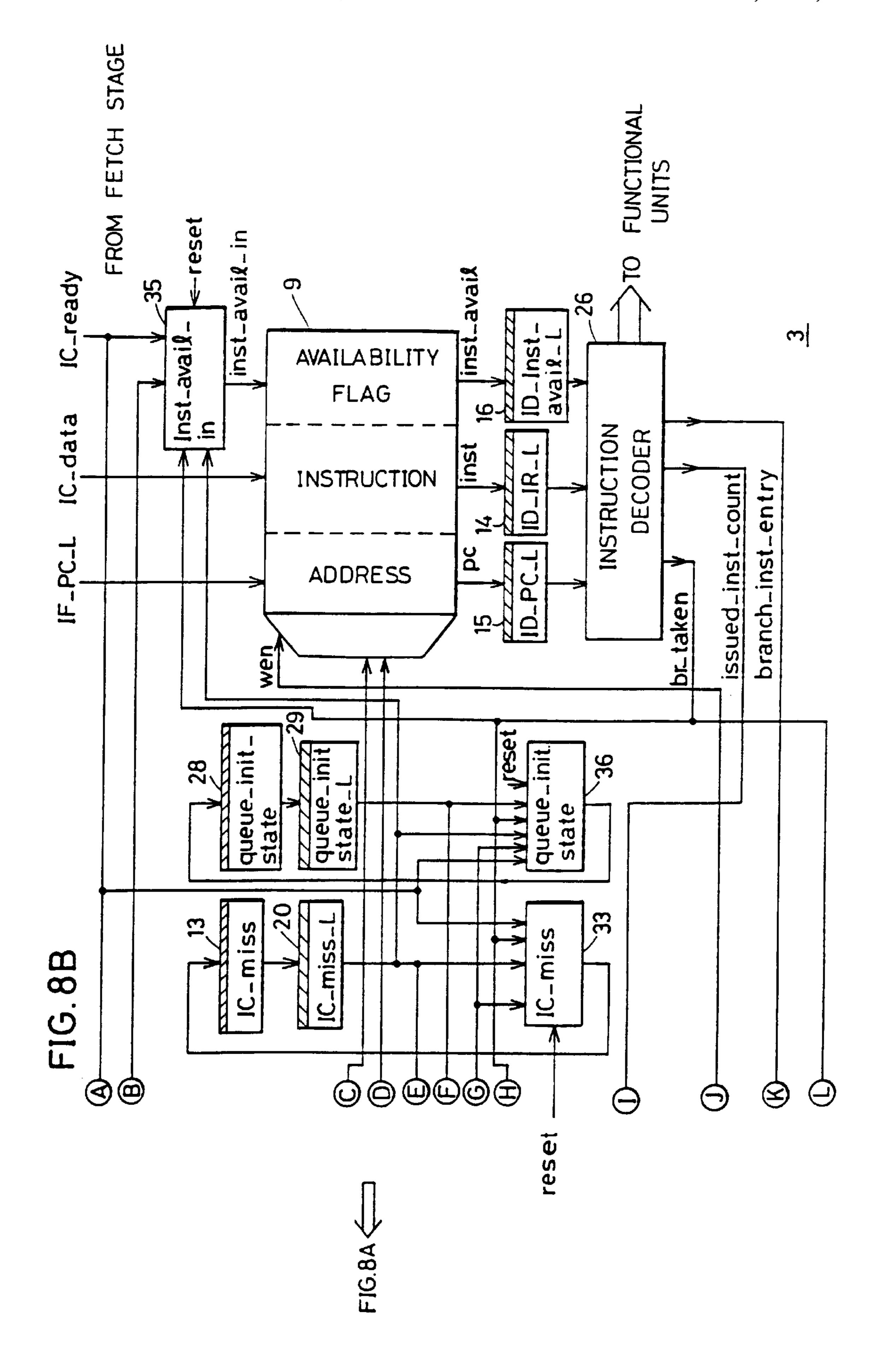

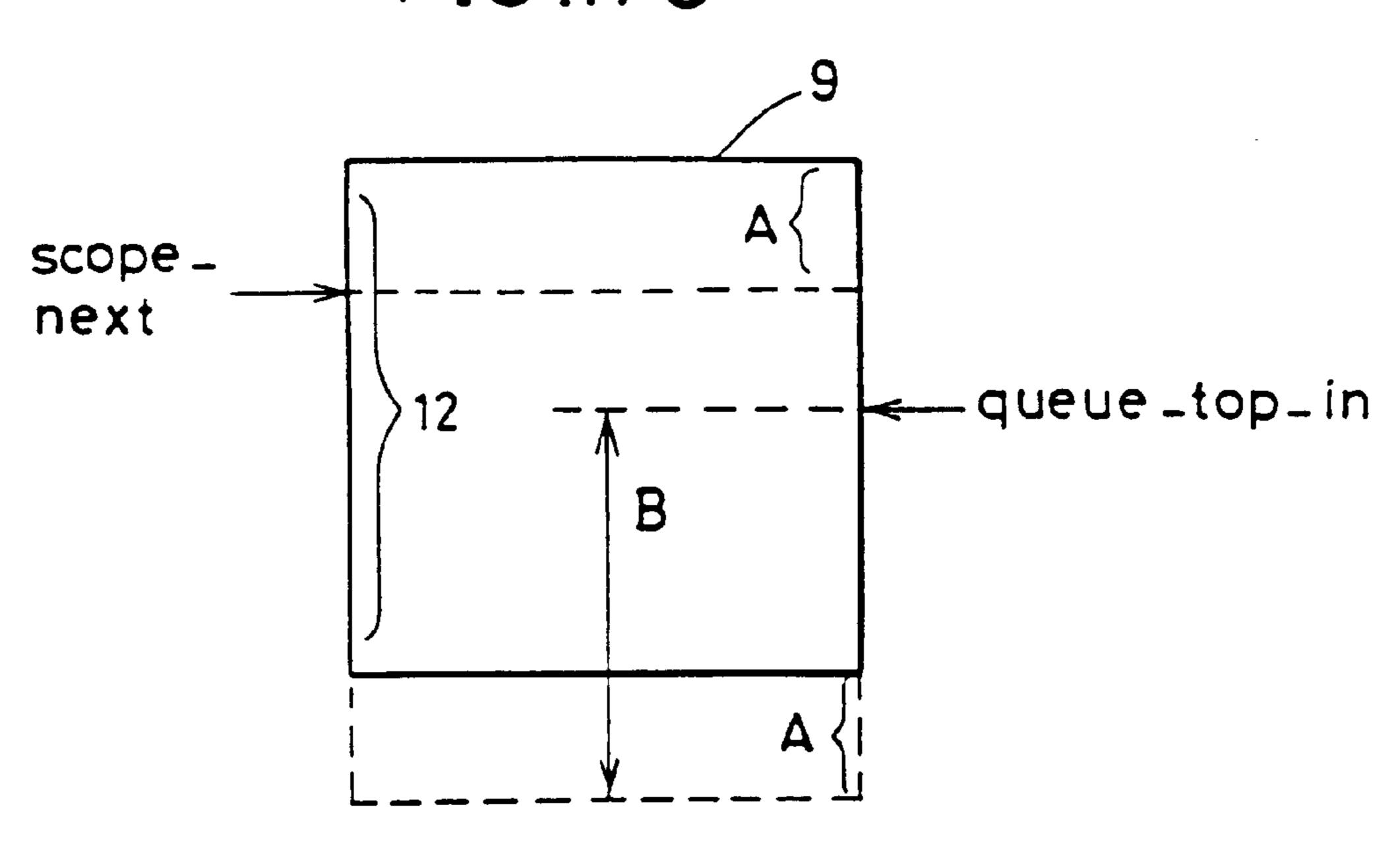

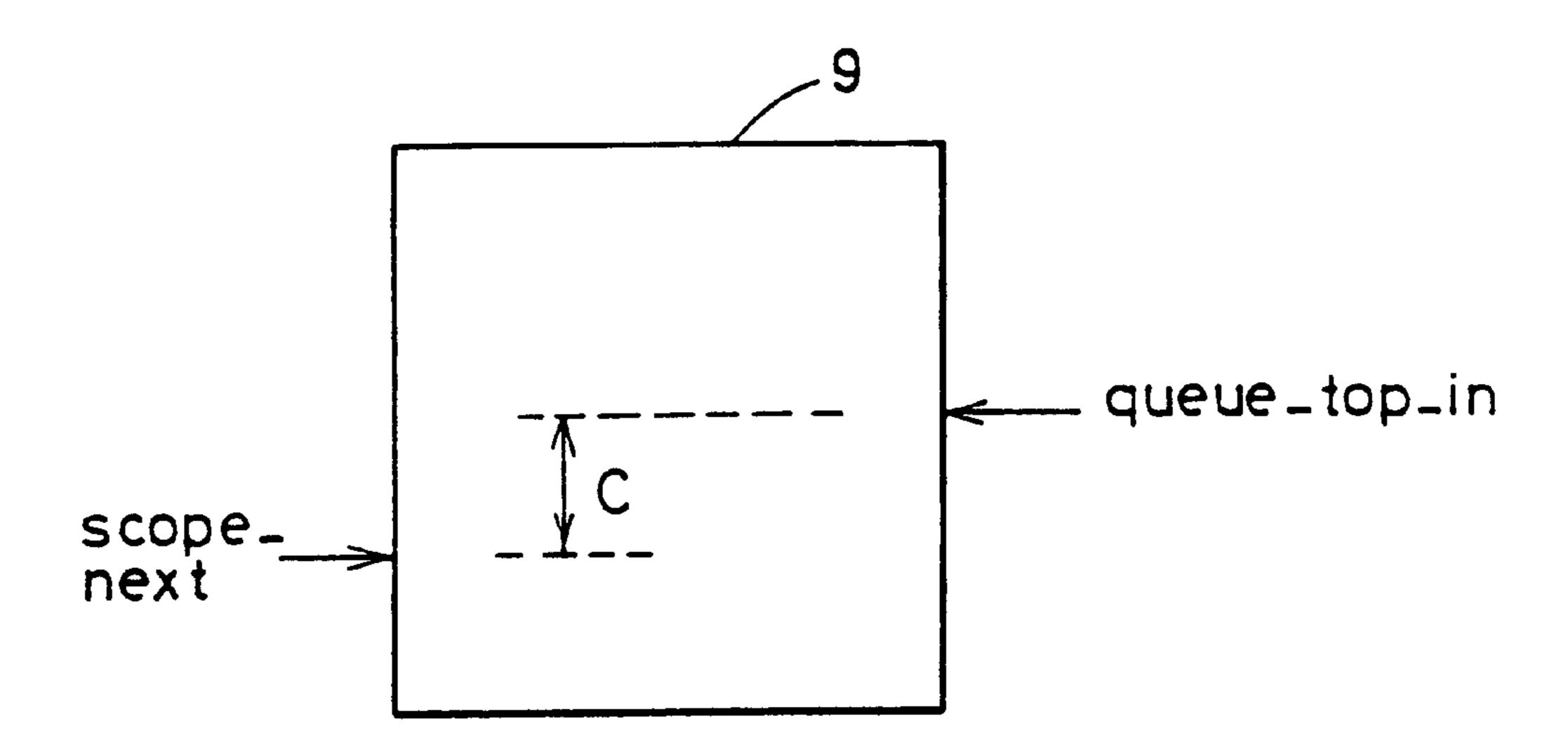

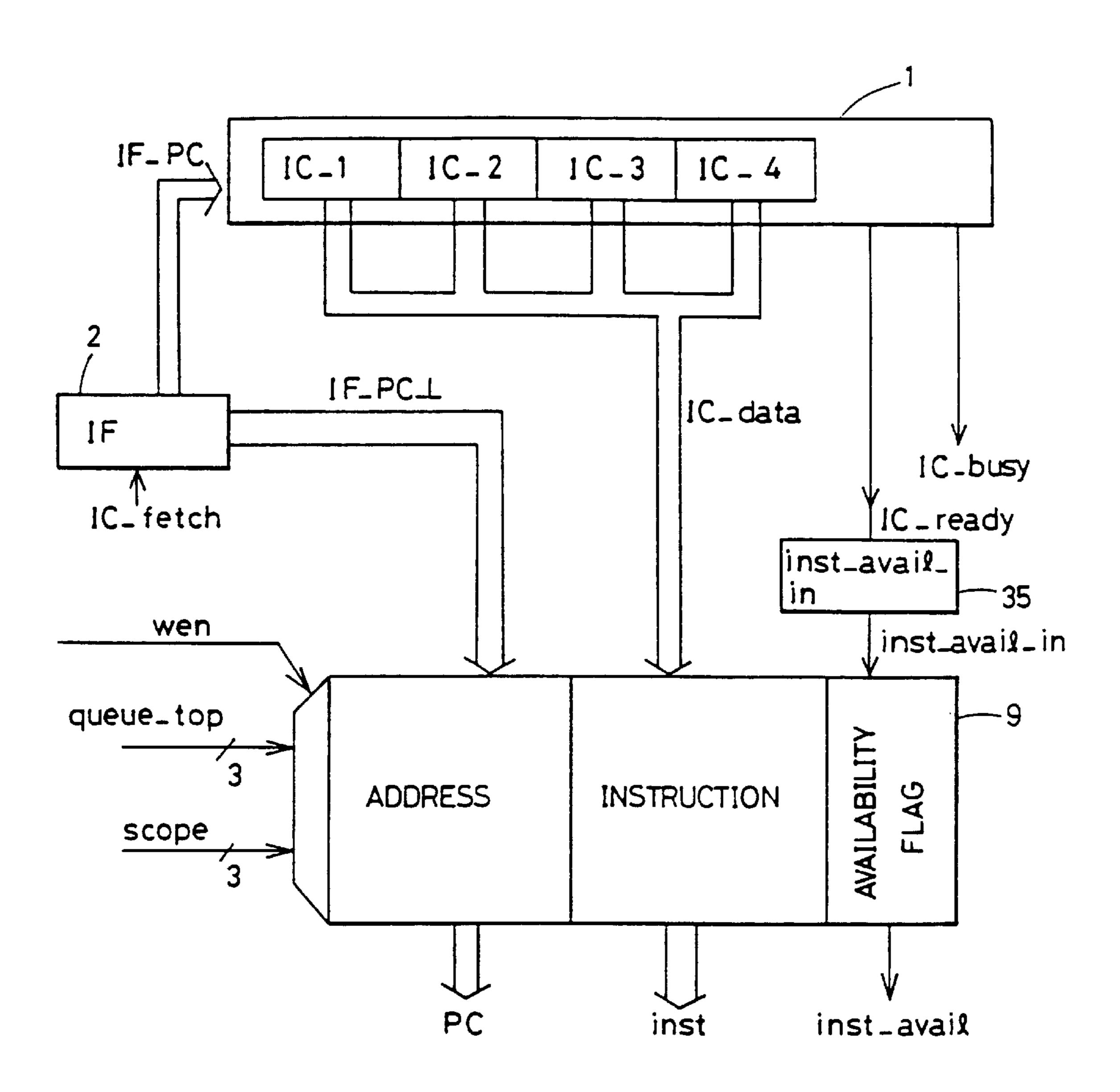

- FIG. 9 shows a conceptional construction of a queue in FIG. **8**;

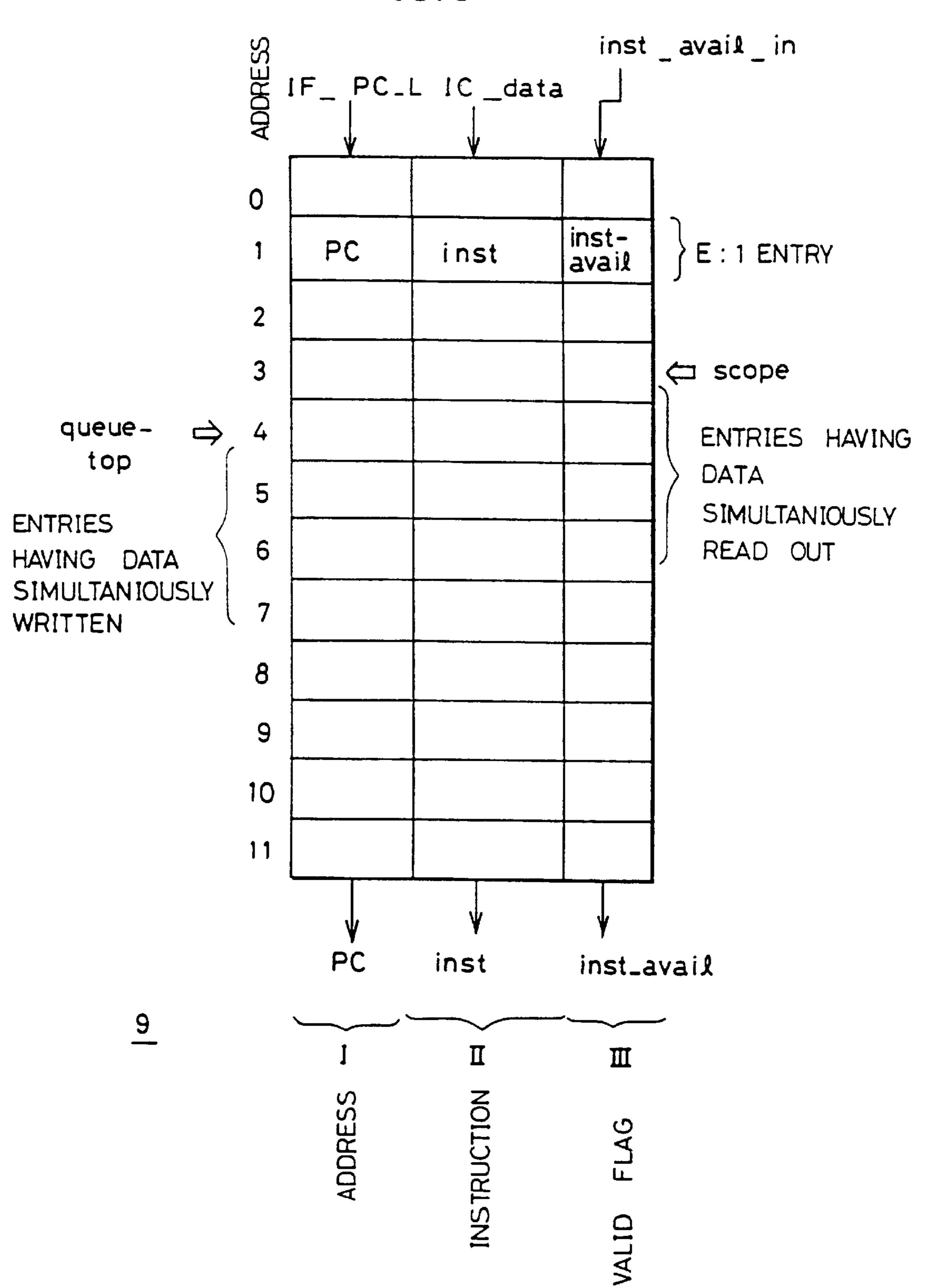

- FIG. 10 shows fundamental movement of addresses of a queue in a parallel processing apparatus according to the invention;

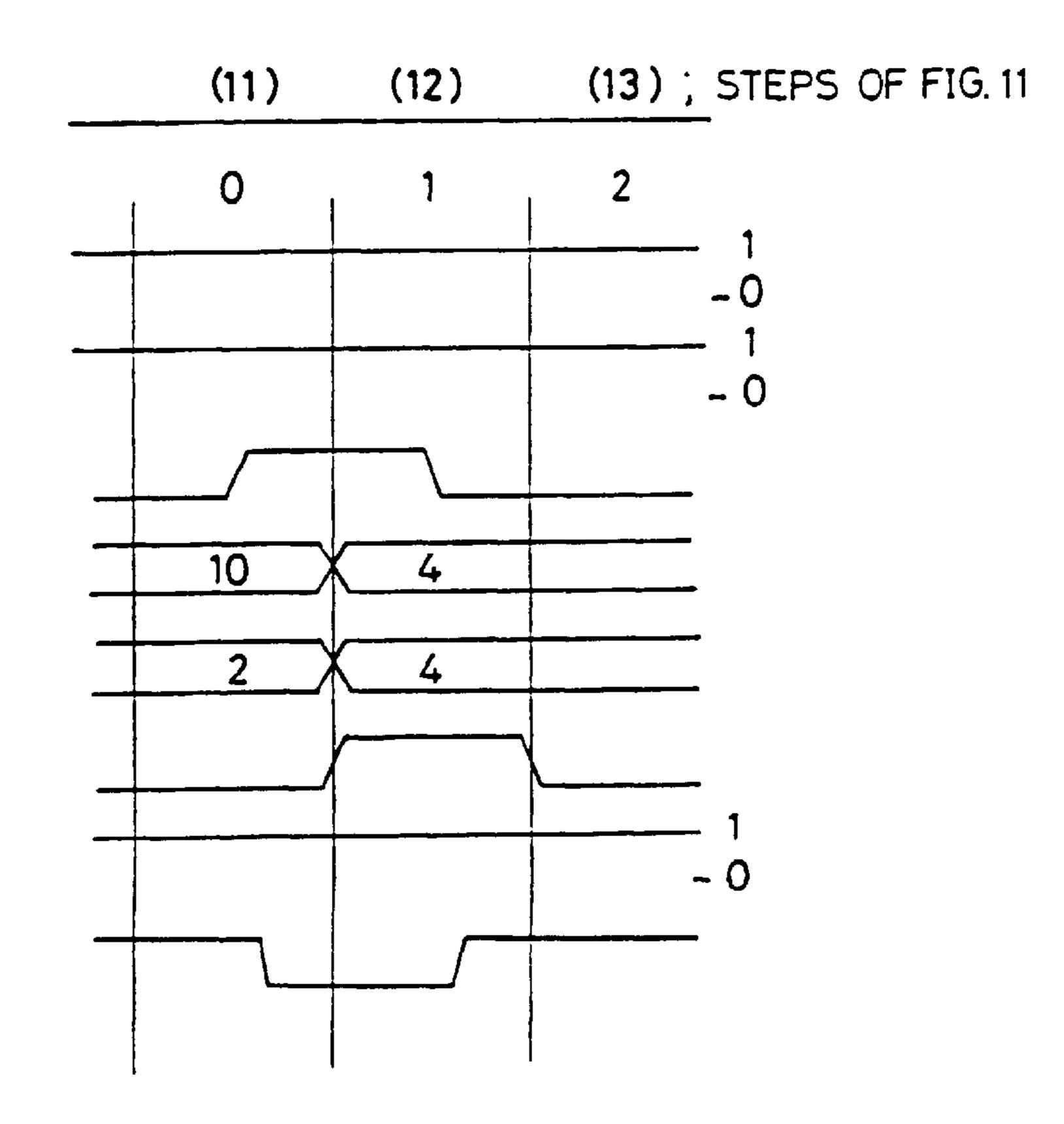

- FIG. 11 shows movement of write/read addresses and availability flags in a queue in a parallel processing apparatus of the invention;

- FIG. 12 shows movement of write/read addresses and availability flags in a queue when an instruction fetch request is issued and an instruction supply is not performed in a parallel processing apparatus of the invention;

- FIG. 13 is a list showing logic for achieving queue-top logic shown in FIG. 8;

- FIG. 14 is a list showing logic for achieving scope next logic shown in FIG. 8;

- FIG. 15 is a list showing logic for achieving instruction fetch logic shown in FIG. 8;

- FIG. 16 is a list showing logic for achieving instruction miss logic shown in FIG. 8;

- logic shown in FIG. 8;

- FIG. 17B is a list showing a logic operation for achieving queue full contained in FIG. 17A;

- FIGS. 17C and 17D shows a logic operation of queue full shown in FIG. 17B;

- FIGS. 18A and 18B shows a second state of a queue;

- FIGS. 19A and 19B shows a third state of a queue;

- FIG. 20 is a list showing logic for achieving queue state logic shown in FIG. 8;

- FIG. 21 is a list showing instruction avail logic of a queue shown in FIG. 8;

- FIG. 22 is a list showing logic for achieving queue initialized state logic shown in FIG. 8;

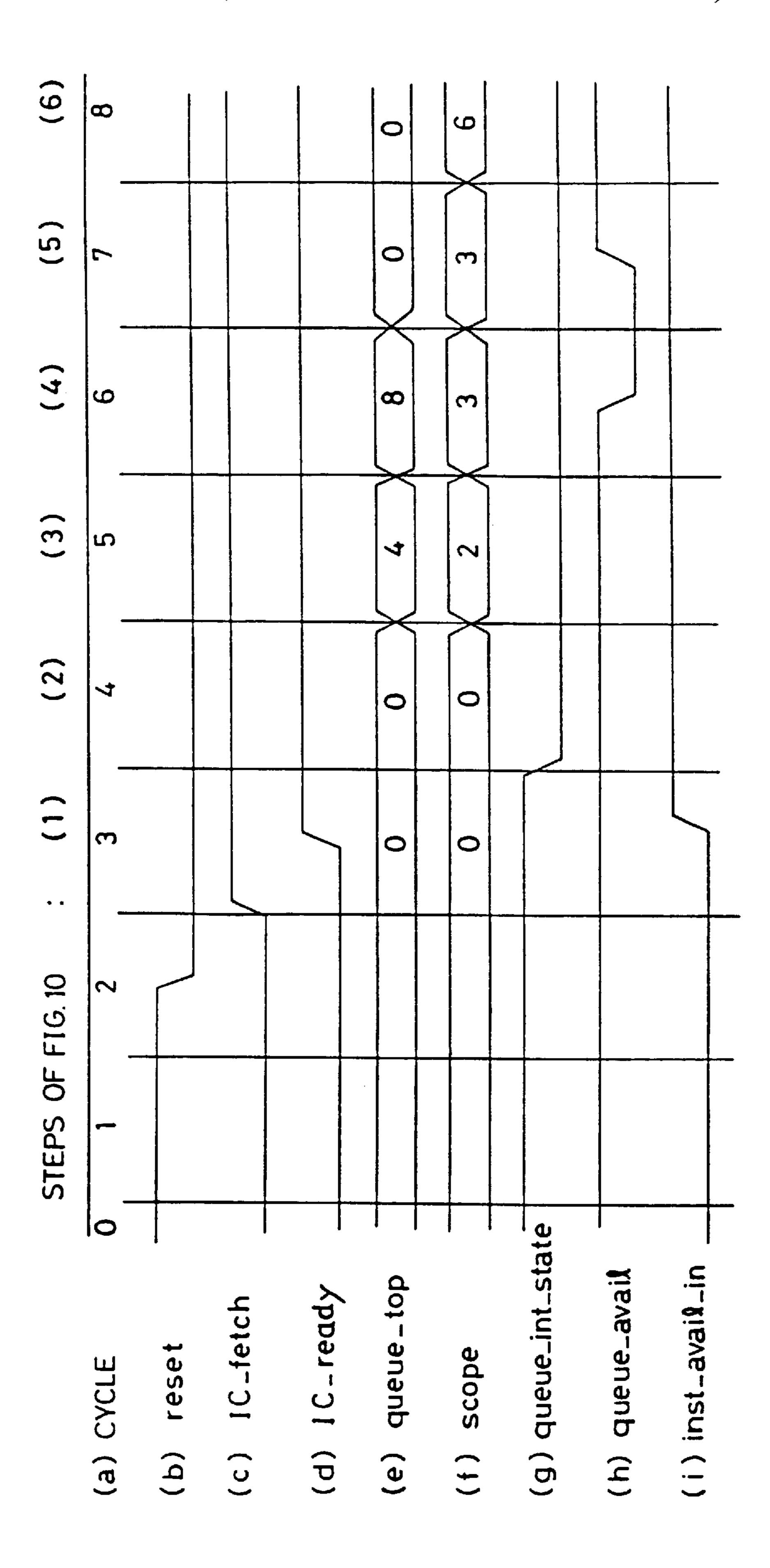

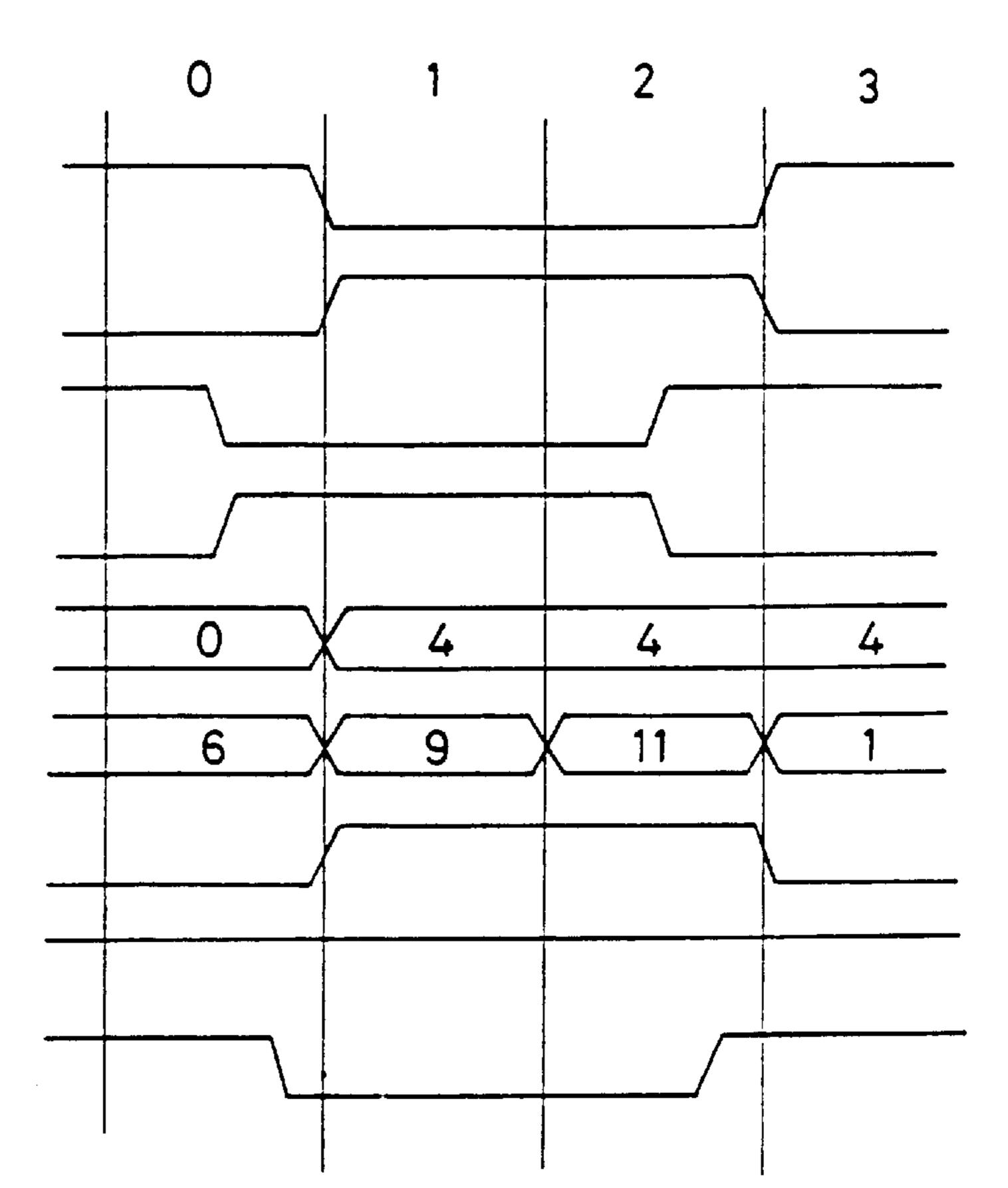

- FIG. 23 is a signal waveform diagram showing operations 65 of respective logics in a basic movement of a queue shown in FIG. 8;

8

- FIG. 24 is a signal waveform diagram showing operations of respective logics of a queue shown in FIG. 8 at a time of generation of branch;

- FIG. 25 is a signal waveform diagram showing operations of respective logics shown in FIG. 8 in a case that instruction supply is not performed with respect to an instruction fetch request;

- FIG. 26 shows a conceptional correlation between instructions, addresses and availability flags applied to a queue from an instruction memory;

- FIG. 27 shows an example of a layout configuration of an instruction applied to a queue;

- FIG. 28 shows an example of a layout configuration of an available address applied to a queue;

- FIG. 29 shows an example of a layout configuration of availability flags applied to a queue;

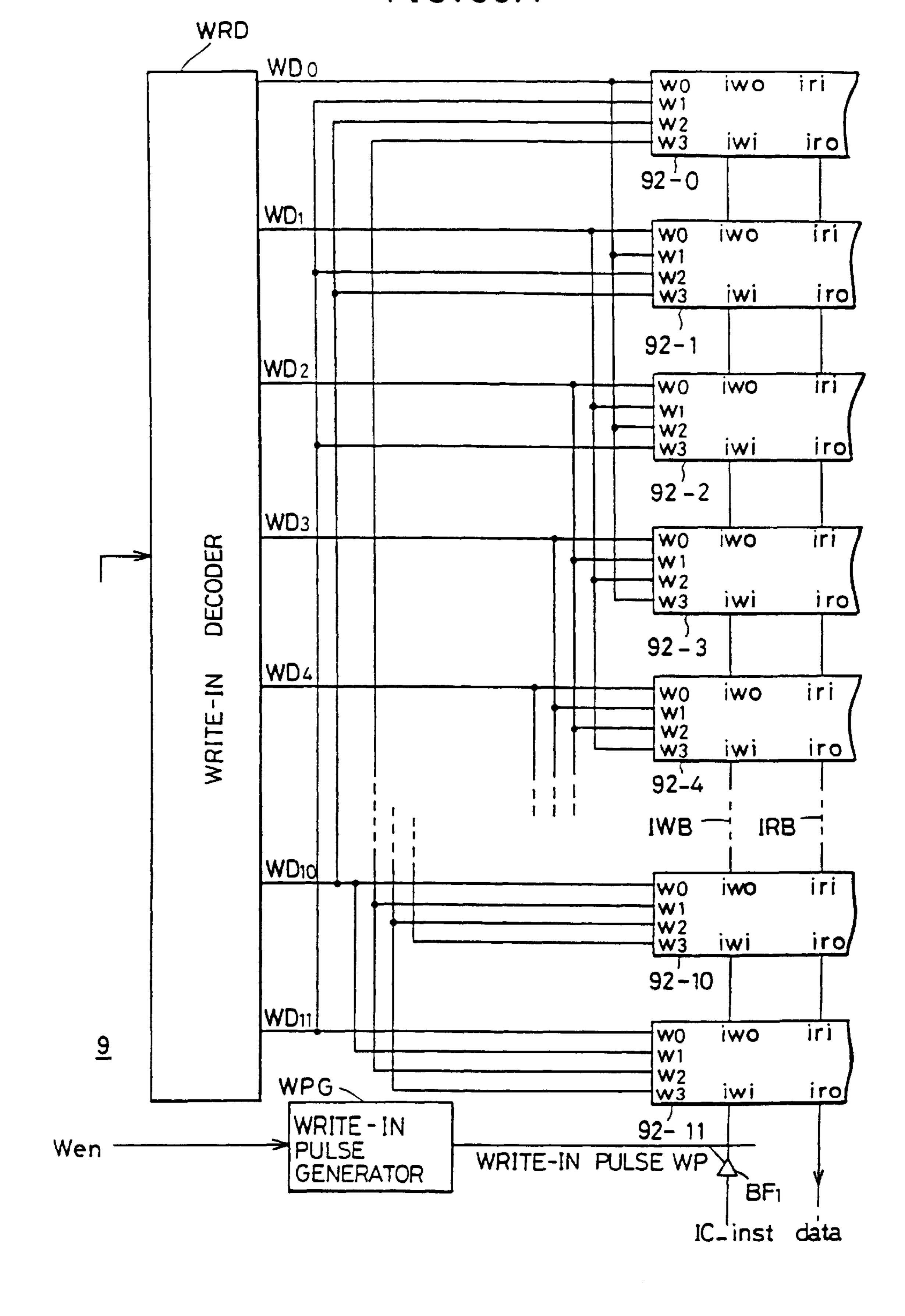

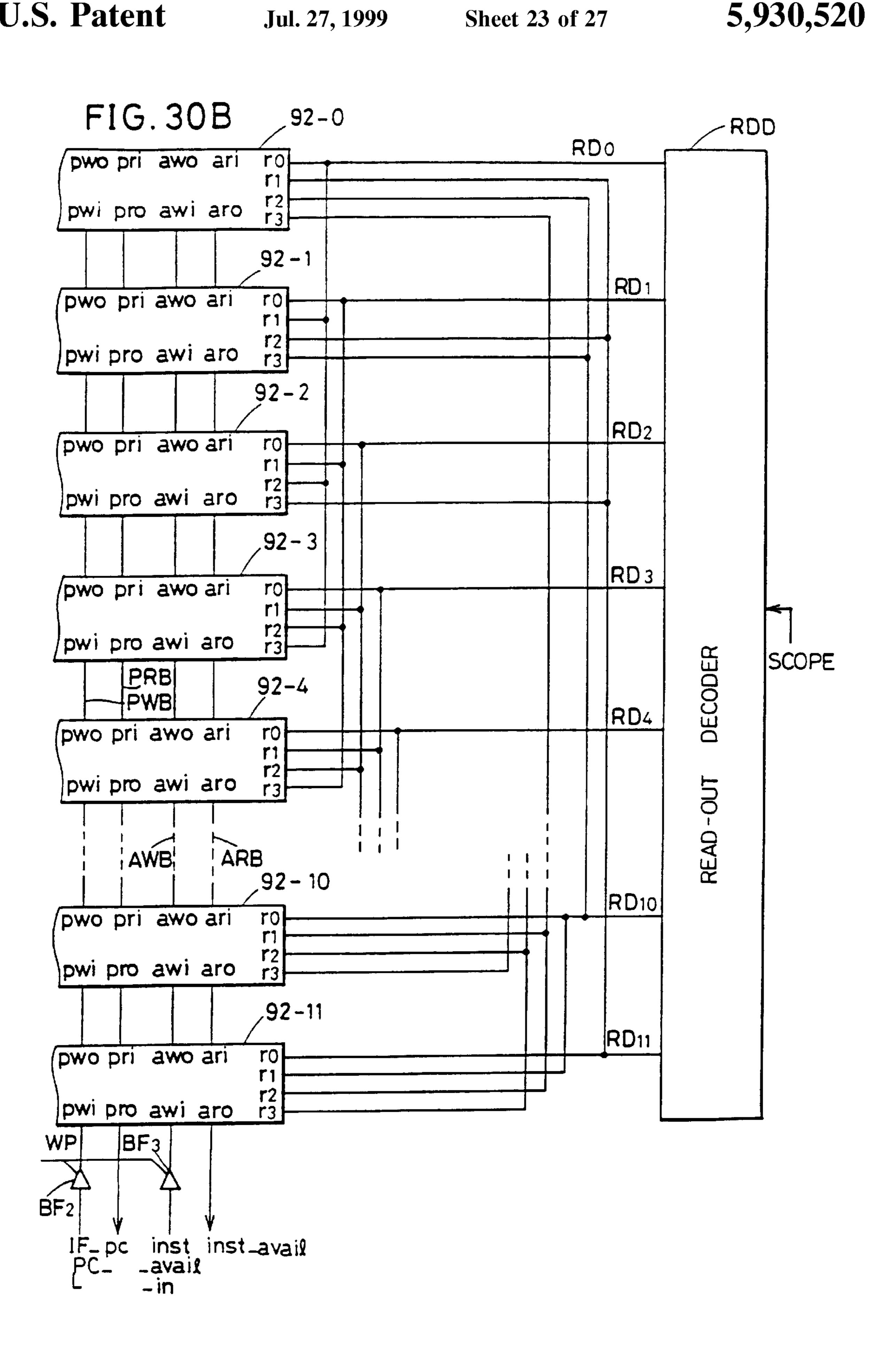

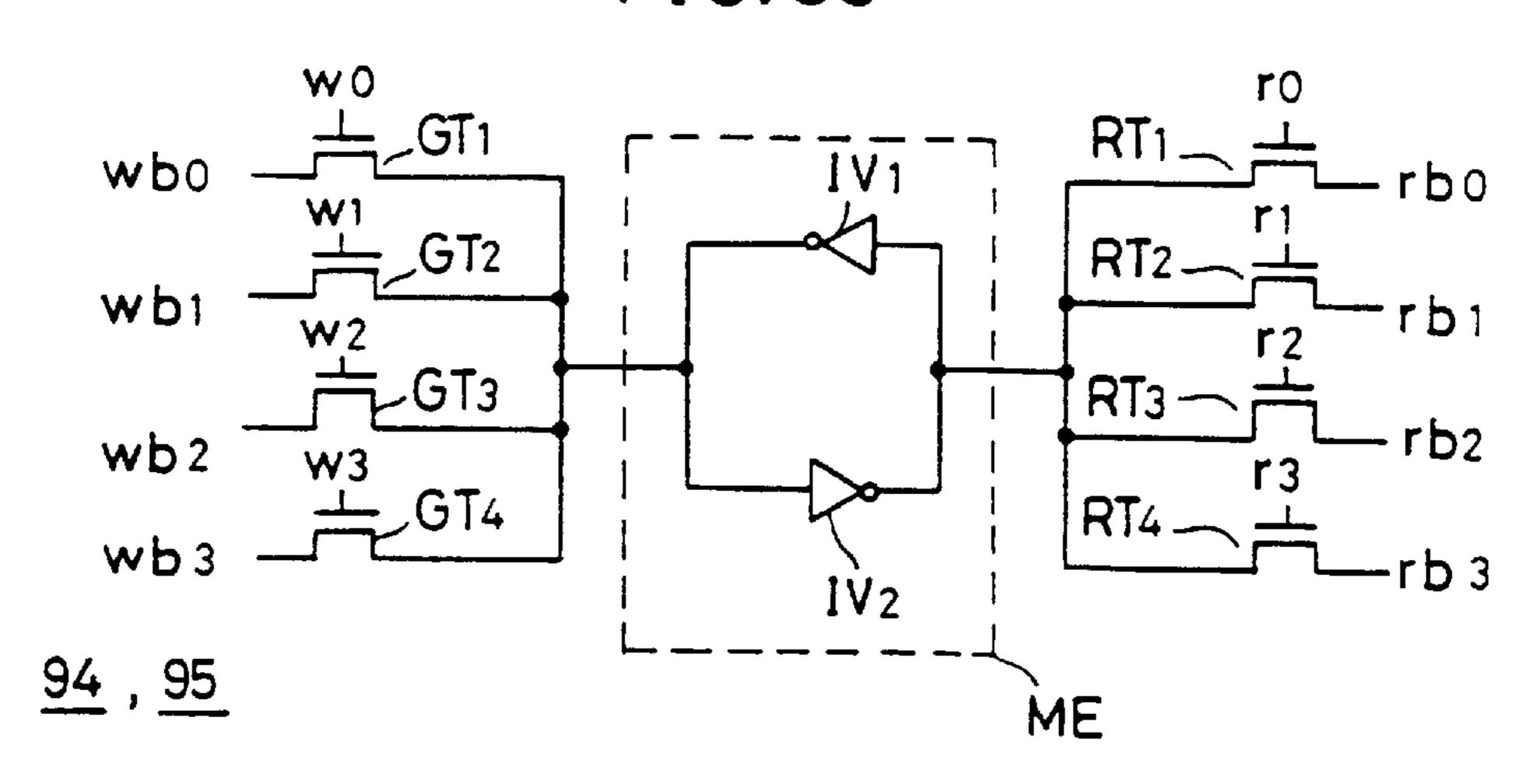

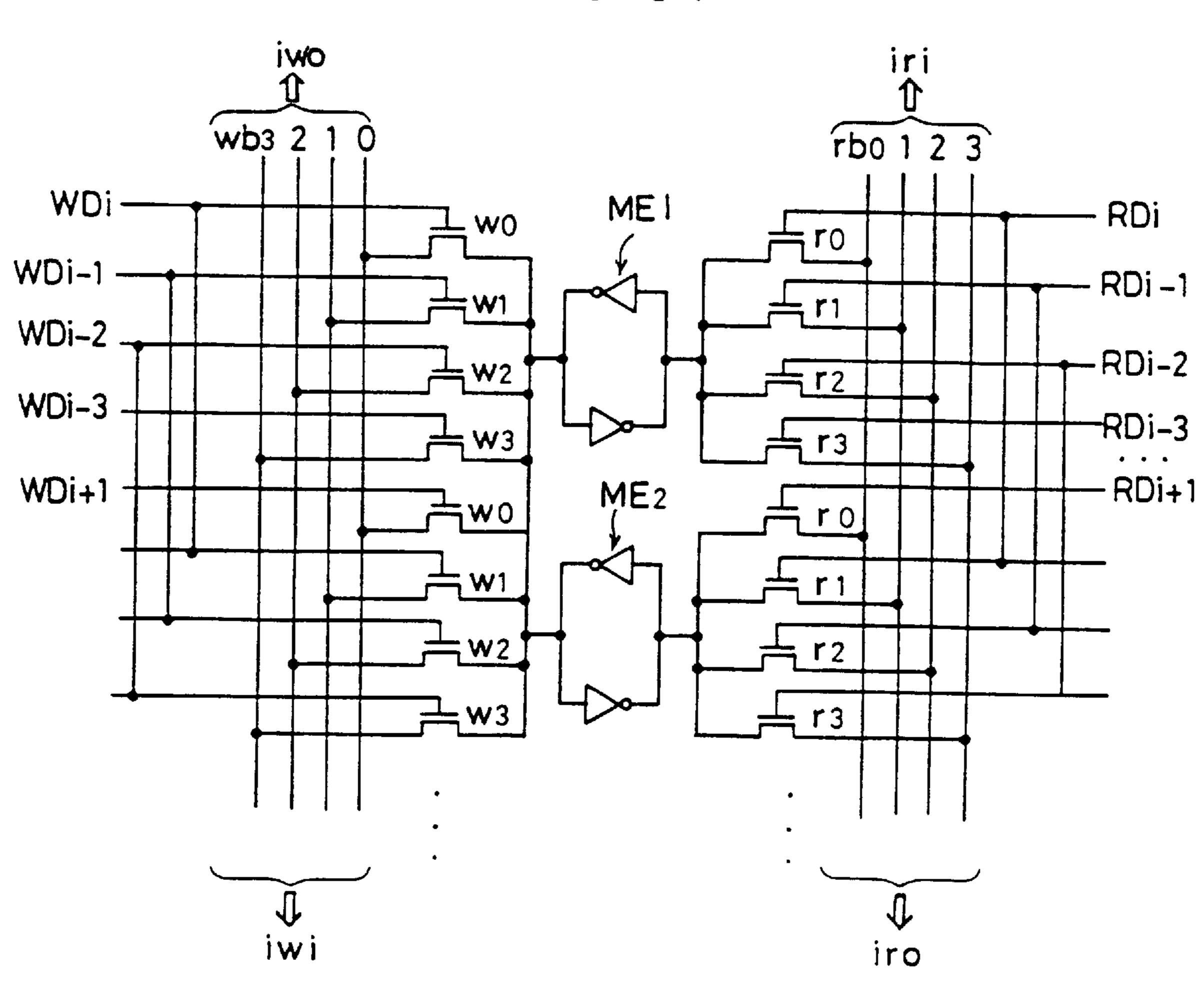

- FIGS. 30(A) and 30(B) show an entire construction of a queue;

- FIG. 31 shows a construction of an entry memory device shown in FIG. 30;

- FIG. 32 shows a construction of an instruction memory device and an address memory device shown in FIG. 31;

- FIG. 33 shows an example of a construction of an instruction and address memory devices as well as an availability flag memory device shown in FIG. 32;

- FIG. 34 shows an example of a coupling configuration of a bit memory device shown in FIG. 33;

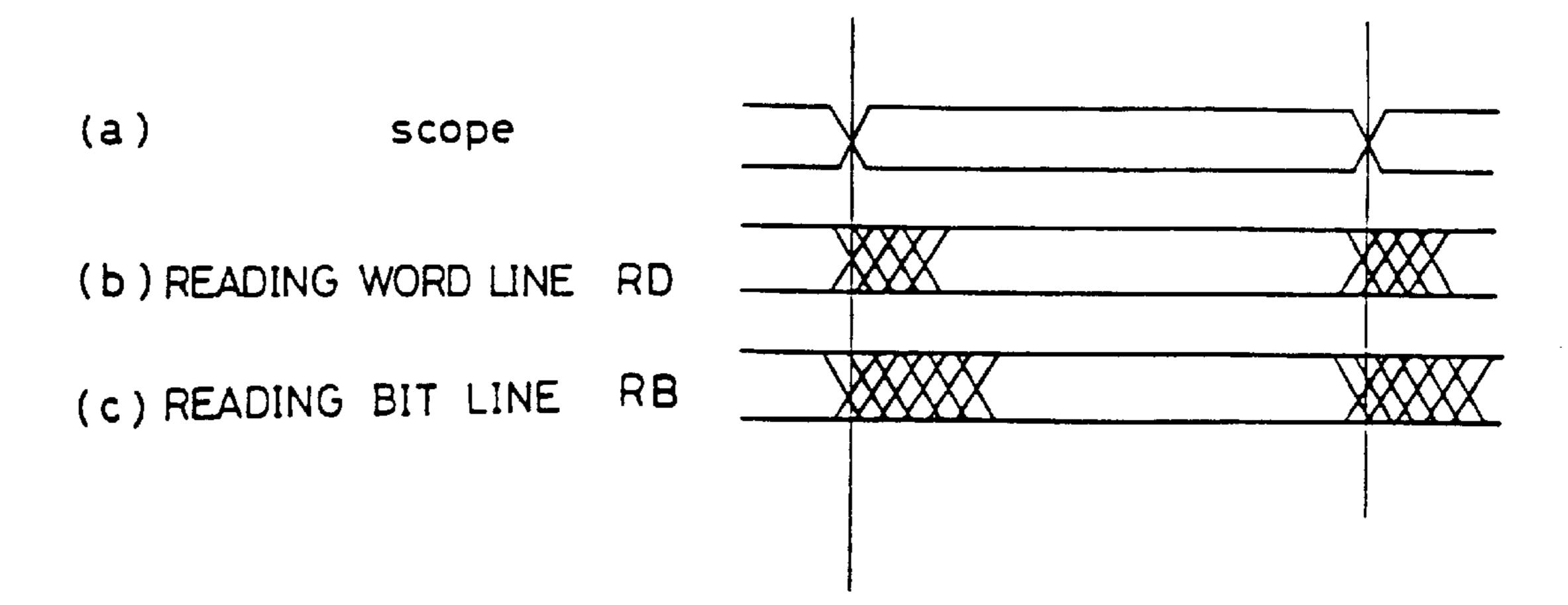

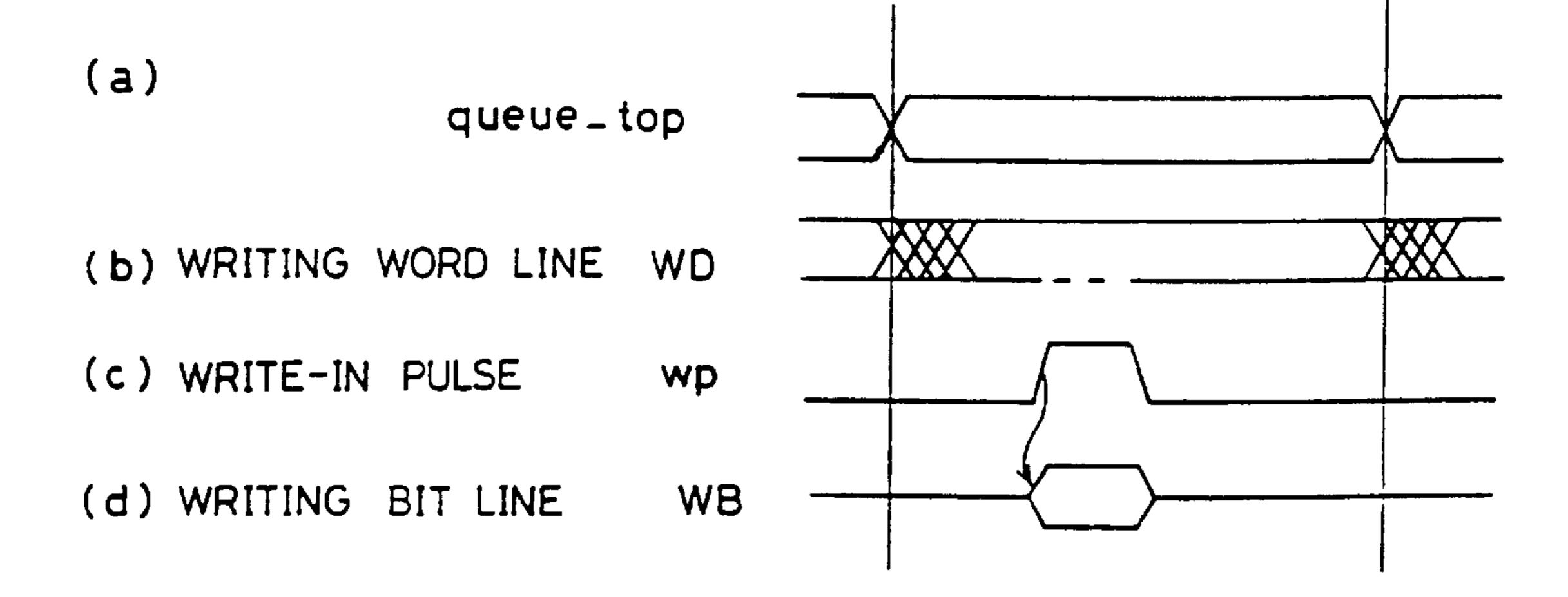

- FIG. 35 is a signal waveform diagram showing an operation of a queue during data reading; and

- FIG. 36 is a signal waveform diagram showing an operation of a queue during data writing.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 8 shows a construction of a major part of a superscalar which is one of parallel processing apparatuses and an embodiment of the invention. The construction shown in FIG. 8 corresponds to an instruction decoding stage of the superscalar. The device shown in FIG. 8 operates in response to the clock signals T and L at two phases which do not overlap each other (see FIG. 7).

Although not shown, the instruction fetching stage (see FIG. 2) fetches a plurality of (four in this embodiment) instructions from an instruction memory in accordance with an instruction fetch request from an instruction decoding stage. A fetched instruction IC\_data and a logic address FIG. 17A is a list showing logic for achieving queue avail 50 IF\_PC\_L of this fetched instruction are supplied to the decoding stage together with a signal IC\_ready which indicates a fact that the instruction is supplied from the instruction memory. The logic address IF\_PC\_L of the fetch instruction is supplied from a pointer which forms an address in the instruction memory and is included in the instruction fetching stage.

> The instruction memory generates and applies a signal IC\_busy to the decoding stage, for example, in such conditions that access to a low-speed main memory (or an 60 external memory) is carried out due to cache miss or the instruction memory is accessed. The above signal IC\_busy indicates that the main memory cannot accept the instruction fetch request.

Referring to FIG. 8, an instruction supplying device, which is an embodiment of the invention, includes a queue 9 formed of a random access memory (RAM) which stores, as one entry, the logic address (IF\_PC\_L) of an instruction

9

fetched from the instruction memory, a fetched instruction (IC\_data) and an availability flag (inst\_avail) indicating availability and unavailability of the fetched instruction. The queue p, of which construction will be described in greater detail later, can store, for example, 12 entries and has a plurality of write ports and a plurality of read ports. Owing to these plurality of write and read ports, contents of a plurality of (four in this embodiment) continuous entries can be simultaneously written or read by designating one write gate and one read gate.

In order to control the reading and writing of the instruction in and from the queue 9 as well as availability and unavailability of the stored instruction, there are provided T-latch circuits 11, 12, 13 and 28 for holding applied signals in response to the clock signals T, L-latch circuits 17, 18, 19, 20 and 29 which are provided correspondingly to the respective T-latch circuits 10–13 and 28 for holding output data (held data) of the corresponding T-latch circuits in response to the clock signals L. There are further provided logic circuits 30, 31, 32, 33, 34, 35, 36 and 50 which generate signals, read and write addresses of the queue 9, operation 20 control signals and signals indicating availability/ unavailability of the instructions, based on held data of the respective L-latch circuits 17–20 and 29, signals br\_taken, issued\_inst\_count and branch\_binst\_entry from the instruction decoder 26.

The T-latch circuit 10 (will be called as a "queue top latch 10") is responsive to the clock signal T to hold an address queue\_top which indicates first addresses of a plurality of entries in which instructions fetched by the queue 9 from the instruction memory is to be written. When simultaneously fetched four instructions are stored in the queue 9, the instructions, their logic addresses and their availability flags are written in following addresses of the queue 9:

queue\_top, queue\_top+1, queue\_top+2, queue\_top+3 wherein "+" represent module addition with respect to a whole entry number (12 in this embodiment) of the queue 9.

The L-latch circuit 17 (will be called as a "queue top L-latch 17") holds the held data of the queue top latch 10 in response to the clock signal L.

The T-latch circuit 11 (will be called as a "scope latch 11") is responsive to the clock signal T to hold, by the clock signal T, the address of the queue 9 in which a first one entry among four entries to be simultaneously read from the queue 9 is registered. That is; the contents of the entries of the following addresses of the queue 9 are simultaneously read: scope, scope+1, scope+2, scope+3

wherein "+" represent module addition with respect to the whole entry number (12 in this embodiment) of the queue 9.

The T-latch circuit (will be called as an "instruction fetch latch") 12 is responsive to the clock signal T to hold a flag IC\_fetch indicating the execution of the instruction fetch. In 50 a cycle in which the instruction fetch request flag IC\_fetch is "1", an instruction fetch request is issued to the instruction fetching stage.

The L-latch circuit (will be called as an "instruction fetch L-latch") 19 is responsive to the clock signal L to hold the 55 flag IC\_fetch latched in the instruction fetch latch 12.

The T-latch circuit (will be called as an "instruction miss latch") 13 is responsive to the clock signal T to hold the flag IC\_miss which indicates a state for waiting an instruction from the instruction memory.

The L-latch circuit (will be called as an "instruction miss L-latch") 20 is responsive to the clock signals L to hold the flag IC\_miss held by the instruction miss latch 13.

The T-latch circuit (will be called as an "initial state latch") 28 is responsive to the clock signal T to hold the flag 65 queue\_init\_state which indicates an initial state of the queue 9.

10

The L-latch circuit (will be called as a "queue initial state L-latch") 29 is responsive to the clock signal L to hold the flag queue\_init\_state held by the queue initial state latch 28.

The logic circuit 30 (will be called as a "queue top logic" **30**") responds to a branch generating signal br\_taken from the instruction decoder 26, the queue initial state flag queue\_init\_state held by the queue initial state L-latch 29, the signal IC\_ready, the write top address queue\_top of the queue 9 from the queue top L-latch 17, and the flag IC\_fetch from the instruction fetch L-latch 19. The queue top logic 30 is also responsive to the read top address scope\_next of the queue 9 in the next cycle from the logic circuit 31, as well as the flag queue\_avail, which indicates whether the queue 9 is available (writable), from the logic circuit 34 and the address branch\_bin\_inst\_entry of the entry at which the branch instruction is registered and which is generated from the instruction decoder 26. In response to the same, the queue top logic 30 forms the write top address queue\_top\_ in of the queue 9 in the next cycle and applied the same to the queue top latch 10 and the logic circuits 34 and 50.

The logic circuit 31 (will be called as a "scope next logic 31") is responsive to the signal br\_taken, the read top address scope\_L from the scope L-latch 18, the issued instruction count data issued\_inst\_count and the address branch\_inst\_entry from the instruction decoder 26. In response to the same, the scope next logic 31 generates the write top address scope-next of the queue 9 in the next cycle, and also generates a flag scope>11 which indicates a fact that this address scope\_next is larger than 11. The signal scope\_next indicating the address scope in the next cycle is applied to the scope latch 11 and the logic circuit 50 and is also applied to the logic circuit 34. The flag scope>11 is applied to the logic circuit 50.

The logic circuit 33 (will be called as an "instruction miss logic 33") is responsive to a flag IC\_fetch\_L from the instruction fetch L-latch 19, a flag IC\_miss\_L from the instruction miss L-latch 20, the flag br\_taken and the signal IC\_ready. In response to the same, the instruction miss logic 33 forms and applies to the instruction miss latch 13 a signal IC\_miss indicating whether it is a state for waiting an instruction.

The logic circuit 36 (will be called as a "queue initialization logic 36") is responsive to the signal queue\_init\_

45 state\_L from the queue initial state L-latch 29, the signal br\_taken, the signal IC\_miss\_L from the instruction miss latch 20, the signal IC\_fetch\_L from the instruction fetch L-latch 19 and the signal IC\_ready. In response to the same, the queue initialization logic 36 forms and applies to the queue initial state latch 28 the signal queue\_init\_state indicating whether the queue 9 is in an initial state.

The logic circuit 34 (will be called as a "queue avail logic 34") is responsive to the address queue\_top\_L from the queue top L-latch 17, the address scope\_next from the scope next logic 31, the signal br\_taken, the address queue\_top\_in from the queue top logic 30 and the signal queue\_state indicating the state (first, second or third state which will be described later) of the queue 9 from the logic circuit 50. In response to the same, the queue avail logic 34 generates and applies to the queue top logic 30 the signal gueue\_avail indicating whether the queue 9 is available.

The logic circuit 32 (will be called as an "instruction fetch logic 32") is responsive to the signal IC\_busy which is applied from the instruction memory or the instruction fetching stage and indicates the state in which the instruction memory cannot accept the instruction fetch request. In response to the same, the instruction fetch logic 32 generates

and applies to the instruction fetch latch 12 the signal IC\_fetch indicating whether the fetch request is to be supplied to the instruction memory.

The logic circuit 35 (will be called as an "instruction avail logic 35") is responsive to the signal IC\_ready, signal IC\_fetch\_L, signal br\_taken and signal IC\_miss\_L to generate the flag inst\_avail\_in indicating whether the instruction contained in the queue 9 is available and to determine a value of the availability flag inst\_avail in the entry of the queue 9.

The logic circuit **50** (will be called as a "queue state logic" **50**") is responsive to the address branch\_inst\_entry from the instruction decoder 26 and the flag queue\_top>11 from the queue top logic 30, as well as the flag scope>11 and address scope\_next from the scope next logic 31. In 15 regions of the addresses from queue\_top to queue\_top+3. response to the same, the queue state logic 50 generates the signal queue\_state indicating an actual state of the queue 9 among the first, second and third states, and applies it to the queue avail logic 34. In the first state described above, the queue 9 is in an initial state, the write top address queue top 20 and read top address scope thereof are "0" or equal to each other, and all the availability flags inst\_avail of the four entries from the address queue\_top are OFF (0). This state is one of the reset state, branch generating state and instruction arrival waiting state. In the second state, the read top address scope is equal to or less than the read top address queue\_top, i.e., a following relationship is established:

scope<queue\_top

This state is a normal state.

In the third state, the write top address queue\_top is equal 30 to or less than the read top address scope, i.e., a following relationship is established:

queue\_top≦scope

This third state is called as a reverse state. By distinguishing the second and third states from each other, it is possible to 35 distinguish whether the queue 9 is empty or full in a state that the address scope\_next is equal to the address queue\_ top\_in. That is; change from the second state to the state of (scope\_next=queue\_top\_in) represents the empty state of the queue 9. Further, change from the third state to the state 40 of (scope\_next=queue\_top\_in) represents the full state of the queue 9. These second and third states will be described in greater detail later.

Between the queue 9 and the instruction decoder 26, there is provided the L-latch circuits 14, 15 and 16 which are 45 responsive to the clock signals L to hold contents of a plurality of entries read from the queue 9. The L-latch circuit 14 (will be called as an "IRL latch 14") holds a plurality of instructions inst simultaneously read from the queue 9.

The L-latch circuit 15 (will be called as a "PCL latch 15") 50 holds addresses PC corresponding to the instructions simultaneously applied from the queue 9.

The L-latch circuit 16 (will be called as an "instruction" avail L-latch 16") holds the availability flag inst\_avail associated to the instructions read from the queue 9.

The instruction decoder 26 is responsive to the addresses, instructions and availability flags from the IRL latch 14, PCL latch 15 and instruction avail L-latch, respectively, to decode the applied instruction for detecting and issuing the instructions allowing parallel execution to the function units. 60 The instructions simultaneously issued to the function units are determined in an ascending order of the addresses from the PCL latch 15, and an instruction having a smaller address is issued earlier than those having larger addresses if the instructions have mutual data dependency.

A fundamental movement of the instruction fetching scheme according to the invention will be described below.

FIG. 9 shows a conceptional construction of the queue 9. In FIG. 9, the queue 9 has memory regions bearing addresses 0–11, and one entry E is stores at each address. Each entry E includes a region I for storing an address (logic address) of the instruction fetched from the instruction memory, a region II for storing the instruction IC\_data fetched from the instruction memory and a region III for storing the flag inst\_avail which indicates whether the corresponding instruction is available. Four instructions each including the address IF\_PC\_L, instruction IC\_data and flag inst\_ avail\_in are transmitted in parallel to the queue 9 and are simultaneously stored in different four address regions. The register regions of the entries of the queue 9 are designated by the addresses queue-top, and they are stored in the

Reading of the instructions from the queue 9 is performed by parallel reading of the four instructions. Designation of the addresses for this reading is performed by the address scope, and the entries registered in the addresses from scope to scope+3 are simultaneously read in parallel. Now, a fundamental operation of the instruction fetch scheme according to the invention will be described with reference to FIG. **10**.

A state (1) is the initial state (first state) immediately after the reset or initialization. In this initial state, both the addresses queue\_top and scope indicate the initial address 0 of the queue 9. In the queue 9, the availability flags starting from queue\_top, i.e., address 0 is set at OFF (0). In this state, since the availability flags indicate OFF (0), the four entries at the addresses 0–3 of the queue 9 are unavailable, and thus issue or execution is inhibited.

In a state (2), instructions are written in four addresses starting from the address 0 indicated by the address queue\_\_ top. Since these written instructions are available instructions, the availability flags corresponding to them are set at ON (1), which indicates that these written instructions are available and that reading, issuing and executing of the instructions of these four entries are allowed. In this state (2), queue\_top is not yet changed. In this state (2), four entries starting from the address 0 indicated by the address scope are read, and are applied to the instruction decoder for decoding.

In the state (2), the instruction decoder issues two instructions, which are determined to allow parallel processing, to the function unit, and the read top address scope is changed to the address 2.

In the cycle of a state (3), the read top address queue\_top has been changed to the address 4, and four address regions starting from this address 4 store the subsequent four instructions 4–7. Availability flags corresponding to these newly written instructions 4–7 are also set simultaneously to be ON.

A state (4) represents a state after the issue of one instruction. Since one instruction was issued, the read top 55 address scope has moved one to indicate the address 3. Further, in this state (4), four new instructions 8–11 have been written in four address regions starting from the address 8 indicated by the write top address queue\_top, and the corresponding availability flags are ON (1). In a cycle of this state, the instructions of four addresses starting from the address 3 indicated by the address scope are read from the queue 9 and are applied to the instruction decoder for decoding.

A state (5) represents a state in which no instruction was issued from the instruction decoder in the last cycle. Since the issued instruction count is 0, the write top address scope has not moved and indicates the address 3. In a cycle of this 13

state (5), the instructions of four addresses starting from the address 3 indicated by the address scope are read from the queue 9 again and are decoded by the instruction decoder. In this state (5), owing to the queue\_top+4 (12 module addition) performed in the last cycle, the write top address queue\_top is 0 (8+4=0) and the address 0 is indicated. Since four address regions starting from the address queue\_top (0) contains instructions which are not yet issued, i.e., instructions of the address 3, thee queue 9 does not perform capturing of the instructions.

A state (6) represents a state in which three instructions were issued from the instruction decoder in the last cycle. Owing to the issue of the three instructions, the read top address scope is shifted by three, and the address 6 is indicated. Instructions 12, 13, 14 and 15 are stored in four 15 address regions starting from the address 0 indicated by the write top address queue\_top. Since the instructions 12–15 are available, the corresponding availability flags are in ON state. Determination of existence of an empty region in the queue 9 is performed by a signal queue\_avail supplied from 20 the queue avail logic 34.

A fundamental operation when branch is caused by a branch instruction will be described below with reference to FIG. 11 showing a flow thereof. It is assumed that the queue 9 is in a state (11), in which the address queue\_top indicates 25 the address 10 and the address scope indicates the address 2. In the state (11), instructions 8, 9, 10 and 11 are written in the addresses 10, 11, 0 and 1. Instructions 2, 3, 4 and 5 stored in the addresses 2, 3, 4 and 5 of the queue 9 are read and applied to the instruction decoder. In a cycle of this state 30 (11), an instruction 2 of the address 4 is assumed to form a branch instruction by which the branch is caused. In a next state (2), an operation is performed as follows.

Since the branch is caused in the instructions 2, contents of addresses higher than the address 3 of the queue 9 is no 35 longer required.

The availability flags of four entries stored in the addresses subsequent to the address queue\_top, i.e., addresses 4–7 are set at OFF (0). The addresses queue\_top and scope are set at the address 4 of the queue 9.

An address of an branch target instruction is sent to the instruction memory in this cycle, and then will be supplied from the instruction memory in the next cycle. That is; the branch target instruction is not written in the queue 9 in this cycle.

The instructions of four entries starting from the address scope can be decoded as an issue target. However, these contents should not be issued to the function units. In order to indicate this inhibition of issue, availability flags of four entries starting from the address queue top are set at OFF (0) 50 in this cycle.

In a state (13), branch target instructions 20–23 are supplied from the instruction memory to the regions of addresses 4–7 starting from the address queue\_top and are written therein. These instructions 20–23 are branch target 55 instructions and thus are to be decoded and issued so that the availability flags thereof are set at ON (1).

In this cycle, the instructions 20–23 of four entries starting from the address scope (queue address 4) are applied to the instruction decoder for decoding.

Then, description will be made with respect to a fundamental operation in a case that an instruction cannot be supplied from the instruction memory in spite of an instruction fetch request from the processor, with reference to FIG. 12 showing a flow thereof.

It is assumed that the queue 9 is in a state (21) shown in FIG. 12. In this state (21), instructions 8–11 are written in

the addresses 0–3 of the queue 9, respectively. The instructions 2, 3, 4 and 5 stored in the addresses 6, 7, 8 and 9 of the queue 9 are applied to the instruction decoder 26 and is decoded as the issue target.

In this cycle, it is assumed that the instructions 2, 3 and 4 are issued to the function units.

It is also assumed that, in this cycle, an instruction fetch request is issued to the instruction memory but the instruction memory cannot supply the instruction in this cycle due to a certain cause (e.g., cache miss, if the instruction memory has a cache configuration).

In a state (22), since the instructions 2, 3 and 4 were issued in the last cycle, the address scope has shifted by three and the address scope is indicated.

The address queue top indicates the address 4. Since an instruction is not supplied from the instruction memory, the instructions stored in the addresses 4, 5, 6 and 7 of the queue 9 are different from those to which the fetch request is applied and thus should not be decoded. Therefore, if an instruction is not supplied from the instructions memory, the availability flags of four entries stored in the addresses subsequent to the addresses queue\_top are set at OFF (0).

In a state (23), an instruction is not yet supplied from the instruction memory, and the processor is in a state for waiting arrival of an instruction. Therefore, writing of instructions in the queue 9 is interrupted. Meanwhile, even if the instruction fetch is not performed, issue of instructions to the function units are continued through the instruction decoder 26 as long as an unissued instruction is in the queue 9. In an example shown in FIG. 12, two instructions were issued in the last cycle (state (22)) and the address scope indicates 11.

In a state (24), since instructions have arrived from the instruction memory, the instructions are written in four entries of the queue 9 starting from the address queue\_top (address 4). That is; the instructions 12–15 are written in the addresses 4–7, respectively.

In the last cycle, two instructions (instructions 7 and 8) were issued, and the address scope indicates the address 1.

Then, description will be made with respect to logics 30–36 for achieving the operation shown in FIGS. 10–12. First, logic achieved by the queue top logic 30 will be described.

- (1) Initial state: This state includes following two states.

- (a) Reset state: signal\_reset=1

- In this state, queue\_top=0

- (b) Initialized state: signal queue\_\_init\_\_state\_L=1

In this state, the write top address of the queue 9 is set at an address held by the queue top L-latch 17. Therefore, a following relationship is established.

queue\_top\_in=queue\_top\_L

Then an uninitialized state, i.e., a case of reset\*init\_state\_L=0, will be described. The above "\*" represents an AND operation.

(2) A branch generation state: signal br\_taken=1

In this state, the address queue\_top is set at an address in which a branch instruction is stored in the queue 9. Therefore, a following relationship is established.

queue\_top\_in=branch\_inst\_entry

The instruction decoder 26 can identify the address in the queue 9 of the applied instructions by receiving the read queue address queue\_top through a path (not shown).

(3) A case that the instruction is not\_supplied in spite of the issued instruction fetch request: IC\_fetch\_L=1 and IC\_ready=0

In this state, since the address queue\_top maintains the same value as the last cycle, a following relationship is established.

queue\_top\_in=queue\_top\_L

(4) In a case that instruction supply is performed in connection with the issued instruction fetch request and there is emptiness in the queue 9:

IC\_fetch\_L=1, IC\_ready=1 and queue\_avail=1

In this case, the address queue\_top will be shifted by four in the next cycle, so that a following relationship is established:

queue\_top\_in=queue+4 wherein "+" is module addition of the module 12. Therefore,

if (queue\_top>11) {queue\_top\_in=queue\_top\_in\_12}

(5) A case that, in spite of the fact that the instruction fetch request is issued and the instruction is supplied, there is no empty region (for four entries) in the queue:

IC\_fetch\_L=1, IC\_ready=1 and queue\_avail=0

This state represents a state in which the writing of the instruction is not performed because there is no region for writing the instructions for four entries in the queue 9. The address queue\_top maintains the same state as the last cycle. Therefore, a following relationship is established.

queue\_top\_in=queue\_top\_L

(6) A case of an instruction arrival waiting state:

This state includes following two cases.

(a) A case that the instruction supply is not performed due to a certain cause such as cache miss in spite of the fact that the instruction fetch request is issued:

IC\_fetch\_L=1 and IC\_ready=0

In this state, queue\_top of the last cycle is maintained, <sup>30</sup> resulting in a following relationship:

queue\_top\_in=queue\_top\_L

(b) A case that access, for example, to the instruction memory is impossible:

IC\_miss\_L=1 and IC\_ready=0

In this state, since an instruction is not supplied, the address queue\_top maintains the last value, resulting in a following relationship:

queue\_top\_in=queue\_top\_L

(7) A case that an instruction is applied in the instruction arrival waiting state due to, for example, cache miss, and an empty region exists in the queue 9:

IC\_miss\_L=1 IC\_ready=1 and queue\_avail=1

In this state, all the applied instructions can be written in 45 the queue 9. In this cycle of this state: a following relationship is established:

queue\_top\_in=queue\_top\_L+4

wherein "+" represents module addition of the module 12.

(8) A case that there is no empty region in the queue 9 in spite of the fact that the instruction is supplied in the instruction arrival waiting state:

IC\_miss\_L=1, IC\_ready=1 and queue\_avail=0

In this state, since the instruction cannot be written in the queue 9, the address queue\_top maintains a value of the last cycle. Therefore, a following relationship is established:

queue\_top\_in=queue\_top\_L

(9) A case that the instruction fetch request is not generated, and it is not in an instruction arrival waiting state:

IC\_fetch\_L=0 and IC\_miss\_L=0

This state is a state in which execution of instructions of the instruction memory is interrupted due to, for example, interruption processing. In this state, the address maintains the value of the last cycle. Therefore, a following relation- 65 ship is established:

queue\_top\_in=queue\_top\_L

16

The logic described above is shown in a list in FIG. 13.