#### US005822605A

### United States Patent [19]

### Higuchi et al.

### [11] Patent Number: 5,822,605

### [45] Date of Patent: Oct. 13, 1998

# [54] PARALLEL PROCESSOR SYSTEM WITH A BROADCAST MESSAGE SERIALIZING CIRCUIT PROVIDED WITHIN A NETWORK

[75] Inventors: Tatsuo Higuchi, Fuchu; Tadaaki Isobe;

Junji Nakagoshi, both of Hadano;

Shigeo Takeuchi, Hanno; Tatsuru

Toba, Fuchu; Yoshiko Yasuda,

Kawasaki; Teruo Tanaka, Hachioji;

Takayuki Nakagawa; Yuji Saeki, both

of Hadano, all of Japan

[73] Assignees: Hitachi, Ltd.; Hitachi ULSI Engineering Corp., both of Tokyo,

Japan

[21] Appl. No.: 408,561

[58]

[22] Filed: Mar. 22, 1995

#### [30] Foreign Application Priority Data

|      | •                     | L 4 L                                   |                                 |

|------|-----------------------|-----------------------------------------|---------------------------------|

| [51] | Int. Cl. <sup>6</sup> | •••••                                   | <b>G06F 13/00</b> ; H04L 12/50  |

| [52] | U.S. Cl.              | • • • • • • • • • • • • • • • • • • • • | <b>395/800.11</b> ; 395/800.12; |

|      |                       | 395/200.68;                             | 395/200.7; 395/311; 395/312     |

### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 5,212,773 | 5/1993  | Hillis 39       | 5/200.73 |

|-----------|---------|-----------------|----------|

| 5,333,279 | 7/1994  | Dunning         | 395/280  |

| 5,377,333 | 12/1994 | Nakagoshi et al | 395/312  |

| 5,379,440 | 1/1995  | Kelly et al     | 395/800  |

395/200.68, 200.7, 311, 312

#### OTHER PUBLICATIONS

T. Boku et al, "A Performance Evaluation of Hyper-Crossbar Network", Technical Report of IEICE, Institute of Electronics, Information and Communication Engineers, CPSY 93–40, (1993, Nov.), pp. 41–48. No translation.

Primary Examiner—Alyssa H. Bowler

Assistant Examiner—John Follensbee

Attorney, Agent, or Firm—Fay, Sharpe, Beall, Fagan,

Minnich & McKee

#### [57] ABSTRACT

In a parallel processor system comprising a plurality of processor elements constituting a network, a source processor element wishing to broadcast data to a plurality of destination processor elements sends a broadcast request message containing the target data to a broadcast exchanger. The broadcast exchanger converts the received message into a broadcast message and sends it over the network to the destinations. A plurality of broadcast request messages, if transmitted parallelly to the broadcast exchanger, are serialized thereby so that only one broadcast message will be transmitted at a time over the network. This prevents deadlock from occurring between different broadcast messages. The routes for transmitting broadcast request messages and those for transmitting broadcast messages are arranged so as not to overlap with one another. This suppresses deadlock between any broadcast request message and broadcast message. The broadcast exchanger is replaced alternatively with one of the partial networks. These schemes all apply where long messages are transmitted through worm-hole routing.

#### 46 Claims, 34 Drawing Sheets

F/G. 1

F/G. 5

F/G. 6

FIG. 7

| DESTINATION PE ADDRESS         | CONTROL BITS B B C R | DATA | 8a                                        |

|--------------------------------|----------------------|------|-------------------------------------------|

| BUFFER<br>EXCHANGER<br>ADDRESS | CONTROL BITS 0 1     | DATA | 8b BROADCAST<br>REQUEST<br>MESSAGE        |

| BUFFER<br>EXCHANGER<br>ADDRESS | CONTROL BITS 1 0     | DATA | 8c BROADCAST<br>MESSAGE                   |

| DESTINATION<br>PE ADDRESS      |                      | DATA | 8d ONE-TO-ONE<br>COMMUNICATION<br>MESSAGE |

FIG. 9 PRIOR ART

F/G. 10

F/G. 11

F/G. 12

5,822,605

F/G. 13

Oct. 13, 1998

| DESTINATION PE ADDRESS         | BE        | 3 P      | OL BITS PE GROUP NUMBER | DATA | 15aع   |                                             |  |

|--------------------------------|-----------|----------|-------------------------|------|--------|---------------------------------------------|--|

| BUFFER<br>EXCHANGER            |           | 1        | OL BITS PE GROUP        | DATA | 15b    | PARTIAL<br>BROADCAST                        |  |

| ADDRESS                        | 0 1       |          | NUMBER                  |      |        | REQUEST<br>MESSAGE                          |  |

| BUFFER<br>EXCHANGER<br>ADDRESS | 10        |          | OL BITS PE GROUP NUMBER | DATA | _15c   | PARTIAL<br>BROADCAST<br>MESSAGE             |  |

|                                |           |          |                         |      |        |                                             |  |

| BUFFER<br>EXCHANGER<br>ADDRESS | CO<br>0 1 | NTF<br>0 | OL BITS                 | DATA | J-15a  | BROADCAST<br>REQUEST<br>MESSAGE             |  |

| BUFFER                         | CO        | NTF      | OL BITS                 | ·    | 150    | BROADCAST                                   |  |

| EXCHANGER<br>ADDRESS           | 1 0       | 0        | *                       | DATA |        | MESSAGE                                     |  |

|                                |           |          |                         |      | -<br>ጉ |                                             |  |

| DESTINATION PE ADDRESS         |           | 0        | OL BITS                 | DATA | _15f   | ONE-TO-ONE<br>COMMUNI-<br>CATION<br>MESSAGE |  |

Oct. 13, 1998

| <del></del>             | <del></del>               |             |           |      |                                                 |

|-------------------------|---------------------------|-------------|-----------|------|-------------------------------------------------|

| SOURCE<br>PE<br>ADDRESS | DESTINATION<br>PE ADDRESS |             | OL BITS   | DATA | 5-5a                                            |

| SOURCE<br>PE<br>ADDRESS | *                         | CONTRO      | OL BITS 1 | DATA | 5b BROADCAST<br>REQUEST<br>MESSAGE              |

| SOURCE<br>PE<br>ADDRESS | *                         | CONTRO      | DL BITS 0 | DATA | 5c BROADCAST<br>MESSAGE                         |

| r r- i                  | DESTINATION<br>PE ADDRESS | CONTRO      | DL BITS   | DATA | _5d ONE-TO-ONE<br>COMMUNI-<br>CATION<br>MESSAGE |

| r                       | DESTINATION<br>PE ADDRESS | CONTRC<br>0 | DL BITS   | DATA | 5e ONE-TO-ONE COMMUNI-CATION                    |

|                         |                           |             |           |      | REQUEST<br>MESSAGE                              |

F/G. 19

F/G. 20

F/G. 21

F/G. 22

## 905 DETOUR INSTRUCTION CKT

5,822,605

F/G. 23

F/G. 24 XB-Y3 XB-Y2 139 138 EX FAULT 136 137 XB-X0 INFORMATION REG 1115 132 1000 1115 XB-Y0 XB-Y1 0000 1000 1117 1118 1116 0000 32 0000 31 11116[31] EX00 EX01 30 1000 SERIALIZING NW NUMBER LREG 32 00 30 00 SB=1 BC=1 PE00 1117 `~133 XB-X1 30 31 <u>31</u> 30 32 33 A STAULT INFORMATION REG 00 00 PE10 PE11 1118 134 XB-X2 31 30 33 00 30 32 00 00 <u>1119</u> 135 XB-X3 30 <u>32</u> <u>30</u> <u>31</u> 33 00 EX32 PE32 EX30 PE30 PE33

F/G. 25

F/G. 26

F/G. 27

F/G. 28

|               | <del>~</del>                          |                 |                                       |          |                                       |                  |              |                                        |            | 7 / 🔿                                 |

|---------------|---------------------------------------|-----------------|---------------------------------------|----------|---------------------------------------|------------------|--------------|----------------------------------------|------------|---------------------------------------|

| SOURCE        | DESTINATION                           | DESTINATION MAX |                                       | MIN      |                                       | CON              | CONTROL BITS |                                        |            | 1/a                                   |

| PE<br>ADDRESS | PE ADDRESS                            |                 | YMAX                                  | XMIN     | YMIN                                  | BC               | P<br>B       | S<br>B                                 | DATA       |                                       |

|               | · · · · · · · · · · · · · · · · · · · | <del></del>     | <u></u>                               | <u> </u> |                                       | ·- <del></del> - |              | ······································ |            | _<br>-, ₁7b                           |

| SOURCE        |                                       | <u>M</u>        | <u>4X</u>                             | <u>M</u> | <u>IN</u>                             | CON              | TROL         | BITS                                   |            | BROADCAST                             |

| PE<br>ADDRESS | *                                     | *               | *                                     | *        | *                                     | 1                | 0            | 1                                      | DATA       | REQUEST<br>MESSAGE                    |

| SOURCE        |                                       | M/              | 4 X                                   | М        | IN                                    | CON              | TROL         | BITS                                   |            | -<br>170<br>PROADCAST                 |

| PE            | *                                     |                 |                                       |          |                                       |                  |              |                                        | DATA       | BROADCAST<br>MESSAGE                  |

| ADDRESS       |                                       | *               | *                                     | *        | *                                     | 1                | 0            | 0                                      |            |                                       |

|               |                                       |                 |                                       |          |                                       |                  |              | <u></u>                                |            | ـــــــــــــــــــــــــــــــــــــ |

| SOURCE        | DESTINATION                           | M/              | λX                                    | M        | N                                     | CON              | TROL         | BITS                                   |            | ONE-TO-ONE                            |

|               | PE ADDRESS                            | ĺ               | *                                     | *        | *                                     | 0                | 0            | 0                                      | DATA       | CATION<br>REQUEST                     |

|               |                                       |                 | · · · · · · · · · · · · · · · · · · · |          | · · · · · · · · · · · · · · · · · · · |                  |              |                                        |            | MESSAGE                               |

| SOURCE        | DESTINATION                           |                 |                                       |          |                                       |                  | _            |                                        |            | ONE-TO-ONE                            |

|               | PE ADDRESS                            |                 | *                                     | *        | *                                     | 0                | 0            | 1                                      | DATA       | COMMUNI-<br>CATION<br>MESSAGE         |

| 17f           |                                       |                 |                                       |          |                                       |                  |              |                                        | -<br>- 17f |                                       |

| SOURCE        | <b>.</b> †                            | MA              | X                                     | M        | <u>N</u>                              | CONT             | ROL          | BITS                                   |            | PARTIAL BROADCAST                     |

| PE<br>ADDRESS | *                                     | *               | *                                     | *        | *                                     | 0                | 1            | 1                                      | DATA       | REQUEST<br>MESSAGE                    |

| 170           |                                       |                 |                                       |          |                                       |                  |              |                                        |            |                                       |

| SOURCE        |                                       | MA              | ·Χ                                    | MI       | N                                     | CONT             | ROL          | BITS                                   |            | PARTIAL                               |

| PE<br>ADDRESS | *                                     | XMAX            | YMAX                                  | XMIN     | YMIN                                  | 0                | 1            | 0                                      | DATA       | BROADCAST<br>MESSAGE                  |

F/G. 30

F/G. 31

F/G. 32

1180 BROADCAST SERIALIZING CKT

F/G. 33

### 710 AND GATE GROUP

1

# PARALLEL PROCESSOR SYSTEM WITH A BROADCAST MESSAGE SERIALIZING CIRCUIT PROVIDED WITHIN A NETWORK

#### BACKGROUND OF THE INVENTION

The present invention relates to a message transmission method and a parallel processor system for use therewith, whereby broadcast messages or partial broadcast messages are transmitted between a plurality of processor elements <sup>10</sup> over a network.

Broadcasting is one of the important data transmission facilities offered by the parallel processor system for transmitting messages between the multiple processor elements configured on the network.

One method for implementing the broadcast facility is disclosed illustratively in Japanese Patent Laid-Open No. Hei 1-267763. The disclosed method involves breaking up n processor elements into factors  $n1 \times n2 \times n3 \times ... \times nn$ , each factor representing a processor element disposed at one of the lattice points constituting an n-dimensional lattice space. The sides making up the lattice space are connected by partial networks each composed of a crossbar switch. This constitutes what is known as a hyper-crossbar network. The partial networks within such a network are each furnished with a circuit for implementing the broadcast facility, whereby data is transmitted parallelly from one processor element to all the other processor elements configured.

Another important data transmission facility of the parallel processor system is a partial broadcast facility. This facility involves transmitting data between the processor elements within a limited processor group on the network. One method for implementing the partial broadcast facility is disclosed illustratively in Japanese Patent Laid-Open No. Hei 5-28122 or U.S. patent application Ser. No. 07/916,663 corresponding thereto now U.S. Pat. No 5,192,580.

One problem to be considered in implementing a network is the possibility of deadlock. The deadlock is a state that the network gets into where one message conflicts with another 40 message in acquiring a transmission route. If the network is in a state of deadlock, neither of the contending messages can proceed from there. On the hyper-crossbar network, for example, a deadlock can occur if each of a plurality of crossbar switches constituting the network receives two or 45 more broadcast messages at the same time. Specifically, to transmit each broadcast message to the multiple output ports of the crossbar switches requires that all of these output ports be ready for use by the broadcast message in question. However, if a different part of the output ports are allocated 50 for a different broadcast message, each of the broadcast messages involved must wait indefinitely to acquire the unallocated output ports for transmission. This problem, encountered when a plurality of broadcast messages are input to any one crossbar switch, is circumvented conven- 55 tionally by use of a broadcast message serializing circuit whereby a plurality of broadcast messages are processed serially. That is, each broadcast message is transmitted after completion of transmission of the preceding message. The scheme is discussed illustratively in Japanese Patent Laid-Open No. Hei 1-267763 cited above.

Parallel processor systems generally utilize the so-called worm-hole routing as their data transmission method. This method, as disclosed illustratively in U.S. Pat. No. 5,212, 773 issued to W. Daniel Hillis, involves taking a message 65 sufficiently longer than any of the diverse buffers within the network, dividing the message into a plurality of parts, and

2

making these message parts advance individually. It may happen that the leading part of a message has arrived at the destination processor element while the trailing part of that message still remains in the source processor element. In such a case, the route used for the message transmission is not allocated as a whole beforehand; the necessary route is secured in steps as the leading part of the message advances. Each of a plurality of route portions constituting the allocated route is released after the trailing part of the message has passed it. That is, each of the component route portions is allocated for transmission of the message solely from the time the leading part of the message has passed that route portion in question until the time the trailing part of the message has passed it. Where a component route portion is being allocated for one broadcast message, that portion cannot be allocated for any subsequent broadcast message. In that case, with a particular route portion allocated for the current message, the attempt by the subsequent broadcast message to have the same route portion allocated for transmission of the latter causes the two messages to keep waiting for the unallocated route portion to be released while each message has part of its necessary route portions allocated. The two messages thus wait indefinitely for the perpetually unavailable route portion to be released. This is how a deadlock results from the contention for a transmission route between a plurality of processor elements transmitting a plurality of broadcast messages over a network such as a hyper-crossbar network composed of a plurality of partial networks.

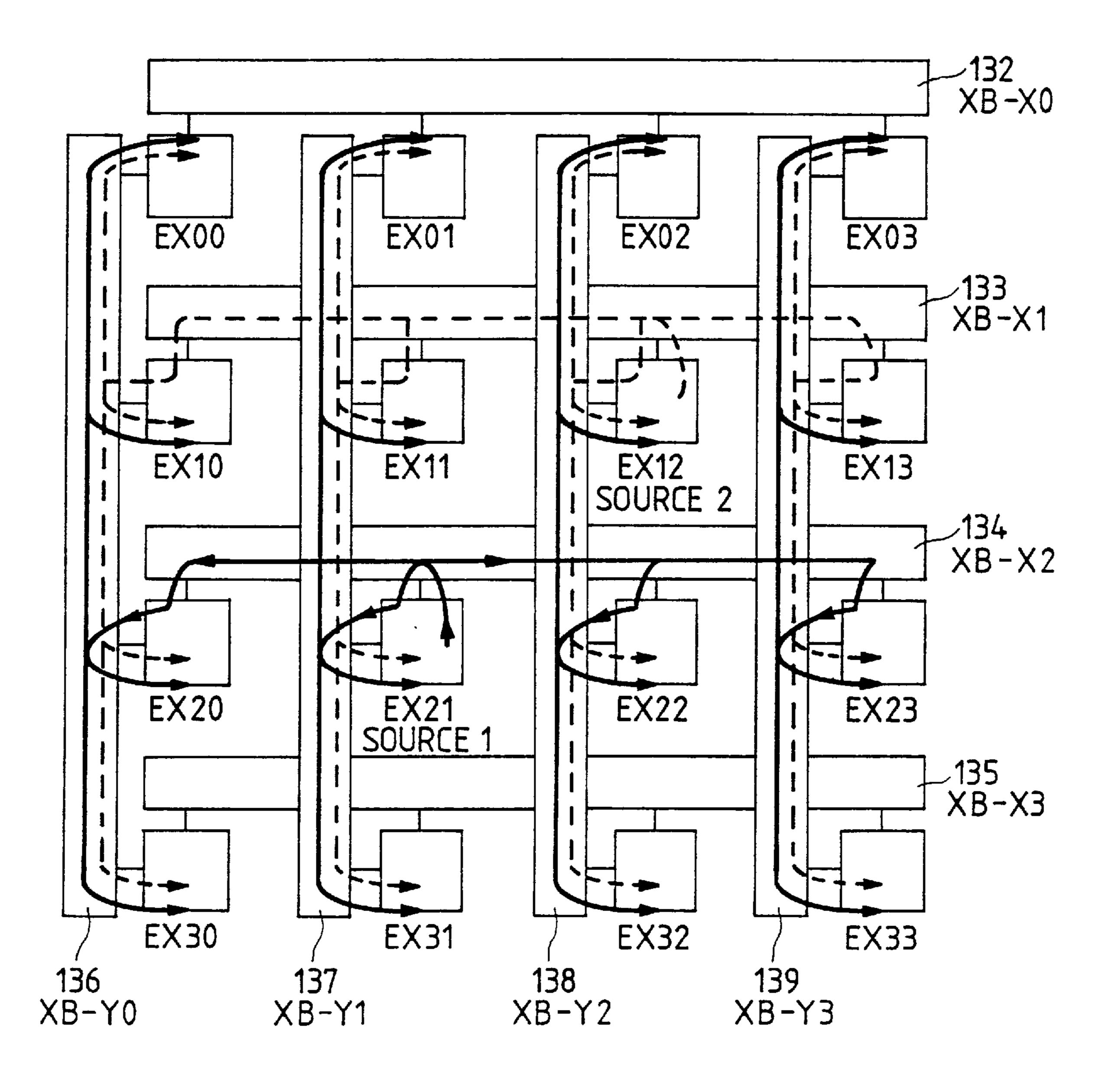

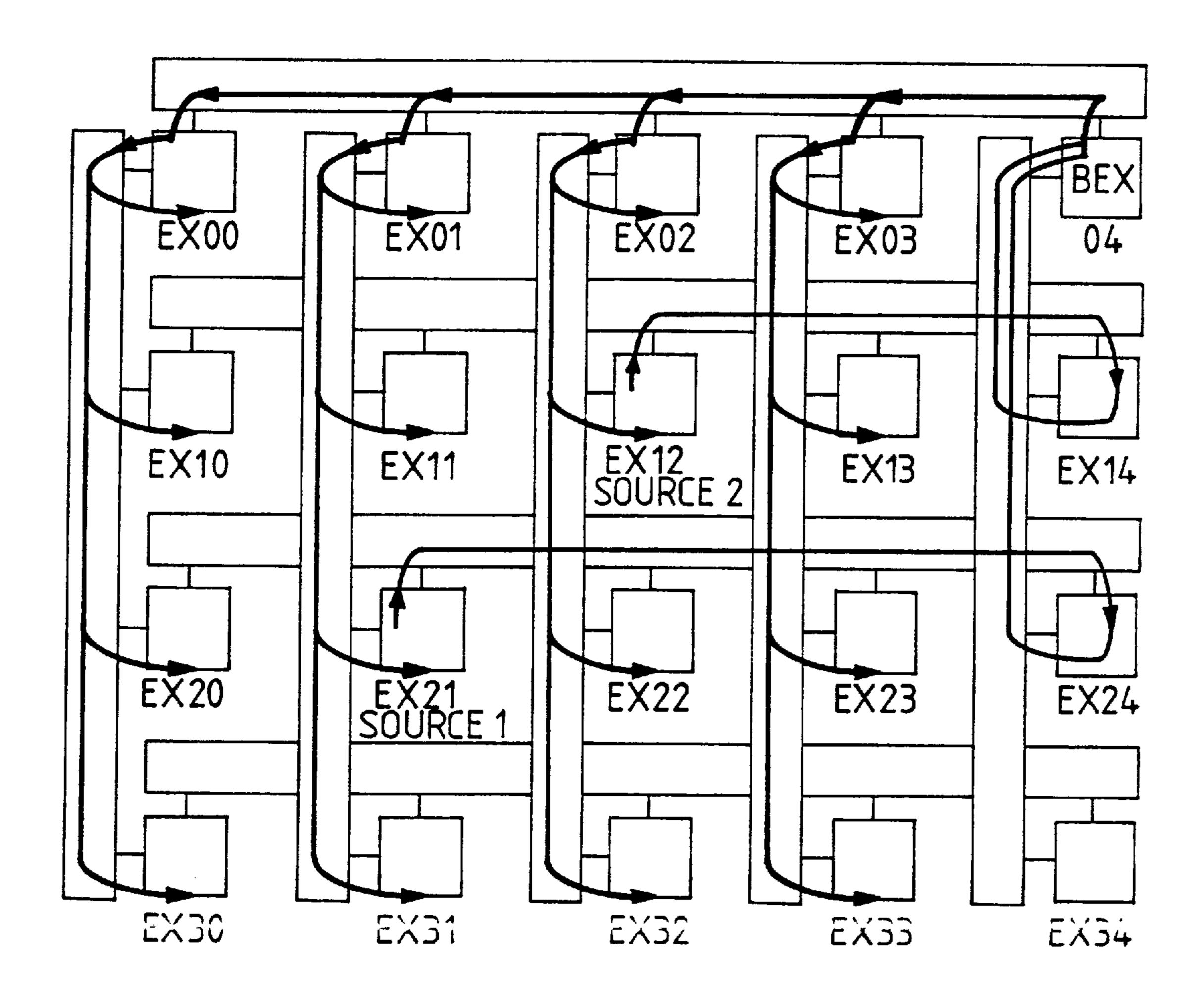

FIG. 9 outlines the structure of the conventional parallel processor system described in Japanese Pat. Laid-Open No. Hei 5-28122 or U.S. patent application Ser. No. 07/916,663 now U.S. Pat. No. 5,192,580 corresponding thereto. Specifically, the network of the processor system comprises a plurality of X-coordinate crossbar switches (each abbreviated to XB-X hereunder) and a plurality of Y-coordinate crossbar switches (XB-Y hereunder). The points of intersection between the XB-Xs and the XB-Ys are each connected to an exchange switch EX. One exchange switch is connected with one processor, which is not shown in FIG. 9 for space reasons. Although Japanese Pat. Laid-Open No. Hei 5-28122 does not describe how the processor system will work if a plurality of broadcast messages are transmitted simultaneously, it is surmised that a deadlock occurs if two or more sources transmit broadcast messages as shown in FIG. 9. According to the message transmission method described in Japanese Pat. Laid-Open No. Hei 5-28122, a source 1 in FIG. 9 transmits a broadcast message to exchange switches EX00 through EX03 using an XB-X0. In turn, the EX00 through EX03 transmit the broadcast message to the EX00 through EX33 using an XB-Y0 through XB-Y3 arranged in the Y-axis direction. Through these EXs, the broadcast message is transmitted to all processor elements PE.

Meanwhile, a source 2 (EX12) transmits a broadcast message to an EX10 through EX13 using an XB-X1. These EXs in turn transmit the broadcast message to the EX00 through EX33 using the XB-Y0 through XB-Y3 in the Y-axis direction, whereby the broadcast message is transmitted to all processor elements PE. In this manner, if broadcast messages do not occur simultaneously, each message is transmitted normally to all processor elements PE. But if a plurality of broadcast messages are transmitted in a substantially simultaneous manner from the source processor element PE, then such messages do not conflict with each other regarding the XB-Xs but they do conflict regarding the XB-Ys. For example, suppose that the broadcast

message from the source 1 has the XB-Y0 and XB-Y1 allocated while the broadcast message from the source 2 has the XB-Y2 and XB-Y3 allocated. In that case, one broadcast message fails to have the XB-Y2 and XB-Y3 allocated while the other message cannot secure the XB-Y0 and XB-Y1. 5 The transmission of both messages thus stops and a deadlock occurs.

The cause of this problem is as follows: where any one broadcast message is to be transmitted over the above network, it is necessary to utilize the entire network for that message alone. Despite this requirement, attempts to secure the network for a plurality of broadcast messages are started simultaneously and independently on a plurality of routes of the network. The problem, in short, stems from such attempts to transmit a plurality of broadcast messages simul- 15 taneously over the network.

One solution to the above problem is proposed in the Technical Report of the Institute of Electronics, Information and Communication Engineers of Japan, Vol. 93, No. 320, pp. 41–48. The proposed solution involves allowing only one of the configured processor elements to be selected for executing the transmission of broadcast messages. Specifically, where it is desired to transmit data from one of the processor elements to the remaining elements, the source processor element sends a broadcast request message comprising the target data to the processor element designated as the broadcast execution processor element. After the broadcast execution processor element has received the broadcast request message, that processor element outputs a broadcast message containing the data onto the network. As a result, even if a plurality of processor elements output broadcast request messages, the broadcast execution processor element serially outputs onto the network a plurality of broadcast messages corresponding to these request messages. The scheme thus prevents the state of deadlock from occurring.

In case of a fault within a hyper-crossbar network, there is a method for transmitting data by detouring around the faulty point. One such method is disclosed illustratively in Japanese Pat. Laid-Open No. Hei 3-209550. The disclosed method involves having each of the component partial networks supplied with fault information about those partial networks connected to each partial network, whereby the transmission of messages to any faulty partial network is prevented. In each partial network, the message from the input port connected to the immediately upstream partial network is not forwarded to the output port connected to the same partial network. This prevents any message from getting into an endless loop on the network. Messages are thus transmitted correctly to the destination processor elements.

Some of the parallel processor systems employing a hyper-crossbar network have two groups of processors connected to the network. One group of processors performs arithmetic operations; the other processor group carries out 55 I/O processing. The scheme is aimed at preventing the I/O processing required of the processor elements from deteriorating their performance in arithmetic operations. One such parallel processor system is disclosed illustratively in Japanese Pat. Laid-Open No. Hei 5-081216 or U.S. Pat. No. 60 5,377,333 corresponding thereto.

# SUMMARY OF THE INVENTION

The method proposed in the Technical Report of the Institute of Electronics, Information and Communication 65 Engineers of Japan, Vol. 93, No. 320 is effective in preventing deadlock, but has the disadvantage of taking extra time

4

in transmitting broadcast messages. Specifically, a processor element that wants to transmit a broadcast message first issues a broadcast request message. The request message is received by the broadcast execution processor element. Thereafter, the broadcast execution processor element sends out a broadcast message including the data from the broadcast request message. In this manner, the proposed method is plagued by the transmission overhead involving the reception of a broadcast request message and the subsequent transmission of a broadcast message.

If the broadcast execution processor element doubles as a processor element for executing arithmetic operations, the processor element must halt its ongoing arithmetic operation when transmitting the broadcast message. This translates into a delay in the execution of the arithmetic operations by that processor element.

Suppose that the processor element located the farthest from the broadcast execution processor element requests message broadcast. In that case, effecting the broadcast requires allocating two routes: one for transmitting a broadcast request message from the source processor element to the broadcast execution processor element, the other for transmitting a broadcast message from the broadcast execution processor element to the source processor element. The transmission distance involved is twice the distance used for transmitting a one-to-one communication message. It thus takes time to complete a broadcast session after a request for message broadcast is made.

The problems above also apply to partial broadcast messages.

The above-mentioned method for detouring around the faulty point on the network, as disclosed in Japanese Pat. Laid-Open No. Hei 3-209550, has the following disadvantage: with one of the configured partial networks at fault, there may occur in a substantially simultaneous manner a combination of a broadcast message and a one-to-one communication message, a combination of a broadcast message and a partial broadcast message, or a combination of a plurality of broadcast messages. In such cases, the attempts to detour around the faulty route portion will result in a deadlock.

It is therefore an object of the present invention to provide a message transmission method and a parallel processor system for use therewith, whereby broadcast messages are transmitted more rapidly than before while the state of deadlock is avoided.

It is another object of the invention to provide a message transmission method and a parallel processor system for use therewith, whereby partial broadcast messages are transmitted more rapidly than before while the state of deadlock is avoided.

It is a further object of the invention to provide a message transmission method and a parallel processor system for use therewith, whereby broadcast messages are transmitted more rapidly than before while the state of deadlock is avoided and a faulty point within the network is detoured.

In achieving the foregoing and other objects of the present invention and according to one aspect thereof, there is provided a message transmission method comprising the steps of:

taking from a source processor element a broadcast request message including the data designated by the source processor element requesting the broadcast of the data to a plurality of processor elements on a network, in order to transmit via the network the broadcast request message from the source processor element to a predetermined position within the network; and

transmitting from the predetermined position within the network a broadcast message including the data retained in the transmitted broadcast request message, to the plurality of processor elements via the network.

Preferably, the broadcast message is transmitted over a transmission route different from the route for transmitting the broadcast request message from the source processor element to the predetermined position within the network.

More specifically, the message transmission method according to the invention comprises the steps of:

taking from a plurality of source processor elements a plurality of broadcast request messages including the data designated by the plurality of source processor elements each requesting the broadcast of the data to a plurality of processor elements on a network, in order to transmit via the network the plurality of broadcast request messages parallelly from the plurality of source processor elements to a plurality of predetermined positions within the network; and

transmitting from the plurality of predetermined positions within the network a plurality of broadcast messages including the data retained in the transmitted broadcast request messages, serially to the plurality of processor elements via the network.

The above step for serially transmitting the multiple broadcast messages preferably includes a step for selecting another broadcast message every time the current broadcast message in its entirety has been transmitted to the predetermined positions.

The above step for serially transmitting the multiple broadcast messages preferably regards a plurality of output positions as the predetermined positions. In this case, the broadcast messages may be transmitted in parallel from these output positions onto the network.

According to another aspect of the invention, there is provided a network for connecting a plurality of processor elements, the network comprising:

- a broadcast request message transmission route for transmitting to a first predetermined position within the network a broadcast request message which is sent by one of the processor elements and which includes the data to be broadcast to the plurality of processor elements;

- a broadcast message supply circuit connected to the first predetermined position and used to convert the broadcast request message transmitted to the position into a broadcast message for requesting the transmission of the data held in the broadcast request message to the plurality of processor elements, the broadcast message supply circuit further supplying the broadcast message to another predetermined position within the network; and

- a broadcast message transmission route for transmitting 55 the broadcast message thus supplied to the plurality of processor elements.

The network above receives a broadcast request message from any one processor element, generates with little delay a broadcast message requested by that broadcast request 60 message, and transmits the generated broadcast message to the multiple processor elements on the network.

Preferably, the broadcast request message transmission route and the broadcast message transmission route have no overlapping portion therebetween. This arrangement pre- 65 vents the two kinds of messages from bringing about a state of deadlock.

6

More preferably, the above network further comprises:

a second broadcast request message transmission route for transmitting to a second predetermined position within the network a second broadcast request message which is sent by another processor element and which includes the data to be broadcast to the plurality of processor elements;

wherein the broadcast message supply circuit has a circuit which is connected to the second predetermined position, which converts the broadcast request messages transmitted to the first and the second predetermined position into a plurality of corresponding broadcast messages, and which outputs the plurality of broadcast messages serially from the second predetermined position onto the network.

With the preferred network above in use, a plurality of broadcast request messages may be transmitted in parallel to the broadcast message supply circuit, and this circuit still supplies the corresponding broadcast messages serially to the network. This arrangement suppresses the state of deadlock caused by the parallel supply of a plurality of broadcast messages to the network.

In another preferred structure according to the invention, the network is constituted by a hyper-crossbar network comprising a plurality of crossbar switches and a plurality of exchange switches connecting these crossbar switches. The broadcast message supply circuit is added to the network as an exchange switch for connecting any two of the plurality of crossbar switches.

In a further preferred structure according to the invention, the above hyper-crossbar network includes an I/O processor element in addition to the configured processor elements. The broadcast message supply circuit is furnished in the position of the exchange switch for connecting the I/O processor element to the hyper-crossbar network. Thus located, the broadcast message supply circuit doubles as the exchange switch for connecting the I/O processor element to the network.

In an even further preferred structure according to the invention, the above hyper-crossbar network comprises a conversion circuit furnished in each of a plurality of exchange switches connected to one particular crossbar switch, the conversion circuit converting a broadcast request message into a broadcast message. That particular crossbar switch includes a broadcast message serializing circuit.

These aspects and variations of the invention permit high-speed transmission of broadcast messages without causing a deadlock by taking advantage of the rapid transmission capability of the hyper-crossbar network. The invention is particularly effective in transmitting broadcast messages by worm-hole routing over the hyper-crossbar network.

These and other objects, features and advantages of the invention will become more apparent upon a reading of the following description and appended drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS

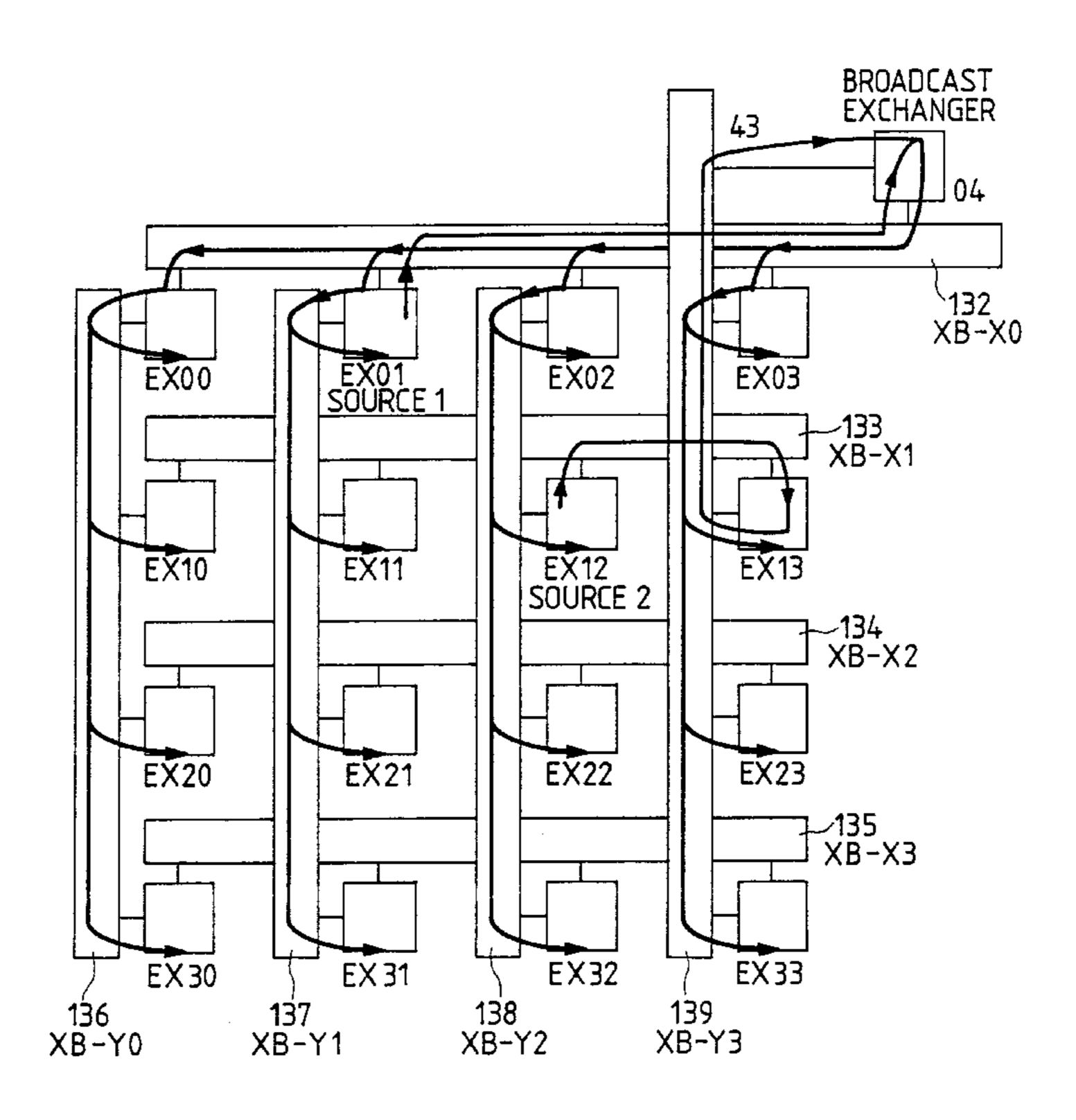

- FIG. 1 is a schematic circuit diagram of a parallel processor system practiced as a first embodiment of the invention;

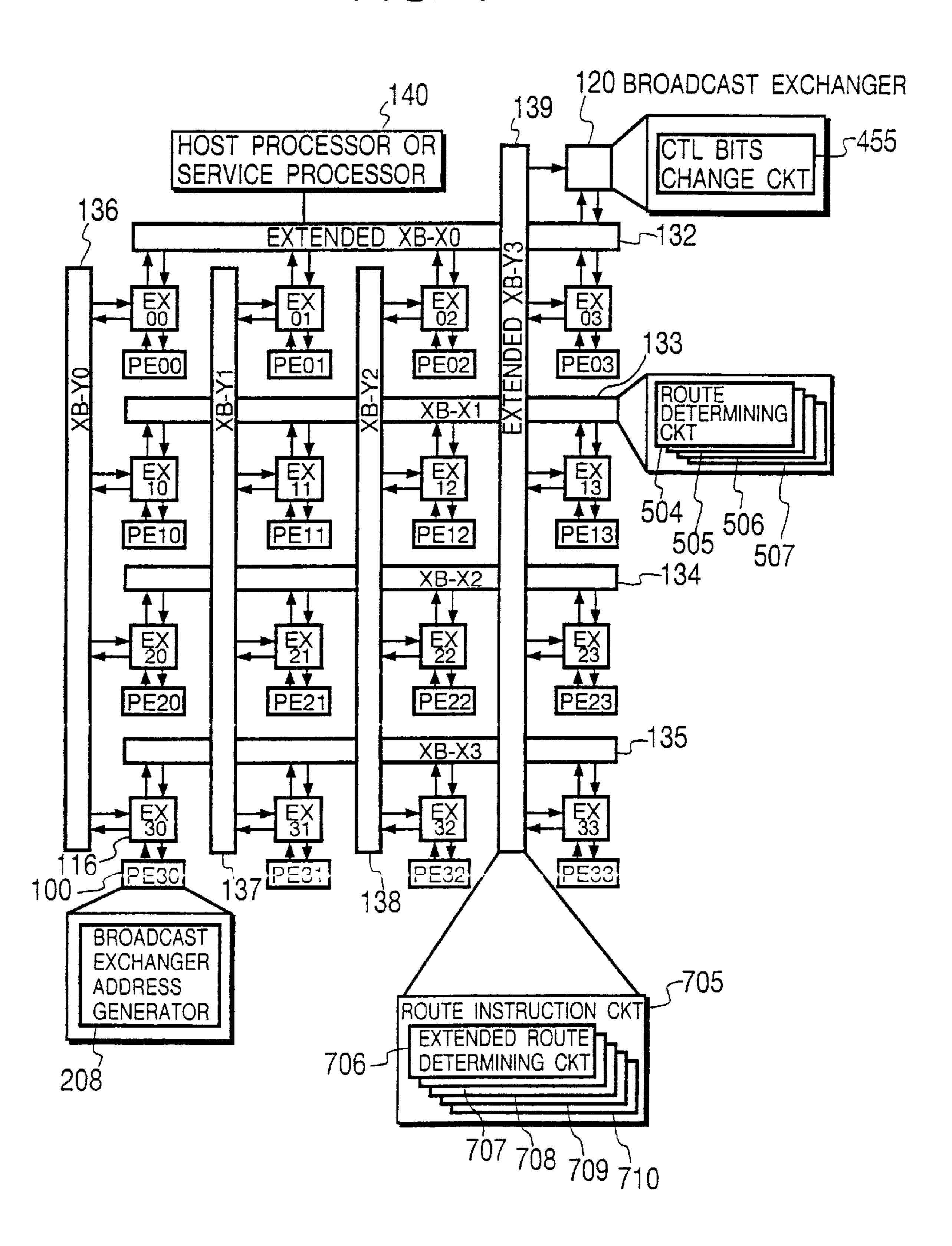

- FIG. 2 is a schematic circuit diagram of a processor element (PE) used by the circuit of FIG. 1;

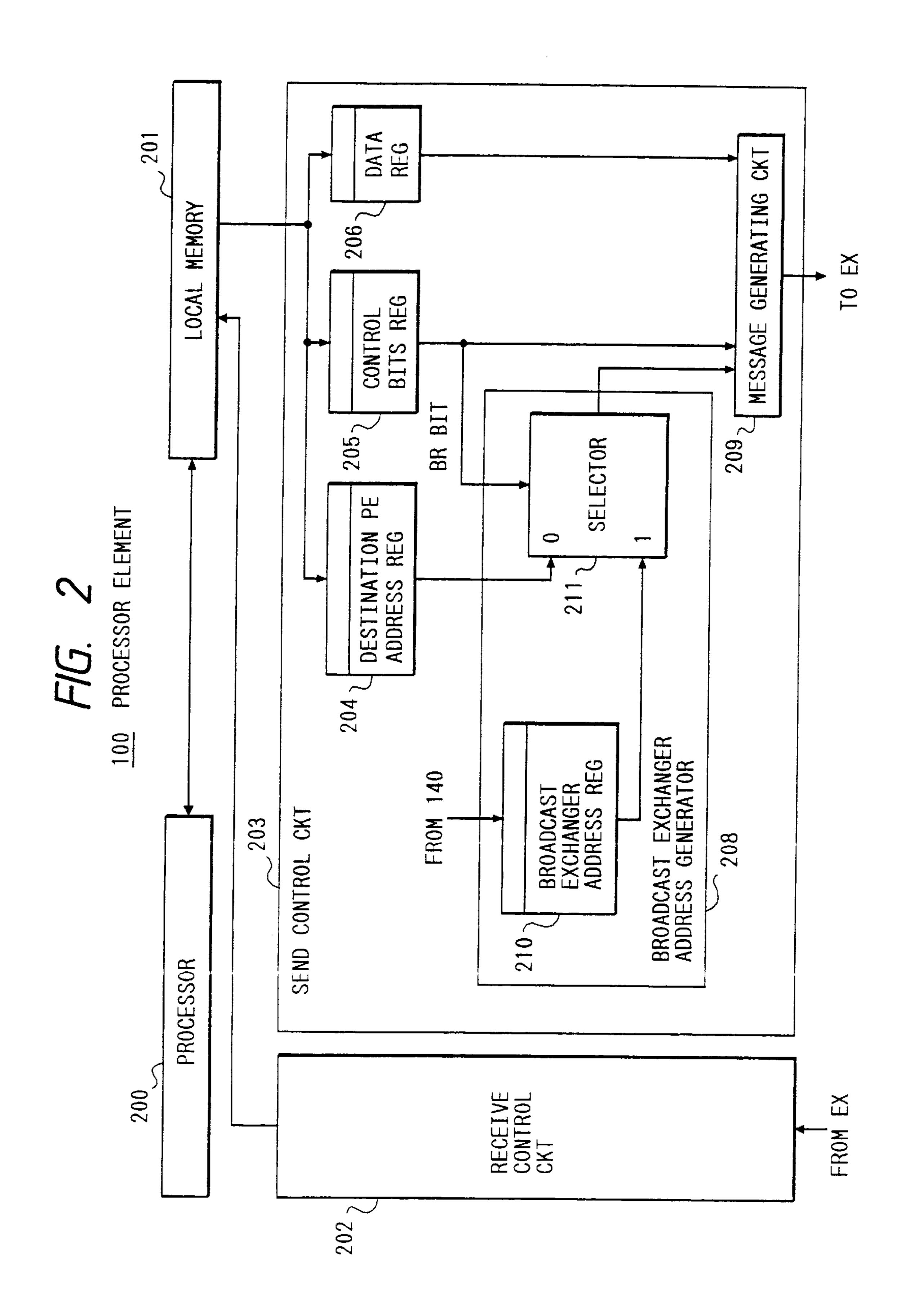

- FIG. 3 is a schematic circuit diagram of an exchange switch (EX) used by the circuit of FIG. 1;

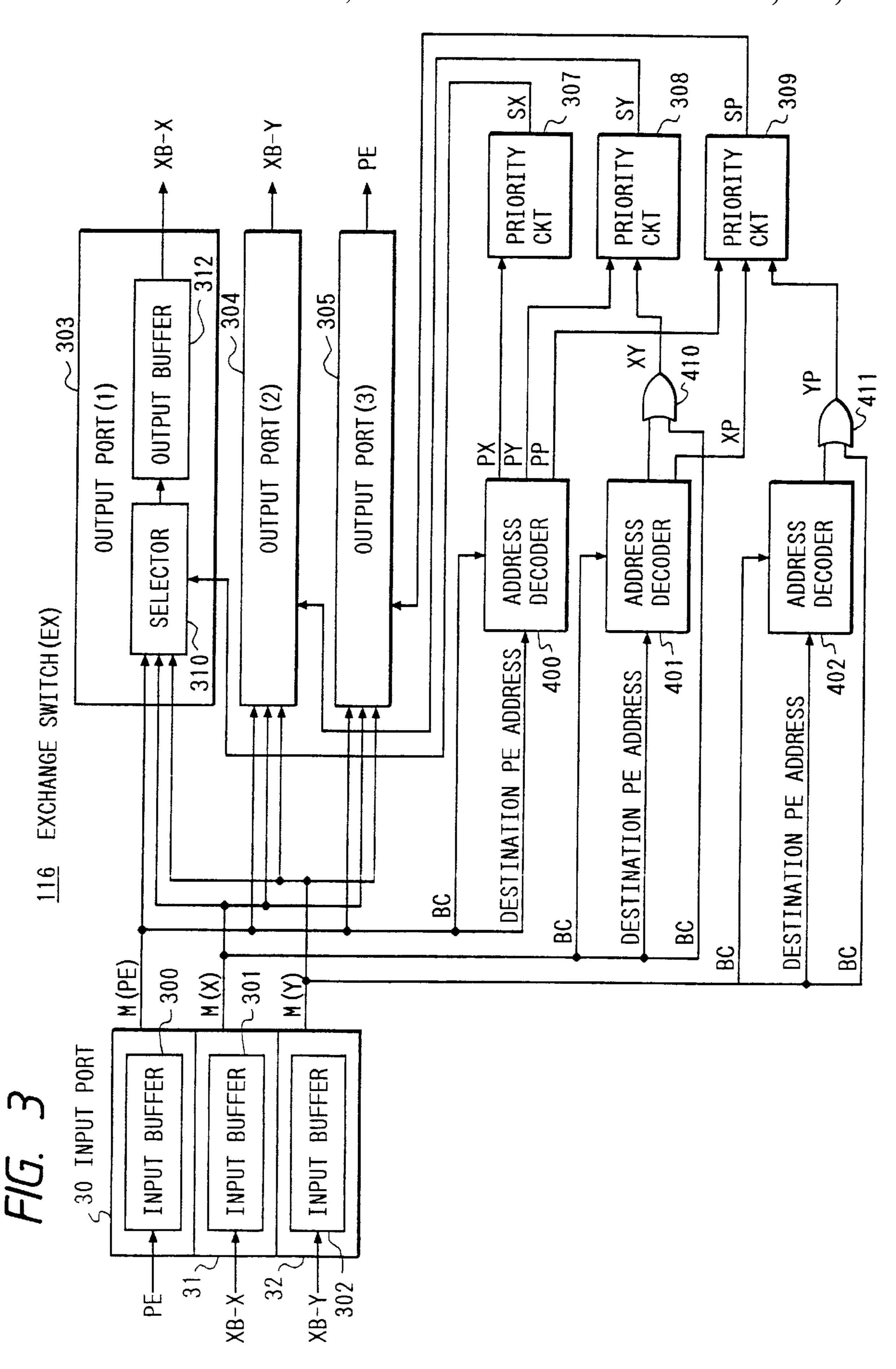

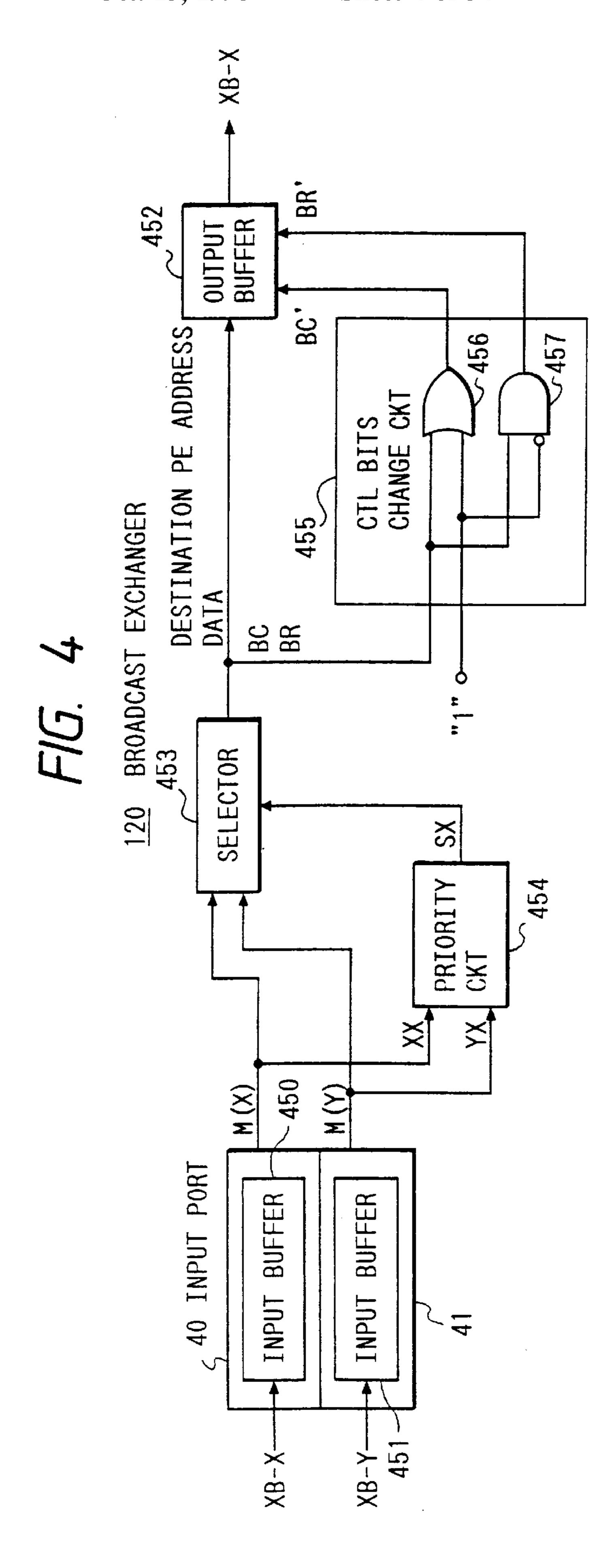

- FIG. 4 is a schematic circuit diagram of a broadcast exchanger (BEX) used by the circuit of FIG. 1;

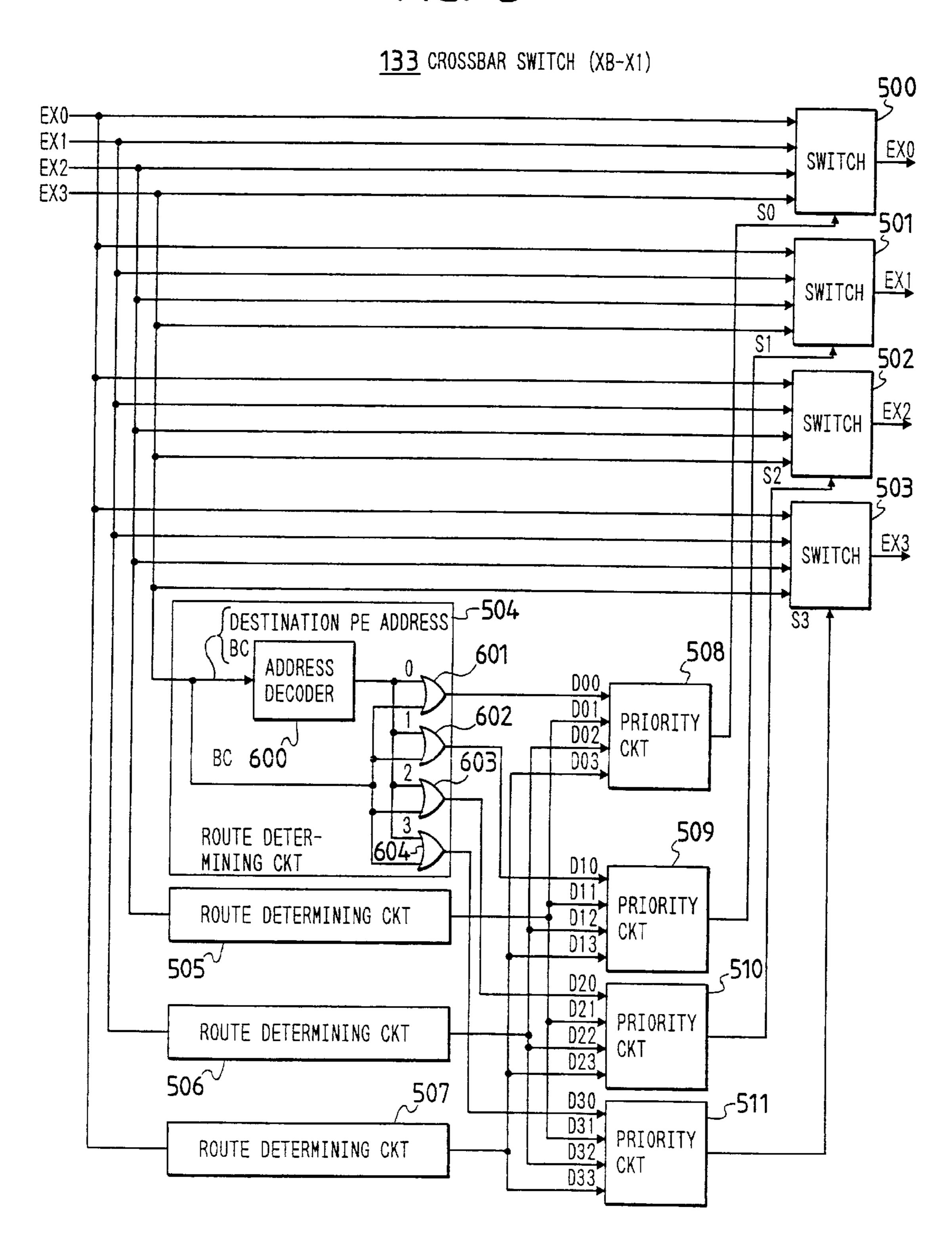

FIG. 5 is a schematic circuit diagram of a crossbar switch (XB) used by the circuit of FIG. 1;

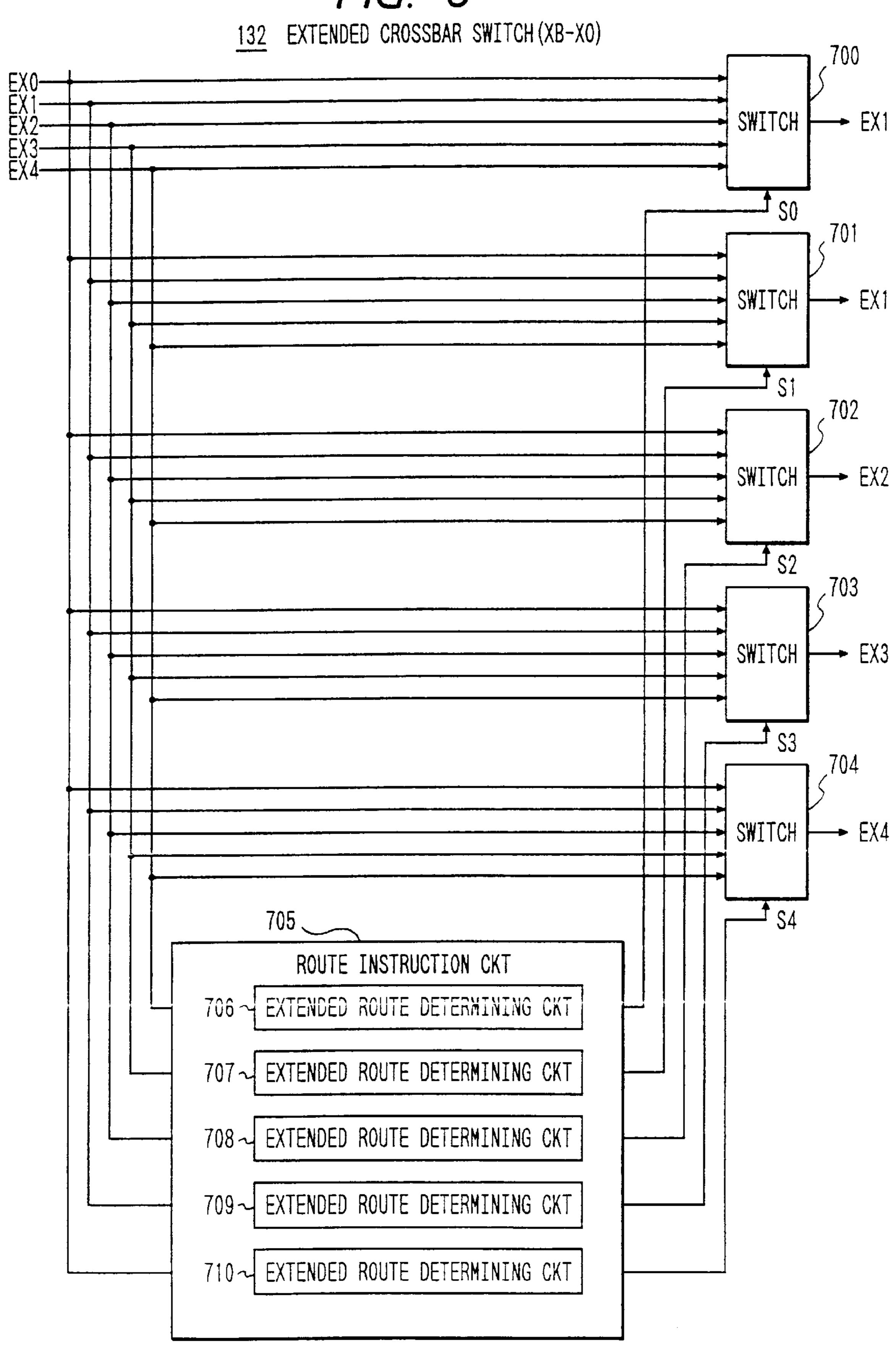

FIG. 6 is a schematic circuit diagram of an extended crossbar switch used by the circuit of FIG. 1;

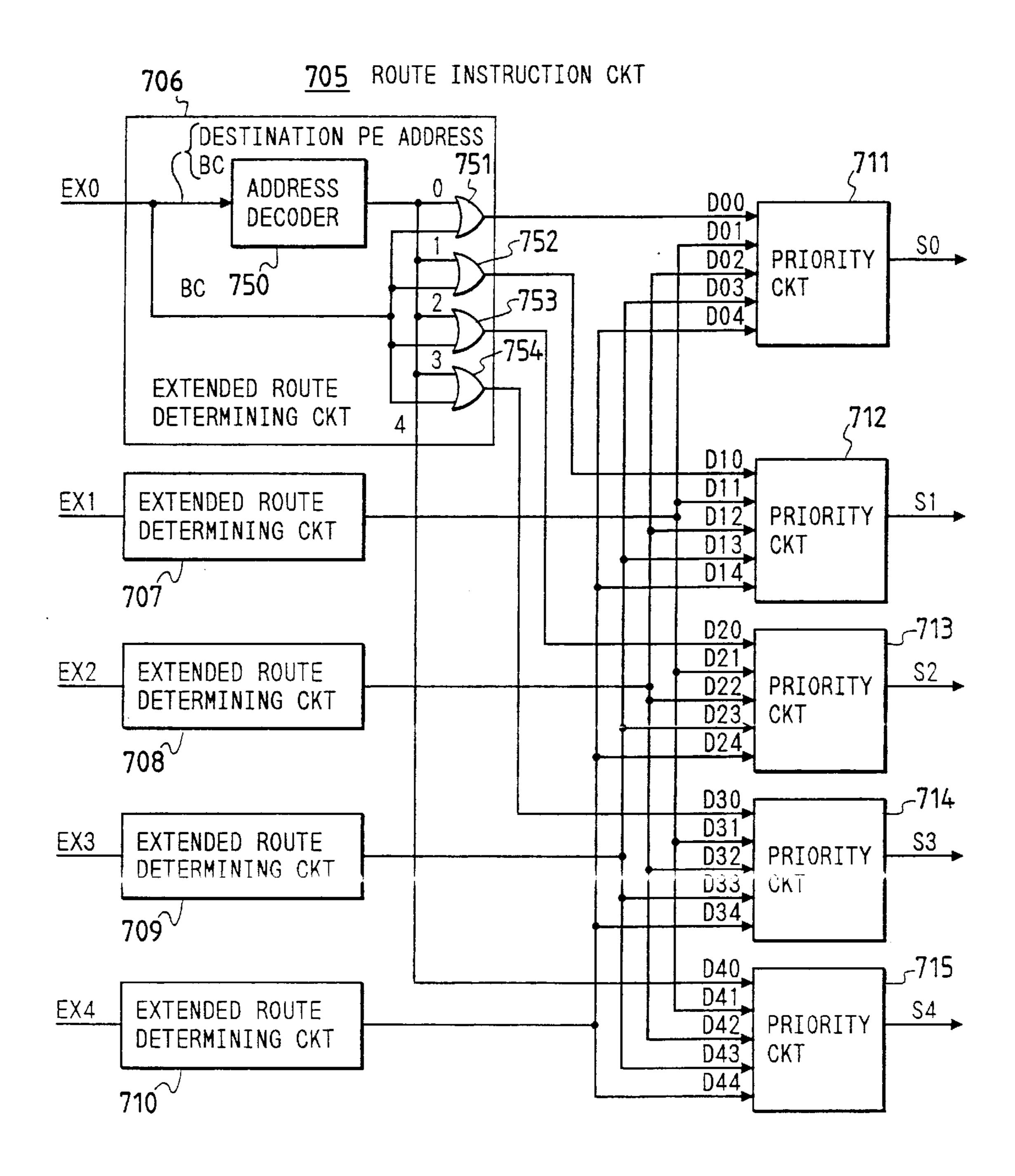

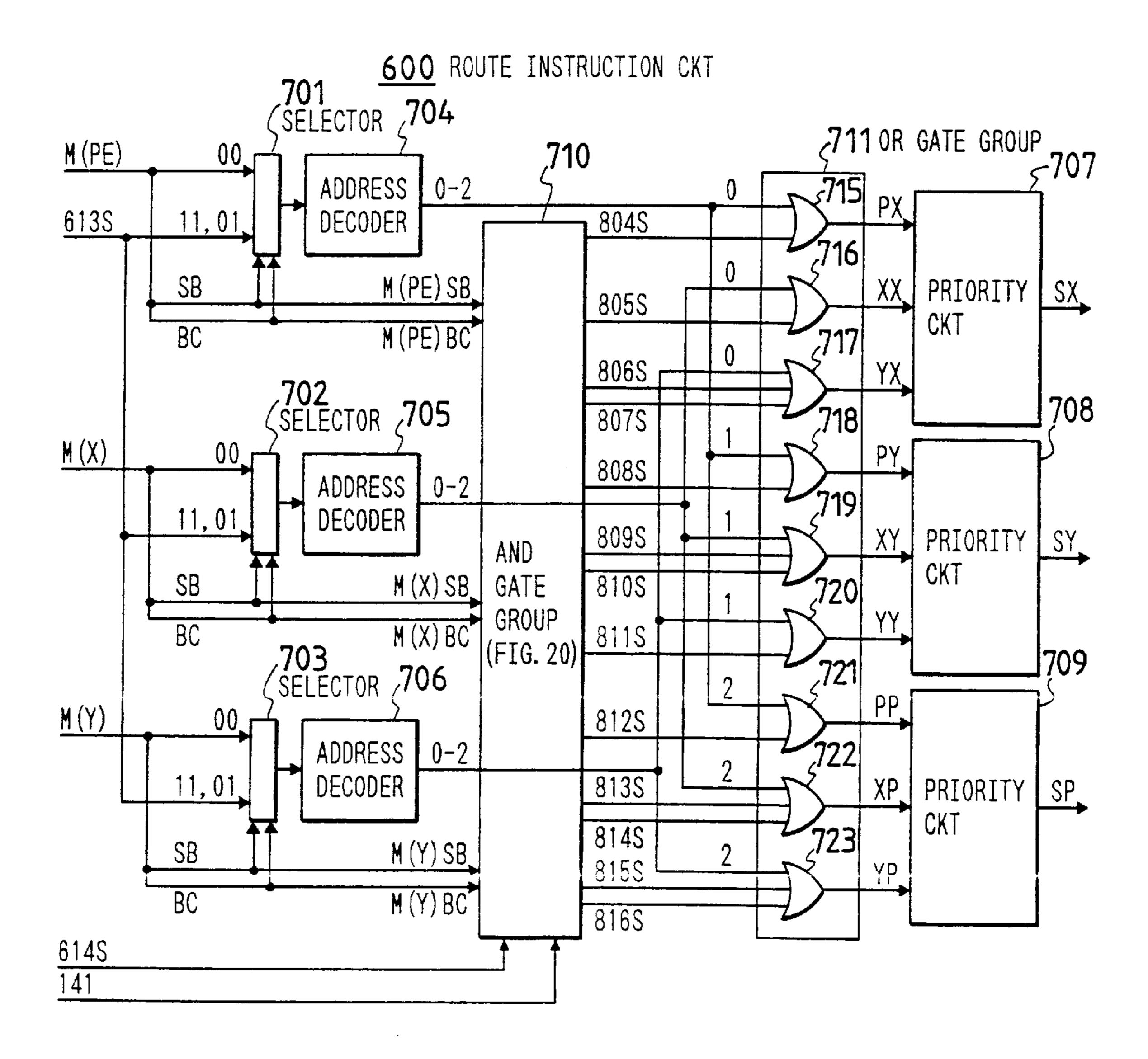

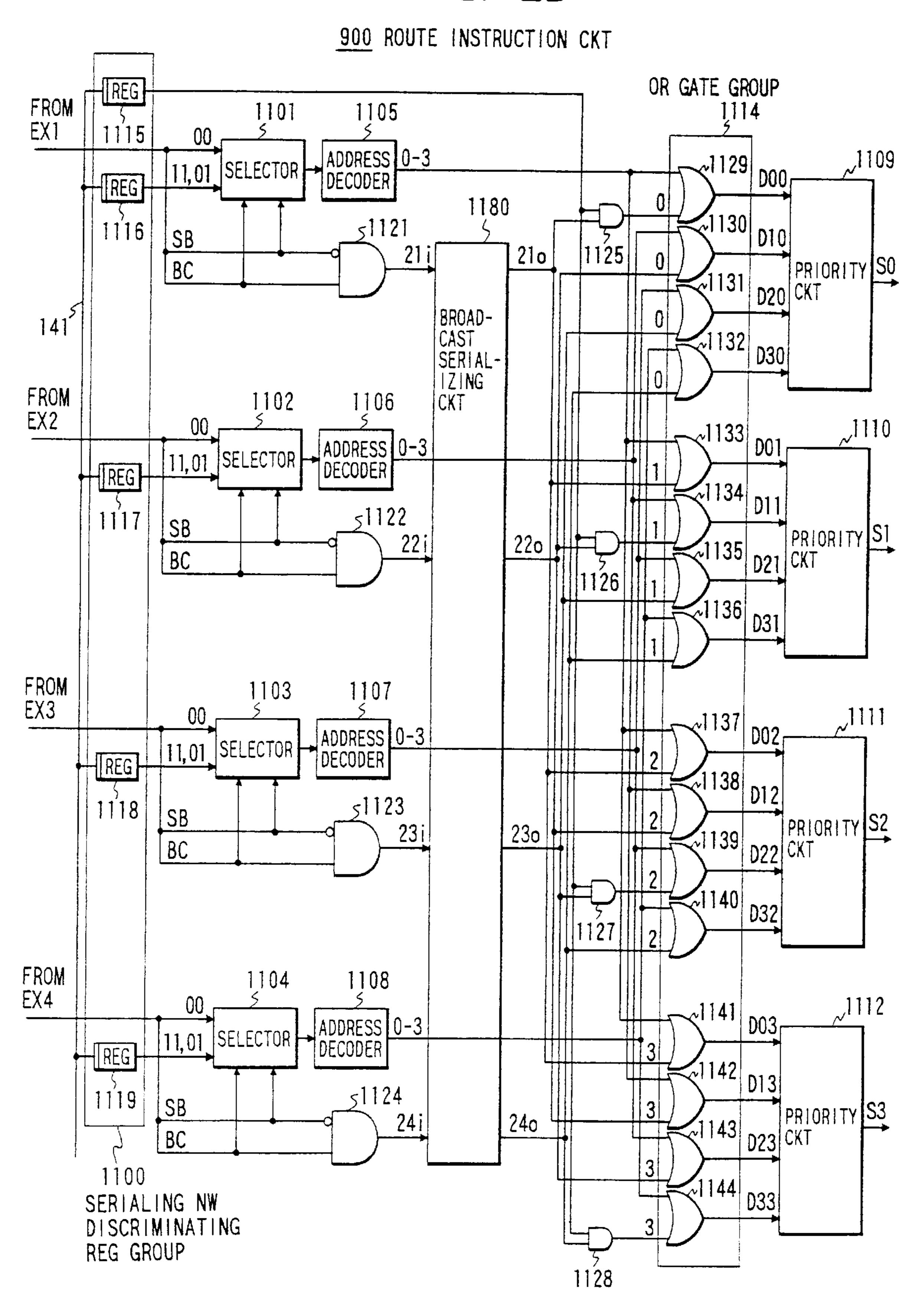

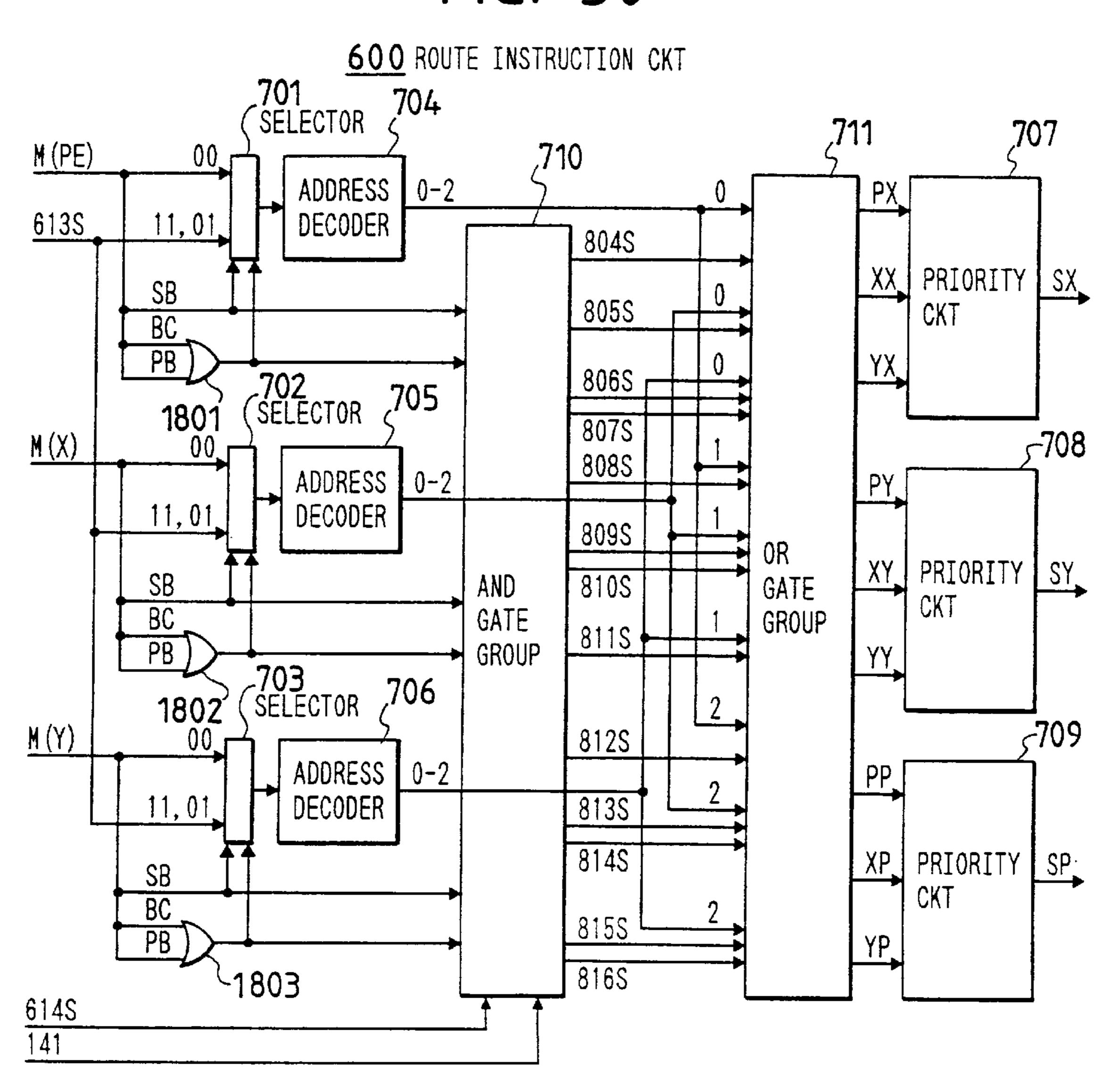

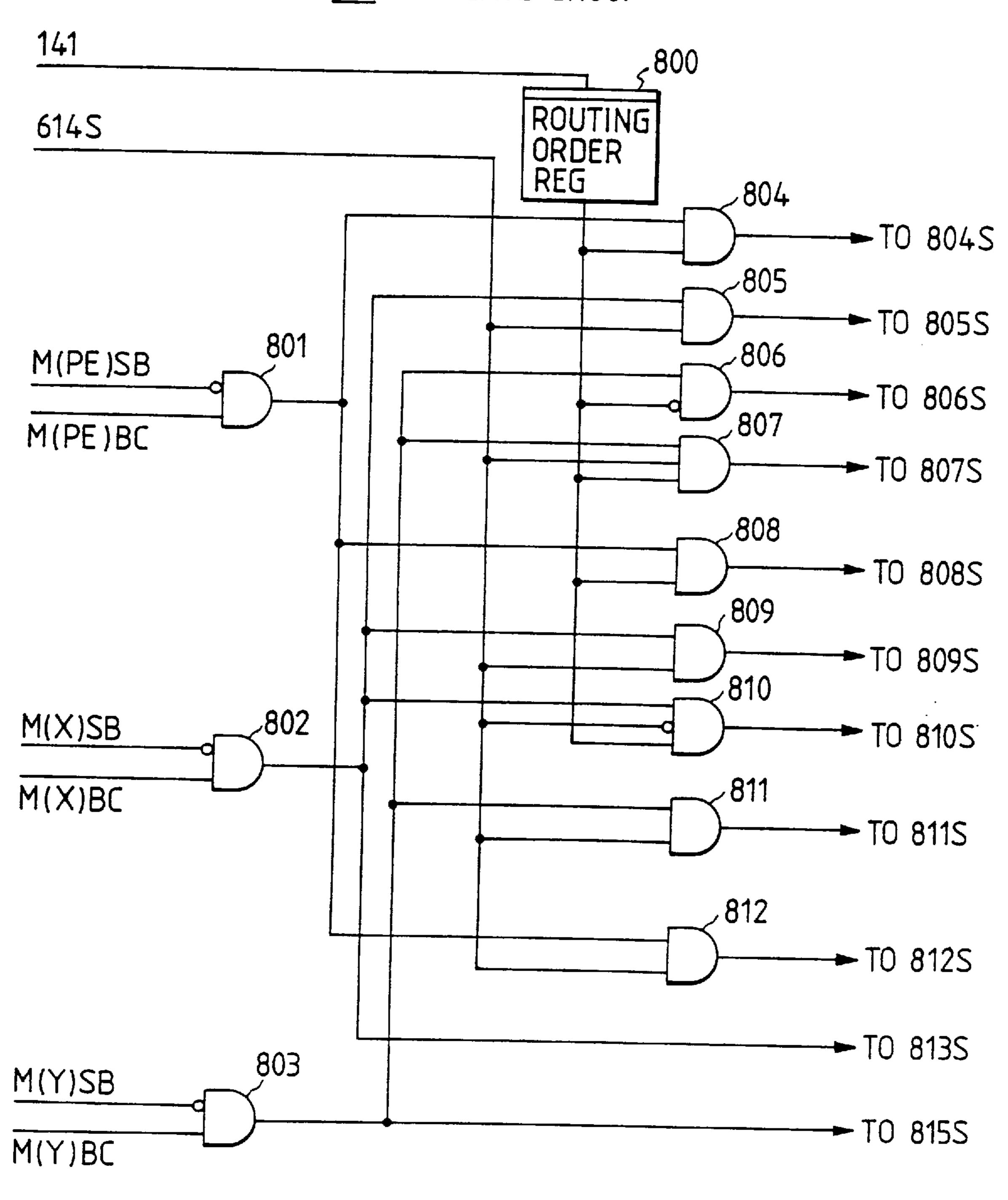

FIG. 7 is a schematic circuit diagram of a route instruction circuit used by the extended crossbar switch of FIG. 7;

FIG. 8 is a view showing message formats used by the circuit of FIG. 1;

FIG. 9 is a view depicting typical routes for transmitting <sub>10</sub> a plurality of broadcast messages conventionally;

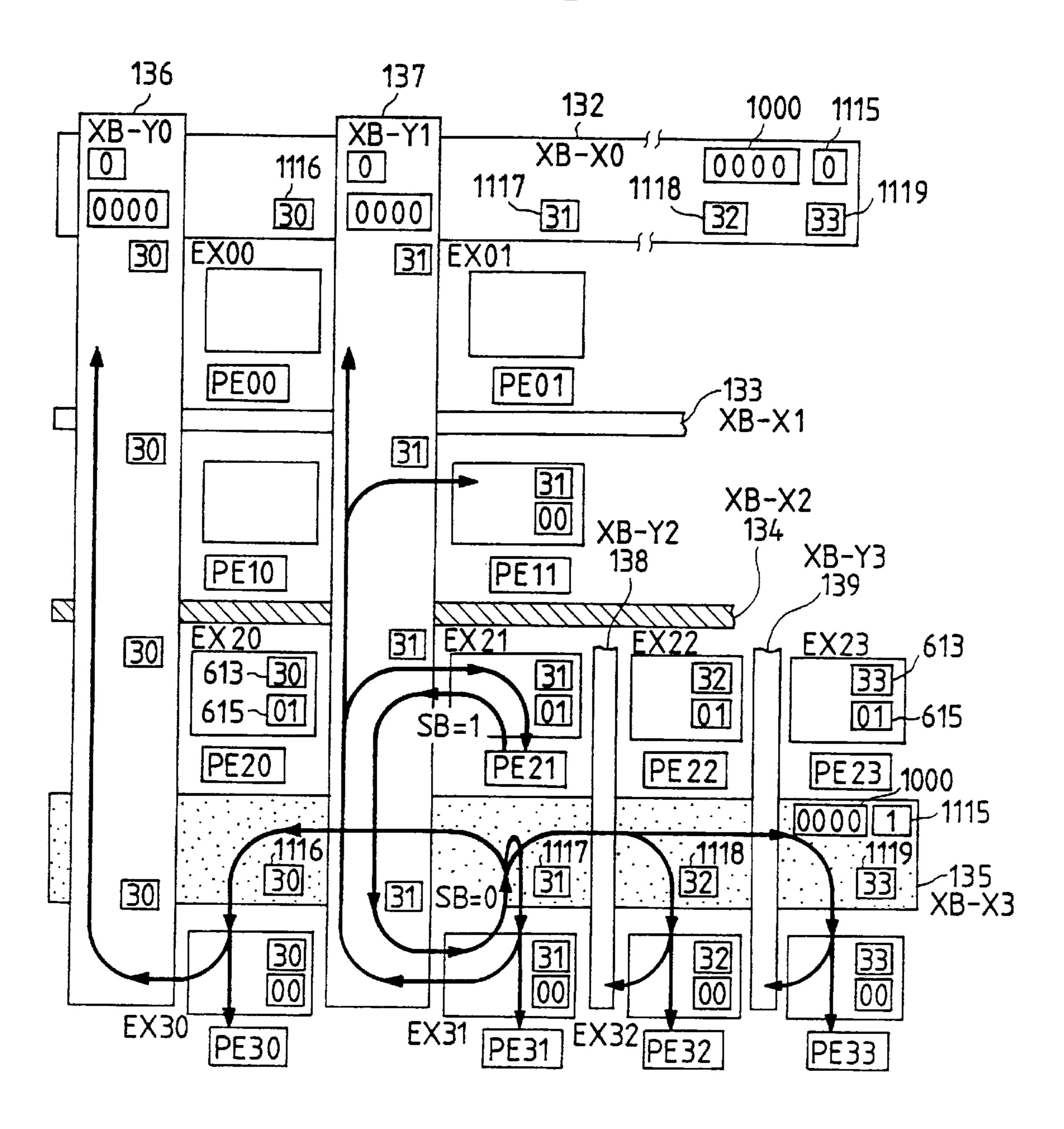

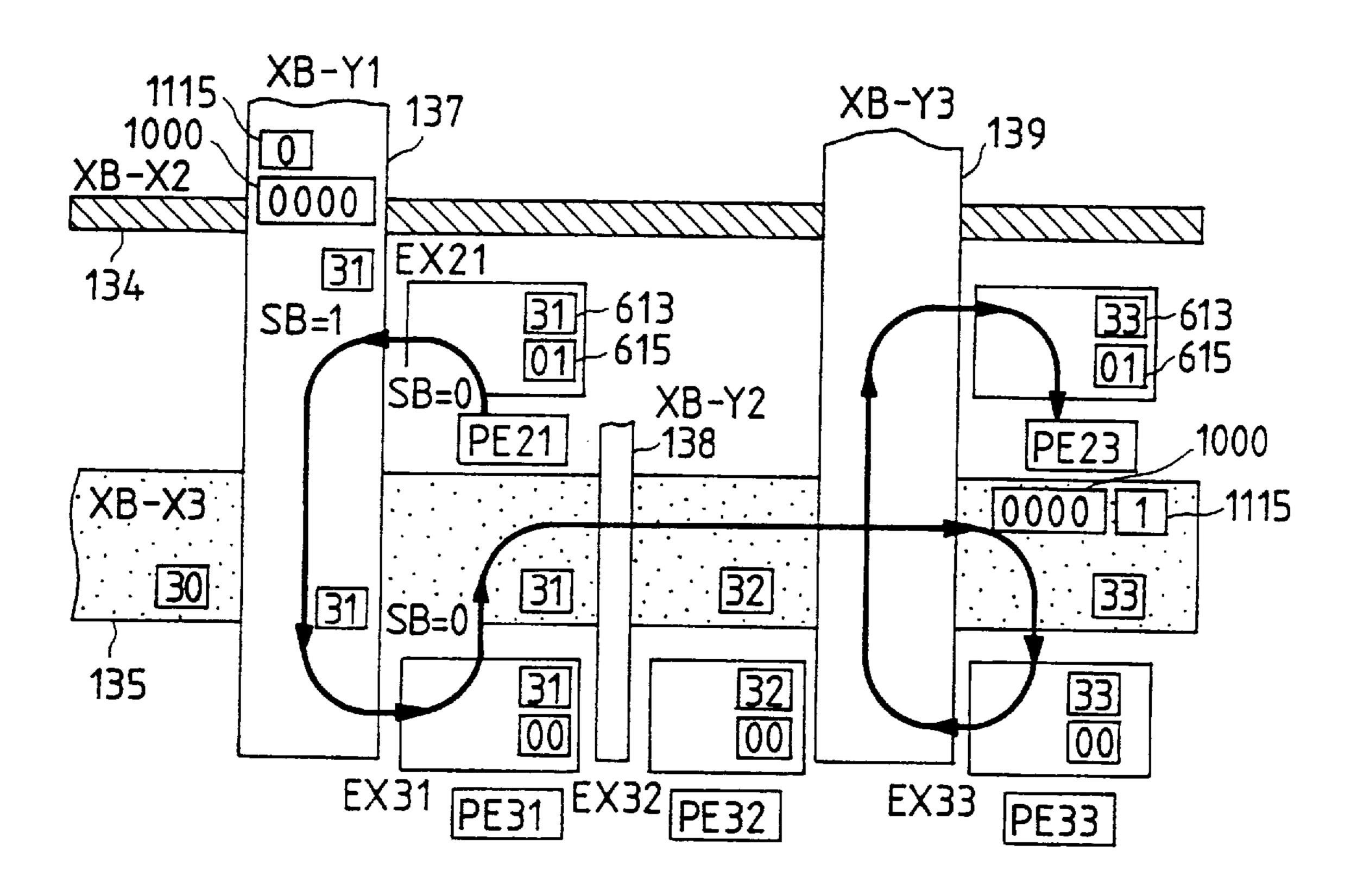

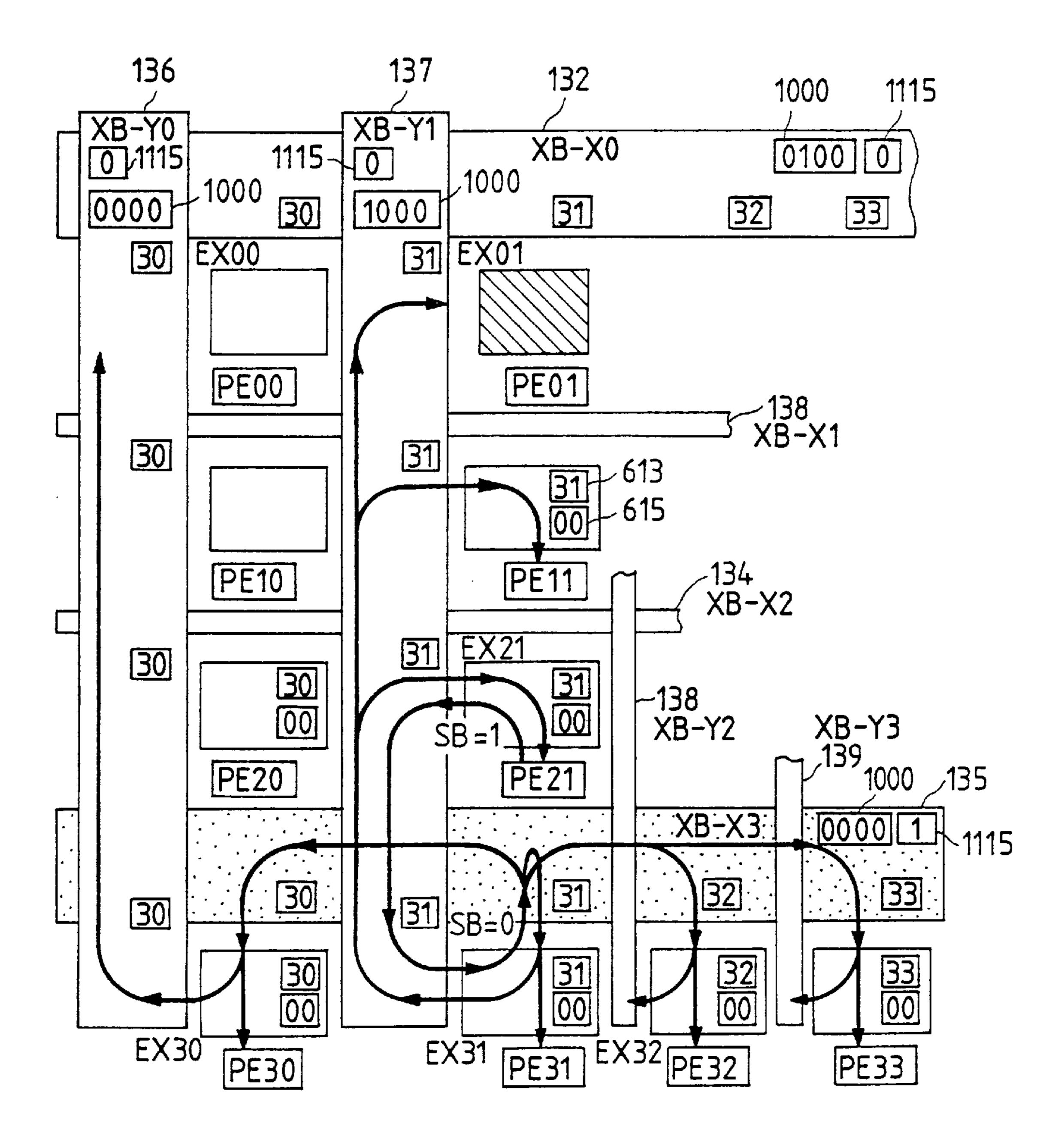

FIG. 10 is a view indicating typical routes for transmitting a plurality of broadcast messages by use of the circuit in FIG. 1;

FIG. 11 is a schematic circuit diagram of a parallel <sup>15</sup> processor system practiced as a second embodiment of the invention;

FIG. 12 is a schematic circuit diagram of a broadcast exchanger (BEX) used by the circuit of FIG. 11;

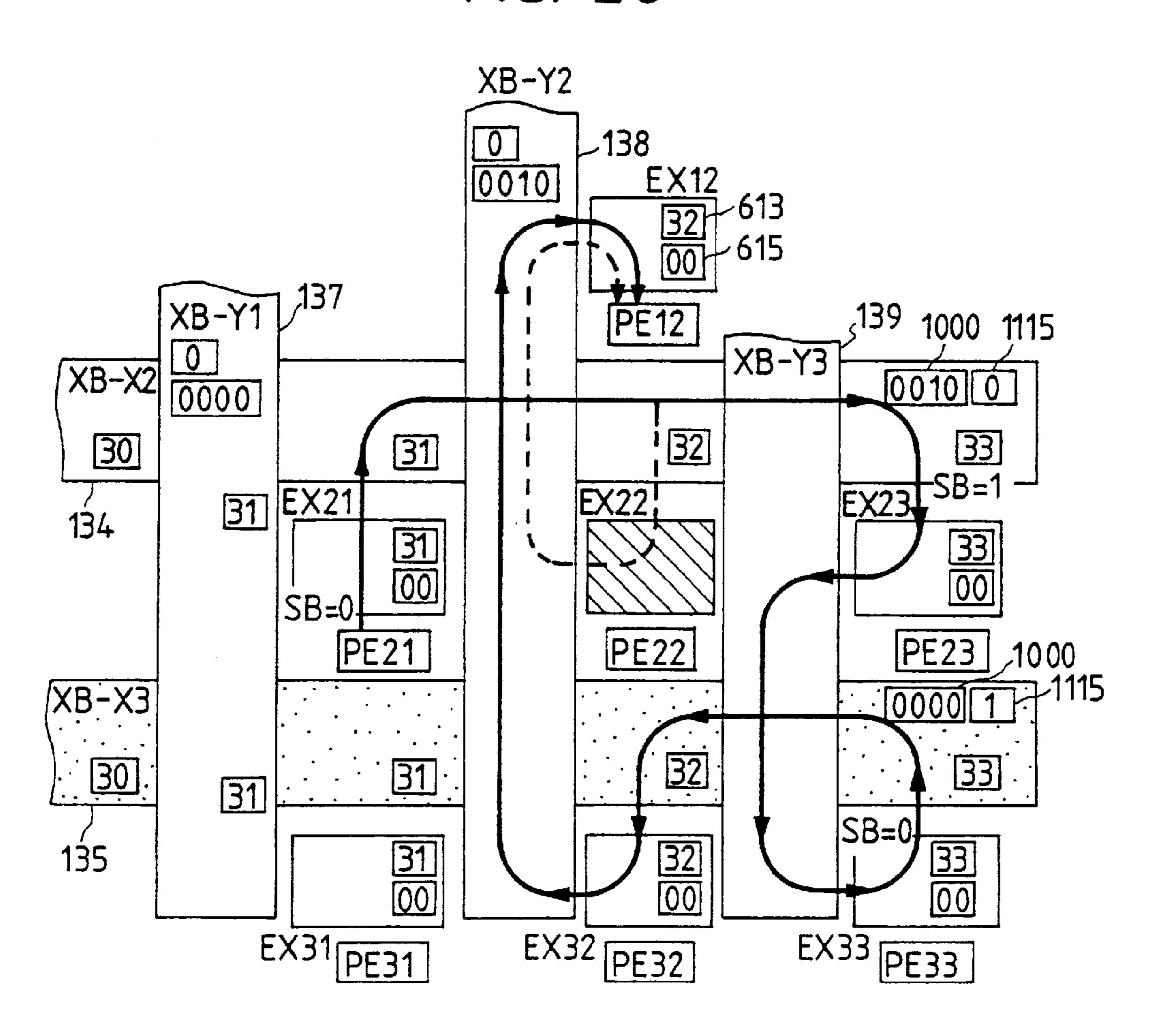

FIG. 13 is a view showing typical routes for transmitting a plurality of broadcast messages by use of the circuit in FIG. 11;

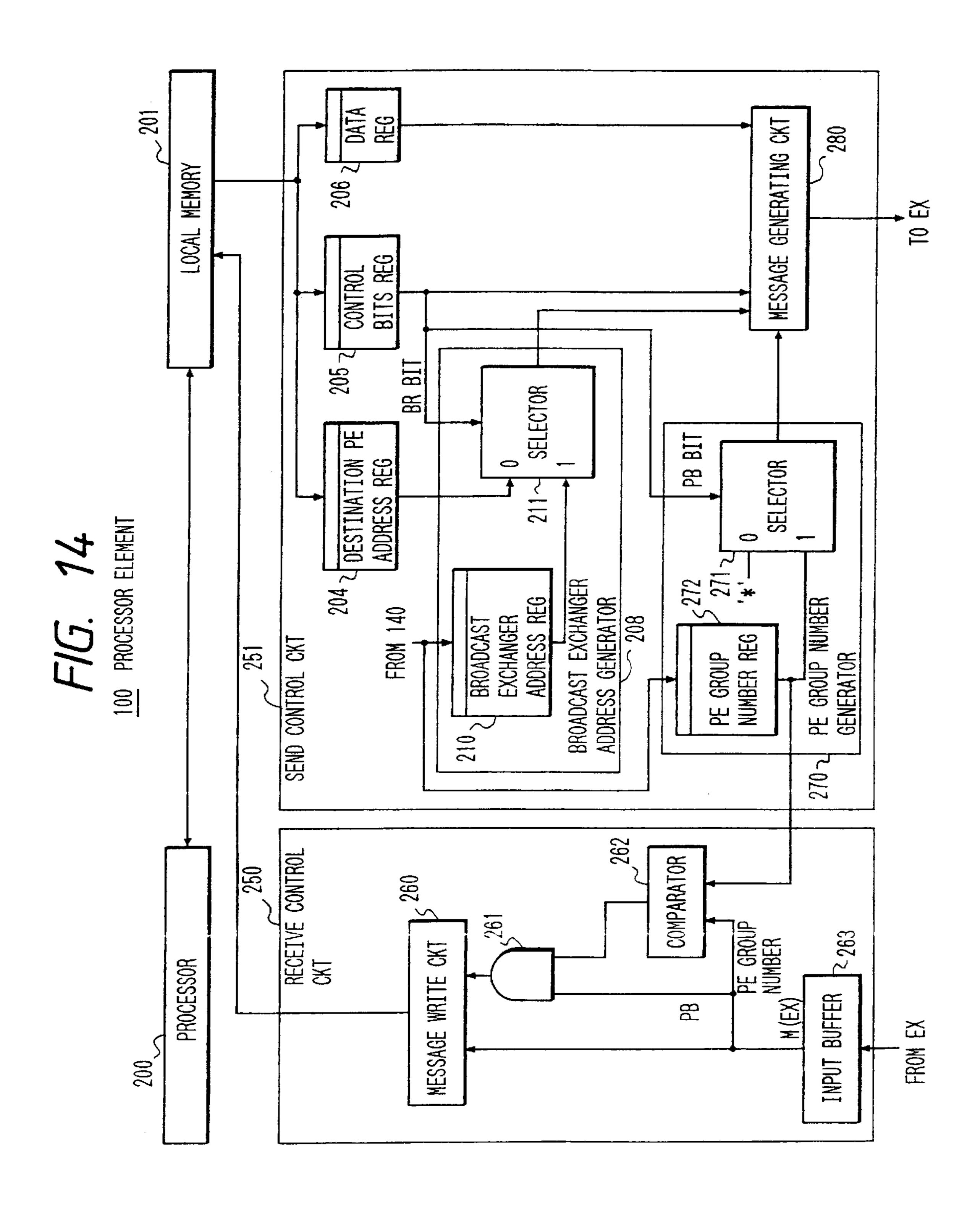

FIG. 14 is a schematic circuit diagram of a processor element (PE) used by a parallel processor system practiced as a third embodiment of the invention;

FIG. 15 is a view depicting message formats used by the third embodiment;

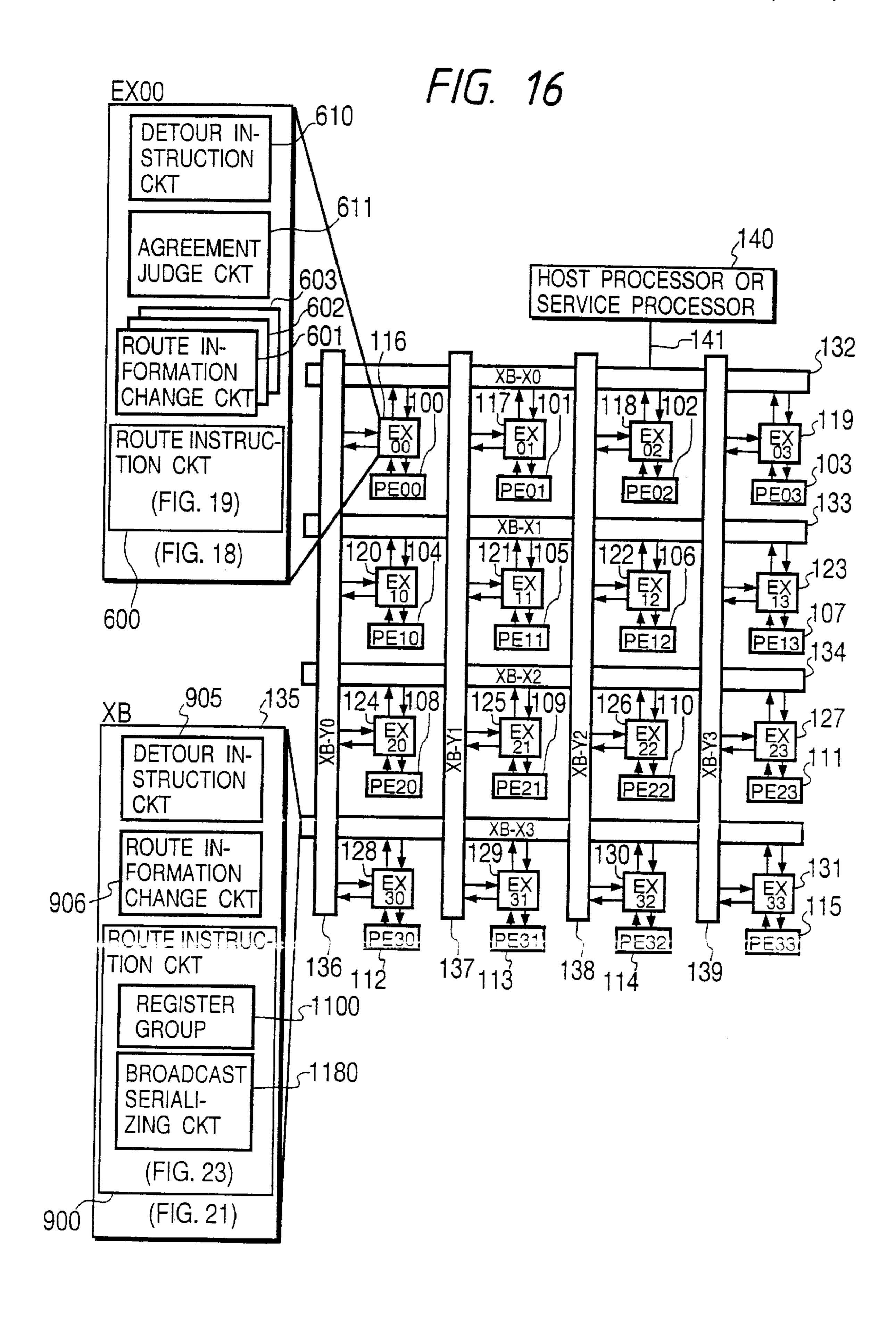

FIG. 16 is a schematic circuit diagram of a parallel processor system practiced as a fifth embodiment of the 30 invention;

FIG. 17 is a view illustrating message formats used by the circuit of FIG. 16;

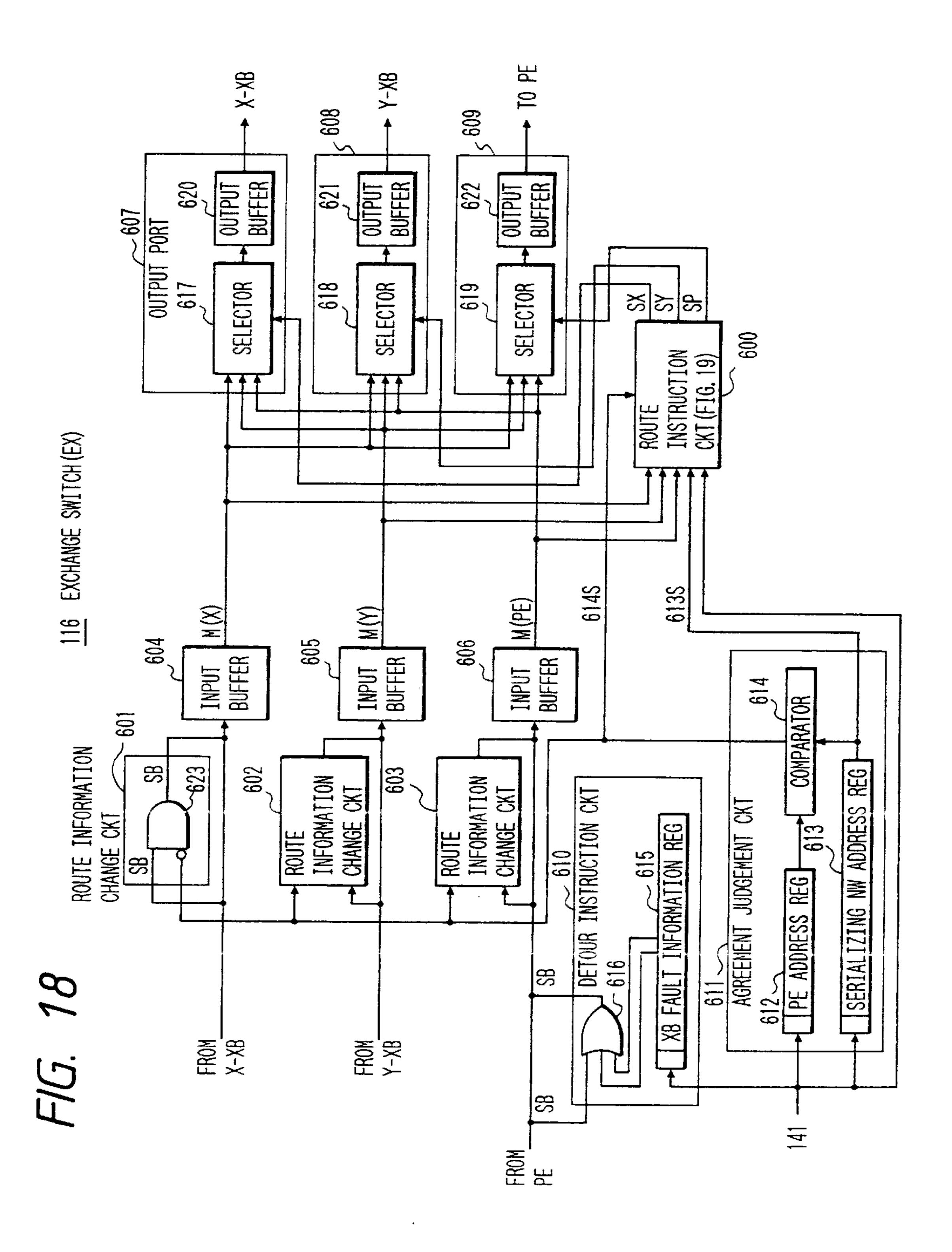

FIG. 18 is a schematic circuit diagram of an exchange switch (EX) used by the circuit of FIG. 16;

FIG. 19 is a schematic circuit diagram of a route instruction circuit used by the circuit of FIG. 18;

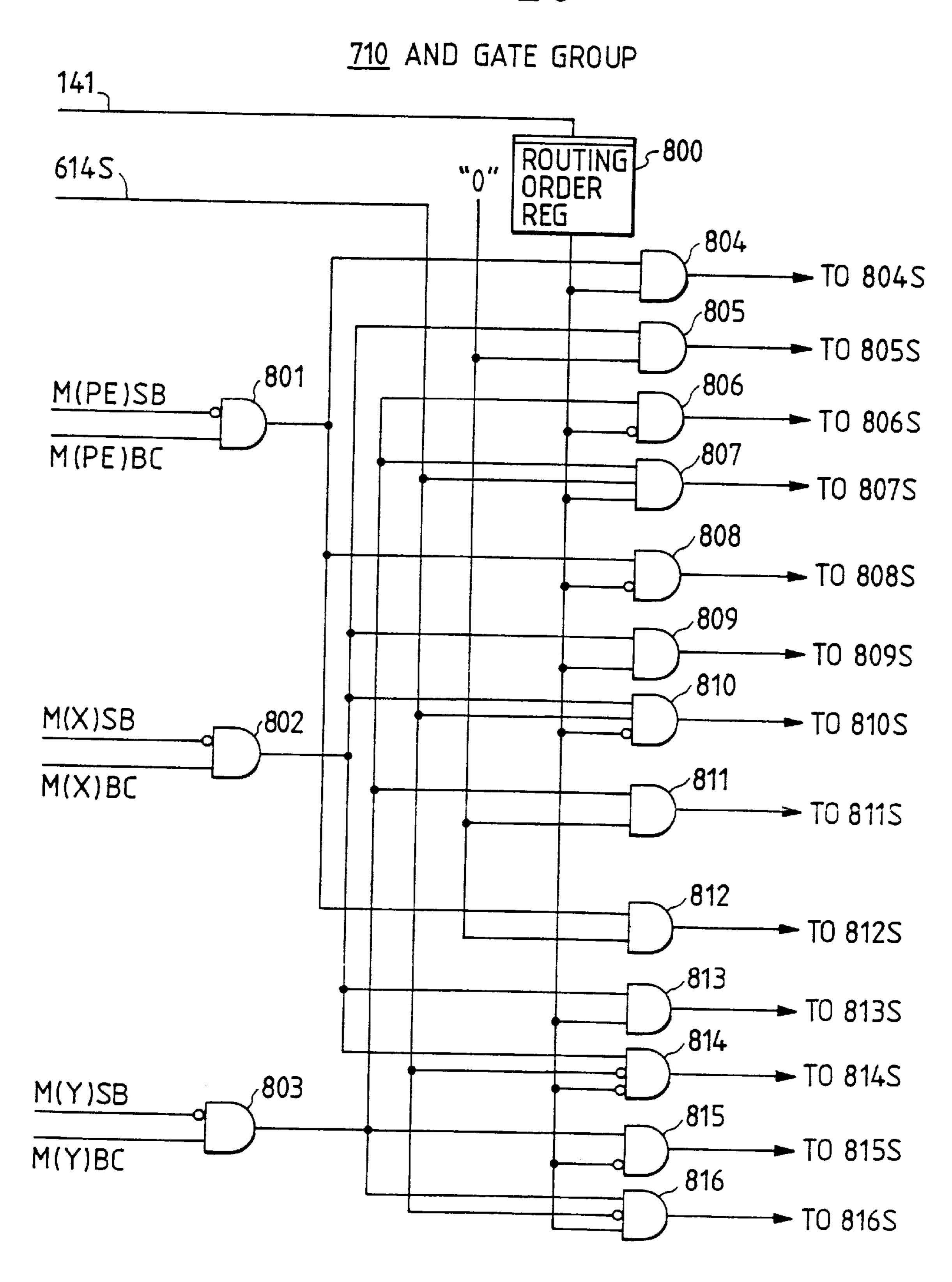

FIG. 20 is a schematic circuit diagram of an AND gate group used by the circuit of FIG. 19;

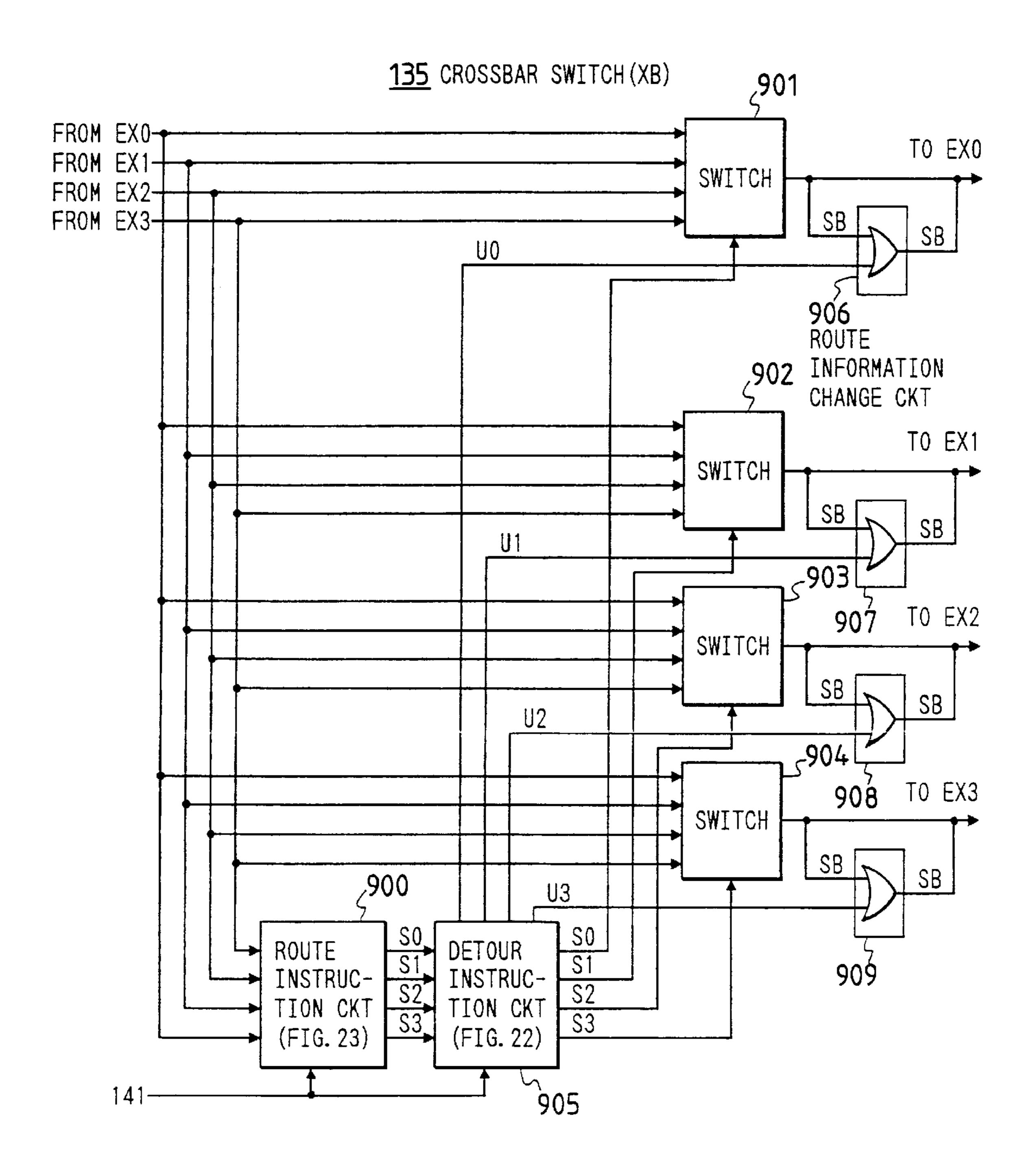

FIG. 21 is a schematic circuit diagram of a crossbar switch used by the fifth embodiment;

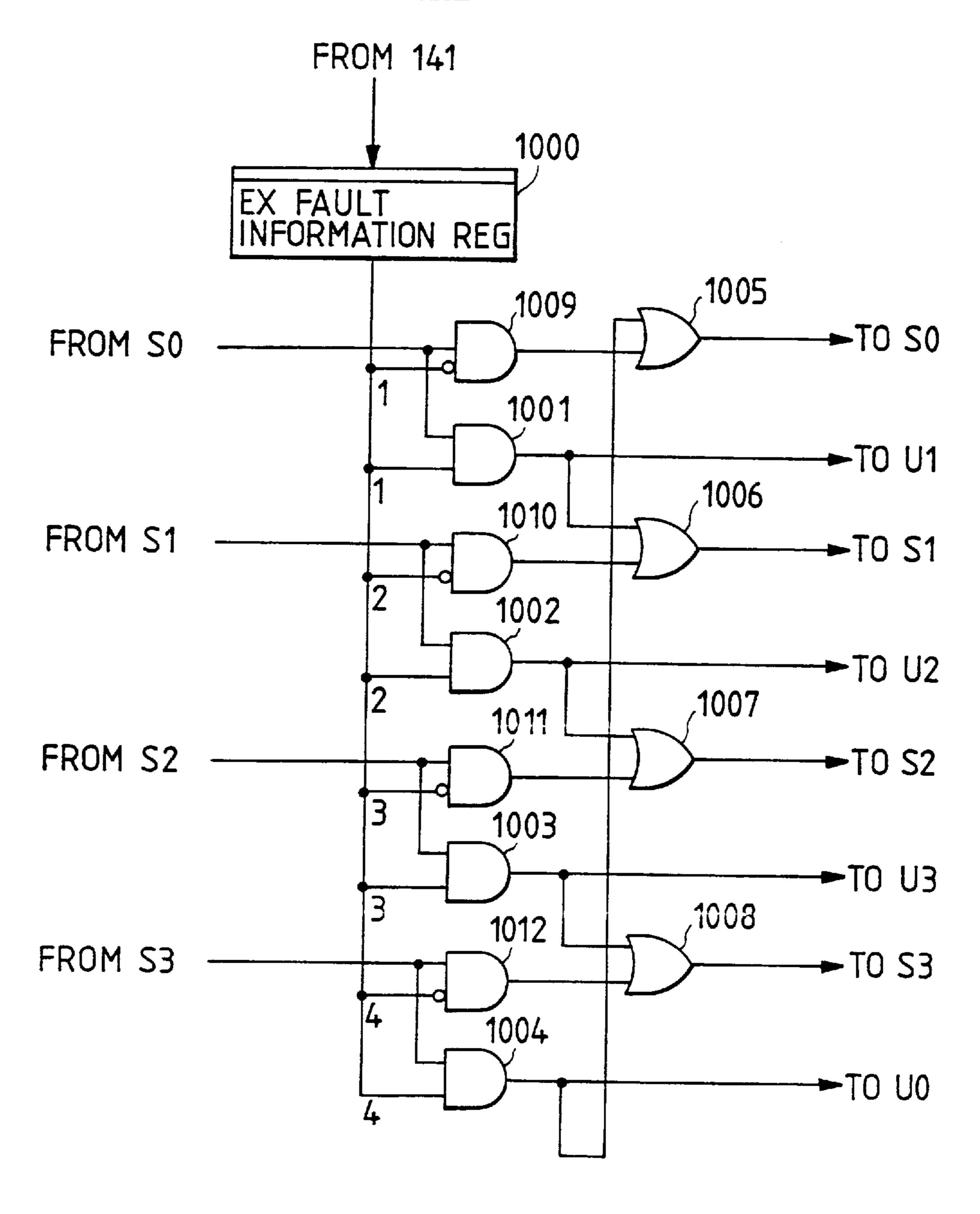

FIG. 22 is a schematic circuit diagram of a detour instruction circuit used by the circuit of FIG. 21;

FIG. 23 is a schematic circuit diagram of a route instruction circuit used by the circuit of FIG. 21;

FIG. 24 is a view showing typical routes for transmitting broadcast messages by use of the circuit in FIG. 16;

FIG. 25 is a view indicating typical routes for transmitting broadcast messages in case of a crossbar switch fault in the circuit of FIG. 16;

FIG. 26 is a view depicting a typical route for transmitting a one-to-one communication message in case of a crossbar switch fault in the circuit of FIG. 16;

FIG. 27 is a view illustrating typical routes for transmitting broadcast messages in case of an exchange switch fault in the circuit of FIG. 16;

FIG. 28 is a view showing a typical route for transmitting a one-to-one communication message in case of an exchange switch fault in the circuit of FIG. 16;

FIG. 29 is a view depicting message formats used by a parallel processor system practiced as a sixth embodiment of the invention;

FIG. 30 is a schematic circuit diagram of a route instruc- 65 tion circuit within an exchange switch used by the sixth embodiment;

8

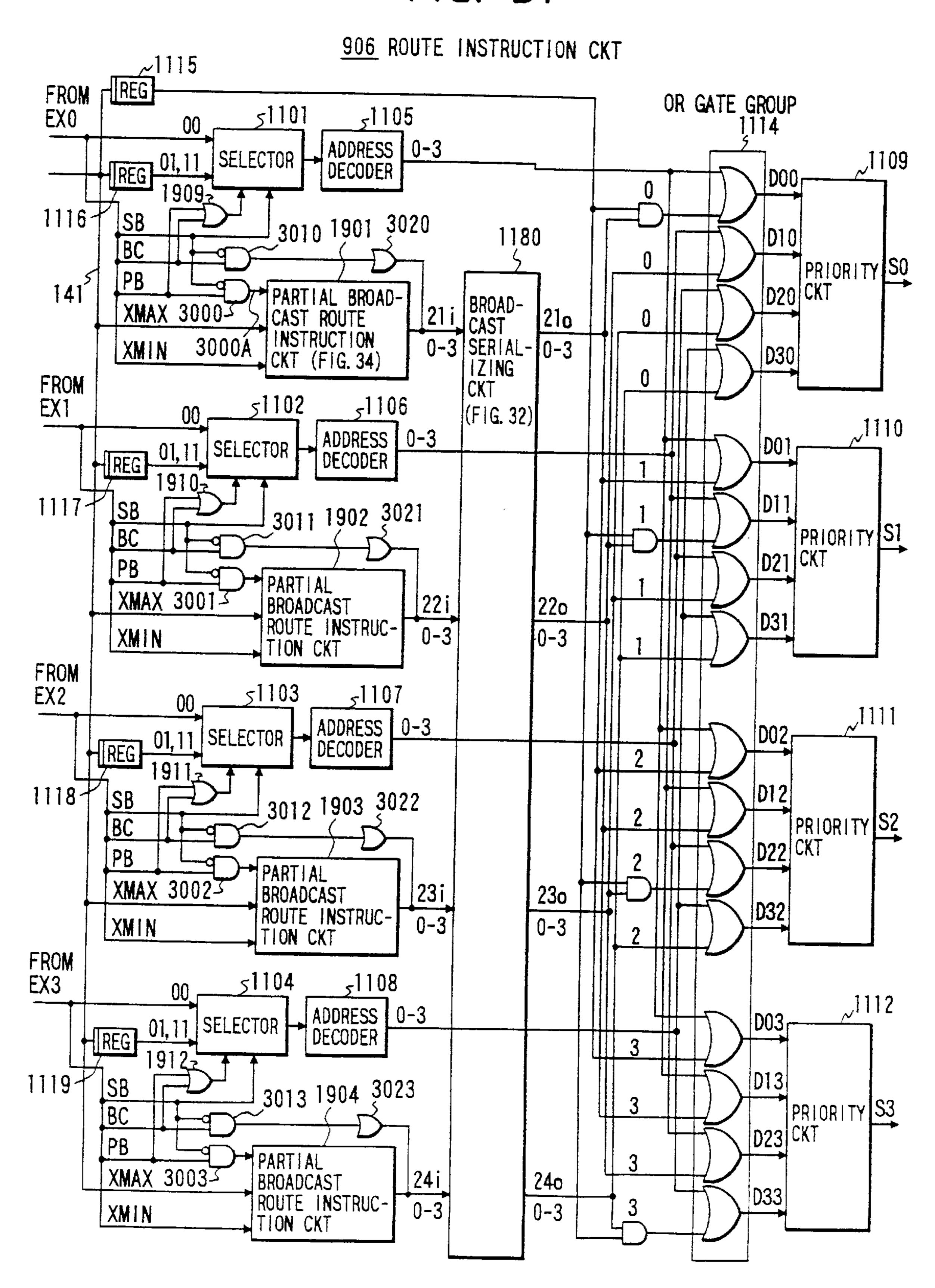

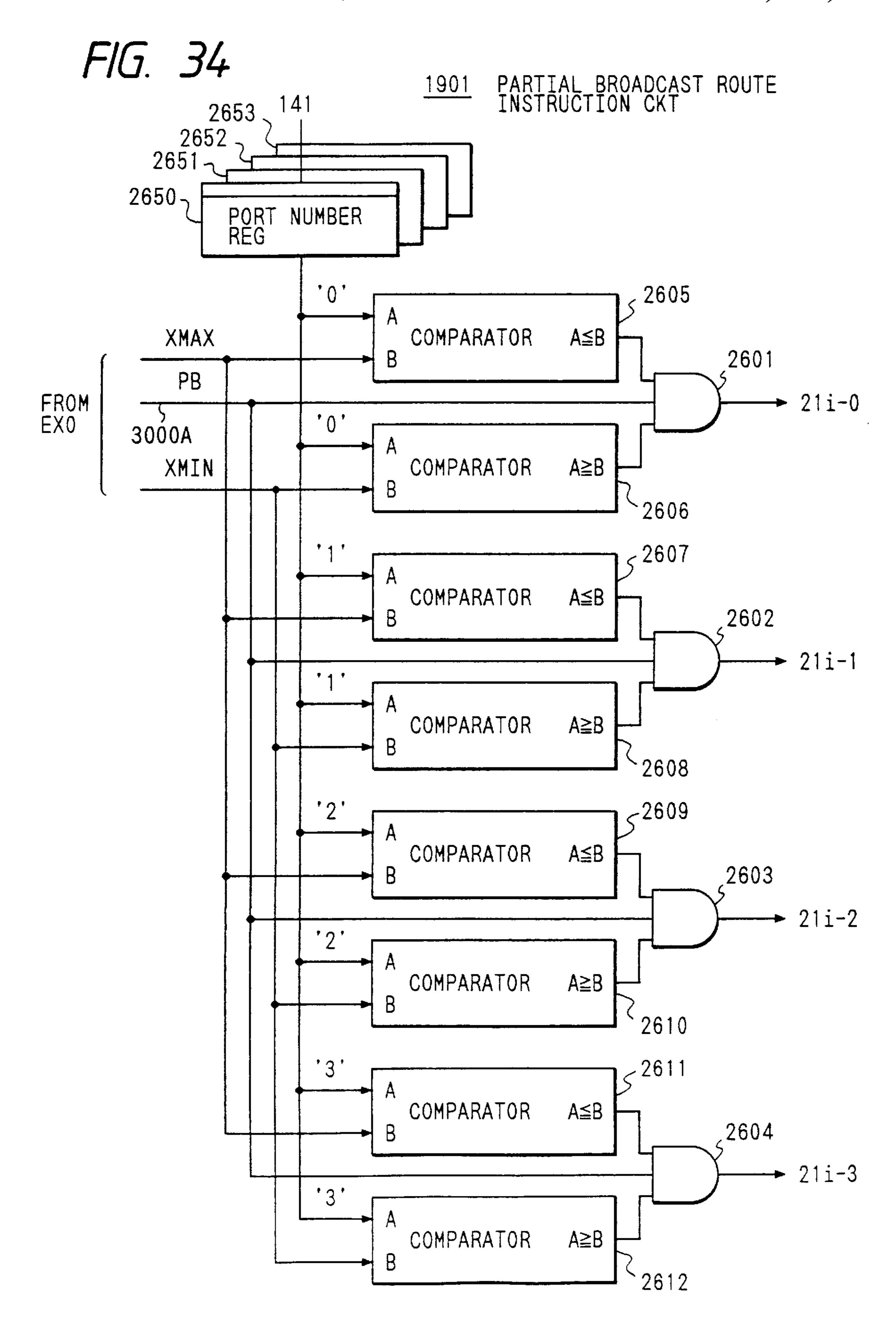

FIG. 31 is a schematic circuit diagram of a route instruction circuit within a crossbar switch used by the sixth embodiment;

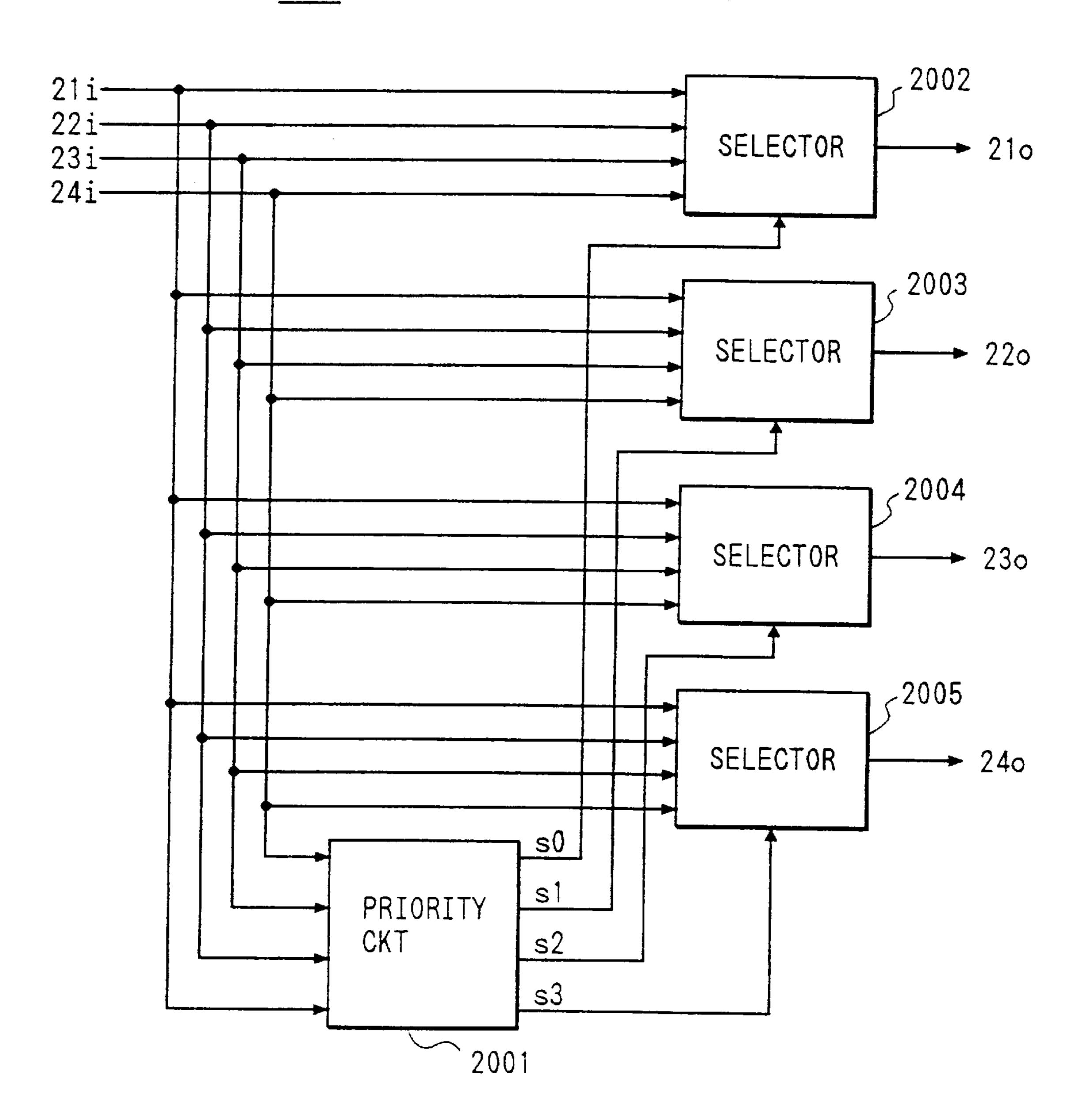

FIG. 32 is a schematic circuit diagram of a broadcast serializing circuit used by the circuit of FIG. 31;

FIG. 33 is a schematic circuit diagram of an AND gate group within an exchange switch used by a parallel processor system practiced as a seventh embodiment of the invention; and

FIG. 34 is a schematic circuit diagram of a partial broadcast route instruction circuit used by the circuit of FIG. 31.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Preferred embodiments of the invention will now be described with reference to the accompanying drawings. In the description that follows, like reference numerals designate like or corresponding parts. Throughout the embodiments described below, like circuit names designate like or similarly structured circuits. The embodiments and their variations in this specification utilize what is disclosed in Japanese Pat. Laid-Open No. Hei 5-28122 or U.S. patent application Ser. No. 07/916,663 now U.S. Pat. No. 5,192, 580 corresponding thereto. The contents of these applications, including the network constitution, the scheme for transmitting broadcast messages, and the techniques for transmitting partial broadcast messages, are incorporated in this specification for reference.

#### <First Embodiment>

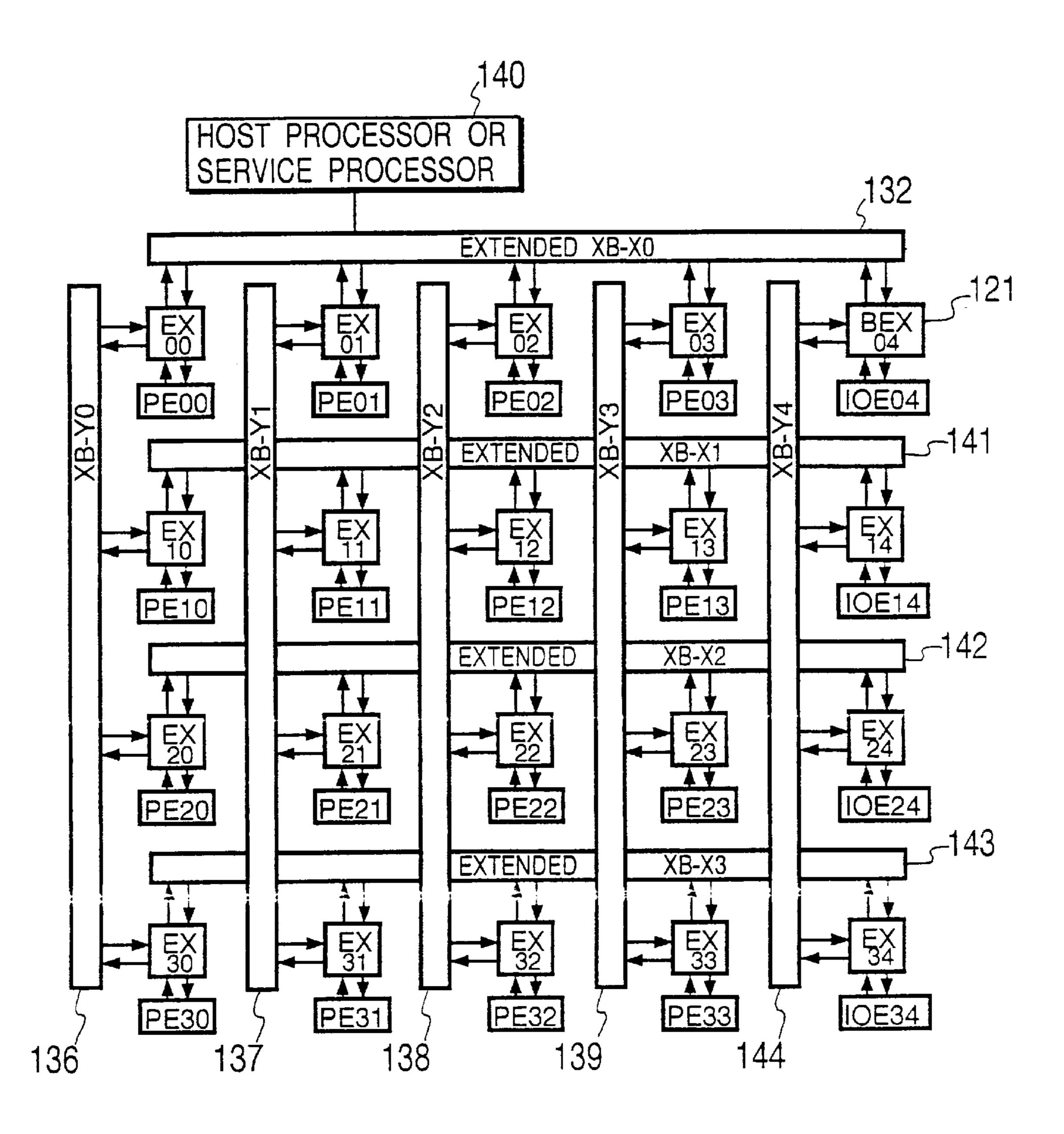

In FIG. 1, reference numerals 132 through 135 are X-coordinate crossbar switches (each abbreviated to XB-X 35 hereunder), and 136 through 139 are Y-coordinate crossbar switches (each abbreviated to XB-Y hereunder). Reference numeral 116 represents an exchange switch (abbreviated to EX) connected to one I/O port of an XB-X as well as to one I/O port of an XB-Y. These crossbar switches and exchange 40 switches constitute a hyper-crossbar network. Reference numeral 100 denotes a processor element (abbreviated to PE) connected to one EX. Reference numeral 120 indicates a broadcast exchanger (BEX) having a broadcast serializing facility specific to the first embodiment. Reference numeral 140 is a host processor or a service processor (SVP) which loads programs and data to the PEs and which retrieves the resultant data from each PE upon completion of program execution thereby. The processor 140 also initializes the network and the PE, monitors the PE and the network for failure, and services the network and the PE in case of fault.

Each PE is given a network address (simply called the address hereunder) representing the combination of X and Y coordinates of a single lattice point in a two-dimensional coordinate space. Each XB-X is installed with respect to a 55 plurality of PEs having the same Y coordinate. Hence each XB-X represents an X-coordinate XB, and each XB-Y denotes a Y- coordinate XB. Each XB-X is specified as XB-Xi, the suffix i representing the Y coordinate i (i=0-3). Each XB-Y is installed with respect to a plurality of PEs 60 having the same X coordinate. Each XB-Y is specified as XB-Yj, the suffix j representing the X coordinate j (j=0-3). In FIG. 1, each PE is identified by its Y and X coordinates. For example, PE03 is the processor element having a Y coordinate of 0 and an X coordinate of 3. Each EX is given the same address as that of the corresponding PE. Each crossbar switch has a plurality of input ports and a plurality of output ports. Upon receipt of a plurality of ordinary

messages (called one-to-one communication messages) through these input ports, a crossbar switch is capable of transmitting these messages parallelly to the output ports designated by the addresses held in the messages. When admitting a broadcast message through one of the input 5 ports, a crossbar switch is also capable of transmitting the message parallelly to the output ports. More specifically, the XB-X1 through XB-X3 and the XB-Y0 through XB-Y2 each comprise three input ports and three output ports connected to a plurality of PEs. The XB-X0 has an addi- 10 tional set of an input and an output port connected to the broadcast exchanger (BEX) 120. Equipped with these extended ports, the XB-X0 is called the extended X-coordinate crossbar switch or the extended XB-X0. Likewise, the XB-Y3 further comprises one output port 15 connected to the broadcast exchanger (BEX) 120. Thus furnished with the extended port, the XB-Y3 is called the extended Y-coordinate crossbar switch or the extended XB-Y3. In the description that follows in which these crossbar switches are not specifically distinguished from one 20 another, they may be simply referred to as XBs. Although FIG. 1 shows four X-coordinate crossbar switches and four Y-coordinate crossbar switches, the quantities are only for illustration purposes. With the first embodiment, messages are transmitted over the network through wormhole routing 25 as described in U.S. Pat. No. 5,212,773 cited above. The transmission technique described in this U.S. patent is incorporated herein for reference regarding the first embodiment and the embodiments that will be discussed later and their variations. The technique above involves first dividing 30 into a plurality of parts a message significantly longer than the capacities of the diverse buffers within the network, and having each of the message parts advance individually through the network. The first embodiment deals with the transmission of a message so long that its trailing part still remains in the source processor element while its leading part has already arrived at the destination processor element. In such a case, the route used for the message transmission is not allocated as a whole beforehand; the necessary route is secured in steps as the leading part of the message 40 advances. Each of a plurality of route portions constituting the allocated route is released after the trailing part of the message has passed it.

9

In the first embodiment, each PE wishing to broadcast data to all other PEs transmits a broadcast request message 45 containing the data to the broadcast exchanger (BEX) 120. Responding serially to a plurality of broadcast request messages from a plurality of PEs, the broadcast exchanger (BEX) 120 transmits serially the broadcast messages requested by these messages to the XB-X0. That is, the 50 broadcast exchanger (BEX) 120 performs the same serializing operation as that on a plurality of broadcast request messages carried out by one of the PEs as described in connection with the prior art. Under the prior art, when any one PE performs the serializing operation, that PE receives 55 a broadcast request message in its entirety and then retransmits a broadcast message containing the data held in the received broadcast request message. However, unlike the other EXs, the broadcast exchanger (BEX) 120 has no corresponding PE connected thereto. That is, the broadcast 60 X coordinate 3 is the same as that of the other PEs connected exchanger (BEX) 120 serializes a plurality of broadcast request messages from the network in preparation for serial retransmission of the corresponding broadcast messages. The broadcast exchanger (BEX) 120 comprises a CTL bit change circuit 455. This circuit converts the control bits 65 contained in, and standing for, each broadcast request message into those representing a broadcast message to be

**10**

retransmitted, whereby a broadcast message is generated. Thus with the first embodiment, unlike under the prior art, the broadcast exchanger (BEX) 120 transmits an already received leading part of a broadcast request message while still receiving concurrently a subsequent part of that message. The scheme minimizes the delay in the broadcast exchanger (BEX) 120 transmitting the broadcast message. Because the broadcast exchanger (BEX) 120 is furnished independently of the PEs for performing arithmetic operations, the performance of the arithmetic operation PEs is not delayed by the intervention of the BEX 120.

Whereas the use of the broadcast exchanger (BEX) 120 offers the benefits outlined above, it could bring about a deadlock involving a broadcast request message and a broadcast message. Specifically, where the first embodiment utilizes worm-hole routing, the following can happen: with the route allocated for transmission of a broadcast request message from one PE up to the broadcast exchanger (BEX) 120, that part of the broadcast request message which has first arrived at the broadcast exchanger (BEX) 120 is sent therefrom as the leading part of the corresponding broadcast message. At this point, if the broadcast message is to employ for its transmission any portion of the already allocated route, the broadcast message waits for that portion of the allocated route to be released. While the broadcast message waits indefinitely for the necessary route portion to be released, the broadcast request message is also unable to advance over the network. Thus occurs a deadlock involving these two messages.

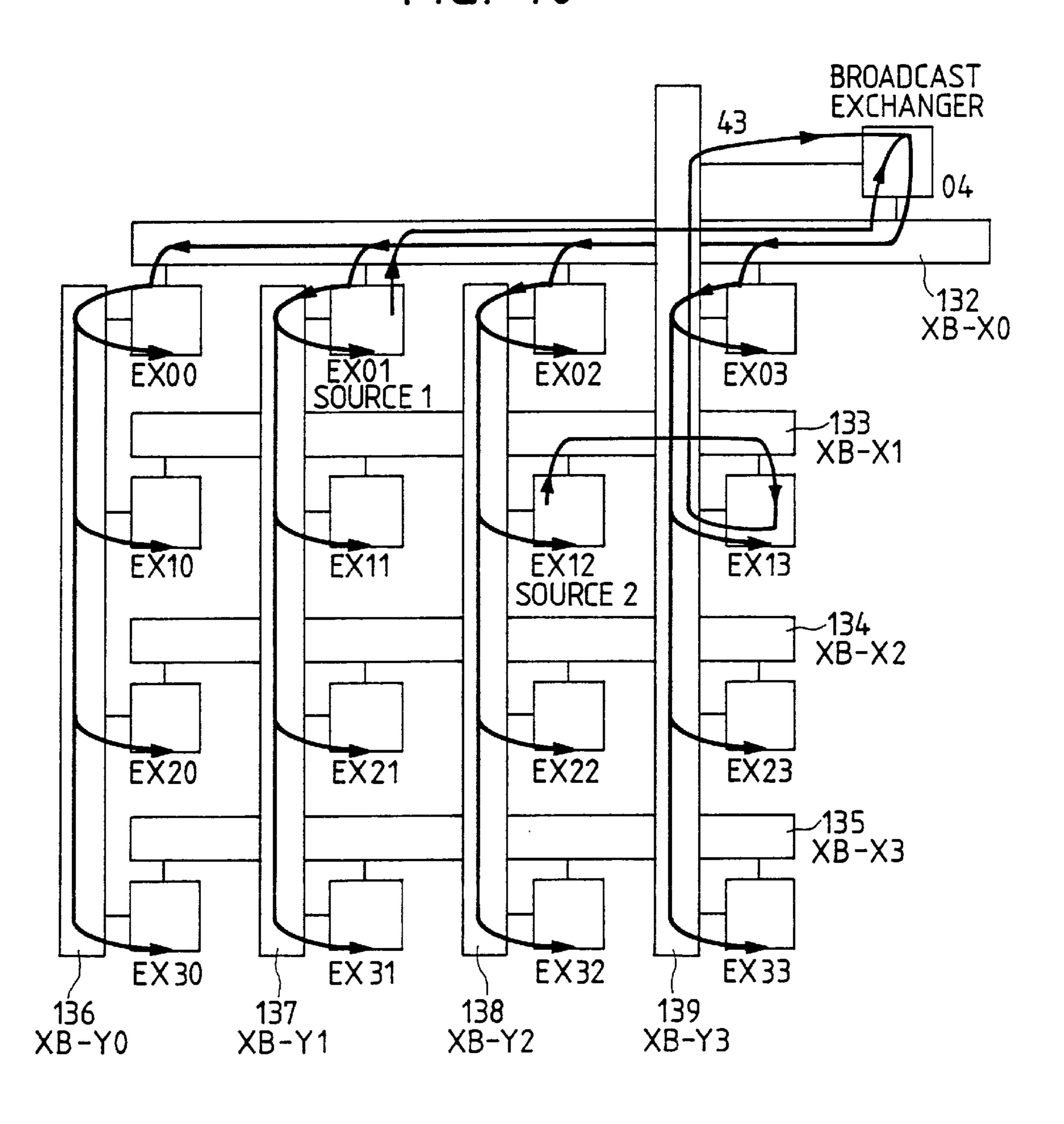

The problem above is circumvented by the first embodiment being arranged so that the route for the broadcast request message will not overlap with that for the broadcast message. FIG. 10 is a view indicating typical routes for transmitting a broadcast request message and a broadcast message by use of the first embodiment. The first embodiment is arranged to transmit an ordinary message (one-toone communication message) from a source PE to a destination PE as follows: the source PE first transmits the message via the EX connected therewith to an XB-X. From that XB-X, the message is transmitted to the EX having the same X coordinate as that in the address of the destination PE. Thereafter, the message is transmitted via that EX to an XB-Y. Past that XB-Y, the message is transmitted to the EX having the same Y coordinate as that in the address of the destination PE. From that EX, the message is transmitted to the destination PE connected thereto.

A broadcast request message sent from a PE connected to an XB-X other than the extended XB-X0, e.g., from source 2 (PE12) connected to an EX12, is also sent to the broadcast exchanger (BEX) 120 in like manner. In this case, the address of the broadcast exchanger (BEX) 120 is used in place of the address of the destination PE. The address of the broadcast exchanger (BEX) 120 used here is a first address related to this BEX for transmitting the broadcast request message via the extended XB-Y3 to the broadcast exchange (BEX) 120. The first address is address 43 consisting of a Y coordinate of 4 and an X coordinate of 3. The Y coordinate 4 is selected to be greater than the X coordinate of any of the EX03 through EX33 connected to the extended XB-Y3. The to this XB-X0. When the PE12 in the source 2 outputs the broadcast request message containing the above first address, that message is transmitted just like a one-to-one communication message from EX12 to XB-X1 to EX13. From the EX13, the broadcast request message is transmitted to the extended XB-Y3. The broadcast request message is then transmitted to the broadcast exchanger (BEX) 120

via the output port which is located within the extended XB-Y3 and which is connected to the broadcast exchanger (BEX) 120. In response to the broadcast request message thus received, the broadcast exchanger (BEX) 120 changes the control bits in that message into those representing a broadcast message which is then forwarded to the XB-X0. The subsequent route for transmitting this broadcast message is the same as that of the conventional method. Specifically, as shown in thick line in FIG. 10, the broadcast message is transmitted parallelly from the XB-X0 to the EX00 through EX03 and on to the XB-Y0 through XB-Y3. From the EX00 connected to the XB-Y0 through XB-Y3, the broadcast message is transmitted to the EX33. Past these EXs, the broadcast message is sent from the PE00 to the PE33. As described, the route for transmitting a broadcast request message does not overlap with the route for trans- 15 mitting a broadcast message. Thus no deadlock occurs with respect to the two messages.

Meanwhile, suppose that one of the PE00 through PE03 connected to the XB-X0 issues a broadcast request message. In that case, the address of the broadcast exchanger (BEX) 20 120 used here is a second address related to the XB-X0 for transmitting the broadcast request message to the broadcast exchanger (BEX) 120. With the first embodiment, the second address is address **04** consisting a Y coordinate of 0 and an X coordinate of 4. The Y coordinate 0 is the same as that 25 of the other EX00 through EX03 connected to this XB-X0. The X coordinate 4 is selected to be greater than the X coordinate of any of these EXs. For example, suppose that the PE01, i.e., source 1, outputs a broadcast request message containing the second address. In such a case, the message 30 is transmitted from the extended XB-X0 directly to the broadcast exchanger (BEX) 120. The subsequent operation of the broadcast exchanger (BEX) 120 is the same as that carried out when a broadcast request message is received from the source 2. In this case, too, the route for transmitting 35 the broadcast request message does not overlap with that for transmitting the broadcast message. Thus no deadlock occurs involving the two messages.

Suppose that, in transmitting its broadcast request message, the source 1 uses as the address of the broadcast 40 exchanger (BEX) 120 the address 43 that the source 2 utilized in transmitting a broadcast request message. In such a case, the message is sent to the XB-Y3 via the XB-X0 and EX03. Past the XB-Y3, the message is transmitted to the broadcast exchanger (BEX) 120. Although the broadcast 45 request message needs to pass through the EX03, the broadcast message corresponding to that message is also required to pass therethrough. With their transmission routes thus overlapping partially, the two messages will bring about a deadlock if they are to be transmitted through worm-hole 50 routing. To avoid the deadlock, the first embodiment uses the address **04** as the address of the broadcast exchanger (BEX) 120 when transmitting a broadcast request message from any PE connected to the XB-X0. The broadcast request message is transmitted from the XB-X0 directly to the 55 broadcast exchanger (BEX) 120 without passage through the EX**03**.

Meanwhile, suppose that a PE other than the PE00 through PE03 transmits a broadcast request message. In such a case, it is impossible to utilize for transmission the 60 second BEX address 04 employed by the source 1 in transmitting its broadcast request message. Because the XB-X1 through XB-X3 to which these PEs are connected have no route corresponding to the X coordinate 4 in the second address, this message cannot be transmitted over this 65 network. For this reason, the first embodiment switches the above-described two BEX addresses as needed.

12

More details of the circuit constituting the first embodiment will now be described. FIG. 8 is a view showing various message formats used by the circuit of FIG. 1. As shown in the common format 8a, each message is composed of a destination PE address field, a control (CTL) bit field and a data field. The destination PE address is the address of the PE that receives the message. The CTL bits represent the attribute of the message in question and contain a BC bit and a BR bit. When set, the BC bit indicates that the message is a broadcast message; when set, the BR bit indicates that the message is a broadcast request message.

In the case of a broadcast request message 8b, the BC bit is set to 0 and the BR bit to 1. The destination PE address is set to be the BEX address (04 or 43).

With a broadcast message 8c, the BC bit is set to 1 and the BR bit to 0. The destination PE address is also set to be the address of the one-to-one communication exchanger (BEX) 120 (04 or 43).

With a broadcast message 8d, both the BC bit and the BR bit are set to 0.

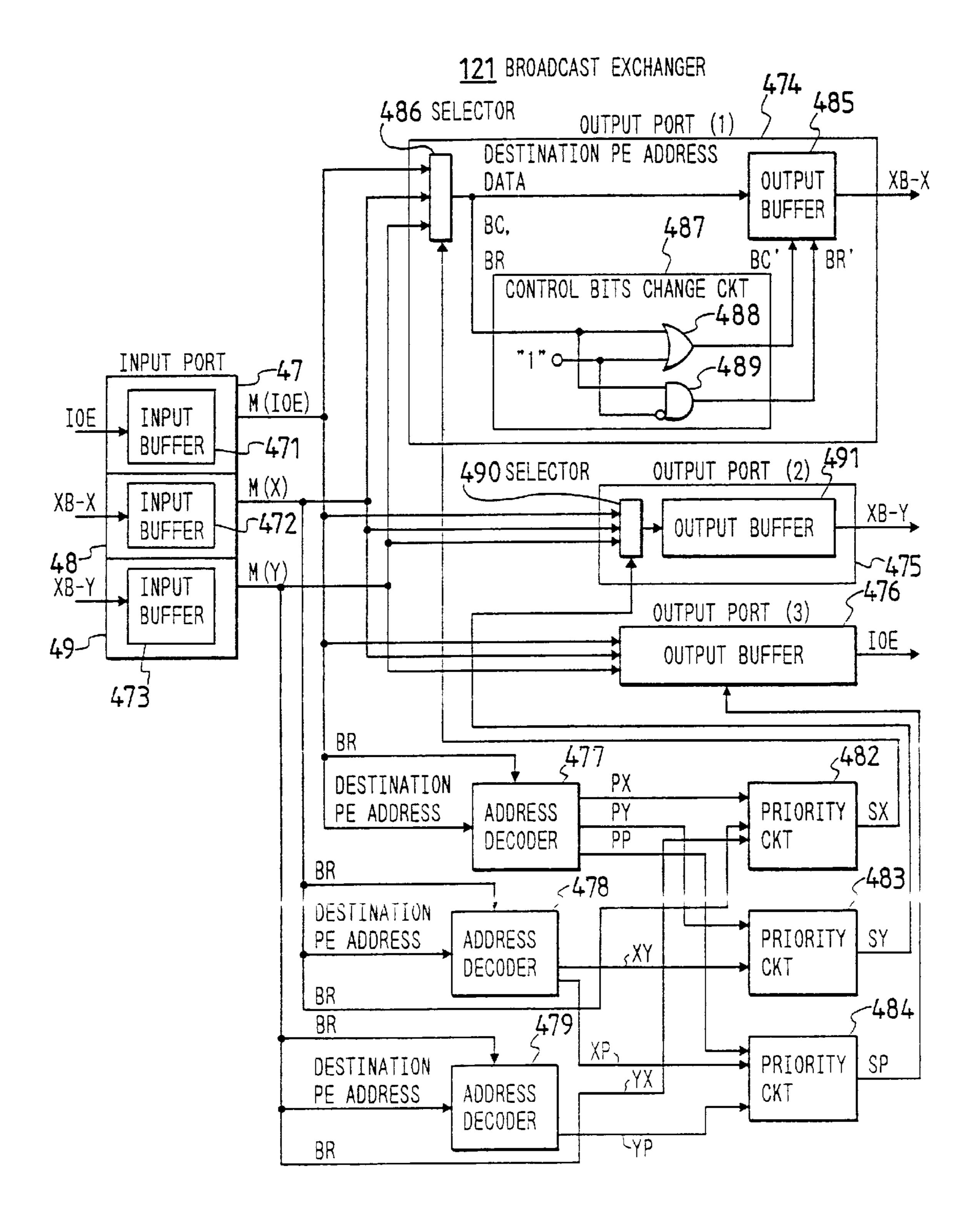

FIG. 4 is a schematic circuit diagram showing the structure of the broadcast exchanger (BEX) 120. The broadcast exchanger (BEX) 120 has its two input ports 40 and 41 connected to the extended XB-X0 and the extended XB-Y3, respectively. Input buffers 450 and 451 retain temporarily the messages input through the ports 40 and 41, respectively. Upon receipt of the messages, the input buffers 450 and 451 supply a priority circuit 454 with signals XX and YX respectively, the signals indicating the presence of the messages to be transmitted. The priority circuit 454 selects one of the broadcast request messages held in the input buffers 450 and 451 for transmission. Having made the selection, the priority circuit 454 supplies a selector 453 with a signal SX indicating which of the signals has been selected. Illustratively, this broadcast exchanger selects messages on a first-in, first-out basis. Given the signal SX, the selector 453 selects accordingly the message to be transmitted. An output buffer 452 retains temporarily the message thus selected.

A control (CTL) bit change circuit 455 changes the BC bit (with a value of 0) and the BR bit (with a value of 1) of the broadcast request message M(X), M(Y) selected by the selector 453, into the bits of a broadcast message. The BC bit is converted to a new BC bit (BC' with a value of 1) by an OR gate 456 that admits a signal 1; the BR bit is converted to a new BR bit (BR' with a value of 0) by an AND gate 457 that has its inversion input terminal receive the signal 1. The BC' and BR' bits are transmitted to the output buffer 452. This rewrites the BC and BR bits of the broadcast message retained in the output buffer 452, whereby the broadcast request message held in the output buffer is converted to the corresponding broadcast message. The broadcast message in the output buffer is broadcast from there to all PEs via the XB-X0.

The first embodiment also performs message transmission through the use of the above-described worm-hole routing. Initially, the input buffer 450 or 451 retains the leading part of the message to be transmitted. When selected by the selector 453, the leading part of the message is sent to the output buffer 452. This leaves empty the input buffer that held the leading part of the message. As a result, a part of the same message subsequent to its leading part is forwarded to the same input buffer from the XB-X0 or XB-Y3. The leading part of the message in the output buffer is transmitted from there to the XB-X0. At the time that the output buffer 452 becomes empty, the subsequent part of the same

message in the same input buffer is selected. Thus the priority circuit 454 keeps selecting the same input buffer once the circuit 454 selects the leading part of a broadcast request message having arrived at the input buffer 451 or 452, until all subsequent parts of that message have been transmitted to the output buffer 452. During that time, the input port 40 or 41 secures the input buffer therein for the message being transmitted and not for any other new message. After one message in its entirety has been selected by the priority circuit 454 and transmitted to the output buffer 10 452, the priority circuit 454 starts selecting anew the input buffer 450 or 451. As a result, the broadcast exchanger (BEX) 120 transmits only one broadcast message at a time. That is, the broadcast exchanger (BEX) 120 selects serially a plurality of broadcast request messages. Only after the 15 entire broadcast message corresponding to one selected broadcast request message has been transmitted, is the next broadcast request message processed. This is how a plurality of broadcast request messages are serialized. Meanwhile, to implement the priority circuit 454 requires furnishing three 20 circuits: one for checking to see if that part of the message which is held in the input buffer 450 or 451 is the leading part or the trailing part of the message, another for checking to see if the output buffer 452 is empty, and another for determining the input buffer in accordance with the output of 25 these checking circuits. These component circuits of the priority circuit 454 are implemented using known techniques and thus will not be discussed further.

Unlike the EXs, the broadcast exchanger (BEX) 120 has no PE corresponding thereto and thus has no output buffer 30 for transmitting messages to PEs. Furthermore, the message received from the XB-X0 or XB-Y3 is transmitted to the XB-X0. Thus the broadcast exchanger (BEX) 120 has no output buffer for transmitting messages to the XB-Y3.

FIG. 2 is a schematic circuit diagram showing the struc- 35 ture of a processor element PE100. The other PEs have the same structure as that of the PE100. With the exception of a circuit 208 for generating a BEX address used to transmit a broadcast request message, the PE structure is basically the same as that of the PEs described in Japanese Pat. Laid- 40 Open No. Hei 5-28122 or U.S. patent application Ser. No. 07/916,663 now U.S. Pat. No. 5,192,580 corresponding thereto. The BEX address generator 208 is composed of a BEX address register 210 for retaining the BEX address and a selector 211. When the BR bit within the CTL bits in a 45 register 205 is found to be 1, the selector 211 selects in place of the destination PE address the address of the broadcast exchanger (BEX) 120 held in the register 210; otherwise the selector 211 selects the destination PE address. In the setup of FIG. 1, upon system start, the host processor or service 50 processor (SVP) 140 may initially set 04 in the register 210 for the PE00 through PE03 and 43 in the register 210 for the other PEs. When outputting a broadcast request message, each PE sets 0 for the BC bit and 1 for the BR bit in the register 205, and sets in the register 206 the data to be 55 broadcast. Then the broadcast request message 8b of FIG. 8 is transmitted. Needless to say, a long broadcast request message is divided into a plurality of parts according to the worm-hole routing convention for serial transmission.

In FIG. 2, reference numeral 200 is a data processor for 60 executing programs; 201 is a local memory for storing data and instruction series; 202 is a receive control circuit that receives a message from the EX corresponding to the PE in question and transmits the received message to the memory 201; and 203 is a send control circuit. The send control 65 circuit 203 comprises registers 204 through 206 for retaining the message contents retrieved from the memory 201, and a

14

message generating circuit **209** for generating a message and transmitting it to the EX corresponding to the PE in question.

FIG. 3 is a schematic circuit diagram showing the structure of an exchange switch EX116. The other EXs have the same structure as that of the EX116. The EX structure is basically the same as that of the EXs described in Japanese Pat. Laid-Open No. Hei 5-28122 or U.S. patent application Ser. No. 07/916,663 now U.S. Pat. No. 5,192,580 corresponding thereto.

Three input ports 30, 31 and 32 of each EX are connected respectively to a PE, XB-X and XB-Y. The messages received through the input ports 30 through 32 are held temporarily in input buffers 300 through 203, respectively. Output ports 303 through 305 send messages to an XB-X, XB-Y and PE, respectively.

When the received message is a one-to-one communication message or a broadcast request message, each EX transmits the message as follows:

(1) The message received from the PE is sent to the XB-X, XB-Y or PE.

The message is sent to the PE if the X and Y coordinates of the destination PE address held in that message coincide with those of the current PE. The message is sent to the XB-Y if the X coordinate of the destination PE address held in that message coincides with the X coordinate of the current PE but the Y coordinate of that destination PE address does not coincide with that of the current PE. Otherwise the message is transmitted to the XB-X.

- (2) The message input from the XB-X is sent to the XB-Y.

- (3) The message input from the XB-Y is sent to the PE. If the received message is a broadcast message, each EX transmits the message as follows:

- (1) The broadcast message input from the XB-X is sent to the XB-Y.

- (2) The broadcast message input from the XB-Y is sent to the PE.

Below is a brief description of the EX circuit structure. Reference numerals 400 through 402 designate address decoders which, if messages M(PE), M(X) and M(Y) input to the input buffers 300 through 302 are a one-to-one communication message or a broadcast request message each, decode the destination PE address in each message to determine the destination to which the message is destined. These address decoders operate when the BC bit is found to be 0 in the messages. The reference characters M(PE), M(X)and M(Y) of the messages indicate that these are message signals (destination PE address, broadcast bit BC, broadcast request bit BR) received from the PE, XB-X and XB-Y connected to the EX. Output signals PX, PY and PP indicate that the messages received from the PEs are sent to the PEs. Likewise, output signals XY and XP indicate that the messages received from the XB-X are sent to the XB-Y and PE. An output signal YP indicates that the message received from the XB-Y is sent to the PE. It should be noted that there is no signal YX that would indicate that the message received from the XB-Y would be sent to the XBX. This is because, as discussed in the Technical Report of the Institute of Electronics, Information and Communication Engineers of Japan, Vol. 93, No. 320, the first embodiment performs dimension order routing whereby all messages are first transmitted in the X-axis direction and then in the Y-axis direction so as to avoid the deadlock of one-to-one communication messages. That is, no message is transmitted first in the Y-axis direction and then in the X-axis direction, i.e., no message received from the XB-Y is initially transmitted to the XB-Y.

Reference numerals 307 through 309 denote priority circuits. These priority circuits select one of three input messages, and output signals SX, SY and SP indicating which of the messages is selected. In this example, the received messages are selected on a first-in, first-out basis. 5 A selector 310 selects the message to be transmitted in accordance with the signal SX from the priority circuit 307. An output buffer 312 retains temporarily the selected message. The output ports 303, 304 and 305 have the same structure. The message received from a PE is either a 10 one-to-one communication message (BC=BR=0) or a broadcast request message (BC=0, BR=1). The address decoder 400 decodes the destination PE address held in the received message in order to determine the PE to which the message is destined. The other address decoders 401 and 402 perform 15 the same process.

If each EX receives a broadcast message from the XB-X, the OR gate 410 sets the signal XY to 1 for transmission of the broadcast message to the XB-Y. If each EX receives a broadcast message from the XB-Y, the OR gate 411 sets the 20 signal YP to 1 for transmission of the broadcast message to the PE. In each EX, as in the broadcast exchanger (BEX) 120, the priority circuits 307, 308 and 309 are arranged to transmit messages through worm-hole routing.

FIG. 5 is a schematic circuit diagram showing the struc- 25 ture of the X-coordinate crossbar switch XB-X1. This XB structure is the same as that of the other XB-Xi (i=2 or 3) or of the Y-coordinate crossbar switches XB-Yj (j=0, 1 or 2). The XB structure is basically the same as that of the XBs described in Japanese Pat. Laid-Open No. Hei 5-28122 or 30 U.S. patent application Ser. No. 07/916,663 now U.S. Pat. No. 5,192,580 corresponding thereto. Upon receipt of a one-to-one communication message or a broadcast message, each of these crossbar switches XBs transmits the message to one output port determined by the destination address 35 designated by that message. For an XB-X, the X coordinate of the destination address is used; for an XB-Y, the Y coordinate of the destination address is utilized. If a broadcast message is input to any one of the input ports of these XBs, the message is transmitted to all EXs connected to the 40 XB in question. With the first embodiment, broadcast messages are transmitted not by the XB-X1 through the XB-X3 but by the XB-Y0 through the XB-Y2.

The crossbar switch structure will now be described briefly. In FIG. 5, I/O signals EX0 through EX3 come from 45 the EX10 through EX13 connected to the crossbar switch in question. The input signals EX0 through EX3 are replaced by signals EX10 through EX13 in the case of the XB-X1 or by signals EX00 through EX30 in the case of the XB-Y0. Broadcast message transmission, to be described below, is 50 actually not utilized by the XB-X1, etc. but by the XB-Y. However, for reasons of expediency, the XB-X1 is used hereunder as an example for illustration.

Reference numerals 500 through 503 represent switches for selecting one of four input ports. Because what is shown 55 here is a crossbar switch XB, the input signals EX0 through EX3 are each connected directly to the inputs of the switches 500 through 503. Thus a message received via any one of the input ports is fed to the switches 500 through 503. Route determining circuits 504 through 507 determine which of the 60 switches the received message is to be sent to. Signals D00, D01, D02 and D03 specify that the input message is to be output to the EX0; these signals are generated from the messages that were input respectively from the EX0, EX1, EX2 and EX3. Signals D10, D11, D12 and D13 designate 65 message output to the EX1; signals D20, D21, D22 and D23 dictate message output to the EX2; and signals D30, D31,

D32 and D33 specify message output to the EX3. These messages are generated respectively from the messages received from the EX0, EX1, EX2 and EX3, and are input to priority circuits 508 through 511. The priority circuits 508 through 511 determine the sequence in which the four received messages are to be transmitted. In this example, the messages are selected for transmission on a first-in, first-out basis.

The route determining circuit 504 comprises an address decoder 600 and OR gates 601 through 604. The other route determining circuits 505 through 507 have the same constitution. When the message input to the XB is a one-to-one communication message or a broadcast request message, the address decoder 600 decodes the destination PE address in that message to determine its destination. Via the OR gates 601 through 604, the address decoder 600 outputs 1 to one of the signals D00 through 30. On the other hand, if the message received from the EX0 is a broadcast message, the outputs of the OR gates 601 through 604 are all set to 1 in order to output 1 to all output signals D00 through D30. This allows the same message to be broadcast to the extended EX0 through EX3 that are connected to the XB-X.

FIG. 6 is a schematic circuit diagram showing the structure of the extended crossbar switch XB-X0. In FIG. 6, I/O signals EX0 through EX3 come from the EX00 through EX03 connected to the crossbar switch in question. A signal EX4 comes from the broadcast exchanger (BEX) 120. The same applies to the extended XB-Y3, except that no input signal from the broadcast exchanger (BEX) 120 is used by the first embodiment. One difference between the extended XB-X0 and the non-extended XB-X1 is that the extended XB-X0 has an additional I/O port. Another difference between the two crossbar switches is the way in which extended route determining circuits 706 through 710 of the extended XB-X0 operate in transmitting broadcast messages. Specifically, as shown in FIG. 7, if the signal from the input port EX is a broadcast message, the extended route determining circuit 706 does not transfer that message to the output port EX4 connected to the broadcast exchanger (BEX) 120. With the first embodiment, the broadcast message is sent from the broadcast exchanger (BEX) 120 only to the input port EX4. This broadcast range limiting facility of the first embodiment is used only by the extended routine determining circuit 710. That is, the broadcast message fed from the broadcast exchanger (BEX) 120 to the XB-X0 is not returned to the same exchanger but sent only to the EX00 through EX03 connected to the XB-X0. If the broadcast message were allowed to be further transmitted to the broadcast exchanger (BEX) 120, the route for transmitting the broadcast request message up to the exchanger 120 would overlap with the route for transmitting the broadcast message starting from the exchanger 120, resulting in a deadlock. The other operations of the extended route determining circuits 706, etc. are the same as those of the non-extended XB-X1, etc. and will not be described further.

As described earlier in reference to FIG. 10, the above circuits allow the sources 1 and 2 to transmit broadcast request messages to the broadcast exchanger (BEX) 120 which in turn transmits broadcast messages to all PEs. Furthermore, the first embodiment has a plurality of sources issue broadcast request messages simultaneously and still allows the broadcast messages corresponding to these request messages to be transmitted serially. Thus message broadcast is implemented without a deadlock.

## <First Variation of the First Embodiment>

Differently from what the first embodiment does, it may be arranged that the broadcast message received from the

extended XB-X0 is transmitted simultaneously to the XB-Y3 and to the PEs and that the broadcast message received from the XB-Y3 is kept from returning to the EX00 through EX03. In such cases, the BEX address in use may be address 43 having the PE00 through PE03 included in a 5 broadcast request message and still no deadlock occurs. Therefore the same BEX address may be stored for the different PEs. To implement this feature, however, requires modifying the EX00 through EX03 so that they will operate differently from the other EXs. With the first embodiment, 10 all EXs may use the same circuit. The end of the message broadcast operation is recognized by detecting the transmission of the broadcast message completed by all EXs, including the EX00 through EX03, to the PEs. This arrangement simplifies structurally the hardware for broadcast end detection.

#### <Second Variation of the First Embodiment>

The network of the first embodiment comprises a plurality of partial networks each composed of a crossbar switch. Alternatively, these crossbar switches may be replaced by, 20 say, a plurality of partial networks each comprising a multistage switch. The same applies to the other embodiments to be explained later.

#### <Third Variation of the First Embodiment>

With the first embodiment, each PE outputs a broadcast request message comprising the address of the broadcast exchanger BEX, the data to be transmitted, and a message mode bit BR identifying the message. The output broadcast request message reaches the EX connected to the PE in 30 question. Thereafter, the EX and a plurality of XBs transmit the message to the broadcast exchanger BEX on the basis of the address held in that message, whereby the corresponding broadcast message is generated. Alternatively, it is possible to arrange the PEs, EXs and XBs so that a PE may transmit 35 to the EX a broadcast request message not designating such a broadcast exchanger address, whereupon the EX changes this broadcast request messages into the corresponding broadcast message. This broadcast message is transmitted to the broadcast exchanger by the EX and by the multiple XBs. 40 This scheme is similar to the method of the fifth embodiment, to be discussed later, and is implemented by use of a circuit similar to that of the fifth embodiment.

### <Fourth Variation of the First Embodiment>

Another variation of the first embodiment is one which 45 utilizes a three-dimensional hyper-crossbar network. The PEs and EXs are represented by three-dimensional coordinates PEijk and EXijk, respectively. Illustratively, an XB-Xij represents the X-coordinate XB connected with the EXij0, EXij1, EXij2 and EXij3. Likewise, an XB-Yik 50 denotes the Y-coordinate XB connected with the EXi0k, EXi1k, EXi2k and EXi3k; and an XB-Zjk stands for the Z-coordinate XB connected with the EX0jk, EX1jk, EX2jk and EX3jk.

In a three-dimensional setup, the extended XB-X0 and SB-Y3 are supplemented by an extended XB composed illustratively of a Z-coordinate XB, e.g., XB-Z0 with its output ports connected to the broadcast exchanger (BEX), the added XB transmitting broadcast request messages to this broadcast exchanger (BEX). Whereas each EX in the 60 two-dimensional setup comprises three inputs and three outputs for the PE, X-coordinate XB and Y-coordinate XB, each EX in the three-dimensional network further includes input and output ports for the Z-coordinate XB. Dimension order routing is allocated to range from an X-coordinate XB 65 through a Y-coordinate XB to a Z-coordinate XB, in that order.

18

The broadcast exchanger (BEX) permits receipt of a broadcast request message from the extended XB-Z0. As with the first embodiment, the corresponding broadcast message is supplied to the extended XB-X0.

In the three-dimensional setup, the message broadcast operation initially involves assigning three addresses to the broadcast exchanger (BEX). One of the three addresses is used for each of the following three PE groups:

group (1) PE00k (k=0, 1, 2 or 3)

address used: 004

group (2) PE0jk (j=1, 2 or 3; k=0, 1, 2 or 3)

address used: 043

group (3) PEijk (i=1, 2 or 3; i=0, 1, 2 or 3; k=0)

group (3) PEijk (i=1, 2 or 3; j=0, 1, 2 or 3; k=0, 1, 2 or 3)

address used: 403 The PEs of group (1) may transmit broadcast request messages to the broadcast exchanger (BEX) using the extended XB-X00 alone; the PEs of group (2) may transmit broadcast request messages to the broadcast exchanger (BEX) using the XB-X0<sub>j</sub> and the extended XB-Y03; the PEs of group (3) may transmit broadcast request messages to the broadcast exchanger (BEX) using the XB-Xij, XB-Yik and the extended XB-Z03. In this manner, the routes for broadcast request messages from all PEs to the broadcast exchanger (BEX) are determined. The routes for a broadcast message from the broadcast exchanger (BEX) to all PEs are allocated through two-dimensional extension. Specifically, the extended XB-X00 first transmits the broadcast message to the EX000 through EX003. From there, the broadcast message is transmitted via the XB-Y00 through XB-Y03 to those EXs among the EX000 through EX033 which have a Z coordinate of 0. Finally, the broadcast message is sent to all EXs by use of all Z-coordinate XBs. From there, the broadcast message is forwarded to each PE. Because no contention occurs between this routing for broadcast message transmission and the above-described routing for broadcast request message transmission to the broadcast exchanger (BEX), no deadlock takes place even as a plurality of sources output broadcast request messages simultaneously. In short, deadlocks are avoided by transmitting a plurality of broadcast messages serially. This is achieved by allocating only one transmission route for a broadcast message within the network and thus eliminating contention between this broadcast routing and the routing for transmitting broadcast request messages to the top of the broadcast route (i.e., BEX).

The same holds true for the network of n dimensions. Specifically, N processor elements constituting the parallel processor system are broken up into factors n1×n2×...nm, each factor representing a processor element disposed at one of the lattice points constituting the n-dimensional lattice space. The network is constituted by having the sides of the lattice space, corresponding to the processor elements, connected by crossbar switches through the use of exchange switches each comprising an (m+1)-input (m+1)-output crossbar switch. Each coordinate system is assigned a single extended XB. The extended ports are connected to the broadcast exchanger (BEX) and the PEs are divided into n groups. Upon initialization, the host processor or service processor SVP sets in each PE the address of the broadcast exchanger (BEX) so that each PE may transmit its message to the BEX.

## <Second Embodiment>

FIG. 11 is a schematic circuit diagram showing the system configuration of a parallel processor system practiced as the