#### US005821622A

# United States Patent [19]

# Tsuji et al.

5,150,233

# [11] Patent Number:

5,821,622

[45] Date of Patent:

Oct. 13, 1998

| [54]                          | LIQUID (                | CRYSTAL DISPLAY DEVICE                                                                                                                               |  |  |  |  |  |

|-------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [75]                          | Inventors:              | Yoshiko Tsuji, Kawasaki; Mitsushi<br>Ikeda; Hisao Toeda, both of<br>Yokohama; Yoshifumi Ogawa,<br>Kawasaki; Toshiyuki Oka, Yokohama,<br>all of Japan |  |  |  |  |  |

| [73]                          | Assignee:               | Kabushiki Kaisha Toshiba, Kawasaki,<br>Japan                                                                                                         |  |  |  |  |  |

| [21]                          | Appl. No.:              | 633,346                                                                                                                                              |  |  |  |  |  |

| [22]                          | Filed:                  | Apr. 17, 1996                                                                                                                                        |  |  |  |  |  |

| Related U.S. Application Data |                         |                                                                                                                                                      |  |  |  |  |  |

| [63]                          | Continuation abandoned. | n-in-part of Ser. No. 208,831, Mar. 11, 1994,                                                                                                        |  |  |  |  |  |

| [30]                          | Foreig                  | gn Application Priority Data                                                                                                                         |  |  |  |  |  |

| Mar.                          | 12, 1993                | [JP] Japan 5-052675                                                                                                                                  |  |  |  |  |  |

| [51]                          | Int. Cl. <sup>6</sup>   |                                                                                                                                                      |  |  |  |  |  |

|                               |                         |                                                                                                                                                      |  |  |  |  |  |

| [58]                          | Field of So             | earch                                                                                                                                                |  |  |  |  |  |

| [56]                          |                         | References Cited                                                                                                                                     |  |  |  |  |  |

|                               | U.S                     | S. PATENT DOCUMENTS                                                                                                                                  |  |  |  |  |  |

| 5,340,491 | 8/1994  | Enomoto et al         |

|-----------|---------|-----------------------|

| 5,373,377 | 12/1994 | Ogawa et al 359/59    |

| 5,459,090 | 10/1995 | Yamazaki et al 437/43 |

#### FOREIGN PATENT DOCUMENTS

| 55-12920 | 1/1980  | Japan . |

|----------|---------|---------|

| 1-231024 | 9/1989  | Japan . |

| 3-9569   | 1/1991  | Japan . |

| 4-280824 | 10/1992 | Japan . |

Primary Examiner—Ngân V. Ngô Attorney, Agent, or Firm—Oblon, Spivak, McClelland, Maier & Neustadt, P.C.

# [57] ABSTRACT

The present invention provides a liquid crystal display device including a plurality of address wiring lines formed of an Mo—W alloy, a plurality of data wiring lines intersecting the address wiring lines, with insulating films interposed at intersection portions of the data wiring lines and the address wiring lines, display regions having pixel electrodes arranged respectively for the intersection portions, and a plurality of switching elements provided adjacent to the intersection portions and having control electrodes connected electrically to the address wiring lines, first main electrodes connected electrically to the data wiring liens, and second main electrodes connected electrically to the pixel electrodes.

#### 12 Claims, 16 Drawing Sheets

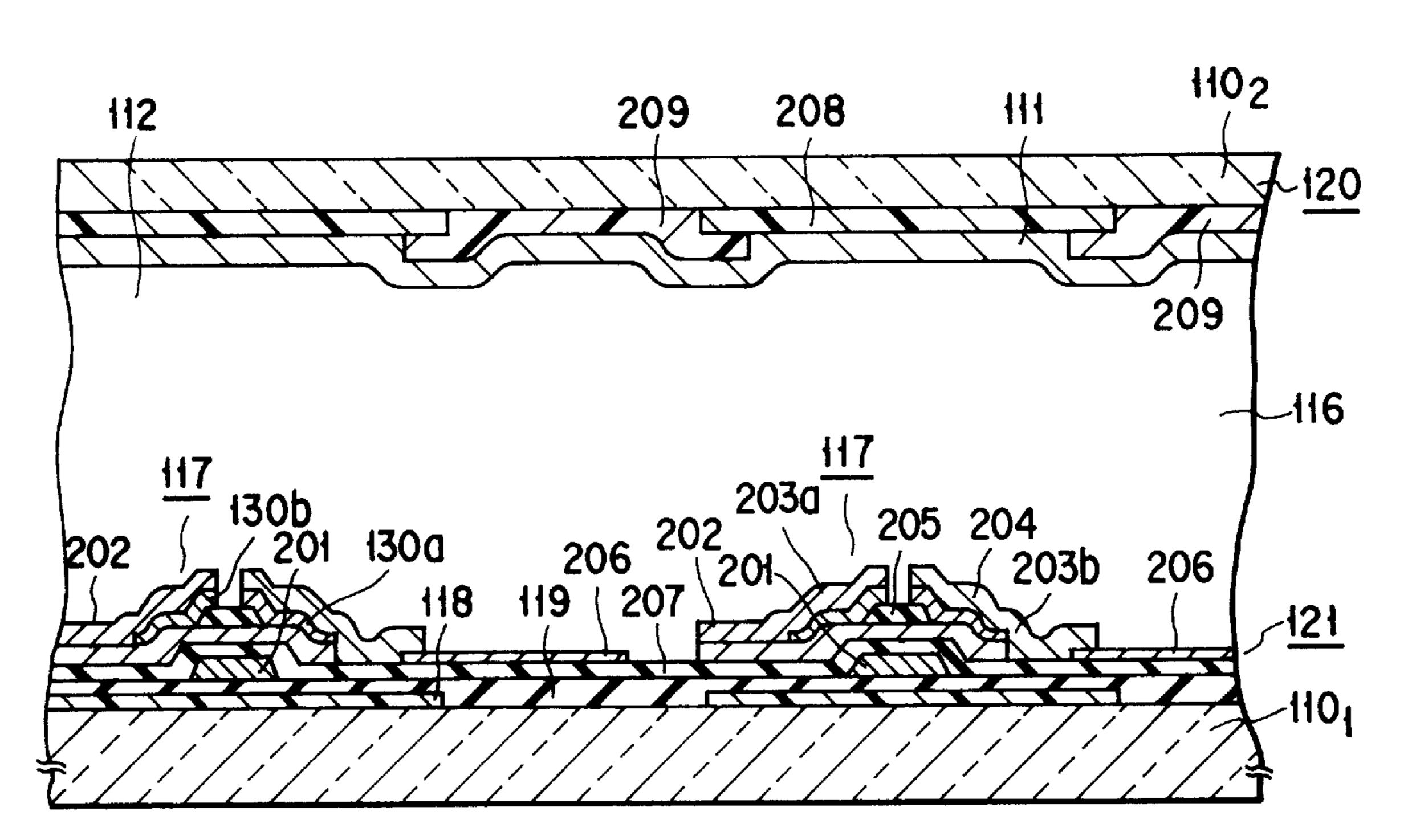

F 1 G. 2

5,821,622

F 1 G. 10B

F 1 G. 12

F I G. 13

5,821,622

F 1 G. 15

F 1 G. 2 1

F I G. 22

F I G. 23

F I G. 24

F I G. 28

F 1 G. 29

F 1 G. 30

Oct. 13, 1998

# LIQUID CRYSTAL DISPLAY DEVICE

This application is a Continuation-in-Part of application Ser. No. 08/208,831, filed on Mar. 11, 1994, now abandoned.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a liquid crystal/display device and, more particularly, to an active matrix type liquid crystal display device.

#### 2. Description of the Related Art

Recently, a great deal of attention has been paid to an active matrix type liquid crystal display element in which a thin-film transistor (to be abbreviated to TFT hereinafter) <sup>15</sup> formed by using an amorphous silicon (to be abbreviated to a-Si hereinafter) film is used as a switching element because there is a possibility of realizing a large-area, high-definition, high-image-quality, inexpensive panel display, i.e., a flat type television set, by forming a TFT array using <sup>20</sup> an a-Si film which can be formed on an inexpensive glass substrate at a low temperature.

In forming a large-area display, however, the total length of address wiring lines greatly increases, and the resistance of the address wiring lines increases. As a result, a gate pulse supplied to each switching element is noticeably delayed due to the resistance of the address wiring lines and capacitances coupled to an address wiring line, and the liquid crystal cannot be properly controlled.

As a means for preventing the delay of a gate pulse while maintaining at least the parameters such as the width of a wiring line, a liquid crystal display device having address wiring lines formed by using a wiring material having a lower resistivity may be developed. More specifically, an Mo—Ta alloy widely used as an address wiring material has a resistivity of about 40  $\mu\Omega$ ·cm, but it is considered to be difficult to realize a large-area display with the resistivity of this material. Especially for a high-definition, direct-view type display having about 1,000 address wiring lines, a 40 wiring material having a resistivity of about 20  $\mu\Omega$ ·cm or less is required. In addition to a low resistivity, such a new wiring material is required to allow tapering to improve the step coverage of an insulating interlayer formed on address wiring lines so as to improve the insulating properties 45 between wiring lines formed on the insulating interlayer and the address wiring lines.

That is, demands have arisen for a reliable liquid crystal display device in which the delay of a gate pulse is prevented and good insulating properties are ensured by forming 50 address wiring lines using such a wiring material. Even if this address wiring line is not applied to a large-area display, there is still a merit. That is, as the resistivity of an address wiring line decreases, the width of the wiring line can be reduced to increase the aperture ratio. From this viewpoint, 55 a new wiring material having the above-described characteristics is desirable.

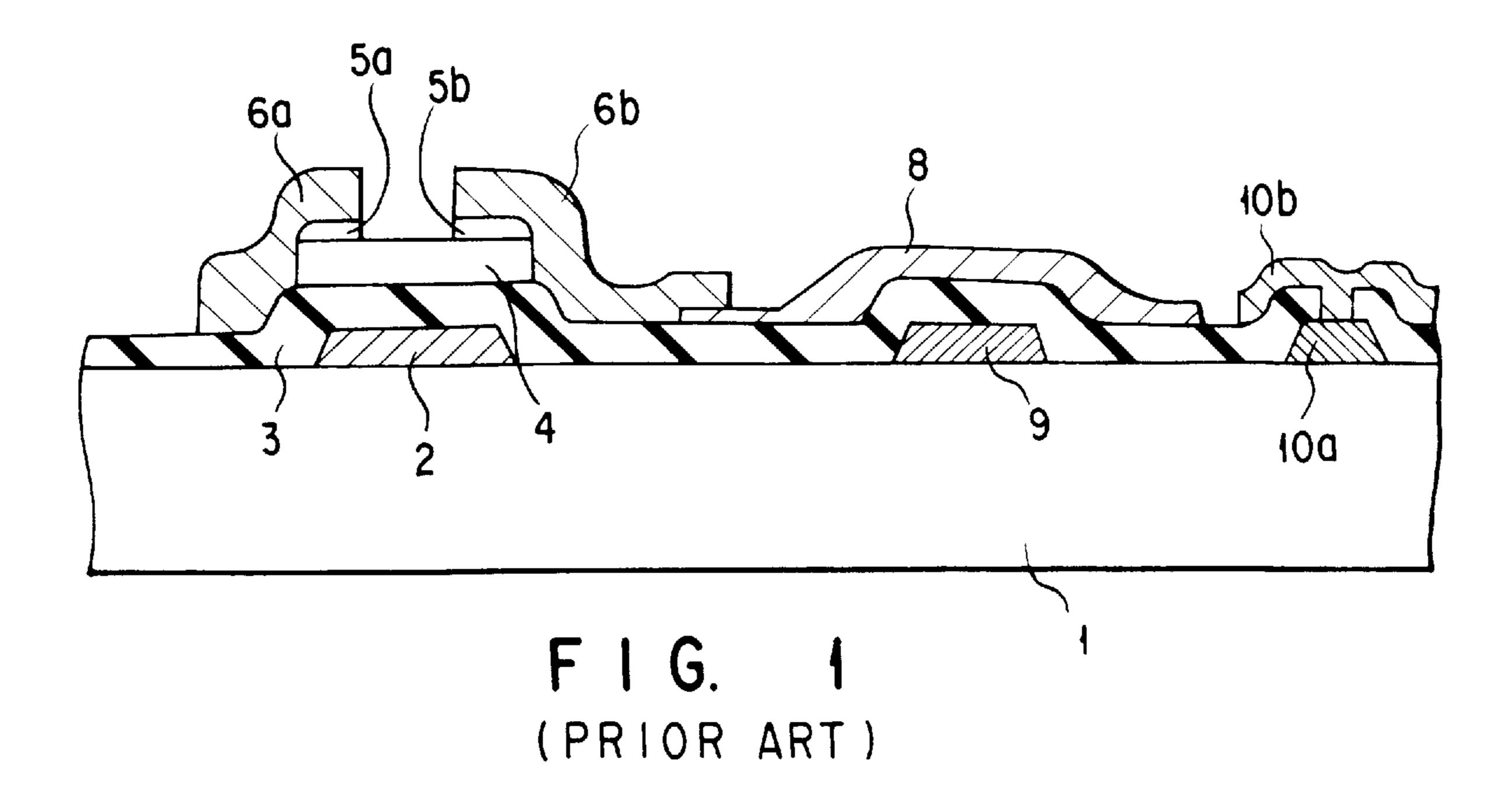

On the other hand, another problem is posed in the conventional liquid crystal display device. FIG. 1 is a sectional view showing a TFT used for the conventional 60 liquid crystal display device. As shown in FIG. 1, a gate electrode 2, an address wiring line, and a Cs line 9 are simultaneously formed on a glass substrate 1 by sputtering an Mo—Ta alloy and patterning. An active layer 4 consisting of a-Si is deposited on the resultant structure on a gate 65 insulating film 3. Thereafter, n<sup>+</sup> a-Si layers 5a and 5b are deposited on both sides of the active layer 4. An ITO pixel

2

electrode 8 is formed on the resultant structure on the gate insulating film 3. Subsequently, an Al source electrode 6a having a junction with the n<sup>+</sup> a-Si layer 5a, an Al drain electrode 6b having junctions with portions of the n<sup>+</sup> a-Si layer 5b and the pixel electrode 8, and a data wiring line are simultaneously formed.

In the TFT shown in FIG. 1, which is used in the conventional liquid crystal display device, since the pixel electrode and the data wiring line are present on the same layer without the mediacy of an insulating film, a short circuit occurs. As a result, a point defect may be produced. In order to prevent such a point defect, an insulating interlayer may be formed after the formation of a source electrode, a drain electrode, which are made of Al usually, and a data wiring line, and a pixel electrode may be formed on the insulating interlayer. However, to realize such a structure, the following requirements must be satisfied:

- (1) A data wiring line and the like need to have excellent resistance to HF as an etchant for an insulating interlayer and an ITO etchant for a pixel electrode.

- (2) A data wiring needs to allow tapering to improve the step coverage of an insulating interlayer so as to improve the insulating properties between the data wiring line and a pixel electrode.

However, there is no known wiring material for data wiring lines that can satisfy these requirements, and hence it is difficult to realize such a structure and improve the reliability of a liquid crystal display device. Especially, in developing a large-area display, it is important to reduce the rate of occurrence of point defects, and the development of such a highly reliable liquid crystal display device is demanded.

In addition, if an Al or Ta alloy is used as material of data wiring lines, an oxide film is formed on the surface of the alloy, resulting in an increase in contact resistance with respect to a metal wiring line as an upper layer. For this reason, the step of removing such an oxide film is required. This step is also required for a contact of a gate wiring line layer 10a and a data wiring line metal layer 10b, i.e., a wiring extraction contact portion in the conventional structure shown in FIG. 1. Furthermore, a barrier metal such as Mo is required to prevent a reaction between ITO and Al, increasing the number of steps.

In addition, if an Al alloy, which has a very high reflectance, is used as data wiring line material, disconnection due to underlayer dust and thinning of a pattern and the like may occur by the exposure light reflection in the photolithographic process, resulting in line defects. Another drawback is posed because of the high reflectance. That is, when stray light such as light reflected by the opposing substrates is rereflected by wiring lines to be radiated on TFTs, a light leakage current may be produced, reducing the contrast in a display operation of the panel due to signal voltage decrease on the pixel.

As described above, in an attempt to realize an active matrix type liquid crystal display device having a large display area, the resistance of address wiring lines increases to cause a noticeable delay of a gate pulse. As a result, the liquid crystal cannot be properly controlled.

#### SUMMARY OF THE INVENTION

The present invention has been made in consideration of the above situation, and has as its object to provide a liquid crystal display device in which a gate pulse is free from a delay, and a high breakdown voltage is ensured with respect to address lines.

The object is accomplished by a liquid crystal display device comprising a plurality of address wiring lines made of an Mo—W alloy, a plurality of data wiring lines intersecting the address wiring lines, with insulating films interposed at intersection portions of data wiring lines and the address wiring lines pixel electrodes arranged respectively for the intersection portions, and a plurality of switching elements, each arranged to be adjacent to a corresponding one of the intersection portions and having a control electrode electrically connected to a corresponding one of the address wiring lines, a first main electrode electrically connected to a corresponding one of the data wiring lines, and a second main electrode electrically connected to a corresponding one of the pixel electrodes.

According to the present invention, since an Mo—W alloy has a low resistivity, an address wiring line formed by using this material serves as a low-resistance component with respect to a gate pulse. Therefore, a gate pulse transferred through this address wiring line is free from a delaying effect due to the wiring resistance of the address wiring line. Hence, a gate pulse without a delay can be supplied to a predetermined switching element for driving a liquid crystal.

In this case, since an Mo—W alloy can be tapered, an insulating interlayer formed on address wiring lines formed by using this material exhibits good step coverage. For this reason, a high breakdown voltage can be ensured between the address wiring lines and other wiring lines formed on the insulating interlayer. Therefore, a reliable liquid crystal display device having a large display area can be realized. 30

In addition, even if this address wiring line is not applied to a large-area display, there is still a merit. That is, as the resistivity of an address wiring line decreases, the width of the wiring line can be reduced, and hence the opening ratio can be increased. Furthermore, since the resistance of an 35 oxide film formed on the surface of each address wiring line is low, no surface layer removal process is required. By using an Mo—W alloy as a signal wiring line or source electrode, no barrier metal is necessary, because good electric contact is obtained. Also, the TFT leakage current is 40 decreased, because light reflection is reduced by small reflectance of the Mo—W alloy.

Additional objects and advantages of the invention will be set forth in the description which follows, and in part will be obvious from the description, or may be learned by practice 45 of the invention. The objects and advantages of the invention may be realized and obtained by means of the instrumentalities and combinations particularly pointed out in the appended claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate presently preferred embodiments of the invention and, together with the general description given above and the detailed description of the preferred embodiments given below, serve to explain the principles of the invention.

- FIG. 1 is a cross-sectional view showing a TFT and a storage capacitance portion used in a conventional liquid crystal display (LCD) device;

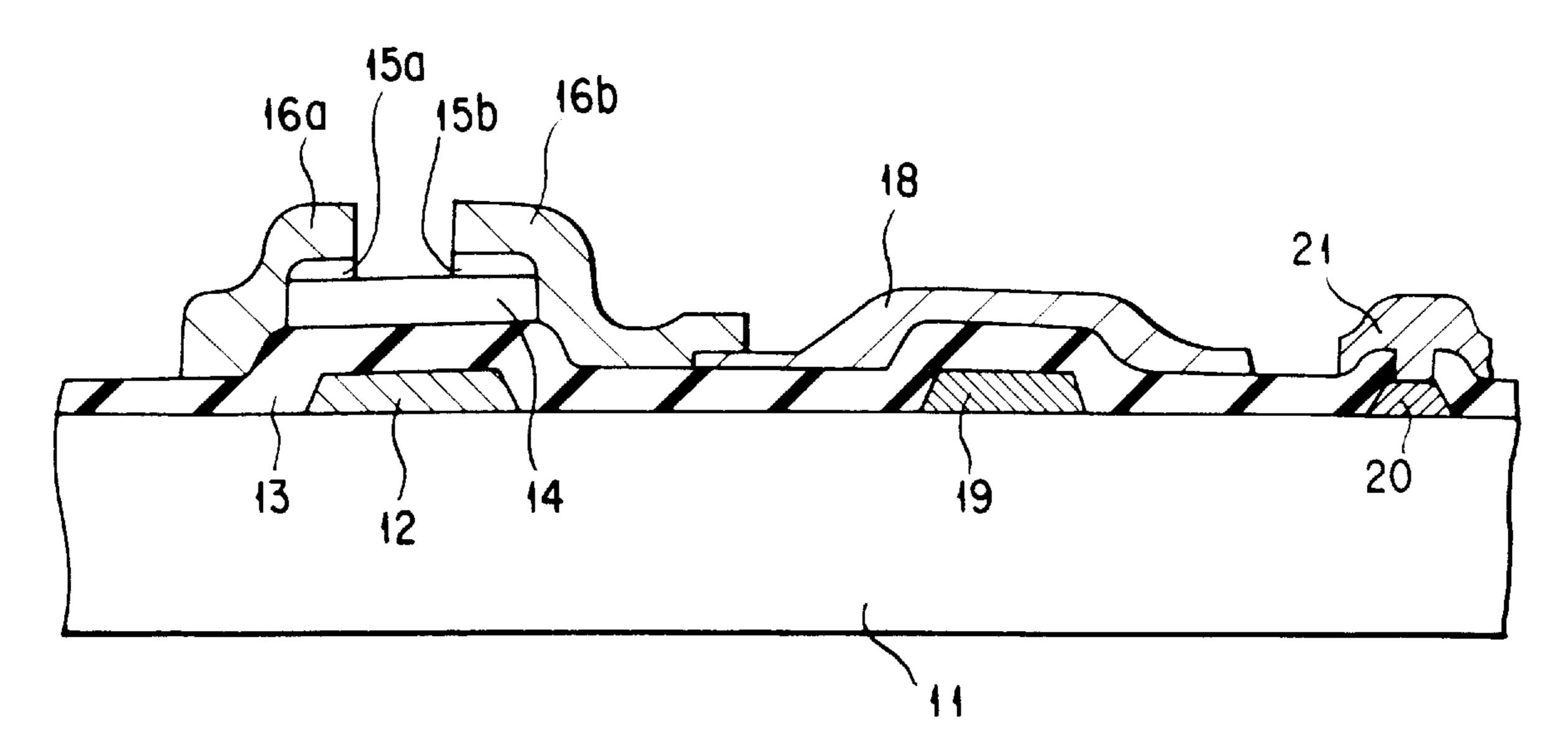

- FIG. 2 is a cross-sectional view showing a TFT and a storage capacitance portion used in an example of an LCD device according to a first embodiment of the present invention;

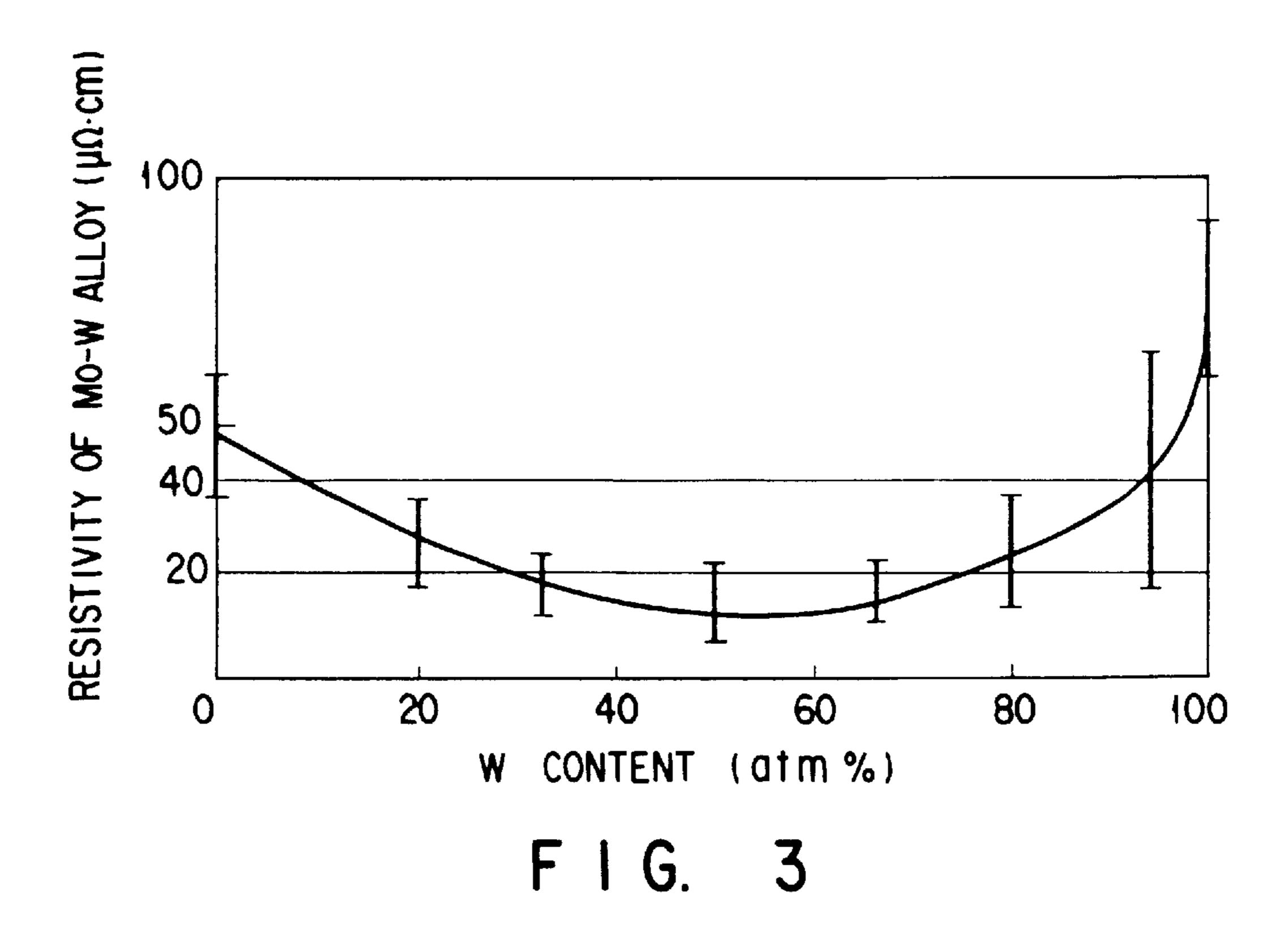

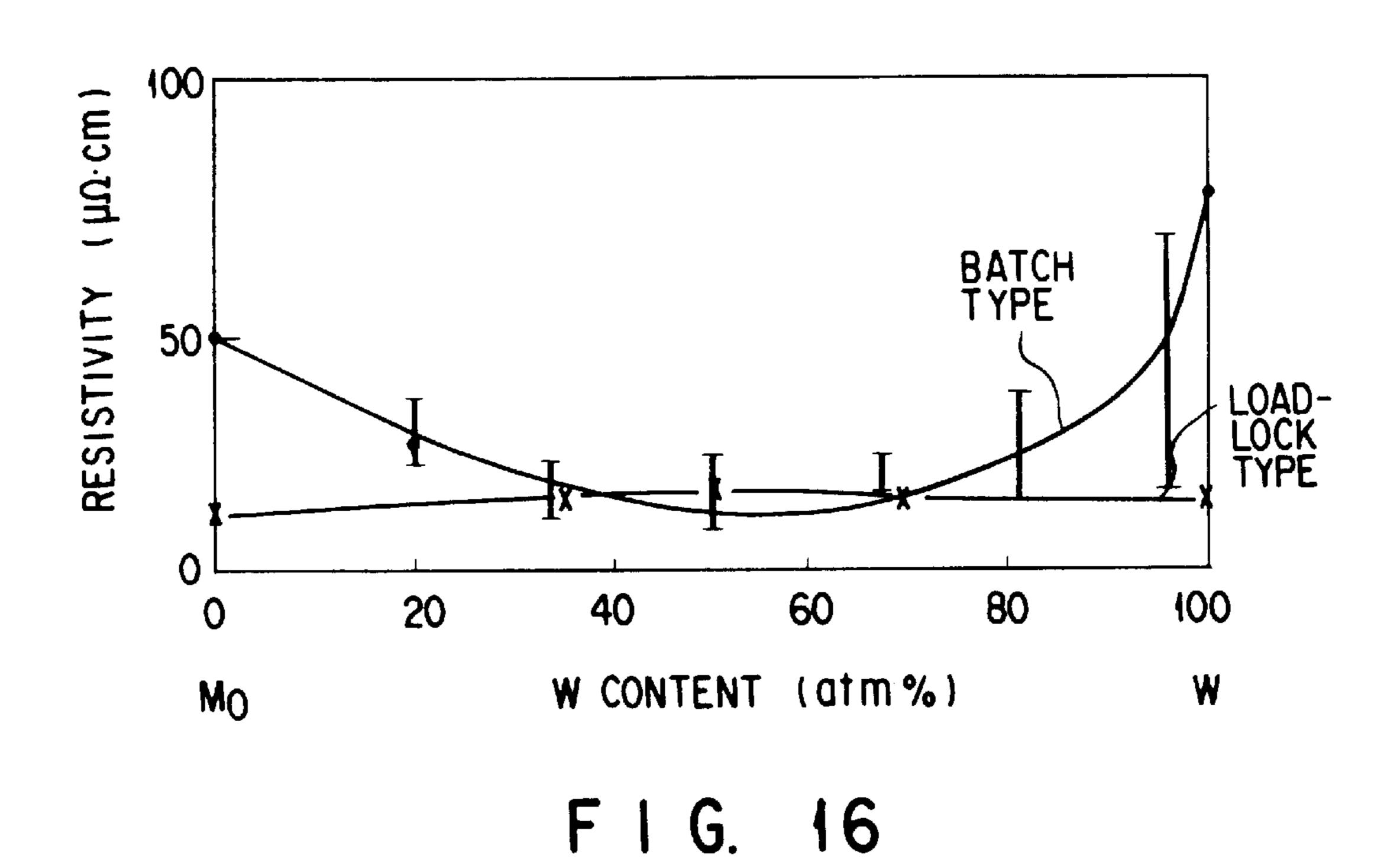

- FIG. 3 and FIG. 16 are graphs showing the relationship 65 between a resistivity of a Mo—W alloy and a W atm % content;

4

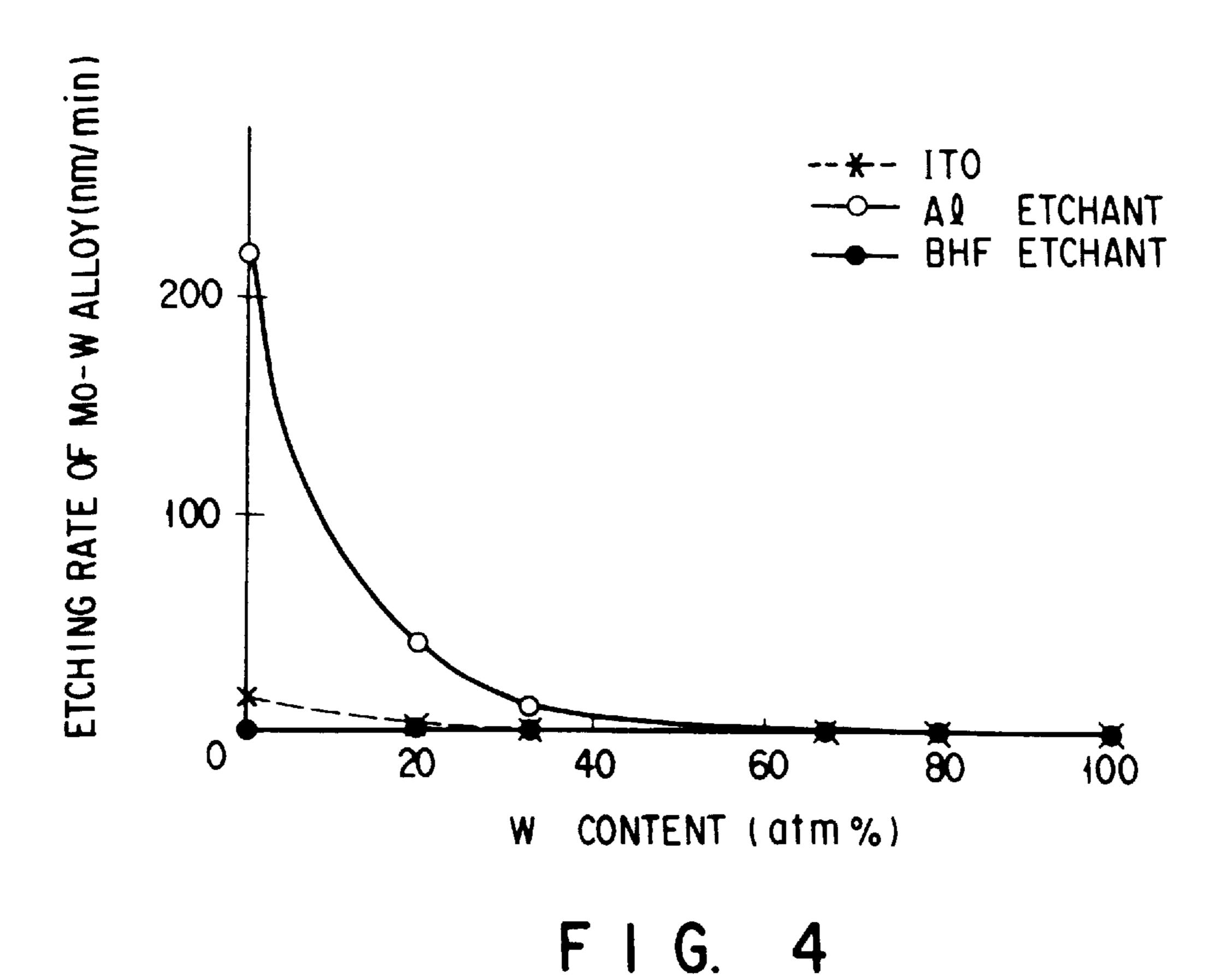

- FIG. 4 is a graph showing the relationship between an etching rate of the Mo—W alloy, with respect to each of etchants, and the W atm % content;

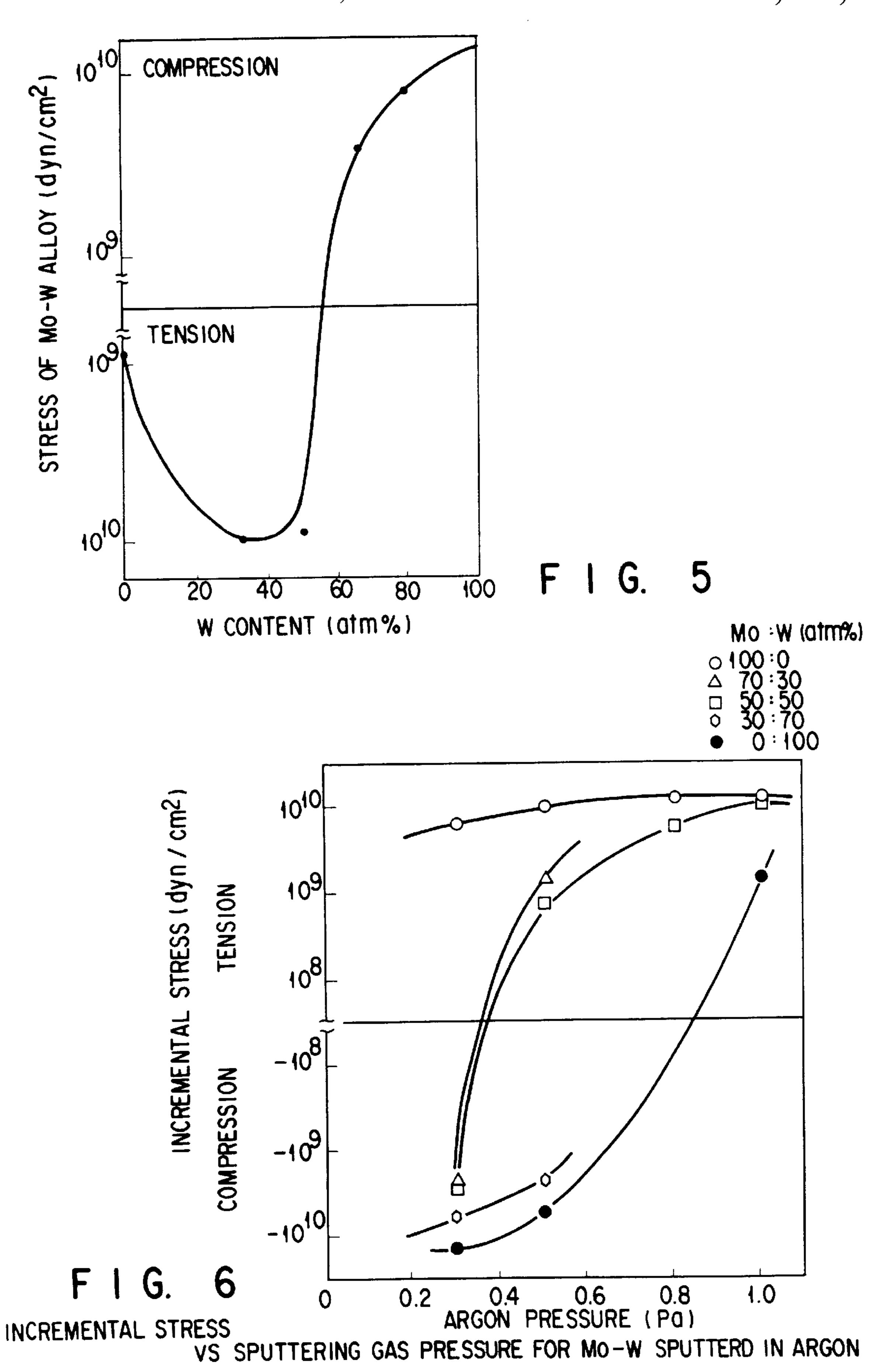

- FIG. 5 and FIG. 6 are graphs showing the stress of the Mo—W alloy and the W atm % content;

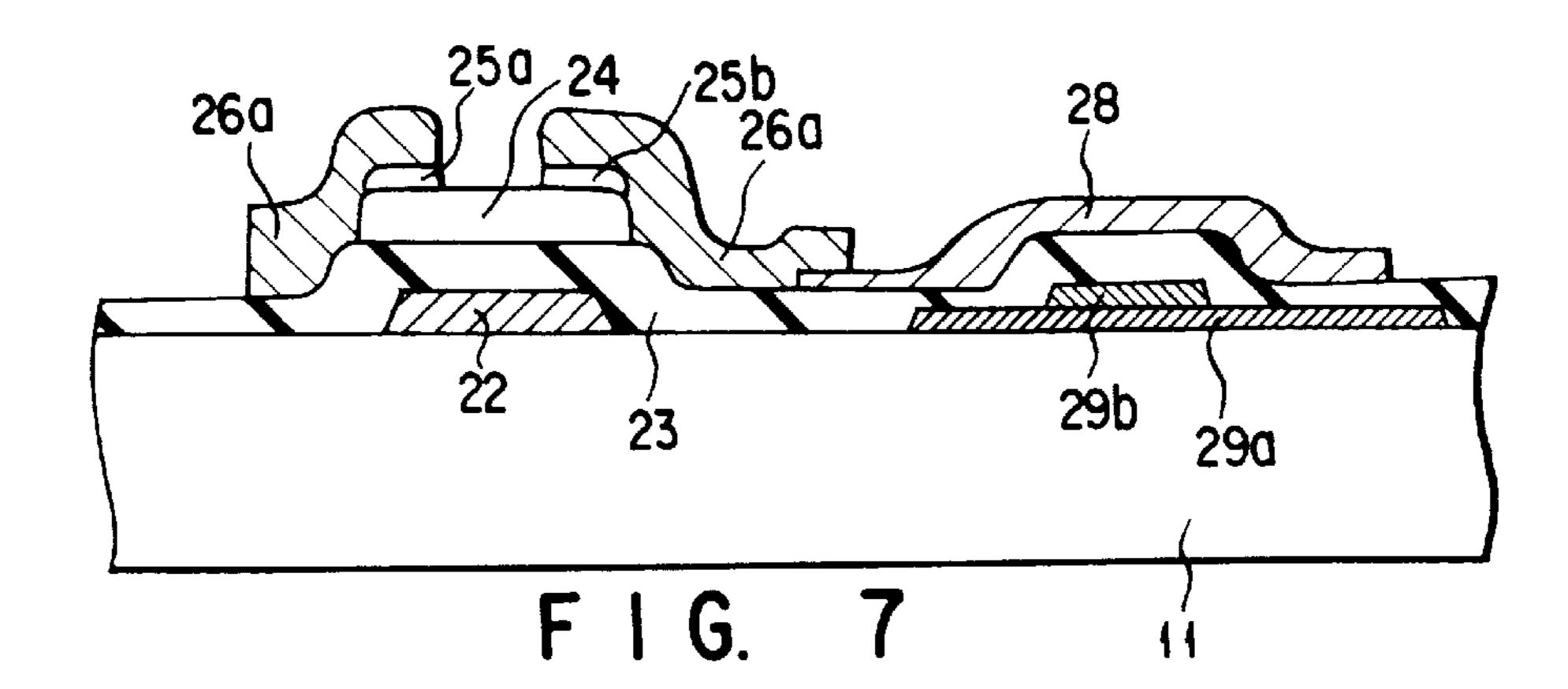

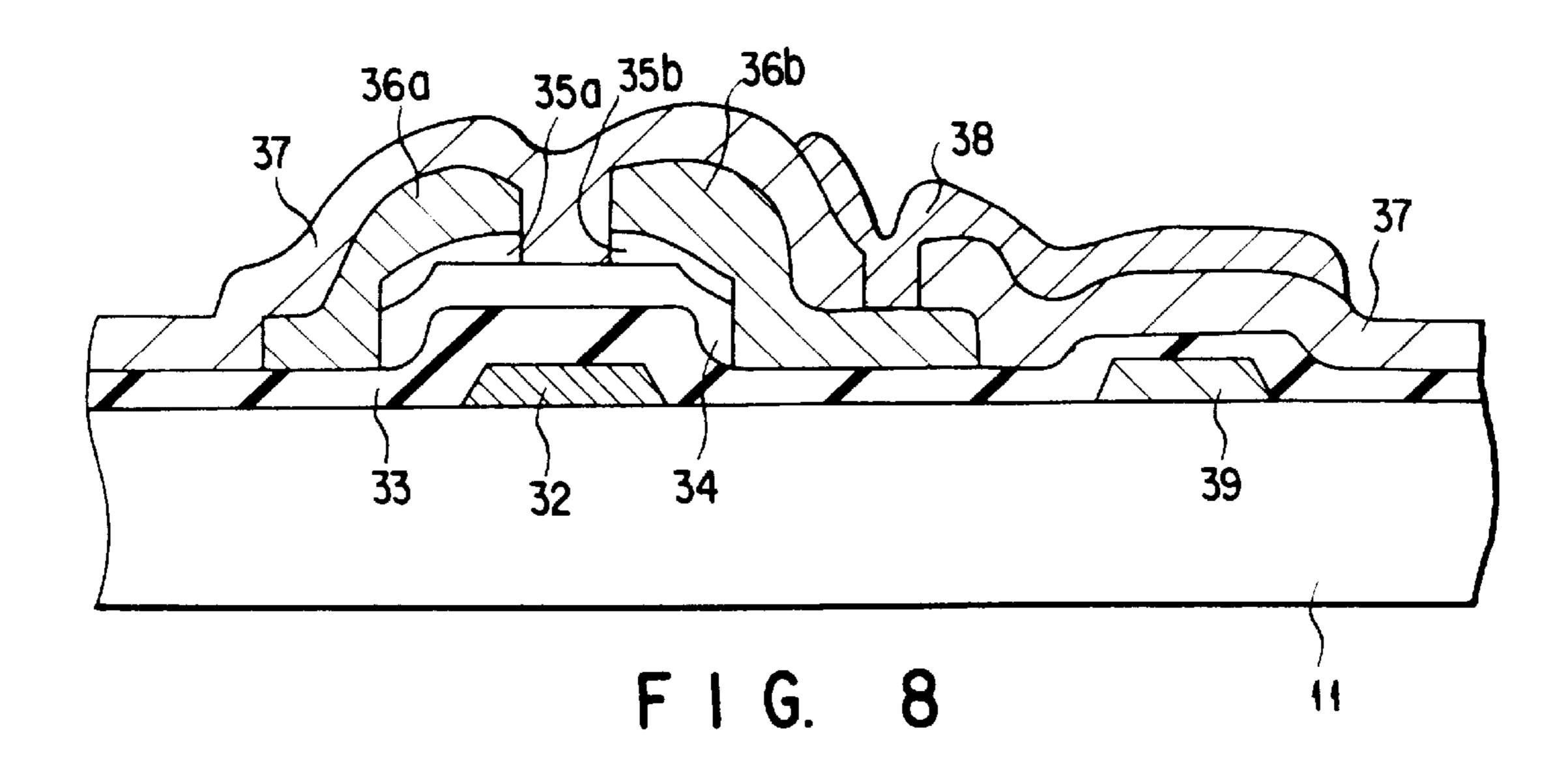

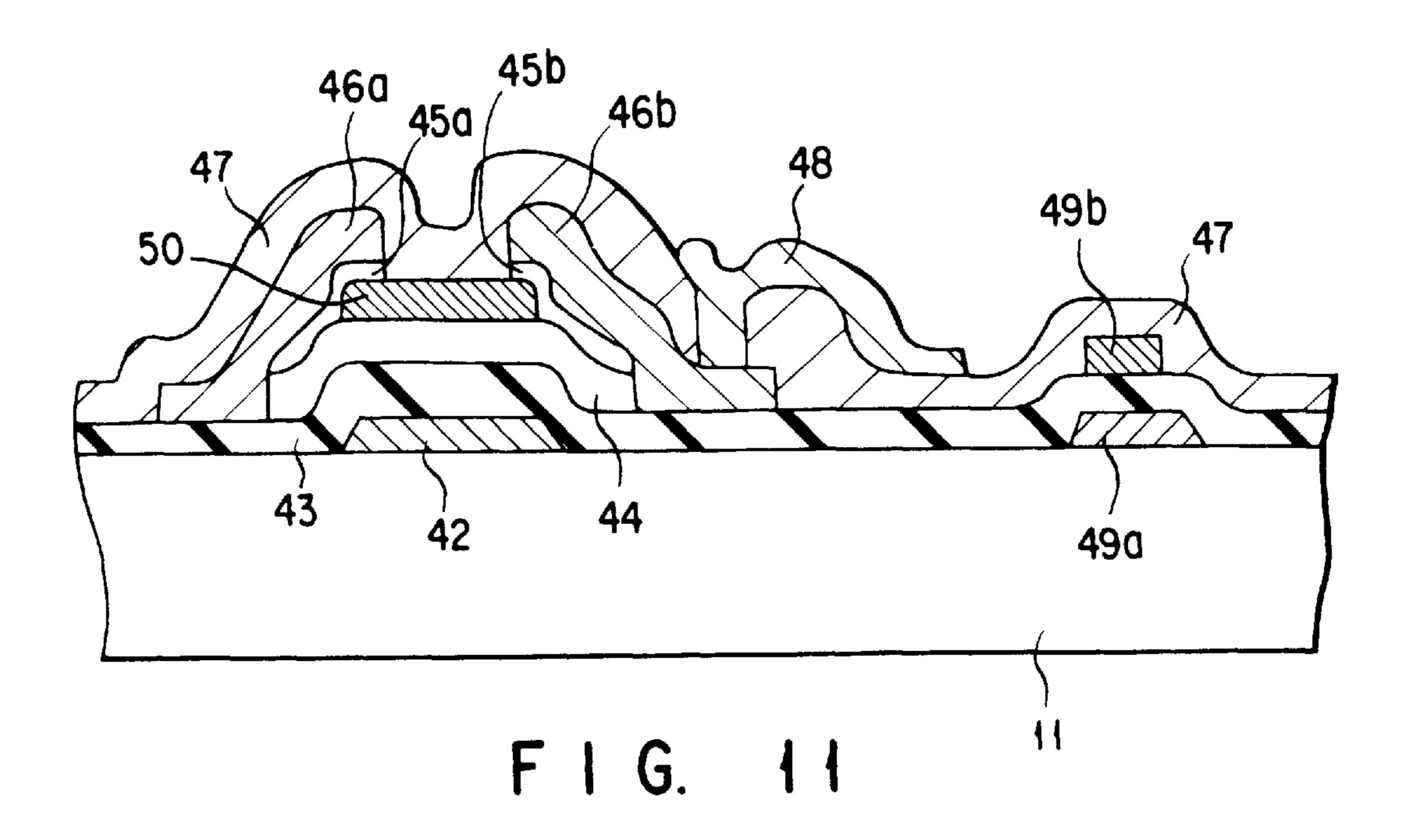

- FIGS. 7, 8 and 11 are cross-sectional views showing TFTs and storage capacitance portions used in other examples of the LCD device according to the first embodiment of the present invention;

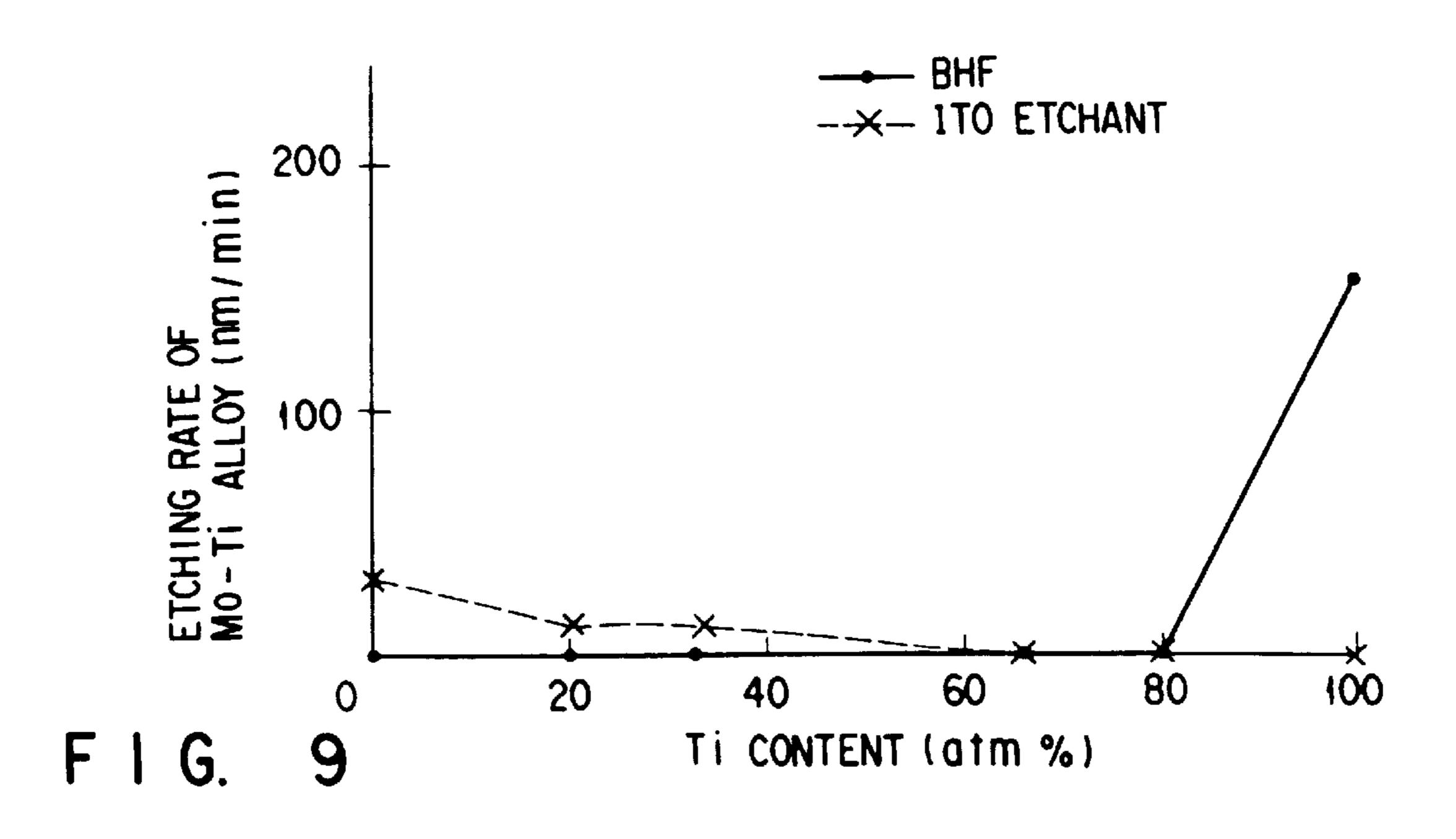

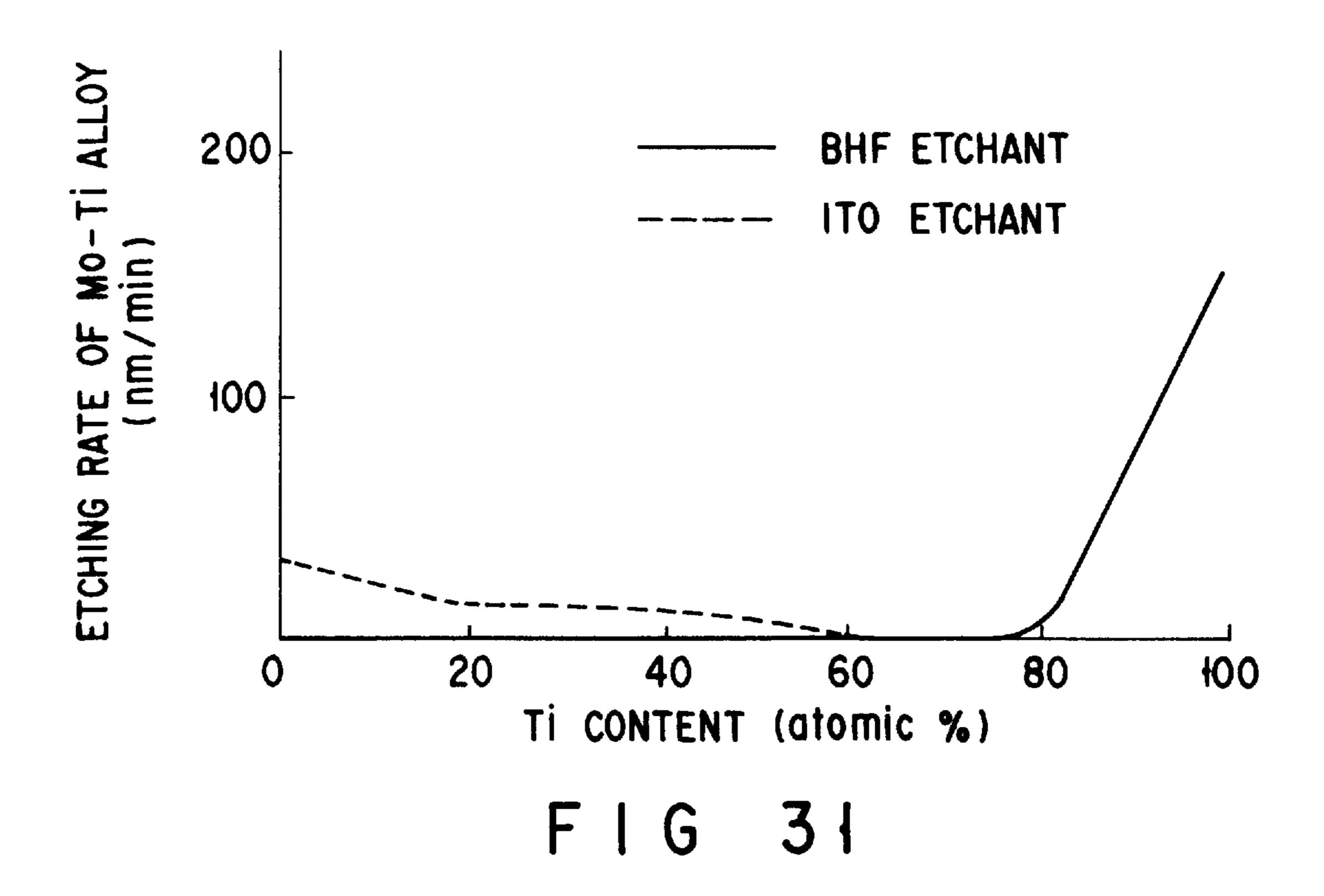

- FIG. 9 is a graph showing the relationship between an etching rate of a Mo—Ti alloy, with respect to each of etchants, and a Ti atm % content;

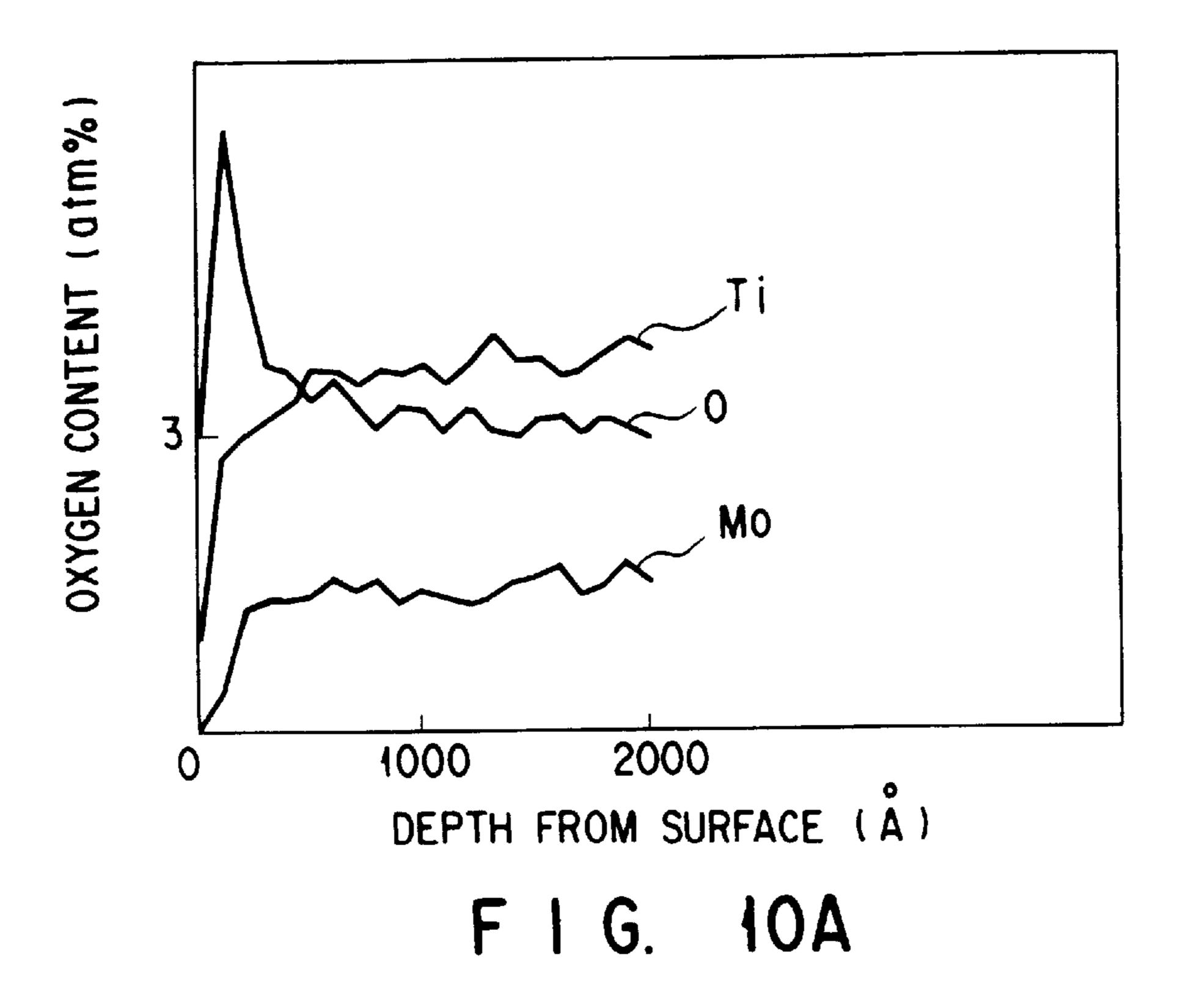

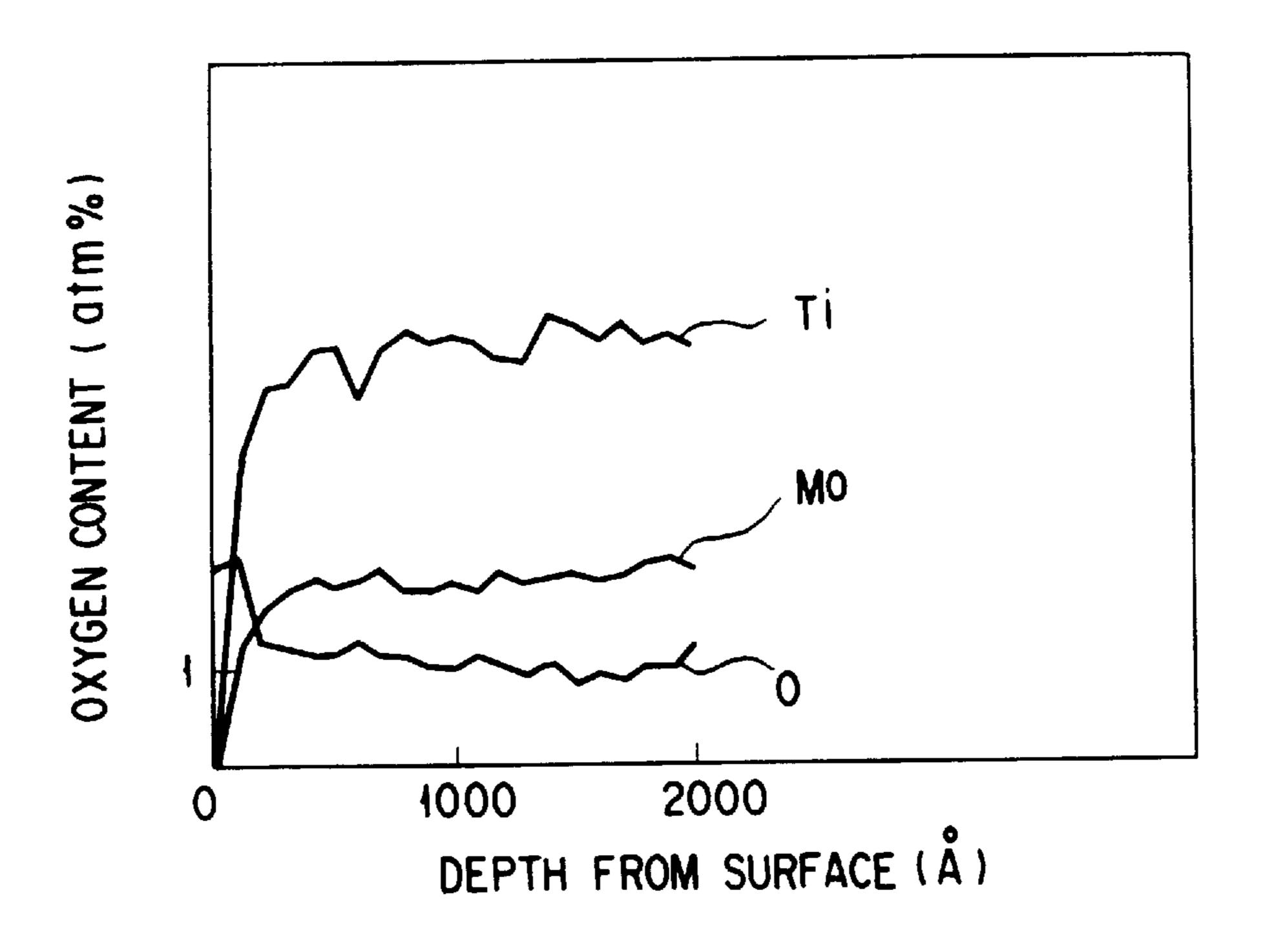

- FIGS. 10A and 10B are graphs illustrating the relationship between an oxygen content of the Mo—Ti alloy and the tapering workability;

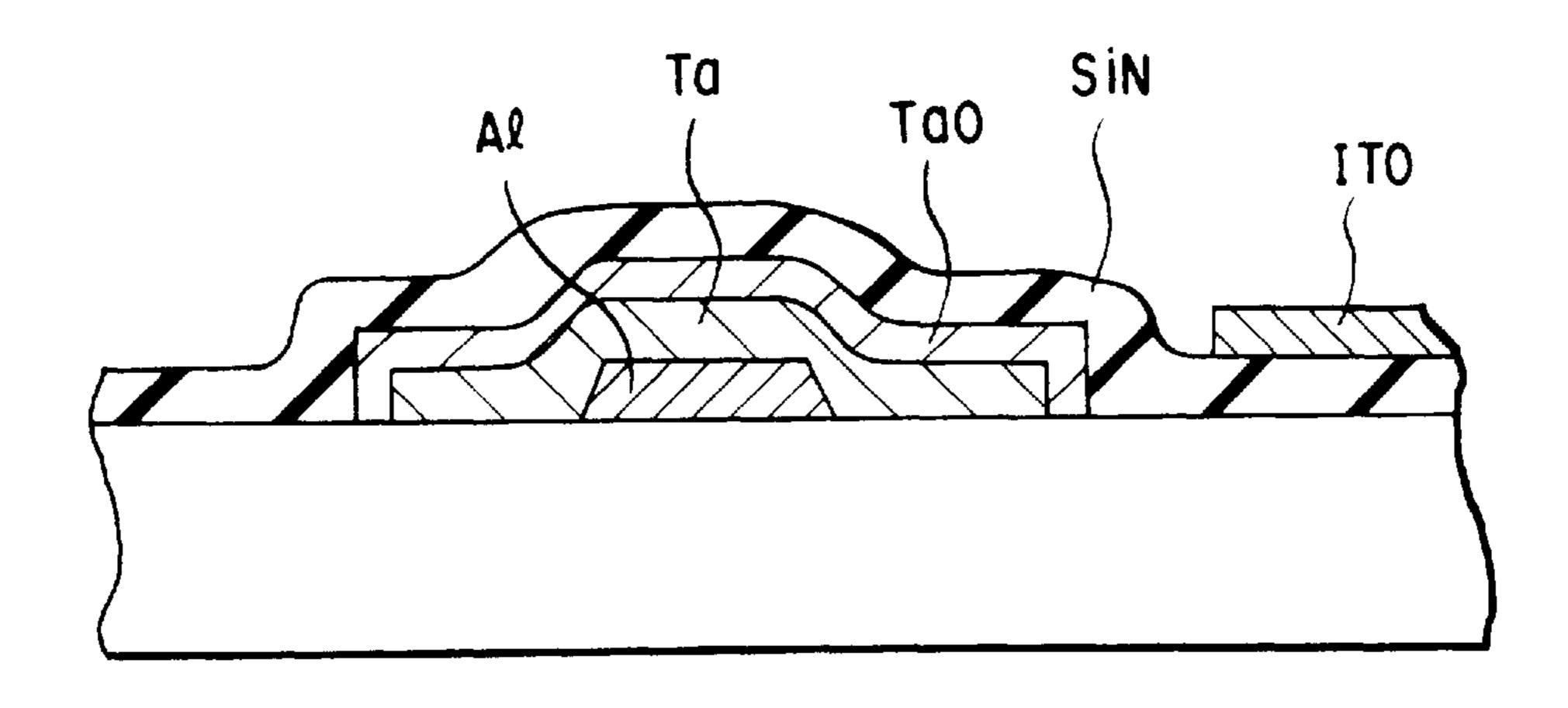

- FIG. 12 is a cross-sectional view showing the structure of a film obtained by an ordinary method;

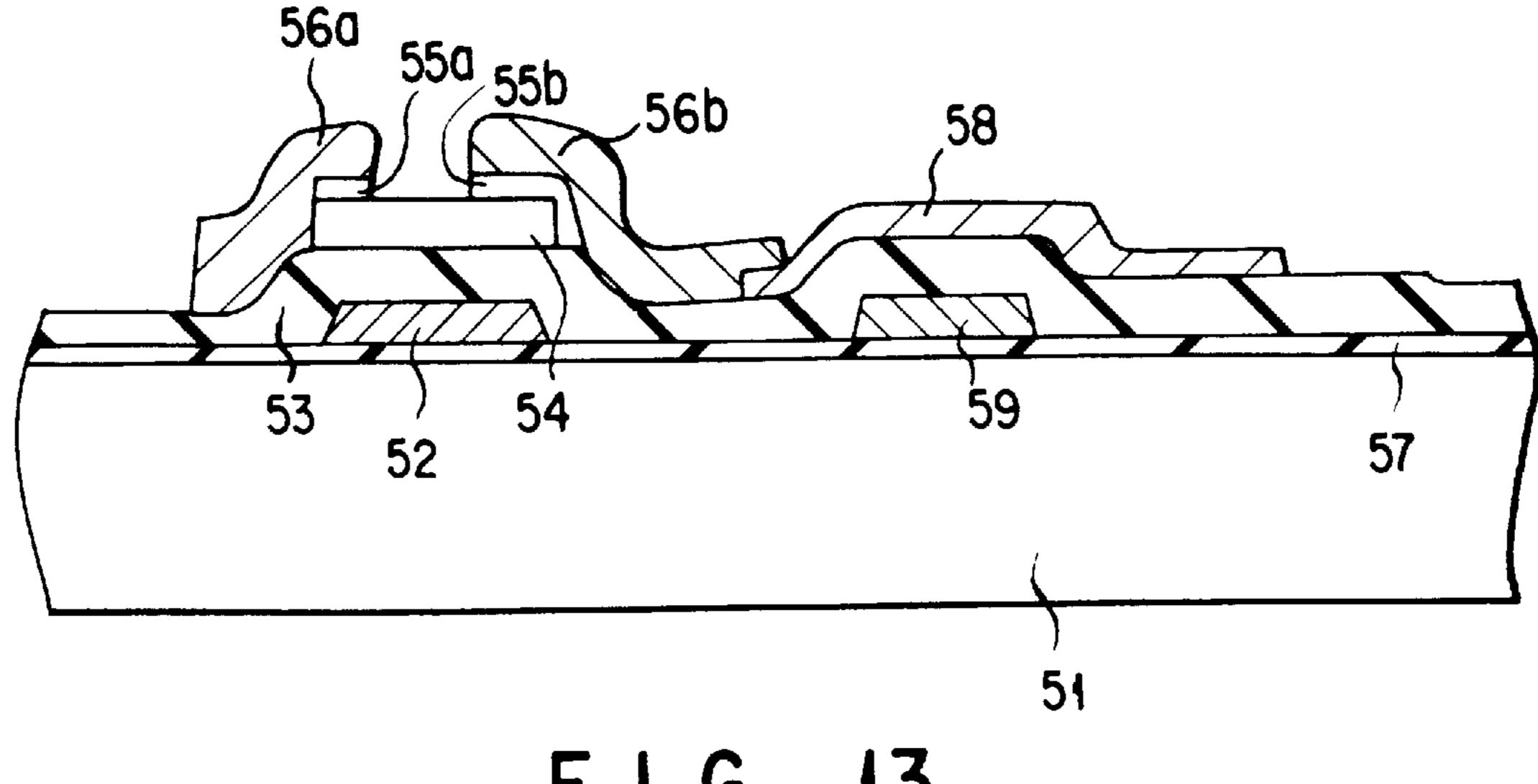

- FIG. 13 is a cross-sectional view showing an LCD device according to a second embodiment of the invention;

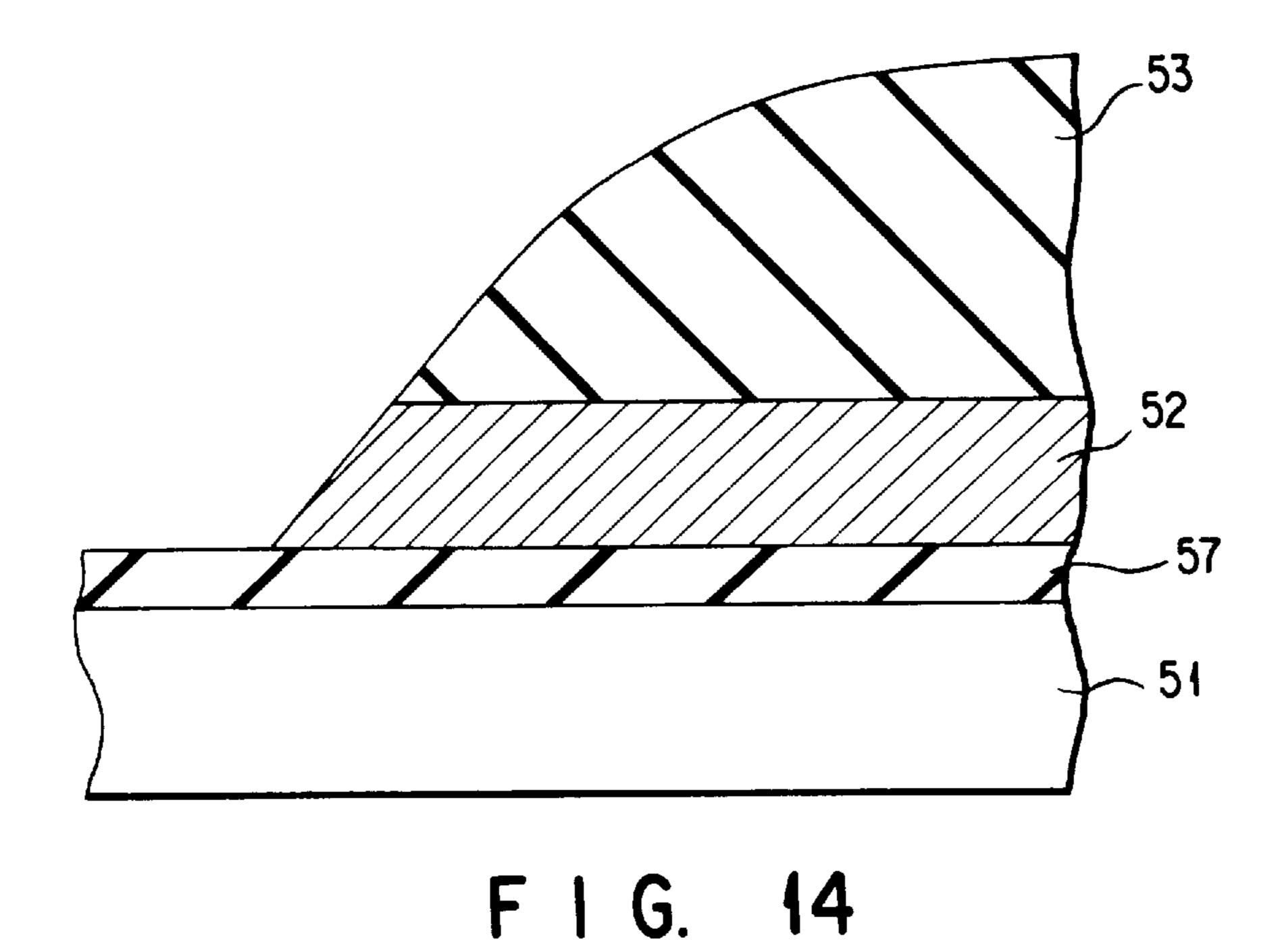

- FIG. 14 is a cross-sectional view showing the state in which the LCD device shown in FIG. 13 has been subjected to a tapering process;

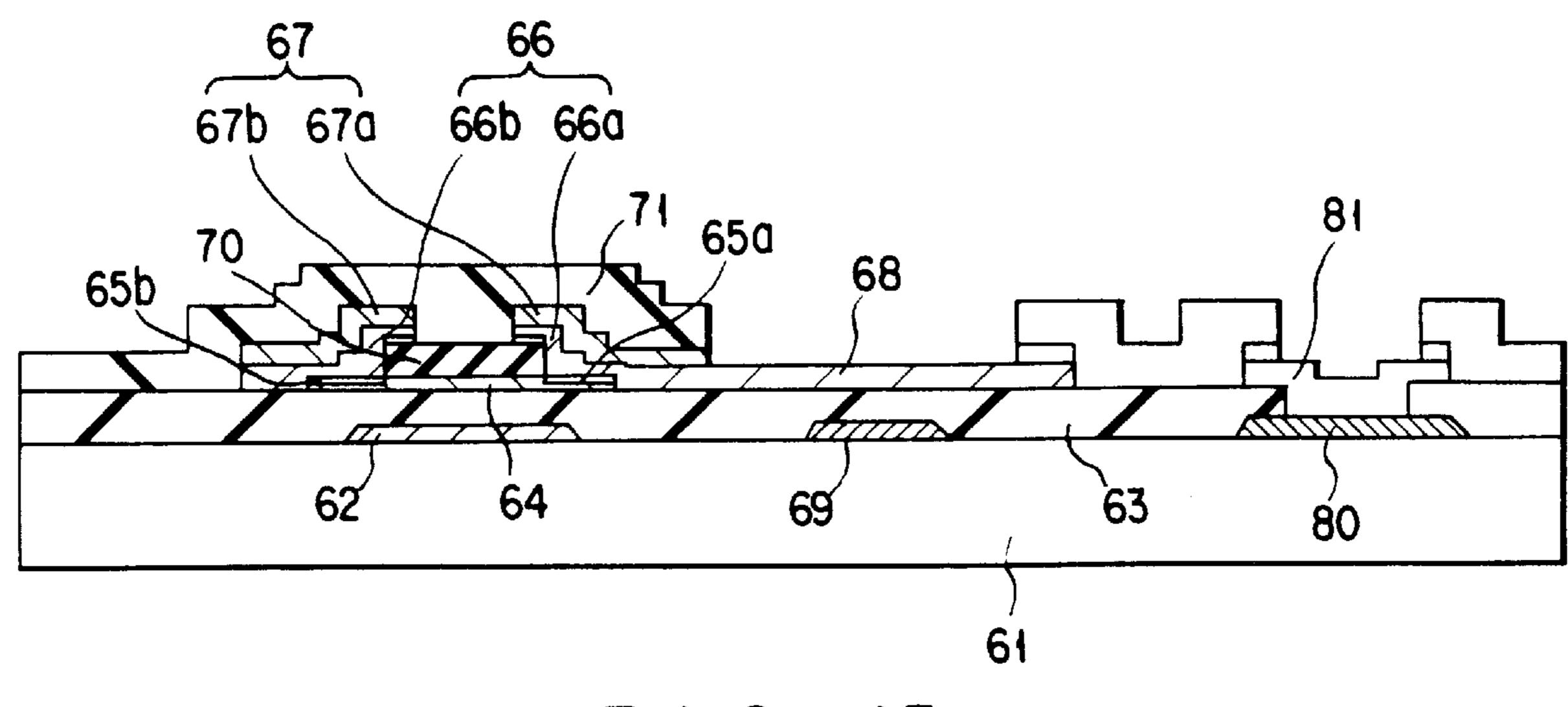

- FIG. 15 is a cross-sectional view showing a TFT and a storage capacitance portion used in an example of an LCD device according to a third embodiment of the invention;

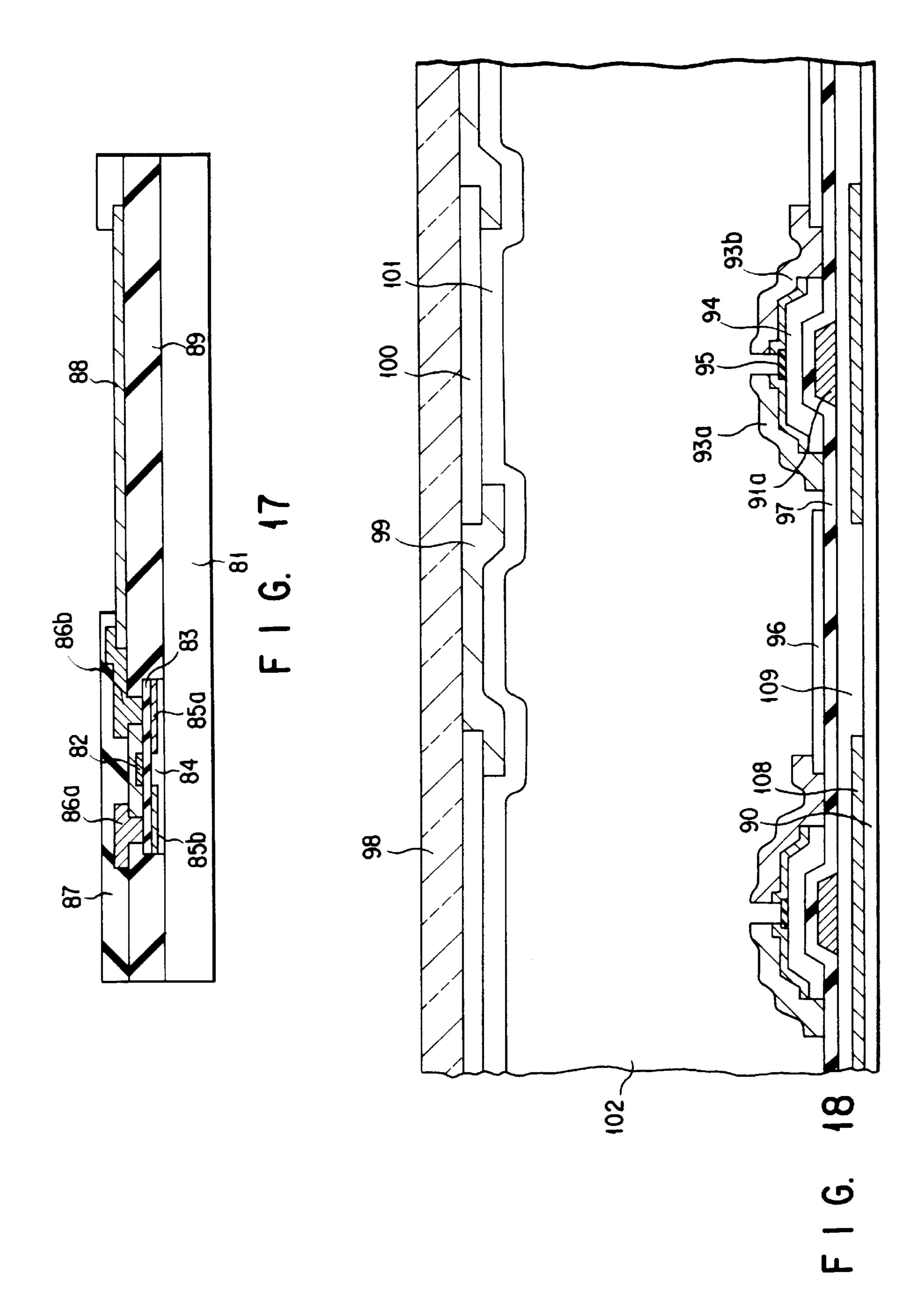

- FIG. 17 is a cross-sectional view showing a TFT and a storage capacitance portion used in an another example of the LCD device according to the third embodiment of the invention;

- FIG. 18 is a cross-sectional view showing an LCD device according to a fourth embodiment of the invention;

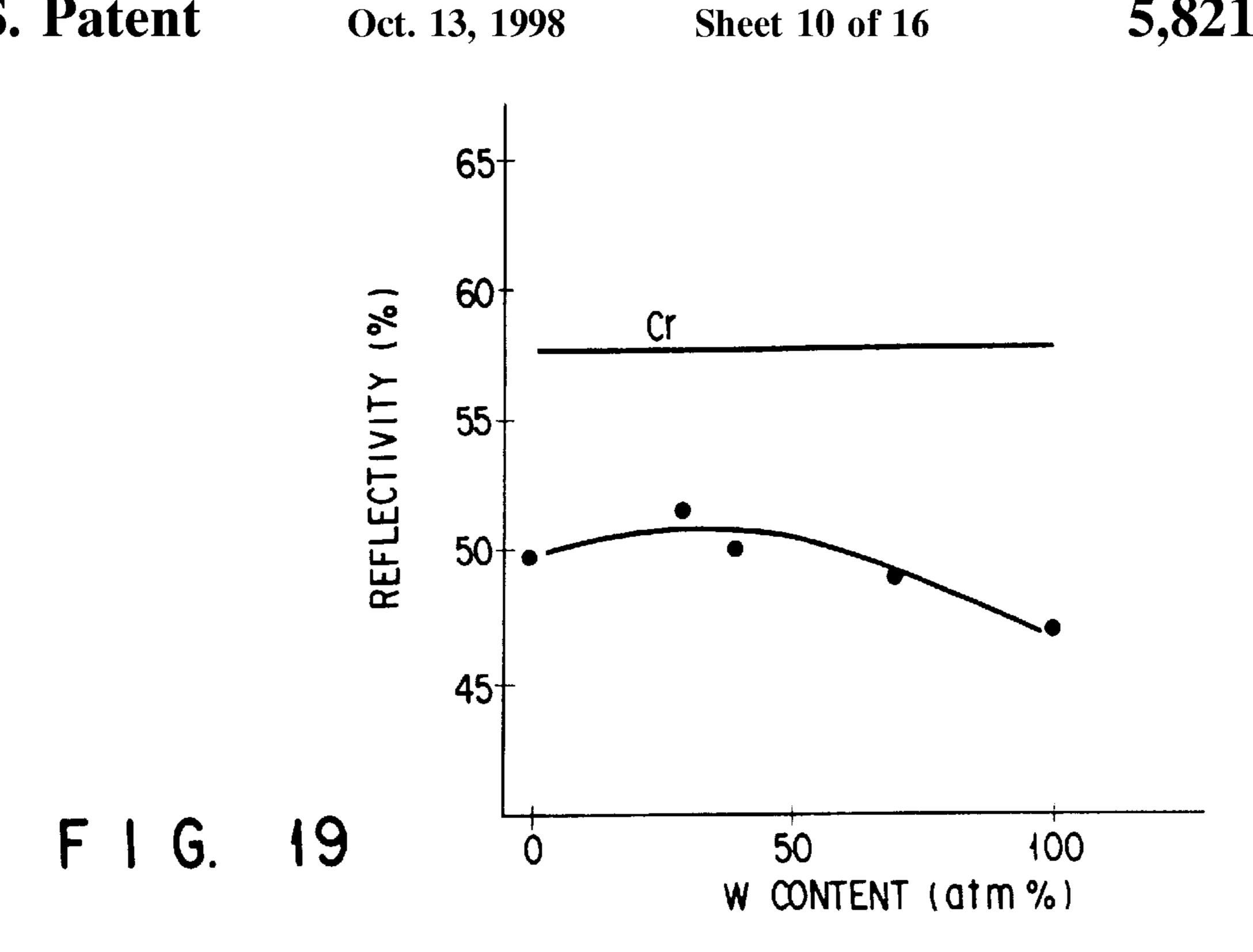

- FIG. 19 is a graph showing the relationship between a reflectance of the Mo—W alloy and the W % content; and

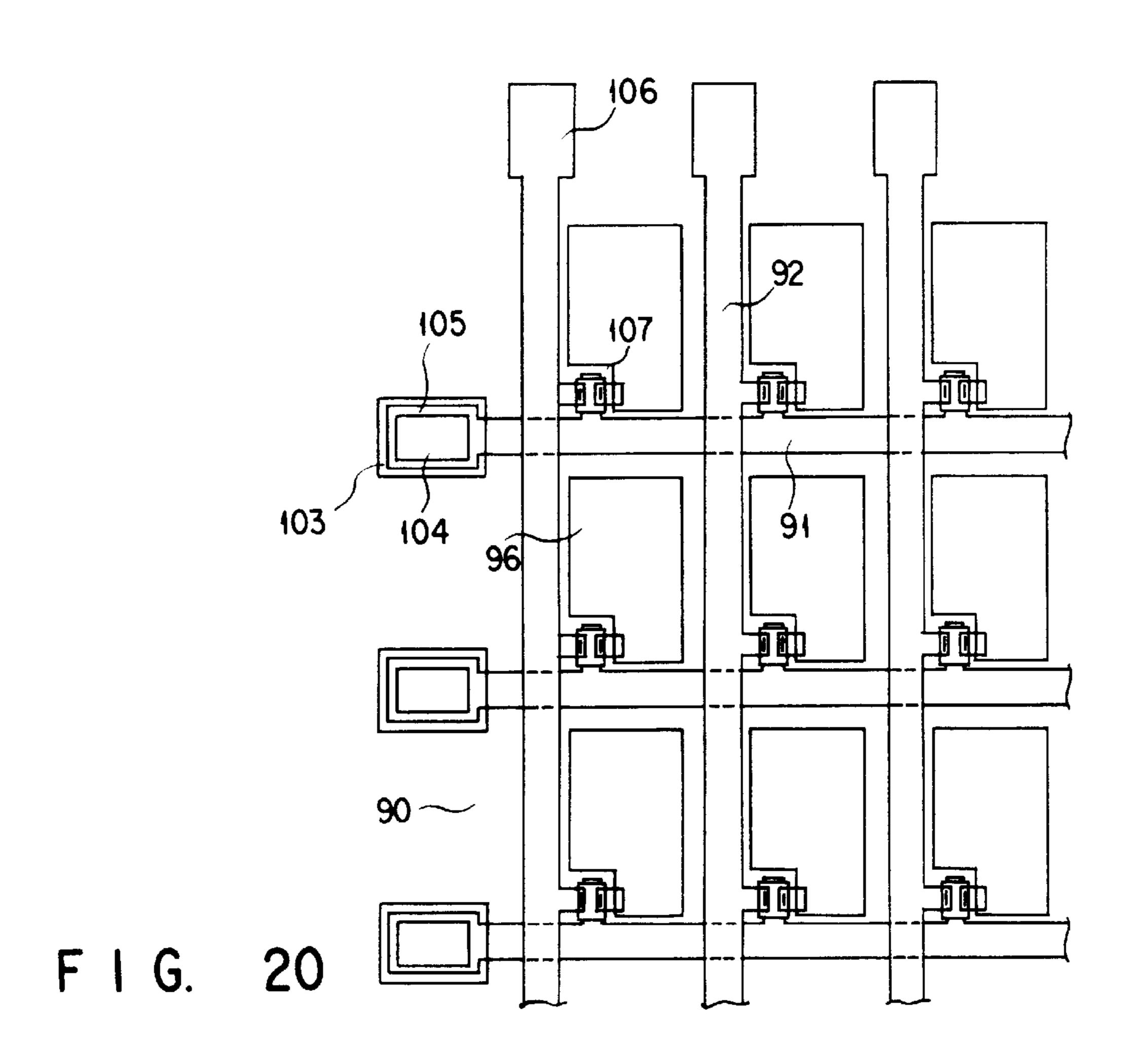

- FIG. 20 is a plan view showing a driving circuit board of the LCD device according to the fourth embodiment of the invention; and

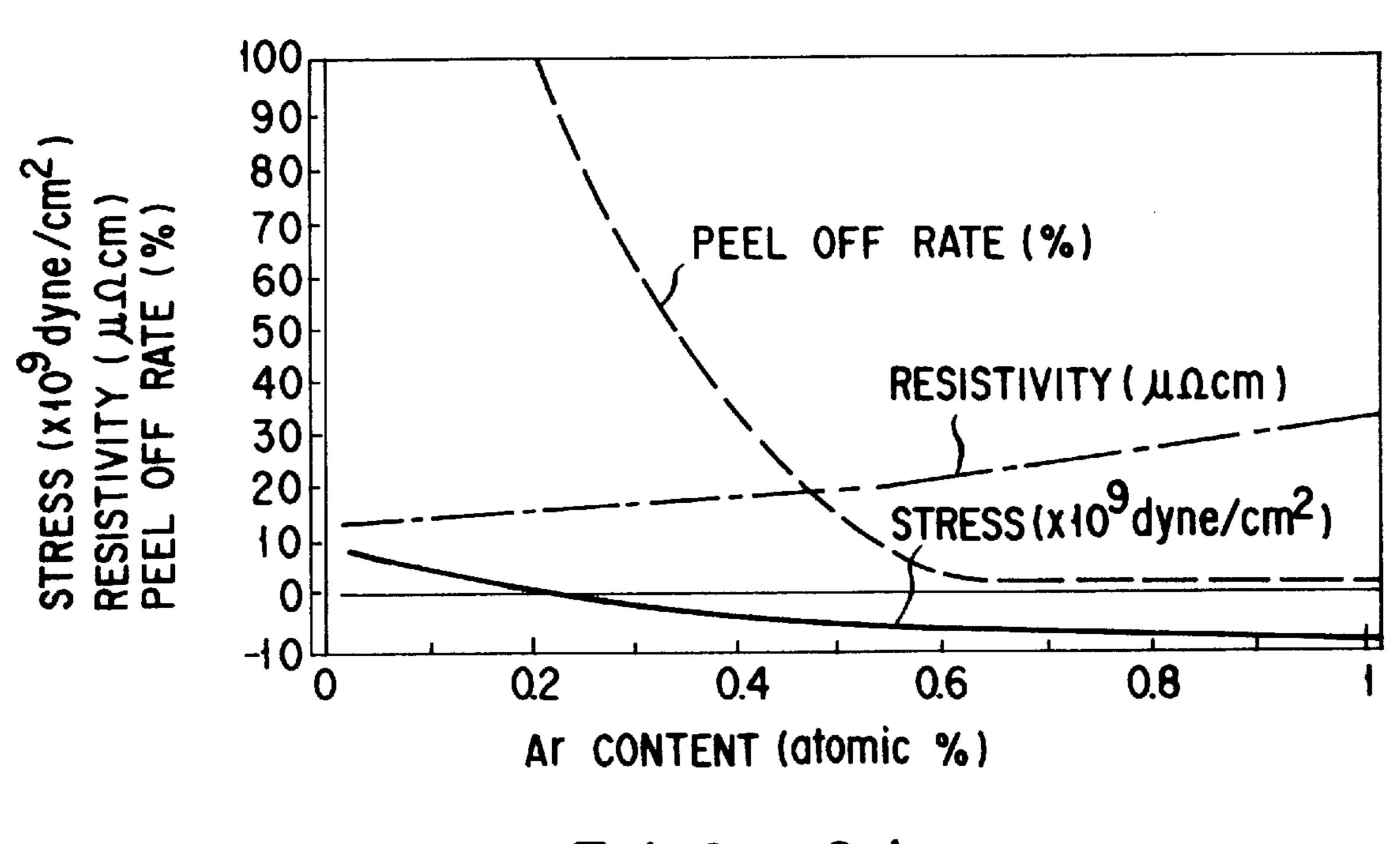

- FIG. 21 is a characteristic diagram illustrating the relationship between the stress, resistivity and film peeling rate, and the Ar amount of the film;

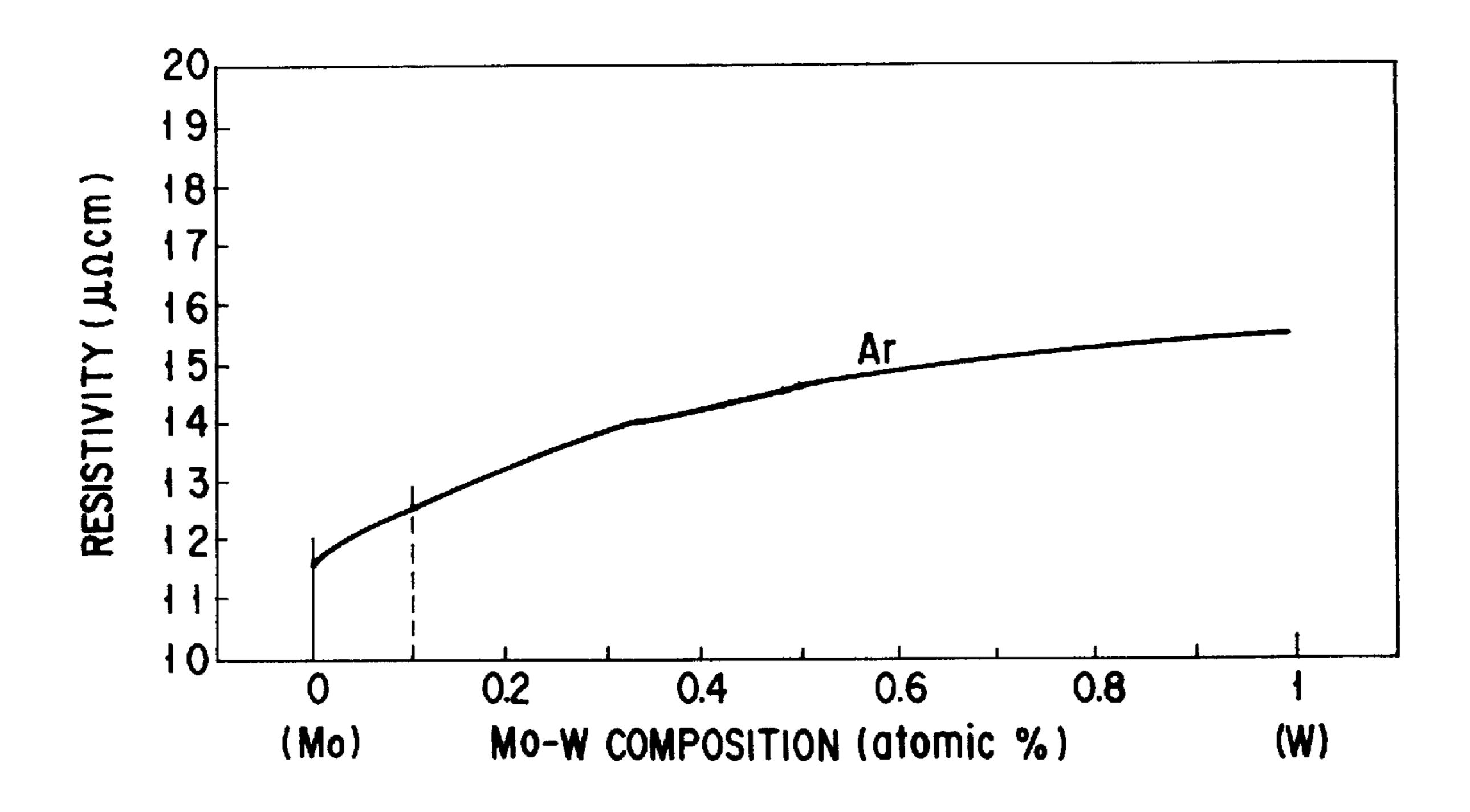

- FIG. 22 is a characteristic diagram illustrating the relationship between the resistivity and the Mo content;

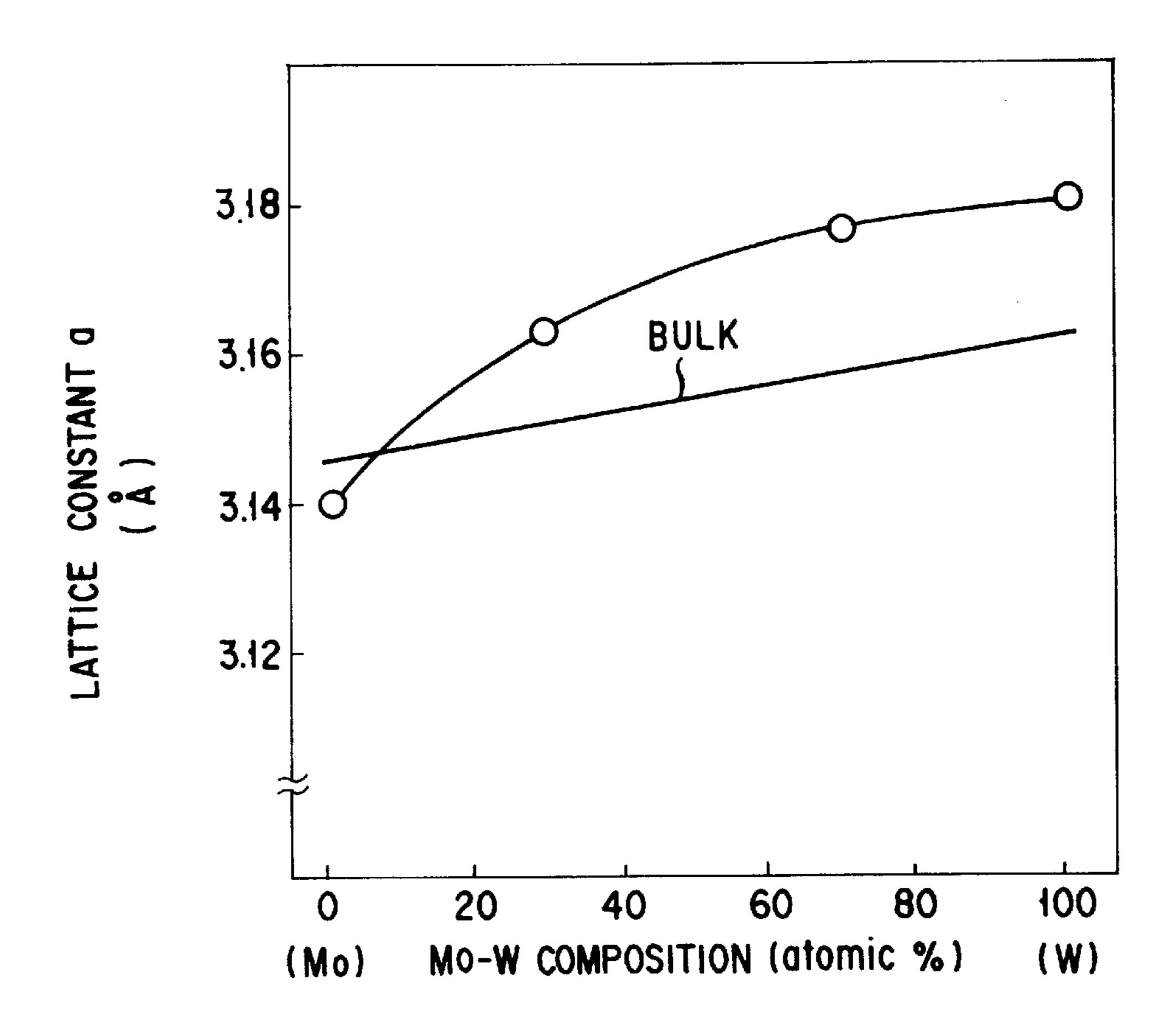

- FIG. 23 is a characteristic diagram illustrating the relationship between the lattice constant measured by X-rays and the Mo content;

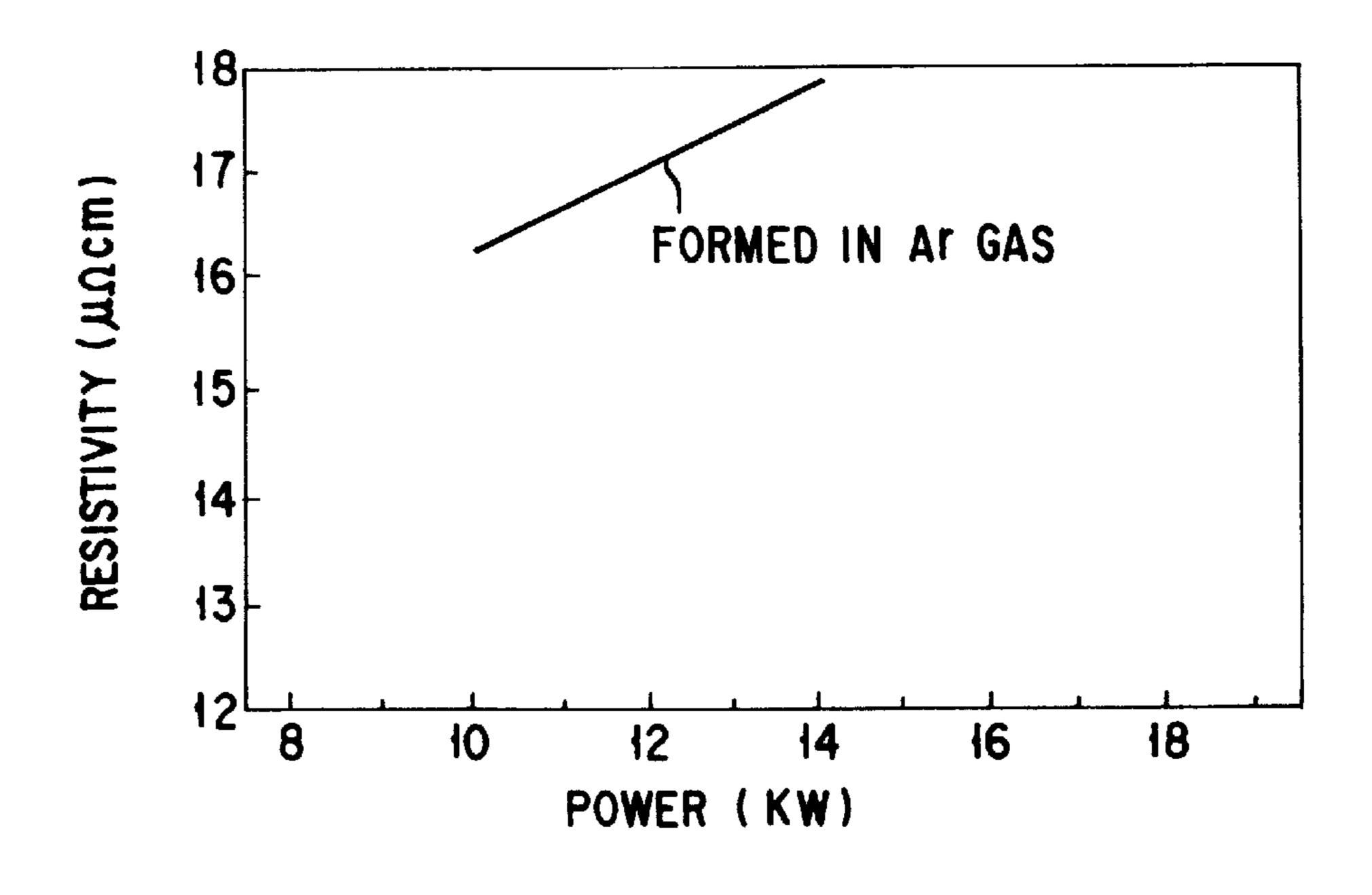

- FIG. 24 is a characteristic diagram illustrating the relationship between the resistivity and the power;

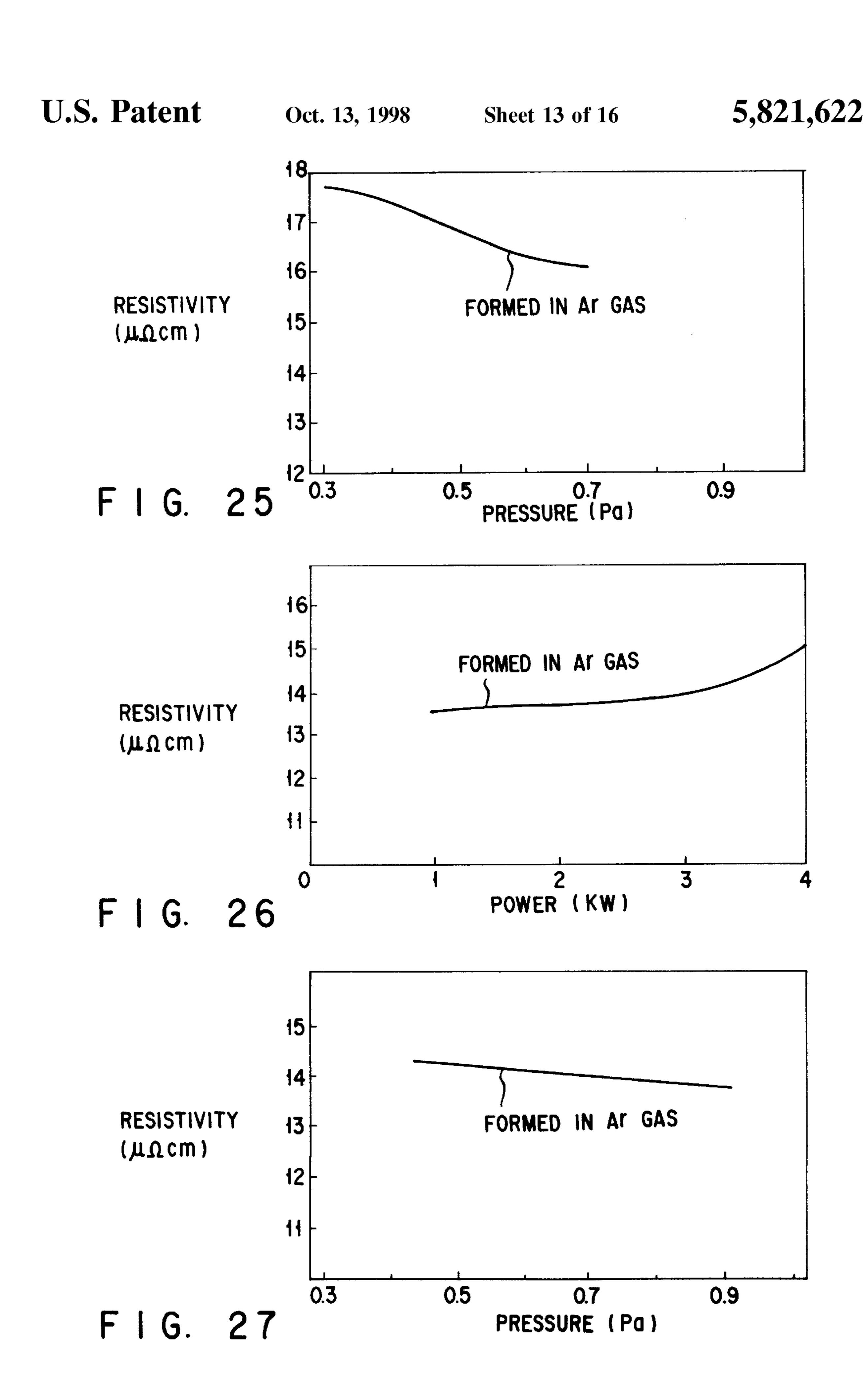

- FIG. 25 is a characteristic diagram illustrating the relationship between the resistivity and the pressure;

- FIG. 26 is a further characteristic diagram illustrating the relationship between the resistivity and power;

- FIG. 27 is a further characteristic diagram illustrating the relationship between the resistivity and the pressure;

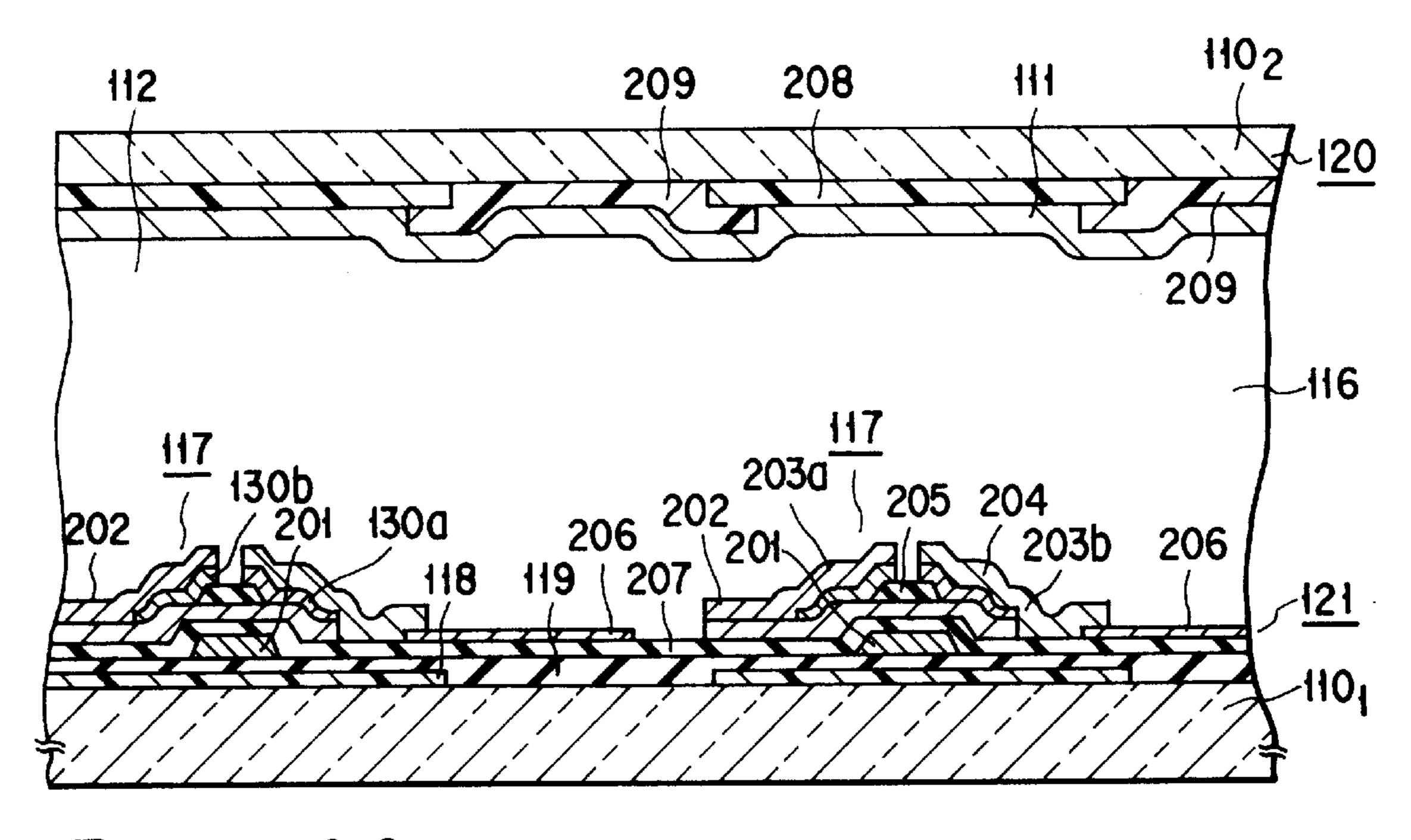

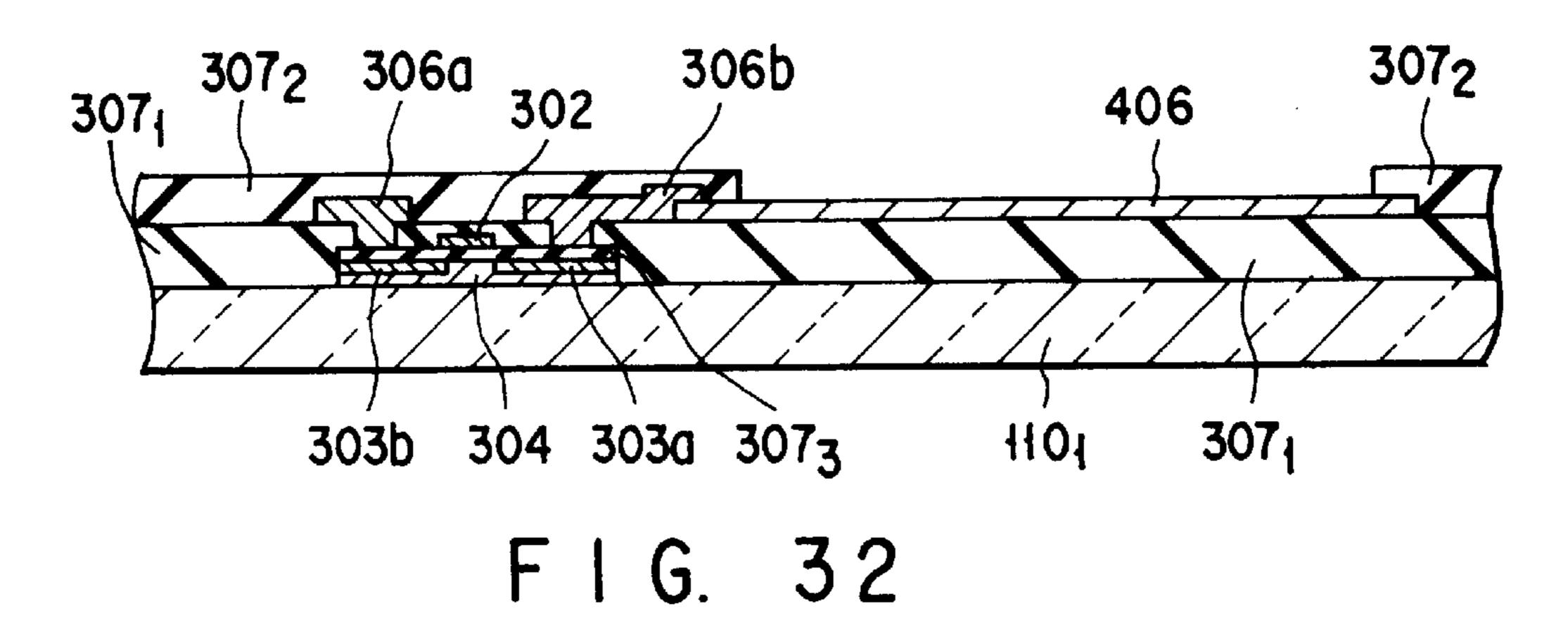

- FIG. 28 is cross sectional view taken along the line A—A in FIG. 29;

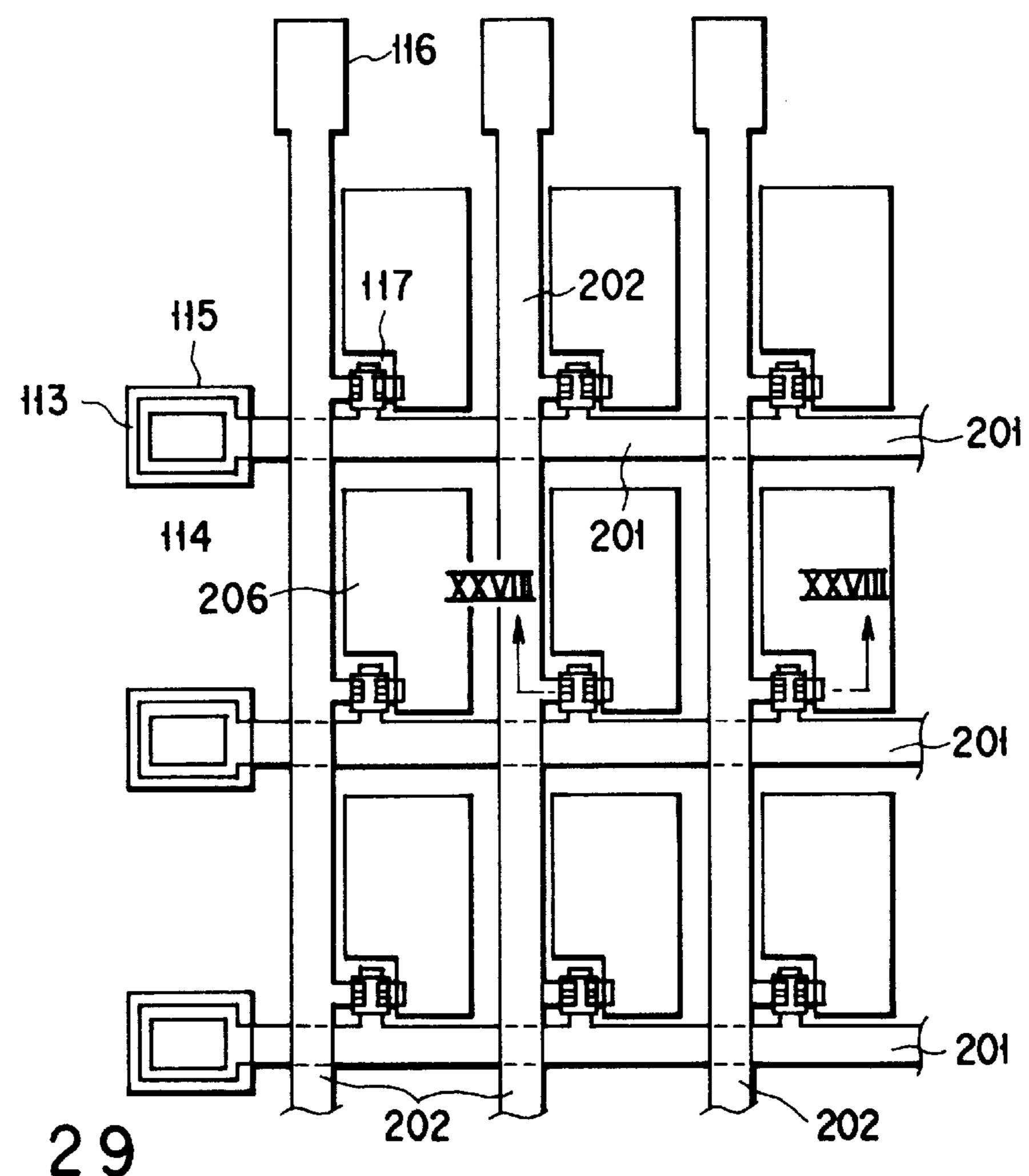

- FIG. 29 is a plan view showing a driving circuit board of a liquid crystal display device employing an electrode wiring material of the present invention;

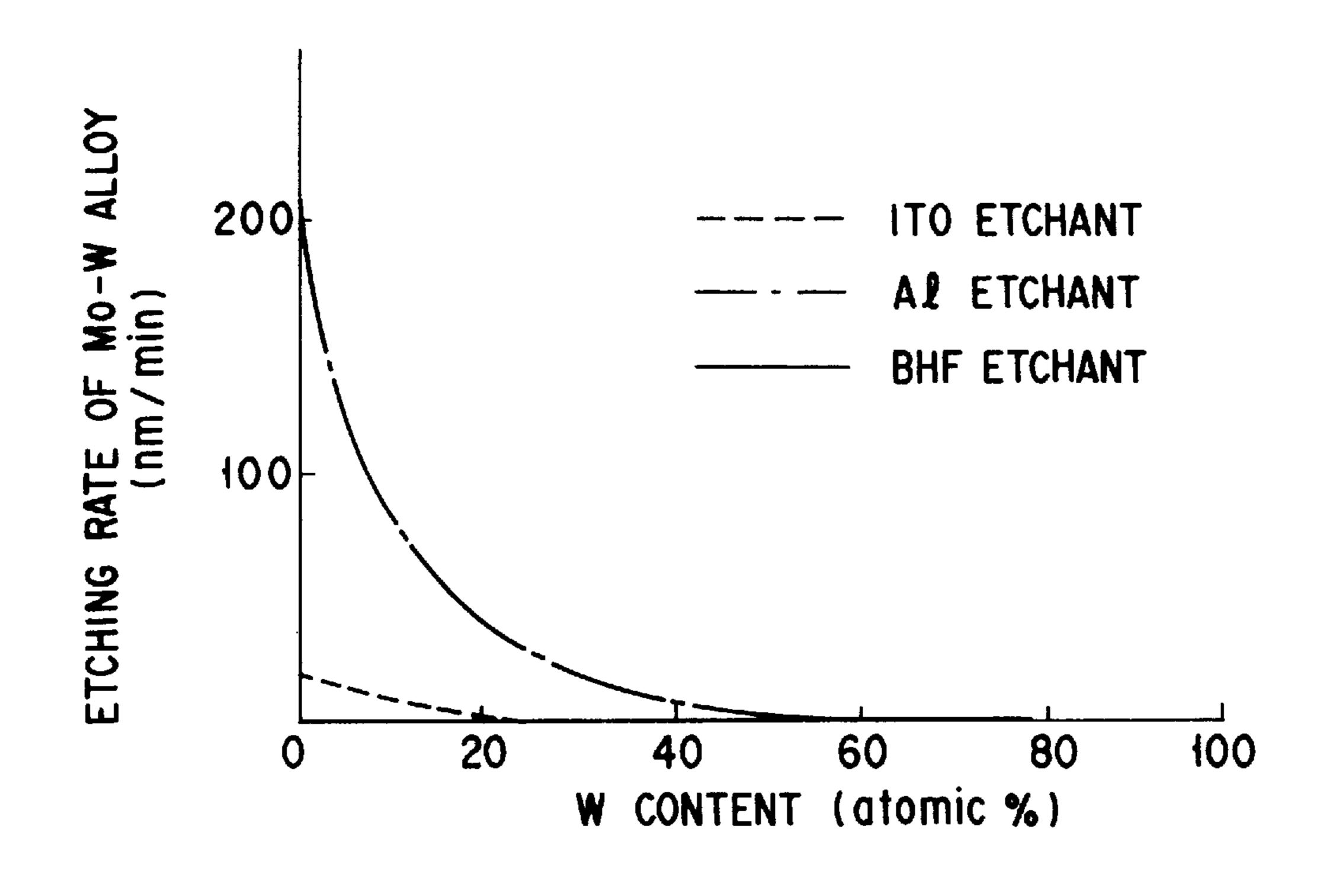

- FIG. 30 is a characteristic diagram showing the relationship between the etching rate of the MoW alloy and the W content;

- FIG. 31 is a characteristic diagram showing the relationship between the etching rate of the MoTi alloy and the W content;

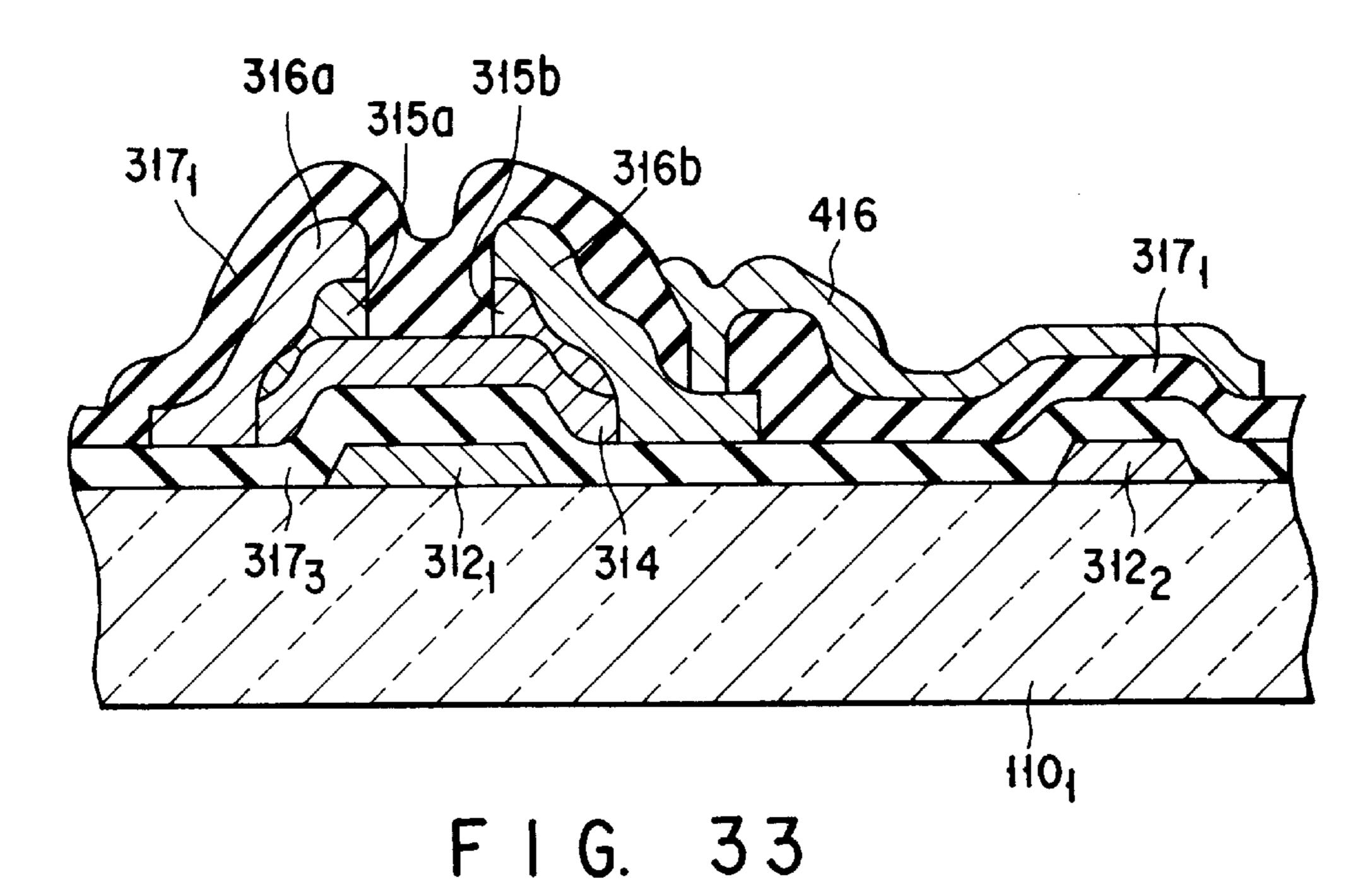

FIGS. 32 and 33 are cross sections showing other examples of the liquid crystal driving circuit board of a liquid crystal display device employing the electrode wiring material of the present invention; and

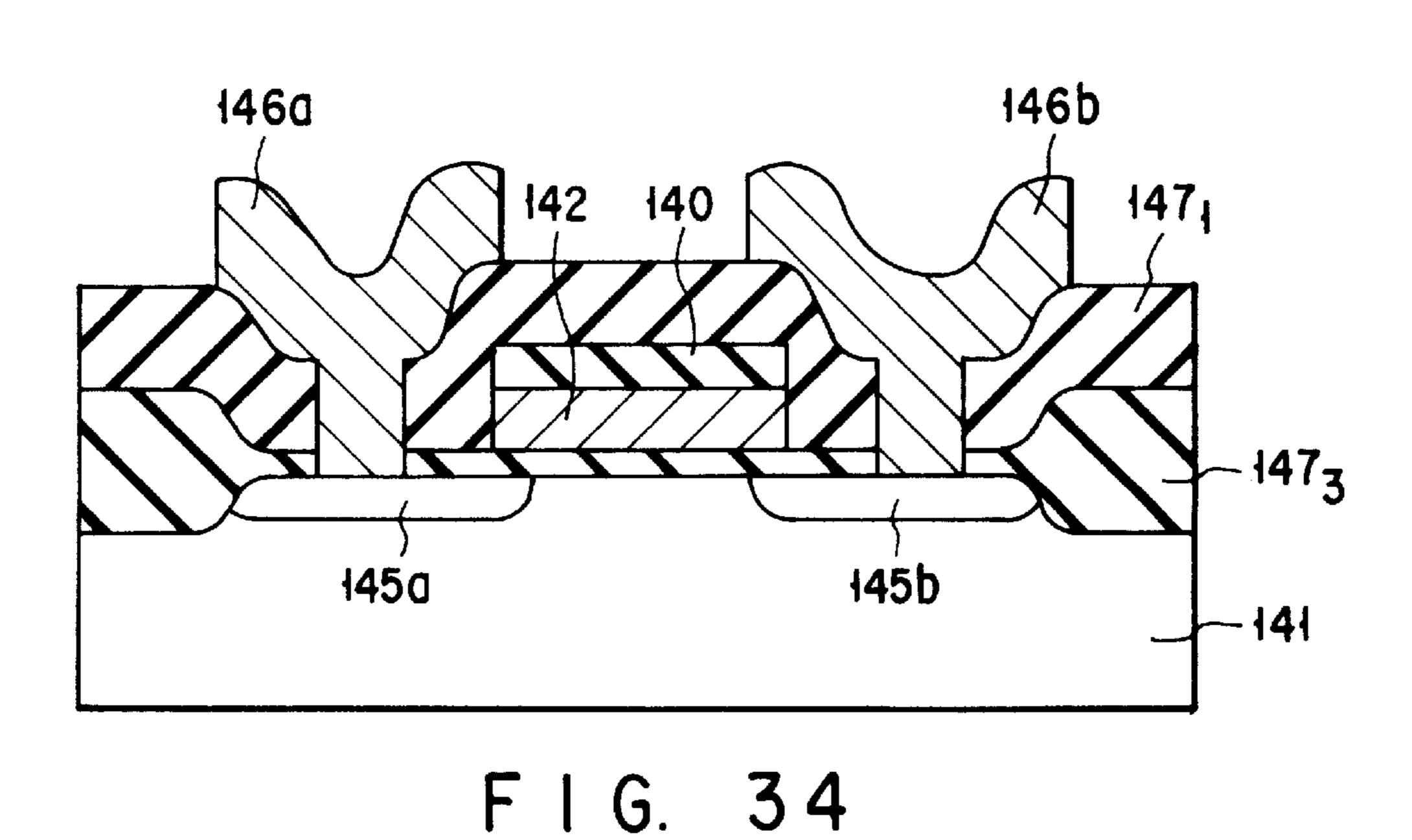

FIG. 34 is a cross sectional view showing the circuit board of a semiconductor device employing the electrode wiring material of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Embodiments of the present invention will be described below with reference to the accompanying drawings. Note that the same reference numerals denote the same parts throughout the embodiments, and a detailed description thereof will be omitted for the sake of simplicity.

#### EMBODIMENT 1

#### (Example 1)

FIG. 2 is a sectional view showing a TFT (switching element) and a capacitor portion which are used for one example of a liquid crystal display device according to the embodiment 1 of the present invention. The arrangement and manufacturing process of the TFT and the capacitor portion will be described below. A gate electrode (control electrode) 12, an address wiring line, and a Cs line 19 are simultaneously formed on a glass substrate 11 by sputtering an Mo—W alloy or Mo—Cr alloy to a thickness of 300 nm and patterning. Thereafter, a 350-nm thick oxide film 13, a 300-nm thick active layer consisting of a-Si, and 50-nm thick n<sup>+</sup> a-Si layers 15a and 15b are continuously formed on the resultant structure by plasma CVD, thus forming an island-shaped a-Si active layer 14. ITO is then sputtered to a thickness of 120 nm to form a pixel electrode 18.  $SiO_x$  of a contact portion 20 is etched by using buffered HF to form a contact hole. A source electrode (first main electrode) 16a, a drain electrode (second main electrode) 16b, a data wiring line, and a contact electrode 21 are simultaneously formed on the resultant structure by sputtering a predetermined wiring metal such as Al and performing wet etching. At this time, an oxide film on the surface of address wiring line electrode of the contact portion needs to be removed before Al or the like is sputtered.

According to tests performed by the present inventors by using a sputtering apparatus whose ultimate degree of vacuum was low, it was found, as shown in FIG. 3, that the resistivity of an Mo—W alloy was much lower than 40  $\mu\Omega$ ·cm (VGA level) and the resistance thereof was below that of Mo or W as a single element with a W content of the Mo—W alloy falling within a preferable range of 10 to 95 atm %, and a more preferable range of 20 to 90 atm %. The resistivity of an Mo—W alloy falling within a range of 30 to 70 atm % was much lower than 20  $\mu\Omega$ ·cm. The address wiring line alloy for use in a 10-inch XGA display (768 columns, 1024 rows) needs to have a resistivity of 20  $\mu\Omega$ ·cm or less.

In addition, it was found that an address wiring line formed by using an Mo—W alloy could be tapered by CDE using a gas mixture of CF<sub>4</sub> and O<sub>2</sub>. It was also found that the address wiring line could be tapered, without degrading a resist, by a wet etching method using an alkaline etchant (pH of 7 to 13) containing an oxidizing agent having a redox potential higher than that of Mo and W and lower than that of Ti.

According to the present invention, since an Mo—W alloy has a low resistivity, an address wiring line formed by

6

using this material exhibits a low resistance. For this reason, no gate pulse delay is caused by the wiring resistance, and a gate pulse without a delay can be supplied to a predetermined switching element. Since an Mo—W alloy can be tapered, an insulating interlayer formed on address wiring lines formed by using this material exhibits good step coverage, thereby ensuring a high breakdown voltage. Therefore, a reliable liquid crystal display device having a large display area can be realized. Note that even if this address wiring line is not applied to a large-area display, there is still a merit. That is, as the resistivity of an address wiring line decreases, the width of the wiring line can be reduced, and hence the aperture ratio can be increased.

According to tests performed by the present inventors, it was found, as shown in FIG. 4, that an Mo-W alloy exhibited excellent chemical resistance when the W content was 20 atm % (atomic %) or more, and more preferably 25 atm % or more. More specifically, it was found that the etching rate of the Mo—W alloy was 10 nm/min or less with an ITO etchant for a pixel electrode material; the Mo—W alloy was not etched at all by BHF as an etchant for an insulating interlayer; and the etching rate of the Mo—W alloy was 30 to 40 nm/min or less even with an Al etching. Especially, it was found that when the W content was 50 atm % or more, the Mo—W alloy was not etched at all. Even if, therefore, a pin hole is formed in the insulating interlayer, wiring lines under the insulating interlayer, such as gate electrodes and data wiring lines, are not corroded by the above etchants. For this reason, the degree of freedom in structure design/process design above the insulating interlayer can be increased. In addition, as shown in FIG. 5, since the stress greatly changes depending on a W composition ratio, a reduction in stress can be achieved by adjusting the W composition ratio.

On the other hand, it was found that the stress was reduced when an Mo—W alloy contained 0.5 atm % or more of O and/or N, but the resistance was increased when the alloy contained 10 atm % or more of O and/or N.

FIG. 6 shows a change in stress measured under different sputtering conditions. As is apparent, the stress greatly changes depending on an Mo/W composition ratio and sputtering conditions (discharging pressure and discharging power). It was found from analysis that this change in stress was due to the Ar content of the film. That is, the stress is reduced when the film contains 0.1 atm % or more of Ar, and the grain size decreased by the crystal growth disturbance and the film resistance increases when the film contains 2 atm % or more of Ar. The same holds true of an inert gas (He, Ne, Kr, or Xe gas) other than Ar, and there is no problem unless the Ar content exceeds 10 atm %.

When a device is to be formed on a glass substrate or a transparent insulating film on a glass substrate, the adhesion property of a film is important. When 0.5 atm % or more of Cr and/or Ti are contained in an Mo—W alloy, the adhesion property of the alloy with respect to an underlying layer is improved, and the alloy can be etched by a gas mixture of CF<sub>4</sub> and O<sub>2</sub>, and good taper can be formed. However, when 10 atm % or more of Cr and/or Ti are contained in an Mo—W alloy, the etching workability of the alloy is degraded, and the resistance is increased.

Stacking of an Mo—W alloy nitride and an Mo—W alloy is also effective in improving the adhesion property with respect to an underlying layer. If 50 atm % or more of N are contained in an Mo—W alloy, the resistance of the alloy abruptly increases. Therefore, the N content of the alloy must be 50 atm % or less. A TiN alloy film also improves the adhesion of the Mo—W film.

It was found when an Mo—W alloy, especially an Mo—W alloy containing 50 atm % or more of W, was annealed in the air for a long time, the resistivity increased 10 times or more. This increase in resistivity was caused by excessive oxidation on the surface of the alloy. However, 5 when an Mo—W alloy nitride film was stacked on the Mo—W alloy film, oxidation was prevented and no increase in resistance occurred. That is, a wiring line which is resistant to oxidation, which can be tapered and which has a low resistance can be formed in the same process as that for an Mo—W alloy by sputtering an Mo—W alloy, sputtering an Mo—W alloy nitride containing 50 atm % or less of N, and dry etching the resultant structure with a gas mixture of CF<sub>4</sub> and O<sub>2</sub> and good taper can be formed. An Mo—W alloy containing 50 atm % or less of N may be formed on the substrate to improve the adhesion of the 15 Mo—W alloy film to the substrate. Such an Mo—W alloy may also be used as an underlayer for a TaN alloy film to attain the same advantage. The surface coverage by a film made of TaN, TaNbN, TaWN or TaMoN alloy has the same effect as the MoWN alloy film.

According to tests performed by the present inventors, it was found that the above description of the Mo—W alloys also applied to Cr—W alloys. When an address wiring line or the like is formed by using this material, the same effects as those described above can be obtained.

The above manufacturing process is only an example, and the thickness of each layer, the film formation methods, and the like can be modified as needed. Even in such a case, the same effects as those of the embodiment can be obtained. In addition, a TFT having a structure different from that of the above TFT may be used. For example, a TFT having an insulating film as a stopper formed on an a-Si channel may be used. Furthermore, a TFT having a capacitor portion which is constituted by the same wiring layer as that of a gate electrode and the same wiring layer as that of a data wiring line may be used.

# (Example 2)

FIG. 7 is a sectional view showing a TFT and a capacitor portion which are used for other example of liquid crystal display device according to the embodiment 1 of the present 40 invention. The arrangement and manufacturing process of the TFT and the capacitor portion will be described below. A Cs line 29a is formed on a glass substrate 11 by sputtering ITO to a thickness of 120 nm and patterning. Thereafter, a gate electrode 22, an address wiring line, and a Cs line 29b 45 are simultaneously formed by sputtering Mo—W to a thickness of 300 nm and patterning. A 350-nm thick silicon oxide or silicon nitride film 23, a 300-nm thick a-Si layer, and 50-nm thick n<sup>+</sup> a-Si layers 25a and 25b are successively formed on the resultant structure by plasma CVD, thus 50 forming an island-shaped a-Si active layer 24. A pixel electrode 28 is then formed by sputtering ITO to a thickness of 120 nm. A contact hole is formed by using an HF solution. A source electrode 26a, a drain electrode 26b, and a data wiring line are simultaneously formed by sputtering a pre- 55 determined wiring metal such as Al and performing wet etching. In this structure, since a capacitor portion is formed between the transparent ITO Cs line 29a and the pixel electrode 28 and both the line 29a and the electrode 28 are transparent, the Cs line portion, which cannot be used as an 60 aperture portion in the prior art, can be used as an aperture portion. Therefore, the aperture ratio can be increased. Although the resistivity of ITO is higher than that of a metal, the resistivity of the Cs line 29a can be sufficiently reduced by stacking the Cs line 29b on the Cs line 29a. At this time, 65 the ITO can contact the Mo—W alloy without a barrier metal.

8

(Example 3)

FIG. 8 is a sectional view showing a TFT and a capacitor portion which are used for other example of a liquid crystal display device according to the embodiment 1 of the present invention. The arrangement and manufacturing process of the TFT and the capacitor portion will be described. A gate electrode 32, an address wiring line, and a Cs line 39 are simultaneously formed on a glass substrate 11 by sputtering a predetermined wiring material such as a Mo—Ta alloy to a thickness of 300 nm and patterning. Thereafter, a 350-nm thick oxide or nitride film 33, a 300-nm thick a-Si layer, and 50-nm thick n<sup>+</sup> a-Si layers 35a and 35b are successively formed on the resultant structure by plasma CVD, thus forming an island-shaped a-Si active layer 34. A contact hole is formed by etching SiOx of a contact portion using diluted HF. An oxide film on the surface of the a-Si active layer 24 is then removed. Subsequently, a source electrode 36a, a drain electrode 36b, and a data wiring line are formed by sputtering an Mo—Ti alloy, a W—Ti alloy, or an Mo—W alloy and performing wet etching. A 300-nm thick oxide film 37 is formed on the resultant structure. A contact hole is formed on the drain electrode 36b by an etching method using an HF solution (for example, an etching rate of about 100 nm/min) or a dry etching method (for example, an etching rate of about 30 to 100 nm/min) using a gas such as CF<sub>4</sub>. In addition, a 120-nm thick ITO is sputtered to form a pixel electrode 38.

According to etching tests performed by the present inventors, as shown in FIG. 9, it was found that an Mo—Ti alloy exhibited excellent chemical resistance with respect to an ITO etchant used to form the pixel electrode 38 and BHF used to form a contact hole when a Ti content was 20 to 80 atm %. In addition, it was found that the Mo—Ti alloy can be etched, without dissolving a resist, by using a weak alkaline etchant (pH of 7 to 13) containing an oxidizing agent having a redox potential higher than that of Ti.

Films formed by using Mo—Ti alloys having different oxygen contents were etched. The oxygen contents of films which were tapered and those of films which were not tapered were checked by using an Auger analysis method. FIGS. 10A and 10B show the results. Although the ordinates in FIGS. 10A and 10B, along which Mo, Ti, and O (oxygen) contents are plotted, have difference scales, the abscissas in the same drawings, along which Mo, Ti, and O (oxygen) contents are plotted, have the same scale. FIG. 10A indicates that the oxygen content of an Mo—Ti alloy is about 3 atm % when tapering can be performed. FIG. 10B indicates that the oxygen content of an Mo—Ti alloy is about 1 atm % when tapering cannot be performed. From the results of these tests, it was found that tapering could be performed when the oxygen content of an Mo—Ti alloy was about 2 atm % or more. In addition, it was found that when the oxygen content of an Mo—Ti alloy exceeded about 8 atm %, the resistivity increased, and hence the alloy could not be used as a wiring material. It was, therefore, found that the oxygen content of an Mo—Ti alloy used as a wiring material was preferably 8 atm % or less, and more preferably fell in the range of 2 to 5 atm \%, in consideration of limitations associated with taper workability and resistivity.

It is, therefore, preferable that the source electrode 36a, the drain electrode 36b, and the data line be formed by sputtering an Mo—Ti alloy having a Ti content of 20 to 80 atm % and an O (oxygen) content of 8 atm % or less, and preferably 2 to 5 atm %, and performing wet etching. In this case, since the data wiring line can be tapered, an insulating interlayer formed on data wiring lines formed by using this

material exhibits good step coverage, thus ensuring a high breakdown voltage. In addition, since an Mo—Ti alloy exhibits good chemical resistance with respect to an ITO etchant used to form the pixel electrode 38 and BHF used to form a contact hole, the chemical resistance of the drain 5 electrode 36b is good, and a contact hole is formed on the drain electrode 36b by using HF. Furthermore, a pixel electrode can be etched by using a solution mixture of hydrochloric acid and nitric acid. For this reason, unlike the conventional structure shown in FIG. 1, the structure shown in FIG. 8, in which the pixel electrode 38 is formed on the data wiring line through the oxide film 37, can be employed to reduce point defects.

According to tests performed by the present inventors, it was found that the same applied to a case wherein a W—Ti <sup>15</sup> alloy was used. The same effects as those described above can be obtained in a case wherein a data wiring line and the like are formed by using this material.

As described above, an Mo—W alloy exhibits excellent chemical resistance when the W content is 20 atm % or more, and preferably 25 atm % or more. In addition, a data wiring line formed by using this material can be tapered, without degrading a resist, by using an alkaline etchant (pH of 7 to 13) containing an oxidizing agent having a redox potential higher than that of Mo and W and lower than that of Ti or by using CF<sub>4</sub>/O<sub>2</sub> gas dry etchant.

Therefore, similar to the cases wherein an Mo—Ti alloy and a W—Ti alloy are used, in a pixel array formed in this manner, since each data wiring line is tapered, the step coverage of an insulating interlayer formed thereon is good, ensuring a high breakdown voltage. In addition, since the drain electrode **36***b* has good chemical resistance, a contact hole can be formed on the drain electrode **36***b* by using HF. Furthermore, a pixel electrode can be processed by a solution mixture of hydrochloric acid and nitric acid. As described above, since the stress greatly changes depending on a W composition ratio, the stress can be reduced, and a low-resistant wiring line can be realized.

It was found that when a wiring line was formed by using 40 an alloy of this example, no hillock was produced unlike an Al wiring line. It was also found that no barrier metal was required because no reaction occurred between the alloy and ITO. In addition, since the alloy has a low reflectance of about 40 to 60% as compared with Al, the rate of occurrence 45 of disconnection due to underlying dust and the like and thinning of a pattern in the photolithographic process are reduced, and line defects are reduced, thus increasing the yield. In order to prevent a reduction in yield in the photolithographic process, photolithography may be performed 50 after a low-reflectance film such as an Mo film is stacked on an Al layer. However, with the use of an Mo—W alloy, the yield can be increased without stacking such a film because of low reflectance. Furthermore, the use of this alloy reduces the amount of re-reflected stray light among wiring lines, 55 such as light reflected by the opposing substrates, which is one of the factors that produce a light leakage current in a TFT. Therefore, the contrast of a panel using this alloy in a display operation can be improved by decreasing the pixel signal voltage as compared with a panel using Al wiring 60 lines.

The above manufacturing process is only an example, and the thickness of each layer, the film formation methods, and the like can be modified as needed. Even in such a case, the same effects as those of the embodiment can be obtained. In 65 addition, a TFT having a structure different from that of the above TFT may be used. For example, a TFT having an

10

insulating film as a stopper formed on a channel may be used. Furthermore, a TFT having a capacitor portion which is constituted by the same wiring layer as that of a gate electrode and the same wiring layer as that of a data wiring line may be used.

## (Example 4)

FIG. 11 is a sectional view showing other example of a liquid crystal display device according to the embodiment 1 of the present invention. This liquid crystal display device is an active matrix type liquid crystal display device which has address wiring lines and the like formed by using an Mo—W or Mo—Cr alloy as in the example 1, and also has data wiring lines formed by using an Mo—Ti, W—Ti, or Mo—W alloy as in the example 3. The device uses a TFT having an insulating film as a stopper formed on a channel in place of the TFT used in the above examples, which is a back channel cut type TFT in which a channel portion is etched. In addition, a capacitor portion is formed by using the same wiring layer as that of a gate electrode and the same wiring layer as that of a data wiring line.

As has been described above, a gate electrode 42, an address wiring line, and a Cs line 49a are simultaneously formed on a glass substrate 11 by using the above wiring metal. Thereafter, an insulating interlayer 43, an a-Si active layer 44, a channel protective film 50, and n<sup>+</sup> a-Si layers 45a and 45b are continuously formed. A source electrode 46a, a drain electrode 46b, a data wiring line, and a Cs line 49b are continuously formed on the resultant structure by using the above wiring metal. Subsequently, an oxide film 47 is formed, and a contact hole is formed on the drain electrode 46b. In addition, a pixel electrode 48 is formed. In this example, the effects in both example 1 and example 3 can be obtained at once. A detailed description of the effects will be omitted for the sake of simplicity.

The present invention is not limited to the embodiment 1 described above. The semiconductor used in the present invention is not limited to a-Si, and p-Si and CdSe may be used. In addition, the insulating film on the data wiring line is not limited to an oxide film, and a nitride film may be used.

Furthermore, the alloy film used in each example described above is not limited to a single-layered structure. Instead of using such a film, a multilayered film constituted by two or more layers made of alloys having difference compositions may be used. For example, a stacked film consisting of a film made of a material containing Mo and W, as main components, and nitrogen and a film made of an Mo—W alloy may be used so that Mo and W may prevent surface oxidation. When an Mo—W—N alloy is formed on the Mo—W wiring line, the oxidation resistance can be improved and the Mo—W—N alloy formed under the Mo—W alloy, adhesion can be improved. In addition, a metal layer consisting of Ta, TaN, TaNbN, TaMoN, TaWN, or the like, or a layer made of an alloy of these metals may be formed on the surface of the above alloy film, i.e., formed as an upper layer, to improve the acid resistance. Moreover, an Al film, a Cu film, an Au film or the like may be stacked as a lower layer of the above Mo—W alloy film to decrease the resistance, as shown in FIG. 12.

The present invention is not limited to the above embodiments. Various changes and modifications can be made without departing from the spirit and scope of the invention.

The importance of the structure of the liquid crystal display device according to the present invention will now be described.

In a liquid crystal display device using a TFT, the wiring resistance needs to be lower, as the screen size and screen resolution increase. For example, in a VGA display for a personal computer, the number of wires is  $480\times(640\times3)$ . In an XGA display for a high-grade personal computer, the 5 number of wires is  $760 \times (1024 \times 3)$ . The wiring resistance needs to be low in order to prevent delay of gate pulses. The pulse delay is determined by a product CR of a wiring resistance R and a capacitance C consisting of a TFT capacitance signal wiring line cross part capacitance and 10 others. If the screen size increases, the length of wiring line increases and inevitably the resistance R increases. As a result, CR increases. If the number of pixels increases, the capacitance C (C= $C_0 \times n$ ;  $C_0$ : capacitance of unit pixel, n: number of pixels) increases and accordingly the product CR <sub>15</sub> increases. Since C is determined by the pixels structure which uniquely determines display quality, the resistance R must be decreased in order to prevent the pulse delay.

In an ordinary design method, the VGA of ordinary design having a 10-inch screen or a larger screen needs to have a 20 resistivity of 40  $\mu\Omega$ ·cm or less, and the XGA a resistivity of 20  $\mu\Omega$ ·cm or less. Thus, as a wiring material of the VGA, MoTa alloy or Cr having a resistivity of about  $40 \,\mu\Omega$  cm can be used. However, in the XGA, neither MoTa nor Cr can be used. This being the case, the XGA normally adopts a 25 structure, as shown in FIG. 12, wherein the surface of a low-resistance Al is coated with Ta having good acid-proof properties. The reason why such a complex structure is adopted is that Al has a low resistivity of about  $4 \mu\Omega$  cm or less but has low acid-resistance and therefore it may be 30 eroded by an Al etchant or ITO etchant. Since the structure shown in FIG. 12 is complex, the manufacturing cost increases and the inside Al is eroded, causing a line defect or a point defect. These defects are inevitable, because Ta pinhole by the dust is inevitable, which causes erosion of 35 bare Al wiring line. If Cu or Mo is used instead of Al, similar defects are generated. Moreover, since an Al film and a Ta film are laminated, the total film thickness increases. Consequently, the coverage of the signal wiring lines crossing these films is degraded, or the stop coverage of the signal 40 wiring lines degrade at crossing the points, resulting in wire breakage. This undesirable event can hardly be avoided, and the yield lowers. As described above, in the structure of the example, by using the Mo—W alloy, an XGA-level wiring resistance can be obtained by a single layer.

It was formed that an MoW film on Al film was inferior in quality to an MoW single layer film. Next, the difference between the signal layer or the SiOx MoW film structure and the MoW/Al film structure will now be described. With respect to samples of both film structures, resistance values, 50 sizes of crystal grain structures and interface reaction products were examined. It was found that the resistance of the MoW film in the MoW/Al structure is greater than that of the Mow film in the MoW/SiOx structure by 4 to 10%. In addition, it was found, by observation by means of an 55 FE-SEM, that the Mo—W grain size of the MoW/SiOx film structure is greater. The reason for this appears to be that the resistance value of the film of the Mo—W alloy, which is influenced by the Mo—W grain size, is greatly influenced by the grain size of the material of the underlying layer. This 60 means that the MOW film formed on the Al film had poor crystallinity. With respect to the MoW/Al film structure, when a MOW film was peeled off by immersion in H<sub>2</sub>O<sub>2</sub>, a component such as (MOx, Al<sub>2</sub>(MO<sub>4</sub>)<sub>3</sub>, M: Mo, W) was observed. It was found that MOW and Al reacted at the 65 interface. Since an MoW—Al alloy has a high resistivity, an MOW film is more effective than a film formed of an MOW

layer and an Al layer. As described above, it is understood that the liquid crystal display device having the structure of the present invention, which comprises an MOW film, has excellent advantages.

#### EMBODIMENT 2

FIG. 13 is a sectional view showing a TFT (switching element) and a capacitor portion which are used for one example of a liquid crystal display device according to an embodiment 2 of the present invention. The arrangement and manufacturing process of the TFT and the capacitor portion will be described below. An insulating film 57 such as silicon dioxide is formed on a glass substrate 11 by PECVD, CVD, sputtering or the like. An Mo—W alloy is sputtered to a thickness of 300 nm to simultaneously form a gate electrode (control electrode) 52, an address wiring line, and a Cs line 59. Thereafter, a 350-nm thick oxide film 53, a 300-nm thick active layer consisting of a-Si, and 50-nm thick n<sup>+</sup> a-Si layers 55a and 55b are continuously formed on the resultant structure by plasma CVD. An island-shaped a-Si active layer 54 is formed by patterning the resultant structure. A pixel electrode 58 is then formed by sputtering ITO to a thickness of 120 nm. SiO<sub>x</sub> of a contact portion is etched by using diluted HF to form a contact hole. A source electrode (first main electrode) 56a, a drain electrode (second main electrode) 56b, and a data wiring line are simultaneously formed by sputtering a predetermined metal such as Al and performing wet etching.

An address wiring line formed by using an Mo—W alloy is processed by CDE (Chemical Dry Etching) using a gas mixture of  $CF_4$  and  $O_2$ . Tapering of the address wiring line is facilitated by interposing a silicon dioxide film between the glass substrate 51 and the address wiring line. However, if an Mo—W film directly on glass substrate, taper etching of Mo—W was difficult especially for the case of larger microwave power of CDE. FIG. 14 shows a cross-section of a tapered portion. As is apparent from FIG. 14, the step coverage of an insulating interlayer formed on the address wiring line is improved, and a high breakdown voltage can be ensured, thereby preventing a short circuit between each address wiring line and each data wiring line and also preventing disconnection of each data wiring line. Therefore, a reliable liquid crystal display device having a large display area can be realized. Note that even if this address wiring line is not applied to a large-area display, there is still a merit. That is, as the resistivity of an address wiring line decreases, the width of the wiring line can be reduced to increase the aperture ratio.

Table 1 shows comparison between XPS analysis results respectively obtained in a case wherein a silicon dioxide film is interposed between a glass substrate and an Mo—W alloy film after CDE etching and in a case wherein an Mo—W alloy film is directly formed on a glass substrate after CDE etching.

As is apparent from Table 1, when an Mo—W alloy is directly formed on a glass substrate, Ba is present in a glass component. From this result, it can be considered that the etching of resist is impaired by a product of reaction between a component in a glass used as a substrate and W or Mo, and that taper etching is subsequently restricted. By interposing a silicon dioxide film between a glass substrate and a metal, a good tapered portion can be formed without causing this reaction. It is confirmed that a good tapered portion can be formed when the W composition ratio of an Mo—W alloy composition falls within the range of 20 to 90 atm %.

Of the elements in a glass substrate, Ba is not only the element that causes such a reaction. For example, Ca and Sr

have similar adverse effects. In addition to silicon dioxide film, other materials such as silicon nitride film can be used as a material for an insulating film interposed between the glass substrate and the Mo—W alloy film as long as they contain no Ba, Sr, and Ca. Ta<sub>2</sub>O<sub>5</sub>, Al<sub>2</sub>O<sub>3</sub> film, and the like 5 can also be used.

**13**

TABLE 1

|                               | С    | N   | О    | F    | Ba  | Si   | Mo  | W   |

|-------------------------------|------|-----|------|------|-----|------|-----|-----|

| ON A GLASS<br>SUBSTRATE       | 29.3 | 9.2 | 20.9 | 29.6 | 5.4 |      | 2.0 | 3.7 |

| ON A SiO <sub>2</sub><br>FILM | 19.0 |     | 50.4 | 2.0  |     | 28.6 |     |     |

The above manufacturing process is only an example, and the thickness of each layer, the film formation methods, and the like can be modified as needed. Even in such a case, the same effects as those of the example 3 can be obtained. In addition, a TFT having a structure different from that of the above-described TFT may be used. For example, a TFT having an insulating film as a stopper formed on a channel may be used. Furthermore, a TFT having a capacitor portion which is constituted by the same wiring layer as that of a gate electrode and the same wiring layer as that of a data wiring line may be used.

Embodiment 2 of the present invention is not limited to above example.

In addition, the semiconductor material used in the present invention is not limited to a-Si, and p-Si and CdSe may be used. Various changes and modifications can be made without departing from the spirit and scope of the invention.

Since ITO is used for a TFT liquid crystal display device, several problems are posed in contacts between wiring lines and ITO. When a wiring line is brought into contact with ITO, the wiring metal is oxidized by ITO to form a barrier oxide having a high resistance, resulting in a contact failure. This poses a serious problem especially in a case wherein an Al alloy or Ta alloy which produces an oxide film having a high resistance is used. For this reason, a barrier metal is required to prevent a reaction between ITO and an Al alloy or Ta alloy, increasing the number of steps. In addition, when an oxide film is formed on the surface of a wiring line, the contact resistance between the wiring line and a metal wiring line as an upper layer increases. For this reason, the step of removing the oxide film is required, increasing the number of steps.

Another problem is that when reactions occur in contact portions between signal wiring lines and a-Si active layer and p-Si layer, the wiring metals are dispersed in the a-Si and p-Si layers to degrade the junction characteristics of n-i or p-i in the contact portions, resulting in a degradation in blocking effect with respect to carriers. This degradation is conspicuous when Al is used as a source/drain metal which is an acceptor impurity. In order to prevent this, a barrier metal is required, resulting in an increase in the number of 55 steps.

This embodiment provides a liquid crystal display device which exhibits the same effects of as the above embodiments, by virtue of the use of MoW, which requires no barrier metals between a signal wiring line metal and ITO and between a signal wiring line metal and n<sup>+</sup> a-Si, and which has signal wiring lines resistant to etching solutions for ITO and the like.

# (Example 5)

FIG. 15 is a sectional view showing a TFT (switching element) and a capacitor portion which are used for one

14

example of a liquid crystal display device according to an embodiment 3 of the present invention. FIG. 15 also shows a driving circuit and a section of a contact portion. The arrangement and manufacturing process of the TFT and the capacitor portion will be described below. A gate electrode (control electrode) 62, an address wiring line, a Cs line 69, and contact pad portion 80 are simultaneously formed on a glass substrate 61 by sputtering an Mo—W alloy to a thickness of 300 nm and performing CDE. Thereafter, a 10 350-nm thick oxide film 63 is formed by plasma CVD or atmospheric pressure CVD, and a 50-nm thick SiN, film 63 a 50-nm thick active layer consisting of a-Si, and a 300-nm thick stopper SiNx film 70 are successively formed by plasma CVD. After the stopper  $SiN_x$  film 70 is etched by using diluted HF, 50-nm thick n<sup>+</sup> a-Si layers 65a and 65b are formed, and an island-shaped a-Si active layer 64 is formed by CDE. An SiO<sub>x</sub> film of the contact portion is etched to form a contact hole. Subsequently, an ITO 66 and an Mo—W or Mo—Cr alloy 67 are sputtered to thicknesses of 100 nm and 300 nm, respectively, and the Mo—W alloy is etched and tapered by wet etching or dry etching using a gas mixture of  $CF_4$  and  $O_2$ . Thereafter, the ITO is etched by using a diluted aqua regia etchant, thereby forming a pixel electrode 68, a signal wiring line, a source electrode (first 25 main electrode) 66a, 67b, a drain electrode (second main electrode) 66b, 67b, a data wiring line, and a contact electrode 81. An SiN, passivation film 71 is formed on the resultant structure by plasma CVD. The SiN<sub>x</sub> and the Mo—W alloy on the pixel and pad portions are etched by RIE or CDE. By forming the signal wiring line and the pixel electrode 68 using the same pattern in this manner, the number of photoetching processes can be decreased by one. In addition, the embodiment 3 of the present invention can be formed by using an Mo—Cr alloy in the same manner as described above.

In the Embodiment 3, an Mo—W/ITO multilayered wiring line is used as a signal wiring line, a gate wiring line is brought into contact with ITO in a contact pad portion. When the Mo—W or Mo—Cr alloy is used, since an oxide film formed on the alloy surface has a low resistance in contrast to a Ta alloy, At, or Cr, an increase in contact resistance poses no problem. Although an oxide film was formed on a gate wiring line, since an oxide film formed on an Mo—W or Mo—Cr alloy had a low resistance, good contact characteristics were obtained without removing the oxide film. The increase in wiring resistance including the contact resistance was 1% or less, posing no problems. In addition, the Id-vd characteristic of the TFT characteristics exhibited good rise characteristics, thus obtaining good 50 Ohmic characteristics. Hence, it was found that a good contact was ensured between each Mo—W wiring line and n<sup>+</sup> a-Si. By using batch type sputter adhesion of H<sub>2</sub>O, O<sub>2</sub>, N<sub>2</sub> on the chamber surface and incorporation of O, N in the sputtered MoW film is inevitable.

The present inventors checked the resistivities of Mo—W alloys. FIG. 16 shows the result. These alloys were formed by using a batch type sputtering apparatus. A load lock type sputtering apparatus with a low back pressure has negligible such O<sub>2</sub> or N<sub>2</sub> impurity. As is apparent from FIG. 16, in the case of the batch type sputtering apparatus, it was found that the resistivity of an Mo—W alloy became much lower than 40 μΩ·cm, and the resistance of the alloy was below that of Mo or W as a signal element when the W content of the Mo—W alloy fell in the range of 10 to 95 atm %, and more preferably in the range of 20 to 90 atm %. In this range, even an Mo—W alloy produced by the batch type sputtering apparatus has a resistivity similar to that of an Mo—W alloy

produced by the load lock type sputtering apparatus. That is, in this range, an inexpensive batch type sputtering apparatus can be used, and Mo—W alloys can be manufactured in a short tact time because sputtering can be performed at a low degree of vacuum.

According to example 5, since pixel and signal wiring lines are formed by using the same mask, no alignment margin is required. Hence, the opening ratio can be increased.

The above manufacturing process is only an example, and the thickness of each layer, the film formation methods, and the like can be modified as needed. Even in such a case, the same effects as those of the Embodiment 3 can be obtained. In addition, a TFT having a structure different from that of the above-described TFT may be used. For example, a back channel type TFT or the like may be used, which is formed by etching an n<sup>+</sup> a-Si layer by using a signal line as a mask without forming an insulating film as a stopper on a channel. Furthermore, a TFT having a capacitor portion which is constituted by the same wiring layer as that of a gate electrode and the same wiring layer as that of a data wiring line may be used.

#### (Example 6)

In the Embodiment 3, the same effects as those described above can be obtained by using a structure having an a-Si active layer formed on a signal wiring line. Similar to example 5, after a gate electrode is formed by using an Mo—W alloy, a 350-nm thick  $SiO_x$  film and a 50-nm thick  $_{30}$ SiN<sub>x</sub> film are formed by plasma CVD, and a contact hole is formed by using diluted HF. An ITO layer and an Mo—W alloy are formed by sputtering. Subsequently, a 50-nm thick n<sup>+</sup> a-Si layer is formed by plasma CVD. The n<sup>+</sup> a-Si layer and the ITO layer are etched by CDE, and the ITO layer is 35 etched by a diluted aqua regia, thereby forming a signal wiring line, a source electrode (a first main electrode), a drain electrode (a second main electrode), and a pixel electrode. The Mo—W alloy film may be formed by thermal CVD. The n<sup>+</sup> a-Si layer may be selectively formed on the 40 Mo—W/ITO layer by using an intermittent plasma constituted by SiH<sub>4</sub>/PH<sub>3</sub> mixture and H<sub>2</sub> gas. After an a-Si layer and a passivation SiN<sub>x</sub> film are formed on the resultant structure by plasma CVD, the a-Si/n<sup>+</sup> a-Si/Mo—W of the pixel portion are etched by RIE, thus completing a TFT 45 array. In this case, in the contact portion, a gate wiring line was brought into contact with the ITO, and a signal wiring metal was brought into contact with the ITO. However, no problem was posed in terms of Ohmic characteristics.

#### (Example 7)

FIG. 17 is a sectional view showing a TFT and a capacitor portion which are used for other example of a liquid crystal display device according to Embodiment 3 of the present invention. The arrangement and manufacturing process of 55 fied. this TFT and capacitor portion will be described below. A 100-nm thick p-Si layer 84 and a 100-nm thick gate oxide film 83 are formed on a glass substrate 81. A gate electrode 82 consisting of an Mo—Ta alloy or an Mo—W alloy is formed on the resultant structure. Subsequently, P ions are 60 doped into  $1\times10^{16}$  cm<sup>-3</sup> by using the gate electrode 82 as a mask to form an n<sup>+</sup> p-Si layer 85a, 85b in a source/drain portion. After an island-shaped a-Si active layer is formed, an insulating interlayer 89 is deposited on the resultant structure to a thickness of 300 nm by thermal CVD. ITO is 65 sputtered to a thickness of 100 nm to form a pixel electrode 88. Insulating interlayer 89 of the contact portion and the

gate portion are etched by using diluted HF to form a contact hole. Thereafter, an Mo—W alloy is sputtered to a thickness of 300 nm to form a source electrode (a first main electrode), a drain electrode (a second main electrode) 86b, and a signal wiring line. After a passivation film 87 consisting of SiN<sub>x</sub> is formed by plasma CVD, a pixel portion and a peripheral circuit connecting portion are etched by RIE, thereby completing a TFT array. In a conventional device, since an Al is used as a metal of a signal wiring line, a metal having a high melting point as a barrier metal is required between an ITO layer and an n<sup>+</sup> p-Si layer. In this embodiment, however, since a signal wiring line was made of an Mo—W alloy, no barrier metal was required, thus decreasing the number of steps. The same effects as those described above were obtained when an Mo—Cr alloy was used.

16

The above manufacturing process is only an example, and the thickness of each layer, the film formation methods, and the like can be modified as needed. Even in such a case, the same effects as those of the embodiment can be obtained. In addition, a TFT having a structure different from that of the above TFT may be used. For example, a TFT having an insulating film as a stopper formed on a channel may be used. Furthermore, a TFT having a capacitor portion which is constituted by the same wiring layer as that of a gate electrode and the same wiring layer as that of a data wiring line may be used.

Embodiment 3 is not limited to the embodiments described above. The semiconductor used in the present invention is not limited to a-Si, and p-Si and CdSe may be used. In addition, the insulating film on the data wiring line is not limited to an oxide film, and a nitride film may be used.

Furthermore, the alloy film used in Embodiment 3 described above is not limited to a single-layered structure. Instead of using such a film, a multilayered film constituted by two or more layers made of alloys having difference compositions may be used. In addition, a metal layer consisting of Ta, TaN, or the like may be formed on the surface of the above alloy film, i.e., formed as an upper layer, to improve the acid resistance. Moreover, an Al film, a Cu film, or the like may be stacked as a lower layer of the above alloy film to decrease the resistance. Embodiment 3 is not limited to the above-described examples. Various changes and modifications can be made without departing from the spirit and scope of the invention.

According to Embodiment 3, since an address or gate wiring line formed by using an Mo—W or Mo—Cr alloy having a low resistivity does not produce a barrier having a high resistance even if it is oxidized upon contact with an ITO layer, no barrier metal is required, thus simplifying the manufacturing process. In addition, since such a wiring line does not react with n<sup>+</sup> a-Si or p-Si, no barrier metal is required. Hence, the manufacturing process can be simplified.

#### EMBODIMENT 4

In a liquid crystal display device, a black matrix is formed on an opposed substrate for image display. The black matrix shields external light incident on an TFT and prevents leakage current increases of the TFT due to the external light. In general, Cr, etc., which are impermeable to light are used as materials of the black matrix. These materials, however, have rather high light reflectance, and external light is reflected by the image display surface. The external light degrades the display quality of the image display screen considerably. The present embodiment aims at pro-

viding a high-quality liquid crystal display device wherein gate pulses are free from delay, the address wiring has a high insulation breakdown voltage, and reflection of external light on the image display screen is reduced by the black matrix.

FIG. 18 shows a sectional view of a liquid crystal display device according to Embodiment 4 of the present invention. Reference numeral 90 denotes a glass substrate. A gate electrode 91a is formed on the glass substrate 90, and the gate electrode 91a extends from address wiring line formed on the substrate 90. A semiconductor layer 94 and a stopper layer 95 are formed and patterned on the gate electrode 91a through an insulating film 97. A drain electrode 93a and a source electrode 93b are formed on the resultant structure. Thus, a TFT is constructed. The source electrode 93b of the TFT is connected to a pixel electrode 96. Thus, a liquid crystal driving circuit board is constituted.

An opposed substrate is formed such that a color filter 99 and a black matrix 100 made of a Mo—W alloy are formed on a glass substrate 98 and an opposed electrode 101 is formed on the resultant structure. The liquid crystal driving circuit and the opposed substrate are arranged to face each other, as shown in FIG. 18, and a liquid crystal material 102 is put between the liquid crystal driving circuit and the opposed substrate. Thus, the liquid crystal display device is constructed.

FIG. 19 is a graph showing a measured result of reflectance of an Mo—W alloy and Cr. As seen from FIG. 19, the reflectance of the Mo—W alloy is lower than that of Cr used as conventional black matrix material throughout all compositions.

In the above liquid crystal display device, since the black matrix formed on the opposed substrate is made of the Mo—W alloy with low reflectance, reflection of external light by the image display surface can be reduced and thereby the display quality can be enhanced. The Mo—W alloy material has substantially the same effect for shielding light incident on the TFT as Cr.

FIG. 20 is a plan view of the driving circuit board of the liquid crystal display device according to Embodiment 4 of 40 the invention. Address wiring lines 91 and data wiring lines 92 crossing the address wiring lines 91 are formed on the glass substrate 90. The address wiring lines 91 have at one end address electrode pads 103 made of the Mo—W alloy. The data wiring lines 92 have at the other end data electrode 45 pads 106 made of the Mo—W alloy. Insulating layers are formed between the address wiring lines 91 and data wiring lines 92 at the intersections thereof. TFTs 107 functioning as switching elements are formed near the intersections. A pixel electrode **96** formed on a pixel region surrounded by 50 the address wiring lines 91 and data wiring lines 92 is connected to one electrode of each of the TFTs 107. The region of the address electrode pad 103 is large enough to include an address electrode 105 and a contact hole 104.

In the liquid crystal display device having the above 55 structure, since the address electrode pads 103 and data electrode pads 106 are formed of the Mo—W alloy, the bonding force acting between these electrode pads and image signal ICs increases and high reliability, and good ohmic contact is obtained, for example, at the time of COG 60 (Chip On Glass) mounting.

Needless to say, the effect achieved by the black matrix 100 formed on the opposed substrate can be obtained by black matrix 108 formed on the liquid crystal driving circuit substrate. In addition, since the reflectance of the Mo—W 65 alloy is low, the Mo—W alloy may be used as material of data wiring line.

18

As has been described above, according to the liquid crystal display device of the present embodiment, the Mo—W alloy is used as black matrix material and thereby the reflection of external light by the image display screen can be reduced and a high display quality can be obtained. Moreover, the reliability of bonding between the ICs and the address and data electrode pads, for example, at the time of COG mounting, can be increased by forming these pads of the Mo—W alloy.

#### EMBODIMENT 5

According to Embodiment 5, there is provided an electrode wiring material containing at least one component selected from the group of Mo and W as a main component, and further containing Ar of 0.0003 atomic % to 5 atomic %. Further, there is provided an electrode wiring material containing W as a main component, or at least one selected from the group of W, Mo and Cr as a main component, and further containing Ar of 0.0003 atomic % to 5 atomic %.

Furthermore, according to Embodiment 5, there is provided an electrode wiring board manufactured by forming an electrode wiring portion on a glass substrate, in which the electrode wiring portion is made of at least one metal selected from Mo and W, and the variation of the lattice constant of a material in the electrode wiring portion, with respect to the lattice constant of the material in a bulk state, is set within ±3%. Further, there is provided an electrode wiring board manufactured by forming an electrode wiring portion on a glass substrate, in which the electrode wiring portion is made of W or at least one metal selected from W, Mo and Cr, and the variation of the lattice constant of a material in the electrode wiring portion, with respect to the lattice constant of the material in a bulk state, is set within ±3%. It should be noted that the significance of that the lattice constants are substantially equal to each other, is the variation of the lattice constant of a material, with respect to the lattice constant of the material in a bulk state is within  $\pm 3\%$ , preferably  $\pm 1\%$ .

First, in the electrode wiring material, the content of Ar with respect to the main component metal is set to 0.0003 atomic % to 5 atomic %. If the content of Ar is less than the lower limit, it is industrially very difficult to form a film, whereas if the content exceeds the upper limit, the resistivity of a film obtained is significantly raised. More preferably, the content of Ar is 0.001 atomic % to 1 atomic %. Most preferably, the content of Ar is 0.2 atomic % to 1 atomic % by considering the peel off rate and the apparatus dependence.

With regard to the electrode wiring board, it is preferable that the electrode wiring portion is formed by a spattering method. Thus, a film having a high adhesion can be formed on a substrate having a large area.

In Embodiment 5, it is preferable that Ti is added to the main component. With this constitution, the adhesion and the resistance to acid are improved at the same time. In embodiment 5, if the main component metal is at least one type selected from Mo and W, the content of W or Mo is in a range of 10 atomic % and 95 atomic %. This results because if the content of W or Mo is in a range of 10 atomic % and 95 atomic %, the margin of the sputtering conditions for achieving a film having a low resistivity is widened.

An example of the electrode wiring board is a substrate on which a liquid crystal display device or a semiconductor device is formed. The electrode wiring material is not made of, for example, W, Mo or the like, which is the conventional electrode wiring material, but also contains Ar at a prede-

termined content in the material. With this structure, the resistivity can be sufficiently reduced, or an excellent corrosion-resistance property as compared to that of Ar, or the like, can be maintained.

With use of such an electrode wiring material, the electrode wiring portion can be formed by making a film by sputtering in a gas atmosphere of, for example, Ar. In this case, it is necessary to adjust the conditions for making films, such as the power and the pressure of the sputtering device.

In the case where an electrode wiring portion is formed by use of the above-described electrode wiring material, Mo and W may be mainly used as a single phase, or the film may be formed along with an alloy of these metals or a metal having a high melting point, such as Cr. By making an alloy as above, the resistance of the electrode wiring portion can be reduced.

Next, Embodiment 5 will now be described in detail on the basis of the results of experiments conducted by the inventors.

First, the relationship between the amount of Ar in the electrode film formed by use of the electrode wiring material according to the present invention will now be described.

With use of a single-sheet load-lock type sputtering apparatus, the temperature of a substrate before the formation of a film was set to 200° C., the film-forming power was set to 10 kW, and the distance between electrodes was set to 5 cm. Then, in an atmosphere of Ar gas of a pressure of 0.9 Pa, MoW containing 65 atomic % of Mo was deposited on a glass substrate, thus forming an MoW alloy film having a thickness of 300 nm (Sample 1). The Ar content in the film of Sample 1 was measured using a fluorescent X-ray apparatus, RIX-1000 (product of RIGAKU DENKI KOGYO), to be 0.3 atomic %. Further, the resistivity of Sample 1 was measured to be 17  $\mu\Omega$ ·cm.

With use of a sputtering apparatus of a type having a great number of diagonal injection components, the temperature of a substrate before the formation of a film was set to  $300^{\circ}$  C., the film-forming power was set to 1 kW, and the distance between electrodes was set to 10 cm. Then, in an atmosphere of Ar gas of a pressure of 0.5 Pa, MoW containing 65 atomic % of Mo was deposited on a glass substrate, thus forming an MoW alloy film having a thickness of 300 nm (Sample 2). The Ar content in the film of Sample 2 was measured to be about 20 atomic %. Further, the resistivity of Sample 2 was measured to be  $50 \ \mu\Omega$ ·cm.

With use of a single-sheet load-lock type sputtering apparatus, the temperature of a substrate before the formation of a film was set to 200° C., the film-forming power was set to 10 kW, and the distance between electrodes was set to 5 cm. Then, in an atmosphere of Ar gas of a pressure of 0.9 Pa, MoW containing 30 atomic % of Mo was deposited on a glass substrate, thus forming an MoW alloy film having a thickness of 300 nm (Sample 3). The Ar content in the film of Sample 3 was measured to be 3 atomic %. Further, the resistivity of Sample 3 was measured to be 25  $\mu\Omega$ 19 cm.

It has been confirmed from the results of the intensive studies of the inventors that the resistivity is drastically increased when the Ar content in the film exceeds 5 atomic 60 %. Further, when the Mo or W content of the film falls outside a range of 10 atomic % to 95 atomic %, the resistivity is increased in a similar manner as above.

As described above, in the case where the resistivity is taken into consideration, it has been confirmed that the 65 amount of addition of Ar to the material should preferably be 5 atomic % or less. However, when the amount of addition

20

of Ar is less than 0.0003 atomic %, the film-forming power used at the formation of a film should be reduced, and the sputtering rate should be decreased to a sufficient level. Further, after the formation of the film, the film constituting materials must be recrystallized. Therefore, in the case where the amount of addition of Ar is less than 0.0003 atomic %, such a structure is not at all industrially suitable.

Furthermore, the inventors of the present invention have used a single-sheet load-lock type sputtering apparatus, forming MoW alloy films having a thickness of 300 nm by depositing MoW containing 65 atomic % of Mo, on a glass substrate, in variable film-formation conditions, thus obtaining MoW alloys having different Ar contents in the films. Thus, the MoW alloy film containing a large amount of Ar can be obtained by increasing the film-forming power, or by decreasing the film-forming pressure.

FIG. 21 is a characteristical diagram illustrating the relationship between each of the stress, the resistivity and the film peel off rate, and the Ar content in the film. It can be understood from FIG. 21 that the stress and the resistivity exhibit excellent characteristics when the Ar content is in a range of 0.0003 atomic % to 5 atomic %. Meanwhile, as can be seen in FIG. 21, the film peel off rate exhibits an increasing tendency in a region where the Ar content is less than 0.4 atomic %. Consequently, in a usage where the adhesion of film is particularly important, the Ar content is preferably set in a range of 0.4 atomic % to 5 atomic %.

In consideration of the above-described circumstances, the Ar content of the electrode wiring material of the present invention is set in a range of 0.0003 atomic % to 5 atomic %. The elements to be added may be mixed into the metal of the main component of the electrode wiring material singly or in combination.

In the case where the elements are mixed into the material in combination, the characteristics of the film are substantially an addition of changes in characteristics affected by the addition of the individual elements.

Next, the film-forming gas dependency and the constitution dependency of the resistivity will now be described with reference to FIG. 22. FIG. 22 is a characteristical diagram illustrating the relationship between the resistivity and the Mo content. The samples were obtained under the following conditions. That is, with use of a small-size single-sheet load-lock type sputtering apparatus, the temperature of a substrate before the formation of a film was set to 150° C., the film formation power was set to 2 kW, and the distance between electrodes was set to 5.5 cm. Then, in an atmosphere of Ar gas of a pressure of 0.9 Pa, films having a thickness of 300 nm were deposited on glass substrates. The Ar contents of the sample films were within a range set by the present invention.

As can be seen from FIG. 22, the larger the content of Mo, the more the resistivity can be lowered. In the case of the formation of a film in an Ar atmosphere, the resistivity can be decreased more when the film is made of a single phase of Mo.

FIG. 23 is a characteristical diagram showing the relationship between the lattice constant measured by X-rays and the Mo content. As can be seen in FIG. 23, by forming a film in an Ar atmosphere, the lattice constant becomes closer to that of the bulk state, achieving a high crystalizability. Thus, the resistivity can be reduced. In practice, those films exhibited low resistivities when the ratio to the lattice constant of the bulk state is within 1.03 times, preferably 1.01 times.

Next, the dependency of the characteristics of the film upon the film-forming conditions will now be described with