US005633831A

# United States Patent [19]

## Tsukude et al.

Appl. No.: 607,497

Filed:

[56]

# [11] Patent Number:

5,633,831

[45] Date of Patent:

May 27, 1997

| [54] |            | NDUCTOR MEMORY DEVICE                              | 4,901,283 | 2/1990  | Hanbury et al 365/222 |

|------|------------|----------------------------------------------------|-----------|---------|-----------------------|

|      | HAVING     | SELF-REFRESHING FUNCTION                           | 5,249,155 | 9/1993  | Arimoto et al         |

|      |            |                                                    | 5,295,110 | 3/1994  | Sakakibara 365/222    |

| [75] | Inventors: | Masaki Tsukude; Kazutami Arimoto,                  | 5,337,282 | 8/1994  | Koike 365/222         |

|      |            | both of Hyogo, Japan                               | 5,469,559 | 11/1995 | Parks et al 365/222   |

|      |            |                                                    | 5,475,646 | 12/1995 | Ogihara 365/222       |

| [73] | Assignee:  | Mitsubishi Denki Kabushiki Kaisha,<br>Tokyo, Japan | 5,488,587 | 1/1996  | Fukumoto 365/222      |

#### FOREIGN PATENT DOCUMENTS

61-57097 3/1986 Japan . 5-198165 8/1993 Japan .

## Related U.S. Application Data

Feb. 27, 1996

[62] Division of Ser. No. 382,557, Feb. 2, 1995, Pat. No. 5,568, 440.

| [30] | Fore                  | eign A       | pplica | tion Prior         | ity Data   |           |

|------|-----------------------|--------------|--------|--------------------|------------|-----------|

|      | . 3, 1994<br>15, 1994 | [JP]<br>[JP] | ***    |                    |            |           |

|      |                       |              |        | <b>365/222</b> ; 3 | 65/226; 36 |           |

| [58] |                       |              |        | 07, 233.5,         | 365/       | 222, 226, |

|      |                       |              | _      |                    |            |           |

### **References Cited**

#### U.S. PATENT DOCUMENTS

Primary Examiner—Tan T. Nguyen

Attorney, Agent, or Firm—Lowe, Price, LeBlanc & Becker

#### [57] ABSTRACT

A timing generating circuit generates a signal SRE defining a period in which a self-refreshing operation is carried out based on a signal extRAS and a signal extCAS. An internal voltage down-converting circuit controls the level of an internal power supply voltage intVcc to be generated in the period defined by the signal SRE lower in the self-refreshing operation than in a normal operation. As a result, a semi-conductor memory device is obtained which reduces current consumption in the self-refreshing operation by simple control in an internal circuit.

### 18 Claims, 27 Drawing Sheets

5,633,831

FIG.2

FIG.3

F/G.4

FIG.5

5,633,831

FIG. 10

FIG. 12

FIG. 13

FIG. 15

|         | (PERIPHERAL · ARRAY)                       | (PERIPHERAL)                  | (ARRAY)               |

|---------|--------------------------------------------|-------------------------------|-----------------------|

|         | ext.Vcc 3.3V                               | ext.Vcc 3.3V                  | ext. Vcc<br>3.34      |

| F/G. 16 | intVcc,a                                   | intVccp<br>Vrefp 2.5V         | intVcca 1.5V<br>Vrefa |

|         | extGND———————————————————————————————————— | extGND  (IN SELF-RE OPERATION |                       |

|         | (ARRAY · PERIPHERAL)  extVcc  2.3V         | (PERIPHERAL)  extVcc  3.3V     | (ARRAY)  extVcc  3.57 |  |

|---------|--------------------------------------------|--------------------------------|-----------------------|--|

| FIG. 17 | intVccp,a<br>Vrefp,a<br>2.5V               | intVccp<br>Vrefp 2.5V          | intVcca<br>Vrefa 2.5V |  |

|         | extGND———————————————————————————————————— | (IN SELF-REFRESHING OPERATION) |                       |  |

FIG. 18

FIG. 19

F/G.20

FIG.21

FIG.23

FIG.25

F1G.2

-1G.28

5,633,831

3050 3062 PSEUDC GENERA CIRCUII INTERNAL DOWN-CO CIRCUIT ext CAS O ext RAS (

## SEMICONDUCTOR MEMORY DEVICE HAVING SELF-REFRESHING FUNCTION

This application is a division of application Ser. No. 08/382,557 filed Feb. 2, 1995 now U.S. Pat. No. 5,568,440.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention generally relates to semiconductor memory devices, and more particularly, to a DRAM 10 (Dynamic Random Access Memory) carrying out a selfrefreshing operation.

#### 2. Description of the Background Art

In the DRAM serving as a semiconductor memory device, a memory cell is self-refreshed. In one method of self- 15 refreshing, a memory cell is refreshed in a refresh cycle generated by an internal circuit of a chip on which the DRAM is formed.

In the self-refreshing operation, a memory cell can be refreshed without an externally applied refresh cycle. More specifically, a relatively long refresh cycle is generated in an internal circuit of a chip, and the refreshing operation is carried out by the internal circuit of the chip in the generated refresh cycle.

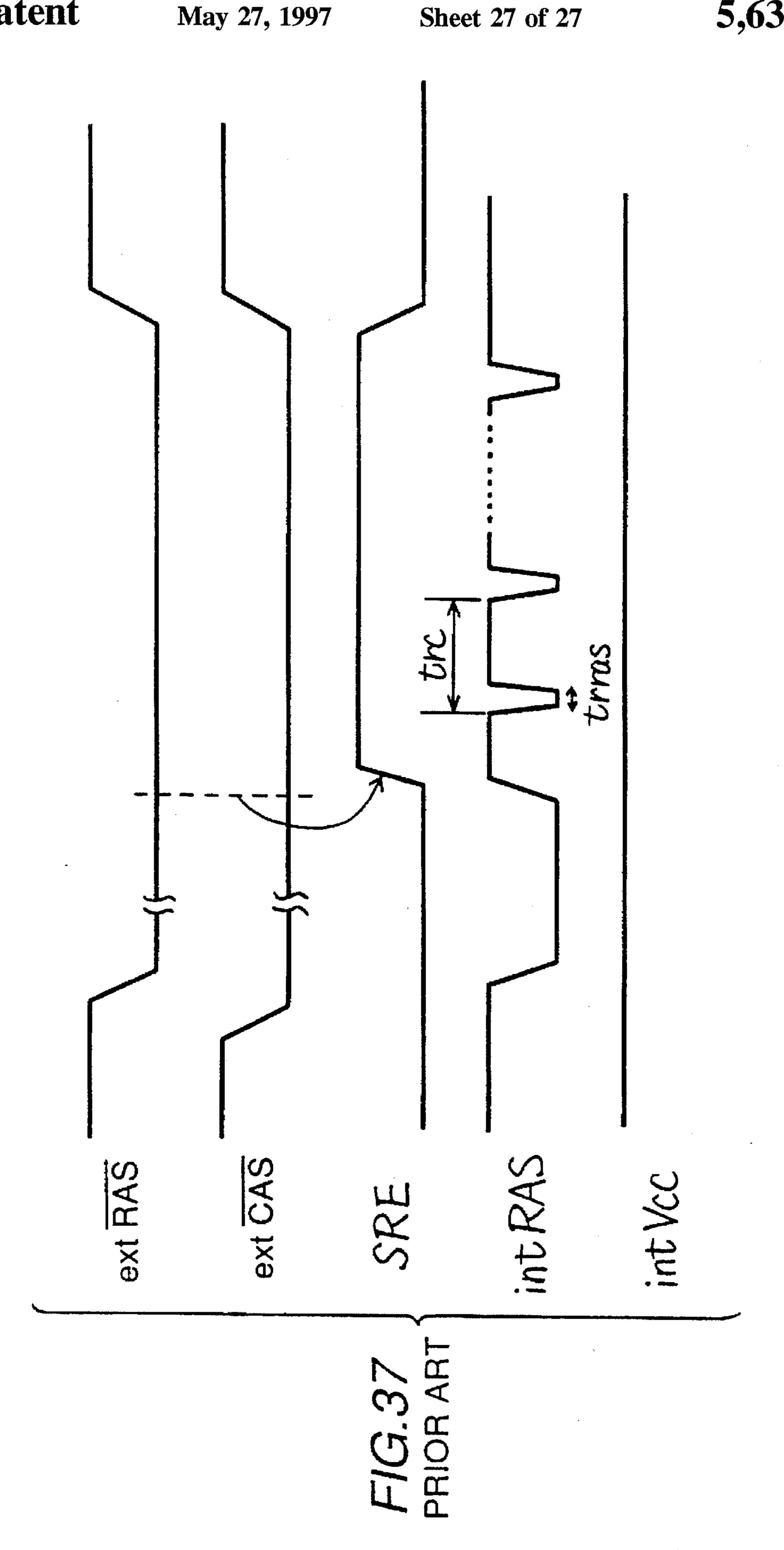

Description will now be given of a conventional selfrefreshing operation. FIG. 37 is a timing chart showing one example of timings of the conventional self-refreshing operation.

Referring to FIG. 37, after an external column address strobe signal extCAS falls to an L or logical low level, an external row address strobe signal extRAS falls to the L level. When these signals both hold the L level for a predetermined period after that timing, that is, a CAS Before RAS timing (hereinafter referred to as a "CBR timing"), a self-refresh enable signal SRE defining a self-refreshing period rises to an H or logical high level.

In response to the signal SRE attaining the H level, an internal row address strobe signal intRAS generates a relatively long refresh cycle tre within a chip. In response to the signal intRAS, the refreshing operation is carried out. Also during the self-refreshing operation, an internal power supply voltage intVcc is held constant.

A problem associated with such a self-refreshing operation is how to make a refresh cycle longer, and how to reduce 45 current consumption both in a stand-by period and an active period in the self-refreshing operation.

However, in a 16 MDRAM and other devices developed thereafter, scale down of a power supply voltage has not caught up with progress of miniaturization. Therefore, in 50 order to implement high integration density while securing reliability of the device, an internal voltage down-converting circuit has been provided in the chip. The internal voltage down-converting circuit generates a low internal power supply voltage obtained by down-converting an external 55 power supply voltage.

In order to implement high speed access in a device operating based on the internal power supply voltage lower than the external power supply voltage, a word line boosted voltage generating circuit has also been provided in the chip. 60

As described above, the internal voltage down-converting circuit and the boosted voltage generating circuit were provided in the chip in the DRAM. Therefore, these circuits increased current consumption in a stand-by period or the like in the self-refreshing operation.

One method of reducing an active current in the selfrefreshing operation is to decrease the external power supply

voltage in the self-refreshing operation. In this method, however, it is necessary to control the power supply voltage out of the chip. Therefore, it was difficult to control increase and decrease of the power supply voltage on a memory board.

#### SUMMARY OF THE INVENTION

One object of the present invention is to provide a semiconductor memory device which can reduce current consumption at the time of self-refreshing by control in an internal circuit.

Another object of the present invention is to reduce current consumption in an internal voltage down-converting circuit.

Still another object of the present invention is to reduce current consumption in a boosted voltage generating circuit.

A further object of the present invention is to implement initialization of a refresh ability without requiring complicated external control in transition from a normal operation to a self-refreshing operation, and in transition from the self-refreshing operation to the normal operation.

According to one aspect of the present invention, a semiconductor memory device which carries out a normal operation and a self-refreshing operation based on a potential swing having a swing width defined by an internal power supply potential difference includes a self-refresh period defining circuit and an internal power supply potential difference generating circuit. The self-refresh period defining circuit generates a self-refresh period definition signal defining a period in which the self-refreshing operation is carried out.

The internal power supply potential generating circuit generates, in response to the self-refresh period definition signal, an internal power supply potential difference so that a potential swing width in the period defined by the signal is smaller than that in the normal operation.

Therefore, the internal power supply potential difference generated by the internal power supply potential difference generating circuit defines the potential swing width so that the potential swing width is smaller in the self-refreshing operation than in the normal operation. Therefore, current consumption in the self-refreshing operation can be reduced by simple control in an internal circuit.

A semiconductor memory device according to another aspect of the present invention which carries out a normal operation and a self-refreshing operation based on a voltage swing having a swing width defined by an internal power supply voltage includes a self-refresh period defining circuit and an internal power supply voltage generating circuit.

The self-refresh period defining circuit generates a selfrefresh period definition signal defining a period in which the self-refreshing operation is carried out.

The internal power supply voltage generating circuit generates, in response to the self-refresh period definition signal, the internal power supply voltage so that it is lower in the period defined by the signal than in the normal operation.

Therefore, the internal power supply voltage generated by the internal power supply voltage generating circuit is made lower in the self-refreshing operation than in the normal operation. Therefore, current consumption in the selfrefreshing operation can be reduced by simple control in an 65 internal circuit.

A semiconductor memory device according to still another aspect of the present invention which carries out a

3

normal operation and a self-refreshing operation based on a voltage swing having a swing width defined by an internal power supply potential difference includes a self-refresh period defining circuit and an internal power supply voltage generating circuit.

The self-refresh period defining circuit generates a self-refresh period definition signal defining a period in which the self-refreshing operation is carried out.

The internal power supply voltage generating circuit generates the internal power supply potential difference, and in response to the self-refresh period definition signal, controls the internal power supply potential difference to be generated.

More specifically, the internal power supply voltage generating circuit controls the internal power supply potential difference to be generated to decrease from a first potential difference to a second potential difference in response to the beginning of the period defined by the self-refresh period definition signal, and to increase from the second potential difference to the first potential difference in response to the end of the period defined by the self-refresh period definition signal.

As described above, at the beginning of the self-refreshing operation, the internal power supply potential difference is decreased from the first potential to the second potential, and, at the end of the self-refreshing operation, the internal power supply potential difference is increased from the second potential difference to the first potential difference. Therefore, the internal power supply potential difference is made smaller in the self-refreshing operation than in the normal operation. Therefore, current consumption in the self-refreshing operation can be reduced by simple control in an internal circuit.

The semiconductor memory device according to this aspect may include a circuit making different in length a period in which the internal power supply potential difference is decreased by the internal power supply voltage generating means and a period in which the internal power supply potential difference is increased by the internal power supply voltage generating circuit.

Since the period in which the internal power supply potential difference is decreased and the period in which the internal power supply potential difference is increased are different in length, stabilization of operation of the semi-conductor memory device suitable for the decrease period and the increase period, respectively, can be implemented.

The semiconductor memory device according to this aspect of the present invention further includes a decrease period definition signal generating circuit, an increase period definition signal generating circuit, a hold period definition signal generating circuit, and a refresh cycle setting circuit. The refresh cycle setting circuit may include a first refresh cycle setting circuit, a second refresh cycle setting circuit, and a third refresh cycle circuit setting circuit.

The decrease period definition signal generating circuit generates a decrease period definition signal activated in the period in which the internal power supply potential difference is decreased from the first potential difference to the second potential difference by the internal power supply 60 voltage generating circuit.

The increase period definition signal generating circuit generates an increase period definition signal activated in the period in which the internal power supply potential difference is increased from the second potential difference to the 65 first potential difference by the internal power supply voltage generating circuit.

4

The hold period definition signal generating circuit generates a hold period definition signal activated in a period in which the internal power supply potential difference is held at the second potential difference by the internal power supply voltage generating circuit.

The refresh cycle setting circuit sets refresh cycles in the self-refreshing operation in response to the decrease period definition signal, the increase period definition signal, and the hold period definition signal.

The refresh cycle setting circuit includes a first refresh cycle setting circuit, a second refresh cycle setting circuit, and a third refresh cycle setting circuit. The first refresh cycle setting circuit sets a first refresh cycle in response to the decrease period definition signal. The second refresh cycle setting circuit sets a second refresh cycle in response to the increase period definition signal. The third refresh cycle setting circuit sets a third refresh cycle in response to the hold period definition signal. The first and second refresh cycles are set shorter than the third refresh cycle.

By thus structured, the first and second refresh cycles set corresponding to the decrease period and the increase period of the internal power supply potential difference are shorter than the third refresh cycle. Therefore, the self-refreshing operation is carried out in a shorter cycle in the increase period and the decrease period of the internal power supply potential difference than in the hold period. Therefore, the semiconductor memory device is less likely to be affected by bump or the like caused by decrease in electric charge stored in a memory cell during the increase period and the decrease period of the internal power supply potential difference, making it possible to stabilize the operation.

In the semiconductor memory device according to this aspect, the internal power supply voltage generating circuit may include a voltage control circuit controlling decrease in the internal power supply potential difference from the first potential difference to the second potential difference and increase in the internal power supply potential difference from the second potential difference to the first potential difference in a plurality of steps.

Since decrease and increase of the internal power supply potential difference are carried out in a plurality of stages, respectively, the internal power supply potential difference does not change abruptly. Therefore, the operation of the semiconductor memory device during the increase period and the decrease period of the internal power supply potential difference can be stabilized, which would be otherwise unstabilized by bump or the like.

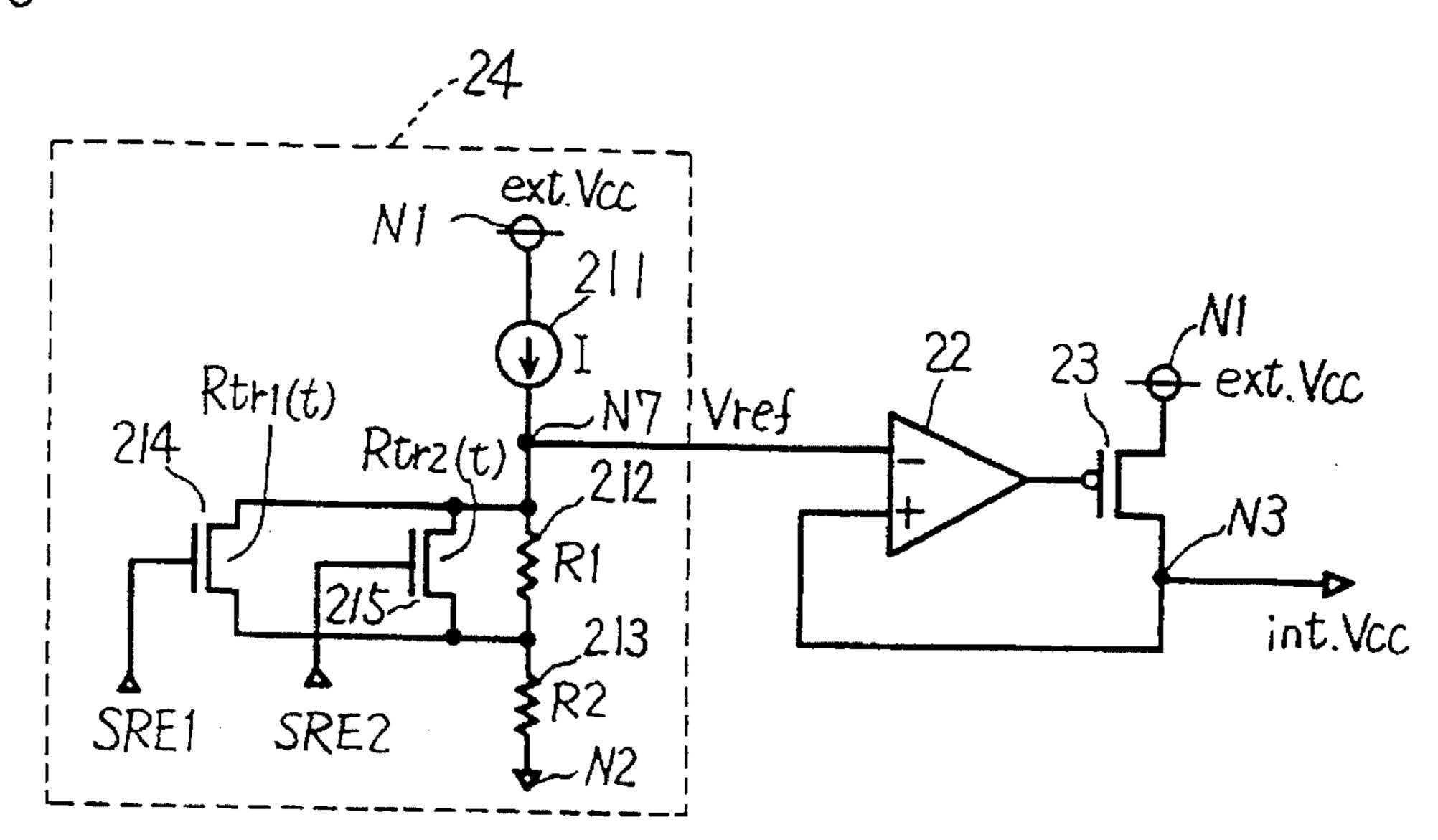

In the semiconductor memory device according to this aspect, at least one internal power supply voltage generating circuit includes a reference voltage generating circuit generating a reference voltage of the internal power supply voltage. The reference voltage generating circuit may include a first potential node, a second potential node, an output node, a constant current generating circuit, a resistor circuit, and a transistor circuit.

The first potential node receives a first potential. The second potential node receives a second potential. The output node provides the reference voltage.

The constant current generating circuit is provided between the first potential node and the output node, and generates a constant current. The resistor circuit is provided between the output node and the second potential node. The transistor circuit is connected in parallel with a part of the resistor circuit, and turned on/off in response to the self-refresh period definition signal.

When the transistor circuit is turned on in response to the self-refresh period definition signal, a resistance value of the

-

resistor circuit is decreased. Therefore, in this case, the voltage at the output node, that is, the reference voltage of the internal power supply voltage, is decreased. As a result, the internal power supply voltage is decreased. Therefore, current consumption in the self-refreshing operation can be 5 reduced.

In the semiconductor memory device according to this aspect, at least one internal power supply voltage generating circuit may include a reference voltage generating circuit, a differential amplifying circuit, a halting circuit, a voltage output node, a power supply node, an N channel transistor, and a transistor control circuit.

The reference voltage generating circuit generates the reference voltage of the internal power supply voltage. The differential amplifying circuit provides a control voltage for controlling the internal power supply voltage based on a difference between the internal power supply voltage to be generated and the reference voltage. The halting circuit halts, in response to the self-refresh period definition signal, operation of the differential amplifying circuit in a period of the self-refreshing operation defined by the signal.

The voltage output node provides the internal power supply voltage. The power supply node receives an external power supply voltage. The N channel transistor is provided between the power supply node and the voltage output node, and supplies the internal power supply voltage based on the external power supply voltage to the output node in response to a signal it receives at its gate electrode.

The transistor control circuit applies, in response to the self-refresh period definition signal, the reference voltage to the gate electrode of the N channel transistor in the period of the self-refreshing operation defined by the signal.

In the self-refreshing operation, the operation of the differential amplifying circuit is halted, and the N channel transistor is rendered conductive. When the N channel transistor is rendered conductive, the internal power supply voltage based on the external power supply voltage is supplied to the voltage output node. Therefore, since the differential amplifying circuit consuming current also at the time of stand-by of the self-refreshing operation is halted at the time of self-refreshing, current consumption in the self-refreshing operation can be reduced.

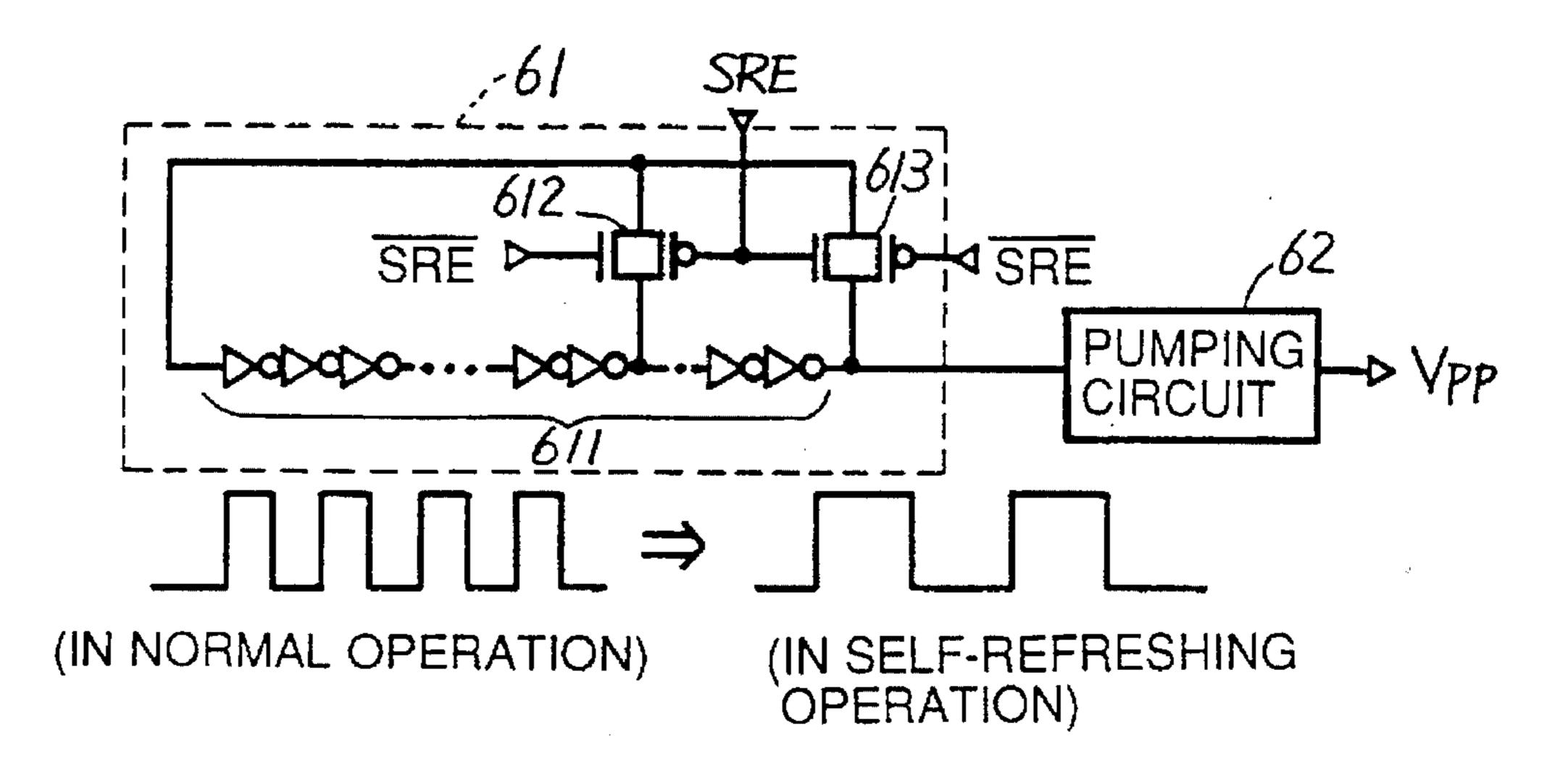

The semiconductor memory device according to this aspect of the present invention further includes a boosted voltage generating circuit generating a boosted voltage. The boosted voltage generating circuit may include a ring oscillating circuit, a pumping circuit, and a frequency changing circuit.

The ring oscillating circuit oscillates a pulse signal. The pumping circuit provides the boosted voltage in response to the pulse signal. In response to the self-refresh period definition signal, the frequency changing circuit makes the frequency of the pulse signal oscillated by the ring oscillating circuit lower in the period of the self-refreshing operation defined by the signal than in the normal operation.

By thus structured, the frequency of the pulse signal oscillated by the ring oscillating circuit is made lower in the self-refreshing operation than in the normal operation. Therefore, the pumping frequency of the pumping circuit 60 becomes lower, and current consumption in the self-refreshing operation can be reduced.

The semiconductor memory device according to this aspect of the present invention may further include a comparing circuit and an external output circuit.

The comparing circuit compares the internal power supply potential difference generated by the internal power

6

supply voltage generating circuit and a predetermined potential difference, and activates an output signal when the internal power supply potential difference and the predetermined potential difference become approximately the same.

The external output circuit receives the output signal of the comparing circuit. When the signal is activated, the external output circuit provides to the outside world a signal at a predetermined level indicating that the internal power supply potential difference has returned to a potential difference in the normal operation.

By thus structured, when the internal power supply potential difference returns to the level of the normal operation at the end of the self-refreshing operation, if the internal power supply potential difference becomes equal or approximately equal to a predetermined value, the output signal of the comparing circuit is activated. A signal at a predetermined level is provided to the outside world by the external output circuit in response to the activation.

Therefore, after completion of the self-refreshing operation, it can be externally known that the internal power supply potential difference has returned to a potential difference in the normal operation.

A semiconductor memory device according to a further aspect of the present invention which carries out a self-refreshing operation based on an internal power supply voltage includes a power supply node, a self-refresh period definition circuit, and an internal voltage down-converting circuit. The internal voltage down-converting circuit includes a reference voltage generating circuit. The reference voltage generating circuit includes an output node, a first reference voltage supplying circuit, a second reference voltage supplying circuit, and a supply stop circuit.

The power supply node receives an external power supply voltage. The self-refresh period defining circuit generates a self-refresh period definition signal defining a period in which the self-refreshing operation is carried out. The internal voltage down-converting circuit down-converts the external power supply voltage, and generates the internal power supply voltage.

The reference voltage generating circuit generates a reference voltage of the internal power supply voltage. The output node provides the reference voltage. The first reference voltage supplying circuit supplies a first constant reference voltage to the output node. The second reference voltage supplying circuit receives the external power supply voltage, and, when the external power supply voltage exceeds a predetermined level for a burn-in test, supplies a second reference voltage in response to the external power supply voltage to the output node.

The supply stop circuit receives the self-refresh period definition signal, and stops supply of the external power supply voltage to the second reference voltage supplying circuit during the period of the self-refreshing operation defined by the signal.

The reference voltage generating circuit provides from the output node a sum of the first reference voltage from the first reference voltage supplying circuit and the second reference voltage from the second reference voltage supplying circuit.

Since the second reference voltage is a reference voltage for a burn-in test, the voltage is not needed in the selfrefreshing operation. Therefore, the second reference voltage supplying circuit is halted by the supply stop circuit in the self-refreshing operation. As a result, current consumption in the self-refreshing operation can be reduced.

A semiconductor memory device according to a further aspect of the present invention which has a memory cell

7

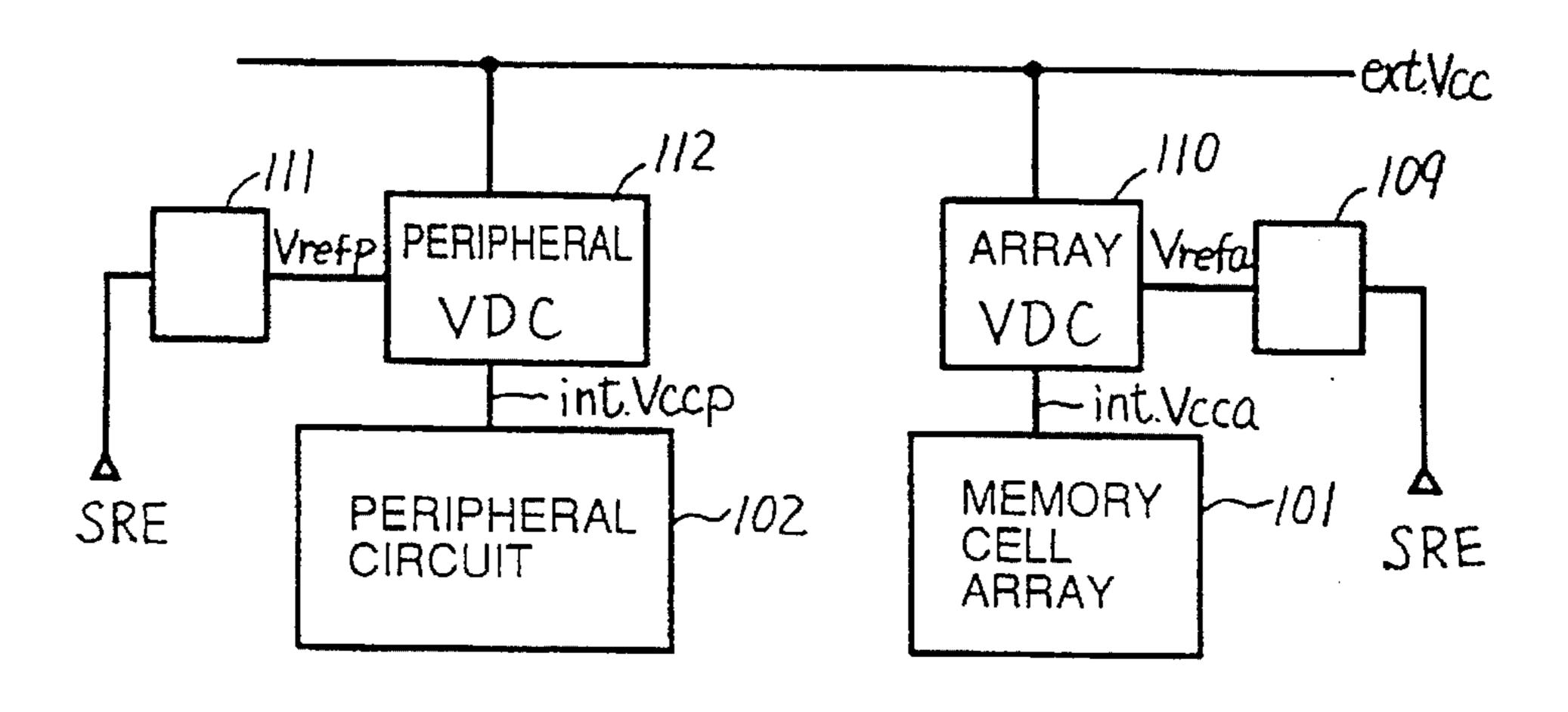

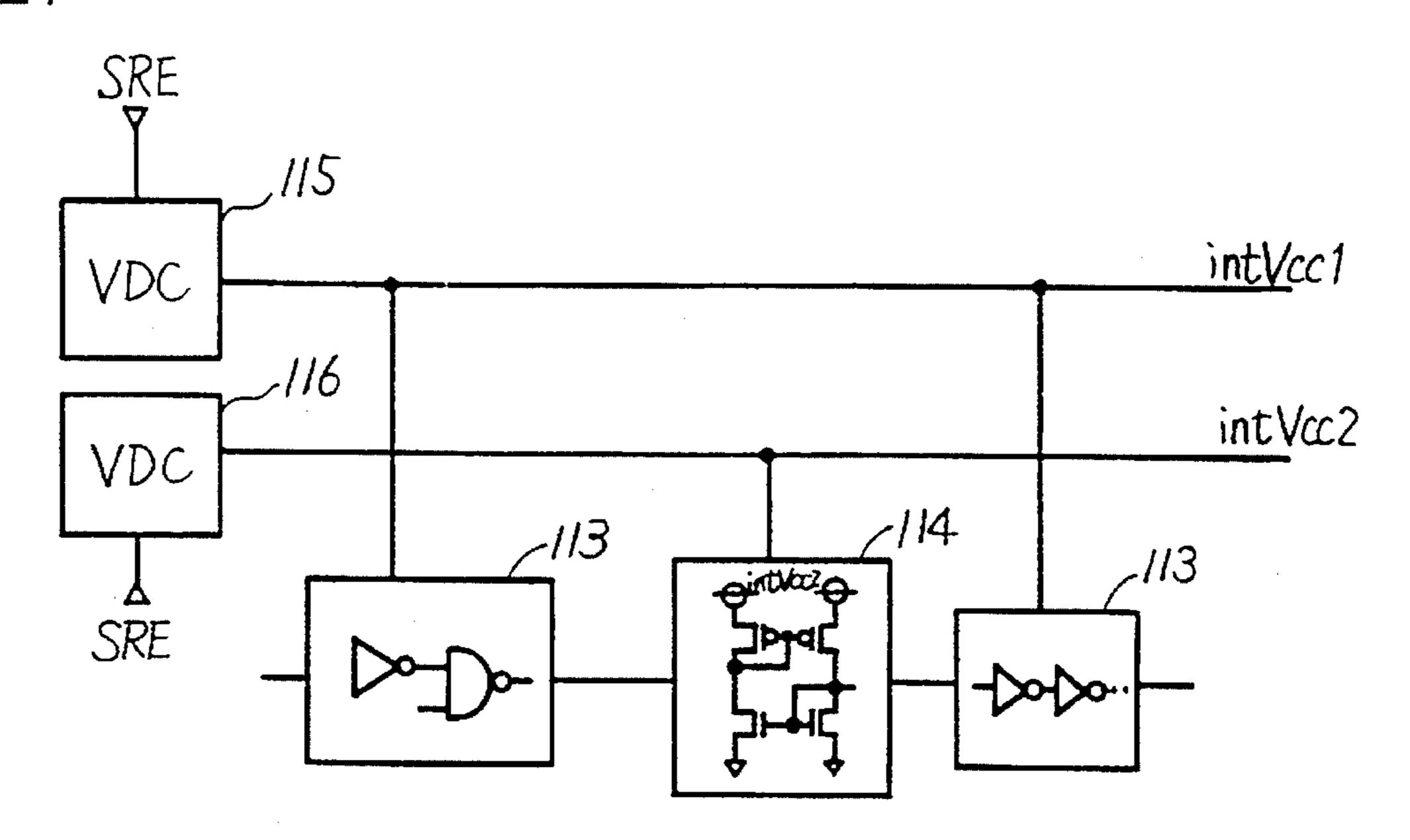

array and a peripheral circuit and carries out a normal operation and a self-refreshing operation based on an internal power supply voltage includes a first internal power supply voltage generating circuit, a second internal power supply voltage generating circuit, a first voltage control circuit, and a second voltage control circuit.

The first internal power supply voltage generating circuit generates a first internal power supply voltage to be supplied to the memory cell array. The second internal power supply voltage generating circuit generates a second internal power 10 supply voltage to be supplied to the peripheral circuit.

The first voltage control circuit controls the first internal power supply voltage generated by the first internal power supply voltage generating circuit to be lower in the self-refreshing operation than in the normal operation.

The second voltage control circuit controls the second internal power supply voltage generated by the second internal power supply voltage generating circuit to be lower in the self-refreshing operation than in the normal operation.

As described above, the first and second internal power supply voltage generating circuits are provided corresponding to the memory cell array and the peripheral circuit. The first and second internal power supply voltages generated by the first and second internal power supply voltage generating circuits are controlled to be lower in the self-refreshing operation than in the normal operation by the first and second voltage control circuits.

Different internal power supply voltages can be supplied to the memory cell array and the peripheral circuit. 30 Therefore, especially in the self-refreshing operation, the memory cell array and the peripheral circuit can be operated based on respective optimal power supply voltages.

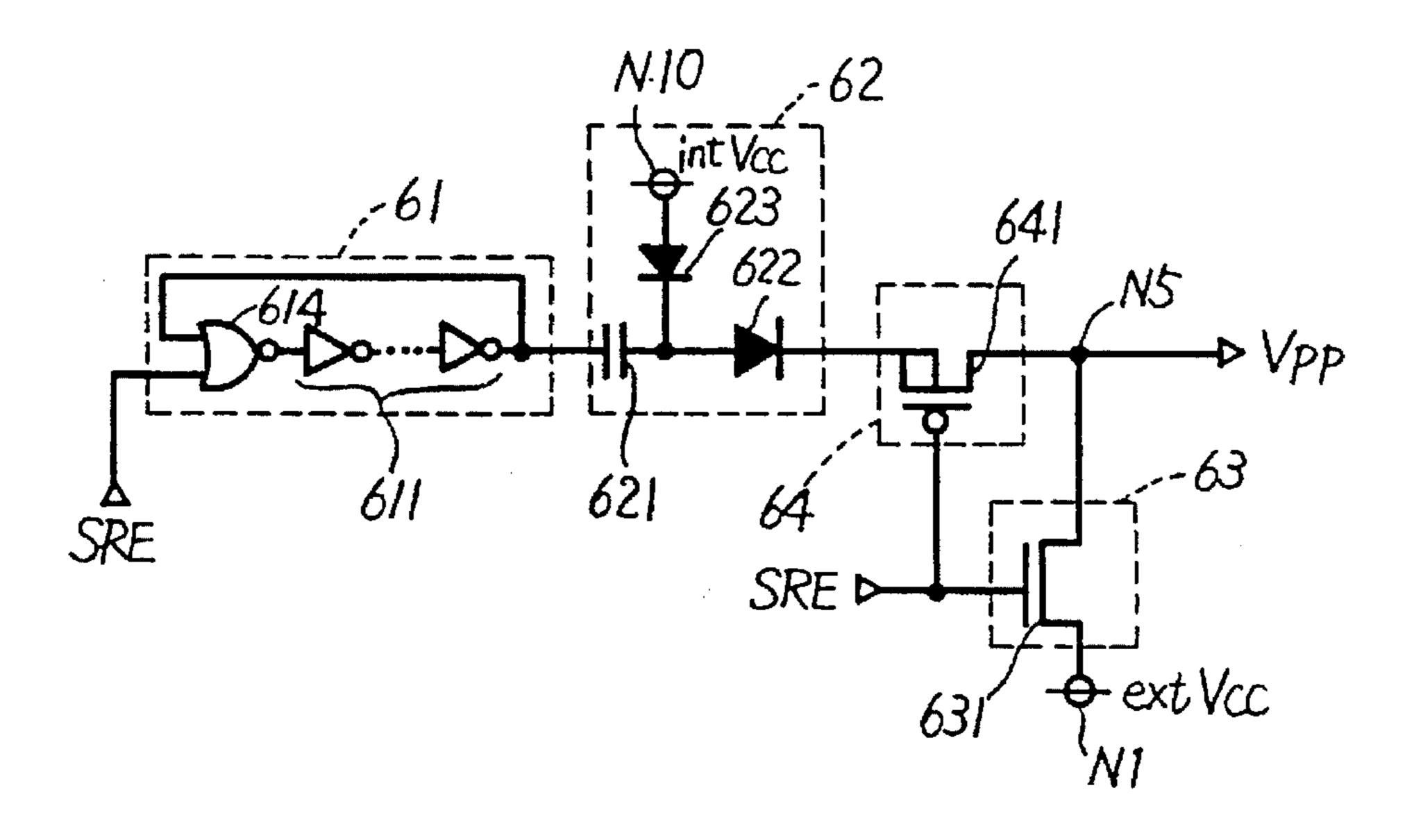

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on an internal power supply voltage and a boosted voltage obtained by boosting the internal power supply voltage includes a self-refresh period defining circuit and a boosted voltage generating circuit. The boosted voltage generating circuit includes a reference power supply node, a boosted voltage output node, a ring oscillating circuit, a pumping circuit, a cut-off circuit, and an N channel transistor.

The self-refresh period defining circuit generates a self-refresh period definition signal defining a period in which the self-refreshing operation is carried out. The boosted voltage generating circuit generates the boosted voltage obtained by boosting the internal power supply voltage.

The reference power supply node receives a predetermined reference power supply voltage. The boosted voltage output node provides the generated boosted voltage.

The ring oscillating circuit oscillates a pulse signal in the normal operation, and stops oscillation of the pulse signal in the self-refreshing operation, in response to the self-refresh period definition signal. The pumping circuit supplies the boosted voltage to the boosted voltage output node in response to the pulse signal.

In response to the self-refresh period definition signal, the cut-off circuit cuts off supply of the boosted voltage from the pumping circuit to the boosted voltage output node in the self-refreshing operation.

The N channel transistor is provided between the reference power supply node and the boosted voltage output node. In response to the self-refresh period definition signal, 65 the N channel transistor is rendered conductive in the self-refreshing operation. The N channel transistor supplies

8

to the boosted voltage output node the boosted voltage lower than the reference power supply voltage by a threshold voltage.

As described above, at the time of self-refreshing, the ring oscillating circuit is halted, and supply of the boosted voltage from the pumping circuit to the boosted voltage output node is cut off in the boosted voltage generating circuit. At the same time, the boosted voltage lower than the reference power supply voltage by the threshold voltage is supplied to the boosted voltage output node through the N channel transistor.

As described above, the operation of the ring oscillating circuit is halted in the self-refreshing operation. Accordingly, the operation of the pumping circuit is also halted, resulting in supply of the boosted voltage through another supply path. Therefore, current consumption at the time of self-refreshing can be reduced.

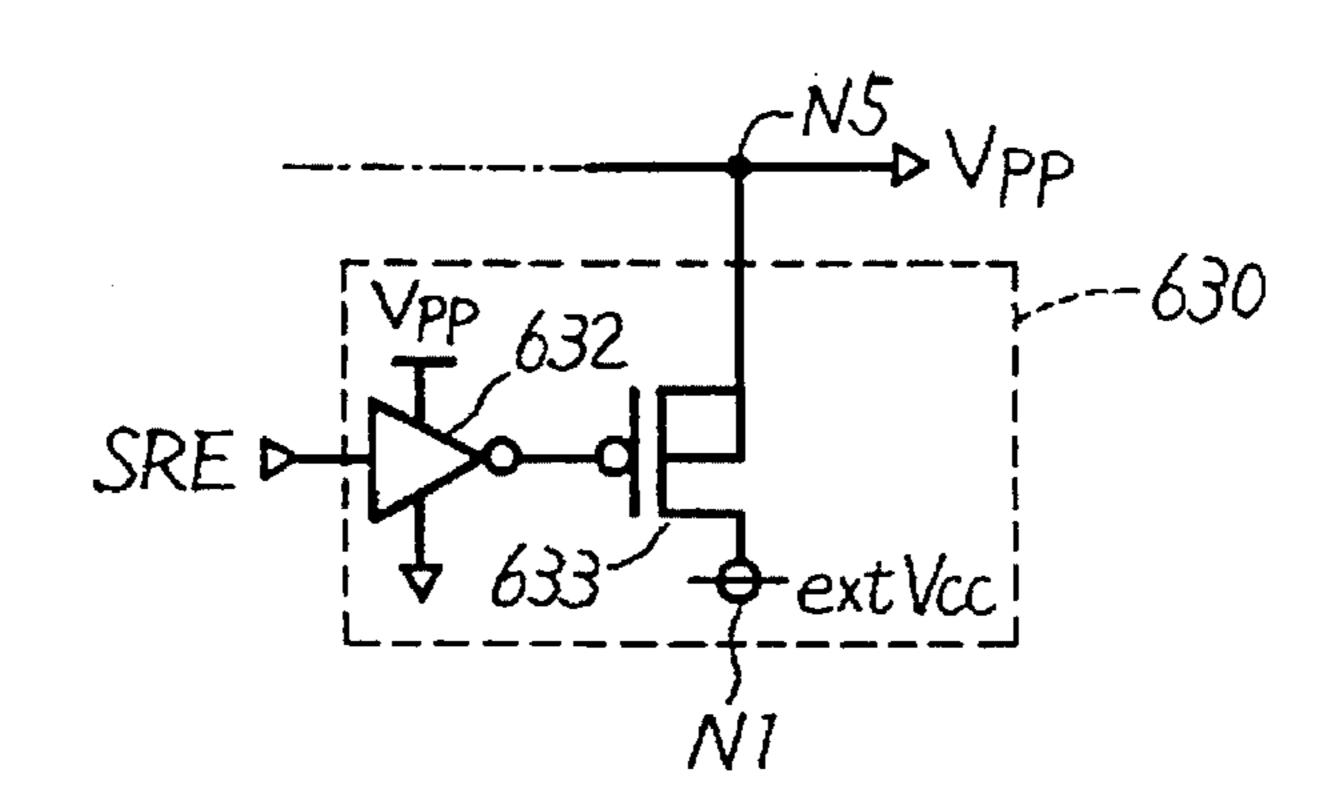

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on an internal power supply voltage and a boosted voltage obtained by boosting the internal power supply voltage includes a self-refresh period defining circuit and a boosted voltage generating circuit. The boosted voltage generating circuit includes a power supply node, a boosted voltage output node, a ring oscillating circuit, a pumping circuit, a cut-off circuit, and an external power supply voltage supplying circuit.

The self-refresh period defining circuit generates a self-refresh period definition signal defining a period in which the self-refreshing operation is carried out. The boosted voltage generating circuit generates the boosted voltage obtained by boosting the internal power supply voltage. The power supply node receives an external power supply voltage. The boosted voltage output node provides the generated boosted voltage. In response to the self-refresh period definition signal, the ring oscillating circuit oscillates a pulse signal in the normal operation, and stops oscillation of the pulse signal in the self-refreshing operation. The pumping circuit supplies the boosted voltage to the boosted voltage output node in response to the pulse signal.

In response to the self-refresh period definition signal, the cut-off circuit cuts off supply of the boosted voltage from the pumping circuit to the boosted voltage output node in the self-refreshing operation. The external power supply voltage supplying circuit receives the external power supply voltage, and, in response to the self-refresh period definition signal, supplies the external power supply voltage to the boosted voltage output node in the self-refreshing operation.

At the time of self-refreshing, the ring oscillating circuit is halted, and supply of the boosted voltage from the pumping circuit to the boosted voltage output node is cut off in the boosted voltage generating circuit. At the same time, the external power supply voltage is supplied from the external power supply voltage supplying circuit to the boosted voltage output node as the boosted voltage.

As described above, the operation of the ring oscillating circuit is halted in the self-refreshing operation. Accordingly, the operation of the pumping circuit is also halted, resulting in supply of the boosted voltage through another supply path. Therefore, current consumption in the self-refreshing operation can be reduced.

Further, since the boosted voltage attains a level of the external power supply voltage, the semiconductor memory device can be used not only when the self-refreshing operation is carried out based on a lower internal power supply voltage than in the normal operation, but also when the

self-refreshing operation is carried out based on the same internal power supply voltage as in the normal operation.

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on an internal power supply voltage includes a CMOS circuit, an analog circuit, a first internal power supply voltage supplying circuit, and a second internal power supply voltage supplying circuit.

The CMOS circuit and the analog circuit operate as a peripheral circuit.

The first internal power supply voltage supplying circuit, provided corresponding to the CMOS circuit, supplies a first internal power supply voltage lower in the self-refreshing operation than in the normal operation.

The second internal power supply voltage supplying circuit, provided corresponding to the analog circuit, supplies a second internal power supply voltage lower in the self-refreshing operation than in the normal operation.

As described above, the CMOS circuit and the analog circuit are supplied with the first and second internal power supply voltages from the corresponding first and second internal power supply voltage supplying circuits, respectively. The first and second internal power supply voltages 25 are made lower in the self-refreshing operation than in the normal operation. As a result, current consumption in the self-refreshing operation can be reduced.

Further, since the internal power supply voltages are supplied from different supply sources, the first and second <sup>30</sup> internal power supply voltages in the self-refreshing operation can be made optimal for stable operation of the CMOS circuit and the analog circuit. As a result, the CMOS circuit and the analog circuit can be operated stably.

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on a potential swing having a swing width defined by a potential difference between a first internal power supply potential and a second internal power supply potential lower than the first internal power supply potential includes a first internal power supply potential generating circuit and a second internal power supply potential generating circuit. The first internal power supply potential generating circuit includes a first potential control circuit, and the second internal power supply potential generating circuit includes a first potential control circuit, and the second internal power supply potential generating circuit includes a second potential control circuit.

The first internal power supply potential generating circuit generates a first internal power supply potential. The second internal power supply potential generating circuit generates a second internal power supply potential.

The first potential control circuit controls the level of the first internal power supply potential to be lower in the self-refreshing operation than in the normal operation by a predetermined width.

The second potential control circuit controls the level of the second internal power supply potential to be higher in the self-refreshing operation than in the normal operation by the same width as the change width of the level of the potential by the first potential control circuit.

The potential swing is controlled to have the same or approximately the same center value in the normal operation and in the self-refreshing operation.

As described above, in the self-refreshing operation, the 65 first internal power supply potential generated by the first internal power supply potential generating circuit and the

second internal power supply potential generated by the second internal power supply potential generating circuit change, respectively.

The level of the first internal power supply potential is made lower by the first potential control circuit in the self-refreshing operation than in the normal operation by a predetermined width. The level of the second internal power supply potential is made higher by the second potential control circuit in the self-refreshing operation than in the normal operation by the same width as that of the change width of the level of the first internal power supply potential.

Therefore, the difference between the internal power supply potentials in the self-refreshing operation is made smaller than the potential difference in the normal operation. Therefore, current consumption in the self-refreshing operation is reduced. Further, in this case, the change of the first internal power supply potential and the change of the second internal power supply potential are equal in width and opposite in the direction. Therefore, a value of ½ level of the internal power supply potential difference which is the center value of the potential swing in the self-refreshing operation can be made unchanged with respect to that in the normal operation.

The value of ½ level of the internal power supply potential difference is a reference potential for writing and reading of data. However, the value does not change even if the internal power supply potential difference is changed. Therefore, the semiconductor memory device is not affected at all by bump when the internal power supply potential difference is changed.

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on a potential swing having a swing width defined by an internal power supply potential difference includes an internal power supply potential difference generating circuit, a first refresh cycle setting circuit, and a second refresh cycle setting circuit.

The internal power supply potential difference generating circuit generates the internal power supply potential difference. The internal power supply potential difference generating circuit decreases the internal power supply potential difference more in the self-refreshing operation than in the normal operation so that the potential swing width is made smaller in at least a predetermined period in the self-refreshing operation than in the normal operation. After holding the internal power supply potential difference at a constant value, the internal power supply potential difference generating circuit increases the internal power supply potential difference in the self-refreshing operation to that in the normal operation.

The first refresh cycle setting circuit sets a standard refresh cycle in the self-refreshing operation.

The second refresh cycle setting circuit sets a refresh cycle in the self-refreshing operation before the internal power supply potential difference is decreased by the internal power supply potential difference generating circuit to a cycle shorter than the standard refresh cycle.

As described above, the internal power supply potential difference generated by the internal power supply potential difference generating circuit is made smaller at least in a predetermined period in the self-refreshing operation than in the normal operation. Therefore, current consumption in the self-refreshing operation can be reduced.

Refreshing in the self-refreshing operation is basically carried out in the standard refresh cycle set by the first

refresh cycle setting circuit. Exceptionally, refreshing before the internal power supply potential difference is decreased is carried out in a cycle shorter than the standard refresh cycle. The shorter refresh cycle is set by the second refresh cycle setting circuit.

Therefore, a memory cell in a severe state in which stored electric charge has been reduced before the beginning of the self-refreshing operation has sufficient electric charge stored therein. Therefore, a refresh ability can be initialized at this time. As a result, the semiconductor memory device is less likely to be affected by bump caused by decrease of the internal power supply potential difference, whereby the operation can be stabilized.

In addition, since refreshing is carried out in a shorter cycle at the beginning of the self-refreshing operation, the memory cell is in a state in which sufficient electric charge is stored. Therefore, the condition regarding a refresh ability required at the beginning of refreshing can be met without external complicated control.

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on a potential swing having a swing width defined by an internal power supply potential difference includes an internal power supply potential difference generating circuit, a first refresh cycle setting circuit, and a second refresh cycle setting circuit.

The internal power supply potential difference generating circuit generates the internal power supply potential difference. The internal power supply potential difference generating circuit decreases the internal power supply potential difference more in the self-refreshing operation than in the normal operation so that the potential swing width is made smaller in at least a predetermined period in the self-refreshing operation than in the normal operation. After holding the internal power supply potential difference at a constant value, the internal power supply potential difference generating circuit increases the internal power supply potential difference in the self-refreshing operation to that in the normal operation.

The first refresh cycle setting circuit sets a standard refresh cycle in the self-refreshing operation.

The second refresh cycle setting circuit sets a refresh cycle in a predetermined period in the self-refreshing operation before the internal power supply potential difference is increased by the internal power supply potential difference generating circuit to a cycle shorter than the standard refresh cycle.

Further, refreshing in the self-refreshing operation is basically carried out in the standard refresh cycle set by the first refresh cycle setting circuit. Exceptionally, the refreshing in a predetermined period before increase of the internal 60 power supply potential difference is carried out in a cycle shorter than the standard refresh cycle. The shorter refresh cycle is set by the second refresh cycle setting circuit.

Therefore, a memory cell in which stored electric charge is reduced before increase of the internal power supply 65 potential difference is brought to a state where sufficient electric charge is stored.

As a result, the semiconductor memory device is less likely to be affected by bump caused by increase in the internal power supply potential difference, and as a result, the operation of the semiconductor memory device can be stabilized.

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on a potential swing having a swing width defined by an internal power supply potential difference includes an internal power supply potential difference generating circuit, a first refresh cycle setting circuit, and a second refresh cycle setting circuit.

The internal power supply potential difference generating circuit generates the internal power supply potential difference generating circuit decreases the internal power supply potential difference more in the self-refreshing operation than in the normal operation so that the potential swing width is made smaller in at least a predetermined period in the self-refreshing operation than in the normal operation. After holding the internal power supply potential difference at a constant value, the internal power supply potential difference generating circuit increases the internal power supply potential difference in the self-refreshing operation to that in the normal operation.

The first refresh cycle setting circuit sets a standard refresh cycle in the self-refreshing operation.

The second refresh cycle setting circuit sets a refresh cycle in the self-refreshing operation after increase of the internal power supply potential difference by the internal power supply potential difference generating circuit to a cycle shorter than the standard refresh cycle.

As described above, the internal power supply potential difference generated by the internal power supply potential difference generating circuit is made smaller in at least a predetermined period in the self-refreshing operation than in the normal operation. Therefore, current consumption in the self-refreshing operation can be reduced.

Refreshing in the self-refreshing operation is basically carried out in the standard refresh cycle set by the first refresh cycle setting circuit. Exceptionally, the refreshing after increase of the internal power supply potential difference is carried out in a cycle shorter than the standard refresh cycle. The shorter refresh cycle is set by the second refresh cycle setting circuit.

Therefore, a memory cell in a severe state in which stored electric charge has been reduced before completion of increase of the internal power supply potential difference is brought to a state where sufficient electric charge is stored. Therefore, at this time, a refresh ability can be initialized. Therefore, the condition regarding the refresh ability required before transition from the refreshing operation to the normal operation can be satisfied without external complicated control.

A semiconductor memory device according to a further aspect of the present invention which carries out a normal operation and a self-refreshing operation based on a potential swing having a swing width defined by an internal power supply potential difference includes a first refresh cycle setting circuit and a second refresh cycle setting circuit.

The first refresh cycle setting circuit sets a standard refresh cycle in the self-refreshing operation.

The second refresh cycle setting circuit sets a refresh cycle in a predetermined period at the beginning of the self-refreshing operation to a cycle shorter than the standard refresh cycle.

As described above, refreshing in the self-refreshing operation is basically carried out in the standard refresh cycle set by the first refresh cycle setting circuit. Exceptionally, in a predetermined period at the beginning of the self-refreshing operation, refreshing is carried out in a refresh cycle shorter than the standard refresh cycle set by the second refresh cycle setting circuit.

Therefore, at the beginning of the self-refreshing operation, a state in which sufficient electric charge is stored in a memory cell can be implemented. As a result, a refresh ability can be initialized at this time.

The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

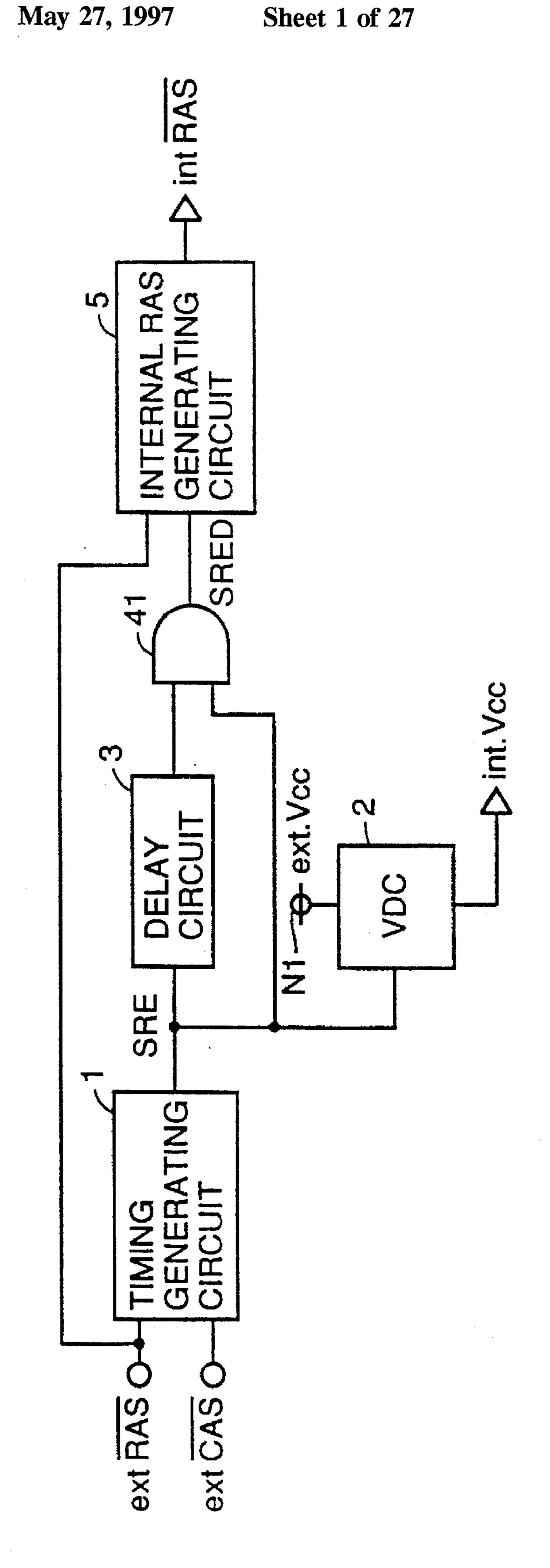

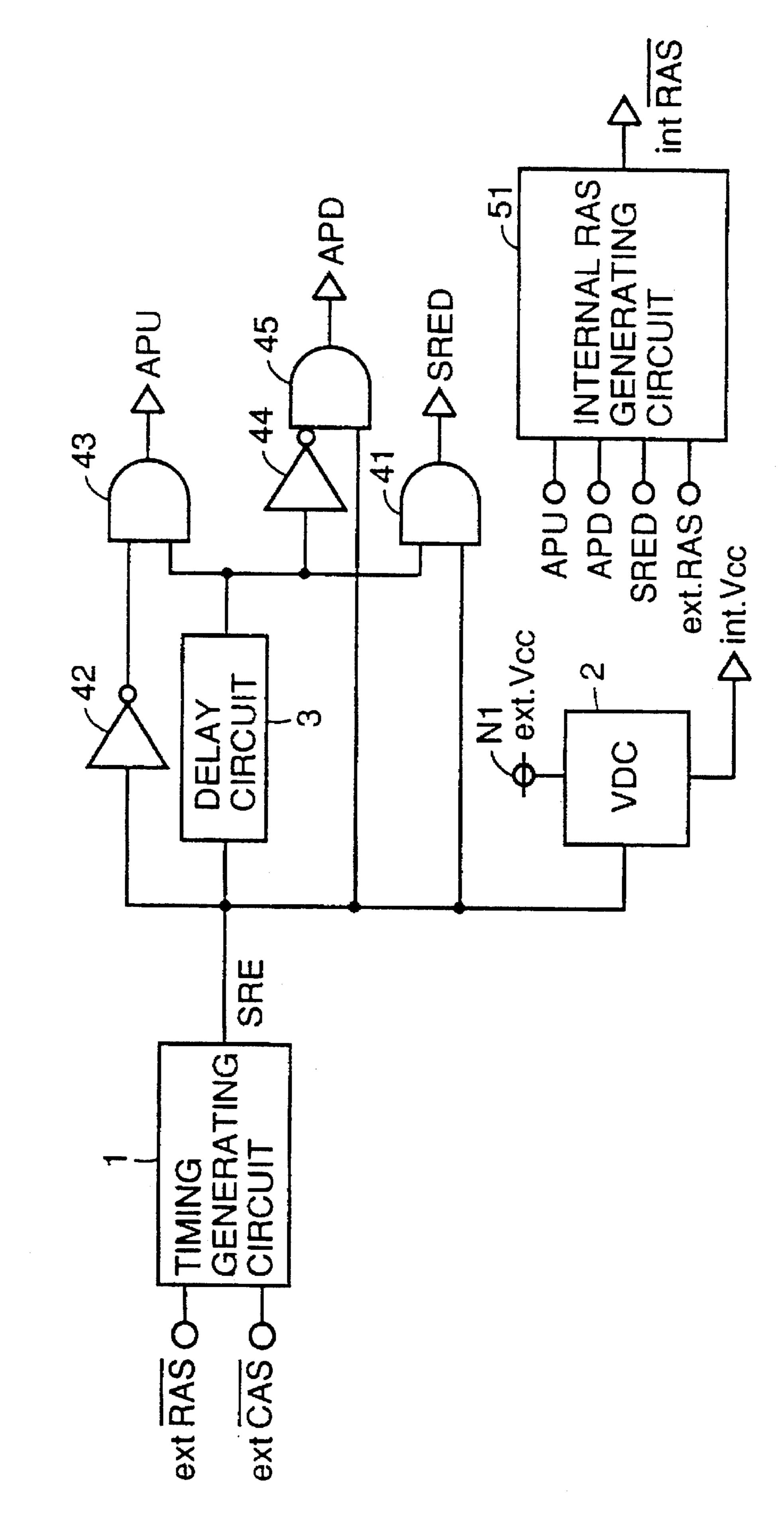

- FIG. 1 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a first embodiment.

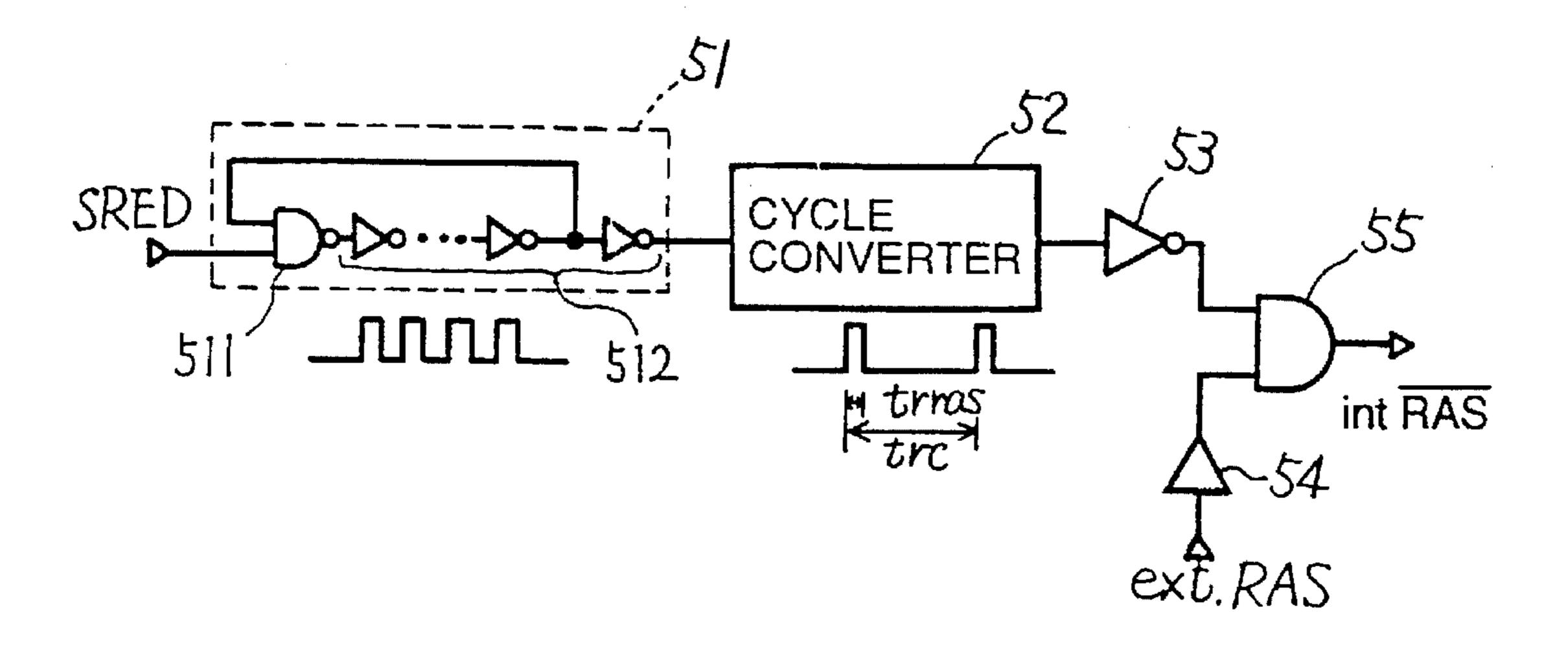

- FIG. 2 is a circuit diagram showing a configuration of an internal RAS generating circuit according to the first embodiment.

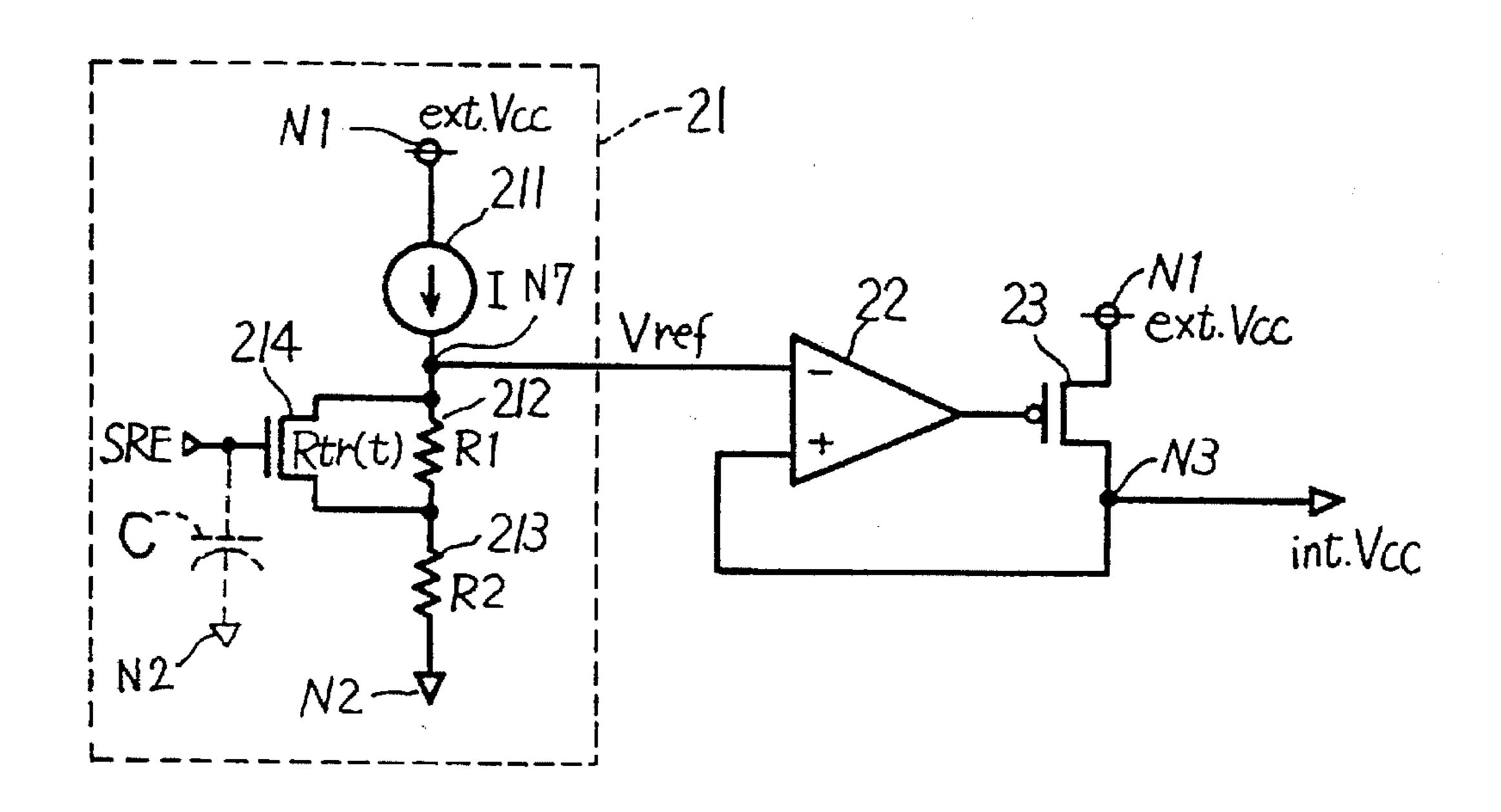

- FIG. 3 is a circuit diagram showing a configuration of an internal voltage down-converting circuit according to the first embodiment.

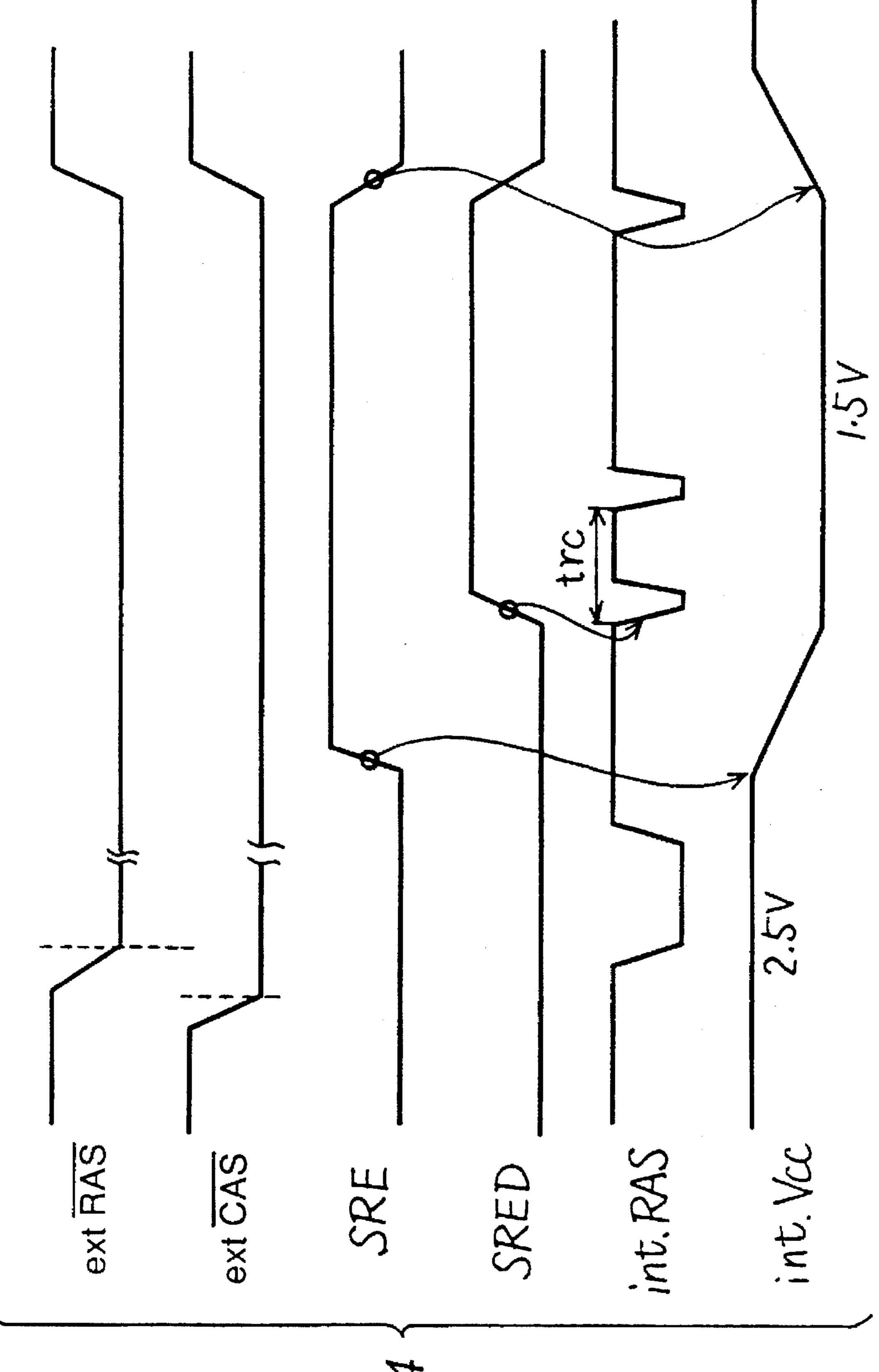

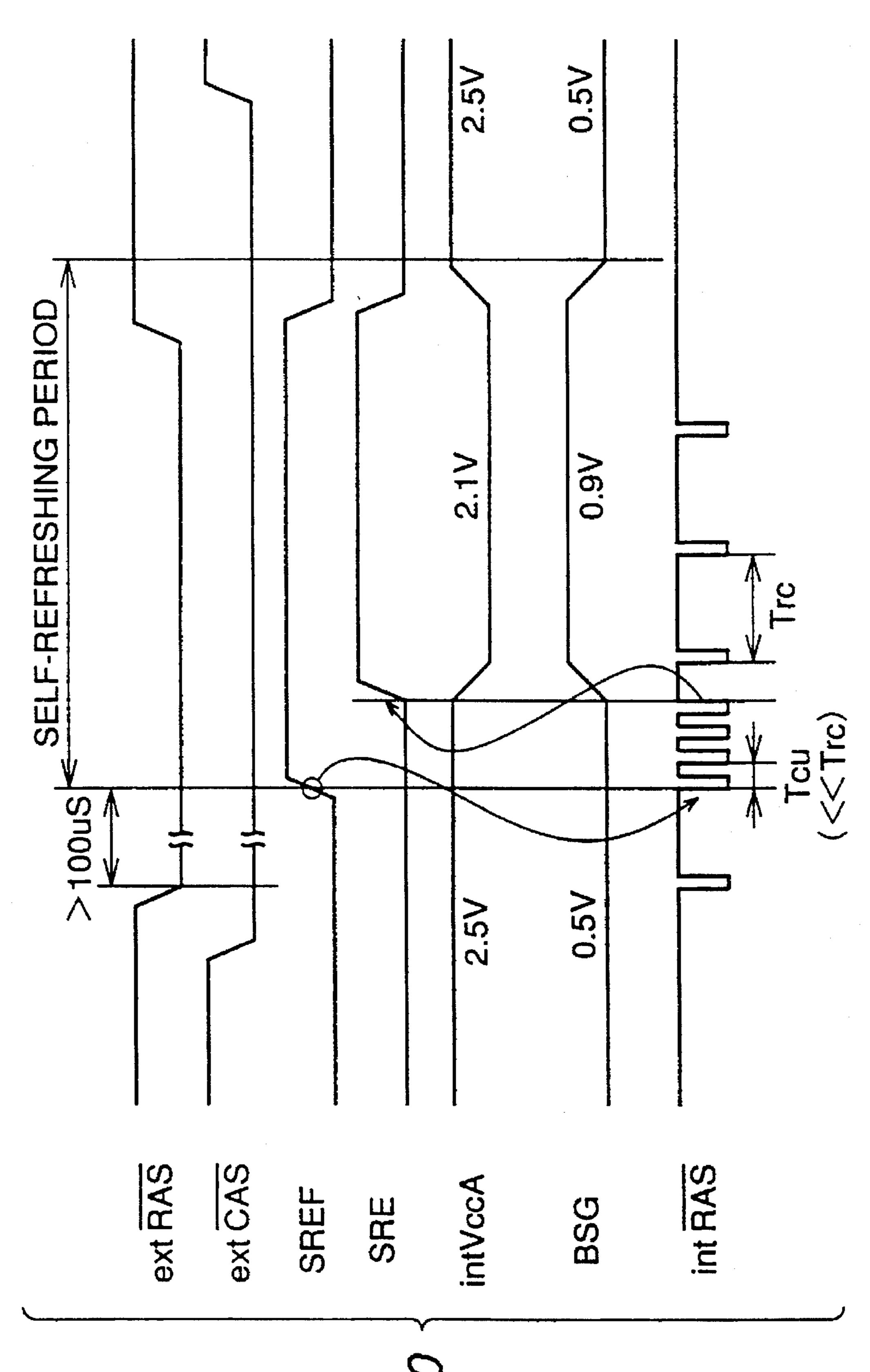

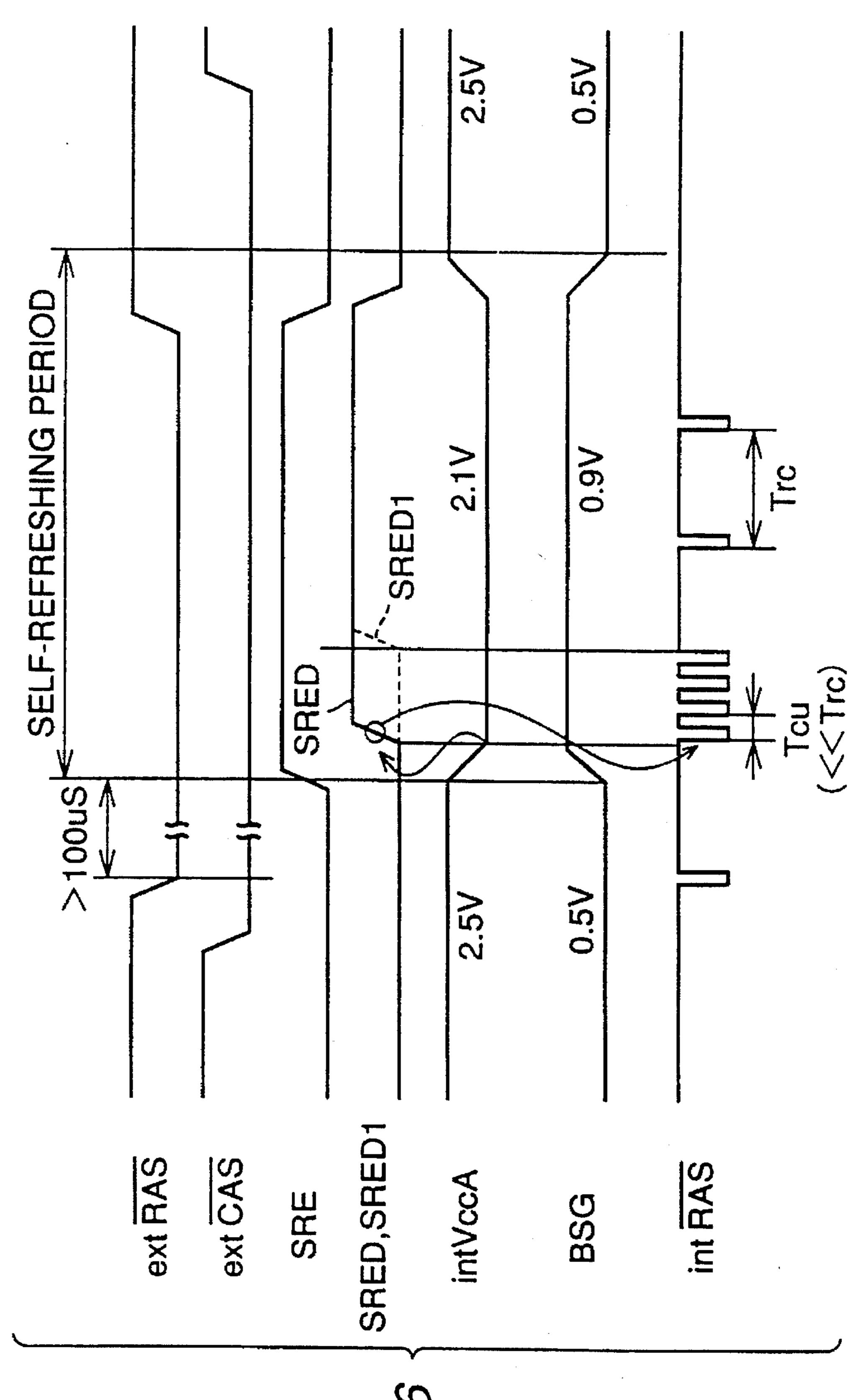

- FIG. 4 is a timing chart showing operation timings of the circuit of FIG. 1 in a self-refreshing operation.

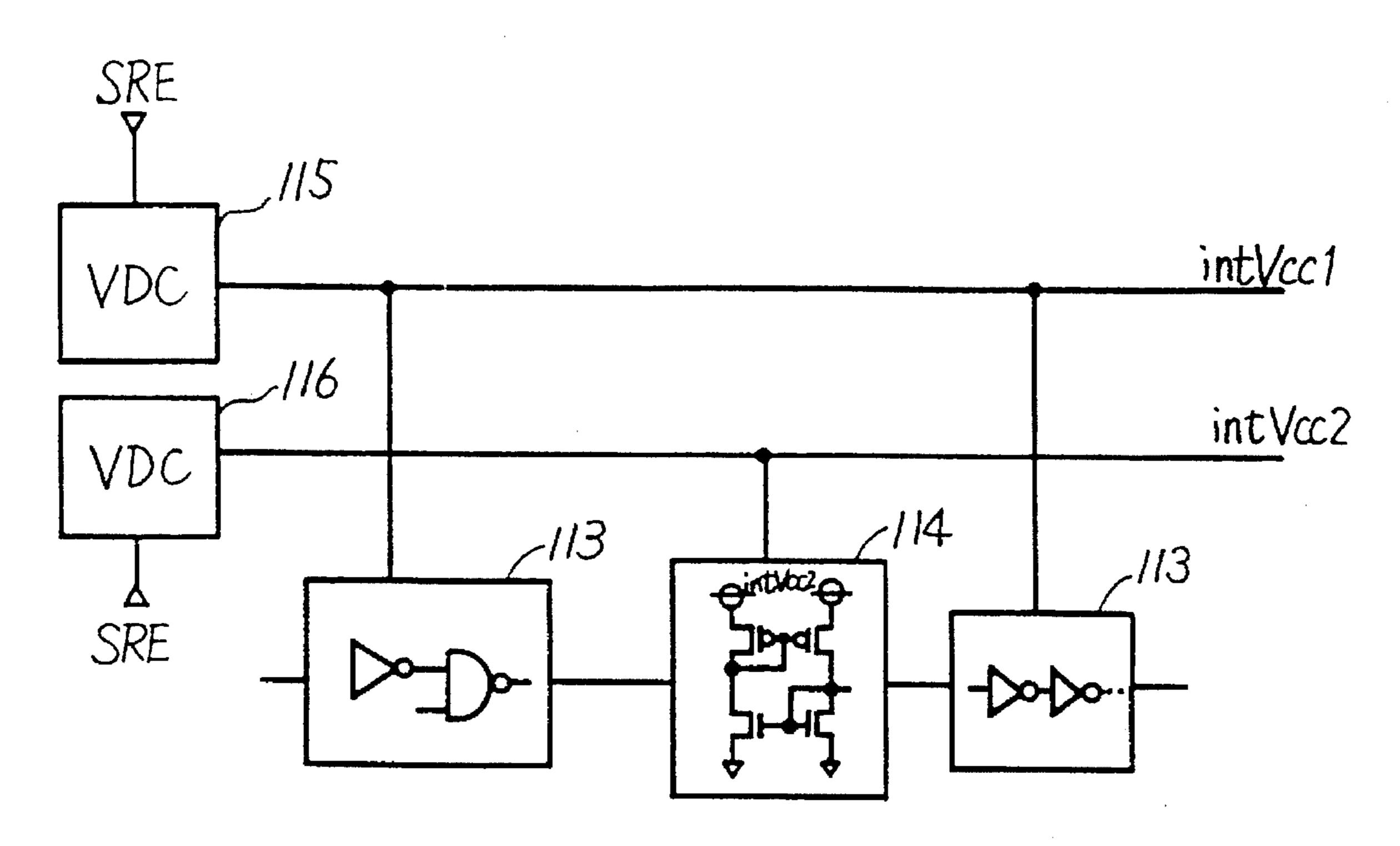

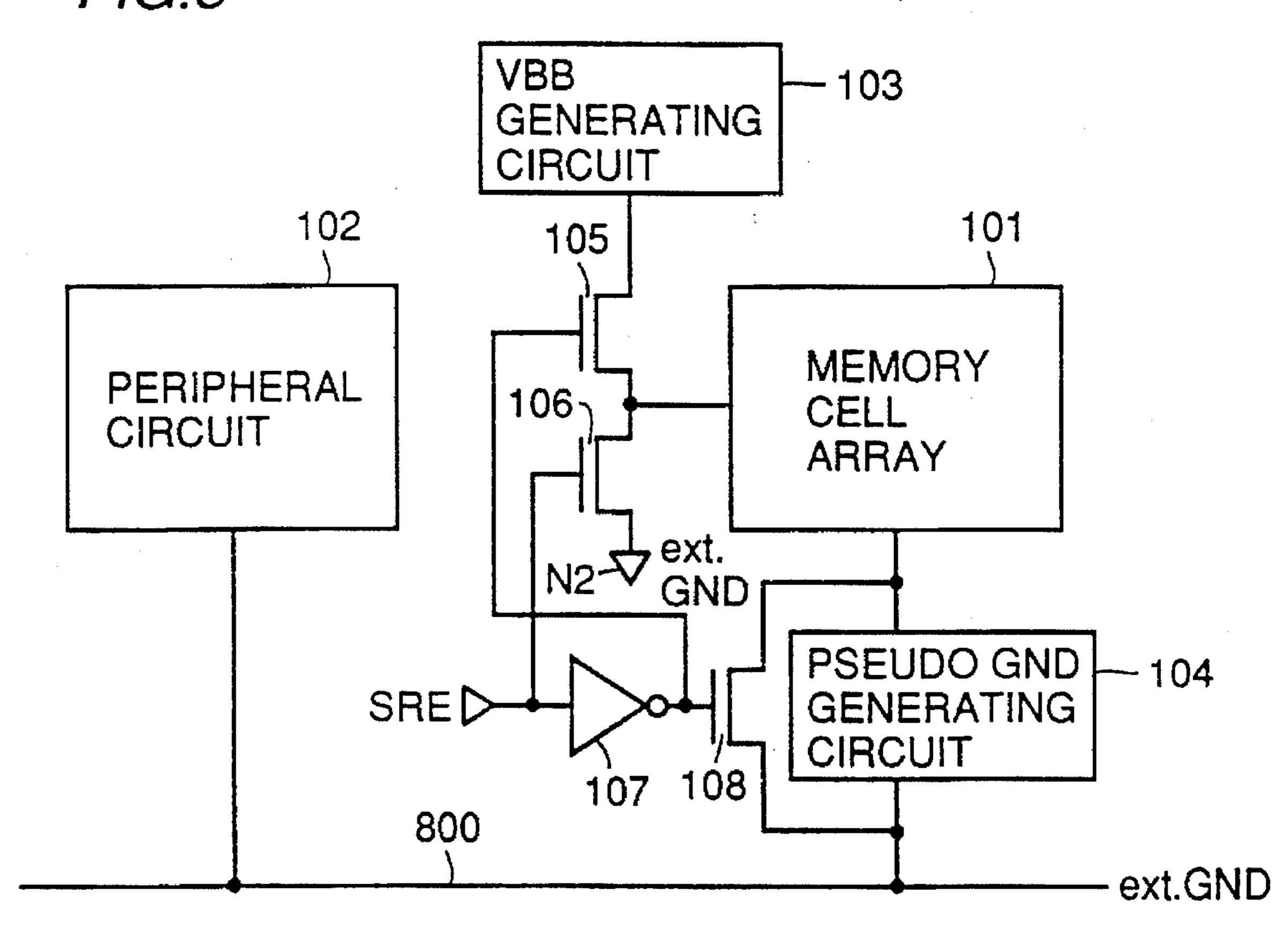

- FIG. 5 is a block diagram showing a circuit portion 30 regarding self-refreshing of a DRAM according to a second embodiment.

- FIG. 6 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a third embodiment.

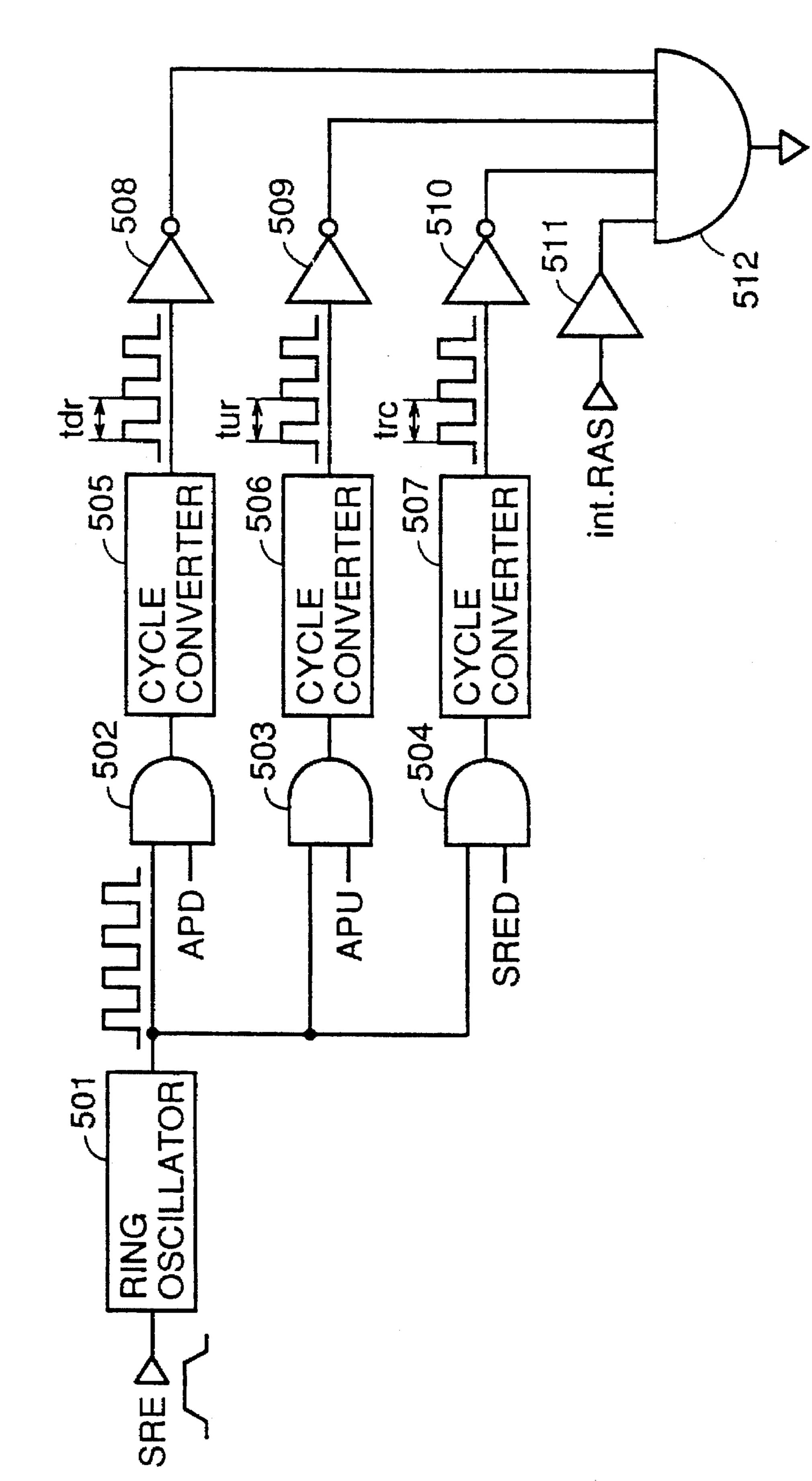

- FIG. 7 is a block diagram showing a configuration of an internal RAS generating circuit according to the third embodiment.

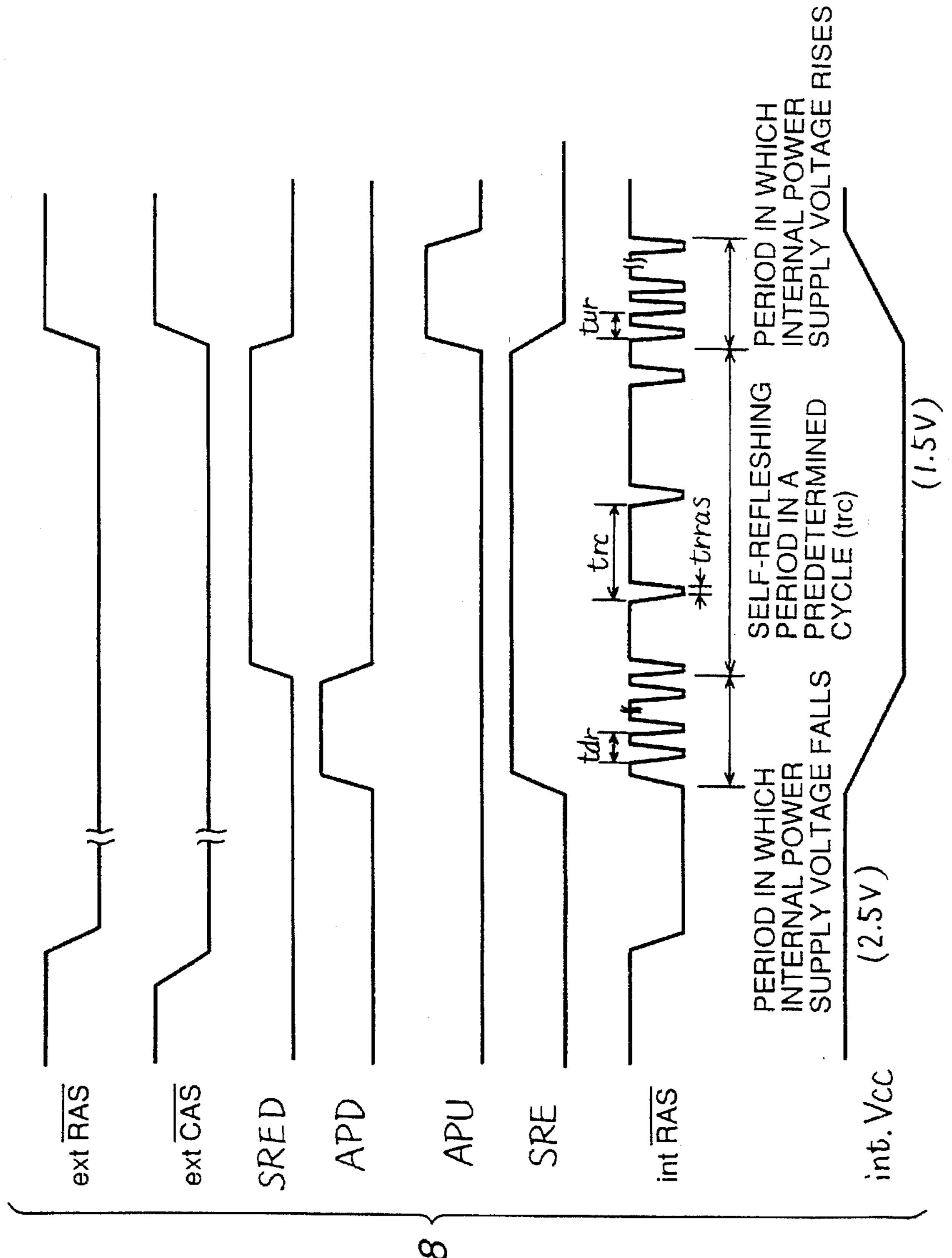

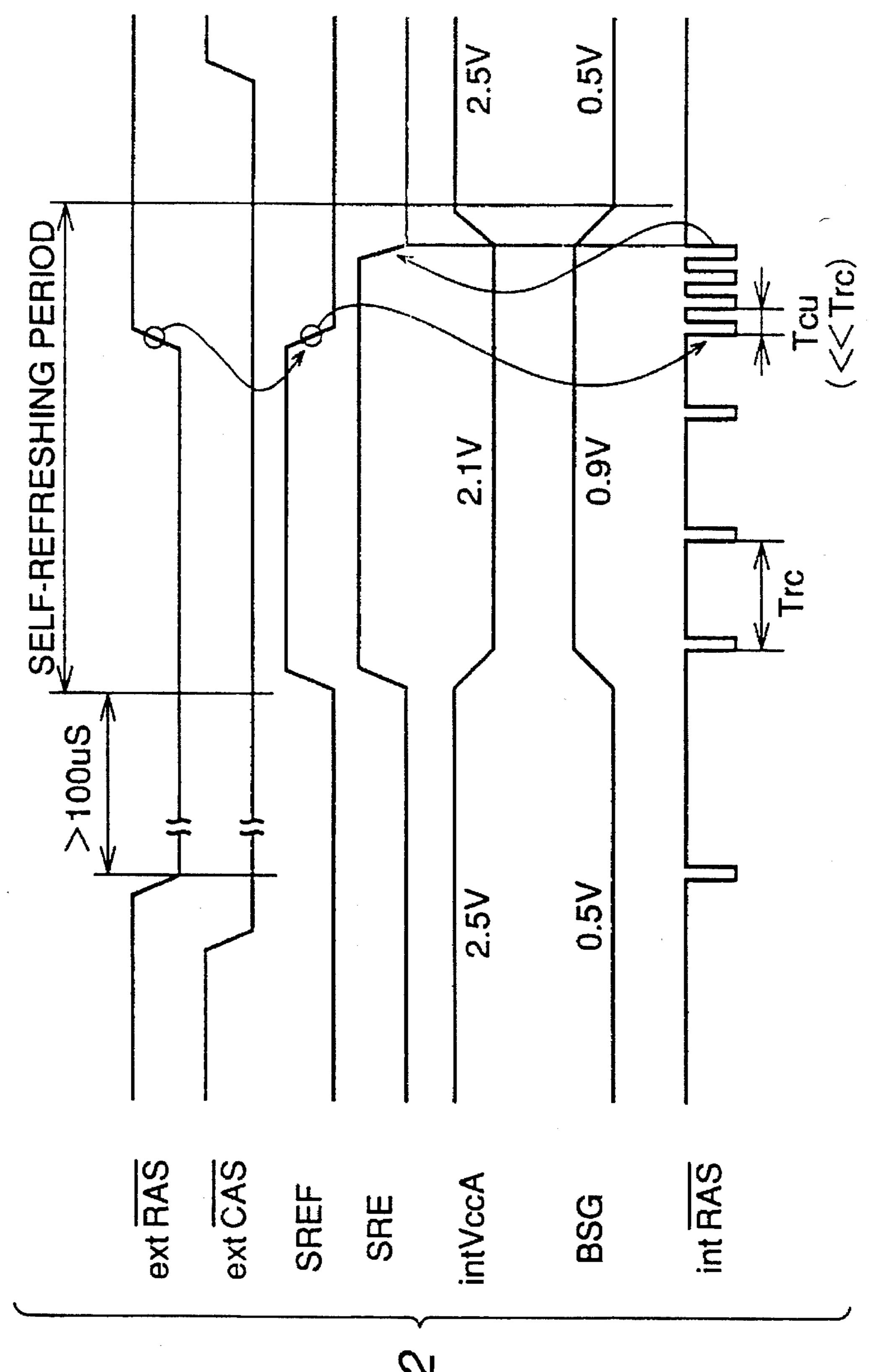

- FIG. 8 is a timing chart showing operation timings of the circuit of FIG. 6 in the self-refreshing operation.

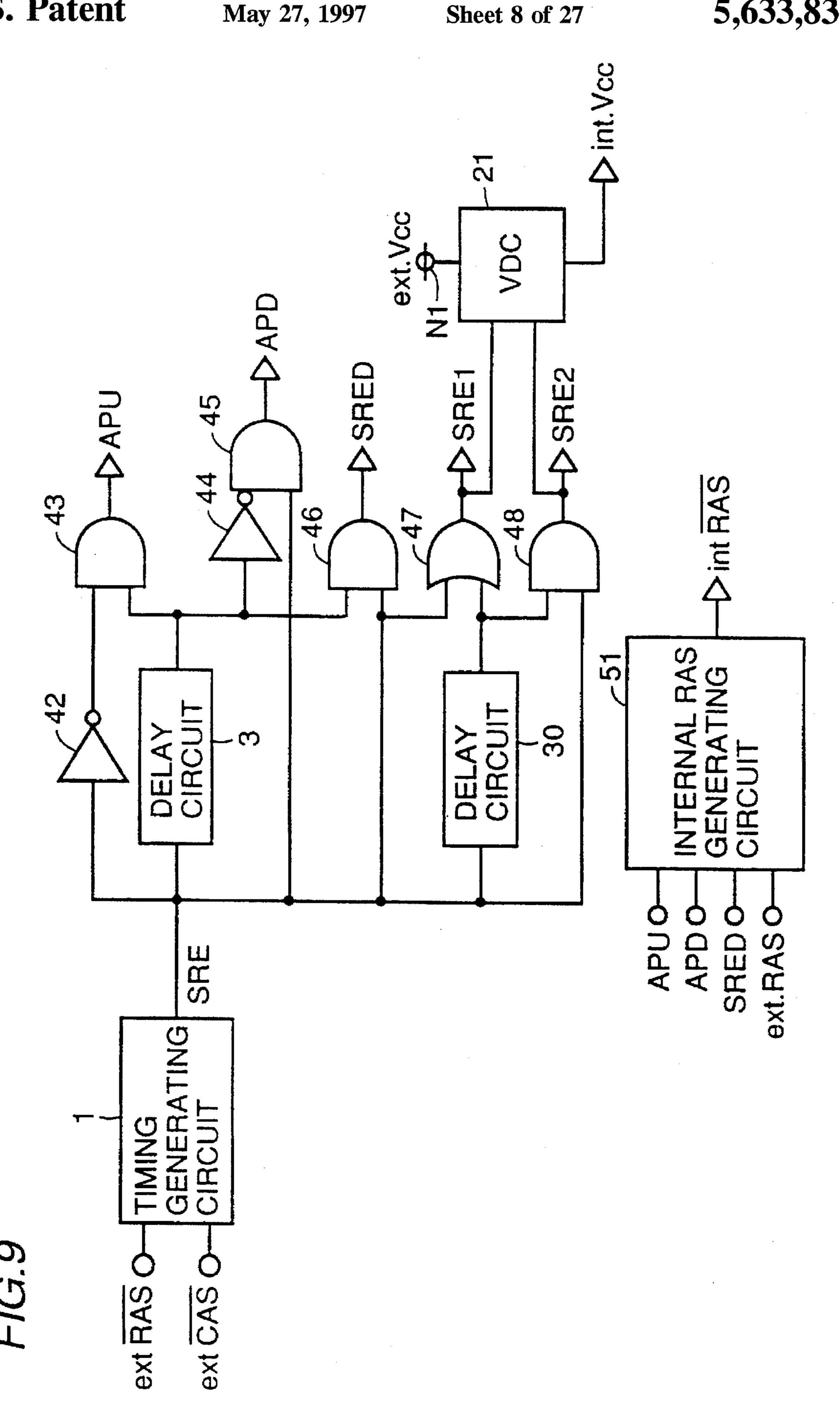

- FIG. 9 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a fourth embodiment.

- FIG. 10 is a circuit diagram showing a configuration of an internal voltage down-converting circuit according to a fourth embodiment.

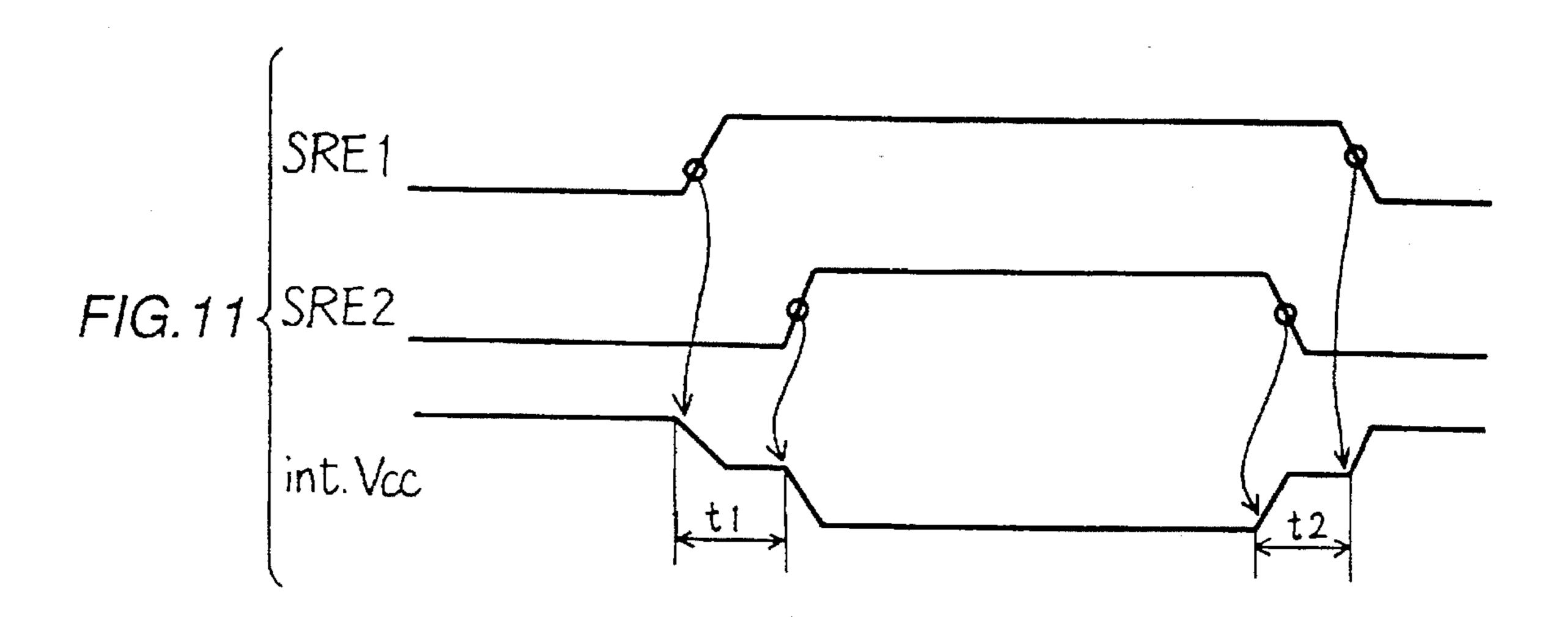

- FIG. 11 is a timing chart showing operation timings of the circuit of FIG. 9 in the self-refreshing operation.

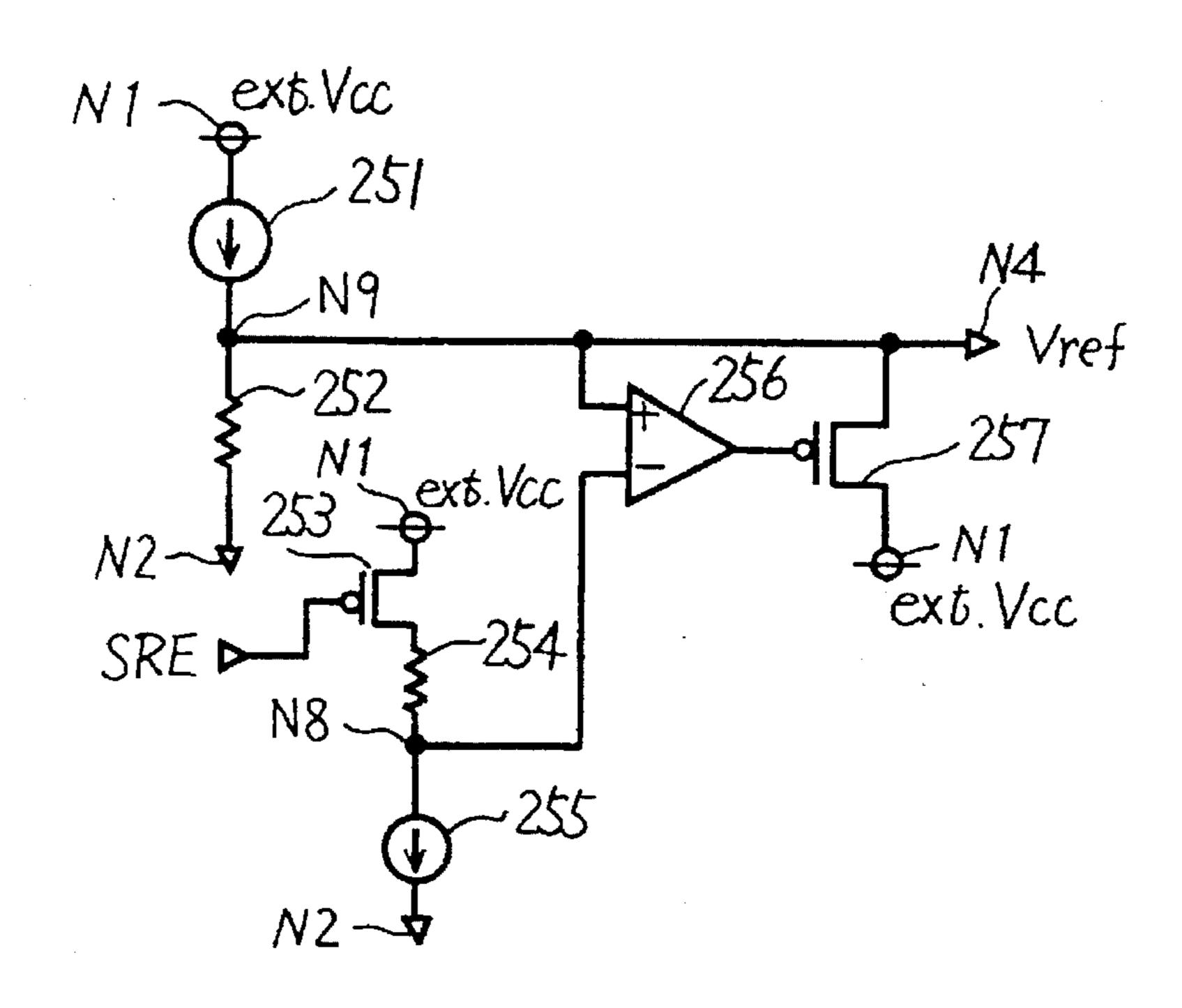

- FIG. 12 is a block diagram showing a configuration of a reference voltage generating circuit of an internal voltage down-converting circuit according to a fifth embodiment.

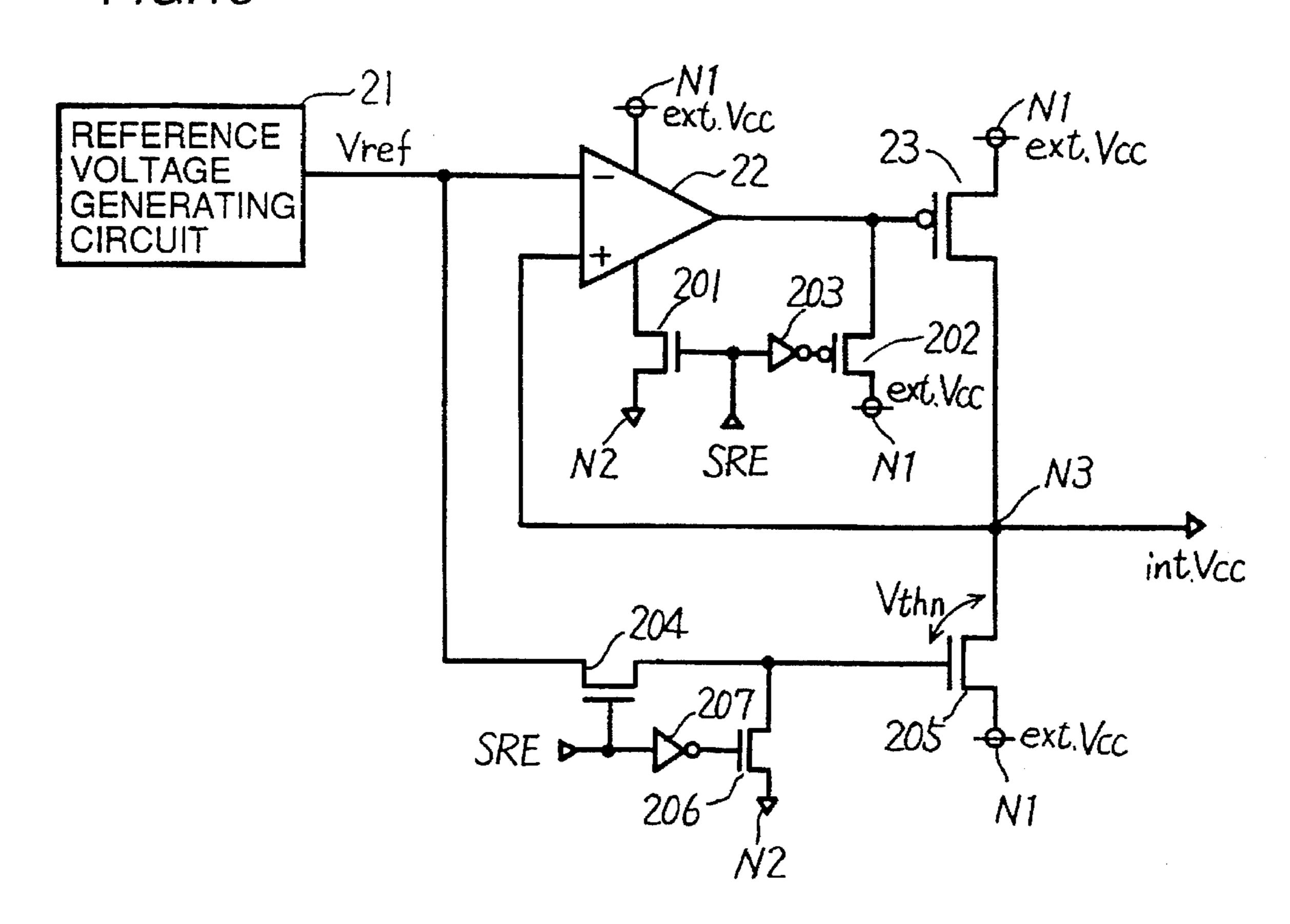

- FIG. 13 is a circuit diagram showing a configuration of an internal voltage down-converting circuit according to a sixth embodiment.

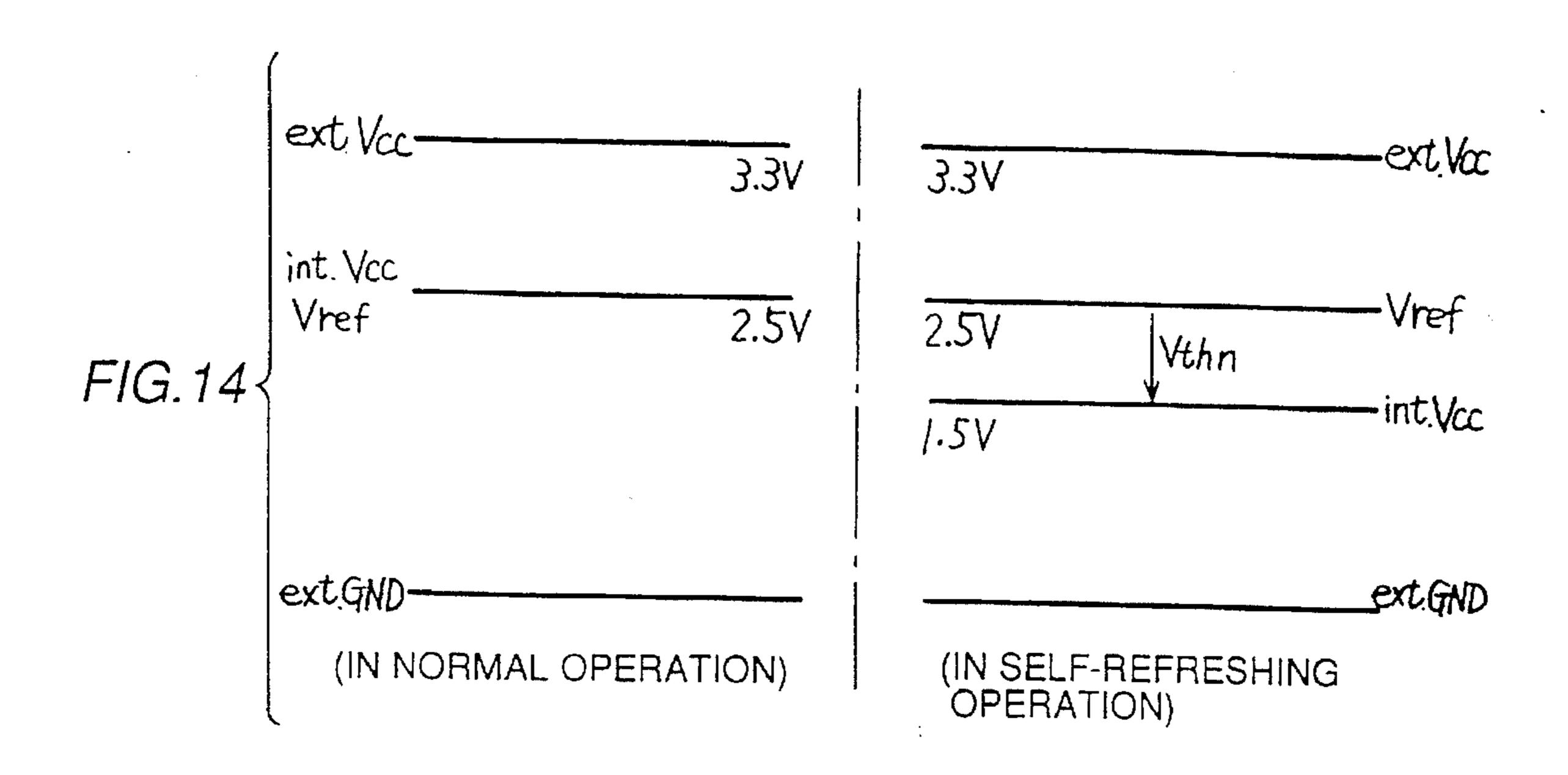

- FIG. 14 is a diagram showing one example of a reference voltage and an internal power supply voltage of the internal voltage down-converting circuit of FIG. 13.

- FIG. 15 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a seventh 60 embodiment.

- FIG. 16 is a diagram showing a method of controlling respective internal power supply voltages of a peripheral circuit and a memory cell array of FIG. 15.

- FIG. 17 is a diagram showing a method of controlling 65 respective internal power supply voltages of the peripheral circuit and the memory cell array of FIG. 15.

- FIG. 18 is a circuit diagram showing a configuration of a boosted voltage generating circuit according to an eighth embodiment.

- FIG. 19 is a circuit diagram showing a configuration of a boosted voltage generating circuit according to a ninth embodiment.

- FIG. 20 is a circuit diagram showing a configuration of an external voltage supplying circuit of a boosted voltage generating circuit according to a tenth embodiment.

- FIG. 21 is a block diagram showing a circuit configuration of a power supply path of a peripheral circuit according to an eleventh embodiment.

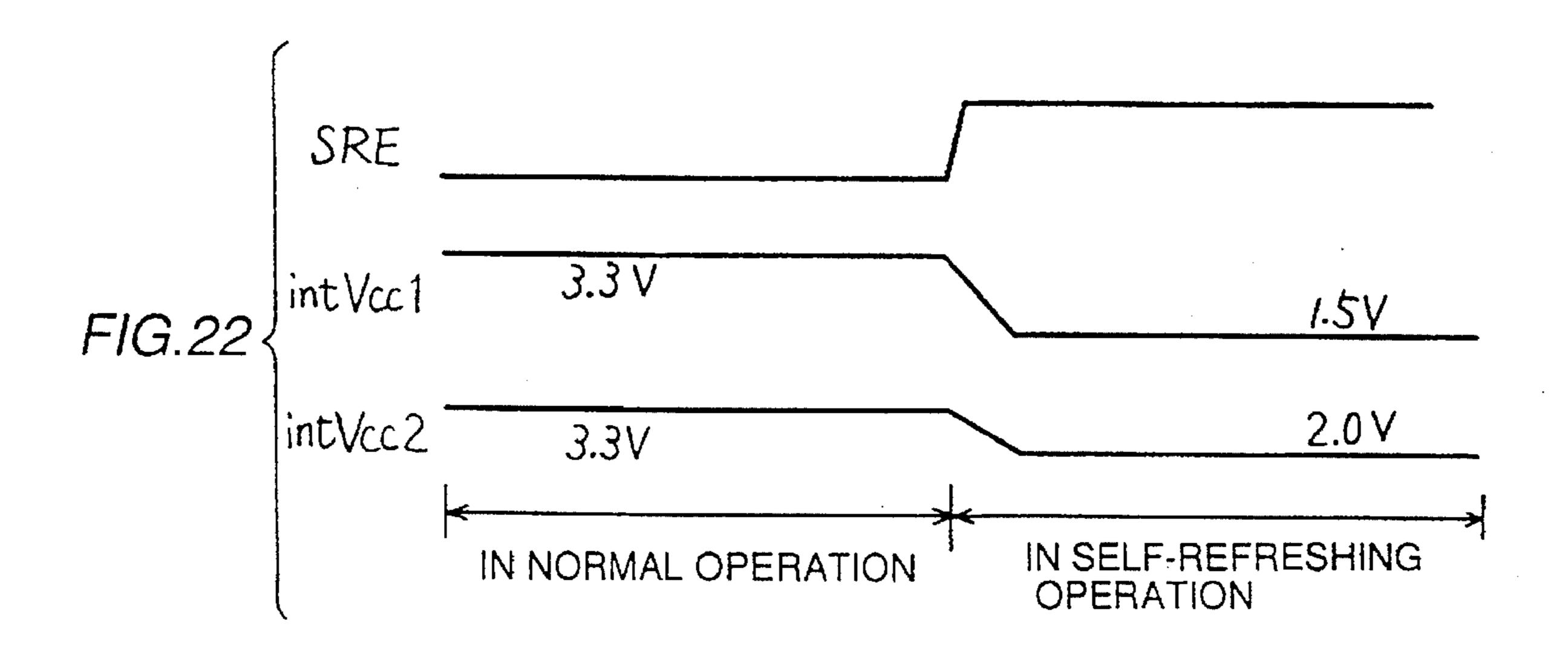

- FIG. 22 is a timing chart showing operation timings of first and second internal voltage down-converting circuits of FIG. 21.

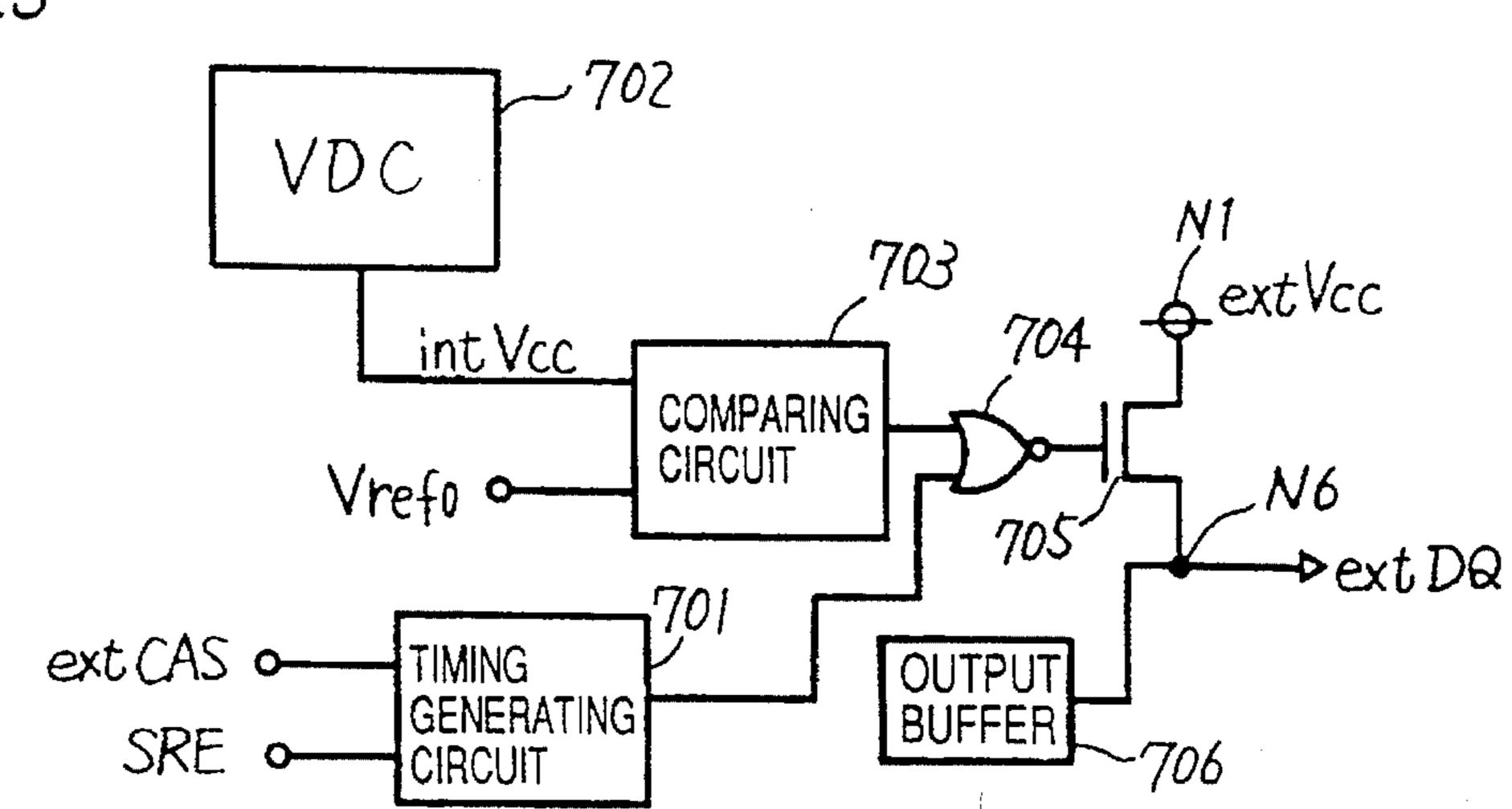

- FIG. 23 is a block diagram of a circuit which provides to the outside world a signal indicating a return state of an internal power supply voltage after completion of selfrefreshing according to a twelfth embodiment.

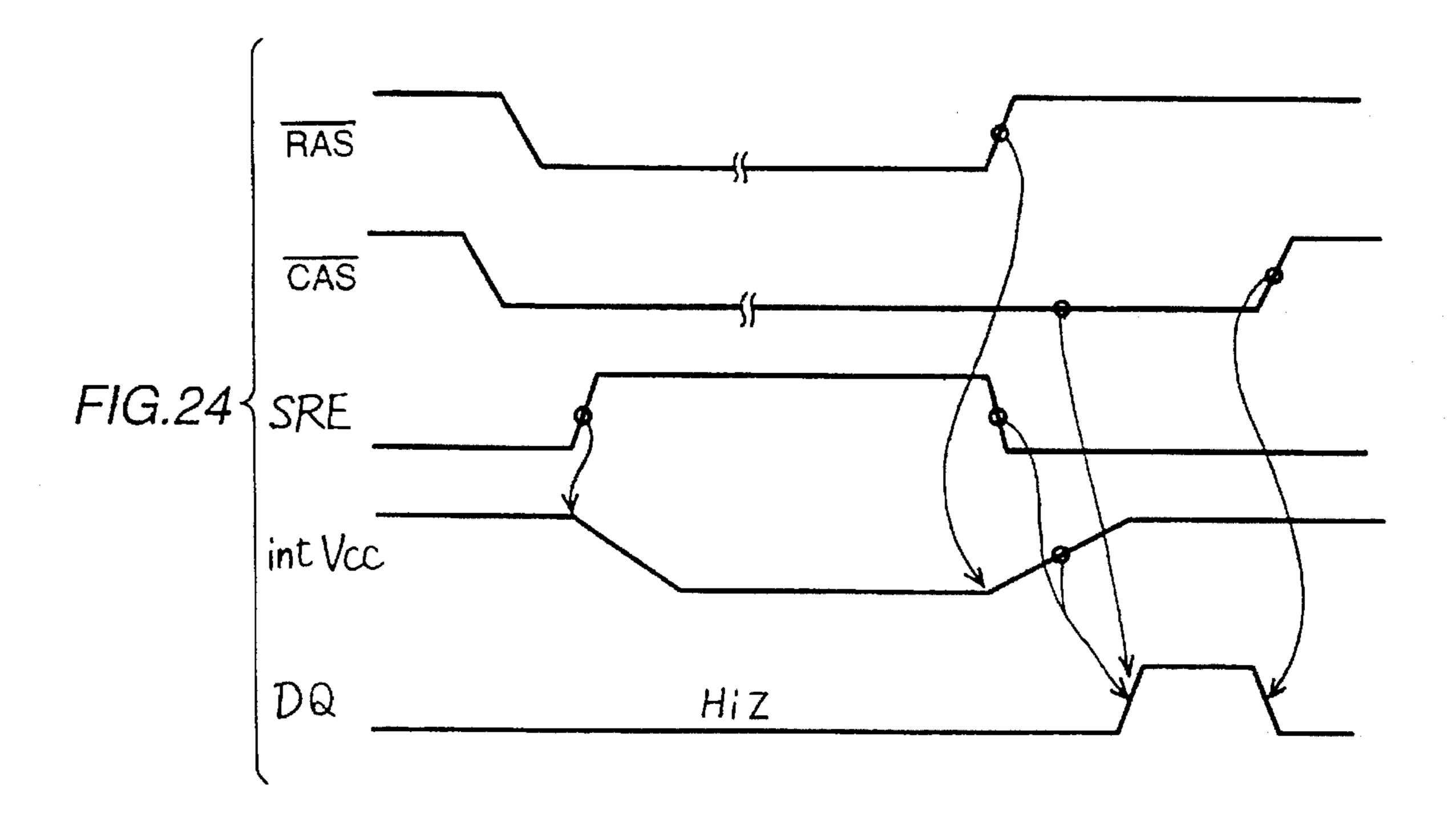

- FIG. 24 is a timing chart showing operation timings of the circuit of FIG. 23.

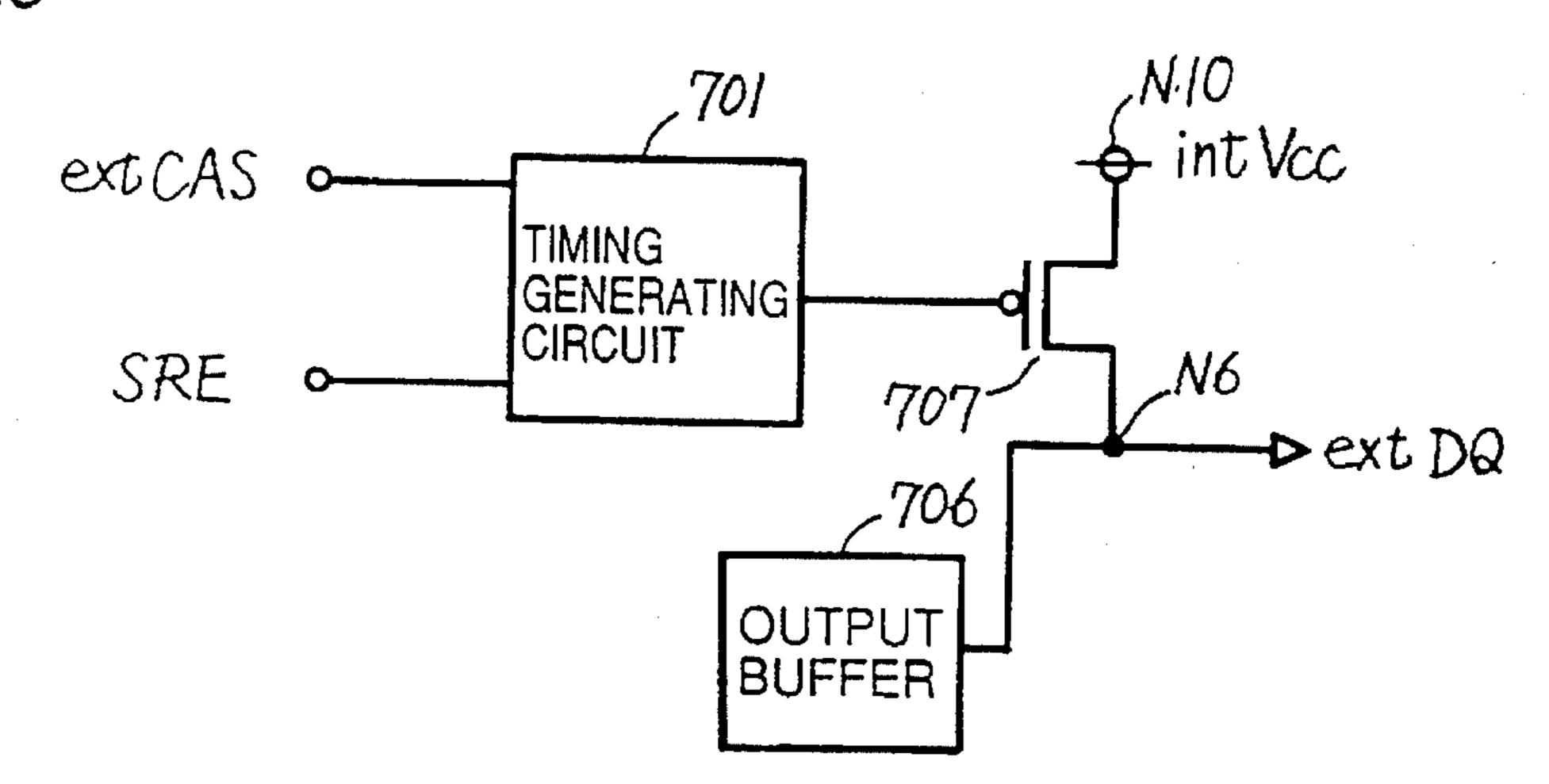

- FIG. 25 is a block diagram of a circuit which provides to the outside world a signal indicating a return state of an internal power supply voltage after completion of selfrefreshing according to a thirteenth embodiment.

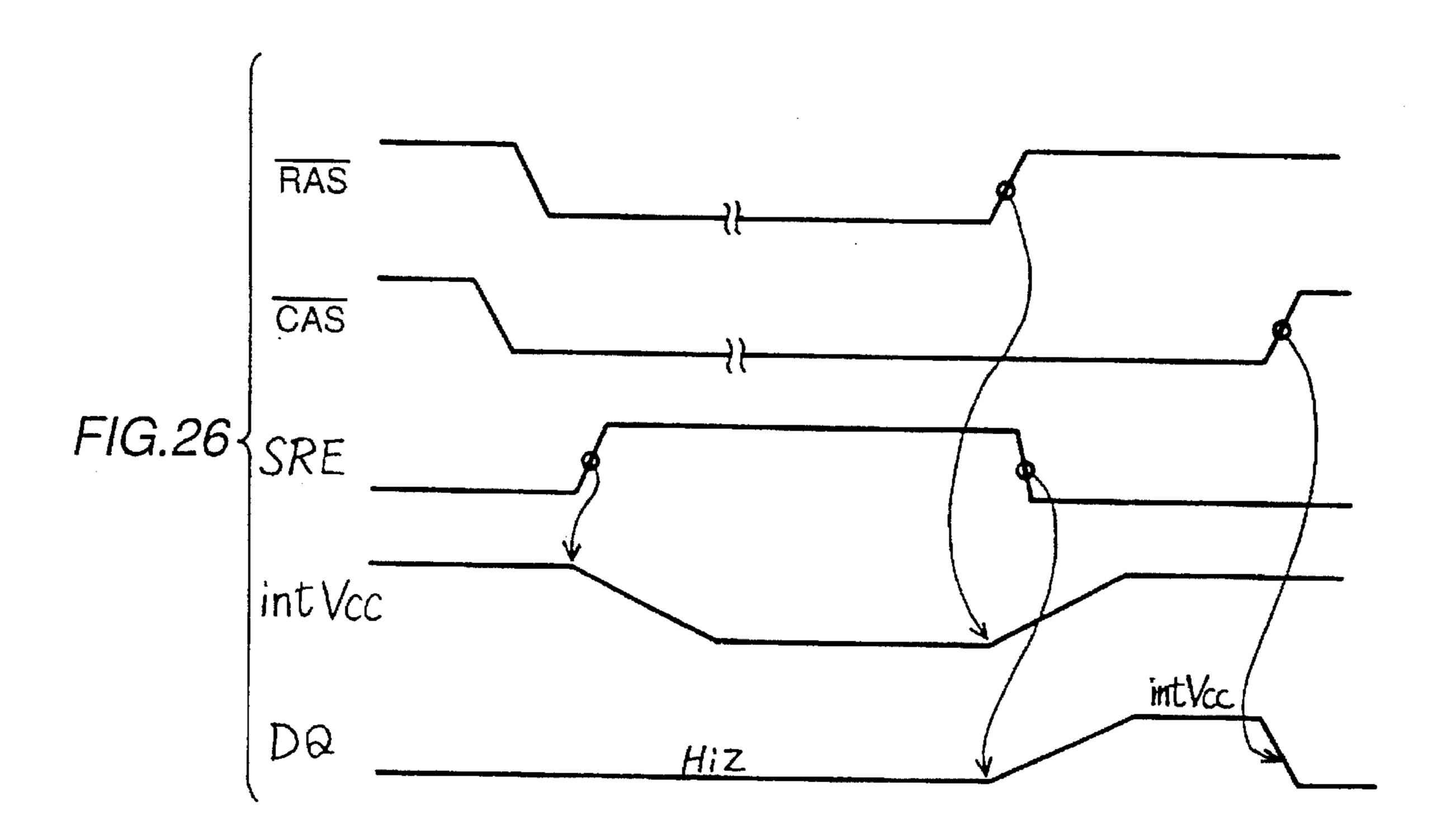

- FIG. 26 is a timing chart showing operation timings of the circuit of FIG. 25.

- FIG. 27 is a diagram showing a circuit portion regarding self-refreshing of a DRAM according to a fourteenth embodiment.

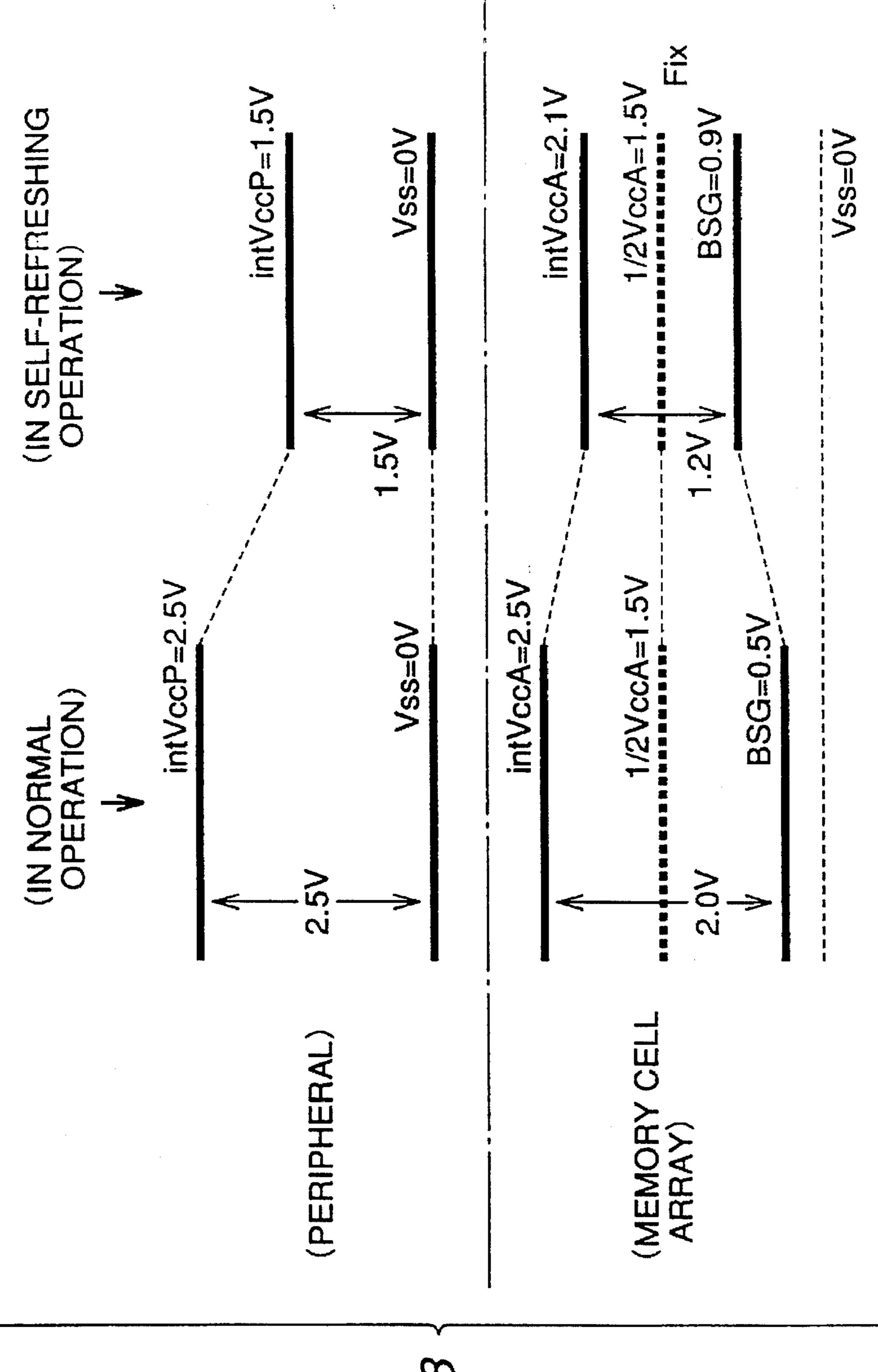

- FIG. 28 is a diagram showing one example of a voltage swing width controlled by the circuit of FIG. 27.

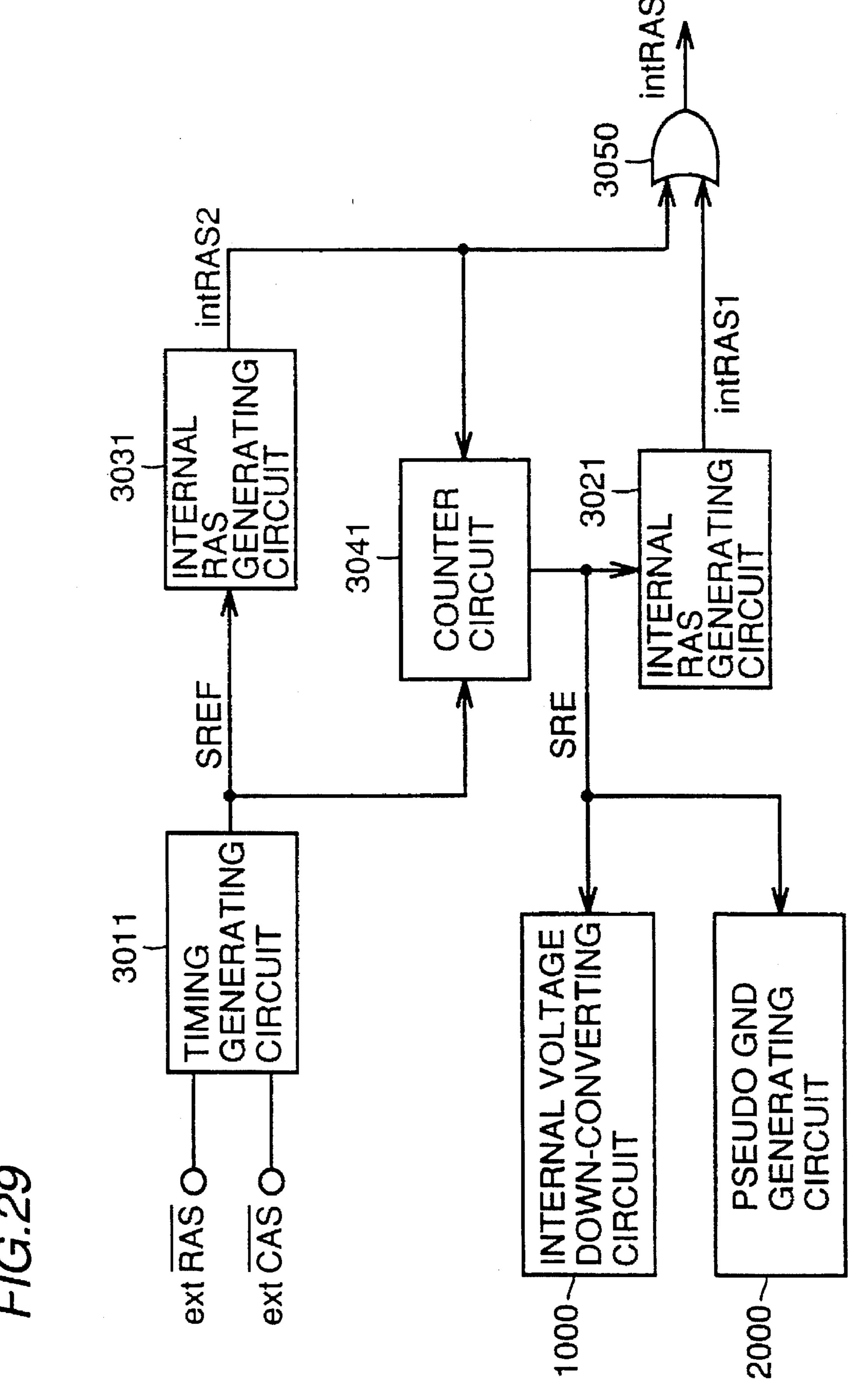

- FIG. 29 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a fifteenth embodiment.

- FIG. 30 is a timing chart showing operation timings of the circuit of FIG. 29 in the self-refreshing operation.

- FIG. 31 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a sixteenth embodiment.

- FIG. 32 is a timing chart showing operation timings of the circuit of FIG. 31 in the self-refreshing operation.

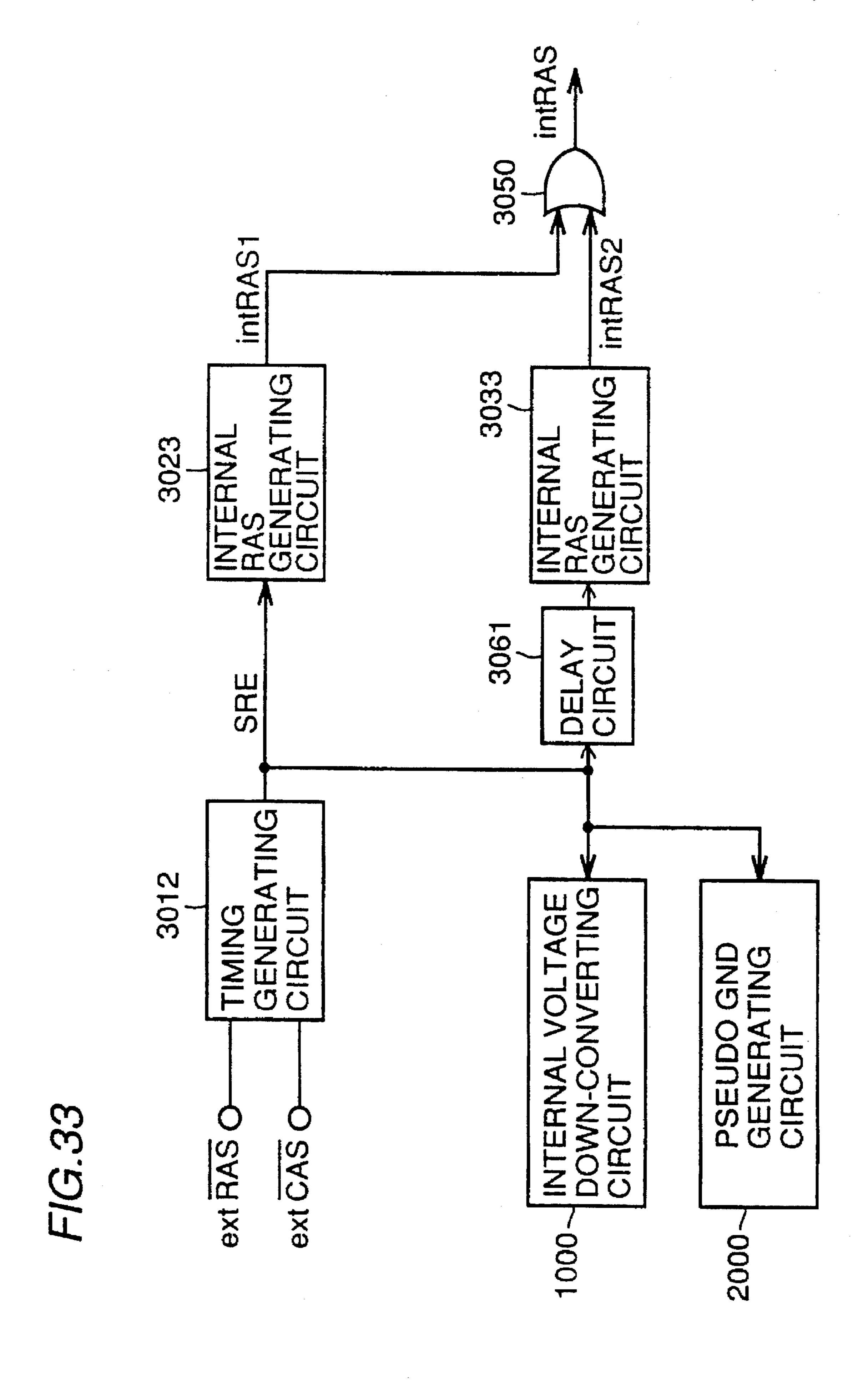

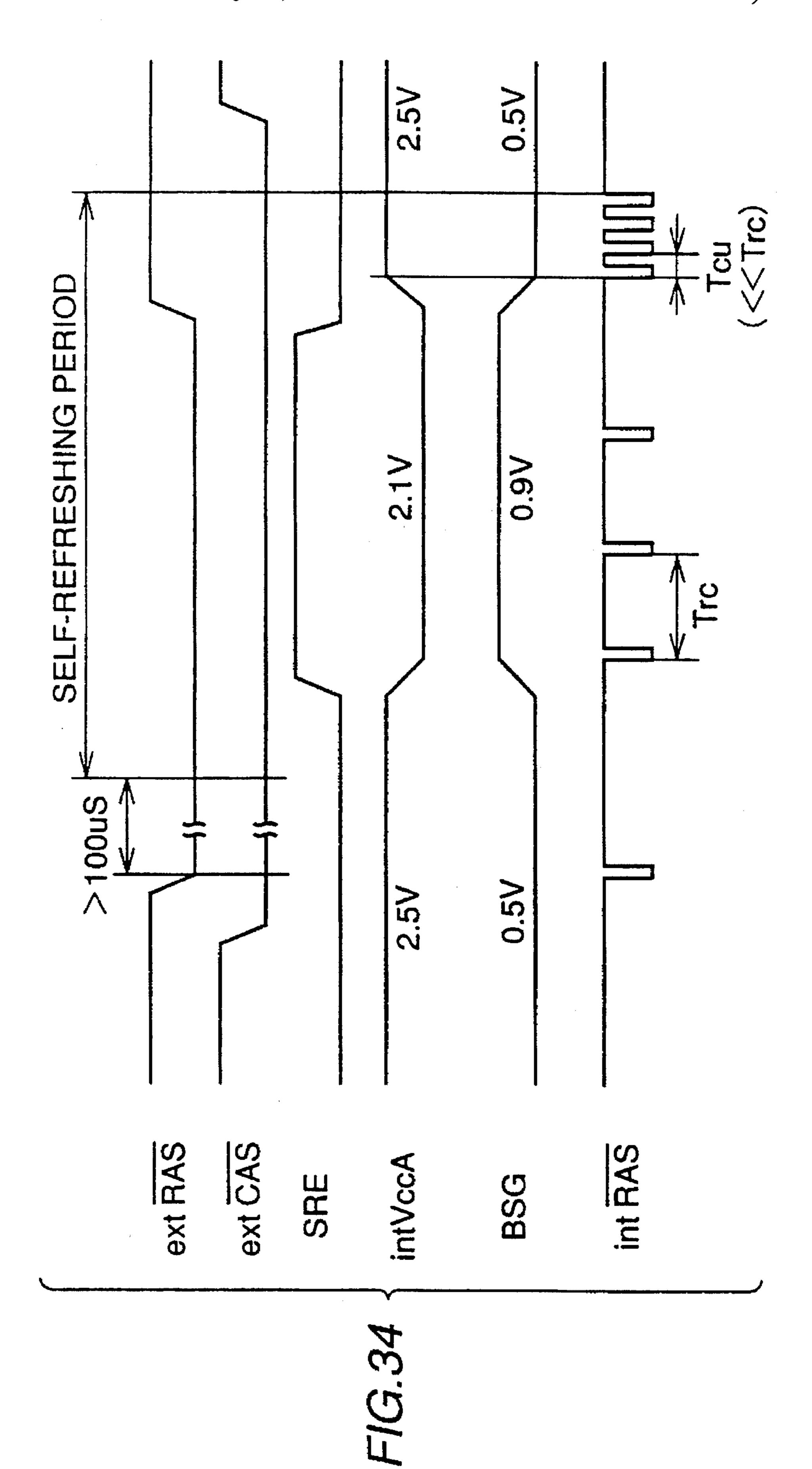

- FIG. 33 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to a seven-teenth embodiment.

- FIG. 34 is a timing chart showing operation timings of the circuit of FIG. 33 in the self-refreshing operation.

- FIG. 35 is a block diagram showing a circuit portion regarding self-refreshing of a DRAM according to an eighteenth embodiment.

- FIG. 36 is a timing chart showing operation timings of the circuit of FIG. 35 in the self-refreshing operation.

- FIG. 37 is a timing chart showing one example of timings in a conventional self-refreshing operation.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

- Embodiments of the present invention will now be described in detail with reference to the drawings.

First Embodiment

- The first embodiment will be described.

- In the following description, a normal operation refers to operation excluding a self-refreshing operation. The normal operation includes a writing operation and a reading operation.

FIG. 1 is a block diagram of a circuit portion regarding self-refreshing of a DRAM according to the first embodiment. Referring to FIG. 1, this circuit includes a timing generating circuit 1, an internal voltage down-converting circuit 2, a delay circuit 3, an AND gate 41, and an internal RAS generating circuit 5.

Timing generating circuit 1 receives an external row address strobe signal extRAS and an external column address strobe signal extCAS, and generates a self-refresh enable signal SRE in response to these signals.

Internal voltage down-converting circuit (VDC) 2 receives an external power supply voltage extVcc from an external power supply node N1 as power supply voltage, and the signal SRE as a control signal. Internal voltage downconverting circuit 2 generates an internal power supply voltage intVcc obtained by down-converting the external power supply voltage extVcc. Internal voltage downconverting circuit 2 controls the level of the internal power supply voltage intVcc in response to the signal SRE.

AND gate 41 receives the signal SRE and a signal obtained by delaying the signal SRE by delay circuit 3, and 20 provides a signal SRED in response to these signals.

Internal RAS generating circuit 5 receives the signal ext RAS and the signal SRED, and generates an internal row address strobe signal intRAS in response to these signals. The signal intRAS is a signal defining a self-refresh cycle. 25

Internal RAS generating circuit 5 of FIG. 1 will now be described in detail.

FIG. 2 is a circuit diagram showing a configuration of internal RAS generating circuit 5 according to the first embodiment. Referring to FIG. 2, internal RAS generating 30 circuit 5 includes a ring oscillator 51, a cycle converter 52, an inverter 53, a buffer 54, and an AND gate 55.

Ring oscillator 51 includes an NAND gate 511 and an inverter group 512 formed of a plurality of series-connected inverters. NAND gate 511 and inverter group 512 are 35 connected in a circular manner. NAND gate 511 receives a signal fed back from one of nodes of inverter group 512, and the signal SRED.

Ring oscillator 51 generates a pulse signal having a predetermined cycle using the signal SRED as a trigger 40 signal. Cycle converter 52 skips pulse signals provided from ring oscillator 51, and generates a pulse signal having a longer cycle than the input pulse signal.

A pulse width trras of the pulse signal generated by cycle converter 52 defines an active period of the self-refreshing 45 operation. Therefore, the pulse width trras of the pulse signal is set to have a sufficient operation margin even in an operating state based on low power supply voltage.

AND gate 55 receives a signal obtained by inverting the pulse signal provided from cycle converter 52 by inverter 50 53, and a signal obtained by the signal extRAS passing through buffer 54. AND gate 55 provides the signal int RAS in response to these signals. More specifically, the internal row address strobe signal intRAS is formed into a pulse signal having a predetermined cycle in a state where 55 of FIG. 1. the signal SRED is at an H or logic high level, and the signal extRAS is at the H level.

Internal voltage down-converting circuit 2 of FIG. 1 will now be described in detail.

internal voltage down-converting circuit 2 according to the first embodiment. Referring to FIG. 3, internal voltage down-converting circuit 2 includes a reference voltage generating circuit 21, a differential amplifier circuit 22, and a PMOS transistor 23.

Reference voltage generating circuit 21 includes a constant current source 211, a resistor 212, a resistor 213, and

an NMOS transistor 214. Constant current source 211 is connected between external power supply node N1 and an output node N7. Resistors 212 and 213 are connected in series between output node N7 and a ground node N2 receiving ground potential. Transistor 214 is connected between output node N7 and a node between resistors 212 and 213. Transistor 214 operates in receipt of the signal SRE at its gate.

Reference voltage generating circuit 21 operates as follows, and generates a reference voltage Vref.

Constant current source 211 generates a constant current i. Therefore, a current from constant current source 211 flows through resistors 212 and 213, and transistor 214. Based on such a current, a resistance value R1 of resistor 15 212, a resistance value R2 of resistor 213, and a resistance value Rtr(t) of transistor 214, the reference voltage Vref which is a voltage at output node N7 is generated. The reference voltage Vref is given by the following expression (1):

$$Vref=I \times \{R1/[1+R1/Rtr(t)+R2]\}$$

(1)

Based on the above expression (1), description will now be given of the reference voltage Vref in the cases where transistor 214 is turned on and off, respectively.

The reference voltage Vref when transistor 214 is completely turned on is given by the following expression (2), wherein Rtr is the on resistance of transistor 214 in this case:

$$Vref=I\times(R1/(1+R1/Rtr)+R2)$$

(2)

The reference voltage Vref when transistor 214 is turned off takes a value given by the following expression (3):

$$Vref=I\times(R1+R2) \tag{3}$$

As described above, the reference voltage Vref generated by reference voltage generating circuit 21 is set lower in the self-refreshing operation in which the signal SRE attains the H level than in the normal operation in which the signal SRE attains an L or logic low level.

Transistor 23 is connected between external power supply node N1 and an output node N3 serving as an internal power supply voltage output node. Differential amplifying circuit 22 receives the reference voltage Vref from reference voltage generating circuit 21 at its negative side input terminal, and the internal power supply voltage intVcc provided from output node N3 at its positive side input terminal.

Differential amplifying circuit 22 differentially amplifies these voltages, and applies the output voltage to the gate of transistor 23. The conductive state of transistor 23 is controlled in response to the voltage which it receives at its gate. Due to change of the conductive state, the internal power supply voltage intVcc is controlled to be the same as the reference voltage Vref.

Description will now be given of operation of the circuit

FIG. 4 is a timing chart showing operation timings of the circuit of FIG. 1 in the self-refreshing operation. Referring to FIG. 4, when a state after the CBR timing is held for a predetermined period, the signal SRE is pulled up to the H FIG. 3 is a circuit diagram showing a configuration of 60 level by timing generating circuit 1. In response to this, internal voltage down-converting circuit 2 pulls down the internal power supply voltage intVcc from, for example, 2.5 V to 1.5 V.

> Then, delayed from the rising of the signal SRE, the output signal of delay circuit 3 attains the H level, causing the signal SRED to rise to the H level. In response to the rising, the signal intRAS provided from internal RAS gen

erating circuit 5 attains a pulse signal state having a predetermined refresh cycle trc, whereby the self-refreshing operation is initiated.

The self-refreshing operation is carried out based on the internal power supply voltage intVcc of, for example, 1.5 V. 5 Therefore, the voltage swing width in this case is 1.5 V which is smaller than 2.5 V in the normal operation.

Then, the signal extRAS rises to the H level. In response to the rising, the signal SRE falls to the L level. This triggers termination of the self-refreshing operation.

In response to the falling of the signal SRE, internal voltage down-converting circuit 2 increases the internal power supply voltage intVcc from, for example, 1.5 V to 2.5 V. In response to the falling of the signal SRE, the signal SRED falls to the L level. In response to the falling, the signal intRAS provided from internal RAS generating circuit 5 stops generation of a pulse, whereby the self-refreshing operation is terminated.

As described above, in the circuit of FIG. 1, the level of the internal power supply voltage intVcc in the self-refreshing operation is controlled to be lower than the level of the internal power supply voltage intVcc in the normal operation. As a result, current consumption in the self-refreshing operation can be reduced.

More specifically, under the condition that the internal power supply voltage intVcc is decreased from 2.5 V in the normal operation to 1.5 V in the self-refreshing operation, current consumption in an active period in the self-refreshing operation is reduced to 1.5/2.5.

As described above, a low internal power supply voltage causes an access speed to decrease. However, since a minimum access speed is enough in the self-refreshing operation, decrease in the access speed is not a big problem. Therefore, it is only necessary that the internal power supply voltage intVcc in the self-refreshing operation is such a voltage as can secure a sufficient margin for the self-refreshing operation.

As described above, in the first embodiment, current consumption in the self-refreshing operation can be reduced by simple control in an internal circuit.

It should be noted that a following circuit may be used as internal voltage down-converting circuit 2 alternatively. Referring to FIG. 3, in the internal voltage down-converting circuit, a capacitor C having a polarity may be provided between the gate of transistor 214 and ground node N2. The capacitor C is an MOS capacitor, for example.

By provision of such capacitor C, it is possible to make different a speed at which the signal SRE which transistor 214 receives at its gate changes from the L level to the H level and a speed at which the signal SRE changes from the H level to the L level because of the capacitance of the capacitor C.

Therefore, it is possible to make different a length of a period in which the internal power supply voltage intVcc is decreased and a length of a period in which the internal power supply voltage intVcc is increased. Preferably, the period in which the internal power supply voltage intVcc is increased is set longer than the period in which the internal power supply voltage intVcc is decreased.

By thus structured, it is possible to increase the internal power supply voltage intVcc slowly in an increase period of the internal power supply voltage, during which the semiconductor memory device is likely to be affected by bump. Therefore, the semiconductor memory device is less likely 65 affected by bump, and the operation of the semiconductor memory device can be stabilized.

Second Embodiment

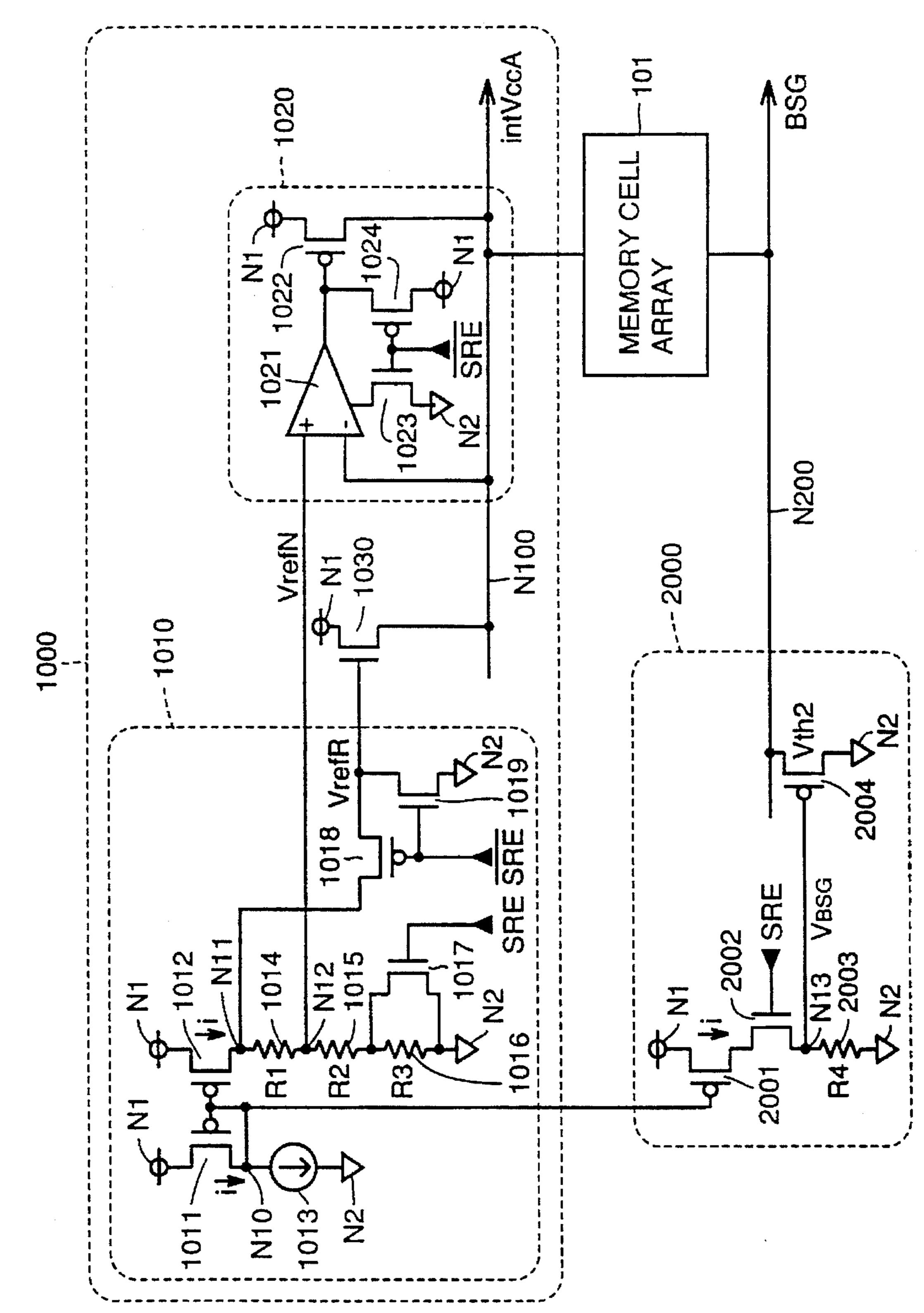

The second embodiment will now be described. In the second embodiment, as another example in which current consumption in the self-refreshing operation is reduced, the case will be described where ground potential of a memory cell array is controlled to be higher than external ground potential extGND in the self-refreshing operation.

FIG. 5 is a block diagram of a circuit portion regarding self-refreshing of a DRAM according to the second embodiment. Referring to FIG. 5, the DRAM includes a memory cell array 101, a peripheral circuit 102, a VBB generating circuit 103, a pseudo GND generating circuit 104, NMOS transistors 105, 106, 108, and an inverter 107.

A ground line 800 receives the external ground potential extGND. Peripheral circuit 102 is connected to ground line 800. Memory cell array 101 is connected to ground line 800 through pseudo GND generating circuit 104 and transistor 108, respectively. In other words, pseudo GND generating circuit 104 and transistor 108 are connected in parallel between memory cell array 101 and ground line 800.

VBB generating circuit 103 generates a substrate potential VBB. Transistors 105 and 106 are connected in series between VBB generating circuit 103 and external ground node N2 receiving the external ground potential extGND. The substrate potential is applied to memory cell array 101 from a node between transistors 105 and 106.

Inverter 107 receives the signal SRE as shown in FIG. 1, and inverts the signal to apply the inverted signal to the gates of transistors 105 and 108. The signal SRE is applied to the gate of transistor 106.

Pseudo GND generating circuit 104 generates a pseudo GND potential. The pseudo GND potential here refers to ground potential at a level between the precharge level of a bit line in memory cell array 101 and the level of the external ground potential extGND.

Specifically, such a pseudo GND potential is generated in pseudo GND generating circuit 104 as follows, for example. Pseudo GND generating circuit 104 includes a pseudo GND line connected to memory cell array 101, and an NMOS transistor connected between the pseudo GND line and ground line 800. Pseudo GND generating circuit 104 generates the pseudo GND potential which is higher than the external ground potential extGND which is a potential of ground line 800 by a threshold voltage of the NMOS transistor, and applies the potential to the pseudo GND line.

Description will now be given of operation of the circuit of FIG. 5.

In the normal operation, the signal SRE is at the L level. In this case, both transistors 105 and 108 are turned on, and transistor 106 is turned off. Therefore, the substrate potential generated by VBB generating circuit 103 is applied to memory cell array 101 through transistor 105. At the same time, the external ground potential extGND is applied to memory cell array 101 through transistor 108.

In the self-refreshing operation, the signal SRE attains the H level. In this case, transistor 106 is turned on, and both transistors 105 and 108 are turned off. Therefore, supply of the substrate potential to memory cell array 101 is stopped. At the same time, the pseudo GND potential from pseudo GND generating circuit 104 is supplied to memory cell array 101 as ground potential.

In such a self-refreshing operation, since the ground potential of memory cell array 101 attains the pseudo GND potential higher than the external ground potential extGND, a voltage swing width of a memory cell is reduced. Therefore, current consumption in the self-refreshing operation is reduced.

Further, since supply of the substrate potential to memory cell array 101 is stopped in the self-refreshing operation, current consumption of VBB generating circuit 103 is reduced. Therefore, current consumption in the selfrefreshing operation is further reduced.

The ground potential of the memory cell array is set to a potential higher than the external ground potential extGND. As a result, a leakage current is reduced, and therefore, it is not necessary to supply the substrate potential to the memory cell array. This is the reason why supply of the 10 substrate potential to memory cell array 101 is stopped in the self-refreshing operation.

In the first embodiment, the internal power supply voltage was decreased in the self-refreshing operation. In the second self-refreshing operation. However, the internal power supply voltage may be decreased, and the ground potential may be increased in the self-refreshing operation. Third Embodiment

The third embodiment will now be described. FIG. 6 is a 20 block diagram of a circuit portion regarding self-refreshing of a DRAM according to the third embodiment.

The circuit of FIG. 6 is different from the circuit of FIG. 1 in the following points. An inverter 44 and an AND gate 45 for generating an internal power supply voltage down 25 activation signal APD defining a period in which the internal power supply voltage is decreased at the beginning of the self-refreshing operation are added to the circuit of FIG. 1.

An inverter 42 and an AND gate 43 for generating an internal power supply voltage up activation signal APU 30 defining a period in which the internal power supply voltage is increased at the end of the self-refreshing operation are further added to the circuit of FIG. 1. In addition, the configuration of an internal RAS generating circuit 51 is different from that of internal RAS generating circuit 5 of 35 a state, a pulse signal having the second cycle tur is provided FIG. 1.

AND gate 43 receives a signal obtained by inversion of the signal SRE by inverter 42, and the output signal of delay circuit 3, and generates the signal APU in response to these signals. AND gate 45 receives a signal obtained by inversion 40 of the output signal of delay circuit 3 by inverter 44, and the signal SRE, and generates the signal APD in response to these signals.

Internal RAS generating circuit 51 receives the signals APU, APD, SRED, and extRAS, and, in response to these 45 signals, generates the signal intRAS at frequencies corresponding to the decrease period, the hold period, and the increase period of the internal power supply voltage intVcc, respectively.

Operation of internal RAS generating circuit 51 will now 50 cycle shorter than the third cycle trc in the hold period. be described in detail.

FIG. 7 is a block diagram showing the configuration of internal RAS generating circuit 51. Referring to FIG. 7, internal RAS generating circuit 51 includes a ring oscillator 501, AND gates 502, 503, 504, cycle converters 505, 506, 55 507, inverters 508, 509, 510, a buffer 511, and a four-input AND gate **512**.

Ring oscillator 501 receives the signal SRE, and generates a pulse signal having a predetermined cycle in response to the signal. AND gate 502 receives the signal APU and the 60 signal APU, and the signal int $\overline{RAS}$ . pulse signal from ring oscillator 501, and generates an output signal in response to these signals. AND gate 503 receives the signal APD and the pulse signal from ring oscillator 501, and generates an output signal in response to these signals. AND gate 504 receives the signal SRED and 65 the pulse signal from ring oscillator 501, and generates an output signal in response to these signals.

**20**

Cycle converter 505 receives the pulse signal from AND gate 502, and, in response to the signal, generates a pulse signal having a first cycle tdr. Cycle converter 506 receives the pulse signal from AND gate 503, and, in response to the 5 signal, generates a pulse signal having a second cycle tur. Cycle converter 507 receives the pulse signal from AND gate 504, and, in response to the signal, generates a pulse signal having a third cycle trc.

The pulse signal generated by cycle converter 505 is inverted through inverter 508, and applied to AND gate 512. The pulse signal generated by cycle converter 506 is inverted through inverter 509, and applied to AND gate 512. The pulse signal generated by cycle converter 507 is inverted through inverter 510, and applied to AND gate 512. embodiment, the ground potential was increased in the 15 Further, extRAS which is an inverted signal of the signal ext RAS is applied to AND gate 512 through buffer 511.

> In response to the four applied signals, AND gate 512 generates the signal int $\overline{RAS}$ .

> In such internal RAS generating circuit 51, the signal SRE and the signal extRAS both attain the H level when the self-refreshing operation is carried out. Therefore, the pulse signal is generated in ring oscillator 501.

> When the signal APD attains the H level in this state, the pulse signal is provided from AND gate 502. Therefore, the pulse signal having the first cycle tdr from cycle converter 505 is inverted by inverter 508, and applied to AND gate 512. In this state, since the signals applied from inverter 509 and inverter 510 to AND gate 512 are both at the H level, the signal intRAS provided from AND gate 512 is formed into a pulse signal having the first cycle tdr.

> Similarly, when the signal SRED attains the H level in such a state, the intRAS provided from AND gate 512 is formed into a pulse signal having the third cycle trc. Similarly, when the signal APU attains the H level in such from AND gate 512.

> As described above, in internal RAS generating circuit 51, a pulse signal having three kinds of cycles is generated as the signal intRAS in response to the signal APD, the signal SRED, and the signal APU, respectively.

> The above described first to third cycles are set to be optimal for the decrease period, the hold period, and the increase period of the internal power supply voltage intVcc, respectively. Since the decrease period and the increase period are transition periods of the internal power supply voltage intVcc, the semiconductor memory device is likely to be affected by bump or the like in these periods. Therefore, in order to decrease the influence of bump or the like, the first cycle tdr and the second cycle tur are set to a

> As a result, the semiconductor memory device is less likely to be affected by bump or the like in the decrease period and the increase period of the internal power supply voltage intVcc in the self-refreshing operation.

> Operation of the circuit of FIG. 6 will now be described. FIG. 8 is a timing chart showing operation timings of the circuit of FIG. 6 in the self-refreshing operation. The operation timings of FIG. 8 are different from those of FIG. 4 in respective changes of the signal SRED, the signal APD, the

> The internal power supply voltage intVcc changes similar to the case of FIG. 4.

> When the signal SRE rises to the H level, the signal APD rises in response to this. The signal APD is held at the H level corresponding to the decrease period of the internal power supply voltage intVcc. As a result, the signal int RAS is formed into a pulse signal having the first cycle tdr

in a period in which the signal APD is at the H level, that is, in the decrease period of the internal power supply voltage intVcc. Accordingly, the self-refreshing operation is carried out in the first cycle tdr.

After a delay time of the signal in delay circuit 3, the signal APD falls to the L level, and the signal SRED rises to the H level. The signal SRED is held at the H level corresponding to a period in which the internal power supply voltage intVcc is held at a low level. The signal intRAS is formed into a pulse signal having the third cycle trc in a 10 period in which the signal SRED is held at the H level, that is, in the hold period of the internal power supply voltage intVcc. Therefore, in the hold time of the internal power supply voltage intVcc, the self-refreshing operation is carried out in the third cycle trc.

Then, the signal SRE falls to the L level. In response to the falling, the signal SRED falls to the L level, and the signal APU rises to the H level. The signal APU is held at the H level corresponding to the increase period of the internal power supply voltage intVcc. Therefore, the signal 20 intRAS is formed into a pulse signal having the second cycle tur in a period in which the signal APU is held at the H level, that is, in the increase period of the internal power supply voltage intVcc. Therefore, in the increase period of the internal power supply voltage intVcc, the self-refreshing 25 operation is carried out in the second cycle tur.

As described above, in the third embodiment, current consumption in the self-refreshing operation can be reduced by simple control in an internal circuit similar to the case of the first embodiment. In addition, in the third embodiment, 30 since self-refreshing is carried out in an optimum cycle in which the semiconductor memory device is less likely to be affected by bump or the like in the decrease period and in the increase period of the internal power supply voltage inVcc, the self-refreshing operation can be more stabilized than the 35 case of the first embodiment.

In the third embodiment, the voltage swing width was reduced by decreasing the internal power supply voltage intVcc in the self-refreshing operation. However, this embodiment is not limited thereto. In this embodiment, the 40 voltage swing width may be reduced by increasing the ground potential as shown in the second embodiment. Both the decrease control and the increase control may be used. Fourth Embodiment

The fourth embodiment of the present invention will now 45 be described.

FIG. 9 is a block diagram of a circuit portion regarding self-refreshing of a DRAM according to the fourth embodiment. Referring to FIG. 9, the circuit of FIG. 9 is different from that of FIG. 6 in the following points.

In order to generate signals SRE1 and SRE2 defining periods in which the internal power supply voltage intVcc is decreased and increased in the self-refreshing operation in a plurality of stages, respectively, a delay circuit 30, an OR gate 47, and an AND gate 48 are provided in addition to the 55 circuit of FIG. 6.

Further, the configuration of an internal voltage down-converting circuit 21 is different from that of internal voltage down-converting circuit 2 of FIG. 6.