### US005384912A

# United States Patent [19]

# Ogrinc et al.

[11] Patent Number:

5,384,912

[45] Date of Patent:

Jan. 24, 1995

# [54] REAL TIME VIDEO IMAGE PROCESSING SYSTEM

[75] Inventors: Michael A. Ogrinc, San Francisco; Robert A. Card, Palo Alto; Chris R.

Burns, Mountain View; Charles P. Clarke, Los Altos; Ronda L. Collier, Scotts Valley; Kevin M. Collins, San Mateo; Stephen E. Crane, Menlo

Park; Clifford Hersh, Berkeley; Brian C. Knittel, Palo Alto; Steven T. Mayer, Los Altos Hills; Lawrence Stead, Mountain View; Andrew E. Wade, Los Altos; Robert L. Lay, San Anselmo; Bradley G. Stewart, San Jose; Raymond Pon, Oakland; Robert Leyland, Novato; John F. Schlag, San

Rafael; Sven Jensen, Palo Alto, all of

Calif.

[73] Assignee: New Microtime Inc., Bloomfield,

Conn.

[21] Appl. No.: **892,607**

[22] Filed: May 29, 1992

## Related U.S. Application Data

[63] Continuation of Ser. No. 116,801, Oct. 30, 1987, abandoned.

[56] References Cited

U.S. PATENT DOCUMENTS

### FOREIGN PATENT DOCUMENTS

0239299 9/1987 European Pat. Off. .... G06F 11/16

Primary Examiner—Phu K. Nguyen Attorney, Agent, or Firm—Skjerven, Morrill, MacPherson, Franklin & Friel

[57] ABSTRACT

A video digital signal processing and display system that allows real time processing of video images with extensive filtering and inter-pixel interpolation. The system includes a front end user and program interface supported by a personal computer, and also includes a microprocessor for controlling the system and specialized video circuitry including an image translator.

The image translator performs image translation, perspective projection, scaling, rotation, border insertion, and formation of composite images. The image translator interacts with the other specialized video circuitry which includes a frame constructor, a keyer and crosspoint switches, and a frame store constructor.

# 10 Claims, 26 Drawing Sheets

FIG. 19

| S. Patent   | Jan. 24, 1995 | Sheet 10 of 26 | 5,384,912   |

|-------------|---------------|----------------|-------------|

|             |               |                |             |

| 00 01 02 03 | 01 02 03 00   | 02 03 00 01    | 03 00 01 02 |

| 10 11 12 13 | 11 12 13 10   | 12 13 10 11    | 13 10 11 12 |

| 20 21 22 23 | 21 22 23 20   | 22 23 20 21    | 23 20 21 22 |

| 30 31 32 33 | 31 32 33 30   | 32 33 30 31    | 33 30 31 32 |

| S0-S3=0     | S0-S3=1       | S0-S3=2        | S0-S3=3     |

| 10 11 12 13 | 11 12 13 10   | 12 13 10 11    | 13 10 11 12 |

| 20 21 22 23 | 21 22 23 20   | 22 23 20 21    | 23 20 21 22 |

| 30 31 32 33 | 31 32 33 30   | 32 33 30 31    | 33 30 31 32 |

| 00 01 02 03 | 01 02 03 00   | 02 03 00 01    | 03 00 01 02 |

| S0-S3=4     | S0-S3=5       | S0-S3=6        | S0-S3=7     |

| 20 21 22 23 | 21 22 23 20 - | 22 23 20 21    | 23 20 21 22 |

| 30 31 32 33 | 31 32 -33 30  | 32 33 30 31    | 33 30 31 32 |

| 00 01 02 03 | 01 02 03 00   | 02 03 00 01    | 03 00 01 02 |

| 10 11 12 13 | 11 12 13 10   | 12 13 10 11    | 13 10 11 12 |

| S0-S3=8     | S0-S3=9       | S0-S3=10       | S0-S3=11    |

| 30 31 32 33 | 31 32 33 30   | 32 33 30 31    | 33 30 31 32 |

| 00 01 02 03 | 01 02 03 00   | 02 03 00 01    | 03 00 01 02 |

| 10 11 12 13 | 11 12 13 10   | 12 13 10 11    | 13 10 11 12 |

| 20 21 22 23 | 21 22 23 20   | 22 23 20 21    | 23 20 21 22 |

| S0-S3=12    | S0-S3=13      | S0-S3=14       | S0-S3=15    |

|             |               |                | FIC 96      |

FIG. 26

| IO         | I1         | I2         | IJ  |  |

|------------|------------|------------|-----|--|

| <b>I</b> 4 | <b>I</b> 5 | <b>I</b> 6 | 17  |  |

| 18         | <b>I</b> 9 | I10        | I11 |  |

| I12        | I13        | I14        | I15 |  |

U.S. Patent

INPUT TABLE

FIG. 27

| МО  | M1  | M2  | МЗ  |

|-----|-----|-----|-----|

| M4  | M5  | M6  | M7  |

| M8  | М9  | M10 | M11 |

| M12 | M13 | M14 | M15 |

OUTPUT TABLE

FIG. 28

| (0,0) (1,0)   | (2,0) $(3,0)$                  | (4,0) | (5,0)  | . (6,0) | ·<br>(7,0) | (8,0) | ·<br>(9,0) |

|---------------|--------------------------------|-------|--------|---------|------------|-------|------------|

| (0,1)         | (3,1)                          | (4,1) | •      | •       | (7,1)      | •     | •          |

| (0,2)         | (3,2)                          | (4,2) | •<br>D | •       | (7,2)      | •     | •          |

| (0,3) [ (1,3) | (2,3) (3,3)                    | (4,3) | (5,3)  | (6,3)   | (7,3)      | (8,3) | (9,3)      |

| (0,4) (1,4)   | $(2,4)$ $(3,4)$ $\odot P(X,Y)$ | (4,4) | (5,4)  | (6,4)   | (7,4)      | (8,4) |            |

| (0,5)   (1,5) | (2,5) (3,5)                    | (4,5) |        | •       | (7,5)      | •     | •          |

| (0,6) $(1,6)$ | (2,6) (3,6)                    | (4,6) |        |         | (7,6)      |       | •          |

| (0,7) (1,7)   | (2,7) (3,7)                    | (4,7) | (5,7)  | (6,7)   | (7,7)      | (8,7) | (9,7)      |

| (0,8)         | . (3,8)                        | (4,8) | •      | •       | (7,8)      | •     | •          |

| (0,9)         | (3,9)                          | (4,9) | •      | •       | (7,9)      |       | •          |

FIG. 29

FIG. 30

FIG. 31

| HORIZONTAL AND | VERTICAL MIRRORED |             |             |     |

|----------------|-------------------|-------------|-------------|-----|

| 33 32 31 30    | 32 31 30 33       | 31 30 33 32 | 30 33 32 31 |     |

| 23 22 21 20    | 22 21 20 23       | 21 20 23 22 | 20 23 22 21 |     |

| 13 12 11 10    | 12 11 10 13       | 11 10 13 12 | 10 13 12 11 |     |

| 03 02 01 00    | 02 01 00 03       | 01 00 03 02 | 00 03 02 01 |     |

| S0-S3=0        | S0-S3=1           | S0-S3=2     | S0-S3=3     |     |

| 23 22 21 20    | 22 21 20 23       | 21 20 23 22 | 20 23 22 21 |     |

| 13 12 11 10    | 12 11 10 13       | 11 10 13 12 | 10 13 12 11 |     |

| 03 02 01 00    | 02 01 00 03       | 01 00 03 02 | 00 03 02 01 |     |

| 33 32 31 30    | 32 31 30 33       | 31 30 33 32 | 30 33 32 31 |     |

| S0-S3=4        | S0-S3=5           | S0-S3=6     | S0-S3=7     |     |

| 13 12 11 10    | 12 11 10 13       | 11 10 13 12 | 10 13 12 11 |     |

| 03 02 01 00    | 02 01 00 03       | 01 00 03 02 | 00 03 02 01 |     |

| 33 32 31 30    | 32 31 30 33       | 31 30 33 32 | 30 33 32 31 |     |

| 23 22 21 20    | 22 21 20 23       | 21 20 23 22 | 20 23 22 21 |     |

| S0-S3=8        | S0-S3=9           | S0-S3=10    | S0-S3=11    |     |

| 03 02 01 00    | 02 01 00 03       | 01 00 03 02 | 00 03 02 01 | FIG |

| 33 32 31 30    | 32 31 30 33       | 31 30 33 32 | 30 33 32 31 |     |

| 23 22 21 20    | 22 21 20 23       | 21 20 23 22 | 20 23 22 21 |     |

| 13 12 11 10    | 12 11 10 13       | 11 10 13 12 | 10 13 12 11 |     |

| S0-S3=12       | S0-S3=13          | S0-S3=14    | S0-S3=15    |     |

| U.S. Patent         | Jan. 24, 19 | 995      | Sheet | 13 of 26    | 5,384,912 |

|---------------------|-------------|----------|-------|-------------|-----------|

| HORIZONTAL MIRROREI |             |          |       |             |           |

| 03 02 01 00 01      | 01 00 03    | 01 00 0. | 3 02  | 00 03 02 01 |           |

| HORIZONTAL MIRRO                                                          | RED         |             |                         |

|---------------------------------------------------------------------------|-------------|-------------|-------------------------|

| 03 02 01 00                                                               | 02 01 00 03 | 01 00 03 02 | 00 03 02 01             |

| 13 12 11 10                                                               | 12 11 10 13 | 11 10 13 12 | 10 13 12 11             |

| 23 22 21 20                                                               | 22 21 20 23 | 21 20 23 22 | 20 23 22 21             |

| 33 32 31 30                                                               | 32 31 30 33 | 31 30 33 32 | 30 33 32 31             |

| S0-S3=0                                                                   | S0-S3=1     | S0-S3=2     | S0-S3=3                 |

| 13 12 11 10                                                               | 12 11 10 13 | 11 10 13 12 | 10 13 12 11             |

| 23 22 21 20                                                               | 22 21 20 23 | 21 20 23 22 | 20 23 22 21             |

| 33 32 31 30                                                               | 32 31 30 33 | 31 30 33 32 | 30 33 32 31             |

| 03 02 01 00                                                               | 02 01 00 03 | 01 00 03 02 | 00 03 02 01             |

| S0-S3=4                                                                   | S0-S3=5     | S0-S3=6     | S0-S3=7                 |

| 23 22 21 20                                                               | 22 21 20 23 | 21 20 23 22 | 20 23 22 21             |

| 33 32 31 30                                                               | 32 31 30 33 | 31 30 33 32 | 30 33 32 31             |

| 03 02 01 00                                                               | 02 01 00 03 | 01 00 03 02 | 00 03 02 01             |

| 13 12 11 10                                                               | 12 11 10 13 | 11 10 13 12 | 10 13 12 11             |

| S0-S3=8                                                                   | S0-S3=9     | S0-S3=10    | S0-S3=11                |

| 33 32 31 30                                                               | 32 31 30 33 | 31 30 33 32 | 30 33 32 31             |

| 03 02 01 00                                                               | 02 01 00 03 | 01 00 03 02 | 00 03 02 01             |

| 13 12 11 10                                                               | 12 11 10 13 | 11 10 13 12 | 10 13 12 11             |

| 23 22 21 20                                                               | 22 21 20 23 | 21 20 23 22 | 20 23 22 21             |

| S0-S3=12                                                                  | S0-S3=13    | S0-S3=14    | S0-S3=15 <i>FIG.</i> 32 |

| VERTICAL MIRROREI 30 31 32 33 20 21 22 23 10 11 12 13 00 01 02 03 S0-S3=0 | 31 32 33 30 | 32 33 30 31 | 33 30 31 32             |

|                                                                           | 21 22 23 20 | 22 23 20 21 | 23 20 21 22             |

|                                                                           | 11 12 13 10 | 12 13 10 11 | 13 10 11 12             |

|                                                                           | 01 02 03 00 | 02 03 00 01 | 03 00 01 02             |

|                                                                           | S0-S3=1     | S0-S3=2     | S0-S3=3                 |

| 20 21 22 23                                                               | 21 22 23 20 | 22 23 20 21 | 23 20 21 22             |

| 10 11 12 13                                                               | 11 12 13 10 | 12 13 10 11 | 13 10 11 12             |

| 00 01 02 03                                                               | 01 02 03 00 | 02 03 00 01 | 03 00 01 02             |

| 30 31 32 33                                                               | 31 32 33 30 | 32 33 30 31 | 33 30 31 32             |

| S0-S3=4                                                                   | S0-S3=5     | S0-S3=6     | S0-S3=7                 |

| 10 11 12 13                                                               | 11 12 13 10 | 12 13 10 11 | 13 10 11 12             |

| 00 01 02 03                                                               | 01 02 03 00 | 02 03 00 01 | 03 00 01 02             |

| 30 31 32 33                                                               | 31 32 33 30 | 32 33 30 31 | 33 30 31 32             |

| 20 21 22 23                                                               | 21 22 23 20 | 22 23 20 21 | 23 20 21 22             |

| S0-S3=8                                                                   | S0-S3=9     | S0-S3=10    | S0-S3=11                |

| 00 01 02 03                                                               | 01 02 03 00 | 02 03 00 01 | 03 00 01 02             |

| 30 31 32 33                                                               | 31 32 33 30 | 32 33 30 31 | 33 30 31 32             |

| 20 21 22 23                                                               | 21 22 23 20 | 22 23 20 21 | 23 20 21 22             |

| 10 11 12 13                                                               | 11 12 13 10 | 12 13 10 11 | 13 10 11 12             |

| S0-S3=12                                                                  | S0-S3=13    | S0-S3=14    | S0-S3=15 <b>FIG. 33</b> |

FIG. 38

FIG. 39

FIG. 41

# REAL TIME VIDEO IMAGE PROCESSING **SYSTEM**

This application is a continuation of application Ser. 5 No. 07/116,801, field Oct. 30, 1987 now abandoned.

# FIELD OF THE INVENTION

This invention relates to a video system for real time processing of video images, and more particularly to 10 modules and chips that support dynamic graphics for television broadcast of video images.

### BACKGROUND OF THE INVENTION

The use of computer-controlled digital signals for video image processing is not new, but generally only the simpler aspects of computer manipulation have been imported into video systems and design. The video system-described here offers a number of innovative 20 improvements, many of which are summarized in the following section and discussed in the detailed description.

#### SUMMARY OF THE INVENTION

The invention described herein has several objects or purposes: (1) to provide burst copying of data to random access memory (RAM) addresses during certain video system blanking intervals; (2) to use multiple banks of slower response dynamic RAMs for purposes 30 of rapid, sequential reading data to and writing data from such memories; (3) to allow inter-pixel interpolation of pixel values; (4) to construct synthetic pixel values for display times at which such values are not available; (5) to provide filter coefficients that can 35 change with each pixel and/or in real time; (6) to allow for flexible border insertion on the screen; (7) to provide certain parameter file and linking technique for sophisticated memory address specification; (8) to provide multi-purpose networks of digital differential analyzers for 40 coordinate generation and manipulation; (9) to provide special paint modes and flexible mini-canvases on the video screens; (10) to utilize logarithms, where appropriate, for arithmetic computations; (11) to provide interfaces for conversion, at the front end and at the rear end of the video system, from conventional slower rate digital systems to the faster rate video system described here; (12) to provide for multiple layer painting and compositing of signals with variable image transparencies; (13) to provide flexible stencils for use in the paint mode; (14) to provide for use of filter coefficients that may be used to form composite pixel values for an arbitrary number of adjacent pixels at the same time; (15) to provide reconfigurable keyers for image mixing 55 to-one keyer to combine a stencil, a paintbrush image, a and related activities; (16) to provide for simultaneous processing of luminance, chrominance, transparency and depth signals associated with video images; (17) to provide special arithmetic modules for special functions used in the video system; and (18) to provide a flexible 60interface between the hardware of the system and various applications-oriented features of the system.

Other objects of the invention, and advantages thereof, will become clear by reference to the following detailed description and accompanying drawings.

The objects of this invention may be realized by methods and apparatus discussed in the Description section and recited in the Claims.

#### DESCRIPTION OF THE DRAWINGS

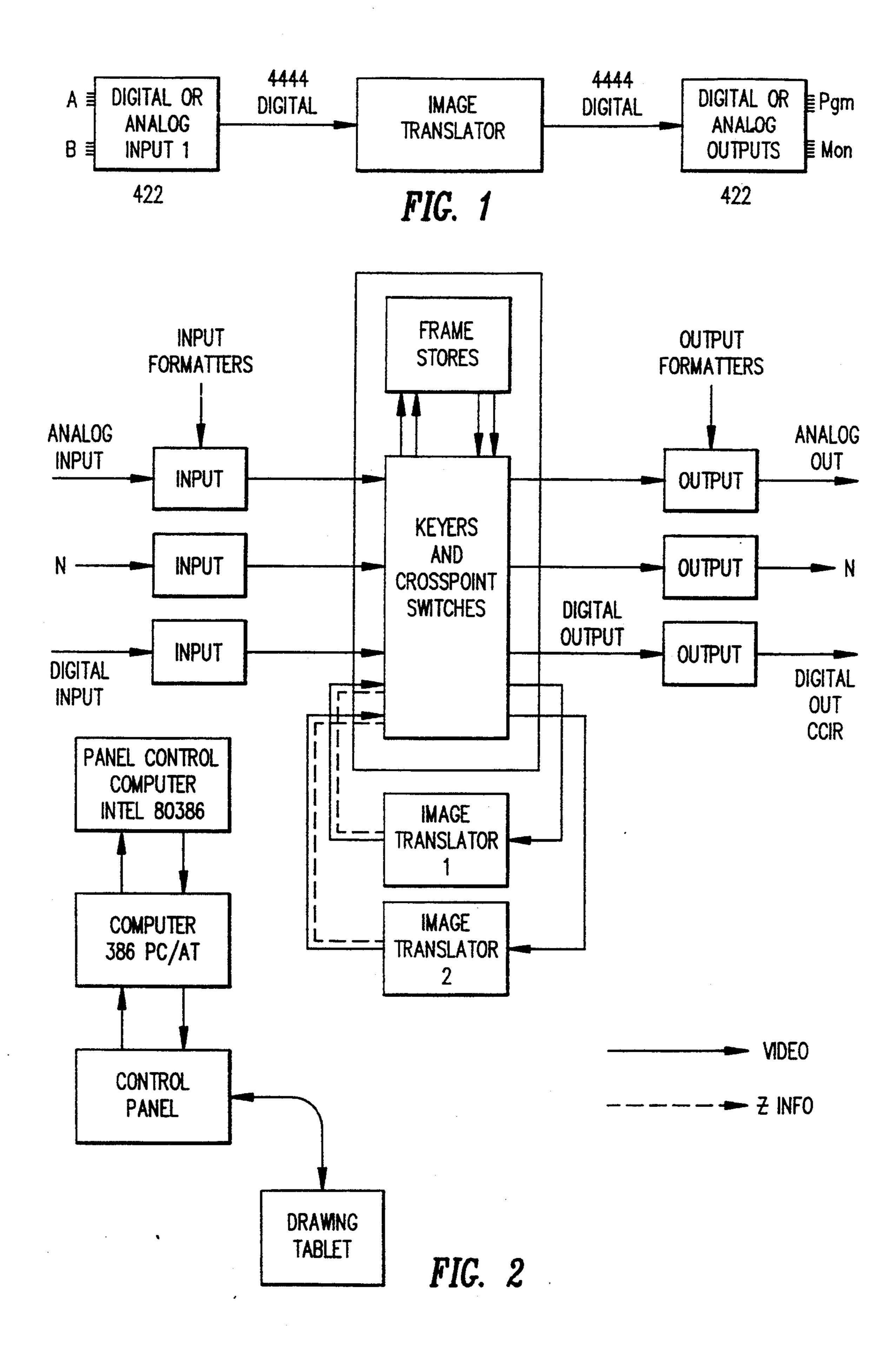

- FIG. 1 is a simplified schematic illustrating Image Translator operation.

- FIG. 2 is a schematic view of the different modules that comprise the Image Translator.

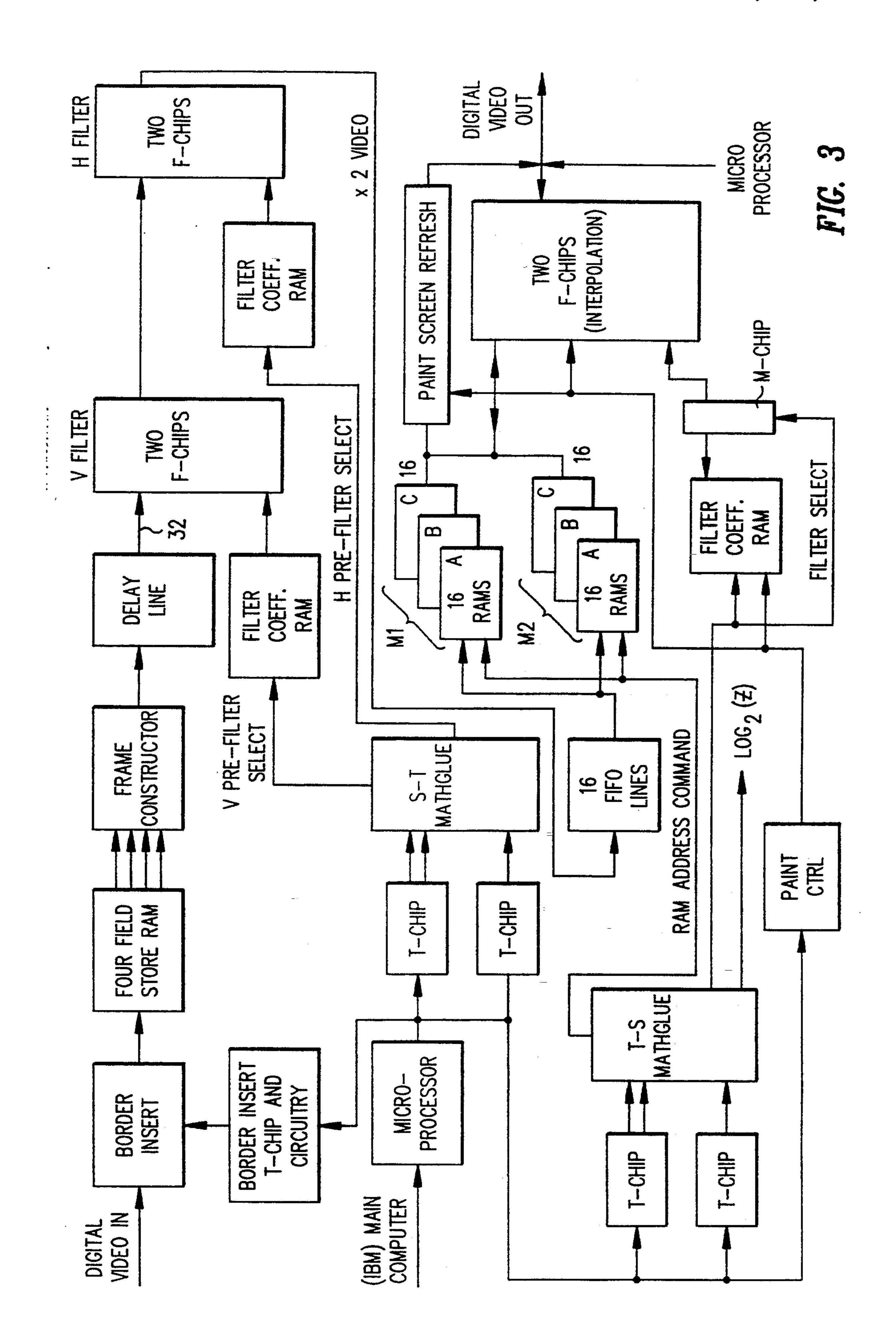

- FIG. 3 is a schematic view of the relationship of the major components of the system and their interconnections.

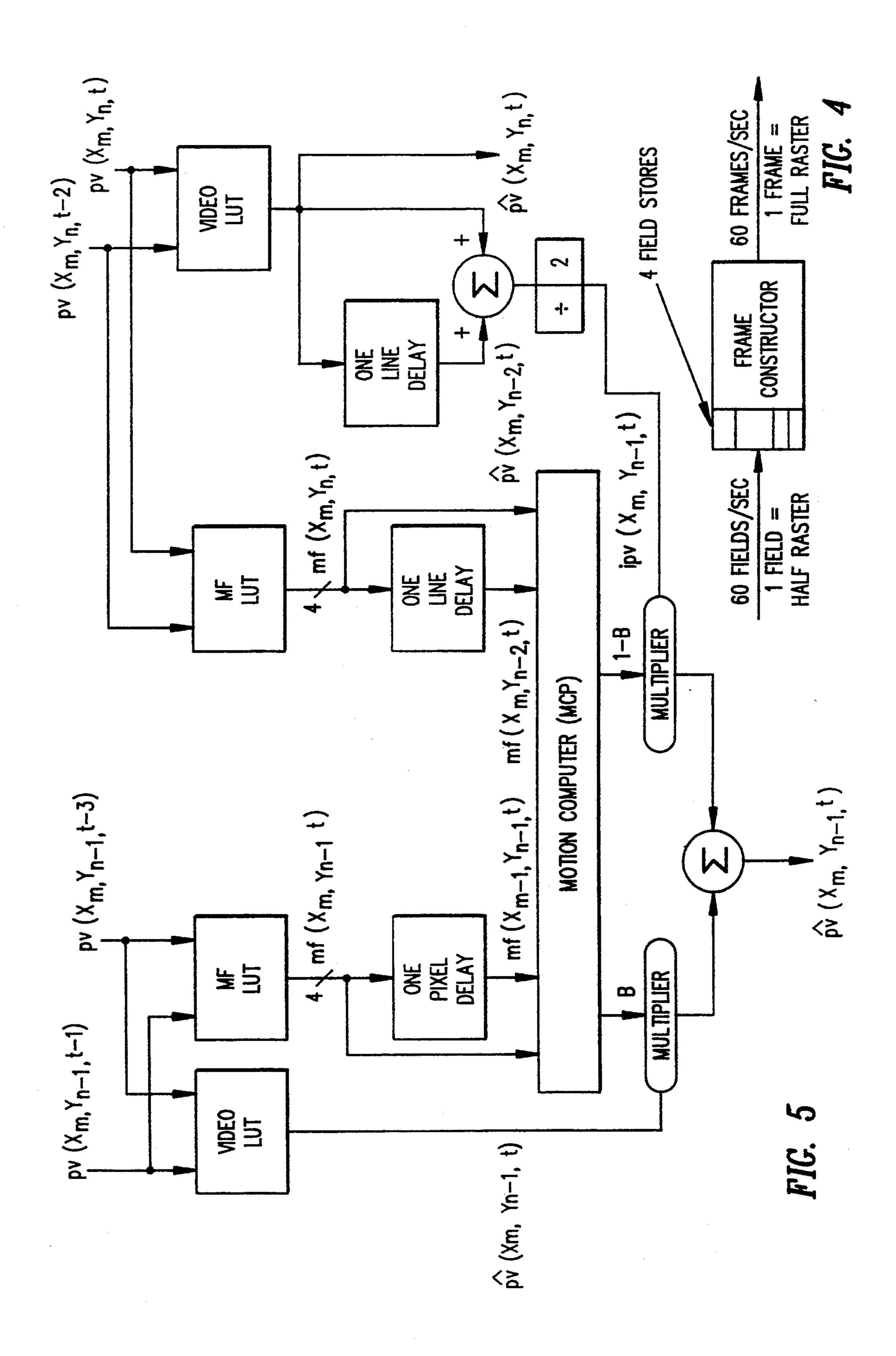

- FIG. 4 is a simplified schematic view of frame constructor operation.

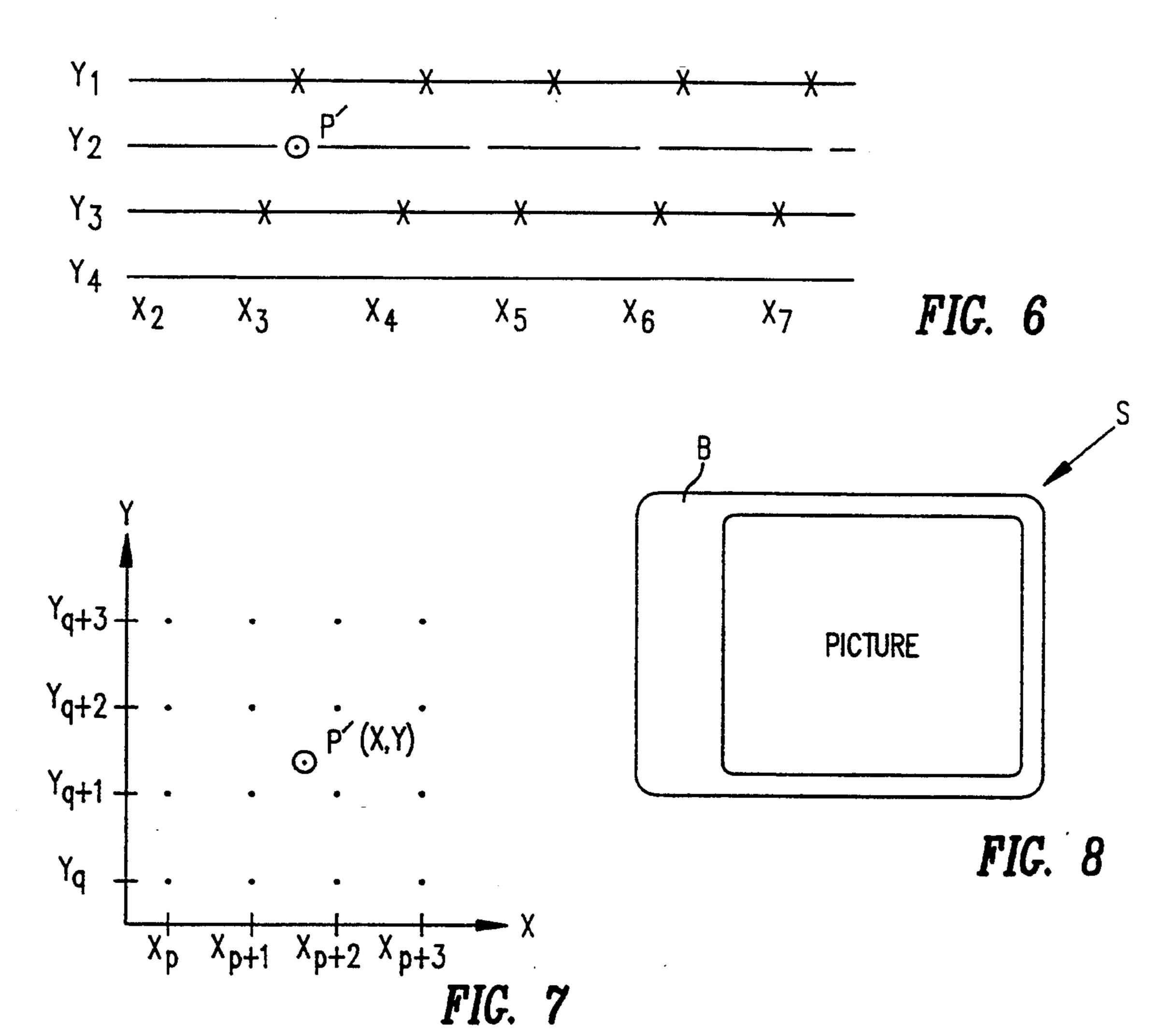

- FIGS. 5 and 6 illustrate construction of a synthetic pixel value at a pixel, used on data fill between even and odd fields in the frame constructor.

- FIG. 7 illustrates the use of averaging of pixel values in a  $4\times4$  pixel array that surrounds a fictitious pixel position p'(x,y).

- FIG. 8 is a front view of a screen image that is to include a predetermined border B.

- FIG. 9 illustrates how a border is formed from image difference signals.

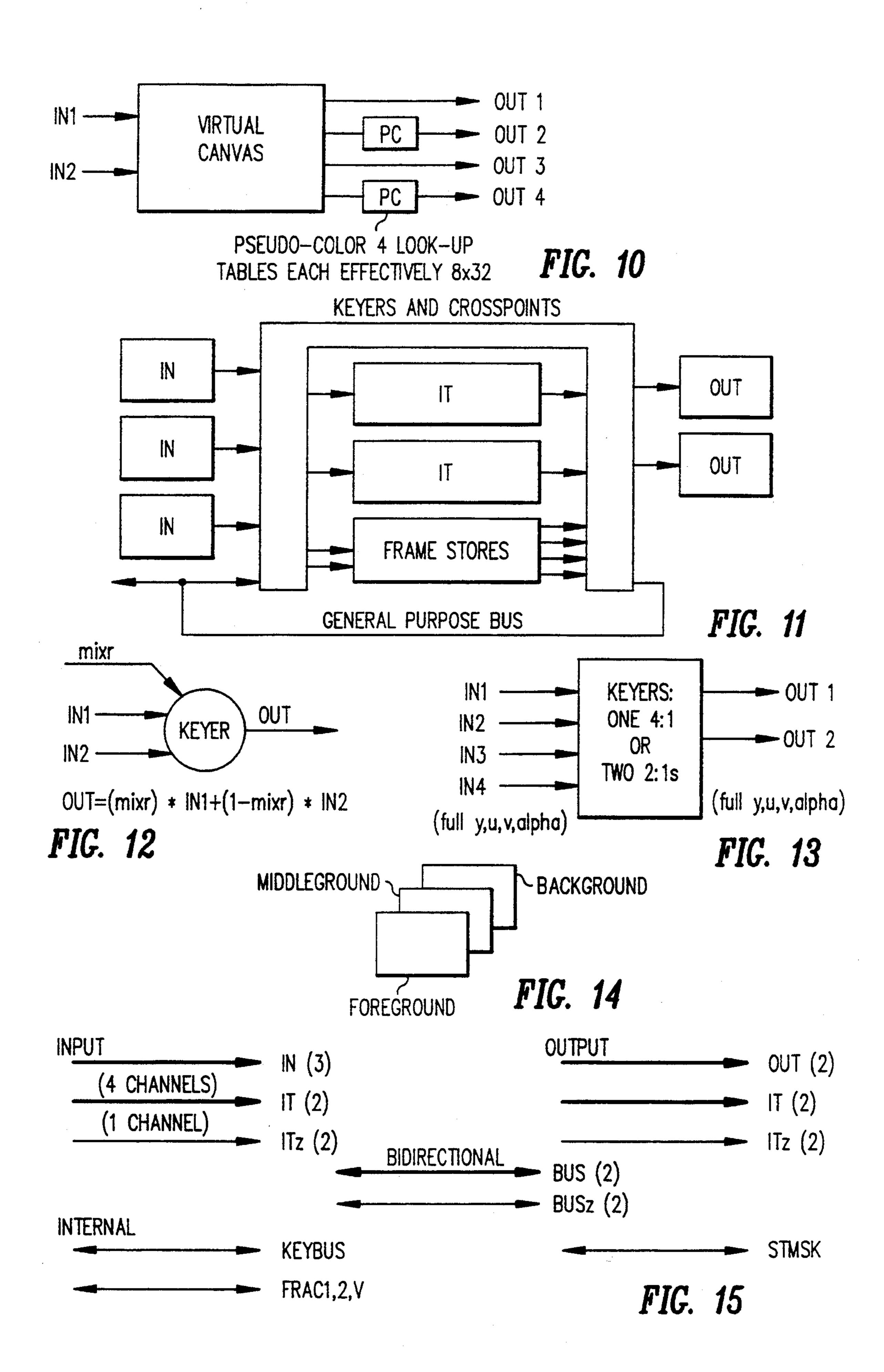

- FIG. 10 is a schematic view of the input and output terminals of the virtual canvas (VC) module.

- FIG. 11 is a schematic view of the FSK buses and crosspoint switches.

- FIG. 12 is a schematic view of a keyer in use to mix two incoming signals.

- FIG. 13 is a schematic view of the input and output terminals of a four-to-one keyer or, alternatively, a pair of two-to-one keyers.

- FIG. 14 is a schematic view illustrating use of a foreground, a middle ground and a background in a composite view.

- FIG. 15 is a schematic view of a general set of keyer buses.

- FIG. 16 is a schematic view illustrating a tile map from the whole screen.

- FIG. 17 is a schematic view of the operation of a  $4\times4$ crosspoint switch upon specific keyer inputs.

- FIG. 18 is a schematic view of the operation of a  $2\times2$ crosspoint switch upon keyer outputs.

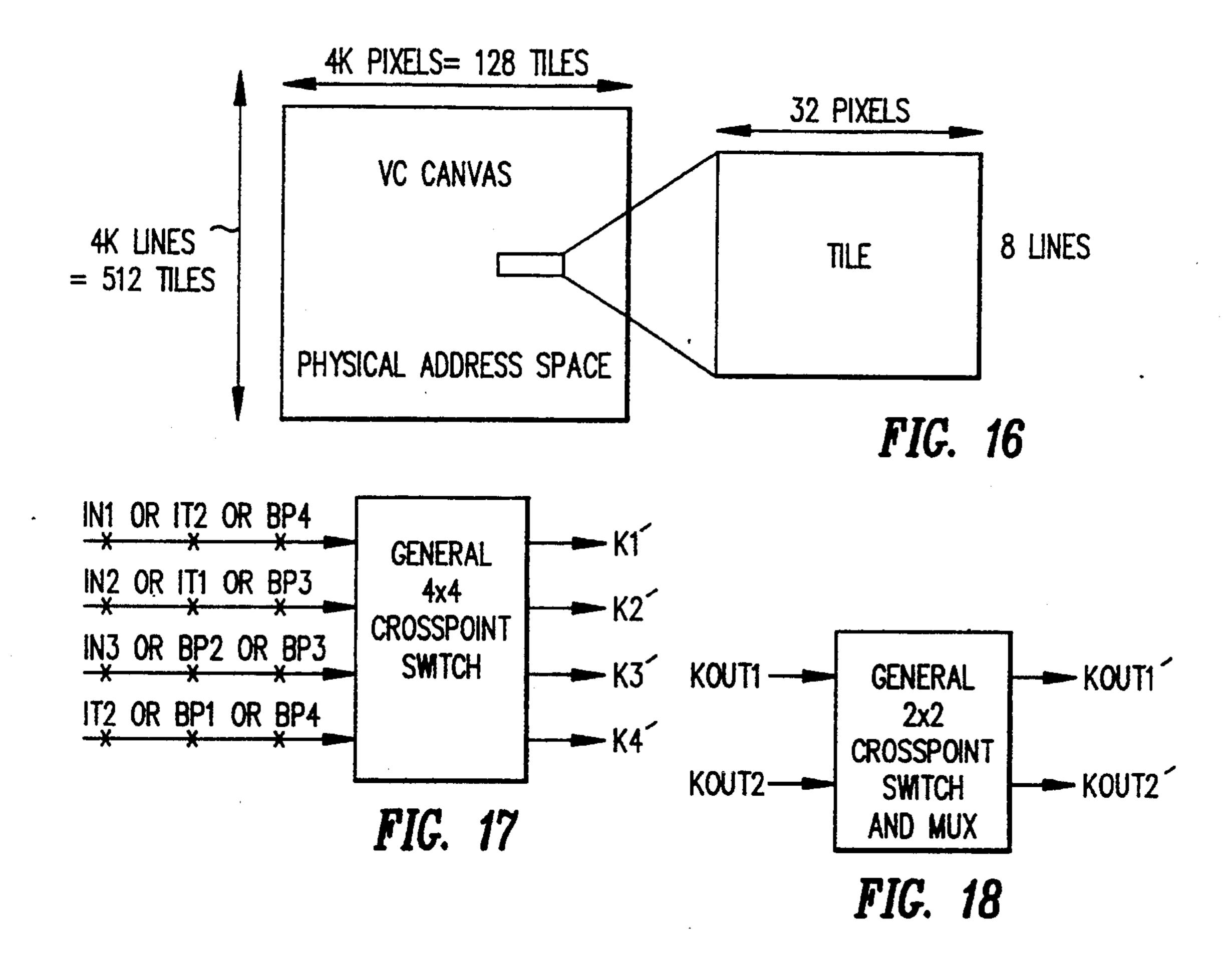

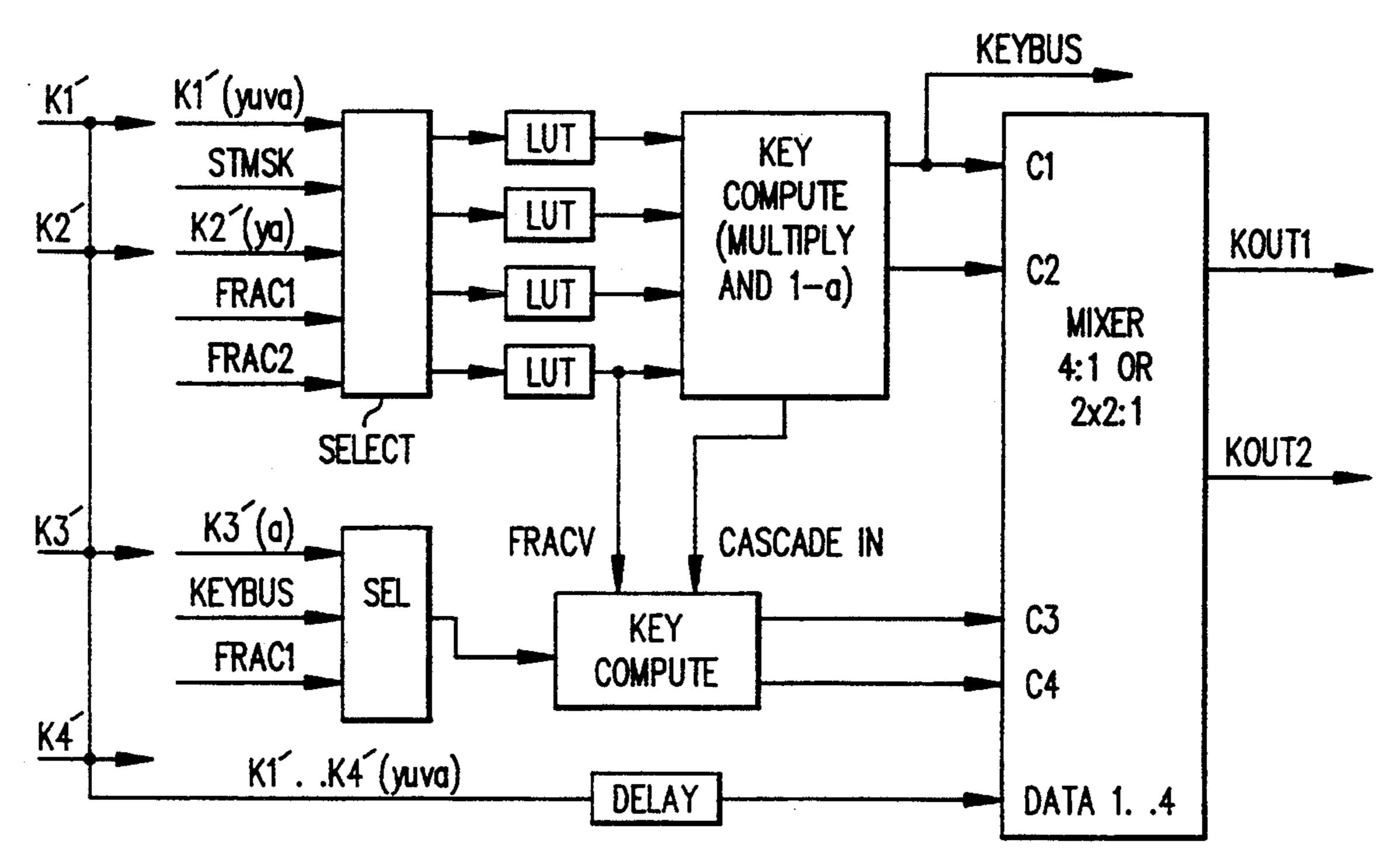

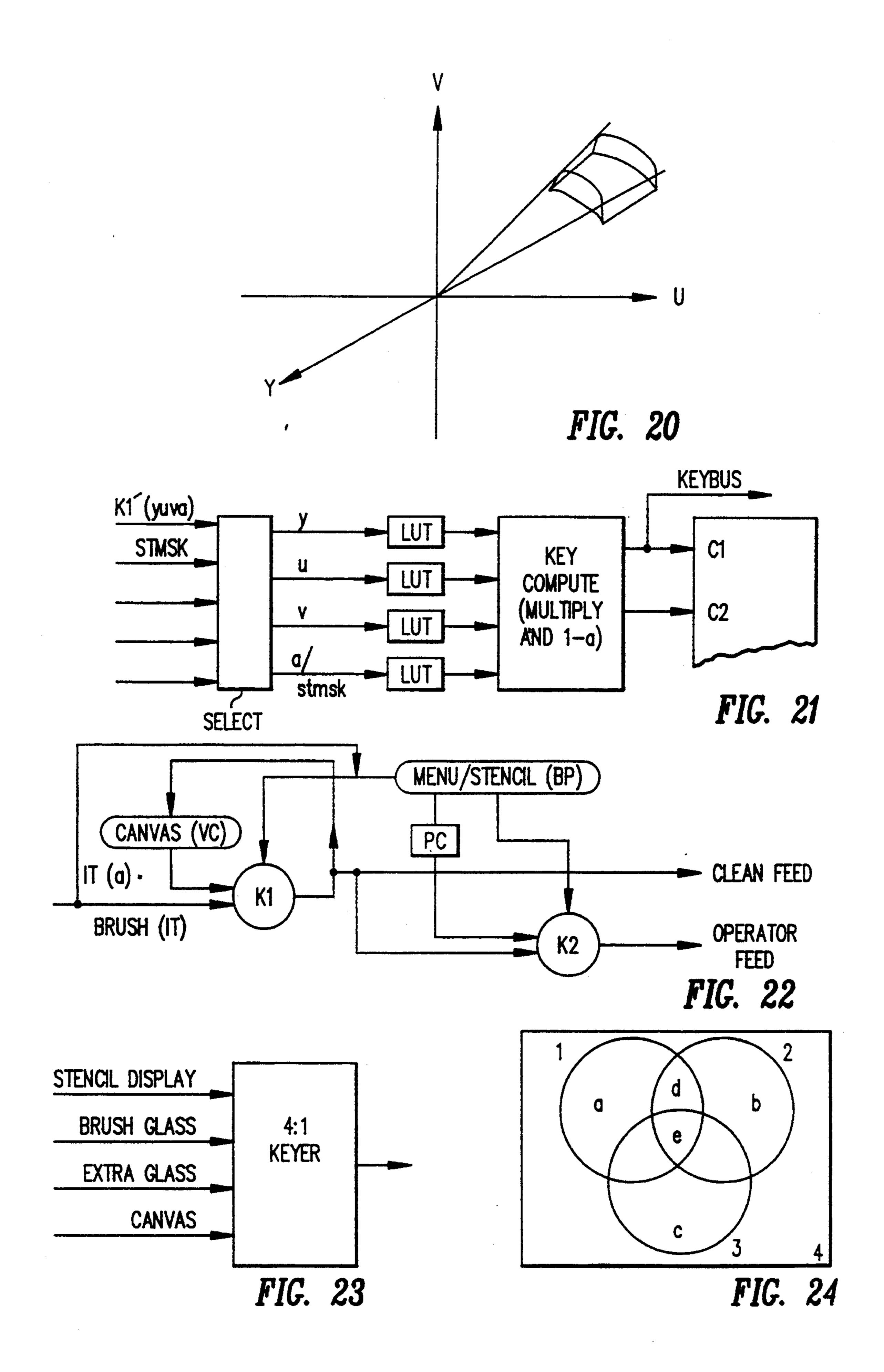

- FIG. 19 is a schematic diagram of the keyer module. FIG. 20 is a graphic view illustrating the use of ranges of the variables Y, U and V to delimit a small volume in luminance/chrominance space.

- FIG. 21 is a schematic view of the luminance/chroma keyer computation ("key compute") module.

- FIG. 22 is a schematic view of the interaction of virtual canvas (VC), the Image Translator (IT) and a stencil through two keyers to form a composite picture of the canvas, the paint brush image and a stencil controlled by the operator.

- FIG. 23 is a schematic view illustrating use of a fourcanvas image and an additional image to form a composite view.

- FIG. 24 is a graphic view or Venn diagram illustrating formation of a composite view from multiple layers with differency assigned opacity factors.

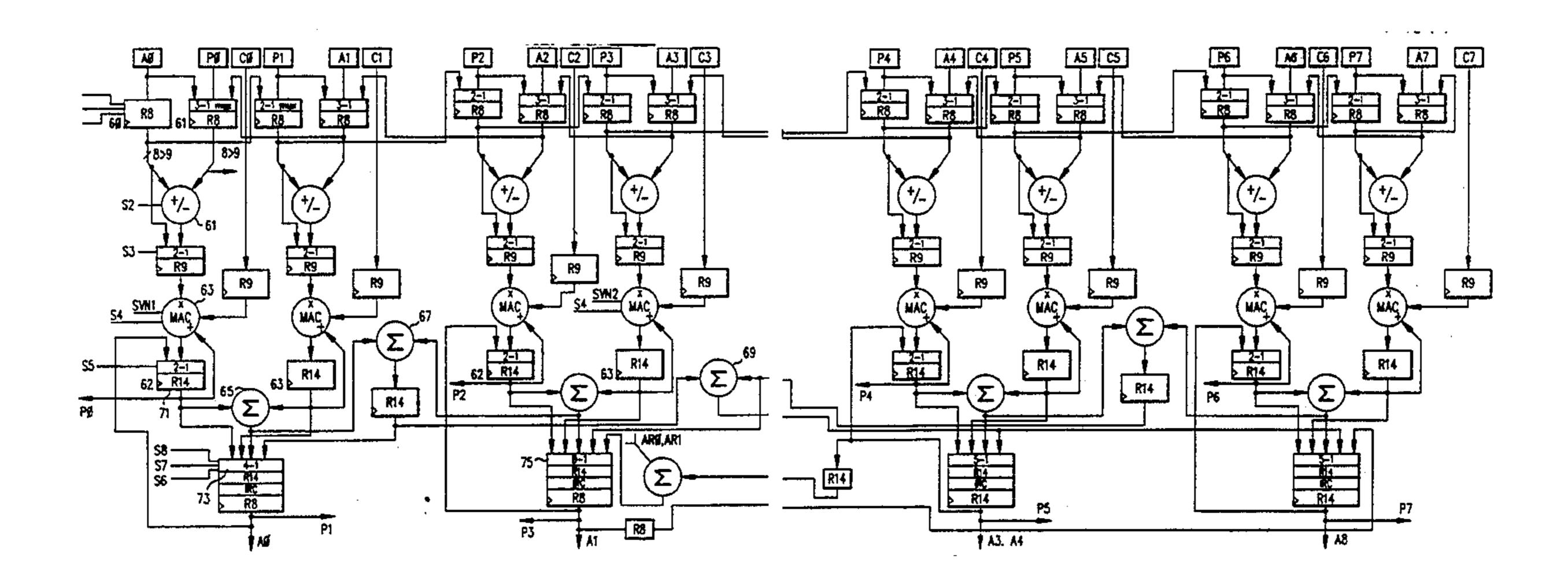

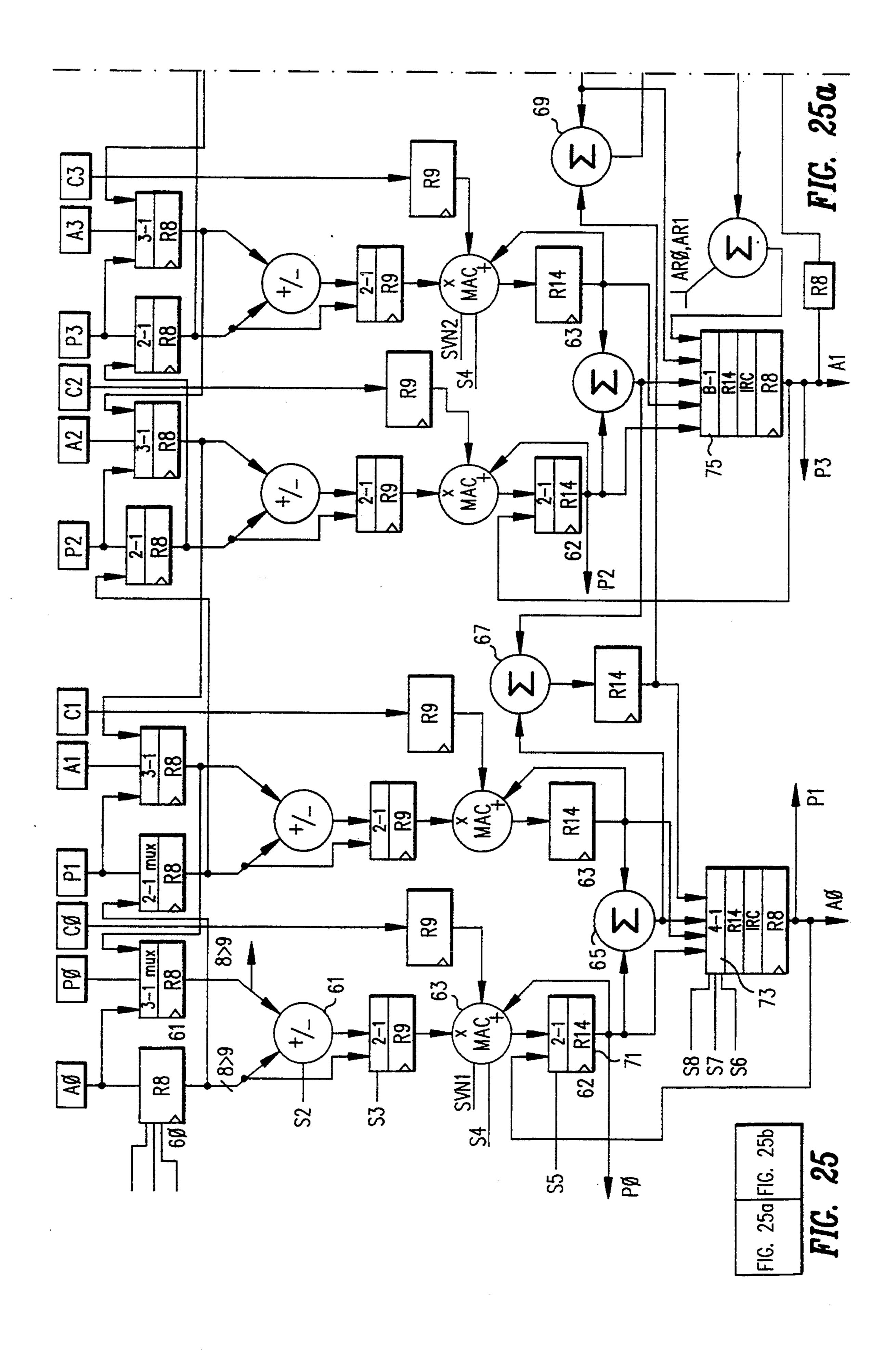

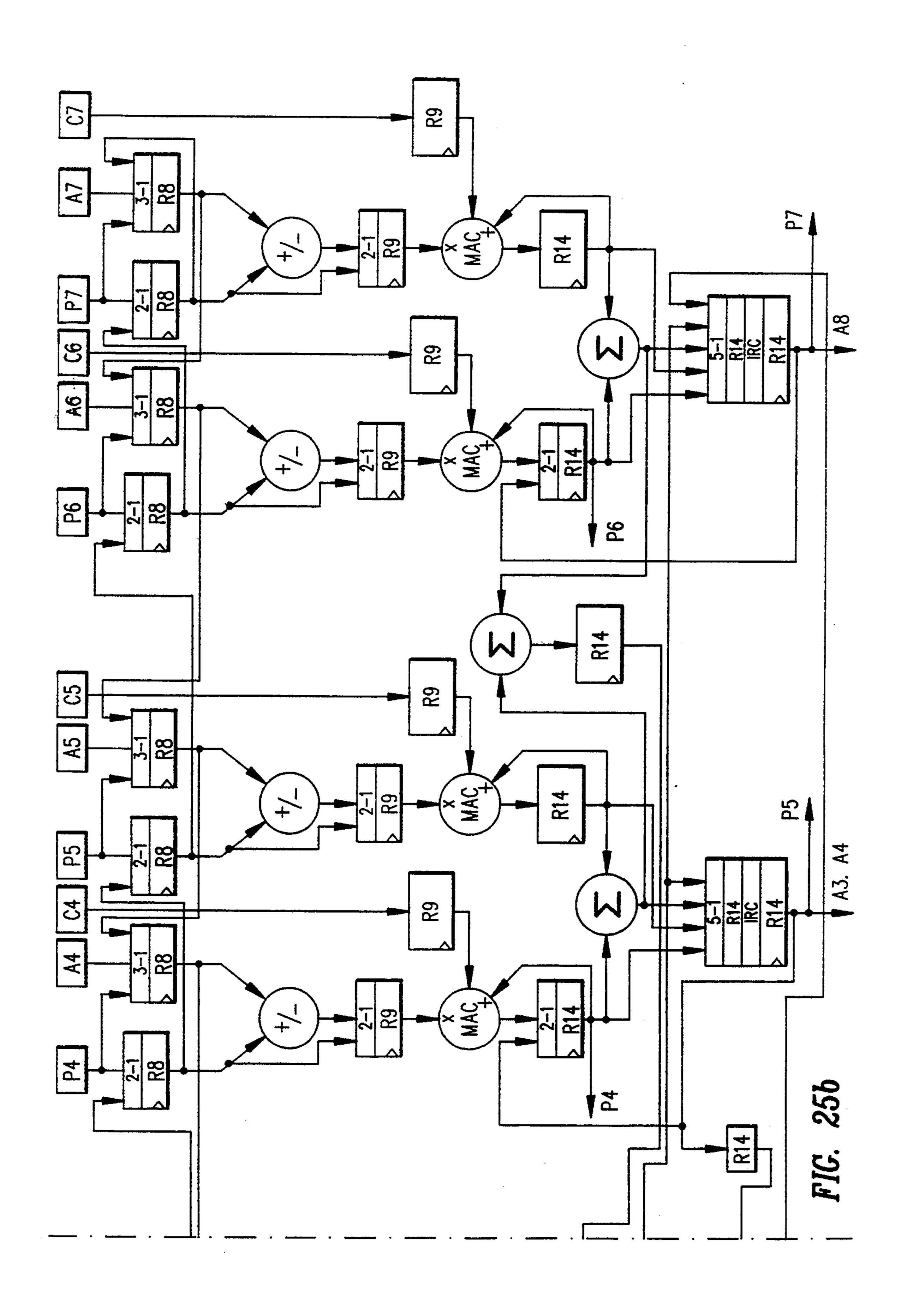

- FIG. 25 is a schematic view of the floorplan of an F-chip, used to filter or compute weighted averages of various signals within the system.

- FIG. 26 illustrates the 16 permutations of a  $4\times4$ 65 block of signals that are available in mode 0 operation of the M-chip, used for inter-pixel interpolation.

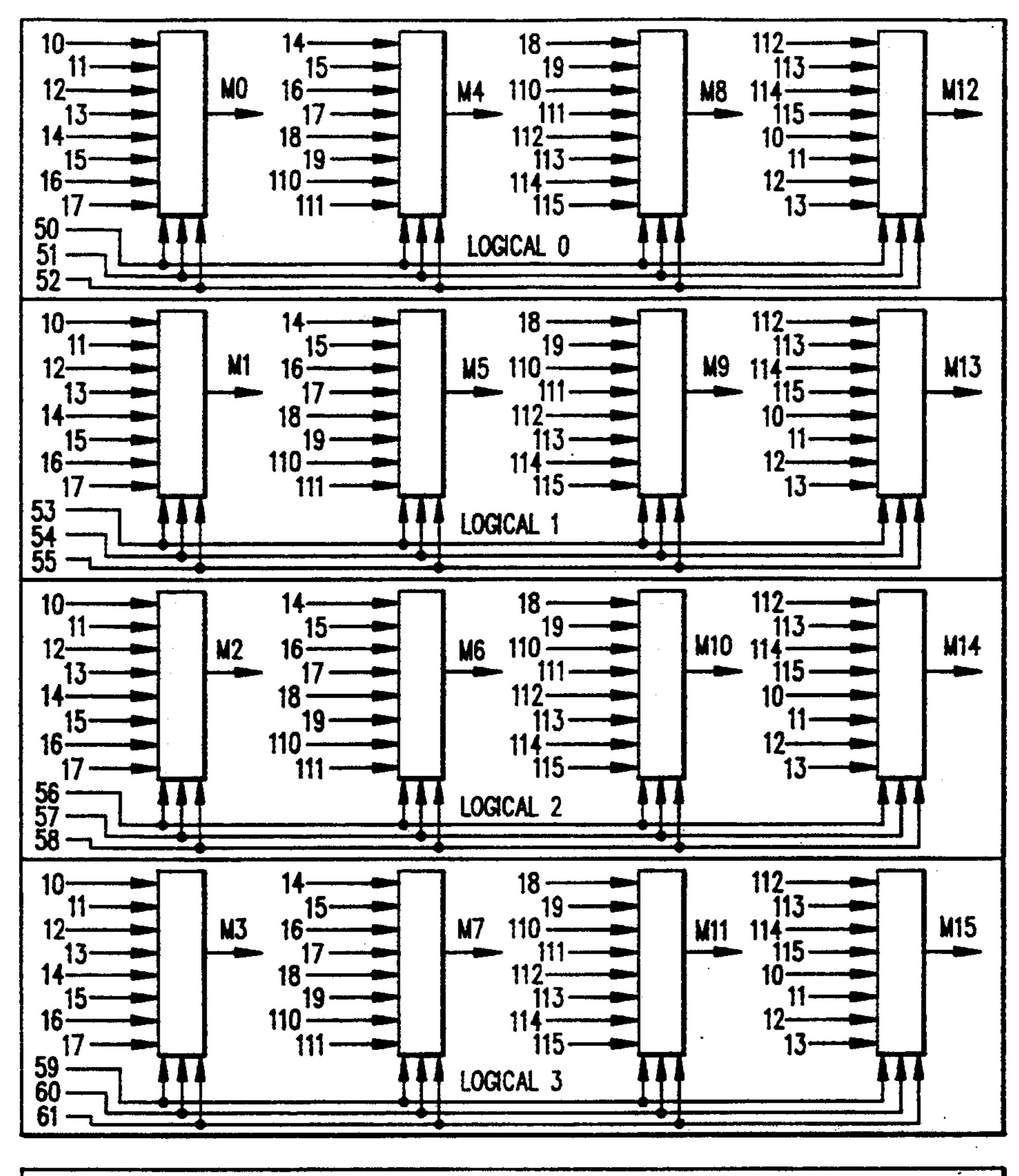

- FIGS. 27 and 28 illustrate the input format (I) and output format (M) for Modes 0, 1, 2 and 3 of the M-chip.

20

FIG. 29 illustrates the use of mode 0 of the M-chip for interpolation.

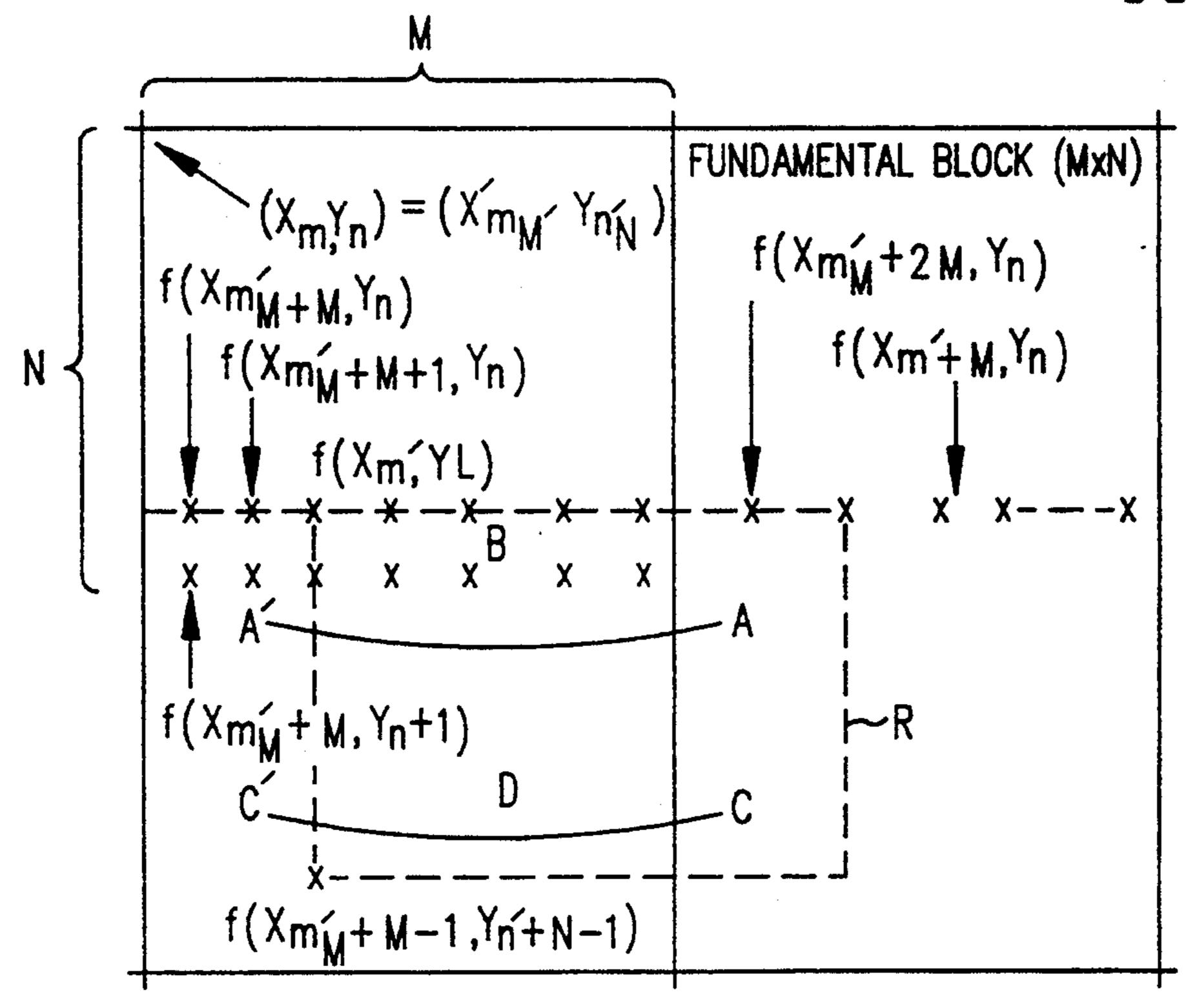

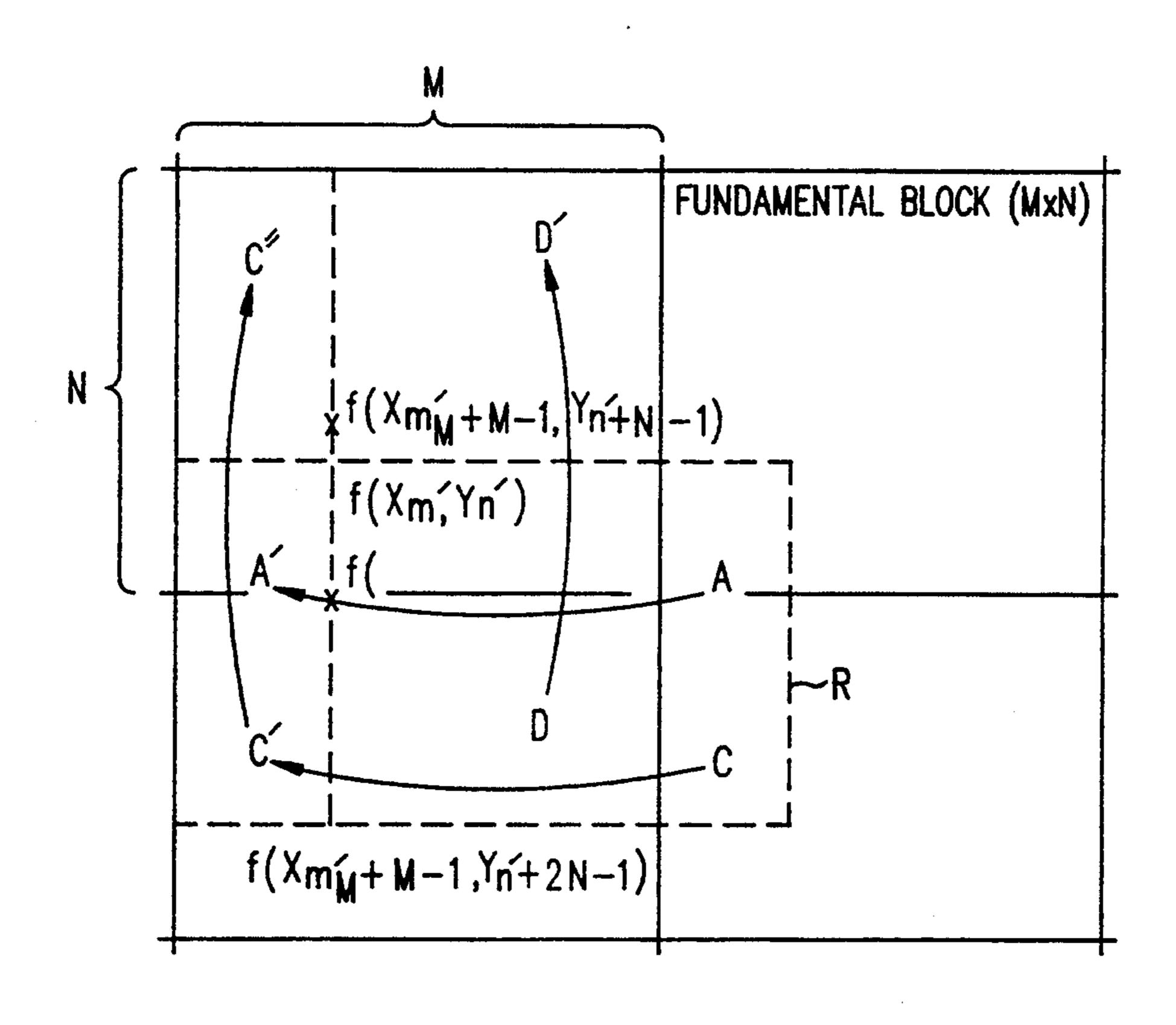

FIGS. 30 and 31 illustrates the effect on the pixel values contained in a certain Target Block of  $M \times N$  pixels of certain transformations on the array of pixel values carried out in conjunction with use of the M-chip in Mode 0 (interpolation).

FIGS. 32, 33 and 34 illustrate the 16 permutations of a 4×4 block of signals that are available in Mode 1 (horizontal mirroring), Mode 2 (vertical mirroring) and mode 3 (both horizontal and vertical mirroring) and Mode 3 (both horizontal and vertical mirroring) of the M-chip.

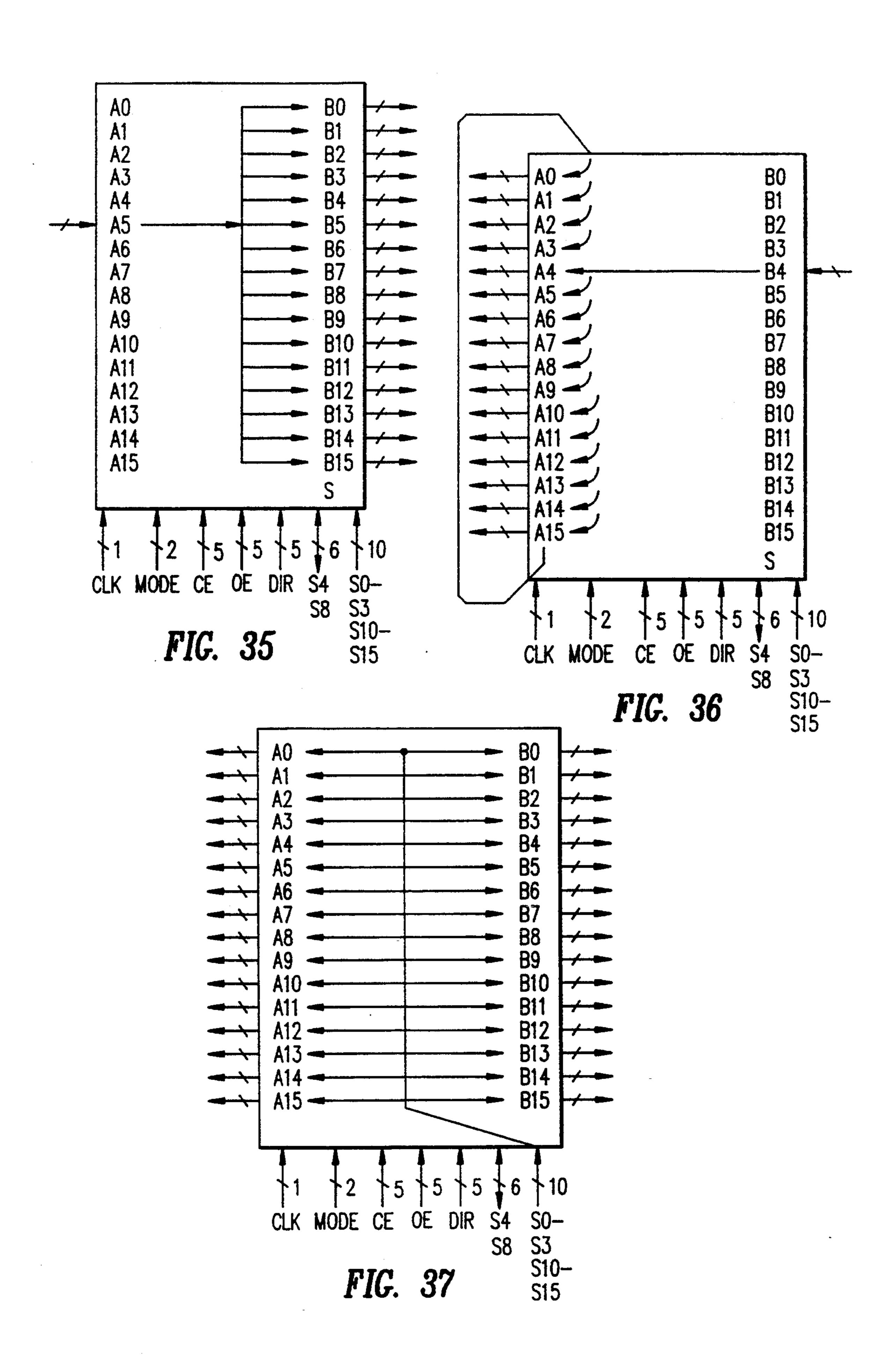

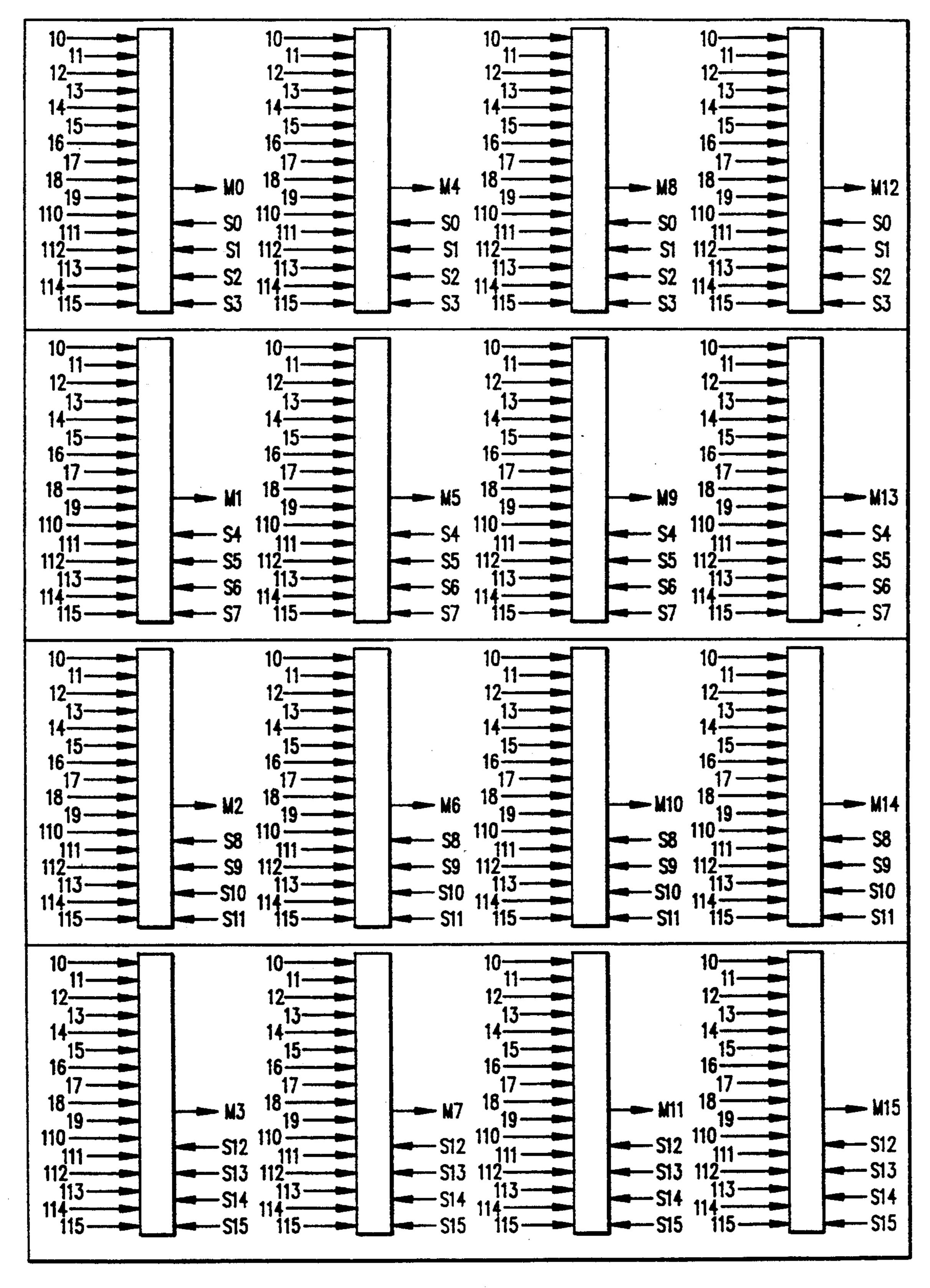

FIGS. 35, 36 and 37 illustrate the use of the M-chip in 15 Mode 4 (broadcast), Mode 5 (16-tap delay line) and Mode 6 (test data broadcast).

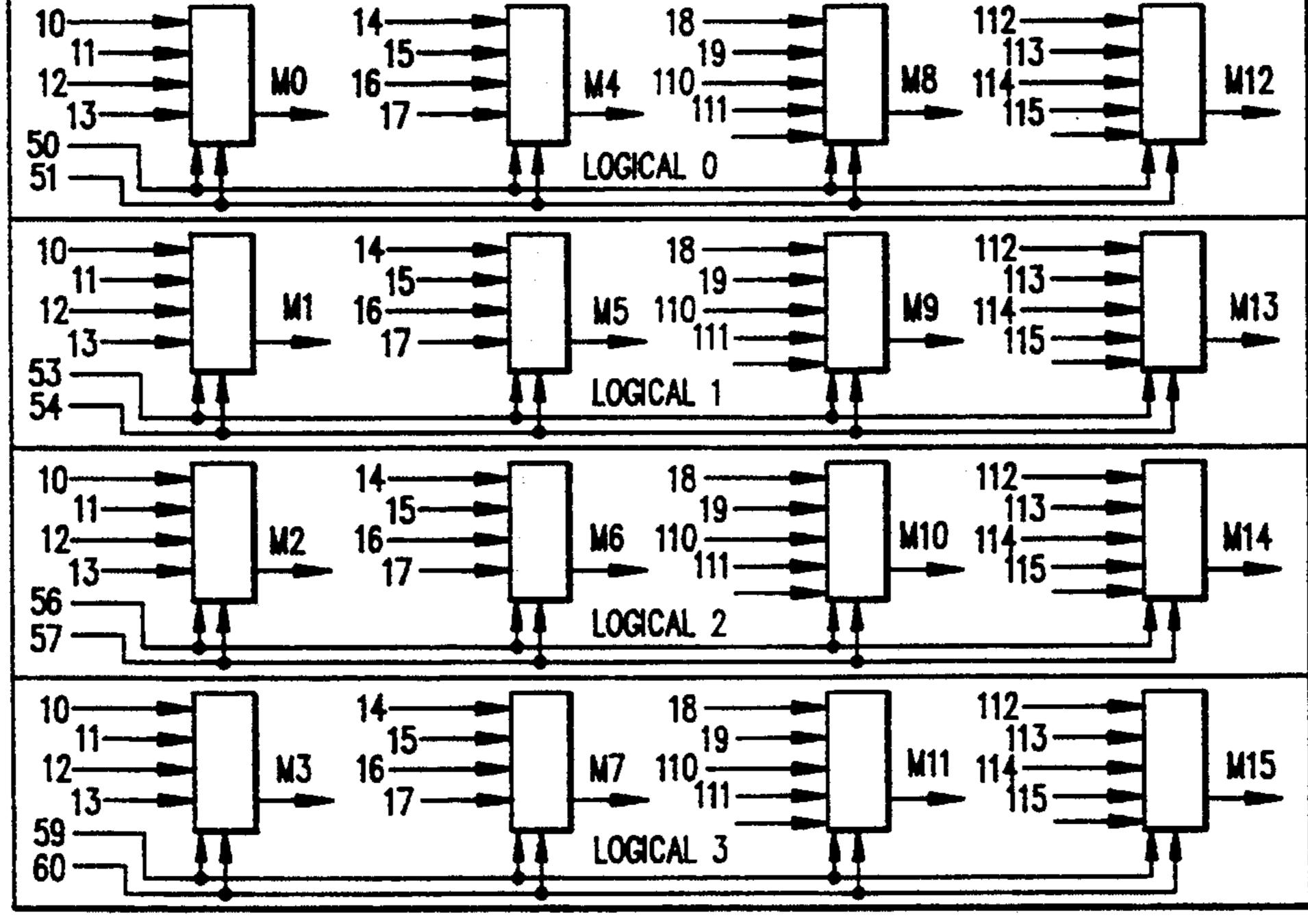

FIGS. 38, 39 and 40 illustrate the use of the M-chip as a multiplexer M-chip in Mode 8 (8-to-1 mux), Mode 9 (4-to-1 mux) and Mode 10 (2-to-1 mux).

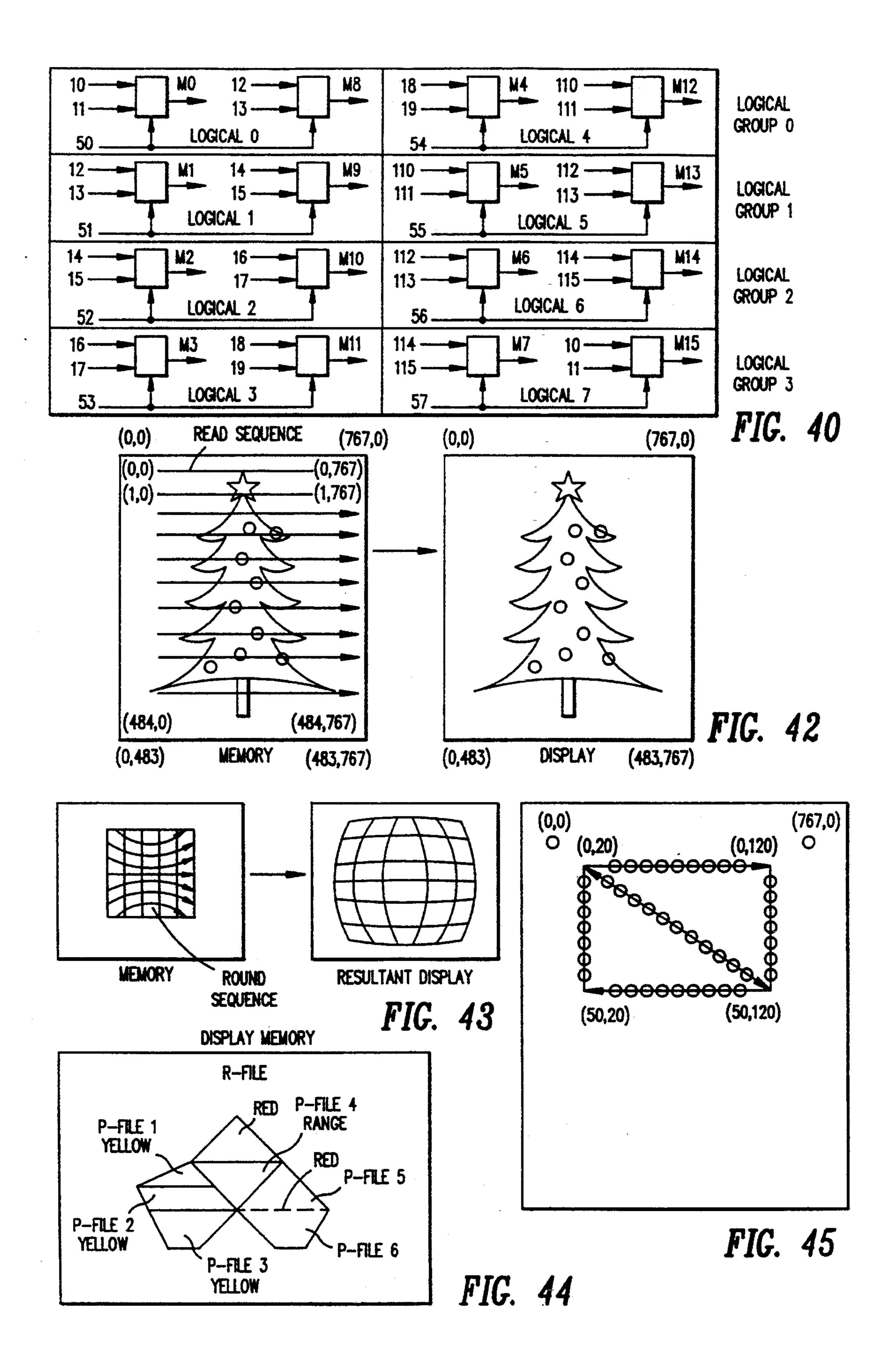

FIG. 41 illustrates the use of the M-chip as a 16-to-1 multiplexer.

FIG. 42 is a schematic view of an untransformed image in memory, represented as a matrix, that is processed by the invention.

FIG. 43 illustrates how the transform operation maps an original image onto a curved surface in the display/transform mode.

FIG. 44 illustrates the use of the invention on the 30 polygon fill mode.

FIGS. 45 illustrates the use of the invention to construct vectors in the vector mode.

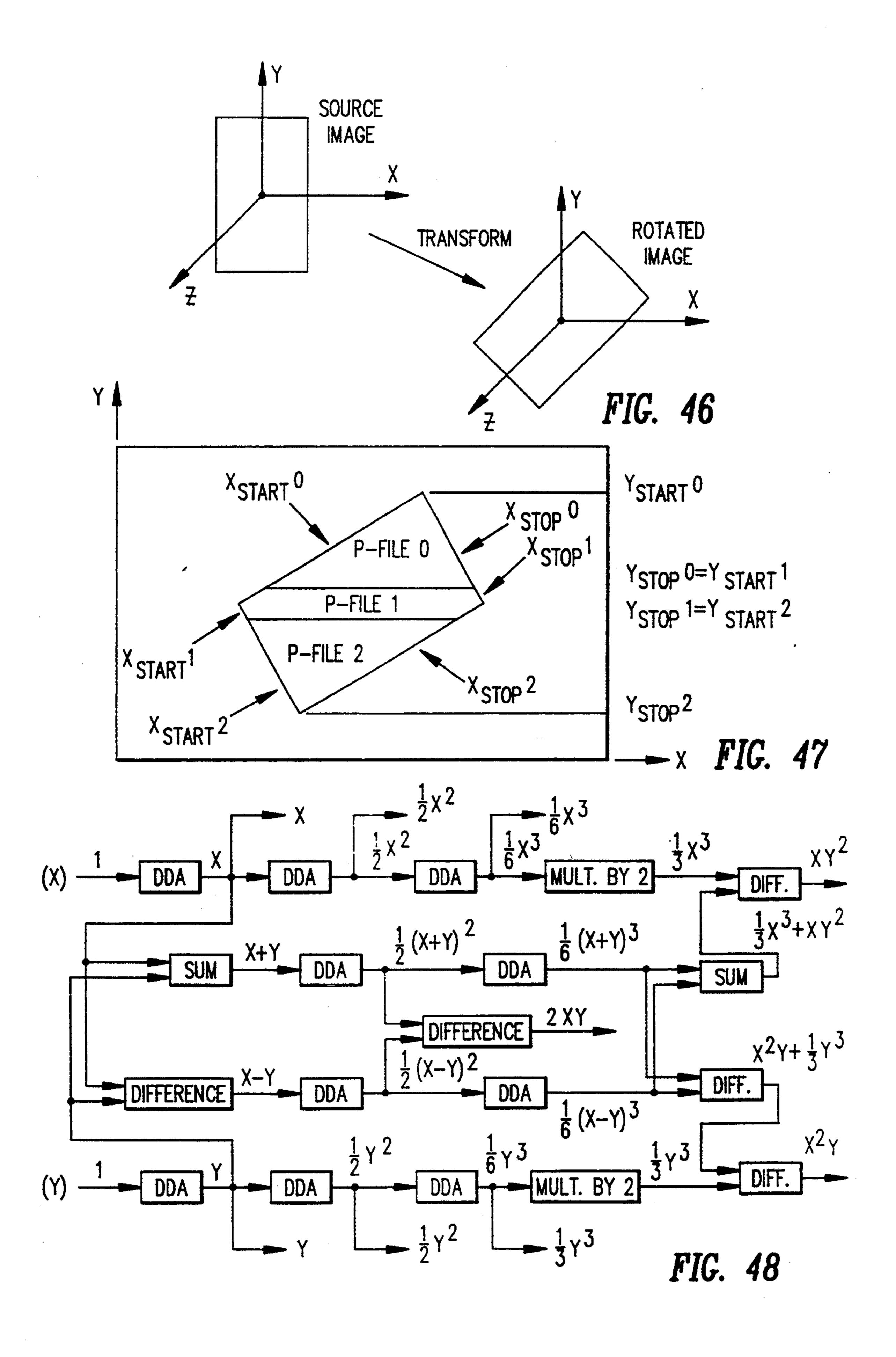

FIGS. 46 and 47 illustrate some of the problems encountered when a figure to be displayed is rotated in a 35 plane that is substantially perpendicular to the viewing axis.

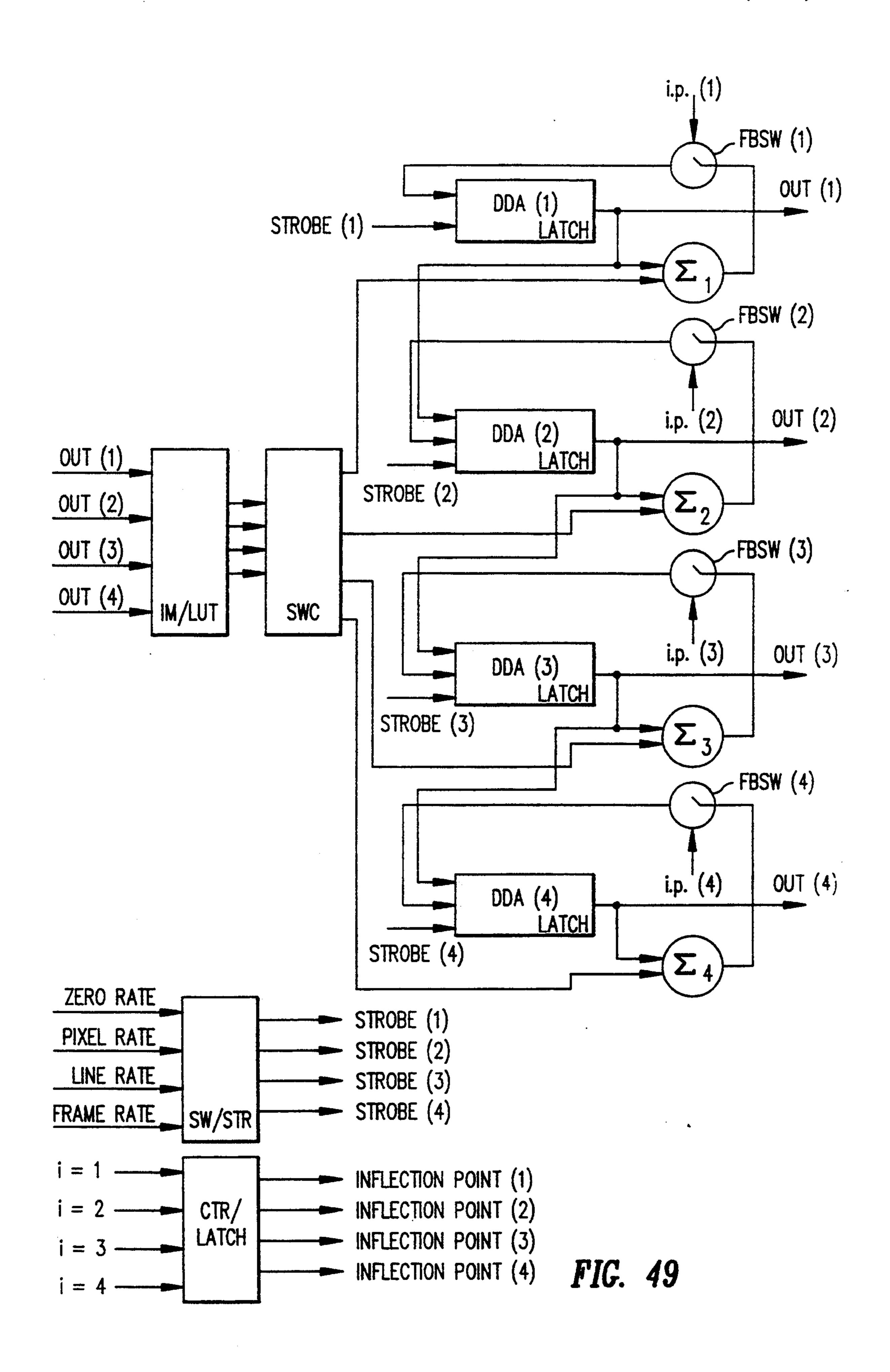

FIG. 48 illustrates schematically a DDA network that is useful in generating the polynomial terms x, y,  $x^2$ , xy,  $y^2$ ,  $x^3$ ,  $x^2y$ ,  $xy^2$  and  $y^3$ .

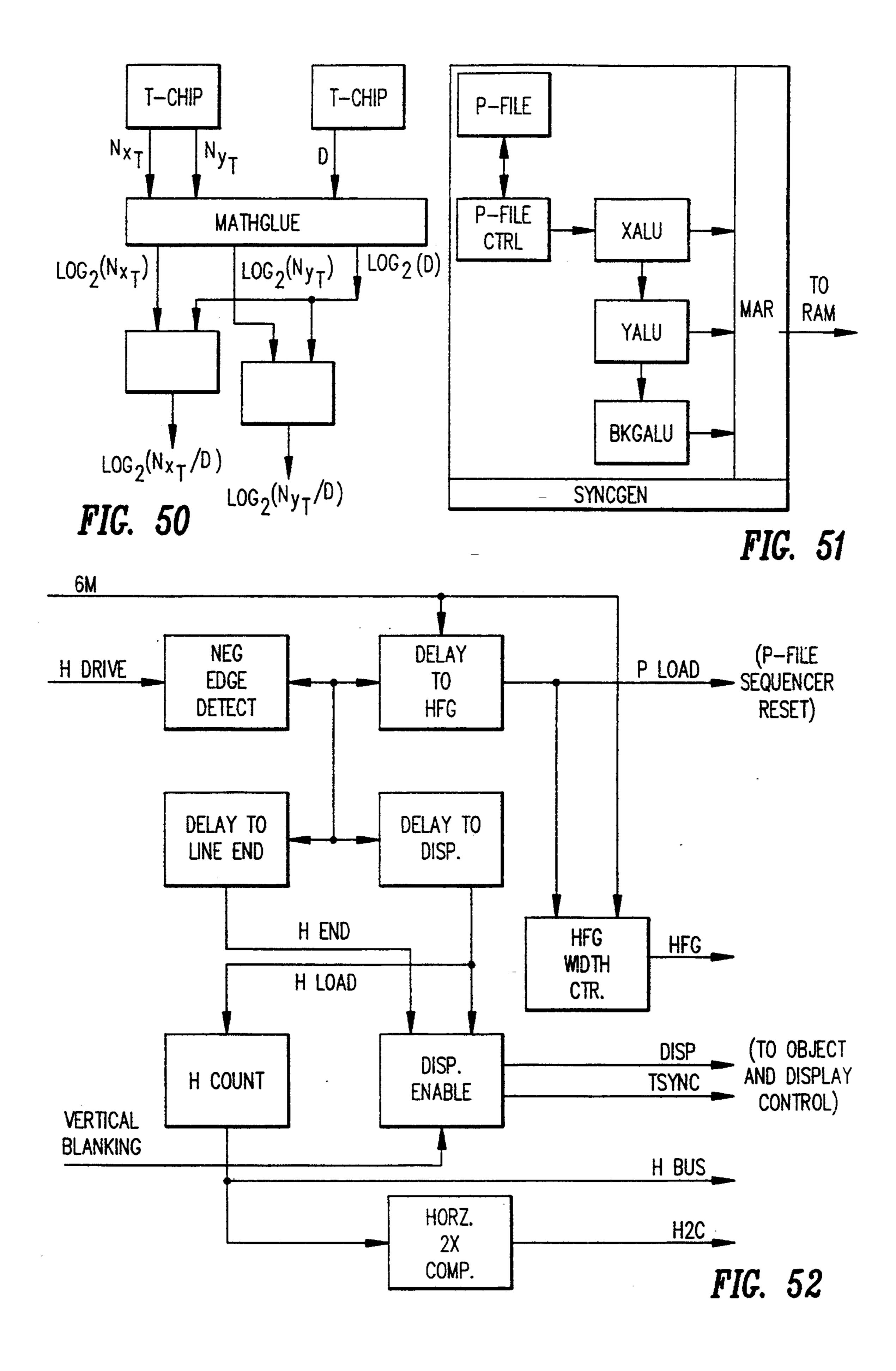

FIG. 50 illustrates schematically the use of two T-chips to form ratios  $N_x/D$  and  $N_y/D$  used in projective coordinate transformations.

FIG. 51 is a schematic view of the arrangement of the T-chip.

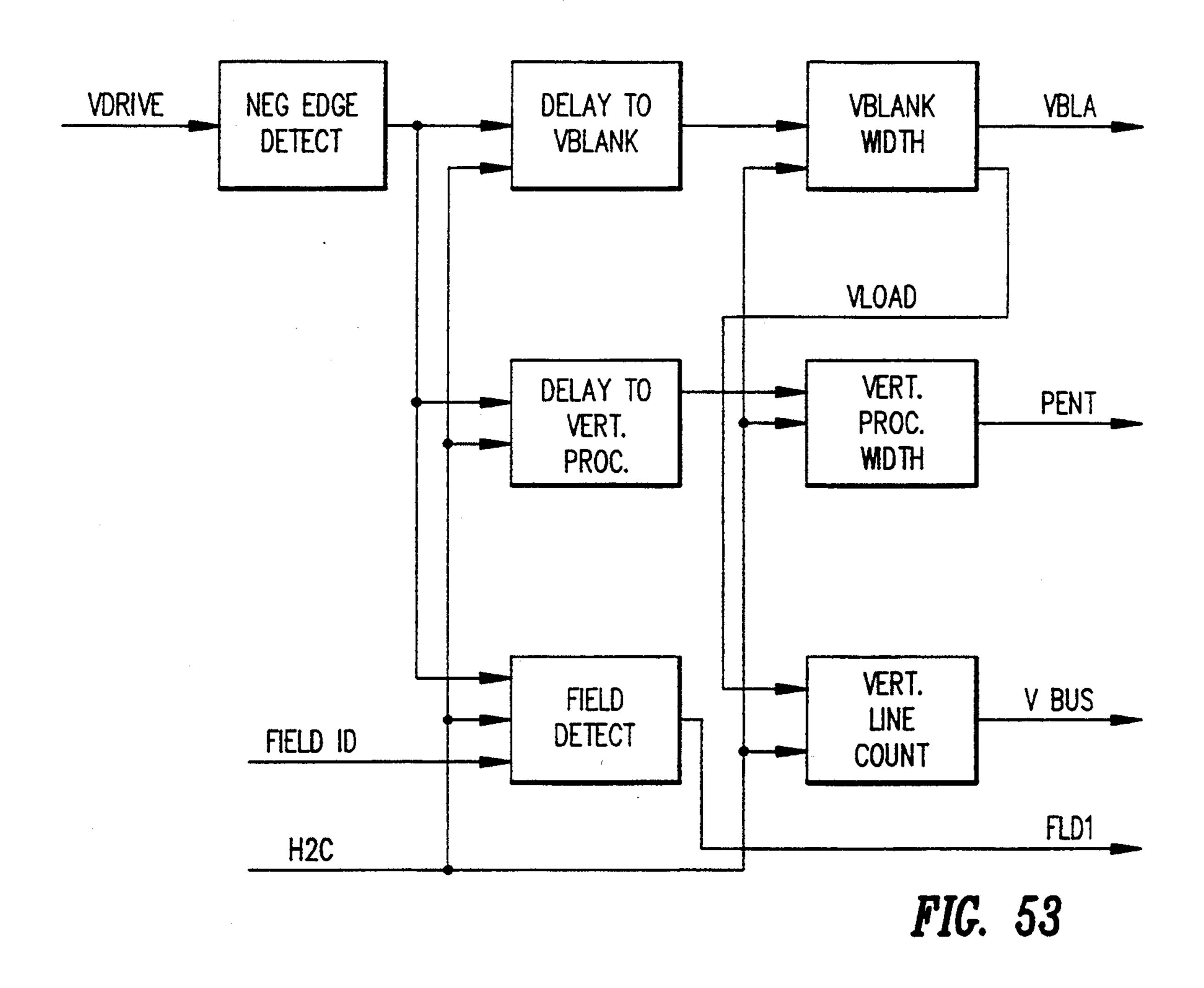

FIG. 52 and 53 illustrate the P-file address generator timing cycles.

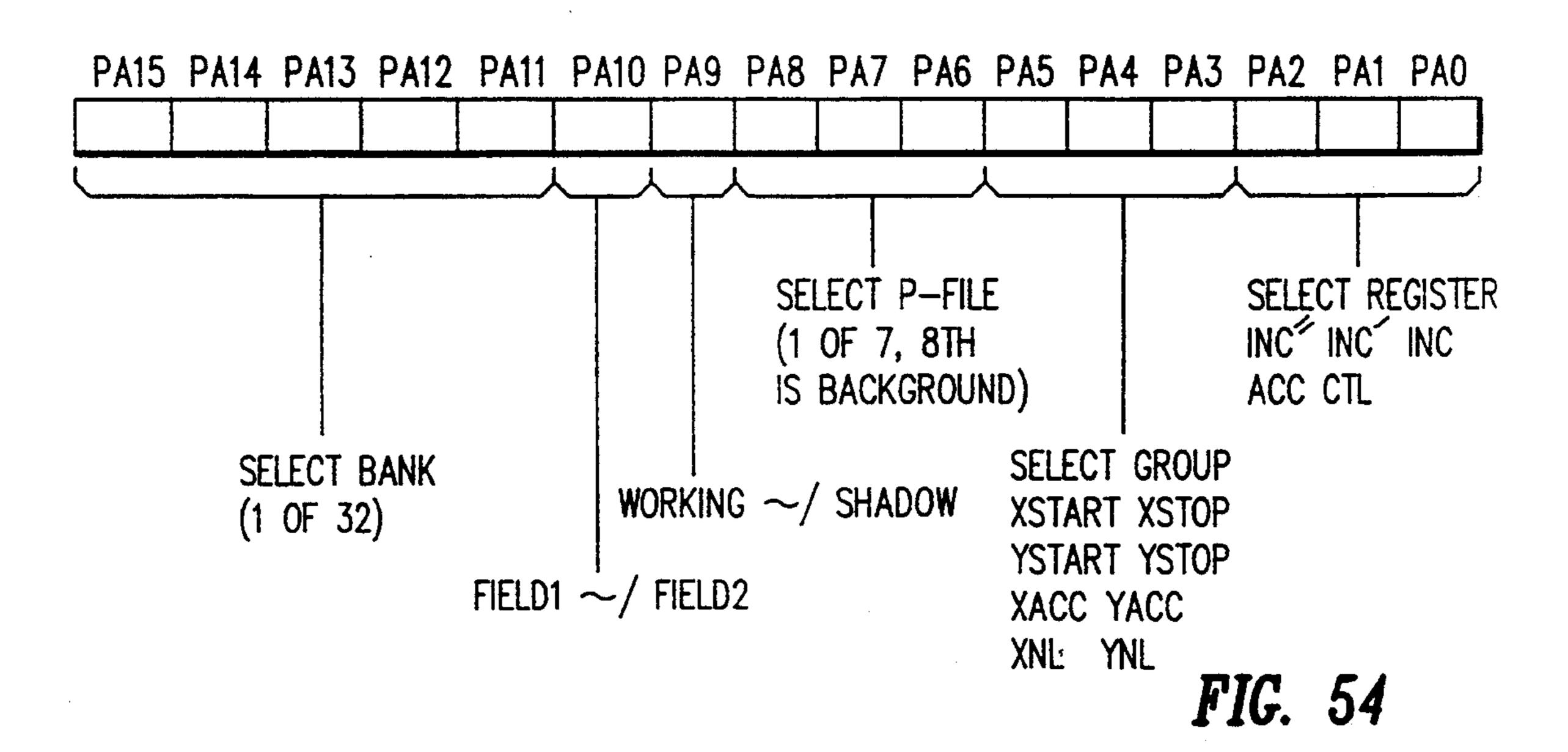

FIG. 54 shows the functional grouping of P-file addresses.

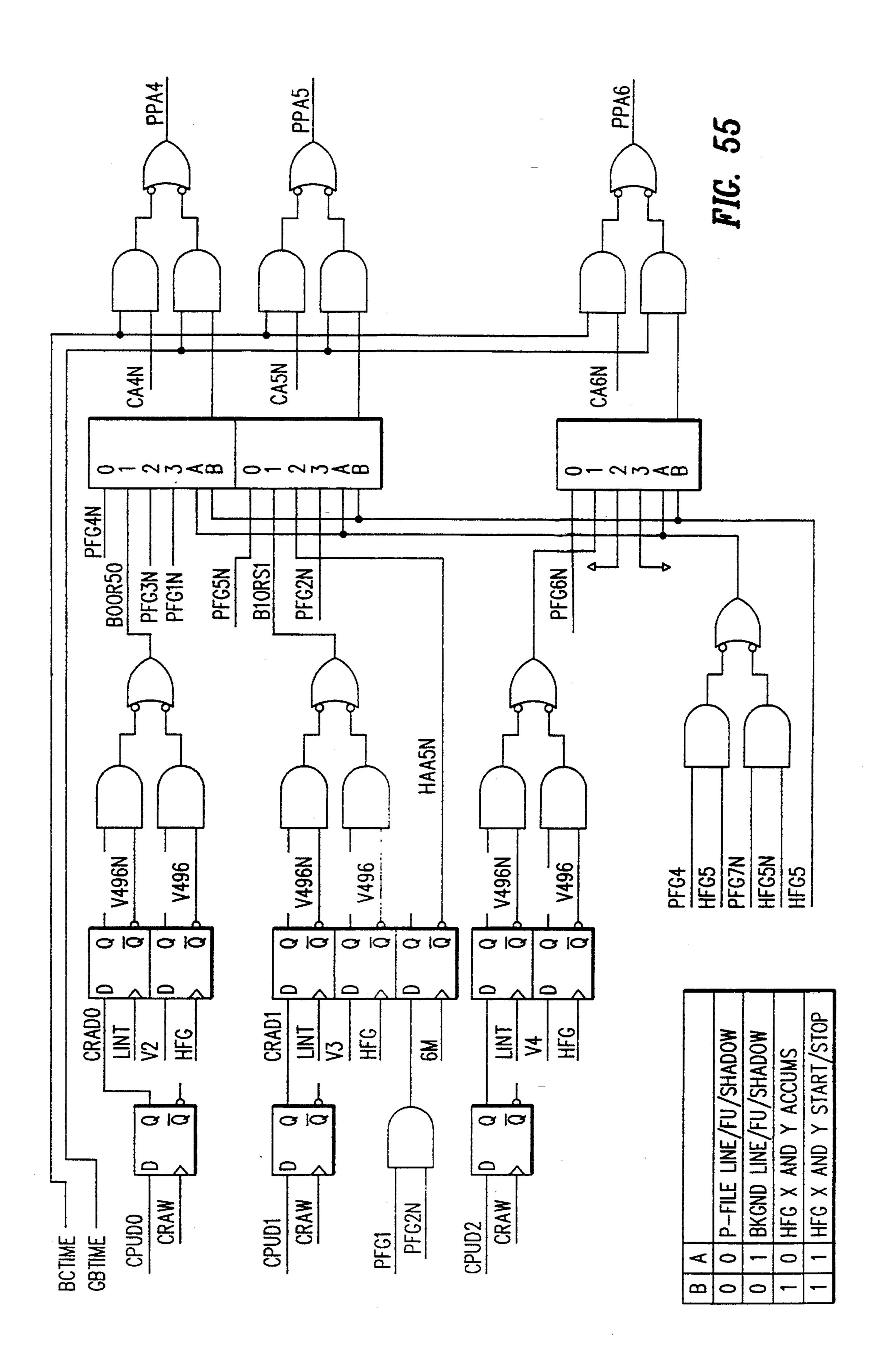

FIG. 55 illustrates how register set address lines are generated from next-line processing information.

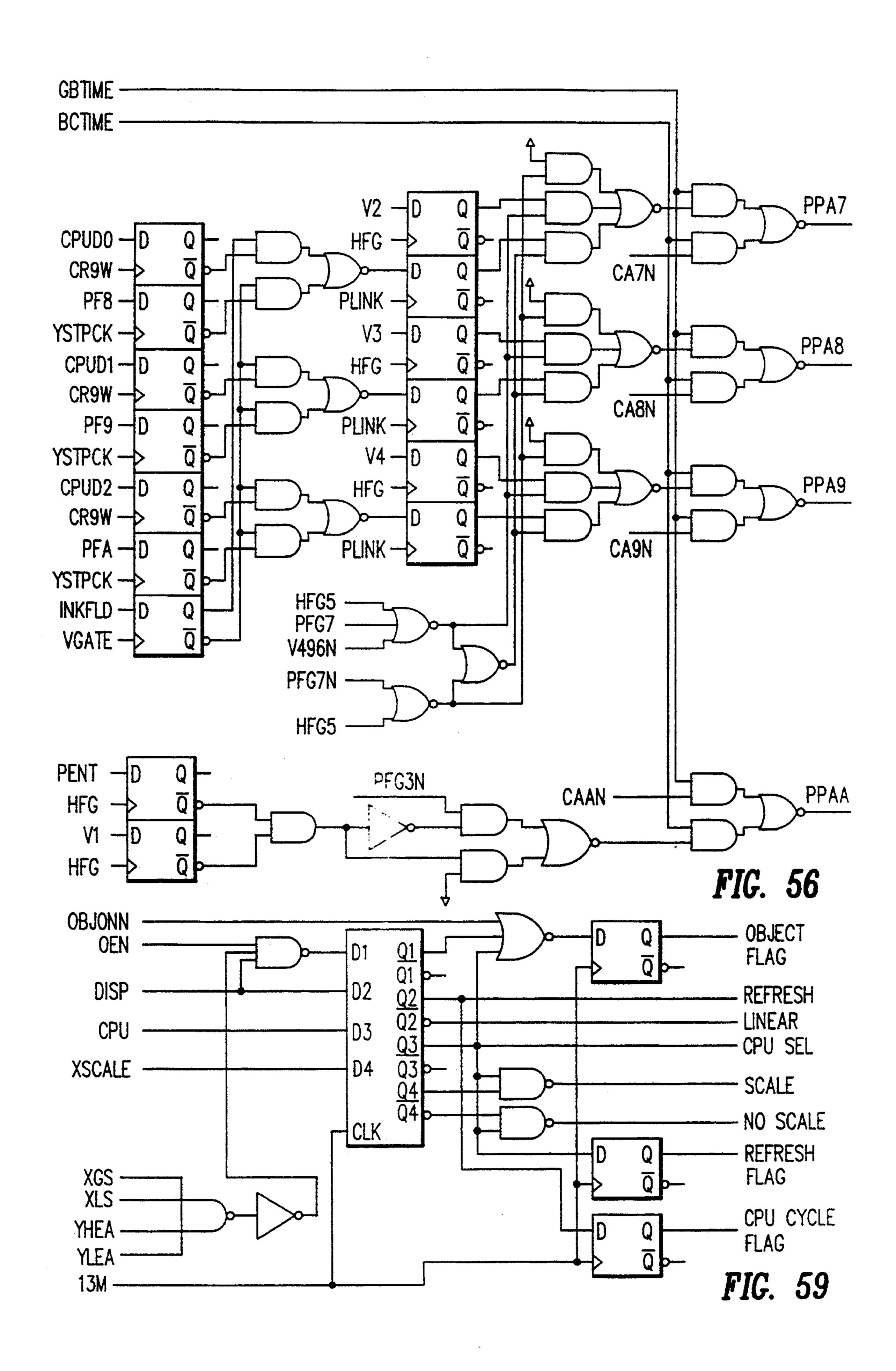

FIG. 56 illustrates the method used to create an active P-file address.

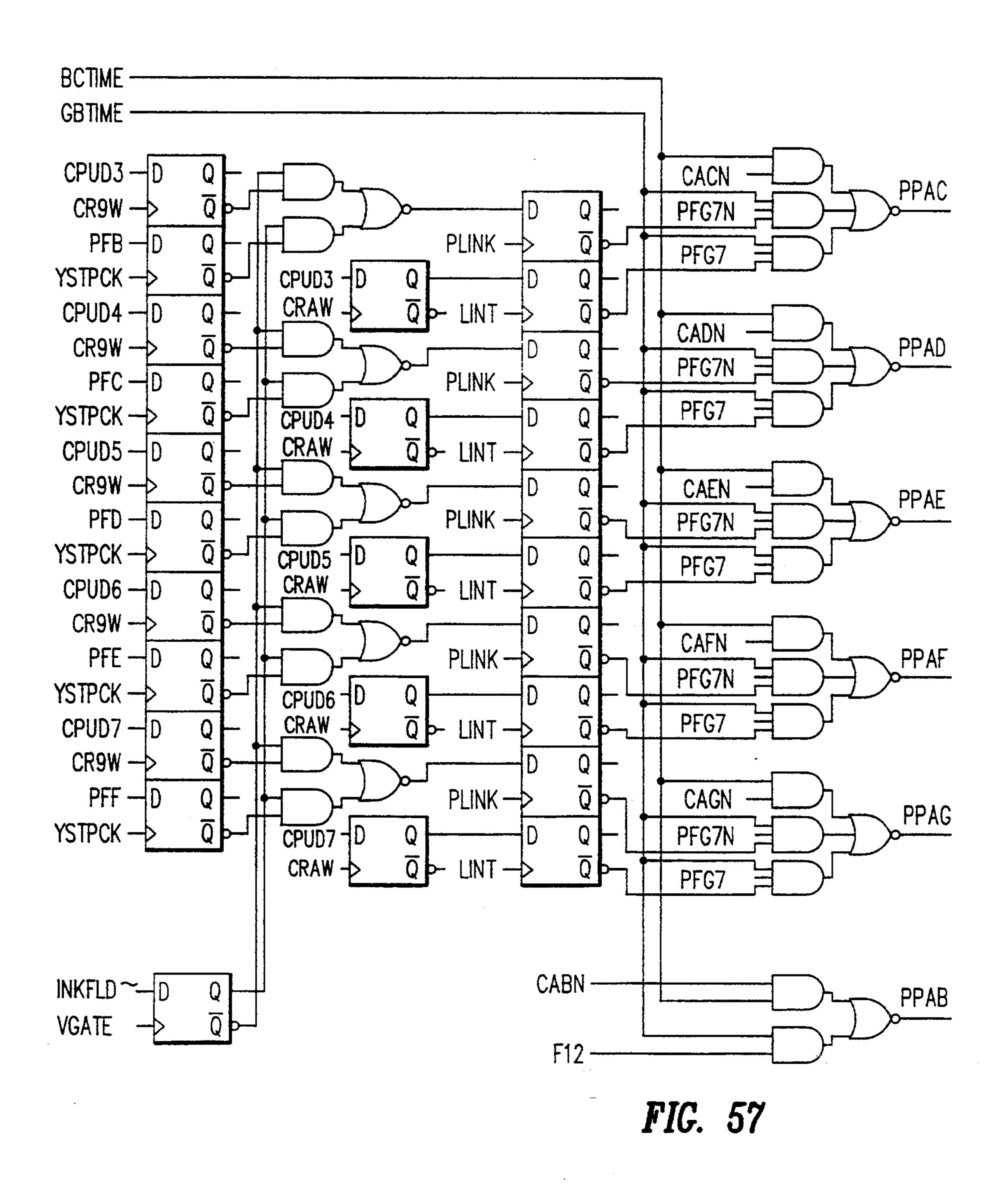

FIG. 57 illustrates the operation of a multiplexer used to transmit an active P-file address (one of 32 such addresses).

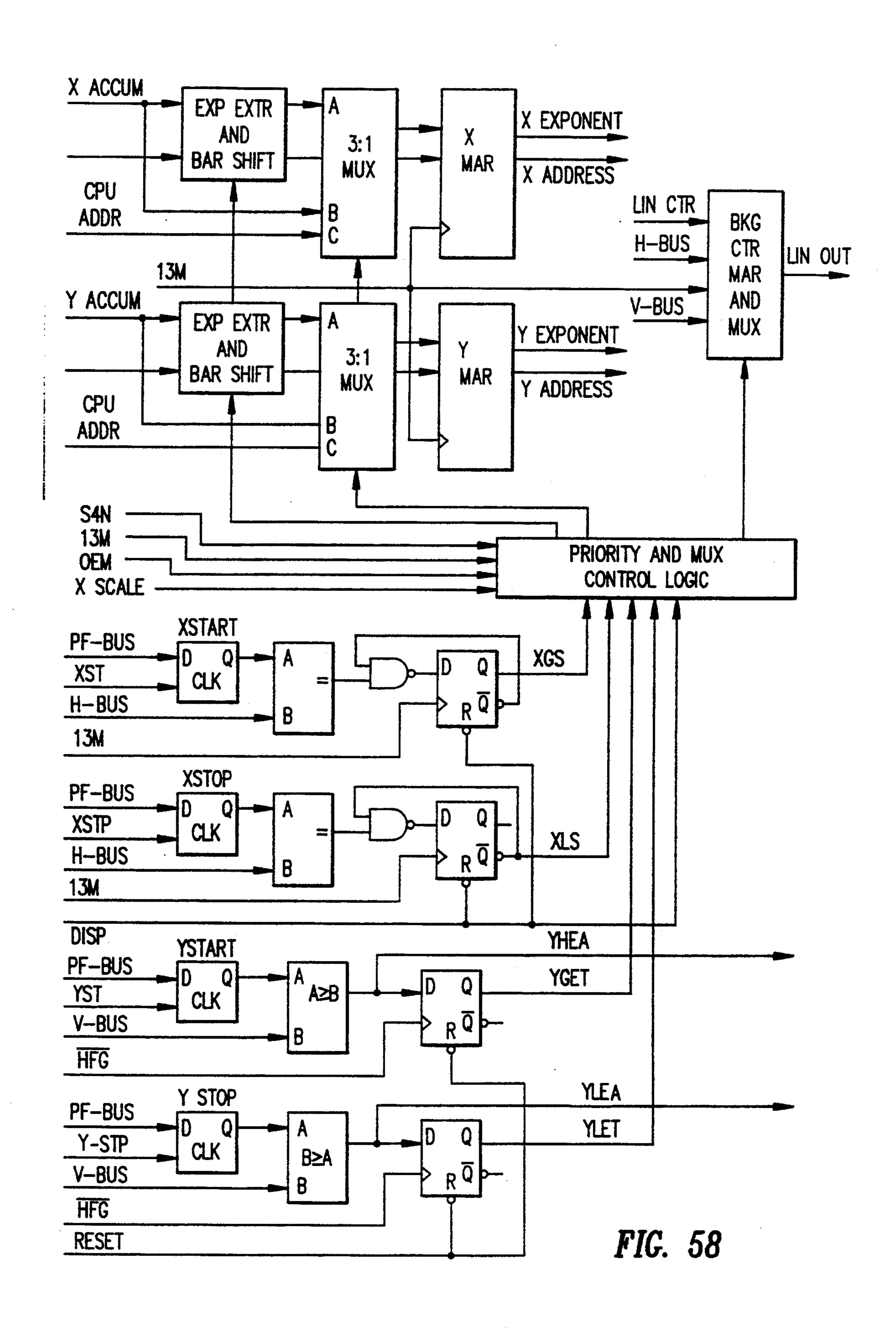

FIG. 58 is a simple block diagram of the memory array register MAR.

FIG. 59 illustrates selection of the next cycle address by the MAR multiplexer.

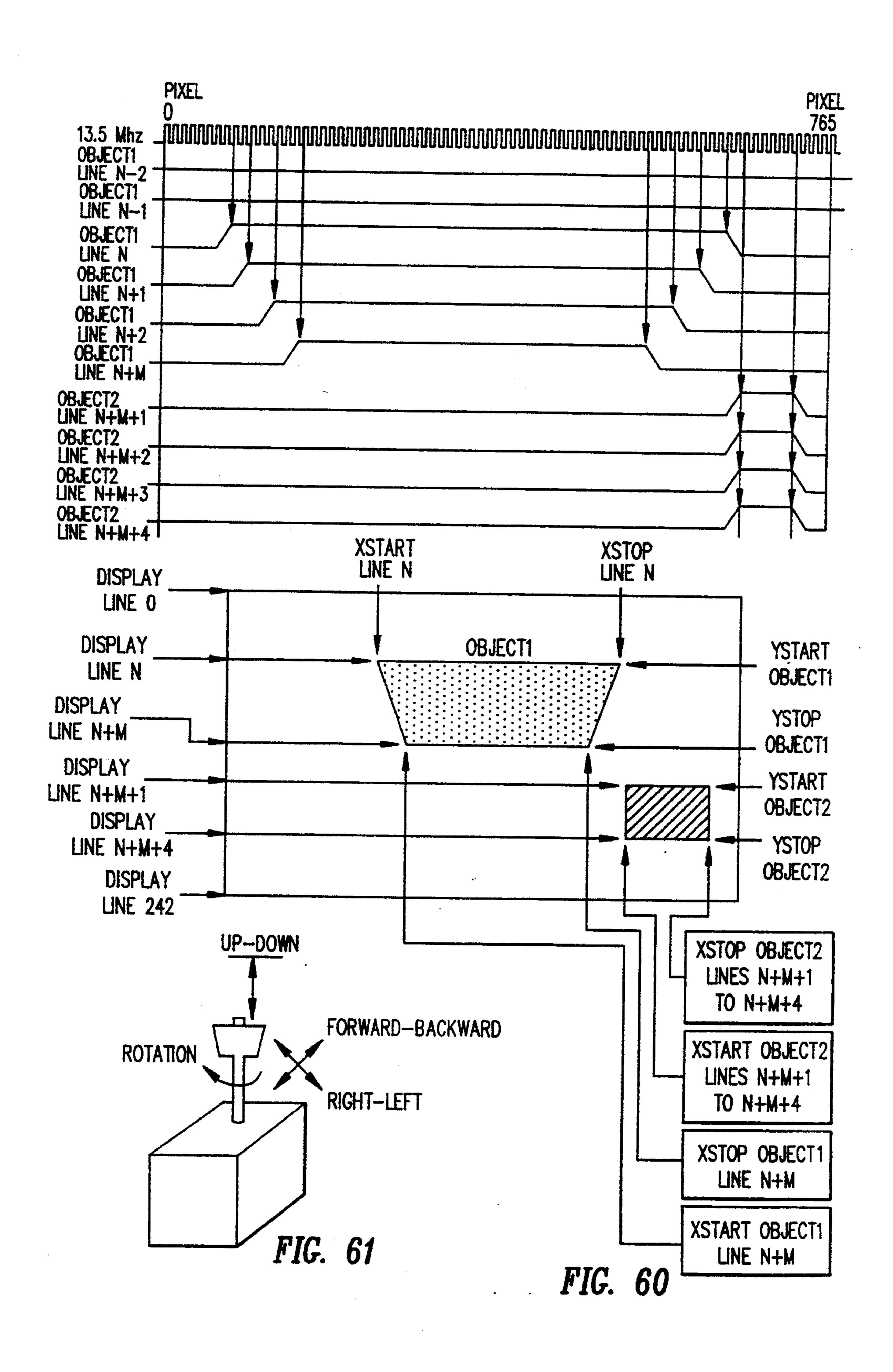

FIG. 60 graphically illustrates how the X and Y comparators, the counters and the BKGALU interact to create a P-file object window.

FIG. 61 is a schematic view of a four-axis joy stick used for control of various quantities that are manipulated in the video system.

# DESCRIPTION OF A PREFERRED EMBODIMENT

The subject invention is a video processing and display system, and some components thereof, that allows real time video signal processing and display. Three levels of technology are involved here. The slowest is the front end user interface and program interface, which can be supported by a personal computer such as the 386 PC/AT. A second level is a 32-bit microprocessor such as the Intel 80386 that runs the control software and specifies real time parameters at the 60 Hz field rate of the system. A third level is the hardware, including several innovative chips and an Image Translator that process the image or composite images at the pixel and sub-pixel levels. Use of a standard computer and standard software interface allows creation of an open system that may be adopted and extended by the user for a variety of applications.

The basic block of the system is an Image Translator (IT), a multi-function module that provides any four-component video information (such as Y, B-Y, R-Y and alpha) at 4444 rates; that is, each of these four channels is supplied at the pixel rate of 13.5 MSPS (13.5 million samples per second, which is approximately four times the NTSC video sub-carrier or reference frequency of 3.58 MSPS), with optional interfaces to receive or transmit B-Y, R-Y and alpha information at the slower rates (6.75 MSPS) used by many companion systems. The IT can perform real time, three-dimensional image translation, perspective projection, scaling, rotation and other computer-intensive graphic operations such as border insertion painting and formation of composite video images.

A Virtual Video Interface (VVI) provides a software interface to the IT and insulates the user or application writer from the sub-pixel processes such as inter-pixel interpolation. The VVI is similar in some respects to standard computer graphics interfaces such as VDI and DGIS; but the VVI has extensions to support video-specific animation operations such as real time video manipulation.

The IT is interfaced to the external video world through universal input and output modules. Each input module provides field rate selection of analog composite signals such as the NTSC standard and analog components input signals such YUV, GBR, YIQ, Betacam, SMPTE and MII. Digital input and output signals at the CCIR 601 standard (422 rate) are also available. Inter-50 connection and formation of composite signals is provided by a digital switch/composite option, the Framestore/Keyer (FSK). The FSK contains 4-24 RAM/based virtual frame buffers and one four-layer, real time mixer/keyer or two two-layer mixer/keyers. Up to four separate images may be used to form a composite image in real time. The FSK also moves screen images spatially and in time. The system determines the degree, using up to eight-bit resolution, of motion associated with a pixel image for purposes of synthetic pixel value construction; this is especially useful where an image is in rapid motion. See FIG. 1 for a schematic view of the relationship of the various control and processing blocks of the system.

The system also contains three innovative chips that perform many special purposes or unique tasks in video processing or display. A T-chip uses digital differential analyzers and special parameter files (P-files) to perform perspective projection, translation, rotation, scaling,

45

5

scrolling and other operations and to provide border insertion using linear or curvilinear border segments. An F-chip that comprises an array of multipliers, adders and other arithmetic units is configurable to provide digital finite impulse response (FIR) filters for use in 5 low pass/high pass, sub-pixel interpolation, video image mixing, painting and similar operations, where all filter coefficients may change in real time. An M-chip, a digital multiplexer, routes video signals and filter coefficients and computer bus signals for operations such as 10 painting and interpolation.

FIG. 1 indicates some of the interconnections between the major elements of the system.

Luminance and Chrominance Specifications

The luminance and chrominance information used for 15 black and white and color display is handled by conventional approaches. A good discussion of this is found in the book Color and Black & White Television Theory and Servicing by Alvin A. Liff, Prentice-Hall, Second Ed., 1985, pp. 88-111. For completeness, a brief summary of 20 this information is given here. Color television makes use of an additive system of color mixing, working with the primary colors of red, green and blue; red and green mixed together (in appropriate proportions) will produce yellow or orange; blue and red mixed together will 25 produce magenta; green and blue mixed together will produce cyan; and the three primary colors mixed together in substantially equal strengths will produce white. The luminance or brightness level Y for a particular color, formed from a mixture of red (R), green (G) 30 and blue (B), is determined from the equation for the "grey scale"

Y=0.299R+0.587G+0.114B

where the parameters R, G and B each vary from 0 to 1.00. If equal amounts of 100 percent red, green and blue color of full strengths are combined (R=G=B=1.00), this yields Y=1.00, which corresponds to the brightest possible shade of grey, namely white. Black is the absence of all color and corresponds to Y=R=G=B=0. Two color difference signals,

R-Y=0.701R-0.587G=0.114B,

B-Y=0.886B-0.299R-0.587G

representing the chrominance or color information, are used together with the luminance signal Y to provide all required color and black and white information. The color difference signal G-Y is easily recovered from the 50 other two difference signals, viz.,

G-Y=-0.508(R-Y)-0.186(B-Y).

The color difference signals R-Y and B-Y are now replaced by the compensated difference signals U=0.877 (R-Y) and V=0.493 (B-Y), respectively, or by a related pair of compensated difference signals CR=0.713(R-Y) and CB=0.564(B-Y). On a conventional two-dimensional (x,y) graph with the x-axis (y-60 axis) being positive toward the right (toward the top), one associates positive U and positive V with the positive y-axis and positive x-axis, respectively. The chrominance information for a particular color is specified by an amplitude and a phase angle on this graph, with 65 the phase angle referenced to the -U axis (negative x-axis). For example, the color yellow (R=G=1.0) corresponds to the coordinates (U,V)=(-0.439,0.096),

which has amplitude 0.449 and phase angle +12.4°. See FIGS. 3-9 of Liff, op. cit., for a graphic representation of the (U,V) graph and amplitude/phase relationships for the different colors. In the network used with the invention, the signals Y, U and V (or, equivalently, Y, R-Y and B-Y) are each assigned a channel with associated sampling rate 13.5 MHz, which, as described by international convention, is approximately four times

the NTSC color subcarrier frequency of 3.5795 MHz

used in the television industry. Image Translator

The Image Translator (IT) is a key portion of the hardware used for image transformation and display. The IT handles a single channel of live video, performs the real time digital effects transformations, mapping two-dimensional images onto a planar or curved surface, for locating that surface in three-dimensional space and performing projections of that surface onto a video screen, and provides the basic "painting" function. With reference to FIG. 2, input video signals enter through the analog input unit IN, are processed by the image translator, and are fed out through the analog output unit OUT. The analog input and output units may interface to various video formats such as RGB, YUV, NTSC, etc., and may convert analog to digital information (within IN) or convert digital to analog information (within OUT) for subsequent processing. The digital I/O unit converts from CC1R 601 standard video to the internal 4444 standard and back again, accomplished in the following manner. At the front end, the chrominance signals U and V, which arrive at only half the rate required by the system, are sent through a multiplexer and an interpolation filter to determine the "in between" or interstitial signal values; the filter in one embodiment may be  $3 \times 1$  and more generally may be up to  $16 \times 1$ . When four successive U (or V) signal data points  $U_n$ ,  $U_{n+1}$ ,  $U_{n+2}$ ,  $U_{n+3}$  arrive and the interstitial signal  $U_{n+3/2}$  is to be constructed, these four real signal values are multiplied by four filter coefficients  $C_i$  (j = 1,2,3,4) from an F-chip in the system to form a sum

$$S = \sum_{j=1}^{4} C_j \cdot U_{n+j}, \quad \sum_{j=1}^{4} C_j = 1.$$

The sum S is designated as the desired signal value  $U_{n+3/2}$ , and these interstitial signal values are computed anew for each n. In one embodiment of the filter used here C2=C3=0.6 and C1=C4=-0.1, but any reasonable choice of coefficients can be used here. As the sequence of real signal values  $U_{n+j}$  arrives, each such signal is multiplexed directly to the IT in FIG. 2. Three consecutive signal values  $U_n$ ,  $U_{n+1}$  and  $U_{n+2}$  are temporarily stored, and when the next consecutive signal value  $U_{n+3}$  arrives the interstitial value  $U_{n+3/2}$  is computed as indicated above and multiplexed into IT for further use.

At the output end of IT in FIG. 2, a decimation filter is used to remove every other U and/or V signal point if the 4444 system is to interface with a 422 system, optionally using multiplexing and filtering. In one embodiment, seven consecutive U signal values  $U_n$ ,  $U_{n+1}$ ,  $U_{n+2}$ ,  $U_{n+3}$ ,  $U_{n+4}$ ,  $U_{n+5}$  and  $U_{n+6}$  are multiplied by predetermined adoptive filter coefficients  $C_j$  (j=0,1,2,3,4,5,6) and summed to yield

$$S' = \sum_{j=0}^{6} C_j U_{n+j}, \sum_{j=0}^{6} C_j = 1,$$

and the sum  $S'=U'_{n+3}$  may replace the middle signal value  $U_{n+3}$ ; the alternate signal values  $U_n$ ,  $U_{n+2}$ ,  $U_{n+4}$ ,  $U_{n+6}, \ldots$  may be deleted by appropriate multiplexing so that the stream of output signals for the U signal becomes ...,  $U'_1$ ,  $U'_3$ ,  $U'_5$ ,  $U'_7$ , ... The seven adoptive filter coefficients used here may be replaced by a larger 10 or smaller number; in one embodiment, these coefficients are symmetric about the central coefficient C'(n+3) so that C'(n+3+k)=C'(n+3-k) (k=0,1,2,... .). If the video system interfaces to a system that can provide or receive data at the full 4444 rate, these ad- 15 justments are not necessary. If the video system interfaces to a system that provides or receives data at other than the 422 rate or the 4444 rate, obvious adjustments can be made in the pre-filtering or post-filtering to accommodate this different rate.

A typical video unit may contain multiple analog and digital input and/or output units, plus a keyer and frame store system. The keyer combines several video signals together from the inputs and the ITs and feeds these to the output units.

FIG. 3 is a schematic view of the IT. The border insert unit inserts a border around the live video, and the total signal is then fed to four time-delayed field stores. Each frame or instantaneous picture on the display screen consists of two interleaved fields, with one 30 field appearing on the odd-numbered horizontal lines (1,3,5,7...) and the other field appearing only on the even-numbered horizontal lines (0,2,4,6,8, . . . ). From these frames of two fields each, the frame constructor produces a full frame of video each 1/60 second (the 35 "frame rate") so that the field rate of each separate field is 1/30 second. The video is pre-filtered by a two-stage, two-dimensional low pass filter (vertical and horizontal) to smooth out any undesirable signals due to aliasing that would otherwise be produced when the image is 40 compressed or rotated in three dimensions or projected onto a surved surface. The video signal is then fed to a random access frame buffer; the frame buffer is actually doubly-buffered so that an output signal is read from one buffer while an input signal is being written into a 45 companion buffer. The output signal is read in an unconventional order, and this produces the transformed image in the interpolator. Post filtering also occurs in the interpolator. Although FIG. 3 shows only one signal line between adjacent modules it should be under- 50 stood that one such line is provided for each signal component (e.g.,  $Y,U,V,\alpha$ ) and that these signals are provided for each of the two fields that comprise a frame.

Generally, this occurs under the control of software 55 associated with the apparatus. The software sets up control parameters at a field rate of 1/60 second. The hardware performs pixel-rate calculations at the rate of one every 74 nsec (1/13.5 MHz).

In FIG. 3, double arrows (===) indicate passage of 60 signals at double the normal video (NTSC) sub-carrier rate, which would produce a full frame every 1/60 second; and quadruple arrows (====) indicate passage of signals at four times the sub-carrier rate. The IT includes a bypass path so that, in the "paint" mode, the 65 video may optionally bypass the pre-filters. The IT also includes a paint refresh path so that the screen can be kept active using the M1, M2 and interpolation filters

only 50 percent of the time; the remaining time is available for using these filters for painting. A feedback path allows information produced by the interpolator to be passed to the field stores for use in the frame constructor.

The video signal passed through the IT contains four full channels, Y, U, V and  $\alpha$ . The luminance or monochrome signal Y carries intensity or brightness information. The color difference signals U and V carry chrominance information, as discussed above. The signal  $\alpha$ represents opacity so that the signal  $1-\alpha$  represents transparency, with  $\alpha=0$  indicating a transparent image and  $\alpha = 1$  indicating a fully opaque image. The  $\alpha$  signal is used when two or more composite signals are superimposed on the display screen. The luminance signal Y and  $\alpha$  each range from 0-255 units; and the chrominance signals U and V range from -128-+127 units, allowing for use of guardbands on the luminance channel and signed number representation of the color signals. Each of the four channel signals Y, U, V and  $\alpha$  is expressed by eight bits and is sampled from the incoming analog signal at 13.5 MHz; this rate is the frequency used in the international standard for digital video, namely CCIR 601. In the conventional CCIR 601 standard, Y is sampled at 13.5 MSPS and U and V are each sampled at 6.75 MSPS (designated 422). Here, the Y, U, V and  $\alpha$  signals are all sampled at 13.5 MSPS so that the corresponding designation might be 4444. Real time interpolation and adaptive decimation filters are included in the digital I/O modules to convert between the internal 4444 standard and the conventional 422 standard, as discussed above.

Returning to FIG. 3, the border insert block inserts a border onto the incoming live video signal. The border crops the picture area; the full area available to store video is limited to the full picture size. The border insert computation is done in a T-chip, is quite flexible and is discussed below. The inside and outside edges of a border may be soft or apodized (gradually merging into the background), or the border may be a standard "hard" border. The border shape may be expressed by polynomials up to second degree in the screen coordinates x and y so that the border shapes may be rectangular, polygonal and even rounded within these limits.

FIGS. 5 and 6 illustrates schematically the operation of the frame constructor, together with the four field stores associated with the frame constructor. Provision of these four field stores allows the video transformations and painting operations to operate on a full frame video (consisting of two interleaved fields) while a second frame is being prepared in a buffer. The human eye can detect flicker and other motion artifacts at a rate of 30 Hz so that a higher rate, 60 Hz, is used here for frame processing and display. In an interlaced raster system, with conventional image processing, if a hand is shown in motion, the position of the fingers of the moving hand will be different in successive fields due to the motion; and this could produce jagged edges where the images of the two interleaved field fail to match. The IT constructs a full frame of video every 1/60 second and does all processing on this full frame. Since the incoming video signal does not contain all information of a frame at precisely the same time, this information is reconstructed by interpolation in time.

Four time-delayed fields of video signals are stored in the frame stores; the most recent field information (here designated t=0, assumed for definiteness to be an even

field), and each of the three previously input fields  $t = -\Delta t$  (odd field),  $t = -2\Delta t$  (even field) and  $t = -3\Delta t$  (odd field). Thus, two snap shots at different times of each of the two fields, even and odd, are then available. These four time-delayed fields are used to generate the 5 most recent estimate of a pixel value pv(x,y), based data from the current field and another synthetic field, which changes at the frame rate of 60 Hz.

FIG. 5 is a schematic view of the apparatus, a part of the IT, that constructs synthetic pixel values from pixel values at adjacent pixel positions and in adjacent field lines, taking account of the presence or absence of rapid change in adjacent pixel values. The apparatus shown will handle one of the four channels of video image information Y, U, V or a. For purposes of discussion here the pixel value at horizontal pixel position  $x_m$ (m=0,1,2,...,767) on video line Yn (n=0,1,2,...,523) at time t will be denoted  $Pv(x_m, y_n; t)$ . Even field lines correspond to lines  $y_0, y_2, y_4, \ldots$ , and odd field lines correspond to lines y<sub>1</sub>, y<sub>3</sub>, y<sub>5</sub>, . . . Thus, for example, the video system does not directly compute or display a pixel value  $pv(x_m, y_2, t)$  in the odd field, although this synthetic pixel value may be needed for some display purposes.

For an arbitrary but fixed display time  $t=t_0$ , let  $t_{-p}=t_0-p\Delta t$  (p=1, 2, 3) be the three immediately preceding pixel rate time intervals ( $\Delta t \sim 74$  nsec here, but  $\Delta t$  is generally unlimited). For illustrative purposes, consider the array of pixel positions shown in FIG. 6, where the pixels at positions  $(x_m, y_n)$  (m=0,1,2,3,...,767;  $n = 0, 2, 4, 6, \ldots, 524$ ) are real pixels on the even field lines and the pixels at positions  $(x_m, y_n)$  (m=0,1,2,3,...., 767; n = 1,3,5,...,523) are real pixels on the odd field lines. When only data from the odd field (lines  $y_1$ ,  $y_3$ ,  $y_5$ ,  $y_5$ ...) are present, at time  $t_0$ , no pixel value  $pv(x_3, y_2; t_0)$ is directly available. This last pixel value is often needed for some purposes, and a synthetic pixel value at this position p' (odd fields) is therefore computed. For  $y=y_1$ , and, separately, for  $y=y_3$ , the two real pixel 40values  $pv(x_3, y; t_0)$  and  $pv(x_3, y; t_{-2})$  are compared by computation of a motion function mf(x3, y; t0) (such as a simple subtraction  $pv(x_3, y; t_0)-pv(x_3, y; t_{-2})$  for these two pixel values. The pixel values are fed to an LUT, which computes a motion function therefrom.

For example, one might form a four-bit output signal from the mf LUT which specifies the degree of motion observed between the two input pixels. Four bits allows up to 16 degrees of motion to be distinguished. The degree of motion assigned to a particular pixel is based 50 upon the difference between the two pixel values (A-B).

The motion functions  $mf(x_3,y_n,t_0)$ ,  $mf(x_3,y_{n-2},t_0)$  and  $mf(x_3,y_{n-1},t_{-1})$  (for n odd) are fed to a motion computer MCP that determines the degree of motion present and generates an output signal  $\beta(t_0)=1$  if no perceived motion is present currently at  $(x_3, y_1)$  and  $(x_3, y_3)$ ,  $\beta(t_0)=0$  if strong or rapid motion is currently present at at least one of these four real pixel positions. If intermediate strength motion is present at these pixel positions, the MCP generate an intermediate output 60 signal  $\beta_i(t_0)(0<\beta_i<1)$ . The intermediate value  $\beta$  may be one of a spectrum of intermediate values lying between 0 and 1; for example, if the MCP output signal has four-bit resolution up to  $14 (=2^4-2)$  different intermediate values  $\beta_i$  may be generated by the MCP.

The synthetic pixel value of (x<sub>3</sub>, y<sub>2</sub>) at time t<sub>0</sub> is formed by

$pv'(x_3,y_2;t_0) = \frac{1}{2}(1-\beta(t_0))[pv(x_3,y_1;t_0)) + pv(x_3,y_3;t_0)] - + \beta(t_0)pv(x_3,y_2;t_{-1}).$

FIG. 5 illustrates one embodiment of this approach for computation of synthetic pixel values.

The frame constructor in FIG. 3 also allows the system to lock down the contents of one to four of the field store signals so that a frame may be frozen. For example, one can freeze two consecutive fields (e.g., odd/even) of video and let the frame constructor algorithm constantly compare that frozen or reference frame to the incoming live video signals. This can be used to filter out backgrounds, as in motion keying in which the moving parts of the picture are extracted from the motionless parts. In this mode, the normal  $\alpha$  channel frame constructor is disabled, and a new output  $\alpha$  is generated based on the motion functions for each of the three components Y, U, V as follows:

$$\alpha(x_m, y_n, t) = f(mf(x_m, y_n, t))$$

$\alpha(x_m, y_{n-1}, t) = g(mf(s_m, y_{n-1}, t))$

where f and g are monotonic, single variable functions, each with a range [0,1]. The frame constructor has four preset modes; (1) normal, in which a full frame of video is constructed from the four fields as described above; (2) freeze all signals (Y,U,V) and  $\alpha$ , which can be used either for field freeze or frame freeze or as an adaptive freeze; (3) freeze  $\alpha$  field only; and (4) motion keying, as discussed above.

The frame constructor hardware used here is quite complete and appears to take more care with these images than does any other unit now available. Some systems are field-based rather than frame-based; these systems use no frame constructor, or they merely copy the even field lines into the odd field line positions and perform their calculations based on only one of the fields. The result is often undesirable image quality in motion video. Other systems use a frame constructor but with one-bit arithmetic so that the switch between the "still" and strong motion limit cases is a hard switch and only equivalent pixels from two previous fields are prepared; the present system uses four-bit arithmetic so that as many as 14 intermediate motion situations can be distinguished from the two limiting cases of no motion and strong motion.

In anticipation that the video may be used for compression, wherein the size of the source images is reduced by a factor greater than one for video display, the image that issues from the frame constructor is pre-filtered by a vertical filter and a horizontal filter to avoid aliasing, twinkling, and other ills that motion video is heir to. To understand the importance of this, consider an image that is compressed by a factor of two in the horizontal and the vertical directions. One simple way to handle this is to sample every second pixel on a horizontal line and to blank out alternate pixels and alternate horizontal lines. In this situation, a one-pixel-wide line might disappear completely or might flash on and off as the picture moves. Our solution is to pass the signal through a low pass filter or to average two adjacent pixels together; this must be done before the image is 65 compressed, because the process of compression would discard necessary video information. Too much filtering will blur the image so that it is important to limit the amount of filtering done here. The more pixels that are

11

averaged together, the better will be the quality of the resulting image.

The IT includes a two-stage pre-filter, which filters the frame constructor output signal vertically (V Select) and then horizontally (H Select). Each filter is a 5 16×1 symmetric, finite impulse response (FIR) filter, and the result resembles a two-dimensional 16×16 filter but without the ability to independently vary some of the cross terms. The filter coefficients are determined by the source-to-target (S-T) Mathglue module shown 10 in FIG. 3, whose input signals are controlled by the software. The software specifies, for each 1/60 second frame, what is to be the transformation from source or live object to the target or output video screen (S-to-T); this is equivalent to specifying the vertices of the raster 15 polygon for each frame. Source-to-target Mathglue logic plus two T-chips determine that transformation down to the pixel level (with time intervals  $\Delta t = 74$ nsec) and feed the necessary coefficients to four F-chips (FIG. 3) that lie downstream from the frame constructor, for filtering of the current signals.

Each T-chip includes several third order digital differential analyzers (DDAs), each of which can solve a third order differential equation in the coordinates x and y. The defining differential equations are downloaded by the software as a description of the change of the video signal for that frame; and the T-chip then integrates these equations across all the pixels in the frame image. Four defining differential equations are needed for the (horizontal and vertical) coordinates so that two T-chips are needed here. The T-chips and Mathglue module in the S-T section compute the derivatives

$$\frac{\partial \Delta}{\partial x}$$

and  $\frac{\partial \Delta}{\partial y}$

at each pixel in the source image. These derivatives contain the information required to select the appropriate pre-filter.

The filter coefficients specify the weights to be associated with each of the 16 neighboring input pixels that are averaged into a interpolated output pixel signal. The filter coefficients are pre-calculated to serve as sets of low pass filters with different bandwidths. To a large extent, the length of the filter (here 16, but this is optional and may be increased or decreased) determines the degree that the picture can be compressed before it appears to break up or to twinkle. In some of the better video image translators currently available, this breakup occurs at about ½ the original image size. In the IT that is part of the subject invention, compression by a factor of up to 4 appears to be possible; with N filter coefficients used, compression, without image breakup, by a factor of up to N/2 would be possible.

The IT performs the transformations for video effects, such as flying the video or rotating the image, as 55 well as facilitating composite operation of the paint brush onto the canvas in the paint mode. The IT contains two frame buffers (double buffers) that are used in an alternating manner. One buffer is written into from the filter board while the contents of the second buffer 60 are being written to the output; then the two buffers swap functions for the next frame. The incoming video signal is written into the frame buffers from the filters during the horizontal blanking interval for the screen image, two lines at a time. Recall that with NTSC 65 video, the horizontal line interval of 63.5 µsec includes some time to scan the active video on the screen ("H retrace") and some time for retracing to the start of the

**12**

line ("H retrace"). During the retrace time, the beam is blanked so that no video signal is output; this is called the horizontal blanking time and is normally  $10.9\pm0.2$  µsec.

During each H active interval, one bank of eight FIFOs is loaded with two lines (each) of active video signal information (192 pixels each x 8 FIFOS=1536 pixels); each FIFO stores one fourth of the line. During the next line interval a second bank of eight FIFOs will be loaded with the next two lines of video data. During the next horizontal line blanking interval, the first bank will once again be written, and this pattern is repeated. Assume for definiteness that field M1 is being displayed. During the H retrace interval, two lines of data are written onto each of three identical frame buffers A, B and C associated with field M2. Sixteen pixel values, one from each of the FIFOs are written simultaneously onto A, B and C at corresponding positions in each buffer utilizing the static column address write capability of the RAMs. Here, static column mode dynamic RAMs may be used for the A, B, C buffers for each field rather than the more expensive static RAMs.

The read operation from a buffer requires full access of a 4×4 pixel neighborhood every 74 nsec as the read out sequence may not be in raster order. This requires very high speed RAMs; and to implement this three banks of identical dynamic RAMs A, B and C are sequentially selected in time so that each RAM need only cycle in a time  $3 \times 74$  nsec=222 nsec. The use of a triple bank (A, B, C) of dynamic RAM's (DRAMs) as an effective static RAM is a novel feature here. The corresponding DRAM addresses, designated here as A-p, B-p and C-p, are written into substanially simulta-35 neously with the same byte or word. The write operation is carried out quickly due to the static column mode of the DRAMs; but the operation of read from a DRAM is relatively slow, requiring as much as 200 nsec for completion of the read cycle. As the read commands arrive serially, the three banks of DRAMs are read sequentially from banks A,B,C,A,B,C,A,B, . . . so that each read operation in a given bank, once begun, has adequate time for completion before answering another read command. That is, if a sequence of read commands arrives that requires reading of the contents of RAM addresses 27,14,89,24,38,11,53 ..., the contents would be read as follows: 27 in A, 14 in B, 89 in C, 24 in A, 38 in B, 11 in C, 53 in A, .... Two banks, rather than three, may be used here if the data read times in the DRAM are no more than about 110 nsec. Such DRAMs are currently available, but they are much more expensive than the slower-read DRAMs for which three banks of DRAMs are used. The frame buffers can be addressed as two independent buffers, each 768 pixels wide, with buffer M1 being 672 lines long and buffer M2 being 692 lines long. These can also be combined as one contiguous buffer 768 pixels wide by 1364 lines long. These addressing modes are accomplished by a novel address computation scheme which permits lines of length 768 instead of the easier 1024. Having lines of length 768 allows both 525 and 625 line television systems to be accommodated by the same hardware.

The target-to-source module (T-S) shown in FIG. 2 determines which pixels are read out and in what order, this is in the inverse of the transformation visible to the user viewing the output. The T-S Mathglue module also uses two T-chips and Mathglue logic, much as the source-to-target module does.

40

50

In general, a pixel location in the target will not map precisely to a pixel location in the source in the T-to-S mode so that some interpolation is required here. The interpolator interpolates a video value by averaging, using appropriate numerical weights, over a  $4\times4$  (more 5 generally,  $M \times N$  with M,  $N \gtrsim 2$ ) pixel area that is approximately centered at the intermediate pixel position p'(x,y) whose value is to be gauged, as illustrated in FIG. 7. The effective position shift occurs through adjustment of filter coefficients associated with adjacent 10 pixels in the chosen  $4\times4$  area. These filter coefficients are pre-calculated and loaded into the coefficient ram by the computer. Fractional raster addresses for p'(x,y) are computed in the T-to-S Mathglue module and are used to select the optimum filter to construct the pixel 15 ification of the border color to be displayed, through value pv(x,y).

### Border Insertion

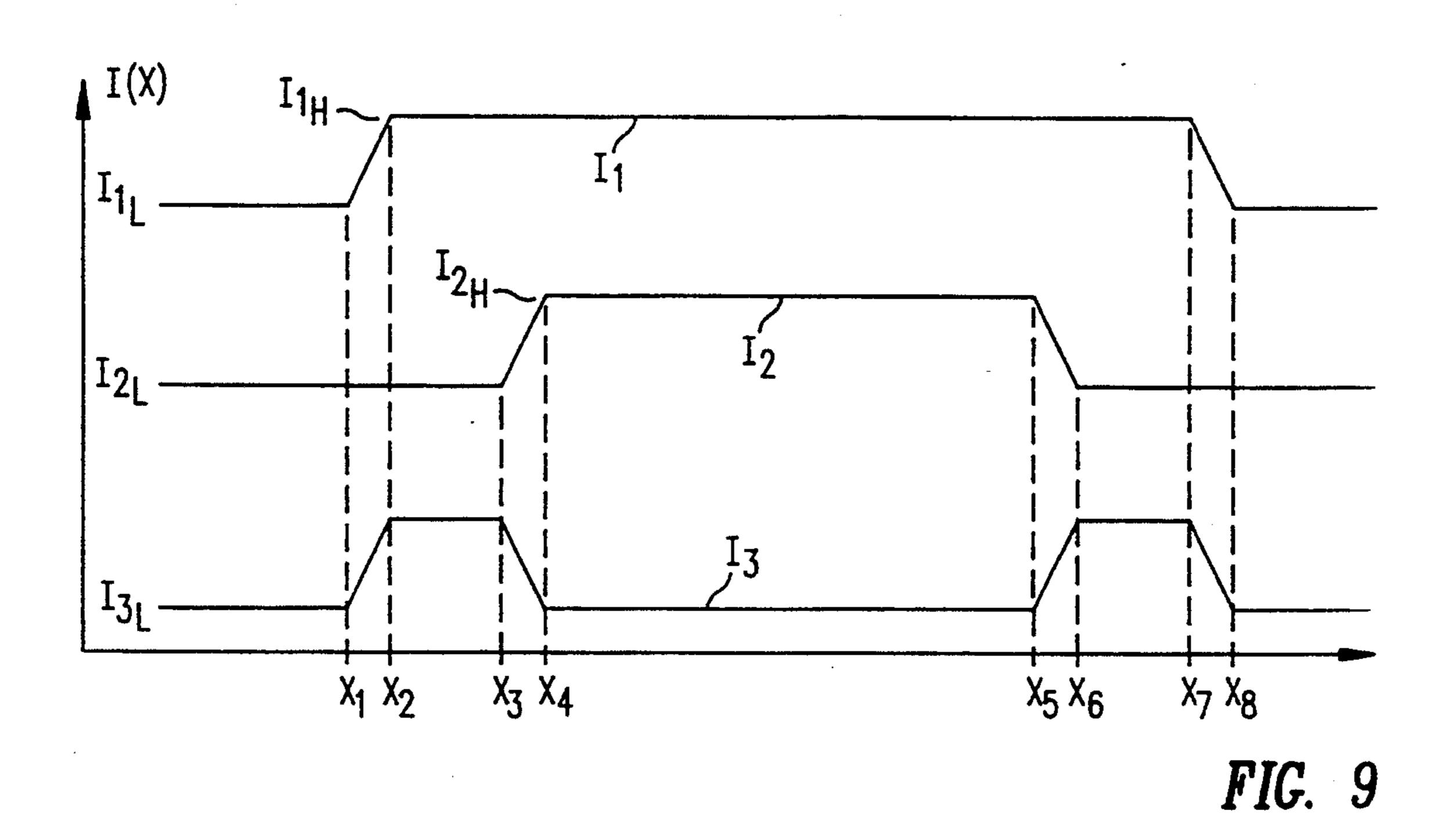

Border insertion on a screen is a task of some complexity, even for a simple rectangular border. With reference to FIG. 8, consider the rectangular border B 20 to be superimposed on the screen S. FIG. 9 illustrates how the border image is generated in one dimension (horizontal), if the left border transition is to occur between horizontal pixel positions x1 and x4 and the right border transition is to occur between pixel posi- 25 tions x5 and x8. A first image I1 is generated for which the image function is

$$I_{1}(x) = 0 x < x_{1}$$

$$= \frac{x - x_{1}}{x_{2} - x_{1}} x_{1} \le x \le x_{2}$$

$$= 1 x_{2} < x < x_{7}$$

$$= \frac{x_{8} - x}{x_{8} - x_{7}} x_{7} \le x \le x_{8}$$

$$= 0 x_{8} < x$$

A second image I<sub>2</sub> is generated for which the image function is

$$I_{2}(x) = 0 x < x_{3}$$

$$= \frac{x - x_{3}}{x_{4} - x_{3}} x_{3} \le x \le x_{4}$$

$$= 1 x_{4} < x < x_{5}$$

$$= \frac{x_{6} - x}{x_{6} - x_{5}} x_{5} \le x \le x_{6}$$

$$= 0 x_{6} < x$$

These two images are subtracted from one another to produce a difference image function  $I_3=I_1-I_2$  are shown in FIG. 9. Where I<sub>3</sub> is positive, the border function is active. Inclusion of the four ramps in I3 allows a reasonably smooth transition (up to eight bits resolu- 55 tion) between the border and the picture enclosed by the border. The slope of the ramps controls the softness or apodization of the border. The slope discontinuity points of the images control the width and symmetry of the border transition regions. For a two-dimensional 60 rectangular border, a second pair of analogous images I4 and I5 is set up in the vertical direction and a difference image function  $I_6=I_4-I_5$  is formed; and the composite image I<sub>3</sub>·I<sub>6</sub> would define the two-dimensional border. The composite image I<sub>3</sub>·I<sub>6</sub> controls two multi- 65 pliers, one for the intensity of the border and a second multiplier that controls the intensity of the image enclosed within the border that is to be mixed on. A com-

puter controlled LUT is inserted between the border arithmetic and these two multipliers to provide nonlinear mixing controls. In particular, inclusion of LUTs allows shaping of the ramps which are the direct output of the border arithmetic T-chip. Such ramps if used directly cause the phenomenon call MACH bonding at the start transition points of the ramp. Borders that are defined by curves of mixed degrees up to three in the coordinates x and y can also be inserted by the T-chip, using an extension of this process in which the border definition points  $x_i$  ( $i=1, 2, \ldots, 8$ ) vary with video screen coordinates x and/or y. In addition to transparency information for a border, the system receives specthe Y, U and V channels.

The two linear ramps on each of the curve I<sub>1</sub> and I<sub>2</sub> in FIG. 9 may be generated using clamped (from below) and clipped (from above) output signals from a DDA. For a constant input signal (of magnitude k<sub>1</sub>) to the DDA, the output signal is of the form  $k_1(t-t_1)$  where t is the time variable of integration and t<sub>1</sub> is the time at which the input to the DDA commences. The horizontal coordinate x shown in FIG. 9 may be made to correspond to the time variable t issuing from the DDA by a linear relation such as  $t=k_2x+t_2$ , where  $k_2$  and  $t_2$  are constants. The output signal of the DDA is then clipped from above at a predetermined value I<sub>1H</sub> and is clamped from below at a second predetermined value  $I_{1L}$  by techniques well known in the art. The clipped/clamped output signal from this DDA then becomes

$$\widetilde{I_1}(t) = \min[I_{1H}, \max[I_{1L}, k_1(t - t_0)]]$$

$$= I_{1L} \quad (t \le t_1 + I_{1L}/k_1)$$

$$= k_1 (t - t_1) \quad (t_1 + I_{1L}/k_1 < t < t_1 + I_{1H}/k_1)$$

$$= I_{1H} \quad (t_1 + I_{1H}/k_1 \le t).$$

Taking account of the linear correspondence of x and t, this may be rewritten as

$$I_{1}(x) = \widetilde{I_{1}}(k_{2}x + t_{1})$$

$$= I_{1L} \quad (x \leq [t_{1} - t_{2} + I_{1L}/k_{2}))$$

$$= k_{1}k_{2}x + k_{1}(t_{2} - t_{1}) ([t_{1} - t_{2} + I_{1L}/k_{1}]/k_{2} < x < [t_{1} - t_{2} + I_{1H}/k_{1}]/k_{2})$$

$$= I_{1H} \quad ([t_{1} - t_{2} + I_{1H}/k_{1}]/k_{2} < t).$$

The controllable variables here are t<sub>1</sub> and k<sub>1</sub>, and one easily verifies that the choices

$$k_1 = (I^1 H - I_1 L)/k_2(x_2 - x_1)$$

$$t_1 = k_2 x_1 + t_2 - I^1 L/k_1$$

will reproduce the desired curve

$$I_1(x) = I_{1L} \quad (x \le x_1)$$

$$= I_{1L} + (I_{1H} - I_{1L}) \frac{x - x_1}{x_2 - x_1} (x_1 < x < x_2)$$

$$= I_{1H} \quad (x \ge x_2).$$

Each of the other linear ramps is similarly generated.

Frame Store/Keyer Module The frame store/keyer (FSK) module is an optional part of the full system and provides three major functions in one hardware module: (1) virtual canvas (VC), which uses a large amount of memory for painting a canvas that is much larger 5 than a single frame, and it also provides various memory management functions; (2) video buses and crosspoint switches that control electronic traffic in the system by providing for flow of the video signals Y, U, V,  $\alpha$ , Z and certain stencil signals, among others; and (3) 10 keyers, which are video mixers that allow combination of multiple video signals with independent transparency factors that are used in image painting and composition.

Virtual canvas is a large memory array in which the video signals Y, U, V and a can be stored and may be 15 used to hold a large canvas that is the equivalent of 6-24 NTSC frames for painting an image or for panning across a scene. VC can also be used to hold the undo buffers, multiple stencils, and menus, all for the painting operations. For formation of composite images, VC can 20 be used to hold the background or multiple layers of images to be composited together, along with the transparency factor associated with each layer. As illustrated in FIG. 10, two input terminals plus four output terminals are available for use with VC, all operating in real 25 time. Two of the output signals pass through lookup tables (LUTs) to provide for effects such as image color mapping, displaying a stencil and similar tasks. The memory array is addressed indirectly by the CPU through a tile map (one tile equals 32 contiguous hori- 30 zontal pixels by eight contiguous vertical lines) that provides considerable flexibility.

The video bus arrangement is shown in FIG. 11. The FSK straddles everything in the system, allowing all signals to flow in and out of the FSK and controlling 35 the intersections. In this embodiment, a video bus submodule has three input terminals and two output terminals; the cumulative limit is four I/O channels. Two additional buses internal to the FSK provide additional paths for keyer and stencil information. The FSK in- 40 cludes a large number of crosspoint switches to interconnect the buses, but in the current embodiment these switches do not include all possible permutations of interconnections. The particular crosspoint connections chosen provide maximum flexibility and include all 45 interconnections that a user might reasonably require. If additional applications are identified, additional crosspoint switches can be added.

The keyers allow mixing or compositing of video signals. As illustrated in FIG. 12, a mixture of two input 50 signals IN1 and IN2 is controlled by the mix ratio mixr that is fed to a third input terminal of the keyer and the output signal OUT=(mixr)\*IN1+(1-mixr)\*IN2, that is the mixture of the two input signals. More generally, a keyer can be dynamically reconfigured as a pair of 55 two-to-one mixers, with two pairs of input terminals and two output terminals, or it may provide a single four-to-one mixer with four input terminals and a single output terminal, as illustrated in FIG. 13. Although the current implementation is limited to a maximum of two 60 four-to-one keyers, in general, one could build nx1 keyers by a simple extension of the concepts presented here. In FIG. 13, for example, two input video signals, each containing the four channels Y, U, V and α, may be composited or mixed or combined into the single 65 output channel signal also Y, U, V and a, under control of the mix ratio mixr. Using this approach, one can effectively paste an object over a background, or blend

two images with variable transparency, or impose a stencil masking part of the canvas from the brush, or perform similar maneuvers.

**16**

Examples of uses of the upper keyer (two-to-one) in FIG. 13 include the following. A one-dimensional smooth scroll may be used for titles or characters as well as general video signals; this involves shifting the video in sub-pixel increments by variably mixing between current and pixel-delayed values to give a smooth effect. A chroma-key may be used with a mask; the chroma-key involves extraction of an  $\alpha$  signal from the chrominance information, wherein a certain range of colors (e.g., a range of blue) could be defined as background and anything other than this range of colors produces an opaque image  $(1-\alpha=0)$ . The upper keyer may be used for a non-additive mix of two video signals, and it may be used in painting, wherein the brush is composited onto the canvas, where a predetermined stencil allows this. A stencil may allow full eightbit resolution and thus allow for partial compositing as well.

Use of the lower keyer also permits one-dimensional scroll independent of the upper keyer scroll. Other lower keyer uses include combination of two video signals based on an overall  $\alpha$  signal, and serving as an externally controlled key between two video signals.

A single four-to-one keyer can provide two-dimensional smooth scroll (horizontal, vertical or diagonal); combine up to four layers of image based on the corresponding α information; provide stencil display; provide a paintbrush with an active stencil; provide direct painting to the canvas; or paint in any three other video channel signals. For example, as illustrated in FIG. 14, a four-to-one keyer could provide a foreground image, a mid-ground image and a background image, each with separate, independent transparency factors. The background might be a city landscape with skyscrapers, the foreground might be other city buildings closer to the viewer, and one or two mid-ground images might provide for action such as an airplane flying at middle distances between the buildings. Note that any or all of these layers could be line input video or painted panels generated in the IT and stored for use in the VC.

With reference to FIG. 10 again, note that VC supports six simultaneous, real time live video access channels, with two being allocated for input signals and four for output signals. The six channels are produced by time slicing on the bus. The control logic, which is based on eight-bit units, would support eight simultaneous channels, but in the current embodiment with the timing margins available only six such channels are provided. The VC input signals can include the output signals from the keyers, the output signals from the ITs, another signal IN3 and bus signals such as BUS2 shown in FIG. 15. In a similar manner, the output signals of VC can be fed to the input terminals of the keyers or to the IT. VC also provides pseudo-color LUTs that provide translation of each of the four video signals Y, U, V and  $\alpha$ . The tables allow any one of the four 8-bit input signals Y, U, V and α used as a lookup address to trigger a corresponding 32-bit output signal, where the table of contents is loaded by software. Double buffers, with both working copies and shadow copies, are available so that the software can load the tables at any time, even during active video output from the VC, without causing delays or other difficulties in the video; the working copy is updated from the shadow copy during the vertical blanking or interrupt interval. To bypass these

LUTs, the contents are merely set up with identity maps.

One anticipated use of these tables is in colorizing or translating recorded colors to false colors. As noted above, the LUT can take any of the four 8-bit signals Y, 5 U, V or  $\alpha$  and convert it to a full 32-bit output; the effect is to use 256 false colors, determined by any one of the four 8-bit input channels, to index into any of  $2^{32}$  full 32-bit Y, U, V, and  $\alpha$  video color and opacity signals. Another anticipated use of these LUTs is to generate a 10 stencil display. Although the stencil and the paint application is only  $\alpha$  information, the user may sometimes wish to view this. In this mode, the  $\alpha$  input signal is used to trigger Y, U, V and  $\alpha$  output signals from the LUT.

Another anticipated use for these LUTs is in color 15 cycle animation, in which several frames of video are to be played back with an animation effect, such as water flowing through a pipe. The video frames are typically unchanged, but the color information is changed for each frame by changing the mapping in the LUTs; the 20 effect is moving color or animation. Using the two LUTs plus four shadow copies plus four input signal components (Y, U, V,  $\alpha$ ), a total of  $2\times4\times4=32$  frames can be produced for an animation sequence by simply changing certain LUT pointers without reloading any 25 of the LUT contents themselves. Arbitrarily long sequences can also be produced by software reloading of the LUT RAMs. Color cycling is commonly used to show flow of material such as water in a pipe or data in a computer, to display reflection highlights or glints 30 moving across an image, to display twinkling stars and similar effects.

The video system implements full 4444 Y, U, V, and a throughout its video path (plus z or log z in some places). This is true within the graphics applications and 35 paint also. In particular, the paint hardware and software treat a as just one more component within the video. Other paint systems have included some aspects which are similar to  $\alpha$  (e.g., stencil), but they treat these as special cases and use them only for a specific purpose. 40 However, the system will perform all painting operations to  $\alpha$  just as it does to Y, U, and V. For example, in choosing the brush color with sliders, there is a slider for α, just as there are for Y, U, and V (or HSV or whatever color specification numbers are used). The 45 hardware compositing of the brush into the canvas with the F-chip composites  $\alpha$  just as it does Y, U, and V. Thus, the artist will automatically build up the matte component as she or he paints, and can, if she or he so chooses, vary that matte component and customize it 50 just as is done for the color and luminosity. The resulting output can be used to combine (key) the painting with other video, live or still or character generator output or external system input. Several detailed technical issues arise in the process of implementing such a full 55 a paint system. These are solved with a combination of hardware and software.

The video system includes a character generator application that produces highest-quality rendered characters that are composited with other video sources 60 (live or still). The characters begin as outline fonts (e.g., from a bit stream) using arcs and lines to define the outlines of each character and symbol in each font. The font renderer, within the character generator, reads the outline format for each character and renders it into a 65 form that can be placed into, or composited with the F-chip into, the full four-component  $(Y,U,V,\alpha)$  in a 32-bit) frame buffer. This is done in real-time, as the user

types in or otherwise requests characters to be added to the video. In order to achieve the real-time response, three key aspects are used: (1) the compositing is done via the F-chip; (2) once rendered, a character is cached (up to the cache memory limit) so that the next time the same character is used it need not be re-rendered. Such caches can also be saved to and restored from disk; and (3) the rendering is done into the  $\alpha$  channel only, so the output need only be eight bits, reducing the processing time and the size of the output for storage and transfer within the system. Once rendered into the  $\alpha$  channel, the character can be colored (by compositing, via the F-chip, a solid color input from a register with the canvas), or can be used as a "see-through" character to show video through the place where the character would be, as a shadow (as in drop shadows). All character generation is done with this technique into both foreground and background areas, which are then combined to produce varied effects including, e.g., neon glows (background very much fuzzed out), drop shadows (background black or gray, slightly offset from foreground), fuzzy shadows for a feeling of threedimensionality, etc. The basic idea of rendering into the α channel not only makes real-time character generation possible, but also facilitates many of the effects used in the character generator.

The physical memory array consists of 256 dynamic RAMs (DRAMs), with either 256 KB or 1 MB memory per chip. The smaller RAM provides eight Mbytes or two Mpixels for information storage. One format uses 736 horizontal pixels for frame width and 484 lines for frame height or 356,224 pixels per frame. Using a 256 KB RAM the VC allows approximately 5.89 frames; with the 1 MB RAM, a total of 23.55 frames is available.

Logical addressing, as sensed by the CPU and as used to generate video input and output signals, is indirect. A tile map, which is a two-dimensional paging system similar to many one-dimensional virtual memory paging systems, is used here for memory addressing. As noted above and illustrated in FIG. 16, a tile is 32 contiguous horizontal pixels in width by 8 contiguous vertical lines in height; these numbers were chosen to provide divisibility into both the NTSC and PAL frame dimensions. Tile size has small enough granularity to provide much flexibility and large enough granularity to avoid the use of ridiculously large amounts of hardware. Each tile can be individually mapped so that, for example, the tiles that contributed to the signal will not necessarily come from memory that is physically contiguous in the frame store and may include tiles scattered across the frame store landscape. This allows one to quickly move parts of the video image by simply changing the pointers rather than by the slower operation of actually copying memory.

As illustrated in FIG. 16, the entire physical address space consists of  $4K \times 4K$  pixels or 128 (horizontal) by 512 (vertical) tiles. Each tile is assignable to any one of the six video channels, with no restrictions on order or on overlap. For example, a single tile could be mapped to an entire video channel where all pixels in that tile represent a single reference color to be used in setup or in compositing or creation of a texture.

Each of the six video channels consists of an array of up to 1K×1K pixels, which is 32 horizontal tiles by 128 vertical tiles by or 4096 tiles. This is a larger address base than is actually needed; actual video channels are about 736 pixels wide by 486 lines high (525 lines, if vertical blanking time is included). The PAL standards

for Europe require 574 lines (active) out of 625 lines. Each of the tiles that comprise the video channel information can be mapped independently to any of the physical tiles on the screen. The mapping of tiles into the video channels is specified by a tile map, which is 5 RAM-loaded by computer access and may be read by any of six display address generators. This mapping operates on a double-buffered RAM so that software can load the shadow copies at any time without concern about video delay or other difficulties, and the working 10 copies can be updated during the vertical blanking interval. The format of the tile map is a two-dimensional array, with the index specifying the tile or tiles in the logical 1K×1K channel and the contents or output signal of the array indicating the physical tile or tiles that fill that part of the logical channel. In this manner, the hardware can scan continuously down the input signals to the array. The tile map format is specified differently for address or input information, which utilizes 16 bits, than for contents or output information, 20 which utilizes 19 bits. The bit assignments for the address mode and the contents mode are shown below in Table 1.

TABLE 1

| Tile Map Format  Meaning   |                                                                                                 |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Address Bits               | Which byte (Y,U,V,α) for byte addressing within a pixel                                         |  |  |  |  |

| 0-4<br>5-11<br>12-14<br>15 | Xtile (0-31)  Ytile (0-127)  channel (0-5 currently)  tile map TMO or TM1 (double buffer spec.) |  |  |  |  |

| Contents Bits              | ourser speed,                                                                                   |  |  |  |  |

| 0-15                       | tile address                                                                                    |  |  |  |  |

| 16–19                      | choice of special attributes such as switching between two tile maps, etc.                      |  |  |  |  |

A video channel output from VC can be smoothly scrolled in one dimension or two dimensions, for example, along any diagonal line. Smooth scrolling uses the keyers to bi-linearly interpolate between two pixel values in order to shift pixel values by sub-pixel increments. For horizontal scrolling, each pixel value is averaged with the preceding pixel value by means of a simple time delay. For vertical scrolling, two VC outputs must be used, with the output of one line time delayed so that the keyer can average the two vertically adjacent pixel values. For diagonal scrolling, both of these 50 time delay mechanisms are used.

The control registers for VC output video channels are similar to the T-chip P-files. Eight registers are used, one for each of the six channels plus two spare registers for possible expansion. Each register set for a single VC 55 output consists of the following information: x<sub>start</sub> (starting pixel of a horizontal line); y<sub>start</sub> (vertical starting line); xinc (increment to be added to current x value for each pixel); yinc (increment to be added to current y for each line); x<sub>scroll</sub> (increment to be added to current x for 60 each frame change); y<sub>scroll</sub> (increment to be added to current y value for each frame change); xcurrent (current x value or pixel address); and y<sub>current</sub> (current y value or line address). At the beginning of each frame: (1)  $X_{start} = X_{start} + X_{scroll}$ , (2)  $y_{start} = y_{start} + y_{scroll}$ , and (3)  $y_{cur}$  65 rent =  $y_{start}$ . At the beginning of each horizontal line; (1)  $y_{current} \rightarrow y_{current} + y_{inc}$ ; and (2)  $x_{current} = x_{start}$ . At each pixel within a horizontal line,  $x_{current} \rightarrow x_{current} + x_{inc}$ .

This formalism generates addresses for output to the video channels and provides some flexibility for the scroll operation. All addresses are logical channel addresses that are interpreted through the tile map to provide physical addresses. Each line ends with the horizontal blanking pulse, which should occur after 23 consecutive horizontal tiles (736 consecutive pixels). One register contains two 3-bit values, which corresponds to one of the keyers, with each of six values specifying one of the six channels to be used for the fractional input for the scroll operation.