#### US005227660A

## United States Patent [19]

## Horiuchi et al.

## [11] Patent Number:

5,227,660

[45] Date of Patent:

Jul. 13, 1993

### [54] SEMICONDUCTOR DEVICE

[75] Inventors: Masatada Horiuchi, Koganei; Kazuo Nakazato, Kokubunji, both of Japan

[73] Assignee: Hitachi, Ltd., Tokyo, Japan

[21] Appl. No.: 648,309

[22] Filed: Jan. 29, 1991

## Related U.S. Application Data

[63] Continuation of Ser. No. 268,738, Nov. 8, 1988, abandoned

| [OJ]       | doned.                | 1 Sc1. 140. 200,730, 140v. 0, 1700, abai | T- |

|------------|-----------------------|------------------------------------------|----|

| [30]       | Foreign A             | pplication Priority Data                 |    |

| No         | v. 9, 1987 [JP]       | Japan 62-28103                           | 3  |

| Nov        | . 20, 1987 [JP]       | Japan 62-29201                           | 9  |

| Jan        | . 25, 1988 [JP]       | Japan 63-1251                            | 8  |

| [51]       | Int. Cl. <sup>5</sup> |                                          | 2  |

| [52]       | U.S. Cl               | <b>257/588;</b> 257/64                   | 4; |

|            |                       | 257/577; 257/62                          | 7  |

| [58]       | Field of Search       | 1 357/61, 59, 60, 34                     | 4, |

| - <b>-</b> |                       | 357/2, 51, 1                             | -  |

FOREIGN PATENT DOCUMENTS

#### [56] References Cited

56-001556 1/1981 Japan .

59-161867 9/1984 Japan . 61-237471 10/1986 Japan .

#### OTHER PUBLICATIONS

1984 IEEE International Solid-State Circuits Conference Digest of Technical Papers, pp. 282-283, by Itoh et al.

Ki Kuchi et al. "A High-Speed Bipolar LSI Process Using Self-Aligned Double Diffusion Polysilicon Technology".

Ghandlai, VLSI Fabrication Principle, 1983, pp. 488-489 357\*60.

Primary Examiner—Mark V. Prenty Attorney, Agent, or Firm—Antonelli, Terry, Stout & Kraus

#### [57] ABSTRACT

This invention relates to a semiconductor device, in which a singlecrystal semiconductor substrate whose principal surface is a (111) plane is etched from the principal surface thereof in the direction perpendicular thereto to form a vertical trench and a lateral trench is formed at the bottom portion of the side wall of the vertical trench by effecting an anisotropic etching with respect to crystallographical axes so that the etching proceeds in the direction of <110> axis, the lateral and the vertical trenches being filled with polycrystalline or amorphous semiconductor or insulator.

#### 14 Claims, 18 Drawing Sheets

FIG.

F I G. 2

F I G. 7

F I G. 8

F I G. 9

# F I G. 10

FIG. 11

F I G. 12

FIG. 14A

F I G. 13

July 13, 1993

1003

F I G. 14B

F I G. 15A

FIG. 16A

July 13, 1993

FIG. 15B

F I G. 16B

1008 1007 1003 1009 1006 1006 1301 1302 1002 1000

FIG. 17A

FIG.

F I G. 18A

F I G. 18B

F I G. 19A

F I G. 19 B

F I G. 20

F I G. 19C

F I G. 21

F I G. 22A

F I G. 22B

F I G. 23

F I G. 24

F I G. 25

F I G. 26

F I G. 27

F I G. 28

2002

F I G. 33

F I G. 34

F I G. 35

F I G. 36

F I G. 37

F I G. 38

40 2110 2111 2070 2030

FIG. 42 PRIOR ART

FIG. 43A PRIOR ART

FIG. 43B PRIOR ART

FIG. 44 PRIOR ART

FIG. 45 PRIOR ART

#### SEMICONDUCTOR DEVICE

This application is a continuation application of application Ser. No. 07/268,738, filed Nov. 8, 1988 and now 5 abandoned.

#### **BACKGROUND OF THE INVENTION**

This invention relates to a semiconductor device and a method for fabricating same, and in particular to a 10 semiconductor device, in which at least a lateral trench is formed in the interior of a single-crystal semiconductor substrate having a principal surface, which trench is filled with a substance other than the singlecrystal semiconductor, and a method for fabricating the same.

Heretofore it is well known to form an n+ or P+ conductivity type buried layer in the interior of a single-crystal semiconductor substrate having a principal surface (JP-A-56-1556), to form a capacitance by burying an insulating material therein (ISSCC 84/FRIDAY, 20 FEB. 24, 1984/CONTINENTAL 5-9/11:45 A.M.), by a buried insulator for taking-out an electrode (JP-A-59-161867, JP-A-61-237471), etc. For forming such various sorts of buried layers, heretofore, the epitaxial technique and a high energy ion implantation technique 25 have been widely utilized. However all these techniques have had several problems.

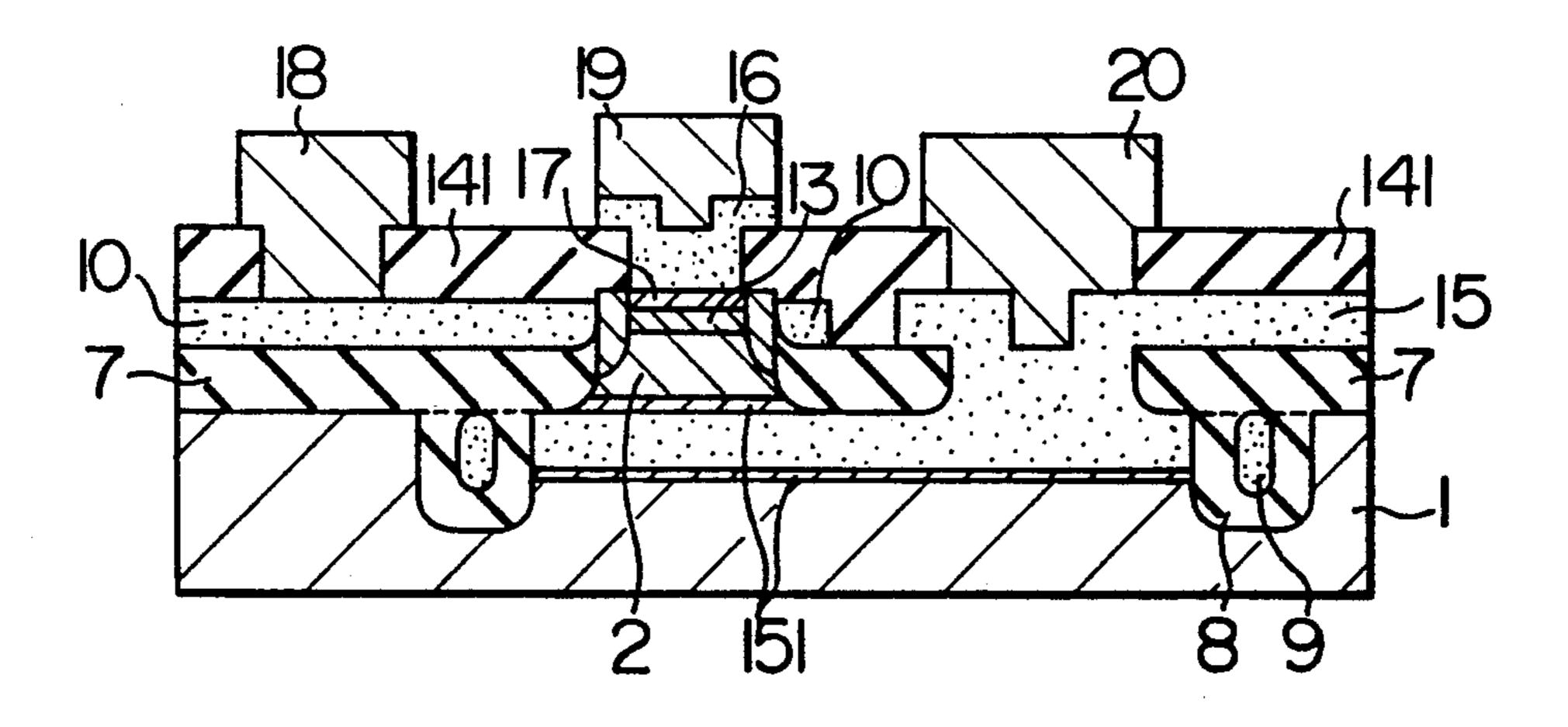

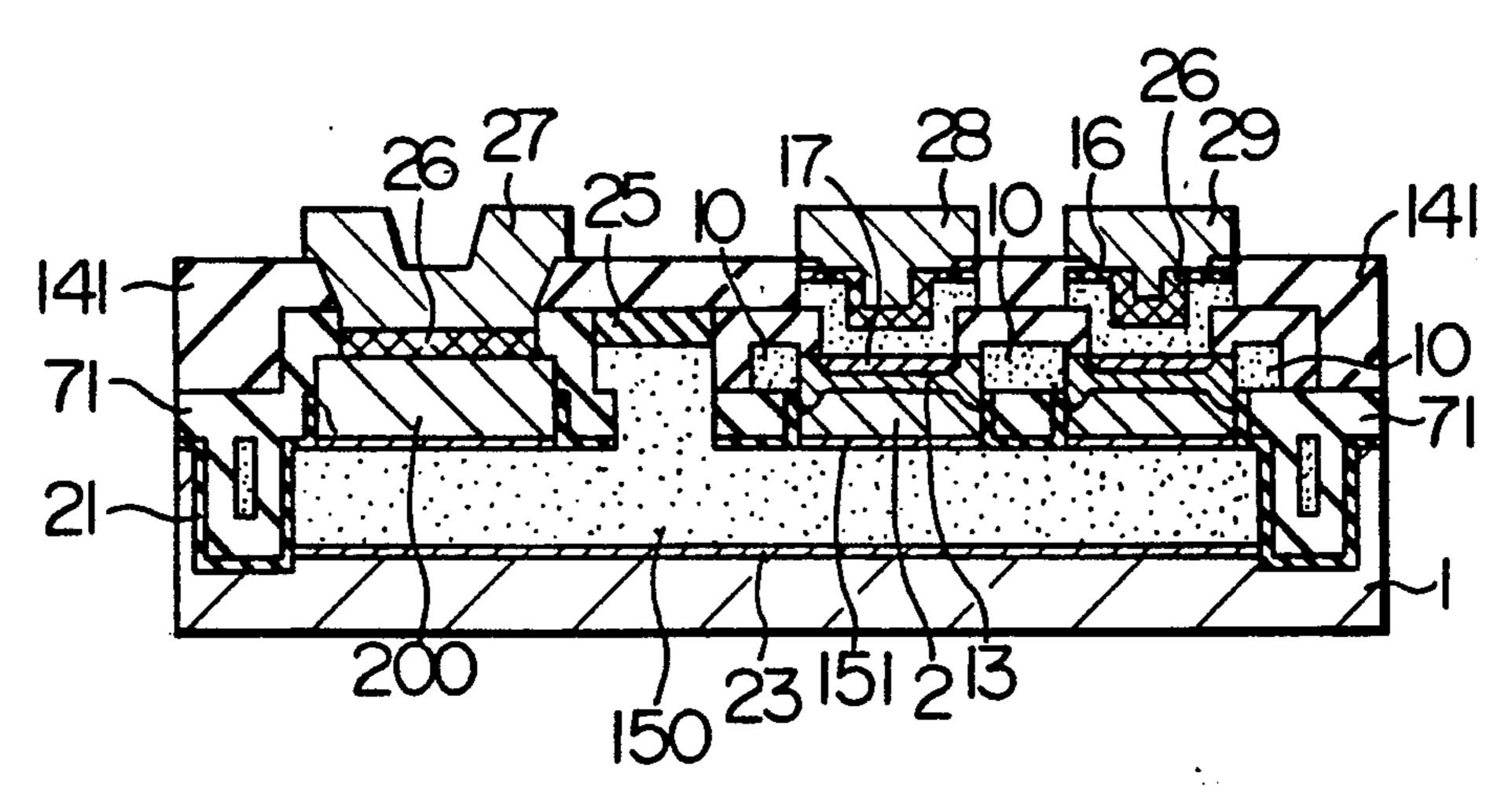

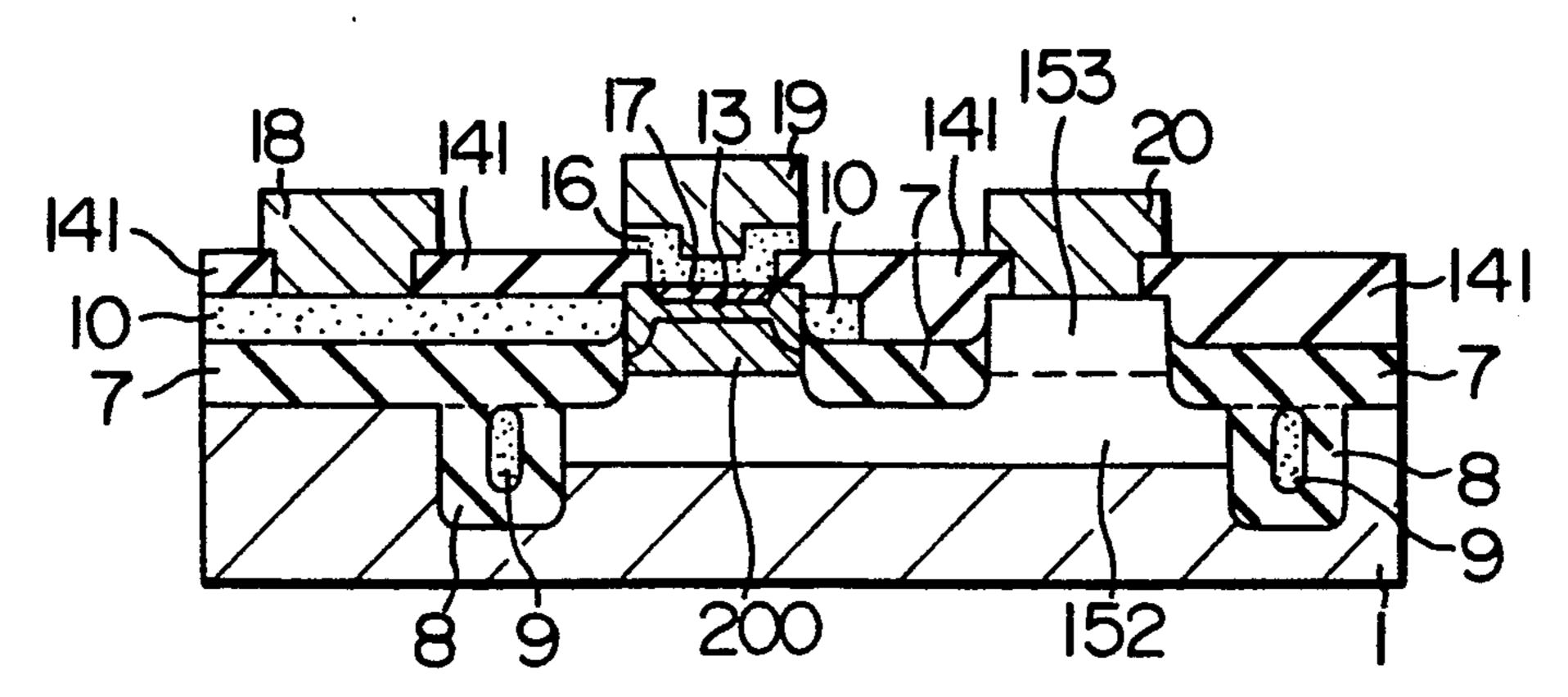

At first consider a bipolar transistor having an n+ conductivity type buried layer disclosed in JP-A56-1556. FIG. 42 shows the construction of this transistor. 30 In the figure reference numeral 1 is a p conductivity type Si substrate: 7 is an isolation insulating layer; 8 is a deep trench isolation insulating layer; 9 is a trench filling Si layer; 10 is a base taking-out electrode; 153 is an n + conductivity type diffusion layer for taking-out an 35 n+ conductivity type buried layer 152; 141 is a surface protecting insulating layer; 16 is an emitter taking-out electrode; 18 is a base electrode; 19 is an emitter electrodes; and 20 is a collector electrode. That is, the epitaxial layer 200 is formed on a collector region consist- 40 ing of an n+ conductivity type diffusion layer 152 and that an intrinsic base region 13, an n+ conductivity type emitter region 17, etc. are constructed within the epitaxial layer 200.

The buried layer may be formed also by the method, 45 by which high energy ions are implanted in the Si substrate.

By the method described above the epitaxial layer 152 is unnecessary and the base region 13 and the emitter region 17 are formed after the formation of the n + 50 conductivity type buried layer.

In the bipolar transistor fabricated by the prior art techniques described above it is required that the n+ conductivity type buried diffusion layer 152 used as the collector has a low resistance for increasing the opera- 55 tion speed of the transistor and an abrupt impurity concentration distribution. In particular, for the n+ conductivity type buried diffusion layer 152 antimony (Sb) has been used as diffused impurities in order to prevent impurity outward diffusion in the step of forming the 60 epitaxial layer 200 on the n + conductivity type buried diffusion layer 152 or variations in the impurity distribution in a succeeding step for high temperature heat treatment. However since the solid solubility of Sb into Si is as low as  $3-5 \times 10^{19}$  cm<sup>-3</sup>, even the sheet resistance 65 of an n+ conductivity type buried diffusion layer 1.5  $\mu$ m thick is essentially as high as 30  $\Omega/\Box$ . Therefore it was difficult to reduce the collector resistance.

Further, during the growth of the epitaxial layer 200 on the n+ conductivity type buried diffusion layer 152 constructed selectively, positional deviations from the buried diffusion layer pattern due to the dependence of the epitaxial growth speed on the crystallographical surface orientation are unavoidable. This caused a hindrance to the reduction of the size and the increase in the degree of integration of elements. Further there was another problem that it was difficult to deal with a large quantity of products in a conventional epitaxial growth apparatus, which raised the production cost.

On the contrary, by the method, by which the n+ conductivity type buried layer 152 is formed by high energy ion implantation, all the problems described 15 above concerning the formation of the epitaxial layer 200 are solved. However, it is known that by the high energy ion implantation implanted ions are not distributed symmetrically with respect to the maximum concentration range, but the distribution has a long tail from the position of the maximum concentration towards the surface of the semiconductor substrate. Therefore there remained a problem that no abrupt impurity distribution could be obtained. Furthermore, the high energy ion implantation method has still another problem that crystal defects are produced during the formation of a high impurity concentration buried layer and that it is difficult to restore the crystallographical property even by a succeeding heat treatment step. Therefore by this method no excellent junction characteristics could be obtained.

Still another problem of the prior art techniques concerning the n+ conductivity type buried diffusion layer 152 consists in that the occupation area required for the taking-out of the collector and the wiring is large, which causes a hindrance to the reduction of the size and the increase in the degree of integration of elements. Furthermore still another problem concerning the increase in the degree of integration consists in that a sufficiently great interval or an element isolating region having a sufficiently great depth is required for isolating adjacent n+ conductivity type buried diffusion layers.

Another problem of the prior art techniques concerns a memory device whose constituent elements are transistors having a prior art structure. That is, in a prior art semiconductor memory device, although the n+ conductivity type buried diffusion layer 152 has been used as a region for storing information, a measure should be taken in the circuit for preventing destruction of stored information due to a large number of electrons produced by  $\alpha$  ray irradiation within the semi conductor substrate 1, so-called soft error misoperation. This has caused a serious problem against the decrease in the storage charge density of the memory device.

An object of this invention is to provide a bipolar transistor including a buried impurity layer having a low resistivity and an abrupt impurity distribution, for which production of crystal misoperation is not feared and which can solve the problems of the prior art techniques, by means of which a transistor of a superfine and super high integration is possible and which transistor is thus not expensive.

Another object of this transistor is to provide a bipolar transistor memory, in which no  $\alpha$ -ray soft errors are produced.

Next the DRAM (Dynamic Random Access Memory) disclosed in ISSCC 84/FRIDAY, FEB. 24, 1984/CONTINENTAL 5-9/11:45 A.M.) will be considered.

~,——·,~~

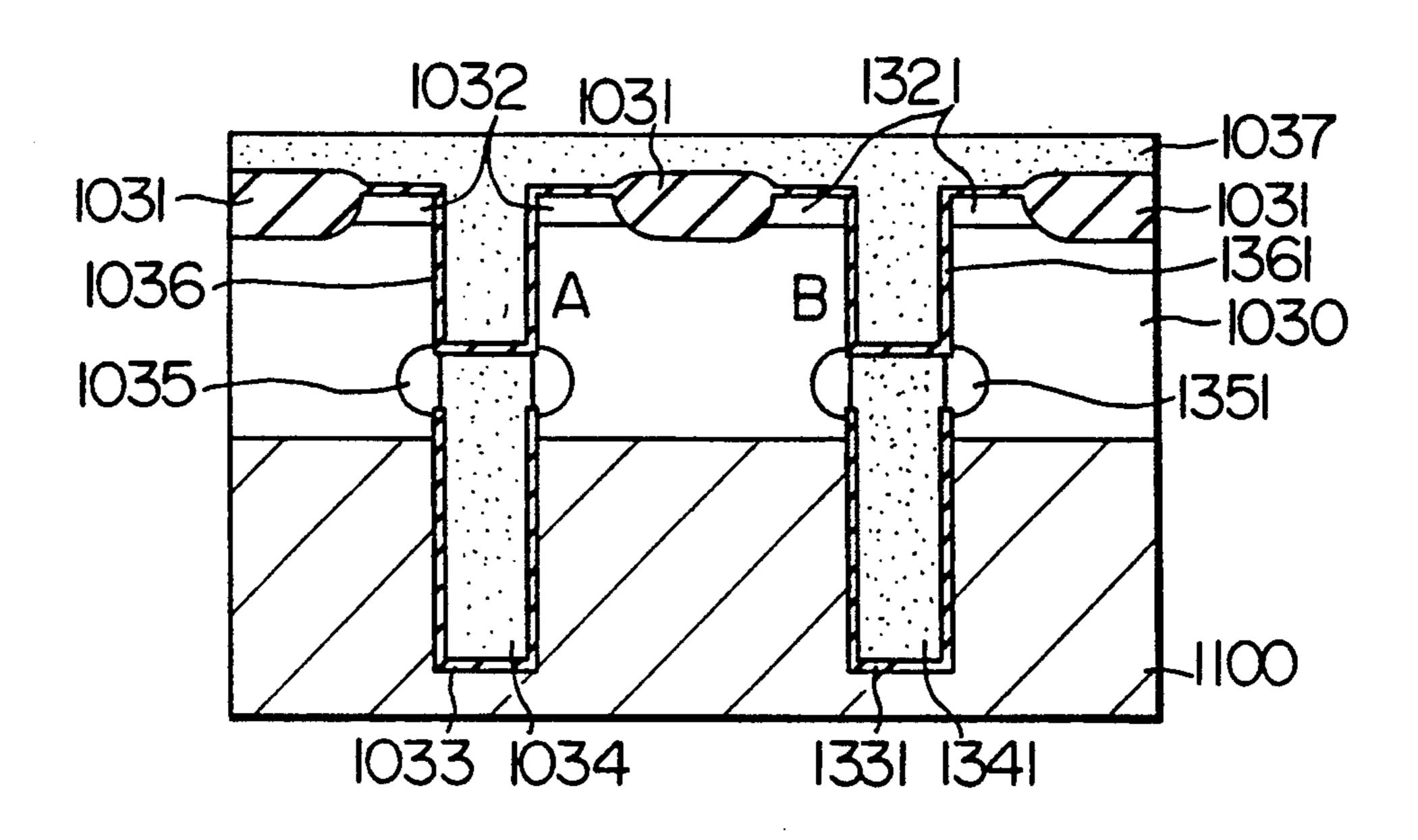

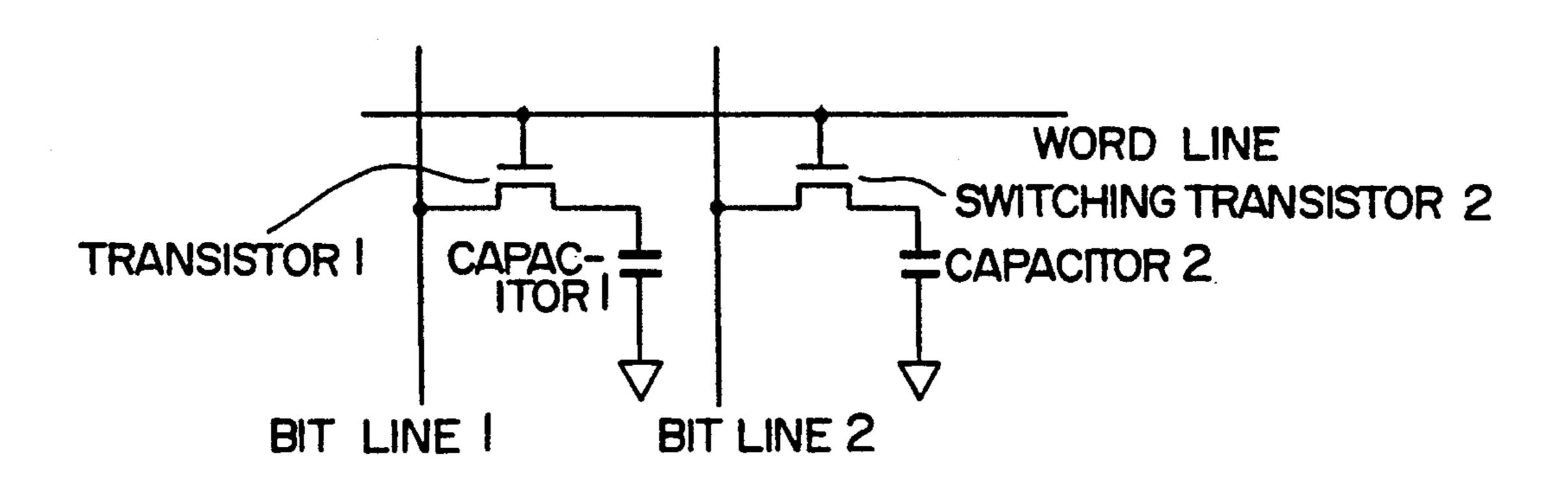

FIG. 43A is a cross-sectional view illustrating the construction of this DRAM and FIG. 43B indicates an equivalent circuit thereof, in which reference numeral 1100 is a p+ conductivity type semiconductor substrate; 1030 is a p— conductivity type epitaxial layer: 1031 is a field oxide layers 1032 and 1321 are n + conductivity type drain diffusion layers, which are bit lines formed in the direction perpendicular to the sheet of the figure; 1033 and 1331 are capacitor oxide layers; and 1034 is a polycrystalline Si storage electrode serving as 10 an electrode of a capacitor element constituted between that p + conductivity type semiconductor element and itself. Further 1035 and 1351 are n + conductivity type buried source diffusion layers and 1036 and 1361 are gate oxide layers of vertical type MOS switching tran- 15 sistors; and 1037 indicates word lines made of polycrystalline Si serving as gate electrodes of switching transistors A and B. In the DRAM cell indicated in FIG. 43A, a transistor and a capacitor element are buried at each intersection of every word line and every bit line. Con- 20 sequently, contrarily to the fact that the reduction of the size of the memory cell having a usual structure is based on the reduction of the size of the processing, the memory cell indicated in FIG. 43B is characterized in that the area of a cell can be significantly reduced with re- 25 spect to the cell having a usual structure in spite of a same design rule.

Although the prior art techniques are efficient for the remarkable reduction of the size of each cell, no attention is paid to mutual interference between adjacent 30 cells. Therefore, they have had a problem that the integration is hindered. That is, in the construction indicated in FIG. 43A, in which adjacent cells are close to each other, current paths are produced between the n+conductivity type drain diffusion layers 1032 and 1321 35 or the n+ conductivity type buried source diffusion layers 1035 and 1351 in the switching transistor portion, which has given rise to a problem that erroneous operations take place. This problem of the production of current paths is more serious between buried sources. 40

Furthermore, the prior art techniques have had a problem that the resistance against erroneous operations due to the  $\alpha$  ray irradiation, so-called soft error misoperation, in not sufficient. Pairs of electron and hole are generated within the semiconductor substrate 45 by the  $\alpha$ -ray irradiation and electrons are diffused towards the surface of the structure. However, in the structure indicated in FIG. 43A, polycrystalline Si storage electrodes 1034 and 1341, which are charge storage regions, are enclosed by oxide layers 1033 and 1331 and 50 no soft error misoperation are produced in these parts. Further the semiconductor substrate is also of P+ conductivity type, the life time of electrons is short, and the resistance against soft error is better than that of the usual construction. However, since electrons diffused to 55 the neighborhood of the surface of the substrate are trapped by the buried source diffusion layer 1035 or 1351. The problem of the erroneous operations due to soft errors is not solved even by the memory cell having the structure as indicated in FIG. 43A.

Another problem of the structure described above concerns the formation of the p-conductivity type epitaxial layer on the p+ conductivity type semiconductor substrate. That is the P conductivity type high impurity concentration substrate is formed usually by using 65 boron (B) as added impurity. However, since the diffusion coefficient of B is great, there is a problem that redistribution of impurity is produced easily by high

temperature heat treatment, which is unavoidable in the fabrication process. Consequently this has given rise to problems that the breakdown voltage of the buried source diffusion layers 1035 and 1351 is lowered by the redistribution of B to the p— conductivity type epitaxial layer 1030, that the threshold voltage of switching transistors is raised, etc. Another problem of the prior art structure described above consists in that the word line 1037 and the storage electrodes 1034 and 1341 are adjacent to each other only through the thin oxide films 1036 and 1361. That is, the potential of the storage electrode is apt to be interfered by the word line signal, which gives rise easily to a problem of write-in thereof, etc.

An object of this invention is to provide a DRAM cell, which can remove the disadvantages of the memory cell having the prior art structure in which no problems such as interference between cells, interference between word lines,  $\alpha$ -ray soft error, etc. are produced; for which redistribution of p+ conductivity type impurities is not feared; and by means of which a superfine and a high density integration are possible.

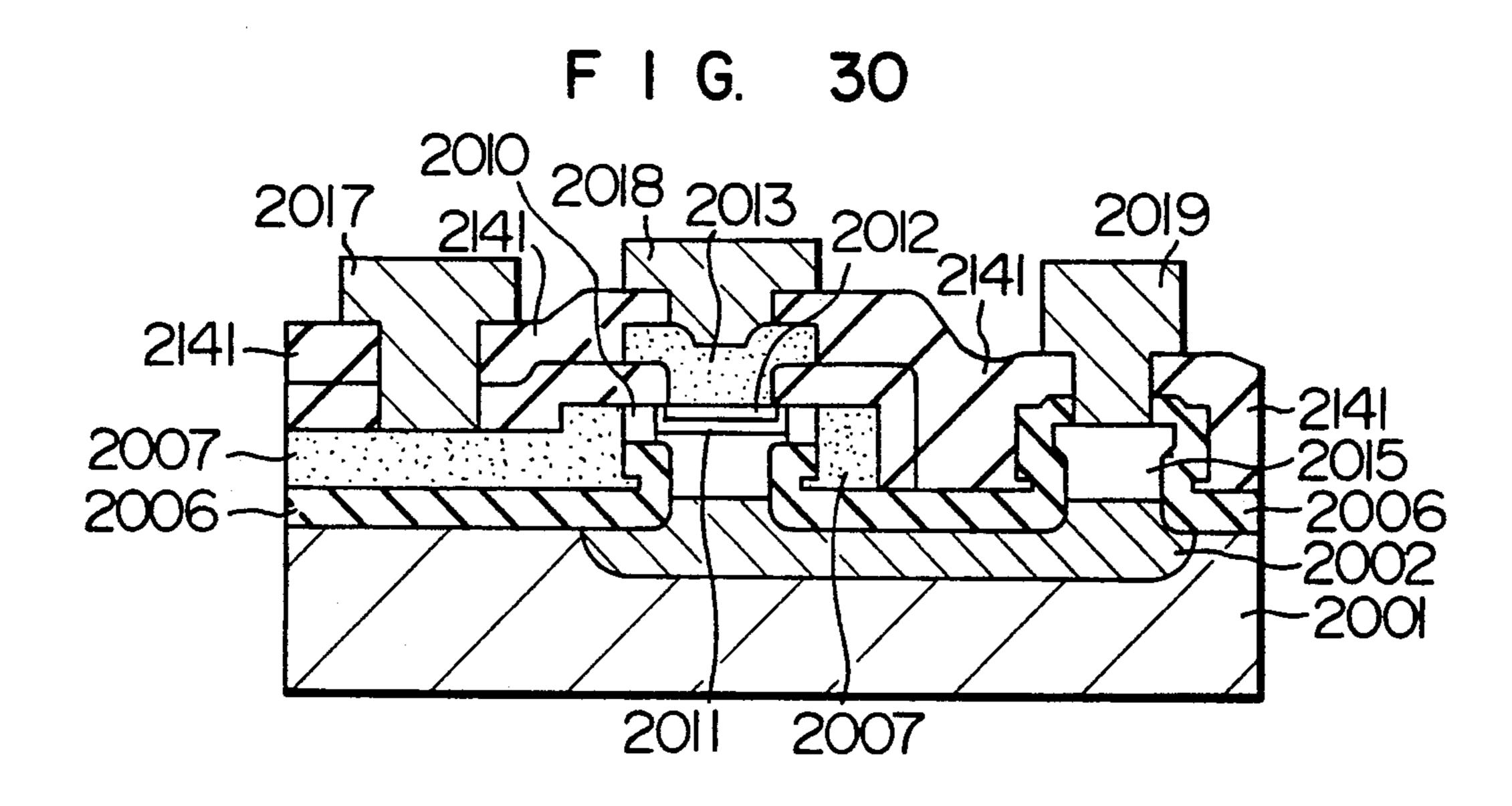

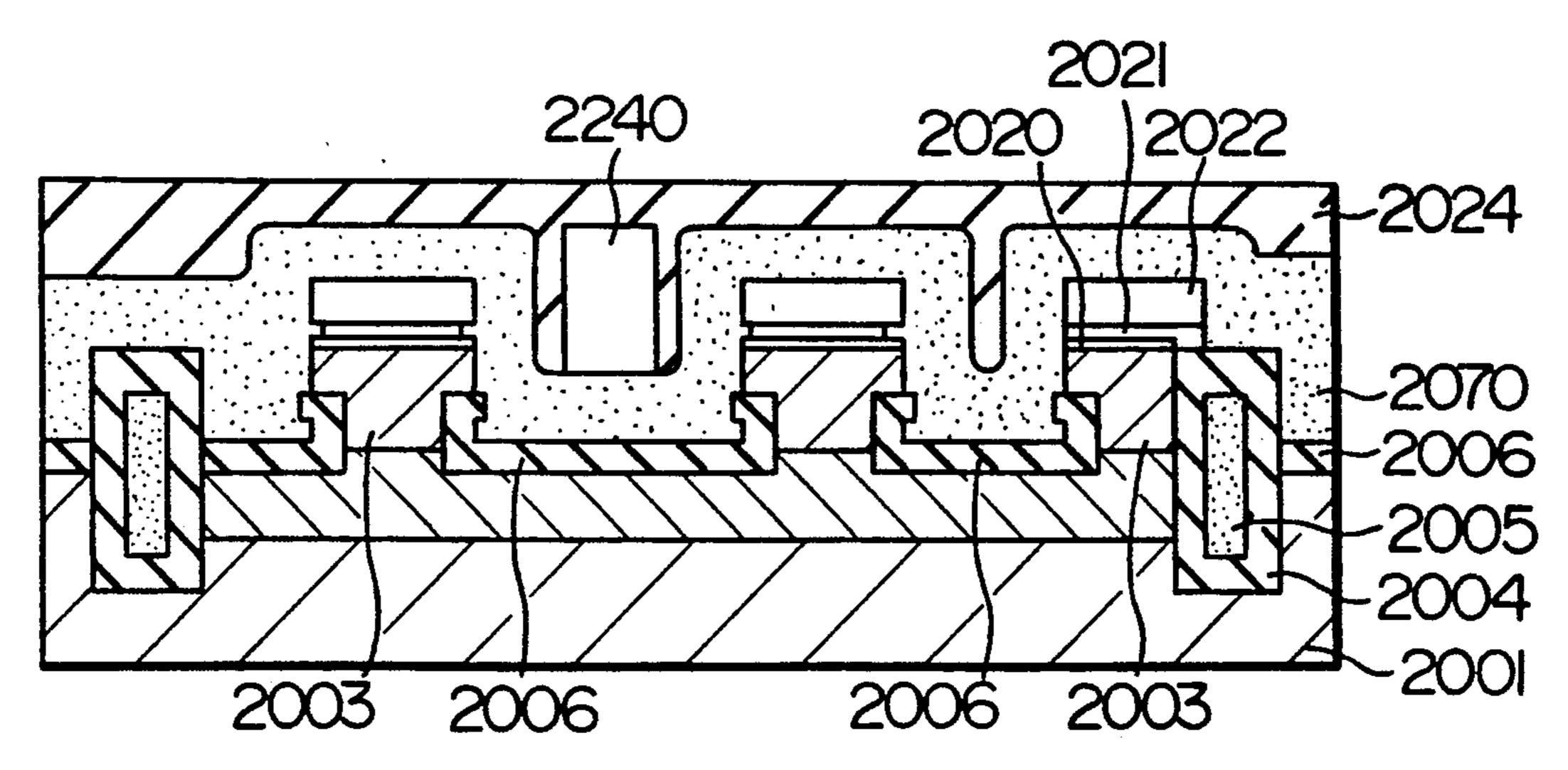

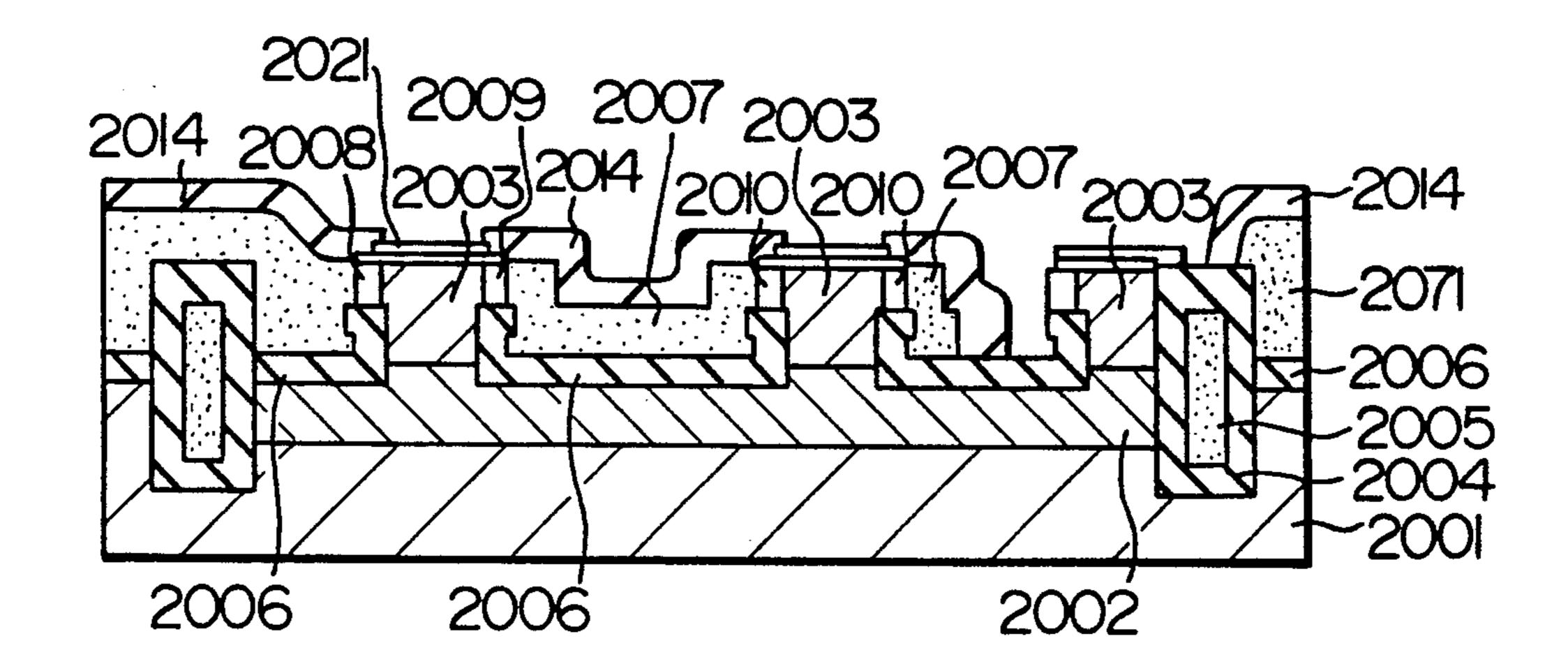

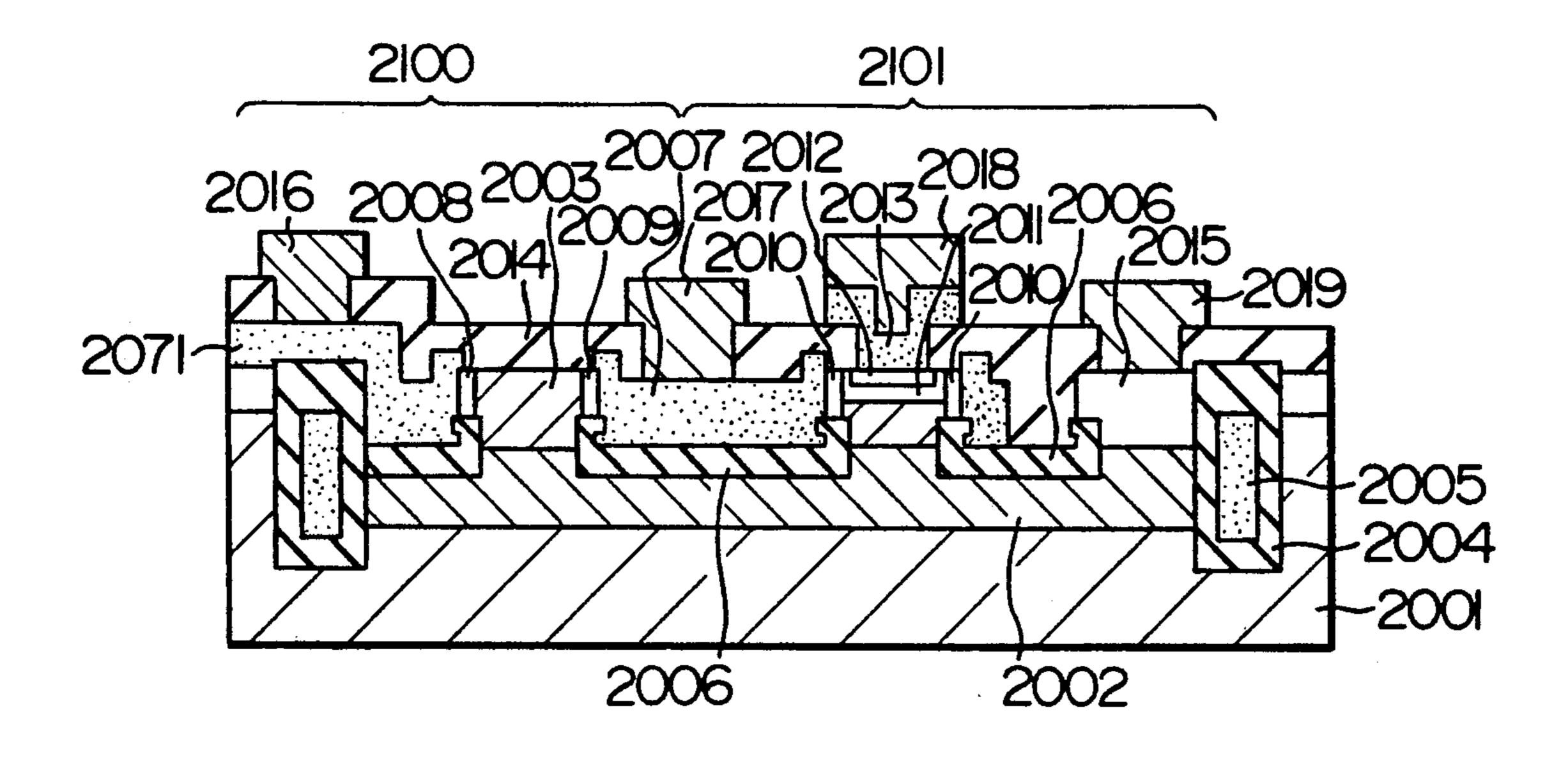

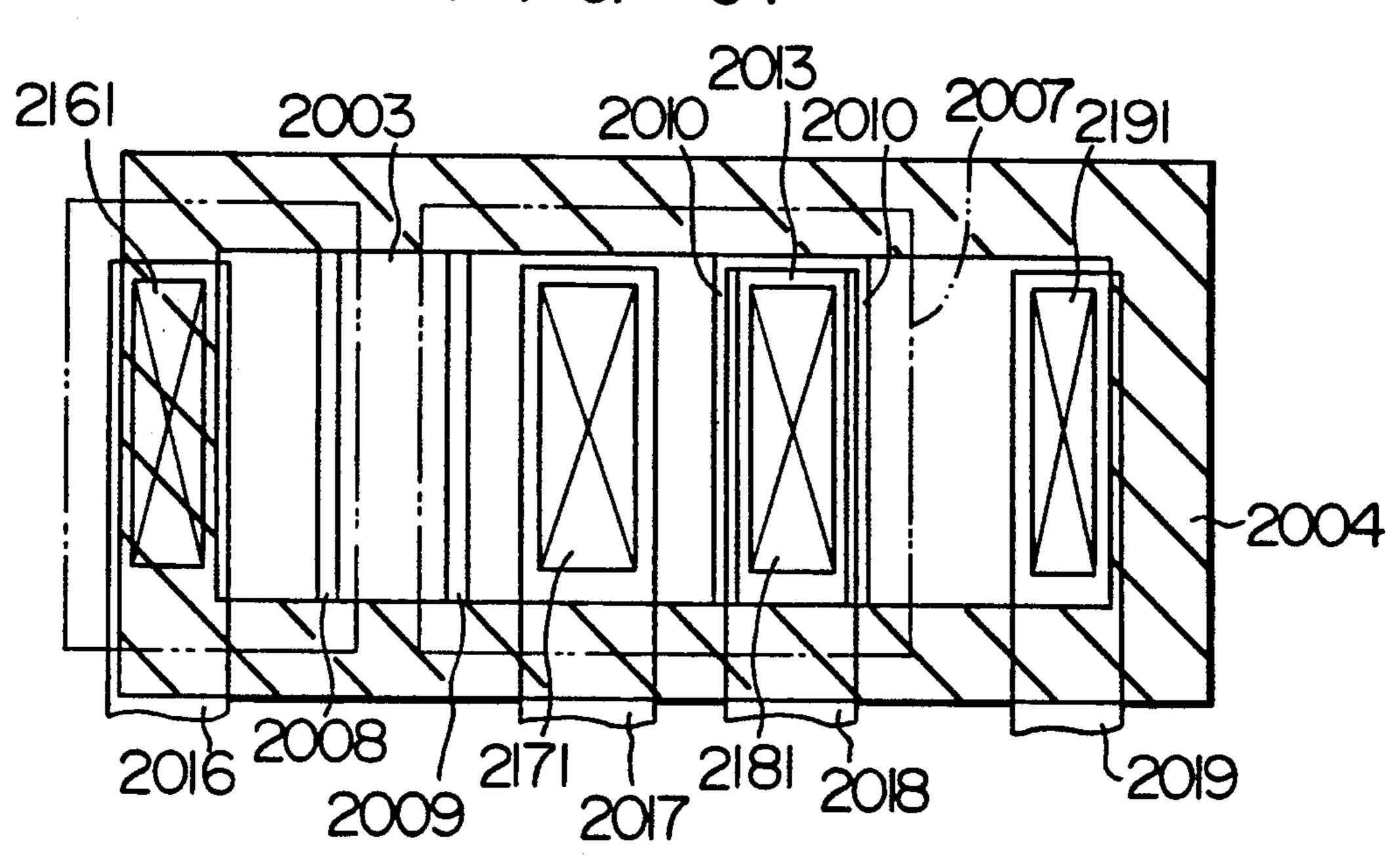

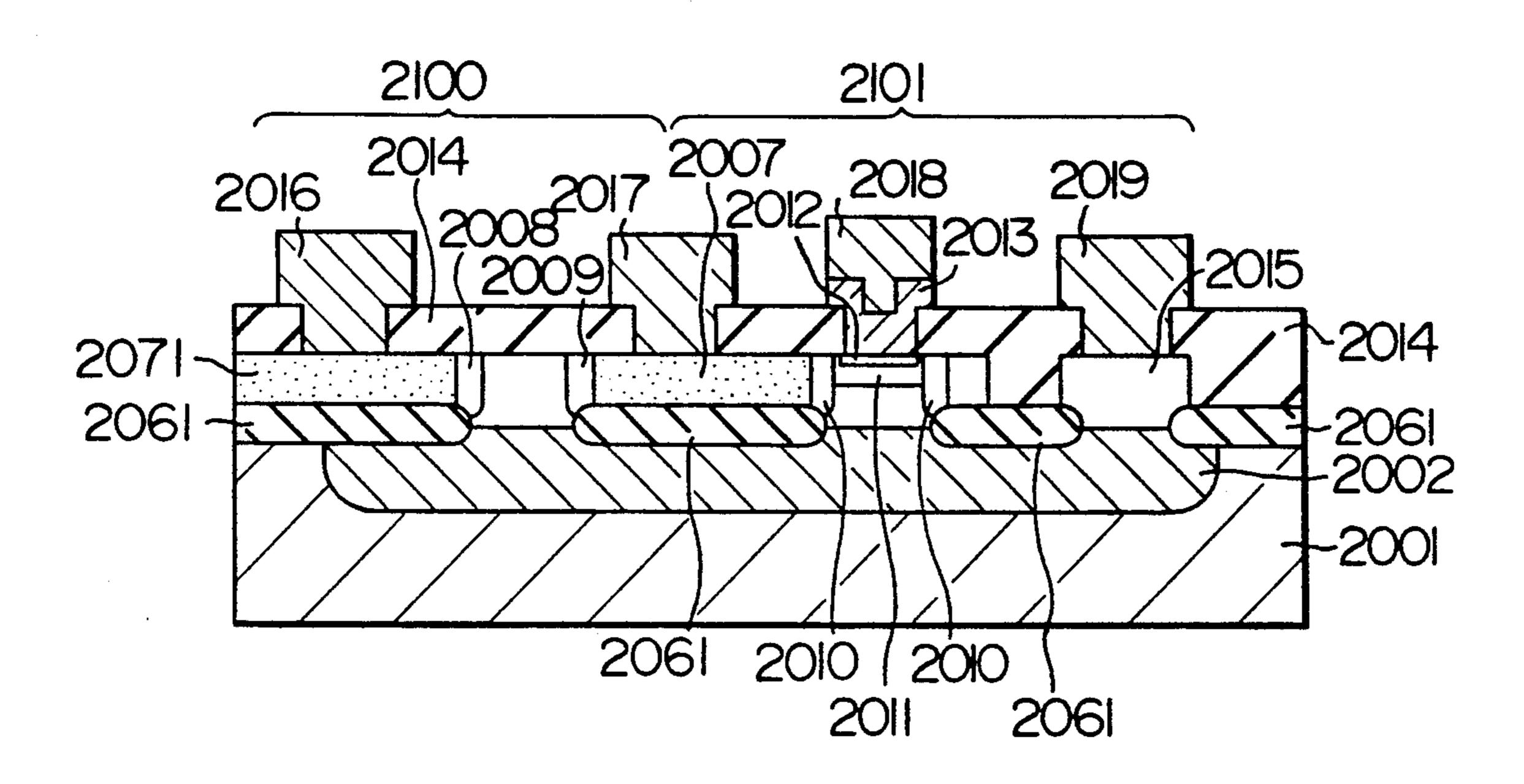

Next a buried insulating layer for taking-out an electrode disclosed in JP-A-59-161867 is indicated in FIG. 44, is which reference numeral 2001 in a p conductivity type Si singlecrystal substrate, whose principal surface is (100) plane; 2100 is lateral type pnp transistor; 2101 is a vertical type npn transistor; 2002 is an n + conductivity type buried layer; 2061 a buried insulating layer made of SiO<sub>2</sub>; 2008, 2009 and 2010 are p + conductivity type diffusion layers, which are the emitter region and the collector region of the lateral type pn transistor 2100 and the graft base region of the vertical type npn transistor 2101, respectively; 2011 is a p conductivity type diffusion layer region, which is the intrinsic base region of the vertical type npn transistor 2101; 2012 and 2015 are the n+ conductivity type emitter region and the n+ conductivity type collector region, respectively, of the vertical type pnp transistor 2101; 2071 is an emitter taking-out electrode of the lateral type pnp transistor 2100 made of polycrystalline Si; 2007 is the collector taking-out electrode of the lateral type pnp transistor 2100, serving also as the base taking-out electrode of the vertical type npn transistors 2101; 2013 is the emitter taking-out electrode of the vertical type npn transistor 2101; 2014 is an insulating layer; 2016, 2017, 2018 and 2019 are the emitter electrode and the collector electrode of the lateral type pnp transistor 2100 and the emitter electrode and the collector electrode of the vertical type npn transistor 2101, respectively, made of metal layers, whose principal component is Al. The collector electrode 2017 of the lateral type pnp transistor 2100 serves also as the base electrode of the vertical type npn transistor 2101.

In a known bipolar transistor having the structure as indicated in FIG. 44, all the base-collector junction outside of the active region of the vertical type npn transistor 2101, and the base-collector and the base-emitter junctions of the lateral type pnp transistor 2100 are replaced by thick insulating layers 2061 so that the parasitic capacitance is significantly reduced. Furthermore, since the graft base 2010 constituted by a p+conductivity type diffusion layer is formed also on a buried insulating layer 2061, the shortest path between the n+conductivity type buried layer 2002 serving as a collector and the base is increased and the base-collector breakdown voltage is improved. Consequently the transistor having the structure indicated in FIG. 44 has

advantages to have a high breakdown voltage and to achieve a high speed operation.

In such a bipolar transistor a thick buried insulating layer 2061 has been formed (1) by selective oxidation of the bottom portion of a trench formed by etching the 5 semiconductor substrate 1 in the direction perpendicular to the principal surface thereof by sputter ion etching, (2) by selective oxidation of a surface obtained by etching isotropically the bottom of the trench, and (3) by making a water-drop-shaped single-crystal region 10 amorphous by implanting ions selectively in the bottom portion of the trench and by selectively oxidizing a surface obtained by selectively removing this amorphous region. By either one of the methods (1) to (3) it is not possible to extend satisfactorily the buried insulat- 15 ing layer 2061 in the lateral direction so as to be positioned below the graft base 2010 and none of them is used in practice. By the method indicated by (1), since the extension of the graft base 2010 formed by using the base taking-out electrode 2007 as a diffusion source due 20 to heat treatment, etc. in the fabrication process is much faster than the oxide film growth of the buried insulating layer 2061, it is almost impossible to construct the buried insulating layer 2061 below the graft base 2010 by the present technique. In the case where it is formed 25 by the method indicated by (2), if the amount of the isotropic etching is increased, it is possible to extend satisfactorily the region of the formation of the buried insulating layer 2061 in the lateral direction. However, since the tunnel making is advanced also in the vertical 30 direction, the n + conductivity type buried layer 2002 is corroded wastefully. Therefore this has given rise to a problem of undesirably increasing the collector resistance and at the same time hindering the reduction of the size. By the method indicated by (3), by which the 35 buried insulating layer 2061 is extended in the lateral direction within the singlecrystal substrate 2001, the degree of the extension in the lateral direction is determined unequivocally by the conditions of the ion implantation on the basis of characteristics of the lateral 40 extension of the amorphous layer by the ion implantation. However, in order to realize a lateral extension of desired size and, in particular, a lateral extension above several 100 nm, it is indispensable to use a high current ion implantation apparatus having a high acceleration 45 energy from several 100 keV to several MeV. Therefore this method has had a drawback that semiconductor devices could not be fabricated in a simple manner with a low cost. Further secondary misoperation due to high energy and high current ion implantation are pro- 50 duced within the singlecrystal substrate 2001, from which the amorphous layer is selectively removed, which has been apt to give rise to a problem to worsen electric characteristics such as increase in leak current, etc.

An object of this invention is to realize a semiconductor device comprising a protruding semiconductor region formed in a surface region of a semiconductor substrate; buried insulating layers formed at least on both the side of the bottom of the protruding semiconductor region on the surface of the semiconductor substrate; a taking-out lead-out electrode layer, which is in contact with a side wall of the protruding semiconductor region and which is formed on the buried insulating layer; and a region doped with impurity, which is 65 formed on the side wall portion in the protruding semiconductor region in contact with the taking-out electrode layer, in which the end portion of the buried

insulating layer formed at the bottom portion of the side wall in the protruding semiconductor region extends satisfactorily towards the central portion of the protruding semiconductor region.

Further, speaking more concretely concerning the bipolar transistor, the object of this invention is to provide a superfine and super high speed bipolar transistor having a buried insulating layer separating the graft base from the high impurity concentration buried collector diffusion layer to a desired extent in the lateral direction in a desired region without impairing the reduction of the size, which can be fabricated with a high controllability by a simple fabrication process.

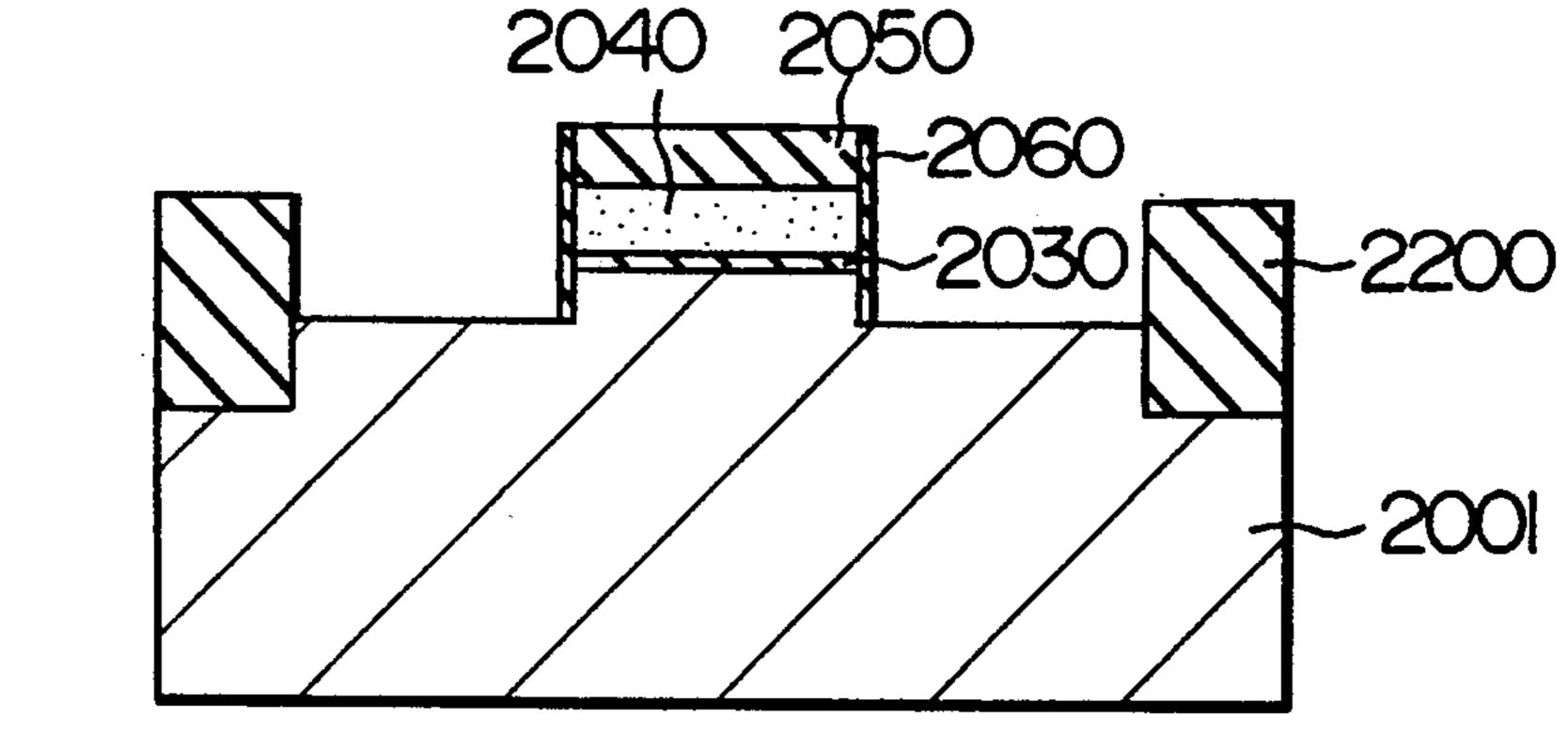

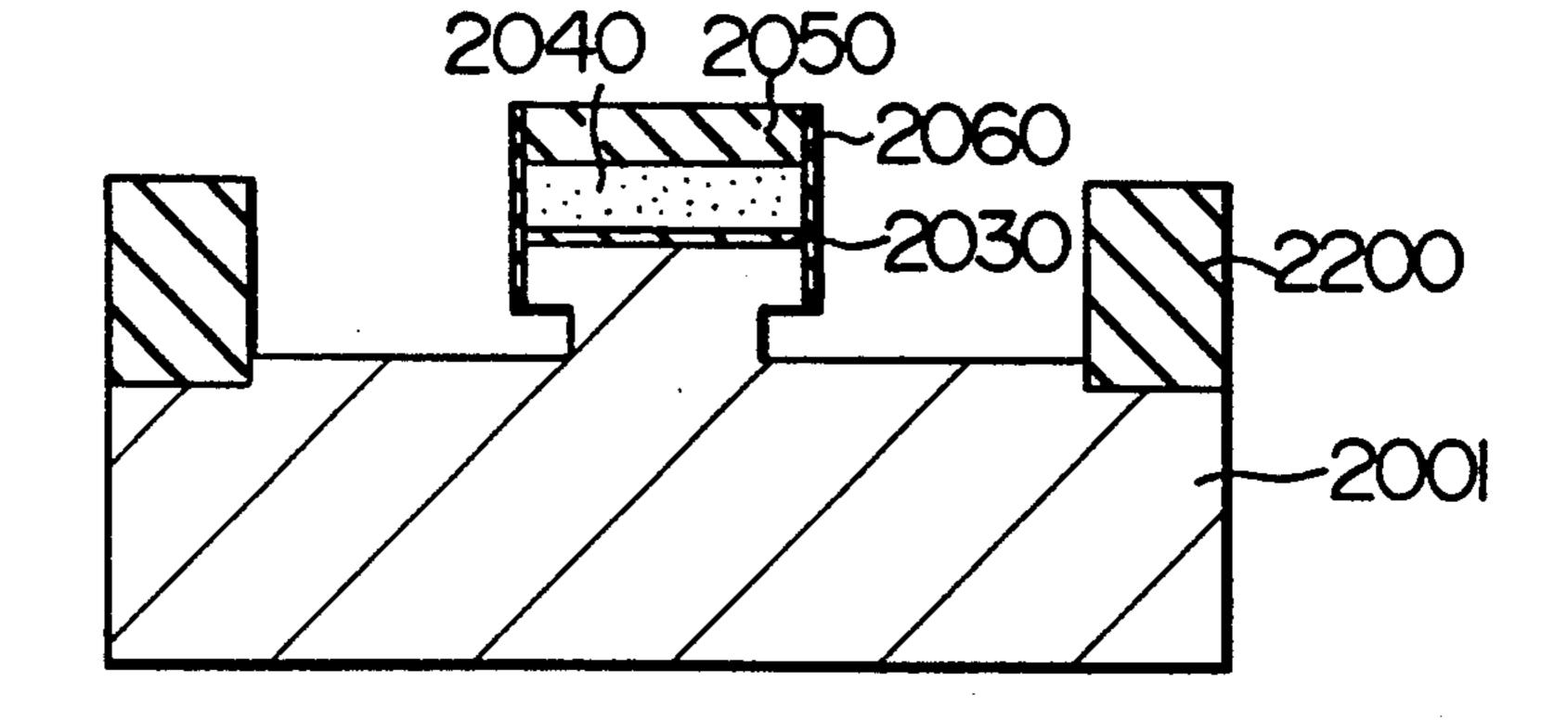

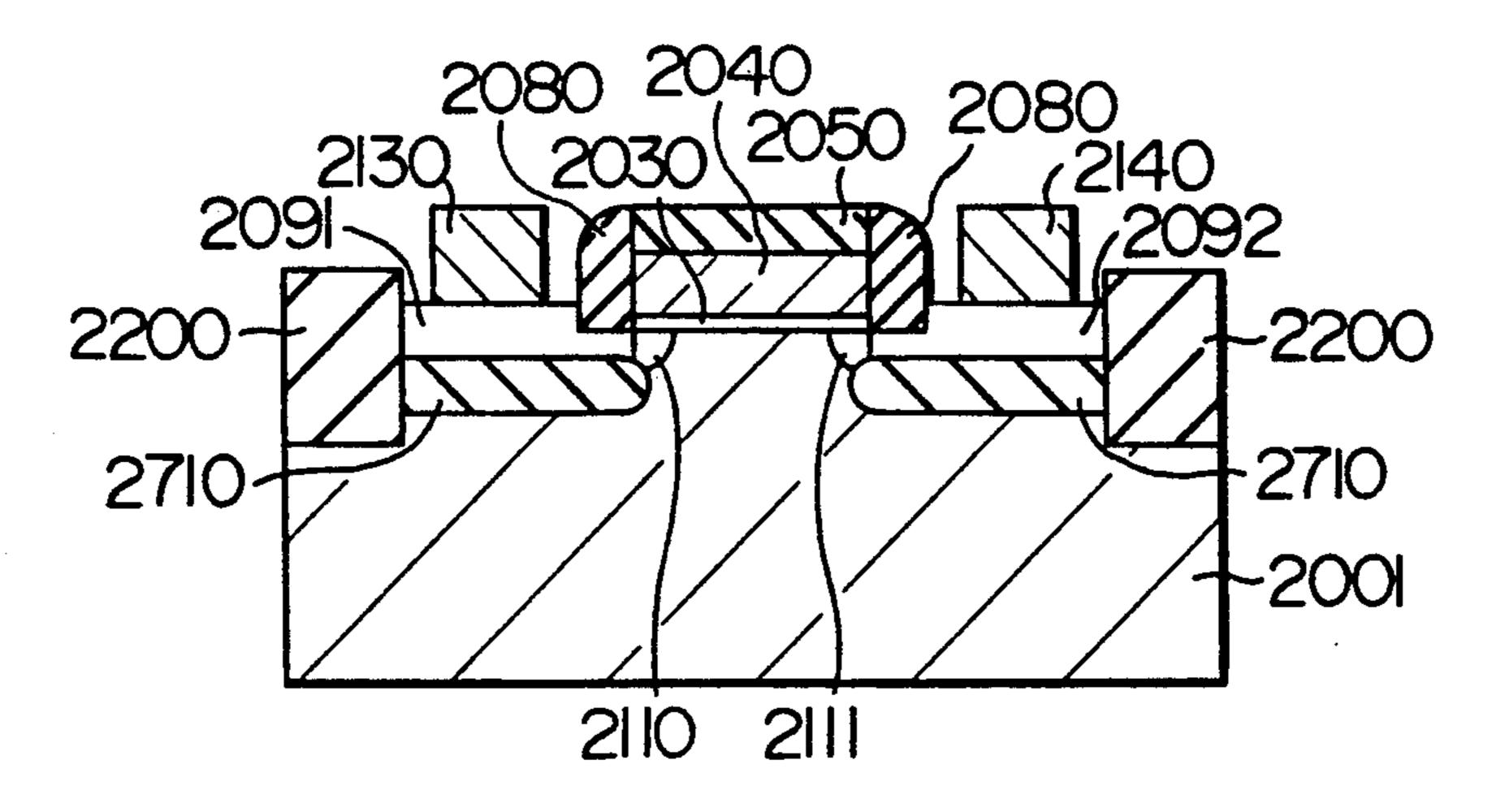

Next the buried insulating layer for taking-out an electrode disclosed in JP-A-61-237471 is indicated in FIG. 45, in which reference numeral 2001 is a p conductivity type Si singlecrystal substrate, for which a (100) plane is usually used as the principal surface from the point of view of reducing surface energy levels; 2200 is an isolation insulating layer separating elements, 2030 is a gate insulating layer; 2040 is a gate electrode; 2050 is a gate protecting insulating layer; 2080 is a gate side wall insulating layer; 2091 is a source taking-out leadout electrode; 2092 is a drain taking-out lead-out electrode; 2710 is a buried insulating layer; 2110 and 2111 are a source diffusion layer and a drain diffusion layer, respectively; and 2130 and 2140 are a source electrode and a drain electrode, respectively. Since in an MOS transistor having the prior art structure indicated in FIG. 45, the buried insulating layer 2710 can be constructed so that it is sufficiently thick, the transistor is characterized in that the parasitic capacitance component can be satisfactorily reduced with respect to that in an MOS transistor having a usual structure and therefore the operation speed is increased.

In such an MOS transistor, the buried insulating layer 2710 has been fabricated by selective oxidation of the etching region on the Si substrate 2001, on which the gate electrode 2040 serving as a mask was formed. Consequently the transistor was not so constructed that the buried insulating layer was extended to the side wall portion of the source-drain junction in the Si substrate region below the gate electrode 2040 and thus it was impossible to realize such a structure.

The structure of the buried insulating layer 2710 will be evaluated by the numerical analyzing method from the point of view of the improvement of the performance, and in particular the increase of the breakdown voltage and the high current density of a superfine MOS transistor and obtained results will be explained. That is, in the structure, in which the buried insulating layer 2710 is formed a the bottom portion of the sourcedrain junction such as in the prior art structure, although the effect to reduce the parasitic capacitance 55 can be obtained, the effect to alleviate the drain high electric field is not obtained at all. Consequently, in an MOS transistor having an extremely short channel, the prior art structure is not at all efficient with respect to the improvement of the effect, because of a strong electric field on the drain side, i.e. the socalled short channel effect and the phenomenon of the lowering of the punchtrough voltage. From the point of view of the short channel effect and the increase of the punchthrough voltage, it is desirable to form a thick insulating layer at the side portion of the drain junction so as to absorb the drain strong electric field.

According to the prior art technique indicated in FIG. 45, a method for burying an insulating layer by the

6

thermal oxidation method or the deposition method at a region, where the side surface of the drain junction is to be formed, after having selectively removed the region by etching using a fluoric acid and nitric acid mixed solution, microwave etching, etc., is also conceivable. However, by the method described above, since the etching proceeds isotropically and there is a problem in its controllability, it is feared that essential disadvantages take place that the semiconductor substrate portion corresponding to the channel region is also etched, 10 that the portion is made to be insulating, etc. and therefore this method is not practical.

Another object of this invention is to construct a thick insulating layer with a good controllability related to the self-alignment with the gate electrode at the side 15 surface portion of the drain junction in the semiconductor substrate right below the gate electrode by the same structure as described for the bipolar transistor.

#### SUMMARY OF THE INVENTION

In order to achieve the above objects, according to this invention, a vertical tunnel is formed in the direction perpendicular to the principal surface of the semiconductor substrate and then a lateral tunnel is formed from the bottom portion of the vertical tunnel in the 25 direction parallel to the principal surface by anisotropic etching depending on the crystallographical orientation. The vertical and lateral tunnels are filled with polycrystalline or amorphous semiconductor doped with impurity or insulator. In order to make it possible 30 to form the lateral tunnel parallel to the principal surface of the semiconductor substrate by the anisotropic etching, according to this invention, a semiconductor, whose principal surface is a (111) plane, is used and the which is perpendicular to <111>. If an N<sub>2</sub>H<sub>4</sub> or kOH solution is used for the anisotropic etching, the etching in the direction of <111> and the etching of a silicon oxide layer and a nitride layer are negligibly small. Consequently the control of the end point of the lateral 40 tunnel can be effected by constructing the whole active region so as to be enclosed by an insulating layer within the deep concave. The isolation from adjacent transistors and the removal of a-ray soft errors can be achieved by isolating the transistor from the semicon- 45 ductor substrate if an insulating layer is formed selectively at the lateral tunnel and the bottom portion of the vertical tunnel before the filling with a semiconductor thin film.

Since the lateral and vertical tunnels described above 50 can be formed even after having formed the base diffusion layer region or the emitter diffusion layer region, it is not necessary to dispose any epitaxial layer and it is possible to shorten remarkably the period, during which the semiconductor body is exposed to a high tempera- 55 ture heat treatment. Consequently it is possible to realize a buried diffusion layer having a high impurity concentration, and moreover an abrupt distribution by using P or As, whose solid solubility is higher than Sb as doped impurity.

Furthermore, if the lateral tunnel and the bottom portion of the vertical tunnel is selectively oxidized before the filling with the semiconductor layer described above, the whole element is completely isolated from the semiconductor substrate. Consequently erro- 65 neous operations such as  $\alpha$ -ray soft errors, interference between adjacent transistors, etc. can be removed completely. Further, if the semiconductor layer is taken-out

on the surface of the semiconductor, it can be used also as electrode wiring. Consequently the area of the collector electrode region is reduced and freedom of the circuit construction is increased, which makes it easier to increase the degree of integration.

The formation of the lateral tunnel according to this invention can be realized by anisotropic etching depending strongly on the crystallographical surface orientation. For example, when an N<sub>2</sub>H<sub>4</sub> or KOH solution is used, the etching speed for Si in the direction <111>and for insulating layers such as SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, etc. is significantly smaller than that for Si in the directions <100> and <110>. Consequently, after having constructed an active region enclosed by a deep trench isolating insulating layer in a semiconductor substrate having a principal surface (111), a vertical tunnel is formed at a desired position in the active region and with the insulating layer left at the upper portion of the vertical tunnel, the anisotropic etching described above 20 is effected. In this way etching proceeds in the direction <110>, which is parallel to the principal surface, and a lateral tunnel, both the ceiling surface and the bottom surface of which ar parallel to the principal surface, is formed all over the active region. The region, where the lateral tunnel is formed, is the region enclosed by the deep trench isolating insulating layer. Therefore the controllability and the reproducibility thereof give rise to no problems.

#### BRIEF DESCRIPTION OF THE DRAWINGS

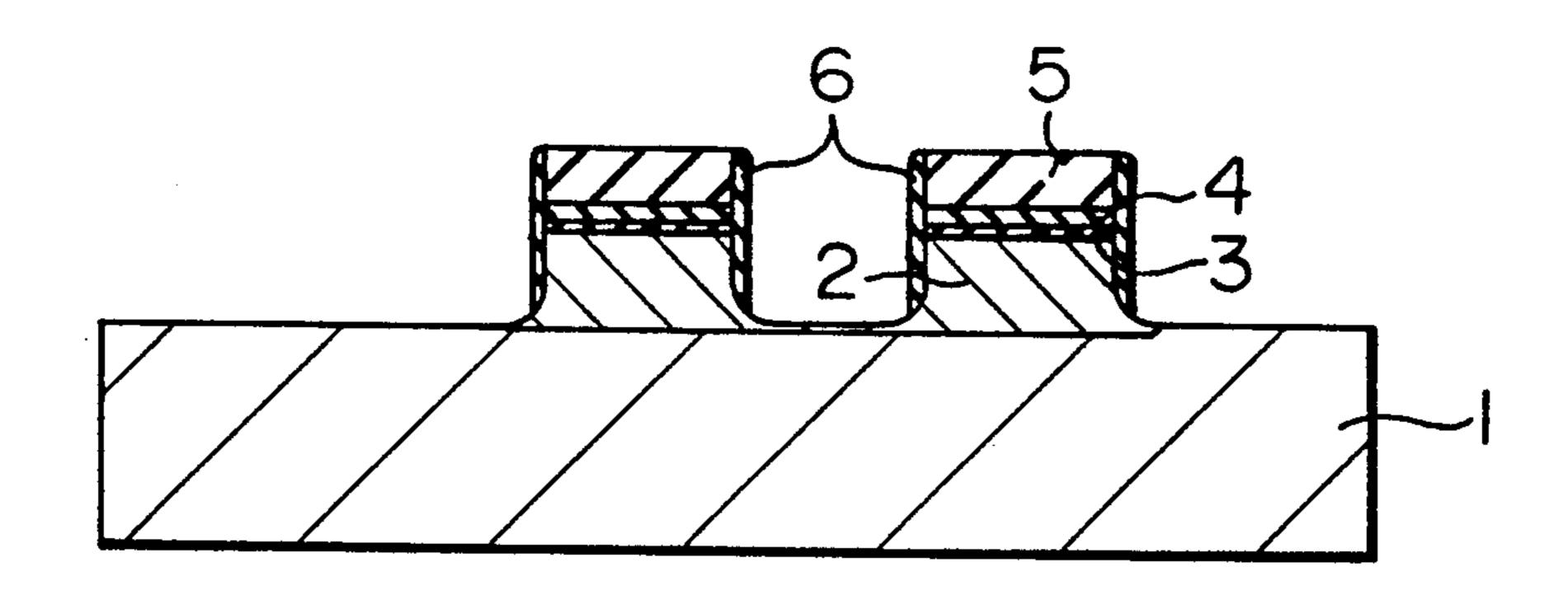

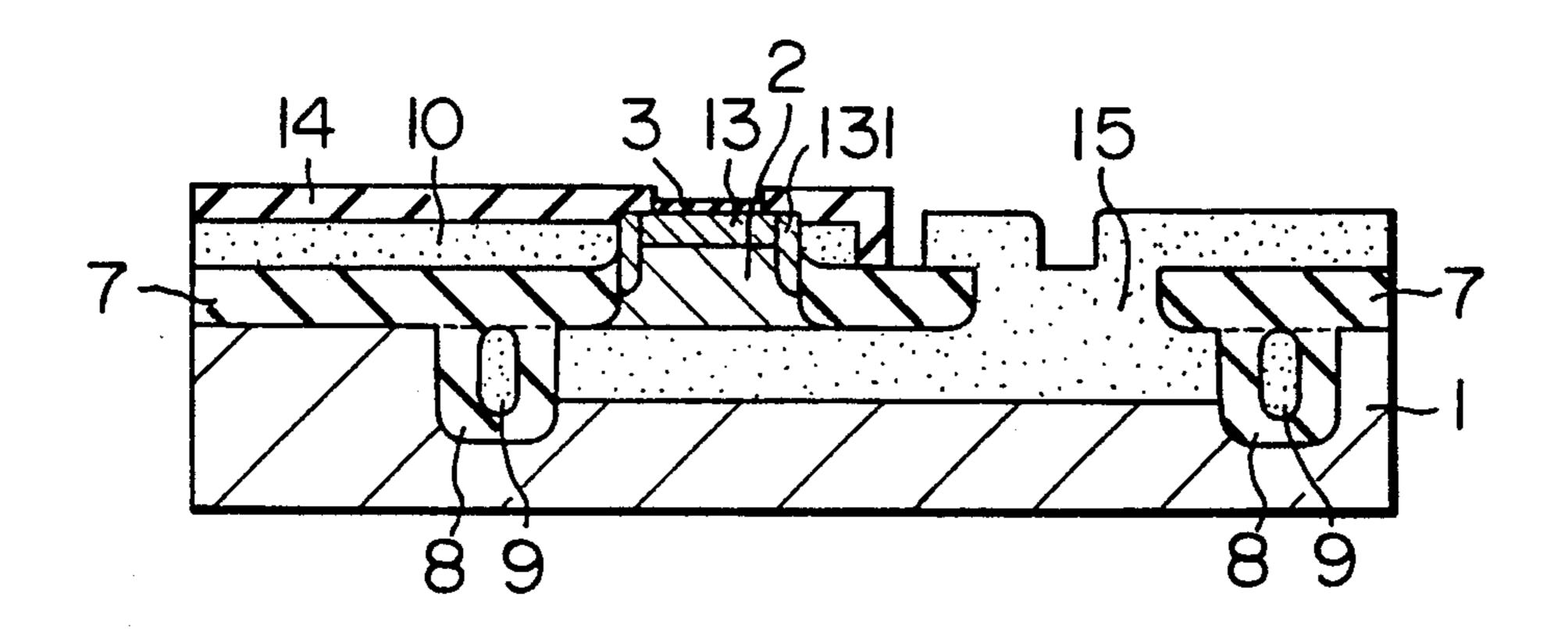

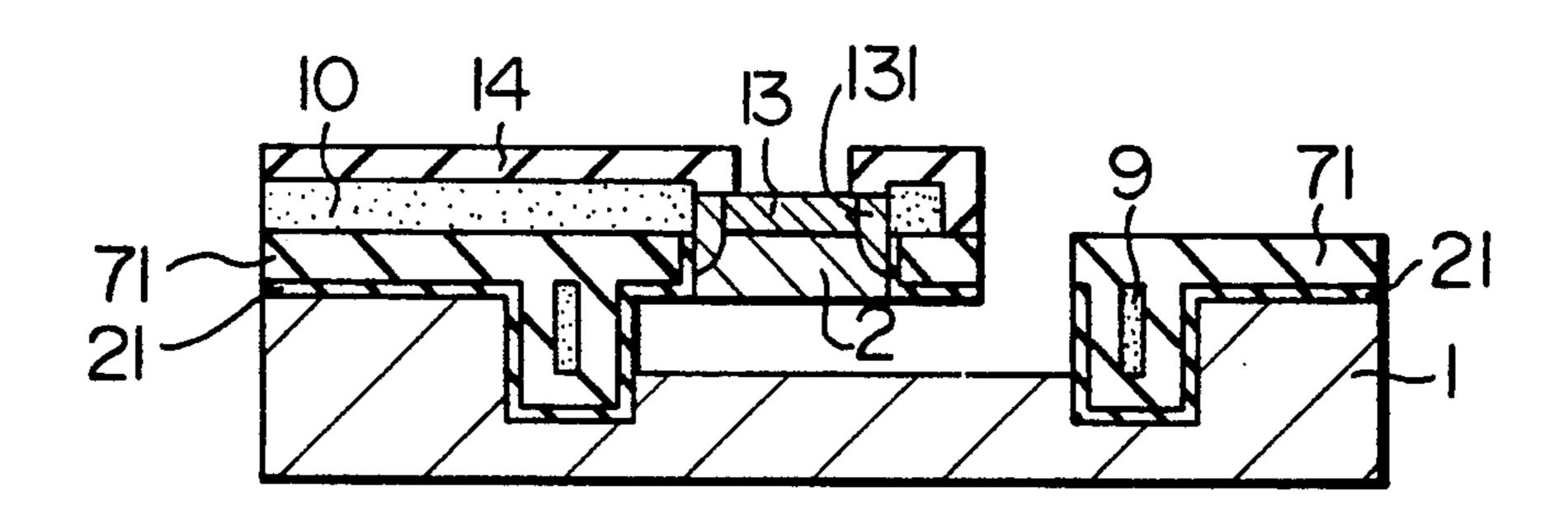

FIGS. 1 to 5 are cross-sectional views illustrating a first embodiment of this invention in the order of the fabrication steps;

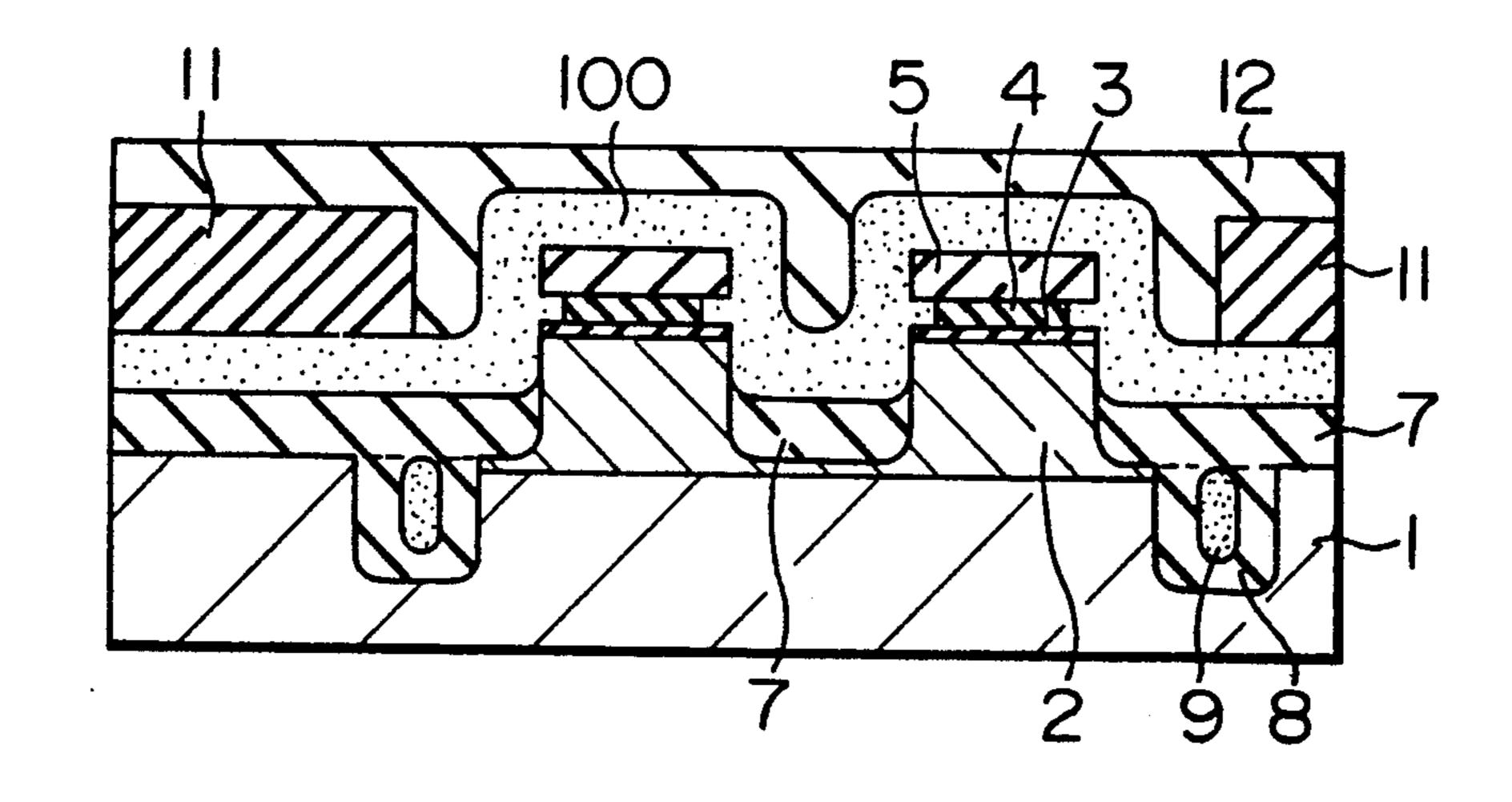

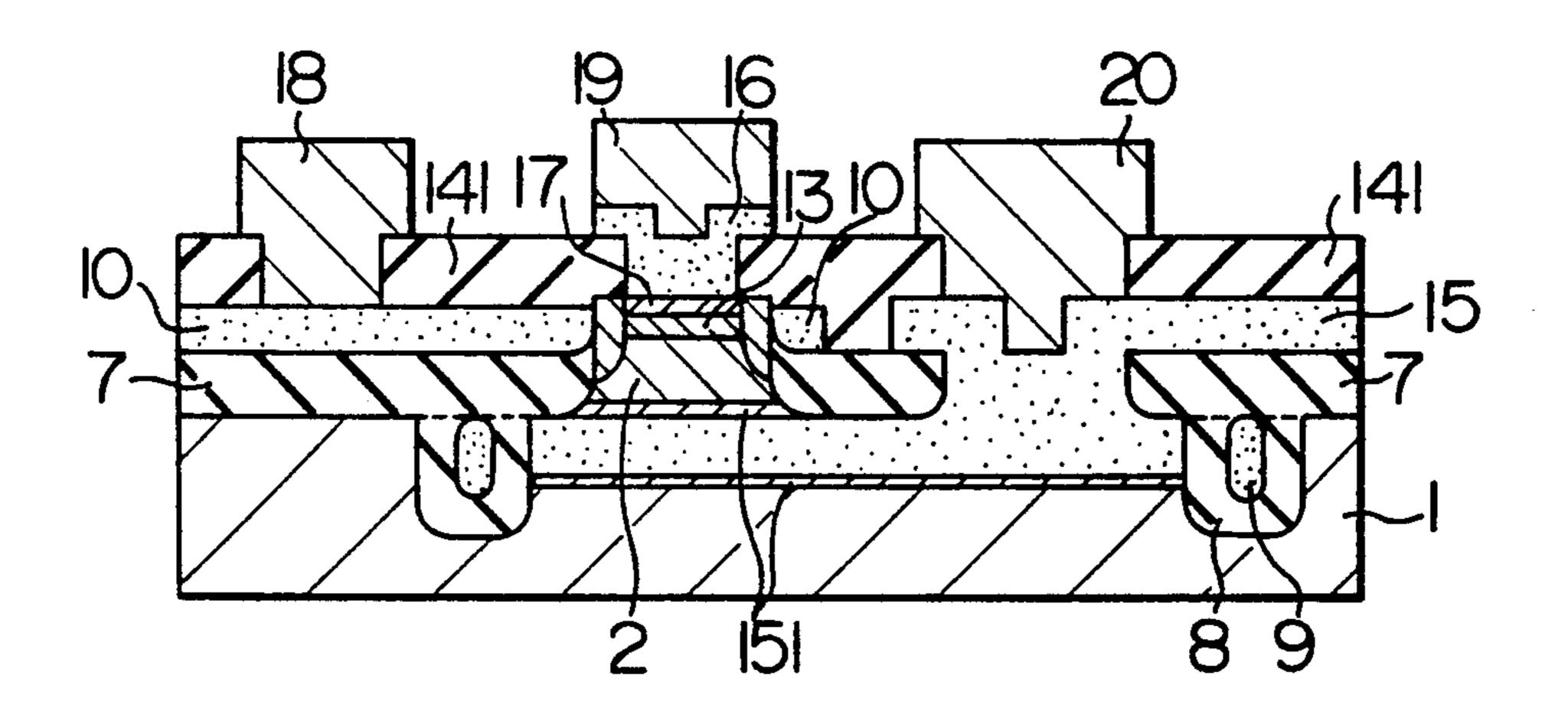

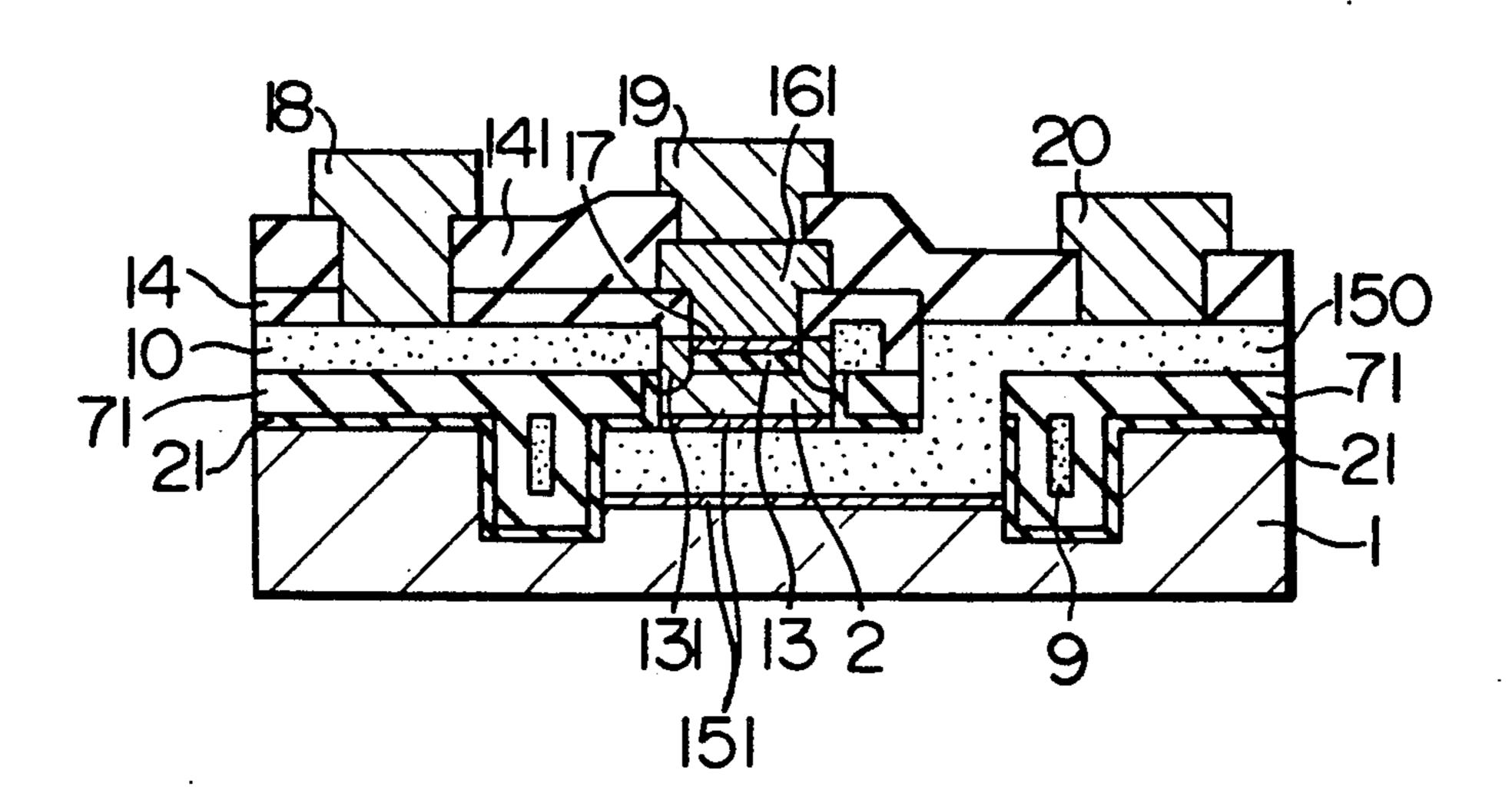

FIGS. 6 to 9 are cross-sectional views illustrating a lateral tunnel is located in the direction of <110>, 35 second embodiment of this invention in the order of the fabrication steps;

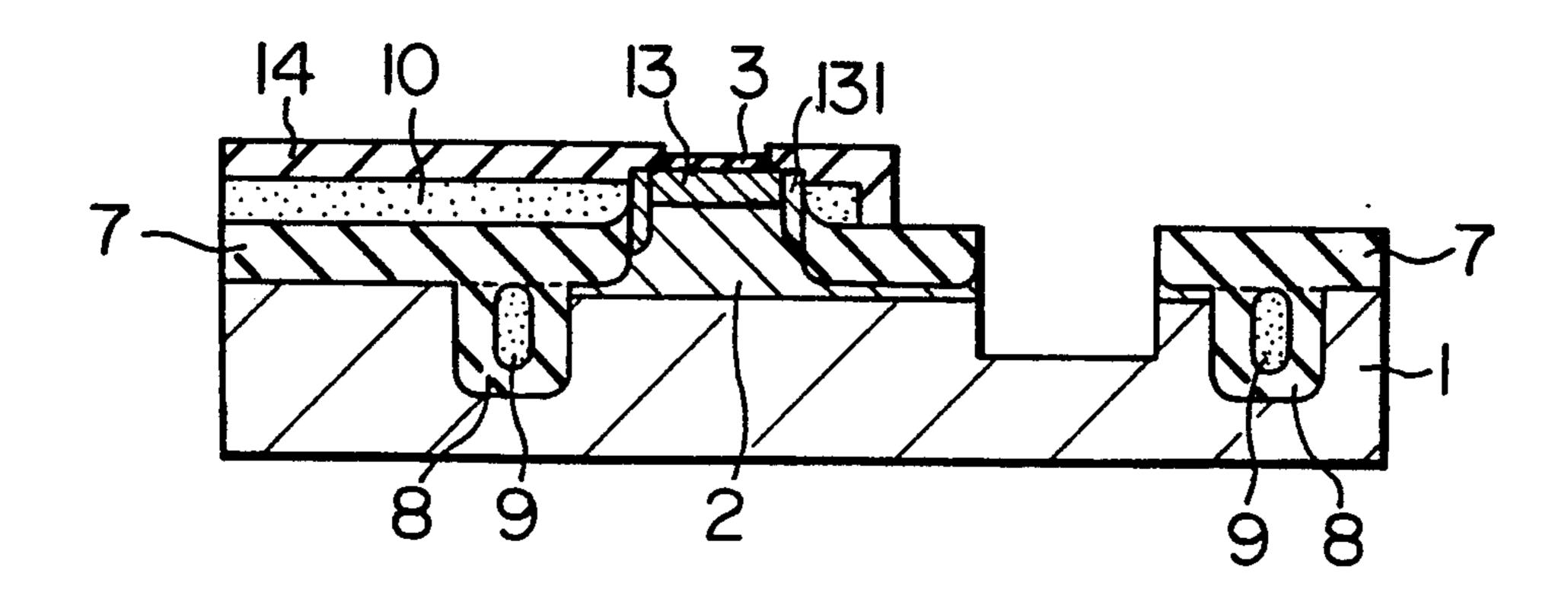

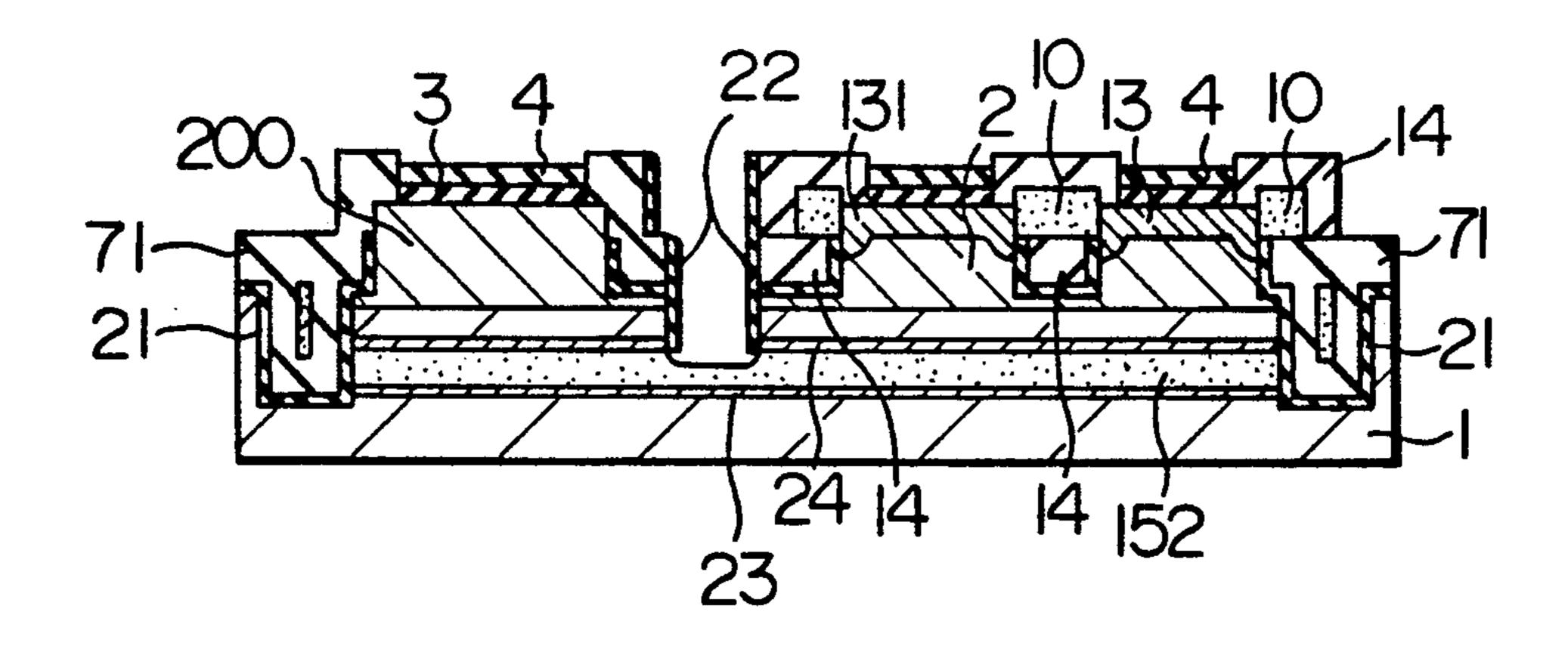

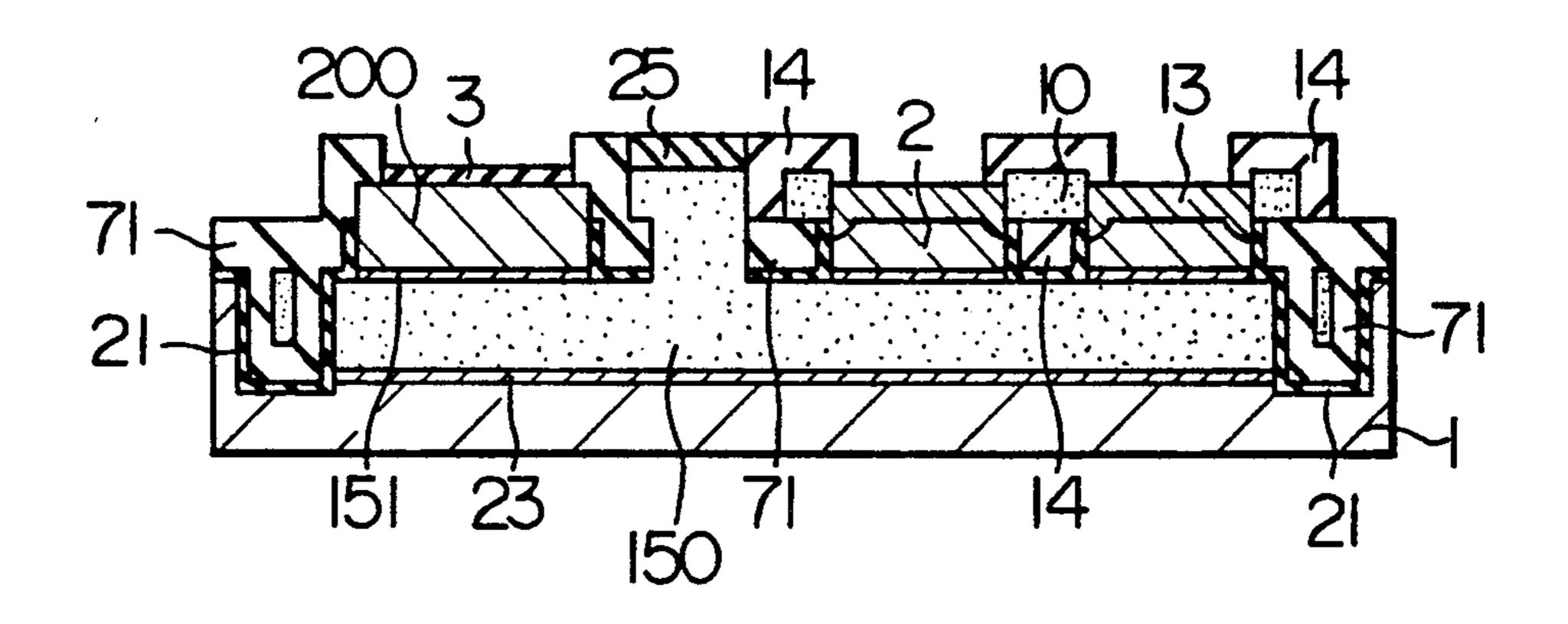

FIGS. 10 to 12 are cross-sectional views illustrating a third embodiment of this invention in the order of the fabrication steps;

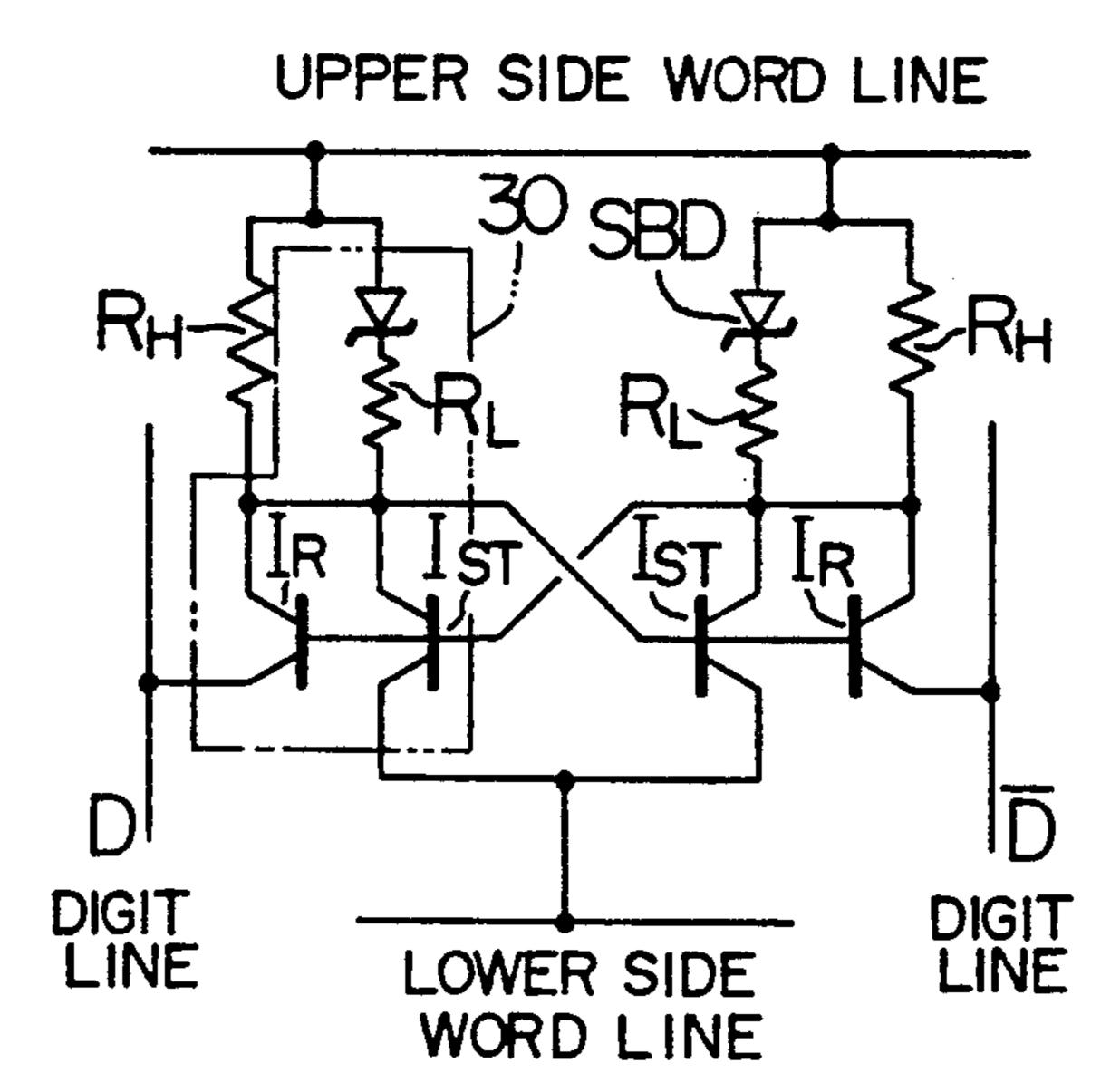

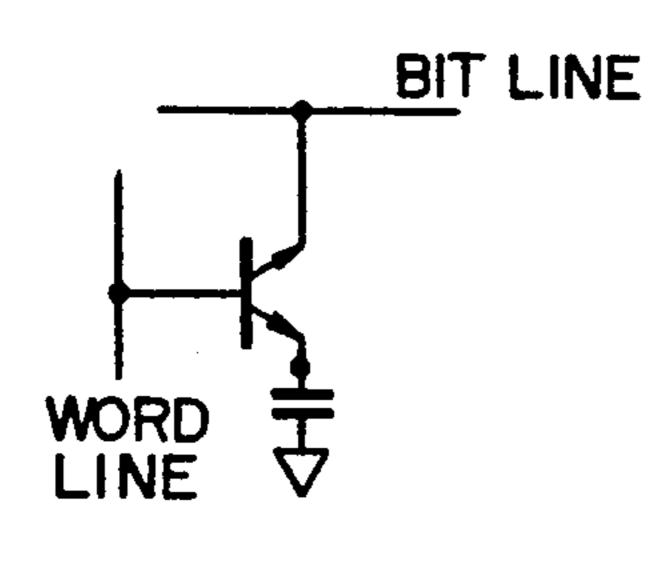

FIG. 13 is an equivalent circuit diagram of a semiconductor device obtained according to the third embodiment;

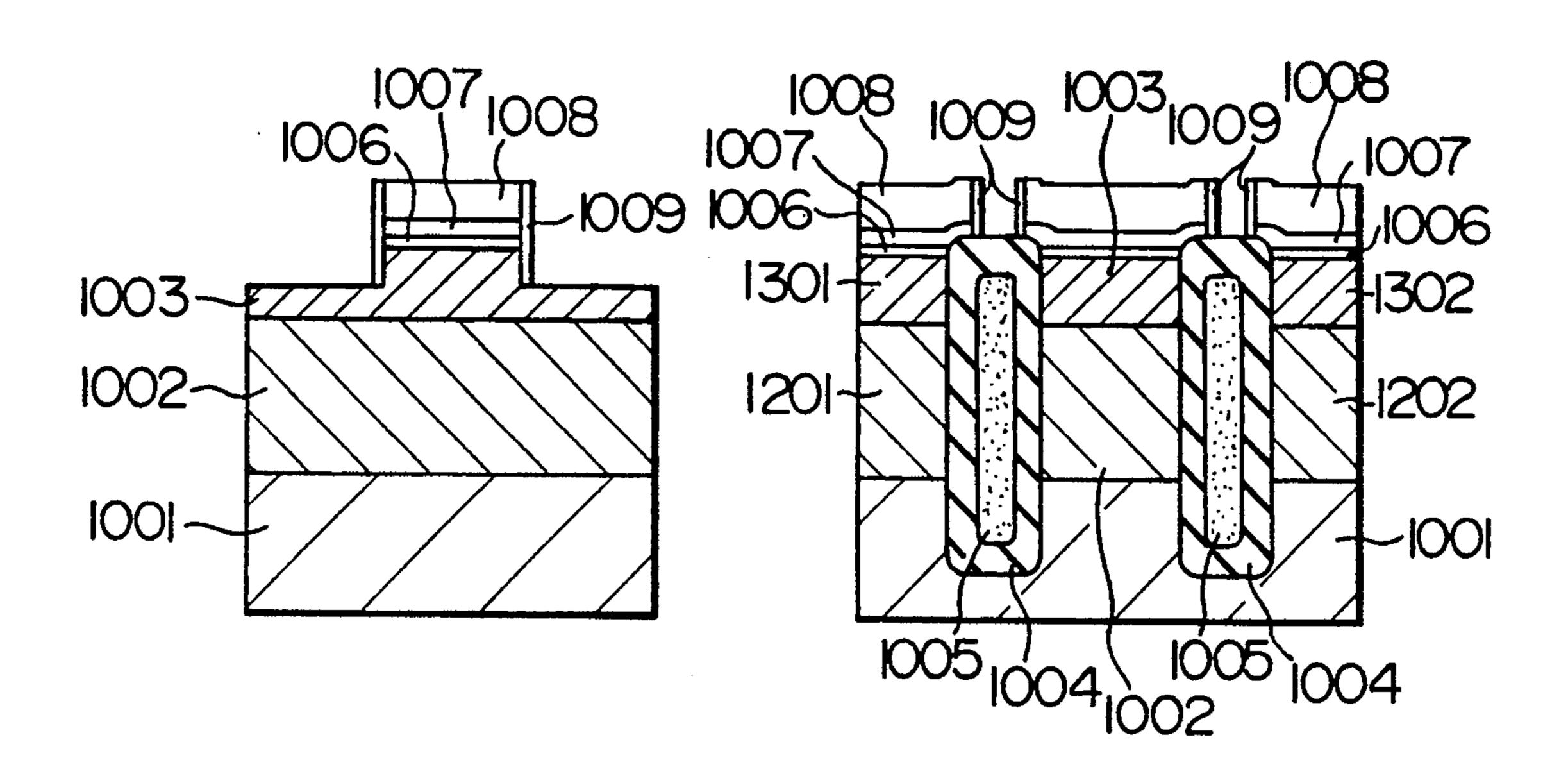

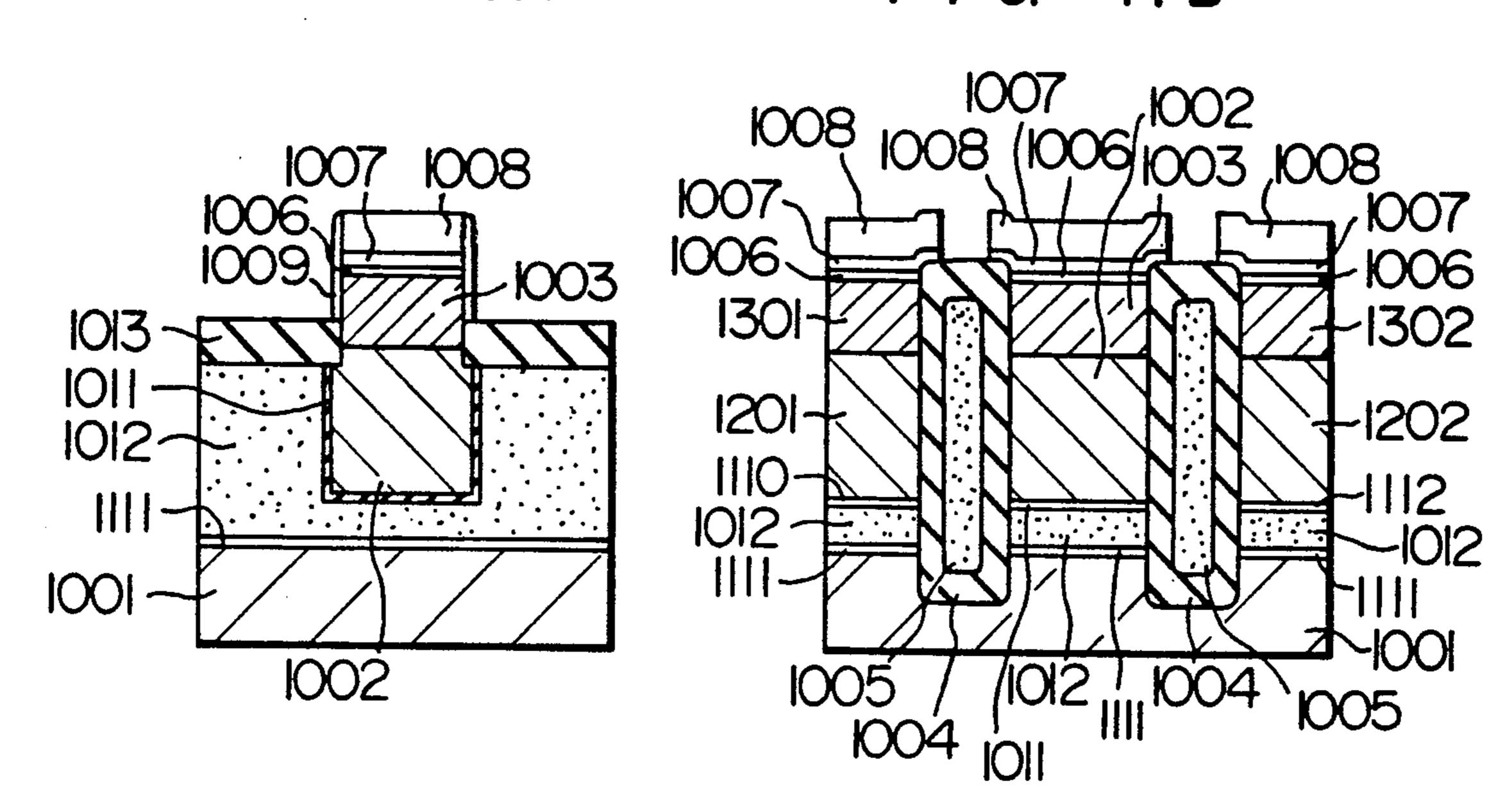

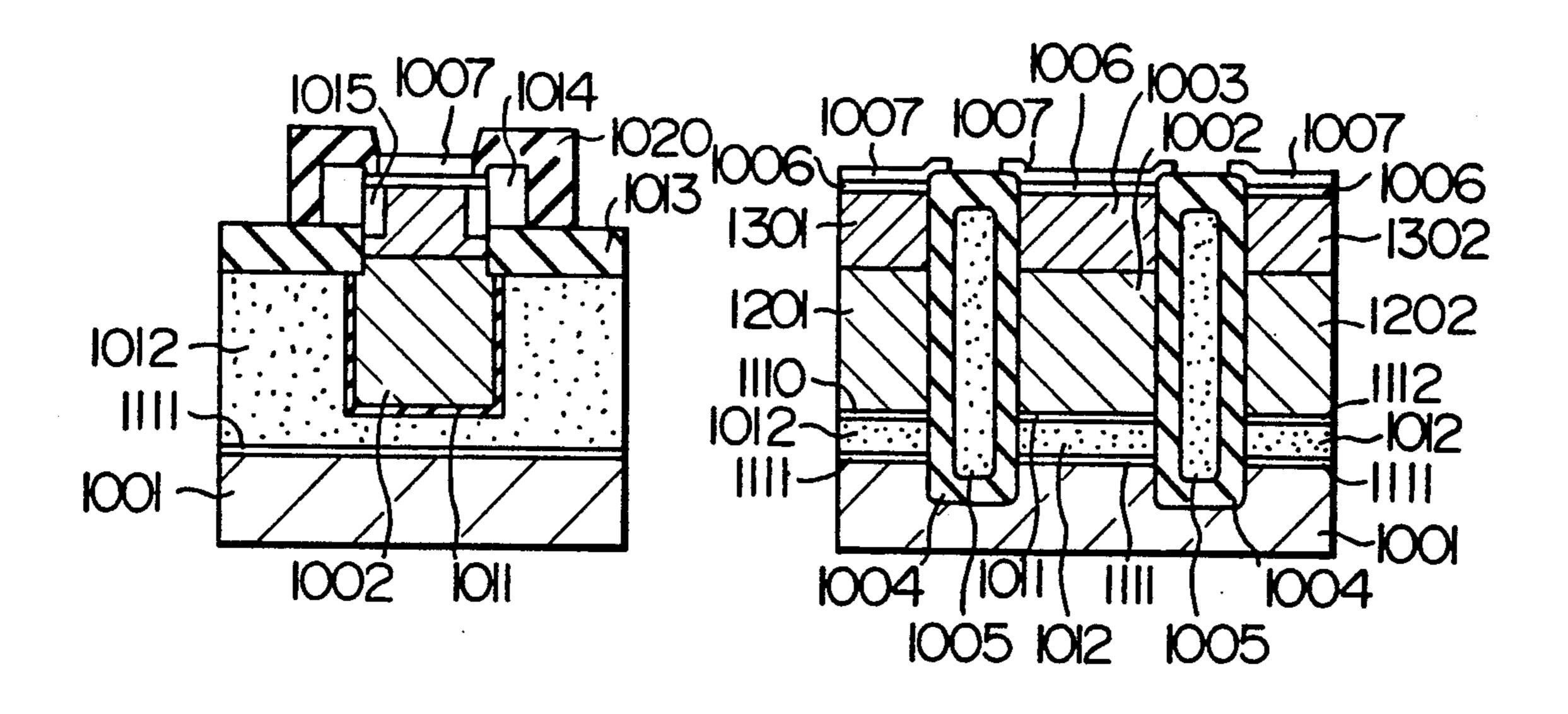

FIGS. 14A, 14B to 19A, 19B are cross-sectional views indicating fabrication steps of a semiconductor memory device, which is a fourth embodiment of this invention, A and B representing cross-sections, which are perpendicular to each other;

FIG. 19C is an equivalent circuit diagram of a semiconductor device obtained according to the fourth embodiment of this invention;

FIG. 20 is a cross-sectional view of a semiconductor memory device, which is a fifth embodiment of this invention;

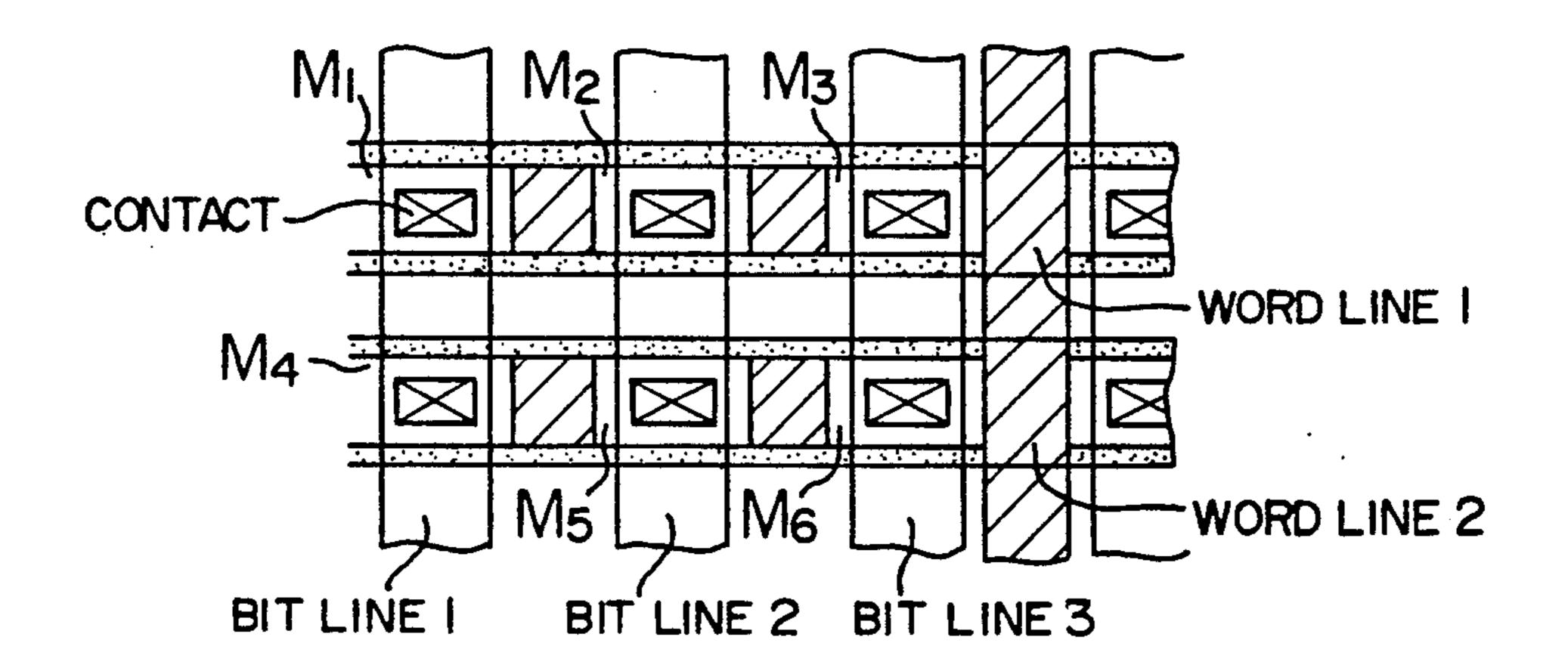

FIG. 21 is a plan view illustrating a semiconductor memory device according to this invention in a simplified manner;

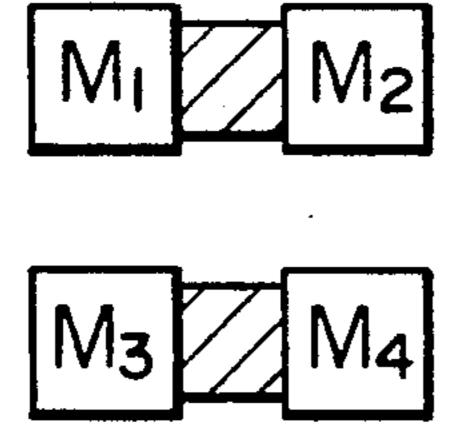

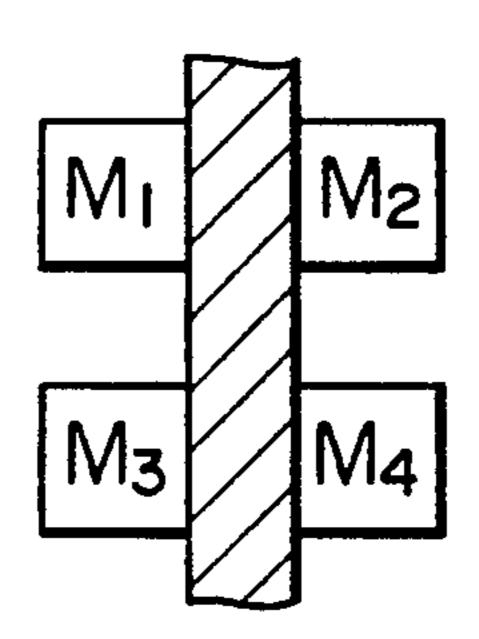

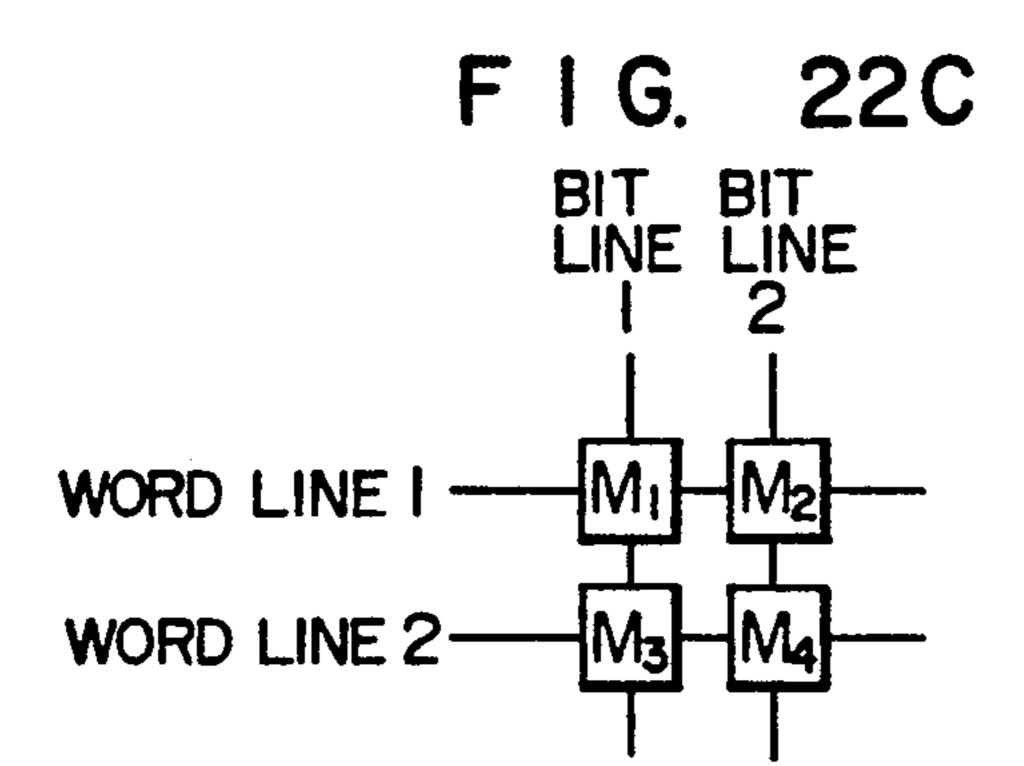

FIGS. 22A and 22B are schematized plan views illustrating the construction of memory cells;

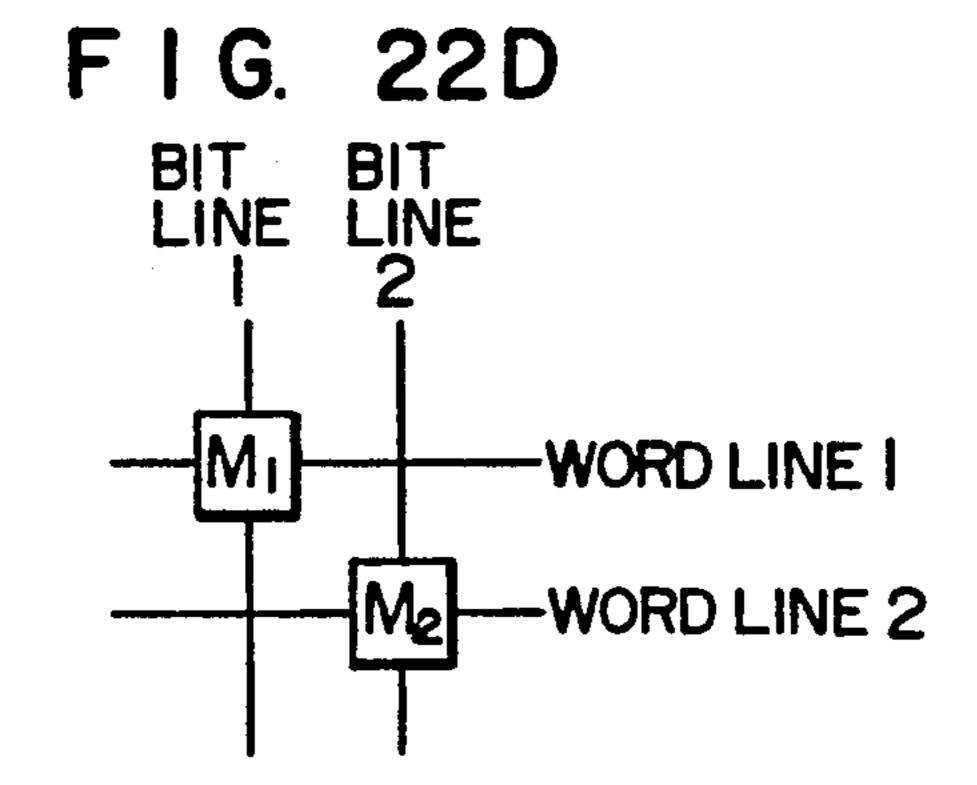

FIGS. 22C and 22D are schemes indicating wiring 60 for memory cells;

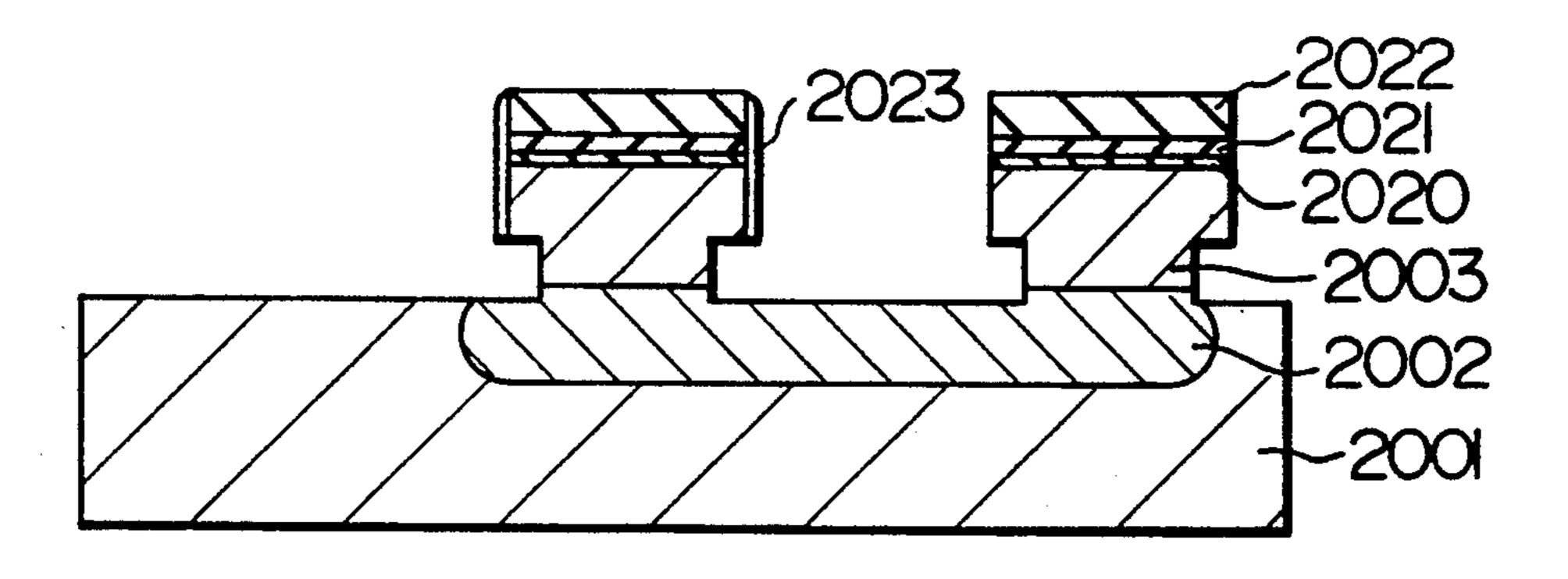

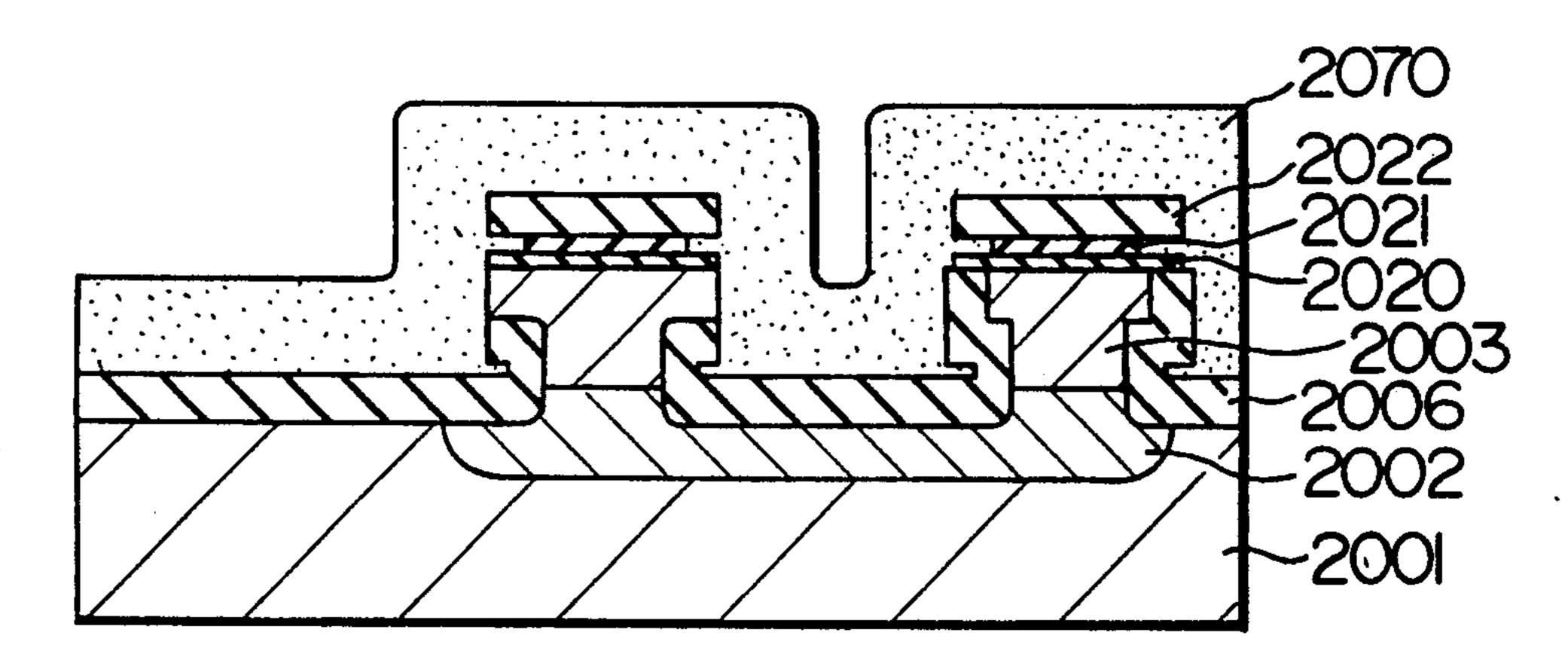

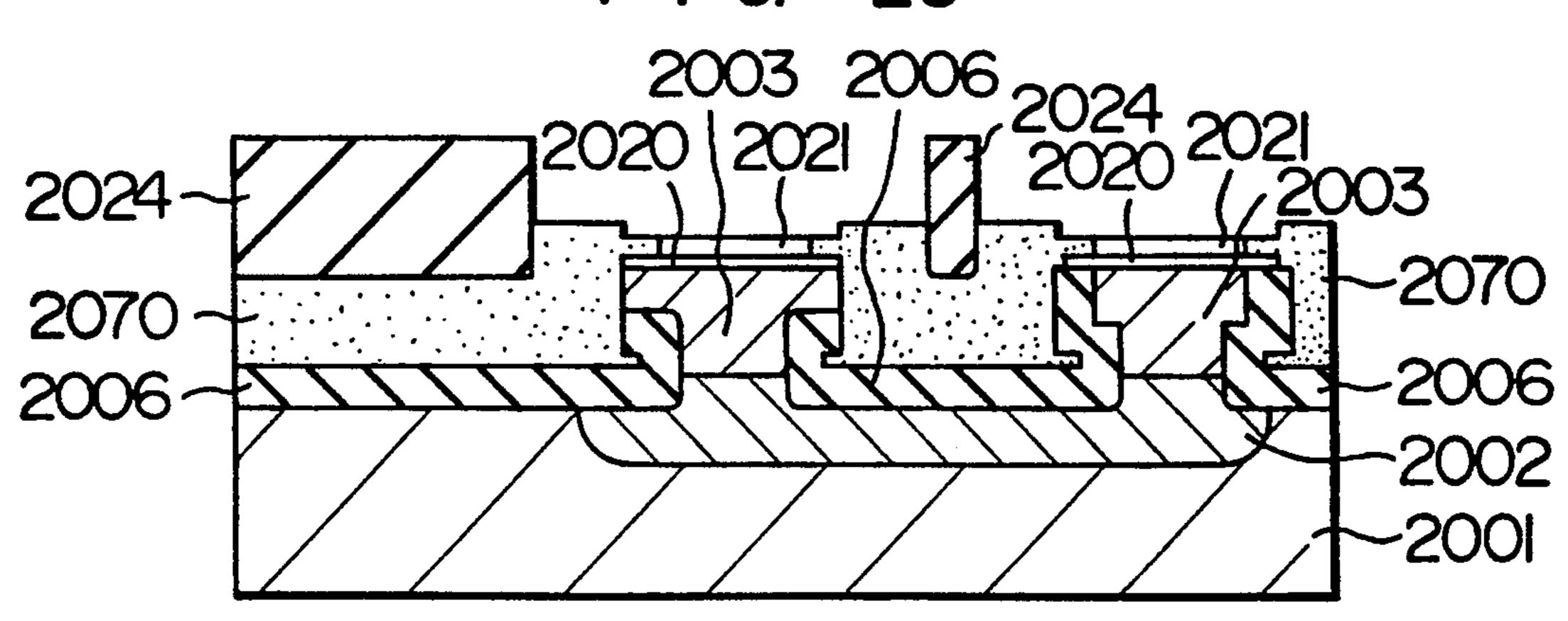

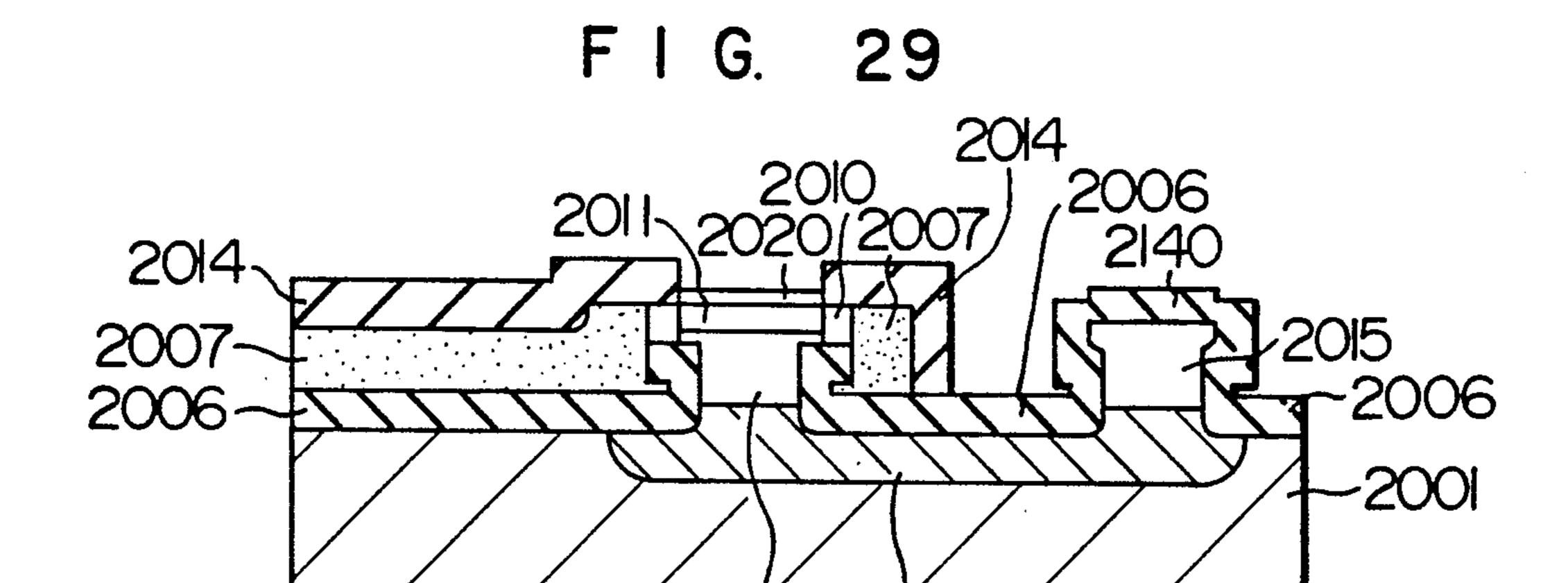

FIGS. 23 to 30 are cross-sectional views illustrating fabrication steps for fabricating a bipolar transistor, which is a sixth embodiment of this invention;

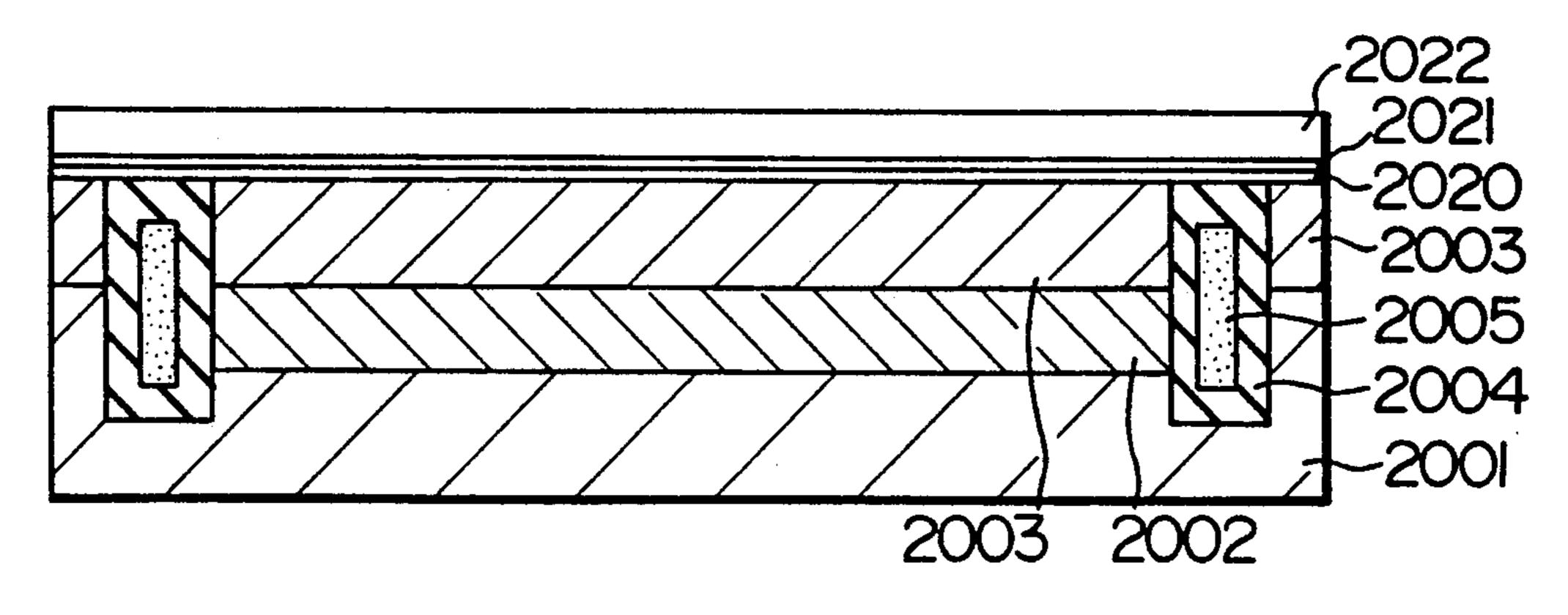

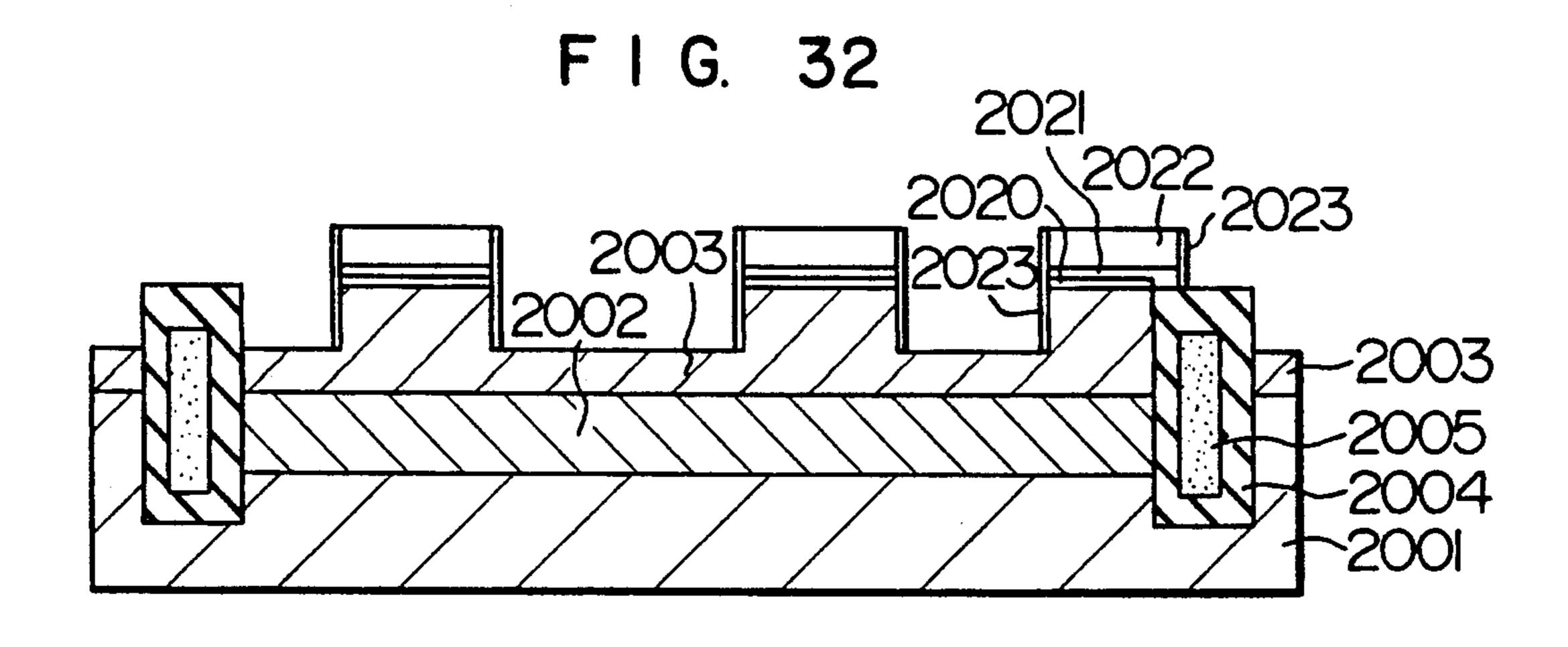

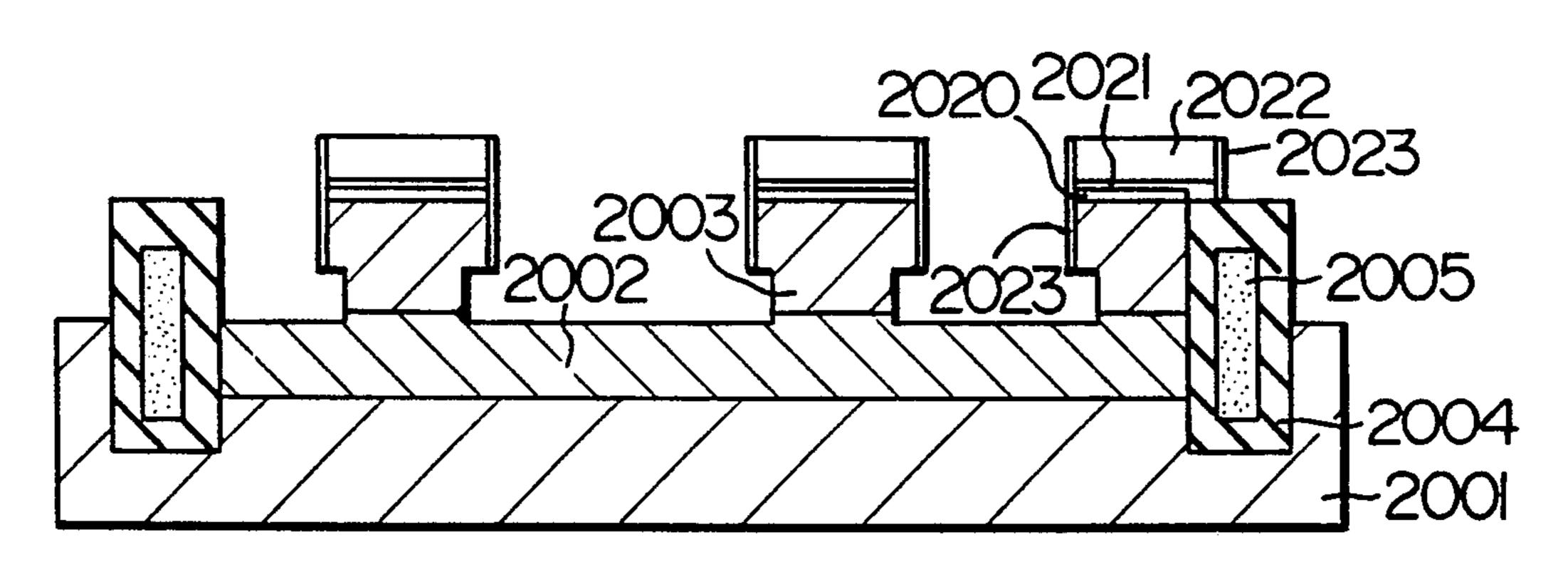

FIGS. 31 to 36 are cross-sectional views illustrating fabrication steps for fabricating another bipolar transistor, which is a seventh embodiment of this invention;

FIG. 37 is a plan view of the bipolar transistor indicated in FIG. 36;

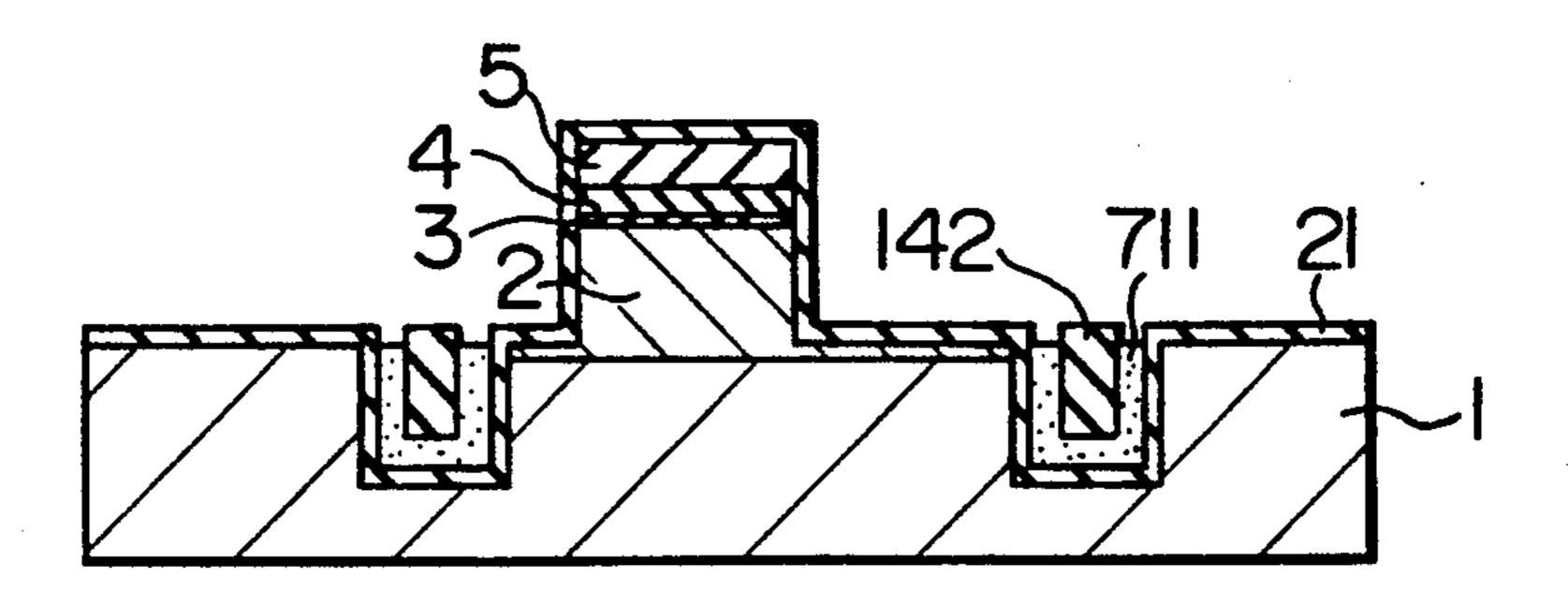

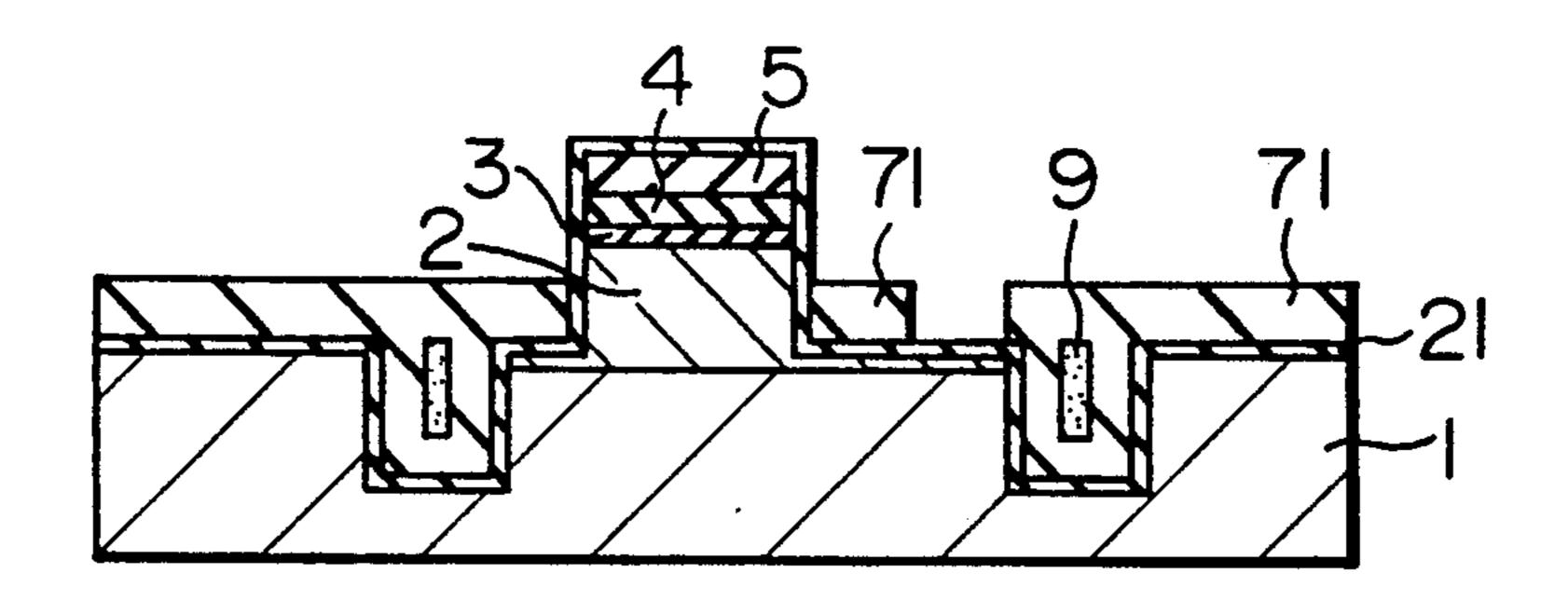

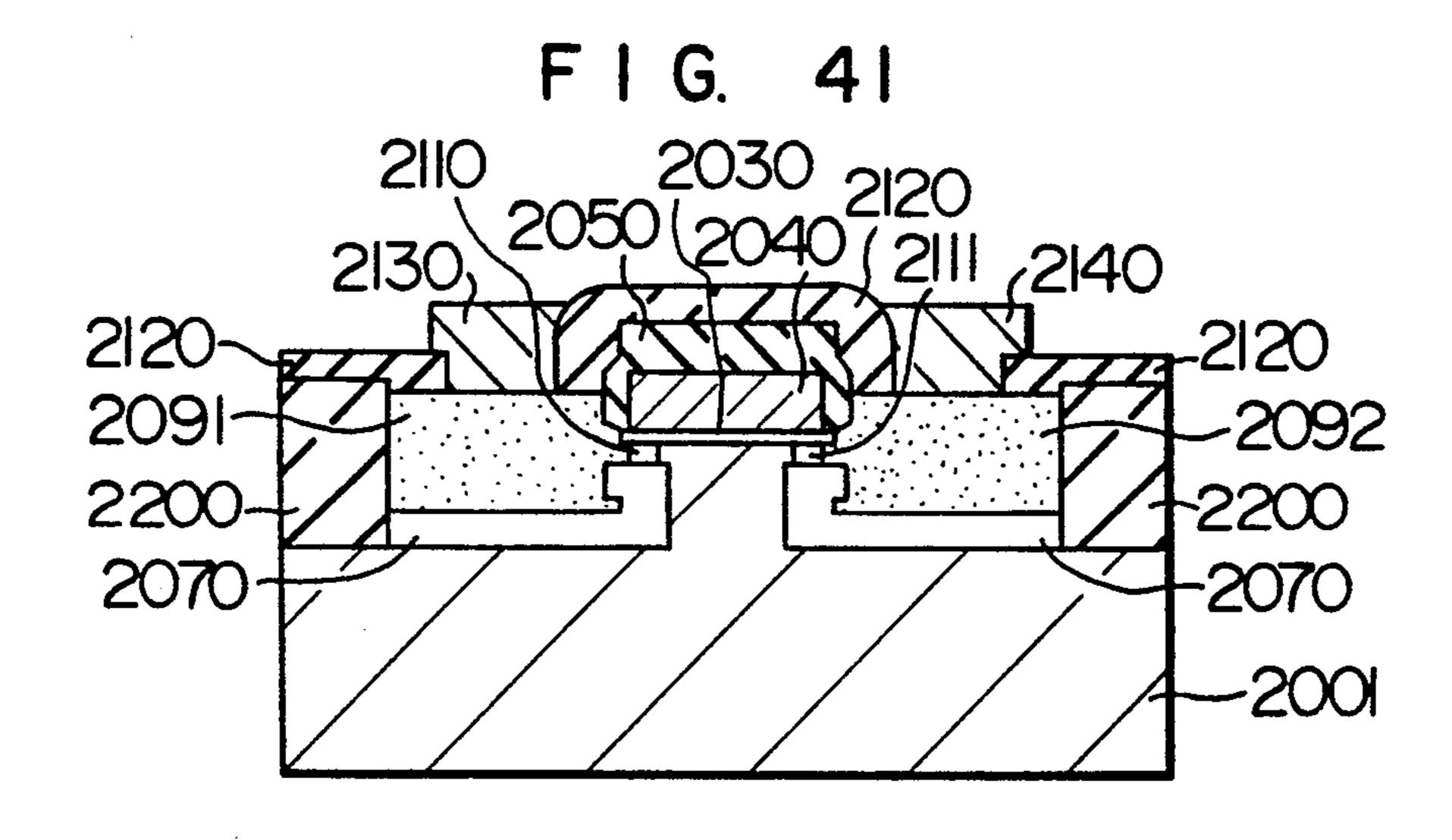

FIGS. 38 to 41 are cross-sectional views illustrating fabrication steps for fabricating an MOS transistor, which is an eighth embodiment of this invention;

FIG. 42 is a cross-sectional view of a prior art semiconductor device having a buried layer;

FIG. 43A is a cross-sectional view of a prior art semiconductor memory device;

FIG. 43B is an equivalent circuit diagram of the device indicated in FIG. 43A;

FIG. 44 is a cross-sectional view of a prior art bipolar transistor; and

FIG. 45 is a cross-sectional view of a prior art MOS transistor.

## DESCRIPTION OF THE PREFERRED EMBODIMENTS

Hereinbelow this invention will be explained in greater detail, using several preferred embodiments. For the sake of the convenience explanation will be made, referring to the drawing, in which attention should be paid to the fact that principal parts are indicated in an enlarged scale. Further, although the material of various parts, the conductivity type of semiconductor layers and the conditions of fabrication will be prescribed in the following description for the purpose of making explanation clearer, it is a matter of course that they are not restricted to those described.

At first an embodiment of this invention concerning the buried diffusion layer in a bipolar transistor will be explained.

#### EMBODIMENT 1

FIGS. 1 to 5 are cross-sectional views illustrating a first embodiment of the semiconductor device according to this invention in the order of the fabrication steps.

In FIG. 1, phosphor (P) ions are selectively implanted in a desired region on a p conductivity type silicon (Si) substrate 1 having a resistivity of 10  $\Omega$ -cm, whose principal surface is (111). Then an n-conduc-40 tivity type diffusion layer 2 having a surface impurity concentration of  $1 \times 10^{15}$  cm<sup>-3</sup> and a junction depth of 0.8 µm is formed by subjecting the substrate 1 to a heat treatment. Eventually the n-conductivity type diffusion layer 2 may be formed over the whole surface of the 45 substrate 1. After that, a silicon dioxide layer (hereinbelow called SiO<sub>2</sub> layer) 3, 50 nm thick by the thermal oxidation method, a silicon nitride layer (hereinbelow called Si<sub>3</sub>N<sub>4</sub> layer) 4, 120 nm thick by the chemical vapor deposition (hereinbelow abbreviated to CVD) 50 method and an SiO<sub>2</sub> layer 5 by the CVD method are formed one after another on the Si substrate 1. Thereafter, the three-layered insulating layer consisting of the SiO<sub>2</sub> layer 5, the Si<sub>3</sub>N<sub>4</sub> layer 4 and the SiO<sub>2</sub> layer 3 is patterned by reactive ion etching (hereinbelow abbrevi- 55 ated to RIE) and further the Si substrate 1 is etched also to a depth of 0.6  $\mu$ m, using the three-layered insulating layer described above as a mask. Subsequently the Si surface thus exposed is etched to a depth of 0.1 µm by using a mixed solution of nitric acid (HNO<sub>3</sub>) and fluoric 60 acid (HF). Then, after having formed a two-layered insulating layer 6 over the whole surface by superposing an SiO<sub>2</sub> film 50 nm thick formed by the thermal oxidation method and an Si<sub>3</sub>N<sub>4</sub> 120 nm thick formed by the CVD method on each other, an etching by the RIE 65 method proceeds only in the direction perpendicular to the principal surface of the Si substrate 1 so that the two-layered insulating layer 6 remains only on the side

wall portion of the three-layered insulating layer 3 to 5 and the Si substrate 1.

Starting from the state indicated in FIG. 1, an SiO<sub>2</sub> layer 450 nm thick is formed by wet thermal oxidation on the exposed surface of the Si substrate 1 by using the two-layered insulating layer 6 as a mask, which SiO<sub>2</sub> layer serves as an isolating insulating layer 7, as indicated in FIG. 2. Then the isolating insulating layer is patterned so as to form a trench 1 µm wide, which encloses an active region, and a trench 2.5 µm deep is formed also on the Si substrate 1 by the RIE method with the same pattern. After having etched off the surface portion 0.1 µm thick within the Si deep trench described previously by using a mixed solution of fluo-15 ric acid and nitric acid, boron (B) ions are implanted under a condition that the acceleration energy is 50 keV and the dose is  $3 \times 10^{13}$  cm<sup>-2</sup>, in order to prevent the channel formation, and a channel step layer (not shown in the figure) is formed at the bottom portion of the 20 deep trench by a succeeding activation heat treatment. Thereafter, an SiO<sub>2</sub> layer 0.2 µm thick is formed on the surface of the Si deep trench by the wet thermal oxidation, which SiO<sub>2</sub> layer serves as a deep trench insulating layer 8 for isolating elements. Then, after having deposited a polycrystalline (or amorphous) Si layer 0.7 µm so as to fill the deep trench, etching process is performed isotropically by microwave plasma etching so that a polycrystalline Si layer 9 is selectively left only in the deep trench. After that, the surface of the polycrystalline Si layer 9 selectively left is oxidized by the wet thermal oxidation so as to form an SiO<sub>2</sub> layer 0.45 µm thick. Then the two-layered insulating layer 6 is removed by using a phosphoric acid solution heated to 180° C. so as to expose the side wall of the Si substrate 1 in the active region. At this time the Si<sub>3</sub>N<sub>4</sub> layer 4 is also side-etched. Then a polycrystalline Si layer 100 0.7 µm thick is deposited over the tunnel surface by the CVD method and a thermal oxidation layer (not shown in the figure) 20 nm thick is formed at the surface portion thereof. Finally a photoresist film 11 is selectively left at places, where the interval between adjacent two protruding regions on the substrate is grater than 1 µm and another photoresist film 12 1 µm thick is applied over the whole surface to flatten the surface.

Starting from the state indicated in FIG. 2, the photoresist layers 12 and 11 are etched by the RIE method to flatten the surface and to expose the polycrystalline Si layer 100 in the protruding regions, as indicated in FIG. 3, and the SiO<sub>2</sub> layer formed on the surface is removed. Subsequently the polycrystalline Si layer 100 on the upper surface of the protruding regions and the upper port of the side wall is removed isotropically by the microwave etching so as to expose the surface of the SiO<sub>2</sub> layer. After having removed the photoresist films 11 and 12, boron ions are implanted in the polycrystalline Si layer 100 left in the recessed portion of the Si substrate under a condition that the acceleration energy is 30 keV and the dose is  $1 \times 10^{16}$  cm<sup>-2</sup> and the SiO<sub>2</sub> layer on the polycrystalline si layer 100 and the SiO<sub>2</sub> layer 5 on the protruding portion are removed. Then the polycrystalline Si layer 100 is patterned and a base taking-out electrode 10 is formed. In this way a p+ conductivity type external base diffusion region 131 is formed by subjecting the whole to a heat treatment. Subsequently, after having formed a protecting insulating layer 14 250 nm thick by oxidizing the base takingout electrode by the wet thermal oxidation, the Si<sub>3</sub>N<sub>4</sub> layer 4 is removed and a p - conductivity type intrinsic

base diffusion layer 13 is formed by boron ion implantation through the SiO<sub>2</sub> layer 3 (implantation energy: 10 keV and dose:  $1 \times 10^{14}$  cm<sup>-2</sup>) and an activation thermal treatment thereof. Then a vertical tunnel is formed on the Si substrate 1 by removal of the SiO<sub>2</sub> layer 3 on the 5 region, where a collector taking-out electrode is to be formed, and by the RIE method. The depth of the vertical tunnel is 0.5  $\mu$ m, measured from the lower end of the isolating insulating layer 7, and about 1.4  $\mu$ m, measured from the principal surface.

Starting from the state indicated in FIG. 3, a lateral tunnel is formed, as indicated in FIG. 4, by a treatment about 120 minutes long using an etching solution, in which 80% hydrated hydrazine (N<sub>2</sub>H<sub>4</sub>), isopropanol and a solution containing appropriate surface active 15 agent at a concentration of about 1% are mixed with a ratio of 200:20:1, at a temperature of 60° C. The etching region is an active region enclosed by the deep trench insulating layer 8 and the lateral tunnel is about 5  $\mu m$ deep in the direction of the axis <011>. In the etching 20 stated above no proceeding of the etching is found at all in the direction of the axis <111>, which is perpendicular to the principal surface. The height of the lateral tunnel is  $0.5 \mu m$  and a bottom and a ceiling surface, which are parallel to the principal surface, are formed. 25 Further the etching stated above is not necessarily effected by using a hydrazine aqueous solution, but it may be effected by using a potassium hydroxide (KOH) aqueous solution or on the basis of the anisotropic gaseous phase dry etching method, etc. At the formation of 30 the lateral tunnel the regions covered by the SiO<sub>2</sub> layers 3, 7, 8 and 14 are not etched at all. After the formation of the lateral tunnel a polycrystalline Si layer 1 µm thick doped with phosphor (P) is deposited so as to fill the lateral and vertical tunnels and patterned to form a 35 layer 21. Further a polycrystalline (or amorphous) Si collector taking-out electrode 15.

Next, as indicated in FIG. 5, a thin SiO<sub>2</sub> layer (not shown in the figure) is formed on the collector takingout electrode by thermal oxidation and at the same time an n + conductivity type collector diffusion layer 151 is 40 formed by solid phase diffusion from the buried region. Then, after having selectively removed the SiO<sub>2</sub> layer 3 on the region, where the emitter is to be formed, a polycrystalline Si layer 16 0.25 µm thick is deposited over the whole surface by the CVD method and an n + 45conductivity type emitter diffusion layer 17 is formed by implantation of As ions under a condition that the acceleration energy is 80 keV and the dose is  $2 \times 10^{16}$ cm<sup>-2</sup> and a succeeding heat treatment. Thereafter an emitter taking-out electrode 16 is formed by patterning 50 the polycrystalline Si layer 3 and an SiO<sub>2</sub> layer is deposited over the whole surface by the CVD method, which layer serves as a surface passivation layer 141, in which contact holes are formed at desired positions. Finally a metal film, whose principal component is Al, is depos- 55 ited by evaporation and patterned according to a desired circuit construction so as to form electrodes and wiring, including a base electrode 18, an emitter electrode 19 and a collector electrode.

Through the fabrication steps described above a ver- 60 tical type npn transistor, which is the semiconductor device, object of this embodiment, is fabricated. According to this invention no step for epitaxial growth is necessary and no problem of positional deviations from the collector buried layer is produced. Further a large 65 number of products can be treated simultaneously and therefore they can be fabricated at a low cost. In addition, since the collector buried diffusion layer can be

formed after the step for the formation of the base diffusion layer 13, the high temperature heat treatment step, to which the collector buried diffusion layer 151 is subjected, is shortened and it is possible to obtain a collector buried diffusion layer 151 keeping an extremely abrupt impurity distribution, for which a redistributed diffusion width is as small as 0.1 µm. Furthermore, since the polycrystalline buried Si layer 7 can be doped with P as impurity, even if it is constructed so as 10 to be as thin as  $0.5 \mu m$ , it can have a sheet resistance of 30  $\Omega/\square$  which is equal to that obtained for a conventional buried diffusion layer 152 doped with Sb and 1.5 µm thick. Thus it is possible to reduce remarkable the collector resistance. The buried polycrystalline Si layer described above acts as the collector taking-out electrode. Therefore, since the area of region necessary for the prior art collector connecting diffusion layer 153 can be significantly reduced and the freedom for the collector wiring is increased, decrease in the element occupation area and increase in the degree of integration are made possible.

FIGS. 6 to 9 are cross-sectional views illustrating another embodiment of this invention in the order of the fabrication steps.

At first, as indicated in FIG. 6, after having etched the Si substrate 1 in the vertical direction at a depth of  $0.5 \mu m$  by the RIE method using the three-layered insulating layer 4 to 5 as a mask in EMBODIMENT 1, a trench 0.8  $\mu$ m wide and 2.5  $\mu$ m deep is formed in the Si substrate 1 so as to enclose the active region. Then an SiO<sub>2</sub> layer 15 nm thick formed by the thermal oxidation method and an Si<sub>3</sub>N<sub>4</sub> layer 30 nm thick formed by the CVD method are superposed on each other on the exposed Si substrate 1 to form a two-layered insulating layer 711 0.15 µm thick is deposited thereon and selectively left in the deep trench. This selective leaving is effected by etching the polycrystalline Si layer 711 by microwave etching after having applied a photoresist resin film 142 so as to flatten the surface and left the photoresist resin film 142 only in the free space of the deep trench by sputter etching.

Starting from the state indicated in FIG. 6, after having removed the photoresist resin film 142, the polycrystalline Si layer 711 is transformed into an SiO<sub>2</sub> layer 0.3 µm thick by the wet thermal oxidation to form an element isolating deep trench insulating layer. Thereafter, as indicated in FIG. 7, a polycrystalline Si layer 9 is again deposited at a thickness of 0.2  $\mu m$  so as to fill the free space in the deep trench. Then the polycrystalline Si layer 0.2 µm thick on the upper portion of the protruding portion and the side wall of the Si substrate is selectively removed by the flattening technique described above. After that, the polycrystalline Si layer 0.2 µm thick stated above is patterned into a desired shape and transformed completely into an SiO2 layer by the wet thermal oxidation except for the deep trench filling portion to form an isolating insulating layer 71 0.4 µm thick. At this time the Si substrate 1 is covered by a two-layered insulating layer 21 and therefore it is not oxidized in the wet thermal oxidation step.

Next, as indicated in FIG. 8, after having selectively removed the two-layered insulating layer 21 in the region, where the base is to be taken-out, a base taking-out electrode 10, a p+ conductivity type external base region 131, a protecting insulating layer 14 and an intrinsic base region 13 are formed one after another according to the same process as that described in EM-

BODIMENT 1. Then, after having removed the two-layered insulating layer in the region, where the collector is to be taken-out, the exposed Si substrate is etched at a depth of 1  $\mu$ m by the microwave etching method and then a lateral tunnel reaching the deep trench insulating layer is formed by using an N<sub>2</sub>H<sub>4</sub> mixed solution according to the process described in EMBODIMENT 1. Thereafter the SiO<sub>2</sub> layer 3 on the region, where the emitter is to be formed, is removed.

Finally, as indicated in FIG. 9, a polycrystalline (or 10 amorphous) Si layer doped with As at a high concentration is deposited so as to fill the vertical and the lateral tunnels and an n+ conductivity type buried collector diffusion layer 151 and an n+ conductivity type emitter diffusion layer 17 are formed by a succeeding activation 15 thermal treatment. Then the polycrystalline Si layer used as a solid phase diffusion source for the n+ conductivity type diffusion layer is patterned to form a collector taking-out electrode 150 and an emitter taking-out electrode 161. Further, a surface passivation 20 layer 141, a base electrode 18, an emitter electrode 19 and a collector electrode 20 are formed according to the process described in EMBODIMENT 1.

Through the fabrication steps described above a vertical type npn transistor, object of this embodiment, is 25 fabricated. According to this embodiment, besides the effects described in EMBODIMENT 1, another effect can be obtained that it is possible to realize an abrupt impurity concentration distribution and to reduce further the thickness of the n - conductivity type diffusion 30 layer 2, because the emitter diffusion layer 17 and the collector buried diffusion layer 151 can be simultaneously formed. Consequently an operation speed, which is still higher than that obtained by the vertical npn transistor based on EMBODIMENT 1, can be 35 obtained. Further according to this embodiment, since the emitter taking-out electrode 161 and the collector taking-out electrode 150 can be formed in a same step, this embodiment has an effect to decrease the number of fabrication steps. Furthermore, according to this inven- 40 tion, since the microwave etching method is used for the formation of the vertical tunnel in the collector taking-out region, it is possible to form the vertical tunnel matched with the isolating insulating layer 71 and the deep trench insulating layer and to reduce fur- 45 ther the element occupation area with respect to that required in EMBODIMENT 1. Further, although vertical type npn transistors have been indicated as examples in EMBODIMENT 1 and this EMBODIMENT, it is a matter of course that this invention can be applied 50 also to a lateral type pnp transistor, in which the emitter diffusion layer 17, the emitter taking-out electrode 161, the emitter electrode 19, and the intrinsic base region 13 are not constructed, but external base regions 131 are disposed, opposite to their position, they being used as 55 the p+ emitter and the p+ collector, the n+ conductivity type buried diffusion layer 151 acting as the base and 150 as the base taking-out electrode.

#### **EMBODIMENT 3**

FIGS. 10 to 12 are cross-sectional views of still another embodiment of this invention in the order of the fabrication steps. Instead of the n— conductivity type diffusion layer 2 in EMBODIMENT 2 described above, an n— conductivity type diffusion layer 200 is formed in 65 a region, where a Schottky barrier is to be formed, under a different ion implantation condition. The ion implantation is effected under a condition that the accel-

eration energy is 160 keV and the dose is  $2 \times 10^{13}$  cm<sup>-2</sup>. After that, the Si substrate 1 is etched in the collector taking-out region at a depth of 0.3 µm according to the process described in EMBODIMENT 2. Subsequently by depositing an Si<sub>3</sub>N<sub>4</sub> layer 22 250 nm thick over the tunnel surface and etching it in the vertical direction by the RIE method, the Si<sub>3</sub>N<sub>4</sub> layer 22 is selectively left only on the side wall of the protruding portion. The Si<sub>3</sub>N<sub>4</sub> layer 22 selectively left on the side wall may be replaced by an SiO<sub>2</sub> layer having a same thickness. After that, the exposed Si substrate 1 is etched again by the RIE method at a depth of 0.3  $\mu m$  and then a lateral tunnel reaching the deep trench insulating layer is formed according to the process described in EM-BODIMENT 2. Thereafter SiO<sub>2</sub> layers 23 and 24 of 0.2 µm thick are formed at the bottom portion and the ceiling surface of the lateral tunnel by the high temperature wet thermal oxidation method (4 at., 1000° C,). Then the lateral tunnel is filled with a polycrystalline Si layer 152 doped with P at a high concentration. The polycrystalline Si layer 152 in the vertical tunnel is selectively removed by the microwave etching method (FIG. 10).

Starting from the state indicated in FIG. 10, after having formed a thin SiO<sub>2</sub> layer (not shown in the figure) on the surface of the exposed polycrystalline Si layer 152 by the thermal oxidation method, the Si<sub>3</sub>N<sub>4</sub> layer 22 is selectively removed so as to expose the side surface of the Si substrate. Subsequently, as indicated in FIG. 11, a lateral tunnel is formed by using again an N<sub>2</sub>H<sub>4</sub> solution to expose the SiO<sub>2</sub> layer 24. The lateral and the vertical tunnels are filled by removing the SiO<sub>2</sub> layer 24 and depositing a polycrystalline Si layer 150 doped with As at a high concentration. Next the poly crystalline Si layer on the principal surface is removed by the microwave etching to flatten the surface and the polycrystalline Si layer 150 exposed at the surface of the vertical tunnel is subjected to wet thermal oxidation to form a thick SiO<sub>2</sub> layer 25. Thereafter the Si<sub>3</sub>N<sub>4</sub> layer 4 is removed and the SiO<sub>2</sub> layer 3 on the regions, where the Schottky barrier diode and the emitter are to be formed, is selectively removed.

Starting from the state indicated in FIG. 11, after having formed an n+ conductivity type emitter diffusion layer 17, an emitter taking-out electrode 16 and a surface passivation layer 141, throughholes are formed in desired positions of the surface passivation layer 141 and a Pt layer 25 nm thick is deposited thereon by evaporation. Then the Pt layer is heated in an oxygen atmosphere to a temperature of 475° C. to form a platinum silicide (designated as PtSi) layer 26 by reactions on the surface of the n — conductivity type diffusion layer 200 and the n+ conductivity type emitter taking-out electrode 16. Pt doesn't react on SiO<sub>2</sub> under the thermal treatment conditions described above. After the formation of the PtSi layer 26, when Pt which has not reacted is removed by using acqua regina, the PtSi layer 27 is selectively left only on the Si substrate 200 and the 60 polycrystalline Si layer (emitter taking-out electrode) 16. After the formation of the PtSi layer 27 a two-layered metal film consisting of a TiN layer 0.1 µm thick formed by the sputtering method and a metal evaporation layer 0.8 µm thick, whose principal component is Al, is deposited thereon and electrodes and wiring including upper side word lines 27, digit lines 28 and lower side word lines 29 are formed according to a desired circuit construction.

Through the fabrication steps described above a bipolar memory, which is the semiconductor device of this embodiment, is fabricated. The cross-sectional view indicated in FIG. 12 corresponds to the cross-section of the element component enclosed by a broken line 30 in 5 the bipolar memory cell indicated in FIG. 13, in which active elements, which are a Schottky barrier type diode (designated as SBD), an npn vertical type transistor for reading-out (designated a Ir) and an npn vertical type transistor for storing (designated as Ist), an upper 10 word line 27, a digit line (designated as D) 28 and a lower word line 29 are indicated. The buried collector semiconductor layer 150 is connected with the base taking-out electrodes of a pair of transistors constituting a flip-flop circuit in another region. Similarly the base 15 taking-out electrodes 10 are connected with the collector taking-out electrode of the pair of transistors constituting the flip-flop circuit.

On the basis of this embodiment, besides the effects concerning the single elements in EMBODIMENT 2 20 described above, an effect can be obtained that the problem of the interference between memory cells and misoperation due to  $\alpha$ -ray soft errors are solved completely by disposing the buried insulating layer (SiO<sub>2</sub>) layer) 23. Consequently, since constituent elements 25 indispensable for a measure against  $\alpha$ -ray soft errors in conventional memory cells, such as capacitive elements connected between memory storage nodes and the upper side power source lines become unnecessary, etc., it becomes possible to realize superfine memory cells 30 and a super high degree of integration. Further, although in this embodiment an example, in which a polycrystalline Si layer is used as the buried collector takingout electrode 150, has been explained, it may be also a two-layered film consisting of a polycrystalline Si layer 35 and a metal layer or a metal layer further or another semiconductor layer having a different band gap. Furthermore the SiO<sub>2</sub> layer 23 is not necessarily restricted to an SiO<sub>2</sub> layer formed by thermal oxidation, but it may be an SiO<sub>2</sub> layer formed by the CVD method, the 40 plasma deposition method, etc. or an insulating layer made of another material such as phosphosilicate glass, borosilicate glass, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, Ti<sub>2</sub>O<sub>5</sub>, Si<sub>3</sub>N<sub>4</sub>, etc.

As it is clear from the explanation in EMBODI-MENTS 1, 2 and 3 described above, according to this 45 invention, no epitaxial step is necessary and all the problems of positional deviations from the collector buried layer, treatment of a small number of product steps, rising of the collector impurity and a high collector resistance are solved. Thus it is possible to obtain a 50 superfine transistor having a collector with an abrupt impurity distribution and a low resistance (which is one third as low as that obtained by the prior art technique) at a low cost. Furthermore, according to this invention, since the collector connection can be constructed by 55 using a polycrystalline semiconductor layer, effects to reduce the collector occupation area and to increase the freedom in the collector wiring can be obtained.

In addition, according to this invention, since it is possible to dispose an insulating layer at the lower part 60 of the buried collector region, effects can be obtained that the constituent elements of the memory cells are more completely isolated from the semiconductor substrate and that the problems of the interference between adjacent cells and the  $\alpha$ -ray soft errors are completely 65 solved. Consequently addition of extra capacitive elements to the memory cells becomes unnecessary and an effect to obtain hyperfine memory cells is obtained.

Now an embodiment of this invention concerning a DRAM consisting of a transistor and a capacitive element will be explained.

#### **EMBODIMENT 4**

FIGS. 14A to 18B are cross-sectional views of a semiconductor memory device, which is a fourth embodiment of this invention, in the order of the fabrication steps, in which the figures, whose number ends by A and the figures, whose number ends by B refer to cross-sectional views, which are perpendicular to each other, the former representing a (211) plane and the latter a (011) plane.

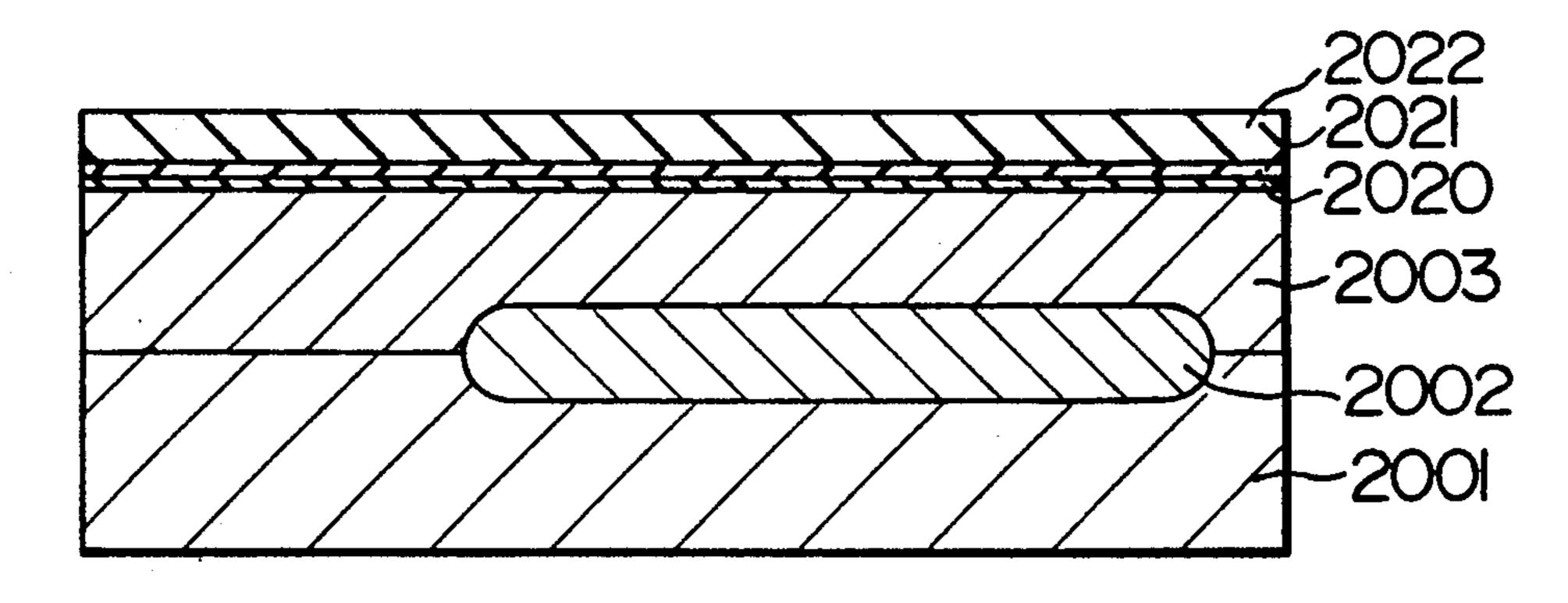

In FIGS. 14A and 14B an n+ conductivity type buried layer 1002 having a depth of 1.5  $\mu$ m and an impurity concentration of  $3\times10^{19}$  cm<sup>-2</sup> is selectively formed by the well-known thermal diffusion method in the surface portion of a p conductivity type silicon (Si) substrate 1 having a resistivity of 10  $\Omega$ cm, whose principal surface is (111). Then an epitaxial layer 1003 0.98  $\mu$ m thick is grown over the whole surface. Thereafter SiO<sub>2</sub> layer 50 nm thick formed by thermal oxidation, an Si<sub>3</sub>N<sub>4</sub> layer 120 nm thick formed by the chemical vapor deposition (designated as CVD) method and a deposited SiO<sub>2</sub> layer 1  $\mu$ m thick (none of them is indicated in the figure) are deposited one after another on the surface of the epitaxial layer 1003 and holes are formed at desired positions.

The epitaxial layer 1003 and the n+ conductivity type buried layer 1002 at the opened positions are processed by reactive ion etching using the two-layered insulating layer as an etching mask to form tunnels (depth 3  $\mu$ m, area of each tunnel  $1 \times 1 \mu m^2$ ) reaching the Si substrate 1. Thereafter an SiO<sub>2</sub> layer 1004 0.3  $\mu$ m thick is formed at the side wall and the bottom of each of the tunnels by the thermal oxidation method, which tunnel is filled with a polycrystalline (or amorphous) si layer 1005. At the filling stated above, although the polycrystalline Si layer is formed also on the two-layered insulating layer described above, the polycrystalline Si layer on the two-layered insulating layer is selectively removed by reactive ion etching so as to leave the polycrystalline Si layer 5 only in the tunnels.

From this state the deposited SiO<sub>2</sub> layer in the two-layered insulating layer is removed by using the polycrystalline Si layer 1004 as an etching mask to expose the Si<sub>3</sub>N<sub>4</sub> layer and a thermal oxidation layer (0.4 µm thick) is formed selectively on the exposed polycrystalline Si layer 5 by using the Si<sub>3</sub>N<sub>4</sub> layer as an oxidation mask. From this state the Si<sub>3</sub>N<sub>4</sub> layer and the thin SiO<sub>2</sub> layer constituting a two-layered insulating layer are selectively removed to expos the surface of the epitaxial layer 1003 (FIGS. 14A and 14B). At this time the Si opening portion constituting the SiO<sub>2</sub> layer 1004 and the polycrystalline Si layer 1005 may be stripe-shaped.

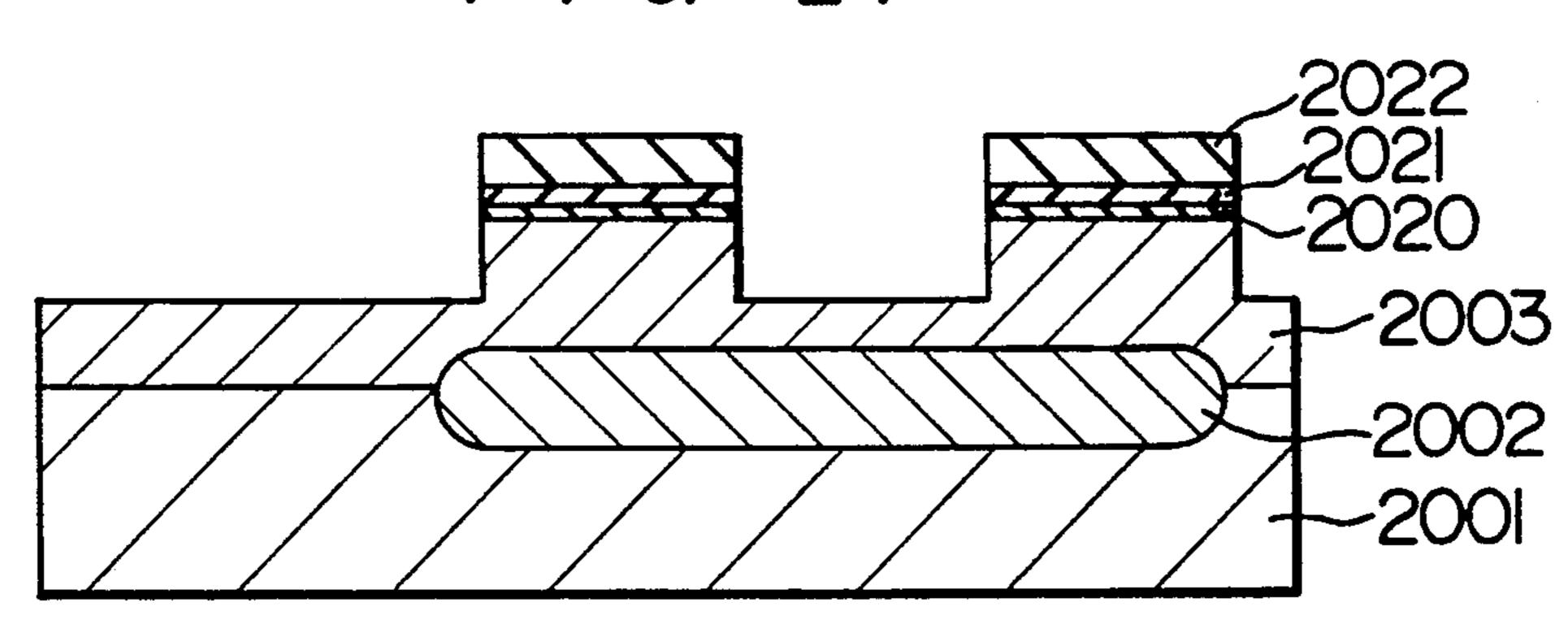

From the sate indicated in FIGS. 14A and 14B, after having formed again a three-layered insulating layer consisting of an SiO<sub>2</sub> layer 1003 50 nm thick formed by thermal oxidation, a deposited Si<sub>3</sub>N<sub>4</sub> layer 1007 120 nm thick and a deposited SiO<sub>2</sub> layer 1008 0.8 µm thick over the whole surface of the epitaxial layer 1003, a part of the three-layered insulating layer 1006 to 1008 is patterned so as to be superposed on the SiO<sub>2</sub> layer 1004 at the Si opening portion. What the three-layered insulating layer 1006 to 1008 constructed by the patterning is to the Si opening SiO<sub>2</sub> layer 1004, the bridge board is to the bridge pier. Then the epitaxial layer is etched in the vertical direction at a depth of 0.3 µm by using the

patterned three-layered insulating layer 1006 to 1008 as a mask. The patterning of the three-layered insulating layer 1006 to 1008 and the etching of the epitaxial layer 1003 are effected by the reactive ion etching method.

After the vertical etching of the epitaxial layer 1003 5 an SiO<sub>2</sub> layer 30 nm thick by the thermal oxidation is formed over the whole surface of the exposed epitaxial layer 3 and then an Si<sub>3</sub>N<sub>4</sub> layer 1009 120 nm thick is deposited over the whole surface. Thereafter the deposited Si<sub>3</sub>N<sub>4</sub> layer is etched only in the direction perpendicular to the principal surface of the Si substrate by the reactive ion etching method so as to leave the deposited Si<sub>3</sub>N<sub>4</sub> layer 1009 only on the side wall of the three-layered insulating layer 1006 to 1008 and on the side wall of the epitaxial layer 1003 (FIGS. 15A and 15B).

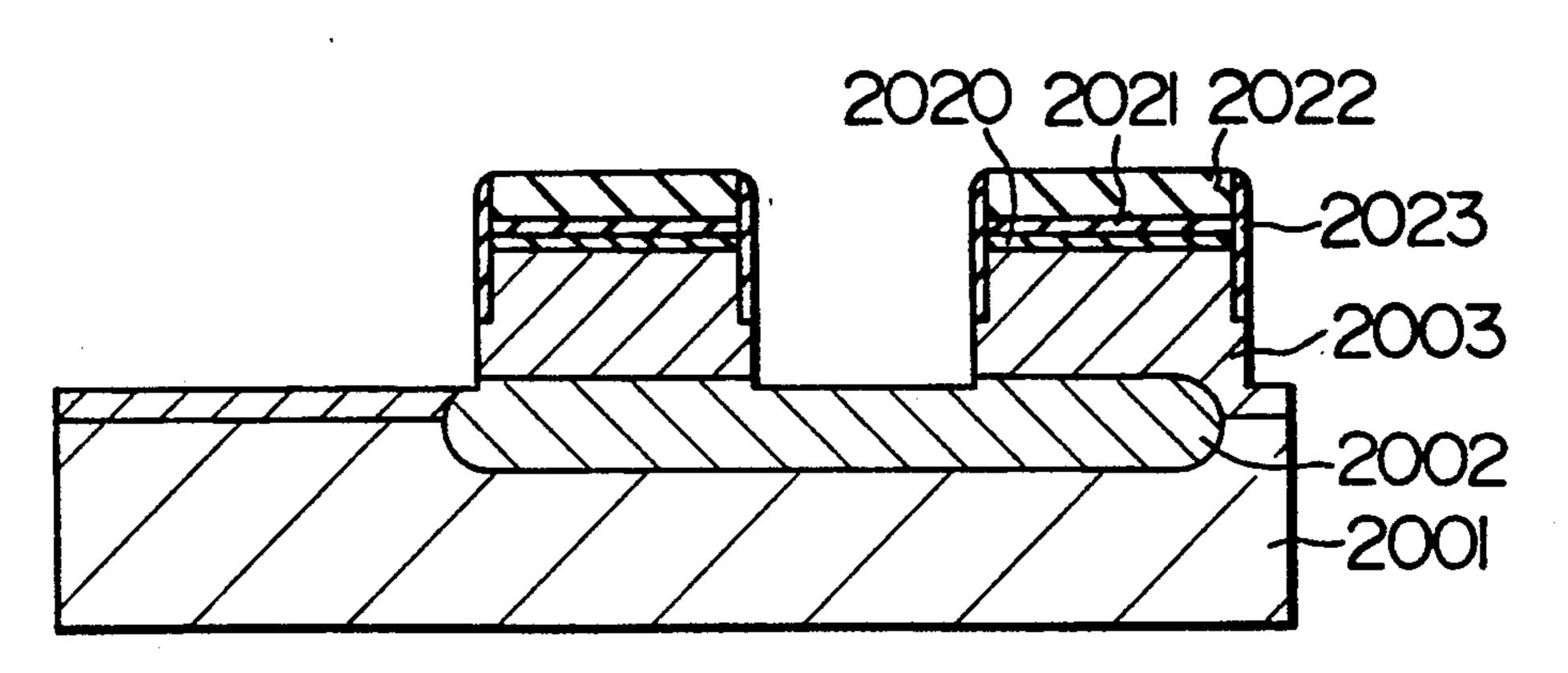

From the state indicated in FIGS. 15A and 15B the epitaxial layer 1003 and the n+ conductivity type buried diffusion layer 1002 are etched in the vertical direction by using the three-layered insulating layer 1006 to 1008 and the Si opening SiO<sub>2</sub> layer 1004 as an etching 20 mask. The depth of the etching is 2.2 µm measured from the surface of the epitaxial layer 1003. From this state, after having deposited an Si<sub>3</sub>N<sub>4</sub> layer 10 30 nm thick over the whole surface, etching is effected again on the surface of the epitaxial layer 1003 and in the vertical 25 direction so as to leave selectively the Si<sub>3</sub>N<sub>4</sub> layer only on the side surface of Si. Further vertical etching is effected again on the Si substrate 1001 at a depth of 0.3 µm (FIGS. 16A and 16B).

In the sate indicated in FIGS. 16A and 16B treatment 30 is effected in about 1 hour by using an etching solution, in which 80% hydrated hydrazine, isopropanol and a solution containing appropriate surface active agent at a concentration of about 1% are mixed with a ratio of 200:20:1 at a temperature of 60° C. Under the etching 35 conditions described above the Si etching speed in the direction of <110> is about 120 nm/min, while that of <111> is negligibly small. Further neither the SiO<sub>2</sub> layer 1004 nor the Si<sub>3</sub>N<sub>4</sub> layer 1010 are etched at all.

In FIGS. 16A and 16B, the cross-sectional view indicated in FIG. 16A represents a (211) plane and that indicated in FIG. 16B a (011) plane. The etching described above proceeds only in the direction parallel to the sheet in FIG. 16A and in the directions perpendicular to the sheet in FIG. 16B (directions of (011) and 45 (011) and it doesn't in the directions of (111) and (111), which are perpendicular to the surface of the epitaxial layer 1003. Consequently in FIG. 16B a structure can be realized, in which the Si singlecrystal region, which is the upper portion above the n+ conductivity type buried diffusion layer 1002, is isolated from the Si substrate 1001 in the state where it is supported by the SiO2 layer 1004 at the Si opening portion.

Furthermore it is not necessary that the etching is effected by using any hydrazine solution, but it may be 55 based e.g. on an anisotropic etching solution such as a hydroxide potassium (KOH) aqueous solution, the gaseous dry etching method, etc.

After having isolated the Si singlecrystal region from the substrate by the anisotropic etching in the direction 60 parallel to the Si (111) plane using the hydrazine solution, the Si<sub>3</sub>N<sub>4</sub> layer 1010 is removed by using a hot phosphoric acid (heated at 160° C.). The removal described above may be effected by the microwave dry etching method.

Next thermal oxidation  $SiO_2$  layers 1011, 1110, 1112 and 1111 are formed 15 nm thick on the side wall and the bottom portion of the n+ conductivity type buried

diffusion layer 2 thus exposed. Then a polycrystalline (or amorphous) Si layer 1012 doped with phosphor is deposited over the whole surface by the gaseous phase chemical reaction using disilane or monosilane, to which phosphine (PH<sub>3</sub>) is added. The gaseous phase chemical reaction stated above may be effected by using monosilane (SiH<sub>4</sub>), etc. and the doping with phosphor may be based on the thermal diffusion method.

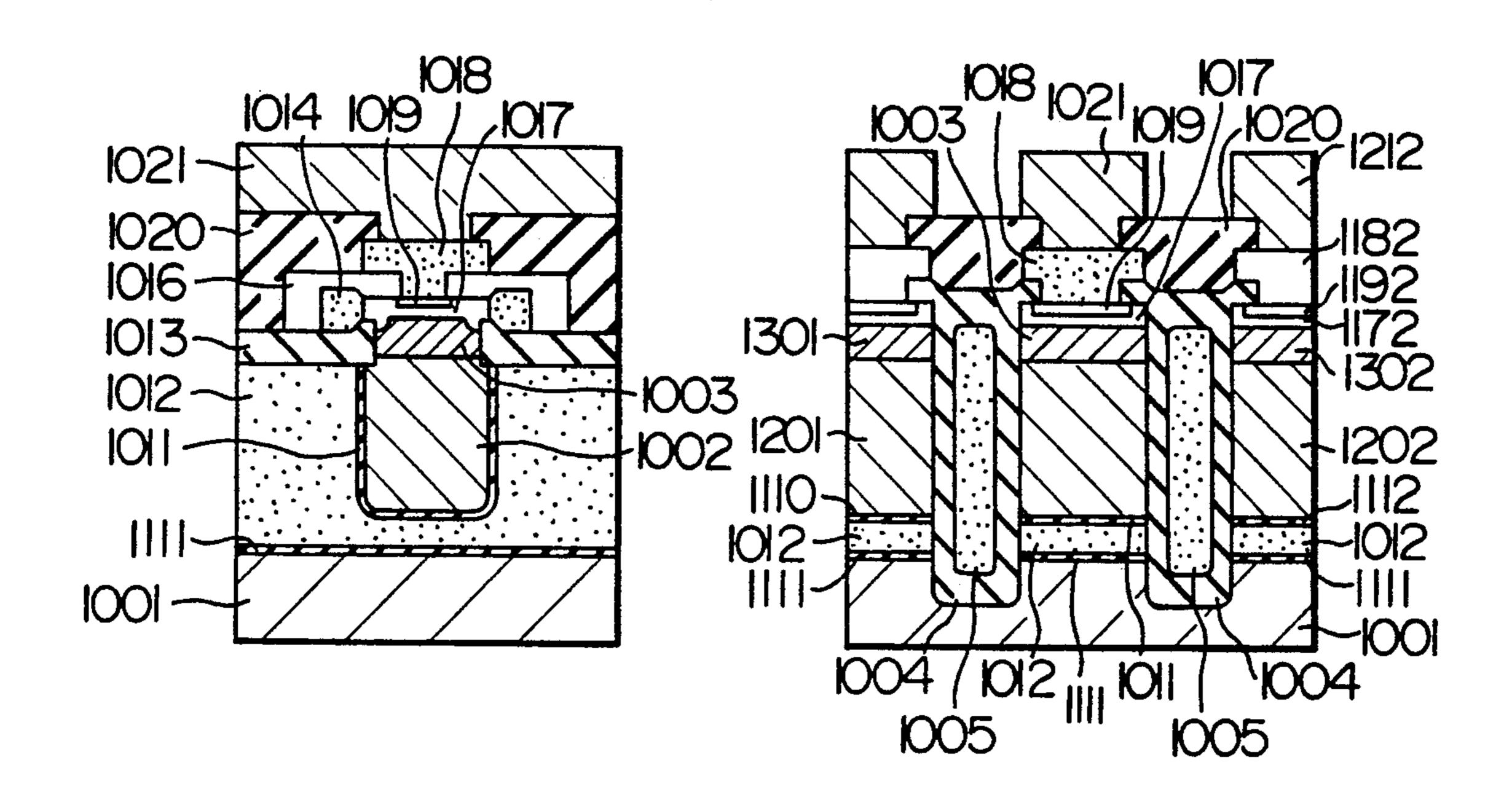

After the deposition of the polycrystalline Si layer 1012, after having coating a photoresist film (not shown in the figure) to the whole surface, the photoresist film stated above is subjected to a whole surface dry etching. The polycrystalline Si layer 1012 or the three-layered insulating layer 1006 to 1008 constituting the protruding 15 portion is exposed and removed at first by microwave dry etching and then the remaining photoresist film is removed. Subsequently the polycrystal line Si layer 1012 is etched by the microwave dry etching to form a plate electrode. The amount of the etching stated above is controlled under a condition that a polycrystalline Si layer on a dummy substrate having same difference in level as that indicated in FIGS. 15A and 15B is removed completely. After the etching stated above the surface of the exposed polycrystalline Si layer 1012 is subjected to the wet thermal oxidation to form a first isolating insulating layer 13, which is an SiO<sub>2</sub> layer 0.4 µm thick (FIGS. 17A and 17B).

From the state indicated in FIGS. 17A and 17B the Si<sub>3</sub>N<sub>4</sub> layer 1009 is removed by using phosphoric acid and a polycrystalline (or amorphous) Si layer 1014 is again deposited thereon. After having implanted boron (B) ions under a condition that the dose is  $1 \times 10^{16}$  cm<sup>-2</sup> and the acceleration energy is 30 keV, an activation heat treatment is effected to form a p+ conductivity type graft base. Then the polycrystalline Si layer 1014 on the first isolating insulating layer 1013 is patterned according to a desired construction to form word lines 1014. Although the patterning has been effected by using reactive ion etching, the polycrystalline Si layer 1014 is also left on the side wall portion of the three layered insulating layer 1006 to 1008 regardless of the pattern stated above and a state can be obtained, where the patterned polycrystalline Si layer is connected with the polycrystalline Si layer on the side wall. At the patterning described above, the polycrystalline Si layer 1014 is left on the three-layered insulating layer 1006 to 1008. After the patterning described above a photoresist film is formed and left on a region, where a recessed portion exists over 1  $\mu m$ , and a photoresist film 1  $\mu m$ thick is applied to the remaining recessed portion so as to flatten the surface. From this state each of the photoresist films (not shown in the figure) is uniformly dryetched so as to expose the surface of the polycrystalline si layer 1014 on the three-layered insulating layer 1006 to 1007, which is selectively removed by the microwave dry etching. Subsequently, after having removed the SiO<sub>2</sub> layer 1008 in the three-layered insulating layer by using a fluoric acid aqueous solution, the photoresist film is removed.

From this state an inter layer insulating layer 1020 0.3 µm thick is formed by wet-oxidizied the polycrystalline Si layer 1014 used as word line. At this time the Si<sub>3</sub>N<sub>4</sub> layer 1007 acts as a mask preventing the oxidation stated above (FIGS. 18A and 18B).

From the state indicated in FIGS. 18A and 18B, after having removed the exposed Si<sub>3</sub>N<sub>4</sub> layer 1007 by using a hot phosphoric acid solution, boron ions are implanted under a condition that the acceleration energy is 10 keV

and the dose is  $1 \times 10^{14}$  cm<sup>-2</sup> and an intrinsic base region 1017 is formed by effecting an activation heat treatment at 900° C. Then, after having removed selectively the SiO<sub>2</sub> layer 1006 so that the principal surface of the Si substrate is exposed, a polycrystalline (or amor- 5 phous) Si layer 1018 is again deposited and arsenic ions are implanted under a condition that the acceleration energy is 80 keV and the dose is  $2 \times 10^{16}$  cm<sup>-2</sup>. Subsequently an emitter region 1019 is formed by effecting an activation heat treatment at 950° C. Thereafter, after 10 having patterned the polycrystalline Si layer 1018 stated above to obtain the emitter taking-out electrode, a surface passivation layer consisting of an SiO<sub>2</sub> layer  $0.4 \mu m$  thick, to which phosphor is added at 4 mol 100%, formed by gaseous phase chemical reaction and 15 an SiO<sub>4</sub> layer 0.2 µm thick formed by the application method is formed to flatten the surface. Thereafter, after having formed throughholes at desired places in the surface passivation layer 1020, a metal layer is deposited over the whole surface by evaporation to obtain 20 wiring and electrodes including bit lines 1021 by patterning (FIGS. 19A and 19B).

A semiconductor memory device of this embodiment is fabricated through the fabrication steps described above. In a memory cell based on this embodiment the 25 area of the emitter-base junction of the transistor constituting the memory cell is almost equal to that of the collector-base junction. Consequently the transistor has a feature that it presents approximately same characteristics, if it is driven with the emitter and the collector 30 replaced by each other. That is, the transistor of the memory cell based on this embodiment has bidirectional operation characteristics that it can be driven with exchanged roles of the emitter and the collector for data write-in and read-out, as indicated by the equivalent 35 circuit in FIG. 19C, contrarily to the fact that it is not desirable to apply a bipolar transistor having the prior art structure, in which the collector-base junction is larger than the emitter-base junction, to the memory cell, for which the bidirectional operation, as described 40 above, is required.

In the memory cell based on this embodiment and indicated in FIGS. 19A and 19B the polycrystalline Si layer 1012 acts as a plate electrode and constitutes a charge storing capacitor element together with the 45 SiO<sub>2</sub> layer 1011 and the n+ conductivity type buried diffusion layer 1002. Data (charge) write-in and readout to and from the capacitor element described above is effected by using the bipolar transistor having the bidirectional characteristics. Consequently the write-in 50 and read-out operation is performed not by the method, by which variations in potential to the bit line 1021 are controlled, but by the current sense method. That is, the write-in control is made possible by the current control method using a sense amplifier circuit.

The memory cell based on this embodiment is characterized in that the capacitor element is constructed in the neighborhood of the n+ conductivity type buried layer 1002. For this structure data holding characteristics, i.e. refresh characteristics are limited by leak curcent at the collector-base junction and since the junction stated above is an n- conductivity type epitaxial-p+ conductivity type graft base junction, leak current smaller than  $10^{-15}$  A/cell and excellent refresh characteristics longer than 0.5 sec can be obtained. On the 65 contrary, in a memory cell fabricated for comparison, in which the charge storing capacitor element is constructed in the emitter taking-out electrode portion on

the emitter region 19 and the n+ conductivity type buried region 1002 is used as a bit line, the leak current is as great as  $10^{-5}$  A/cell and it presents bad refresh characteristics. It is thought that this is due to the fact that the refresh characteristics are limited by the high impurity concentration junction characteristics of the p+ conductivity type graft base-n+ conductivity type emitter junction.

As described above the memory cell based on this embodiment can be realized by modifying slightly the fabrication steps for a usual bipolar transistor. Consequently it has characteristics that peripheral circuits can be constructed by using bipolar transistors and the operation speed can be increased by one order of magnitude with respect to a DRAM based on conventional MOS transistors. That is, for a 4K-bit DRAM fabricated according to this embodiment, characteristics that the access time is shorter than 10 ns are verified. Further, in the memory cell according to this embodiment, it is so constructed that the base taking-out electrode 1014 used as a word line is connected at the side wall of the base region 1017 and that the base taking-out electrode 1014 at the connection portion is formed by self-alignment with the singlecrystal region. That is, in a plan view (per unit cell), there is only one contact tunnel for the connection of the bit line 1021 with the emitter region 19 and increase in the charge storing capacitance can be achieved without increasing the cell area. The increase in the storing capacitance can be easily achieved by increasing the area of the side wall portion of the n+ conductivity type buried layer. Consequently the occupation area of the memory cell according to this embodiment can be reduced to 8  $\mu$ m<sup>2</sup>, which is about  $\frac{2}{3}$ time as large as that of a memory cell consisting of a usual MOS transistor and a capacitor element on the basis of a same design rule (line width and interval of 0.8) μm). In the comparison described above the storing capacitance is 30 fF for both the cases.

The memory cell according to this embodiment corresponds to a so-called cross-point memory; in which a transistor and a capacitor element are formed right below the intersection of a word line with a bit line. However the memory cell according to this embodiment differs essentially from the prior art cross point memory as indicated in FIGS. 43A and 43B.

That is, in a memory device according to this embodiment unit cells are so constructed that adjacent two of them are isolated from each other by a plate electrode consisting of a polycrystalline Si layer 1012 and that all of them are isolated completely from the Si substrate 1001. Consequently fatal disadvantages such as interference between different cells, soft error misoperation due to  $\alpha$ -ray irradiation, etc. can be essentially solved 55 and in fact they are not found at all, which disadvantages were serious for the prior art memory cell indicated in FIGS. 43A and 43B. In particular, concerning the interference between different cells, no misoperation are found in the case where the interval between two adjacent cells is 0.5 µm and thus it is verified that a still increased degree of integration can be realized, as the design rule advances.

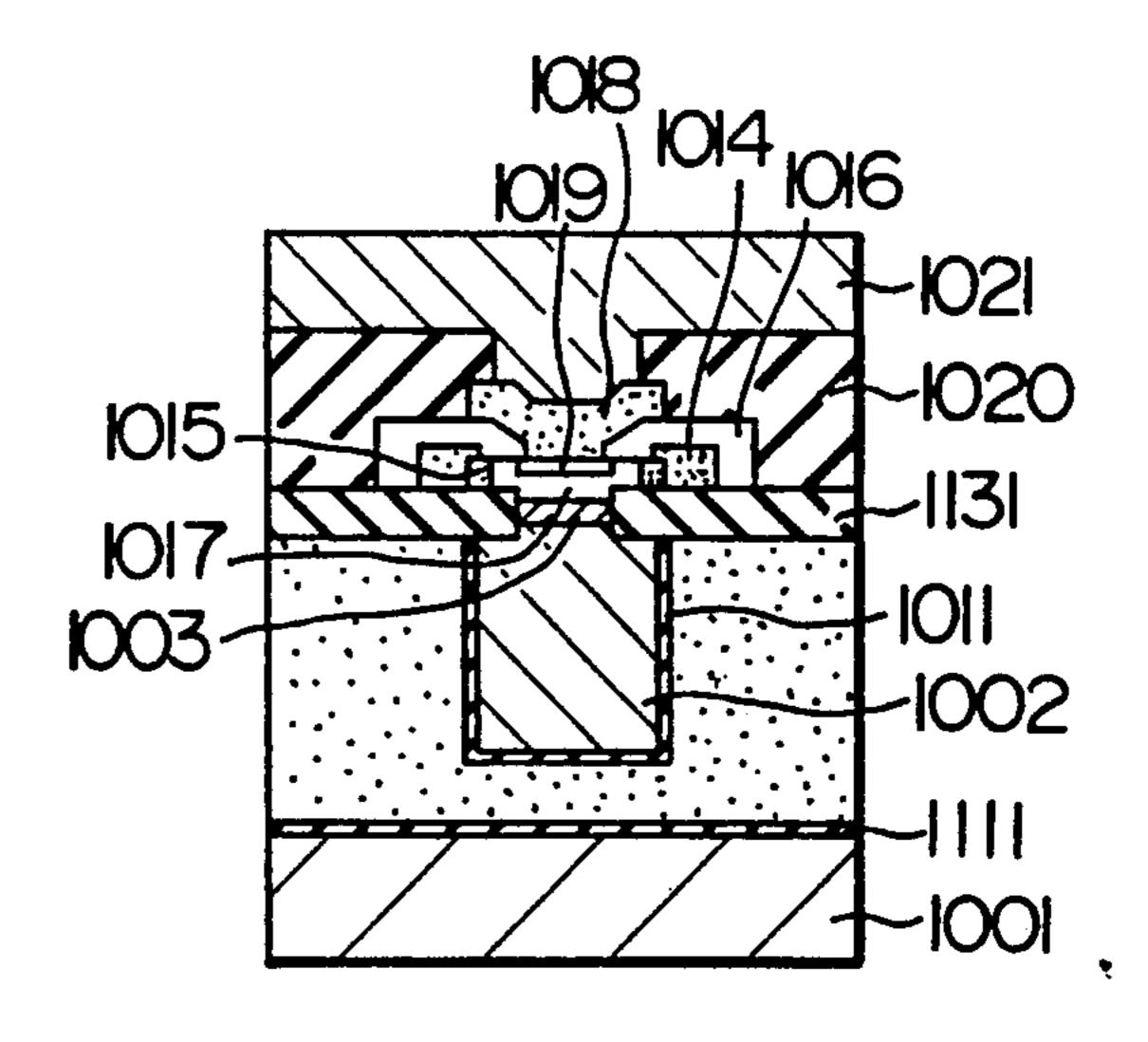

## EMBODIMENT 5

FIG. 20 is a cross-sectional view illustrating still another embodiment of this invention; FIG. 21 is a plan view there of; and FIGS. 22A, 22B, 22C and 22D are schemes showing an SiO<sub>2</sub> layer at an opening portion

supporting an active region in the fabrication process and the construction of unit cells.

In FIGS. 17A and 17B referred to for EMBODI-MENT 4 described above, after having formed an isolating insulating layer 1013 0.1 µm on the polycrystalline Si layer 1012 doped with impurity, the lower portion of the Si<sub>3</sub>N<sub>4</sub> layer 1010 at the side wall of the protruding portion of the Si substrate is selectively removed to expose the surface of the Si singlecrystal. The exposition stated above can be realized by forming further selectively a third Si<sub>3</sub>N<sub>4</sub> layer on the side wall of the Si<sub>3</sub>N<sub>4</sub> layer 1010 and removing it selectively as the construction of the Si<sub>3</sub>N<sub>4</sub> layers 1009 and 1010 in FIGS. 16A and 16B.

After having exposed the Si surface at a region adjacent to the isolating insulating layer 1013 disposed on the side wall of the protruding Si single-crystal, it is subjected to a treatment in 30 minutes in a hydrazine mixed solution stated previously held at  $50^{\circ}$  C. to etch it selectively at a depth of 0.3  $\mu$ m in the direction of 20 <110>. In this state a wet oxidation is effected to grow an oxide layer also on the selectively etched surface while increasing the thickness of the isolating insulating layer and another isolating insulating layer 1131 is formed so as to insulate the lower portion of the region, 25 where the graft base 1115 is to be formed, from the n+ conductivity type buried layer 1002. Thereafter, a semiconductor memory device is fabricated on the basis of EMBODIMENT 4 described previously.