### United States Patent [19]

#### Carey

[11] Patent Number:

5,039,628

[45] Date of Patent:

Aug. 13, 1991

#### [54] FLIP SUBSTRATE FOR CHIP MOUNT

[75] Inventor: David H. Carey, Austin, Tex.

[73] Assignee: Microelectronics & Computer

Technology Corporation, Austin, Tex.

[21] Appl. No.: 479,487

[22] Filed: Feb. 12, 1990

#### Related U.S. Application Data

[62] Division of Ser. No. 157,778, Feb. 19, 1988, Pat. No. 4,926,241.

| [51] | Int. Cl. <sup>5</sup> |         |

|------|-----------------------|---------|

|      |                       |         |

|      |                       | 437/209 |

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,082,394 | 4/1978 | Gedney et al         |

|-----------|--------|----------------------|

| 4,322,778 | 3/1982 | Barbour et al        |

| 4,652,974 | 3/1987 | Ryan.                |

| 4,665,468 | 5/1987 | Dohyn.               |

| 4,667,219 | 5/1987 | Lee et al            |

| 4,667,220 | 5/1987 | Lee et al            |

| 4,682,207 | 7/1987 | Akasaki et al.       |

| 4,685,033 | 8/1987 | Inoue.               |

| 4,749,120 | 6/1988 | Hatada 228/123       |

| 4,811,082 | 3/1989 | Jacobs et al         |

| 4,820,013 | 4/1989 | Fuse                 |

| 4,851,862 | 7/1989 | Newman et al 346/107 |

#### FOREIGN PATENT DOCUMENTS

981799 1/1976 Canada.

176245 2/1986 European Pat. Off. .

62-31146 2/1987 Japan.

62-165350 7/1987 Japan.

#### OTHER PUBLICATIONS

Blodgett, "Microelectronic Packaging", Scientific American, Jul. 1983, pp. 86-96. "TAB Technology Tackles High Density Interconnec-

"TAB Technology Tackles High Density Interconnections", Electronic Packaging & Production, Dec. 1984, pp. 34–39.

Primary Examiner—Olik Chaudhuri

Assistant Examiner—Andrew Griffis

Attorney, Agent, or Firm—Fulbright & Jaworski

#### [57] ABSTRACT

A substrate for attaching electrical devices having an interconnect wiring structure and a support for the interconnect, the support having a number of vias, or throughholes, extending therethrough and electrically connected to the interconnect. The substrate allows for attachment of the electrical devices on the side of the support opposite the interconnect at the vias, rather than on the interconnect itself. By so doing, the chips can be packed more density since the area between the chips normally reserved for engineering change pads, test pads and the like is not required, these functions being performed on the interconnect on the opposite side of the substrate.

#### 18 Claims, 3 Drawing Sheets

U.S. Patent

2

#### FLIP SUBSTRATE FOR CHIP MOUNT

This is a division of application Ser. No. 157,778, filed 02/19/88 now U.S. Pat. No. 4,926,241.

#### BACKGROUND OF THE INVENTION

The present invention relates to an improved substrate design for application in integrated circuitry. Specifically, the present invention relates to a substrate 10 design for attaching and interconnecting electrical and electronic devices, especially integrated circuit chips.

Current multi-chip circuitry design requires attachment to a substrate of electrical and electronic devices, oftentimes in the form of integrated circuit (I.C.) chips. 15 The substrate, which includes an interconnect wiring structure and a support therefor, electrically connects the chips. Presently known attachments involve the attachment of the chips directly to the interconnect, thus forming a multilayer structure of support-intercon- 20 nect-chips.

The interconnect surface serves a number of services in addition to chip attachment. For example, the interconnect surface provides for test pads for testing the attached circuitry and underlying wiring, for engineering change pads for rewiring the circuitry, for termination resistors, for repair to the circuitry, and so on. These different functions and their attendant structures compete with chip attachment structures for room on the interconnect. As a result, the chip packing density is 30 less than optimal because space must be left between the chips for these other various structures. As more and more structure is required on the interconnect surface, the chip density declines. Optimally, the chip density should approach 100% in a planar multi-chip module. 35

Accordingly, there exists a need for a substrate structure which is capable of supporting the many structures and functions required of such substrates, while optimizing chip density.

#### SUMMARY OF THE INVENTION

It is therefore an object of the present invention to provide a substrate for attaching electrical and electronic devices which provides high chip density.

Another object of the present invention is to provide 45 a substrate design having high chip density, while at the same time providing surface area for the related functions of testing, repairing, changing, and the like.

Yet another object of the invention is to provide a substrate which achieves the high chip density proper- 50 ties mentioned above and which further provides for discretionary wiring interconnect.

Still yet another object of the invention is to provide. a substrate which uses the more rugged support surface of the substrate for device attachment so that the integ- 55 rity of the delicate interconnect is not jeopardized by soldering and bonding.

It is also an object of the present invention to provide a method for attaching electrical devices to a substrate which optimizes chip density.

Thus, there is provided in accordance with one aspect of the present invention, a substrate for attaching electrical and electronic devices comprising a wiring interconnect and a support structure for supporting the interconnect which includes means on one side thereof 65 for attaching to the interconnect, means on the other side thereof for attaching to electrical and electronic devices, and a plurality of vias extending therethrough

and electrically connecting the devices to the interconnect. The vias are preferably arranged in a grid design or in alignment with outer lead bondsites of a chip having Peripheral bonding and can be electrically connected to the integrated circuit chip. Additionally, the vias can be filled completely with a conductive material or simply can be coated along their walls with a conductive material.

In accordance with another aspect of the present invention, there is provided a method for attaching an electrical device to a substrate which comprises the step of attaching the device to the substrate at at least one via extending through the substrate, wherein the via is electrically connected to an interconnect structure on the opposite side of the substrate.

The present invention provides for "brickwalling" of the attached electrical devices, primarily I.C. chips. "Brickwalling" refers to that condition in which the chips are placed on the substrate very near one another, much like the positioning of brick in a brickwall. In so doing, the density on the chips per unit area of substrate is increased, approaching 100%. The density measurement here refers to the density as measured in the surface plane of the support. Further, the thin-film interconnect surface is freed for testing, engineering changes, terminations, module input/output ("I/O") and decoupling.

Another advantage of the present substrate is that chip attachment occurs on the support surface and not on the thin-film interconnect. The support provides a more robust, planar surface reducing concerns for interconnect damage during bonding.

Still another advantage of the present substrate is that the vias can provide for a self-alignment between the chip and the substrate.

Also, if a silicon support is used for the substrate, a better thermal coefficient of expansion match exists between the chip and substrate. Accordingly, large area controlled collapse chip connection (C4) can be considered.

Other objects, features and advantages of the present invention will be apparent from a review of the detailed description of preferred embodiments which follows, when considered together with the drawings, a brief description of which follows.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In the drawings:

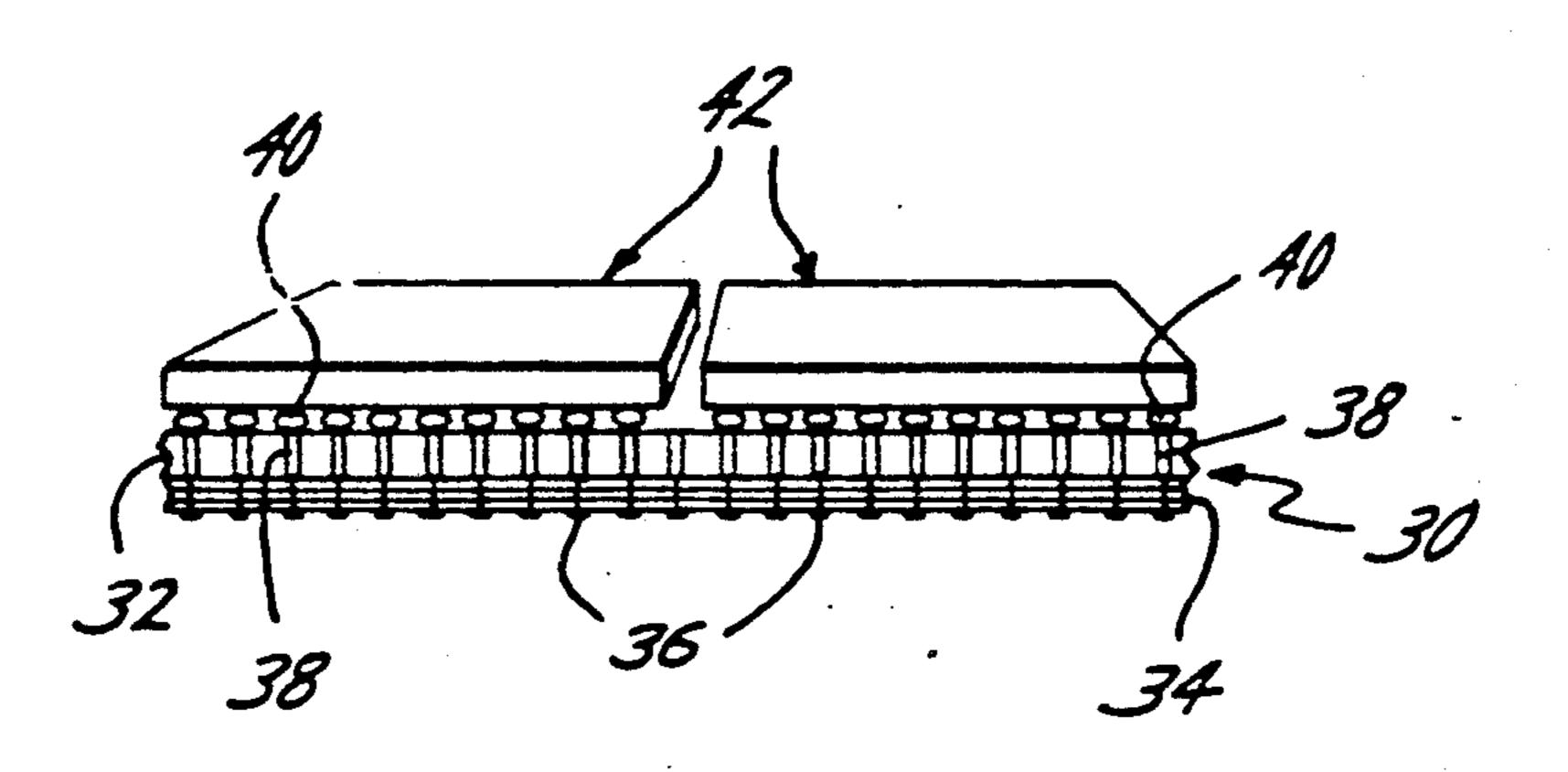

FIG. 1 is a cross-sectional view of a prior art substrate.

FIG. 2 is a plan view of the substrate of FIG. 1.

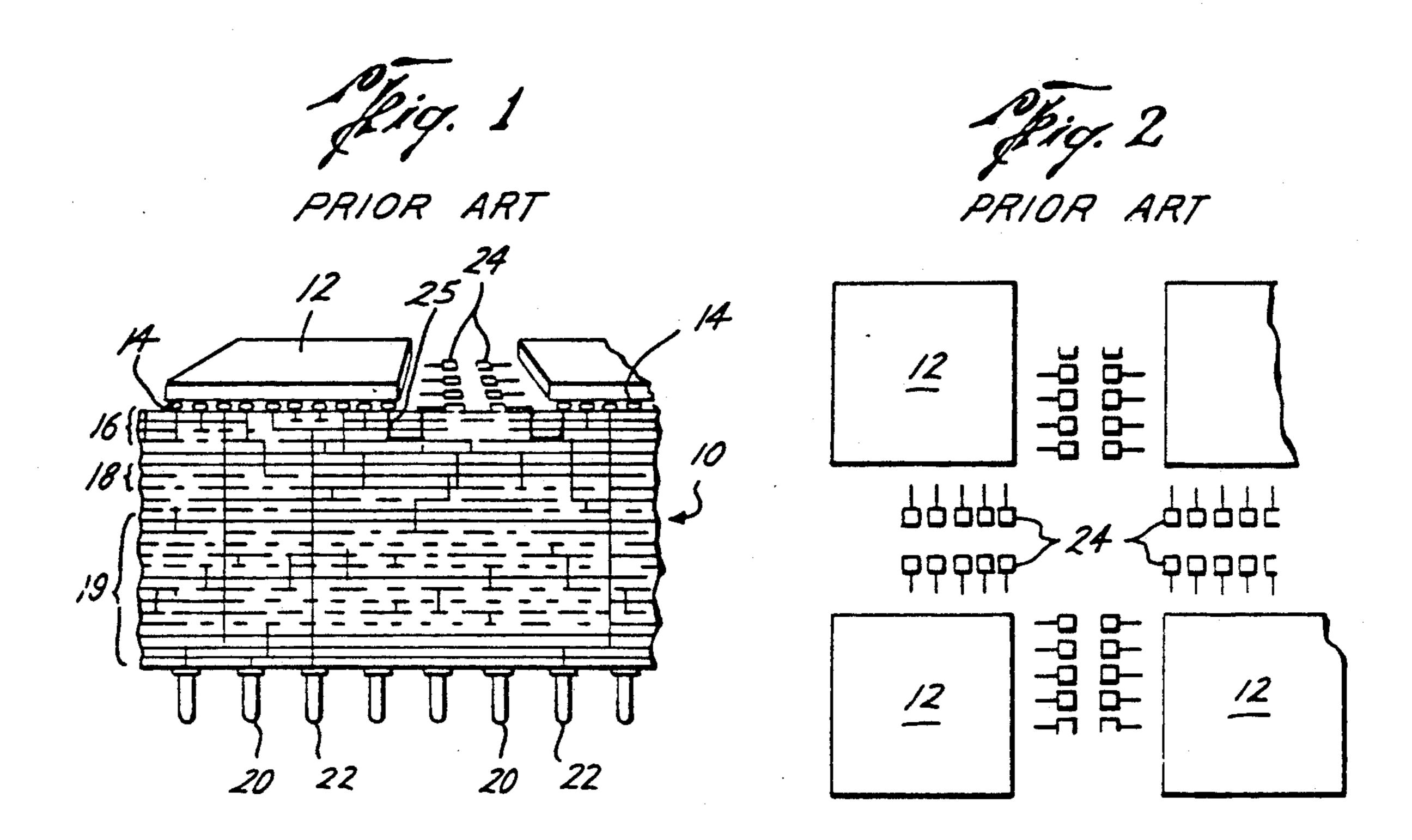

FIG. 3 is a cross-sectional view of a substrate according to the present invention.

FIG. 4 is a plan view of the substrate of FIG. 3.

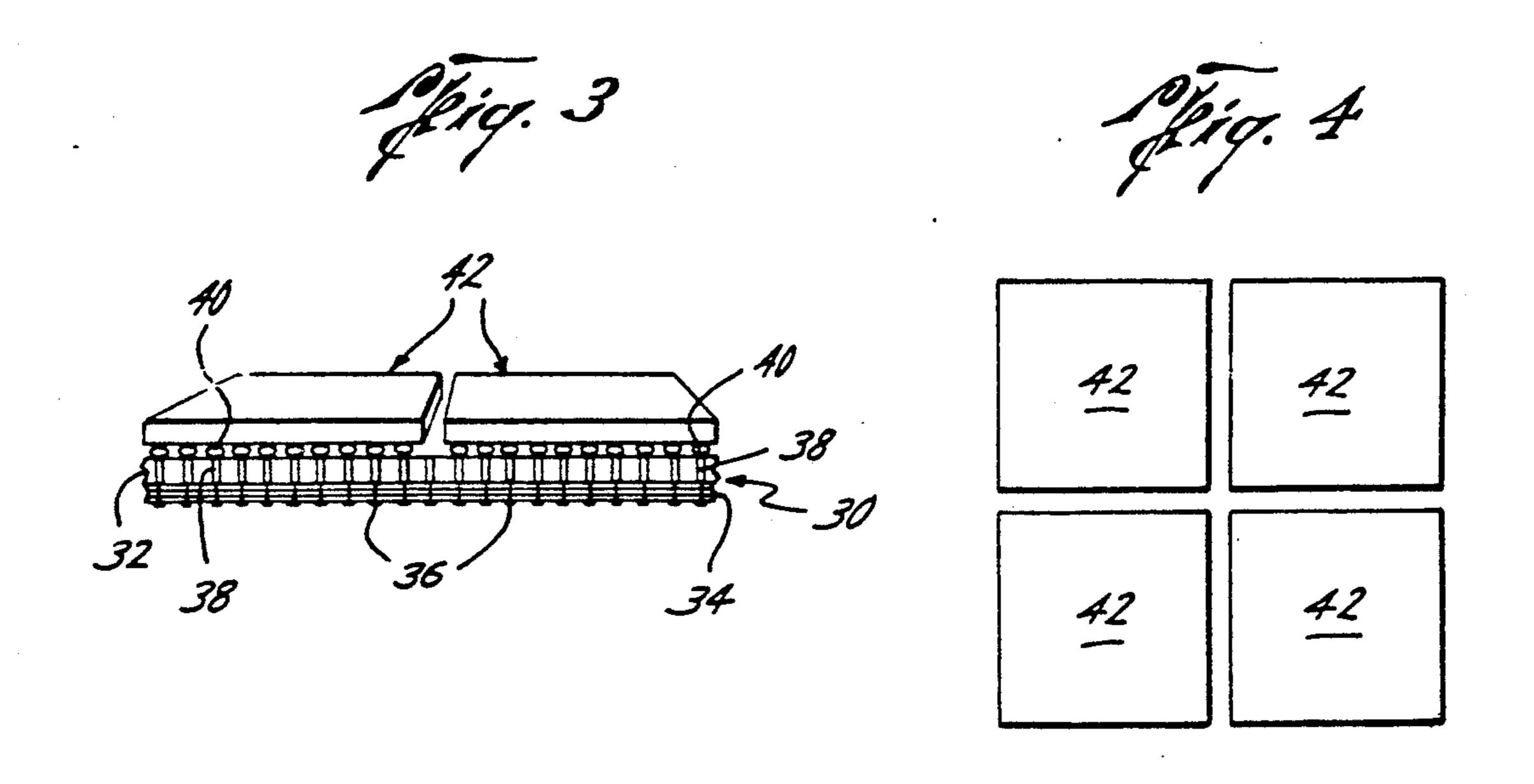

FIG. 5 is an exploded isometric view of a substrate according to the present invention and a chip for attachment thereto.

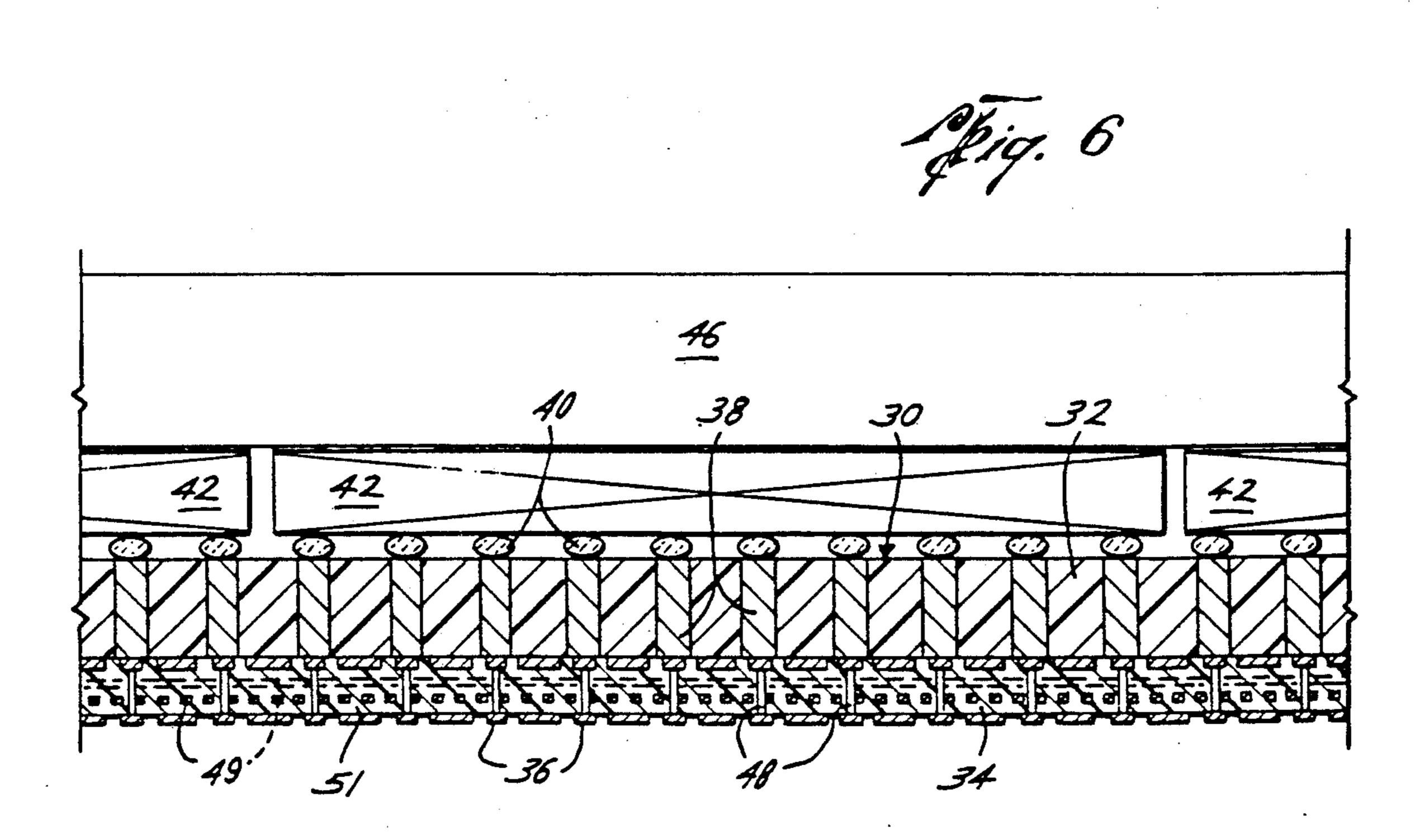

FIG. 6 is an enlarged cross-sectional view of a substrate according to the present invention.

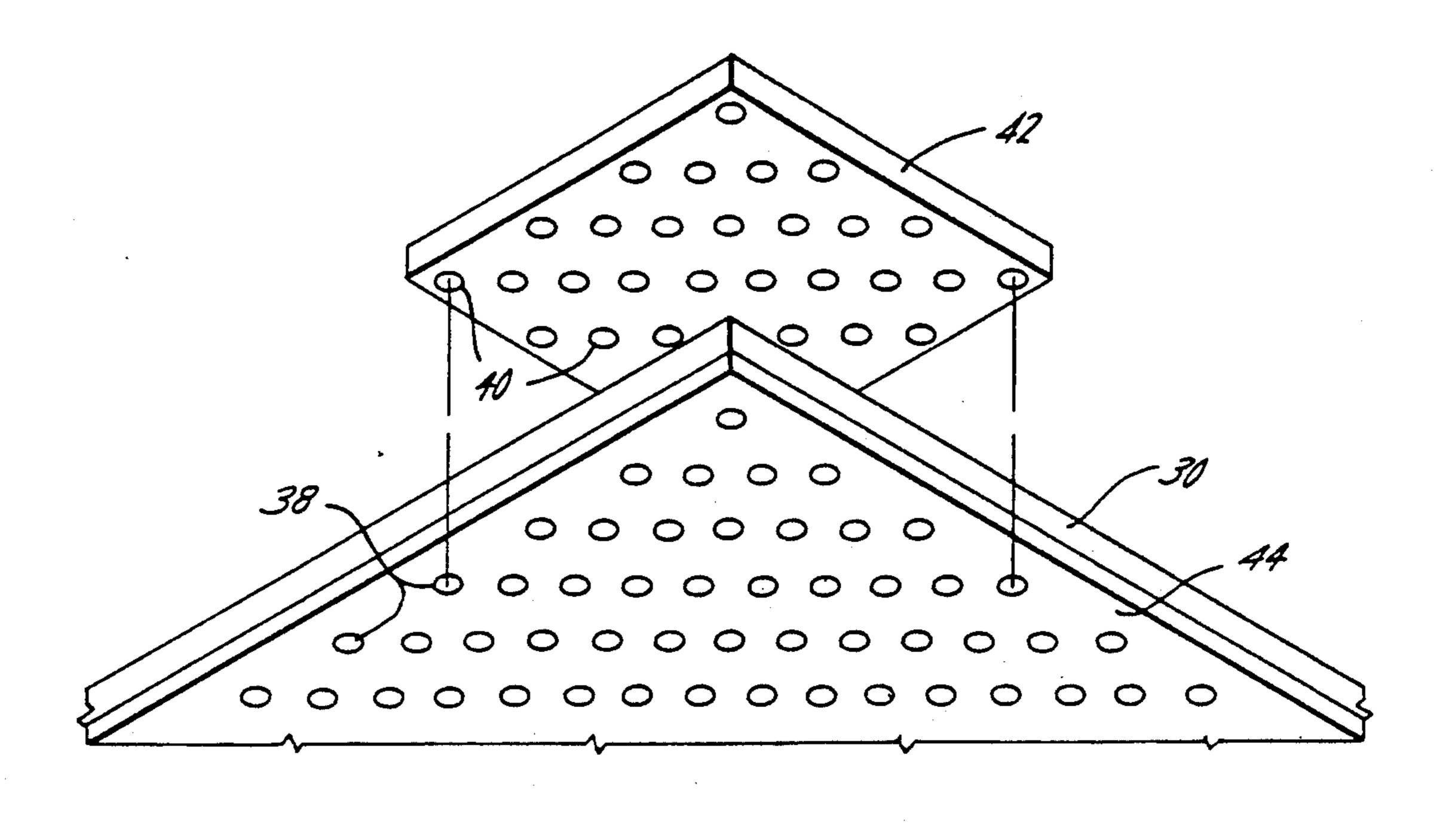

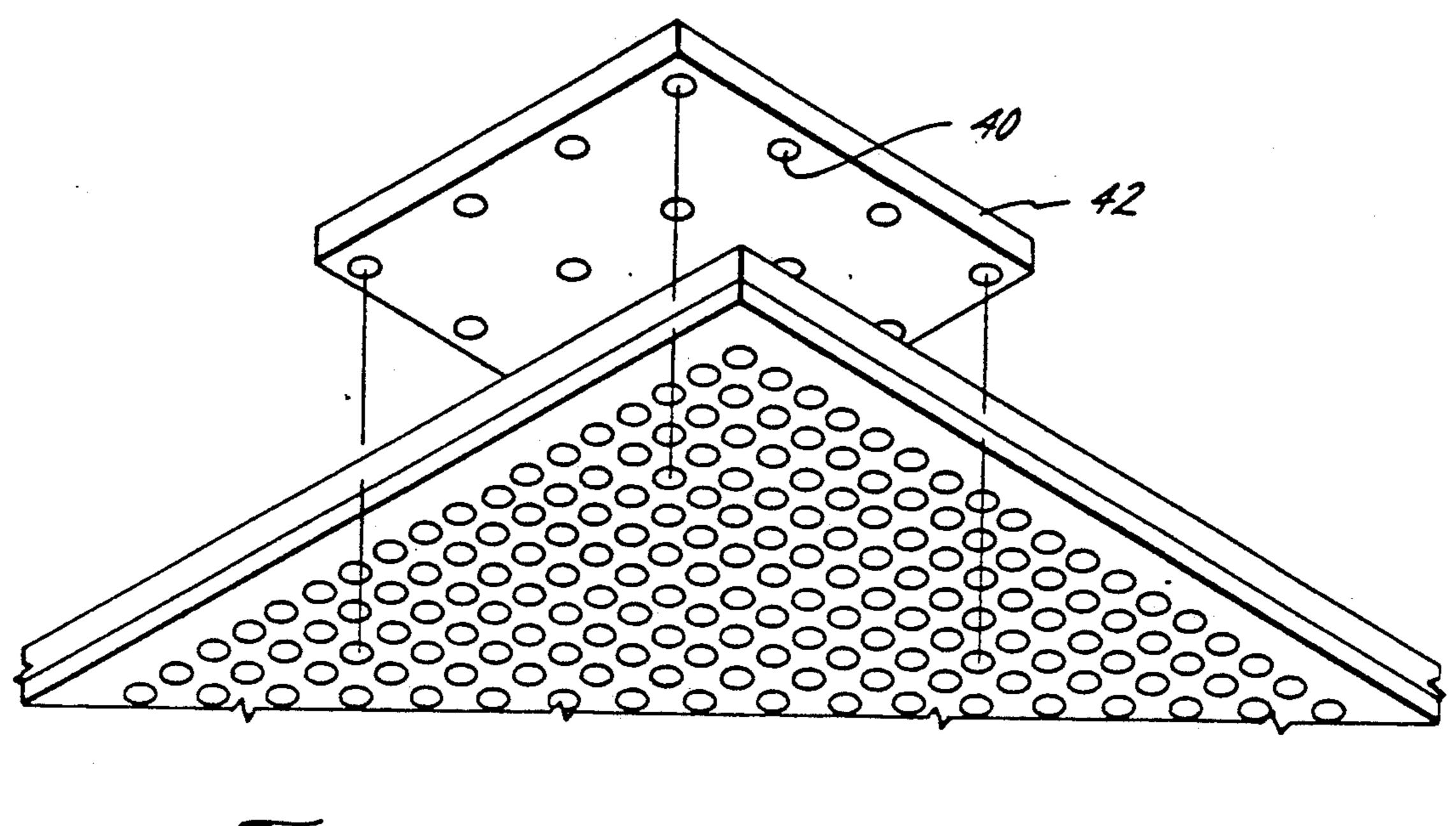

FIG. 7 is an exploded isometric view of a substrate similar to the substrate of FIG. 5.

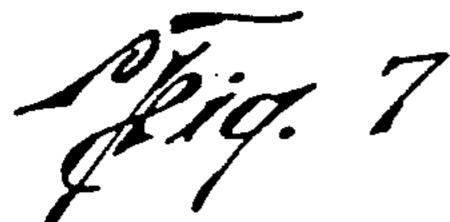

FIG. 8 is an exploded isometric view of a substrate according to the present invention, but with vias aligned with leads from the inner bond sites of the chip. The figure also shows a cutaway of the substrate detailing the thin-film interconnect structure.

4

## DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

Recent developments in integrated circuitry have led to a continuing increase in the number of semiconductor 5 chips per unit area to be attached to the underlying substrate. As the demand for chip space increases, it encroaches on and highlights the competing demand for space on the interconnect substrate between the chip and the structures for performing other important func- 10 tions, such as repairing and testing.

FIG. 1 shows a prior art substrate 10 having chips 12 attached thereto. The substrate is a multilayer structure having redistribution layers 16 near the top of the substrate, followed by an interconnect structure 18 of x- 15 and y-wiring. The remaining substrate structure comprises signal distribution and signal reference layers and power distribution and module I/O layers (19). The lower portion of the substrate includes a number of signal pins 20 and ground pins 22. The interconnect 18 20 of the substrate electrically connects the numerous electrical devices, primarily chips, that comprise a typical multi-chip modular package.

FIG. 1 illustrates the competing demand for chip attach space and the demand for space to perform other 25 important functions. As can be seen, a significant area of the surface of the substrate 10 is utilized for attachment of the chip 12. At the same time, space is required on the substrate surface for test pads 24. As shown, a line 25 extends from the chip bondsites or nodes 14 to pads 24. 30 The pads provide an accessible mechanism for testing the viability of the individual chip attach points.

FIG. 2 illustrates the chip/test pad structure and the competition between the structures and their attendant functions for substrate surface.

The chip attach space problem is magnified in those structures which, unlike the flip-chip bonding of FIGS.

1 and 2, utilize outer lead, peripheral or area bonding OLB's. In these embodiments, the chip bondsites are brought to the periphery of the chips by lead lines. The 40 advantage in the design is the accessibility of the bondsites to testing. The disadvantage is that the chip effectively uses more surface area for attachment.

In order to solve the problem of interconnect surface availability, the present invention utilizes a "flip" substrate. In other words, the substrate can be viewed as being flipped so that its thin-film interconnect is on the side of the substrate opposite the chip. The support structure of the substrate thus is adjacent to the chip. In order to achieve the necessary attachment between the 50 chip and interconnect, vias, or passageways, are provided from bondsites on the interconnect through the support to chip attach pads at the support surface immediately adjacent the chip. The vias are filled or coated with an electrically conductive material or otherwise 55 designed to provide an electrical connection between the interconnect and the chip.

FIG. 3 illustrates a substrate according to the present invention. The substrate 30 includes a support structure 32 and a thin-film interconnect structure 34. The inter-60 connect is a photolithographically defined set of strip transmission lines which interconnect chips in multichip modules, cards and boards. The interconnect is designed to provide a number of surface access pads 36. In presently available designs these pads would be di-65 rectly attached to the chip, either at the chip's inner bondsites or nodes 14 (FIG. 1) or at outer bondsites ("OLB's") as previously described:

According to the present invention, however, the surface access pads are directly attached to the chips by posts from the lower interconnect surface to sites at the interconnect/support interface. These Posts, in turn, are electrically connected to vias 38 which extend vertically through the support 32.

The vias are electrically conductive passageways connecting the interconnect to the nodes of the chips. The vias may be filled completely or the walls may be coated with a conductive material or may be otherwise treated so long as a conductive connection is made between interconnect and chip.

The vias terminate at their upper end at points which mate with the particular chip attach scheme. In FIG. 3, the vias 38 mate directly with the nodes 40 of the chips 42.

An advantage of the present structure is that surface access pads 36 can be smaller than the corresponding chip attach pads of presently available interconnects. In the latter structures, the pads are required to have a certain area in order to facilitate and assure adequate contact with the chips. Since the connections are now made at the vias and translated to the access pads 36, the pads may be smaller. As such, additional wiring is achievable on the interconnect.

FIG. 4 is a plan view illustrating the close arrangement achieved by adjacent chips 42. This view shows why the present structure is said to Provide for "brick-walling" chips.

FIG. 5 shows how a chip 42 is attached to a substrate 30 so as to align the vias 38 with the nodes 40 of the chip or chip package. FIG. 5 also shows that the remainder of the interconnect surface 44 is available for performing additional functions necessary for such modular packages. A nonexhaustive list of functions includes engineering changing, repair, testing, module I/O attachment, terminations and decoupling.

An additional advantage of the present structures is that the location of the vias may be designed so that they are aligned with the particular nodes 40 of different chips. This ensures proper electrical contact between the two structures.

FIG. 6 shows the chip and substrate attachment in more detail. The chips 42 are shown having a heat sink 46 or cold plate on their side opposite the substrate 30. The heat sink 46 is a standard item in modules of this type and is necessary to dissipate the heat build-up in chips. The nodes 40 of the chips are illustrated to be in alignment with and electrically connected to the vias 38 of the support 32. The vias, in turn, attach to Posts 48 which terminate at surface access pads 36. The interconnect 34 is shown as a series of x and y wires 49 extending through and surrounded by a non-conductive, insulative material 51.

FIG. 7 is similar to FIG. 5, except that the number of nodes 40 on the chip 42 is less than what is shown in FIG. 5.

FIG. 8 illustrates an embodiment of the present substrate having a peripheral via arrangement corresponding to lead lines 50 extending from the chip. As shown, the vias 38 extend through the substrate and will attach to the chip along the beam leads 50. As mentioned earlier, this arrangement offers the advantage that the chip to substrate bond is uncovered and is more accessible to inspection, compared to the bonds shown in FIGS. 5-7. A disadvantage to this arrangement, of course, is the additional space taken up by each chip. This reduces the chip density on the substrate.

It is preferred that the vias be arranged in a regular grid Pattern. Such an arrangement adapts with a "discretionary" interconnect, such as that described in copending U.S. application Ser. No. 102,172, filed Sept. 29, 1987 now abandoned in preference to a continuation 5 application Ser. No. 07/344,534 filed April 25, 1989. This makes possible a completely standardized substrate employing the advantages described above. The regular pattern allows a regular device attach scheme such as area "tape automated bonding" (TAB) or controlled 10 collapse chip connection (C4). If the latter approach is employed, a near-100% device packing density can be realized with the advantage of higher performance over less densely packed devices. The regular pattern also allows a continuous sheet of connections to be devel- 15 oped at the interface between chip and substrate. The increased spacing between attachment points gained by the use of a regular area grid patterns, instead of dense peripheral or linear attach, also enhances the manufacturing and assembly of electronic modules.

FIG. 8 also shows the x- and y-wiring scheme of the interconnect. As illustrated, the interconnect comprises a first set of transmission wires 52 extending in the ydirection and a second set of wires 54 extending in the x-direction orthogonal to the first set of wires. The vias 25 38 are shown extending through the wires.

Of course, other interconnect schemes can be used, for example, multiple x and y wire planes, diagonal wiring, reference planes, and the like can be envisioned. Also, though not shown in the drawings, reference and 30 voltage planes can be included in the substrate.

The substrate can be formed from a support material through which a number of vias are created. The support material can be selected from any number of materials which provide the needed support to the intercon- 35 nect and the thermal and physical properties for proper package operations. Examples of advantageous support materials are silicon, ceramic, glass, and metals. Particularly preferred are those materials having advantageous thermal coefficient of expansion (TCE) match with the 40 chip. This aspect will be described in more detail below.

The vias can be formed by a number of techniques. For example, the via pattern may be established by a photoresist and then etched away. The vias can then be back-filled or coated with a conductive material. Other 45 techniques for forming the vias include punching of green ceramic, laser drilling, photo-machining, and crystalligraphic etching. Suggested conductive materials include copper, tungsten, gold, and nickel. The choice of conductive material is based upon the adhe- 50 sion characteristics with the chosen support material and the method chosen for rendering the hole conductive.

The vias are arranged depending on the specifications of the chip. As already discussed, the vias can be posi- 55 tioned in any number of positions, with the grid pattern preferred due to its ease in manufacture and bonding. Further, the shape of the vias is not controlling as long as the proper electrical connection is achieved between the interconnect and chip.

Once the support is formed, the thin-film interconnect is processed onto the support. The interconnect structure comprises a plurality of thin transmission lines surrounded by a non-conductive, insulative material. A suggested material for the transmission lines is copper 65 surrounded by polyimide. The transmission lines are arranged in a network and interconnected depending on user needs. The transmission lines may be a customized

network or a discretionary network as disclosed in copending application U.S. Ser. No. 102,172 now abandoned in preference to a continuation application Ser. No. 07/344,534 filed Apr. 25, 1989 mentioned above. It may be advantageous to "personalize" or interconnect the wiring network prior to chip attachment.

Once the substrate is complete, the I.C. chips are mounted onto the non-interconnect side of the substrate. The present invention offers a still further advantage at this step in the operation. The support surface is a more rugged surface than is the interconnect. Thus, by attaching the chips to the support rather than the interconnect, the integrity of the delicate interconnect is not jeopardized by the soldering or bonding of the chips. Also, the support allows for lower thermal expansion mismatch with the chip. This reduces the development of a shearing force between the chip and the substrate at the chip attach points.

The chips can be attached to the vias by a variety of well-known techniques, such as soldering, thermocompression bonding, pressure contact, and the like.

Thus, the present invention provides an improved substrate for attaching and connecting the many electrical devices, typically in the form of I.C. chips, necessary in digital circuitry. The present substrate provides improved device packing density by the migration of area-consuming functions, such as test/engineering change pads, termination resistors, etc. to a different plane from the chip attachment plane. Further, the substrate does not jeopardize the delicate interconnect during device attachment since the attachment is done on the more rugged support surface.

The present invention, therefore, is well adapted to carry out the objects and attain the ends and advantages mentioned, as well as others inherent therein. While presently preferred embodiments of the invention have been described for the purpose of disclosure, numerous changes in the details of construction and arrangement of parts may be made without departing from the spirit of the present invention and the scope of the appended claims.

What is claimed is:

60

1. A method for manufacturing an integrated circuit packaging structure comprising the steps of:

providing an integrated circuit element including a plurality of internal circuits integrated into a single semi-conductor element, said integrated circuit element having an upper surface and a lower surface, with an array of conductive nodes protruding from said lower surface to provide electrical coupling to said internal circuits;

providing a support substrate having an upper surface and a lower surface with a plurality of through vias extending from said upper surface to said lower surface, said through vias being formed in a pattern corresponding to said array of conductive nodes on said lower surface of said integrated circuit element;

providing said substrate with conductor means within said through vias extending from said substrate upper surface to said substrate lower surface; providing an electrical interconnect layer with a plurality of electrically conductive interconnect elements distributed within an electrically insulating material, said interconnect layer having an upper surface and a lower surface;

further providing said interconnect layer with a plurality of conductive coupling elements extending 35

7

from, said upper surface to said lower surface of said interconnect layer, said coupling elements being arranged in a pattern corresponding to said array of conductive nodes on said integrated circuit element and being adapted for conductive 5 coupling to said interconnect elements within said interconnect layer and for conductive contact from said lower surface by external sources; and

mounting said lower surface of said integrated circuit element adjacent said upper surface of said sub- 10 strate so as to align said conductive nodes with said through vias and to electrically couple said conductive nodes with said conductor means;

mounting said upper surface of said interconnect layer adjacent said lower surface of said substrate 15 so as to align said coupling elements with said through vias and to electrically couple said coupling elements with said conductor means.

2. The method of claim 1 wherein said integrated circuit element and said support substrate are formed of 20 material having equal coefficients of thermal expansion.

3. The method of claim 1, wherein said conductor means within said through vias in said substrate are formed by substantially filling said through vias with a conductive material.

4. The method of claim 1, wherein said through vias are formed by boring through said substrate from said upper surface to said lower surface, said formed vias being defined by a vias wall, and wherein said conductor means within said through vias are formed by lining 30 said vias wall with a conductive material.

5. The method of claim 1, wherein said electrical interconnect layer is formed to include a plurality of electrical conductor elements distributed within a layer of polyimide insulating material.

6. The method of claim 5 wherein said electrical conductor elements are formed of copper.

7. The method of claim 1 further comprising the step of soldering said conductive nodes of said integrated circuit element to said conductor means of said sub- 40 strate.

8. The method of claim 1 further comprising the step of thermo bonding said conductive nodes of said integrated circuit element to said conductor means of said substrate.

9. The method of claim 1 further comprising the step of coupling said conductive nodes of said integrated circuit to said conductor means of said substrate by pressure contact.

10. the method of claim 1, wherein said conductive 50 rial. coupling elements of said interconnect layer are formed by providing a conductive lead extending from said are upper surface to said lower surface of said interconnect upper layer.

11. The method of claim 10, wherein said conductive 55 coupling elements are formed having an upper end and a lower end, said upper and lower ends being adjacent said upper and lower surfaces of said interconnect layer, and further comprising the step of providing said conductive elements with a conductive pad electrically 60 coupled to said lower end of said conductive elements.

12. The method of claim 1, wherein said support substrate is formed to include a conductive voltage plane.

13. A method of manufacturing an integrated circuit 65 packaging structure comprising the steps of:

providing an integrated circuit element with a plurality of internal circuits integrated into a single semi8

conductor element, said integrated circuit element having an upper surface, a lower surface and a peripheral edge;

further providing said integrated circuit element with a plurality of conductive leads extending from said peripheral edge to provide electrical coupling to said internal circuits;

providing a support substrate having an upper surface and a lower surface with a plurality of through vias extending from said upper surface to said lower surface, said through vias being formed in a pattern corresponding to the arrangement of said conductive leads of said integrated circuit element;

providing said substrate with conductor means within said through vias and extending from said substrate upper surface to said substrate lower surface;

providing an electrical interconnect layer comprising a plurality of electrically conductive interconnect elements distributed within an electrically insulating material, said interconnect layer having an upper surface and a lower surface;

further providing said interconnect layer with a plurality of conductive coupling elements extending from said upper surface to said lower surface of said interconnect layer, said coupling elements being arranged in a pattern corresponding to the arrangement of said conductive leads of said integrated circuit element and being adapted for conductive coupling to said interconnect elements within said interconnect layer and for conductive contact from said lower surface by external sources; and

mounting said lower surface of said integrated circuit element adjacent said upper surface of said substrate so as to align said conductive leads with said through vias and to electrically couple said conductive leads with said conductor means;

mounting said upper surface of said interconnect layer adjacent said lower surface of said substrate so as to align said coupling elements with said through vias and to electrically couple said coupling elements with said conductor means.

14. The method of claim 13 wherein said integrated circuit element and said support substrate are formed of material having equal coefficients of thermal expansion.

15. The method of claim 13 wherein said conductor means within said through vias are formed by substantially filling said through vias with a conductive material

16. The method of claim 13 wherein said through vias are formed by boring through said substrate from said upper surface to said lower surface, said formed vias being defined by a vias wall, and wherein said conductor means within said through vias are formed by lining said vias wall with a conductive material.

17. A method of manufacturing an integrated circuit packaging structure of the type adapted to receive an integrated circuit element including a plurality of internal circuits integrated into a single semi-conductor element, the single semi-conductor element being of the type having an upper surface and a lower surface and being formed having an array of conductive nodes protruding from the lower surface to provide electrical coupling to the internal circuits, said packaging structure method comprising the steps of:

providing a support substrate having an upper surface and a lower surface;

forming a plurality of through vias in said substrate extending from said upper surface to said lower surface in a pattern corresponding to the array of conductive nodes of the lower surface of the integrated circuit element;

providing conductor means within said through vias extending from said substrate upper surface to said substrate lower surface;

providing an electrical interconnect layer having a plurality of electrically conductive interconnect 10 elements distributed within an electrically insulating material, and having an upper surface and a lower surface with a plurality of conductive coupling elements extending from said upper surface to said lower surface of said interconnect layer; and 15 wherein said coupling elements are arranged in a pattern corresponding to the array of conductive nodes on the integrated circuit element and adapted for conductive coupling to said interconnect elements within said interconnect layer and 20 for conductive contact from said lower surface by external sources; and

mounting the lower surface of the integrated circuit element adjacent the upper surface of the substrate so as to align the conductive nodes with said 25 through vias and to electrically couple the conductive nodes with said conductor means;

mounting said upper surface of said interconnect layer adjacent said lower surface of said substrate so as to align said coupling elements with said 30 through vias and to electrically couple said coupling elements with said conductor means.

18. A method of manufacturing an integrated circuit packaging structure of the type adapted to receive an integrated circuit element including a plurality of inter- 35 nal circuits integrated into a single semi-conductor element, the semi-conductor element being formed having an upper surface a lower surface, and a peripheral edge and having a plurality of conductive leads extending from the peripheral edge to provide electrical coupling 40

to the internal circuits, said method comprising the steps of:

providing a support substrate having an upper surface and a lower surface with a plurality of through vias formed therein extending from said upper surface to said lower surface, said through vias being formed in a pattern corresponding to the arrangement of the conductive leads of the integrated circuit element;

further providing said substrate with conductor means within said through vias extending from said substrate upper surface to said substrate lower surface;

providing an electrical interconnect layer comprising a plurality of electrically conductive interconnect elements distributed within an electrically insulating material, said interconnect layer having an upper surface and a lower surface;

providing said interconnect layer with a plurality of conductive coupling elements extending from said upper surface to said lower surface of said interconnect layer, said coupling elements being arranged in a pattern corresponding to the arrangement of the conductive leads of the integrated circuit element and being adapted for conductive coupling to said interconnect elements within said interconnect layer and for conductive contact from said lower surface by external sources; and

mounting the lower surface of said integrated circuit element adjacent said upper surface of said substrate so as to align said conductive leads with said through vias and to electrically couple said conductive leads with said conductor means;

mounting said upper surface of said interconnect layer adjacent said lower surface of said substrate so as to align said coupling elements with said through vias and to electrically couple said coupling elements with said conductor means.

45

50

55

60

# UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO. : 5,039,628

DATED : August 13, 1991 INVENTOR(S): David H. Carey

It is certified that error appears in the above-indentified patent and that said Letters Patent is hereby corrected as shown below:

On The Title Page, In The Abstract, line 9, "density" should be —densely—.

Col. 2 line 4, change "Peripheral" to --peripheral--.

Col. 2 line 12, after "substrate" delete --at--.

Col. 4 line 4, change "Posts" to --posts--.

Col. 4 line 28, change "Provide" to --provide--.

Col. 5 line 2, change "Pattern" to --pattern--.

Col. 7 line 50, change "the" to --The---.

Col. 9 line 38, after "upper surface" insert --,--.

Signed and Sealed this

Twenty-third Day of November, 1993

Attest:

BRUCE LEHMAN

Attesting Officer

Commissioner of Patents and Trademarks