# United States Patent [19] Shinohara

LEAD FRAME FOR A SEMICONDUCTOR DEVICE AND A METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE USING THE LEAD FRAME Toshiaki Shinohara, Hyogo, Japan Inventor: Mitsubishi Denki Kabushiki Kaisha, [73] Assignee: Tokyo, Japan Appl. No.: 108,907 Filed: Oct. 13, 1987 [30] Foreign Application Priority Data Int. Cl.<sup>5</sup> ..... H01L 29/60 [58] [56] References Cited U.S. PATENT DOCUMENTS FOREIGN PATENT DOCUMENTS

| [11] | Patent Number:  | 4,942,455     |

|------|-----------------|---------------|

| [45] | Date of Patent: | Jul. 17, 1990 |

|          | •      |       |        |

|----------|--------|-------|--------|

| 53-32675 | 3/1978 | Japan | 357/70 |

|          |        | Japan |        |

|          |        |       |        |

Primary Examiner—Rolf Hille Assistant Examiner—Steven Ho Yin Loke Attorney, Agent, or Firm—Lowe, Price, LeBlanc, Becker & Shur

# [57] ABSTRACT

A lead frame for a semiconductor device and a method for manufacturing the semiconductor device using the frame, the lead frame comprising a dice pad, inner leads, tie bar, outer leads and a thin metal layer of lead which is hard to melt and is easily transformed formed on the surface of that portion of the inner leads, outer leads and the tie bar which is not covered with the sealing resin. In injection molding of a resin material on the lead frame with a semiconductor chip therein, the gap between the lead frame and the mold is filled while the thin metal layer is transformed by the clamping pressure, so that the bur may be prevented from being generated.

3 Claims, 5 Drawing Sheets

FIG.1

PRIOR ART

FIG.3

PRIOR ART

FIG.5

Jul. 17, 1990

FIG.6

FIG.7

Jul. 17, 1990

FIG.9

## LEAD FRAME FOR A SEMICONDUCTOR DEVICE AND A METHOD FOR MANUFACTURING A SEMICONDUCTOR DEVICE USING THE LEAD FRAME

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a lead frame for a semiconductor device and a method for manufacturing a semiconductor device using the lead frame and, more specifically, it relates to a lead frame employed in a method for manufacturing a resin-sealed type semiconductor device and to a method for manufacturing a semiconductor device using the lead frame.

## 2. Description of the Prior Art

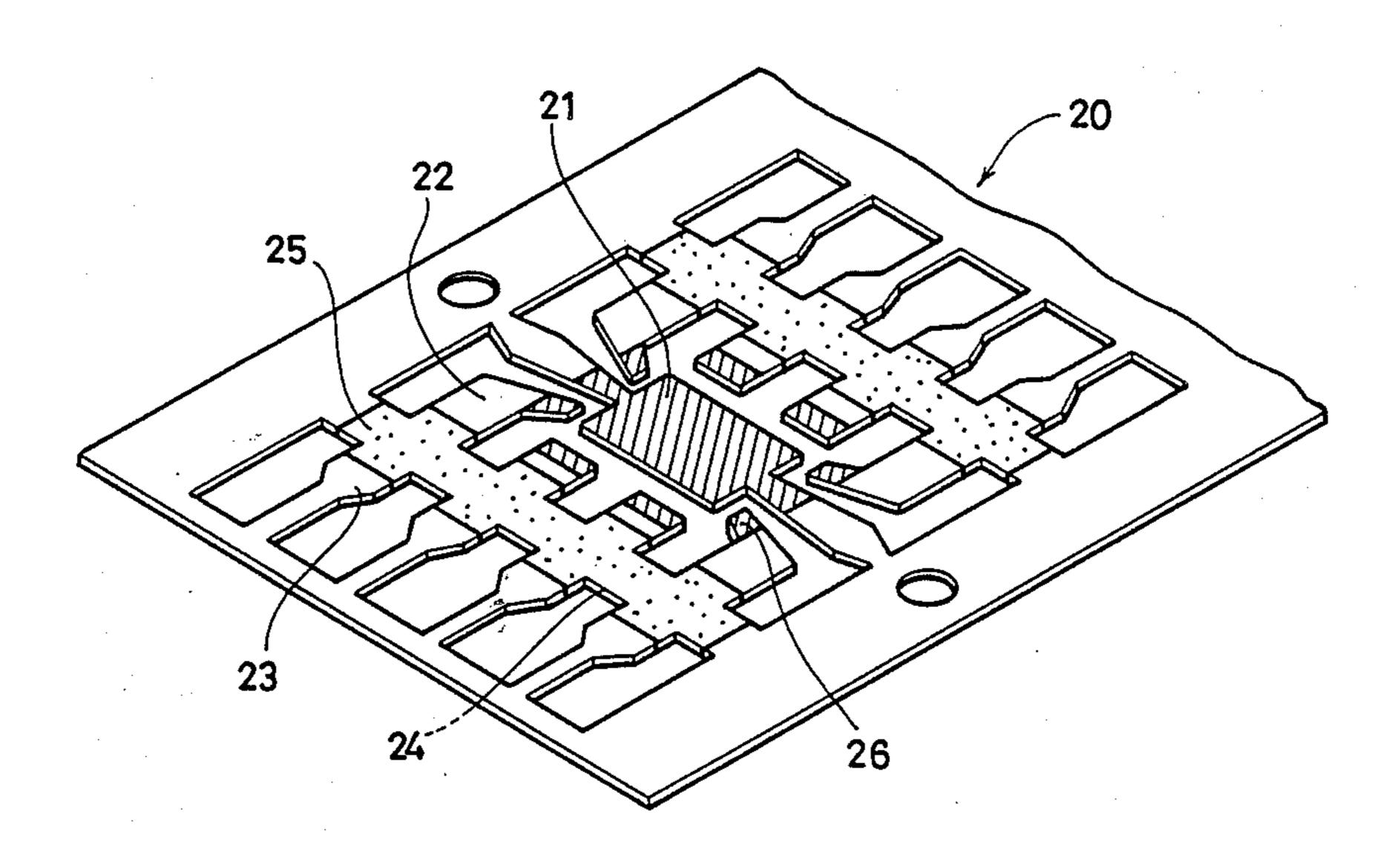

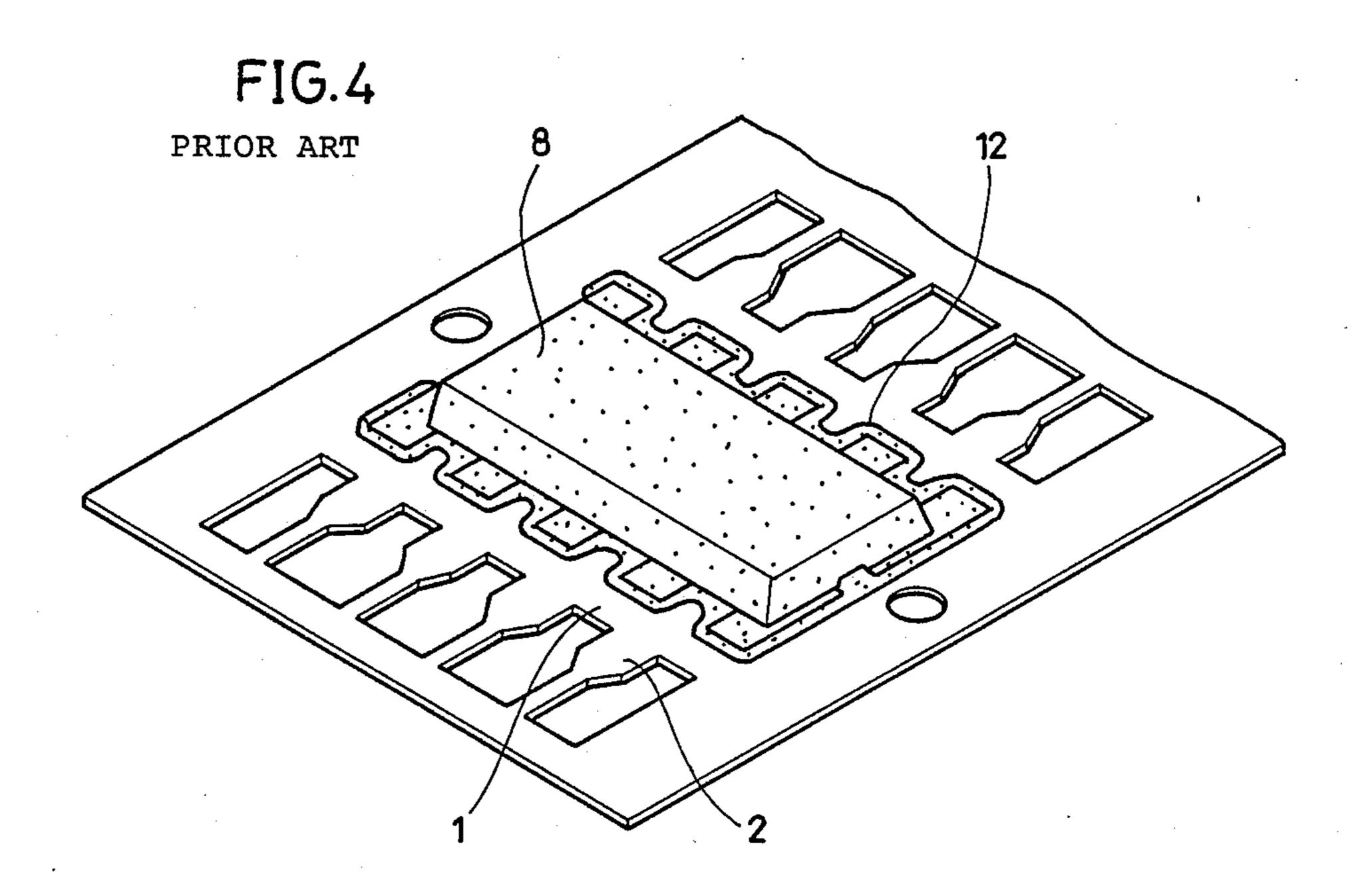

FIG. 1 shows a lead frame employed in a method of manufacturing a conventional integrated circuit. The lead frame has a prescribed pattern which is formed by etching or pressing a thin metal plate. Referring to the figure, a tie bar 1 connects outer leads 2. Inner leads 3 extend to the side of a central die pad 4 and after sealing, they will be contained in the resin. Meanwhile, hatched portions in the figure show the Ag or Au plated portions which facilitate the junction of semiconductor 25 chips and the connection by Au wire, etc., between the electrodes of the semiconductor chip and the inner leads 3.

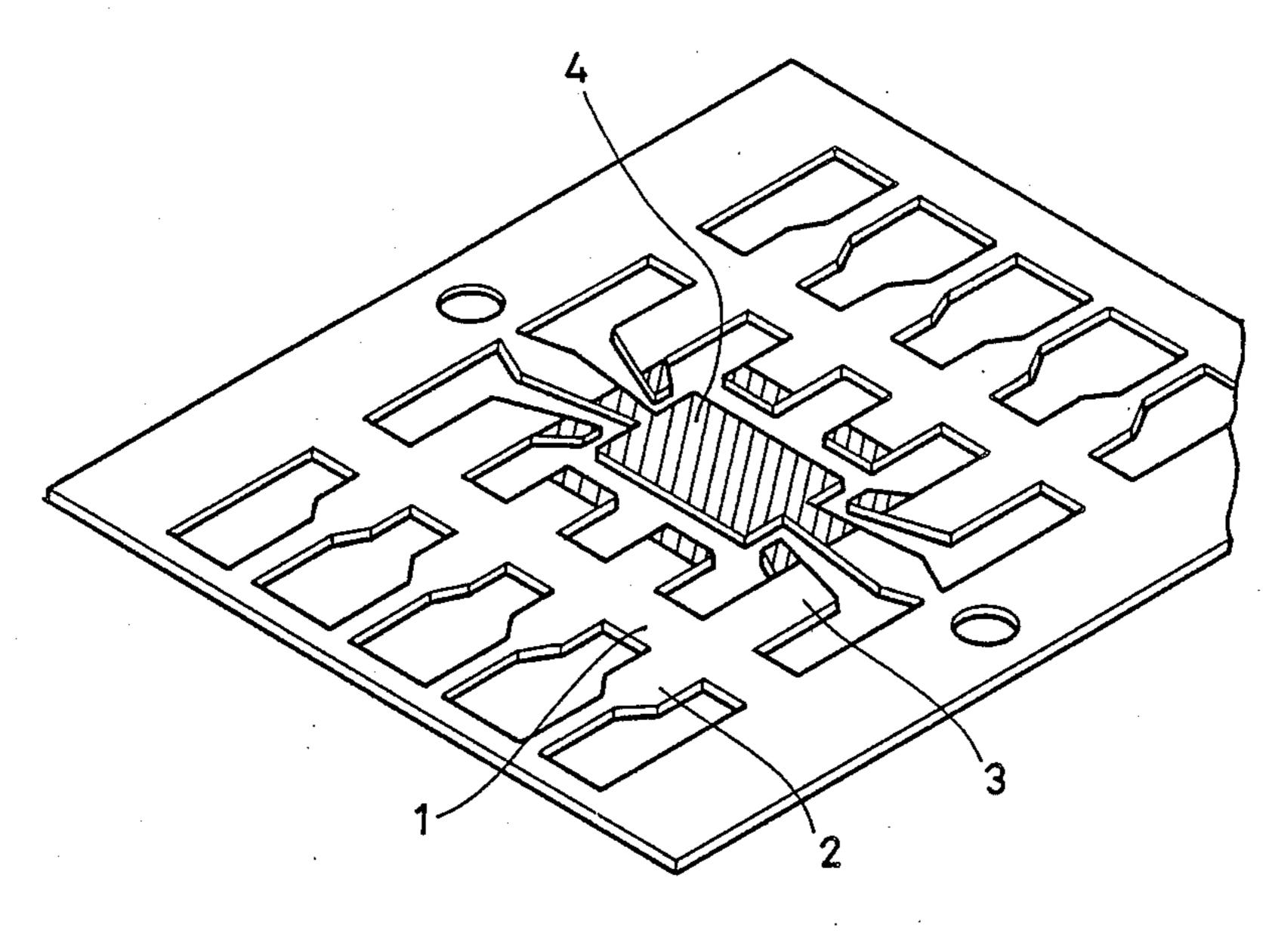

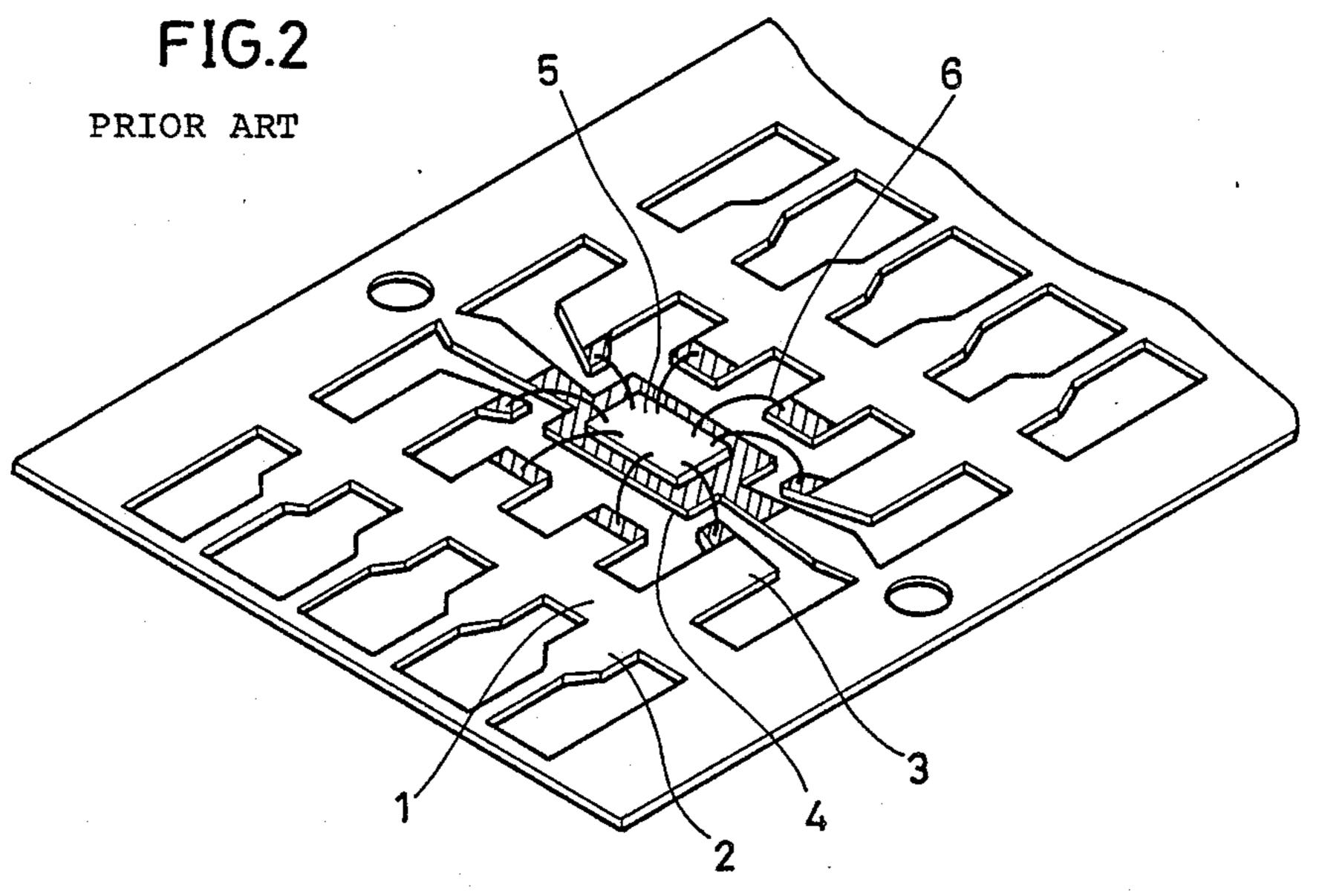

Referring to FIG. 2, a chip 5 is attached to the die pad 4 and the electrodes of the chip 5 and the inner leads 3 30 are in electrical connection to each other by fine lead wires 6 of, for example, Au. After the structure of FIG. 2 is obtained, a lead frame 11 is interposed between the upper mold 9 and the lower mold 10 of an injection mold, as shown in FIG. 3. Then, a thermosetting resin 35 such as epoxy resin is injected to the cavity using the low pressure transfer molding, etc., to form a resin layer 8. The molded frame is shown in FIG. 4.

A thin film 12 (hereinafter referred to as a bur) which is formed by the resin entered the gap between the mold 40 and the frame. The bur 12 occurs according to the flatness precision of the mold, the dispersion of plate thickness of the lead frame, uniformity of pressure of the press clamping the mold, the fluidity of the sealing resin and the die ware due to the frame treatment. The bur 45 causes an inconvenience in that the plating can not be carried out on the outer lead in a subsequent process. Therefore, the bur 12 is eliminated by dry honing or the wet honing after molding. In addition, a bur eliminating method using high water pressure is employed after the 50 electrolytic flash cutting.

A conventional lead frame is formed as described above. However, the bur eliminating process as above is essentially an undesired one. Meanwhile, when the honing is carried out, a package as well as the bur is damsed, the surface of the lead frame is made rough and the frame becomes slender, causing a probem such as the generation of plating needle deposition or less lead strength. There is also a problem in the bur eliminating method using electrolysis and high water pressure. 60 Namely, a thick bur can not perfectly be eliminated according to the method. In addition, the necessary bur eliminating process and facilities as above increases product cost.

#### SUMMARY OF THE INVENTION

The present invention eliminates the above described problems and a primary object of the present invention

is to suppress the generation of bur as much as possible during the resin sealing process, and to dispense with a special bur eliminating process and facilities, without damaging the resin and the lead.

A lead frame according to the present invention comprises a die pad for mounting a chip placed in the central portion, inner leads, a tie bar and outer leads disposed around the die pad, a thin metal layer which is hard to melt and easily transformed, formed on the surface of that portion of the inner leads, outer leads and tie bar which are not covered by the sealing resin.

The thin metal layer of the present invention has less hardness so that it is transformed to fill the gap between the mold and the lead frame when the lead frame is clamped with the mold in the molding process. When the resin is injected into the cavity of the mold, the resin hardly enters the gap between the mold and the lead frame since the thin metal layer occupies the gap. Consequently, undesired generation of the bur can be prevented.

These objects and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a perspective view of a conventional lead frame.

FIG. 2 is a perspective view showing a step of a method for manufacturing a semiconductor device using the conventional lead frame of FIG. 1.

FIG. 3 is a cross sectional view showing another step of the manufacturing method using the conventional lead frame.

FIG. 4 is a perspective view showing a further step of the manufacturing method using the conventional lead frame.

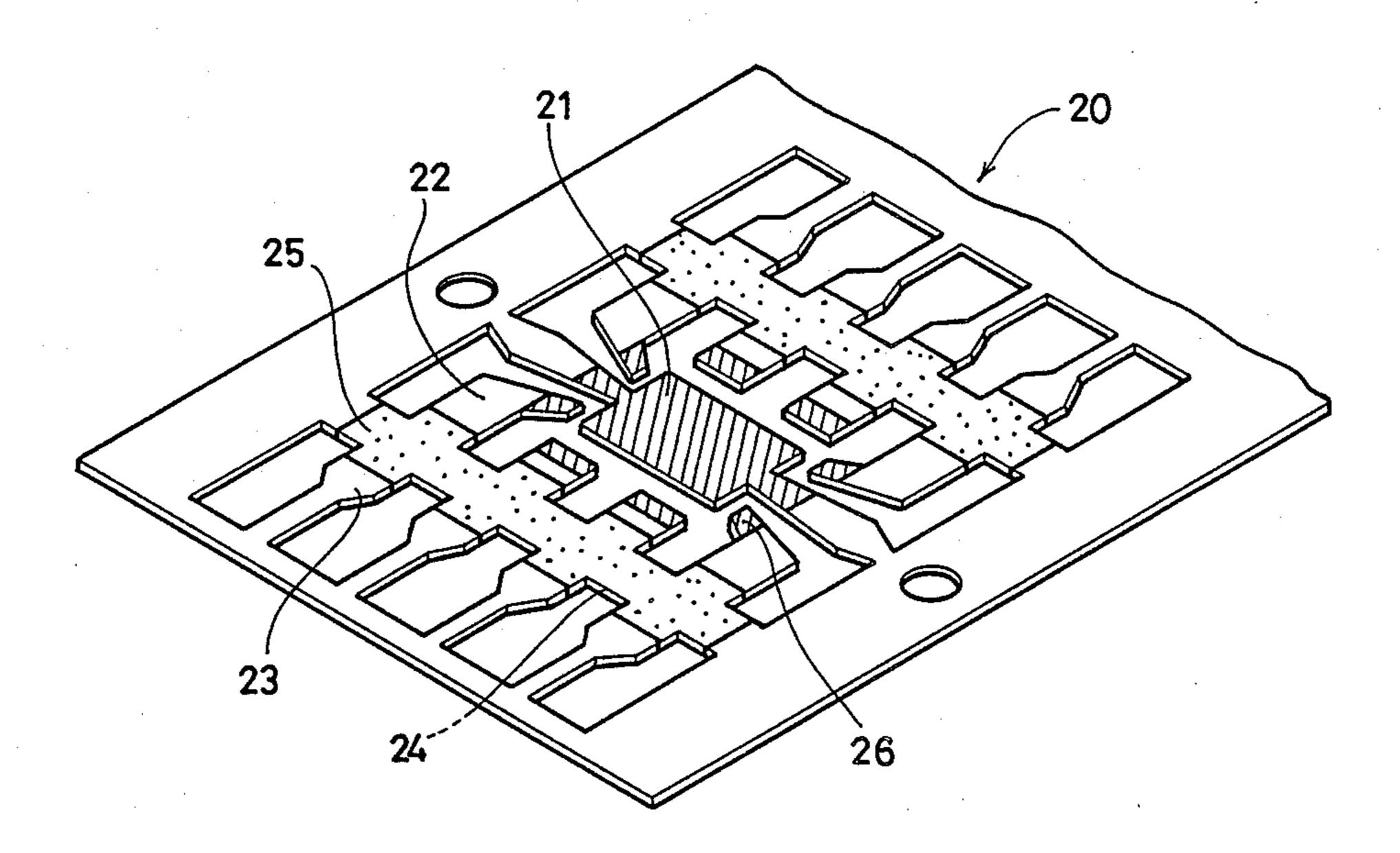

FIG. 5 is a perspective view showing a step of a method for manufacturing a semiconductor device using a lead frame of one embodiment of the present invention.

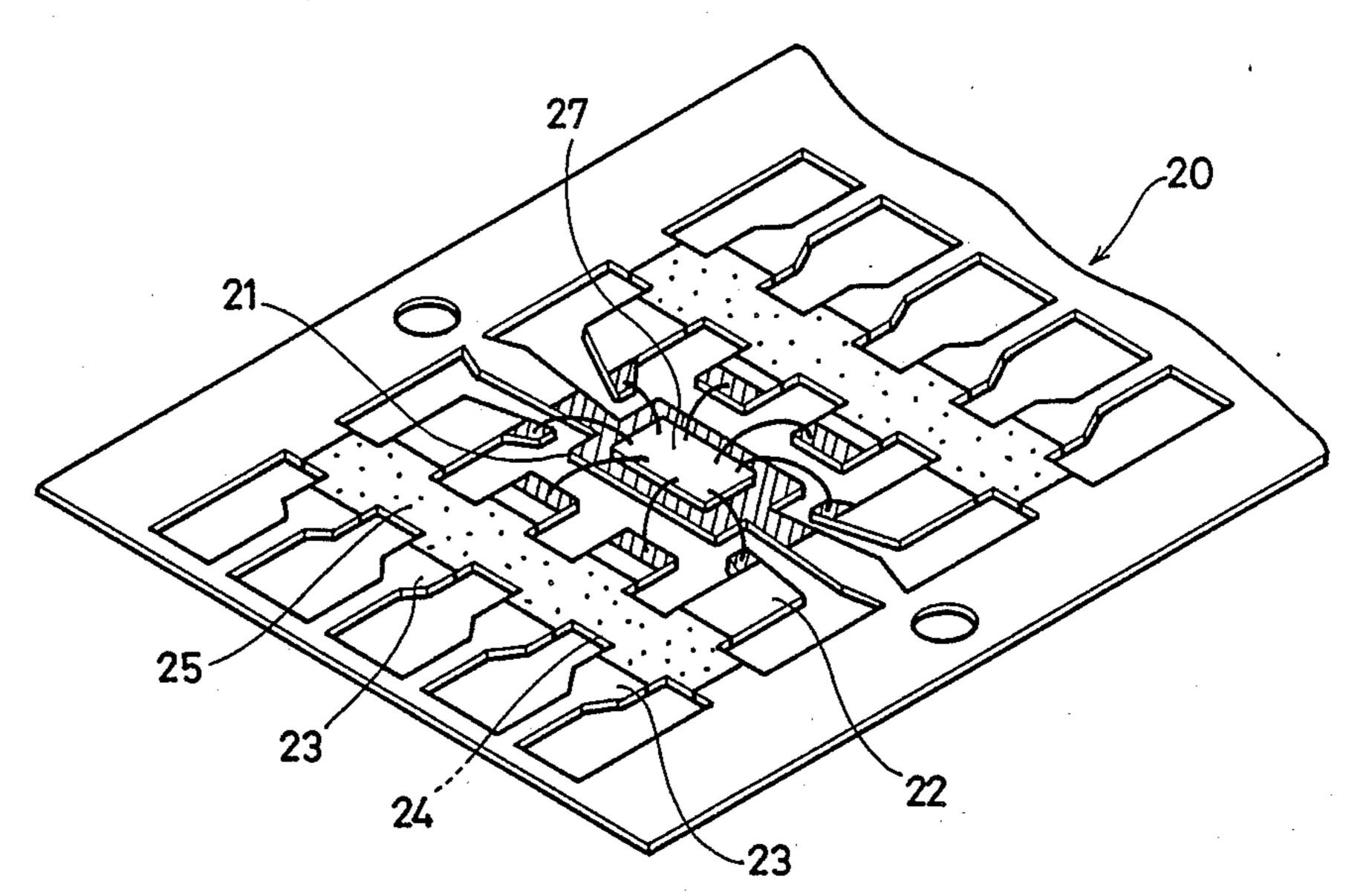

FIG. 6 is a perspective view showing another step of the manufacturing method using the lead frame of the present invention.

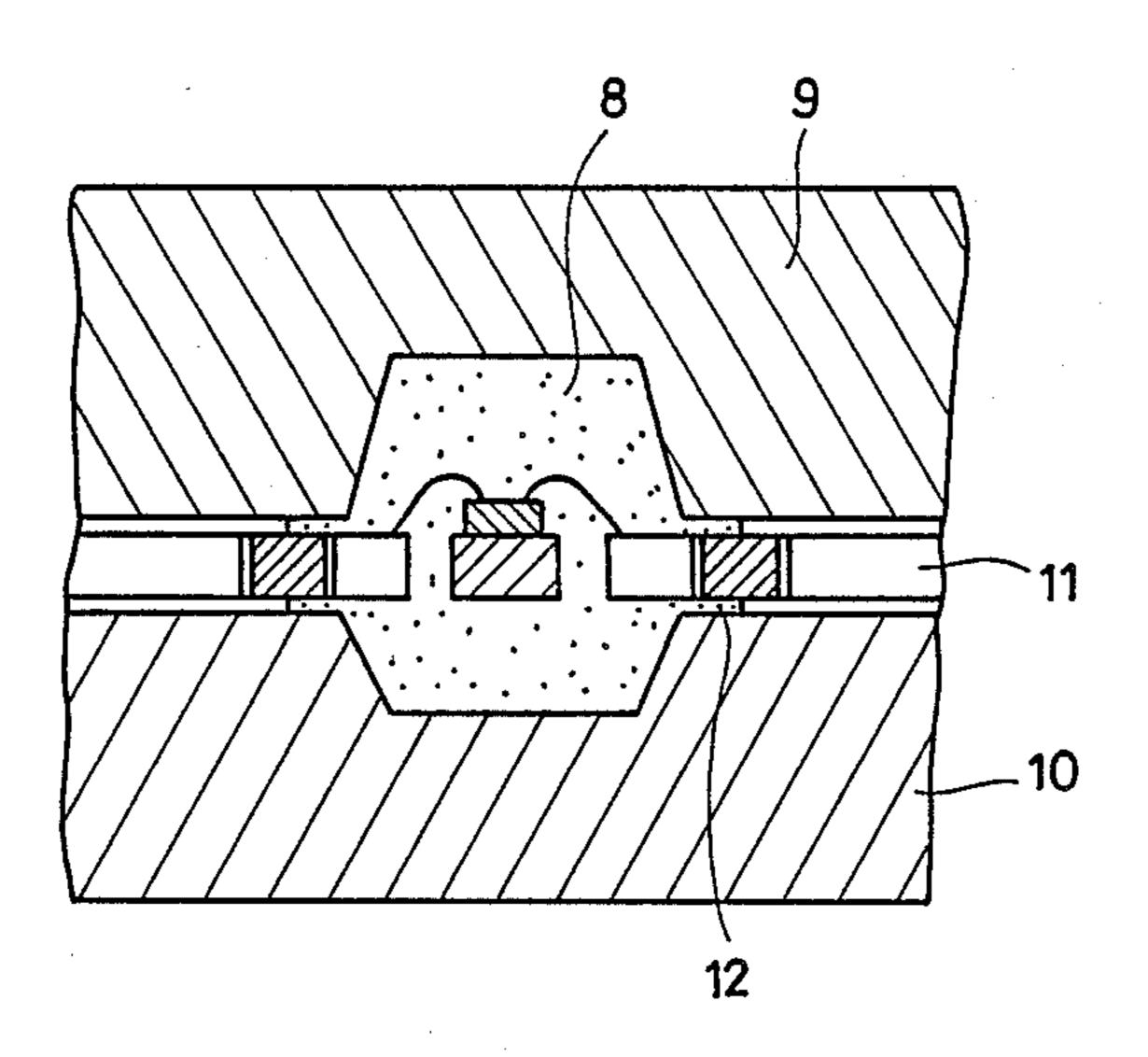

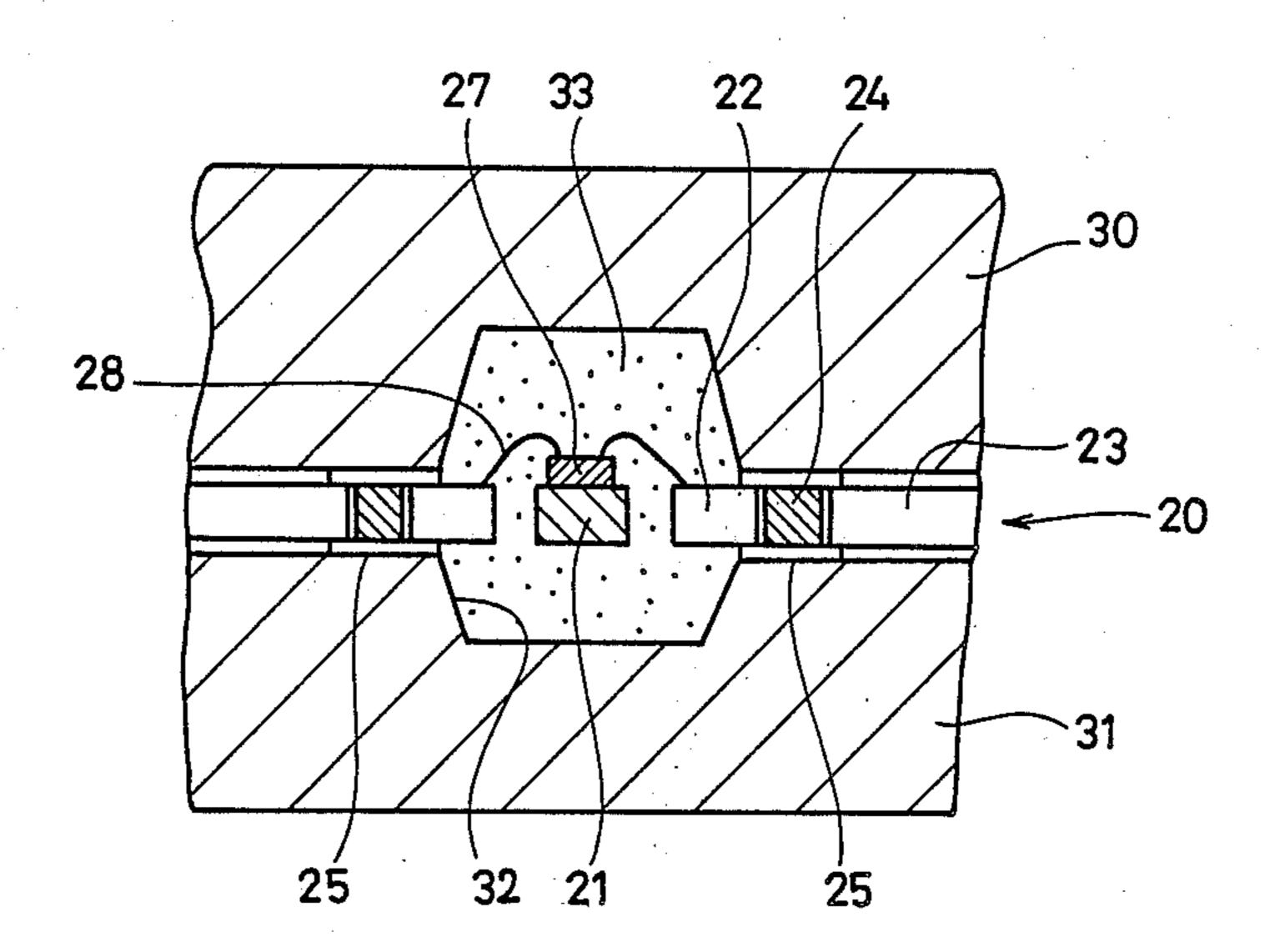

FIG. 7 is a cross sectional view showing a further step of the manufacturing method using the lead frame of the present invention.

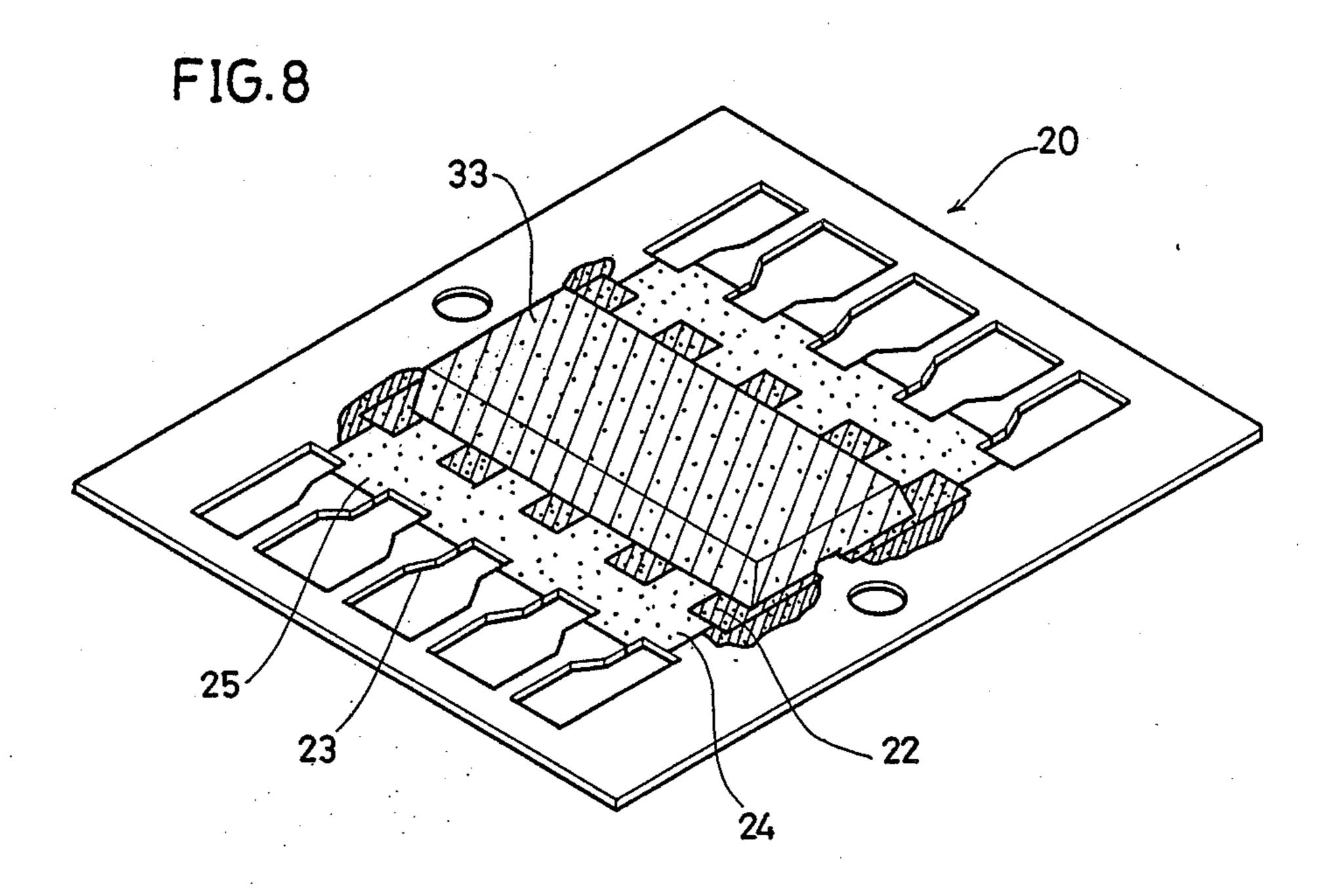

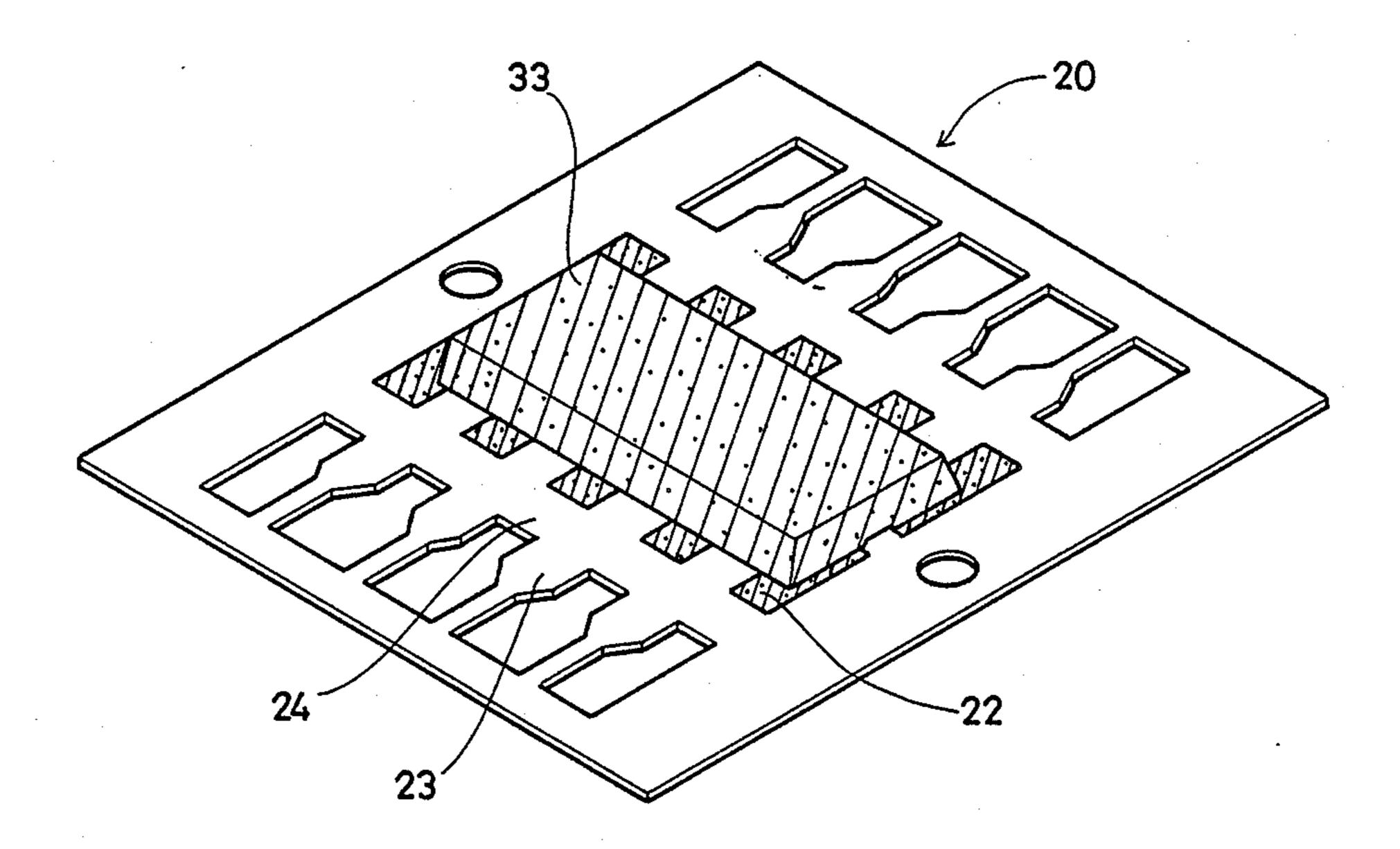

FIGS. 8 and 9 are perspective views showing the resin sealing process.

# DESCRIPTION OF THE PRFERRED EMBODIMENTS

According to FIG. 5, a lead frame 20 is formed of a thin metal plate and it has a prescribed pattern formed by etching or pressing. The lead frame 20 has a die pad 21 for mounting a chip in the central position. A plurality of inner leads 22 are disposed around the die pad 21 with spacing between each other. A plurality of outer leads 23 are formed around the inner leads 22. The inner leads 22 and the outer leads 23 are connected integrally by a tie bar 24.

Lead plated portions 25 are formed on the surface of those portions of the inner leads 22, the outer leads 23 and the tie bar 24 which will not be covered with the sealing resin (package) in the subsequent molding process. The lead plated portions 25 are formed on the

upper surface, the rear surface and the side of the inner leads 22, the outer leads 23 and the tie bar 24 from the external periphery of the sealing resin which is provided in the subsequent process to the portion slightly extending over the tie bar 24. The range usually corre- 5 sponds to that range of the final product which remains exposed with no covering of the sealing resin. The plating thickness of the lead plating portion 25 is in the range of about  $1\mu \sim 20\mu$ , according to the dimension accuracy of the mold or the lead frame and to the pres- 10 sure of clamping of the press. A range of  $5\mu \sim 10\mu$  is preferable.

Referring to FIG. 5, the hatched portions are the Ag or Au plated portions 26 which facilitate the junction of the semiconductor chip and the connection between the 15 electrodes of the semiconductor chip and the inner leads 22 by, for example, Au wires. The above described lead plated portions 25 can be more easily formed by simultaneously plating in the plating process of the plated portion 26.

Next, a method for manufacturing a semiconductor device using the said lead frame 20 will be described.

First, a semiconductor chip 27 is attached to the die pad 21 in the central portion of the lead frame 20 of FIG. 5, as shown in FIG. 6, and then fine wires 28 (e.g. 25 Au) are applied to electrically connect the electrode of the chip 27 and the inner leads 22. The junction temperature of the semiconductor chip 27 is about 200° C. when resin junction is carried out, while the junction temperature of the fine wire 28 is about 250° C.

Then, as shown in FIG. 7, the lead frame 20 is interposed between the upper mold 30 and the lower mold 31 of the metal mold. Then, a thermosetting resin such as epoxy resin is injected in the cavity 32 using, for example, the low pressure transfer molding, forming a 35 resin layer 33. The temperature of the mold is about 180° C. at the time of resin sealing.

Now, the melting point of the lead is 327° C., so that the lead plated portions 25 do not melt during the manufacturing process. Meanwhile, lead has less hardness so 40 that it is easily transformed when the lead frame 20 is pressed by the mold and it eliminates the gap between the mold and the lead frame 20. Therefore, the lead plated portions 25 occupy the gap between the metal mold and the lead frame 20, preventing entrance of the 45 introduced resin. Consequently, the undesired bur is not generated at that portion. Namely, the lead plated portions 25 occupy the gap between the lead frame 20 and the upper mold 30 and the lower mold 31 by the deformation due to the clamping pressure of the press, pre- 50 venting the out flow of the resin which otherwise forms the bur. Meanwhile, if the resin outflows between the lead plated portion 25 and the mold, the bur will be deposited on the lead plated portion 25.

After the resin sealing, usually a solder plating is 55 carried out on the outer leads 23 in order to enhance the facility of lead soldering. During this process, by dipping the lead plating into a solution for pealing or removing the layer (15% solution of nitric acid), the lead plating can be easily removed and, at the same time, the 60 metal layer is a thin substantially pure lead metal layer. bur deposited on the lead plating is completely eliminated. FIG. 8 is a perspective view of the lead frame 20 after the molding process. When this structure is subjected to the peeling process, the lead plated portions 25

on the leads 22, 23 and the tie bar 24 are completely eliminated as shown in FIG. 9. Even if the resin is deposited on the lead plated portions 25, it will be completely eliminated with the melting of the lead plated portions 25.

As described above, by providing a soft thin metal layer such as lead on the lead frame of the resin outflowing portion during the resin sealing of the manufacturing process of a semiconductor device, the generation of burs during the sealing process can be prevented and, if there is a little outflow, it will be completely eliminated during the peeling process of the plating process. In addition, conventional bur eliminating processes and facilities such as honing can be eliminated.

Although lead is used as a plating material in the above described embodiment, other metals (for example Ag, Sn) can be used. These metals must not melt at the temperature of the semiconductor chip junction, the fine wire connection for electrically connecting the electrodes of the semiconductor chip and the inner leads and the resin sealing. They must also have a hardness such that they are easily deformed when the lead frame is pressed by the metal mold during the molding process. Although plating is employed in the above described embodiment as a method for depositing lead onto the lead frame 20, other method such as pressure welding of a thin film or frame coating can be employed.

Although the present invention has been described and illustrated in detail, it is clearly understood that the same is by way of illustration and example only and is not to be taken by way of limitation, the spirit and scope of the present invention being limited only by the terms of the appended claims.

What is claimed is:

- 1. In a lead frame of a resin sealed type semiconductor device package wherein the lead frame includes a die pad disposed in a central portion thereof with an inner lead, a tie bar and an outer lead formed around the die pad with the tie bar disposed between the inner and outer lead, a chip mounted to the pad and wires connecting the chip to a metal plated surface of the inner lead, and molded resin material covering the chip and at least portions of said metal plated surface of the inner lead and the wires, the improvement comprising said molded resin material having at least a pair of border edges free of burs or bur residues and overlying a surface of the inner lead, said border edges free of burs or bur residues being formed by disposing a thin metal layer on predetermined surfaces of at least the inner lead with edges of said thin metal layer defining said border edges of resin material disposed to cover said chip and metal plated surface portions of the inner lead, with said thin metal layer having a melting temperature greater than the temperature of liquid resin material with said thin metal layer removed from the lead frame subsequent to solidification of the resin material.

- 2. In the lead frame of claim 7, wherein said thin

- 3. A lead frame for a semiconductor device according to claim 2, wherein the thickness of said thin lead metal layer is about  $1\mu \sim 20\mu$ .