## United States Patent [19]

### Ueda et al.

[11] Patent Number:

4,918,434

[45] Date of Patent:

Apr. 17, 1990

| [54] | T.V. GAMI                                                                                                                                                                                                | E SYSTEM                                                         |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| [75] | Inventors:                                                                                                                                                                                               | Hiroo Ueda, Toyonaka; Hiromitsu<br>Yagi, Itami, both of Japan    |  |  |

| [73] | Assignees:                                                                                                                                                                                               | Nintendo Co., Ltd., Kyoto; Ricoh Co., Ltd., Tokyo, both of Japan |  |  |

| [21] | Appl. No.:                                                                                                                                                                                               | 344,540                                                          |  |  |

| [22] | Filed:                                                                                                                                                                                                   | Apr. 25, 1989                                                    |  |  |

|      | Relat                                                                                                                                                                                                    | ed U.S. Application Data                                         |  |  |

| [60] | [60] Continuation of Ser. No. 28,005, Mar. 18, 1987, abandoned, which is a continuation of Ser. No. 709,342, Mar. 6, 1985, abandoned, which is a division of Ser. No. 564,091, Dec. 21, 1983, abandoned. |                                                                  |  |  |

| [30] | Foreign                                                                                                                                                                                                  | 1 Application Priority Data                                      |  |  |

|      | 22, 1982 [JP<br>23, 1982 [JP                                                                                                                                                                             | -                                                                |  |  |

| [52] | U.S. Cl                                                                                                                                                                                                  |                                                                  |  |  |

| [56] |                                                                                                                                                                                                          | References Cited                                                 |  |  |

|      | U.S. F                                                                                                                                                                                                   | ATENT DOCUMENTS                                                  |  |  |

| 4,106,056 | 8/1978 | Naguma et al 358/47 |

|-----------|--------|---------------------|

| •         |        | Russo               |

| 4,271,409 | 6/1981 | Filliman            |

| 4,442,428 | 4/1984 | Dean et al 340/703  |

Primary Examiner—David K. Moore

Assistant Examiner—Jeffery A. Brier

Attorney, Agent, or Firm—Nixon & Vanderhye

#### [57] ABSTRACT

A T.V. game system for displaying a desired picture on the screen of a raster scanning type T.V. set includes a motion picture pattern generator, a still picture pattern generator, a central processing unit for controlling the overall operation of the system under the control of the operator, and a picture processing unit for combining motion and still picture patterns to form a video signal to be supplied to the T.V. set, whereby the picture processing unit includes a motion picture attribute table memory which stores information relating to motion picture pattern for the next following frame during the horizontal blanking period and a temporary memory which stores information relating to motion picture pattern to be displayed in the next following line by accessing the motion picture attribute table memory during the scanning of current line.

#### 14 Claims, 7 Drawing Sheets

Fig. 1b PRIOR ART

Fig. 2 PRIOR ART

Apr. 17, 1990

Fig. 4a

Sheet 3 of 7

| VERTICAL POSITION   | 0  |

|---------------------|----|

| CHARACTER NO.       | 0  |

| ATTRIBUTE           | 0  |

| HORIZONTAL POSITION | 0  |

|                     |    |

| VERTICAL POSITION   | 63 |

| CHARACTER NO.       | 63 |

| ATTRIBUTE           | 63 |

| HORIZONTAL POSITION | 63 |

U.S. Patent

#### T.V. GAME SYSTEM

This is a continuation of application Ser. No. 07/028,005, filed Mar. 18, 1987, now abandoned, which 5 is a continuation of Ser. No. 709,342, filed Mar. 6, 1985, now abandoned, which in turn is a divisional of Ser. No. 564,091, filed Dec. 21, 1983, now abandoned.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention generally relates to image processing technology for combining two or more picture patterns into a single picture frame for display on a picture tube such as a T.V. set, and particularly to an image processing system for displaying a picture frame by combining a motion picture pattern, which may be varied under the control of the operator, with a still picture pattern which defines the background of picture frame. More specifically, the present invention relates to a T.V. 20 game system in which motion picture information and still picture information are controlled independently from each other and they are combined into a series of frames which are then displayed on the T.V. screen.

#### 2. Description of the Prior Art

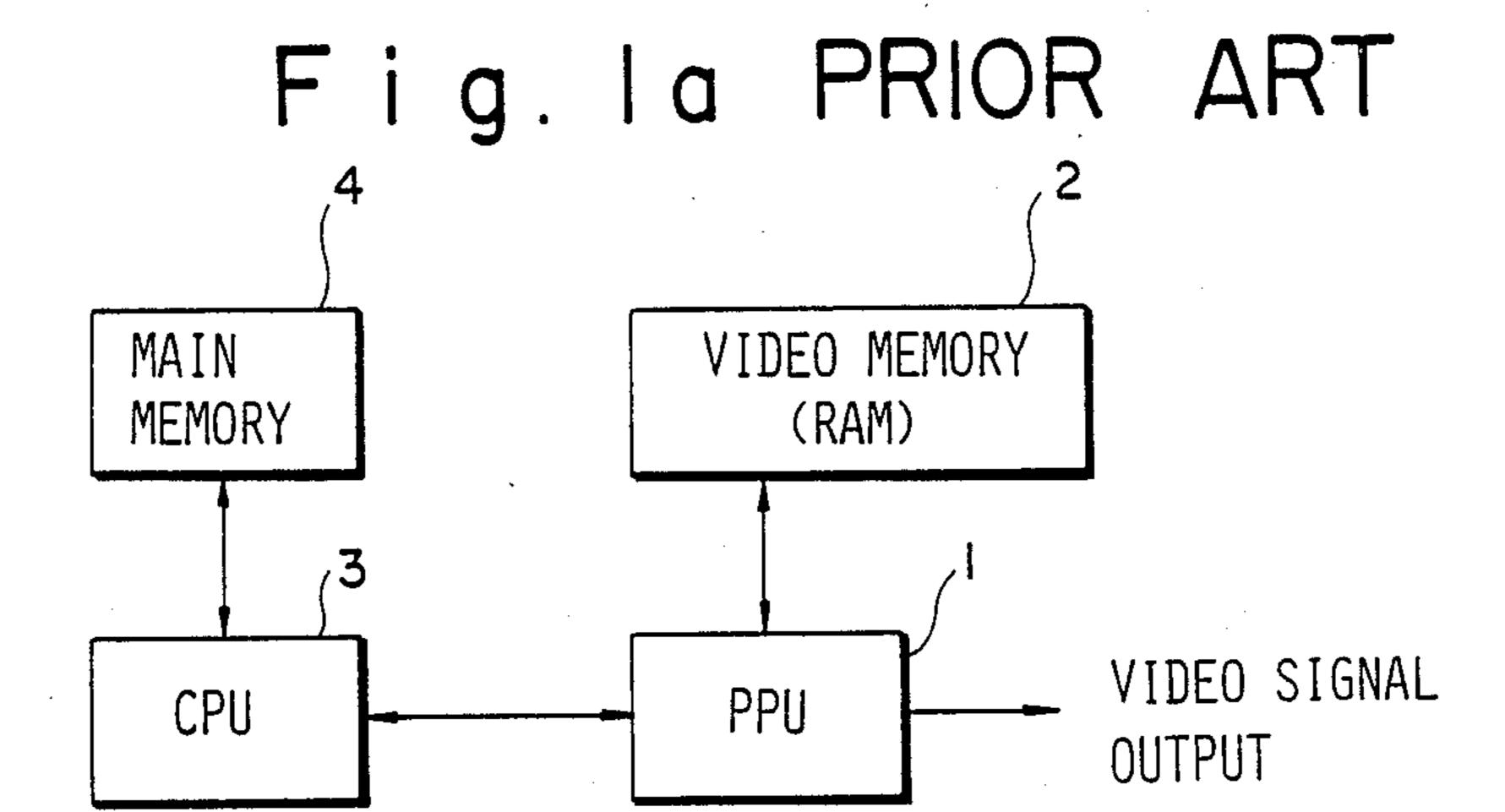

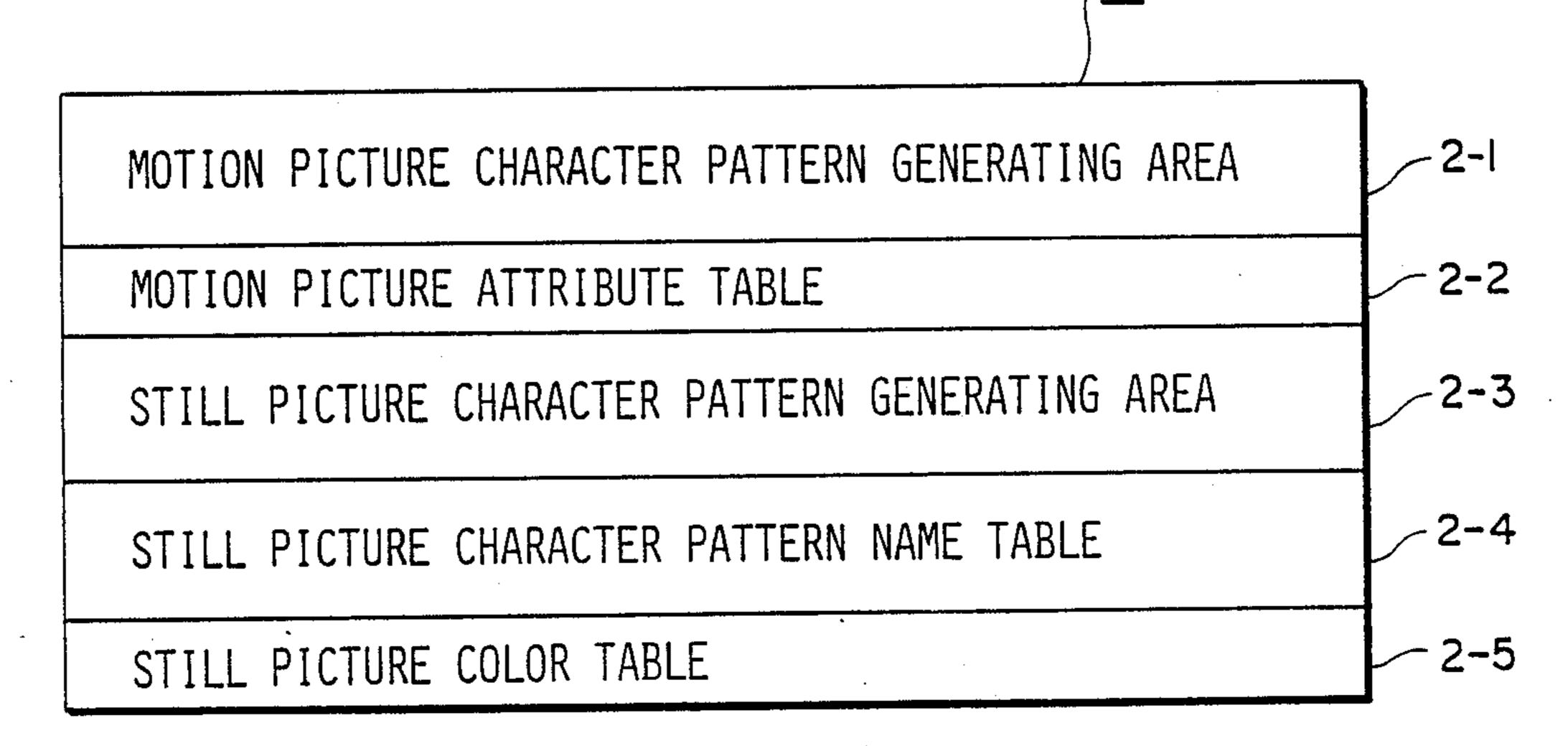

FIG. 1a shows a prior art T.V. game system which includes a picture processing unit (hereinafter, also referred to as "PPU") 1 which comprises a random access memory (hereinafter, also referred to as "RAM") and is connected to a video memory 2 and to a central pro- 30 cessing unit (hereinafter, also referred to as "CPU") 3, which, in turn, is connected to a main memory 4. In the system of FIG. 1a, under the control of CPU 3, motion and still picture data are transferred from the main memory 4 to the video memory 2 to be stored therein 35 temporarily, and then the PPU 1 receives appropriate data from the video memory 2 and to supply an output as a video signal to a T.V. set (not shown) for display under the control of the CPU 3. A memory map contained in the video memory 2 is shown in FIG. 1b, and, 40 as shown, the memory map includes a motion picture character pattern generating area 2-1, a motion picture attribute table 2-2 which is rewritten for each frame to be displayed during the vertical blanking period, a still picture character pattern generating area 2-3, a still 45 picture character pattern name table 2-4 and a still picture color table 2-5.

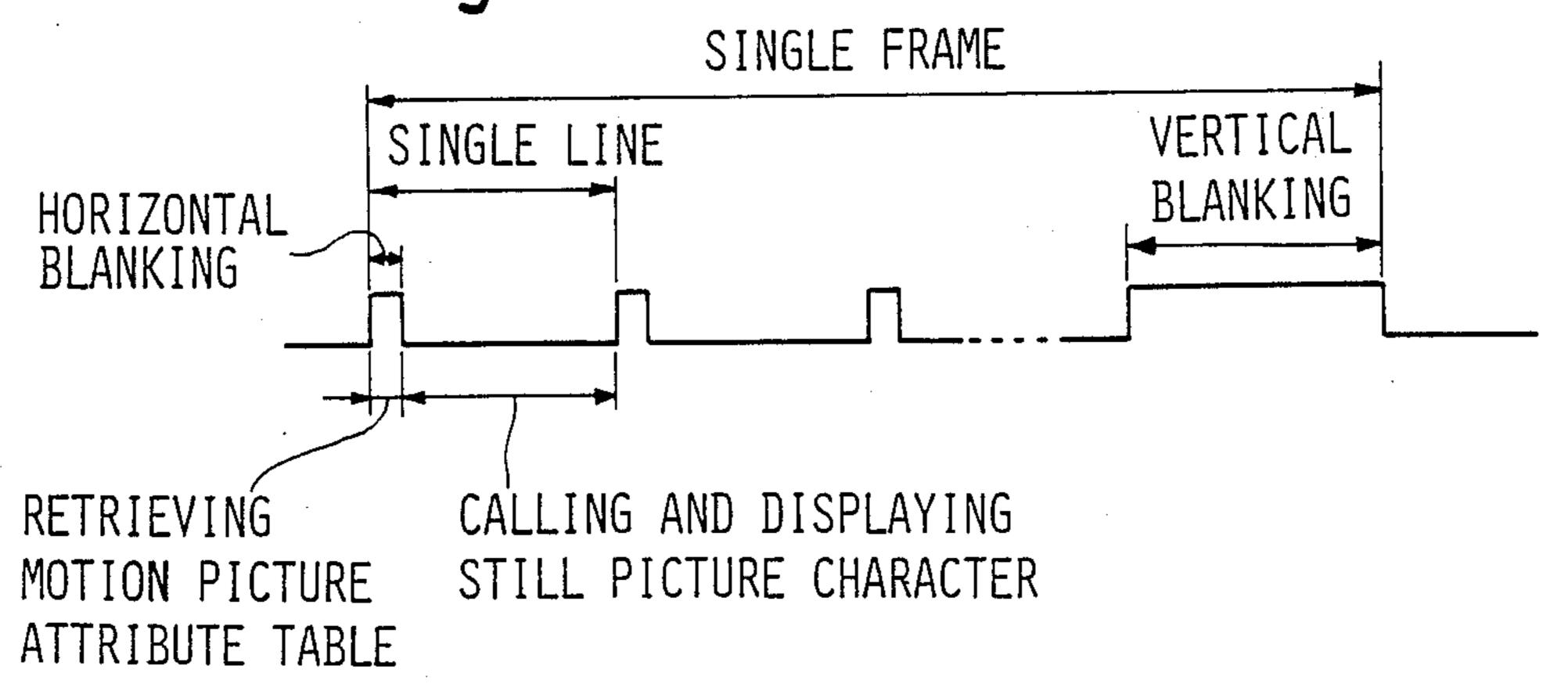

Described the operation of the above-described system with reference to FIG. 2, during the horizontal blanking period in carrying out scanning along horizon- 50 tal line sectors, the motion picture attribute table 2-2 is accessed under the control of the operator thereby retrieving the attributes of motion picture pattern to be displayed in the next scanning line. Then, on the basis of the thus retrieved attributes, desired motion picture 55 character pattern data is outputted from the motion character pattern generating area 2-1 during the same horizontal blanking period thereby generating a motion. picture pattern. On the other hand, as the line scanning of the display screen proceeds, a pattern name and a 60 color code are read out from the addresses, which corresponds to a display position, of still picture character pattern name table 2-4 and the still picture color table 2-5, respectively. On the basis of the pattern name thus read out, a pattern data is outputted from the still pic- 65 ture character pattern generating area 2-3 so that a still picture pattern is generated in real time. If there occurs a collision between the still picture pattern data and the

motion picture pattern data at the same position on the display screen, either one of them is allowed to be displayed in accordance with a predetermined priority.

In the above-described prior art system, since external address and data buses are used to call and obtain still picture character data during the line scanning period and also the number of pins usable for interconnections between components is limited, the retrieving of the motion picture attribute table and the calling of motion picture character pattern data on the basis of the result of such retrieval must all be carried out during the horizontal blanking period. For this reason, the number of motion picture characters which may be displayed during a single line scanning period is rather limited so is the kind of motion picture characters which may be displayed in a single frame. As a result, displayed pictures tend to be dull and they do not change as fast as pleasing to a viewer.

#### SUMMARY OF THE INVENTION

Therefore, it is a primary object of the present invention to obviate the above-described disadvantages of the prior art and to provide an improved image processing system.

Another object of the present invention is to provide an image processing system which is suitable for application as a T.V. game system.

A further object of the present invention is to provide an image processing system capable of displaying the increased number and kinds of moving characters without increasing the number of pins when constructed in the form of ICs.

A still further object of the present invention is to provide an improved color encoder particularly suited for use in a T.V. game system.

A still further object of the present invention is to provide an improved T.V. game system.

Other objects, advantages and novel features of the present invention will become apparent from the following detailed description of the invention when considered in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1a is a block diagram showing a prior art T.V. game system;

FIG. 1b is a schematic illustration showing the structure of the memory map employed in the video memory 2 shown in FIG. 1a;

FIG. 2 is a timing chart which is useful for explaining the operation of the system shown in FIGS. 1a and 1b;

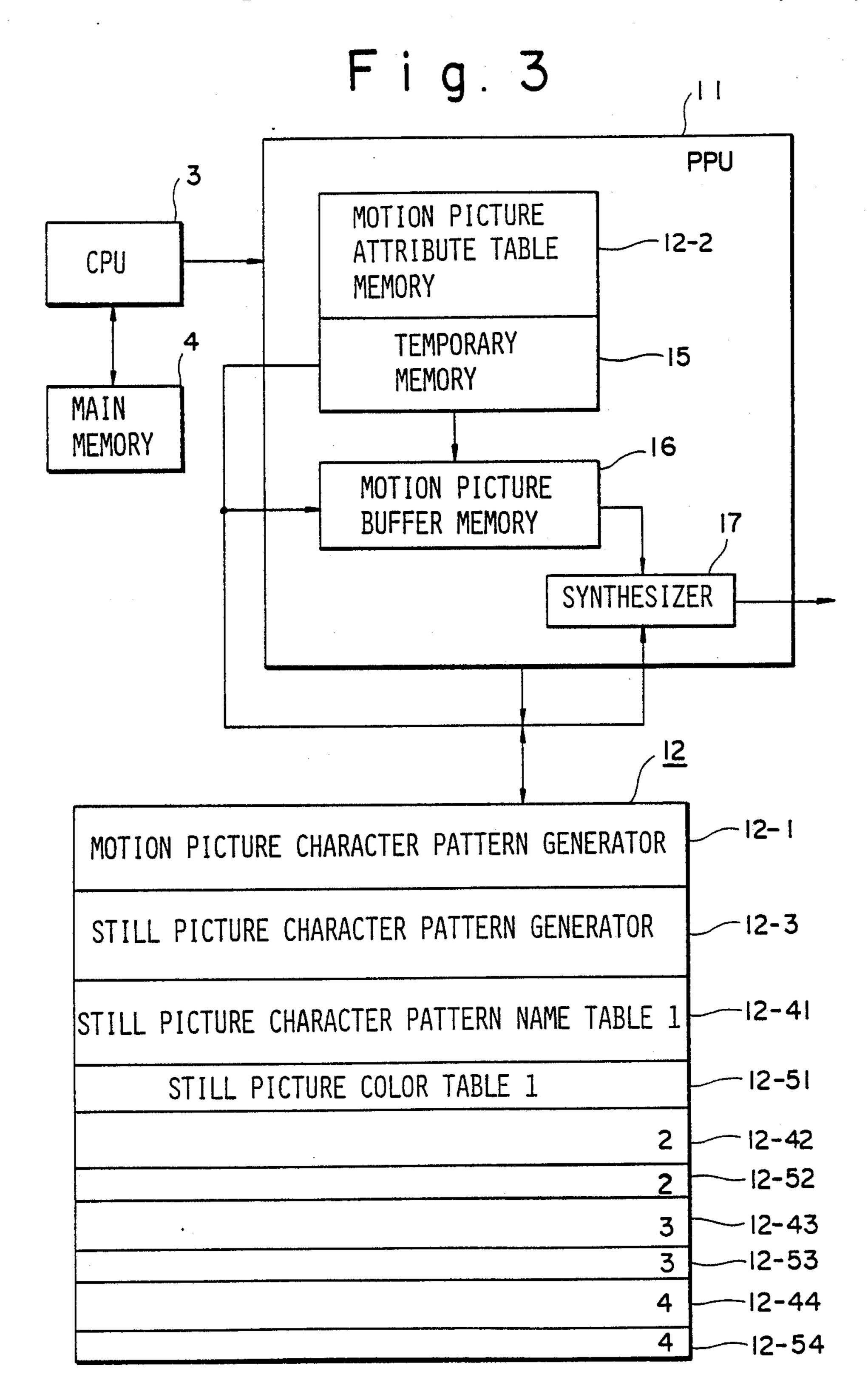

FIG. 3 is a block diagram showing the T.V. game system constructed in accordance with one embodiment of the present invention;

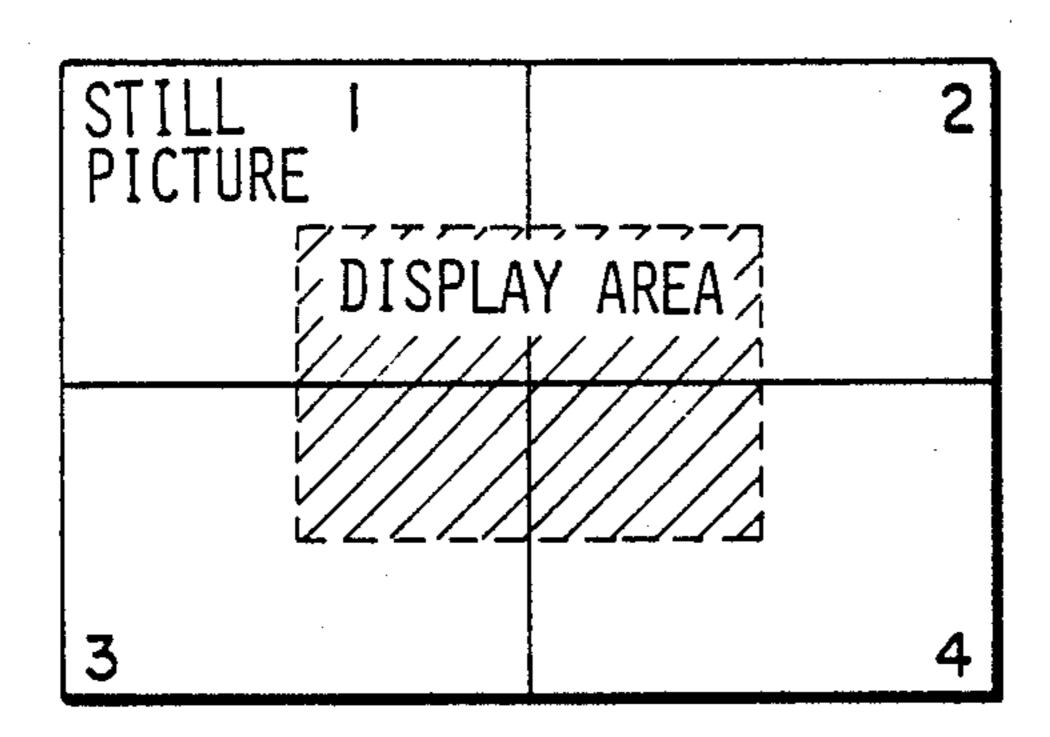

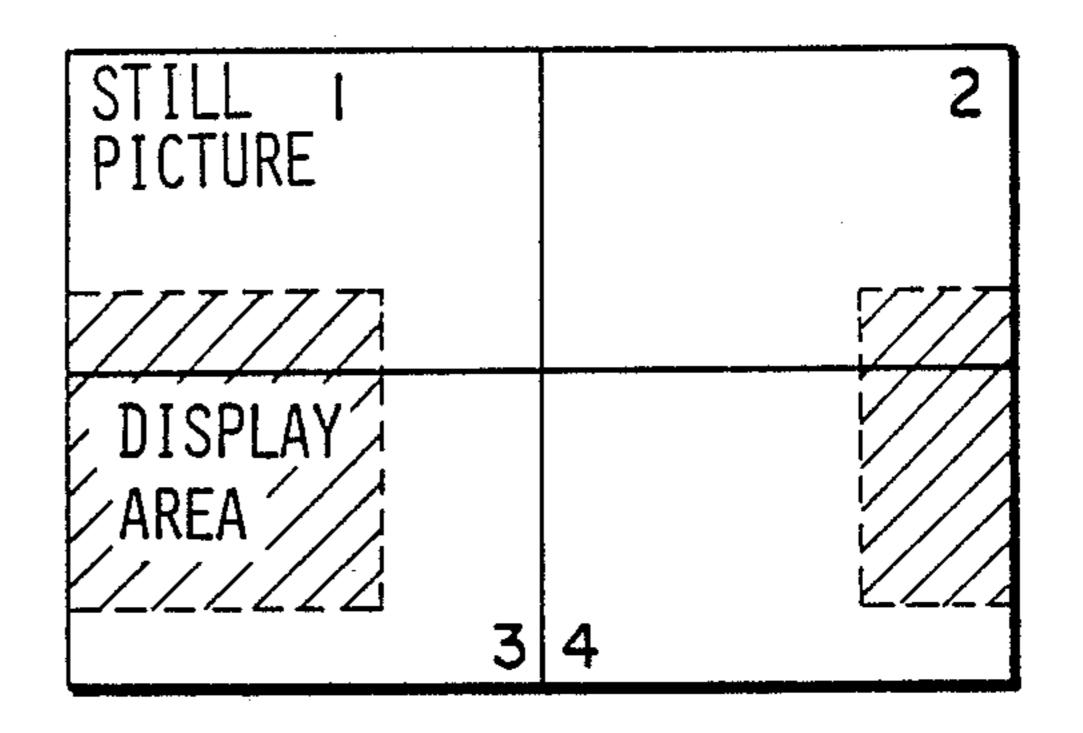

FIGS. 4a and 4b are schematic illustrations showing examples of displaying the background on the T.V. screen;

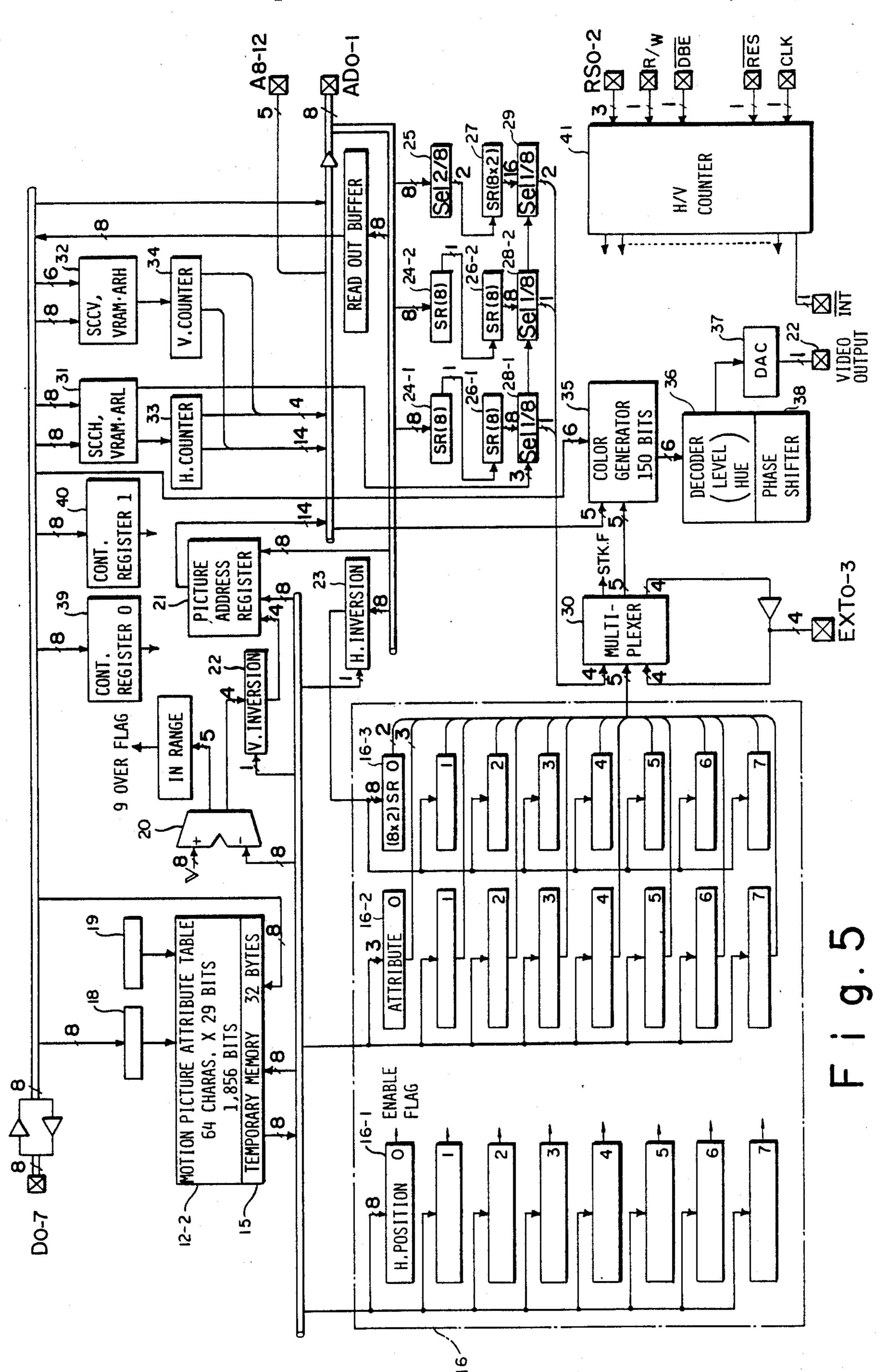

FIG. 5 is a block diagram showing the detailed structure of the system shown in FIG. 3;

FIG. 6 is a schematic illustration showing the memory map of the motion picture attribute table memory 12-2 shown in FIG. 5;

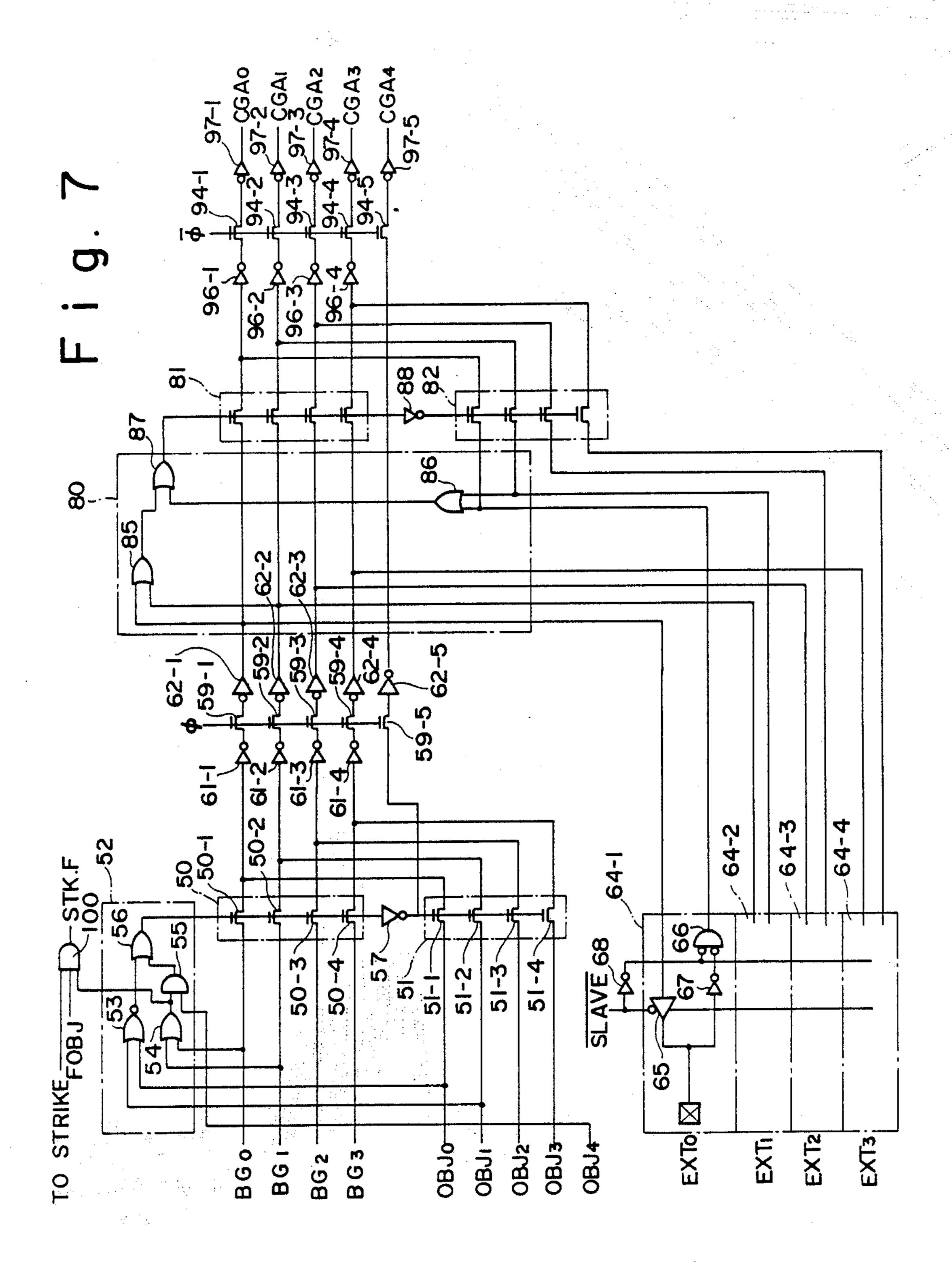

FIG. 7 is a circuit diagram partly in logic symbols showing the detailed structure of the multiplexer 30 shown in FIG. 5;

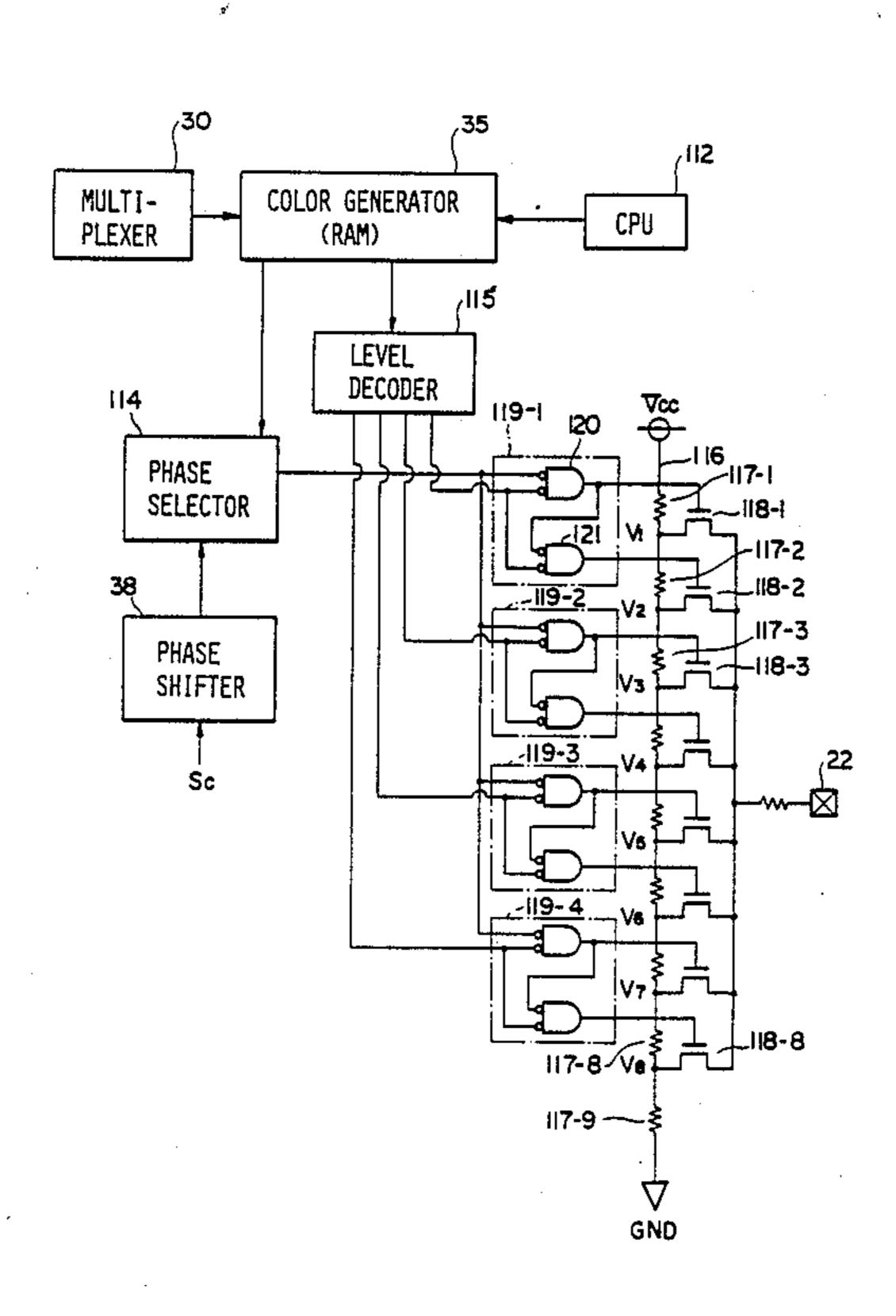

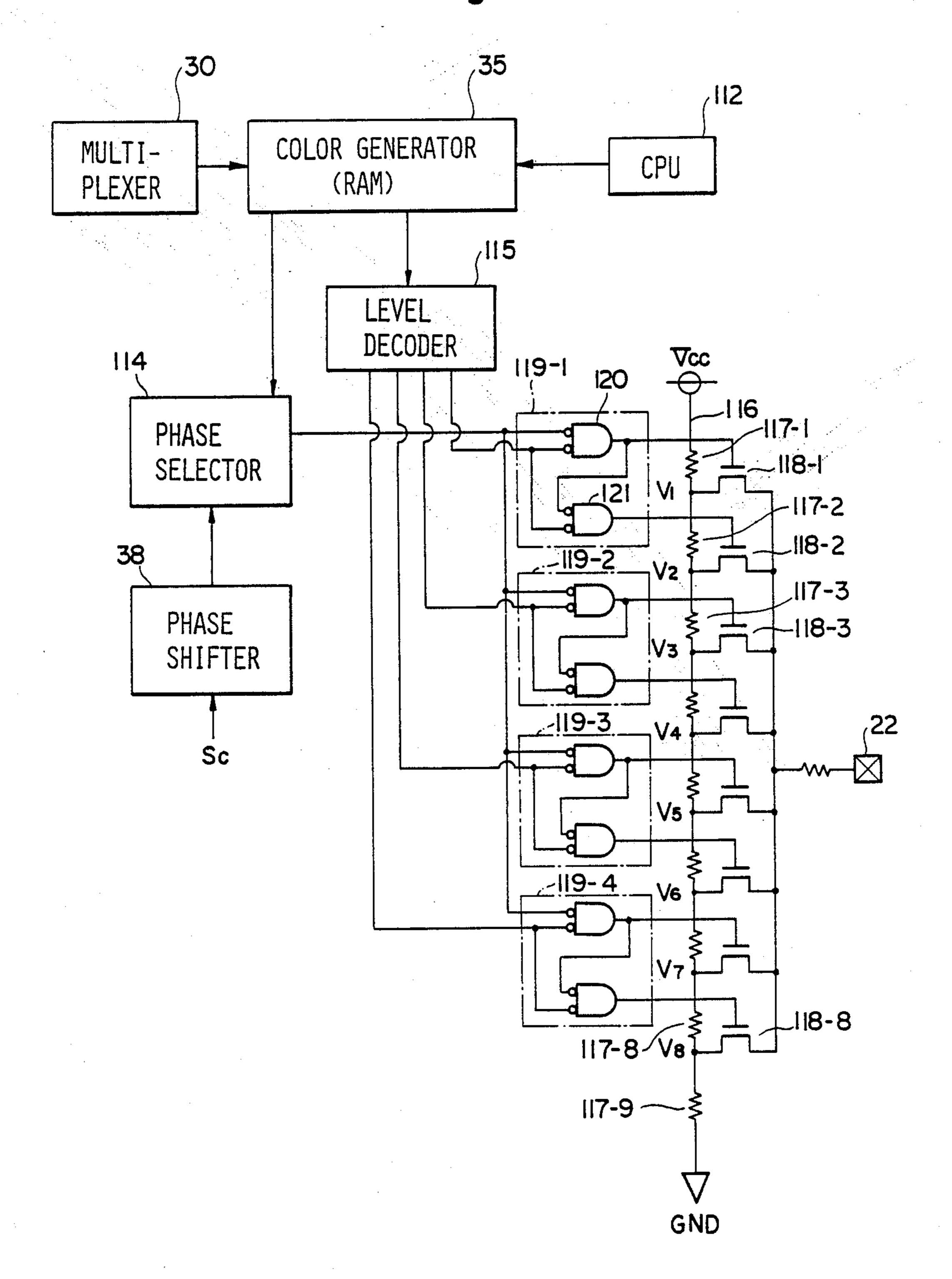

FIG. 8 is a block diagram showing the detailed structure of the color generator 35 shown in FIG. 5;

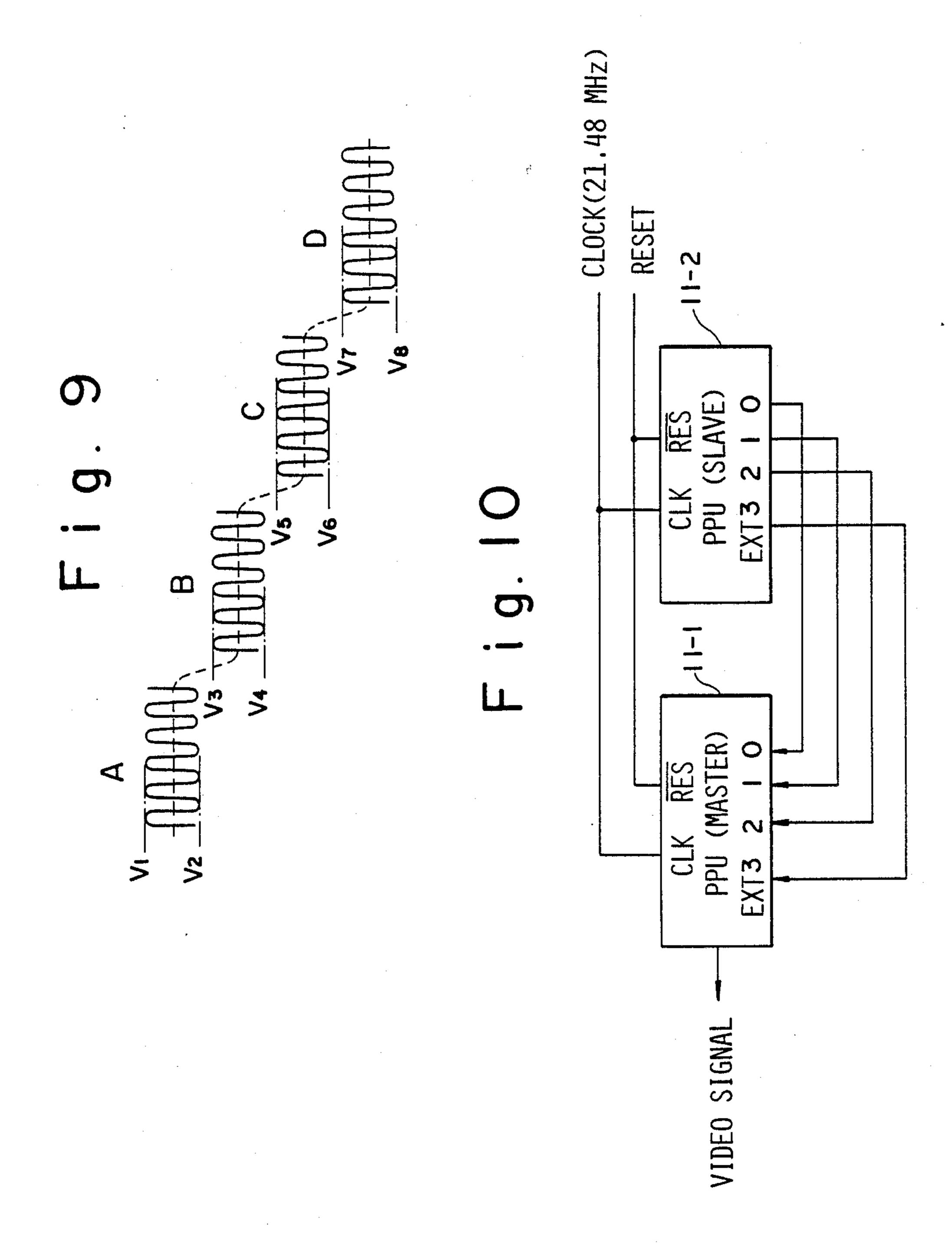

FIG. 9 is a schematic illustration showing color signals at different levels which may be produced as outputs from the structure of FIG. 8; and

FIG. 10 is a block diagram showing another embodiment in which two picture processing units (PPU) are 5 provided as connected to each other.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 3 is a block diagram showing the image process- 10 ing system constructed when applied as a T.V. game system in accordance with one embodiment of the present invention. As shown, the present image processing system or T.V. game system includes a picture processing unit ("PPU") 11 provided with a motion picture 15 attribute table memory 12-2 which is typically comprised of a RAM and which is rewritten for each frame with the information supplied from the video memory, as different from PPU 1 of the prior art system shown in FIG. 1a. PPU 11 also includes a temporary memory 15 20 which is also typically comprised of a RAM. The temporary memory 15 stores the motion picture character data for a single scanning line by retrieving the motion picture attribute table memory 12-2 and it is rewritten for each scanning line. Also provided in PPU 11 is a 25 motion picture buffer memory 16 which is typically comprised of a RAM whose contents are rewritten for each scanning line and which stores the attributes and pattern data of the motion picture character stored in the temporary memory 15. PPU 11 further includes a 30 synthesizer 17 which is connected to receive an output signal from the motion picture buffer memory 16 and an output signal from a still picture character pattern generator 12-3 or an output signal supplied from an external circuit, as the case may be, to supply a particular signal, 35 which is a combination of two or more input signals, as its output in accordance with predetermined conditions.

A video memory 12 is provided external to PPU 11 and it includes a motion picture character pattern generator 12-1, a still picture character pattern generator 40 12-3 typically comprised of a ROM or RAM, four still picture character pattern name tables 12-41 through 12-44 typically comprised of RAMs and four still picture color tables 12-51 through 12-54 typically comprised of RAMs. As shown in FIG. 3, PPU 11 is also 45 connected to CPU 3 which controls the overall operation of the present system and which is connected to a main memory 4.

In operation, when a main switch (not shown) is turned on or programs containing different games are 50 changed, the contents of the still picture character pattern name tables 12-41 through 12-44 and still picture color tables 12-51 through 12-54 are rewritten in accordance with the main memory 4 under the control of CPU 3. Then, at the first vertical blanking period of a 55 single frame, the contents of the motion picture attribute table memory 12-2 are also rewritten in accordance with the main memory 4 under the control of CPU 3.

In PPU 11, during line scanning, the motion picture character pattern to be displayed in the next scanning 60 line is retrieved from the motion picture attribute table memory 12-2 and stored into the temporary memory 15, and, then, during the horizontal blanking period, the motion picture character pattern generator 12-1 is retrieved on the basis of the data then stored in the tempo- 65 rary memory 15 via address and data buses, thereby causing the data necessary to display a motion picture character for the next line to be stored into the motion

picture buffer memory 16. After initiation of line scanning, when the corresponding horizontal position has been reached, the motion picture character pattern data is supplied to the synthesizer 17 from the motion picture buffer memory 16, and at the same time the still picture character pattern name tables 12-41 through 12-44 and the color tables 12-51 through 12-54 are retrieved in real time via address and data buses so that the still picture character pattern data thus retrieved and defining the background of a displayed picture is supplied from the still picture character pattern generator 12-3 to the synthesizer 17.

In the embodiment illustrated in FIG. 3, the still picture character pattern name tables 12-41 through 12-44 and the still picture color tables 12-51 through 12-54 are larger in area by four times than the display area or screen. Accordingly, a desired still picture may be displayed on the display screen by using only one of the four still picture character pattern name tables, or, alternatively, the display area may be set at any location within the scope of four frames to define a desired background to be displayed on the screen as shown in FIGS. 4a and 4b. The display area may be shifted horizontally as well as vertically independently from each other in a scrolling fashion with a dot as a unit. Such a scrolling technique is disclosed, for example, in the Japanese Patent Laid-open Pub. No. 55-96186.

It is to be noted that in the video memory 12 the motion picture character pattern generator 12-1 and the still picture character pattern generator 12-3 may not only be used separately form each other as described above but also be used in common. That is, the same character pattern generator may be accessed by an address for motion picture and another address for still picture thereby producing both of motion picture and still picture characters from the same character pattern generator. Such a structure is advantageous because an increased number of characters may be generated using a character pattern generator of the same capacity as compared with the case in which a character pattern generator is not used in common.

An assumption is made here that the display area or screen has the width of 256 dots in the horizontal direction and the height of 240 dots in the vertical direction and a character constituting a motion picture or still picture is defined by a matrix of 8 dots by 8 dots. It is also assumed that the max. number of motion pictures to be displayed on a single horizontal line is eight and thus 64 motion pictures may be displayed on the screen at maximum at the same time. Furthermore, in the motion picture character pattern generator 12-1 and the still picture character pattern generator 12-3, a single dot or picture element to be displayed on the screen is represented by two bits and thus a single character formed by 8 dots by 8 dots is represented by 16 bytes.

FIG. 5 shows the detailed structure of PPU 11 shown in FIG. 3. Now, it will first be described as to the structure for displaying a motion picture character pattern. The motion picture attribute table memory 12-2 for storing the attributes of motion picture characters for a single frame has a capacity to store sixty-four motion picture characters as shown in FIG. 6 and it has areas for storing a vertical position (8 bits), a character number (8 bits), an attribute (5 bits) and a horizontal position (8 bits) for each character to be displayed. The attribute data includes 1 bit for each of horizontal and vertical inversions, 1 bit for determining the priority between

display.

Storage of data from CPU 3 into the motion picture attribute table 12-2 is carried out via input terminals  $D_{0-7}$  and its storage position is determined by a motion 5 picture attribute memory address register 18. While the previous line is being scanned, the retrieval of the motion picture character to be displayed on the next following line is carried out by a comparator 20 using a vertical position data. At the comparator 20, the signal 10 indicating the vertical position of the next line to be displayed is compared with the vertical position data of each character stored in the motion picture attribute table memory 12-2 to determine whether they agree (in-range) or not. The motion picture character which 15 without change. has been found to be in-range is then stored into the temporary memory 15 by means of a temporary memory register 19. The temporary memory 15 is provided with an area capable of storing eight motion picture characters at the same time. Accordingly, if nine or 20 more motion picture characters have been found to be in-range, only eight of them are stored into the temporary memory 15 with a flag indicating the presence of nine or more being posted.

motion and still picture characters and 2 bits for color

The motion picture buffer memory 16 whose con- 25 tents are rewritten during the horizontal blanking period also has the memory area capable of storing eight motion picture characters to be displayed on the next line, and, in the buffer memory 16, for each motion picture character, a horizontal position area (8 bits) 30 16-1, an attribute area (3 bits) 16-2 and a pair of shift registers (8 bits) 16-3 are allocated. The horizontal position area 16-1 stores a horizontal position data supplied from the temporary memory 15, and this area is structured in the form of a down-counter which down- 35 counts in accordance with the scanning along a horizontal scanning line, and when the count has reached "0", the motion picture character is supplied as its output. The attribute area 16-2 stores a bit for determining the priority and two bits of color data and thus three 40 bits in total among the attribute data stored in the temporary memory 15. Each of the shift registers 16-3 stores 8-bit data supplied as an output from the motion picture character pattern generator 12-1 in accordance with the character number of motion picture character 45 in the temporary memory 15. The reason why a pair of shift registers 16-3 are provided in parallel is that a picture element is represented by two bits.

In FIG. 5 is also provided a picture address register 21 which retrieves the character pattern generator 12-1 50 or 12-3 from terminals  $AD_{0-7}$  through buses by means of motion picture character data, which has been found to be in-range, during the horizontal blanking period and of still picture character data during the line scanning period and calls or obtains corresponding charac- 55 ter pattern data. In case where a vertical inversion data is contained in the motion picture character data, the retrieving operation is carried out with the vertical address inverted within the motion picture character pattern in accordance with a signal supplied from an 60 inverter 22. There is also provided a horizontal inverter 23 which functions to supply the retrieved motion picture character pattern data with the order of transmission reversed to the shift register 16-3 of motion picture buffer memory 16 if a horizontal inversion signal is 65 contained in the motion picture character data.

Next, a description will be made as to the structure for displaying a still picture (background) character

6

pattern. As line scanning proceeds, still picture character pattern data of the corresponding position is supplied through the terminals AD<sub>0-7</sub> in accordance with a signal from the picture address register 21. This character pattern data is comprised of a two bit data for character pattern and another two bit data for color display for a single dot on the display screen, so that the character pattern data and color display data are inputted to the shift registers 24-1, 24-2 and a selector 25, respectively, which are then inputted to selectors 28-1, 28-2 and 29 in the form of 8 and 16 bits through shift registers 26-1, 26-2 and 27, respectively. In the case where no scrolling operation is to take place, these data are then outputted to a multiplexer 30 in the order mentioned without change.

The structure of FIG. 5 also includes a register 31 which has a dual function as a horizontal scroll register (SCCH) and as a video memory address register (VRAM.ARL) for counting the lower address of video memory and another register 32 having a dual function as a vertical scroll register (SCCV) and as a video memory address register (VRAM.ARH) for counting the upper address of video memory. In the scroll registers 31 and 32 are set offset values (scrolling initiation position) at the time of scrolling in the order of that in the horizontal direction and that in the vertical direction, and the selection of selectors 28-1, 28-2 and 29 is carried out in accordance with these offset values. On the other hand, when used as video memory address registers 31 and 32, upon completion of read out/write in operation of video memory 12, values of 1 and 32 are respectively added automatically. Also provided as connected to the registers 31 and 32 are horizontal and vertical counters 33 and 34, respectively.

The multiplexer 30 constitutes part of the synthesizer 17 shown in FIG. 3 and it receives motion picture character pattern data and still picture character pattern data and moreover another motion picture character pattern data from terminals EXT<sub>0-3</sub>, as the case may be. The multiplexer 30 then supplies its output signal to a color generator 35 in accordance with the priority order determined by the attribute data within the motion picture character pattern data. If desired, the multiplexer 30 may so function to supply its output signal to the exterior through the terminals EXT<sub>0-3</sub>. In the case where a collision occurs between a particular motion picture character pattern data and a still picture character pattern data in the multiplexer 30, a flag (STK.F) for that effect is raised.

The color generator 35 is typically comprised of a RAM and it is accessed by a 6-bit code comprised of a 2-bit code designating one of four levels and a 4-bit code designating one of 12 kinds of phases (hue), so that selection is made by a 4-bit data representing a character pattern data supplied as an output from the multiplexer 30. A decoder 36 is provided as connected to receive an output signal from the color generator 35 as its input thereby converting it into a level selection signal and a phase selection signal. Also provided as connected to receive an output signal from the decoder as its input is a digital-to-analog converter (DAC) 37 which serves to have its input converted into and supplies as its output an analog video signal. A phase shifter 38 is provided as connected to the decoder 36.

It is to be understood that the synthesizer 17 of FIG. 3 is constructed by those elements of multiplexer 30, color generator 35, decoder 36, DAC 37 and phase shifter 38. Also provided are control registers 39 and 40

for determining the operating mode of PPU 11 and they receive data from CPU 3 via a counter 41.

FIG. 7 shows in detail the structure of multiplexer 30. As shown, the multiplexer 30 includes a transmission gate 50 for transmitting a 4-bit still picture character 5 pattern data (BGO-BG3) and it includes four MOS transistors 50-1 through 50-4 each corresponding to each bit. Also provided is another transmission gate 51 for transmitting a 4-bit portion (OBJO-OBJ3) among a 5-bit motion picture character pattern and it is provided 10 with four MOS transistors 51-1 through 51-4 one for each bit. Provided in the multiplexer 30 is a priority determining circuit 52 for determining to transmit either one of the still picture character pattern data BGO-BG3 forming a background of displayed picture and the 15 motion picture character pattern data OBJO-OBJ3 and it is so structured that a NOR circuit 53 receives OBJ0 and OBJ1 as its two inputs and an OR circuit 54 receives BG0 and BG1 as its two inputs. Data OBJ4 which determines the priority order and an output from 20 the OR circuit 54 are supplied as two inputs to an AND circuit 55 whose output is supplied as one input to another OR circuit 56 which also receives as its the other input an output from the NOR circuit 53. The OR circuit 56 is connected to supply its output to the gate of 25 each the MOS transistors 50-1 through 50-4 and to supply its inverted output to the gates of MOS transistors 51-1 through 51-4 via an inverter 57.

As a result, depending upon a combination of BG0, BG1, OBJ0, OBJ1 and OBJ4, either one of the transmis- 30 sion gates 50 and 51 is turned on, so that BG0-BG3 or OBJ0-OBJ3 and the ouput signal from the inverter 57 indicating the result of the priority order determination are transferred through inverters 61-1 through 61-4 and 62-1 through 62-5 via transmission gate transistors 59-1 35 through 59-5, which are turned on and off in accordance with a clock signal  $\phi$ .

Turn-over circuits 64-1 through 64-4 are also provided and they are appropriately activated by a slave signal SLAVE to thereby cause the terminals EXT0- 40 EXT3 to function either as input or output terminals when two PPUs are connected to each other. The turnover circuit 64-1 includes a driver circuit 65 which receives as its input either of data BG0 or OBJ0 and which also receives the SLAVE signal for controlling 45 the passage of data therethrough. Moreover, in order to control data input via the terminal EXT0, the turn-over circuit 64-1 includes a NAND circuit 66 which has one input connected to receive the data supplied via the terminal EXT0 through an inverter 67 and the remain- 50 ing input connected to receive the SLAVE signal via another inverter 68. The other turn-over circuits 64-2 through 64-4 are similarly structured.

Also provided is a master/slave priority order determining circuit 80 which causes a transmission gate 81 or 55 82 to be turned on in accordance with the SLAVE signal and input signals from BG0, BG1 (or OBJ0, OBJ1) and EXT0, EXT1 terminals, thereby determining to transfer the data from either one of the master and slave PPUs. BG0 and BG1 (or OBJ0 and OBJ1) are supplied 60 as inputs to an OR circuit 85 and the data supplied through the EXT0 and EXT1 terminals are inputted to a NOR circuit 86. The circuit 80 includes another OR circuit 87 which has its one input connected to receive an output signal from the OR circuit 85 and the remain-65 ing input connected to receive an output signal from the NOR circuit 86 and the OR circuit 87 is connected to supply its output signal to the gate of each of MOS

transistors provided in a transmission gate 81 and to supply its inverted output signal to the gate of each of MOS transistors in another transmission gate 82 via an inverter 88.

The data transferred through the transmission gate 81 or 82 then passes through inverters 96-1 through 96-4 and transmission gate MOS transistors 94-1 through 94-4 which are controlled by a clock signal φ and inverters 97-1 through 97-4 to be supplied as address signals CGAO-CGA3 for addressing the color generator 35 shown in FIG. 5. As a signal CGA4 which indicates whether CGA0-CGA3 are either BG0-BG3 or OBJ0-OBJ3, an output signal supplied from the priority determining circuit 52 is used after having been inverted by an inverter 94-5.

There is also provided an AND circuit 100 which functions to raise a collision flag (STK.F) when a collision has occurred between BG0-BG3 and OBJ0-OBJ3.

The operation of priority order determining circuit 52 of the multiplexer 30 shown in FIG. 7 may be summarized in the following table.

| 5 | OBJ0 + OBJ1 | BG0 + BG1 | OBJ4 | Data transferred thru<br>gate 50 or 51 |

|---|-------------|-----------|------|----------------------------------------|

|   | 0           | 0         | 0    | BG                                     |

|   | 0           | 1         | 0    | BG                                     |

|   | 1           | 0         | 0    | OBJ                                    |

|   | 1           | 1         | 0    | OBJ                                    |

|   | 0           | 0         | 1    | BG                                     |

| ) | 0           | 1         | 1    | BG                                     |

|   | 1           | 0         | 1    | OBJ                                    |

|   | 1           | 1         | 1    | · BG                                   |

Next, in the case where two PPUs are provided as connected to each other and the present PPU serves as a master, the SLAVE signal is "1". In the turn-over circuits 64-1 through 64-4, the NAND circuit 66 receives at its one input "0" through the inverter 68, so that the NAND circuit 66 is enabled thereby allowing data to be inputted through the terminals EXT0-EXT3. On the other hand, the driver circuit 65 is disbled since the SLAVE signal is "1", thereby inhibiting data to be outputted. Conversely, in the case where the present PPU serves as a slave, the SLAVE signal is "0" so that the NAND circuit 66 becomes disabled and the driver circuit 65 becomes enabled, thereby setting up the condition in which data may be outputted through terminals EXT0-EXT3.

Now, the operation of the master/slave priority order determining circuit 80 may be summarized as in the following table.

| 5 | BG0 + BG1<br>(OBJ0 + OBJ1) | EXT0 + EXT1 | SLAVE | Data transferred<br>thru gate 81 or 82 |

|---|----------------------------|-------------|-------|----------------------------------------|

|   | 0                          |             | 0     | internal data                          |

|   | 0                          |             | 0     | internal data                          |

|   | 1                          |             | 0     | internal data                          |

|   | 1                          |             | 0     | internal data                          |

|   | 0                          | 0           | 1     | internal data                          |

| 0 | 0                          | 1           | 1     | EXT data                               |

|   | 1                          | 0           | i     | internal data                          |

|   | 1                          | 1           | 1     | internal data                          |

Now, the color generator 35, decoder 36, DAC 37 and phase shifter 38 will be described in detail with particular reference to FIG. 8.

The color generator 35 is comprised of a RAM and capable of storing thirty-two 6-bit color codes, one of

T, J I O, T J T

which is supplied as its output after having been selected by a 5-bit address signal CGA0-CGA4 supplied from the multiplexer 30. The color code signals stored in the color generator 35 may be rewritten under the control of a CPU 112.

Provided in the structure of FIG. 8 is a phase shifter 38 which divides six times (3.58 MHz  $\times$ 6) of the frequency of chrominance subcarrier (Sc) and produces twelve kinds of chrominance subcarriers different in phase from each other. Provided as connected to re- 10 ceive an output signal from the phase shifter 38 is a phase selector 114 which receives a 4-bit data among a 6-bit color code signal supplied from the color code generator 35 thereby selectively outputting one of the twelve kinds of chrominance subcarriers different in 15 phase supplied from the phase shifter 38. There is also provided a level decoder 115 which receives a 2-bit data among a 6-bit color code signal supplied from the color generator 35 and converts it into a level selection signal having four different levels. It is to be noted that the 20 decoder 38 of FIG. 5 includes the phase shifter 114 and the level decoder 115.

Also provided as shown in FIG. 8 is a resistor ladder 116 which includes nine resistors 117-1 through 117-9 connected in series between a supply voltage  $V_{CC}$  and 25 ground (GND). From each of the nodes between the adjacent resistors, an output signal having a voltage level divided proportionately may be obtained through the corresponding one of MOS transistors 118-1 through 118-8 which together form a transmission gate. 30 Gate circuits 119-1 and 119-4 are provided as appropriately connected to control two of the transistors 118-1 through 118-8 at the same time. Each of the gate circuits 119-1 through 119-4 includes two NAND circuits 120 and 121, each of which has its one input connected to 35 D in FIG. 9. receive the same level selection signal supplied from the level decoder 115. Furthermore, in each of the gate circuits 119-1 through 119-4, one 120 of the pair of NAND circuits has the other input commonly connected to receive the same chrominance subcarrier 40 signal having a desired phase supplied from the phase selector 114; whereas, the other NAND circuit 121 has its the other input connected to receive an output signal of the one NAND circuit 120. Each of the NAND circuits 120 and 121 has its output connected to the gate 45 of corresponding one of MOS transistors 118-1 through 118-8. It is to be noted that the DAC 37 of FIG. 5 includes the resistor ladder 116, transistors 118-1 through 118-8 and gate circuits 119-1 through 119-4.

The operation of the structure shown in FIG. 8 will 50 now be described with particular reference to FIG. 9. When a single data is outputted from the multiplexer 30, there is outputted a single color code signal (6bits) from the color generator 35. The phase selector 114 then receives only four bits among the thus supplied color 55 code signal thereby selecting one out of twelve kinds of chrominance subcarriers different in phase one from another to be supplied to all of the gate circuits 119-1 through 119-4. On the other hand, the level decoder 115 receives a 2-bit data from the same color code signal to 60 supply a level selection signal to one of the gate circuits 119-1 through 119-4.

Now, suppose that, for example, the gate circuit 119-1 is selected by the level decoder 115, then a low level signal is applied to one input of each of the NAND 65 circuits 120 and 121 in the gate circuit 119-1 and a high level signal is applied to one input of each of the NAND circuits 120 and 121 in each of the remaining gate cir-

cuits 119-2 through 119-4. Under the condition, if the phase difference pulse signal from the phase selector 114 is a low level signal, in the gate circuit 119-1, the NAND circuit 120 supplies a high level output signal and the NAND circuit 121 supplies a low level output signal, so that the transistor 118-1 connected to the node of the resistor ladder at voltage V<sub>1</sub> is turned on and the transistor 118-2 connected to the node at voltage V<sub>2</sub> is turned off. On the other hand, if the chrominance subcarriers signal is a high level signal, then the NAND circuits 120 and 121 of gate circuit 119-1 supply low and high level signals, respectively, and, thus, the transistor 118-1 connected to the node at voltage V<sub>1</sub> is turned off and the transistor 118-2 connected to the node at voltage V<sub>2</sub> is turned on. Under the circumstances, the outputs from all of the other gate circuits 119-2 through 119-4 are at low level, and, thus, the transistors 118-3 and 118-8 are all maintained off.

10

As a result, an output signal obtained from the output terminal 22 under the condition is a color signal which is defined by a chrominance subcarriers phase difference pulse having an intended phase and an amplitude which varies between two voltage levels V<sub>1</sub> and V<sub>2</sub> in an oscillatory manner, as indicated by a signal A in FIG. 9, whereby the center of amplitude indicates luminance or degree of brightness. In this color signal, the amplitude indicates chroma and the phase indicates hue.

When another level is selected by the decoder 115 in accordance with another output signal from the multiplexer 30, for example when the gate 119-2 is selected, there is outputted a color signal having an amplitude which varies between two voltage levels V<sub>3</sub> and V<sub>4</sub> as shown by a signal B in FIG. 9. Similarly, color signals for other color code levels are shown by signals C and D in FIG. 9.

If another chrominance subcarrier having a different phase has been selected in accordance with a 4-bit code for phase selection in the color code signal supplied from the color generator 35, another color signal having a different phase (hue) with one of the signals A through D in FIG. 9 having particular amplitudes (chroma) and voltage levels (luminance) is outputted. A color signal thus supplied as an output is then added with a burst signal and a sync signal to be formed into a color video signal which may be supplied to any of conventional T.V. sets (not shown) for display on the screen.

Since each of the twelve different kinds of chrominance subcarriers can take four different levels (amplitudes and voltage levels) in the present embodiment, color may be produced in 48 different representations. However, since the output signal from the multiplexer 30 has a 5-bit structure, color may be produced in 32 different representations at a time. In view of this, provision is made of the color generator 11 capable of storing thirty-two 6-bit color codes in the present embodiment so that although only thirty-two kinds may be selected by the color data generator 10, color may be represented in forty-eight different ways at maximum with a 6-bit color code signal by rewriting the contents of the color generator 35 by CPU 112. Thus, the maximum number of different color representations in the present embodiment is 48, and four of the remaining codes may be allocated to white, gray (2) and black.

FIG. 10 shows another embodiment of the present invention in which two PPUs 11-1 and 11-2 are coupled together to synthesize the character patterns in these PPUs 11-1 and 11-2. Let us assume that use is made of

the SLAVE signal and PPUs 11-1 and 11-2 function as a master and a slave, respectively. With PPUs 11-1 and 11-2 interconnected as shown in FIG. 10, a square wave having sharp rising and falling edges is applied to a clock terminal CLK and a reset signal is employed for 5 initial synchronization between the two PPUs 11-1 and 11-2. Under the condition, the character pattern data of slave PPU 11-2 is outputted from terminals EXT0-3 to be inputted to the terminals EXT0-3 of master PPU 11-1, whereby synthesization of character pattern data 10 takes place within the master PPU 11-1 with the determination of priority order as described with reference to FIG. 7.

With the structure shown in FIG. 10, as a video output signal, any of possible combinations between still or 15 motion picture character pattern in master PPU 11-1 and still or motion picture character pattern in slave PPU 11-2 may be obtained and displayed on the screen.

As described in detail above, in accordance with the present invention, provision is made of a motion picture 20 attribute table memory capable of storing information relating to a motion picture pattern for the next following frame during the vertical blanking period and a temporary memory for storing motion picture information to be displayed in the next following line, and, 25 therefore, since the retrieval of motion picture attribute table memory can be done during the preceding line scanning operation, it is only necessary to retrieve the character pattern generator for those motion picture characters thus retrieved and found to be in-range dur- 30 ing the horizontal blanking period. As a result, without requiring an increase in the number of connection pins, the number and kinds of motion picture character patterns which may be called or accessed during the horizontal blanking period can be increased.

While the above provides a full and complete disclosure of the preferred embodiments of the present invention, various modifications, alternate constructions and equivalents may be employed without departing from the true spirit and scope of the invention. Therefore, the 40 above description and illustration should not be construed as limiting the scope of the invention, which is defined by the appended claims.

What is claimed is:

1. A color encoder which is connected to a color 45 television receiver such that a color image can be displayed by the color television receiver, comprising:

first means for generating a predetermined number of phase signals, each having a frequency which is related to the frequency of a reference frequency 50 signal, each of said predetermined number of phase signals being different in phase from each other and each corresponding to a hue capable of being output to said color television receiver;

second means for generating color code signals in- 55 cluding a hue code for designating the hue to be output and a level selection code for designating a color level to be output;

third means for selecting one of said phase signals obtained from said first means in accordance with 60 said hue code included in one of said color code signals output from said second means;

fourth means for generating an amplitude selection signal in accordance with said level selection code included in the one of said color code signals; and 65 fifth means, responsive to the amplitude selection signal from said fourth means, for generating a color signal by changing the level of the phase

signal selected by said third means to have a predetermined amplitude selected by said amplitude selection signal and which is associated with the chroma of the color signal and varies between two voltages at least one of which is also selected by said amplitude selection signal, an average value of said level-changed phase signal being associated with the degree of brightness of the color signal.

2. A color encoder as in claim 1 wherein said fifth means includes:

means for providing said color signal with a frequency and phase signal component corresponding to said phase signal selected by said third means;

means for varying the amplitude of said signal component between said two voltages; and

means for providing said color signal component with a center amplitude determined by said at least one voltage.

- 3. A color encoder in accordance with claim 1, further including means for generating a color subcarrier signal as said reference signal.

- 4. A color encoder in accordance with claim 1, wherein said fifth means includes:

an output terminal for outputting said color signal;

- a voltage divider including a plurality of resistors connected in a series connection having first and second ends, said plurality of resistors being interconnected at a corresponding plurality of series connection points, a predetermined voltage being applied across said first and second ends of said series connection;

- a plurality of switching elements, each switching element being coupled at one end to a corresponding one of said plurality of series connection points and each switching element having another end which is commonly connected to said output terminal; and

- a driving circuit means for enabling a predetermined one of said plurality of switching elements in response to said phase signal selected by said third means and said amplitude selection signal generated by said fourth means.

- 5. A color encoder in accordance with claim 4, wherein respective one ends of adjacent switching elements are connected to adjacent series connection points, and said driving circuit means includes gate means for controlling the adjacent switching elements in response to said amplitude selection signal from said fourth means.

- 6. A color encoder in accordance with claim 5, wherein said gate means includes a gate circuit means for supplying said phase signal selected by said third means to said adjacent switching elements in response to said amplitude selection signal provided by said fourth means.

- 7. A color encoder in accordance with claim 1, wherein said second means includes storing means for storing a plurality of color code signals.

- 8. A color encoder in accordance with claim 7, further comprising processing means for selectively altering color code signals stored in said storing means.

- 9. A color encoder in accordance with claim 7, further including multiplexer means for addressing said storing means and for causing said storing means to output a selected color code signal.

- 10. A color encoder in accordance with claim 9, further including:

external memory means for storing at least color related data; and

means for receiving said color related data from said external memory means and for coupling said color related data to said multiplexer means.

11, A color encoder for producing signals representing a color image displayable by a color television receiver, said color encoder comprising:

control means for generating a digital color code signal including a hue code representing a hue and a level selection code, said control means including means for encoding said level selection code with any one of plural different level values representing corresponding different color signal chroma/b-rightness levels;

phase means, connected to receive a reference frequency signal and said hue code, for generating a phase signal having a frequency which is related to the frequency of said reference frequency signal 20 and having a phase responsive to said hue code, said phase corresponding to a hue for display by said color television receiver;

first voltage level pair providing means for providing a first voltage pair defining a first color signal am- 25 plitude;

second voltage level pair providing means for providing a second voltage pair defining a second color signal amplitude different from said first color signal amplitude; and

color signal generating means connected to receive said selected phase signal and said level selection code and operatively connected to said first and second voltage level pair providing means for selecting one of said first and second voltage level pair providing means in response to said level selection code and for generating a color signal having an amplitude defined by the voltage pair produced by the selected voltage level pair providing means at a frequency and phase corresponding to said selected phase signal.

12. A color encoder as in claim 11 wherein said color signal generating means comprises means for generating a varying color signal having an amplitude associated 45 with chroma, a phase associated with hue, and a center amplitude associated with degree of brightness, said amplitude and center amplitude both being selected in response to said level selection code.

13. A method of providing a color signal representing 50 a color image for display by a color television receiver, said method comprising the following steps:

generating a plurality of phase signals each having a frequency which is related to the frequency of a reference frequency signal, each of said plurality of phase signals being different in phase from one another and each corresponding to a different hue for display by said color television receiver;

generating a digital color code signal including a hue code designating a hue and a level selection code designating at least one further color parameter;

selecting one of said plurality of phase signals in response to said hue code;

generating an amplitude selection signal in response to said level selection code;

selecting a predetermined amplitude in response to said amplitude selection signal; and

selecting at least one voltage in response to said amplitude selecting signal; and

generating a color signal, including changing the level of the phase signal selected by said phase signals selecting step to have said selected predetermined amplitude associated with the chroma of the color signal by varying said phase signal level between said selected voltage and a further voltage related to said selected voltage by said selected predetermined amplitude.

14. A method of producing signals representing a color image displayable by a color television receiver, said method comprising the following steps:

generating a digital color code signal including a hue code representing a hue and a level selection code representing a chroma/brightness level;

encoding said level selection code with any one of plural different level values representing corresponding plural different color signal chroma/brightness levels;

generating a phase signal having a frequency which is related to the frequency of a reference frequency signal and a phase responsive to said hue code;

producing a first voltage level pair defining a first signal amplitude;

producing a second voltage level pair defining a second signal amplitude different from said first signal amplitude;

selecting one of said first voltage level pair and said second voltage level pair in response to said level selection code; and

generating a color signal having an amplitude defined by said selected voltage level pair which varies between the voltage levels of said selected voltage level pair at a frequency and phase corresponding to said selected phase signal.