# Andrews

[45] Date of Patent:

May 3, 1988

| [54] VECTOR IMAGE PROCESSING SYSTEM                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [75] Inventor: Barry A. Andrews, Auburn, Wash.                                                                                                                                                                                                                                                                                 |

| [73] Assignee: The Boeing Company, Seattle, Wash.                                                                                                                                                                                                                                                                              |

| [21] Appl. No.: 536,385                                                                                                                                                                                                                                                                                                        |

| [22] Filed: Sep. 27, 1983                                                                                                                                                                                                                                                                                                      |

| [51] Int. Cl. <sup>4</sup>                                                                                                                                                                                                                                                                                                     |

| [56] References Cited                                                                                                                                                                                                                                                                                                          |

| U.S. PATENT DOCUMENTS                                                                                                                                                                                                                                                                                                          |

| 4,215,401       7/1980       Holsztynski et al.       382/49         4,363,104       12/1982       Nussmeier       382/41         4,442,543       4/1984       Sternberg et al.       382/49         4,484,349       11/1984       McCubbrey       382/27         4,524,455       6/1985       Holsztynski et al.       382/41 |

| Primary Examiner—Leo H. Boudreau                                                                                                                                                                                                                                                                                               |

| Attorney, Agent, or Firm—H. Donald Nelson                                                                                                                                                                                                                                                                                      |

| [57] ABSTRACT                                                                                                                                                                                                                                                                                                                  |

Hybrid parallel internally pipelined Vector Image Processors (24, 41, 54) which may also be externally pipelined. The exemplary Processors (24, 41, 54) include n processing elements ( $PE_a-PE_n$ )—wherein "n" is any whole integer but, when greater than "1", the elements are arranged in parallel in a one-dimensional column—for processing a two-dimensional XY PIXEL image

array (25, 25', 38, 52) wherein each element ( $PE_a-PE_n$ ) includes: (i) multiple cascaded latches (N1, N2, N3) in a one-dimensional row; (ii) a neighborhood functional unit (NFU<sub>n</sub>) for performing NEIGHBORHOOD TRANSFORMS; (iii) an arithmetic logic unit (ALU) for performing ARTIHMETIC/LOGIC TRANS-FORMS; (iv) means  $(48_n, 49_n, 50_n)$  for transferring data in the latches (N1, N2, N3) to the neighborhood functional unit (NFU<sub>n</sub>) and to the neighboring north/south processors; (v) means  $(48_n, 49_n)$  for transferring data in the latches (N1, N2) to the arithmetic logic unit (ALU); and (vi), means  $(48_{n-1} \dots 50_{n-1}, 48_{n+1} \dots 50_{n+1})$  for inputting image boundary and PIXEL neighbor data to the neighborhood functional unit  $(NFU_n)$ . Where the number of rows ("X") of PIXEL data is greater than the number ("n") of processors ( $PE_a-PE_n$ ), the system processes adjacent strips  $(38_a-38_d)$  of PIXEL rows with all PIXELS in a given column ("Y") within each strip  $(38_a-38_d)$  being processed in parallel and with all columns of PIXELS in each strip being processed in internally pipelined form. This latter system includes border Memories (22<sub>NB</sub>, 22<sub>SB</sub>) for storing boundary data for each strip  $(38_a-38_d)$  and for cross-feeding the north and south rows of PIXEL output data in each strip to respective ones of the border Memories  $(22_{SB}, 22_{NB})$  for use in processing adjacent strips.

78 Claims, 13 Drawing Sheets

4,742,552

FIG. 3

O 1 2

A O O O

B O O I

C O I I

FIG. 6

| 0 | X | X |

|---|---|---|

| 0 | ш | X |

| 0 | X | X |

FIG. 11a

|          | 2  | 3  | 4  |   |

|----------|----|----|----|---|

|          | 8  | 9  | 0  |   |

|          | 17 | 8  | 19 |   |

|          | 24 | 25 | 26 |   |

| FIG. 12c | 28 | 29 |    | • |

| X | X | 0 |

|---|---|---|

| X | Ш | 0 |

| X | X | 0 |

FIG. 11b

| Α | В | С |

|---|---|---|

| Q | Ш | F |

| G | Η |   |

FIG. 8

FIG. 12d

FIG. 14b

FIG. 14c

FIG. 14d

## **VECTOR IMAGE PROCESSING SYSTEM**

#### **BACKGROUND OF THE INVENTION**

#### Technical Field

The present invention relates generally to image processing systems for processing digitally encoded image data derived from a suitable conventional sensor on a high-speed real time basis; and, more particularly, to a 10 Vector Image Processor (hereinafter termed "VIP") and Vector Image Processing System employing a parallel internally pipelined architecture enabling processing of n rows of digitally encoded binary data in the form of an XY array of picture elements (hereinafter referred to as "PIXELS"), and wherein the n PIXELS (where "n" can be any desired whole integer) in each column are shifted sequentially through the VIP in column-by-column internally pipelined form, thereby minimizing the complexity of the processor in terms of 20 size, hardware and attendant expenses, while optimizing processor speed so as to enable performance of specific image processing operations on a real time basis.

To this end, the present invention is directed to a VIP and Vector Image Processing System having a onedimensional column of n (where "n" is any desired whole integer) parallel processor elements (hereinafter "PES") through which an XY array of digitally encoded PIXEL data is sequentially shifted in column-bycolumn internally pipelined form and wherein the VIP is programmed to permit a selected one or selected ones of conventional well-known image processing operations such, merely by way of example, as: (i) neighboroperations (hereinafter generally "NEIGHBOR TRANSFORMS")—e.g., spatial filtering operations such as expansion, contraction and thinning used to modify image features and/or measure image characteristics based upon relationships between each PIXEL and its neighbors—typically, NEIGH-BOR TRANSFORMS might, for example, include edge or boundary detection, size determination, bright- 40 ness measurement, etc.—(ii) arithmetic operations (hereinafter generally termed ("ARITHMETIC TRANSFORMS") such as "add", "subtract" and "multiply" for smoothing images, altering brightness levels, and comparing two images one to another or a given 45 image at two spaced points in time; and (iii), logic operations (hereinafter generally termed "LOGIC TRANS-FORMS")—e.g., Boolean operations—such as AND, OR, and XOR (inclusive OR) for superimposing images, detecting changes, extracting objects of interest 50 and/or removing unwanted details.

The foregoing representative TRANSFORMS are identified solely for the purpose of indicating exemplary types of processing operations commonly employed in image processing techniques and are not considered to 55 be all inclusive or limiting. The particular processing operations to be carried out are generally well known and conventional, vary widely dependent upon the specific use for which the special purpose image processor is intended; are not critical to the present invention; 60 and, consequently, are not described in detail in the ensuing specification.

The present invention finds particularly advantageous application in such fields as, merely by way of example: blood cell counting; picture enhancement; 65 innumerable industrial applications such as, for example, sorting parts in an assembly line based upon the size of the parts, detection of defective parts, and/or orien-

tation of parts to conform to a particular pattern for permitting subsequent automated machining and/or assembly operations—i.e., robotics; aerial and/or space reconnaissance; target tracking and/or identification; target seeking or location; guidance systems; and, numerous like applications, to name but a few of the possible technical fields within which the invention might find application.

### BACKGROUND ART

During the past three decades and continuing into the 1980's, considerable efforts have been devoted in attempts to design image processors suitable for use in a wide variety of technical fields and differing applications. Prior to the advent of the present invention, such efforts have been primarily directed to developing conventional computers programmed for image processing. Unfortunately, however, conventional computers, when programmed for image processing, are extremely inefficient for most high speed applications. This is in part due to: (i) the tremendous volume of digitally encoded data present in a typical two-dimensional XY PIXEL array—for example, a typical image may contain from 10<sup>3</sup> to 10<sup>7</sup> PIXELS—and, consequent processing time with conventional computers may require up to several minutes, or even hours, of computational operations; (ii) the desire for operation on a real time basis; and (iii), the specialized nature of image processing algorithms. Consequently, in an effort to overcome these disadvantages, numerous special purpose, single instruction multiple data ("SIMD") image processors have been developed which, in general, fall into one of two distinct categories-viz., (i) a parallel Binary Array Processor (BAP); or (ii), a serial or Pipelined Processor.

BAP architectures have, in turn, generally fallen into one of two categories—viz., (i) a fully parallel processor or a locally parallel processor. Typical examples of fully parallel processors include: (i) the Cellular Logic Image Processor (CLIP); (ii) the Massively Parallel Processor (MPP); and (iii), the SOLOMON Processor. The CLIP, developed by M. J. B. Duff and his associates in the United Kingdom, has progressed through a series of models identified as CLIP I, CLIP II, CLIP III and CLIP IV; and, in CLIP IV, for example, the processor is designed to operate on all PIXELS in a  $96 \times 96$ PIXEL array simultaneously and, therefore, requires a total of 9,216 PES. The MPP, originally designed by NASA for processing satellite data and, more recently redesigned by Kenneth Batcher at Goodyear Aerospace, has been designed to simultaneously process all PIXELS in an  $128 \times 128$  PIXEL array and, as a consequence, the MPP requires 16,384 PES.

Fully parallel processors such as the CLIP series, MPP and SOLOMON have a number of disadvantages. In general, they employ fixed hardware construction designed to deal with images of a specific maximum size—e.g.,  $96 \times 96$  in the case of the CLIP IV;  $128 \times 128$  in the case of the MPP; etc. However, if such fully parallel processors are used to process smaller images, then some (often a large percentage) of their capacity is wasted. If they are used to process larger images, then neighborhood relations are lost at the edges of the processor. This requires special treatment such, for example, as dividing the image frames into segments with boundaries that cut into objects; and, as a consequence, the resulting sliced objects do not permit of accurate spatial filtering operations.

In addition to the foregoing problems, fully parallel processors implemented as single integrated circuits ("ICs") have severe interconnection problems due to the fact that they employ a separate PE for each PIXEL to be processed. Where neighborhood operations are to 5 be performed—and, assuming a  $3\times3$  neighborhood—a fully parallel array processor designed to handle a 16×16 PIXEL image array would require a total of 376 pins just for neighbor communications with other 16×16 ICs. Memory interface requirements further 10 exacerbate this problem. That is, two pins are required for each PE-viz. one for data input and one for data output—in order to perform a single operation for each cycle of the image buffer. Thus, the exemplary  $16 \times 16$ parallel array processor described above would require 15 an additional 512 pins for high speed operations. A single pin can, of course, be multiplexed, but this will at least halve the speed of operation dependent upon the number of signals multiplexed—i.e., if three signals are multiplexed, the speed of operation will be only one- 20 third the speed of operation for a single signal; four signals multiplexed reduce the speed to one-fourth, etc. In addition to the foregoing communication pins, control and clock pins are also required. Consequently, fully parallel processors tend to be relatively large and 25 complex, highly pin limited, extremely inflexible, and extremely expensive.

A locally parallel processor is, in effect, simply a smaller version of a fully parallel processor, and is derisigned to analyze only a subsection or window of an 30 overall XY PIXEL image array. Typical examples of locally parallel processors are the Coulter diff3 (a  $10 \times 3$ PIXEL window) and the Preston-Herron Processor (PHP) which employs an 18×3 PIXEL window. As in the case of a fully parallel processor—e.g., CLIP IV, 35 MPP, SOLOMON, etc.—locally parallel processors have generally required sufficient hardware to simultaneously process all PIXELS in a given XY array (e.g., a  $3 \times 10$  array in the diff3, or an  $18 \times 3$  array in the PHP). Thus, in the fully parallel BAP, the XY array of PES is 40 coextensive with the maximum size XY PIXEL image array to be processed and can require up to literally thousands of PES, associated memories, and the necessary hardware interconnections; while locally parallel BAPs, which are designed to include a smaller two-di- 45 mensional XY array of PES, still require a large number of associated memories and the necessary hardware interconnections which are mandated by the two-dimensional PE array.

Articles of interest describing the foregoing types of 50 fully parallel and/or locally parallel BAP architecture designs, as well as various advantages and disadvantages thereof, include: Computer Architectures For Image Processing In The U.S.A., Anthony P. Reeves, SIGNAL PROCESSING, Vol. 3, pp. 217-230 (1981), 55 0165-1684/81/0000-0000, published by North-Holland Publishing Company; and, A General-Purpose High-Speed Logical Transform Image Processor, J. M. Herron, J. Farley, K. Preston, Jr., and H. Sellner, IEEE TRANSACTIONS ON COMPUTERS, Vol. C-31, 60 computer architects have designed what are known as No. 795–800 pp. (August 1982) 0018-9340/82/0800-0795.

A modified version of a conventional BAP is the PYRAMID, which, in a sense, also comprises a locally parallel processor; but, wherein each PE is used to 65 process several PIXELS. A current known PYRAMID design requires a  $4 \times 16$  tile size wherein each of four PES on a single chip is responsible for sixteen PIXELS

with each operation being applied successively to each of sixteen PIXEL rows by four PES operating in parallel. The PYRAMID is constructed by interconnecting tiles to form arrays or levels, with the largest array being the baseplane and with successively smaller arrays being stacked thereabove—hence, the name PYRAMID. It has been suggested that the principal advantage of a pyramidal architecture is that lower resolution images can be processed more rapidly than higher resolution images; and, a pyramidal architecture permits operations at various resolutions with each array or level having 50% of the resolution and 25% of the image area of the array or level immediately therebelow. Unfortunately, however, one of the highly desirable purposes of image processing is the ability to conduct spatial filtering operations such as size measurements and/or comparisons. Since the purpose of spatial filtering is to discriminate between objects having different spatial characteristics, operation at high resolution is highly desirable. Moreover, the time required to move images to progressively higher levels at progressively lower resolutions tends to be a real disadvantage, particularly when working with relatively large pyramidal structures.

Pyramidal architectures have numerous disadvantages in terms of complexity, cost and flexibility. In general, a pyramidal architecture requires one-third more PES than a two-dimensional XY parallel array processor; and, in addition, requires interlevel communication, additional control circuits for each level, and more complex software and microcode to handle multilevel operations. As with the fully parallel array processors discussed above, the PYRAMID is also generally designed to handle images of a fixed maximum size. Consequently, when dealing with smaller images, capacity is wasted; and, when dealing with larger images, spatial filtering operations are either not possible or their accuracy is seriously denigrated unless additional circuitry is provided to allow segments to be overlapped. Pyramidal architectures, by employing shared PES and pin multiplexing, have tended to reduce the interconnection problems inherent in fully parallel processors; but, at a real cost or trade-off in terms of performance which is decreased by a factor of at least sixteen (16) when compared to a fully parallel array processor such, for example, as a  $4 \times 16$  processor.

In U.S. Pat. No. 4,060,713-Golay, the pantentee discloses a BAP wherein the two-dimensional array of PIXELS are arranged such that every PIXEL in the array, except for the edge PIXELS, is surrounded by six (6) neighboring PIXELS disposed in an hexagonal array. Golay further describes in considerable detail various NEIGHBORHOOD TRANSFORM operations to be performed with respect to each PIXEL on a PIXELby-PIXEL basis including, for example, such neighborhood operations as spatial filtering—i.e., expansion, contraction, hole isolation, etc.

In an effort to overcome at least some of the foregoing disadvantages inherent in known BAP designs, serial processors or "Pipelined Processors". A well known example of such a Pipelined Processor is the CYTOCOMPUTER developed by Environmental Research Institute of Michigan. An excellent description of Pipelined Processors in general, and the CYTO-COMPUTER in particular, appears in the aforesaid article by Anthony P. Reeves entitled Computer Architectures For Image Processing In The U.S.A., SIGNAL

PROCESSING, supra, at pp. 223-225; and, those interested in a detailed description of such processors are referred thereto and to U.S. Pat. Nos. 4,167,728-Sternberg, 4,174,514-Sternberg, 4,290,049-Sternberg et al and 4,301,443-Sternberg et al. Thus, the Sternberg '728 pa- 5 tent describes a Pipelined Processor having a chain of PES with the output of each PE providing the input to the next PE in the pipelined chain. In Sternberg's '514 patent, a Pipelined Processor is disclosed having parallel pipelines wherein each PE operates on a window or 10 subsection of an image with the window contents being brought into position by means of shift registers and a raster scan technique. In the Sternberg et al '049 patent, the patentees describe an image processing technique for selecting the maximum PIXEL value in a  $3\times3$  15 neighborhood; while the Sternberg et al '443 patent describes a portion of the CYTOCOMPUTER circuit.

The CYTOCOMPUTER serial processor has two primary advantages when compared to a BAP such as those discussed above—viz., it has no pin limitations 20 and it does not require an image buffer memory since it can be connected directly to a sensor. However, the precision of the CYTOCOMPUTER serial processor as currently designed is limited to eight (8) bits, a major disadvantage when working with sensors having dy- 25 namic ranges of ten (10) or twelve (12) bits. While the CYTOCOMPUTER can be modified to provide ten (10) or twelve (12) bits of precision, most of the capacity would be wasted when working with binary images. Moreover, the CYTOCOMPUTER has inherent disad- 30 vantages in connection with data rates and latency—i.e., the built in time delay resulting from processing data in step-by-step pipeline fashion as measured from the time of entry of a PIXEL into the pipeline through the time of exit thereof. In short, the CYTO- 35 COMPUTER has very limited utility in connection with real time applications; it has too little precision for infra-red sensors and the like; it is incapable of handling the data rate for many of such sensors; it requires too many chips for use with commonly used image process- 40 ing algorithms; it has limited arithmetic capability; and, it employs a fixed execution sequence; to name but a few of the disadvantages inherent with this type of serial image processor.

Other prior patent disclosures of interest include U.S. 45 Pat. Nos.: 4,224,600—Sellner (a fully parallel microprocessor based BAP suitable for use with binary images and said to be an improvement based on the aforesaid Golay U.S. Pat. Nos. 4,060,713); 4,229,797—Ledley (a high speed video processor employing a video 50 crossbar switch, D/A converters, x/y delay buffers, etc.); 4,309,691-Castleman (a processing system employing multiple cascaded or pipelined general purpose microcomputers); 4,334,241—Kashioka et al (a special purpose pattern matching circuitry); 4,334,274—Augi 55 et al (a special purpose digital circuit employed to determine whether an object or Blob in a digital image lies within a closed boundary); 4,325,085—Gooch (a digital circuit for compressing facsimile data for storage or transmission); 4,143,401—Coviello and 60 4,258,394—Kennedy (digital circuits for use in edge detection of gray scale images); 4,330,833—Pratt et al (a digital filtering technique for enhancement of digital images); 3,809,902—Cofer et al (a facsimile recorder used to produce a picture of electrolytic cells); 65 4,302,775—Widergren et al (a digital video compression system); 4,238,768—Mitsuya et al (a special purpose digital circuit for digitally encoding image data for

6

storage or transmission through a data channel); 4,297,727—Ogawa et al (facsimile apparatus employing a microcomputer as a central controller); 4,184,206—Harano (an apparatus for assigning the most accurate value to a PIXEL as the input image is digitized); and, 4,254,467—Davis et al (a vector to raster processor for converting graphics data to a form suitable for plotting or display). Attention is also directed to an article entitled Architecture For A Digital Programmable Image Processing Element, Stanley A. White, CONFERENCE: ICASSP 81, PROCEEDINGS OF THE 1981 IEEE INTERNATIONAL CONFERENCE ON ACOUSTICS, SPEECH AND SIGNAL PROCESSING, pp. 658-661 (30 Mar.-1 Apr., 1981).

### SUMMARY OF THE INVENTION

An image processing system including special purpose processing hardware and methods for processing digitally encoded binary and gray scale data output from a sensor in a two-dimensional XY PIXEL image array and wherein the system includes a onedimensional column of n PES (wherein "n" can be any desired whole integer) arranged in parallel for parallel processing of such rows of PIXELS in the two-dimensional array and wherein the columns of PIXELS in the array are relatively fed or shifted in column-by-column fashion through the Vector Image Processor (VIP) of the invention in internally pipelined sequential order; and, wherein the PIXELS in each column are processed in parallel while permitting a NEIGHBORHOOD, ARITHMETIC or LOGIC TRANSFORM to be conducted simultaneously on a plurality of PIXELS in each column.

To this end, and in accordance with one relatively narrow specific embodiment of the invention, the image processing system or VIP of the present invention includes a single PE having: (i) a plurality of latches in a two-dimensional neighborhood array—for example, a two-dimensional AB neighborhood array wherein both "A" and "B" are equal to three (3), thus forming a  $3 \times 3$ neighborhood array; (ii) a neighborhood functional unit (hereinafter referred to as "NFU"); and (iii), at least one of an arithmetic unit (hereinafter referred to as "AU"), a logic unit (hereinafter referred to as "LU"), or a comosite arithmetic logic unit (hereinafter referred to as "ALU"); and, wherein n rows of digitally encoded PIXEL data (where "n" is equal to the value of "A" in the AB neighborhood array) contained within the twodimensional PIXEL image array are relatively shifted through the VIP in column-by-column pipelined fashion with n adjacent PIXELS—for example, three (3) adjacent PIXELS-in each horizontal row being processed being shifted into, held for processing in, and shifted out of n—e.g., three (3)—cascaded latches and wherein: (a) the digitally encoded data stored in all nine (9) latches in the AB neighborhood array at any given instant of time is fed to the NFU for performing a selected NEIGHBORHOOD TRANSFORM; or (b), while the digitally encoded PIXEL data in two (2) adjacent latches in a given row containing the particular PIXEL of interest being processed is fed to one of an AU, LU or ALU for performing an ARITHMETIC or LOGIC TRANSFORM.

In a more generalized and practical embodiment of the invention, n PES (where "n" is any desired whole integer greater than "1") are arranged in parallel in a one-dimensional columnar array with each PE including: (i) a plurality of cascaded latches—for example,

A more specific object of the invention is the provision of a VIP having a plurality of n parallel bit-serial synchronous PES under the control of a general purpose counter so as to permit handling of image processing functions on a real time basis.

Yet another object of the present invention is the provision of a Vector Image Processor (VIP) comprising a hybrid parallel/pipelined architecture, and, more

three (3) latches—in a one-dimensional row; (ii) an NFU; and (iii), at least one of an AU, a LU, or an ALU; and, wherein the NFU is provided with data input from the latches contained in its PE and is simultaneously provided with data input from the latches in the neighboring north and south PES. In this latter more generalized form of the invention, the digitally encoded PIXEL data contained within n rows of data in an XY PIXEL image array is progressively and relatively shifted through the VIP containing n PES in internally 10 pipelined column-by-column fashion for permitting simultaneous parallel processing of n PIXELS in each successive column being processed to permit a NEIGH-BORHOOD, ARITHMETIC or LOGIC TRANS-FORM.

Yet another object of the present invention is the provision of a Vector Image Processor (VIP) comprising a hybrid parallel/pipelined architecture, and, more specifically, a parallel internally pipelined architecture which may, optionally, be configured as a parallel internally and externally pipelined architecture.

In another of its important aspects, it is an object of

In those instances where the value "X" in the two-dimensional XY PIXEL image array is greater than the value "n" for the number of PES contained within the VIP, adjacent strips each containing "n" rows of PIXEL image data are successively processed by the 20 VIP; and, in such instances, the VIP is provided with edge memories for inputting digitally encoded data representative of: (i) either the northernmost image border or boundary, or the southernmost row of digitally encoded PIXEL data in the adjacent northern 25 strip; and, (ii), either the southernmost image border or boundary or the northernmost row of digitally encoded PIXEL data in the bordering southern strip, so as to permit spatial filtering of data at the northern and southern edges of each strip of digitally encoded data being 30 processed. The VIP system of the present invention further permits of external pipelining of a plurality of VIPs with the digitally encoded data output from one VIP being input to the next adjacent downstream VIP for conducting a further processing operation thereon. 35

the invention to provide a special purpose image processing system characterized by its high speed real time operational characteristics and its ability to process digitally encoded image data derived from any suitable sensor such as a video image derived from a TV sensor, an imaging IR sensor, a laser radar, or any other sensor capable of generating digitally encoded video image data in a two-dimensional XY array of discrete PIX-ELS and wherein the two-dimensional XY array is relatively shifted through the VIP in column-by-column internally pipelined fashion.

More specifically, it is a general aim of the present invention to provide a highly simplified image processing system architecture which overcomes the disadvantages inherent in conventional BAP and serial, or pipelined, image processing architectures and which is capa- 40 ble of performing any selected preprogrammed NEIGHBORHOOD, ARITHMETIC or LOGIC operation on a two-dimensional digitally encoded PIXEL image array on a real time basis while employing only a minimal amount of hardware that can be packaged in an 45 optionally sized configuration at minimal expense. Stated differently, it is a general objective of the invention to provide a special purpose image processor for handling computationally expensive tasks which would otherwise place too great a load on a conventional 50 computer or Central Processing Unit (CPU) due to: (i) the tremendous volume of data in typical digitally encoded two-dimensional XY PIXEL image arrays; and (ii), the specific nature of image processing algorithms; yet, wherein the special purpose image processor is 55 characterized by its ability to carry out its image processing functions on a real time basis.

In another of its more specific aspects, it is an object of the invention to provide a VIP characterized by its simplicity and having a one-dimensional columnar array—i.e., a vector—of PES characterized by their flexibility and their ability to handle a two-dimensional XY PIXEL image array in parallel internally pipelined fashion—viz., wherein a plurality of rows of digitally encoded image data in the form of PIXELS are fed in parallel column-by-column internally pipelined fashion through the VIP which serves to process the data employing bit-serial arithmetic wherein each PIXEL is fed as a stream of one or more bits of any desired length, and which is capable of handling digitally encoded binary and/or gray scale data with equal ease.

In one of its more important aspects, it is an object of the present invention to provide a Vector Image Processor (VIP) employing a one-dimensional columnar 60 array of n parallel PES for permitting a preprogrammed processing operation on digitally encoded PIXEL data oriented in a two-dimensional XY PIXEL image array in parallel internally pipelined fashion, yet which does not require shift registers, microprocessors, video cross-65 bar switches, D/A converters, and/or similar hardware employed in conventional types of images processing systems.

In another of its more detailed aspects, it is an object of the invention to provide a special purpose VIP characterized by its ability to perform well known image processing operations such as: noise filtering; spatial filtering—i.e., detection of size, shape and brightness or contrast of an object, target or "Blob" of interest; pattern matching; superimposition of two images; detection of image changes; extraction of objects of interest; removal of unwanted details; modification of image features; measurement of image characteristics by NEIGHBORHOOD TRANSFORMS such as expansion, contraction or the like based upon the relationships between each PIXEL of interest and its nearest neighboring PIXELS—e.g., its eight (8) surrounding PIXELS in a two-dimensional  $3\times3$  neighborhood or its six (6) surrounding PIXELS in a Golay-type neighborhood.

cessing functions on a real time basis.

In one of its more important aspects, it is an object of the present invention to provide a Vector Image Processor (VIP) employing a one-dimensional columnar array of n parallel PES for permitting a preprogrammed

In yet another of its more detailed aspects, the invention provides for a VIP comprising a one-dimensional columnar array of PES wherein each PE processes a single PIXEL at a time and which, therefore, requires very little circuitry, thus enabling implementation of up to on the order of sixty-four (64) or more PES on a single integrated circuit (IC).

A further general aim of the present invention is the provision of a special purpose one-dimensional columnar VIP employing a plurality of parallel PES wherein each scan of a two-dimensional XY PIXEL image array serves to perform a single processing operation—which may comprise a NEIGHBORHOOD TRANSFORM, an ARITHMETIC TRANSFORM, or a LOGIC

TRANSFORM such as a Boolean logic operation—over an entire two-dimensional XY PIXEL image array permitting multiple processing operations to be conducted by processing such digitally encoded image representative binary and/or gray scale data 5 through: (i) a series of externally pipelined VIPs; (ii) iteratively through a single VIP; and/or (iii) iteratively through n externally pipelined VIPS; thereby allowing desired trade-offs between speed and complexity so as to meet specific operating requirements.

A further objective of the invention is the provision of an image processing system which permits the processor to rapidly scan an overall two-dimensional XY image of digitally encoded binary and/or gray scale PIXEL data to locate objects or areas of interest, and to 15 then isolate on segments of the overall image and conduct a desired NEIGHBORHOOD, ARITHMETIC or LOGIC processing operation thereon, all on a real time basis.

## DESCRIPTION OF THE DRAWINGS

These and other objects and advantages of the present invention will become more readily apparent upon reading the following detailed description and upon reference to the attached drawings, in which:

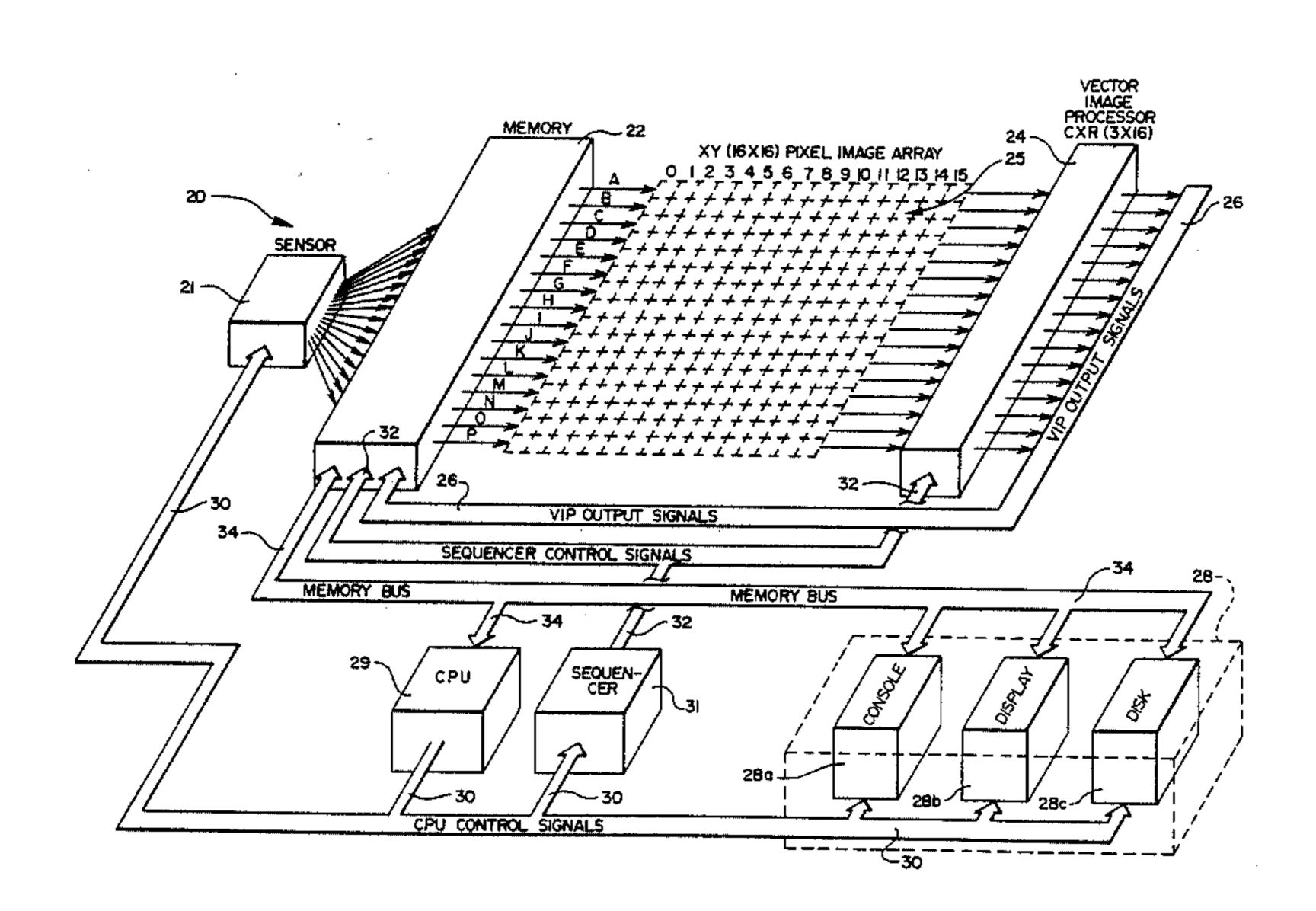

FIG. 1 is a three-dimensional block-and-line drawing in highly simplified diagrammatic form, here illustrating an image processing system of the type including: (i) a suitable Sensor for detecting targets or other image type objects and inputting digitized data representative 30 thereof into the image processing system; (ii) a Central Processing Unit ("CPU"); (iii) a Memory; (iv) one or more peripherals such, for example, as a Console, Display and/or Disk; (v) a Vector Image Processor ("VIP") embodying features of the present invention; 35 and (vi), a Sequencer; it being understood that the broken line representation of the two-dimensional XY PIXEL image array here shown is an imaginary diagrammatic pictorial representation provided solely for purposes of clarity and to facilitate an understanding of 40 the invention and is, therefore, to be distinguished from the other hardware components shown in solid lines;

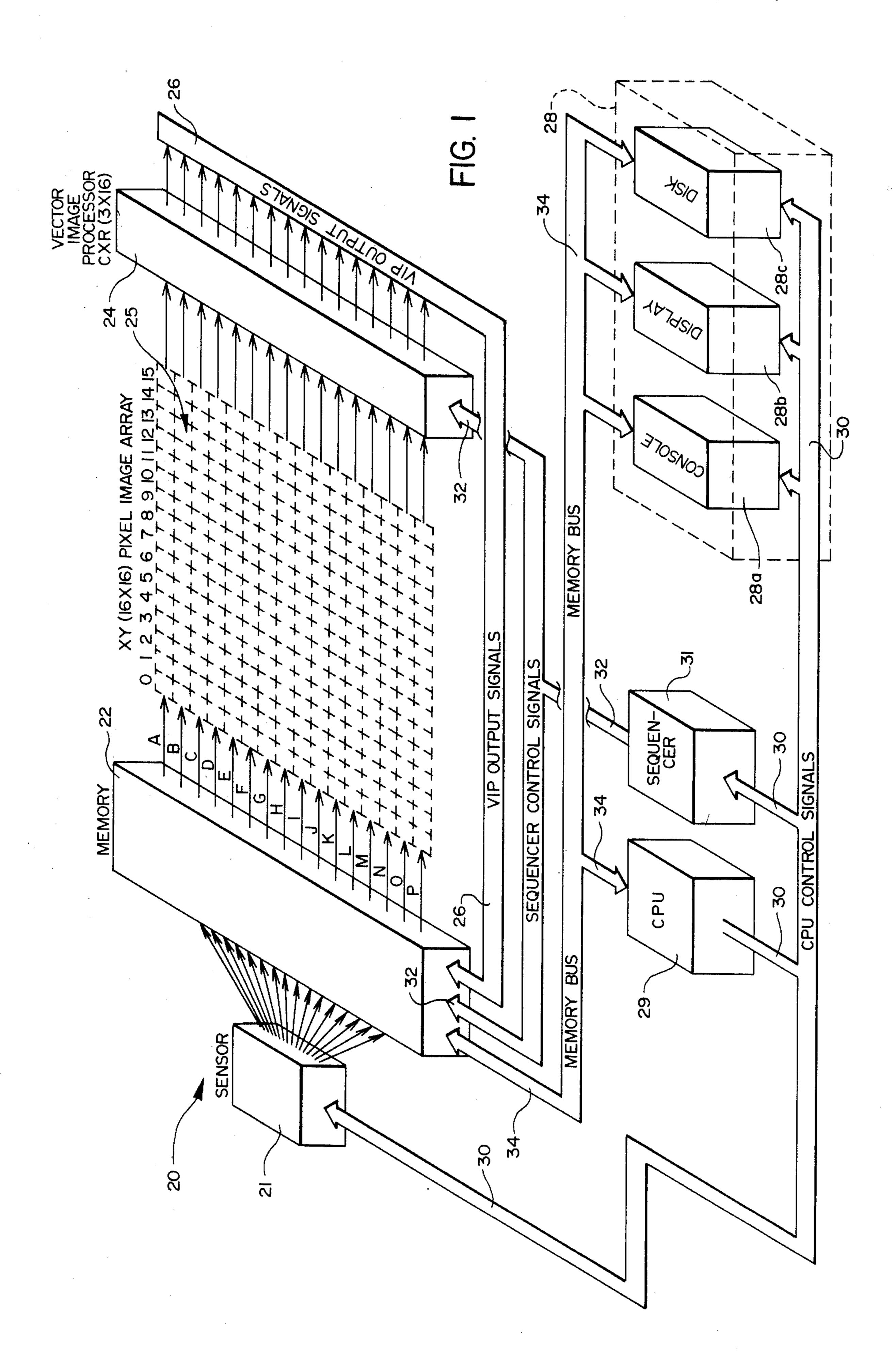

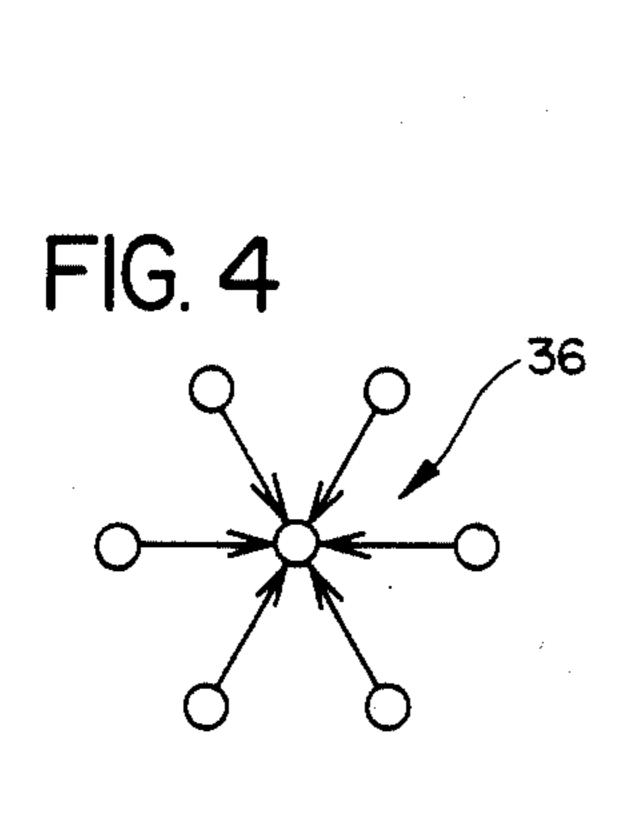

FIG. 2 is a fragmentary block-and-line drawing depicting—in highly diagrammatic, somewhat imaginary pictorial format—a typical two-dimensional XY 45 PIXEL image array suitable for processing in accordance with the present invention, here particularly illustrating a plurality of typical overlapping two-dimensional AB (here, 3×3) PIXEL neighborhoods;

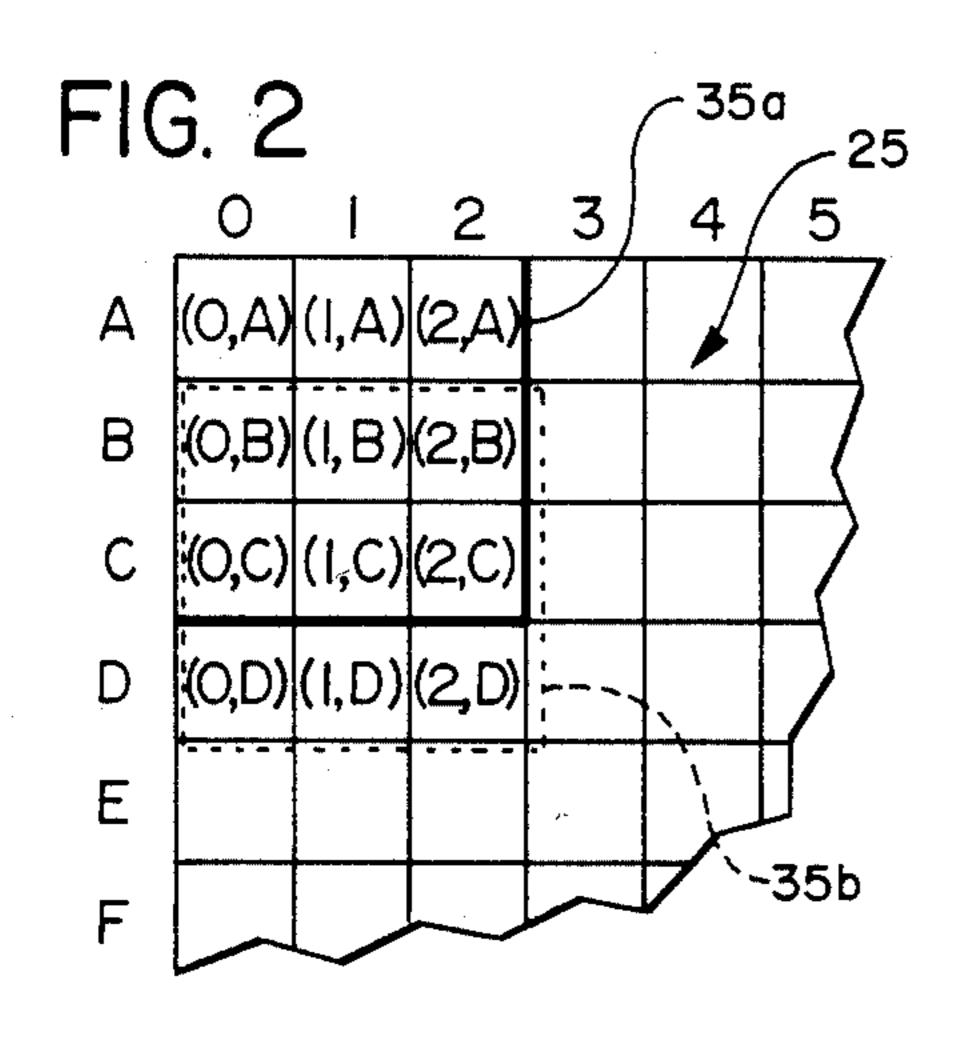

FIG. 3 is a highly diagrammatic drawing representa-50 tive of an exemplary  $3\times3$  AB PIXEL neighborhood wherein the nine (9) PIXELS illustrated have, or may have been threshold to have, binary values of either "0" or "1", here particularly illustrating an arrangement wherein the binary values of the PIXELS in the "A" 55 horizontal row and in the "0" vertical column are such that they respectively define the upper (hereinafter referred to as "north") and left (hereinafter referred to as "west") boundaries or borders of an image;

FIG. 4 is a diagrammatic line drawing representative 60 of a typical PIXEL image array known as a "Golay Surround", an array which may also be processed utilizing equipment and processes embodying features of the present invention;

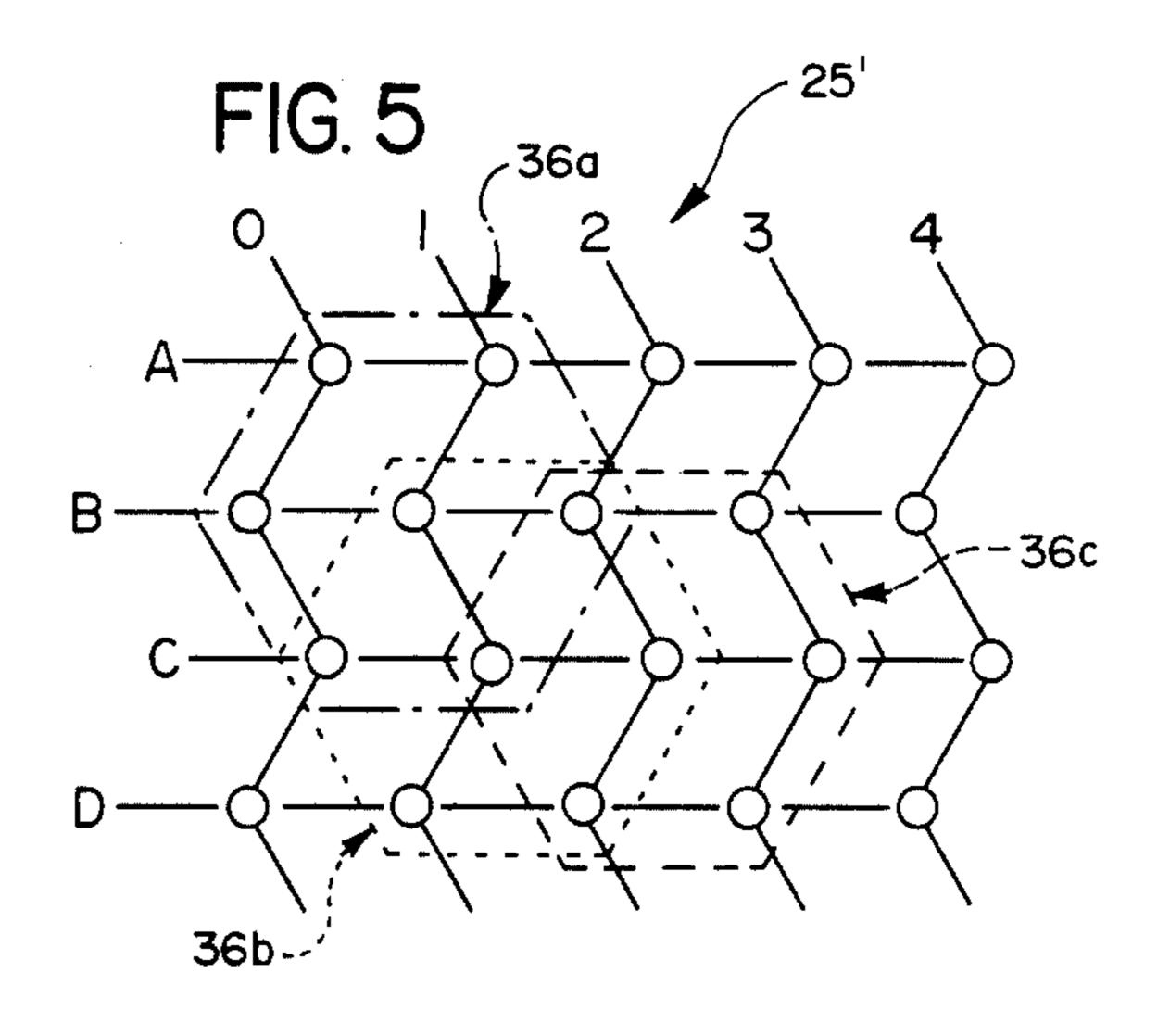

FIG. 5 is a diagrammatic line drawing representative 65 of a plurality of overlapping neighboring Golay Surrounds which may, for purposes of an understanding of the invention, be considered to also define a two-dimen-

10

sional XY PIXEL image array wherein at least one of either the horizontal rows or the vertical columns of PIXELS—here the vertical columns "0" through "4"—are offset to define saw-tooth shaped lines;

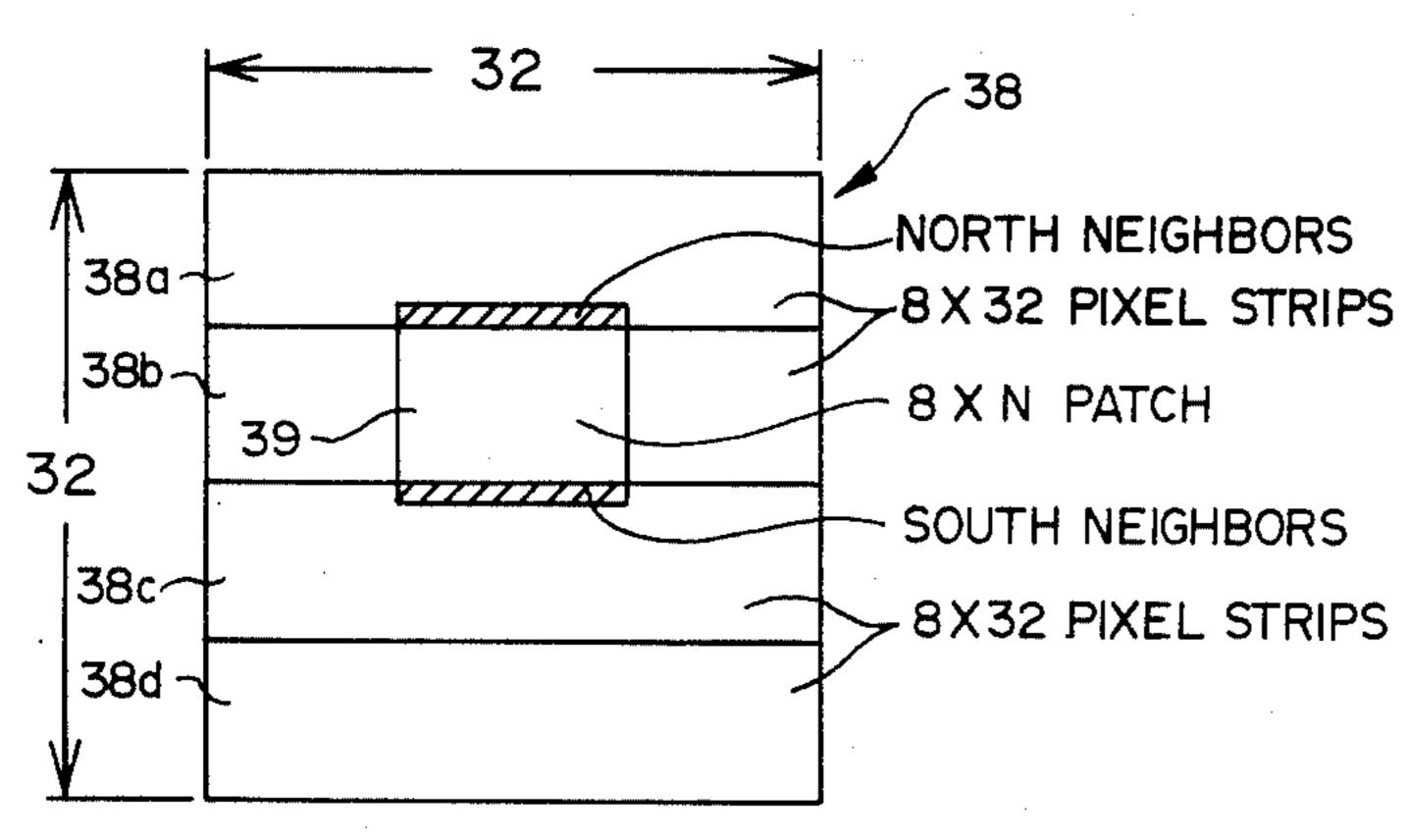

FIG. 6 is a diagrammatic block-and-line drawing here representative of an exemplary two-dimensional XY (32×32) PIXEL image array defined by four adjacent 8×32 PIXEL strips and illustrating also a typical 8×N patch (where "N" can be any desired integer representative of the number of vertical columns of PIXELS to be processed);

FIG. 7 is a line drawing representative of a fragmentary XY PIXEL image array depicted in diagrammatic format and defining an object of "Blob" formed by forty-one centrally located PIXELS having binary values or binary thresholded values of "1" surrounded by a plurality of PIXELS having binary values or binary thresholded values of "0" indicative of the absence of a target, object or Blob of interest;

FIG. 8 is a diagrammatic line drawing representative of a typical  $3\times3$  PIXEL neighborhood wherein the centermost PIXEL "E" may be considered representative of any given PIXEL in the particular XY PIXEL image array being processed—e.g., the XY PIXEL image array shown in FIG. 7;

FIGS. 9a and 9b are diagrammatic line drawings representative of  $3\times3$  PIXEL neighborhoods and here indicative of an algorithm that may be employed during an exemplary neighborhood functional operation wherein a given object or Blob is horizontally eroded for purposes of determining the height thereof;

FIGS. 10a through and including 10c are respectively representative of the first, second and third operational stages performed in accordance with the algorithm in an horizontal erosion process to determine the height of the Blob depicted in FIG. 7;

FIGS. 11a and 11b are similar to FIG. 9a and 9b, respectively, but are here illustrative of an algorithm that may be employed in a vertical erosion process to determine the width of a particular object or Blob;

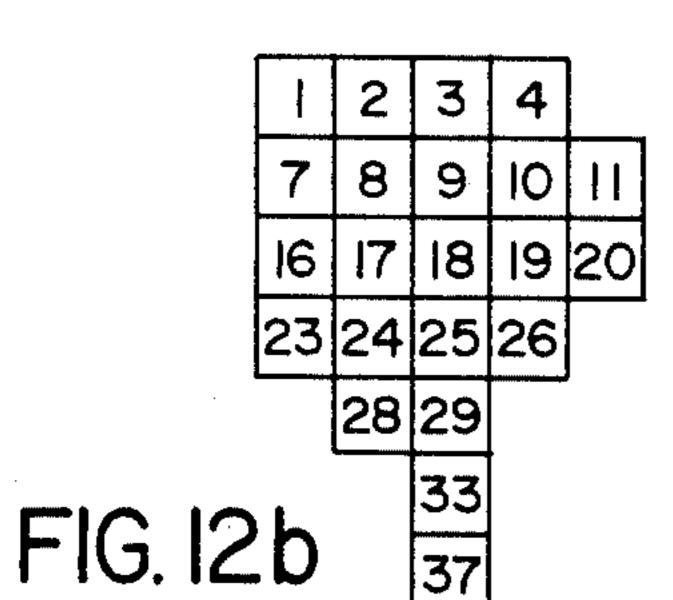

FIGS. 12a through 12d are similar to FIGS. 10a through 10c, but are here illustrative of the first, second, third and fourth operational stages performed in accordance with an algorithm for determining the width of the object or Blob depicted in FIG. 7;

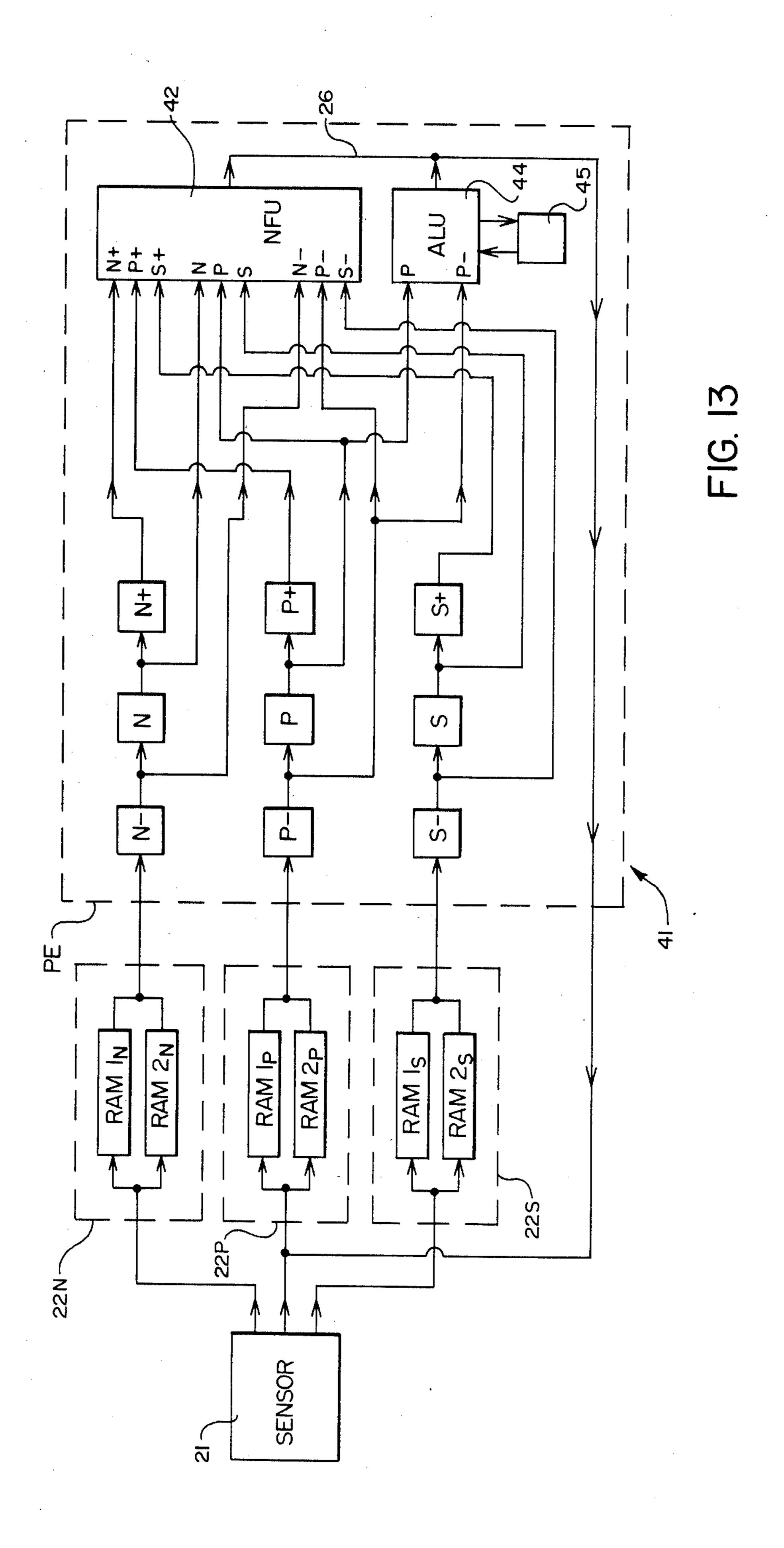

FIG. 13 is a highly diagrammatic block-and-line diagram, with parts removed for purposes of clarity, here depicting a single exemplary processor element ("PE") embodying features of the present invention and suitable for use in carrying out the methods of the present invention;

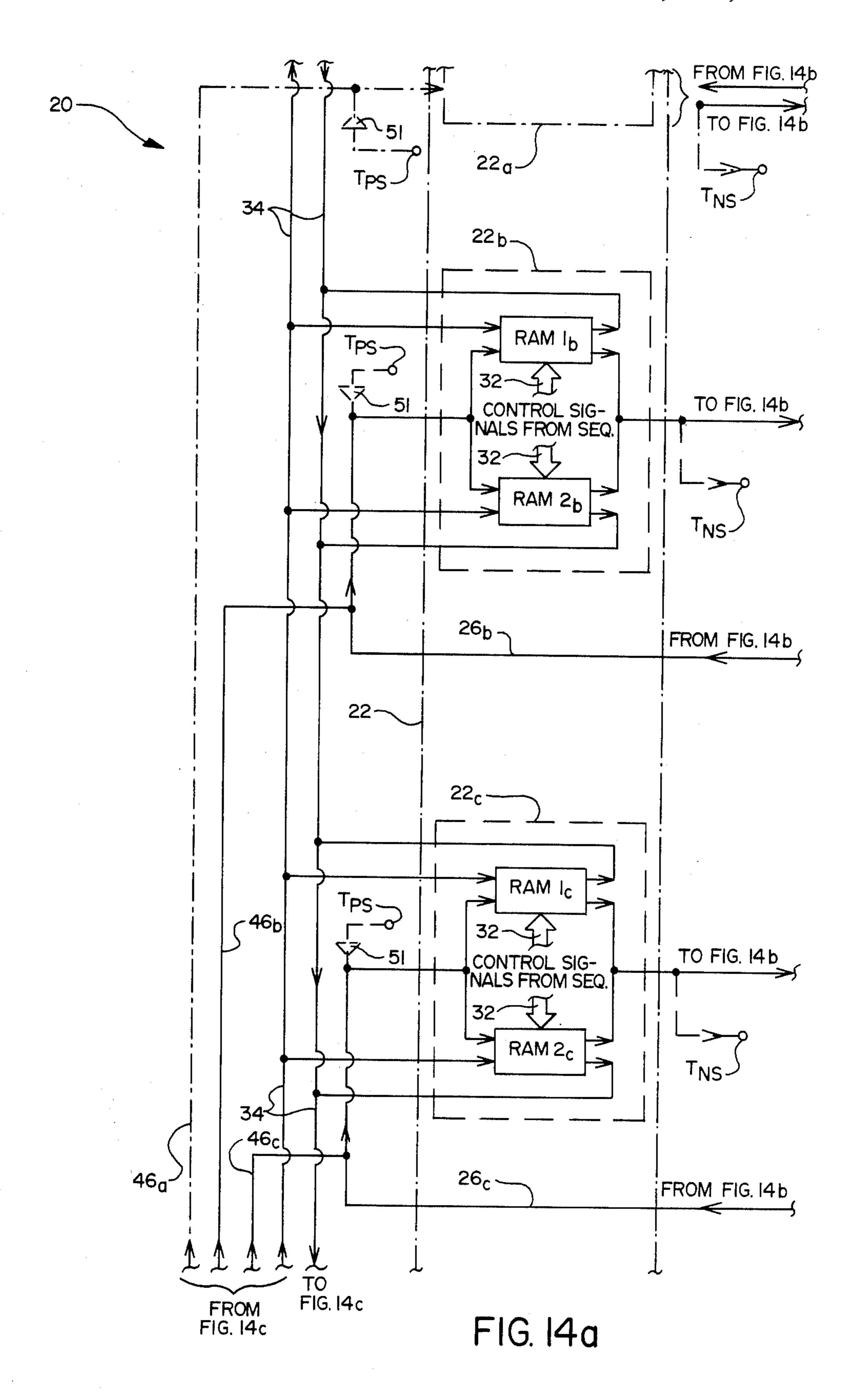

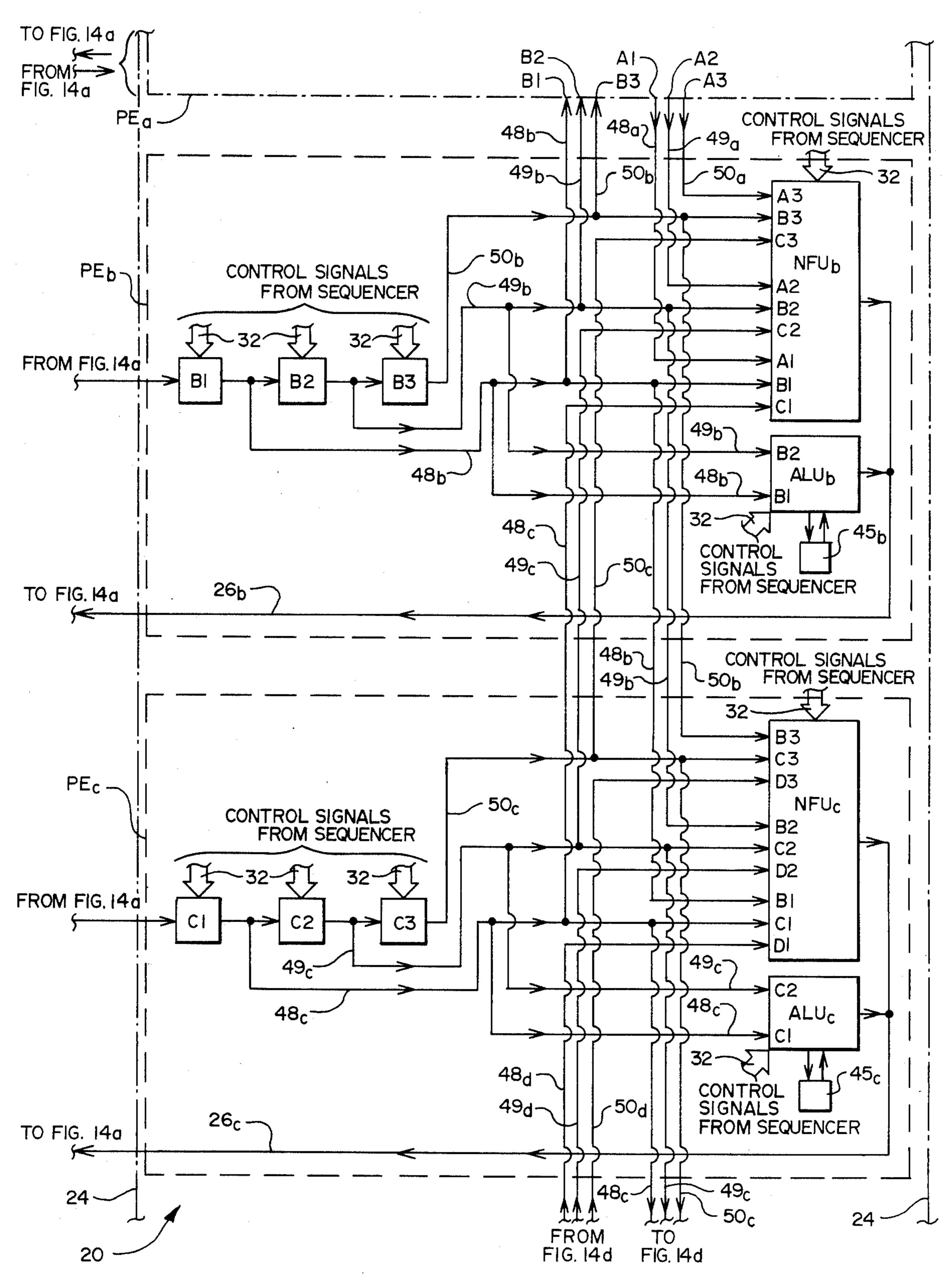

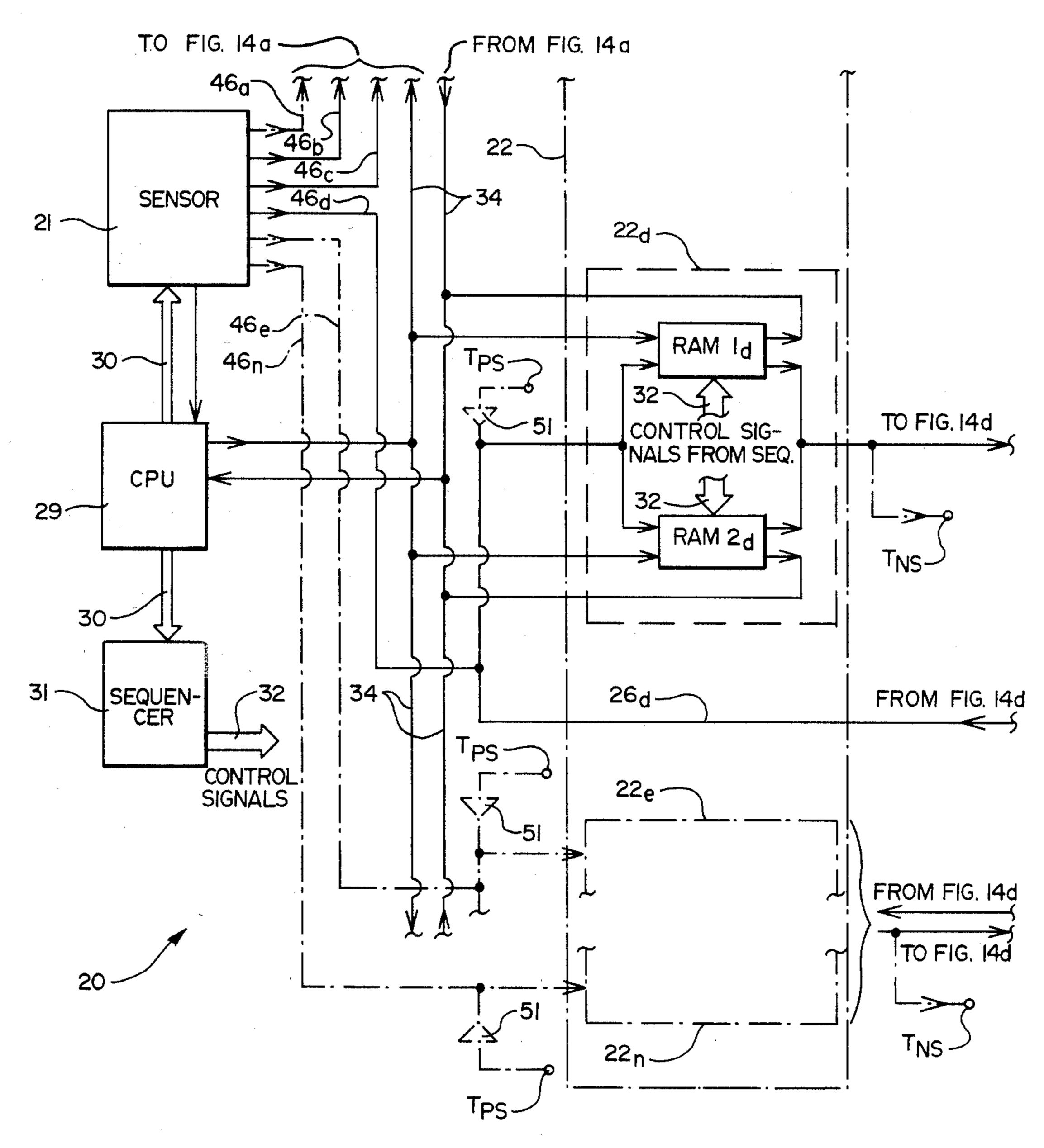

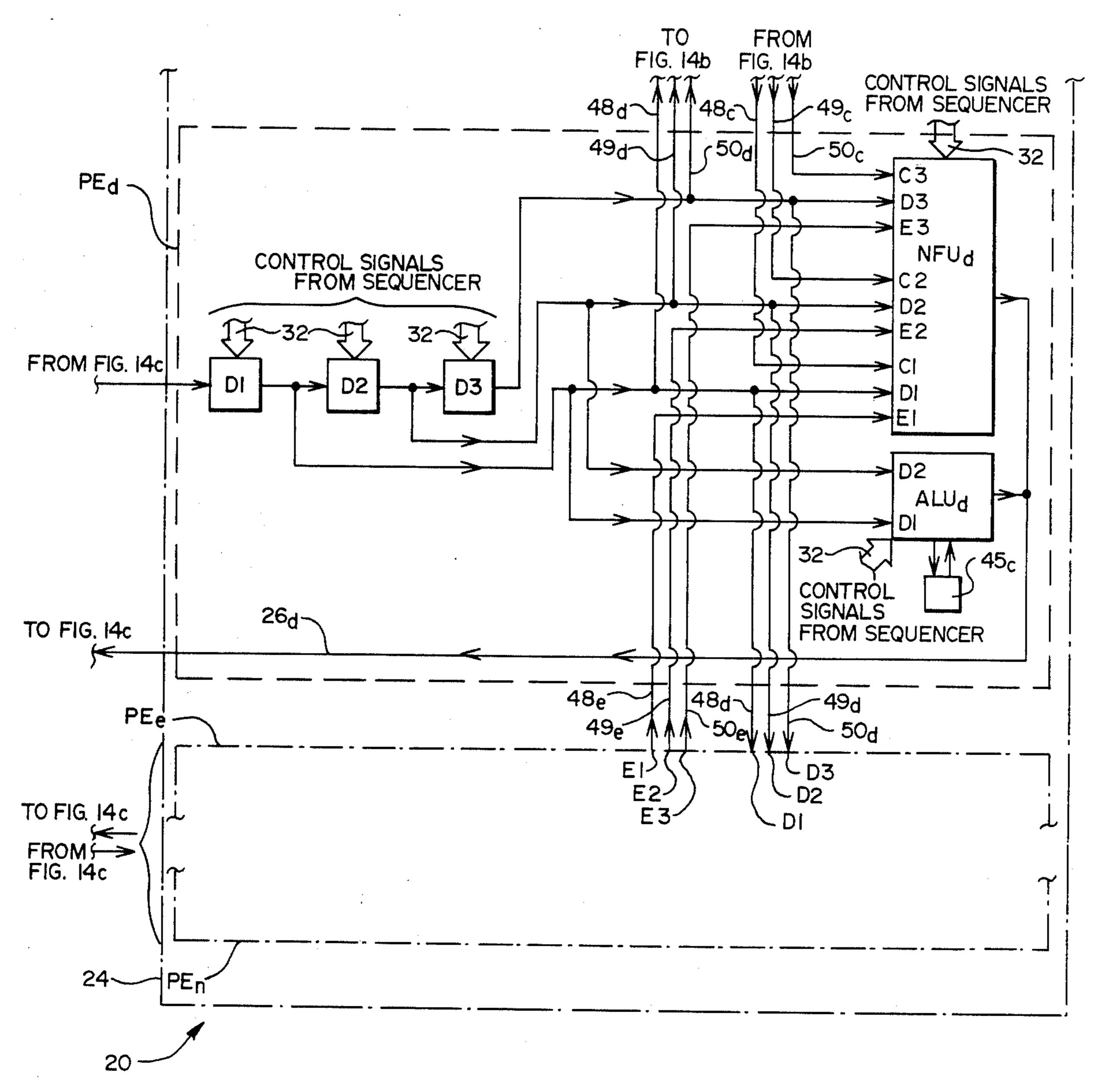

FIGS. 14a, 14b, 14c, and 14d are somewhat more detailed block-and-line drawings which, when placed in side-by-side (FIGS. 14a and 14b; and, FIGS. 14c and 14d) and top-to-bottom (FIGS. 14a and 14c; and, FIGS. 14b and 14d) relation and viewed conjointly, respectively portray the upper left quadrant (FIG. 14a), upper right quadrant (FIG. 14b), lower left quadrant (FIG. 14c), and lower right quadrant (FIG. 14d) of an overall image processing system incorporating an exemplary Vector Image Processor (VIP) embodying features of the present invention, such exemplary VIP having n processor elements ("PES") where "n" can be any whole integer and is here shown as comprising anywhere from three (3) to six (6), or more, processor elements ("PES");

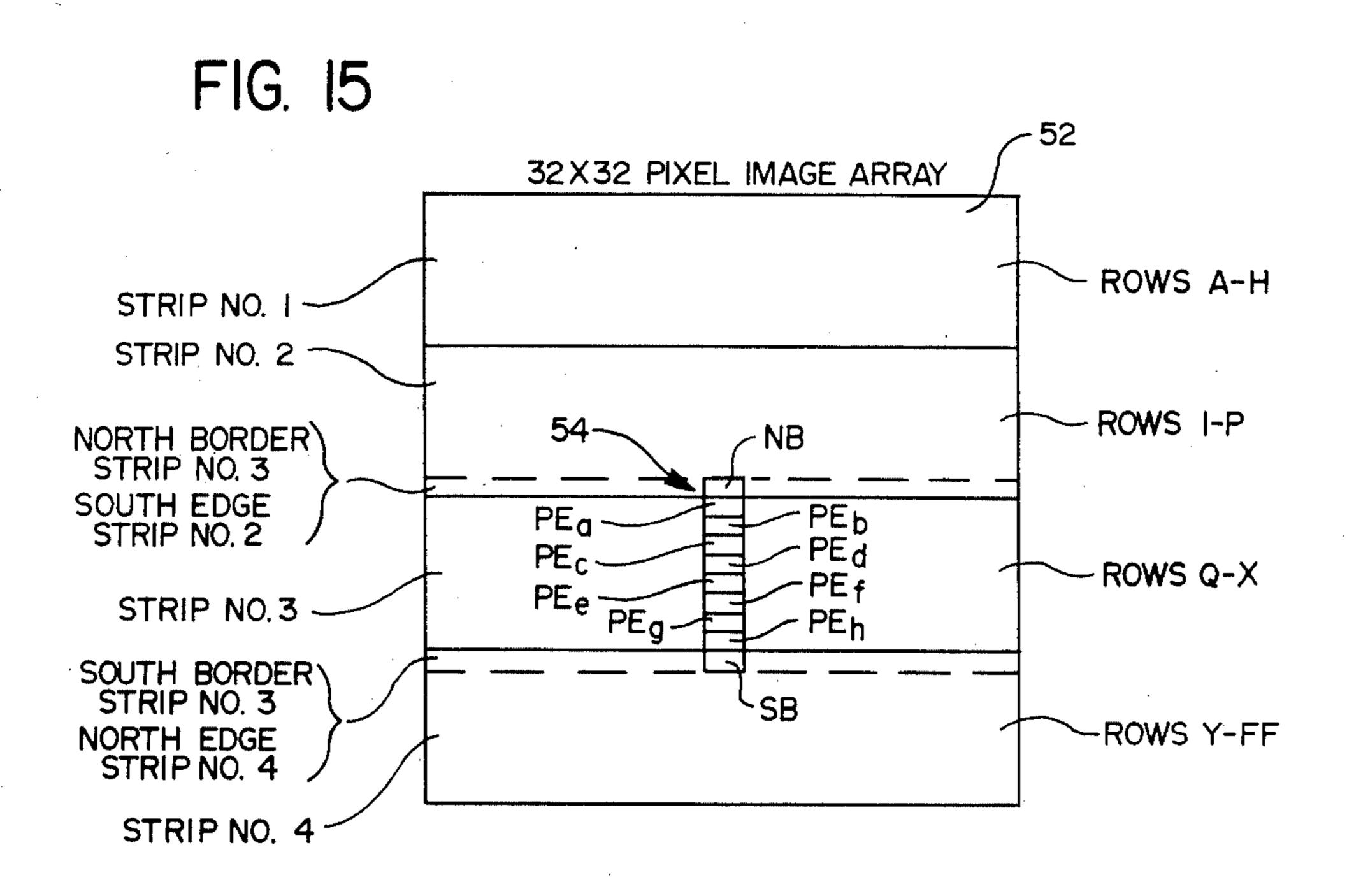

FIG. 15 is a diagrammatic block-and-line drawing, somewhat similar to FIG. 6 and again representative of

an exemplary IX (32×32) PIXEL image array defined by four adjacent 8×32 PIXEL strips, but here depicting the PIXEL data being processed by an exemplary Vector Image Processor ("VIP") including eight (8) parallel processor elements  $PE_a-PE_h$  in conjunction 5 with north and south border memories, with the VIP here shown during processing of data in the third strip from the top of the two-dimensional XY PIXEL image array and with the north border memory providing north neighbor inputs to the northernmost processor 10 element PEa from the neighboring PIXELS in the southernmost row of PIXELS in the neighboring north or second strip, while the south border memory provides south neighbor inputs to the southernmost processor element  $PE_h$  from the neighboring PIXELS in the 15 northernmost row of PIXELS in the neighboring south or fourth strip;

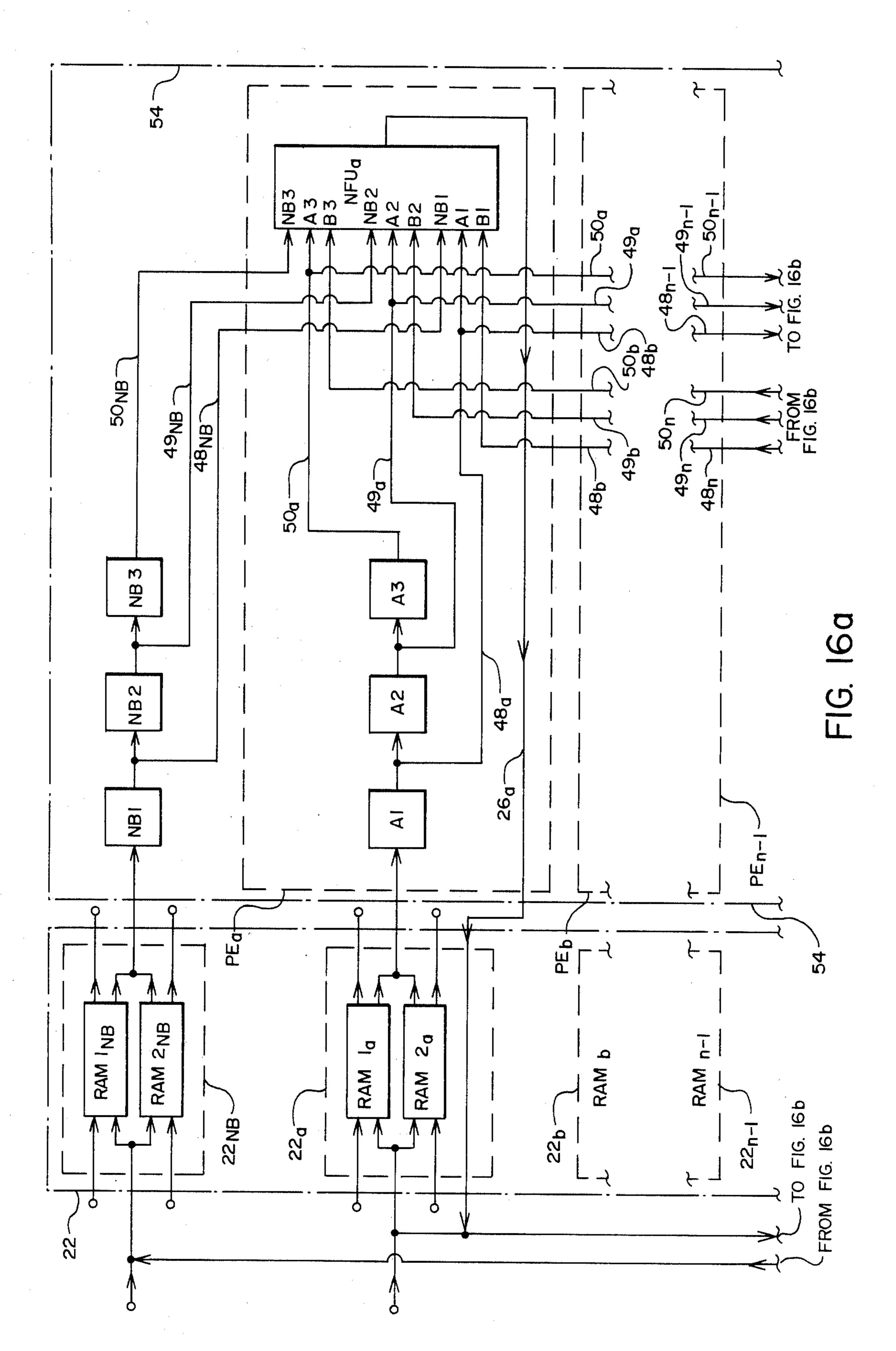

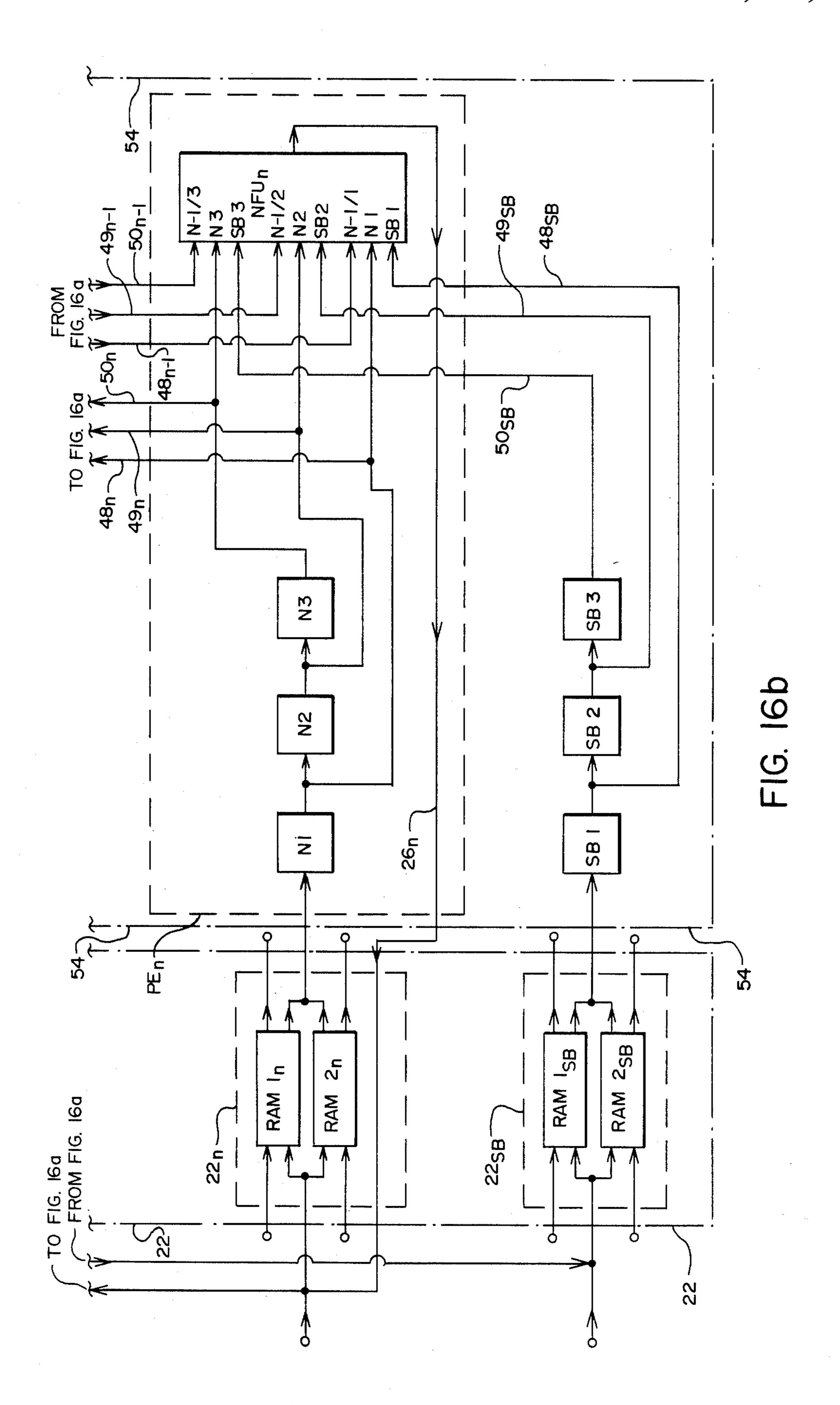

FIGS. 16a and 16b, when placed in top-to-bottom relation and considered conjointly, comprise a highly diagrammatic block-and-line drawing, somewhat simi- 20 lar to FIGS. 14a through 14d, but, in considerably less detail and with parts removed for purposes of clarity, here showing a Vector Image Processor ("VIP") embodying features of the invention and employing n processor elements—for example, eight (8) processor ele- 25 ments  $PE_a-PE_h$  as shown in FIG. 15—and the interconnections employed in an exemplary form of the invention suitable for providing north and south border inputs to respective ones of the northernmost and southernmost processor elements from respective ones of the 30 southernmost and northernmost rows of PIXELS in the neighboring north and south PIXEL strips, respectively; and,

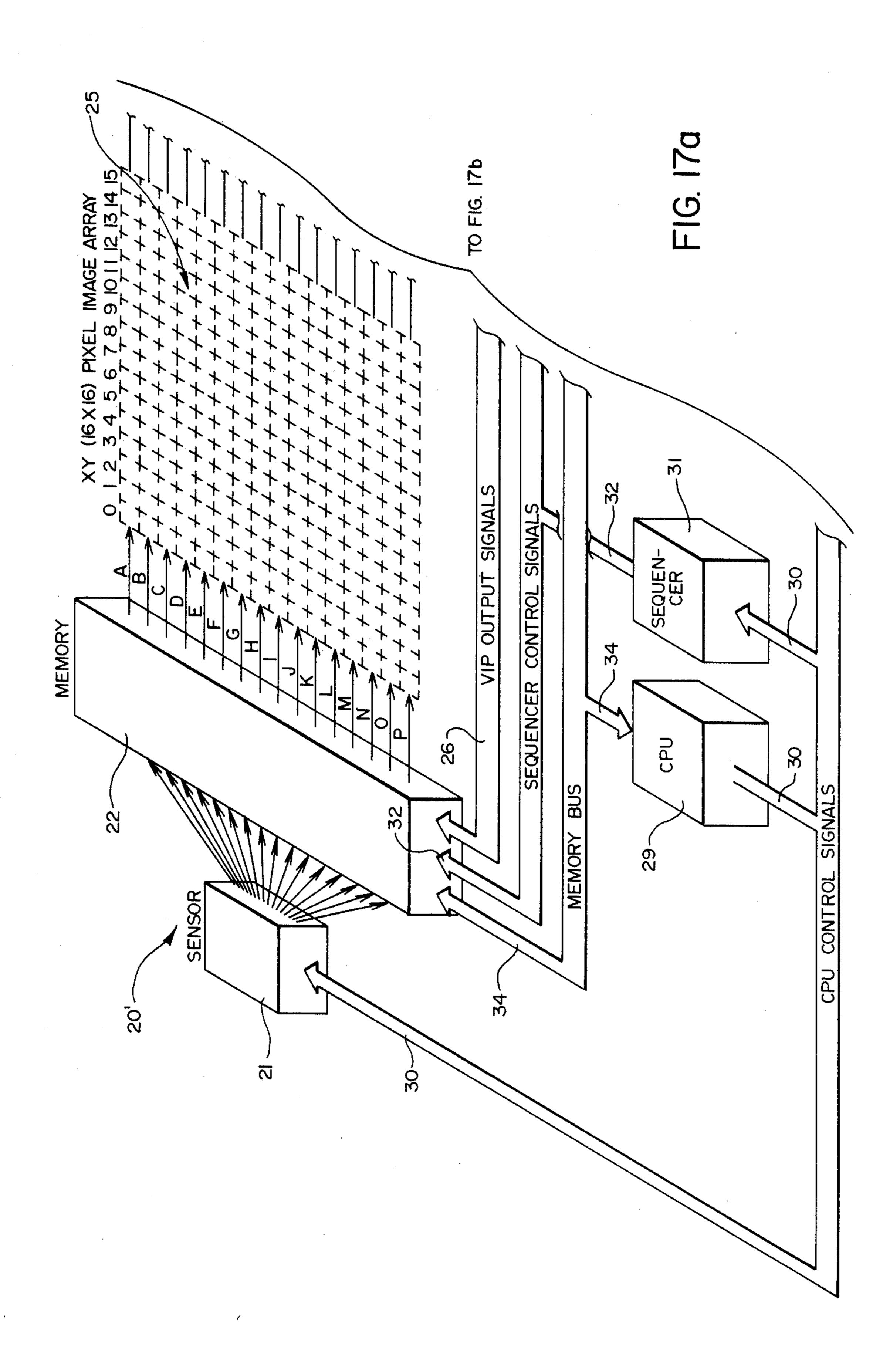

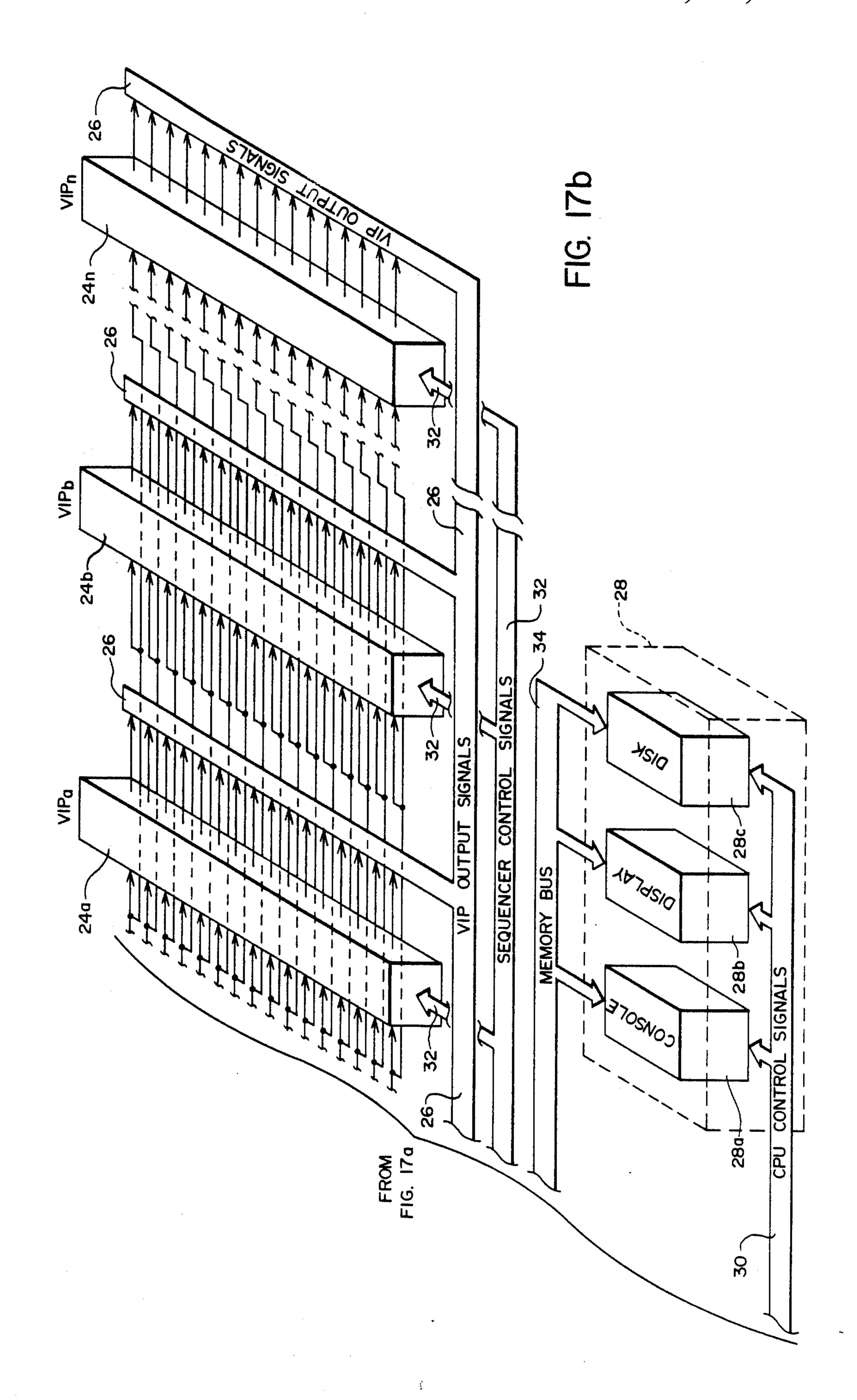

FIGS. 17a and 17b, when placed in side-by-side relation and considered conjointly, comprise a highly dia- 35 grammatic three-dimensional block-and-line drawing somewhat similar to FIG. 1, but here illustrating a plurality of Vector Image Processors ("VIPs") embodying features of the present invention configured in externally pipelined format.

While the invention is susceptible of various modifications and alternative forms, specific embodiments thereof have been shown by way of example in the drawings and will herein be described in detail. It should be understood, however, that it is not intended 45 to limit the invention to the particular forms disclosed; but, on the contrary, the intention is to cover all modifications, equivalents and alternatives falling within the spirit and scope of the invention as expressed in the appended claims.

# DETAILED DESCRIPTION

Before turning to the drawings and to a detailed description of the invention and a typical environment within which it fines particularly advantageous applica- 55 tion, and in an effort to facilitate an understanding of the ensuing description, it should be noted than an exemplary two-dimensional XY PIXEL image array is commonly referred to as having "X" horizontal rows of PIXEL data disposed in "Y" vertical columns wherein 60 Herron et al, IEEE TRANSACTIONS ON COM-"X" and "Y" may have any whole integer value—for example, XY arrays having  $8\times8...16\times16...32\times32$  $...96\times96...128\times128...$ , etc. configurations. While the invention is not, in any sense, limited to any particular size array, those skilled in the art will appreciate that 65 typical sensors of the type commonly employed in conjunction with image processing systems will commonly output a video image containing a tremendous volume

of digitally encoded binary and/or gray scale data in a two-dimensional XY PIXEL image array containing, merely by way of example, from 10<sup>3</sup> to 10<sup>7</sup> PIXELS disposed in horizontal rows and vertical columns. However, it will be understood that references in the ensuing specification and claims to "row" and/or "column" are not to be considered as limiting but, rather, have been set out simply to facilitate an understanding of the invention since the Vector Image Processor ("VIP") of the invention is equally applicable to processing, in parallel, horizontal rows of PIXELS in internally pipelined column-by-column form, and to processing, in parallel, vertical columns of PIXELS in internally pipelined row-by-row form. In the first instance, the Vector Image Processor of the invention would comprise a one-dimensional columnar array of parallel processing elements ("PES"); whereas in the latter instance, it would comprise a one-dimensional row of parallel processing elements ("PES"). Moreover, in either case, the particular number of processing elements ("PES") employed may vary widely dependent namely upon design and/or cost considerations, operating speed requirements, anticipated maximum image size, etc.; and, indeed, there may be any desired number of processing elements ranging from one (1) to one hundred twentyeight (128), or even significantly more.

**12**

It will also be understood that terms such as top ("north"), bottom ("south"), left ("west"), and right ("east") have been used herein simply for purposes of facilitating an understanding of the invention; and, such terms have not been used in a limiting sense.

It will further be understood by those skilled in the art that the particular TRANSFORM employed—viz., a NEIGHBORHOOD TRANSFORM, an ARITH-METIC TRANSFORM or a LOGIC TRANSFOR-M—will, for the most part, be quite conventional and may vary widely dependent upon the particular environment within which the invention is employed. Consequently, while exemplary NEIGHBORHOOD 40 TRANSFORMS for detecting edges and/or sizes of objects of interest will be described herein in some detail, such description is solely for purposes of facilitating an understanding of the invention and has been set forth in the area of neighborhood logic operations as contrasted with arithmetic operations ("add", "subtract", "multiply") and logic operations (AND, OR, XOR) simply because it is believed that neighborhood logic operations may not enjoy as widespread familiarity among persons skilled in the art pertaining to computer 50 architecture as arithmetic and/or logic operations. Nevertheless, all of such operations and the algorithms for performing the same are believed to be well known to persons knowledgeable in the art pertaining to image processing; and, therefore, will not be exhaustively described in detail herein.

Those interested in ascertaining further details of such logic and/or arithmetic image processing operations and algorithms are referred, for example, to such discussions as are set forth in the aforesaid articles by: PUTERS, Vol. C-31, No. 8, pp. 795-800 (August, 1982); Reeves, SIGNAL PROCESSING, Vol.3, pp. 217-230 (1981); and, White, CONFERENCE: ICASSP 81, PROCEEDINGS OF THE 1981 IEEE INTER-NATIONAL CONFERENCE ON ACOUSTICS, SPEECH AND SIGNAL PROCESSING, Atlanta, Ga. (Mar. 30-Apr. 1, 1981); all of which have been more fully identified above; as well as the following

additional articles: Pattern Detection and Recognition, Unger, PROCEEDINGS OF THE IRE, p. 737 (1959); Feature Extraction, Goley, and Hexagonal Pattern Transformers, Preston, Jr., IEEE TRANSACTIONS ON COMPUTERS, Vol. C-20, No. 9 (September, 5 1971); The Texture Analyzer, JOURNAL OF MICROS-COPY, Vol. 95, Part II, pp. 349–356 (April, 1972); Random Sets And Integral Geometry, G. Matheron, Wiley (1975); Integral Geometry As A Tool In Pattern Perception, Albert B. J. Novikoff, PRINCIPLES OF SELF- 10 ORGANIZATION, edited by Von Foerstn and Zopf, Pergamon Press (1962); and Stereology And Structuring Elements, JOURNAL OF MICROSCOPY, Vol. 95, Part I, pp. 93-103 (February, 1972). Reference may also be had to the descriptions set forth in the aforesaid U.S. 15 Pat. Nos. 4,060,713—M. J. E. Golay; 4,224,600—Sellner; 4,167,728—Sternberg; and, 4,174,514—Sternberg. It will be understood that the foregoing bibliography of articles and patents is by no means exhaustive.

Finally, to facilitate readibility of the ensuing descrip- 20 tion, reference will hereinafter be made to the following acronyms which are, or will be, quite familiar to persons skilled in computer architecture and/or image processing techniques:

ALU—an arithmetic logic unit;

AU—an arithmetic unit—e.g., an adder/subtractor/-multiplier;

BAP—a binary array processor—either fully or locally parallel;

CPU—a central processing unit;

EPROM—an erasable programmable read only memory;

FLIR—a forward looking infra-red sensor;

IC—an integrated circuit;

LU—a logic unit—e.g., a Boolean logic device;

NFU—a neighborhood functional unit;

PE—a processing element;

PIXEL—a digitally encoded picture element;

PLA—a programmable logic array;

PROM—a programmable read only memory;

RAM—a random access memory;

ROM—a read only memory;

SAR—a synthetic aperture radar sensor;

SIMD—a single instruction multiple data processor;

SLA—a storage logic array; and,

VIP—a Vector Image Processor embodying features of the present invention.

A. The Environment Of The Invention

Turning now to the drawings, there has been illustrated in FIG. 1, in highly diagrammatic, block-and-line 50 form, an exemplary image processing system, generally indicated at 20, comprising a Sensor 21, a video image buffer Memory 22 for receiving digitally encoded binary and/or gray scale image representative PIXEL data from the Sensor 21; and, a one-dimensional image 55 processor, here a VIP 24 embodying features of the invention for processing, in internally pipelined column-by-column format, the "X" rows of PIXEL data output from the Memory 22 in the form of a two-dimensional XY PIXEL image array which is here generally 60 illustrated in highly diagrammatic, pictorially imaginary form at 25. In the exemplary image processing system 20 shown in FIG. 1, the two-dimensional XY PIXEL image array comprises a  $16 \times 16$  array having sixteen (16) horizontal "X" rows of PIXELS labelled as 65 rows "A" through "P" from north to south, and sixteen (16) vertical "Y" columns of PIXELS labelled as columns "0" through "15" from west to east. As shown,

the processed data is output from the VIP in parallel row format and sequentially in internally pipelined column-by-column format and is fed to the image buffer Memory 22 via a VIP output signal three-state bus 26.

As is quite conventional with the illustrative type of image processing system 20 here shown—except, of course, for the inclusion of the exemplary VIP 24 embodying the invention—the system 20 may include one or more peripherals 28 such, for example, as a Console 28a, a Display 28b and/or a Disk Memory 28c, all under the control of a host CPU 29 which provides control signals via bus 30 to the Sensor 21, peripherals 28a, 28b and/or 28c, and a Sequencer 31. In the illustrative image processing system 20, Sequencer 31 provides control signals for the image buffer Memory 22 and the VIP 24 under the control of CPU 29 via signal bus 32; it being understood by those skilled in the art that the particular control, clock and similar signals, and the timing thereof, will vary widely dependent upon the environment within which the image processing system 20 is to be employed and the particular operational instructions desired by the user/programmer; and, since such control, clock and similar signals, as well as the programming thereof, are completely conventional and form no part of the present invention except for enabling the continuous operational mode whereby the digitally encoded data is shifted through the system and processed, they will not be further detailed herein. Finally, the exemplary image processing system 20 includes a three-state Memory bus 34 which serves to provide data/communication paths coupling the image buffer Memory 22, one or more peripherals 28a-28c, and CPU 29 together.

In the exemplary image processing system 20 illus-35 trated environmentally in FIG. 1, it will be understood that the particular details of the Sensor 21 are not critical to the present invention and will vary widely dependent upon the particular field and environment within which the system 20 is employed. Thus, the Sensor 21 may comprise a FLIR, an imaging infra-red (IR) sensor, a sonic or laser radar, a SAR, a TV sensor, or any similar sensor characterized by its ability to output a video image on a real time basis and in the form of digitally encoded PIXEL data in a two-dimensional PIXEL image array 25. And, as previously indicated, such sensors will typically output a two-dimensional XY PIXEL image array containing on the order of from 10<sup>3</sup> to 10<sup>7</sup> discrete PIXELS. Similarly, the image buffer Memory 22, peripherals 28, CPU 29 and Sequencer 31 are entirely conventional in construction and mode of operation and may be programmed as required and/or desired to meet the various operational parameters and objectives set for the image processing system 20. Accordingly, such components are not described in greater detail in the ensuing description.

B. Image Arrays/Neighborhoods/TRANSFORMS General Information

Referring now to FIG. 2, there has been illustrated, in pictorially imaginary form, a fragmentary portion of a typical two-dimensional XY PIXEL image array 25 here comprising fragmentary portions of vertical columns identified as "0" through "5" and horizontal rows identified as "A" through "F". Thus, any given PIXEL may be identified by its "X" and "Y" coordinate addresses, thereby enabling entry into, storage within, and/or withdrawal from comparable address positions in Memory 22 (FIG. 1). As shown in FIG. 2, the illustrative PIXELS describe a series of overlapping AB

neighborhoods—for example, the  $3\times3$  neighborhood 35a circumscribed by the relatively heavy solid line surrounding PIXEL locations (0,A) through (2,A), (0,B) through (2,B), and (0,C) through (2,C); and, the overlapping  $3 \times 3$  neighborhood 35b circumscribed by 5 the broken line surrounding PIXEL locations (0,B) through (2,B), (0,C), through (2,C), and (0,D) through (2,D). In like manner, other overlapping  $3 \times 3$  neighborhoods (not shown) can be readily defined by any selected group of nine (9) neighboring PIXELS located at 10 the intersections of any three adjacent vertical columns and any three adjacent intersecting horizontal rows.

It has been found that for most special purpose image processing applications, it is highly advantageous to employ  $3 \times 3$  neighborhoods since PES embodying the 15 invention can be readily implemented with a single data input terminal, six (6) neighbor input terminals (the two additional neighbor input terminals being derived from the data input terminal), six (6) neighbor output terminals, and a single data output terminal together with the 20 necessary control and clock terminals; thereby enabling implementation of up to on the order of sixty-four (64) or more PES on a single IC. However, as will become apparent as the ensuing description proceeds, the invention is not limited to use with  $3\times3$  PIXEL neighbor- 25 hoods, but, rather, it can be employed with Golay Surrounds—a seven (7) PIXEL neighborhood wherein each PIXEL of interest has six (6) immediate neighbors;  $2\times2$  neighborhoods;  $5\times5$  neighborhoods; etc. Of course, as the neighborhoods increase in size, considera- 30 bly more interconnections are required since each PIXEL of interest has considerably more neighbors for example, in a  $5\times5$  neighborhood, the centermost PIXEL of interest has twenty four (24) neighbors, thus significantly increasing the number of PE interconnec- 35 tions required.

As is conventional with SIMD image processors including BAPs (both fully parallel and locally parallel) and/or Pipelined Processors, the PIXEL data may be digitally encoded binary and/or gray scale data—in- 40 deed, the VIP 24 (FIG. 1) of the present invention can function equally well with either and/or both types of digitally encoded bits. However, for many spatial filtering operations and the like, it may be preferable to work with digitally encoded binary data having, or thre- 45 sholded to have, a binary value of "0" ("False") or "1" ("True"). For example, in edge or boundary detection with respect to objects, or "Blobs", of interest, the presence of a binary "0" value is indicative of the absence of a Blob of interest; whereas the presence of a binary "1" 50 value is indicative of the presence of a Blob of interest. Considering, for example, the  $3\times3$  neighborhood 35a shown in FIG. 2, and assuming that the nine (9) PIX-ELS defining such neighborhood have, or have been thresholded to have, binary values of "0" or "1" as 55 shown in FIG. 3, then it will be observed that a Blob of interest—i.e., as indicated by binary values of "1"—appears at PIXEL locations (2,B), (1,C) and (2,C), while all other PIXELS in the  $3\times3$  neighborhood 35a have binary values of "0" indicating the absence of a Blob of 60 northernmost and southernmost rows of PIXELS in interest. Thus, the presence of PIXELS (0,A) through (2,A) having binary values of "0" in row "A" will provide neighbor data for the associated PE (not shown in FIG. 3) indicative that row "A" defines the north boundary or border of the object within that  $3 \times 3$  65 neighborhood, such object being defined by PIXEL locations (2,B), (1,C) and (2,C). Similarly, the presence of PIXELS having binary values of "0" at all PIXEL

locations in column "0" provides neighbor data for the associated PE indicating that column "0" defines the west border or boundary of the object within that  $3 \times 3$ neighborhood. The algorithms for enabling the foregoing edge detection computations are completely conventional and well known to persons skilled in the art; and, therefore, will not be described herein.

Turning next to FIG. 4, there has been illustrated a conventional PIXEL neighborhood, generally indicated at 36, more commonly known in the art as a "Golay Surround". See, e.g., U.S. Pat. No. 4,060,713 issued to M. J. E. Golay for a more complete description of NEIGHBORHOOD TRANSFORMS involving the use of Golay Surrounds. Suffice it to say that a typical Golay Surround 36 is defined by a centermost PIXEL of interest surrounded by six (6) PIXELS configured in an hexagonal array—i.e., the neighborhood 36 comprises a total of seven (7) PIXELS. As will be more clearly evident upon inspection of FIG. 5, a fragmientary portion of a PIXEL image array 25' has been illustrated wherein the array is defined by a plurality of overlapping Golay Surround neighborhoods, three of which are shown at 36a, 36b, and 36c. For purposes of the present invention, the PIXEL image array 25' shown in FIG. 5 may be considered the full equivalent of the rectilinear two-dimensional XY PIXEL image array 25 depicted in FIGS. 1 and 2; and, it may be processed by the VIP 24 (FIG. 24) of the present invention in the same fashion as the PIXEL image array 25. Thus, the PIXEL image array 25' depicted fragmentarily in FIG. 4 is defined by discrete PIXELS located at the intersections of parallel, linear, horizontal rows "A" through "D" and parallel, saw-tooth-shaped, vertical columns "0" through "4"; and, therefore, the array 25' also comprises a two-dimensional XY PIXEL image array.

To further facilitate an understanding of the present invention, it will be understood by those skilled in the art that the image processor employed—here a VIP 24 (FIG. 1) embodying the invention—does not necessarily have to be configured to have a PE for each and every row in a typical two-dimensional XY PIXEL image array. For example, and as best shown in FIG. 6, a given two-dimensional XY PIXEL image array 38 can be processed by sequentially scanning discrete adjacent strips of PIXELS wherein each strip consists of n rows of PIXELS (where "n" is equal to the number of PES in the VIP—not shown in FIG. 6—and, wherein "n" may be equal to any desired whole integer). Thus, the exemplary XY PIXEL image array 38 depicted in FIG. 6 comprises a  $32 \times 32$  array consisting of four (4) adjacent horizontal strips 38a, 38b, 38c and 38d with each strip being  $8 \times 32$ . This illustrative form of PIXEL image array assumes, therefore, that the VIP to be employed will comprise a one-dimensional columnar processor including eight (8) parallel PES together with associated north and south Memories for inputting north and south border data enabling the equipment to carry out NEIGHBORHOOD TRANSFORMS on the each such strip.

Thus, when processing the illustrative  $32 \times 32$  array 38 shown in FIG. 6, the PIXEL data contained in the eight (8) rows of PIXELS defining the northernmost strip 38a will be fed to, and shifted relatively through, a one-dimensional VIP (not shown) embodying the features of the invention having north and south border Memories and eight (8) parallel PES, with the VIP

scanning and analyzing the PIXELS contained within the strip 38a from edge-to-edge (e.g., from west-to-east) followed by sequential edge-to-edge scanning of the eight (8) rows of PIXEL data contained within each of strips 38b, 38c and 38d. A first processing operation 5 programmed into the VIP might, for example, comprise a rapid scan of the overall XY PIXEL image array 38 in strip-by-strip internally pipelined format to locate areas and/or objects of interest, followed by a second, and perhaps one or more additional, processing operation(s) 10 in a localized area where an object of interest has been detected, here shown as an 8×N patch 39 located centrally within strip 38b. It will be appreciated as the ensuing description proceeds that when the VIP 24 (FIG. 1) comprises a one-dimensional processor having 15 sixteen (16) parallel PES, the  $32 \times 32$  array 38 shown in FIG. 6 would consist of only two (2) strips, each 16×32. Similarly, if the VIP 24 includes only four (4) PES arranged in a one-dimensional columnar array, then the image array 38 depicted in FIG. 6 would be 20 defined by eight (8) adjacent  $4 \times 32$  strips.

As previously indicated, the various ARITHMETIC TRANSFORMS and LOGIC TRANSFORMS (such as Boolean logic operations) employed in image processing techniques are completely conventional and 25 well known to persons skilled in the art; and, therefore, they will not be further described herein. However, while NEIGHBORHOOD TRANSFORMS are also generally known in the art, they are believed to be less widely understood—albeit, that they have been de- 30 scribed in some detail in, for example, the aforesaid U.S. Pat. No. 4,060,713 issued to M. J. E. Golay, the aforesaid Sternberg patents, and numerous of the aforesaid literature references, to name but a few of available published TRANSFORM descriptions. Therefore, to 35 insure that NEIGHBORHOOD TRANSFORM operations of the type referred to in the present detailed description will have real meaning to the leader, one typical NEIGHBORHOOD TRANSFORM that can be performed will be described hereinbelow—viz., a spa- 40 tial filtering termed "contraction" or "erosion" as might be employed to determine the size of an object or Blob of interest.

Thus, referring to FIG. 7, there has been illustrated, in pictorially imaginary form, a fragmentary portion of 45 a two-dimensional XY PIXEL image array 25 containing a plurality of PIXELS disposed in horizontal rows and vertical columns wherein the PIXELS have, or have been thresholded to have, binary values of "0" ("False") or "1" ("True"). As here shown by way of 50 example, it will be noted that forty-one (41) of the centrally located PIXELS, here respectively numbered "1" through "41", define a Blob 40 or object of interest-i.e., these forty-one (41) numbered PIXELS have binary values of "1", while all other surrounding PIX- 55 ELS have binary values of "0" indicative of the absence of significant object data. It will further be assumed that the image processing system 20 (FIG. 1) has been programmed such that once a Blob of interest—e.g. Blob 40—has been detected, at least one ensuing processing 60 operation will be to determine the size of the Blob. To accomplish this, each PIXEL of interest within the horizontal and vertical boundaries of the Blob 40 is processed or analyzed based upon its relation with its neighboring PIXELS. Thus, as shown in FIG. 8, each 65 PIXEL of interest to be processed is identified as "E" and its relation to each of the eight (8) neighboring PIXELS "A" through "D" and "F" through "I" is

determined in accordance with algorithms for detecting the size of the Blob 40. One such algorithm—viz., an "erosion" or "contraction" algorithm for determining the height of the Blob 40—has been pictorially illustrated in FIGS. 9a and 9b where the PIXEL E of interest is shown as being located adjacent the north boundary in FIG. 9a as indicated by the binary value "0" in the three north neighbors and as being located adjacent the south boundary in FIG. 9b as indicated by the binary value "0" in the three south neighbors, it being understood that the values "X" are "I don't cares". The height detection or "horizontal erosion" algorithm pictorially depicted in FIGS. 9a and 9b can be expressed as follows:

$$E = \overline{A}\overline{B}\overline{C} + \overline{G}\overline{H}\overline{I}$$

[EQ. I]

and, is designed to cause the Blob 40 to undergo a series of contractions which will eventually cause the Blob 40 to disappear; with the number of contractions or Steps required to make the Blob disappear providing an indication of the size of the Blob.

Smaller objects or Blobs will, of course, disappear before larger objects or Blobs and, consequently, when the size of any given Blob is known, the contraction process can be halted before the Blob of interest disappears, at which point smaller Blobs will have already disappeared; and, the Blob of interest can then again be enlarged through a series of "expansion" or "dilation" steps (not described herein, but which are completely conventional) to restore the Blob of interest to its original size and, if desired, the Blob can be restored, at least approximately, to a shape similar to its original shape by "masking"—i.e., ANDing—the processed Blob with the original Blob. However, the smaller objects will not be restored since they have been removed from the image.

Thus, in processing the Blob 40 depicted in FIG. 7 in accordance with the algorithm of Equation I and as depicted in FIGS. 9a and 9b, the first Step as shown by comparison of FIGS. 7 and 10a results in elimination of those PIXELS numbered "1" through "5", "12" and "13" adjacent the upper or northern boundary (FIGS. 7 and 9a) and those PIXELS numbered "14", "21", "22", "39", "40" and "41" adjacent the lower or southern boundary (FIGS. 7 and 9b), since, in each instance, the eliminated PIXEL is bounded by three northern or three southern neighbors having binary values of "0" ("False"). Similarly, during Step 2 (Cf., FIGS. 10a and 10b), those PIXELS numbered "6" through "11" are eliminated by virtue of the fact that their northern boundary neighbors have binary values of "0"; and, PIXELS "36" through "38" are eliminated by virtue of the fact that their three southern neighbors also have binary values of "0". In Step 3 (Cf., FIGS. 10b and 10c), the upper boundary portion of the "horizontal erosion" algorithm (FIG. 9a) serves to eliminate PIXELS "15" through "20", while the lower boundary portion of the algorithm (FIG. 9b) serves to eliminate PIXELS "32" through "35". Finally, in Step 4 (not shown), the "horizontal erosion" algorithm of Equation I and FIGS. 9a and 9b serves to eliminate all remaining PIXELS numbered "23" through "31". Thus, the entire "contraction" or "horizontal erosion" process defined by the algorithm of Equation I requires four (4) Steps in the exemplary instance, with each Step removing all PIX-ELS in the north and south rows of the Blob 40 having three northern or southern neighbors with binary values

of "0", thereby establishing that the height of the original Blob 40 is eight (8) PIXELS—i.e., four Steps×two PIXEL rows/Step.

To determine the width of the Blob 40, a similar "contraction" process known as "vertical erosion" is 5 performed; and, the algorithm for this operation is pictorially illustrated in FIGS. 11a and 11b and is defined by the following equation:

$$E = \overline{ADG} + \overline{CFI}$$

[EO. II]

Thus, as shown in FIG. 11a, the "vertical erosion" algorithm of Equation II serves to eliminate the left or westernmost PIXELS whose neighboring boundary PIXELS have binary values of "0"; and, as shown in 15 FIG. 11b, those right or easterly PIXELS having neighbors with binary values of "0" will be eliminated. Thus, in Step 1 (Cf., FIGS. 7 and 12a) the westerly PIXELS "5", "14", "27", "36" and "40" and the easterly PIX-ELS "13", "22", "31", "35" and "39" are eliminated; in <sup>20</sup> Step 2 (Cf., FIGS. 12a and 12b) the westerly PIXELS "6", "15", "32" and "41" and the easterly PIXELS "12", "21", "30", "34" and "38" are eliminated; in Step 3 (Cf., FIGS. 12b and 12c) the westerly PIXELS "1", "7", "16", "23" and "37" and the easterly PIXELS <sup>25</sup> "11", "20", "33" and "37" are eliminated; and, in Step 4 (Cf., FIGS. 12c and 12d) the westerly PIXELS "2", "8", "17", "24" and "28" and the easterly PIXELS "4", "10", "19" and "26" are eliminated; thus leaving only a "18", "25" and "29". Such remaining PIXELS are eliminated during Step 5 (not illustrated) by that portion of the "vertical erosion" algorithm pictorially illustrated in FIG. 11a; and, consequently, the successive Steps of the algorithm as set forth in Equation II and FIGS. 11a and 11b are indicative of a Blob 40 having an original width of nine (9) PIXELS.

Knowing that the Blob 40 of FIG. 7 has a height of eight (8) PIXELS and a width of nine (9) PIXELS, the 40 image processing system 20 (FIG. 1) is now capable of proceeding with any additional desired computational processing operation. For example, the image can be again "contracted" or "eroded" to eliminate all objects having a height less than eight (8) PIXELS and all 45 objects having a width less than nine (9) PIXELS; and, thereafter, it can be "expanded" or "dilated" to its original size (and, if desired, to a shape approximating its original shape) so as to eliminate from the image all objects smaller than Blob 40.

## VECTOR IMAGE PROCESSOR AND METHOD OF PROCESSING IN ACCORDANCE WITH THE INVENTION

In accordance with the present invention, methods 55 and apparatus in the form of a special purpose Vector Image Processing System are provided wherein the VIP 24 (FIG. 1) or the modified VIP shown generally at 41 in FIG. 13 comprise a one-dimensional columnar array of n PES (where "n" can be any whole integer; 60 and, where the PES are disposed in parallel in those instances where "n" is "2" or more) and wherein n rows of PIXEL data contained within a two-dimensional XY PIXEL image array—e.g., the array 25 shown by way of example in FIG. 1—are fed to, and relatively shifted 65 through, the VIP 24 (or the VIP 41) which serves to process each PIXEL of interest in internally pipelined column-by-column form and, in those instances where

"n" is greater than "1", wherein the "n" PIXELS in each column are processed in parallel.

### C. Single PE VIP Embodiment

To this end, and as best illustrated by reference to FIG. 13, a modified form of VIP, generally indicated at 41, has been shown as comprising a single processing element PE wherein all hardware components and interconnections are implemented on a single IC. As here shown, the processing element PE is fed with digitally [EQ. II] 10 encoded data originally derived from a Sensor 21 and stored in Memories 22N, 22P and 22S (i.e., specific Memory locations in the image buffer Memory 22 shown in block form in FIG. 1) at address positions corresponding to the XY address positions of the two dimensional XY PIXEL image array—e.g., the array 25 of FIG. 1. Data contained within the Memories 22N, 22P and 22S is, upon command by the Sequencer (not shown in FIG. 13, but identical to the Sequencer 31 depicted in FIG. 1) under the control of a host CPU 29, shifted in parallel and in internally pipelined column-bycolumn form through three parallel sets of cascaded latches (N-, N, N+), (P-, P, P+) and (S-, S, S+)which form part of the exemplary processing element PE. It will be understood by those skilled in the art that such latches may simply take the form of shift register stages of D-type flip flops of completely conventional construction and which need not be further described in detail herein.

Assuming, for example, that the VIP 41 of FIG. 13 is single vertical column containing PIXELS "3", "9", 30 being used to process the 16×16 PIXEL image array 25 as shown in FIG. 1, and assuming further that the VIP 41 scans the rows of PIXELS sequentially from west to east within each row and scans the rows sequentially from north to south with such sixteen rows hereinbelow being termed rows "A" through "P", then during scanning of row "A"—viz., the northernmost row of PIX-ELS—the digitally encoded bits corresponding to the sixteen (16) PIXELS contained within row "A" will be stored in the Memory 22P associated therewith; the digitally encoded bits corresponding to the sixteen (16) PIXELS contained within the adjacent southerly row "B" will be stored in the south Memory 22S; and, digitally encoded bits representative of the north boundary (not shown) of the PIXEL image array 25 in FIG. 1 will be stored in north Memory 22N. In addition, although not shown in FIG. 1 or 13, it will be understood by those skilled in the art that memory locations will be provided in Memory 22 (FIG. 1) for storage of digitally encoded data bits representative of the east, west and 50 south boundaries of the two-dimensional XY PIXEL image array 25.

Thus, the arrangement is such that the VIP 41 (FIG. 13) is configured to process the digitally encoded PIXEL data in the two-dimensinoal XY PIXEL image array—e.g., the array 25 of FIG. 13—on a PIXEL-by-PIXEL basis commencing with row "A" and sequentially proceeding through rows "B" through "n" (in FIG. 1, row "n" is row "P"). To this end, upon the first shift command emanating from the Sequencer 31 (FIG. 1), digitally encoded data is shifted from the Memories 22N, 22P and 22S into respective ones of the latches N-, P- and S-; and, such data is representative of the western boundary of the image—i.e., the contents of latch N— will be data representative of the western edge of the northern boundary; and, the contents of latches P— and S— will be the data representative of the western boundaries of rows "A" and "B" respectively. Upon the second shift command, the data stored

in latches N-, P- and S- is shifted, in parallel, into respective ones of latches N, P and S; while digitally encoded data representative of the north boundary of the westernmost column—e.g., column "0" 1)—in the two-dimensional XY PIXEL image array is 5 shifted into latch N-, and digitally encoded data representative of the westernmost column "0" PIXELS in rows "A" and "B" is respectfully shifted into latches P— and S—. Upon the third shift command emanating from the Sequencer 31 (FIG. 1): the data stored in 10 latches N, P and S is respectively shifted to the N+, P+ and S+ latches; data in the N-, P- and Slatches is respectively shifted into the N, P and S latches; and, data representative of the north boundary and second most westerly column—e.g., column "1" 15 (FIG. 1)—of PIXELS in row "A" and "B" is respectively shifted into latches N-, P- and S-.

The processing element PE is now enabled by the Sequencer 31 under control of the CPU 29 (FIG. 1) for conducting its first NEIGHBORHOOD, ARITHME- 20 TIC or LOGIC TRANSFORM through suitable control enable signals shown only diagrammatically in FIG. 1—it being understood, of course, that the processing element PE could also have been enabled by the Sequencer 31 to perform an ARITHMETIC or LOGIC 25 TRANSFORM in the interval between the second and third shift commands. Assuming, for example, that a NEIGHBORHOOD TRANSFORM is to be conducted, and recognizing that the westernmost PIXEL of the northernmost row in the two-dimensional XY 30 PIXEL image array of FIG. 1—viz., PIXEL (0,A)—is now stored in latch P, it will be appreciated that data representative of the eight neighboring PIXEL positions are stored in latches N-, N, N+, P-, P+, S-, S and S+; and, all such data is input to the correspond- 35 ingly labeled terminals of an NFU 42 mounted on processing element PE.