[11] Patent Number:

4,485,414

[45] Date of Patent:

Nov. 27, 1984

# [54] SERVO SYSTEM FOR POSITIONING A MOVABLE TRANSDUCING HEAD ASSEMBLY

[75] Inventor: Billy R. Baker, Redwood City, Calif.

[73] Assignee: Ampex Corporation, Redwood City,

Calif.

[21] Appl. No.: 297,291

[22] Filed: Aug. 28, 1981

### Related U.S. Application Data

[63] Continuation-in-part of Ser. No. 138,206, Jul. 7, 1980, abandoned, which is a continuation of Ser. No. 956,816, Nov. 1, 1978, abandoned.

130.23, 130.24, 106, 107, 108, 109; 358/312, 334

### [56] References Cited

### U.S. PATENT DOCUMENTS

| 4,093,885<br>4,099,211<br>4,139,871<br>4,143,405<br>4,148,082<br>4,163,993<br>4,179,717<br>4,364,098 | 7/1978<br>2/1979<br>3/1979<br>4/1978<br>8/1979<br>12/1979 | Brown       360/77         Hathaway       360/77         Yoshida et al.       360/70         Kubota       360/10.2         Okada et al.       360/77         Ravizza       360/77         Maxey       360/84         Hirota et al.       360/108 |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### FOREIGN PATENT DOCUMENTS

2088115 6/1982 United Kingdom .......... 360/130.23

#### OTHER PUBLICATIONS

Johnson, "Video Color Recording System", IBM Tech. Disc. Bul., vol. 9, No. 11, Apr. 1967, pp. 1584-1585.

Primary Examiner—Donald E. McElheny, Jr. Attorney, Agent, or Firm—Ralph L. Mossino; Joel D. Talcott

### [57] ABSTRACT

A method and apparatus for accurately positioning a transducing means along a desired path for recording parallel tracks of information being transmitted at varying rates. The apparatus also is arranged to control the transducing means so that accurately follows the tracks during reproducing at various tape transport speeds. In a magnetic recording/reproducing apparatus having transducing means operably supported by rotation means for scanning a magnetic tape along a plurality of adjacent sets of tracks, the rotation means including movable means carrying the transducing means and in response to electrical signals effecting movement of the transducing means in opposite directions from a home position in which the movement is generally transverse to the direction of the sets of tracks, wherein the improvement includes the signal producing means being operable to produce signals in response to the transverse position data for positioning the transducing means to either accurately simultaneously record a set of tracks along a desired path or simultaneously reproduce from the tracks and, during recording, to record additional sets of tracks subsequent to the completion of the preceding set of tracks along paths parallel to the selected path, the selected path being determined as a function of the speed and direction of transport of the tape.

### 44 Claims, 20 Drawing Figures

Nov. 27, 1984

## SERVO SYSTEM FOR POSITIONING A MOVABLE TRANSDUCING HEAD ASSEMBLY

This is a continuation in part of my prior application, 5 Ser. No. 138,206, filed Apr. 7, 1980, now abandoned, which is a continuation of Ser. No. 956,816, filed Nov. 1, 1978, now abandoned.

## CROSS-REFERENCE TO RELATED APPLICATIONS

Billy Richard Baker, Ser. No. 956,777, now U.S. Pat. No. 4,212,043, entitled "Magnetic Transducing Head Mount", and assigned to the same assignee as the present invention.

#### BACKGROUND OF THE INVENTION

The present invention generally relates to information recording and reproducing and, more specifically, to a recording and reproducing apparatus and a method 20 for achieving high density recording of information transmitted at varying speeds.

The extensive research and development effort in the field of data recording and reproducing has resulted in many significant improvements in apparatus that record 25 and reproduce information with respect to tape as well as other mediums. While there have been many different formats that have been developed for data recording and reproducing, the format wherein signals are recorded on magnetic tape as the tape is transported in a 30 helix around a cylindrically-shaped tape guide drum has exhibited many distinct advantages in terms of relative simplicity of the tape transport drive and control mechanism, the necessary electronics involved, the number of transducing heads, and the efficient use of tape, in 35 terms of the quantity of tape that is required for recording a given amount of material. By helically wrapping the tape around a tape guide as it is scanned by a rotating head, a single transducing head assembly can be utilized for reproducing or playing back the information 40 that is recorded on the tape. When a single head assembly is used in a helical tape recording apparatus, two recognized alternatives are available for wrapping the tape about the tape guide for scanning by the rotating head, which are generally referred to as the "alpha" 45 wrap and the "omega" wrap.

In apparatus employing the alpha wrap, the tape is introduced to the tape guide drum from one side and is helically wrapped completely around the drum so that it exits on the opposite side. It is referred to as the alpha 50 wrap for the reason that the tape path about the tape guide drum generally conforms to the Greek symbol alpha ( $\alpha$ ) when one views the tape path from above. In apparatus employing the omega wrap, the tape introduced to the tape guide drum along a path that is gener- 55 ally radial relative to the tape guide drum, is passed around a guide post that directs the tape into contact with the surface of the drum, is helically wrapped around the drum or a portion thereof, and is passed around another guide post so that it exits the drum also 60 in a direction generally radial relative to the drum. The tape path about the tape guide drum generally conforms to the shape of the Greek symbol omega  $(\Omega)$  when it is viewed from above. Both of these wrap configurations are helical in that the tape is wrapped around the tape 65 guide drum in a helical manner, with the tape exiting the tape path about the drum surface at a different axially displaced position relative to the position at which the

tape enters the tape path. In other words, if the axis of the drum is vertically oriented, the tape leaves the drum surface at an axial position that is either higher or lower than the axial position at which it first contacts the surface. As the tape is passed around the tape guide drum, a rotating head assembly records data information signals along discrete parallel tracks that are oriented at an angle relative to the longitudinal direction of the tape so that a track length greatly in excess of the 10 width of the tape can be achieved. The angular orientation of the recorded tracks is a function of both the speed of the tape being transported around the tape guide drum as well as the speed of rotation of the scanning head itself. The resultant angle therefore varies 15 depending upon the relative speeds of both the rotating scanning head and tape being transported.

It should therefore be appreciated that if information signals are recorded on a tape at a predetermined angle which results from a precise rotational scanning head speed and tape transport speed, the subsequent reproducing of the information signal should be performed at the same speeds or the transducing head will not follow the track with precision. This assumes, however, that the head is rotating in the same equatorial plane. If the tape speed is changed during the reproduction of recorded information, such as reduced or stopped, the transducing head scans the tape at a different angle relative to the longitudinal direction of the tape, and therefore, will no longer precisely follow the recorded track and may even cross onto an adjacent track. The failure to precisely follow the track in registry during playback results in improper reproduction of the recorded information. While various prior art systems have been proposed to attempt to reduce such undesirable effects due to the lack of registry, many of such systems have not been entirely successful. Moreover, some prior art systems experience tracking difficulties during reproducing at the tape and head speeds that are intended to be identical to those that were used during recording.

One prior art system employs two transducing heads with switching means that are adapted to select the transducing head which has the maximum output. This approach suffers because neither head is always precisely on the recorded track throughout its length. As a result, the signal-to-noise ratio is poor. Other systems for reproduction of helically recorded signals have attempted to minimize the effect of mistracking by using synchronization pulse lineup techniques and the like, and by modifying the head-to-tape scan angle by changing the orientation of the axis of the tape guide drum about which the tape passes during recording and reproducing.

More recently, the above problems were overcome or substantially mitigated in a recording apparatus described in U.S. Pat. No. 4,165,523, entitled "Automatic Scan Tracking" by Richard A. Hathaway. Further description of this recording apparatus is set forth in U.S. Pat. No. 4,151,569, and U.S. Pat. No. 4,151,570. The apparatus described in these patents is directed to successfully achieving altered time base reference effects in the art of recording and reproducing information signals on a medium with a single transducing head. More particularly, such apparatus employs a cantilevered bimorph element anchored at one end and having the transducing head located on the second free end such that the head may be moved. This arrangement is satisfactory for single track recording and reproducing

but cannot be moved sufficiently for a multiplicity of parallel tracks, such as, for example, 27 or more extremely narrow parallel tracks. An arrangement is therefore required that can move a multiple transducing head assembly a large distance, such as, for example, within the range of 0.02 to 0.04 inch. Moreover, if a multiplicity of transducing heads are employed in a single head assembly for recording and reproducing from a corresponding multiplicity of extremely narrow parallel tracks of data on a medium, accurate tracking becomes more critical and a different arrangement is preferred.

### BRIEF SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide an improved method and apparatus for achieving high density information recording and reproducing at varying rates.

More particularly, it is an object of the present invention to provide an improved method and apparatus of the foregoing type which effects precise repositioning and control of the tracking of a transducer with respect to a plurality of tracks along a medium of a recording and reproducing apparatus.

Furthermore, it is an object of the present invention to provide an improved method and apparatus of the foregoing type which achieves accurate repeatability with an altering time base reference in an information recording apparatus, without sacrificing the quality of 30 the reproduced signal.

Another object of the present invention is to provide an improved method and apparatus of the foregoing type which operates at virtually infinitely variable relative head to tape speeds within predetermined limits, 35 both in record and reproduce modes of operation.

Other objects and advantages will become apparent upon reading the following detailed description, while referring to the attached drawings.

#### GENERAL DESCRIPTION OF THE DRAWINGS

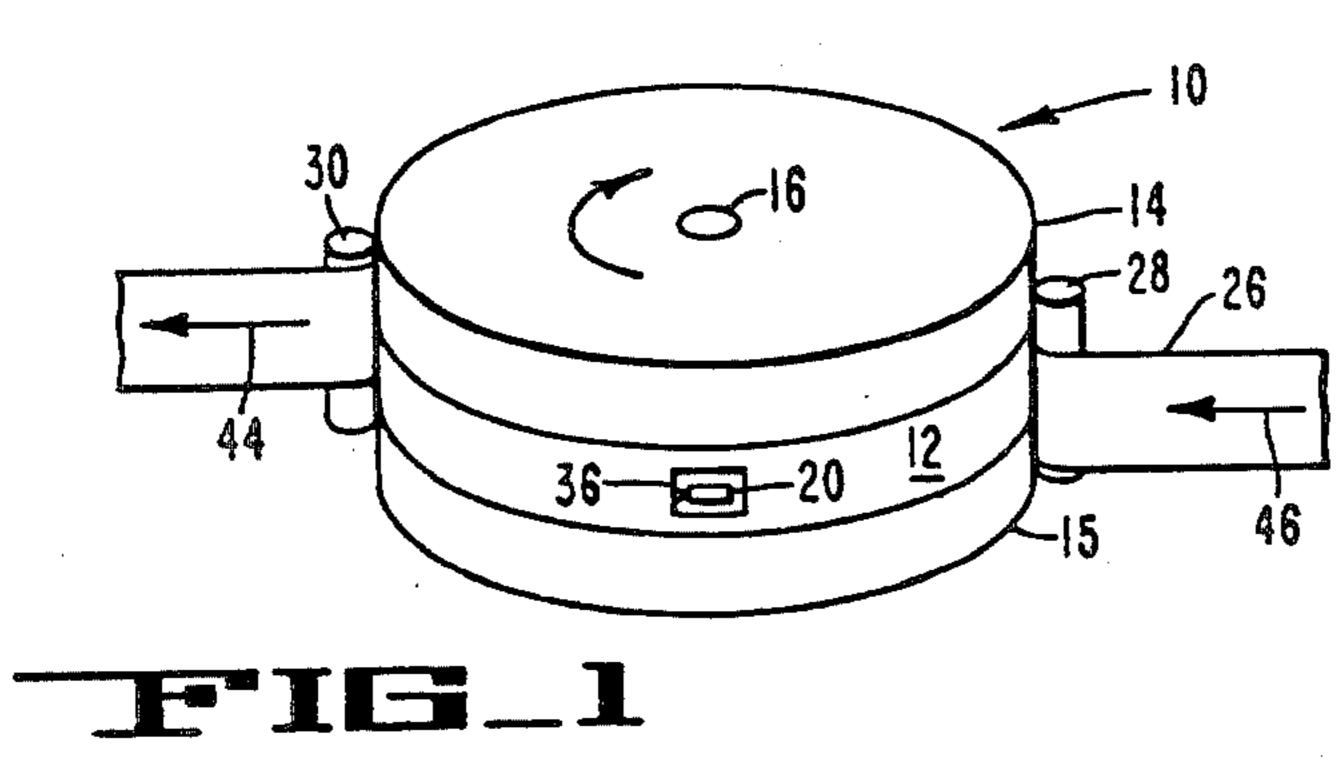

FIG. 1 is a perspective view of an omega wrap helical tape guide drum simplified for the sake of clarity and embodying the present invention;

FIG. 2 is a broken-away elevational view of the tape <sup>45</sup> guide drum shown in FIG. 1;

FIG. 2a is a fragmentary cross-sectional plan view of the structure shown in FIG. 2, and taken on the plane of lines 2a-2a of FIG. 2;

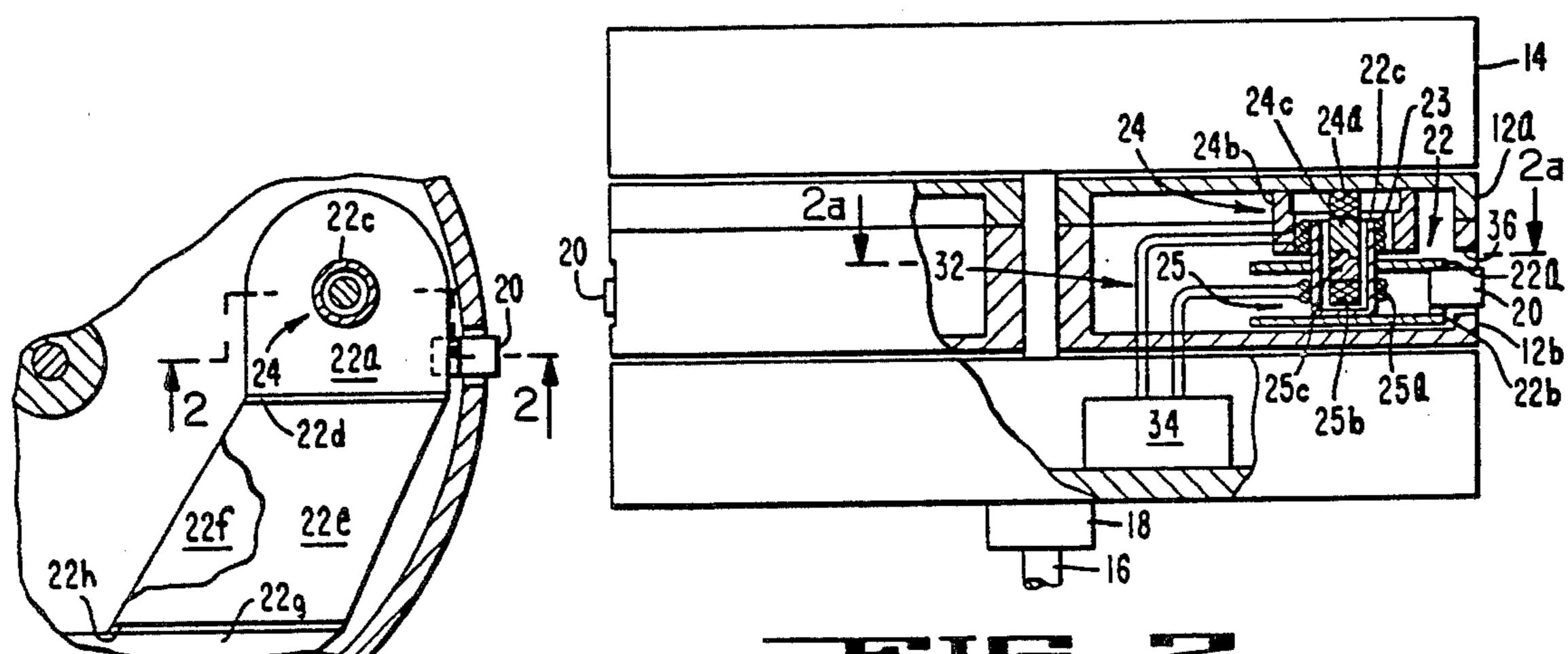

FIG. 3 is an enlarged segment of magnetic tape having several sets of tracks recorded thereon;

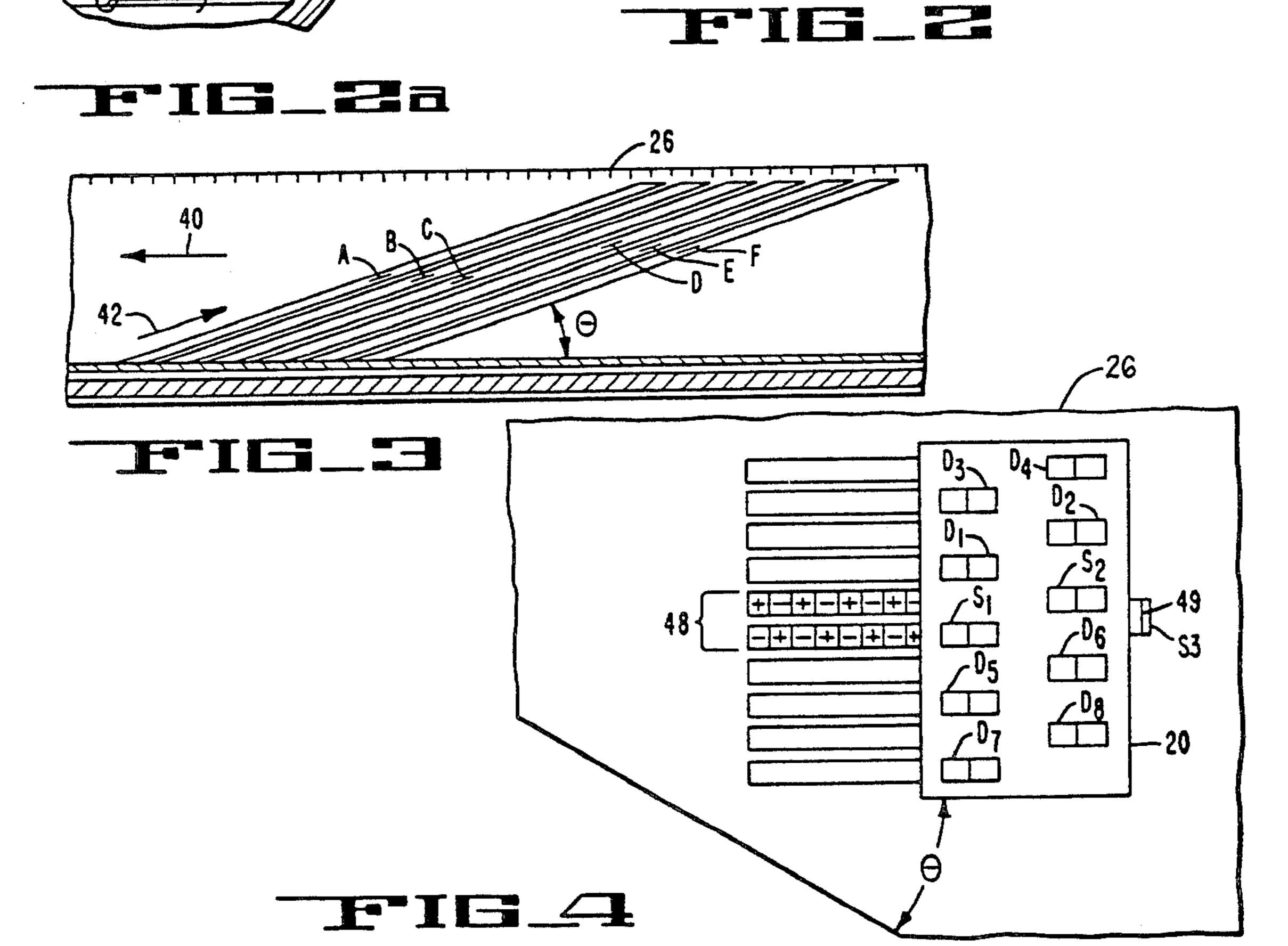

FIG. 4 is an amplification of a portion of a set of the tracks shown in FIG. 3;

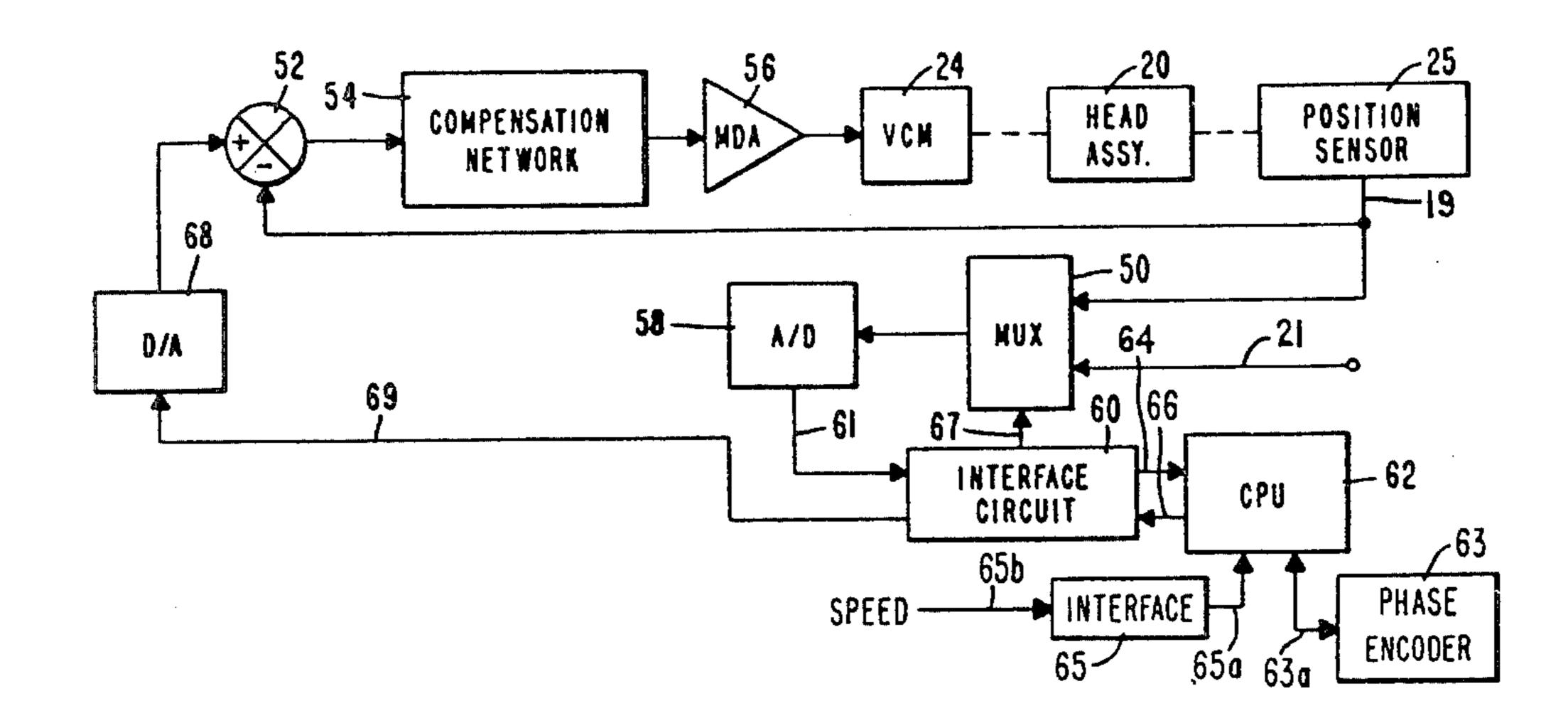

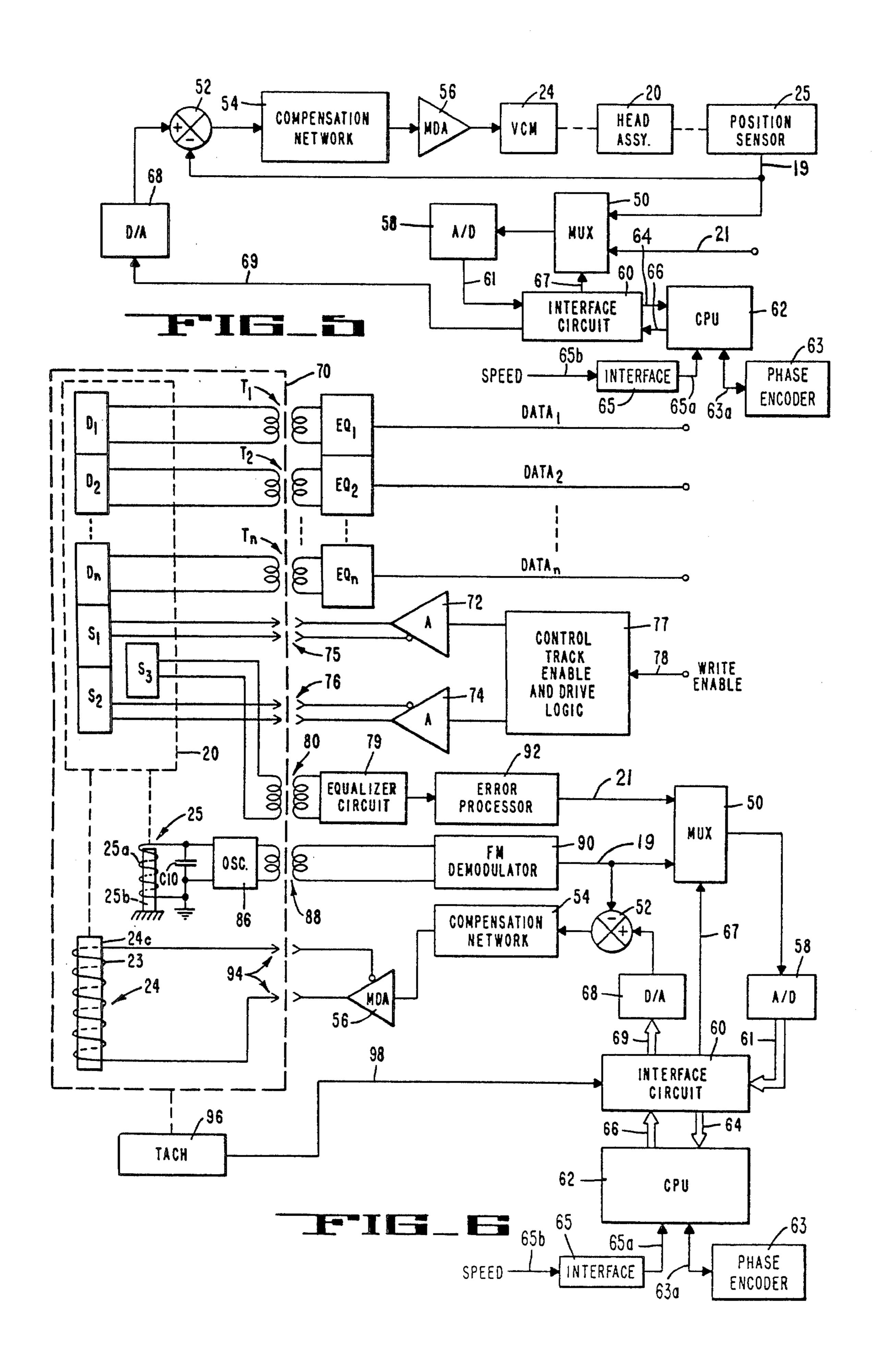

FIG. 5 is an overall block diagram of the system of this invention;

FIG. 6 is a more detailed block schematic diagram of the system of this invention;

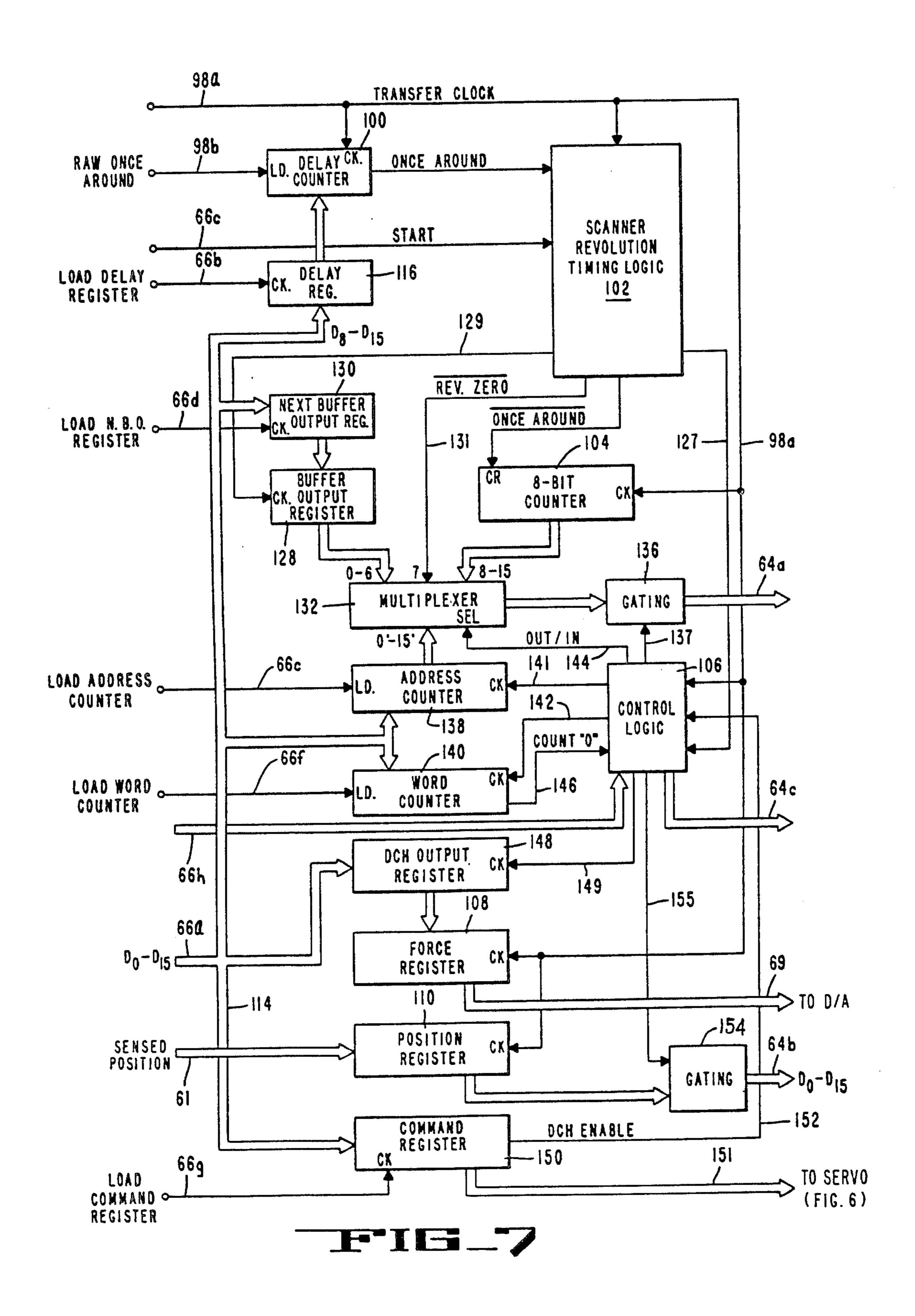

FIG. 7 is a block diagram of the interface circuit illustrated in the diagram of FIG. 6;

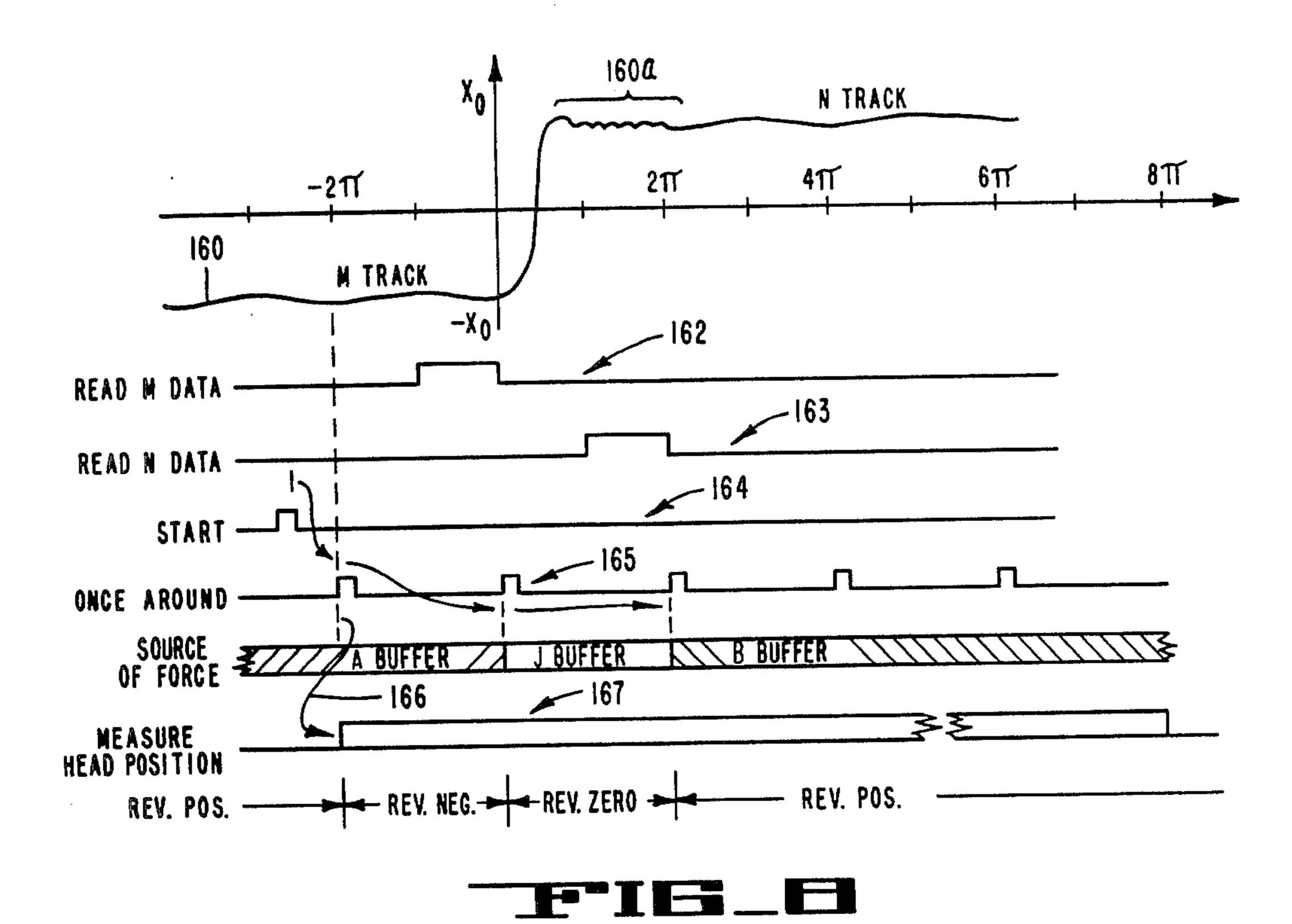

FIG. 8 is a diagram illustrating the timing relationship for a position jump or reset of the magnetic head assembly;

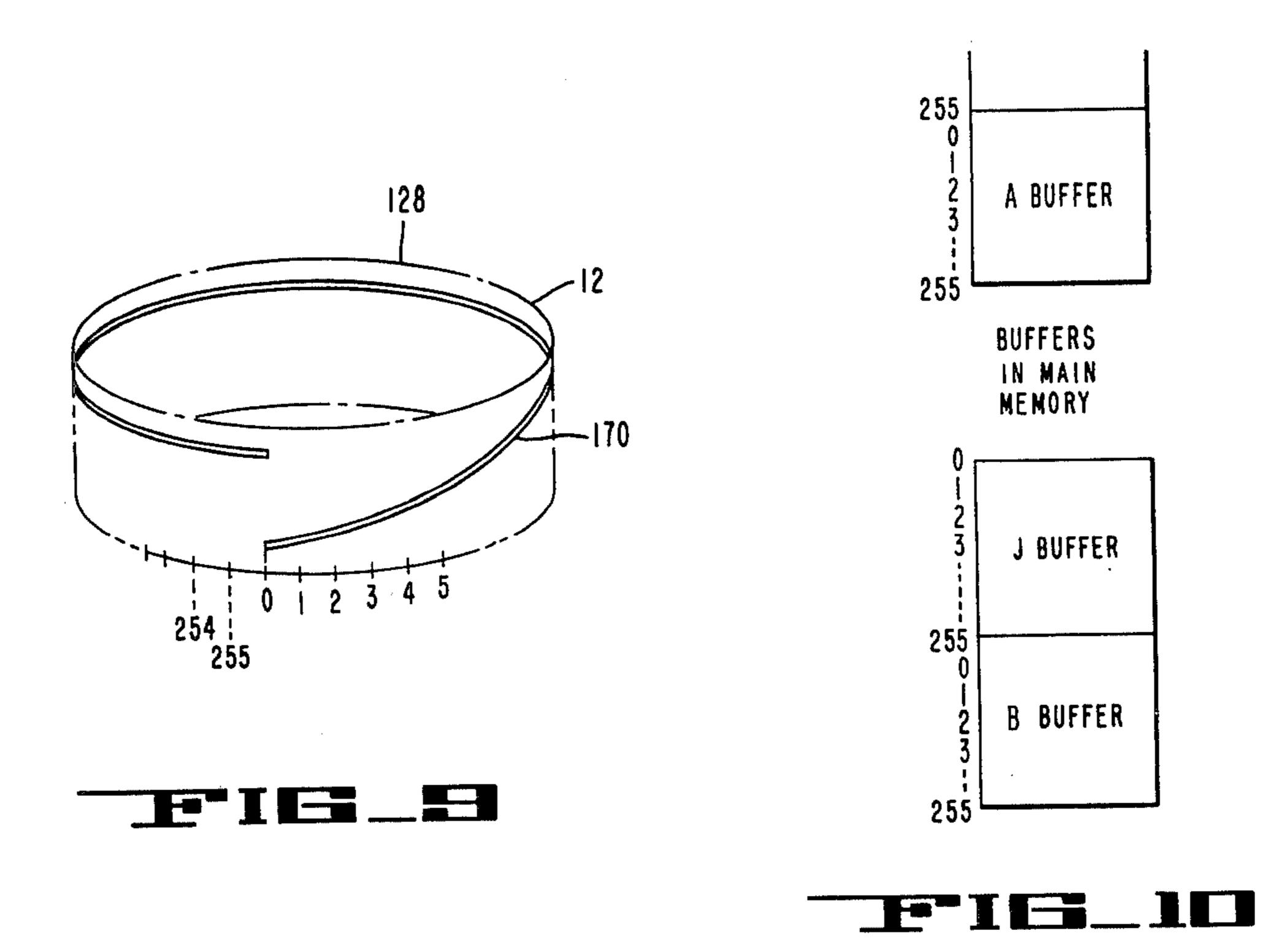

FIG. 9 is a pictorial diagram of a helical track around the tape guide drum;

FIG. 10 is a map of buffers within the main memory of the central processing unit (CPU) utilized in the system embodying the present invention;

4

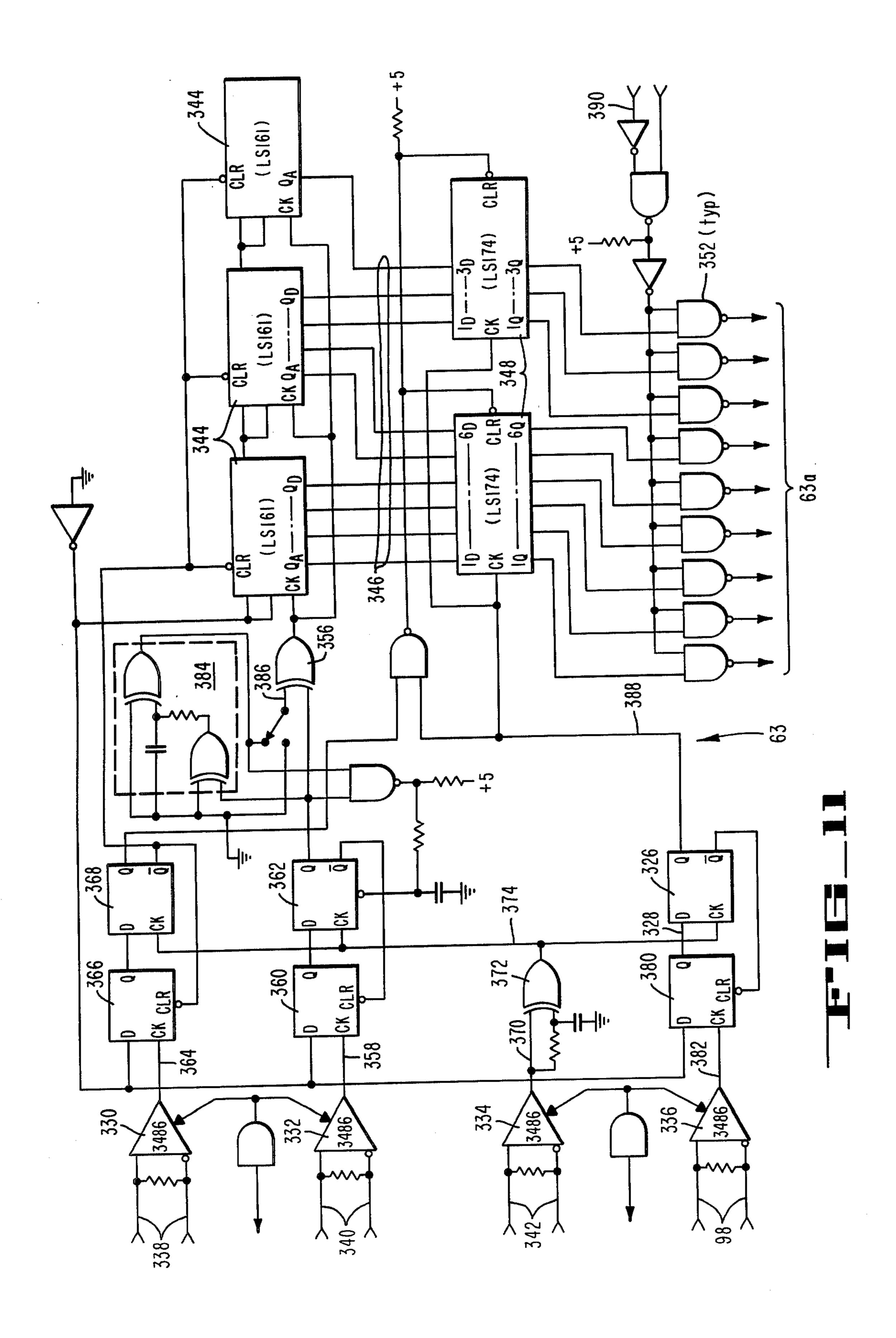

FIG. 11 is an electrical schematic diagram of the phase encoder portion of the circuitry shown in the block diagram of FIGS. 5 and 6;

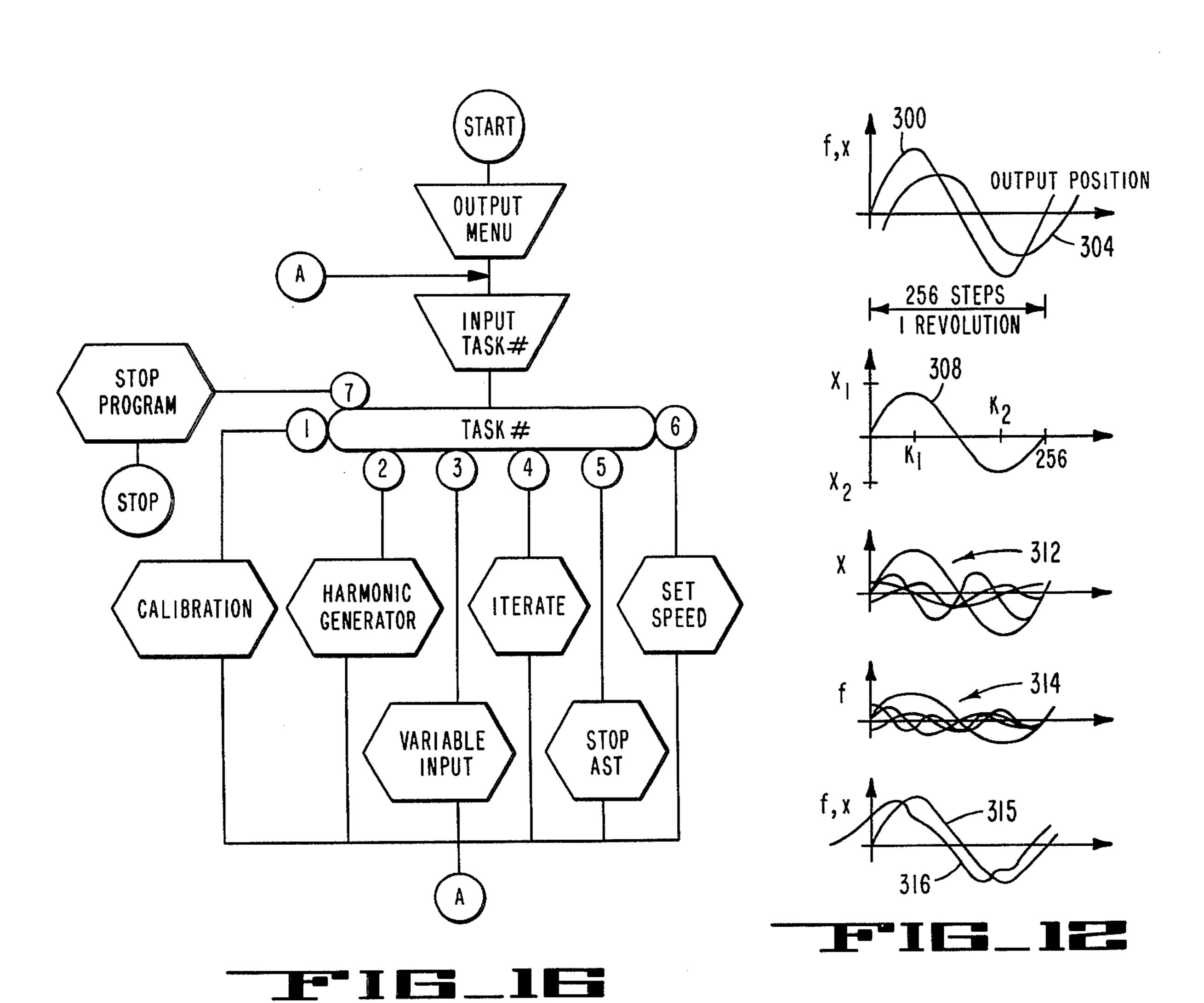

FIG. 12 is a waveform diagram of a force data computation;

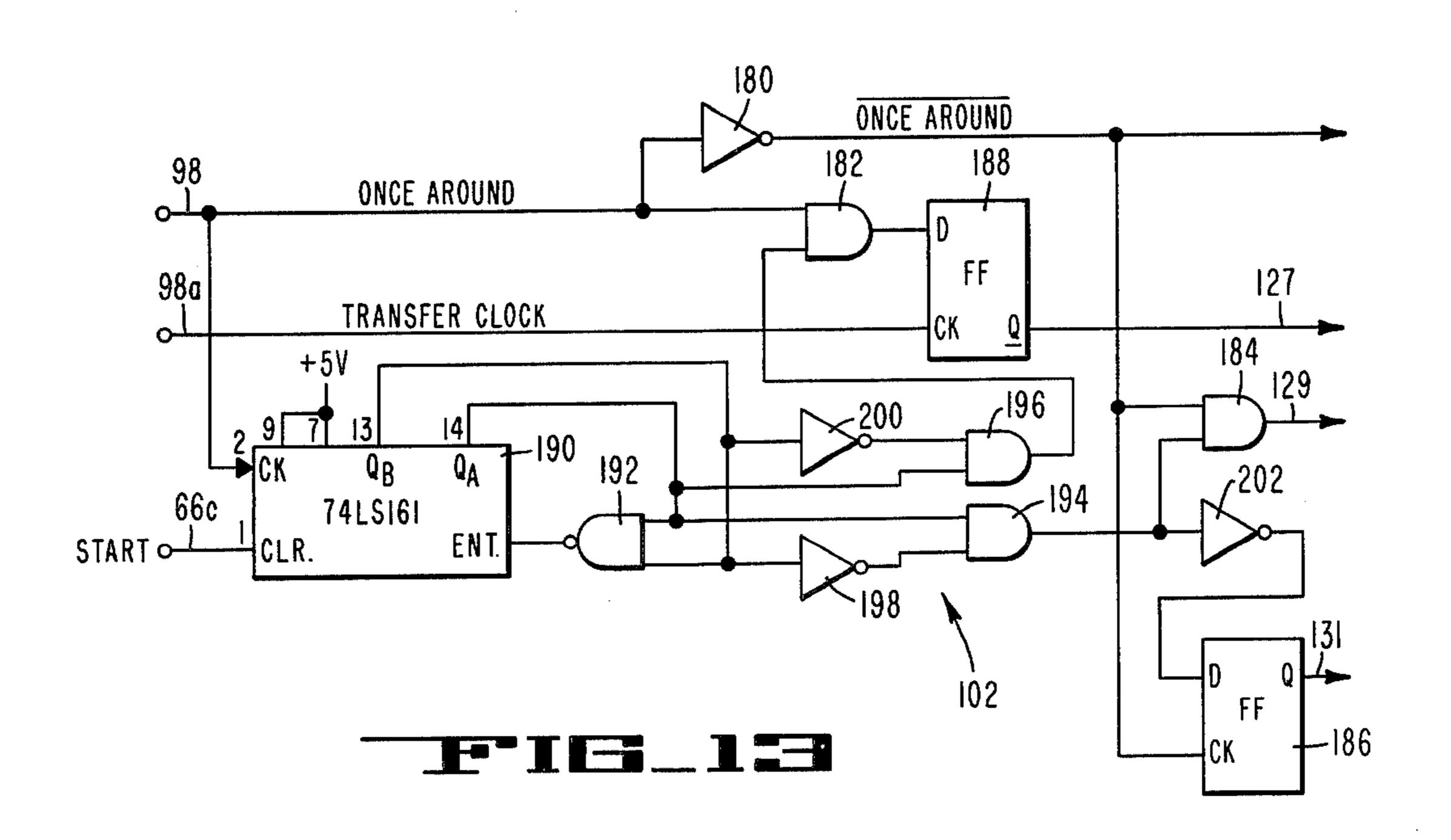

FIG. 13 is a schematic diagram of another interface the timing logic circuit within the central processing unit used with the system of this invention which is illustrated in FIG. 7;

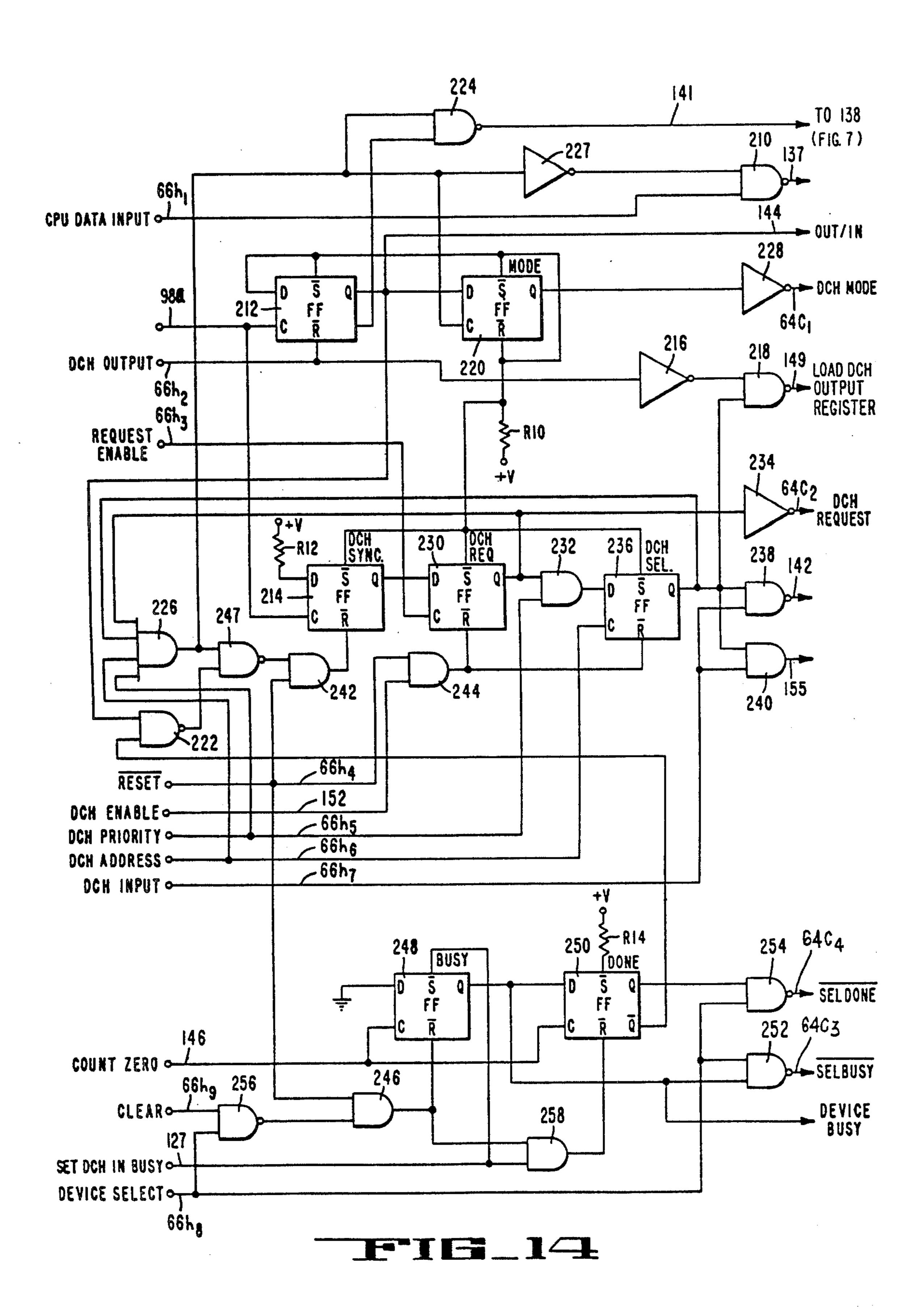

FIG. 14 is a schematic diagram of the scanner revolution logic used in the circuit of FIG. 7;

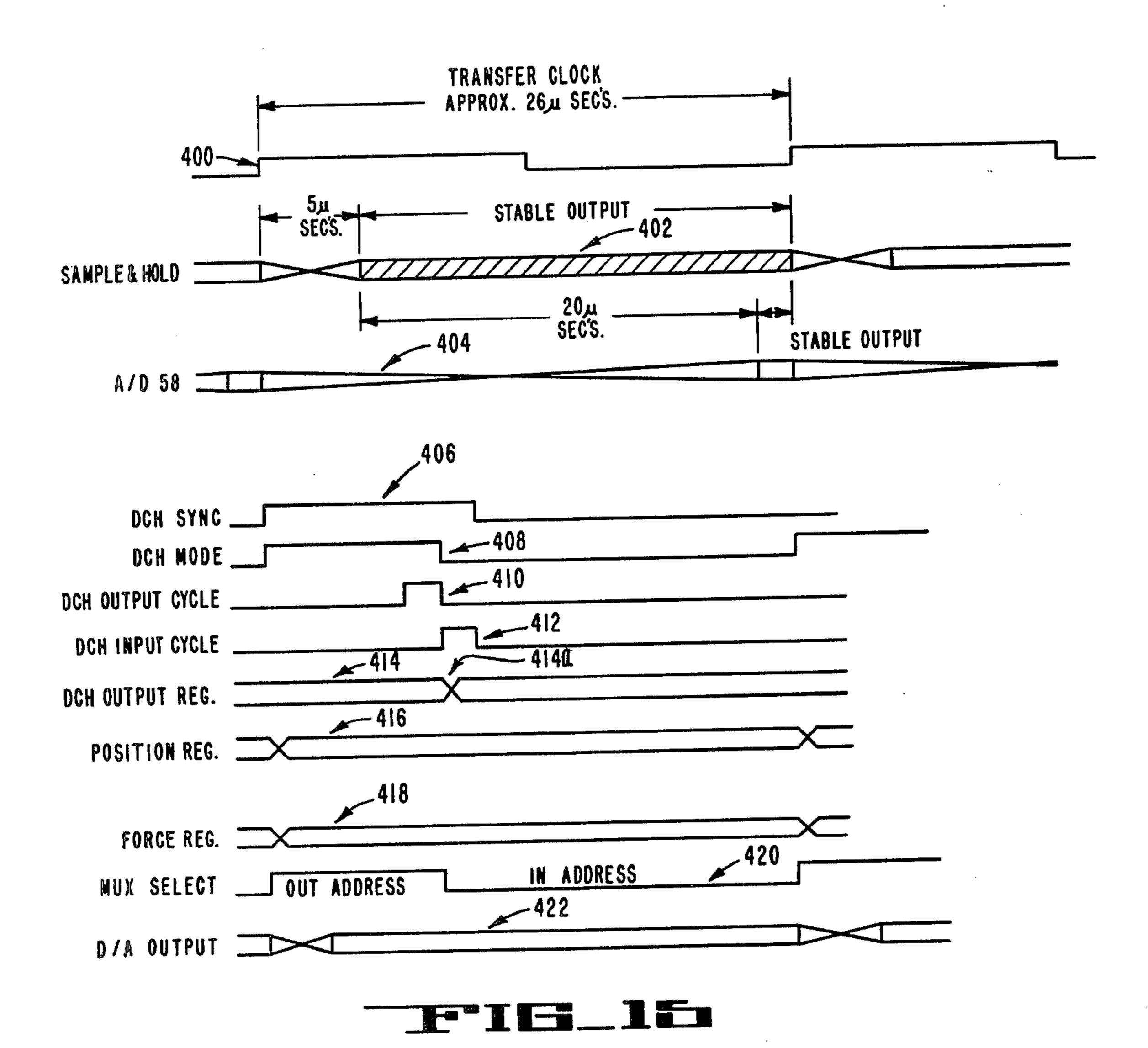

FIG. 15 is a timing diagram illustrating operation of the circuit shown in FIG. 7;

FIG. 16 is a simplified flow diagram of the software program executed by the CPU during various operations of the apparatus;

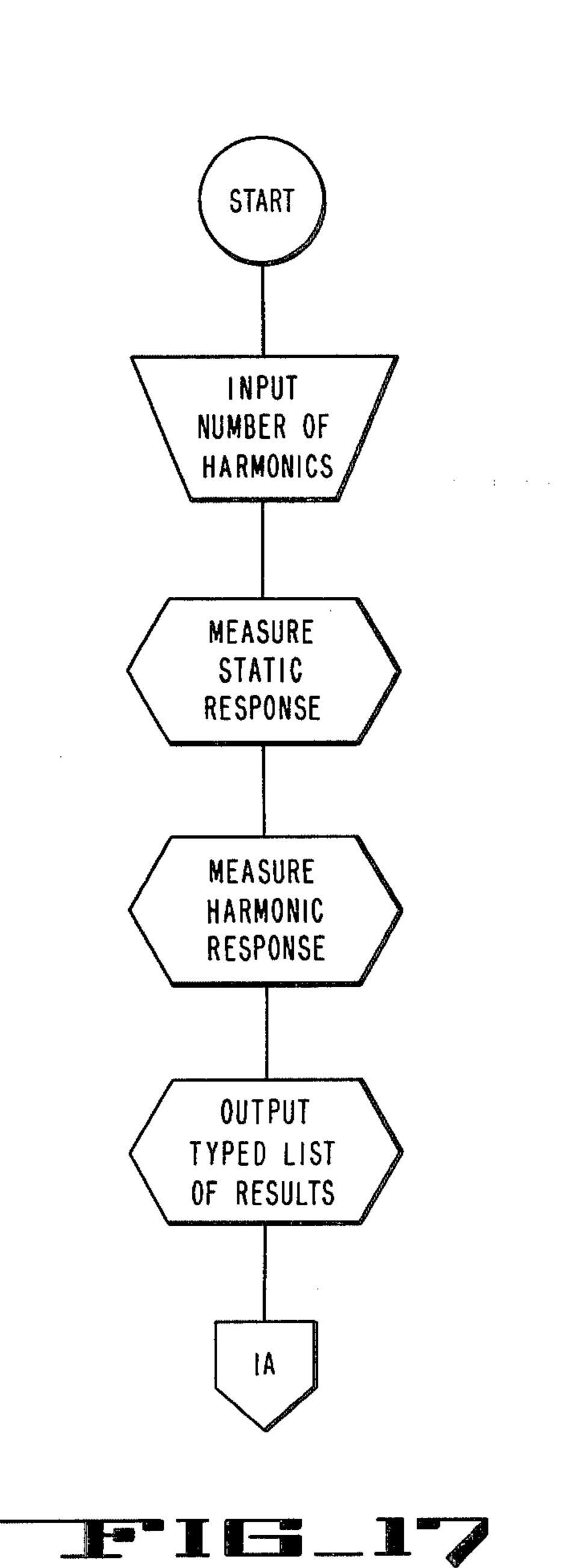

FIG. 17 is a simplified flow diagram of the software program executed by the CPU during calibration of the apparatus; and

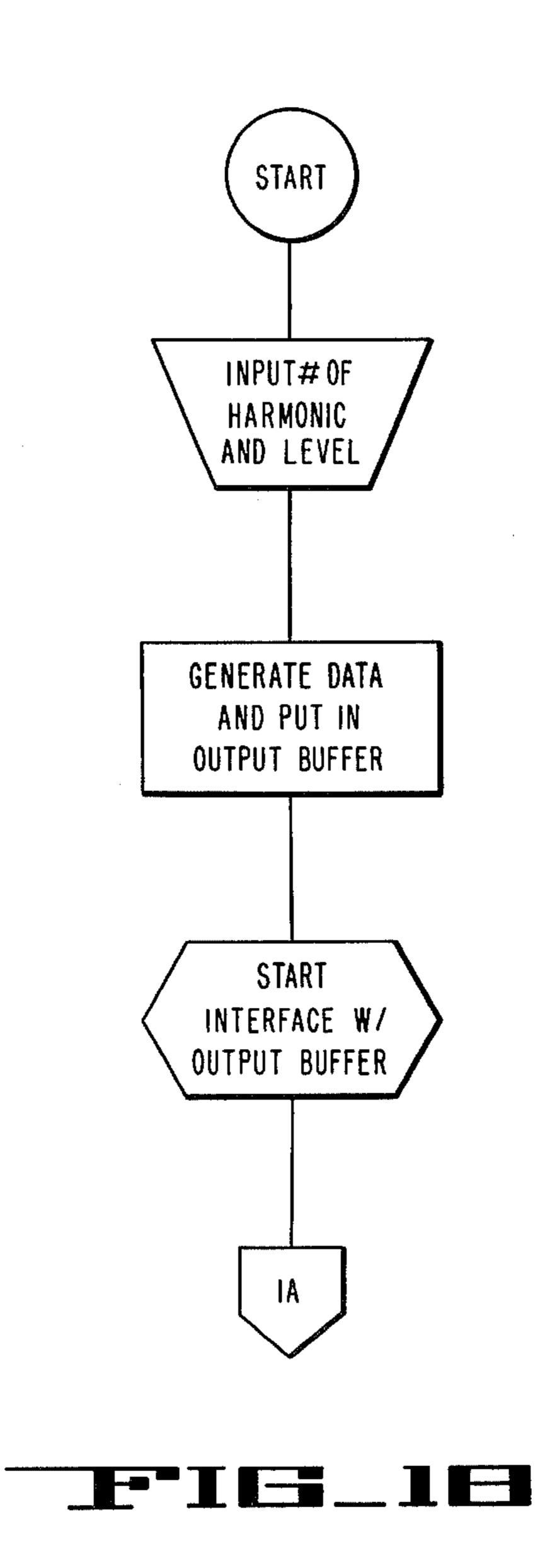

FIG. 18 is a simplified flow diagram of the software program executed by the CPU during the generation of force data using various harmonics.

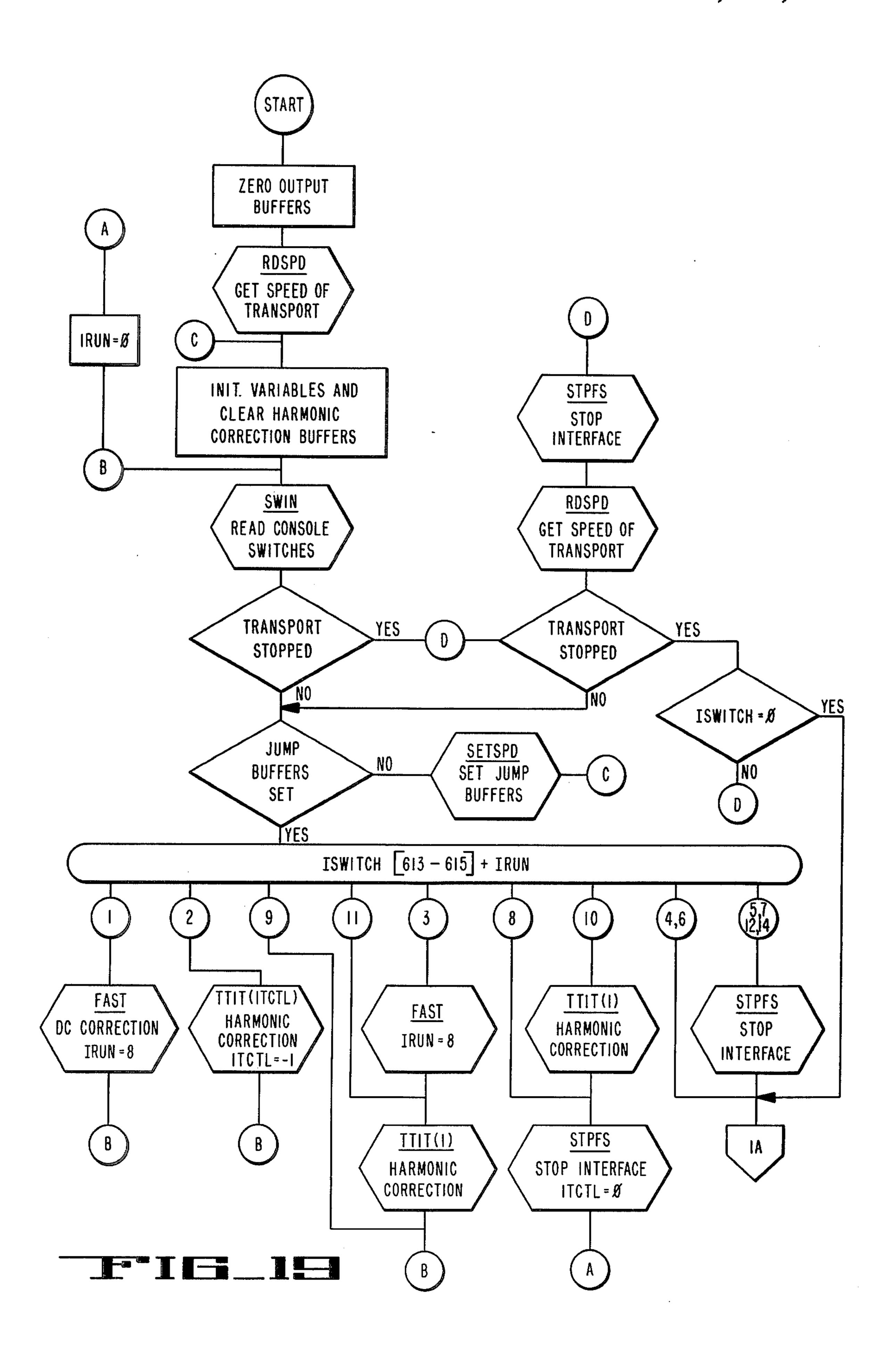

FIG. 19 is a simplified flow diagram of the software program executed by the CPU in performing the iteration task illustrated in FIG. 16.

## DETAILED DESCRIPTION OF THE INVENTION

While the present invention will be specifically described in connection with a helical tape recording apparatus, it is equally applicable to other types of recording apparatus, such as a disc recorder or a longitudinal or quadruplex-type tape recorder. Additionally, while the present invention will be described in conjunction with the recording and reproducing of information on magnetic tape with the use of electromagnetic transducing heads, the present invention is also applicable to optical recorders or the like using appropriate recording mediums.

It should also be understood that the present invention is applicable to arrangements where the scanning head can move in either rotational direction and the tape can be introduced either above or below the exit path and moved around the tape guide drum in either direction. The relationships of head rotation, tape transport direction and manner of tape guiding, i.e., introducing the tape above or below the path of its exit, can represent up to eight different configurational relationships of which only one will be specifically described herein, as shown in FIG. 1 of the drawings.

Broadly stated, the present invention is directed to a method and apparatus for accurately positioning a transducing means along a desired path for recording parallel tracks of information being transmitted at varying rates and for reproducing recorded information at varying relative head to tape transport rates. In the event data recording at high rates and on a relatively continuous basis is to be achieved, the transport speed of the tape must be increased and, conversely, for data 60 recording of data that occurs intermittently or at lower rates, the transport speed must be slowed down to maintain a relatively high density of recorded data. Since changing and tape transport speed changes the head-totrack angle as well, it is apparent that the transducing means must be appropriately moved a prescribed amount to record sets of tracks of information parallel to one another if the tape transport speed is different while recording different sets. The amount and direction of movement of the transducing means is a function of the relative head to tape transport speed and direction. During a reproduce mode of operation, the apparatus permits the tracks to be accurately followed, even though the relative head to tape transport speed is varied within wide limits.

The present invention comprises means for moving the transducing head assembly transversely relative to the longitudinal direction of the sets of tracks of the information and thereafter selectively alters or changes 10 the position of the head assembly so as to correctly position the head to commence recording of another set of tracks parallel to the previously recorded set of tracks. It should be understood that during a constant speed recording operation, one complete revolution of 15 the scanning head assembly causes the transducing head assembly to scan the tape to record a set of tracks at a predetermined angular orientation relative to the length of the tape and at the end of the scan of the tape, the movement of the tape causes the recording head assem- 20 bly to be gradually displaced relative to the length of the tape a predetermined distance downstream in position to begin recording the next adjacent successive set of tracks. In this manner, the sets of tracks are recorded parallel to one another and, assuming the transport 25 speed of the tape and the speed of rotation of the rotating drum carrying the record transducing head assembly is maintained constant, the set of tracks will have a constant spacing relative to adjacent sets of tracks, i.e., the track center-to-track center distance between sets of 30 tracks will be substantially constant in the absence of geometric errors that can be introduced due to stretching, or other temperature or humidity-induced dimensional changes of the tape, or by faulty tensioning mechanisms in the tape transport or the like.

If, however, data transmitted at different rates is to be recorded, the head assembly is preferably deflected so as to record the data at the same angle on the tape regardless of the data transmission rate. Provision is made in the system of this invention to deflect the head assem- 40 bly by a sufficient amount during the record mode of operation so as to always record the set of tracks at an angle corresponding to the undeflected head position at the highest relative head to tape speed of operation. Thus, the slower the information is transmitted, the 45 greater the head assembly must be deflected to record the sets of tracks parallel to one another at an angle to the length of the tape that would be achieved at the highest relative head to tape speed of operation. The system also has provision for deflecting the head assem- 50 bly in an appropriate manner so that during reproducing the head assembly will properly follow the set of tracks at the proper angle to obtain accurate reproducing of the data that is recorded on the tracks, even though the relative head to tape transport speed may be 55 changed or varied during reproducing. Stated in other words, during reproducing operations the path that is followed by the transducing heads while the head assembly is rotating will have a precise angular relationship relative to the longitudinal direction of the tape 60 (often referred to as "normal") during reproducing at any relative head to tape transport speed that is same as the path followed by the transducing head when the relative head to tape speed is normal and the transducing head is undeflected. By virtue of the fact that the 65 widths of the tracks contemplated herein are extremely narrow, i.e., on the order of about 1 mil, variation of the head from a prescribed path required to follow the

tracks accurately is extremely critical. The system of the present invention includes a computer means for generating the appropriate path control signals that the transducing means accurately follow the tracks during either recording or reproducing. During recording, the system generates force data signals for application to the deflecting head mounting mechanism carrying the transducing heads so that the tracks are recorded at the appropriate selected angle relative to the lengthwise direction of the tape even though the relative head to tape speed may change. Also, the system generates force data signals for application to the deflecting head mounting mechanism to cause the transducing means to accurately follow the recorded tracks during reproducing even when the relative head to tape transport speed is other than the normal relative head to tape transport speed.

Turning now to the drawings and particularly to FIGS. 1, 2 and 2a, there is shown a helical tape guide drum assembly, indicated generally at 10, with portions broken away from explanation purposes. The helical tape guide drum assembly and constituent parts thereof are described in greater detail in the above-cited U.S. Pat. No. 4,212,043. Briefly, for purpose of the present discussion, the drum assembly 10 is shown to comprise a rotatable center drum portion 12 consisting of an upper disc portion 12a and a lower disc portion 12b; and stationary upper and lower mandrel or guide portions 14 and 15, respectively. The center rotating portion 12 is fixed to a shaft 16 which is rotatably journaled in bearing 18 that is mounted on the lower drum 15. The shaft 16 is driven by a motor (not shown) operatively connected thereto in a conventional manner. The drum assembly 10 has a pair of diametrically opposed transducing head assemblies 20 carried by the rotatable drum portion 12 and is shown to be mounted on a head support element 22, which is disclosed in the above-mentioned U.S. Pat. No. 4,212,043. The head support element 22 comprises a pair of parallel plate assemblies 22a and 22b spaced apart and joined by a hollow tubular assembly 22c. As shown in FIG. 2a, the assembly 22 is joined by a pair of spring flexure hinges 22d to a pair of rigid parallel plate-shaped link members 22e and 22f, which in turn are joined to a solid base block 22g, forming part of the lower rotatable drum portion 12b, as by means of another pair of spring flexure hinges 22h. The flexure hinge assembly permits the head assembly 20 to be relatively free to move up and down in directions parallel to the drum axis. To drive the head assembly in such motion, there is provided a linear motor structure comprising a voice coil 23 mounted on an extending portion of the tubular assembly 22c, and driven by signals from a driving circuit 34 (to be explained further hereafter with reference to FIGS. 5 and 6); and, a stator comprising a permanent magnet assembly 24 consisting of a magnet 24a affixed to the upper rotating disc 12a, which is made of carbon steel, and outer and inner pole piece elements 24b and 24c which are also mounted on disc 12a so as to, respectively, circumvallate coil 23, and be circumvallated thereby. Also, a position sensing transducer 25 is provided for the head mounting assembly, comprising a coil 25a, also mounted on the tubular assembly 22c so as to circumvallate a ferrite member 25b that is mounted on an aluminum spacer element 25c extending from the pole piece 24b. The coil 25a is coupled to a sensing circuit within the driving circuit 34 so as to provide electrical signals indicative of the position

of the head assembly 20, all of which will be described in detail hereinafter.

As best shown in FIG. 1, the drum assembly 10 is part of a helical omega wrap tape recorder which has magnetic tape 26 advancing toward the drum in the direction of the arrows as shown. More specifically, the tape is introduced to the drum surface from the right as shown in the drawing and is fed around a guide 28 which brings the tape into contact with the outer surface of the stationary lower portion 15 whereupon the 10 tape travels around approximately 180° of the drum periphery until it passes around a second guide 30 which changes direction of the tape as it exits the drum assembly after it has been either recorded or played back.

The movable element 22 is effective to move the transducing head 20 mounted thereto in a vertical direction as shown in FIG. 2 in accordance with electrical signals that are applied to the voice coil motor 24 through conductors 32 from circuitry schematically 20 illustrated by block 34. The head assembly 20 is mounted so as to extend approximately 1 to 2 mils beyond the outer surface of the rotating drum portion 12 through an opening 36 in the outer surface thereof. The element 22 is coupled to the voice coil motor 24 so as to 25 suspend the transducing head assembly in the opening 36 for controlled positioning with respect to the magnetic tape. Thus, the movable element 22 is adapted to move up or down (when viewing the drawings in a conventional manner) and displace the transducing 30 head assembly in response to applied electrical signals by means of the conductors 32.

If the transport speed of the magnetic tape, for example, is changed relative to the speed at which the information was recorded, the effective angle of the path 35 followed by the head assembly 20 relative to the length of the tape 26 is changed and error correcting signals will be produced for the purpose of having the transducing head of the assembly 20 follow the track. Since the element 22 is movable in either direction, the tape 40 can be transported around the tape guide drum assembly 10 at either a faster or slower speed relative to the record speed and the element 22 can position the head assembly 20 to follow the set of tracks being reproduced for either condition.

In accordance with an aspect of the present invention and referring to FIG. 3, a segment of tape 26 having a number of sets of tracks A through F recorded thereon is shown together with arrows 40 and 42 which illustrate the direction of tape motion around the tape guide 50 drum assembly 10 and the direction of head scan relative to the tape itself, respectively. As stated hereinabove, the transducing head assembly 20 includes a multiplicity of individual transducing heads which record or reproduce a corresponding multiplicity of par- 55 allel tracks. The term "sets of tracks" as used herein refers to the multiplicity of tracks recorded by the transducing head assembly during a single pass across the tape. The orientation of the sets of tracks and the arrows shown in FIG. 3 coincide with what is produced by the 60 movements of the rotatable drum portion 12 and tape 26 shown in FIG. 1 (see arrows 44 and 46). With a constant transport speed and angular velocity of the rotating drum portion 12, sets of tracks A through F will be substantially straight and parallel to one another at an 65 angle  $\theta$  (of about 17°, for example) relative to the longitudinal direction of the tape, with the rightward set of tracks shown in the drawing being subsequently proR

duced during the recording operation. Since set B, for example, is recorded immediately after set A is recorded during constant head rotation and tape transport speeds, it should also be appreciated that if these speeds are maintained during the reproducing or playback operation, the transducing head assembly 20 will play back set B during a successive revolution immediately after having reproduced the information from set A. If, however, the transport speed is changed during the recording operation, the angle of the recorded sets of tracks would likewise change. The system of the present invention is also directed to maintaining a constant angle  $\theta$  of the recorded set of tracks relative to the longitudinal direction of the tape during the record 15 mode of operation even though the speed of the tape movement may change.

If conditions were ideal and no disturbances occur that cause mistracking, then the head assembly 20 simply follows the successive adjacent sets of tracks without adjustment during reproduction, since no error signals would be produced for transversely moving the head assembly 20 relative to the sets of tracks. Stated in other words, the transducing head is automatically in position to begin reproducing the subsequent set of tracks B after completing reproduction of the information from track set A. It should also be appreciated that even if the tape transport speed is varied during reproduction relative to the transport speed during record, and the angle of the path followed by the transducing head relative to the tape thereby changed, and the head is transversely moved to maintain accurate tracking through playback of the set of tracks, at the end of the set being scanned, the head is nevertheless in a position to begin scanning the next adjacent downstream set of tracks, i.e., set B, in the event the scan of track set A was ending. This occurs even when the tape is stopped or is traveling slower or faster than the transport recording speed.

To record information that is transmitted at varying speeds on a tape or other medium, it is necessary to vary or adjust the transport speed of the tape around the scanning head assembly. That is, to record the information at a high rate of speed, the transport speed is increased relative to a normal speed, and to record at a slow rate of speed, it is necessary to reduce speed of transport of the tape around the tape guide drum relative to the normal speed.

In accordance with the present invention, the apparatus can be placed in different modes of operation wherein the recording or reproducing of information can be effectively increasing or decreased by adjusting the transport speed of the tape, while appropriately controlling the operation of the scanning head assembly. It should be understood that the scanning head assembly moves at a constant rotational velocity and that the data that is either being recorded or reproduced occurs when the transducing heads are activated to perform the intended operating function. When the information is being recorded on a generally continuous basis, the tape transport speed is at its predetermined maximum and every revolution of the rotating scanning head assembly will record the sets of tracks during operation. This will generally be referred to as the normal transport speed during record.

However, if the data that is to be recorded occurs intermittently, then it may not be necessary for the recording to be continuously performed and in such case, there may be revolutions of the scanning head

assembly where the transducing heads are not energized so that data is not recorded during those revolutions. In such case, the tape obviously does not need to be moved. If the data that is being provided to the recording apparatus is received at a relatively lower rate than 5 is typically recorded and there is a desire for the recording apparatus to apply the data to tape at a higher density as would occur during continuous receipt of the data, for example, then the data may be incrementally stored in a suitable memory and thereafter read out 10 during selective revolutions of the scanning drum assembly with the scanning drum assembly being controlled to record the tracks at a particular angular orientation relative to the lengthwise direction of the tape even though the tape is being transported at a slower 15 than normal speed. The end result is the tracks are recorded at a density and and angular orientation that is the same as that obtained when data is received continuously for recording at a normal tape transport speed.

It should also be appreciated that data may be re- 20 ceived by the recording apparatus in a continuous manner but at a data rate that is slower than could be recorded on the medium by the recording apparatus. In such event, the data may also be stored in a suitable memory and then read out for recording at a much 25 higher data rate or density, with recording being done intermittently. Stated in other words, there may be rotations of the scanner head assembly wherein recording is not being performed, and it should be appreciated that in this situation, the tape would not be transported 30 at the normal tape transport speed.

From either of these examples, it can be appreciated that a suitable buffer interposed between an incoming low data rate data stream or streams can appropriately be used with the recording apparatus and very high 35 density recording can then be accomplished on tape which will result in a savings of tape surface which is an economic benefit. If recording is accomplished in the above-described manner, it should also be appreciated that the data could be reproduced at normal transport 40 speed and the data reproducing continuously at the high density data rate typifying normal data reproduction at the normal tape transport speed.

It should also be appreciated that during reproducing, the high speed or full packing density data may be 45 reproduced and again written into a buffer and while the data is read from the buffer and is sent onwardly to other apparatus or through some information channel at a lower data rate, the reproducing apparatus of the present invention can have the tape stopped and the 50 reproducing transducing heads inactivated until the buffer is emptied, at which time the buffer is loaded again. In this latter type of operation, it should be appreciated that the tape transport speed would be less than the normal speed and there will be intermittent times 55 when the reproducing heads are not activated. Also during this type of operation, the movable element 22 is necessarily provided with force data signals for accurately following the tracks, since at a reduced transport speed or even when the tape is stopped, the scan angle 60 series of discrete states with each state being oppositely of the rotatable transducing head relative to the longitudinal direction of the tape is required to be different from the normal angle. From the foregoing examples, it is apparent that the apparatus is effective to automatically position the transducing head assembly to follow a 65 set of recorded tracks from their beginning to their end, and thereafter adjust the position of the head assembly (if adjustment is needed) to the beginning of the proper

10

set of tracks. In addition, the apparatus is effective to automatically maintain the same angle of the recorded sets of tracks during the record mode of operation even though the speed of the relative head to tape movement may change.

Also, the present invention provides for resetting or transversely moving the transducing head assembly at the end of the scan of a set of tracks to a position corresponding to the start of a set other than the next successive adjacent set under certain predetermined conditions. The decision to transversely move or adjust the head assembly depends upon the mode in which the apparatus is operating and whether the amount of transverse movement is within the predetermined limits that can be achieved. In other words, if the head assembly is moved its maximum amount in one direction, it can not be moved further in that direction. The total range of movement should be within practical limits determined by the characteristics of the element 22 and the voice coil motor 24.

An amplification of an exemplary single set of tracks on the tape 26 is shown in FIG. 4, along with a diagram of a typical transducing head assembly 20. The head assembly includes a multiplicity of individual transducing heads. Though 11 heads are shown, i.e., D<sub>1</sub> through  $D_8$  and  $S_1$  through  $S_3$ , it should be understood that additional heads could be included in the head assembly 20. In the exemplary embodiment described and illustrated herein, the heads D<sub>1</sub> through D<sub>8</sub> are read/write heads disposed for recording or reproducing information or data. The heads  $S_1$  and  $S_2$  are disposed for recording a pair of parallel tracks of control information referred to herein as control tracks 48, which control tracks are read by the control track read head S<sub>3</sub>. The control tracks and associated heads are disposed for tracking alignment of the transducing head assembly 20 during the record and reproduce modes of operation. By way of example, each of the control tracks 48 is divided into a series of discrete states, with each state being oppositely polarized in an alternating fashion as shown. Also, the sequence of polarization is offset between each of the two control tracks. The read head S<sub>3</sub> has a gap 49 whose width dimension equals the distance between the centers of the adjacent control tracks 48 and nominally the read head is positioned with its gap extending from the center of one control track to the center of the second control track. Thus, the head S<sub>3</sub> will reproduce an alternating signal as the head assembly 20 scans the set of control tracks. When the head assembly drifts off track, the amplitude of the signal reproduced from the track in the direction of the drift will increase. This increase in amplitude is used by circuitry of the apparatus to reposition the head assembly back on track. Such an arrangement is explained in greater detail in U.S. Pat. Nos. 3,838,453 entitled "Track Following System For Magnetic Tape Recorder", and 3,534,344 entitled "Method and Apparatus For Recording and Detecting Information". While the abovedescribed scheme for the control tracks uses the polarized in an alternating fashion as shown and described, it should be appreciated that a separate signal of different frequency recorded in each of the tracks would provide similar error signal information.

Referring now to FIG. 5, a block diagram of the system of the present invention is illustrated wherein the voice coil motor (VCM) 24 is shown mechanically coupled to the transducing head assembly 20. The posi-

tion sensor 25 is also mechanically coupled to the assembly 20. The output from the position sensor 25 is coupled by line 19 to one of two inputs of a multiplexer 50 and to one of two inputs of a summing junction 52. The output of the summing junction 52 is coupled to an input terminal of a conventional servo compensation network 54. The output of the compensation network 54 is coupled to an input of a motor drive amplifier (MDA) 56, and the output of the MDA is coupled to an input of the voice coil motor 24. Accordingly, it may be seen that the output of the sensor 25 forms a feedback network by means of the summing junction 52 for the motor drive amplifier driving of the voice coil motor 24, which feedback network is also referred to herein as an "inner loop".

As stated above, the control track read head S<sub>3</sub> provides a means for tracking the position of the heads 20 during playback operations. The signal reproduced by the read head S<sub>3</sub> is provided over line 21 to a second input to a multiplexer 50. The output of the multiplexer 20 50 is coupled to an input of an analog-to-digital (A/D) converter 58, and the output of the A/D converter is coupled to an input of an interface circuit 60 by means of a line 61. It is the function of the interface circuit 60 to transmit signals to and receive signals from a central 25 processing unit (CPU) 62, which CPU may typically comprise a NOVA 1220 minicomputer as manufactured by Data General Corporation. Any other minicomputer, or a microprocessor of sufficient capability, may also satisfactorily be used in implementing the present 30 invention. It is the function of the CPU 62 to compute and generate force data signals for moving the head assembly as a function of various input data and system parameters. Various information and control signals from the interface circuit 60 are transmitted to the CPU 35 62 by means of lines 64, and in a similar manner information and control signals from the CPU 62 are transmitted to the interface circuit 60 by means of lines 66. It is noted that in the description hereof a single line in a drawing may represent a multiplicity of lines.

In addition to the information and control signals that are provided to the CPU 62 from the interface circuit 60, a phase encoder circuit 63 also provides information via line 63a to the CPU for the purpose of providing data indicating the physical relationship between the 45 heads-to-tape relative to the rotational position of the scanning head assembly, all of which is used by the CPU to properly calculate the path or trajectory of the transducing heads so that the proper path, during either recording or reproducing, is followed during operation. 50 Additionally, an interface 65 which receives transport speed information via line 65b is applied to the CPU through line 65a. The data relating to tape speed is also used by the CPU 62 in computing the force data signals for driving each of the transducing heads along the 55 appropriate and correct path during operation.

Another output of the interface circuit 60 is coupled to the select input terminal of the multiplexer 50, by means of a line 67, which effects selection of input signals from the sensor 25 or the control track read head 60 S<sub>3</sub>. Data from the CPU 62 transmitted on lines 66 to the interface circuit 60 are transmitted therethrough to a digital-to-analog (D/A) converter 68 on lines 69, and an output of the D/A converter is applied to the second input of the summing junction 52.

As will be described more comprehensively herein, the CPU 62 computes a series of binary numbers, which when taken sequentially determine the amount of de-

flection force (or force data) to be applied to the head assembly 20 during the recording or reproduction of a set of data tracks. The digital-to-analog converter 68 translates this sequence of binary numbers into an analog signal representative thereof, which analog signal is applied to the MDA 56 through the summing junction 52 and compensation network 54. The MDA 56 applies a current through the windings of the voice coil motor 24 to thereby effect the force deflection. The sensor 25 provides a means for feeding back information representative of the position of the voice coil motor 24 which information is supplied to the CPU 62 through the multiplexer 50, the A/D converter 58, and the interface circuit 60. Alternatively, the position of the head assembly 20 may be detected by the read head S<sub>3</sub> during a reproduction operation, which information is transmitted along a similar path. The CPU 62, interface circuit 60, multiplexer 50 and the converters 58 and 68 in combination with the read head S<sub>3</sub> and the sensor 25 form a second feedback network, which is sometimes referred to herein as an "outer loop".

To more fully appreciate the servo system of the present invention, reference is made to FIG. 6 wherein a more detailed block diagram of the servo system is illustrated. The rotating portion of the circuitry illustrated in FIG. 6 is shown within a dashed line 70. Included within this rotating portion of the circuitry is the voice coil motor 24, the sensor 25, and the magnetic head assembly 20 (also enclosed within dashed lines). The magnetic head assembly 20 typically comprises a multiplicity of read/write heads,  $D_1$ ,  $D_2$ ...  $D_n$ , the control track write heads  $S_1$  and  $S_2$ , and the control track read head S<sub>3</sub>. Though only three data heads are illustrated in FIG. 6, it is understood that numerous other heads could be connected in a similar manner. The control track write heads S<sub>1</sub> and S<sub>2</sub> are coupled to outputs of amplifiers 72 and 74 by means of slip rings 75 and 76, respectively; and, these amplifiers are driven by a control track enable and drive logic 77 in response to a write enable signal supplied on a line 78. Alternatively, rotating transformers may be used for coupling signals between the rotating and the fixed circuitry. In addition, optical signal couplers may be employed for either the slip rings or the rotating transformers.

1.

The read head  $S_3$  is coupled to an equalizer circuit 79 by means of a rotating transformer 80. Outputs of the data heads  $D_1, D_2 \ldots D_n$  are coupled to equalization circuits  $EQ_1, EQ_2 \ldots EQ_n$  by means of rotating transformers  $T_1, T_2 \ldots T_n$ , respectively. The outputs of the equalization circuits  $EQ_1, EQ_2 \ldots EQ_n$  are coupled to data lines extending from the head assembly 20 to conventional read/write circuitry (not shown).

The sensor 25 typically comprises a coil 25a mechanically coupled to the head assembly 20, which coil is wound around a permanently fixed core 25b for magnetic coupling therebetween. Also, the coil is electrically coupled to input terminals of an oscillator circuit 86, and a capacitor C10 is coupled across these input terminals. One terminal of the capacitor C10 is coupled to ground potential. The output terminals of the oscillator 86 are coupled to one side of a rotating transformer 88. The oscillator 86 may typically comprise an integrated circuit, Model No. MC1648 as manufactured by Motorola Semiconductor. The stationary windings of the transformer 88 are coupled to input terminals of a conventional FM demodulator 90. In operation, the oscillator 86 causes the tank circuit formed from the coil 25a and the capacitor C10 to oscillate at a frequency

**.3**

determined by the position of the core 25b within the coil 25a. When the coil 25a is moved to different positions around the core 25b, the frquency of oscillation is changed, which change in frequency is coupled to the FM demodulator circuit 90 across the transformer 88. 5 The output of this demodulator is coupled to one of two inputs of the multiplexer 50 and to the negative input terminal of the summing junction 52. Accordingly, such changes in the frequency of oscillation cause the FM demodulator 90 to provide a voltage indicative of the 10 position of the head assembly 20, which is a function of the frequency of oscillation of the tank circuit. This signal is coupled through the multiplexer 50 to the input terminal of the A/D converter 58, transmitted in binary form to the interface circuit 60 along the lines 61, and 15 then supplied to the CPU 62 on the lines 64.

Thus, the position of each of the head assemblies 20 relative to the drum assembly 10, i.e., the vertical position thereof, can be accurately measured and information regarding same provided to the CPU 62 for use in 20 generating the necessary force data signals for controlling the head assemblies 20. This is done for controlling the head assemblies when they are in transducing relation with the magnetic tape, as well as during the period of each rotation where they are not in proximity to the 25 tape and are being appropriately positioned to again be in transducing relation to the tape for a subsequent revolution. In the event it is necessary to move the head assemblies a relatively large distance, for example, resetting the transducing head assembly for placing it in 30 position to reproduce sets of tracks, it may be necessary to generate force data signals for providing the large scale movement for such purpose. The vertical position information concerning the transducing head assembly 20, particularly, when out of engagement with the tape 35 26, is provided by the sensor 25 and circuitry associated with it.

The position of the magnetic head assembly relative to the recorded tracks on tape may also be detected during a reproduction operation by the control track 40 read head S<sub>3</sub>. The signals from the read head S<sub>3</sub> are coupled across the rotating transformer 80 to the input terminal of the equalizer circuit 79 and the output terminal of this equalizer circuit is coupled to the input of an error processor circuit 92, which functions to detect 45 any tracking error of the head assembly. An exemplary error processor circuit is explained further in the aforementioned U.S. Pat. No. 3,838,453.

The output terminal of the processor circuit 92 is coupled to the second input terminal of the multiplexer 50 50. Accordingly, during a read operation the read head S<sub>3</sub> provides a signal indicative of the instantaneous position of the head assembly 20 with respect to the recorded tracks thereof, which information is converted to binary form by the A/D converter 58 and supplied to 55 the CPU 62 along the same above-described path.

The drive signal for the voice coil motor 24 is derived in the CPU 62 in the form of binary numbers, which numbers are transmitted over the lines 66 to the interface circuit 60, and these binary numbers are converted 60 to an analog signal by the D/A converter 68. The output of the D/A converter 68 is an analog signal coupled to the positive terminal of the summing junction 52 through the compensation network to the input of the MDA 56. The windings of the voice coil motor 24 are 65 coupled to the MDA 56 by means of slip rings 94.

The speed of rotation of the moving assembly outlined by the dashed line 70 is detected by a tachometer

96. Output terminals of the tachometer 96 are coupled to the interface circuit 60 on lines 98 to thereby provide synchronization signals to be described further hereinafter.

Referring now to FIG. 7, a block diagram of the interface circuit 60 is shown in greater detail. The line 98a of the lines 98 from the tachometer 96 transmits a TRANSFER CLOCK signal or pulse from the tachometer to a clock input terminal (CK) of a delay counter 100. In one embodiment, the tachometer 96 provides 256 pulses per revolution of the rotating head assembly. Also, the TRANSFER CLOCK signal is applied to one of three input terminals of a scanner revolution timing logic 102, to the clock input terminal of an 8-bit counter 104, to an input terminal of a control logic 106, to the clock input terminal of a force register 108 and to the clock input terminal of a position register 110. Line 98b of the lines 98 transmits a signal identified herein as RAW ONCE AROUND to the load (LD) input terminal of the counter 100. The RAW ONCE AROUND signal is a single pulse generated for each revolution of the center rotating portion 12 of the drum assembly 10.

Lines 66a of the lines 66 from the CPU 62 are coupled to an internal data bus 114. The signals transmitted on the lines 66a comprise 16 data bits referred to herein as D<sub>0</sub> through D<sub>15</sub>. The internal data bus 114 couples either certain ones or all of the data bit lines 66a to various registers or counters within the interface circuit 60 as will be described further hereinafter. Eight of the data bit lines, D<sub>8</sub> through D<sub>15</sub>, of the bus 114 are coupled to input terminals of a delay register 116, which register is clocked in response to a data output control signal identified herein as LOAD DELAY REGISTER supplied on a line 66b from the CPU 62.

The output of the delay register 116 is coupled to input terminals of the delay counter 100. The data bits stored within the delay register 116 form a binary word representative of an amount of time delay, which binary number is loaded into the delay counter 100 in response to the RAW ONCE AROUND signal on the line 98b. The time delay is provided as a means of off-setting with precision an electrical-to-mechanical timing reference so as to accurately but simply align the operation of the various components of the system.

The counter 100 is decremented by the TRANSFER CLOCK signal, and when a count of the binary number loaded therein is complete, a carry out (C<sub>0</sub>) output signal (identified herein as ONCE AROUND) is supplied to a second input terminal of the scanner revolution timing logic 102. Thus, the ONCE AROUND signal is equal to the RAW ONCE AROUND signal delayed by the amount of time required to count down the binary number loaded into the counter 100.

A third input to the logic 102 is supplied on line 66c from the CPU 62, and is a control signal identified herein as START. In response to the START signal being applied to the logic 102, a first output signal is supplied on a line 127 to an input terminal of the control logic 106. The signal supplied on the line 127 causes the control logic 106 to transmit DONE or BUSY status signals to the CPU 62 on the lines 64c. A second output signal from the logic 102 is supplied to the clock (CK) input terminal of a buffer output register 128 on a line 129, which signal causes the contents of a next-buffer-output register 130 to be loaded into the register 128. A third output signal from the logic 102 is supplied on a line 131 to an input terminal (terminal No. 7) of a multiplexer 132. This signal is referred to herein as REV.

ZERO, and is provided in response to the next ONCE AROUND signal incrementing a counter within the logic 102, which will be explained further hereinbelow. Yet another output signal, referred to herein as ONCE AROUND, is supplied to the clear (CR) input terminal of the 8-bit counter 104. The output terminals of the counter 104 are coupled to additional input terminals (Nos. 8-15) of the multiplexer 132.

The eight most significant bit lines (D<sub>0</sub> through D<sub>7</sub>) of the data bus 114 are coupled to input terminals of the 10 next-buffer-output register 130. The clock input terminal of this register is coupled to a data output control signal line 66d from the CPU 62, which control signal is referred to herein as LOAD N.B.O. REGISTER. The output terminals of the register 130 are coupled to input 15 terminals of the buffer-output register 128, and the output terminals of the register 128 are coupled to input terminals (Nos. 0-6) of the multiplexer 132.

The multiplexer 132 in this embodiment is a 16-bit multiplexer. The outputs of the register 128 comprise 20 seven lines, the REV. ZERO output signal line 131 from the logic 102 comprises a single line, and the output of the 8-bit counter 104 comprises eight lines, all of which in combination form one set of the two selectable sets of 16-bit input terminals to the multiplexer. The 25 16-bit output terminals of the multiplexer 132 are coupled to a gating circuit 136, which is enabled by a signal supplied on a line 137 from the control logic 106. The output terminals of the gating circuit 136 are coupled to the lines 64a which are coupled to the ADDRESS BUS 30 of the CPU 62.

The internal data bus 114 is also coupled to input terminals of a 16-bit ADDRESS COUNTER 138 and to a WORD COUNTER 140. The counter 138 is loaded in response to a data output control signal desig- 35 nated as LOAD ADDRESS COUNTER supplied by the CPU 62 on a line 66e, and this counter is incremented in response to a clock signal the from the control logic 106 supplied on a line 141. In a similar manner, the WORD COUNTER 140 is loaded in response to a 40 data output control signal designated as LOAD WORD COUNTER supplied by the CPU 62 on a line 66f, and is decremented in response to a clock signal supplied on a line 142 from the logic 106. Output terminals of the ADDRESS COUNTER 138 are coupled to the alter- 45 nate set of 16 input terminals (Nos. 0'-15') of the multiplexer 132.

In operation, the ADDRESS COUNTER 138 is loaded with data present on the bus 114 in response to the control signal on the line 66e, and is incremented by 50 the clock signal supplied on the line 141 from the logic 106. Memory addresses are supplied through the multiplexer 132 to the gating circuit 136 in response to the state of an OUT/IN control signal supplied on a line 144 from the control logic 106. The WORD COUNTER 55 140 is decremented by the clock signals on the line 142 in response to each transfer of an address on the lines 64a to the CPU, and when the counter 140 reaches a count of zero, a COUNT ZERO signal indicative thereof is supplied to the logic 106 on a line 146. The 60 COUNT ZERO signal causes the gating circuit 136 to be disabled, thereby inhibiting any additional transfer of data to the CPU.

The internal data bus 114 is also coupled to input terminals of a data channel (DCH) output register 148 65 and to a command register 150. The DCH output register 148 is loaded with data on the bus 114 in response to a clock signal from the control logic 106 on a line 149.

The output terminals of the register 148 are coupled to input terminals of the force register 108. The force register 108 is loaded in response to the transfer clock signals, and the output of this register is supplied to the D/A converter 68 (FIG. 6) on the lines 69. The binary numbers representative of the position to which the head assembly 22 must be deflected are supplied on the lines 69 from the force register 108, which binary numbers were computed by the CPU 62.

The command register 150 is loaded with data on the bus 114 in response to a data output control signal designated as LOAD COMMAND REGISTER, and supplied on a line 66g from the CPU 62. The binary numbers stored in the register 150 are provided on the lines 151 as control signals to the servo mechanism illustrated in FIG. 6, which signals will be explained further hereinbelow. In addition, a single data bit position of the command register 150 provides a DCH ENABLE signal on a line 152 to the data control logic 106. Additional control signals are applied to the control logic 106 on lines 66h from the CPU 62. In a similar manner, control signals are supplied to the CPU 62 from the control logic 106 on lines 64c.

The position of the head assembly as detected by either the control track read head S<sub>3</sub> or the sensor 25 (FIG. 6), which position signal is converted to a series of binary numbers by the A/D converter 58, is applied to input terminals of the position register 110 of the lines 61. The position register 110 is loaded in response to the TRANSFER CLOCK signal applied to the clock input terminal thereof. The output terminals of the position register 110 are coupled to a gating circuit 154, which gating circuit is enabled by a signal from the control logic 106 on a line 155. The output of the gating circuit 154 is coupled to the DATA BUS (not shown) within the CPU 62 by means of the lines 64b.

In general, the primary function of the interface circuit 60 is to route position data to the CPU 62 from the SENSED POSITION of the head assembly 20 for storage in a main memory, and to extract data from the CPU memory for conversion to a forcing signal for driving the voice coil motor 24. When position data is to be stored in the main memory, address locations for storing such position data are provided by the contents of the ADDRESS COUNTER 138, through the multiplexer 132 and the gating circuit 136. The initial address location for storage of the position data is determined by the CPU 62, which initial address is stored in the counter 138. Additional memory address locations, sequentially consecutive from the initial address location, are provided by incrementing the counter 138 with clock signals supplied on the line 141 from the logic 106.

The position data to be stored in the main memory is provided at the output of the gating circuit 154 on the lines 64b. In particular, each binary word (typically 16 data bits per word) of position data supplied on the lines 61 is temporarily stored in the register 110 before being transferred through the gating circuit 154 simultaneously with the address locations transferred through the gating circuit 136.

There are practical limits, however, to the size of main memories used with the CPU. Thus, a selection is made in the CPU for the maximum number of words of position data to be stored in the main memory at any one time. Of course, new data may be stored in the CPU memory by "writing over" data previously stored therein. The selection of the number of words of position data to be stored is represented by a binary number

which is stored in the WORD COUNTER 140. Each time the ADDRESS COUNTER 138 is incremented, the WORD COUNTER 140 is decremented. When the word counter reaches a count of zero, the gating circuits 136 and 154 are disabled. Accordingly, only a 5 preselected number of words of position data are stored in the main memory at any given time.

When the main memory is providing force data signals to drive the voice coil motor 24 so as to position the head assembly 20, data is extracted from the main mem- 10 ory at address locations provided by the opposite set of input terminals (Nos. 0–15) of the multiplexer 132. That is, the multiplexer 132 is selected by the level of the OUT/IN signal on the line 144 to transfer the combination of the outputs from the buffer output register 128 15 and the 8-bit counter 104 along with the state of the REV. ZERO signal on the line 131 through the gating circuit 136 to the lines 64a in the form of an initial main memory address for extracting the force data.

As previously mentioned and as should be appreci- 20 ated from the foregoing detailed description, the force data is used to properly position the head assemblies 20 to follow the correct path during recording as well as reproducing. The position information is utilized by the CPU to generate the force data since the force data 25 which moves the head assemblies is necessarily a function of the present position the head assemblies, as well as where they should be moved to be correctly positioned. The speed and amount of movement of the head assemblies is therefore determined by their present posi- 30 tion as well as the desired position. The sense head  $S_3$  is used to generate error information for use in controlling the transducing head assembly 20 so that it accurately follows the tracks while the transducing heads are scanning the tracks during reproduction therefrom, the posi- 35 tion information provided by the sensor 25 is useful and necessary during the portion of each rotation of the transducing heads when they are off the tape and are being positioned for scanning a subsequent set of tracks during a subsequent rotation of the assembly 20. During 40 a record operation, it should be appreciated that the position information is needed for the CPU to generate the forcing signals, particularly if the tape transport speed is less than normal and the prescribed or intended path of the transducing heads is that which would be 45 produced if the tape transport speed were normal.

To more fully appreciate the operation of the servo system described thus far, reference is made to FIGS. 8, 9 and 10. FIG. 8 shows the timing relationship for a jump or reset of the head assembly 20 from a set of 50 tracks M to an adjacent set of tracks N. Such a jump of the head assembly would occur while the head is not scanning the tape (i.e., off tape) and would be necessary once the head assembly has been deflected to its maximum deflection limit in one direction.

That is, if the head assembly is gradually deflected for each revolution of the rotatable transducing head assembly 20 and is always deflected in the same direction, it is necessary to jump or reset the position of the head assembly, once maximum deflection thereof has been 60 for the A buffer or other similar output buffer. reached. Waveform 160 illustrates the actual jump movement of the head assembly with respect to its angle of rotation. Note that the jump begins when the head assembly 20 is located approximately at a reference angle  $\phi$  or 0° and is completed within approxi- 65 mately 180° of rotation of the assembly. However, due to the well-known phenomenon of inertia there will be an oscillatory motion of the head assembly. To mitigate

this oscillation the forcing signals applied to the voice coil motor are modified to counteract the inertial oscillations. There still remains a minute amount of oscillatory motion, which is represented by portion 160a of the waveform 160.

18

Waveforms 162 and 163 represent the time at which data may be read from the tracks M and N by one transducing head assembly following an intervening jump movement. Waveform 164 represents the time at which the CPU 62 enables the hardware, which signal is also referred to herein as START. Waveform 165 represents the ONCE AROUND signal provided at the output of the delay counter 100. Following the START signal from the CPU 62, the next subsequent ONCE AROUND signal initiates operation of the servo system. As shown by the sequence arrow 166, measurement of the position of the head assembly 20 is initiated by generation of the waveform 167. Also, the first ONCE AROUND transition initiates the extraction of force data from JBUF buffer within the CPU main memory at REV. ZERO time to effect the jump from track M to N. The JBUF buffer contains force data for providing a jump from one set of tracks to another and is also especially adapted for the mass of a particular head assembly 20 so as to mitigate inertial oscillatory motion following a jump (as shown by portion 160a of the waveform 160). Note in FIG. 7 that the complement of the ONCE AROUND signal, namely, the (ONCE AROUND) signal, clears the 8-bit counter 104. The cleared state of this counter in combination with a first state of the REV. ZERO signal, and the contents of the register 128, provide the address to the JBUF buffer location of the main memory. The next subsequent transition of the ONCE AROUND signal clears the 8-bit counter 104. However, the state of the REV. ZERO signal changes, and this causes the issuance of another memory address location signal which controls the head assemblies for following the N set of tracks. The new address location contains forcing data computed by the CPU for driving the voice coil motor as the transducing head assembly scans the set of tracks N. If the address of the J buffer identifies a location in the buffer containing data indicating a jump from one set of tracks to another was required, then the voice coil motor is controlled by the voice data obtained from the J buffer to accomplish the jump as is desired. During the course of the execution of the jump, the A buffer is provided with another address, so that at the completion of the jump, the voice coil motor controlling the head assemblies is provided with the appropriate data to follow another set of tracks. However, during the execution of the jump using the data from the J buffer, if another address is not provided, then the CPU automatically obtains data from the B buffer which operates to 55 keep the transducing head assembly from moving so that it will not undergo large excursions which would be undesirable and possibly damaging to the assembly. The B buffer is a circulating buffer whose contents are circulated at its output until a new address is provided

The actual position of the head assembly is measured while the transducing heads are in transducing relation with the tape, i.e., for about 180°, or about  $\frac{1}{2}$  of each revolution of the transducing head assembly 20 and the tracking information is provided to input buffers. There are three input buffers, each of which receive 128 samples or words. While three input buffers are used, three are provided only because of synchronizing require-

ments with other routines performed by the CPU. The input buffers load position information regarding the head assembly or receive error information from the sense head S<sub>3</sub>, the latter of which is typically used during the reproducing. After the 128th sample is received 5 in an input buffer, an interrupt is provided which indicates that the data is received and ready for use, and the interrupt routine then begins executing to control the buffers.

Referring to FIG. 9, the rotatable center drum por- 10 tion 12 is shown in phantom line. The trace of the head assembly movement during a jump is illustrated by band 170. In the illustrated embodiment, the center drum portion is rotated at 9,000 RPM and 256 sample intervals per revolution are provided. Consequently, each 15 sample interval is approximately 26 microseconds. It should be appreciated that the inner loop described with reference to FIG. 5 has a bandwidth of about 4 kHz and a response time of approximately 1 millisecond and it is for this reason that the computer controlled 20 outer loop is necessary to generate predicted correction of errors in the trajectory of the path followed by the transducing head assembly 20 that are caused by other factors such as stretching of the tape, bearing run out (which is sometimes referred to as wobble), changes in 25 temperature and humidity, all of which affect the accuracy with which a track is followed by the head assembly during operation. The computer aided outer loop effectively samples and averages the error waveform signature during operation and finds the harmonic con- 30 tent of the error and uses the data to generate a correction waveform that effectively predicts the error on the basis of what has been determined and thereby causes the transducing heads that are carried by the deflectable head mounting assembly 22 to follow the proper path to 35 obtain accurate reproducing.

FIG. 10 illustrates maps of the ABUF, JBUF and BBUF buffers within the main memory. Since there are 256 samples per revolution, each buffer contains 256 address locations for storing the 256 samples, or words, 40 of the force data to be applied to the head assembly 20.

The broad organization of the software for the computer that controls the movement of the head assemblies is illustrated in FIGS. 16–19, with FIG. 16 providing the broad general operation of the CPU 62. The afore- 45 mentioned Data General Nova computer operates with a main program of the system that is named MILE 3, which performs the interface between the operator and the hardware system comprising the overall apparatus. The computer displays prompts and requests the neces- 50 sary parameter for each of seven separate tasks which will be hereinafter described. The computer has a front panel containing a number of switches as is standard for the Nova computer which controls the submodes of one of the seven tasks, namely the task named "iteration" 55 which is the task that is used during normal operation in either the recording or reproducing modes. The available tasks that can be selected from the total number of tasks which are on the displaced directory or menu include the following: (1) calibrate; (2) output single 60 harmonic; (3) change values for window, delay, N fit, gain; (4) iterate, including sense switches 13, 14 and 15; (5) stop control of automatic scan tracking; (6) set speed; and (7) stop program. The overall operation is shown in the diagram of FIG. 16, which illustrates that 65 after the basic program is started, the output menu is displayed and an operator can designate one of the appropriate input paths, which is then carried out by the

**20**

CPU. Most of the tasks are located "in line" in the MILE 3 system program, while certain major and other more complex tasks are located in subroutine modules which are shown in the following table.

### Table 1

TTIT—harmonic correction

FAST—low frequence correction

JMPINIT—set up parameters for filling a jump buffer

JMPFILL—fill a jump buffer

SETSPD—set up speed constants

RDSPD—read speed from interface

SWIN—read sense switches

CMCAS—send a command to the interface

STCAS—start the interface and read/write data

RDCAS—read another set of data

FILON—integration of a set of real numbers

LMSQ—least mean square fit

Upon start up, the apparatus is calibrated and this procedure is carried out using the flow chart shown in FIG. 17 in conjunction with the diagrams shown in FIG. 12. In this calibration stage, the CPU considers the inner loop or computer controlled loop to be a black box so that if a forcing function of sin  $\omega t$  is applied to the input of the black box there will be a resulting displacement of  $f = f_o R \sin(\omega t + \phi)$  where R is an attenuation factor and  $\phi$  is the phase angle or lag of the output with respect to the input. During the calibration stage, sinusoidal forcing functions are used to drive the outer loop and the computer records the corresponding displacement of the system using the sensor 25. Fourier transforms are then used to determine the attenuation factor R and the phase delay  $\phi$  for each harmonic of the once around frequency of the rotating drum assembly 10. The desired displacement is then analyzed by Fourier methods to determine the various component frequencies, including their amplitudes and phases. From the previously recorded response characteristics of the inner loop, it is then possible to determine the requisite forcing function in terms of its harmonics. These harmonics are then combined to form a truncated Fourier series and this forcing function produces the desired output of the inner loop.

The diagrams shown in FIG. 12 illustrate the various sine waves which are produced as a result of the Fourier analysis to generate the required forcing function to provide the desired output characteristic. The movement of the head assembly is generally depicted by the waveform 315 (and 308) and the forcing data that is required as a result of the analysis to move the head assembly in accordance with the movement depicted by waveform 315 is shown by the waveform 316. The desired pattern of movement of the head assembly 20 is represented by waveforms 308 and 315 and several harmonics of the computations are illustrated by waveforms 312 and 314.

Returning to FIG. 16, the task 2, which is that of outputting a single harmonic, results in the production of a sinusoidal forcing function at a selected harmonic of the rotating assembly's fundamental frequency. The amplitude of the forcing function may range from 0 to 32,767 bits in the illustrated embodiment. The amplitude corresponding to 32,767 bits is that which will approximately produce 40 mils of transducing head assembly movement, which corresponds to the full output range of the digital-to-analog converter. The data is put into a 512 integer array and the address of the array is output

to the interface 60. The interface is commanded to continuously fetch data from the array until stopped and the interface may be stopped by invoking task 5 explicitly or implicitly by invoking any other task which uses the interface.

The third task which is that of changing the values of four parameters that are preset for a particular rotating assembly, and includes those labeled "window", "delay", "N fit" and "gain", can be changed and usually necessarily have to be changed if a particular rotating 10 assembly is changed for a particular apparatus. Broadly stated, the "delay" parameter involves the controlling of a delay counter in the interface which adjusts for any angular misalignment of the heads relative to tape. Since the once around signal is derived from a tach 15 pickup, its placement relative to head position is critical in determining when the head is on tape.

The "window" parameter represents that portion of the rotation of the head assembly wherein the transducing heads are in transducing relation with the tape. The 20 window parameter number should not exceed 128 and represents the number of samples that are present in the input buffer as a result of the transducing heads being in transducing relation to the tape.

The "N fit" parameter represents the number of sam- 25 ples to perform a straight line fit for developing the off tape forcing function and this is nominally set at 40 samples. These 40 samples are located at the beginning portion as well as the end portion of the path that is followed while the transducing heads are on tape and 30 the 40 samples are averaged to eliminate noise.

The "gain" parameter represents the number of units required at the input of the interface to force a movement of the head assembly so that the transducing heads move exactly 0.001 inch and is nominally set at 1600. 35 Stated in other words, it also represents the change of input that is needed to drive the digital-to-analog converter to provide an output that effects a 0.001 inch displacement of the transducing head assembly 20. It is a conversion between the internal computer word and 40 external physical movement of the head assemblies.

"Iteration" of the task number 4, is shown in the flow diagram of FIG. 19 and is the basic operating process which controls the movement of the head assembly with harmonic and D.C. correction, as well as with 45 speed change strategy. As previously mentioned, the interface 60 works with two sets of buffers, i.e., the input and output sets of buffers, with the input set providing position or error data, while the output set contains the composite forcing function or force data sig- 50 nals which control the trajectory of the transducing heads during operation. Each revolution of the rotating head assembly 20 provides 128 points of data describing the 180° of revolution of the transducing head assembly 20, during which time the transducing head is in trans- 55 ducing relation with the tape and requires 256 points of data for controlling the head mounting assembly carrying the transducing heads. As defined, the sample points 0 through 127 occur when the heads are scanning the tape, and sample points 128 through 255 occur when the 60 transducing heads are off tape.

The harmonic analysis occurs only when the interrupt service routine is idle, and both the harmonic analysis and interrupt service routines use both input and output data, so several buffers of each set of input and 65 output buffers are used. All of the input and output buffers are either handled by the harmonic correction routine or the D.C correction routine but never by