### Faust et al.

[30]

[52]

[45] Jan. 4, 1983

| [54]                          | COMBINING THYRISTOR CIRCUITS OF VARIOUS CIRCUIT CONFIGURATIONS                                             |                                                                            |  |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|

| [75]                          | Inventors:                                                                                                 | Werner Faust, Wettingen; Peter Etter, Oberehrendinger, both of Switzerland |  |  |  |

| [73]                          | Assignee:                                                                                                  | BBC Brown Boveri & Company,<br>Limited, Baden, Switzerland                 |  |  |  |

| [21]                          | Appl. No.:                                                                                                 | 150,882                                                                    |  |  |  |

| [22]                          | Filed:                                                                                                     | May 19, 1980                                                               |  |  |  |

| Related U.S. Application Data |                                                                                                            |                                                                            |  |  |  |

| [60]                          | Division of Ser. No. 867,945, Jan. 9, 1978, Pat. N<br>4,232,235, which is a continuation of Ser. No. 700,5 |                                                                            |  |  |  |

Foreign Application Priority Data

Int. Cl.<sup>3</sup> ...... H03K 17/72

U.S. Cl. ...... 307/252 R; 307/318;

Sweden ...... 857575

361/56; 361/91; 363/68

Jun. 28, 1976, abandoned.

Jul. 2, 1975 [SE]

| [58] | Field of Search | 307/252 J, 252 M, 252 N,       |

|------|-----------------|--------------------------------|

|      | 307/252 A, 318  | 3, 305, 252 R; 363/68; 361/56, |

|      |                 | 91, 111; 323/229, 231          |

U.S. PATENT DOCUMENTS

## [56] References Cited

| 3,242,416 | 3/1966  | White        | 307/252 N |

|-----------|---------|--------------|-----------|

| 3,651,375 | 3/1972  | Ebersohl     | 307/252 N |

| 4,232,235 | 11/1980 | Faust et al. | 307/252 R |

Primary Examiner—John Zazworsky Attorney, Agent, or Firm—Orville N. Greene

#### [57] ABSTRACT

Thyristors included in circuit configurations are, in turn, connected in series circuit fashion such that n circuit configurations are so interconnected, where n is a real integer equal to or greater than 2. The circuit configurations provide a combination of functions such as current limiting, voltage distribution, assumption of storage load, limitation of commutation voltage and limitation of search voltage. The combined circuit configurations provide the most practical arrangement of desired characteristics to meet the requirements for specific applications.

### 8 Claims, 67 Drawing Figures

Jan. 4, 1983

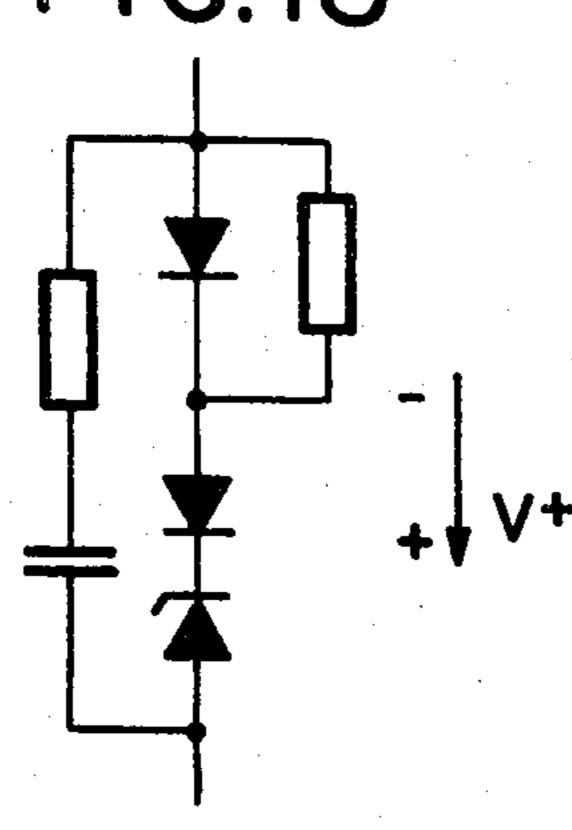

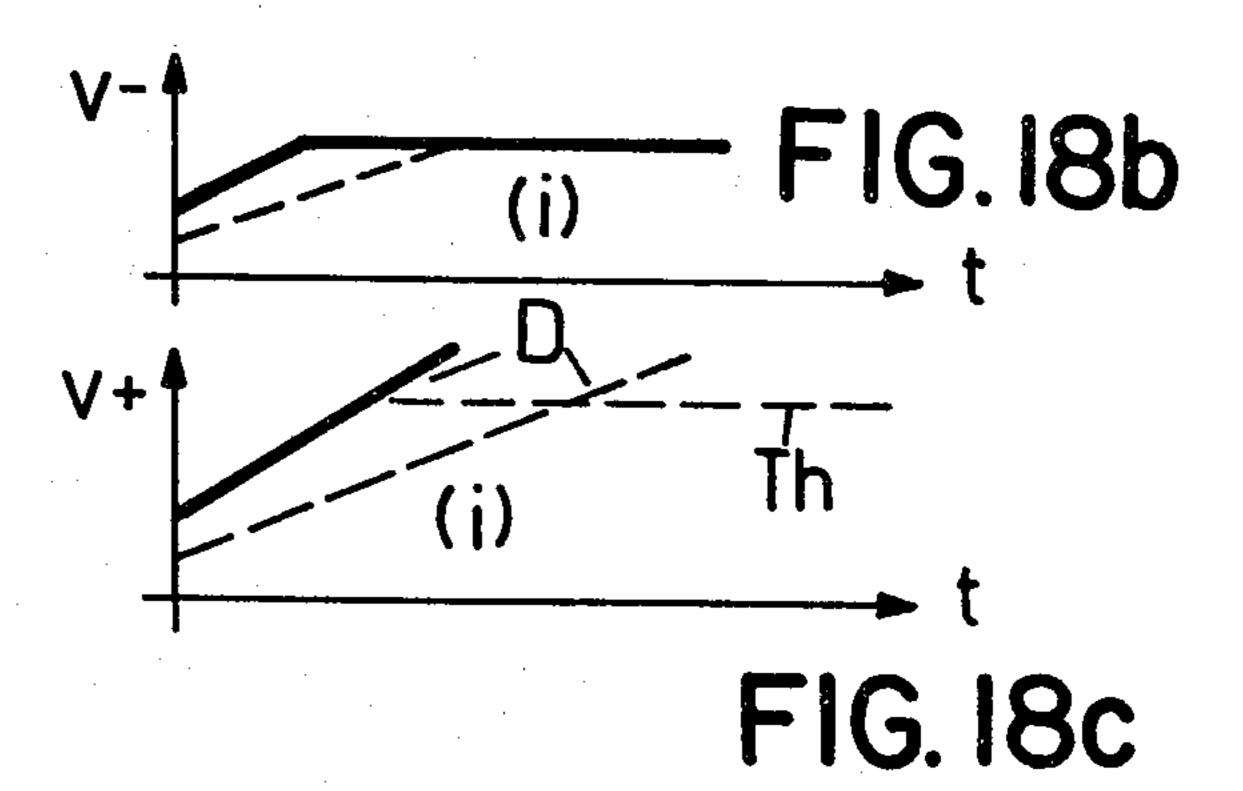

F1G.18

t=0 FIG. 18a

FIG. 19

FIG. 19a

V+

(i)

FIG. 19c

V

(ii)

FIG. 19b

### COMBINING THYRISTOR CIRCUITS OF VARIOUS CIRCUIT CONFIGURATIONS

This is a divisional of U.S. application Ser. No. 5 867,945, filed Jan. 9, 1978 (now U.S. Pat. No. 4,232,235, issued Nov. 4, 1980), which is a continuation of U.S. application Ser. No. 700,560, filed June 28, 1976 (now abandoned).

### **BACKGROUND OF THE INVENTION**

The present invention relates to thyristors and more particularly to circuit configurations each including at least one thyristor, which circuit configurations are connectible in series in order to obtain a resultant series circuit in which the desired characteristics are optimized.

Normally the following points are of primary consideration when considering the use in connection of thyristors:

I. Equalization of the various thyristor properties which result from the voltage distribution.

II. The most practical distribution of total voltage on the individual thyristors in accordance with external voltage stress, as well as voltage limitation of the individual thyristors, particularly with respect to maintaining surge voltage in the most practical range of the surge front with minimum loss.

In more specific terms, circuit arrangements employing thyristors should ideally meet the following criteria:

1. Voltage distribution in accordance with operating frequency.

2. Take-up of the storage load.

3. Limitation of the commutation voltage.

4. Voltage limitation at the thyristor.

5. dv/dt-limitation by surge voltage load.

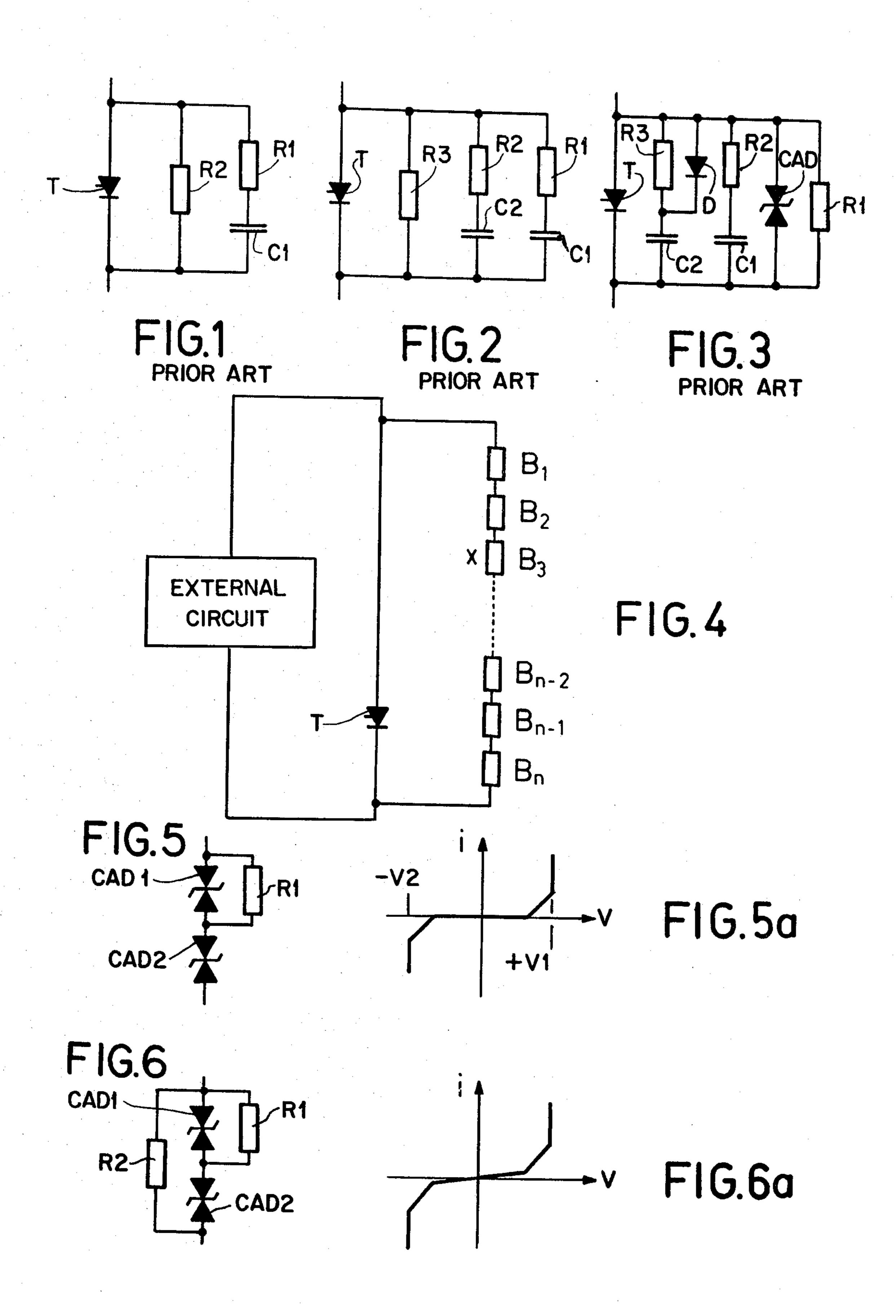

A great number of various circuit arrangements for thyristor circuits have been proposed. Typical of these are the following three circuits (shown in FIGS. 1-3 herein).

FIG. 1 shows a circuit configuration in which R1-C1 and R2 branches are connected in parallel with one another and with a thyristor T. Note, for example, the ASEA Publication 16 (1971) Vol. 2, page 39 entitled 45 "Thyristor Values For The Expanded HGÜ-Gotland Arrangement". The circuit configuration of FIG. 1 fulfills to a limited extent the above requirements 1 and 2, but for a number of reasons is not voltage limiting.

The arrangement of FIG. 2 includes three parallel 50 paths consisting of the elements R1-C1, R2-C2 and R3, respectively, which are connected in parallel with one another and with thyristor T. The resulting configuration is useful in a larger frequency range compared with the circuit of FIG. 1. However, the circuit of FIG. 2 is 55 not voltage limiting (see CIGRE International Conference on Large High-Tension Electric Systems-1972 Session Aug. 28-Sept. 6, pages 14 and 61).

Finally, FIG. 3 shows the circuit configuration of the HGÜ-valve for the Power Plant "Cabora Bassa" in 60 Mozambique, which is a cooperative development of the HGÜworking agreement of AEG, BBC and Seimans. The circuit of FIG. 3 fulfills requirements 1-3 above. The voltage limitation of thyristor T (requirement 4) comes about through the use of a CAD element 65 condition ("Controlled Avalanche Diode" = diode which Homogeneous Avalanche Breakdown), while requirement 5, the dv/dt limitation by surge voltage

load is obtained through the diode D and the R3-C2 circuit branch.

### BRIEF DESCRIPTION OF THE INVENTION

The invention is based upon the need for appreciably increasing the voltage exploitation of thyristors, while at the same time providing a cost reducing design. This is achieved by the employment of a scheme in which the final circuit configuration comprises a series connection of n circuits, at least two of which have different impedances or different V-I (voltage-current) characterisite curves and wherein at least one of the circuit configurations is equipped with a voltage limiting element.

The above arrangement permits a greater adaptability of the resultant circuit to take advantage of the special properties of the thyristors as well as taking fully into account all of the possible requirements imposed upon the final circuit design. The resultant series circuit can, for example, provide a differing characteristic for each voltage direction and solve different problems such as, for example, a sharp limitation of the commutation overshoot and sharp limitation of the voltage stress imposed upon the thyristors. This is particularly advantageous when dealing with series connected thyristors, in that the limited prohibiting stress is in the negative direction (breakthrough voltage) and the sweep voltage (blocking voltage) is widely spread, especially if the thyristors in the prohibited direction show no "controlled avalanche" behavior (homogeneous avalanche 30 breakthrough).

### BRIEF DESCRIPTION OF THE FIGURES

FIGS. 1-3 show schematic diagrams of three different embodiments of circuit configurations employing thyristors.

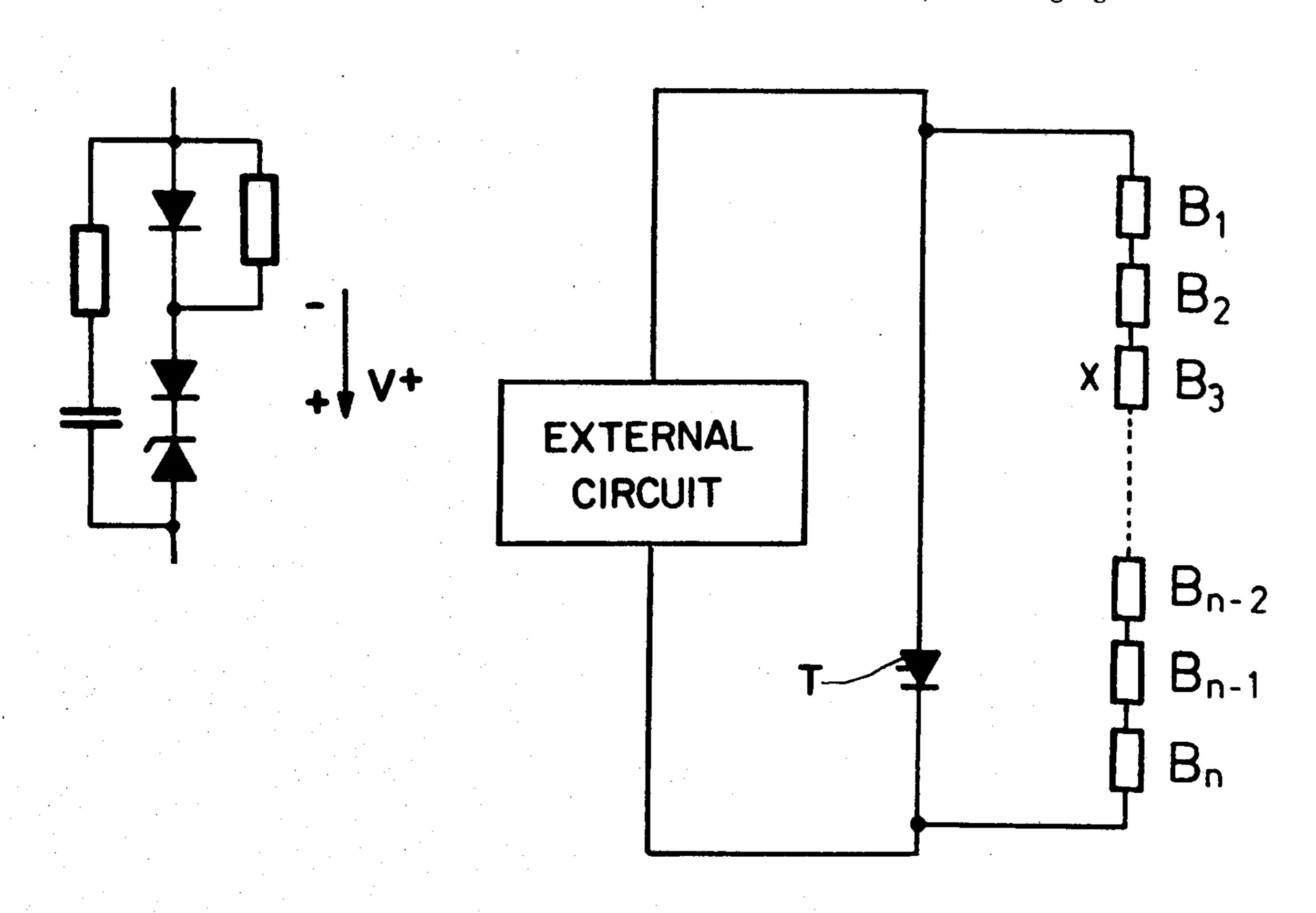

FIG. 4 shows a simplified block diagram of n series connected groups and embodying the principles of the present invention.

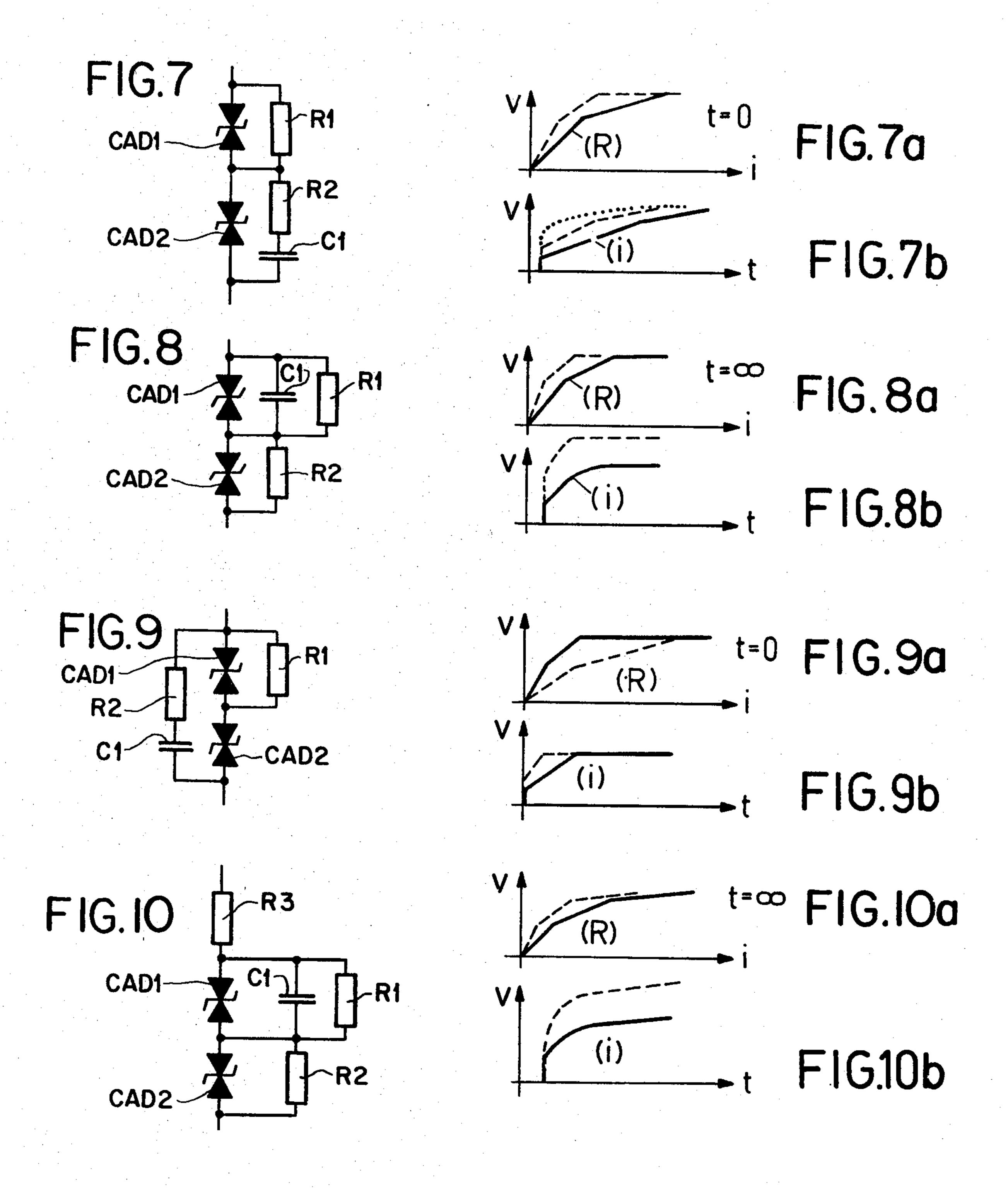

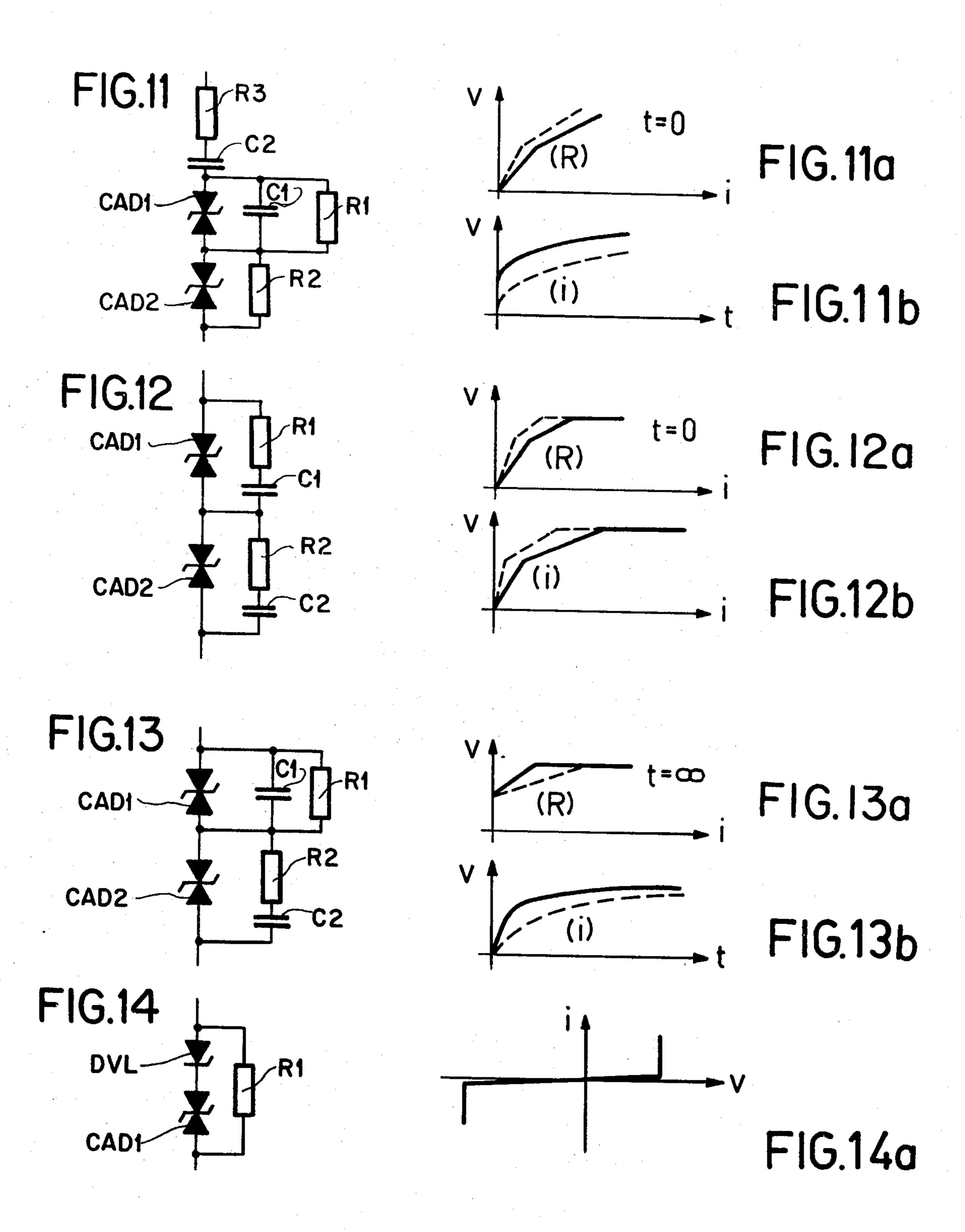

FIGS. 5-25 show schematic diagrams of individual circuit configurations which may be selectively employed in various combinations in a series connected circuit of the type shown in FIG. 4.

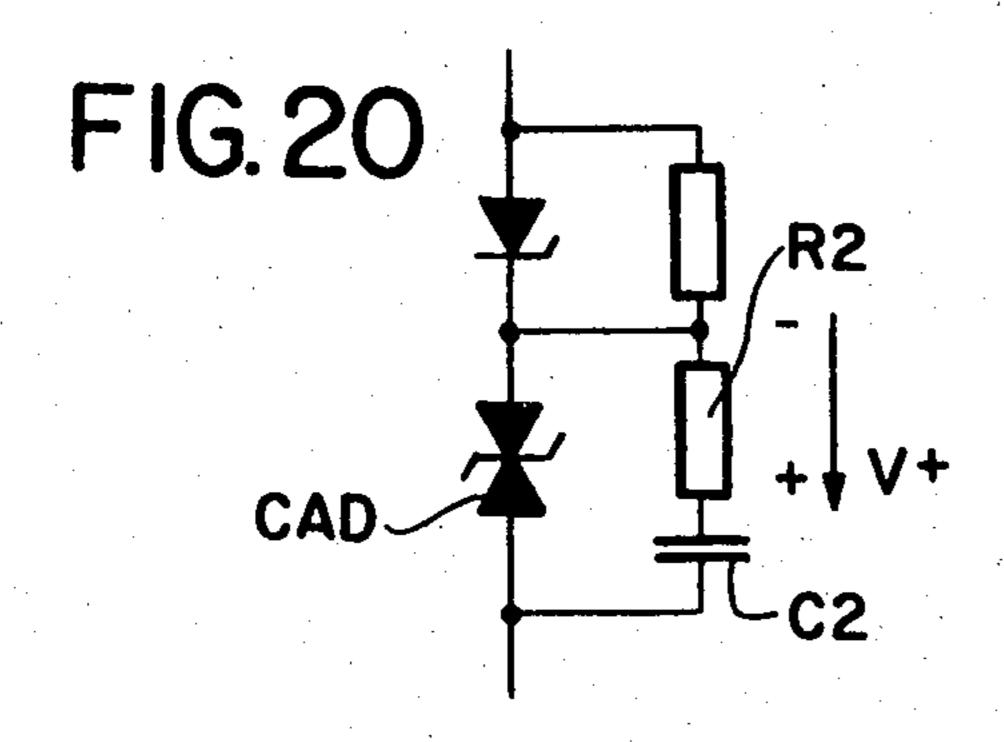

FIGS. 5a-25a show the voltage-current characteristic curves for the circuits 5-25, respectively.

FIGS. 7b-13b show the voltage-time characteristic curves for the circuits of 7-13, respectively.

FIGS. 16b-22b show the negative polarity voltagetime characteristic curves for the circuits of FIGS. 16-22, respectively; and

FIGS. 16c-22c show the positive polarity voltage-time characteristic curves for the circuits of FIGS. 16-22, respectively.

# DETAILED DESCRIPTION OF THE INVENTION AND THE PREFERRED EMBODIMENTS THEREOF

Referring now to the drawings, wherein like identifying characters indicate like elements, there is shown in FIG. 4 a thyristor T with anode and cathode and a plurality of series connected sub-circuits Bl-Bn connected in parallel with thyristor T. The opposite terminals of thyristor T are also connected to opposite terminals of an external circuit. According to the invention, the series connected sub-circuits comprise a plurality of series connected circuit configurations B1, B2, ..., Bn of different impedances. At least one of the sub-circuit configurations (for example, note the circuit configuration B3 denoted with an "X") is provided with a voltage

and CAD2 can be achieved only by long high overvoltage across the circuited thyristor.

limiting element. Those sub-circuit configurations in the Figures to be described hereinbelow represent the circuit configurations which may be combined to provide a resultant series circuit which meet the desired objectives. Other additional conventional circuit configurations such as, for example, a dv/dt limitation circuit arrangement may also be utilized (for example, note the parallel branch of FIG. 3, including the elements R3-C2).

FIGS. 5 and 6 show two series connected elements 10 CAD1 and CAD2, each of which represent series opposed diodes with controlled avalanche behavior or, in other words, homogeneous avalanche breakthrough. In FIG. 5, CAD1 has a resistor R1 connected in parallel therewith. The current-voltage characteristic curve for 15 the circuit of FIG. 5 is shown in FIG. 5a. Both of the CAD elements limit the total voltage across the thyristor (T in FIG. 4). The resistance causes a current flow (i) through the circuit if the total breakdown voltage of CAD2 is exceeded. In this way, by reducing (for example, by halving) the thyristor limiting voltage, a known limitation of the thyristor voltage to a desired current (for example, a few amperes), will be obtained. These currents can, for example, occur at the end of the current flow time following the carrier storage effect. In this way, the commutating overshoot can be limited and can be lowered.

The characteristic voltage-current curves of FIGS. 5 and 6 are shown respectively in FIGS. 5a and 6a. Due to the bidirectional nature of the CAD elements, the voltage limiting characteristics are obtained as shown at +v1 and -v2 of FIG. 5a, for example.

In the following examples it will be assumed that at least two sub-circuit configurations are connected al- 35 though certainly more than two may be employed, if desired.

In the circuit in accordance with FIG. 7, CAD1 and R1 are connected in parallel while CAD2 is connected in parallel with the series branch circuit comprised of 40 with the circuits of FIGS. 5-9. R2 and C1. The voltage limitation and the piecewise static voltage-current characteristic curves are obtained through the circuit of FIG. 7 (as shown by FIGS. 7a and 7b). The branch path comprised of R2-C1 additionally cooperate to provide a known time relation, as the 45 loading of the capacitor requires a certain time interval, for example, before being charged up to the storage load of the thyristors. At time t=0, only the resistances draw current. The breakthrough voltage of CAD2 will eventually be achieved first within a fixed predeter- 50 mined time delay which is dependent upon the values of C1 and R2, as well as the magnitude of the current i. Again, there exists a certain, although not strongly expressed limitation of the commutating overshoot if the back current is small.

In the circuit according to FIG. 8, R1 and C1 are connected in parallel with one another and are further connected in parallel with CAD1. R2 is connected in parallel with CAD2. At time t=0, C1 is assumed to have no voltage across its plates and can discharge 60 again over the parallel connected resistor R1. As a result the voltage on the circuit will be much stronger than the circuits previously described, and approached through the breakthrough voltage, and will be limited only by CAD2 having R2 connected in parallel there- 65 with. With this circuit configuration, the commutating overvoltage can be effectively fully limited. Thus, the established full voltage limit through elements CAD1

Again, FIGS. 8a and 8b show the voltage-current and the voltage-time characteristic curves wherein R (resistance) serves as the parameter for FIG. 8a while i (current) serves as the parameter for FIG. 8b (as well as subsequent Figures).

The circuit of FIG. 9 is comprised of a combination of the circuit of FIG. 5, together with the series branch comprised of R2-C1 connected in parallel across the series connected elements CAD1 and CAD2. The values of C1 and R2 are appropriately chosen for the particular storage load. Upon the occurrence of higher thyristor voltage, the piece-wise voltage-current characteristic curve of FIG. 9a will be operative. With this arrangement, the special voltage limitation results again for the commutating oscillations as long as the magnitude of the current i into the circuit of FIG. 9 is not too large.

With regard to the circuits shown in FIGS. 10 and 11, a respectively, resistor R3 is connected in series with the series connected elements CAD1 and CAD2, and a resistor R3 and a capacitor C2 are series connected with the elements CAD1 and CAD2. The voltage limitation effect is, as a result, only weakly expressed and otherwise, the circuit construction is substantially similar to that shown in FIG. 8.

In FIG. 12, the elements CAD1 and CAD2 each have connected thereacross a series circuit branch comprised 30 of R1-C1 and R2-C2 respectively, which serve as differential time constants. The values for the elements in one of the two series circuit branches is chosen for the particular storage loads. The values of the elements in the second series circuit branch are chosen to provide a larger time constant and will only be loaded by overvoltages of a longer time interval. In this way, a certain limitation of the commutation overvoltage can be achieved. Furthermore, the thyristor voltage T (FIG. 4) will be limited by the CAD elements as is the case

In the circuit of FIG. 13, there is provided a parallel RC circuit (R1-C1) and a series RC circuit (R2-C2), each of these branch circuits being respectively connected across CAD1 and CAD2. The voltage limitation effect for commutation overshoot is similar to that obtained in the circuit of FIG. 8, but essontially more strongly expressed than the other wiring circuit configurations, wherein "wiring" when used in connection with a thyristor means the connection of a wiring circuit directly in parallel with the thyristor and with no other element. Again, the limitation of the total thyristor voltage is obtained through the employment of the two series connected CAD circuit elements CAD1 and CAD2).

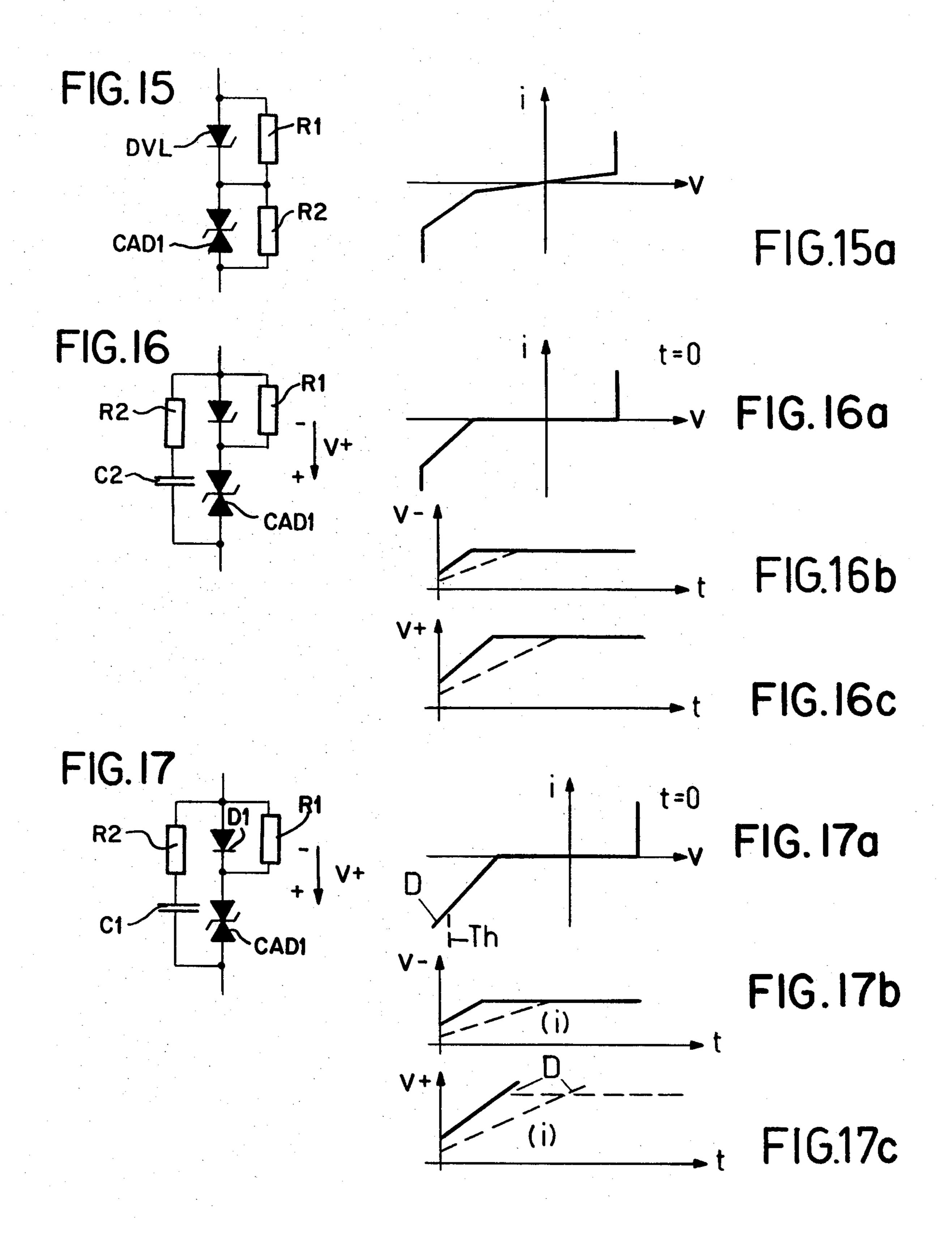

FIG. 14 provides an asymmetrical voltage-current characteristic curve as shown in FIG. 14a. The breakthrough voltages differ for the respective positive and negative voltage directions. With this object in mind, a voltage limiting diode, i.e., a diode DVL with a controlled avalanche behavior, is further connected in series with CAD1. A circuit of this type is advantageous for use with thyristors employed in non-symmetrical voltage applications, for example, in cases where the sweep voltage may be lower than the breakthrough voltage of the inverse direction (i.e. the high resistance or backward direction). In FIG. 15 there is shown a resistance R1 connected in parallel with avalanche diode DVL and a resistance element R2 connected in

5

parallel with CAD1. This circuitry provides an asymmetric voltage-current characteristic curve as shown in FIG. 15a, which curve is similar to that obtained through the circuit configuration of FIG. 5. In FIG. 5, however, a symmetrical voltage-current characteristic 5 curve is obtained. The voltage asymmetry of the circuit is obtained, while the limitation of the commutating overshoot is necessary only in the inverse direction.

In the backward direction of the thyristors, a limitation of the thyristor voltage can be achieved by some- 10 what of a half-thyristor voltage, if the current is not too high. Furthermore, we have obtained herein the voltage limitation by full thyristor voltage.

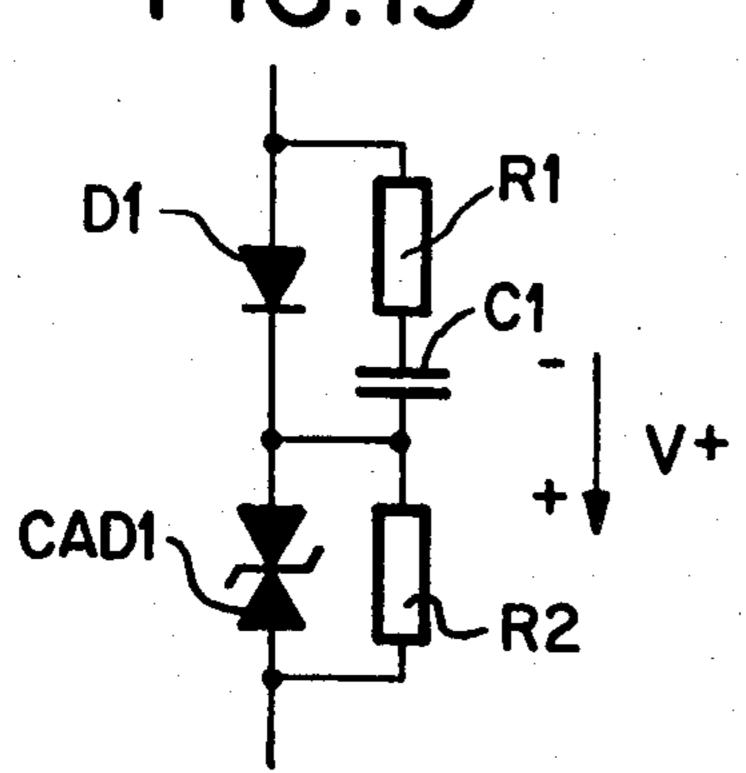

In the arrangement of FIG. 16, the series connected branch circuit of R2-C2 is connected in parallel across 15 diode element T2 and element CAD1 in order to take up the storage load and to limit the commutating overshoot. The voltage limiting operation of the commutating overshoot becomes still higher. The operation of the circuit in the backward or reverse direction is similar to 20 that of the circuit shown in FIG. 9. The voltage-current characteristic curve is shown in FIG. 16a as being asymmetrical in nature while FIGS. 16b and 16c show the voltage-time characteristic curve for forward and reverse voltage operation.

The circuit configuration of FIG. 17 differs from that of FIG. 16 in that a conventional diode D1 (replacing a voltage limiting diode) is connected in series with element CAD1 thereby eliminating the voltage limitation characteristic. This configuration is adequate, for example, if the thyristor is provided with a controlled avalanche behavior in the inverse direction.

The circuit configuration in accordance with FIG. 18 is used for those applications in which the voltage direction, for example, the inverse direction, employs conventional diodes and for the blocking direction employs voltage limiting diodes.

The circuit configuration of FIG. 19 employs for the inverse direction of the thyristors an arrangement similar to that of the circuit shown in FIG. 7 in which limi- 40 tation of the thyristor total voltage in the inverse direction and limitation of the commutation overshoot is provided. In place of a series circuit branch of R1-C1 placed in parallel with the diodes, separate parallel connected R and C circuit branches may also be uti- 45 lized. There is a better accommodation of the commutation overshoot in that no voltage loss needs to be considered at a resistance. The voltage limitation is merely foreseen for the blocking direction.

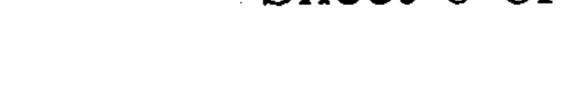

The circuit of FIG. 20 differs from that shown in 50 FIG. 19 in that the series R-C branch (R2-C2) is connected in parallel with the CAD element and further because the circuit is operational for both voltage directions. This can be advantageous for a dv/dt limitation of the thyristor voltage. Otherwise, the retention is similar 55 in both the circuits shown in FIGS. 19 and 20.

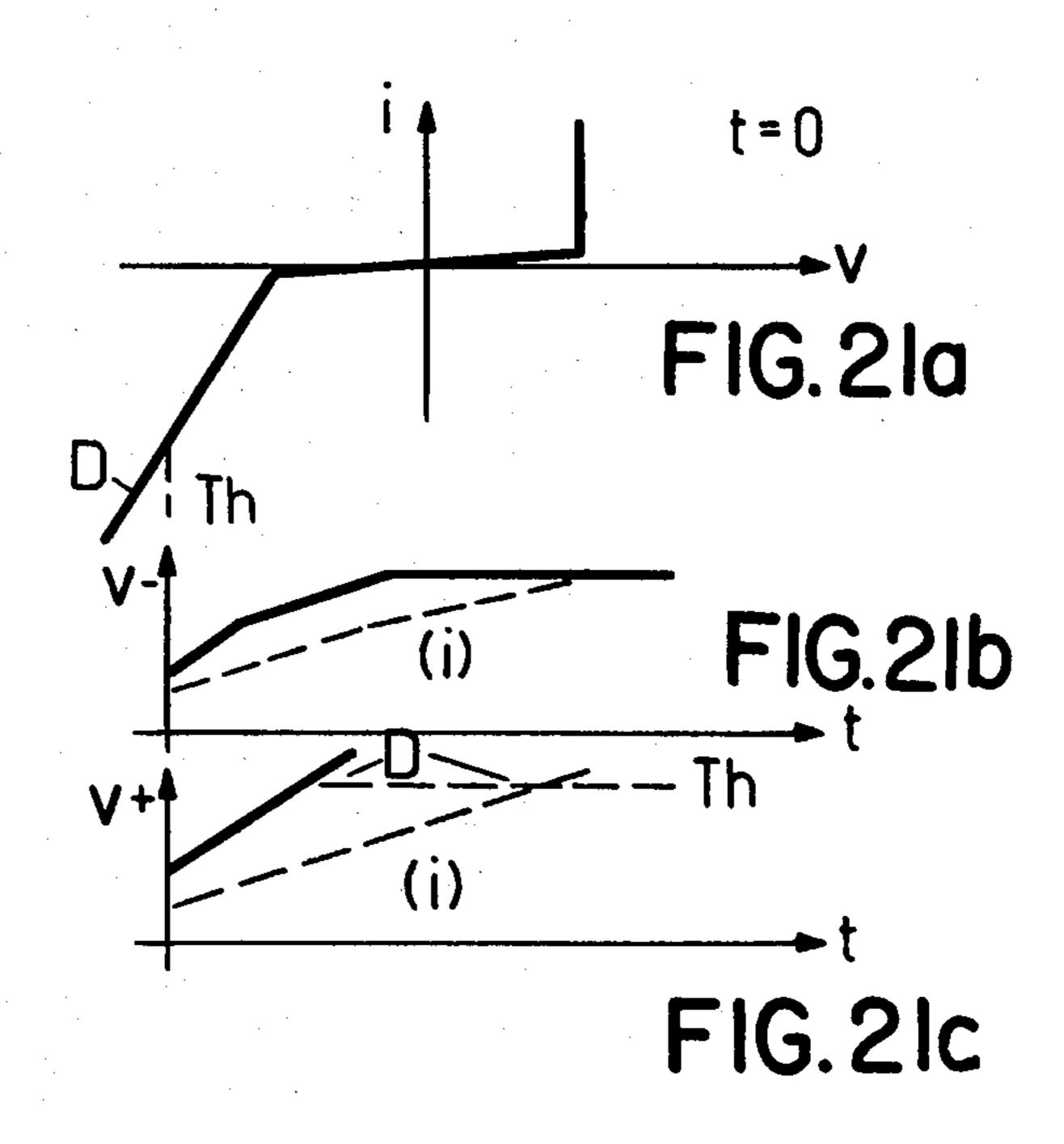

In the characteristic curves 21a-21c, the letter D means diode and Th means thyristor (as is the case with the subsequent waveform diagrams).

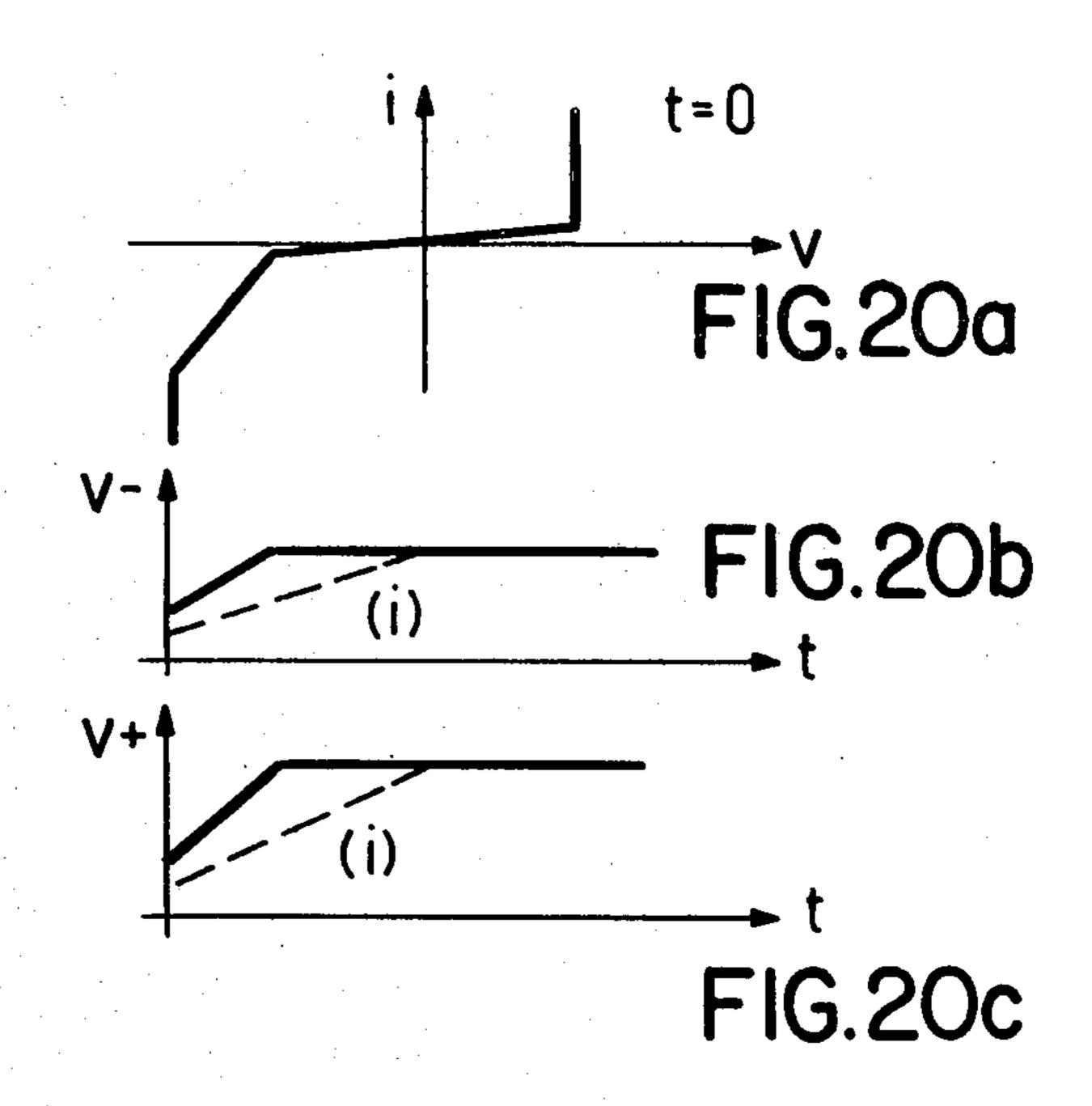

In the circuit of FIG. 21 a pair of series connected 60 R-C differentiating time constant circuit branches are employed as shown at R1-C1 and R2-C2. The diodes D1 and D2 exhibit voltage limiting retention for the blocking direction of the thyristors which is not the case for the inverse direction. The latter is, for example, not 65 necessary if the thyristor exhibits self-controlled avalanche behavior. Operationally, the circuit of FIG. 21 behaves similar to that shown in FIG. 12.

6

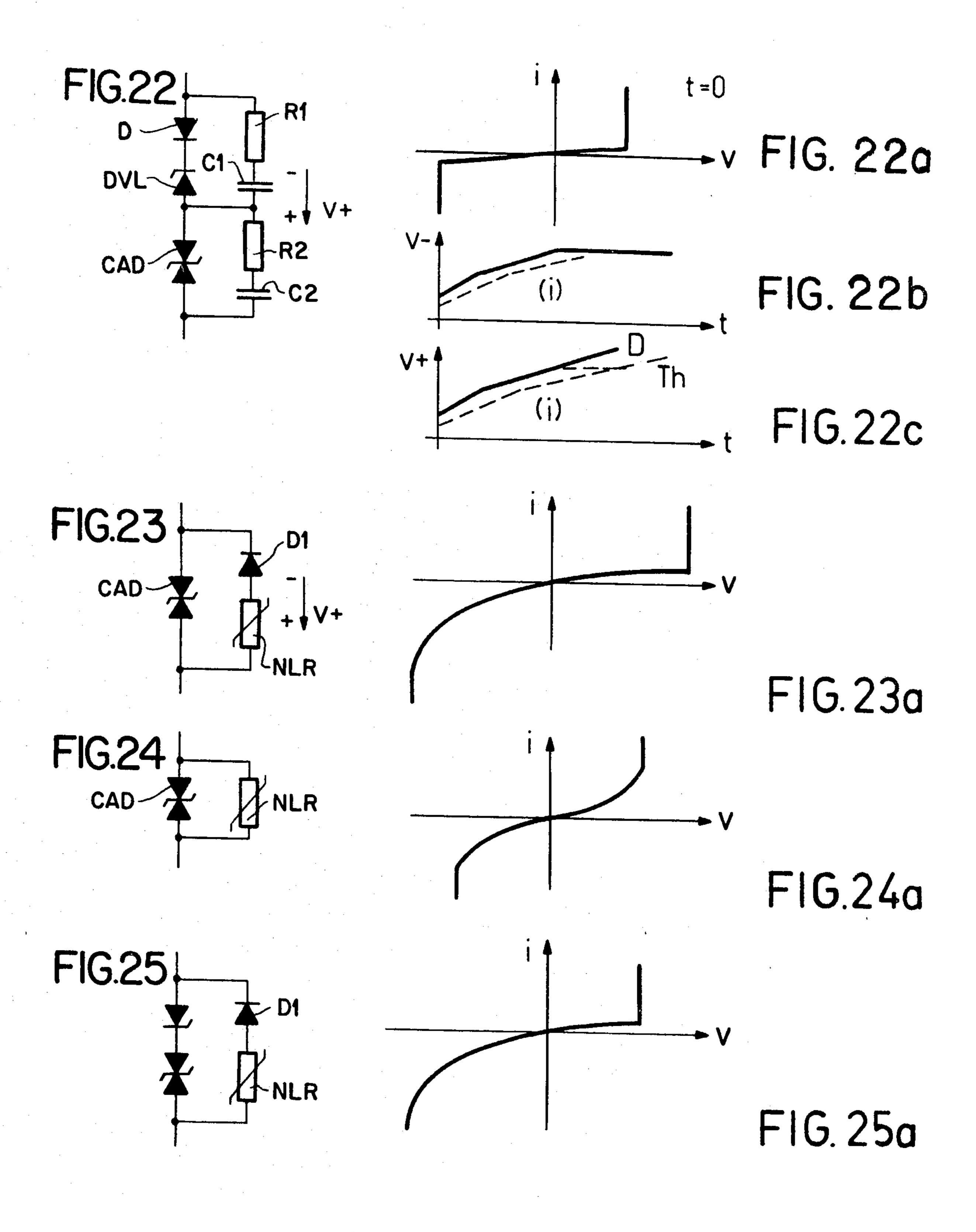

The circuit configuration of FIG. 22 also employs first and second R-C series connected branches (R1-C1 and R2-C2) and is operationally similar to FIG. 12 for the inverse direction of the thyristors, since the diode D1 is not a voltage limiting diode.

The circuit configurations of FIGS. 23-25 employ voltage limiting resistors (NLR) having non-linear characteristic curves and employ CAD elements with sharply limiting voltage-current characteristic curves. The non-linear resistor is utilized for limitation of the commutation overvoltage, while the CAD element limits the thyristor voltage.

In the circuit of FIG. 23, NLR comes into the circuit only during the inverse direction of the thyristor (due to the diode D1) since it is only in this voltage direction that the commutation overvoltage is to be limited.

In the circuit configuration of FIG. 24, the voltage-current characteristic curve (FIG. 24a) can be seen to be symmetrical.

The voltage-current characteristic curve (FIG. 25a) for the circuit configuration of FIG. 25 can be seen to be asymmetrical. The non-linear resistance is active only in the inverse direction (due to diode D1) and is therefore only operational in this direction to limit the commutation overvoltage.

It should again be noted that the thyristor, in the blocking and inverse direction, has differentiating properties. In the blocking direction there is limited dv/dt stability, reverses and eventually lower voltage strength. In the inverse direction, the storage effect steps up commutation overshoot and eventually controlled avalanche behavior. Through the use of circuit configurations having asymmetric voltage characteristics an optimalization for both voltage directions is made possible.

Although there has been described a preferred embodiment of this novel invention, many variations and modifications will now be apparent to those skilled in the art. Therefore, this invention is to be limited, not by the specific disclosure herein, but only by the appending claims.

What is claimed is:

- 1. A circuit, comprising:

- (A) first and second nodes;

- (B) an input and an output lead connected to said first and second nodes, respectively, each of said input and output leads coupled to an external circuit; and

- (C) a thyristor circuit including first and second parallel branches each coupled between said first and second nodes;

- (1) said first branch consisting of a thyristor, the anode of said thyristor being directly coupled to one of said first and second nodes, the cathode of said thyristor being directly coupled to the other of said first and second nodes; and

- (2) said second branch including a plurality of series connected sub-circuits, each of said sub-circuits including at least one electrical element, at least two of said sub-circuits having different voltage-current characteristic curves, at least one of said sub-circuits including first and second sub-branches connected together in parallel, said first sub-branch containing first and second series connected diodes connected in opposed polarity fashion, said first diode being a standard diode, said second diode exhibiting controlled avalanche behavior and said second sub-branch including a resistor.

- 2. The circuit of claim 1, wherein said second subbranch further includes a capacitor coupled in series with said resistor. TO THE STATE OF TH

- 3. The circuit of claims 1 or 2, wherein said first 5 sub-branch further contains a second standard diode coupled in series with said first standard diode.

- 4. The circuit of claim 3, wherein said first sub-branch further contains a second resistor coupled in parallel 10 with said second standard diode.

- 5. The circuit of claims 1 or 2, wherein a second one of said sub-circuits includes third and fourth sub-branches connected together in parallel, said third subbranch containing third and fourth series connected diodes connected in opposed polarity fashion, said third diode being a standard diode, said fourth diode exhibiting controlled avalanche behavior, said fourth subbranch including a second resistor coupled in series with a second capacitor.

- 6. A circuit, comprising:

- (A) first and second nodes;

(B) an input and an output lead connected to said first and second nodes, respectively, each of said input and output leads coupled to an external circuit; and

- (C) a thyristor circuit including first and second parallel branches each coupled between said first and second nodes;

- (1) said first branch consisting of a thyristor, the anode of said thyristor being directly coupled to one of said first and second nodes, the cathode of said thyristor being directly coupled to the other of said first and second nodes; and

- (2) said second branch including a plurality of series connected sub-circuits, each of said sub-circuits including at least one electrical element, at least two of said sub-circuits having different voltage-current characteristic curves, at least one of said sub-circuits including first and second sub-branches connected together in parallel, said first sub-branch containing a controlled avalanche diode comprising first and second series connected diodes connected in opposed polarity fashion and exhibiting controlled avalanche behavior, and said second sub-branch including a non-linear resistor.

- 7. The circuit of claim 6, wherein said second subbranch further includes a diode coupled in series with said non-linear resistor.

- 8. The circuit of claim 7, wherein said first sub-branch further contains an additional diode coupled in series with said first and second series connected diodes.

and the second s

The Collins of the State of State of the Asset of the Collins of t