## Pohlman, III et al.

Dec. 7, 1982 [45]

| [54] |            | ED ADDRESS, SINGLE AND<br>E BIT MICROPROCESSOR                                                                |

|------|------------|---------------------------------------------------------------------------------------------------------------|

| [75] | Inventors: | William B. Pohlman, III, Los Gatos;<br>Bruce W. Ravenel, III, Sunnyvale;<br>James F. McKevitt, III, San Jose; |

Stephen P. Morse, San Francisco, all

of Calif.

Intel Corporation, Santa Clara, Calif. Assignee:

Appl. No.: 873,777

[22] Filed: Jan. 31, 1978

U.S. Cl. 364/200 [52]

Field of Search ... 364/200 MS File, 900 MS File, [58] 364/748, 749; 340/347 DD

[56] References Cited

## U.S. PATENT DOCUMENTS

| 3,657,705 | 4/1972 | Mekota, Jr. et al | 364/200 |

|-----------|--------|-------------------|---------|

| 3,786,436 | 1/1974 | Zelinski et al    |         |

| 3,818,460 | 6/1974 | Beard et al.      | •       |

| 3,938,096 | 2/1976 | Brown et al.      | 364/200 |

| 3,949,378 | 4/1976 | Crabb et al       | 364/200 |

| 3,976,976 | 8/1976 | Khosharian        |         |

| 4,037,211 | 7/1977 | Ikuta et al       | •       |

| 4,042,911 | 8/1977 | Bourke et al      |         |

| 4,079,455 | 3/1978 | Ozga              | •       |

| 4,092,715 | 5/1978 | Scriver           |         |

Primary Examiner—Gareth D. Shaw Assistant Examiner—Thomas M. Heckler Attorney, Agent, or Firm-Blakely, Sokoloff, Taylor & Zafman

#### [57] **ABSTRACT**

The addressable memory space within the retrievable capacity of the microprocessor is necessarily limited by the bit length of the address word. This in turn, is limited by the bit length of the word which the microprocessor may compute or manipulate. By appropriate organization of multiple registers, an extended or expanded memory space may be achieved without the necessity of increasing the word length of the digital information manipulated by the microprocessor. In addition, the microprocessor can be fabricated to be capable of both eight bit and sixteen bit operation by appropriate organization and coordination of a plurality of register files. By virtue of this register file organization and coordination additional improved operations may be achieved, such as direct coupling by the microprocessor between the memory and separate dedicated data processing chips, simplified string instructions and the condensation of entire classes of instructions into single generic instruction formats.

26 Claims, No Drawings

## EXTENDED ADDRESS, SINGLE AND MULTIPLE BIT MICROPROCESSOR

#### **BACKGROUND OF THE INVENTION**

1. Field of the Present Invention

The present invention relates to the field of microprocessors and in particular relates to the organization of microprocessors as that organization limits or relates to the use and structure of microprocessor instructions.

2. Description of the Prior Art

Since their inception, digital computers have continuously become more efficient, expanding into new applications with each major technological improvement. The advent of minicomputers allow digital computers to be included as a permanent part of various process control systems. Unfortunately, the size and cost of minicomputers in dedicated applications has limited their use. Capacity and ability of such dedicated minicomputers has been limited in part due to a fixed or limited word length upon which the operation of the microprocessor is based.

Thus, prior art microprocessors typically assumed a certain memory structure or by reason of their internal organization were subject to certain limitations with 25 respect to the manner and means in which digital information could be stored and retrieved from a memory and later manipulated within the microprocessor itself. These limitations led to restrictions as to how multiple byte words were to be stored within a memory with 30 respect to word length boundaries, and restrictions as to the structure of instructions which were decoded in the microprocessor to manipulate the digital information. As a result, instruction sets from microprocessors necessarily were limited in the power of the instruction, and 35 in the number of instructions which could be accommodated. Typically prior art microprocessors, by virtue of their architectural organization, would require a large number of distinct instructions or comparatively complex instructions in order to perform relatively simple 40 tasks.

The present invention, as disclosed herein, overcomes each of these disadvantages in the manner and by the means as set forth in the following brief summary.

### BRIEF SUMMARY OF THE INVENTION

The present invention is an improvement in a data processing system. The data processing system includes a memory unit for storing digital information. Such digital information includes instructions, addresses, and 50 data. The data processing system also includes a processor unit for processing the digital information communicated between the processor unit and the memory unit. The improvement comprises a first plurality of registers in the processor unit for storing bytes of digital informa- 55 tion. A second plurality of registers is also included in the processor unit for storing words of digital information. The word is an integral number of bytes of digital information. At least some of the second plurality of registers are relocation registers wherein each of the 60 relocation registers has associated therewith a plurality of assumed bits to extend the effective bit length of the word in each such relocation register. As a result, the data processing system may be afforded an extended memory space beyond the word length limitation of the 65 first and second plurality of registers.

The present invention may also be viewed as a data processing system comprised of a memory having an

addressable memory space used for storing digital information, a first plurality of registers, a second plurality of registers, an arithmetic logic unit, and a control means. The first plurality of registers temporarily stores a corresponding plurality of single bytes. The second plurality of registers temporarily stores a corresponding plurality of multiple byte words having a maximum bit length. The arithmetic logic unit selectively performs arithmetic and logical operations upon the digital information. The control means is coupled to the memory, to the first and second plurality of registers and to the arithmetic logic unit in order to selectively transfer digital information therebetween and to selectively generate a plurality of discrete command signals thereto in response to a plurality of instructions. The control means includes an extended address means for generating an extended digital word having a bit length greater than the maximum bit length.

One way in which the extended address means generates the extended digital word, typically used for addressing in an extended memory space, is by summing selected bits of the contents of a selected one of the second plurality of registers with a predetermined digital word. The remaining unselected bits of the contents of the selected register are then placed as a prefix or suffix with respect to the sum to form an extended digital word. In the case where it is a prefix, carries may ripple through the prefix. The selected register, or relocation register, is selected by the control means in response to an address instruction.

The data processing system of the present invention is used with a conventional memory and comprises an upper control means for transferring digital information to and from the memory and a lower control means for processing the digital information wherein the operation of the upper and lower control means are overlapping and asynchronous. The upper control means includes a file of registers which in turn includes a plurality of registers forming an ordered first-in-first-out queue of registers. Digital instructions obtained from the memory are temporarily stored in the queue until requested by the lower control unit for execution. The queue is filled in whole or in part to allow the lower control unit to run at maximum speed. The lower control unit runs in an overlapping manner in that the data processing system of the present invention processes the digital information in the lower control means by executing an instruction while simultaneously decoding a subsequent instruction. In particular, the upper and lower control means processes single byte and multiple byte instructions. The upper and lower control means has an upper and lower file respectively of single byte and multiple byte registers. The upper and lower file of registers are selectively coupled by a bus which has a plurality of separate bus lines equal in number to the number of bits in the multiple byte register. Selected ones of the upper and lower files of registers are selectively coupled to the bus as a source or destination register by and in response to a plurality of bus registers. The bus registers in turn are responsive to the single byte and multiple byte instructions. By this scheme, the lower control means can execute both single byte and multiple byte instructions without duplication of hardware and in a simple manner.

The lower control means includes an instruction register coupled to the queue. A group decode ROM has its inputs coupled to the instruction register. The group

decode ROM generates a plurality of group decode signals which are indicative of the genera of the single byte and multiple byte instructions being received and decoded by the lower control means. A microcode address register has inputs coupled to the queue. A microcode address incrementing register is included and is coupled to a microcode ROM. The microcode ROM stores a multiplicity of microcode instructions. The outputs of the microcode ROM are selectively coupled to the first and second file of registers and to an 10 arithmetic and logic unit which may include a plurality of temporary registers and status registers. A loader means selectively enables and loads a byte from the queue into the instruction register and microcode address register. The loader also enables the microcode address incrementing register in microcode ROM. The loader is characterized by having a plurality of cyclic states. The microcode ROM is taken to include a ROM-OUT control means for selectively generating a next-tothe-last clock signal, NXT, on the next to the last clock of a selected plurality of the multiplicity of microcode instructions in the microcode ROM. The signal, NXT, triggers the loader means to recycle through at least part of the plurality of cyclic states.

In addition, the data processing system of the present invention includes a subroutine translation ROM having inputs coupled to the queue and outputs coupled to the microcode ROM. A subroutine translation ROM also has its outputs coupled to the microcode address 30 register and the microcode address incrementing register to load therein a selected microcode address in response to predetermined ones of the output of the microcode ROM. In addition, the subroutine translation ROM may load a selected microcode address into the 35 microcode address register and microcode address incrementing register in response to a selected bit field in the second byte of a multiple byte instruction. The subroutine translation ROM may also have associated therewith, a subroutine register by which the micro- 40 code address stored within the microcode address register and microcode address incrementing register may be temporarily stored or saved during a microcode jump.

The data processing system may also include an ALU opcode register having inputs coupled to the queue and outputs coupled to an arithmetic and logic unit included within a lower control means. The ALU opcode register temporarily stores the predetermined bit field from the single byte and multiple byte instructions while the microcode ROM is communicating ALU opcode instructions to the arithmetic and logic unit in response to the second byte of the single and multiple byte instructions.

Many other advantages and benefits result by virtue 55 of the organization recited above and are best understood and will be described in the Detailed Description of the Preferred Embodiments in association with the accompanying figures.

### BRIEF DESCRIPTION OF THE DRAWINGS

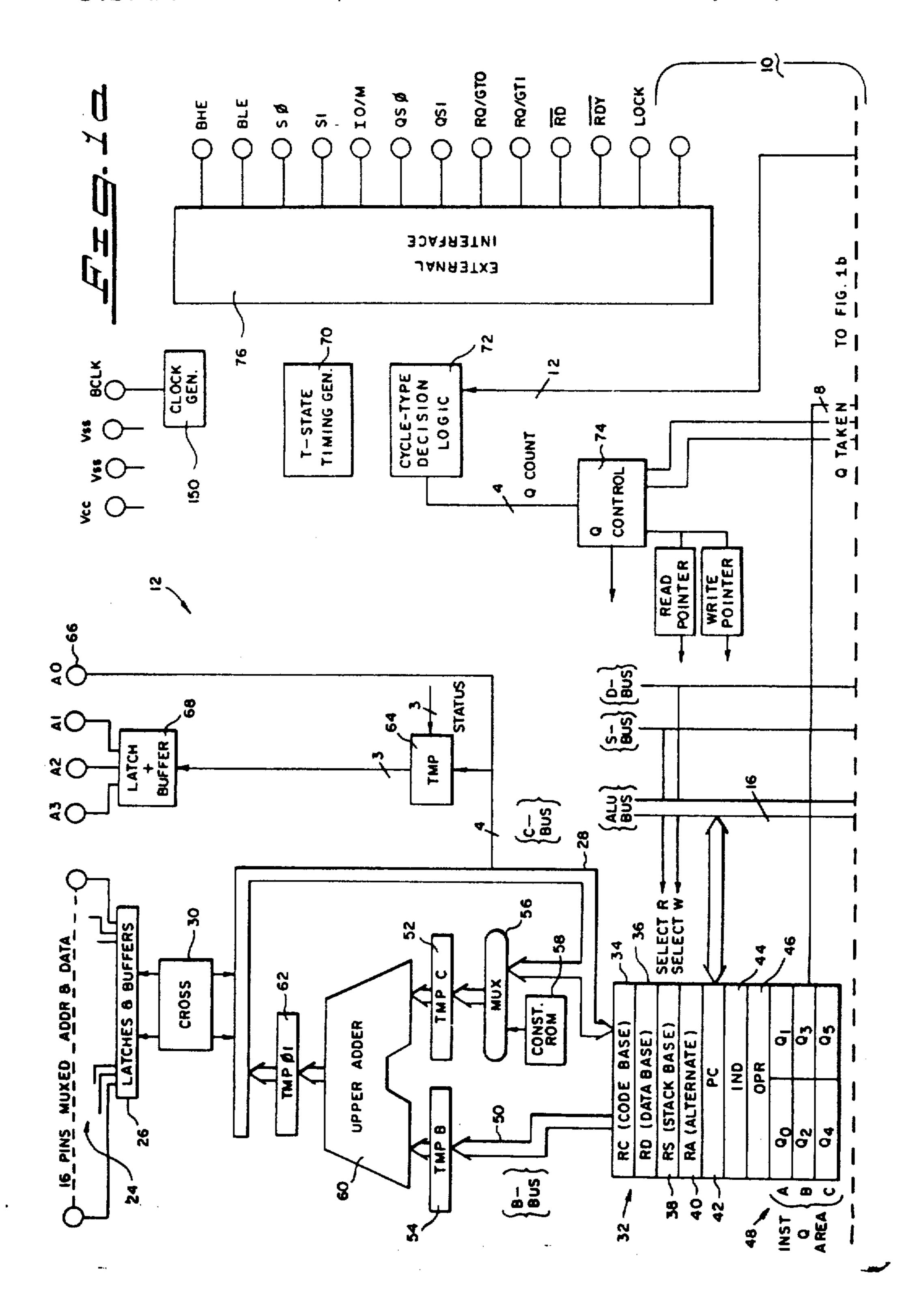

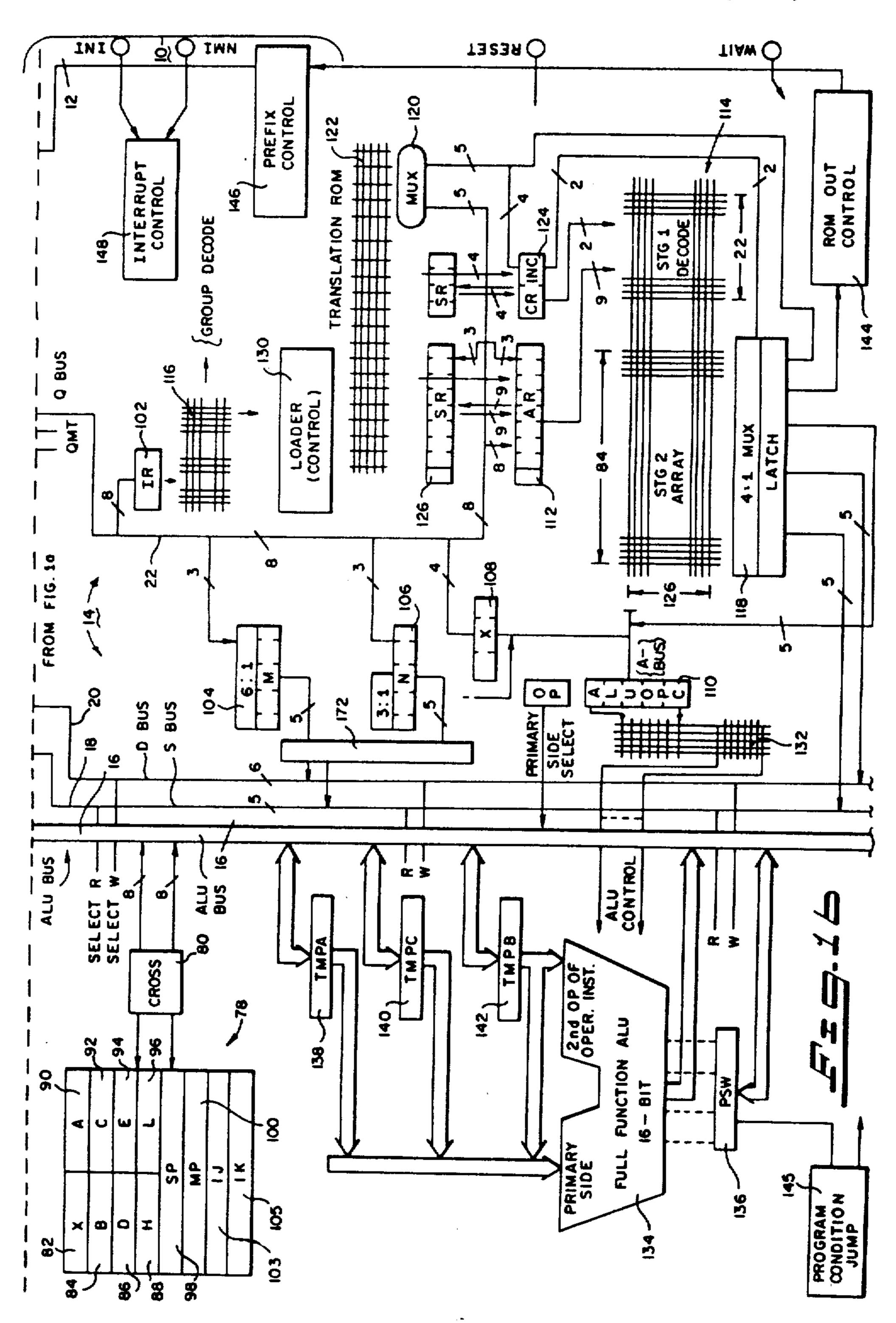

FIGS. 1A and 1B are a simplified block diagram of the internal organization of a microprocessor incorporating the present invention.

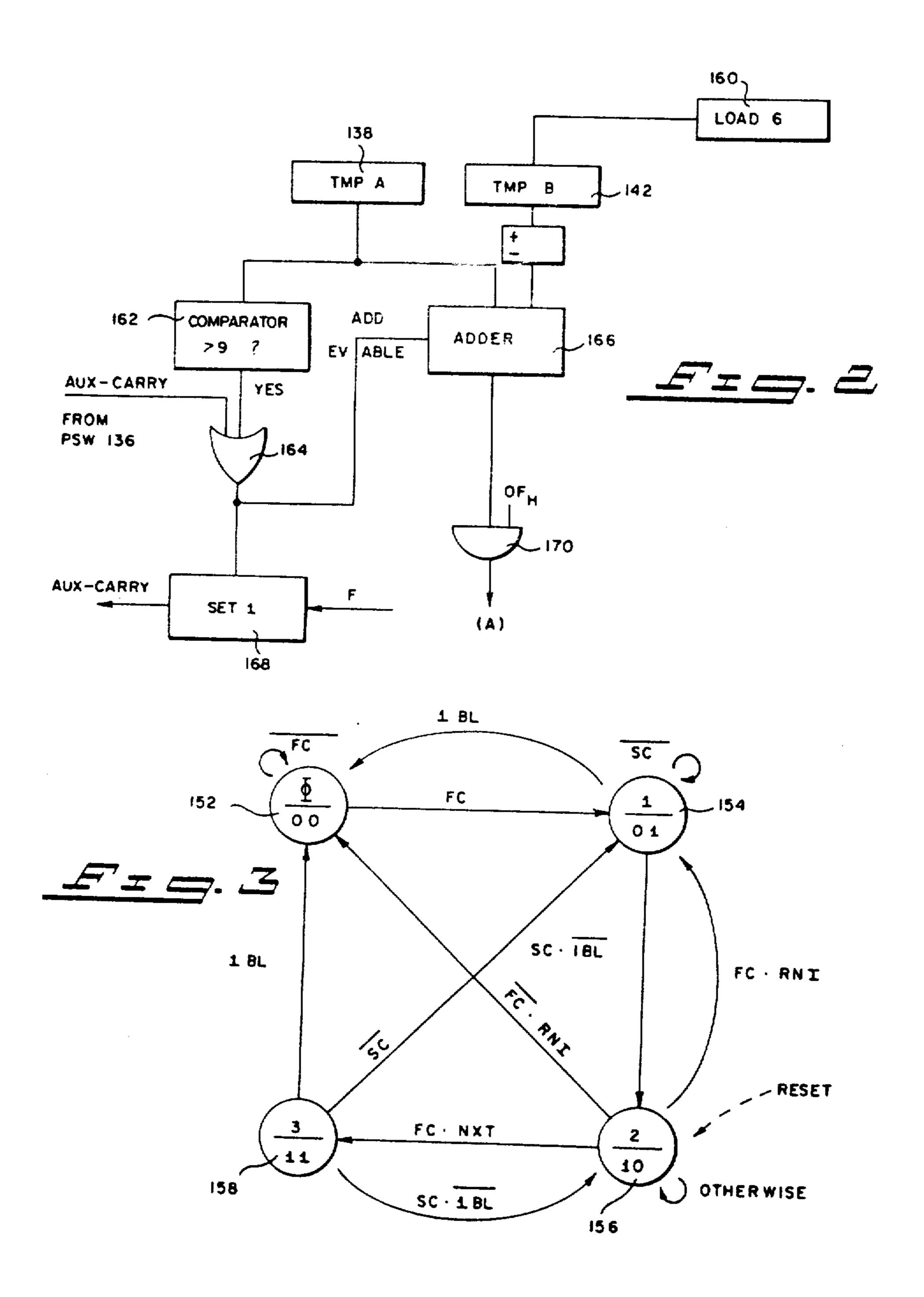

FIG. 2 is an equivalent logical circuit to dedicated 65 ALU circuitry used in ASCII instructions.

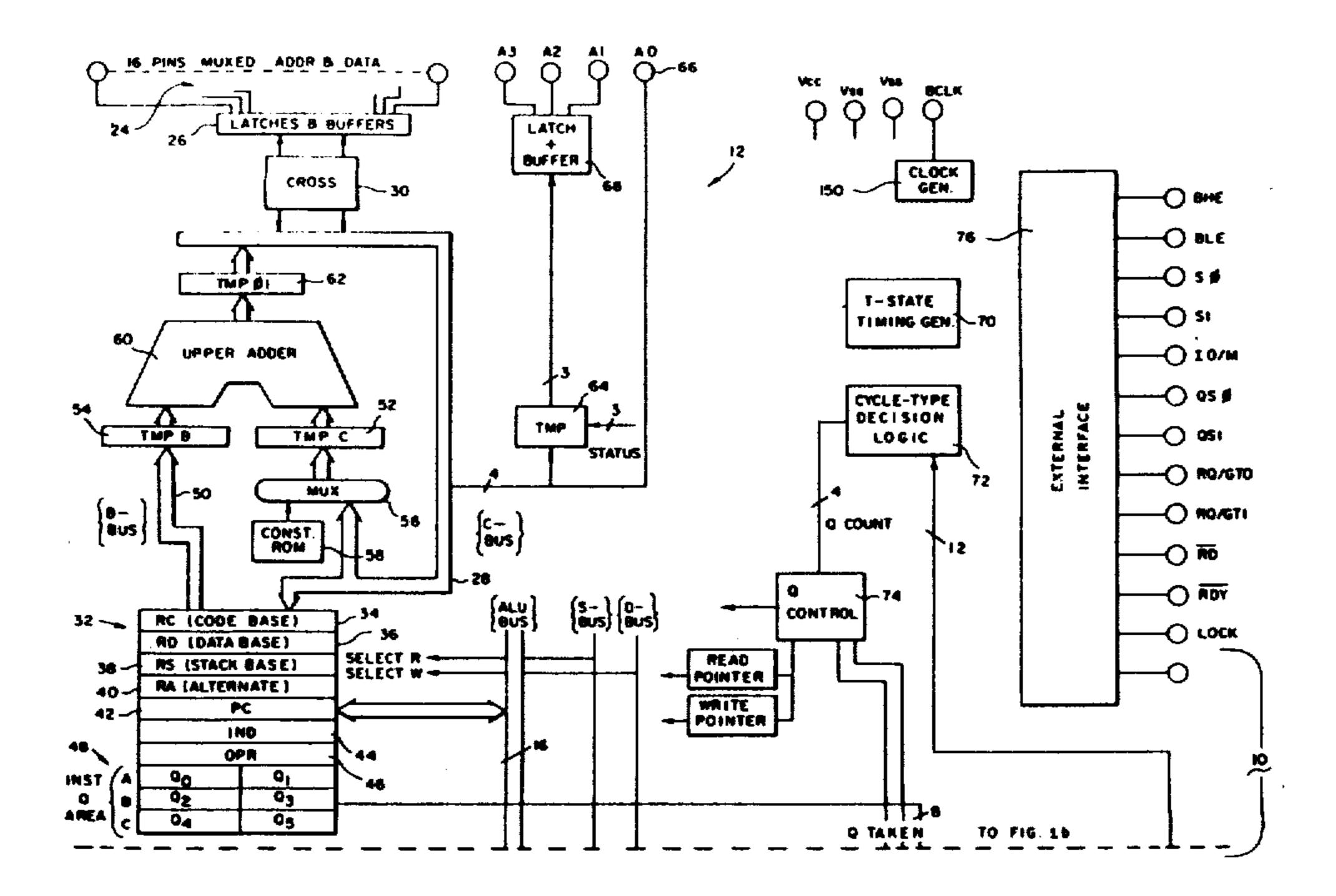

FIG. 3 is a symbolic state diagram for the lower control unit loader circuit.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIGS. 1A and 1B are simplified diagrammatic block diagrams of a central processor 10 organized according to the present invention. Central processing unit or CPU 10 is characterized by the division of CPU 10 into an upper control means 12 diagrammatically shown in FIG. 1A and a lower control means 14, diagrammatically shown in FIG. 1B. As shown in FIGS. 1A and 1B upper unit or means 12 is coupled to lower unit or means 14 primarily by an ALU bus 16, an S or source bus 18, a D or destination bus 20, and a Q bus 22. It must be also understood that there are a plurality of discrete command lines or buses connecting upper unit 12 and lower unit 14 in a manner which shall be described below.

Upper control unit 12 is the only portion of CPU 10 which is directly involved in the exchange of information with an external memory unit. As is well known to the art, all CPU's are used in combination with one or more memory systems, which in the present illustration shall be assumed to be a one megabyte semiconductor memory. Other types of memories or input/output devices well known to the art may be coupled, directly or indirectly, to the external address and data bus coupled to the address and data bus, input/output pins 24, of CPU 10.

Sixteen of the address and data bus pins 24 are coupled to a latch and input/output buffer 26, well known to the art. Binary information is coupled to a C bus 28 through a simple cross-over circuit 30. The sixteen pins are organized into two bytes of eight bits each to form a single sixteen bit word. Circuit 30 selectively couples the two bytes forming a sixteen bit word to C bus 28 either in a normal order or reverse order. The use and explanation of cross-over circuit 30 is described in greater detail below.

Upper control unit 12 has an upper register file 32 which includes four-16 bit relocation registers 34 through 40 also denoted as registers RC, RD, RS and RA respectively. Upper register file 32 also includes a 16 bit program counter 42 denoted as register PC; a 16 bit indirect register 44, also denoted as register IND; a 16 bit operand register 46 also denoted as register OPR. In addition, register file 42 includes an instruction queue buffer 48, which in the embodiment illustrated, is shown as six paired 8 bit registers also denoted as registers Q0 and Q5. Register file 32 is coupled through C bus 28 and B bus 50 to temporary registers 52 and 54 respectively. C bus 28 is coupled to temporary register 52 through a multiplexer 56 which also has as its inputs the outputs of a constant read only memory or ROM 58. The outputs of temporary registers 52 and 54 are coupled to an adder 60 which in turn has its output coupled to a temporary register 62. The output of temporary register 62 is similarly coupled to C bus 28 to permit communication with the external address and data bus. Four lines of C bus 28 60 are singled out to form the first 4 bits of the 20 bit address. One line is coupled to the zeroeth order address pin 66 or A0, while the remaining three lines are coupled through a temporary register 64 to an address latch and buffer 68 having as its output, the three address bits A1 through A3.

Upper register file 32 is also coupled to ALU bus 16, S bus 18, D bus 20 and Q bus 22 to communicate with lower control unit 14 in a manner described below.

Finally, the upper control unit 12 also includes a T-state generator 70, a cycle decision logic circuit 72 and a Q control circuit 74. Each of these circuits are described below and are publicly marketed in a product under the trademark, Intel 8086. Upper control unit 12 5 also includes an external interface circuit 76 which is described in greater detail in a co-pending application assigned to the same assignee as the present invention filed on June 30, 1978 and entitled "APPARATUS AND METHOD FOR COOPERATIVE AND CONCURRED COPROCESSING OF DIGITAL INFORMATION".

Cycle decision logic circuit 72 provides the proper commands to relocation registers 32 through 40 to execute the memory READ and WRITE cycles with 15 proper timing. Relocation registers 32 through 40 are accessed through discrete control lines not shown in FIG. 1A in addition to being treated as ordinary digital information registers subject to the manipulation and control by the instructions. Queue control circuit 74 20 maintains a count of bytes in the instruction queue and their ordering. This information is provided to logic circuit 72 to effect the proper computations with respect to program counter 42, operand register 46 and indirect register 44 in the memory READ and WRITE 25 operations described below, interrupt operations and their subsequent address and program counter corrections. Constant read only memory 58 selectively provides a series of integer values, such as +6 to -6, to adder 60 to be used during the relocation address cor- 30 rections and program counter corrections discussed below. T-state timer circuitry 70 provides a plurality of flip-flop defined T-states to cycle upper control unit 12 through the instruction FETCH, READ and WRITE cycles and such other cycles, such as INTERRUPT 35 cycles, which are typically required of a general purpose microprocesser. Queue control circuitry 74, cycle decision logic circuitry and T-state timing generator 70 employ random logic organized according to principles well known to the art to effect the functions described 40 above.

Lower control unit 14 similarly has a lower or main register file 78 coupled to ALU bus 16 through a cross-over circuit 80 similar to that of cross-over circuit 30. Main register file 78 is also appropriately coupled to S 45 bus 18 and D bus 20. Main register file 78, in the illustrated embodiment, includes eight paired, 8 bit registers 82 through 96 also denoted as X, B, D, H, A, C, E, and L, respectively. Similarly, main file 78 includes a 16 bit stack pointer register 98 also denoted as register SP, a 50 16 bit memory pointer register 100 or register MP and two 16 bit index registers 103 and 105 or registers IJ and IK respectively.

Q bus 22 from upper control unit 12 is coupled to a plurality of registers and decoders in lower control unit 55 14. All eight bit lines of Q bus 22 are coupled to an instruction decoder 102 denoted as register IR. Similarly, the three least significant bits are coupled to an M register 104 whose output in turn is coupled to S bus 18 and D bus 20. Bits 3 through 5, the fourth through sixth 60 most significant bits, are coupled to an N register 106 which also has its output coupled to S bus 18 and D bus 20. Bits 3 through 5 are also loaded into an X register 108 which has an output coupled to an ALU opcode register 110. Finally, all 8 bits of Q bus 22 are coupled to 65 a main array register or AR register 112. The output of AR register 112 is coupled to the first stage decoder of main ROM array 114 which contains most or all of the

6

microcode program. Similarly, the output of instruction register 102 is coupled to a group decode ROM 116. The microcode output from stage two of ROM 114 is coupled through a 4 to 1 multiplexer and latch 118. Five bits of the output of the latch is coupled to a 2 to 1 multiplexer 120, the output of which is similarly coupled to the input of a translation ROM 122. AR register 112 is paired with a counting and incrementing register or CR register 124. The output of translation ROM 122 is coupled to AR register 112 and CR register 124 which are similarly coupled in a bidirectional manner with a corresponding subroutine or SR register 126 and subroutine incrementing register 128 respectively. The operation of group decode ROM 116, translation ROM 122 and main ROM 114 are coordinated by a loader circuit 130 by discrete command lines not shown. The detailed operation of lower control unit 14 will be described below.

The output of multiplexer and latch 118 is similarly coupled to S bus 18 and D bus 20 and to ALU opcode register 110. The contents of opcode register 110 are translated by an ALU ROM 132 which provides the ALU control signals to a full function, 16 bit ALU circuit 134 which provides the arithmetic and logical operations for CPU 10. ALU 134 has its output coupled to ALU bus 16 and is coupled with the program status word or PSW register 136 which is used to test and manipulate the state of the plurality of flags. PSW 136 includes such conventional flag bits as carry, aux-carry, zero, sign, parity, overflow, direction, interrupt-enable and trap. The input to ALU 134 is provided by means of three temporary registers 138 through 142. The input to each of the registers 138 through 142 is derived from ALU bus 16. Both lower register file 78 and the temporary registers 138-142 are coupled to S bus 18 and S bus 20 by which these registers are selectively accessed.

Lower control unit 14 also contains certain random logic which facilitates operation and coordination of over-all functions of CPU 10. For example, the output of latch multiplexer 118 is coupled to a ROM-OUT control circuit 144 which has at least part of its outputs coupled to a prefix control circuit 146.

ROM-OUT circuitry 144 includes conventional random logic circuitry which generates an internal command signal, RUN-NEXT-INSTRUCTION, RNI, described in greater detail below. In addition, ROM-OUT control generates the next-to-last clock instruction, NXT, also described below. The communication between lower control unit 14 and upper control unit 12 is principally through the output bus connecting ROM-OUT control 144 to decision logic circuit 72. The communication between the upper and lower unit generally pertains: to memory reading and writing; to relocation register computations and manipulations; to correction operations with respect to the relocation of registers and program counter; to interrupt acknowledge operations; to input and output operations; and to clearing of queue 48 and suspension of overall microprocesser operation during a HALT mode. A large part of ROM-OUT control circuit 144 is coupled to program condition jump circuit 145 which provides the random logic needed to test conditions set-up in microcode jumps, some examples of which are given in the following tables.

A prefix control circuit 146 provides the required random logic for various prefix bytes in a conventional manner. In addition, prefix control circuit 146 provide the random logic for a base prefix instruction employed

in the present invention. The circuit comprises three flip-flops denoted BPE, BPL and BPH. The first flipflop, BPE, will be enabled in response to a discrete command generated by group decode ROM 116 in response to the loading of a BASE prefix into instruc- 5 tion register 102. The BASE prefix will indicate that a selected relocation register is to be used as a stack relocation register and data relocation register for the duration of the following instruction instead of the normally assumed registers when a stack address is made through 10 MP, i.e., other than a push or pop instruction. The relocation register which is to be selected when the BASE prefix is used is determined by the state of the flip-flops BPL and BPH. Flip-flops BPL and BPH comprise a two bit field which is drawn from a relocation register 15 instruction which will load, store, push or pop the contents of a specified relocation register. The BASE prefix allows the actual relocation register, which is normally assumed by program convention for use by an instruction accessing a relocation register, to be changed to 20 that designated in the BASE prefix byte. Flip-flop BPL and BPH in prefix control circuitry 146 are coupled directly to the bit field corresponding to the relocation register designated within the BASE prefix and will be loaded when BPE has been enabled. On the next fol- 25 lowing instruction, BPE will be disenabled together with BPL and BPH and will remain disenabled until flip-flop BPE is again enabled by the occurrence of a base prefix byte.

Suitable interrupt control circuitry 148 may also be 30 provided to service interrupt requests and to check the state of instruction execution to determine when CPU 10 could acknowledge an interrupt request. Interrupt control circuitry 148 is described in greater detail in the co-pending application entitled "APPARATUS AND 35 METHOD FOR COOPERATIVE AND CONCURRED COPROCESSING OF DIGITAL INFORMATION", filed June 30, 1978, Serial No. 921,082 assigned to same assignee of the present invention. This circuitry, as well as other circuitry described below, 40 comprise the main functional blocks of lower control unit 14 whose internal operation and cooperation with upper control unit 12 may now be described and understood.

The present invention employs a six byte, first-in- 45 first-out queue 48. CPU 10 is a two-level fetch ahead system. Inasmuch as there is no advantage in upper control unit 12 of fetching bytes faster than lower control unit 14 can execute them, and inasmuch as there is no advantage in lower control unit 14 executing faster 50 than upper control unit 12 can fetch them, the queue is only so large as to allow enough bytes to be stockpiled so that the queue will be able to fetch enough bytes during the slow instructions to allow the fast instructions to run at full speed. The only other requirement is 55 that at least two bytes of the queue must be empty before a new instruction is fetched inasmuch as two byte instructions are permitted. When these factors are considered, together with the execution time for the instruction set, the optimum queue length is six. It is to be 60 understood that other queue lengths may be optimal depending upon the nature of the instruction set, and the execution speeds of the CPU according to the principles disclosed herein.

Upper control unit 12 and the lower control unit 14 65 are essentially unsynchronized in their operation with one another, although they both run from clock 150. The function of upper unit 12 is to run all external cy-

cles, to maintain a program counter, PC 42 and relocation registers 34-40 at the proper relocation offset for all addresses, and to maintain the six byte instruction stream look ahead queue 48. Lower control unit 14 executes all instructions, reset and interrupt sequences, provides data and basic 16 bit addresses to upper control unit 12, and maintains main register file 78 and PSW 136. Interface to the outside world is almost exclusively the domain of upper control unit 12 with the exception of certain interrupt functions handled directly in lower control unit 14.

The microprocessor of the present invention, although an ambidextrous 8 or 16 bit machine, operates in an extended memory space, which in the presently illustrated embodiment is accessed through a 20 bit address. Adder 60, which is a dedicated adder, performs the function of adding the relocation number to the base address and incrementing or decrementing the addresses if required by offset 16 bit accesses. Adder 60 is also used to provide a post-fetch correction to any given address and to apply corrections to PC 42 described in greater detail below.

PC 42 is not a real or true program counter in that it does not, nor does any other register within CPU 10, maintain the actual execution point at any time. PC 42 actually points to the next byte to be input into queue 48. The real program counter is calculated by instruction whenever a relative jump or call is required by subtracting the number of accessed instructions still remaining unused in queue 48 from PC 42. However, it is to be understood that in other embodiments a true program counter could be included within the CPU organization if desired.

The memory space used in combination with the present invention organizes digital information into 8 bit bytes. Any two consecutive bytes can be paired-up to form a 16 bit word without the necessity that the bytes be stored on even address boundaries. The convention used in the present invention is that the most significant 8 bits of the word are stored in the byte having the higher numerical memory address.

Relocation registers 34-40 are used to obtain an address in an extended memory space as follows. Four low order bits are appended to the 16 bits of any one of the relocation registers thereby providing the 20 bit base address of a page. RC register 34 serves as a code relocation register; RD location register 36 serves as a data relocation register; RS relocation register 38 serves as a stack relocation register; and RA relocation register 40 serves as an alternate relocation register accessible with the base prefix instruction as described and by block move instructions. A 20 bit memory address corresponding to a 16 bit data stack or code address is obtained by adding a 16 bit base address to the appropriate relocation register. For example, the memory code address is obtained from adding the 16 bits of the program counter, PC 42, with RC register 34. In general, address lines A0-A3 are therefore directly tapped from register file 32 via C bus 28 and the least significant 4 bits of the selected register whose contents is added to the contents of the relocation register, are directly coupled to the address/data pins A0-A3. The next 12 bits from the selected register are then added to the 16 bits of the chosen relocation register in adder 60 and coupled through crossover circuit 30 to latch and input buffer 26. Consequently, the memory space is divided into pages of 16 words each, each word having a 16 bit length. Data is then accessed from the memory and

placed upon C bus 28 to the appropriate register of upper file 32, namely one of the Q registers 48.

According to a command signal generated by loader circuit 130, described in greater detail below, one of the bytes from queue 48 will be accessed and coupled to Q bus 22 while Q control circuitry 74 maintains the proper fetch rate and control of upper control circuit 12 functions. The three least significant bits of the fetched byte will be inserted into M register 104 whose basic function is to hold the source bus code of the main operand 10 of the instruction. Register 104 translates the register field of the first byte into the proper S and D bus code. Similarly, bits 3 through 5 are loaded into N register 106 whose basic function is to hold the destination bus code of the second operand of the instruction. X register 108 15 loads bits 3-6 of the byte and assumes that the opcode of the instruction is an ALU opcode. The entire byte is loaded into AR register 112. Since some of the instructions do not contain ALU opcodes, and since some instructions are two byte instructions, the assumptions 20 made with respect to the significance of information loaded into registers 104, 106, 108 and 112 are sometimes incorrect. Any incorrect assumption is later corrected after the byte, which was loaded into instruction register 102, is properly decoded by group decode 25 ROM 116. The correction scheme and procedure will be described in greater detail below.

Microcode control of the present invention consists principally of a main PLA or ROM 114 supported by two others, namely translation ROM 122 used to de- 30 code full length microcode jump addresses and a group decode ROM 116 to decode machine language opcodes for purposes of higher level organization. Nevertheless, many control functions are not handled through the ROMS but by random logic such as the prefix instruc- 35 tions described below, one clock non-ALU instructions, opcode decoding, direction bit, the 1 bit, various idiosyncrasies in flag handling, and certain differences between 8 or 16 bit data operations.

The opcode inserted into register AR is translated 40 into a ROM starting address by treating the first stage of ROM 14 as a PLA by using the opcode itself directly as the ROM address for that instruction's microcode sequence. Each opcode is provided with a space in ROM 114 for the microcode sequence associated with that 45 opcode. The opcode address itself cannot be incremented because of the danger of overflowing into the instruction opcode space of an adjoining opcode. Thus, a four bit incrementing register 124 is added and initially zeroed when the opcode is loaded into register AR 112. 50 A ninth bit is added to register 112 to provide more programming space. The extra bit, ARX, is also initially reset. CR register 124 is then incremented across the 16 separate microcode states allowed each instruction while AR remains fixed and can only be changed by a 55 2 BR is a decoded command signal generated by group long jump or return. A microcode subroutine is provided by register 126 used in combination with ROM 122 which encodes a 13 bit long jump address from a 5 bit microcode tag applied by ROM 114 through multiplexer 120.

The ROM microcode program does not control its own cycling. When the microcode routine for an instruction has been executed, ROM 114 passes lower unit control 14 back to the master timing circuit, loader 130, whose function is to load the next instruction from Q 65 bus 22 into the appropriate lower unit control registers. When all new opcode and field information is loaded into lower control unit 14 and the ROM starting address

for ROM 114 is properly initialized, loader 130 enables ROM 114 and passes control of lower control unit 14 to

The lower unit control thus alternates between a master four-state counter, loader circuit 130, and main microcode ROM 114. The function of the loader is to move instruction bytes containing opcode and register fields from instruction queue 48, across Q bus 22 and into the appropriate lower unit registers IR 104, M 104, N 106, X 108 and AR 112. Once ROM 114 is properly initialized, loader 130 permits ROM 114 to run by raising a ROM enable signal, ROME, to a binary 1. Main microcode ROM 114 does not have legitimate "off" states. Execution is stopped by resetting ROME to zero which will gate-off the key ROM outputs. The incrementing register CR 124 will continue counting regardless of the state of ROME. If ROM 114 is running, it must sense the end of an instruction execution sequence and send a discrete command signal, run the next instruction, RNI, to loader 130 to indicate that the current sequence of microcode instructions is over and that a new instruction is to be loaded.

An instruction decode overlap is maintained by another discrete control signal next, NXT. If ROM 114 can identify the unique next-to-last clock of the microcode sequence, it will send signal NXT to loader 130. If such is effected, the loading of the new instruction will overlap the execution of the last, thereby increasing throughput. Under these conditions loader 130 and ROM 114 will operate simultaneously without any break of ROM operation. The first execution clock of the new instruction will be directly followed by the last execution clock of the prior instruction.

Loader 130 generates two key timing signals for every sequence in lower control unit 14. These signals are a first clock, FC, indicating the first step of a load procedure and a second clock, SC, following FC at the next or some later clock indicating the second step of the load procedure. The first byte of an opcode is clocked across Q bus 22 at FC. The second byte, if any, will move across at SC. The significance of SC is greater than merely the loading of the second byte because it is only under and after the timing signal SC, that the output of group decoder ROM 116 is valid for the instruction being loaded. Thus, timing signal SC occurs regardless of how many bytes actually move across Q bus 22. The state diagram of loader 130 is diagrammatically illustrated in FIG. 2 and is simplified and depicted logically in the following equations:

$FC = [(00) + (10)(NXT + RNI)] \cdot \overline{MT}$  and,

$SC = [(01) + (11)][2BR \cdot MT].$

decode ROM 116 indicating that the instruction at hand has at least two bytes and requires use of ROM 114 for decoding. MT is a signal generated by Q control circuitry 74 indicating that queue 48 is empty and that 60 more bytes need to be fetched.

Referring now to FIG. 2, it should be noted that the operation of loader 130 is based upon two flip-flops in a manner well known to the art. In the zero state 152, the flip-flops are set at (00), the lower control unit 14 is not executing, and the first byte of the new instruction has not been located. The timing signal, FC, occurs on the transition out of zero state 152. In first order state 154, defined by (01) on the loader flip-flops, no instruction is

being executed, the timing signal FC has occurred for the new instruction and the timing signal SC has not occurred. SC is generated on transition out of first state 154. If the internal command signal one byte logic, 1 BL, is generated from group decode ROM 116, loader 5 130 returns to zero state 152. The command signal 1BL indicates that the current instruction is recognized as a one byte logic instruction, in other words a one byte instruction which is not decoded by the use of ROM 114 but by random logic. However, upon generation of 10 the timing signal SC and the nonoccurrence of 1BL, loader 130 will move to second state 156 defined by the flip-flop condition (10). The second condition is the run or execution state wherein the timing signals SC and FC have occurred and loader 130 is waiting for the com- 15 mand signals NXT or RNI from ROM 114 to indicate that a new instruction is to be run or the next to the last clock pulse has been executed of the microcode sequence.

As indicated in the above logic equation, when in the 20 second state if either the internal command signals in NXT or RNI are generated by ROM 114, loader 130 will either return to the first state in the case of the validity of RNI or to a third state in the case of receipt of NXT. Third state 158, defined by flip-flop configura- 25 tion (11), is a mirror image of the first state with the exception that the prior instruction is still executing. If the timing signal FC is no longer active and ROM 114 indicates a new instruction is to be run, loader 130 returns to the zeroeth state to begin the fetch anew. While 30 in the third state if the instruction is not a one byte logic type instruction and the timing signal SC is still valid, that is the instruction is a two byte ROM type instruction or queue 48 is not empty, loader 130 returns to the second state. If the timing signal SC has gone inactive, 35 loader 130 returns to the first state configuration, otherwise if the next instruction is a one byte logic, loader 130 will be forced to the zeroeth state to turn and maintain ROM 116 off. The timing signals FC and SC are also used throughout the various registers within lower 40 control unit 14 to set the time at which the register operates in its intended function according to well known principles.

Execution is enhanced in CPU 10 of the present invention by eliminating much of the instruction over- 45 head as possible. In other words, the opcodes are assigned so that almost in all cases only the first byte of a multiple byte instruction is required to form the entire microcode address. The timing signal FC represents the only clock pulse in which the first byte is read by lower 50 control unit 14. Since instruction register 102 still has its prior value, there is no current information as to the nature of the new instruction. Therefore, all lower control unit registers attached to Q bus 22 make a probablistic guess as to the nature of the new instruction and load 55 from the first byte on the timing signal, FC accordingly. More particularly, instruction register IR 102 loads the first byte normally. M register 104 assumes the instruction could be a one byte instruction and thus it forms up the 16 bit register source bus code by taking the three 60 least significant bits of byte one as a register field. N register 106 assumes that the instruction is a relocation register instruction by forming up a 16 bit relocation register destination bus code from bits 3 and 4 of the first byte as a relocation register field. X register 108 65 assumes the first byte may have ALU opcodes in bits 3 through 6 and loads these bits accordingly. AR register 112 and CR register 124 assume that byte one is a suffi-

cient starting address and loads byte one into register AR 112, resets CR register 124 and starts accessing the microcode location in ROM 114. If any first guess was incorrect, it is corrected at the timing signal SC since at that time the output of group decode ROM 116 is then available as discrete command signals coupled to selected decoders and the above registers to cause the bit field to be redecoded under a different interpretation if necessary.

CPU 10 of the present invention has nine distinct addressing modes. The location of an operand in an instruction employed by the present invention is specified by various fields in the instruction. In particular, these fields include a register field or a combination of a mode field and an R/M field. The register field is a three bit field which specifies one of the 8 or 16 bit registers described above to be the location of the operand, hence the first two addressing modes. The register/memory field or R/M field is a three bit field in the instruction which specifies an 8 or 16 bit register or registers which are contained or used to locate the operand. The three bits designate eight ways in which certain registers can be employed for operand accessing in possible combination with two displacement bytes in the instruction. The mode field is a two bit field in the instruction which specifies whether the operand is contained in the indicated register or at a memory location pointed at by the register contents, and indicates the manipulation to be made on the displacement bits, if any. In particular, a register which is indicated can be either the location of the operand or can point to the location of the operand in memory. A W or word field is a one bit field in the instruction used in combination with one of the mode field codes to specify whether the operand is a byte or work quantity. Any of the registers and combinations of the 8 bit registers in upper file 78 may be the location, and certain ones may point to the location in memory of the operand specified in the instruction. An automatic address subroutine is intialized by loader circuit 130 at clock SC when required, that is whenever the instruction is a two bit ROM instruction and obtains the operand from a location in memory. The steps followed by the address subroutine are substantially similar to a normal long jump wherein the microcode address is saved except that movement of data into and out of AR register 112, CR register 124 and SR register 126 are under the control of loader circuit 130 rather than ROM 114. The mode and register/memory fields are directly loaded into translation ROM 122 through multiplexer 120 from Q bus 22 to obtain one of the nine starting subroutine microcode addresses by a direct decode. As a result the addressed operand is automatically loaded into the appropriate upper file registers, usually OPR register 46 in the same manner as a normal instruction fetch as described above.

The operation and organization of the present invention can be better understood by considering in detail the execution of a number of specific instructions which are particularly unique to a CPU utilizing the present invention.

CPU 10 may execute what is defined as string instructions consisting of a set of primitive one byte instructions which can be performed either once or repeatedly. When used as a repeated operation the string instructions permit a complete string or loop operation to be hardware executed as opposed to typical software execution. When used in the form of a single operation, the string instructions permit the writing of a tight software loop which could be used to perform more complex string instructions. All primitive string instructions use BC registers 84 and 92 respectively as a loop counter and IJ register 103 and if necessary IK register 105 as 5 pointers to operands in memory. If a direction flag in PSW 136 has been cleared, the operand pointers are incremented after being used, otherwise they are decremented automatically by ALU 134. Other software instructions are provided in the instruction set for set-10 ting or clearing the direction flag in PSW 136.

The primitive string instructions are MOVE, COM-PARE, SEARCH, LOAD, and STORE. The MOVE primitive moves a string of characters, i.e. 8 bit bytes, from one block of memory to another. The COMPARE 15 primitive permits comparing two character strings to determine after which character the strings become unequal and thus help to establish a lexigraphical ordering between the strings. The SEARCH primitive permits searching for a given character in a character 20 string. The STORE primitive is used for filling in a string of characters with a given value. Typically, the STORE primitive and the LOAD primitive are used as building block instructions to form tight software loops that perform complex string instructions. Each of the 25 primitive instructions also has the ability to operate on words as well as characters or bytes. Included among the string instructions is a prefix, REPEAT, which provides for rapid loop control in a hardware repeated string operation. Any of the primitive instructions can 30 be preceded with the one byte prefix, REPEAT, which will repeat the instruction as long as the loop count is not zero. The test for the loop count is made prior rather than after each repetition of the loop so that the initial loop count of zero will not cause any executions 35 of the primitive string instruction. During each repetition of the loop, the loop counter is decremented. Dur-

ing the repetition of any string instruction the PC program counter 42 remains pointing at the repeat prefix byte and is not updated until after the last repetition of the string instruction. This fact, together with the continuous updating of the operand pointers and count register, allow that the repeated instruction to be correctly resumed if it is interrupted. External interrupt will be permitted prior to each repetition of the primitive string instruction.

A loop instruction provides the same control as the REPEAT prefix but in tight software loops to perform complex string operations. A loop instruction decrements the loop count in register BC and performs a relative branch, typically to the start of the loop, if either the count has not become zero or the zero flag of PSW 136 is not at a specified setting. A form of loop instruction is also available that does not test the zero flag. The loop instruction is typically placed at the end of the loop and tests for loop repetitions after each execution of the loop. This means that if the loop counts were initially zero, the loop will still be executed. A SKIP instruction is introduced to prevent undesireable repetitions. A SKIP instruction performs a relative branch if register BC contains a zero and does so without altering the contents of BC. Translate, XLAT, is another primitive string instruction used as a building block in tight loops. The XLAT instruction allows a byte fetch from one string to be translated before being stored into a second string or compared to a given byte. Translation is performed by using the value in the A register 90 to index into a table pointed at by HL register 88 and 96. The translated value obtained from the table then replaces the value initially held in a register

The machine language code for the string instructions are set forth below in summary form.

TABLE 1

| <del></del>                          | STRING INSTRUCTIONS                                                                                   | ······································ |

|--------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------|

| STRING LOAD  Mnemonic:  Description: | 7654321 0<br>1010110 w<br>LDS (w=0)<br>LDSW (w=1)                                                     |                                        |

|                                      | if $w=0$ then $((IJ)) \longrightarrow (A)$<br>else $((IJ))+1,(IJ)) \longrightarrow (XA)$              |                                        |

| Flags Affected: STRING STORE         | if (DIRECTION)=1 then (IJ)-(1+w) $\longrightarrow$ (IJ) else (IJ) + (1+w) $\longrightarrow$ (IJ) None |                                        |

| Mnemonic:  Description:              | 7654321 0<br>1010101 w<br>STS (w=0)<br>STSW (w=1)                                                     |                                        |

|                                      | if $w=0$ then $(A) \longrightarrow ((IK))$<br>else $(XA) \longrightarrow ((IK))+1,(IK))$              |                                        |

|                                      | if (DIRECTION)=1 then $(IK)-(1+w) \longrightarrow (IK)$<br>else $(IK) + (1+w) \longrightarrow (IK)$   |                                        |

### TABLE 1-continued

## STRING INSTRUCTIONS Flags Affected: None STRING COMPARE 7654321 0 1010011 w Mnemonic: CMPS (w=0)CMPSW (w=1)Description: if w = 0 then ((IJ)) - ((IK))nowhere but flags are set else ((IJ)+1,(IJ))-((IK)+1,(IK))nowhere but flags set if (DIRECTION)=1 then $(IJ)-(1+w)\longrightarrow (IJ)$ $(IK)-(1+w) \longrightarrow (IK)$ else $(IJ)+(1+w)\longrightarrow (IJ)$ $(IK)+(1+w) \longrightarrow (IK)$ Flags Affected: CARRY, AUX-CARRY, SIGN, ZERO, PARITY, OVERFLOW STRING SEARCH 7654321 0 1010111 w Mnemonic: SRCHS(w=0)SRCHSW (w=1)Description: if w=0 then (A)-((IK))nowhere but flags are set else (XA)-((IK)+1,(IK))nowhere but flags are set if (DIRECTION) = 1 then (IK) $-(1+w) \longrightarrow (1K)$ else $(IK)+(1+w) \longrightarrow (IK)$ Flags Affected: CARRY, AUX-CARRY, SIGN, ZERO, PARITY, OVERFLOW STRING MOVE 7654321 0 1010010 w Mnemonic: MOVS (w=0)MOVSW (w=1)Description: if w=0 then $((IJ)) \longrightarrow ((IK))$ else $((IJ)+1,(IJ)) \longrightarrow ((IK)+1,(IK))$ if (DIRECTION)=1 then $(IJ)-(1+w) \longrightarrow (IJ)$ $(1K)-(1+w) \longrightarrow (1K)$ else $(IJ)+(1+w)\longrightarrow (IJ)$ $(iK)+(i+w) \longrightarrow (iK)$ Flags Affected: None REPEAT PREFIX Repeat: 7654321 0 1111001 z Description: while (BC) <> 0

#### TABLE 1-continued

| STRING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|

| perform primitive string instruction in succeeding byte  (BC) — → (BC)  if primitive instruction is one specified to affect 2ERO lag and (ZERO) <> z then ent's while 'loop end-of-white  (PC) + 2 → (PC)  LOOP  7 6 5 4 3 2 1 0  1 1 0 0 0 1 0  1 1 0 0 0 1 0  (BC) — 1 → (BC)  if (BC) <> 0 then (PC) + displacement → (PC) where "displacement" is an 8-bit signed number  None  SKIP  None  SKIP  7 6 5 4 3 2 1 0  1 1 1 0 0 0 1 1 1  Memonic:  SKP disp  Description:  if (BC) = 0 then (PC) + displacement → (PC) where "displacement" is an 8-bit signed number  None  TIGHT LOOP INSTRUCTIONS  Translate:  7 6 5 4 3 2 1 0  1 1 0 1 0 1 1 1  Mnemonic:  Description:  (HL) + (A) → (A)  None  LPW disp for z = 1 (means LooP While) LPU disp for z = 0 (means LooP While) LPU disp for z = 0 (means LooP Untill)  (BC) — 1 → (BC)  if (ZERO) = z and (BC) <> 0 then (PC) + displacement → (PC) where "displacement → (PC) where "displacement → (PC)  T(ZERO) = z and (BC) <> 0 then (PC) + displacement → (PC) where "displacement → (PC)  if (ZERO) = z and (BC) <> 0 then (PC) + displacement → (PC) where "displacement → (PC) w |                         | STRING INSTRUCTIONS                                                                                  |

| if primitive instruction is one specified to of affect ZERO flag and (ZERO) $< > z$ then ear while' loop end-of-while  (PC) +2 $\rightarrow$ (PC)  LOOP  (PC) +2 $\rightarrow$ (PC)  LOOP  7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | perform primitive string instruction                                                                 |

| DOOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | if primitive instruction is one specified to affect ZERO flag and (ZERO) <> z then exit 'while' loop |

| I   1   0   0   1   0     0   0   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LOOP                    |                                                                                                      |

| Description: $(BC)-1 \longrightarrow (BC)$ if $(BC) <> 0$ then $(PC) + \text{displacement} \longrightarrow (PC)$ where "displacement" is an 8-bit signed number  Flags Affected:  SKIP $\frac{7.6543210}{11100011} \frac{7.6543210}{\text{displacement}}$ Mnemonic:  SKP disp  Description:  if $(BC)=0$ then $(PC)+$ displacement $\longrightarrow (PC)$ where "displacement" is an 8-bit signed number  Flags Affected:  None  TIGHT LOOP INSTRUCTIONS  Translate: $\frac{7.6543210}{11010111}$ Mnemonic:  XLAT  Description: $((HL)+(A)) \longrightarrow (A)$ Flags Affected:  None $\frac{7.6543210}{111000012} \frac{7.6543210}{\text{displacement}}$ Mnemonic:  LOOP AND TEST ZERO $\frac{7.6543210}{(111000012)} \frac{7.6543210}{\text{displacement}}$ Mnemonic: $LPW \text{ disp for } z=1 \pmod{Mile}$ $LPW \text{ disp for } z=0 \pmod{Mile}$                                                              | Mnemonic:               | 1 1 1 0 0 0 1 0 displacement                                                                         |

| PC   displacement → (PC)   where "displacement" is an 8-bit signed number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description:            |                                                                                                      |

| ## Affected:    SKIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |                                                                                                      |

| T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Flags Affected:         | where "displacement" is an 8-bit signed number                                                       |

| Mnemonic:  Description:  if $(BC)=0$ then $(PC)$ + displacement $\longrightarrow$ $(PC)$ where "displacement" is an 8-bit signed number  None  TIGHT LOOP INSTRUCTIONS  Translate:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>SKIP</u>             | 76543210 76543210                                                                                    |

| where "displacement" is an 8-bit signed number    TIGHT LOOP INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                                                                                      |

| TIGHT LOOP INSTRUCTIONS  Translate:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |                                                                                                      |