| , 1982 |

|--------|

|        |

| [54] | NETWOR        | ISION MULTIPLEX SWI<br>K WITH AN ASSOCIATIVE<br>STORE OF THE REGISTE<br>R TYPE | Æ                                     |

|------|---------------|--------------------------------------------------------------------------------|---------------------------------------|

| [76] | Inventor:     | Michel J. Servel, Le Rhu<br>Lannion, France, 22300                             | en Servel,                            |

| [21] | Appl. No.:    | 148,007                                                                        |                                       |

| [22] | Filed:        | May 8, 1980                                                                    | . · .                                 |

| [30] | Foreig        | n Application Priority Data                                                    | · · · · · · · · · · · · · · · · · · · |

| Ma   | y 11, 1979 [F | R] France                                                                      | 79 12080                              |

|      | U.S. Cl       | arch                                                                           | 370/66                                |

| [56] |               | References Cited                                                               |                                       |

|      | U.S.          | PATENT DOCUMENTS                                                               | · · · · · · · · · · · · · · · · · · · |

|      |               |                                                                                | 450 466                               |

#### [57] ABSTRACT

A time division multiplex switching network comprises a data word circulating store and a random address circulating store. These two circulating stores are synchronous and have data word registers and random address registers respectively associated two by two. The bytes in the time-slots of an incoming supermultiplex highway are written in the data word registers and addresses depending on the outgoing time slots which are to be connected are written in the random address registers. These addresses are incremented at each step of the random address circulating store. When the incremented address reaches a predetermined value, a data word is read in the data word circulating store.

### 3 Claims, 9 Drawing Figures

FIG.3

FIG.6

## FIG.4

FIG.5

| • | F1G.7    |

|---|----------|

|   | <b>)</b> |

| - | TABLE    |

|       |                    | T                  |                      | <b>1</b>             | ·<br>T              | ·                   | <del></del>    | <del></del>            | <del>y</del>         |                  | <del></del>            |                          |

|-------|--------------------|--------------------|----------------------|----------------------|---------------------|---------------------|----------------|------------------------|----------------------|------------------|------------------------|--------------------------|

|       | A 0, 956           | A0, 957            | A0,958               | A0, 959              | Ao, 9 <b>6</b> 0    | 0,961               | Ao, 962        | Ao, 963                | 0, 964               | 0,965            | 0,966                  | Ao, 967                  |

|       | A1,955<br>R0,956   | 95                 | A 1, 957<br>R 0, 958 |                      |                     | A 1, 960 / R 0, 961 | 961            | 2 2                    | A 1,963 A<br>R 0,964 | 1,964 A<br>0,965 | 1,965 A<br>0,966       | 1,966<br>0,967           |

|       | (A2,954<br>R1,955  | 8, 8               | 0, 0                 | 2,957                | 2, 958<br>1, 959    | 2, 959<br>1, 960    | ,960           | 2,961<br>1,962         | 2, 962<br>1, 963     | 2, 963<br>1, 964 | 2, 964 A<br>1, 965 R   | 12, 965 A<br>11, 966 R   |

| 6.7   | A3,953<br>R2,954   | 1 71 .             | 95                   | 3,95                 | 3,957<br>2,958      | 958                 | 959            | 3,960<br>2,961         | 3,961 2,962          | 3, 962<br>2, 963 | A 3,963 A<br>R 2,964 R | 13, 964 A<br>2, 965 R    |

| (File | A4,952<br>R3,953   | A4,953<br>R3,954   | 4, 8)                | 4,95                 | 4,956<br>3,957      | 4,957<br>3,958      | ,958<br>,959   | 4,95 <b>9</b><br>3,960 | 4,960<br>3,961       | 4,961<br>3,962   | A4, 962 A<br>R3, 963 F | A4,963 A<br>R3,964 R     |

| BLE   | A 5,951<br>R 4,952 | A5,952<br>R4,953   | 5,954,95             | A 5,954<br>R4,955    | A5,955<br>R4,956    | A5,956/<br>R4,957   | 6              | امما                   |                      | 5,960            | 5, 961                 | 5,962                    |

| TABL  | A6, 950<br>R5, 951 | A6,951<br>R5,952   | 5, 7,                | A 6,953<br>R 5,954   | A 6,954<br>R 5,955  | 6,955<br>5,956      | 6,956<br>5,957 | 6, 957<br>5, 958       | 6,958<br>5,959       | 6,959<br>5,960   | 6,960<br>5,961         | A6,961 A<br>R5,962 R     |

|       | A 7,949<br>R 6,950 | A7, 950<br>R6, 951 | 7, 9                 | A 7, S52<br>R6, 953  | A 7, 953<br>R6, 954 |                     | တတ             | A 7, 956<br>R6, 957    | 7,957 6,958          | 7, 958<br>6, 959 | 7, 959                 | A7,960<br>R6,961         |

|       | A 8,948<br>R 7,949 | A8,949<br>R7,950   | 8 1                  | 8,95<br>7,95         | 95                  | 8,953               | 8,954          | 8, 95 5                | 956                  | 7, 958           | 8, 958<br>7, 959       | A 8, 959 /<br>R 7, 960 F |

|       | R8,947             |                    | A9,949<br>R8,950     | •                    | <b>-</b> 1          | · 7                 |                | ~ >                    |                      | 956              | 9, 957<br>8, 958       | R8, 959                  |

|       | R9,947             | R 9, 948           | R9,949               | R <sub>9</sub> , 950 | R9,951              | Rg, 952             | R9,953         | R 9, 954               | R 9, 955             | R9, 956          | R9, 957                | Rg, 958                  |

.

|     |      | A 0,956              | A <sub>0,957</sub>               | A0,958             | Ao, 959              | Ao, 9 <b>6</b> 0    | Ao, 961              | Ao, 962            | Ap, 963              | A <sub>0</sub> , 964 | Ao, 965              | A <sub>0</sub> , 966 | Ao, 967            |

|-----|------|----------------------|----------------------------------|--------------------|----------------------|---------------------|----------------------|--------------------|----------------------|----------------------|----------------------|----------------------|--------------------|

|     |      | (A1,955)<br>R0,956   | A1, 956/<br>R0, 957              | ` `                | A 1, 958<br>R 0, 959 | A1,959<br>R0,960    | A 1, 960<br>R 0, 961 | A1,961<br>R0,962   | A 1,962<br>R 0,963   | A 1,963<br>R 0,964   | A 1, 964<br>R 0, 965 |                      | A1,966<br>R0,967   |

|     | †    | (A2,954<br>R1,955    | <sup>7</sup> A2, 955/<br>R1, 956 | A 2,956<br>R 1,957 | A 2, 957<br>R 1, 958 | A 2, 958<br>R1, 959 | A2, 959<br>R1, 960   | A 2,960<br>R 1,961 | A 2,961<br>R1,962    | A 2, 962<br>R 1, 963 | A 2, 963<br>R 1, 964 | A 2, 964<br>R 1, 965 | A2,965<br>R1,966   |

|     | G.8) | A3,953<br>R2,954     | A3,954/<br>R2,955                | ָס ס               | 95,                  | A3,957<br>R2,958    | , 95<br>, 95         | 95,                | A 3, 960<br>R 2, 961 | ם ס                  | l ' * _7_~           | ^ _~                 | A3, 964<br>R2, 965 |

|     |      | A4,952<br>R3,953     |                                  | A4,954<br>R3,955   | <b>1</b> • •         | اصُ                 | 95                   | 5.5                | 5                    | A4,960<br>R3,961     | i                    |                      | 1 - 1              |

|     | BLE  | A 5,951<br>R 4,952   | 1 0,                             | A5,953<br>R4,954   | A 5,954<br>R4,955    | A 5,955<br>R4,956   | 3 67                 | A 5,957<br>R 4,958 | A'5, 958<br>R4,959   |                      | A 5, 960<br>R 4, 961 | ا ص ف                | A5,962<br>R4,963   |

|     | T    | A 6, 950<br>R5, 951  | ·                                | 6,3                | 35,                  | .95<br>.95          | 36,                  |                    | A 6, 957<br>R 5, 958 | A 6,958<br>R 5,959   | ا ص مي               | 96,                  | A 6,961<br>R 5,962 |

|     |      | A 7, 949<br>R 6, 950 | 0.0                              | ס ס                | 0,0                  |                     | 6,0                  | i                  |                      | A7,957<br>R6,958     | 1 ~ ~                |                      | 0 0                |

|     |      | A 8,948<br>R 7,949   | 0,0                              |                    | N N                  | 20 20               | 95,                  | 95,                | 0,0                  | 95,                  |                      |                      |                    |

|     |      | A9,947<br>R8,948     | - ·                              | 0,0                | 0,0                  | 9, 95,              | ο (α<br>ο (α         | ,95                | 9,9                  |                      | ס ָס                 | 95                   | ف ف                |

|     |      | R9, 947              | Rg 948                           | R9 949             | $\mathcal{O}$        |                     | Rg 952               | R9,953             | R9,954               | Rg, 955              | R9,956               | _ \                  | Rg, 958            |

| · · |      | •                    | <sup>2</sup> 951                 | t 952 -            | t 953                | -954-               | . 955                | -926-              | , 957                | 6958                 | -626 <sub>3</sub>    | .096                 | , 961              |

|     | •    |                      |                                  |                    |                      |                     |                      |                    |                      |                      |                      |                      |                    |

# TIME DIVISION MULTIPLEX SWITCHING NETWORK WITH AN ASSOCIATIVE BUFFER STORE OF THE REGISTER COUNTER TYPE

#### **BACKGROUND OF THE INVENTION**

Field of the Invention

The present invention relates to improvements made to time-division multiplex switching networks and, more particularly, to switching networks of this type in which the buffer store is an associative type store addressable by its contents and constructed using coupled charge devices (CCD).

Description of the Prior Art

U.S. Pat. No. 3,971,892 includes a description of a 15 time-division multiplex switching network comprising an input stage having plurality of incoming multiplex highways and a supermultiplexer converting the said incoming multiplex highways into one incoming supermultiplex highway; an output stage having outgoing 20 supermultiplex highway and a superdemultiplexer converting the said outgoing supermultiplex highway into a plurality of outgoing multiplex highways; a buffer store having a write in input connected to the incoming supermultiplex highway and a read out output con- 25 nected to the outgoing supermultiplex highway; and means for sequentially writing, in data storage locations of the buffer store, the words present in the time-slots of the incoming supermultiplex highway. The said buffer store is a circulating store addressable by its contents. 30 The buffer store includes random address store locations associated with the said data store locations and a fixed address store giving the addresses of the component time-slots of the outgoing supermultiplex highway. Plural comparator means, each associated with a data 35 store location, and a random address store location compare the random addresses written in the address store locations with the fixed addresses of the component time-slots of the outgoing supermultiplex highway to control read out of the word associated with a given 40 random address when there is identity between the said given random address and a fixed address.

Assuming that there are N multiplex highways in a supermultiplex highway and 32 time-slots in each multiplex highway, the address (j-i) modulo 32N is written in 45 the random address store location associated with the data store location containing the word in time-slot of address i in the incoming supermultiplex highway and the circulating store advances stepwise. When random address (j-i) is equal to fixed address (j-i) assigned to a 50 given step of the circulating store, the word is read out and transferred into time-slot of address j in the outgoing supermultiplex highway.

#### SUMMARY OF THE INVENTION

The object of the invention is to provide a time-division multiplex switching network in which the fixed address memories included in the stages of the circulating store and the comparators associated with these fixed address memories are done eliminated.

In the prior art, the words and their associated random addresses progress unchanged in the circulating store from the input stage thereof up to the stage having a fixed address equal to the random address. In the invention, the associative buffer store is arranged as a 65 counter and the random address which is written in the circulating store at the input stage thereof is incremented to each circulation step; the reading of the data 2

word is ordered in the circulating store stage when the counter overflows.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The invention will now be described in detail in relation to the accompanying drawings in which:

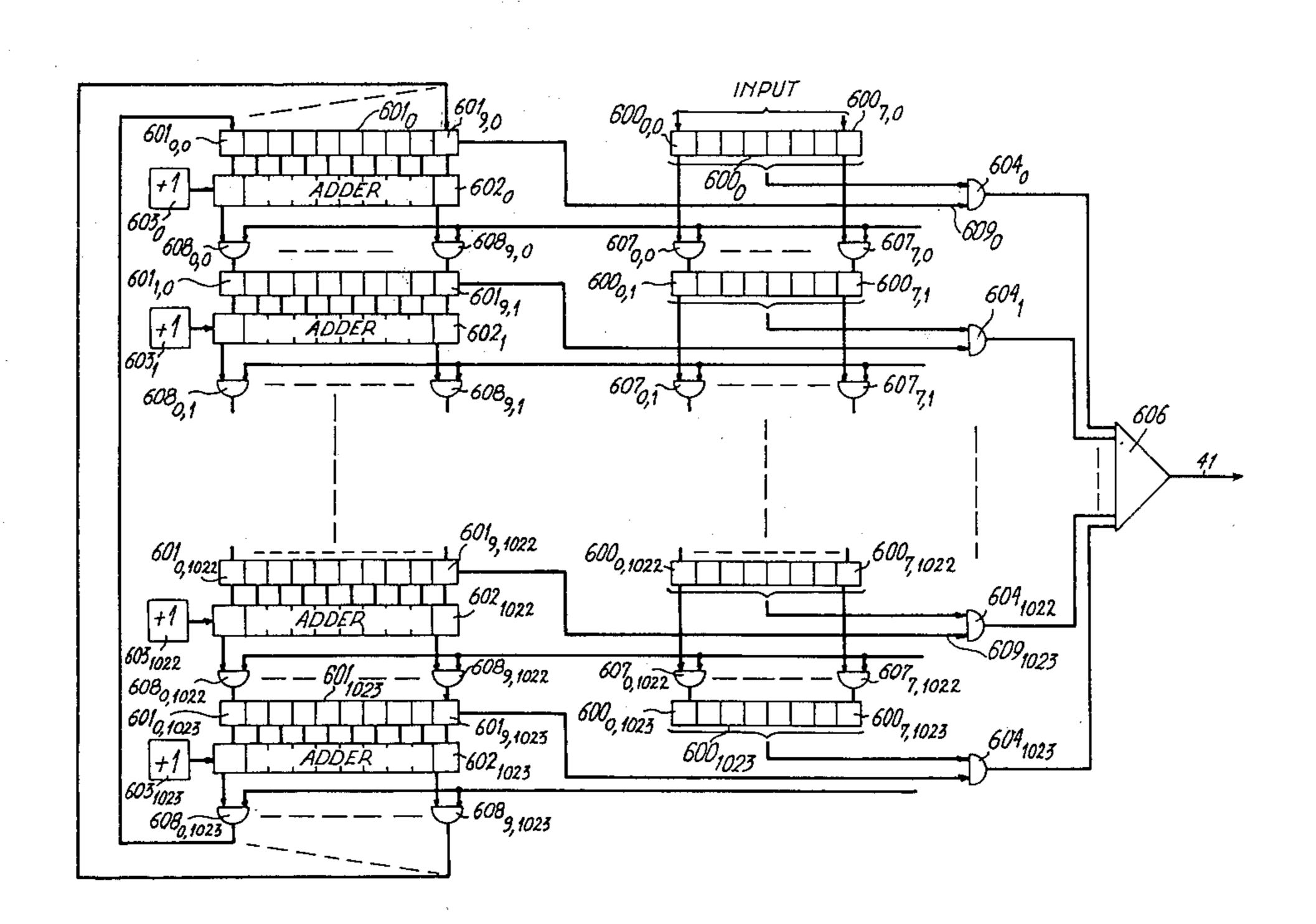

FIG. 1 is a circuit diagram of the time-division multiplex switching network described in the aforementioned patent;

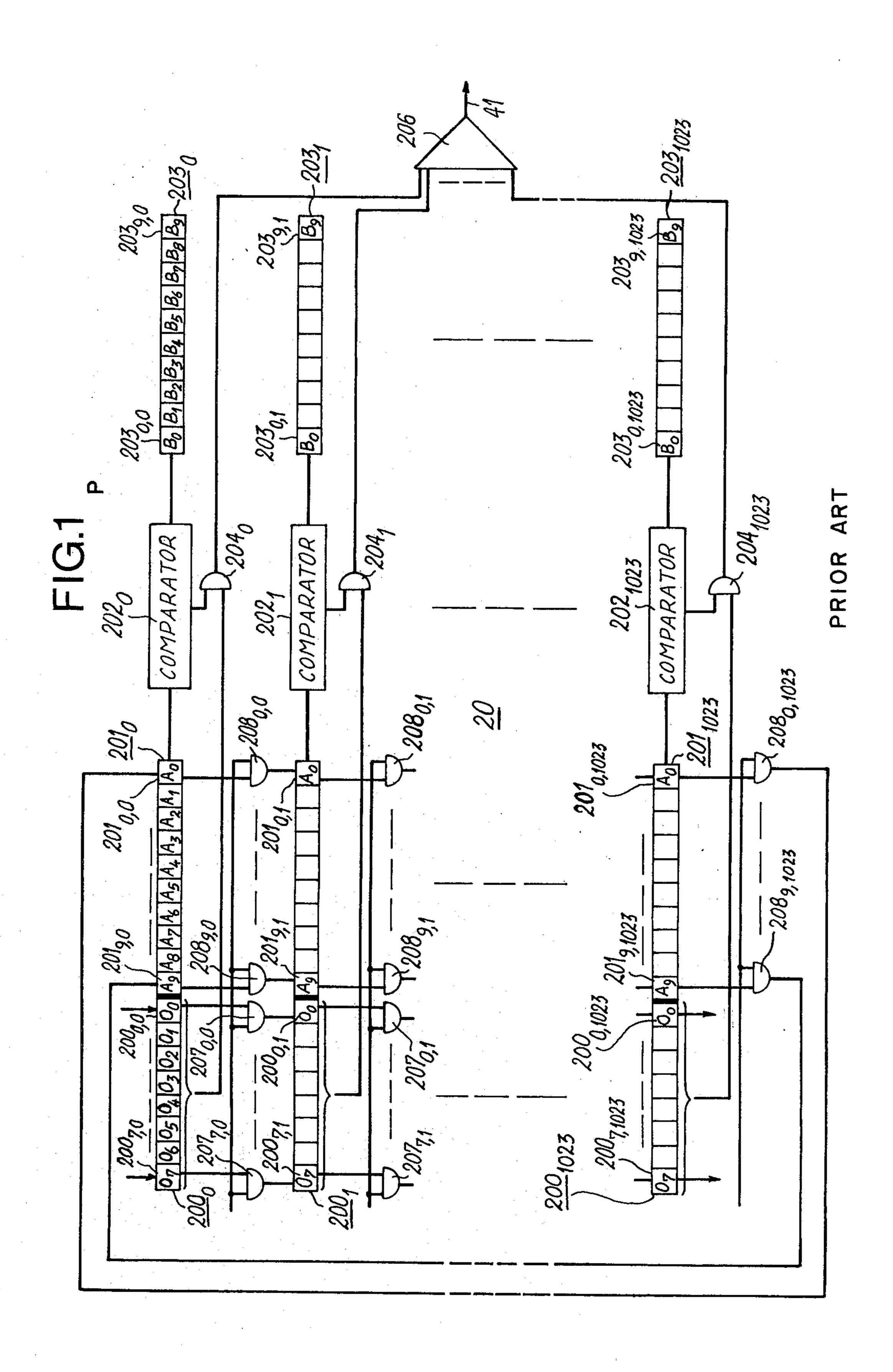

FIG. 2 is a circuit diagram of the time-division multiplex switching network in accordance with the invention;

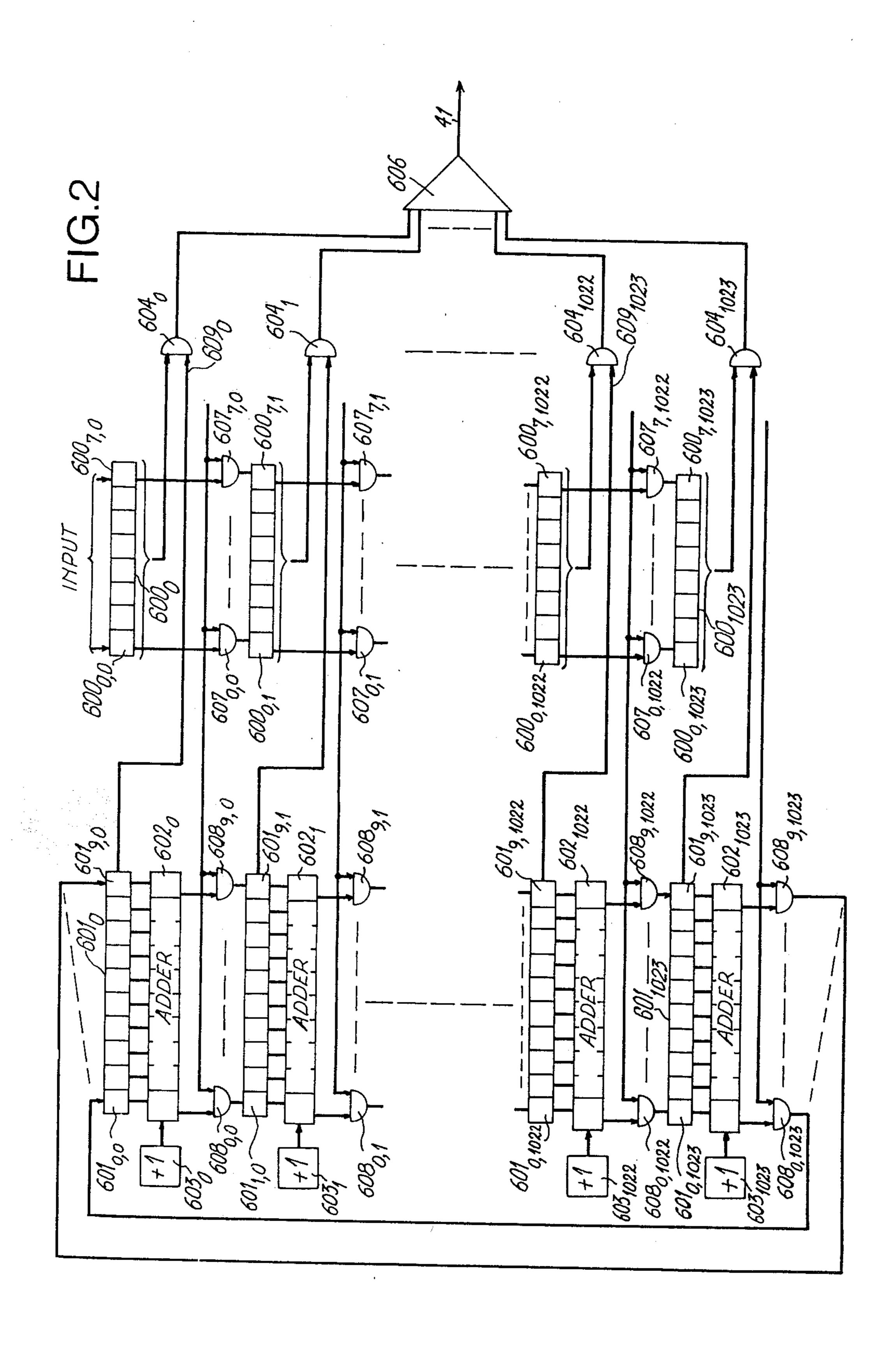

FIG. 3 is a circuit diagram of the principle of an associative buffer store with count down;

FIGS. 4, 5 and 6 are circuit diagrams of that part of the associative buffer store; and which serves as a control store;

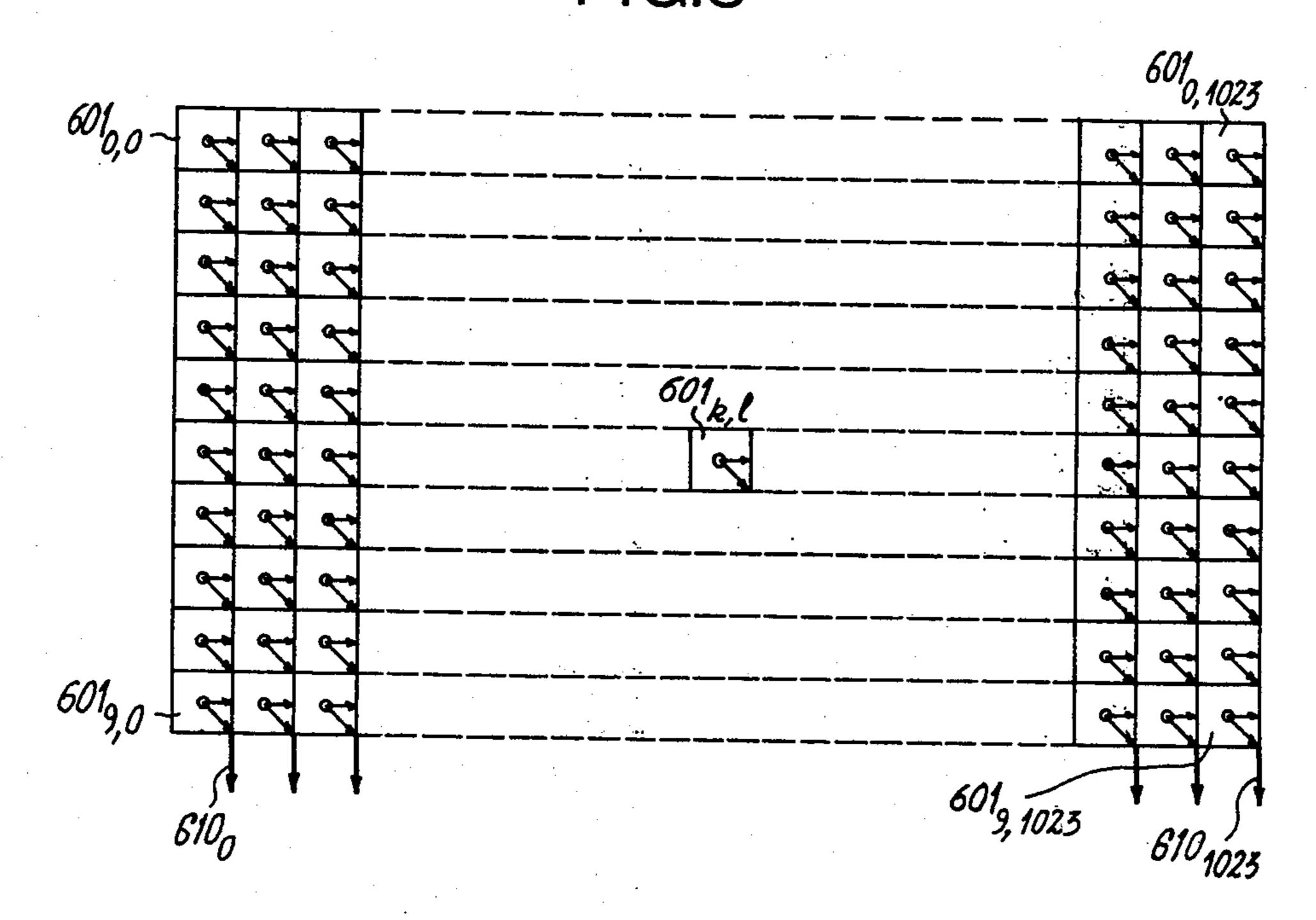

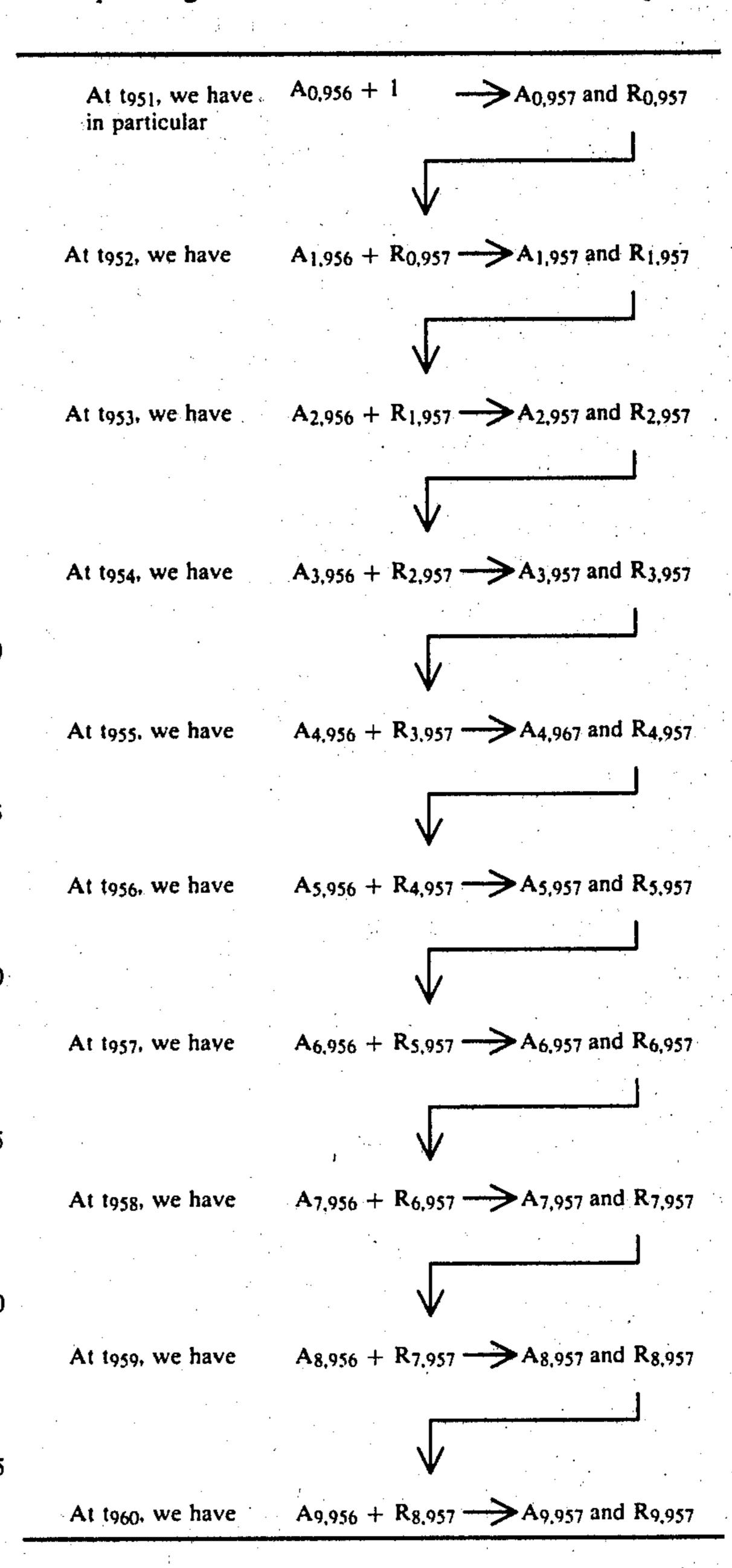

FIGS. 7, 8 and 9 are tables showing how the increment or decrement by one unit of the address word is performed at the rate of one bit weight per one memory step.

## DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring first to FIG. 1 which relates to the prior art, each store location of buffer store 20 comprises a data octet area 200<sub>0</sub> to 200<sub>1023</sub> respectively, a random address area 201<sub>0</sub> to 201<sub>1023</sub> respectively, a comparator 202<sub>0</sub> to 202<sub>1023</sub> respectively and a fixed address area 203<sub>0</sub> to 203<sub>1023</sub> respectively. Address areas 203<sub>0</sub> to 203<sub>1023</sub> form a read only memory, a wired memory for example. In other words, these areas unalterably contain the binary numbers 0 to 1023.

Inputs of AND gates 204<sub>0</sub> to 204<sub>1023</sub> are respectively connected to octet areas 200<sub>0</sub> to 200<sub>1023</sub> and comparators 202<sub>0</sub> to 202<sub>1023</sub>; outputs of the AND gates are connected to OR-gate 206, connected to outgoing supermultiplex highway 41. The comparators each receive a fixed address coming from the read only memory.

Buffer store 20 is the circulating type. The data octet areas are eight-bit ones and the random address areas have ten bits. Consequently, there are eight unit memories 200<sub>0,0</sub> to 200<sub>7,0</sub> in memory area 200<sub>0</sub> and the same is so in the other data octet memory areas. There are ten unit memories 201<sub>0,0</sub> to 201<sub>9,0</sub> in the random address memory area 201<sub>0</sub> and the same is so in the other random address memory areas.

AND-gates 207<sub>0,0</sub> to 207<sub>7,0</sub> are connected to the outputs of unit memories 200<sub>0,0</sub> and to 200<sub>7,0</sub> to the inputs of unit memories 200<sub>0,1</sub> to 200<sub>7,1</sub> The buffer store part concerning the data octets is not looped; it receives at each frame the eight-bit words present in the time-slots of the incoming supermultiplex highway.

AND-gates  $208_{0,0}$  to  $208_{9,0}$  connect the outputs of unit memories  $201_{0,0}$  to  $201_{9,0}$  to the inputs of unit memories  $201_{0,1}$  to  $201_{9,1}$ . Similarly AND-gates  $208_{0,1023}$  to  $208_{9,1023}$  connect the outputs of unit memories  $201_{0,1023}$  to  $201_{9,1023}$  to the inputs of unit memories  $201_{0,0}$  to  $201_{9,0}$ .

It can thus be seen that a data octet and a random address may be written respectively in input stages 200<sub>0</sub> and 201<sub>0</sub> and that the octet together with the random address cyclically move around the circulating store, the octet path being non-looped and the address path being looped.

The manner in which the associative circulating store works is as follows:

Assume that time-slot of address 0 in the incoming supermultiplex highway is to be connected to time-slot of address j in the outgoing supermultiplex highway. The incoming octet is written in register 2000 during time interval to and address j is written in register 2010 during the same time interval to. Due to the circulation, the octet, together with the address of the outgoing time-slot, progress stepwise, advancing one step per time interval. At any moment, the random address may 10 be compared with the fixed address written in the stage of the read only memory 203 which is associated with the stage of the buffer store in which octet and random address are actually lying. In particular, at time interval  $t_i$ , the octet and the random address are respectively in  $^{15}$ registers 200; and 201; which are associated with stage 203; of read only memory 203, the comparison of the random and fixed addresses is positive and the octet of address 0 is read out and transferred into time-slot of 20 address j in the outgoing supermultiplex highway.

Now assume that time-slot of address i in the incoming supermultiplex highway is to be connected to time-slot of address j in the outgoing supermultiplex highway. The incoming octet is then written in register  $200_0$  25 at time interval  $t_i$  and the random address (which now is merely j) is written in register  $201_0$  at time interval  $t_i$ . At time interval  $t_i$  the octet and the random address are respectively in registers  $200_{(1024-i)}$  and  $201_{(1024-i)}$ . At time interval  $t_i$ , the octet and the random address are respectively in registers  $200_{(1024-i+j)}$  and  $201_{(1024-i+j)}$ . Consequently, j is not written at time interval  $t_i$  in register  $201_0$ ; but instead (1024-i+j) modulo 1024, that is (j-i), is written in register  $201_0$ . The result of this is that if i=0, j is written at time interval  $t_0$  in register  $201_0$ .

FIG. 2 is an illustration of the associative circulating buffer store in accordance with the invention. It comprises  $8 \times 1024 = 8192$  information bit-memories and  $10 \times 1024 = 10240$  random address bit-memories. The 40 information bit-memories are designated by:

The information bit memories are arranged in a circulating store in which a eight-bit data word can occupy 1024 successive word locations.

The random address bit-memories are designated by:

The random address bit memories are arranged in a circulating store in which a ten-bit address word can occupy 1024 successive word locations.

The address bit-memories are also located in counters.

As already said, while the address memory is looped  $_{65}$  from stage  $601_{1023}$  ( $601_{0,1023}$  to  $601_{9,1023}$ ) to stage  $601_0$  ( $601_{0,0}$  to  $601_{9,0}$ ), the data memory is not looped. Gates

607<sub>0,0</sub> to 607<sub>7,0</sub>

607<sub>0,1023</sub> to 607<sub>7,1023</sub>

connect the stages of the data part of the buffer store. Gates

608<sub>0,0</sub> to 608<sub>9,0</sub>

608<sub>0,1023</sub> to 608<sub>9,1023</sub>

connect the stages of the address part of the buffer store. Finally gates

604<sub>0</sub> to 604<sub>1023</sub>

connect the stages of the data part of the buffer store to an OR-gate connected to the outgoing supermultiplex highway 41.

It can be seen that FIG. 2 resembles FIG. 1 to a certain extent. However, the random addresses written in the address locations when they pass from one given word location to the next. In contrast, in the FIG. 1 system the random addresses are circulated without modification and are, at each successive location, compared with fixed addresses. This incrementation is performed by means of adders 6020 to 6021023 and unity sources 603<sub>0</sub> to 603<sub>1023</sub> Counters 601<sub>0</sub> to 601<sub>1023</sub> overflow when they reach 1024. Assume that incoming time-slot of address i is connected to outgoing time-slot of address j, and that the incoming time-slot contains a word which is written at time interval tin input data register  $600_0$  while address (1024-j+i) is written in input address register 601<sub>0</sub>. When this address arrives in register  $601_{(j-1)}$  at time interval  $t_j$ , i.e. after (j-i) time intervals, the address becomes

$$1024-(j-i)+(j-i)=1024$$

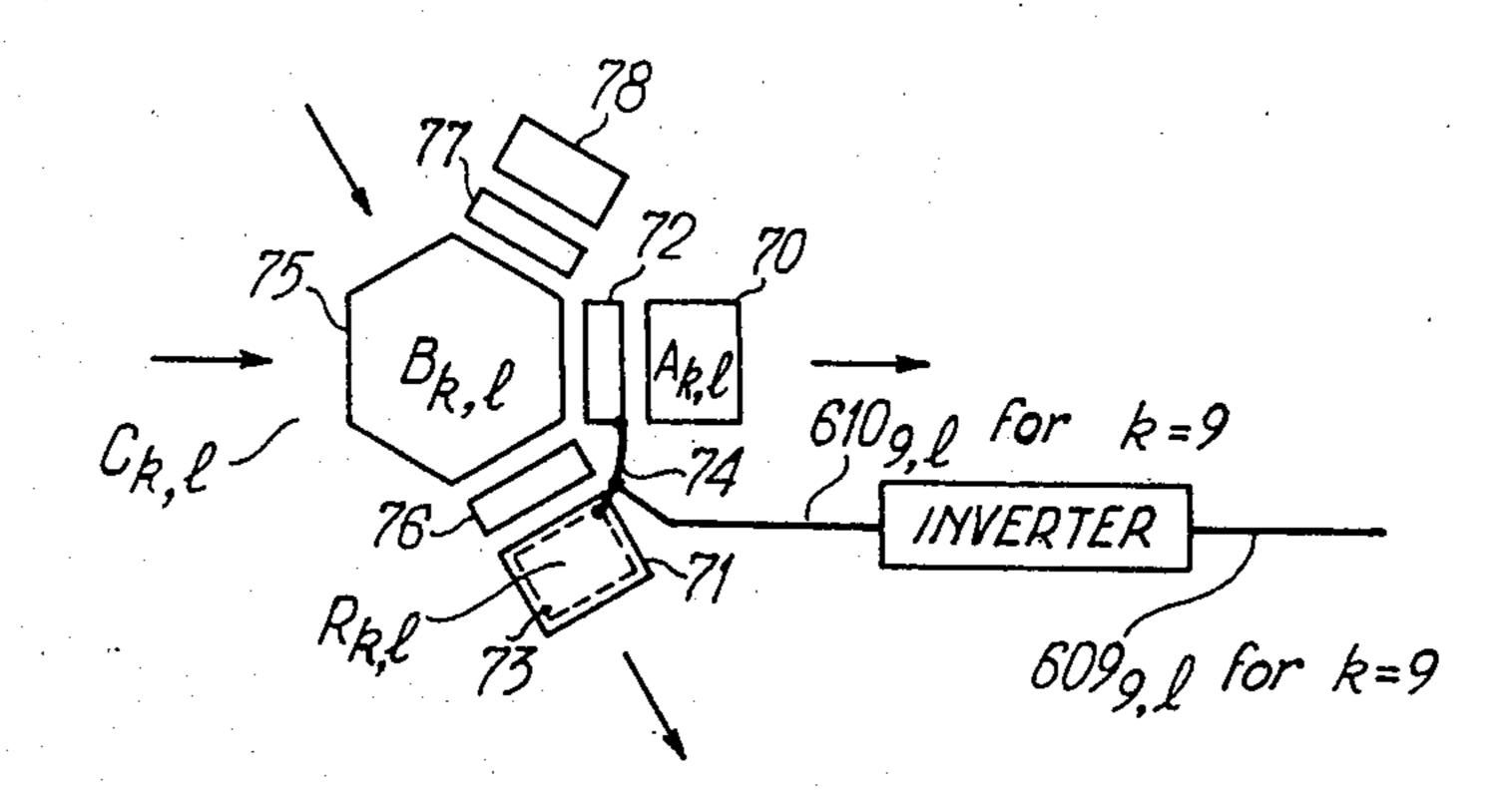

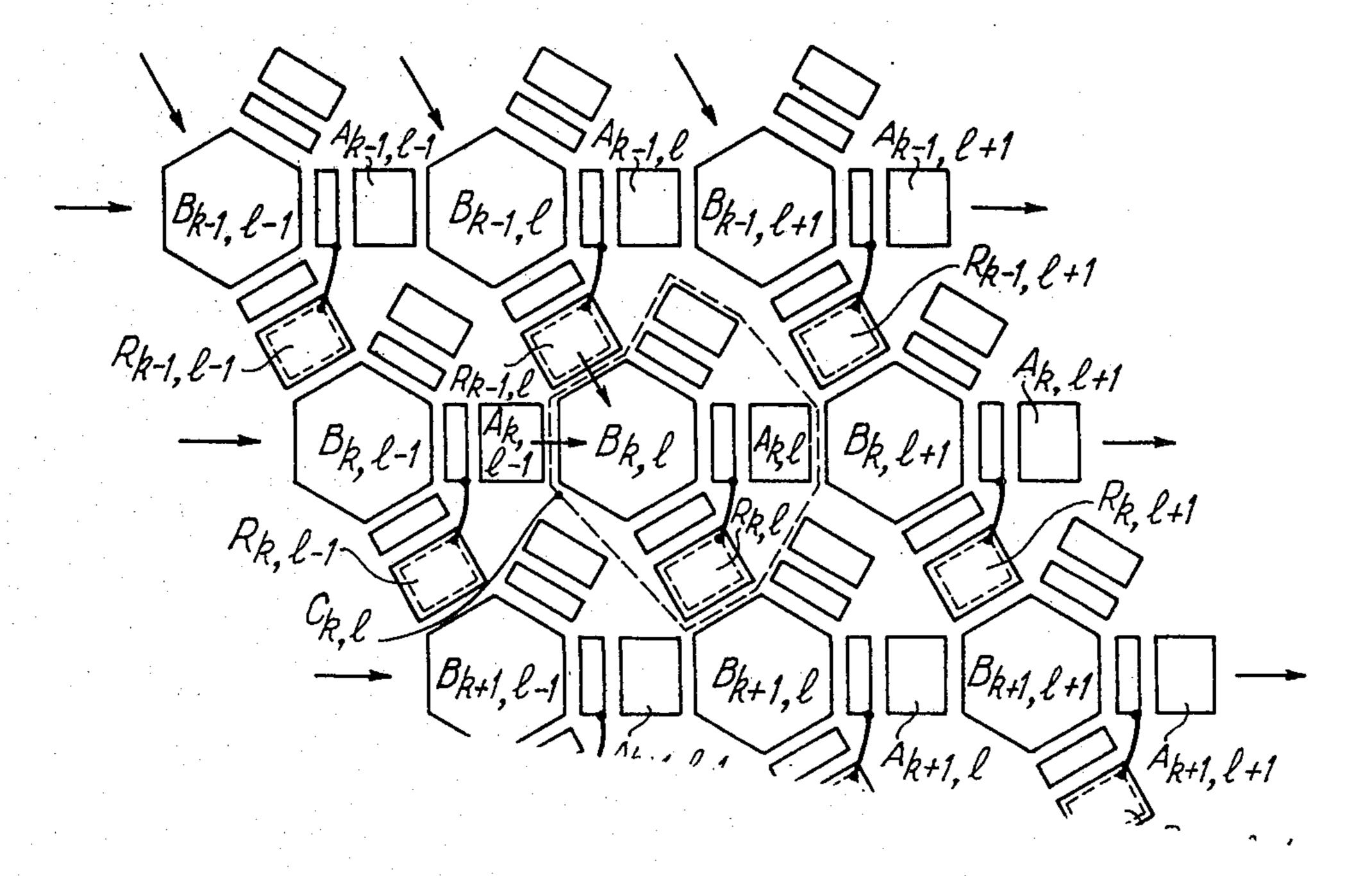

Counter  $601_{(j-i)}$  overflows and operates gate  $604_{(j-i)}$  via wire  $609_{(j-i)}$  and the octet in circulation leaves at time, interval  $t_j$  Reference is now made to FIG. 3, wherein each stage of the address part of the buffer store assigned to the octet reading control comprises a plurality of cells  $C_{k,l}$  with  $0 \le k \le 9$  and  $0 \le l \le 1023$ . In FIG. 3, the horizontal arrows in cells  $C_{k,l}$  represent the progression of the address words, whereas the diagonal arrows represent the progression of the carry over values. On the line of index k=0, the previous carry over is replaced by a binary digit 1.

FIG. 4 is an illustration of how a cell  $C_{k,l}$  is set up in a coupled charge device.

Unit memory 70 temporarily stores the address bit  $A_{k,l}$  resulting from the addition which takes place in cell  $C_{k,l}$ . Unit memory 71 temporarily stores carry over bit  $R_{k,l}$  resulting from the carry over of the addition which takes place in cell  $C_{k,l}$ . Control electrode 72 controls coupling of the charge of  $B_{k,l}$  to  $A_{k,l}$  depending on the potential of electrode 72. Equipotential link 73 connects cell 72 to change sensor 73. CCD (charge coupled device) adder 75 receives the charges due to the previous carry over  $R_{(k-1),l}$  and the previous address bit  $A_{k,(l-1)}$ . Potential barrier 76 enables the excess of charge of cell  $B_{k,l}$   $R_{k,l}$ . Finally, electrode 77 allows to be coupled to cell the contents of cell  $B_{k,l}$  to be cleared after an addi-

tion operation and PN junction 78 makes it possible to absorb the previous charge if necessary.

FIG. 5 is a view of an assembly of 9 cells such as that described in FIG. 4.

Cell  $C_{k,l}$  operates in the following manner.

It can be seen that the address part of the circulating buffer store shown in FIG. 3 has 1024 output wires 610<sub>0</sub> to 610<sub>1023</sub> respectively connected to cells C<sub>9.0</sub> to  $C_{9,1023}$ . Each of wires  $610_0$  to  $610_{1023}$  is respectively connected to a wire, 6090 to 6091023 by means of an 10 inverter circuit, discussed infra. Wire 609 (j-i) controls gate  $604_{(j-i)}$  which allows the reading at time interval  $t_i$ of the data word entered at time interval t<sub>i</sub>. On each clock pulse defining a time interval, the charges representative of the logic levels derived from cells  $R_{(k-1),l-15}$ and  $A_{k,(l-1)}$  are transferred to cell  $B_{k,l}$  where they are added. Potential barrier 76 allows any surplus charge to pass to cell  $R_{k,l}$ . (Surplus charge is coupled to cell  $R_{k,l}$ the contents of cells only if  $A_{k(l-1)}$  and R(k-1), are both binary one values. The contents of cell  $R_{k,l}$  conse- 20quently represents the carry over of the addition. Next solely the absence of charges in cell  $R_{k,l}$  makes for the transfer of the contents of cell  $B_{k,l}$  into cell  $A_{k,l}$ , it thus follows that the result of the addition is to be found in  $\mathbf{A}_{k,l}$ .

A final clock pulse on the electrode 77, FIG. 4, enables the binary signal of cell  $B_{k,l}$  to be set back to zero. Tables I to IV herebelow summarize the possible cases.

TABLE I

|          | •                   |                  |                |         |                              |      |

|----------|---------------------|------------------|----------------|---------|------------------------------|------|

| The      | initial situation   | is $A_{k,(l-1)}$ | $= 0; R_{(k)}$ | -1),l=0 |                              |      |

|          | $A_{k,(l-1)}$       |                  |                |         | $\exists i \mathbf{A}_{k,l}$ |      |

| 1st time | 0                   | 0                | 0              | 0       | 0                            |      |

| 2nd time | 4. <b>0</b> - 4- 4- | 0                | 0              | 0       | 0                            |      |

| 3rd time | 0                   | 0                | 0              | 0       | 0                            | ``35 |

| 4th time | 0 '                 | 0 .              | 0              | 0       | 0                            |      |

4 79 8 1 to 16 12 13 1 72

TABLE II

| The                                    | initial situation is $A_{k,(l-1)} = 0$ ; $R_{(k-1),l} = 0$ |                         |                    |           |           |      |  |  |

|----------------------------------------|------------------------------------------------------------|-------------------------|--------------------|-----------|-----------|------|--|--|

|                                        | $A_{k,(l-1)}$                                              | _                       | $\mathbf{B}_{k,l}$ | $R_{k,l}$ | $A_{k,l}$ | _    |  |  |

| 1st time                               | 0                                                          | <i>1,</i> € 1, € 0, * 1 | 1 .                | . 0       | 0         | -    |  |  |

| 2nd time                               | 0                                                          | 0                       | 1                  | 0         | 0         |      |  |  |

| 3rd time                               | . 0                                                        | . 0                     | 0                  | 0         | 1 .       |      |  |  |

| 4th time                               | 0                                                          | 0                       | 0                  | 0         | 1         | . A1 |  |  |

| —————————————————————————————————————— |                                                            | ·                       |                    |           |           | - 47 |  |  |

TABLE III

| The i    | nitial situatio | n is $A_{k,(l-1)}$ | $= 1; R_{(k)}$     | -1), l = 0   |                    | <u> </u> |

|----------|-----------------|--------------------|--------------------|--------------|--------------------|----------|

|          | $A_{k,(l-1)}$   | $R_{(k-1),l}$      | $\mathbf{B}_{k,l}$ | $R_{k,l}$    | $\mathbf{A}_{k,l}$ | _ 50%    |

| 1st time | 0               | 0                  | 1                  | 0            | 0                  | - 50     |

| 2nd time | C 4-0           | 0                  | 1                  | < <b>0</b> . | 0                  |          |

| 3rd time | 0               | 0                  | 0                  | 0            | 0                  |          |

| 4th time | 0               | 0                  | 0                  | 0            | 0                  |          |

TABLE IV

| \$           | The in   | nitial situatio | n is $A_{k,(l-1)}$ | $= 1; R_{(k=1)}$   | 1)./ =    | Subjects           |

|--------------|----------|-----------------|--------------------|--------------------|-----------|--------------------|

|              |          | $A_{k,(l-1)}$   | $R_{(k-1),l}$      | $\mathbf{B}_{k,l}$ | $R_{k,l}$ | $\mathbf{A}_{k,l}$ |

| ,            | 1st time | 0               | 0                  | 1 + 1              | 0         | · 0                |

|              | 2nd time | 0               | 0                  | 1                  | 1         | 0                  |

|              | 3rd time | √ <b>0</b> a≥ . | <b>* 0.</b>        | 137137 3           | 1         | <b>.</b> ( ) 0     |

| <u>.</u> 10' | 4th time | 0               | 0                  | 0.4                | 1         | . · · O            |

The reading of the data octet from one of the octet registers is controlled by the carry over in cell C<sub>9,1</sub>. 65 With this in mind, the potential derived in charge sensor 73 in FIG. 4 must be considered. However, this potential allows the octet to be read only when the value of

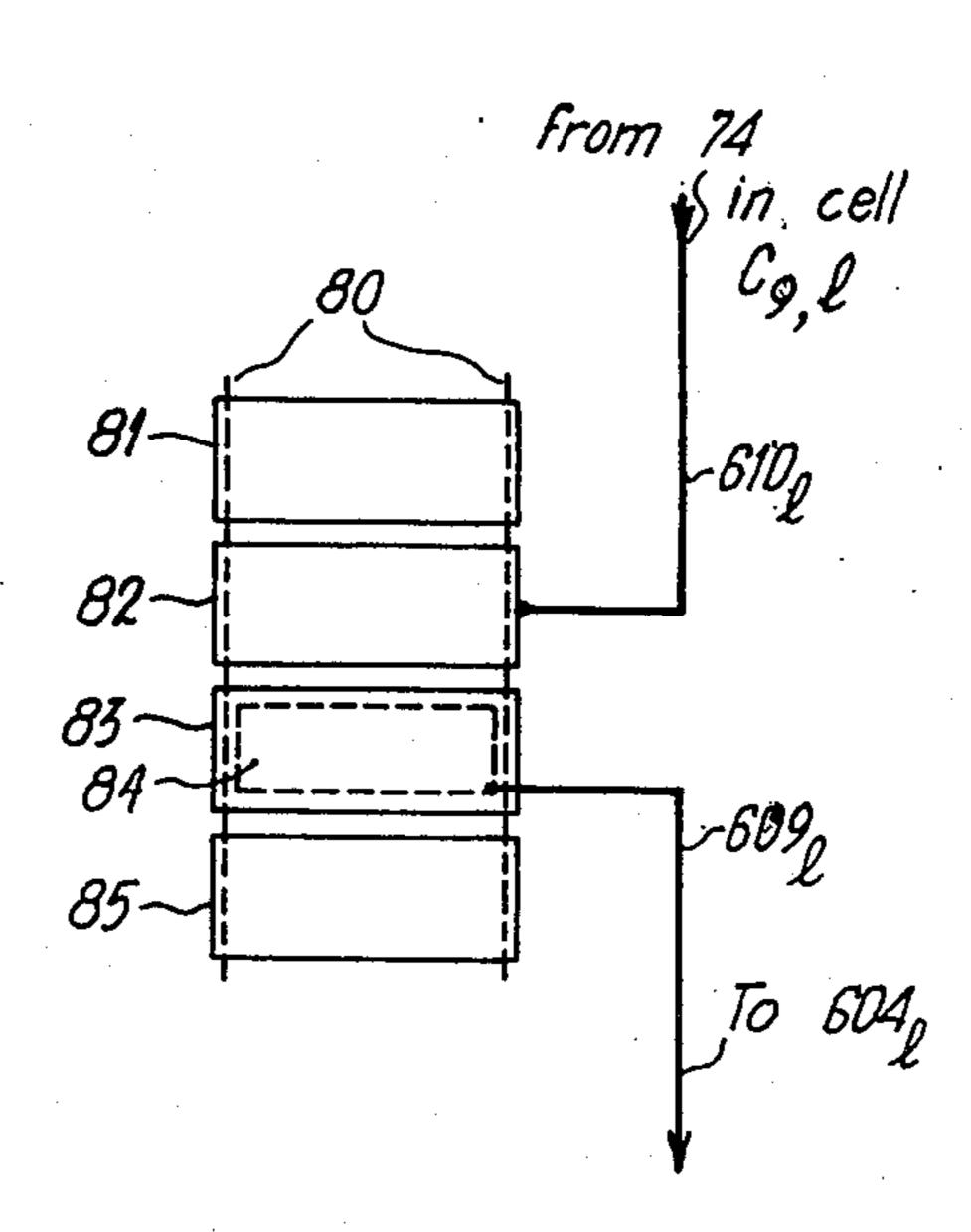

the charge packet representative of the carry over is zero; the sign should thus be inverted. Sensor 73 is therefore connected to an inverter-regenerator, a device quite familiar to those of ordinary skill in the charge coupled device field. Such an inverter is shown in FIG. 6, wherein isolating diffused part 80 localizes the charges in the cell. PN junction 81 is biased to generate charges. 82 is an electrode connected to charge sensor 73 of cell C<sub>9,l</sub>. Clock electrode 83 controls the progression of the charges. Charge sensor 84 is connected to the output gate 604<sub>l</sub> of the octet register 600<sub>l</sub>. Finally non-biased PN junction 85 absorbs the charges.

Thus reading of the octet is controlled by control charge sensor 84.

The manner in which the address part of the buffer store works is described from the following example.

Assume that incoming time-slot of address i=3 in the incoming supermultiplex highway is to be connected to outgoing time-slot of address j=960 in the outgoing supermultiplex highway. At time interval  $t_3$ , the octet of address i=3 is written in register  $600_0$  and, at time interval  $t_{960}$ , i.e. 957 clock pulses later, it is to be read from register  $600_{957}$ . An address or control word is written at time interval  $t_3$  in address register  $601_0$ . The address word reaches the value 1024 after it has circulated around to register  $600_{957}$ ; this address word is normally

$$1024-(j-i)=67=0001000011$$

The foregoing reasoning assumes that, at each stage of the circulating store, a complete addition (including the propagation of the carry-overs) of unitary and the address word in the address register of this stage takes place.

In this system of complete addition at each stage, the operation of the address part of the buffer store can be summarized by the following table:

| <br> |   | tim            | number o<br>address<br>register             |     | address word                      |    |

|------|---|----------------|---------------------------------------------|-----|-----------------------------------|----|

| <br> |   | t <sub>0</sub> | 601 <sub>102</sub> 1<br>601 <sub>1022</sub> | . • | 64 = 0001000000 $65 = 0001000001$ | ۲, |

| . :  | A | t <sub>2</sub> | 601 <sub>1023</sub>                         |     | 66 = 0001000010                   |    |

| <b>- '</b> ". |            | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |                                          | _ |

|---------------|------------|---------------------------------------|---------------------------------------|------------------------------------------|---|

|               | writing-in | t <sub>3</sub>                        | 6010                                  | $67 = 0 \ 0 \ 0 \ 1 \ 0 \ 0 \ 0 \ 1 \ 1$ |   |

| <i>:</i> ·    |            |                                       |                                       |                                          |   |

| t951 | 601948 | $1015 = 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1$     |

|------|--------|--------------------------------------------|

| t959 | 601956 | $1023 = 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1$ |

| reading-out t960 | 601957 | 1024 = 10000000000 |

|------------------|--------|--------------------|

| •                |        |                    |

$$t_{1023}$$

$601_{1020}$   $63 = 00001111111$

In keeping with another characteristic of the invention, the addition of unity to the address when the address passes from one stage of the buffer store to the following stage is distributed over a number of stages equal to the number of bits in the number where the counters overflow; thus the addition is not performed once at each stage.

Under these conditions and supposing that the number for which the counters overflow has eleven bits, the addition of +1 to the address occurs in ten clock pulses by initially adding +1 to the address bit of binary weight 0; then during the following time interval the

carry from this first addition is added to the address bit of binary weight 1, then during the following time interval the carry over of this second addition is added to the address bit of binary weight 2, and so forth.

Table V hereinbelow represents a portion of the address part of the buffer store contained in the register and counter. In each box of TABLE V, there are two unit memories  $A_{k,(l-1)}$  and  $R_{(k-1),l}$ . Each box of a horizontal line corresponds to a bit of an address word. Each box of a column corresponds to one of the 1024 10 positions of the address part of the buffer store. The following sketch represents the locations in Table V of the added bits

(1)

$$A_{k,(l-1)} + R_{(k-1),l} \longrightarrow A_{k,l} \text{ and } R_{k,l} \text{ (carry over)}$$

$$A_{k,(l-1)} = A_{k,(l-1)} R_{(k-1),l}$$

$$R_{k,l} = A_{k,l} A_{k,l}$$

Table V therefore represents the following additions:

$$A_{0,956} + 1$$

$\longrightarrow A_{0,957}$  and  $R_{0,957}$   $\longrightarrow A_{1,956}$  and  $R_{1,956}$   $\longrightarrow A_{2,954} + R_{1,955}$   $\longrightarrow A_{2,955}$  and  $R_{2,955}$   $\longrightarrow A_{4,956} + R_{3,957}$   $\longrightarrow A_{4,957}$  and  $R_{4,957}$

These additions are represented in Table V of FIG. 7 by brackets connecting the two digits to be added and a vertical arrow to the resulting sum and a diagonal arrow to the carry over. These operations occur at each interval of time; 10240 elementary operations of the 45 type indicated in Equation (1) therefore take place during each interval of time.

Coming back to the above example at time  $t_3$ , the address word lies at stage 0 (stage  $601_0$ ); the same is true of the data octet (stage  $600_0$ ). The address progresses 50 through the address register and counter by undergoing successive additions.

Closer consideration of the staggered addition process corresponding to position or stage 957 reveals that this position corresponds to the output of the data octet 55 at time t960 since the octet was entered in t3.

Table VI is a repeat of Table V with the addition of the time references corresponding to this particular case.

In T<sub>952</sub>, on one line appears:

| $A_{0.957} + 1$                         | <b>→</b>      | A0,958 and R0,958                         |

|-----------------------------------------|---------------|-------------------------------------------|

| $A_{1,956} + R_{0,957}$                 |               | A1,957 and R1,957                         |

| $A_{2,955} + R_{1,956}$                 |               | A2,955 and R2,956                         |

| $A_{3,953} + R_{2,955}$                 | $\rightarrow$ | A3,955 and R3,955                         |

| $A_{4,953} + R_{3,954}$                 |               | A4,954 and R4,954                         |

| $A_{5,952} + R_{4,953}$                 | $\rightarrow$ | A5,953 and R5,953                         |

| $A_{6,951} + R_{5,952}$                 | <b></b> ≯·    | A <sub>6,952</sub> and R <sub>6,952</sub> |

| $A_{7,950} + R_{6,951}$                 | •             | A7,951 and R7,951                         |

| • • • • · · · · · · · · · · · · · · · · |               |                                           |

|                         | -continued |                                           |

|-------------------------|------------|-------------------------------------------|

| $A_{8,949} + R_{7,950}$ | <b>→</b>   | A <sub>8,950</sub> and R <sub>8,950</sub> |

| $A_{9,948} + R_{8,949}$ | ·          | A9,949 and R9,949                         |

These ten elementary operations correspond to the control word at time t952.

The calculation follows through t953, t854 . . . etc. Consider the series leading up to the complete addition corresponding to a determined number in ten steps:

The last carry over R<sub>9,957</sub> is the one which causes the reading of the data octet at time t<sub>960</sub>.

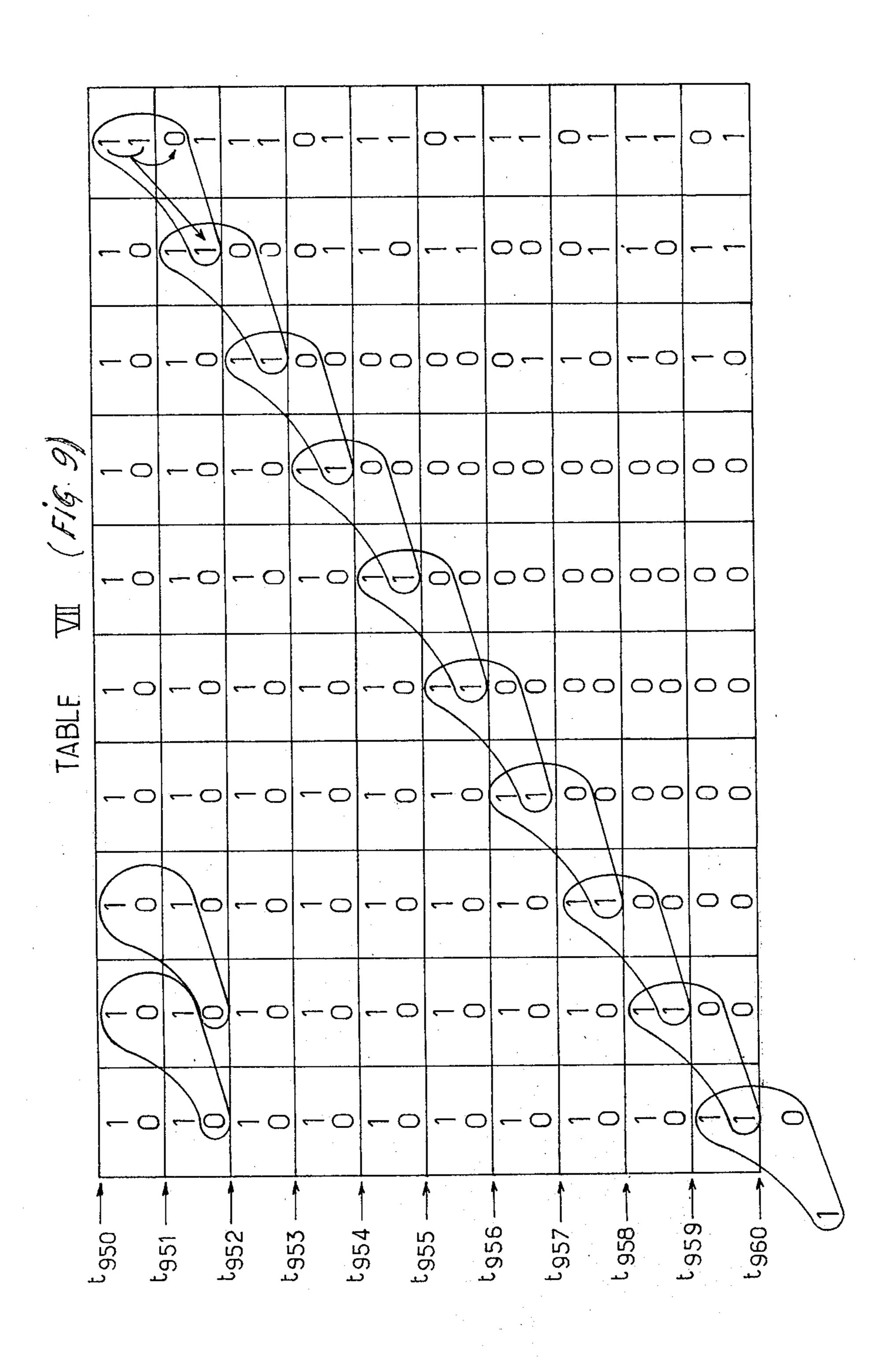

Table VII resumes the digital example of connecting incoming time-slot 3 to outgoing time-slot 960. In this table, each line represents an address word with its carry overs as before; however in this case, the table indicates the development of the address word in time by leaving the other address words out of consideration.

The first line of Table VII represents the address word at time  $t_{950+\epsilon}$ ; in the second line of the Table

20.

25

30

55

65

representing  $t_{951+\epsilon}$ , the same word has advanced by one open line, etc.

In Table VII, the addition process can be followed on the digital example. In particular, the diagonal indicated by the closed loops represents the propagation of the 5 addition in ten clock pulses terminating in overflowing of the counter at the value of 1024.

At time t<sub>3</sub>, an address other than 67 must be initialized. The initialized address results from the following analysis:

If it is assumed that the writing of an address in the address part of the buffer store occurs at time t<sub>3</sub> as specified hereinabove, only the most significant bit is exact at that moment. The previous bit had a correct value at position 1023. At position 0, the value of the previous 15 bit must be deducted from the value

$$67 + 1 = 0001000100$$

in binary

The street of the street

The previous bit had a correct value at position 1022. At position 0, it must therefore be deducted from the value

$$67 + 2 = 0001000101$$

in binary

The street of the street

And so forth.

The following table indicates the value of the bits which are written in register  $601_0$  instead of 67.

| ·               |                                                         | 35                                                    |

|-----------------|---------------------------------------------------------|-------------------------------------------------------|

| 9876543210      |                                                         | <del></del>                                           |

| 0001000011 .    | 67                                                      |                                                       |

| 0001000100<br>↑ | 67 + 1                                                  |                                                       |

| 0001000101      | 67 + 2                                                  | 40                                                    |

| 0001000110      | 67 + 3                                                  |                                                       |

| 0001000111      | 67 + 4                                                  |                                                       |

| 0001001000      | 67 + 5                                                  | 45                                                    |

| 0001001001      | 67 + 6                                                  |                                                       |

| 0001001010      | 67 + 7                                                  |                                                       |

| 0001001011      | 67 + 8                                                  | 50                                                    |

| 0001001100      | 67 + 9                                                  |                                                       |

|                 | 0001000011  0001000100  0001000100  0001000100  0001001 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

The value to be written in position 0 (stage 601<sub>0</sub>) is therefore (without taking the remainders into account)

0001001010 (indicated by the arrows pointing upward)

More generally speaking, let i still be the incoming time-slot to be connected to outgoing time-slot j. Put  $j-i=a \pmod{1024}$ .

Let "." represent the logic "AND" operation, "+" the logic "OR" operation and "plus" the arithmetic "binary addition" operation.

To connect time-slot i and j, the following word is written at the input of the address store at time t:

[

$$(a.2^8)$$

.  $(a plus 1.2^8)$

|   |     | , • | 1   |

|---|-----|-----|-----|

| - | con | tın | ued |

| • • • • • • • • • • • • • • • • • • • |                                                                                   |  |

|---------------------------------------|-----------------------------------------------------------------------------------|--|

| ·                                     | + (a plus $1.2^7$ ). (a plus $2.2^7$ )                                            |  |

| • • • • •                             | $+$ (a plus $2.2^6$ ). (a plus $3.2^6$ )                                          |  |

|                                       | + (a plus $3.2^5$ ). (a plus $4.2^5$ )                                            |  |

|                                       | + (a plus 4.2 <sup>4</sup> ) . (a plus 5.2 <sup>4</sup> )                         |  |

| 0                                     | + (a plus $5.2^3$ ). (a plus $6.2^3$ )                                            |  |

| •                                     | + (a plus $6.2^2$ ). (a plus $7.2^2$ )                                            |  |

| <i>:</i>                              | + (a plus $7.2^1$ ). (a plus $8.2^1$ )                                            |  |

| 5                                     | + (a plus $8.2^{\circ}$ ). (a plus $9.2^{\circ}$ )<br>+ $2^{-1}$ ] $\times 2^{1}$ |  |

The remainders to be initialized take the following values:

[  $(a.2^8)$  .  $(a plus 1.2^8)$ +  $(a plus 1.2^7)$  .  $(a plus 2.2^7)$ +  $(a plus 2.2^6)$  .  $(a plus 3.2^6)$ +  $(a plus 3.2^5)$  .  $(a plus 4.2^5)$ +  $(a plus 4.2^4)$  .  $(a plus 5.2^4)$ +  $(a plus 5.2^3)$  .  $(a plus 6.2^3)$ +  $(a plus 6.2^2)$  .  $(a plus 7.2^2)$ +  $(a plus 7.2^1)$  .  $(a plus 8.2^1)$ +  $(a plus 8.2^0)$  .  $(a plus 9.2^0)$ +  $(a plus 8.2^0)$  .  $(a plus 9.2^0)$

What we claim is:

1. A time division multiplex switching network com-40 prising:

in an input stage, a plurality of incoming multiplex highways and a supermultiplexer converting the said incoming multiplex highways into one incoming supermultiplex highway;

in an output stage, an out-going supermultiplex highway and a superdemultiplexer converting the said out-going supermultiplex highway into a plurality of out-going multiplex highways;

a circulating buffer store addressable by its content and comprising an input data word register and further data word registers forming a data word partial circulating store and an input random address register and further random address registers forming a random address partial circulating store, said data word partial circulating store and said random address partial circulating store operating synchronously and having associated data word registers and random address registers;

means for successively writing in the input data word register the words present in the incoming timeslots of the incoming supermultiplex highway;

means for successively writing in the input random address register addresses depending on the outgoing time slots to be connected to the incoming time slots;

means for steppedly incrementing by 1 the addresses written in the input random address register each time said addresses pass from a random address

register to the next of the random address partial circulating store, and

means for reading out the word stored in a data word register associated with a random address register when the incremented address stored therein has reached a predetermined value

2. A time division multiplex switching network as set forth in claim 1, in which the means for steppedly incre- 10 menting by 1 the addresses written in the input random address register consists in a unit addend register forming a counter with said random address register, said counter overflowing for a predetermined value and said 15

reading means are operated when the incremented address has reached said counter overflowing value

3. A time division multiplex switching network as set forth in claim 1 in which the random addresses have k bits and the means for steppedly incrementing by 1 the addresses written in the input random address register are distributed addition means synchronous with the circulating buffer store successively adding 1 to the bit of binary weight 0 in a first addition, adding the carry over of said first addition to the bit of binary weight 1, in a second addition, adding the carry over of the (k-1)th addition to the bit of binary weight (k-1) in a (k-1)th addition, the carry over of said (k-1)th addition controlling said reading out means.

20

·ZJ

30

33

40

45