## Morihisa

Mar. 30, 1982 [45]

| [54] | CRYSTAL OSCILLATOR IMPLEMENTEI WITH CMOS TECHNOLOGY                                                      |                                         |  |

|------|----------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| [75] | Inventor:                                                                                                | Mitsuo Morihisa, Nara, Japan            |  |

| [73] | Assignee:                                                                                                | Sharp Kabushiki Kaisha, Osaka,<br>Japan |  |

| [21] | Appl. No.:                                                                                               | 57,989                                  |  |

| [22] | Filed:                                                                                                   | Jul. 16, 1979                           |  |

|      | Relat                                                                                                    | ted U.S. Application Data               |  |

| [62] | Division of Ser. No. 868,432, Jan. 10, 1978, abando<br>which is a division of Ser. No. 760,522, Jan. 19, |                                         |  |

| [62] | Division of Ser. No. 868,432, Jan. 10, 1978, abandoned, |  |  |  |  |  |

|------|---------------------------------------------------------|--|--|--|--|--|

|      | which is a division of Ser. No. 760,522, Jan. 19, 1977, |  |  |  |  |  |

|      | Pat. No. 4,091,338.                                     |  |  |  |  |  |

| [30] | Foreign Applicatio    | n Priority Data            |

|------|-----------------------|----------------------------|

| Jan  | 19, 1976 [JP] Japan . | 51-5220                    |

| Mar  | 18, 1976 [JP] Japan.  | 51-30041                   |

| Jul  | 12, 1976 [JP] Japan.  | 51-83238                   |

| [51] | Int. Cl. <sup>3</sup> | Н03В 5/36                  |

| [52] |                       | 331/116 FE; 331/158        |

| [58] | Field of Search 3     | 31/116 R, 116 FE, 108 C,   |

|      | 331/108 <b>D</b> , 1  | 58, 159; 368/156, 157, 167 |

| [56] | Reference             | s Cited                    |

## U.S. PATENT DOCUMENTS 2,981,899 4/1961 Hahuel ...... 331/116 R

| 3,040,272 | 6/1962 | Hukee 331/159 X   |  |

|-----------|--------|-------------------|--|

| 3,824,495 | 7/1974 | Gerum 331/159 X   |  |

| 3,979,693 | 9/1976 | Saari 331/116 R X |  |

### OTHER PUBLICATIONS

Olson, "Standard MOS NOR gate serves as 100-KHz clock", Electronic Design, vol. 13, Jun. 21, 1969, pp. 90, 91.

Primary Examiner—Siegfried H. Grimm Attorney, Agent, or Firm-Birch, Stewart, Kolasch & Birch

#### [57] **ABSTRACT**

In a crystal oscillator for solid state wristwatches, the input of an impedance converter is connected to the output of a complementarily connected transistor amplifier which performs linear operation within its essential operating range, to thereby stabilize and decrease the output impedance of the amplifier on the average. The impedance converter includes one or more active elements such as MOSFET's, junction type FET's and bipolar transistors. A quartz resonator is connected between the input of the complementarily connected transistor amplifier and the output of the impedance converter.

#### 3 Claims, 24 Drawing Figures

.

F1G. 4

F1G. 5

F1G. 7

.

•

Mar. 30, 1982

F1G. 9

F1G. 12

F1G. 17

Mar. 30, 1982

U.S. Patent Mar. 30, 1982

Mar. 30, 1982

2

# CRYSTAL OSCILLATOR IMPLEMENTED WITH CMOS TECHNOLOGY

This is a divisional of application Ser. No. 868,432, 5 filed Jan. 10, 1978, now abandoned, which is a divisional of application Ser. No. 760,522, filed Jan. 19, 1977 and now U.S. Pat. No. 4,091,338.

#### BACKGROUND OF THE INVENTION

The present invention relates to CMOS amplifiers useful for crystal oscillators.

In the past, a CMOS analog amplifier as illustrated in FIG. 1 was employed as an amplifier in crystal oscillators for a variety of electronic apparatuses for example 15 solid state wristwatches to fulfill low power consumption requirements. The amplifier includes a basic inverter consisting of a P-channel MOS transistor P and an N-channel MOS transistor N, and a resistor  $R_f$  of a high resistance value connected between an input terminal  $V_{in}$  and an output terminal  $V_{out}$  of the complementary MOS inverter for biasing purposes. Advantageously, the circuit exhibits high gain, low power dissipation performance characteristics while retaining simple circuit construction.

Nevertheless, one difficulty is experienced in reducing the output impedance in the vicinity of the operating center of the CMOS inverter. If the output impedance is forced into a low impedance state, there is a requirement that the mutual conductance of the P-channel and N-channel MOS transistors be increased while the threshold level voltage  $V_{th}$  thereof be decreased. Those requirements result in an increase in dissipation of current. In addition, because the output impedance is constructed by active elements such as MOS transistors, 35 the output impedance is greatly varied in accordance with input and output potential levels, power supply voltages, temperatures, etc.

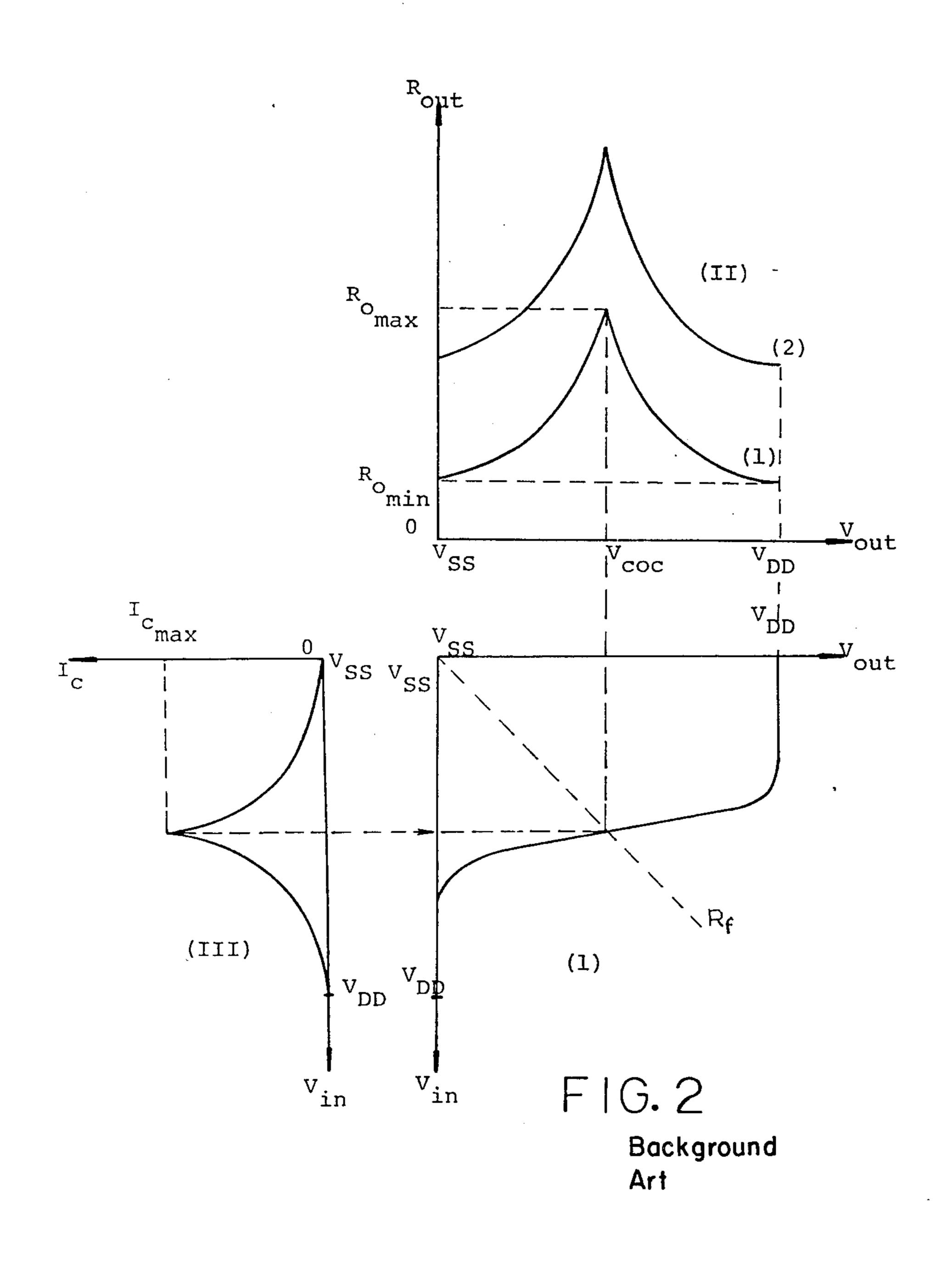

FIG. 2 depicts interrelation among an input voltage  $V_{in}$ , an output voltage  $V_{out}$ , output impedance  $R_{out}$ , 40 current  $I_c$  flowing through P- and N- MOS transistors when supplied with a voltage  $(V_{DD}-V_{SS})$ , which occur within the CMOS analog amplifier of FIG. 1.

The graph (I) in FIG. 2 shows a  $V_{in}$ - $V_{out}$  characteristic of a conventional CMOS transistor, indicating that 45  $V_{in}$  is biased at the substantially same as  $V_{out}$  via the bias resistor  $R_f$  and thus the CMOS operating center  $V_{coc}$  is given. The graph (II) shows the dependency of the output impedance  $R_{out}$  upon variations in the output voltage  $V_{out}$ , indicating that  $R_{out}$  tends to take a maximum at the operating center  $V_{coc}$  and reduce when the power supply potential approximates either  $V_{DD}$  or  $V_{SS}$ . Analysis of the graph (II) also reveals the fact that a reduction in the power supply voltage ( $V_{DD}$ - $V_{SS}$ ) and a temperature rise permit the output impedance  $R_{out}$  to 55 be increased as suggested by the curves (1) and (2).

The graph (III) shows variations in the current  $I_c$  flowing through the CMOS when supplied with  $(V_{DD}-V_{SS})$ , as a function of the input potential  $V_{in}$ . While the current  $I_c$  has a peak at the operating center, the same is 60 correspondingly reduced in accordance with a degree of deviation from the operating center  $V_{coc}$ .

FIG. 3 shows an example wherein the above discussed type of the amplifier is applied to timekeeping crystal oscillators having a frequency of about 32.768 65 KHz. A quartz resonator is denoted as X and phase shifting or frequency adjustment capacitors are denoted as C<sub>1</sub> and C<sub>2</sub>. When the crystal impedance value (here-

inafter referred to as the CI of the quartz resonator X is relatively small (typically, in the order of several tens  $K\Omega$ ), the crystal oscillator of FIG. 3 is satisfactory for practical use of timekeeping devices. The critical conditions for practical use of timekeeping devices are that changes in oscillation frequency due to power supply voltage change  $\Delta f/f.V$  be below 1.0 sec/day.V, dissipation of current under a voltage supply of 1.6 V be below 5  $\mu$ A, the lowest oscillation initiating voltage be below 1.4 V and the oscillation initiating period be within 8 seconds.

However, if CI of the quartz resonator X is increased beyond 100 K $\Omega$ , the circuit of FIG. 1 can fulfill these requirements no longer. In the event that CI is several hundred K $\Omega$ , oscillation will be very difficult. It is believed that this is caused by the above disadvantages mentioned with respect to the CMOS analog amplifier of FIG. 1.

In a characteristic diagram of FIG. 2, the difficulty in reducing the output impedance Romax in the vicinity of the operating center  $V_{coc}$  causes the period of time required for initiating oscillation to be considerably longer because it is difficult to excite the quartz resonator in order to initiate oscillation. In addition, the difficulty in reducing the average of the output impedance  $R_{out}$  implies an increase in the oscillation initiating voltage is required.

The greater the variations in the output impedance  $R_{out}$  of the amplifier as a function of power voltage variations, the greater the regulation of the oscillation frequency. Although silver batteries recommended for use in solid state wristwatches can provide a comparatively stable discharge voltage when loaded with a light-load, their temperature dependencies vary from battery to battery to thereby adversely effect the performances of the oscillator.

When the CI of the quartz resonator is increased in this way, the attenuation factor of a feed-back system including a phase shifter is correspondingly increased. As a consequence, the difficulty in initiating oscillation is still not avoided since the maximum and average of the output impedance  $R_{out}$  of the amplifier remain unchanged at their high values.

Accordingly, it is a primary object of the present invention to provide an improved amplifier suited for effectively exciting quartz resonators of relatively high CI, which has the advantage of comparatively high gain, comparatively low output impedance, minimized variations in output impedance, and minimized power dissipation.

## BRIEF DESCRIPTION OF DRAWINGS

Other objects and novel features of the present invention are set forth in the appended claims and the present invention as to its organization and its mode of operation will best be understood from a consideration of the following detailed description of the preferred embodiments taken in connection with the accompanying drawings, wherein:

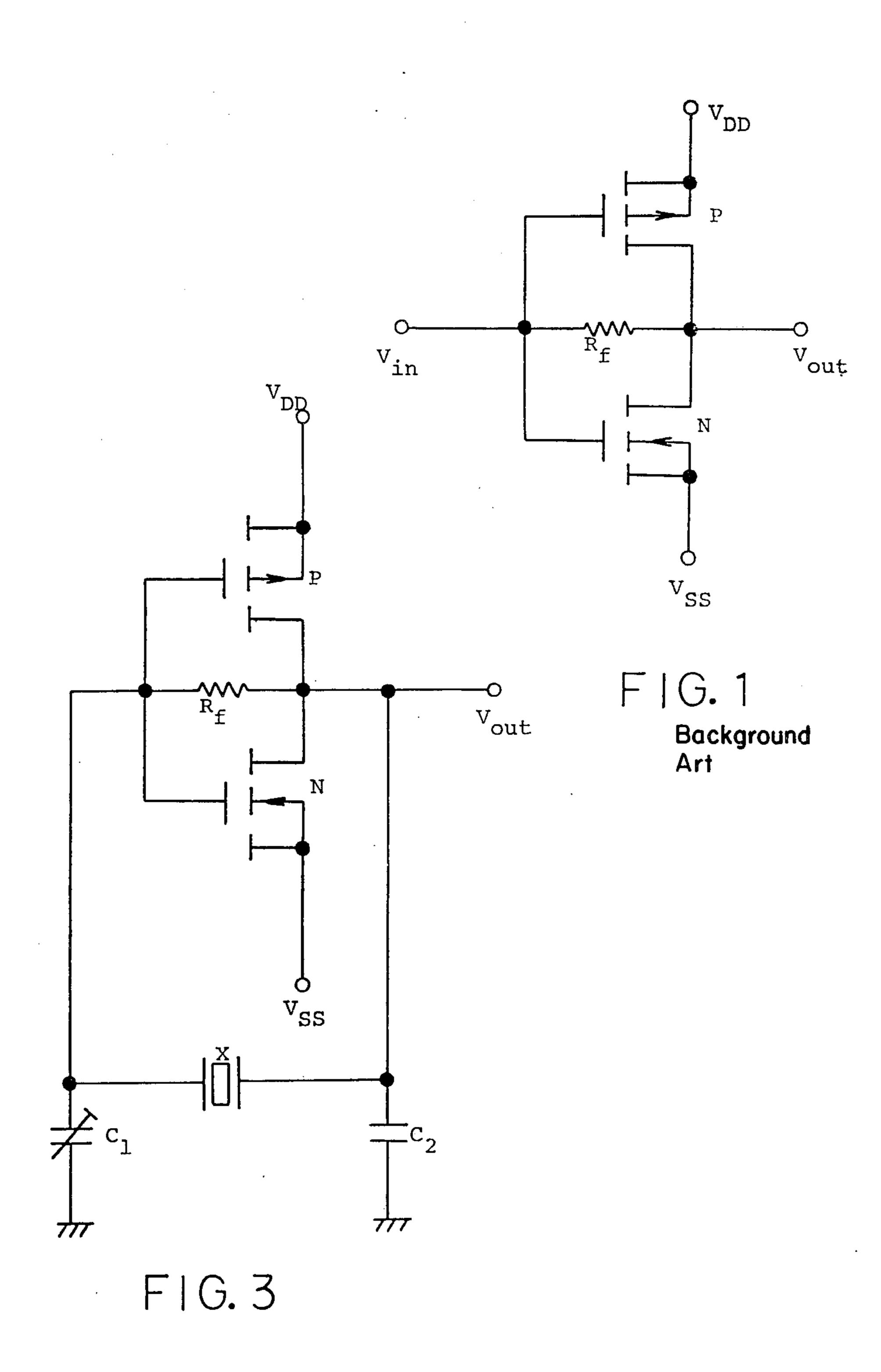

FIG. 1 is a circuit diagram of a prior art CMOS analog amplifier;

FIG. 2 is a graph showing the operating characteristics of the analog amplifier of FIG. 1;

FIG. 3 is a circuit diagram of an example of applications of the analog amplifier of FIG. 1; P FIG. 4 is a circuit diagram of one preferred form of an analog amplifier constructed in accordance with the present invention;

may be useful.

3

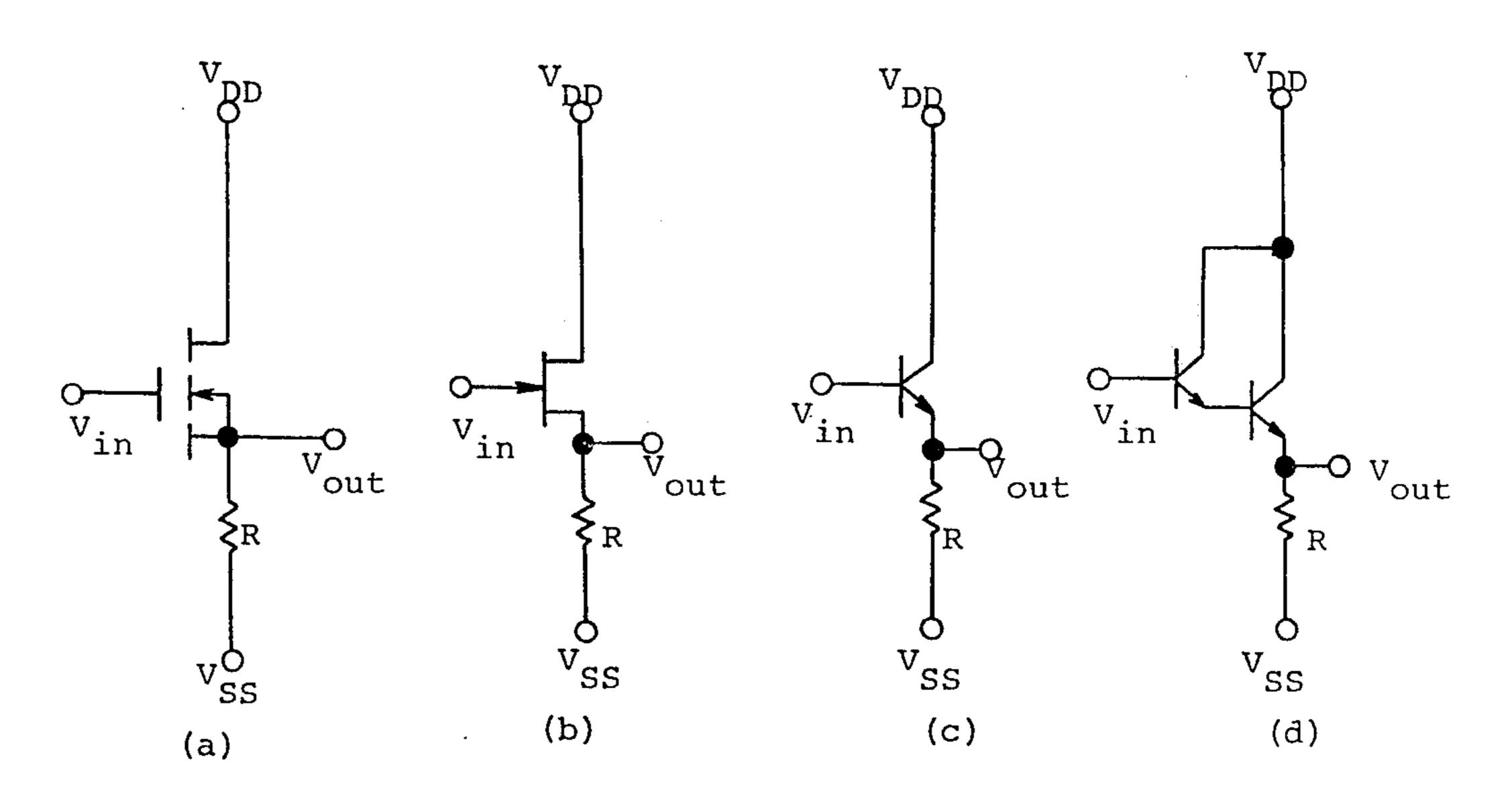

FIGS. 5(a), 5(b), 5(c) and 5(d) are circuit diagrams of examples of the essential implementations of the circuit of FIG. 4;

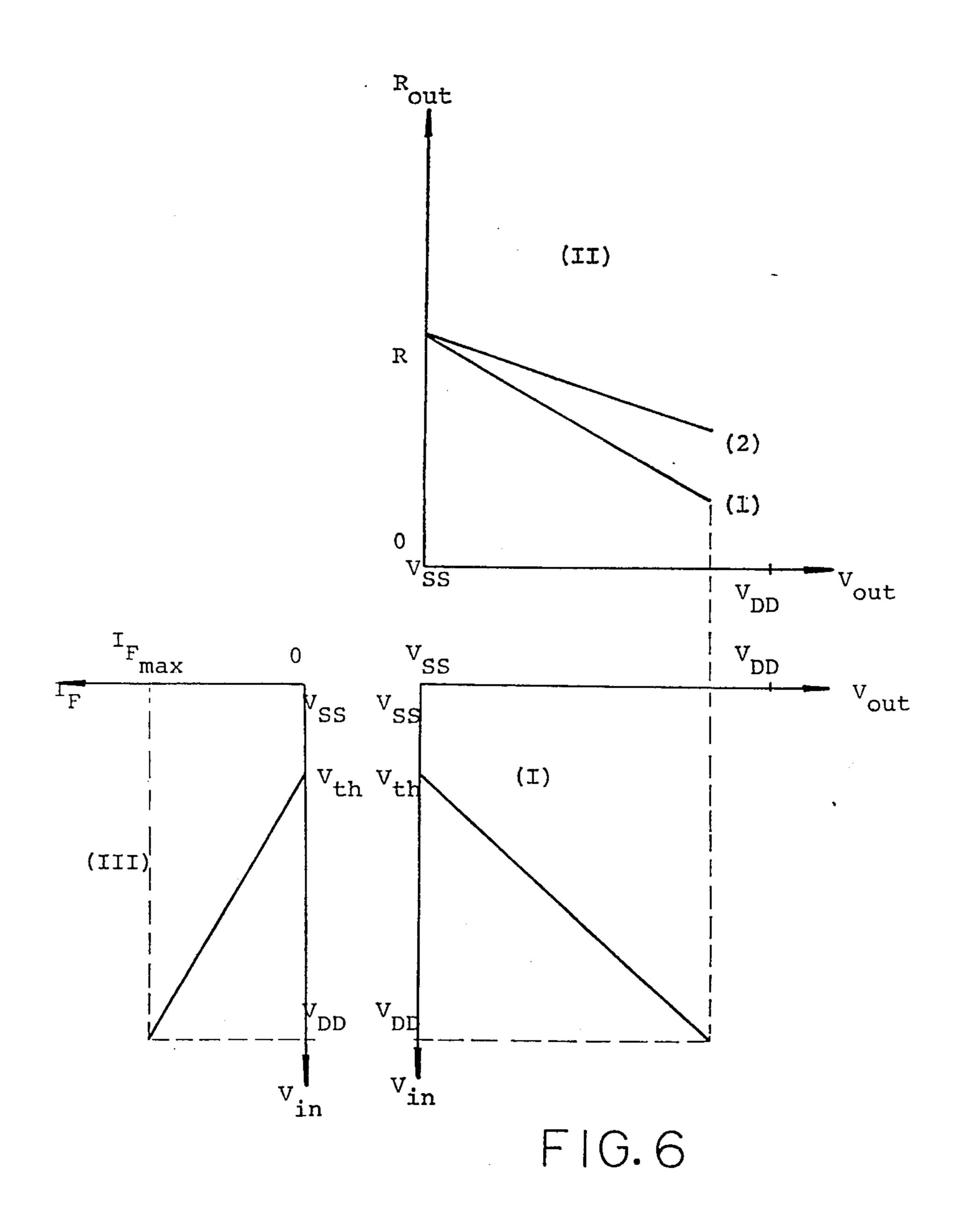

FIG. 6 is a graph showing operating characteristics of the example shown in FIG. 5(a);

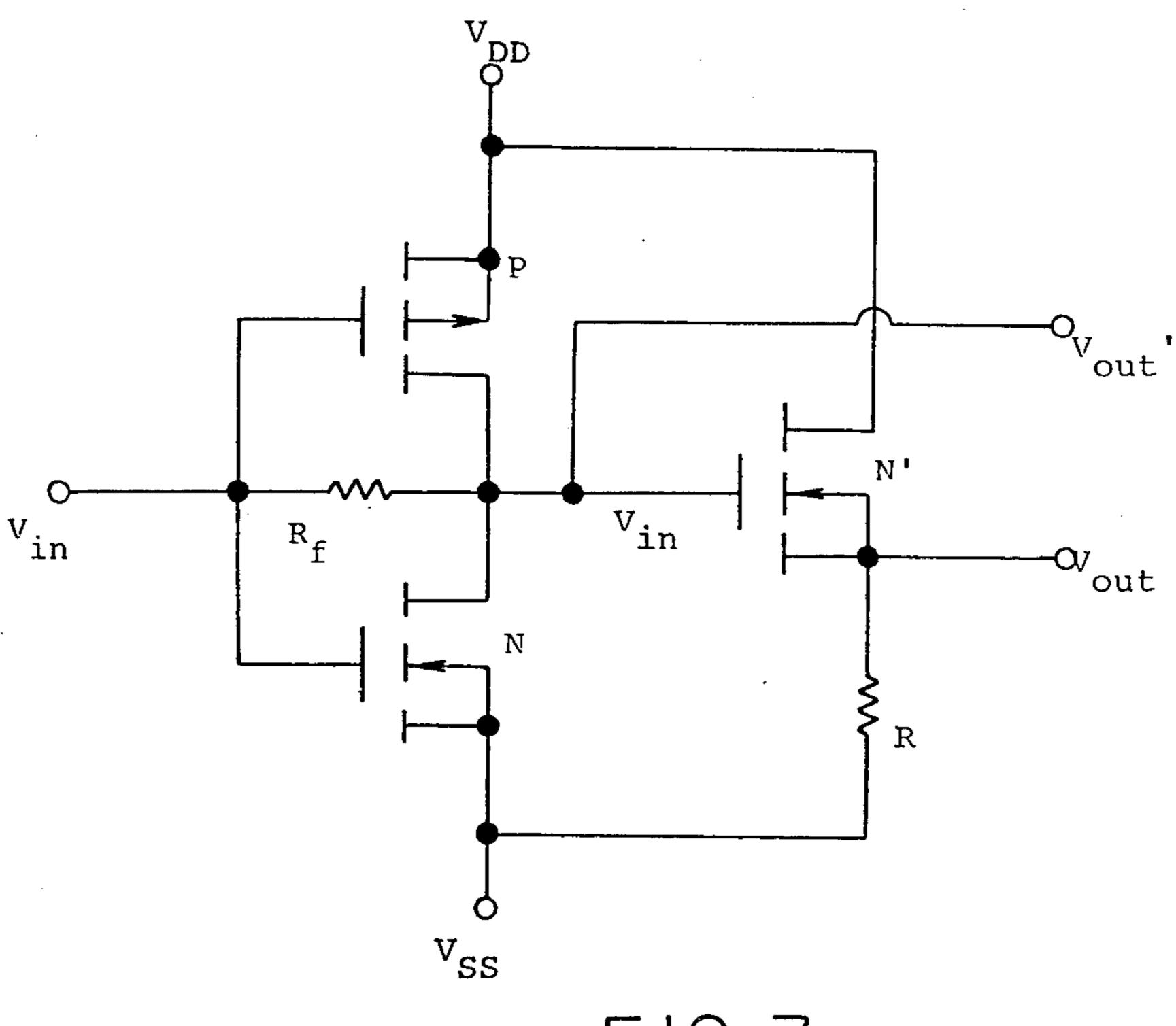

FIG. 7 is a circuit diagram of another preferred form of the present invention;

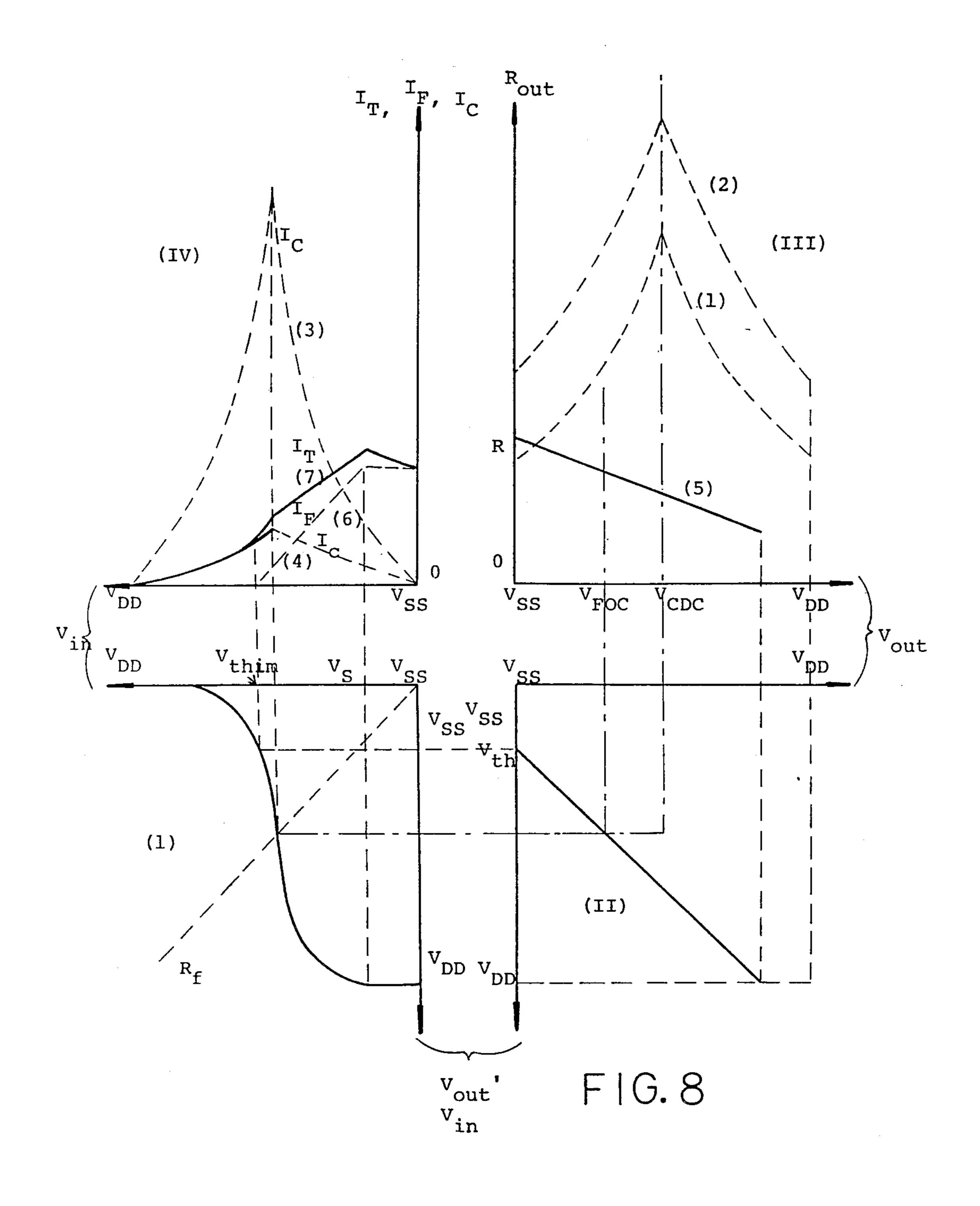

FIG. 8 is a graph showing operating characteristics of the circuit of FIG. 7 for illustration of operation;

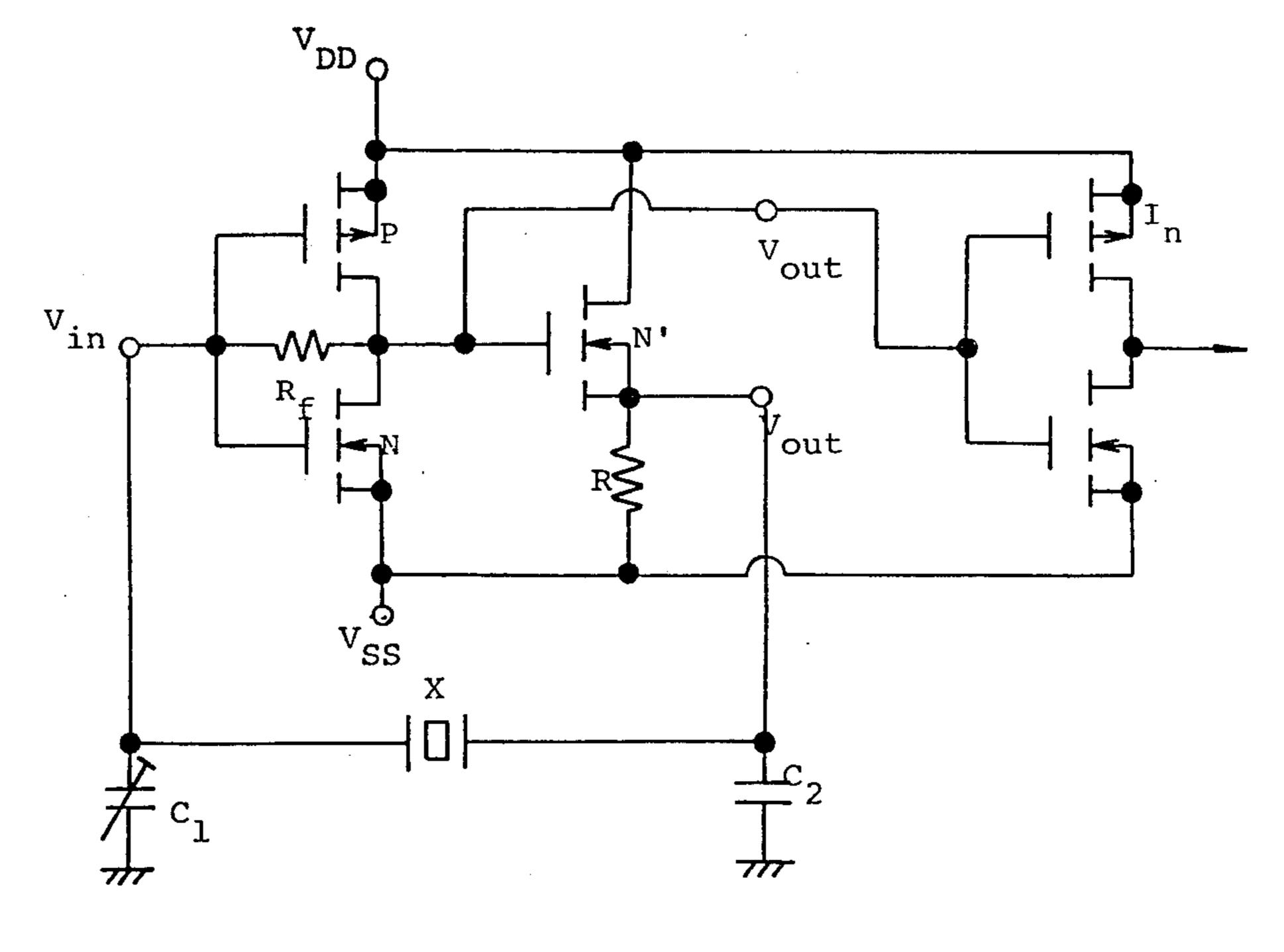

FIG. 9 is a circuit diagram of an example of application of the present invention;

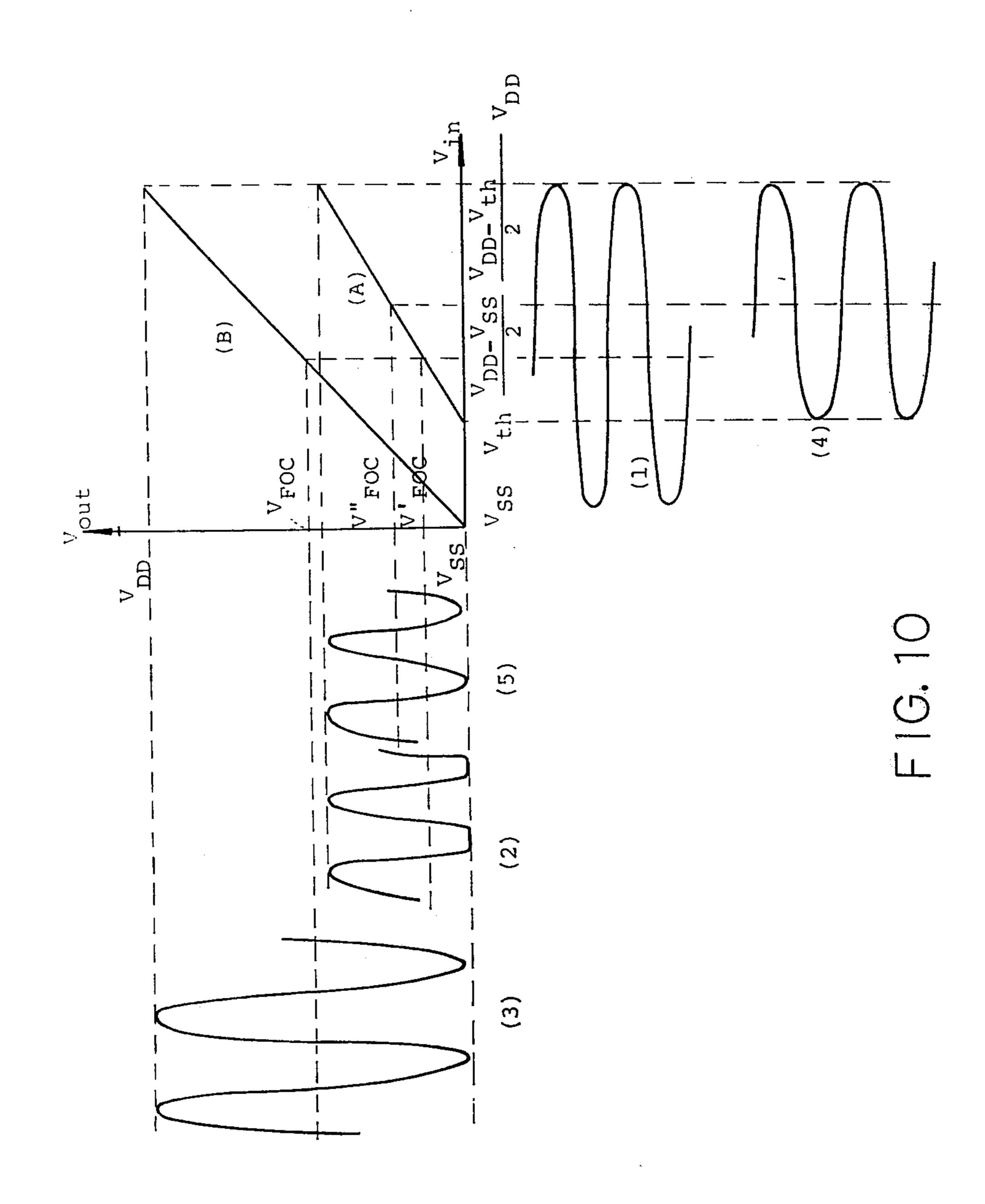

FIG. 10 is a graph showing operating characteristics of the embodiment of FIG. 7;

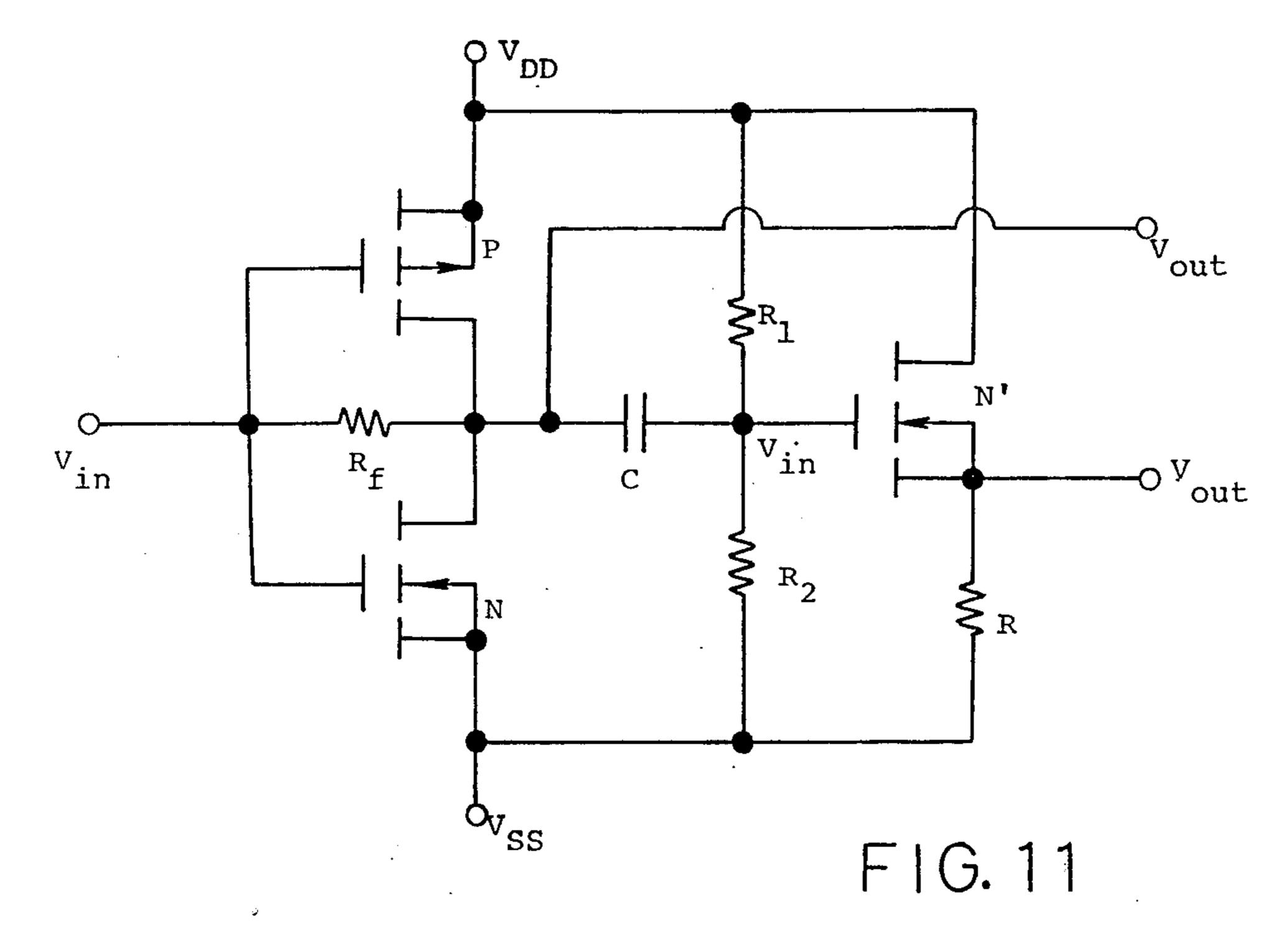

FIG. 11 is a circuit diagram of still another preferred form of the present invention;

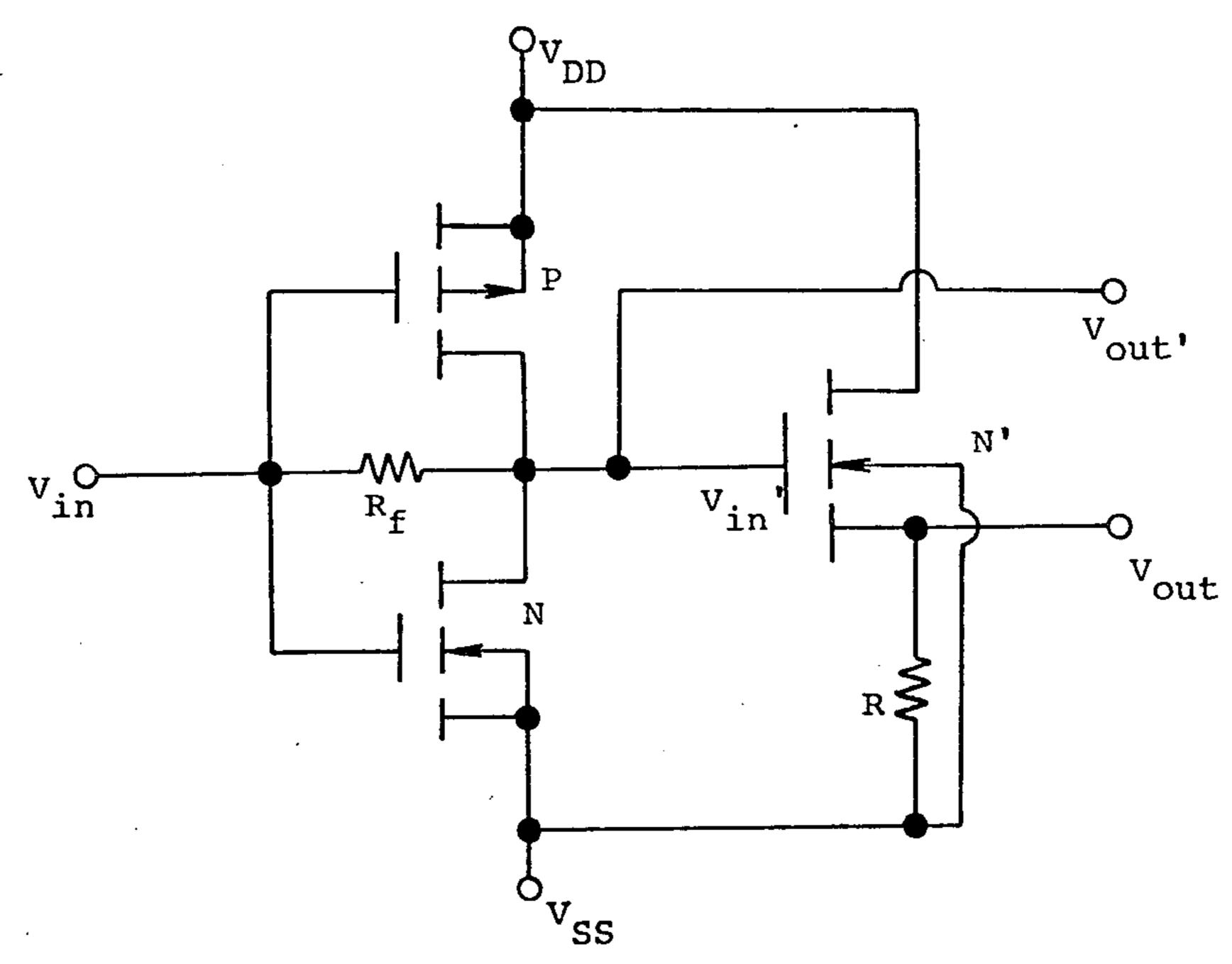

FIG. 12 is a circuit diagram of another preferred form of the present invention;

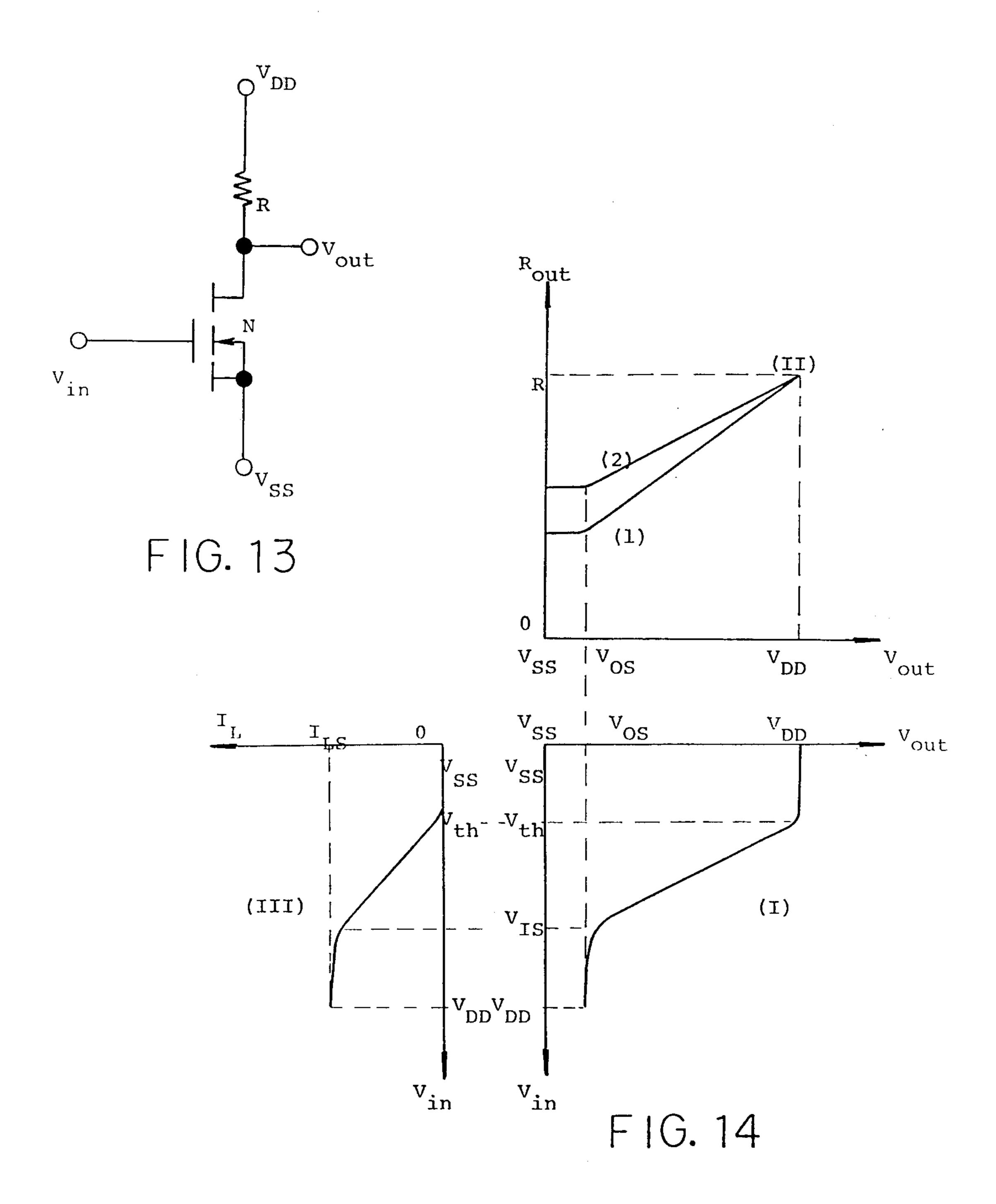

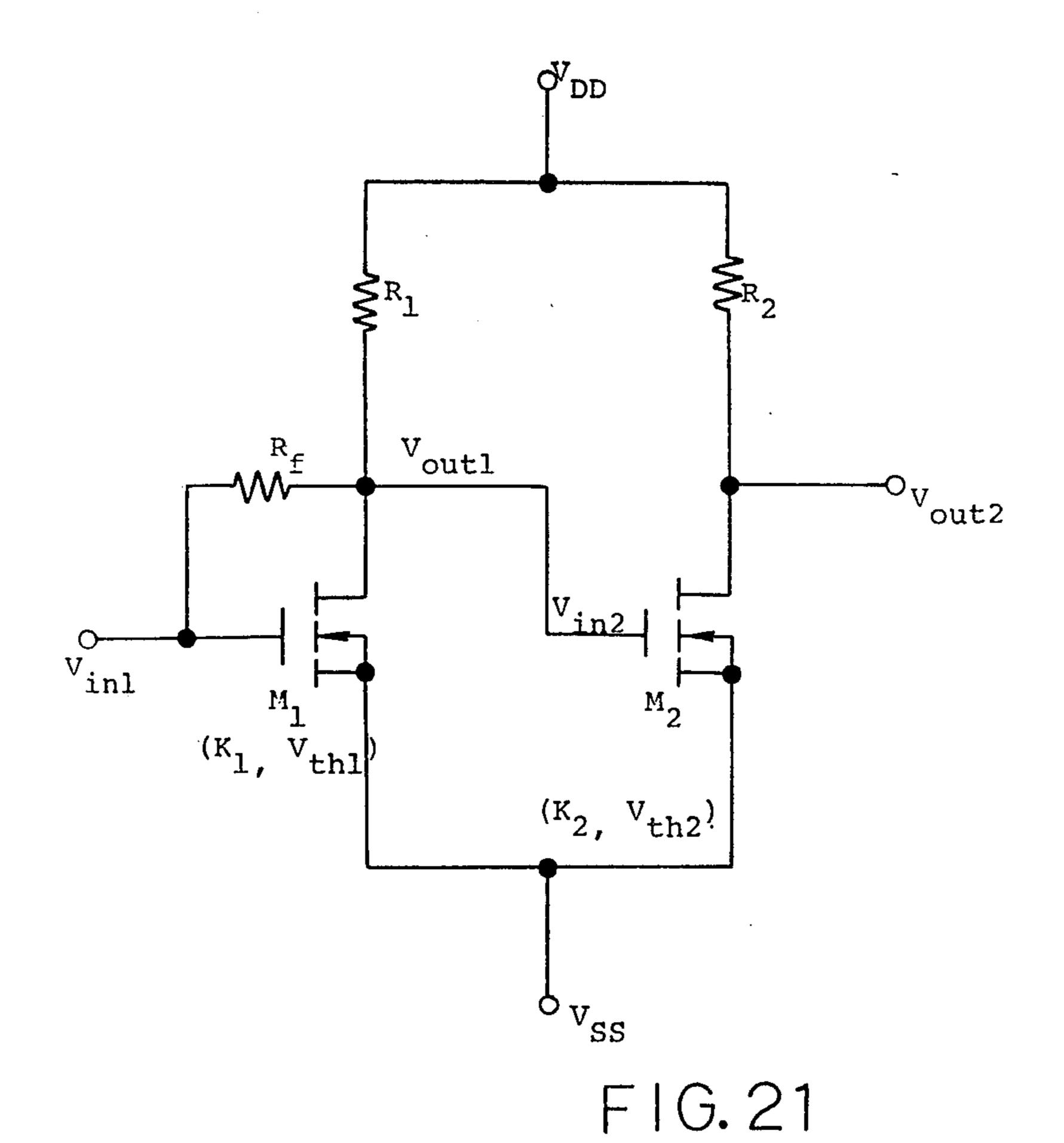

FIG. 13 is a circuit diagram of a resistor load MOS amplifier;

FIG. 14 is a graph showing operating characteristics 20 lished by only passive elements. of the amplifier of FIG. 13;

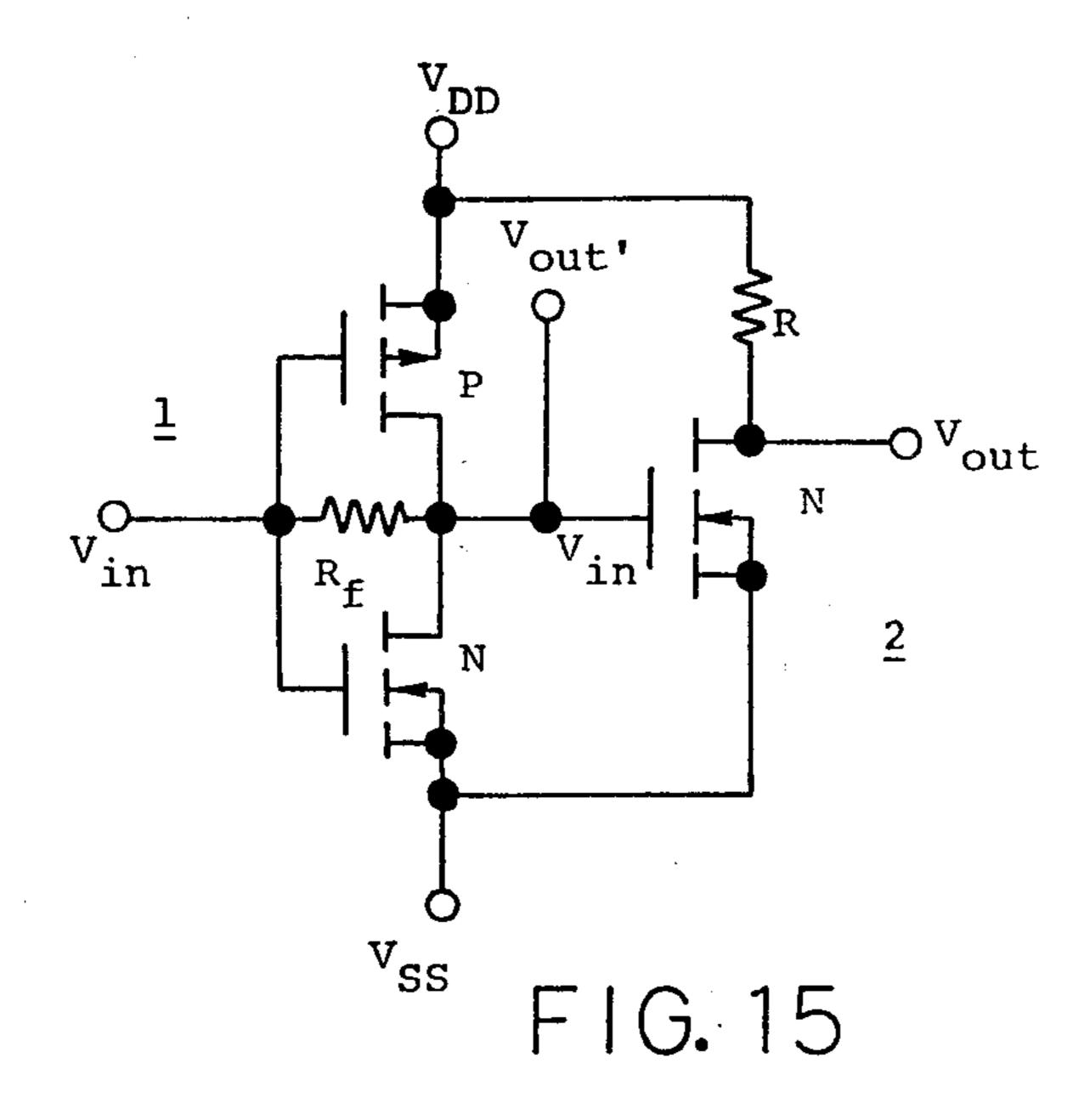

FIG. 15 is a circuit diagram of one preferred form of the present invention utilizing the resistor-loaded MOS amplifier;

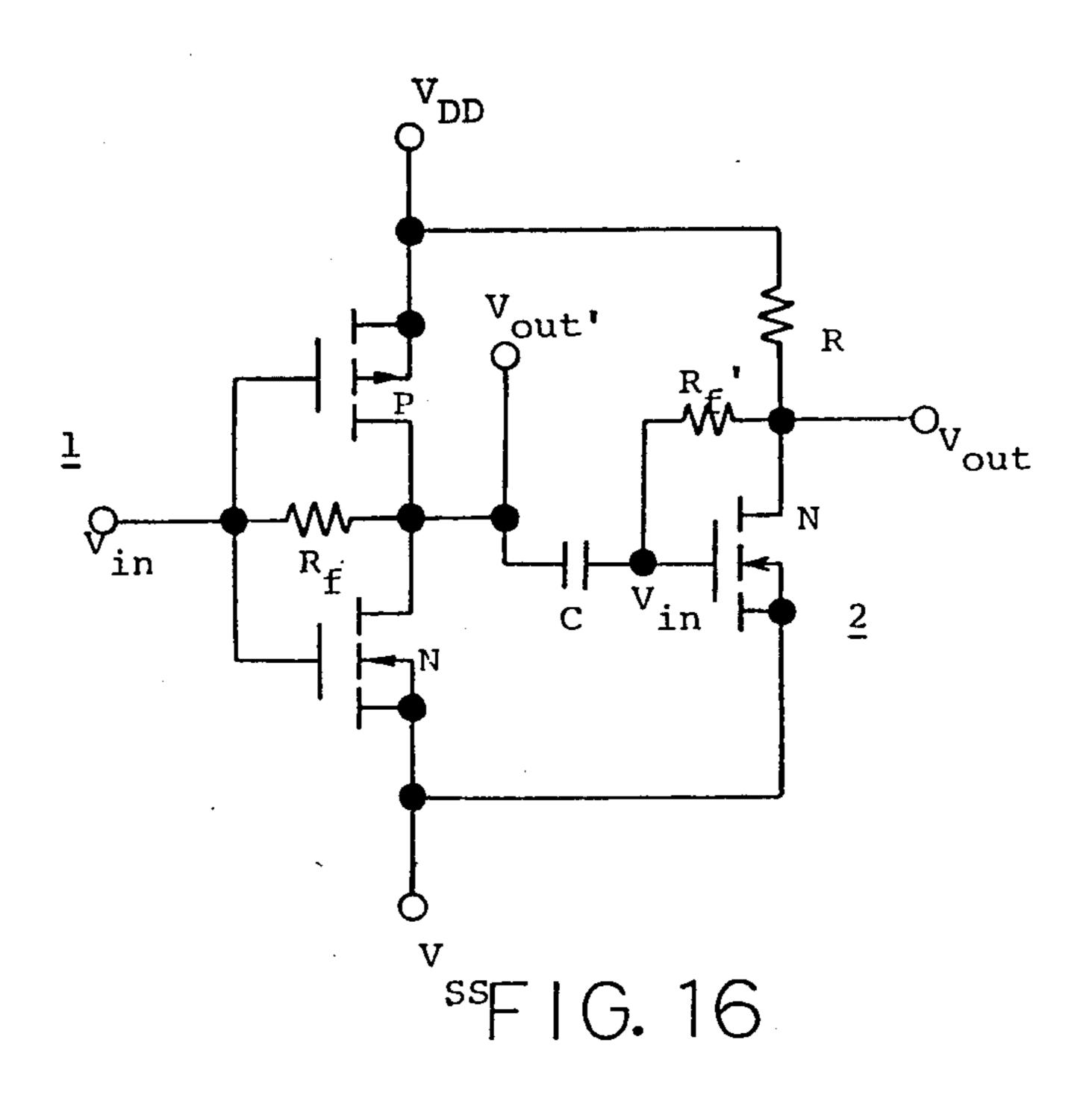

FIG. 16 is a circuit diagram of another preferred form 25 increase current consumption. of the present invention utilizing the resistor-loaded  $V_{in}$ , output voltage  $V_{out}$ , output voltage  $V_{o$

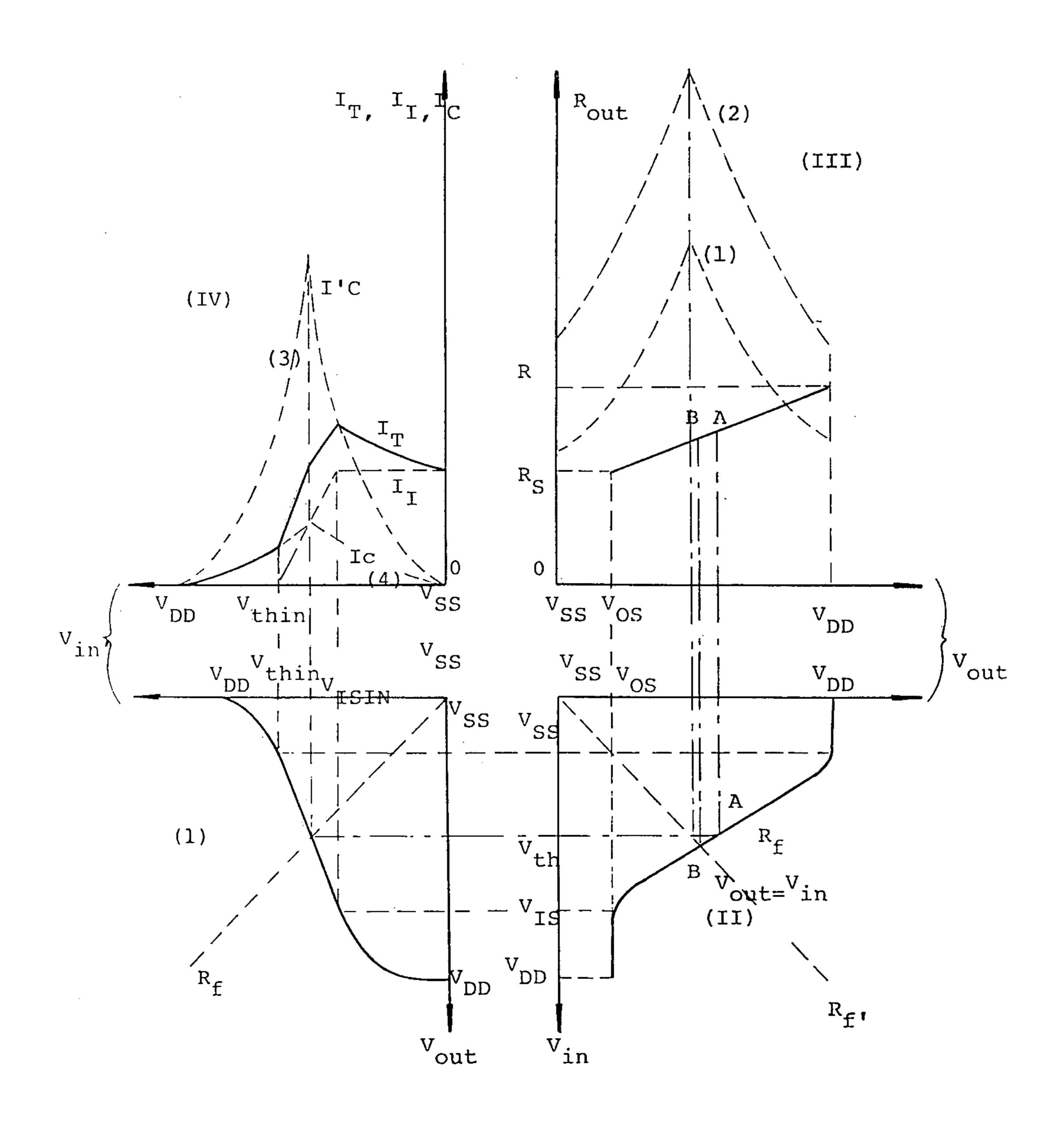

FIG. 17 is a graph of characteristic curves for the purpose of illustration of operation of the embodiments of FIGS. 15 and 16;

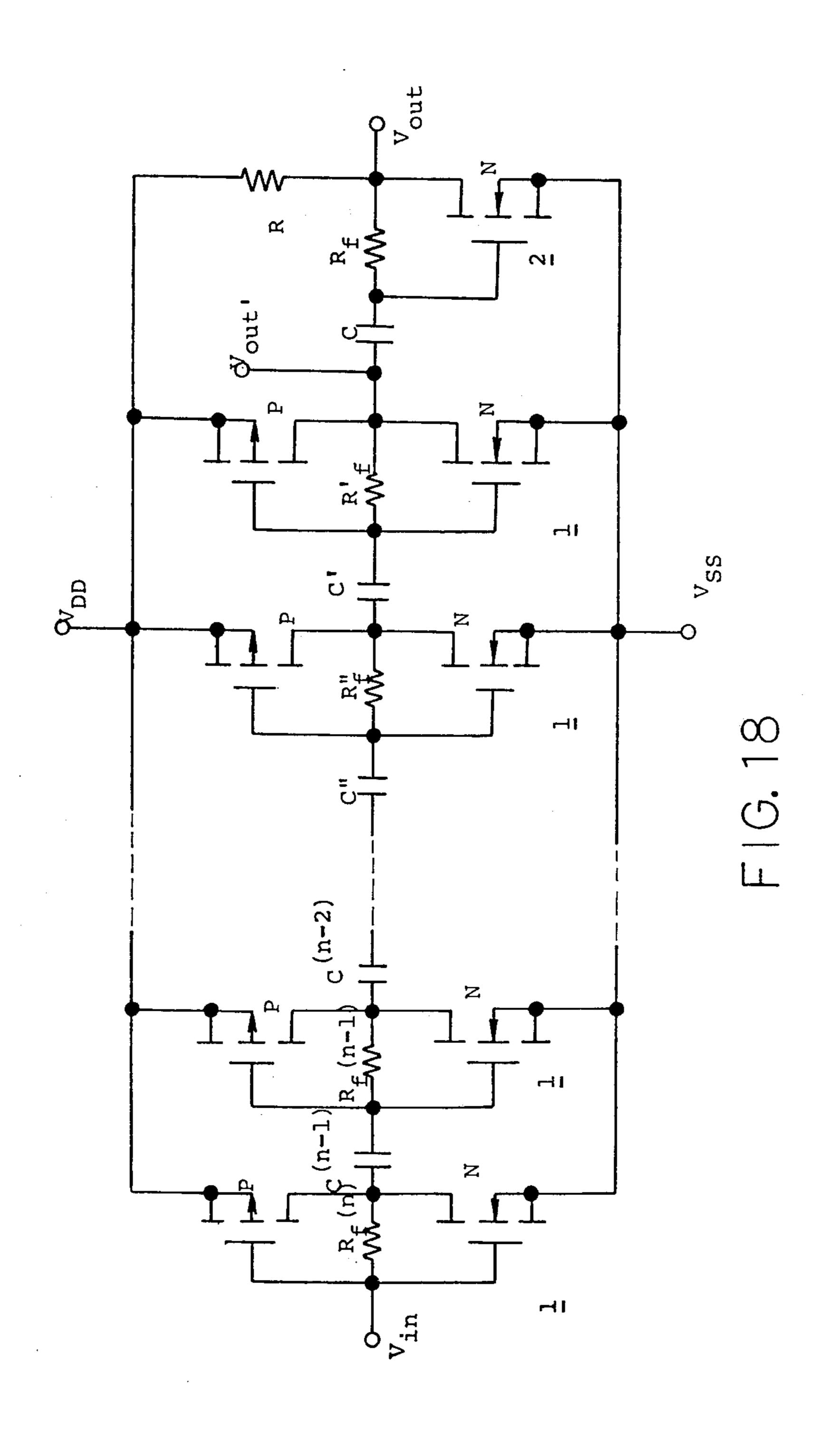

FIG. 18 is a circuit diagram of a multi-stage amplifier utilizing the portion of the circuit of FIG. 16;

FIG. 19 is a circuit diagram of an oscillator utilizing the multi-stage amplifier of FIG. 18;

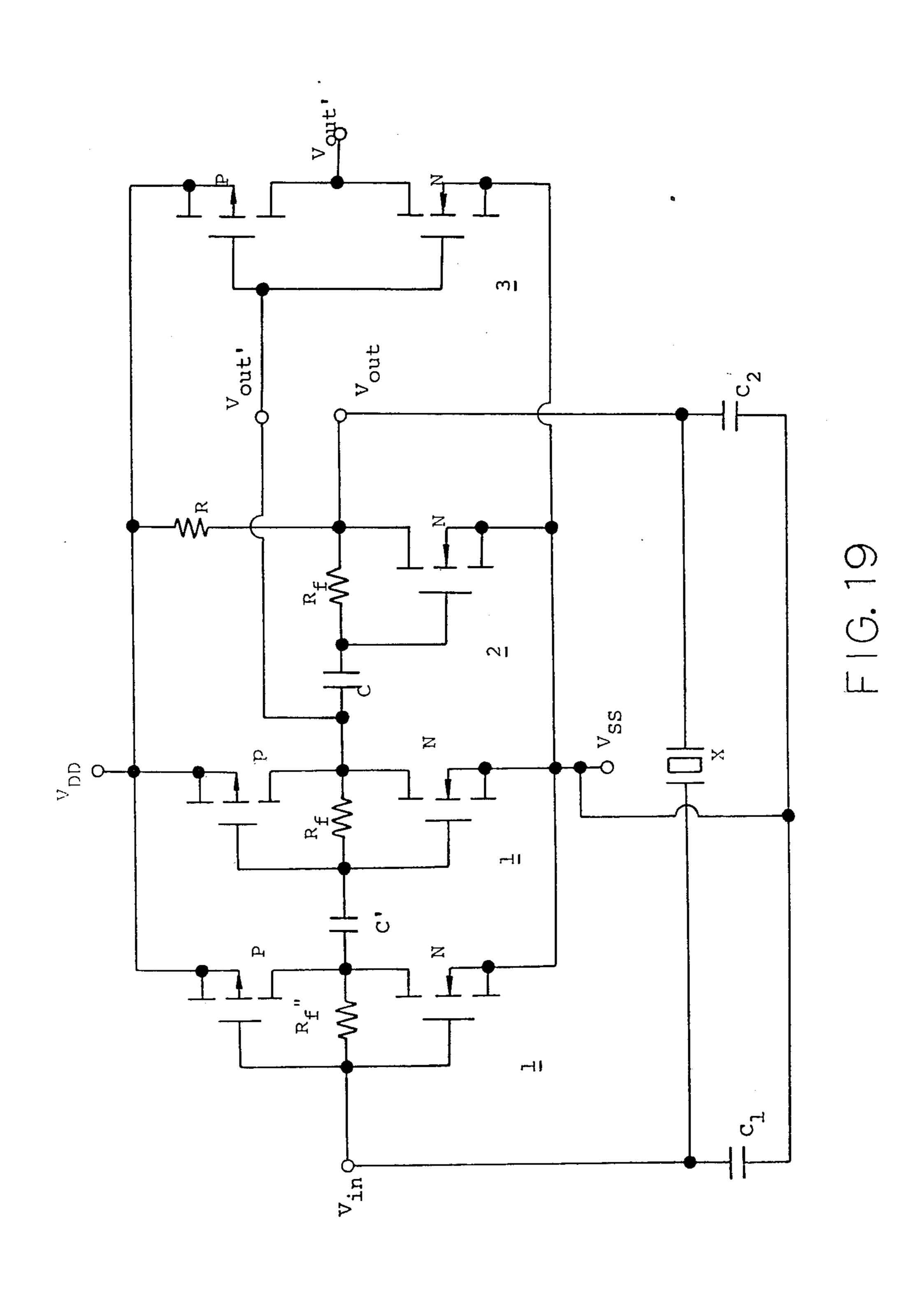

FIG. 20 is a graph showing frequency characteristic 35 of the amplifier of FIG. 9;

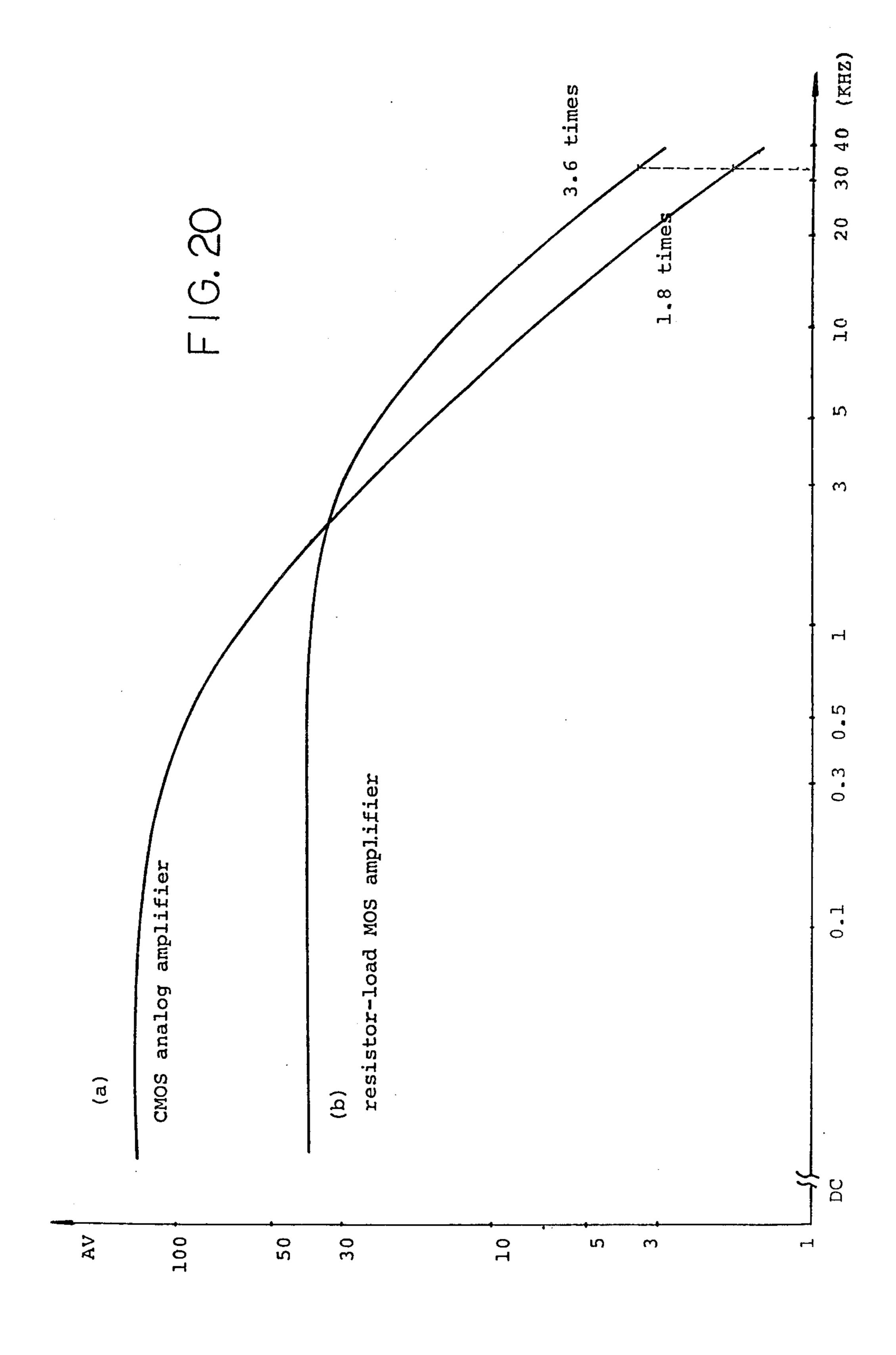

FIG. 21 is a circuit diagram of one preferred form of the present invention effective to improve the frequency characteristic of FIG. 20;

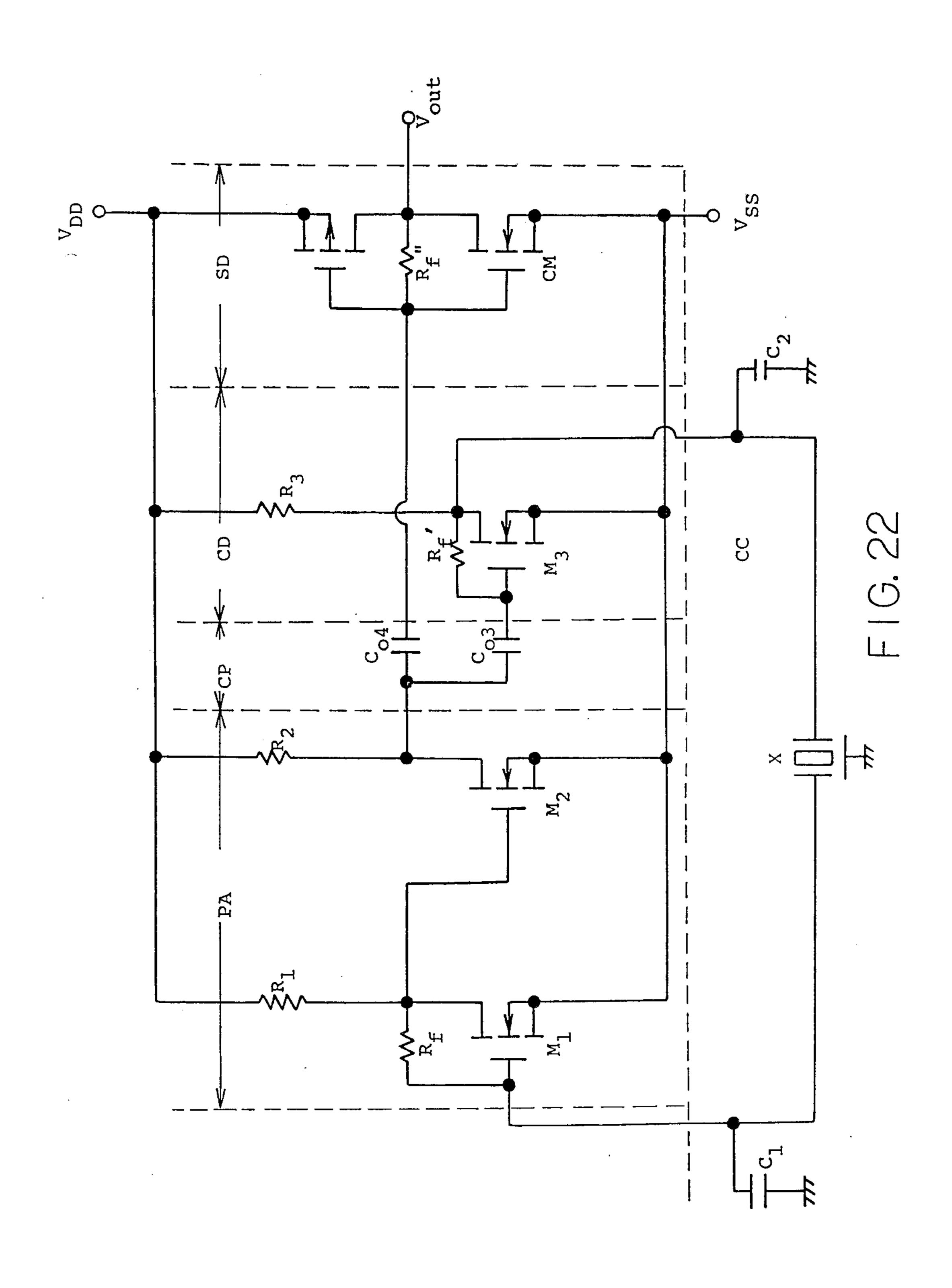

FIG. 22 is a circuit diagram of an oscillator incorpo- 40 rating the embodiment of FIG. 21 thereinto; and

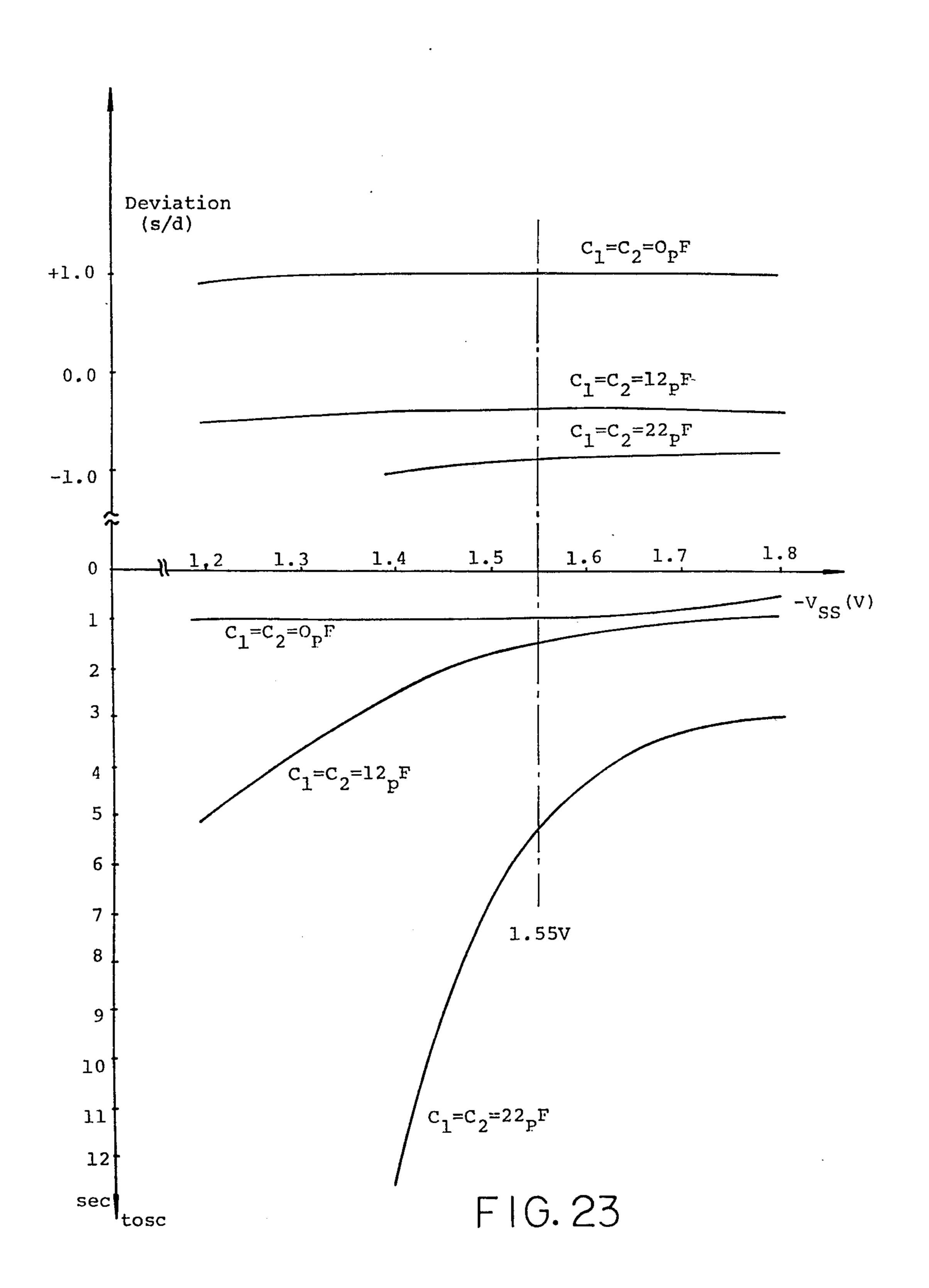

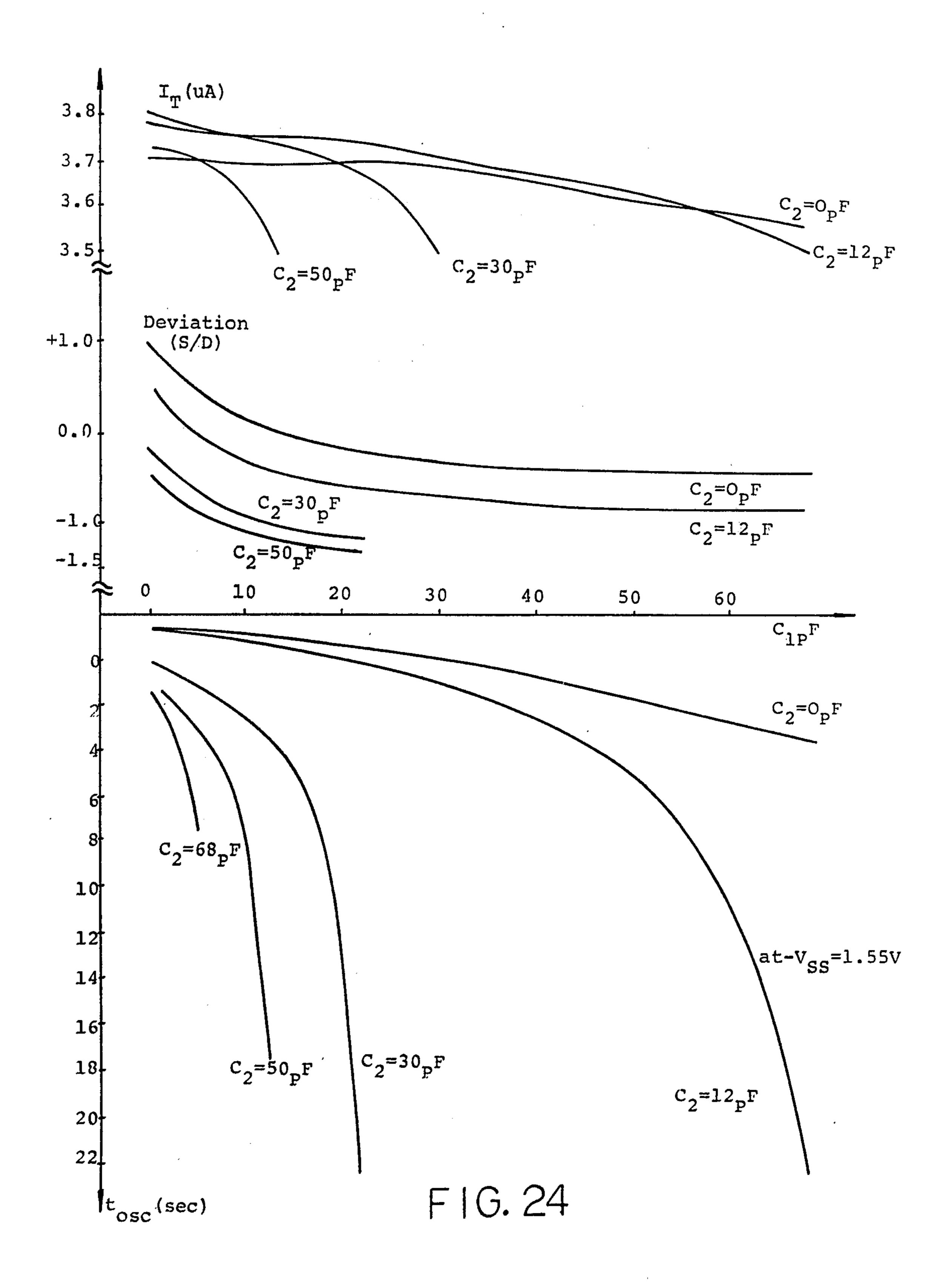

FIGS. 23 and 24 are graphic representations of operating characteristics of the circuit of FIG. 22.

### DETAILED DESCRIPTION OF INVENTION

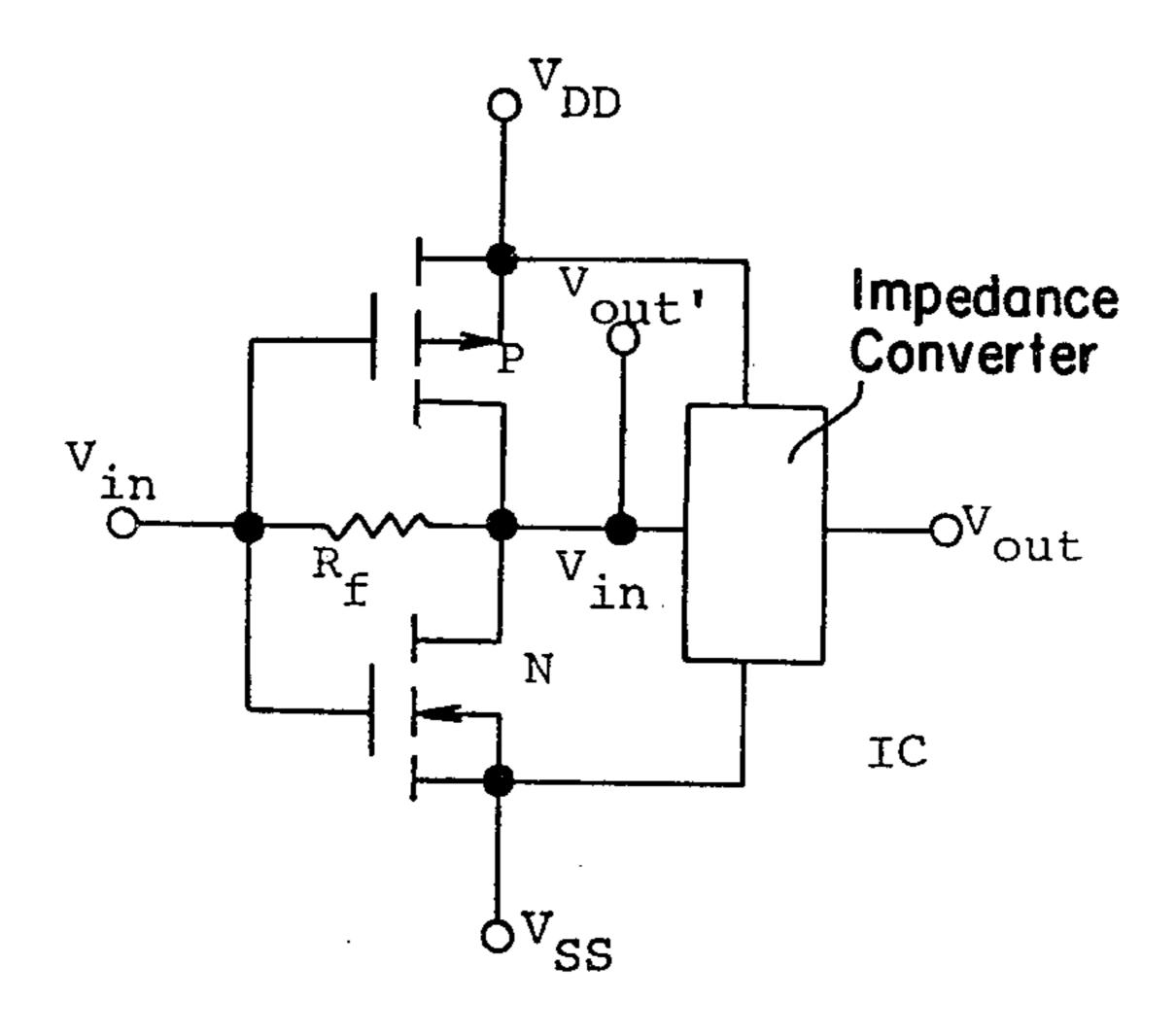

Attention is initially called to FIG. 4 of the drawings which illustrates a basic construction of an amplifier embodying the present invention. A CMOS analog amplifier having high gain and low power consumption properties as briefly described above is provided at its 50 output with an impedance converter IC which has a considerably higher input impedance and a considerably lower output impedance, for the purposes of reducing the output impedance of the CMOS analog amplifier. The resulting circuit arrangement assures low out- 55 put impedance and low power consumption while keeping the high gain properties of the CMOS scheme.

The impedance converter IC may take a variety of forms some of which are shown in FIGS. 5(a) through 5(d).

In case where the basic circuit construction is in the form of CMOS as described above, a MOSFET follower as suggested in FIG. 5(a) is most beneficial because of its simplicity of integrated circuit manufacture. However, when taking only the function of the impedance converter into account, a junction type FET of FIG. 5(b), or bipolar transistors of FIGS. 5(c) and 5(d) may be equally applicable. In any case, since the output

impedance of the CMOS analog amplifier is considerably high, it is recommended that the input impedance of the impedance converter IC be as high as possible. To this end, for the emitter follower of FIG. 5(c)  $\beta$  should be as high as possible. In case of FIG. 5(d), a Darlington Connection may be used. Moreover, super- $\beta$  transistors may be employed. Other elements may be employed as far as they do not interfere with the performances of the impedance converter. In the case of FET's, P-channel or N-channel enhancement mode or depletion mode

FET's are optionally selectable. In the case of bipolar

transistors, either PNP type or NPN type transistors

In the examples of FIGS. 5(a) through 5(d) there is provided a resistor R as a passive element at their output portions. This causes variations in the output impedance due to variations in power supply voltage and temperature to be greatly reduced as compared with the circuit of FIG. 1 wherein the output impedance is established by a plantage alaments.

The output impedance itself may be optionally determined by the resistor R and the gm of the transistors. However, in determining and more particularly reducing the output impedance, care must be taken not to increase current consumption.

FIG. 6 illustrates correlation among input voltage  $V_{in}$ , output voltage  $V_{out}$ , output impedance  $R_{out}$ , current I<sub>f</sub>flowing through the MOSFET and the resistor R when supplied with power voltage  $V_{DD}$ - $V_{SS}$ , etc.

The graph (I) shows  $V_{in'}$  versus  $V_{out}$  characteristic of a MOSFET follower. The presence of the threshold voltage  $V_{th}$  inherent to the MOSFET develops no output  $V_{out}$  while the input  $V_{in'}$  changes from  $V_{ss}$  to  $V_{th}$ . The gain should not be more than 1 from the viewpoint of the operating principle of the follower amplifier. In other words, the maximum of the output  $V_{out}$  never reaches  $V_{DD}$  in contrast with the CMOS scheme.

The graph (II) indicates the development of the output impedance  $R_{out}$  of the MOSFET follower as a function of variations in the output potential  $V_{out}$ . Since the MOSFET is in the pinch off state before the input  $V_{in}$  changes from  $V_{ss}$  to  $V_{th}$ , the output impedance  $R_{out}$  is the very output resistor R. As the input  $V_{in}$  exceeds the voltage  $V_{th}$  and advances toward the voltage  $V_{DD}$ , the internal resistance of the MOSFET is correspondingly reduced, thereby accomplishing a reduction of the output impedance  $R_{out}$ .

Within the graph (II), the curve (1) represents the output impedance  $R_{out}$  when power supply voltage is between  $V_{DD}$ - $V_{SS}$  and at room temperature, whereas the curve (2) represents the same when the power supply voltage is between  $V_{DD}$ - $V_{SS}$  and at a higher than room temperature. It will be clear from the curves that the output impedance in the case (2) is higher than in the case (1).

The graph (III) depicts the current  $I_F$  flowing across the power terminals  $V_{DD}$  and  $V_{SS}$  of the MOSFET follower when supplied with  $V_{DD}$ - $V_{SS}$ , as a function of the input potential  $V_{in}'$ . Since the MOSFET is in the pinch off state, it permits little or no current  $I_F$  till the input  $V_{in}'$  reaches the voltage  $V_{th}$ . However, when the input  $V_{in}'$  is increased beyond the voltage  $V_{th}$  to approach the voltage  $V_{DD}$ , the ON resistance of the MOSFET is decreased and the current  $I_F$  is increased.

An amplifier arrangement which employs as a buffer means for the CMOS analog amplifier, the MOSFET follower having the above discussed properties, is illustrated in FIG. 7. An N-channel MOSFET forming the

4

follower circuit is denoted as N'. While the output terminal of the CMOS analog amplifier is commonly connected to the input terminal of the next succeeding stage MOS follower, both are respectively denoted as  $V_{out}$ ,  $V_{in}$  for the sake of explanation only. A total of the 5 consumption current I<sub>c</sub> of the CMOS analog amplifier and the consumption current I<sub>F</sub> of the MOS follower is denoted as  $I_T$  as shown in FIG. 8.

FIG. 8 illustrates some of the operating characteristics of the CMOS analog amplifier. The graph (I) de- 10 picts relationship between the input potential  $V_{in}$  and the output potential  $V_{out}$ ; the graph (II) depicts relationship between the input potential  $V_{in}$  and the output potential  $V_{out}$  within the MOS follower; the graph (III) depicts relationship between the output potential  $V_{out}$  15 and the output impedance Rout; and the graph (IV) depicts relationship between the input potential  $V_{in}$  and the consumption current I<sub>c</sub> and I<sub>F</sub> and the total consumption current  $I_T$ . These graphs are provided for comparison between the basic CMOS amplifier of FIG. 20 2 and the MOSFET follower of FIG. 7.

It is obvious from relationship between the curve (I) in the graph (III) and the curve (3) in the graph (IV) and relationship between the curve (2) in the graph (III) and the curve (4) in the graph (IV) that intention to reduce 25 the output impedance Rout leads to an increase in the consumption current  $I_c$ .

Analysis of the curve (5) in the graph (III) reveals that the output impedance Rout always stands below the resistance value of the output resistor R for all of the 30 possible output potentials by employment of the MOS follower driver. While the output voltage is biased with the operating center  $V_{FOC}$  of the MOS follower output, the peak of the output impedance Rout does not stand in the vicinity of the operating center  $V_{FOC}$  in contrast 35 with the basic CMOS amplifier.

Accordingly, the circuit of FIG. 7 is effective since the output impedance Rout at the operating center should be low.

As stated earlier, in case of the basic CMOS amplifier 40 of FIG. 1, the only way to reduce the output impedance is to increase gm of the P- and N-MOS transistors or to decrease  $V_{th}$ . This results in an increase in consumption current. However, since pursuant to the circuit of FIG. 7 the output of the CMOS analog amplifier is utilized 45 only to drive a gate capacitor of the next succeeding state MOS follower, the output impedance of the CMOS amplifier may be sufficiently high as not to disturb the frequency characteristic of the amplifier. For example, the characteristics as suggested by the curve 50 (2) of the graph (III) and the curve (4) of the graph (IV) may be employed. In other words, it is not difficult to reduce the voltage gain even if P- and N-MOS transistors within the CMOS scheme assume smaller gm. This enables the consumption current  $I_c$  in the CMOS ampli- 55 fier region to be largely reduced.

Moreover, since the circuit of FIG. 7 is such that the output impedance Rout is established by the MOS follower including one passive element (that is, the resistor temperature) but excluding one active element (that is, the MOS transistor), the output impedance Rout of the MOS follower circuit is scarcely varied due to variations in the input and output potentials, the power supply voltage, temperature, etc.

The following describes the consumption current  $I_F$ in the MOS follower circuit. The curve (6) in the graph (IV) of FIG. 8 illustrates changes in the consumption

current I<sub>F</sub> in the MOS follower circuit as a function of changes in the input potential  $V_{in}$ . No current  $I_F$  flows till the input potential  $V_{in}$  is increased from  $V_{SS}$  to  $V_{th}$ . As  $V_{in}$  approaches  $V_{DD}$  through  $V_{th}$ ,  $I_F$  is increased. When  $V_{DD}$  is exceeded,  $I_F$  takes a maximum.

Voltage  $V_s$ , an input voltage  $V_{in}$  of the CMOS amplifier, is sufficient to permit the output voltage  $V_{out}$  of the CMOS amplifier to continue saturating at the voltage  $V_{DD}$ . Voltage  $V_{thin}$ , also an input voltage  $V_{in}$  of the CMOS amplifier is sufficient to permit the input potential  $V_{in}$  of the MOS follower to reach the voltage  $V_{th}$ .

No current I<sub>F</sub> will flow during a period of time where the input voltage  $V_{in}$  is between the voltage  $V_{DD}$  and the voltage  $V_{thin}$ .

The current  $I_F$  is increased as the voltage changes from the voltage  $V_{thin}$  to the voltage  $V_s$ . But,  $I_F$  becomes constant during transition from  $V_s$  to  $V_{ss}$ . When variations in the consumption current  $I_c$ , responsive to variations in the input voltage  $V_{in}$  are described by the curve (4) in the graph (IV) of FIG. 8, the total consumption current  $I_T$  will be  $I_F + I_c$  as viewed from the curve (7).

In the circuit of FIG. 7 it is possible to utilize the output  $V_{out}$  since it has relatively good linearity and a relatively good amplitude characteristic. The output  $V_{out}$  is, therefore, useful when driving a light-load.

Accordingly, when the amplifier embodying the present invention is combined with quartz resonators of higher CI in crystal oscillators for solid state timekeeping devices, the amplifier gives excellent oscillation characteristics. More particularly, it is possible to reduce the oscillation initiating duration, the oscillation initiating voltage and the oscillating frequency deviation and power consumption. In addition, signals of large amplitude are obtainable through the utilization of the output terminal  $V_{out}$  to assure a simplicity in a pulse re-shaping circuit of the next succeeding stage. FIG. 9 is an example wherein excitation of the crystal oscillator, having requirement for lowered output impedance, is through the output  $V_{out}$  of the MOS follower and signal stretching is through the output  $V_{out}$  of the CMOS amplifier. The output is re-shaped easily by introduction into a CMOS re-shaping circuit  $I_n$ .

An example of practical conditions is as follows: the MOS transistor N' within the MOS follower amplifier is an N-channel one wherein  $\beta \div 400 \,\mu v/V$  and Vth=0.7 V at 1  $\mu$ A; the resistor R is 470 K $\Omega$ ; the quartz resonator X has a nominal oscillation frequency of 32.768 KHz; CI is 265 KΩ; capacitors C<sub>1</sub> and C<sub>2</sub> are respectively 19 pF and 81 pF. When  $V_{DD}-V_{SS}=1.6V$  and room temperature 25° C.,  $I_F=1.35~\mu A$ ,  $I_c=1.95~\mu A$ ,  $I_F=3.20 \mu A$ , the oscillation initiating duration =6 sec., the minimum oscillation initiating voltage and oscillation frequency deviation against power voltage variations is 0.8 sec/day V. These results are completely satisfactory to timekeeping crystal oscillators.

For comparison purposes, if the quartz oscillator is excited by the CMOS amplifier without using the MOS follower, the following unfavorable results are given: R; the only factor causing variations in its resistance is 60 the consumption current is 5.8 µA; the oscillation initiating duration is over 40 sec.; the oscillation initiating voltage is 1.6 V; the frequency deviation is 2.5 sec/day V. Input-output waveform characteristics of the MOS follower stage when biased via the Rf are illustrated in 65 FIG. 10, wherein the curve (A) represents relationship between the follower input voltage Vin' and the follower output voltage  $V_{out}$  in case where the threshold voltage  $V_{th}$  of the MOS transistor N' of FIG. 7 is not

ignored as compared with the power supply voltage  $V_{DD}$ - $V_{SS}$ . The curve (B) shows the case where the threshold voltage  $V_{th}$  is extremely low as compared with the power voltage  $V_{DD}$ - $V_{SS}$  or zero. For the MOS follower having the characteristics shown by the curve 5 (A), the operating center of the output  $V_{out}$  is  $V_{FOC}$  when the input of the MOS follower is biased with the voltage

$$\left(\frac{V_{DD}-V_{SS}}{2}\right)$$

via  $R_f$  within the CMOS amplifier. When the input  $V_{in'}$  takes the signal waveform (1), the output  $V_{out}$  will take 15 the somewhat disturbed waveform (2). For the MOS follower having the characteristic shown by the curve (B), the waveform of the output  $V_{out}$  contains little distortion. As a matter of fact, the MOS follower as shown by the curve (B) intends to increase the consumption current. Meanwhile, when a large amplitude signal is not necessary but waveform distortion must be small, the CMOS amplifier and the MOS follower can be AC coupled through a capacitor C as suggested in FIG. 11. By a couple of resistors  $R_1$  and  $R_2$ , the source 25 follower input  $V_{in'}$  is biased with

$$\left(\frac{V_{DD}-V_{th}}{2}\right)$$

to attain the waveform (5) containing little distortion. In this instance  $V_{out}$  has the operating center  $V_{FOC}$ .

As shown in FIG. 12, current limiting effects are expected if a substrate potential is declined to  $V_{ss}$  and 35 voltage drop is developed between a substrate and a source due to the resistor R.

The consumption current is therefore reduced even though the resistor R is not high.

Another approach to reduce and stabilize the output 40 impedance without a considerable large reduction in the consumption current is suggested in FIG. 13 showing employment of a resistor-load MOS amplifier.

FIG. 14 illustrates the output potential  $V_{out}$ , the output impedance  $R_{out}$ , the current  $I_L$  flowing through 45 N-channel MOS transistor N and the resistor R, etc., as a function of the input potential  $V_{in}$ .

The graph (I) in FIG. 14 represents the  $V_{in}$ - $V_{out}$  characteristics of the resistor-load amplifier. Due to the presence of the threshold voltage  $V_{th}$  inherent to the 50 MOS transistors, the output potential  $V_{out}$  remains unchanged at  $V_{DD}$  till the input potential  $V_{in}$  changes from  $V_{ss}$  to  $V_{th}$ . However, during voltage transition from  $V_{th}$  to  $V_{IS}$  the output potential  $V_{out}$  is greatly varied from  $V_{DD}$  to  $V_{OS}$ . As well, during transition from  $V_{IS}$  to 55  $V_{DD}$  the output potential  $V_{out}$  is held at the saturated value  $V_{OS}$ .

The graph (II) shows the development of the output impedance  $R_{out}$  as a function of variations in the output potential  $V_{out}$ . When the input potential  $V_{in}$  changes 60 from  $V_{ss}$  to  $V_{in}$ , the MOS transistor is held at the pinch off state and therefore the output impedance  $V_{out}$  is constituted by only the output resistor R. As the input potential  $V_{in}$  is increased via  $V_{th}$  to  $V_{IS}$ , the on resistance of the MOS transistor is correspondingly reduced 65 with an accompanying gradual reduction in the output impedance  $R_{out}$ . The output potential  $V_{out}$  is held at the saturated state  $V_{OS}$  till the input potential  $V_{in}$  is varied

from  $V_{IS}$  to  $V_{DD}$ . Thus, the output impedance  $R_{out}$  becomes unchanged. The curve (1) in the graph (II) shows the output impedance  $R_{out}$  under the power supply voltage  $V_{DD}$ - $V_{SS}$  and at room temperature, whereas the curve (2) shows the same under the conditions where the power supply voltage is lower than  $V_{DD}$ - $V_{SS}$  and the circumambient temperature is higher than room temperature.

The graph (III) shows the current I<sub>L</sub> flowing across the power supply terminals V<sub>DD</sub> and V<sub>SS</sub> of the resistor-load MOS amplifier when supplied with V<sub>DD</sub>-V<sub>SS</sub>, as a function of the input potential V<sub>in</sub>. Since the MOS transistor is at the pinch off state when the input potential V<sub>in</sub> is varied from V<sub>SS</sub> to V<sub>th</sub>, no current I<sub>L</sub> flows. But, as the input potential V<sub>in</sub> is increased via V<sub>th</sub> to V<sub>IS</sub>, the ON resistance of the MOS transistor is reduced to thereby increase the current I<sub>L</sub>. If V<sub>IS</sub> is exceeded, the current I<sub>L</sub> is saturated at I<sub>LS</sub>.

As noted earlier, the amplifier of FIG. 13 supplies current through the load resistor R when its active elements are conductive. The output impedance  $R_{out}$  is formed by the constant resistor R and the internal impedance of the MOS transistor N. The number of the MOS transistors as the active elements is reduced from two to one such that variations in the output impedance  $R_{out}$  due to the input and output voltage levels, the power supply voltage and the temperature are further minimized.

FIG. 15 is one preferred form of the present invention which is predicated upon a combination of the complementarily coupled transistor amplifier and the above discussed resistor-load transistor amplifier. In the prior art amplifier, while the output impedance is relatively high and its variations due to the input and output levels and the power supply voltage are relatively large, the voltage gain is high and the input impedance is high. In accordance with the amplifier described with respect to FIGS. 13 and 14, the input impedance is high but the output impedance is relatively low and its variations due to the input and output levels and the power supply voltage also is relatively low.

The embodiment of FIG. 15 comprises a CMOS amplifier 1 including a P-channel MOS transistor P, an N-channel MOS amplifier N and a bias resistor R<sub>f</sub> provided between its input and output, and a resistor-load MOS amplifier 2 of which the load resistor R is is connected to the drain of the N-channel MOS transistor N. The output node of the CMOS amplifier 1 is connected to the input node of the resistor-load MOS amplifier 2. With such an arrangement, the input node of the resistor-load MOS amplifier 2 is biased.

In case where DC amplification is not needed and variations in the bias level at the input node of the resistor-load amplifier should be minimized, DC level is cut via a capacitor C and a resistor R<sub>f</sub> establishes self biasing as suggested in FIG. 16.

FIG. 17 illustrates various characteristics for the purpose of explanation of operation of the circuits shown in FIGS. 15 and 16. In FIG. 17, the graph (I) represents relationship between the input potential  $V_{in}$  and the output potential  $V_{out}$  within the CMOS amplifier 1; the graph (II) represents the relationship between the input potential  $V_{in}$  and the output potential  $V_{out}$  within the resistor-load MOS amplifier 2; the graph (III) represents the relationship between the output potential  $V_{out}$  and the output impedance  $R_{out}$ ; and the graph (IV) represents the relationship between the

9

input potential  $V_{in}$  in the CMOS amplifier 1 and the consumption current  $I_c$  in the CMOS amplifier 2, the counterpart  $I_I$  in the resistor-load amplifier 2 and the sum thereof  $I_T(=I_c+I_I)$ . It is obvious from relationship between the curve (1) in the graph (III) and the curve (3) in the graph (IV) and relationship between the curve (2) in the graph (III) and the curve (4) in the graph (IV) that the consumption circuits  $I_c$  and  $I_c$  are unavoidably increased if the output impedance  $R_{out}$  is sought to be reduced.

It will be noted that the operating center of the resistor-load MOS amplifier 1 is somewhat shifted depending upon whether the DC coupling of FIG. 15 or the AC coupling of FIG. 16 is employed. Such fact is depicted on the graphs (II) and (III) in FIG. 17. A shows 15 the operating center in case of the DC coupling while B shows the same in case of the AC coupling.

As illustrated in the graph (I) in FIG. 17, the output potential  $V_{out}$  and the output impedance  $R_{out}$  are constant until the input potential  $V_{in}$  is varied from  $V_{DD}$  to 20  $V_{thin}$ . Under these circumstances the consumption current  $I_I$  of the resistor-load MOS amplifier 2 is zero and hence the total consumption current  $I_T$  is only the consumption current  $I_c$  of the CMOS amplifier.

Therefore, as viewed from the graphs (II) and (III), 25 the output potential  $V_{out}$  is approximately equal to  $V_{OS}$  and the output impedance  $R_{out}$  is gradually decreased to the resistance  $R_S$  during the period where the input  $V_{in}$  is advanced from  $V_{thin}$  toward  $V_{ISN}$ . Simultaneously, the consumption current  $I_I$  and in other words  $I_T$  are 30 increased.

During a period where  $V_{in}$  is varied from  $V_{ISIN}$  to  $V_{SS}$  the resistor-load MOS amplifier 2 is saturated so that the output potential  $V_{out}$  and the output impedance  $R_{out}$  are substantially settled at  $V_{OS}$  and  $R_S$ . The consumption current  $I_I$  becomes constant and the consumption current  $I_C$  is gradually reduced, thereby reducing the total of the consumption current  $I_T$ .

As suggested in FIG. 18, the CMOS amplifier 1 may be provided in a multi-stage fashion. In case where the 40 number of the amplifier stages is an even number, inversion is developed between the input  $V_{in}$  and the output  $V_{out}$ . In the given example, the respective ones of the CMOS amplifiers are AC coupled via a series of capacitors C, C', ... C (n-1).

In FIG. 19, a two-stage CMOS amplifier 1 is provided and the output  $V_{out}$  of the resistor-load MOS amplifier 2 is employed to excite the quartz resonator X.

Attention must be paid to the frequency characteristics of the respective amplifiers. In FIG. 20, (a) represents the frequency characteristic of the CMOS amplifier and (b) represents the counterpart of the resistor-load amplifier, wherein the input signal is 10 mVp-p, the voltage supply is 3.0 V and the output floating capacitance is 8 pF.

In the case of the CMOS amplifier, the voltage gain is about 130 at a low frequency range but only 1.8 in the vicinity of the oscillating frequency of the quartz resonator X (i.e., 32.768 KHz). In contrast to this, for the resistor-load amplifier the voltage gain is about 40 at a 60 low frequency range and about 3.6 in the vicinity of the oscillating frequency 32.768 KHz. The resistor-load amplifier, therefore, manifests the better frequency characteristics although the current consumption is equal. Furthermore, since the gain within the DC and 65 low frequency region is lower for the resistor-load amplifier, a multi-stage arrangement of the resistor-load amplifier is possible in principle.

10

FIG. 21 is an example of a two-stage direct coupling resistor-load amplifier. Detailed analysis of the bias characteristics of the resistor-load amplifier of FIG. 21 is as follows.

Biasing is basically accomplished by the resistor  $R_f$  provided between the drain and the gate of the first stage MOS transistor  $M_1$ . Therefore, when the input and output potentials of the transistor  $M_1$  are respectively  $V_{in1}$  and  $V_{out1}$ .

$$V_{out1} = V_{in1} \tag{1}$$

If the threshold voltage of the first stage MOS transistor  $M_1$  is  $V_{th1}$ ,  $V_{th1} > 0$ .

$$V_{out1} > V_{in1} - V_{th1} \tag{2}$$

This shows the fact that the MOS transistor  $M_1$  is in the saturated state. Therefore, current  $i_{DS}$  flowing through the MOS transistor is as follows.

$$i_{DS} = k_1 (V_{in1} - V_{th1})^2$$

$$= k_{1'} \cdot \frac{W}{L} (V_{in1} - V_{th1})^2$$

$$= \frac{\mu \epsilon o x}{2 to x} \cdot \frac{W}{L} (V_{in1} - V_{th1})^2$$

(3)

If current flowing through the load resistor  $R_1$  is  $i_L$ ,

$$i_L = \frac{V_{DD} - V_{out1}}{R_1} \tag{4}$$

Because the next succeeding state is a MOS gate load, no DC current flows.

$$i_{DS}=i_{L} \tag{5}$$

The equations (3) and (4) are substituted into the equation (5).

$$V_{out} = V_{DD} - k_1 R_1 (V_{in1} - V_{th1})^2$$

(6)

The equation (1) is substituted into the above.

$$K_1R_1 V_{out1}^2 + (1 - 2K_1R_1V_{th1}) V_{out1} + K_1R_1V_{th1}^2 - V_{DD} = 0$$

(7)

That is,

$$V_{out1} = V_{th1} + \frac{\sqrt{1 + 4K_1R_1(V_{DD} - V_{th1}) - 1}}{2K_1R_1} = V_{in1}$$

In this manner, the first stage amplifier is biased via the bias resistor  $R_f$  and provides the output potential which is determined by  $V_{th1}$  of the MOS transistor  $M_1$ ,  $K_1$ , the load resistor  $R_1$  and the power supply voltage  $V_{DD}$  without regard to  $R_f$ .

The input-output relationship of the second-stage resistor-load MOS amplifier is as follow wherein  $K_2$  is the constant of the MOS transistor  $M_2$ ,  $V_{th2}$  is the threshold voltage of  $M_2$  and  $R_2$  is the load resistor.

$$K_1R_1 = K_2R_2 \tag{9}$$

If the following is established,

$$V_{th1} = V_{th2} \tag{10}$$

From the equation (8),

$$V_{out2} = V_{in2} = V_{out1} = V_{in1} \tag{11}$$

It thus can be considered from temperature-dependent variations in  $K_1$ ,  $K_2$ ,  $V_{th1}$ ,  $V_{th2}$ , that the resistors  $R_1$  and  $R_2$  are not varied when implemented with integrated circuit technology. The equation (11) therefore seems almost practical for use. The amplifier of FIG. 21 eliminates the need for capacitor coupling and exhibits the substantially stable performance characteristics.

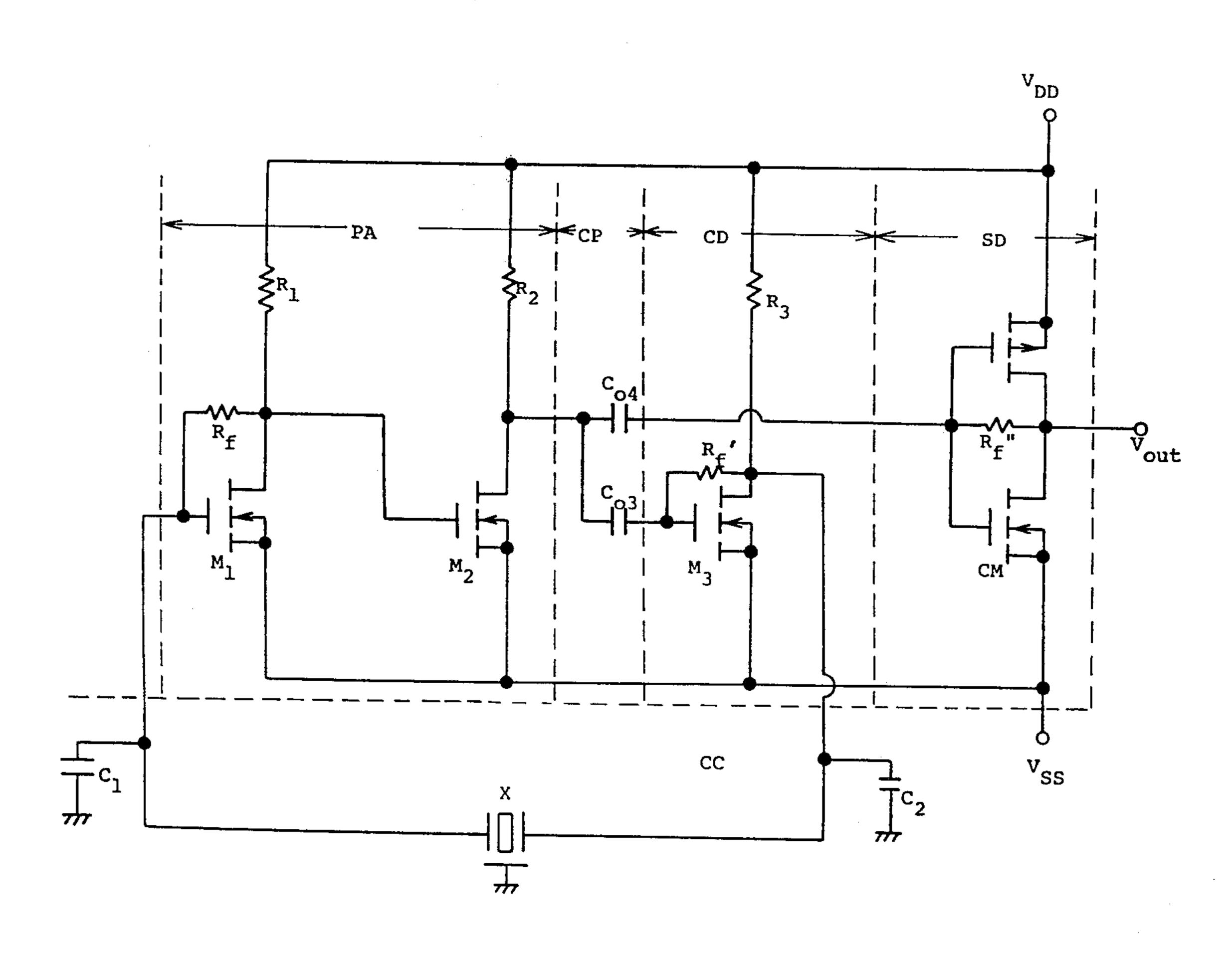

FIG. 22 shows an application of the amplifier of FIG. 21 to an oscillator containing a quartz resonator of higher CI. A quartz enabling stage CD, an impedance converter, consists of a load resistor R<sub>3</sub> and a MOS transistor M<sub>3</sub> and serves to excite a quartz circuit CC. 15 Biasing is accomplished by R<sub>f</sub>. A preamplifier PA as suggested by FIG. 21 is coupled via a capacitor C<sub>03</sub> with the quartz enabling stage CD.

FIG. 23 illustrates deviation in sec/day and the period of time required for initiating oscillation  $t_{osc}$  as a 20 function of the power supply voltage  $V_{ss}$  and external capacitors  $C_1$  and  $C_2$ . The greater the deviation the greater the capacitors  $C_1$  and  $C_2$ . The most favorable results are obtained at 0-0.5 S/D.  $V_{out}$ . When the external capacitors are not coupled, the period  $t_{osc}$  is reduced 25 to a minimum (shorter than 1.0 sec.). FIG. 24 depicts the total consumption current  $I_T$  ( $\mu$ A), the deviation (sec/day) and the oscillation period  $t_{osc}$  (sec.) when the power supply voltage  $V_{DD}$ - $V_{SS}$  is 1.55 V and the external capacitors  $C_1$  and  $C_2$  are altered.

While only certain embodiments of the present invention have been described, it will be apparent to those skilled in the art that various changes and modifications may be made therein without departing from the spirit and scope of the invention as claimed.

What is claimed is:

1. A high impedance crystal oscillator comprising: vibrating crystal means for creating a signal; and

a resistor load amplifier means for amplifying the signal created by said vibrating crystal means, said 40 resistor load amplifier means including:

first and second bias voltage means, said first bias voltage means having a voltage different from said second bias voltage means;

- first and second impedances, each having first and 45 second terminals, the first terminal of each impedance being connected to said first bias voltage means;

- a first semiconductor switch having a control terminal, an output terminal, and a third terminal, 50 the control terminal of said first semiconductor switch receiving said signals created by said vibrating crystal means, the output terminal of said first semiconductor switch being connected to the second terminal of said first impedance, 55 and the third terminal of said first semiconductor switch being connected to said second bias voltage means;

- a second semiconductor switch having a control terminal, an output terminal, and a third termi- 60 nal, the control terminal of said second semiconductor switch being connected to the output terminal of said first semiconductor switch, the output terminal of said second semiconductor switch being connected to the second terminal of 65

said second impedance, and the third terminal of said second semiconductor switch being connected to said second bias voltage means;

whereby the output of said second semiconductor switch is the output of said resistor load amplifier means and is used to excite said vibrating crystal means into vibration, said output of said resistor load amplifier means being of a constant frequency regulated by said vibrating crystal means;

a resistor load impedance converter means for reducing the output impedance of said resistor load amplifier means to more easily excite said vibrating crystal means, said resistor load impedance converter having an input connected to the output of said resistor load amplifier means and an output connected to said vibrating crystal means, said resistor load impedance converter including:

a third impedance having first and second terminals, the first terminal of said third impedance being connected to said first bias voltage means;

a third semiconductor switch having a control terminal, an output terminal, and a third terminal, the control terminal of said third semiconductor switch connected to the output terminal of said second semiconductor switch, the output terminal of said third semiconductor switch being connected to the second terminal of said third impedance and to said vibrating crystal means, the third terminal of said third semiconductor switch being connected to said second bias means; and

fourth impedance means for biasing said third semiconductor switch, said fourth impedance means being connected between the control and output terminals of said third semiconductor switch.

2. The high impedance crystal oscillator of claim 1 further comprising:

reshaping circuit means for amplifying and reshaping the output of said resistor load amplifier means, said reshaping circuit means having an input and an output, the input being connected to the output of said resistor load amplifier means and the output of said reshaping circuit means being the output of said high impedance crystal oscillator, said reshaping circuit means including;

fifth impedance having first and second terminals; fourth semiconductor switch having an input terminal, an output terminal, and a control terminal; fifth semiconductor switch having an input terminal, an output terminal, and a control terminal; and

wherein the first terminal of said fifth impedance and the control terminal of said fourth and fifth switches are connected together and to the output of said resistor load amplifier means, and the second terminal of said fifth impedance and the output terminals of said fourth and fifth switches are connected together and form the output of said high impedance crystal oscillator.

3. The high impedance crystal oscillator of any of claims 1 and 2 wherein said semiconductor switches are MOSFETs.

\* \* \* \*