# Fujita et al.

[45] Nov. 10, 1981

| [54] | MATRIX DRIVING METHOD FOR      |  |  |

|------|--------------------------------|--|--|

|      | ELECTRO-OPTICAL DISPLAY DEVICE |  |  |

[75] Inventors: Hiroo Fujita, Sayama; Akira Tsuzuki,

Tokyo; Shigeru Morokawa, Higashiyamato, all of Japan

[73] Assignee: Citizen Watch Company Limited,

Tokyo, Japan

[21] Appl. No.: 57,461

[22] Filed: Jul. 13, 1979

### Related U.S. Application Data

[63] Continuation-in-part of Ser. No. 784,746, Apr. 5, 1977, abandoned.

| [30] | Foreign Application Priority Data |                                  |  |

|------|-----------------------------------|----------------------------------|--|

| Α    | pr. 6, 1976 [JP] Japa             | an 51/38536                      |  |

|      |                                   |                                  |  |

| [58] | Field of Search                   | 350/332<br>340/765, 784; 350/332 |  |

| [56] | Refere                            | nces Cited                       |  |

## U.S. PATENT DOCUMENTS

| 3,781,863<br>3,922,667<br>4,019,178<br>4,038,564<br>4,041,481<br>4,044,346<br>4,050,064<br>4,078,374 | 11/1975<br>4/1977<br>7/1977<br>8/1977<br>8/1977<br>9/1977<br>3/1978 | Fujita       340/765         Ueda et al.       340/805         Hashimoto et al.       340/765         Hakata       340/803 X         Sato       340/787         Akahane et al.       340/765         Hashimoto et al.       340/784 X         Kondo       350/332 X |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| , ,                                                                                                  | •                                                                   |                                                                                                                                                                                                                                                                     |

| , ,                                                                                                  |                                                                     |                                                                                                                                                                                                                                                                     |

| 4,050,064                                                                                            | 9/1977                                                              | Hashimoto et al 340/784 X                                                                                                                                                                                                                                           |

| 4,078,374                                                                                            | 3/1978                                                              | Kondo 350/332 X                                                                                                                                                                                                                                                     |

| 4,091,377                                                                                            | 5/1978                                                              | Shimoi                                                                                                                                                                                                                                                              |

| 4,110,967                                                                                            | 9/1978                                                              | Fujita 350/332 X                                                                                                                                                                                                                                                    |

| 4,142,182                                                                                            | 2/1979                                                              | Kmetz 340/765                                                                                                                                                                                                                                                       |

| 4,186,395                                                                                            | 1/1980                                                              | Fujita et al 340/765                                                                                                                                                                                                                                                |

|                                                                                                      |                                                                     |                                                                                                                                                                                                                                                                     |

Primary Examiner—David L. Trafton Attorney, Agent, or Firm—Jordan and Hamburg

#### [57] ABSTRACT

A matrix driving method for driving an electro-optical display device including digit and segment electrodes arranged in a matrix configuration, in which digit and segment drive signals are applied to digit and segment electrodes in such a manner that the digit drive signals applied to all the digit electrodes have potentials equal in level with each other during a prescribed time interval during which the potential of a first segment drive signal inducing a state of non-display at all the digit electrodes is equal to the potential of each of the digit drive signals. During the prescribed time intervals, the potential difference between a second segment drive signal inducing a state of display at one of the digit electrodes and a state of non-display at the other digit electrode and each of the digit drive signals is maintained in a first predetermined value whereby the root mean square value of the potential difference between the second segment drive signal and the digit drive signal applied to the other digit electrode is substantially equal to that of the potential difference between the first segment drive signal and each of the digit drive signals. During the prescribed time interval, further, the potential difference between a third segment drive signal inducing a state of display at all the digit electrodes and each of the digit drive signals is maintained in a second predetermined value whereby the root mean square value of the potential difference between the second segment drive signal and the digit drive signal applied to the one of the digit electrodes is substantially equal to that of the potential difference between the third segment drive signal and each of the digit drive signals.

## 4 Claims, 34 Drawing Figures

Sheet 1 of 26

Fig. IA

Fig. 2

Fig. 3

Fig. 6

U.D. I alcit Mov. 10, 1901

Fig. 7

Fig. 8

Fig. 11

Fig. 12

$$r_2 - c_{12} = {0 \atop -v} - {1 \atop -2v}$$

(2)

$$r_1 - c_0 = 0$$

$$-V$$

$$(3)$$

$$r_2 - c_1 \stackrel{\vee}{=} 0$$

(6)

Fig. 14

(4)

1Vo 0 -1Vo

Fig. 16

.

Fig. 19

Fig. 20

•

•

Fig. 24

•

.

Fig. 26  $\phi_1$   $\phi_2$   $A_1 = \phi_1$   $P_2$   $P_3$   $A_3 = P_4$   $P_5$   $P_6$   $A_4 = P_5 + P_6$   $A_4 = P_5 + P_6$   $A_1 = \Phi_1$   $\Phi_2$   $\Phi_3$   $\Phi_4$   $\Phi_5$   $\Phi_6$   $\Phi_6$   $\Phi_6$   $\Phi_6$   $\Phi_6$   $\Phi_7$   $\Phi_8$   $\Phi_8$

•

•

Fig. 27

Fig. 28

.

•

Fig. 29

•

# MATRIX DRIVING METHOD FOR ELECTRO-OPTICAL DISPLAY DEVICE

This application is a continuation in part of patent 5 application Ser. No. 784,746, filed Apr. 5, 1977, now abandoned.

This invention relates to a method for driving an electro-optical display device such as a liquid crystal display device and, more particularly, to a method for 10 driving an electro-optical display device having digit and segment electrodes arranged in a matrix configuration.

In recent years, electro-optical display devices such as liquid crystal display devices have been increasingly 15 used in various applications such as electronic timepieces, desk calculators, etc., because of low power consumption. It is known in the art that there are two types of arrangements for the electrodes of the liquid crystal display devices, i.e., a static type arrangement 20 and a matrix type arrangement. In the static type arrangement, the liquid crystal display device comprises a common electrode and a plurality of groups of segment electrodes displaced from and disposed opposite the common electrode. The segment electrodes of each 25 group are not interconnected and independently driven from each other. This arrangement is advantageous in that a driver circuit for each segment electrode can be manufactured in a simple construction. However, this has drawbacks in that a number of driver circuits are 30 required and increases the number of leads from the liquid crystal display device, increasing packaging cost and complexity.

In the matrix type arrangement, the liquid crystal display device comprises a plurality of digit electrodes, 35 and a plurality of segment electrodes displaced from and disposed opposite all of the digit electrodes. The segment electrodes relative to each digit electrode are interconnected, and the digit electrodes are provided independently from each other. Generally, the digit 40 electrodes are driven in a time multiplexed relationship. With this arrangement, the number of leads from the liquid crystal display device is remarkably reduced, representing a considerable saving in packaging cost and complexity. However, this suffers from drawbacks 45 in the design of driver circuits because of low display contrast.

It is, therefore, an object of the present invention to provide a method for driving an electro-optical display device in a matrix mode which can overcome the short-50 comings encountered in the prior art.

It is another object of the present invention to provide a driving method for driving an electro-optical display device in a matrix mode so as to provide a remarkably increased operation margin to increase display contrast.

These and other, objects, features and advantages of the present invention will become more apparent from the following description when taken in conjunction with the accompanying drawings, in which:

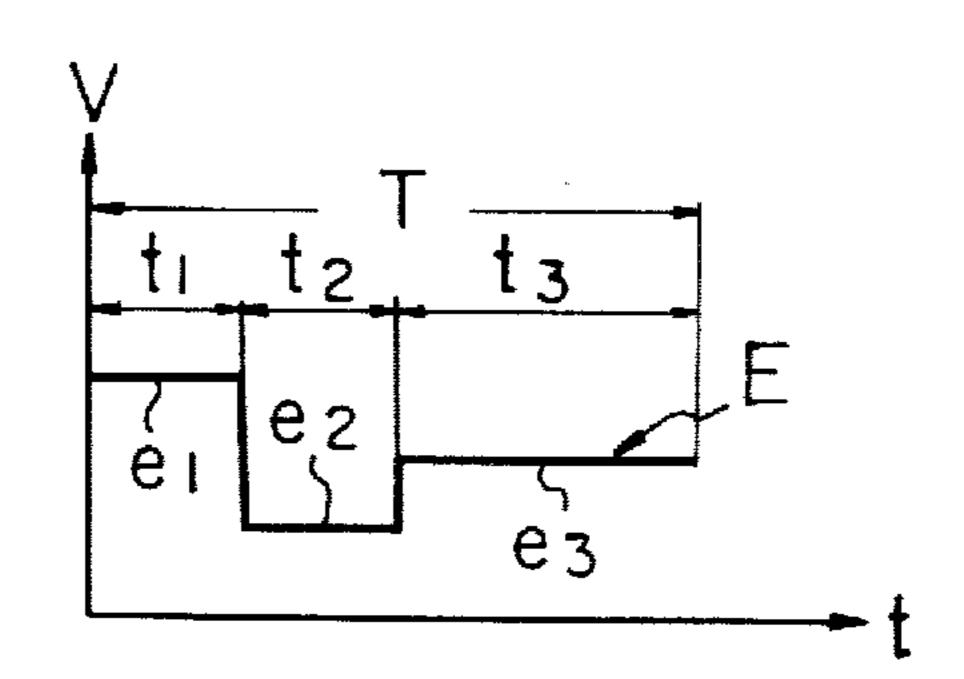

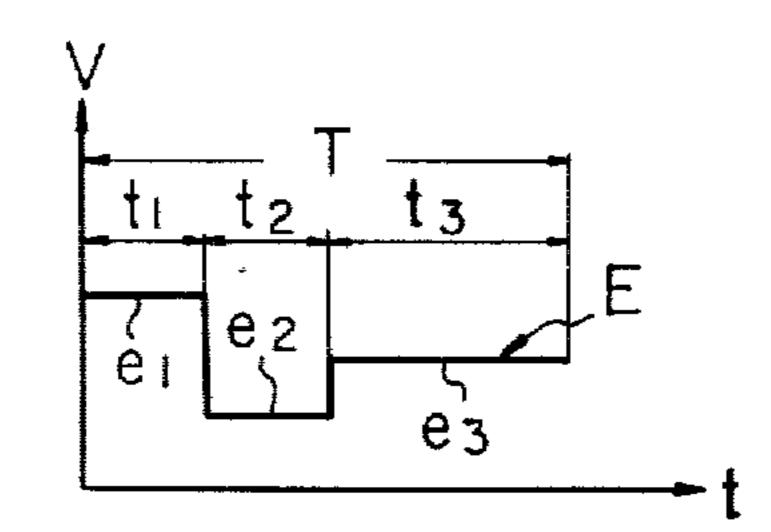

FIG. 1A is an example of a timing chart for an example of a conventional drive signal to be used for driving an electro-optical display device;

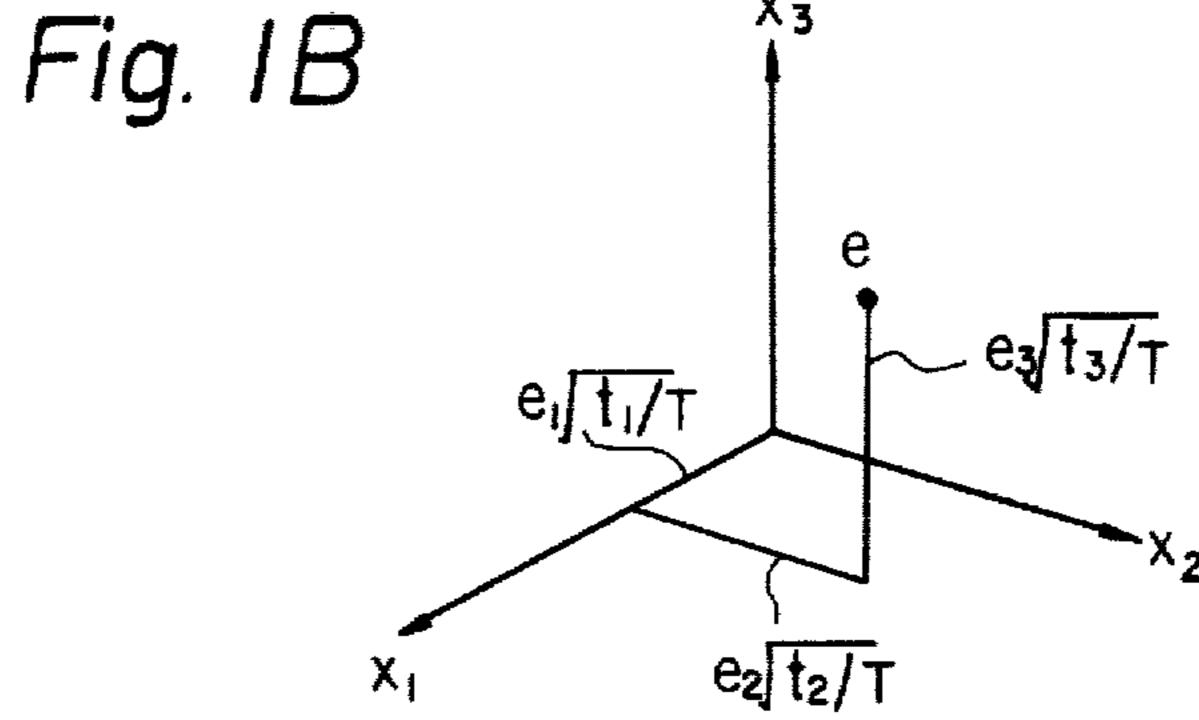

FIG. 1B is a vector diagram of the drive signal shown in FIG. 1A;

FIG. 2 is a schematic view of an example of a conventional electro-optical display device arranged in a matrix configuration;

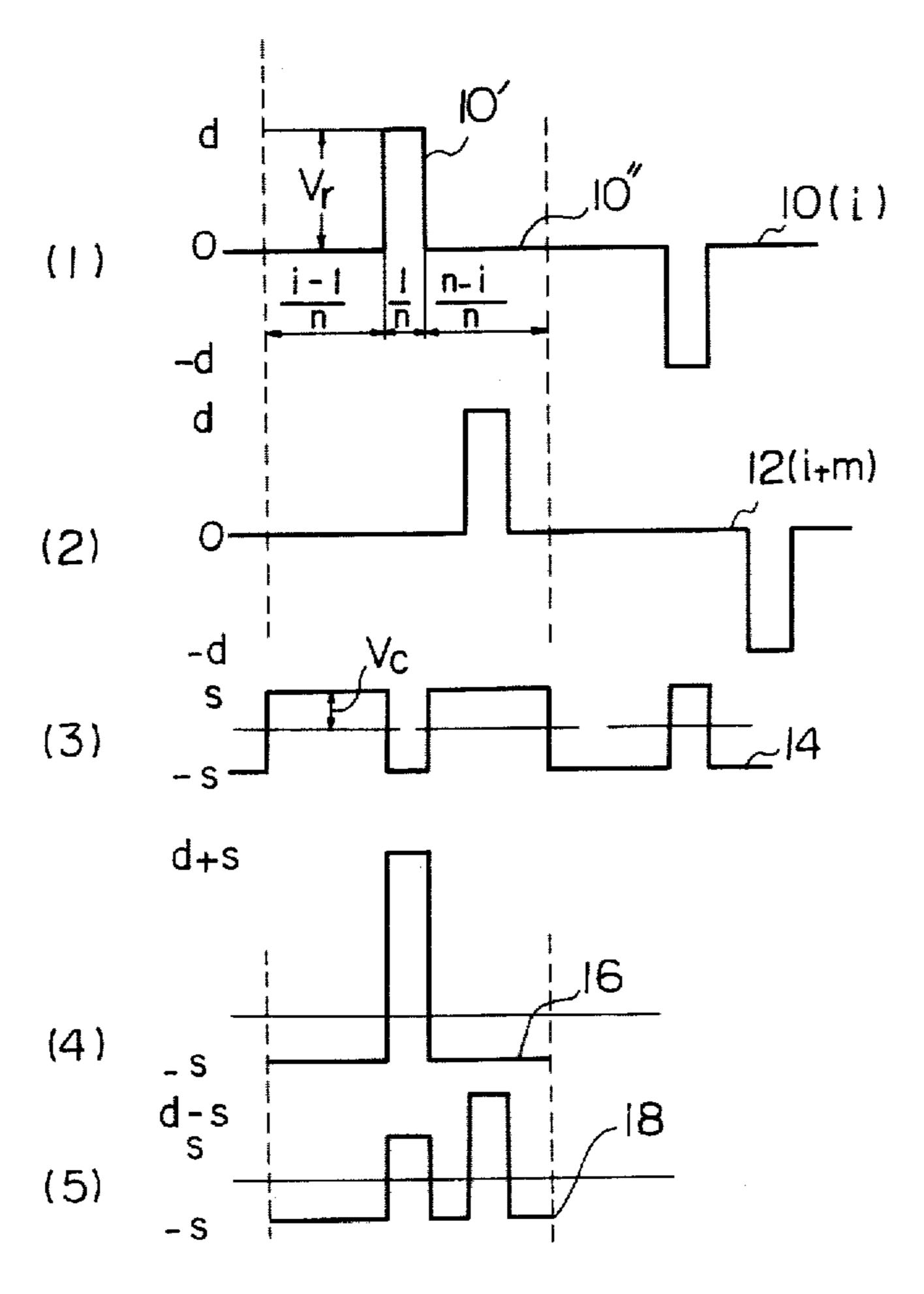

FIG. 3 is a timing chart for illustrating another example of conventional digit and segment drive signals to be used for driving the display device shown in FIG. 2;

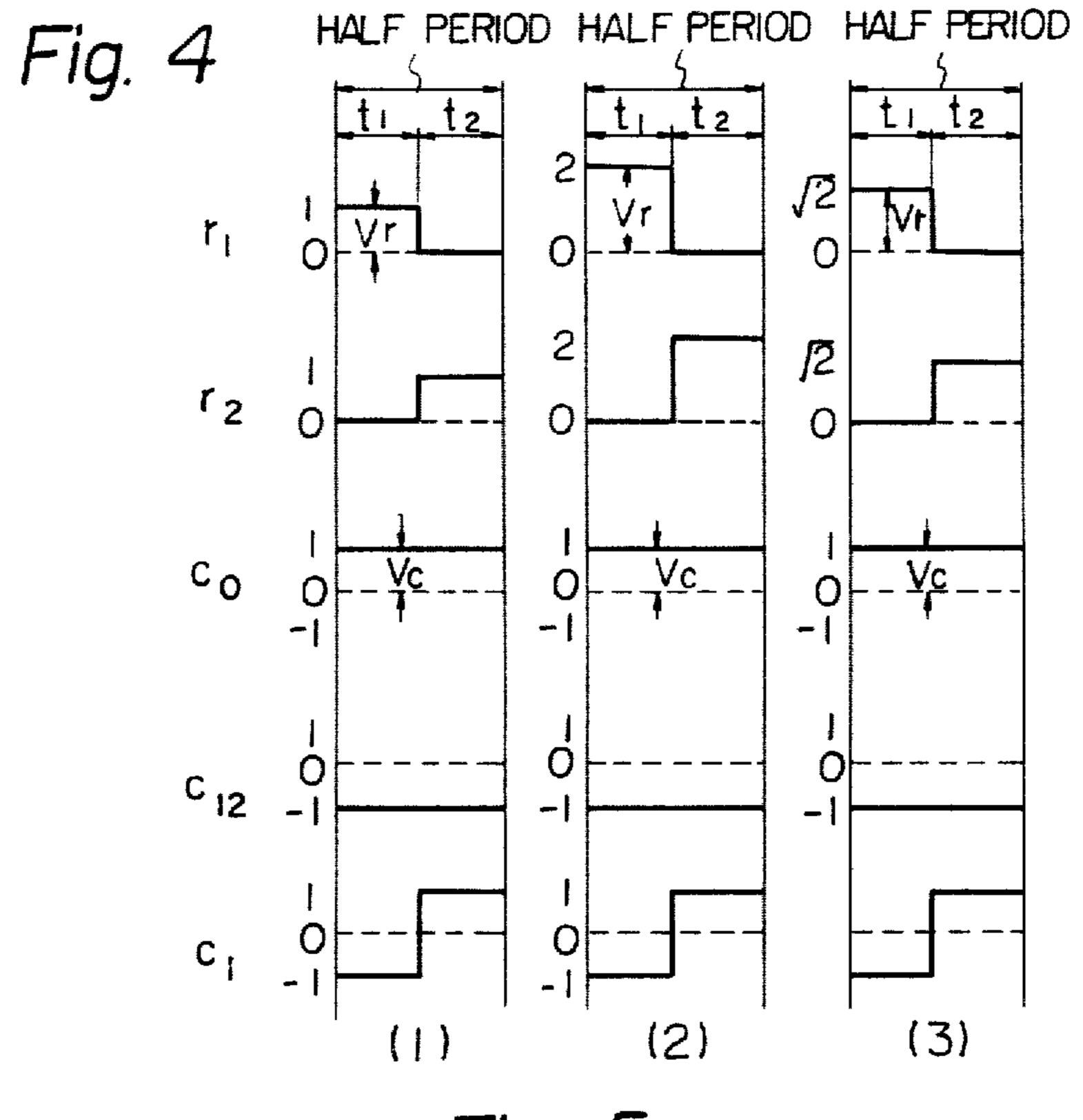

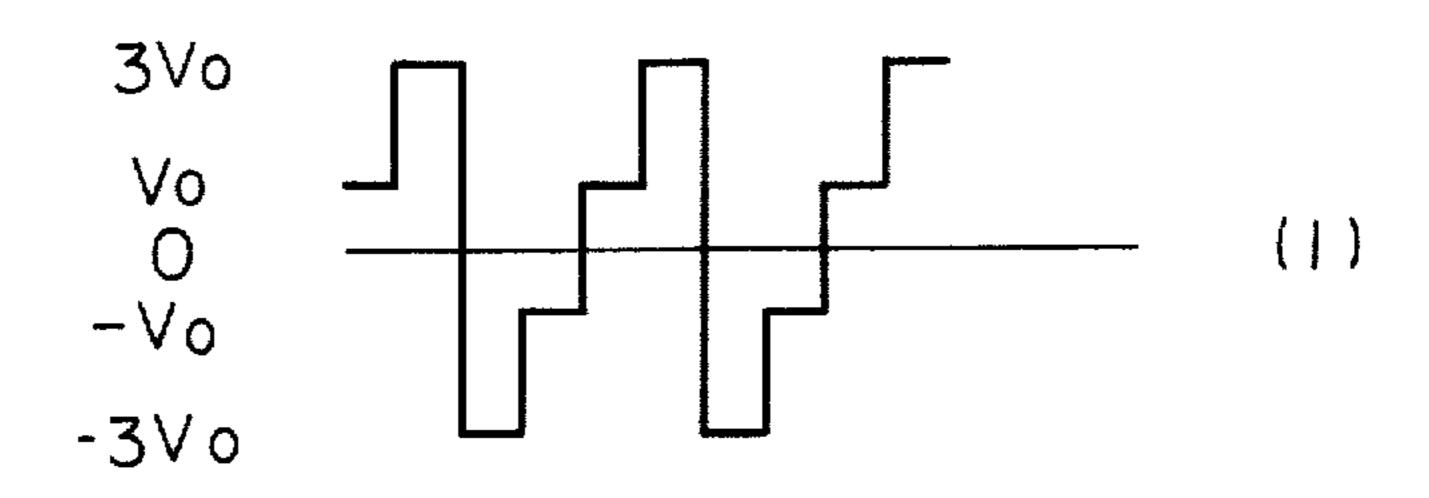

FIG. 4 is a timing chart of another example of conventional digit and segment drive signals;

FIG. 5 shows vector diagrams for the drive signals shown in FIG. 4;

FIG. 6 is a timing chart for another example of conventional drive signals;

FIG. 7 is a timing chart for illustrating the potential differences across the electrodes of the display device;

FIG. 8 is a timing chart for another example of prior art drive signals;

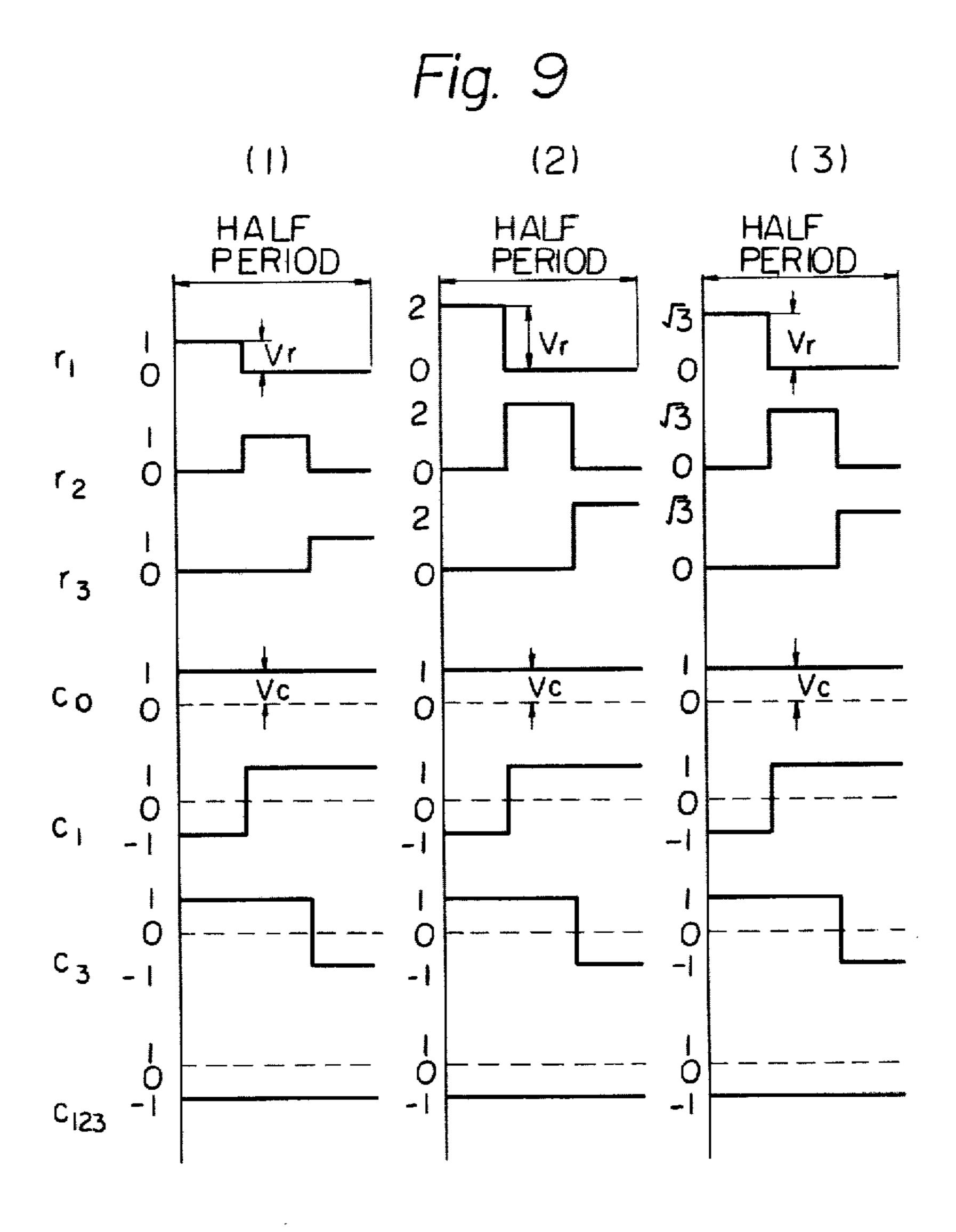

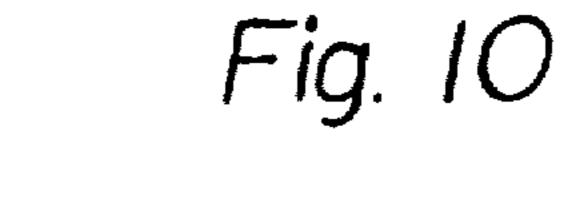

FIG. 9 is a timing chart for illustrating a prior art concept of the method of the present invention;

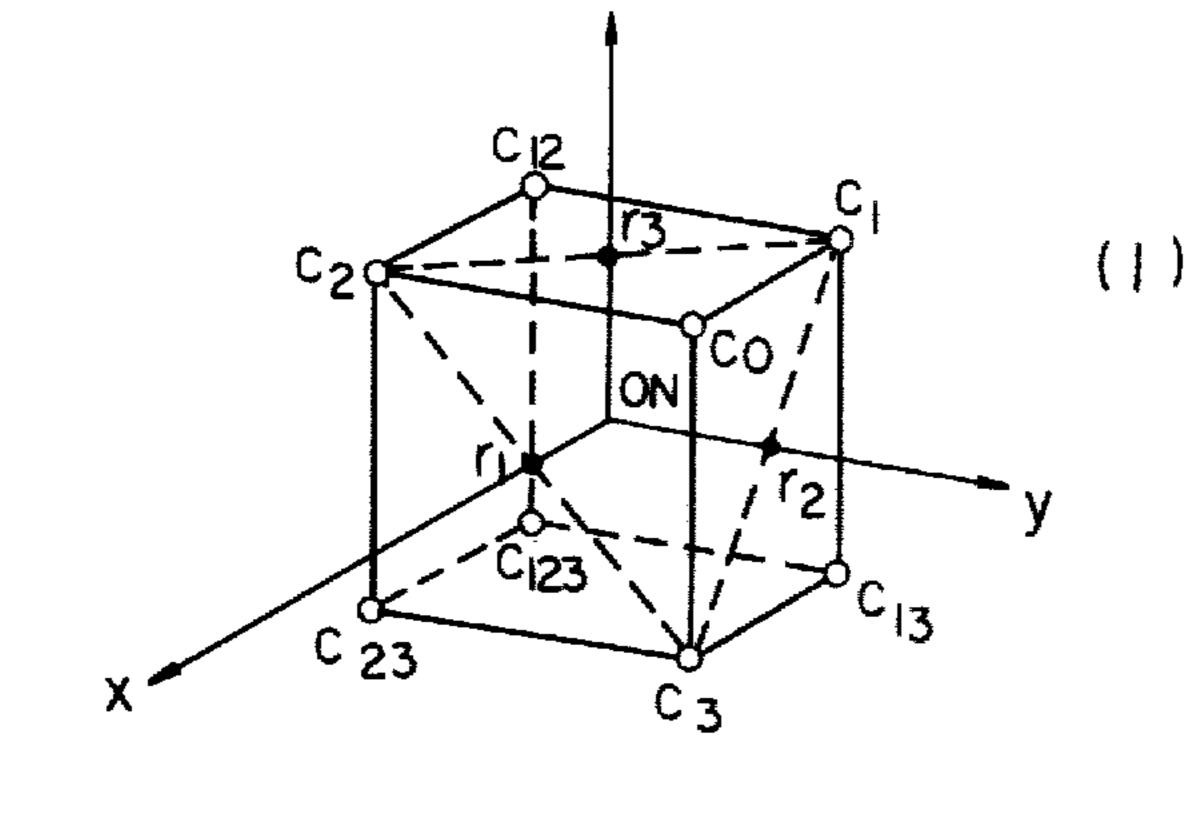

FIG. 10 shows vector diagrams for the drive signals shown in FIG. 9;

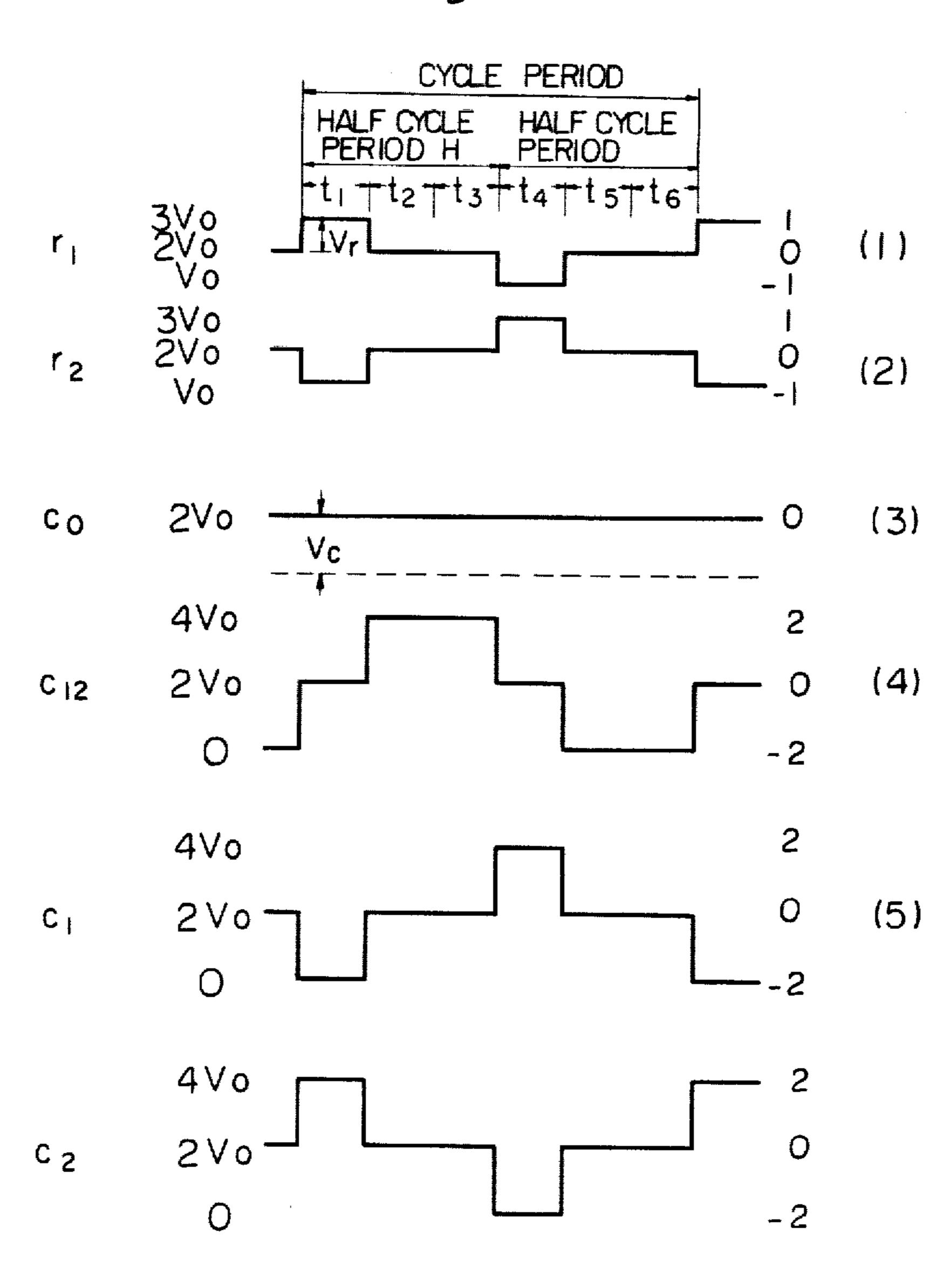

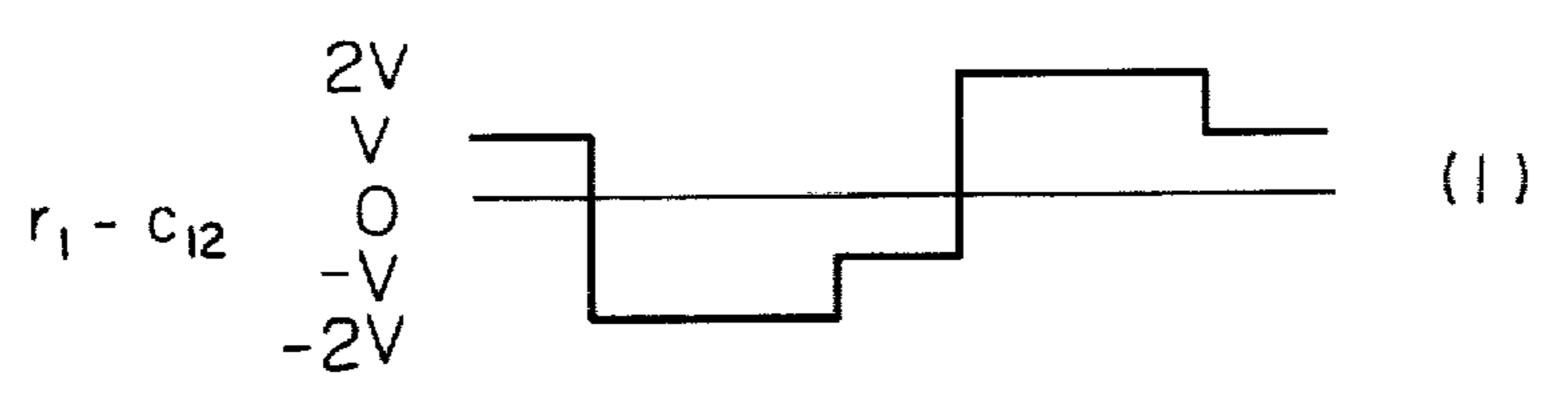

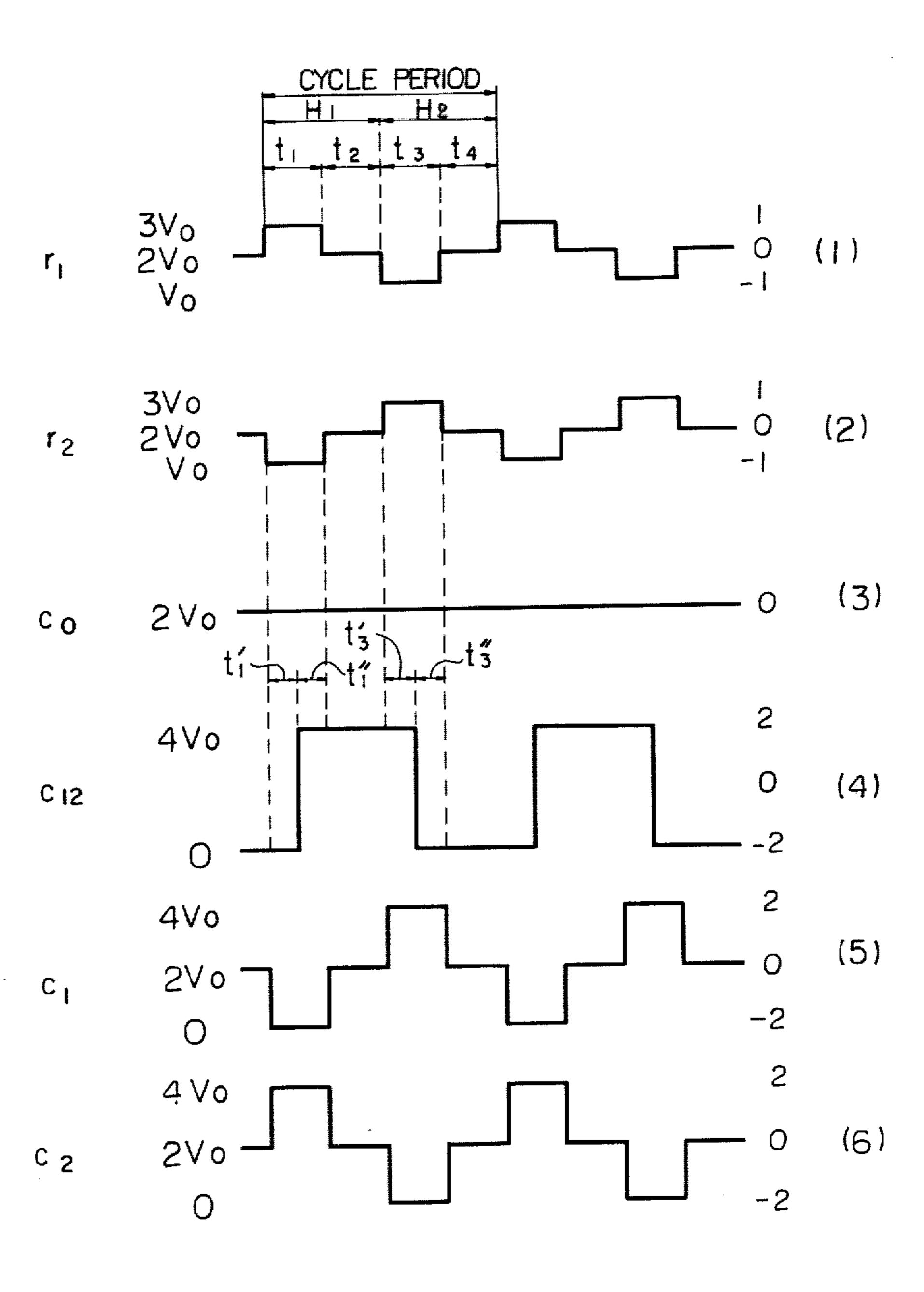

FIG. 11 is a timing chart for a preferred example of digit and segment drive signals used in a method of the present invention;

FIG. 12 shows the potential differences across the electrodes applied with the drive signals shown in FIG. 11;

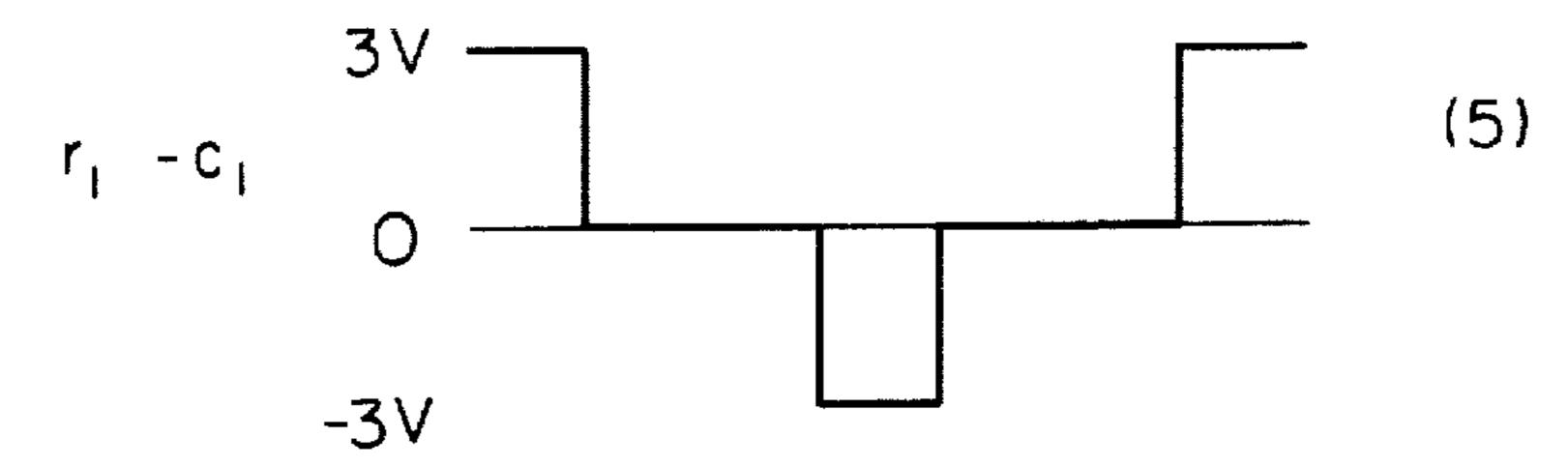

FIG. 13 shows vector diagrams for the drive signals shown in FIG. 11;

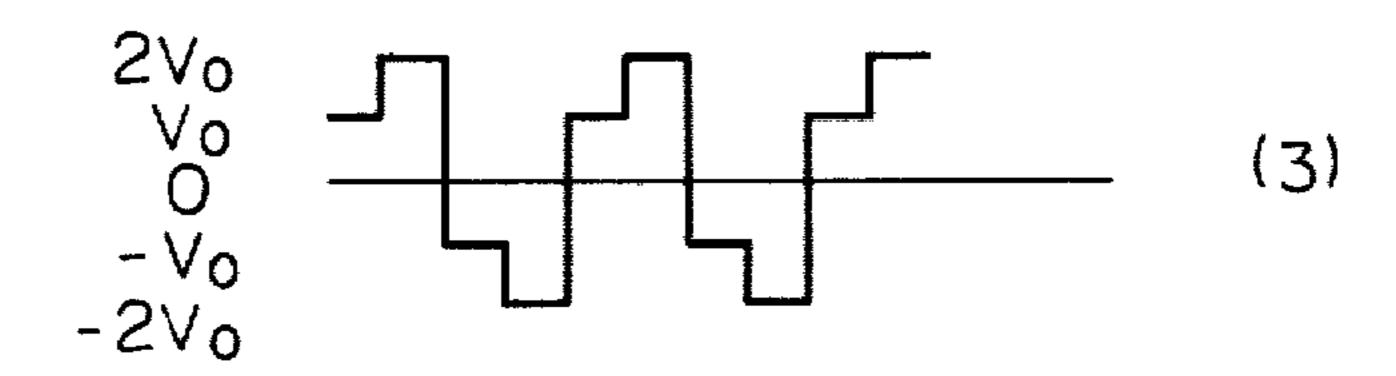

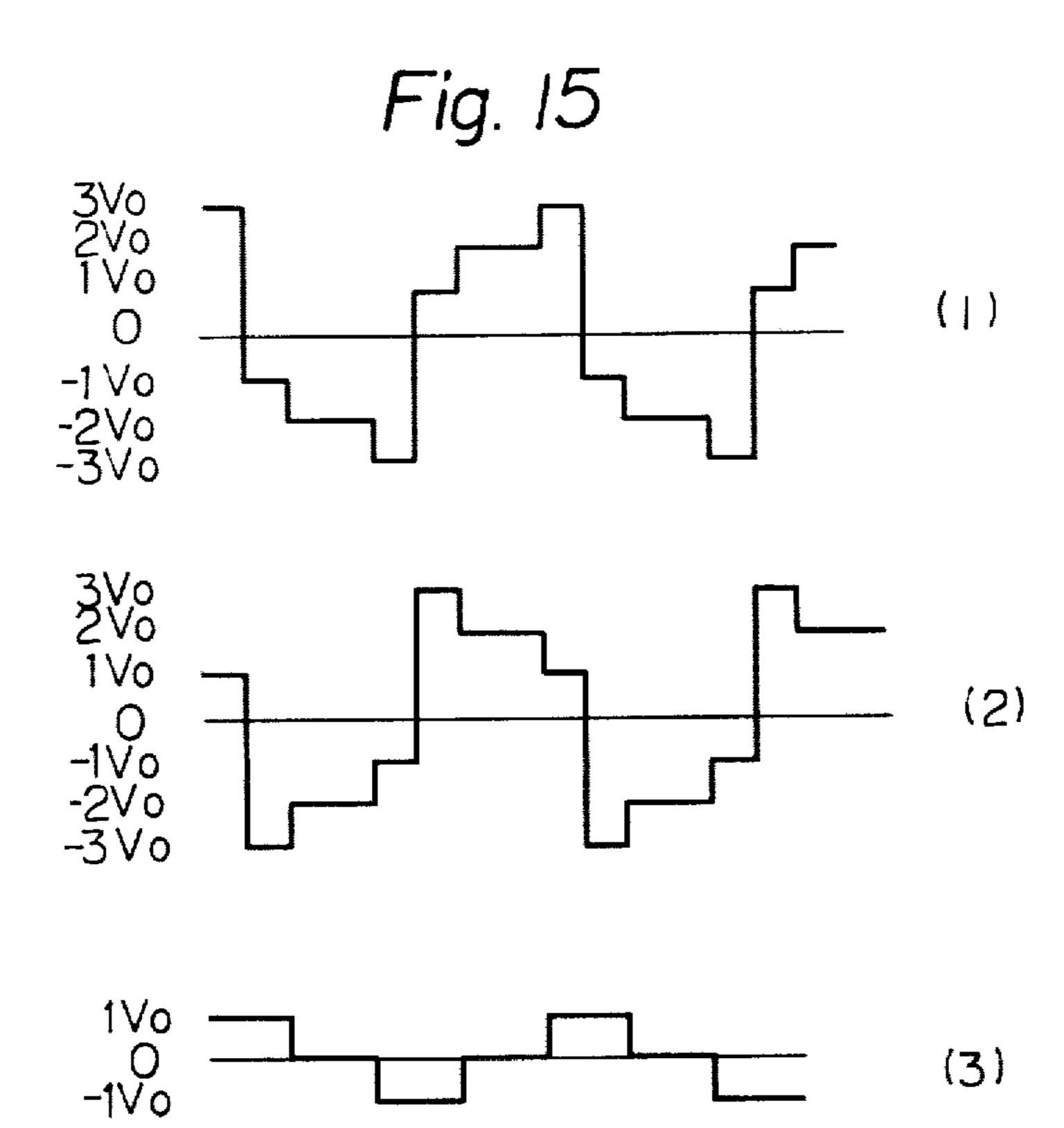

FIG. 14 is a timing chart for another preferred example of digit and segment drive signals according to the present invention;

FIG. 15 shows the potential difference across the electrodes applied with the drive signals shown in FIG. 14;

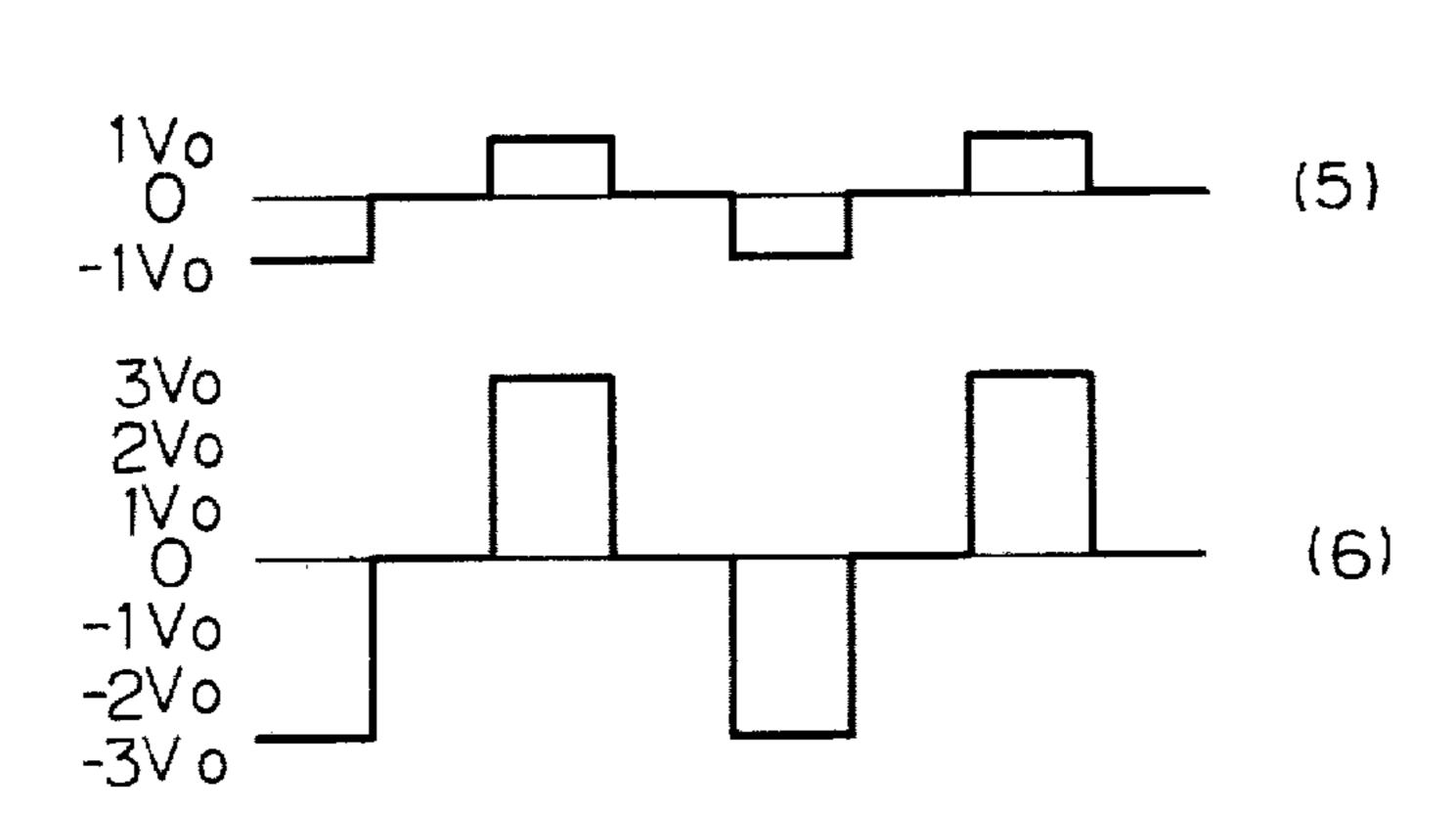

FIG. 16 is a timing chart for another preferred example of digit and segment drive signals according to the present invention;

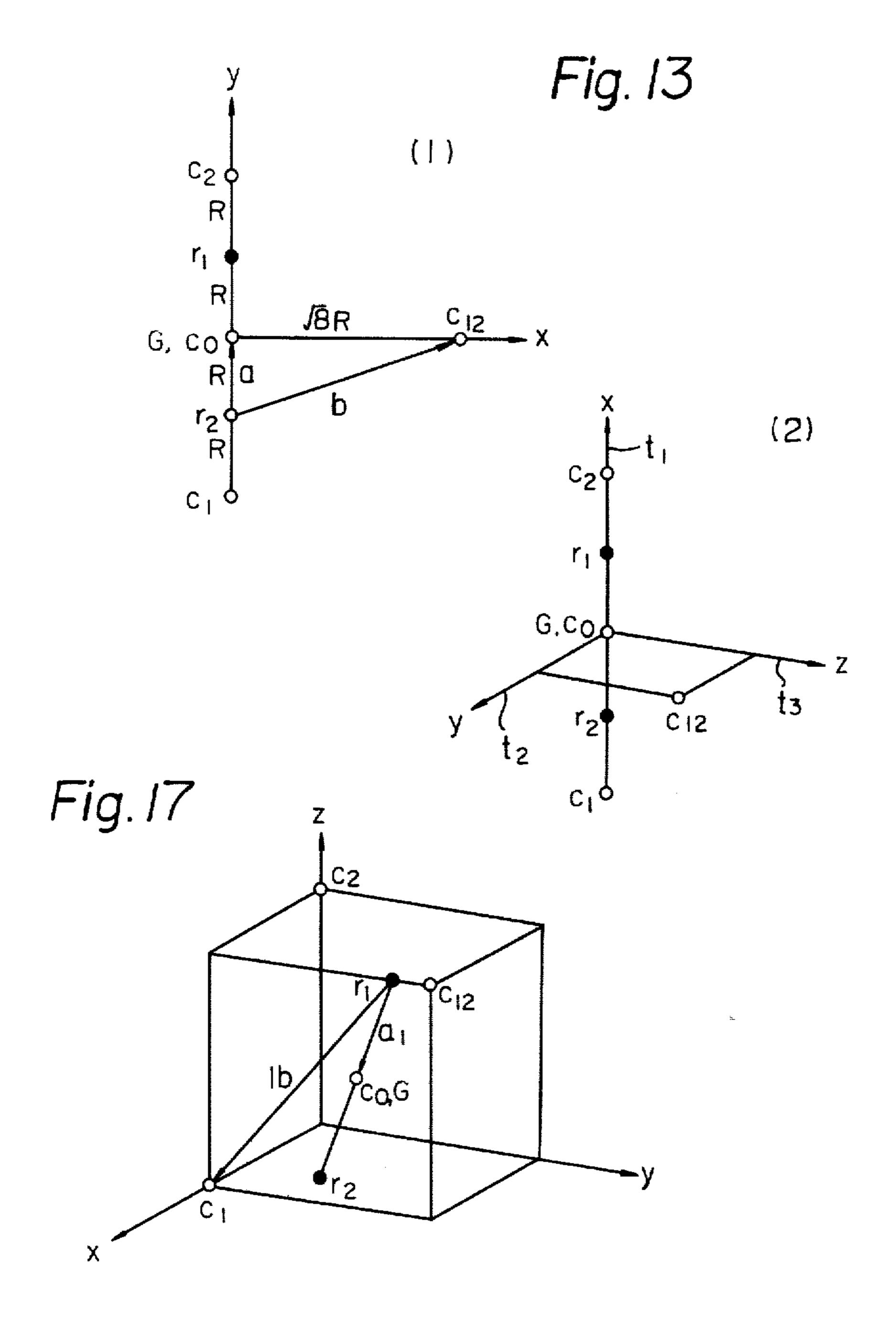

FIG. 17 is a vector diagram for one of the drive signals shown in FIG. 16;

FIG. 18 shows the potential differences across the electrodes applied with the drive signals shown in FIG. 17;

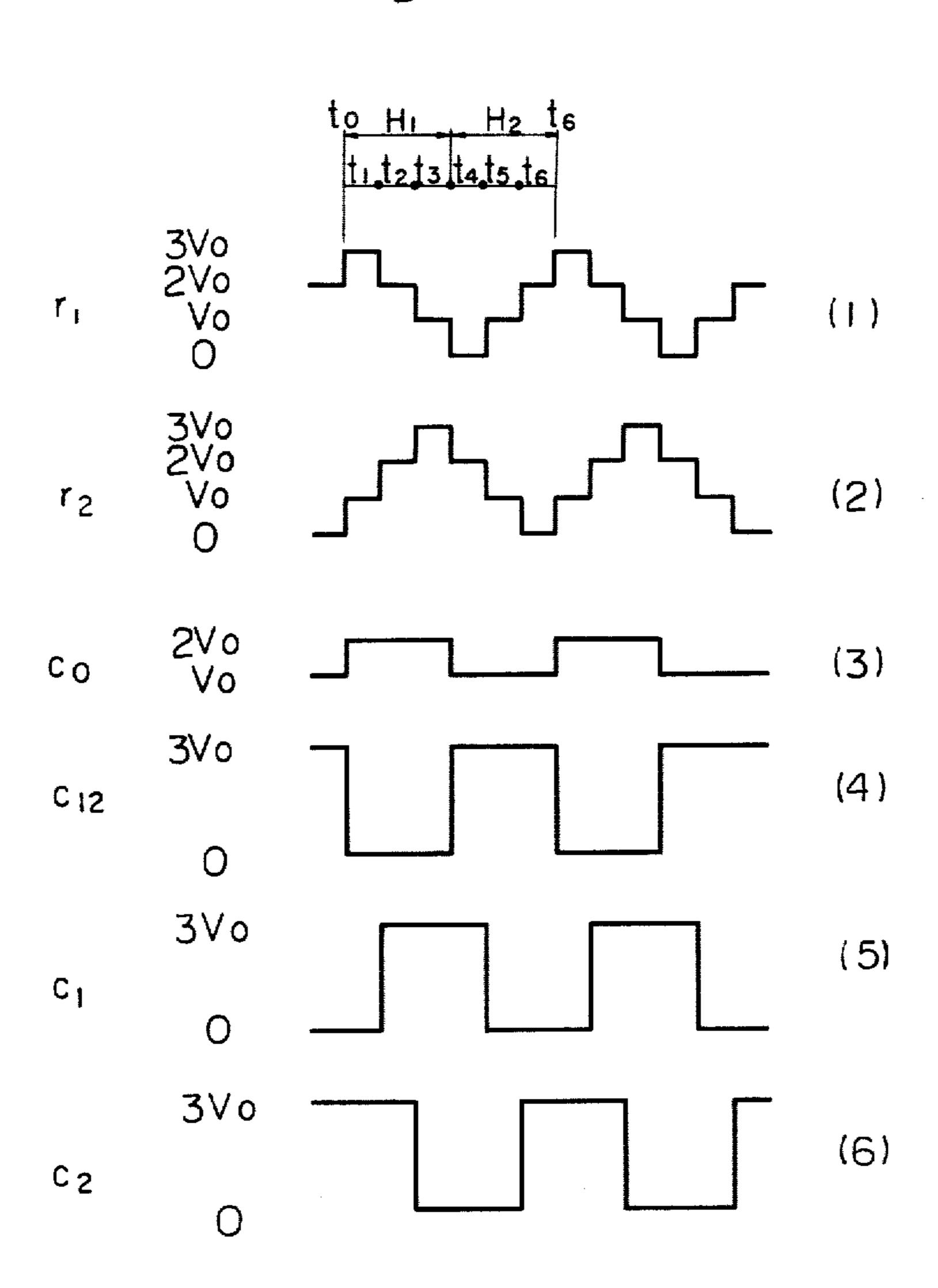

FIG. 19A is a timing chart for another preferred example of digit and segment drive signals according to the present invention;

FIG. 19B is a schematic view of an example of an electro-optical display device arranged in a matrix configuration for the digit and segment drive signals shown in FIG. 19A;

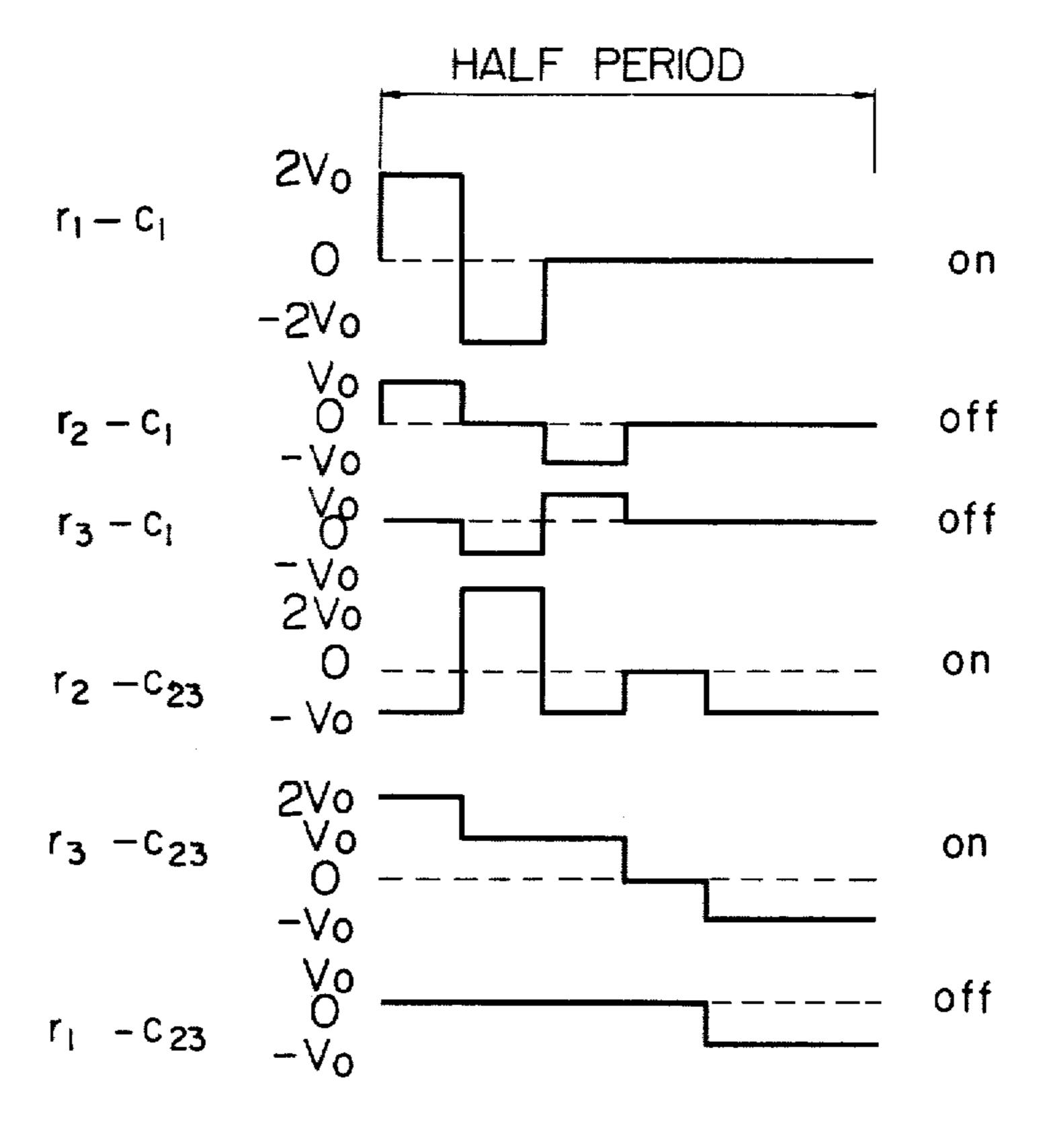

FIG. 20 shows the potential differences across the electrodes applied with the drive signals shown in FIG. 19;

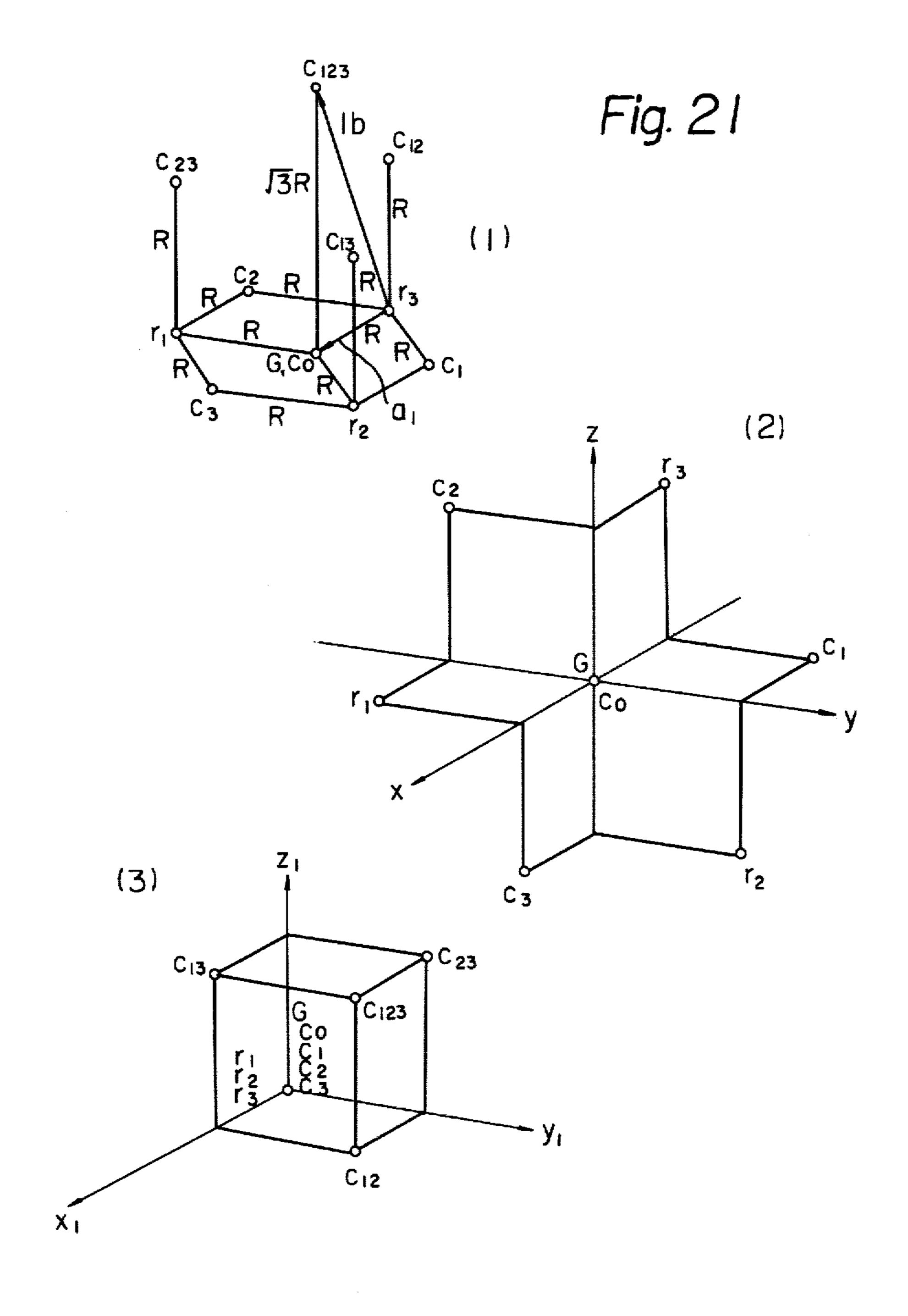

FIG. 21 shows the vector diagrams for the drive signals shown in FIG. 19;

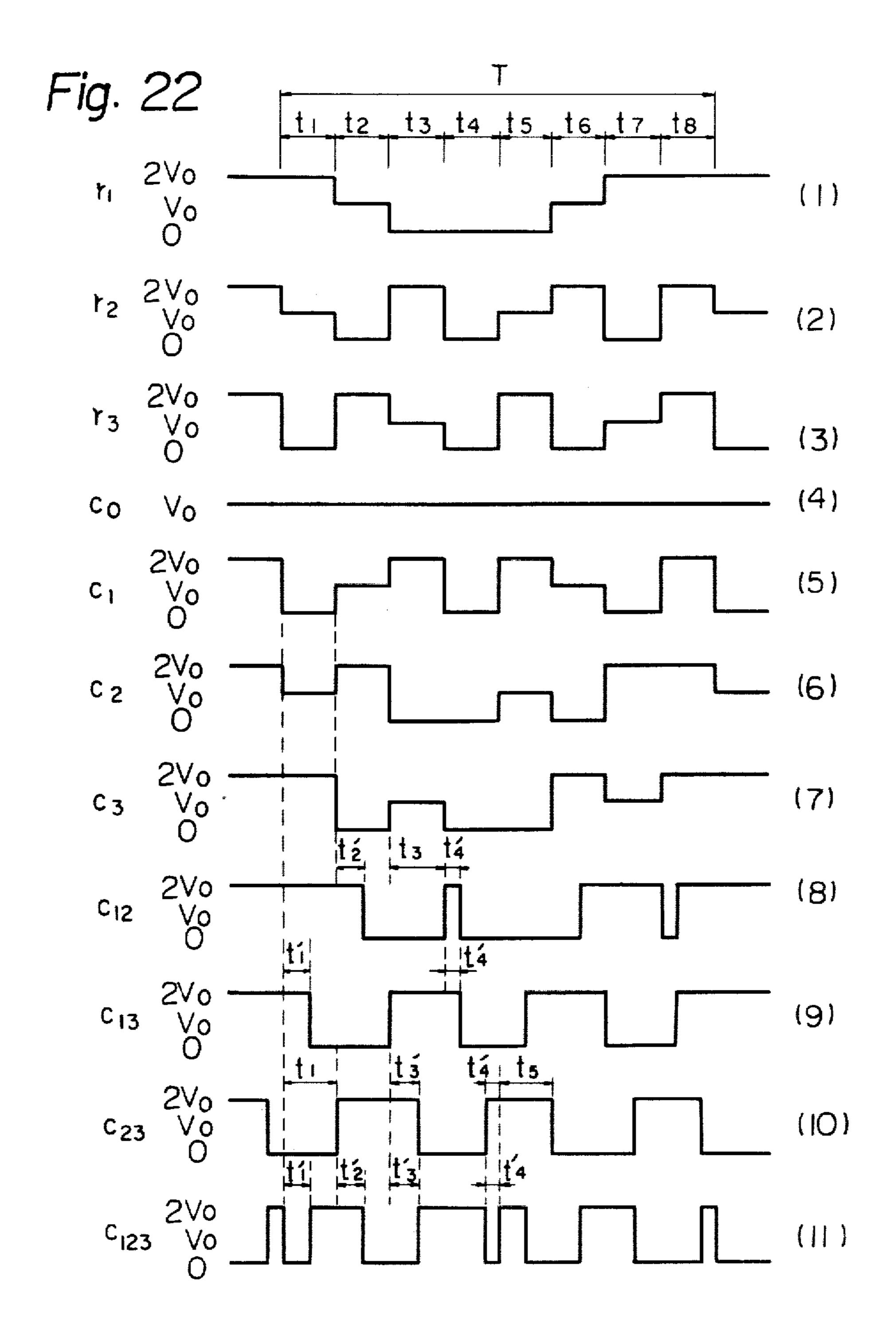

FIG: 22 is a timing chart for another preferred example of digit and segment drive signals according to the present invention;

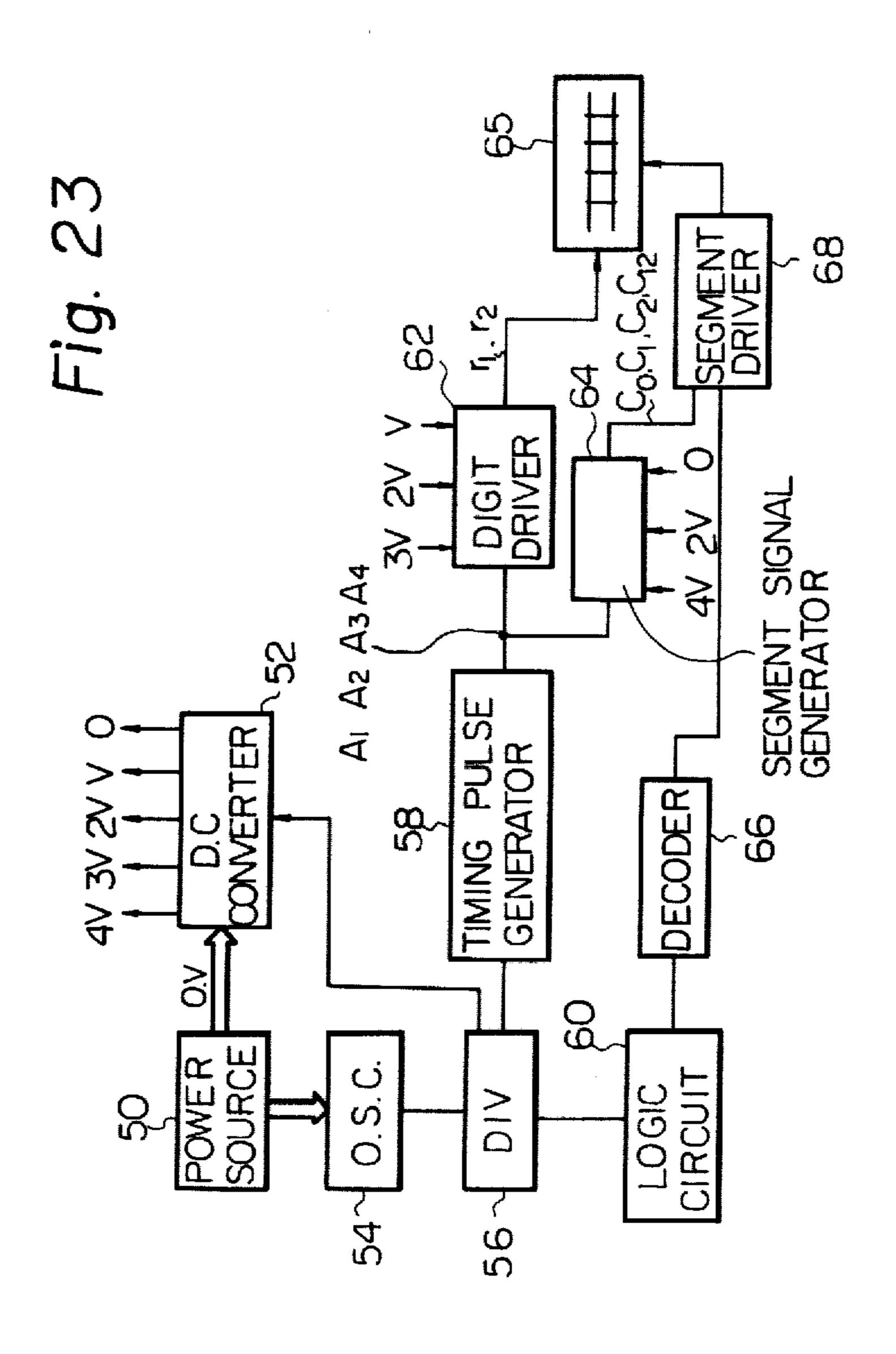

FIG. 23 is a block diagram of an example of a driver circuit to carry out a method of the present invention;

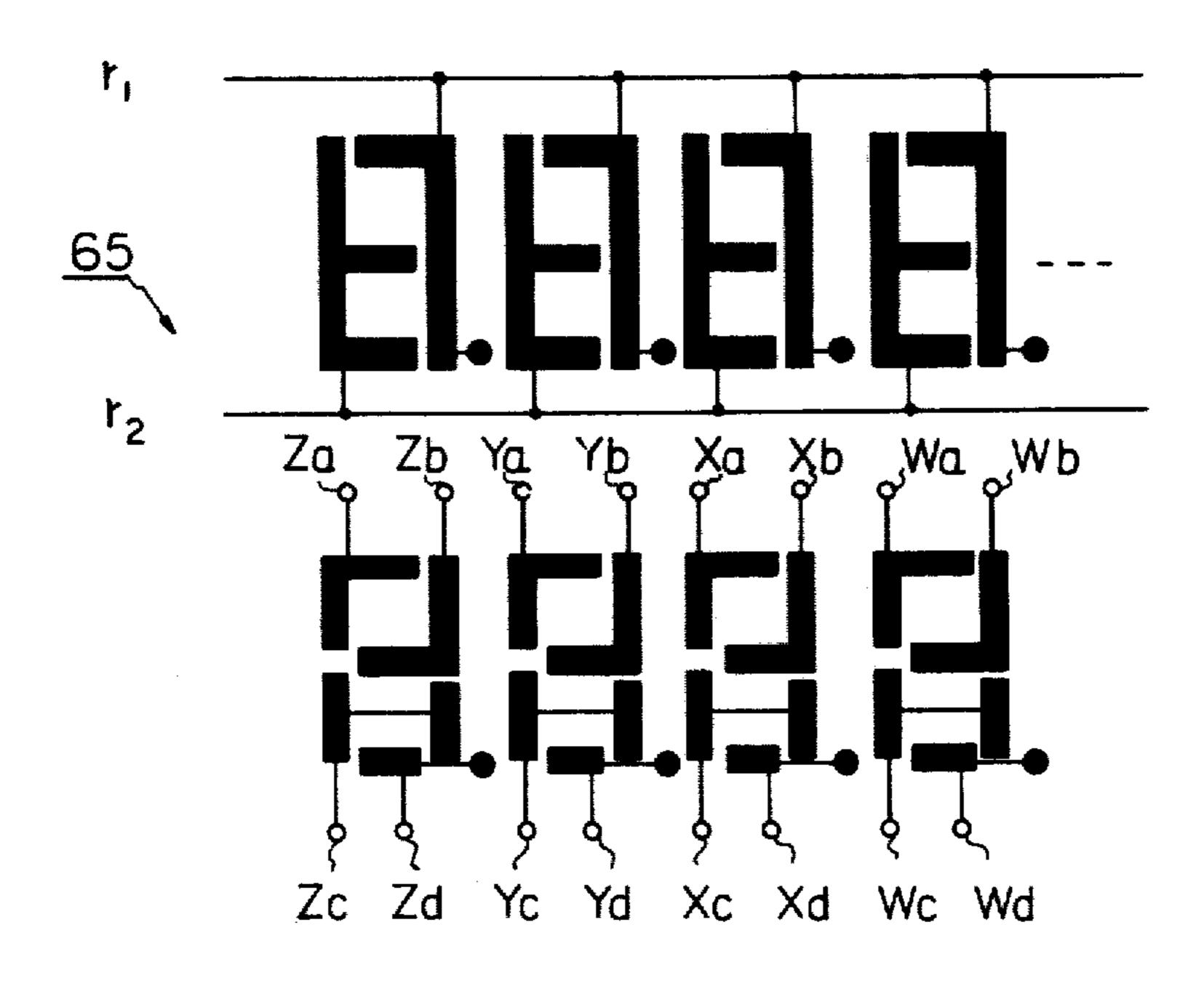

FIG. 24 is a view showing an example of an arrangement of a display device shown in FIG. 23;

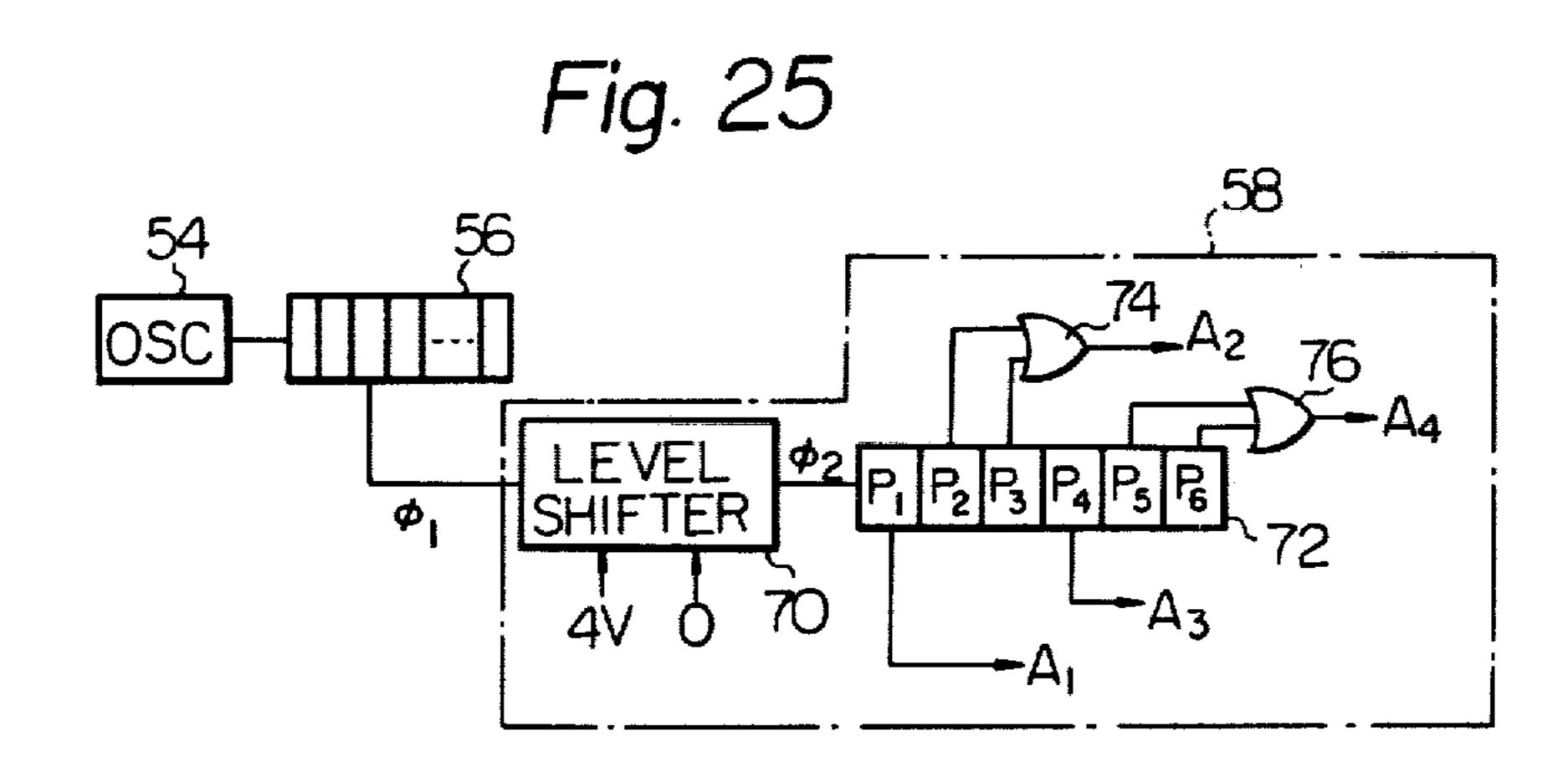

FIG. 25 is a detail circuitry for a timing pulse genera-60 tor shown in FIG. 23;

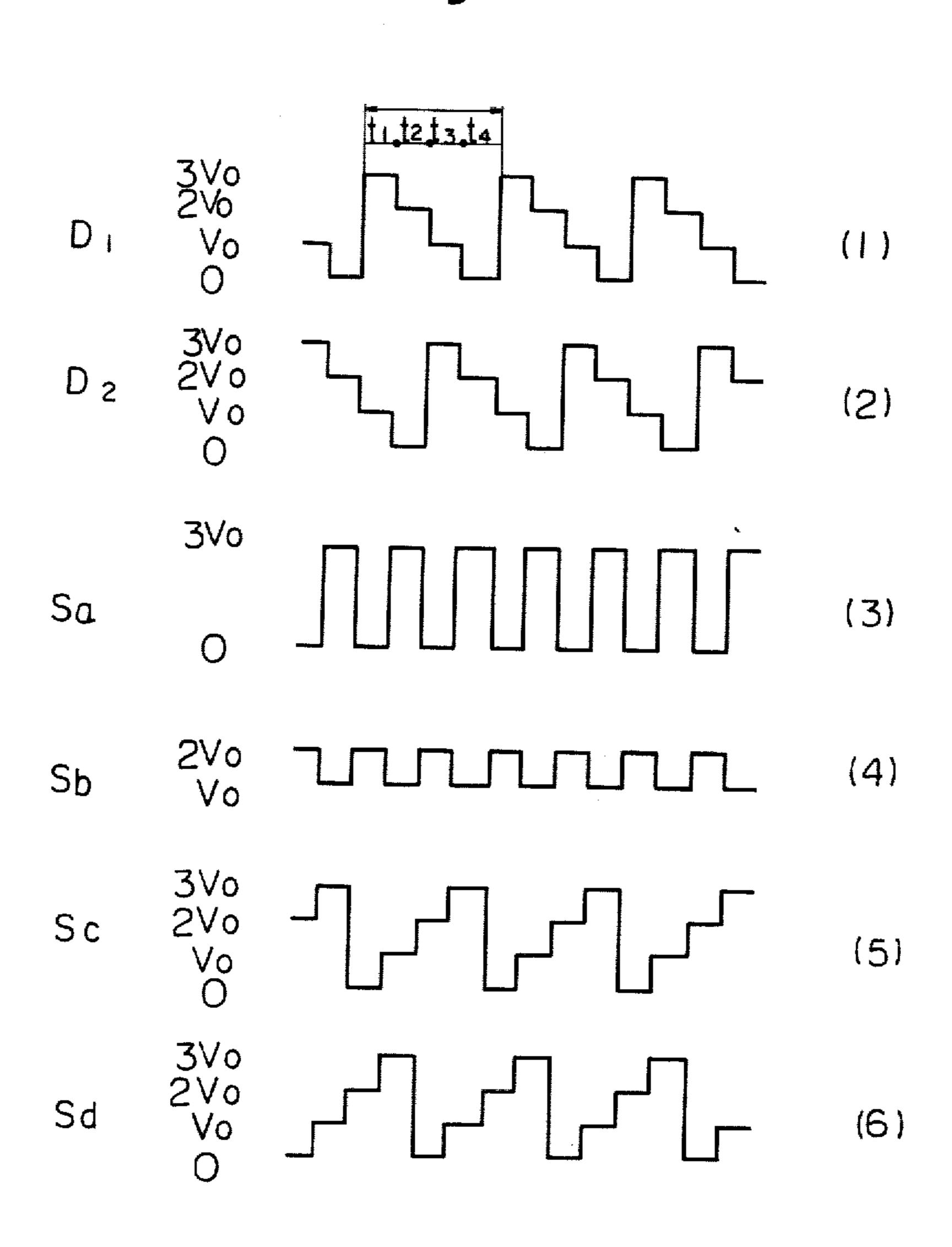

FIG. 26 is a timing chart for timing signals generated by the circuit shown in FIG. 25;

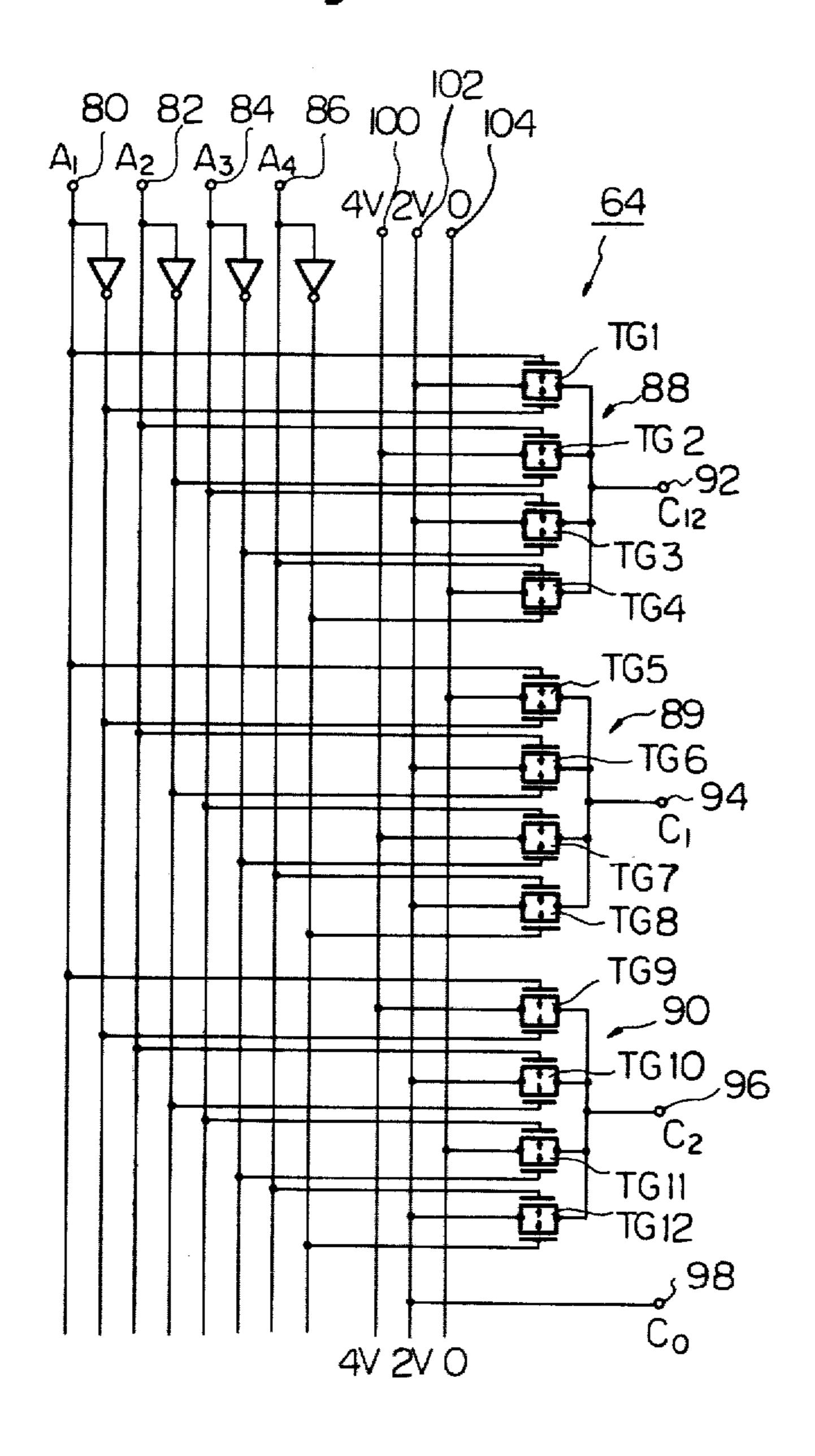

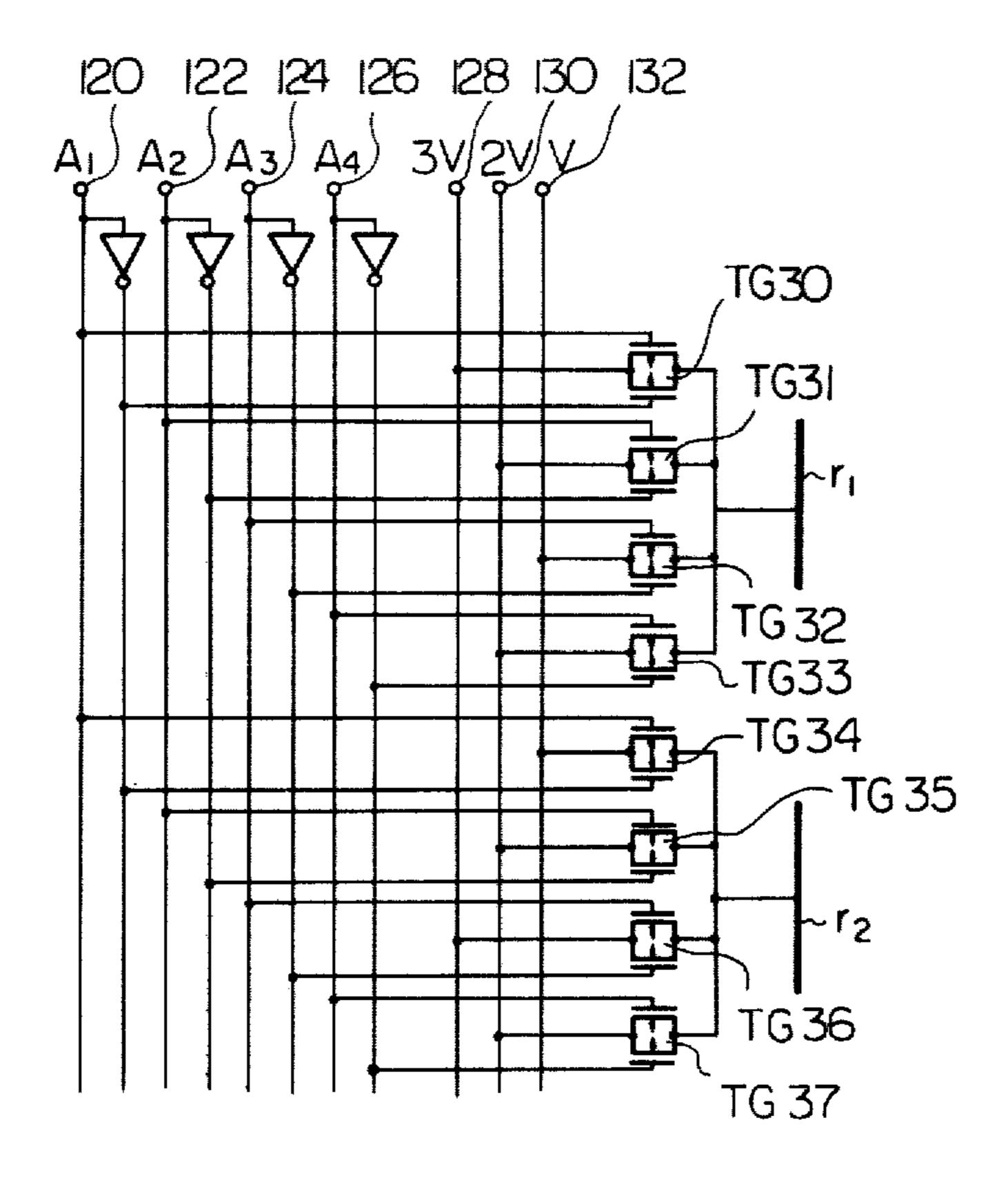

FIG. 27 is a detail circuitry for a segment signal generator shown in FIG. 23;

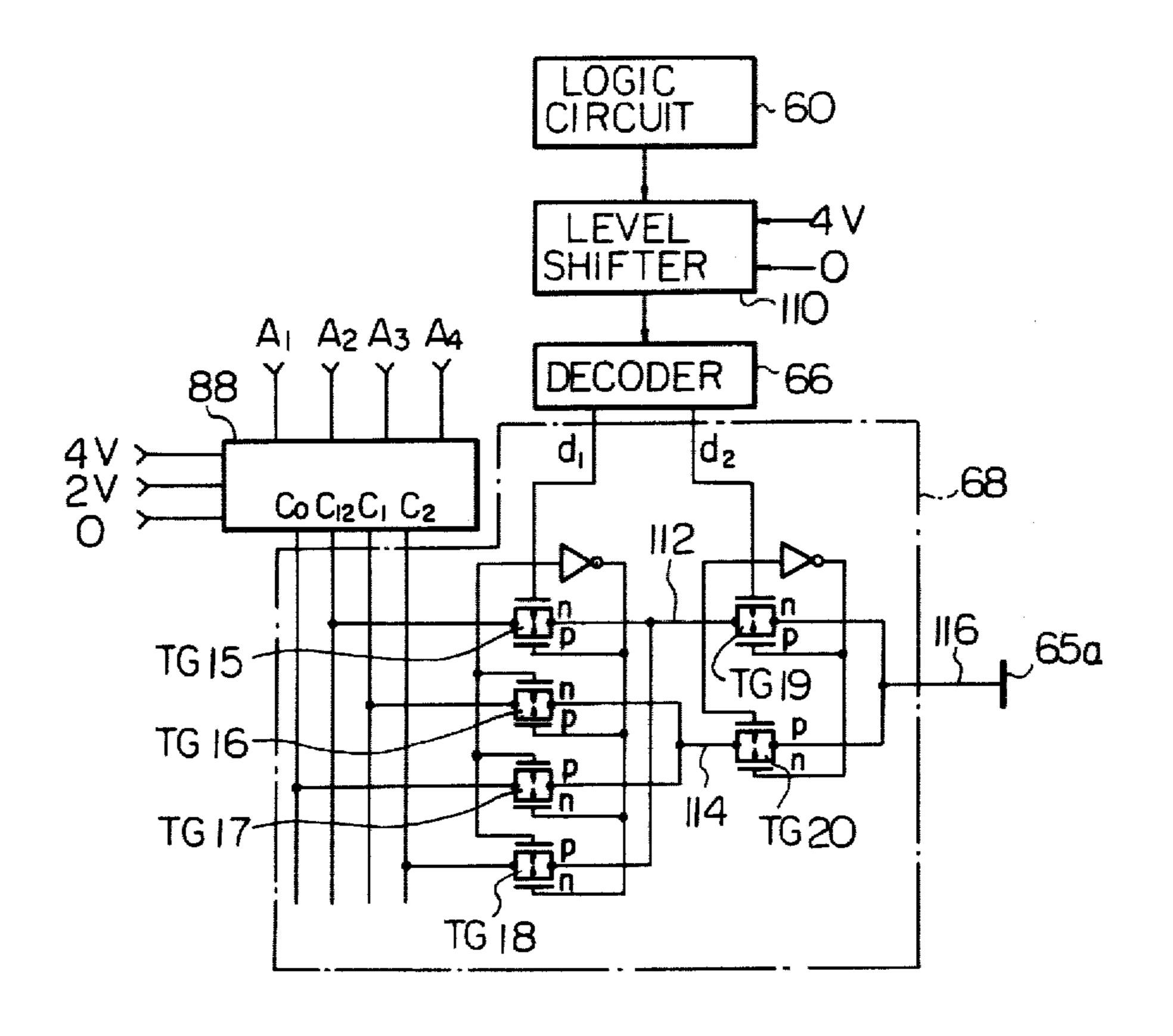

FIG. 28 is a detail circuitry for a segment driver shown in FIG. 23;

FIG. 29 is a detail circuitry for a digit driver shown in FIG. 23;

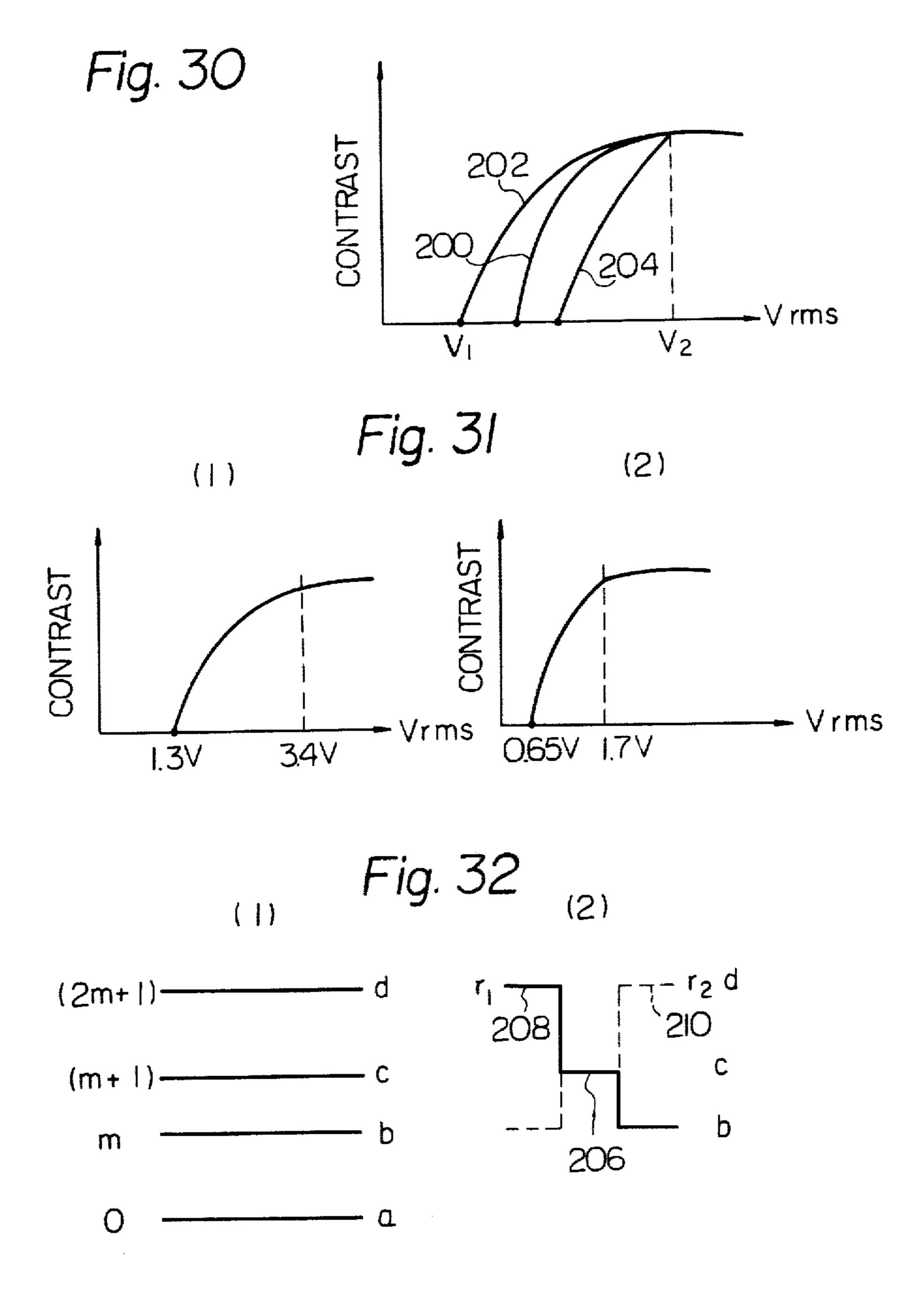

FIG. 30 is a graph illustrating voltage characteristics for a liquid crystal;

FIG. 31 shows graphs illustrating voltage-contrast curves for a liquid crystal when driving is accomplished by a driving method according to the present invention; 5 and

FIG. 32 shows diagrams illustrating the relationship between the potential levels and the drive signals used in a driving method of the present invention.

Before entering to a detailed description of the present invention, an explanation will be given to how to convert a potential of a driving signal to vector quantities with reference to FIGS. 1A and 1B. A signal cycle or half cycle T of the driving signal waveform is divided into a number of intervals  $t_1, t_2, \ldots t_j$ .  $t_i$  is assumed as the width (duration) of the i-th interval, and the potential of the driving signal over each such interval is assumed to be constant and is assigned as  $e_i$ . The j-dimension vector e having the i-th component which specified  $e_i \sqrt{t_i/T}$  will be herein defined as a vector corresponding to the driving waveform E (FIG. 1) and expressed in the following equation:

$$e = \begin{pmatrix} e_1 \sqrt{t_1/T} \\ e_2 \sqrt{t_2/T} \\ e_j \sqrt{t_j/T} \end{pmatrix}$$

(1)

FIG. 1B shows the vector diagram indicating the components of the vector e. FIGS. 1A and 1B shows examples of the waveforms of the driving signal and the vector diagram in which j=3.

The root mean square value  $V_{k1}$  of the potential representative of the difference between two signals  $A_k$  and  $A_l$  becomes:

$$V_{kI} = \sqrt{\frac{1}{T}} \int_{0}^{T} (A_k - A_l)^2 \cdot dt = \sqrt{\frac{1}{T}} \sum_{i=1}^{j} (a_{ki} - a_{li})^2 \cdot t_i$$

This is equivalent to the distance between  $a_k$  and  $a_1$  in the j-dimension space, namely

$$a_k \bar{\mathbf{a}}_l = \sqrt{\sum_{i=1}^{j} (a_{ki} \sqrt{ti/T} - a_{li} \sqrt{t_i/T})^2}$$

The signal waveforms  $A_1, A_2, \ldots A_n$  may be brought into correspondence with another set of vectors  $a_1', a_2', \ldots a_n'$  by an interval dividing method which is different from that given above. These vectors may be different from  $a_1, a_2, \ldots a_n$  even in dimension number, but  $a_1, a_2, \ldots a_n$  and  $a_1', a_2', \ldots a_n'$  are congruent. In other words, it is possible to bring them into coincidence by rotational movement, parallel movement and a reversal transformation.

The transformation from vectors  $a_1, a_2, \ldots a_n$  to signal waveforms will be carried out by a procedure 60 which is the reverse of that stated above. However, this transformation is not a one-to-one correspondence because in this case  $t_1, t_2, \ldots t_n$  can be arbitrarily selected according to formula (1).

However, when the method of selecting  $t_1, t_2, \ldots t_n$  65 is changed and a transformation made to other signals  $A_1'$ ,  $A_2'$ , the root mean square values of the potential differences between signals, that is signals  $A_1$ ,  $A_2$ , ...

4

$A_n$  and signals  $A_1'$ ,  $A_2'$ , ...  $A_n'$ , maintain the same relation. The root mean square value of the potential differences also maintain the same relation for  $A_1''$ ,  $A_2''$ , ...  $A_n''$  in which a transformation is made to signal waveforms from vectors  $a_1'$ ,  $a_2'$ , ...  $a_n'$ , obtained by the rotational movement, parallel movement and reverse transformation of vectors  $a_1$ ,  $a_2$ , ...  $a_n$ . Accordingly, it can be understood that signal waveform groups  $A_1$ ,  $A_2$ , ...  $A_n$ ; and  $A_1''$ ,  $A_2''$ , ...  $A_n''$  constitute components of one set A. Likewise,  $a_1$ ,  $a_2$ , ...  $a_n$  and  $a_1'$ ,  $a_2'$  ...  $a_n'$  constitute components of one set A over the vector space, with which set A may be considered to be in one-to-one correspondence.

Considering the transformation from vector to waveform in a practical light, it is preferable that the waveform be as simple as possible; in particular, the simplicity of the signal waveform has a great effect upon the number of gates in the driving circuit. It follows that there are cases in which prior to transforming the vectors it is better to perform a suitable transformation of coordinates to change the vector dimension number before making the transformation to the waveforms.

A convenient method of dealing with the transformation of vector coordinates is to apply a matrix as shown below. For a transformation from j-dimension vectors  $a_1, \ldots a_n$  to 1-dimension vectors  $a'_1, \ldots a'_n$ , we have

Vectors  $a_n$ ,  $a'_n$  are thus represented respectively by matrix with j rows and l rows, and  $(a'_1, a'_2 \dots a'_n)$  with l rows and n columns are represented by the following matrix:

$$\begin{pmatrix} X_{1}', X_{2}' \dots X_{n}' \\ Y_{1}', Y_{2}' \dots Y_{n}' \\ Z_{1}', Z_{2}' \dots Z_{n}' \end{pmatrix}$$

Assume that K represents a matrix with 1 rows and n columns. To represent a unit matrix I with 1 rows and 1 columns, use is made of a matrix N with 1 rows and n columns where  $N^T \cdot N = I$  so that  $(a_1', a_2', \ldots a_n') = N \cdot (a_1, a_2 \ldots a_n) + K$

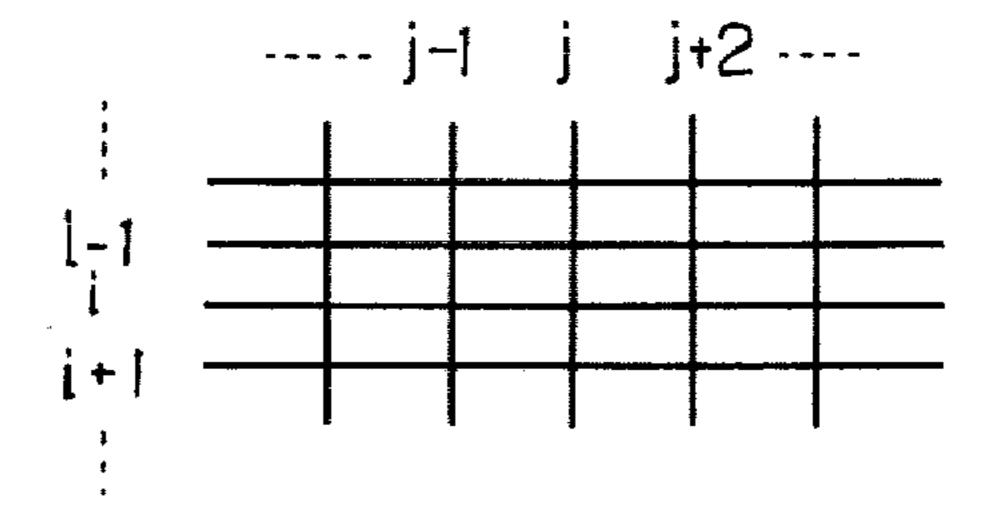

Referring now to FIG. 2, there is shown a model matrix layout in which the i order represents a group of digit electrodes while the j order denotes a group of segment electrodes. Discussion will now be directed toward the relationships between digit driving signals and address signals applied to the j segment electrodes.

FIG. 3 shows typical voltage waveforms which are applied in the prior art to the digit and segment electrodes. Discussion will be made with respect to one-half the driving period. In FIG. 3, ±d will be taken as the voltage impressed upon the digit electrodes while ±s

represents the voltage impressed upon the segment electrodes. In FIG. 3, reference numeral 10 denotes the waveform of the voltage applied to the i-th digit electrode and reference numeral 12 the waveform of the voltage applied to the (i+m)-th digit electrode. Reference numeral 14 denotes the waveform of the voltage impressed upon segment electrode j.

Hereinaster the matrix driving system will be described, using an integer n representing a n digits (n ≤ 2). In general, the timing relationship between waveforms 10 and 12 will be assumed as follows: the portion denoted by reference numeral 10' will be represented by 1/n and the portion 10" by (n-i)/n. In other words, n represents the number of the digit electrodes and 1/n the duty.

FIGS. 3(4) and 3(5) represent the voltage difference between the electrodes. Here, reference numeral 16 denotes the voltage waveform for an intersection i.j, and 18 the voltage waveform for an intersection (i+m).j. To obtain the root mean square (rms) voltage 20 of the waveform shown in FIG. 3(4), the following equation is employed:

$$Vrms = \sqrt{\frac{n-1}{n} s^2 + \frac{1}{n} (s+d)^2}$$

while the equation for the rms voltage of the waveform in FIG. 3(5) is given by

$$Vrms = \sqrt{\frac{n-1}{n} s^2 + \frac{1}{n} (d-s)^2}$$

where (4) denotes a display state and (5) a non-display state. Letting s=1, the operation margin  $\alpha$  can be obtained from

$$\alpha = \sqrt{\frac{(n-1) + (d+1)^2}{(n-1) + (d-1)^2}}$$

The operation margin is thus the value which represents the minimum ratio of the rms voltage during a period in which there is a display to the rms voltage during a 45 period in which there is no display; accordingly, the values of n and d determine the operation margin. It follows then that when driving a 2-digit matrix with n=2,  $\alpha=\sqrt{5}$  for d=1 and for d=2. When d=1, this corresponds to so-called  $\frac{1}{2}$  biasing whereas  $\frac{1}{3}$  biasing 50 corresponds to a case where d=2. From the above equation (2) it will be seen that when  $d=\sqrt{n}$ , the operation margin  $\alpha$  becomes the maximum value, i.e.,

$$\alpha = \frac{\sqrt{n+1}}{\sqrt{n-1}}.$$

It is apparent from the above description that in a conventional system the maximum operation margin is 60  $(\sqrt{2}+1)$  for matrix driving with n=2. Such systems are premised on the fact that there is no overlapping of phases or potential levels with regard to the signals which drive the respective digits.

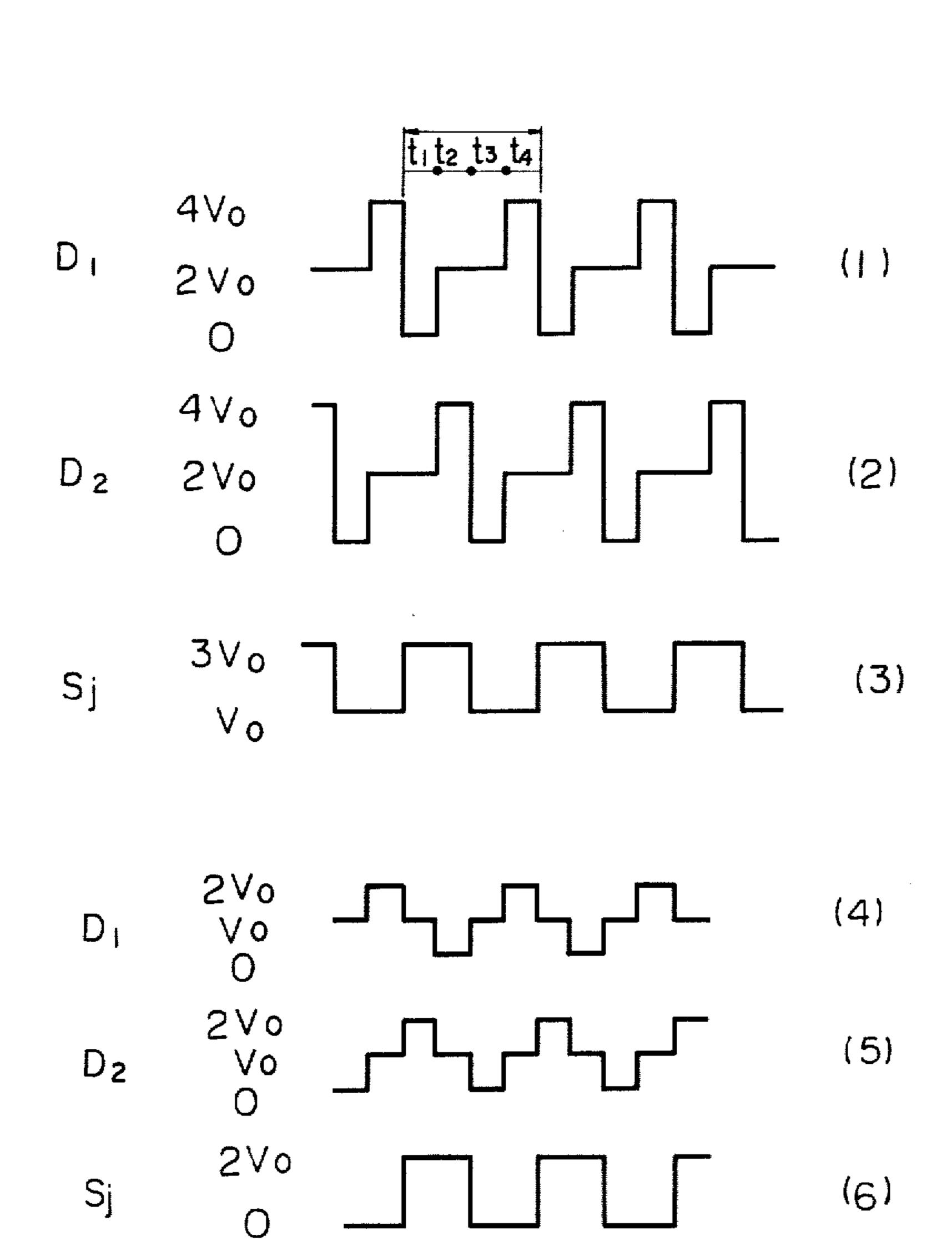

FIG. 4 shows the waveform diagrams for the driving 65 signals to be applied to digit and segment electrodes in various prior art driving methods in which n=2, and FIG. 5 shows vector diagrams for the signals shown in

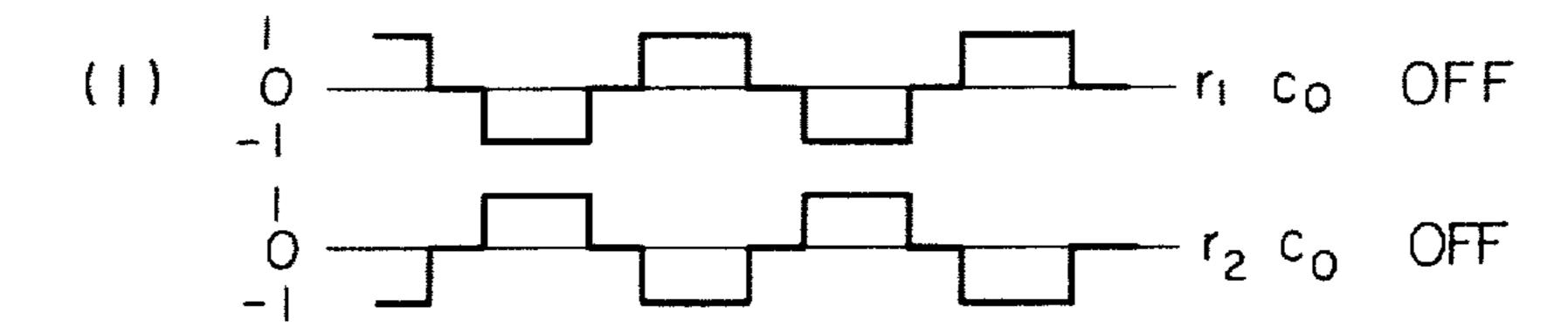

FIG. 4. In FIG. 4, r<sub>1</sub> represents the waveform impressed upon a first digit electrode, and r<sub>2</sub> the waveform impressed upon a second digit electrode. Similarly, co represents the waveform impressed upon a segment electrode to induce a non-display state at intersections between the segment electrode and both the first and second digit electrodes. C<sub>12</sub> represents the waveform by which the segments at both the corresponding intersections are in a state of display. Similarly, C1 is the waveform by which the segment at an intersection with the first digit electrode and the second digit electrode is in state of non-display. FIG. 4(1) represents a group of waveforms for the driving signals in the 1 biasing method in which  $V_r = V_c$ . FIG. 4(2) represent the waveform for the driving signals in the 3 biasing method in which  $V_r=2$   $V_c$ . Similarly, FIG. 4(3) represents the waveforms for the driving signals in which  $V_r = \sqrt{2} \cdot V_c$ .

In FIG. 5(1), a convenient set of X and Y axes is chosen and r<sub>1</sub> and r<sub>2</sub> indicative of varying potentials of corresponding digit drive signals r<sub>1</sub>' and r<sub>2</sub>' are resolved as vectors into X and Y components along these axes. In FIG. 5(1), the symbols C<sub>0</sub>, C<sub>1</sub> and C<sub>12</sub> represent varying potentials of the corresponding segment drive signals 25 Co, C1 and C12. The symbol G represents the mean value in potential of the digit drive signals at each time instant. The time interval  $t_1$  is resolved into the X axis, and the time interval t<sub>2</sub> is resolved into the Y axis. In FIG. 5(1), r<sub>1</sub> has a potential value of 1 during the time 30 interval t<sub>1</sub>, and r<sub>2</sub> has a potential value of 0 during the time interval t2. Similarly, r2 has a value of 0 during the time interval t<sub>1</sub> and has a value of 1 during the time interval t2. Resolving co at co-ordinates (1, 1), c1 at co-ordinates (-1, 1),  $c_2$  at co-ordinates (1, -1) and  $c_{12}$ at co-ordinates (-1, -1) produces a square with the length of each side having a potential value of 2. G is plotted at co-ordinates (1/2, 1/2). Vector a represents the rms voltage Vost indicative of the state of non-display, and vector b represents the rms voltage Von indicative 40 of the state of display. Since the operation margin  $\alpha$  is expressed by the ratio of  $V_{on}$  to  $V_{off}$ , the following equation holds:

$$\alpha = |b|/|a| = \sqrt{5}/1 = \sqrt{5}$$

In a case shown in FIG. 5(2), G is plotted at the same point as  $C_0$ , and  $|a| = \sqrt{2}$  and  $|b| = \sqrt{10}$ . Therefore, the operation margin  $\alpha$  is  $\sqrt{5}$ . Similarly, in a case of FIG. 5(3) G is plotted at a point  $(\sqrt{2}/2, \sqrt{2}/2)$ . In this example, since  $|a| = 2(2 - \sqrt{2})$  and  $|b| = 2(2 + \sqrt{2})$ , the operation margin  $\alpha$  is  $1 + \sqrt{2}$ .

The relationship in the three cases among  $r_1$ ,  $r_2$ ,  $c_0$ ,  $c_1$ ,  $c_2$  and  $c_{12}$  with respect to the half period is expressed by the following matrixes:

$$(r_1, r_2, c_0, c_1, c_2, c_{12}) =$$

$$\begin{pmatrix} 1 & 0 & 1 & -1 & 1 & -1 \\ 0 & 1 & 1 & 1 & -1 & -1 \end{pmatrix}$$

$$\begin{pmatrix} 2 & 0 & 1 & -1 & 1 & -1 \\ 0 & 2 & 1 & 1 & -1 & -1 \end{pmatrix}$$

$$\begin{pmatrix} \sqrt{2} & 0 & 1 & -1 & 1 & -1 \\ 0 & \sqrt{2} & 1 & 1 & -1 & -1 \end{pmatrix}$$

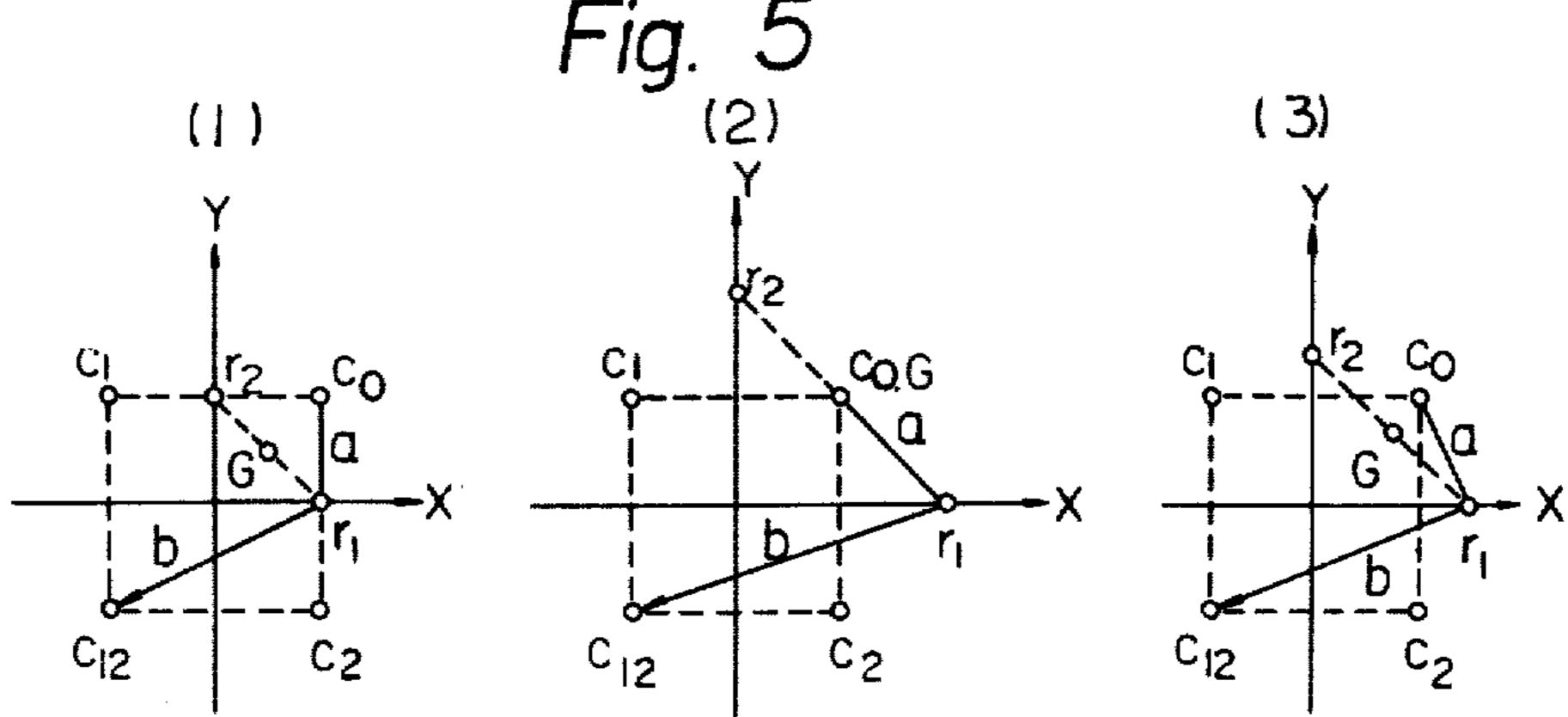

FIGS. 6 (1, 2, 3) shows the actual waveforms for the situation described with reference to FIG. 4(2), i.e.,

with n=2, Vc=1 and Vr=2. FIG. 6(1) shows the

In this case, the rms voltage  $V_{off}$  in the non-display state is  $\sqrt{2}$  and rms voltage  $V_{on}$  in the display state is  $\sqrt{6}$ . Therefore, the operation margin  $\alpha$  is  $\sqrt{3}$ .

waveform impressed upon a digit electrode D1, and FIG. 6(2) shows the waveform impressed upon a digit electrode D2. Similarly, FIG. 6(3) shows the waveform impressed upon any segment electrode Sj to display only in the digit D1. As may be appreciated from the drawings, five potential levels, namely 0, Vo, 2 Vo, 3 Vo and 4 Vo are employed. By combining these waveforms a liquid crystal may be driven at an operational margin of  $\sqrt{5}$ .

In FIG. 9(2),  $V_r = 2 V_c$ , and the rms voltage  $V_{off}$  is 1 while the rms voltage  $V_{on}$  is  $\sqrt{11/3}$ . Therefore, the operation margin  $\alpha$  is  $\sqrt{11/3}$ .

FIGS. 6(4), (5) and (6) correspond as in FIG. 4(1) to a case in which Vc=Vr=1 and show the waveforms which are impressed upon a digit electrode D1, a digit electrode D2, and any segment electrode Sj to display only in the digit D1, respectively. As previously ex- 15 plained, the obtainable operation margin  $\alpha$  is  $\sqrt{5}$ . Here,

In FIG. 9(3),  $V_r = \sqrt{3} \cdot V_c$ , and the rms voltage  $V_{off}$  is  $\sqrt{2(3-\sqrt{3})}$  while the rms voltage  $V_{on}$  is  $\sqrt{2(3+\sqrt{3})}$  so that the operation margin  $\alpha$  is

three potentials 0, Vo and 2 Vo are employed.

FIG. 7 illustrates the waveforms which are obtained across the electrodes of a liquid crystal by making use of the waveforms shown in FIG. 6. FIG. 7(1) shows the waveforms for a display state when Vr=2, and FIG. 7(2) the waveforms for a non-display state when Vr = 2. Similarly, FIGS. 7(3) and (4) depict the respective waveforms for display and non-display states when Vr=1.

FIGS. 10(1), (2) and (3) show the vector diagrams for the waveforms used in FIGS. 9(1), (2) and (3), respectively.

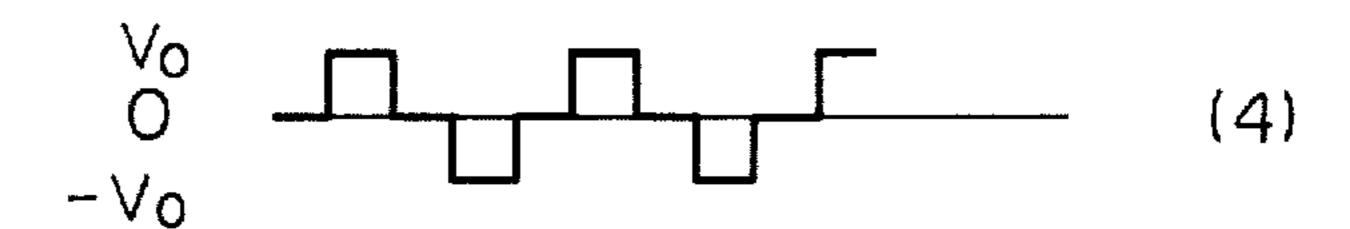

FIG. 8 depicts the waveforms for matrix driving in accordance with conventional systems when n=2 and four potentials, namely 0, Vo, 2 Vo and 3 Vo are employed. FIGS. 8(1) and (2) show the waveforms which are impressed upon a digit electrode D1 and a digit electrode D2, respectively. It can be understood from FIG. 8(1) that the driving signal for these digit electrodes consists of four equal intervals t<sub>1</sub>, t<sub>2</sub>, t<sub>3</sub> and t<sub>4</sub> which comprise one period (or cycle time). If the potentials for the D1 digit signal and D2 digit signal over each of these intervals are added, the sums are 4 Vo for t<sub>1</sub>, 2 Vo for t<sub>2</sub>, 4 Vo for t<sub>3</sub> and 2 Vo for t<sub>4</sub>, thus repetitively alternating between 4 Vo and 2 Vo. In other words, either a potential of 0 or 3 Vo appears once 40 during each unit time interval without overlapping each another and at no time do identical potential levels appear during any of the intervals t<sub>1</sub> through t<sub>4</sub>.

In FIG. 10, r<sub>1</sub>, r<sub>2</sub> and r<sub>3</sub> indicative of varying potentials of the corresponding digit drive signals  $r_1$ ,  $r_2$  and  $r_3$ in FIG. 9 are resolved as vectors into X, Y and Z axes, respectively. c1, c2, c3, c12, c13 and c23 correspond to voltage potentials of the segment drive signals producing display at one or two digits. From these vector diagrams, it will be possible to grasp the potential difference across the electrodes.

FIGS. 8(3), (4), (5) and (6) show the waveforms of signals impressed upon any segment electrode Sj to 45 induce the display or non-display state for a matrix where n=2. Signal Sa in FIG. 8(3) is a segment drive signal when intersections  $D1S_i$  and  $D2S_i$  are both in a display state. Similarly, signal Sb in FIG. 8(4) is the corresponding signal when D1S; and D2S; are both in a 50 state of non-display, signal Sc in FIG. 8(5) is the corresponding signal when  $D1S_i$  is in a display state and D2S<sub>i</sub> in a state of non-display, and signal Sd in FIG. 8(6) is the corresponding signal when  $D1S_i$  is in a state of non-display and D2S; is in a display state. In this case the 55 waveforms across the electrodes of the liquid crystal are as illustrated by FIG. 7(1) and (2), and the operation margin  $\alpha$  is  $\sqrt{5}$ .

From the above description, it will be understood that the waveforms of the drive signals consist of a half-period (for example t<sub>1</sub>, t<sub>2</sub> in FIGS. 6 and 8) and another half-period (for example t<sub>3</sub>, t<sub>4</sub>). Each halfperiod is sub-divided into n equal parts and each interval is assigned to a respective digit. Interval t<sub>1</sub> corresponds to a 1st digit, and interval t<sub>2</sub> to a 2nd digit; if the digit driving voltages are now represented with the mean value of all the digit driving signals taken as a reference, then a large driving voltage will be generated for the 1st digit driving signal over the interval t<sub>1</sub>, the 2nd digit driving signal over the interval t2, and the ith digit driving signal over the interval ti, and the voltage will drop to a low level over the other intervals. In addition, the segment signal voltage during interval to and the segment signal voltage during interval ti are both determined by the state of display or non-display of the 1st digit and ith digit, respectively, in accordance with the pattern that decides which digits should be displayed by the segment signal. It is preferable that the voltage for the segment signal during the non-display state be close to the mean voltage of all the digit driving signals; even so, the rms value of the driving voltage does not fall to 0 during a state of non-display. Moreover, if we consider the driving voltage at the ith intersection when the ith digit is to be displayed, then this voltage is exactly the same as the driving voltage at the ith intersection when the ith digit is not to be displayed during the half-period from which interval t<sub>i</sub> is omitted, and the rms value of the driving voltage differs only by the difference in voltage applied over the interval t<sub>i</sub>.

FIG. 9 shows the waveform diagrams of driving signals used in three-digit matrix driving method with 60 n=3. In FIG. 9,  $r_1$ ,  $r_2$  and  $r_3$  represent digit drive signals, and c<sub>0</sub>, c<sub>1</sub>, c<sub>3</sub>, c<sub>123</sub> represent segment drive signals, respectively. In FIG. 9(1), the voltage potential  $V_r$  of the digit drive signal is equal to the voltage potential  $V_c$ of the segment drive signal  $V_c$  and expressed as:

In a matrix driving method of the present invention, the driving waveform for a half cycle time is not divided in its entirety into separate components for each digit electrode and, in contrast, digit and segment drive signals are applied to digit and segment electrodes in such a manner that the digit drive signals applied to all the digit electrodes have potentials equal in level with each other during a prescribed time interval during which the potential of a first segment drive signal inducing a state of non-display at all the digit electrodes is equal to the potential of each of the digit drive signals. During the prescribed time interval, the potential differ-

ence between a second segment drive signal inducing a state of display at one of the digit electrodes and a state of non-display at the other digit electrode and each of the digit drive signals is maintained in a first predetermined value whereby the root mean square value over a complete cycle of the potential difference between the second segment drive signal and the digit drive signal applied to the other digit electrodes is substantially equal to that of the potential difference between the first segment drive signal and each of the digit drive signals. 10 During the prescribed time interval, further, the potential difference between a third segment drive signal inducing a state of display at all the digit electrodes and each of the digit drive signals is maintained at a second predetermined value whereby the root mean square 15 value over a complete cycle of the potential difference between the second segment drive signal and the digit drive signal applied to the said one of the digit electrodes is substantially equal to that of the potential difference between the third segment drive signal and each 20 of the digit drive signals.

More specifically, the potential of the first segment drive signal inducing the state of non-display at all of the intersections (hereinafter referred to as display intersections) between the segment and digit electrodes 25 has a level equal to a reference potential which is substantially equal to the mean value of all the digit drive signals. The potential of each digit drive signal in turn is selected to have a value larger than the reference potential during a respective first time interval within one- 30 half of the cycle period. During a second time interval corresponding to the prescribed time interval mentioned above within one-half of the cycle time, the potentials of all the digit drive signals are selected to be equal to each other. The potentials of the segment drive 35 for a suitable interval  $\tau$ . Vo is a function of time or a signals inducing the state of display at only the i-th digit's display intersections and the potential of the segment drive signal inducing the state of non-display at the i-th digit's display intersections are selected to be unequal in level during the first time interval. Further, 40 the potential of the second segment drive signal applied to a given segment electrode inducing the state of display at the display intersections of only a given digit electrode is selected to have a level by which the maximum potential difference is provided between the given 45 digit electrode and the given segment electrode. In this case, it is possible to increase the root means square (rms) value of the driving voltage for a state of display by raising the voltage of the segment drive signal in comparison to that of the prior art, or by increasing the 50 driving time interval in which the segment drive signal is applied, or by a combination of such methods. The third segment drive signal inducing the state of display at the display intersections of all the digit electrodes is selected to have a first potential equal to the reference 55 potential during the first time interval and a second potential equal to the maximum value during the second time interval.

A driving method according to the present invention will now be described in general with reference to a 60 matrix in which n=2. A voltage waveform for a digit drive signal impressed upon a digit electrode r<sub>1</sub> is expressed by

$$Vr_1 = V1 + Vo$$

,

a voltage waveform for a digit drive signal impressed upon a digit electrode r<sub>2</sub> is expressed by

$$Vr_2 = -Vi + Vo$$

a voltage waveform for a segment drive signal when display intersections of both digit electrode are to be brought to a state of non-display is expressed by

$$VCo = Vo$$

,

a voltage waveform for a segment drive signal indicative of a display state for both digit electrodes is expressed by

$$VC_{12} = V2 + V_0$$

,

a voltage waveform for a segment drive signal indicative of a display state for a 1st digit electrode and nondisplay state for a 2nd digit electrode is expressed by

$$VC_1 = -2V1 + Vo$$

, and

a voltage waveform for a segment drive signal indicative of a non-display state for a 1st digit electrode and a display state for a 2nd digit electrode is expressed by

$$VC_2 = 2V1 + Vo.$$

Here, V1 and V2 are AC voltages which do not include a DC component;

they are chosen so as to satisfy

$$\int_{\tau} V_1 \cdot V_2 \cdot dt = 0$$

$$\int_{\tau} (V_2)^2 \cdot dt = 8 \int_{\tau} (V_1)^2 dt$$

constant. By way of example, the following possibilities are acceptable: Vo=0,  $V1=\sin \omega t$ , and  $V2=\sqrt{8}\sin t$  $\omega/2t$ . In such a case the rms value of the driving voltage for the display and non-display states is 3, a significant improvement over the conventional value of  $\nabla 5$  when n=2. In order to obtain a waveform for a case in which a switchable DC power source is used for the driving operation, it is permissible to adopt a step-like voltage waveform for Vo, V1 and V<sub>2</sub>. Two such examples are illustrated in FIGS. 11 and 14.

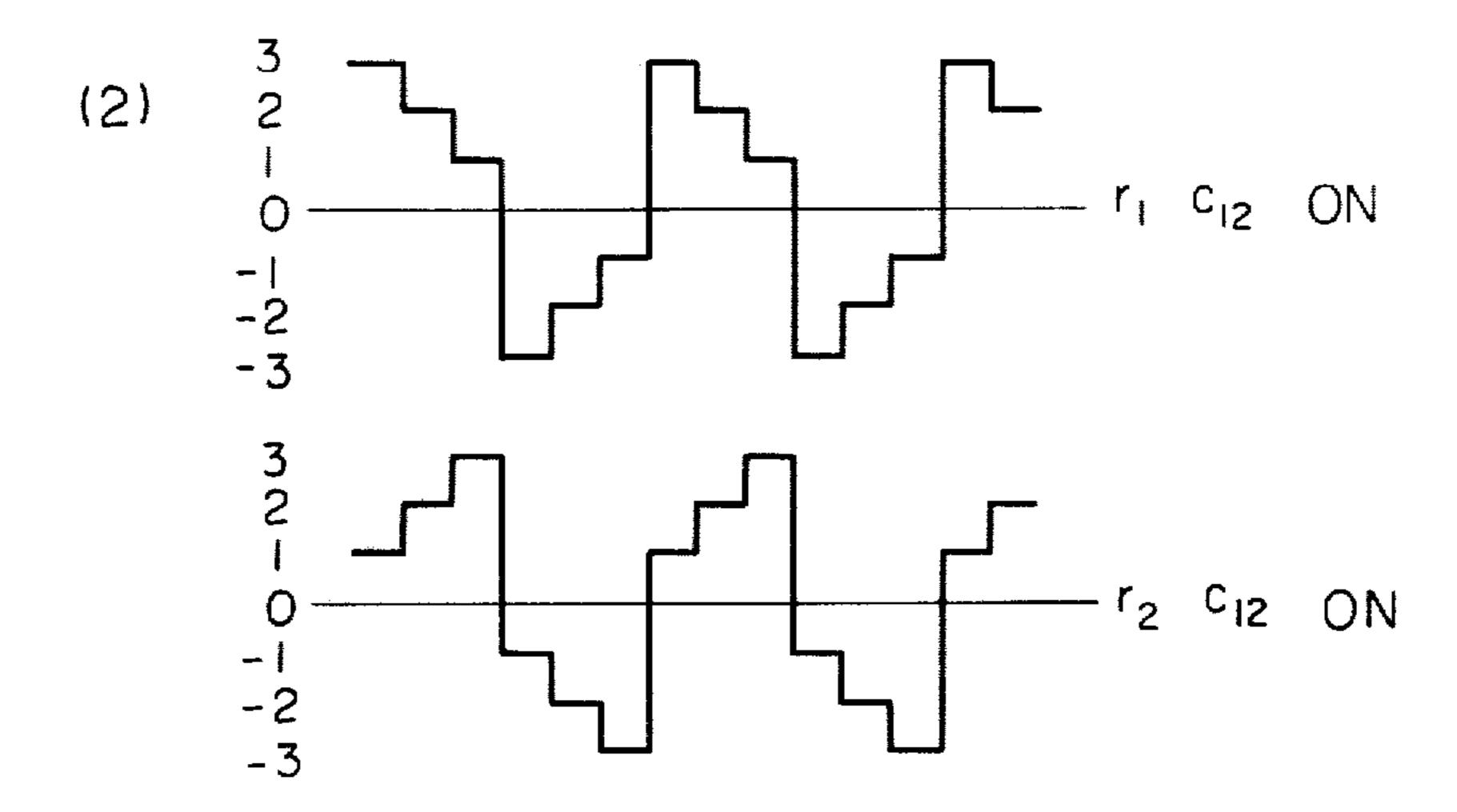

FIGS. 11(1) and (2) show one preferred example of the waveforms of the digit drive signals which are impressed upon respective digit electrodes  $r_1'$  and  $r_2'$ . In FIG. 11(1) it can be seen that the waveform is composed of six equal time intervals t1, t2, t3, t4, t5 and t6 which constitute one cycle period. The potential levels over these time intervals (hereinafter referred to as t1, t2, t3, t4, t5 and t6) of the  $r_1$  digit signal are t1=3 Vo, t2=2 Vo, t4=Vo, t5=2 Vo and t6=2 Vo, while the potentials for the  $r_2$  digit signal are  $t1 = V_0$ ,  $t2 = 2 V_0$ , t3=2 Vo, t4=3 Vo, t5=2 Vo and t6=2 Vo all of these potentials being based upon the minimum potential O of the segment drive signal which is taken as a reference potential.

FIGS. 11(3), (4), (5) and (6) show the waveforms of segment drive signals  $C_0$ ,  $C_{12}$ ,  $C_1$  and  $C_2$  which are impressed upon any segment electrode Sj.

Signal Co in FIG. 11(3) is the waveform of the segment drive signal when a non-display of  $r_1S_j$  and  $r_2S_j$  is 65 indicated, signal C<sub>12</sub> in FIG. 11(4) is the waveform of the segment drive signal when r<sub>1</sub>Sj and r<sub>2</sub>Sj are to be displayed, signal C<sub>1</sub> in FIG. 11(5) is the waveform for a display of r<sub>1</sub>Sj and a non-display of r<sub>2</sub>Sj, and signal C<sub>2</sub>

in FIG. 11(6) is the waveform for a non-display of r<sub>1</sub>S<sub>1</sub> and a display of r<sub>2</sub>Sj. In this example, t1 and t4 are the previously described driving intervals for all of the non-display segment signals and at the same time they also correspond to the intervals during which there is a 5 maximum absolute value of the digit driving signal voltage with respect to the reference potential level 2 Vo. Here, the potential levels of the digit drive signals are equal to each other during intervals t2, t3, t5 and t6. In addition, two segment signals are compared and the 10 times at which they do not present the same potential level are t1 and t4 for C<sub>1</sub> and C<sub>2</sub> and for C<sub>0</sub> and C<sub>1</sub> and for  $C_0$  and  $C_2$ ; all times for  $C_1$  and  $C_{12}$ ,  $C_2$  and  $C_{12}$ . Segment signals C<sub>1</sub> and C<sub>2</sub> possess a higher absolute voltage over the respective intervals t1, t4, and al- 15 though a large absolute potential difference then exists between C<sub>1</sub> and r<sub>1</sub> driving signals, a small absolute potential difference exists between C<sub>1</sub> and r<sub>2</sub> driving signals during the same interval. A large absolute potential difference also exists between C<sub>12</sub> and r<sub>1</sub>, r<sub>2</sub> digit drive 20 signals during the intervals t2 and t3.

It will now be understood that in accordance with the present invention the digit drive signals r<sub>1</sub> and r<sub>2</sub> have first and second voltage potentials 3 Vo and Vo which have the same potential difference but opposite in polar- 25 ity with respect to a reference potential 2 Vo during a first time interval t1 of half cycle period H and have a voltage potential 2 Vo serving as a reference potential during a second time interval t2 or t3 of the half cycle period H, with the reference potential taking a value 2 30 Vo intermediate between the first and second voltage potentials 3 Vo and Vo. A first segment drive signal Co has a potential level equal to the reference potential 2 Vo during the first and second time intervals t1 and t2, inducing a state of non-display at said display elements 35 on all of said digit electrodes. A second segment drive signal C<sub>1</sub> or C<sub>2</sub> has a fourth voltage potential 0 or 4 Vo larger in amplitude level than the first and second voltage potentials Vo and 3 Vo during the first time interval t1 and the same potential as the reference potential 2 Vo 40 during the second time interval t2, inducing a state of display at said display elements on one of said digit electrodes. A third segment drive signal C<sub>12</sub> has the same potential as the reference potential 2 Vo during the first time interval t<sub>1</sub> and a voltage potential 4 Vo, 45 during the second and third time intervals t2 and t3, inducing a state of display at said display elements on all of said digit electrodes.

FIG. 12 shows the waveforms for the potential difference across the electrodes. FIGS. 12(1), (2), (3), (4), (5) 50 and (6) are the respective waveforms for the intersections  $r_1 \times C_{12}$ ,  $r_2 \times C_{12}$ ,  $r_1 \times C_0$ ,  $r_2 \times C_0$ ,  $r_1 \times C_1$ , and  $r_2 \times C_1$ . If a square wave with a peak value of  $\sqrt{8}$  Vo is employed as the  $C_{12}$  waveform it is possible to do away with the intervals t2, t3, t5, t6, and 3 can still be obtained 55 as the ratio of the rms value of the display to the nondisplay driving voltage.

FIG. 13 shows the vector diagrams illustrating the relationship between the digit and segment drive signals value of 2 V, of the segment drive signal  $C_0'$  is plotted as a vector at the origin 0 and the potentials 3 V and 4 V are illustrated as having values 1 and 2, respectively, for a sake of simplicity of description. In FIG. 13(1), the potentials  $r_1$  and  $r_2$  of digit drive signals  $r_1$  and  $r_2$  are 65 plotted on the Y axis and symmetrical with respect to the potential  $C_0$  of the segment drive signal  $C_0$  plotted on the intersection between the X and Y axes. Assume

that  $\overline{r_1r_2}=2$  R. In this case,  $r_1$  is plotted as a vector on the point (O,R) indicative of the potential, and  $r_2$  is plotted as a vector on the point (O, -R) indicative of the potential. Plotting  $C_2$  as a vector on the point (0,2)R) and  $C_1$  on the point (O, -2 R), then the following relation holds:

$$|\overline{r_2C_2}| = |\overline{r_1C_1}| = 3R$$

Here, the potential differences between r<sub>1</sub> and C<sub>12</sub> and between  $r_2$  and  $C_{12}$ , represented by  $r_1C_{12}$  and  $r_2C_{12}$ , are equal to each other when C<sub>12</sub> falls on the X axis and the distance between the points  $C_0$  and  $C_{12}$  is  $\sqrt{8}$  R. Therefore, the absolute value of the vector a is equal to R and the absolute value of the vector b is equal to 3 R. From this it will be seen that the operation margin is 3 which is much greater than that obtained in the prior art driving method.

In the vector diagram of FIG. 13(1), since  $C_0$  is set to the reference potential 0 to which G is also set, the potential of each point at a certain time instant in interval t<sub>1</sub> is expressed as:

$$C_1 = -2$$

$r_2 = -1$

$C_{12} = 0$

$r_1 = 1$

$C_2 = 2$

From the above equations it will be seen that it is possible practically to obtain driving waveforms with the use of four voltage sources and varying in potential at five different levels.

FIG. 13(2) shows the vector diagram defined in the three dimensions using X, Y and Z axes. In this vector diagram, the time interval t<sub>1</sub> is assigned to the X axis, t<sub>2</sub> to the Y axis and t<sub>3</sub> to the Z axis. The potentials of various drive signals are expressed by the following matrix:

$$r_1 \quad r_2 \quad C_0 \quad C_1 \quad C_2 \quad C_{12}$$

$$= \left( \begin{array}{cccccc} 1 & -1 & 0 & -2 & 2 & 0 \\ 0 & 0 & 0 & 0 & 0 & 2 \\ 0 & 0 & 0 & 0 & 0 & 2 \end{array} \right)$$

$$(0 \quad 0 \quad 0 \quad 0 \quad 0 \quad 2)$$

The above relation represents the potentials at the time intervals t<sub>1</sub>, t<sub>2</sub> and t<sub>3</sub> which constitutes one-half of cycle time of the drive signals. The potentials in another half cycle time will be obtained by multiplying the value of -1 to each of the potentials listed above. It is to be noted that the difference between the potential of the segment drive signal inducing a state of display at one of the digit electrodes and the mean value of all the digit signals is preferably selected to have a value two times the difference between the mean value of the potentials of all the digit drive signals and the potential of the digit drive signal applied to the digit electrode which is to be in a state of display.

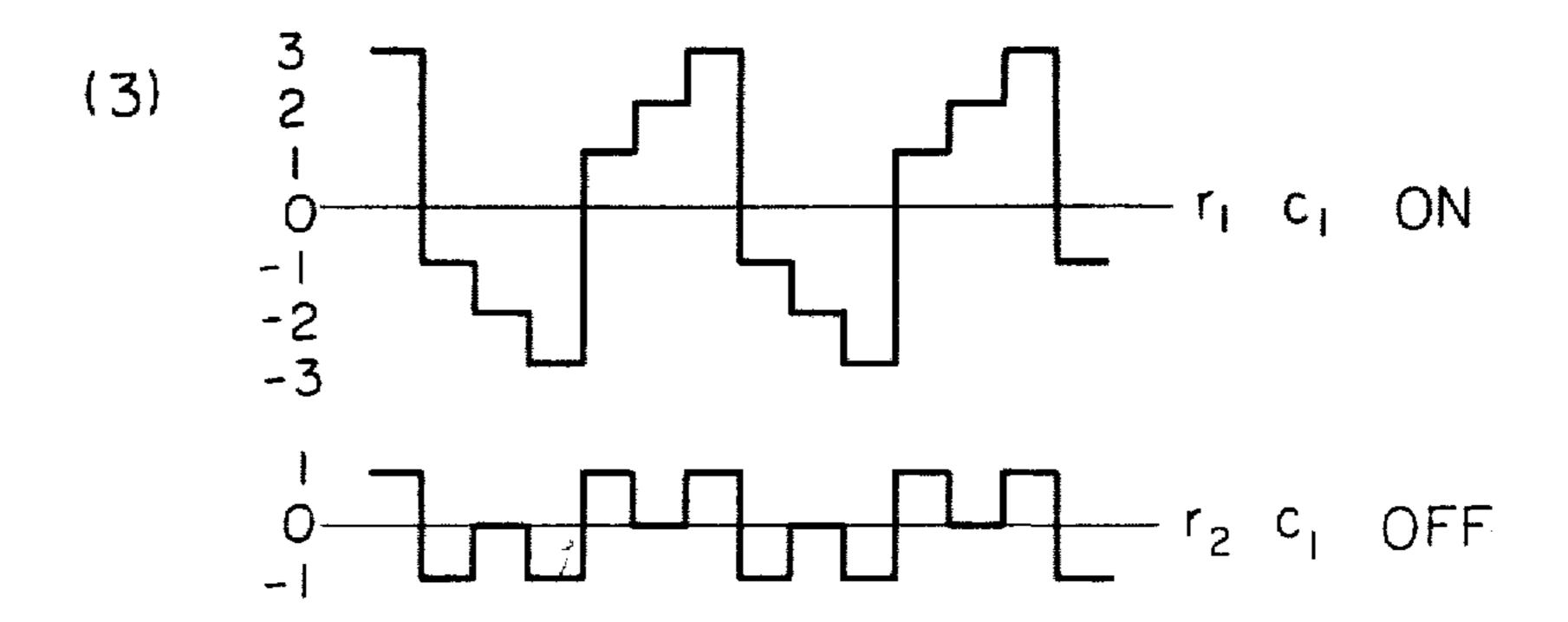

FIGS. 14(1) and (2) shows another preferred example used in FIG. 11. In FIG. 13, the potential C<sub>0</sub>, having a 60 of the waveforms of digit drive signals which are impressed upon respective digit electrodes r<sub>1</sub>' and r<sub>2</sub>'. In FIG. 14(1) it can be seen that the waveform is composed of four equal time intervals t1, t2, t3 and t4 which constitute one cycle period. The potential levels over the 1st half cycle time and 2nd half cycle period (hereinafter referred to as t1, t2, t3, and t4) of the r<sub>1</sub> digit signal are t1=3 Vo, t2=2 Vo, t3=Vo and t4=2 Vo, while the potentials for the  $r_2$  digit signal are  $t1 = V_0$ ,  $t2 = 2 V_0$ ,

t3=3 Vo and t4=2 Vo, all of these potentials being based upon the minimum potential of the segment driving signal which is taken as a standard.

FIGS. 14(3), (4), (5) and (6) show the waveforms of the segment drive signals which are impressed upon any segment electrode Si.

Signal Co in FIG. 14(3) is the waveform of the segment electrode driving signal when a non-display of r<sub>1</sub>Sj and r<sub>2</sub>Sj is indicated, signal C<sub>12</sub> in FIG. 14(4) is the waveform of the segment electrode driving signal when 10 r<sub>1</sub>Sj and r<sub>2</sub>Sj are to be displayed, signal C<sub>1</sub> in FIG. 14(5) is the waveform for a display of r<sub>1</sub>Sj and a non-display of r<sub>2</sub>Sj, and signal C<sub>2</sub> in FIG. 14(6) is the waveform for a non-display of r<sub>1</sub>Sj and a display of r<sub>2</sub>Sj. In this example, t1 and t3 are the previously described driving inter- 15 vals for all of the non-display segment signals and at the same time they also correspond to the intervals during which there is an increase in the absolute value of the digit driving signal voltage with respect to the reference potential level 2 Vo. Here, the potential levels of the 20 two digit drive signals are equal to each other during intervals t2 and t4. In addition, two segment signals are compared and the times at which they do not present the same potential level are t<sub>1</sub> and t<sub>3</sub> for c<sub>0</sub> and c<sub>1</sub>, c<sub>0</sub> and c2, t1", t2 and t3" for c1 and c12, t1', t2 and t3' for c2 and 25 c<sub>12</sub>. Segment signals c<sub>1</sub> and c<sub>2</sub> possess a higher absolute voltage of over the intervals t<sub>1</sub>, t<sub>3</sub> than is the case with the prior art, and although a large driving voltage is generated between c1 and the r1 driving signal, a small driving voltage generated between c1 and r2 driving 30 signal over the same interval will suffice. A large driving voltage is also generated between c12 and the r1, r2 digit driving signals over the intervals t2, t4 as well as t1, t3. It is to be understood that FIGS. 11 and 14 show examples in which the potential of the segment drive 35 signal inducing the state of non-display at display intersections of all the digit electrodes is equal to the mean value of the potentials of all the digit drive signals, i.e., the vector Co is brought into coincidence with the vector G and the vectors C<sub>1</sub>, r<sub>1</sub> and G are disposed on the 40 same axis.

In FIG. 14, more specifically, the first digit drive signal r<sub>1</sub> has a first voltage potential 3 V<sub>0</sub> during a first time interval to of a first half cycle period Ho and a reference potential 2 Vo during a second or remaining 45 time interval t2 of the first half cycle period H1. The second digit drive signal r<sub>2</sub> has a second voltage potential Vo which is opposite in polarity to the voltage potential 3 Vo of the first digit drive signal r<sub>1</sub> during the first time interval t<sub>1</sub>. During a first time interval t<sub>3</sub> of 50 another half cycle period H<sub>2</sub> the first digit drive signal  $r_1$  has a voltage potential  $V_O$ , and the second digit drive signal  $r_2$  has a voltage potential 3  $V_0$ , which provides the same voltage difference as that between 2 Vo and  $\mathbf{V}_{O}$  and is opposite in polarity to the voltage potential 55 Vo of the first digit drive signal r<sub>1</sub> with respect to the reference potential 2 Vo. During the second time interval t4 of another half cycle period H2, the first and second digit drive signals r<sub>1</sub> and r<sub>2</sub> have the reference potential 2 Vo. A segment drive signal Co has a voltage 60 potential equal to the reference potential 2 Vo during the first and second time intervals t<sub>1</sub> and t<sub>2</sub> of the first half cycle period H<sub>1</sub> and during the first and second time intervals t<sub>3</sub> and t<sub>4</sub> of another half cycle period H<sub>2</sub>, inducing a state of non-display at display elements on all 65 of the digit electrodes because of a minimum potential difference between the digit electrodes and the segment electrodes as seen in FIGS. 15(3) and (4). A segment

signal C<sub>12</sub> has a voltage potential 0 during a time period t<sub>1</sub>, of the first time interval t<sub>1</sub> of the half cycle period H<sub>1</sub> and a voltage potential 4 Voduring another time period t<sub>1</sub> of the first time interval t<sub>1</sub>. During the second time interval t<sub>2</sub> of the first half cycle period H<sub>1</sub> the segment drive signal  $C_{12}$  has the voltage potential 4  $V_O$ , so that the maximum potential difference exists between the digit and segment electrodes as shown in FIGS. 15(1) and (2), inducing a state of display at display elements on all the digit electrodes. The segment drive signal C<sub>1</sub> has a voltage potential 0 during the first time interval t of the first half cycle period H<sub>1</sub>, a voltage potential 2 Vo during the second time interval to of the first half cycle period H<sub>1</sub>, a voltage potential 4 V<sub>0</sub> during the first time interval t<sub>3</sub> of the second half cycle period H<sub>2</sub>, and a voltage potential 2 V<sub>O</sub> during the second time interval t<sub>4</sub> of the second half cycle period H<sub>2</sub>. Thus, the maximum potential difference exists between the segment drive signal c1 and the digit drive signal r1, inducing a state of display at display elements on the first digit electrode applied with digit drive signal r<sub>1</sub>. The segment drive signal c<sub>2</sub> has a voltage potential 4 V<sub>0</sub> during the first time interval t<sub>1</sub> of the first half cycle period H<sub>1</sub>, a voltage potential 2 Voduring the second time interval t<sub>2</sub> of the first half cycle period H<sub>1</sub>, a voltage potential 0 during the first time interval t<sub>3</sub> of the second half cycle period H<sub>2</sub>, and a voltage potential 2 V<sub>0</sub> during the second time interval H<sub>2</sub> of the second half cycle period H<sub>2</sub>. Thus, the maximum potential difference exists between the segment drive signal C<sub>2</sub> and the digit drive signal r<sub>2</sub>, inducing the state of display at the display elements on the digit electrode applied with digit drive signal r<sub>2</sub>. It will thus be seen that during the second time intervals t<sub>2</sub> and t<sub>4</sub> of the first and second half cycle periods H<sub>1</sub> and H<sub>2</sub> the segment drive signals c<sub>1</sub> and c<sub>2</sub> have the voltage potential equal to the reference voltage potential, but during the first time intervals t<sub>1</sub> and t<sub>3</sub> of the half cycle periods the segment drive signals ca and  $c_2$  have the voltage potential 0 or 4  $V_0$ .

FIGS. 15(1), (2), (3), (4), (5) and (6) are the respective waveforms for the intersections  $c_{12} \times r_1$ ,  $c_{12} \times r_2$ ,  $c_0 \times r_2$ ,  $c_0 \times r_1$ ,  $c_2 \times r_1$ ,  $c_2 \times r_2$ . If a square wave with a peak value of  $\sqrt{8}$  Vo is employed as the  $c_{12}$  waveform, it is possible to do away with the intervals  $t_2$ ,  $t_4$ , and 3 can still be obtained as the ratio of the root mean square value of the display to the non-display driving voltage.

FIG. 16 shows another example of the waveform diagram for drive signals. In the example of FIG. 16, each of the digit drive signals r<sub>1</sub> and r<sub>2</sub> have a reference voltage potential 2 Vo during a first half cycle H<sub>1</sub> of a cycle period and a reference voltage potential Voduring a second half cycle time H<sub>2</sub>. During a first time interval t<sub>1</sub> of the first half cycle time H<sub>1</sub>, the first digit drive signal r<sub>1</sub> has a voltage potential 3 V<sub>O</sub> and the second digit drive signal  $r_2$  has a voltage potential  $V_0$ which provides the same voltage difference as that between the potential 3 V<sub>O</sub> of the first digit drive signal r<sub>1</sub> and the reference potential 2 V<sub>O</sub> during the first time interval t<sub>1</sub>. During the second time interval t<sub>2</sub> of the first half cycle time H<sub>1</sub>, both the first and second digit drive signals  $r_1$  and  $r_2$  have the voltage potential equal to the reference voltage potential 2 Vo. During a third time interval t<sub>3</sub> of the first half cycle time H<sub>1</sub>, the first digit drive signal r<sub>1</sub> has a voltage potential vo and the second digit drive signal r<sub>2</sub> has a voltage potential 3 V<sub>O</sub> of the same potential difference as that of the first digit drive signal  $r_1$  relative to the reference potential 2  $V_0$  but opposite in polarity with respect to the reference poten-

tial 2  $V_O$ . As previously noted, the reference voltage potential of the first and second digit drive signals r<sub>1</sub> and r<sub>2</sub> is V<sub>O</sub> during the second half cycle time H<sub>2</sub>. During a first time interval t<sub>4</sub> of the second half cycle time H<sub>2</sub>, the first digit drive signal  $r_1$  has a voltage potential 0 and the 5 second digit drive signal  $r_2$  has a voltage 2  $V_0$  of the same potential difference as that of the first digit drive signal r<sub>1</sub> but opposite in polarity to the first digit drive signal  $r_1$  with respect to the reference potential  $V_0$ . During a second time interval to of the second half cycle 10 time  $H_2$ , the first and second digit drive signals  $r_1$  and  $r_2$ have a voltage potential equal to the reference potential  $V_O$ . During a third time interval  $t_0$  of the second half cycle time  $H_2$ , the first digit drive signal  $r_1$  has a voltage potential 2 V<sub>O</sub> and the second digit drive signal r<sub>2</sub> has a 15 voltage potential 0 of the same potential difference as that of the first digit drive signal r<sub>1</sub> but opposite in polarity thereto with respect to the reference potential  $V_0$ .

In FIG. 16, a segment drive signal C<sub>0</sub> has a voltage potential equal to the reference potential 2  $V_O$  of the 20 digit drive signals during the first half cycle time H<sub>1</sub> and has a voltage potential equal to the reference potential  $V_O$  of the digit drive signals during the second half cycle time H<sub>2</sub>, providing a minimum voltage difference between the digit drive signal and the segment drive 25 signal  $C_0$ , as shown in FIG. 18(1), to induce a state of non-display at display elements on all of the digit electrodes. A segment drive signal  $C_{12}$  has a voltage potential 0 during the first half cycle time H<sub>1</sub> and has a voltage potential 3  $V_O$ during the second half cycle time  $H_2$ , 30 providing a maximum voltage difference between the segment drive signal  $C_{12}$  and either one of the first and second digit drive signals r<sub>1</sub> and r<sub>2</sub>, as shown in FIG. 18(2) to induce a state of display at all the display elements on both the first and second digit electrodes. A 35 third segment drive signal C<sub>1</sub> has a voltage potential 0 during the first time interval t<sub>1</sub> of the first half cycle time  $H_1$  and a voltage potential 3  $V_0$  during the second and third time intervals t<sub>2</sub> and t<sub>3</sub> of the first half cycle time  $H_1$ . The segment drive signal  $C_1$  has a voltage 40 potential 3 V<sub>O</sub> during the first time interval t<sub>4</sub> of the second half cycle time H<sub>2</sub> and a voltage potential 0 during the second and third time intervals t<sub>5</sub> and t<sub>6</sub> of the second half cycle time H<sub>2</sub>, providing a maximum voltage difference between the first digit drive signal 45 and the segment drive signal C<sub>1</sub> and a minimum voltage difference between the digit drive signal r<sub>2</sub> and the segment drive signal c<sub>2</sub> as shown in FIG. 18(3). In this case, the display elements associated with the first digit electrode applied with the first digit drive signal r<sub>1</sub> are 50 turned on while the display elements associated with the second digit electrode applied with the second digit drive signal r<sub>2</sub> are turned off. Similarly, a segment drive signal c<sub>2</sub> has a voltage potential 3 V<sub>O</sub>during the first and second time intervals t<sub>1</sub> and t<sub>2</sub> of the first half cycle time 55 H<sub>1</sub> and a voltage potential 0 during the third time interval t<sub>3</sub> of the first half cycle time H<sub>1</sub>. The segment drive signal c<sub>2</sub> also has a voltage potential 0 during the first and second time intervals t<sub>4</sub> and t<sub>5</sub> of the second half cycle time and a voltage potential 3 Voduring the third 60 time interval to of the second half cycle time H2. Thus, a maximum voltage difference is provided between the segment drive signal c2 and the digit drive signal r2 while a minimum voltage difference is provided between the segment drive signal c2 and the digit drive 65 signal  $r_1$ , as shown in FIG. 18(3). In this instance, the display elements associated with the digit electrode applied with the digit drive signal raare turned on while

the display elements associated with the digit electrode applied with the digit drive signal r<sub>1</sub> are turned off.

FIGS. 16(1) and (2) show digit driving waveforms which are applied to respective digit electrodes  $r_1'$  and r<sub>2</sub>'. In FIG. 16(1) it can be seen that the waveform is composed of 6 equal time intervals t<sub>1</sub>, t<sub>2</sub>, t<sub>3</sub>, t<sub>4</sub>, t<sub>5</sub>, and t<sub>6</sub> which constitute one period. The potential levels over the 1st half cycle time H<sub>1</sub> and 2nd half cycle time H<sub>2</sub> (hereinafter referred to as  $t_1, t_2, \ldots t_6$ ) of the  $r_1$  digit signal are  $t_1=3$  Vo,  $t_2=2$  Vo,  $t_3=V$ o,  $t_4=0$ ,  $t_5=V$ o, and  $t_6=2$  Vo, while the potentials for the D2 digit signal are  $t_1 = V_0$ ,  $t_2 = 2 V_0$ ,  $t_3 = 3 V_0$ ,  $t_4 = 2 V_0$ ,  $t_5 = V_0$ , and  $t_6=0$ , all of these potentials being based upon Vo which is taken as a reference potential. If the potentials over each of the intervals t<sub>1</sub>, t<sub>2</sub>... for the r<sub>1</sub> digit signal and  $r_2$  digit signal are added, we are left with  $t_1 = 4 \text{ Vo}$ ,  $t_2 = 4 \text{ Vo}, t_3 = 4 \text{ Vo}, t_4 2 \text{ Vo}, t_5 2 \text{ Vo}, \text{ and } t_6 = 2 \text{ Vo}. \text{ If a}$ comparison is made to the waveforms shown in FIG. 8, it will be seen that in FIG. 16 intervals t<sub>2</sub> and t<sub>5</sub> have been added; in other words, intervals have been added over which the potentials of the  $r_1$  and  $r_2$  digit signals coincide.

FIG. 16(3), (4), (5) and (6) show the waveforms which are impressed upon any segment electrode Sj. Signal Co in FIG. 16(3) is the waveform of the segment electrode driving signal when a non-display of  $r_1Sj$  and  $r_2Sj$  is indicated, signal  $c_{12}$  in FIG. 16(4) is the waveform of the segment electrode driving signal when  $r_1Sj$  and  $r_2Sj$  are to be displayed, signal  $c_1$  in FIG. 16(5) is the waveform for a display of  $r_1Sj$  and a non-display of  $r_2Sj$ , and signal  $c_2$  in FIG. 16(6) is the waveform for a non-display of  $r_1Sj$  and a display of  $r_2Sj$ . The segment electrode driving signals which satisfy all states are a combination of the potentials (Vo·2 Vo) and (0·3 Vo), and their frequency is the same as the frequency of the digit driving signals.

FIG. 17 show the vector diagram for the drive signals shown in FIG. 16. Here, the potentials of the various drive signals are expressed by the following matrix:

$$=\begin{pmatrix} (r_1 & r_2 & c_0 & c_1 & c_2 & c_{12}) \\ 0 & 2 & 1 & 3 & 0 & 3 \\ 1 & 1 & 1 & 0 & 0 & 3 \\ 2 & 0 & 1 & 0 & 3 & 3 \end{pmatrix}$$

In this case, the vectors a and b are written as:

$$|a| = \sqrt{1^2 + 1^2} = \sqrt{2}$$

$|b| = \sqrt{3^2 + 2^2 + 1^2} = \sqrt{14}$

Therefore, the operation margin  $\alpha$  is obtainerd as:

$$\alpha = \sqrt{7}$$

In this example, the varying potential  $C_0$  of the segment drive signal  $C_0$  is plotted as a vector at a point intermediate between potentials  $r_1$  and  $r_2$  and coincides with G; Angle  $C_1Gr_1$  and  $C_2Gr_2$  define obtuse angles. This means that the potential of the segment drive signal inducing a state of non-display at all the digit electrodes is equal to the mean value of the potentials of all the digit drive signals.

It can thus be understood that the driving method of the present invention, in contrast to that of the prior art, is provided with intervals over which there is coinci-

dence between the phases of the digit electrode driving signals as well as coincidence between their potentials. In this case, if a non-display is indicated for segments at matrix intersections, the segment electrodes may be applied with a voltage at the same level as the digit 5 signal potentials when these potentials are in coincidence, whereas they are applied with differing voltage levels at other times. It should be appreciated that in the examples of FIGS. 11 and 14 the digit and segment drive signals have five potential levels different from 10 each other by equal steps and in the example of FIG. 16 the digit and segment drive signals have four potential levels differing from each other by equal steps.

FIG. 18 shows the waveforms which appear across the electrodes in a case where the waveforms of FIG. 15 17 are applied to a liquid crystal. FIG. 18(1) shows examples of potential waveforms between digit and segment electrodes when a state of non-display is desired at all of the digit electrodes, and FIG. 18(2) examples in which a display is desired at all of the digit electrodes. FIG. 18(3) shows an example in which a display is desired at the first digit electrodes and a state of non-display is desired at the second digit electrode.

In FIG. 18(2) the rms voltage is  $\sqrt{14/3}$  Vo, while the rms voltage is  $\sqrt{\frac{2}{3}}$  Vo according to FIG. 18(1), thereby 25 giving an operation margin of  $\alpha = \sqrt{7}$ . In other words, the operation margin can be widened from  $\sqrt{5}$  to  $\sqrt{7}$  by providing an interval over which the potential levels of the two digit driving signals of FIG. 17 coincide.

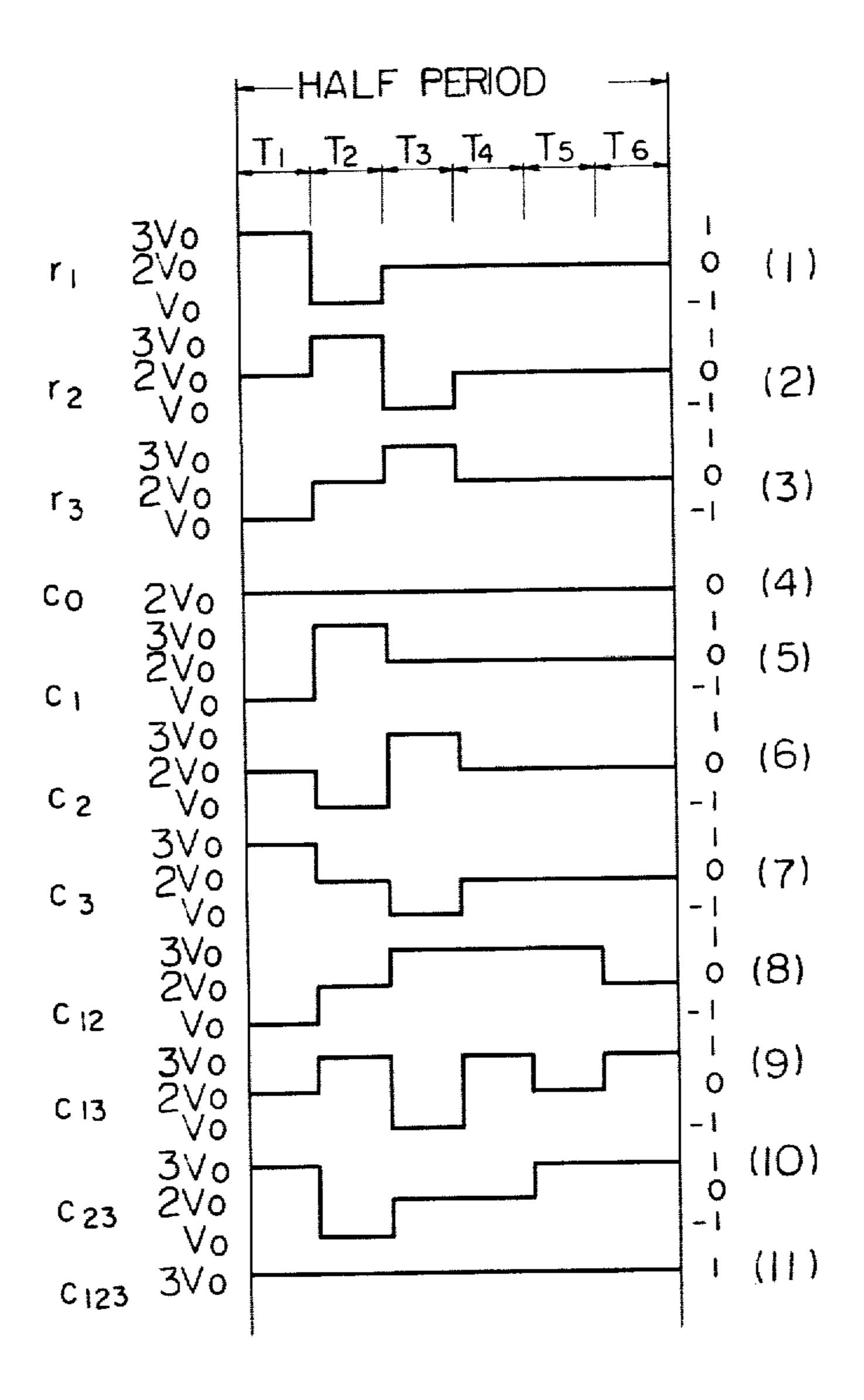

FIG. 19A shows the waveform diagram of other 30 example of driving signals used in the method of the present invention with n=3. In the waveform diagram of FIG. 19A, a digit drive signal r<sub>2</sub> has a reference voltage potential 2  $V_O$  and digit drive signals  $r_1$  and  $r_3$  have voltage potentials 3  $V_O$  and  $V_O$ , respectively, during a 35 first time interval t<sub>1</sub> of a half cycle period, with the voltage potentials 3  $V_O$  and  $V_O$  being of the same amplitude level relative to the reference voltage potential 2 V<sub>O</sub> but opposite in polarity to one another with respect to the reference voltage potential 2  $V_0$ . During a sec- 40 ond time interval t<sub>2</sub> of the half cycle period, the digit drive signal r<sub>3</sub> has a voltage potential equal to the reference potential 2  $V_0$  and the digit drive signals  $r_1$  and  $r_2$ have voltage potentials  $V_O$  and 3  $V_O$ , respectively, which have the same potential difference relative to the 45 reference potential 2 V<sub>O</sub> and are opposite in polarity to one another with respect to the reference potential 2 V<sub>O</sub>. During a third time interval of the half cycle period, the digit drive signal r<sub>1</sub> has the reference potential and the digit drive signals r<sub>2</sub> and r<sub>3</sub> have the voltage 50 r<sub>3</sub>Sj. potentials  $V_O$  and 3  $V_O$ , respectively, which have the same potential difference relative to the reference potential 2 V<sub>O</sub> but are opposite in polarity to one another with respect to the reference potential 2 V<sub>O</sub>. During fourth to six time intervals  $t_4$  to  $t_6$ , all of the digit drive 55 signals  $r_1$  to  $r_3$  have the reference potential 2  $V_{O}$ .

In FIG. 19A, a segment drive signal c<sub>0</sub> has a voltage potential equal to the reference potential 2 V<sub>O</sub>during all of the time intervals t<sub>1</sub> through t<sub>6</sub> of the half cycle period, providing a minimum voltage difference between 60 the segment drive signal c<sub>0</sub> and any one of the digit drive signals r<sub>1</sub> and r<sub>2</sub> to induce a state of non-display at all the display elements associated with the digit electrodes applied with the digit drive signals r<sub>1</sub> through r<sub>3</sub>. A segment drive signal c<sub>1</sub> has such a voltage potential to 65 provide a maximum voltage difference between the segment drive signal c<sub>1</sub> and the digit drive signal r<sub>1</sub> to induce a state of display at the display elements associ-

ated with only the digit electrode applied with the digit drive signal r<sub>1</sub>. More specifically, the segment drive signal c<sub>1</sub> has a voltage potential V<sub>O</sub> during the first time interval t<sub>1</sub> and a voltage potential 3 V<sub>0</sub> during the second time interval t<sub>2</sub>. During the remaining time intervals t<sub>3</sub> through t<sub>6</sub>, the segment drive signal c<sub>1</sub> has a reference voltage 2 Vo. Thus, a maximum voltage difference is provided between the first digit drive signal r<sub>1</sub> and the segment drive signal c<sub>1</sub> during the first and second time intervals t<sub>1</sub> and t<sub>2</sub> as shown in FIG. 20 so that the display elements associated with the digit electrode applied with the digit drive signal reare turned on during the first and second time intervals t<sub>1</sub> and t<sub>2</sub>. During the remaining time intervals to through to, a minimum voltage difference is provided between the segment drive signal  $c_1$  and the digit drive signal  $r_1$  so that the display elements associated with the digit electrode applied with the digit drive signal reare turned off during the time intervals t<sub>3</sub> through t<sub>6</sub>. A voltage difference between the digit drive signal r<sub>2</sub> and the segment drive signal  $c_1$  exists as shown in the waveform  $r_2 - c_1$  of FIG. 20 and the display elements are turned off. Likewise, a voltage difference exists between the digit drive signal r3 and the segment drive signal c1 as shown by the waveform  $r_3-c_1$  of FIG. 20 and the display elements are turned off. A segment drive signal c<sub>2</sub> has voltage potentials of such a value to provide a maximum voltage difference between the segment drive signal c2 and the digit drive signal r<sub>2</sub> during the time intervals t<sub>2</sub> and t<sub>3</sub> of the half cycle period.

FIGS. 19A(4), (5), (6), (7), (8), (9), (10) and (11) show the waveforms which are impressed upon any segment electrode Sj. Signal Co in FIG. 19A(4) is the waveform of the segment electrode driving signal when a non-display of r<sub>1</sub>Sj, r<sub>2</sub>Sj and r<sub>3</sub>Sj is indicated, signal c<sub>12</sub> in FIG. 19A(8) is the waveform of the segment electrode driving signal when r<sub>1</sub>Sj and r<sub>2</sub>Sj are to be displayed and r<sub>3</sub>Sj is to be non-displayed, signal c<sub>1</sub> in FIG. 19A(5) is the waveform for a display of r<sub>1</sub>Sj and a non-display of r<sub>2</sub>Sj and r<sub>3</sub>Sj, and signal c<sub>2</sub> in FIG. 19A(6) is the waveform for a non-display of r<sub>1</sub>Sj and r<sub>3</sub>Sj and a display of r<sub>2</sub>Sj.

Similarly, signal  $C_3$  in FIG. 19A(7) is the waveform for a display of  $r_3S_j$  and a non-display of  $r_1S_j$  and  $r_2S_j$ , signal  $C_{13}$  in FIG. 19A(9) is the waveform for a display of  $r_1S_j$  and  $r_3S_j$  and a non-display of  $r_2S_j$ , signal  $C_{23}$  in FIG. 19A(10) is the waveform for a display of  $r_2S_j$  and  $r_3S_j$  and a non-display of  $r_1S_j$ , and signal  $C_{123}$  in FIG. 19A(11) is the waveform for a display of  $r_1S_j$ ,  $r_2S_j$  and  $r_3S_j$ .

It is to be appreciated that in the example of FIG. 19A, the difference between the potential of the segment drive signal inducing a state of display at one of the digit electrodes and the potential of the mean value of all the digit drive signals is equal to the potential difference between the mean value of the potentials of all the digit drive signals and the potential of the digit drive signal applied to the digit electrode which is to be in a state of display. It should also be appreciated that the digit drive signals  $r_1$ ,  $r_2$  and  $r_3$  have first, second and third potential levels Vo, 2 Vo and 3 Vo, respectively, and that the three digit drive signals concurrently have the different potential levels during the time intervals  $t_1$ ,  $t_2$  and  $t_3$  and have the same potential level during the time intervals  $t_4$ ,  $t_5$  and  $t_6$ .

FIG. 19B shows a model matrix layout for the digit and segment drive signals shown in FIG. 19A, wherein the three digit electrodes are employed.

19

FIG. 20 shows an example of the waveforms for the potential difference across the digit and segment electrodes with the drive signals used in FIG. 19A.

FIG. 21(1) shows the vector diagram for the drive signals shown in FIG. 19A. In FIG. 21(1), a varying potential  $C_0$  of the segment drive signal  $C_0$  indicative of the non-display state of all the digit electrodes  $r_1'$ ,  $r_2'$ and r3' is plotted as a vector at a potential intermediate among potentials  $r_1$ ,  $r_2$  and  $r_3$  of the digit drive signals  $r_1'$ ,  $r_2'$  and  $r_3'$ . Let  $\overline{C_0r_1} = \overline{C_0r_2} = \overline{C_0r_3} = R$ .  $r_1r_2r_3$  define 10 an equilateral triangle about  $C_0$  as a center with the line segment having the length of  $\sqrt{3}$ -R. In this case,  $C_1$   $C_2$ C<sub>3</sub> are expressed as:

$$|\overline{r_1C_3}| = |\overline{r_2C_3}| = |\overline{r_2C_1}| = |\overline{r_3C_1}| = |\overline{r_3C_1}| = |\overline{r_1C_2}| = R$$

$$\frac{1}{T} \quad (r_1 - r_j)^2 dt = \frac{1}{T} \quad r_i^2 dt - \frac{2}{T} \quad r_i r_j dt + |\overline{r_3C_2}| = R$$

Therefore, r<sub>1</sub> C<sub>3</sub> r<sub>2</sub> C<sub>1</sub> r<sub>3</sub> C<sub>2</sub> define an equilateral hexagon 20 about C<sub>0</sub> as a center. Each point of C<sub>12</sub>, C<sub>13</sub>, C<sub>23</sub>, C<sub>123</sub> are selected such that  $\overline{r_1C_{23}} = R$  and  $\overline{r_2C_{23}} = \overline{r_3C_{23}}$ . The of  $C_{123}$  is selected point such  $r_1C_{123}=r_2C_{123}=\overline{r_3}C_{123}$ . The vectors a and b are expressed as:

$$|a| = R$$

$$|\mathbf{b}| = 2\mathbf{R}$$

Therefore, the operation margin  $\alpha$  is obtained as:

$$\alpha = 2$$

FIG. 21(2) shows an example of the diagram in which the arrangement of FIG. 21(1) is applied to the points of 35 a three-dimentional lattice. In FIG. 21(2) potentials  $C_{12}$ , C<sub>13</sub>, C<sub>23</sub> and C<sub>123</sub> of the corresponding segment drive signals C<sub>12</sub>', C<sub>13</sub>', C<sub>23</sub>' and C<sub>123</sub>' can be represented as vectors at points within three-dimensional space; however, by doing so the points indicative of potentials will 40 no longer rest at the points of a regular lattice. In order to permit the potential indicating points to lie at the points of a regular lattice, at least 4-dimensions are required. Therefore, the potentials r<sub>1</sub>, r<sub>2</sub>, r<sub>3</sub>, C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub> are plotted as vectors on the X, Y and Z axes. FIG. 45 21(3) shows an example of the diagram in which  $C_{12}$ , C<sub>13</sub>, C<sub>23</sub> and C<sub>123</sub> lie on the regular lattice defined by the X', Y' and Z' axes with the potentials  $r_1$ ,  $r_2$ ,  $r_3$ ,  $C_0$ ,  $C_1$ ,  $C_2$  and  $C_3$  being at the origin of the X', Y' and Z' axes. If the matrix is used to show this, the following is the 50 result:

From the above it will be seen that the half frame time consists of six equal time intervals t<sub>1</sub> through t<sub>6</sub>. The potentials for the remaining frame time can be obtained by multiplying each element of the above matrix by -1. It should now be understood that in FIG. 21(2) the 65 potentials  $C_0$ ,  $C_1$ ,  $C_2$  and  $C_3$  are plotted in terms of the time  $t_1$ ,  $t_2$  and  $t_3$  assigned to the X, Y and Z axes whereas in FIG. 21(3) the potentials  $C_{12}$ ,  $C_{13}$ ,  $C_{23}$  and  $C_{123}$  are

plotted in terms of the times t4, t5 and t6 assigned to the X', Y' and Z' axes.

It will now be appreciated that the waveforms of the matrix drive signals can be represented in vector space as previously noted. The set of digit drive signals capable of displaying a complete pattern is given by:

$$1/T\int_{0}^{\tau}r_{i}^{2}dt=R^{2}$$

$$1/\Gamma \int_{-\tau}^{\tau} r_i r_j dt = -R^2/n - 1$$

Therefore, the digit drive signal is located on the surface of a sphere of radius R with the origin as a center. It can be understood from

$$\frac{1}{T} = (r_1 - r_j)^2 dt = \frac{1}{T} = r_i^2 dt - \frac{2}{T} = r_i r_j dt + \frac{1}{T} = r_j^2 dt = \frac{2n}{n-1} R^2$$

that the distance between mutual drive signals is given by  $\sqrt{2n/n}-1R$ . For a two-digit matrix,  $r_1$  and  $r_2$  become points of symmetry with respect to the origin. For a three-digit matrix, r<sub>1</sub>, r<sub>2</sub>, r<sub>3</sub> define an equilateral trian-25 gle with a side of  $\sqrt{3}$  R. For a four-digit matrix, the points lie at the corners of an equilateral tetrahedron. In the case of an n-digit matrix, the points lie at the apices of an equilateral n(n-1)(n-2)/6 body in the n-1 dimension space. It can be understood that the digit drive 30 signals of the prior art satisfy these conditions. Hereinafter such digit drive signals will be referred to as digit drive signals which possess symmetry.

The segment drive signal Cm which displays the worst pattern is given by:

$$Cm = -A\Sigma r_i = -\sqrt{\frac{n-1}{m(n-m)}} \sum_i r_i$$

$$=-\sqrt{\frac{m(n-1)}{n-m}\cdot\frac{\sum r_i}{m}}$$

Where  $\Sigma$  is the sum total with regard to digit electrodes which are to be in the state of display. Therefore, the segment drive signal Cm can readily be obtained from the position of the centroid  $\Sigma r_i/m$  of the digit drive signal for the digit electrode which is to be in the state of display. It can be understood that the varying potential difference between the potential of the segment drive signal inducing a state of display at one of the digit electrodes and the mean value of the potentials of all the digit electrodes is in a proportional relationship with the varying potential difference between the mean value of the potential of all the digit drive signals and the potential of the digit drive signal applied to the digit electrode which is to be in a state of display.