G,

.

300

.

FIG. 3.

.

j.

÷

#### INVENTOR.

ELORED C. NELSON,

BY

Seymour M. Benberg HIS ATTORNEY.

## Sept. 2, 1958

-

.

### E. C. NELSON

### 2,850,566

### HIGH-SPEED PRINTING SYSTEM

Filed Sept. 8, 1953

8 Sheets-Sheet 3

ELORED C. NELSON,

.

ù

J.

.

.

.

.

.

.

.

### 2,850,566

Sept. 2, 1958

.

.

٩.

ELORED C. NELSON,

OR" GATE

.

.

.

.

ELDRED C. NELSON BY Br Henry Heyman HIS ATTORNEY

#### Sept. 2, 1958 н 2,850,566 E. C. NELSON

HIGH-SPEED PRINTING SYSTEM

8 Sheets-Sheet 8

Filed Sept. 8, 1953

.

1<u>6</u>5.

## AGENT.

# United States Patent Office

### 2,850,566 Patented Sept. 2, 1958

#### 2,850,566

#### **HIGH-SPEED PRINTING SYSTEM**

Eldred C. Nelson, Los Angeles, Calif., assignor, by mesne assignments, to Hughes Aircraft Company, a corporation of Delaware

Application September 8, 1953, Serial No. 379,045

14 Claims. (Cl. 178-23)

### 2

One of the principal disadvantages of these prior art printing systems is that they require tremendous multiplication of electrical circuitry and components, such as vacuum tubes, and are therefore almost prohibitively expensive. Other logical consequences of their inherent δ complexity are unreliability of the system as a whole and excessive size and weight. Another significant disadvantage of these prior art systems is that they are incapable of printing at speeds in excess of five to ten lines per second, even when the intelligence information is restricted to numerical information alone. The present invention, on the other hand, obviates the above and other disadvantages of the prior art printing systems by providing a reliable and relatively inexpensive serially operable high-speed printing system for printing the information characters in a line of intelligence information by sequentially comparing each information character with each type character which is sequentially presented to be printed. According to the fundamental concept of this invention, a plurality of serially applied electrical information signals corresponding respectively to the information characters in the line of intelligence information are sequentially compared with an electrical character signal corresponding to the type character in printing position on an associated printing cylinder to selectively actuate a plurality of associated printing transducers to print on a printing medium the type characters corresponding to the information characters. More particularly, according to the preferred embodiment of the present invention, the electrical information signals correspond respectively to the binary-coded numerical equivalents of the information characters and are serially applied to a single electronic comparator network where they are compared with an electrical character signal which is binary coded in accordance with the rotation of the printing cylinder. The comparator network functions to produce a comparator output signal each time an information character in the line of intelligence information corresponds to the type character in printing position. Each comparator output signal is applied in turn to a distributor network which is connected to the printing transducers and which is responsive to the application of a comparator output signal for selectively energizing the printing transducers. The transducer energized corresponds to the spacing in the line of intelligence information of the information character being compared in the comparator network, thereby printing in the corresponding space on the printing medium the type character corresponding to the information character being compared. Each line of intelligence information is compared sequentially with the type characters which may be printed by continuously recirculating the electrical information signals and by applying these signals to the comparator network once for each different electrical character signal. Accordingly, one comparator output signal is produced for each information character, thereby selectively energizing the printing transducers to print the type characters corresponding to all of the information characters in 60 the line of intelligence information. The printing system of the present invention may include either the conventional straight-line printing cylinder, or a continuously rotatable skeyed-type printing cylinder similar to those disclosed in copending U. S. patent application, Serial No. 360,998, for "Printing Cylinders for High-Speed Printing Systems," by R. A. Hartley, filed June 11, 1953. In addition, by employing an interference type printing transducer similar to that disclosed in copending U. S. patent application, Serial No. 377,818, for "High-Speed Electromechanical Printing Transducer," by S. M. Fomenko et al., filed October 1, 1953, identical information characters in the line of intelligence informa-

This invention relates to a high-speed printing system, 15 and more particularly to a serially operable high-speed printing system in which the information characters in a line of intelligence information to be printed are sequentially compared with each type character which is sequentially presented to be printed.

Relatively recent advances in the field of high-speed electronic data-processing machines have fostered the need for reliable high-speed output devices to convert processed intelligence information in the form of electrical signals to visual indications of the results of the data- 25 processing operation. In particular, there has been an ever increasing need in the art for high-speed printing systems to rapidly convert the electrical output signals from the data-processing machine to a printed record.

The high-speed printing systems of the prior art have 30 one basic mode of operation, namely parallel, wherein all like characters in the line of intelligence information are printed simultaneously, the printing being accomplished by selectively energizing a plurality of printing transducers to bring an intermittently movable printing 35 medium into engagement with a rotatable straight-line printing cylinder having a plurality of longitudinally aligned rows of type characters disposed about its periphery. The number of printing transducers employed is dependent upon the number of line spaces or columns 40 in the line of intelligence information to be printed, one transducer being provided for each column on the printing medium. In these high-speed printing systems of the prior art, each printing transducer is coupled to an associated electronic register, usually a flip-flop counter, the number of counters corresponding to the number of printing transducers incorporated in the system. In operation the signals corresponding to the information characters in the line of intelligence information to be printed are 50 first entered, either serially or in parallel, into the counters corresponding to the spacing of the information characters in the line of intelligence information. The counters are then pulsed in parallel by an electrical pulse signal generated by the associated printing cylinder as it 55 rotates, the count in each counter changing one number for each pulse received, one pulse being received each time the printing cylinder has rotated sufficiently to place the succeeding row of type characters in printing position. As each counter becomes full or empty, depending upon whether a count-up or count-down counting sequence is employed, the counter generates an electrical output signal for energizing its associated printing transducer to print on the printing medium the type character 65 in printing position on the printing cylinder. Thus, if several counters have the same information signals entered therein prior to the pulsing operation, the counters will generate output signals simultaneously for energizing their associated printing transducers simultaneously to print 70 the same information character in their respectively associated columns or spaces on the printing medium.

3

tion may be printed either in sequence, with a skewedtype cylinder, or simultaneously with a straight-line cylinder.

Another basic feature of the high-speed printing system of this invention is the use of logical network theory to 5provide simplified electronic circuits which further increase the inherent reliability and speed of the system and which further decrease both the initial and operating expense of the system. In practice it has been found that the printing system of the present invention is capable of 10printing intelligence information, represented by as many as sixty different type characters, at speeds in excess of fifteen lines per second.

It is, therefore, an object of this invention to provide

of the information character being compared in response to each comparison signal.

The novel features which are believed to be characteristic of the invention, both as to its organization and method of operation, together with further objects and advantages thereof, will be better understood from the following description considered in connection with the accompanying drawings, in which a preferred embodiment of the invention is illustrated by way of example. It is to be expressly understood, however, that the drawings are for the purpose of illustration and description only, and are not intended as a definition of the limits of invention.

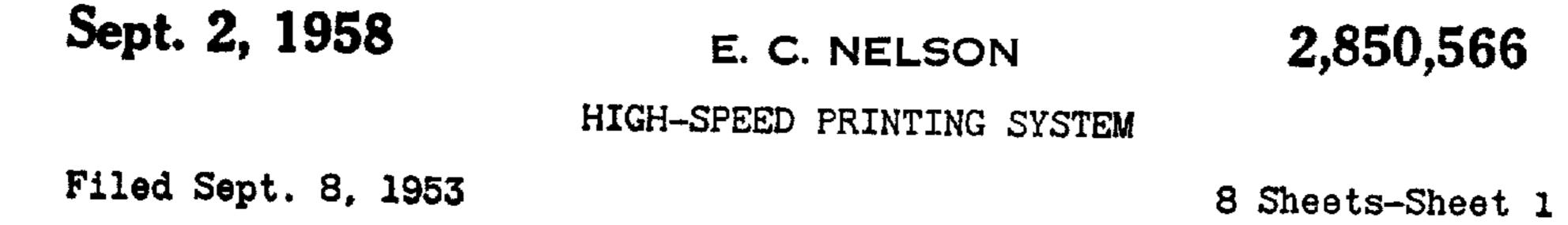

Fig. 1 is a block diagram of a high-speed printing sys-

a reliable and relatively inexpensive serially operable 15 tem, according to the present invention; high-speed printing system capable of printing intelligence information, at speeds in excess of fifteen lines per second.

Another object of this invention is to provide a logically designed high-speed printing system for printing the information characters in a line of intelligence informa- 20 tion as corresponding type characters on a printing medium by sequentially comparing the information characters with each type character which may be printed.

It is also an objecct of this invention to provide a highspeed printing system for printing a line of intelligence in- 25 formation by sequentially comparing the information characters in the line of intelligence information with each type character which may be printed to selectively energize a plurality of associated printing transducers to print in corresponding column spaces on a printing 30 medium the type characters corresponding to each of the information characters.

An additional object of this invention is to provide a high-speed printing system for printing the information characters in a line of intelligence information, stored in 35 the form of coded binary numbers, by sequentially comparing electrical information signals, corresponding to the binary numbers, with electrical signals corresponding to the type character in printing position to produce electrical output signals for selectively energizing a plurality 40 of printing transducers, corresponding to the column spacing of the information characters. Still another object of this invention is to provide a high-speed printing system in which electrical signals corresponding to the sequential information characters in a 45 line of binary-coded intelligence information are sequentially compared with electrical signals corresponding to the type character in printing position for energizing a printing transducer, corresponding to the column spacing of the information character being compared, each time 50 the information character being compared corresponds to the type character in printing position. It is another object of this invention to provide a highspeed printing system for printing a line of binary-coded intelligence information by sequentially comparing all of 55 the information characters in the line of intelligence information with electrical signals corresponding to each of the type characters which may be printed for selectively energizing a plurality of printing transducers, corresponding in number to the number of information characters in the line of intelligence information, to print on a printing medium the type characters corresponding to the information characters in the line of intelligence. It is still another object of this invention to provide a high-speed printing system for printing intelligence information, serially presented as electrical information signals corresponding to a plurality of binary-coded information characters, by sequentially comparing the information signals with electrical signals corresponding to the sequential type characters which are in printing position to produce an electrical comparison signal each time an information character corresponds to the type character in printing position, and by selectively energizing a printing transducer corresponding to the column spacing 75

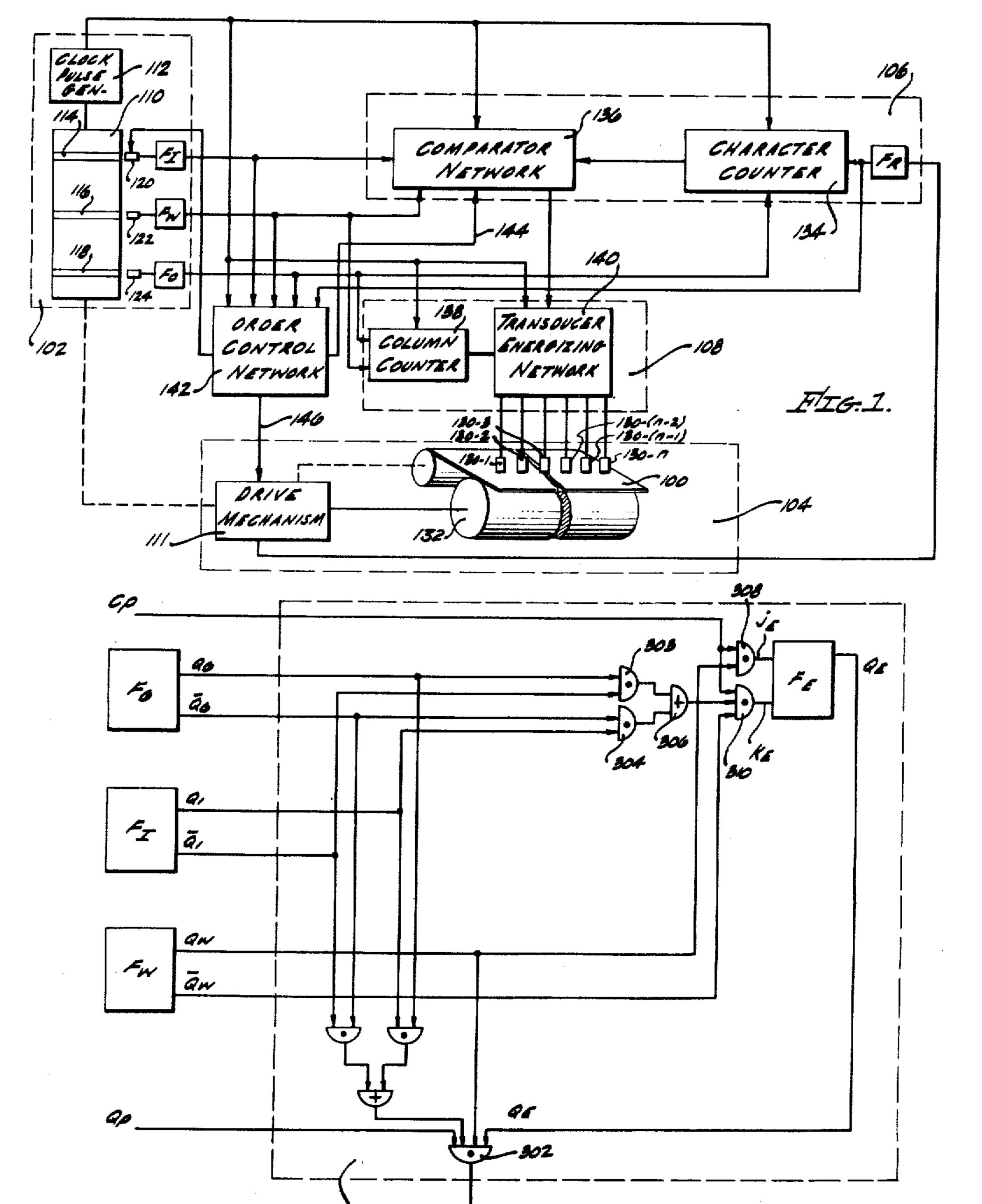

Fig. 2 is a schematic diagram of one form of character counter which may be utilized in the printing system of Fig. 1;

Fig. 3 is a schematic diagram of a serially operable comparator network which may be employed with the character counter shown in Fig. 2 in the high-speed printing system of Fig. 1;

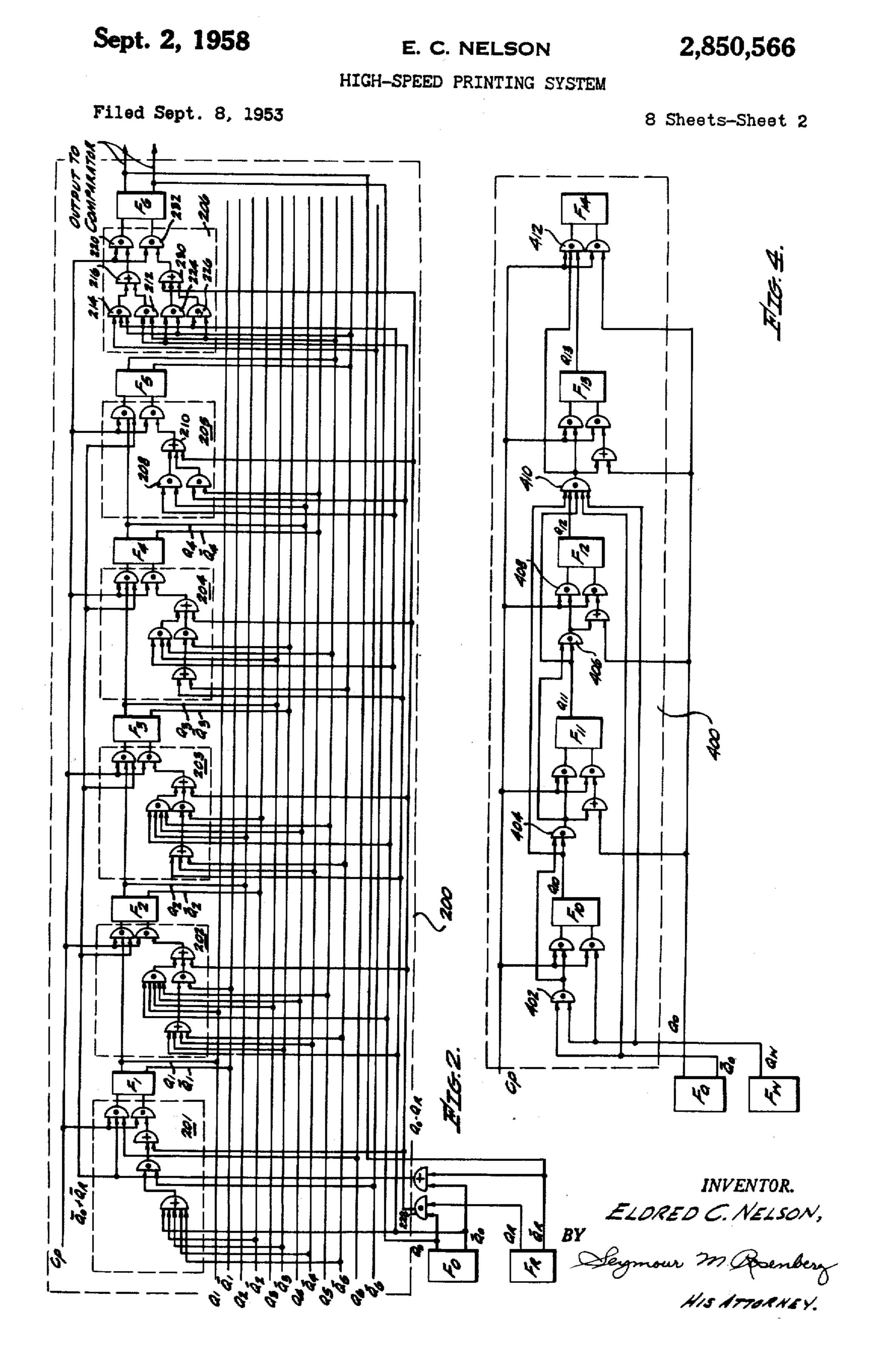

Figs. 4 and 5 are schematic diagrams of a column counter and a transducer energizing network, respectively, which may be employed in combination in the highspeed printing system of Fig. 1 for controlling the energization of the printing transducers;

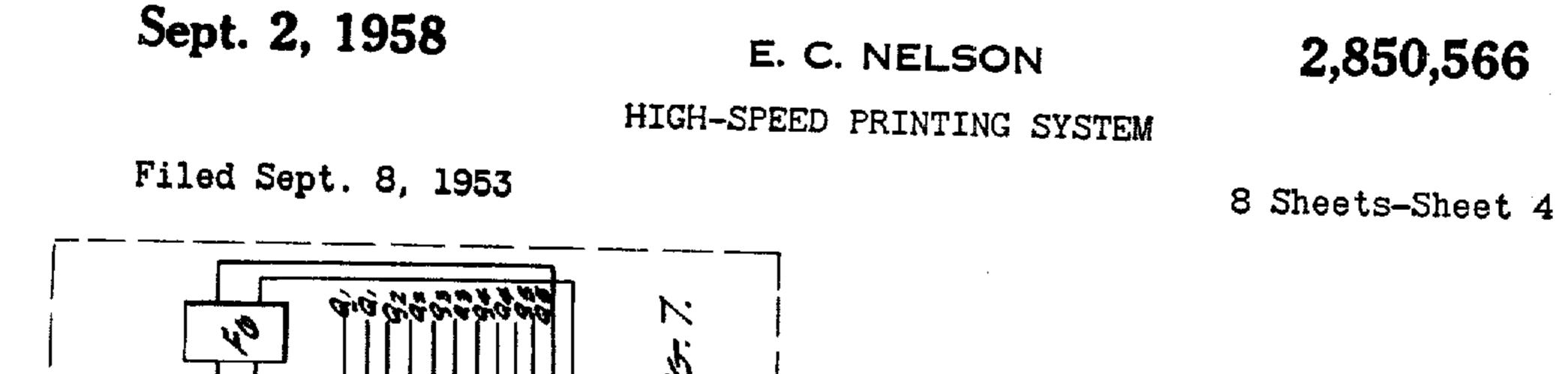

Fig. 6 is a schematic diagram, partly in block diagram form, of one type of order control network which may be utilized to control the operational functions of the high-speed printing system of Fig. 1;

Fig. 7 is a schematic diagram of a modified character counter which may be employed with the serial comparator of Fig. 3 in the high-speed printing system of this invention;

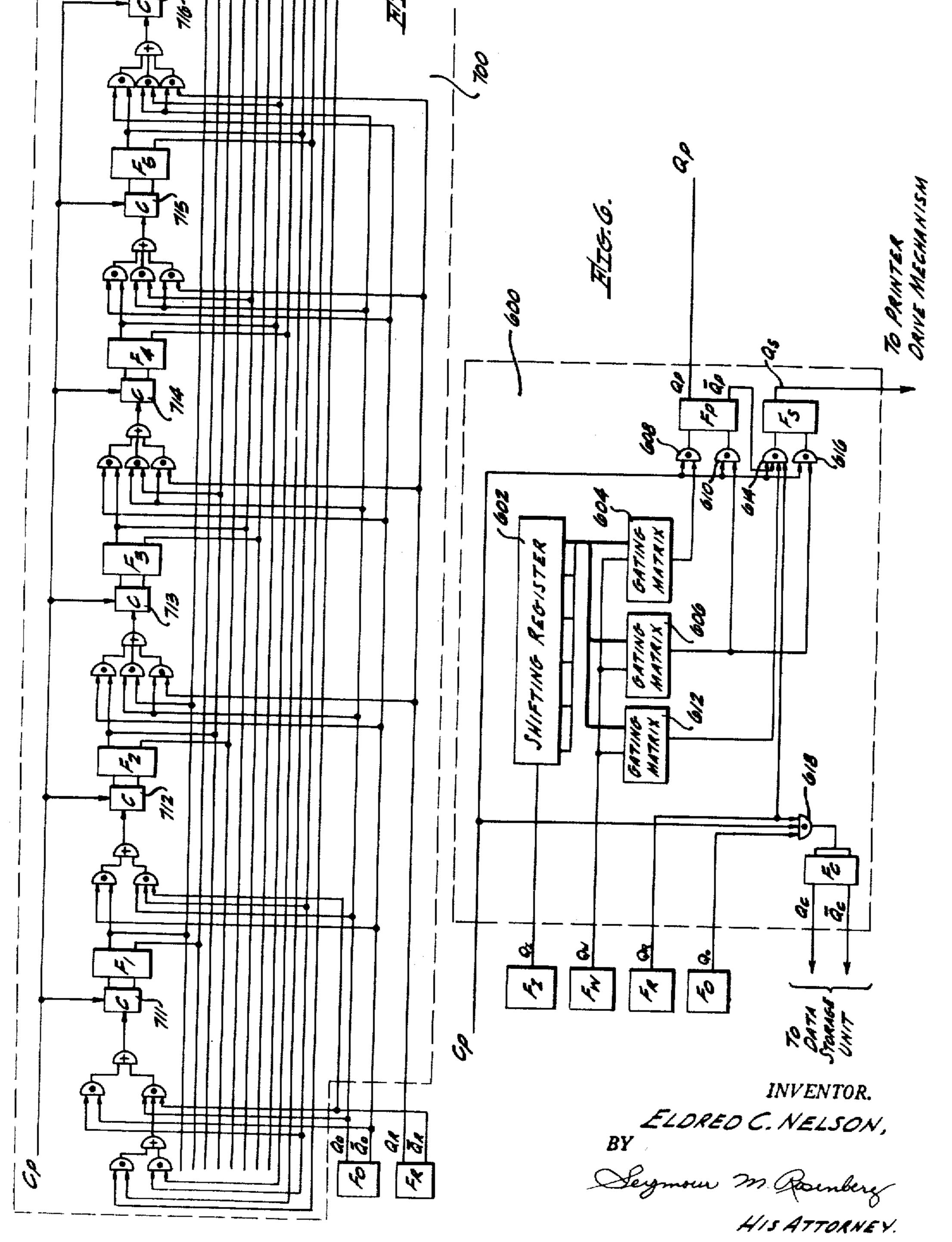

Figs. 8 and 9 are schematic diagrams of a modified column counter and a transducer energizing network, respectively, which may be employed in the high-speed printing system of this invention;

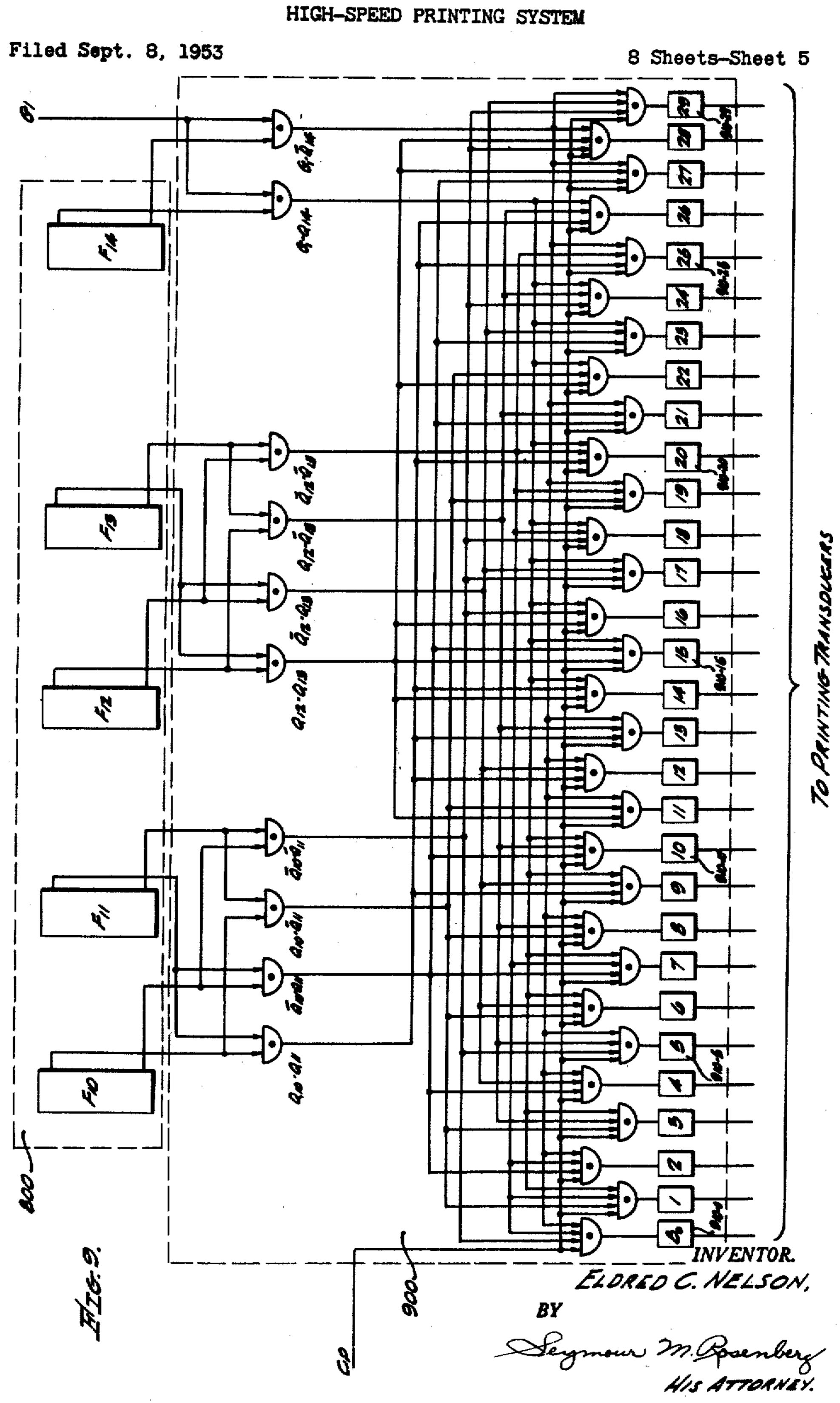

Fig. 10 is a schematic diagram of a different type of character counter which may be utilized in the high-speed printing system of Fig. 1;

Fig. 11 is a schematic diagram of a parallel comparator circuit which may be utilized in cooperation with the character counter shown in Fig. 10 in the high-speed printing system of Fig. 1;

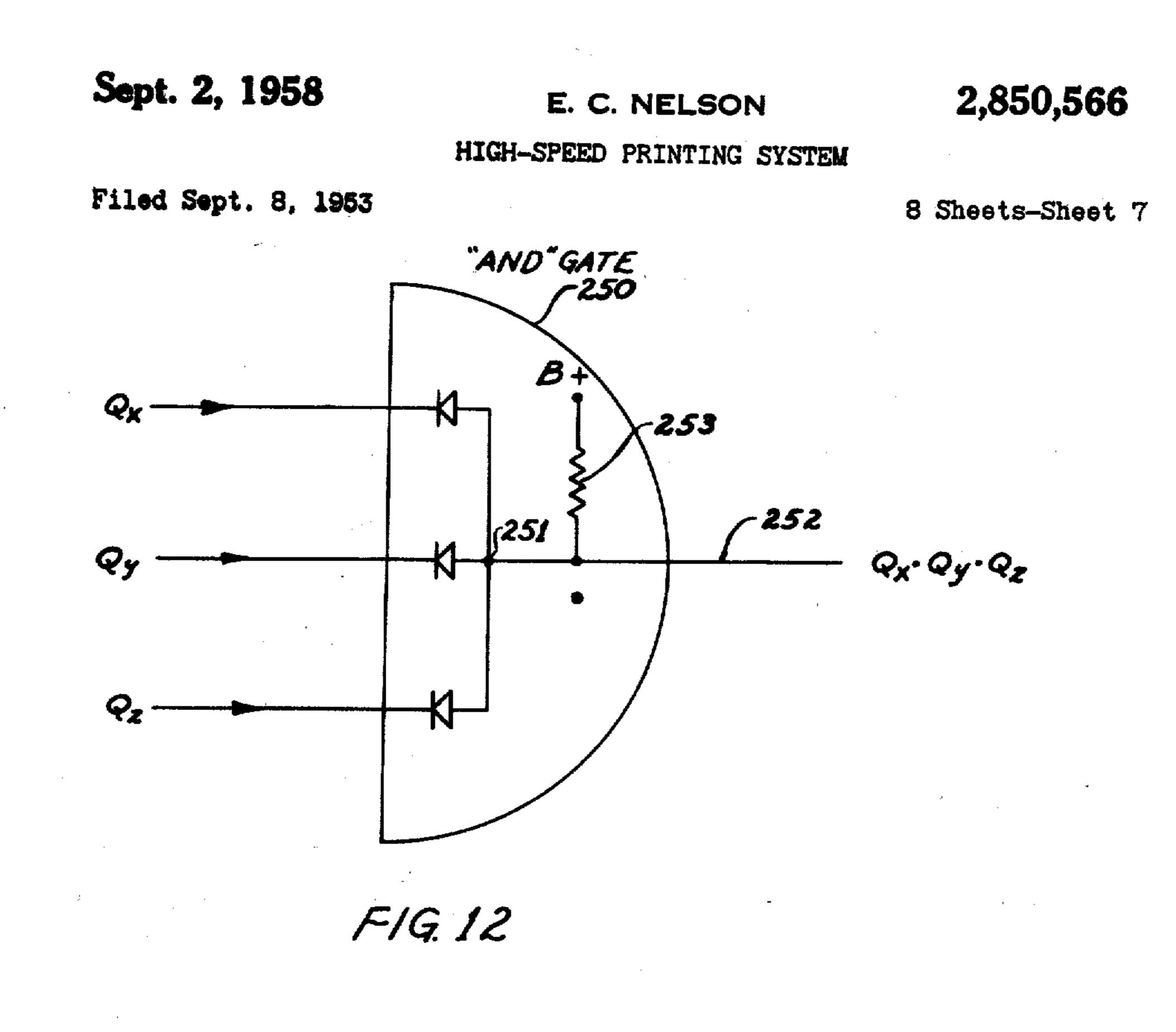

Fig. 12 is a circuit diagram illustrating a typical "and" gate employing diode rectifiers;

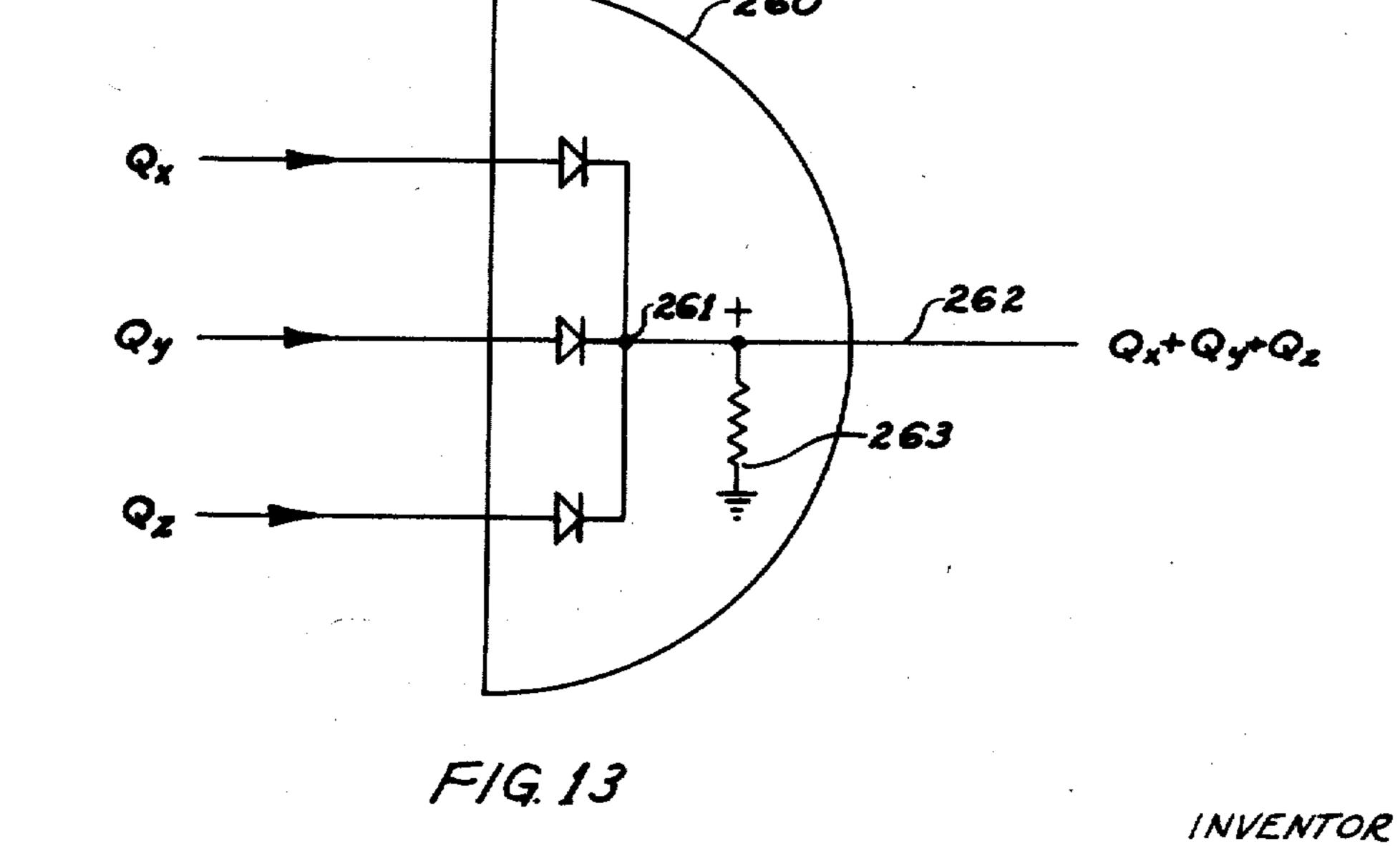

Fig. 13 is a circuit diagram illustrating a typical "or" gate;

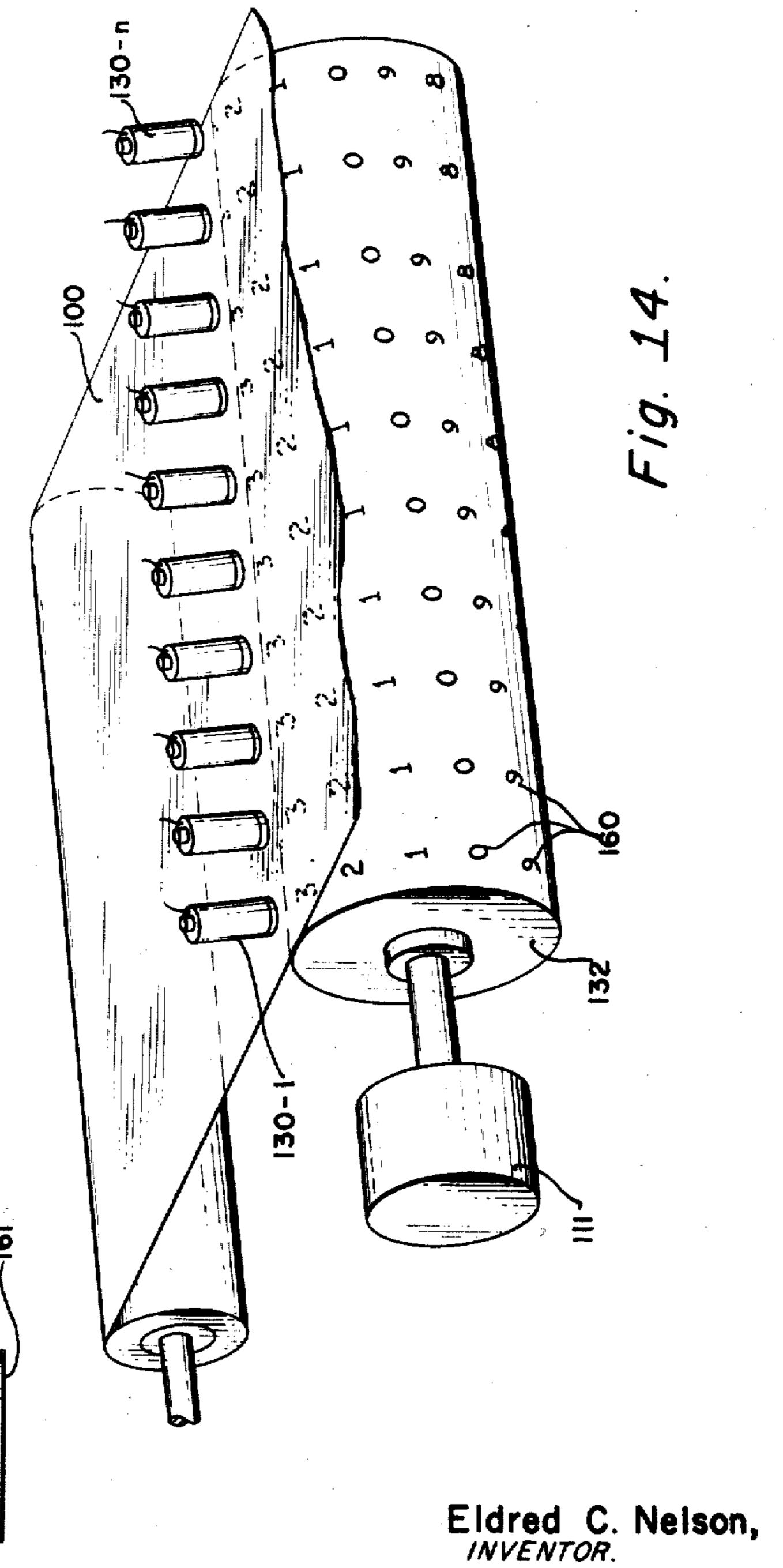

Fig. 14 is a perspective view schematically illustrating a printing cylinder mechanism; and

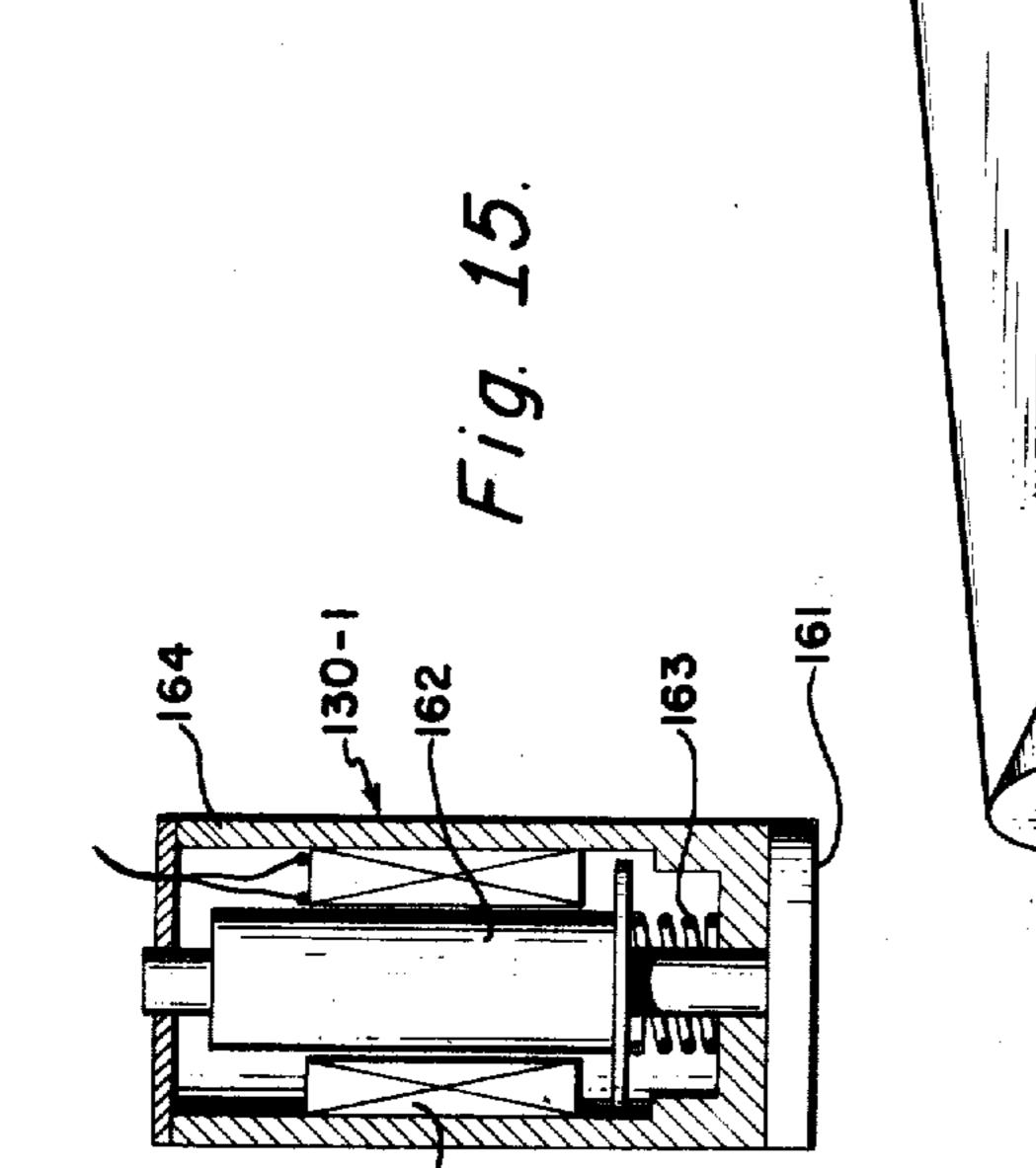

Fig. 15 is a sectional view illustrating a type of printing transducer.

Referring now to the drawings, there is shown in Fig. 1 a serially operable high-speed printing system, according to the present invention, for printing on a printing medium 100 intelligence information stored in the form of binary-coded electrical signals in a data storage unit 102. The high-speed printing system includes four basic com-60 ponents, namely, data storage unit 102 for storing the intelligence information to be printed, a high-speed printer 104 for printing on medium 100 the type characters corresponding to the information characters in the stored intelligence information, a logical control network 106 65 for synchronizing the operation of data storage 102 with printer 104 to control the printing sequence of the individual characters of the stored intelligence information, and a distributor network 108 for selectively controlling the operation of printer 104 so that each information char-70acter is printed in the proper space on printing medium 100. In order to simplify the description of the high-speed printing system of this invention, it will first be assumed that one full line of intelligence information to be printed

#### 5

is stored in data storage unit 102. It will also be assumed for purposes of illustration that each line of intelligence information includes a predetermined number of information characters corresponding to the number of characters which may be printed on one line of printing medium 100, 5 each information character being represented by a sixdigit electrical signal weighted in the 32-16-8-4-2-1 binary code. The time interval required to serially present each binary digit signal of each information character at the output circuit of the data storage unit will 10 hereinafter be termed a digit time interval, while the time required to serially present the six-digit signal corresponding to an information character will be termed a word time interval. Similarly, the time required to serially present the full line of stored intelligence information 15 at the output circuit of the data storage unit will hereinafter be termed a line time interval, while the time required to print the full line of intelligence information will be termed a line printing interval. Data storage unit 102 preferably includes a magnetic 20 memory unit, such as a rotatable magnetic drum 110, an associated clock pulse generator 112, and associated electronic circuits. Magnetic drum 110 is mechanically coupled to and rotated by a drive source 111 in printer 104, and includes at least three magnetic tracks 114, 116, and 25 118 respectively, for storing binary-coded intelligence information and order signals in the form of magnetized cells on the drum periphery. The associated electrical circuits of data storage unit 102 include three reading circuits 120, 122, and 124 which 30 are positioned adjacent magnetic tracks 114, 116, and 118, respectively, and are responsive to the magnetization of their associated tracks for producing electrical signals corresponding to the binary values represented by the magnetization of the tracks. The electrical signals 35 produced by reading circuits 120, 122, 124 are applied, in turn, to three respectively associated flip-flop or bistable multivibrator circuits  $F_I$ ,  $F_W$ , and  $F_O$  to set these flipflops to conduction states corresponding to the binary values represented by the applied signals. Thus, if the 40 magnetization of a particular cell on a magnetic track corresponds to the binary value one, the associated flipflop is set to the conduction state corresponding to the binary value one, whereas the flip-flop is set to the other conduction state if the magnetization of the cell on the 45 associated magnet track corresponds to the binary value zero. It will be assumed that one complete line of binarycoded intelligence information is serially entered on magnetic track 114 through an associated writing circuit, not 50 shown, so that the complete line of intelligence information may be serially read by reading circuit 120 once during each line time interval, thereby serially presenting at the output circuit of flip-flop  $F_{I}$  electrical voltagestate signals corresponding to the sequential binary digits 55 of each of the successive information characters in the stored line of intelligence information. It will also be assumed for purposes of illustration that the intelligence information is serially presented at the output circuit of flip-flop F<sub>I</sub> in the order of least significant binary digit 60 first.

### 6

polarity, one clock pulse occurring during each digit time interval. It will hereinafter be assumed that each clock pulse is relatively sharp negative electrical pulse which occurs at the beginning of each digit time interval. High-speed printer 104 includes three basic elements, namely, drive mechanism 111, a rotatable printing cylinder 132 coupled to the drive mechanism, and a transducer network including a plurality of selectively energizable printing transducers 130-1, 130-2, 130-3, ... 130-(n-2), 130-(n-1), and 130-(n, respectively, positioned adjacent printing cylinder 132 and adapted to cooperate with the printing cylinder for printing intelligence information on printing medium 100.

The printing transducers are operable under the control of distributor network 108 and are preferably of the type disclosed in copending U.S. patent application, Serial No. 377,956, for "Electromechanical Transducers," by E. M. Baldwin et al., filed October 1, 1953. These transducers are preferred because of their relatively high efficiency and their exceptionally high operating speeds. It will be recognized however, that other printing transducers may be utilized with the high-speed printing system of this invention. Printing cylinder 132 may be a skewed-type printing cylinder similar to those disclosed in the aforementioned copending application by Richard A. Hartley, or may be of the conventional straight-line type in which a plurality of rows of type characters are longitudinally disposed about the periphery of the printing cylinder. In each of these two basic forms of printing cylinders, one row of type characters is provided for each different type character which may be printed, each row including a plurality of identical type characters corresponding in number to the number of printing transducers employed in the printer.

A typical example of such a cylinder is illustrated in Fig. 14. In an effort to simplify this illustration, the type characters on the face of the cylinder are represented only as numerals. These type characters are generally designated 160 and range from 0 through 9, circumferentially. The type of printing cylinder herein illustrated involves skewed rows of type characters in which each row represents a different type character and the characters in individual rows are identical. The rows are skewed in an amount wherein the character at one end of one row occupies a position in a plane axially of the cylinder, approximately overlapping the number at the other end of an adjacent row. The minimum number of characters in each row usually corresponds to the number of different characters circumferential of the cylinder. The characters are spaced in the rows as required to provide proper type spacing for printing purposes. A printing transducer is associated with each circumferential ring of characters. These transducers are arranged in spaced relation axially of the cylinder in correspondence with the axial spacing of the characters on the printing cylinder. The printing transducers lie in an axial plane which substantially parallels the axis of rotation of the printing cylinder and are preferably radially disposed of the printing cylinder. Assuming clockwise rotation of the printing cylinder as viewed, the first character of a skewed row which appears beneath a printing transducer is on the left side of the printing cylinder. Continued rotation of the cylinder thus sequentially brings the characters, from left to right of a row, beneath the respective printing transducers. Thus, by controlling the printing transducers in time sequence with the appearance of the characters in a skewed row beneath the respective transducers and further controlling the transducers each time a character in the line of intelligence information to be printed, corresponds to the characters of the type row in printing position, a complete line of characters may be printed across a printing medium such as a web or a sheet of paper passing over the printing cylinder beneath the transducers,

Magnetic track 116 and its associated reading circuit are utilized to set flip-flop  $F_w$  to the conduction state corresponding to the binary value one during the sixth or last digit time interval of each word time interval. Flip- 65 flop  $F_0$ , on the other hand, is set to the conduction state corresponding to the binary value one during the sixth or last digit time interval of the last word time interval of each line time interval. In other words, flip-flop  $F_0$  is set to the conduction state corresponding to the binary 70 value one during the last digit time interval of each circulation of the intelligence information by the magnetic drum.

Clock pulse generator 112 is utilized to produce a periodically recurring electrical clock pulse of predetermined 75

In keeping with the numbering in Fig. 1 of the drawings the transducers are identified as 130-1 through 130-n. It is to be appreciated, however, that in the interest of drawing convenience, a printing cylinder bearing only numeral-type characters has been illustrated in Fig. 14, 5 having a definite length sufficient only to contain the required number of type numbers in the respective skewed rows. Thus, the cylinder is not illustrated with an intermediate break as in Fig. 1. In Fig. 14, the driving means is schematically represented as 111 and the connection 10 of the drive mechanism 111 to the roll of printing material has not been shown. Such details are within the skill of the ordinary mechanic.

7

A type of printing transducer which might be employed

### 8

periphery which subtends a radial angle  $\theta$ , the ratio of the rotational speeds of magnetic drum 110 and printing cylinder 132 may be shown to be

## 360*m*

Logical control network 106 is provided to compare the electrical information signals with electrical signals corresponding to the type character which is in a printing position relative to the printing transducers. The logical control network includes a character counter 134 which presents an electrical character signal corresponding to the type character in printing position, and a comparator network 136 which is connected to clock pulse generator 112, flip-flop  $F_I$ , and character counter 134 for producing and applying to distributor network 108 an electrical output signal each time an information character in the line of intelligence information corresponds to the type character in printing position. Character counter 134 is connected to clock pulse generator 112 and to flip-flop  $F_0$  in order to change the count in the character counter during the last digit time interval of each line time interval to correspond to the next succeeding type character which may be printed. In addition, the character counter is connected to the output circuit of a flip-flop  $F_R$  which is set to the conduction state corresponding to the binary value one during the last line time interval of each line printing interval in order to reset the count in the character counter to zero after each line of intelligence information has been printed on the printing medium. Flip-flop  $F_R$  may be actuated from drive mechanism 111, as shown in Fig. 1, or may be actuated from a line time interval counting circuit in the data storage unit if desired. The function of distributor network 108 is to selectively actuate the printing transducers, in response to output signals from the comparator network, to print each information character in the line of intelligence information as a corresponding type character in its proper line spacing on printing medium 100. The distributor network includes a column counter 138 which is connected to the output circuit of flip-flop  $F_w$  and to clock pulse source 112 in order to count the number of word time intervals in each line time interval. Thus, the electrical output signal from column counter 138 corresponds to the spacing in the line of intelligence information of the character being compared in comparator network 136. In addition, the column counter is connected to the output circuit of flip-flop Fo for resetting the counter to zero count during the last digit time interval of each line time interval. The distributor network also includes a transducer energizing network 140 which is connected to each of the printing transducers and to the output circuits of column counter 138 and comparator network 136. The 55transducer energizing network is operable under the control of column counter 138 for sequentially rendering the printing transducers energizable and is responsive to an output signal from the comparator network for energizing the particular printing transducer which corresponds to the line spacing of the information character being compared. The high-speed printing system of this invention also includes an order control network 142 which is connected to flip-flops  $F_I$  and  $F_W$  and to clock pulse generator 112, and which is responsive to predetermined binary-coded electrical signals in the line of intelligence information for controlling certain operational sequences of the printing system. For example, the order control network may be utilized to actuate the printing system to skip or slough a predetermined number of lines on the printing medium between successive printings of two lines of intelligence information. Again, the order control network may be utilized for indicating when additional intelligence in-

15with the arrangement herein illustrated appears in Fig. 15 and is identified 130-1. Since the printing transducers are identical, this illustration, of course, is typical of all of the transducers. Reference is made hereinabove to a patent application of E. N. Baldwin et al. for "Electromechanical Transducer." The transducer therein illus- 20 trated differs in principle from that illustrated in Fig. 15 depending primarily upon the kinetic energy stored in a rotating body for supplying mechanical energy for operating the printing hammer. The representation in Fig. 15 in this application is purely of a schematic nature to 25 indicate an operable arrangement for actuating the type hammer and is not to be construed as representing a preferred way or the only way of actuating the type hammer.

In Fig. 15 type hammer 161 is driven by a solenoid 30 plunger 162 which is spring loaded by a spring 163 to the retracted position illustrated. The solenoid plunger 162 is slidably mounted in a housing 164 of magnetic material and the plunger mass is axially eccentric with respect to the magnetic field produced by an annular coil 165 dis- 35 posed within the magnetic housing and through which the solenoid plunger strokes. It will be appreciated that energization of coil 165 produces a magnetic field linking the solenoid plunger 162 and the plunger moves in a direction tending to center its mass in the magnetic field. 40 The direction of motion being downwardly, as viewed, compressing spring 163 and displacing type hammer 161 downwardly. For the position of the printing transducers illustrated in Fig. 14 this downward displacement of the type hammer impinges printing sheet 100 against the char- 45 acters on the printing cylinder transferring the character impression by means of a carbon tape, not shown, or other suitable printing transfer medium, on to the underside of the printing sheet 100. The manner in which the selective and synchronous control of the transducers 50 is achieved for printing a line of intelligence information is described hereinafter. Further details as to a practical type of printing transducer and further details with respect to the printing cylinder per se may be had by reference to the aforesaid copending applications of E. M. Baldwin et al. and Richard A. Hartley, respectively. Printing cylinder 132 is preferably continuously rotated by drive mechanism 111, although intermittent rotation of the type cylinder is permissible with the conventional printing cylinders of the prior art. The speed of rota- 60 tion of the printing cylinder relative to that of magnetic drum 110 is such that the complete line of intelligence information is serially presented at the output circuit of flip-flop  $F_I$  once for each row of type characters on the printing cylinder, or in other words, a different row 65 of type characters is presented for printing during each successive line time interval. For example, if it is assumed that printing cylinder 132 includes m rows of type characters uniformly spaced about the printing cylinder periphery, and that the complete line of intel- 70 ligence information is scanned once per revolution of magnetic drum 110, the magnetic drum is rotated through *m* revolutions for each revolution of the printing cylinder. If, on the other hand, m rows of type characters are disposed about only a portion of the printing cylinder 75 formation should be entered on magnetic drum 110.

### 9

In addition to instituting these operations, the order control network may be employed to temporarily suppress or prevent the printing cf characters on the printing medium while other operations are being performed. As shown in Fig. 1, therefore, the order control network is connected to comparator network 136 by a conductor 144 and to drive mechanism 111 in printer 104 by a conductor 146 in order to provide "on-off" control of the printing operation and to provide for sloughing of printing medium 100. In operation, the control network 10 presents a relatively high-level voltage on conductor 144 when it senses that printing operations should be performed, and a relatively low-level voltage at all other times.

### 10

the 30 identical type characters in a first row on printing cylinder 132 is capable of printing the numeral 0 through an intervening carbon paper or print ribbon onto an advancing paper record medium, whenever the paper is pressed against the type character by a printing transducer. The type characters in succeeding rows of print cylinder 132 can print the numerals and characters 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, etc., respectively. It will be noted that the binary number 011111 is utilized to represent a blank space in the line of intelligence information and does not actually represent a type character. Consequently, the character counter may be constructed to skip this particular count, or, on the other hand, a vacant type row may be provided on the printing In order to more clearly describe the operation of the 15 cylinder periphery. In addition, it will be noted that the binary number 111101 is utilized for actuating control network 142 to stop the printing operation, whereas the binary number 111110 is employed to signify that printing operations should be resumed. To further illustrate the arrangement of the type characters upon printing cylinder 132, in the following Table I-A, the numerals 0 through 9 and the alphabetical characters A through D are arranged in rows and columns in the same relative positions in which the corresponding type characters are disposed on the surface of the described embodiment of printing cylinder 132.

high-speed printing system of the present invention, it will be assumed that the printing system is capable of printing 60 different characters corresponding, respectively, to 60 of the 64 possible code combinations of the six-digit binary code. It will also be assumed that two 20 of the remaining four combinations of digits correspond to order control signals which are recognizable by order control network 142 for separating the printing operation from the other operational functions of the printing system, and that one of the remaining two binary numbers 25 corresponds to a blank space. The following illustra-

#### Table I-A

0 0  $2 \ 2 \ 2$ 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 5 - 5 -5 - 5 66 6 6 6 6 6 77 **8 8 8 8 8 8 8 8 8** 9 9 9 9 9 9 9 9 9 888888888888 9999999999999 8 9

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

tive table correlates the six-digit binary code with the order control signals and the 60 different type characters which may be printed:

Table I

|                |               |        |                      |                                       | i              |      |

|----------------|---------------|--------|----------------------|---------------------------------------|----------------|------|

| Binary         | Type          | Binary | Type                 | Binary                                | Type character |      |

| Number         | character     | number | character            | number                                |                | 4    |

| <u></u>        |               | ·      |                      | · · · · · · · · · · · · · · · · · · · |                | •    |

| 000000         |               | 010101 | -                    |                                       |                |      |

| 000000         | 0             | 010101 |                      | 101010                                |                |      |

| 000001         | l l           | 010110 | M                    | 101011                                | •              |      |

| 000010         | $\frac{2}{2}$ | 010111 |                      | 101100                                | %              |      |

| 000011         | 3             | 011000 | 0                    | 101101                                | %<br>@<br>&    |      |

| 001000         | 4             | 011001 | P                    | 101110                                | Č              | . سو |

| 000101         | 5             | 011010 | Q                    | 101111                                |                | 5    |

| 000110         | 6             | 011011 | Q<br>R               | 110000                                | 1              |      |

| 000111         | 7             | 011100 | S                    | 110001                                |                |      |

| 001000         | 8             | 011101 | $\tilde{\mathbf{T}}$ | 110010                                | 6              |      |

| <b>601</b> 001 | 9             | 011110 | <b>n</b>             | 110011                                | _JL_           |      |

| 001010         | Ā             | 011111 | (Blank)              | 110100                                | ===            |      |

| 001011         | B             | 100000 | V                    | 110100                                | *              |      |

| 001100         | õ             | 100001 | ŵ                    |                                       |                |      |

| 001101         | Ď             | 100010 | • F I                |                                       | <b>Jun</b>     | 5    |

| 001110         | т<br>Т        | 100011 | X<br>Y               |                                       | · +            |      |

| 001111         | E<br>F        |        | Ž                    | 111000                                | -              |      |

| 010000         | - <u>5</u>    |        | Z,                   | 111001                                | Φ              |      |

| 010001         | G<br>H        | 100101 | 1                    | 111010                                | <b></b>        |      |

|                | <b>–</b>      | 100110 | 1                    | 111011                                | i              |      |

| 010010         | ÷ į           | 100111 | \$                   | 111100                                | c/o            |      |

| 010011         | J             | 101000 | <b>,</b> t           | 111101                                | Stop printing; |      |

| 010100         |               |        |                      |                                       | order follows. | 6(   |

| 010100         | K             | 101001 | #                    | 111110                                | Resume print-  |      |

|                |               |        | -                    |                                       | ing.           |      |

|                |               | ļ      |                      | 111111                                | D.             |      |

|                |               |        |                      |                                       |                |      |

|                |               | ii     |                      | <b>ا</b>                              |                |      |

Additional rows of type characters are provided on **4**0 printing cylinder 132 for the printing of the remaining characters of the alphabet and for the printing of punctuation marks and other indicia as indicated in Table I. An individual printing transducer is associated with each column of type characters on printing cylinder 132. Thus, 45 for the described 30-column printing cylinder, there are provided 30 printing transducers designated 130-1, 130-2, to 130-n, respectively, where n is equal to 30.

These printing transducers, as shown in Fig. 1, may be arranged in a single row adjacent printing cylinder 132 50 and parallel to the rows of type characters, each printing transducer being positioned with respect to the type characters in its associated column so that it is operable when appropriately energized by network 140 for hammering the intervening portion of record medium 109 against the printing face of the type character in its associated column which has reached a printing position immediately opposite the printing transducer. The engagement of record medium 100 with the type character which has reached printing position causes the character to be 30 printed upon the record medium. Thus, for example, printing transducer 130-1 is selectively operable for printing any one of the 60 type characters contained in the first column of printing cylinder 132 upon the corresponding first column of record medium 100, while the printing transducer 130-3 is similarly operable for printing a predetermined character in the third print column of record medium 109. The particular embodiment of the invention which is to be described is adapted for printing a complete line of information during a single revolution of printing cylinder 132. If it be assumed that a line of intelligence information which is to be printed contains the numeral 0 at the 12th, 29th, and 30th columns, then as that row of print cylinder 132 which comprises 30 identical 0 type characters attains the printing position, transducers 130-12, 130-29,

If it is assumed that character counter 134 counts sequentially in the conventional six-digit binary code, the 65 rows of type characters on printing cylinder 132 are positioned about the periphery of the printing cylinder in accordance with the sequence of characters set forth in Table I. For example, in a conventional straight line embodiment of printing cylinder 132, each row of type char- 70 acters on the printing cylinder may comprise 30 identical raised or elevated type characters disposed longitudinally along the surface of the cylinder in a line substantially parallel to the axis of the cylinder. In accordance with the sequence of type characters shown in Table I, each of 75

and 130-30 are energized by network 140 to print the desired character in the named columns. Similarly, as succeeding rows of type characters attain the printing position, the appropriate transducers are energized, so that by the time a complete revolution of print cylinder 132 5 has been completed, the complete line of intelligence information is printed upon record medium 100.

The described sequence of operations will be clarified at a later point in the specification by the information presented in Table II, and by the descriptive material 10 supplied in connection with Table II.

When the high-speed printing system of Fig. 1 is placed in operation, character counter 134 and column counter 138 may assume any arbitrary counts, due to circuit transients and allied phenomena, and may not respectively represent the type character in printing position and the proper line spacing of information characters, as desired. As printing cylinder 132 finishes its first revolution, however, the character counter is reset to zero count during the last digit time interval of the last line time 20 interval through the combined signals from flip-flop  $F_{R}$ ,

### 12

counter, in turn, control transducer energizing network 140 for sequentially rendering each of the printing transducers energizable in accordance with the column count. Consequently, the printing transducer corresponding to the line spacing of the compared information character is selectively energized to print each time an electrical signal is applied to the transducer energizing network from comparator network 136.

It may be recalled that the complete line of intelligence information is continuously recirculated in data storage unit 102 and is serially applied to the comparator network once during each line time interval. Accordingly, the information signals representing each character in the line of intelligence information are compared with each different count to which the character counter is in-15 dexed, thereby enabling the high-speed printing system of this invention to print the complete line of intelligence information during only one revolution of the printing cylinder. The following table inllustrates the sequence in which a typical 30-space line of intelligence information may be printed:

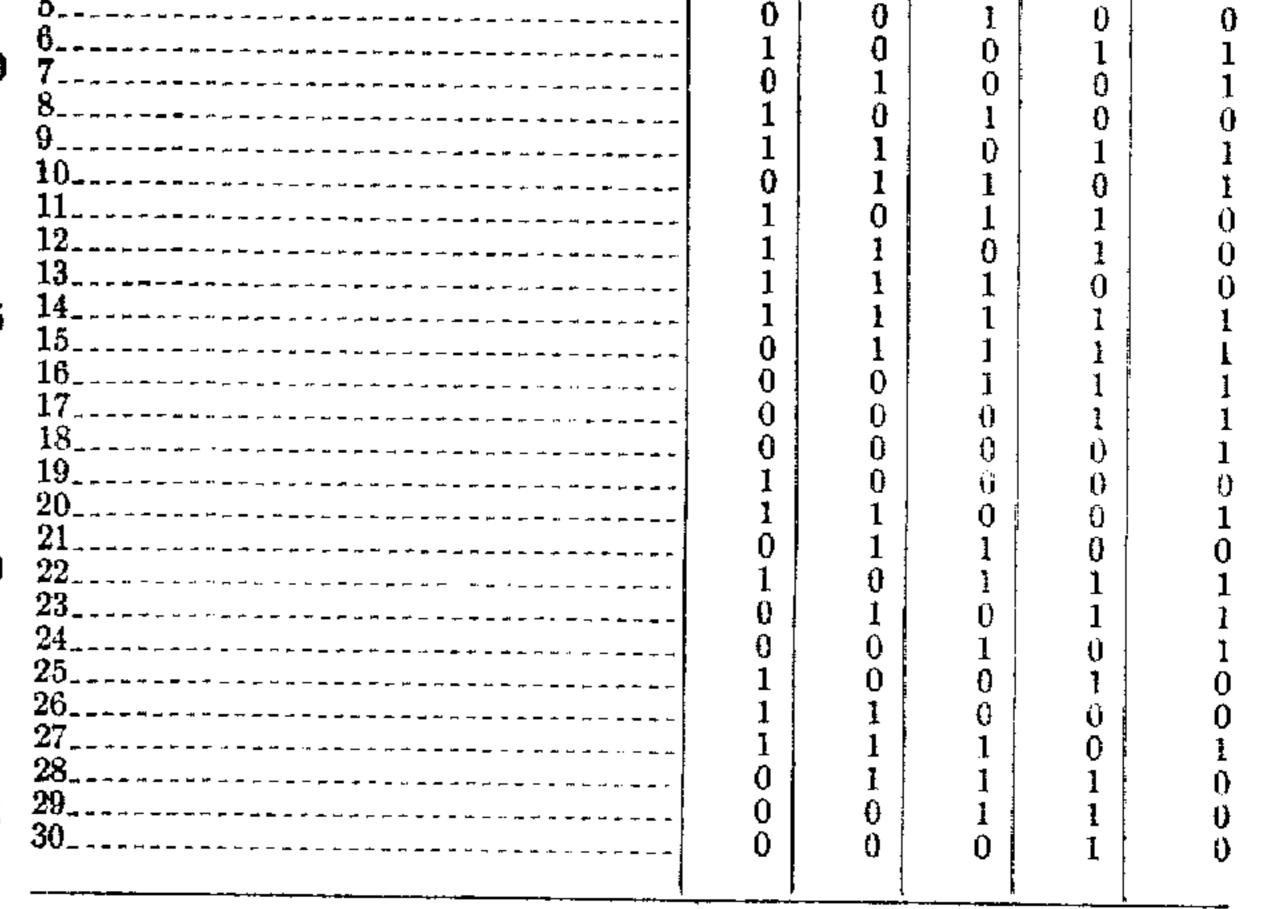

Table II

|                           |                                        |   |    |                                         |   |         |                                      |   |     |   |    | L  | ine | spac | lng | or | colu                                     | mns | 3                                       |                                        |    |                                        |    |    |    | _                   |    |    |    |    |

|---------------------------|----------------------------------------|---|----|-----------------------------------------|---|---------|--------------------------------------|---|-----|---|----|----|-----|------|-----|----|------------------------------------------|-----|-----------------------------------------|----------------------------------------|----|----------------------------------------|----|----|----|---------------------|----|----|----|----|

|                           | 0                                      | 1 | 2  | 3                                       | 4 | 5       | 6                                    | 7 | 8   | 9 | 10 | 11 | 12  | 13   | 14  | 15 | 16                                       | 17  | 18                                      | 19                                     | 20 | 21                                     | 22 | 23 | 24 | 25                  | 26 | 27 | 28 | 29 |

| Line to be printed        | A                                      | С | c  | 0                                       | U | N       | Т                                    |   | #   | 3 | 2  | 0  | 7   |      |     |    | 3                                        |     | С                                       | A<br>                                  | M  |                                        |    | @  |    | \$                  | 5  | •  | 0  | 0  |

| Line time intervals:<br>1 | AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA |   | Ĭč | 000000000000000000000000000000000000000 |   | NNNNNNN | T<br>T<br>T<br>T<br>T<br>T<br>T<br>T |   | ### |   |    |    |     |      |     |    | ω το |     | 000000000000000000000000000000000000000 | AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA | ſ  | 00000000000000000000000000000000000000 |    | @@ |    | <del>60 69 69</del> | 5  |    |    |    |

$F_0$  and clock pulse generator 112. Similarly, at the end  $_{45}$ of the first line time interval, the column counter is reset to zero count by the combined effects of the clock pulse signals and the output signals from flip-flop Fo. Consequently, as the printing cylinder and the magnetic drum continue to rotate thereafter, the binary counts stored in 50 the character counter and in the column counter are continuously indexed from data storage unit 102 and printer 104, thereby respectively presenting electrical output signals corresponding to the type character in printing position and the information character being com- 55 pared.

Assume now that a line of intelligence information has been entered on magnetic track 114 of the magnetic drum and that a high-level voltage is applied to comparator network 136 from order control network 142 to indicate that 80 the intelligence information is to be printed. The complete line of intelligence information is serially applied to comparator network 136 from flip-flop  $F_I$  once during each line time interval, the binary digit signals corresponding to each information character being compared 65 with the binary digit signals corresponding to the type character in printing position. Each time an information character signal correspondings to a type character signal, an electrical output signal is applied to transducer energizing network 140. During the comparison interval, the count in column counter 138 is advanced once each word time interval in accordance with the spacing in the line of intelligence information of the characters being compared. The electrical signals corresponding to the count in the column 75 pared are identical, the comparator network applies an

Printing medium 100 may be advanced continuously by drive mechanism 111 during the line printing operation or may be advanced intermittently when the complete line of intelligence information has been printed. Each of these techniques is discussed in more detail in the above-mentioned copending application by Hartley. In addition, the printing medium may be more rapidly advanced a predetermined number of lines when desired by the application to drive mechanism 111 of an electrical signal from order control network 142. This function of the order control network will be described in more detail below with regard to Fig. 6.

It will be recognized, of course, that the high-speed printing system shown in Fig. 1 may employ numerous component circuits well known to the art and is especially adaptable to the use of various component circuits well known in the field of electronic high-speed digital computing machinery. Several different electronic circuits which may be employed in the high-speed printing system of this invention will now be described. As set forth above, the electronic circuits utilized in character counter 134 and comparator network 136 are preferably selected to serially compare the information characters in the line of intelligence information with the count stored in the character counter. More particu-70 larly, the logical control network preferably untilizes a serially operable comparator network, for comparing the successive binary information character signals with the correspondingly weighted character counter signals, least significant binary digits first. If the signals being com-

### 13

electrical output signal to distributor network 108 during the last digit time interval of the associated word time interval.

It will be recognized that if a serial comparator network is to be utilized in logical network 106, character 5 counter 134 should not only be capable of counting in the binary system of numbers during the last digit time interval of each line time interval, but should also be able to operate as a six binary digit circulating register in order to serially apply to the comparator network, 10 during each word time interval, the six successive binary digits of the binary-coded character count. In addition, the character counter should be capable of being reset to zero count at the end of each revolution of the printing cylinder to insure that the character count corre- 15 sponds to the type character in printing position. Referring now to Fig. 2, there is shown a high-speed electronic character counter 200 for accomplishing the above-mentioned results, counter 200 including six flipflops,  $F_1$ ,  $F_2$ ,  $F_3$ ,  $F_4$ ,  $F_5$ , and  $F_6$ , respectively, and six 20 respectively associated gating matrices 201, 202, 203, 204, 205, and 206 which intercouple the input circuits of their associated flip-flops with the output circuits of flip-flops  $F_{O}$  and  $F_{R}$  for controlling the operation of the counter. In order to more clearly describe the structure and op- 25 eration of the character counter shown in Fig. 2 and of the other electrical circuits to be described later, it will be advantageous to first consider briefly the electrical connections of a typical flip-flop circuit and to describe how the mechanization and function of specific gating ma-30trices may be expressed in terms of logical or Boolian algebraic equations. Each flip-flop or bistable multivibrator includes two input terminals, hereinafter termed the *j*-input and the kinput terminals, respectively, and two output terminals 35 for producing complementary bivalued electrical output signals hereinafter termed Q and  $\overline{Q}$ , respectively. Signals applied separately to the *j*-input and *k*-input terminals set the flip-flop to conduction states corresponding to the binary values one and zero, respectively, while signals applied simultaneously to both input terminals trigger or change the conduction state of the flip-flop. The jand k-inputs to any particular flip-flop will hereinafter be designated by a numerical sub-script corresponding to the numerical designation of the particular flip-flop. 45 When the flip-flop is in the conduction state corresponding to the binary value one, signals Q and  $\overline{Q}$  have relatively high-and-low level voltages, respectively, whereas signals Q and  $\overline{Q}$  have relatively low-and-high level volt- 50 ages, respectively, when the conduction state of the flipflop corresponds to the binary value zero. The Q and  $\overline{Q}$ output signals from any particular flip-flop will hereinafter be designated by a numerical subscript corresponding to the numerical designation of the flip-flop which 55 produces the output signals. For example, the complementary output signals from flip-flop Fo will be designated  $Q_0$  and  $\overline{Q}_0$ , while the output signals from  $F_R$  will be designated  $Q_R$  and  $\overline{Q}_R$ , respectively. A typical flipflop circuit is shown in Fig. 4 of the copending U. S. 60 patent application, Serial No. 322,665, for "Arithmetic Units for Binary-Coded Decimal Computers," by Eldred C. Nelson, filed November 26, 1952. Each of gating matrices 201 through 206 includes one or more logical "and" and "or" gates, such as gates 208 65 and 210, respectively, which are interconnected and mechanized in accordance with logical equations representing the various functions of the character counter, such as shift, count, and reset. In operation, each "and" gate produces a high-level output signal corresponding to the 70 binary value one, only when all of the associated input signals are likewise at their high-level values; whereas each "or" gate produces a high-level output signal when any one or all of the associated input signals are at their high-level values. The above-mentioned copending ap- 75

### 14

plication by Nelson also includes a detailed description of the structure of logical gating circuits and the manner in which they may be mechanized in accordance with logical equations. It will be understood, of course, that both the logical gating circuits and the flip-flop circuits may include either vacuum tubes or passive element electronic devices, such as semiconductor diodes and transistors.

For purpose of illustration and further clarification, there is shown in Fig. 12 a typical "and" gate 250, empolying diode rectifiers and adapted for combining three arbitarary input signals  $Q_x$ ,  $Q_y$ , and  $Q_z$  to produce an output signal  $Q_x \cdot Q_y \cdot Q_z$  which is at its high level only when all of the input signals are at their high levels. As shown in Fig. 12, within "and" gate 250, each of the input signals  $Q_x$ ,  $Q_y$ , and  $Q_z$  is applied to the cathode of a respectively associated diode rectifier, the anodes of these three diodes being connected together at a common terminal 251. Terminal 251 is connected to an output conductor 252 and is also coupled through a resistor 253 to a source of positive voltage, not shown. In operation, if it be assumed that the level of the voltage source is higher than the high level of any of the input signals, then it is clear that if all of the input signals are at their high levels, the voltage at terminal 251 will be maintained at the common high level. However, if any of the input signals should be at its low level, the associated diode will conduct strongly to maintain the voltage at terminal 251 at the low level. It should be clear that additional signals may be combined in the "and" gate through provision of additional diode rectifiers. A typical "or" gate 260 is illustrated in Fig. 13. "Or" gate 260 is adapted for combining the arbitrary input signals  $Q_x$ ,  $Q_y$ , and  $Q_z$  to produce a corresponding output signal  $Q_x + Q_y + Q_z$ . Within "or" gate 260, each of the input signals  $Q_x$ ,  $Q_y$ , and  $Q_z$  is applied to the anode of a respectively associated diode rectifier, the cathodes of the three diodes being connected together at a common terminal 261. Terminal 261 is connected to an output conductor 262 and is also coupled through a resistor 263 to a point at ground potential. In operation, if any of the input signals is at its high level, the associated diode will conduct strongly to thereby maintain terminal 261 at the high voltage level. Considering first the shifting function of the character counter shown in Fig. 2, it may be recalled that in order to operate with a serially operable comparator network, the binary count in the character counter must be circulated through the counter once during each word time interval. If it is assumed that the output signals from flip-flop  $F_8$  are applied to the comparator network and that the least significant binary digit of the stored count is normally stored in this flip-flop, it is clear that the binary number stored in the counter must be circulated from left to right, as viewed in Fig. 2, in order to sequentially present the successively higher weighted binary digit signals at the output terminals of flip-flop  $F_6$ . The shifting function of counter 200 may, therefore, be expressed by the following logical equations:

$^{n}1S = \Sigma 6 \cdot \Sigma 0 \cdot \nabla P$ (2) $j_{2s} = Q_1 Q_0 C_p$ (3)  $k_{2S} = \overline{Q}_1 \cdot \overline{Q}_0 \cdot Cp$ (4)  $j_{3S} = Q_2 \cdot \overline{Q}_0 \cdot Cp$ (5)  $k_{3S} = \overline{Q}_2 \cdot \overline{Q}_0 \cdot Cp$ (6)  $j_{4S} = Q_3 \cdot \overline{Q}_0 \cdot Cp$ (7)  $k_{4S} = \overline{Q}_3 \cdot \overline{Q}_0 \cdot Cp$ (8)  $j_{5S} = Q_4 \cdot \overline{Q}_0 \cdot Cp$ (9)  $k_{5S} = \overline{Q}_4, \overline{Q}_0, Cp$ (10) $j_{\theta S} = Q_5 \cdot \overline{Q}_0 \cdot Cp$ (11) $k_{6S} = \overline{Q}_5 \cdot \overline{Q}_0 \cdot Cp$ (12)

15

2,850,566

where the dot (.) represents the logical "and" function, Cp represents the clock pulse signal, and  $\overline{Q}_0$  is a signal indicating that it is not the last digit time interval of a line time interval. For example, if it is not the last digit time interval of a line time interval  $(\overline{Q}_0)$ , "and" the binary digit one is stored in flip-flop  $F_{\theta}$  (Q<sub> $\theta$ </sub>), the clock pulse signal is applied to the *j*-input of flip-flop  $F_1$  in accordance with Equation 11 to set the flip-flop to the conduction state corresponding to the binary digit value one. If prior to the application of the clock pulse, flipflop  $F_5$  was in its conduction state corresponding to the binary digit value zero  $(\overline{Q}_5)$ , the clock pulse signal is simultaneously applied to the k-input of flip-flop  $F_{\beta}$  in accordance with Equation 12 to set flip-flop  $F_8$  to the 15 conduction state coresponding to the binary value zero. Thus the six-digit binary number stored in character counter 200 is completely circulated once each six clock pulses, or in other words, once per word time interval, thereby serially presenting at the output circuit of flip-20flop  $F_6$  electrical signals corresponding to the sequential binary digits of the stored binary count. Considering now the counting function of counter 200, it may be recalled that the stored count must be advanced to the next binary count during the last digit time 25 interval of each line time interval  $(Q_0)$ . It is apparent, however, that in the digit time interval preceding the receipt of signal  $(Q_0)$ , or in other words, during the fifth digit time interval of the last word time interval, the least significant binary digit of the character count is 30 stored in flip-flop  $F_5$ . Accordingly, during the last digit time interval of the line time interval (Q<sub>0</sub>), the stored count must be changed to correspond to the next succeeding type character in printing position and must simultaneously be shifted one digit in order to store the 35 least significant binary digit of the new count in flipflop **F**<sub>6</sub>.

### 16

the above logical equations are simplified forms and may be transformed to other equivalent forms by applying logical network theory. A comprehensive treatment of this subject may be found in copending U. S. patent application, Serial No. 327,131, for "Binary-Coded Flip-Flop Counters," by Robert Royce Johnson, filed December 20, 1952. It will also be recognized that if the count is always reset to zero before the counter has achieved its maximum count, the term  $(Q_6.Q_2.Q_3.Q_4.Q_5)$  in Equation 14 may be omitted since this term is only employed for setting flip-flop F<sub>6</sub> to zero after the maximum count has been achieved.

The combined gating functions of character counter 200 may be determined by combining Equations 1 through 12 with Equations 13 through 24 and introducing a reset function for resetting all flip-flops to zero at the end of each revolution of the printing cylinder. The reset function is derived from flip-flops  $F_{\mathbf{R}}$  and  $F_{\mathbf{O}}$  and is expressed by the function  $k_R = Q_O Q_R$  which indicates that a reset pulse is applied to the k-input of each of the counter flipflops during the last digit time interval before printing cylinder 132 starts its next revolution. In addition to providing a reset pulse, it is also desirable to inhibit the application of a clock pulse signal to the j-input of any flip-flop during the digit time interval when the counter is being reset to zero in order to prevent a flip-flop from being triggered to the conduction state corresponding to the binary value one. This may be accomplished by including the "or" function  $j_R = (\overline{Q}_O + \overline{Q}_R)$  in the *j*-input functions to all flip-flops, thus signifying that a pulse may not be applied to a *j*-input when the counter is being reset. For example, referring for the moment particularly to flip-flop  $F_1$ , combined shifting-counting-reset functions  $j_1$  and  $k_1$  may be obtained for the j and k inputs, respectively, of flip-flop  $F_1$  by combining the  $j_{1S}$  (shift) function, the  $j_{1C}$  (count) function, and the  $j_{R}$  (reset) function, to form the  $j_1$  function, and by combining the  $k_{1S}$ ,  $k_{1C}$ , and  $k_{\rm R}$  functions to form the  $k_1$  function. The desired function  $j_1$  may be defined in the following manner:

For example, if the binary number 011101 is being

circulated in the character counter once during each word time interval, the position of the count in flip-flops  $F_1$  40 through  $F_6$  during the penultimate digit time interval of the line time interval is such that the most significant binary digit is stored in flip-flop  $F_6$  while the least significant digit is stored in flip-flop  $F_5$ , thereby giving the appearance that the binary number 111010 is stored in 45 the counter. During the next digit time interval, therefore, the count must be changed to the next succeeding binary number 011110 with the least significant binary digit again stored in flip-flop  $F_6$  and the most significant binary digit again stored in flip-flop  $F_1$ . 50

The counting function of character counter 200 may be expressed by the following logical equations:

$$j_1 = (j_{1S} + j_{1C}) \cdot j_R$$

(25a)

Remembering that:

$$\begin{array}{l}

j_{1S} = Q_6 . \overline{Q}_0 . Cp & (1) \\

j_{1C} = Q_0 . Q_6 . Cp & (13) \\

j_R = (\overline{Q}_0 + \overline{Q}_R) . Cp & (25b)

\end{array}$$

Then it is clear that:

$j_1 = (Q_6.\overline{Q}_0.Cp + Q_6.Q_0.Cp).(\overline{Q}_0 + \overline{Q}_R).Cp$  (25c) Equation 25c may be simplified by factoring Cp from one of its terms:

5  $j_1 = (Q_6 \cdot \overline{Q}_0 + Q_6 \cdot Q_0) \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp \cdot Cp$  (25d) In the logical algebra, a term such as A.A is equal to A. Similarly,  $Cp \cdot Cp = Cp$ . Therefore:

$$j_1 = (Q_6 \cdot \overline{Q}_0 + Q_6 \cdot Q_0) \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp \qquad (25e)$$

<sup>60</sup> Equation 25*e* may be further simplified by factoring out  $Q_6$  to obtain:

| (4CQO)(Q3)Q5TQ3)Q5TQ5DP                             | (21) |

|-----------------------------------------------------|------|

| $j_{5C} = Q_0 Q_4 C_p$                              | (22) |

| $k_{5C} = Q_0 \cdot Q_4 \cdot C_p$                  |      |

| j <sub>6C</sub> =Q <sub>0</sub> .Q <sub>5</sub> .Ср | (23) |

| $k_{BC} = Q_0 Q_5 C_p$                              | (24) |

where the plus (+) represents the logical nonexclusive "or" function. For example, Equation 20 signifies that a clock pulse signal (Cp) is applied to the k-input terminal of flip-flop  $F_4$  when it is the last word time interval of a line time interval  $(Q_0)$  "and" either binary ones are stored in flip-flops  $F_3$  and  $F_5$   $(Q_3.Q_5)$  "or" (+) binary zeros are stored in flip-flops  $F_3$  and  $F_5$   $(\overline{Q_3.Q_5})$ .

It will be recognized by those skilled in the art that 75

$j_1 = (\overline{Q}_0 + Q_0) \cdot Q_0 \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp \qquad (25f)$

65 Those skilled in the art will readily recognize that  $(\overline{Q}_0 + Q_0) = 1$ , since the signals  $\overline{Q}_0$  and  $Q_0$  are complementary and, therefore, one of these signals must be at its high (1-representing) level, while the other signal is at its low (0-representing) level.  $(\overline{Q}_0 + Q_0)$  must, there-70 fore, equal (1+0) which is, in turn, equal to 1. By substituting 1 for the term  $(\overline{Q}_0 + Q_0)$  in Equation 25f there is obtained a complete simplified logical Equation 25 for the desired shifting-counting-reset function  $j_1$ :

$$j_1 = Q_6 \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp \tag{25}$$

#### 17

The desired shifting-counting-reset function  $k_1$ , which may be defined by the logical Equation  $k_1 = k_{1s} + k_{1c} + k_R$ , may be similarly derived from the corresponding separate shift, count, and reset functions.

In the same manner, the j and k gating functions for 5 each of the flip-flops of character counter 200 may be similarly derived.

The complete gating functions of character counter 200, including the shifting, counting and reset functions may be expressed by the following simplified logical equations: 10

#### (Gating matrix 201)

$$i_1 = Q_{\theta} \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp \qquad (25)$$

$$k_1 = [\overline{Q}_{\theta} \cdot (\overline{Q}_0 + \overline{Q}_2 + \overline{Q}_3 + \overline{Q}_4 + O_5) + Q_0 \cdot Q_0] \cdot Cp \quad (26)$$

### 18

1 or 0 value in accordance with the foregoing rules. The signals  $(\overline{Q}_5)$ ,  $(Q_0)$ , and  $(\overline{Q}_R)$  are combined in an "and" gate 214 to produce an electrical output signal corresponding to the term  $(\overline{Q}_5, Q_0, \overline{Q}_R)$ . The output signals from each of "and" gates 212 and 214 are then combined in an "or" gate 216 to produce a high-level (1-representing) electrical output signal corresponding to the term  $(Q_5.\overline{Q}_0 + \overline{Q}_5.Q_0.\overline{Q}_R)$ , the output signal from the "or" gate being applied to a clock pulse "and" gate 220 which is connected to the *j*-input of flip-flop  $F_{\theta}$  and has an additional input terminal connected to the clock pulse generator for receiving the clock pulse signal (Cp). Each clock pulse "and" gate is structurally similar to the other "and" gates and differs only functionally in that it is selectively operable to pass the applied clock pulse signal to its associated flip-flop input circuit, only when all of the voltage-state signals applied to the input terminals of the "and" gate are at their high-level (1-representing) values. Equation 36 is similarly mechanized by three "and" gates 224, 226, and 228 corresponding to the terms  $(Q_5,Q_0)$ ,  $(Q_5,Q_0)$ , and  $(Q_0,Q_R)$ , respectively, an "or" gate 230, and a clock pulse "and" gate 232 having its 25 output terminal connected to the k-input of flip-flop  $\mathbf{F}_{\theta}$ . Gate 228 is located outside of gating matrix 206 because the combined signal  $(Q_0, Q_R)$  is also applied to matrices 201 through 205 for partially mechanizing Equations 26, 28, 30, 32, and 34. It will be recognized by those skilled in logical algebra, of course, that Equations 25 through 3036 may be transformed by Boolian algebra to permit modified mechanizations of the equations, and consequently, the mechanization of the gating matrices shown in Fig. 2 is merely illustrative. In the foregoing description of the structure of charac-35ter counter 200, the following pattern of explanation has been followed: First, logical Equations 1 through 12 were presented and fully explained, these equations being representative of gating structure which could accomplish the desired shifting function of counter 200. Next, logical Equations 13 through 24 were presented which were representative of gating structure for the accomplishment of the counting function of character counter 200, and also for the accomplishment of an additional shift of information within character counter 200 in conjunction with each increase of count in the counter. Next, the reset function  $Q_0 Q_R$ , for the k-inputs to the flip-flops of counter 200, was presented and explained, and an associated reset function  $\overline{Q}_{o} + \overline{Q}_{R}$ , for the inhibition of clock pulse signals to the *j*-inputs of the flip-flops of counter 200 during the reset interval, was also presented and described. Then, to obtain the complete combined shifting-counting-and reset functions represented by logical Equations 25 to 36, the separate corresponding shift functions, count functions, and reset functions were com-55 bined and simplified in accordance with the laws of the logical algebra.

$\sim 1 \simeq 1 \simeq 0 = 1 \simeq 0 \simeq R = 0 P (20)$ (Gating matrix 202)  $j_2 = Q_1 \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp$ (27) $k_2 = [Q_0, Q_1, Q_3, Q_4, Q_5 + \overline{Q}_1, (\overline{Q}_0 +$  $\overline{Q}_3 + \overline{Q}_4 + \overline{Q}_5) + Q_0 Q_R ].Cp$ (28) 20 (Gating matrix 203)  $j_3 = Q_2 (\overline{Q}_0 + \overline{Q}_R) C_p$ (29) $k_3 = \{\overline{Q}_0, Q_2, Q_4, Q_5 + \overline{Q}_2, (\overline{Q}_0 + \overline{Q}_4 + \overline{Q}_5) + Q_0, Q_R\}, Cp \quad (30)$ (Gating matrix 204)  $j_4 = Q_3 \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot Cp$ (31)  $\mathbf{k}_4 = [\mathcal{Q}_0, \mathcal{Q}_3, \mathcal{Q}_5 + \overline{\mathcal{Q}}_3, (\overline{\mathcal{Q}}_0 + \overline{\mathcal{Q}}_5) + \mathcal{Q}_0, \mathcal{Q}_R].C_p$ (32) (Gating matrix 205)  $j_5 = Q_4 \cdot (\overline{Q}_0 + \overline{Q}_R) \cdot C_p$ (33)  $k_5 = [Q_0 \cdot Q_4 + \overline{Q}_0 \cdot \overline{Q}_4 + Q_0 \cdot Q_R] \cdot Cp$ (34) (Gating matrix 206)

> $j_{\theta} = [(Q_{5}, \overline{Q}_{0} + \overline{Q}_{5}, Q_{0}), (\overline{Q}_{0} + \overline{Q}_{R})].C_{p}$  $= (Q_5.\overline{Q}_0 + \overline{Q}_5.Q_0.\overline{Q}_R).C_p$ (35)  $k_6 = [\overline{Q}_5 \cdot \overline{Q}_0 + Q_5 \cdot Q_0 + Q_0 \cdot Q_R] \cdot Cp$

(36)

The mechanization of logical Equations 25 through 36 40 will be understood more readily by considering the structure of gating matrix 206 which is mechanized according to Equations 35 and 36. In mechanizing the *j*-input function to flip-flop  $F_6$  the signals (Q<sub>5</sub>) and ( $\overline{Q}_0$ ) are first combined in an "and" gate 212 to produce an output 45 signal corresponding to the term  $(Q_5,Q_0)$ . Signal  $(Q_5, \overline{Q}_0)$  will have a high (1-representing) level only when both signal  $(Q_5)$  "and" signal  $(\overline{Q}_0)$  are at their high (1) levels. In the symbology of the logical algebra, 50 if  $(Q_5)$  is at a high level  $(Q_5=1)$  "and"  $(\overline{Q}_0)$  is at a high level ( $\overline{Q}_0=1$ ), then  $Q_5.\overline{Q}_0=1.1=1$  and, therefore, signal  $(Q_5, \overline{Q}_0)$  will then be at a high (1-representing) level. On the other hand, if  $Q_5=1$  and  $Q_0=0$ , then signal  $(Q_5, \overline{Q}_0) = (1.0) = 0$  and will, therefore, be at a low (0) level. Finally, if  $Q_5=0$  and  $\overline{Q}_0=0$ , then  $Q_5.\overline{Q}_0=0$ 0.0=0, and is, therefore, at a low (0) level.

From the foregoing it is clear that the level of an output signal produced by the interaction of two-level 60 electrical signals in an "and" gate can be discovered by first substituting the appropriate 1 or 0 values for the corresponding symbols in the logical expression which represents the "and" gate, and then applying the ordinary rules of multiplication; namely, that 1.1=1, 1.0=0, and 650.0=0. It can also be demonstrated in a similar manner that, for an "or" gate, the level of its output signal is related to the levels of its input signals in accordance with the following rules which closely resemble the ordinary rules of addition; namely, that 1+0=1, 0+0=0, 70 and 1+1=1. Even for a very complicated gating function, composed of a plurality of "and" and "or" gates, the level of an output signal can be discovered in the same manner by systematic substitution of appropriate 1 or 0 values for the input signals and reduction to a final 75

Equation 25, for example, which is descriptive of the gating function for the *j*-input of flip-flop  $F_1$  was obtained by combining the right hand terms of Equations 1 and 13 with the reset function  $\overline{Q}_0 + \overline{Q}_R$ . It should be noted that Equation 1 is representative of the shift function for the *j*-input to flip-flop  $F_1$ , and that Equation 13 is representative of the count function for the *j*-input of flip-flop  $F_6$ . It will be understood that each of the other combined gating functions is similarly obtained by combining the corresponding shift, count, and reset functions for the associated flip-flop inputs. Finally, the exact and definite correspondence between the terms of the logical equations and the corresponding gating structures of Fig. 2 was clarified, by way of example, by relating each of the terms of Equations 35 and 36 to the corresponding gates shown in Fig. 2, it being understood that the terms of each of the other logical equations is similarly mech-

#### 19

anized by exactly corresponding gating structurees shown in Fig. 2.

To those skilled in the art, the foregoing derivation of the combined gating functions 25 through 36, from separate elementary shift, count, and reset functions, is suf- 5 ficient to establish the validity of these functions and, therefore, the operability of the structure of the corresponding gating matrices 201 to 206 for the accomplishment of the desired combined shifting-counting-reset functions. However, to further illustrate the operations 10 of counter 200, and to more directly relate the controlling or descriptive logical equations to the gating matrices which they represent, it will be helpful to follow the numerical examples provided below. In these examples the functions  $j_{6}$  and  $\bar{k}_{6}$  are evaluated, first for the reset of 15 Reducing, there is obtained: counter 200 at the last digit time of a line printing interval, then for the cyclical shift of counter 200 during the immediately succeeding line time interval, and finally for the advance or increase by one of the character count stored in counter 200 during the last digit time of this line 20time interval. During this described sequence of operations, each of the counter flip-flops,  $F_1$  through  $F_6$ , is first set to the 0 state, by the reset operation, to store the binary number 000000 in the counter. Then, during the shift operation, this number 000000 is continuously shifted in cylical fashion around the counter. Finally, during the count operation, flip-flop  $F_{\theta}$  is changed from the 0 state to the 1 state, thereby increasing the character count by 1 from the binary number 000000 to the binary number 000001. During reset, each of the flip-flops  $F_1$  through  $F_6$  is to be set to the zero state without regard to its former state. It is clear that during reset a clock pulse signal Cp must be applied to the k-input of each of the flip-flops of counter 200, while the clock pulse signal must be prevented from reaching the *j*-input of each of the flip-flops. Expressed in the logical algebra, the requirement for successful reset is that during reset, each of the gating func-

### 20

It will be remembered that during shift, flip-flops  $F_R$ and  $F_0$  are both in the 0 state.

Therefore, during shift:

$Q_0=0$  $Q_R=0$  $\overline{Q}_R = 1$   $\overline{Q}_O = 1$

From Equations 35 and 36:

$$j_6 = (Q_5 \cdot \overline{Q}_0 + \overline{Q}_5 \cdot Q_0 \overline{Q}_R) \cdot Cp$$

$$k_6 = [\overline{Q}_5 \cdot \overline{Q}_0 + Q_5 \cdot Q_0 + Q_0 \cdot Q_R] \cdot Cp$$

Substituting values:

$j_{6} = (Q_{5}.1 + \overline{Q}_{5}.0.1).Cp$   $k_{6} = [\overline{Q}_{5}.1 + Q_{5}.0 + 0.0].Cp$

$j_6 = (Q_5 + 0).Cp$   $k_8 = [\overline{Q_5} + 0 + 0].Cp$

In final form, during shift:

$j_6 = Q_5.Cp$   $k_6 = \overline{Q}_5.Cp$

In the same manner, it may be shown that during shift,  $j_1 = Q_6, Cp, j_2 = Q_1, Cp, j_3 = Q_2, Cp, j_4 = Q_2, Cp, j_5 = Q_4, Cp,$ and that  $k_1 = \overline{Q}_6 \cdot Cp, \ k_2 = \overline{Q}_1 \cdot Cp, \ k_3 = \overline{Q}_2 \cdot Cp, \ k_4 = \overline{Q}_3 \cdot Cp,$ 25  $k_5 = \overline{Q}_4.Cp.$