US 20190013200A1

### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2019/0013200 A1

Lagally et al.

Jan. 10, 2019 (43) Pub. Date:

#### HIGH-QUALITY, SINGLE-CRYSTALLINE SILICON-GERMANIUM FILMS

Applicant: Wisconsin Alumni Research Foundation, Madison, WI (US)

Inventors: Max G. Lagally, Madison, WI (US);

Thomas Francis Kuech, Madison, WI (US); Yingxin Guan, Madison, WI (US); Shelley A. Scott, Madison, WI (US); Abhishek Bhat, Madison, WI

(US); Xiaorui Cui, Middleton, WI (US)

Appl. No.: 15/643,111

Jul. 6, 2017 (22)Filed:

#### **Publication Classification**

Int. Cl. (51)

H01L 21/02 (2006.01)H01L 21/78 (2006.01)C30B 29/52 (2006.01) C30B 25/02 (2006.01)C30B 29/08 (2006.01)C30B 29/68 (2006.01)

U.S. Cl. (52)

> CPC .. *H01L 21/02694* (2013.01); *H01L 21/02395* (2013.01); *H01L 21/02463* (2013.01); *H01L* 21/02461 (2013.01); H01L 21/02532 (2013.01); *H01L 31/035254* (2013.01); *H01L 21/7813* (2013.01); *C30B 29/52* (2013.01); *C30B 25/02* (2013.01); *C30B 29/08* (2013.01); C30B 29/68 (2013.01); H01L 21/0262 (2013.01)

#### (57)**ABSTRACT**

High-quality, single-crystalline silicon-germanium  $(Si_{(1-x)})$ Ge<sub>x</sub>) having a high germanium content is provided. Layers of the high-quality, single-crystalline silicon-germanium can be grown to high sub-critical thicknesses and then released from their growth substrates to provide  $Si_{(1-x)}Ge_x$  films without lattice mismatch-induced misfit dislocations or a mosaic distribution of crystallographic orientations.

## HIGH-QUALITY, SINGLE-CRYSTALLINE SILICON-GERMANIUM FILMS

#### REFERENCE TO GOVERNMENT RIGHTS

[0001] This invention was made with government support under 144-LS09 awarded by the Department of Energy and under 144-PRJ91IC awarded by the National Science Foundation. The government has certain rights in the invention.

#### **BACKGROUND**

[0002]  $Si_{(1-x)}Ge_x$  single-crystal thin films have been grown epitaxially on silicon. However, the thickness of these films is limited because, beyond a certain thickness (referred to as the critical thickness), the strain induced in the  $Si_{(1-x)}Ge_x$  by the lattice mismatch between the growth substrate and the  $Si_{(1-x)}Ge_x$  begins to plastically relax, which results in the formation of lattice mismatch-induced misfit dislocations in the  $Si_{(1-x)}Ge_x$ . Moreover, as the Ge content of the  $Si_{(1-x)}Ge_x$ increases, the critical thickness of the film decreases. As a result, high-quality, single-crystalline films of  $Si_{(1-x)}Ge_x$ with a high Ge content cannot be grown on silicon to adequate thicknesses for many practical processing techniques and device applications. High-Ge-content  $Si_{(1-x)}Ge_x$ single-crystal thin films can be grown epitaxially on germanium. However, the critical thickness of these films decreases with increasing silicon content and, therefore, high-quality  $Si_{(1-x)}Ge_x$  films with thicknesses useful for many device applications can only be achieved for  $Si_{(1-x)}Ge_x$ films with a very high Ge content when germanium is used as the growth substrate.

[0003] High Ge content  $Si_{(1-x)}Ge_x$  has been grown epitaxially over compositionally graded, plastically relaxed growth substrates. Unfortunately, the plastically relaxed growth substrates are characterized by lattice mismatch-induced misfit dislocations and their associated threading dislocations, and these propagate through the  $Si_{(1-x)}Ge_x$ . Moreover, the resulting  $Si_{(1-x)}Ge_x$  films are characterized by a non-uniform strain distribution and small-angle tilt boundaries, which degrade the crystal quality and, therefore, the performance of devices incorporating the  $Si_{(1-x)}Ge_x$ .

#### **SUMMARY**

[0004] High-quality, single-crystalline silicon-germanium  $(Si_{(1-x)}Ge_x)$  and electronic devices incorporating the films as active layers are provided.

[0005] One embodiment of a high-quality single-crystal-line  $Si_{(1-x)}Ge_x$  material is a layer of single-crystalline  $Si_{(1-x)}Ge_x$ , where  $0.4 \le x < 1$ , having a thickness of at least 40 nm, wherein the single-crystalline  $Si_{(1-x)}Ge_x$  does not comprise a mosaic distribution of crystallographic orientations.

[0006] One embodiment of an electronic device that incorporates high-quality, single-crystalline  $Si_{(1-x)}Ge_x$  includes: a first electrode; a second electrode; and a layer of single-crystalline  $Si_{(1-x)}Ge_x$ , where  $0.4 \le x < 1$ , in electrical communication with the first electrode and the second electrode, the layer of single-crystalline  $Si_{(1-x)}Ge_x$  having a thickness of at least 40 nm, wherein the single-crystalline  $Si_{(1-x)}Ge_x$  does not comprise a mosaic distribution of crystallographic orientations. The first and second electrodes can be in electrical communication with the single-crystalline  $Si_{(1-x)}Ge_x$  via direct physical contact with the single-crystalline  $Si_{(1-x)}Ge_x$  or through an intervening material that separates the electrodes from the single-crystalline  $Si_{(1-x)}Ge_x$ .

[0007] Other principal features and advantages of the invention will become apparent to those skilled in the art upon review of the following drawings, the detailed description, and the appended claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0008] Illustrative embodiments of the invention will hereafter be described with reference to the accompanying drawings, wherein like numerals denote like elements.

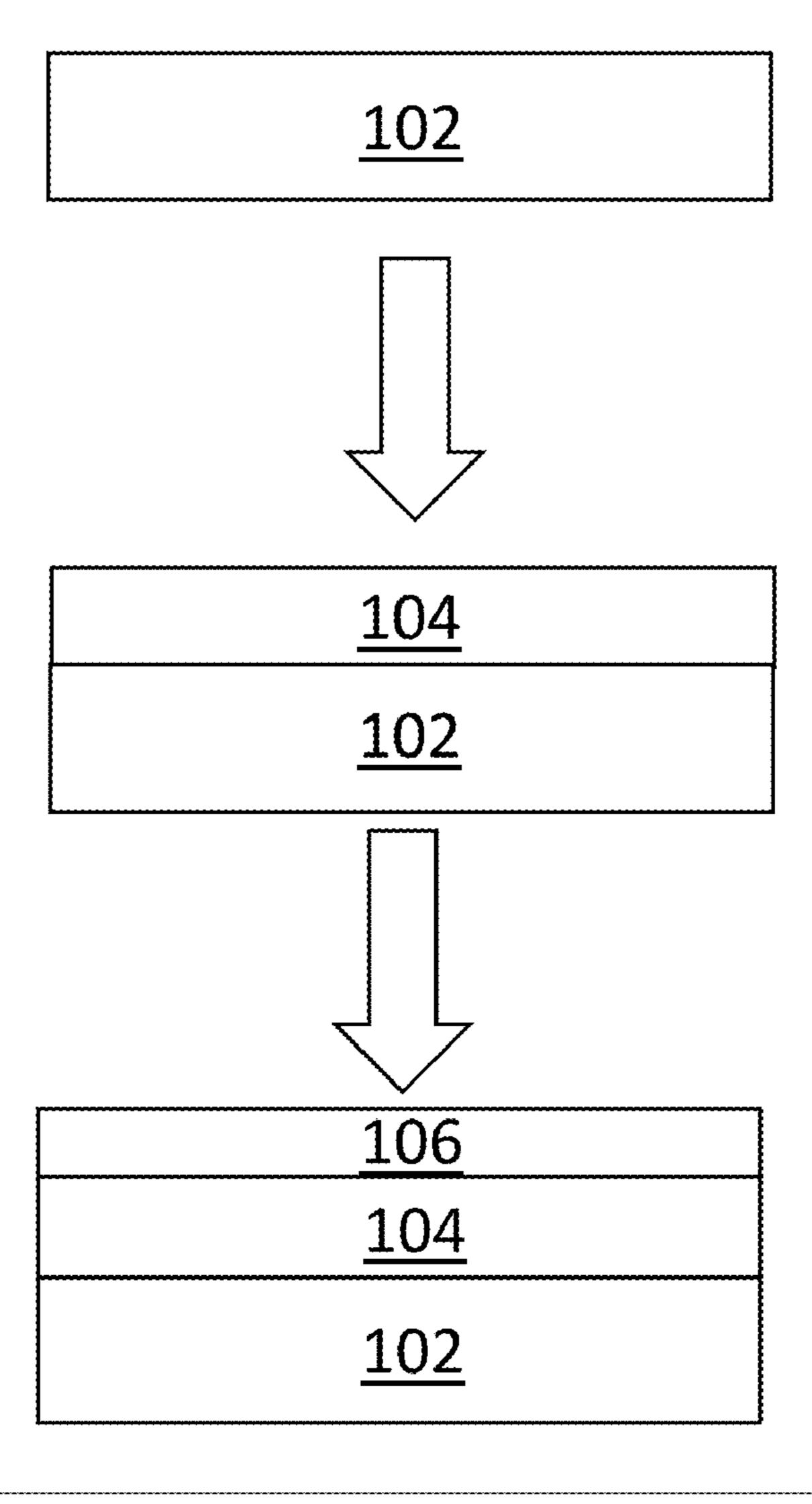

[0009] FIG. 1 is a schematic diagram of a method for growing high-quality, single-crystalline silicon-germanium on a sacrificial growth layer.

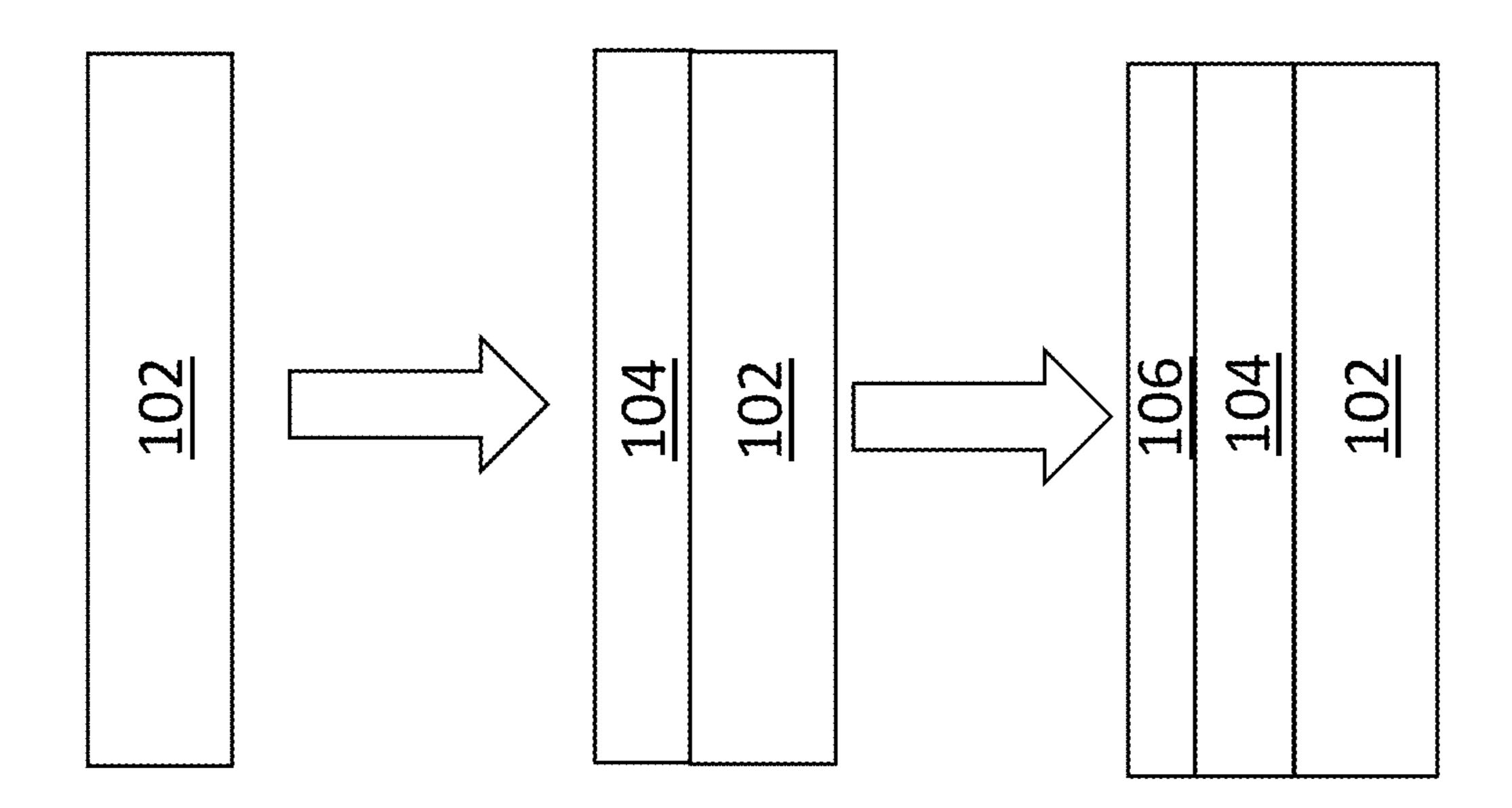

[0010] FIG. 2 is a schematic diagram of a method for releasing the high-quality, single-crystalline silicon-germanium from the underlying heterostructure.

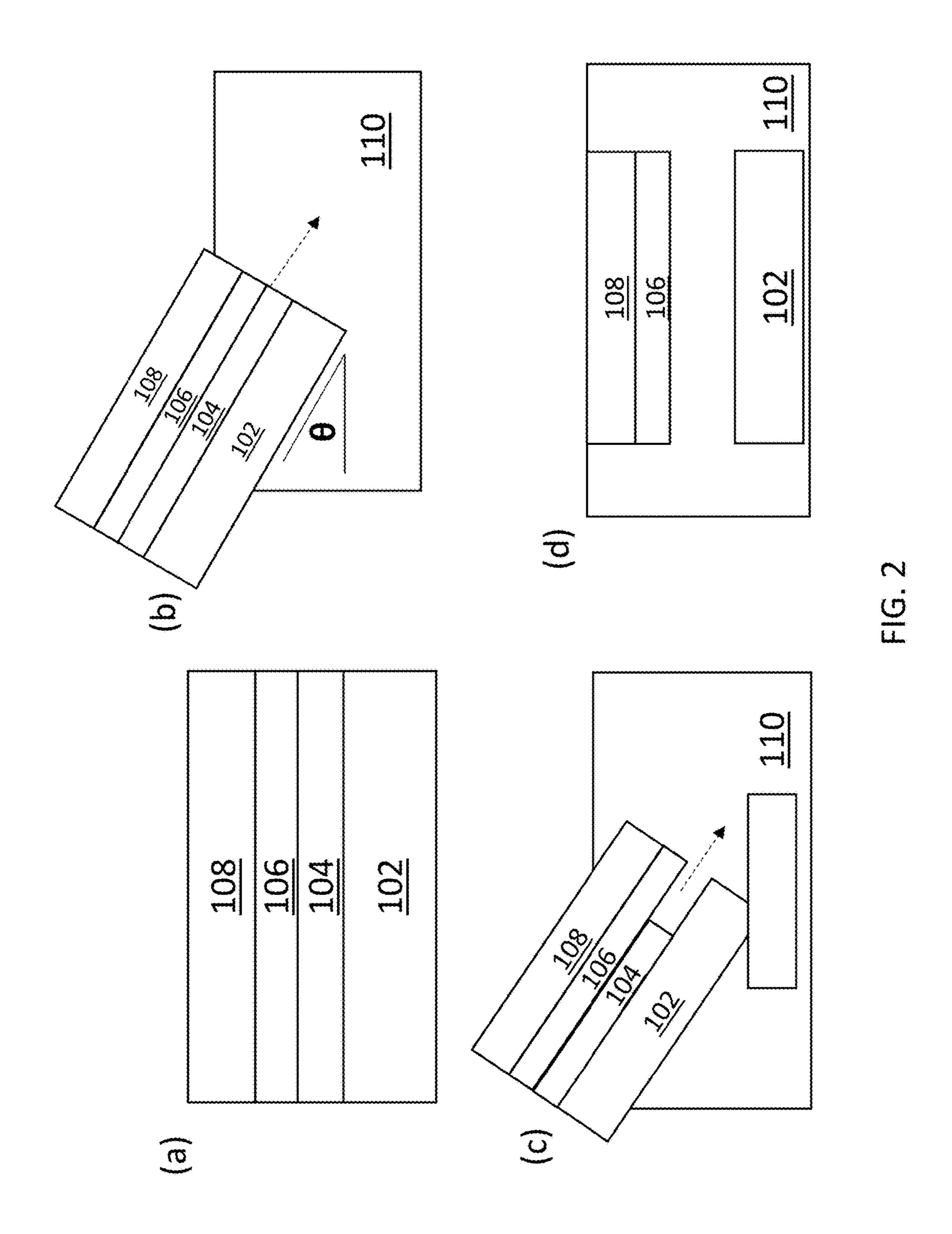

[0011] FIG. 3 is a schematic diagram of another method for growing high-quality, single-crystalline silicon-germanium on a sacrificial growth layer.

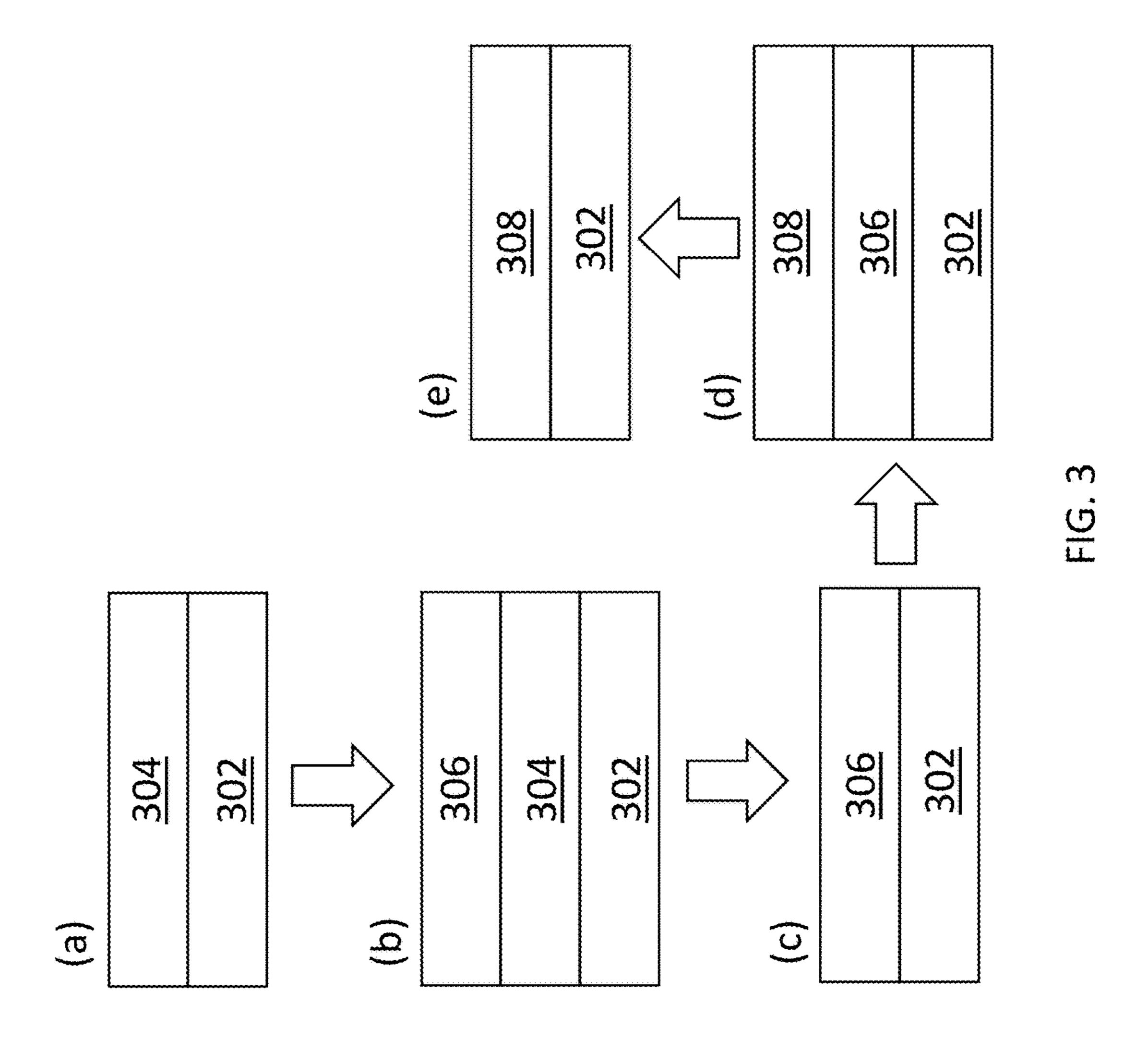

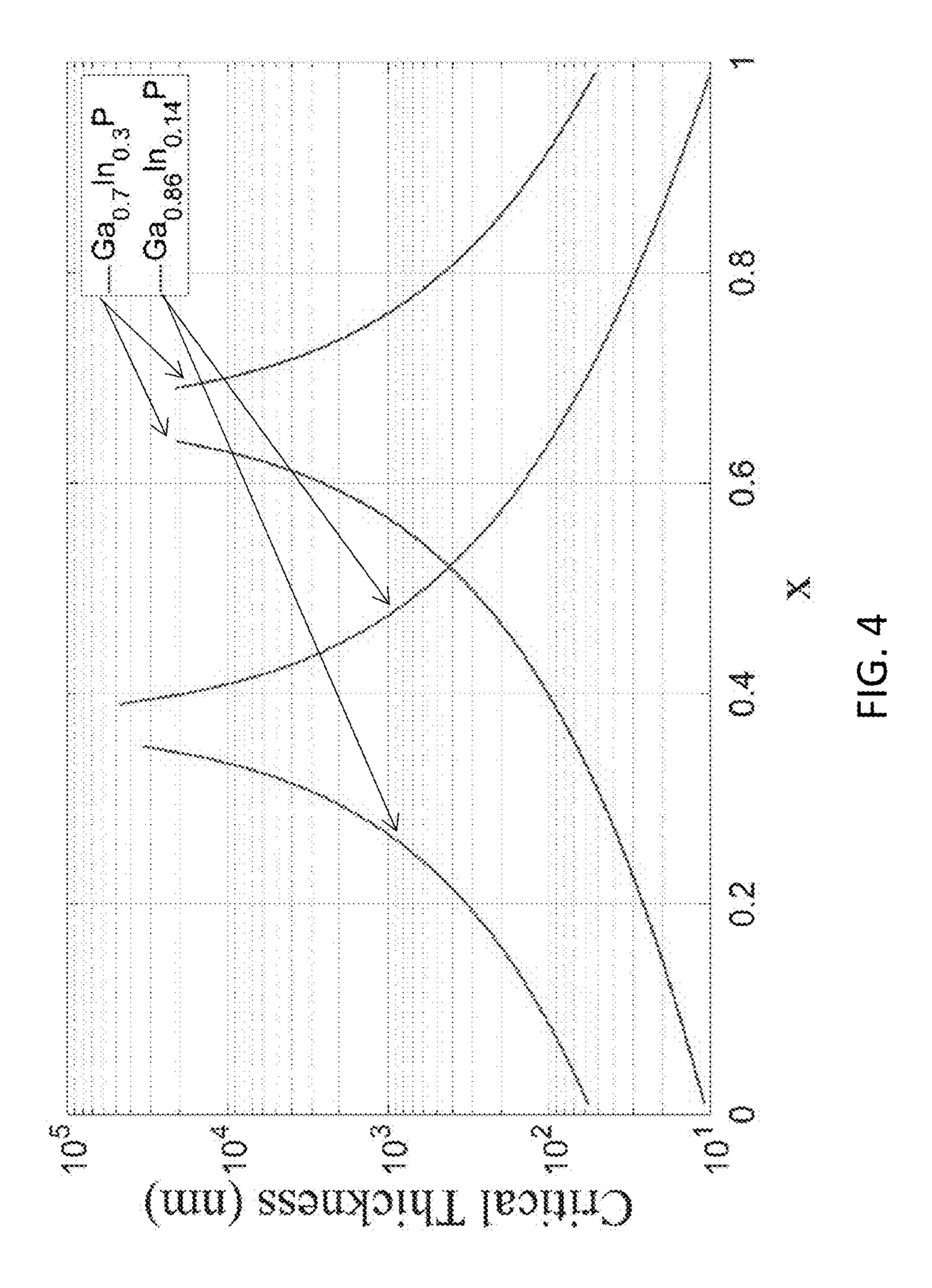

[0012] FIG. 4 is a graph showing the relationship between the critical thickness and the germanium content for  $Si_{(1-x)}$   $Ge_x$  grown on two GaInP alloys.

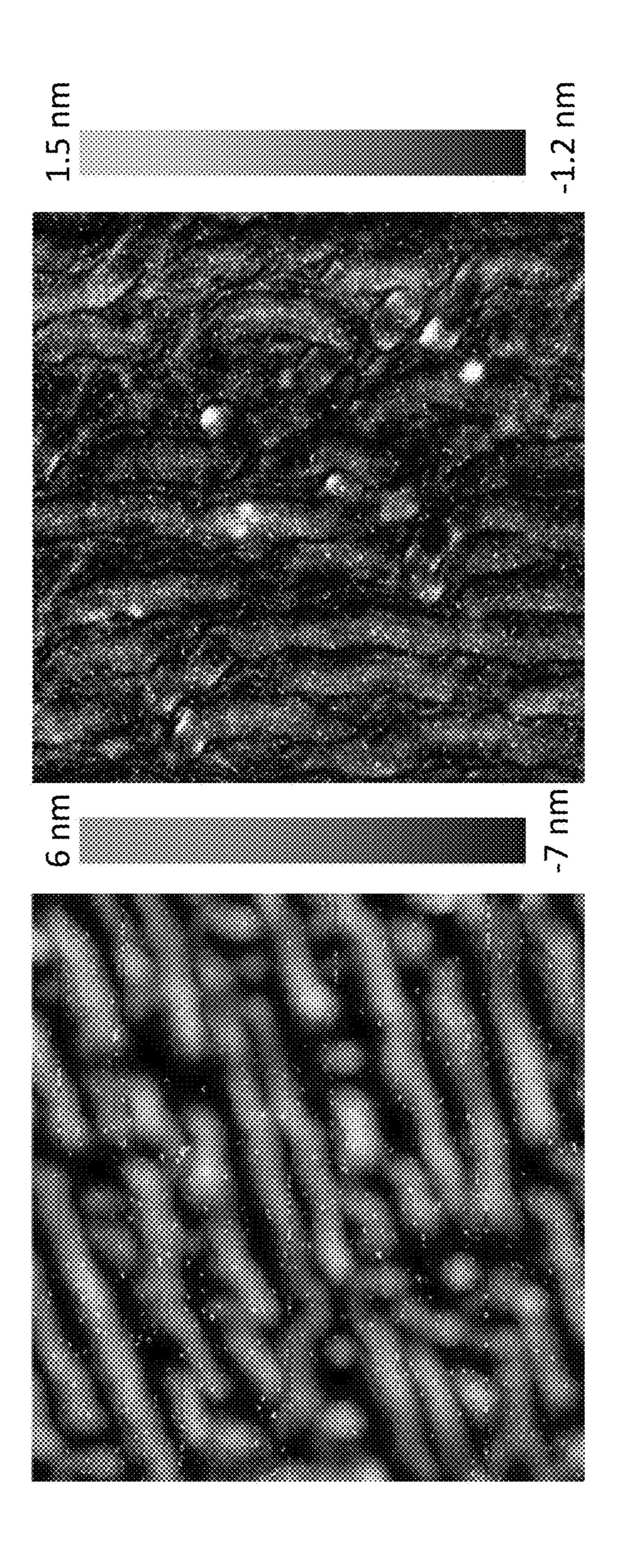

[0013] FIG. 5A is an atomic force microscope image of a layer of single-crystalline Ge as-grown on a GaAs base substrate with an AlAs sacrificial layer. FIG. 5B is an atomic force microscope image of the Ge film after being released from the growth heterostructure and transferred to a host substrate of oxidized silicon.

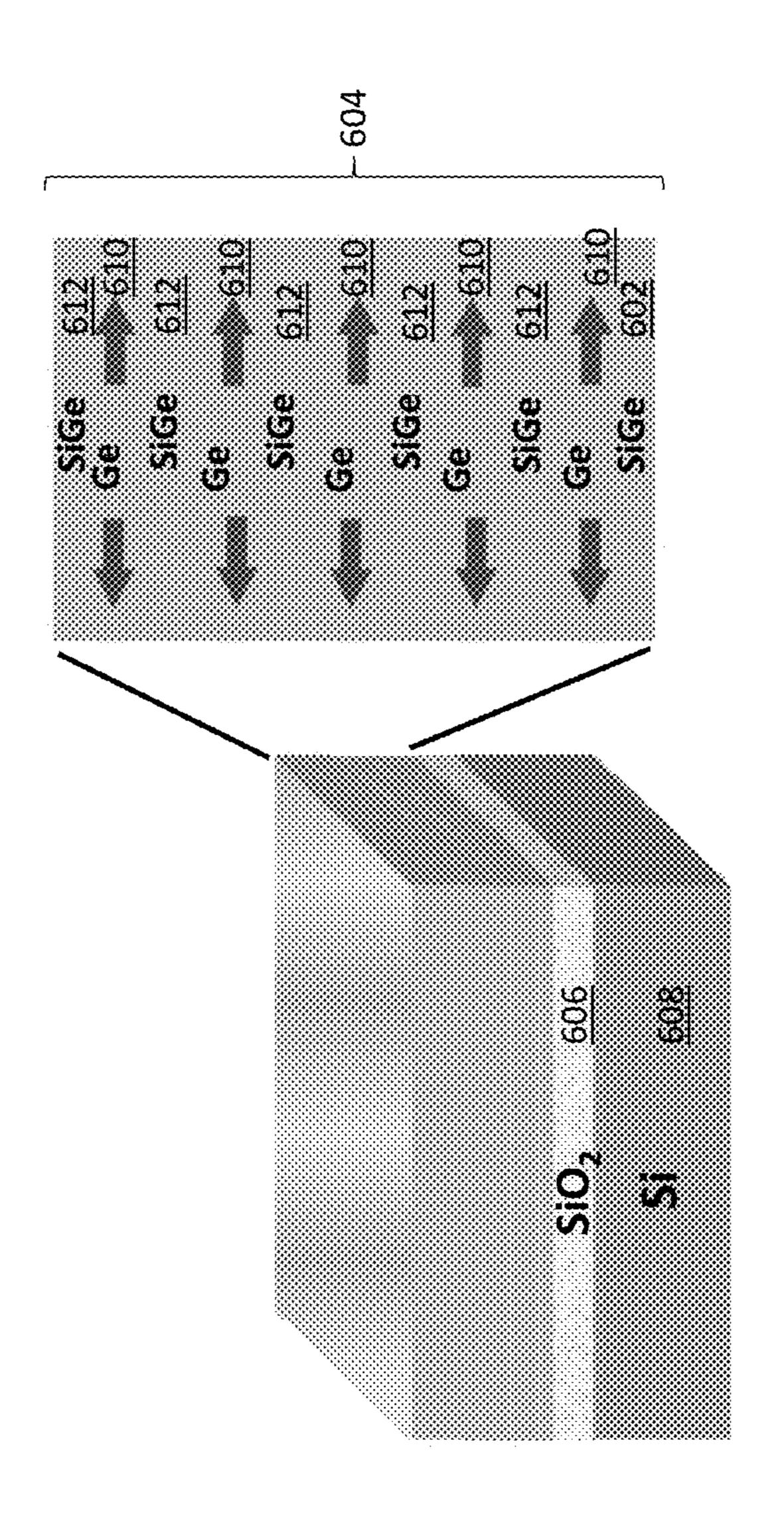

[0014] FIG. 6 is a schematic diagram of a SiGe/Ge quantum well structure for THz radiation grown on an elastically relaxed SiGe NM transferred to SiO<sub>2</sub>. The arrows indicate that the Ge layers are under compression.

[0015] FIG. 7 is a schematic diagram of a MOSFET that includes a  $Si_{(1-x)}Ge_x$  film as a channel layer.

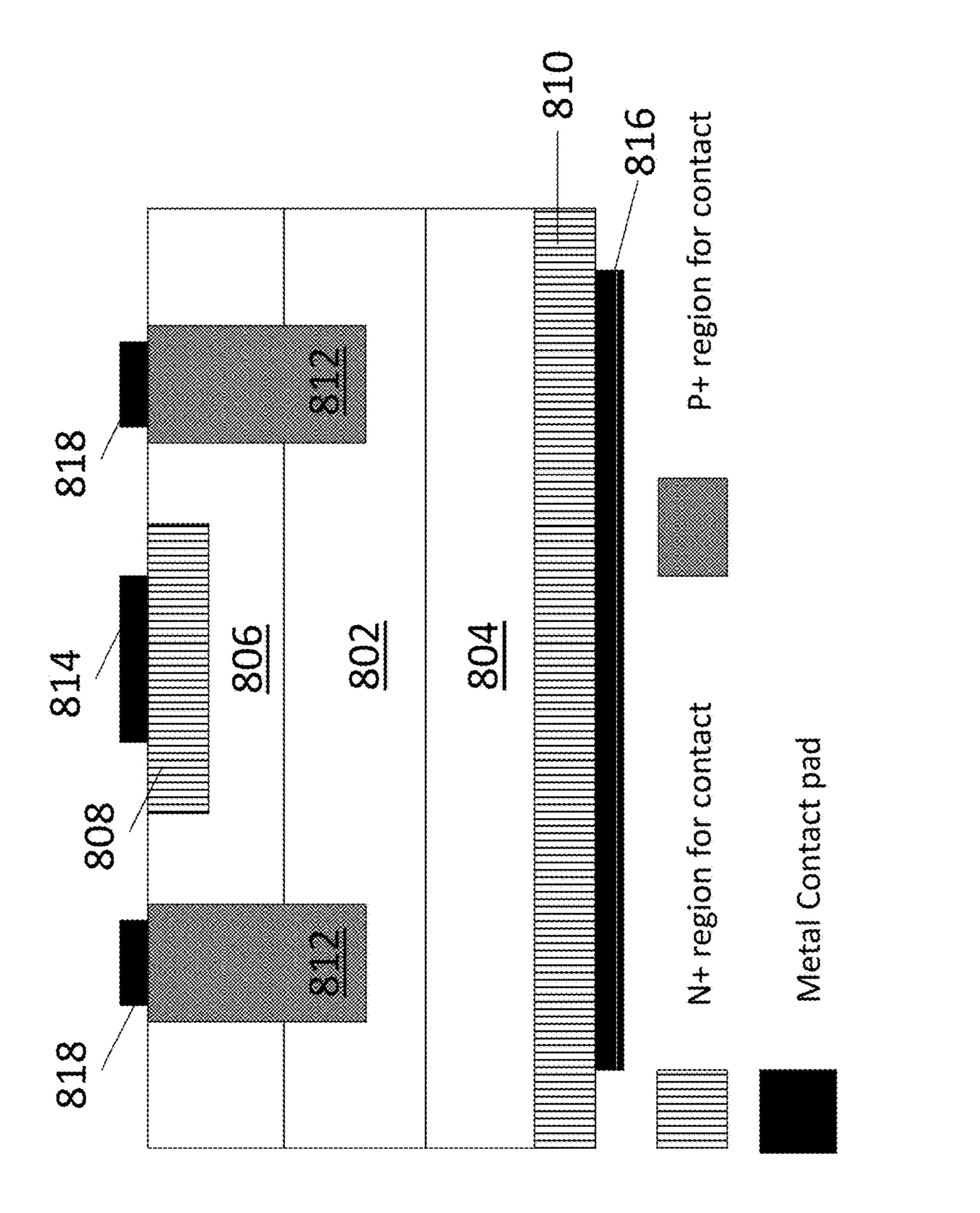

[0016] FIG. 8 is a schematic diagram of an HBT that includes a  $Si_{(1-x)}Ge_x$  film as a base layer.

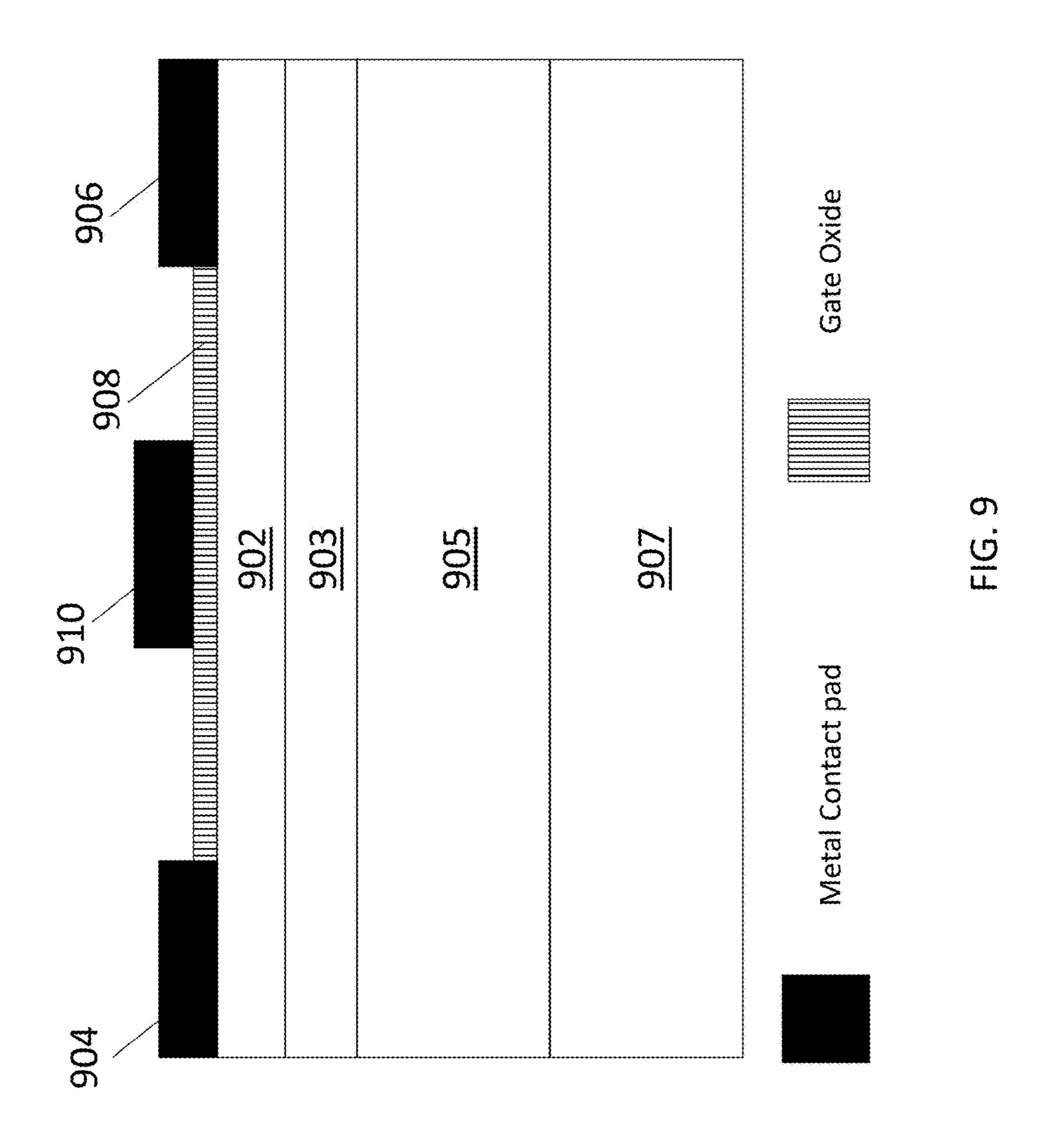

[0017] FIG. 9 is a schematic diagram of a MODFET that includes a  $Si_{(1-x)}Ge_x$  film as a spacer layer.

#### DETAILED DESCRIPTION

[0018] High-quality, single-crystalline silicon-germanium  $(Si_{(1-x)}Ge_x)$  films, including films having commercially practical thicknesses and high germanium contents, are provided. Also provided are methods of forming films of the high-quality, single-crystalline silicon-germanium.

[0019] The high-quality, single-crystalline silicon-germanium films are free of the lattice mismatch-induced misfit dislocations and their associated threading dislocations that would result from the epitaxial growth of the films above their critical thicknesses or from the epitaxial growth of the films on plastically relaxed, compositionally graded growth substrates. The silicon-germanium films also lack the strain variations and small-angle tilt boundaries that characterize films grown on plastically relaxed, compositionally graded growth substrates. The formation of these strain variations in materials grown epitaxially on a plastically relaxed, compositionally graded growth substrate can be explained as follows: when the compositionally graded substrate is plastically relaxed, a non-uniform distribution of misfit dislocations is formed in the growth substrate, which results in a non-uniform strain distribution in the epitaxial layer grown on top. This strain variation can be detected using micro-Raman spectroscopy, as illustrated in Paskiewicz, D. M. et

al. "Nanomembrane-based materials for Group IV semiconductor quantum electronics." *Scientific Reports* 4 (2014).

[0020] In addition, the plastic relaxation of the graded growth substrate results in the formation of crystallites having small misorientations with respect to each other, which are observed as small-angle tilt boundaries. These small-angle tilt boundaries are transferred to the epitaxial layer grown on the plastically relaxed substrate. As a result, the epitaxial layer grown on the plastically relaxed substrate is characterized by a mosaic distribution of crystallographic orientations, which can be observed as a crosshatch pattern in a micro-Raman map of the crystalline structure, as described in Paskiewicz, et al. These misfit dislocationinduced, small-angle tilt boundaries that can be detected as a crosshatch pattern in a micro-Raman map of the crystalline structure (referred to herein as small-angle tilt boundaries) are not present in the high-quality, single-crystalline silicongermanium made by the methods described herein.

[0021] The high-quality, single-crystalline silicon-germanium, which has a (001) orientation, can be grown epitaxially on a sacrificial growth layer having a low lattice mismatch with the  $Si_{(1-x)}Ge_x$ . Using sacrificial growth layers having low lattice mismatches with the silicon-germanium allows for the growth of high-germanium-content, singlecrystalline silicon-germanium layers with high critical thicknesses. The sacrificial growth layer may be grown on an underlying support substrate with which it has a low lattice mismatch. After the growth of the  $Si_{(1-x)}Ge_x$  layer is completed, it can be released as an unstrained  $Si_{(1-x)}Ge_x$  film from the sacrificial growth layer and any underlying support substrate by selectively removing the sacrificial growth layer. Alternatively, the  $Si_{(1-x)}Ge_x$  layer can be bonded to a host substrate before being released from its sacrificial growth substrate, whereby the host substrate prevents the elastic relaxation of the strain in the  $Si_{(1-x)}Ge_x$ . As a result, the bonded and transferred  $Si_{(1-x)}Ge_x$  at least partially retains the strain imparted to it by the sacrificial growth substrate. [0022] In other embodiments, the  $Si_{(1-x)}Ge_x$  film is one layer of a multilayered heterostructure that is grown epitaxially on a sacrificial growth layer. After the growth of the epitaxial heterostructure is completed, it can be released from the sacrificial growth layer, whereby elastically strained layers in the heterostructure partially elastically relax via elastic strain sharing with the other layers in the heterostructure. During elastic stain sharing between the layers, layers that are under a compressive strain become partially relaxed through the introduction of a tensile strain in their adjacent layers, such that the global average strain in the heterostructure is zero.

**[0023]** Some embodiments of the growth methods use a GaAs support substrate with an overlying  $Ga_yAl_{1-y}As$  sacrificial growth layer, where  $0 \le y < 1$ . The low lattice mismatch between the GaAs, the GaAlAs, and the SiGe allows for the epitaxial growth of high-quality, single-crystalline  $Si_{(1-x)}Ge_x$  on the  $Ga_yAl_{(1-y)}As$ , where  $0.8 \le x < 1$ , with critical thicknesses of up to about 230 nm, or greater. Alternatively, a layer of GaAs can be grown epitaxially over the  $Ga_yAl_{(1-y)}As$  sacrificial layer and the  $Si_{(1-x)}Ge_x$  can be grown directly on that layer of GaAs. The  $Si_{(1-x)}Ge_x/GaAs$  bilayer can then be released by the selective removal of the  $Ga_yAl_{(1-y)}As$  sacrificial layer.

[0024] In another embodiment, a sacrificial layer of  $Ga_z$ In  $_{(1-z)}P$ , where  $0.75 \le z < 0.98$  is used as a growth layer for the  $Si_{(1-x)}Ge_x$ . The  $Ga_zIn_{(1-z)}P$  sacrificial layer can be prepared

by growing the  $Ga_zIn_{(1-z)}P$  on GaP to a thickness below its critical thickness, etching away the GaP to release the strain in the  $Ga_zIn_{(1-z)}P$ , and then transferring and bonding the  $Ga_zIn_{(1-z)}P$  to a host substrate to provide a growth layer for the  $Si_{(1-x)}Ge_x$  that has an appropriate lattice constant. Over the released, transfer-bonded  $Ga_zIn_{(1-z)}P$ , a layer of  $Si_{(1-x)}Ge_x$ , where  $0.2 \le x \le 0.5$ , can be grown epitaxially to a critical thickness of up to 1  $\mu$ m, or greater.  $Si_{(1-x)}Ge_x$  having a lower critical thickness can be grown for  $Si_{(1-x)}Ge_x$  alloys having germanium contents outside that range.

[0025] Alternatively, a sacrificial layer of  $Ga_zIn_{(1-z)}P$ , where 0.5<z<0.75, can be prepared by growing the  $Ga_zIn_{(1-z)}P$  on GaAs to a thickness below its critical thickness and then etching away the GaAs to release the strain in the  $Ga_zIn_{(1-z)}P$  to provide a growth layer for the  $Si_{(1-x)}Ge_x$  that has an appropriate lattice constant. Over the released  $Ga_zIn_{(1-z)}P$ , a layer of  $Si_{(1-x)}Ge_x$ , where  $0.5 \le x \le 0.8$ , can be grown epitaxially to a critical thickness of up to 1  $\mu$ m, or greater.  $Si_{(1-x)}Ge_x$  having a lower critical thickness can be grown for  $Si_{(1-x)}Ge_x$  alloys having germanium contents outside that range.

The critical thickness of the  $Si_{(1-x)}Ge_x$  will depend on the germanium content of the silicon-germanium and on the composition of the substrate upon which it is grown. This is illustrated in the graph of FIG. 4, which shows the relationship between the germanium content, x, and the critical thickness for  $Si_{(1-x)}Ge_x$  grown on  $Ga_{0.7}In_{0.3}P$  and Ga<sub>0.86</sub>In<sub>0.14</sub>P. As shown in the graph, using the present methods,  $Si_{(1-x)}Ge_x$  films with critical thicknesses in the range from 10 nm (or lower) to 10 µm can be grown with germanium contents in the range of  $0.2 \le x < 1$ . Therefore, by using the appropriate growth substrate,  $Si_{(1-x)}Ge_x$  layers having a wide range of germanium contents and sub-critical thicknesses can be grown. The grown layers can then be released from their sacrificial growth substrates to provide free-standing films that are free of lattice-mismatch-induced threading dislocations. By way of illustration only, highquality, single-crystalline  $Si_{(1-x)}Ge_x$  films with  $x \ge 0.2$  can be grown to a thickness of at least 30 nm. This includes films of  $Si_{(1-x)}Ge_x$  with:  $x \ge 0.3$ ;  $x \ge 0.35$ ;  $x \ge 0.4$ ;  $x \ge 0.45$ ;  $x \ge 0.5$ ;  $x \ge 0.55$ ;  $x \ge 0.6$ ;  $x \ge 0.65$ ;  $x \ge 0.7$ ;  $x \ge 0.75$ ;  $x \ge 0.8$ ;  $x \ge 0.85$ ;  $x \ge 0.8$ 9; and x≥0.95. Illustrative ranges for the Ge content of the  $Si_{(1-x)}Ge_x$  include:  $0.2 \le x \le 0.99$ ;  $0.2 \le x \le 0.90$ ;  $0.2 \le x \le 0.80$ ;  $0.3 \le x \le 0.99$ ;  $0.4 \le x \le 0.99$ ;  $0.5 \le x \le 0.99$ ;  $0.55 \le x \le 0.95$ ;  $0.6 \le x \le 0.95$ ;  $0.7 \le x \le 0.95$ ;  $0.6 \le x \le 0.85$ ;  $0.7 \le x \le 0.85$ ; and 0.7≤x≤0.8. High-quality, single-crystalline germanium layers (i.e., x=1) can also be grown with the methods described herein. Various embodiments of these layers can be grown to sub-critical thickness of: at least 40 nm; at least 50 nm; at least 60 nm; at least 70 nm; at least 80 nm; at least 90 nm; at least 100 nm; at least 200 nm; at least 300 nm; at least 500 nm; at least 1 μm; and at least 5 μm. Illustrative ranges for the layer thicknesses include 30 nm to 5 µm, 50 nm to 250 nm, and 100 nm to 230 nm.

**[0027]** If the  $Si_{(1-x)}Ge_x$  films are grown on imperfect growth layers that contain misfit dislocations and threading dislocations, those defects may propagate into the growing  $Si_{(1-x)}Ge_x$  layer. Therefore, some embodiments of the  $Si_{(1-x)}Ge_x$  films may contain misfit dislocations and associated threading dislocations, although such dislocations are not induced by the plastic relaxation of strain caused by the lattice mismatch between the growth substrate and the  $Si_{(1-x)}Ge_x$  films during film growth. These dislocation defects, when present, are present at low densities. For

example, some embodiments of the  $Si_{(1-x)}Ge_x$  films have misfit dislocation densities and threading dislocation densities of less than  $1\times10^5$  cm<sup>-2</sup>. This includes embodiments of the  $Si_{(1-x)}Ge_x$  films having misfit dislocation densities and threading dislocation densities of less than  $1\times10^4$  cm<sup>-2</sup> and further includes embodiments of the  $Si_{(1-x)}Ge_x$  films having misfit dislocation densities and threading dislocation densities of less than  $1\times10^3$  cm<sup>-2</sup>.

[0028] The high-quality, single-crystalline silicon-germanium can be formed as large-area, free-standing films with low surface roughnesses. For example, films of the highquality, single-crystalline silicon-germanium can have a wafer-scale, or larger, area, as measured by the area of the upper surface of the film. This includes films of the highquality, single-crystalline silicon-germanium that have areas of at least 1 mm<sup>2</sup>, at least 10 mm<sup>2</sup>, at least 5 cm<sup>2</sup>, at least 10 cm<sup>2</sup>, at least 50 cm<sup>2</sup>, and at least 100 cm<sup>2</sup>. The films can be formed as regular geometric shapes (e.g., squares, rectangles, circles, etc.) or irregular shapes. Embodiments of the films of high-quality, single-crystalline silicon-germanium may have a root mean square (rms) roughness of 2.5 nm or lower, 2 nm or lower, 1 nm or lower, 0.6 nm or lower, 0.5 nm or lower, and 0.4 nm or lower, where the rms roughness of the films can be determined based on Atomic Force Microscopy (AFM).

[0029] One embodiment of a method for making the high-quality, single-crystalline silicon-germanium is shown in FIG. 1 and FIG. 2. The method starts with a gallium arsenide (GaAs) support substrate 102 (FIG. 1, top panel), such as a GaAs wafer, upon which a thin layer of  $Ga_yAl_{(1-y)}As$  104, where  $0 \le y < 1$ , is grown (FIG. 1, middle panel) to a sub-critical thickness. The  $Ga_yAl_{(1-y)}As$  may have a gallium content in the range of, for example,  $0 \le y < 0.5$ , including  $0 \le y < 0.2$ . A layer of high-Ge-content, single-crystalline  $Si_{(1-x)}Ge_x$  (or pure germanium) 106 is then grown to the desired, sub-critical thickness on the  $Ga_yAl_{(1-y)}As$  layer (FIG. 1, bottom panel). The  $Ga_yAl_{(1-y)}As$  and the  $Si_{(1-x)}Ge_x$  can be grown using epitaxial growth processes, such as metal organic chemical vapor deposition (MOCVD), as illustrated in the Example.

[0030] As shown in FIG. 2, a layer of photoresist 108 is then applied to the upper surface of  $Si_{(1-x)}Ge_x$  106 in the GaAs/GaAlAs/SiGe (or GaAs/GaAlAs/Ge) heterostructure (panel (a)) by, for example, spin-coating. The front edge of the heterostructure is then inserted into an etchant solution 110 that selectively etches  $Ga_{\nu}Al_{(1-\nu)}As$  104, relative to  $Si_{(1-x)}Ge_x$  106 and photoresist 108 (panel (b)). As a result,  $Ga_{\nu}Al_{(1-\nu)}As$  104 dissolves, beginning at its front edge, releasing  $Si_{(1-x)}Ge_x$  106 and photoresist 108 (panel (c)). As the heterostructure continues to be fed into etchant solution 110 (panel (c)),  $Ga_{\nu}Al_{(1-\nu)}As$  104 is progressively etched away and  $Si_{(1-x)}Ge_x$  106 and photoresist 108 are progressively released, until the complete release of the  $Si_{(1-x)}Ge_x$ and the photoresist layers has occurred (panel (d)). GaAs substrate 102 then sinks, while  $Si_{(1-x)}Ge_x$  106 and photoresist 108 remain at the surface of etchant solution 110. The etchant solution may comprise a dilute solution of hydrochloric acid (HCl) and/or hydrofluoric acid (HF). For example, a dilution of 1:100 49% HF:H<sub>2</sub>O or a dilution of 1:12 (including 1:6 to 1:8) 37% HCl:H<sub>2</sub>O could be used.

[0031] The photoresist is desirably selected such that it renders the released SiGe/photoresist bilayer buoyant in the etchant solution and also induces a tensile strain on the  $Si_{(1-x)}Ge_x$  layer. This has the advantage of flexing the  $Si_{(1-x)}Ge_x$  layer.

$_{x}$ )Ge $_{x}$  layer upward toward the surface and away from the bulk of the etchant solution as it is released, so that the exposure of the Si $_{(1-x)}$ Ge $_{x}$  to any harmful etching reaction products can be reduced. In addition, by flexing the released portion of the SiGe/photoresist bilayer away from the rest of the heterostructure, the photoresist can help gaseous etching reaction products to escape more easily. Suitable photoresists include electron-beam (E-beam) photoresists, such as novolak-based photoresists, including S1813 available from Dow (Shipley), and acrylate-styrene co-polymer resists, such as ZEP520, a copolymer of  $\alpha$ -chloromethacrylate and  $\alpha$ -methylstyrene, available from Zeon Chemicals. Other polymers that render the released SiGe/photoresist bilayer buoyant in the etchant solution and induce a tensile strain on the Si $_{(1-x)}$ Ge $_{x}$  layer could also be used.

[0032] The angle and rate at which the heterostructure is introduced and fed into the etchant solution should be designed to allow for the escape of gaseous etchant reaction products from the etch front. This is important because gas bubbles that are trapped between the  $Si_{(1-x)}Ge_x$  and the release layer during the etching process can rupture and create holes in, or otherwise damage, the  $Si_{(1-x)}Ge_x$ . Suitable feed angles include those in the range from  $10^\circ$  to  $60^\circ$ , including  $15^\circ$  to  $30^\circ$ , wherein the feed angle,  $\theta$ , is the angle formed between the surface of the etchant solution and the surface of the heterostructure, as shown in FIG. 2. Suitable feed rates include those in the range from 0.1 mm/h to 2.2 mm/h, including those in the range from 0.4 mm/hr to 1.2 mm/h.

[0033] An alternative embodiment of a method for making the high-quality, single-crystalline silicon-germanium is shown in FIG. 3. The method starts with an unstrained layer of GaAs 304 on a host substrate 302 (panel (a)). For example, the unstrained GaAs layer can be obtained by a release and transfer method in which a layer of crystalline GaAs is grown epitaxially on a substrate. That substrate is then selectively etched away, releasing the GaAs layer in an unstrained state. The released, unstrained layer can then be transferred to a host substrate 302. Methods for the release and transfer of thin crystalline GaAs layers (also referred to a nanomembranes or "NMs") can be found in J. A. Rogers, M. G. Lagally, and R. G. Nuzzo. "Synthesis, assembly and applications of semiconductor nanomembranes." Nature 477.7362 (2011): 45-53. (Alternatively, the crystalline device layer of a semiconductor-on-insulator (e.g., siliconon-insulator; SOI) can be used as the growth substrate.) A thin layer of  $Ga_zIn_{(1-z)}P$ , where  $0 \le z \le 1$ , 306 is then epitaxially grown to a sub-critical thickness on GaAs layer 304 (panel (b)). GaAs layer 304 is then selectively etched away, which releases the layer of  $Ga_zIn_{(1-z)}P$  306 and elastically relaxes any lattice mismatch-induced strain in the Ga<sub>z</sub>In<sub>(1-</sub> z)P (panel (c)). The elastically relaxed  $Ga_zIn_{(1-z)}P$  306 can have a lattice that is closely matched to the  $Si_{(1-x)}Ge_x$  and can serve as a new sacrificial growth layer for the epitaxial growth of a  $Si_{(1-x)}Ge_x$  layer 308 (panel (d)). If desired, the thickness of the released, relaxed  $Ga_zIn_{(1-z)}P$  layer 306 can be increased by further epitaxial growth prior to proceeding with the growth of the  $Si_{(1-x)}Ge_x$ . The  $Ga_zIn_{(1-z)}P$  and the  $Si_{(1-x)}Ge_x$  can be grown using epitaxial growth processes, such as MOCVD. Finally, the layer of  $Ga_zIn_{(1-z)}P$  306 can be selectively etched away to release  $Si_{(1-x)}Ge_x$  layer 308 (panel (e)), using, for example, HCl as an etchant. Although not shown in FIG. 3, a layer of photoresist could be deposited on

the  $Si_{(1-x)}Ge_x$  layer 308 prior to its release, and the release of  $Si_{(1-x)}Ge_x$  layer 308 could be carried out using the process shown in FIG. 2.

[0034] Although the methods of FIGS. 1-3 are illustrated and described in terms of forming high-quality, single-crystalline silicon-germanium layers, these methods can also be used for the epitaxial growth and release of high-quality, single-crystalline germanium layers.

[0035] The released  $Si_{(1-x)}Ge_x$  layer (or Ge layer) is a free-standing film (or "nanomembrane") in that it does not require a support substrate to provide it with structural integrity and is not fixed to a substrate at an epitaxial interface. As used herein the term "epitaxial interface" refers to an interface in which the crystallographic orientation of an overlying layer is controlled by that of its underlying layer, such that the two layers have the same lattice constant (i.e., crystalline arrangement), at least in the area of the interface. An epitaxial interface may include strains and stresses at the interface, induced by a lattice mismatch between the two materials. In contrast to such epitaxial interfaces, non-epitaxial interfaces have crystallographic orientations that are independent from (e.g., different from) those of their neighboring layers and are free from lattice mismatch-induced strains and stresses.

[0036] Before or after the  $Si_{(1-x)}Ge_x$  layer (or the Ge layer) has been released from its growth substrate, it can be bonded to a variety of host substrates, including host substrates upon which the  $Si_{(1-x)}Ge_x$  (or Ge) could not be grown epitaxially and/or flexible substrates, such as polymeric substrates. If the released  $Si_{(1-x)}Ge_x$  film or the Ge film is bonded to a flexible host substrate, it can be mechanically stretched and/or compressed after transfer. This is advantageous because it makes it possible to introduce a tensile or compressive uniaxial, biaxial, or shear stain in the material. The host substrate can also be a semiconductor substrate composed of, for example, a Group III-V semiconductor, a Group II-VI semiconductor, or a Group IV semiconductor, such as silicon, germanium, or another  $Si_{(1-x)}Ge_x$  alloy having a different germanium content (i.e., a different x value).

[0037] After a layer of  $Si_{(1-x)}Ge_x$  is released from its sacrificial growth layer—either as a single-layer or as part of a multilayered heterostructure—one or more additional semiconductor layers can be grown epitaxially on the  $Si_{(1-x)}Ge_x$ . These additional layers may be strained or unstrained, depending upon their lattice mismatch with the  $Si_{(1-x)}Ge_x$  and the strain state of the released  $Si_{(1-x)}Ge_x$ . For example, materials that can be grown over the  $Si_{(1-x)}Ge_x$  include Ge, InGaP, or even a thin layer of Si.

[0038] The high-quality, single-crystalline layers of silicon-germanium and the high-quality, single-crystalline layers of germanium can be incorporated in a variety of electronic devices, including optical and optoelectronic devices. The layers can be incorporated as strain-free layers, as elastic strain sharing sub-layers in a multilayered heterostructure, or as strained layers bonded to a host substrate. For example, the silicon-germanium and/or germanium layers can be incorporated into a quantum well structure for a terahertz radiation source or a terahertz radiation detector. One example of a quantum well structure is composed of alternating layers of  $Si_{(1-x)}Ge_x$  and Ge that provide a series of Ge quantum well layers, each sandwiched between a pair of  $Si_{(1-x)}Ge_x$  barriers. The schematic diagram in FIG. 6 shows a terahertz (THz) radiation source that includes such

a quantum well structure. The radiation source can be formed by growing a single-crystalline layer of  $Si_{(1-x)}Ge_x$ with the desired Ge content on a sacrificial growth substrate, as described herein, and releasing the layer as a  $Si_{(1-x)}Ge_x$ film 602. Released film 602 can be transferred and bonded to a host substrate that includes a thin dielectric layer 606, such as SiO<sub>2</sub>, on a base substrate 608, such as a silicon handle wafer. The bonding of  $Si_{(1-x)}Ge_x$  film **602** to dielectric layer 606 can be carried out by subjecting the transferred film and the dielectric layer to a heat treatment at an elevated temperature that is, a temperature above room temperature. For example, the bonding of  $Si_{(1-x)}Ge_x$  film **602** to dielectric layer 606 can be carried out at temperatures of at least 500° C., including temperatures in the range from 500° C. to 1000° C. (Alternatively, in order to retain the strain in  $Si_{(1-x)}Ge_x$  film 602, that film can be bonded to dielectric layer 606 before it is released from its sacrificial growth substrate.) A quantum well structure 604 composed of alternating layers of Ge 610 quantum wells and SiGe 612 barriers can then be grown epitaxially on  $Si_{(1-x)}Ge_x$  film 602. In the embodiment shown in FIG. 6,  $Si_{(1-x)}Ge_x$  film 602 and SiGe layers 612 are elastically relaxed and Ge layers 610 are grown with a compressive strain (as indicated by the arrows). (Alternatively, in order to provide a quantum well heterostructure in which the elastic strain is shared between the well layers and the barrier layers, the quantum well stack can be grown on  $Si_{(1-x)}Ge_x$  film **602** before it is released from the sacrificial growth substrate.) The THz radiation source further includes a first electrode (not shown) in electrical communication with the upper surface of the quantum well structure and a second electrode (not shown) in electrical communication with the lower surface of the quantum well structure.

[0039] Other devices into which the high-quality, single-crystalline layers of silicon-germanium and the high-quality, single-crystalline layers of germanium can be incorporated include transistors, including field effect transistors and heterojunction bipolar transistors (HBT), complementary metal oxide semiconductor (CMOS) devices, quantum cascade lasers, tunable light emitters, infrared photodetectors, and other sensors.

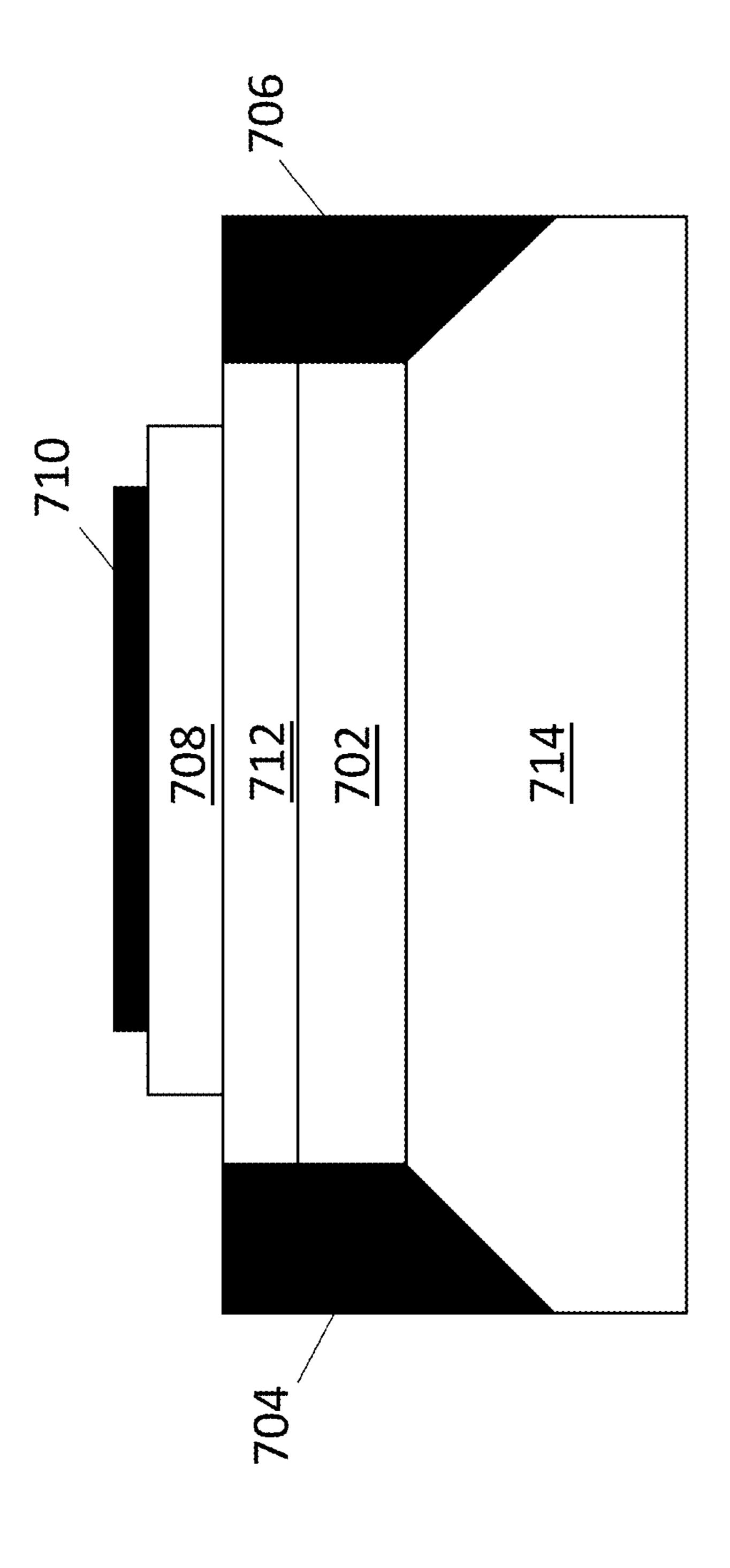

[0040] A cross-sectional view of one embodiment of a metal oxide semiconductor field effect transistor (MOSFET) that includes a high-quality, single-crystalline  $Si_{(1-x)}Ge_x$  film is shown in FIG. 7. In the MOSFET, the  $Si_{(1-x)}Ge_x$  film 702, which provides the channel layer for the transistor, separates, and is in electrical communication with, a source electrode 704 and a drain electrode 706. A gate stack disposed over  $Si_{(1-x)}Ge_x$  film 702 includes a gate oxide 708 and a gate electrode 710. A spacer layer 712, such as a Si layer, separates  $Si_{(1-x)}Ge_x$  film 702 from gate oxide 708.  $Si_{(1-x)}Ge_x$  film 702 is bonded to base substrate 714, which may be a Si handle wafer.

[0041] A cross-sectional view of one embodiment of an HBT that includes a high-quality, single-crystalline  $Si_{(1-x)}$   $Ge_x$  film is shown in FIG. 8. In the HBT, a P-type doped  $Si_{(1-x)}Ge_x$  film 802, which provides the Base for the transistor, positioned between an N-type doped Emitter (e.g., n-Si) 804 and an N-type doped Collector (e.g., n-Si) 806 to form an N/P/N heterostructure. A heavily N-type doped region (e.g., n++ Si) in Collector 806 provides a collector contact region 808 and a heavily N-type doped region (e.g., n++ Si in Emitter 804 provides an emitter contact region 810. Heavily P-type doped regions (p++) extending into Base 802

provide base contact regions 812. Finally, metal contact pads 814, 816, and 818 in electrical communication with collector contact region 808, emitter contact region 810, and base emitter regions 812, provide collector contact, emitter contact, and base contacts, respectively.

[0042] A cross-sectional view of one embodiment of a modulation-doped field effect transistor (MODFET) that includes a high-quality, single-crystalline  $Si_{(1-x)}Ge_x$  film is shown in FIG. 9. In the MODFET, a Ge film 903 provides the channel layer for the transistor. Ge film 903 overlies a SiGe buffer layer 905 on a Ge substrate 907. Ge film 903 is spaced apart from an overlying gate oxide 908 by a spacer layer of the  $Si_{(1-x)}Ge_x$  902. A source electrode 904 and a drain electrode 906 are in electrical communication through spacer layer 902 and a gate electrode 910 is disposed over gate oxide 908.

[0043] The transistors can be fabricated using the epitaxy and transfer printing methods described herein. As a result, the  $Si_{(1-x)}Ge_x$  films in the transistors can be strained, unstrained, or in a strain sharing state with an adjacent layer and they can have an epitaxial or a non-epitaxial relationship with their adjacent layers.

#### Example

[0044] This example illustrates methods for growing high-quality, single-crystalline germanium on a sacrificial layer, followed by the release and transfer of that layer to a host substrate.

### Ge/AlAs/GaAs Heterostructure Growth

[0045] The Ge/GaAs/AlAs heterostructures were grown in a low pressure (0.1 bar) metal-organic vapor phase epitaxy (MOVPE) system. Germane (GeH<sub>4</sub>), arsine (AsH<sub>3</sub>), triethyl gallium (TEGa) and trimethyl aluminum (TMAl) were employed as the Ge, As, Ga and Al precursors for the growth. Hydrogen was used as the carrier gas with a total flow rate of 0.31 mol/min. The growth temperatures for the AlAs layer and the Ge layer were 750° C. and 565° C., respectively. The thicknesses of the AlAs layer and the Ge layer were 200-1000 nm and 70-100 nm, respectively, as determined by Scanning Electron Microscopy (SEM). The dislocation defect density can be measured by the etch-pit method. The etch-pit method is used to determine the dislocation defect density when this density is in a relatively low range (<1×10<sup>6</sup> cm<sup>-2</sup>). (See, D. J. Stirland, 'The Relationship between Etch Pit Density and Dislocation Density for (001) GaAs', Journal of Crystal Growth, 7 (1986) 493-502.)

#### Etching

[0046] The sample was first cleaned by acetone and isopropyl alcohol (IPA), followed by a prebake at 100° C. for 60 seconds. A deionized-water (DI) cleaning was not performed, in order to retain the Ge oxide layer that was observed to help in the bond between the sample and photoresist layer.

[0047] The resist was then spun onto the sample, forming a smooth and flexible layer that could keep the nanomembrane (NM) in shape during etching. The compressive stress in the resist layer needed to be well controlled in order to curve the NM from the edge and open access for the etchant.

Three resists were tried, including Shipley photoresist 1813, PMMA, and ZEP 520A. All three worked quite well for the process.

[0048] PR 1813 showed the best result for the selected sample and etchant. The recipe used for all resists included spin coating at 4000 rpm for 30 seconds followed by hard baking for 3 minutes at 100° C. (PR 1813) or 90 seconds at 180° C. (PMMA and ZEP).

[0049] Following the photoresist coating, the sample was transferred to a holder for immersion in the etchant solution. An angle of about 20° to the etchant was found to be ideal, with a range from 15-30 degrees yielding comparable results. The etchant used was diluted hydrochloric acid (1:8) 37% (vol.) HCl:H<sub>2</sub>O). Observations suggest that this allowed for a well-controlled etch, since the surface tension from the liquid was sufficient to float a large-area NM with the help of the resist layer. The etching started from the edge of the sample where the sacrificial layer was etched, and the released template layer was dragged up by the intact resist, floating on the etchant surface and therefore opening the gap between template layer and the substrate that facilitated the circulation of etchant as well as continuous etching. The immersion rate was controlled at around 0.8 mm/hour to provide enough time for the escape of produced gasses from the interface.

[0050] Once the etching was complete, the NM with intact resist floated freely on the surface of the etchant solution, and could be gently picked up by the desired substrate. A soft baking at 70° C. for 30 minutes was then performed in order to evaporate the excess water at the interface between the NM and substrate, so that the bond between the two layers would become relatively strong.

[0051] Suitable solvents, such as acetone and isopropyl alcohol, were subsequently used for photoresist removal. Finally, a hard bake at 100° C. for 60 minutes was done to strengthen the contact between the NM and the substrate.

#### AFM Characterization

[0052] The surface roughness of both the as-grown and transferred Ge NM was characterized separately by AFM. A Bruker Bioscope Catalyst AFM was operated under tapping mode for a 10 µm scan window with a lateral resolution of 20 nm. In the comparison experiment shown in FIGS. 5A and 5B, the grown Ge (FIG. 5A) was cleaned with acetone IPA and DI H<sub>2</sub>O prior to the taking of measurements. The Ge NM was transferred to a polished Si wafer (FIG. 5B) and cleaned with hydrofluoric acid (HF) and DI water immediately before the roughness characterization in order to minimize the influence of the germanium oxide.

[0053] The word "illustrative" is used herein to mean serving as an example, instance, or illustration. Any aspect or design described herein as "illustrative" is not necessarily to be construed as preferred or advantageous over other aspects or designs. Further, for the purposes of this disclosure and unless otherwise specified, "a" or "an" means "one or more".

[0054] The foregoing description of illustrative embodiments of the invention has been presented for purposes of illustration and of description. It is not intended to be exhaustive or to limit the invention to the precise form disclosed, and modifications and variations are possible in light of the above teachings or may be acquired from practice of the invention. The embodiments were chosen and described in order to explain the principles of the invention

and as practical applications of the invention to enable one skilled in the art to utilize the invention in various embodiments and with various modifications as suited to the particular use contemplated. It is intended that the scope of the invention be defined by the claims appended hereto and their equivalents.

- 1. Single-crystalline silicon-germanium comprising a layer of single-crystalline  $Si_{(1-x)}Ge_x$ , where  $0.4 \le x < 1$ , having a thickness of at least 40 nm, wherein the single-crystalline  $Si_{(1-x)}Ge_x$  does not comprise a mosaic distribution of crystallographic orientations and the single-crystalline silicongermanium is not bonded to a layer of silicon with which it forms an epitaxial interface.

- 2. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  is unstrained.

- 3. Single-crystalline silicon-germanium comprising a layer of single-crystalline  $Si_{(1-x)}Ge_x$ , where  $0.4 \le x < 1$ , having a thickness of at least 40 nm, wherein the single-crystalline  $Si_{(1-x)}Ge_x$  does not comprise a mosaic distribution of crystallographic orientations and the layer of unstrained, single-crystalline  $Si_{(1-x)}Ge_x$  is a free-standing layer.

- 4. The single-crystalline silicon-germanium of claim 2, wherein the unstrained layer of single-crystalline  $Si_{(1-x)}Ge_x$  is bonded to a host substrate at a non-epitaxial interface.

- 5. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  is strained.

- 6. The single-crystalline silicon-germanium of claim 5, wherein the strained layer of single-crystalline  $Si_{(1-x)}Ge_x$  is bonded to a host substrate at a non-epitaxial interface that prevents the strain in the layer of single-crystalline  $Si_{(1-x)}Ge_x$  from relaxing.

- 7. The single-crystalline silicon-germanium of claim 5, wherein the strained layer of single-crystalline  $Si_{(1-x)}Ge_x$  is joined with a layer of a second semiconductor at an epitaxial interface, wherein elastic strain is shared between the layer of single-crystalline  $Si_{(1-x)}Ge_x$  and the layer of the second semiconductor.

- **8**. The single-crystalline silicon-germanium of claim **7**, wherein the second semiconductor is a Group III-V semiconductor.

- 9. The single-crystalline silicon-germanium of claim 8, wherein the Group III-V semiconductor is GaAs.

- 10. The single-crystalline silicon-germanium of claim 8, wherein the Group III-V semiconductor is GaInP.

- 11. The single-crystalline silicon-germanium of claim 1, wherein the layer has a thickness of at least 50 nm.

- 12. The single-crystalline silicon-germanium of claim 1, wherein the layer has a thickness of at least 100 nm.

- 13. The single-crystalline silicon-germanium of claim 1, wherein the layer has a thickness of at least 500 nm.

- 14. The single-crystalline silicon-germanium of claim 1, wherein  $x \ge 0.5$ .

- 15. The single-crystalline silicon-germanium of claim 1, wherein  $x \ge 0.8$

- 16. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  has an area of at least 1 mm<sup>2</sup>.

- 17. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  has an area of at least 10 mm<sup>2</sup>.

- 18. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  has a thickness in the range from 50 nm to 10  $\mu$ m.

- 19. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  has an rms surface roughness of no greater than 2 nm.

- 20. The single-crystalline silicon-germanium of claim 1, wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  has an rms surface roughness of no greater than 1 nm.

- 21. An electronic device comprising:

- a first electrode;

- a second electrode; and

- a layer of single-crystalline  $Si_{(1-x)}Ge_x$ , where  $0.4 \le x < 1$ , in electrical communication with the first electrode and the second electrode, the layer of single-crystalline  $Si_{(1-x)}Ge_x$  having a thickness of at least 40 nm, wherein the single-crystalline  $Si_{(1-x)}Ge_x$  does not comprise a mosaic distribution of crystallographic orientations and the single-crystalline silicon-germanium is not bonded to a layer of silicon with which it forms an epitaxial interface.

- 22. Single-crystalline silicon-germanium comprising a layer of single-crystalline  $Si_{(1-x)}Ge_x$ , where  $0.4 \le x < 1$ , having a thickness of at least 40 nm, wherein the single-crystalline  $Si_{(1-x)}Ge_x$  does not comprise a mosaic distribution of crystallographic orientations, and further wherein the layer of single-crystalline  $Si_{(1-x)}Ge_x$  forms at least one epitaxial interface with another semiconductor and the concentration of lattice mismatch-induced misfit dislocations at the at least one epitaxial interface is no greater than  $1 \times 10^5$  cm<sup>-2</sup>.

- 23. The single-crystalline silicon-germanium of claim 22, wherein the concentration of lattice mismatch-induced misfit dislocations at the at least one epitaxial interface is no greater than  $1\times10^3$  cm<sup>-2</sup>.

- 24. The single-crystal silicon-germanium of claim 22, wherein the at least one epitaxial interface is free of lattice mismatch-induced misfit dislocations.

\* \* \* \* \*