US 20120032232A1

# (19) United States

# (12) Patent Application Publication IWABUCHI et al.

(10) Pub. No.: US 2012/0032232 A1 (43) Pub. Date: Feb. 9, 2012

## (54) **SEMICONDUCTOR DEVICE**

(75) Inventors: Akio IWABUCHI, Niiza-shi (JP);

Hironori AOKI, Niiza-shi (JP)

(73) Assignee: SANKEN ELECTRIC CO., LTD,

Niiza-shi (JP)

(21) Appl. No.: 13/243,600

(22) Filed: Sep. 23, 2011

(30) Foreign Application Priority Data

## **Publication Classification**

(51) Int. Cl. *H01L 29/778* (2006.01)

# (57) ABSTRACT

A semiconductor device protects against concentration of electric current at a front end portion of one of the electrodes thereof The semiconductor device includes a substrate, a compound semiconductor layer formed on the substrate and having a channel layer based on a hetero junction, a first main electrode formed on the compound semiconductor layer, a second main electrode formed on the compound semiconductor surrounding the first main electrode and having a linear region and an arc-shaped region, a control electrode formed on the compound semiconductor layer and disposed opposite to the first main electrode and the second main electrode, an electric current being made to flow between the first main electrode and the second main electrode and the arc-shaped region of the second main electrode.

Fig.1

Fig.2

Fig.6

Fig.7

Fig.9

Fig. 12

#### SEMICONDUCTOR DEVICE

#### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to a semiconductor device. More particularly, the present invention relates to a semiconductor device equipped with an electrode having an arc-shaped part.

[0003] 2. Description of the Related Art

[0004] Nitride-based compound semiconductors such as gallium nitride-based ones are expected to find applications in the field of low loss and high power devices with high breakdown voltage because they have a high breakdown electric field. Nitride-based compound semiconductor devices having a finger type electrode structure have been disclosed in recent years (See, for example, Patent Document 1).

[0005] [Citation List]

[0006] [Patent Document]

[0007] Patent Document 1: Jpn. Pat. Appln. Laid-Open Publication No. 2009-60049

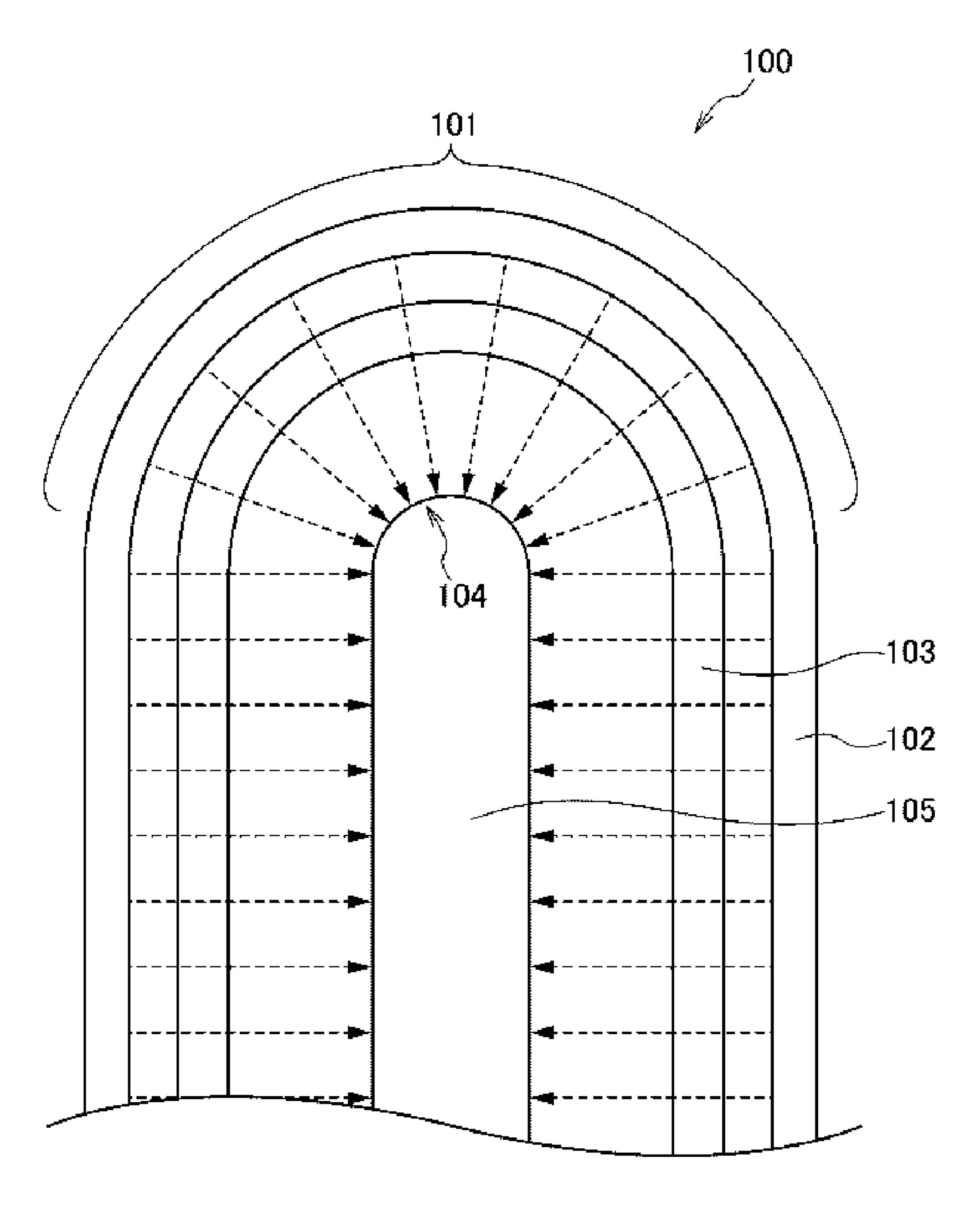

[0008] In semiconductor devices having a finger type electrode structure, the electrode structure includes a linear part and an arc-shaped part linked to the linear part. When an electrode having an arc-shaped part is employed, there arises a problem of concentration of electric current at a front end portion of the electrode. This phenomenon will be described below by referring to FIG. 12 . FIG. 12 is a schematic plan view of a part of the electrode section having an arc-shaped part of a nitride semiconductor-based high electron mobility transistor (GaN-HEMT) when an electric current is made to flow through the transistor. In FIG. 12, the electrode section 100 includes a source electrode 102 and a gate electrode 103, each having an arc-shaped part 101 and a drain electrode 105 having a front end portion 104. The arrows in FIG. 12 indicate how an electric current flows from the source electrode to the drain electrode. As seen from FIG. 12, the electric current flowing from the arc-shaped part 101 of the source electrode 102 to the front end portion 104 of the drain electrode 105 is concentrated at the front end portion 104. The portion of the drain electrode 105 where the electric current is concentrated shows a voltage fall greater than the portion thereof where the electric current is not concentrated so that the semiconductor device can emit heat from the former portion and ultimately be broken down.

# SUMMARY OF THE INVENTION

[0009] It is desirable to provide a semiconductor device of the type under consideration that can protect the device against any breakdown attributable to concentration of electric current at a front end portion of one of the electrodes thereof having such a front end portion.

[0010] According to the present invention, a semiconductor device is configured as described below.

[0011] A semiconductor device, which is referred to as the first semiconductor device according to the present invention hereinafter, includes:

[0012] a substrate;

[0013] a compound semiconductor layer formed on the substrate and having a two-dimensional carrier gas layer based on a hetero-junction;

[0014] a first main electrode formed on the compound semiconductor layer;

[0015] a second main electrode formed on the compound semiconductor layer so as to surround the first main electrode in a plan view and having a linear region and an arc-shaped region;

[0016] a control electrode formed between the first main electrode and the second main electrode on the compound semiconductor layer;

[0017] an electric current being made to flow between the first main electrode and the second main electrode by way of the two-dimensional carrier gas layer; and

[0018] an electric current limiting section for limiting the electric current from flowing between the first main electrode and the arc-shaped region of the second main electrode.

[0019] Thus, according to the present invention, an electric current limiting section is provided between the first main electrode and the arc-shaped region of the second main electrode of a semiconductor device according to the present invention so that the concentration of electric current at a front end portion of the first main electrode is alleviated and the semiconductor device is protected against any breakdown attributable to concentration of electric current.

### BRIEF DESCRIPTION OF THE DRAWINGS

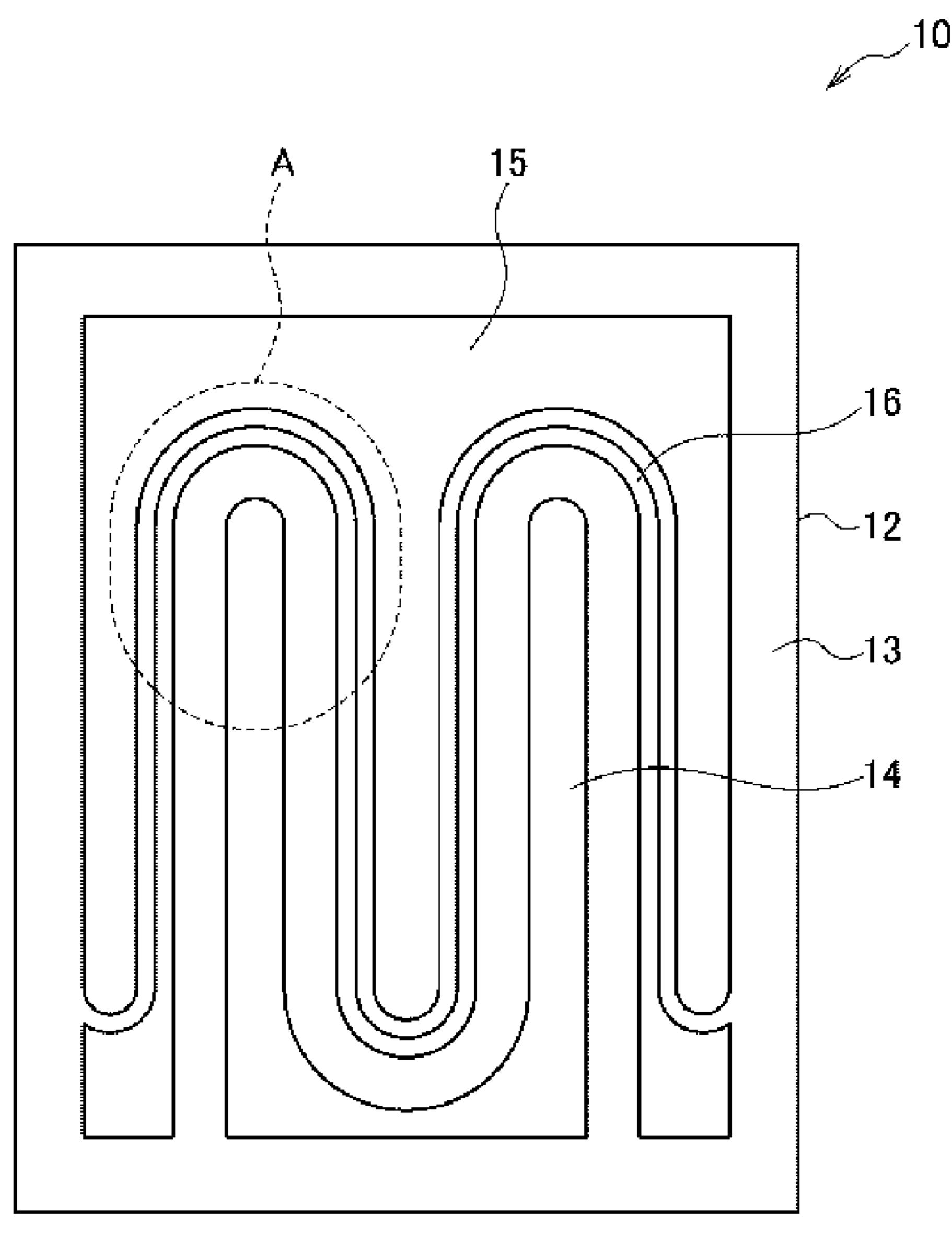

[0020] FIG. 1 is a schematic plan view of the semiconductor device according to a first embodiment of the present invention;

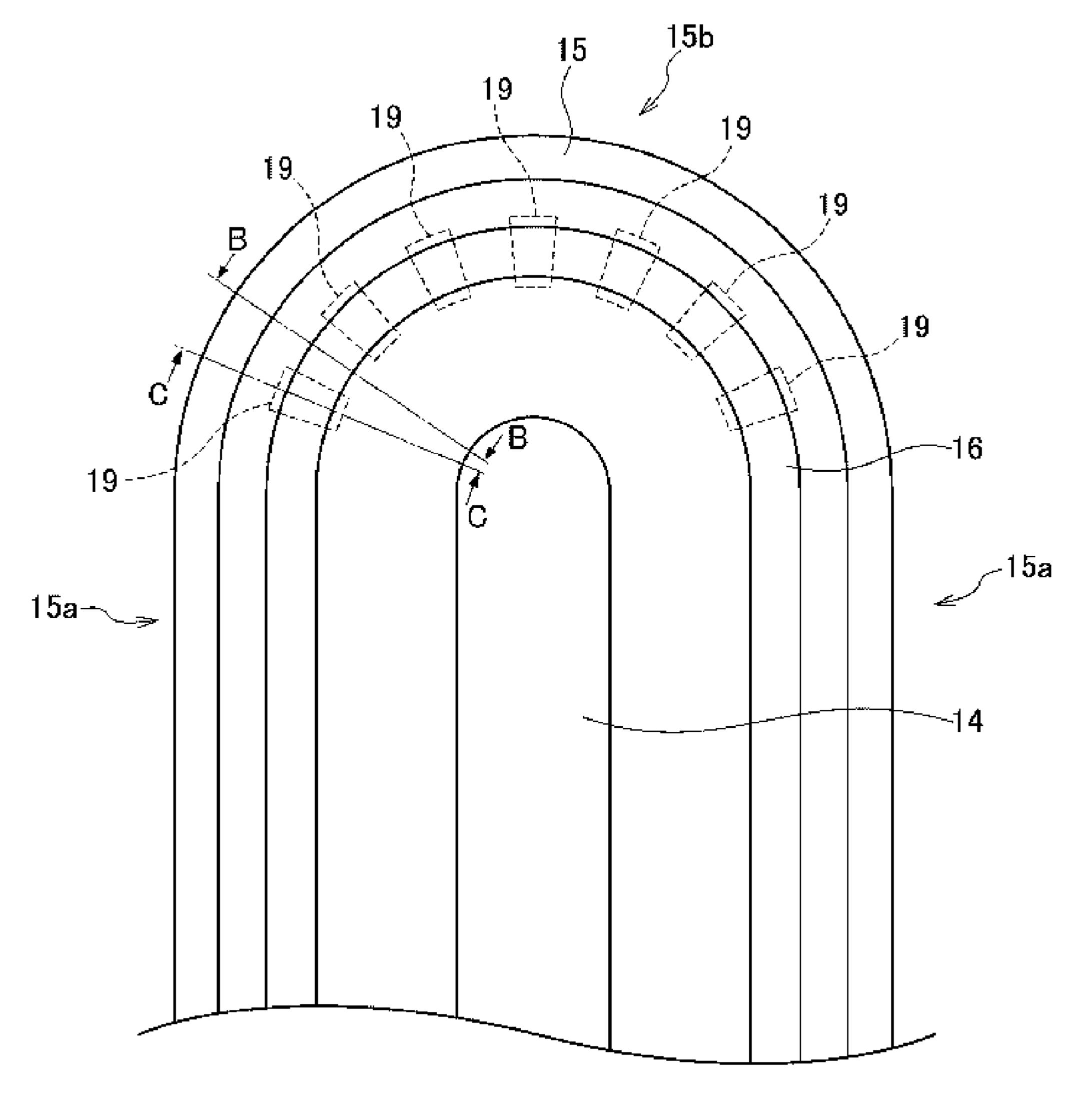

[0021] FIG. 2 is an enlarged schematic view of area A in FIG. 1;

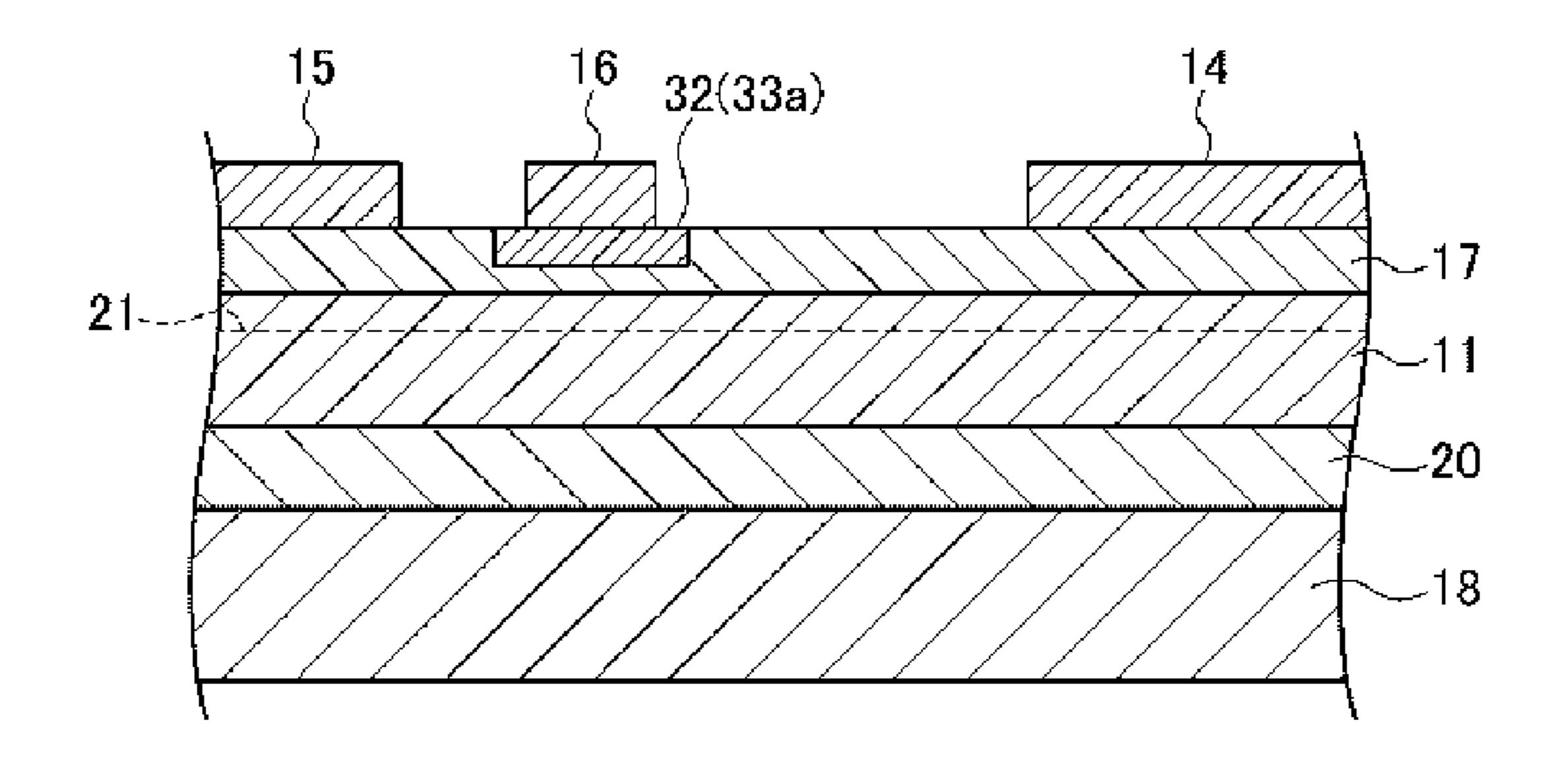

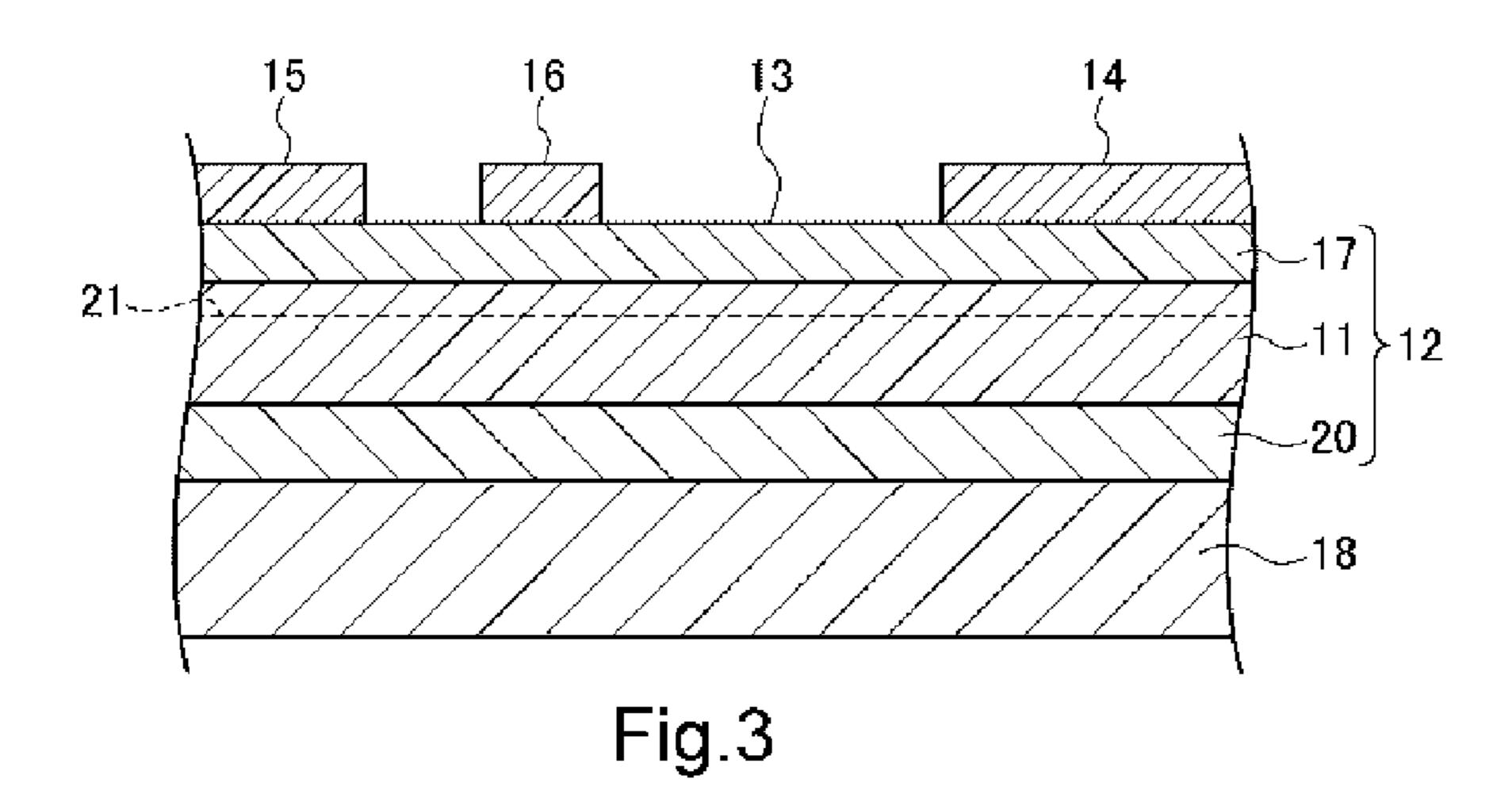

[0022] FIG. 3 is a schematic cross-sectional view taken along line B-B in FIG. 2;

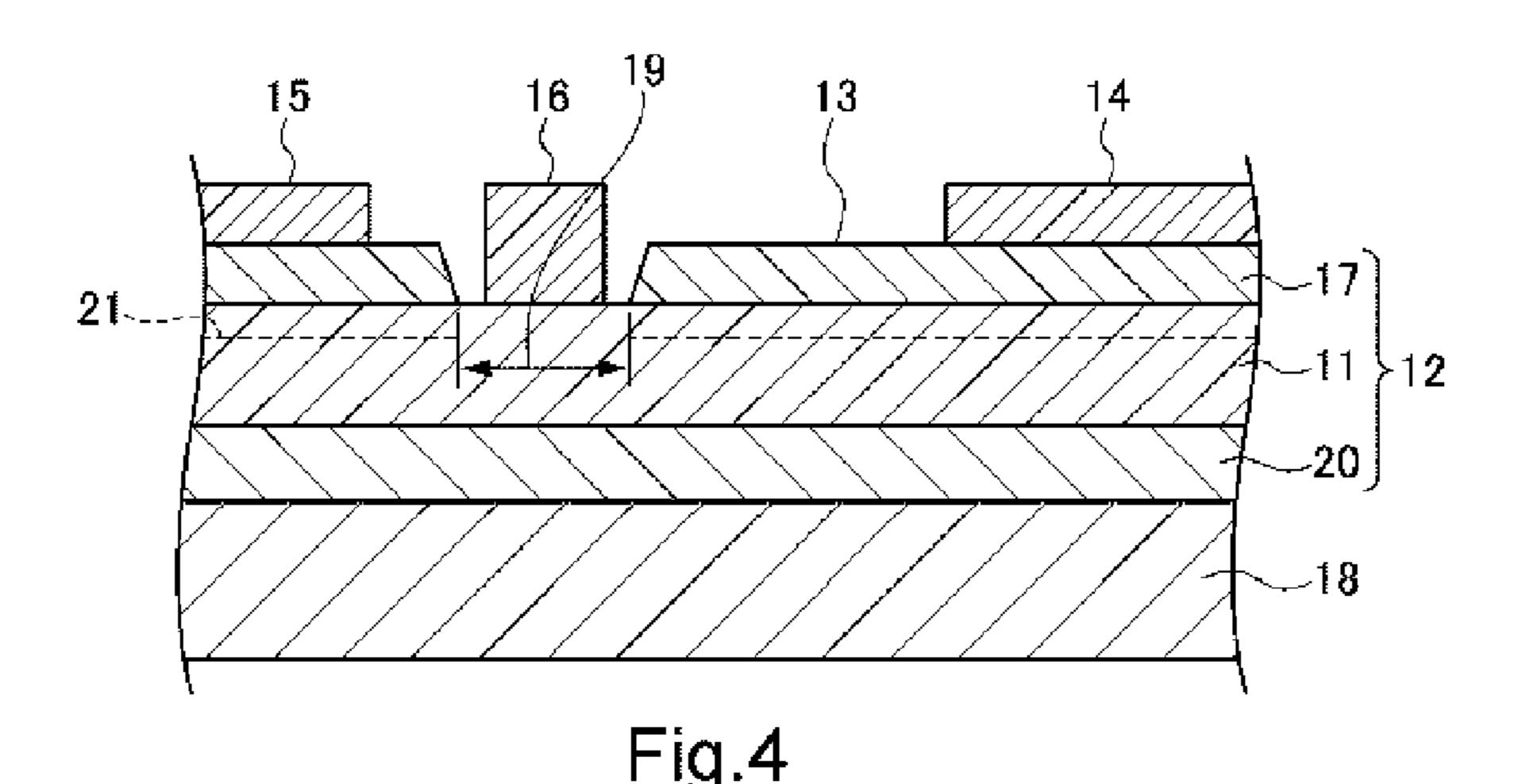

[0023] FIG. 4 is a schematic cross-sectional view taken along line C-C in FIG. 2;

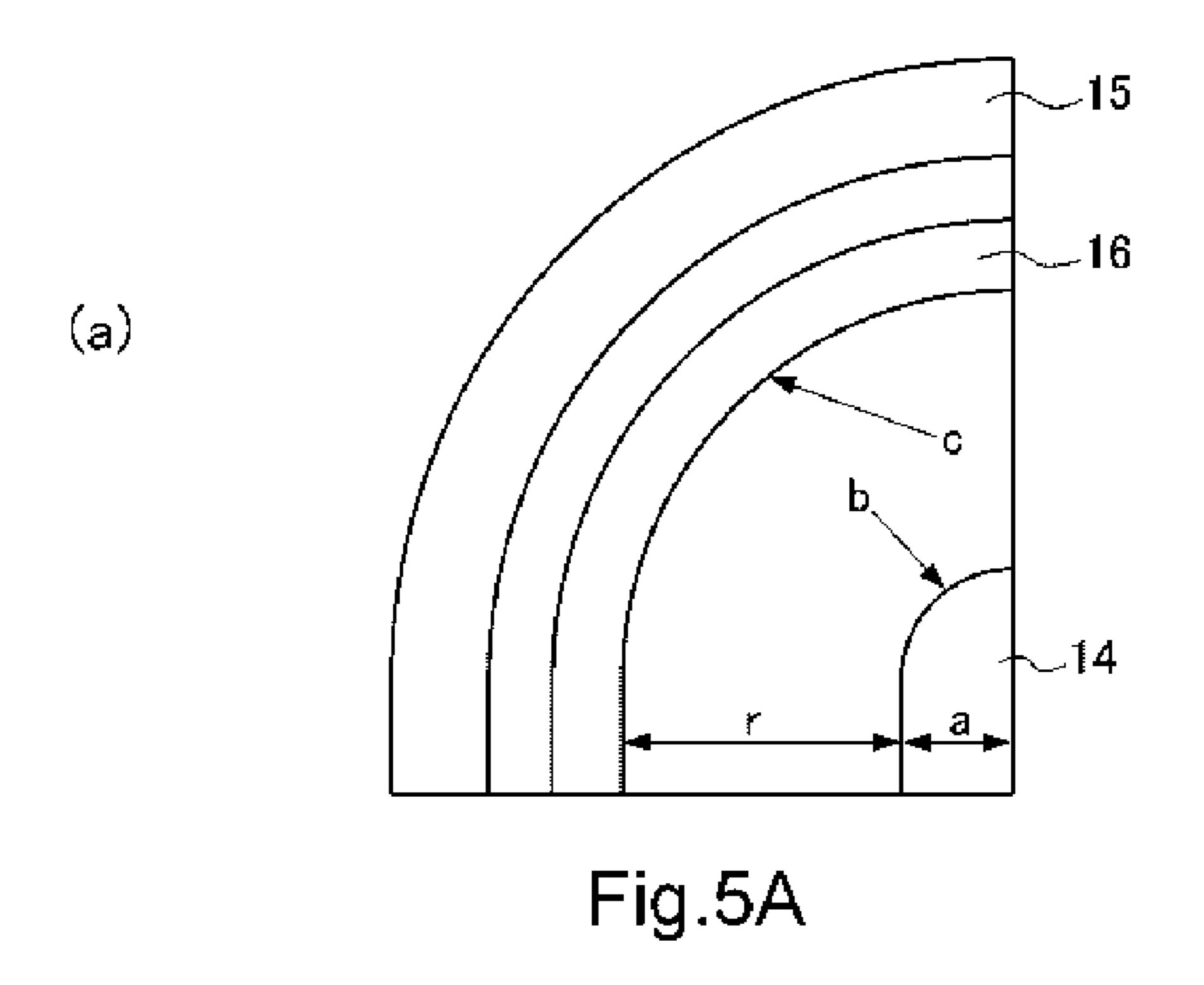

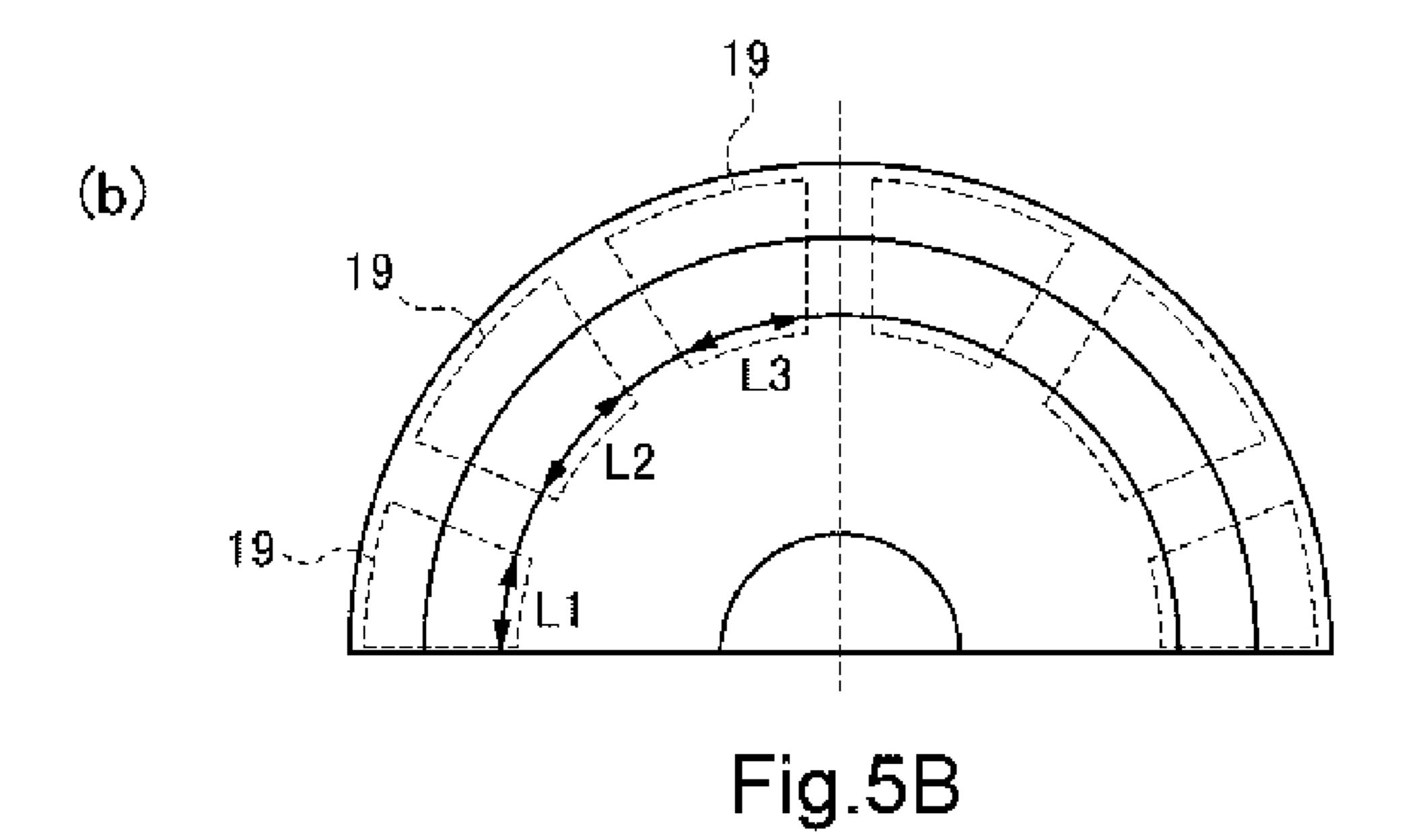

[0024] FIGS. 5A and 5B are schematic views of the semiconductor device according to the first embodiment of the present invention, illustrating the dimensions of the electric current limiting section thereof;

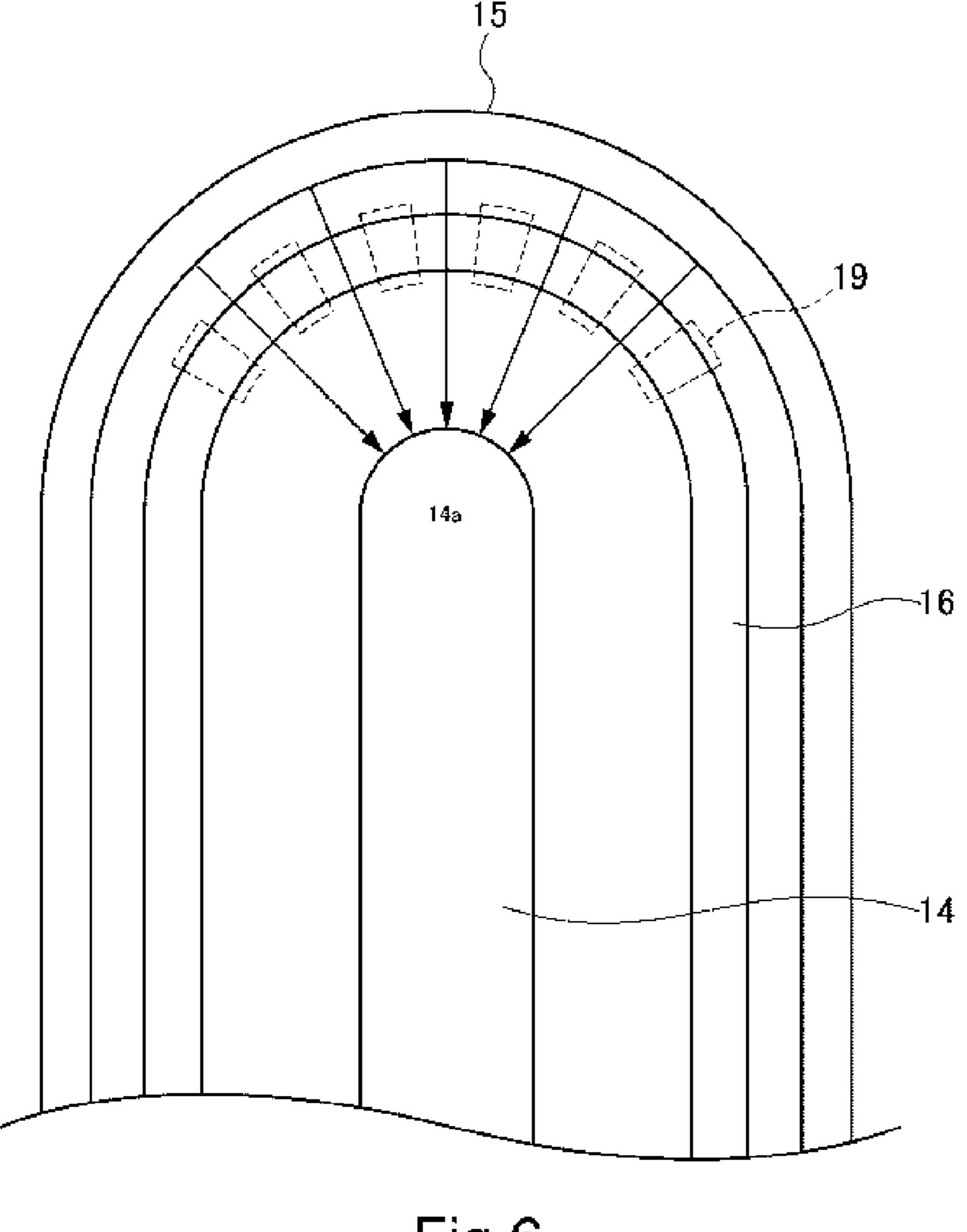

[0025] FIG. 6 is a schematic view of the semiconductor device according to the first embodiment of the present invention, illustrating the operation thereof;

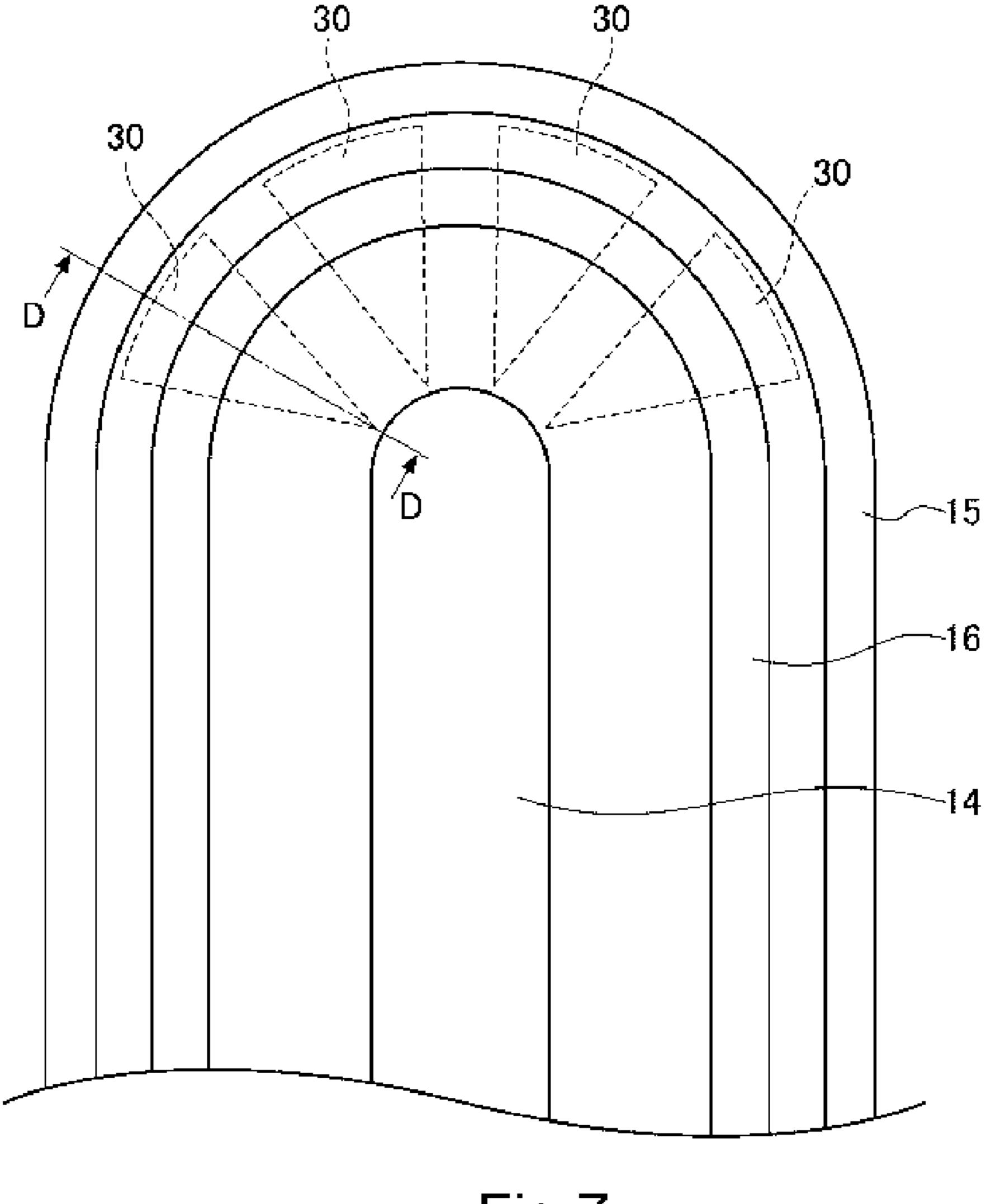

[0026] FIG. 7 is a schematic view of an embodiment formed by modifying the semiconductor device of the first embodiment;

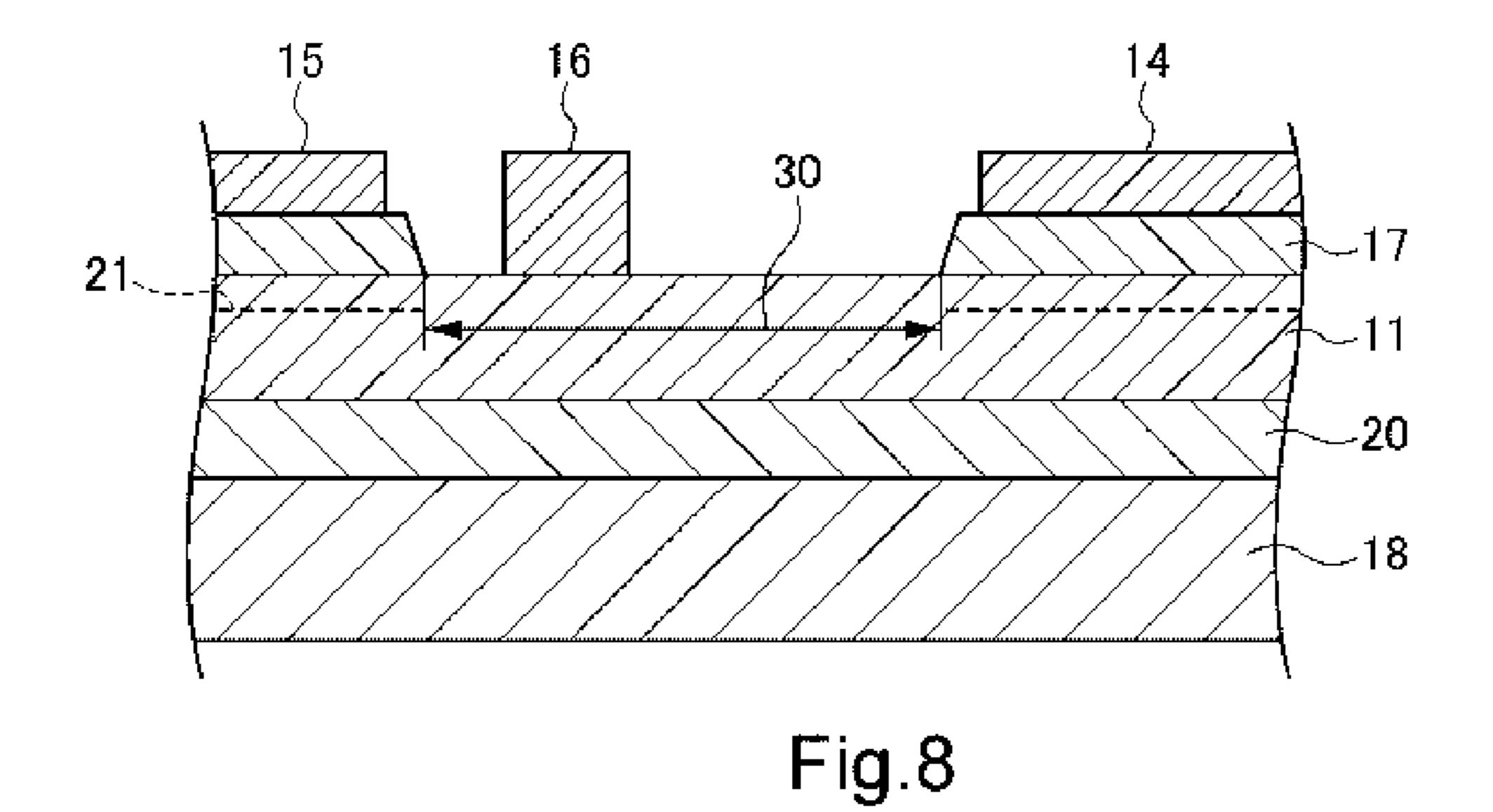

[0027] FIG. 8 is a schematic cross-sectional view taken along line D-D in FIG. 7;

[0028] FIG. 9 is a schematic cross-sectional view of the semiconductor device according to a second embodiment of the present invention;

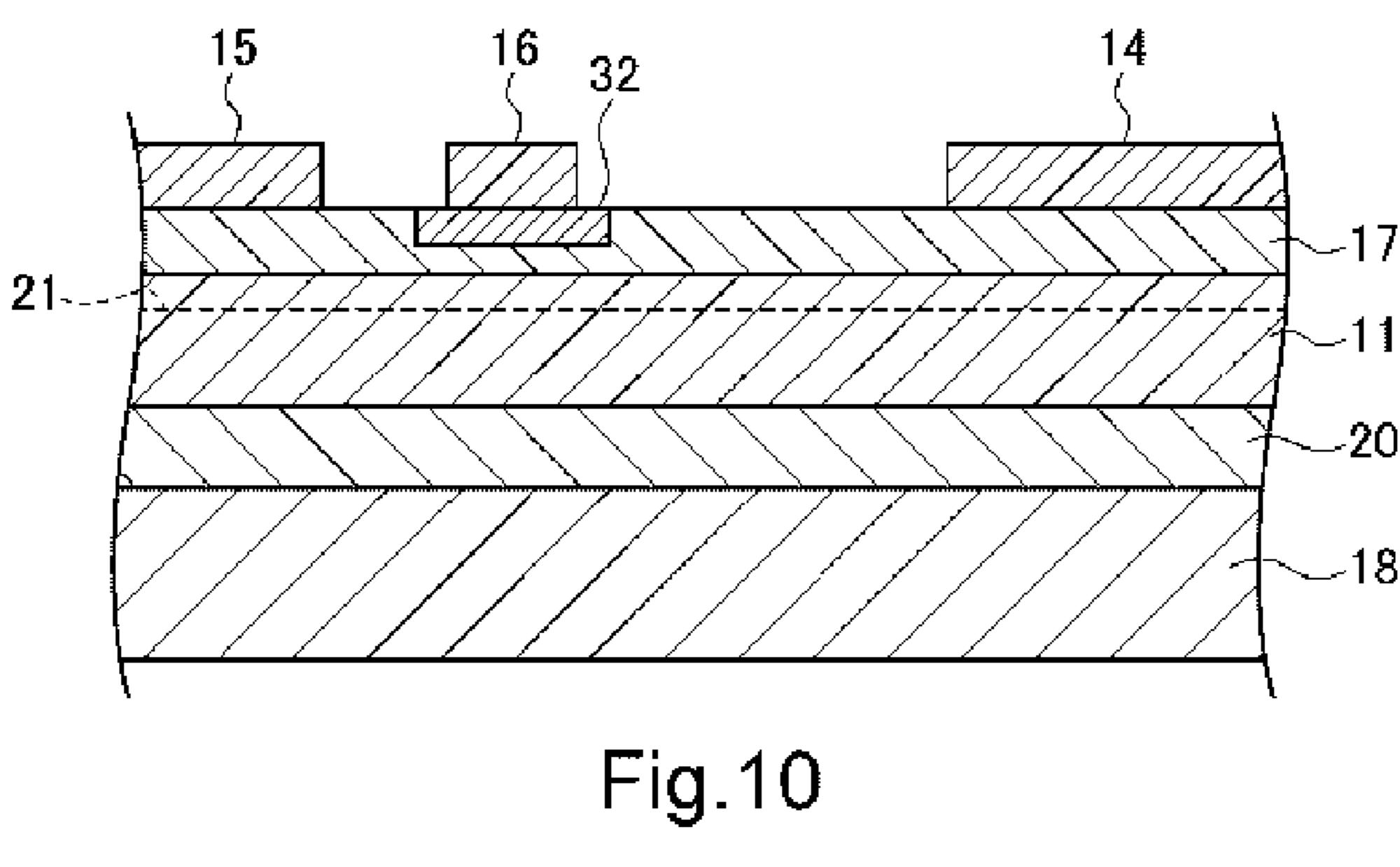

[0029] FIG. 10 is a schematic cross-sectional view of the semiconductor device according to a third embodiment of the present invention;

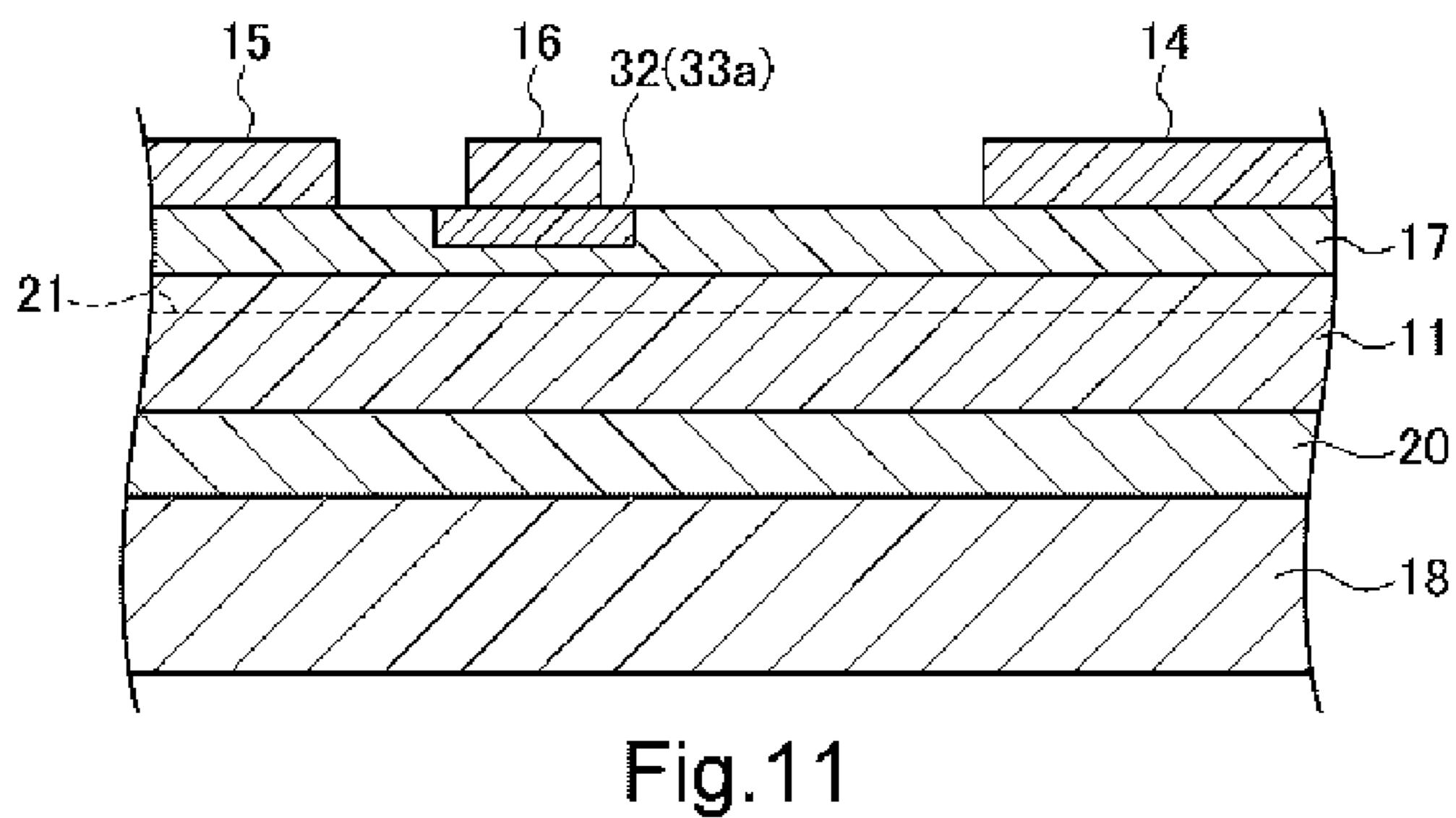

[0030] FIG. 11 is a schematic cross-sectional view of the semiconductor device according to a fourth embodiment of the present invention; and

[0031] FIG. 12 is a schematic view of a known semiconductor device.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0032] Now, the present invention will be described in greater detail by referring to the accompanying drawings that illustrate preferred embodiments of the invention.

[0033] The semiconductor device according to the first embodiment of the present invention will be described below

by referring to FIGS. 1 through 4. FIG. 1 is a schematic plan view of the semiconductor device according to the first embodiment of the present invention. FIG. 2 is an enlarged schematic view of area A in FIG. 1. FIG. 3 is a schematic cross-sectional view taken along line B-B in FIG. 2. FIG. 4 is a schematic cross-sectional view taken along line C-C in FIG. 2.

[0034] As shown in FIGS. 1 through 4, the semiconductor device 10 according to the first embodiment of the present invention has a semiconductor layer 12 formed by a plurality of layers including a channel layer 11 made of a nitride-based compound semiconductor, a buffer layer 20 and a carrier supply layer 17, a first main electrode 14, a second main electrode 15, the first main electrode 14 and the second main electrode being formed on the main surface 13 of the semiconductor layer 12, and a control electrode 16 arranged between the first main electrode 14 and the second main electrode 15 on the main surface 13. The control electrode (gate electrode) 16 controls the principal current that flows between the first main electrode 14 and the second main electrode 15 through the channel layer 11. In the following description, it is assumed that the first main electrode 14 is a drain electrode 14 and the second main electrode 15 is a source electrode 15. Alternatively, however, it may be so assumed that the first main electrode 14 is a source electrode and the second main electrode 15 is a drain electrode. In any case, a semiconductor device according to the present invention will be described in terms of a first main electrode, a second main electrode and a control electrode.

[0035] As shown in FIG. 1, the second main electrode 15 and the first main electrode 14 are comb-shaped with their plural teeth extending vertically on the sheet of FIG. 1. The third electrode 16 is arranged between the second main electrode 15 and the first main electrode 14.

[0036] The second main electrode 15 and the first main electrode 14 that are arranged on the semiconductor layer 12 make an ohmic contact (low resistance contact) with the electron supply layer (carrier supply layer) 17. The second main electrode 15 and the first main electrode 14 may be formed as laminates of titanium (Ti) and aluminum (Al).

[0037] The control electrode 16 may be a metal film that is a laminate of, for example, nickel (Ni), gold (Au) and titanium (Ti) and make a Shottky contact with the carrier supply layer 17. The control electrode 16 may alternatively be formed by using a material that makes a Schottky contact with nitride-based compound semiconductors. Examples of such a material include Ni, platinum (Pt), palladium (Pd), rhodium (Rh) and copper (Cu).

[0038] As shown in FIG. 3, the semiconductor layer 12 that is formed by a plural layers including a buffer layer 20, a channel layer 11 and a carrier supply layer 17 is arranged on a substrate 18. The substrate 18 is preferably a silicon substrate that can be made to show a large diameter in order to manufacture nitride-based compound semiconductor devices at low cost. An impurity may be doped to the silicon substrate to make the substrate a conductive substrate. Alternatively, the substrate 18 may be a ceramic semiconductor substrate or an SiC substrate. Still alternatively, the substrate 18 may be made of a material selected from silicon carbide, sapphire, spinel, ZnO, gallium nitride, aluminum nitride or some other material on which a III-group nitride material can grow.

[0039] FIG. 2 is an enlarged schematic view of area A in FIG. 1. The semiconductor device 10 has a substrate 18, a compound semiconductor layer (semiconductor layer) 12

that includes a channel layer 11 formed on the substrate 18 and based on a hetero junction, a first main electrode 14 formed on the compound semiconductor layer 12, a second main electrode 15 formed on the compound semiconductor layer 12 so as to surround the first main electrode 14 and including a linear region 15a and an arc-shaped region 15b, and a control electrode 16 formed on the compound semiconductor layer 12 between the first main electrode 14 and the second main electrode 15. In the semiconductor device 10, an electric current is made to flow between the first main electrode 14 and the second main electrode 15. An electric current limiting section 19 is provided between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 to limit the electric current flowing between them.

[0040] With the above-described arrangement, the electric current limiting section 19 is preferably a part between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 where the two-dimensional carrier gas layer is partially removed.

[0041] More specifically, the electric current limiting section 19 is a part where the two-dimensional carrier gas layer 21 is removed by partially removing the carrier supply layer 17 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 by means of recess etching. More specifically, the electric current limiting section 19 may be a part where the two-dimensional carrier gas layer 21 is partially removed in an area located right under the control electrode between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15.

[0042] FIG. 3 is a schematic cross-sectional view taken along line B-B in FIG. 2. The semiconductor layer 12 shown in FIG. 3 has a structure formed by sequentially laying a buffer layer 20, a channel layer 11 and a carrier supply layer 17, each of which is made of a nitride-based compound semiconductor, in the above-described order. In the following description, the carriers supplied to the channel layer 11 by the carrier supply layer 17 are assumed to be electrons. In other words, the two-dimensional carrier gas layer 21 is a two-dimensional electron gas layer (to be referred to as 2DEG layer hereinafter) and electrons flows from the source electrode 15 to the drain electrode 14 by way of the 2DEG layer 21.

[0043] The buffer layer 20 is produced on the substrate 18 to alleviate the lattice mismatch, if any, between the substrate 18 and the channel layer 11, although the buffer layer 20 may be omitted.

[0044] The channel layer 11 arranged on the buffer layer 20 is a layer for obtaining the 2DEG layer 21 as a current path (channel) located near the hetero-junction interface with the carrier supply layer 17. The channel layer 11 is typically formed by epitaxial growth of undoped GaN, which is free from any impurity, to a thickness of about 0.5 to 10 μm by way of a MOCVD process. An appropriate channel layer 11 can be formed by using an III-group nitride material such as  $Al_{\nu 1}Ga_{\nu 2}In_{(1-\nu 1-\nu 2)}N$  (0≤y1<1, 0y2≤1, y1+y2≤1). In this embodiment, the channel layer 11 is formed as a non-doped GaN layer having a film thickness of about 5 to 6 μm. The channel layer 11 can be formed on the buffer layer 20 by means of a known semiconductor growth process such as a metalorganic vapor phase epitaxy (MOVPE) process or a molecular beam epitaxy (MBE) process.

[0045] The carrier supply layer 17 arranged on the channel layer 11 is made of a nitride semiconductor showing a band

gap greater than the channel layer 11 and having a lattice constant different from the channel layer 11. The carrier supply layer 17 is expressed by  $Al_xM_yGa_{1-x-y}N$  ( $0 \le x < 1$ ,  $0 \le y < 1$ ,  $0 \le x + y \le 1$ ), where M is indium (In) or boron (B). X in the composition ratio is preferably 0.1 to 0.5 and more preferably 0.3. While undoped  $Al_xGa_{1-x}N$  can be adopted for the carrier supply layer 17, a nitride semiconductor made of  $Al_xGa_{1-x}N$  to which an n-type impurity is added can also be adopted for the carrier supply layer 17.

[0046] The carrier supply layer 17 is formed on the channel layer 11 by way of an epitaxial growth process such as a MOCVD process. The film thickness of the carrier supply layer 17 is so selected as to produce a known 2DEG layer 21 on the basis of a hetero junction between the channel layer 11 and the carrier supply layer 17. Specifically, the film thickness of the carrier supply layer 17 is preferably about 5 to 50 nm, which is thinner than the channel layer 11, and more preferably about 5 to 30 nm.

[0047] Alternatively,  $Al_xGa_{1-x}N$  to which an n-type impurity is doped may be adopted for the carrier supply layer 17. A spacer layer made of undeoped AlN may be arranged between the carrier supply layer 17 and the channel layer 11 made of GaN. A contact layer typically made of n-type AlGaN may be arranged between the source electrode 15 and the drain electrode 14, and the carrier supply layer 17. The carrier supply layer 17 can be formed on the channel layer 11 by way of a known semiconductor growth process such as a metalorganic vapor phase epitaxy (MOVPE) process or a molecular beam epitaxy (MBE) process.

[0048] FIG. 4 is a schematic cross-sectional view taken along line C-C in FIG. 2. The cross-sectional view taken along line C-C differs from the cross-sectional view taken along line B-B in that a part formed by partially removing the carrier supply layer 17 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 is arranged. The part formed by removing the carrier supply layer 17 operates as an electric current limiting section 19. No electric current flows through the electric current limiting section 19 because a two-dimensional carrier gas (2DEG) layer is not formed there. More specifically, the electric current limiting section 19 is formed by partially removing the carrier supply layer 17 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 by means of recess etching. The electric current limiting section 19 maybe formed by partially removing the carrier supply layer located right under the control electrode 16 between the first main electrode 14 and the arc-shaped region **15***b* of the second main electrode **15**. Otherwise, the crosssectional view taken along line C-C is same as the crosssectional view taken along line B-B.

[0049] FIGS. 5A and 5B are schematic views, illustrating the dimensions of the electric current limiting section 19. Referring to FIG. 5A, the illustrated dimensions show relationships as described below. Assume that the width of the first main electrode 14 (the diameter of the arc-shaped part) is 2a and the peripheral length of the arc-shaped region of the first main electrode 14 is b while the peripheral length of the end section at the side of the first main electrode 14 of the arc-shaped part of the control electrde 16 is c and the distance from the end of the first main electrode 14 to the corresponding end of the control electrode 16 is r, the relationships of  $b=2\pi a/4$  and  $c=2\pi(a+r)/4$  hold true. With this arrangement, concentration of electric current is apt to take place because of

the relationship of b<c. Concentration of electric current can be alleviated by making the relationship between b and c close to b=c.

[0050] In this embodiment, the relationship between b and c is made to become close to b=c by forming an electric current limiting section 19 as shown in FIG. 5B. More specifically, if the total length of the parts of the end section of the control electrode 16 at the side of the first main electrode 14 from right under which 2DEG is removed is L (L=L1+L2+L3 in FIG. 5B), 2DEG is removed from right under the control electrode 16 so as to make L=c-b=πr/2 hold true. While an electric current limiting section 19 is preferably so arranged as to make the above formula hold true to be strict, the region of the electric current limiting section 19 can be appropriately selected so long as the effect of alleviating concentration of electric current is obtained.

[0051] Now, the operation of the semiconductor device 10 according to the first embodiment of the present invention will be described below by referring to FIG. 6. When a voltage is applied between the first main electrode 14 and the second main electrode 15, 2DEG is formed in the region where no electric current limiting section 19 is formed so that consequently an electric current flows between the first main electrode 14 and the second main electrode 15. On the other hand, no 2DEG 21 is formed in the electric current limiting section 19 because the carrier supply layer 17 is removed from there so that consequently no electric current flows through the electric current limiting section 19. Thus, an electric current flows only in the parts indicated by arrows in FIG. 6. As a result, concentration of electric current is suppressed at the end section of the second main electrode 15.

[0052] As described above, according to the present invention, concentration of electric current is alleviated at the front end section 14a of the first main electrode 14 because of the provision of the electric current limiting section 19 so that it is possible to provide a semiconductor device 10 that is protected against any breakdown attributable to concentration of electric current.

[0053] Now, a method of manufacturing the nitride-based compound semiconductor device according to the first embodiment of the present invention will be described below. Note, however, that the method is described below only as an example and any of various other methods including those obtained by modifying the method to be described below can be used to manufacture a nitride-based compound semiconductor device according to the present invention.

[0054] (Step 1)

[0055] Firstly, a buffer layer 2, a channel layer 11 and a carrier supply layer 17 are sequentially formed on a substrate 18 by epitaxial growth in the above-mentioned order to produce a semiconductor layer 12 as a laminate. The channel layer 11 is formed as an undoped GaN layer typically having a film thickness of 0.5 to  $10\,\mu m$  by way of a MOCVD process and the carrier supply layer 17 thereon is formed as an undoped AlGaN layer, which may typically be made of a nitride semiconductor showing a band gap greater than the channel layer 11 and having a lattice constant different from the channel layer 11, by way of a MOCVD process.

[0056] (Step 2)

[0057] A recess etching operation is partially conducted in areas of the carrier supply layer 17 for producing a control electrode. In other words, the carrier supply layer 17 is partially removed.

[0058] (Step 3)

[0059] Then, a first electroconductor layer is formed on the semiconductor layer 12 by way of an evaporation process to produce the second main electrode 15 and the first main electrode 14 on the semiconductor layer 12. A laminate structure of Ti and Al, for example, can be adopted for the first electroconductor layer. Thereafter, the second main electrode 15 and the first main electrode 14 are formed by wet etching the first electroconductor layer, using a patterned photoresist film as a mask, by way of a photolithography process.

[0060] (Step 4)

[0061] Subsequently, an insulating film is formed on the semiconductor layer 12, the second main electrode 15 and the first main electrode 14 and the parts of the insulating film where the control electrode 16 and the semiconductor layer contact with each other are removed by way of a photolithography process and a wet etching process to produce an aperture section.

[0062] (Step 5)

[0063] Thereafter, a second electroconductor layer is formed by way of a sputtering process in order to produce the control electrode 16. More specifically, the second electroconductor layer is so formed as to bury the aperture section of the insulating film and produce a Schottky junction between the second electroconductor layer and the semiconductor layer 12 at the aperture section, and followed by a lift-off process. The second electroconductor layer may be formed as a laminate of Ni, Au and Ti, for instance.

[0064] <Modified Embodiment>

FIGS. 7 and 8 schematically illustrate of an embodiment formed by modifying the semiconductor device of the first embodiment. FIG. 7 is a view that corresponds to FIG. 2 illustrating the first embodiment. FIG. 8 is a schematic crosssectional view taken along line D-D in FIG. 7. The nitridebased compound semiconductor device illustrated in FIGS. 7 and 8 differs from the first embodiment of the present invention illustrated in FIGS. 1 through 6 in that the electric current limiting section 30 thereof is produced by removing the twodimensional carrier gas layer 21 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 in a part other than and in addition to the part right under the control electrode 16. Otherwise, this modified embodiment is same as the nitride-based compound semiconductor device of the first embodiment illustrated in FIGS. 1 through **6**.

[0066] For the nitride-based compound semiconductor device illustrated in FIGS. 7 and 8, the carrier supply layer 17 is partially removed by removing 2DEG 21 in the part where the control electrode is formed by deposition and also in a part other than the former part by recess etching.

[0067] Thus, when a voltage is applied between the first main electrode 14 and the second main electrode 15 of the nitride-based compound semiconductor device formed by modifying the first embodiment of the present invention, an electric current flows between the first main electrode 14 and the second main electrode 15 because 2DEG 21 is formed in the region where the electric current limiting section 30 is not found. On the other hand, no 2DEG 21 is formed in the electric current limiting section 30 so that consequently no electric current flows through the electric current limiting section 30. As a result, concentration of electric current is suppressed at the end section of the second main electrode 15.

Thus, this modified embodiment can suppress concentration of electric current just like the first embodiment illustrated in FIGS. 1 through 6.

[0068] Now, the semiconductor device according to the second embodiment of the present invention will be described below. In the second embodiment, the electric current limiting section 31 is a part where the carrier concentration of the two-dimensional carrier gas layer is partially reduced between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15. FIG. 9 is a schematic cross-sectional view of the semiconductor device of the second embodiment of the present invention that corresponds to the cross-sectional view taken along line D-D in FIG. 7. The second embodiment of the present invention differs from the first embodiment in that the thickness of the carrier supply layer 17 is reduced around the control electrode 16 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 in the region for forming the electric current limiting section 31 if compared with the thickness of the carrier supply layer 17 of the other region as shown in FIG. 9. Otherwise, this embodiment is same as the nitride-based compound semiconductor device of the first embodiment illustrated in FIGS. 1 through 6. Therefore, the components same as those of the first embodiment are denoted by the same reference symbols and will not be described here repeatedly.

[0069] When manufacturing the nitride-based compound semiconductor device shown in FIG. 9, the carrier supply layer 17 is partially subjected to a recess etching process to make the carrier supply layer 17 thinner in the area where the gate electrode is to be formed by deposition in Step 2 of the above-described manufacturing method of the first embodiment. Thus, the carrier concentration of the 2DEG 21 is reduced.

[0070] Thus, when a voltage is applied between the first main electrode 14 and the second main electrode 15 of the nitride-based compound semiconductor device according to the second embodiment of the present invention, 2DEG 21 is formed in the region where no electric current limiting section 31 is formed so that consequently an electric current flows between the first main electrode 14 and the second main electrode 15. On the other hand, the electric current limiting section 31 is a high resistance region because the electron concentration of 2DEG 21 is held low there so that consequently the electric current flowing through the electric current limiting section 31 is suppressed. As a result, concentration of electric current is suppressed at the end section 14a of the first main electrode 14. Thus, this embodiment can suppress concentration of electric current just like the first embodiment illustrated in FIGS. 1 through 6.

[0071] Now, the semiconductor device according to the third embodiment of the present invention will be described below. In the third embodiment, the electric current limiting section 32 is a part located right under the control electrode 16 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 where the carrier concentration of the two-dimensional carrier gas layer 21 is partially reduced. In the above-described arrangement, the electric current limiting section 32 is preferably a part where the carrier concentration of the two-dimensional carrier gas layer 21 is partially reduced by doping the compound semiconductor layer junctioned to the channel layer between the first main electrode and the arc-shaped region of the second main electrode with fluorine ions.

[0072] FIG. 10 is a schematic cross-sectional view of the semiconductor device of the third embodiment of the present invention that corresponds to the cross-sectional view taken along line D-D in FIG. 7. As seen from FIG. 10, the third embodiment of the present invention differs from the first embodiment illustrated in FIGS. 1 through 6 in that the electric current limiting section 32 is a part where the carrier concentration of the two-dimensional carrier gas layer is partially reduced by doping the compound semiconductor layer (carrier supply layer 17) junctioned to the channel layer 11 between the first main electrode and the arc-shaped region of the second main electrode with fluorine ions. Otherwise, this embodiment is same as the nitride-based compound semiconductor device of the first embodiment illustrated in FIGS. 1 through 6. Therefore, the components same as those of the first embodiment are denoted by the same reference symbols and will not be described here repeatedly.

[0073] When manufacturing the nitride-based compound semiconductor device as illustrated in FIG. 10, the carrier concentration of 2DEG is reduced in the area of the carrier supply layer where the control electrode is to be formed by deposition by doping the carrier supply layer with fluorine ions there in the step corresponding to Step 2 of the method of manufacturing the first embodiment. The operation of fluorine ion doping can be conducted byway of a fluorine-based gas plasma process.

[0074] Thus, the nitride-based compound semiconductor device according to the third embodiment can suppress concentration of electric current just like the second embodiment. [0075] Now, the semiconductor device according to the fourth embodiment of the present invention will be described below. In the fourth embodiment, the electric current limiting section 32 is a part located right under the control electrode 16 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 where the carrier concentration of the two-dimensional carrier gas layer 21 is partially reduced. With the above-described arrangement, preferably, the electric current limiting section 32 is a part where the carrier concentration of the two-dimensional carrier gas layer is partially reduced by making the compound semiconductor layer 33a junctioned to the channel layer 11 between the first main electrode 14 and the arc-shaped region 15b of the second main electrode 15 a p-type semiconductor layer.

[0076] FIG. 11 is a schematic cross-sectional view of the semiconductor device of the fourth embodiment of the present invention that corresponds to the cross-sectional view taken along line D-D in FIG. 8. As seen from FIG. 11, the fourth embodiment differs from the first embodiment illustrated in FIGS. 1 through 6 in that the carrier concentration of the two-dimensional carrier gas layer 21 is partially reduced by forming a p-type semiconductor layer 33a on the channel layer 11 between the first main electrode 14 and the arcshaped region 15b of the second main electrode 15. Otherwise, this embodiment is the same as the nitride-based compound semiconductor device of the first embodiment illustrated in FIGS. 1 through 6. Therefore, the components same as those of the first embodiment are denoted by the same reference symbols and will not be described here repeatedly.

[0077] When manufacturing the nitride-based compound semiconductor device as illustrated in FIG. 11, the carrier concentration of 2DEG is reduced in the area of the carrier supply layer where the gate electrode is formed by deposition by doping a p-type impurity such as Mg by ion injection in Step 2.

[0078] Thus, the nitride-based compound semiconductor device of the fourth embodiment can suppress concentration of electric current just like the second embodiment.

[0079] While the electric current limiting section is arranged right under the control electrode in each of the above-described second through fourth embodiments, the present invention is by no means limited thereto and an electric current limiting section may be formed in a part other than right under the control electrode.

[0080] The first through fourth embodiments of the present invention are described above summarily in terms of configuration, shape, size and positional arrangement only to such an extent that the present invention is understandable and carried out. Additionally, the numerical values and the compositions (materials) of the components listed above are only shown as examples. Therefore, the present invention is by no means limited to the above-described embodiments, which may be modified, altered and/or combined in various different ways without departing from the technical spirit and scope of the present invention.

[0081] A semiconductor device according to the present invention can find applications in the field of power devices that are required to operate at a high frequency and with high breakdown voltage.

[0082] 10 semiconductor device

[0083] 11 channel layer

[0084] 12 semiconductor layer

[0085] 13 main surface

[0086] 14 first main electrode (drain electrode)

[0087] 15 second main electrode (source electrode)

[0088] 16 control electrode

[0089] 17 carrier supply layer

[0090] 18 substrate [0091] 19 electric current limiting section

[0092] 20 buffer layer

[0093] 21 two-dimensional carrier gas layer

What is claimed is:

1. A semiconductor device comprising:

a substrate;

- a compound semiconductor layer formed on the substrate and having a two-dimensional carrier gas layer based on a hetero-junction;

- a first main electrode formed on the compound semiconductor layer;

- a second main electrode formed on the compound semiconductor layer so as to surround the first main electrode in a plan view and having a linear region and an arcshaped region;

- a control electrode formed between the first main electrode and the second main electrode on the compound semiconductor layer;

- an electric current being made to flow between the first main electrode and the second main electrode by way of the two-dimensional carrier gas layer; and

- an electric current limiting section for limiting the electric current from flowing between the first main electrode and the arc-shaped region of the second main electrode.

- 2. The semiconductor device according to claim 1, wherein the electric current limiting section is a part, where carrier concentration of the two-dimensional carrier gas layer formed between the first main electrode and the arc-shaped region of the second main electrode is partly reduced.

- 3. The semiconductor device according to claim 1, wherein the electric current limiting section is a part, where carrier

concentration of the two-dimensional carrier gas layer formed between the first main electrode and the arc-shaped region of the second main electrode right under the control electrode is partly reduced.

- 4. The semiconductor device according to claim 1, wherein the electric current limiting section is a part, where the two-dimensional carrier gas layer is removed between the first main electrode and the arc-shaped region of the second main electrode.

- 5. The semiconductor device according to claim 1, wherein the compound semiconductor layer includes a channel layer in which the two-dimensional carrier gas layer is formed, and a carrier supply layer formed on the channel layer to produce a hetero junction, and the electric current limiting section is a

part between the first main electrode and the arc-shaped region of the second main electrode where the carrier supply layer is partly thinned.

- 6. The semiconductor device according to claim 1, wherein the electric current limiting section is a part, where the compound semiconductor layer junctioned to the channel layer is doped with fluorine ions, between the first main electrode and the arc-shaped region of the second main electrode.

- 7. The semiconductor device according to claim 1, wherein the electric current limiting section is a part, where p-type semiconductor layer is formed in the compound semiconductor layer junctioned to the channel layer between the first main electrode and the arc-shaped region of the second main electrode.

\* \* \* \* \*