US 20110108081A1

### (19) United States

# (12) Patent Application Publication

Werthen et al.

## (10) Pub. No.: US 2011/0108081 A1

(43) Pub. Date: May 12, 2011

### (54) PHOTOVOLTAIC POWER CONVERTER

(75) Inventors: **Jan-Gustav Werthen**, Cresskill, NJ

(US); Qiang Liu, San Jose, CA

(US)

(73) Assignee: JDS Uniphase Corporation,

Milpitas, CA (US)

(21) Appl. No.: 11/958,487

(22) Filed: **Dec. 18, 2007**

### Related U.S. Application Data

(60) Provisional application No. 60/871,108, filed on Dec. 20, 2006, provisional application No. 60/871,125, filed on Dec. 20, 2006.

#### **Publication Classification**

(51) Int. Cl.

H01L 31/05 (2006.01)

H01L 31/0248 (2006.01)

(57) ABSTRACT

The invention provides a photovoltaic power converter that includes a multilayer structure supported by a substrate having a base layer of a semiconductor material of a first conductivity type and a first emitter layer of a semiconductor material of a second conductivity type opposite said first conductivity type forming a p-n junction region therebetween, and a first current blocking layer of a semiconductor material of the second conductivity type interposed between the substrate and the first multilayer structure. The emitter layer is carbon doped.

FIG. 2 (Prior Art)

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 8

FIG. 9

PPC-9LW: Input Power = 100 mW at 1436 nm

FIG. 10

### PHOTOVOLTAIC POWER CONVERTER

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The present invention claims priority from U.S. Provisional Patent Application No. 60/871,108 filed Dec. 20, 2006, entitled "InP-based Photovoltaic Power Converter for Long-Distance Power Delivery (>>1 km)", and U.S. Provisional Patent Application No. 60/871,125 filed Dec. 20, 2006, entitled "Novel Ultra-High Efficiency Photovoltaic Power Converter for High Power Delivery", both of which are incorporated herein by reference for all purposes.

### TECHNICAL FIELD

[0002] The present invention generally relates to devices that convert optical power into electrical power, and in particular relates to segmented semiconductor optical power converting devices having a current blocking layer.

### BACKGROUND OF THE INVENTION

[0003] Devices for converting optical power into electrical power are used in many applications, perhaps most known of which is the conversion of sunlight into electricity, for which silicon-based photovoltaic cells, also referred to as photocells or solar cells, are typically used. For this type of application, an array of photovoltaic cells with a relatively large total photosensitive area is typically used.

[0004] Another application for optical power converters that has recently emerged is a remote optical powering of electronic modules. In this type of applications, optical power may be provided by a high-power laser and delivered to the module via an optical fiber, where it is converted into an electrical power signal. In such applications, the optical light is typically comes in the form of a well-confined infra-red beam of high intensity, typically in the wavelength range between about 900 nm and 1600 nm corresponding to a low absorption window of typical optical fibers. The optical power converter for such applications has a relatively small, preferably circular photosensitive area of a few square millimeters or less, and is based on compound semiconductors such as InP, GaAs and their alloys, that are more suitable for absorbing infra-red light than silicon. An example of such a GaAs device is disclosed in U.S. Pat. No. 5,342,451 issued to Virshup, which is incorporated herein by reference.

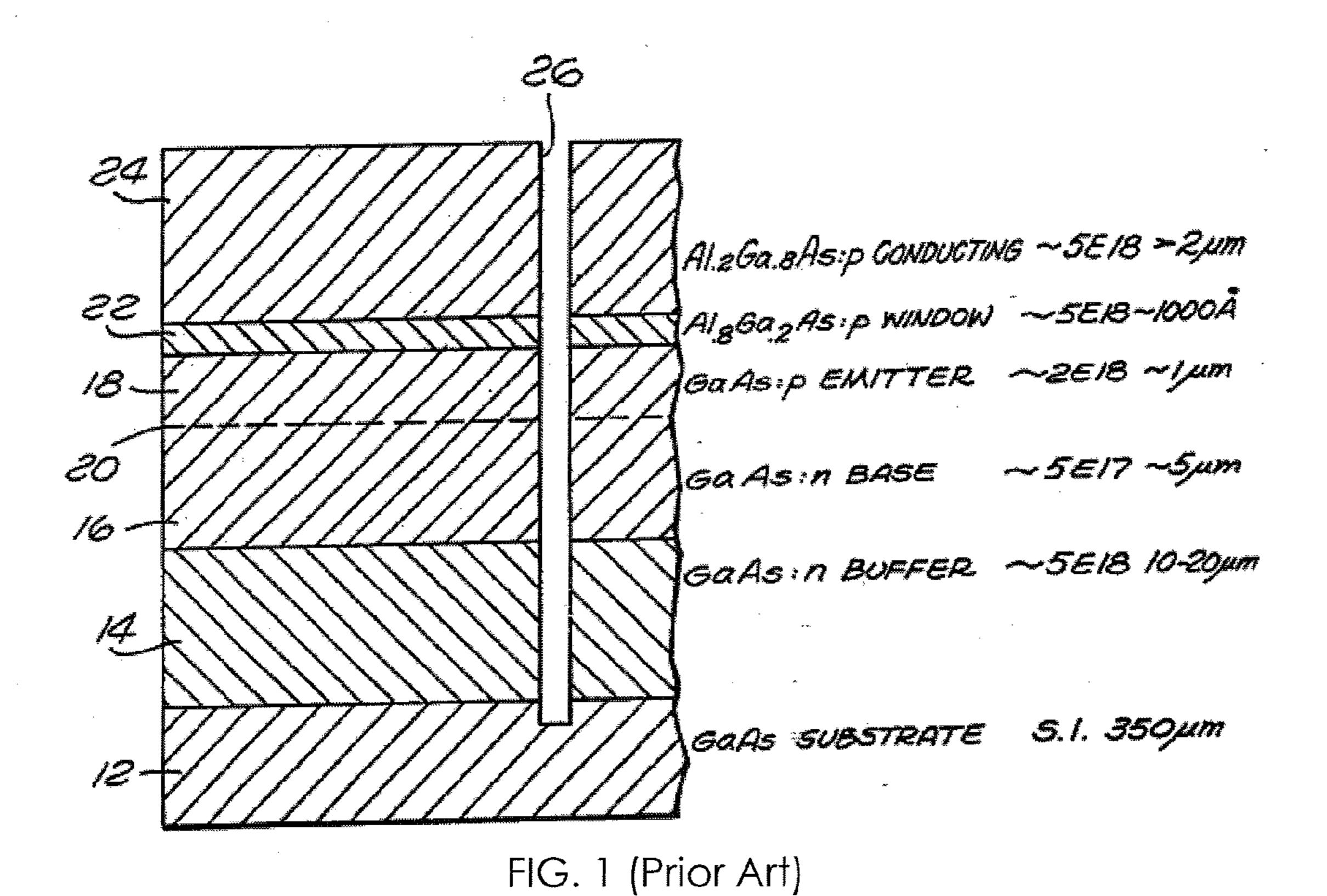

[0005] As described in the Virshup patent and illustrated in FIG. 1, which reproduces FIG. 2 of Virshup, a typical semiconductor optical power converter includes a pn junction 20 formed between a base layer 16, which may typically be n-type, and an emitter layer 18, which may typically be p-type. The base and emitter layers 16, 18 are sandwiched between a highly conductive buffer layer 14 placed on an isolating substrate 12, and a highly conductive, optically transparent window layer 22, which can be followed by a thicker conducting layer 24. A cap layer (not shown in FIG. 1) is placed on top of the window layer and electrical contacts (not shown in FIG. 1) such as metal grid lines are deposited onto this cap layer. Between the metal grid lines, which are typically as narrow as 3 microns, the cap layer is etched away, allowing the incident light to penetrate through the transparent window layer and be absorbed by the underlying pn junction 20. In order to complete the circuit, the n-portion of the pn junction has to be reached, typically by an etching technique. The depth of this etch is usually a few microns to

ensure that the n-type layer 16 is reached. Once metal has been deposited onto this exposed n-type layer, connection to both the n-type and the p-type polarities can be made. As photons are incident and absorbed by the pn junction 20, carriers are generated, and, in the presence of the electrical field created by the pn junction, swept away and collected at the electrical contacts, creating a voltage difference between them. By connecting to an external circuit, electrical power can be extracted.

[0006] An open circuit voltage that a single pn junction can deliver is limited by the bandgap of the used semiconductor material, and is typically less than 1 Volt. By connecting a number of these pn junctions in series in a lateral configuration, individual voltages are summed to produce an output voltage that can reach 12 volts or more. In order to create such individual pn junction elements, etching between adjacent segments is typically done. This has to be deep enough to isolate the pn junctions from each other, with a typical depth of about 25 microns. To complete the series connections, air bridges are formed between adjacent pn junctions. One side of such an air bridge is connected to the exposed n-type portion of the pn junction; the other to the p-type portion of the neighbouring pn junction.

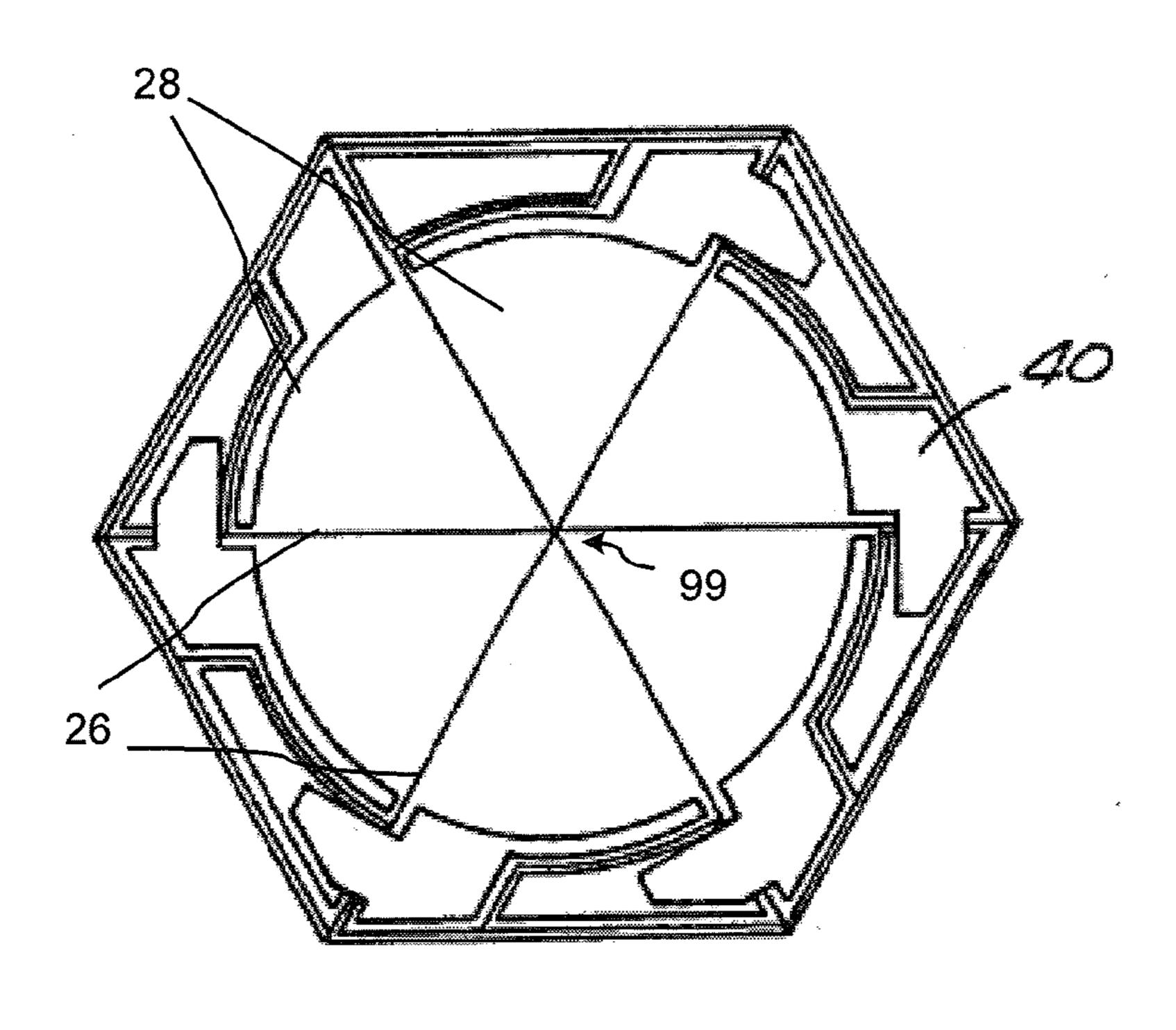

[0007] For applications wherein the optical power is delivered by a confined optical beam with a circular cross-section, such as that emanating from an optical fiber. As illustrated in FIG. 2, which is reproduced from FIG. 3 of the Virshup patent, these multiple pn junctions are typically created by dividing a circular photosensitive area of a semiconductor chip into a plurality of pie-shaped device segments 28 that are separated from each other by etched trenches 26, and connected in series by the interconnecting bridges 40; although 6 segments are shown, in a typical device there may be anywhere from two to sixteen or more such segments.

[0008] One drawback of the prior art optical power converters relates to their limited light conversion efficiency, which has been typically less than 50%, so that more than half of optical power of the incident light was lost. One reason for the relatively low light conversion efficiency of the prior art optical power converters is the appearance of leakage currents in such devices that tend to degrade the device performance under light intensities above a few milliwatts (mW). These leakage currents are electrical currents that were found to be flowing through the substrate between the segments 28, especially under intense light illumination, despite the presence of deep etched trenches separating them and low doping levels of the substrate. Another reason relates to a relatively high rate of non-radiative recombination of the photo-generated carriers within the p-n junction region of the prior art optical power converters, which reduces the internal quantum efficiency of the device and thus the available photocurrent.

[0009] Another drawback of the prior art power converters that they are limited to operation in the wavelengths range of 0.8 to 0.9 microns ( $\mu m$ ). To the best of our knowledge, no optical power converters heretofore existed that can efficiently convert optical power into electrical power for light in the wavelengths range between 1.3 and 1.55  $\mu m$ , where optical fibers have low attenuation. Therefore, operating distances at which optical power can be efficiently transmitted has been limited to a few hundred meters at best, or less.

[0010] An object of the present invention is to overcome at least some of the shortcomings of the prior art by providing an

improved optical power converter that has lower leakage currents, lower internal resistance and improved light conversion efficiency.

[0011] Another object of the present invention is to provide an efficient optical power converter for operating in the wavelength range of 1.3  $\mu m$  to 1.55  $\mu m$ .

### SUMMARY OF THE INVENTION

[0012] In accordance with the invention, a photovoltaic power converter is provided, comprising a substrate of a semiconductor material, and a first multilayer structure supported by the substrate comprising a first base layer of a semiconductor material of a first conductivity type disposed over the substrate, said first base layer having a first bandgap, a first emitter layer of a semiconductor material of a second conductivity type opposite said first conductivity type and adjacent said first base layer to form a first junction region therebetween, said first emitter layer having a second bandgap that is equal or greater than the first band gap, and a first conducting layer of a semiconductor material of the second conductivity type disposed over the first emitter layer, said first conducting layer having a third bandgap that is wider than any of the first and second band gaps. A first current blocking layer of a semiconductor material of the second conductivity type is interposed between the substrate and the first multilayer structure. A base electrical contact is disposed in electrical communication with the first base layer, and an emitter electrical contact is disposed on said conducting layer in electrical communication with the first emitter layer for developing a voltage relative to the base electrical contact in response to radiation of selected wavelengths being incident on the first emitter layer.

[0013] In accordance with one aspect of this invention, at least one of the first emitter layer and the conducting layer is carbon doped so as to have an acceptor impurity concentration in the rage of  $2\times10^{18}$  to  $1\times10^{19}$  cm<sup>-3</sup>.

[0014] The photovoltaic power converter of this invention may further comprise a plurality of trenches extending through the first multilayer structure and the current blocking layer and further partially extending into the substrate so as to form a plurality of spatially separated device segments supported by the substrate, each of said device segments comprising a first metal contact in electrical communication with the first base layer within the device segment, said first metal contact disposed on the first base layer in an opening in the first emitter layer, and a second metal contact disposed over the conducting layer of the device segment in electrical communication with the first emitter layer. A plurality of electrical interconnects is provided for electrically connecting each but one first metal contact to a respective adjacent second metal contact so at for form a chain of device segments connected in series, wherein one of said first metal contacts that remains unconnected to any of the second metal contacts is the base electrical contact, and one of said second metal contacts that remains unconnected to any of the first metal contacts is the emitter electrical contact.

[0015] According to one aspect of the invention, the semiconductor material of each of the substrate, first base and emitter layers is GaAs, and the semiconductor material of the conducting layer is an alloy of one of AlGaAs and InGaP.

[0016] According to another aspect of the present invention the semiconductor material of the substrate and the current blocking layer is InP, the semiconductor material of the first base and emitter layers is an alloy of one of InGaAs and

InGaAsP, and the semiconductor material of the conducting layer is an alloy of one of InP and InGaAsP.

[0017] In one embodiment of the invention, the semiconductor material of the substrate is GaAs having substantially intrinsic conductivity with a doping level less than  $10^{-15}$ cm<sup>-3</sup>; the current blocking layer comprises p-doped GaAs having an acceptor impurity concentration in the range  $5\times10^{17}$  to  $1\times10^{19}$  cm<sup>-3</sup> and a thickness in the range of 0.1 to 0.3 μm; the buffer layer comprises n-doped GaAs having a donor impurity concentration in the range  $5 \times 10^{17}$  to  $2 \times 10^{18}$ cm<sup>-3</sup> and a thickness in the range of 1 to 10  $\mu$ m; the first base layer comprises one of GaAs and an alloy of AlGaAs with an aluminum concentration not greater than 35%, a donor impurity concentration in the range  $5 \times 10^{17}$  to  $1 \times 10^{19}$  and has a thickness in the range of 1 to 3 µm; the first emitter layer comprises carbon doped layer of one of GaAs and an alloy of AlGaAs with an Al content not greater than 35%, and has a thickness in the range of 0.6 to 1 µm and an acceptor impurity concentration in the range  $2 \times 10^{18}$  to  $5 \times 10^{18}$ ; and, the conducting layer is p-type comprising of one of: Zn or Be doped InGaP, and carbon doped AlGaAs with an aluminum concentration not greater than 35%, and has a bandgap that is wider than bandgaps of the first emitter and base layers, a thickness in the range of 1 to 3 μm, and a donor impurity concentration in the range  $2 \times 10^{18}$  to  $2 \times 10^{19}$ .

[0018] In another embodiment of the invention, the semiconductor material of the substrate is semi-insulating indium phosphate (InP); the current blocking layer comprises p-doped InP having an acceptor impurity concentration of  $5 \times 10^{17}$  cm<sup>-3</sup> or greater and a thickness in the range of 0.2 to 0.3 µm; the buffer layer comprises n-doped InP having a donor impurity concentration of  $5 \times 10^{17}$  or greater and a thickness in the range of 5 to 10 µm; the first base comprises an alloy of InGaAs that is lattice-matched to InP and has a donor impurity concentration of  $5 \times 10^{17}$  or greater and a thickness in the range of 1 to 3 µm; the first emitter layer comprises a p-doped alloy of InGaAs that is lattice-matched to InP and has an acceptor impurity concentration of  $2 \times 10^{18}$ or greater and a thickness in the range of 0.5 to 1.5 µm; and, the conducting layer comprises p-doped InP that has a donor impurity concentration of  $2 \times 10^{18}$  or greater and a thickness in the range of 1.5 to 2.5  $\mu$ m.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0019] The invention will be described in greater detail with reference to the accompanying drawings which represent preferred embodiments thereof and in which like reference labels are used to indicate like elements, wherein:

[0020] FIG. 1 is a diagram illustrating a prior art layer structure of a semiconductor optical power converter;

[0021] FIG. 2 is a plan view of the prior art segmented semiconductor optical power converter;

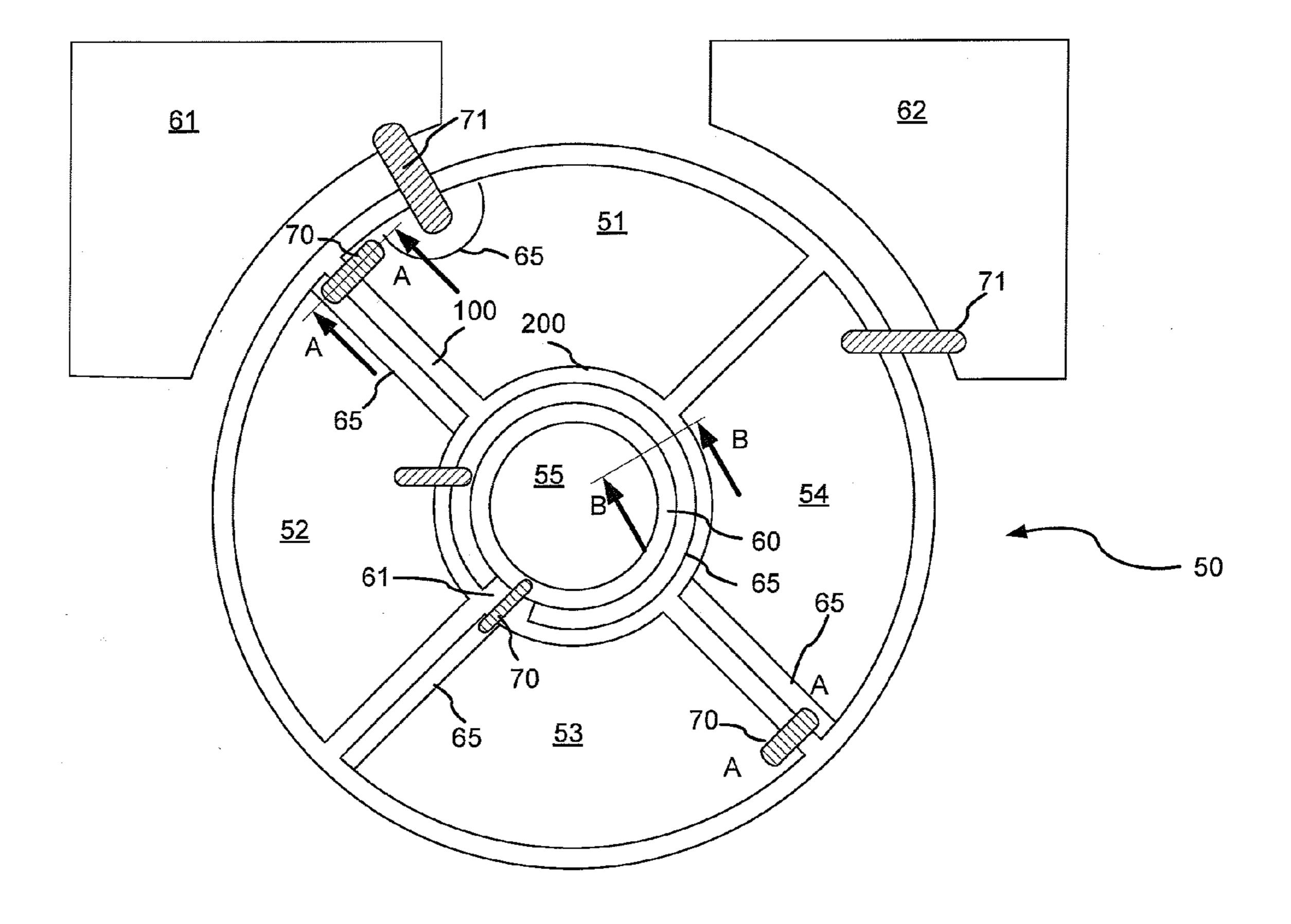

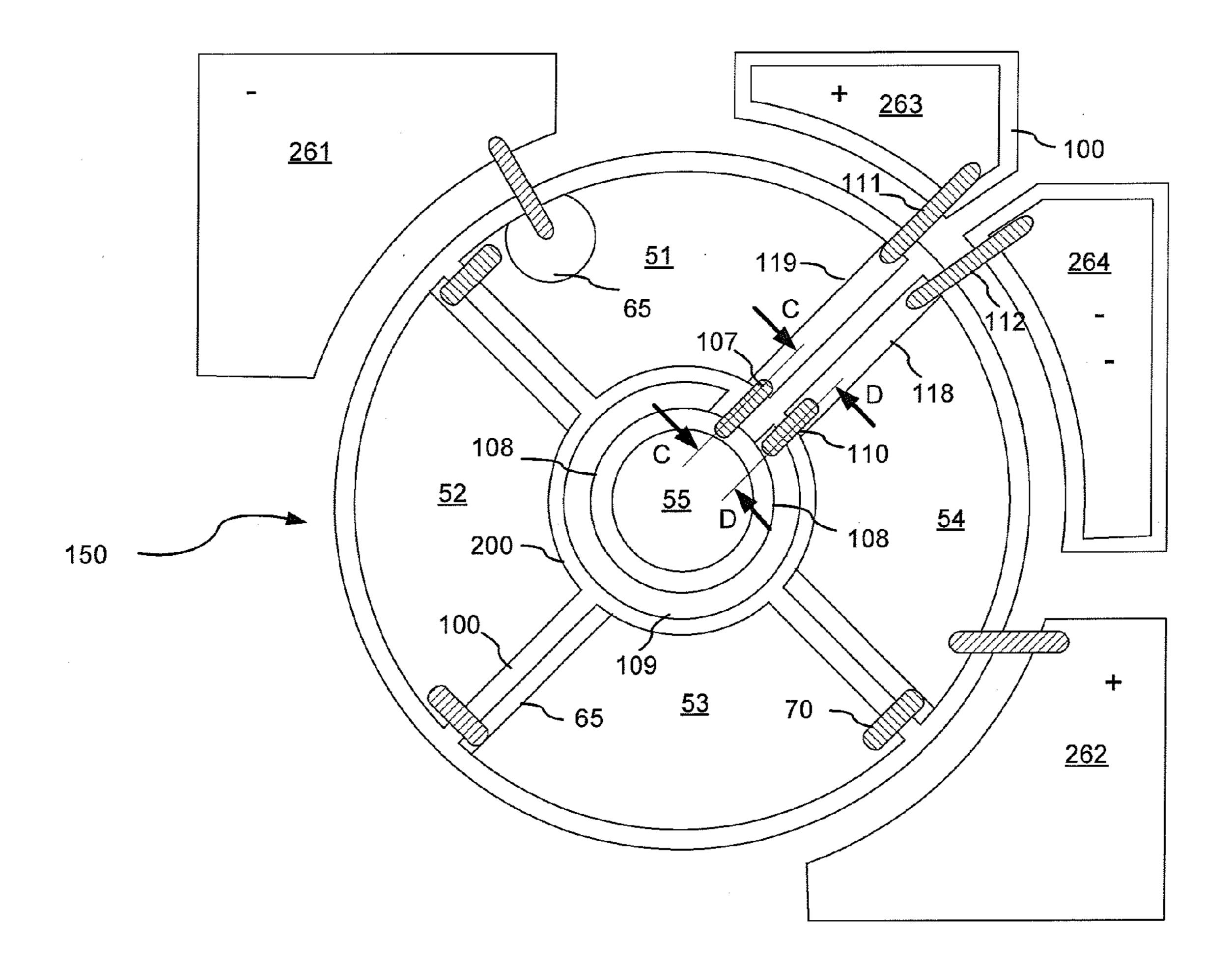

[0022] FIG. 3 is a plan view of a photovoltaic power converter having a center section according to one embodiment of the present invention;

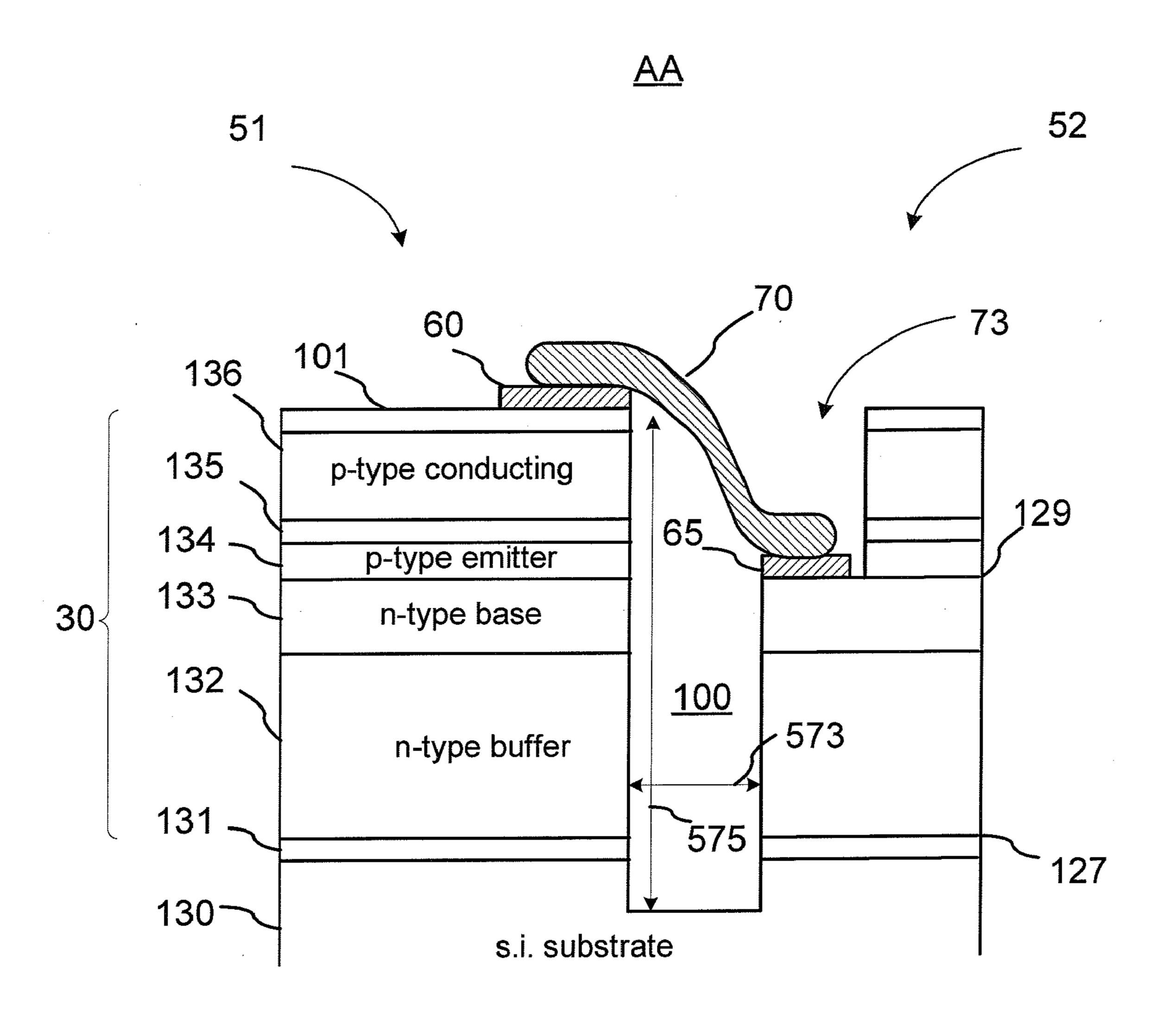

[0023] FIG. 4 is a cross-sectional view of the photovoltaic power converter of FIG. 3 as taken along line A-A, illustrating an exemplary layer structure thereof;

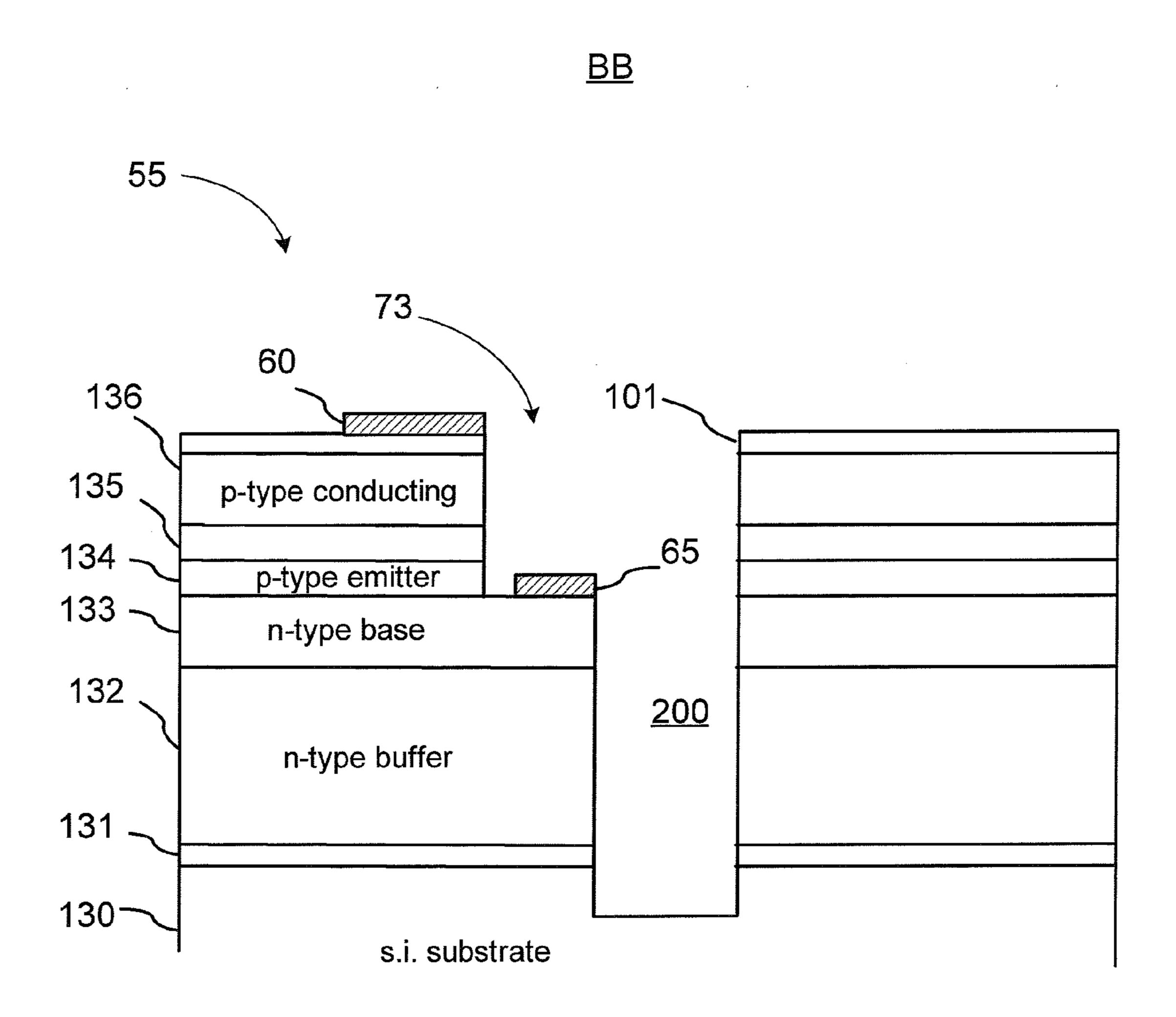

[0024] FIG. 5 is a cross-sectional view of the photovoltaic power converter of FIGS. 3 and 4 as taken along line B-B of FIG. 3;

[0025] FIG. 6 is a plan view of a photovoltaic power converter having an independently addressable center section;

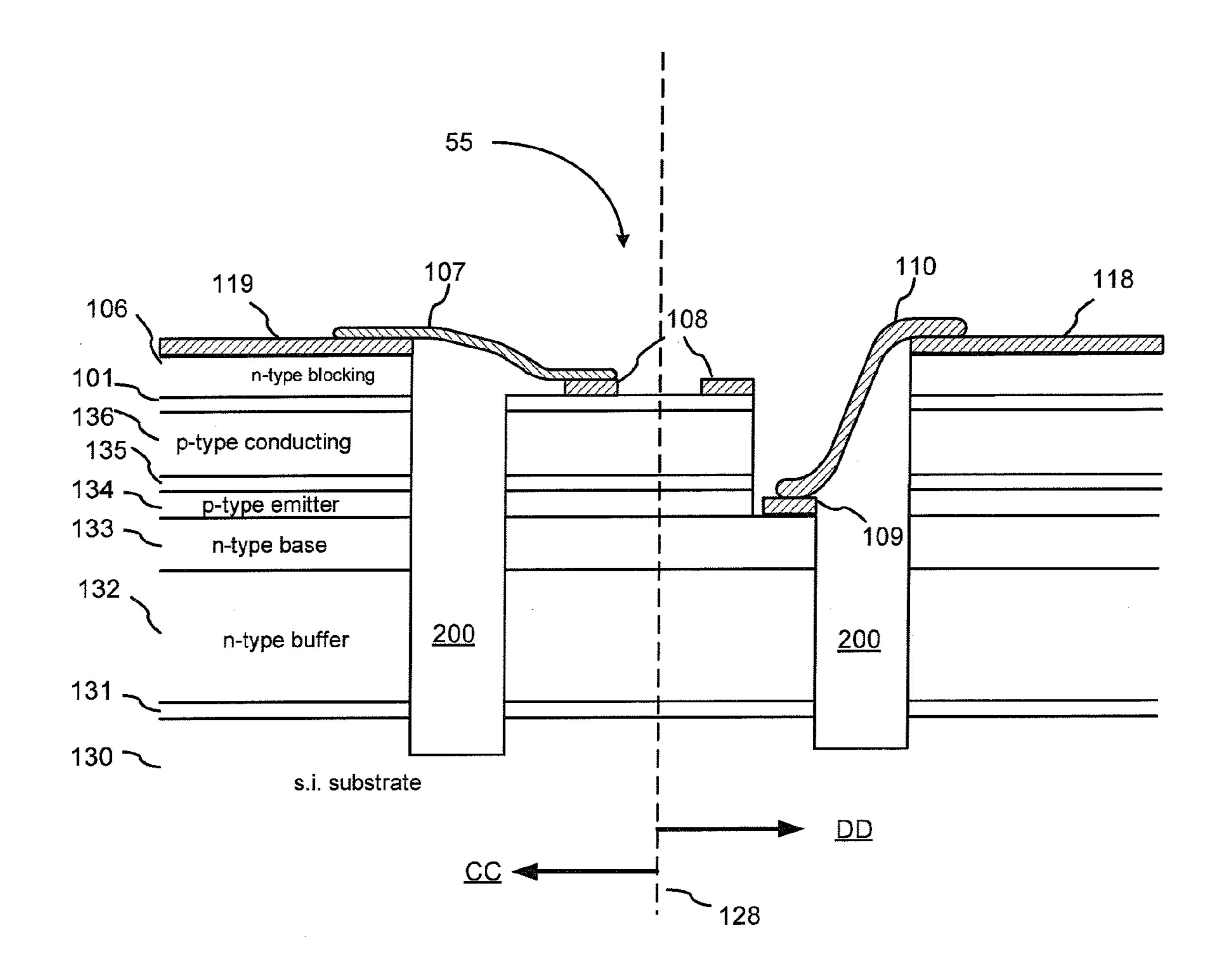

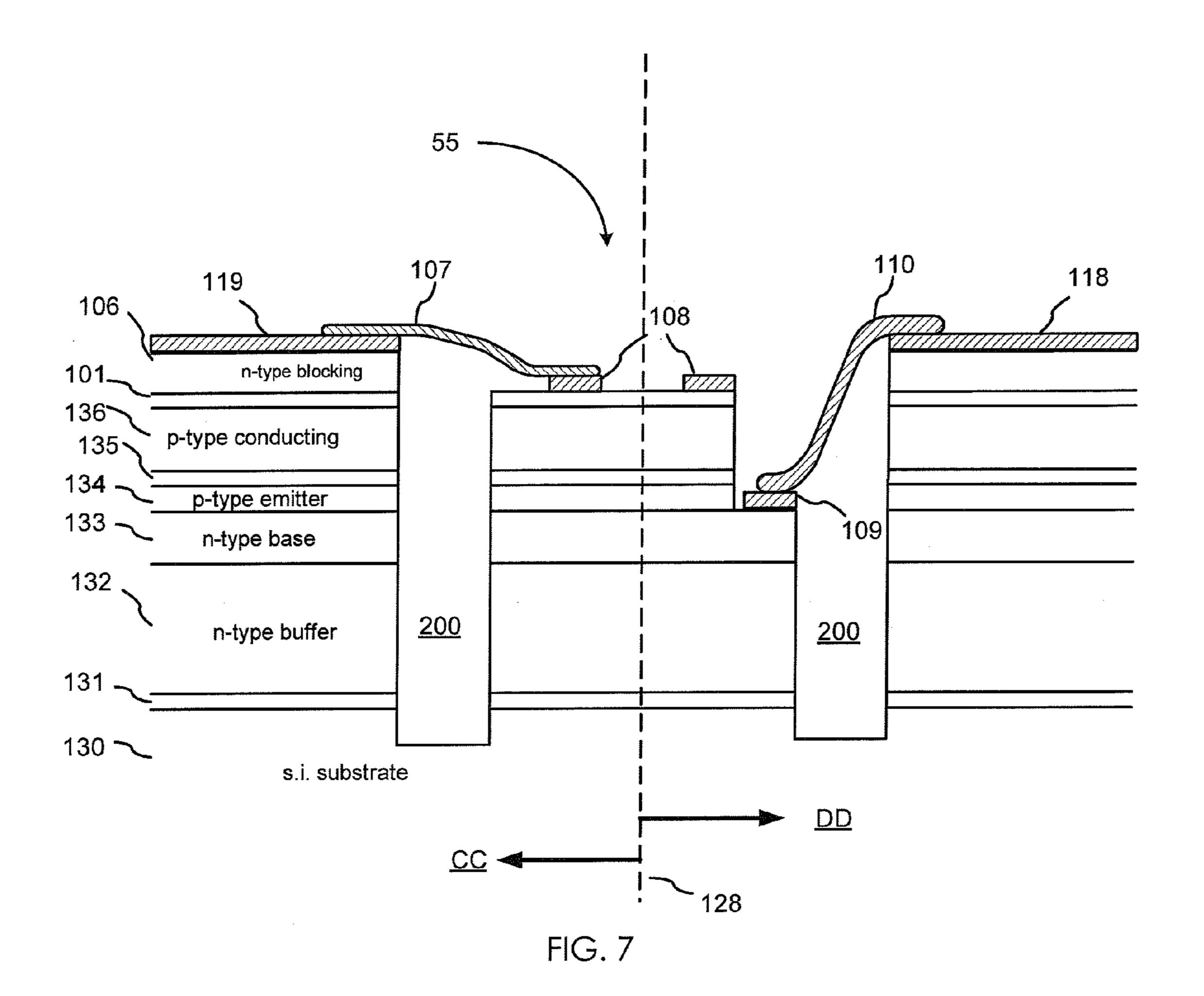

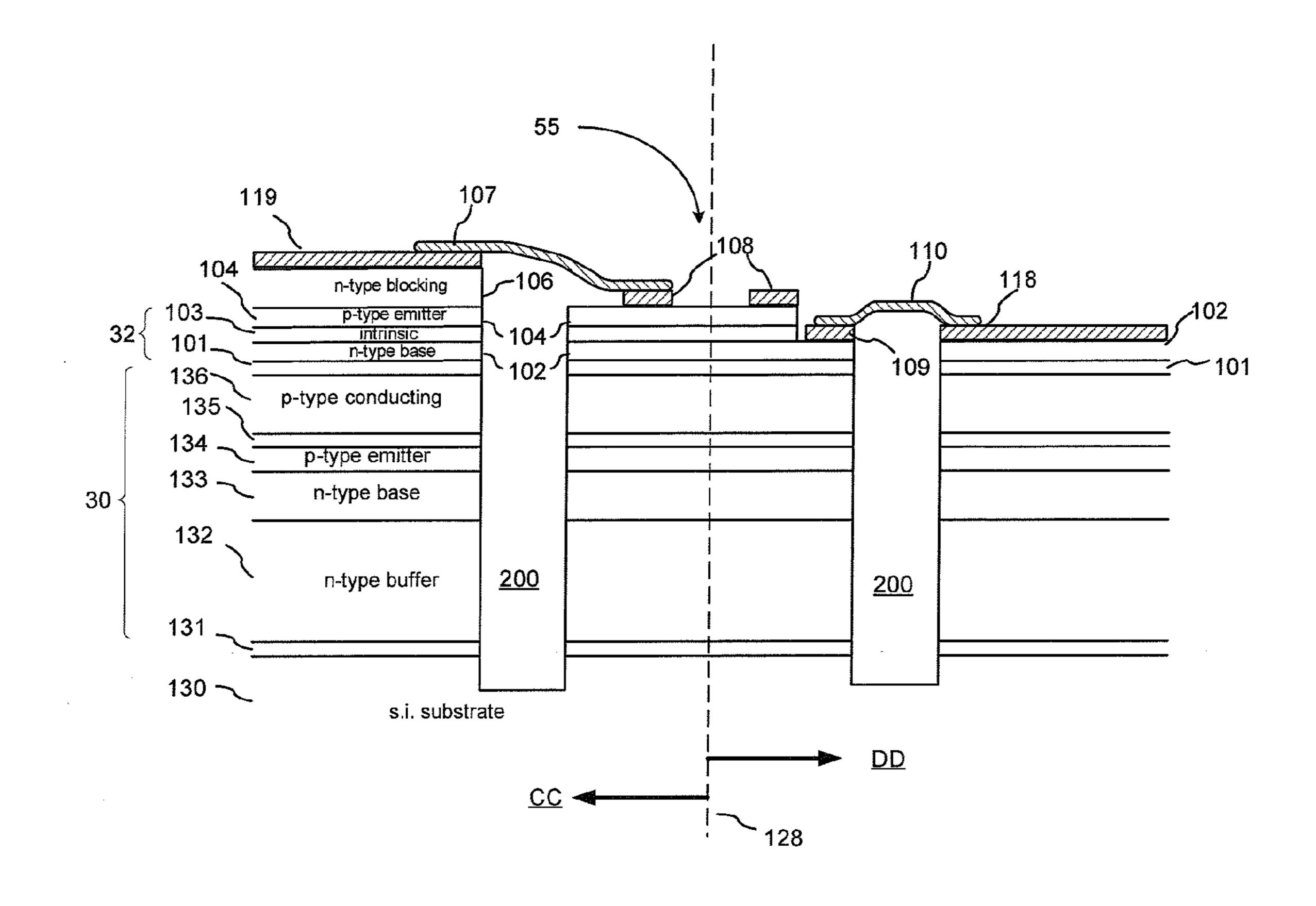

[0026] FIG. 7 provides cross-sectional views of an exemplary embodiment of the photovoltaic power converter of FIG. 6 as taken along lines C-C and D-D of FIG. 6;

[0027] FIG. 8 provides cross-sectional views of an alternative embodiment of the photovoltaic power converter of FIG. 6 as taken along lines C-C and D-D of FIG. 6;

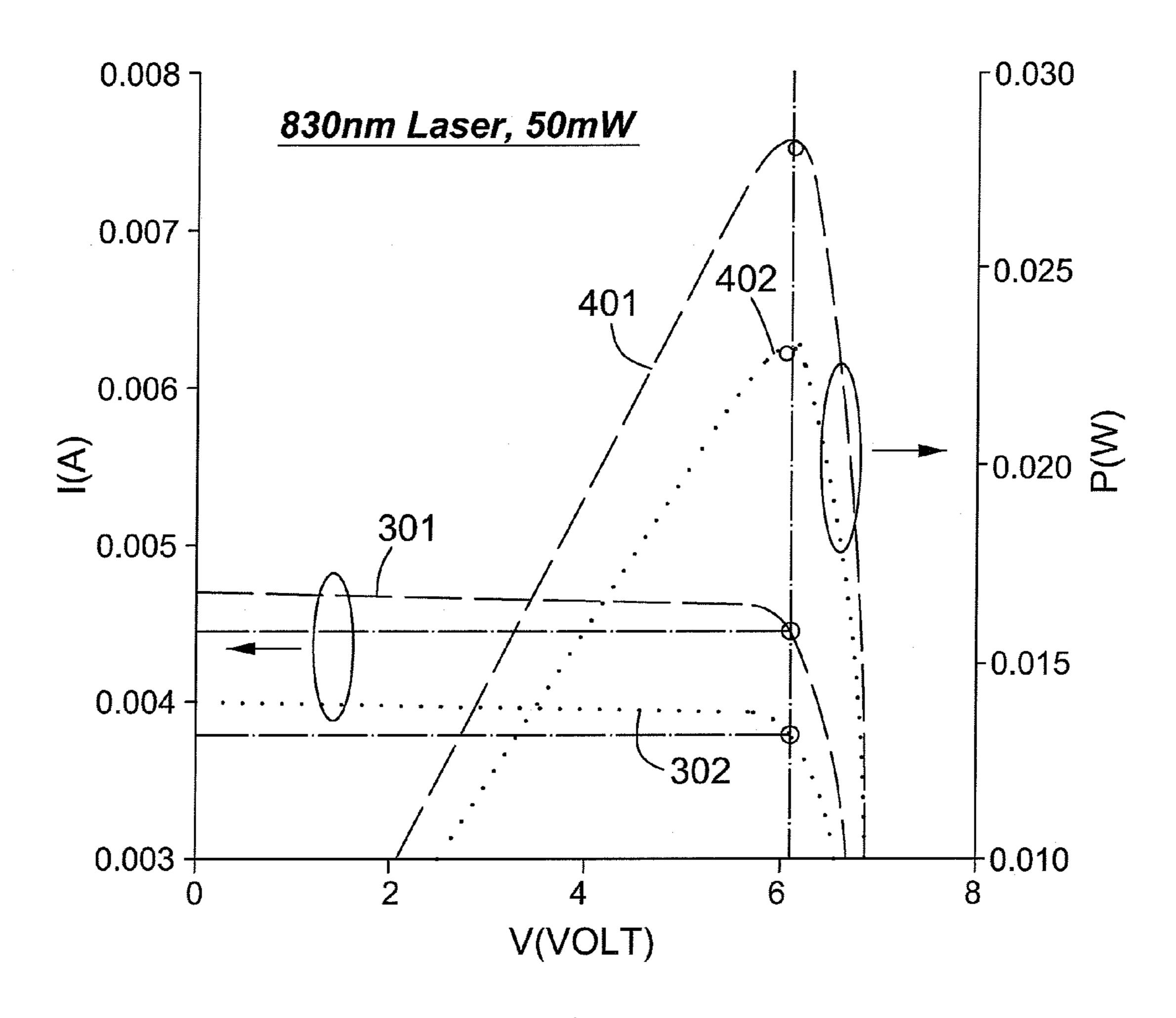

[0028] FIG. 9 is a graph showing current-voltage (I-V) and output power-voltage (P-V) characteristics of a GaAs/Al-GaAs photovoltaic power converter of the present invention under 50 mW illumination.

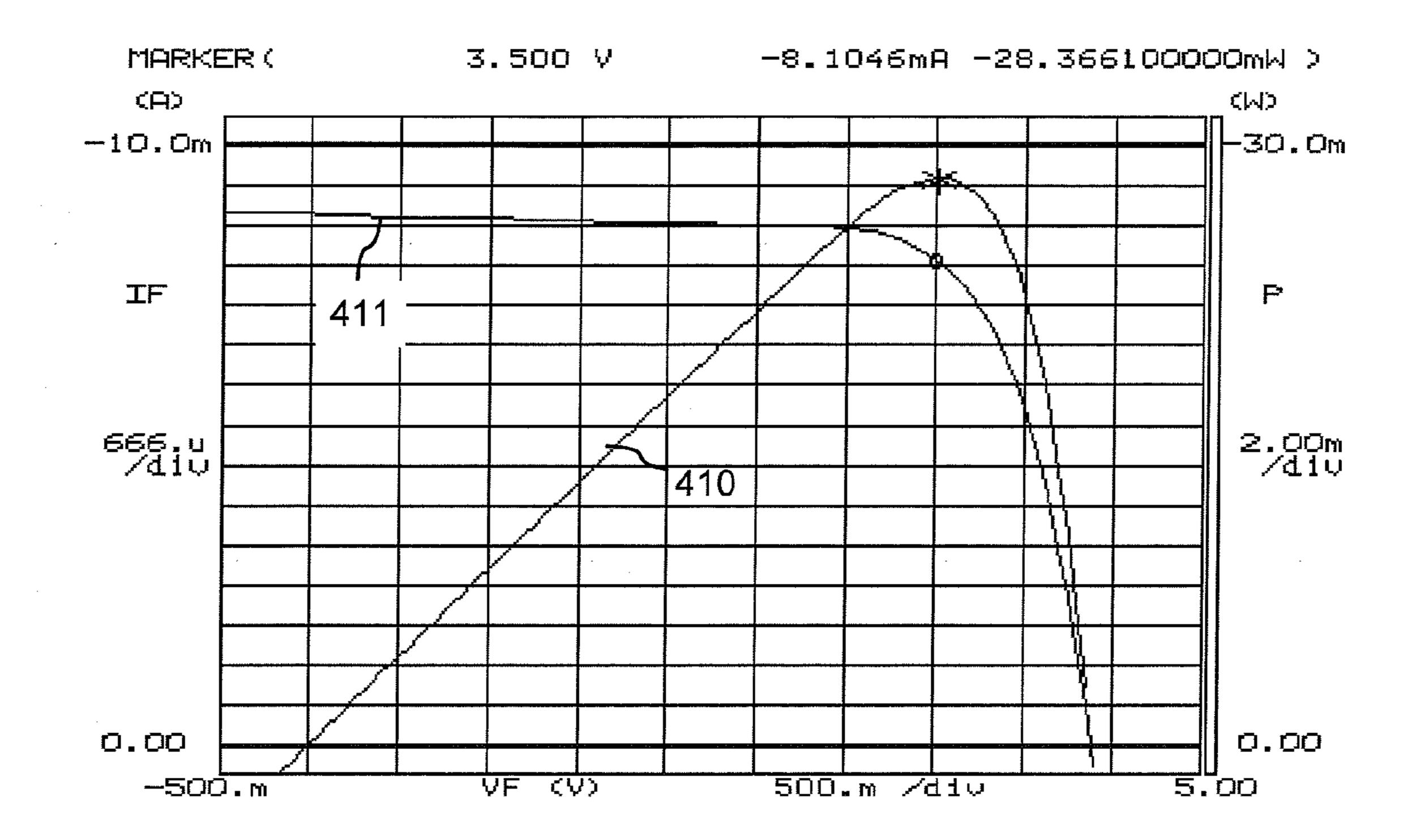

[0029] FIG. 10 is a graph showing current-voltage (I-V) and output power-voltage (P-V) characteristics of an InGaAs/InP photovoltaic power converter of the present invention under 1430 nm, 100 mW illumination;

### DETAILED DESCRIPTION

[0030] Exemplary embodiments of the photovoltaic power converter (PPC) of the present invention will now be first described with reference to FIGS. 3, 4 and 5.

[0031] Referring first to FIG. 3, the PPC 50 includes a plurality of device segments 51-55 arranged in a circular pattern, with a central portion, or segment 55 and a plurality of segments 51-54 that are disposed around the central segment 55 surrounding said central segment and forming a ring-like structure. The segments **51-54**, which will also be referred to herein as the ring segments, and the central segment 55 are separated from each other by narrow trenches 100, 200. A circular, or more generally, endless trench 200 separates the central segment 55 from the ring segments 51-54, while the trenches 100 extend radially therefrom to separate the ring sections 51-54 from each other. The trenches 100, 200 are etched in an epitaxially grown semiconductor wafer using one of known in the art etching techniques for etching high aspect ratio features such as Reactive Ion Etching (RIE). Electrical interconnects 70 in the form of air bridges connect the segments 51-55 in series between contact pads 61 and 62, as described hereinbelow in further detail, so that a voltage developed across each of the segment when the device is illuminated with light of suitable wavelengths is summed to generate a respectively higher output voltage  $V_{out}$ between the contact pads 61 and 62. Although the PPC 50 is shown in FIG. 3 to have four ring segments, other embodiments may have either lower or, greater number of ring segments so as to provide a higher output voltage. Generally, devices based on lower energy band gap materials will require a greater number of device segments to achieve a certain value of the desired output voltage  $V_{out}$ , for example 6V. For example, InP based devices described hereinbelow may have 12 or greater device segments, while 5 device segments may be suitable for GaAs based devices.

[0032] Turning now to FIG. 4, a cross-section of a portion of the PPC 50 along a line 'A-A' is shown to illustrate a layer structure of the PPC 50; it includes a semi-insulating or insulating substrate 130, a first current blocking layer 131, and a first multilayer structure 30, which in turn includes a buffer layer 132 of a first semiconductor material having a first conductivity type, a first base layer 133 of the first semiconductor material of the first conductivity type having a first energy bandgap, a first emitter layer 134 of a second semi-conductor material of a second conductivity type opposite to the first conductivity type so as to form a p-n junction region 129 therebetween, the first emitter layer having a second bandgap, and a conducting layer 136 of the third semiconductor material having the second conductivity type. The first

and second semiconductor materials are such that they absorb the incident light and generate photo-induced minority carriers in the emitter and base layers, which are then pulled by an electrical field of the p-n junction 129 in the adjacent emitter or base layer where they become majority carriers and charge the first emitter and base layers 134, 133, which are referred to hereinafter as the first active layers, with electrical charges of opposite polarities to create a photo-induced voltage. The third semiconductor material of the conducting layer 136 is transparent to the incident light and has a third band gap that is wider than the bandgaps of any of the first and second semiconductor materials forming the first base and emitter layers 133, 134. An optional contact or cap layer 101 of the second conductivity type that is transparent to the incident light may be deposited on top of the conducting layer 136 to assist in forming a good ohmic contact with first metal contacts 60 and grid lines (not shown). The terms "bandgap" and "energy bandgap" are used herein interchangeably to refer to the energy difference between the top of the valence band and the bottom of the conduction band of a semiconductor material.

The buffer layer 132 underlying the base layer 133 is relatively thick as compared to both the base and emitter layers 133, 134. In operation, the buffer layer serves as a second conducting layer assisting the flow of photogenerated carriers of the first polarity to a respective first metal contact 65; it should have a low sheet resistance preferably less than 1 ohm-cm<sup>2</sup>. Both the substrate **130** and the first current blocking layer 131 may be of the first semiconductor material, i.e. same as the buffer and first base layers 132, 133, to assist in the epitaxial growth of the high-quality base layer 133 having low density of defects that would give rise to non-radiative recombination of the photo-induced carriers. The second semiconductor material, i.e. the material of the first emitter layer has preferably the same or higher energy band gap and substantially the same lattice constant as the first semiconductor material, and may be same as the first semiconductor material.

[0034] The substrate 130 should have high resistivity so as to resist leakage therethrough of the photo-generated carriers that flow in the buffer layer 132, which would reduce the output voltage of the PPC 50 and thereby degrade the PPC's performance. Since high-quality substrates of most suitable semiconductor materials that are undoped and have intrinsic conductivity are only semi-insulating, the substrate 130 may be an intrinsic or semi-insulating substrate of the first semi-conductor material preferably having a resistivity of no less than 10<sup>7</sup> ohm-cm. In the selection of substrates, a good choice is an undoped GaAs or InP substrate having no more than 10<sup>15</sup> cm<sup>-3</sup> of background doping. Such background doping will ensure no direct current conduction in the substrate but does not prevent undesirable photo-induced current conduction in the substrate.

[0035] Advantageously, the first current blocking layer 131, which is according to the invention interposed between the semi-insulating substrate 130 and the buffer layer 132, has the second conductivity type that is opposite to the first conductivity type of the buffer layer 132, and therefore forms a p-n junction 127 with the buffer layer 132 that blocks the majority carries of the buffer layer 132 from flowing into the substrate 130, so as to further suppresses the leakage currents between the device segments through the substrate 130. The p-n junction 127 between the current blocking layer 131 and

the buffer layer 132 is referred to hereinafter as the current blocking junction 127 or the first current blocking junction. [0036] In the embodiments described herein the first conductivity type is the n-type conductivity, and the second conductivity type is the p-type conductivity, although in other embodiments of the invention the first conductivity type may be the p-type conductivity, and the second conductivity type may be the n-type conductivity. The n-type refers to the conductivity type of a semiconductor material doped with doping material or materials giving rise to donor impurities wherein the majority carriers are electrons, and the p-type refers to the conductivity type of a semiconductor material doped with doping material or materials giving rise to acceptor impurities wherein the majority carriers are holes. The terms "n(p)-type" and "n(p)-doped" are used herein interchangeably when refer to as semiconductor material of a respective conductivity type. The term 'doping level' used herein below refers to a net concentration of donor or acceptor impurities in the respective n-type or p-type semiconductor material.

[0037] The first base layer may be doped so as to have a donor impurity concentration in the range of  $5\times10^{17}$  to  $1\times10^{19}$  cm<sup>-3</sup>. The first base layer may be doped so as to have an acceptor impurity concentration greater than  $5\times10^{17}$  cm<sup>-3</sup>, or preferably in the range of  $2\times10^{18}$  to  $1\times10^{19}$  cm<sup>-3</sup>, and most preferably in the range of  $3\times10^{18}$  to  $5\times10^{18}$  cm<sup>-3</sup>. In other embodiments, the first base layer may have a donor impurity concentration that is increasing away from the junction region 129 towards the current blocking layer 131 from less than  $2\times10^{17}$  cm<sup>-3</sup> to at least  $2\times10^{18}$  cm<sup>-3</sup>. Similarly, the emitter layer may have an acceptor impurity concentration that is increasing away from the junction region 129 towards the conducting layer 136 from a level of less than  $2\times10^{17}$  cm<sup>-3</sup> to at least  $2\times10^{18}$  cm<sup>-3</sup>.

[0038] In a first preferred embodiment, the semiconductor materials of the substrate 130, the current blocking layer 131, the buffer layer 132, the first base and emitter layers 133, 134 are gallium arsenide (GaAs), the semiconductor material of the conducting and optional window layers 136, 135 is one or both of indium gallium phosphate (InGaP) and aluminum gallium arsenide (AlGaAs), and of the optional cap layer is GaAs.

[0039] More particularly, the substrate 130 is formed from substantially undoped GaAs having the background doping level no greater than  $10^{-15}$  cm<sup>-3</sup> and may have a thickness of several hundred microns (µm), for example in the range of 350 μm to 650 μm. The current blocking layer 131 epitaxially grown on the substrate 130 is a p-type GaAs having an acceptor impurity concentration in the range of  $5 \times 10^{17}$  cm<sup>-3</sup> to  $1\times10^{19}$  cm<sup>-3</sup> or for example about  $2\times10^{18}$  cm<sup>-3</sup> and a thickness in the range of 0.2 to 0.3 microns for example 0.25 microns. The buffer layer 132 is an n-type highly-doped GaAs epitaxially grown on the current blocking layer 131 and having a donor concentration in the range of  $5 \times 10^{17}$  cm<sup>-3</sup> to  $2\times10^{18}$  cm<sup>-3</sup> and a thickness in the range of 1 to 10 microns for example 5 μm. The first base layer 133 is epitaxially grown on the buffer layer 132, is also of n-type GaAs having a donor concentration in the range of  $5 \times 10^{17}$  cm<sup>-3</sup> to  $2 \times 10^{18}$  cm<sup>-3</sup>, for example  $1 \times 10^{18}$  cm<sup>-3</sup> and a thickness of approximately 3 microns. The first emitter layer 134 is epitaxially grown on the first base layer 133 and is of p-type GaAs having an acceptor impurity concentration in the range of  $2 \times 10^{18}$  cm<sup>-3</sup> to  $1\times10^{19}$  cm<sup>-3</sup>, and preferably in the range of  $3\times10^{18}$  cm<sup>-3</sup> to  $5 \times 10^{18}$  cm<sup>-3</sup> and a thickness in the range of 0.2 to 1 micron,

for example  $0.8 \mu m$ . The p-n junction 129 is formed between the first base layer 133 and the first emitter layer 134.

[0040] The semiconductor material of the optional window layer 135, which may be epitaxially grown on the first emitter layer 134, is of a first alloy of GaAs, such as AlGaAs or, more particularly,  $Al_xGa_{1-x}As$ , with the relative aluminum content x>50%, for example x=80%. The window layer 135 has the same or higher p-type conductivity as the first emitter layer 134. The AlGaAs is selected because of its transparency to the selected wavelengths of radiation at which the PPC 50 operates, and for passivation of the first emitter layer 134 so as to reduce the rate of non-radiative recombination of the photo-induced carriers on the interface of the first emitter layer 134 with the following layer. The window layer 135 may have an acceptor concentration of  $5\times10^{18}$  cm<sup>-3</sup> and a thickness in the range of 0.02 and 0.1 µm, for example 0.08 µm.

[0041] The conducting layer 136 may be a highly p-doped layer with an acceptor impurity concentration level in the range of  $2\times10^{18}$  cm<sup>-3</sup> to  $2\times10^{19}$  cm<sup>-3</sup>, and preferably  $3\times10^{18}$ cm<sup>-3</sup> or greater, so as to reduce the sheet resistance of the conducting layer 136. The semiconductor material of the conducting layer 136 may be a second alloy of aluminum gallium arsenide, such as  $Al_xGa_{1-x}As$ , with the aluminum content preferably less than 50%, for example 20%, and a thickness in the range of 1 to 3  $\mu$ m, for example 2  $\mu$ m. The aluminum content x of the second alloy of AlGaAs of the conducting layer 136 should be sufficiently high to ensure the transparency of the conducting layer 136 to the incident radiation of the selected wavelength. On the other hand, reducing the aluminum content in the conducting layer is beneficial for reducing the sheet resistance thereof as it reduces the undesirable oxidization of the layer.

[0042] Therefore, an alternative embodiment of the invention utilizes an aluminum free conducting layer 136 such as a p-doped layer of an alloy of InGaP, for example having a material composition  $In_xGa_{1-x}P$  with x in the range of 0.5 to 0.54. Such a layer can be epitaxially grown either over the window layer 135 of the first alloy of AlGaAs with a high Al content over 50%, or can be directly grown on the first emitter layer of p-doped GaAs 134.

[0043] Another aspect of the present invention relates to the use of carbon (C) as the preferred doping material that is utilized in preferred embodiments of the invention for the p-doped layers of the PPC 50, such as the current blocking layer 131, the first emitter layer 134, the optional window layer 135, and the conducting layer 136, instead of more traditional p-doping materials such as beryllium (Be) and zinc (Zn) that are typically used in GaAs and InP-based optoelectronic devices. Advantageously, the use of carbon doping enables to strengthen the electrical field in the p-doped emitter layer 134 and across the p-n junction region 129, and increase the internal quantum efficiency of the PPC. Traditional dopants, such as zinc, have possible detrimental effects associated with high doping levels greater than 5e17, such as the decrease in a minority carrier lifetime, whereas carbon doping is not associated with these effects, or at least to a considerably lesser degree. Carbon doping enables the highly doped GaAs or InGaAs to preserve good minority carrier lifetimes and hence contributes to a high quantum efficiency in the active layers 133/134, i.e. a high proportion of photo-generated electron and holes that leave the p-n junction region 129 without non-radiatively recombining therein. Accordingly, using carbon as the doping material, the p-doping level of the emitter layer 134 may be as high as  $5 \times 10^{18}$

cm<sup>-3</sup> without substantially decreasing the quantum efficiency of the device. Contrary to that, the use of conventional doping materials such as Zn at high doping levels, for example greater than  $2\times10^{18}$  cm<sup>-3</sup>, in the p-layer of the p-n junction 129 may lead to the addition of non-radiative recombination centers and a decreased minority carrier life time, resulting in a lowering of the quantum efficiency and thus smaller photocurrents and/or output voltages that the PPC can produce. Furthermore, spatial distribution of carbon within the semiconductor host material is more stable than that of conventional acceptor impurities such as Zn and Be. By being stable, the carbon doping enables sharper, high gradient interface to be formed between the p-type and the n-type portions of the p-n junction region 129, contributing to a stronger electrical field associated with the p-n junction and a better efficiency with which the photo-generated minority carriers are pulled from the p-n junction 129 to contribute to the photocurrent. The carbon doping of the conducting layer 136 enables a reduced sheet resistance of the conducting layer 136 by providing a higher quality material at elevated doping levels, especially in combination with aluminum-less InGaP material of the conducing layer 16.

[0044] The aforedescribed embodiment, wherein the semiconductor material of the base layer 133 and the emitter layer 134 is GaAs, is directed to the optical to electrical power conversion of light having wavelengths in the range of 0.8 to 0.9 µm, as defined by the GaAs energy bandgap and the AlGaAs/InGaP energy bandgap of the conducting layer. One skilled in the art would appreciate however that light of shorter or longer wavelengths can be converted using the PPC 50 by utilizing alloys of AlGaAs or InGaAs lattice matched to the GaAs substrate as the buffer and emitter layers 133, 134, and suitably adjusting the material composition of the conducting layer 136. For example, an alloy of  $Al_xGa_{(1-x)}As$  with the Al content x from 5% to 35% may be utilized for the first active layers 133, 134, and another alloy of  $Al_xGa_{(1-x)}As$  with a higher concentration of Al or an alloy of InGaP having a higher bandgap than the material of the first active layers 133, 134 may be used for the conducting layer 136. By utilizing alloys of AlGaAs or InGaAs grown over the GaAs substrate as the first active layers 133/134, the PPC 50 may be manufactured that is suitable for power conversion of light in the wavelength range from about 0.7 µm to about 1.3 µm. The energy band gap of the conducting layer 136 may be between 0.15 and 0.5 eV greater than the energy band gap of the emitter layer 134 so as to ensure the transparency of the conducting layer 136 for the incident light that is absorbed in the first active layers 133/134.

[0045] Other embodiments of the PPC 50 utilize a layer structure that is epitaxially grown on indium phosphate (InP) substrates, and are suitable for converting light at wavelengths in the 1.2  $\mu$ m-1.6  $\mu$ m range, where most commercial optical fibers has a low optical loss. By way of example, in one such embodiment the PPC 50 may utilize the following semiconductor materials in its layer structure. The semiconductor material of the substrate 130 is a semi-insulating InP doped with Iron (Fe) to  $10^{16}$  cm<sup>-3</sup> and has a high resistivity of 10<sup>7</sup> ohm-cm. The current blocking layer **131** is a layer of p-doped InP having a thickness in the range of 0.2 to 0.3 μm, for example 0.25  $\mu$ m, and doping level of  $5\times10^{17}$  cm<sup>-3</sup> or greater; the buffer layer 132 is a layer of n-doped InP having a thickness in the range of 5 to 10 μm, for example 7 μm, and a donor impurity concentration of  $5 \times 10^{17}$  or greater; the semiconductor material of the first base layer 133 is an n-doped

alloy of InGaAs that is lattice-matched to InP and has a thickness in the range of 1 to 3  $\mu$ m, for example 3  $\mu$ m, and a donor impurity concentration of  $5 \times 10^{17}$  or greater; the first emitter layer 134 is a p-doped layer of one of an alloy of InGaAs that is lattice-matched to InP and has a thickness in the range of 0.5 to 1.5  $\mu$ m, for example 1  $\mu$ m, and an acceptor impurity concentration in the range of  $2 \times 10^{18}$  cm<sup>-3</sup> to  $1 \times 10^{19}$ cm<sup>-3</sup>, or preferably in the range of  $3\times10^{18}$  cm<sup>-3</sup> to  $5\times10^{18}$ cm<sup>-3</sup>, with carbon as the preferred doping material; the conducting layer 136 is a p-doped layer of InP, and has a thickness in the range of 1.5 to 2.5  $\mu$ m, for example 2  $\mu$ m, and an acceptor impurity concentration in the range of  $2 \times 10^{18}$  cm<sup>-3</sup> to  $2\times10^{19}$  cm<sup>-3</sup>, and preferably greater than  $3\times10^{18}$ . The doping material for the p-doped InP layers 131, 136 can be, for example, beryllium (Be). The semiconductor material of the contact layer 101 is p-doped InGaAs, with carbon as a preferred doping material, and the doping level approximately  $2 \times 10^{18}$  cm<sup>-3</sup> or greater, and a thickness of 0.1 to 0.2 μm.

[0046] Turning now back to FIG. 3, the device segments 51-55 of the PPC 50 are fabricated in a PPC wafer of the aforedescribed layer structure by forming the trenches 100, 200 which extend through the first multiplayer structure 30, the current blocking layer 131, and partially extend into the substrate 130, so that the device sections 51-55 are electrically and spatially separated from each other and supported by the substrate that is at least semi-insulating, i.e. has a resistivity of no less than 10<sup>7</sup> ohm-cm so as to reduce, in cooperation with the current blocking layer 131, leakage currents between the device segments.

[0047] The depth of the trenches is defined by the total thickness of the first multi-layer structure 30, and may be in the range of 10 to 20  $\mu$ m. An aspect ratio of trenches 100, 200, which is defined as the ratio of the trench depth 575 to the trench width 575 as indicated with respectively labeled arrows in FIG. 4, should be suitably high so as to minimize the fraction of the incident light that reaches the substrate material at the bottom of the trenches, since said light may get absorbed in the substrate material generating photo-carriers and thereby causing an undesirable increase in the substrate conductance, thus potentially causing a conductance path to be created in the substrate between the device segments, leading to a reduction in the light conversion efficiency of the PPC. Therefore the trenches 100, 200 should be suitably narrow, with the trench width 573 preferably in the range between 2 μm and 10 μm, for example 5 μm or less, with the aspect ratio greater than 4 and preferably greater than 5. The current blocking layer 131 blocks the majority carriers of the buffer layer 132 from flowing into the substrate, thereby preventing leakage currents between the device segments through the substrate 130 from occurring, resulting in a considerable improvement in the light conversion efficiency of the PPC 50 compared to a similar device in the absence of the current blocking layer 131. The terms light conversion efficiency and power conversion efficiency are used herein interchangeably to mean the ratio of electrical power provided by the PPC to an external electrical circuit to the optical power of light incident on the PPC.

[0048] In each of the device segments 51-55, a first metal contact 65 is disposed on the first base layer 133 in electrical communication therewith, and a second metal contact 60 is disposed on the optional cap layer 101 or, in the absence of such layer, directly on the conducting layer 136, to be in electrical communication with the first emitter layer 134.

Electrical interconnects 70 in the form of metallic air bridges are then formed to connect each but one of the first metal contacts 65 to a second metal contact of an adjacent device segment so that all the device segments 51-55 are connected in series. When light of selected wavelengths in the absorption range of the first active layers 133/134 and the transmission range of the conducting layer 136 is incident upon the PPC **50**, voltages that are developed across the p-n junction region 129 of each of the device segments 51-55 are added so as to produce a higher summed voltage  $V_{out}$  between the first and second metal contacts that remain unconnected to any of the other first and second metal contacts. These first and second metal contacts that remain unconnected to metal contacts of other segments are referred to herein as base and emitter electrical contacts, respectively; they may be connected with air bridges 71 to the contact pads 61 and 62 to assist in connecting the PPC **50** to an external circuit.

[0049] As illustrated in FIG. 3 by way of example, the second metal contact 60 of the device segment 51 may be connected with the air bridge 70 to the first metal contact 65 of the device segment **52**, as further shown in a cross-sectional view in FIG. 4. The second metal contact 60 of this device segment 51 may be connected with an air bridge to the first metal contact 65 of the central segment 55, with the second metal contact thereof 60 being connected to the first metal contact 65 of the device segment 53. The first and second contacts 65, 60 of the central segment 55 have both the shape of a ring and are referred to hereinafter as the first and second ring contacts. They are located at the circumference of the central segment 55, with the first ring contact 65 being adjacent to the circular trench 200 and the second ring contact 60 located within the central segment 55 next to the first ring contact 65 that is located in the opening 73, as illustrated in FIG. 5, which shows a cross-sectional view of another portion of the PPC **50** along the 'B-B' line indicated in FIG. **3**. The first ring contact 65 has a gap 61 therein over which the air bridge 70 connects the second ring contact 60 to the first metal contact 65 of the next device segment 53, the second metal contact of which is connected with another air bridge 70 to the first metal contact 65 of the last device segment 54. This interconnect configuration results in the device segments 51, 52, 55, 53, and 54 being serially connected in the stated order, with the output voltage  $V_{out}$  that is developed under suitable illumination between the emitter and base electrical contacts, i.e. between the second metal contact 65 of the device segment **54** and the first metal contact **60** of the device segment 51, being approximately the sum of voltages developed across the p-n junctions 129 of each of the device segments **51-55**. The metal pads **61** and **62**, to which the remaining metal contacts of the device segments 54 and 51 are connected with the air bridges 71, serve as anode and cathode terminals of the PPC **50**, respectively.

[0050] The first and second metal contacts 65, 60 can be deposited in a single metallization step, that may be followed by a contact patterning step and a fabrication of the air bridges 70, 71, for example as described in the Virshup patent. The second metal contacts 60 in the outer device segments 51-54 are preferably deposited so as to overlap with one of the metal grid lines on the cap layer 101, while the central segment 55 may not have any grid lines and the respective second ring contact 60 is deposited directly on the contact cap layer 101. The widths of the first and second ring contacts 65, 60 of the central segment 55 should be suitably small as to leave most of the surface area of the contact layer 101 of the central

segment **55** open to the incident light. By way of example, the diameter of a circle that defines the outer circumference of the ring segments **51-54** is 1800  $\mu m$ , the diameter of the central circular segment **55** is 250  $\mu m$ , and each of the ring contacts **65**, **60** has a width in the range of 10 to 50  $\mu m$ .

[0051] Prior to depositing the first metal contact 65, a portion of the first base layer 133 in each device segment is exposed at a selected location of the respective device segment preferably near a trench separating it from an adjacent device section, by selectively etching away a top portion of the multilayer structure 30 up to the first base layer 133 so as to form an opening 73 in the first emitter layer 134 wherein the first metal contact 65 is then deposited, as illustrated in FIG. 4 which shows a cross-sectional view of a portion of the PPC 50 along the 'A-A' line indicated in FIG. 3.

[0052] The device segments layout of the PPC 50, wherein one device segment 55 is centrally located and surrounded by a group of device segments 51-54 that are disposed at the circumference of the central segment 55, is a novel feature of the present invention that advantageously provides for a higher optical power conversion efficiency as compared to the prior art "pie-wedge" layout of FIG. 1, wherein the trenches **26** all converge in the center of the PPC effectively forming a hole in the center of the photosensitive surface of the device. This prior art layout may significantly reduce the conversion efficiency of the prior art optical power converters in applications wherein the incident light is in the form of a beam which intensity reduces away from the beam axis, such as the Gaussian or near-Gaussian beams emanating from single mode optical fibers. Advantageously, the PPC 50 of the present invention eliminates this drawback of the prior art devices by utilizing a centrally located device segment 55, which enables to utilize light at the center of the incident beam where light intensity is maximal. By "tailoring" the geometry of the PPC segments to the light input density distribution, negative effects of an uneven illumination pattern may largely be avoided. We found that, by utilizing a suitably dimensioned central device segment 55, the power conversion efficiency of the PPC 50 can be increased by up to 25% for a PPC with 5 device segments. We also found that for efficiently converting the optical power of a Gaussian beam into electrical power, the central segment 55 should preferably have a photosensitive surface having an area between 15% and 25%, and more preferably about 20%, of the total area of the photosensitive surface of the PPC **50**. However, in applications wherein the intensity of the incident light is substantially uniform across the photosensitive surface of the PPC **50**, the photosensitive surfaces of the device segments 51-55 should be equal in area. Note that the term "photosensitive surface" is used herein to refer to the surface of the PPC through which the incident light reaches the active layers of the device where it is absorbed and converted to electricity. The photosensitive surface of the PPC **50** is a portion of the total light receiving surface of all the device segments 51-55, as shown in FIG. 3, that is not covered by metal. The term "photosensitive area" is used herein to refer to an area of the respective photosensitive surface. Another advantage provided by the central segment 55 is the reduction of the undesirable voltage drop in the device associated with the resistive path the carriers generated at the device center have to travel to reach the contact pads 61, 62. By capturing the light in a centrally located segment, the current does not have to travel a long distance through resistive material, but can be collected directly near the central segment and fed out via metallic grid

lines having low resistance to the perimeter of the device. In the prior art, there were no means of the collections of the current from the inner portion of the device.

[0053] Referring now to FIG. 6, another embodiment of the invention provides a PPC 150, wherein the central segment 55 is connected independently of the ring segments 51-54 and is electrically isolated therefrom. The PPC 150 is now a fourport device, having a first device portion embodied by the central device segment 55, which is electrically isolated from a second device portion as embodied by the ring segments 51-54, and can be electrically addressed independently therefrom. The ring segments 51-54 are connected in series between the contact pads 261 and 262, and form a section of the PPC 150 that is referred to herein as the ring device section or simply as the ring section. Note that in FIGS. 3-7 like numerals are used to indicate like elements to simplify the description and assist in understanding of the shown embodiments, with the exception that the first and second ring contacts of the central segment 55 are now labeled with reference numerals 109 and 108, respectively to distinguish them from the first and second metal contacts 65, 60 of the ring segments 51-55. Instead of being connected to the first and second metal contacts of respective ring segments as in the PPC 50, the first and second ring contacts 109, 108 of the central segment 55 of the PPC 150 are connect to contact pads 263 and 264 by means of conducting pathways 118 and 119 that are preferably less than 15 □m wide, are located next to a trench 100 separating two ring segments of the device. The conducting pathways 118 and 119 are disposed over the device segments 51 and 54 extending from the inner to outer circumference thereof, but are insulated therefrom by a second current blocking layer 106, which is epitaxially grown on the cap layer 101 and has a conductivity type that is opposite to the conductivity of the cap layer 101.

[0054] This second current blocking layer is illustrated in FIG. 7, showing cross-sectional views of portions of the PPC 150 along the lines 'C-C' (to the left of a dashed line 128), and 'D-D' (to the right of the dashed line 128). In the afore-described embodiment wherein the semiconductor material of the substrate 130 and the first active layers 133/134 is GaAs, and the conducting and cap layers 136, 101 are p-type, the second current blocking layer 106 may be an n-doped GaAs with a doping level of at least  $5\times10^{17}$  cm<sup>-3</sup> and a thickness in the range of 1 to 5  $\mu$ m. The pathways 119, 118 can be formed in the same or separate metallization step as the first and second metal contacts 65, 60 followed by a contact patterning step, after which the second blocking layer 106 is removed everywhere except for directly under the narrow metal pathways 118, 119.

[0055] The device segments 51-54 are connected in series by the air bridges 70 between the contact pads 261 and 262, with the first metal contact 65 of each of the device segments 51-54, except for the device segment 51, connected to the second metal contact 60 of a next adjacent ring device segment so at to form a serially connected chain of device segments 51-54, with the first metal contact 65 of the first device segment 51 in the chain connected to the contact pad 261 with a first air bridge 71, and the second metal contact 60 of the device segment 54 connected to the contact pad 262 with the second air bridge 71. The contact pads 263 and 264 function as anode and cathode terminals of the first, or central portion 55 of the PPC 150, while the contact pads 261 and 262 function as the anode and cathode terminals of the second, or ring portion of the PPC 150 comprised of the serially con-

nected ring device segments **51-54**. The conducting pathways **118** and **119** are also referred to herein as the third and forth metal contacts, respectively. They extend outwardly across the ring device section and are electrically insulated from the device segments thereof for connecting to an external circuit independently of the device segments **51-54** of the ring section.

Advantageously, the PPC **150** can function as an integrated device combining a PPC and a more conventional photodetector (PD), with a PPC portion of the device corresponding to the ring portion 51-54, and the PD portion of the device corresponding to the central portion 55. When illuminated by light of suitable wavelengths having a modulation component carrying data, the PPC 150 can provide both electrical power in the form of a 5V or higher voltage signal across the device terminals 261, 262 to be used, for example, for driving external electrical circuitry, and a detected data at the terminals 263, 264. Moreover, the central portion 55 of the device can be forward biased using the anode and cathode terminals 263, 264 thereof, forcing its active layers 133/134 to emit rather than absorb light, so that the central portion of the PPC 150 can function as an LED, for example to transmit rather than detect optical data.

[0057] Accordingly, this aspect of the invention provides a four port PPC that has two independently addressable portions, as opposed to the prior art optical power converter of FIG. 1 and the novel PPC 50 of the present invention, which both are two-port devices. Advantageously, the independently addressable portions of the PPC 150 can be used to perform two different functions, for example to perform optical power conversion and optical data reception or transmission simultaneously within the same device.

[0058] In the embodiment of FIG. 7, the central and ring portions of the PPC 150 utilize different spatial regions of the same p-n junction 129 to detect or emit light, and to convert light into electrical power, respectively. However, the p-n junction 129 may not be optimal for receiving or emitting optical data signals, i.e. for performing the LED and PD functions. Moreover, in some applications the optical data signal and the optical power can be carried by different wavelengths of light.

[0059] With reference to FIG. 8, another embodiment the PPC 150 includes a second multiplayer structure 32, for example of a p-i-n type, disposed on the first multilayer structure 30 within center segment 55, which may be optimized for operating as a PD or an LED. This second multilayer structure 30 may include a second base layer 102 of the first conductivity type epitaxially grown on the cap layer 101, followed by an undoped or intrinsic layer 103 epitaxially grown on the second base layer 102, and a second emitter layer 104 of the second conductivity type epitaxially grown over the intrinsic layer 103. The second current blocking layer 106 is then epitaxially grown on top of the second emitter layer 104. After forming the conducting pathways 118, 119 using metallization and patterning steps, the second current blocking layer 106 is removed everywhere except under the conducting pathways 118, 119, where it provides electrical insulation from the underlying semiconductor structure.

[0060] The second multilayer structure 32 is kept within the central segment 55, but may be removed everywhere within the ring segments 51-54, except from under the pathways 118, 119. The first ring contacts 109 of the central segment 55 is disposed on an exposed portion of the second base layer 102 in an opening in the intrinsic and second emitter layers

103, 104 as shown to the right of the dashed line 128 in FIG. 8, to be in electrical communication with the second base layer 102. The second ring contact 108 of the central segment 55 is disposed on the second emitter layer 104 to be in electrical communication therewith. In the illustrated embodiment wherein the second emitter layer 104 is p-type and the second base layer 102 is n-type, the first ring contact 109 and the second ring contact 108 may be formed using known in the art n-type and p-type metallization techniques, respectively, for example an Au/Ge/Au metallization or the n-type metal contacts 108, 118, 119, and 65, and Ti/Pt/Au metallization for the p-type metal contacts 109 and 60. The metal air bridge 107 connects the second emitter layer 104 via the second ring contact 108 to the conducting pathway 119, which is in turn connected with the air bridge 111 to the anode terminal 263 of the p-i-n structure of the central portion 55 of the PPC 150. Similarly, the metal air bridge 111 connects the second base layer 102 via the first ring contact 109 to the conducting pathway 118, which is in turn connected with the air bridge 112 to the cathode terminal 264 of the p-i-n structure of the central portion 55 of the PPC 150. The anode and cathode terminals 263, 264 are separated from the rest of the device by the etched trenches 100 which are bridged with the air bridges 111 and 112.

[0061] By way of example, in a GaAs based device having the first multilayer structure as described hereinabove, the semiconductor material of the second base layer 102 can be n-doped GaAs having a donor impurity concentration of approximately  $5 \times 10^{17}$  cm<sup>-3</sup> to  $2 \times 10^{18}$  cm<sup>-3</sup> and a thickness in the range of 1 to 5 microns for example 3 µm, the semiconductor material of the intrinsic layer 103 can be undoped GaAs having a background doping level preferably less than  $10^{16}$  cm<sup>-3</sup> and a thickness in the range of 0.5 to 1.5 microns for example 0.8 μm, and the semiconductor material of the second emitter layer 104 can be p-doped GaAs having an acceptor impurity concentration of approximately  $5 \times 10^{17}$  $cm^{-3}$  to  $2 \times 10^{18}$  cm<sup>-3</sup> and a thickness in the range of 0.5 to 1 microns for example 0.8 µm. The second current blocking layer 106 may be again n-doped GaAs having a donor impurity concentration of approximately  $5 \times 10^{17}$  cm<sup>-3</sup> to  $2 \times 10^{18}$ cm<sup>-3</sup> and a thickness in the range of 0.5 to 2 microns, for example 1.0 µm. In other GaAs based embodiments of the PPC 150, the second multilayer structure 32 can utilize an alloy of AlGaAs or InGaAs and have a wider or narrower energy bandgap than that of the first active layers 133/134, so as to absorb and convert into photo-carriers a different set of wavelengths than is absorbed in the active layers of the ring segments **51-54**. Such embodiments can be advantageous in applications wherein the optical power and data are delivered by light of differing wavelengths.

[0062] In another exemplary embodiment, the semiconductor material of the substrate 130 is the semi-insulating InP, with the layers 131-136 and 101 as described hereinabove with reference to the InP based embodiment of the PPC 50, with the first active layers 133/134 of an alloy of InGaAs lattice matched to InP and having an energy bandgap corresponding to a wavelengths of approximately 1.48  $\mu$ m. In this embodiment of the PPC 150 the semiconductor material of the second base layer 102 may be an n-doped alloy of InGaAsP with the alloy composition such as to have an energy band gap corresponding to a wavelength of 1.3  $\mu$ m, having a donor impurity concentration of approximately  $1\times10^{18}$  cm<sup>-3</sup> and a thickness in the range of 1 to 3 microns for example 2  $\mu$ m. The semiconductor material of the intrinsic

layer 103 may be an undoped alloy of InGaAsP of the same alloy composition as the second base layer 102 having a thickness of in the rage of 0.5 to 1.5 µm, for example about 1 μm, and the semiconductor material of the second emitter layer 104 can be p-doped InGaAsP of the same alloy composition as the second base layer 102 and having an acceptor impurity concentration in the range of  $5 \times 10^{17}$  to  $5 \times 10^{18}$  cm<sup>-3</sup> or approximately  $2 \times 10^{18}$  cm<sup>-3</sup> and a thickness in the range of 0.5 to 1.5 μm or approximately 1 μm. The second current blocking layer 106 may be n-doped InGaAs having a donor impurity concentration of approximately  $5 \times 10^{18}$  cm<sup>-3</sup> to  $2\times10^{19}$  cm<sup>-3</sup> and a thickness of 0.2 microns. This embodiment of the PPC 150 is suitable for detecting an optical data signal at a 1.3 µm wavelength, and for converting into electrical power light from a high-power laser operating at 1480 nm, such as a 1480 nm diode pump laser. The doping material of the InP and InGaAsP device layers may be Zn or Be.

[0063] One skilled in the art would appreciate that different combinations of ternary materials such as InGaAs and InGaP and quaternary materials such as different alloys of InGaAsP can be epitaxially grown over an InP substrate to form the first and second multilayer structures 30, 32, resulting in various embodiments of the PPC 150 operating in a range of wavelengths from about 1.2 μm to about 1.6 μm. Conventional growth techniques such as MBE and MOCVD can be utilized for the epitaxial growth of the ternary and quaternary layers, with metamorphic growth enabling to incorporate latticemismatched layers into the layer structure of the PPC without substantially degrading the device performance. By way of another example, the second multilayer structure 32 may utilize an alloy of InGaAsP or InGaP and have a wider or narrower energy bandgap than that of the first active layers 133/134, so as to absorb and convert into photo-carriers a different set of wavelengths than is absorbed in the active layers of the ring segments 51-54. Such embodiments can be advantageous in applications wherein the optical power and data are delivered by light of differing wavelengths.

### PPC Measurement Results

[0064] FIG. 9 shows a measured I-V characteristic 301 and the P-V characteristic **401** of a GaAs-based PPC **50** of the present invention in comparison with respective I-V characteristic 302 and the power conversion efficiency 402 of the prior-art GaAs-based PPC as shown in FIGS. 1 and 2. The measurements were performed by illuminating the devices with light at a wavelength of 830 nm and optical power of 50 mW. The maximum power conversion efficiency obtained with the GaAs-based PPC 50 of the present invention is approximately 55% vs. the 45% conversion efficiency of the prior art power converter, and occurs at the output voltage V<sub>2117</sub> of approximately 6.3 volts, with the corresponding electrical current being approximately 4.5 milliamps. The improvement in the conversion efficiency and the output current achieved by the PPC 50 of the present invention over the state-of-the-art GaAs-based power converter is almost 25%, with the power conversion efficiency of the PPC of the present invention being close to the theoretical maximum. The improvement may be attributed to the following factors: i) carbon doping of the p-type layers; this includes the improved minority carrier lifetimes in the carbon-doped p-type emitter layer 134, which partly results from the favorable field patterns that arise from the extra-high doping of the window and conducting layers 135, 136 so as to induce an even stronger field for newly photo-generated carriers to be swept across the

p-n junction, and the lower sheet resistance of the carbon-doped layers, including the p-type emitter layer, the p-type window layer and the p-type conductivity layer; the lowered sheet resistance improves the achievable voltage while the current remains high, all leading to higher power output; ii) the novel geometry of the device segments that eliminates the hole in the device center by adding the center segment; this leads to better utilization of the available surface area and its interaction with the light intensity profile; and, the addition of the current blocking layer 131, which significantly reduces, and possibly eliminates, any or all photo-induced conductivity between adjacent segments and this, in turn, increases the voltage that is generated under the illumination across each individual device segment.

[0065] FIG. 10 shows a current-voltage (I-V) characteristic 411 and an output power (P-V) characteristic 410 of an InPbased PPC manufactured according to the present invention, with the first multilayer structure 30 including the InGaAs active layers 133/134 and the InP current blocking layer 131 as described hereinabove. The maximum power conversion efficiency of the device exceeds 28%, and occurs at the output voltage  $V_{out}$  of 3.5 volts, with the corresponding output electrical current of 8.1 milliamps. The wavelength of the incident light was 1436 nanometers, and its power was 100 mW, providing a maximum output power from the PPC of about 28.4 mW. Such a high power conversion efficiency is a remarkable achievement for optical power converters operating in the 1310-1550 nm wavelength range, significantly exceeding reported performance parameters of all such devices known heretofore. The measured device had 9 wedge-shaped device segments.

[0066] Advantageously, the InP-based PPC of the present invention may be used to realize a key objective for the photonic power technology, namely increasing the distance over which optical power can be transmitted with sufficient efficiency for driving remote devices such as sensors and data interfaces. For distances over 1 km, the long wavelength light in the range of 1310 to 1550 nm must be used, due to a relatively high attenuation in optical fiber for wavelengths outside of this range. For shorter wavelengths, for example 980 nm and below, the light attenuation in typical optical fibers is greater than 3 dB/km, which may be prohibitive for optically powering devices at distances greater than a few hundred meters. However, for wavelengths of 1310 nm and above, the attenuation of light in optical fibers is about or less than 0.1 dB/km, making the InP-based PPC of the present invention a more suitable choice of power converter than the GaAs based devices, when optical power needs to be delivered over distances of 1 km or greater. As a further advantage, the PPC of the present invention can be mounted in receptacles suitable for alignment to a single-mode fiber, so that the use of the InP based PPC of the present invention extends the benefits of remote optical powering to longer distances.

[0067] Note that the particular embodiments of the photovoltaic power converter of the present invention described hereinabove may utilize portions of other embodiments and are by way of example only, and alternative embodiments of many elements can be employed in particular applications of the invention as would be evident for those skilled in the art. For example, other embodiments of the PPC of the present invention may have device segments that are arranged in a circular pattern wherein a first group of the device segments is centrally positioned and is surrounded by a second group of the device segments comprising at least two device segments.

In the embodiment described herein, the first group of the device segments consist of the single device segment 55, but other embodiments may be envisioned where the first group consists of more than one device segments separated by additional trenches, which may also be connected in series or be isolated from each other and individually addressable. Other embodiments may include devices wherein the base layers are p-doped, while the emitter layers are n-doped. In yet other embodiments the second multilayer structure in the central portion of the PPC may be optimized to generate light and may either have no intrinsic layer between the second base and emitter layers, or the intrinsic layer may be less than 0.1  $\square$ m thick so that a quantum well structure is formed.

[0068] Of course numerous other embodiments may be envisioned without departing from the spirit and scope of the invention.

We claim:

- 1. A photovoltaic power converter comprising: a substrate of a semiconductor material;

- a first multilayer structure supported by the substrate comprising:

- a first base layer of a semiconductor material of a first conductivity type disposed over the substrate, said first base layer having a first bandgap,

- a first emitter layer of a semiconductor material of a second conductivity type opposite said first conductivity type and adjacent said first base layer to form a first junction region therebetween, said first emitter layer having a second bandgap that is equal or greater than the first band gap, and

- a first conducting layer of a semiconductor material of the second conductivity type disposed over the first emitter layer, said first conducting layer having a third bandgap that is wider than any of the first and second band gaps;

- a first current blocking layer of a semiconductor material of the second conductivity type interposed between the substrate and the first multilayer structure;

- a base electrical contact in electrical communication with the first base layer; and,

- an emitter electrical contact disposed on said conducting layer in electrical communication with the first emitter layer for developing a voltage relative to the base electrical contact in response to radiation of selected wavelengths being incident on the first emitter layer.

- 2. A photovoltaic power converter according to claim 1, wherein the current blocking layer has a thickness of at least 0.1  $\mu$ m and a doping level in the range of  $5\times10^{17}$  to  $1\times10^{19}$  cm<sup>-3</sup>.

- 3. A photovoltaic power converter according to claim 1, further comprising a buffer layer of a semiconductor material of the first conductivity type disposed between the current blocking layer and the first base layer.

- 4. A photovoltaic power converter according to claim 1, wherein the first conductivity type is n-type, and the second conductivity type is p-type.

- 5. A photovoltaic power converter according to claim 4, wherein the first emitter layer is carbon doped so as to have an acceptor impurity concentration in the rage of  $2\times10^{18}$  to  $1\times10^{19}$  cm<sup>-3</sup>.

- 6. A photovoltaic power converter according to claim 4, wherein the first conducting layer and the first current blocking layer are doped with carbon so as to produce an acceptor concentration in the first conducting layer in the rage of

- $2\times10^{18}$  to  $2\times10^{19}$  cm<sup>-3</sup>, and to produce an acceptor impurity concentration in the first current blocking layer  $5\times10^{17}$  cm<sup>-3</sup> or greater.

- 7. A photovoltaic power converter according to claim 4, wherein the semiconductor material of the substrate is GaAs.

- 8. A photovoltaic power converter according to claim 7, wherein the semiconductor material of each of the first buffer, base, and emitter layers is GaAs.

- 9. A photovoltaic power converter according to claim 8, wherein the semiconductor material of the conducting layer is an alloy of one of AlGaAs and InGaP.

- 10. A photovoltaic power converter according to claim 9, further comprising a window layer of an alloy of  $Al_xGa_{(1-x)}As$  characterized by x greater than 50%, which is interposed between the first emitter layer and the first conducting layer.

- 11. A photovoltaic power converter according to claim 7, wherein the semiconductor material of the first base and emitter layers is an alloy of one of InGaAs and AlGaAs.

- 12. A photovoltaic power converter according to claim 4, wherein the semiconductor material of the substrate, the current blocking layer and the buffer layer is InP.

- 13. A photovoltaic power converter according to claim 12, wherein the semiconductor material of the first base and emitter layers is an alloy of one of InGaAs and InGaAsP.

- 14. A photovoltaic power converter according to claim 12, wherein the semiconductor material of the conducting layer is an alloy of one of InP and InGaAsP.

- 15. A photovoltaic power converter according to claim 1, comprising:

- a plurality of trenches extending through the first multilayer structure and the current blocking layer and further partially extending into the substrate so as to form a plurality of spatially separated device segments supported by the substrate, each of said device segments comprising:

- a first metal contact in electrical communication with the first base layer within the device segment, said first metal contact disposed on the first base layer in an opening in the first emitter layer, and

- a second metal contact disposed over the conducting layer of the device segment in electrical communication with the first emitter layer, and,

- a plurality of electrical interconnects for electrically connecting each but one first metal contact to a respective adjacent second metal contact so at for form a chain of device segments connected in series, wherein one of said first metal contacts that remains unconnected to any of the second metal contacts is the base electrical contact, and one of said second metal contacts that remains unconnected to any of the first metal contacts is the emitter electrical contact.

- 16. A photovoltaic power converter according to claim 15, wherein the trenches have a width that is 5  $\mu$ m or less.

- 17. A photovoltaic power converter according to claim 15, wherein the trenches are characterized by a depth to width ratio that is equal to 5 or greater.

- 18. A photovoltaic power converter according to claim 4, wherein:

- the semiconductor material of the substrate is GaAs having substantially intrinsic conductivity with a doping level less than  $10^{-15}$  cm<sup>-3</sup>;

- the current blocking layer comprises p-doped GaAs having an acceptor impurity concentration in the range  $5\times10^{17}$  to  $1\times10^{19}$  cm<sup>-3</sup> and a thickness in the range of 0.1 to 0.3 um:

- the buffer layer comprises n-doped GaAs having a donor impurity concentration in the range  $5\times10^{17}$  to  $2\times10^{18}$  cm<sup>-3</sup> and a thickness in the range of 1 to 10  $\mu$ m;

- the first base layer comprises one of GaAs and an alloy of AlGaAs with an aluminum concentration not greater than 35%, a donor impurity concentration in the range  $5\times10^{17}$  to  $1\times10^{19}$  and has a thickness in the range of 1 to 3  $\mu m$ ;

- the first emitter layer comprises carbon doped layer of one of GaAs and an alloy of AlGaAs with an Al content not greater than 35%, and has a thickness in the range of 0.6 to 1  $\mu$ m and an acceptor impurity concentration in the range  $2\times10^{18}$  to  $5\times10^{18}$ ; and,

- the conducting layer is p-type comprising of one of: Zn or Be doped InGaP, and carbon doped AlGaAs with an aluminum concentration not greater than 35%, and has a bandgap that is wider than bandgaps of the first emitter and base layers, a thickness in the range of 1 to 3  $\mu$ m, and a donor impurity concentration in the range  $2\times10^{18}$  to  $2\times10^{19}$ .

- 19. A photovoltaic power converter according to claim 4, wherein

- the semiconductor material of the substrate is semi-insulating indium phosphate (InP);

- the current blocking layer comprises p-doped InP having an acceptor impurity concentration of  $5\times10^{17}$  cm<sup>-3</sup> or greater and a thickness in the range of 0.2 to 0.3  $\mu$ m;

- the buffer layer comprises n-doped InP having a donor impurity concentration of  $5\times10^{17}$  or greater and a thickness in the range of 5 to 10  $\mu$ m;

- the first base comprises an alloy of InGaAs that is lattice-matched to InP and has a donor impurity concentration of  $5\times10^{17}$  or greater and a thickness in the range of 1 to 3  $\mu m$ ;

- the first emitter layer comprises a p-doped alloy of InGaAs that is lattice-matched to InP and has an acceptor impurity concentration of  $2\times10^{18}$  or greater and a thickness in the range of 0.5 to 1.5  $\mu$ m; and,

- the conducting layer comprises p-doped InP that has a donor impurity concentration of  $2\times10^{18}$  or greater and a thickness in the range of 1.5 to 2.5  $\mu m$ .

\* \* \* \* \*