US 20100164070A1

### (19) United States

## (12) Patent Application Publication OKAHISA et al.

(10) Pub. No.: US 2010/0164070 A1 (43) Pub. Date: Jul. 1, 2010

# (54) GROUP III NITRIDE SEMICONDUCTOR CRYSTAL SUBSTRATE AND SEMICONDUCTOR DEVICE

(75) Inventors: **Takuji OKAHISA**, Itami-shi (JP);

Tomohiro Kawase, Itami-shi (JP); Tomoki Uemura, Itami-shi (JP); Muneyuki Nishioka, Itami-shi (JP); Satoshi Arakawa, Itami-shi (JP)

Correspondence Address:

DRINKER BIDDLE & REATH (DC) 1500 K STREET, N.W., SUITE 1100 WASHINGTON, DC 20005-1209 (US)

(73) Assignee: SUMITOMO ELECTRIC

INDUSTRIES, LTD

(21) Appl. No.: 12/719,719

(22) Filed: Mar. 8, 2010

### Related U.S. Application Data

(63) Continuation of application No. 12/273,101, filed on Nov. 18, 2008.

(30) Foreign Application Priority Data

#### **Publication Classification**

(51) **Int. Cl.**

H01L 29/20 (2006.01)

(57) ABSTRACT

A group III nitride semiconductor crystal substrate has a diameter of at least 25 mm and not more than 160 mm. The resistivity of the group III nitride semiconductor crystal substrate is at least  $1\times10^{-4}~\Omega$ ·cm and not more than 0.1  $\Omega$ ·cm. The resistivity distribution in the diameter direction of the group III nitride semiconductor crystal is at least -30% and not more than 30%. The resistivity distribution in the thickness direction of the group III nitride semiconductor crystal is at least -16% and not more than 16%.

FIG.1

FIG.2

FIG.3

FIG.4

FIG.6

FIG.7

FIG.8

FIG.9

FIG. 1(

FIG.11

FIG.12

FIG.13

FIG.14

FIG.15

SCHOTTKY

DRIFT RESISTANCE

SUBSTRATE RESISTANCE

ELECTRODE RESISTANCE

# GROUP III NITRIDE SEMICONDUCTOR CRYSTAL SUBSTRATE AND SEMICONDUCTOR DEVICE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to a group III nitride semiconductor crystal substrate and a semiconductor device.

[0003] 2. Description of the Background Art

Gallium nitride (GaN) type semiconductor materials are known to have superior properties such as a large bandgap that is approximately 3 times that of silicon (Si), a high breakdown electric field that is approximately 10 times that of silicon, and also a high saturation electron velocity. Research and development of the gallium nitride type semiconductor material for use in devices of high frequency and high power output in the field of radio communication are actively in progress, and has already come to the stage of practical use in devices directed to base stations for cellular phones. Moreover, the expectation of covering the two competing demands of high breakdown voltage and low loss, i.e. low ON-state resistance, that was difficult in conventional Si power devices, has attracted attention in the application to power devices. Since the logic value of the ON-resistance is inversely proportional to the breakdown electric field raised to the power of three, it may be possible to significantly reduce the ON-resistance in a power device based on gallium nitride to approximately 1/1000 that of a device based on silicon. Thus, group III nitride semiconductor crystals such as gallium nitride crystals stand out to be a promising material for optical devices such as an LED (Light Emitting Diode) and for electronic devices such as a transistor.

[0005] With regards to such group III nitride semiconductor crystals, Japanese Patent Laying-Open No. 2006-193348 (Patent Document 1) discloses a group III nitride semiconductor substrate having a specific resistance of at least  $1 \times 10^4$  $\Omega$ ·cm. In a fabrication method of the group III nitride semiconductor substrate, vapor phase growth such as HVPE (Hydride Vapor Phase Epitaxy), MOCVD (Metal Organic Chemical Vapor Deposition), or MBE (Molecular Beam Epitaxy) is employed to grow epitaxially a group III nitride semiconductor employing dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>) and tetrachlorosilane (SiCl<sub>4</sub>: silicon tetrachloride) for the doping raw material of silicon (Si) qualified as the impurity element. [0006] Japanese National Patent Publication No. 2007-519591 (Patent Document 2) discloses a monocrystalline gallium nitride that has an average density of less than  $1\times10^6$ cm<sup>-2</sup> and a dislocation density standard deviation ratio of less than 25%. In the fabrication method thereof, silane (SiH<sub>4</sub>) and the like are employed as the doping raw material of silicon. [0007] Further, Japanese Patent Laying-Open No. 2005-101475 (Patent Document 3) discloses a III-V group nitride type semiconductor substrate characterized in that the carrier concentration distribution at the outermost surface of the substrate is substantially uniform. In a fabrication method thereof, dichlorosilane is employed as the doping raw material in HVPE.

[0008] When a group III nitride semiconductor crystal is to be grown by vapor phase growth such as HVPE, MOCVD or MBE, the concentration of n type impurities (dopant) in the group III nitride semiconductor crystal must be controlled in order to regulate the n type conductive property of the group III nitride semiconductor crystal. Silane and dichlorosilane employed as the doping gas in the aforementioned Patent

Documents 1-3 to dope silicon qualified as then type impurity may be decomposed before arriving at the underlying substrate and adhere to the reaction tube at the growth temperature of the group III nitride semiconductor crystal.

[0009] The doping gas employed in the aforementioned Patent Documents 1-3 may react with nitrogen gas or ammonia gas to generate an  $Si_xN_y$  (silicon nitride) type compound (x and y are arbitrary integers).

[0010] It was difficult to control the concentration of silicon in the doping gas if the doping gas directed to supplying silicon was decomposed or caused reaction prior to arriving at the underlying substrate. As a result, the concentration of silicon taken into the group III nitride semiconductor crystal will vary, disallowing adjustment of the concentration of silicon taken into the group III nitride semiconductor crystal. Therefore, it was difficult to control the resistivity of the group III nitride semiconductor crystal with silicon as a dopant. Particularly, this problem was further noticeable when HVPE was employed since the decomposition of the doping gas and/or reaction with another gas was significant due to the entire heating of the reaction tube.

[0011] A possible consideration is to supply the doping gas at high rate for the purpose of preventing thermal decomposition of the doping gas or reaction with the raw material gas. However, the concentration distribution of the doping gas supplied to the underlying substrate will be degraded if the doping gas is supplied at high rate, leading to significant degradation in the in-plane distribution of the resistivity in the group III nitride semiconductor crystal.

[0012] Thus, there was a problem that the property such as the ON-resistance is degraded in the case where the resistivity is not regulated and a semiconductor device is fabricated employing a group III nitride semiconductor crystal substrate of high resistivity.

[0013] Further, in the case where a semiconductor device is fabricated employing a group III nitride semiconductor crystal substrate having poor resistivity in-plane distribution, the yield was degraded since the property such as the ON-resistance of the semiconductor device will vary.

### SUMMARY OF THE INVENTION

[0014] In view of the foregoing, an object of the present invention is to provide a group III nitride semiconductor crystal substrate, allowing the resistivity to be reduced and preventing degradation in the resistivity in-plane distribution.

[0015] Another object of the present invention is to provide a semiconductor device that can have degradation in properties prevented and the yield improved.

[0016] As a result of diligent research on the doping conditions of silicon, the inventors found that, by employing silicon tetrafluoride gas as the doping gas, or by setting the growth rate of a group III nitride semiconductor crystal substrate to at least 200 µm/h and not more than 2000 µm/h based on the usage of silicon tetrachloride gas as the doping gas, decomposition of the doping gas can be prevented and reaction per se of the doping gas with another gas can be suppressed or the effect of the reaction reduced, at the stage of doping silicon. Thus, there was obtained a group III nitride semiconductor crystal substrate allowing the resistivity to be reduced by readily controlling the resistivity and preventing degradation in the resistivity in-plane distribution.

[0017] Specifically, the group III nitride semiconductor crystal substrate of the present invention is directed to a group III nitride semiconductor crystal substratet having a diameter

of at least 25 mm and not more than 160 mm. The resistivity of the group III nitride semiconductor crystal substrate is at least  $1\times10^{-4} \Omega$ ·cm and not more than  $0.1 \Omega$ ·cm. The resistivity distribution in the diameter direction of the group III nitride semiconductor crystal substrate is at least -30% and not more than 30%. The resistivity distribution in the thickness direction of the group III nitride semiconductor crystal substrate is at least -16% and not more than 16%.

[0018] By virtue of the resistivity being not more than 0.1  $\Omega$ ·cm, the group III nitride semiconductor crystal substrate of the present invention can be conveniently selected as an n type substrate employed in semiconductor devices such as an electronic device or light-emitting device, improved in properties such as low ON-resistance and high breakdown voltage. Further, since it is not necessary to dope silicon in high concentration by virtue of the resistivity being at least  $1\times10^{-4} \,\Omega\cdot\text{cm}$ , generation of a pit or defect as well as a crack can be suppressed during growth of the group III nitride semiconductor crystal. In the case where the resistivity distribution in the diameter direction is at least -30% and not more than 30% and the resistivity distribution in the thickness direction is at least -16% and not more than 16% in the group III nitride semiconductor crystal substrate, variation in properties can be suppressed, when semiconductor devices are produced using the group III nitride semiconductor crystal substrate. Thus, the yield can be improved.

[0019] In the case where the diameter is at least 25 mm, generation at a plane orientation different from the growing plane can be suppressed. Therefore, a group III nitride semiconductor crystal substrate of favorable crystallinity can be obtained. Since an underlying substrate having a diameter of not more than 160 mm is readily available, a nitride semiconductor crystal substrate having a diameter of not more than 160 mm can be obtained readily.

[0020] Preferably in the group III nitride semiconductor crystal substrate set forth above, the resistivity distribution in the diameter direction is at least -20% and not more than 20%, and the resistivity distribution in the thickness direction is at least -10% and not more than 10%.

[0021] Since the variation in properties, when semiconductor devices are produced using the group III nitride semiconductor crystal substrate, can be further suppressed, the yield can be further improved.

[0022] Preferably in the group III nitride semiconductor crystal substrate set forth above, the thickness is at least 2 mm and not more than 160 mm.

[0023] In the case where the thickness is at least 2 mm, a plurality of group III nitride semiconductor crystal substrates having a desired thickness can be obtained by slicing the group III nitride semiconductor crystal substrate at the required thickness. In the case where the thickness is not more than 160 mm, a group III nitride semiconductor crystal substrate can be grown readily in terms of facilities. Therefore, the cost can be reduced.

[0024] The group III nitride semiconductor crystal substrate set forth above preferably has a thickness of at least 100  $\mu$ m and not more than 1000  $\mu$ m.

[0025] In the case where the thickness is at least 100  $\mu m$ , a group III nitride semiconductor crystal substrate having generation of a crack during handling suppressed can be obtained. In the case where the thickness is not more than 1000  $\mu m$ , the substrate is conveniently employed for a semiconductor device. Thus, the fabrication cost per one group III nitride semiconductor crystal substrate can be reduced.

[0026] The group III nitride semiconductor crystal substrate preferably has a resistivity of at least  $1\times10^{-3} \ \Omega\cdot\text{cm}$  and not more than  $8\times10^{-3} \ \Omega\cdot\text{cm}$ .

[0027] In the case where the resistivity is at least  $1\times10^{-3}$   $\Omega\cdot\text{cm}$ , it is not necessary to dope silicon in high concentration. Therefore, generation of a pit or defect as well as a crack during growth of a group III nitride semiconductor crystal can be suppressed. In the case where the resistivity is not more than  $8\times10^{-3}$   $\Omega\cdot\text{cm}$ , the substrate can be conveniently selected as an n type substrate used in semiconductor devices such as an electronic device or light-emitting device.

[0028] In the group III nitride semiconductor crystal substrate set forth above, the concentration of silicon is at least  $5\times10^{16}$  cm<sup>-3</sup> and not more than  $5\times10^{20}$  cm<sup>-3</sup>, more preferably at least  $3\times10^{18}$  cm<sup>-3</sup> and not more than  $5\times10^{19}$  cm<sup>3</sup>.

[0029] In the case where the concentration of silicon is at least  $5\times10^{16}$  cm<sup>-3</sup>, the concentration of silicon taken in can be controlled readily. In the case where the concentration of silicon is at least  $3\times10^{18}$  cm<sup>-3</sup>, the concentration of silicon taken in can be controlled more readily. In the case where the silicon concentration is not more than  $5\times10^{20}$  cm<sup>-3</sup>, generation of a pit or defect as well as a crack during growth of a group III nitride semiconductor crystal can be suppressed. In the case where the silicon concentration is not more than  $5\times10^{19}$  cm<sup>-3</sup>, a group III nitride semiconductor crystal substrate of favorable crystallinity can be obtained.

[0030] The group III nitride semiconductor crystal substrate set forth above preferably has a dislocation density of not more than  $1\times10^7$  cm<sup>-2</sup>.

[0031] By employing the group III nitride semiconductor crystal substrate in a semiconductor device such as an electronic device or light-emitting device, properties such as the electric property and optical property can be stabilized.

[0032] Preferably in the group III nitride semiconductor crystal substrate set forth above, the main face has an angle of at least –5 degrees and not more than 5 degrees relative to any one of a (0001) plane, (1-100) plane, (11-20) plane and (11-22) plane.

[0033] Accordingly, a group III nitride semiconductor crystal of favorable crystallinity can be further grown on the main face. Thus, a semiconductor device of more favorable property can be obtained.

[0034] Preferably in the group III nitride semiconductor crystal substrate set forth above, the full width at half maximum (FWHM) of the rocking curve in X-ray diffraction is at least 10 arcsec and not more than 500 arcsec.

[0035] Accordingly, a group III nitride semiconductor crystal of favorable crystallinity can be additionally grown on the group III nitride semiconductor crystal substrate. Therefore, a semiconductor device of more favorable property can be obtained.

[0036] Preferably, the group III nitride semiconductor crystal substrate set forth above is formed of an  $Al_xIn_yGa_{(1-x-y)}N$  ( $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $x+y \le 1$ ) crystal. Preferably, the group III nitride semiconductor crystal substrate set forth above is formed of a gallium nitride crystal.

[0037] Accordingly, an extremely effective group III nitride semiconductor crystal can be grown.

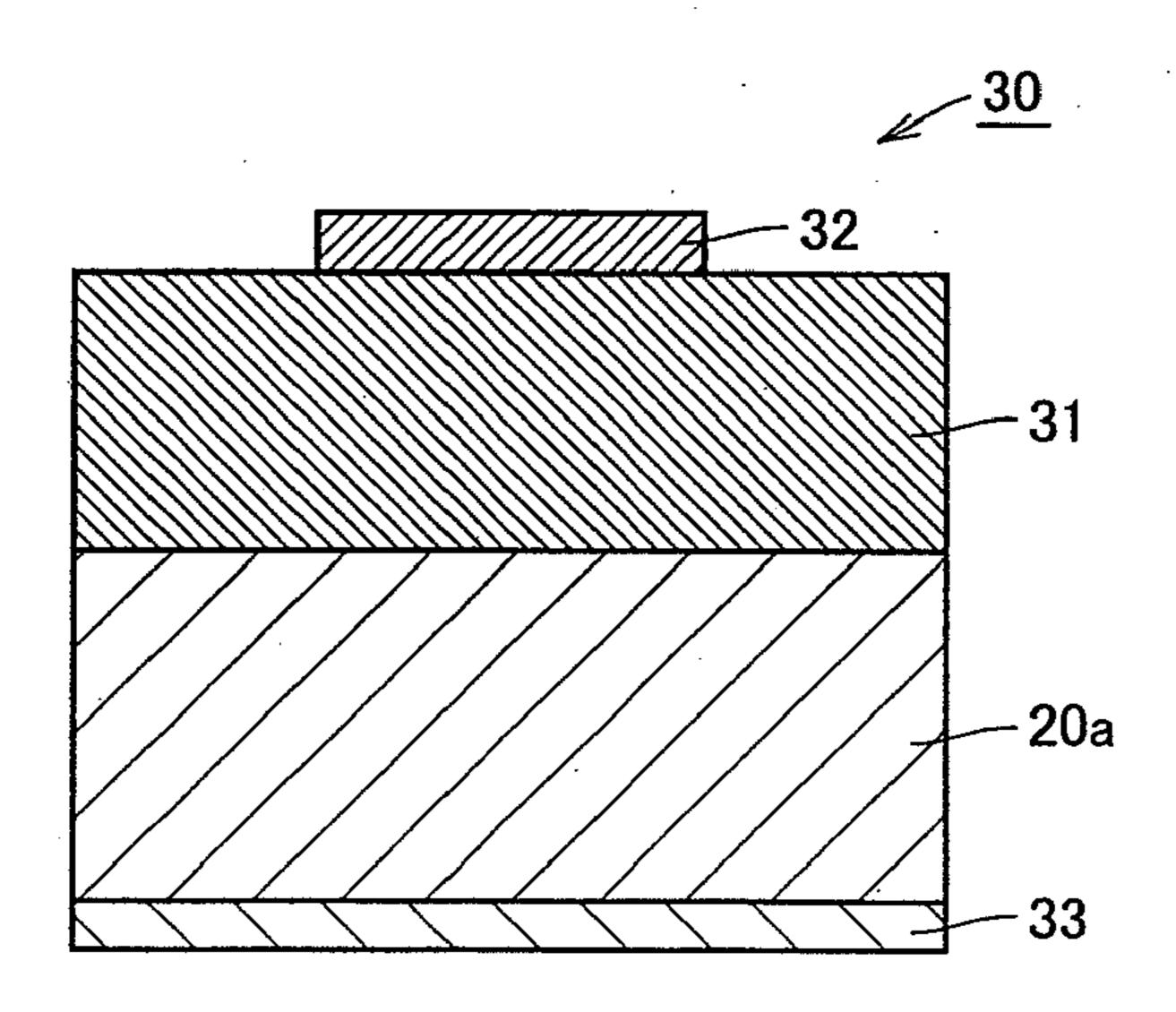

[0038] A semiconductor device of the present invention includes any of the group III nitride semiconductor crystal substrate set forth above, and an epitaxial layer formed on the group III nitride semiconductor crystal substrate.

[0039] According to the semiconductor device of the present invention, the group III nitride semiconductor crystal

substrate having the resistivity in-plane distribution suppressed is employed, allowing variation in properties to be suppressed. Therefore, the yield can be improved. Further, since the group III nitride semiconductor crystal substrate having low resistivity is employed, degradation in properties such as low ON-resistance and high breakdown voltage can be prevented.

[0040] In the present invention, "group III" implies group IIIB in the former IUPAC (The International Union of Pure and Applied Chemistry) system. Namely, a group III nitride semiconductor crystal implies a semiconductor crystal including nitrogen, and at least one element of boron (B), aluminium (Al), gallium (Ga), indium (In) and thallium (TI). Further, "doping gas" implies gas used to dope impurities (dopant).

[0041] According to the group III nitride semiconductor crystal substrate of the present invention, the resistivity can be reduced, and degradation in the resistivity in-plane distribution can be prevented.

[0042] Further, according to the semiconductor device of the present invention, degradation in properties can be prevented, and the yield improved.

[0043] The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

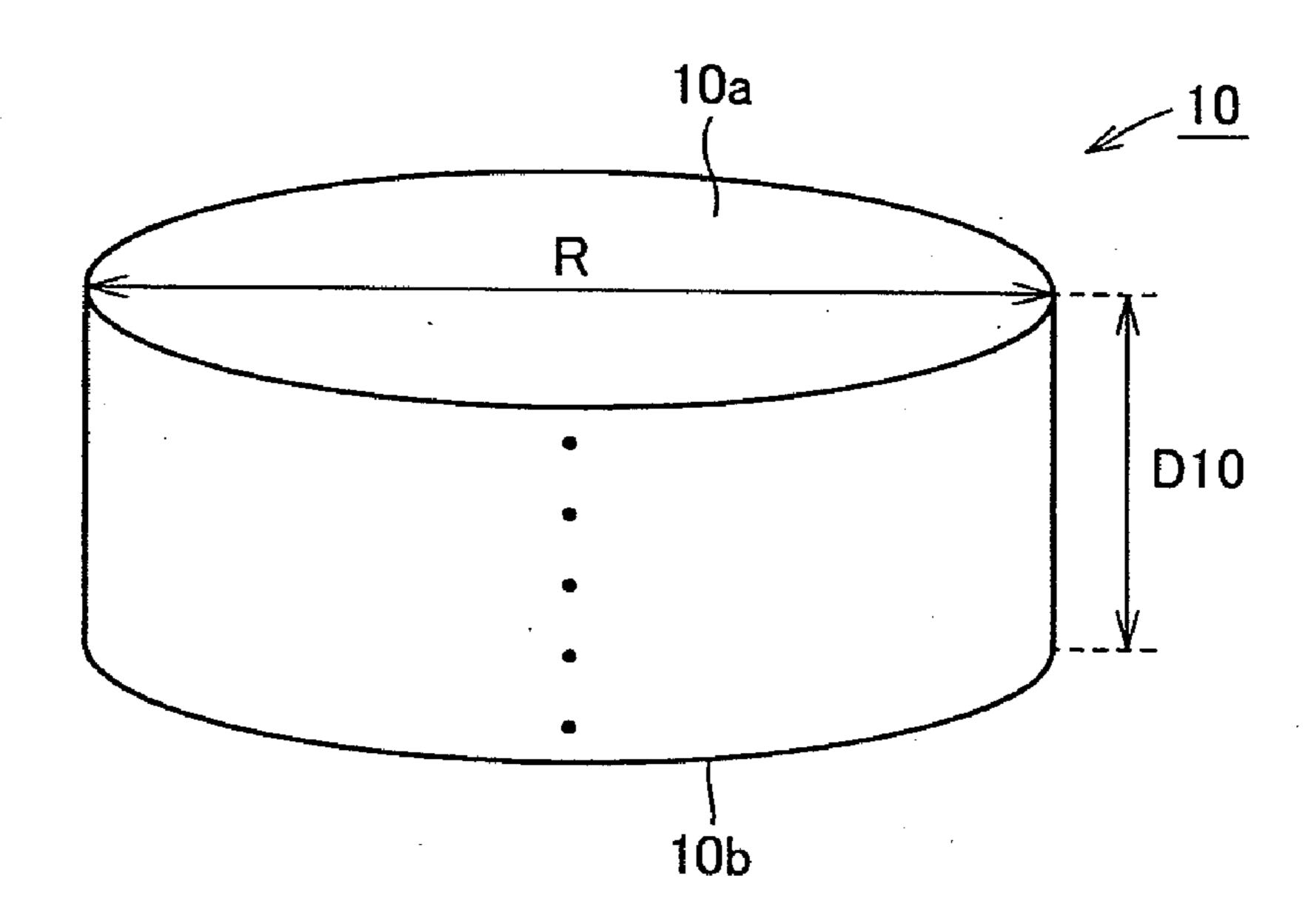

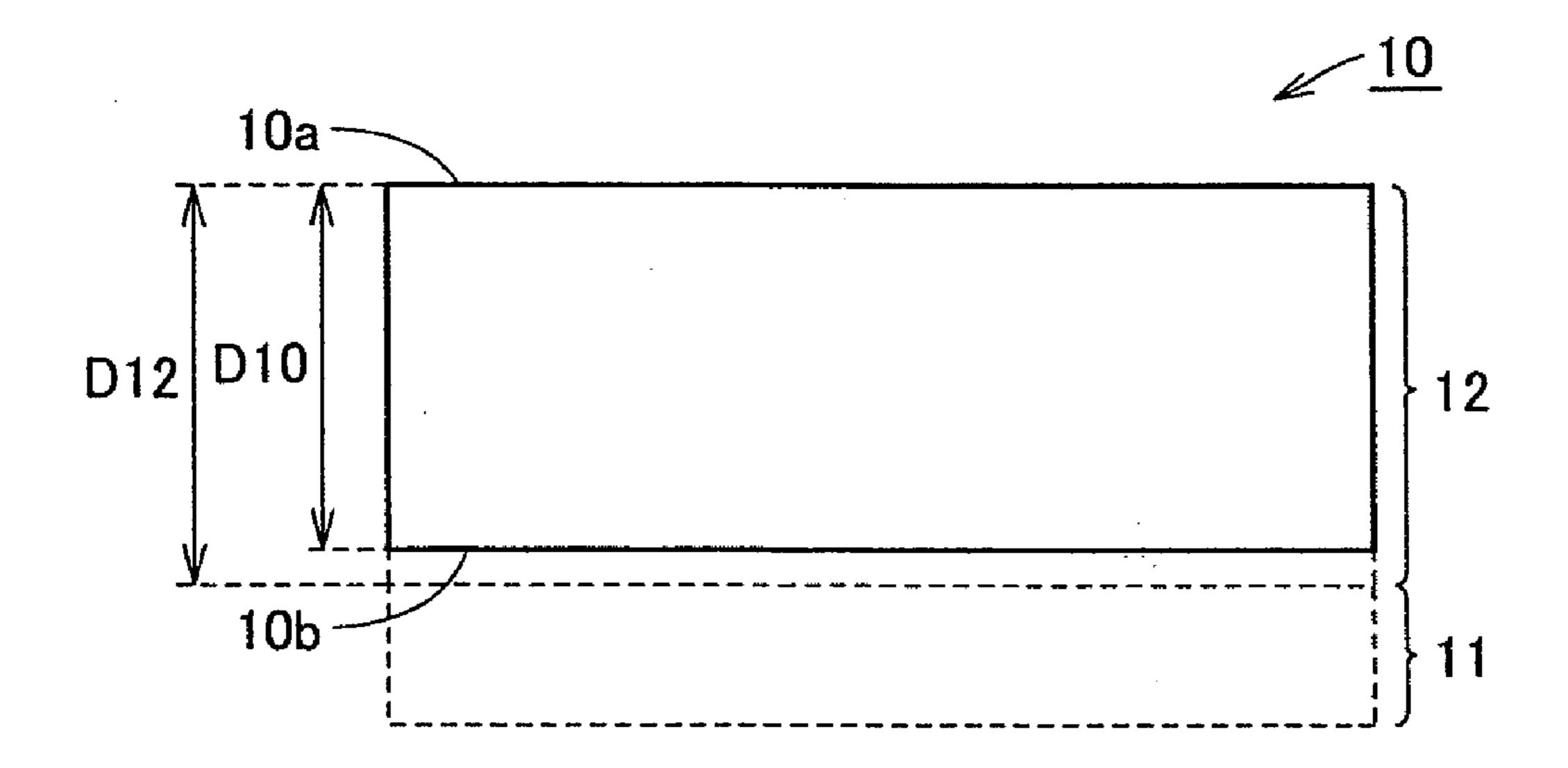

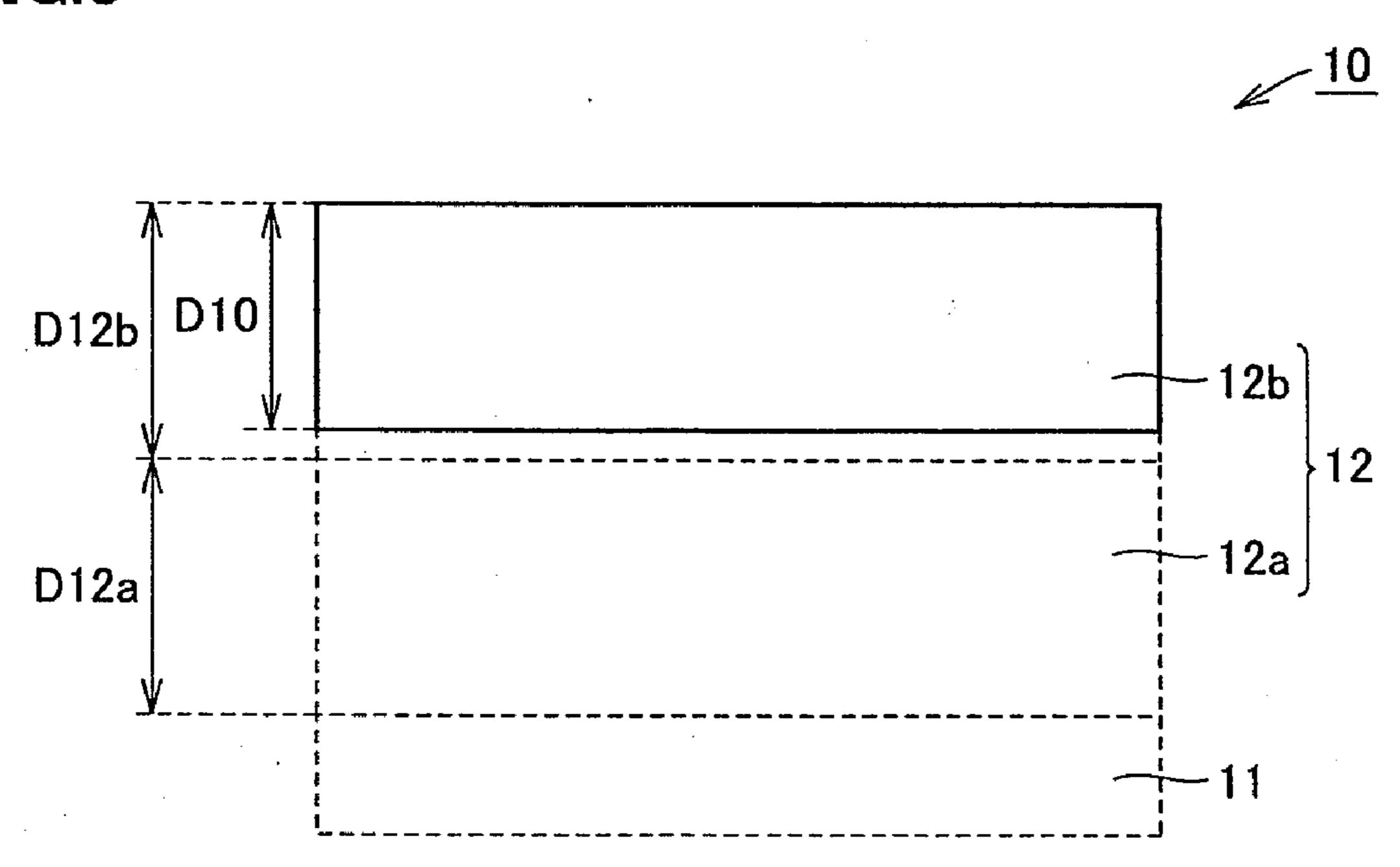

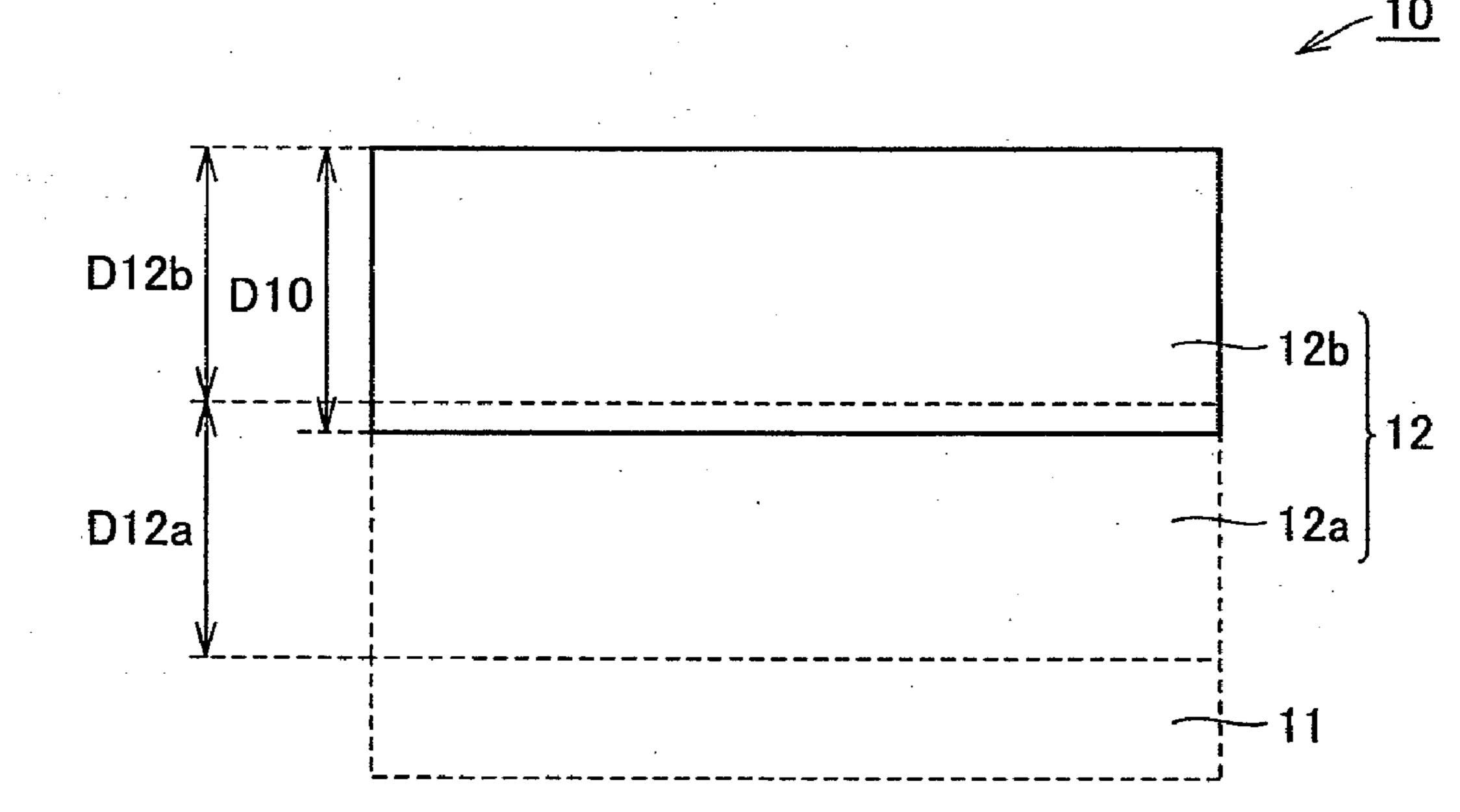

[0044] FIG. 1 is a schematic perspective view of a gallium nitride crystal substrate according to a first embodiment of the present invention.

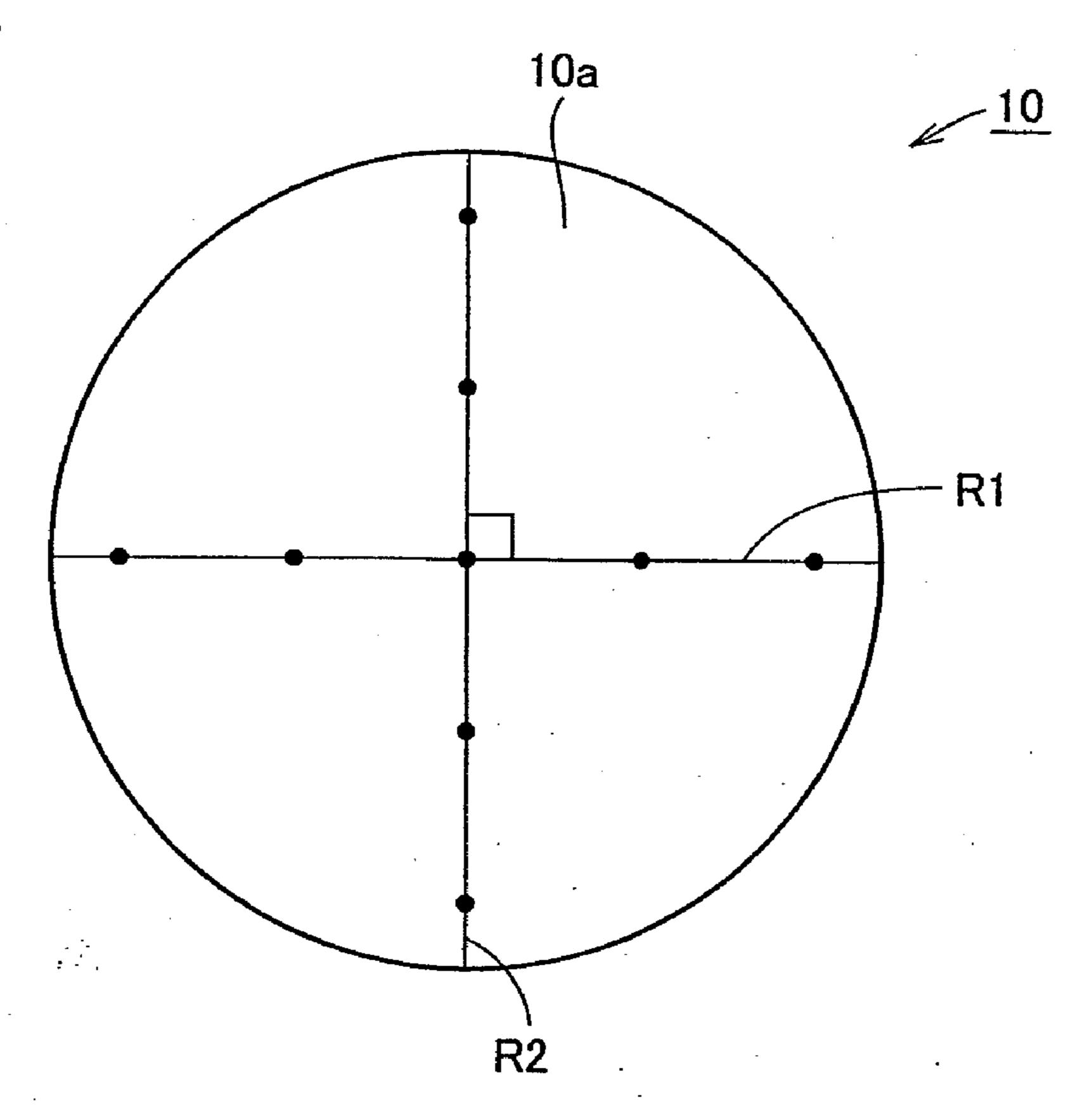

[0045] FIG. 2 is a schematic top view of a gallium nitride crystal substrate of the first embodiment.

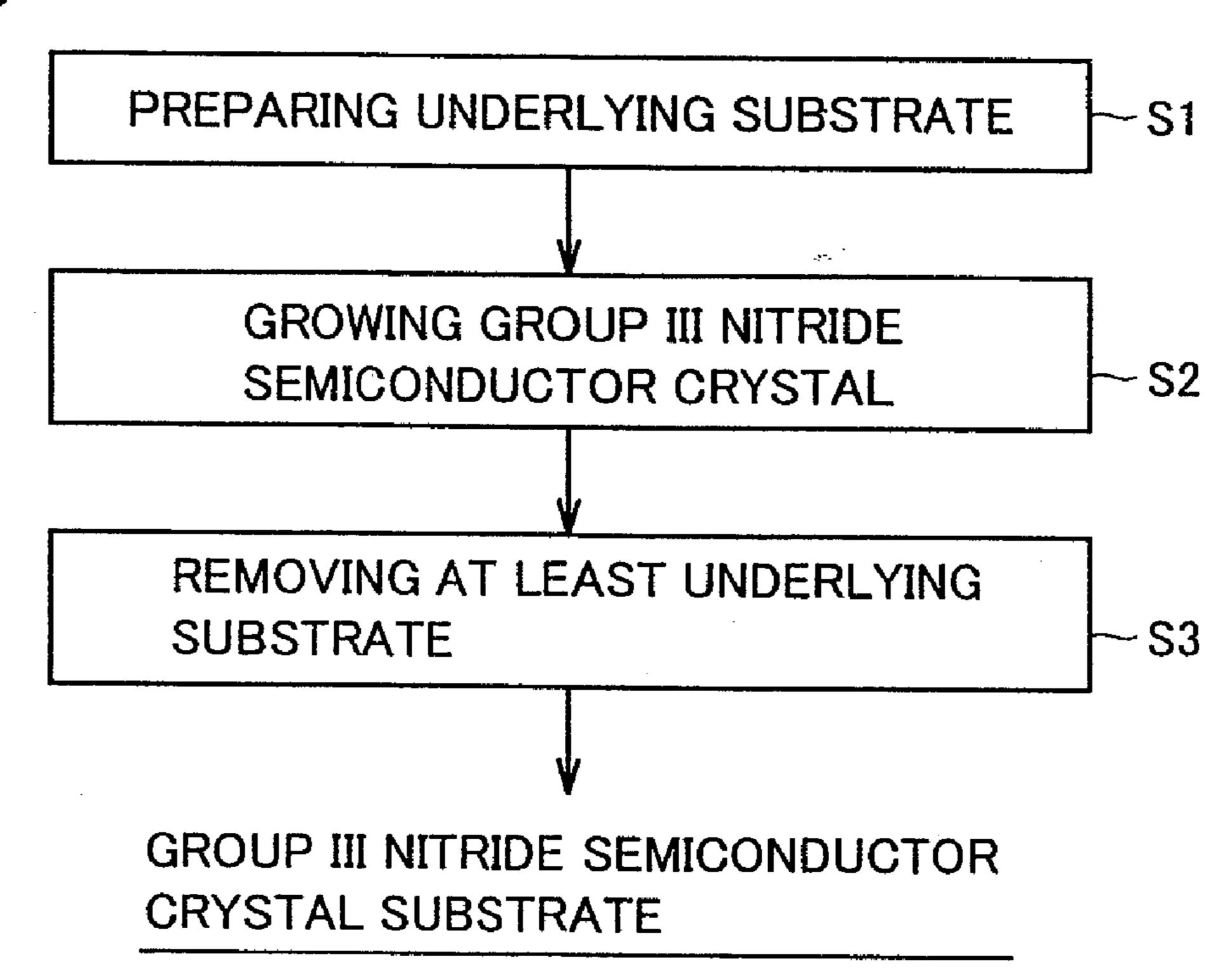

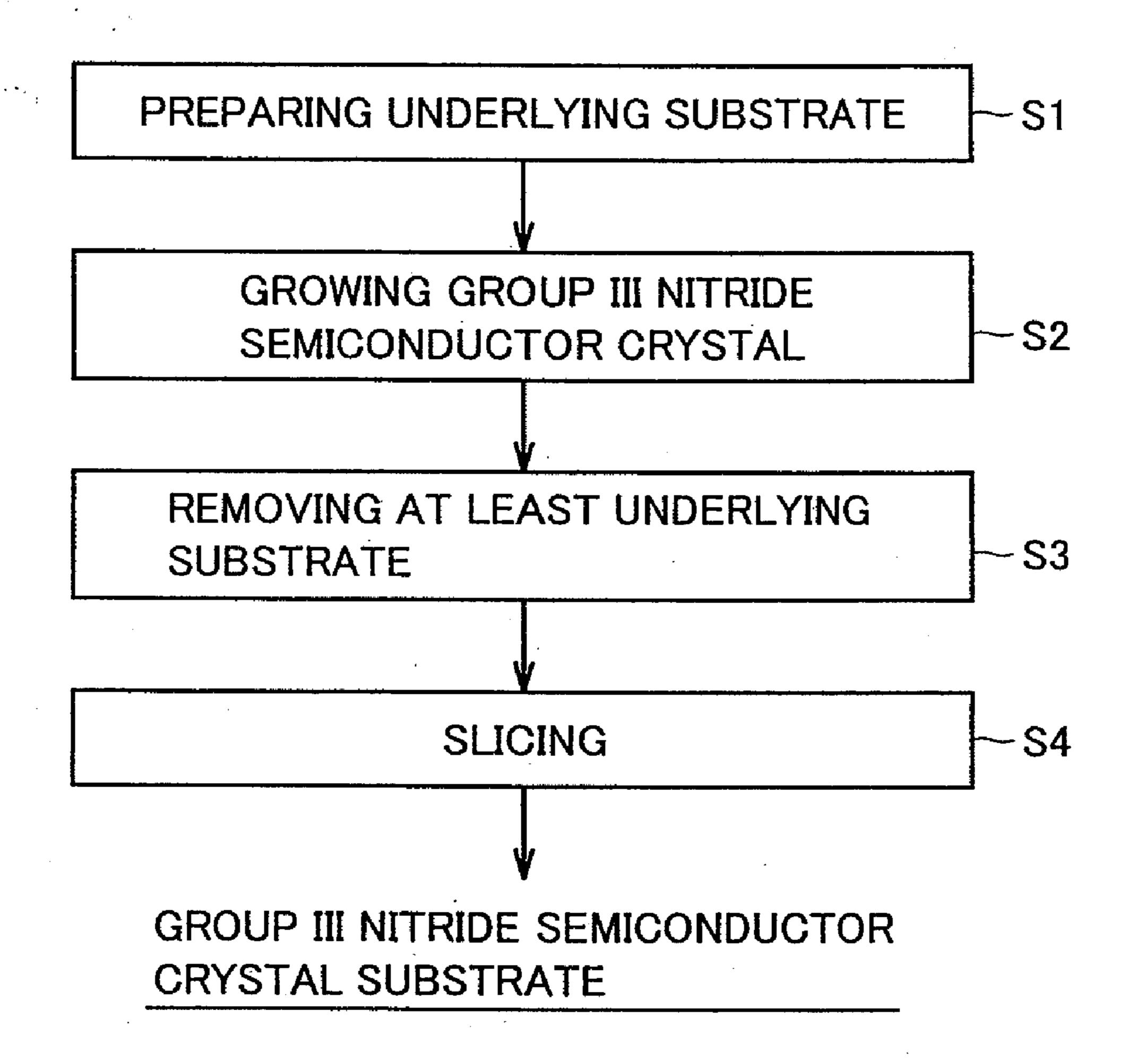

[0046] FIG. 3 is a flowchart of a fabrication method of a group III nitride semiconductor crystal substrate of the first embodiment.

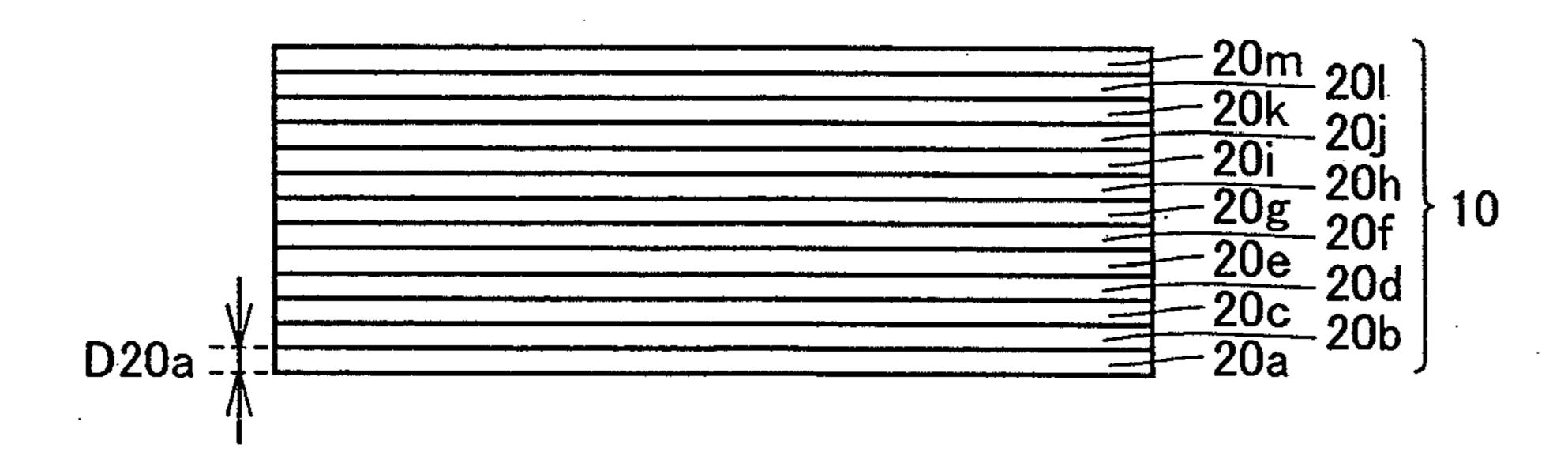

[0047] FIG. 4 is a schematic view representing a state of growing a group III nitride semiconductor crystal in the first embodiment.

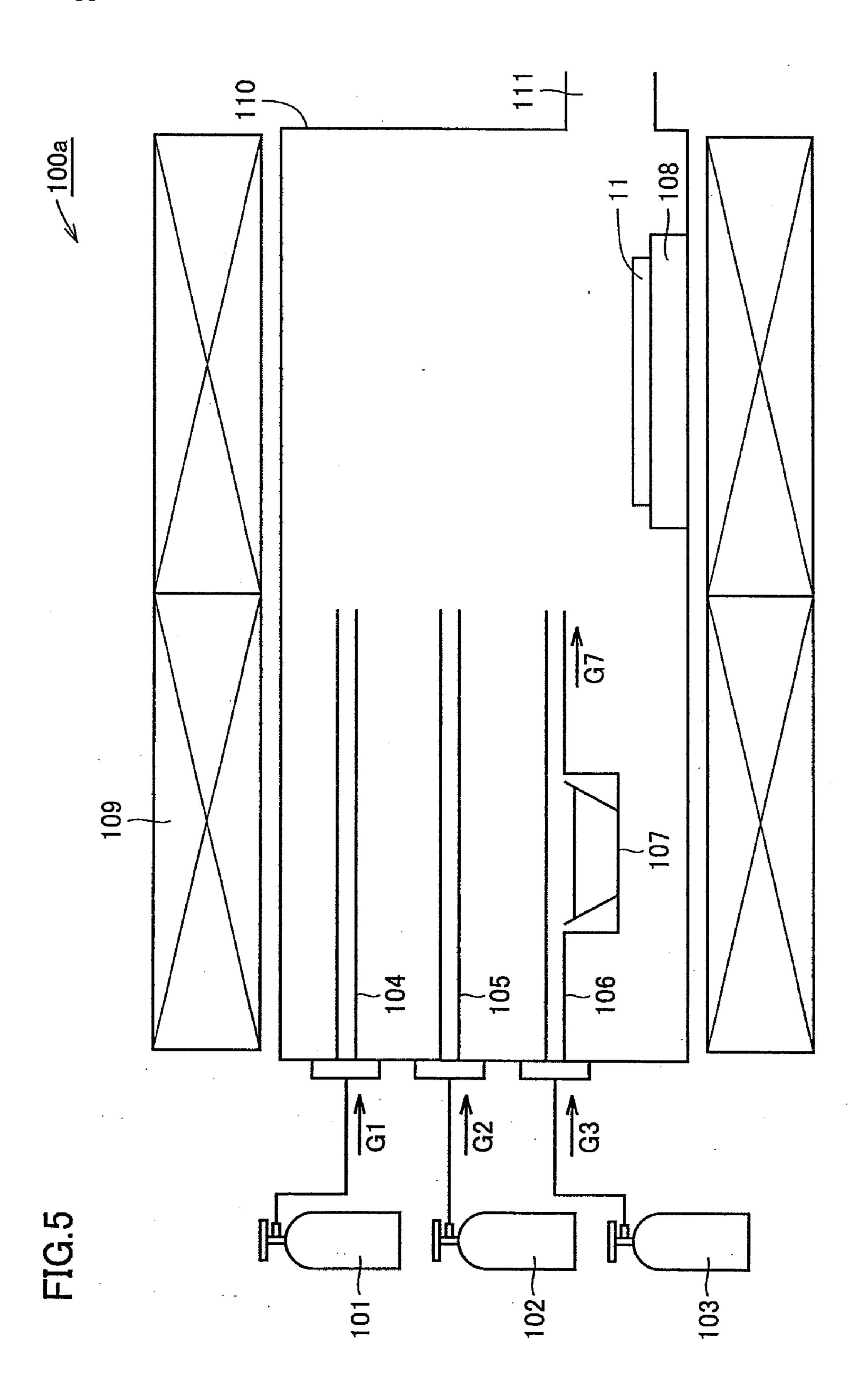

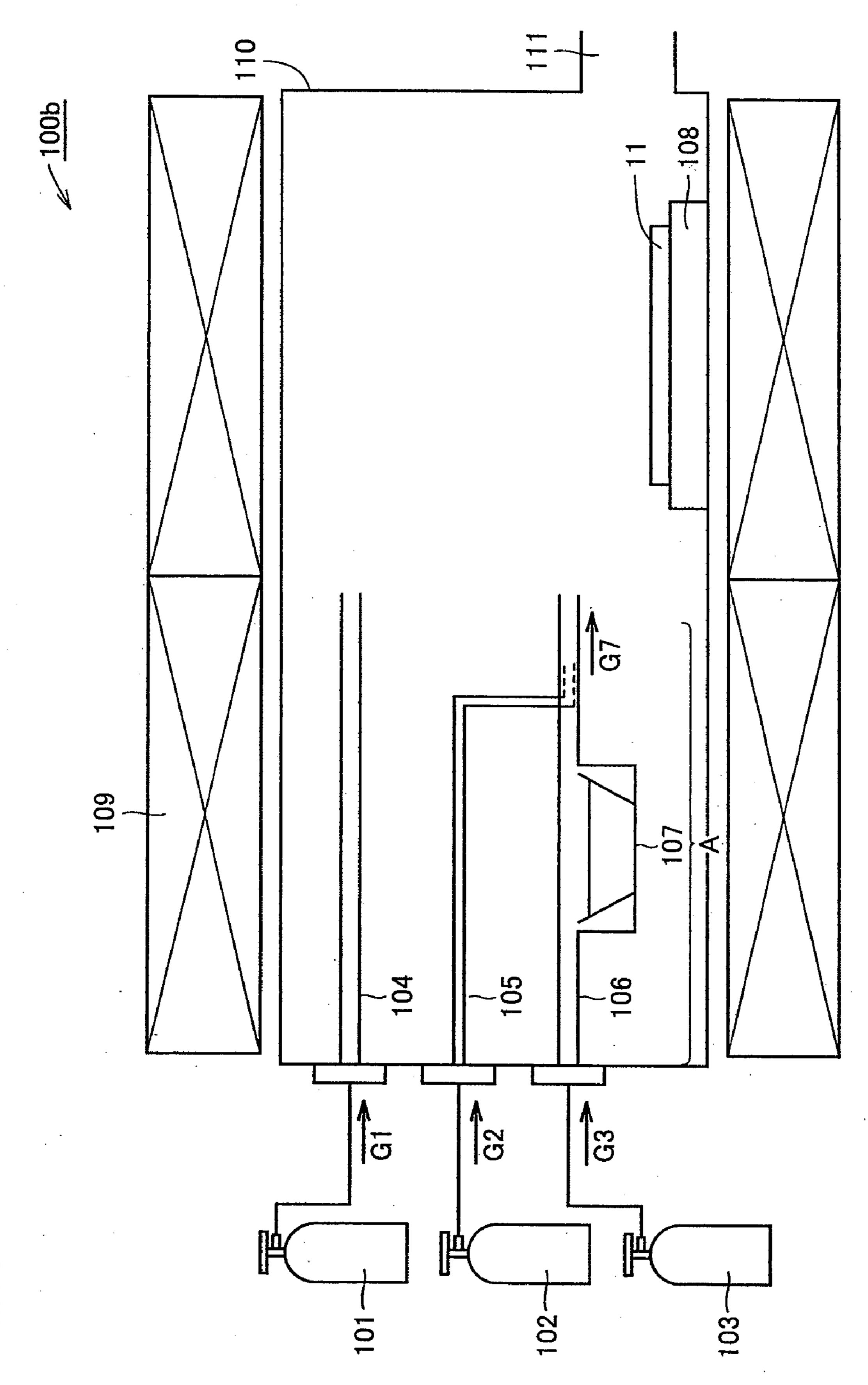

[0048] FIG. 5 is a schematic view of an HVPE apparatus employed in a growing method of a group III nitride semiconductor crystal of the first embodiment.

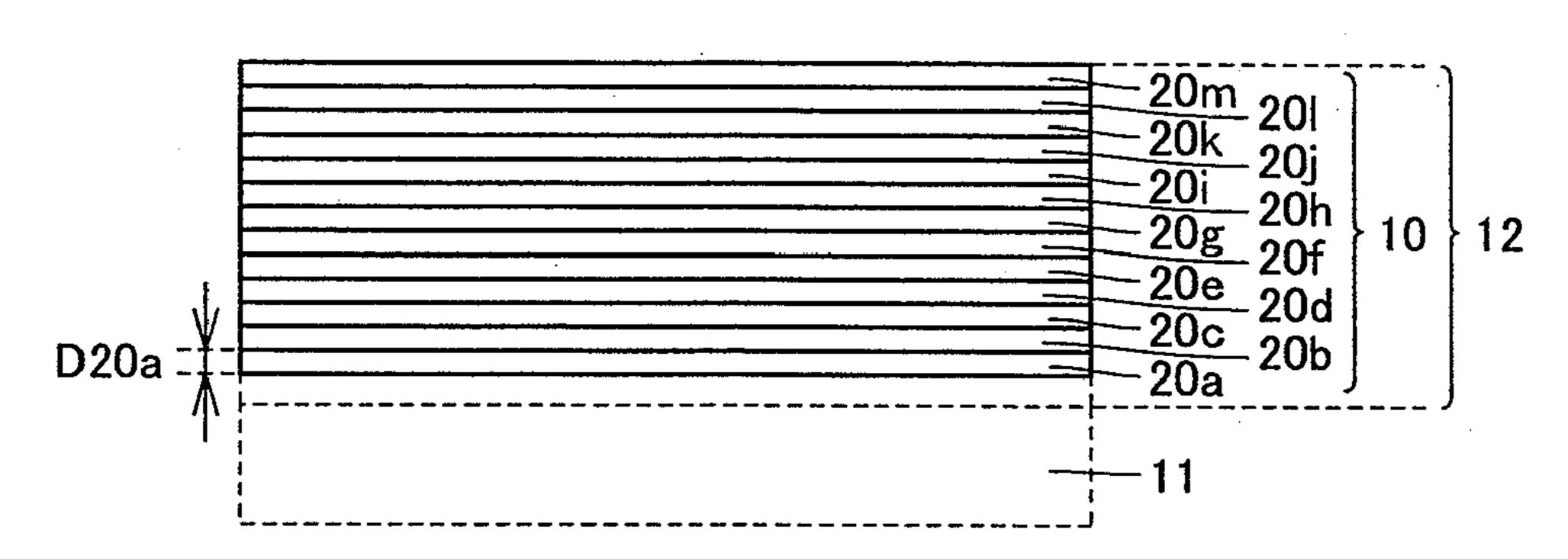

[0049] FIG. 6 is a schematic diagram of a group III nitride semiconductor crystal representing a state of at least the underlying substrate removed in the first embodiment.

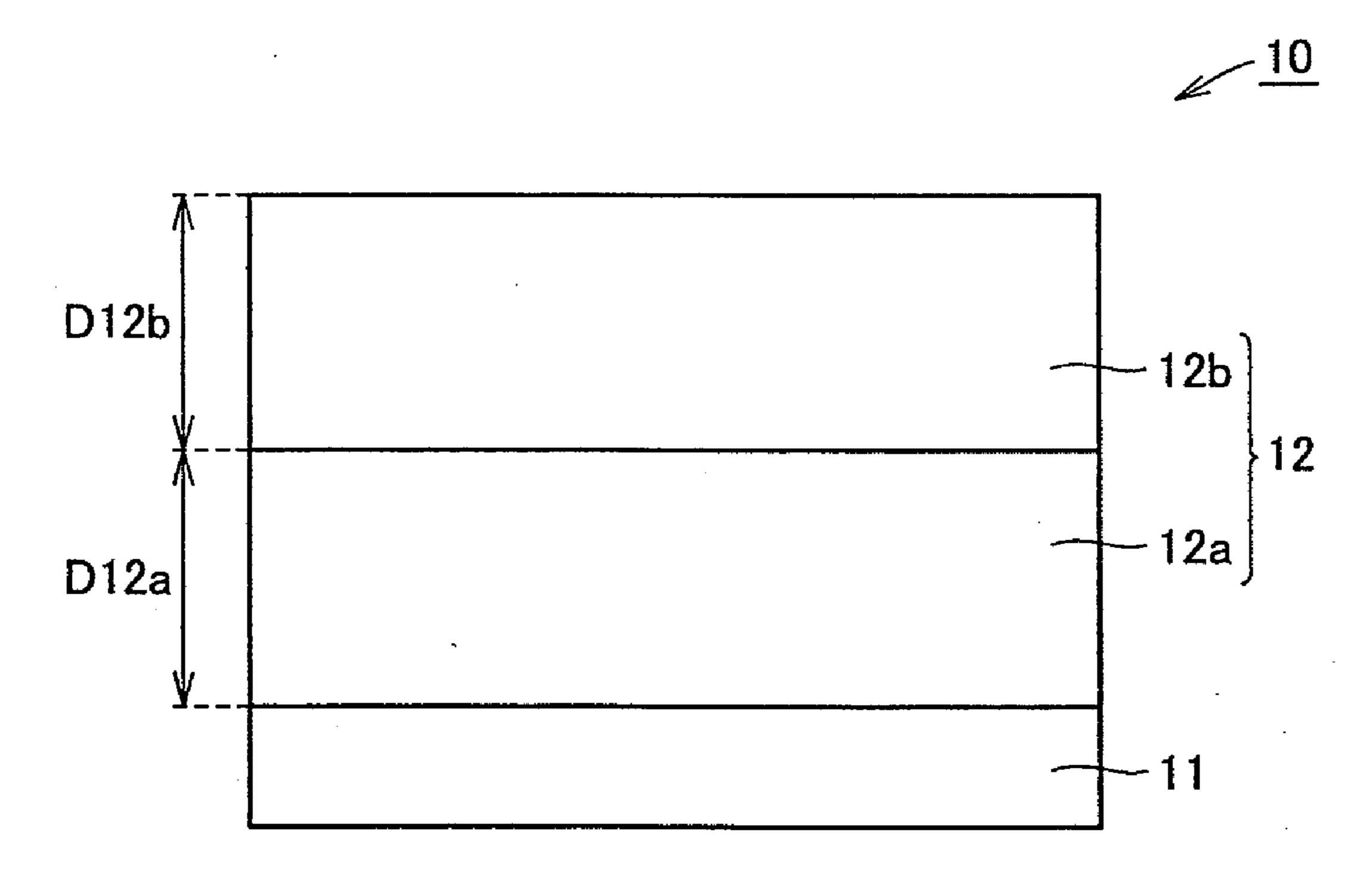

[0050] FIG. 7 is a schematic diagram of a grown state of a group III nitride semiconductor crystal according to a first modification of the first embodiment.

[0051] FIG. 8 is a schematic diagram of a group III nitride semiconductor crystal representing a state of at least the underlying substrate removed in the first modification of the first embodiment.

[0052] FIG. 9 is a schematic diagram of a group III nitride semiconductor crystal representing a state of at least the underlying substrate removed in a second modification of the first embodiment.

[0053] FIG. 10 is a schematic view of another HVPE apparatus employed in a growing method of a group III nitride semiconductor crystal according to a second embodiment of the present invention.

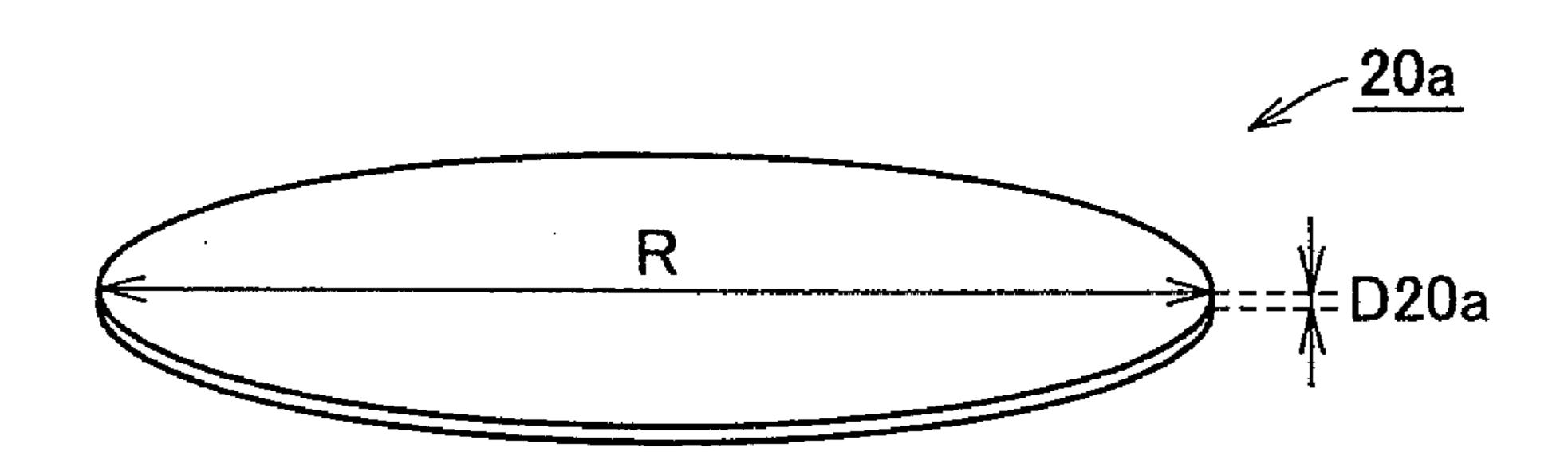

[0054] FIG. 11 is a schematic perspective view of a group III nitride semiconductor crystal substrate according to a third embodiment of the present invention.

[0055] FIG. 12 is a flowchart of a fabrication method of a group III nitride semiconductor crystal substrate of the third embodiment.

[0056] FIG. 13 is a schematic diagram of a group III nitride semiconductor crystal substrate representing a slicing state of the third embodiment.

[0057] FIG. 14 is a schematic diagram of a fabrication method of a group III nitride semiconductor crystal substrate according to a modification of the third embodiment.

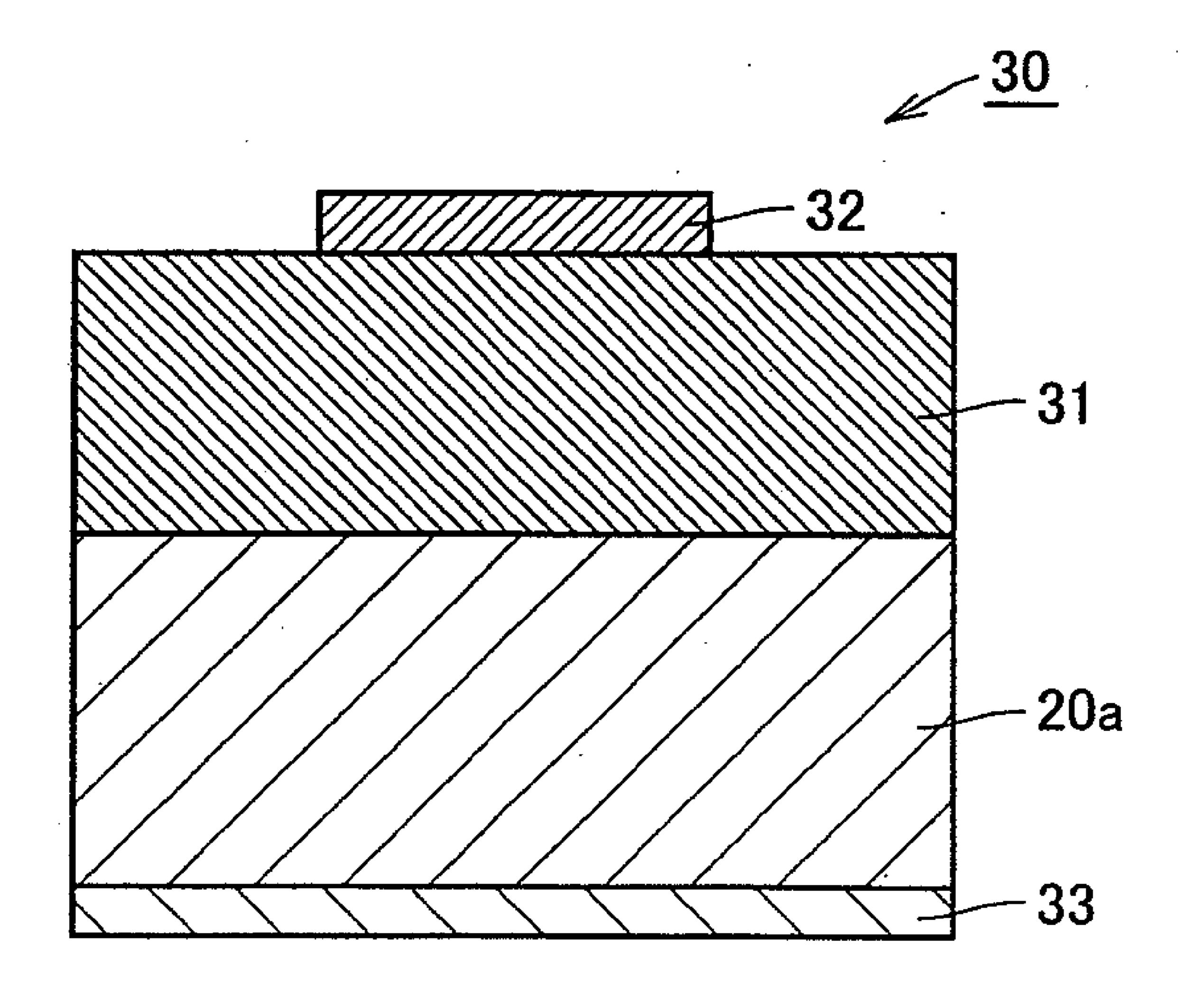

[0058] FIG. 15 is a schematic sectional view of a semiconductor device according to a fourth embodiment of the present invention.

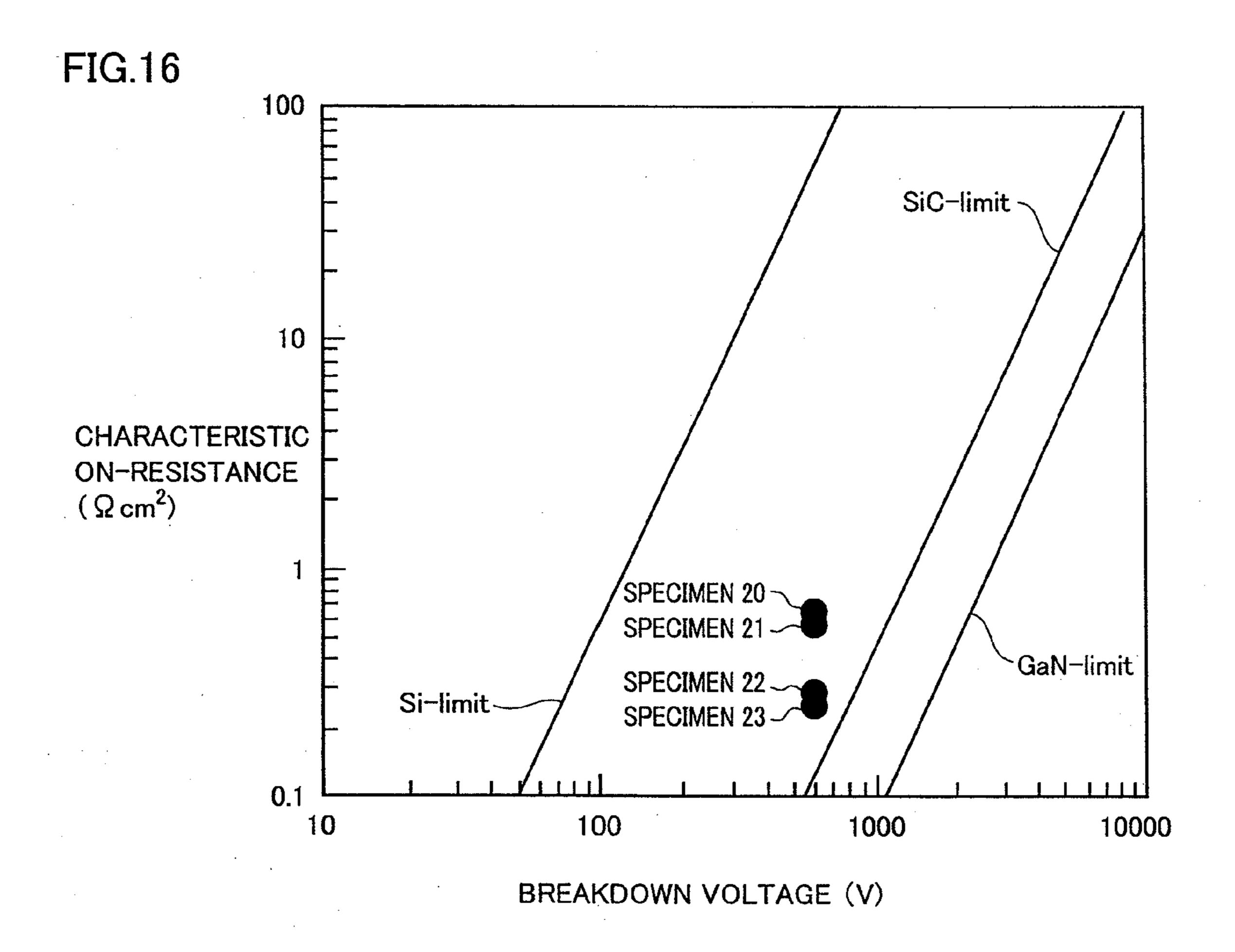

[0059] FIG. 16 is a diagram representing the relationship between the characteristic ON-resistance and reverse breakdown voltage of Schottky barrier diodes of Specimens 20-23 in Example 3.

[0060] FIG. 17 is a diagram to describe the theoretical threshold value of Example 3.

## DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0061] Embodiments of the present invention will be described hereinafter with reference to the drawings. In the drawings, the same or corresponding elements have the same reference characters allotted, and description thereof will not be repeated.

### First Embodiment

[0062] A group III nitride semiconductor crystal substrate according to an embodiment of the present invention will be described hereinafter with reference to FIGS. 1 and 2. As shown in FIGS. 1 and 2, a group III nitride semiconductor crystal substrate 10 is formed of a group III nitride semiconductor crystal 12 (refer to FIG. 4) having silicon doped as the impurity. Group III nitride semiconductor crystal substrate 10 includes a main face 10a.

[0063] As shown in FIGS. 1 and 2, a group III nitride semiconductor crystal substrate 10 of the present embodiment has a diameter R that is at least 25 mm and not more than 160 mm, preferably at least 45 mm and not more than 130 mm. A diameter R of at least 25 mm is advantageous in that the crystallinity of group III nitride semiconductor crystal substrate 10 is rendered favorable since the occurrence of a different plane orientation at main face 10a is prevented. In the case where diameter R is at least 45 mm, the crystallinity of group III nitride semiconductor crystal substrate 10 is rendered more favorable. A diameter R of 160 mm is advantageous in that the cost can be reduced since the underlying substrate is readily available. In the case where diameter R is not more than 130 mm, the cost can be further reduced.

[0064] Group III nitride semiconductor crystal substrate 10 has a thickness D10 of at least 2 mm and not more than 160 mm, preferably at least 6 mm and not more than 50 mm. In the case where D10 is at least 2 mm, a plurality of group III nitride semiconductor crystal substrates having a desired thickness can be obtained by slicing group III nitride semiconductor crystal substrate 10 to the desired thickness. A thickness D10 of at least 6 mm is advantageous in that more group III nitride semiconductor crystal substrates of a desired thickness can be obtained from one group III nitride semiconductor crystal substrate 10, leading to reduction in cost. In the case where thickness D10 is not more than 160 mm, a group III nitride semiconductor crystal can be grown readily in terms of facili-

ties. Therefore, the cost can be reduced. In the case where thickness D10 is at least 50 mm, the cost can be further reduced.

[0065] The resistivity of group III nitride semiconductor crystal substrate 10 is at least  $1 \times 10^{-4} \Omega \cdot \text{cm}$  and not more than  $0.1 \ \Omega \cdot \text{cm}$ , preferably at least  $1 \times 10^{-3} \ \Omega \cdot \text{cm}$  and not more than  $1\times10^{-2}~\Omega$ ·cm, more preferably at least  $1\times10^{-3}~\Omega$ ·cm and not more than  $8\times10^{-2}~\Omega$ ·cm. The resistivity of at least  $1\times10^{-4}$  $\Omega$ ·cm is at advantageous in that silicon does not have to be doped in high concentration. Therefore, the generation of a pit or defect, as well as a crack during growth of a group III nitride semiconductor crystal can be suppressed. In the case where the resistivity is at least  $1 \times 10^{-3} \Omega \cdot \text{cm}$ , the generation of a pit, defect, and crack can be further suppressed. In the case where the resistivity is not more than  $0.1 \Omega \cdot cm$ , the substrate is conveniently employed in light-emitting devices and electronic devices. In the case where the resistivity is not more than  $1\times10^{-2}\,\Omega$ ·cm, the substrate is conveniently selected as an n type substrate used in light-emitting devices and optical devices, particularly power devices. In the case where the resistivity is not more than  $8\times10^{-3}$   $\Omega\cdot\text{cm}$ , the substrate is further conveniently selected as an n type substrate used in light-emitting devices and optical devices, particularly power devices.

[0066] As used herein, "resistivity" is a value measured by the method set forth below. First, main face 10a of group III nitride semiconductor crystal substrate 10 is subjected to polishing and dry etching. Then, the resistivity is measured at each site of the total of 9 points such as the nine dots shown in FIG. 2, i.e. 5 points along an arbitrary diameter R1 including one point around the center, two points around either ends, and respective intermediate points between the center and either end (two points), and 4 points along a diameter R2 orthogonal to diameter R1, including two points around either ends and respective intermediate points between the center and either end (two points), by the four probe method at room temperature. Then, the average value of the resistivity at these nine points is calculated. Although a method of measuring the resistivity with respect to main face 10a has been described, the resistivity may be measured for another face. For example, a face parallel to main face 10a is obtained by slicing substantially the middle plane in the thickness direction between main face 10a and a face 10b opposite surface to main face 10a. Then, the resistivity at the nine points on the obtained face is measured in a similar manner, from which the resistivity average value can be calculated. Alternatively, the resistivity of nine points on a face orthogonal to main face 10amay be measured, from which the resistivity average value can be calculated.

[0067] The resistivity distribution in the diameter direction of group III nitride semiconductor crystal substrate 10 is at least –30% and not more than 30%, preferably at least –20% and not more than 20%, and more preferably at least –17% and not more than 17%. The range of –30% to 30% is advantageous in that, when semiconductor devices are produced using group III nitride semiconductor crystal substrate 10, variation of the performance in the diameter direction is suppressed and the yield improved. The range of –20% to 20% is advantageous in that, when semiconductor devices are produced, variation of the performance is suppressed and the yield improved. The range of –17% to 17% is advantageous in that, when semiconductor devices are produced, variation of the performance is further suppressed and the yield further improved.

[0068] As used herein, "resistivity distribution in the diameter direction" refers to a value measured by a method set forth below. First, main face 10a of group III nitride semiconductor crystal substrate 10 is subjected to polishing and dry etching. Then, the resistivity is measured at each site of the total of 9 points such as the nine dots shown in FIG. 2, i.e. 5 points along an arbitrary diameter R1 including one point around the center, two points around either ends, and respective intermediate points between the center and either end (two points), and 4 points along a diameter R2 orthogonal to diameter R1, including two points around either ends and respective intermediate points between the center and either end (two points), by the four probe method at room temperature. Then, the average value of the resistivity at these nine points is calculated. With regards to the values of resistivity at the nine points, the value defined by (largest value-average value)/average value is taken as the upper limit of the resistivity distribution in the diameter direction, and the value defined by (smallest value–average value)/average value is taken as the lower limit of the resistivity distribution in the diameter direction. Although a method of measuring the resistivity with respect to main face 10a has been described, the resistivity may be measured for another face.

[0069] The resistivity distribution in the thickness direction of group III nitride semiconductor crystal substrate 10 is at least –16% and not more than 16%, preferably at least –10% and not more than 10%, more preferably at least –9% and not more than 9%. The range of –16% to 16% is advantageous in that, when semiconductor devices are produced using this group III nitride semiconductor crystal substrate, variation of the performance in the thickness direction can be suppressed and the yield improved. The range of –10% to 10% is advantageous in that, when semiconductor devices are produced, variation of the performance can be suppressed and the yield improved. The range of –9% to 9% is advantageous in that, when semiconductor devices are produced, variation of the performance is further suppressed and the yield further improved.

[0070] As used herein, "resistivity distribution in the thickness direction" refers to a value measured by a method set forth below. First, main face 10a of group III nitride semiconductor crystal substrate 10 is subjected to polishing and dry etching. Then, the resistivity is measured at each site of the total of 5 points at respective arbitrary thickness such as the five dots shown in FIG. 1, i.e. one point in the proximity of main face 10a, one point in the proximity of a face 10bopposite to main face 10a, and 3 points between main face 10a and opposite face 10b, by the four probe method at room temperature. The average of the 5 values of resistivity is calculated. With regards to the values of resistivity at the five points, the value defined by (largest value–average value)/ average value is taken as the upper limit of the resistivity distribution in the thickness direction, and the value defined by (smallest value-average value)/average value is taken as the lower limit of the resistivity distribution in the thickness direction.

[0071] The concentration of silicon in group III nitride semiconductor crystal 12 is preferably at least  $5\times10^{16}$  cm<sup>-3</sup> and not more than  $5\times10^{20}$  cm<sup>-3</sup>, more preferably at least  $3\times10^{18}$  cm<sup>-3</sup> and not more than  $5\times10^{19}$  cm<sup>-3</sup>. In the case where the silicon concentration is at least  $5\times10^{16}$  cm<sup>-3</sup>, the concentration of the silicon taken in can be readily controlled since silicon is introduced effectively. Therefore, a group III nitride semiconductor crystal substrate 10 containing silicon

of high concentration can be obtained. In the case where the silicon concentration is at least  $3\times10^{18}$  cm<sup>-3</sup>, the concentration of silicon taken in can be controlled more readily. In the case where the silicon concentration is not more than  $5\times10^{20}$  cm<sup>-3</sup>, generation of a pit or defect as well as a crack during growth of a group III nitride semiconductor crystal can be suppressed. In the case where the silicon concentration is not more than  $5\times10^{19}$  cm<sup>-3</sup>, the crystallinity is rendered further favorable.

[0072] As used herein, "silicon concentration" refers to a value measured by a method set forth below. First, main face 10a of group III nitride semiconductor crystal substrate 10 is subjected to polishing and dry etching. Then, the silicon concentration is measured at each site of the total of 9 points such as the nine dots shown in FIG. 2, i.e. 5 points along an arbitrary diameter R1 including one point around the center, two points around either ends, and respective intermediate points between the center and either end (two points), and 4 points along a diameter R2 orthogonal to diameter R1, including two points around either ends and respective intermediate points between the center and either end (two points), by SIMS (Secondary Ion-microprobe Mass Spectrometer) at room temperature. Then, the average value of the silicon concentration at the nine points is calculated. Although a method of measuring the silicon concentration with respect to main face 10a has been described, the silicon concentration may be measured at nine points in another face, or at arbitrary 9 points based on a combination of two or more faces.

[0073] The dislocation density of group III nitride semiconductor crystal substrate 10 is preferably not more than  $1\times10^7$ cm<sup>-2</sup>, more preferably not more than  $1 \times 10^6$  cm<sup>-2</sup>. A dislocation density of not more than  $1 \times 10^7$  cm<sup>-2</sup> is advantageous in that, when group III nitride semiconductor crystal substrate 10 is employed in an electronic device, the electric property can be improved, and when group III nitride semiconductor crystal substrate 10 is employed in an optical device, the optical property can be improved. A semiconductor device of more favorable property can be obtained. In the case where the dislocation density is not more than  $1\times10^6$  cm<sup>-2</sup>, the performance in usage of a semiconductor device can be further improved. Although the dislocation density is preferably as low as possible, the lower limit is, for example, at least  $1\times10^3$  cm<sup>-2</sup>. In the case where the dislocation density is at least  $1 \times 10^3$  cm<sup>-2</sup>, group III nitride semiconductor crystal substrate 10 can be produced at low cost.

[0074] As used herein, "dislocation density" is the etch pit density obtained from the number of etch pits counted on an etched surface of the nitride semiconductor crystal that has been immersed in a KOH—NaOH (potassium hydroxide-sodium hydroxide) mixture melt of 350° C., using the Nomarski microscope or a scanning electron microscope (SEM).

[0075] The concentration of oxygen in group III nitride semiconductor crystal substrate 10 is not more than  $5\times10^{16}$  cm<sup>-3</sup>, preferably not more than  $2\times10^{16}$  cm<sup>-3</sup>. Although gas containing oxygen is not employed as doping gas in the present embodiment, the oxygen in the reaction tube will be taken into the growing group III nitride semiconductor crystal as a dopant. Although oxygen is an n type dopant, identical to silicon, the efficiency of being taken into the c-plane is poor. Particularly, the introduction efficiency differs depending upon the plane orientation. Oxygen is known to have poor controllability as an n type dopant. By preventing the introduction of oxygen down to the concentration of not more than  $5\times10^{16}$  cm<sup>-3</sup>, silicon will become dominant in terms of the n

type carrier concentration. Therefore, control over the silicon concentration allows the carrier concentration of group III nitride semiconductor crystal 12 to be controlled. The crystallinity can be rendered further favorable by setting the oxygen concentration to preferably not more than  $2 \times 10^{16}$  cm<sup>-3</sup>. Although the oxygen concentration is preferably as low as possible, the lower limit is  $5 \times 10^{15}$  cm<sup>-3</sup> or above in consideration of the lowest measurable level for detection in SIMS analysis.

[0076] Main face 10a of group III nitride semiconductor crystal substrate 10 is preferably at the angle of at least -5 degrees and not more than 5 degrees relative to any one of a (0001) plane, (1-100) plane, (11-20) plane and (11-22) plane. A group III nitride semiconductor crystal of favorable crystallinity can be additionally grown on such a main face 10a. Therefore, the usage thereof in an electronic device and a light-emitting device allows improvement in the electric property and optical property, respectively. A semiconductor device of further favorable property can be obtained.

[0077] Each individual plane is represented by (). Moreover, although it is crystallographically defined to attach "–" (bar sign) above the numeral for a negative index, the negative sign is attached in front of a numeral in the present specification.

[0078] The full width at half maximum of the rocking curve in the X-ray diffraction of group III nitride semiconductor crystal substrate 10 is preferably at least 10 arcsec and not more than 500 arcsec, preferably at least 20 arcsec and not more than 100 arcsec. The value of not more than 500 arcsec is advantageous in that a semiconductor device of further favorable property is obtained since a group III nitride semiconductor crystal of favorable crystallinity can be further grown on main face 10a of group III nitride semiconductor crystal substrate 10. In the case where the value is not more than 100 arcsec, a group III nitride semiconductor crystal of further favorable crystallinity can be additionally grown on main face 10a. In the case where the value is at least 10 arcsec, the cost can be reduced since a group III nitride semiconductor crystal constituting group III nitride semiconductor crystal substrate 10 can be readily grown. The cost can be further reduced in the case where the value is at least 20 arcsec.

[0079] As used herein, "full width at half maximum of a rocking curve" implies a measured value of the full width at half maximum of a rocking curve at the (0004) plane by XRD (X-ray diffraction), and becomes an index representing the in-plane orientation. The lower value of the full width at half maximum of a rocking curve, the higher favorable crystallinity.

[0080] The group III nitride semiconductor crystal constituting a group III nitride semiconductor crystal substrate 10 is preferably an  $Al_xIn_yGa_{(1-x-y)}N$  ( $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $x+y \le 1$ ) crystal, more preferably a gallium nitride crystal.

[0081] A fabrication method of a group III nitride semiconductor crystal substrate of the present embodiment will be described with reference to FIGS. 3 and 4. First, a growing method of a group III nitride semiconductor crystal constituting a group III nitride semiconductor crystal substrate will be described.

[0082] As shown in FIGS. 3 and 4, an underlying substrate 11 is prepared (step S1). Underlying substrate 11 is a substrate directed to growing group III nitride semiconductor crystal 12 thereon.

[0083] At the preparing step (step S1), underlying substrate 11 preferably formed of a material including at least one type

selected from the group consisting of silicon (Si), sapphire (Al<sub>2</sub>O<sub>3</sub>), gallium arsenide (GaAs), silicon carbide (SiC), gallium nitride (GaN), and aluminium nitride (AlN) is prepared. Alternatively, a spinel type crystal substrate such as MgAl<sub>2</sub>O<sub>4</sub> is preferably prepared as underlying substrate 11. Moreover, in order to reduce the difference in lattice constant, underlying substrate 11 is preferably formed of a composition identical to that of group III nitride semiconductor crystal 12 to be grown. For a gallium nitride substrate, the monocrystalline gallium nitride substrate disclosed in Japanese Patent Laying-Open No. 2001-102307, for example, can be employed.

[0084] The prepared underlying substrate 11 has a diameter of at least 25 mm and not more than 160 mm, preferably at least 45 mm and not more than 130 mm. Underlying substrate 11 having a diameter of at least 25 mm is advantageous in that group III nitride semiconductor crystal 12 of favorable crystallinity can be grown since growing a group III nitride semiconductor crystal 12 constituting group III nitride semiconductor crystal substrate 10 on a plane of a different plane orientation can be prevented. In the case where the diameter of underlying substrate 11 is at least 45 mm, group III nitride semiconductor crystal 12 of further favorable crystallinity can be grown. In the case where the diameter of underlying substrate 11 is not more than 160 mm, the cost can be reduced since it is available readily. In the case where the diameter of underlying substrate 11 is not more than 130 mm, the cost can be further reduced.

[0085] Then, a group III nitride semiconductor crystal 12 doped with silicon is grown on underlying substrate 11 by vapor phase growth (step S2). For the doping gas, silicon tetrafluoride gas, for example, may be employed. In the present embodiment, silicon tetrafluoride gas alone is employed for the doping gas.

[0086] The growing method is not particularly limited as long as it corresponds to vapor phase growth. For example, HVPE, MOCVD, MBE, or the like can be employed to grow group III nitride semiconductor crystal 12. In the present embodiment, group III nitride semiconductor crystal 12 is grown by HVPE. By virtue of the high crystal growth rate, HVPE is advantageous in that a group III nitride semiconductor crystal 12 of great thickness D12 can be grown by controlling the growing time.

[0087] An HVPE apparatus 100a employed in the growing method of a group III nitride semiconductor crystal in the present embodiment will be described with reference to FIG. 5. As shown in FIG. 5, HVPE apparatus 100a includes a first raw material gas cylinder 101, a doping gas cylinder 102, a second raw material gas cylinder 103, a first gas introduction pipe 104, a doping gas introduction pipe 105, a second gas introduction pipe 106, a source boat 107, a susceptor 108, a heater 109, a reaction tube 110, an exhaust pipe 111, and an exhaust gas treatment device. HVPE apparatus 100a is based on a horizontal type reaction tube, for example. Alternatively, HVPE apparatus 100a may be a vertical type reaction tube.

[0088] Reaction tube 110 is a vessel to hold underlying substrate 11 therein and grow a group III nitride semiconductor crystal on underlying substrate 11. A quartz reaction tube, for example, may be employed for reaction tube 110. Raw material containing an element constituting a group III nitride semiconductor crystal to be grown is supplied to each of first raw material gas cylinder 101, second raw material gas cylinder 103 and source boat 107. Doping gas cylinder 102 is filled with gas containing silicon qualified as the dopant. In the present embodiment, doping gas cylinder 102 is filled

with silicon tetrafluoride gas as the doping gas. First gas introduction pipe 104, doping gas introduction pipe 105, and second gas introduction pipe 106 are provided at reaction tube 110 to introduce first raw material gas G1, doping gas G2, and second raw material gas G3, respectively, from outside reaction tube 110. Source boat 107 stores and holds a metal raw material of the group III nitride semiconductor crystal, and is disposed in second gas introduction pipe 106.

[0089] Susceptor 108 holds underlying substrate 11. In reaction tube 110, susceptor 108 is disposed such that the face on which underlying substrate 11 is held is located below first gas introduction pipe 104, doping gas introduction pipe 105 and second gas introduction pipe 106. Susceptor 108 is disposed horizontally in reaction tube 110. Alternatively, susceptor 108 may be configured with underlying substrate 11 disposed vertically. HVPE apparatus 100a may further include a local heating mechanism such as a resistance heater for underlying substrate 11.

[0090] A heater 109 is disposed outside reaction tube 110, capable of heating the entire interior of reaction tube 110 to at least 700° C. and not more than 1500° C., for example. Exhaust pipe 111 is provided at reaction tube 110 to output the gas subsequent to reaction outside of reaction tube 110. The exhaust gas treatment device is configured to allow disposal of the gas subsequent to reaction from exhaust pipe 111 so as to reduce environmental load.

[0091] In the growing step (step S2), the prepared underlying substrate 11 is held on susceptor 108, as shown in FIG. 5. At this stage, a plurality of underlying substrates 11 may be held on susceptor 108.

[0092] First and second raw material gas cylinders 101 and 103 filled with first and second raw material gasses G1 and G3, respectively, are prepared. In addition, the metal raw material is supplied to source boat 107. First raw material gas G1, second raw material gas G3 and the metal raw material are the raw material for a group III nitride semiconductor crystal 12 to be grown. When group III nitride semiconductor crystal 12 to be grown is gallium nitride, ammonia (NH<sub>3</sub>) gas, hydrogen chloride (HCl) gas, and gallium (Ga), for example, may be employed for the first raw material gas, second raw material gas, and the metal raw material supplied to source boat 107, respectively. Further, a doping gas cylinder 102 filled with silicon tetrafluoride gas is prepared.

[0093] Then, source boat 107 is heated. Reaction gas G7 is generated by the reaction of second raw material gas G3 from second gas introduction pipe 106 with the raw material at source boat 107. First raw material gas G1 from first gas introduction pipe 104, doping gas G2, and reaction gas G7 are delivered (supplied) to strike the surface of underlying substrate 11 for reaction. At this stage, a carrier gas to carry these gases to underlying substrate 11 may be employed. Inert gas such as nitrogen  $(N_2)$  gas, hydrogen  $(H_2)$  gas and argon (Ar) gas may be employed for the carrier gas.

[0094] According to HVPE, the interior of reaction tube 110 is heated by means of heater 109 to a temperature that allows group III nitride semiconductor crystal 12 to be grown at an appropriate rate. The temperature for growing group III nitride semiconductor crystal 12 is preferably at least 900° C. and not more than 1300° C., more preferably at least 1050° C. and not more than 1200° C. In the case where group III nitride semiconductor crystal 12 is grown at the temperature of 900° C. or higher, generation of a defect at group III nitride semiconductor crystal 12 can be prevented. In addition, development at a plane orientation different from the plane orienta-

tion for growth (for example, a pit or the like in the case of a c-plane) can be suppressed. Namely, a group III nitride semiconductor crystal 12 of favorable crystallinity can be grown stably with respect to the plane orientation of growth. In the case where group III nitride semiconductor crystal 12 is grown at the temperature of 1050° C. or higher, the crystallinity can be rendered more favorable. In the case where group III nitride semiconductor crystal 12 is grown at the temperature of 1300° C. or lower, degradation in crystallinity can be suppressed since decomposition of the growing group III nitride semiconductor crystal 12 can be suppressed. In the case where group III nitride semiconductor crystal 12 is grown at the temperature of 1200° C. or lower, degradation in crystallinity can be further suppressed.

[0095] The partial pressure of silicon tetrafluoride gas in growing group III nitride semiconductor crystal 12 is preferably at least  $2.0 \times 10^{-7}$  atm and not more than  $1.0 \times 10^{-5}$  atm. In the case where the partial pressure of silicon tetrafluoride is  $2.0 \times 10^{-7}$  atm, silicon qualified as the n type dopant can be taken in group III nitride semiconductor crystal 12 sufficiently. In the case where the partial pressure of silicon tetrafluoride is not more than  $1.0 \times 10^{-5}$  atm, silicon can be doped with higher controllability since the generation of an Si<sub>x</sub>N<sub>y</sub> (silicon nitride) type compound can be further suppressed. In consideration of the concentration of silicon doped into group III nitride semiconductor crystal 12, the partial pressure of silicon tetrafluoride gas is not more than  $1.0 \times 10^{-5}$  atm. The total of respective partial pressures (entirety) of each of the raw material gas, carrier gas, doping gas, and the like in reaction tube 110 is 1 atm. The concentration of silicon tetrafluoride gas is proportional to the partial pressure.

[0096] By adjusting the flow rate of first raw material gas G1, the flow rate of second raw material gas G3, or the amount of the raw material in source boat 107, the thickness of the group III nitride semiconductor crystal to be grown can be modified appropriately. Group III nitride semiconductor crystal 12 is preferably grown such that the thickness D12 thereof is at least 100 µm and not more than 1100 µm, for example. By virtue of the high crystal growth rate in HVPE, a group III nitride semiconductor crystal 12 having a large thickness can be grown by controlling the growing time. In the case where thickness D12 is at least 100 µm, a group III nitride semiconductor crystal 12 that can be employed singularly as the substrate for various types of semiconductor devices can be grown readily. By setting thickness D12 to not more than 1100 μm, a group III nitride semiconductor crystal substrate 10 having the aforementioned thickness D10 can be obtained by the step of removing at least underlying substrate 11 (step S3) that will be described afterwards.

[0097] At the growing step (step S2), the doping gas is supplied to underlying substrate 11 such that the concentration of silicon in group III nitride semiconductor crystal 12 is preferably at least  $5\times10^{16}$  cm<sup>-3</sup> and not more than  $5\times10^{20}$  cm<sup>-3</sup>, more preferably at least  $3\times10^{18}$  cm<sup>-3</sup> and not more than  $5\times10^{19}$  cm<sup>-3</sup>. In the case where the silicon concentration is at least  $5\times10^{16}$  cm<sup>-3</sup>, the concentration of silicon taken in group III nitride semiconductor crystal 12 can be readily controlled by adjusting the concentration of doping gas G2. In the case where the silicon concentration is at least  $3\times10^{18}$  cm<sup>-3</sup>, the concentration of silicon taken in group III nitride semiconductor crystal 12 can be controlled more readily. In the case where the silicon concentration is not more than  $5\times10^{20}$  cm<sup>-3</sup>, generation of a pit or defect, as well as generation of a crack, at group III nitride semiconductor crystal 12 during growth,

can be suppressed. In the case where the silicon concentration is not more than  $5\times10^{19}$  cm<sup>-3</sup>, generation of a pit or defect at group III nitride semiconductor crystal **12**, as well as generation of a crack, can be suppressed.

[0098] In the growing step (step S2), group III nitride semiconductor crystal 12 is grown such that the resistivity is at least  $1 \times 10^{-4} \,\Omega$ ·cm and not more than  $0.1 \,\Omega$ ·cm, preferably at least  $1\times10^{-3}$   $\Omega\cdot\text{cm}$  and not more than  $1\times10^{-2}$   $\Omega\cdot\text{cm}$ , more preferably at least  $1\times10^{-3}~\Omega$ ·cm and not more than  $8\times10^{3}$  $\Omega$ ·cm. In the case where the resistivity is at least  $1\times10^{-4}$  $\Omega$ ·cm, silicon does not have to be doped in high concentration. Therefore, the event of group III nitride semiconductor crystal 12 rendered fragile due to impurities being taken in can be suppressed. As a result, a group III nitride semiconductor crystal 12 can be grown having generation of a pit or defect, as well as a crack suppressed. In the case where the resistivity is at least  $1\times10~\Omega$ ·cm, a group III nitride semiconductor crystal 12 further suppressed in the generation of a pit, defect and crack can be grown. In the case where the resistivity is not more than  $0.1 \Omega \cdot cm$ , a group III nitride semiconductor crystal 12 that can be conveniently employed for an electronic device or light-emitting device can be grown. In the case where the resistivity is not more than  $1\times10^{-2}~\Omega\cdot\text{cm}$ , a group III nitride semiconductor crystal 12 conveniently selected for an electronic device or light-emitting device, particularly a power device, can be grown. In the case where the resistivity is not more than  $8 \times 10^{-3}$   $\Omega \cdot \text{cm}$ , a group III nitride semiconductor crystal 12 further conveniently selected for an electronic device or light-emitting device, particularly a power device, can be grown.

[0099] In addition, group III nitride semiconductor crystal 12 is grown such that the resistivity distribution in the diameter direction is at least –30% and not more than 30%, preferably at least –20% and not more than 20%, more preferably at least –17% and not more than 17%. The range of –30% to 30% is advantageous in that, for producing semiconductor devices, there can be grown group III nitride semiconductor crystal 12 having variation of the performance in the diameter direction suppressed and the yield improved. The range of –20% to 20% is advantageous in that, when semiconductor devices are produced, variation of the performance can be suppressed and the yield improved. The range of –17% to 17% is advantageous in that, when semiconductor devices are produced, variation of the performance can be further suppressed and the yield further improved.

[0100] Group III nitride semiconductor crystal 12 is grown such that the resistivity distribution in the thickness direction is at least -16% and not more than 16%, preferably at least -10% and not more than 10%, more preferably at least -9% and not more than 9%. The range of –16% to 16% is advantageous in that group III nitride semiconductor crystal 12 is grown such that, when used for producing semiconductor devices, variation of the performance in the thickness direction can be suppressed and the yield improved. The range of -10% to 10% is advantageous in that group III nitride semiconductor crystal 12 is grown such that, when used for producing semiconductor devices, variation of the performance in the thickness direction can be suppressed and the yield improved. The range of -9% to 9% is advantageous in that, group III nitride semiconductor crystal 12 is grown such that, when semiconductor devices are produced, variation of the performance is further suppressed and the yield further improved.

[0101] Preferably in the growing step (step S2), group III nitride semiconductor crystal 12 is an  $Al_xIn_yGa_{(1-x-y)}N$  ( $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $x+y \le 1$ ) crystal, preferably a gallium nitride crystal. Accordingly, an extremely effective group III nitride semiconductor crystal 12 can be grown.

[0102] In the growing step (step S2), the doping gas is supplied to underlying substrate 11 such that the concentration of oxygen in group III nitride semiconductor crystal 12 is not more than  $5 \times 10^{16}$  cm<sup>-3</sup>. Although gas containing oxygen is not employed as doping gas in the present embodiment, the oxygen in reaction tube 110 will be taken into the growing group III nitride semiconductor crystal 12. Although oxygen is an n type dopant, identical to silicon, the efficiency of being taken into the c-plane is poor. Particularly, the introduction efficiency differs depending upon the plane orientation. Oxygen is known to have poor controllability as an n type dopant. By preventing the introduction of oxygen down to the concentration of not more than  $5 \times 10^{16}$  cm<sup>-3</sup>, more preferably down to the concentration of not more than  $2 \times 10^{16}$  cm<sup>-3</sup>, the resistivity of group III nitride semiconductor crystal 12 can be controlled stably. Although the oxygen concentration is preferably as low as possible, the lower limit is  $5 \times 10^{15}$  cm<sup>-3</sup> or above in consideration of the lowest measurable level for detection in SIMS analysis. In the growing step (step S2), group III nitride semiconductor crystal 12 is grown such that the dislocation density of group III nitride semiconductor crystal 12 is preferably not more than  $1 \times 10^7$  cm<sup>2</sup>, more preferably not more than  $1 \times 10^6$  cm<sup>-2</sup>. A dislocation density of not more than  $1\times10^7$  cm<sup>-2</sup> is advantageous in that, when employed in an electronic device, the electric property can be improved, and when employed in an optical device, the optical property can be improved. A group III nitride semiconductor crystal 12 of more favorable property can be obtained. In the case where the dislocation density is not more than  $1 \times 10^6$  cm<sup>-2</sup>, the performance in usage of a semiconductor device can be further improved. Although the dislocation density is preferably as low as possible, the lower limit is, for example, at least  $1 \times 10^3$  cm<sup>-2</sup>. In the case where the dislocation density is at least  $1 \times 10^3$  cm<sup>-2</sup>, a group III nitride semiconductor crystal 12 can be produced at low cost.

[0103] In the growing step (step S2), group III nitride semiconductor crystal 12 is grown such that the main face of group III nitride semiconductor crystal 12 is preferably at the angle of at least -5 degrees and not more than 5 degrees relative to any one of a (0001) plane, (1-100) plane, (11-20) plane and (11-22) plane. A group III nitride semiconductor crystal of favorable crystallinity can be additionally grown on the main face. Therefore, the usage thereof in an electronic device and a light-emitting device allows improvement in the electric property and optical property, respectively. A semiconductor device of further favorable property can be obtained.

[0104] In the growing step (step S2), group III nitride semiconductor crystal 12 is grown such that the full width at half maximum of a rocking curve in the X-ray diffraction is preferably at least 10 arcsec and not more than 500 arcsec, more preferably at least 20 arcsec and not more than 100 arcsec. The value of not more than 500 arcsec is advantageous in that a semiconductor device of further favorable property is obtained since a group III nitride semiconductor crystal of favorable crystallinity can be further grown on group III nitride semiconductor crystal 12. In the case where the value is not more than 100 arcsec, a group III nitride semiconductor crystal of further favorable crystallinity can be additionally grown thereon. In the case where the value is at least 10

arcsec, the cost can be reduced since a group III nitride semiconductor crystal 12 can be readily grown. The cost can be further reduced in the case where the value is at least 20 arcsec.

[0105] Then, the heating by heater 109 is stopped, and the temperature of source boat 107, group III nitride semiconductor crystal 12, and underlying substrate 11 is reduced down to approximately the room temperature. Then, underlying substrate 11 and group III nitride semiconductor crystal 12 are taken out from reaction tube 110.

[0106] Thus, a group III nitride semiconductor crystal 12 can be grown on underlying substrate 11 shown in FIG. 4.

[0107] Referring to FIG. 6, at least underlying substrate 11 is removed to produce a group III nitride semiconductor crystal substrate 10 constituted of group III nitride semiconductor crystal 12 having a thickness D10 of at least 100  $\mu$ m (step S3).

[0108] The crystallinity is often not favorable in the neighborhood of the interface between group III nitride semiconductor crystal 12 and underlying substrate 11. It is therefore preferable to fabricate a group III nitride semiconductor crystal substrate 10 by further removing the region of group III nitride semiconductor crystal 12 where the crystallinity is not favorable. Thus, a group. III nitride semiconductor crystal substrate 10 having a main face 10a and a face 10b opposite to main face 10a is produced, as shown in FIG. 6.

[0109] The removing method includes the method of, for example, cutting, grinding, and the like. Cutting refers to dividing (slicing) mechanically at least underlying substrate 11 from group III nitride semiconductor crystal 12 by means of a slicer having a peripheral cutting edge of a diamond electrolytic deposited wheel or a wire saw. Grinding refers to mechanically grinding away at least underlying substrate 11 by a grinding equipment with a diamond grindstone.

[0110] The face to be removed from group III nitride semiconductor crystal 12 is not limited to a face parallel to the surface of underlying substrate 11. For example, a face having an arbitrary inclination with respect to the surface may be sliced. It is to be noted that main face 10a preferably has an angle of at least -5 degrees and not more than 5 degrees relative to any one of a (0001) plane, (1-100) plane, (11-20) plane and (11-22) plane, as set forth above.

[0111] Main face 10a and opposite face 10b of group III nitride semiconductor crystal substrate 10 may be further subjected to polishing or surface treatment. The polishing method or the surface treatment method is not particularly limited, and an arbitrary method may be employed.

[0112] By carrying out the steps set forth above (steps S1-S3), a group III nitride semiconductor crystal substrate 10 shown in FIGS. 1 and 2 can be fabricated. Namely, there is obtained a group III nitride semiconductor crystal substrate 10 having a resistivity of at least  $1\times10^{-4} \Omega \cdot \text{cm}$  and not more than 0.1  $\Omega \cdot \text{cm}$ , a resistivity distribution in the diameter direction of at least -30% and not more than 30%, and a resistivity distribution in the thickness direction of at least -16% and not more than 16%.

[0113] First Modification

[0114] A fabrication method of a group III nitride semiconductor crystal substrate according to a first modification of the present embodiment will be described hereinafter with reference to FIGS. 7 and 8.

[0115] As shown in FIG. 7, the growing method of a group III nitride semiconductor crystal substrate of the present modification is basically similar to that of the first embodi-

ment set forth above, and differs in that two layers of group III nitride semiconductor crystal are grown at the growing step (step S2).

[0116] Specifically, as shown in FIG. 7, group III nitride semiconductor crystal 12 doped with silicon by using silicon tetrafluoride gas as the doping gas provided on underlying substrate 11 by vapor phase growth is a first group III nitride semiconductor crystal 12a. Then, a second group III nitride semiconductor crystal 12b doped with silicon by using silicon tetrafluoride gas as the doping gas is grown in a similar manner on first group III nitride semiconductor crystal 12a. Thus, there are produced underlying layer 11, first group III nitride semiconductor crystal 12a on underlying substrate 11, and second group III nitride semiconductor crystal 12b on first group III nitride semiconductor crystal 12a.

[0117] Then, at least underlying substrate 11 is removed, as shown in FIG. 8, to fabricate a group III nitride semiconductor crystal substrate constituted of at least one of first and second group III nitride semiconductor crystals 12a and 12b having a thickness D10 of at least 100 µm. In the present modification, a group III nitride semiconductor crystal substrate constituted of second group III nitride semiconductor crystal 12b is fabricated by removing first group III nitride semiconductor crystal 12a and a portion of second group III nitride semiconductor crystal 12b. In this case, a group III nitride semiconductor crystal substrate 10 of further favorable crystallinity can be obtained by taking first group III nitride semiconductor crystal 12a as a buffer layer directed to matching with underlying substrate 11 in the lattice constant, and growing second group III nitride semiconductor crystal 12b of further favorable crystallinity thereon.

[0118] Second Modification

[0119] A fabrication method of a group III nitride semiconductor crystal substrate according to a second modification of the present embodiment will be described hereinafter with reference to FIG. 9.

[0120] As shown in FIG. 9, the fabrication method of a group III nitride semiconductor crystal substrate of the present modification is basically similar to the fabrication method of a group III nitride semiconductor crystal substrate in the first modification, and differs in that a group III nitride semiconductor crystal substrate 10 including first and second group III nitride semiconductor crystals 12a and 12b is fabricated by removing a portion of first group III nitride semiconductor crystal 12a in the step of removing at least the underlying substrate (step S3).

[0121] In group III nitride semiconductor crystal substrate 10 of the present modification, the two layers of group III nitride semiconductor crystals 12a and 12b may be of the same composition or of different compositions. Furthermore, the growing method of a group III nitride semiconductor crystal of the present invention is not particularly limited to the method of growing one or two layers of group III nitride semiconductor crystal. Three or more layers of a group III nitride semiconductor crystal may be grown.

[0122] As set forth above, group III nitride semiconductor crystal substrate 10 of the present embodiment and modifications thereof has a resistivity is at least  $1\times10^{-4} \Omega \cdot \text{cm}$  and not more than 0.1  $\Omega \cdot \text{cm}$ , a resistivity distribution in the diameter direction of at least -30% and not more than 30%, and a resistivity distribution in the thickness direction of at least -16% and not more than 16%.

[0123] In the present embodiment and modifications thereof, silicon tetrafluoride gas is used as the doping gas in

growing group III nitride semiconductor crystal 12 doped with silicon under the condition that decomposition of the doping gas is to be prevented and reaction per se with another gas is suppressed. Silicon tetrafluoride gas is characterized in that, as compared to other doping gases directed to doping silicon, the gas per se is not readily decomposed, and does not easily react with another gas such as the raw material gas for the group III nitride semiconductor crystal and the carrier gas. Particularly, it is to be noted that silane, disilane, chlorosilane, dichlorosilane, monochlorosilane and tetrachlorosilane react with ammonia gas that is the raw material of nitrogen (N) at a temperature in the vicinity of the room temperature, whereas silicon tetrafluoride gas does not react with ammonia gas even if raised up to 1200° C. Therefore, the event of the silicon tetrafluoride gas being decomposed prior to arrival at underlying substrate 11 to adhere to a region other than underlying substrate 11 and/or generation of an  $Si_xN_v$  (silicon nitride) type compound (x and y are arbitrary integers) caused by the reaction of silicon in the silicon tetrafluoride can be suppressed. Accordingly, control over the concentration of tetrafluoride gas qualified as the doping gas allows the concentration of silicon serving as the dopant to be controlled readily. As a result, the amount of silicon taken in group III nitride semiconductor crystal 12 can be regulated at a constant level. Thus, the resistivity of group III nitride semiconductor crystal 12 can be readily controlled.

[0124] Since the amount of silicon in the silicon tetrafluoride gas can be controlled readily, it is not necessary to supply the silicon tetrafluoride gas to underlying substrate 11 at a high rate. Therefore, doping gas can be supplied uniformly to underlying substrate 11 since first group III nitride semiconductor crystal 12 can be grown by supplying doping gas at an appropriate flow rate directed to growing the crystal. Therefore, degradation in the resistivity in-plane distribution of group III nitride semiconductor crystal 12 to be grown can be prevented.

[0125] Group III nitride semiconductor crystal substrate 10 of the present embodiment and modifications thereof is based on group III nitride semiconductor crystal 12 having the resistivity reduced by readily controlling the resistivity and degradation in the resistivity in-plane distribution prevented. By virtue of the resistivity being not more than  $0.1 \Omega \cdot \text{cm}$ , group III nitride semiconductor crystal substrate 10 is conveniently selected as an n type substrate employed in electronic devices and light-emitting devices improved in the properties such as the low ON-resistance and high breakdown voltage. Since the resistivity is at least  $1 \times 10^{-4} \,\Omega \cdot \text{cm}$ , it is not necessary to dope silicon in high concentration. Therefore, generation of a pit or defect as well as a crack during growth of a group III nitride semiconductor crystal can be suppressed. In the case where the resistivity distribution in the diameter direction is at least –30% and not more than 30% and the resistivity distribution in the thickness direction of the group III nitride semiconductor crystal substrate is at least –16% and not more than 16%, variation in the properties, when semiconductor devices are produced using the group III nitride semiconductor crystal substrate, can be suppressed. Therefore, the yield can be improved.

### Second Embodiment

[0126] A group III nitride semiconductor crystal substrate according to a second embodiment of the present invention is similar to group III nitride semiconductor crystal substrate 10 of the first embodiment shown in FIGS. 1 and 2. The fabri-

cation method of a group III nitride semiconductor crystal substrate of the second embodiment differs from the fabrication method of a group III nitride semiconductor crystal of the first embodiment.

[0127] Specifically, the fabrication method of the present embodiment differs from the fabrication method of the first embodiment in that silicon tetrachloride gas is used as the doping gas to grow a group III nitride semiconductor crystal. [0128] In detail, group III nitride semiconductor crystal 12 doped with silicon by using silicon tetrachloride gas as the doping gas is grown on underlying substrate 11 by vapor phase growth (step S2). In the present embodiment, silicon tetrachloride gas alone is employed for the doping gas. Elements differing from those of the first embodiment will be described in detail hereinafter.

[0129] In the case where the doping gas is silicon tetrachloride gas, the growth rate of group III nitride semiconductor crystal 12 is at least 200 μm/h and not more than 2000 μm/h, preferably at least 300 μm/h and not more than 600 μm/h. In the case where the growth rate of group III nitride semiconductor crystal 12 is at least 200 μm/h, group III nitride semiconductor crystal 12 is grown to fill an Si<sub>x</sub>N<sub>y</sub>, layer of a minute amount, when formed at the growing face of group III nitride semiconductor crystal 12, since the growth rate of group III nitride semiconductor crystal 12 is sufficiently higher than the growth rate of the  $Si_xN_v$  layer. Therefore, the influence of an  $Si_xN_v$  layer being formed can be suppressed. Accordingly, control of the concentration of silicon qualified as the dopant is facilitated by adjusting the concentration of the silicon tetrachloride gas. As a result, the concentration of silicon taken in can be regulated at a constant level. Thus, the resistivity of group III nitride semiconductor crystal 12 can be readily controlled. In the case where the growth rate of group III nitride semiconductor crystal 12 is at least 300 µm/h, the resistivity of group III nitride semiconductor crystal 12 can be controlled more readily. In the case where the growth rate of group III nitride semiconductor crystal 12 is not more than 2000 μm/h, degradation of the crystallinity of group III nitride semiconductor crystal 12 to be grown is suppressed. In the case where the growth rate of group III nitride semiconductor crystal 12 is not more than 600 µm/h, degradation in the crystallinity of group III nitride semiconductor crystal 12 can be further suppressed.

[0130] The partial pressure of the silicon tetrachloride gas during growing group III nitride semiconductor crystal 12 is preferably at least  $1 \times 10^{-6}$  atm and not more than  $2 \times 10^{-4}$  atm. In the case where the partial pressure of the silicon tetrachloride gas is at least  $1 \times 10^{-6}$  atm, silicon qualified as the n dopant can be sufficiently taken in group III nitride semiconductor crystal 12. In the case where the partial pressure of the silicon tetrachloride gas is not more than  $2 \times 10^{-4}$  atm, silicon can be doped with further favorable controllability since the generation of an  $Si_xN_\nu$  (silicon nitride) type compound can be further suppressed. In consideration of the concentration of silicon doped into group III nitride semiconductor crystal 12, the partial pressure of silicon tetrachloride gas is not more than  $1.0 \times 10^{-5}$  atm. The total of respective partial pressures (entirety) of each of the gases in reaction tube 110 such as the raw material gas, carrier gas, and doping gas is 1 atm. The concentration of the silicon tetrachloride gas is proportional to the partial pressure.

[0131] The rate of supplying doping gas G2 is preferably at least 100 cm/min and not more than 1000 cm/min, more preferably at least 250 cm/min and not more than 500 cm/min. By setting the rate within this range, variation in the concentration distribution of doping gas G2 that is supplied can be suppressed.

[0132] Thus, group III nitride semiconductor crystal 12 can be grown on underlying substrate 11 shown in FIG. 4. Using this group III nitride semiconductor crystal 12, a group III nitride semiconductor crystal substrate is fabricated in a manner similar to that of the first embodiment. Thus, there is obtained a group III nitride semiconductor crystal substrate having a resistivity of at least  $1 \times 10^{-4} \,\Omega$ ·cm and not more than  $0.1 \,\Omega$ ·cm, a resistivity distribution in the diameter direction of at least -30% and not more than 30%, and a resistivity distribution in the thickness direction of at least -16% and not more than 16%.

[0133] The remaining elements in the growing method of a group III nitride semiconductor crystal 12 and the fabrication method of a group III nitride semiconductor crystal substrate are similar to those in the growing method of a group III nitride semiconductor crystal 12 and the fabrication method of a group III nitride semiconductor crystal substrate 10 of the first embodiment. The same elements have the same reference characters allotted, and description thereof will not be repeated.

[0134] The fabrication method of the present embodiment is applicable to, not only the first embodiment, but also to modifications thereof.

[0135] In the growing method of a group III nitride semi-conductor crystal 12 in the first modification of the first embodiment shown in FIGS. 6 and 7, first group III nitride semiconductor crystal 12a preferably has a relatively low silicon concentration of not more than  $1\times10^{17}$  cm<sup>-3</sup>, and second group III nitride semiconductor crystal 12b has a relatively high silicon concentration exceeding  $1\times10^{17}$  cm<sup>-3</sup>. In this case, there can be obtained a second group III nitride semiconductor crystal 12b having growth inhibition caused by the formation of an Si<sub>x</sub>N<sub>v</sub> film prevented.

[0136] [Modification]

[0137] An HVPE apparatus 100b shown in FIG. 10 has a configuration basically similar to that of HVPE apparatus 100a set forth above, provided that doping gas introduction pipe 105 has a smaller diameter, and that doping gas introduction pipe 105 and second gas introduction pipe 106 interconnect each other at the exit side.

[0138] HVPE apparatus 100b is characterized in that the flow rate of doping gas G2 is increased due to the smaller diameter of doping gas introduction pipe 105. The diameter of doping gas introduction pipe 105 is set to realize a flow rate of doping gas G2 that can maintain a favorable resistivity in-plane distribution.

[0139] By the interconnection between doping gas introduction pipe 105 and second gas introduction pipe 106, the timing of the contact between doping gas G2 and first raw material gas G1 is delayed. HVPE apparatus 100b is characterized in that the duration of doping gas G2 brought into contact with first raw material gas G1 at a region A is shortened. In the case where second raw material gas G3 has low reactivity with doping gas G2 and first raw material gas G1 has high reactivity with doping gas G2, reaction of doping gas G2 with first raw material gas G1 can be suppressed. Accordingly, controllability in the concentration of the supplied silicon can be improved. Therefore, group III nitride semiconductor crystal 12 is preferably grown using HVPE apparatus 100b of FIG. 10. HVPE apparatus 100b of FIG. 10 is conveniently selected in the case where silicon tetrachloride is employed for the doping gas.

[0140] In the case where group III nitride semiconductor crystal 12 is grown in HVPE apparatus 100b, the supply rate of doping gas G2 is preferably at least 250 cm/min. In this case, thermal decomposition of doping gas G2 at region A can

be suppressed when region A attains a high temperature of 800° C. or above in HVPE apparatus 100b.

[0141] This fabrication method of the present modification can be applied to, not only the second embodiment, but also the first embodiment and modifications thereof.

[0142] In the present embodiment and modification thereof, silicon tetrachloride gas is employed as the doping gas, and the growth rate of group III nitride semiconductor crystal 12 constituting group III nitride semiconductor crystal substrate 10 is set to at least 200 µm/h and not more than 2000 μm/h in growing a group III nitride semiconductor crystal 12 doped with silicon under the condition that decomposition of doping gas is prevented and the influence of reaction with another gas is reduced when silicon is doped. Silicon tetrachloride gas is characterized in that, as compared to other gases directed to doping silicon such as silane, disilane, trichlorosilane, dichlorosilane and monochlorosilane, the gas per se is not readily decomposed. Therefore, the event of the silicon tetrachloride gas being decomposed before reaching underlying substrate 11 to adhere to a site other than underlying substrate 11 can be prevented.