US 20080090322A1

## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2008/0090322 A1

Mech et al.

Apr. 17, 2008 (43) Pub. Date:

METHOD OF FORMING AN IMPLANTABLE (54)ELECTRONIC DEVICE CHIP LEVEL HERMETIC AND BIOCOMPATIBLE ELECTRONICS PACKAGE USING SOI WAFERS

Inventors: Brian V. Mech, Stevenson Ranch, CA

(US); Robert J. Greenberg, Los Angeles, CA (US); Gregory J. Delmain, Minnetrista, MN (US)

Correspondence Address:

SECOND SIGHT MEDICAL PRODUCTS, INC. 12744 SAN FERNANDO ROAD **BUILDING 3 SYLMAR, CA 91342 (US)**

11/893,153 (21)Appl. No.:

Aug. 15, 2007 (22)Filed:

#### Related U.S. Application Data

Division of application No. 10/360,988, filed on Feb. 7, 2003, now Pat. No. 7,190,051.

Provisional application No. 60/440,806, filed on Jan. (60)17, 2003.

#### **Publication Classification**

Int. Cl.

(2006.01)H01L = 31/00

U.S. Cl. ..... **438/64**; 257/E31

#### (57)**ABSTRACT**

The invention is directed to a hermetically packaged and implantable integrated circuit for electronics that is made my producing streets in silicon-on-insulator chips that are subsequently coated with a selected electrically insulating thin film prior to completing the dicing process to yield an individual chip. A thin-layered circuit may transmit light, allowing a photodetector to respond to transmitted light to stimulate a retina, for example. Discrete electronic components may be placed in the three-dimensional street area of the integrated circuit package, yielding a completely integrated hermetic package that is implantable in living tissue.

Fig. 1

Fig. 2

Fig. 3

Fig. 5

# METHOD OF FORMING AN IMPLANTABLE ELECTRONIC DEVICE CHIP LEVEL HERMETIC AND BIOCOMPATIBLE ELECTRONICS PACKAGE USING SOI WAFERS

## CROSS REFERENCE TO RELATED APPLICATION

[0001] This application is a divisional of U.S. application Ser. No. 10/360,988, "Chip Level Hermetic and Biocompatible Electronics Package Using SOI Wafers", filed Feb. 7, 2003, the disclosure of which is incorporated herein by reference, which claims the benefit of U.S. Provisional Application No. 60/440,806, "Chip Level Hermetic and Biocompatible Electronics Package Using SOI Wafers", filed Jan. 17, 2003, the disclosure of which is incorporated herein by reference.

#### FIELD OF THE INVENTION

[0002] This invention relates to a hermetic integrated circuit and a method of making an integrated electronic circuit by utilizing silicon-on-insulator (SOI) techniques.

#### BACKGROUND OF THE INVENTION

[0003] This invention relates to electrically insulating thin film processes that are hermetic and that are used to encapsulate integrated circuits (ICs) for the purpose of forming a protective package for an electronic circuit, where the ICs are applicable to devices that are implanted in living tissue, such as neural prostheses or retinal electrode arrays. The package may have electrical feedthroughs to connect electrically to the outside environment. The electric circuit may interface with the outside environment optically (for example, infrared or laser) or via electromagnetic means, such as radio frequency (RF) and thus it may not need an exposed feedthrough. Additionally, the hermetic film may be made selectively electrically conductive in certain regions to facilitate signal transmission or power transmission.

[0004] The main drawback to thin film packaging of electronic circuits that are implanted in living tissue is that the process is typically three-dimensional since the entire IC needs to be packaged (encapsulated in a thin film). This results in long deposition times that add cost and that could exceed the thermal budget of the electronic circuits, thereby destroying the device. The invention describes a device and means for reducing the required deposition process time by allowing an equivalent package to be constructed in a two-dimensional deposition that covers several chips at the same time at the wafer level.

#### SUMMARY OF THE INVENTION

[0005] In accordance with a preferred embodiment of this invention, the apparatus of the instant invention is a hermetic and biocompatible electronics package that is made by applying silicon-on-insulator (SOI) technology and thin film deposition technology to enable large-scale production of individual integrated circuits for electronic packages that may be implantable in living tissue.

[0006] The SOI wafer is diced partially through its thickness. The spaces between the chips, die, or reticules are scored or semi-diced by one of several known means, in order to produce three-dimensional streets. The depth of these three-dimensional streets passes completely through

the silicon layer and partially through the insulating layer. The three-dimensional streets are then coated along with the silicon layer to yield a hermetic electronics package that is suitable for implantation in living tissue.

[0007] In accordance with an alternative embodiment, the thin silicon layer may be transparent to light, thus allowing light to strike a photodetector on the surface away from the light source. This may have application in neural prostheses or retinal electrode arrays, for example, where light passes through the integrated circuit, strikes a photodetector, which in turn stimulates the retina to enable vision in a non-functioning eye. In this case, it passes through the insulator then through the silicon/integrated circuit layer.

[0008] A further embodiment places discrete electronic circuit components in the street area of the integrated circuit. The discrete component is then coated and thus part of the hermetically sealed, implantable electronics package.

[0009] The novel features of the invention are set forth with particularity in the appended claims. The invention will be best understood from the following description when read in conjunction with the accompanying drawings.

#### OBJECTS OF THE INVENTION

[0010] It is an object of the invention to produce a hermetically sealed integrated circuit using silicon-on-insulator technology and thin film deposition technology.

[0011] It is an object of the invention to produce a light transparent thin-layered integrated circuit chip using silicon-on-insulator techniques.

[0012] It is an object of the invention to produce a discrete integrated circuit that has discrete electronic components hermetically protected wherein select components are located in the street area of the integrated circuit.

[0013] Other objects, advantages and novel features of the present invention will become apparent from the following detailed description of the invention when considered in conjunction with the accompanying drawing.

### BRIEF DESCRIPTION OF THE DRAWINGS

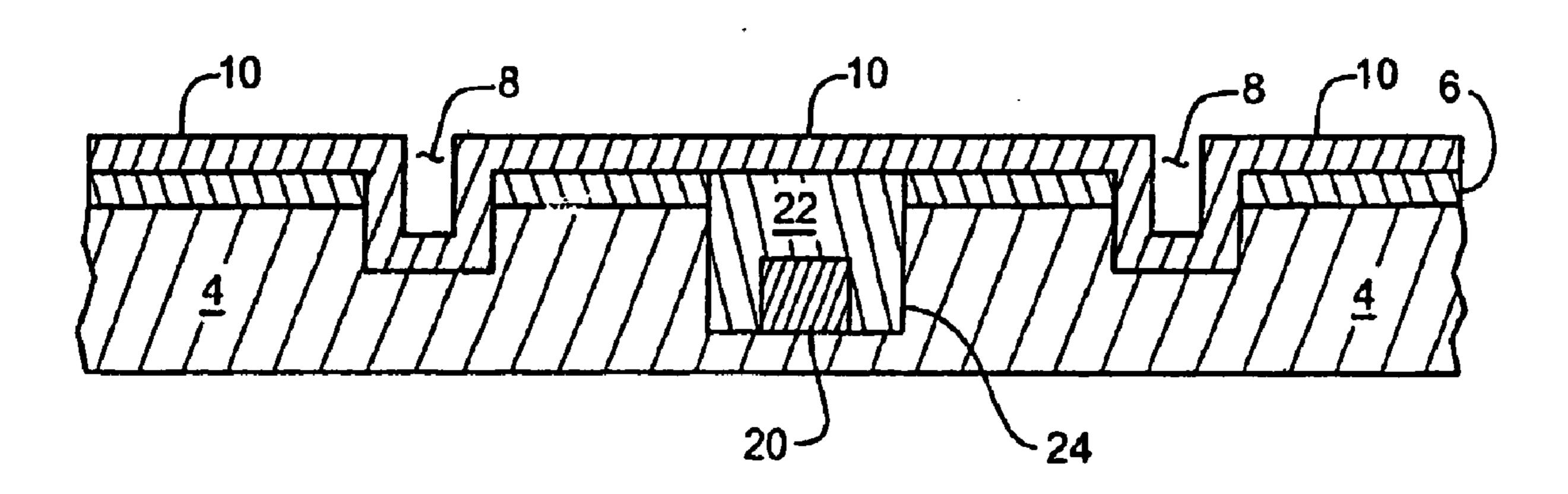

[0014] FIG. 1 illustrates a cross sectional side view of the silicon-on-insulator chip assembly.

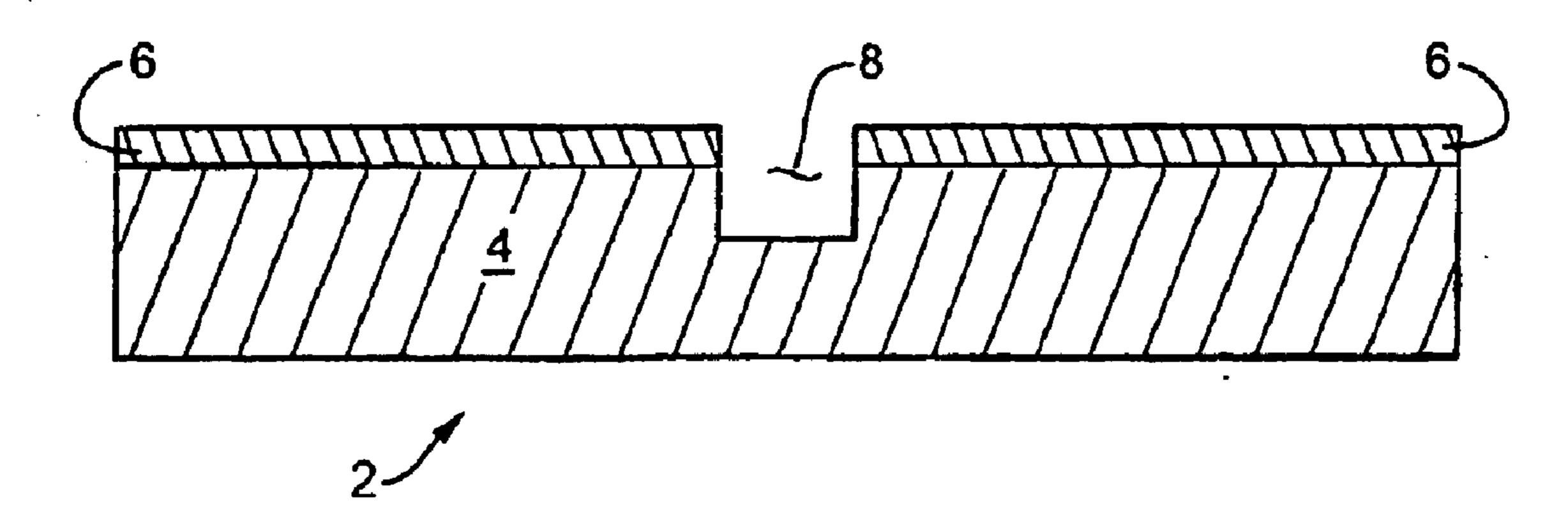

[0015] FIG. 2 depicts a cross sectional side view of the silicon-on-insulator chip assembly showing the insulating thin film.

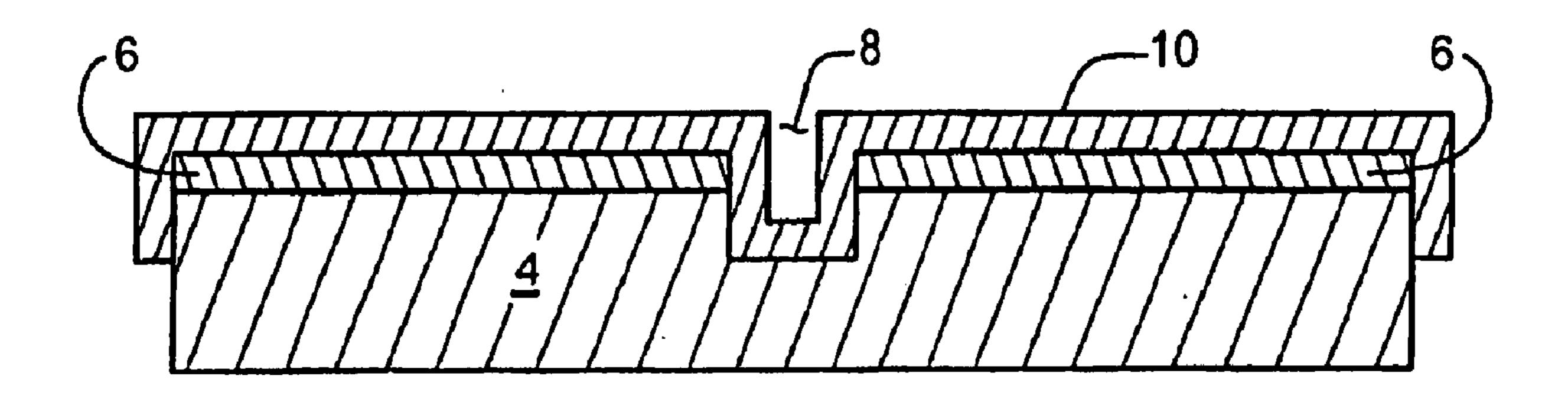

[0016] FIG. 3 depicts a cross sectional side view of a single silicon-on-insulator chip.

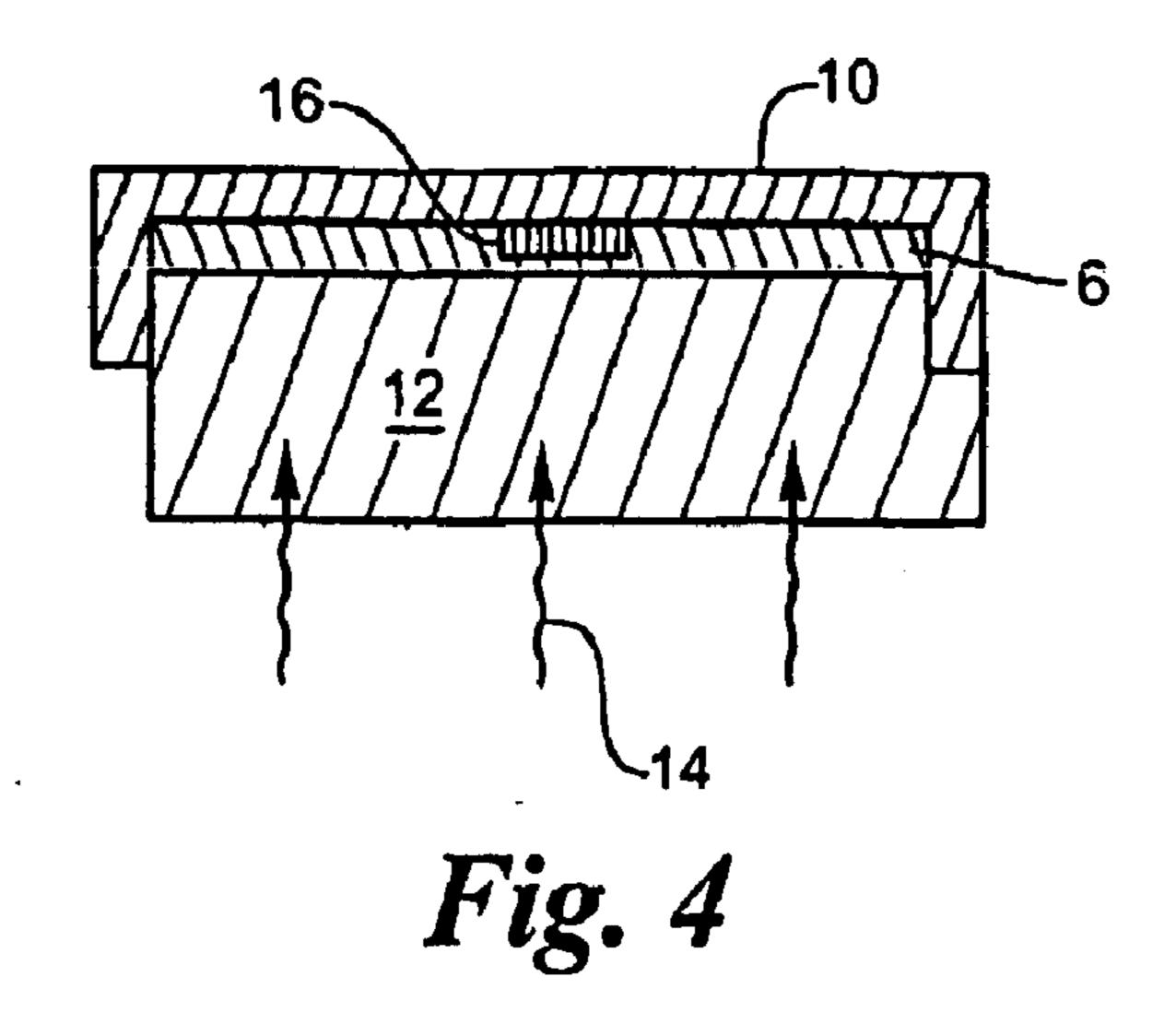

[0017] FIG. 4 illustrates a cross-sectional side view of a light transparent insulator with a photoelectric cell.

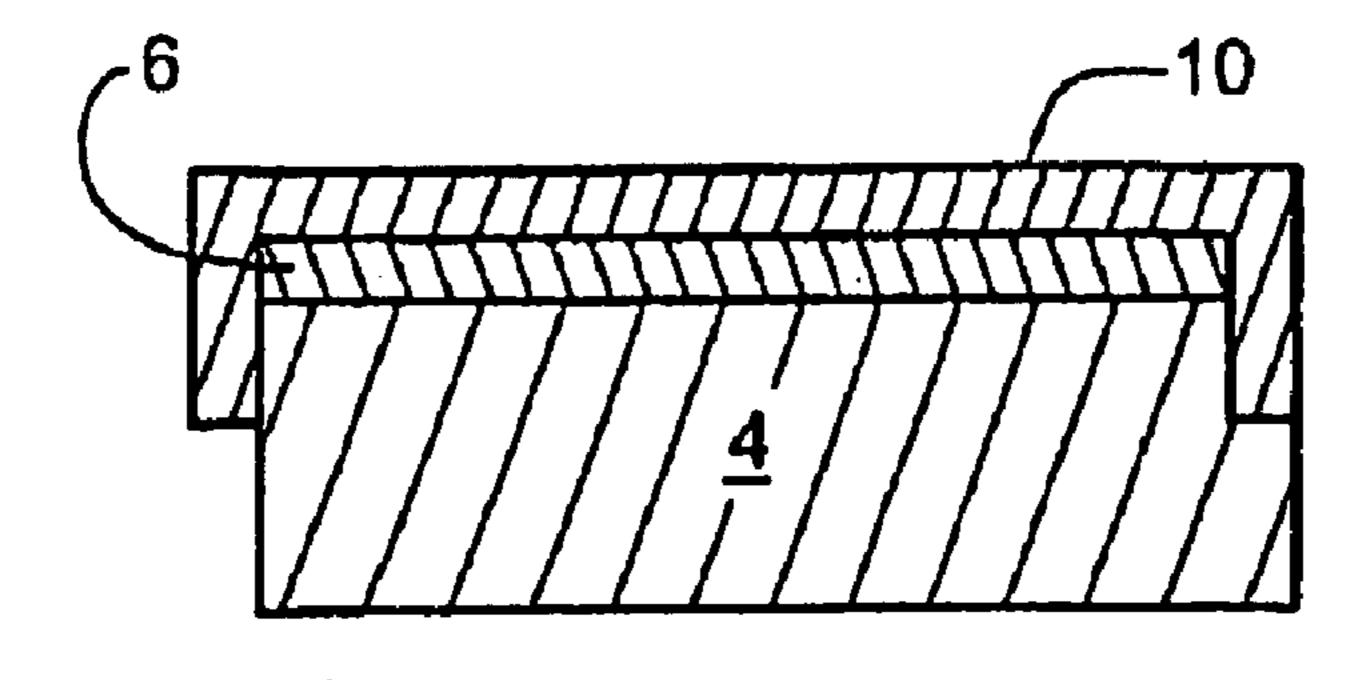

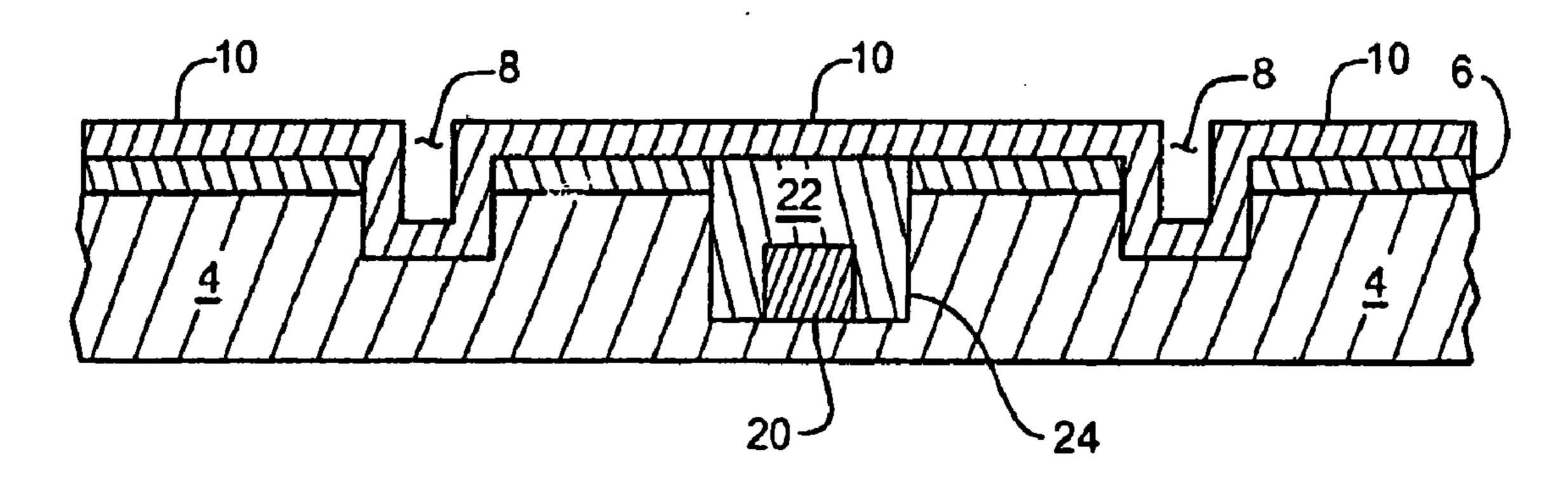

[0018] FIG. 5 depicts a hermetically coated silicon-on-insulator IC with a discrete component.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

[0019] Starting with a base substrate wafer facilitates reducing process time. A silicon-on-insulator (SOI) wafer is used as the starting substrate as opposed to a standard silicon wafer. The invention is not limited to a silicon wafer, and it is envisioned that alternative semiconductors may be

employed, such as gallium arsenide. In the case, where the integrated circuit (IC) is suitable for implantation in living tissue, a silicon-on-sapphire (SOS) or a silicon-on-diamond (SOD) wafer forms alternate embodiments, because the insulating layer is both biocompatible and bio-inert. A preferred embodiment is to the broader class of SOI wafers for electronic circuits for forming ICs for electronic circuits.

[0020] Using these wafers, the circuitry is designed using an electronics process that is known to one skilled in the art (e.g., 0.5 um CMOS) and this process is conducted to produce a wafer of functional die, such as ICs or chips). Typically, such wafers are post-processed, such as being thinned and polished, then diced into individual chips that are placed into their own packages. In a preferred embodiment, a wafer 2 is diced part of the way through, such that the spaces between the chips, die, or reticules are semi-diced by one of several known means in order to produce a three-dimensional street 8 having a depth that passes completely through a silicon layer 6 and partially through an insulator substrate 4, as shown in FIG. 1.

[0021] The insulator substrate 4 is preferably comprised of silica, although in alternative embodiments it may be comprised of glass or oxide materials that are electrical insulators. For implantation in living tissue, the insulator substrate 4 is preferably selected from a group of materials that are biocompatible and bio-inert, such as sapphire, diamond, silica, or oxide ceramics.

[0022] The main advantage of such a technique is that it eliminates the need to cover the back of the ICs with an electrically insulating and hermetic thin film, while permitting a single coating deposition process at the wafer level. The wafer level deposition of the insulating thin film 10 covers the sides of the three-dimensional street 8, eliminating the need for any further deposition coatings. Choices for the deposition process for the insulating thin film 10 and material selection are known in the art. Candidate materials include diamond, such as ultra-nanocrystalline diamond (UNCD) or ceramics, such as alumina.

[0023] The thin film process is preferably a physical vapor deposition such as Ion Beam Assisted Deposition (IBAD), which like physical vapor deposition processes, is line-of-sight deposition, it none the less is capable of uniformly covering high aspect ratio features. In an alternative embodiment, a CVD process (which is not line of sight), such as microwave plasma chemical vapor deposition (MPCVD), is selected because it is also well suited to this requirement as it naturally fills in regions such as the three-dimensional street 8. After a blanket deposition of the insulating thin film 10 over the entire wafer (which may be accomplished in several layers) the resulting structure appears as presented in FIG. 2.

[0024] A further alternative embodiment utilizes an IC package that is at least partially transparent to light 14, as illustrated in FIG. 4, where the light 14 is preferably visible light. In alternative embodiments, the light 14 may include other types of electromagnetic radiation that is detectable with a sensor that is specific to the transmitted radiation. By using an SOI device, the insulator 12 may be chosen to have favorable transmission properties for electromagnetic radiation 14. A preferred embodiment has a photoelectric cell 16, which includes, but is not limited to, photo detectors,

cadmium sulfide crystals, light sensors, phototransistors, or photodiodes that are located on a surface away from the light source.

[0025] In alternative embodiments, the photoelectric cell 16 may be any electronic circuit that responds to exposure to electromagnetic radiation 14 by generating an electric impulse. In FIG. 4, the photoelectric cell 16 is located in the silicon layer 6 and is separated from the transparent insulator 12 by a portion of the silicon layer 6. The invention is not limited to silicon layer 6 and it is envisioned that alternative semiconductor materials may be employed, such as gallium arsenide. In alternative embodiments, the photoelectric cell 16 is in direct contact with transparent insulator 12. The photoelectric cell 16 may be located on the surface of the insulator 12, in an alternative embodiment.

[0026] A preferred application is a device such as a neural prosthesis where the prosthesis may alternately be a retinal electrode array or demultiplexer, wherein the transmitted light 14 stimulates a photoelectric cell 16, which in turn stimulates the retina, enabling a non-functioning eye to detect and see visible light. Alternative embodiments enable other types of electromagnetic radiation 14, such as infrared or ultraviolet radiation, to be detected after the radiation passes through the transparent insulator 4.

[0027] In yet another embodiment, FIG. 5, a discrete electronic component 20 is placed in a hole 24 that passes part of the way through the thickness of insulator substrate 4. The hole 24 is formed by any of the techniques that are know in the art, such as reactive ion etching, laser ablation, wet etching, dry etching, or combinations of these techniques. The hole **24** is filled with an electrically insulating fill 22, preferably epoxy. After final dicing into a packaged chip, the discrete component 20 is hermetically protected in the three-dimensional street 8 of the hermetically packaged and implantable IC, having been covered with the electrically insulating thin film 10. In a preferred embodiment, the discrete component 20 is a capacitor, although in alternative embodiments the discrete component 20 may be a resistor, filter, inductor, or a combination of these electronic circuitry elements.

[0028] The advantages of this packaging approach for an implantable IC chip is that all electronic circuitry is in a single package with internal electrical leads that are hermetically sealed in the package, thereby eliminating the need for external connections and feedthroughs, which are notoriously difficult to hermetically seal for long-term living tissue implant applications.

[0029] The chips can be singulated completely by a second dicing cut in the previously formed three-dimensional street 8 using known techniques, such as laser cutting, standard dicing, or a similar procedure. The resulting packaged chip is depicted in FIG. 3.

[0030] Using the disclosed techniques, a wafer that contains numerous discrete chips, perhaps hundreds of discrete chips, is packaged in a fraction of the time that it previously took to package just one chip.

[0031] Obviously, many modifications and variations of the present invention are possible in light of the above teachings. It is therefore to be understood that, within the scope of the appended claims, the invention may be practiced otherwise than as specifically described.

What we claim is:

- 1. A method of forming an implantable electronic device, comprising the steps of:

- selecting a silicon-on-insulator chip assembly that comprises a silicon layer and an insulator substrate that has a thickness, said silicon layer bonded to said insulator substrate;

- making a street that passes through said silicon layer and that passes partially through said thickness of said insulator substrate;

- coating said silicon layer and said street with a coating; and

- extending said street through said thickness of said insulator substrate.

- 2. The method according to claim 1, further comprising the steps of:

- selecting said insulator substrate that is transparent to electromagnetic radiation; and

- mounting at least one photoelectric cell on said insulator substrate to detect said electromagnetic radiation.

- 3. The method according to claim 1, further comprising the steps of:

- selecting a discrete electronic component; and

- embedding said discrete electronic component in said insulator substrate.

- 4. The method according to claim 1, further comprising the steps of:

- selecting said coating from the group consisting of diamond, ultra-nanocrystalline diamond, ceramics, or alumina; and

- depositing said coating by ion beam assisted deposition.

- 5. The method according to claim 1 wherein said silicon layer comprises an integrated circuit.

- 6. The method according to claim 1 wherein said insulator substrate has an exposed area of said insulator substrate that is covered by said hermetic electrically insulating thin film.

- 7. The method according to claim 1 wherein said hermetic electrically insulating thin film is comprised of alumina.

- 8. The method according to claim 1 wherein said hermetic electrically insulating thin film is comprised of diamond.

- 9. The method according to claim 1 wherein said hermetic electrically insulating thin film is biocompatible.

- 10. The method according to claim 1 wherein said at least one discrete electronic component is further comprised of a capacitor.

- 11. The method according to claim 1 wherein said at least one discrete electronic component is embedded.

- 12. The method according to claim 1 wherein said insulator substrate is transparent to light.

- 13. The method according to claim 1 wherein said silicon layer contains at least one photoelectric cell that produces an electric impulse when stimulated by electromagnetic radiation.

- 14. The method according to claim 1 wherein said silicon layer contains at least one photoelectric cell that produces an electric impulse when stimulated by light.

- 15. The method according to claim 1 wherein said insulator substrate is glass.

- 16. The method according to claim 1 wherein said insulator substrate is sapphire.

- 17. The method according to claim 1 wherein said electronics package comprises a neural prosthesis.

\* \* \* \*