US 20040099215A1

# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2004/0099215 A1 Danek et al.

## May 27, 2004 (43) Pub. Date:

#### CHAMBER FOR CONSTRUCTING A FILM (54)ON A SEMICONDUCTOR WAFER

Inventors: Michal Danek, Sunnyvale, CA (US); (75)Marvin Liao, Singapore (SG); Eric Englhardt, Palo Alto, CA (US); Mei Chang, Saratoga, CA (US); Yeh-Jen Kao, San Jose, CA (US); Dale R. DuBois, Los Gatos, CA (US); Alan F.

Morrison, San Jose, CA (US)

Correspondence Address: **Patent Counsel** Applied Materials, Inc. 3050 Bowers Avenue P. O. Box 450A Santa Clara, CA 95052 (US)

Assignee: Applied Materials, Inc.

Appl. No.: 10/716,096 (21)

Nov. 18, 2003 Filed:

## Related U.S. Application Data

Continuation of application No. 08/808,246, filed on (63)Feb. 28, 1997, now Pat. No. 6,699,530. Continuation of application No. 08/680,913, filed on Jul. 12, 1996, now abandoned. Continuation of application No. 08/677,218, filed on Jul. 9, 1996, now abandoned.

Continuation of application No. 08/677,185, filed on Jul. 9, 1996, now Pat. No. 6,155,198.

Continuation of application No. 08/567,461, filed on Dec. 5, 1995, now abandoned.

Continuation of application No. 08/498,990, filed on Jul. 6, 1995, now abandoned.

### **Publication Classification**

(51) Int. Cl.<sup>7</sup> ...... C23C 16/00 (52)

#### (57)**ABSTRACT**

The construction of a film on a wafer, which is placed in a processing chamber, may be carried out through the following steps. A layer of material is deposited on the wafer. Next, the layer of material is annealed. Once the annealing is completed, the material may be oxidized. Alternatively, the material may be exposed to a silicon gas once the annealing is completed. The deposition, annealing, and either oxidation or silicon gas exposure may all be carried out in the same chamber, without need for removing the wafer from the chamber until all three steps are completed. A semiconductor wafer processing chamber for carrying out such an in-situ construction may include a processing chamber, a showerhead, a wafer support and a rf signal means. The showerhead supplies gases into the processing chamber, while the wafer support supports a wafer in the processing chamber. The rf signal means is coupled to the showerhead and the wafer support for providing a first rf signal to the showerhead and a second rf signal to the wafer support.

FIG. 1

FIG. 2

FIG. 3(a)

FIG. 4

FIG. 8

FIG. 14

FIG. 15(a)

FIG. 15(b)

FIG. 15(c)

FIG. 18

|         | TABL                                      |              |                    |

|---------|-------------------------------------------|--------------|--------------------|

| EXAMPLE | DESCRIPTION                               | THICKNESS, Å | RESISTIVITY, µΩ-cm |

|         |                                           |              |                    |

| CONTROL |                                           | ~200         | 16,000             |

|         | H <sub>2</sub> ADDED                      | ~200         | 81,200             |

| 25      | NF3 ADDED                                 | ~200         | 2,200              |

| C3      | H <sub>2</sub> /NF <sub>3</sub> ADDED     | ~400         | 1×10 <sup>6</sup>  |

| C4      | MIXED H <sub>2</sub> N <sub>2</sub> ADDED | ~200         | 39,500             |

|           | TABLE                                       |              |                    |

|-----------|---------------------------------------------|--------------|--------------------|

| SAMPLE    | DESCRIPTION                                 | THICKNESS, Å | RESISTIVITY, µΩ-cm |

|           |                                             |              |                    |

| C5        | H <sub>2</sub> PLASMA PRE/POST              | ~200         | 13,500             |

| C6        | N <sub>2</sub> PLASMA PRE/POST              | ~200         | 15,500             |

| <b>C7</b> | NF <sub>3</sub> FLOW PRIOR TO<br>DEPOSITION | ~200         | 16,500             |

| 77      |

|---------|

| ע.<br>פ |

| _       |

|           | [                     |          |         |       |       | . <u>-</u> |       |       | <u> </u> |       |       |

|-----------|-----------------------|----------|---------|-------|-------|------------|-------|-------|----------|-------|-------|

|           | PERCENT<br>CHANGE     | •        | 130     | 43    | 56    | 31         | 39    | 19    | 21       | . 7   | 2     |

|           | μΩ-cm                 | 24 HOURS | 25,385  | 6,623 | 3,623 | 2,662      | 3,827 | 2,549 | 1,915    | 1,203 | 933   |

|           | RESISTIVITY,          | INITIAL  | 11,020  | 4,620 | 2,870 | 2,027      | 2.762 | 2,150 | 1,630    | 1,154 | 913   |

|           | TIME,<br>THICKNESS, Å |          | 226     | 731   | 707   | 654        | 579   | 604   | 909      | 376   | 220   |

| TABLE III | TIME,<br>SEC          |          |         | 30    | 30    | 30         | 9     | 09    | 9        | 30    | 30    |

|           | POWER,<br>WATTS       |          | -       | 100   | 100   | 100        | 100   | 100   | 100      | 100   | 100   |

|           | THICKNESS PER CYCLE,  |          | 100     | 200   | 333   | 250        | 200   | 333   | , 250    | 100   | . 50  |

|           | NUMBER OF<br>CYCLES   |          | 2       | . 2   | ~     | 4          | 2     | 3     | 4        | 2     | 5     |

|           | SAMPLE                |          | CONTROL | EX. 1 | EX. 2 | EX. 3      | EX. 4 | EX. 5 | EX. 6    | EX. 7 | EX. 8 |

FIG. 24

| L | ハ |

|---|---|

|   | ح |

| - |   |

|       | I                 | <br>j | <del></del> |      |      |

|-------|-------------------|-------|-------------|------|------|

|       | °, °,             | 18.1  | 20.9        | 18.6 | 21.9 |

|       | N <sub>2</sub> ,% | 32.4  | 20.0        | 32.6 | 22.8 |

| TABLE | 02,%              | 8.6   | 17.2        | 8.2  | 14.3 |

|       | DEPTH, Å          | 42    | 188         | 397  | 543  |

FIG. 27

FIG. 29

FIG. 31

| TABLE V   |                                       |  |  |  |

|-----------|---------------------------------------|--|--|--|

| CONTROL   | $3.48 \times 10^{22} \text{ cm}^{-3}$ |  |  |  |

| EXAMPLE 7 | $3.96 \times 10^{22} \text{ cm}^{-3}$ |  |  |  |

| EXAMPLE 8 | $3.94 \times 10^{22} \text{ cm}^{-3}$ |  |  |  |

FIG. 32

1G. 34B

FIG. 340

FIG. 37

FIG. 38A

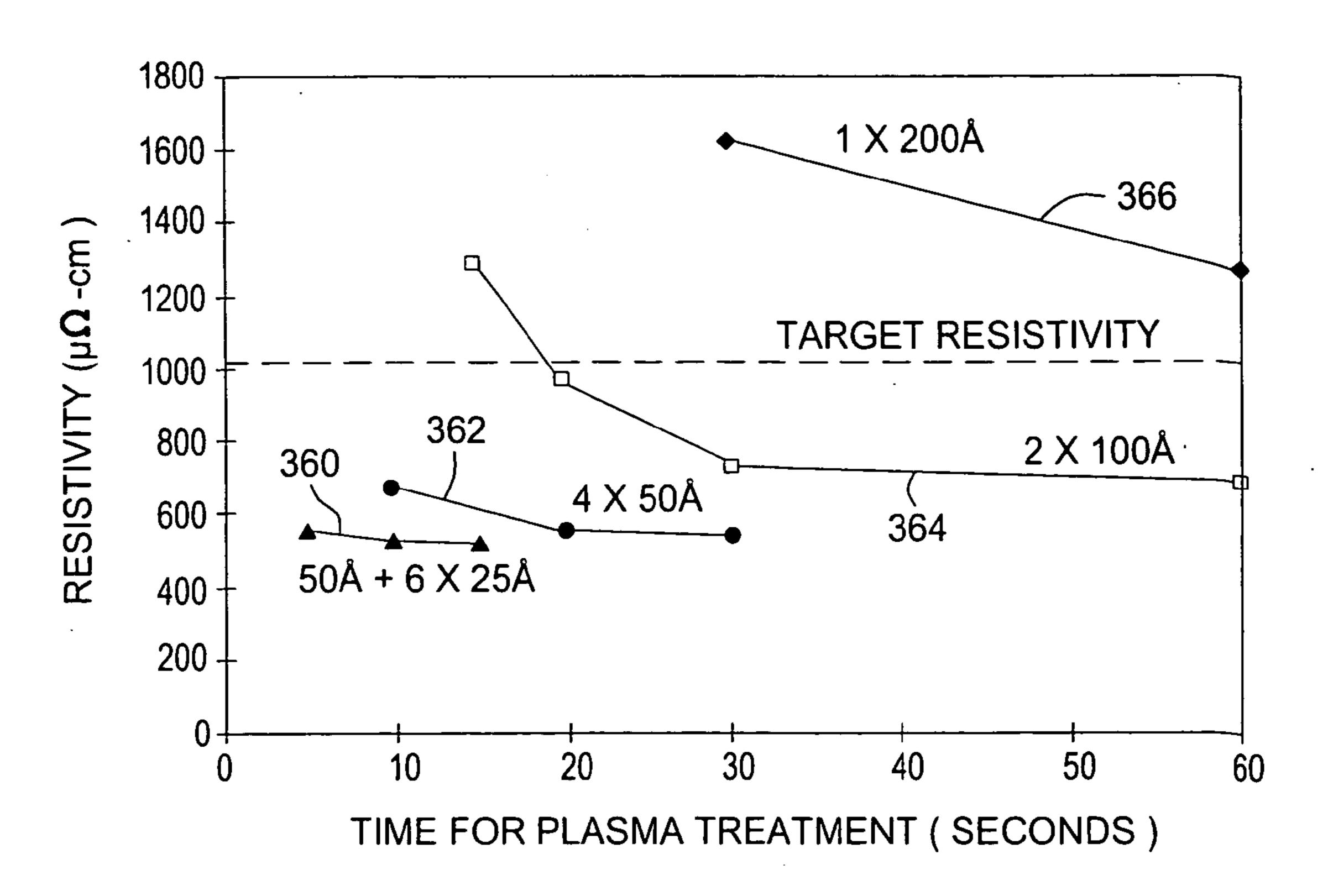

SATURATION OF PLASMA TREATMENT AT 50 Å INTERVAL

|                                                           |                        | TABLE VI                               |                                |                                |

|-----------------------------------------------------------|------------------------|----------------------------------------|--------------------------------|--------------------------------|

| GAS                                                       | RESISTIVITY (page -cm) | RESISTIVITY<br>AGING @ 50 HOURS<br>(%) | OXYGEN<br>CONCENTRATION<br>(%) | CARBON<br>CONCENTRATION<br>(%) |

| N <sub>2</sub> /H <sub>2</sub>                            | 570 - 630              | 11 - 12                                | 7                              | · ·                            |

| N <sub>2</sub> /H <sub>2</sub> + N <sub>2</sub>           | 450-500                | 7 - 8                                  | 10.8                           | 12                             |

| N <sub>2</sub> /H <sub>2</sub><br>+<br>N <sub>2</sub> /He | 440-480                | 3-7                                    | 9.1                            | 10.5                           |

| $N_{2}/H_{2}$ $N_{2}$ $+$ $+$ $N_{2}/H_{2}$               | 540-600                | 11 - 12                                | 10.5                           | 12.3                           |

五 (G. 42)

SEVERE

2.0%

**D**/80.

235

300 Å (NO OXIDATION)

MINOR

3.7%

n/sg.

630

(20 SECONDS OXIDATION)

200 Å

NONE

2.7%

250 **\Omega/SQ**.

(20 SECONDS OXIDATION)

300 Å

SEVERE

2.2%

410 **\O**/SQ.

200 Å (NO OXIDATION)

SUBSTRATE DEFECTS

SHEET RESISTANCE UNIFORMITY STANDARD DEVIATION

RESISTANCE

SHEET

FILM THICKNESS

|                                                                                                    | Z                                                   |                                                                                          |                                                                                       |                                                                                    |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| CHARACTERIZATION OF STUFFING VERSUS DEPOSITION  E RESISTIVITY COMPOSITION, ATOMIC PERCENT  μ Ω -cm | HYDROGEN<br>(H)                                     |                                                                                          |                                                                                       | 10                                                                                 |

|                                                                                                    | SILICON<br>(Si)                                     |                                                                                          |                                                                                       | 2                                                                                  |

|                                                                                                    | NITROGEN<br>(N)                                     |                                                                                          | 52.8                                                                                  | 49.7                                                                               |

|                                                                                                    | TITANIUM<br>(Ti)                                    |                                                                                          | 35.2                                                                                  | 25.3                                                                               |

| RESISTIVITY p n n -cm                                                                              |                                                     |                                                                                          | ~520                                                                                  | ~2400                                                                              |

| CHARAC                                                                                             |                                                     |                                                                                          | SILICON STUFFED<br>TIN                                                                | DEPOSITED TISICN                                                                   |

|                                                                                                    | MPLE COMPOSITION, ATOMIC POSITION, ATOMIC P. 12 -cm | MPLE RESISTIVITY COMPOSITION, ATOMIC PER μ Ω -cm TITANIUM NITROGEN SILICON (Ti) (N) (Si) | MPLE RESISTIVITY COMPOSITION, ATOMIC PER μ α -cm TITANIUM NITROGEN (Si) (Ti) (N) (Si) | SAMPLE RESISTIVITY COMPOSITION, ATOMIC PER LITANIUM NITROGEN SILICON (Ti) (N) (Si) |

FIG. 49

## CHAMBER FOR CONSTRUCTING A FILM ON A SEMICONDUCTOR WAFER

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of the following United States Patent Applications:

[0002] U.S. patent application Ser. No. 08/808,246, entitled "CHAMBER FOR CONSTRUCTING A FILM ON A SEMICONDUCTOR WAFER", filed on Feb. 28, 1997;

[0003] U.S. patent application Ser. No. 08/680,913, entitled "PLASMA BOMBARDING OF THIN FILMS", filed on Jul. 12, 1996;

[0004] U.S. patent application Ser. No. 08/677,218, entitled "IN-SITU CONSTRUCTION OF AN OXIDIZED FILM ON A SEMICONDUCTOR WAFER", filed on Jul. 9, 1996;

[0005] U.S. patent application Ser. No. 08/677,185, entitled "CHAMBER FOR CONSTRUCTING AN OXIDIZED FILM ON A SEMICONDUCTOR WAFER", filed on Jul. 9, 1996;

[0006] U.S. patent application Ser. No. 08/567,461, entitled "PLASMA ANNEALING OF THIN FILMS", filed on Dec. 5, 1995; and

[0007] U.S. patent application Ser. No. 08/498,990, entitled "BIASED PLASMA ANNEALING OF THIN FILMS", filed on Jul. 6, 1995.

[0008] Each of the aforementioned related patent applications is hereby incorporated by reference.

### BACKGROUND OF THE INVENTION

[0009] A. Field of the Invention

[0010] The present invention is directed toward the field of manufacturing integrated circuits.

[0011] B. Description of the Related Art

[0012] When manufacturing integrated circuits, deposition processes are employed to deposit thin layers of insulative material and conductive material onto wafers. Deposition has been performed through various well known processes, such as chemical vapor deposition ("CVD") and physical vapor deposition ("PVD" or "sputtering").

[0013] In a CVD process, a wafer is loaded into a chemical vapor deposition chamber. Conventional CVD processes supply reactive gases to the wafer surface where heat-induced chemical reactions take place to form a thin film layer over the surface of the wafer being processed. One particular CVD application is the deposition of a titanium containing compound, such as titanium nitride, over a wafer from a process gas that includes a metallo-organic compound. One such compound is tetrakis (dialkylamido) titanium (Ti(NR<sub>2</sub>)<sub>4</sub>) having the following structural formula:

[0014] wherein R at each occurrence independently is in an alkyl group, of, for example, 1-5 carbon atoms. For example, it is common to use tetrakis(dimethylamido) titanium (TDMAT), which has the formula  $Ti(N(CH_3)_2)_4$ .

[0015] A carrier gas, such as helium, argon, nitrogen, or hydrogen brings the compound into the chamber, so that it may be infused with energy. The energy may be generated through a thermal heat source, in the case of thermal CVD, or a radio frequency ("rf") signal source, in the case of plasma enhanced CVD. The energized chemical vapor reacts with the wafer's surface to form a thin layer of material on the wafer. When the TDMAT chemical vapor is used, a titanium nitride film is deposited on the wafer's surface.

[0016] In a sputtering process, a wafer is placed in a physical vapor deposition ("PVD") chamber, and the chamber is filled with a gas, such as argon. A plasma containing positively charged ions is generated from the gas, by creating an electrical field in the chamber. The positively charged ions accelerate and collide into a target material, which is mounted in the chamber. Atoms of the target material are thereby separated from the target and deposited on the wafer to form a layer of target material on the surface of the wafer.

[0017] In a traditional sputtering process, the bombardment of the target material by the positively charged ions is enhanced by providing a negative bias to the target material. This is achieved by providing a radio frequency signal to an electrode that supports the target material.

[0018] A separate rf signal may be inductively coupled to the chamber for generating positively charged ions in a high density plasma PVD chamber. A high density plasma PVD chamber may include another rf signal coupled to a wafer support for improving the attraction of the target material to the wafer.

[0019] A deposition chamber, such as a CVD chamber or a PVD chamber, may be used to deposit diffusion barriers in an integrated circuit. Diffusion barriers inhibit the diffusion of a contact metal, such as aluminum and copper, into the active region of a semiconductor device that is built on a silicon substrate. This prevents the interdiffusion of a contact metal into the substrate. Unlike an insulative layer of material, a diffusion barrier forms a conductive path through which current may flow. For example, a diffusion barrier may be employed to overlie a silicon substrate at the base of a contact hole.

[0020] A severe interdiffusion between a contact metal and a silicon substrate can begin to take place when the integrated circuit is heated to temperatures in excess of 450° C. If an interdiffusion is allowed to occur, the contact metal penetrates into the silicon substrate. This causes an open contact in the integrated circuit and renders the integrated circuit defective.

[0021] In the fabrication of integrated circuits, there has been an increased use of aluminum and copper metalization processes operating at high temperatures, in excess of 450° C. Therefore, it desirable to have diffusion barriers with a greater ability to inhibit the diffusion of contact metals, such as aluminum and copper.

[0022] Traditionally, diffusion barriers have been made thicker to accommodate such a desire. However, smaller geometries are being employed in the fabrication of integrated circuits. The smaller geometries decrease the dimensions of contact holes, thereby making it desirable for diffusion barriers to become thinner and more conformal.

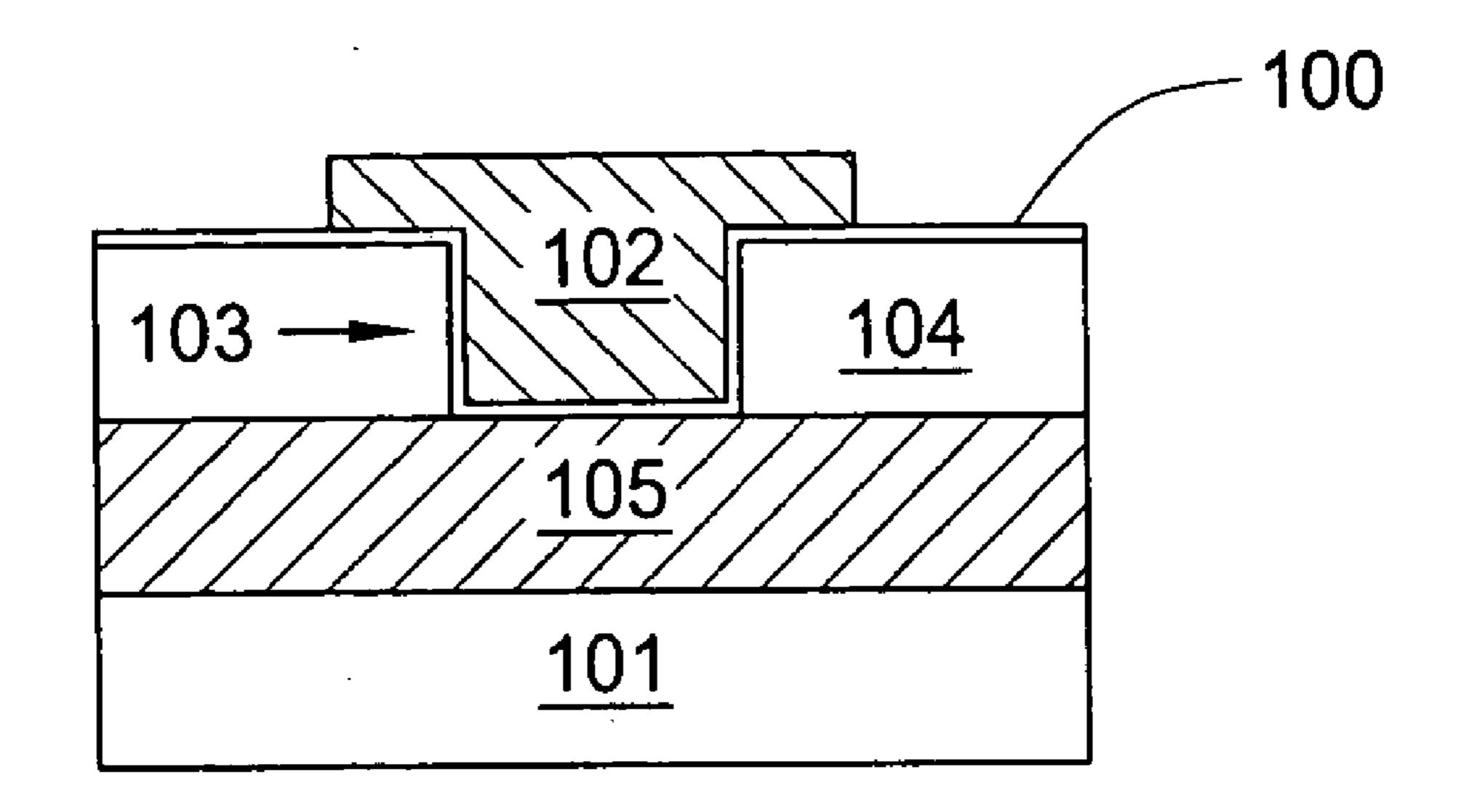

[0023] FIG. 1 illustrates a diffusion barrier 100 that resides between a conductive region 105 of a silicon substrate 101 and a contact plug 102. A contact hole 103 is formed in an insulative layer of material 104, such as silicon dioxide, which overlies the substrate 101. The diffusion barrier 100 is ideally formed so that it is thin and substantially conforms to the contours of the surface of the contact hole 103.

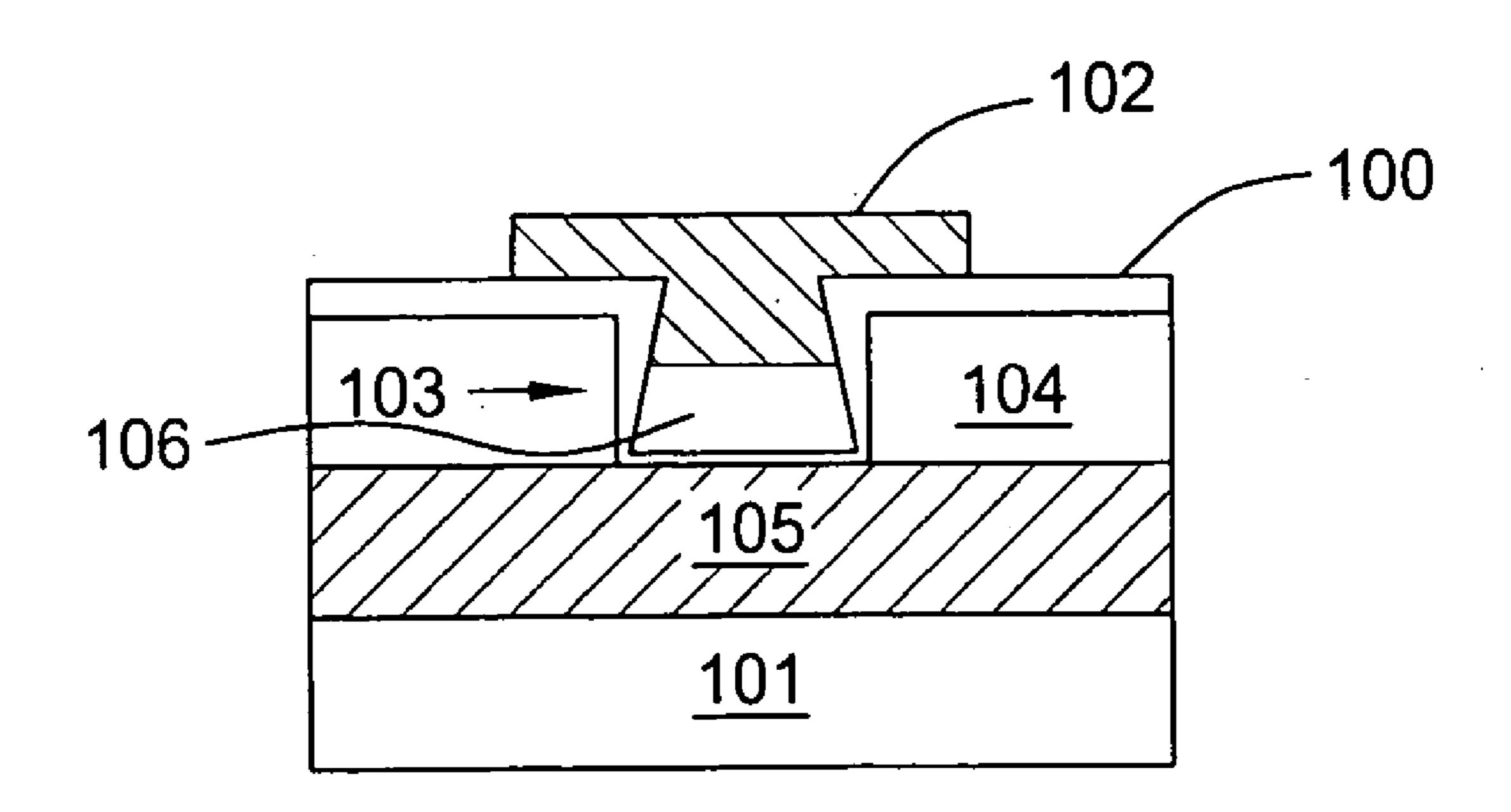

[0024] If the diffusion barrier 100 is thin and highly conformal, the contact metal 102 is able to form a sufficiently conductive ohmic contact with the silicon substrate's conductive region 105. If the diffusion barrier 100 is too thick or poorly formed, as shown in FIG. 2, it will prevent the contact metal 102 from forming a sufficiently conductive ohmic contact with the substrate region 105.

[0025] In FIG. 2, the poorly formed diffusion barrier 100 severely narrows the opening of the contact hole 103. The narrow opening causes the contact metal 102 to form so that it does not reach the base of the contact hole 103. As a result, a void 106 is formed.

[0026] In order to ensure a good ohmic contact between the contact metal 102 and the substrate region 105, it is desirable for the resistance of the diffusion barrier 100 to be minimal. Typically, a resistivity value of 1,000  $\mu\Omega$ -cm or less is acceptable. One material that has been successfully employed as a diffusion barrier is titanium nitride (TiN).

[0027] However, some deposition processes, such as those using TDMAT, provide an unstable barrier layer having high resistivity. In the case of TDMAT, this is partly due to a significant fraction of the deposited barrier material being composed of a carbon (hydrocarbons, carbides, etc.). Further, the titanium, a chemically reactive metal, may not be completely reacted in the film. It would be desirable to treat such a layer of barrier material with a post-deposition processing, so that its resistivity is reduced and stabilized.

[0028] In manufacturing an integrated circuit, it is desirable to perform successive steps of the manufacturing process, such as deposition and post-deposition processing, in the same chamber ("in-situ"). In-situ operations reduce the amount of contamination that a wafer is exposed to by decreasing the number of times that the wafer is required to be transferred between different pieces of manufacturing equipment. In-situ operations also lead to a reduction in the number of expensive pieces of manufacturing equipment that an integrated circuit manufacturer must purchase and maintain.

[0029] Accordingly, it would be desirable to construct a highly conformal thin diffusion barrier with an increased

ability to inhibit the diffusion of contact metals, such as aluminum or copper. Additionally, it is desirable for such a diffusion barrier to have a resistance that allows the diffusion barrier to form a good path for current flow. It would also be desirable to construct such a diffusion barrier in-situ.

#### SUMMARY OF THE INVENTION

[0030] An apparatus and method in accordance with the present invention provides for carrying out the in-situ construction of a highly conformal diffusion barrier with improved resistivity. By practicing aspects of the present invention, the diffusion barrier's ability to impede the diffusion of contact metals, such as aluminum or copper, may be enhanced. Such an enhancement of the diffusion barrier will not significantly enlarge its thickness or resistivity beyond acceptable limits.

[0031] A semiconductor processing apparatus, which enables practicing embodiments of the present invention, may include a processing chamber, showerhead, wafer support, and rf signal means. In one embodiment of the present invention, the semiconductor wafer processing apparatus is capable of performing chemical vapor deposition.

[0032] The showerhead is adapted to supply gases in the processing chamber. The wafer support provides for supporting a wafer in the processing chamber. The rf signal means may be coupled to both the showerhead and the wafer support for providing a first rf signal to the showerhead and a second rf signal to the wafer support. Alternatively, the rf signal means may only be coupled to provide a rf signal to the wafer support.

[0033] The wafer support is supported in the processing chamber by a support arm. The support arm couples the rf signal means to the wafer support. The support arm also couples a thermocouple housed in the wafer support to a temperature determination device for measuring the temperature of the wafer support. The thermocouple is electrically isolated from the rf signal means.

[0034] When practicing an aspect of the present invention, a film may be constructed on a wafer. First, a layer of material is deposited on the wafer. The material may be a binary metal nitride  $M_xN_y$  or a ternary metal silicon nitride  $M_xSi_yN_z$  (where M may be titanium Ti, Zirconium Zr, hafnium Hf, tantalum Ta, Molybdenum Mo, Tungsten W, and other metals). The deposition of the material may be carried out by a variety of means, such as chemical vapor deposition and physical vapor deposition.

[0035] After the material is deposited, the material is plasma annealed, so as to reduce the resistivity of the layer of material. The plasma annealing may include an exposure of the material to an environment containing ions and electrically biasing the layer of the material to cause the ions to impact the material.

[0036] Alternatively, the annealing may consist of multiple annealing steps that are performed sequentially with different gases. For example, a first annealing step may employ a mixture of nitrogen and hydrogen, while a subsequent annealing step uses a mixture of nitrogen and helium. The subsequent annealing step removes hydrogen molecules from the material to reduce its resistivity.

[0037] Once the annealing is completed, the layer of material may be oxidized. The oxidation enhances the material's ability to inhibit the diffusion of contact metals, such as aluminum. Alternatively, the annealed layer of material may be exposed to a silane gas to enhance the material's ability to inhibit the diffusion of contact metals, such as copper.

[0038] In accordance with the present invention, the deposition, annealing, and either oxidation or silane exposure may all be performed in a single chamber, without need for removing the wafer from the chamber before all three operations are completed. Accordingly, the deposition, annealing and either oxidation or silane exposure of the material may be performed in-situ.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0039] Further details of the present invention are explained with the help of the attached drawings in which:

[0040] FIG. 1 illustrates a contact plug in an integrated circuit, which includes a diffusion barrier.

[0041] FIG. 2 illustrates a contact hole in an integrated circuit that is obstructed by a diffusion barrier.

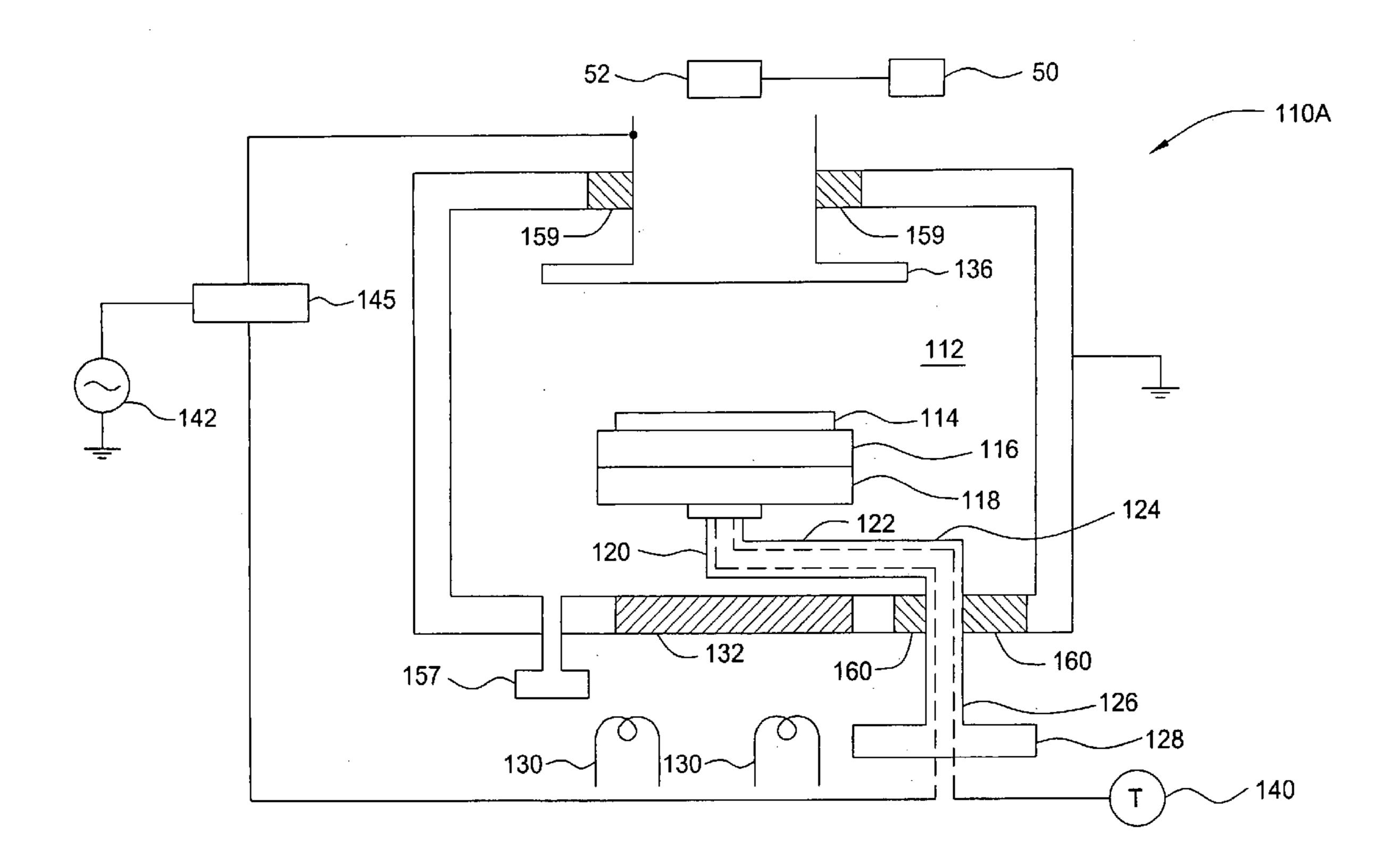

[0042] FIG. 3(a) illustrates a chemical vapor deposition chamber.

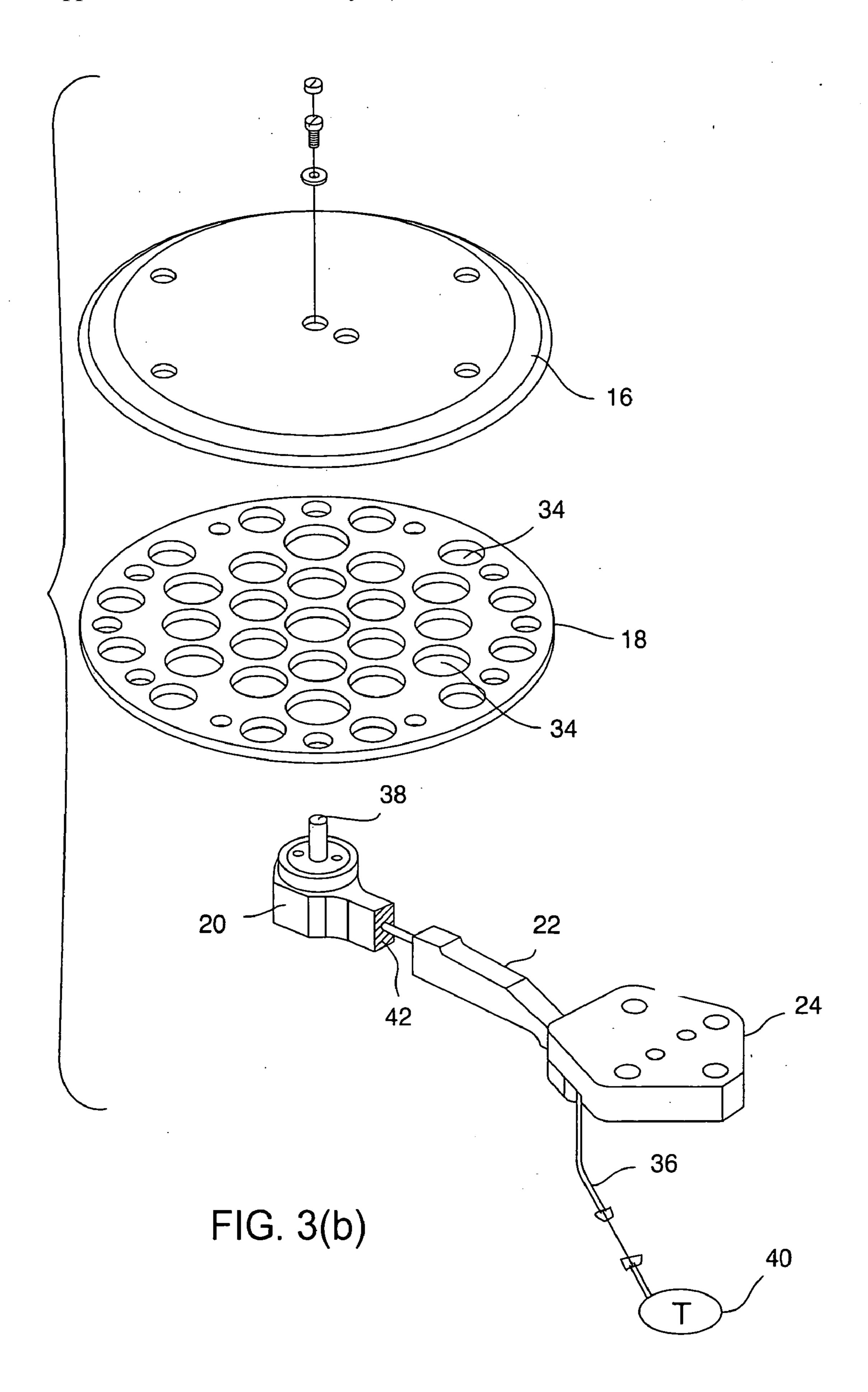

[0043] FIG. 3(b) illustrates a wafer support and support arm for the chamber shown in FIG. 3(a).

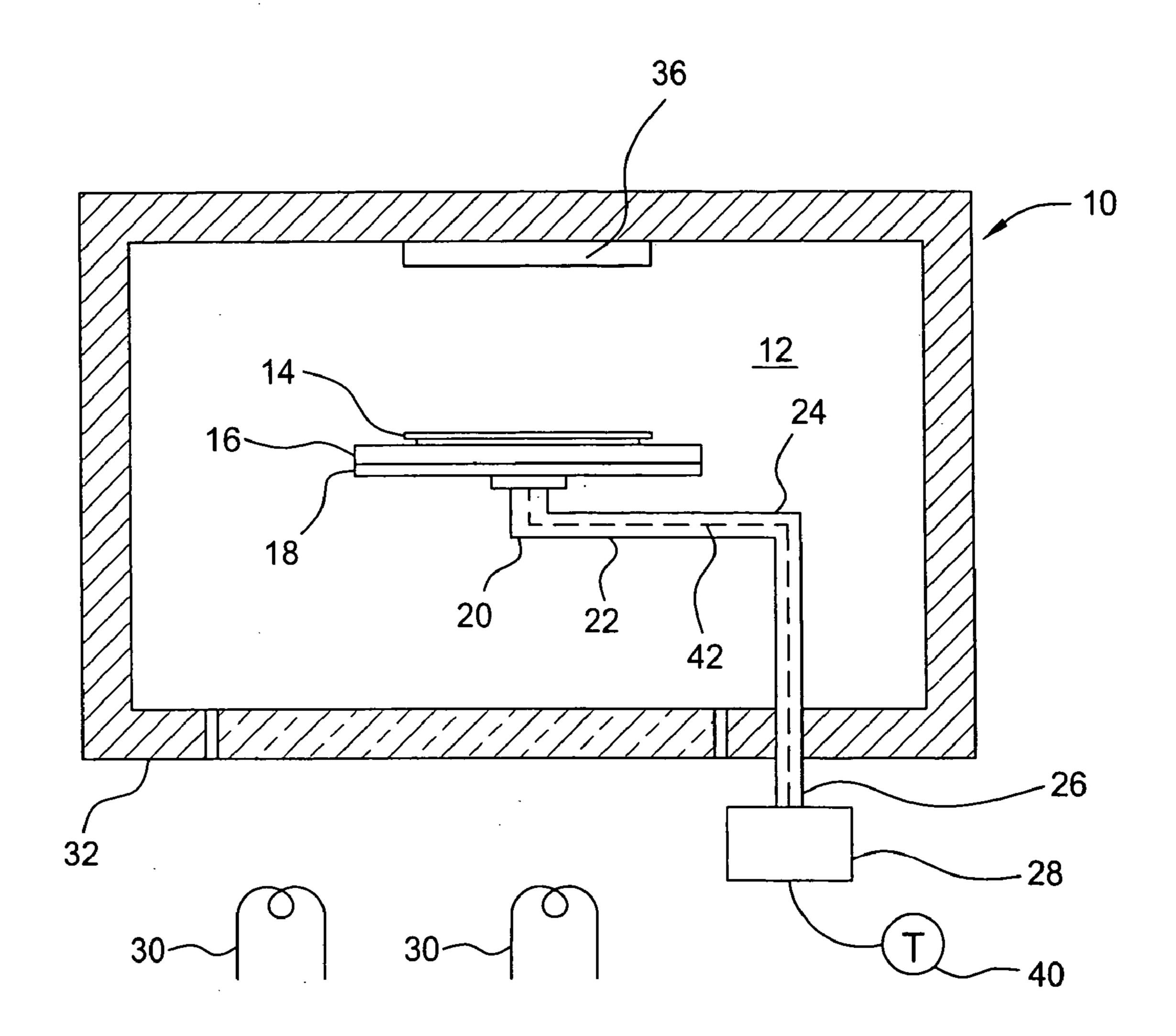

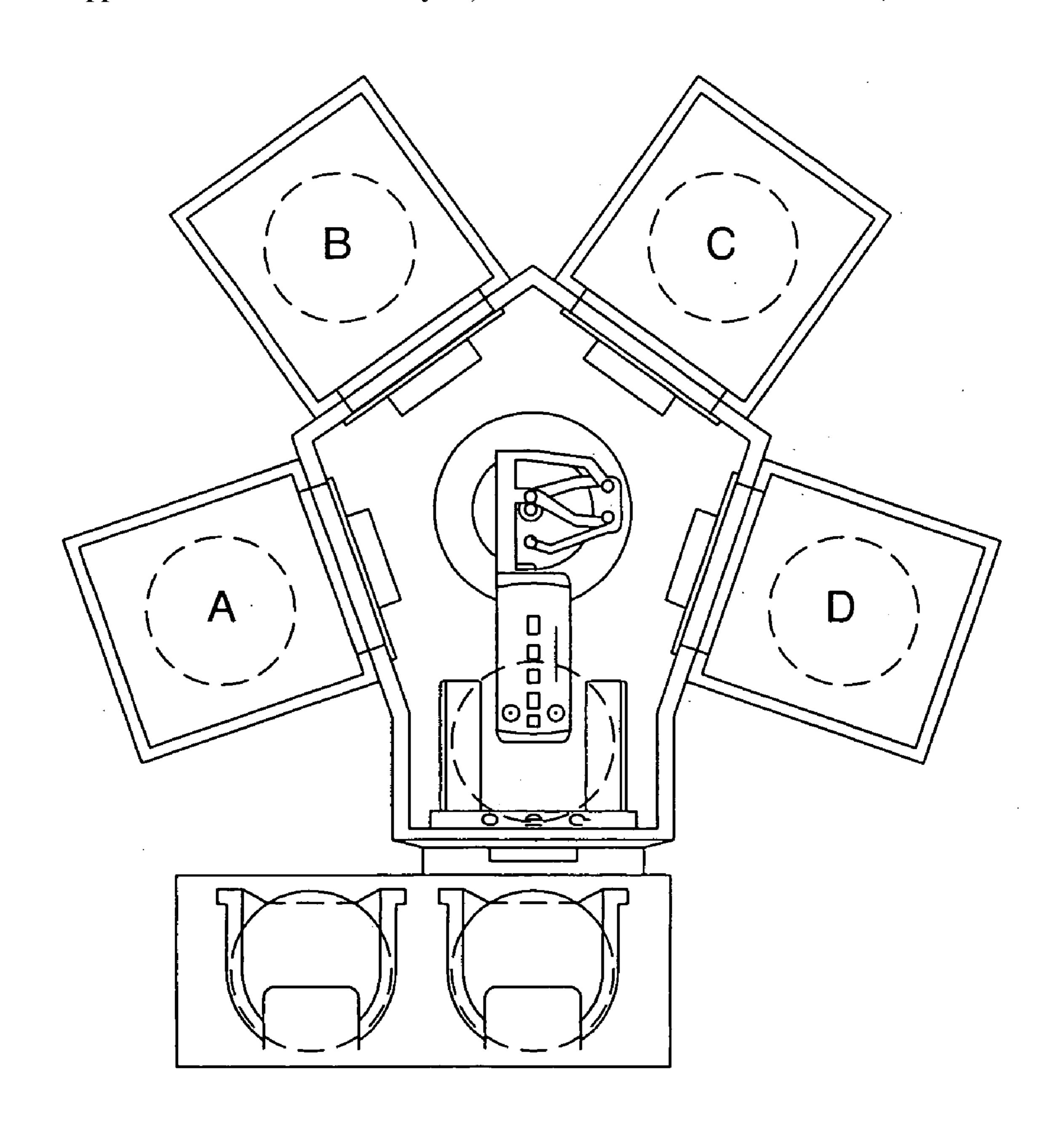

[0044] FIG. 4 illustrates a multichamber processing apparatus.

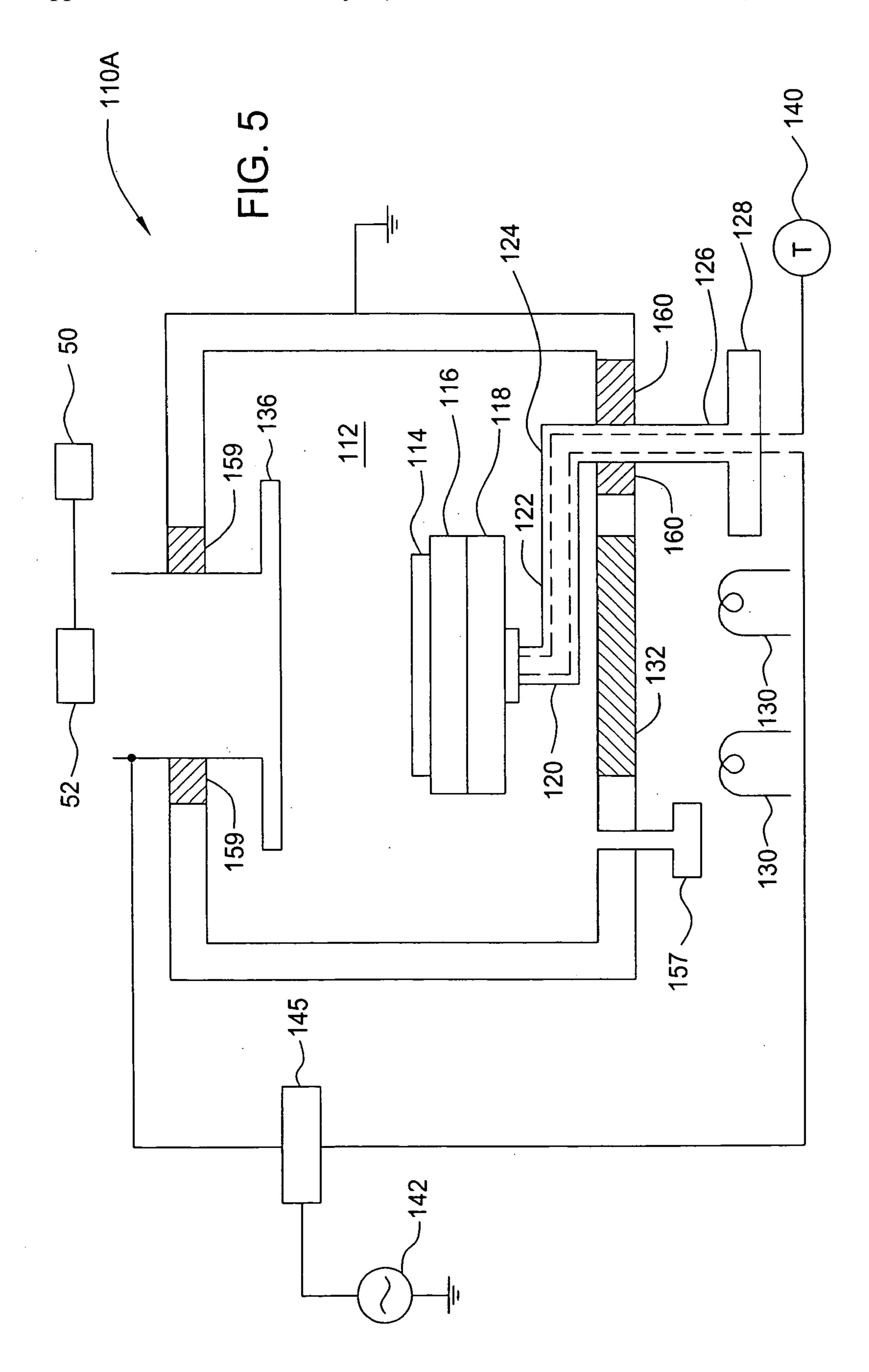

[0045] FIG. 5 illustrates one embodiment of a wafer processing chamber in accordance with the present invention.

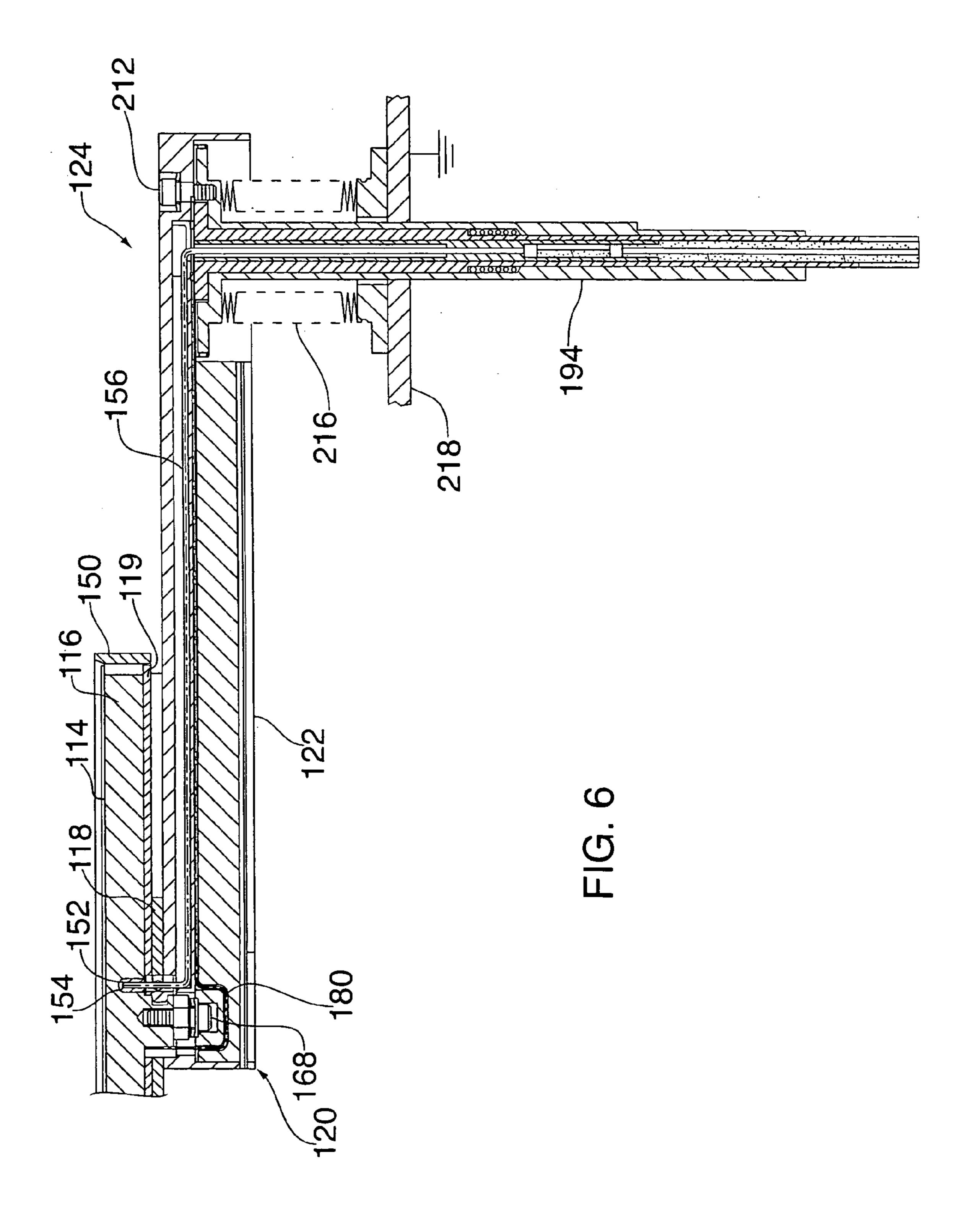

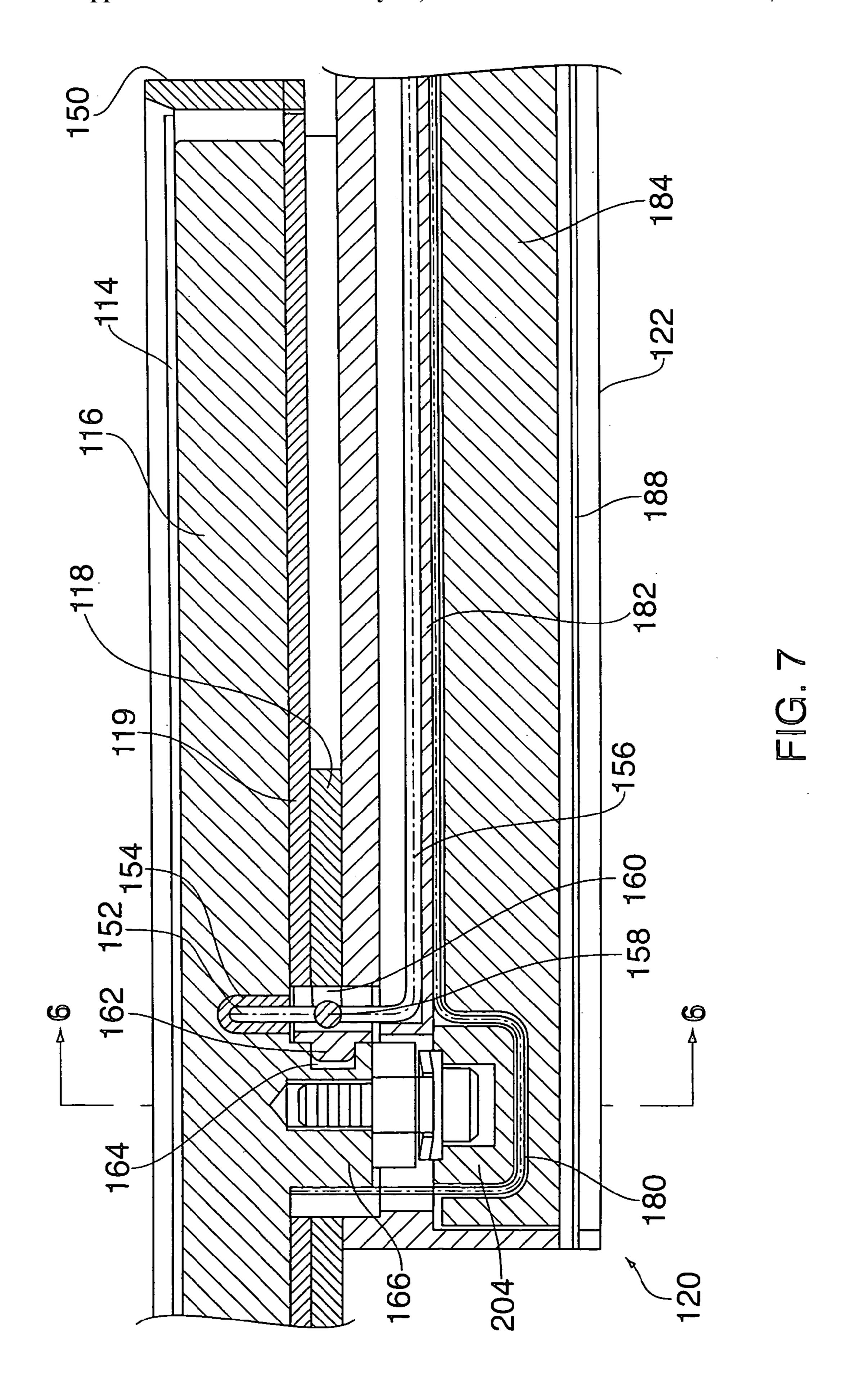

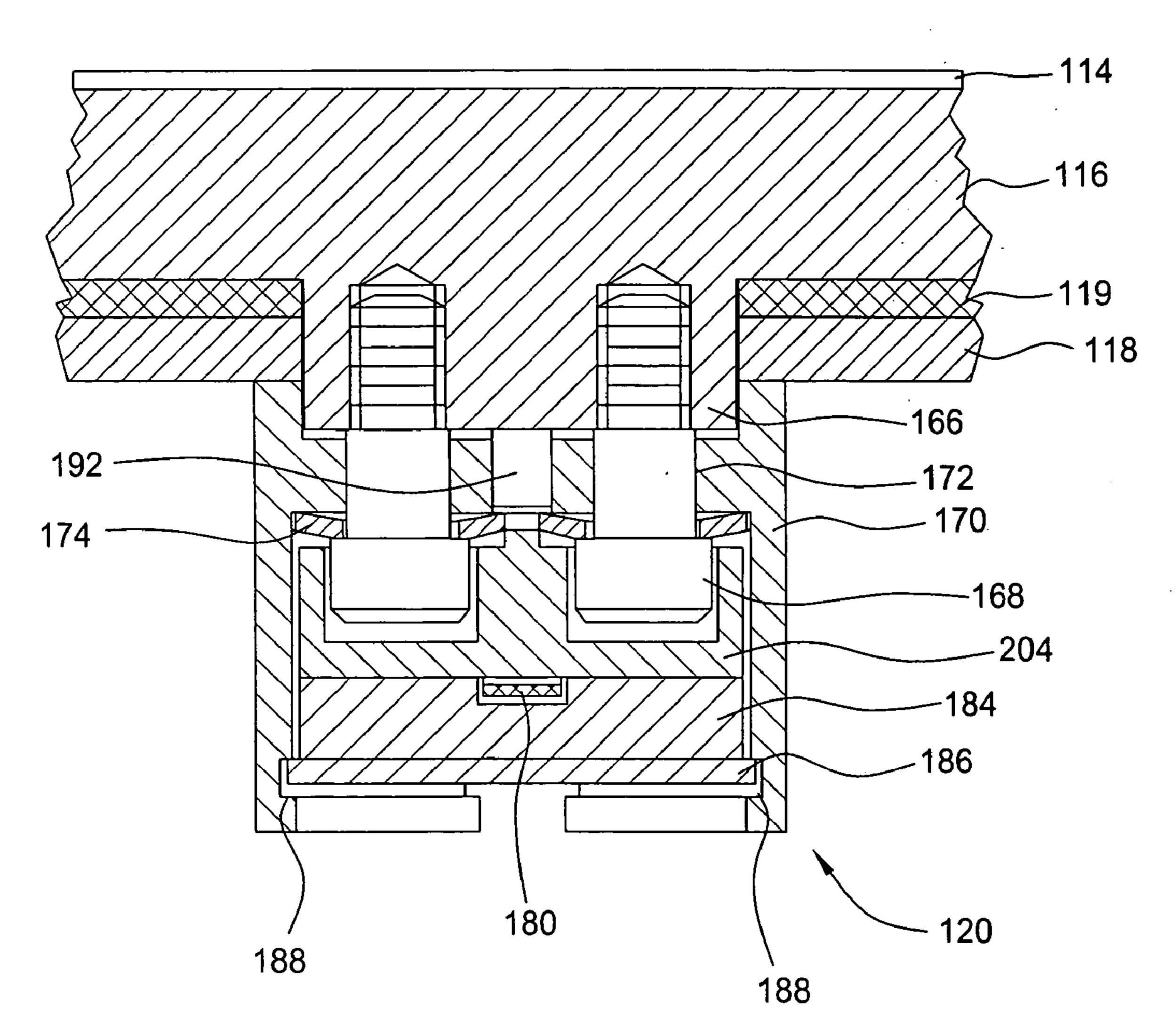

[0046] FIG. 6 illustrates a longitudinal cross-section through the wafer support and support arm shown in FIG. 5.

[0047] FIG. 7 illustrates an enlarged cross-section of the support arm shown in FIG. 6 at the point where the support arm supports the wafer support.

[0048] FIG. 8 illustrates a partial cross-section along lines 6-6 in FIG. 7.

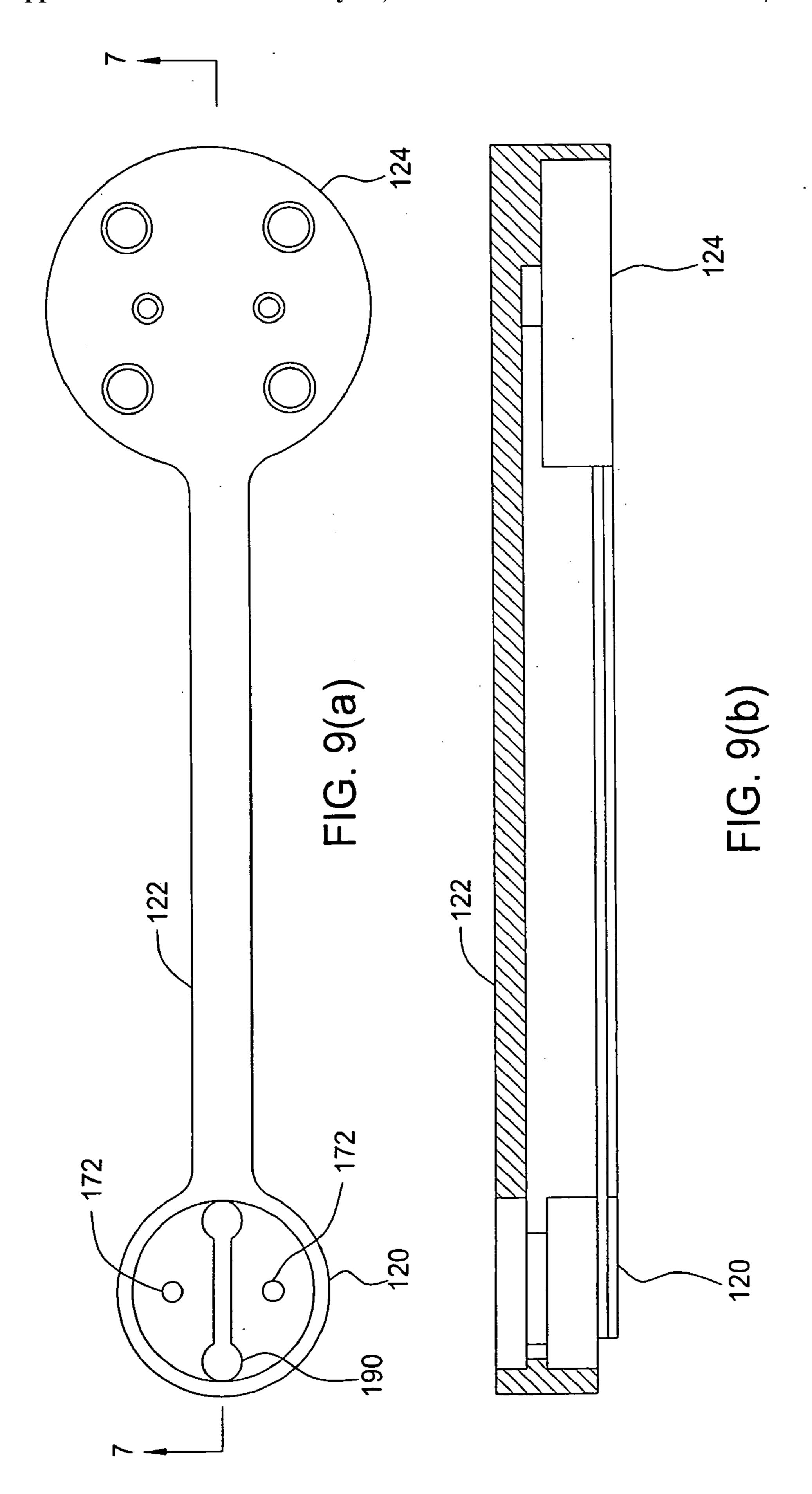

[0049] FIG. 9(a) illustrates a top view of the support arm shown in FIG. 6.

[0050] FIG. 9(b) illustrates a longitudinal cross-section along line 7-7 in FIG. 9(a).

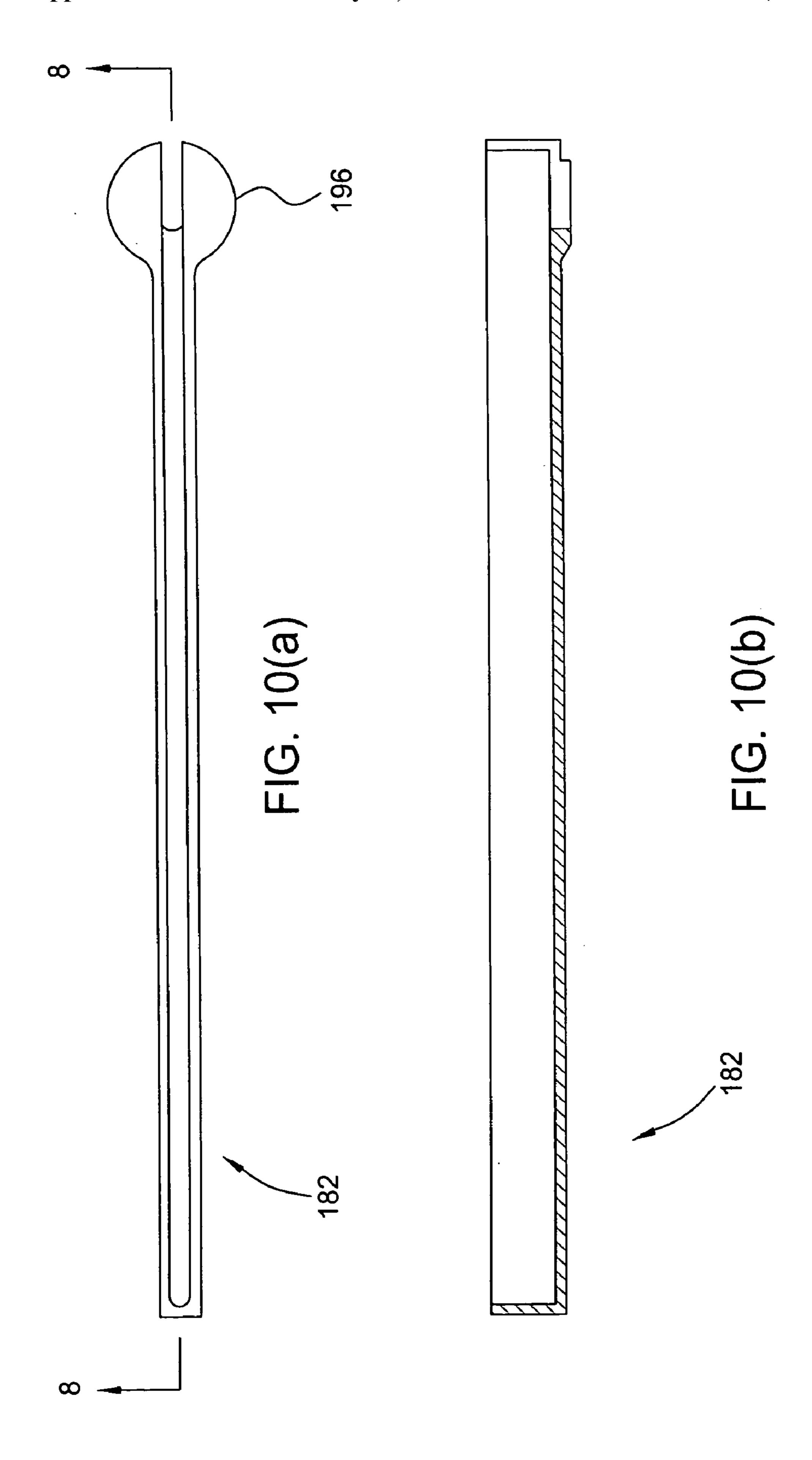

[0051] FIG. 10(a) illustrates a plan view of a thermocouple isolator in the support arm shown in FIG. 6.

[0052] FIG. 10(b) illustrates a longitudinal section along line 8-8 in FIG. 10(a).

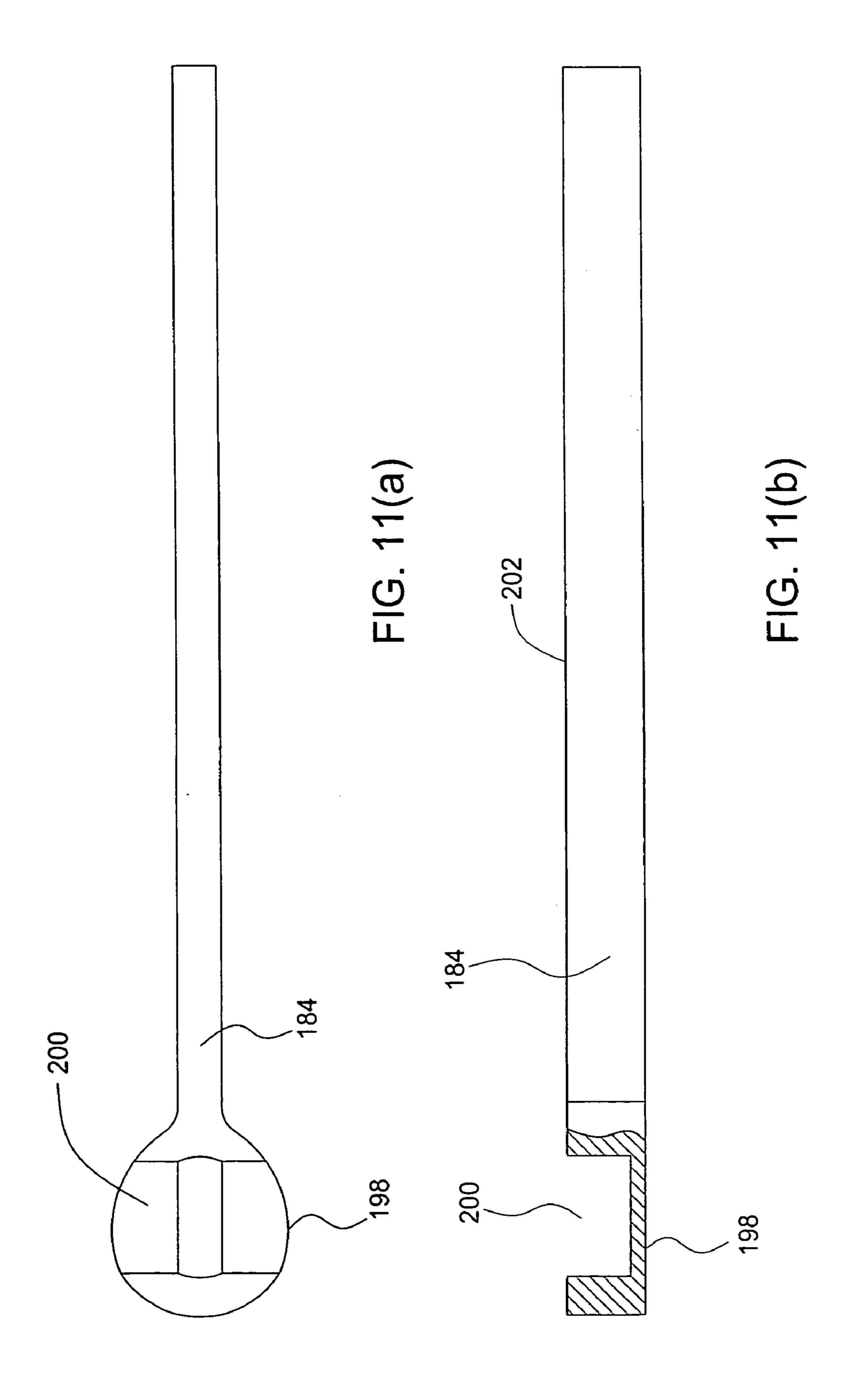

[0053] FIG. 11(a) illustrates a plan view of a rf power strip isolator in the support arm shown in FIG. 6.

[0054] FIG. 11(b) illustrates a partially sectioned elevation of the isolator shown in FIG. 11(a).

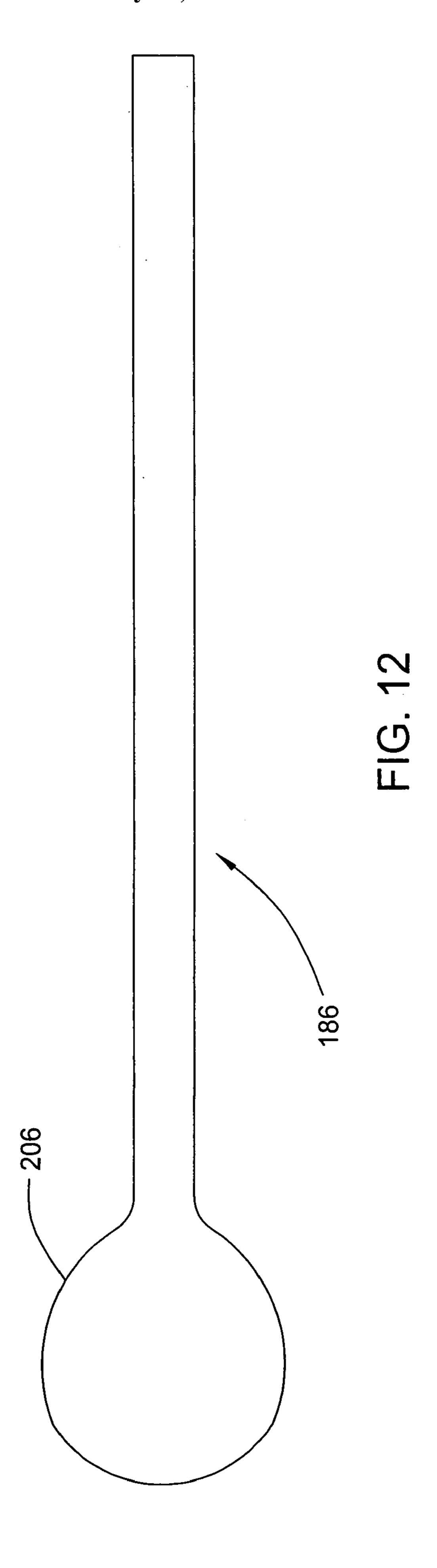

[0055] FIG. 12 illustrates a plan view of an underside retaining plate of the support arm shown in FIG. 6.

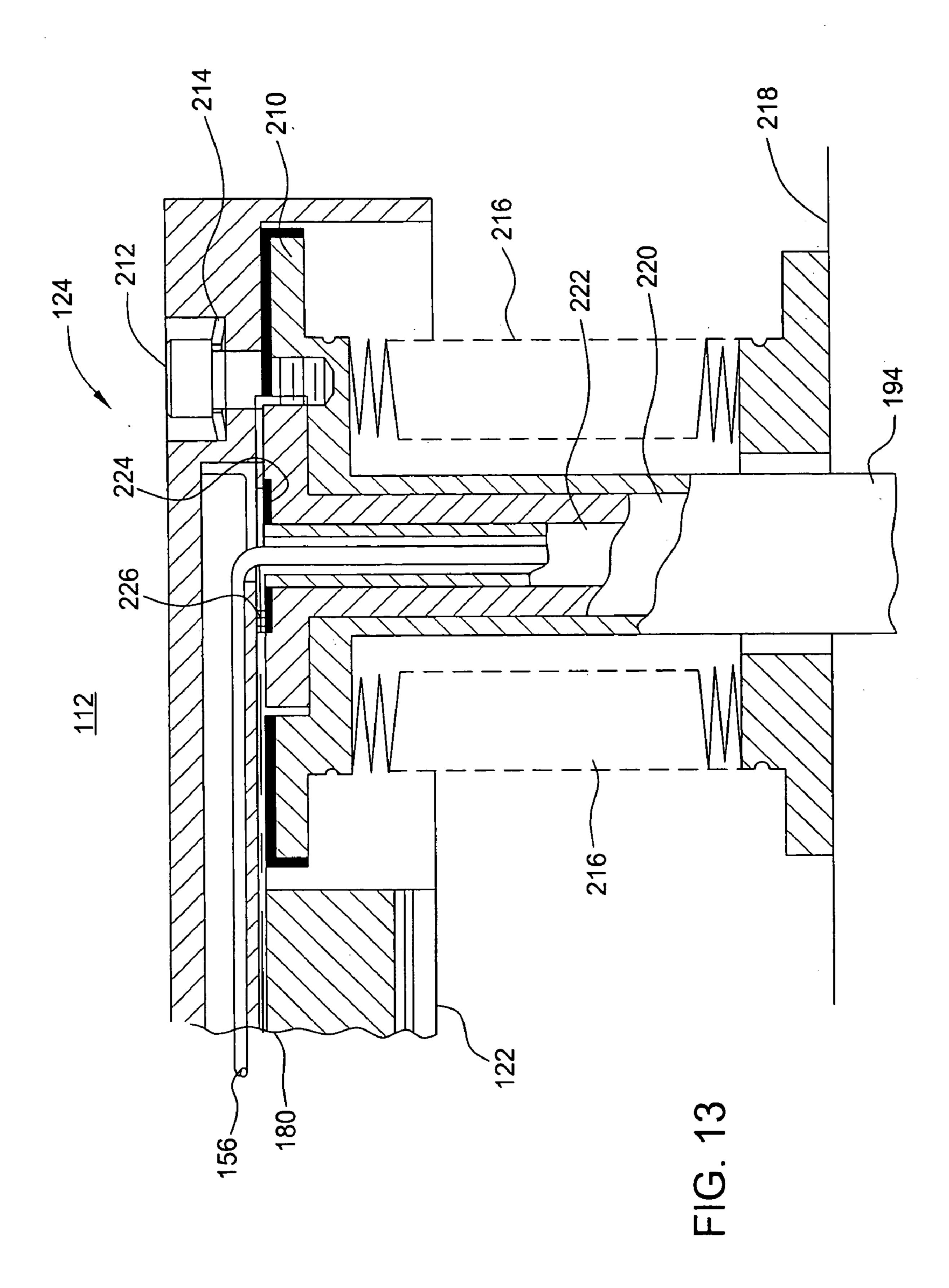

[0056] FIG. 13 illustrates a cross-section showing details on the fixed end of the support arm shown in FIG. 6.

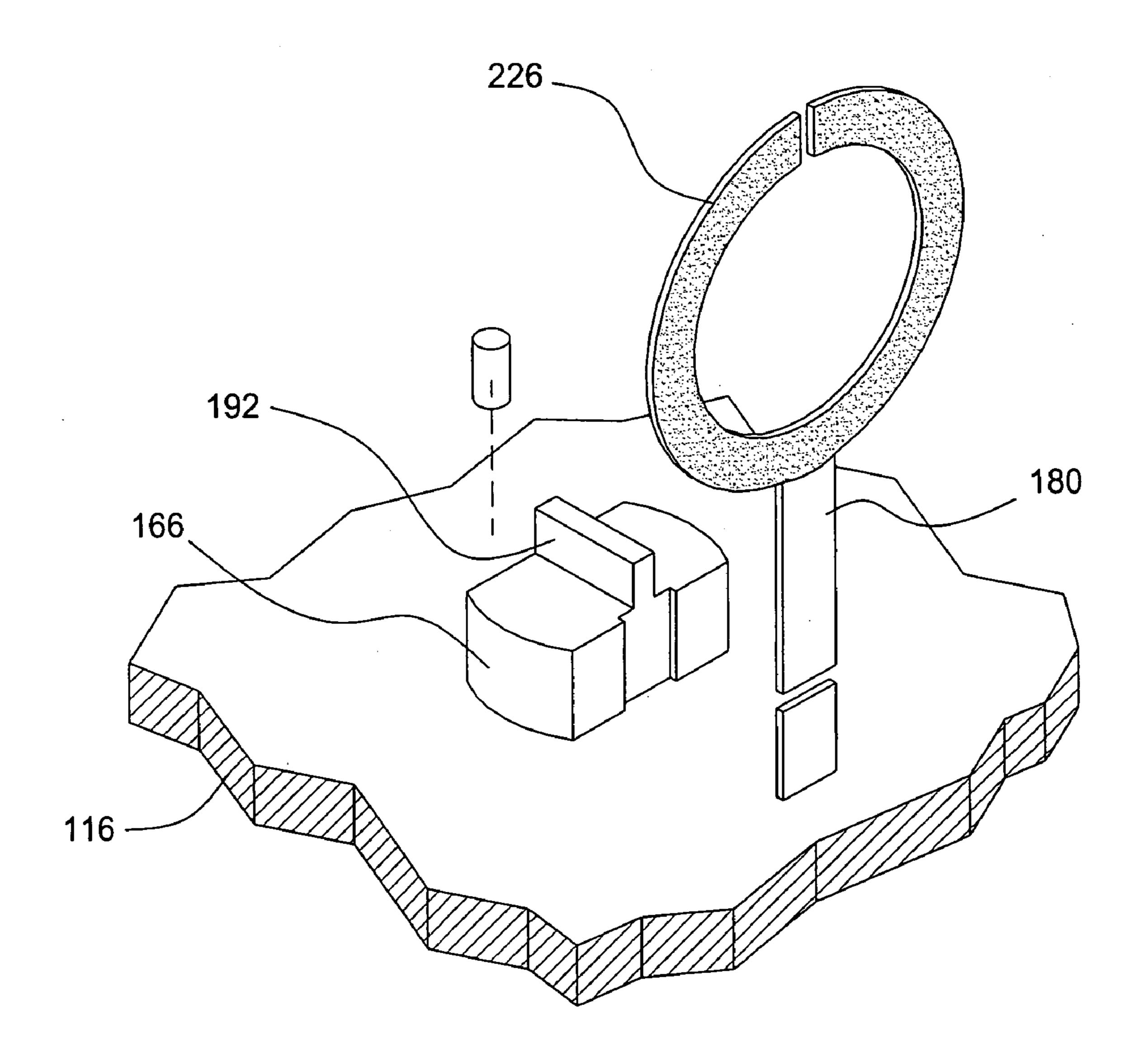

[0057] FIG. 14 illustrates connector details of the rf power strip located in the support arm shown in FIG. 6.

[0058] FIGS. 15(a)-15(c) illustrate embodiments of the matching network that is shown in FIG. 5.

[0059] FIG. 16 illustrates an alternate embodiment of a semiconductor wafer processing chamber in accordance with the present invention.

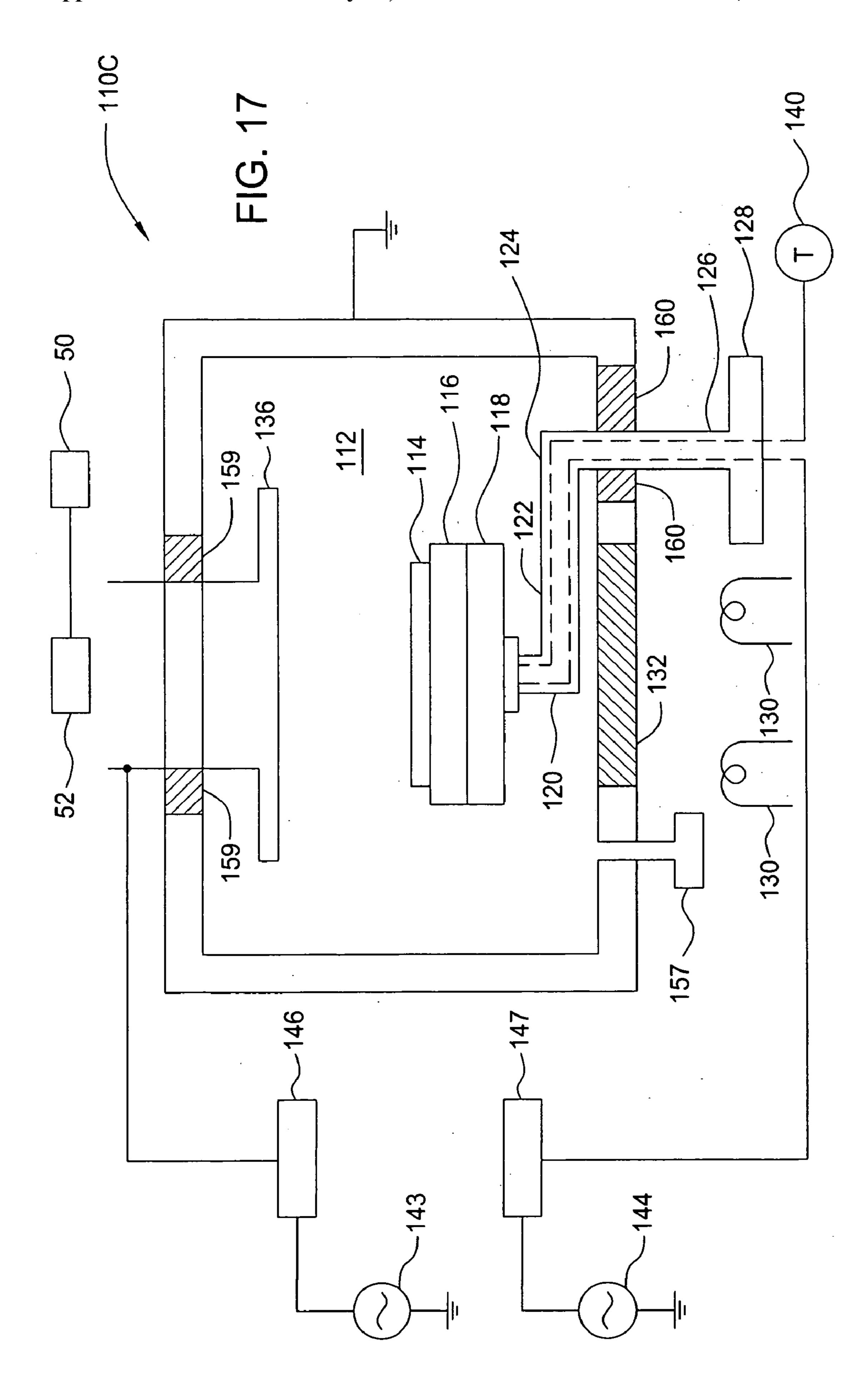

[0060] FIG. 17 illustrates an alternate embodiment of a semiconductor wafer processing chamber in accordance with the present invention.

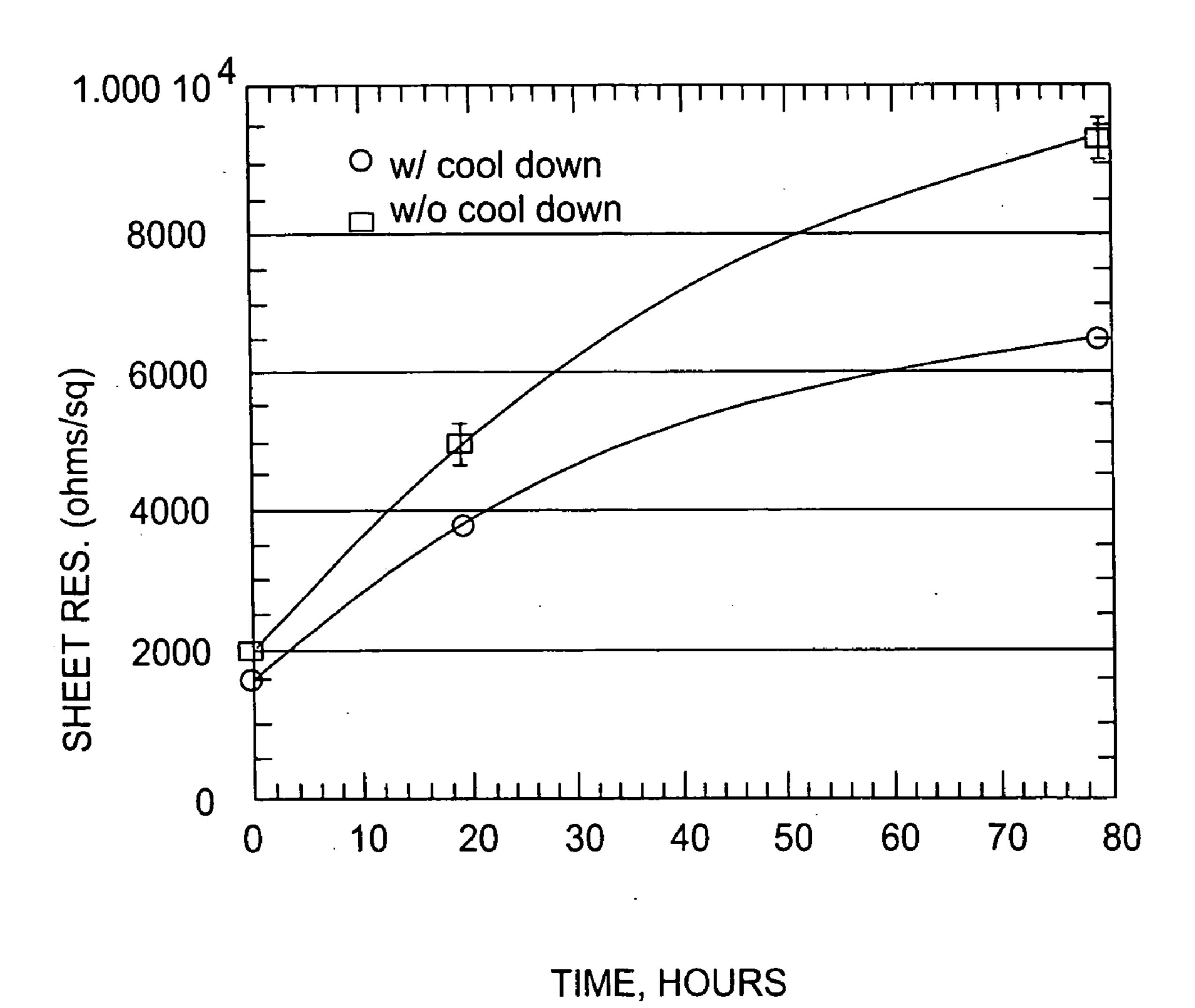

[0061] FIG. 18 illustrates a graph of sheet resistance versus time for titanium nitride film deposited by using a conventional deposition process.

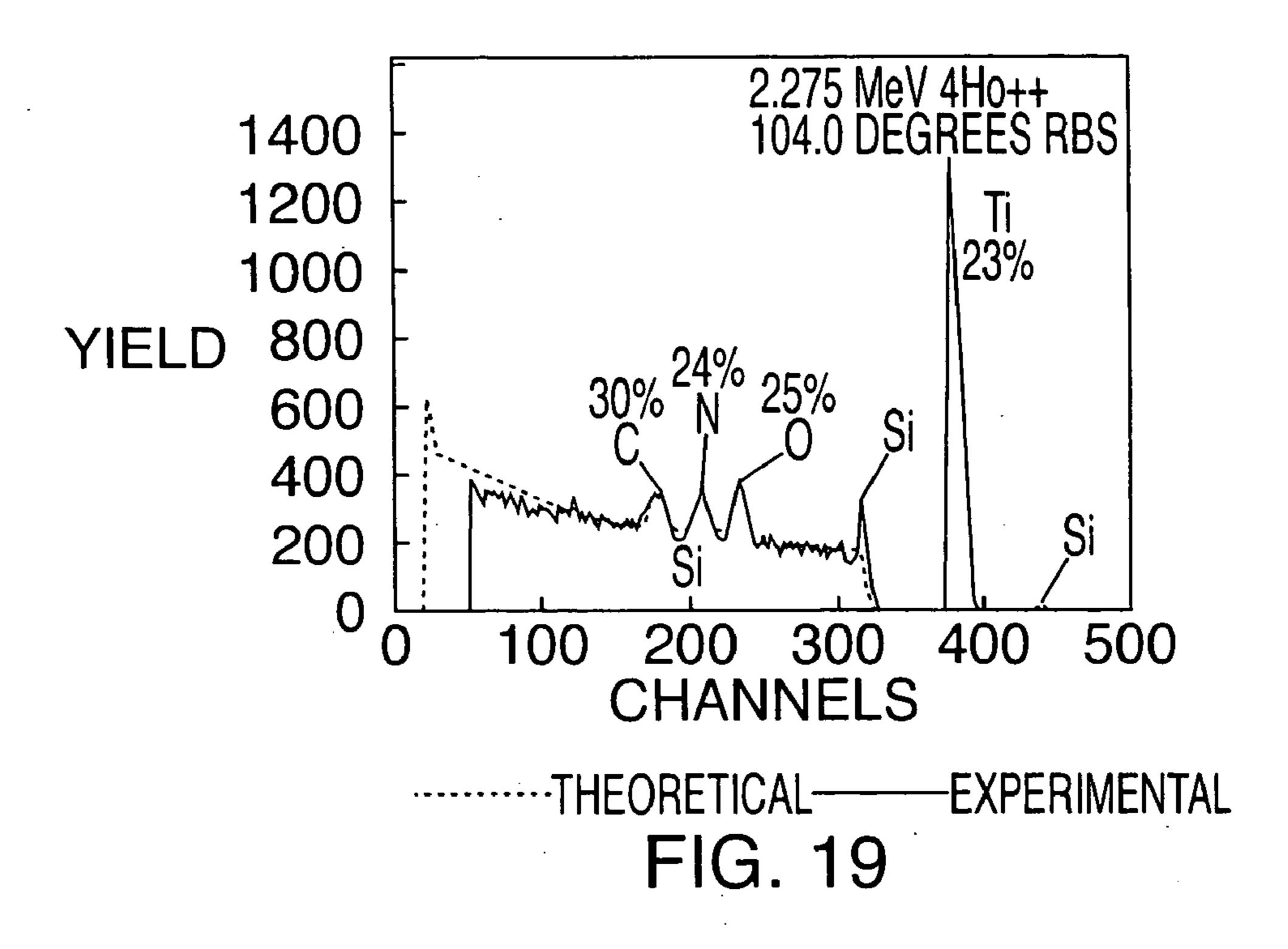

[0062] FIG. 19 illustrates a Rutherford backscattering spectrum of a titanium nitrate film deposited on a silicon wafer using a conventional deposition process.

[0063] FIG. 20 illustrates Table I.

[0064] FIG. 21 illustrates Table II.

[0065] FIG. 22 illustrates Table III.

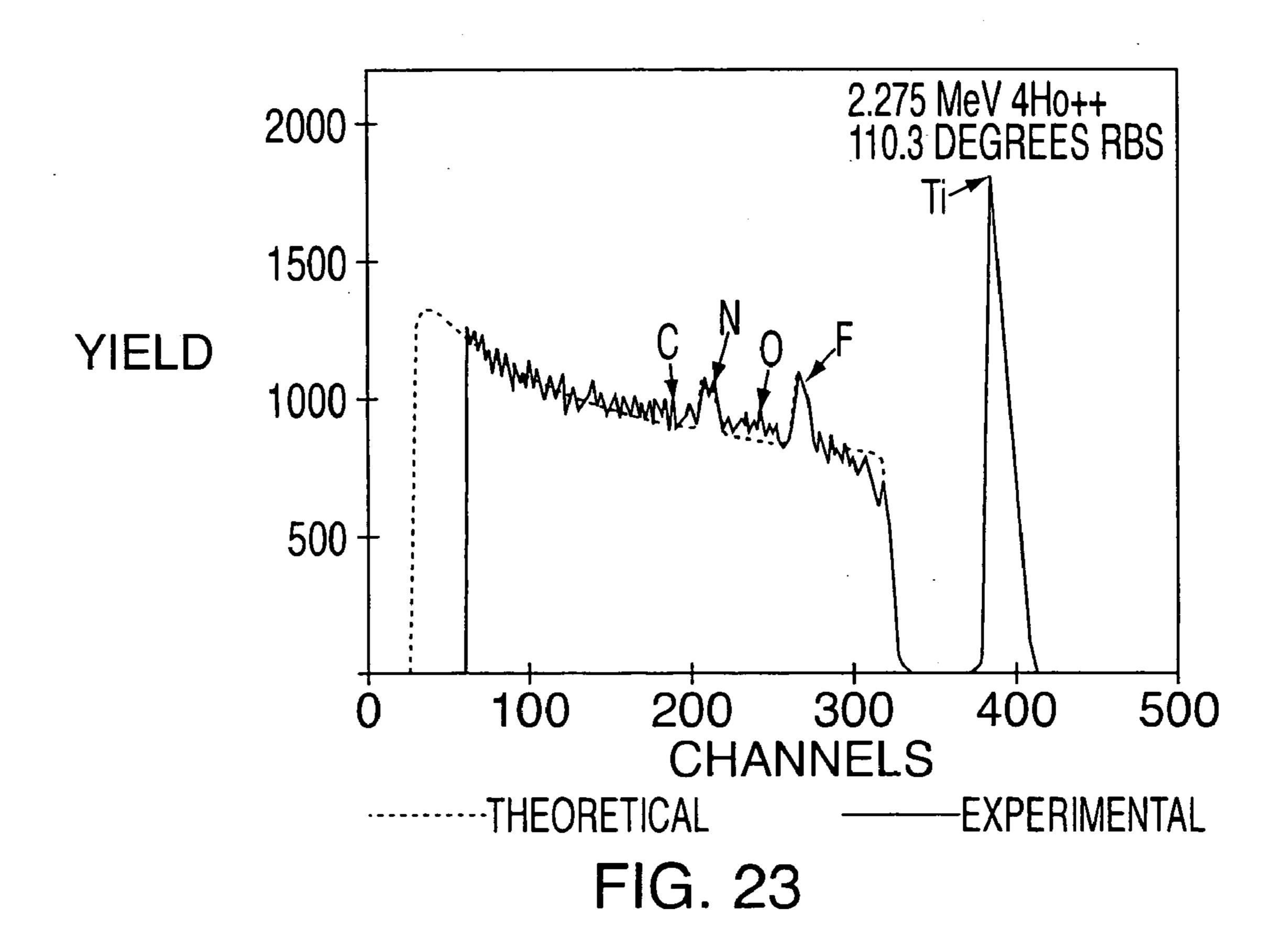

[0066] FIG. 23 illustrates a Rutherford backscattering spectrum of a titanium nitride film deposited using chemical vapor deposition with a gas flow of NF<sub>3</sub>.

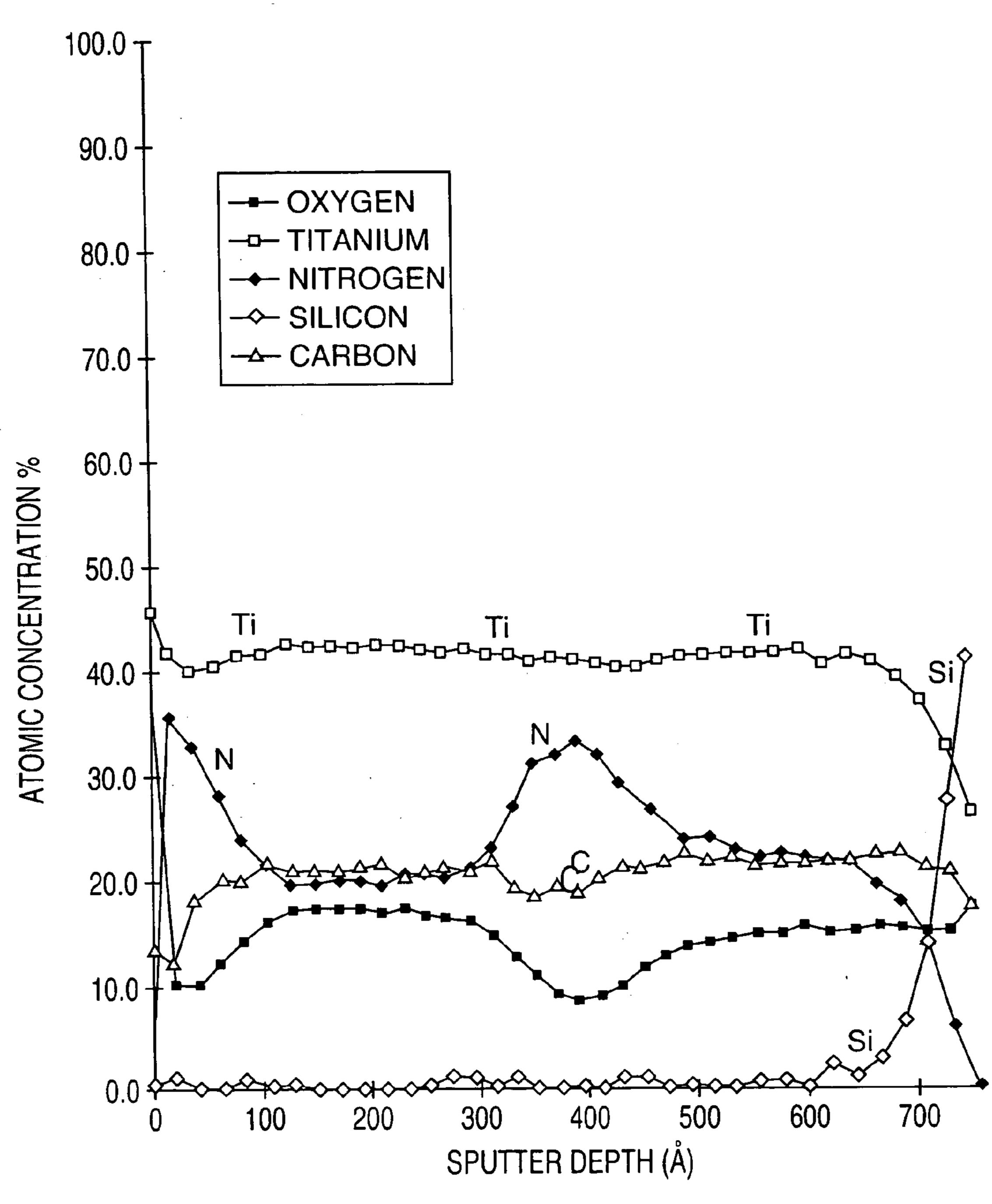

[0067] FIG. 24 illustrates an Auger sputter analysis graph of a titanium nitride film in accordance with the present invention.

[0068] FIG. 25 illustrates Table IV.

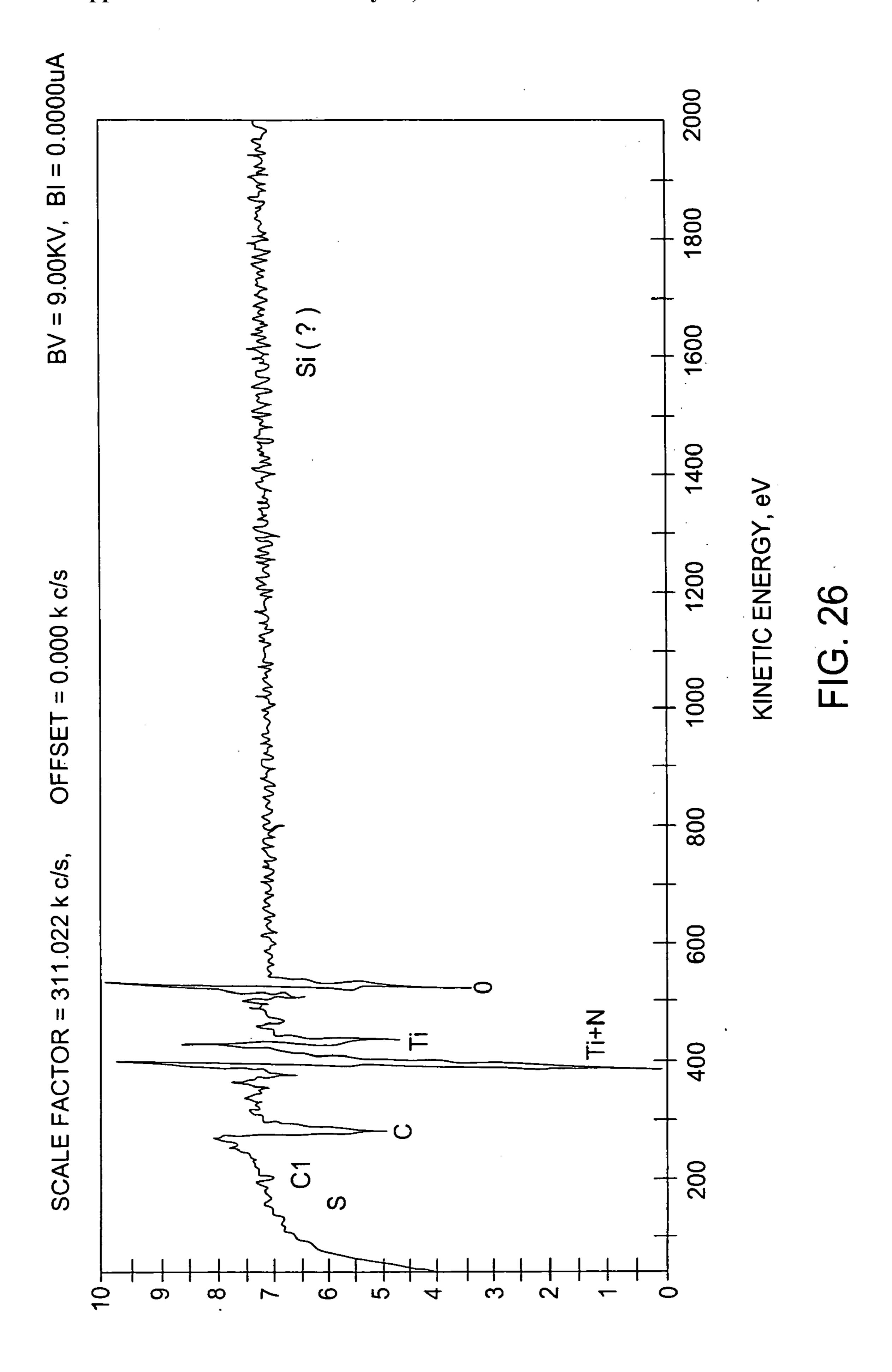

[0069] FIG. 26 illustrates an Auger surface spectrum of elements of another titanium nitride film in accordance with the present invention.

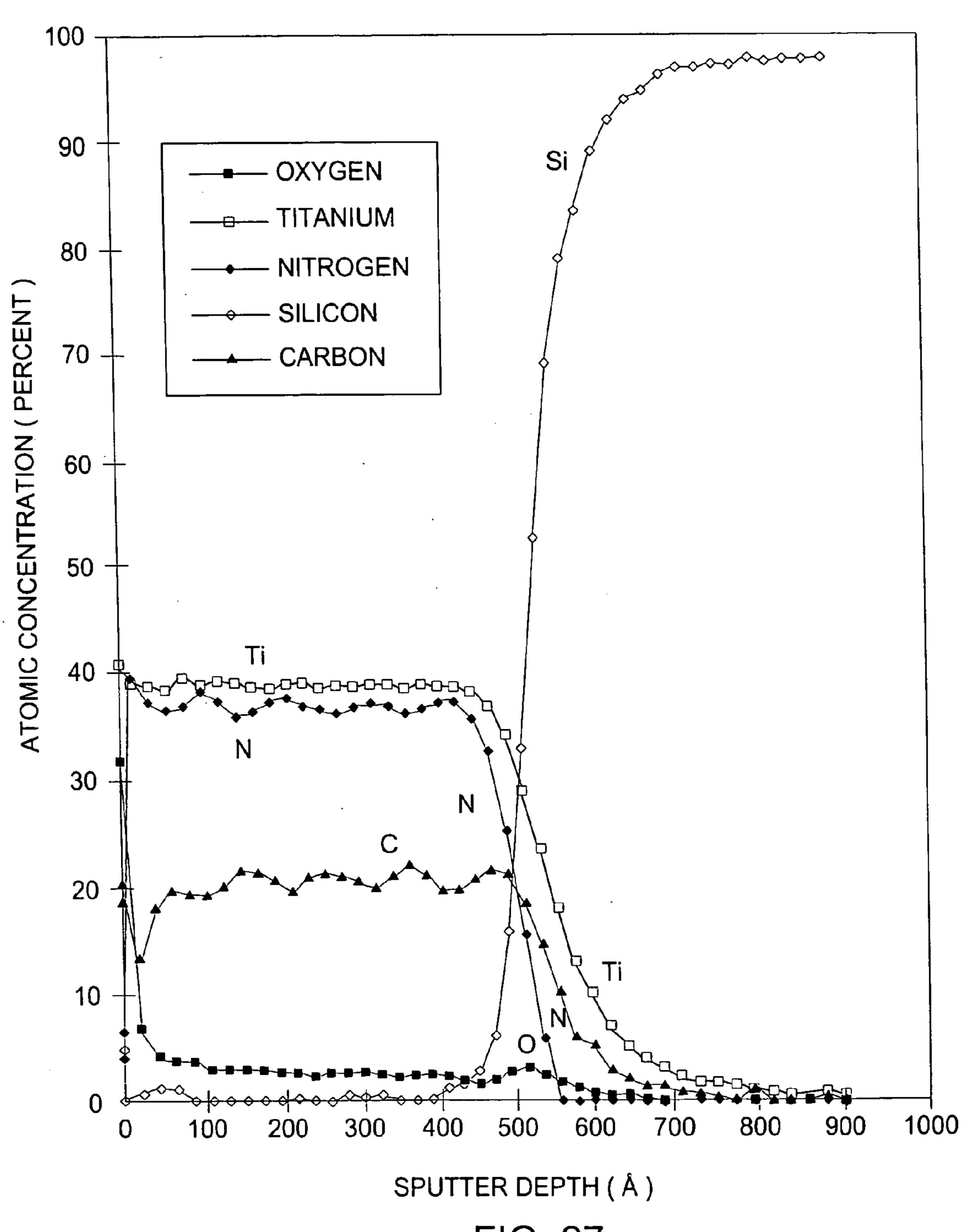

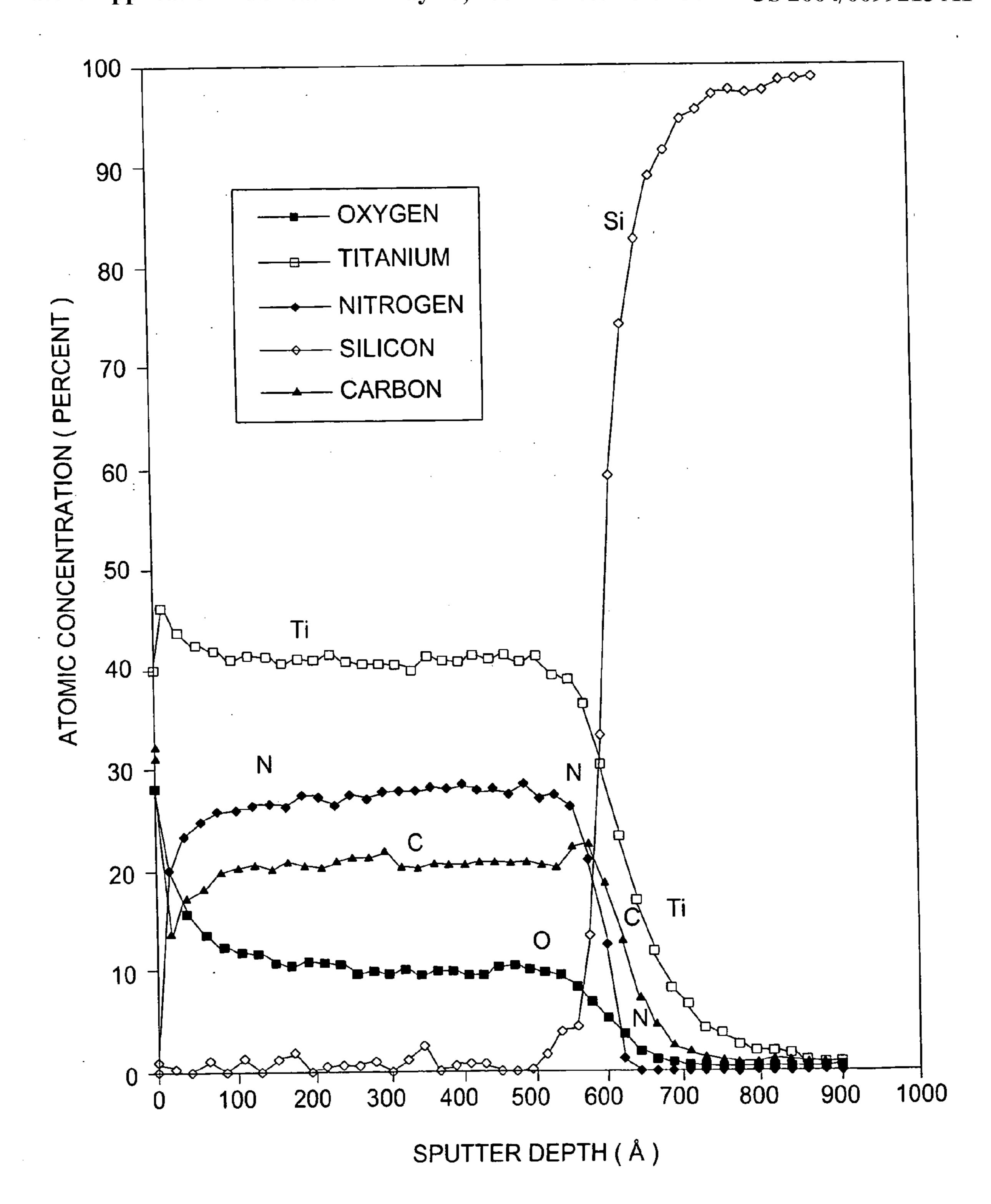

[0070] FIG. 27 illustrates a graph of the atomic concentration of various elements in the titanium nitride film of FIG. 26.

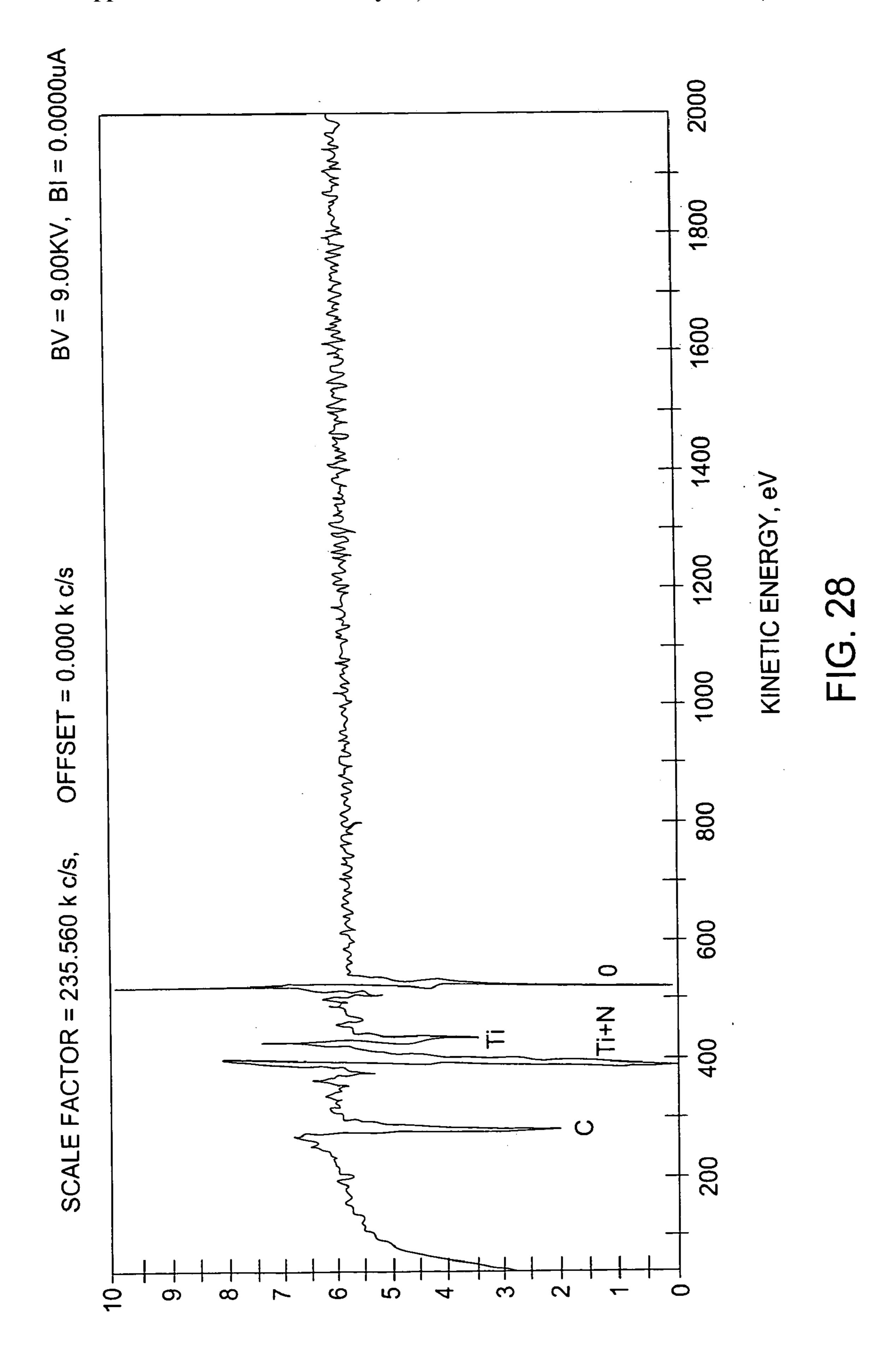

[0071] FIG. 28 illustrates an Auger surface spectrum of elements of a Control titanium nitride film.

[0072] FIG. 29 illustrates a graph of the atomic concentration of various elements in the Control titanium nitride film of FIG. 28.

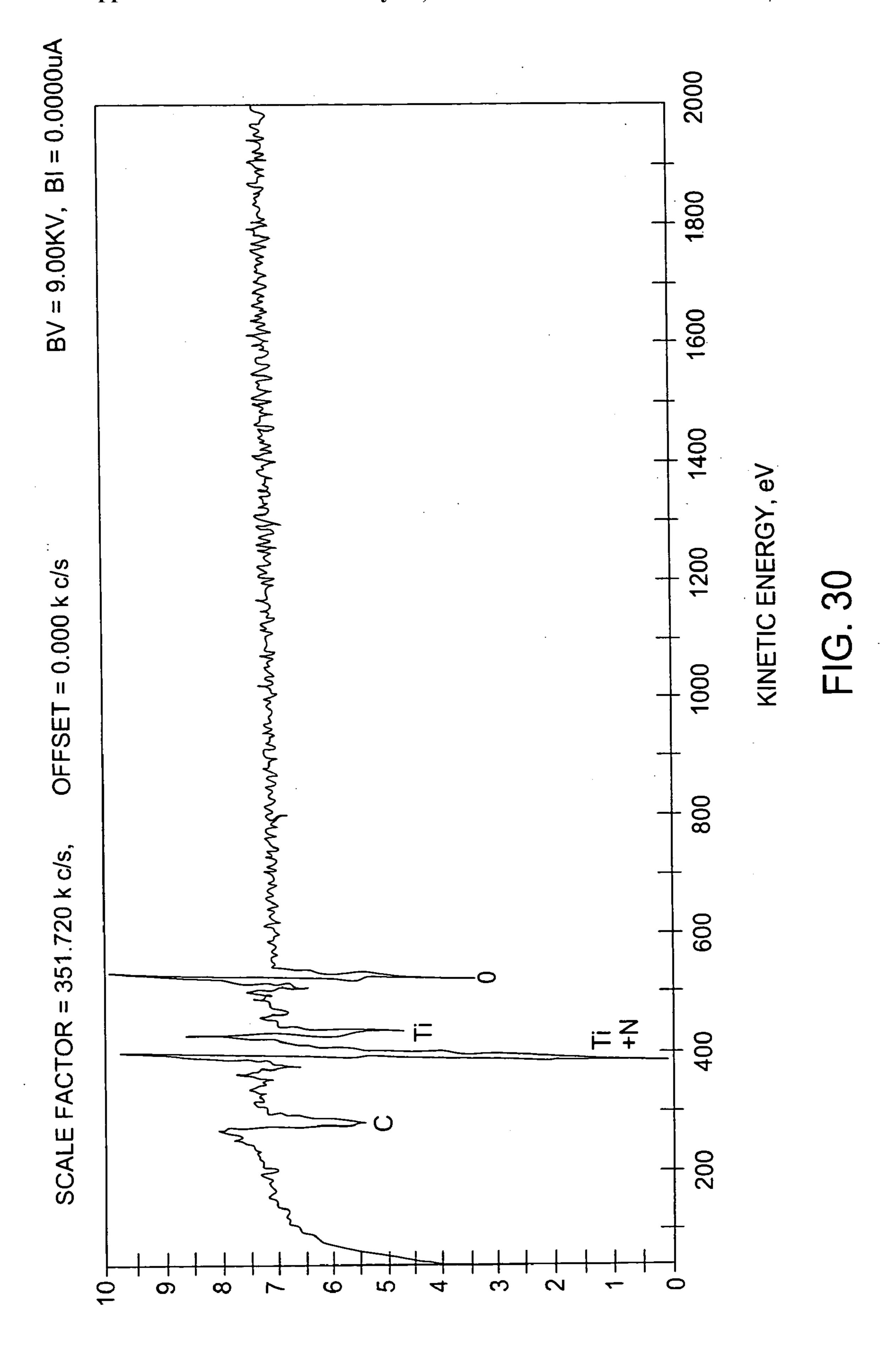

[0073] FIG. 30 illustrates an Auger surface spectrum of elements of another titanium nitride film in accordance with the present invention.

[0074] FIG. 31 illustrates a graph of the atomic concentration of various elements in the titanium nitride film of FIG. 30.

[0075] FIG. 32 illustrates Table V.

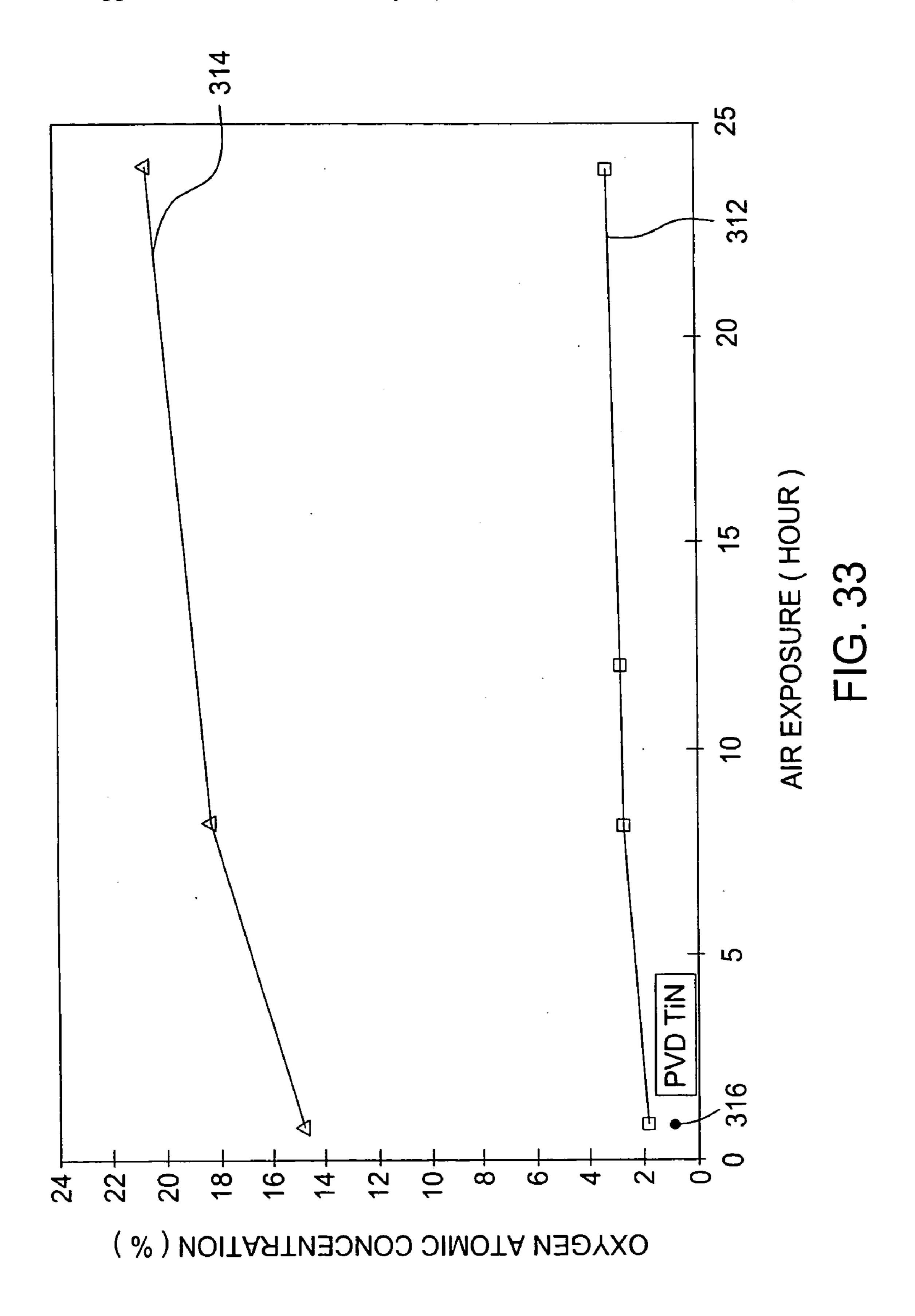

[0076] FIG. 33 illustrates the absorption of oxygen by films produced in accordance with the present invention.

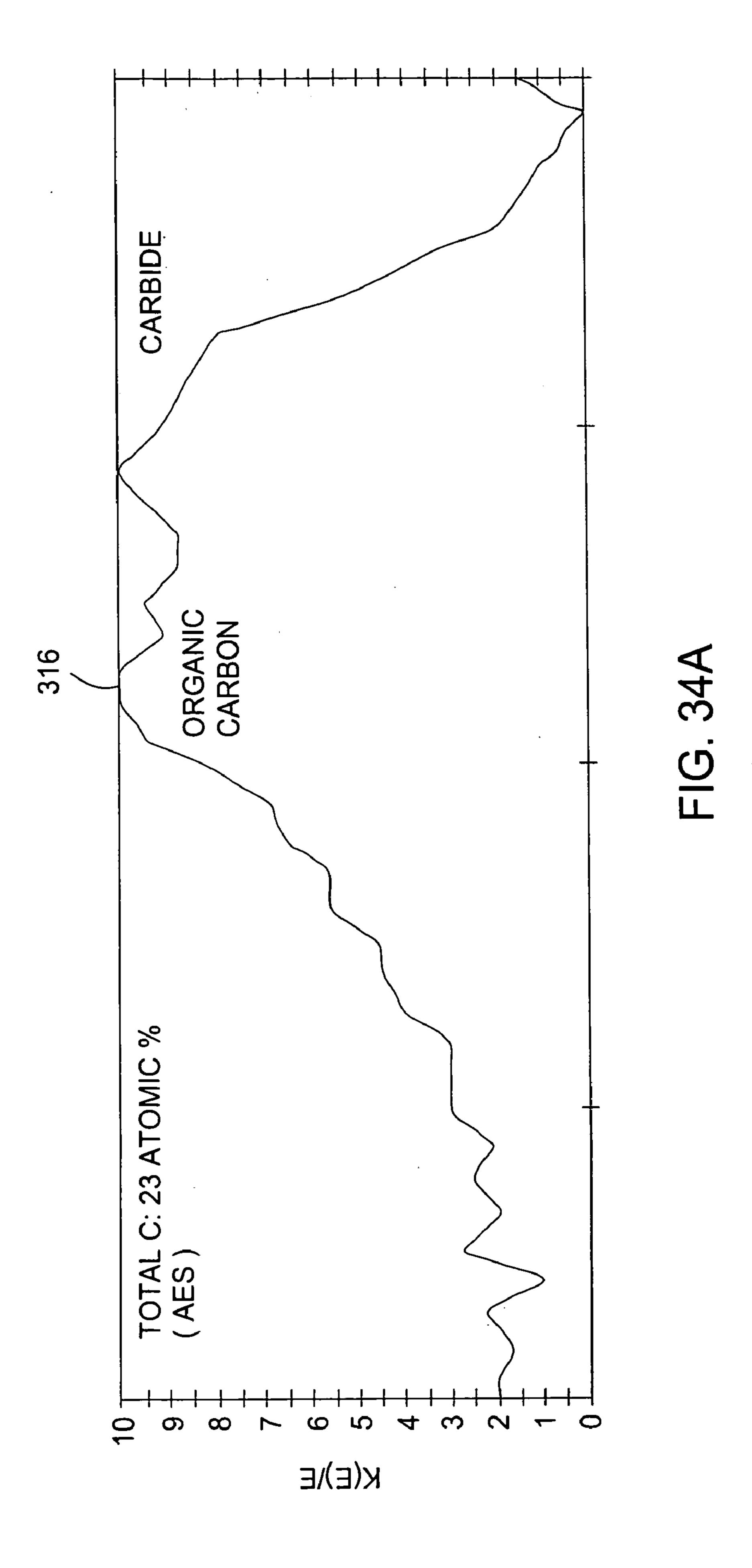

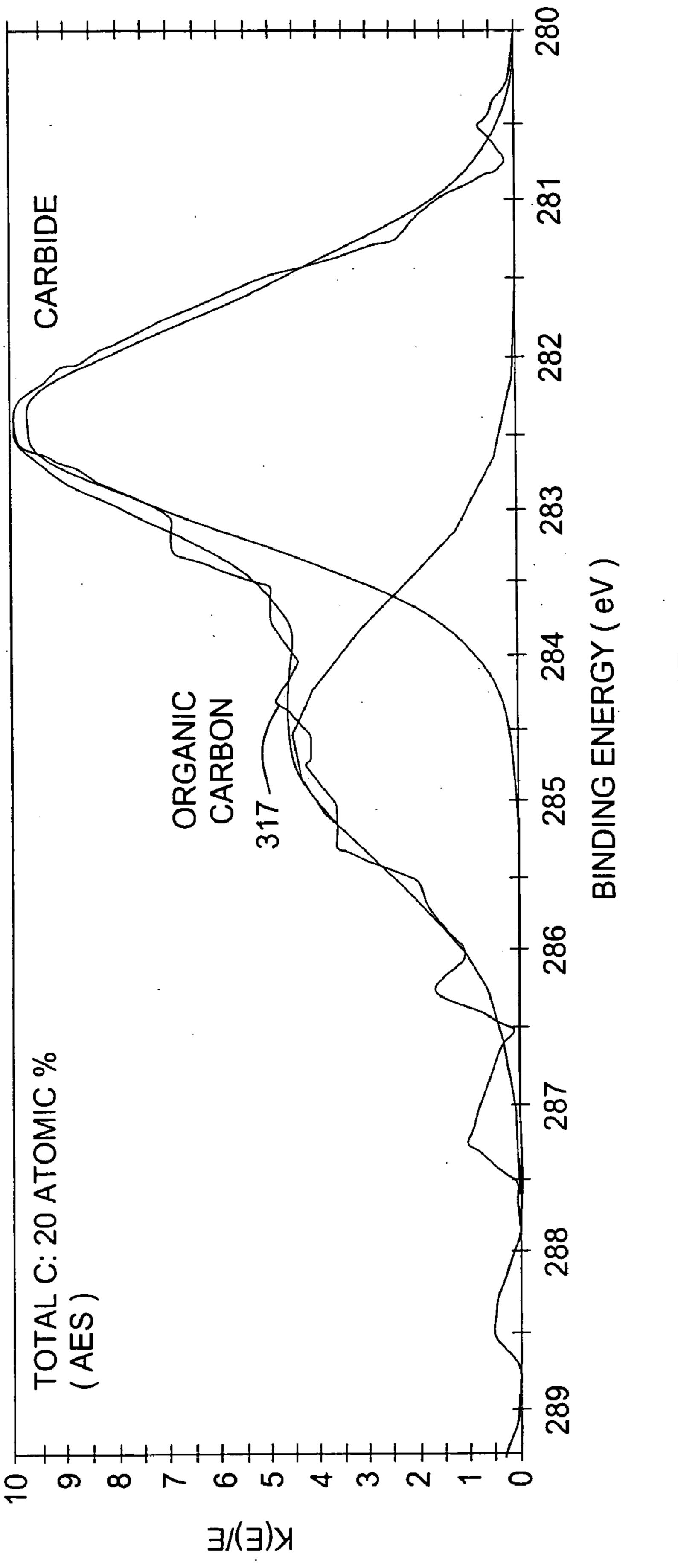

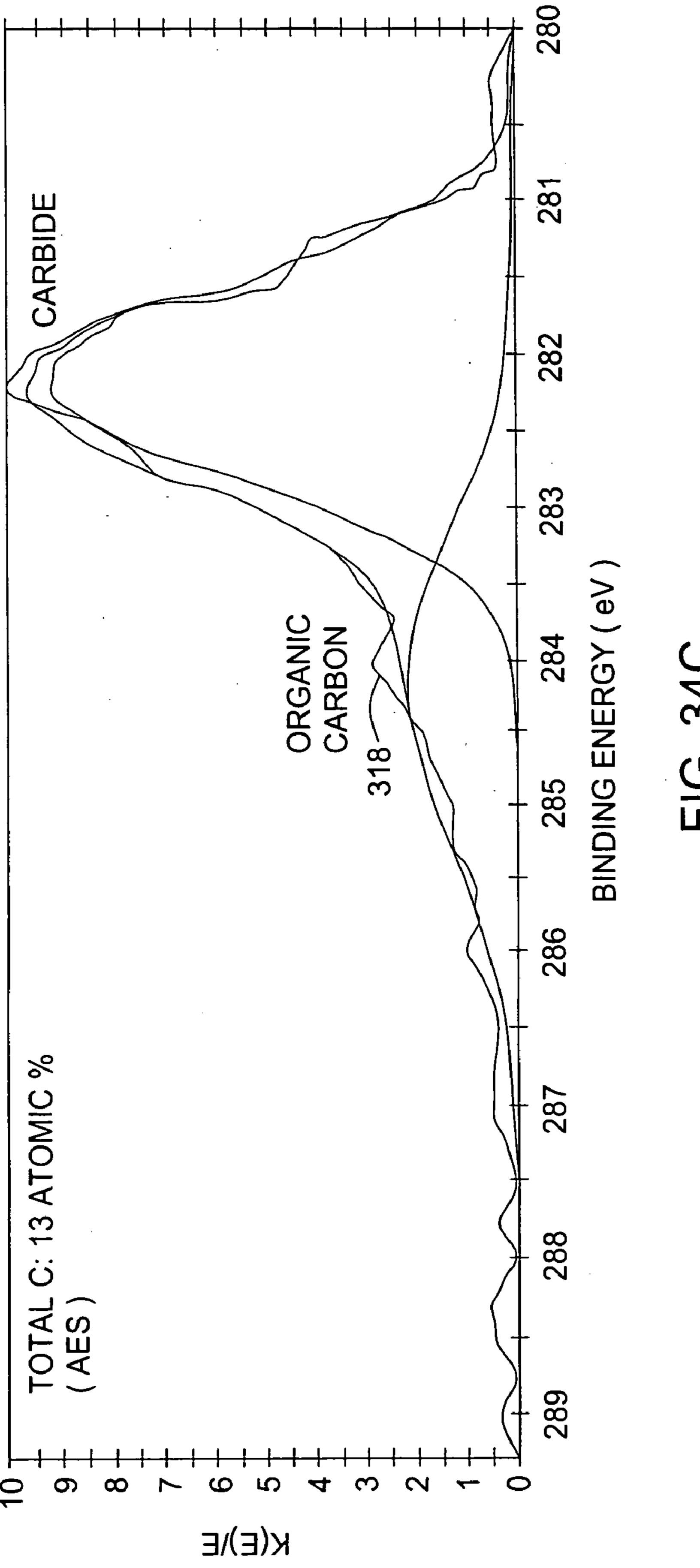

[0077] FIGS. 34(a)-34(c) illustrate the reduction of organic carbon content of films produced in accordance with the invention.

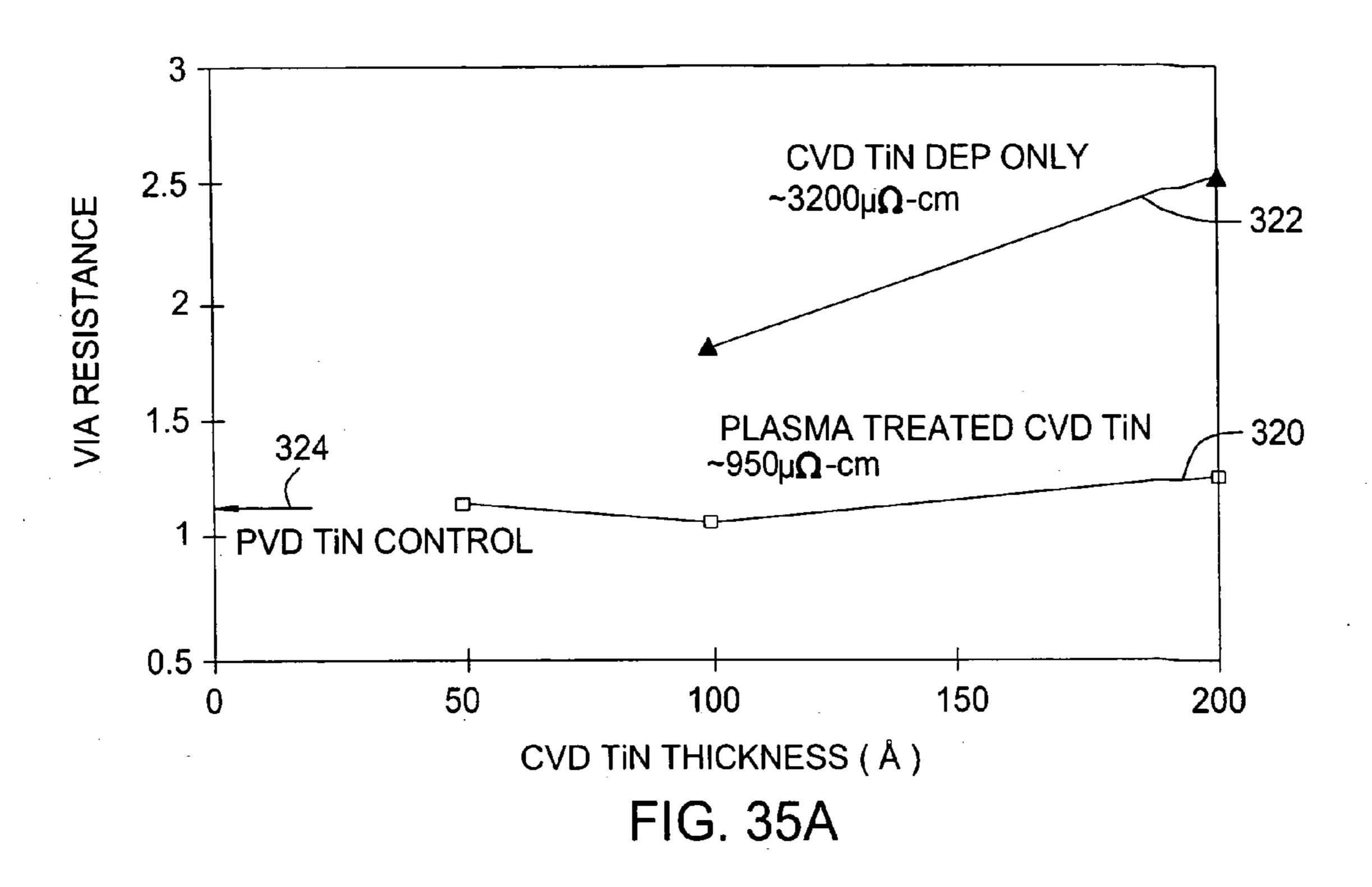

[0078] FIGS. 35(a)-35(b) illustrate the improved film resistance in vias and salicide contacts formed in accordance with the present invention.

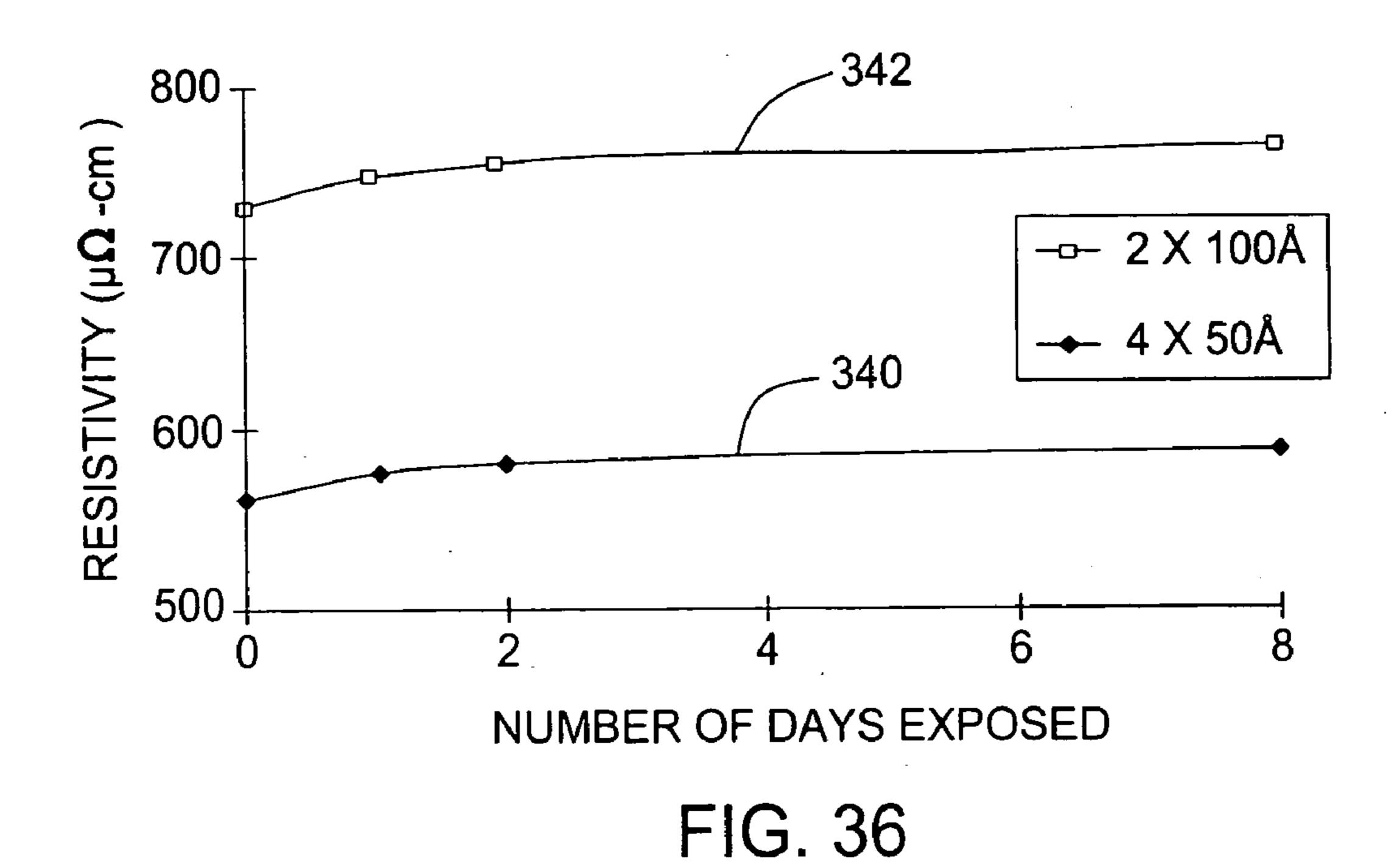

[0079] FIG. 36 illustrates the resistivities of films produced using different numbers of cycles of deposition and plasma treatment.

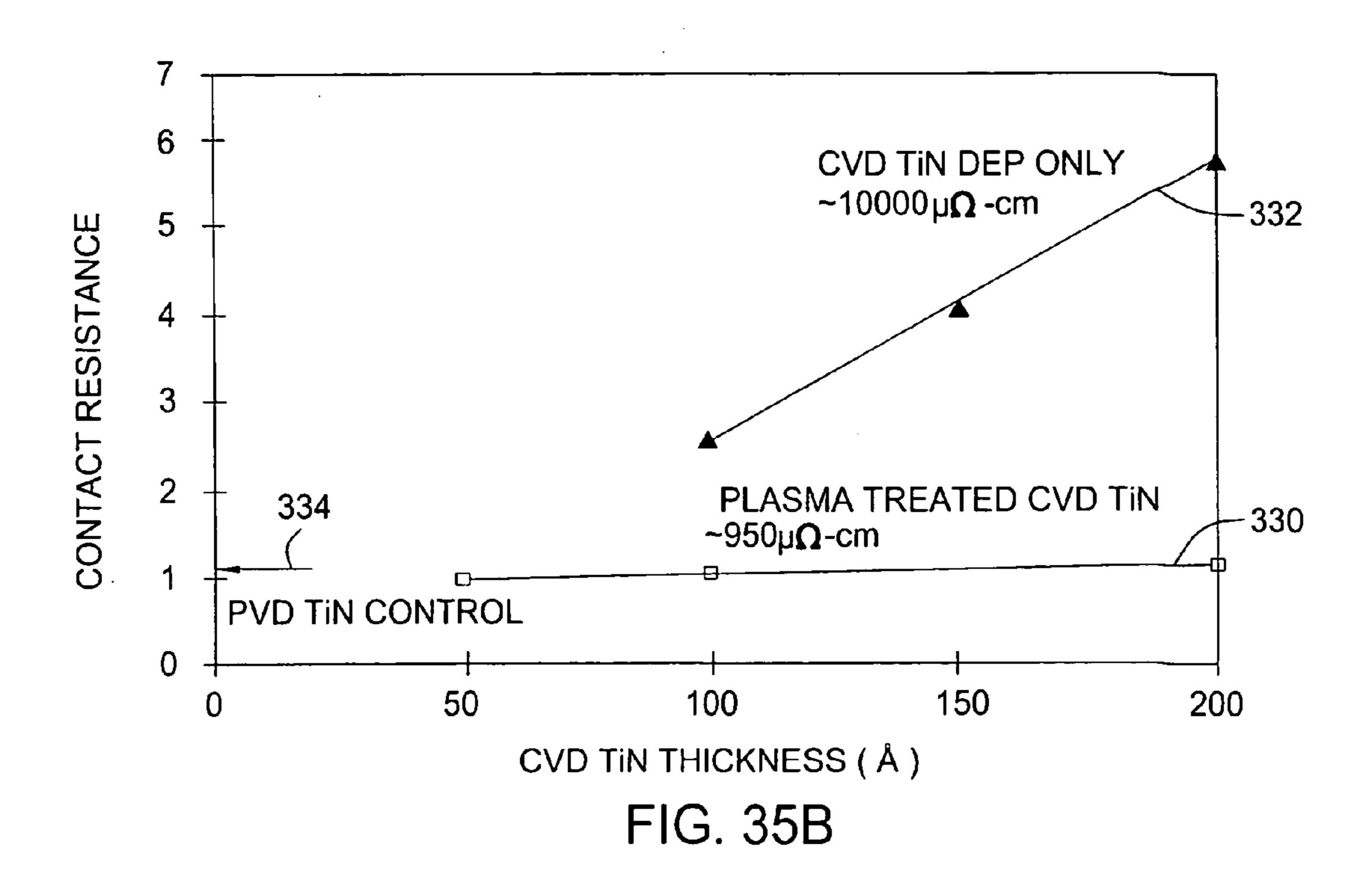

[0080] FIG. 37 illustrates a plot of film resistivity and bias voltage as a function of plasma process pressure.

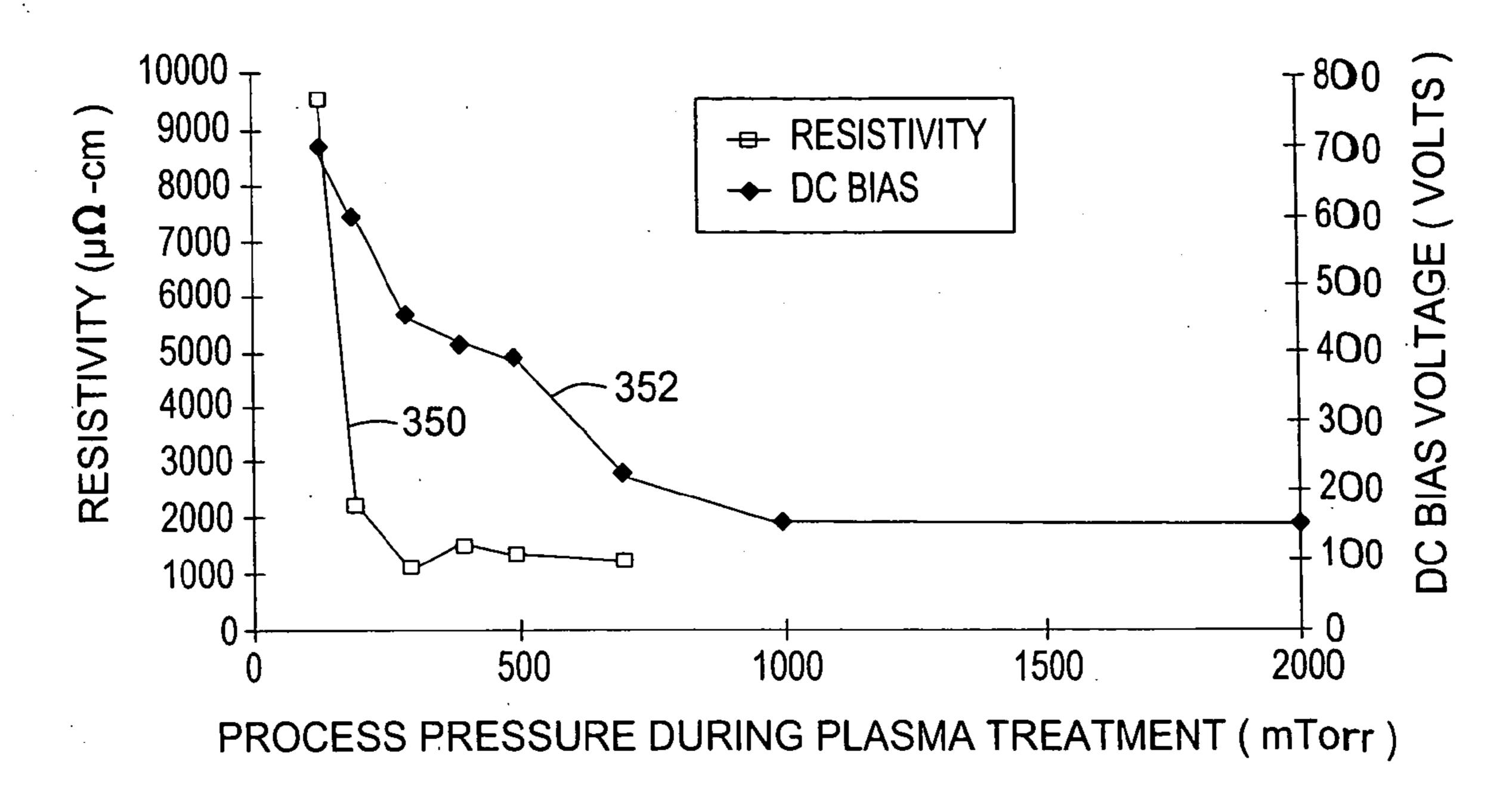

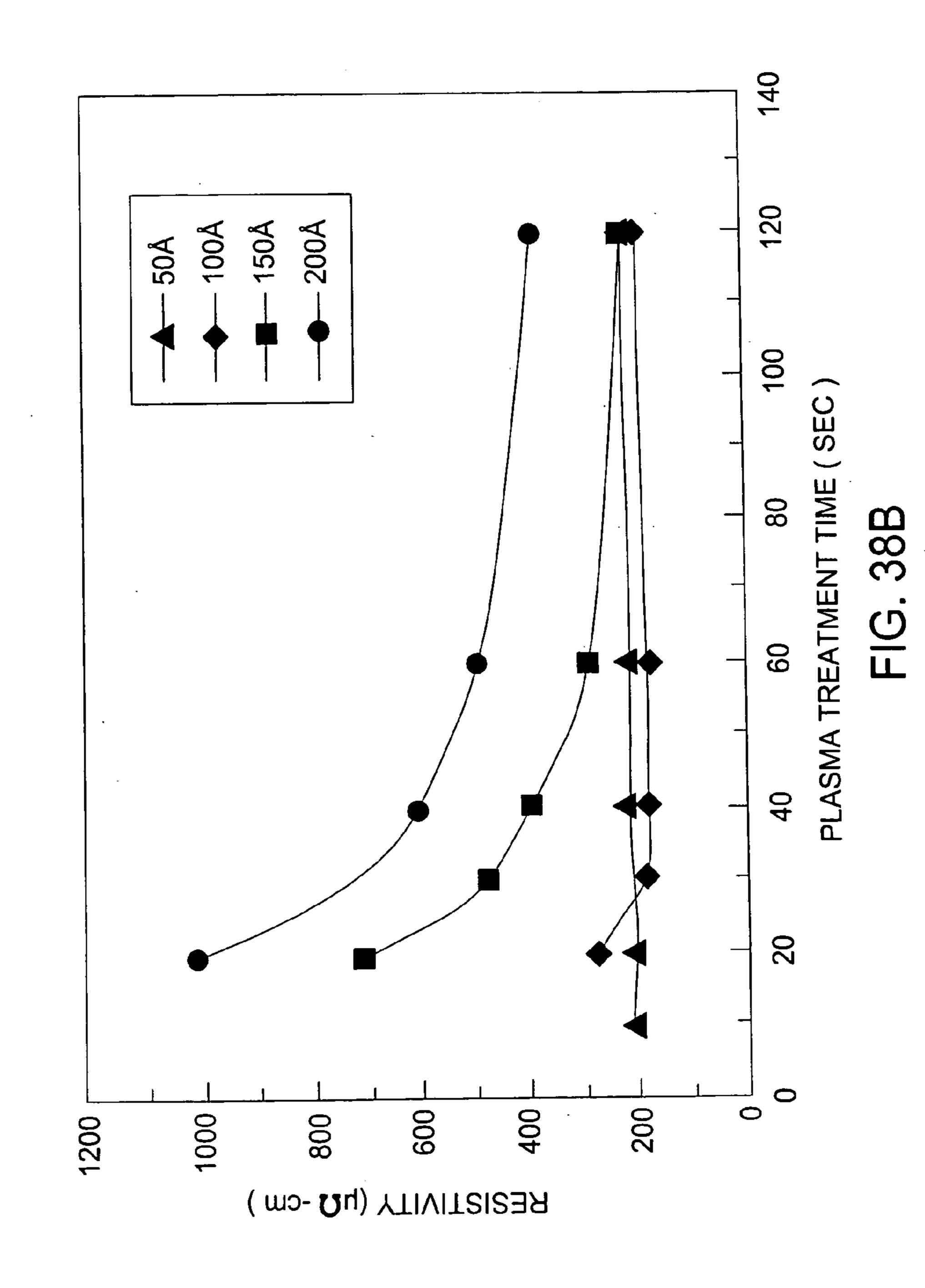

[0081] FIG. 38(a) illustrates the effects of annealing duration and frequency on film resistivity.

[0082] FIG. 38(b) illustrates a further example of the effects of annealing duration on film resistivity.

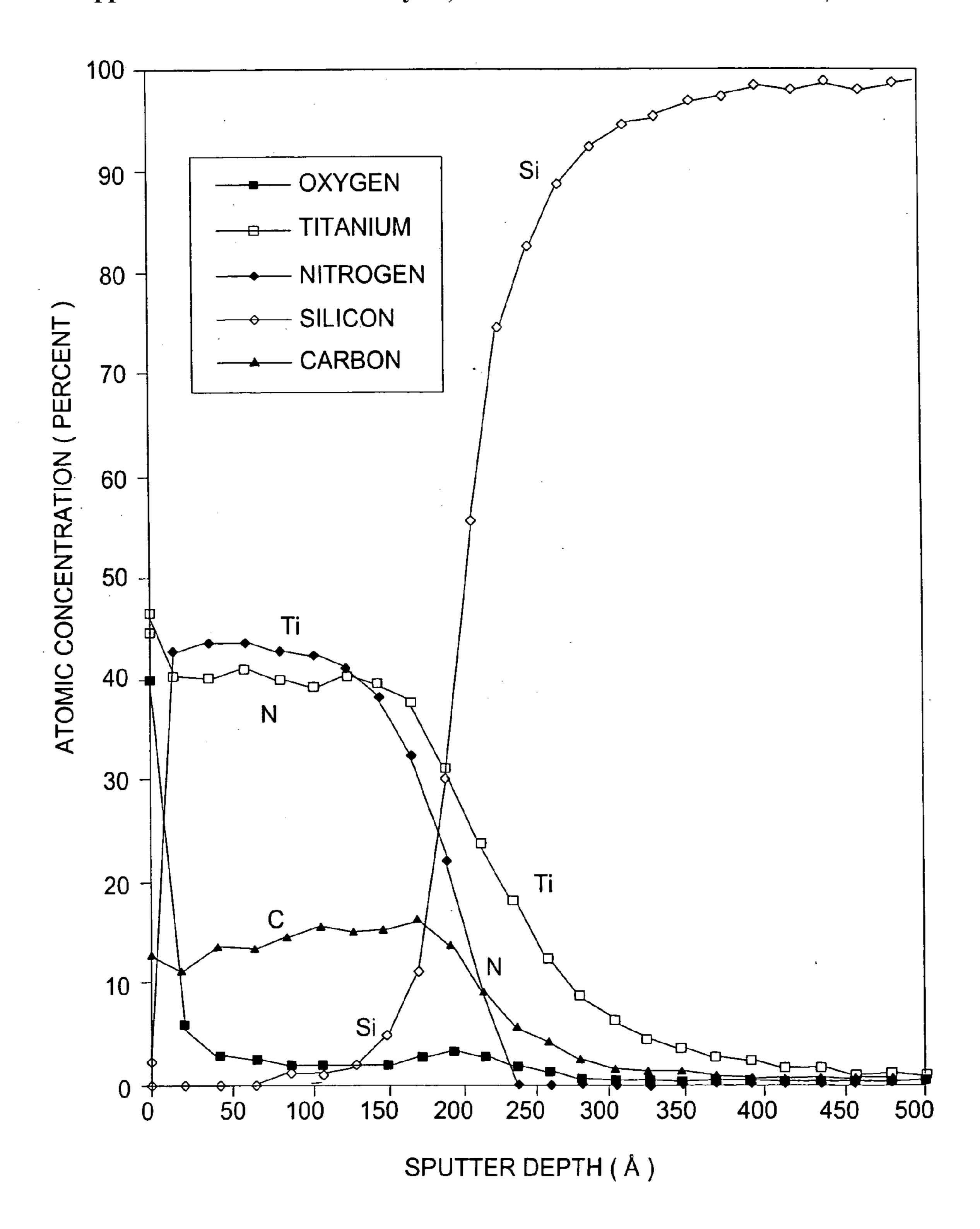

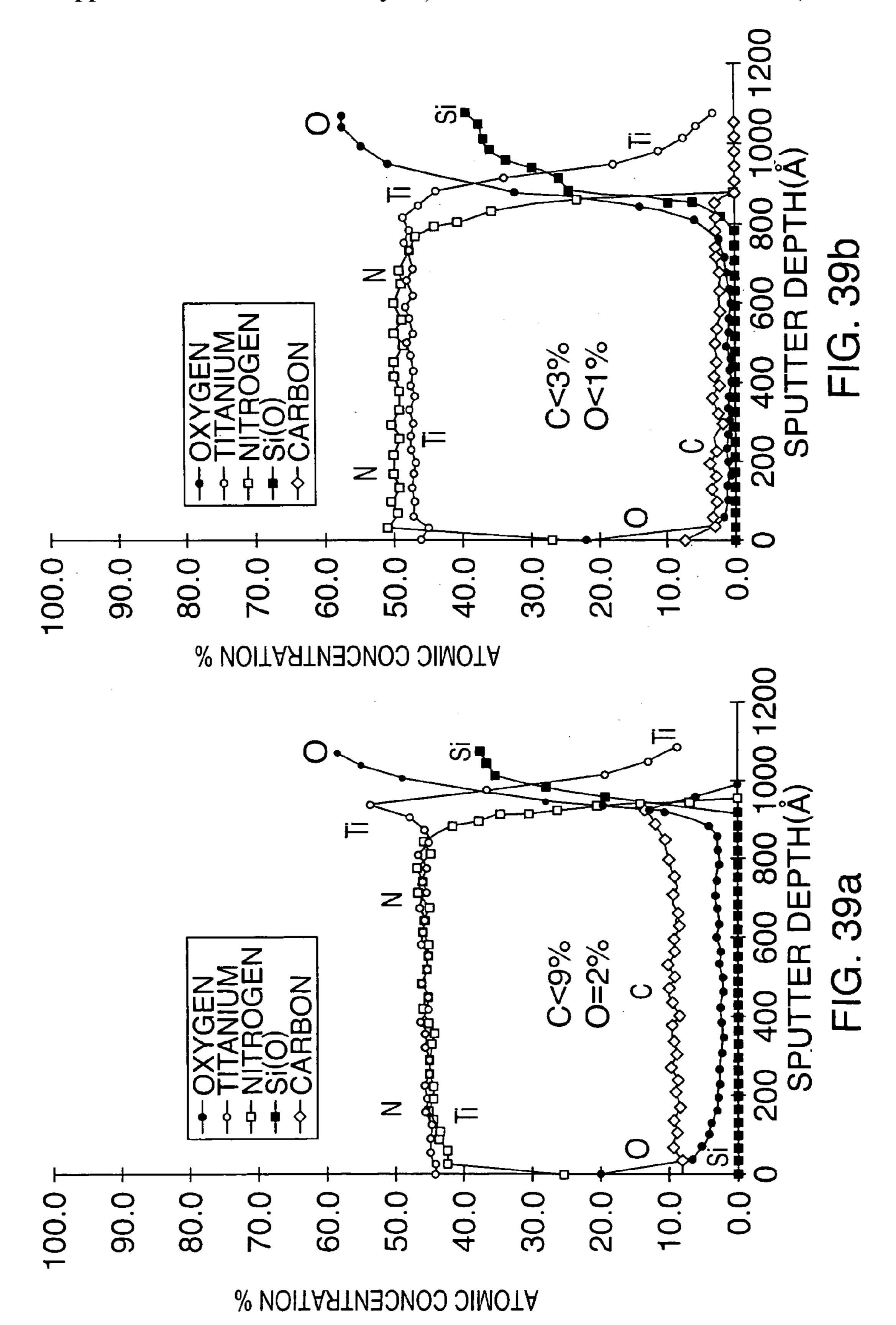

[0083] FIGS. 39(a)-39(b) illustrate Auger electron spectroscopic depth profiles for titanium nitride films formed by successively depositing and annealing layers of titanium nitride.

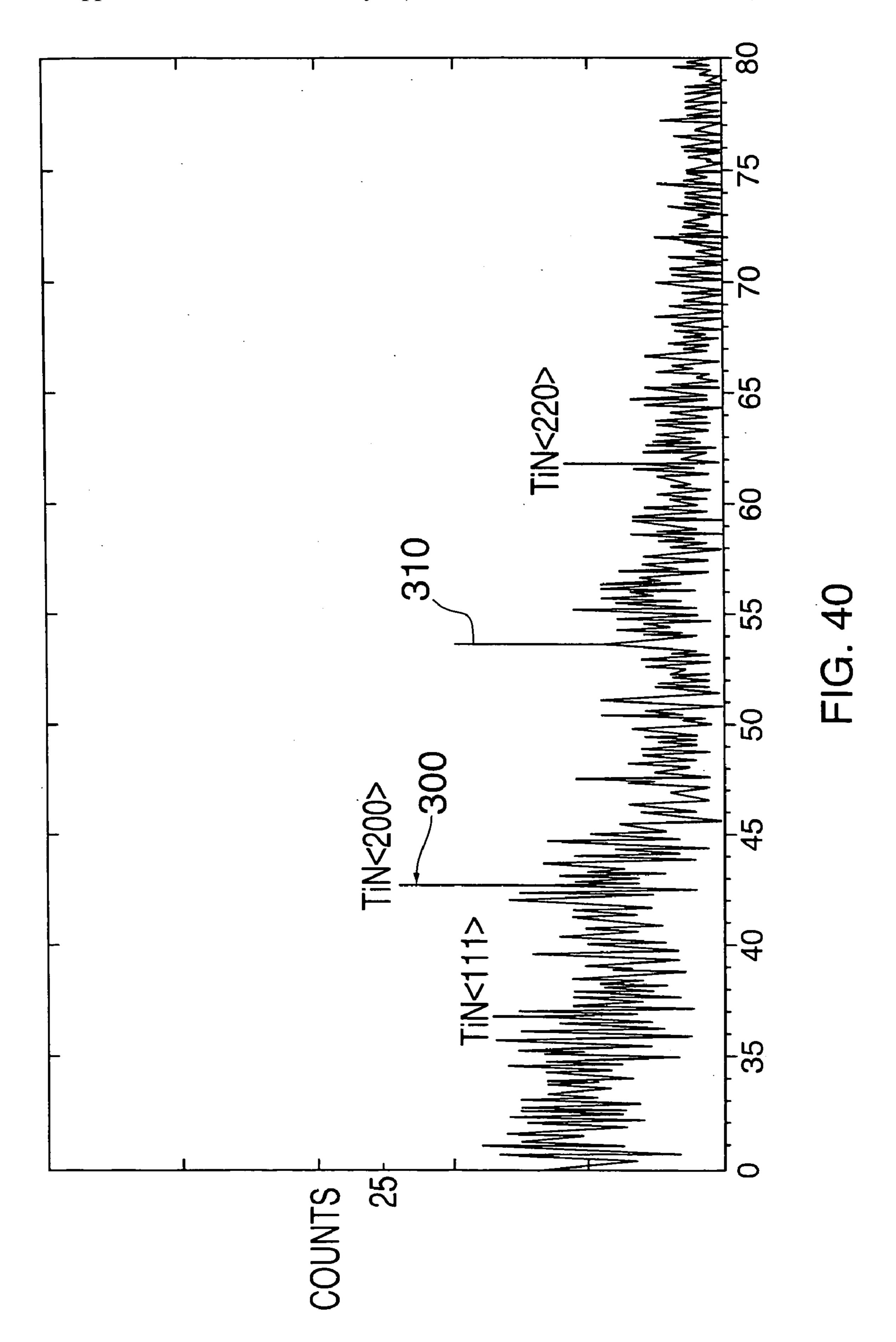

[0084] FIG. 40 illustrates an x-ray diffraction glancing angle scan of a 1,000 Å titanium nitride layer deposited on a silicon wafer using conventional chemical vapor deposition.

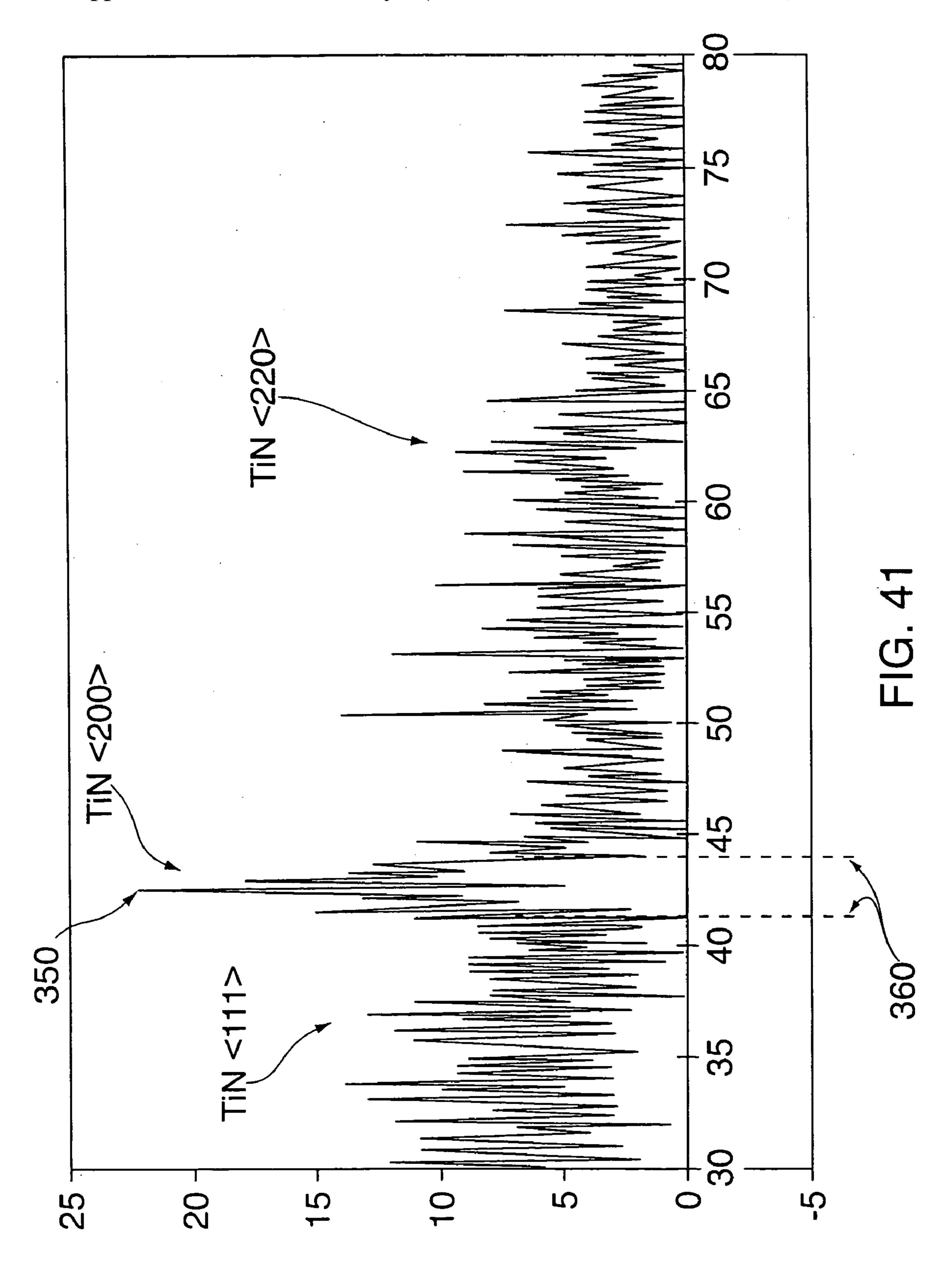

[0085] FIG. 41 is an x-ray diffraction glancing angle scan of a 1,000 Å titanium nitride layer deposited on a silicon wafer and annealed in accordance with the present invention.

[0086] FIG. 42 illustrates Table VI.

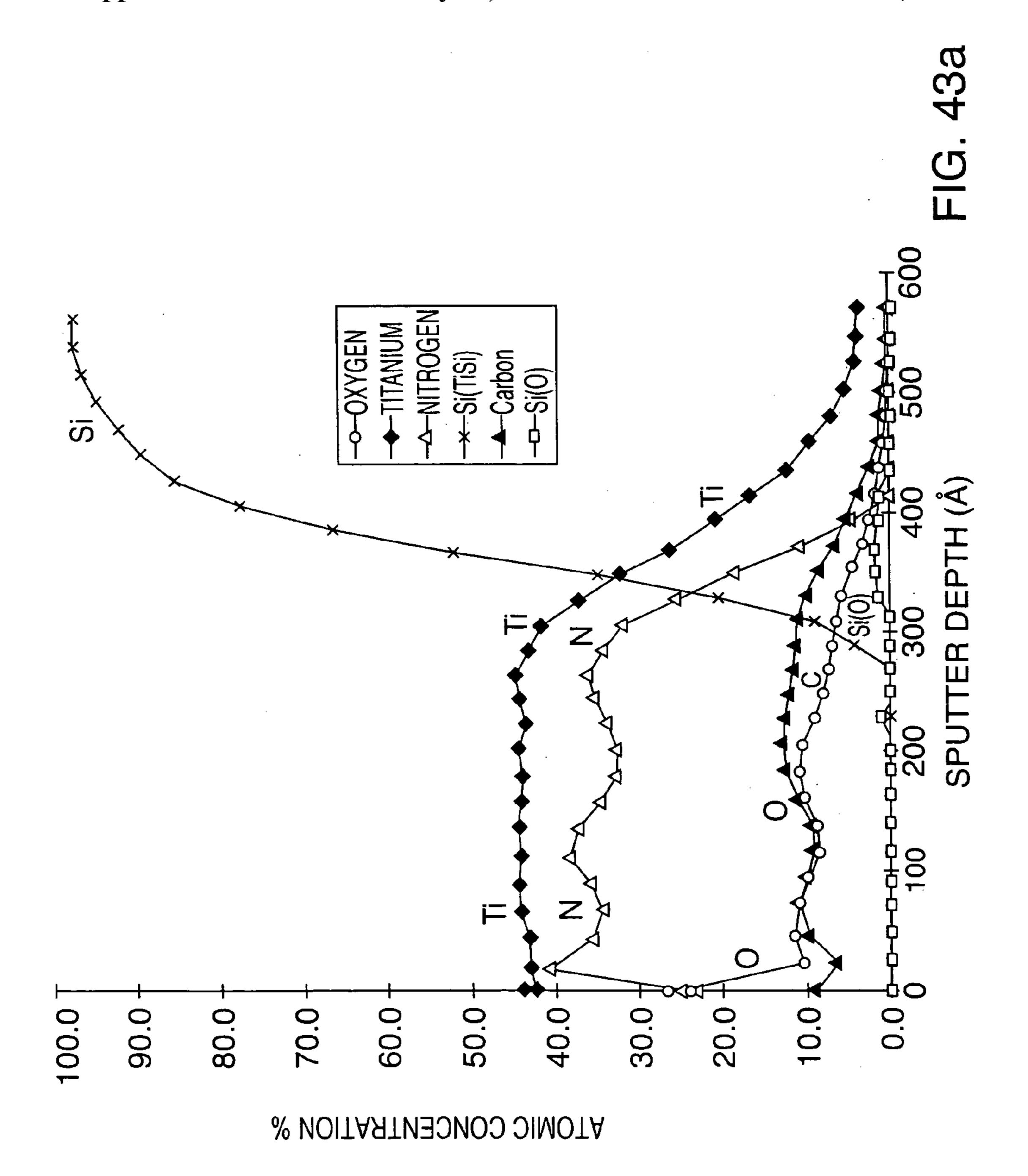

[0087] FIGS. 43(a)-43(b) illustrate the chemical composition of non-oxidized and oxidized diffusion barriers, respectively, that are formed in accordance with one embodiment of the present invention.

[0088] FIG. 44 illustrates the resistance characteristics of diffusion barriers that are formed in accordance with one embodiment of the present invention.

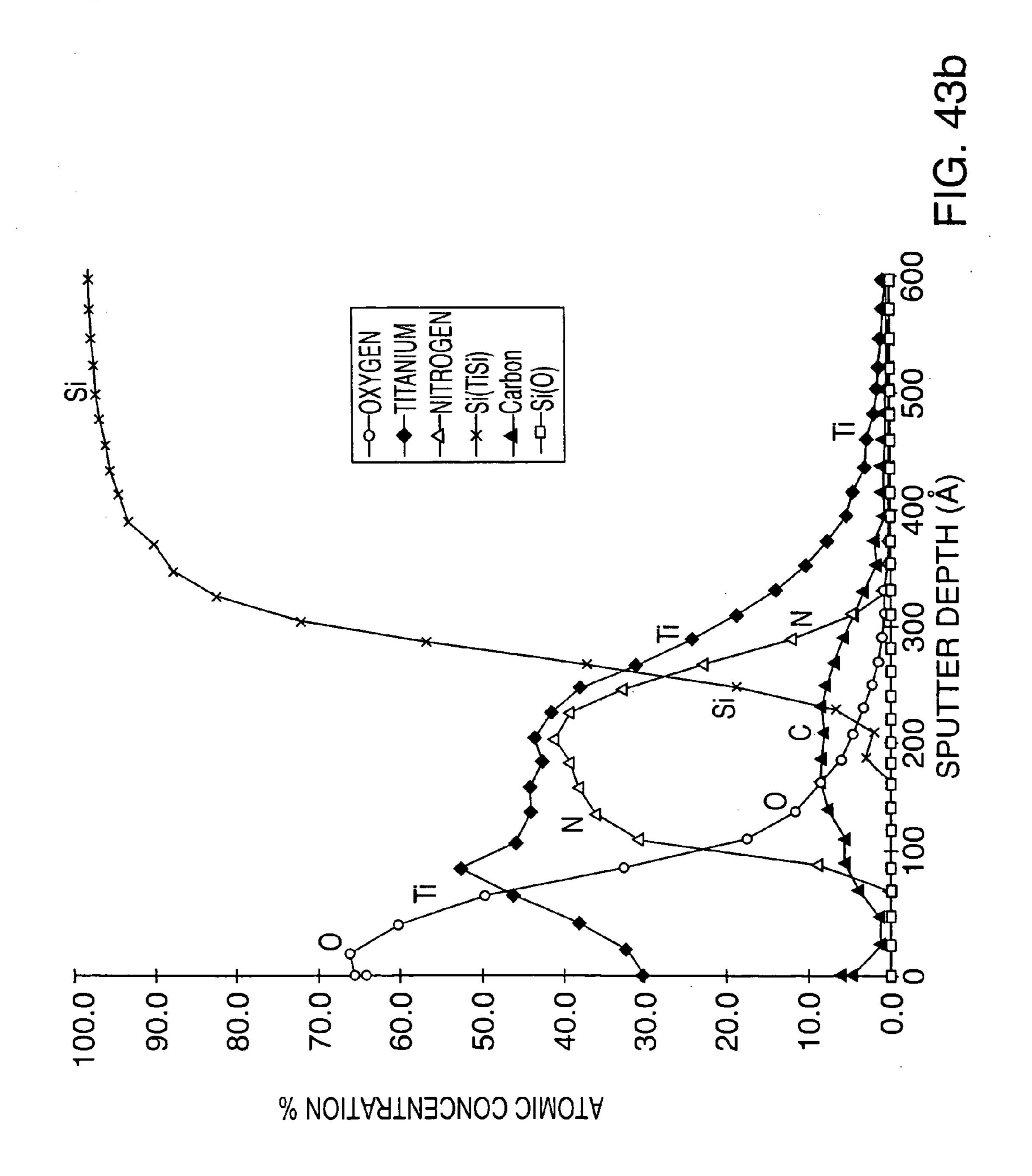

[0089] FIG. 45 illustrates an Auger depth profiling of a film formed using silicon stuffing in accordance with the present invention.

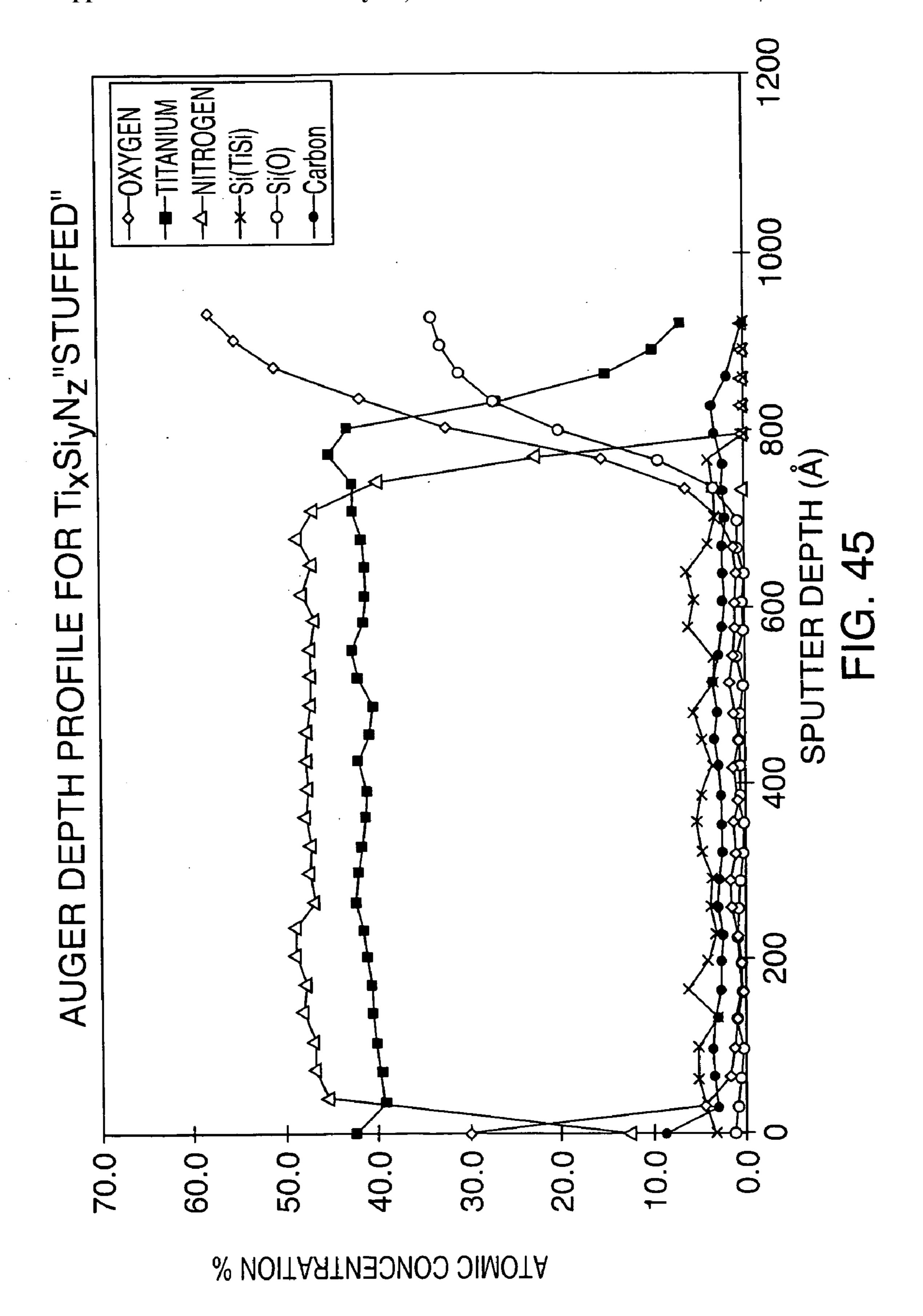

[0090] FIG. 46 illustrates an Auger depth profiling of a film formed by deposition of a material containing silicon in accordance with the present invention.

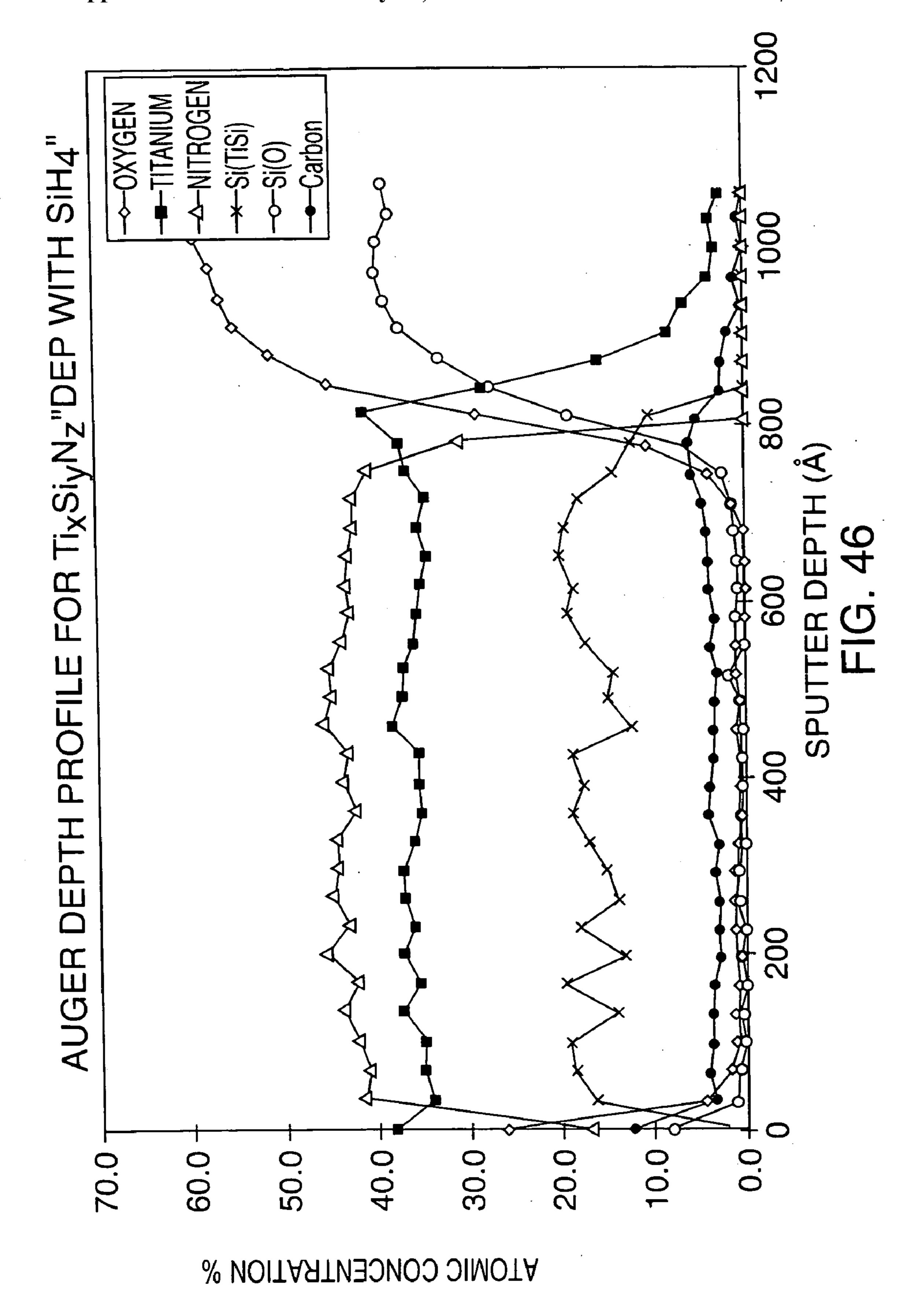

[0091] FIG. 47 illustrates a comparison of the resistivity and composition of the films shown in FIG. 45 and FIG. 46.

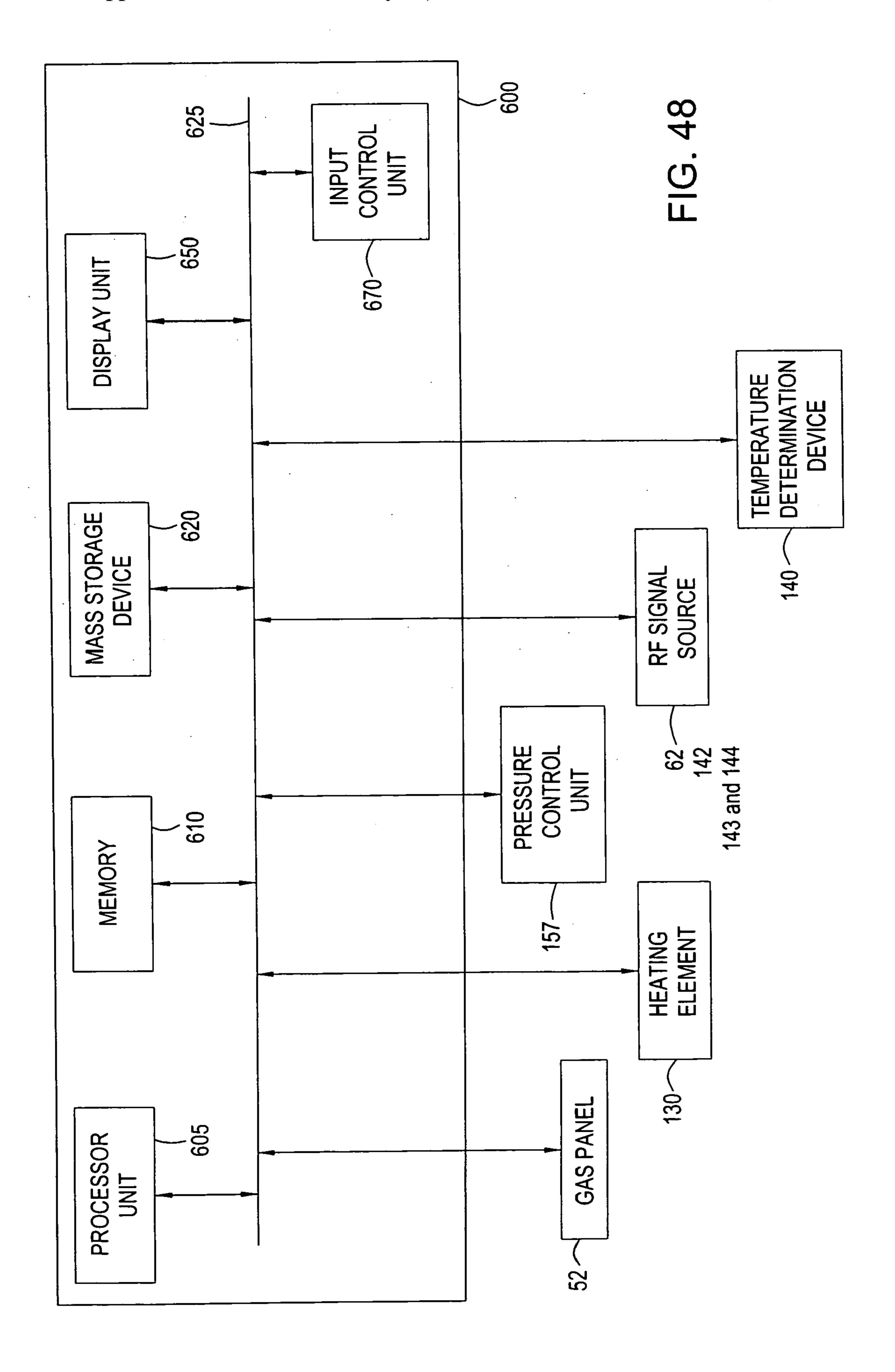

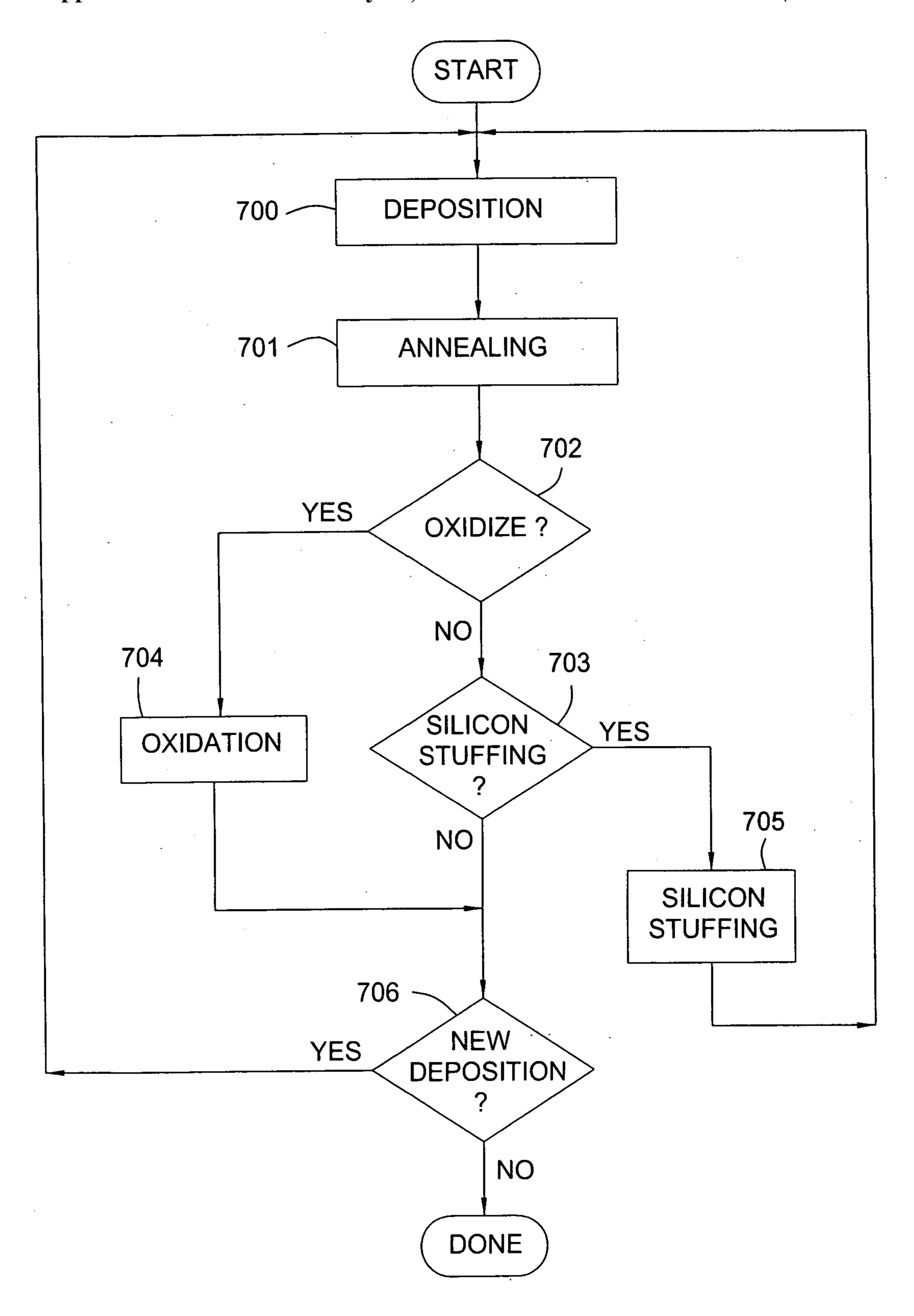

[0092] FIG. 48 illustrates a control unit for controlling a chamber that is used for constructing a film on a substrate in accordance with the present invention FIG. 49 illustrates a sequence of operations performed by the control unit in FIG. 48 in one embodiment of the present invention.

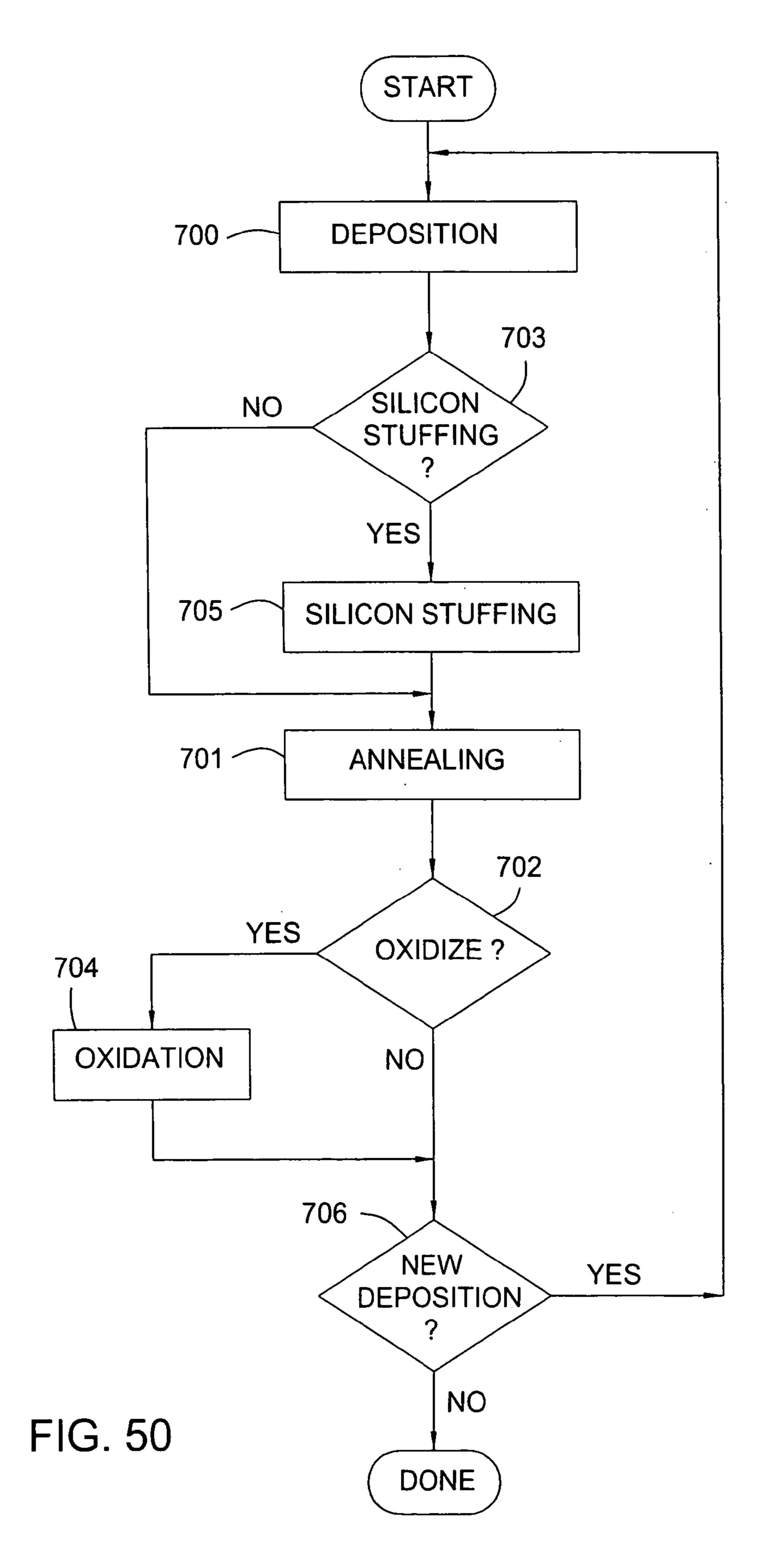

[0093] FIG. 50 illustrates a sequence of operations performed by the control unit in FIG. 48 in an alternate embodiment of the present invention.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0094] A. Chambers for Processing Wafers

[**0095**] 1. Overview

[0096] FIGS. 3(a) and 3(b) jointly depict a traditional CVD chamber 10. The CVD chamber 10 includes a processing chamber 12 in which a wafer 14 is supported by a wafer support 16, such as a susceptor. The wafer support 16 is supported by a circular disk 18, which is typically made of a material such as alumina ceramic. The disk 18 rests on

the free end 20 of a support arm 22. The support arm 22 defines a cantilever with its fixed end 24 mounted to a stem 26. The stem 26 is capable of vertical displacement under action of a displacement mechanism 28. The displacement mechanism 28 operates to move the support arm 20 vertically within the processing chamber 12.

[0097] During the processing of a wafer 14, gas is injected into the processing chamber 12, via a showerhead 36. The showerhead 36 is typically mounted directly above the wafer 14.

[0098] In operation, the interior of the processing chamber 12 is heated by a set of infrared lamps 30 mounted beneath the CVD chamber 10. The lamps 30 irradiate the interior of the processing chamber 12 through a quartz window 32, which is located between the lamps 30 and the interior of the processing chamber 12. The lamps 30 serve to heat both the interior of the processing chamber 12 and the wafer support 16. As a result, a wafer 14 on the wafer support 16 is also heated.

[0099] To enhance the heating of the wafer support 16, the ceramic supporting plate 18, as shown in FIG. 3b, includes a number of holes 34 formed therethrough. The typical arrangement of holes 34 shown in FIG. 3b makes it apparent why the plate 18 is often referred to as a "Swiss Cheese" plate.

[0100] Thermal CVD wafer processing is very sensitive to the wafer temperature. To ensure that the wafer remains at an appropriate temperature, the temperature of the wafer support 16 is measured by a thermocouple 38. The thermocouple 38 is supported at the free end 20 of the support arm 22 and mounted within the body of the wafer support 16. An electrically conductive cable 42 couples the thermocouple to a temperature determination device 40, which is mounted outside the processing chamber 12. The cable 42 typically runs along a bore formed centrally within the support arm 22.

[0101] FIG. 4 depicts a multichamber vacuum system, which is suitable for carrying out the manufacture of a wafer including integrated circuits. Chamber A will provide for the pre-cleaning of a substrate upon which the integrated circuits are to be formed. After pre-cleaning, the substrate is transferred to a CVD chamber B, so that a film may be deposited onto the substrate. The substrate will then be transferred to a post-deposition treatment chamber C for improving the quality of the deposited film.

[0102] If it is desirable to "stuff" the film with a substance that enhances the film's operation as a diffusion barrier, the substrate may be transferred to chamber D in which such "stuffing" may be performed. For example, the film may be a layer of titanium nitride material, which is to be stuffed with oxygen to reduce the diffusivity of the film for aluminum. The stuffing of a titanium nitride barrier layer with oxygen is disclosed in U.S. Pat. No. 5,378,660, entitled BARRIER LAYERS AND ALUMINUM CONTACTS and issued to Ngan, et al.

[0103] Either of the above described systems may be employed for practicing aspects of the present invention. However, neither system provides the ability to deposit a material on a wafer and perform post deposition processing on the material to form a film within a single chamber. Such post deposition processing may include annealing, oxidizing, exposure to silicon, or a combination thereof.

[0104] 2. A Chamber for In-situ Operations

[0105] FIG. 5 illustrates a semiconductor wafer processing chamber 110A in accordance with the present invention. The wafer processing chamber 110A provides for performing a series of in-situ deposition and post-deposition processing steps on a semiconductor wafer 114. In accordance with the present invention, the chamber 110A depicted in FIG. 5 may be a chemical vapor deposition chamber as is described in detail in U.S. patent application Ser. Nos. 08/567,461 and 08/677,185.

[0106] Wafer processing chamber 110A eliminates the need for employing multiple chambers to deposit and treat a material in accordance with the present invention. For instance, the wafer processing chamber 110A may be employed to form a film on a wafer by depositing a material on the wafer and annealing the deposited material to stabilize and reduce its resistance. As a result, the wafer will not be exposed to damaging impurities that are outside of the chamber 110A during the formation of the film.

[0107] As shown in FIG. 5, the semiconductor wafer processing chamber 110A includes a processing chamber 112, which is coupled to ground. A semiconductor wafer 114 may be supported in the processing chamber 112 on a wafer support 116, which may be the same as the wafer support 16 shown in FIGS. 3(a) and 3(b). The wafer support 116 may be a susceptor, a pedestal, a resistive heater, or any other suitable means for supporting the wafer 114.

[0108] In FIG. 5, the wafer support 116 is a susceptor, which is the type of wafer support that is often used when lamps are employed to irradiate the wafer support 116. The susceptor is made of anodized aluminum and is supported by a conventional alumina ceramic support plate 118, which is similar to the support plate 18 in FIG. 3b.

[0109] The combination of the support plate 118, wafer support 116 and wafer 114 is supported on a free end 120 of a cantilevered alumina support arm 122. A fixed end 124 of the support arm 122 is mounted to a generally vertically moveable stem 126, which is electrically isolated from the processing chamber by isolator 160. The vertically moveable stem 126 is vertically displacable under the action of a displacement mechanism 128.

[0110] The processing chamber 112 and its contents are heated by means of conventional lamps 130, which irradiate the wafer support 116 through a conventional quartz window 132. The semiconductor wafer processing chamber 110A further includes a temperature determination device 140. The temperature determination device 140 is coupled to the wafer support 116 to sense the temperature of the wafer support 116. A vacuum pump, pressure gauge and pressure regulator valve are all included in a pressure control unit 157. The pressure control unit 157 adjusts the pressure in the processing chamber 112 and exhausts both carrier gases and reaction by-products from the processing chamber 112.

[0111] A showerhead 136 is placed above the wafer support 116 in the processing chamber 112 and is electrically isolated from the chamber 112 by means of isolator 159. The showerhead 136 is supplied with processing gases from a gas panel 52. The gas panel 52 is controlled by a gas panel controller 50 in the form of a computer.

[0112] In order to perform post-deposition annealing, the semiconductor wafer processing chamber 110A includes a rf

source 142. The rf source 142 applies rf power to the showerhead 136, which operates as a first electrode, and the wafer support 116, which operates as a second electrode. The rf source 142 may be capable of providing signals with frequencies less than 1 MHZ, and preferably providing signals with a frequency of 350 KHz. Providing rf signals to the two electrodes 136 and 116 overcomes challenges that are not present in providing rf signals to two electrodes in other traditional semiconductor wafer processing chambers, such as a PVD chamber.

[0113] In embodiments of the present invention, it is possible to prevent the application of excessive negative bias to the showerhead 136. Excessive negative bias on the showerhead 136 can cause increased ion bombardment of the showerhead 136 which results in the generation of contaminant particles.

[0114] It is desirable to have a great deal of ion bombardment of a target electrode in a traditional PVD chamber. In a traditional PVD chamber, a target electrode supports a target of material to be deposited. The target electrode is given significant negative bias, so that ions readily collide with the target material to provide for deposition of the target material.

[0115] Further, the negative biasing of a wafer support and the control of wafer temperature in a traditional sputtering process are typically not critical. This is not true in embodiments of the present invention. Controlling negative bias on the wafer support 116 is desirable for establishing an optimum level of ion flux towards the wafer 114. Accurately setting the temperature of the wafer 114 is desirable for performing both deposition and post-deposition processing of deposited material.

[0116] Accordingly, the wafer support 116 provides the dual function of being coupled to an rf source 142 and housing a thermocouple temperature sensing mechanism (not shown). The rf source 142 provides for controlling the negative biasing of the wafer support 116, and the thermocouple provides for monitoring the temperature of the wafer 114.

[0117] The wafer support 116 and support arm 122 are designed to isolate the rf source signals from the thermocouple signals, so that accurate wafer temperature readings may be made. This isolation enables both the rf source signals and thermocouple signals to be accurately transferred within the chamber 110A, so that the wafer 114 is both biased and heated properly. The details of the wafer support arm 122 are described below with reference to FIGS. 6-14.

[0118] 3. The Wafer Support Arm

[0119] Referring generally to FIGS. 6-9(b), wafer 114 is supported on the wafer support 116 which is itself supported by a conventional "Swiss Cheese" alumina ceramic support plate 118. A thin quartz plate 119 is located between the support plate 118 and the wafer support 116. The quartz eliminates arcing between the support plate 116 and other components in the wafer processing chamber 110A. The quartz plate 119 is transparent to radiate energy provided by the lamps 130. This allows the lamps 130 to quickly heat the wafer support 116.

[0120] The wafer support 116 is encircled by a quartz shield 150. The quartz shield 150 rests on the alumina

support plate 118 (partially shown in FIG. 7) to extend above the wafer support 116 and define a wafer receiving pocket within which both the wafer support 116 and the wafer 114 reside. The quartz shield 150 has its upper edge chamfered outwards to receive the wafer 114 more easily when the wafer 114 is transferred to and from the wafer support 116. The quartz shield 150 primarily functions to shield the edge of the wafer support 116 from attracting an arc.

[0121] In processing, the temperature of the wafer support 116 is measured by a thermocouple 152 mounted in the wafer support 116. The thermocouple 152 is mounted within an alumina nitride sheath 154 which snugly fits within the body of the wafer support 116. The sheath 154 provides electrical insulation between the thermocouple 152 and the body of the wafer support 116. Although the sheath 154 is electrically highly resistive, it remains a good conductor of heat. The sheath 154 has a low thermal mass and thus low thermal inertia making it suitable for use with the thermocouple 152. Further, the sheath 154 is chemically stable within the processing environment of the processing chamber 112.

[0122] The thermocouple 152 is connected to the temperature determination device 140 by an electrically conductive cable 156. As will be described below, the cable 156 passes along a central portion of the support arm 122 and is electrically insulated from any radio frequency energy within the processing chamber 112.

[0123] The thermocouple 152 is held in position by a small nickel sphere 158 which is crimped over the conductive cable 156. The sphere 158 is retained in a slot 160 formed in a keyed ceramic retaining element 162. The keyed retaining element 162 keys into a groove 164 formed in a central protruding stub 166 on the underside of the wafer support 116. This arrangement ensures that the thermocouple 152 can be removed relatively easily and replaced once the wafer support 116 is separated from the support arm 122. The above-described arrangement ensures that the thermocouple 152 is held firmly in place within the body of the wafer support 116, while maintaining electrical isolation between the wafer support 116 and the thermocouple 152.

[0124] The wafer support 116 is secured to the support arm 122 by a pair of bolts 168, which screw into the central stub 166. FIG. 8 show that the support arm 120 is primarily constituted by an inverted U-shaped ceramic section 170. The bolts 168 pass through respective holes 172 passing through the horizontal portion of the U-shaped section 170. To prevent excessive bearing of the bolts 168 onto the horizontal portion of the U-shaped section 170, each head is spaced from the horizontal portion by means of a Belvedere spring washer 174. Preventing excessive bearing of the head of the bolt 168 onto the ceramic U-shaped section 170 is important, since ceramic, particularly thin section ceramic, is relatively brittle. Excessive bearing force may cause the U-shaped section 170 to break.

[0125] An rf conductive strip 180 passes along the support arm 122. The strip 180 is electrically connected to the underside of the wafer support 116 at the stub 166. The rf conductive strip 180 is coated with a high temperature elastomeric dielectric material, such as polyimide, such as materials available from Dupont Electric under the trade name Pyralin.

[0126] This polyimide coating provides an electric insulation for the rf conductive strip 180. In addition, the rf conductive strip 180 is electrically isolated from the conductive cable 156 by means of a ceramic isolator 182. The details of the ceramic isolator will be discussed below with reference to FIGS. 10(a) and 10(b). Further, the rf conductive strip 180 is isolated from the interior of the processing chamber 112 by the "legs" of the inverted U-shaped section 170 and by isolator 184. The details of isolator 184 will be described below with reference to FIGS. 11(a) and 11(b).

[0127] During assembly, the thermocouple 152 and its associated sheath 154 is inserted into the wafer support 116. The thermocouple's lead cable 156 is then fed into the U-shaped section 170. The wafer support 116 is fastened onto the U-shaped section 170, by means of bolts 168. The isolator 182 is placed over the conductive cable 156 to isolate the conductive cable 156 from the rf strip 180. The rf conductive strip 180 is then laid onto isolator 182, and isolator 184 is positioned over the rf conductive strip 180.

[0128] Thereafter, a flat ceramic retainer 186 is slotted into grooves 188 formed close to the free ends of the "legs" of the U-shaped section 170. The retainer 186 acts as a retainer for all the various pieces which are located within the body of the U-shaped section 170. The details of the retainer 186 are shown in FIG. 12.

[0129] As illustrated in FIGS. 9(a) and 9(b), the support arm 122 is constituted by a relatively slender central portion with enlarged portions at its free and fixed ends, 120 and 124, respectively. The free end 120 of the support arm 122 has two bolt holes 172 formed respectively on either side of a slot 190 formed in the upper surface of the free end 120. This slot 190 receives a keyed formation 192 extending downward from the stub 166 on the bottom of the wafer support 116. This keyed formation 192 mates with the slot 190 and further stabilizes the wafer support 116 when it is positioned on the support arm 122. The details of the keyed formation 192 are shown in FIGS. 8 and 14. The fixed end 124 of the support arm 122 is secured to a vertically movable stem 194, the details of which will be described with reference to FIG. 13.

[0130] From FIGS. 10(a) and 10(b) it can be seen that the isolator 182 is in the form of a U-shaped channel within which conductive cable 156 rests. The U-shaped channel has an enlarged portion 196 formed at one end. The enlarge portion 196 covers the rf conductive strip 180 at the fixed end 124 of the support arm 122.

[0131] As shown in FIGS. 11(a) and 11(b), the isolator 184 has an enlarged portion 198 which is sized to fit relatively snugly within the free end 120 of the support arm 122. The enlarged portion 198 has a channel 200 formed therein. When the apparatus is assembled, the rf conductive strip 180 lies on the upper surface 202 of the insulator 184. The rf conductive strip 180 also bends to follow the internal contour of the channel 200. This arrangement is illustrated in FIG. 7 and provides for separating the rf conductive strip 180 from the connecting bolts 168. As can be seen from FIG. 7, a suitable spacer element 204 is provided to fit into the channel 200 and provide isolation between the rf conductive strip 180 and the bolts 168.

[0132] The details of the retainer 186 are illustrated in FIG. 12. The retainer 186 is generally spoon-shaped with an

enlarged portion 206 sized to be received within the groove formed at the free end 120 of the support arm 122. During assembly, the retainer 186 is inserted into the slot 188 from the free end 120 of the support arm 122.

[0133] The fixed end 124 of the support arm 122 is connected to the stem 194 as illustrated in FIG. 13. The stem 194 is a hollow tube which flares at its upper end to define flanges 210 to which the fixed end 124 of the support arm 122 is bolted by bolts 212. To prevent excessive bearing force between the bolts 212 and ceramic fixed end 124, a Belleville spring washer 214 is provided between each bolt 212 and the fixed end 124 of the support arm 122.

[0134] A stainless steel bellows 216 is positioned between the flanges 210 and the lower wall of the processing chamber 112. The bellows 216 allow the support arm 122 to be moved vertically up and down, while at the same time providing a seal around the stem 194 as it passes through the wall 218 of the processing chamber 112.

[0135] As indicated previously, the stem 194 is in the form of a hollow tube. An electrically non-conductive tube 220 is located inside the tube forming the stem 194. The non-conductive tube 220 is typically made of a polyimide material and provides electrical isolation between the processing chamber 112 and a hollow rf conducting tube 222. The rf conducting tube 222 is connected to the rf source 142 and the rf conductive strip 180. The conductive cable 156 communicating between the thermocouple 152 and the temperature determination device 140 passes down the central bore formed in the rf conductive tube 222.

[0136] FIG. 14, when read with FIG. 13, illustrates how the connection is made between the rf conductive strip 180 and the rf conductive tube 222. As shown in FIG. 13, the rf conductive tube 222 flares at its upper end to define a circular flange 224. The rf conductive strip 180, as illustrated in FIG. 14, ends in a circular conductive hoop 226. When the support arm 122 is assembled, the hoop 226 is placed on the circular flange 224 of the rf conductive tube 222.

[0137] This provides a rf conductive connection to the rf conductive strip 180 which is coupled to the wafer support 116. This connection allows for easy assembly and disassembly of the support art 122. The connection also allows for a certain amount of rotational freedom (above the longitudinal access of stem 194) when the fixed end 124 of the support arm 122 is being positioned onto the flange 210 of the stem 194.

### [0138] 4. The Matching Network

[0139] In accordance with the present invention, the rf source 142 is coupled to both the wafer support 116 and the showerhead 136 through a matching network 145. The matching network 145 is a resistor/inductor/capacitor network. The matching network 145 matches the load impedance to the source impedance, in order to maximize the power delivered by the source at a given frequency. The matching network 145 also splits rf power between the wafer support 116 and the showerhead 136 and sets the phase shift of the rf signals provided to the showerhead 136 and the wafer support 116.

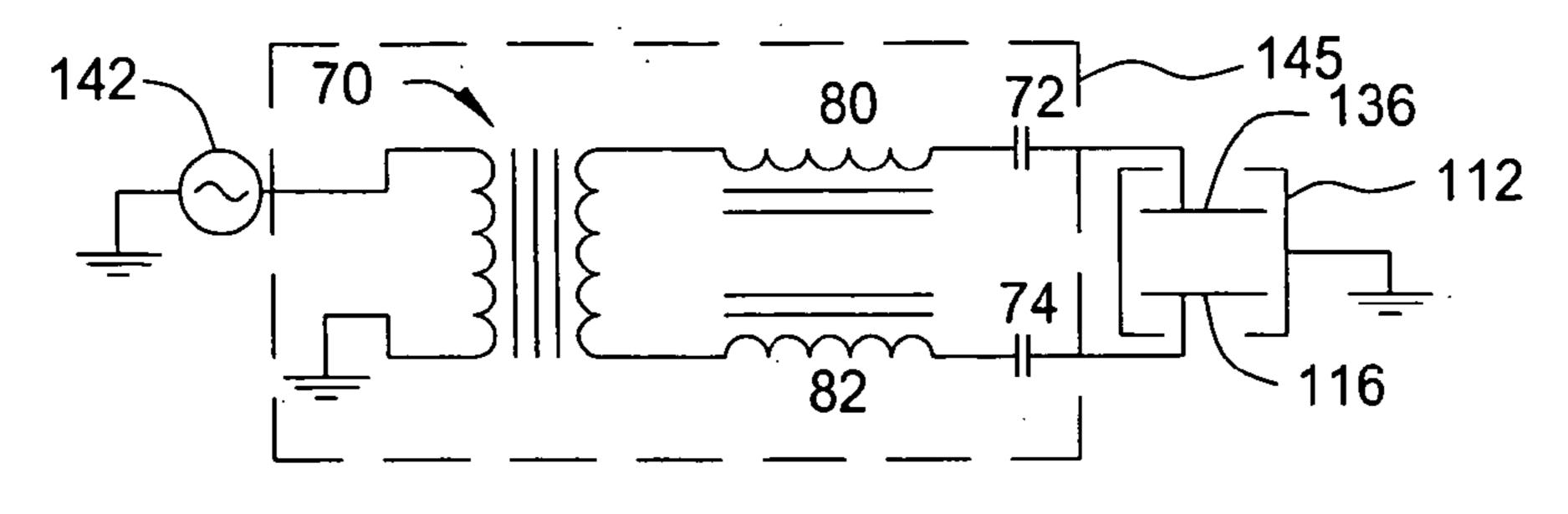

[0140] A matching network 145 used in one embodiment of the present invention is illustrated in FIG. 15A. The matching network 145 shown in FIG. 15A includes a load

match transformer 70, two inductors 80 and 82, and two capacitors 72 and 74. The load match transformer 70 is coupled at one end to the rf source 142 and ground, and on another end to the inductors 80 and 82. The inductors 80 and 82 are coupled to the showerhead 136 and wafer support 116, respectively, through capacitors 72 and 74, respectively.

[0141] The load match transformer 70 may have a primary to secondary turns ratio ranging from 1:1 to 1:4, with 1:1.22 being typical. In accordance with the present invention, the primary coil of the load match transformer 70 may have 18 turns, and the secondary coil of the load match transformer 70 may have 47 turns. The inductors 80 and 82 each have an inductance of  $50 \mu\text{H}$ , and the capacitors 72 and 74 each have a capacitance of  $0.01 \mu\text{F}$ .

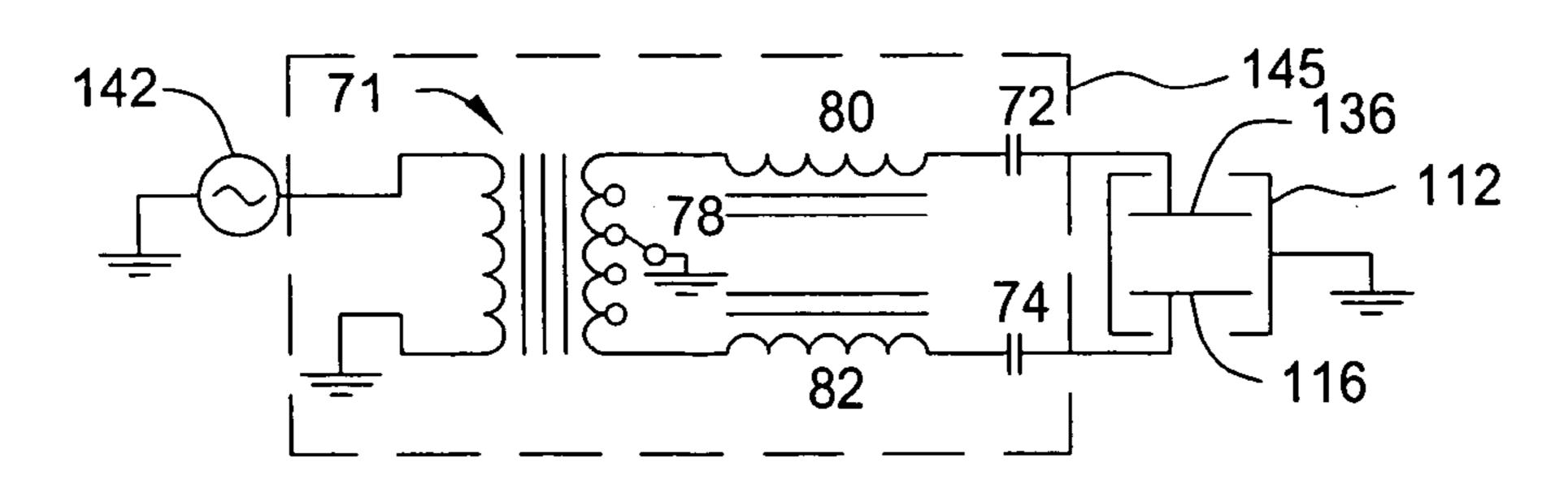

[0142] The power split and the phase shift between the rf signals at the showerhead 136 and wafer support 116 may be altered by modifying the turns ratio of the load match transformer 70. Alternatively, as shown in FIG. 15B, a load match transformer 71 may have a selectable ground tap 78. The selectable ground tap 78 allows for the selection of variable ground tap positions to change the power split and phase shift between the rf signals at the showerhead 136 and the wafer support 116.

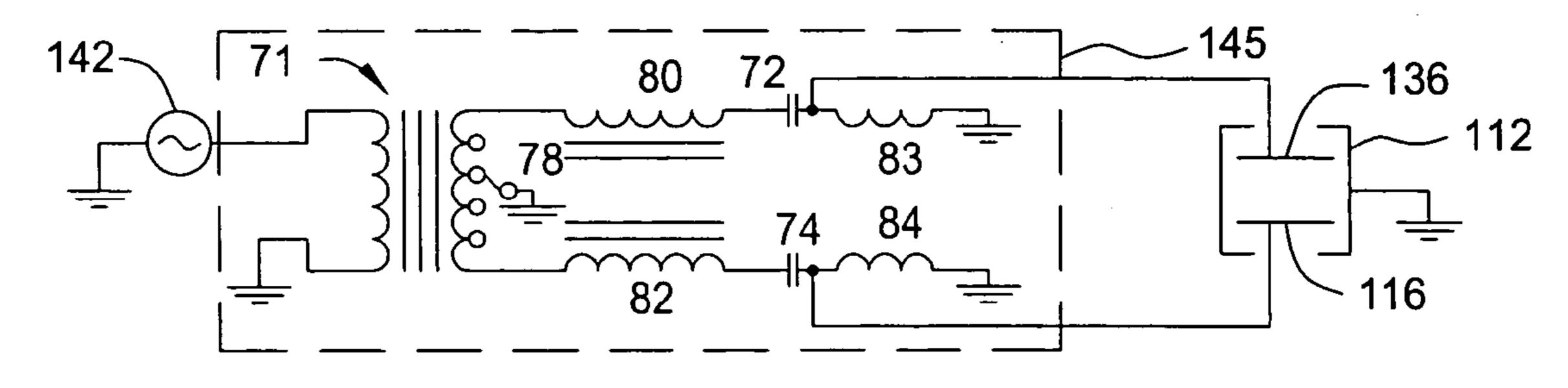

[0143] Yet another embodiment of the matching network 145 is shown in FIG. 15C. Capacitor 72 and the showerhead 136 are both coupled to ground through an inductive choke 83. Capacitor 74 and the wafer support 116 are both coupled to ground through an inductive choke 84. Inductive choke 83 and inductive choke 84 may each have a value of  $500 \mu H$ . When such an embodiment is employed, the showerhead 136 and the wafer support 116 do not become DC biased.

[0144] Coupling both the showerhead 136 and the wafer support 116 to the rf source 142 through the matching network 145 is advantageous when the processing chamber 110 is employed for plasma annealing and/or oxidation. The phase shift between the rf signals at the showerhead 136 and the wafer support 116 may be set to provide for enhancing the uniformity of a plasma generated during post-deposition processing. An out of phase relationship between the showerhead 136 and the wafer support 116 signals causes the ions in the plasma to be more attracted to the wafer support 116 than the grounded processing chamber 112. The out of phase relationship also increases the voltage potential between the showerhead 136 and the wafer support 116, thereby enhancing the uniformity of the ion flux towards the wafer 114.

[0145] Adjusting the power split of the signals at the showerhead 136 and the wafer support 116 enables the intensity of ion bombardment of the wafer 114 and the showerhead 136 to be controlled. Negative biasing of the wafer support 116, during plasma generation, generally causes ions to increase their acceleration towards the wafer 114. Excessive negative biasing of the wafer support 116 causes ions to bombard the wafer 114 with such energy that the wafer 114 becomes damaged. Excessive negative biasing of the showerhead 136, during plasma generation, generally causes ions to bombard the showerhead 136 and create contaminant particles.

[0146] In embodiment of the present invention, the power split of the rf source's 145 signal may be selected by a chamber 110A operator. The power split may be set so that the negative biases of the showerhead 136 and the wafer support 116 minimize the potential for the aforementioned contamination and wafer damaging ion bombardment.

[0147] In accordance with the present invention, the matching network 145 may be configured to supply rf signals to the wafer support 116 and the showerhead 136 having the same power and frequency, but being 180 degrees out of phase. This efficiently couples rf power to the showerhead 136 and the wafer support 116 for transforming gases in the processing chamber 112 into plasma.

[0148] Embodiments of an rf split power configuration may be seen by reference to U.S. Pat. No. 5,314,603, entitled PLASMA PROCESSING APPARATUS CAPABLE OF DETECTING AND REGULATING ACTUAL RF POWER AT ELECTRODE WITHIN CHAMBER and issued to Sugiyama, et al., or to U.S. Pat. No. 4,871,421, entitled SPLIT-PHASE DRIVER FOR PLASMA ETCH SYSTEM and issued to Ogle, et al.

### [0149] 5. Chamber Operation

[0150] During a deposition process, the gas panel controller 50 causes the gas panel 52 to supply a CVD process gas, such as TDMAT, to the showerhead 136. Through the showerhead 136, the process gas is introduced into the processing chamber 112 and transported to the heated wafer 114. As a result, a thin film of material deposits on the upper surface of the wafer 114. When TDMAT is employed, the thin film of material that is formed is titanium nitride TiN.

[0151] During a post-deposition process that is performed in the semiconductor wafer processing chamber 110A, annealing, oxidation, or exposure to silicon may be performed, as will be described below. During a plasma annealing process, a plasma gas, such as nitrogen; hydrogen, argon, or a combination thereof is supplied to the showerhead 136 by the gas panel 52 under control of the gas panel controller 50. During a post-deposition oxidation process, an oxygen based gas, such as  $O_2$  or a  $N_2/O_2$  mixture is supplied to the showerhead 136 by the gas panel 52 under control of the gas panel controller 50. During a silicon exposure process, a silicon based gas, such as silane (SiH<sub>4</sub>), is supplied to the showerhead 136 by the gas pannel 52 under control of the gas panel controller 50.

[0152] In both the plasma annealing process and the oxidation process, the gas supplied by the showerhead 136 is transformed into a plasma containing positively charged ions that react with the wafer 114. In the silicon exposure process, the gas is infused with energy through the heating of the wafer 114 and wafer support 116. Any carrier gas that is employed during either the deposition or post-deposition processing, as well as any by-products from the deposition or post-deposition processing, are exhausted from the processing chamber 112 by the pressure control unit 157.

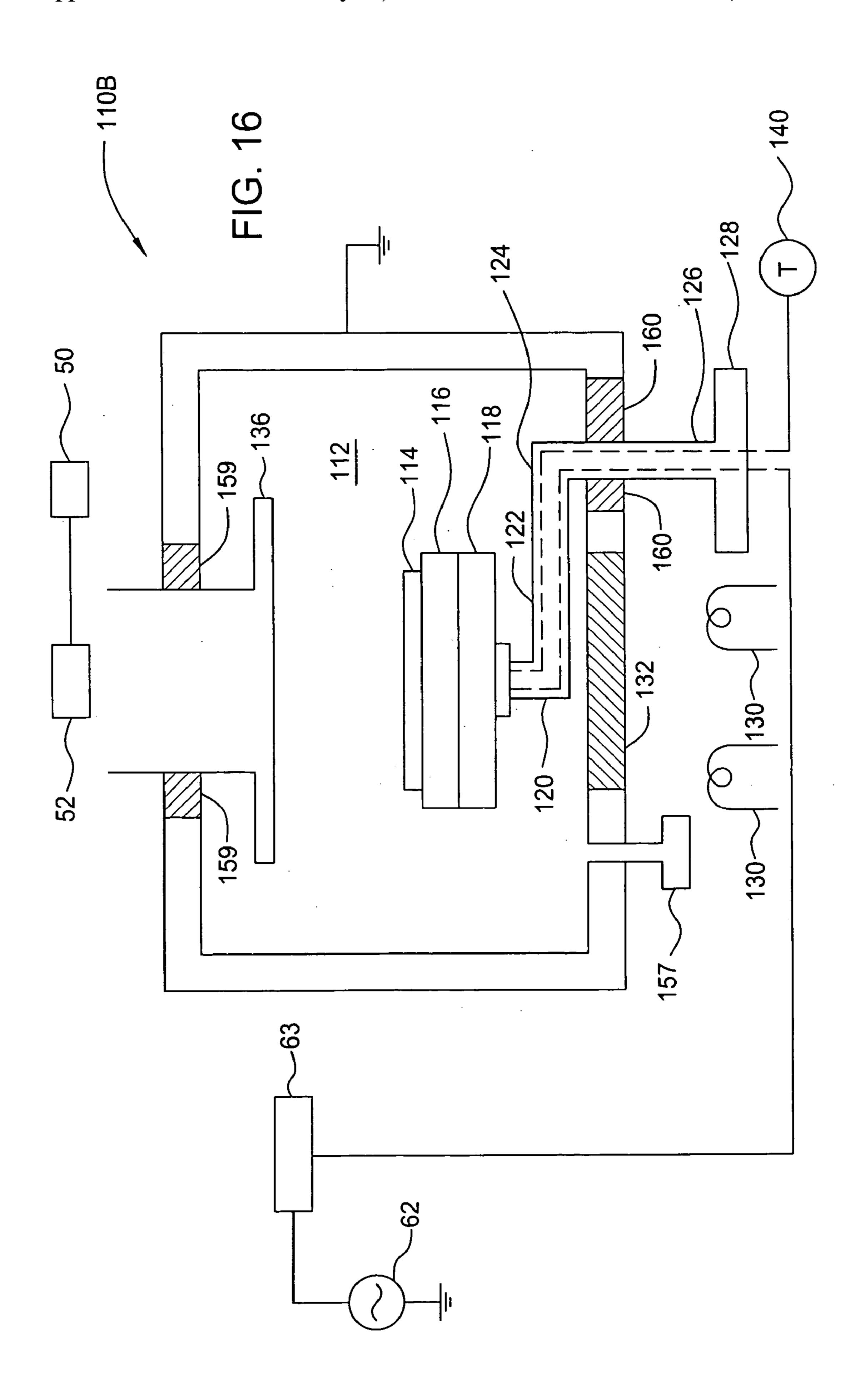

### [0153] 6. Alternative Chamber Configurations

[0154] FIG. 16 illustrates a semiconductor wafer processing chamber 110B that incorporates an alternative embodiment of the present invention for carrying out a process in accordance with the present invention. The semiconductor wafer processing chamber 110B shown in FIG. 16 is the same as the chamber 110A depicted in FIG. 5, except that the showerhead 136 is not coupled to an rf source. An rf source 62 is coupled to the wafer support 116 through a matching network 63, and the showerhead 136 is grounded.

[0155] The matching network 63 uses conventional means for matching the load impedance of the wafer support 116 to the impedance of the rf source 62. The matching maximizes the power delivered by the rf source 62 at a given frequency. In accordance with the present invention, the matching network 63 and rf source 62 may be configured to supply an rf signal to the wafer support 116, so that sufficient rf energy is provided for plasma annealing or oxidation without causing the wafer 114 to become excessively negative biased.

[0156] FIG. 17 illustrates a semiconductor wafer processing chamber 110C that incorporates an alternative embodiment of the present invention and is capable of carrying out a process in accordance with the present invention. The semiconductor wafer processing chamber 110C in FIG. 17 is the same as the chamber 110A depicted in FIG. 5, except that the showerhead 136 and the wafer support 116 are each couplet to a different rf source 143 and 144, respectively. Rf source 143 is coupled to the showerhead 136 through matching network 146, and rf source 144 is coupled to the wafer support 116 through matching network 147.

[0157] The matching networks 146 and 147 each use conventional means for matching the load impedance of the showerhead 136 and wafer support 116, respectively, to a source impedance. The matching maximizes the power delivered by each source at a given frequency. Preferably, the rf sources 143 and 144 are coupled together (not shown) to provide for controlling the phase shift and power split between the rf signals provided to the showerhead 136 and the wafer support 116. In accordance with the present invention, the matching networks 146 and 147 and rf sources 143 and 144 may be configured to supply rf signals to the wafer support 116 and the showerhead 136 that have the same power and frequency, but are 180 degrees out of phase.

[0158] In yet another embodiment of the present invention, the wafer support 116 in any of FIGS. 5, 16, or 17 may be a resistive heater. The resistive heater supports the wafer 114 and incorporates a resistive coil for heating the wafer 114.

[0159] The semiconductor wafer processing chambers shown in FIGS. 5, 16, and 17 may be employed to carry out a number of processes. In a further aspect of the present invention, a process is provided for forming a diffusion barrier. It will be recognized that the process of the present invention may be advantageously performed in the aforementioned apparatuses. However, it should be further recognized that the disclosed method may be performed in any number of suitable chambers.

[0160] B. Film Construction

[**0161**] 1. Overview

[0162] Embodiments of the present invention provide for the construction of a film with an improved resistivity value in an integrated circuit. One film that may be constructed is a diffusion barrier. However, other films that are intended to inhibit the diffusion of contact metals, such as aluminum and copper, may also be constructed using embodiments of the present invention.

[0163] In accordance with the present invention, a layer of material is deposited on a substrate, such as a semiconductor wafer. The material is then plasma annealed to reduce the resistivity of the deposited material. Subsequently, a new

layer of the material is deposited on the previously deposited material. The material is once again annealed to reduce the material's resistivity. The deposition and annealing of the material may be repeated several timed to form a film that resides on the upper surface of the wafer.

[0164] Another aspect of the present invention provides for the annealed material on the wafer to be stuffed with molecules. The stuffing enhances the material's ability to inhibit the diffusion of contact metals, such as aluminum or copper. In order to enhance the film's operation as a barrier to aluminum, the stuffing may be achieved through oxidation of the annealed material. In order to enhance the film's operation as a barrier to copper, the stuffing may be achieved through exposing the annealed material to silane (SiH<sub>4</sub>). Alternatively, reduced diffusion of copper may be obtained by depositing a material that is a ternary metal silicon nitride.

[0165] Yet another aspect of the present invention provides for the deposition, annealing, and stuffing of the material on the wafer to be performed in-situ.

[0166] 2. Annealing to Lower Film Resistivity

[0167] In accordance with the present invention, a film may be formed on a wafer by depositing a layer of material on the wafer and plasma annealing the layer of material, so as to reduce its resistivity.

[0168] The layer of material is deposited on a wafer in a chamber that is capable of performing a traditional chemical vapor deposition, such a chamber 10 in FIG. 3(a), chamber 110A in FIG. 5, chamber 110B in FIG. 16 or chamber 110C in FIG. 17. The deposition of a titanium nitride material may be achieved through the use of a metallo-organic titanium compound, preferably tetrakis (dialkylamido) titanium (Ti  $(NR_2)_4$ ).

[0169] A carrier gas, such as helium, argon, nitrogen, or hydrogen, brings the titanium compound into the chamber. In the chamber, the titanium compound is reacted with remotely generated reactive species, such as halogen, ammonium or hydrogen radicals. To facilitate the deposition of the titanium nitride, the wafer temperature is set to be about 200-600° C., and the processing chamber pressure is set to be about 0.1-100 Torr.

[0170] The deposited titanium nitride contains significant amounts of carbon, thereby causing the resulting titanium nitride films to be chemically reactive. Consequently, oxygen is absorbed into the film, when the film is exposed to air or other oxygen containing gases. Since the oxygen absorption is uncontrolled, the stability of the film is impaired and the resistivity of the film is adversely increased. This may result in the reliability of devices formed on the wafer being poor.

[0171] After exposure to air, the sheet resistivity of the deposited titanium nitride film can increase to values of about  $10,000 \,\mu\Omega$ -cm/sq up to about  $100,000 \,\mu\Omega$ -cm/sq. This is highly undesirable when the deposited titanium nitride is operating as a barrier layer for conductive contacts and vias. For a barrier layer, a resistivity on the order of about 1,000  $\mu\Omega$ -cm or less is desirable.

[0172] In accordance with the present invention, the deposited titanium nitride film is plasma annealed with an inert plasma containing high energy ions. The ions are

obtained by applying a DC bias voltage to the wafer. The DC bias voltage may be applied to the wafer by a low power rf source coupled to the wafer support and providing sufficient power to form a plasma from a precursor gas. The application of a voltage of about 100 to 1,000 volts to the wafer is sufficient. For example, 400 volts having only 100 watts of rf power may be applied to form a plasma. This is sufficient to produce high energy ions and to passivate or densify a titanium nitride film so that it remains stable overtime.

[0173] When titanium nitride films that are annealed in accordance with the present invention are exposed to air, oxygen, or water vapor, the oxygen is either not absorbed or absorbed to a much lesser extent than if no bias voltage had been applied to the wafer. Titanium nitride films deposited and annealed in accordance with the present invention are more crystalline, contain more nitrogen, and have a reduced oxygen and carbon content compared to titanium nitride films that are produced by the conventional thermal CVD of metallo-organic titanium compounds. The deposited titanium nitride films that are annealed according with the present invention also have a low and stable sheet resistivity.

[0174] The exact mechanism of the present invention is not known. However, it is believed that the high energy ion bombardment of the deposited material on a biased substrate densifies the film.

[0175] a. Nitrogen Plasma

[0176] In one embodiment of the present invention, the gas used to form the plasma for the annealing of deposited titanium nitride may be any gas, but is preferably a non-oxygen-and-carbon containing gas such as nitrogen, ammonia, or argon. Nitrogen is the most effective for passivation of the titanium nitride material. Alternatively, the deposited material can be bombarded with ions generated from a nongaseous species, such as ion sources. The plasma treatment of the deposited titanium nitride does not adversely affect particle performance, step coverage, deposition rate or barrier performance of the deposited material.

[0177] Titanium nitride has been deposited on a silicon wafer under the following conditions in a conventional vacuum chemical vapor deposition chamber 10. The pressure in the processing chamber 12 was 0.45 Torr, and the wafer support 16 was set to a temperature of 420° C. A helium flow of 400 sccm was used through a bubbler containing Ti(NR<sub>2</sub>)<sub>4</sub>, and a flow of nitrogen dilutant was set at 100 sccm. An argon purge gas was flowed in the processing chamber at 200 sccm following the deposition of the titanium nitride. A conventional CVD process for depositing titanium nitride is disclosed in U.S. Pat. No. 5,246,881 issued to Sandhu, et al.

[0178] As a result, titanium nitride was deposited at a deposition rate of about 425 Å per minute. The resultant titanium nitride film was very uniform in thickness, having a four wafer thickness variation of only 3.03%. However, the sheet resistivity (average of 4 wafers) was high at 11,360  $\mu\Omega$ -cm/sq. The resistivity was also unstable.

[0179] FIG. 18 is a graph of sheet resistivity of the deposited titanium nitride in  $\Omega$ /sq versus time in hours. The measurements denoted by a  $\square$  were taken from films withdrawn from the deposition chamber after the desired film thickness was obtained. The measurements denoted by a  $\square$  were taken from films cooled to a temperature of 150°

C. prior to removing them from the deposition chamber. Although the sheet resistivity of the  $\bigcirc$  films is lower than those of the  $\square$  films, both films are unstable, and the sheet resistivity increases with time. These properties are undesirable for a diffusion barrier.

[0180] Rutherford backscattering measurements were made on the deposited titanium nitride film. The resulting spectrum is given in FIG. 19. The peaks for carbon, C, nitrogen, N, and oxygen, O, are marked on the spectrum, as is the silicon interface. The content of various material in the titanium nitride is as follows: carbon content about 30%, nitrogen content about 24%, oxygen content about 25%, and titanium content about 23%. This shows that the deposited titanium nitride material contains comparatively high levels of carbon and oxygen impurities.

[0181] In an effort to reduce the titanium nitride's sheet resistivity, the deposition method of the titanium nitride was varied by the addition of various gases during the deposition procedure. The results are given in Table I, which appears in FIG. 20. The Control layer of titanium shown in Table I was deposited using the method set forth immediately above. The most successful run of reducing the sheet resistivity of the titanium nitride included a flow of NF<sub>3</sub>(7 sccm) during deposition. This reduced the sheet resistivity to 2,200  $\mu\Omega$ -cm. However, Rutherford backscattering spectra of the NF<sub>3</sub> treated material (see FIG. 23) that fluorine is incorporated as an impurity in the film. The incorporation of the fluorine is undesirable.

[0182] Next, pre- and post-deposition flow of gases and plasma treatment were used to determine whether such treatment would affect the sheet resistivity of a deposited titanium nitride. In two cases, a plasma was initiated before and after chemical vapor deposition of titanium nitride. The plasma was generated using a low power of 100 watts and without biasing the substrate silicon wafer receiving the titanium nitride deposition. The results are summarized in Table II, which appears in FIG. 21. None of the pre- and post-deposition treatments had much effect on the sheet resistivity of the deposited titanium nitride. Thus, it was highly unexpected that the application of a bias voltage to the wafer in a plasma would decrease the sheet resistivity and cause it to remain stable over time.

[0183] Aspects of the present invention will be further described by means of the following examples, but the invention is not meant to be limited to the details described therein. A series of tests was conducted in which a bias voltage of 400 volts was applied to a silicon wafer substrate having a layer of titanium nitride thereon. The titanium nitride was deposited on the wafer in a chamber such as chamber 110B of FIG. 16 and annealed with a plasma at an applied rf power of about 100 watts. Deposition and biasing were cycled sequentially. The two steps were cycled up to five times. A summary of depositions thickness, number of cycles and resistivity obtained over time are given Table III, which appears in FIG. 22. The Control was deposited in five uninterrupted steps, but without being annealed in a plasma between depositions.

[0184] The data in Table III shows that titanium nitride resistivity can be markedly reduced and stability dramatically improved by a post deposition annealing of the titanium nitride. In each of the Examples in Table III, the resistivity and change in resistivity over time is improved

over the Control case. The initial resistivity of the annealed titanium nitride is lower, and the resistivity increases less over time.

[0185] FIG. 24 is a graph an Auger analysis of the titanium nitride film of Example 1. The graph displays the atomic concentration of elements in the film versus the film's sputter edge depth in angstroms. The titanium nitride was biased twice for 30 seconds (see Table III; above). As shown in FIG. 24, the titanium concentration remains steady, but the graph clearly shows that the film surface nitrogen concentration is high, while carbon and oxygen concentrations are low. This reduction in carbon and oxygen impurity levels continues for a depth of about 100 Å. At a 400 Å depth, when the film was first annealed with high energy nitrogen ions, the nitrogen concentration rises, while the carbon and oxygen concentrations decrease. The graph of FIG. 24 also shows a change in the elemental composition of the film after annealing in accordance with the present invention. The change in elemental analysis with depth is shown in Table IV, which appears in FIG. 25.

[0186] Since a 100 Å thick layer of titanium nitride is adequate for a barrier layer, the present post-deposition annealing is ideal for improving the stability and reducing the resistivity of titanium nitride barrier layers. An Auger spectrum showing surface elements present on the post deposition annealed titanium nitride of Example 7 is shown in FIG. 26. This spectrum shows that the bulk of material deposited is titanium nitride with some titanium present. Carbon and oxygen are present at the surface as impurities.

[0187] However, Auger sputtering analysis of the Example 7 film, as shown in FIG. 27, shows that the oxygen concentration drops markedly in the bulk of the film to a low level. Carbon is the only other major impurity besides oxygen, but it remains unaffected by the present annealing process. In a depth of 200 Å, concentrations of various elements in the film in atomic percent are: oxygen, 2.8%; carbon, 20.9%; titanium 38.8%; and nitrogen, 37.5%. No silicon was present.

[0188] As a comparison, surface Auger analysis of the Control film is shown in FIG. 28, and sputter Auger analysis of the Control film is shown in FIG. 29. The oxygen content of the Control film is significantly higher. At 200 Å depth, the concentration of elements of the control film in atomic percent are: oxygen, 10.8%; carbon, 20.7%; titanium, 41.0%; and nitrogen, 27.5%. No silicon was present.

[0189] Surface Auger analysis of the titanium nitride film of Example 8 is shown in FIG. 30, and sputter Auger analysis versus depth in angstrom is shown in FIG. 31. The oxygen content of this film was low. At 43 Å depth, the concentration of elements in atomic percent are: oxygen, 3.1%; carbon, 13.7%; titanium, 40.0%; and nitrogen, 43.2%. No silicon was present.

[0190] Rutherford backscattering was used to determine the density in atoms/cm<sup>3</sup> of the Control and Example titanium nitride deposited films. The data is summarized in Table V, which appears in FIG. 32. As seen from the data in Table V, plasma annealing, including the bombardment of the deposited titanium nitride with high energy ions, increases the density of the titanium nitride film as compared to the Control film.

[0191] The present invention is not limited to titanium nitride barrier layers. The present invention may also improve properties and chemical compositions of other materials such as aluminum, copper, tantalum, tantalum pantoxide, silicides, other nitrides. For example, properties and chemical compositions of binary metal nitride  $M_xN_y$  and ternary metal silicon nitride  $M_xSi_yN_z$  (where M may be. Ti, Zr, Hf, Ta, Mo, W and other metals) may be improved by practicing aspects of the present invention. Substrates other than a silicon wafer can also be used such as stainless steel, metals, oxides, glasses, and suicides.

[0192] The deposition and plasma annealing can be performed in a single CVD chamber fitted with a precursor gas and plasma capability, such as chambers 110A, 110B and 110C. When employing chamber 110A, 110B, or 110C, films of titanium nitride can be deposited and directly thereafter annealed in the same chamber. Alternatively, more than one chamber may be employed when an apparatus such as the one shown in FIG. 3(a) is employed in practicing the present invention. When more than one chamber is employed a vacuum is preferably maintained during the transfer of the substrate from the CVD chamber 10 to an annealing chamber.

[0193] The following procedure may be followed when the plasma annealing of deposited titanium nitride is performed in chamber 110B. The wafer 114 resides on the wafer support 116 and is spaced about 0.3 to 0.8 inches, preferably 0.6 to 0.7 inches, from the showerhead 136. Energetic ions are obtained by applying rf energy to the substrate from the rf signal source at about 350 KHz at a power of 100 to 500 watts. This translates to about 0.3 to 1.6 watts of power per square centimeter (CM<sup>2</sup>) of surface area of the wafer 114.

[0194] With the negatively powered wafer support 116 and the showerhead 136 and chamber walls grounded, a DC self-bias voltage between 50 to 1,000 volts is induced. Preferably, the DC self-bias voltage is between 200 to 800 volts, between the wafer 114 and ground. This is sufficient to attract ions to impact the wafer 114 surface at high energy. As a result, the deposited titanium nitride is passivated or densified so that it remains stable over time.

[0195] FIG. 33 is a graph of atomic oxygen concentration versus air exposure time for two different layers of titanium nitride formed in accordance with the present invention. Both titanium nitride films were deposited and plasma annealed in the same chamber. The chamber was similar to chamber 110B, which is described above.

[0196] For each film, a 200 Å thick titanium nitride film was formed by cycling deposition and annealing. To do this, a 100 Å layer was deposited and thereafter annealed, followed by the deposition and annealing of a second 100 Å layer. Annealing was achieved using an N<sub>2</sub> plasma. The percentage of atomic oxygen concentration was measured for the two films repeatedly over a period of over 24 hours and is reflected by plot 312.