#### US012467950B2

# (12) United States Patent

# Fitzgerald

# (10) Patent No.: US 12,467,950 B2 (45) Date of Patent: Nov. 11, 2025

# (54) SYSTEMS AND METHOD FOR COAXIAL MEASUREMENT OF RF SIGNAL PERFORMANCE

(71) Applicant: BAE Systems Information and

Electronic Systems Integration Inc.,

Nashua, NH (US)

(72) Inventor: Jeffrey Fitzgerald, Lunenburg, MA

(US)

(73) Assignee: BAE Systems Information and

Electronic Systems Integration Inc.,

Nashua, NH (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 168 days.

(21) Appl. No.: 18/153,479

(22) Filed: Jan. 12, 2023

### (65) Prior Publication Data

US 2024/0241154 A1 Jul. 18, 2024

(51) **Int. Cl.**

$G01R \ 1/067$  (2006.01)

(52) **U.S. Cl.**

CPC ..... *G01R 1/06772* (2013.01); *G01R 1/06766* (2013.01)

#### (58) Field of Classification Search

CPC .. G01R 27/28; G01R 35/005; G01R 31/2822; G01R 1/06772; G01R 1/06766; G01R 27/06; G01R 31/2837; G01R 31/3191; G01R 31/00; G01R 27/04; G01R 31/002; G01R 29/0878; G01R 35/007; G01R 31/001; G01R 31/2886; G01R 23/16; G01R 31/2834; G01R 31/31917; G01R 1/067; G01R 31/2853; G01R 31/31901;

G01R 31/31709; G01R 31/316; G01R 23/02; G01R 31/2612; G01R 31/2851; G01R 27/2623; G01R 27/2664; G01R 21/133; G01R 29/26; G01R 31/003; (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

DE 19924315 A1 \* 11/2000 ............ G01R 31/045 Primary Examiner — Vinh P Nguyen (74) Attorney, Agent, or Firm — Sand, Sebolt & Wernow LPA; Gary McFaline

### (57) ABSTRACT

A coaxial pad probe for coupling with a preexisting coaxial cable having a first end and a second end opposite to the first end and remote from an analyzing device. The coaxial pad probe includes a probe operably engaged with the second end of the preexisting coaxial cable. The probe is configured to directly contact a coaxial input/output (IO) connection provided on a mixed signal die or a coplanar IO connection provided on the mixed signal die for measuring an S-parameter measurement of the mixed signal die. The probe may include a support structure operably engaged with second end of the preexisting coaxial cable. The probe may also include a probe tip operably engaged with the support structure and configured to directly contact with the selected coaxial IO connection provided on the mixed signal die or the coplanar IO connection provided on the mixed signal die.

### 17 Claims, 33 Drawing Sheets

## (58) Field of Classification Search

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,617,864    | B2*  | 9/2003  | Inoue    | G01R 1/06772               |

|--------------|------|---------|----------|----------------------------|

|              |      |         |          | 333/33                     |

| 7,609,077    | B2 * | 10/2009 | Campbell |                            |

| 7.764.072    | D2*  | 7/2010  | Ctmi d   | 324/755.11<br>COLD 1/06772 |

| 7,764,072    | DZ ' | 7/2010  | Strid    | 324/149                    |

| 7,898,273    | B2 * | 3/2011  | Gleason  |                            |

| , ,          |      |         |          | 324/754.06                 |

| 10,854,993   |      |         | Franzini | H01Q 5/50                  |

| 12,210,039   |      | 1/2025  | O'Brien  | G01R 1/06772               |

| 2012/0013358 | A1*  | 1/2012  | Wang     | G01R 1/06772               |

|              |      |         |          | 324/755.01                 |

<sup>\*</sup> cited by examiner

Producing a semiconductor package, wherein the at least one section and the at least another section are formed of pure metal materials

FIG.8

FIG. 11

FIG. 12

FIG. 13A

FIG. 13B

FIG. 13C

FIG. 14

FIG. 15

Y1,Y2

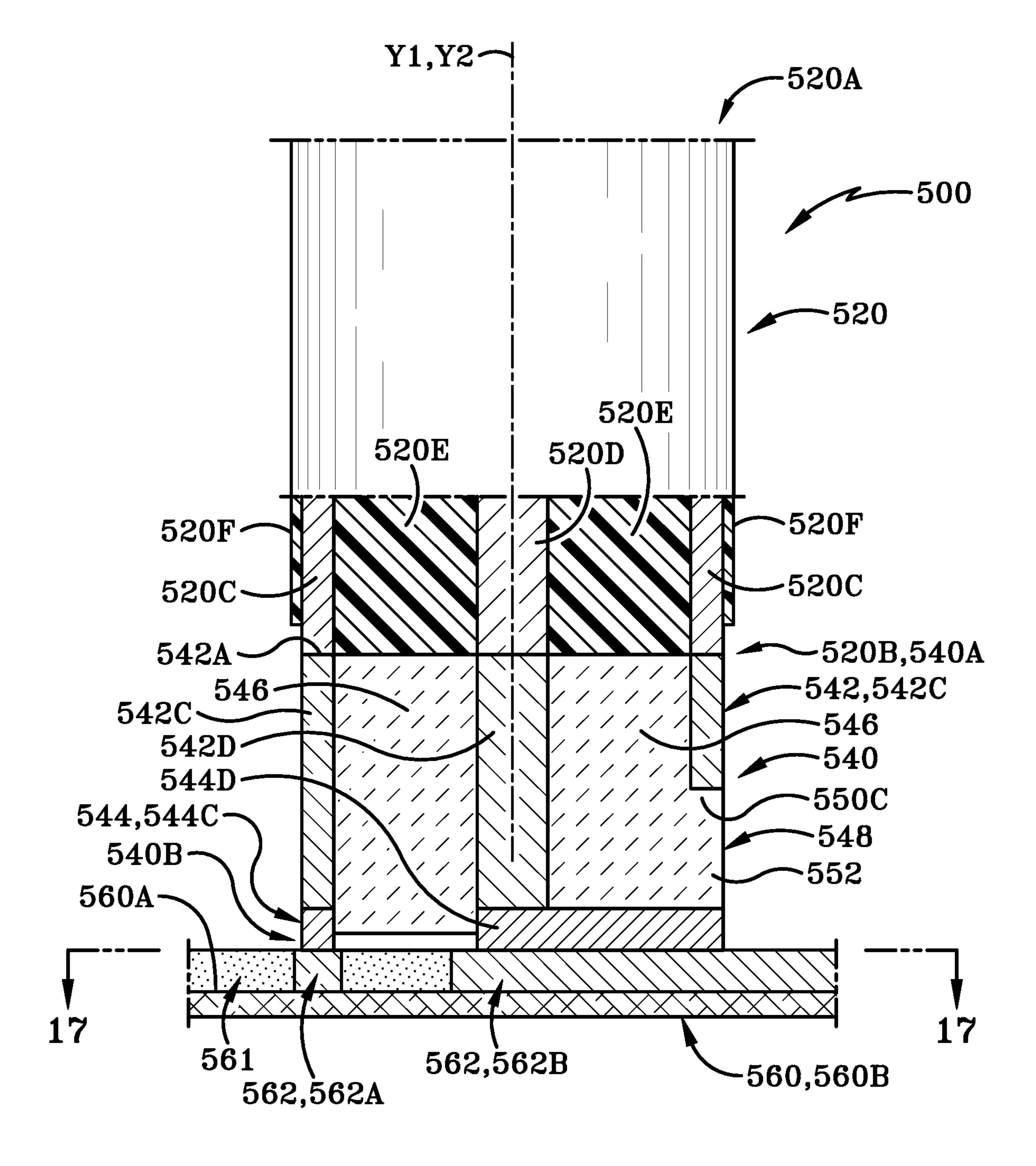

FIG. 16

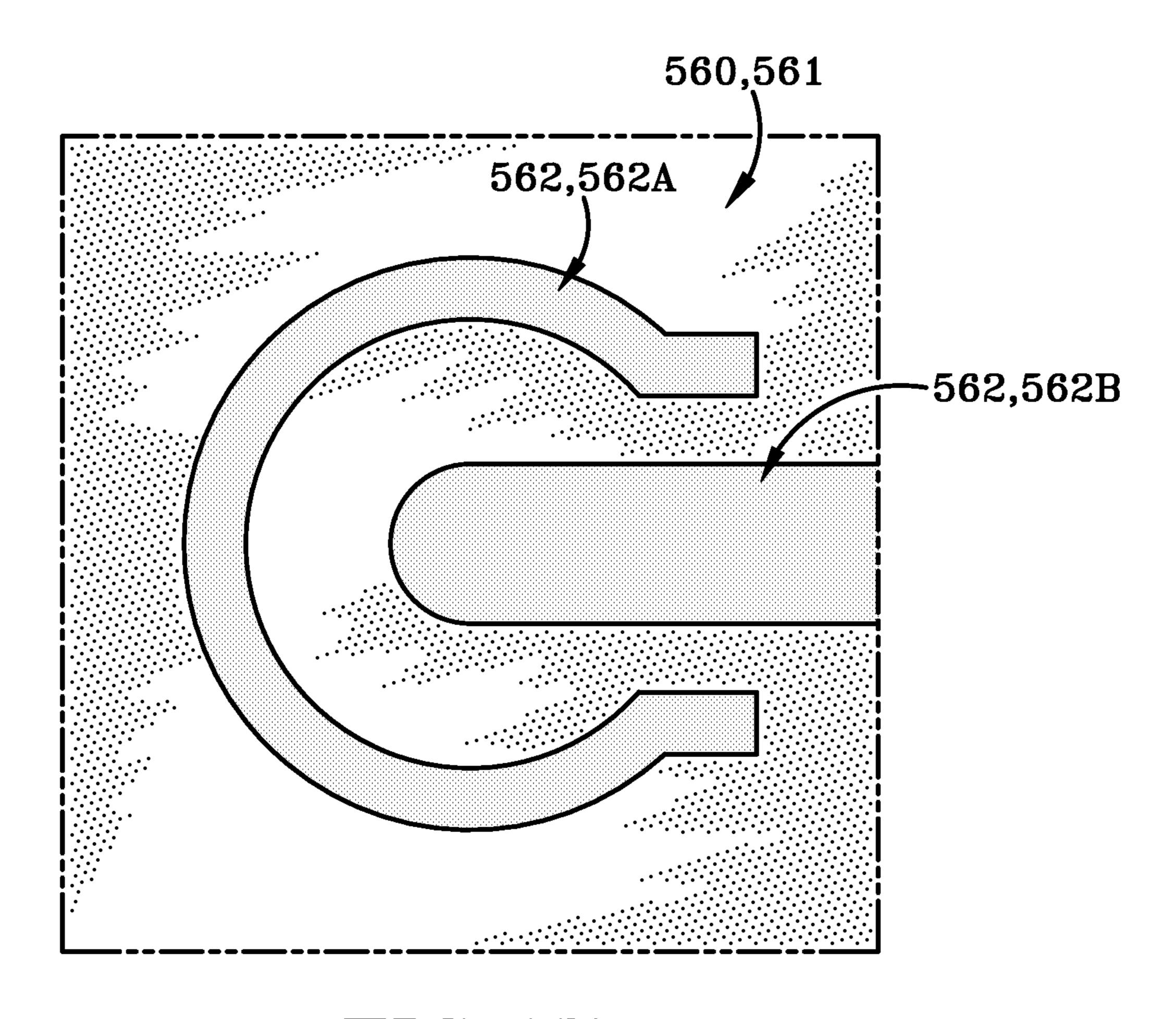

FIG. 17

FIG. 20

1

# SYSTEMS AND METHOD FOR COAXIAL MEASUREMENT OF RF SIGNAL PERFORMANCE

#### TECHNICAL FIELD

The present disclosure generally relates to interconnecting various dies to create semiconductor packages, coaxial input/output (IO) connections provided on dies, and coaxial probing tools for measuring RF signal performance and integrity.

#### **BACKGROUND**

In the field of electronics, semiconductor packages or integrated circuit packages include one or more semiconductor materials and components that are encapsulated in a supporting case or package to prevent damage, corrosion, or other harmful events to the integrated circuit. Once manufactured, these semiconductor packages may be mounted and/or interconnected with a printed-circuit board (or PCB). Generally, however, mounting and/or interconnecting these semiconductor packages to a PCB require specific methods and techniques to ensure electrical designs, mechanical 25 designs, and thermal designs are met as dictated by the implantation of the semiconductor packages.

To combat these design hurdles, semiconductor packages may use various devices, such as interposers, substrates, and other devices or the like, to interconnect semiconductor dies 30 and other electrical devices in a single semiconductor packages. However, such methods of interconnecting electrical devices require various electrical, mechanical, and thermal designs. In one instance, a first set of electrical devices may need to be positioned at the perimeter of the interposer or 35 substrate for electrical purposes while a second set of electrical devices may need to be positioned towards the center of the interposer or substrate; such specific design parameters may impede or hinder performance of the semiconductor package and/or increase the overall size, shape, 40 and configuration of the semiconductor package. In another instance, conventional electrical connections, such as wiring bonding, solder balls, copper pillars, silicon bridges, etc., may be required to electrically interconnect various dies together along with other electrical component based on the 45 implementation of the semiconductor package; such use of these electrical connections may impede or hinder performance of the semiconductor package and/or increase the overall size, shape, and configuration of the semiconductor package.

Furthermore, testing and/or probing of bond pads, such as bond pads of radio frequency input/output connections, as provided on the semiconductor dies is rather difficult and costly for users of these semiconductor pads. Given the size, shape, and configuration of specific bond pads on a small 55 semiconductor die, the probing of these specific bond pads with convention coaxial probes may become tedious and time consuming. In conventional probe tips of coaxial probes, these probe tips generally comprise of a coaxial cable that transitions to independent spring fingers and/or 60 tips in a ground-signal-ground coplanar wavelength configured to match general radio frequency input/output connections. However, these conventional probe tips may lack the specific characteristics of shielding for test purposes. Moreover, conventional coaxial probes used to test bond pads of 65 radio frequency input/output connections are rather costly for users. Even with such costs, these conventional probes

2

also lack in operating over a wider ranges of frequencies given the configuration of these coaxial probes.

#### **SUMMARY**

In one aspect, an exemplary embodiment of the present disclosure may provide a semiconductor package. The semiconductor package may include at least one section having at least one die and at least one electrical structure operably engaged directly with the at least one die. The semiconductor package may also include at least another section having at least another die and at least another electrical structure operably engaged directly with the at least another die. The at least one section and the at least another section directly engage with one another via wafer bonding of the at least one electrical structure and the at least another electrical structure. The at least one section and the at least another section are also formed entirely of metal materials.

This exemplary embodiment or another exemplary embodiment may further include that the at least one section comprises: at least one complaint support structure operably engaged with the at least one die and the at least one electrical structure; wherein the at least one die and the at least one electrical structure are encased by the at least one compliant support structure. This exemplary embodiment or another exemplary embodiment may further include that the at least one complaint support structure further includes a stochastic structure or a non-stochastic structure. This exemplary embodiment or another exemplary embodiment may further include that the at least another section comprises: at least another compliant support structure operably engaged with the at least another die and the at least another electrical structure; wherein the at least another die and the at least another electrical structure are encased by the at least another compliant support structure. This exemplary embodiment or another exemplary embodiment may further include that the at least another complaint support structure further includes a stochastic structure or a non-stochastic structure. This exemplary embodiment or another exemplary embodiment may further include at least one air cavity structure provided between the at least one die and the at least one electrical structure of the at least one section or the at least another die and the at least another electrical structure of the at least another section. This exemplary embodiment or another exemplary embodiment may further include that the at least one section further comprises: a first temporary carrier operably engaged at a first position with each of the at least one die and remote from the at least one electrical structure. This exemplary embodiment or another 50 exemplary embodiment may further include that the at least one section further comprises: at least one air cavity structure provided between the at least one die and the at least one electrical structure of the at least one section; and a first temporary carrier operably engaged at a first position with each of the at least one air cavity structure and remote from the at least one electrical structure. This exemplary embodiment or another exemplary embodiment may further include that the at least one section further comprises: a second temporary carrier operably engaged at a second position with the at least one die and remote from the at least one electrical structure; wherein when the first temporary carrier is removed from the at least one die and the at least one electrical structure, the second temporary carrier operably engages with the at least one die, and wherein when the first temporary carrier engages the at least one die and the at least one compliant structure, the second temporary carrier does not engage the at least one die. This exemplary embodiment

or another exemplary embodiment may further include that the at least another section further comprises: a third temporary carrier operably engaged at a first position with each of the at least another die and remote from the at least another electrical structure. This exemplary embodiment or another exemplary embodiment may further include that the at least another section further comprises: a fourth temporary carrier operably engaged at a second position with the at least another die and remote from the at least another electrical structure; wherein when the third temporary carrier is removed from the at least another die, the fourth temporary carrier operably engages with the at least another die.

In another aspect, an exemplary embodiment of the present disclosure may provide a method. The method may 15 comprise steps of providing at least one die engaged directly with an end of at least one electrical structure that forms at least one section; providing at least another die engaged directly with an end of at least another electrical structure that forms at least another section; providing at least one 20 compliant support structure positioned about the at least one die; providing at least another compliant support structure positioned about the at least another die; providing another end of the at least one electrical structure engaged directly with another end of the at least another electrical structure; 25 wherein the another end of the at least one electrical structure is opposite to the end of the at least one electrical structure; and wherein the another end of the at least another electrical structure is opposite to the end of the at least another electrical structure; and producing a semiconductor 30 package, wherein the at least one section and the at least another section are formed entirely of metal materials.

This exemplary embodiment or another exemplary embodiment may further include steps of providing at least one temporary carrier directly engaged with an end of the at 35 least one die; and providing at least another temporary carrier directly engaged with the at least one compliant support structure and towards an opposite end of the at least one die; wherein the steps of providing the at least one temporary carrier directly engaged with the end of the at 40 least one die and providing at least another temporary carrier directly engaged with the at least one compliant support structure and towards the opposite end of the at least one die are completed prior to the step of providing the at least one die directly with the end of the at least one electrical 45 structure that forms the at least one section. This exemplary embodiment or another exemplary embodiment may further include a step of providing an air cavity structure between the at least one die one of the at least one temporary carrier. This exemplary embodiment or another exemplary embodi- 50 ment may further include a step of removing the at least one temporary carrier from the at least one die and the at least one compliant support structure prior to the step of providing the at least one die directly engaged directly with the end of the at least one electrical structure that forms the at least one section. This exemplary embodiment or another exemplary embodiment may further include steps of providing at least one temporary carrier directly engaged with an end of the at least another die; and providing at least another temporary carrier directly engaged with the at least another 60 compliant support structure and towards an opposite end of the at least another die; wherein the steps of providing at least one temporary carrier directly engaged with the end of the at least another die and providing at least another temporary carrier directly engaged with the at least another 65 compliant support structure and towards the opposite end of the at least another die are completed prior to the step of

4

providing the at least another die directly with the end of at least another electrical structure that forms the at least another section. This exemplary embodiment or another exemplary embodiment may further include a step of providing an air cavity between the at least another die and the at least one temporary carrier. This exemplary embodiment or another exemplary embodiment may further include a step of removing the at least one temporary carrier from the at least another die and the at least one compliant support structure prior to the step of providing at least another die directly with the end of the at least another electrical structure that forms the at least another section. This exemplary embodiment or another exemplary embodiment may further include steps of providing a plurality of solder balls with one of the at least one section and the at least another section; and testing the semiconductor package via the plurality of solder balls. This exemplary embodiment or another exemplary embodiment may further include steps of providing a plurality of solder balls with one of the at least one section and the at least another section; and providing a second semiconductor package with the semiconductor package.

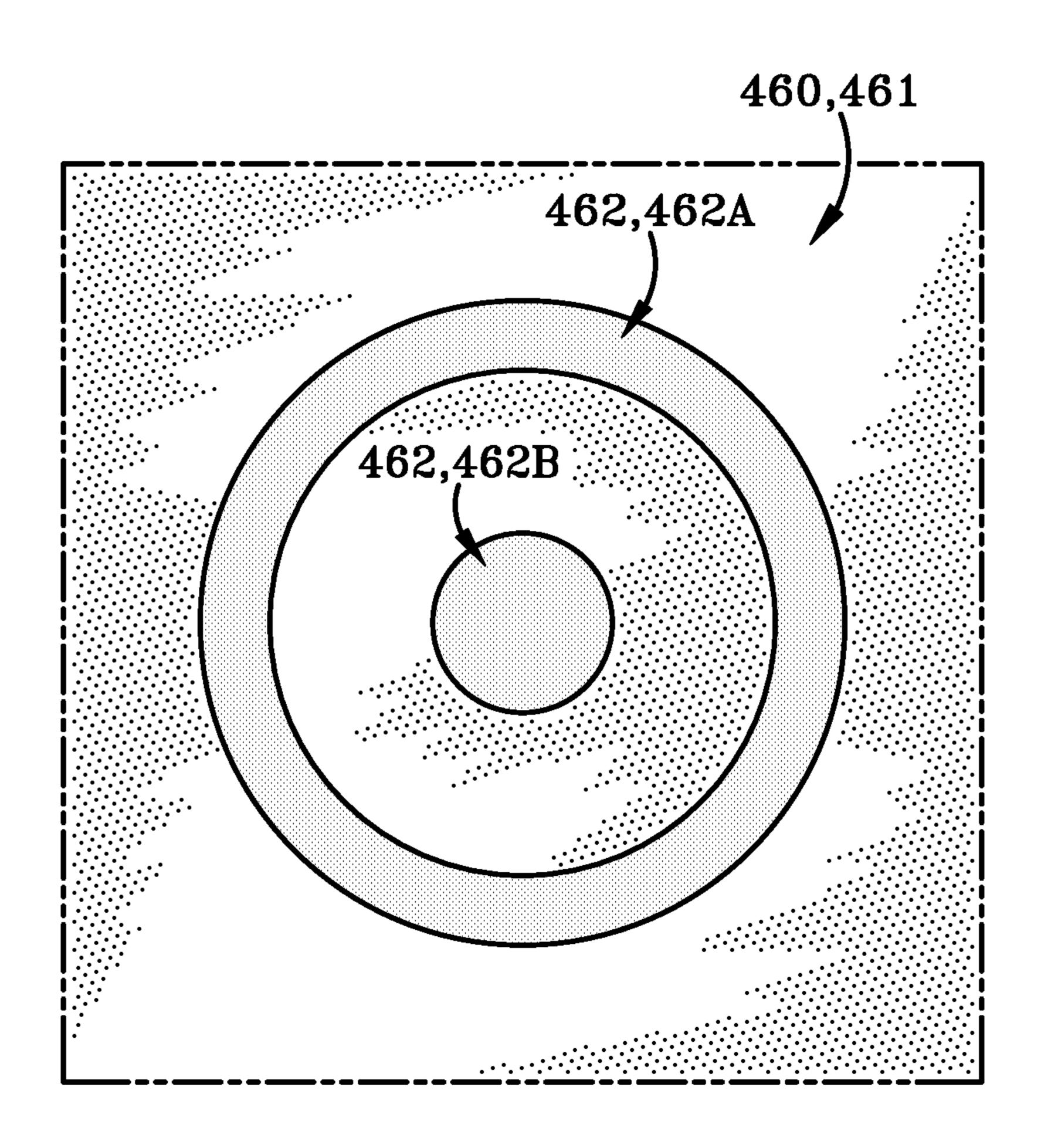

In yet another aspect, an exemplary embodiment of the present disclosure may provide a semiconductor package. The semiconductor package may comprise an interconnect; a mixed signal die having a first surface operably engaged with the interconnect and a second surface opposite to the first surface; and at least one set of input/output (IO) connections on the mixed signal die. The at least one set of IO connections is configured to be electromagnetically shielded in a non-linear geometry from at least another set of IO connections that is different from the at least one set of IO connections.

This exemplary embodiment or another exemplary embodiment may further include that the at least one set of IO connections further comprises: at least one radio frequency (RF) connection formed on the mixed signal die; wherein at least one bond pad of the at least one RF connection is configured to be electromagnetically shielded in a non-linear geometry from the at least another set of IO connections adjacent to the at least one RF connection. This exemplary embodiment or another exemplary embodiment may further include that the at least one set of IO connections further comprises: at least one radio frequency (RF) connection formed on the mixed signal die; the at least one RF connection comprises: a first bond pad; and a second bond pad circumferentially surrounded by the first bond pad in a continuous, non-linear geometry to electromagnetically shield the second bond pad. This exemplary embodiment or another exemplary embodiment may further include that the at least one set of IO connections further comprises: at least one radio frequency (RF) connection formed to the second surface of the mixed signal die; the at least one RF connection comprises: a first bond pad; and a second bond pad circumferentially surrounded by the first bond pad in a continuous, curvilinear shape to electromagnetically shield the second bond pad. This exemplary embodiment or another exemplary embodiment may further include at least one electromagnetic interference (EMI) fence formed to the second surface of the mixed signal die and formed with the at least one RF connection; wherein the at least one EMI fence is configured to electromagnetically shield the second bond pad of the at least one RF connection. This exemplary embodiment or another exemplary embodiment may further include that the at least one EMI fence comprises: a first end formed with the first bond pad of the at least one RF connection; a second end opposite to the first end and remote

from the first bond pad of the at least one RF connection; and at least one curve formed between the first end and the second end. This exemplary embodiment or another exemplary embodiment may further include that the at least one set of IO connections further comprises: at least another RF 5 connection on the mixed signal die and positioned adjacent to the at least one RF connection; the at least another RF connection comprises: a first bond pad; and a second bond pad circumferentially surrounded by the first bond pad in a continuous, non-linear geometry to electromagnetically shield the second bond pad. This exemplary embodiment or another exemplary embodiment may further include at least another EMI fence on the mixed signal die and formed with EMI fence is configured to electromagnetically shield the second bond pad of the at least one RF connection. This exemplary embodiment or another exemplary embodiment may further include that the at least another EMI fence comprises: a first end formed with the first bond pad of the 20 at least another RF connection; a second end opposite to the first end and remote from the first bond pad of the at least another RF connection; and at least another curve shape formed between the first end and the second end. This exemplary embodiment or another exemplary embodiment 25 may further include that the first bond pad further comprises: a first surface; a second surface extending from the first surface; a circumferential wall extending between the first surface and the second surface; wherein each of the first surface, the second surface, and the circumferential wall is continuous and uninterrupted. This exemplary embodiment or another exemplary embodiment may further include that the mixed signal die comprises: a first peripheral edge; a second peripheral edge being perpendicular to the first the first peripheral edge and perpendicular to the second peripheral edge; and a fourth peripheral edge being parallel with the second peripheral edge and perpendicular to the third peripheral edge; wherein the at least one RF connection is located interior to the first peripheral edge, the second 40 peripheral edge, the third peripheral edge, and the fourth peripheral edge. This exemplary embodiment or another exemplary embodiment may further include that the mixed signal die comprises: a first peripheral edge; a second peripheral edge being perpendicular to the first peripheral 45 edge; a third peripheral edge being parallel with the first peripheral edge and perpendicular to the second peripheral edge; and a fourth peripheral edge being parallel with the second peripheral edge and perpendicular to the third peripheral edge; wherein the at least one RF connection is 50 located proximate to at least one of the first peripheral edge, the second peripheral edge, the third peripheral edge, and the fourth peripheral edge.

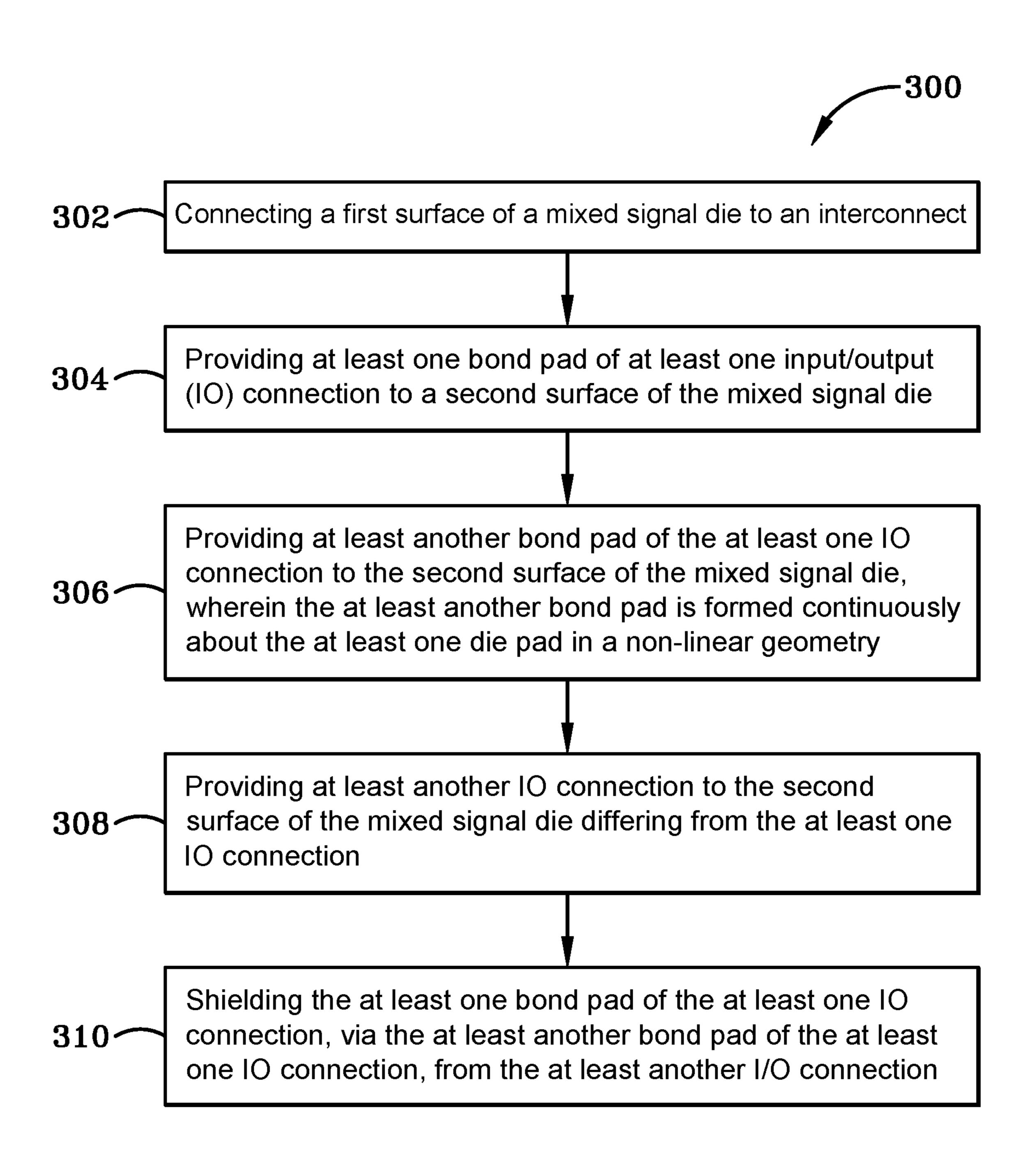

In yet another aspect, an exemplary embodiment of the present disclosure may provide a method. The method may 55 comprise steps of connecting a first surface of a mixed signal die to an interconnect; providing at least one bond pad of at least one input/output (IO) connection on the mixed signal die; providing at least another bond pad of the at least one IO connection on the mixed signal die, wherein the at least 60 another bond pad is formed continuously about the at least one die pad in a non-linear geometry; providing at least another IO connection on the mixed signal die differing from the at least one IO connection; and shielding the at least one bond pad of the at least one IO connection, via the at least 65 another bond pad of the at least one IO connection, from the at least another I/O connection.

This exemplary embodiment or another exemplary embodiment may further include that the at least one IO connection is a radio frequency (RF) connection. This exemplary embodiment or another exemplary embodiment may further include steps of engaging an inner conductor of a coaxial cable with the at least one bond pad of the at least one IO connection; and engaging an outer conductor of the coaxial cable with the at least one another pad of the at least one IO connection; wherein the coaxial cable is directly connected to the mixed signal die. This exemplary embodiment or another exemplary embodiment may further include a step of providing the at least one bond pad of the at least one IO connection and the at least one bond pad of the at least IO connection proximate to at least one of a first the at least another RF connection; wherein the at least one 15 peripheral edge of the mixed signal die, a second peripheral edge of the mixed signal die, a third peripheral edge of the mixed signal die, and a fourth peripheral edge of the mixed signal die or remote from a first peripheral edge of the mixed signal die, a second peripheral edge of the mixed signal die, a third peripheral edge of the mixed signal die, and a fourth peripheral edge of the mixed signal die. This exemplary embodiment or another exemplary embodiment may further include a step of providing at least one electromagnetic interference (EMI) fence formed to the second surface of the mixed signal die and formed with the at least one IO connection; wherein the at least one EMI fence is configured to electromagnetically shield the first bond pad of the at least one IO connection. This exemplary embodiment or another exemplary embodiment may further include steps of providing at least one bond pad of a third input/output IO connection to the second surface of the mixed signal die; providing at least another bond pad of the third IO connection to the second surface of the mixed signal die, wherein the at least another bond pad of the third IO connection is peripheral edge; a third peripheral edge being parallel with 35 formed continuously about the at least one die pad in a non-linear geometry; providing a fourth IO connection to the second surface of the mixed signal die differing from the at least one IO connection; and shielding the at least one bond pad of the third IO connection, via the at least another bond pad of the third IO connection, from the fourth I/O connection. This exemplary embodiment or another exemplary embodiment may further include steps of engaging an inner conductor of a second coaxial cable with the at least one bond pad of the third IO connection; and engaging an outer conductor of the second coaxial cable with the at least one another pad of the third IO connection; wherein the second coaxial cable is directly connected to the mixed signal die. This exemplary embodiment or another exemplary embodiment may further include a step of providing at least another EMI fence formed to the second surface of the mixed signal die and formed with the third IO connection; wherein the at least another EMI fence is configured to electromagnetically shield the at least one bond pad of the third IO connection.

In yet another aspect, an exemplary embodiment of the present disclosure may provide a coaxial pad probe for coupling with a preexisting coaxial cable having a first end and a second end opposite to the first end and remote from the analyzing device. The coaxial pad probe may comprise of a probe operably engaged with the second end of the preexisting coaxial cable. The probe may be configured to directly contact a coaxial input/output (IO) connection provided on a mixed signal die or a coplanar IO connection provided on the mixed signal die for measuring S-parameter measurement of the mixed signal die.

This exemplary embodiment or another exemplary embodiment may further include that the probe defines a tapered configuration. This exemplary embodiment or

another exemplary embodiment may further include that the probe comprises: a support structure operably engaged with second end of the preexisting coaxial cable; and a probe tip operably engaged with the support structure and configured to directly contact with the selected coaxial IO connection 5 provided on the mixed signal die or the coplanar IO connection provided on the mixed signal die. This exemplary embodiment or another exemplary embodiment may further include that the support structure comprises: a first end of the support structure operably engaged with the second end of 10 the preexisting coaxial cable and defining a first diameter; and a second end of the support structure opposite to the first end of the support structure and operably engaged with the probe tip and defining a second diameter; wherein the first diameter is greater than the second diameter. This exemplary 15 embodiment or another exemplary embodiment may further include that the probe tip comprises: a first end of the probe tip operably engaged with the second end of the support structure; a second end of the probe tip opposite to the first end of the probe tip and configured to directly contact with 20 the selected coaxial IO connection provided on the mixed signal die or the coplanar IO connection provided on the mixed signal die; a first diameter defined at the first end; and a second diameter defined at the second end that is equal with the first diameter. This exemplary embodiment or 25 another exemplary embodiment may further include that the support structure comprises: a first end of the support structure operably engaged with the second end of the preexisting coaxial cable and defining a first diameter; and a second end of the support structure opposite to the first end 30 of the support structure and operably engaged with the probe tip and defining a second diameter; wherein the first diameter and the second diameter are equal with one another. This exemplary embodiment or another exemplary embodiment prises: a first outer connection operably engaged with an outer conductor of the preexisting coaxial cable at the second end of the preexisting coaxial cable. This exemplary embodiment or another exemplary embodiment may further include that the support structure further comprises: a first 40 inner connection operably engaged to an inner conductor of the preexisting coaxial cable at the second end of the preexisting coaxial cable; wherein the first inner connection is positioned inside of the first outer connection and is free from connecting with the first outer connection. This exem- 45 plary embodiment or another exemplary embodiment may further include that the support structure further comprises: a dielectric component operably engaged with the first outer connection and the first inner connection; wherein the dielectric component suspends the first inner connection 50 inside of the first outer connection. This exemplary embodiment or another exemplary embodiment may further include that the probe tip further comprises: a second outer connection operably engaged with the first outer connection; wherein the second outer connection and the outer conductor 55 are in electrical communication with one another via the first outer connection. This exemplary embodiment or another exemplary embodiment may further include that the probe tip further comprises: a second inner connection operably engaged with the first inner connection; wherein the second 60 inner connection is positioned inside of the second outer connection and is free from connecting with the second outer connection; wherein the second inner connection and the inner conductor are in electrical communication with one another via the first inner connection of the support struc- 65 ture. This exemplary embodiment or another exemplary embodiment may further include that the probe tip further

comprises: a dielectric component operably engaged with the second outer connection and the second inner connection; wherein the air dielectric suspends the second inner connection inside of the second outer connection. This exemplary embodiment or another exemplary embodiment may further include a protruding structure extending from the support structure and the probe tip; wherein the protruding structure is configured to directly contact the coplanar IO connection provided on the mixed signal die for measuring S-parameter measurement of the mixed signal die. This exemplary embodiment or another exemplary embodiment may further include that the protruding structure further comprises: a first end operably engaged with the support structure and the probe tip; a second end opposite to the first end and remote from the support structure and the probe tip; and a side passageway extending between the first end and the second end. This exemplary embodiment or another exemplary embodiment may further include that the support structure further comprises: a first outer connection operably engaged with an outer conductor of the preexisting coaxial cable at the second end of the preexisting coaxial cable; and a first inner connection operably engaged to an inner conductor of the preexisting coaxial cable at the second end of the preexisting coaxial cable and is positioned inside of the first outer connection and is free from connecting with the first outer connection; wherein the probe tip further comprises: a second outer connection operably engaged with the first outer connection; and a second inner connection operably engaged to the first inner connection and is free from connecting with the first outer connection; wherein the second inner connection is positioned inside of the second outer connection and positioned inside of the protruding structure.

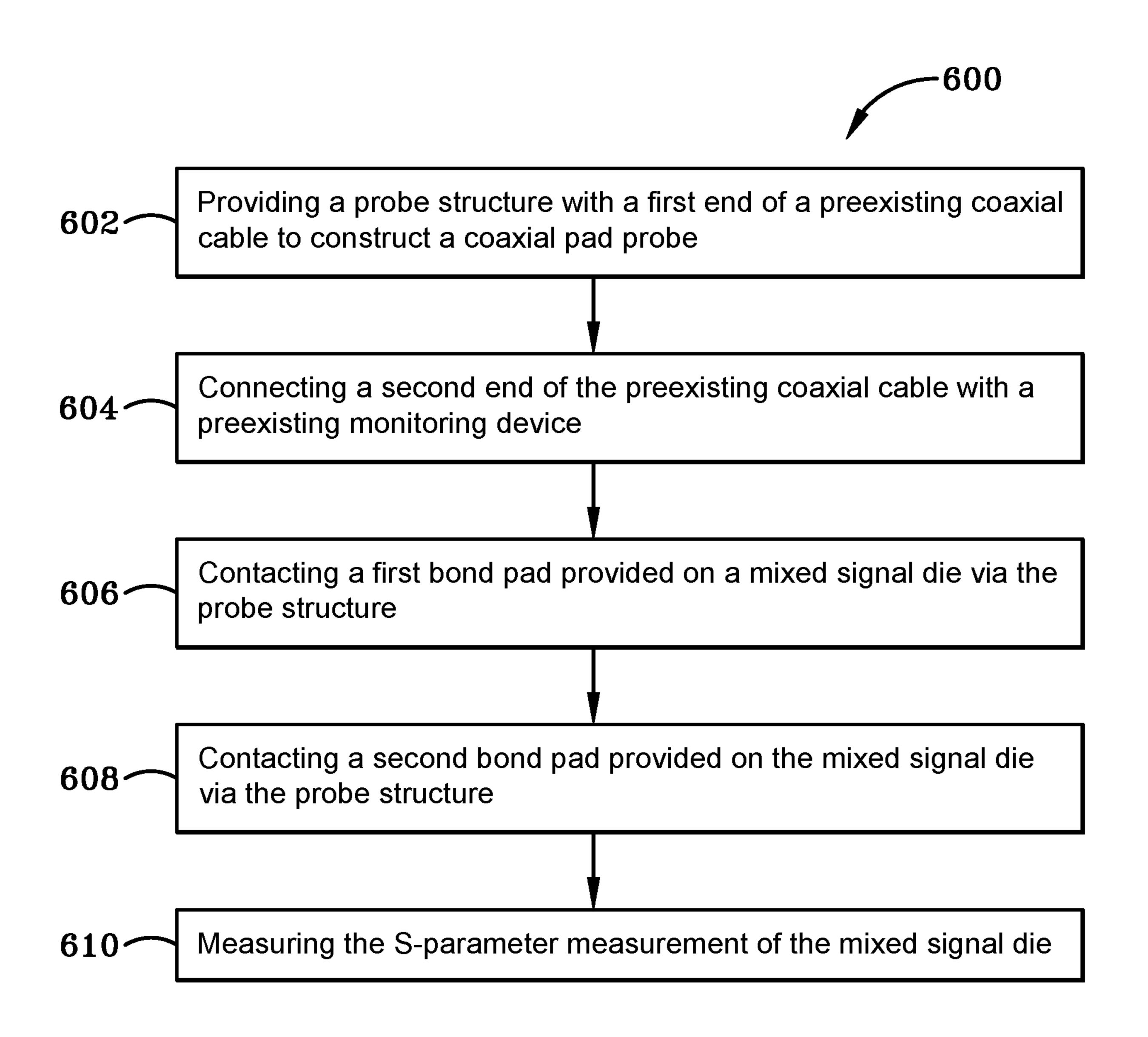

In yet another aspect, an exemplary embodiment of the may further include that the support structure further com- 35 present disclosure may provide a method for measuring an S-parameter measurement of a mixed signal die. The method may comprise steps of connecting a first end of a coaxial cable with an analyzing device; providing a probe with a second end of the coaxial cable to construct a coaxial pad probe; contacting a first bond pad provided on the mixed signal die with the probe; contacting a second bond pad provided on the mixed signal die with the probe; and measuring the S-parameter measurement of the mixed signal die.

> This exemplary embodiment or another exemplary embodiment may further include that the step of measuring the S-parameter measurement of the mixed signal die is accomplished by measuring an electrical signal at a coaxial input/output (IO) connection provided on the mixed signal die or a coplanar IO connection provided on the mixed signal die. This exemplary embodiment or another exemplary embodiment may further include that the step of providing the probe with the first end of the coaxial cable further comprises: providing a first outer connection of a support structure of the probe with an outer conductor of the coaxial cable; providing a first inner connection of the support structure of the probe with an inner conductor of the coaxial cable; providing a second outer connection of a probe tip of the probe with the first outer connection of the support structure; and providing a second inner connection of the probe tip of the probe with the first inner connection of the support structure. This exemplary embodiment or another exemplary embodiment may further include that the step of contacting the first bond pad provided on the mixed signal die further comprises: contacting the second outer connection with the first bond pad provided on the mixed signal die; and wherein the step of contacting the second

bond pad provided on the mixed signal die further comprises: contacting the second inner connection with the second bond pad provided on the mixed signal die; wherein the mixed signal die is a coaxial IO connection. This exemplary embodiment or another exemplary embodiment 5 may further include that the step of providing the probe with the first end of the coaxial cable further comprises: providing a first outer connection of a support structure of the probe with an outer conductor of the coaxial cable; providing a first inner connection of the support structure of the 10 probe with an inner conductor of the coaxial cable; providing a second outer connection of a probe tip of the probe with the first outer connection of the support structure; providing a second inner connection of the probe tip of the 15 probe with the first inner connection of the support structure; providing a protruding structure with the first outer connection and the second outer connection; wherein the second inner connection is provided inside of the protruding structure. This exemplary embodiment or another exemplary 20 embodiment may further include that the step of contacting the first bond pad provided on the mixed signal die further comprises: contacting the second outer connection and the protruding structure with the first bond pad provided on the mixed signal die; and wherein the step of contacting the 25 second bond pad provided on the mixed signal die further comprises: contacting the second inner connection with the second bond pad provided on the mixed signal die; wherein the mixed signal die is a coplanar IO connection.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

Sample embodiments of the present disclosure are set forth in the following description, are shown in the drawings 35 and are particularly and distinctly pointed out and set forth in the appended claims.

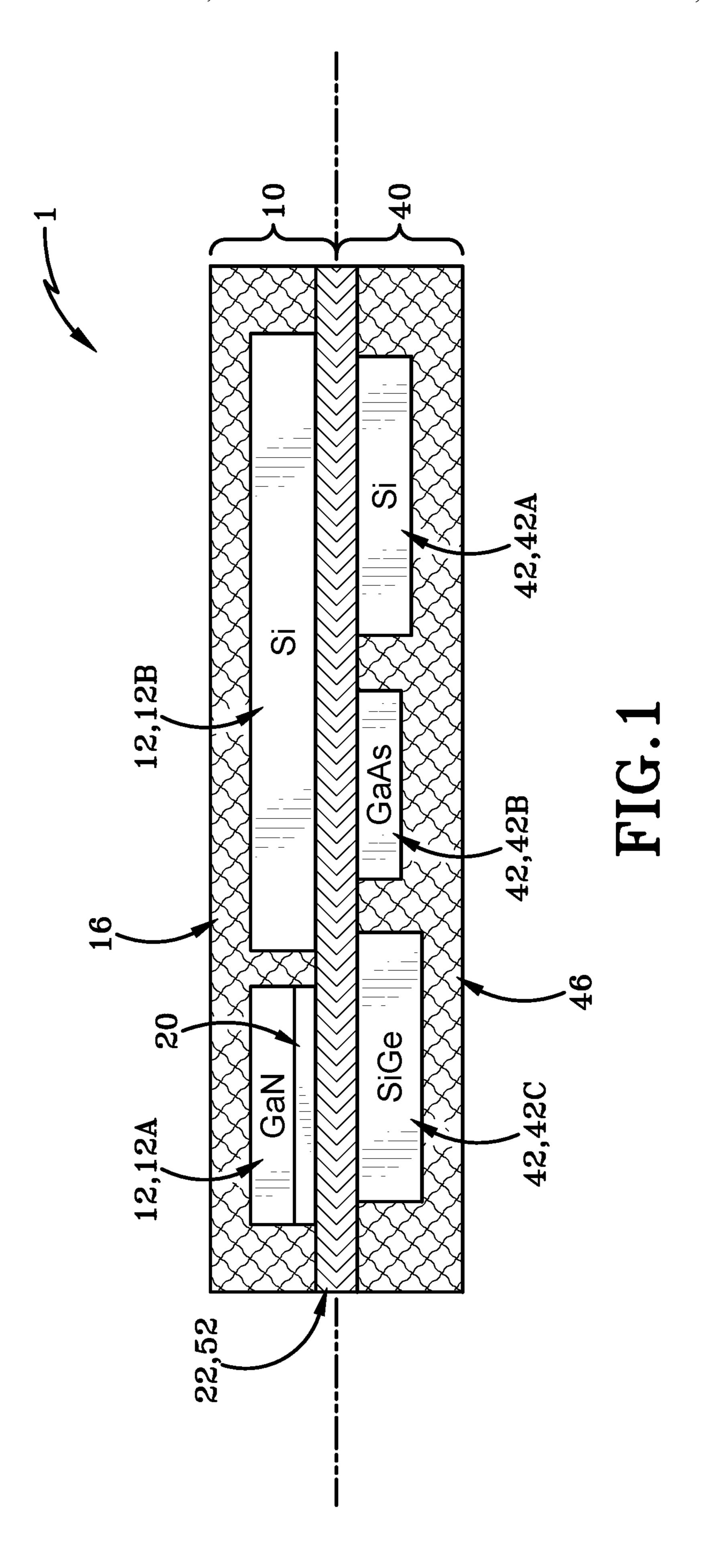

- FIG. 1 is a section view of a semiconductor package according to one aspect of the present disclosure.

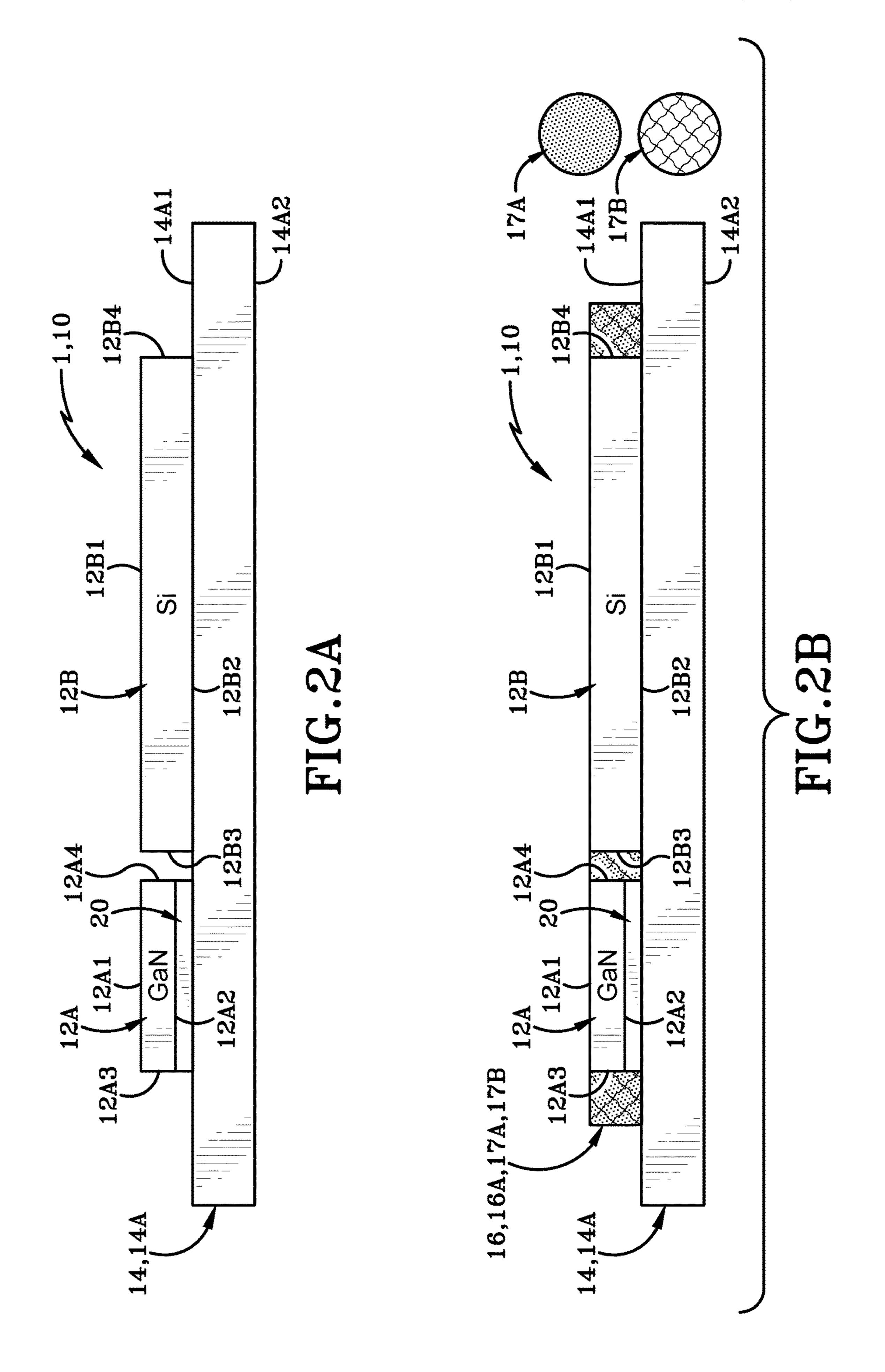

- FIG. 2A is a side elevation view of a first section of the 40 semiconductor package, wherein one or more dies are operably engaged with a first temporary carrier of the first section.

- FIG. 2B is a side elevation view similar to FIG. 2A, but a first a compliant support structure operably engages with the one 45 section. or more dies and the first temporary carrier.

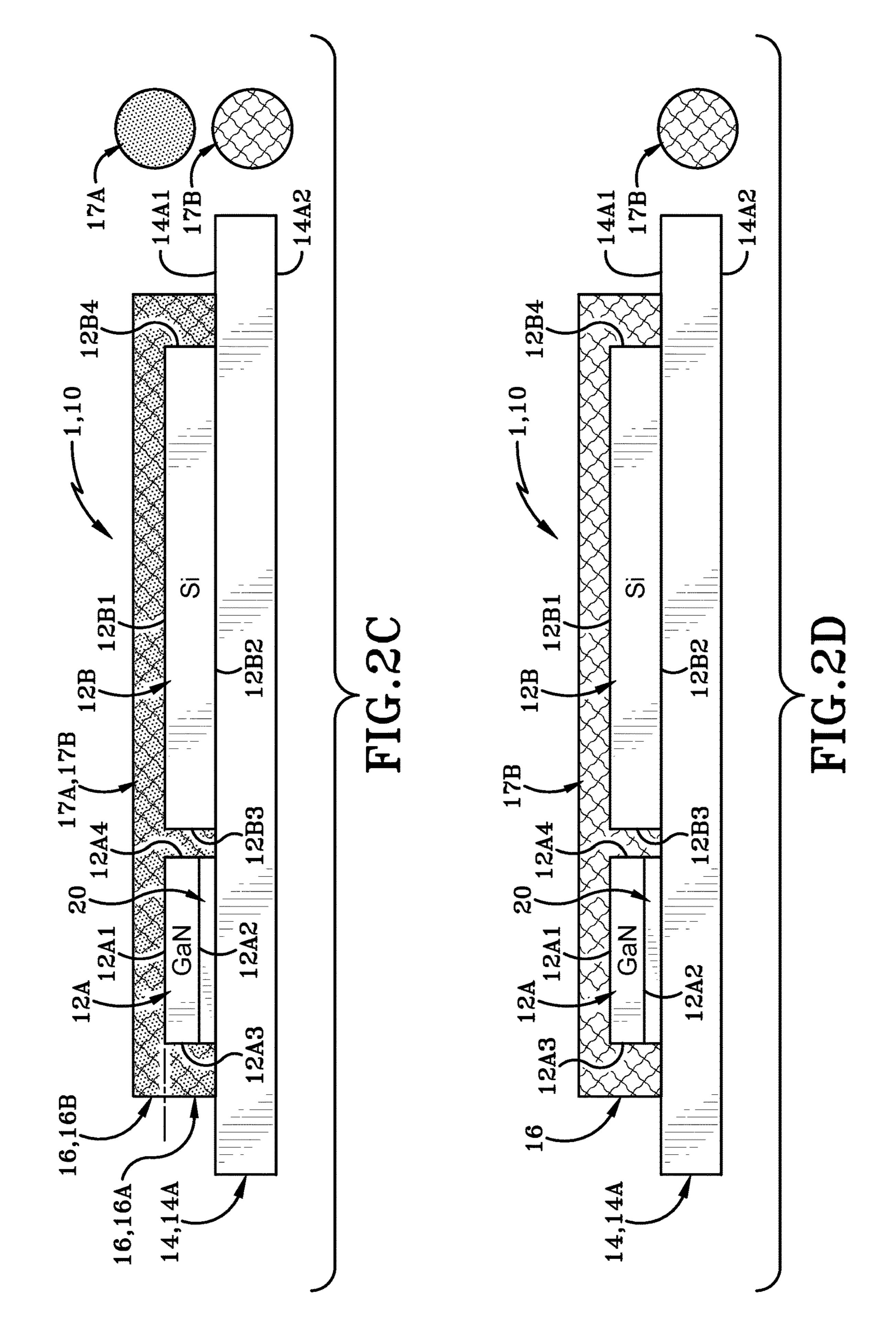

- FIG. 2C is a side elevation view similar to FIG. 2B, but a thermal conductive structure operably engages with the compliant support structure.

- FIG. 2D is a side elevation view similar to FIG. 2C, but 50 a temporary support of compliant support structure is removed.

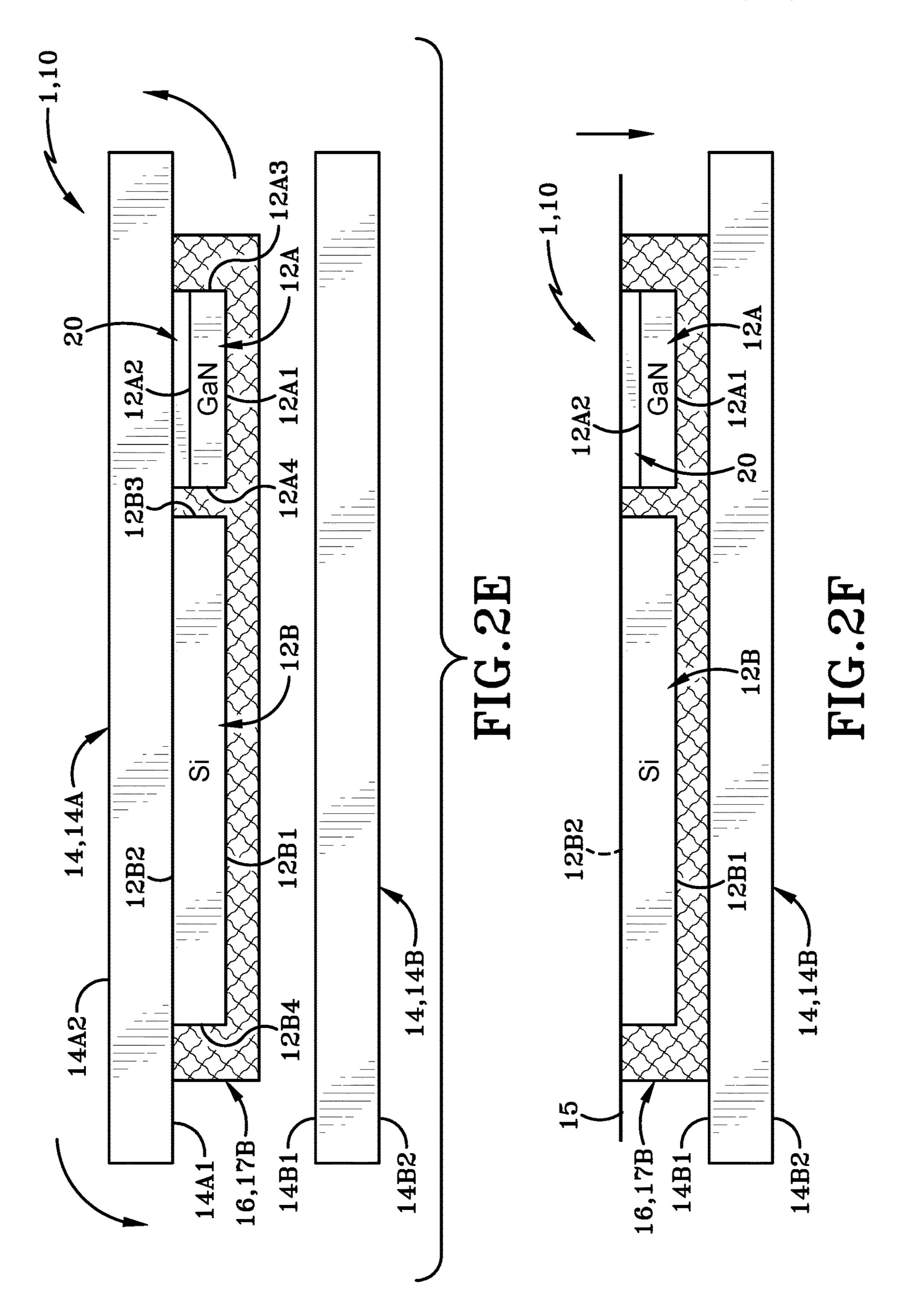

- FIG. 2E is a side elevation view similar to FIG. 2D, but the first section is inverted and a second temporary carrier is introduced to the first section.

- FIG. 2F is a side elevation view similar to FIG. 2E, but the first temporary support is removed from the first section and second temporary carrier operably engages with the compliant support structure.

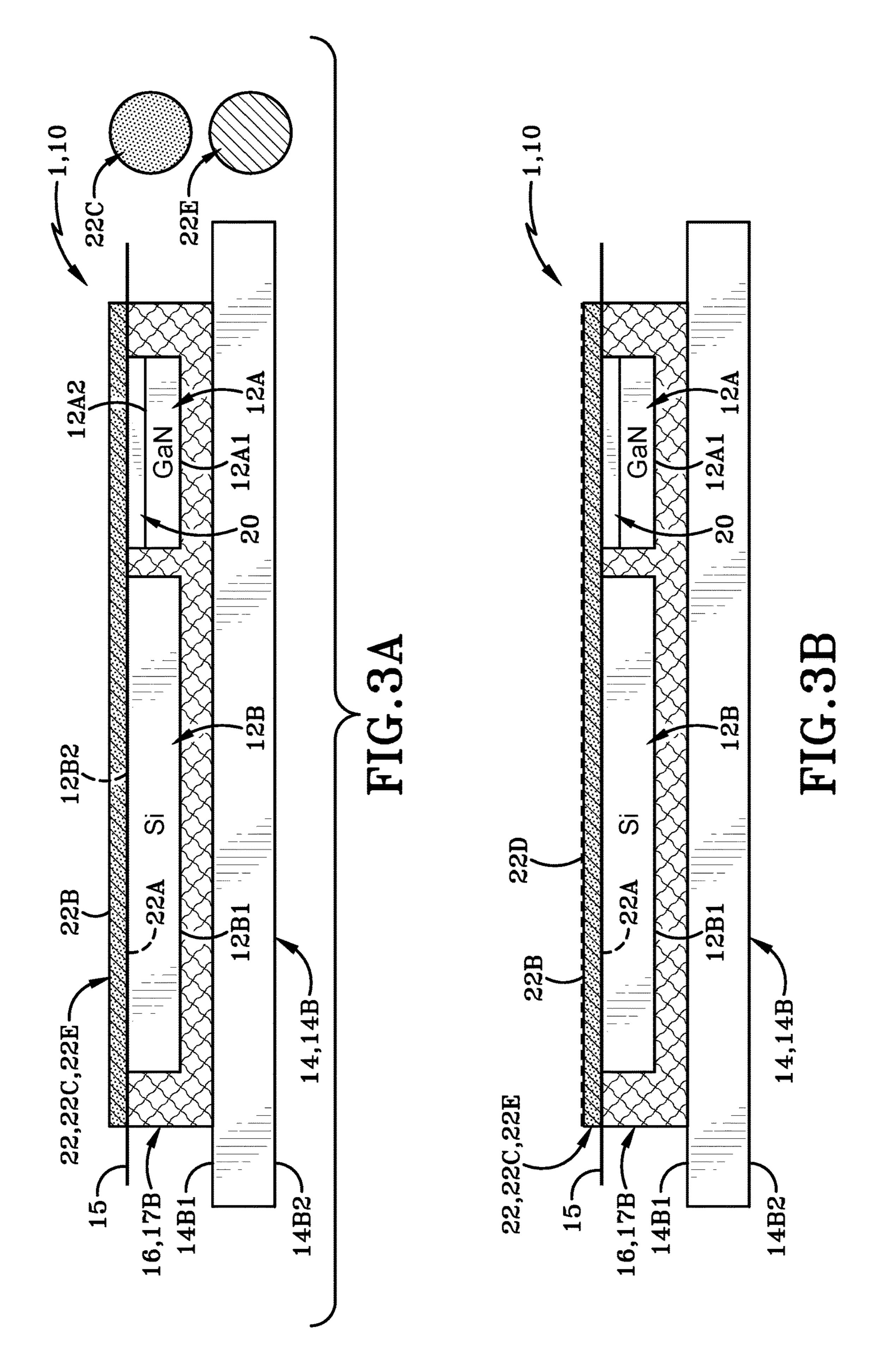

- FIG. 3A is a side elevation view of operably engaging an 60 electrical structure with the first section.

- FIG. 3B is a side elevation view similar to FIG. 3A, but an exterior dielectric is operably engaged with the electrical structure.

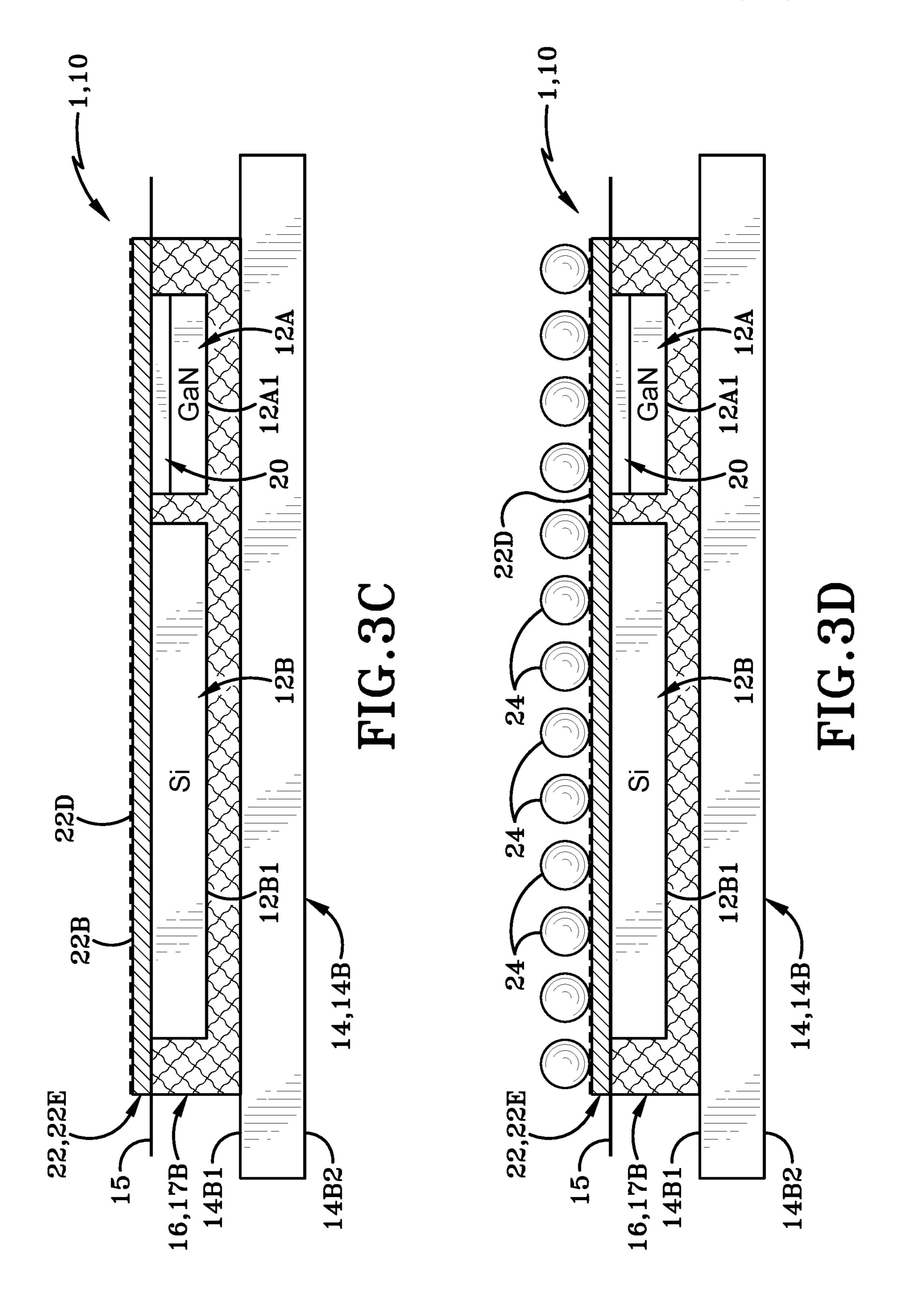

- FIG. 3C is a side elevation view similar to FIG. 3B, but 65 a first temporary dielectric is removed from the electrical structure.

**10**

- FIG. 3D is a side elevation view similar to FIG. 3C, but a plurality of solder balls operably engages with the electrical structure of the first section.

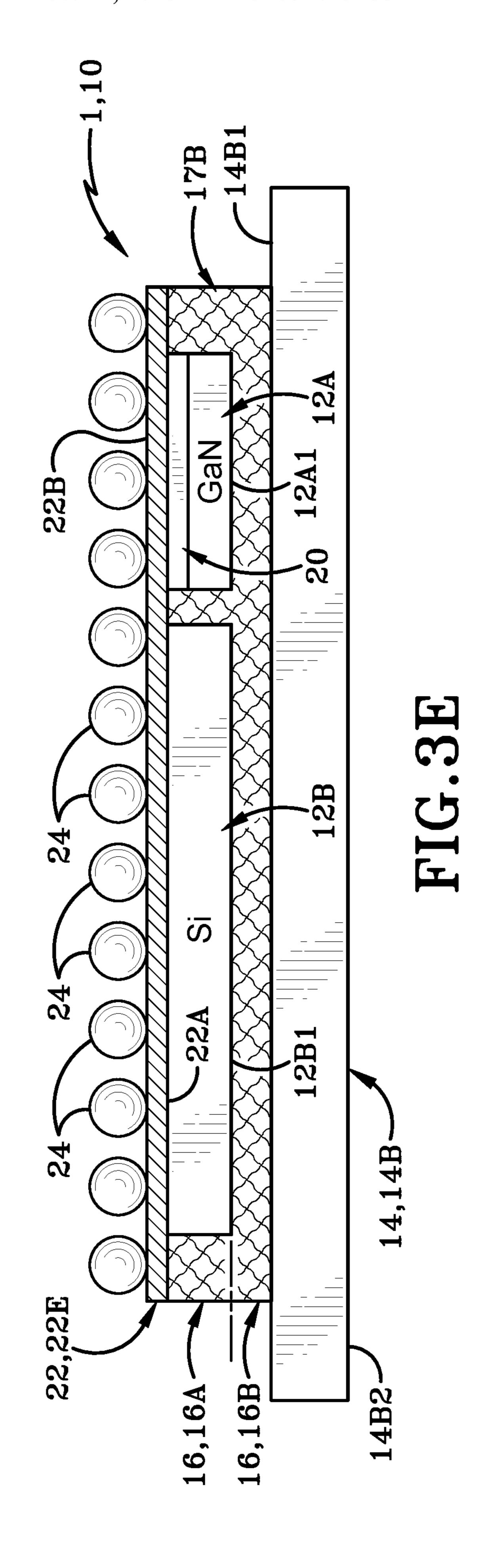

- FIG. 3E is a side elevation view similar to FIG. 3D, but a second temporary dielectric is removed from the electrical structure.

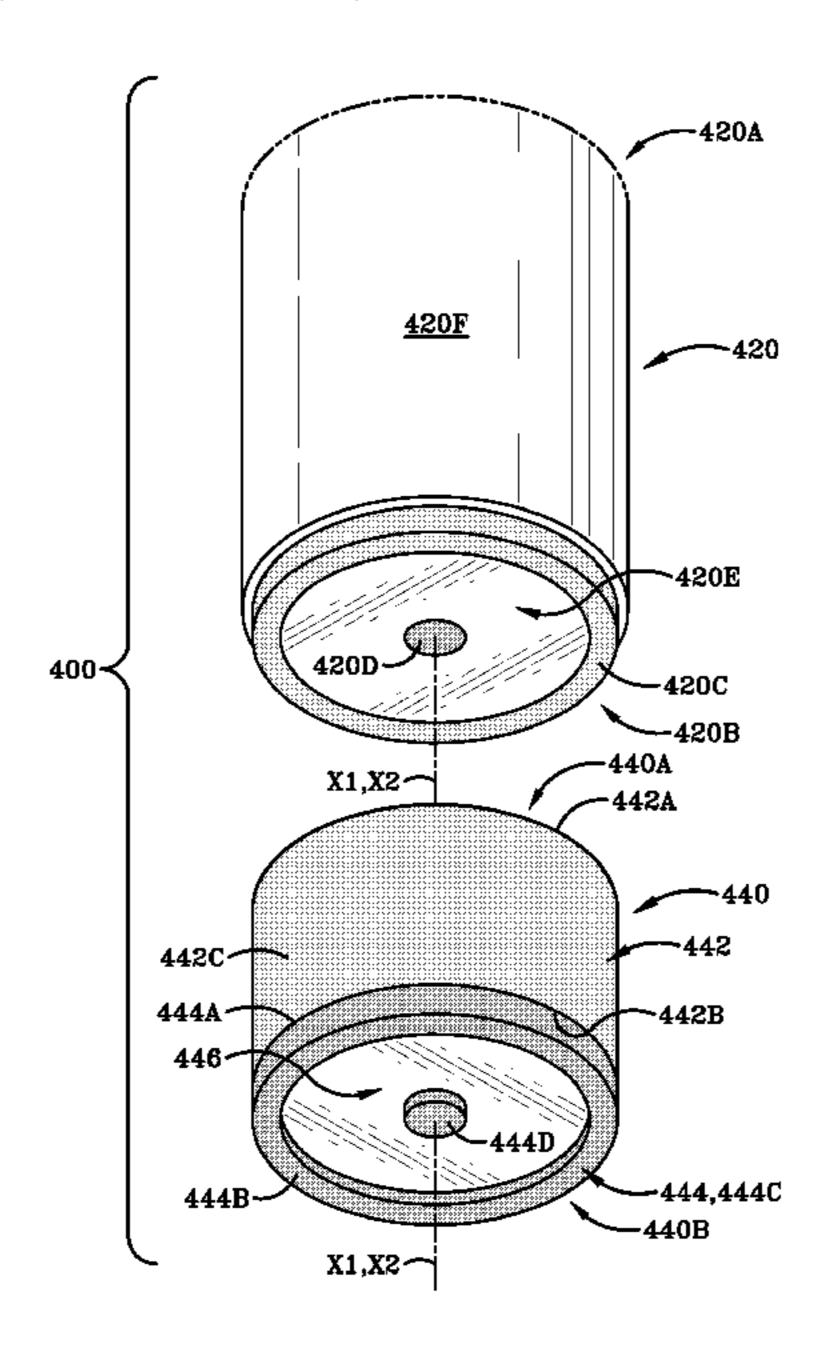

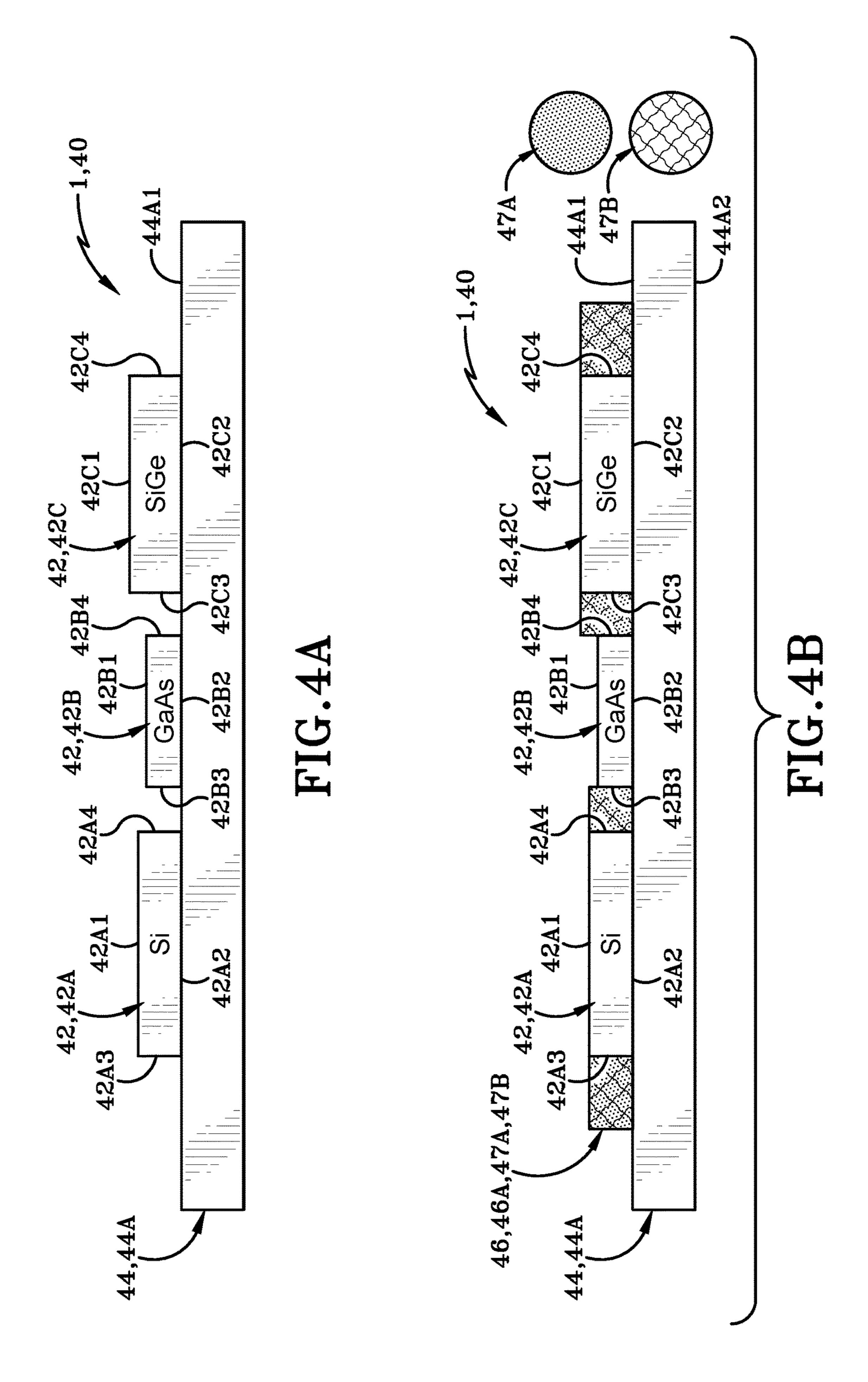

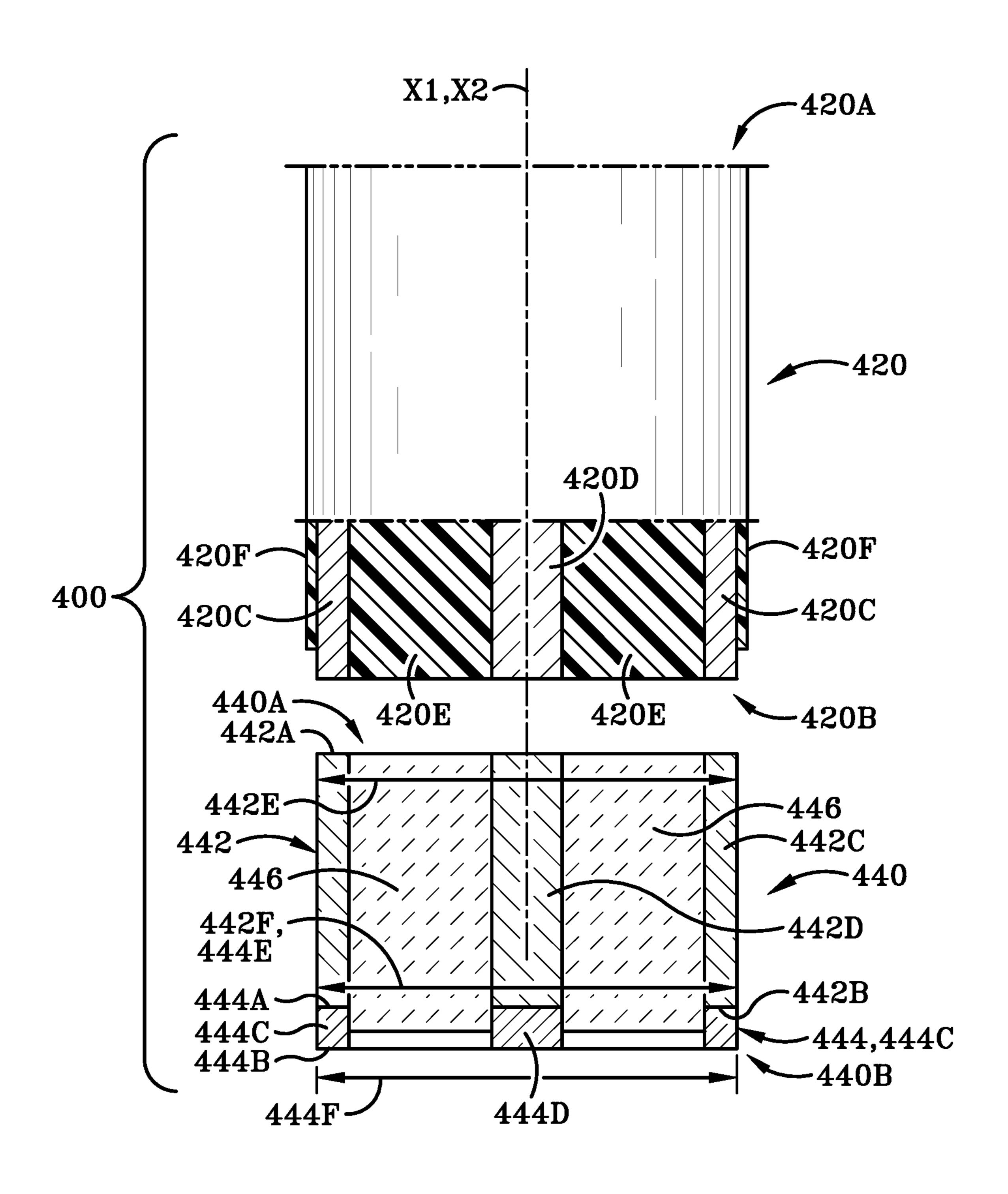

- FIG. 4A is a side elevation view of manufacturing a second section of the semiconductor package, wherein one or more dies are operably engaged with a first temporary carrier of the second section.

- FIG. 4B is a side elevation view similar to FIG. 4A, but a compliant support structure operably engages with the one or more dies and the first temporary carrier.

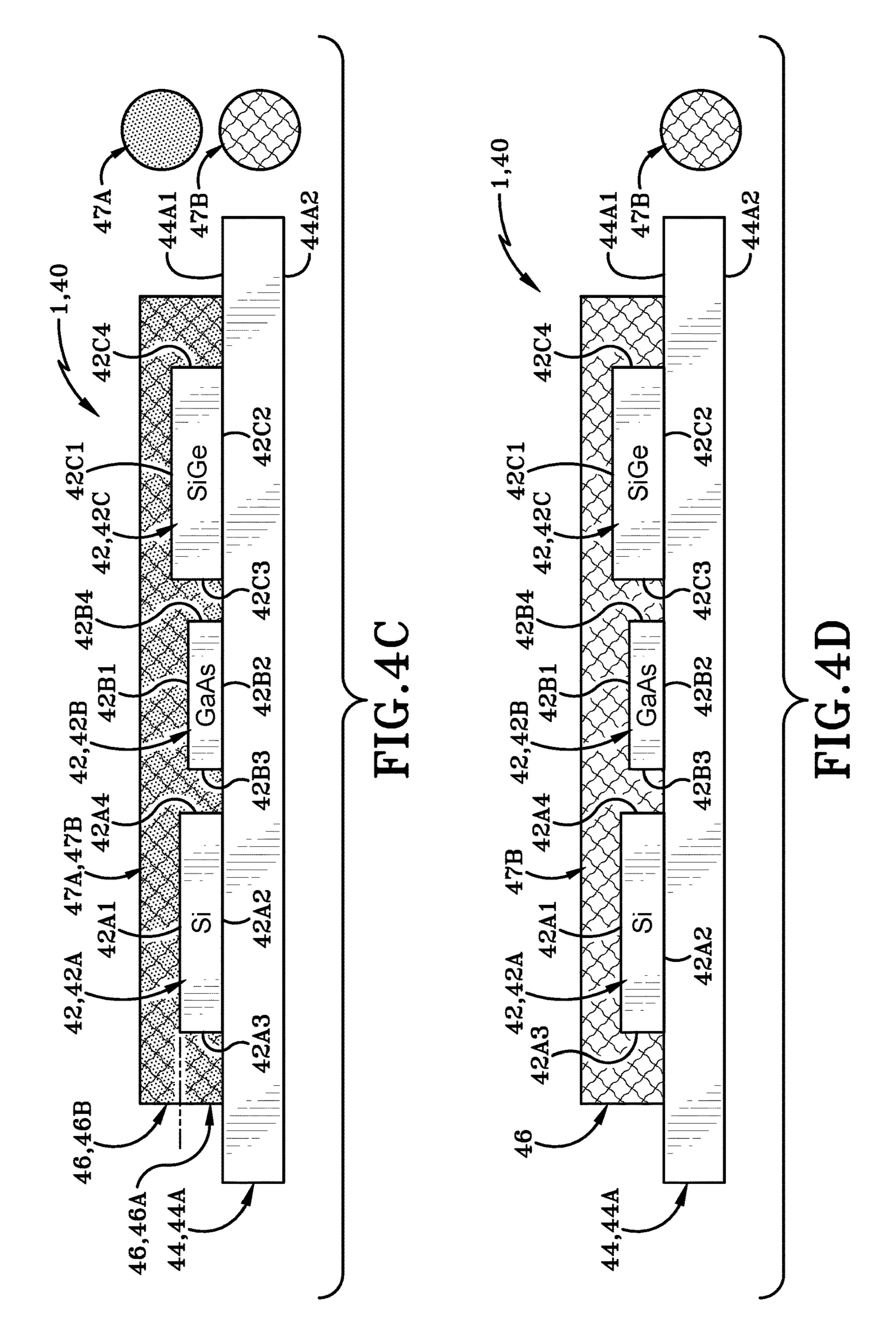

- FIG. 4C is a side elevation view similar to FIG. 4B, but a thermal conductive structure operably engages with the compliant support structure.

- FIG. 4D is a side elevation view similar to FIG. 4C, but a temporary support of compliant support structure is removed.

- FIG. 4E is a side elevation view similar to FIG. 4D, but irises are added to the compliant support structure.

- FIG. 4F is a side elevation view similar to FIG. 4E, but the second section is inverted and a second temporary carrier is introduced to the first section.

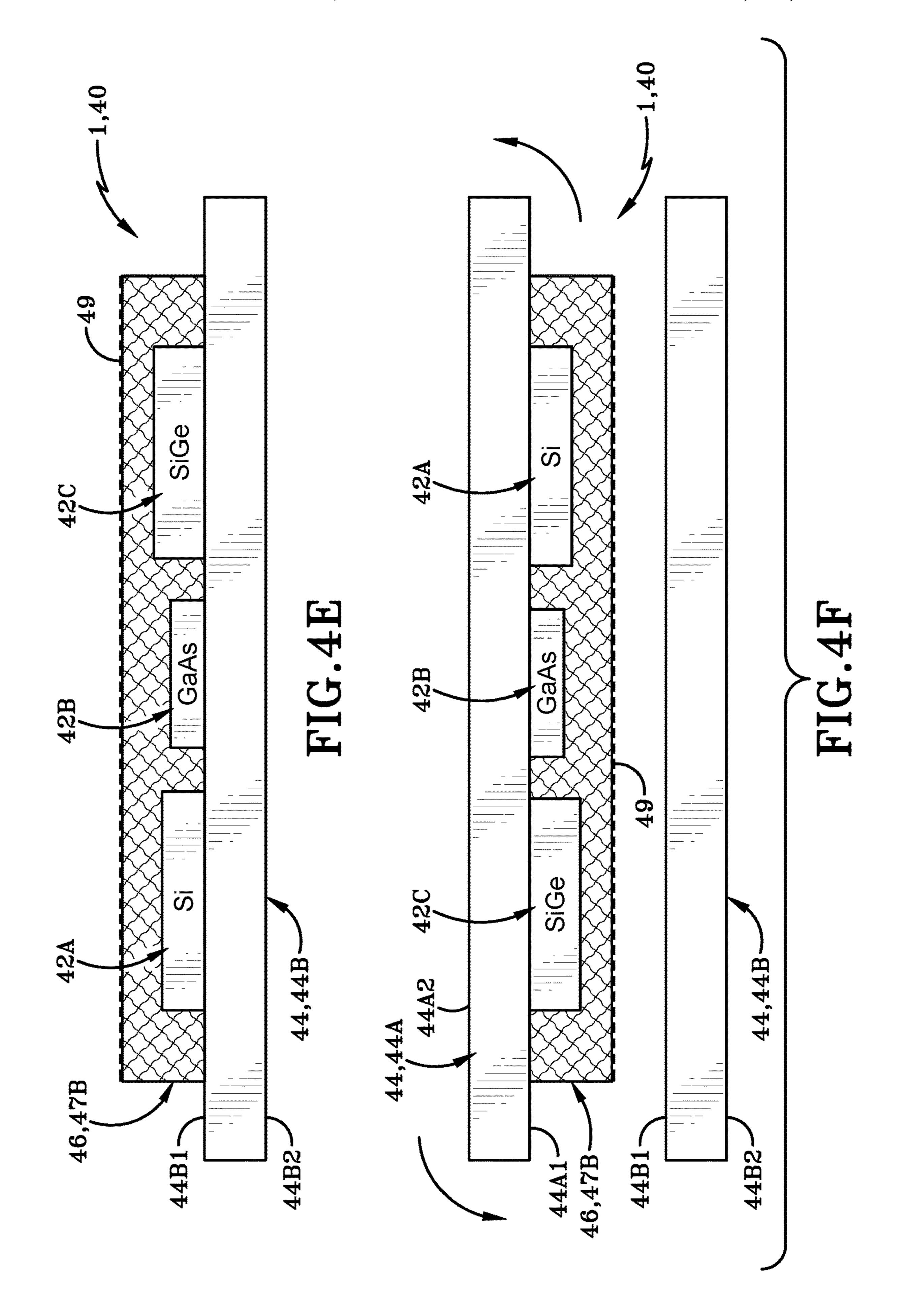

- FIG. 4G is a side elevation view similar to FIG. 4F, but the first temporary support is removed from the second section and second temporary carrier operably engages with the complaint support structure.

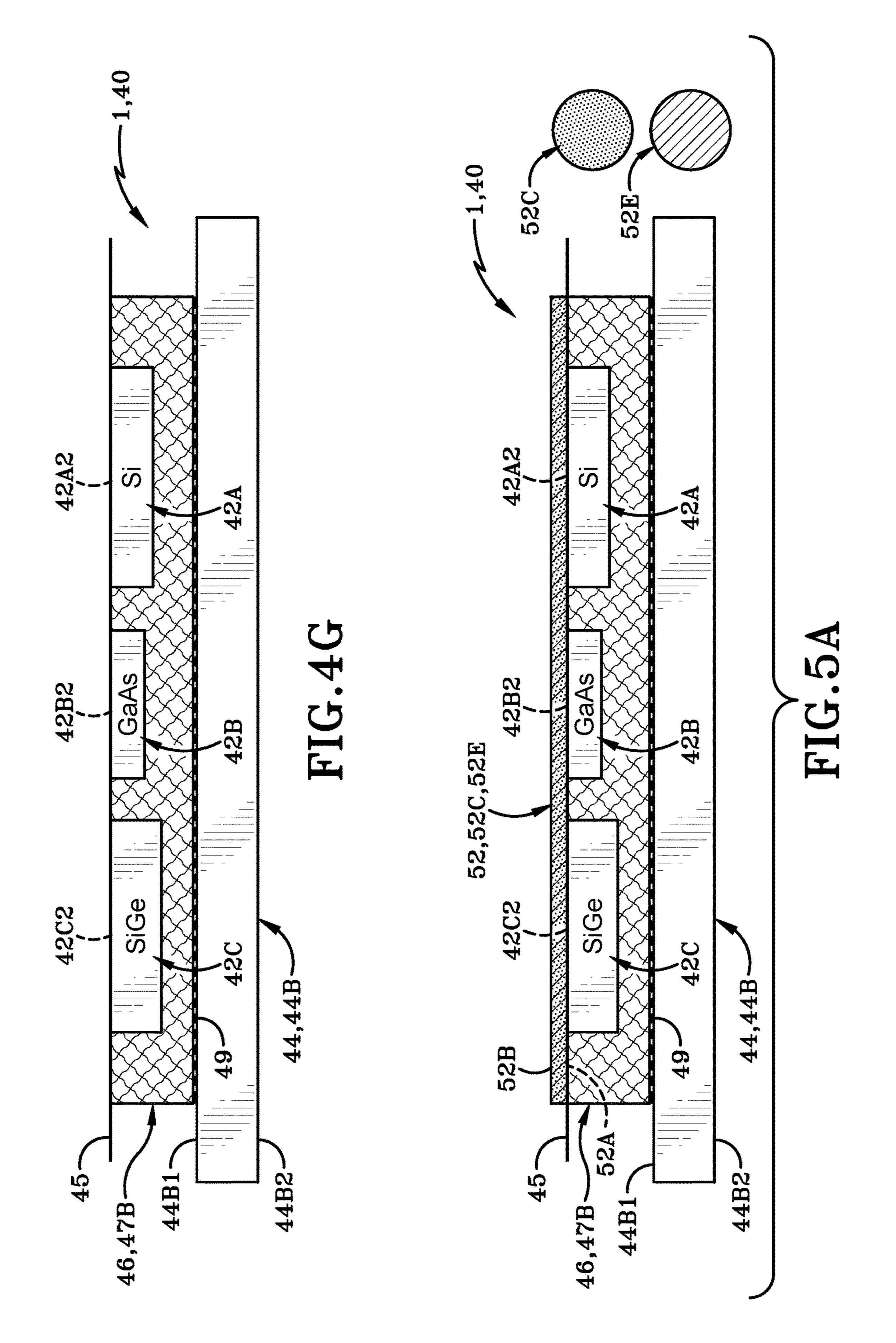

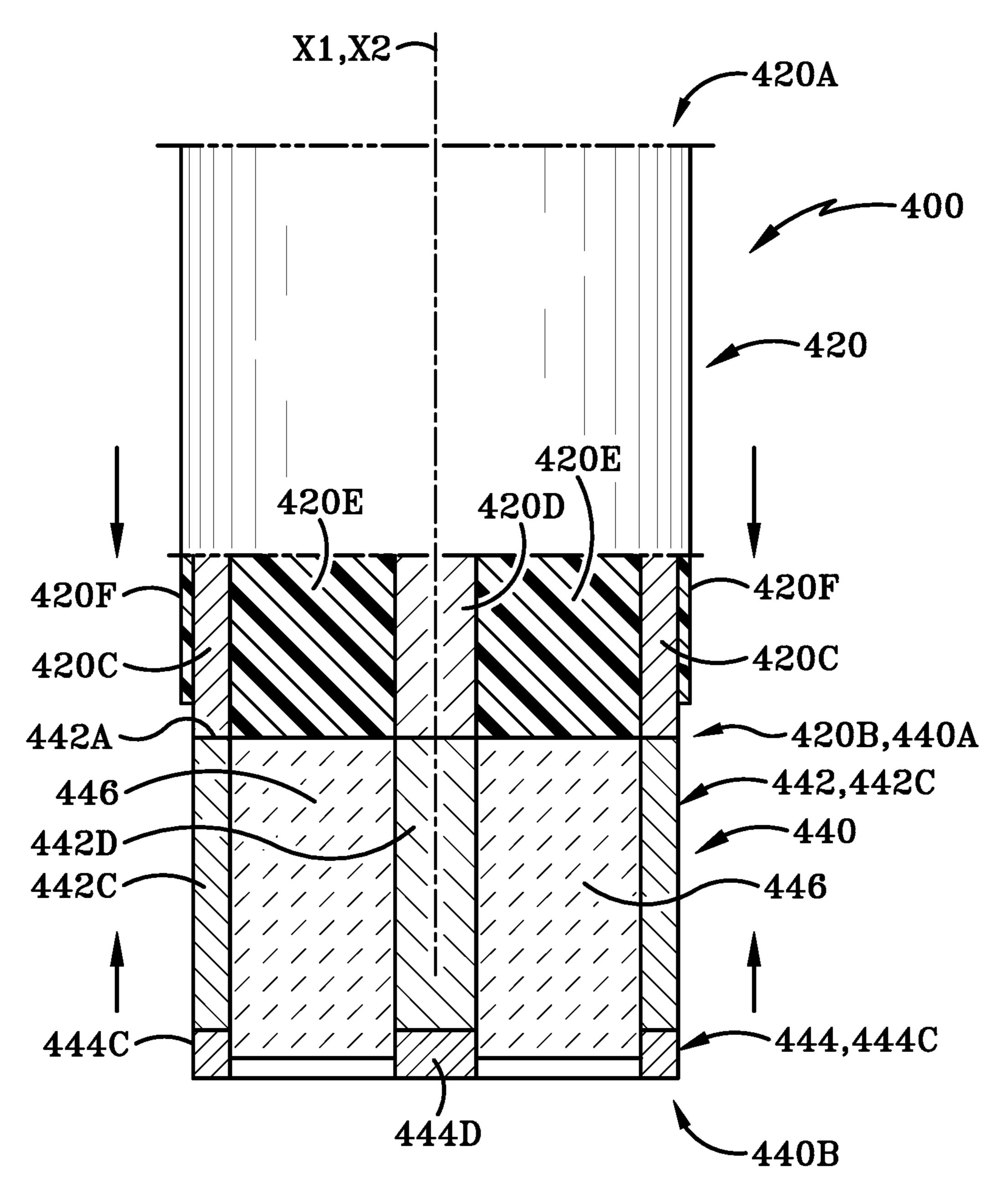

- FIG. **5**A is a side elevation view of operably engaging an electrical structure with the second section.

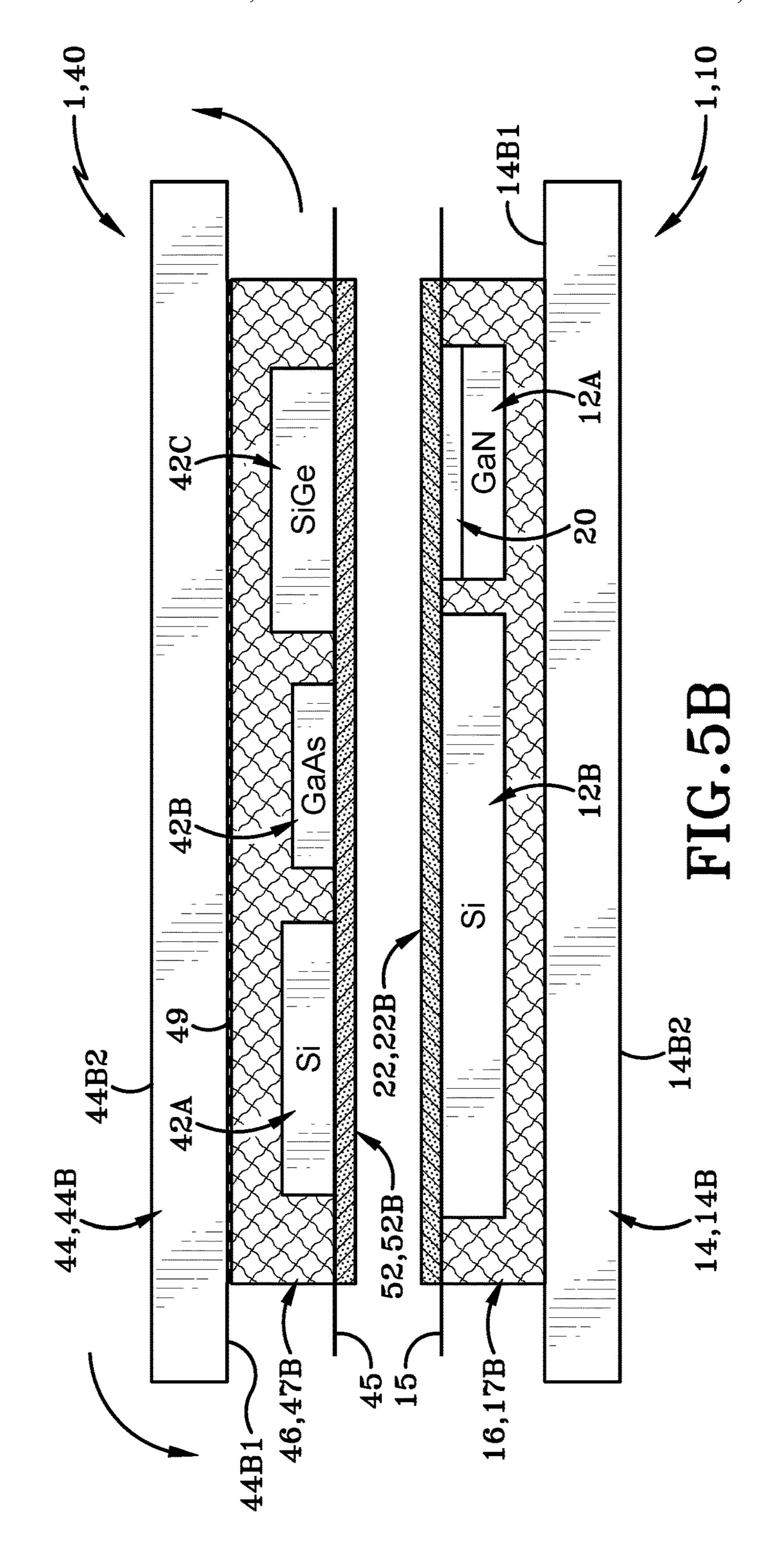

- FIG. 5B is a side elevation view similar to FIG. 5A, but the second section is inverted and aligned with the first section.

- FIG. 5C is a side elevation view similar to FIG. 5B, but the electrical structure of the second section operably engages with the electrical structure of the first section.

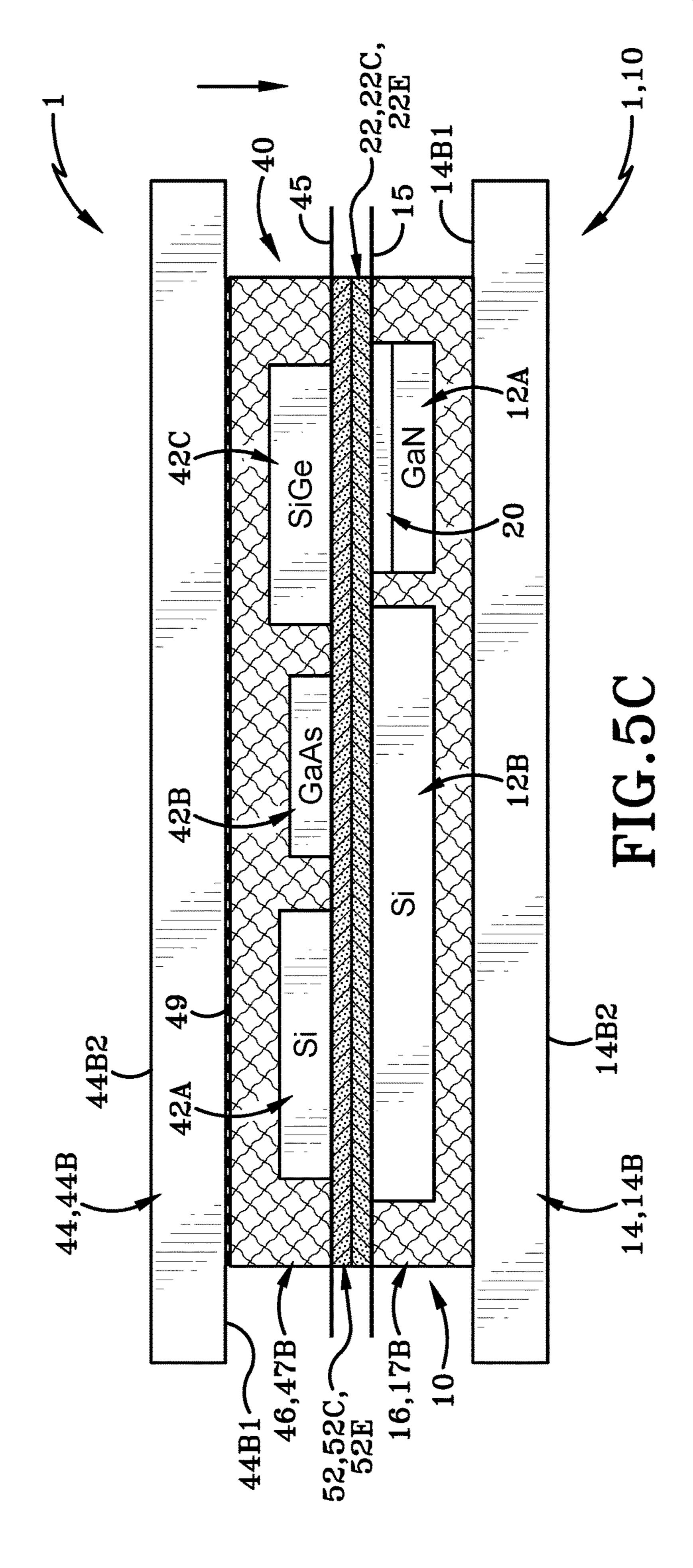

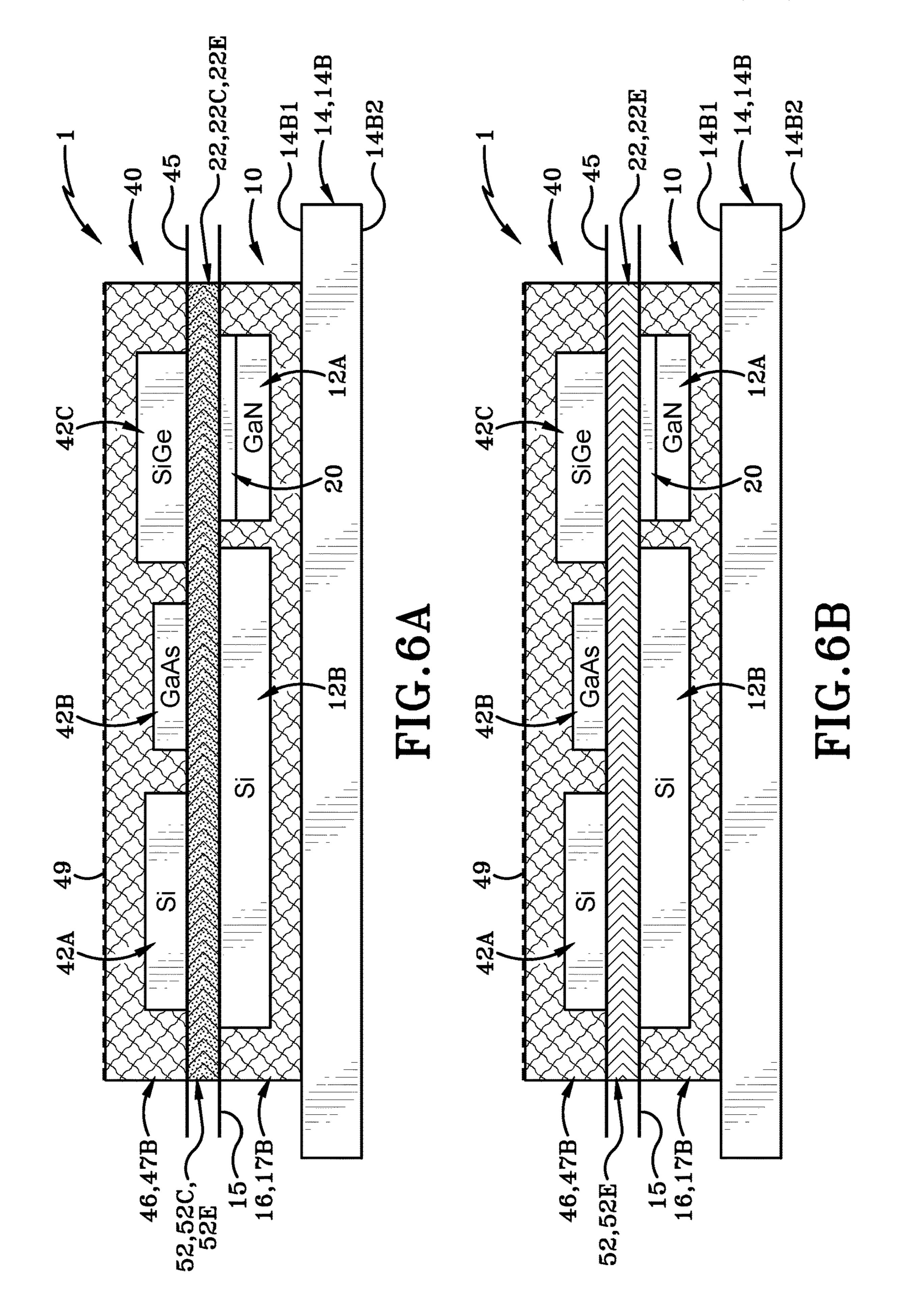

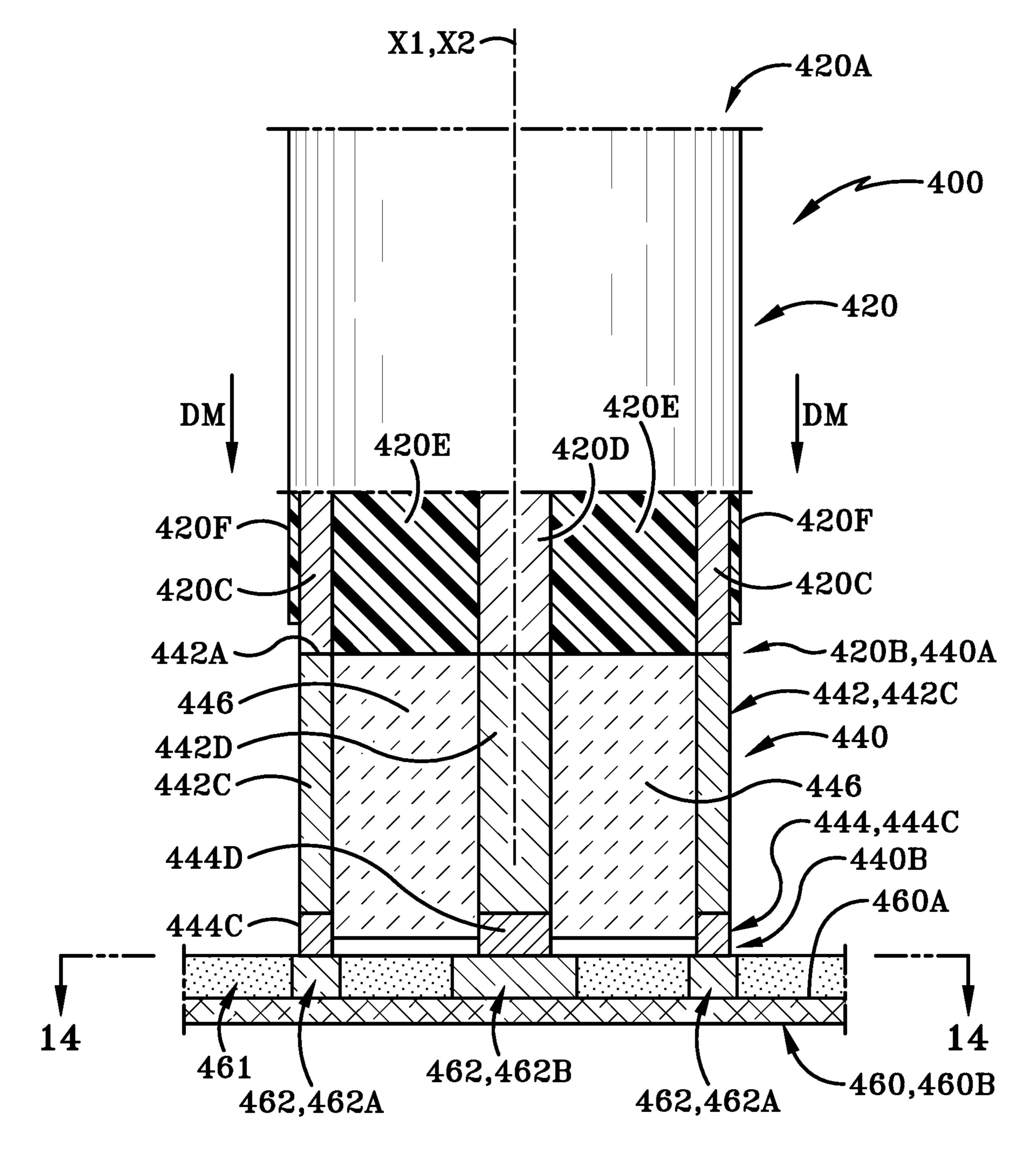

- FIG. **6**A is a side elevation view of the second temporary carrier of the second section being removed from the compliant support structure along with plating exterior dielectric to the second section.

- FIG. **6**B is a side elevation view similar to FIG. **6**A, but a first temporary dielectric is removed from the second section.

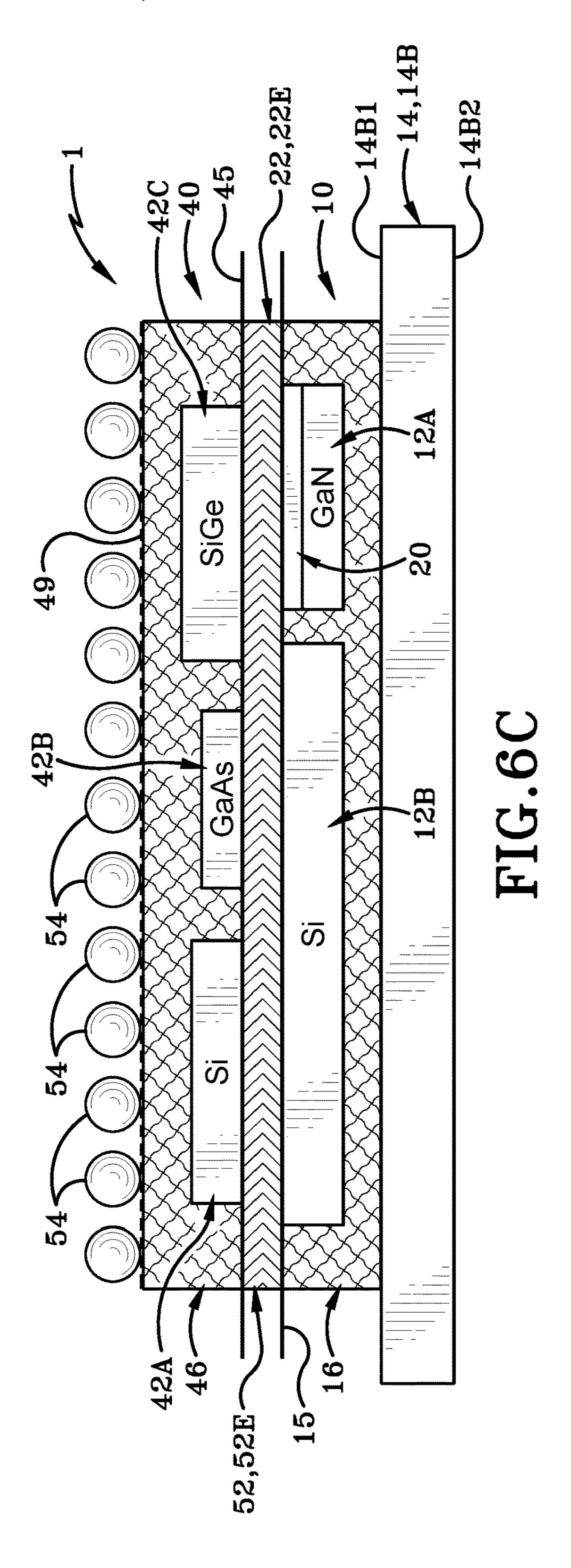

- FIG. 6C is a side elevation view similar to FIG. 6B, but a plurality of solder balls operably engages with the electrical structure of second section.

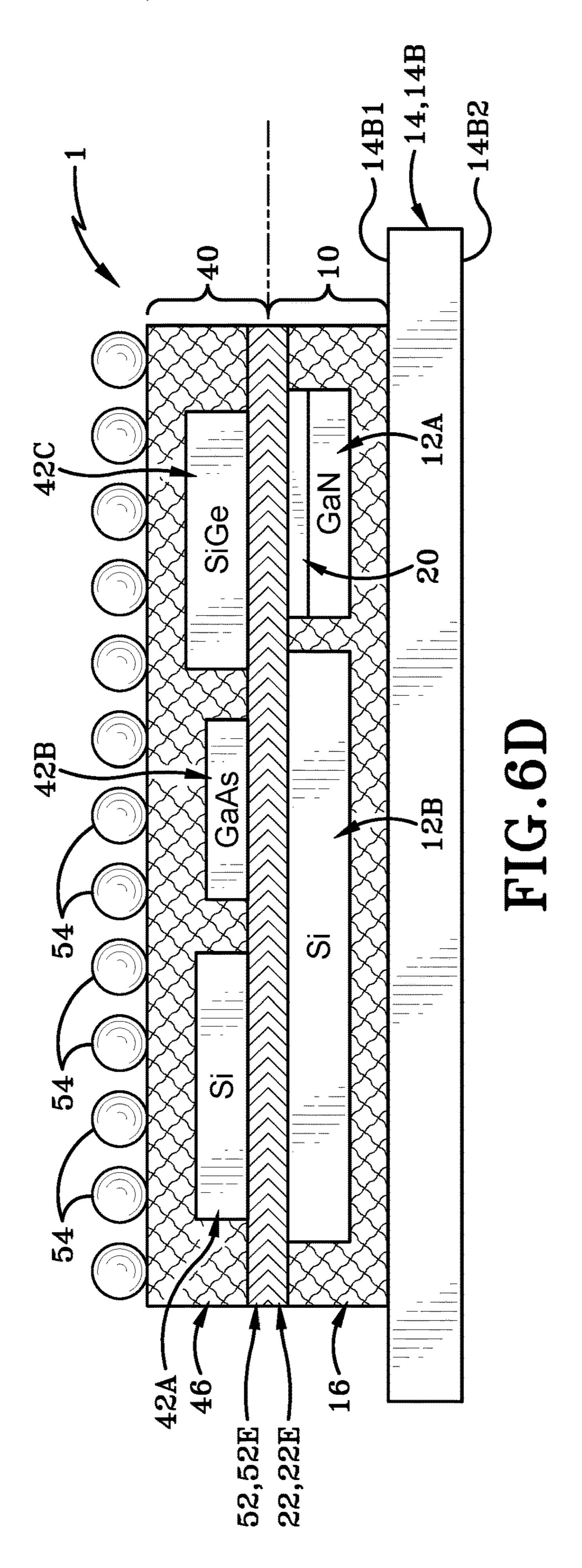

- FIG. **6**D is a side elevation view similar to FIG. **6**C, but a second temporary dielectric is removed from the second section.

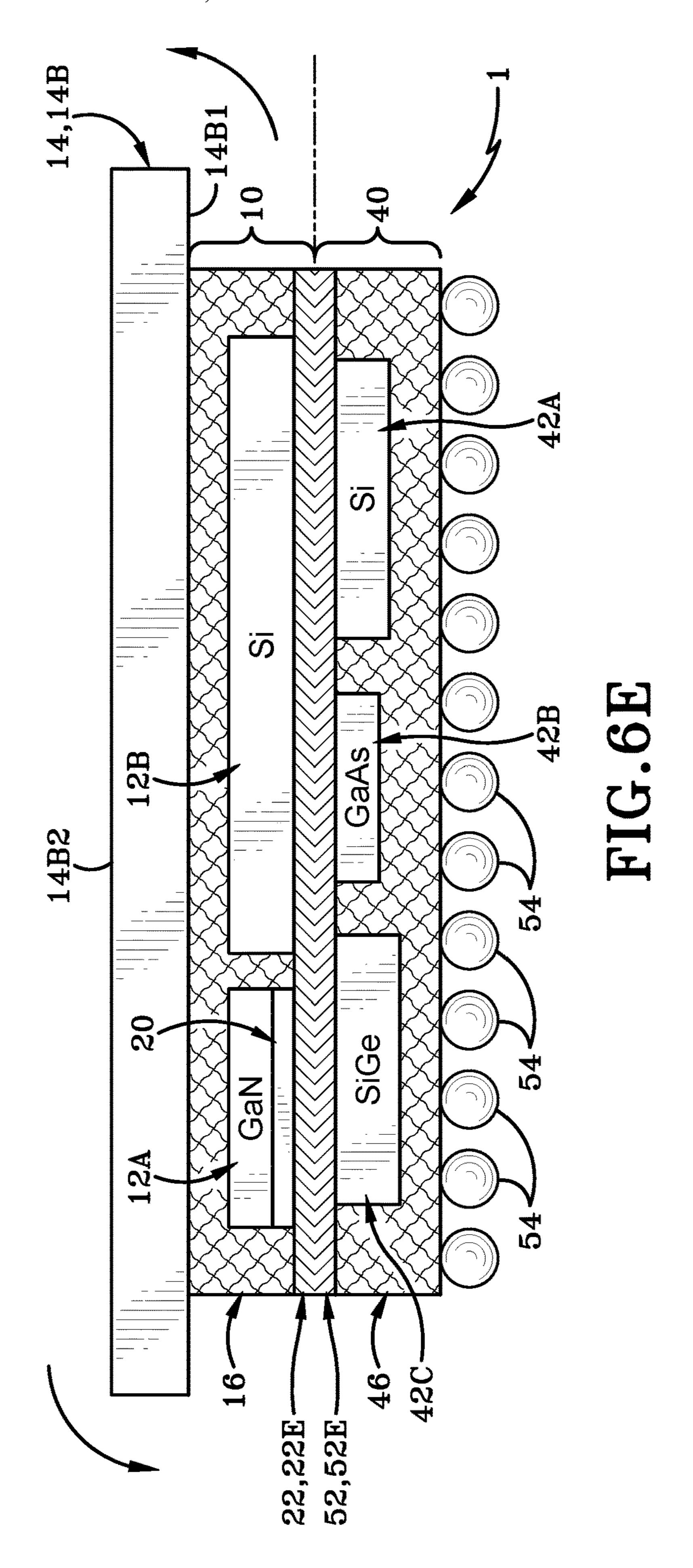

- FIG. **6**E is a side elevation view similar to FIG. **6**D, but the combination of the first section and second section is inverted.

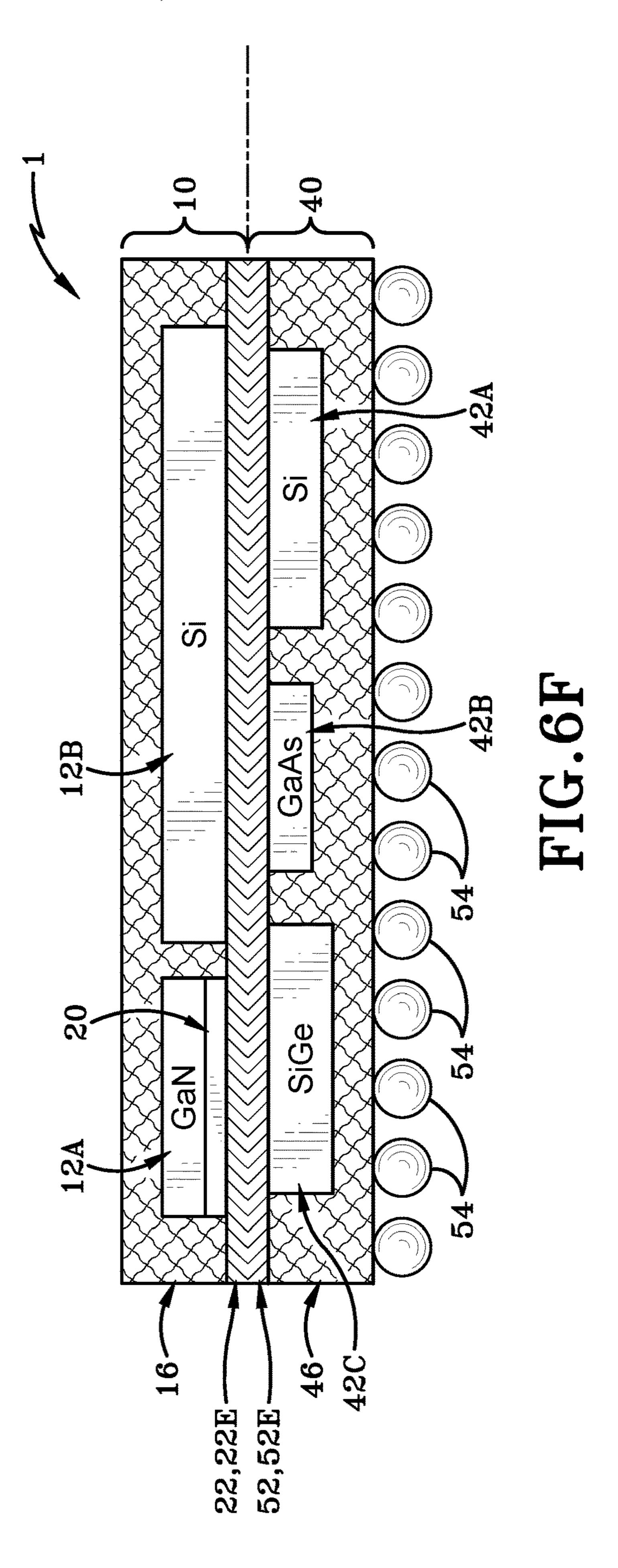

- FIG. 6F is a side elevation view similar to FIG. 6E, but the second temporary carrier is removed from the first section.

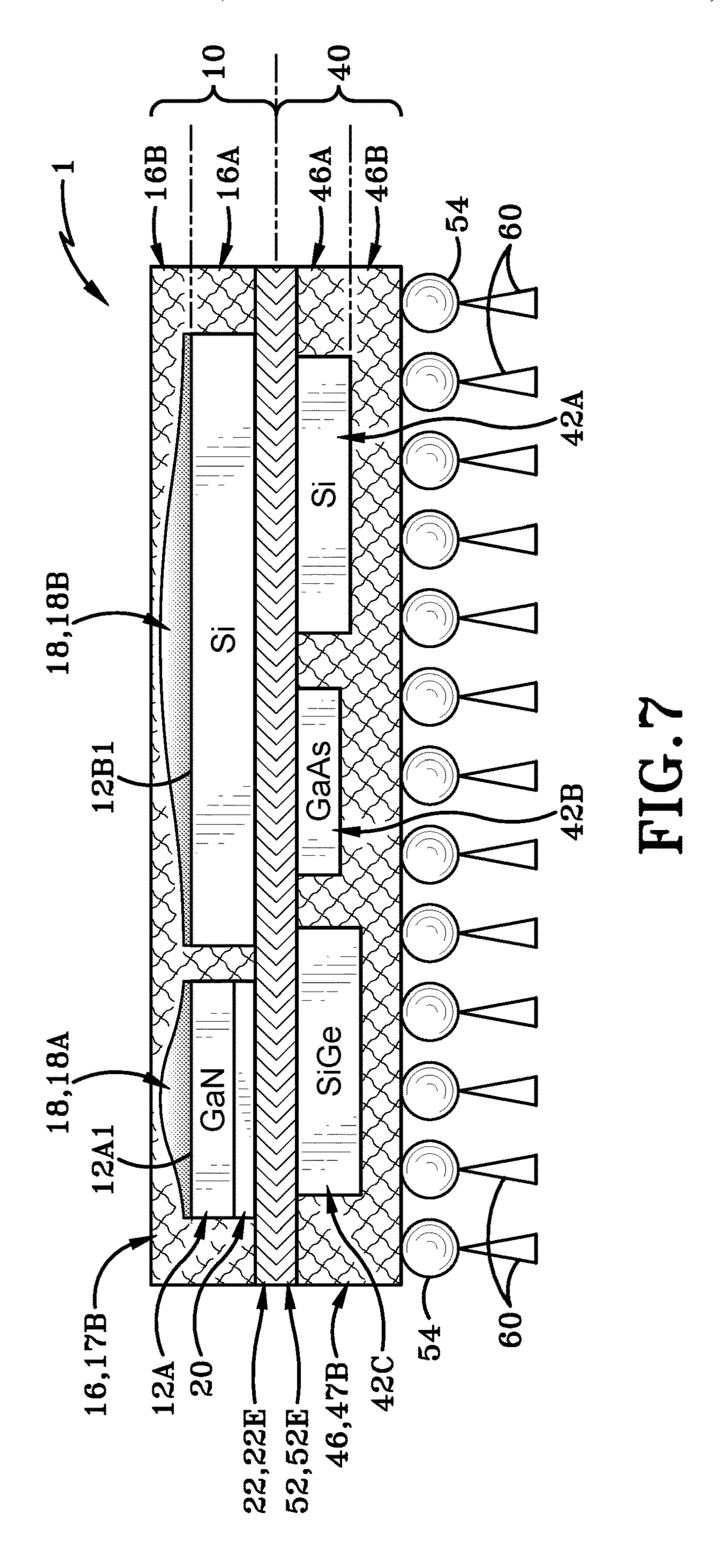

- FIG. 7 is a side elevation view of testing the semiconductor package.

- FIG. 8 is an exemplary method flowchart.

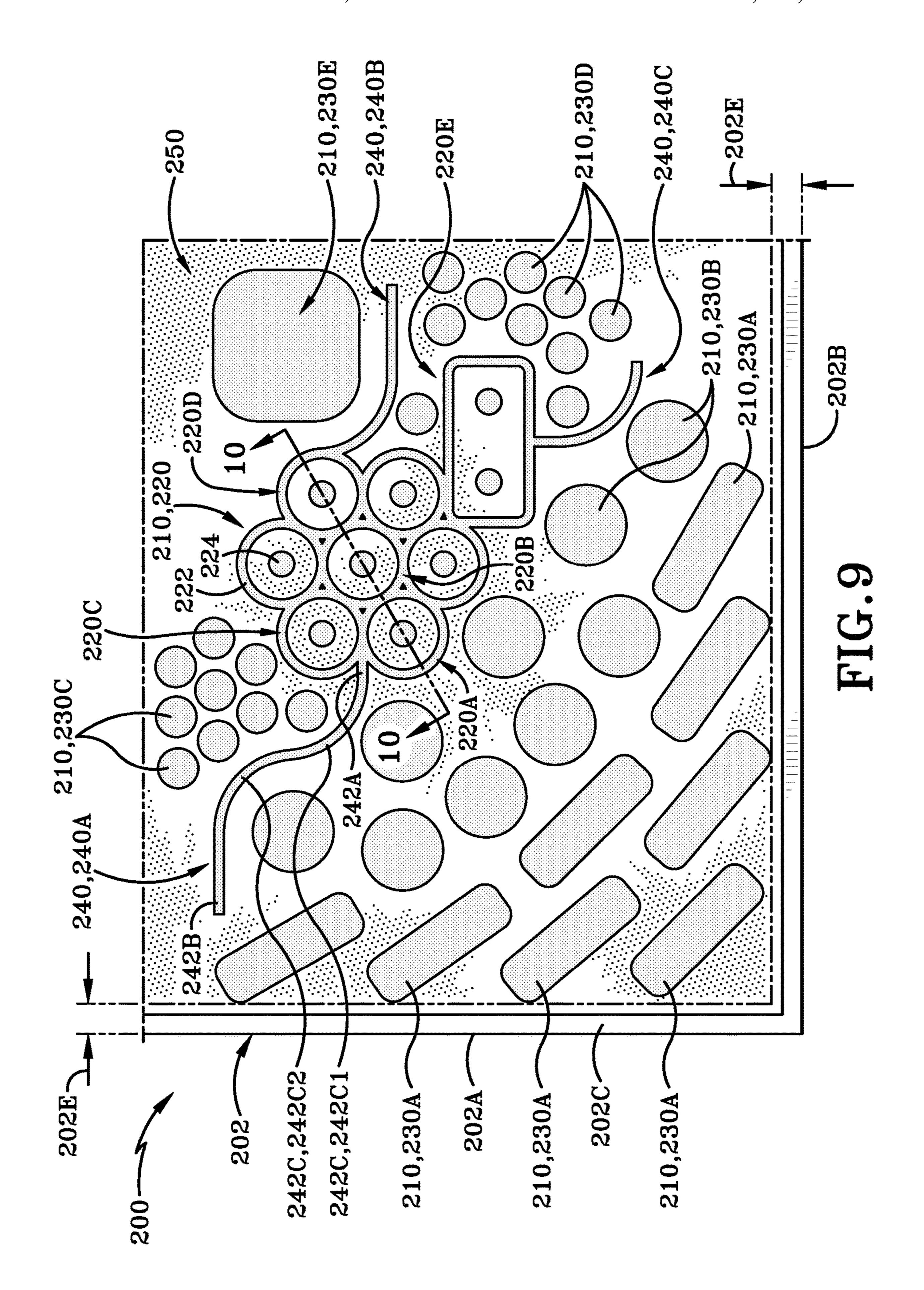

- FIG. 9 is a top plan view of a semiconductor die having sets of input/output (IO) connections in accordance with one aspect of the present disclosure.

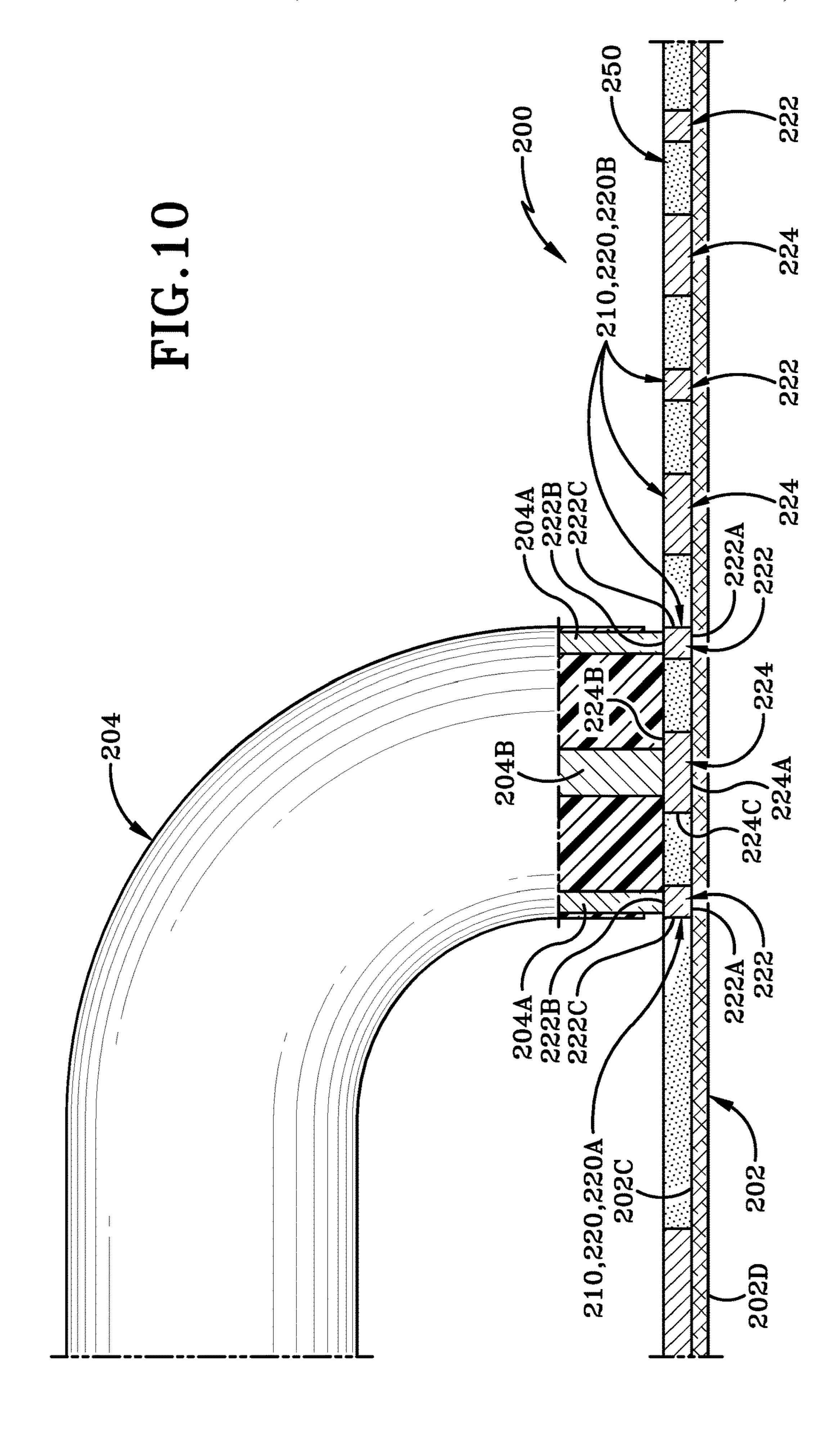

- FIG. 10 is a cross-sectional view of the semiconductor die taken in the direction of line 10-10 shown in FIG. 9.

- FIG. 11 is another exemplary method flowchart.

- FIG. 12 is a bottom, front, side isometric perspective view of a coaxial pad probe in accordance with one aspect of the

present disclosure, wherein a probe and a preexisting coaxial cable of the coaxial pad probe are exploded away from one another.

FIG. 13A is a partial sectional view of the coaxial pad probe shown in FIG. 12, wherein the probe and the preexisting coaxial cable are exploded away from one another.

FIG. 13B is another partial sectional view similar to FIG. 13A, but the probe is provided with the preexisting coaxial cable.

FIG. 13C is another partial sectional view similar to FIG. 10 13B, but the probe directly contacts a coaxial IO pad of a semiconductor die.

FIG. 14 is a top plan view of the coaxial IO pad of the semiconductor die taken in the direction of line 14-14 shown in FIG. 13C.

FIG. 15 is a bottom, front, side isometric perspective view of a coaxial pad probe in accordance with another aspect of the present disclosure, wherein a probe and a preexisting coaxial cable of the coaxial pad probe are exploded away from one another.

FIG. 16 is a partial sectional view of coaxial pad probe shown in FIG. 15, but the probe directly contacts a coplanar IO pad of a semiconductor die.

FIG. 17 is a top plan view of the coplanar IO pad of the semiconductor die taken in the direction of line 17-17 shown 25 in FIG. 16.

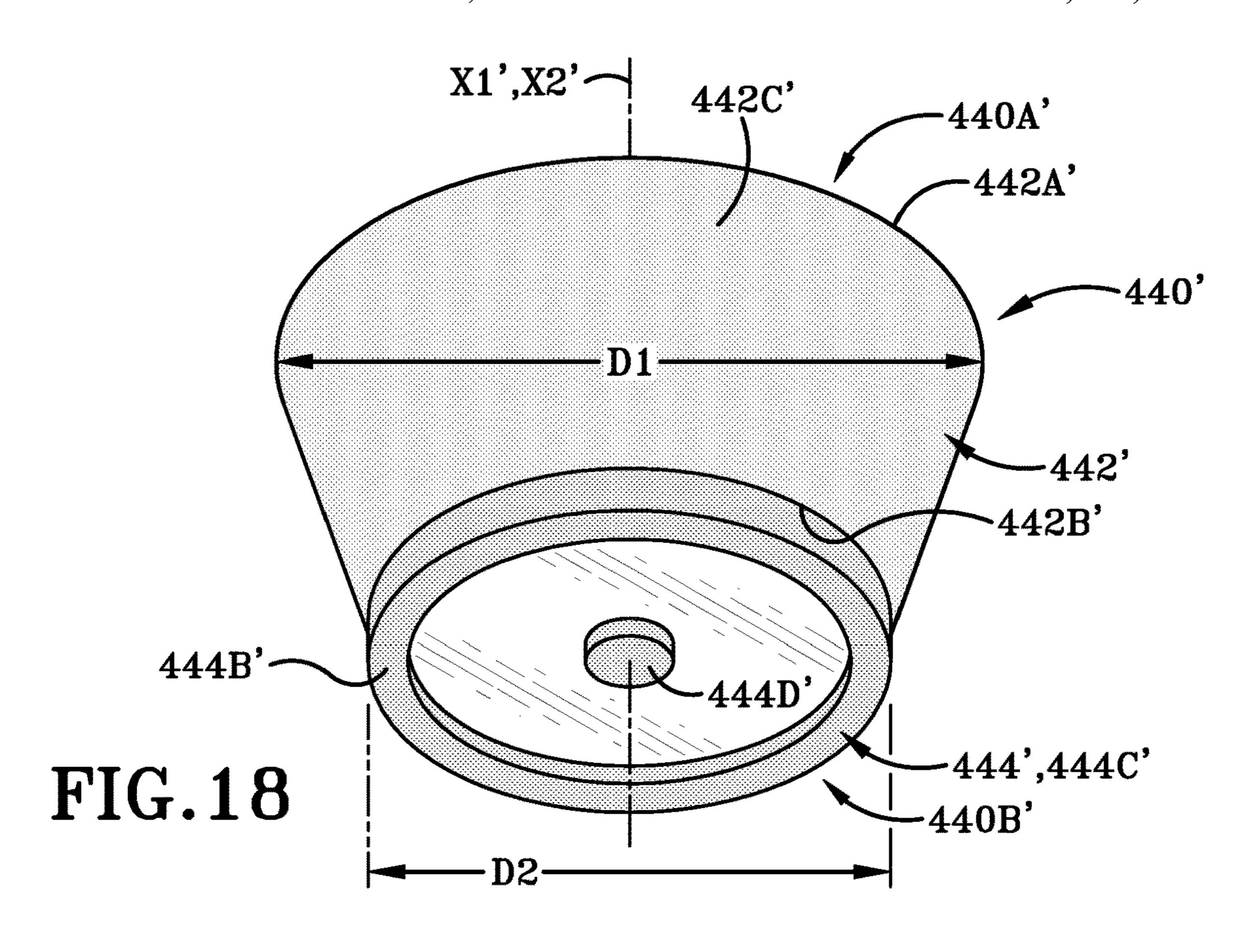

FIG. 18 is a bottom, front, side isometric perspective view of an alternative probe of the probe shown in FIG. 12.

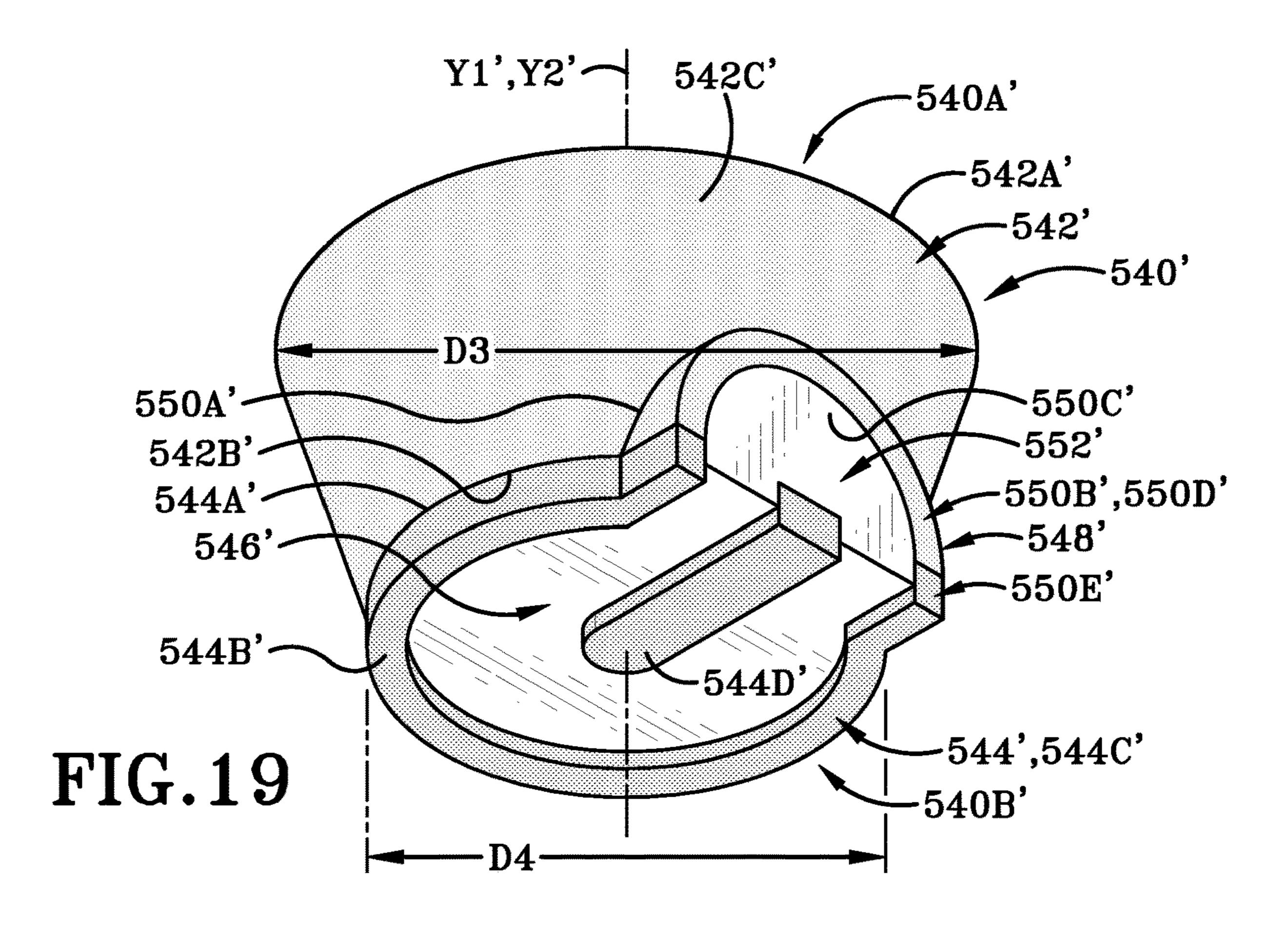

FIG. 19 is a bottom, front, side isometric perspective view of an alternative probe of the probe shown in FIG. 15.

FIG. 20 is another exemplary flowchart.

Similar numbers refer to similar parts throughout the drawings.

## DETAILED DESCRIPTION

FIGS. 1-7 illustrate a semiconductor package 1 that adaptively interconnects at least one mixed signal die or semiconductor die with an additive wafer level packaging technology for incorporating radio frequency (RF) devices, 40 passive electrical devices, and optical couplings provided in a compliant interconnect. With respect to compliant interconnects, the semiconductor package 1 described and illustrated may incorporate at least one interconnect that has coefficient of thermal expansion (or CTE) compliant geometries and thermal management solutions and/or structures free from using solder alloys or epoxy mold compounds between the at least one mixed signal die and the compliant interconnect. Such components and elements of the semi-conductor package 1 are described in more detail below.

It should be appreciated that the term "compliant" or other derivatives similar to "compliant" describing complaint interconnects simply means that the each interconnect may meet a desired coefficient of thermal expansion for desired structural geometries of each interconnect and/or desired thermal management solutions or gradient heat dissipation geometries of each interconnect. Stated differently, the term "compliant" or other derivatives similar to "compliant" describing complaint interconnects simply means that any usable or suitable material may be used for package thermal management that will not compromise or hinder the performance of the interconnect during operation.

Referring to FIGS. 1-3E, the semiconductor package 1 includes at least one portion or first section 10 that includes at least one mixed signal die or semiconductor die (herein-65 after "die") generally referred to as numeral 12. The at least one die 12 may include any suitable elements and/or com-

12

ponents for generating various mixed signals dictated by the implementation of the semiconductor package 1. In at least one instance, semiconductor package 1 includes a first die 12A and a second die 12B in this specific implementation of semiconductor package 1 where the first die 12A and the second die 12B may be configured to generate mixed signals. In other exemplary instances, semiconductor package 1 may include any suitable number of semiconductor dies configured to generate mixed signals dictated by the implementation of the semiconductor package 1.

As illustrated in FIGS. 1-3E, the first die 12A includes a first surface or inactive surface 12A1 that is free from input and output locations. First die 12A also includes a second surface or active surface 12A2 that is opposite to the inactive surface 12A1 and includes the input and output locations of the first die 12A. First die 12A may also include a first side 12A3 defined between the inactive surface 12A1 and the active surface 12A2 and is free from input and output locations. First die 12A may also include a second side 12A4 defined between the inactive surface 12A1 and the active surface 12A2 that is opposite to the first side 12A3 and is free from input and output locations.

Similarly, as illustrated in FIGS. 1-3E, the second die 12B includes a first surface or inactive surface 12B1 that is free from input and output locations. Second die 12B also includes a second surface or active surface 12B2 that is opposite to the inactive surface 12B1 and includes the input and output locations of the second die 12B. Second die 12B may also include a first side 12B3 defined between the inactive surface 12B1 and the active surface 12B2 and is free from input and output locations. Second die 12B may also include a second side 12B4 defined between the inactive surface 12B1 and the active surface 12B2 that is opposite to the first side 12B3 and is free from input and output locations.

The first die 12A and the second die 12B may be formed of any suitable semiconductor materials conventionally and commercially available in the field of semiconductor packages. In one aspect, first die 12A may be formed of a first material (e.g., gallium nitride), and the second die 12B may be formed of a second material (e.g., silicon) that is different than the first material of the first die 12A. In another aspect, first die 12A may be formed of a first material, and the second die 12B may be formed of a second material that is the same as the first material of the first die 12A. It should be appreciated that a first die and a second die of a semiconductor package may be formed of any suitable semiconductor materials discussed herein and conventionally and commercially available in the field of semiconductor packages.

Referring to FIGS. 2A-3E, the first section 10 also includes at least one temporary carrier or temporary workpiece holder, generally referred to as numeral 14, that operably engages with that least one die 12. The at least one temporary carrier 14 may include any suitable elements and/or components or structural configuration for operably engaging with at least one die 12 as dictated by the implementation of the semiconductor package 1. In at least one instance, semiconductor package 1 includes a first temporary carrier 14A that operably engages with the first die 12A and the second die 12B and a second temporary carrier 14B that operably engages with a compliant support structure of the first section 10, which is described in more detail below. In other exemplary instances, semiconductor package 1 may include any suitable number of temporary carriers configured operably engage with at least one die described and illustrated herein.

Referring to FIG. 2A, the first temporary carrier 14A includes a first surface or engaging surface 14A1 that is configured to operably engage with the at least one die 12. In the illustrated embodiment, the engaging surface 14A1 of the first temporary carrier 14A is configured to operably 5 engage with the first die 12A and the second die 12B. In other exemplary embodiments, the engaging surface 14A1 of the first temporary carrier 14A is configured to operably engage with any suitable number of dies as dictated by the implementation of the semiconductor package 1. As 10 described in more detail below, the first temporary carrier **14**A is configured to be removed and/or separated from the first die 12A and the second die 12B upon manufacturing the semiconductor package 1; as such, the first temporary carrier **14A** is a removable and/or separable component from the 15 first die 12A and the second die 12B. First temporary carrier 14A also includes a second surface or non-engaging surface **14A2** that is opposite to the engaging surface **14A1** and remote from the first die 12A and the second die 12B. During manufacturing processes, the second surface **14A2** may rest 20 on a work surface or support surface as the first section 10 is being manufactured.

It should be appreciated that the first die 12A and the second die 12B may be operably engaged at any suitable location on the engaging surface 14A1 of first temporary 25 carrier 14A as dictated by the shape, size, and configuration of the first temporary carrier 14A.

Referring to FIG. 2E, the second temporary carrier 14B also includes a first surface or engaging surface 14B1 that is configured to operably engage with at least one compliant 30 support structure of first section 10 of semiconductor package 1, which is described in more detail below. In other exemplary embodiments, the engaging surface 14B1 of the second temporary carrier 14B is configured to operably engage with any suitable number of compliant support 35 structures as dictated by the implementation of the semiconductor package 1. As described in more detail below, the second temporary carrier 14B is configured to be removed and/or separated from a compliant support structure upon manufacturing the semiconductor package 1; as such, the 40 second temporary carrier 14B is a removable and/or separable component from the compliant support structure at the engaging surface 14B1. Second temporary carrier 14B also includes a second surface or non-engaging surface 14B2 that is opposite to the engaging surface 14B1 and remote from a 45 compliant support structure of first section 10 of semiconductor package 1. During manufacturing processes, the second surface 14B2 may rest on a work surface or support surface as the first section 10 is being manufactured.

Referring to FIG. 2F, an interconnect dielectric 15 may be 50 provided between the first die 12A and the second die 12B and the first temporary carrier 14A. Such use of the interconnect dielectric 15 may protect the active surfaces 12A2, 12B2 of the first die 12A and the second die 12B until the semiconductor package 1 is constructed. As such, interconnect dielectric 15 may be temporary and removable from the first die 12A and the second die 12B once the semiconductor package 1 is constructed.

As best seen in FIGS. 2B-2D, at least one compliant support structure 16A may be provided in the first section 10 of semiconductor package 1. In the illustrated embodiment, first section 10 includes a single compliant support structure 16A formed about the perimeter of the first section 10 while encapsulating and/or encasing the first die 12A and the second die 12B inside of the compliant support structure 65 16A. Compliant support structure 16A is also operably engaged with the first temporary carrier 14A, specifically

**14**

with the engaging surface 14A1 of first temporary carrier 14A. The compliant support structure 16A is configured to provide translational support to the first die 12A and the second die 12B in the horizontal or lateral directions to prevent the first die 12A and the second die 12B from shifting or rotating along the engaging surface 14A1 of the first temporary carrier 14A.

It should be understood that compliant support structure **16**A and/or thermally conductive structure **16**B may include a temporary or removable support 17A and a permanent support 17B. As best seen in FIG. 2B, the temporary support 17A is initially applied to the first die 12A, second die 12B, and the first temporary carrier 14A via suitable fabrication methods such as adaptive direct write lithography and other fabrication methods of the like. In this embodiment, temporary support 17A may be a cured polymer network that is formed on and about the first die 12A, second die 12B, and the first temporary carrier 14A. Additionally, the temporary support 17A may also include a preferably thin-metal coating. Once the temporary support 17A is cured, the temporary support may be removed to leave the permanent support 17B engaged with the engaging surface 14A1 of the first temporary carrier 14A along with the first die 12A and the second die 12B. The permanent support 17B may also be a desired CTE-compliant structure as dictated by the implementation of semiconductor package 1.

The compliant support structure 16A may also define any suitable structural configuration in order to provide translational support to the first die 12A and the second die 12B in the horizontal or lateral directions so that the first die 12A and the second die 12B are restricted from shifting or rotating along the engaging surface 14A1 of the first temporary carrier 14A. Such structural configuration of the compliant support structure 16A may be based on various considerations, including the size, shape, and materials of the first die 12A and the second die 12B. In one instance, a compliant support structure described and illustrated herein may be an open-cell foam stochastic three-dimensional structure that forms about at least one die of a semiconductor package and that engages with at least one temporary carrier of the semiconductor package. In another instance, a compliant support structure described and illustrated herein may be a non-stochastic lattice structure that forms about at least one die of a semiconductor package and that engages with at least one temporary carrier of the semiconductor package.

While the compliant support structure 16A and the thermally conductive structure 16B may include the temporary support 17A and the permanent support 17B, the compliant support structure 16A and the thermally conductive structure 16B may include any suitable number of supports. In one example, a compliant support structure 16A described and illustrated herein may form a single CTE-compliant structure with the first die 12A, the second die 12B, and the first temporary structure 14 without depositing a temporary support structure, such as temporary support 17A.

As best seen in FIG. 7, first section 10 of semiconductor package 1 may also include at least one thermally conductive structure 16B formed with the compliant support structure 16A and formed about the first die 12A and the second die 12B. In the illustrated embodiment, a first thermally conductive portion of thermally conductive structure 16B may be engaged with the compliant support structure 16A and formed about the first die 12A, and a second thermally conductive portion of thermally conductive structure 16B is engaged with the compliant support structure 16A and formed about the second die 12B. The thermally conductive structure 16B is configured to conduct heat away from the

first die 12A and the second die 12B upon operation of the first die 12A and the second die 12B. Stated differently, thermally conductive structure **16**B is configured to provide thermal dissipation from the first die 12A and the second die **12**B in order to enable for higher-level assemblies, which is described in more detail below.

Each of the first and second thermally conductive portion of the thermally conductive structure **16**B may also have any suitable structural configuration for conducting heat away from the first die 12A and the second die 12B as dictated by the implementation of semiconductor package 1. In one instance, first and second thermally conductive portion of the thermally conductive structure 16B may be solid and away from the first die 12A and the second die 12B. In another instance, first and second thermally conductive portion of the thermally conductive structure 16B may be hollow thermally conductive structures and/or cavities for conducting heat away from the first die 12A and the second 20 die **12**B.

Referring to FIG. 2A, first section 10 of semiconductor package 1 may include at least one air cavity structure 20 formed between at least one die 12 and at least one temporary carrier 14. In the illustrated embodiment, a single air 25 cavity structure 20 is formed between the first die 12A and the first temporary carrier 14A. More particularly, air cavity structure 20 operably engages with the active surface 12A2 of first die 12A and the first surface 14A1 of first temporary carrier 14A. The use of the air cavity structure 20 with at 30 least one die 12 and at least one temporary carrier 14 may provide various advantages, including singulation, cleaning, deposit getters to the air cavity, temporary storage, and other various advantages of the like provided by the air cavity structure 20.

The air cavity structure 20 described and illustrated may be formed of any suitable materials that are standard and/or commercially available in the semiconductor package market. In one instance, an air cavity structure described and illustrated may be formed of a glass material. In another 40 instance, an air cavity structure described and illustrated may be formed of a plastic material. In yet another instance, an air cavity structure described and illustrated may be formed of a metal material. In yet another instance, an air cavity structure described and illustrated may be formed of 45 a ceramic material.

While air cavity structure 20 is formed between the first die 12A and the first temporary carrier 14A, the air cavity structure 20 or any number of air cavity structures may be formed between any die and/or temporary carrier provided 50 in a first portion of a semiconductor package. In one example, an air cavity structure may be formed between the second die 12B and the first temporary carrier 14A in which air cavity structure operably engages with the active surface **12B2** of second die **12B** and the first surface **14A1** of first 55 temporary carrier 14A.

First section 10 of the semiconductor package 1 includes at least one compliant electrical structure or interconnect generally referred to as numeral 22. The at least one electrical structure 22 may include any suitable electrical elements and/or components dictated by the implementation of the semiconductor package 1. In at least one instance, semiconductor package 1 includes a single electrical structure 22 in this specific implementation of semiconductor package 1 where the electrical structure 22 may be config- 65 ured to electrically connect the first die 12A and the second die 12B with specific electrical elements and/or components

**16**

provided in the electrical structure 22. Such elements and components of the electrical structure 22 are described in more detail below.

As best seen in FIG. 3A, the electrical structure 22 includes a first surface or first electrical engaging surface 22A that electrically connects with the first die 12A and the second die 12B. More particularly, the first surface 22A of electrical structure 22 electrically connects with the inactive surface 12A1 of the first die 12A and the inactive surface 10 **12B1** of the second die **12B**. Electrical structure **22** also includes a second surface or second electrical engaging surface 22B that is opposite to the first surface 22A. Second surface 22B of electrical structure 22 may electrically engage with any suitable components or elements provided compact thermally conductive structures for conducting heat 15 in semiconductor package 1. In one instance, second surface 22B of electrical structure 22 may electrically connect with a plurality of solder balls 24 for testing purposes of first section 10 or for constructing higher-level assemblies. In another instance, second surface 22B of electrical structure 22 may electrically connect with another electrical structure of a second section of semiconductor package 1, which is described in more detail below.

> It should be understood that electrical structure **22** of first section 10 may include various input and output connections and/or contours defined along the first surface 22A and/or the second surface 22B as dictated by the implantation of the semiconductor package 1. As such, desired electrical components (e.g., radio frequency devices, passive electrical devices, digital electrical devices, ground electrical elements, power electrical devices, etc.) may be engaged at specific input and output connections and/or contours defined along the first surface 22A and/or the second surface 22B. While not illustrated herein, additional supports or shielding features may be provided on the first surface 22A and/or the second surface 22B for structural support. Electrical structure 22 may also include a deposited conductive metal (e.g., copper or suitable conductive metals of the like) prior to or subsequent to the inclusion of the desired electrical components.

Such creation of input and output connections and/or contours defined along the first surface 22A and/or the second surface 22B may be performed by any suitable methods and techniques used in the semiconductor package field. In one instance, adaptive direct write lithography may be used to create various input and output connections and/or contours defined along the first surface 22A and/or the second surface 22B as dictated by the implantation of the semiconductor package 1.

Electrical structure 22 of first section 10 may also include at least one temporary dielectric applied to one or both of the first surface 22A and the second surface 22B. As best seen in FIGS. 3A and 3B, a first temporary dielectric or interior temporary dielectric 22C is applied between the first surface 22A and second surface 22B of the electrical structure 22, and a second temporary dielectric or exterior temporary dielectric 22D is applied to the second surface 22B of the electrical structure 22. Such inclusion of first temporary dielectric 22C and second temporary dielectric 22D may be performed by any suitable methods and techniques used in the semiconductor package field. In one instance, adaptive direct write lithography may be used to include first temporary dielectric 22C and second temporary dielectric 22D to first surface 22A and second surface 22B of electrical structure 22.

Still referring to FIGS. 3A and 3B, electrical structure 22 of first section 10 may also include and/or incorporate at least one permanent dielectric to add electromechanical

support to signal transmission lines, ground transmission lines, power transmission lines, shielding structures, or other electrical devices. In this illustrated embodiment, a permanent dielectric 22E is incorporated into the electrical structure **22** to add electromechanical support to signal transmission lines, ground transmission lines, power transmission lines, shielding structures, or other electrical devices. Such inclusion of permanent dielectric 22E may be performed by any suitable methods and techniques used in the semiconductor package field. In one instance, adaptive direct write lithography may be used to include permanent dielectric 22E to the electrical structure 22 at appropriate and/or desired locations based on mechanical simulations performed on the electrical structure 22. In one instance, the supports provided in the permanent dielectric 22E may be cantilevered from surrounding metal features. In another instance, the supports provided in the permanent dielectric 22E may be positioned on the center from metal below or directly attached to at least one die 12 surface.

While the permanent dielectric 22E is separate from the first temporary dielectric 22C and the second temporary dielectric 22D, a permanent dielectric may be incorporated with one or both of a first temporary dielectric or second temporary dielectric for assembly purposes. In one instance, 25 a pre-fabricated dielectric component may be installed into a cavity of a second temporary dielectric where the pre-fabricated dielectric component is encapsulated and remains as a permanent support.

As stated previously, electrical components may be introduced into the electrical structure 22 by any suitable methods and techniques. In one instance, electrical components may be permanently added into the electrical structure 22 upon manufacturing and/or building of the electrical structure 22. In this same instance, an electrical component may 35 be incorporated as a layered or interdigital structure using a deposition process (as described above) or an additive manufacturing process (e.g., plasma spray methods). In another instance, prefabricated and/or existing electrical components may be added to the electrical structure 22 once 40 the electrical structure 22 is built.

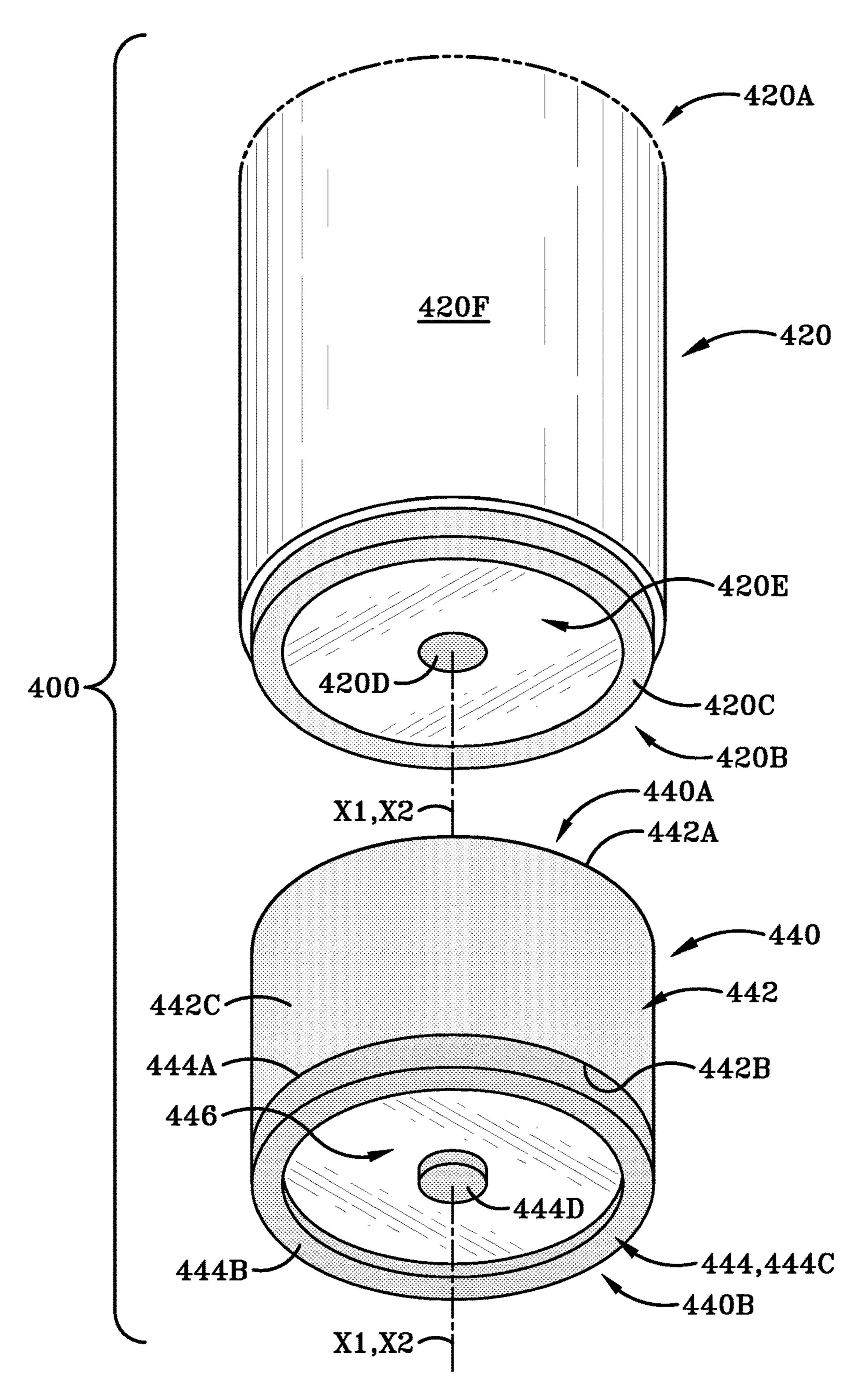

Referring to FIGS. 4A-5A, the semiconductor package 1 includes at least another portion or second section 40 that includes at least another mixed signal die or semiconductor die (hereinafter "die") generally referred to as numeral 42. 45 The at least another die 42 may include any suitable elements and/or components for generating various mixed signals dictated by the implementation of the semiconductor package 1. In at least one instance, semiconductor package 1 includes a first die 42A, a second die 42B, and a third die 50 **42**C in this specific implementation of semiconductor package 1 where the first die 42A, the second die 42B, and the third die 42C may be configured to generate mixed signals. In other exemplary instances, semiconductor package 1 may include any suitable number of semiconductor dies config- 55 ured to generate mixed signals dictated by the implementation of the semiconductor package 1.

As illustrated in FIGS. 4A-5A, the first die 42A includes a first surface or inactive surface 42A1 that is free from input and output locations. First die 42A also includes a second 60 surface or active surface 42A2 that is opposite to the inactive surface 42A1 and includes the input and output locations of the first die 42A. First die 42A may also include a first side 42A3 defined between the inactive surface 42A1 and the active surface 42A2 and is free from input and output 65 locations. First die 42A may also include a second side 42A4 defined between the inactive surface 42A1 and the active

18

surface 42A2 that is opposite to the first side 42A3 and is free from input and output locations.

Similarly, as illustrated in FIGS. 4A-5A, the second die 42B includes a first surface or inactive surface 42B1 that is free from input and output locations. Second die 42B also includes a second surface or active surface 42B2 that is opposite to the inactive surface 42B1 and includes the input and output locations of the second die 42B. Second die 42B may also include a first side 42B3 defined between the inactive surface 42B1 and the active surface 42B2 and is free from input and output locations. Second die 42B may also include a second side 42B4 defined between the inactive surface 42B1 and the active surface 42B2 that is opposite to the first side 42B3 and is free from input and output locations.

Similarly, as illustrated in FIGS. 4A-5A, the third die 42C includes a first surface or inactive surface 42C1 that is free from input and output locations. Third die 42C also includes a second surface or active surface 42C2 that is opposite to the inactive surface 42C1 and includes the input and output locations of the third die 42C. Third die 42C may also include a first side 42C3 defined between the inactive surface 42C1 and the active surface 42C2 and is free from input and output locations. Third die 42C may also include a second side 42C4 defined between the inactive surface 42C1 and the active surface 42C2 that is opposite to the first side 42C3 and is free from input and output locations.

The first die 42A, the second die 42B, and the third die 42C may be formed of any suitable semiconductor materials conventionally and commercially available in the field of semiconductor packages. In one aspect, first die 42A may be formed of a first material (e.g., silicon), the second die 42B may be formed of a second material (e.g., gallium arsenide), and the third die 42C may be formed of a third material (e.g., silicon-germanium) where each of the first material, the second material, and the third material are different from one another. In another aspect, first die 42A may be formed of a first material, the second die 42B may be formed of a second material, and the third die 42C may be formed of a third material where the first material, the second material, and the third material are the same materials. It should be appreciated that a first die, a second die, and a third die of a semiconductor package may be formed of any suitable semiconductor materials discussed herein and conventionally and commercially available in the field of semiconductor packages.

Referring to FIGS. 4A-4F, the second section 40 also includes at least one temporary carrier or temporary workpiece holder, generally referred to as numeral 44, that operably engages with that least one die 42. The at least one temporary carrier 44 may include any suitable elements and/or components for operably engaging with at least one die 42 as dictated by the implementation of the semiconductor package 1. In at least one instance, semiconductor package 1 includes a first temporary carrier 44A that operably engages with the first die 42A, the second die 42B, and a third die 42C. In the same instance, semiconductor package 1 also includes a second temporary carrier 44B that operably engages with a compliant support structure of the second section 40, which is described in more detail below. In other exemplary instances, semiconductor package 1 may include any suitable number of temporary carriers configured operably engage with at least one die described and illustrated herein.

Referring to FIG. 4A, the first temporary carrier 44A includes a first surface or engaging surface 44A1 that is configured to operably engage with the at least one die 42.

In the illustrated embodiment, the engaging surface 44A1 of the first temporary carrier 44A is configured to operably engage with the first die 42A, the second die 42B, and the third die 42C. In other exemplary embodiments, the engaging surface 44A1 of the first temporary carrier 44A is 5 configured to operably engage with any suitable number of dies as dictated by the implementation of the semiconductor package 1. As described in more detail below, the first temporary carrier 44A is configured to be removed and/or separated from the first die 42A, the second die 42B, and the third die 42C upon manufacturing the semiconductor package 1; as such, the first temporary carrier 44A is a removable and/or separable component from the first die 42A, the second die 42B, and the third die 42C. First temporary carrier 44A also includes a second surface or non-engaging surface 44A2 that is opposite to the engaging surface 44A1 and remote from the first die 42A, the second die 42B, and the third die 42C.

It should be understood that the first die 42A, the second below. die 42B, and the third die 42C may be operably engaged at any suitable location on the engaging surface 44A1 of first temporary carrier 44A.

Referring to FIG. 4F, the second temporary carrier 44B also includes a first surface or engaging surface **44B1** that is 25 configured to operably engage with at least one compliant support structure of second section 40 of semiconductor package 1, which is described in more detail below. In other exemplary embodiments, the engaging surface 44B1 of the second temporary carrier 44B is configured to operably 30 engage with any suitable number of compliant support structures as dictated by the implementation of the semiconductor package 1. As described in more detail below, the second temporary carrier 44B is configured to be removed and/or separated from a compliant support structure upon 35 manufacturing the semiconductor package 1; as such, the second temporary carrier 44B is a removable and/or separable component from the compliant support structure at the first engaging surface 44B1. Second temporary carrier 44B also includes a second surface or non-engaging surface 40 44B2 that is opposite to the engaging surface 44B1 and remote from a compliant support structure of second section 40 of semiconductor package 1.

Referring to FIG. 4G, an interconnect dielectric 45 may be provided between the first die 42A, the second die 42B, 45 the third die 42C, and the first temporary carrier 44A. Such use of the interconnect dielectric 45 may protect the active surfaces 42A2, 42B2, 42C2 of the first die 42A, the second die 42B, and the third die 42C until the semiconductor package 1 is constructed. As such, interconnect dielectric 45 may be temporary and removable from the first die 42A, the second die 42B, and the third die 42C once the semiconductor package 1 is constructed.

As best seen in FIGS. 4B-4E, at least one compliant support structure 46A may be provided in the second section 55 40 of semiconductor package 1. In the illustrated embodiment, second section 40 includes a single compliant support structure 46A formed about the perimeter of the second section 40 while encapsulating and/or encasing the first die 42A, the second die 42B, and the third die 42C inside of the 60 compliant support structure 46A. Compliant support structure 46A is also operably engaged with the first temporary carrier 44A, specifically with the engaging surface 44A1 of first temporary carrier 44A. The compliant support structure 46A is configured to provide translational support to the first die 42A, the second die 42B, and the third die 42C in the horizontal or lateral directions to prevent the first die 42A,

**20**

the second die 42B, and the third die 42C from shifting or rotating along the engaging surface 44A1 of the first temporary carrier 44A.

As best seen in FIG. 4C, second section 40 of semiconductor package 1 may also include a thru-interconnect structure 46B formed with the compliant support structure **46**A and formed about the first die **42**A, the second die **42**B, and the third die **42**C. In the illustrated embodiment, thruinterconnect structure 46B may be engaged with the compliant support structure 46A and formed about the first die 42A, the second die 42B, and the third die 42C. In one instance, the thru-interconnect structure **46**B is configured to enable electrical connection between solder balls (described in more detail below) and the first die 42A, the second die **42**B, and the third die **42**C. In another instance, the thruinterconnect structure **46**B is configured to enable electrical connection between solder balls and the first die 42A, the second die 42B, and the third die 42C in order to enable for higher-level assemblies, which is described in more detail

It should be understood that compliant support structure **46**A and thru-interconnect structure **46**B may include a temporary or removable support 47A and a permanent support 47B. As best seen in FIG. 4B, the temporary support 47A is initially applied to the first die 42A, second die 42B, third die 42C, and the first temporary carrier 44A via suitable fabrication methods such as adaptive direct write lithography and other fabrication methods of the like. In this embodiment, temporary support 47A may be a cured polymer network that is formed on and about the first die 42A, second die 42B, third die 42C, and the first temporary carrier 44A. Additionally, the temporary support 47A may also include a preferably thin-metal coating. Once the temporary support 47A is cured, the temporary support may be removed to leave the permanent support 47B engaged with the engaging surface 44A1 of the first temporary carrier 44A along with the first die 42A, the second die 42B, and the third die 42C. The permanent support 47B may also be a CTE-compliant structure that is dictated by the implementation of semiconductor package 1.

The compliant support structure **46**A may also define any suitable structural configuration in order to provide translational support to the first die 42A, the second die 42B, and the third die 42C in the horizontal or lateral directions so that the first die 42A, the second die 42B, and the third die 42C are prevented from shifting or rotating along the engaging surface 44A1 of the first temporary carrier 44A. Such structural configuration of the compliant support structure **46**A may be based on various considerations, including the size, shape, and materials of the first die 42A, the second die **42**B, and the third die **42**C. In one instance, a compliant support structure described and illustrated herein may be an open-cell foam stochastic three-dimensional structure that forms about at least one die of a semiconductor package and that engages with at least one temporary carrier of the semiconductor package. In another instance, a compliant support structure described and illustrated herein may be a non-stochastic lattice structure that forms about at least one die of a semiconductor package and that engages with at least one temporary carrier of the semiconductor package.

While the compliant support structure 46A and thruinterconnect structure 46B may include the temporary support 47A and the permanent support 47B, the compliant support structure 46A and thru-interconnect structure 46B may include any suitable number of supports. In one example, a compliant support structure 46A and thru-interconnect structure 46B described and illustrated herein may

form a single CTE-compliant structure with the first die 42A, the second die 42B, the third die 42C and the first temporary carrier 44A without depositing a temporary support structure, such as temporary support 47A.