## US012430280B2

US 12,430,280 B2

Sep. 30, 2025

## (12) United States Patent

Doddi et al.

(10) Patent No.:

(45) **Date of Patent:**

### **References Cited** (56)

2004/0236815 A1 11/2004 Mirsky et al. 2011/0179212 A1 7/2011 Hartman 6/2016 Morris et al. 2016/0179718 A1 11/2016 Lee 2016/0342566 A1 2017/0235701 A1 8/2017 Pethe et al. 2022/0222198 A1\* G06F 13/4273 7/2022 Lanka ..... 2022/0327083 A1 10/2022 Das Sharma et al.

U.S. PATENT DOCUMENTS

## OTHER PUBLICATIONS

International Search Report and Written Opinion—PCT/US2024/ 042867—ISA/EPO—Nov. 26, 2024.

\* cited by examiner

Primary Examiner — Idriss N Alrobaye Assistant Examiner — Dayton Lewis-Taylor (74) Attorney, Agent, or Firm — Muncy, Geissler, Olds & Lowe, P.C.

#### **ABSTRACT** (57)

Various embodiments include methods and devices for implementing Universal Chiplet Interconnect Express (UCIe) link configuration for multi-module chiplets of a computing device. Embodiments may include transitioning a UCIe link in an active state having a first sideband that is active to the UCIe link in a reset state, and initializing at least one sideband for the UCIe link that is a different functional sideband of a multi-module chiplet than the first sideband following the reset state of the UCIe link. Embodiments may include reading sideband data configured to represent a functional sideband of the multi-module chiplet, and initializing the functional sideband as the at least one sideband. Embodiments may include reading sideband data configured to represent at least two functional sidebands of the multi-module chiplet, and initializing at least one functional sideband of the at least two functional sidebands as the at least one sideband.

## 27 Claims, 18 Drawing Sheets

## MECHANISM TO IMPROVE THE RELIABILITY OF SIDEBAND IN CHIPLETS

Applicant: QUALCOMM Incorporated, San

Diego, CA (US)

Inventors: Ravindranath Doddi, Hyderabad (IN); Umamaheshwaran V, Salem (IN); **Afreen Haider**, Muzaffarpur (IN); Lekhya Pavani Godavarthi, Hyderabad (IN); Harinatha Reddy Ramireddy, Hyderabad (IN); James Lionel Panian, San Marcos, CA (US); Ramacharan Sundararaman, San Jose, CA (US); Santhosh Reddy

Assignee: Qualcomm Incorporated, San Diego, (73)

CA (US)

Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 64 days.

**Akavaram**, Hyderabad (IN)

Appl. No.: 18/466,299

Sep. 13, 2023 (22)Filed:

#### (65)**Prior Publication Data**

US 2025/0086136 A1 Mar. 13, 2025

Int. Cl. (51)G06F 13/42 (2006.01)

G06F 15/78 (2006.01)

U.S. Cl. (52)CPC ..... *G06F 13/4282* (2013.01); *G06F 15/7825* (2013.01)

## Field of Classification Search

None

See application file for complete search history.

FIG. 1

സ

五 (五) (4)

| Active<br>Sideband   | Functional<br>Sideband 0 | Functional<br>Sideband 1 | Functional<br>Sideband 2 | Functional<br>Sideband 3 |

|----------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| Active<br>Sideband 0 | 0                        |                          | 0                        |                          |

| Active<br>Sideband 1 |                          |                          |                          |                          |

FG. 5

<u>「</u>

U.S. Patent US 12,430,280 B2 Sep. 30, 2025 Sheet 7 of 18 -1006 1000 Reset -1008 TRAIN SBINIT **ERROR** -1010 **MBINIT** -1004 -1012 MBTRAIN L1/L2 -1014 LINKINIT -1002 ACTIVE PHYRETRAIN

FIG. 10

FIG. 11A

FIG. 11B

FIG. 11C

FIG. 12A

FIG. 12B

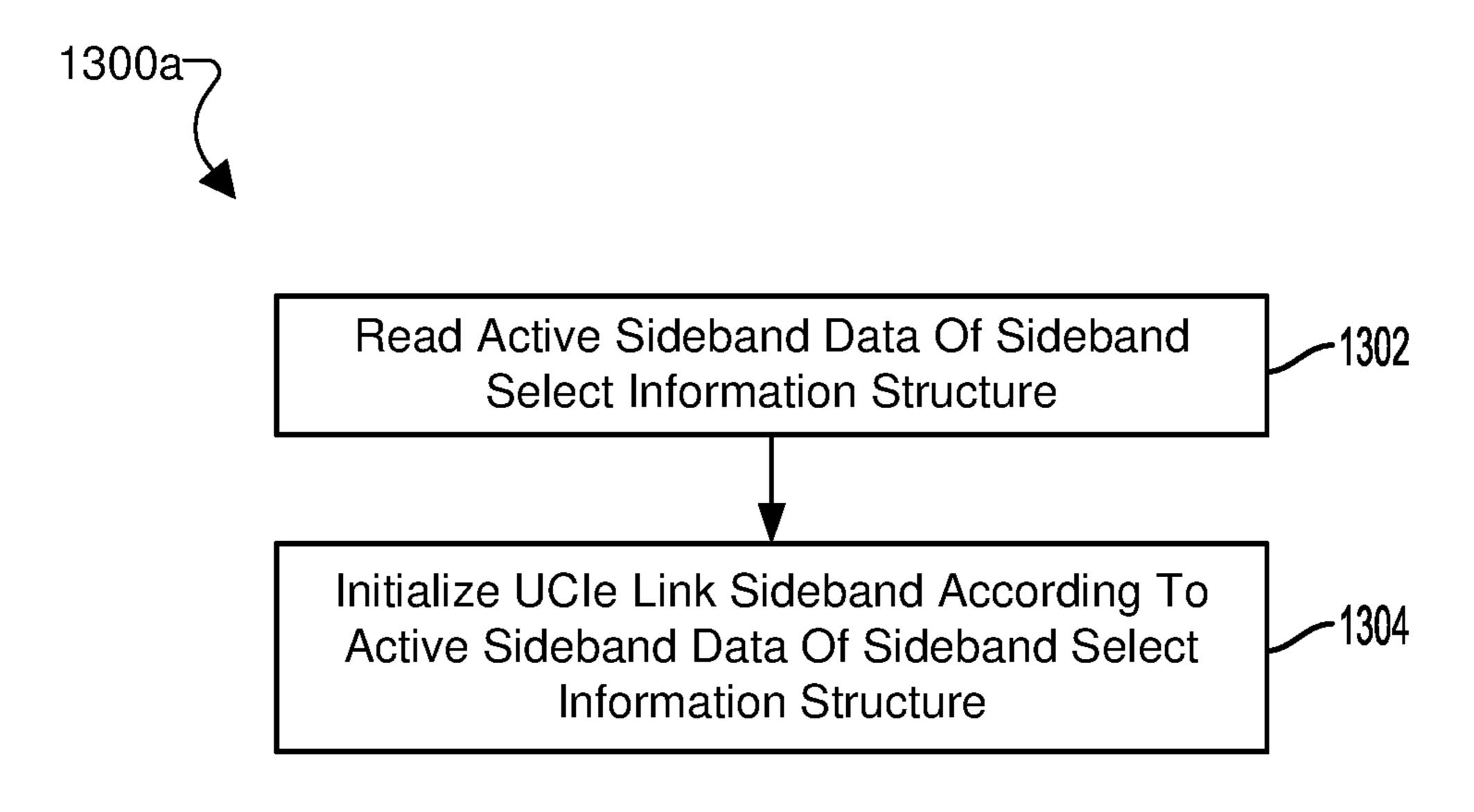

FIG. 13A

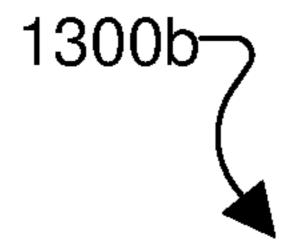

FIG. 13B

Sep. 30, 2025

FIG. 17B

FIG. 17C

# MECHANISM TO IMPROVE THE RELIABILITY OF SIDEBAND IN CHIPLETS

## BACKGROUND

The Universal Chiplet Interconnect Express (UCIe) specification provides for chiplets to operate in multi-module (or interface) configurations, either in a pair of 2 or 4 modules (or interfaces). The multi-module configurations are applicable to both standard (low bandwidth) and advanced (high bandwidth) packages. In multi-module configurations, after the initialization of the sidebands and mainbands, only one sideband of one module will be configured to send the required messages and other sidebands of the other modules will be in powered off state.

### **SUMMARY**

Various aspects provide methods include methods and 20 apparatuses for implementing such methods for configuring the Universal Chiplet Interconnect Express (UCIe) link between multi-module chiplets of a computing device. Various aspects may include transitioning a UCIe link in an active state having a first sideband that is active to the UCIe 25 link in a reset state, and initializing at least one sideband for the UCIe link that is a different functional sideband of a multi-module chiplet than the first sideband following the reset state of the UCIe link. Some aspects may further include reading active sideband data configured to represent 30 a functional sideband of the multi-module chiplet from a sideband select information structure, in which initializing the at least one sideband for the UCIe link that is a different functional sideband of the multi-module chiplet than the first sideband following the reset state of the UCIe link may 35 include initializing the functional sideband represented by the active sideband data.

Some aspects may further include receiving a sideband configuration signal having active sideband data configured to represent a functional sideband of the multi-module 40 chiplet, in which the functional sideband includes the at least one sideband for the UCIe link that is a different functional sideband of the multi-module chiplet than the first sideband, and setting a value at a sideband select information structure based on the active sideband data.

Some aspects may further include reading aggregate sideband data configured to represent at least two functional sidebands of the multi-module chiplet from a sideband aggregate information structure, in which initializing the at least one sideband for the UCIe link that is a different 50 functional sideband of the multi-module chiplet than the first sideband following the reset state of the UCIe link may include initializing the at least one functional sideband of the at least two functional sidebands represented by the aggregate sideband data. In some aspects, the at least two functional sidebands represented by the aggregate sideband data may include the first sideband and the at least one sideband or the at least one sideband and not the first sideband.

Some aspects may further include initializing the first sideband for the UCIe link following the reset state of the 60 UCIe link. Some aspects may further include identifying that a process implemented using the at least one sideband is complete, and clearing aggregate sideband data configured to represent at least two functional sidebands of the multi-module chiplet from a sideband aggregate information 65 structure, in which the at least two functional sidebands include the at least one sideband.

2

Some aspects may further include identifying that another multi-module chiplet supports a UCIe link using at least two sidebands, in which initializing the at least one sideband for the UCIe link that is a different functional sideband of the multi-module chiplet than the first sideband following the reset state of the UCIe link occurs following identifying that the another multi-module chiplet supports a UCIe link using at least two sidebands.

In some aspects, transitioning the UCIe link in the active state having the first sideband that is active to the UCIe link in the reset state may include transitioning the UCIe link in the active state to the UCIe link in the reset state link based on an elapsed period. Some aspects may further include receiving a sideband configuration signal having a sideband timer data, setting a value at a sideband timer information structure based on the sideband timer data, updating the value at the sideband timer information structure, and comparing the value of the sideband timer information structure to a threshold sideband timer value, in which the elapsed period is based on comparing the value of the sideband timer information structure to the threshold sideband timer value.

Further aspects include a computing device including a memory, a processor, multi-module chiplets connected via a UCIe link, and/or a UCIe link configuration device configured to perform operations of any of the methods summarized above. Further aspects include a multi-module chiplet connected via a UCIe link, and a UCIe link configuration device configured to perform operations of any of the methods summarized above. Further aspects include a multi-module chiplet having means for performing functions of any of the methods summarized above. Further aspects include a computing device having means for performing functions of any of the methods summarized above.

## BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated herein and constitute part of this specification, illustrate example embodiments of various embodiments, and together with the general description given above and the detailed description given below, serve to explain the features of the claims.

FIG. 1 is a component block diagram illustrating an example computing device suitable for implementing various embodiments.

FIG. 2 is a component block diagram illustrating an example of a multi-module chiplet configuration of a Universal Chiplet Interconnect Express (UCIe) system of the computing device suitable for implementing various embodiments.

FIG. 3 is a component block diagram illustrating an example of a multi-module chiplet configuration of a chiplet configured for UCIe link sideband selection suitable for implementing various embodiments.

FIG. 4 is a component block and information structure diagram illustrating an example of a sideband select information structure for UCIe link sideband selection suitable for implementing various embodiments.

FIG. **5** is an information structure diagram illustrating an example information structure for implementing UCIe link sideband selection according to an embodiment.

FIG. 6 is a component block and information structure diagram illustrating an example of a sideband select timer information structure for UCIe link sideband selection suitable for implementing various embodiments.

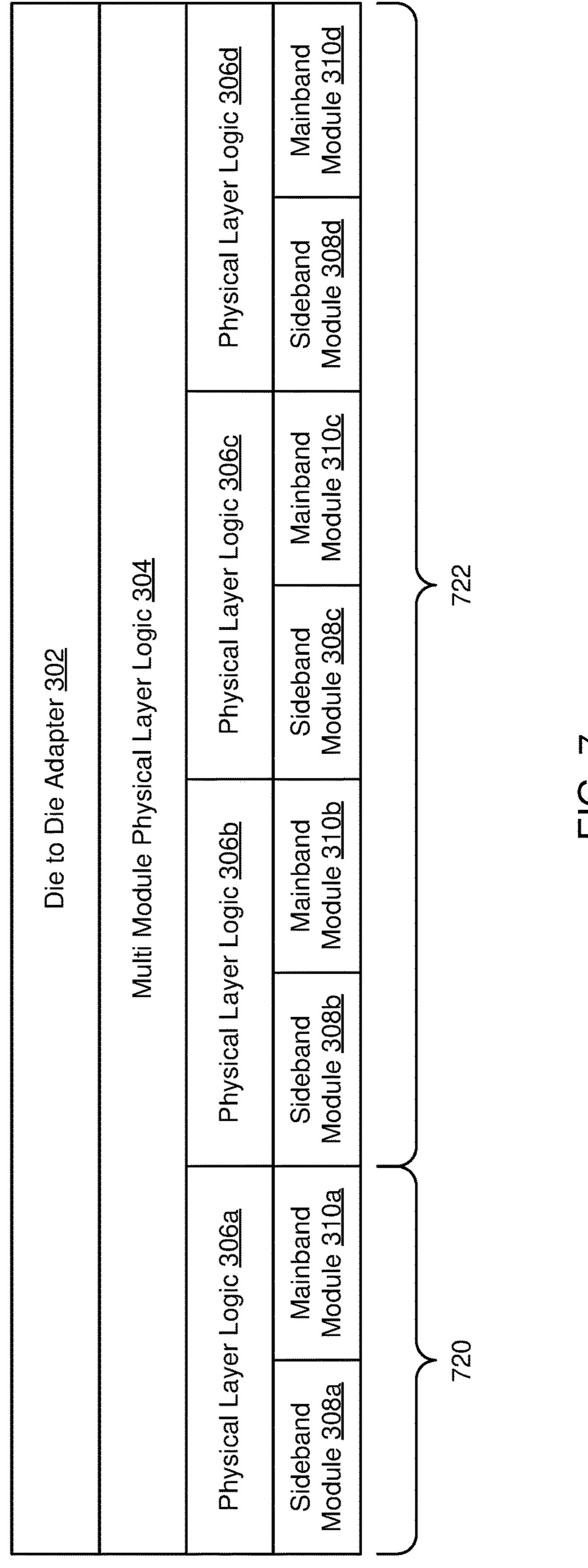

FIG. 7 is a component block diagram illustrating an example of a multi-module chiplet configuration of a UCIe

communication module configured for UCIe link sideband aggregation suitable for implementing various embodiments.

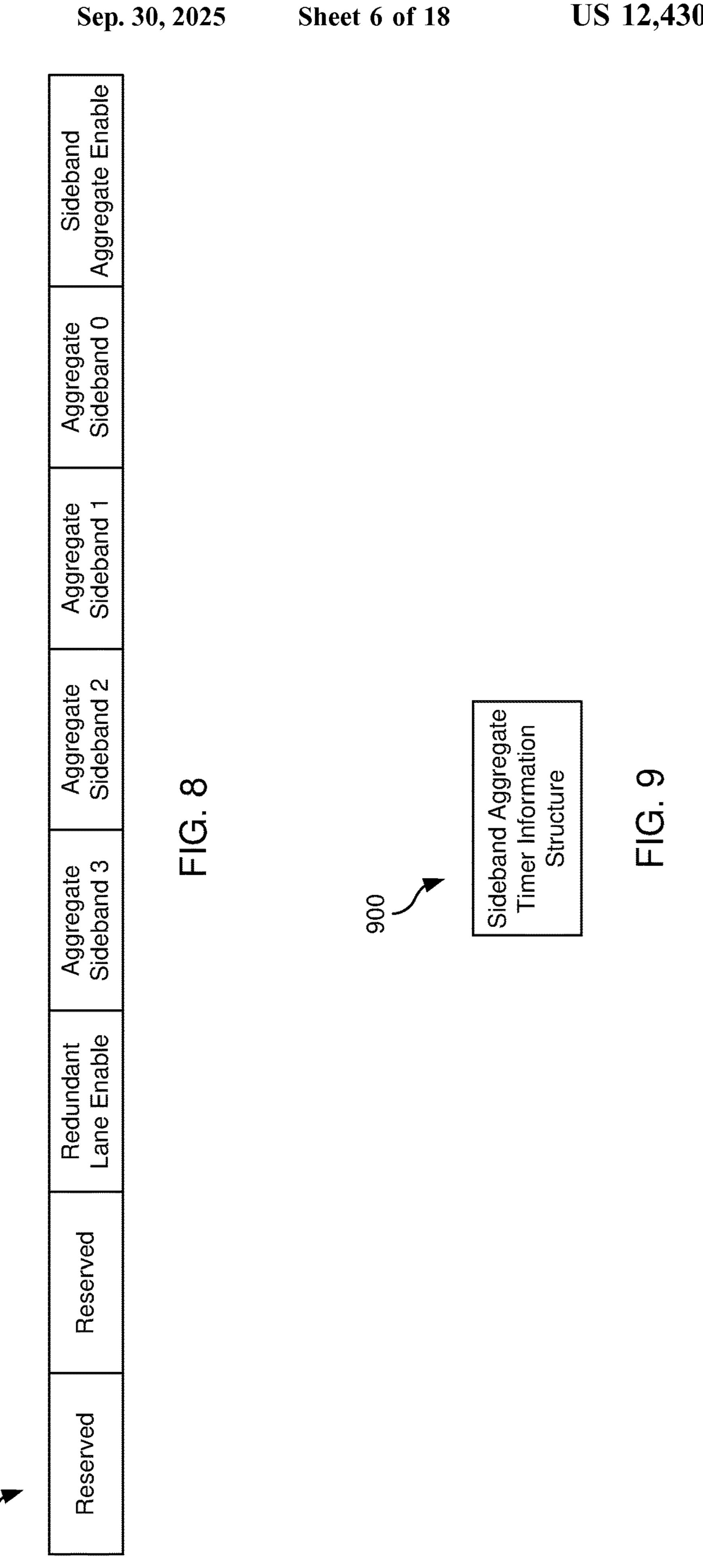

FIG. **8** is a component block and information structure diagram illustrating an example of a sideband aggregate 5 information structure for UCIe link sideband aggregation suitable for implementing various embodiments.

FIG. 9 is a component block and information structure diagram illustrating an example of a sideband aggregate timer information structure for UCIe link sideband aggre- 10 gation suitable for implementing various embodiments.

FIG. 10 is a graph flow diagram illustrating an example UCIe link training status and state machine suitable for implementing various embodiments.

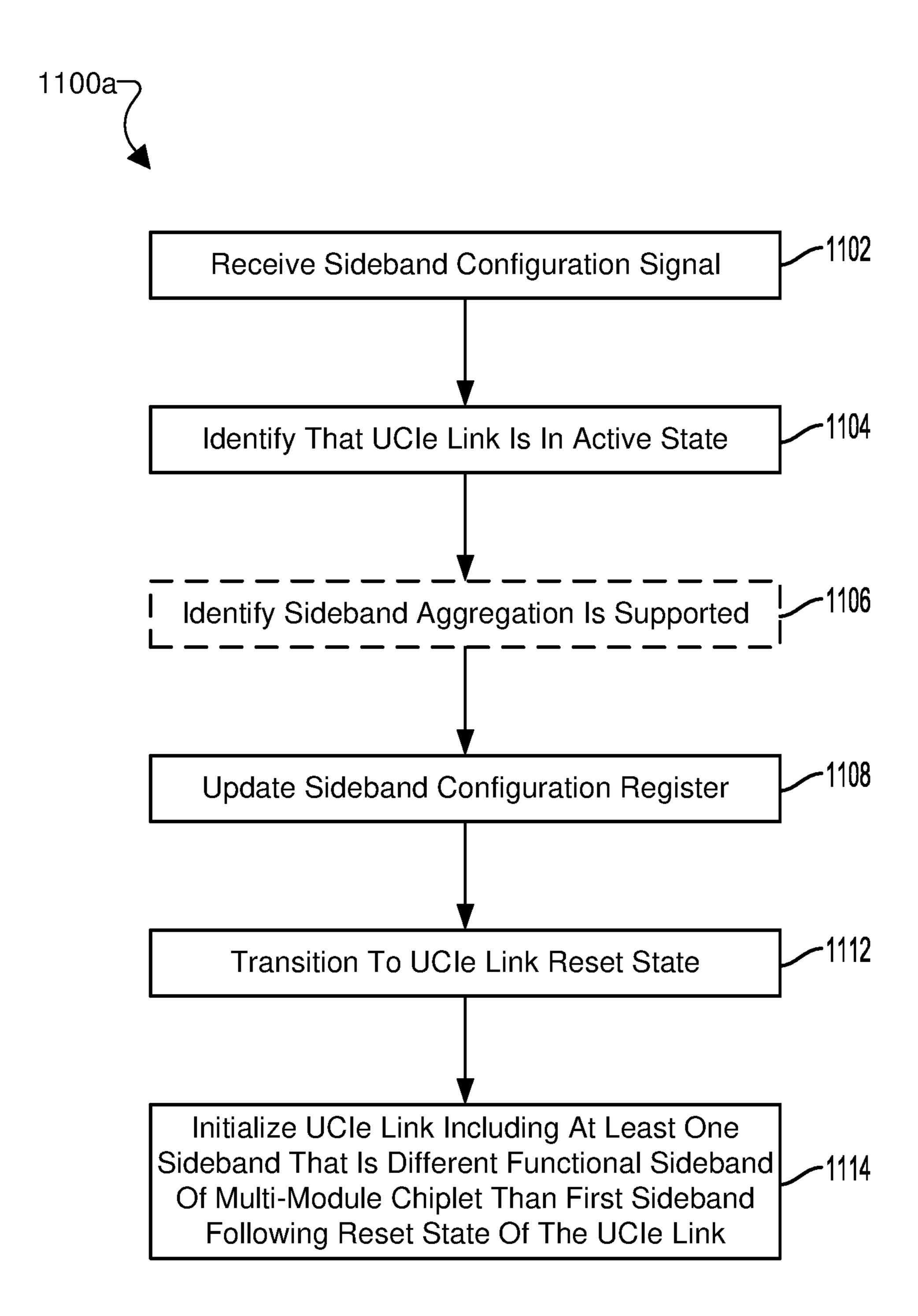

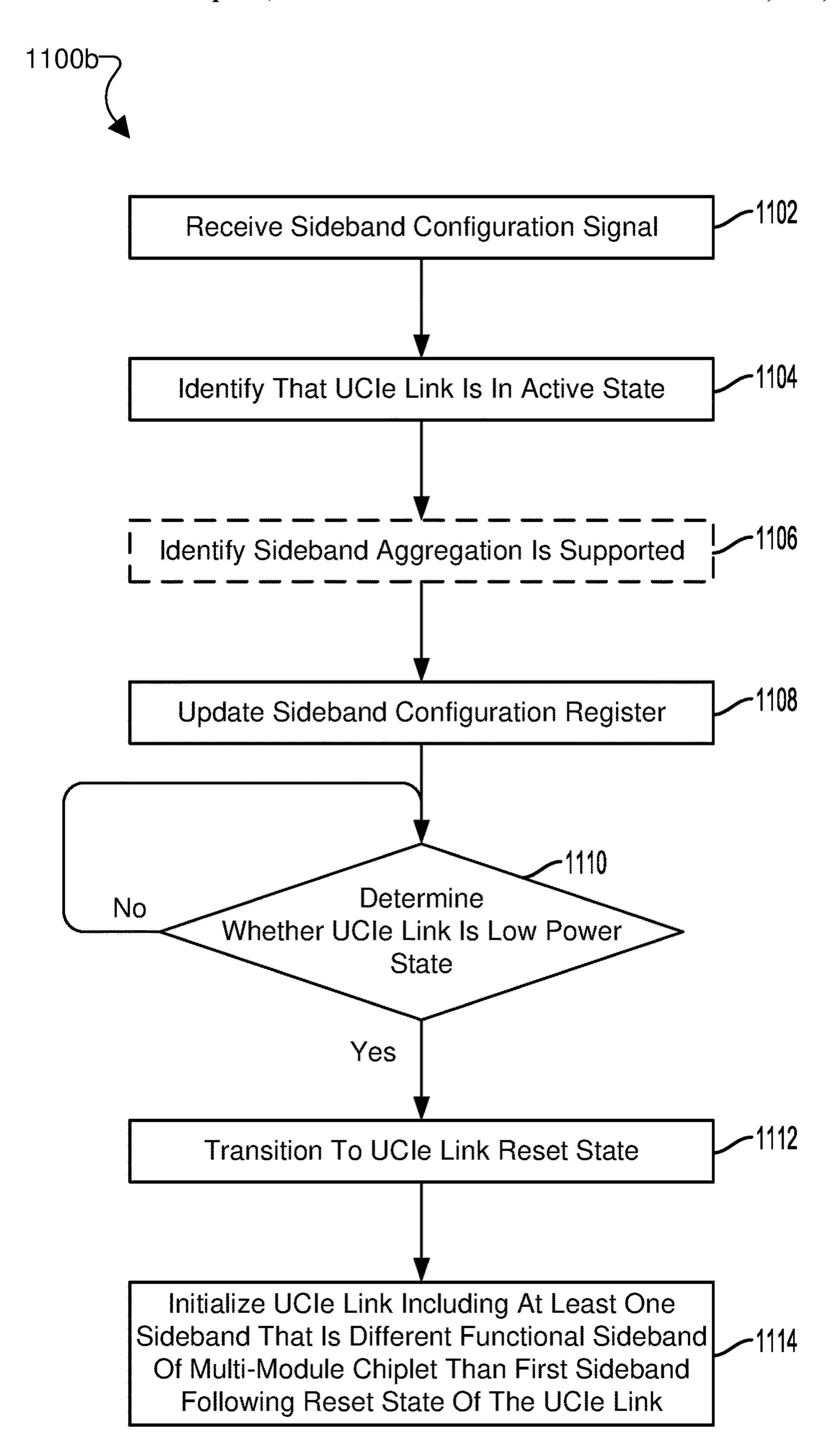

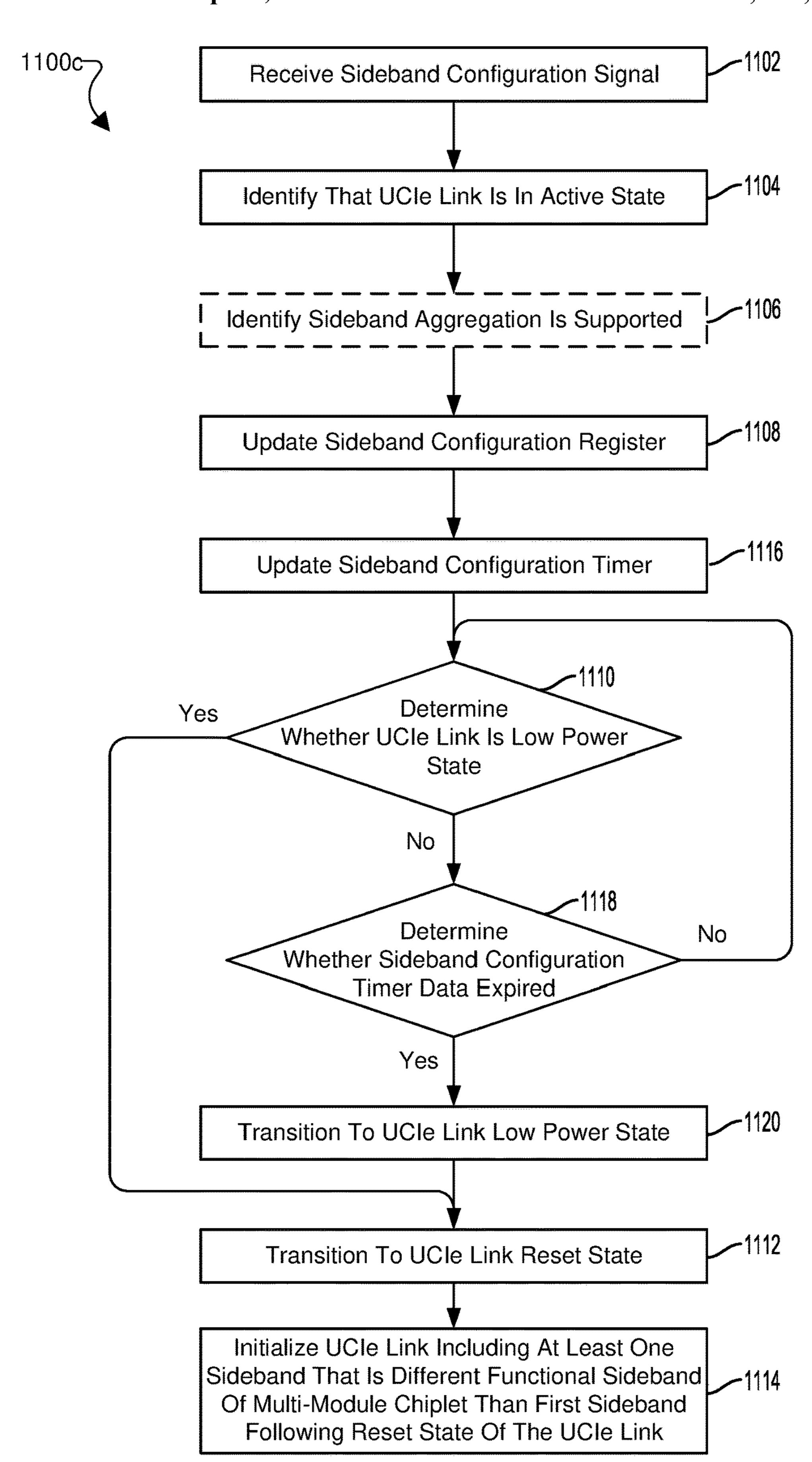

FIGS. 11A-11C are process flow diagrams illustrating 15 example methods for implementing multi-module chiplet configured UCIe link sideband configuration according to an embodiment.

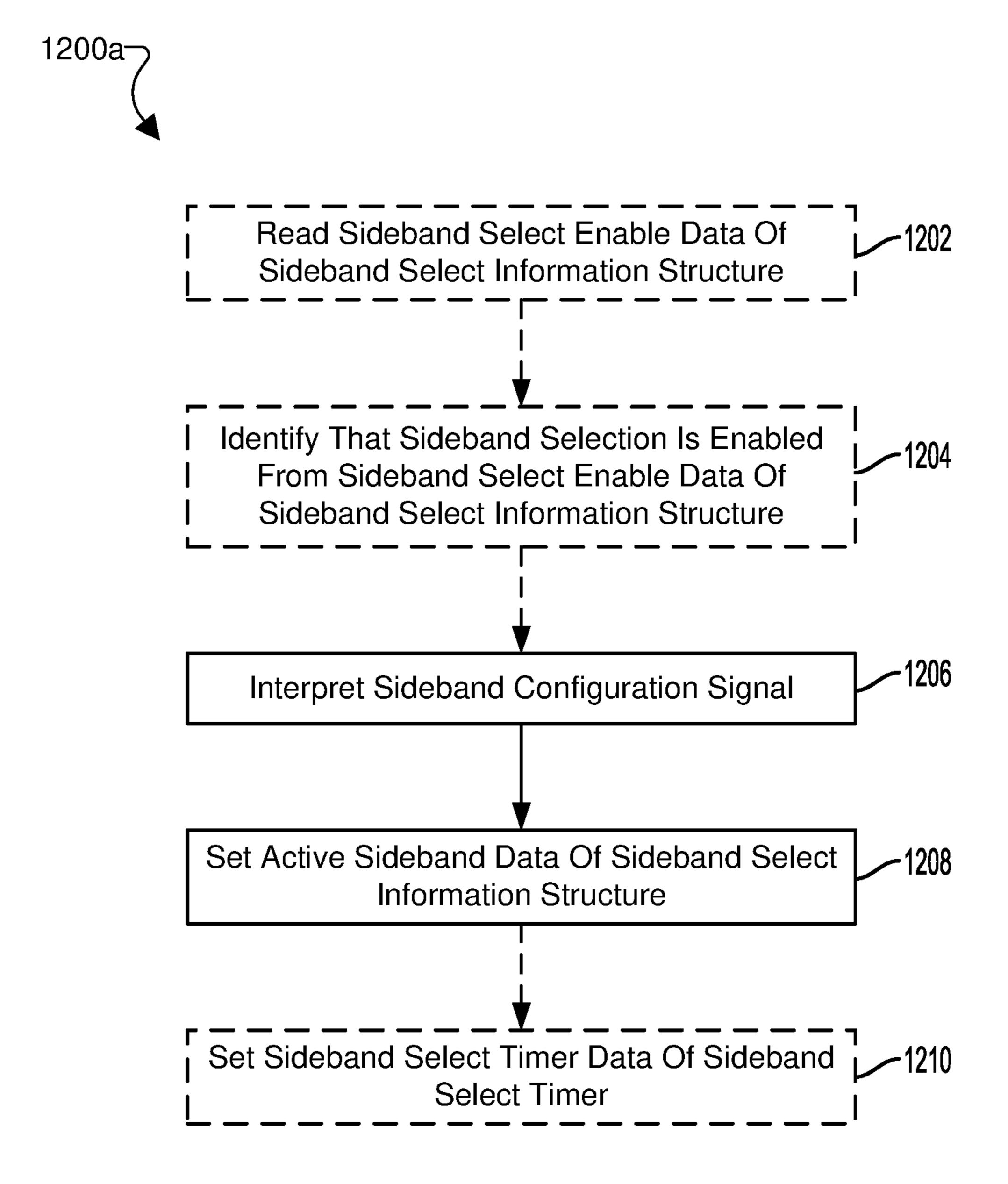

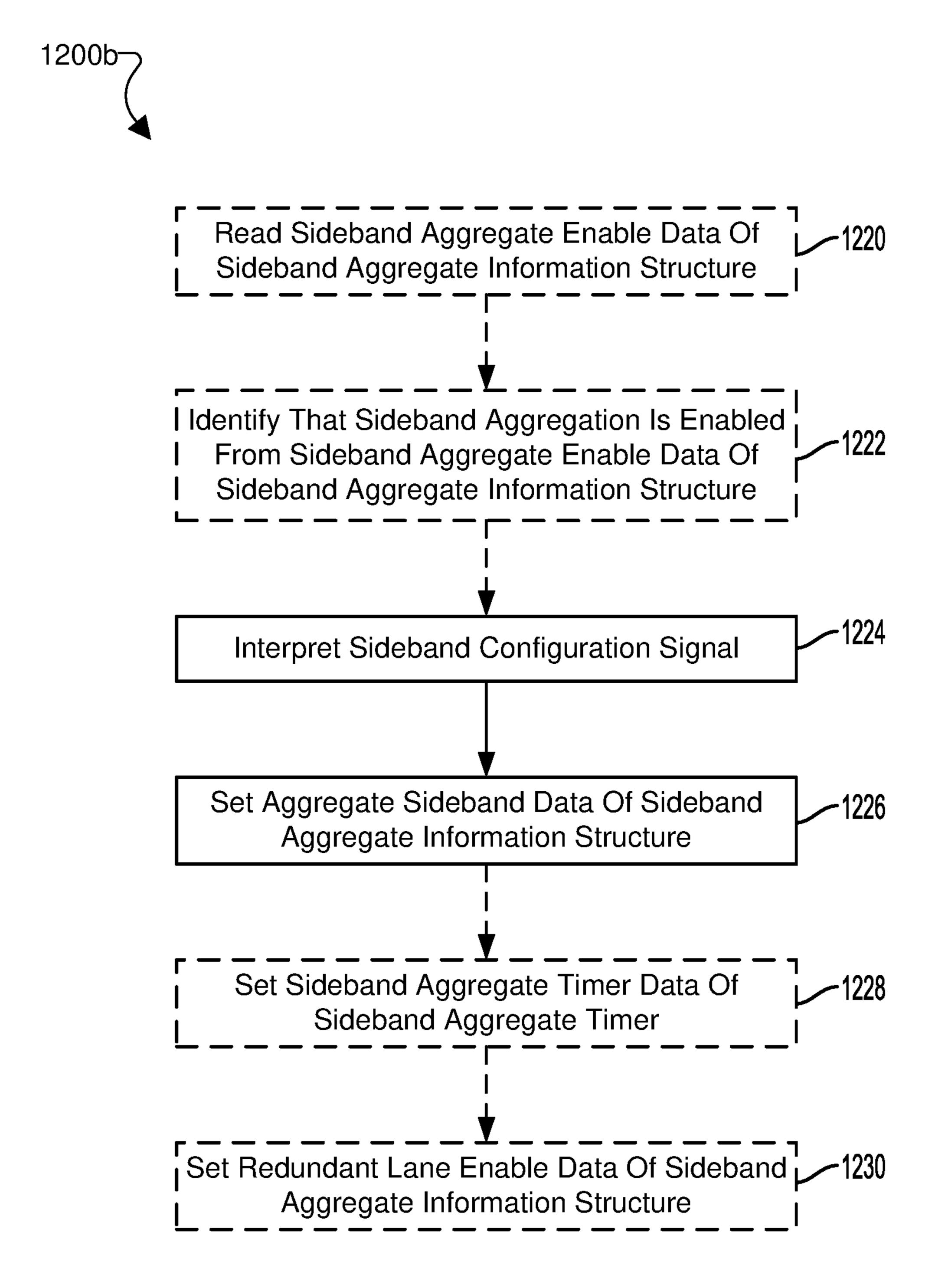

FIGS. 12A and 12B are process flow diagrams illustrating example methods for implementing multi-module chiplet <sup>20</sup> configured UCIe link sideband configuration according to an embodiment.

FIGS. 13A and 13B are process flow diagrams illustrating example methods for implementing multi-module chiplet configured UCIe link sideband configuration according to an <sup>25</sup> embodiment.

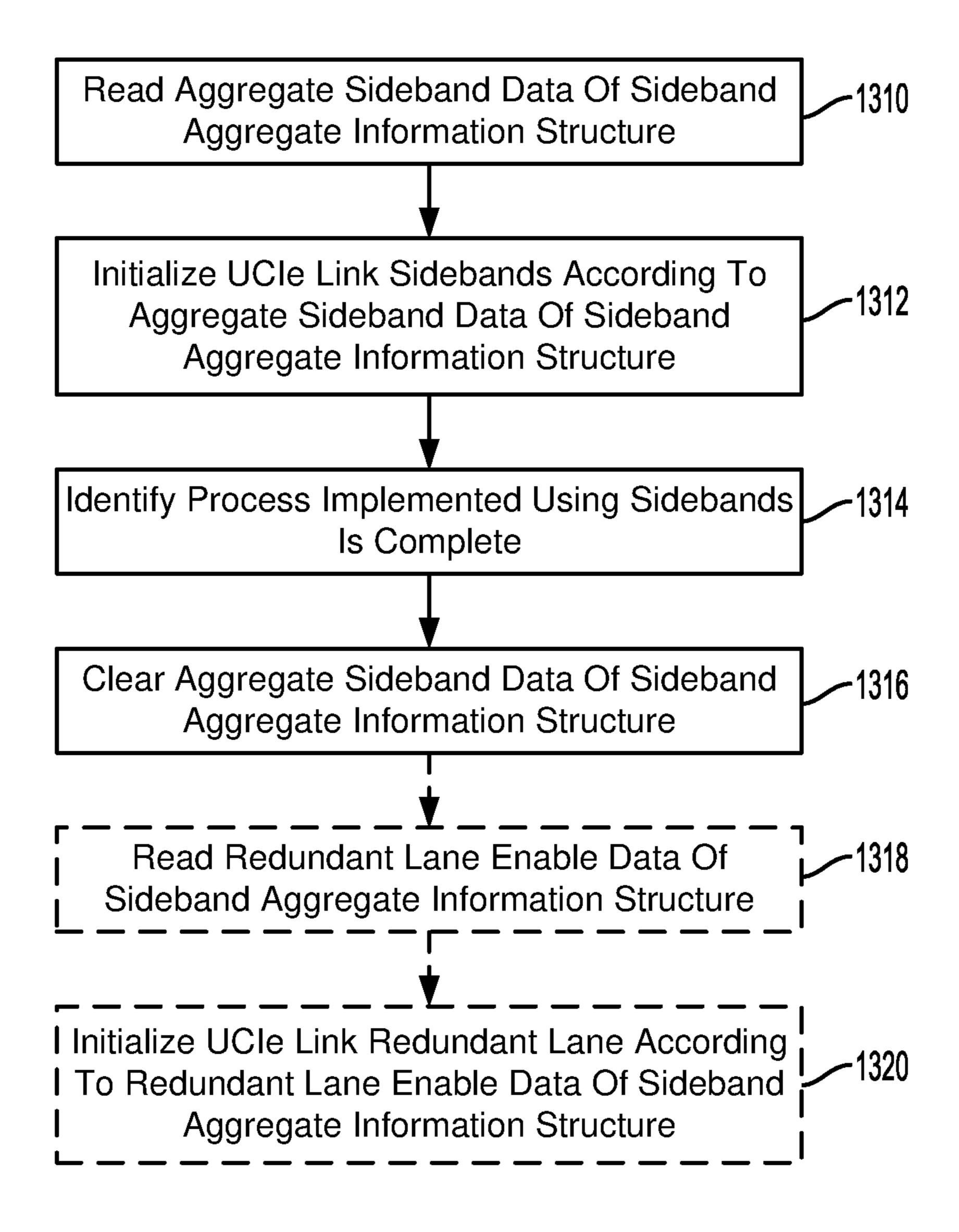

FIG. 14 is a component block diagram illustrating an example mobile computing device suitable for implementing various embodiments.

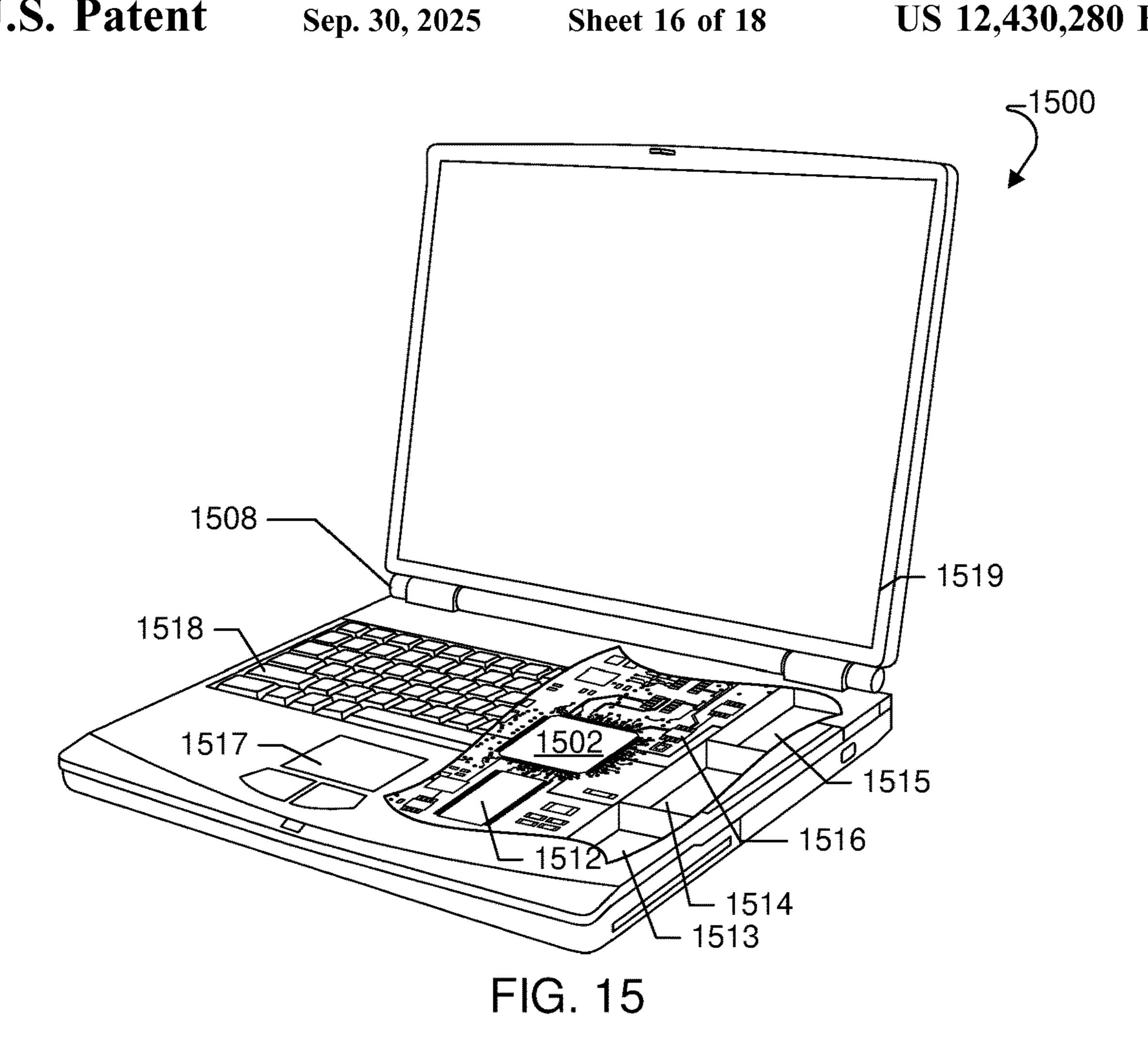

FIG. **15** is a component block diagram illustrating an <sup>30</sup> example mobile computing device suitable for implementing various embodiments.

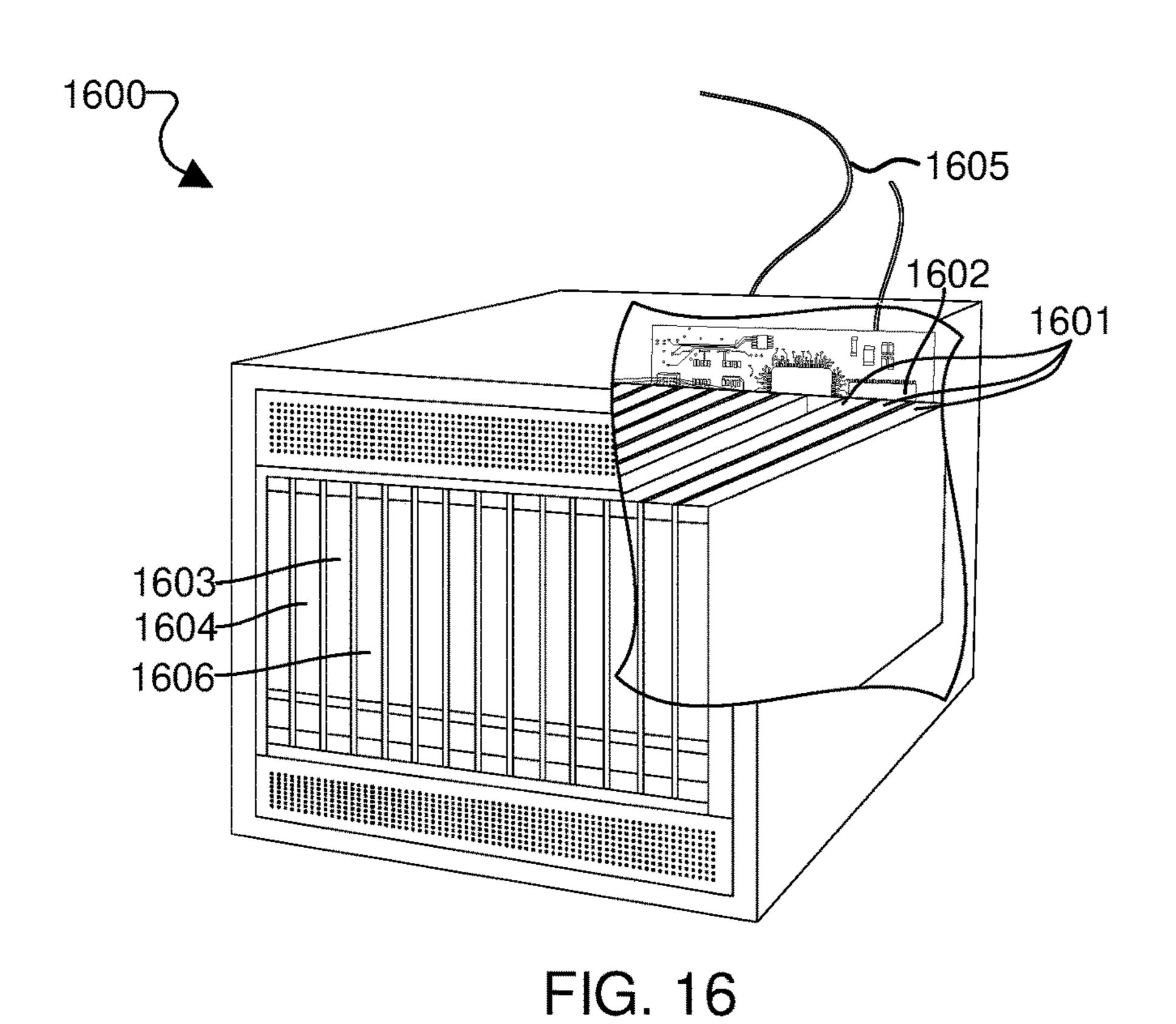

FIG. 16 is a component block diagram illustrating an example server suitable for implementing various embodiments.

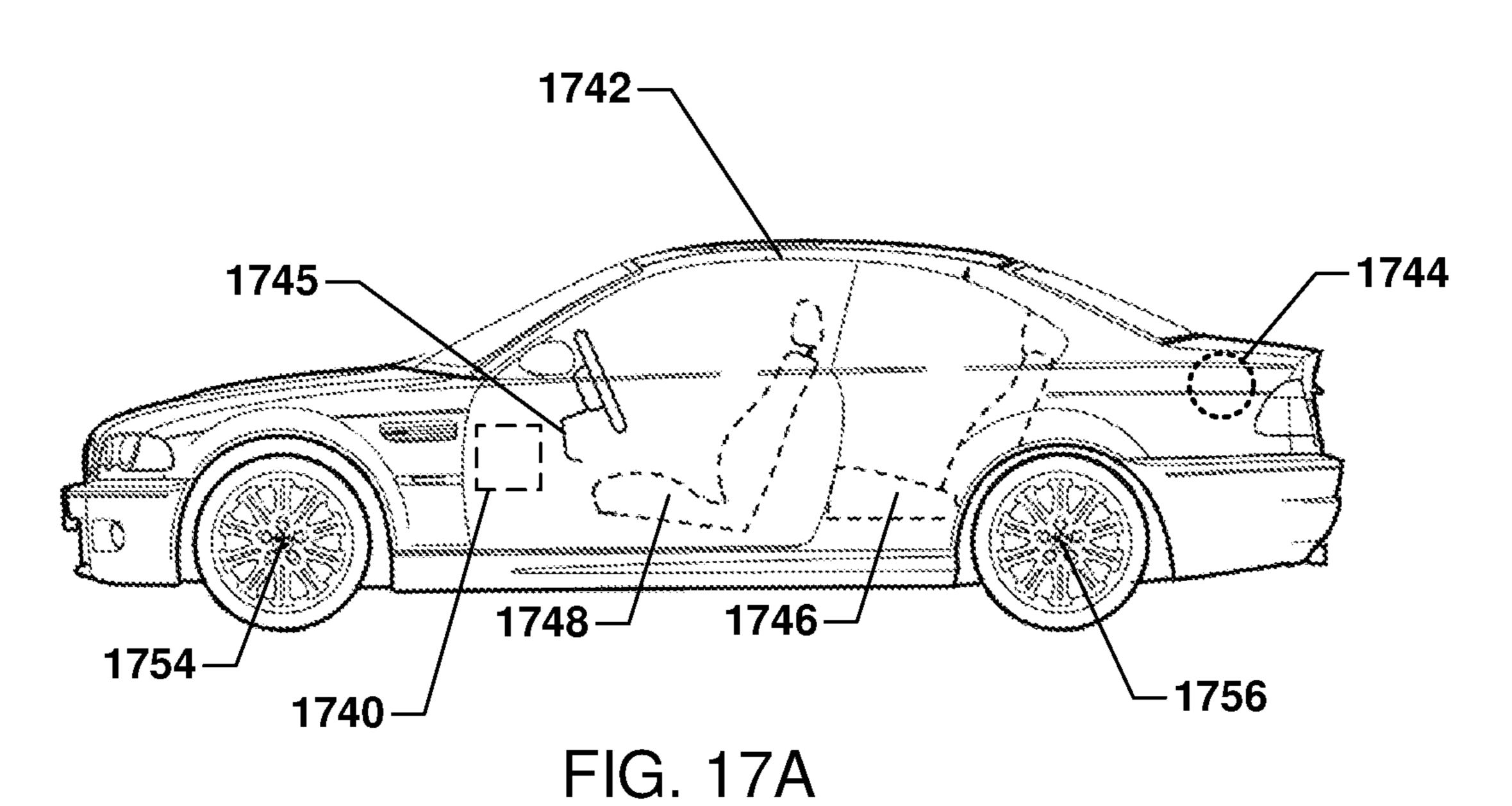

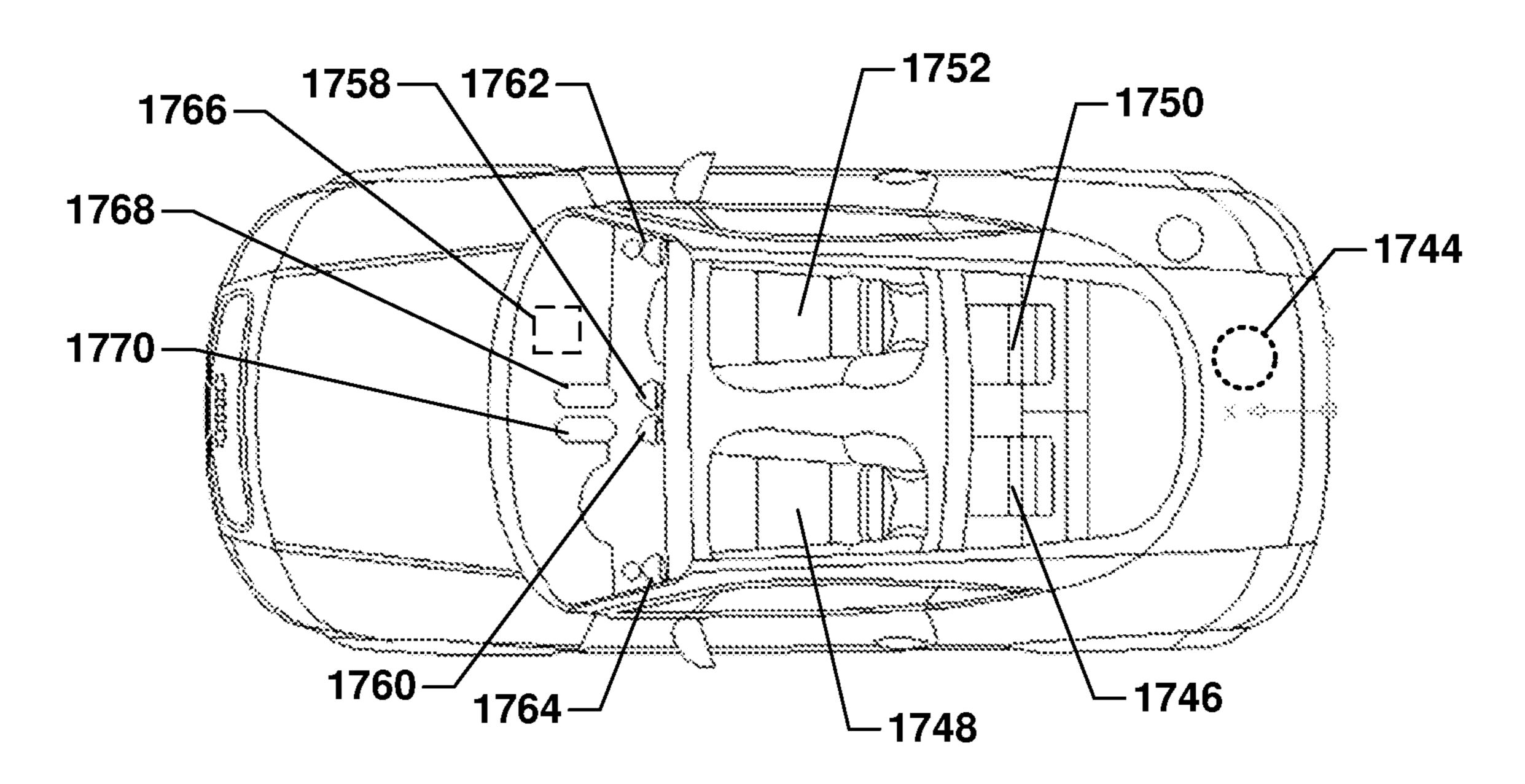

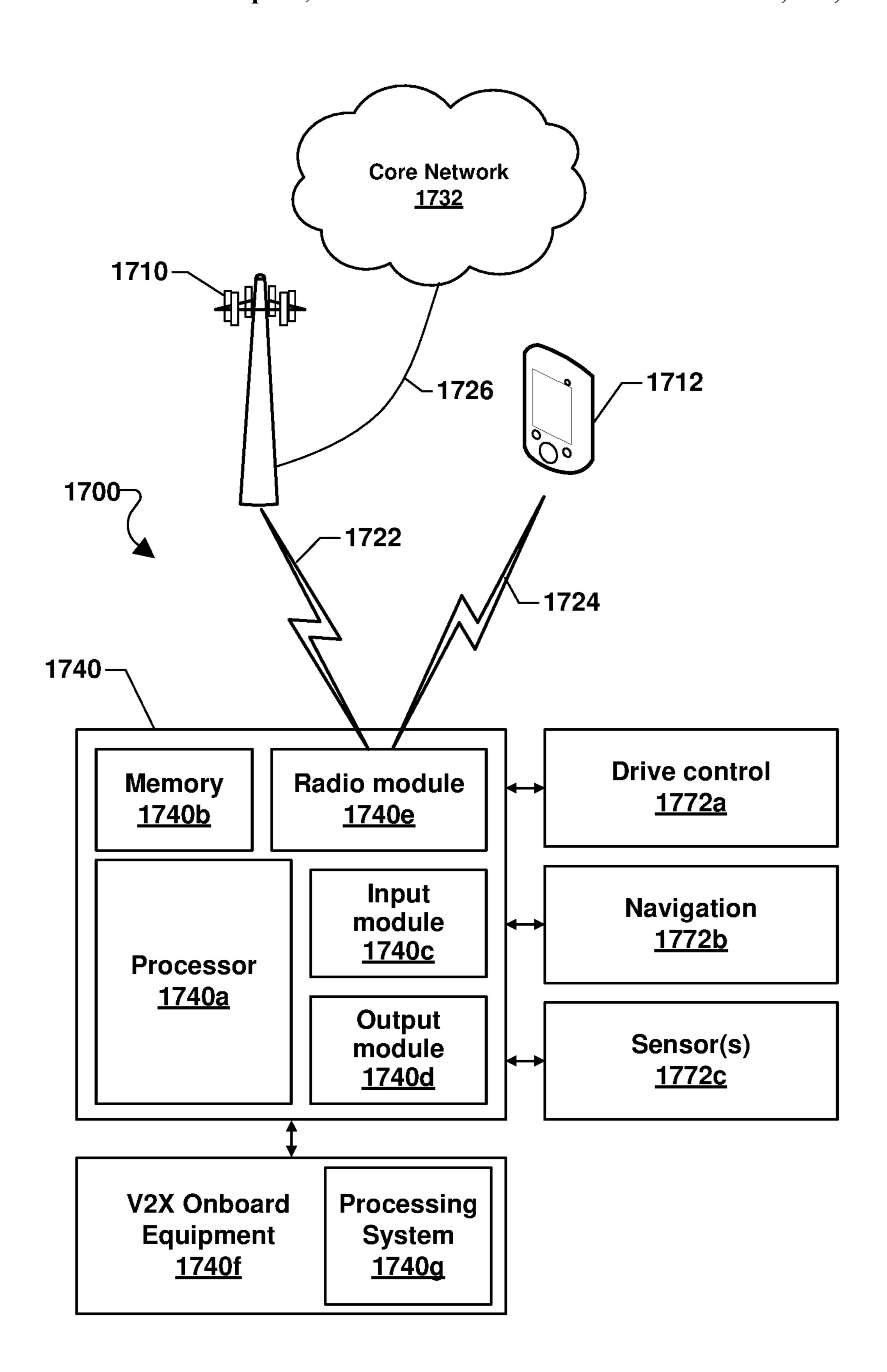

FIGS. 17A-17C are component block diagrams illustrating an example embedded vehicle computing system suitable for implementing various embodiments.

## DETAILED DESCRIPTION

Various embodiments will be described in detail with reference to the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts. References 45 made to particular examples and implementations are for illustrative purposes, and are not intended to limit the scope of the claims.

Various embodiments include methods, and computing devices implementing such methods of implementing multi- 50 module chiplet configured Universal Chiplet Interconnect Express (UCIe) link sideband configurations. Various embodiments of a multi-module chiplet configured UCIe link sideband configuration may include sideband selection in which a sideband of a UCIe link may be changed from a 55 sideband of one UCIe communication module to a sideband of another UCIe communication module during runtime. Various embodiments of a multi-module chiplet configured UCIe link sideband configuration may include sideband aggregation in which one or more sidebands of one or more 60 UCIe communication modules may be initialized in addition to a sideband of a UCIe communication module previously initialized for a UCIe link. Various embodiments may include configuring one or more sidebands of a UCIe link in response to a sideband configuration signal by updating a 65 sideband configuration register and using the sideband configuration register settings while training the UCIe link.

4

Various embodiments may include triggering training the UCIe link based on the UCIe link entering a low power state, which may occur in response to a UCIe link power usage policy and/or a sideband configuration timer.

The term "computing device" is used herein to refer to stationary computing devices including personal computers, desktop computers, all-in-one computers, workstations, super computers, mainframe computers, embedded computers (such as in vehicles and other larger systems), computing systems within or configured for use in vehicles, servers, multimedia computers, and game consoles. The terms "computing device" and "mobile computing device" are used interchangeably herein to refer to any one or all of cellular telephones, smartphones, personal or mobile multi-media players, personal data assistants (PDA's), laptop computers, tablet computers, convertible laptops/tablets (2-in-1 computers), smartbooks, ultrabooks, netbooks, palm-top computers, wireless electronic mail receivers, multimedia Internet enabled cellular telephones, mobile gaming consoles, wireless gaming controllers, and similar personal electronic devices that include a memory, and a programmable processor.

The term "chiplet" is used herein to describe an integrated circuit that is communicably connected to at least one other chiplet in a package via a die-to-die interconnect scheme, such as UCIe. Each chiplet may be configured for specific a function(s). For example, each chiplet may be designed for data storage functions, signal processing functions, input/ output (I/O) functions, etc. Multiple chiplets may be configured as a system-on-chip (SoC). The chiplets of a package may be connected to a shared semiconductor substrate and to each other via a shared semiconductor interposer, such as in a 2.5D package. The chiplets may be stacked such that at least one chiplet may be connected to the shared semicon-35 ductor substrate and/or the shared semiconductor interposer through another chiplet, such as in a 3D package. Stacked chiplets may be connected to one or more other chiplets via the shared semiconductor interposer.

Various embodiments are described in terms of code, e.g., processor-executable instructions, for ease and clarity of explanation, but may be similarly applicable to any data, e.g., code, program data, or other information stored in memory. The terms "code," "data," and "information" are used interchangeably herein and are not intended to limit the scope of the claims and descriptions to the types of code, data, or information used as examples in describing various embodiments.

The UCIe specification provides for chiplets that operate in multi-module (or interface) configurations, either in a pair of 2 or 4 modules (or interfaces). The multi-module configurations are applicable to both standard (low bandwidth) and advanced (high bandwidth) packages. In multi-module configurations, after the initialization of the sidebands and mainbands, only one sideband of one module will be configured to send the required messages and other sidebands of the other modules will be in powered off state.

The one active sideband in multi-module configurations have some limitations. For example, in the cases of 2.5D and 3D packaging technologies, it is possible to have thermal hot spots at different points of an SoC. If the active sideband is always fixed, any hotspot close to the module of the active sideband can introduce data integrity issues. As another example, in use cases like firmware loading, patch downloading, configuration management, security protocol and data module (SPDM) information exchange, and the like, latency is introduced because the single active sideband must be shared to complete the management activities.

Various embodiments address and overcome the foregoing problems by enabling runtime configuration of the sidebands of multi-module configured UCIe connected chiplets (referred to herein in as "multi-module chiplets") at runtime by selecting a different sideband than the single active sideband and/or aggregating one or more additional sidebands to the single active sideband. The multi-module chiplets may include multiple communication modules that may each enable a mainband connection and/or a sideband connection. Runtime configuration of the sidebands of the multi-module chiplets may include training a UCIe link between multi-module chiplets to use the sidebands of one or more of the communication modules.

Various embodiments provide additional benefits over current UCIe link between multi-module chiplets implementations, increasing reliability of the sidebands as a result of reducing hardware stress for a sideband by changing the sidebands periodically and/or episodically. Additionally, during sideband failures, faulty sidebands may be switched 20 for functional sidebands to re-establish communication.

Selecting a different sideband than the single active sideband may include the multi-module chiplets training the UCIe link to use the different sideband of a different communication module than the communication module of 25 the single active sideband. The different communication module may be at a different location of a multi-module chiplet than a location of the communication module of the single active sideband. The different module may be located further from a hotspot of an SoC, of which the multi-module 30 chiplet is a component, than the communication module of the single active sideband. The additional distance from the hotspot may lessen a detrimental impact of the hotspot on data integrity of data communications of the different sideband compared to data communications of the single active 35 sideband.

Selecting a sideband that is different than the single active sideband may effectively change the active sideband for the multi-module chiplet at runtime. To change the active sideband, data configured to set the active sideband may be 40 changed from data representing a current active sideband to data representing a next active sideband from among at least one other inactive sideband. For example, the data stored at a sideband configuration register configured to set the active sideband (referred to herein as a "sideband select register") 45 may be changed from data representing the current active sideband to data representing the next active sideband. In some embodiments, the data configured to set the active sideband may be set according to a signal from a software and/or firmware executed at the multi-module chiplet. The 50 multi-module chiplet may interpret the data configured to set the active sideband at runtime and change the active sideband using the data configured to set the active sideband as the next active sideband rather than the current active sideband.

In some embodiments, changing the active sideband may be triggered during a normal course of UCIe link management, such as during execution of a UCIe link training process during runtime. The UCIe link training process may be triggered by a UCIe link transitioning from an active state 60 to a low power state (e.g., "L2" state) and to a reset state. The sideband select register may be a sticky register configured to retain the data at the sideband select register through the reset state. The multi-module chiplet may interpret the data configured to set the active sideband from the 65 sideband select register during the UCIe link training process, such as at a sideband initialization state. The UCIe link

6

may be trained using the data configured to set the active sideband as the next active sideband rather than the current active sideband.

A sideband configuration timer, referred to herein as sideband select timer, may also be implemented to trigger changing the active sideband. In some embodiments, the sideband select timer may be set according to a signal from the software and/or firmware executed at the multi-module chiplet. The sideband select timer may be configured to signal to the multi-module chiplet to implement the link training process to change the active sideband based on an elapsed period of the sideband select timer.

Aggregating one or more additional sidebands to the single active sideband may include training the UCIe link to use the one or more additional sidebands of one or more additional communication modules to the communication module of the single active sideband. Using more sidebands than only the single active sideband increases throughput, reducing latency, between the multi-module chiplets to execute the management activities, such as firmware loading, patch downloading, configuration management, SPDM information exchange, etc.

Aggregating one or more additional sidebands to the single active sideband may effectively configure multiple active sidebands from the multiple sidebands for the multimodule chiplet at runtime. To configure multiple active sidebands, a data configured to set the multiple active sidebands may be set. For example, the data stored at a sideband configuration register configured to set the multiple active sidebands, referred to herein as sideband aggregate register, may be set. The data may be set to indicate which of the multiple sidebands are the multiple active sidebands. In some embodiments, the data configured to set the multiple active sidebands may be set according to a signal from the software and/or firmware executed at the multi-module chiplet. The multi-module chiplet may interpret the data configured to set the multiple active sidebands at runtime and set the multiple active sidebands.

In some embodiments, configuring the multiple active sidebands may be triggered during a normal course of UCIe link management, such as during execution of a UCIe link training process during runtime. The UCIe link training process may be triggered by a UCIe link transitioning from an active state to a low power state (e.g., "L2" state) and to a reset state. The sideband aggregate register may be a sticky register configured to retain the data at the sideband aggregate register through the reset state. The multi-module chiplet may interpret the data configured to set the multiple active sidebands from the sideband aggregate register during the UCIe link training process, such as at a sideband initialization state. A UCIe link may be trained using the data configured to set the multiple active sidebands.

A sideband configuration timer, referred to herein as sideband aggregate timer, may also be implemented to trigger configuring the multiple active sidebands. In some embodiments, the sideband aggregate timer may be set according to a signal from the software and/or firmware executed at the multi-module chiplet. The sideband aggregate timer may be configured to signal to the multi-module chiplet that the chiplet should implement the UCIe link training process to configure the multiple active sidebands based on an elapsed period of the sideband aggregate timer.

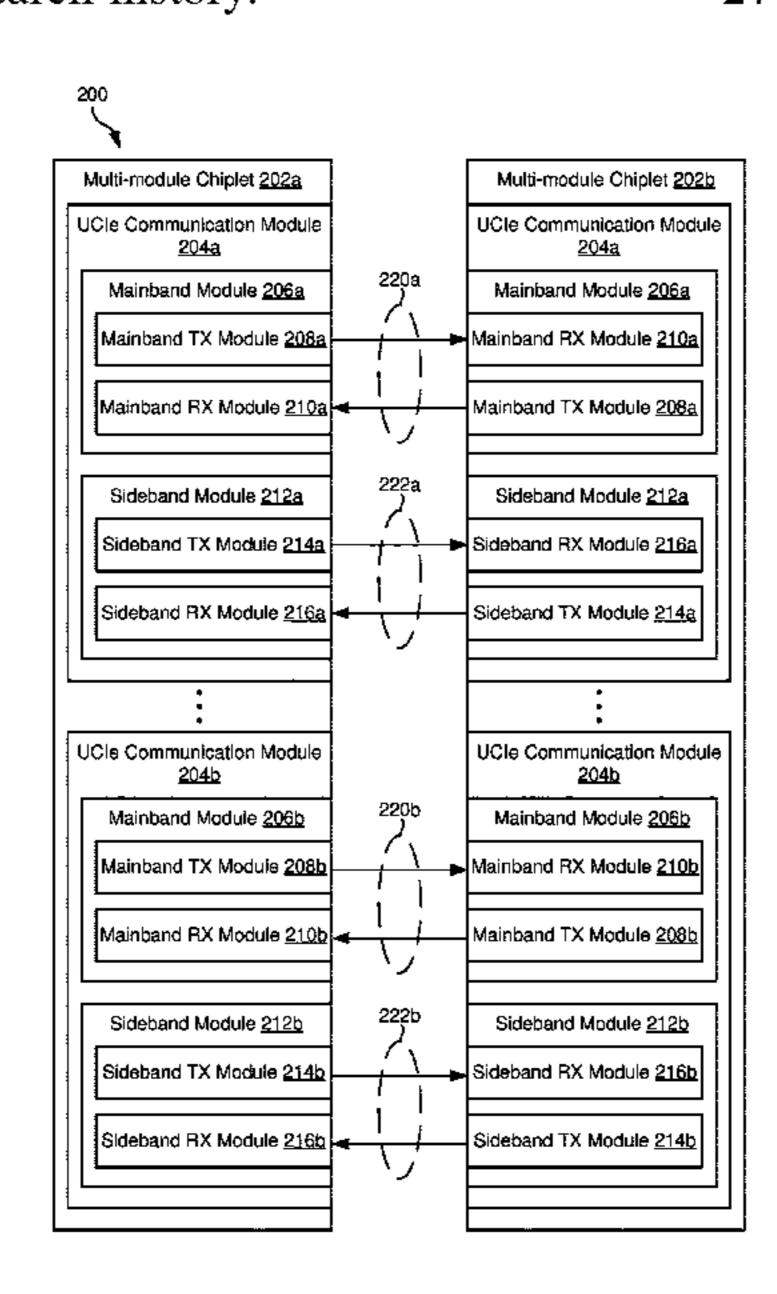

FIG. 1 is a component block diagram illustrating an example computing device 100 suitable for implementing any of the various embodiments. Various embodiments may be implemented on a number of single processor and/or

multiprocessor computer systems, including a system-on-chip (SoC) or system in a package.

With reference to FIG. 1, the illustrated example computing device 100 (which may be a system-in-a-package in some embodiments) may include any combination of one or 5 more SoCs 102, 104 coupled to a clock 106, a voltage regulator 108, at least one subscriber identity module (SIM) and/or a SIM interface 168, a DRAM 170, a Universal FLASH Storage (UFS) device 172, a wireless transceiver **166** configured to send and receive wireless communications via an antenna (not shown) to/from wireless computing devices, such as a base station, wireless device, and/or computing device. In some embodiments, the first SoC 102 may operate as a central processing unit (CPU) of the software application programs by performing the arithmetic, logical, control and input/output (I/O) operations specified by the instructions. In some embodiments, the second SoC 104 may operate as a specialized processing unit. For example, the second SoC 104 may operate as a specialized 20 5G processing unit responsible for managing high volume, high speed (e.g., 5 Gbps, etc.), and/or very high frequency short wavelength (e.g., 28 GHz mmWave spectrum, etc.) communications.

The first SoC **102** may include a digital signal processor 25 (DSP) 110, a modem processor 112, a graphics processor 114, an application processor (AP) 116, one or more coprocessors 118 (e.g., vector co-processor) connected to one or more of the processors, memory 120, custom circuitry 122, system components and resources 124, a host controller 162, 30 an interconnection/bus module 126, one or more sensors 130 (e.g., accelerometer, temperature sensor, pressure sensor, optical sensor, infrared sensor, analog sound sensor, etc.), a thermal management unit 132, and a thermal power envelope (TPE) component 134. The second SoC 104 may 35 include a low power processor 152, a power management unit 154, an interconnection/bus module 164, a BT controller 156, memory 158, and one or more various additional processors 160, such as an applications processor, packet processor, etc.

Each processor 110, 112, 114, 116, 118, 152, 160 may include one or more cores, and each processor/core may perform operations independent of the other processors/cores. For example, the first SoC 102 may include a processor that executes a first type of operating system (e.g., 45 FreeBSD, LINUX, OS X, etc.) and a processor that executes a second type of operating system (e.g., MICROSOFT WINDOWS 10). In addition, any or all of the processors 110, 112, 114, 116, 118, 152, 160 may be included as part of a processor cluster architecture (e.g., a synchronous processor cluster architecture, an asynchronous or heterogeneous processor cluster architecture, etc.).

The first and second SoC 102, 104 may include various system components, resources, and custom circuitry for managing sensor data, analog-to-digital conversions, wireless data transmissions, and for performing other specialized operations, such as decoding data packets and processing encoded audio and video signals for rendering in a web browser or audio/video application. For example, the system components and resources 124 of the first SoC 102 may include power amplifiers, voltage regulators, oscillators, phase-locked loops, peripheral bridges, data controllers, memory controllers, system controllers, access ports, timers, and other similar components used to support the processors and software clients running on a computing device. The 65 system components and resources 124 and/or custom circuitry 122 may also include circuitry to interface with

8

peripheral devices, such as cameras, electronic displays, wireless communication devices, external memory chips, etc.

The first and second SoC 102, 104 may communicate via interconnection/bus module 150. In some embodiments, the interconnection/bus module may be a connection established by transceiving (i.e., receiving and transmitting) components within both the SoC 102 and SoC 104. For example, the low power processor 152 may include a universal asynchronous receiver-transmitter (UART) and the application processor 116 may include a multiple signal messages (MSM) UART driver that is communicatively connected to the UART of the low power processor 152.

The various processors 110, 112, 114, 116, 118, may be computing device 100 that carries out the instructions of software application programs by performing the arithmetic, logical, control and input/output (I/O) operations specified by the instructions. In some embodiments, the second SoC 104 may operate as a specialized processing unit. For example, the second SoC 104 may operate as a specialized processing unit responsible for managing high volume, high speed (e.g., 5 Gbps, etc.), and/or very high frequency short wavelength (e.g., 28 GHz mmWave spectrum, etc.)

The first SoC 102 may include a digital signal processor (DSP) 110, a modem processor 112, a graphics processor

The first and/or second SoCs 102, 104 may further include an input/output module (not illustrated) for communicating with resources external to the SoC, such as a clock 106, a voltage regulator 108, one or more wireless transceivers 166, and at least one SIM and/or SIM interface 168 (i.e., an interface for receiving one or more SIM cards). Resources external to the SoC (e.g., clock 106, voltage regulator 108) may be shared by two or more of the internal SoC processors/cores. The at least one SIM 168 (or one or more SIM cards coupled to one or more SIM interfaces) may store information supporting multiple subscriptions, including a first 5GNR subscription and a second 5GNR subscription, etc.

In addition to the example computing device 100 discussed above, various embodiments may be implemented in a wide variety of computing systems, which may include a single processor, multiple processors, multicore processors, or any combination thereof.

In some embodiments, the various processors of the SoC 102 and SoC 104 may be located within a same SoC. For example, the application processor 116 and low power processor 152 may be located within a same SoC, such as in a single SoC of a wearable device.

In some embodiments, any of the components integral to the SoCs 102, 104 may be composed of one or more multi-module chiplets configured to communicate with other multi-module chiplets according to UCIe protocols for multi-module chiplet configurations.

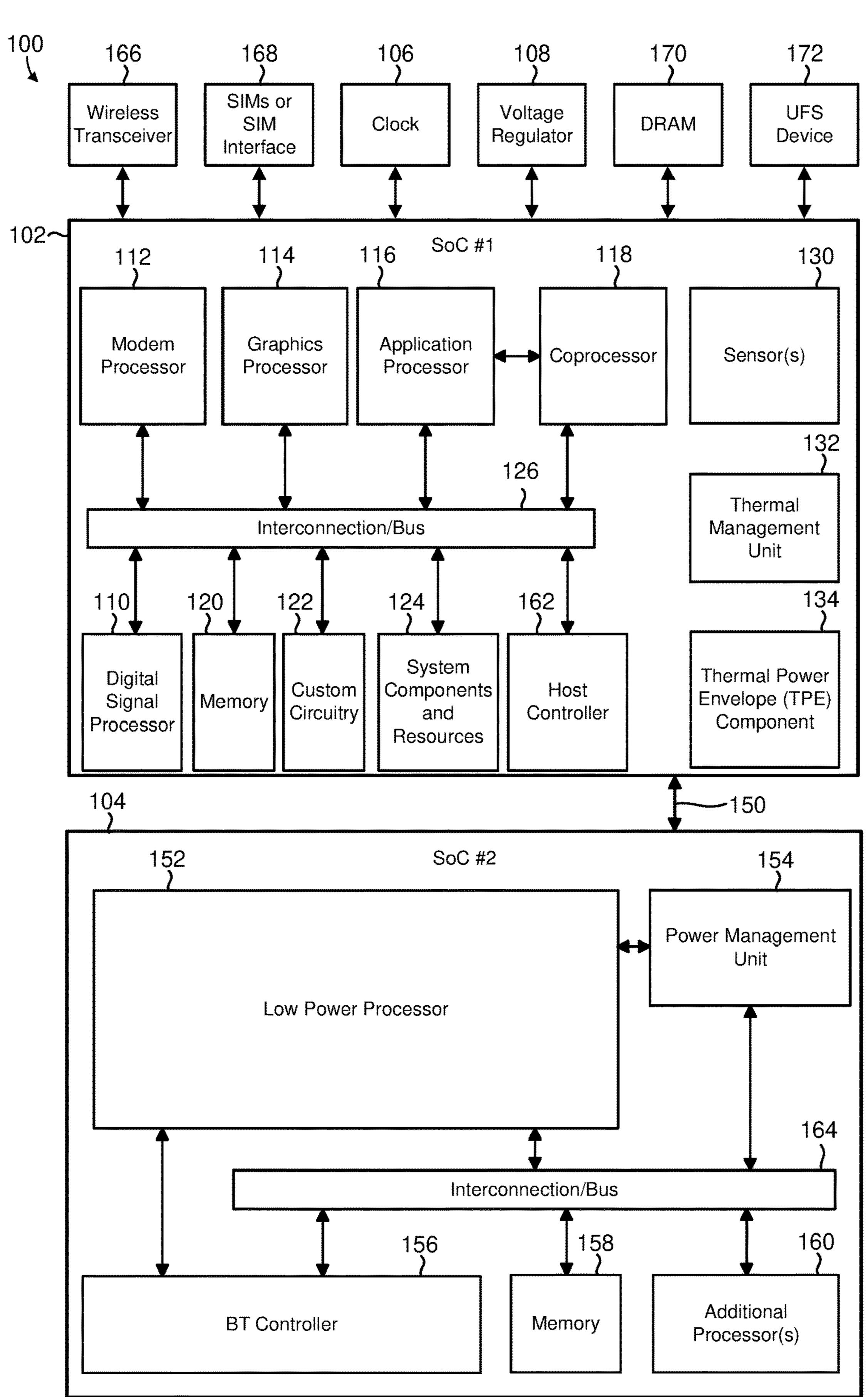

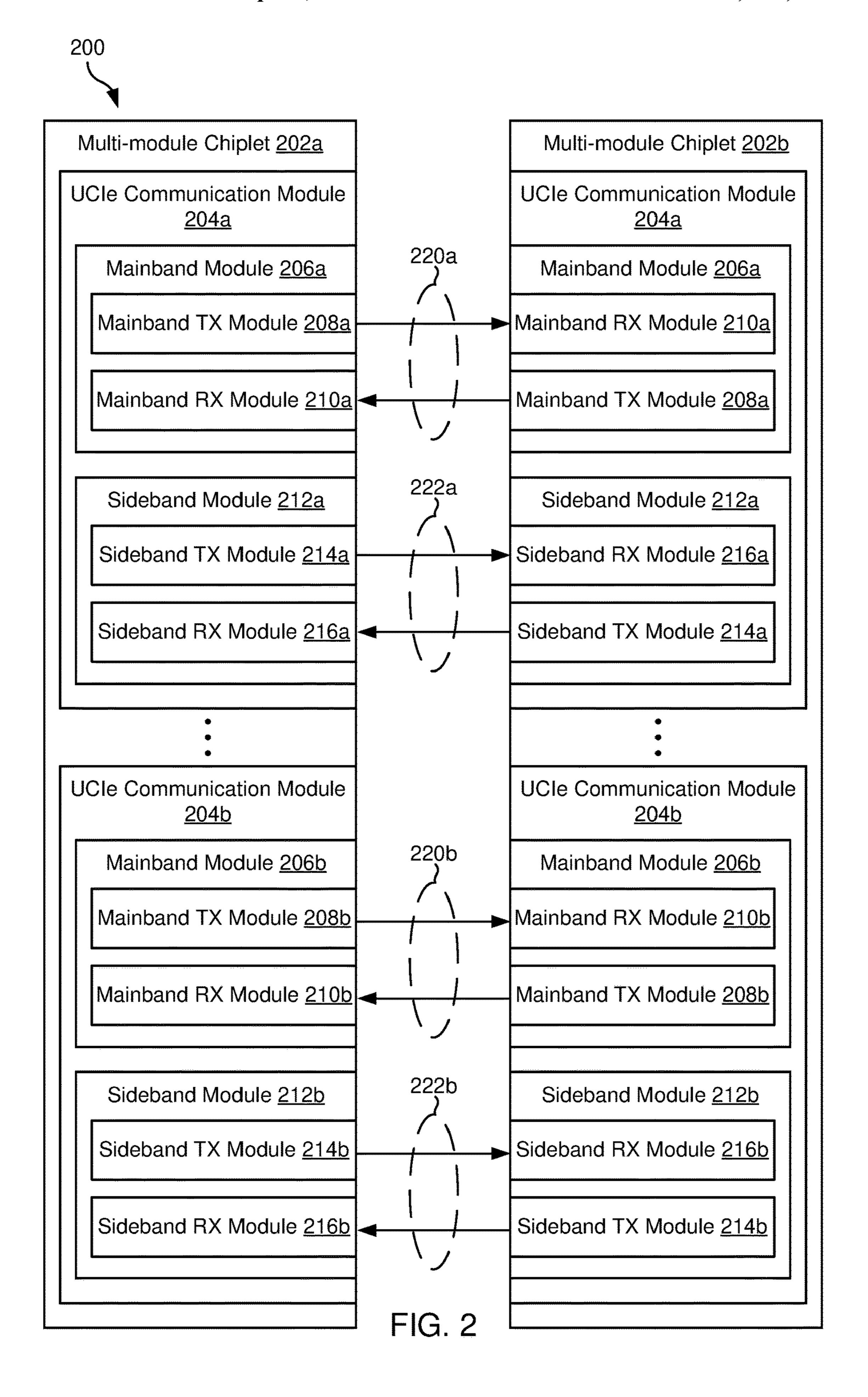

FIG. 2 illustrates an example multi-module chiplet configurations of a UCIe system 200 of the computing device (e.g., computing device 100 in FIG. 1) suitable for implementing various embodiments. With reference to FIGS. 1 and 2, the UCIe system 200 may include two or more multi-module chiplets 202a, 202b. The multi-module chiplet 202a, 202b may be integral to an SoC (e.g., SoC 102, 104 in FIG. 1). Each multi-module chiplet 202a, 202b may include two or more UCIe communication modules 204a, 204b.

Each UCIe communication module 204a, 204b may include components for implementing a UCIe link for communication with at least one other multi-module chiplet

**202***a*, **202***b* according to UCIe protocols for multi-module chiplet configurations. For example, each UCIe communication module 204a, 204b may include components for implementing a mainband 220a, 220b of the UCIe link, such as a mainband module 206a, 206b having a mainband transmission (TX) module 208a, 208b and a mainband reception (RX) module 210a, 210b. The mainband transmission (TX) module 208a, 208b of one multi-module chiplet 202a, 202b may send transmissions via the mainband 220a, 220b that may be received by the mainband reception (RX) module 210a, 210b of another multi-module chiplet 202a, 202b. As another example, each UCIe communication module 204a, 204b may include components for implementsideband module 212a, 212b having a sideband transmission (TX) module 214a, 214b and a sideband reception (RX) module 216a, 216b. The sideband transmission (TX) module **214***a*, **214***b* of one multi-module chiplet **202***a*, **202***b* may send transmissions via the sideband 222a, 222b that may be 20received by the sideband reception (RX) module 216a, 216b of another multi-module chiplet 202a, 202b.

Typically, only one sideband module **212***a*, **212***b* of any multi-module chiplet 202a, 202b may be activated for a UCIe link to implement one sideband **222***a*, **222***b*. That one 25 sideband module 212a, 212b may be persistently activated for the UCIe link without modifying which of the two or more sideband modules 212a, 212b of the multi-module chiplet 202a, 202b may be activated. For example, the sideband module 212a of the multi-module chiplet 202a 30 may be active and may enable the sideband 222a. At the same time, the sideband module **212***b* of the multi-module chiplet 202a may be inactive and may disable the sideband **222***b*.

202b may change which of the two or more sideband modules 212a, 212b may be activated for the UCIe link at runtime by selecting an inactive sideband module 212a, 212b to replace the active sideband module 212a, 212b. For example, the multi-module chiplet 202a may change the 40 active sideband module from the sideband module **212***a* to the sideband module 212b, disabling sideband 222a and enabling sideband 222b.

Embodiments enable that the multi-module chiplet 202a, **202***b* may increase the number of active sideband modules 45 212a, 212b to more than one sideband module 212a, 212b, such as two or more sideband modules 212a, 212b, for the UCIe link at runtime by selecting at least one inactive sideband module 212a, 212b in addition to the active sideband module **212***a*, **212***b*. For example, the multi-module chiplet 202a may activate the sideband module 212b in addition to having the active sideband module 212a, enabling the sideband 222b in addition to the enabled sideband 222a.

module chiplets 202a, 202b each having two UCIe communication modules 204a, 204b and two sidebands 222a, 222bfor clarity and ease of explanation, but does not limit the scope of the specification and claims to this number of multi-module chiplets, to this number of UCIe communica- 60 tion modules per multi-module chiplet, and to this number of sidebands per multi-module chiplet. One of skill in the art will realize that the descriptions of the UCIe system 200 with two multi-module chiplets 202a, 202b each having two UCIe communication modules 204a, 204b and two side- 65 bands 222a, 222b are similarly applicable to UCIe system with more than two multi-module chiplets, to multi-module

**10**

chiplets having more than two UCIe communication modules, and/or to multi-module chiplets having more than two sidebands.

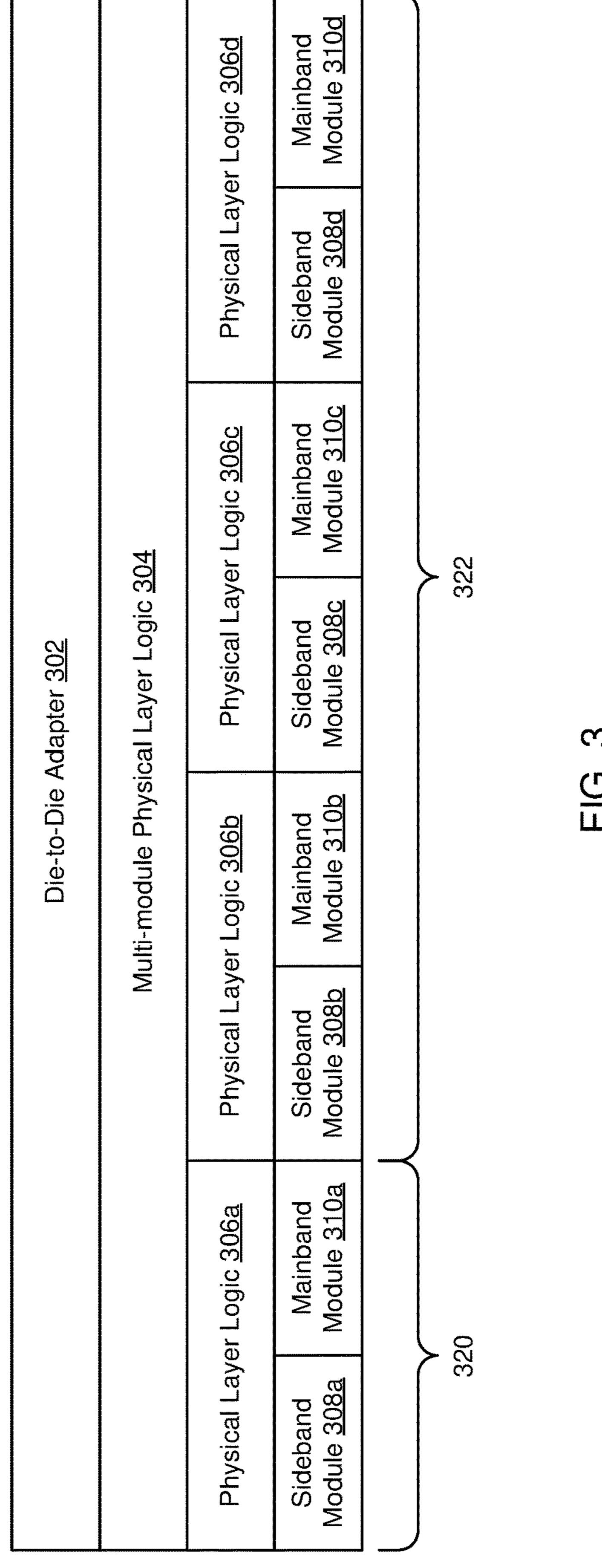

FIG. 3 illustrates an example of a multi-module chiplet configuration of a multi-module chiplet 300 (e.g., multimodule chiplet 202a, 202b in FIG. 2) configured for UCIe link sideband selection for implementing various embodiments. With reference to FIGS. 1-3, the multi-module chiplet 300 may be one of multiple multi-module chiplets 300 10 integral to an SoC (e.g., SoC 102, 104 in FIG. 1). The multi-module chiplet 300 may include a die-to-die adapter 302, a multi-module physical layer logic 304, two or more physical layer logics 306a, 306b, 306c, 306d (e.g., UCIe communications module 204a, 204b in FIG. 2), and a ing a sideband 222a, 222b of the UCIe link, such as a 15 sideband module 308a, 308b, 308c, 308d (e.g., sideband module 212a, 212b in FIG. 2) and a mainband module 310a, **310**b, **310**c, **310**d (e.g., mainband module **206**a, **206**b in FIG. 2) per physical layer logic 306a, 306b, 306c, 306d.

> The die-to-die adapter 302 may be configured to implement link state management and parameter negotiation between multi-module chiplets 300. The die-to-die adapter 302 may also be configured to implement optional support for additional data reliability safeguards via cyclic redundancy checks and link-level retries.

The multi-module physical layer logic 304 may be configured to manage and implement the connections via interconnects between multi-module chiplets 300 of the same package. For example, the multi-module physical layer logic 304 may implement transmitting and receiving voltage signals representing commands and/or data between higher layers (not shown) of the multi-module chiplet 300 and the at least one of the two or more physical layer logics 306a, 306b, 306c, 306d of the multi-module chiplet 300. As another example, the multi-module physical layer logic 304 Embodiments enable that the multi-module chiplet 202a, 35 may manage to which and from which of the two or more physical layer logics 306a, 306b, 306c, 306d to transmit and/or receive voltage signals. For example, the multimodule physical layer logic 304 may transmit and/or receive voltage signals from at least one of the two or more physical layer logics 306a, 306b, 306c, 306d that is active, associated with an active sideband module 308a, 308b, 308c, 308d and/or an active mainband module 310a, 310b, 310c, 310d. In some embodiments, the multi-module physical layer logic 304 may implement UCIe link training using UCIe link sideband selection for which an active sideband module 308a, 308b, 308c, 308d may be changed at runtime, enabling and disabling the associated sidebands (e.g., sideband 222a, 222b FIG. 2) at runtime. In some embodiments, the multi-module physical layer logic 304 may implement UCIe link training using UCIe link sideband aggregation for which multiple active sideband modules 308a, 308b, 308c, 308d may be implemented at runtime, enabling the associated sidebands at runtime.

Each physical layer logic 306a, 306b, 306c, 306d may be The example illustrated in FIG. 2 shows two multi- 55 configured to manage and implement the connections via interconnects between multi-module chiplets 300 of the same package. For example, each physical layer logic 306a, 306b, 306c, 306d may implement transmitting and receiving voltage signals representing commands and/or data between the multi-module physical layer logic 304 and the interconnects with other multi-module chiplets 300. An active physical layer logic 306a, 306b, 306c, 306d may transmit and/or receive voltage signals via an associated active sideband module 308a, 308b, 308c, 308d and/or an associated active mainband module 310a, 310b, 310c, 310d. In some embodiments, each physical layer logic 306a, 306b, 306c, 306d may implement UCIe link training using UCIe link sideband

selection for which an active sideband module 308a, 308b, 308c, 308d may be changed at runtime, enabling and disabling the associated sidebands at runtime. In some embodiments, the multi-module physical layer logic 304 may implement UCIe link training using UCIe link sideband 5 aggregation for which multiple active sideband modules 308a, 308b, 308c, 308d may be implemented at runtime, enabling the associated sidebands at runtime.

In the following example, a physical layer logic 306a, 306b, 306c, 306d and an associated sideband module 308a, 10 308b, 308c, 308d may be referred to interchangeably. The example is described in terms of sideband modules 308a, 308b, 308c, 308d for clarity and ease of explanation. In the example illustrated in FIG. 3, a UCIe link may be configured with a default enabled sideband by activating, by default, a 15 sideband module 308a from a group of default sideband modules 320. In this example, the group of default sideband modules 320 includes a single sideband module 308a. The multi-module chiplet 300 may also include a group of functional, inactive sideband modules **322**. In this example, 20 the group of functional, inactive sideband modules 322 may include at least one of a remainder of sideband modules 308b, 308c, 308d of the multi-module chiplet 300. By implementing UCIe link training using UCIe link sideband selection, the UCIe link configuration may be changed from 25 using this default enabled sideband to another enabled sideband by deactivating the sideband module 308a activated by default and activating one of the sideband modules 308b, 308c, 308d of the group of functional, inactive sideband modules **322**. Similarly, further configurations of the 30 UCIe link may again change enabled sidebands by enabling any of the disabled, functional sideband modules 308a, 308b, 308c, 308d from the group of default sideband modules 320 and the group of functional, inactive sideband modules 322.

In the following examples described with reference to FIGS. 4-6, a sideband module (e.g., sideband module 212a, 212b in FIG. 2, sideband module 308a, 308b, 308c, 308d in FIG. 3) and an associated sideband (e.g., sideband 222a, 222b) may be referred to interchangeably. The examples are 40 described in terms of sidebands for clarity and ease of explanation.

FIG. 4 illustrates an example of a sideband select information structure 400 for UCIe link sideband selection suitable for implementing various embodiments. With reference 45 to FIGS. 1-4, the sideband select information structure 400 may be configured to store data for implementing UCIe link sideband selection. In some embodiments, the sideband select information structure 400 may be and/or may be stored at a memory (e.g., memory **120**, **158** in FIG. **1**), such 50 as a sideband select register. The sideband select information structure 400 may be persistent, or sticky, such that the sideband select information structure 400 may retain data through a reset state of a UCIe link training process. The sideband select information structure 400 may be a compo- 55 nent of a multi-module chiplet (e.g., multi-module chiplet **202***a*, **202***b* in FIG. **2**, multi-module chiplet **300** in FIG. **3**). The sideband select information structure 400 may be accessible by a UCIe communications module (e.g., UCIe communications module 204a, 204b in FIG. 2), a multi-module 60 physical layer logic (e.g., multi-module physical layer logic 304 in FIG. 3), and/or a physical layer logic (e.g., physical layer logic 306a, 306b, 306c, 306d in FIG. 3).

The sideband select information structure 400 may include at least one active sideband data (e.g., active sideband 1, active sideband 0) and at least two functional sideband data (e.g., functional sideband 3, functional sideband sideband sideband 3, functional sideband sideband 3, functional sideband sideban

12

band 2, functional sideband 1, functional sideband 0). The functional sideband data may be configured to represent which sidebands of the multi-module chiplet are functional.

For example, each sideband may be associated with a location in the sideband select information structure 400, and the value at the location may represent whether the associated sideband is functional. As a non-limiting example, a value of "1" at a location in the sideband select information structure 400 may indicate the associated sideband is functional and a value of "0" at the location in the sideband select information structure 400 may indicate the associated sideband is not functional. Thus in this example, if functional sideband 2="0" and functional sideband 0, functional sideband 1, and functional sideband 3 each="1", then sideband 2 is not functional and sidebands 0, 1, and 3 are functional. As another example, each sideband and/or combination of sidebands may be associated with a value, and the value at a location in the sideband select information structure 400 may represent the sideband(s) associated with the value as a functional sideband(s). As a non-limiting example, for four sidebands the value may be from 0 to 15, where different values correspond to different combinations of functional sideband, such as: if value="3", then sideband 2 is functional and sidebands 0, 1, and 3 are not functional; if value="6", then sidebands 0 and 2 are functional and sidebands 1 and 3 are not functional; if value="13", then sidebands 0, 2, and 3 are functional and sideband 1 is not functional; etc.

The active sideband data may be configured to represent which functional sideband is the active, or enabled, sideband. For example, the active sideband data may be one or more data for which different values may be associated with different functional sidebands. As another example, the active sideband data may be one or more data for which different values may be associated with different locations of functional sideband data at the sideband select information structure 400.

An example of how the active sideband data may relate to the functional sideband data is illustrated in FIG. 5. With reference to FIGS. 1-5, a table 500 illustrates an example of how different values of two active sideband data (e.g., active sideband 1, active sideband 0) may represent which of the functional sidebands, represented by functional sideband data (e.g., functional sideband 3, functional sideband 2, functional sideband 1, functional sideband 0), is the active sideband. For example: active sideband data of values "00" may represent functional sideband 0 as the active sideband; active sideband data of values "01" may represent functional sideband 1 as the active sideband; active sideband data of values "10" may represent functional sideband 2 as the active sideband; and active sideband data of values "11" may represent functional sideband 3 as the active sideband. In some embodiments, one of the values of active sideband data may be a default value at the sideband select information structure 400 resulting in activating the associated functional sideband by default.

In some embodiments, the sideband select information structure 400 may include a sideband select enable data for which different values may represent whether the multimodule chiplet may implement UCIe link sideband selection. For example, the sideband select enable data having a value enabling UCIe link sideband selection may enable the multi-module chiplet to implement UCIe link sideband selection. Alternatively, the sideband select enable data having a value disabling UCIe link sideband selection may disable the multi-module chiplet from implementing UCIe link sideband selection.

In some embodiments, a software and/or firmware executed by the multi-module chiplet may write data to the sideband select information structure 400. For example, the software and/or firmware may write values of the active sideband data to the sideband select information structure 500. The software and/or firmware may be configured to implement a process for UCIe link sideband selection based on any combination of criteria, such as a measure, estimation, and/or requirement of a level data integrity for UCIe communication between multi-module chiplets.

The software and/or firmware may write values of the active sideband data to indicate which functional sideband to select for a next UCIe link training. The values of the active sideband data written by the software and/or firmware may be different from the values previously at the active sideband 15 data, resulting in a different functional sideband than a current active sideband being activated during the next UCIe link training.

The multi-module chiplet may read the values of the active sideband data during the next UCIe link training and 20 train the UCIe link including activating the functional sideband represented by the values of the active sideband data. In some embodiments, reading the values of the active sideband and training the UCIe link including activating the functional sideband represented by the values of the active 25 sideband data may be implemented by a UCIe communications module, a multi-module physical layer logic, and/or a physical layer logic.

The examples illustrated in FIGS. 3-5 show four sideband modules 308a, 308b, 308c, 308d and/or four sidebands per 30 multi-module chiplet 300 for clarity and ease of explanation, but do not limit the scope of the specification and claims to this number of sideband modules and to this number of sidebands per multi-module chiplet. One of skill in the art will realize that the descriptions of the examples with four 35 sideband modules 308a, 308b, 308c, 308d and/or four sidebands per multi-module chiplet 300 are similarly applicable to any number greater than one, such as two or eight, of sideband modules and/or sidebands per multi-module chiplet.

FIG. 6 illustrates an example of a sideband select timer information structure 600 for UCIe link sideband selection suitable for implementing various embodiments. With reference to FIGS. 1-6, the sideband select timer information structure 600 may be configured to store data for imple- 45 menting UCIe link sideband selection. In some embodiments, the sideband select timer information structure 600 may be and/or may be stored at a memory (e.g., memory 120, 158 in FIG. 1), such as a sideband select timer. The sideband select timer information structure 600 may be a 50 component of a multi-module chiplet (e.g., multi-module chiplet 202a, 202b in FIG. 2, multi-module chiplet 300 in FIG. 3). The sideband select timer information structure 600 may be accessible by a UCIe communications module (e.g., UCIe communications module 204a, 204b in FIG. 2), a 55 multi-module physical layer logic (e.g., multi-module physical layer logic 304 in FIG. 3), and/or a physical layer logic (e.g., physical layer logic 306a, 306b, 306c, 306d in FIG. 3).

The sideband select timer information structure **600** may be configured to store as data a sideband select timer value 60 that may be periodically, continuously, and/or episodically incremented and/or decremented. In some embodiments, a software and/or firmware executed by the multi-module chiplet may write sideband select timer data to the sideband select timer information structure **600**. For example, the 65 software and/or firmware may write the sideband select timer value to the sideband select timer information structure.

14

ture **600**. The software and/or firmware may be configured to implement a process for UCIe link sideband selection based on any combination of criteria, such as a measure, estimation, and/or requirement of a level of data integrity for UCIe communication between multi-module chiplets. The software and/or firmware may write the sideband select timer value to indicate when to implement a next UCIe link training implementing UCIe link sideband selection.

A threshold sideband select timer value may trigger UCIe link training implementing UCIe link sideband selection. In some embodiments, the multi-module chiplet may read the sideband select timer value, and, based on the sideband select timer value, decide (e.g., determine or take an action) to implement UCIe link training, which may implement UCIe link sideband selection based on data of a sideband select information structure (e.g., sideband select information structure (e.g., sideband select information structure 400 in FIG. 4). In some embodiments, reading the sideband select timer value and deciding (e.g., determining or taking an action) to implement UCIe link training may be implemented by a UCIe communications module, a multi-module physical layer logic, and/or a physical layer logic.

FIG. 7 illustrates an example of a multi-module chiplet configuration of a chiplet 700 (e.g., multi-module chiplet **202***a*, **202***b* in FIG. **2**, multi-module chiplet **300** in FIG. **3**) configured for UCIe link sideband aggregation for implementing various embodiments. With reference to FIGS. 1-7, the multi-module chiplet 700 may be one of multiple multimodule chiplets 700 integral to an SoC (e.g., SoC 102, 104) in FIG. 1). The multi-module chiplet 700 may include a die-to-die adapter 302, a multi-module physical layer logic 304, two or more physical layer logics 306a, 306b, 306c, 306d (e.g., UCIe communications module 204a, 204b in FIG. 2), and a sideband module 308a, 308b, 308c, 308d(e.g., sideband module 212a, 212b in FIG. 2) and a mainband module 310a, 310b, 310c, 310d (e.g., mainband module 206a, 206b in FIG. 2) per physical layer logic 306a, 306b, 306c, 306d. The die-to-die adapter 302, the multimodule physical layer logic 304, the two or more physical layer logics 306a, 306b, 306c, 306d, the sideband modules 308a, 308b, 308c, 308d, and the mainband modules 310a, 310b, 310c, 310d may be configured as described herein for the same reference numbered components with reference to FIG. **3**.

In the following example, a physical layer logic 306a, 306b, 306c, 306d and an associated sideband module 308a, 308b, 308c, 308d may be referred to interchangeably. The example is described in terms of sideband modules 308a, 308b, 308c, 308d for clarity and ease of explanation. In the example illustrated in FIG. 7, a UCIe link may be configured with a default enabled sideband by activating, by default, a sideband module 308a from a group of default sideband modules 720. In this example, the group of default sideband modules 720 includes a single sideband module 308a. The multi-module chiplet 700 may also include a group of functional, inactive sideband modules 722. In this example, the group of functional, inactive sideband modules 722 may include at least one of a remainder of sideband modules 308b, 308c, 308d of the multi-module chiplet 700. By implementing UCIe link training using UCIe link sideband aggregation, the UCIe link configuration may be changed from using only this default enabled sideband to using the default enabled sideband and at least one other enabled sideband by activating at least one of the sideband modules 308b, 308c, 308d of the group of functional, inactive sideband modules 722. By implementing UCIe link training using UCIe link sideband aggregation, the UCIe link con-

figuration may be changed from using only this default enabled sideband to using at least two enabled sidebands by activating at least two of the sideband modules 308b, 308c, 308d of the group of functional, inactive sideband modules 722 and deactivating the default enabled sideband. Similarly, further configurations of the UCIe link may again change enabled sidebands by enabling any combination of the disabled, functional sideband modules 308b, 308c, 308d from the group of functional, inactive sideband modules 722.

In the following examples described with reference to FIGS. 8 and 9, a sideband module (e.g., sideband module 212a, 212b in FIG. 2, sideband module 308a, 308b, 308c, 308d in FIG. 3) and an associated sideband (e.g., sideband 222a, 222b) may be referred to interchangeably. The 15 examples are described in terms of sidebands for clarity and ease of explanation.

FIG. 8 illustrates an example of a sideband aggregate information structure **800** for UCIe link sideband aggregation suitable for implementing various embodiments. With 20 reference to FIGS. 1-8, the sideband aggregate information structure 800 may be configured to store data for implementing UCIe link sideband aggregation. In some embodiments, the sideband aggregate information structure 800 may be and/or may be stored at a memory (e.g., memory 120, 158 in FIG. 1), such as a sideband aggregation register. The sideband aggregate information structure **800** may be persistent, or sticky, such that the sideband aggregate information structure 800 may retain data through a reset state of a UCIe link training process. The sideband aggregate information structure 800 may be a component of a multi-module chiplet (e.g., multi-module chiplet 202a, 202b in FIG. 2, multi-module chiplet 300, 700 in FIGS. 3 and 7). The sideband aggregate information structure 800 may be accessible by a UCIe communications module (e.g., UCIe com- 35 munications module 204a, 204b in FIG. 2), a multi-module physical layer logic (e.g., multi-module physical layer logic 304 in FIGS. 3 and 7), and/or a physical layer logic (e.g., physical layer logic 306a, 306b, 306c, 306d in FIGS. 3 and

The sideband aggregate information structure **800** may include at least two aggregate sideband data (e.g., aggregate sideband 3, aggregate sideband 2, aggregate sideband 1, aggregate sideband 0). The aggregate sideband data may be configured to represent which sidebands of the multi-module 45 chiplet are active, enabled, and/or are functional. For example, when implementing UCIe link sideband aggregation, at least two, such as two and/or four, sidebands of the multi-module chiplet may be aggregated or concurrently active, and the aggregate sideband data of the sideband 50 aggregate information structure **800** may be configured to indicate to the multi-module chiplet which of the sidebands are active.

For example, each sideband may be associated with a location in the sideband aggregate information structure 55 800. The aggregate sideband data at each location may be configured to represent which sideband is an active, or enabled, sideband based on an association of the location with sideband and a value of the aggregate sideband data at the location. For example, the aggregate sideband data may 60 be data for which different values may represent an active state or an inactive state of the sideband associated with the location of the aggregate sideband data in the sideband aggregate information structure 800. As a non-limiting example, a value of "1" at locations in the sideband aggregate information structure 800 may indicate the associated sideband is active and a value of "0" at the locations in the

**16**

sideband aggregate information structure **800** may indicate the associated sideband is not active. In this example, if aggregate sideband 1 and aggregate sideband 2 each="0" and aggregate sideband 0 and aggregate sideband 3 each="1", then sidebands 1 and 2 are not active and sidebands 0 and 3 are active.

In some embodiments, each sideband and/or combination of sidebands may be associated with a value, and the value at a location in the sideband aggregate information structure 800 may represent the sideband(s) associated with the value as an active sideband(s). As a non-limiting example, for four sidebands the value may be from 0 to 11, where different values correspond to different combinations of functional sideband, such as: if value="3", then sideband 2 is active and sidebands 0, 1, and 3 are not active; if value="6", then sidebands 0 and 2 are active and sidebands 1 and 3 are not active; if value="0", then sidebands 2 and 3 are active and sidebands 0, 1, 2 and 3 are active; if value="11", then sidebands 0, 1, 2 and 3 are active.

In some embodiments, the sideband aggregate information structure 800 may include functional sidebands and may exclude nonfunctional side sidebands. In some embodiments, the sideband aggregate information structure 800 may include nonfunctional side sidebands that may be associated with locations in the sideband aggregate information structure 800 that may be prevented from being set with a value of aggregate sideband data configured to represent an active state.

For example, any two or more, such as four, functional sidebands may be aggregated, or active at the same time. Values of the aggregate sideband data at the two or more locations of the sideband aggregate information structure **800** may be set to represent an active state for the functional associated sidebands. In some embodiments, a value of the aggregate sideband data at one of the locations of the sideband aggregate information structure 800 may be a default value resulting in activating the associated functional sideband by default. Values of the aggregate sideband data at any one or more, such as three, other locations of the 40 sideband aggregate information structure **800** may be set to represent an active state of the associated functional sidebands. In some embodiments, the default value may be modified to be set to represent an inactive state of the associated functional sideband, and two or more other locations of the sideband aggregate information structure 800 may be set with values of the aggregate sideband data to represent an active state of the associated functional sidebands.

In some embodiments, the sideband aggregate information structure **800** may include a sideband aggregate enable data for which different values may represent whether the multi-module chiplet may implement UCIe link sideband aggregation. For example, the sideband aggregate enable data having a value enabling UCIe link sideband aggregation may enable the multi-module chiplet to implement UCIe link sideband aggregation. Alternatively, the sideband aggregate enable data having a value disabling UCIe link sideband aggregation may disable the multi-module chiplet from implementing UCIe link sideband aggregation.

In some embodiments, the sideband aggregate information structure **800** may include a redundant lane enable data for which different values may represent whether the multimodule chiplet may implement redundant lanes for a UCIe link. For example, the multi-module chiplet may be configured as an advanced package with redundant lane capabilities. The redundant lane enable data having a value enabling redundant lanes for the UCIe link may enable the multi-

module chiplet to implement redundant lanes for the UCIe link, such as part of a mainband of the UCIe link. Alternatively, the redundant lane enable data having a value disabling redundant lanes for the UCIe link may disable the multi-module chiplet from implementing redundant lanes for the UCIe link.

In some embodiments, a software and/or firmware executed by the multi-module chiplet may write data to the sideband aggregate information structure 800. For example, the software and/or firmware may write values of the aggregate sideband data to the sideband aggregate information structure 800. The software and/or firmware may be configured to implement a process for UCIe link sideband aggregation based on any combination of criteria, such as for firmware loading, patch downloading, configuration update/ management, security protocol and data module (SPDM) information exchange, other management activities, etc. between multi-module chiplets. The software and/or firmware may write values of the aggregate sideband data to 20 indicate which functional sidebands to select for a next UCIe link training. The values of the aggregate sideband data written by the software and/or firmware may be different from the values previously at the aggregate sideband data, resulting in a different combination of functional sidebands <sup>25</sup> than one or more current active sidebands being activated during the next UCIe link training. The multi-module chiplet may read the values of the aggregate sideband data during the next UCIe link training and train the UCIe link including activating the combination of functional sidebands represented by the values of the aggregate sideband data. In some embodiments, reading the values of the aggregate sideband data and training the UCIe link including activating the combination of functional sidebands represented by the values of the aggregate sideband data may be implemented by a UCIe communications module, a multi-module physical layer logic, and/or a physical layer logic.

The examples illustrated in FIGS. 7 and 8 show four sideband modules 308a, 308b, 308c, 308d and/or four 40 sidebands per multi-module chiplet 700 for clarity and ease of explanation, but do not limit the scope of the specification and claims to this number of sideband modules and to this number of sidebands per multi-module chiplet. One of skill in the art will realize that the descriptions of the examples 45 with four sideband modules 308a, 308b, 308c, 308d and/or four sidebands per multi-module chiplet 700 are similarly applicable to any number greater than one, such as two or eight, of sideband modules and/or sidebands per multi-module chiplet.

FIG. 9 illustrates an example of a sideband aggregate timer information structure 900 for UCIe link sideband aggregation suitable for implementing various embodiments. With reference to FIGS. 1-9, the sideband aggregate timer information structure 900 may be configured to store 55 data for implementing UCIe link sideband aggregation. In some embodiments, the sideband aggregate timer information structure 900 may be and/or may be stored at a memory (e.g., memory 120, 158 in FIG. 1), such as a sideband aggregate timer. The sideband aggregate timer information 60 structure 900 may be a component of a multi-module chiplet (e.g., multi-module chiplet 202a, 202b in FIG. 2, multimodule chiplet 300, 700 in FIGS. 3 and 7). The sideband aggregate timer information structure 900 may be accessible by a UCIe communications module (e.g., UCIe communi- 65 cations module 204a, 204b in FIG. 2), a multi-module physical layer logic (e.g., multi-module physical layer logic

**18**

304 in FIGS. 3 and 7), and/or a physical layer logic (e.g., physical layer logic 306a, 306b, 306c, 306d in FIGS. 3 and 7)

The sideband aggregate timer information structure 900 may be configured to store as data a sideband aggregate timer value that may be periodically, continuously, and/or episodically incremented and/or decremented. In some embodiments, a software and/or firmware executed by the multi-module chiplet may write sideband aggregate timer data to the sideband aggregate timer information structure 900. For example, the software and/or firmware may write the sideband aggregate timer value to the sideband aggregate timer information structure 900. The software and/or firmware may be configured to implement a process for UCIe 15 link sideband aggregation based on any combination of criteria, such as a measure, estimation, and/or requirement of a level of data integrity for UCIe communication between multi-module chiplets. The software and/or firmware may write the sideband aggregate timer value to indicate when to implement a next UCIe link training implementing UCIe link sideband aggregation.

A threshold sideband aggregate timer value may trigger UCIe link training implementing UCIe link sideband aggregation. In some embodiments, the multi-module chiplet may read the sideband aggregate timer value, and based on the sideband aggregate timer value, decide (e.g., determine or take an action) to implement UCIe link training, which may implement UCIe link sideband aggregation based on data of a sideband aggregate information structure (e.g., sideband aggregate information structure **800** in FIG. **8**). In some embodiments, reading the sideband aggregate timer value and deciding (e.g., determining or taking an action) to implement UCIe link training may be implemented by a UCIe communications module, a multi-module physical layer logic, and/or a physical layer logic.

FIG. 10 illustrates an example UCIe link training status and state machine (LTSSM) 1000 suitable for implementing various embodiments. With reference to FIGS. 1-10, the UCIe LTSSM 1000 may be implemented for UCIe link training, including transitions between states of the LTSSM 1000, by a multi-module chiplet (e.g., multi-module chiplet 202a, 202b in FIG. 2, multi-module chiplet 300, 700 in FIGS. 3 and 7), including by a UCIe communications module (e.g., UCIe communications module 204a, 204b in FIG. 2), a multi-module physical layer logic (e.g., multi-module physical layer logic 304 in FIGS. 3 and 7), and/or a physical layer logic (e.g., physical layer logic 306a, 306b, 306c, 306d in FIGS. 3 and 7).

During the active state **1002** ("active") of a UCIe link, the 50 UCIe link may be previously initialized and the UCIe communications module and/or components of the UCIe communications module may be powered and enabled to send and receive transactions via the UCIe link. Also during the active state 1002, a multi-module chiplet of the UCIe link executing a software and/or firmware may receive a sideband configuration signal from the software and/or firmware. The sideband configuration signal may include sideband configuration data (e.g., active sideband data and/ or sideband select enable data; aggregate sideband data, sideband aggregate enable data, and/or redundant lane enable data). Receiving the sideband configuration signal may prompt the multi-module chiplet to write the sideband configuration data to a sideband configuration information structure (e.g., sideband select information structure 400 in FIG. 4, sideband aggregate information structure 800 in FIG. 8). In some embodiments, the sideband configuration signal may include sideband configuration timer data (e.g.,

sideband select timer data, sideband aggregate timer data). Receiving the sideband configuration signal may prompt the multi-module chiplet to write the sideband configuration timer data to a sideband configuration timer information structure (e.g., sideband select timer information structure 600 in FIG. 6, sideband aggregate timer information structure 900 in FIG. 9).

The UCIe link may transition from the active state to a low power state 1004 ("L1/L2"). During the low power state 1004, power provided to the UCIe communications module 10 and/or components of the UCIe communications module may be lowered to a level such that the UCIe link may be inactive or no longer initialized and transactions may not be sent or received via the UCIe link. The power provided to the UCIe communications module and/or components of the 15 UCIe communications module may be lowered to a level also sufficient to maintain data relating to previous initialization of one or more sidebands, including sideband configuration data, and a mainband of the UCIe link. The power provided to the UCIe communications module and/or com- 20 ponents of the UCIe communications module may be lowered relative to power provided during the active state 1002. The UCIe link may transition from the active state 1002 to the low power state 1004 periodically and/or episodically during normal operation. In some embodiments, the side- 25 band configuration timer information structure may be implemented to ensure that the UCIe link transition from the active state to the low power state occurs within a designated period, which may be related to the sideband configuration timer data written to the sideband configuration timer information structure. For example, the sideband configuration timer data may set value at the sideband configuration timer information structure to use as the period. The sideband configuration timer information structure may time the period and be configured to identify that the period has 35 elapsed. In some embodiments, the sideband configuration timer information structure may identify the period has elapsed actively, such as by issuing a sideband configuration timer signal to the multi-module chiplet configured to represent that the period has elapsed and that may prompt the 40 multi-module chiplet to transition the UCIe link from the active state to the low power state. In some embodiments, the sideband configuration timer information structure may identify the period has elapsed passively, such as by retaining a value configured to indicate to the multi-module 45 chiplet that the period has elapsed and the multi-module chiplet may be prompted to transition the UCIe link from the active state to the low power state based on reading the retained value at the sideband configuration timer information structure.

The UCIe link may transition from the low power state 1004 to a reset state 1006 ("reset"). During the reset state 1006, the UCIe link may be reset. For example, the UCIe link may be reset by clearing data relating to the UCIe link from the UCIe communications module and/or components of the UCIe communications module and/or interrupting the connection of the UCIe link. Clearing the data relating to the data relating to the UCIe link and/or interrupting the connection of the UCIe link may involve toggling power to the UCIe communications module and/or components of the UCIe communications module. The sideband configuration information structure may be persistent, or sticky, such that the sideband configuration information structure may retain the sideband configuration data through the reset state.

The UCIe link may transition from the reset state **1006** to 65 a sideband initialize state **1008** ("sbinit"). During the sideband initialize state **1008** the multi-module chiplet may use

**20**

the sideband configuration data from the sideband configuration information structure to initialize, or activate or enable, one or more sidebands. In some embodiments, the multi-module chiplet implementing UCIe link sideband selection may initialize a sideband different from a sideband that was active prior to the reset state based on the sideband configuration data. In some embodiments, the multi-module chiplet implementing UCIe link sideband aggregation may initialize two or more sidebands, such as four, which may include a combination of a sideband that was active and at least one sideband that was inactive prior to the reset state, and/or at least two sidebands different from the sideband that was active prior to the reset state, based on the sideband configuration data.

The UCIe link may transition from the sideband initialize state 1008 to a mainband initialize state 1010 ("mbinit"), to a mainband train state 1012 ("mbtrain"), to a UCIe link initialize state 1014 ("linkinit"), and to the active state 1002 ("active"). The multi-module chiplet may implemented the UCIe link in the active state 1002 using the one or more sidebands initialized during the sideband initialize state.

In some embodiments, the LTSSM 1000 may also include a physical layer retrain ("phyretrain") state for retraining the UCIe link and a train error ("trainerror") state for handling an error during UCIe link training.

FIGS. 11A-11C illustrate example methods 1100a, 1100b, 1100c for implementing multi-module chiplet configured UCIe link sideband configuration according to various embodiments. With reference to FIGS. 1-11C, the methods 1100a, 1100b, 1100c may be implemented in a computing device (e.g., computing device 100, SoC 102, 104 in FIG. 1, UCIe system 200 in FIG. 2), in hardware (e.g., UCIe communications module 204a, 204b in FIG. 2, multi-module physical layer logic 304, physical layer logic 306a, 306b, 306c, 306d in FIGS. 3 and 7), in software (e.g., UCIe communications module 204a, 204b in FIG. 2, multi-module physical layer logic 304, physical layer logic 306a, 306b, 306c, 306d in FIGS. 3 and 7) executing in a processor (e.g., multi-module chiplet 202a, 202b, 300, 700 in FIGS. 2, 3, and 7), or in a combination of a software-configured processor and dedicated hardware (e.g., multi-module chiplet **202***a*, **202***b*, **300**, **700** in FIGS. **2**, **3**, and **7**), that includes other individual components, such as various memories/ caches (e.g., sideband select information structure 400 in FIG. 4, sideband select timer information structure 600 in FIG. 6, sideband aggregate information structure 800 in FIG. 8, sideband aggregate timer information structure 900 in FIG. 9) and various memory/cache controllers. In order to encompass the alternative configurations enabled in various 50 embodiments, the hardware implementing the methods 1100a, 1100b, 1100c is referred to herein as a "UCIe link configuration device."

Blocks 1102-1114 of the methods 1100a, 1100b, 1100c described with reference to FIGS. 11A-11C may be implemented in a similar manner and are described in detail once for the methods 1100a, 1100b, 1100c unless otherwise specified.

With reference to FIG. 11A, in the method 1100a, in block 1102, the UCIe link configuration device may receive a sideband configuration signal. The UCIe link configuration device executing a software and/or firmware may receive the sideband configuration signal from the software and/or firmware. The sideband configuration signal may include sideband configuration data (e.g., active sideband data and/or sideband select enable data; aggregate sideband data, sideband aggregate enable data, and/or redundant lane enable data). In some embodiments, the sideband configuration

ration signal may include sideband configuration timer data (e.g., sideband select timer data, sideband aggregate timer data). In some embodiments, the UCIe link configuration device receiving the sideband configuration signal in block 1102 may include a multi-module chiplet (e.g., multi-module chiplet 202a, 202b, 300, 700 in FIGS. 2, 3, and 7), a UCIe communications module (e.g., UCIe communications module 204a, 204b in FIG. 2), a multi-module physical layer logic (e.g., multi-module physical layer logic (e.g., physical layer 10 logic 306a, 306b, 306c, 306d in FIGS. 3 and 7).

In block 1104, the UCIe link configuration device may identify that the UCIe link is in an active state (e.g., active state 1002 in FIG. 10). Identifying that the UCIe link is in an active state may be implemented via various methods, 15 such as reading and interpreting a value of a state register for the UCIe link, a power level indicator for the UCIe link, etc. In some embodiments, the UCIe link configuration device identifying that the UCIe link is in an active state in block 1104 may include the multi-module chiplet, the UCIe communications module, the multi-module physical layer logic, and/or the physical layer logic.