#### US012399638B2

## (12) United States Patent

#### Gorobets et al.

## (54) TLC DATA PROGRAMMING WITH HYBRID PARITY

(71) Applicant: Sandisk Technologies, Inc., Milpitas,

CA (US)

(72) Inventors: Sergey Anatolievich Gorobets,

Edinburgh (GB); Alan D. Bennett, Edinburgh (GB); Liam Parker, Edinburgh (GB); Yuval Shohet, Acton, MA (US); Michelle Martin, Westford, MA (US)

(73) Assignee: Sandisk Technologies, Inc., Milpitas,

CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 15 days.

(21) Appl. No.: 18/515,758

(22) Filed: Nov. 21, 2023

(65) Prior Publication Data

US 2024/0086097 A1 Mar. 14, 2024

#### Related U.S. Application Data

(62) Division of application No. 17/202,163, filed on Mar. 15, 2021, now Pat. No. 11,861,195.

(51) Int. Cl.

$G06F \ 3/06$  (2006.01)  $G06F \ 11/10$  (2006.01)

(52) U.S. Cl.

CPC ...... *G06F 3/064* (2013.01); *G06F 3/0626* (2013.01); *G06F 3/0673* (2013.01); *G06F 11/1004* (2013.01)

(58) Field of Classification Search

None

See application file for complete search history.

### (10) Patent No.: US 12,399,638 B2

(45) **Date of Patent:** Aug. 26, 2025

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

8,279,668 B2 10/2012 Cho et al. 8,499,215 B2 7/2013 Kong et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 105359218 A 2/2016 CN 107403646 A 11/2017 (Continued)

#### OTHER PUBLICATIONS

Benoit et al. "Efficient Checkpoint/Verification Patterns for Silent Error Detection," ICL Research Report, RR-1403, May 2014, 16 pages.

(Continued)

Primary Examiner — Brian R Peugh (74) Attorney, Agent, or Firm — PATTERSON + SHERIDAN, LLP

#### (57) ABSTRACT

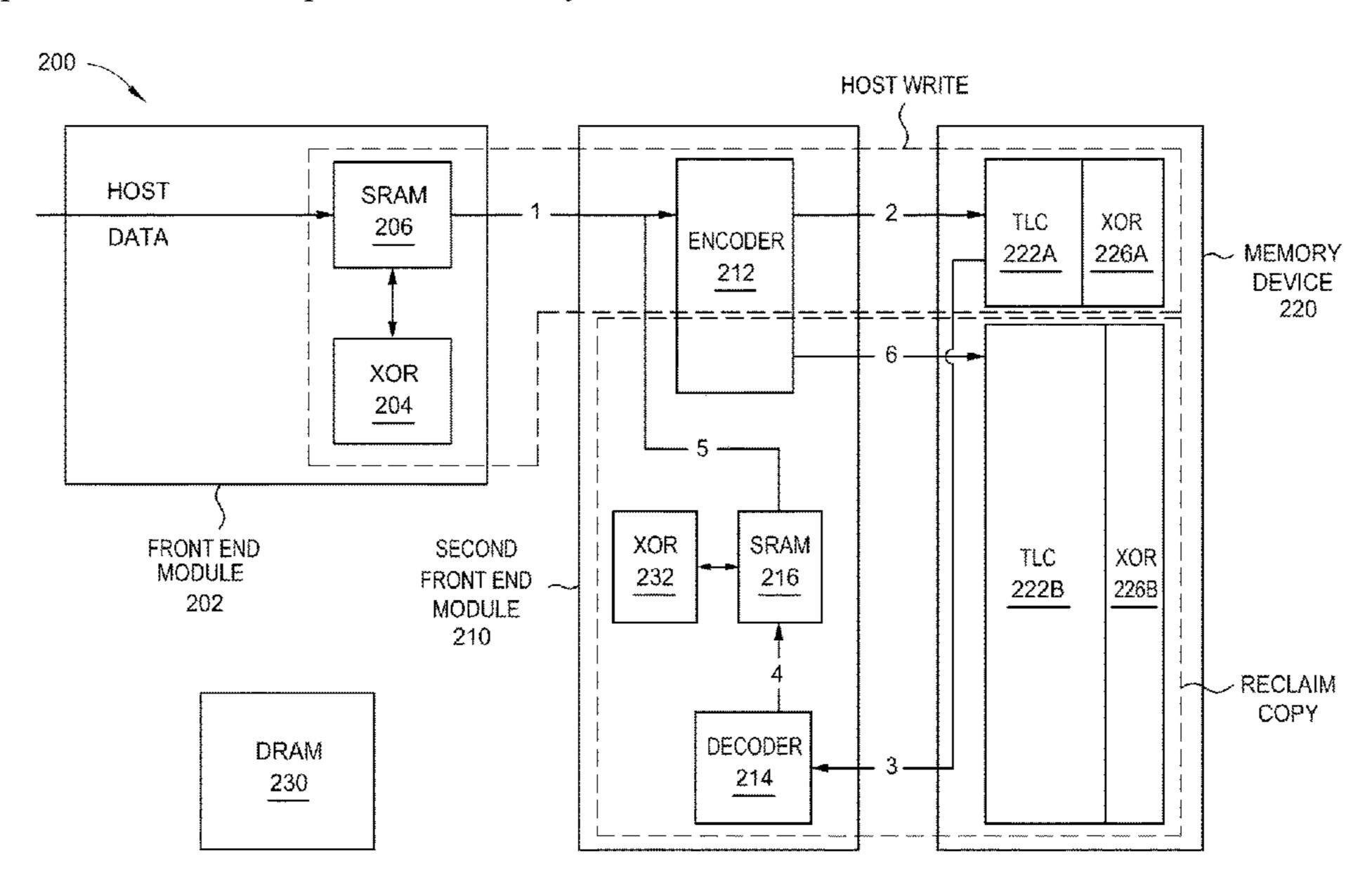

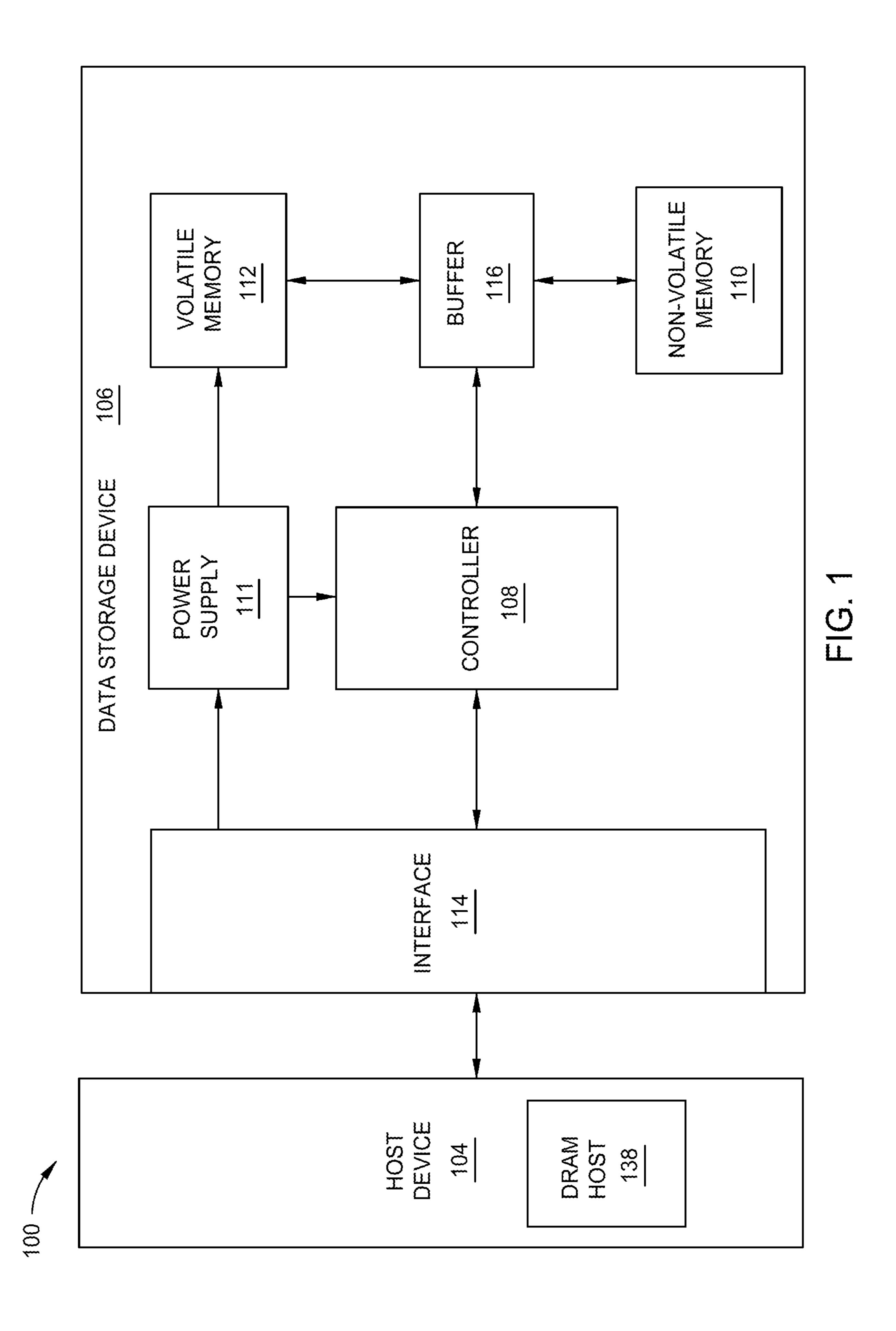

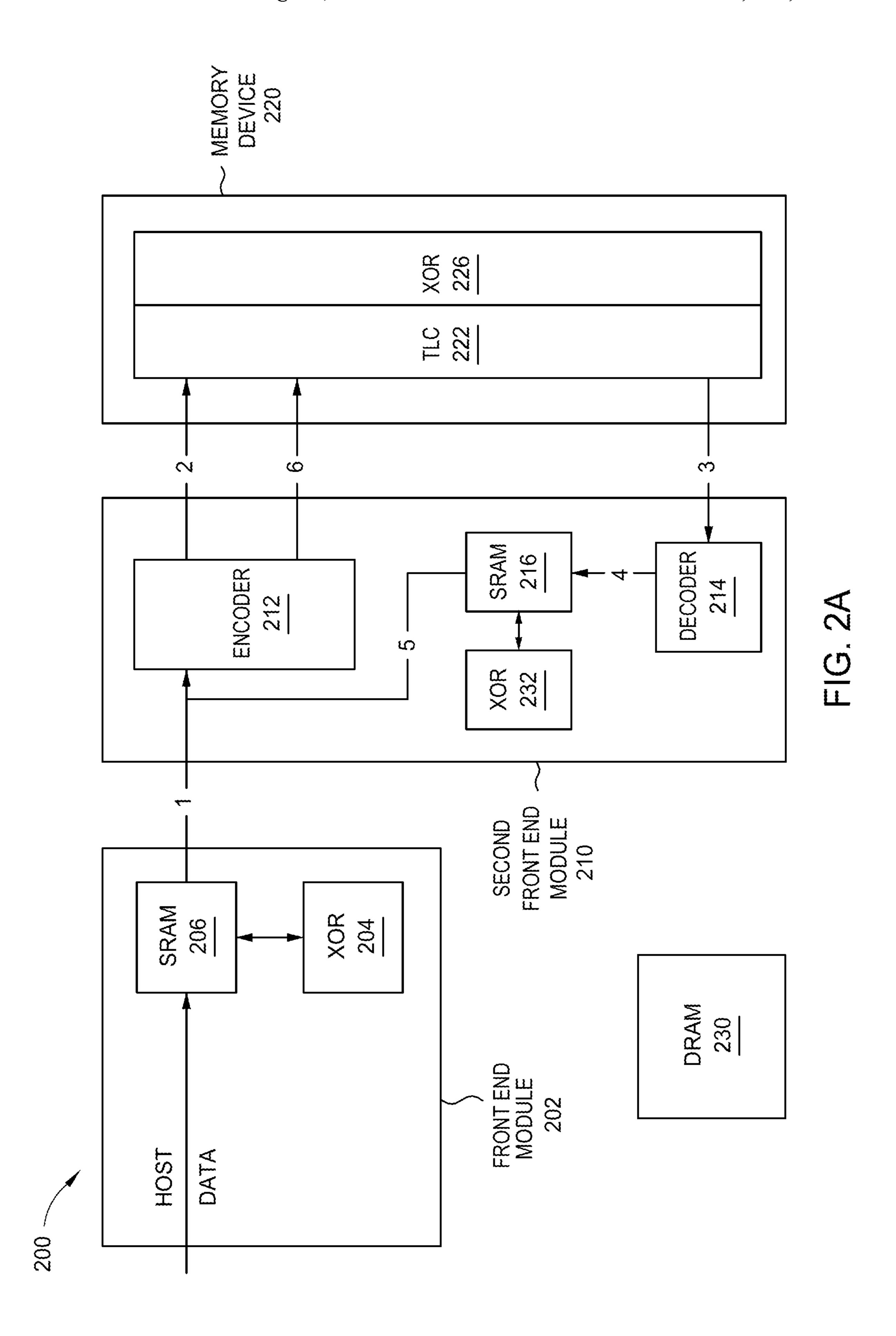

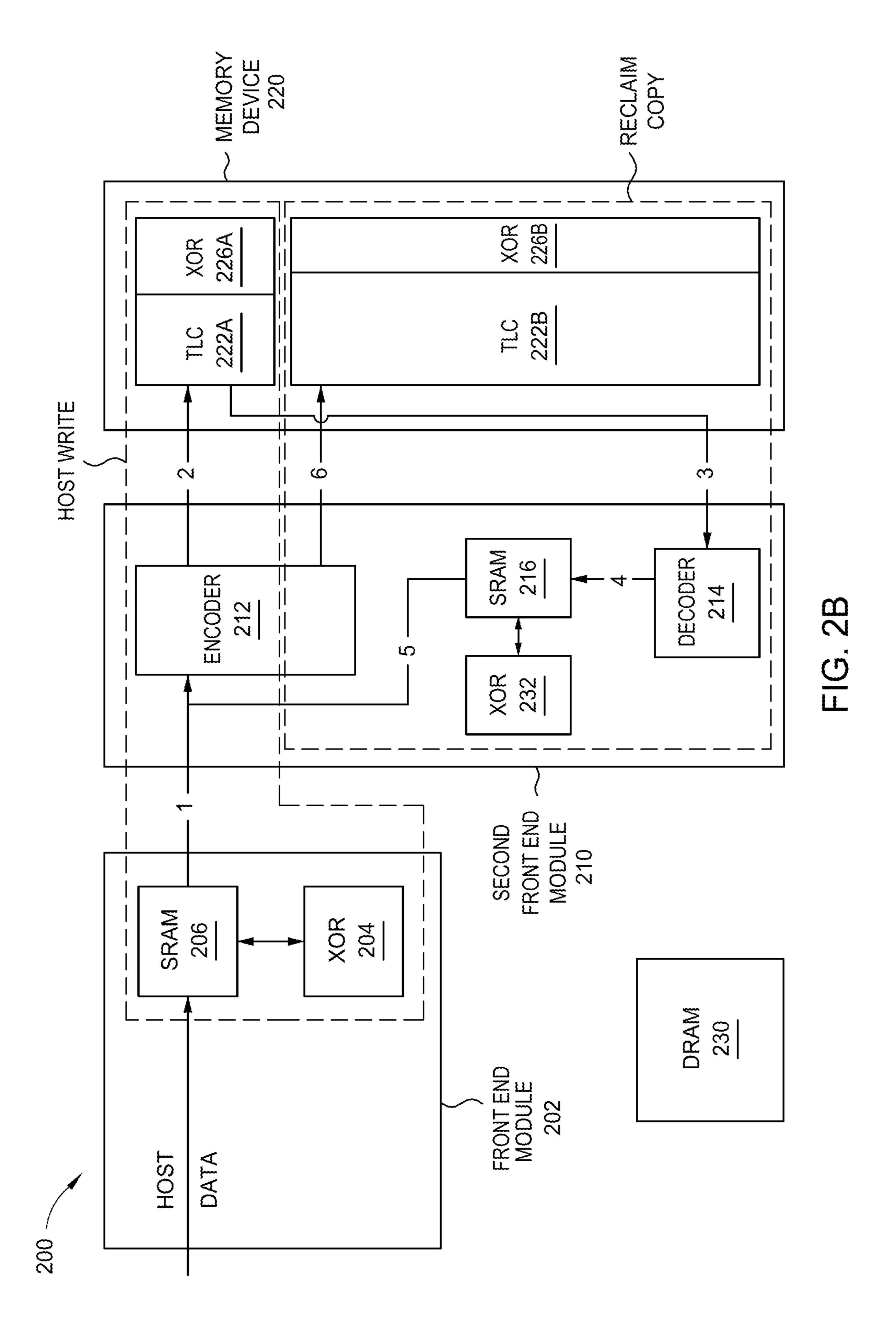

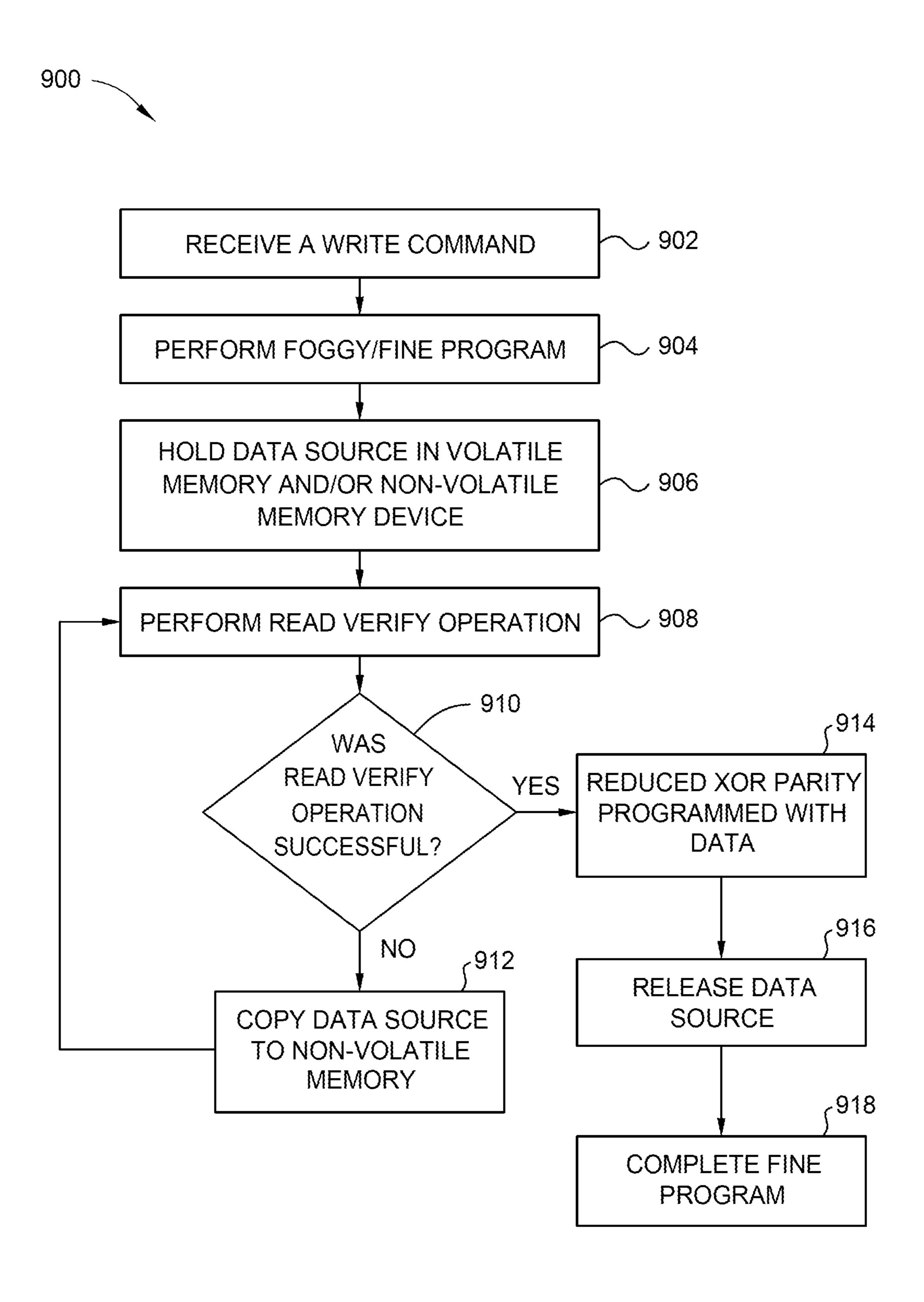

The present disclosure generally relates to improving programming to data storage devices, such as solid state drives (SSDs). A first memory device has a first XOR element and a second memory device has a second XOR element. The ratio of the first XOR element to the capacity of the first memory device is substantially smaller than the ratio of the second XOR element to the capacity of the second memory device. A read verify operation to find program failures is executed on either a wordline to wordline basis, an erase block to erase block basis, or both a wordline to wordline basis and an erase block to erase block basis. Because the program failures are found and fixed prior to programming to the second memory device, the second XOR element may be decreased substantially.

#### 20 Claims, 12 Drawing Sheets

# US 12,399,638 B2 Page 2

| (56) Referen                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ces Cited                                                                                                                          | CN 111415699 A 7/2020<br>CN 111710358 A 9/2020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U.S. PATENT                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DOCUMENTS                                                                                                                          | EP 2513907 A1 10/2012<br>WO 2011075597 A1 6/2011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8,898,374 B2 11/2014<br>8,902,652 B1 12/2014<br>9,135,155 B2 9/2015<br>9,619,321 B1 4/2017<br>10,025,662 B2 7/2018<br>10,101,942 B1 10/2018<br>10,204,007 B2 2/2019<br>10,339,000 B2 7/2019<br>10,769,014 B2 9/2020<br>10,789,126 B2 9/2020<br>11,309,051 B2 4/2022<br>2012/0008389 A1 1/2012<br>2017/0315867 A1 11/2017<br>2018/0025776 A1 1/2018<br>2019/0354478 A1* 11/2019<br>2020/0110661 A1 4/2020<br>2020/0183779 A1 6/2020<br>2020/0194064 A1 6/2020 | Huang et al. Sharon et al. Haratsch et al. Yang et al. Parker et al. Zhang et al. Yang et al. Cariello Singidi et al. Asami et al. | OTHER PUBLICATIONS  Cai et al. "Error characterization, Mitigation, and Recovery in Flash-Memory-Based Solid-State Drives," Proceedings of the IEEE, vol. 105, No. 9, pp. 1666-1704, Sep. 2017, doi: 10.1109/JPROC. 2017.2713127, <a href="https://arxiv.org/pdf/1706.08642.pdf">https://arxiv.org/pdf/1706.08642.pdf</a> . International Search Report and the Written Opinion for International Application No. PCT/US2020/066420 mailed Apr. 7, 2021, 11 pages. Huilong, Y., et al., "NAND flash memory large capacity image stored invalid block management", Microelectronics and Computer, Issue 2, 2010.  Xinfeng, Y., et al., "Design of Low Error Rate Digital Telemetry System for Reentry Vehicle", Beijing Aerospace Long March Aircraft Research Institute, vol. 8, No. 7, 2020.  Zuolo, L., et al., "LDPC soft decoding with improved performance in 1X-2X MLC and TLC Nand flash-based solid state drives", IEEE, vol. 7, Issue 3, 2019. |

| CN 110928722 A                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3/2020                                                                                                                             | * cited by examiner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

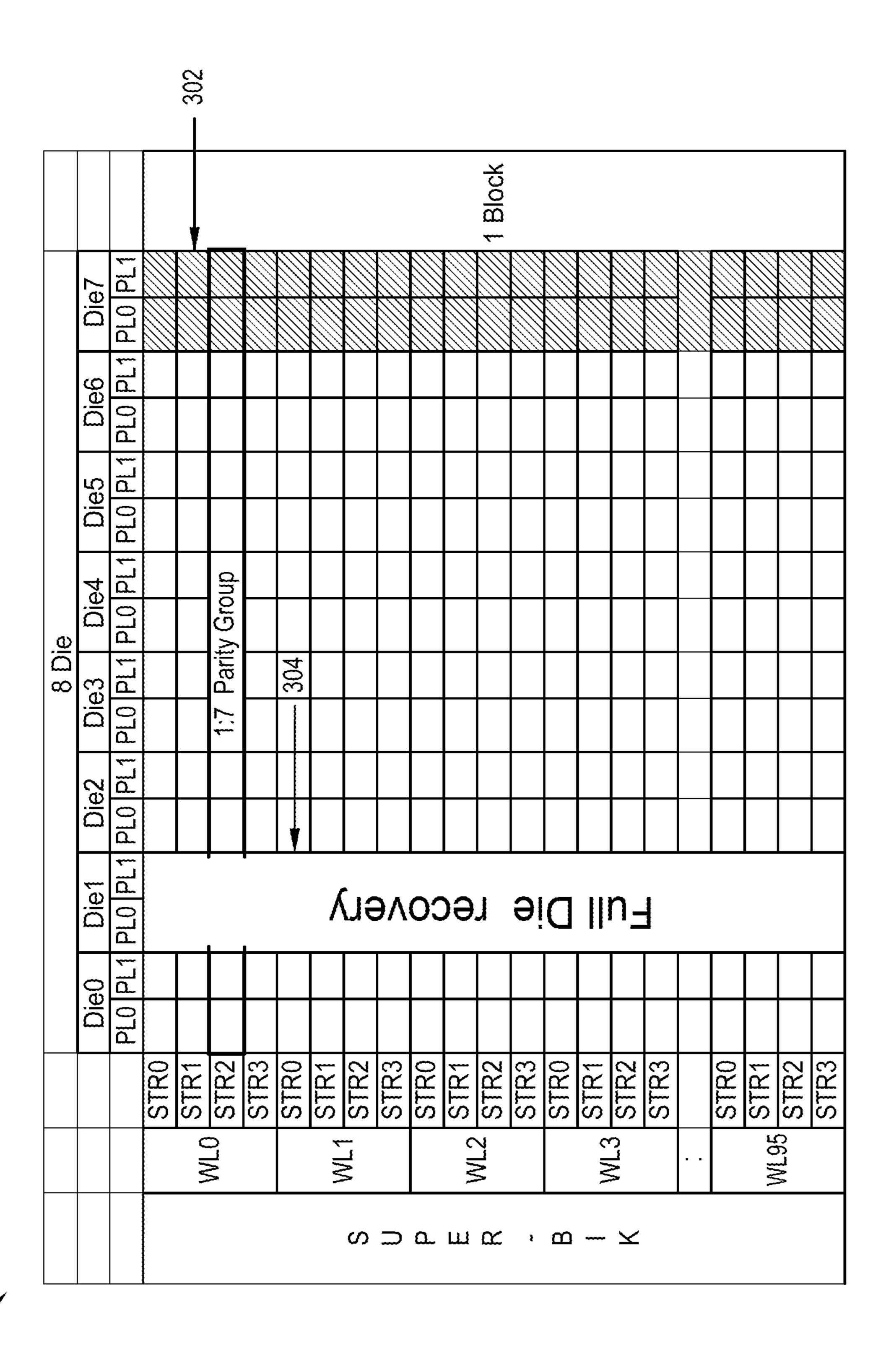

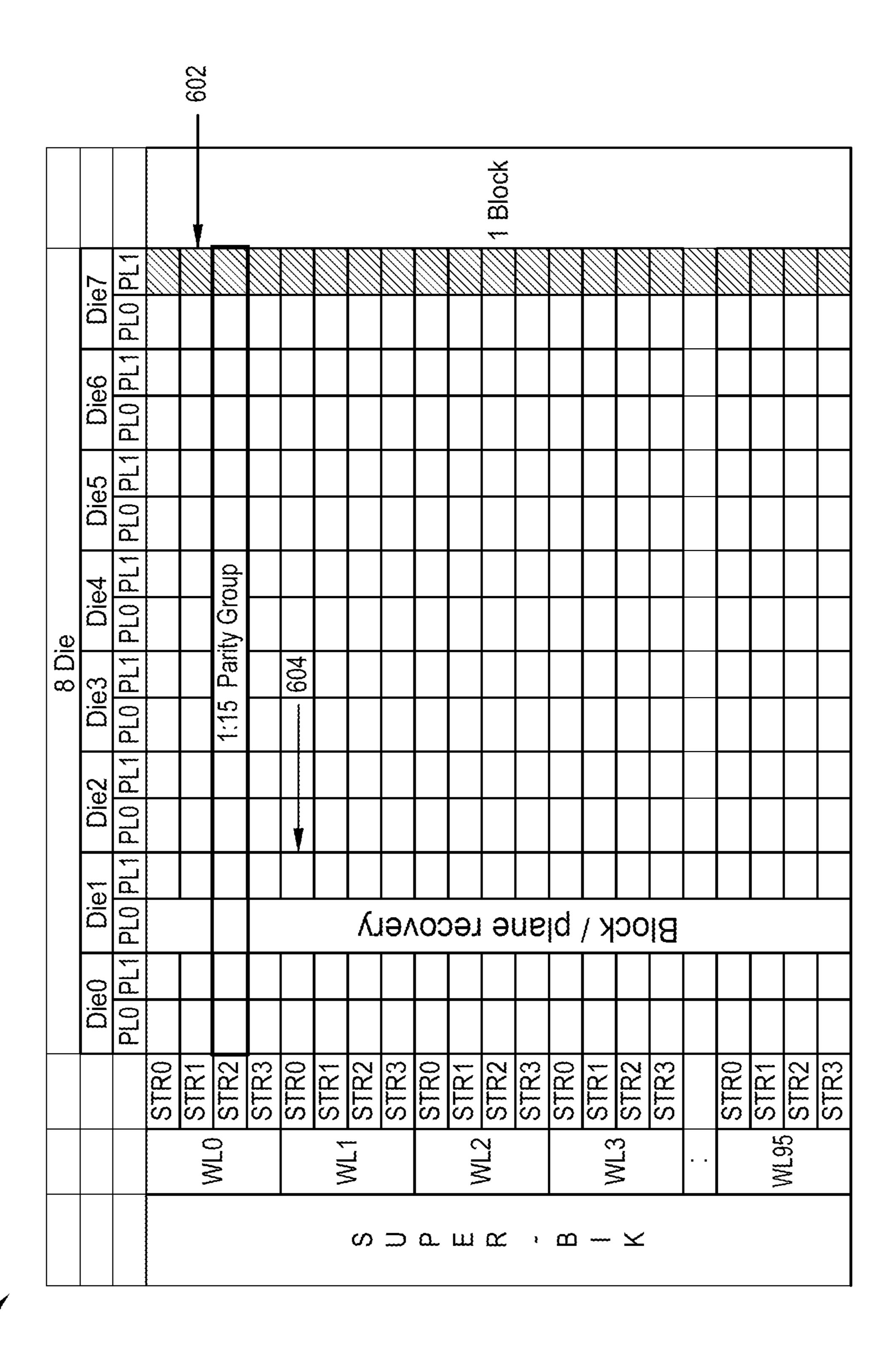

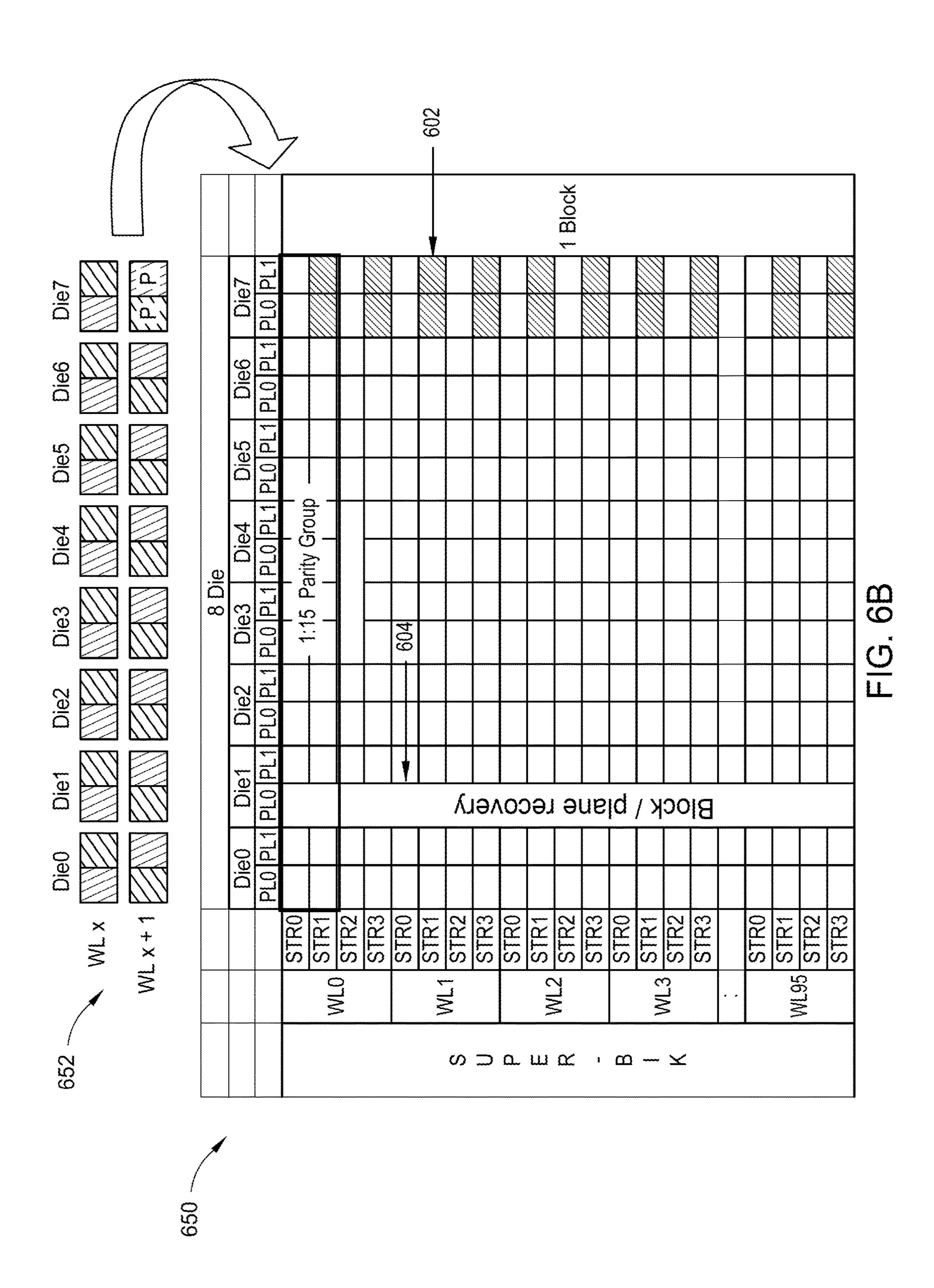

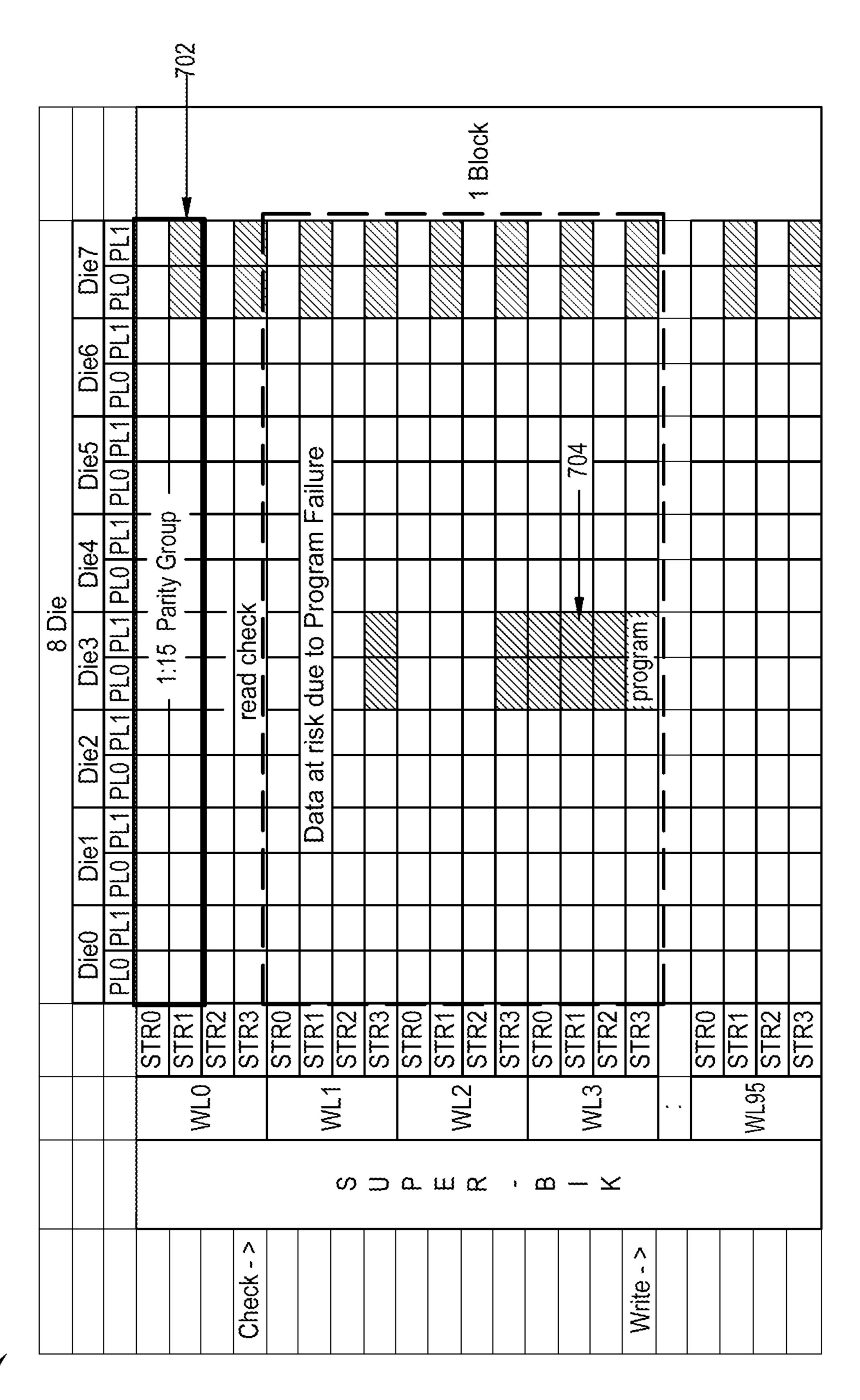

FIG. 3

|      |                                           | The error                     | s to be fixed                 | d using XOR                  | in NAND                     |                        |                             |                                       |                                  |

|------|-------------------------------------------|-------------------------------|-------------------------------|------------------------------|-----------------------------|------------------------|-----------------------------|---------------------------------------|----------------------------------|

|      | Source of UECC data errors                | PSF<br>program<br>failures    | Silent p<br>failt             | nt program<br>failures       | wear, DR                    | XOR PA                 | ARITY                       |                                       |                                  |

|      | input metric                              | B                             | 3FR/PE cycl                   | le                           | SFR                         |                        |                             |                                       |                                  |

|      | category                                  | WL-WL<br>short and<br>smaller | WL-WL<br>short and<br>smaller | 1-EB,<br>2-EB,<br>plane, die | random<br>UECC CWs<br>(SFR) | XOR<br>Parity<br>level | parity<br>ratio<br>examples | Temp data<br>source or<br>XOR holding | Read Verify<br>/ EPWR**<br>level |

|      | OLC. baseline. Full Die Redundancy (1:3   | \ <del></del>                 | Darity ratio)                 |                              |                             |                        |                             |                                       |                                  |

|      |                                           |                               | `<br>`<br>                    |                              |                             | T<br>C                 | 4:34                        | z/a*                                  |                                  |

|      | alc (copy from SLC or alc)                |                               | >                             |                              |                             | T<br>C                 | 1,34                        | 2WL deep                              |                                  |

|      |                                           |                               |                               |                              |                             |                        |                             |                                       |                                  |

|      | QLC ESS drive path (conver                | ntional, 32 c                 | die super-bl                  | ocks)                        |                             |                        |                             |                                       |                                  |

|      | SLC blocks (host writes)                  | >                             | >                             | >                            |                             | e.g. FDR               | 1,31                        |                                       |                                  |

|      | alc (copy from SLC or alc)                |                               |                               |                              |                             |                        |                             |                                       |                                  |

| 402  | 1. no extra checks                        |                               | >                             | >                            | <b>&gt;</b>                 | less than SLCs         | 1:63                        | 2WL deep                              |                                  |

| 404  | 2, with FW read verify/ EPWR              |                               |                               | <b>&gt;</b>                  | >                           | even less              | 1:127                       | 2WL deep                              |                                  |

|      | 3. with FW read verify/ EPWR              |                               | >                             |                              |                             | even less              | 1:255                       | 1-EB deep                             |                                  |

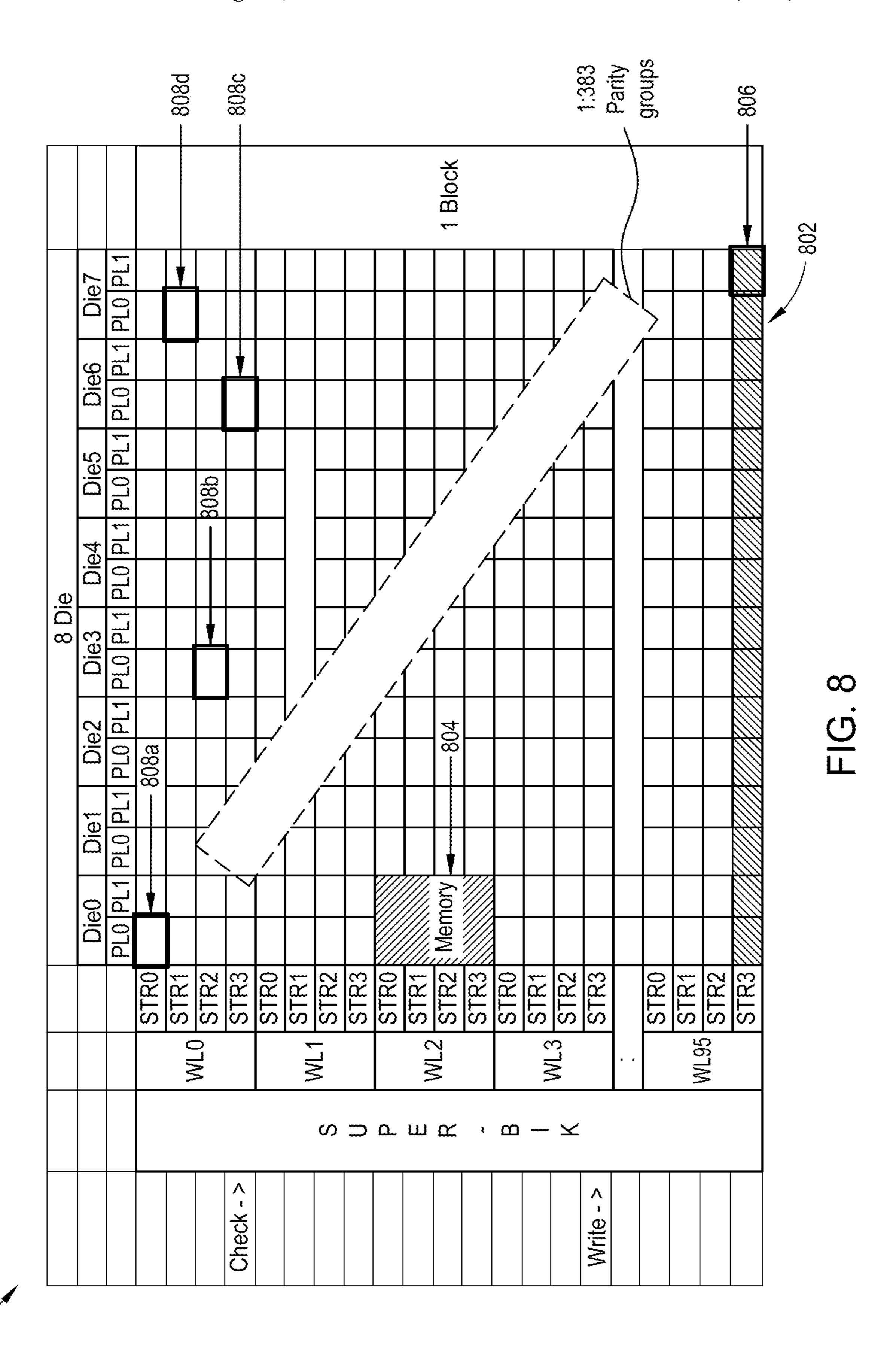

|      | 4. with FW read verify/ EPWR              |                               |                               |                              | >                           | even less              | 1:383                       | 1-EB deep                             |                                  |

| 406- | 5. with FW read verify/ EPWR              |                               |                               |                              |                             | none                   | none                        | 1-EB deep                             |                                  |

|      | EPWR = FW Read Verify - may not detect    |                               | 100% of errors                | رن<br>ا                      |                             |                        |                             |                                       |                                  |

|      | *limited by host buffers, may add extra   | d extra temp                  | parity (Q-Parity)             | arity)                       |                             |                        |                             |                                       |                                  |

|      | ** exact data verification design depends | depends on                    | the failure                   | type and geometry            | netry, Smaller              | error require hig      | higher verification         | tion overhead.                        |                                  |

下 (C, 4

| w/ PSF (SELSTRING                                                                                                                                |         |    |     | <b>7</b>                                | **************************************  |                                        |     |     |     | *************************************** | *************************************** |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------|----|-----|-----------------------------------------|-----------------------------------------|----------------------------------------|-----|-----|-----|-----------------------------------------|-----------------------------------------|------------|

|                                                                                                                                                  |         | P  | ane | )<br>0 (                                |                                         | ······································ | Pla | ane | ; 1 |                                         | Lege                                    | end        |

|                                                                                                                                                  | WL(N-x) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | OK         |

|                                                                                                                                                  | WL(N-1) |    |     |                                         |                                         |                                        | 十   |     |     |                                         |                                         | UECC/Shor  |

|                                                                                                                                                  | WL(n)   |    |     |                                         |                                         |                                        | 十   |     |     |                                         |                                         | PSF        |

|                                                                                                                                                  |         | 50 | 51  | 52                                      | 53                                      | 1                                      | 50  | 51  | 52  | 53                                      |                                         |            |

| w/ PSF (SELSTRING) + UECC<br>on WL + UECC on (SELSTRING)                                                                                         |         |    |     | *************************************** |                                         |                                        |     |     |     |                                         |                                         |            |

|                                                                                                                                                  |         | P  | ane | 9 0                                     |                                         |                                        | Pla | ane | 1   | ***                                     | Lege                                    | nd         |

|                                                                                                                                                  | WL(N-x) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | OK         |

|                                                                                                                                                  | WL(N-1) |    |     |                                         |                                         | <u> </u>                               | 十   |     |     |                                         |                                         | UECC/Shor  |

|                                                                                                                                                  | WL(n)   |    |     |                                         |                                         | ·····                                  |     |     |     |                                         |                                         | PSF        |

| ***************************************                                                                                                          |         | 50 | 51  | 52                                      | 53                                      | Į                                      | 50  | 51  | 52  | 53                                      |                                         | ·····      |

| w/ PSF (SELSTRING) + UECC<br>on WL + UECC on (SELSTRING)<br>+ UECC on WLn-1 + UECC on<br>Previous Strings                                        |         |    |     | **************************************  | **************************************  |                                        |     |     |     | *************************************** |                                         |            |

|                                                                                                                                                  |         | PI | ane | • O                                     |                                         |                                        | Pla | ane | 1   |                                         | Lege                                    | end        |

| ······································                                                                                                           | WL(N-x) |    |     |                                         |                                         |                                        |     | ·   |     |                                         |                                         | OK         |

|                                                                                                                                                  | WL(N-1) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | UECC/Short |

|                                                                                                                                                  | WL(n)   |    |     |                                         |                                         |                                        | 十   |     |     |                                         |                                         | PSF        |

|                                                                                                                                                  |         | 50 | 51  | ŧ                                       | 53                                      | Į.                                     | 50  | 51  | 52  | 53                                      |                                         |            |

| w/ PSF (SELSTRING) + PSF WL<br>ADJ + PSF (SELSTRING) ADJ +<br>UECC on WL + UECC on (SEL<br>STRING) + UECC on WL ADJ +<br>UECC on (SELSTRING) ADJ |         |    |     | **************************************  | **************************************  |                                        |     |     |     |                                         |                                         |            |

|                                                                                                                                                  |         | P  | ane | 9 0                                     | *************************************** |                                        | Pla | ne  | 1   | *************************************** | Lege                                    | end        |

|                                                                                                                                                  | WL(N-x) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | OK         |

|                                                                                                                                                  | WL(N-1) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | UECC/Short |

| **************************************                                                                                                           | WL(n)   |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | PSF        |

|                                                                                                                                                  |         | 50 | 51  | 52                                      | 53                                      | Ş                                      | 50  | 51  |     | 53                                      |                                         |            |

| w/ PSF (SELSTRING) + UECC on<br>WL + UECC on (SELSTRING) +<br>UECC on Previous Strings + UECC<br>WL ADJ + UECC on<br>Previous String ADJ         |         |    |     | *************************************** |                                         |                                        |     |     |     |                                         |                                         |            |

|                                                                                                                                                  |         | PI | ane | 0                                       |                                         |                                        | Pla | ne  | 1   |                                         | Lege                                    | end        |

|                                                                                                                                                  | WL(N-x) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | OK         |

|                                                                                                                                                  | WL(N-1) |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | UECC/Short |

| •                                                                                                                                                | WL(n)   |    |     |                                         |                                         |                                        |     |     |     |                                         |                                         | PSF        |

|                                                                                                                                                  |         | 50 | 51  | 1                                       | 53                                      | į                                      | 50  | 51  | 52  | 53                                      |                                         |            |

FIG. 5A

| More WL) ADJ + UECC on 1 UECC (SELSTRING) ADJ +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                    |                                         |        |      |      |          |                                         |          |    |      | •                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------|--------|------|------|----------|-----------------------------------------|----------|----|------|-----------------------------------------------------------------------|

| Previous Strings ADJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1521 /1 1 \                                                                                        | PI                                      | ane    | 9 () |      | P        | ane                                     | 9 1      |    | Lege |                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WL(N-x)                                                                                            |                                         |        |      |      |          |                                         |          |    |      | OK                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WL(N-1)                                                                                            | 7777                                    | 7777   | 777  |      |          | 7777                                    | 7777     |    |      | UECC/Short                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WL(n)                                                                                              |                                         |        | ; ;  |      |          |                                         |          |    |      | PSF                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                    | 50                                      | 51     | 52   | 53   | 50       | 51                                      | 52       | 53 |      | possible UECC                                                         |

| / PSF (SELSTRING) + UECC (<br>UECC on WLn-1 + UECC on (S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SELSTRING) +                                                                                       | *************************************** |        |      |      |          |                                         |          |    |      |                                                                       |

| UECC on Previous Strings + Proceedings (SELSTRING) AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    | *************************************** |        |      |      |          | *************************************** |          |    |      |                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                    | PI                                      | ane    | 9 0  |      | P        | ane                                     | 1        |    | Lege | end                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WL(N-x)                                                                                            |                                         |        |      |      |          |                                         |          |    |      | OK                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WL(N-1)                                                                                            |                                         |        |      |      |          |                                         |          |    |      | UECC/Short                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WL(n)                                                                                              |                                         |        |      |      |          |                                         |          |    |      | PSF                                                                   |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ***************************************                                                            | 50                                      | 51     | 52   |      | 50       | 51                                      | 1        | 53 |      | possible UECC                                                         |

| pMg g g g g g g g g g g g g g g g g g g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    | 4                                       |        |      |      | -        | <u> </u>                                |          |    | _    |                                                                       |

| Single WL UECC Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sile                                                                                               | · <del>-</del> ······                   | eri    |      | s (n |          | Shane                                   | <b></b>  |    | Lege | end                                                                   |

| Single WL UECC Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sile<br>WL(N-x)                                                                                    | · <del>-</del> ······                   |        |      | s (n |          |                                         | <b></b>  |    | Lege |                                                                       |

| Single WL UECC Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    | · <del>-</del> ······                   |        |      | S (n |          |                                         | <b></b>  |    | Lege | OK                                                                    |

| Single WL UECC Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WL(N-x)                                                                                            | · <del>-</del> ······                   |        |      | S (n |          |                                         | <b></b>  |    |      |                                                                       |

| Single WL UECC Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WL(N-x) WL(N-1)                                                                                    | P                                       | ane    | 9 0  |      | P        |                                         | <b>1</b> | 53 | Lege | OK<br>UECC/Short<br>PSF                                               |

| All WL UECC Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | WL(N-x) WL(N-1)                                                                                    | P                                       | ane    |      |      | P        | ane                                     | <b>1</b> | 53 |      | OK<br>UECC/Short<br>PSF                                               |