#### US012162279B2

# (12) United States Patent

# Shimamura

## PRINTING APPARATUS

Applicant: BROTHER KOGYO KABUSHIKI

KAISHA, Nagoya (JP)

Inventor: Yasuhiro Shimamura, Nagoya (JP)

Assignee: Brother Kogyo Kabushiki Kaisha, (73)

Nagoya (JP)

Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 76 days.

Appl. No.: 17/822,180

(22)Aug. 25, 2022 Filed:

(65)**Prior Publication Data**

> US 2023/0094405 A1 Mar. 30, 2023

Foreign Application Priority Data (30)

(JP) ...... 2021-161820 Sep. 30, 2021

Int. Cl. (51)B41J 2/045

(2006.01)

U.S. Cl. (52)CPC ...... **B41J 2/04546** (2013.01); **B41J 2/0451** (2013.01); **B41J 2/0455** (2013.01); **B41J 2/04551** (2013.01)

(58) Field of Classification Search

CPC .... B41J 2/04546; B41J 2/0451; B41J 2/0455; B41J 2/04551; B41J 2/0452; B41J 2/04541; B41J 2/04581

See application file for complete search history.

#### (56)**References Cited**

# U.S. PATENT DOCUMENTS

2007/0146403 A1 6/2007 Sayama et al. 2007/0177169 A1 8/2007 Han

(10) Patent No.: US 12,162,279 B2

(45) Date of Patent: Dec. 10, 2024

5/2008 Suzuki 2008/0122888 A1 2013/0083106 A1 4/2013 Tsukamoto

7/2013 Yanaka ..... 2013/0182025 A1\* B41J 2/04541

347/10

(Continued)

#### FOREIGN PATENT DOCUMENTS

JP S5888469 A 6/1983 2001-54947 A 2/2001 (Continued)

#### OTHER PUBLICATIONS

EP Office Action dated Jun. 25, 2024 from application EP 22 155 761.4.

(Continued)

Primary Examiner — Sharon Polk (74) Attorney, Agent, or Firm — Scully, Scott, Murphy & Presser, PC

#### **ABSTRACT** (57)

There is provided a printing apparatus including: a nozzle configured to discharge a liquid by an energy generating element; a selector configured to select, based on a print job, a driving waveform corresponding to a printing method indicated by the print job, from a plurality of driving waveforms different from each other; a signal generator configured to generate a time division multiplex signal, based on data indicating the driving waveform selected by the selector; and a separator configured to separate a driving waveform signal indicating the driving waveform selected by the selector from the time division multiplex signal generated by the signal generator. The energy generating element is configured to be driven by the driving waveform signal separated by the separator.

#### 14 Claims, 17 Drawing Sheets

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 2017/0113461 A | 1 4/2017   | Netsu et al.     |                 |

|----------------|------------|------------------|-----------------|

|                |            |                  |                 |

| 2018/0201012 A | .1 7/2018  | Miyagishi        |                 |

| 2018/0272705 A | 1* 9/2018  | Ono              | $B41J\ 2/04581$ |

| 2019/0126611 A | .1 5/2019  | Lahiri et al.    |                 |

| 2021/0060935 A | .1 3/2021  | Kashimura et al. |                 |

| 2022/0314617 A | 1* 10/2022 | Hiwada           | B41J 2/14201    |

#### FOREIGN PATENT DOCUMENTS

| TD | 2000 126612 4 | C/2000 |

|----|---------------|--------|

| JР | 2008-126612 A | 6/2008 |

| JP | 2010-64465 A  | 3/2010 |

| JP | 2010142978 A  | 7/2010 |

| JP | 2011-20330 A  | 2/2011 |

| JP | 2017080891 A  | 5/2017 |

| JP | 2017-113965 A | 6/2017 |

| JP | 2019-512413 A | 5/2019 |

#### OTHER PUBLICATIONS

Related U.S. Appl. No. 17/693,614, filed Mar. 14, 2022.

Official Action dated Nov. 24, 2023 from related application, namely, U.S. Appl. No. 17/693,614, filed Mar. 14, 2022.

Extended European Search Report dated Jul. 22, 2022 of EP Patent Application No. 22155761.4.

Notice of Reasons for Refusal dated Jan. 9, 2024 of Japanese Patent Application No. 2021-143754 with computer generated translation. Related U.S. Appl. No. 17/693,677, filed Mar. 14, 2022.

Notice of Reasons for Refusal dated Jan. 9, 2024 received from the Japanese Patent Office in related JP 2021-161820 together with English language translation.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 5

|        | ADDRESS X | TIME ta(X) |

|--------|-----------|------------|

|        | 8         | 2 µs       |

|        | 7         | 1 45       |

| Da ~~~ | 6         | 2 µs       |

|        | 5         | 1 45       |

|        | 4         | 5 # 5      |

|        | 3         | 1 4 5      |

|        | 2         | 5 #s       |

|        |           | 1 µs       |

|        | 0         | 2 µs       |

| ADDRESS X | VOLTAGE | ~~~ |

|-----------|---------|-----|

| 8         | O       |     |

| 7         | VŤ      |     |

| 6         | V2      |     |

| 5         | V 1     |     |

| 4         | 0       |     |

| 3         | V1      |     |

| 2         | V2      |     |

| *         | V       |     |

| Q         | 0       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADDRESS X | TIME tb(X)   | *******                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|-----------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4         | 5#s          |                                         |

| Ob The second se | 3         | 1 4 8        | 000000000000000000000000000000000000000 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2         | 9 # s        | ,,,,,,,,,,,,,,,,,,                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | 1 <i>U</i> S |                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0         | 4 # s        |                                         |

| ADDRESS X | VOLTAGE |      |

|-----------|---------|------|

| 4         | O       | C () |

| 3         | V 1     |      |

| 2         | V2      |      |

| 4         | V1      |      |

| O         | 0       |      |

|          | ADDRESS X | TIME tc(X) |

|----------|-----------|------------|

| <u> </u> | 4         | 11 µs      |

|          | 3         | 1 4 5      |

|          | 2         | 5ីµទ       |

|          | Je s      | 1 µ s      |

|          | 0         | 2 µ s      |

| ADDRESS X | VOLTAGE |  |

|-----------|---------|--|

| 4         | O       |  |

| 3         | V1      |  |

| 2         | V2      |  |

| ***       | V1      |  |

| 0         | 0       |  |

|       | ADDRESS X | TIME td(X)   |     |

|-------|-----------|--------------|-----|

|       | 4         | 5 µ s        | •   |

| Dd ~~ | 3         | 1 <i>u</i> s | · · |

|       | 2         | 5 µ s        |     |

|       | ***       | 1µs          |     |

|       | 0         | 8 <i>µ</i> s |     |

| ADDRESS X | VOLTAGE |  |

|-----------|---------|--|

| 4         | O       |  |

| 3         | V 1     |  |

| 2         | V2      |  |

|           | V1      |  |

| O         | 0       |  |

FIG.

aaaaaaaaaaaaaaaaaaaaaaa \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* ~~~<del>~</del> experimental states of the sta minimumum, ...... processing the second · harrows the contract of the co \*\*\*\*\*\*\*\*\*\*\*\*\* mummin 🎮 transmining the Management of the Control of the Con O mmmmmm faceautication for parameter has

Height

FIG. 8

FIG. 1

FIG. 12

FIG. 1

FIG. 15A

FIG. 15B

FIG. 16

#### PRINTING APPARATUS

#### REFERENCE TO RELATED APPLICATIONS

This application claims priority from Japanese Patent <sup>5</sup> Application No. 2021-161820 filed on Sep. 30, 2021. The entire content of the priority application is incorporated herein by reference.

#### **BACKGROUND ART**

There is a printer which generates first to fourth driving pulses having different amplitudes, as driving signals for driving a piezoelectric element of each of nozzles. The first to fourth driving pulses are continuously generated during one cycle for printing one pixel. One of the first to fourth driving pulses is selected and applied to the piezoelectric element of each of the nozzles. Each of the nozzles discharges or ejects an ink in an amount corresponding to the amplitude of the selected driving pulse so as to form a dot having a desired size.

#### DESCRIPTION

According to a first aspect of the present disclosure, there is provided a printing apparatus including:

- a nozzle configured to discharge a liquid by an energy generating element;

- a selector configured to select, based on a print job, a 30 driving waveform corresponding to a printing method indicated by the print job, from a plurality of driving waveforms different from each other;

- a signal generator configured to generate a time division multiplex signal, based on data indicating the driving 35 waveform selected by the selector; and

- a separator configured to separate a driving waveform signal indicating the driving waveform selected by the selector from the time division multiplex signal generated by the signal generator.

The energy generating element is configured to be driven by the driving waveform signal separated by the separator. According to a second aspect of the present disclosure, there is provided a printing apparatus including:

- a nozzle configured to discharge a liquid by an energy 45 generating element;

- a signal generator configured to generate a time division multiplex signal, transmittable via a single signal line, based on a plurality of pieces of data each indicating one of a plurality of driving waveforms different from 50 each other; and

- a separator configured to separate a driving waveform signal indicating the one of the plurality of driving waveforms from the time division multiplex signal generated by the signal generator.

Both a first period of time and a second period of time are included in a same one cycle of the time division multiplex signal.

The second period of time is different from the first period of time.

A number of the data to be used by the signal generator so as to generate the time division multiplex signal during the first period of time is smaller than a number of the data to be used by the signal generator so as to generate the time division multiplex signal during the second period of time. 65

The energy generating element is configured to be driven by the driving waveform signal separated by the separator.

2

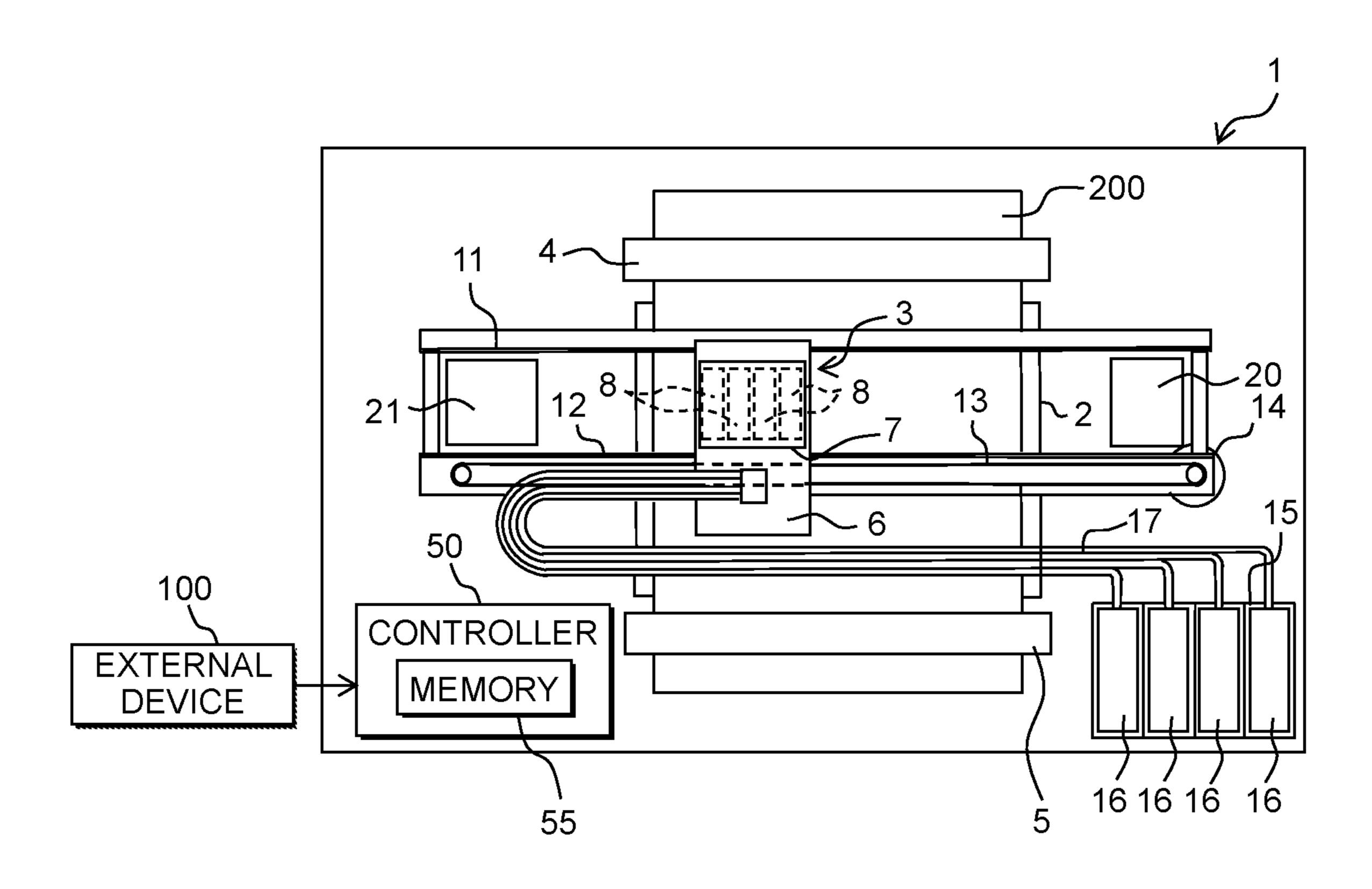

FIG. 1 is a plan view schematically depicting a printing apparatus.

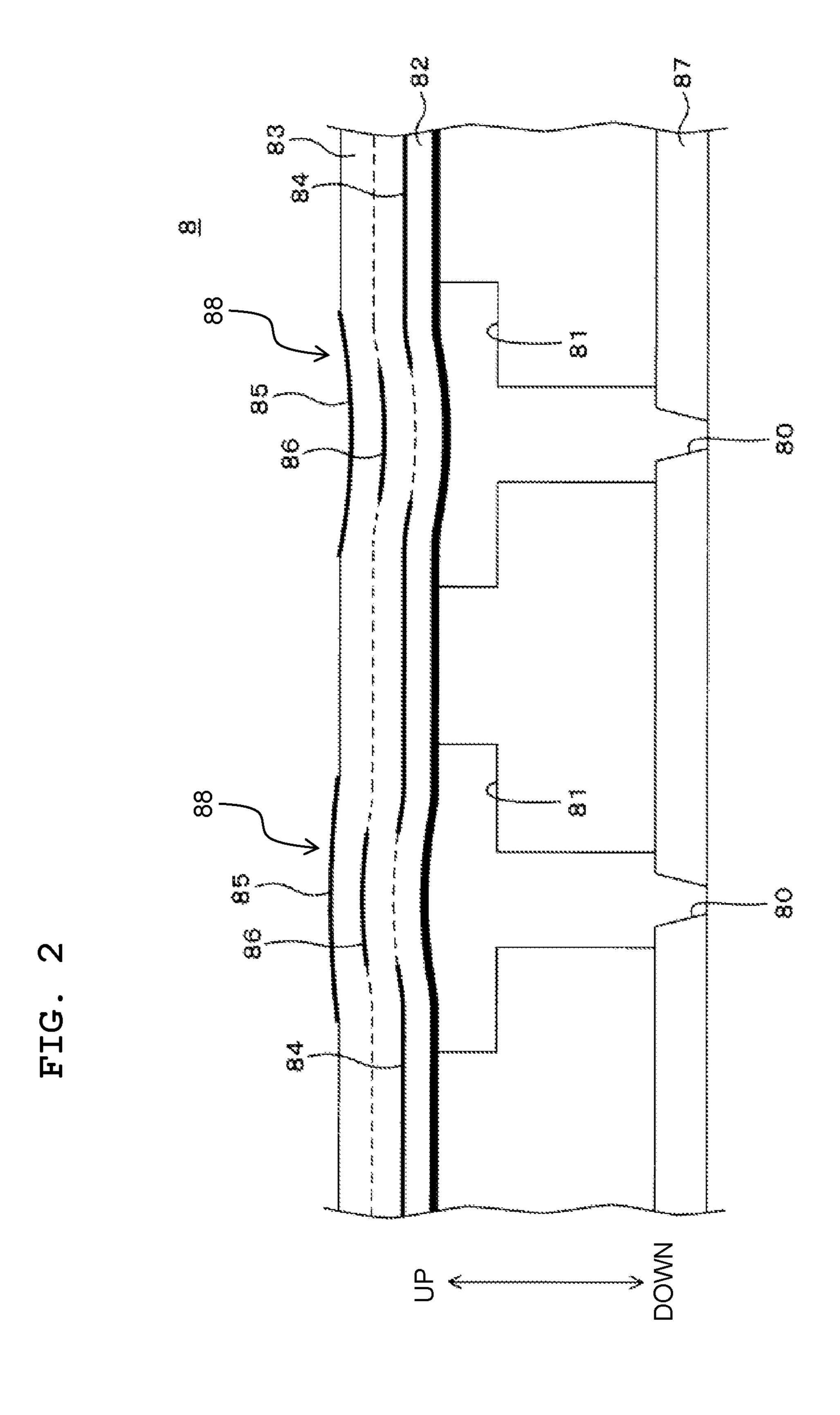

FIG. 2 is a partial enlarged cross-sectional view schematically depicting an ink-jet head.

FIG. 3 is a block diagram of a controller.

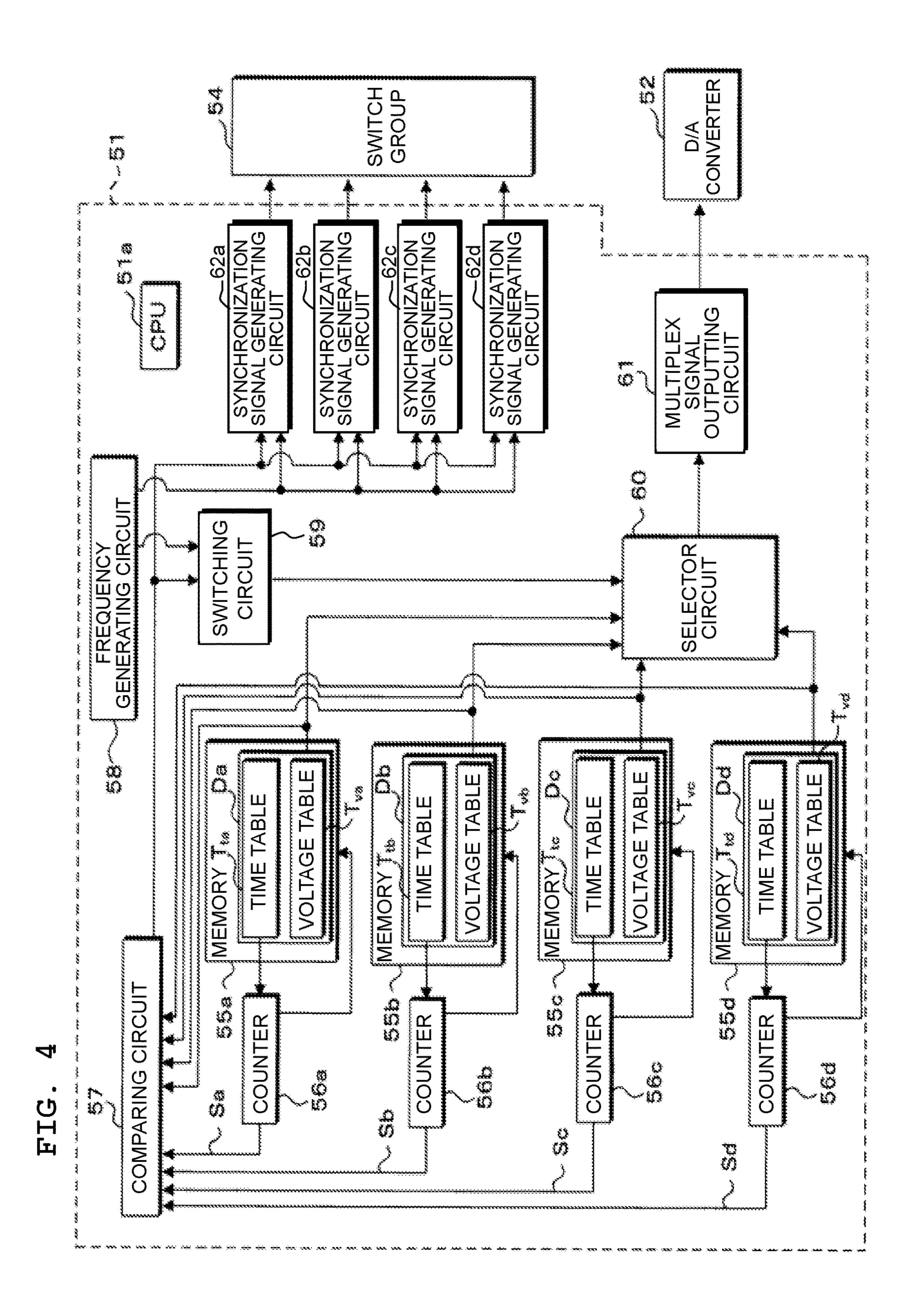

FIG. 4 is a block diagram of a control circuit.

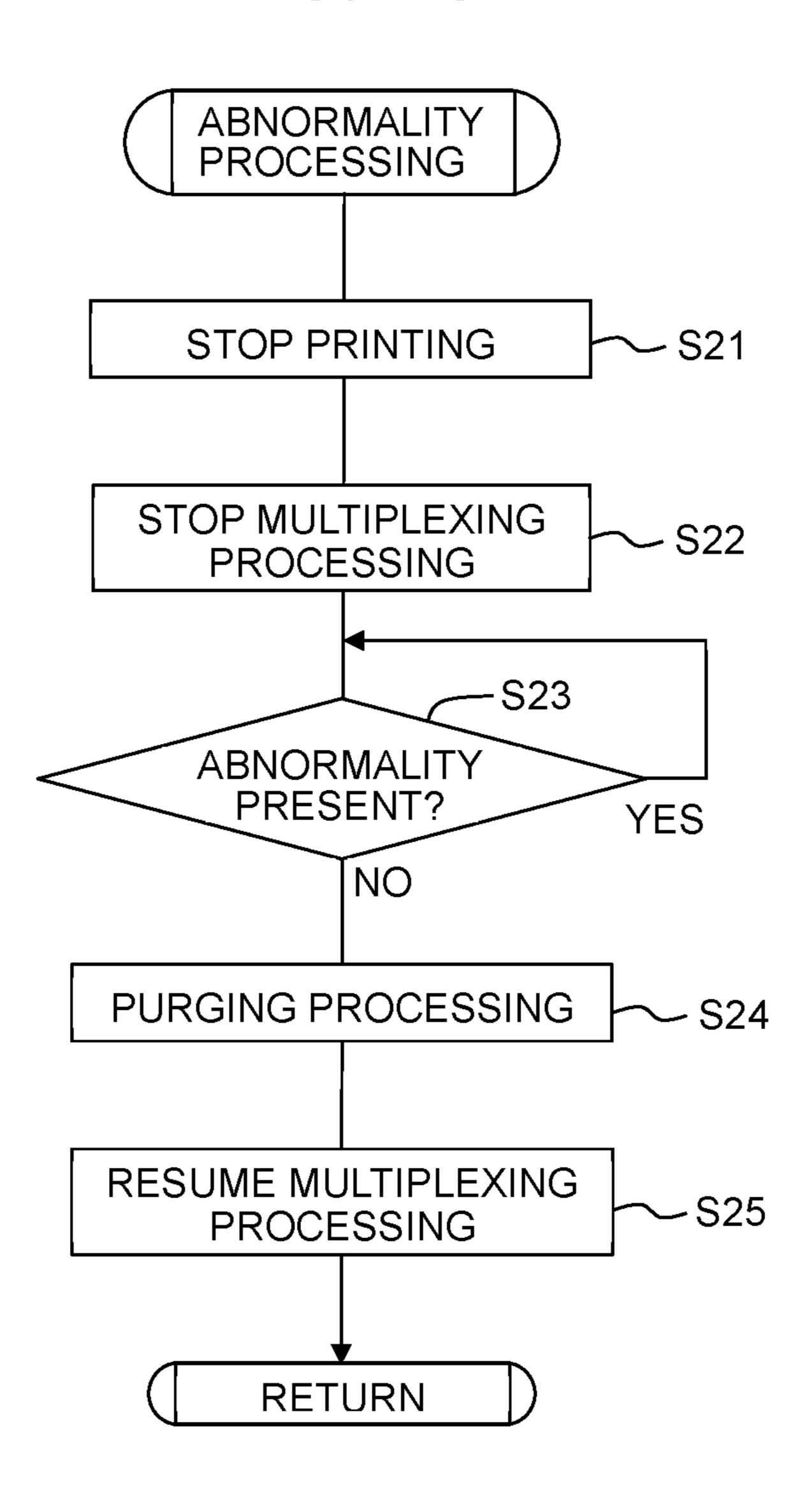

FIG. 5 is a conceptual diagram depicting an example of a time table and an example of a voltage table.

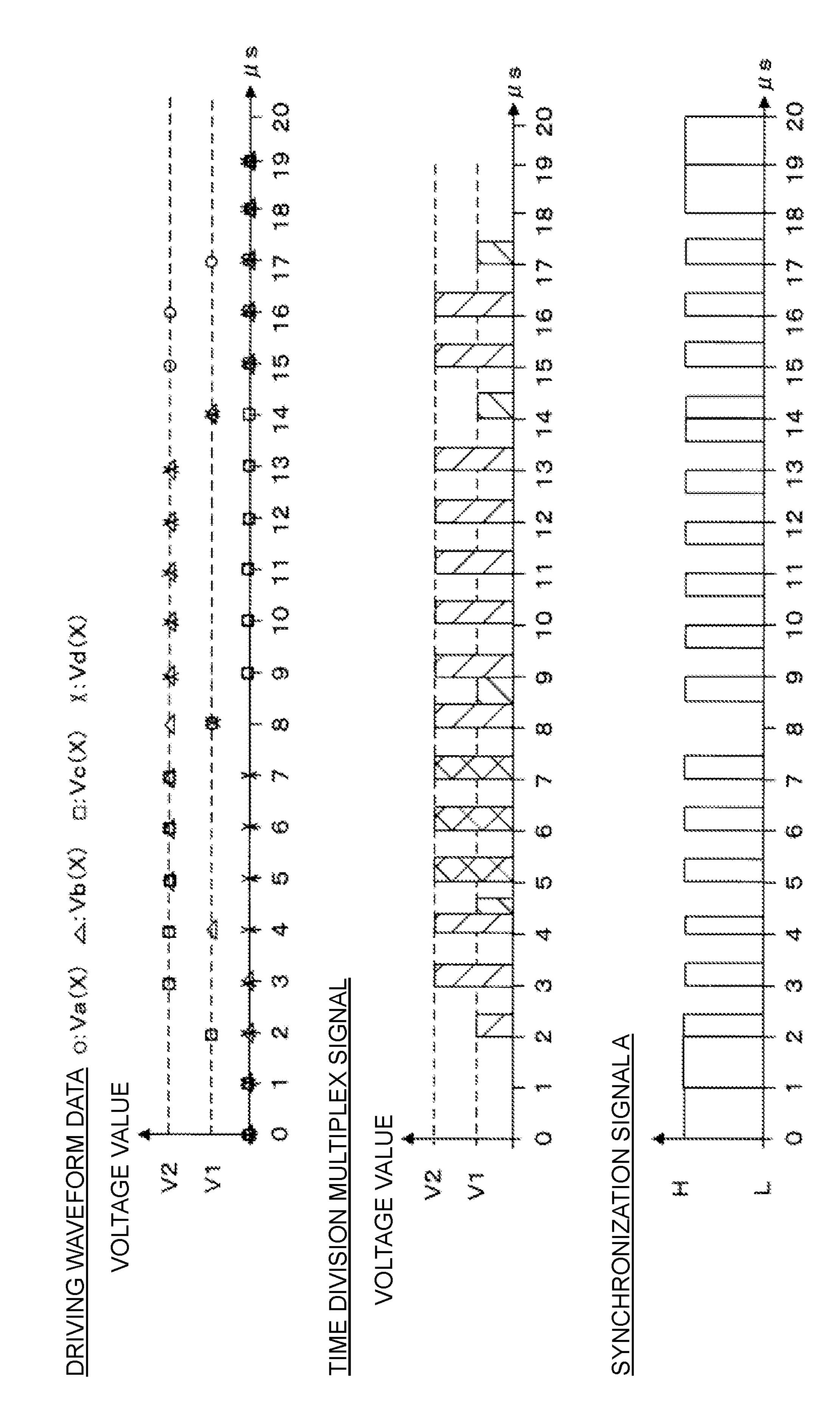

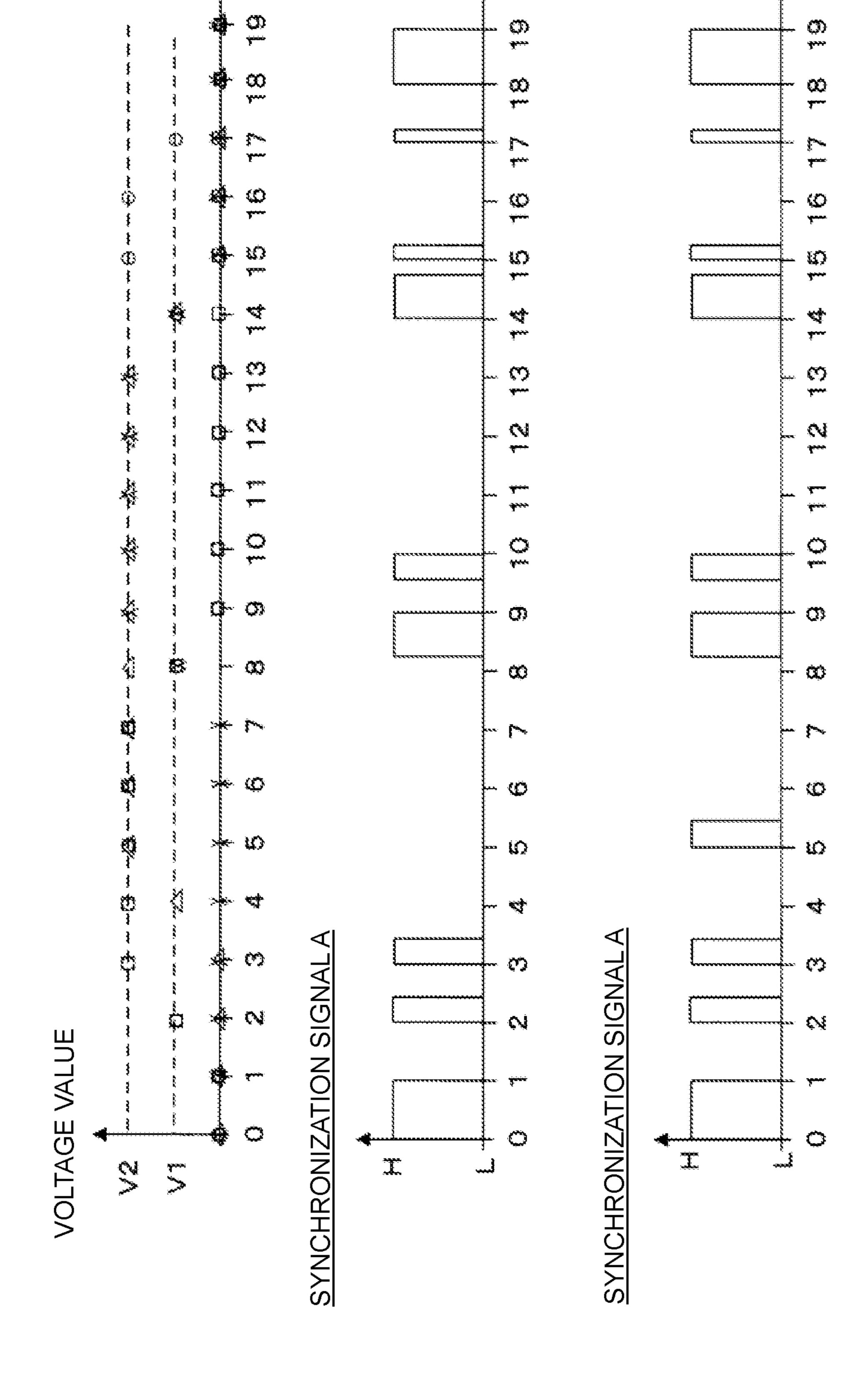

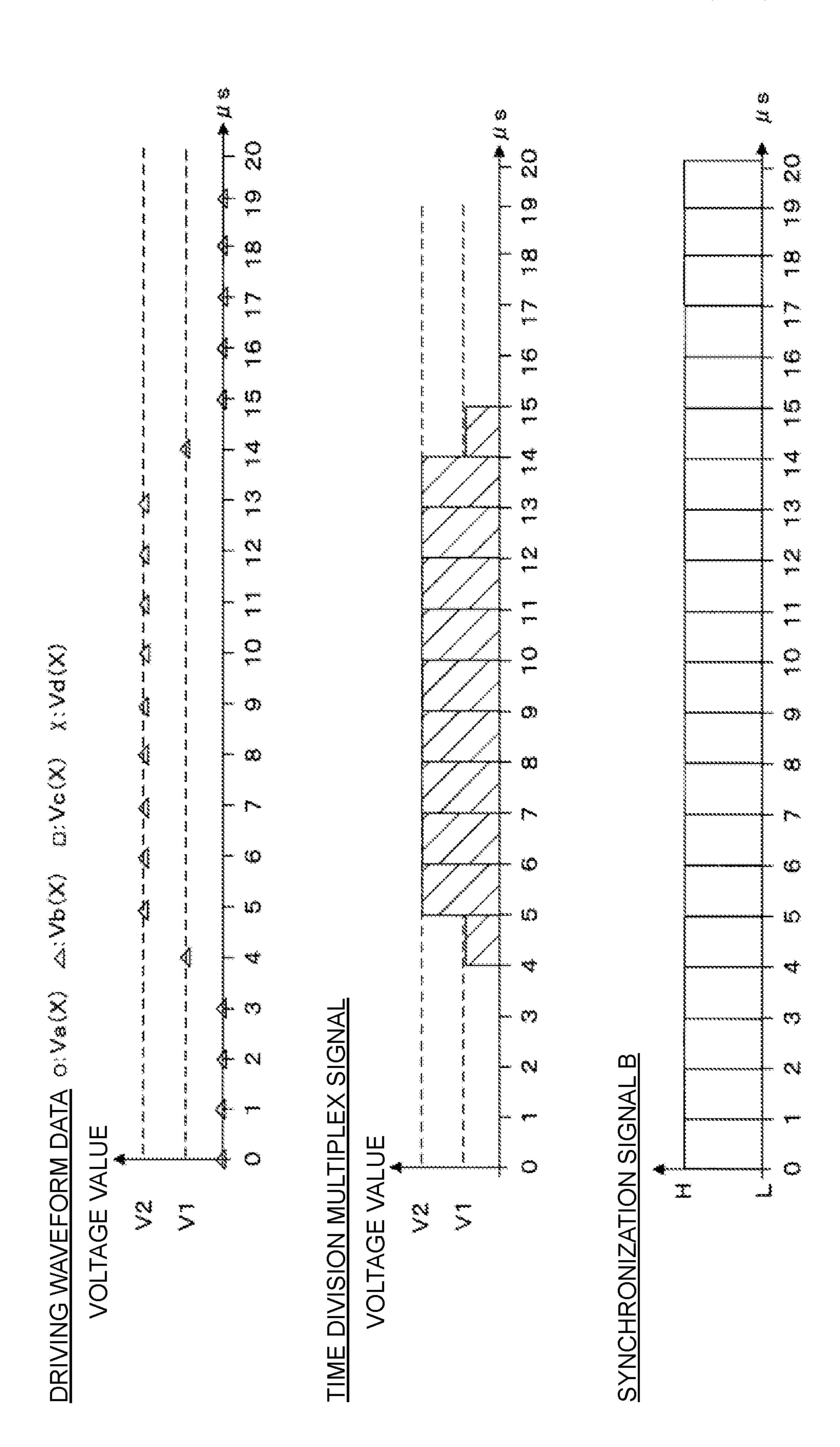

FIG. 6 is a graph of driving waveform data of one cycle which is plotted in time series, a graph indicating a time division multiplex signal, and a graph indicating a synchronization signal.

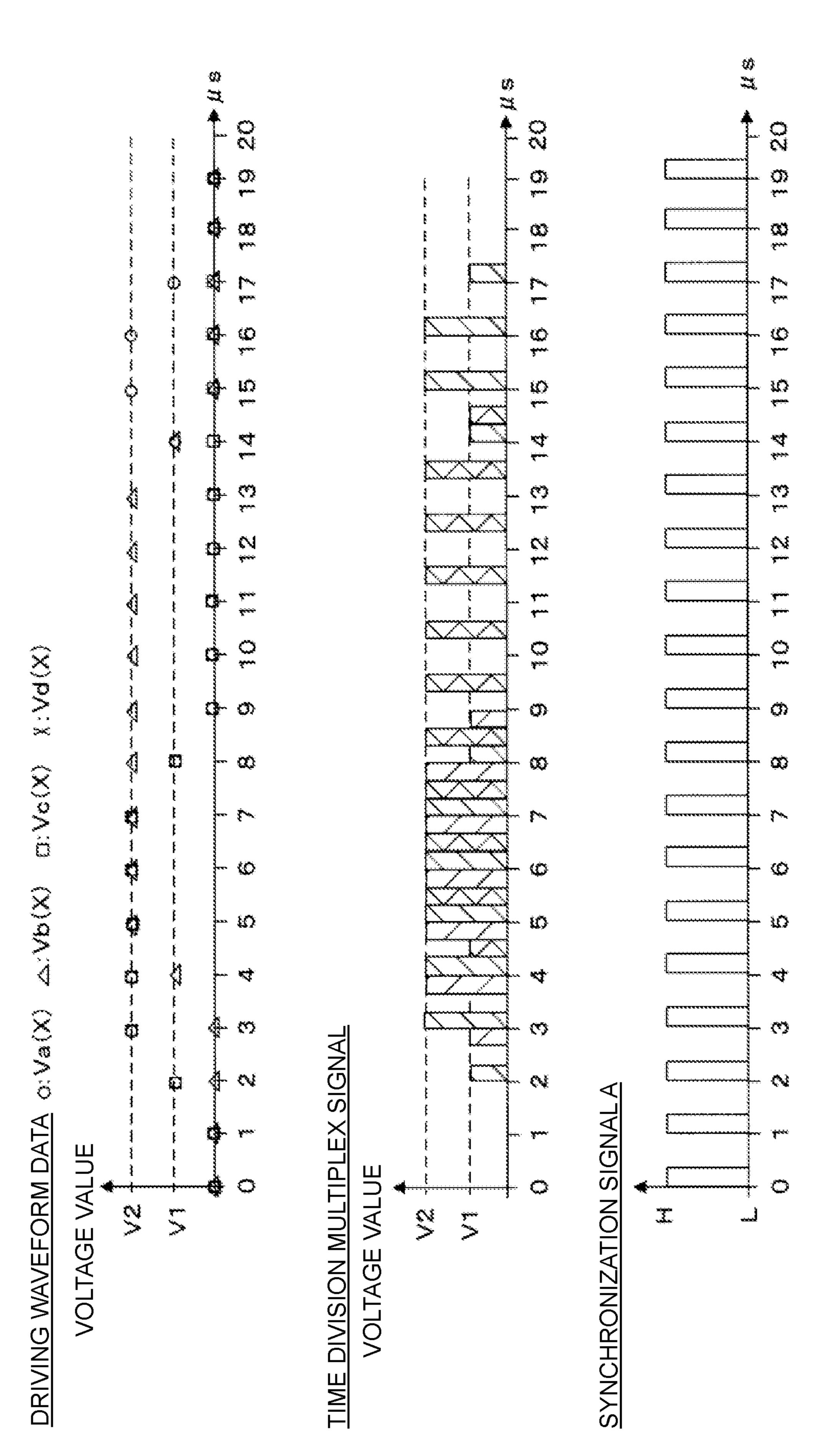

FIG. 7 is graphs indicating synchronization signals.

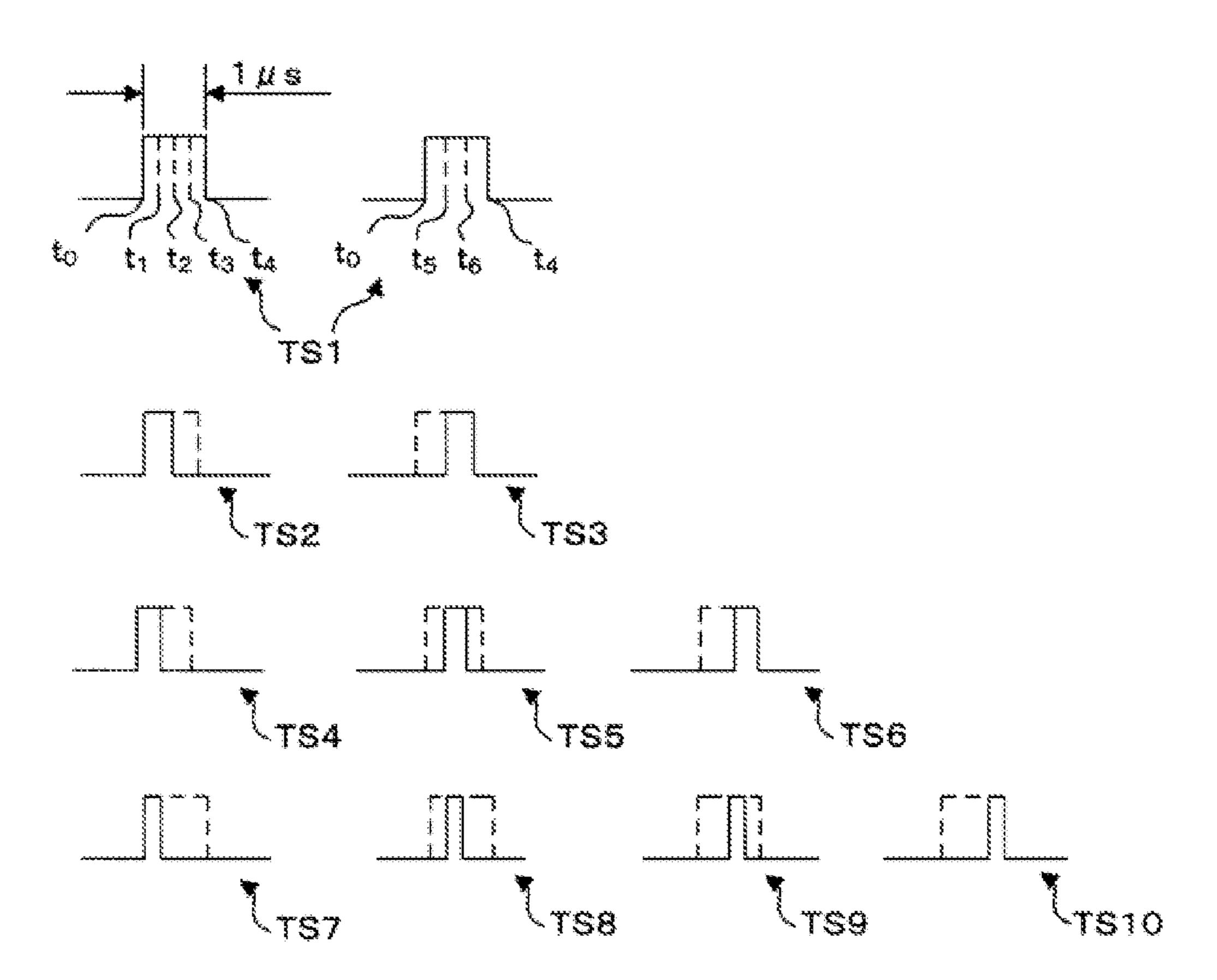

FIG. 8 is a view explaining time slots.

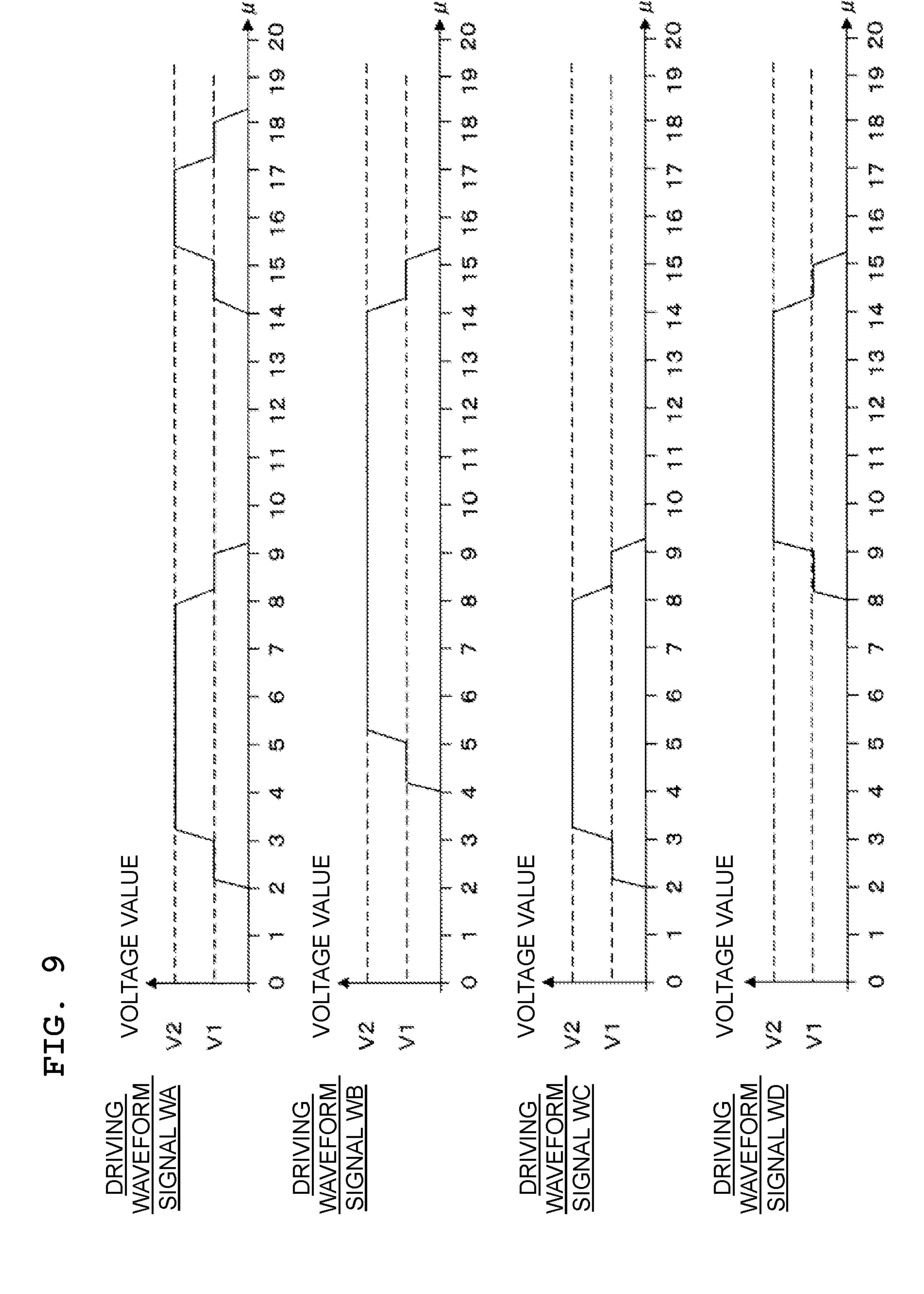

FIG. 9 is a schematic view of driving waveform signals inputted to an actuator by opening and closing of a n-th switch.

FIG. 10 is a graph of driving waveform data of one cycle which is plotted in time series and graphs indicating synchronization signals.

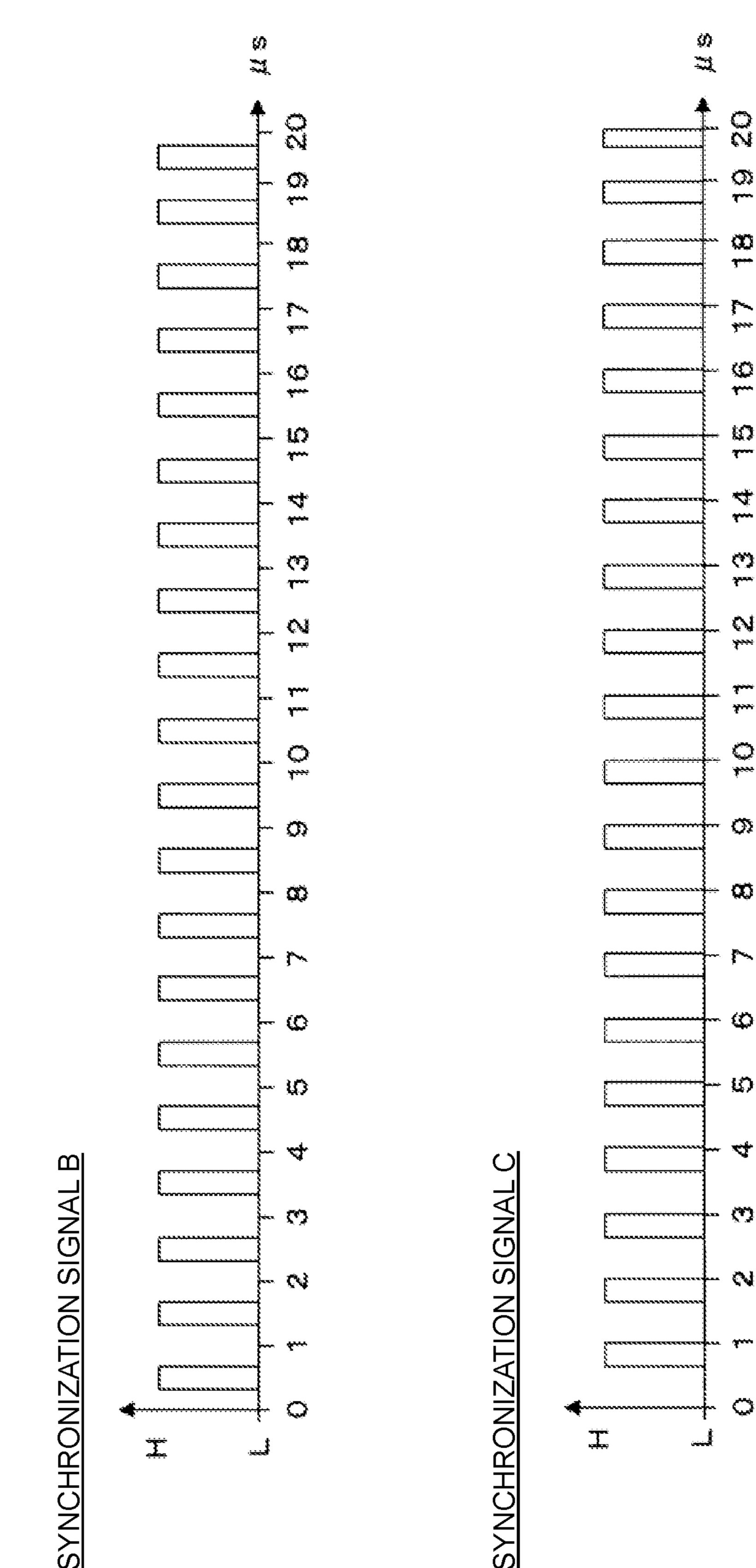

FIG. 11 is a graph of driving waveform data of one cycle which is plotted in time series, a graph indicating a time division multiplex signal, and a graph indicating a synchronization signal in a case of executing a low resolution printing.

FIG. 12 is graphs indicating synchronization signals.

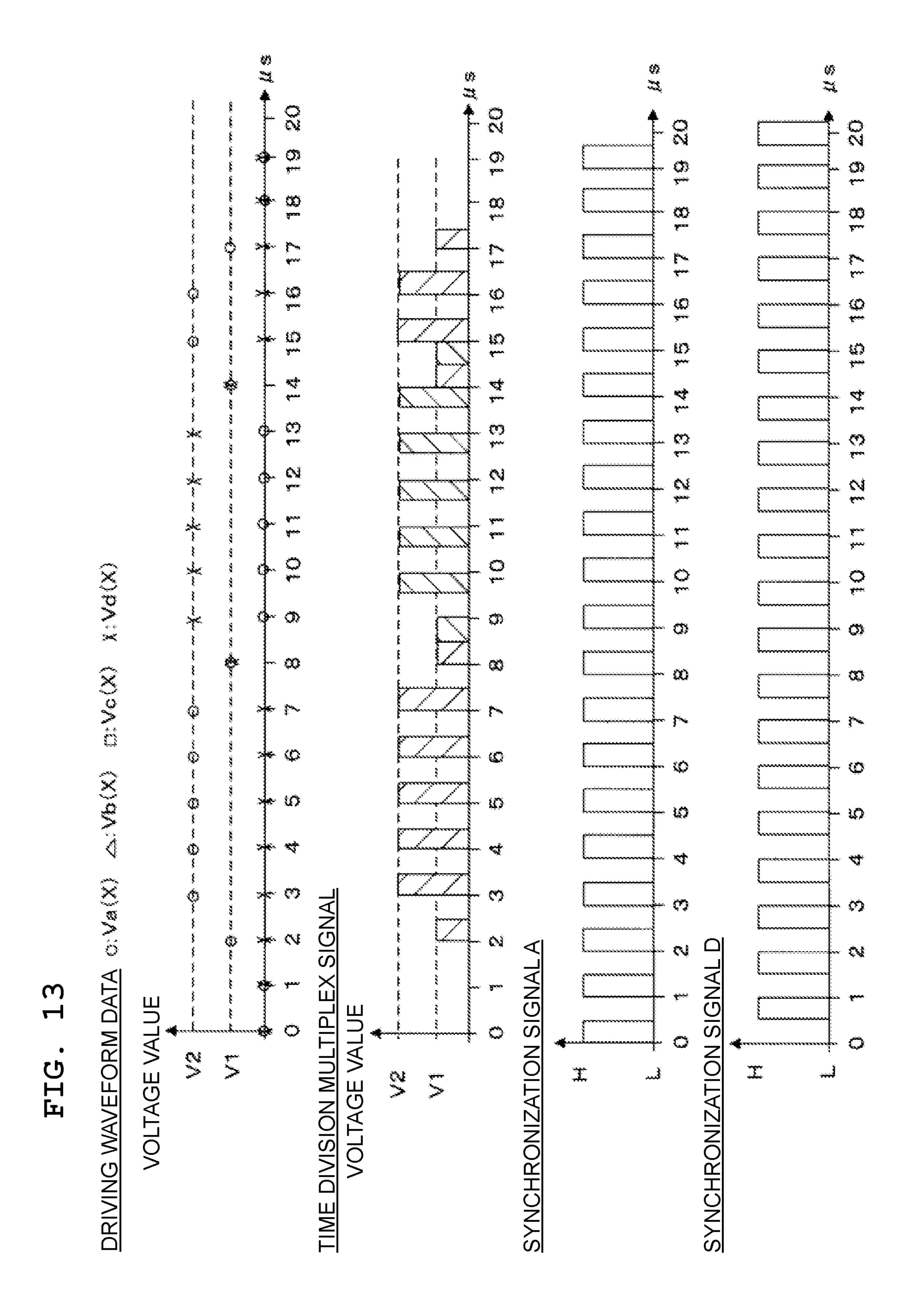

FIG. 13 is a graph of driving waveform data of one cycle which is plotted in time series, a graph indicating a time division multiplex signal, and graphs indicating synchronization signals in a case of executing a high speed printing.

FIG. 14 is a graph of driving waveform data of one cycle which is plotted in time series, a graph depicting a time division multiplex signal, and a graph depicting a synchronization signal in a case of executing a first printing.

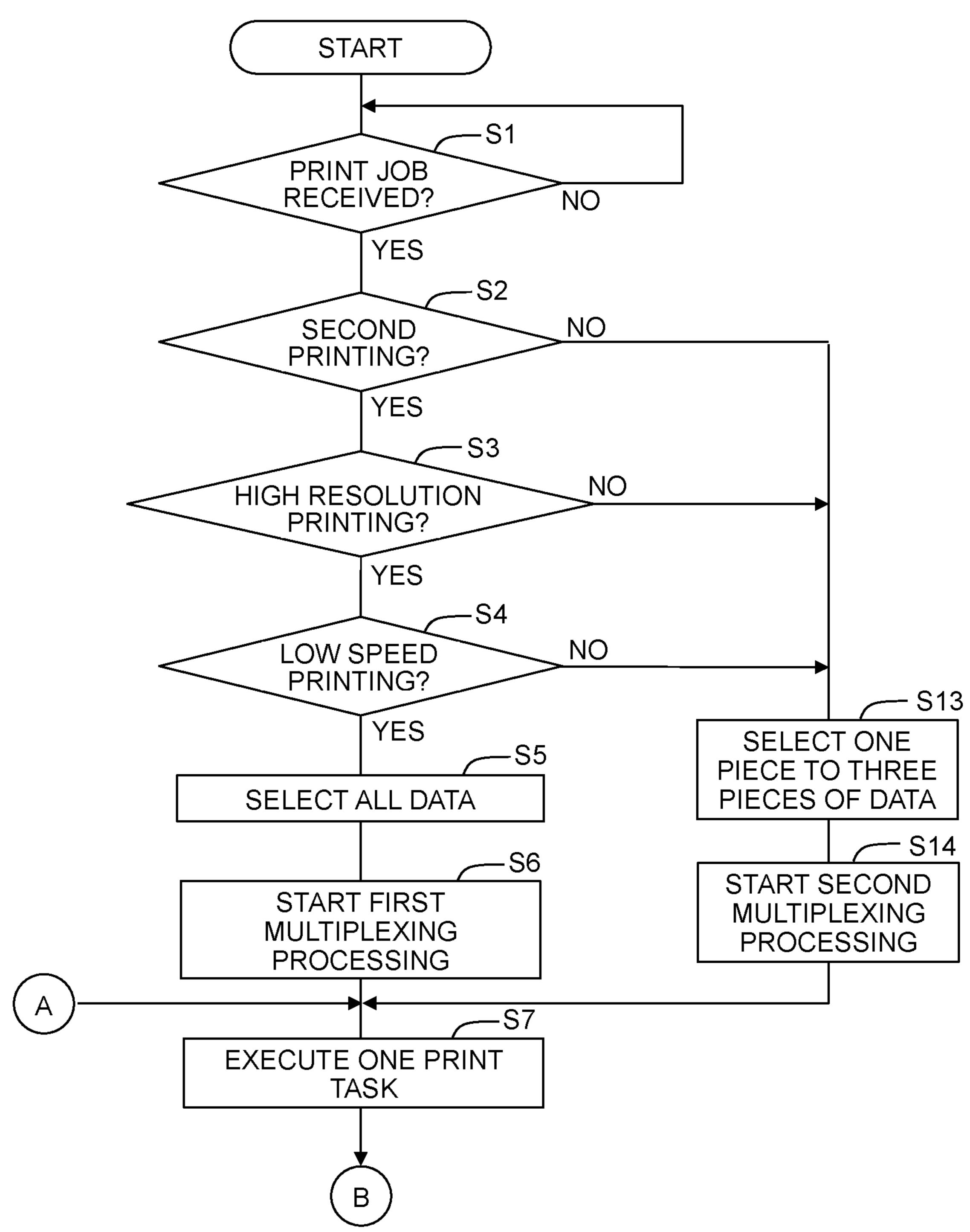

FIG. 15A and FIG. 15B are flow charts explaining a printing processing by a CPU.

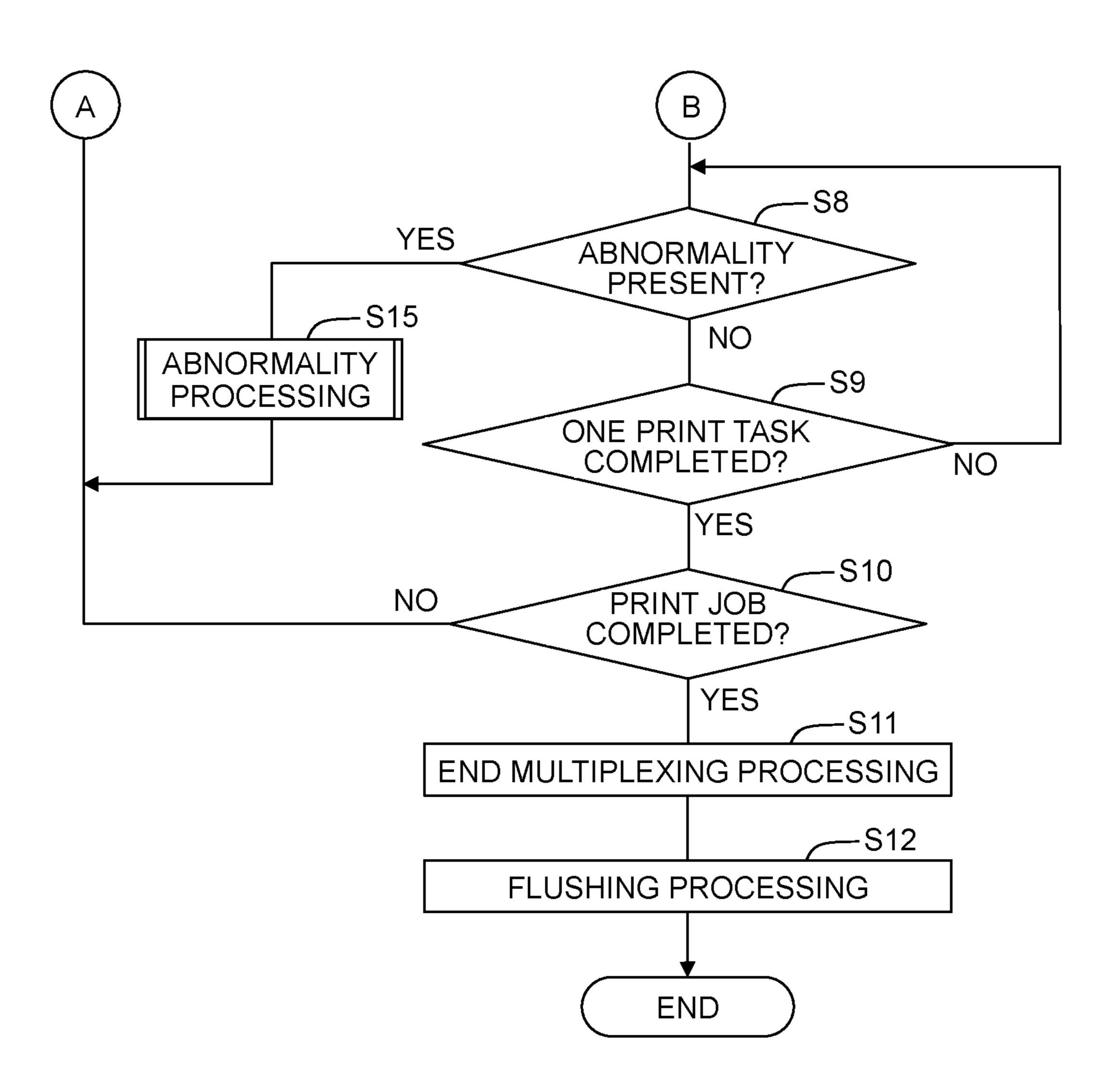

FIG. 16 is a flow chart explaining an abnormality processing by the CPU.

In the above-described printer, although the four driving pulses are continuously generated during one cycle, only one driving pulse is selected. On this account, the time, which is allotted to the three driving pulses that are not selected, is the waiting time of the nozzle.

The present disclosure has been made taking the foregoing circumstances into consideration, an object of which is to provide a printing apparatus which is capable of reducing the waiting time of a nozzle by adjusting the amplitude of a driving waveform applied to an energy generating element (energy application element).

In the printing apparatus according to an aspect of the present disclosure, the time division multiplex signal is generated based on the plurality of pieces of data each indicating one of the driving waveforms which are mutually different. The driving waveform signal which corresponds to any one of the mutually different driving signals is separated from the generated time division multiplex signal. The energy generating element is configured to be driven by the separated driving waveform signal. By separating any one of the driving waveform signals, it is possible to adjust the shape of the driving waveform to be applied to the energy generating element. Further, the one cycle for printing one pixel includes only a cycle of any one of the driving 60 waveforms, and does not include a cycle of another waveform. Accordingly, it is possible to reduce the waiting time of the nozzle.

### FIRST EMBODIMENT

A first embodiment of the present disclosure will be explained below on the basis of the drawings depicting a

printing apparatus according to the first embodiment. FIG. 1 is a plan view schematically depicting the printing apparatus. In the following explanation, the front, rear, left, and right depicted in FIG. 1 are used. The front-rear direction corresponds to a conveying direction, and the left-right 5 direction corresponds to a moving direction. Further, the surface side of FIG. 1 corresponds to the upper side and the underside corresponds to the lower side. In the explanation, the up-down direction is also used.

As depicted in FIG. 1, the printing apparatus 1 is provided 10 with, for example, a platen 2, an ink discharge device 3, and conveying rollers 4, 5. Recording paper 200, which is a recording medium, is placed on the upper surface of the platen 2. The ink discharge device 3 records an image by discharging or ejecting an ink to the recording paper 200 15 placed on the platen 2. The ink discharge device 3 is provided with, for example, a carriage 6, a subtank 7, four ink-jet heads 8, and a circulating pump (not depicted).

Two guide rails 11, 12, which guide the carriage 6 and which extend in the left-right direction, are provided over or 20 above the platen 2. An endless belt 13, which extends in the left-right direction, is connected to the carriage 6. The endless belt 13 is driven by a carriage driving motor 14. The carriage 6 is reciprocatively moved in the moving direction in an area opposed to or facing the platen 2 while being 25 guided by the guide rails 11, 12 in accordance with the driving of the endless belt 13. More specifically, the carriage 6 performs a first movement in which the carriage 6 moves the heads 8 from a certain position to another position from the left to the right in the moving direction, and a second 30 movement in which the carriage 6 moves the heads 8 from the another position to the certain position from the right to the left in the moving direction, in a state in which the carriage 6 supports the four ink-jet heads 8.

the guide rails 11, 12. The cap 20 and the flushing receiver 21 are arranged under or below the ink discharge device 3. The cap **20** is arranged at right end portions of the guide rails 11, 12, and the flushing receiver 21 is arranged at left end portions of the guide rails 11, 12. Note that the cap 20 may 40 be arranged at the left end portions of the guide rails 11 and 12 and that the flushing receiver 21 may be arranged at the right end portions of the guide rails 11 and 12.

The subtank 7 and the four ink-jet heads 8 are carried on the carriage 6, and the subtank 7 and the four ink-jet heads 45 8 are reciprocatively moved (reciprocate) in the moving direction together with the carriage 6. The subtank 7 is connected to a cartridge holder 15 via tubes 17. An ink cartridge 16 of one color or ink cartridges 16 of a plurality of colors (four colors in this embodiment) is/are installed to 50 the cartridge holder 15. The four colors are exemplified, for example, by black, yellow, cyan, and magenta.

Four ink chambers (not depicted) are formed at the inside of the subtank 7. The four color inks, which are supplied from the four ink cartridges 16, are stored in the four ink 55 chambers respectively.

The four ink-jet heads 8 are arranged side by side in the moving direction on the lower side of the subtank 7. A plurality of nozzles 80 (see FIG. 2) are formed in the lower corresponds to one color ink, and is connected to one ink chamber of the subtank 7. That is, the four ink-jet heads 8 correspond to the four color inks respectively, and are connected to the four ink chambers, respectively, of the subtank 7.

The ink-jet head 8 is provided with an ink supply port (not depicted in the drawings) and an ink discharge port (not

depicted in the drawings). The ink supply port and the ink discharge port are connected to the ink chamber of the subtank 7, for example, via tubes. A circulating pump (not depicted in the drawings) intervenes between the ink supply port and the ink chamber.

The ink, which is fed from the ink chamber of the subtank 7 by the circulating pump, passes through the ink supply port to flow into the ink-jet head 8, and the ink is discharged (ejected) from the nozzles 80. The ink, which has not been discharged from the nozzles 80, passes through the ink discharge port, and the ink returns to the ink chamber of the subtank 7. The ink is circulated between the ink chamber of the subtank 7 and the ink-jet head 8. The four ink-jet heads 8 discharge the four color inks supplied from the subtank 7 onto the recording paper 200, while being moved in the moving direction together with the carriage 6.

As depicted in FIG. 1, the conveying roller 4 is arranged on the upstream side (rear side) in the conveying direction with respect to the platen 2. The conveying roller 5 is arranged on the downstream side (front side) in the conveying direction with respect to the platen 2. The two conveying rollers 4, 5 are synchronously driven by a motor (not depicted). The two conveying rollers 4, 5 convey the recording paper 200 placed on the platen 2 in the conveying direction orthogonal to the moving direction. The printing apparatus 1 is provided with a controller 50. The controller 50 is provided with, for example, a CPU or a logic circuit (for example, FPGA), and a memory (storage) 55 such as a nonvolatile memory and a RAM or the like. The controller 50 receives a print job and driving waveform data from an external device 100, and the controller 50 stores the print job and the driving waveform data in the memory 55. The controller 50 controls the driving of, for example, the ink discharge device 3 and the conveying roller 4 on the basis of A cap 20 and a flushing receiver 21 are provided between 35 the print job so as to execute the printing processing.

> FIG. 2 is a partial enlarged cross-sectional view schematically illustrative of each of the four ink-jet heads 8. Each of the ink-jet heads 8 is provided with a plurality of pressure chambers 81. The plurality of pressure chambers 81 constitute a plurality of pressure chamber arrays. A vibration plate **82** is formed on the upper side of the pressure chamber **81**. A layered piezoelectric member 83 (an example of an "energy generating element") is formed on the upper side of the vibration plate 82. A first common electrode 84 is formed between the piezoelectric member 83 and the vibration plate **82** on the upper side of each of the plurality of pressure chambers 81.

A second common electrode 86 is provided at the inside of the piezoelectric member 83. The second common electrode **86** is arranged on the upper side of each of the pressure chambers 81 and on the upper side of the first common electrode **84**. The second common electrode **86** is arranged at a position at which the second common electrode **86** does not face (is not opposed to) the first common electrode 84. An individual electrode 85 is formed on the upper surface of the piezoelectric member 83, at a location on the upper side of each of the plurality of pressure chambers 81. The individual electrode 85 vertically faces the first common electrode **84** and the second common electrode **86** with the surface of each of the ink-jet heads 8. One ink-jet head 8 60 piezoelectric member 83 intervening therebetween. The vibration plate 82, the piezoelectric member 83, the first common electrode 84, the individual electrode 85, and the second common electrode 86 constitute an actuator 88.

A nozzle plate 87 is provided under or below the respec-65 tive pressure chambers 81. A plurality of nozzles 80, which vertically penetrate, are formed through the nozzle plate 87. Each of the plurality of nozzles 80 is arranged on the lower

side of each of the plurality of pressure chambers 81. The plurality of nozzles 80 constitute a plurality of nozzle arrays which extend, respectively, along the pressure chamber arrays.

The first common electrode **84** is connected to a COM 5 terminal, i.e., the ground in this embodiment. The second common electrode **86** is connected to a VCOM terminal. The VCOM voltage is higher than the COM voltage. The individual electrode **85** is connected to a switch group **54** (see FIG. **3**). The High or Low voltage is applied to the individual electrode **85**, which in turn deforms the piezoelectric member **83**, and vibrates the vibration plate **82**. The ink in the pressure chamber **81** is discharged via the nozzle **80** in accordance with the vibration of the vibration plate **82**.

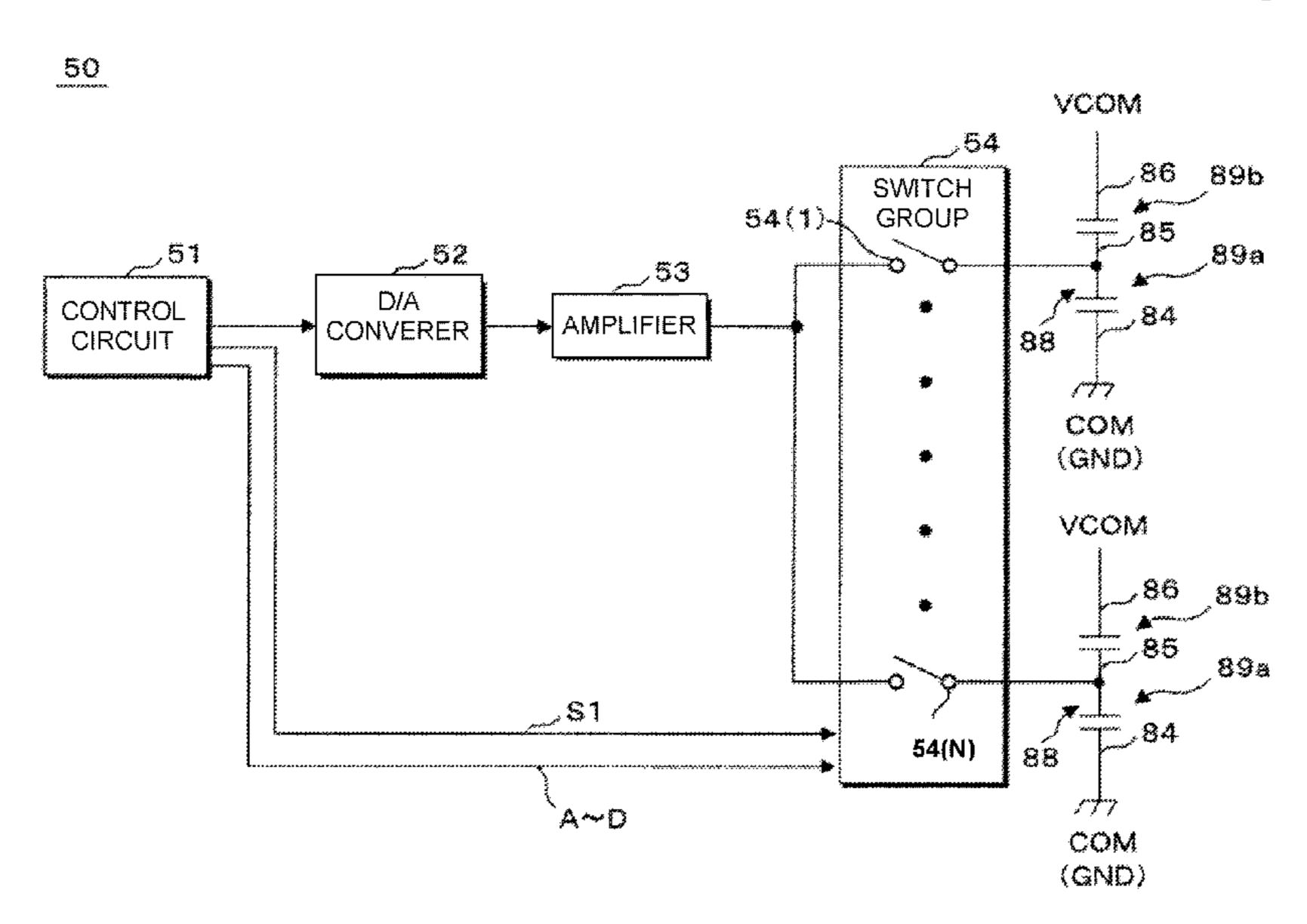

FIG. 3 is a block diagram of the controller 50. The 15 and 0. controller 50 is provided with a control circuit 51, a digital—

analog converter (D/A converter) 52, an amplifier 53 and a 54.

The draw and the

The digital-analogue converter 52 converts a digital signal into an analog signal. The amplifier 53 amplifies the analog signal. The switch group 54 is provided with a plurality of n-th switches 54(n) (n=1, 2, ..., N). Each of the plurality of n-th switches 54(n) is constructed, for example, by an analog switch IC. One end of each of the plurality of nth switches 54(n) is connected to the amplifier 53 via a common bus. The other end of each of the plurality of n-th switches 54(n) is connected to the individual electrode 85 which corresponds to one of the plurality of nozzles 80. In other words, one piece of the n-th switch 54(n) is provided with respect to one piece of the actuator 88.

A first capacitor **89***a* is constructed by the individual electrode **85**, the first common electrode **84**, and the piezo-electric member **83**. A second capacitor **89***b* is constructed by the individual electrode **85**, the second common electrode **86**, and the piezoelectric member **83**.

FIG. 4 is a block diagram of the control circuit 51. The control circuit 51 is provided with a CPU 51a, four memories 55a to 55d, four counters 56a to 56d, a comparing circuit (a comparator) 57, a frequency generating circuit 58, a switching circuit 59 (an example of "a switcher" and/or "a 40 selection signal outputting circuit"), a selector circuit 60, a multiplex signal outputting circuit 61 and four synchronization signal generating circuits 62a to 62d.

Driving waveform data Da to Dd are stored, respectively, in the memories **55***a* to **55***d*. Each of the driving waveform 45 data Da to Dd is data indicating a voltage waveform to be applied to the individual electrode **85**, namely, a driving waveform for driving the actuator **88**, and is quantized data. The respective driving waveform data Da to Dd indicate mutually different driving waveforms.

FIG. 5 is the conceptual view depicting an example of time tables  $T_{ta}$  to  $T_{td}$  and voltage tables  $T_{va}$  to  $T_{vd}$ . The memory 55a stores the driving waveform data Da. The driving waveform data Da includes the time table  $T_{ta}$  and the voltage table  $T_{va}$ . In the time table  $T_{ta}$ , a time ta(X) 55 associated with an address X (X=0, 1, 2, . . . ) is stored. In the present embodiment, ta(0) to ta(8) are, respectively, 2 µs, 1 µs, 5 µs, 1 µs, 5 µs, 1 µs, 2 µs, 1 µs and 2 µs. In the voltage table  $T_{va}$ , a voltage value Va(X) associated with the address X is stored. In the present embodiment, Va(0) to Va(8) are, 60 respectively, 0, V1, V2, V1, 0, V1, V2, V1 and 0. V2 is a voltage value greater than V1. V1 is represented by a numerical value, and is, for example, 256. V2 is represented by a numerical value, and is, for example, 512.

The memory 55b stores the driving waveform data Db. 65 57. The driving waveform data Db includes the time table  $T_{tb}$  Solution and the voltage table  $T_{vb}$ . In the time table  $T_{tb}$ , a time tb(X) out

6

associated with the address X is stored. In the present embodiment, tb(0) to tb(4) are, respectively, 4  $\mu$ s, 1  $\mu$ s, 9  $\mu$ s, 1  $\mu$ s and 5  $\mu$ s. In the voltage table T<sub>vb</sub>, a voltage value Vb(X) associated with the address X is stored. In the present embodiment, Vb(0) to Vb(4) are, respectively, 0, V1, V2, V1 and 0.

The memory 55c stores the driving waveform data Dc. The driving waveform data Dc includes the time table  $T_{tc}$  and the voltage table  $T_{vc}$ . In the time table  $T_{tc}$ , a time tc(X) associated with the address X is stored. In the present embodiment, tc(0) to tc(4) are, respectively, 2  $\mu$ s, 1  $\mu$ s, 5  $\mu$ s, 1  $\mu$ s and 11  $\mu$ s. In the voltage table  $T_{vc}$ , a voltage value Vc(X) associated with the address X is stored. In the present embodiment, Vc(0) to Vc(4) are, respectively, 0, V1, V2, V1 and 0.

The memory **55***d* stores the driving waveform data Dd. The driving waveform data Dd includes the time table  $T_{td}$  and the voltage table  $T_{vd}$ . In the time table  $T_{td}$ , a time td(X) associated with the address X is stored. In the present embodiment, td(0) to td(4) are, respectively, 8  $\mu$ s, 1  $\mu$ s, 5  $\mu$ s, 1  $\mu$ s and 5  $\mu$ s. In the voltage table  $T_{vd}$ , a voltage value Vd(X) associated with the address X is stored. In the present embodiment, Vd(0) to Vd(4) are, respectively, 0, V1, V2, V1 and 0.

The CPU 51a causes the memory 55a to output, to the counter 56a, the times of the time table  $T_{ta}$  in the order of the address, and causes the memory 55a to output, to the selector circuit 60 and the comparing circuit 57, the voltages of the voltage table  $T_{\nu\alpha}$  in the order of the address. For so example, the memory 55a stores the address X as a parameter. The CPU **51***a* sets the address X to be 0 (zero). The memory 55a refers to the address 0, and outputs ta(0) of the time table  $T_{ta}$ , namely, 2 µs, to the counter **56**a; the counter 56a, into which ta(0) is inputted, outputs a comparison 35 timing signal Sa to the comparing circuit **57**. The counter **56***a* measures the inputted time 2  $\mu$ s, and after the measurement, the counter 56a outputs an address increment signal Spa to the memory 55a. In a case that the address increment signal Spa is inputted to the memory 55a, the memory 55aincrements the address X by 1 (one), refers to the address 1, and outputs ta(1) of the time table  $T_{ta}$ , namely, 1 µs, to the counter 56a. The counter 56a, into which ta(1) is inputted, outputs the comparison timing signal Sa to the comparing circuit 57. In such a manner, every time the time ta(X) is inputted from the time table  $T_{ta}$ , the counter **56**a outputs the comparison timing signal Sa to the comparing circuit 57; every time the counter **56***a* completes the measurement of the time ta(X), the counter 56a outputs the address increment signal Spa to the memory 55a.

In a case that the CPU 51a sets the address X to be 0 (zero), the memory 55a outputs the voltage value Va(0) of the voltage table  $T_{va}$ , namely 0 (zero), to the selector circuit 60 and the comparing circuit 57. Afterwards, in a case that the address increment signal Spa is inputted to the memory 55a, the memory 55a increments the address X by 1 (one), and outputs the voltage value Va(1), namely V1, to the selector circuit 60 and the comparing circuit 57. In such a manner, in a case that the address X is set to be 0 (zero) and every time the address increment signal Spa is inputted to the memory 55a, the memory 55a outputs the voltage value of the voltage table  $T_{va}$  to the selector circuit 60 and the comparing circuit 57. Namely, the memory 55a outputs the voltage value of the voltage table  $T_{va}$ , in the order of address, to the selector circuit 60 and the comparing circuit 57.

Similarly, the CPU 51a causes the memory 55b to 55d to output, respectively, the times tb(X) to td(X) of the time

table  $T_{ta}$  to  $T_{td}$  to the counters **56**b to **56**d, respectively, in the order of address; the counters **56**b to **56**d output, respectively, the timing signals Sb to Sd to the comparing circuit **57** every time the times tb(X) to td(X) are inputted, respectively, to the counter **56**b to **56**d. Every time the time 5 corresponding to the address X lapses, the counters **56**b to **56**d output, respectively, the address increment signals SPb to Spd to the memories **55**b to **55**d, respectively.

Similarly, in a case that the address X is set to be 0 (zero) and every time the address increment signals Spb to Spd are 10 inputted to the memories 55b to 55d, respectively, the memories 55b to 55d output, respectively, the voltage values Vb(X) to Vd(X) of the voltage table  $T_{va}$  to  $T_{vd}$  to the selector circuit 60 and the comparing circuit 57. Namely, the memories 55b to 55d output, respectively, the voltage values 15 Vb(X) to Vd(X) to the selector circuit 60 and the comparing circuit 57, in the order of address.

FIG. 6 includes a graph of the driving waveform data Da to Dd of one cycle plotted in time series, a graph indicating a time division multiplex signal, and a graph indicating a 20 synchronization signal A. FIG. 7 includes graphs indicating synchronization signals B to D, respectively. FIG. 8 is a view explaining time slots.

An upper view of FIG. 6 is a graph of the driving waveform data Da to Dd plotted in time series, wherein the 25 horizontal axis of the graph is time (µs), and the vertical axis of the graph is voltage value. A circle represents the voltage value Va(X) of the voltage table  $T_{va}$ , a triangle represents the voltage value Vb(X) of the voltage table  $T_{vb}$ , a square represents the voltage value Vc(X) of the voltage table  $T_{vc}$ , 30 and a cross (x) represents the voltage value Vd(X) of the voltage table  $T_{vd}$ , each being corresponded to the time of the time table and plotted every 1 µs. In the following, "µs" is appropriately omitted regarding the plotted time (plotted point of time). The plot is 20 pieces of plots ranging from a 35 point of time 0 (zero) to point of time 19. The voltage value of point of time k (k=0, 1, 2, ... 19) indicates a voltage value in a range of point of time k to point of time  $k+1 \mu s$ . In FIG. 6, the period of time in the range of point of time 0 to point of time 20, namely, 20 µs is one cycle of the time division 40 multiplex signal.

A middle view of FIG. 6 indicates a time division multiplex signal generated based on the driving waveform data Da to Dd, a lower view of FIG. 6, and FIG. 7 indicate the synchronization signals A to D generated, respectively, in 45 the synchronization signal generating circuits 62a to 62d. The synchronization signals A to D are each a pulse signal having a high level (H) interval (time period) and a low level (L) interval (time period). Here, the details of the time division multiplex signal will be conceptually explained. The driving waveform data Da has, conceptually, quantized data Ak (k=0, 1, 2, ..., K), the driving waveform data Db has, conceptually, quantized data Bk (k=0, 1, 2, . . . K), the driving waveform data Dc has, conceptually, quantized data Ck (k=0, 1, 2, ..., K), and the driving waveform data Dd has, 55 conceptually, quantized data Dk (k=0, 1, 2, . . . K). In a case that the actuator 88 is to be driven, the control circuit 51 accesses the memory 55, obtains the driving waveform data Da, Db, Dc and Dd, and generates time series data. In the time series data, conceptually, data Ak, Bk, Ck, Dk are 60 successively arranged while providing time intervals  $\Delta t$ ; the data Ak, Bk, Ck and Dk are arranged in an order of A0, B0, C0, D0, A1, B1, C1, D1 . . . , AK, BK, CK and DK. The time series data is a digital signal. Note that the time interval  $\Delta t$ is the reciprocal of a predetermined sampling frequency. The 65 quantized data Ak, Bk, Ck, Dk are arranged in the order of A0, B0, C0, D0, A1, B1, C1, D1, . . . , AK, BK, CK and DK

8

for every time (at a time interval) corresponding to the reciprocal of the predetermined sampling frequency. In other words, the data length of the quantized data Ak, Bk, Ck, Dk is not more than a length corresponding to the reciprocal of the predetermined sampling frequency.

Further, the quantized data A0 is continuous with the quantized data B0, the quantized data B0 is continuous with the quantized data C0, and the quantized data C0 is continuous with the quantized data D0. In other words, the quantized data C0, the quantized data D0, any other quantized data, and any data of any other waveform are absent between the quantized data A0 and the quantized data B0. Further, the quantized data A0, the quantized data D0, any other quantized data, and any data of any other waveform are absent between the quantized data B0 and the quantized data C0. Further, the quantized data A0, the quantized data B0, any other quantized data, and any data of any other waveform are absent between the quantized data C0 and the quantized data D0.

The control circuit 51 outputs the time series data to the digital-analogue converter **52**. As depicted in FIG. **3**, the digital-analogue converter 52 converts the time series data into the analog signal, and outputs the converted analog signal to the amplifier 53. The amplifier 53 amplifies the inputted analog signal, and outputs the amplified analog signal to the switch group 54. As depicted in FIG. 3, the analog signal, which is amplified by the amplifier 53, constructs the time division multiplex signal. In the time division multiplex signal, it is assumed that a portion corresponding to data Ak-1 is a first portion, a portion corresponding to the data Ak is a second portion, a portion corresponding to data Bk-1 is a third portion and a portion corresponding to the data Bk is a fourth portion. On this assumption, the third portion is present (aligned) between the first portion and the second portion, and the second portion is present (aligned) between the third portion and the fourth portion. Note that a similar relationship holds also between the data Bk and the data Ck, a similar relationship holds also between the data Ck and the data Dk, and a similar relationship holds also between the data Dk and the data Ak. In other words, the first portion is continuous with the third portion, the third portion is continuous with the second portion, and the second portion is continuous with the fourth portion. That is, the second portion, the fourth portion, and any other waveform are absent between the first portion and the third portion in the time division multiplex signal. Further, the first portion, the fourth portion, and any other waveform are absent between the third portion and the second portion in the time division multiplex signal. Further, the first portion, the third portion, and any other waveform are absent between the second portion and the fourth portion in the time division multiplex signal. The control circuit 51, the digital-analogue converter 52, the amplifier 53, and the memory 55 construct a "signal generator".

FIG. 8 indicates, as time slots, TS1 to TS10 each having a pulse shape. Each of TS1 to TS10 has a high level interval and a low level interval, wherein the high level interval corresponds to a time during which the n-th switch 54(n) is closed, and the low level interval corresponds to a time during which the n-th switch 54(n) is opened. In FIG. 8, one time slot is indicated while being quadrisected (equally divided) into four segments by a point of time t1, a point of time t2 and a point of time t3, with a start point of time of one time slot being defined as "t0", and an end point of time of one time slot being defined as "t4". Further, in FIG. 8, one time slot is indicated while being trisected (equally divided) into three segments by a point of time t5 and a point of time

t6, with a start point of time of one time slot being defined as "t0", and an end point of time of one time slot being defined as "t4".

As indicated in FIG. 8, TS1 is a high level interval between the point of time t0 to point of time t4, and does not 5 have any low level interval. TS2 is a high level interval between point of time t0 and point of time t2, and is a low level interval between point of time t2 and point of time t4. TS3 is a high level interval between point of time t2 and point of time t4, and is a low level interval between point of 10 time t0 and point of time t2. TS4 is a high level interval between point of time t0 and point of time t5, and is a low level interval between point of time t5 and point of time t4. TS5 is a high level interval between point of time t5 and t6, 15 value. and is a low level interval each between point of time t0 and point of time t5 and between point of time t6 and point of time t4. TS6 is a high level interval between point of time t6 and point of time t4, and is a low level interval between point of time t0 and point of time t6. TS7 is a high level interval 20 between point of time t0 and point of time t1, and is a low level interval between point of time t1 and point of time t4. TS8 is a high level interval between point of time t1 and point of time t2, and is a low level interval each between point of time t0 and point of time t1 and between point of 25 time t2 to point of time t4. TS9 is a high level interval between point of time t2 and point of time t3, and is a low level interval each between point of time to and point of time t2 and between point of time t3 to point of time t4. TS10 is a high level interval between point of time t3 and point of 30 time t4, and is a low level interval between point of time t0 and point of time t3.

TS1 to TS10 are classified into mutually different four sampling frequencies wherein TS1 corresponds to a first sampling frequency, TS2 and TS3 correspond to a second 35 sampling frequency, TS4 to TS6 correspond to a third sampling frequency, and TS7 to TS10 correspond to a fourth sampling frequency. For example, in a case that the fourth sampling frequency corresponds to 24 MHz, the third sampling frequency corresponds to 18 MHz, the second sampling frequency corresponds to 12 MHz and the first sampling frequency corresponds to 6 MHz.

In a case that any one of the comparison timing signals Sa to Sd is inputted to the comparing circuit 57, the comparing circuit 57 compares the voltage values inputted, respec- 45 tively, from the voltage tables  $T_{va}$  to  $T_{vd}$ . The points of time at which any one of the comparison timing signals Sa to Sd is inputted to the comparing circuit 57 are the points of time 0 (zero), 2, 3, 4, 5, 8, 9, 14, 15, 17 and 18 in the upper view of FIG. 6. The comparing circuit 57 allocates a common one 50 time slot with respect to same voltage values, and allocates mutually different time slots to mutually different voltage values. Note that in a case that any one of the comparison timing signals Sa to Sd is not inputted to the comparing circuit 57, namely, at each of a certain point of time among 55 the points of time 1, 6, 7, 10 to 13, 16 and 19 in the upper view of FIG. 6, the comparing circuit 57 allocates a time slot, which is same as that allocated to a preceding point of time preceding the certain point of time by one, to each of the same voltage values.

In a case that there are four same voltage values, TS1 is allocated to each of the four same voltage values. In a case that there are three same voltage values, TS2 is allocated to each of the three same voltage values, and T3 is allocated to a remaining one voltage value; or TS3 is allocated to each of the three same voltage values, and T2 is allocated to a remaining one voltage value.

10

In a case that there are two same voltage values and that remaining two voltage values are mutually different, TS4 is allocated to each of the two same voltage values, and T5 and TS6 are allocated to remaining two voltage values, respectively; or TS5 is allocated to each of the two same voltage values, and T4 and TS6 are allocated to remaining two voltage values, respectively; or TS6 is allocated to each of the two same voltage values, and T4 and TS5 are allocated to remaining two voltage values, respectively.

In a case that two voltage values are a first voltage value, that remaining two voltage values are a second voltage value and that the first voltage value and the second voltage value are different from each other, TS2 is allocated to the first voltage value, and TS3 is allocated to the second voltage value.

In a case that four voltage values are mutually different, TS7 to TS10 are allocated, respectively, to the four different voltage values.

The comparing circuit 57 associates the time slots with the respective voltage values Va(X) to Vd(X), and outputs the time slots and the respective voltage values Va(X) to Vd(X) which are associated with each other to the switching circuit 59 and the respective synchronization signal generating circuits 62a to 62d. The frequency generating circuit 58 generates a reference frequency (24 MHz in the present embodiment), and outputs the reference frequency to the switching circuit 59 and the respective synchronization signal generating circuits 62a to 62d.

For example, as depicted in the upper view of FIG. 6, at the point of time 0, the voltage values Va(X) to Vd(X) are each 0 (zero). In this situation, the comparing circuit 57 associates TS1 with the voltage values Va(X) to Vd(X), and outputs TS1 and the voltage values Va(X) to Vd(X) which are associated with each other to the switching circuit **59** and the respective synchronization signal generating circuits 62a to 62d. The switching circuit 59 selects one voltage value from the four voltage values Va(X) to Vd(X), for example, the voltage value Va(X). The selection is performed, for example, based on a priority order which is previously set. In a case that same voltage values are included at a certain point of time, for example, a priority order of Va(X)>Vb (X)>Vc(X) and Vd(X) is previously set, and a voltage value of which priority is highest is set among the same voltage values. Note that the order of priority may be appropriately set, the priority of Vb(X), Vc(X) or Vd(X) may be made the highest, or the order of priority may be set in accordance with a magnitude of usage frequency. In the following, the selection is made in a similar method in a case of selecting any one voltage value among the same voltage values.

In a case that the switching circuit **59** selects one voltage value, the switching circuit **59** generates a frequency of 6 MHz based on the reference frequency and TS1. The switching circuit **59** associates TS1, the frequency of 6 MHz and the voltage value Va(X) with each other, and outputs TS1, the frequency of 6 MHz and the voltage value Va(X) which are associated with each other to the selector circuit 60. As depicted in the middle view of FIG. 6, the selector circuit 60 refers to the voltage value Va(X) inputted from the switching circuit **59**, selects the voltage value Va(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{vd}$ , respectively, and generates a signal of which voltage value is 0 (zero) during a period of time (time) from the point of time 0 (zero) to the point of time 1 µs. In other words, the control circuit **51** generates a time division multiplex signal including a driving waveform signal which collates (combines or collects) the four voltage values of the voltage values Va(X) to Vd(X) to one.

For example, as depicted in the upper view of FIG. 6, the voltage values Va(X) and Vc(X) are both V1 and the voltage values Vb(X) and Vd(X) are both 0 (zero) at the point of time 2. In this situation, the comparing circuit 57 associates TS2 and the voltage values Va(X) and Vc(X), and outputs 5 TS2 and the voltage values Va(X) and Vc(X) which are associated with each other to the switching circuit **59** and the synchronization signal generating circuits 62a to 62d; and the comparing circuit 57 associates TS3 and the voltage values Vb(X) and Vd(X), and outputs TS3 and the voltage 10 values Vb(X) and Vd(X) which are associated with each other to the switching circuit 59 and the synchronization signal generating circuits 62a to 62d. The switching circuit 59 selects one voltage value from the two voltage values Va(X) and Vc(X), for example, the voltage value Va(X), and 15 selects one voltage value from the two voltage values Vb(X)and Vd(X), for example, the voltage value Vb(X). The switching circuit 59 generates, with respect to the voltage value Va(X), a frequency of 12 MHz, based on the reference frequency and TS2. The switching circuit **59** generates, with respect to the voltage value Vb(X), a frequency of 12 MHz, based on the reference frequency and TS3. The switching circuit **59** associates TS2, the frequency of 12 MHz and the voltage value Va(X) with each other, and outputs TS2, the frequency of 12 MHz and the voltage value Va(X) which are 25 associated with each other to the selector circuit 60; and the switching circuit **59** associates TS3, the frequency of 12 MHz and the voltage value Vb(X) with each other, and outputs TS3, the frequency of 12 MHz and the voltage value Vb(X) which are associated with each other to the selector 30 circuit 60.

As depicted in the middle view of FIG. 6, the selector circuit **60** refers to the voltage value Va(X) inputted thereinto from the switching circuit 59, selects the voltage value Va(X) from the four voltage values Va(X) to Vd(X) inputted 35 from the voltage tables  $T_{va}$  to  $T_{vd}$ , respectively, and generates a signal of which voltage value is V1 during a period of time from the point of time 2  $\mu$ s to the point of time 2.5  $\mu$ s. The selector circuit 60 refers to the voltage value Vb(X)inputted thereinto from the switching circuit **59**, selects the 40 voltage value Vb(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{va}$ , respectively, and generates a signal of which voltage value is 0 (zero) during a period of time from the point of time 2.5 µs to the point of time 3 µs. In other words, the control circuit 45 51 generates a time division multiplex signal including a driving waveform signal which collates the two voltage values of the voltage values Va(X) and Vc(X) to one, and a driving waveform signal which collates the two voltage values of the voltage values Vb(X) and Vd(X) to one.

For example, as depicted in the upper view of FIG. 6, the voltage values Va(X) and Vc(X) are both V2, the voltage value Vb(X) is V1, and the voltage value Vd(X) is 0 (zero) at the point of time 4. In this situation, the comparing circuit 57 associates TS4 and the voltage values Va(X) and Vc(X), 55 and outputs TS4 and the voltage values Va(X) and Vc(X)which are associated with each other to the switching circuit 59 and the respective synchronization signal generating circuits 62a to 62d; and the comparing circuit 57 associates TS5 and the voltage value Vb(X), and outputs TS5 and the 60 voltage value Vb(X) which are associated with each other to the switching circuit **59** and the respective synchronization signal generating circuits 62a to 62d. The comparing circuit 57 associates TS6 and the voltage value Vd(X), and outputs TS6 and the voltage value Vd(X) which are associated with 65 each other to the switching circuit 59 and the respective synchronization signal generating circuits 62a to 62d. The

12

switching circuit **59** selects one voltage value from the two voltage values Va(X) and Vc(X), for example, the voltage value Va(X). The switching circuit **59** selects the voltage values Vb(X) and Vd(X). The switching circuit **59** generates, with respect to the voltage value Va(X), a frequency of 18 MHz, based on the reference frequency and TS4. The switching circuit 59 generates, with respect to the voltage value Vb(X), a frequency of 18 MHz, based on the reference frequency and TS5. The switching circuit 59 generates, with respect to the voltage value Vd(X), a frequency of 18 MHz, based on the reference frequency and TS6. The switching circuit **59** associates TS4, the frequency of 18 MHz and the voltage value Va(X) with each other, and outputs TS4, the frequency of 18 MHz and the voltage value Va(X) which are associated with each other to the selector circuit 60; the switching circuit **59** associates TS5, the frequency of 18 MHz and the voltage value Vb(X) with each other, and outputs TS5, the frequency of 18 MHz and the voltage value Vb(X) which are associated with each other to the selector circuit **60**; and the switching circuit **59** associates TS6, the frequency of 18 MHz and the voltage value Vd(X) with each other, and outputs TS6, the frequency of 18 MHz and the voltage value Vd(X) which are associated with each other to the selector circuit **60**.

As depicted in the middle view of FIG. 6, the selector circuit 60 refers to the voltage value Va(X) inputted thereinto from the switching circuit 59, selects the voltage value Va(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{vd}$ , respectively, and generates a signal of which voltage value is V2 during a period of time from the point of time 4  $\mu$ s to the point of time 4+(1/3)  $\mu$ s. The selector circuit **60** refers to the voltage value Vb(X) inputted thereinto from the switching circuit 59, selects the voltage value Vb(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{vd}$ , respectively, and generates a signal of which voltage value is V1 during a period of time from the point of time  $4+(\frac{1}{3})$  µs to the point of time 4+(2/3) µs. The selector circuit 60 refers to the voltage value Vd(X) inputted thereinto from the switching circuit **59**, selects the voltage value Vd(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{vd}$ , respectively, and generates a signal of which voltage value is 0 (zero) during a period of time from the point of time 4+(2/3) µs to the point of time 5 µs. In other words, the control circuit 51 generates a time division multiplex signal including a driving waveform signal which collates the two voltage values of the voltage values Va(X)and Vc(X) to one, a driving waveform signal indicating the voltage value Vb(X), and a driving waveform signal indi-50 cating the voltage value Vd(X).

For example, as depicted in the upper view of FIG. 6, the voltage values Va(X), Vb(X) and Vd(X) are each V1 and the voltage value Vc(X) is 0 (zero) at the point of time 14. In this situation, the comparing circuit 57 associates TS2 and the voltage values Va(X), Vb(X) and Vd(X), and outputs TS2 and the voltage values Va(X), Vb(X) and Vd(X) which are associated with each other to the switching circuit 59 and the respective synchronization signal generating circuits 62a to 62d; and the comparing circuit 57 associates TS3 and the voltage value Vc(X), and outputs TS3 and the voltage value Vc(X) which are associated with each other to the switching circuit 59 and the respective synchronization signal generating circuits 62a to 62d. The switching circuit 59 selects one voltage value from the three voltage values Va(X)Vb(X) and Vd(X), for example, the voltage value Va(X). The switching circuit **59** selects the voltage value Vc(X). The switching circuit 59 generates, with respect to the

voltage value Va(X), a frequency of 12 MHz, based on the reference frequency and TS2. The switching circuit **59** generates, with respect to the voltage value Vc(X), a frequency of 12 MHz, based on the reference frequency and TS3. The switching circuit **59** associates TS2, the frequency of 12 MHz and the voltage value Va(X) with each other, and outputs TS2, the frequency of 12 MHz and the voltage value Va(X) which are associated with each other to the selector circuit **60**. The switching circuit **59** associates TS3, the frequency of 12 MHz and the voltage value Vc(X) with each other, and outputs TS3, the frequency of 12 MHz and the voltage value Vc(X) which are associated with each other to the selector circuit **60**.

As depicted in the middle view of FIG. 6, the selector circuit 60 refers to the voltage value Va(X) inputted thereinto 15 from the switching circuit 59, selects the voltage value Va(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{vd}$ , respectively, and generates a signal of which voltage value is V1 during a period of time from the point of time 14 µs to the point of time 14.5 20  $\mu$ s. The selector circuit **60** refers to the voltage value Vc(X) inputted thereinto from the switching circuit 59, selects the voltage value Vc(X) from the four voltage values Va(X) to Vd(X) inputted from the voltage tables  $T_{va}$  to  $T_{va}$ , respectively, and generates a signal of which voltage value is 0 25 (zero) during a period of time from the point of time 14.5 μs to the point of time 15 μs. In other words, the control circuit 51 generates a time division multiplex signal including a driving waveform signal which collates the three voltage values of the voltage values Va(X), Vb(X) and Vd(X) to one, 30 and a driving waveform signal which indicates the voltage value Vc(X).

As described above, the voltage value used for generating the time division multiplex signal during the period of time from the point of time 0 to the point of time 1 µs included 35 in one cycle of the time division multiplex signal is only the voltage value Va(X). In other words, the number (quantity) of the driving waveform data to be used is 1 (one). The voltage value used for generating the time division multiplex signal during the period of time from the point of time 2  $\mu$ s 40 to the point of time 3 µs included in the one cycle is the voltage values Va(X) and Vb(X). In other words, the number (quantity) of the driving waveform data to be used is 2 (two). The voltage value used for generating the time division multiplex signal during the period of time from the point of 45 time 4  $\mu$ s to the point of time 5  $\mu$ s included in the one cycle is the voltage values Va(X), Vb(X) and Vd(X). In other words, the number (quantity) of the driving waveform data to be used is 3 (three).

The selector circuit 60 outputs the respective signals 50 generated to the multiplex signal outputting circuit 61; and the multiplex signal outputting circuit 61 outputs the time division multiplex signal to the digital-analog convertor 52 (see the middle view of FIG. 6). As depicted in FIG. 3, the time division multiplex signal is amplified by the amplifier 55 53, and inputted into each of the plurality of n-th switches 54(n).

As described above, the frequency generating circuit **58** outputs the reference frequency to the respective synchronization signal generating circuits **62***a* to **62***d*; and the 60 comparing circuit **57** associates the time slots and the respective voltage values Va(X) to Vd(X), and outputs the time slots and the respective voltage values Va(X) to Vd(X) which are associated with each other to the respective synchronization signal generating circuits **62***a* to **62***d*.

As depicted in the lower view of FIG. 6, the synchronization signal generating circuit 62a refers to the time slot

14

associated with the voltage value Va(X), and generates the synchronization signal A. The time slot associated with the voltage value Va(X) is TS1 during a period of time from the point of time 0 (zero) to the point of time 2, and the synchronization signal A is in a state of the high level during the period of time from the point of time 0 (zero) to the point of time 2. The time slot associated with the voltage value Va(X) is TS2 during a period of time from the point of time 2 to the point of time 3; the synchronization signal A is in a state of the high level during a period of time from the point of time 2 to the point of time 2.5, and is in a state of the low level during a period of time from the point of time 2.5 to the point of time 3. The time slot associated with the voltage value Va(X) is TS2 during a period of time from the point of time 3 to the point of time 4; the synchronization signal A is in a state of the high level during a period of time from the point of time 3 to the point of time 3.5, and is in a state of the low level during a period of time from the point of time 3.5 to the point of time 4. The time slot associated with the voltage value Va(X) is TS4 during a period of time from the point of time 4 to the point of time 5; the synchronization signal A is in a state of the high level during a period of time from the point of time 4 to the point of time  $4+(\frac{1}{3})$ , and is in a state of the low level during a period of time from the

point of time  $4+(\frac{1}{3})$  to the point of time 5. The time slot associated with the voltage value Va(X) is TS2 during a period of time from the point of time 5 to the point of time 8; the synchronization signal A is in a state of the high level during a period of time from the point of time 5 to the point of time 5.5, and is in a state of the low level during a period of time from the point of time 5.5 to the point of time 6. The synchronization signal A is in a state of the high level during a period of time from the point of time 6 to the point of time 6.5, and is in a state of the low level during a period of time from the point of time 6.5 to the point of time 7. The synchronization signal A is in a state of the high level during a period of time from the point of time 7 to the point of time 7.5, and is in a state of the low level during a period of time from the point of time 7.5 to the point of time 8. The time slot associated with the voltage value Va(X) is TS3 during a period of time from the point of time 8 to the point of time 9; the synchronization signal A is in a state of the low level during a period of time from the point of time 8 to the point of time 8.5, and is in a state of the high level during a period of time from the point of time 8.5 to the point of time 9. The time slot associated with the voltage value Va(X) is TS3 during a period of time from the point of time 9 to the point of time 14; the synchronization signal A is in a state of the low level during a period of time from the point of time 9 to the point of time 9.5, and is in a state of the high level during a period of time from the point of time 9.5 to the point of time 10. The synchronization signal A is in a state of the low level during a period of time from the point of time 10 to the point of time 10.5, and is in a state of the high level during a period of time from the point of time 10.5 to the point of time 11. The synchronization signal A is in a state of the low level during a period of time from the point of time 11 to the point of time 11.5, and is in a state of the high level during a period of time from the point of time 11.5 to the point of time 12. The synchronization signal A is in a state of the low level during a period of time from the point of time 12 to the point of time 12.5, and is in a state of the high level during a period of time from the point of 65 time 12.5 to the point of time 13. The synchronization signal A is in a state of the low level during a period of time from the point of time 13 to the point of time 13.5, and is in a state

of the high level during a period of time from the point of time 13.5 to the point of time 14.

The time slot associated with the voltage value Va(X) is TS2 during a period of time from the point of time 14 to the point of time 18; the synchronization signal A is in a state of 5 the high level during a period of time from the point of time 14 to the point of time 14.5 and is in a state of the low level during a period of time from the point of time 14.5 to the point of time 15. The synchronization signal A is in a state of the high level during a period of time from the point of 10 time 15 to the point of time 15.5 and is in a state of the low level during a period of time from the point of time 15.5 to the point of time 16. The synchronization signal A is in a state of the high level during a period of time from the point of time 16 to the point of time 16.5, and is in a state of the 15 low level during a period of time from the point of time 16.5 to the point of time 17. The synchronization signal A is in a state of the high level during a period of time from the point of time 17 to the point of time 17.5, and is in a state of the low level during a period of time from the point of time 17.5 20 to the point of time 18. The time slot associated with the voltage value Va(X) is TS1 during a period of time from the point of time 18 to the point of time 20; the synchronization signal A is in a state of the high level during the period of time from the point of time 18 to the point of time 20. 25 Namely, the driving waveform signal is separated from the time division multiplex signal based on the first sampling frequency, the second sampling frequency or the third sampling frequency corresponding to the respective periods of time. Each of during the period of time from the point of 30 time 0 to the point of time 2.5, during the period of time from the point of time 13.5 to the point of time 14.5, and during the period of time from the point of time 18 to the point of time 20, the synchronization signal A is continuously in the state of the high level.

As depicted in the upper view of FIG. 7, the synchronization signal generating circuit 62b refers to the time slot associated with the voltage value Vb(X), and generates the synchronization signal B. The time slot associated with the voltage value Vb(X) is TS1 during a period of time from the 40 point of time 0 (zero) to the point of time 2, and the synchronization signal B is in a state of the high level during the period of time from the point of time 0 (zero) to the point of time 2. The time slot associated with the voltage value Vb(X) is TS3 during a period of time from the point of time 45 2 to the point of time 4; the synchronization signal B is in a state of the low level during a period of time from the point of time 2 to the point of time 2.5, and is in a state of the high level during a period of time from the point of time 2.5 to the point of time 3. The synchronization signal B is in a state 50 of the low level during a period of time from the point of time 3 to the point of time 3.5, and is in a state of the high level during a period of time from the point of time 3.5 to the point of time 4. The time slot associated with the voltage value Vb(X) is TS5 during a period of time from the point 55 of time 4 to the point of time 5; the synchronization signal B is in a state of the low level each of during a period of time from the point of time 4 to the point of time  $4+(\frac{1}{3})$  and during a period of time from the point of time  $4+(\frac{2}{3})$  to the point of time 5; and the synchronization signal B is in a state 60 of the high level during a period of time from the point of time  $4+(\frac{1}{3})$  to the point of time  $4+(\frac{2}{3})$ .

The time slot associated with the voltage value Vb(X) is TS2 during a period of time from the point of time 5 to the point of time 15; the synchronization signal B is in a state of 65 the high level during a period of time from the point of time 5 to the point of time 5.5, and is in a state of the low level

**16**