#### US012096626B2

# (12) United States Patent

#### Parekh

## (10) Patent No.: US 12,096,626 B2

## (45) **Date of Patent:** Sep. 17, 2024

# (54) 3D NAND FLASH MEMORY DEVICES, AND RELATED ELECTRONIC SYSTEMS

(71) Applicant: Micron Technology, Inc., Boise, ID (US)

Inventor: Kunal R. Parekh, Boise, ID (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 18/149,318

(22) Filed: Jan. 3, 2023

(65) Prior Publication Data

US 2023/0143455 A1 May 11, 2023

#### Related U.S. Application Data

(63) Continuation of application No. 16/905,385, filed on Jun. 18, 2020, now Pat. No. 11,563,018.

(51) Int. Cl.

H10B 41/27 (2023.01)

G11C 5/02 (2006.01)

(Continued)

(52) U.S. Cl.

CPC ...... *H10B 41/27* (2023.02); *G11C 5/025* (2013.01); *G11C 5/06* (2013.01); *H01L* 23/5226 (2013.01);

(Continued)

(58) Field of Classification Search

CPC ...... H10B 41/27; H10B 43/27; G11C 5/025; G11C 5/06; H01L 23/5226; H01L 23/53214; H01L 23/53228

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,925,809 A 5/1990 Yoshiharu et al. 6,165,247 A 12/2000 Kodas et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 107768376 A 3/2018 CN 107887395 A 4/2018 (Continued)

#### OTHER PUBLICATIONS

Choe et al., YMTC is China's First Mass Producer of 3D NAND Flash Memory Chips, https://www.techinsights.com/blog/ymtc-chinas-first-mass-producer-3d-nand-flash-memory-chips, (Mar. 12, 2020), 3 pages.

(Continued)

Primary Examiner — Tu-Tu V Ho (74) Attorney, Agent, or Firm — TraskBritt

#### (57) ABSTRACT

A microelectronic device comprises a memory array region, a control logic region underlying the memory array region, and an interconnect region vertically interposed between the memory array region and the control logic region. The memory array region comprises a stack structure comprising vertically alternating conductive structures and insulating structures; vertically extending strings of memory cells within the stack structure; at least one source structure vertically overlying the stack structure and coupled to the vertically extending strings of memory cells; and digit line structures vertically underlying the stack structure and coupled to the vertically extending strings of memory cells. The control logic region comprises control logic devices for the vertically extending strings of memory cells. The interconnect region comprises structures coupling the digit line structures to the control logic devices. Methods of forming a microelectronic device, and memory devices and electronic systems are also described.

#### 18 Claims, 10 Drawing Sheets

| (51)                                                              | Int. Cl.                     |                  |                                    | 2018                   | /0269329 A1                          | 9/2018            | Balakrishnan et al.                  |

|-------------------------------------------------------------------|------------------------------|------------------|------------------------------------|------------------------|--------------------------------------|-------------------|--------------------------------------|

| (51)                                                              | G11C 5/06                    |                  | (2006.01)                          |                        | /0358476 A1                          |                   | Balakrishnan et al.                  |

|                                                                   |                              | 2                | ` /                                | 2019                   | /0043836 A1                          | 2/2019            | Fastow et al.                        |

|                                                                   | H01L 23/52                   |                  | (2006.01)                          |                        | /0088493 A1                          |                   | Watanabe et al.                      |

|                                                                   | H01L 23/53                   |                  | (2006.01)                          |                        | /0096906 A1                          |                   | Lindsay et al.                       |

|                                                                   | H10B 43/27                   |                  | (2023.01)                          |                        | /0206861 A1<br>/0221557 A1           |                   | Beigel et al.<br>Kim et al.          |

| (52)                                                              | U.S. Cl.                     |                  |                                    |                        | /0221337 A1<br>/0229089 A1           |                   | Zhou et al.                          |

|                                                                   | CPC <b>H0</b> 1              | <i>1L 23/532</i> | 14 (2013.01); H01L 23/53228        |                        | /0279952 A1                          |                   |                                      |

| (2013.01); <b>H10B</b> 43/27 (2023.02)                            |                              |                  | 2019                               | /0355786 A1            |                                      |                   |                                      |

| (58) Field of Classification Search                               |                              |                  |                                    | /0393238 A1            |                                      | Lim et al.        |                                      |

| (00)                                                              |                              |                  |                                    |                        | /0006380 A1                          |                   | Van et al.                           |

|                                                                   |                              |                  | r complete search history.         |                        | /0013792 A1<br>/0013798 A1           |                   | Parekh et al.<br>Parekh              |

|                                                                   | See applican                 | ion me io        | r complete scarch mistory.         |                        | /0013790 AT                          |                   | Zhu et al.                           |

| (56)                                                              |                              | Referen          | ces Cited                          |                        | /0066745 A1                          |                   | Yu et al.                            |

| (50)                                                              |                              | ICICICII         | ecs Citeu                          |                        | /0083245 A1                          |                   | Fayrushin et al.                     |

|                                                                   | U.S.                         | <b>PATENT</b>    | DOCUMENTS                          |                        | /0098776 A1                          |                   | Sugisaki                             |

|                                                                   |                              |                  |                                    |                        | /0135541 A1<br>/0159133 A1           |                   | Wu et al.<br>Yan et al.              |

|                                                                   | 7,087,452 B2                 |                  | Joshi et al.                       |                        | /0159135 A1                          |                   | Sills et al.                         |

|                                                                   | 7,372,091 B2                 | 5/2008           |                                    |                        | /0185406 A1                          |                   | Li et al.                            |

|                                                                   | 7,897,485 B2<br>8,042,082 B2 |                  | Parekn<br>Solomon                  |                        | /0219815 A1                          |                   | Elsherbini et al.                    |

|                                                                   | /                            |                  | Samachisa et al.                   |                        | /0227397 A1                          |                   | Yada et al.                          |

|                                                                   | , ,                          |                  | Ramaswamy et al.                   |                        | /0258816 A1                          |                   | Okina et al.                         |

|                                                                   | 9,397,145 B1                 |                  |                                    |                        | /0258876 A1<br>/0258904 A1           |                   |                                      |

|                                                                   | 9,449,652 B2                 |                  | ~ ~                                |                        |                                      |                   | Elsherbini et al.                    |

|                                                                   | 9,515,083 B2                 |                  |                                    |                        |                                      |                   | Cheng H01L 27/0688                   |

|                                                                   | 9,530,790 B1<br>9,553,263 B1 |                  |                                    |                        | /0074711 A1                          |                   | Suzuki et al.                        |

|                                                                   | 9,590,012 B2                 |                  |                                    |                        | /0082939 A1                          |                   | Matsuda                              |

|                                                                   | 9,653,617 B2                 |                  | Zhou et al.                        |                        | /0134778 A1<br>/0296316 A1           | 5/2021<br>9/2021  |                                      |

|                                                                   | , ,                          |                  | Balakrishnan et al.                |                        | /0290510 A1<br>/0343690 A1           |                   |                                      |

|                                                                   | 9,922,716 B2                 |                  | •                                  |                        |                                      | 12/2021           |                                      |

|                                                                   |                              |                  | Lindsay et al.<br>Pellizzer et al. |                        | /0028830 A1                          |                   | •                                    |

|                                                                   | 0,381,362 B1                 |                  |                                    |                        | /0238631 A1                          |                   |                                      |

|                                                                   | 0,665,580 B1                 |                  | Hosoda et al.                      |                        | /0336646 A1<br>/0416029 A1           |                   | Ontalus et al.                       |

| 10                                                                | 0,847,220 B2                 | 11/2020          | Castro                             |                        | /0410029 A1<br>/0301191 A1           | 12/2022<br>9/2023 | Ferrari et al.                       |

|                                                                   | 1,282,815 B2                 |                  | Parekh et al.                      | 2023                   | ,0501151 711                         | <i>J,</i> 2025    | r critari ce tar.                    |

| 11,417,676 B2 8/2022 Meotto et al.<br>11,751,408 B2 9/2023 Parekh |                              |                  | FOREIG                             | N PATE                 | NT DOCUMENTS                         |                   |                                      |

|                                                                   | 5/0113669 A1                 |                  | Cheng et al.                       |                        |                                      |                   |                                      |

|                                                                   | /0151083 A1                  |                  | Matsui et al.                      | $\overline{\text{CN}}$ |                                      | 7865 A            | 8/2018                               |

|                                                                   | /0265076 A1                  | 12/2005          |                                    | CN                     |                                      | 0213 A            | 8/2019<br>6/2020                     |

|                                                                   | 0/0076690 A1                 |                  | Khandros et al.                    | CN<br>JP               | 2002-103                             | 7636 A<br>3299 A  | 6/2020<br>4/2002                     |

|                                                                   | //0288702 A1<br>//0019165 A1 |                  | Roohparvar<br>Lin et al.           | JР                     | 2010-153                             |                   | 7/2010                               |

|                                                                   | /0168482 A1                  |                  | Park et al.                        | JP                     | 2016-062                             | 2901 A            | 4/2016                               |

| 2011                                                              | /0159645 A1                  | 6/2011           | Pekny                              | JP                     | 2019-024                             |                   | 2/2019                               |

|                                                                   | /0309431 A1                  |                  | Kidoh et al.                       | JP<br>vp               | 2019-220                             |                   | 12/2019                              |

|                                                                   | /0047321 A1                  |                  | Yoon et al.                        | KR<br>KR               | 10-2009-0034<br>10-2014-0113         |                   | 4/2009<br>10/2014                    |

|                                                                   | /0161094 A1<br>/0181602 A1   |                  | Huo et al.<br>Fukuzumi et al.      | KR                     | 10-2015-0085                         |                   | 7/2015                               |

|                                                                   | /0224426 A1                  |                  | Nam et al.                         | KR                     | 10-2020-0008                         | 8606 A            | 1/2020                               |

| 2013                                                              | /0126622 A1                  | 5/2013           | Finn                               | KR                     | 10-2020-0037                         |                   | 4/2020                               |

|                                                                   | /0130468 A1                  |                  | Higashitani et al.                 | TW                     |                                      | 1319 A            | 3/2015<br>7/2018                     |

|                                                                   | /0001583 A1                  |                  | Teh et al.                         | TW<br>TW               |                                      | 5556 A<br>3153 A  | 7/2018<br>10/2018                    |

|                                                                   | /0061750 A1<br>/0063938 A1   |                  | Kwon et al.<br>Oh et al.           | TW                     |                                      | 1407 B            | 10/2019                              |

|                                                                   | /00033336 A1<br>/0124726 A1  | 5/2014           |                                    | TW                     | 201946                               | 5057 A            | 12/2019                              |

|                                                                   | /0175637 A1                  |                  | Stuber et al.                      | TW                     |                                      | 8568 B            | 2/2020                               |

|                                                                   | /0204675 A1                  |                  | Cho et al.                         | WO                     | 2008/063                             | 3251 A2           | 5/2008                               |

|                                                                   | 5/0091180 A1                 |                  | Ong et al.                         |                        |                                      |                   |                                      |

|                                                                   | /0243708 A1<br>/0278675 A1   |                  | Ravasio et al.<br>Finn et al.      |                        | OT.                                  | HER PU            | BLICATIONS                           |

|                                                                   | /02/80/3 A1<br>/0348987 A1   |                  | Lee et al.                         | т.,                    | .: 1 G 1                             | D                 | 4 1' 4' NE DOTE/EIGOCO1/             |

|                                                                   | 6/0049201 A1                 |                  | Lue et al.                         |                        |                                      | -                 | or Application No. PCT/US2021/       |

|                                                                   | /0079164 A1                  |                  | Fukuzumi et al.                    |                        | 5, mailed Sep. 7                     |                   | pages.  A Fine-Grained 3D CMOS Inte- |

|                                                                   | /0104715 A1                  |                  | Pachamuthu et al.                  |                        | • •                                  |                   | E Transactions on Nanotechnology,    |

|                                                                   | 5/0268304 A1<br>5/0343727 A1 |                  | Ikeda et al.<br>Kim et al.         | _                      | 5, No. 4, Jul. 20                    |                   |                                      |

|                                                                   | 7/0343727 A1<br>7/0025421 A1 |                  | Sakakibara et al.                  |                        |                                      |                   | ion Micron Mobile TLC 3D NAND,       |

|                                                                   | //0054036 A1                 |                  | Dorhout et al.                     | Industr                | ry-Leading Storag                    |                   | ns for Flagship Smartphones, (2018), |

|                                                                   | /0092649 A1                  |                  | Takaoka                            | 9 page                 |                                      |                   | C                                    |

|                                                                   | /0148802 A1                  |                  | Dorhout et al.                     |                        |                                      |                   | for Application No. 110119677,       |

|                                                                   | 3/0053768 A1<br>3/0108741 A1 |                  | Kim et al.                         |                        | Jan. 26, 2022, 9<br>n Opinion of the | - <b>-</b>        | onal Searching Authority for Appli-  |

|                                                                   | 70108741 A1<br>3/0158689 A1  |                  | Li et al.<br>Mumford               |                        | -                                    |                   | 5, mailed Sep. 7, 2021, 3 pages.     |

2018/0158689 A1

6/2018 Mumford

cation No. PCT/US2021/033305, mailed Sep. 7, 2021, 3 pages.

## US 12,096,626 B2

Page 3

### (56) References Cited

#### OTHER PUBLICATIONS

YMTC, About Xtacking, http://www.ymtc.com, visited Apr. 20, 2020, 3 pages.

<sup>\*</sup> cited by examiner

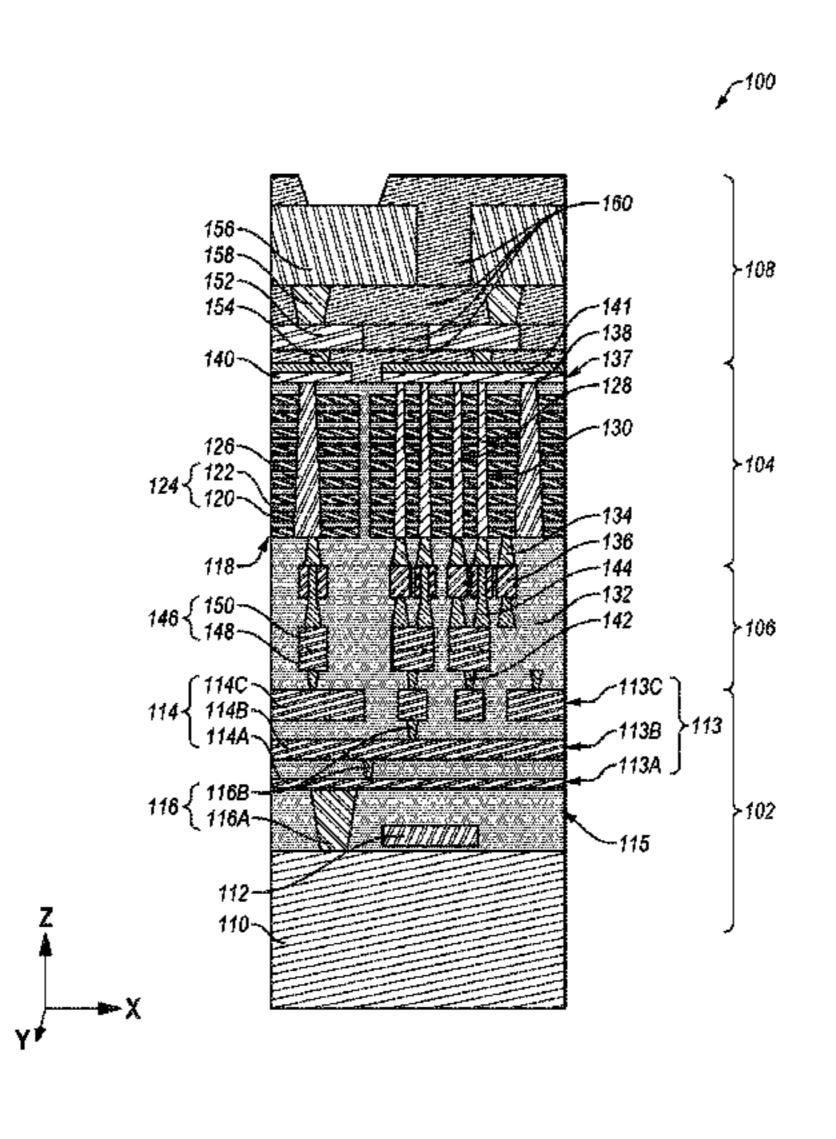

FIG. 1

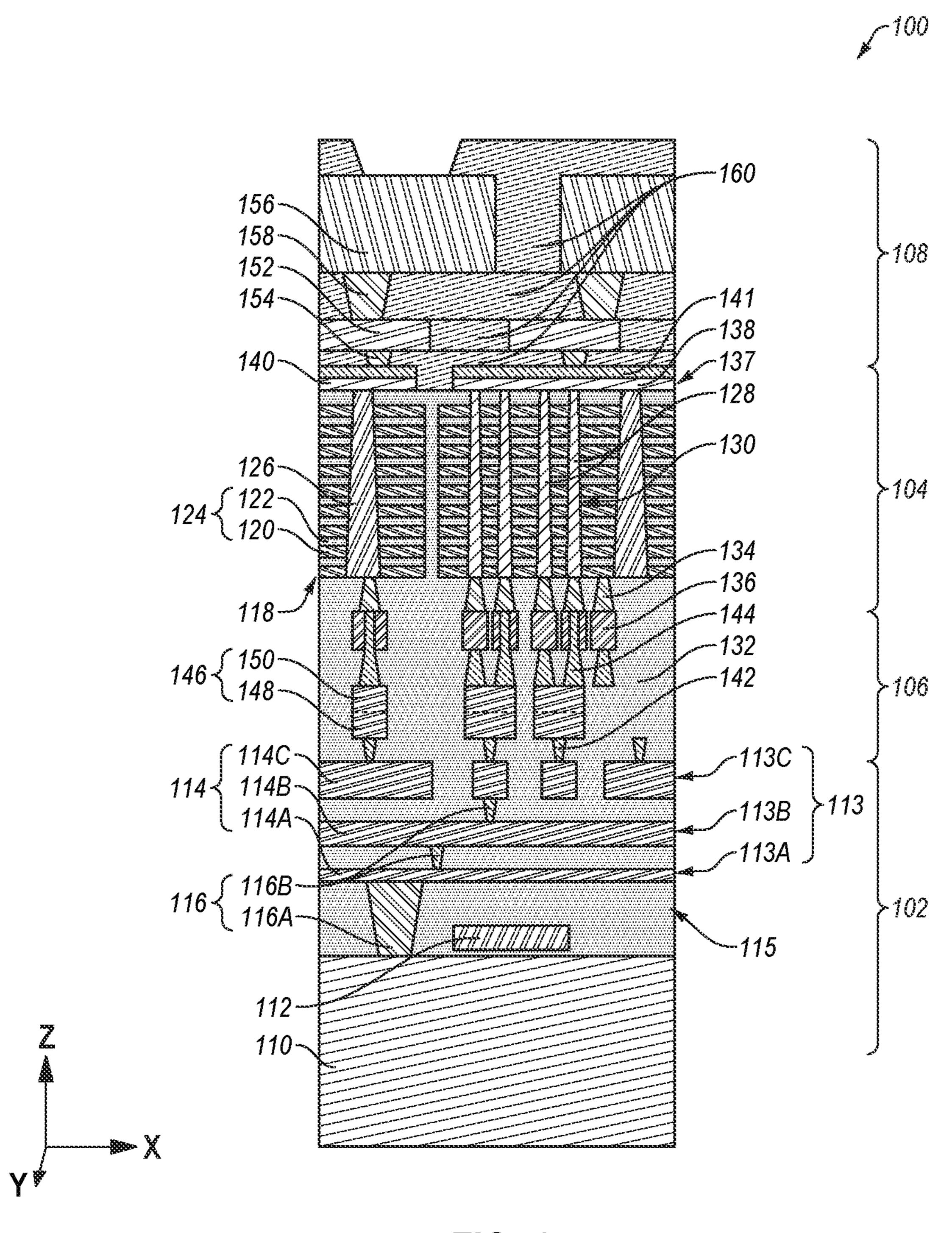

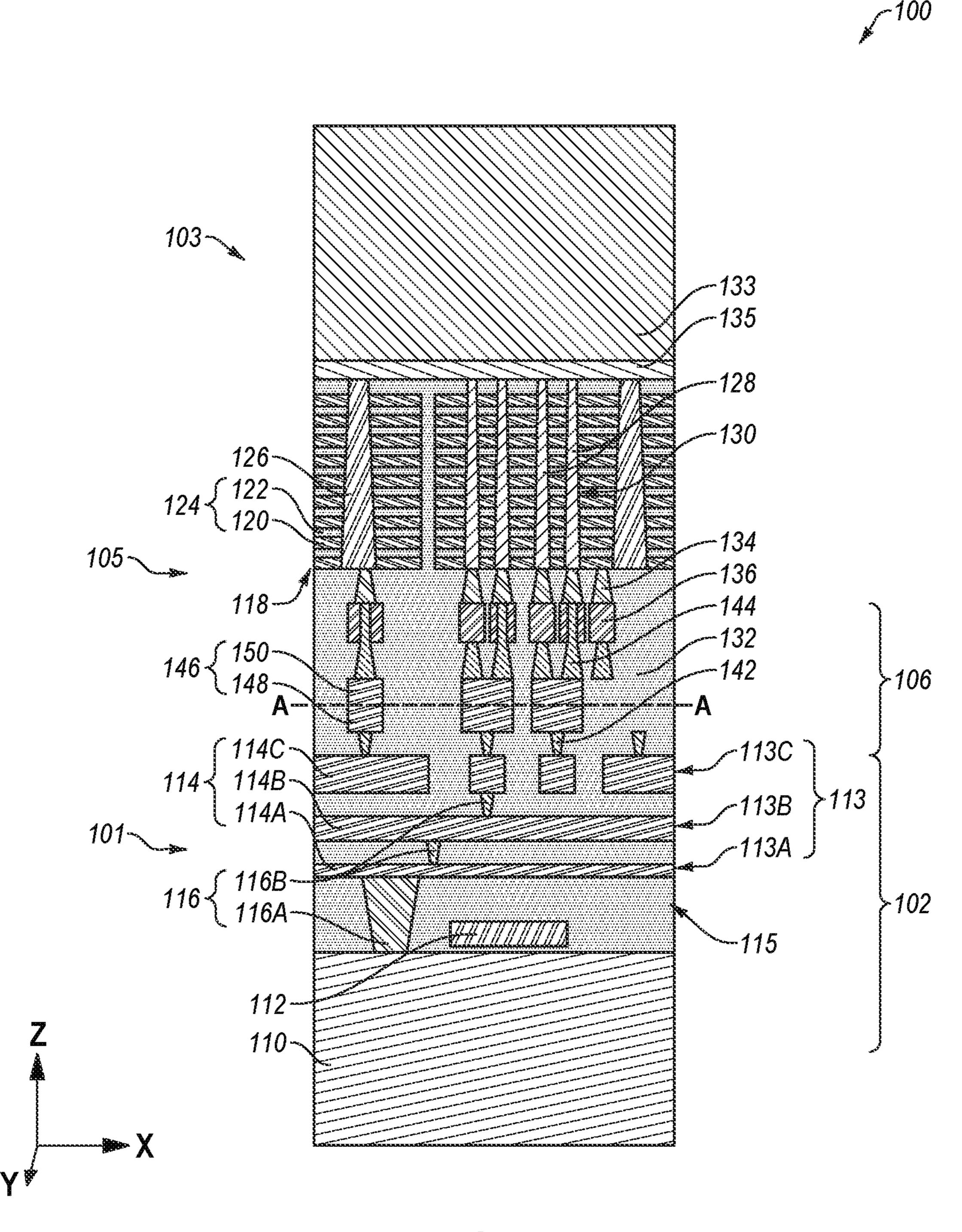

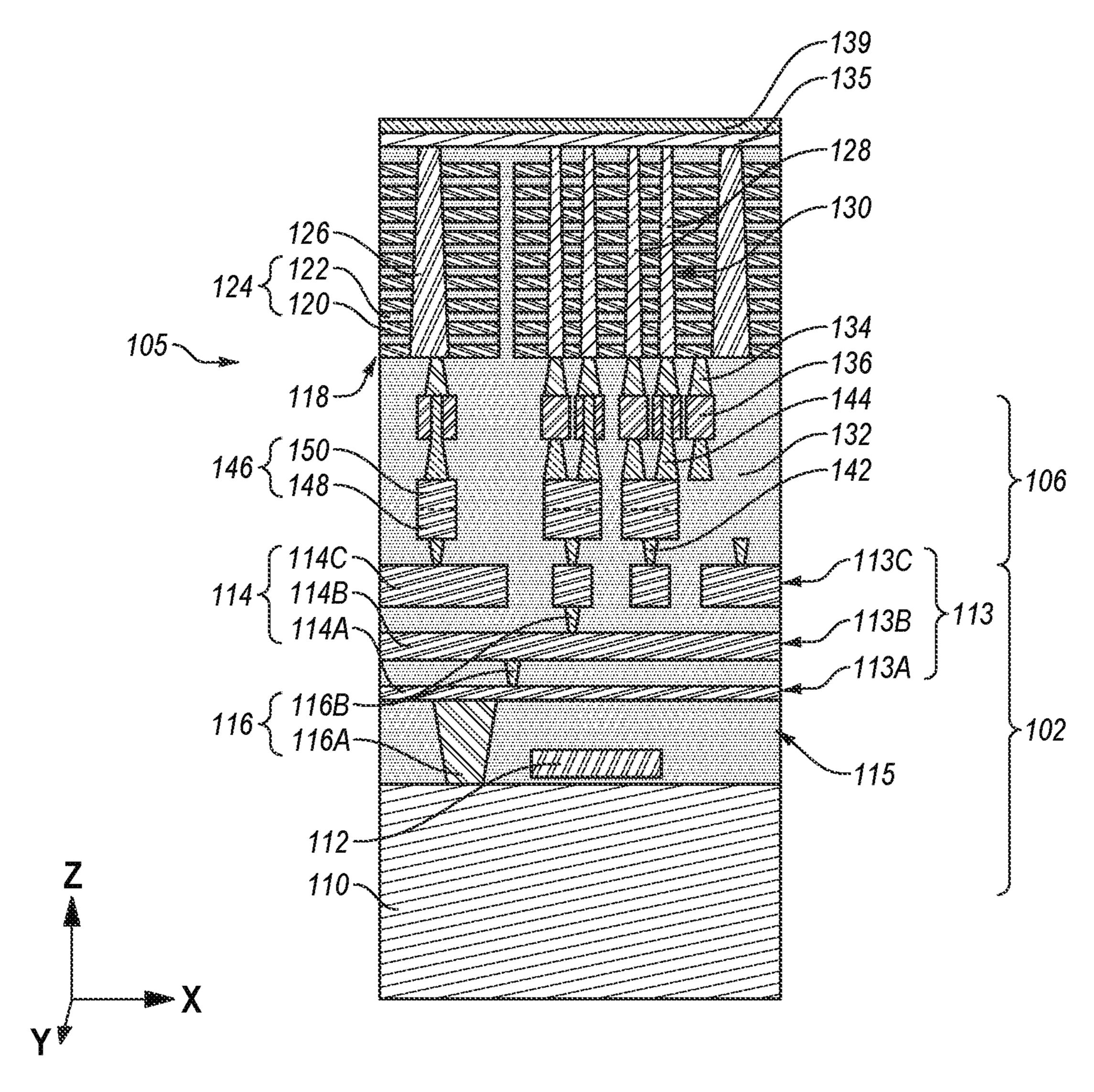

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 2D

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

# 3D NAND FLASH MEMORY DEVICES, AND RELATED ELECTRONIC SYSTEMS

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. patent application Ser. No. 16/905,385, filed Jun. 18, 2020, now U.S. Pat. No. 11,563,018, issued Jan. 24, 2023, which is related to U.S. patent application Ser. No. 16/905,452, filed Jun. 18, 10 2020, now U.S. Pat. No. 11,705,367, issued Jul. 18, 2023, listing Kunal R. Parekh as inventor, for "METHODS OF MICROELECTRONIC DEVICES, AND FORMING RELATED MICROELECTRONIC DEVICES, MEMORY DEVICES, ELECTRONIC SYSTEMS, AND ADDI- 15 TIONAL METHODS." This application is also related to U.S. patent application Ser. No. 16/905,698, filed Jun. 18, 2020, now U.S. Pat. No. 11,705,367, issued Jul. 18, 2023, listing Kunal R. Parekh as inventor, for "MICROELEC-TRONIC DEVICES AND ELECTRONIC SYSTEMS." 20 This application is also related to U.S. patent application Ser. No. 16/905,747, filed Jun. 18, 2020, now U.S. Pat. No. 11,557,569, which will issue Jan. 17, 2023, listing Kunal R. Parekh as inventor, for "MICROELECTRONIC DEVICES INCLUDING SOURCE STRUCTURES OVERLYING 25 STACK STRUCTURES, AND RELATED ELECTRONIC SYSTEMS." This application is also related to U.S. patent application Ser. No. 16/905,763, filed Jun. 18, 2020, now U.S. Pat. No. 11,335,602, issued May 17, 2022, listing Kunal R. Parekh as inventor, for "METHODS OF FORM- <sup>30</sup> ING MICROELECTRONIC DEVICES, AND RELATED MICROELECTRONIC DEVICES AND ELECTRONIC SYSTEMS." This application is also related to U.S. patent application Ser. No. 16/905,734, filed Jun. 18, 2020, now U.S. Pat. No. 11,380,669, issued Jul. 5, 2022, listing Kunal <sup>35</sup> R. Parekh as inventor, for "METHODS OF FORMING MICROELECTRONIC DEVICES." The disclosure of each of the foregoing documents is hereby incorporated herein in its entirety by reference.

#### TECHNICAL FIELD

The disclosure, in various embodiments, relates generally to the field of microelectronic device design and fabrication. More specifically, the disclosure relates to microelectronic 45 devices, and related methods, memory devices, and electronic systems.

#### **BACKGROUND**

Microelectronic device designers often desire to increase the level of integration or density of features within a microelectronic device by reducing the dimensions of the individual features and by reducing the separation distance between neighboring features. In addition, microelectronic 55 device designers often desire to design architectures that are not only compact, but offer performance advantages, as well as simplified designs.

One example of a microelectronic device is a memory device. Memory devices are generally provided as internal 60 integrated circuits in computers or other electronic devices. There are many types of memory devices including, but not limited to, non-volatile memory devices (e.g., NAND Flash memory devices). One way of increasing memory density in non-volatile memory devices is to utilize vertical memory 65 array (also referred to as a "three-dimensional (3D) memory array") architectures. A conventional vertical memory array

2

includes vertical memory strings extending through openings in one or more decks (e.g., stack structures) including tiers of conductive structures and dielectric materials. Each vertical memory string may include at least one select device coupled in series to a serial combination of vertically stacked memory cells. Such a configuration permits a greater number of switching devices (e.g., transistors) to be located in a unit of die area (i.e., length and width of active surface consumed) by building the array upwards (e.g., vertically) on a die, as compared to structures with conventional planar (e.g., two-dimensional) arrangements of transistors.

Control logic devices within a base control logic structure underlying a memory array of a memory device (e.g., a non-volatile memory device) have been used to control operations (e.g., access operations, read operations, write operations) on the memory cells of the memory device. An assembly of the control logic devices may be provided in electrical communication with the memory cells of the memory array by way of routing and contact structures. However, processing conditions (e.g., temperatures, pressures, materials) for the formation of the memory array over the base control logic structure can limit the configurations and performance of the control logic devices within the base control logic structure. In addition, the quantities, dimensions, and arrangements of the different control logic devices employed within the base control logic structure can also undesirably impede reductions to the size (e.g., horizontal footprint) of a memory device, and/or improvements in the performance (e.g., faster memory cell ON/OFF speed, lower threshold switching voltage requirements, faster data transfer rates, lower power consumption) of the memory device.

#### BRIEF DESCRIPTION OF THE DRAWINGS

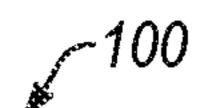

FIG. 1 is simplified, partial cross-sectional view of a microelectronic device, in accordance with embodiments of the disclosure.

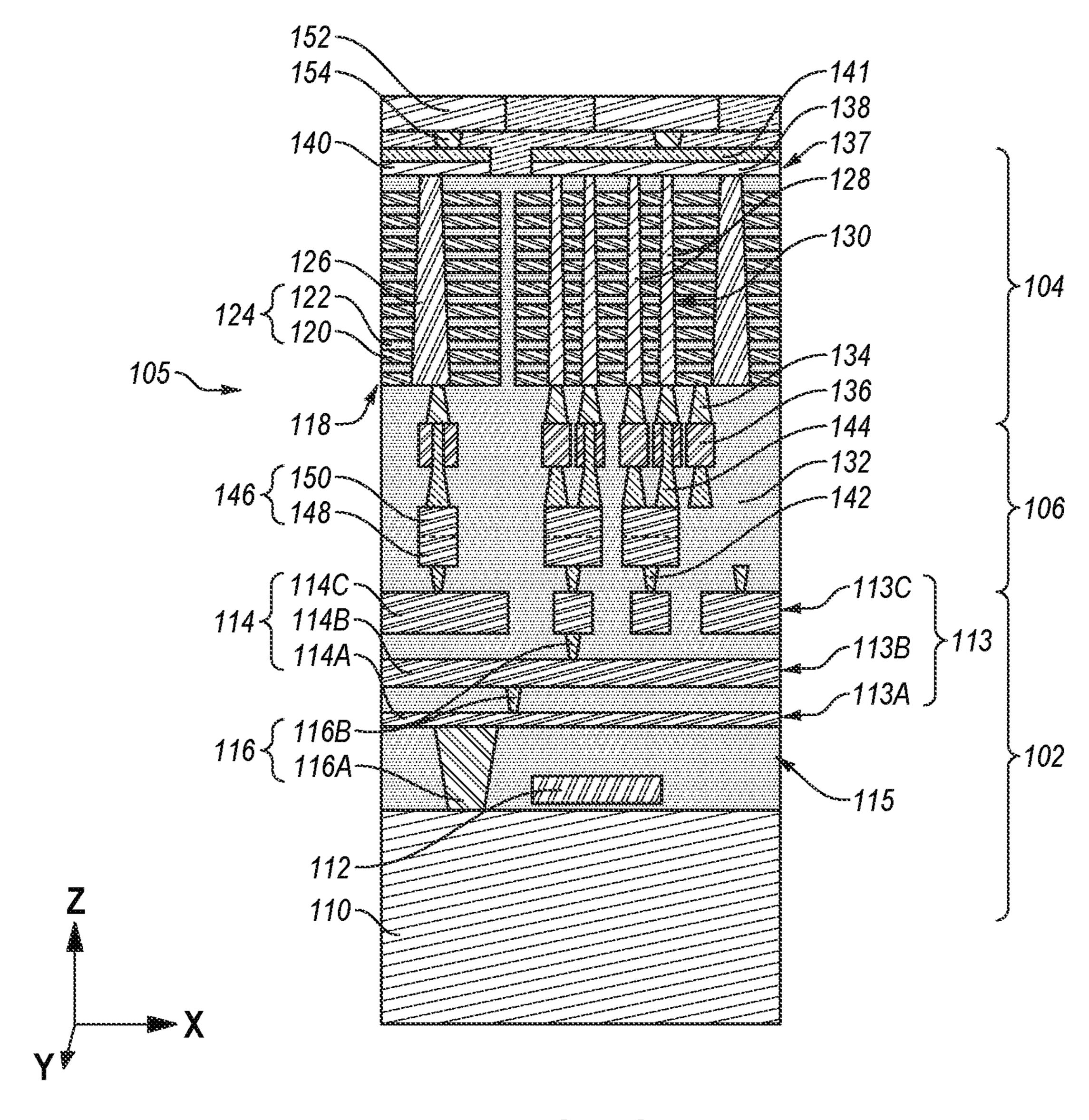

FIGS. 2A through 2D are simplified, partial cross-sectional views illustrating a method of forming the microelectronic device shown in FIG. 1, in accordance with embodiments of the disclosure.

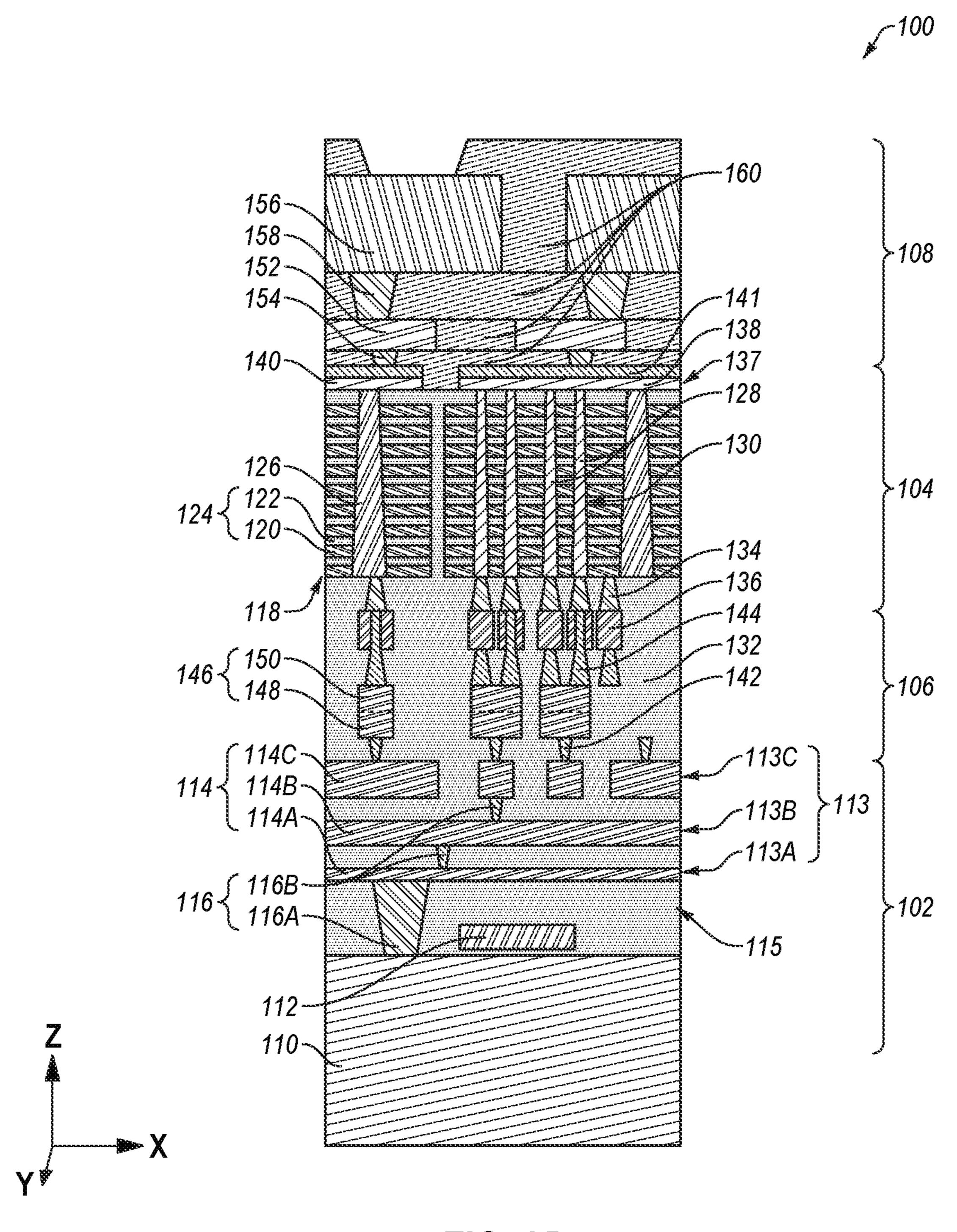

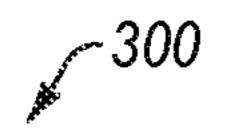

FIG. 3 is simplified, partial cross-sectional view of a microelectronic device, in accordance with additional embodiments of the disclosure.

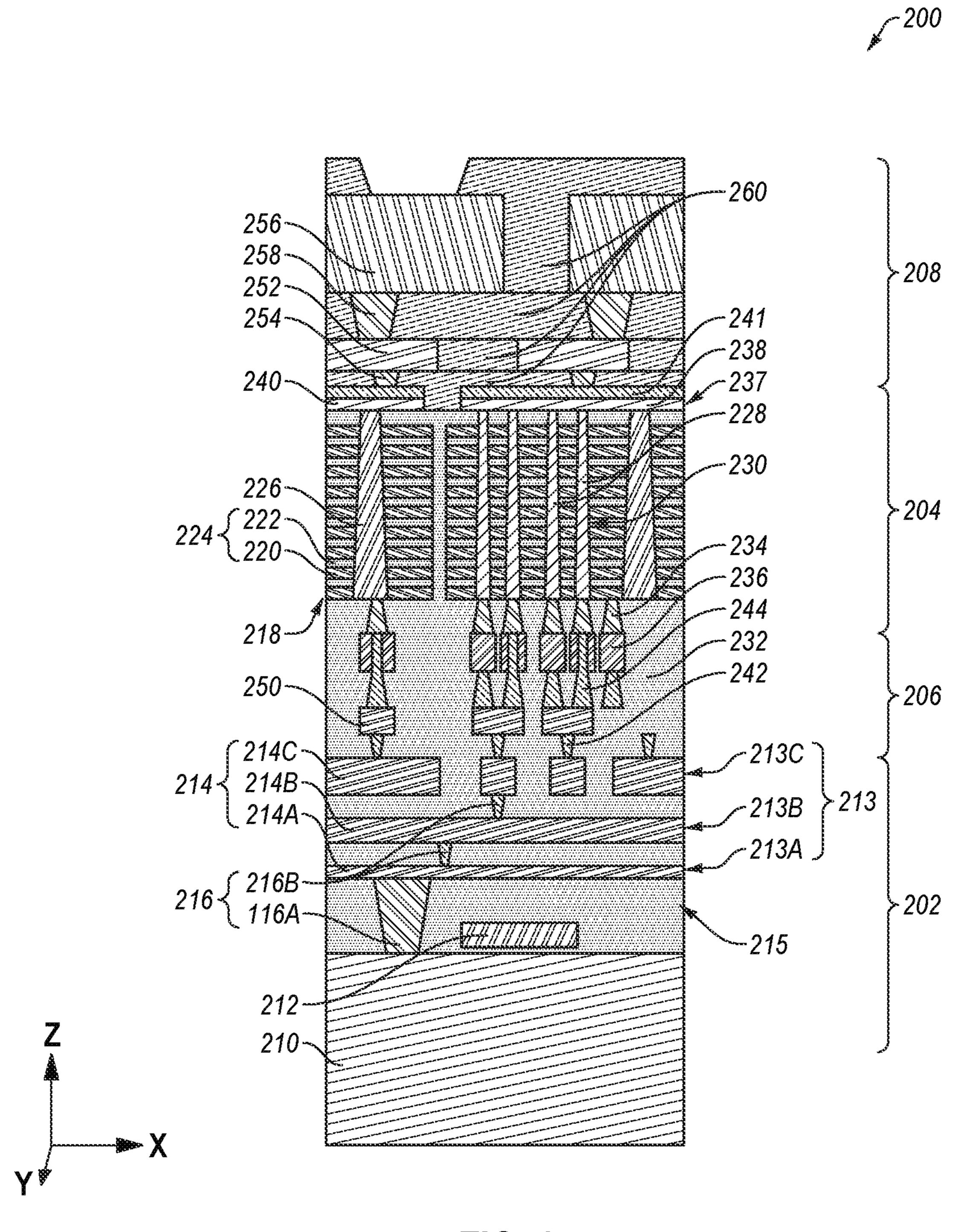

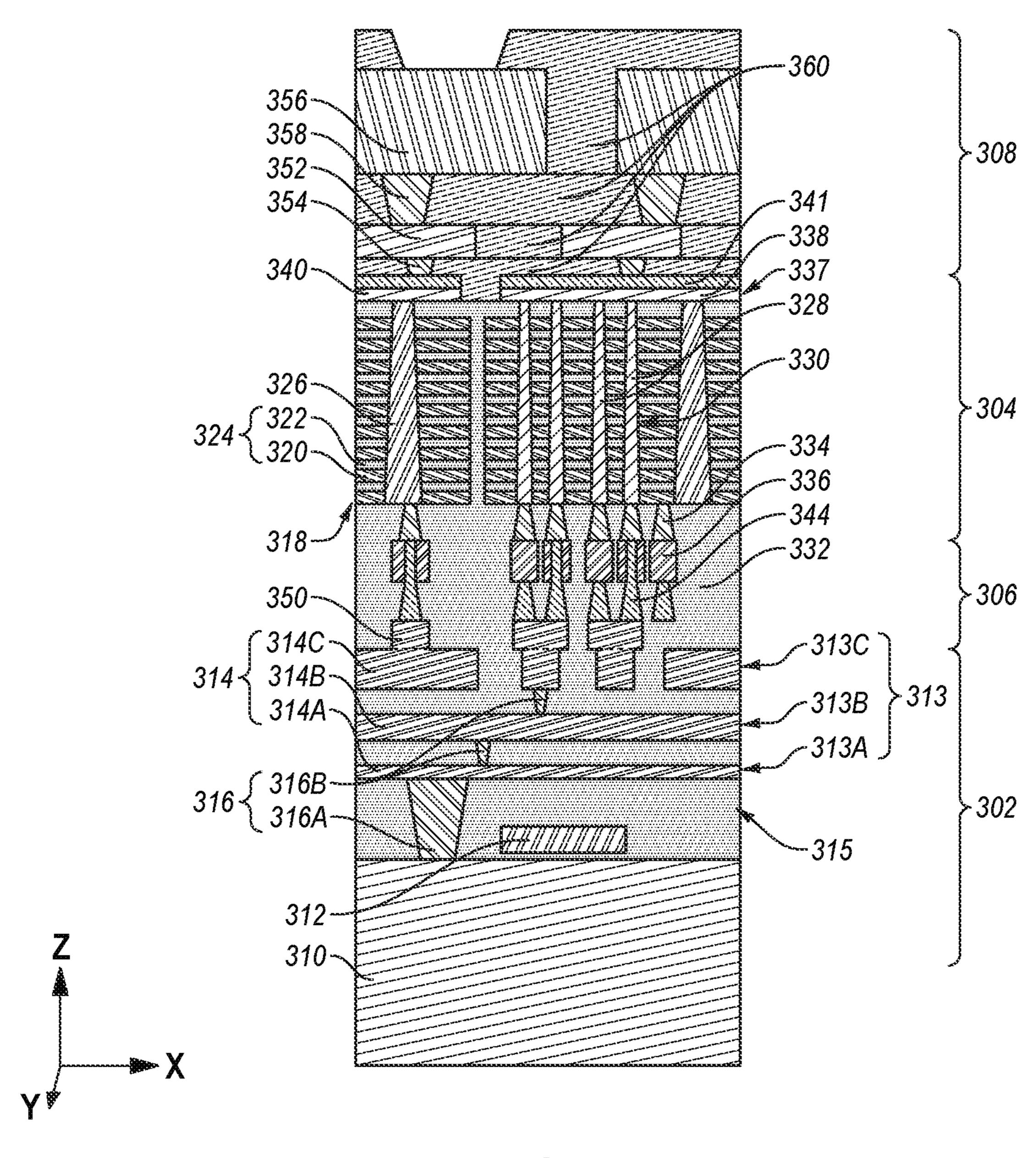

FIG. 4 is simplified, partial cross-sectional view of a microelectronic device, in accordance with further embodiments of the disclosure.

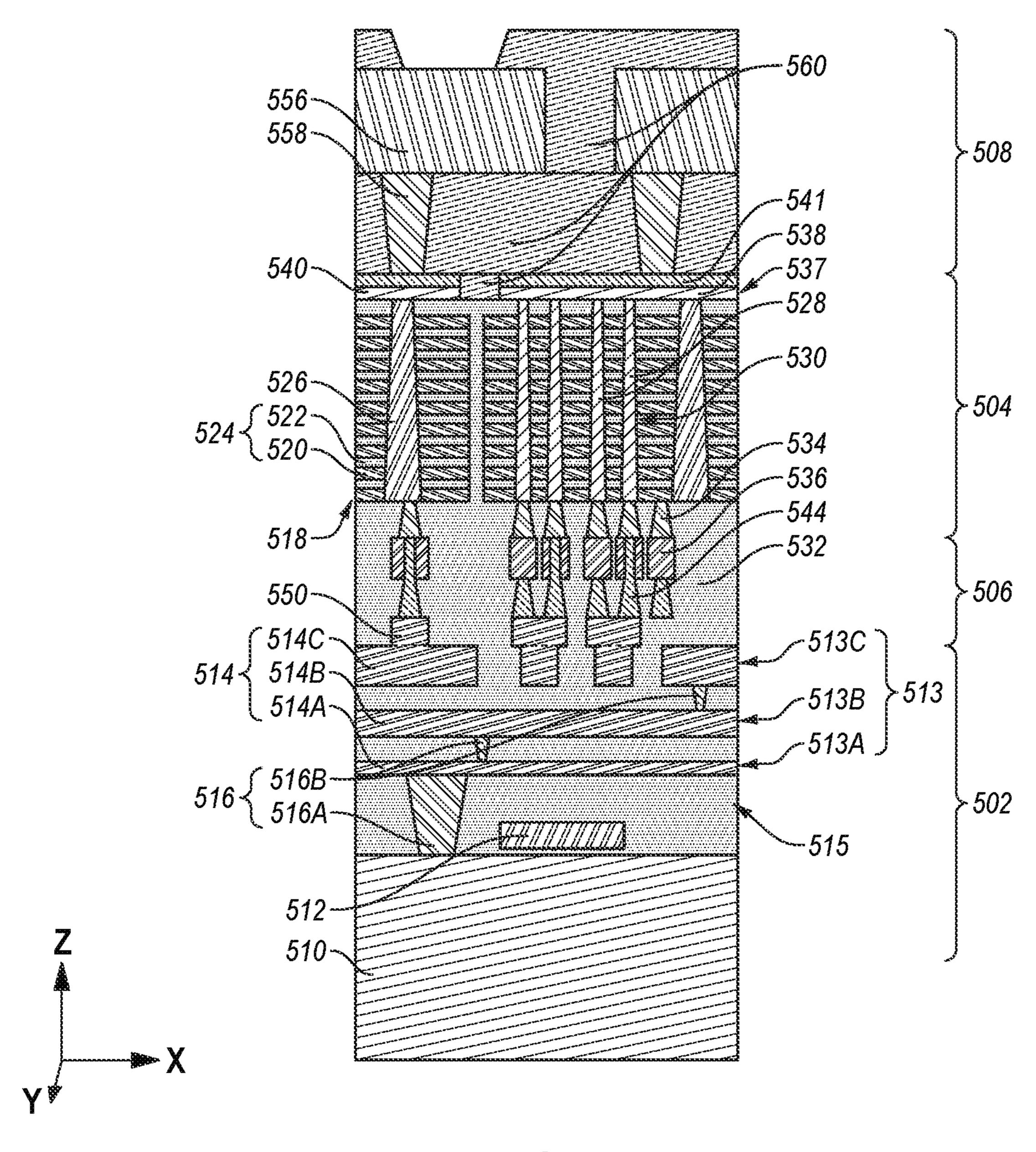

FIG. **5** is simplified, partial cross-sectional view of a microelectronic device, in accordance with yet additional embodiments of the disclosure.

FIG. 6 is simplified, partial cross-sectional view of a microelectronic device, in accordance with yet further embodiments of the disclosure.

FIG. 7 is a schematic block diagram of an electronic system, in accordance with an embodiment of the disclosure.

#### DETAILED DESCRIPTION

The following description provides specific details, such as material compositions, shapes, and sizes, in order to provide a thorough description of embodiments of the disclosure. However, a person of ordinary skill in the art would understand that the embodiments of the disclosure may be practiced without employing these specific details. Indeed, the embodiments of the disclosure may be practiced in conjunction with conventional microelectronic device

fabrication techniques employed in the industry. In addition, the description provided below does not form a complete process flow for manufacturing a microelectronic device (e.g., a memory device, such as 3D NAND Flash memory device). The structures described below do not form a 5 complete microelectronic device. Only those process acts and structures necessary to understand the embodiments of the disclosure are described in detail below. Additional acts to form a complete microelectronic device from the structures may be performed by conventional fabrication techniques.

Drawings presented herein are for illustrative purposes only, and are not meant to be actual views of any particular material, component, structure, device, or system. Variations from the shapes depicted in the drawings as a result, for 15 example, of manufacturing techniques and/or tolerances, are to be expected. Thus, embodiments described herein are not to be construed as being limited to the particular shapes or regions as illustrated, but include deviations in shapes that result, for example, from manufacturing. For example, a 20 region illustrated or described as box-shaped may have rough and/or nonlinear features, and a region illustrated or described as round may include some rough and/or linear features. Moreover, sharp angles that are illustrated may be rounded, and vice versa. Thus, the regions illustrated in the 25 figures are schematic in nature, and their shapes are not intended to illustrate the precise shape of a region and do not limit the scope of the present claims. The drawings are not necessarily to scale. Additionally, elements common between figures may retain the same numerical designation. 30

As used herein, a "memory device" means and includes microelectronic devices exhibiting memory functionality, but not necessarily limited to memory functionality. Stated another way, and by way of non-limiting example only, the term "memory device" includes not only conventional 35 memory (e.g., conventional volatile memory, such as conventional dynamic random access memory (DRAM); conventional non-volatile memory, such as conventional NAND memory), but also includes an application specific integrated circuit (ASIC) (e.g., a system on a chip (SoC)), a micro-40 electronic device combining logic and memory, and a graphics processing unit (GPU) incorporating memory.

As used herein, the term "configured" refers to a size, shape, material composition, orientation, and arrangement of one or more of at least one structure and at least one 45 apparatus facilitating operation of one or more of the structure and the apparatus in a pre-determined way.

As used herein, the terms "vertical," "longitudinal," "horizontal," and "lateral" are in reference to a major plane of a structure and are not necessarily defined by earth's 50 gravitational field. A "horizontal" or "lateral" direction is a direction that is substantially parallel to the major plane of the structure, while a "vertical" or "longitudinal" direction is a direction that is substantially perpendicular to the major plane of the structure. The major plane of the structure is 55 defined by a surface of the structure having a relatively large area compared to other surfaces of the structure. With reference to the figures, a "horizontal" or "lateral" direction may be perpendicular to an indicated "Z" axis, and may be parallel to an indicated "X" axis and/or parallel to an 60 indicated "Y" axis; and a "vertical" or "longitudinal" direction may be parallel to an indicated "Z" axis, may be perpendicular to an indicated "X" axis, and may be perpendicular to an indicated "Y" axis.

As used herein, features (e.g., regions, structures, devices) 65 described as "neighboring" one another means and includes features of the disclosed identity (or identities) that are

4

located most proximate (e.g., closest to) one another. Additional features (e.g., additional regions, additional structures, additional devices) not matching the disclosed identity (or identities) of the "neighboring" features may be disposed between the "neighboring" features. Put another way, the "neighboring" features may be positioned directly adjacent one another, such that no other feature intervenes between the "neighboring" features; or the "neighboring" features may be positioned indirectly adjacent one another, such that at least one feature having an identity other than that associated with at least one the "neighboring" features is positioned between the "neighboring" features. Accordingly, features described as "vertically neighboring" one another means and includes features of the disclosed identity (or identities) that are located most vertically proximate (e.g., vertically closest to) one another. Moreover, features described as "horizontally neighboring" one another means and includes features of the disclosed identity (or identities) that are located most horizontally proximate (e.g., horizontally closest to) one another.

As used herein, spatially relative terms, such as "beneath," "below," "lower," "bottom," "above," "upper," "top," "front," "rear," "left," "right," and the like, may be used for ease of description to describe one element's or feature's relationship to another element(s) or feature(s) as illustrated in the figures. Unless otherwise specified, the spatially relative terms are intended to encompass different orientations of the materials in addition to the orientation depicted in the figures. For example, if materials in the figures are inverted, elements described as "below" or "beneath" or "under" or "on bottom of" other elements or features would then be oriented "above" or "on top of" the other elements or features. Thus, the term "below" can encompass both an orientation of above and below, depending on the context in which the term is used, which will be evident to one of ordinary skill in the art. The materials may be otherwise oriented (e.g., rotated 90 degrees, inverted, flipped) and the spatially relative descriptors used herein interpreted accordingly.

As used herein, the singular forms "a," "an," and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise.

As used herein, "and/or" includes any and all combinations of one or more of the associated listed items.

As used herein, the phrase "coupled to" refers to structures operatively connected with each other, such as electrically connected through a direct Ohmic connection or through an indirect connection (e.g., by way of another structure).

As used herein, the term "substantially" in reference to a given parameter, property, or condition means and includes to a degree that one of ordinary skill in the art would understand that the given parameter, property, or condition is met with a degree of variance, such as within acceptable tolerances. By way of example, depending on the particular parameter, property, or condition that is substantially met, the parameter, property, or condition may be at least 90.0 percent met, at least 95.0 percent met, at least 99.0 percent met, at least 99.9 percent met, or even 100.0 percent met.

As used herein, "about" or "approximately" in reference to a numerical value for a particular parameter is inclusive of the numerical value and a degree of variance from the numerical value that one of ordinary skill in the art would understand is within acceptable tolerances for the particular parameter. For example, "about" or "approximately" in reference to a numerical value may include additional numerical values within a range of from 90.0 percent to

of from 95.0 percent to 105.0 percent of the numerical value, within a range of from 97.5 percent to 102.5 percent of the numerical value, within a range of from 99.0 percent to 101.0 percent of the numerical value, within a range of from 99.5 percent to 100.5 percent of the numerical value, or within a range of from 99.9 percent to 100.1 percent of the numerical value.

As used herein, "conductive material" means and includes electrically conductive material such as one or more of a 10 metal (e.g., tungsten (W), titanium (Ti), molybdenum (Mo), niobium (Nb), vanadium (V), hafnium (Hf), tantalum (Ta), chromium (Cr), zirconium (Zr), iron (Fe), ruthenium (Ru), osmium (Os), cobalt (Co), rhodium (Rh), iridium (Ir), nickel (Ni), palladium (Pd), platinum (Pt), copper (Cu), silver (Ag), 15 gold (Au), aluminum (Al)), an alloy (e.g., a Co-based alloy, an Fe-based alloy, an Ni-based alloy, an Fe- and Ni-based alloy, a Co- and Ni-based alloy, an Fe- and Co-based alloy, a Co- and Ni- and Fe-based alloy, an Al-based alloy, a Cu-based alloy, a magnesium (Mg)-based alloy, a Ti-based 20 alloy, a steel, a low-carbon steel, a stainless steel), a conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide), and a conductivelydoped semiconductor material (e.g., conductively-doped 25 polysilicon, conductively-doped germanium (Ge), conductively-doped silicon germanium (SiGe)). In addition, a "conductive structure" means and includes a structure formed of and including conductive material.

As used herein, "insulative material" means and includes 30 electrically insulative material, such as one or more of at least one dielectric oxide material (e.g., one or more of a silicon oxide (SiO<sub>x</sub>), phosphosilicate glass, borosilicate glass, borophosphosilicate glass, fluorosilicate glass, an aluoxide (NbO<sub>x</sub>), a titanium oxide (TiO<sub>x</sub>), a zirconium oxide  $(ZrO_x)$ , a tantalum oxide  $(TaO_x)$ , and a magnesium oxide (MgO<sub>x</sub>)), at least one dielectric nitride material (e.g., a silicon nitride (SiN<sub>v</sub>)), at least one dielectric oxynitride material (e.g., a silicon oxynitride (SiO<sub>x</sub>N<sub>v</sub>)), at least one 40 dielectric oxycarbide material (e.g., silicon oxycarbide (Si- $O_xC_v$ ), at least one hydrogenated dielectric oxycarbide material (e.g., hydrogenated silicon oxycarbide  $(SiC_xO_vH_z)$ ), and at least one dielectric carboxynitride material (e.g., a silicon carboxynitride (SiO<sub>x</sub>C<sub>z</sub>N<sub>v</sub>)). Formulae 45 including one or more of "x," "y," and "z" herein (e.g., SiO<sub>x</sub>,  $AlO_x$ ,  $HfO_x$ ,  $NbO_x$ ,  $TiO_x$ ,  $SiN_v$ ,  $SiO_xN_v$ ,  $SiO_xC_v$ ,  $SiC_xO_vH_z$ ,  $SiO_xC_zN_v$ ) represent a material that contains an average ratio of "x" atoms of one element, "y" atoms of another element, and "z" atoms of an additional element (if any) for every one 50 atom of another element (e.g., Si, Al, Hf, Nb, Ti). As the formulae are representative of relative atomic ratios and not strict chemical structure, an insulative material may comprise one or more stoichiometric compounds and/or one or more non-stoichiometric compounds, and values of "x," "y," 55 and "z" (if any) may be integers or may be non-integers. As used herein, the term "non-stoichiometric compound" means and includes a chemical compound with an elemental composition that cannot be represented by a ratio of welldefined natural numbers and is in violation of the law of 60 definite proportions. In addition, an "insulative structure" means and includes a structure formed of and including insulative material.

Unless the context indicates otherwise, the materials described herein may be formed by any suitable technique 65 including, but not limited to, spin coating, blanket coating, chemical vapor deposition ("CVD"), atomic layer deposi-

6

tion ("ALD"), plasma enhanced ALD, physical vapor deposition ("PVD") (e.g., sputtering), or epitaxial growth. Depending on the specific material to be formed, the technique for depositing or growing the material may be selected by a person of ordinary skill in the art. In addition, unless the context indicates otherwise, removal of materials described herein may be accomplished by any suitable technique including, but not limited to, etching (e.g., dry etching, wet etching, vapor etching), ion milling, abrasive planarization, or other known methods.

FIG. 1 is a simplified, partial cross-sectional view of a microelectronic device 100 (e.g., a memory device, such as a 3D NAND Flash memory device), in accordance with embodiments of the disclosure. With the description provided below, it will be readily apparent to one of ordinary skill in the art that microelectronic devices described herein may be included in various relatively larger devices and various electronic systems.

Referring to FIG. 1, the microelectronic device 100 may include a control logic region 102, a memory array region 104, a first interconnect region 106, and a second interconnect region 108. As shown in FIG. 1, the first interconnect region 106 may vertically overlie (e.g., in the Z-direction) and be in electrical communication with the control logic region 102, and the memory array region 104 may vertically overlie and be in electrical communication with the first interconnect region 106. The first interconnect region 106 may be vertically interposed between and in electrical communication with the control logic region 102 and the memory array region 104. In addition, the second interconnect region 108 may vertically overlie and be in electrical communication with the memory array region 104. The memory array region 104 may be vertically interposed minum oxide (AlO<sub>x</sub>), a hafnium oxide (HfO<sub>x</sub>), a niobium 35 between and in electrical communication with the first interconnect region 106 and the second interconnect region **108**.

The control logic region 102 of the microelectronic device 100 may include a semiconductive base structure 110, gate structures 112, first routing structures 114, and first contact structures 116. Portions of the semiconductive base structure 110, the gate structures 112, the first routing structures 114, and the first contact structures 116 form various control logic devices 115 of the control logic region 102, as described in further detail below.

The semiconductive base structure **110** (e.g., semiconductive wafer) of the control logic region 102 comprises a base material or construction upon which additional features (e.g., materials, structures, devices) of the microelectronic device 100 are formed. The semiconductive base structure 110 may comprise a semiconductive structure (e.g., a semiconductive wafer), or a base semiconductive material on a supporting structure. For example, the semiconductive base structure 110 may comprise a conventional silicon substrate (e.g., a conventional silicon wafer), or another bulk substrate comprising a semiconductive material. In some embodiments, the semiconductive base structure 110 comprises a silicon wafer. In addition, the semiconductive base structure 110 may include one or more layers, structures, and/or regions formed therein and/or thereon. For example, the semiconductive base structure 110 may include conductively doped regions and undoped regions. The conductively doped regions may, for example, be employed as source regions and drain regions for transistors of the control logic devices 115 of the control logic region 102; and the undoped regions may, for example, be employed as channel regions for the transistors of the control logic devices 115.

As shown in FIG. 1, the gate structures 112 of the control logic region 102 of the microelectronic device 100 may vertically overlie (e.g., in the Z-direction) portions of the semiconductive base structure 110. The gate structures 112 may individually horizontally extend between and be 5 employed by transistors of the control logic devices 115 within the control logic region 102 of the microelectronic device 100. The gate structures 112 may be formed of and include conductive material. A gate dielectric material (e.g., a dielectric oxide) may vertically intervene (e.g., in the 10 Z-direction) between the gate structures 112 and channel regions (e.g., within the semiconductive base structure 110) of the transistors.

The first routing structures 114 may vertically overlie (e.g., in the Z-direction) the semiconductive base structure 15 110, and may be electrically connected to the semiconductive base structure 110 by way of the first contact structures 116. The first routing structures 114 may serve as local routing structures for the microelectronic device 100. A first group 116A of the first contact structures 116 may vertically 20 extend between and couple regions (e.g., conductively doped regions, such as source regions and drain regions) of the semiconductive base structure 110 to one or more of the first routing structures 114. In addition, a second group 116B of the first contact structures 116 may vertically extend 25 between and couple some of the first routing structures 114 to one another.

The control logic region 102 may include multiple tiers 113 (e.g., levels) of the first routing structures 114. By way of non-limiting example, as shown in FIG. 1, the control 30 logic region 102 may include three (3) tiers 113 of the first routing structures 114. Within each individual tier 113, the first routing structures 114 included therein may horizontally extend in paths having desired geometric configurations (e.g., shapes, sizes). As shown in FIG. 1, a first tier 113A 35 may include a first portion 114A of the first routing structures 114; a second tier 113B vertically overlying the first tier 113A may include a second portion 114B of the first routing structures 114; and a third tier 113C vertically overlying the second tier 113B may include a third portion 40 114C of the first routing structures 114. In additional embodiments, the control logic region 102 may include a different quantity of the tiers 113 of the first routing structures 114, such as greater than three (3) tiers 113 of the first routing structures 114, or less than three (3) tiers 113 of the 45 first routing structures 114.

The first routing structures 114 may each individually be formed of and include conductive material. By way of non-limiting example, the first routing structures 114 may be formed of and include one or more of at least one metal, at 50 least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide). In some embodiments, the first routing structures 114 are formed of and include Cu. In additional embodiments, 55 the first routing structures 114 are formed of and include W.

The first contact structures 116 (including the first group 116A and the second group 116B thereof) may each individually be formed of and include conductive material. By way of non-limiting example, the first routing structures 114 60 may be formed of and include one or more of at least one metal, at least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide). In some embodiments, the first 65 contact structures 116 are formed of and include Cu. In additional embodiments, the first contact structures 116 are

8

formed of and include W. In further embodiments, the first contact structures 116 of the first group 116A of the first contact structures 116 are formed of and include first conductive material (e.g., W); and the first contact structures 116 of the second group 116B of the first contact structures 116 are formed of and include a second, different conductive material (e.g., Cu).

As previously mentioned, portions of the semiconductive base structure 110 (e.g., conductively doped regions serving as source regions and drain regions, undoped regions serving as channel regions), the gate structures 112, the first routing structures 114, and the first contact structures 116 form various control logic devices 115 of the control logic region 102. In some embodiments, the control logic devices 115 comprise complementary metal oxide semiconductor (CMOS) circuitry. The control logic devices 115 may be configured to control various operations of other components (e.g., memory cells within the memory array region 104) of the microelectronic device 100. As a non-limiting example, the control logic devices 115 may include one or more (e.g., each) of charge pumps (e.g., V<sub>CCP</sub> charge pumps,  $V_{NEGWL}$  charge pumps, DVC2 charge pumps), delay-locked loop (DLL) circuitry (e.g., ring oscillators),  $V_{dd}$  regulators, string drivers, page buffers, and various chip/deck control circuitry. As another non-limiting example, the control logic devices 115 may include devices configured to control column operations for arrays (e.g., memory element array (s), access device array(s)) within the memory array region 104 of the microelectronic device 100, such as one or more (e.g., each) of decoders (e.g., local deck decoders, column decoders), sense amplifiers (e.g., equalization (EQ) amplifiers, isolation (ISO) amplifiers, NMOS sense amplifiers (NSAs), PMOS sense amplifiers (PSAs)), repair circuitry (e.g., column repair circuitry), I/O devices (e.g., local I/O devices), memory test devices, array multiplexers (MUX), and error checking and correction (ECC) devices. As a further non-limiting example, the control logic devices 115 may include devices configured to control row operations for arrays (e.g., memory element array(s), access device array(s)) within the memory array region 104 of the microelectronic device 100, such as one or more (e.g., each) of decoders (e.g., local deck decoders, row decoders), drivers (e.g., word line (WL) drivers), repair circuitry (e.g., row repair circuitry), memory test devices, MUX, ECC devices, and self-refresh/wear leveling devices.

Still referring to FIG. 1, the memory array region 104 of the microelectronic device 100 may include a stack structure 118, digit line structures 134 (e.g., bit line structures, data line structures), and a source tier 137 including one or more source structure(s) 138 and one or more contact pad(s) 140. The stack structure 118 may be vertically interposed between the digit line structures 134 and the source tier 137. The digit line structures 134 may vertically underlie (e.g., in the Z-direction) the stack structure 118, and may be coupled (e.g., electrically connected) to features (e.g., pillar structures, filled vias) within the stack structure 118, and additional features (e.g., contact structures) within the first interconnect region 106 of the microelectronic device 100. The source tier 137 may vertically overlie (e.g., in the Z-direction) the stack structure 118. The source structure(s) 138 and the contact pad(s) 140 of the source tier 137 may be coupled (e.g., electrically connected) to features (e.g., pillar structures, filled vias) within the stack structure 118 and additional features (e.g., additional contact structures) within the second interconnect region 108 of the microelectronic device 100.

The stack structure 118 of the memory array region 104 includes a vertically alternating (e.g., in the Z-direction) sequence of conductive structures 120 and insulative structures 122 arranged in tiers 124. Each of the tiers 124 of the stack structure 118 may include at least one of the conductive structures 120 vertically neighboring at least one of the insulative structures 122. In some embodiments, the conductive structures 120 are formed of and include tungsten (W) and the insulative structures 122 are formed of and include silicon dioxide (SiO<sub>2</sub>). The conductive structures **120** and insulative structures **122** of the tiers **124** of the stack structure 118 may each individually be substantially planar, and may each individually exhibit a desired thickness.

126 may vertically extend through the stack structure 118. The deep contact structure(s) 126 may be configured and positioned to electrically connect one or more components of the microelectronic device 100 vertically overlying the stack structure 118 with one or more other components of 20 the microelectronic device 100 vertically underlying the stack structure 118. The deep contact structure(s) 126 may be formed of and include conductive material. In some embodiments, the deep contact structure(s) are formed of and include W.

As shown in FIG. 1, the memory array region 104 further includes cell pillar structures 128 vertically extending through the stack structure 118. The cell pillar structures 128 may each individually include a semiconductive pillar (e.g., a polycrystalline silicon pillar, a silicon-germanium pillar) at 30 least partially surrounded by one or more charge storage structures (e.g., a charge trapping structure, such as a charge trapping structure comprising an oxide-nitride-oxide ("ONO") material; floating gate structures). Intersections of the cell pillar structures 128 and the conductive structures 35 120 of the tiers 124 of the stack structure 118 may define vertically extending strings of memory cells 130 coupled in series with one another within the memory array region 104 of the microelectronic device 100. In some embodiments, the memory cells 130 formed at the intersections of the 40 conductive structures 120 and the cell pillar structures 128 within the tiers 124 of the stack structure 118 comprise so-called "MONOS" (metal-oxide-nitride-oxide-semiconductor) memory cells. In additional embodiments, the memory cells 130 comprise so-called "TANOS" (tantalum 45) nitride-aluminum oxide-nitride-oxide-semiconductor) memory cells, or so-called "BETANOS" (band/barrier engineered TANOS) memory cells, each of which are subsets of MONOS memory cells. In further embodiments, the memory cells comprise so-called "floating gate" memory 50 cells including floating gates (e.g., metallic floating gates) as charge storage structures. The floating gates may horizontally intervene between central structures of the cell pillar structures 128 and the conductive structures 120 of the different tiers 124 of the stack structure 118.

With continued reference to FIG. 1, the digit line structures 134 may be vertically interposed between the stack structure 118 and the first interconnect region 106 underlying the stack structure 118. Individual digit line structures 134 may be coupled to individual vertically extending 60 strings of memory cells 130. In some embodiments, the digit line structures 134 directly physically contact the cell pillar structures 128. In additional embodiments, conductive contact structures may vertically intervene between the digit line structures **134** and the cell pillar structures **128**, and may 65 couple the digit line structures **134** to the vertically extending strings of memory cells 130.

**10**

The digit line structures 134 may each individually be formed of and include conductive material. By way of non-limiting example, the digit line structures 134 may each individually be formed of and include a metallic material comprising one or more of at least one metal, at least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide). In some embodiments, the digit line structures 134 are each 10 individually formed of and include W.

As shown in FIG. 1, digit line cap structures 136 may directly vertically underlie the digit line structures **134**. The digit line cap structures 136 may cover lower surfaces of the digit line structures 134. The digit line cap structures 136 As shown in FIG. 1, one or more deep contact structure(s) 15 may be formed of and include insulative material. By way of non-limiting example, the digit line cap structures 136 may each individually be formed of and include a dielectric nitride material, such as SiN<sub>v</sub> (e.g., Si<sub>3</sub>N<sub>4</sub>). As described in further detail below, conductive contact structures (e.g., digit line contact structures) may vertically extend through the digit line cap structures 136 and to the digit line structures 134 to couple the digit line structures 134 to additional features thereunder.

> With continued reference to FIG. 1, the source tier 137 25 may be vertically interposed between the stack structure **118** and the second interconnect region 108 overlying the stack structure 118. Within the source tier 137, the source structure (s) 138 and the contact pad(s) 140 may horizontally neighbor one another (e.g., in the X-direction, in the Y-direction). The source structure(s) 138 may be electrically isolated from the contact pad(s) 140, and may be positioned at substantially the same vertical position (e.g., in the Z-direction) as the contact pad(s) 140. At least one insulative material may be horizontally interposed between the source structure(s) 138 and the contact pad(s) 140, as described in further detail below.

The source structure(s) 138 of the source tier 137 may be coupled to the vertically extending strings of memory cells 130. In some embodiments, the source structure(s) 138 directly physically contact the cell pillar structures 128. In additional embodiments, conductive contact structures may vertically intervene between the source structure(s) 138 and the cell pillar structures 128, and may couple the source structure(s) 138 to the vertically extending strings of memory cells 130. In addition, the source structure(s) 138 may be coupled to additional structures (e.g., contact structures, routing structures, pad structures) within the second interconnect region 108, as described in further detail below.

The contact pad(s) 140 of the source tier 137 may be coupled to the additional conductive features (e.g., conductive contact structures, conductive pillars, conductively filled vias) within the stack structure 118. For example, as shown in FIG. 1, the contact pad(s) 140 may be coupled to the deep contact structure(s) 126 vertically extending 55 through the stack structure **118**. In some embodiments, the contact pad(s) 140 directly physically contact the deep contact structure(s) 126. In additional embodiments, additional contact structures may vertically intervene between the contact pad(s) 140 and the deep contact structure(s) 126, and may couple the contact pad(s) 140 to the deep contact structure(s) 126. In addition, the contact pad(s) 140 may be coupled to additional structures (e.g., contact structures, routing structures, pad structures) within the second interconnect region 108, as described in further detail below.

The source structure(s) 138 and the contact pad(s) 140 may each be formed of and include conductive material. A material composition of the source structure(s) 138 may be

substantially the same as a material composition of the contact pad(s) 140. In some embodiments, the source structure(s) 138 and the contact pad(s) 140 are formed of and include conductively doped semiconductive material, such as a conductively doped form of one or more of a silicon 5 material, such as monocrystalline silicon or polycrystalline silicon; a silicon-germanium material; a germanium material; a gallium arsenide material; a gallium nitride material; and an indium phosphide material. As a non-limiting example, the source structure(s) 138 and the contact pad(s) 140 may be formed of and include epitaxial silicon (e.g., monocrystalline silicon formed through epitaxial growth) doped with at least one dopant (e.g., one or more of at least another dopant). As another non-limiting example, the source structure(s) 138 and the contact pad(s) 140 may be formed of and include polycrystalline silicon doped with at least one dopant (e.g., one or more of at least one n-type dopant, at least one p-type dopant, and at least another 20 dopant).

As shown in FIG. 1, optionally, strapping structures 141 may be located on or over the source structure(s) 138 and the contact pad(s) 140. The strapping structures 141 may be vertically interposed between the source structure(s) 138 and 25 the contact pad(s) 140 and additional features (e.g., additional structures, additional materials) within the second interconnect region 108. If present, the strapping structures **141** may be formed of and include conductive material. A material composition of the strapping structures **141** may be 30 selected to lower contact resistance (relative to configurations wherein the strapping structures 141 are absent) between conductive structures within the second interconnect region 108 and each of source structure(s) 138 and the non-limiting example, the strapping structures 141 (if any) may be formed of and include a metallic material comprising one or more of at least one metal, at least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a 40 conductive metal carbide, a conductive metal oxide). In some embodiments, the strapping structures **141** are formed of and include tungsten silicide (WSi<sub>x</sub>). In additional embodiments, the strapping structures **141** are formed of and include one or more of (e.g., a stack of) W and tungsten 45 nitride (WN<sub>r</sub>).

With continued reference to FIG. 1, the first interconnect region 106 of the microelectronic device 100 may be vertically interposed between the control logic region 102 and the memory array region **104** of the microelectronic device 50 100. The first interconnect region 106 may couple features of the control logic region 102 with features of the memory array region 104. As shown in FIG. 1, the first interconnect region 106 may include second contact structures 142 coupled to the first routing structures **114** of the control logic 55 region 102, third contact structures 144 (e.g., digit line contact structures) coupled to the digit line structures 134 of the memory array region 104, and connected bond pads 146 extending between and coupling the second contact structures **142** and the third contact structures **144**. The connected 60 bond pads 146 may include first bond pads 148 on (e.g., vertically overlying and directly adjacent) the second contact structures 142, and second bond pads 150 on (e.g., vertically underlying and directly adjacent) the third contact structures **144**. The first bond pads **148** and the second bond 65 pads 150 may be physically connected to one another to form the connected bond pads 146.

The second contact structures **142** of the first interconnect region 106 may vertically extend from and between the first bond pads 148 and some of the first routing structures 114 of the control logic region 102. In some embodiments, the second contact structures 142 comprise conductively filled vias vertically extending through dielectric material interposed between the first bond pads 148 and the first routing structures 114. The second contact structures 142 may be formed of and include conductive material. By way of 10 non-limiting example, the second contact structures 142 may be formed of and include one or more of at least one metal, at least one alloy, and at least one conductive metalcontaining material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a one n-type dopant, at least one p-type dopant, and at least 15 conductive metal oxide). In some embodiments, each of the second contact structures **142** is formed of and includes Cu.

The third contact structures **144** of the first interconnect region 106 may vertically extend from and between the second bond pads 150 and the digit line structures 134 of the memory array region 104. In some embodiments, the third contact structures 144 comprise additional conductively filled vias vertically extending from the digit line structures **134**, through the digit line cap structures **136** and additional insulative material (described in further detail below), and to the second bond pads 150. The third contact structures 144 may be located at desired positions along lengths (e.g., in the Y-direction) of the digit line structures 134. The third contact structures 144 may be formed of and include conductive material. By way of non-limiting example, the third contact structures 144 may be formed of and include one or more of at least one metal, at least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide). In some embodiments, contact pad(s) 140 of the source tier 137. By way of 35 the third contact structures 144 are formed of and include

> The connected bond pads 146 of the first interconnect region 106 may vertically extend from and between the second contact structures 142 and the third contact structures **144**. The first bond pads **148** of the connected bond pads **146** may vertically extend from and between the second contact structures 142 and the second bond pads 150 of the connected bond pads 146; and the second bond pads 150 of the connected bond pads 146 may vertically extend from and between the third contact structures 144 and the first bond pads 148 of the connected bond pads 146. While in FIG. 1, the first bond pad 148 and the second bond pad 150 of each connected bond pad 146 are distinguished from one another by way of a dashed line, the first bond pad 148 and the second bond pad 150 may be integral and continuous with one another. Put another way, each connected bond pad 146 may be a substantially monolithic structure including the first bond pad 148 as a first region thereof, and the second bond pad 150 as a second region thereof. For each connected bond pad 146, the first bond pad 148 thereof may be attached to the second bond pad 150 thereof without a bond line.

> The connected bond pads 146 (including the first bond pads 148 and the second bond pads 150 thereof) may be formed of and include conductive material. By way of non-limiting example, the connected bond pads 146 may be formed of and include one or more of at least one metal, at least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide). In some embodiments, each of the connected bond pads 146 (including the first bond pad 148 and the second bond pad 150 thereof) is formed of and includes Cu.

Still referring to FIG. 1, at least one insulative material 132 may cover and surround the second contact structures **142**, the third contact structures **144**, and the connected bond pads 146. The at least one insulative material 132 may also cover and surround portions of one or more of the digit line 5 structures 134, the digit line cap structures 136, the first routing structures 114, and the first contact structures 116. In some embodiments, the insulative material **132** is formed of and includes at least one dielectric oxide material, such as  $SiO_x$  (e.g.,  $SiO_2$ ). In additional embodiments, the insulative 10 material 132 is formed of and includes at least one low-k dielectric material, such as one or more of  $SiO_xC_v$ ,  $SiO_xN_v$ ,  $SiC_xO_vH_z$ , and  $SiO_xC_zN_v$ . The insulative material **132** may be substantially homogeneous, or the insulative material 132 may be heterogeneous. As used herein, the term "homoge- 15 neous" means relative amounts of elements included in a feature (e.g., a material, a structure) do not vary throughout different portions (e.g., different horizontal portions, different vertical portions) of the feature. Conversely, as used herein, the term "heterogeneous" means relative amounts of 20 elements included in a feature (e.g., a material, a structure) vary throughout different portions of the feature. If the insulative material **132** is heterogeneous, amounts of one or more elements included in the insulative material 132 may vary stepwise (e.g., change abruptly), or may vary continu- 25 ously (e.g., change progressively, such as linearly, parabolically) throughout different portions of the insulative material **132**. In some embodiments, the insulative material **132** is substantially homogeneous. In additional embodiments, the insulative material 132 is heterogeneous. The insulative 30 material 132 may, for example, be formed of and include a stack of at least two different dielectric materials.

With continued reference to FIG. 1, the second interconnect region 108 of the microelectronic device 100 may vertically overlie the memory array region 104 of the 35 from about 100 nanometers (nm) to about 5 micrometers microelectronic device 100. The second interconnect region 108 may include second routing structures 152 and conductive pads 156. The second routing structures 152 may vertically overlie the source tier 137 (including the source structure(s) 138 and the contact pad(s) 140 thereof) of the 40 memory array region 104, and may be coupled to the source structure(s) 138 and the contact pad(s) 140 by way of fourth contact structures 154. The fourth contact structures 154 may extend between the second routing structures 152 and the source structure(s) 138 and the contact pad(s) 140 of the 45 source tier 137. If present, the strapping structures 141 may vertically intervene between the fourth contact structures 154 and the source structure(s) 138 and the contact pad(s) **140**. The conductive pads **156** may vertically overlie the second routing structures 152, and may be coupled to the 50 second routing structures 152 by way of fifth contact structures 158. The fifth contact structures 158 may extend from and between the second routing structures 152 and the conductive pads 156.

The second routing structures 152 and the conductive 55 pads 156 may serve as global routing structures for the microelectronic device 100. The second routing structures 152 and the conductive pads 156 may, for example, be configured to receive global signals from an external bus, and to relay the global signals to other components (e.g., 60 structures, devices) of the microelectronic device 100.

The second routing structures 152, the fourth contact structures 154, the conductive pads 156, and the fifth contact structures 158 may each be formed of and include conductive material. By way of non-limiting example, the second 65 routing structures 152, the fourth contact structures 154, the conductive pads 156, and the fifth contact structures 158

14

may each individually be formed of and include one or more of at least one metal, at least one alloy, and at least one conductive metal-containing material (e.g., a conductive metal nitride, a conductive metal silicide, a conductive metal carbide, a conductive metal oxide). In some embodiments, the second routing structures 152 and the fourth contact structures 154 are each formed of and include Cu, the conductive pads 156 are formed of and include Al, and the fifth contact structures 158 are formed of and include W. In additional embodiments, the second routing structures 152 are formed of and include Cu, the conductive pads 156 are formed of and include Al, and the fourth contact structures **154** and the fifth contact structures **158** are each formed of and include W.

The second routing structures 152, the fourth contact structures 154, the conductive pads 156, and the fifth contact structures 158 may each individually have a desired vertical thickness (e.g., dimension in the Z-direction). Thicknesses of the second routing structures 152 and the conductive pads 156 may be selected at least partially based on the material compositions of the second routing structures 152 and the conductive pads 156 and functions of the second routing structures 152 and the conductive pads 156 within the microelectronic device 100. By way of non-limiting example, if the second routing structures 152 comprise Cu, a relatively greater vertical thickness may facilitate relatively lower electrical resistance, and a relatively smaller vertical thickness may facilitate one or more relatively lower electrical capacitance and relatively greater density. At least in embodiments wherein the second routing structures 152 comprise Cu and are employed receive and relay global signals within the microelectronic device 100, the second routing structures 152 may be formed to have relatively greater thicknesses, such as thicknesses within a range of  $(\mu m)$ .

Still referring to FIG. 1, at least one additional insulative material 160 may cover and surround the second routing structures 152, the fourth contact structures 154, the conductive pads 156, and the fifth contact structures 158. The at least one additional insulative material 160 may also cover and surround portions of the source structure(s) 138 and the contact pad(s) 140. A material composition of the additional insulative material 160 may be substantially the same as or may be different than a material composition of the insulative material 132. In some embodiments, the additional insulative material 160 is formed of and includes at least one dielectric oxide material, such as SiO<sub>x</sub>(e.g., SiO<sub>2</sub>). In additional embodiments, the additional insulative material 160 is formed of and includes at least one low-k dielectric material, such as one or more of  $SiO_xC_v$ ,  $SiO_xN_v$ ,  $SiC_xO_vH_z$ , and  $SiO_xC_zN_v$ . The additional insulative material 160 may be substantially homogeneous, or the additional insulative material 160 may be heterogeneous. If the additional insulative material 160 is heterogeneous, amounts of one or more elements included in the additional insulative material 160 may vary stepwise (e.g., change abruptly), or may vary continuously (e.g., change progressively, such as linearly, parabolically) throughout different portions of the additional insulative material 160. In some embodiments, the additional insulative material 160 is substantially homogeneous. In additional embodiments, the additional insulative material 160 is heterogeneous. The additional insulative material 160, for example, be formed of and include a stack of at least two different dielectric materials.

Thus, a microelectronic device according to embodiments of the disclosure comprises a memory array region, a control

logic region underlying the memory array region, and an interconnect region vertically interposed between the memory array region and the control logic region. The memory array region comprises a stack structure comprising vertically alternating conductive structures and insulating 5 structures; vertically extending strings of memory cells within the stack structure; at least one source structure vertically overlying the stack structure and coupled to the vertically extending strings of memory cells; and digit line structures vertically underlying the stack structure and 10 coupled to the vertically extending strings of memory cells. The control logic region comprises control logic devices configured to effectuate a portion of control operations for the vertically extending strings of memory cells. The interconnect region comprises structures coupling the digit line 15 structures of the memory array region to the control logic devices of the control logic region.

Furthermore, a memory device according to embodiments of the disclosure comprises a memory array region, a first interconnect region vertically underlying the memory array 20 region, a control logic region vertically underlying the first interconnect region, and a second interconnect region vertically overlying the memory array region. The memory array region comprises a stack structure, strings of memory cells, one or more source structures, and data line structures. 25 The stack structure comprises a vertically alternating sequence of conductive structures and insulating structures. The strings of memory cells vertically extend through the stack structure. The one or more source structures vertically overlie the stack structure and are coupled to the strings of 30 memory cells. The data line structures vertically underlie the stack structure and are coupled to the strings of memory cells. The first interconnect region comprises conductive pad structures coupled to the data line structures. The control conductor (CMOS) circuitry including conductive routing structures coupled to the conductive pad structures. The second interconnect region comprises additional conductive routing structures coupled to the one or more source structures.

FIGS. 2A through 2D are simplified, partial cross-sectional views illustrating embodiments of a method of forming the microelectronic device 100 of FIG. 1. With the description provided below, it will be readily apparent to one of ordinary skill in the art that the methods and structures 45 described herein may be used in various devices and electronic systems.

Referring to FIG. 2A, a first microelectronic device structure **101** (e.g., a first die) may be attached (e.g., bonded) to a second microelectronic device structure 103 to form a 50 microelectronic device structure assembly 105. In FIG. 2A, the vertical boundaries of the first microelectronic device structure 101 relative to the second microelectronic device structure 103 prior to the attachment of the first microelectronic device structure 101 to the second microelectronic 55 device structure 103 to form the microelectronic device structure assembly **105** are depicted by the dashed line A-A. The first microelectronic device structure 101 may be attached to the second microelectronic device structure 103 without a bond line.

As shown in FIG. 2A, the first microelectronic device structure 101 may be formed to include the control logic region 102 of the microelectronic device 100 (FIG. 1), including the semiconductive base structure 110, the gate structures 112, the first routing structures 114, and the first 65 contact structures 116 thereof. The first microelectronic device structure 101 may also be formed to include the

**16**