### US012093187B1

## (12) United States Patent Shveidel et al.

## (10) Patent No.: US 12,093,187 B1

#### Sep. 17, 2024 (45) **Date of Patent:**

## READ I/O PROCESSING TECHNIQUES USING REMOTE MAPPING RESOLUTION

# WITH LOGICAL ADDRESS SPACE SLICING

## Applicant: **Dell Products L.P.**, Hopkinton, MA (US)

## Inventors: Vladimir Shveidel, Pardes-Hana (IL);

Uri Shabi, Tel Mond (IL); Dror **Zalstein**, Givatayim (IL)

#### **Dell Products L.P.**, Hopkinton, MA (73)

(US)

#### Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

## Appl. No.: 18/129,283

#### Mar. 31, 2023 (22)Filed:

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | G06F 12/00  | (2006.01) |

|      | G06F 3/06   | (2006.01) |

|      | G06F 12/06  | (2006.01) |

|      | G06F 12/109 | (2016.01) |

|      | G06F 13/16  | (2006.01) |

## U.S. Cl.

(2013.01); *G06F 3/0667* (2013.01); *G06F 3/0683* (2013.01); *G06F 12/06* (2013.01); **G06F** 13/1668 (2013.01); G06F 2212/657 (2013.01)

#### Field of Classification Search (58)

CPC .... G06F 3/0604; G06F 3/0677; G06F 3/0683; G06F 3/0617; G06F 12/10; G06F 2212/202; G06F 2212/65

See application file for complete search history.

#### **References Cited** (56)

### U.S. PATENT DOCUMENTS

| 11,409,454 B1*   | 8/2022  | Shveidel G06F 3/0635   |

|------------------|---------|------------------------|

| 2021/0011776 A1* | 1/2021  | Thirumalai G06F 3/067  |

| 2021/0149816 A1* | 5/2021  | Bak G06F 12/1441       |

| 2022/0342552 A1* | 10/2022 | Oohira G06F 3/065      |

| 2023/0083104 A1* | 3/2023  | Xiang G06F 3/0659      |

|                  |         | 707/692                |

| 2023/0333766 A1* | 10/2023 | Xiang G06F 3/0619      |

|                  |         | Vankamamidi G06F 3/064 |

## OTHER PUBLICATIONS

U.S. Appl. No. 18/160,404, filed Jan. 27, 2023, entitled System and Method for Managing Data Portion Ownership in a Storage Cluster, to Vladimir Shveidel, et al.

U.S. Appl. No. 18/134,881, filed Apr. 14, 2023, entitled Exclusive Ownership of Logical Address Slices and Associated Metadata, to Vasudevan Subramanian, et al.

## \* cited by examiner

Primary Examiner — John A Lane (74) Attorney, Agent, or Firm — Muirhead and Saturnelli, LLC

#### **ABSTRACT** (57)

Logical address space portions and virtual layer blocks (VLBs) can be partitioned into multiple sets. Each of multiple nodes in a system can be assigned exclusive ownership of one of the multiple sets. In at least one embodiment, for a read I/O which is received at a first node and directed to a logical address LA1 that is owned by a second node, the first node can request that the second owning node perform resolution processing for LA1. The second node can return either a VLB address or a PLB address based on whether the second node owns a VLB used in mapping LA1 to a corresponding physical location PA1 which includes content C1 stored at LA1. The second node can set a flag in its response to indicate whether a returned address is a VLB address or a PLB address.

## 20 Claims, 15 Drawing Sheets

FIG. 2E

FIG. 3

FIG. 81

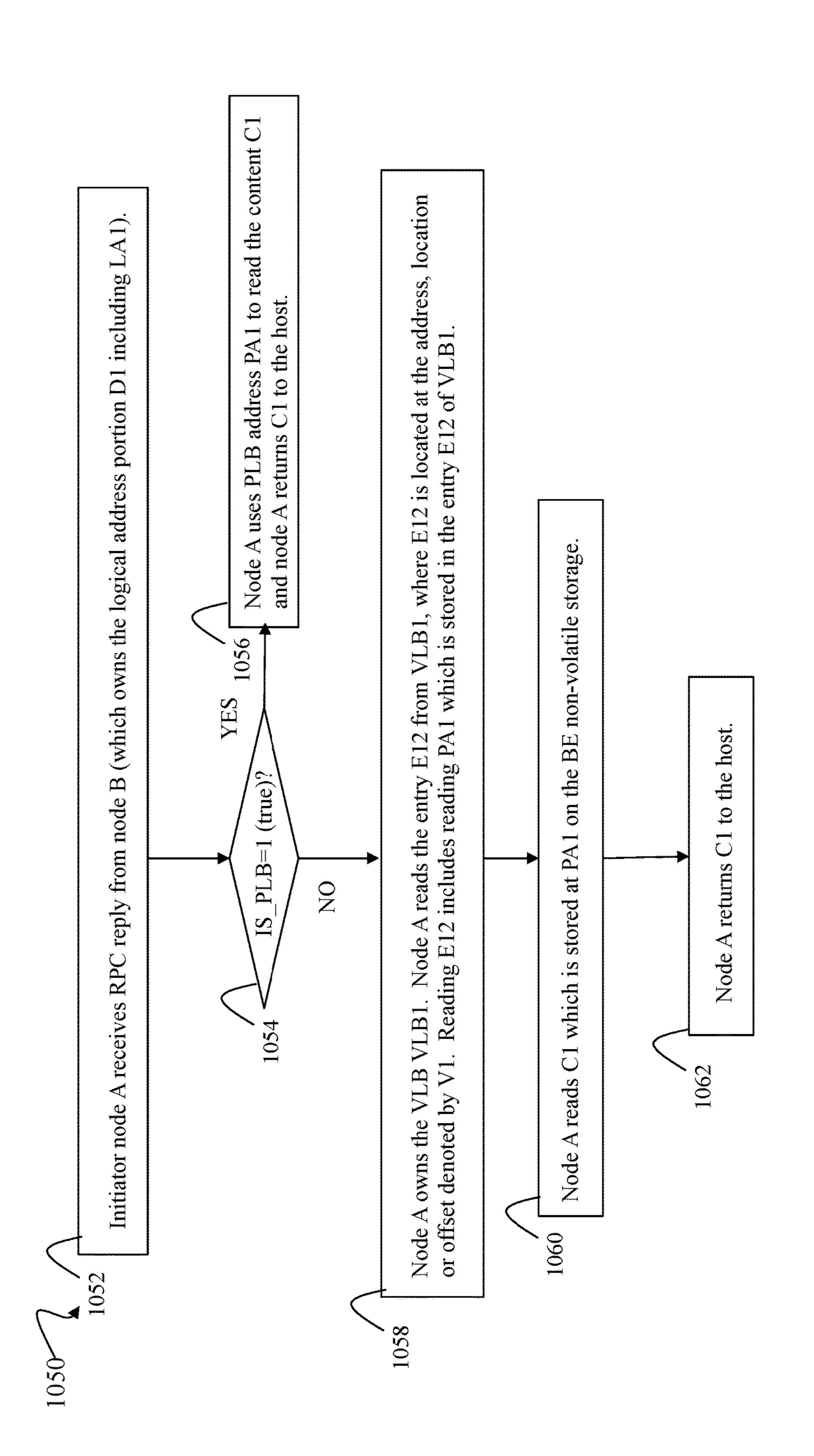

FIG. 104

FIG. 10E

## READ I/O PROCESSING TECHNIQUES USING REMOTE MAPPING RESOLUTION WITH LOGICAL ADDRESS SPACE SLICING

### BACKGROUND

Systems include different resources used by one or more host processors. The resources and the host processors in the system are interconnected by one or more communication connections, such as network connections. These resources 10 include data storage devices such as those included in data storage systems. The data storage systems are typically coupled to one or more host processors and provide storage services to each host processor. Multiple data storage systems from one or more different vendors can be connected 15 to provide common data storage for the one or more host processors.

A host performs a variety of data processing tasks and operations using the data storage system. For example, a host issues I/O operations, such as data read and write 20 operations, that are subsequently received at a data storage system. The host systems store and retrieve data by issuing the I/O operations to the data storage system containing a plurality of host interface units, disk drives (or more generally storage devices), and disk interface units. The host 25 systems access the storage devices through a plurality of channels provided therewith. The host systems provide data and access control information through the channels to a storage device of the data storage system. Data stored on the storage device is provided from the data storage system to 30 the host systems also through the channels. The host systems do not address the storage devices of the data storage system directly, but rather, access what appears to the host systems as a plurality of files, objects, logical units, logical devices or logical volumes. Thus, the I/O operations issued by the 35 host are directed to a particular storage entity, such as a file or logical device. The logical devices generally include physical storage provisioned from portions of one or more physical drives. Allowing multiple host systems to access the single data storage system allows the host systems to 40 share data stored therein.

## SUMMARY OF THE PRESENT DISCLOSURE

Various embodiments of the techniques herein can include 45 PA1 from E2 of the first VLB. a computer-implemented method, a system and a nontransitory computer readable medium. The system can include one or more processors, and a memory comprising code that, when executed, performs the method. The nontransitory computer readable medium can include code 50 stored thereon that, when executed, performs the method. The method can comprise: receiving, at a first node from a host, a read I/O operation requesting to read content C1 from a first logical address LA1, where the first node and a second node are included in a data storage system; determining that 55 LA1 is owned by the second node but not owned by the first node; sending, from the first node to the second node, a first request requesting that the second node perform first resolution processing for LA1; and responsive to receiving the first request at the second node, the second node performing 60 said first resolution processing for LA1, wherein said first resolution processing includes: mapping LA1 to a first entry E1 of a first metadata (MD) leaf object, wherein E1 includes a first virtual layer block (VLB) address which corresponds to a first VLB of a virtual block layer; determining whether 65 the second node owns the first VLB; responsive to determining the second node does not own the first VLB, sending

a first response from the second node to first node, where the first response includes the first VLB address and includes a first indicator with a first setting which indicates that the first response includes a VLB address type; and responsive to determining that second node does own the first VLB, performing first processing including: the second node using the first VLB address to obtain a first physical address or location PA1 on non-volatile storage, wherein C1 is stored at PA1; and sending the first response from the second node to the first node, wherein the first response includes PA1 and includes the first indicator with a second setting which indicates that the first response includes a physical layer block (PLB) address type.

In at least one embodiment, the VLB address type can be an indirect pointer or address used to indirectly access stored content. The PLB address type can be a physical address or location of stored content on non-volatile storage. Processing can include: receiving, at the first node from the second node, the first response; determining, by the first node, whether the first indicator of the first response has the first setting or the second setting; and responsive to determining that the first indicator has the first setting, the first node determining that the first response includes the VLB address type, and the first node performing second processing which includes using the first VLB address to read C1 from PA1.

In at least one embodiment, the first VLB address can identify a VLB entry E2 of the first VLB, wherein E2 includes PA1, and wherein the second processing can include: reading, by the first node, the first VLB from non-volatile storage; caching, by the first node, the first VLB in a local cache of the first node; reading, by the first node, PA1 from E2 of the first VLB; reading, by the first node, C1 which is stored at PA1 on non-volatile storage; and returning, by the first node, C1 to the host in a read I/O response. Responsive to determining that the first indicator has the second setting, the first node can determine that the first response includes the PLB address type, and third processing can be performed which includes: reading, by the first node, C1 from PA1; and returning, by the first node, C1 to the host in a read I/O response. The second node using the first VLB address to obtain PA1 can further comprise: reading, by the second node, the first VLB from non-volatile storage; caching, by the second node, the first VLB in a local cache of the second node; and reading, by the second node,

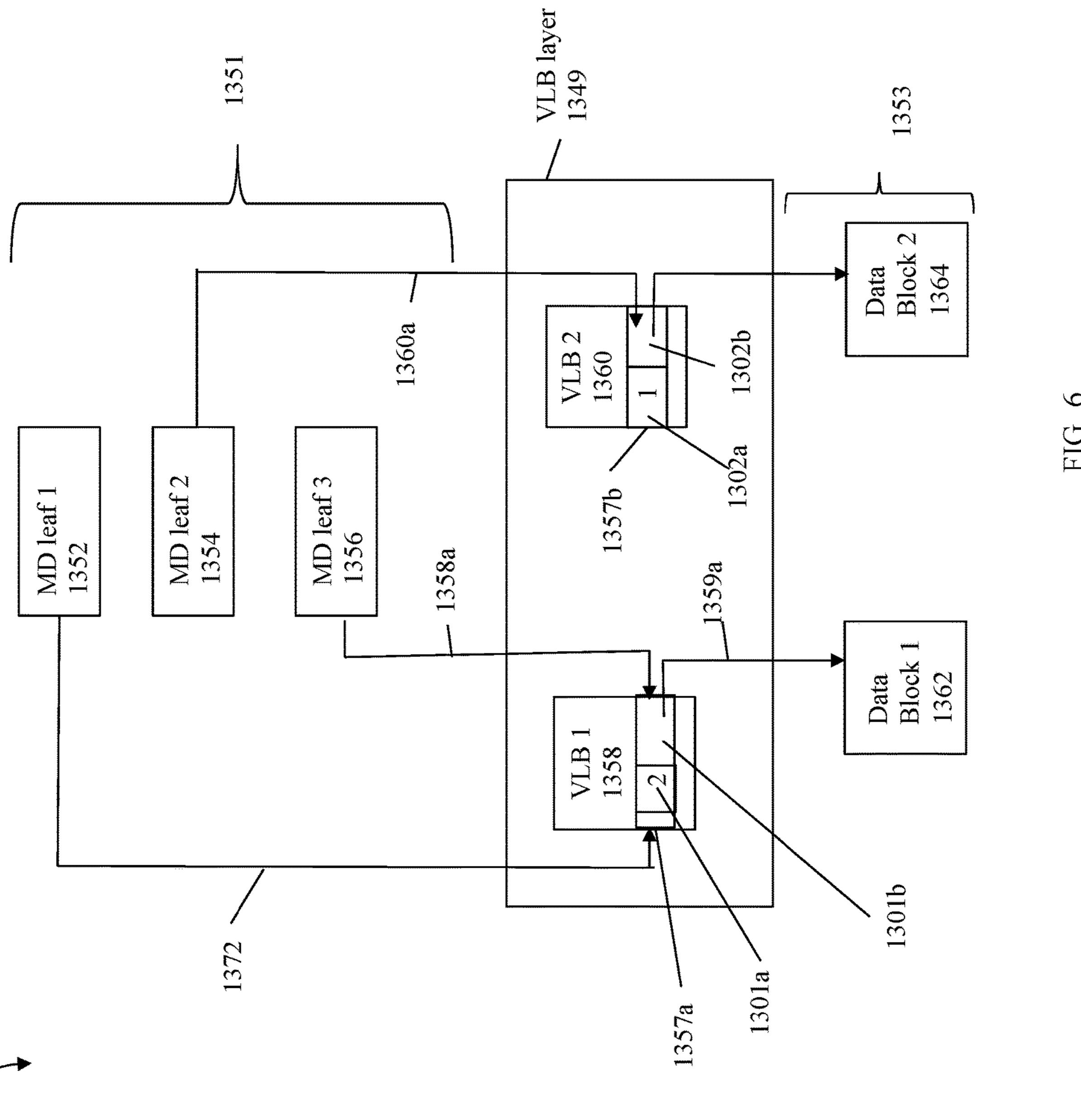

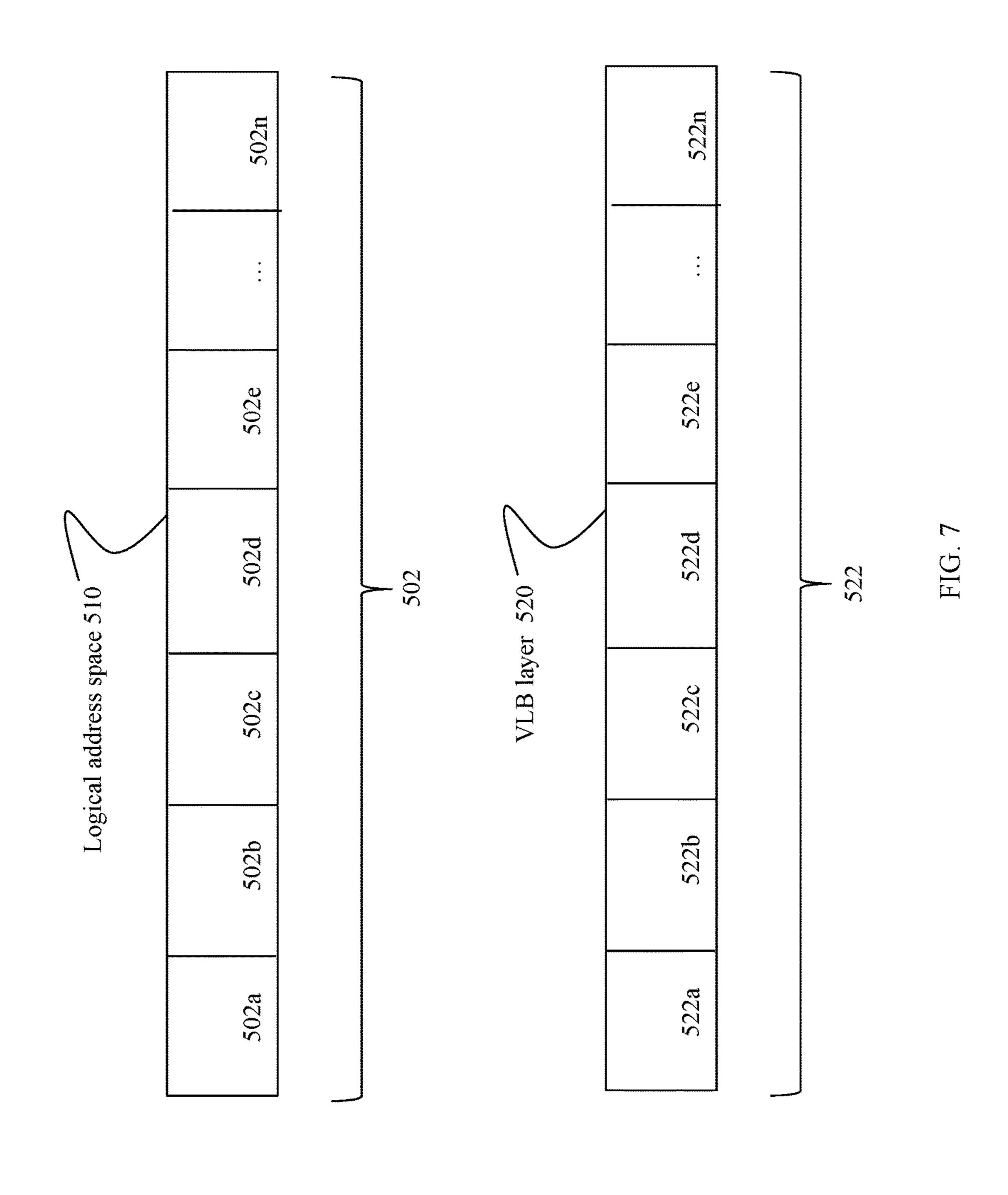

In at least one embodiment, processing can include: partitioning a plurality of virtual layer blocks (VLBs) of the virtual block layer into a plurality of sets including a first set and a second set, wherein the first node is assigned exclusive ownership of VLBs in the first set and wherein the second node is assigned exclusive ownership of VLBs in the second set. Processing can include: partitioning a logical address space into a plurality of logical address portions; dividing the plurality of logical address portions into a plurality of logical address sets including a first logical address set and a second logical address sets, wherein the first node is assigned exclusive ownership of logical address portions of the first logical address set, and wherein the second node is assigned exclusive ownership of logical address portions of the second logical address set.

Various embodiments of the techniques herein can include a computer-implemented method, a system and a nontransitory computer readable medium. The system can include one or more processors, and a memory comprising code that, when executed, performs the method. The nontransitory computer readable medium can include code stored thereon that, when executed, performs the method.

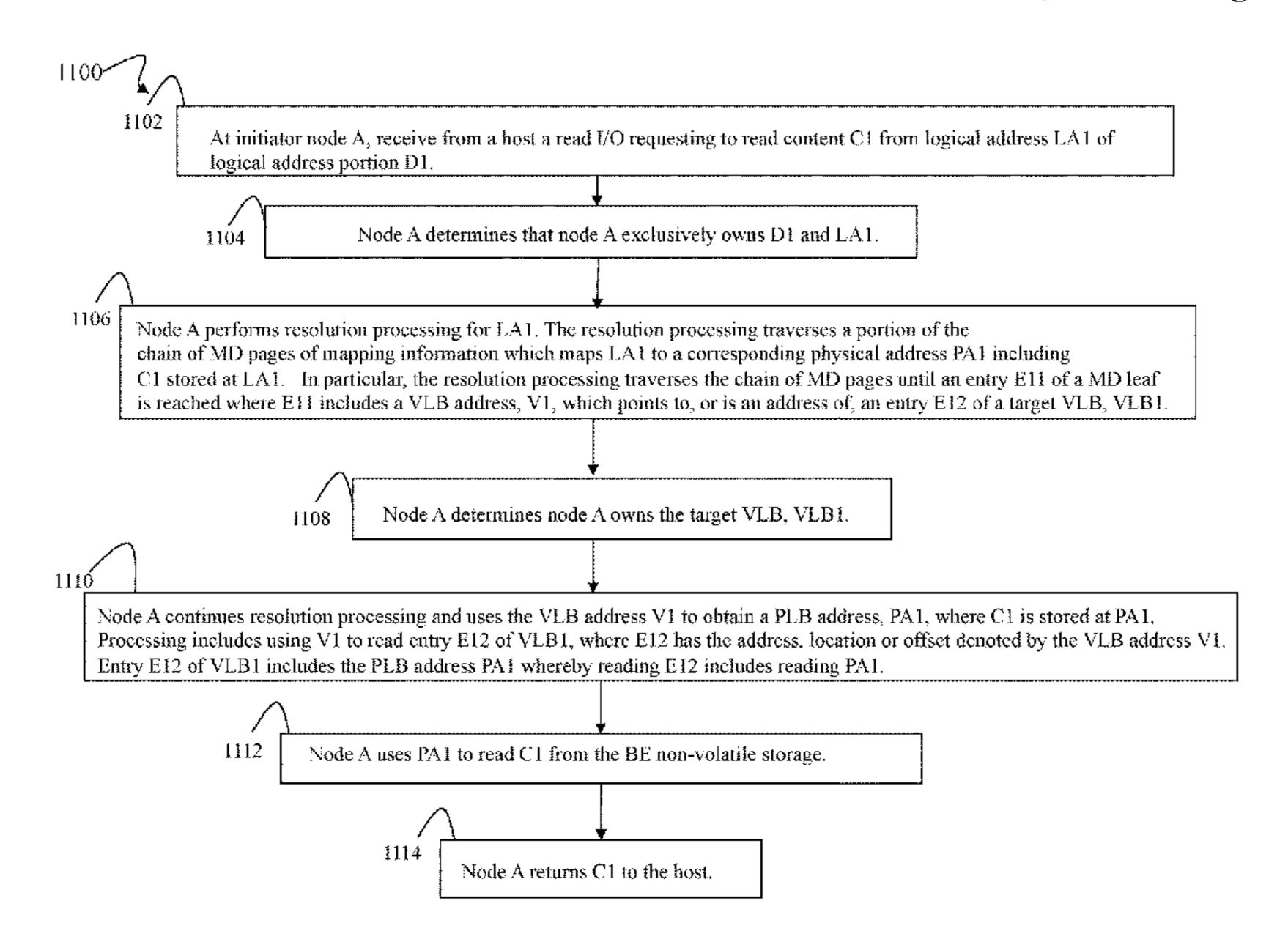

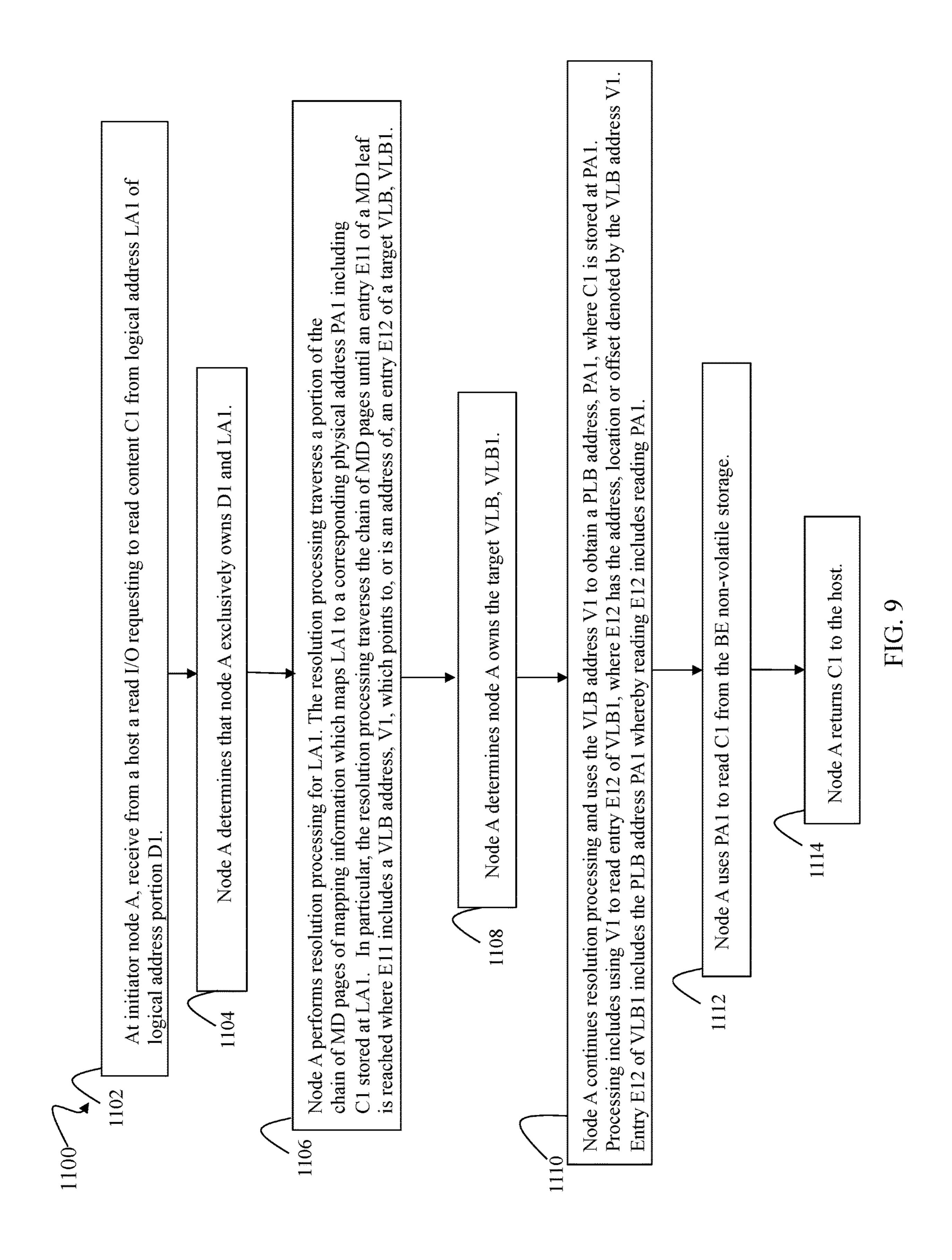

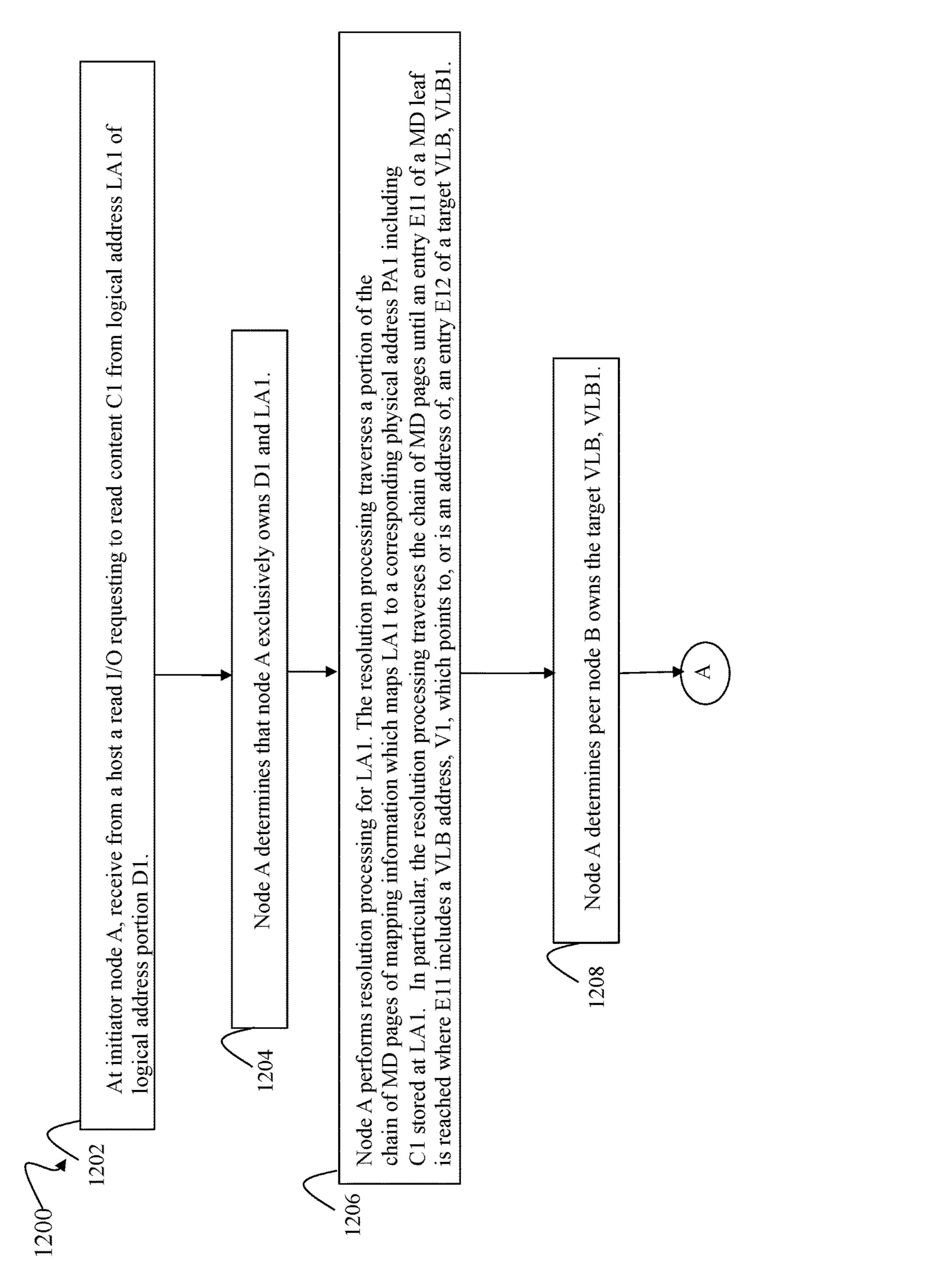

The method can comprise: receiving, at a first node from a host, a read I/O operation requesting to read content C1 from a first logical address LA1, where the first node and a second node are included in a data storage system; determining that LA1 is owned by the first node; the first node performing 5 first resolution processing for LA1, wherein the first resolution processing includes the first node mapping LA1 to a first entry E1 of a first metadata (MD) leaf object, wherein E1 includes a first virtual layer block (VLB) address which corresponds to a first VLB of a virtual block layer; deter- 10 mining, by the first node, whether the first node or the second node owns the first VLB; responsive to determining that the first node owns the first VLB, performing first processing including: the first node using the first VLB address to obtain a first physical address or location PA1 on 15 non-volatile storage, wherein C1 is stored at PA1; the first node reading C1 from PA1; and the first node returning C1 to the host in a read I/O response.

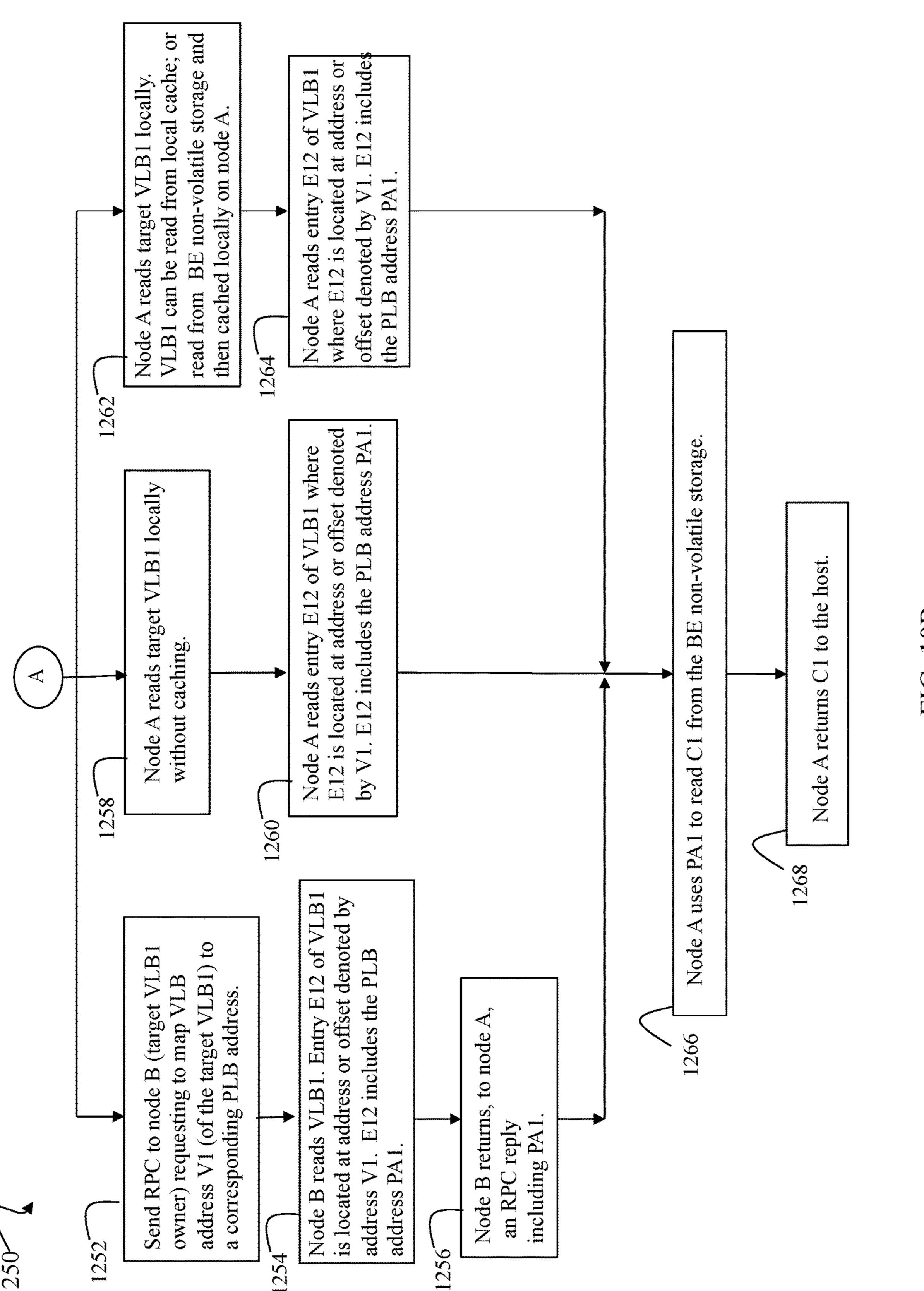

In at least one embodiment, the first VLB address can identify a second entry E2 of the first VLB, and wherein the 20 first node using the first VLB address to obtain a first physical address or location PA1 on non-volatile storage can further include: the first node reading the first VLB from non-volatile storage; the first node caching the first VLB in a local cache of the first node; and the first node reading PA1 25 from E2 of the first VLB. Processing can include: determining, by the first node, that the second node owns the first VLB; and responsive to determining that the second node owns the first VLB, performing second processing including: selecting one option from a plurality of processing 30 options; performing processing of the selected one option to obtain PA1 for the first node; the first node using PA1 to read C1 from non-volatile storage; and the first node returning C1 in a read I/O response to the host.

In at least one embodiment, the plurality of options can include a first option, and wherein processing of the first option can include: sending a request, from the first node to the second node, requesting that the second node map the first VLB address of the first VLB to a corresponding physical address, PA1; receiving, by the second node, the 40 request; reading, by the second node, the first VLB from non-volatile storage; storing the first VLB in a local cache of the second node; reading, by the second node, PA1 from E2 of the first VLB; and the second node returning a response to the first node, wherein the response includes PAL.

In at least one embodiment, the plurality of options can include a second option, wherein processing of the second option can include: the first node reading the first VLB from non-volatile storage and not caching the first VLB locally on the first node; and the first node reading PA1 from E2 of the 50 first VLB.

In at least one embodiment, the plurality of options can include a third option, wherein processing of the third option can include: the first node reading the first VLB from non-volatile storage; the first node caching the first VLB 55 locally on the first node; and the first node reading PA1 from E2 of the first VLB.

In at least one embodiment, selecting the one option from the plurality of options can include evaluating one or more criteria dynamically at runtime to select said one option 60 from the plurality of options. The one or more criteria can select the one option in accordance with one or more metrics including any of: latency introduced by issuing a request from the first node to the second node; a VLB page cache hit rate with respect a first local cache of the first node; a VLB 65 page cache hit rate with respect a second local cache of the second node; and a current utilization of backend non-

4

volatile storage including PA1 where C1 is stored. The one or more criteria can include a first criterion which indicates to select a first option of the plurality of options if the latency is less than a specified threshold, and wherein the first option can include issuing the request, from the first node to the second node, requesting that the second node map the first VLB address of the first VLB to a corresponding physical address, PAL. The one or more criteria can include a second criterion which indicates to select a second option of the plurality of options or a third option of the plurality of options if the latency is not less than the specified threshold and if the current utilization of backend non-volatile storage is less than a utilization threshold, wherein the second option and the third option can both include the first node locally reading the first VLB from backend non-volatile storage.

### BRIEF DESCRIPTION OF THE DRAWINGS

Features and advantages of the present disclosure will become more apparent from the following detailed description of exemplary embodiments thereof taken in conjunction with the accompanying drawings in which:

FIG. 1 is an example of components that may be included in a system in accordance with the techniques of the present disclosure.

FIG. 2A is an example illustrating the I/O path or data path in connection with processing data in at least one embodiment in accordance with the techniques of the present disclosure.

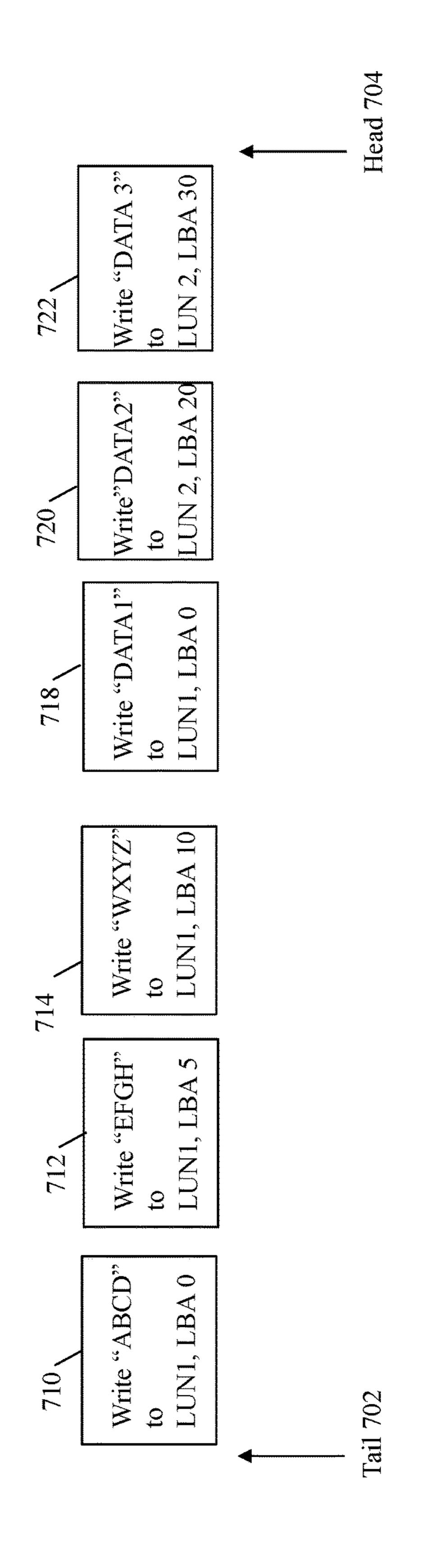

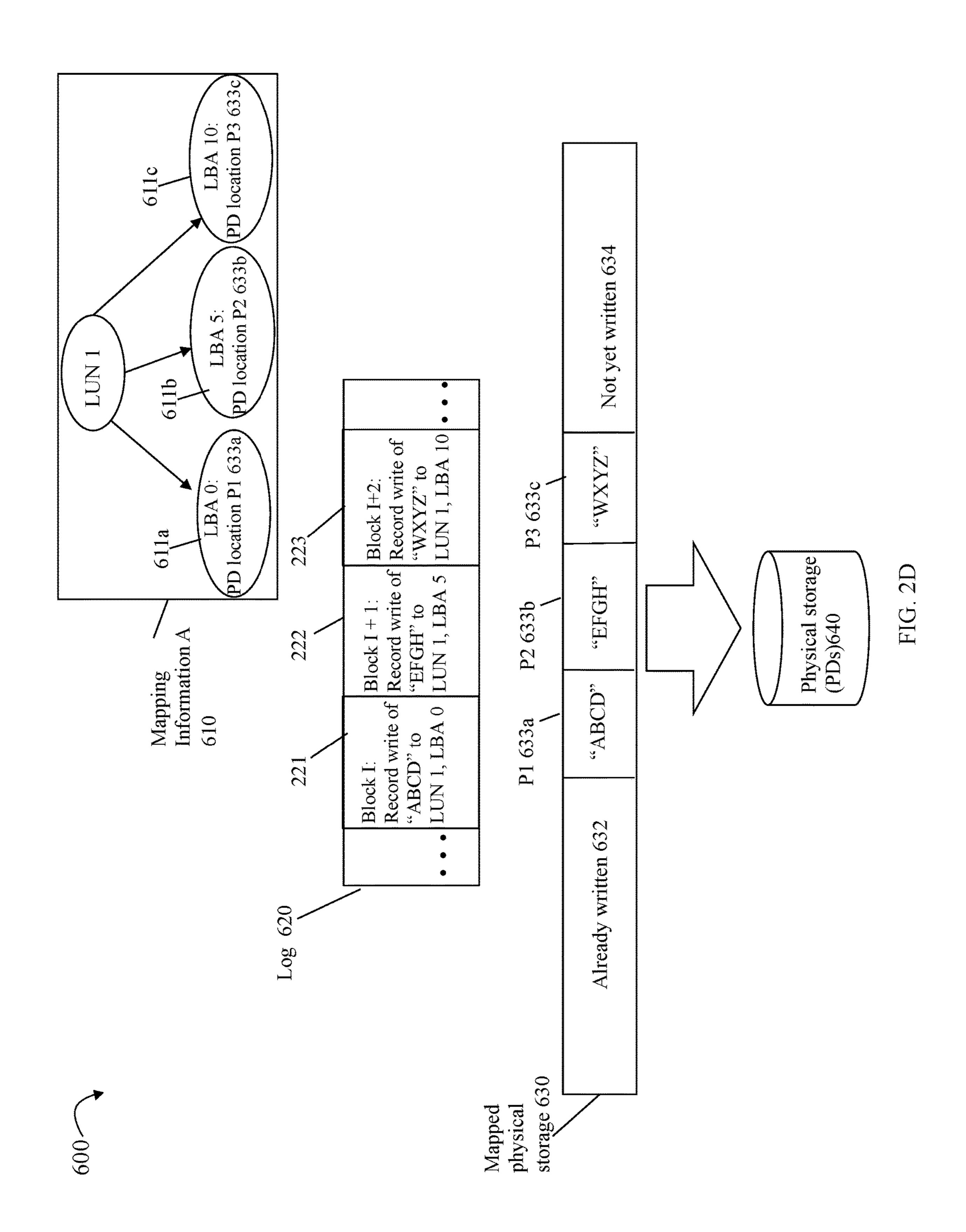

FIGS. 2B, 2C and 2D are examples illustrating use of a log or journal recording client operations in at least one embodiment in accordance with the techniques of the present disclosure.

In at least one embodiment, the plurality of options can clude a first option, and wherein processing of the first option can include: sending a request, from the first node to e second node, requesting that the second node map the

FIG. 7 is an example illustrating a partitioned logical address space and a partitioned VLB layer in at least one embodiment in accordance with the techniques of the present disclosure.

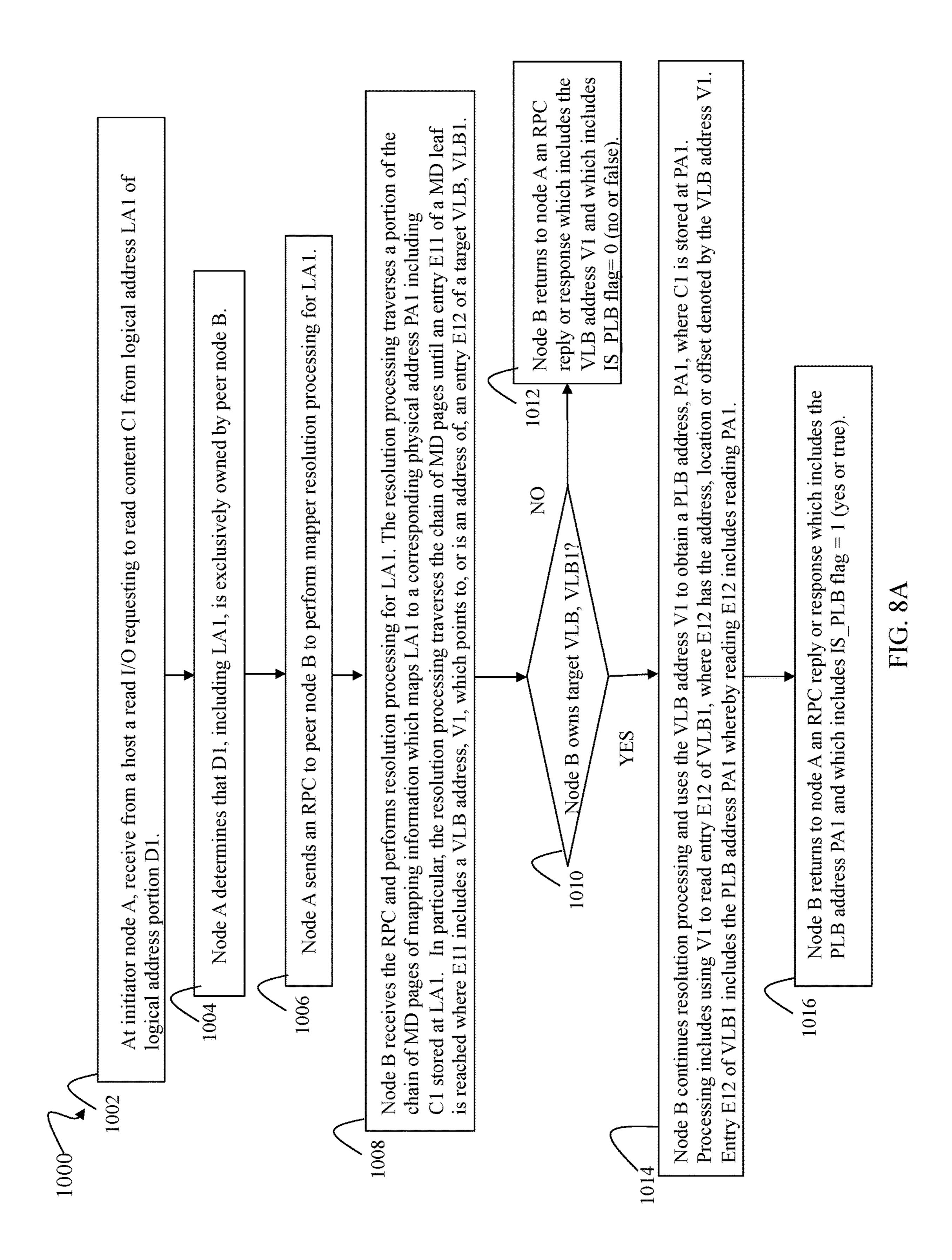

FIGS. 8A, 8B, 9, 10A and 10B are flowcharts of processing steps that can be performed in at least one embodiment in accordance with the techniques of the present disclosure.

## DETAILED DESCRIPTION OF EMBODIMENT(S)

Existing systems, such as data storage systems, can maintain and utilize a data cache to store frequently accessed pages of data. The data cache can be, for example, a form of fast volatile memory such as a volatile form of random access memory (RAM). In particular, the data cache can be used as a read data cache to store user data which is frequently read. For a read I/O requesting read data, the read data which is stored in the cache results in a cache hit or read cache hit. For a read cache hit, the requested read data can be retrieved from the cache and returned to the requester or originator of the read I/O. If the requested read data is not in the cache, a cache miss or read cache miss results where the requested read data can be retrieved from longer term backend (BE) non-volatile storage. A cache miss as compared to a cache hit results in an I/O performance penalty and increased I/O latency in order to service the read I/O and return the requested read data to the requester. The data cache can provide for read cache hits and optimized perfor-

mance such as by providing for improved I/O latency and improved utilization of system resources. Generally, the data cache, and cache memory in general, can be characterized as a critical and expensive resource which can have a limited size or capacity. Accordingly, it is important for systems to utilize the data cache, and more generally cache storage, efficiently to provide for optimal performance.

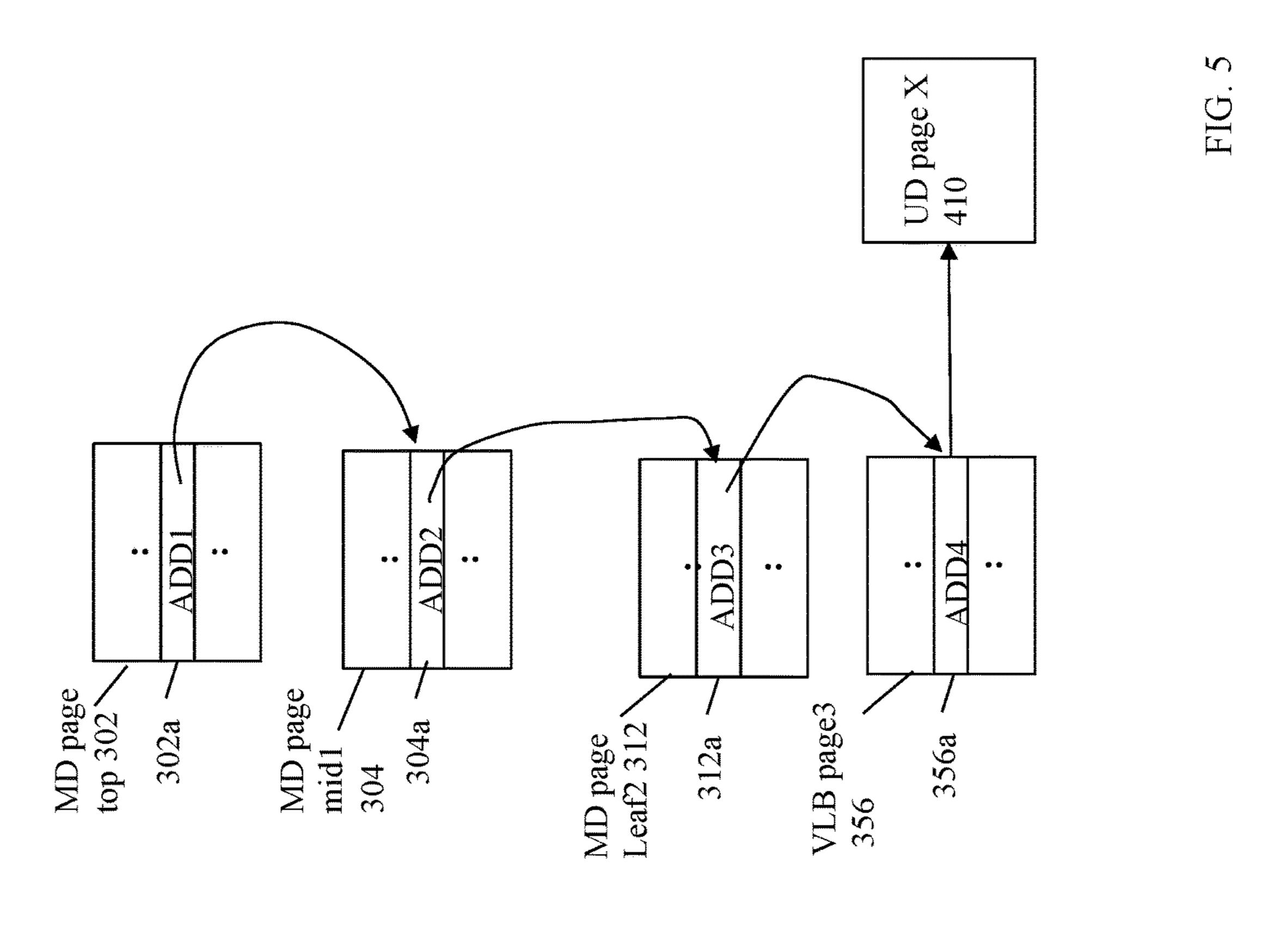

In at least one existing system, mapping information can be used to map a logical address to a corresponding physical storage location or address storing the user data or content 10 of the logical address. The mapping information can be a chain of metadata (MD) pages traversed to obtain the content of a logical address from its corresponding physical storage location or address on BE non-volatile storage. Thus, a read cache miss with respect to a read I/O requesting 15 to read user data from a logical address can result in a cache miss with respect to the data cache noted above. Read cache miss processing can incur a performance penalty as noted above, at least in part, due to the traversal of the chain of MD pages of the mapping information. The MD pages of map- 20 ping information can also be stored on BE non-volatile storage. Thus, traversing the chain of MD page can include retrieving each MD page of the chain from BE non-volatile storage thereby incurring additional performance penalties to access. To further improve performance, a system can also 25 store the mapping information, such as the chain of MD pages, in the cache. However, as with the user data and the limited size of the cache, not all mapping information or MD pages for all user data can be stored in the cache. As a result, accessing the multiple layers or levels of MD pages which 30 can be needed for accessing the read data to service a read cache miss can result in additional cache misses thereby incurring an additional performance penalty to access any uncached MD pages of mapping information from BE non-volatile storage.

Some system can include multiple processing nodes where the multiple processing nodes can service I/Os. In such systems, cache usage can be even more inefficient across the multiple processing nodes since the same MD and/or user data or content for servicing I/Os can be cached 40 in node-local caches of all the multiple processing nodes. For example, pages of the same user data and/or MD can be cached locally in caches of the multiple processing nodes. To improve upon the foregoing, an architecture can be utilized which partitions ownership of the logical address 45 space of user data or content among the multiple processing nodes. In one such architecture, a node assigned a particular logical address can be designated as the exclusive owner of the logical address. A node can service I/Os directed to logical addresses owned by the node. If the node receives an 50 I/O directed to a logical address not owned by the node, the receiving node can forward the I/O for servicing or processing to the owning node. Generally, an exclusive ownership assignment can also be characterized as a strong ownership. In contrast, a non-exclusive ownership assignment can also 55 be characterized as a weak ownership.

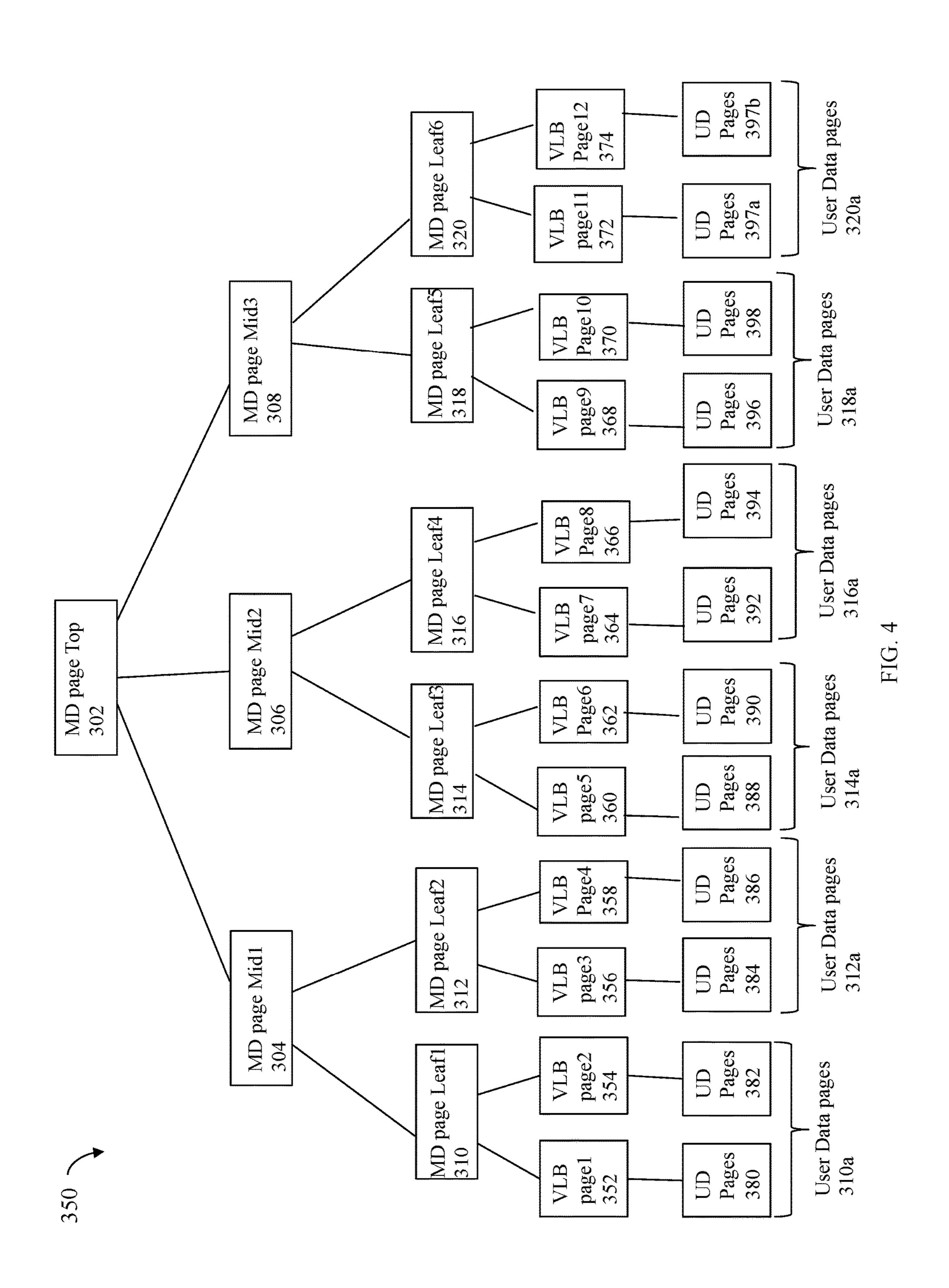

The architecture can also assign strong ownership to some MD pages and assign weak ownership to other MD pages. Strong ownership of a MD page assigned to a node can denote exclusive ownership of the assigned MD page by the 60 node. Weak ownership of a MD page can indicate that the MD page can be owned by more than one node and thus can denote non-exclusive ownership of the MD page shared by multiple nodes. Thus, those MD pages having associated weak ownership can lead to caching inefficiencies since the 65 same weakly owned MD page can be cached locally in local caches of multiple nodes. In particular, a virtual layer of the

6

mapping information can include multiple virtual layer blocks (VLBs) used in connection with mapping user data logical addresses to corresponding physical locations or addresses containing content stored at corresponding logical addresses. VLBs can be weakly owned and thus can be regularly cached in duplicate in multiple local caches of multiple nodes.

Accordingly, described in the present disclosure are techniques that overcome the foregoing drawbacks and provide for improved and efficient cache usage.

In at least one embodiment, the techniques of the present disclosure provide for assigning ownership of the VLBs of the virtual layer among the multiple nodes of the system. In at least one embodiment, the VLBs of the virtual layer can be partitioned into multiple sets, where exclusive ownership of one of the multiple sets of VLBs is assigned to a corresponding one of the multiple nodes. In at least one embodiment, exclusive ownership of each VLB can be assigned to a single one of the nodes.

In at least one embodiment, a node which receives an I/O operation can be referred to as the initiator node with respect to that particular I/O operation.

In at least one embodiment, exclusive ownership, such as with respect to a portion of logical address space as well as a VLB or other metadata portion may include a strong ownership or include the exclusive locking by a particular node, where such ownership is not shared with another node. In at least one embodiment, a storage node assigned exclusive ownership over a logical address or a metadata portion does not yield access to that logical address or metadata portion to another node.

In at least one embodiment, an architecture can be utilized which partitions ownership of the logical address space of user data or content among the multiple processing nodes. In at least one embodiment, a node assigned a particular logical address can be designated as the exclusive owner of the logical address. If the node receives an I/O directed to a logical address not owned by the node, the receiving node can forward or redirect the I/O for servicing or processing to the owning node. In at least one embodiment, the I/Os can include read I/Os. For a read I/O directed to a target logical address LA1 where the read I/O is received by an initiator node which does not own LA1, the initiator node can issue a remote procedure call (RPC) to its peer node to service the read, where the peer node owns LA1. In at least one embodiment, the RPC for the read I/O can be a request from the initiator node to a peer node (owner of LA1) to perform processing in connection with MD pages of mapping information for LA1. In particular, the RPC for the read I/O can be a request for the peer node (which owns the logical address LA1) to perform mapping resolution processing for LA1. The resolution processing can include mapping LA1 to a corresponding VLB address or physical layer block (PLB) address. The resolution processing can be in accordance with the chain of MD pages of mapping information for LA1. The resolution processing can include traversing one or more of the MD pages of the chain of mapping information for LA1. The VLB address can be a location or address of an offset or entry of a VLB included in the chain of MD pages of mapping information used to map LA1 to a corresponding PLB address. The PLB address can be a physical location or address of a PLB (or physical location or address within a PLB) including the content C1 stored at LA1. Thus, the VLB address can be an indirect pointer or address used to indirectly access the content C1 stored at LA1. The PLB address can be a pointer to, or address of, a

physical storage location on BE non-volatile storage, where the physical storage location contains the content C1 stored at LA1.

In at least one embodiment, the peer node, which owns LA1 and receives the RPC from the initiator node, can return either a VLB address V1 or a PLB address PAL. In at least one embodiment, the peer node can return a PLB address if the peer node is the exclusive owner of the VLB, VLB1, where V1 is an address or offset of an entry within VLB1, where V1 is included in the mapping information used to map LA1 to PA1, and where PA1 is the physical address or location of C1 stored at LAL. If the peer node receiving the RPC owns LA1 and also owns VLB1 including V1, the peer node continues performing additional resolution processing 15 cient use of cache by having the VLB owning node perform using V1. In particular, V1 can denote an address, offset or location of an entry E1 within VLB1, where E1 includes the PLB address PAL. In this manner, the resolution processing can include mapping LA1 to V1, and then reading the contents stored at V1 (e.g., the contents stored at entry E1 of 20 VLB1), where PA1 is the contents stored at V1.

In at least one embodiment, the peer node receiving the RPC can return the VLB address V1 if the peer node is not the exclusive owner of the VLB, VLB1, where VLB1 includes the VLB address V1, where V1 is included in the 25 mapping information used to map LA1 to PA1, and where PA1 is the physical address or location of C1 stored at LA1. In connection with the foregoing case, V1 is the address of an entry E1 in VLB1 where PA1 is included in the entry E1 of VLB1. If the peer node receiving the RPC owns LA1 but does not own VLB1 including V1, the peer node can simply return V1 (an address or pointer to the entry E1 of VLB1) without performing the additional resolution processing noted above.

In at least one embodiment, in response to the RPC, the peer node owning LA1 can return information including either the VLB address V1 or the PLB address PA1 depending on whether the peer node owns VLB1 which includes a corresponding entry, location or address denoted by V1. In 40 such an embodiment, the flag IS\_PLB can be included in an RPC response or reply sent from the peer node to the initiator node, where the initiator node sent the RPC. The IS\_PLB flag can denote the address or pointer type returned as either a VLB address type or a PLB address type. The 45 initiator node can then examine the IS\_PLB flag to interpret the returned address as either a VLB address or a PLB address. If the IS\_PLB flag=1 (e.g., is true or on) and thus denotes a PLB address, the initiator can directly read the content C1 using the returned PLB address PAL. If the 50 IS\_PLB flag=0 (e.g., is false or off) and thus denotes a VLB address, the initiator owns the VLB, VLB1, including the returned VLB address, V1. In this latter case the initiator node accesses VLB1 to read contents stored at the address, address V1. In at least one embodiment, V1 can be an address or location of an entry or offset E1 within the VLB1, where E1 includes PAL. Thus, E1 of VLB1 can be accessed to read PA1, and the PA1 can be accessed by the initiator node to read the contents C1 stored at LA1. C1 can then be 60 returned to the host or other client which issued the read I/O reading from LA1.

If the initiator node which receives the read I/O operation to read C1 from LA1 is the owner of LA1 and also the owner of the VLB, VLB1, included in the mapping information for 65 LA1, the initiator node can perform all necessary resolution processing for LA1. In this case, the initiator node, which

8

owns LA1 and VLB1, may not issue an RPC to its peer node. Rather, the VLB access to VLB1 is done locally on the owning initiator node.

In at least one embodiment, for a read I/O directed to logical address LA1, the node designated as the exclusive owner of LA1 can map LA1 to a corresponding VLB address, V1, where V1 is included in the mapping information for LA1. Additionally in at least one embodiment, the particular node designated as the exclusive owner with 10 respect to a target VLB (which includes an entry E1 having the address V1) can map the VLB address V1 to a corresponding PLB address denoting a physical address or location PA1 containing the content C1 stored at LA1.

In this manner, the foregoing scenarios provide for effimapper resolution processing with respect to a target logical address LA1 of a read I/O operation. As a result in such embodiments, the VLB can be read and accessed, and correspondingly cached, on only the owning node of the VLB but not the peer node. As a result of the foregoing scenarios in accordance with the techniques of the present disclosure, access and reading of a VLB by a non-owning node can be avoided in such scenarios, whereby the nonowning node with respect to a VLB can avoid caching the VLB which it does not own.

In at least one embodiment, an initiator node receiving a read I/O directed to the logical address LA1 can exclusively own LA1 but not exclusively own the target VLB included in the chain of MD pages of mapping information mapping 30 LA1 to a corresponding PLB address PA1 containing content C1 stored at LA1. In at least one embodiment in this case, the initiator node can issue an RPC to the peer node which owns the target VLB, where the target VLB includes an entry E1, where E1 includes the corresponding PLB 35 address PAL. The peer node owning the target VLB can access and read its entry E1 thereby reading PA1 from E1. The peer node can then return PA1 in response to the RPC. After the initiator node receives the RPC response from the peer node which owns the target VLB, the initiator node can access PA1 and read the content C1, and then return C1 to the host or other client which issued the read I/O.

In at least one embodiment, an initiator node receiving a read I/O directed to the logical address LA1 can exclusively own LA1 but not own the target VLB included in the chain of MD pages of mapping information mapping LA1 to a corresponding PLB address PA1 containing content C1 stored at LA1. In at least one embodiment, one of multiple options can be selected in order to access the target VLB and obtain PA1 from a corresponding entry E1 of the target VLB. In at least one embodiment, one or more of the multiple options can include relaxation or removal of some of the restrictions resulting from exclusive VLB ownership. In particular, the second and third options noted below and discussed elsewhere herein provide for a relaxation or location or entry thereof denoted by the returned VLB 55 removal of some of the restrictions of exclusive VLB ownership whereby the non-owning VLB node can be allowed to limited access and/or caching of a VLB which it does not own. In at least one embodiment, such limited access and/or caching by a non-owning node with respect to a target VLB can be performed in connection with a limited usage case or scenario where the initiator node receives the read I/O directed to LA1 and exclusively owns LA1 but where the peer node owns the target VLB of the mapping information mapping LA1 to its corresponding PLB address PA1 containing content C1 stored at LA1.

In at least one embodiment, the multiple options can include a first, second and third option. The first option can

include issuing an RPC as noted above to the peer node which owns the target VLB. The second option can include the initiator node (which does not own the target VLB) reading the target VLB, such as from a corresponding location on non-volatile BE storage; and then reading PA1<sup>-5</sup> from the corresponding entry E1 of the target VLB. In this second option, the target VLB read locally by the nonowning initiator node from BE non-volatile storage may not be cached by the non-owning initiator node. The third option can include the initiator node (which does not own the target 10 VLB) reading the target VLB, such as from a corresponding location on non-volatile BE storage; and then reading PA1 from the corresponding entry E1 of the target VLB. In this third option, the target VLB read locally by the non-owning 15 initiator node from BE non-volatile storage can be cached by the non-owning initiator node. With this third option in at least one embodiment, the initiator node can have a relatively small local cache of un-owned VLBs (e.g., VLBs which are exclusively owned by the peer node but not the 20 initiator node). With this third option in at least one embodiment, the small local cache of un-owned VLBs can include hot or frequently accessed VLBs which are owned by the peer node.

In at least one embodiment including the three options 25 noted above, one or more criteria can be specified to provide for dynamically selecting one of the three options at runtime in accordance with the current evaluation of the one or more criteria. In at least one embodiment, the one or more criteria can include one or more metrics. In at least one embodiment, 30 the one or more criteria can include the latency introduced if the RPC of the first option is performed. The latency can be determined in any suitable manner. In at least one embodiment, the latency can be estimated based on prior actual issuances of the RPC of the first option alone, or in 35 combination with, current utilization or data traffic of an internode link or connection between the initiator and peer nodes where the RPC would be issued over the internode link or connection. Generally, the higher the latency and/or the higher the internode link utilization, the more motivation 40 to select another option other than the first option. In at least one embodiment, the one or more criteria can include a VLB cache hit rate with respect to the peer node which owns the target VLB. Generally, the higher the VLB cache hit rate of the owning node of the target VLB, the greater the motiva- 45 tion to send the RPC request by selecting the first option rather than reading the target VLB locally from BE nonvolatile storage (as with the second or third options). In at least one embodiment, the one or more criteria can include a current utilization of BE non-volatile storage. Generally, 50 the higher the BE utilization, the greater the motivation to send the RPC request by selecting the first option rather than selecting the second or third options which read the target VLB locally from BE non-volatile storage. In at least one embodiment, the one or more criteria can include a local 55 VLB cache hit rate of the initiator node if a local VLB cache is used to cache VLB pages not owned by the initiator node. Generally, the higher the local VLB cache hit rate, the more motivation to use the local VLB cache and not send an RPC request (e.g., not select the first option but rather select the 60 above-noted second or third option which is performed locally on the initiator node which received the read I/O operation).

In at least one embodiment, the criteria can indicate to select the first option and send a peer RPC request if the 65 latency is less than a specified maximum latency threshold, if the VLB cache hit rate of the peer node is above a

**10**

specified hit rate threshold, and if the BE utilization is greater than a specified utilization threshold.

In at least one embodiment, the criteria can indicate to select the first option to send a peer RPC request if the latency is less than a specified maximum latency threshold, and if the VLB cache hit rate of the peer node is above a specified hit rate threshold.

In at least one embodiment, the criteria can indicate to select the first option to send a peer RPC request if the latency is less than a specified maximum latency threshold, and if the BE utilization is greater than a specified utilization threshold.

In at least one embodiment, the criteria can indicate to select the second or third option (and not send a peer RPC request) if the latency is more than a specified maximum latency threshold, and/or if the internode link utilization is greater than a specified utilization threshold.

In at least one embodiment, the criteria can include a function F which includes one or more independent variables used to make a selection provided as an output of the function F. The one more independent variables can include one or more of: the latency introduced if the RPC of the first option is performed; current utilization of an internode link or connection between the initiator and peer nodes where the RPC would be issued over the internode link or connection; a VLB cache hit rate with respect to the peer node which owns the target VLB; a current utilization of BE non-volatile storage; and a local VLB cache hit rate of the initiator node if a local VLB cache is used to cache VLB pages not owned by the initiator node. Generally, the function F can make a selection from multiple specified or predefined options such as discussed above. In at least one embodiment, F can be used to select one of the specified options in accordance with a weighting of the multiple independent variables.

The foregoing and other aspects of the techniques of the present disclosure are described in more detail in the following paragraphs.

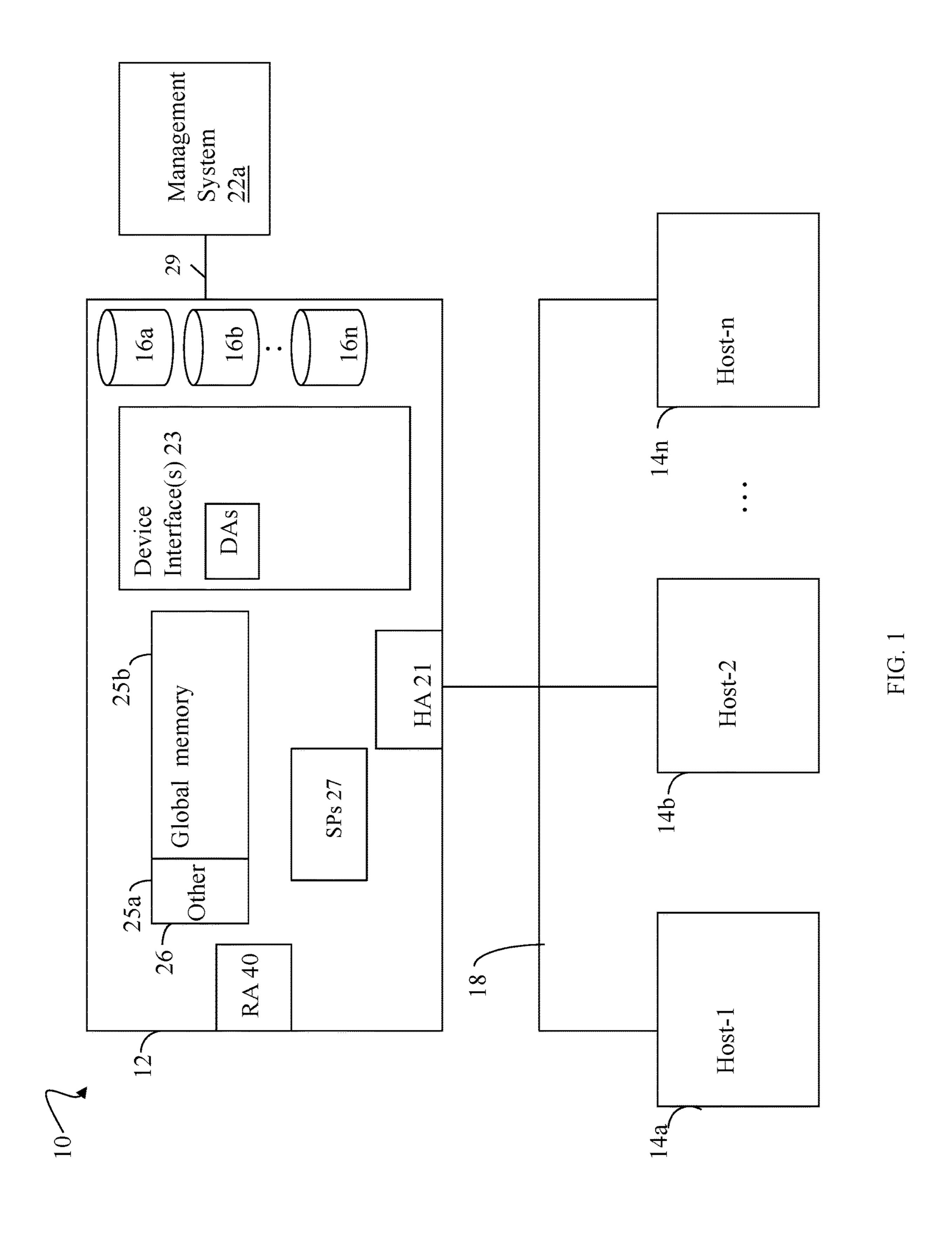

Referring to the FIG. 1, shown is an example of an embodiment of a SAN 10 that is used in connection with performing the techniques described herein. The SAN 10 includes a data storage system 12 connected to the host systems (also sometimes referred to as hosts) 14a-14n through the communication medium 18. In this embodiment of the SAN 10, the n hosts 14a-14n access the data storage system 12, for example, in performing input/output (I/O) operations or data requests. The communication medium 18 can be any one or more of a variety of networks or other type of communication connections as known to those skilled in the art. The communication medium 18 can be a network connection, bus, and/or other type of data link, such as a hardwire or other connections known in the art. For example, the communication medium 18 can be the Internet, an intranet, a network, or other wireless or other hardwired connection(s) by which the host systems 14a-14n access and communicate with the data storage system 12, and also communicate with other components included in the SAN **10**.

Each of the host systems 14a-14n and the data storage system 12 included in the SAN 10 are connected to the communication medium 18 by any one of a variety of connections as provided and supported in accordance with the type of communication medium 18. The processors included in the host systems 14a-14n and data storage system 12 can be any one of a variety of proprietary or commercially available single or multi-processor system, such as an Intel-based processor, or other type of commer-

cially available processor able to support traffic in accordance with each particular embodiment and application.

It should be noted that the particular examples of the hardware and software included in the data storage system 12 are described herein in more detail, and can vary with 5 each particular embodiment. Each of the hosts 14a-14n and the data storage system 12 can all be located at the same physical site, or, alternatively, be located in different physical locations. The communication medium 18 used for communication between the host systems 14a-14n and the 10 data storage system 12 of the SAN 10 can use a variety of different communication protocols such as block-based protocols (e.g., SCSI, FC, iSCSI), file system-based protocols (e.g., NFS or network file server), and the like. Some or all of the connections by which the hosts 14a-14n and the data 15 storage system 12 are connected to the communication medium 18 can pass through other communication devices, such as switching equipment, a phone line, a repeater, a multiplexer or even a satellite.

Each of the host systems 14a-14n can perform data 20 operations. In the embodiment of the FIG. 1, any one of the host computers 14a-14n issues a data request to the data storage system 12 to perform a data operation. For example, an application executing on one of the host computers 14a-14n performs a read or write operation resulting in one 25 or more data requests to the data storage system 12.

It should be noted that although the element 12 is illustrated as a single data storage system, such as a single data storage array, the element 12 also represents, for example, multiple data storage arrays alone, or in combination with, 30 other data storage devices, systems, appliances, and/or components having suitable connectivity to the SAN 10 in an embodiment using the techniques herein. It should also be noted that an embodiment can include data storage arrays or other components from one or more vendors. In subsequent 35 examples illustrating the techniques herein, reference is made to a single data storage array by a vendor. However, as will be appreciated by those skilled in the art, the techniques herein are applicable for use with other data storage arrays by other vendors and with other components than as 40 described herein for purposes of example.

In at least one embodiment, the data storage system 12 is a data storage appliance or a data storage array including a plurality of data storage devices (PDs) 16a-16n. The data storage devices 16a-16n include one or more types of data 45 storage devices such as, for example, one or more rotating disk drives and/or one or more solid state drives (SSDs). An SSD is a data storage device that uses solid-state memory to store persistent data. SSDs refer to solid state electronics devices as distinguished from electromechanical devices, 50 such as hard drives, having moving parts. Flash devices or flash memory-based SSDs are one type of SSD that contains no moving mechanical parts. In at least one embodiment, the flash devices can be constructed using nonvolatile semiconductor NAND flash memory. The flash devices include, for 55 example, one or more SLC (single level cell) devices and/or MLC (multi level cell) devices.

In at least one embodiment, the data storage system or array includes different types of controllers, adapters or directors, such as an HA 21 (host adapter), RA 40 (remote 60 adapter), and/or device interface(s) 23. Each of the adapters (sometimes also known as controllers, directors or interface components) can be implemented using hardware including a processor with a local memory with code stored thereon for execution in connection with performing different operations. The HAs are used to manage communications and data operations between one or more host systems and the

12

global memory (GM). In an embodiment, the HA is a Fibre Channel Adapter (FA) or other adapter which facilitates host communication. The HA 21 can be characterized as a front end component of the data storage system which receives a request from one of the hosts 14a-n. In at least one embodiment, the data storage array or system includes one or more RAs used, for example, to facilitate communications between data storage arrays. The data storage array also includes one or more device interfaces 23 for facilitating data transfers to/from the data storage devices 16a-16n. The data storage device interfaces 23 include device interface modules, for example, one or more disk adapters (DAs) (e.g., disk controllers) for interfacing with the flash drives or other physical storage devices (e.g., PDS 16a-n). The DAs can also be characterized as back end components of the data storage system which interface with the physical data storage devices.

One or more internal logical communication paths exist between the device interfaces 23, the RAs 40, the HAs 21, and the memory 26. An embodiment, for example, uses one or more internal busses and/or communication modules. In at least one embodiment, the global memory portion 25b is used to facilitate data transfers and other communications between the device interfaces, the HAs and/or the RAs in a data storage array. In one embodiment, the device interfaces 23 performs data operations using a system cache included in the global memory 25b, for example, when communicating with other device interfaces and other components of the data storage array. The other portion 25a is that portion of the memory used in connection with other designations that can vary in accordance with each embodiment.

The particular data storage system as described in this embodiment, or a particular device thereof, such as a disk or particular aspects of a flash device, should not be construed as a limitation. Other types of commercially available data storage systems, as well as processors and hardware controlling access to these particular devices, can also be included in an embodiment.

The host systems 14a-14n provide data and access control information through channels to the storage systems 12, and the storage systems 12 also provide data to the host systems 14*a-n* also through the channels. The host systems 14*a-n* do not address the drives or devices 16a-16n of the storage systems directly, but rather access to data is provided to one or more host systems from what the host systems view as a plurality of logical devices, logical volumes (LVs) also referred to herein as logical units (e.g., LUNs). A logical unit (LUN) can be characterized as a disk array or data storage system reference to an amount of storage space that has been formatted and allocated for use to one or more hosts. A logical unit has a logical unit number that is an I/O address for the logical unit. As used herein, a LUN or LUNs refers to the different logical units of storage referenced by such logical unit numbers. The LUNs have storage provisioned from portions of one or more physical disk drives or more generally physical storage devices. For example, one or more LUNs can reside on a single physical disk drive, data of a single LUN can reside on multiple different physical devices, and the like. Data in a single data storage system, such as a single data storage array, can be accessible to multiple hosts allowing the hosts to share the data residing therein. The HAs are used in connection with communications between a data storage array and a host system. The RAs are used in facilitating communications between two data storage arrays. The DAs include one or more types of device interfaced used in connection with facilitating data transfers to/from the associated disk drive(s) and LUN (s)

residing thereon. For example, such device interfaces can include a device interface used in connection with facilitating data transfers to/from the associated flash devices and LUN(s) residing thereon. It should be noted that an embodiment can use the same or a different device interface for one or more different types of devices than as described herein.

In an embodiment in accordance with the techniques herein, the data storage system as described can be characterized as having one or more logical mapping layers in which a logical device of the data storage system is exposed 10 to the host whereby the logical device is mapped by such mapping layers of the data storage system to one or more physical devices. Additionally, the host can also have one or more additional mapping layers so that, for example, a host side logical device or volume is mapped to one or more data 15 storage system logical devices as presented to the host.

It should be noted that although examples of the techniques herein are made with respect to a physical data storage system and its physical components (e.g., physical hardware for each HA, DA, HA port and the like), the 20 techniques herein can be performed in a physical data storage system including one or more emulated or virtualized components (e.g., emulated or virtualized ports, emulated or virtualized DAs or HAs), and also a virtualized or emulated data storage system including virtualized or emulated components.

Also shown in the FIG. 1 is a management system 22a used to manage and monitor the data storage system 12. In one embodiment, the management system 22a is a computer system which includes data storage system management 30 software or application that executes in a web browser. A data storage system manager can, for example, view information about a current data storage configuration such as LUNs, storage pools, and the like, on a user interface (UI) in a display device of the management system 22a. Alternatively, and more generally, the management software can execute on any suitable processor in any suitable system. For example, the data storage system management software can execute on a processor of the data storage system 12.

Information regarding the data storage system configura- 40 tion is stored in any suitable data container, such as a database. The data storage system configuration information stored in the database generally describes the various physical and logical entities in the current data storage system configuration. The data storage system configuration infor- 45 mation describes, for example, the LUNs configured in the system, properties and status information of the configured LUNs (e.g., LUN storage capacity, unused or available storage capacity of a LUN, consumed or used capacity of a LUN), configured RAID groups, properties and status infor- 50 mation of the configured RAID groups (e.g., the RAID level of a RAID group, the particular PDs that are members of the configured RAID group), the PDs in the system, properties and status information about the PDs in the system, data storage system performance information such as regarding 55 various storage objects and other entities in the system, and the like.

Consistent with other discussion herein, management commands issued over the control or management path include commands that query or read selected portions of the 60 data storage system configuration, such as information regarding the properties or attributes of one or more LUNs. The management commands also include commands that write, update, or modify the data storage system configuration, such as, for example, to create or provision a new LUN 65 (e.g., which result in modifying one or more database tables such as to add information for the new LUN), and the like.

14

It should be noted that each of the different controllers or adapters, such as each HA, DA, RA, and the like, can be implemented as a hardware component including, for example, one or more processors, one or more forms of memory, and the like. Code can be stored in one or more of the memories of the component for performing processing.

The device interface, such as a DA, performs I/O operations on a physical device or drive 16a-16n. In the following description, data residing on a LUN is accessed by the device interface following a data request in connection with I/O operations. For example, a host issues an I/O operation that is received by the HA 21. The I/O operation identifies a target location from which data is read from, or written to, depending on whether the I/O operation is, respectively, a read or a write operation request. In at least one embodiment using block storage services, the target location of the received I/O operation is expressed in terms of a LUN and logical address or offset location (e.g., LBA or logical block address) on the LUN. Processing is performed on the data storage system to further map the target location of the received I/O operation, expressed in terms of a LUN and logical address or offset location on the LUN, to its corresponding physical storage device (PD) and location on the PD. The DA which services the particular PD performs processing to either read data from, or write data to, the corresponding physical device location for the I/O operation.

It should be noted that an embodiment of a data storage system can include components having different names from that described herein but which perform functions similar to components as described herein. Additionally, components within a single data storage system, and also between data storage systems, can communicate using any suitable technique described herein for exemplary purposes. For example, the element 12 of the FIG. 1 in one embodiment is a data storage system, such as a data storage array, that includes multiple storage processors (SPs). Each of the SPs 27 is a CPU including one or more "cores" or processors and each have their own memory used for communication between the different front end and back end components rather than utilize a global memory accessible to all storage processors. In such embodiments, the memory 26 represents memory of each such storage processor.

Generally, the techniques herein can be used in connection with any suitable storage system, appliance, device, and the like, in which data is stored. For example, an embodiment can implement the techniques herein using a midrange data storage system as well as a higher end or enterprise data storage system.

The data path or I/O path can be characterized as the path or flow of I/O data through a system. For example, the data or I/O path can be the logical flow through hardware and software components or layers in connection with a user, such as an application executing on a host (e.g., more generally, a data storage client) issuing I/O commands (e.g., SCSI-based commands, and/or file-based commands) that read and/or write user data to a data storage system, and also receive a response (possibly including requested data) in connection such I/O commands.

The control path, also sometimes referred to as the management path, can be characterized as the path or flow of data management or control commands through a system. For example, the control or management path is the logical flow through hardware and software components or layers in connection with issuing data storage management command to and/or from a data storage system, and also receiving responses (possibly including requested data) to such control

or management commands. For example, with reference to the FIG. 1, the control commands are issued from data storage management software executing on the management system 22a to the data storage system 12. Such commands, for example, establish or modify data services, provision storage, perform user account management, and the like. Consistent with other discussion herein, management commands result in processing that can include reading and/or modifying information in the database storing data storage system configuration information.

The data path and control path define two sets of different logical flow paths. In at least some of the data storage system configurations, at least part of the hardware and network connections used for each of the data path and control path differ. For example, although both control path and data path 15 generally use a network for communications, some of the hardware and software used can differ. For example, with reference to the FIG. 1, a data storage system has a separate physical connection 29 from a management system 22a to the data storage system 12 being managed whereby control 20 commands are issued over such a physical connection 29. However, user I/O commands are never issued over such a physical connection 29 provided solely for purposes of connecting the management system to the data storage system. In any case, the data path and control path each 25 define two separate logical flow paths.

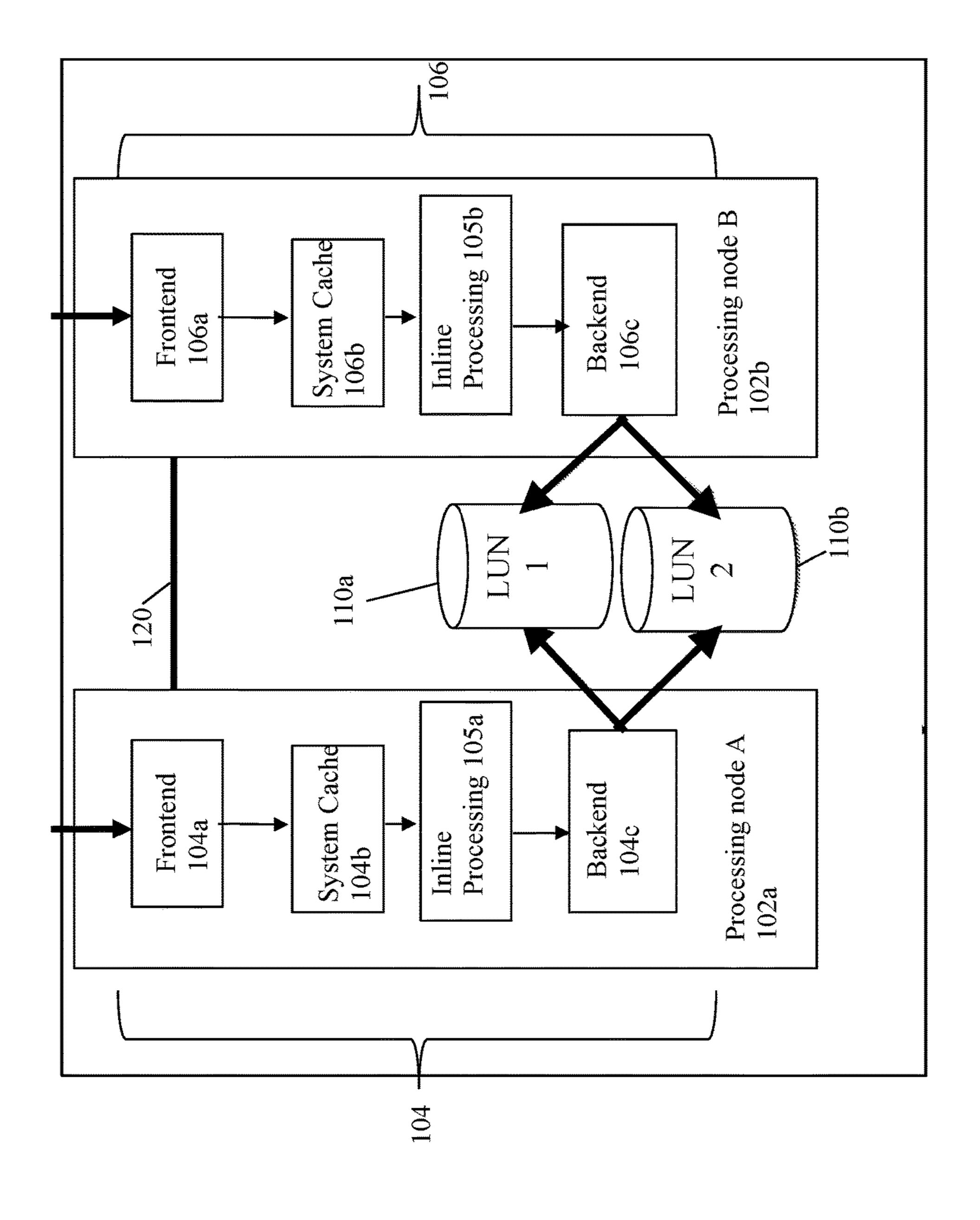

With reference to the FIG. 2A, shown is an example 100 illustrating components that can be included in the data path in at least one existing data storage system in accordance with the techniques of the present disclosure. The example 30 100 includes two processing nodes A 102a and B 102b and the associated software stacks 104, 106 of the data path, where I/O requests can be received by either processing node **102***a* or **102***b*. In the example **200**, the data path **104** of processing node A 102a includes: the frontend (FE) com- 35 ponent 104a (e.g., an FA or front end adapter) that translates the protocol-specific request into a storage system-specific request; a system cache layer 104b where data is temporarily stored; an inline processing layer 105a; and a backend (BE) component 104c that facilitates movement of the data 40 between the system cache and non-volatile physical storage (e.g., back end physical non-volatile storage devices or PDs accessed by BE components such as DAs as described herein). During movement of data in and out of the system cache layer 104b (e.g., such as in connection with read data 45 from, and writing data to, physical storage 110a, 110b), inline processing can be performed by layer 105a. Such inline processing operations of 105a can be optionally performed and can include any one of more data processing operations in connection with data that is flushed from 50 system cache layer 104b to the back-end non-volatile physical storage 110a, 110b, as well as when retrieving data from the back-end non-volatile physical storage 110a, 110b to be stored in the system cache layer 104b. In at least one embodiment, the inline processing can include, for example, 55 performing one or more data reduction operations such as data deduplication or data compression. The inline processing can include performing any suitable or desirable data processing operations as part of the I/O or data path.

In a manner similar to that as described for data path 104, 60 the data path 106 for processing node B 102b has its own FE component 106a, system cache layer 106b, inline processing layer 105b, and BE component 106c that are respectively similar to the components 104a, 104b, 105a and 104c. The elements 110a, 110b denote the non-volatile BE physical 65 storage provisioned from PDs for the LUNs, whereby an I/O can be directed to a location or logical address of a LUN and

**16**

where data can be read from, or written to, the logical address. The LUNs 110a, 110b are examples of storage objects representing logical storage entities included in an existing data storage system configuration. Since, in this example, writes, or more generally I/Os, directed to the LUNs 110a, 110b can be received for processing by either of the nodes 102a and 102b, the example 100 illustrates what can also be referred to as an active-active configuration.

In connection with a write operation received from a host and processed by the processing node A 102a, the write data can be written to the system cache 104b, marked as write pending (WP) denoting it needs to be written to the physical storage 110a, 110b and, at a later point in time, the write data can be destaged or flushed from the system cache to the physical storage 110a, 110b by the BE component 104c. The write request can be considered complete once the write data has been stored in the system cache whereby an acknowledgement regarding the completion can be returned to the host (e.g., by component the 104a). At various points in time, the WP data stored in the system cache is flushed or written out to the physical storage 110a, 110b.

In connection with the inline processing layer 105a, prior to storing the original data on the physical storage 110a, 110b, one or more data reduction operations can be performed. For example, the inline processing can include performing data compression processing, data deduplication processing, and the like, that can convert the original data (as stored in the system cache prior to inline processing) to a resulting representation or form which is then written to the physical storage 110a, 110b.

In connection with a read operation to read a block of data, a determination is made as to whether the requested read data block is stored in its original form (in system cache 104b or on physical storage 110a, 110b), or whether the requested read data block is stored in a different modified form or representation. If the requested read data block (which is stored in its original form) is in the system cache, the read data block is retrieved from the system cache 104b and returned to the host. Otherwise, if the requested read data block is not in the system cache 104b but is stored on the physical storage 110a, 110b in its original form, the requested data block is read by the BE component 104c from the backend storage 110a, 110b, stored in the system cache and then returned to the host.

If the requested read data block is not stored in its original form, the original form of the read data block is recreated and stored in the system cache in its original form so that it can be returned to the host. Thus, requested read data stored on physical storage 110a, 110b can be stored in a modified form where processing is performed by 105a to restore or convert the modified form of the data to its original data form prior to returning the requested read data to the host.

Also illustrated in FIG. 2A is an internal network interconnect 120 between the nodes 102a, 102b. In at least one embodiment, the interconnect 120 can be used for internode communication between the nodes 102a, 102b.

In connection with at least one embodiment in accordance with the techniques of the present disclosure, each processor or CPU can include its own private dedicated CPU cache (also sometimes referred to as processor cache) that is not shared with other processors. In at least one embodiment, the CPU cache, as in general with cache memory, can be a form of fast memory (relatively faster than main memory which can be a form of RAM). In at least one embodiment, the CPU or processor cache is on the same die or chip as the processor and typically, like cache memory in general, is far

more expensive to produce than normal RAM used as main memory. The processor cache can be substantially faster than the system RAM used as main memory. The processor cache can contain information that the processor will be immediately and repeatedly accessing. The faster memory 5 of the CPU cache can for example, run at a refresh rate that's closer to the CPU's clock speed, which minimizes wasted cycles. In at least one embodiment, there can be two or more levels (e.g., L1, L2 and L3) of cache. The CPU or processor cache can include at least an L1 level cache that is the local 10 or private CPU cache dedicated for use only by that particular processor. The two or more levels of cache in a system can also include at least one other level of cache (LLC or lower level cache) that is shared among the different CPUs. The L1 level cache serving as the dedicated CPU 15 cache of a processor can be the closest of all cache levels (e.g., L1-L3) to the processor which stores copies of the data from frequently used main memory locations. Thus, the system cache as described herein can include the CPU cache (e.g., the L1 level cache or dedicated private CPU/processor 20 cache) as well as other cache levels (e.g., the LLC) as described herein. Portions of the LLC can be used, for example, to initially cache write data which is then flushed to the backend physical storage such as BE PDs providing non-volatile storage. For example, in at least one embodi- 25 ment, a RAM based memory can be one of the caching layers used as to cache the write data that is then flushed to the backend physical storage. When the processor performs processing, such as in connection with the inline processing 105a, 105b as noted above, data can be loaded from the main 30 memory and/or other lower cache levels into its CPU cache.

In at least one embodiment, the data storage system can be configured to include one or more pairs of nodes, where each pair of nodes can be generally as described and represented as the nodes 102a-b in the FIG. 2A. For 35 local processor(s), local memory, and the like. example, a data storage system can be configured to include at least one pair of nodes and at most a maximum number of node pairs, such as for example, a maximum of 4 node pairs. The maximum number of node pairs can vary with embodiment. In at least one embodiment, a base enclosure 40 can include the minimum single pair of nodes and up to a specified maximum number of PDs. In some embodiments, a single base enclosure can be scaled up to have additional BE non-volatile storage using one or more expansion enclosures, where each expansion enclosure can include a number 45 of additional PDs. Further, in some embodiments, multiple base enclosures can be grouped together in a load-balancing cluster to provide up to the maximum number of node pairs. Consistent with other discussion herein, each node can include one or more processors and memory. In at least one 50 embodiment, each node can include two multi-core processors with each processor of the node having a core count of between 8 and 28 cores. In at least one embodiment, the PDs can all be non-volatile SSDs, such as flash-based storage devices and storage class memory (SCM) devices. It should 55 be noted that the two nodes configured as a pair can also sometimes be referred to as peer nodes. For example, the node A 102a is the peer node of the node B 102b, and the node B 102b is the peer node of the node A 102a.

In at least one embodiment, the data storage system can 60 be configured to provide both block and file storage services with a system software stack that includes an operating system running directly on the processors of the nodes of the system.

In at least one embodiment, the data storage system can 65 be configured to provide block-only storage services (e.g., no file storage services). A hypervisor can be installed on

each of the nodes to provide a virtualized environment of virtual machines (VMs). The system software stack can execute in the virtualized environment deployed on the hypervisor. The system software stack (sometimes referred to as the software stack or stack) can include an operating system running in the context of a VM of the virtualized environment. Additional software components can be included in the system software stack and can also execute in the context of a VM of the virtualized environment.

In at least one embodiment, each pair of nodes can be configured in an active-active configuration as described elsewhere herein, such as in connection with FIG. 2A, where each node of the pair has access to the same PDs providing BE storage for high availability. With the active-active configuration of each pair of nodes, both nodes of the pair process I/O operations or commands and also transfer data to and from the BE PDs attached to the pair. In at least one embodiment, BE PDs attached to one pair of nodes are not shared with other pairs of nodes. A host can access data stored on a BE PD through the node pair associated with or attached to the PD.

In at least one embodiment, each pair of nodes provides a dual node architecture where both nodes of the pair can be generally identical in terms of hardware and software for redundancy and high availability. Consistent with other discussion herein, each node of a pair can perform processing of the different components (e.g., FA, DA, and the like) in the data path or I/O path as well as the control or management path. Thus, in such an embodiment, different components, such as the FA, DA and the like of FIG. 1, can denote logical or functional components implemented by code executing on the one or more processors of each node. Each node of the pair can include its own resources such as its own local (i.e., used only by the node) resources such as

Consistent with other discussion herein, a cache can be used for caching write I/O data and other cached information. In one system, the cache used for caching logged writes can be implemented using multiple caching devices or PDs, such as non-volatile (NV) SSDs such as NVRAM devices that are external with respect to both of the nodes or storage controllers. The caching devices or PDs used to implement the cache can be configured in a RAID group of any suitable RAID level for data protection. In at least one embodiment, the caching PDs form a shared non-volatile cache accessible to both nodes of the dual node architecture. It should be noted that in a system where the caching devices or PDs are external with respect to the two nodes, the caching devices or PDs are in addition to other non-volatile PDs accessible to both nodes. The additional PDs provide the BE nonvolatile storage for the nodes where the cached data stored on the caching devices or PDs is eventually flushed to the BE PDs as discussed elsewhere herein. In at least one embodiment, a portion of each node's local volatile memory can also be used for caching information, such as blocks or pages of user data and metadata. For example, such nodelocal cached pages of user data and metadata can be used in connection with servicing reads for such user data and metadata.

In the following paragraphs, the one or more caching devices or PDs may be referred to as a data journal or log used in the data storage system. In such a system, the caching devices or PDs are non-volatile log devices or PDs upon which the log is persistently stored. It should be noted that as discussed elsewhere herein, both nodes can also each have local volatile memory used as a node local cache for storing data, structures and other information. In at least one

embodiment, the local volatile memory local to one of the nodes is used exclusively by that one node.

In a data storage system, minimizing the latency of I/O requests is a critical performance metric. In at least one data storage system using the dual node architecture such as 5 described in connection with FIG. 2A, for write operations, latency can be affected by the amount of time taken to store the write data in the log where the write data is visible to both nodes or controllers of the system.

Consistent with other discussion herein, the log file used 10 to log user operations, such as write I/Os, can be used to optimize write operation latency. Generally, a write operation writing data is received by the data storage system from a host or other client. The data storage system then performs processing to persistently record the write operation in the 15 log. Once the write operation is persistently recorded in the log, the data storage system can send an acknowledgement to the client regarding successful completion of the write operation. At some point in time subsequent to logging the write operation the log, the write operation is flushed or 20 destaged from the log to the BE PDs. In connection with flushing the recorded write operation from the log, the data written by the write operation is stored on non-volatile physical storage of a BE PD. The space of the log used to record the write operation that has been flushed can now be 25 reclaimed for reuse.

It should be noted that the flushing of the log can be performed in response to an occurrence of any one or more defined conditions. For example, the log can be flushed in response to determining that the amount of reclaimed log 30 space available for use and allocation is less than a specified threshold amount or size.

In at least one embodiment, a metadata (MD) structure of mapping information can be used in accordance with the techniques herein.

The mapping information can be used, for example, to map a logical address, such as a LUN and an LBA or offset, to its corresponding storage location, such as a physical storage location on BE non-volatile PDs of the system. Consistent with discussion elsewhere herein, write requests 40 or operations stored in the log can be flushed to the BE PDs (non-volatile) providing storage locations for the written data. For example, a logged write operation that writes first data to a logical address can be flushed whereby the logged first data is written out to a physical storage location on a BE 45 PD. The mapping information can be used to map the logical address to the physical storage location containing the content or data stored at the logical address. In at least one embodiment, the mapping information includes a MD structure that is hierarchical structure of multiple layers of MD 50 pages or blocks.

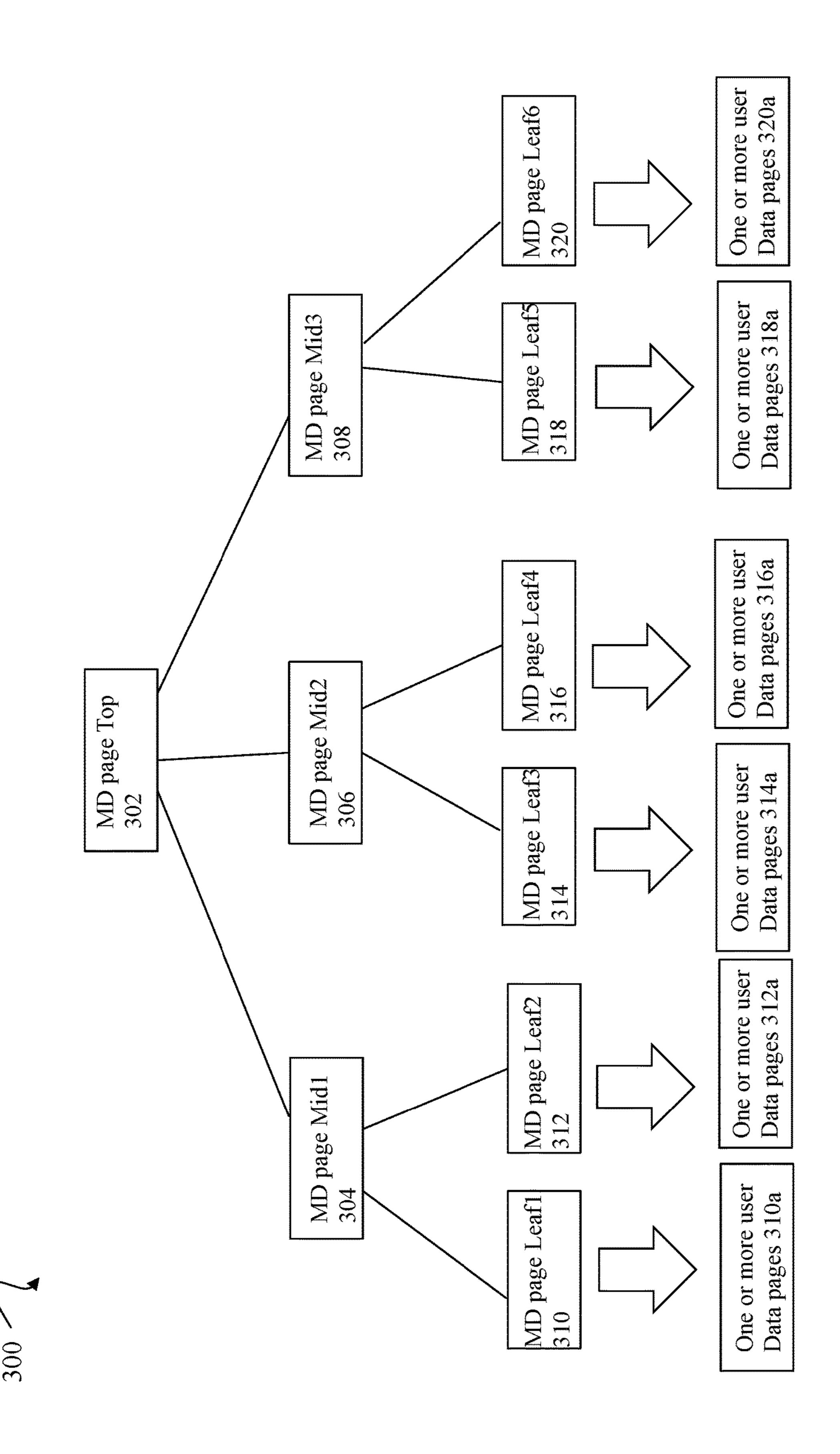

In at least one embodiment, the mapping information or MD structure for a LUN, such as a LUN A, can be in the form of a tree having a plurality of levels of MD pages. More generally, the mapping structure can be in the form of any 55 ordered list or hierarchical structure. In at least one embodiment, the mapping structure for the LUN A can include LUN MD in the form of a tree having 3 levels including a single top or root node (TOP node), a single mid-level (MID node) and a bottom level of leaf nodes (LEAF nodes), where each 60 of the MD page leaf nodes can point to, or reference (directly or indirectly) one or more pages of stored data, such as user data stored on the LUNA. Each node in the tree corresponds to a MD page including MD for the LUN A. More generally, the tree or other hierarchical structure of various MD pages 65 of the mapping structure for the LUN A can include any suitable number of levels, such as more than 3 levels where

**20**

there are multiple mid-levels. In at least one embodiment the tree of MD pages for the LUN can be a B+ tree, also sometimes referred to as an "N-ary" tree, where "N" indicates that each node in the tree structure can have up to a maximum of N child nodes. For example, in at least one embodiment, the tree of MD pages for the LUN can specify N=512 whereby each node in the tree structure can have up to a maximum of N child nodes. For simplicity of illustration, the tree structure of MD pages, corresponding to the mapping structure in at least one embodiment, is represented in FIG. 3 as including only 3 levels where each node in the tree can have at most 3 child nodes. Generally, the techniques herein can be used with any layered or hierarchical structure of MD pages.

Before describing in more detail the mapping information of MD pages that can be used in an at least one embodiment to map a logical address to a corresponding physical storage location or address, further details are described in connection with using a log for logging user or client operations, such as write I/Os.

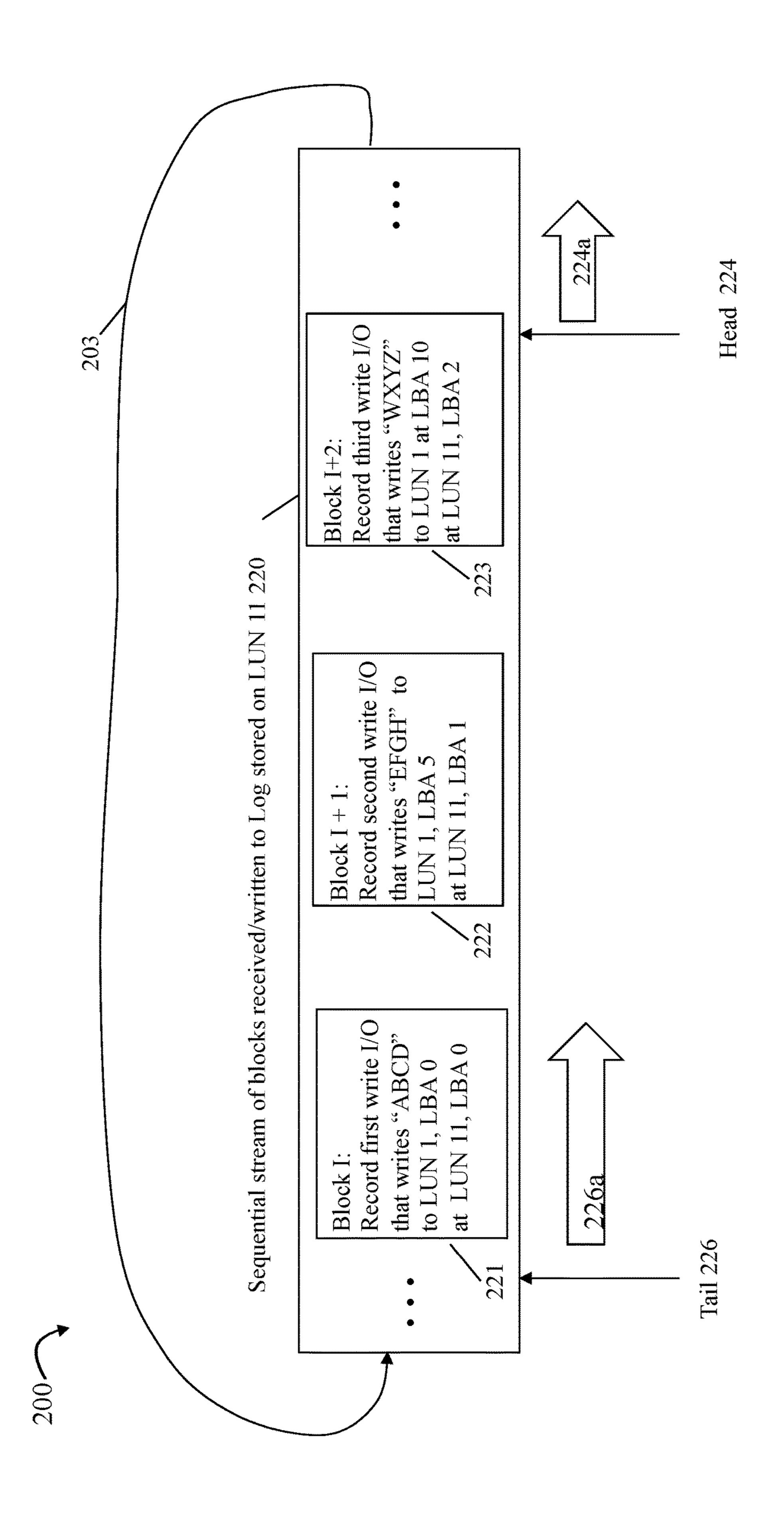

Consistent with other discussion herein, the log can be used to optimize write operation latency. Generally, the write operation writing data is received by the data storage system from a host or other client. The data storage system then performs processing to persistently record the write operation in the log. Once the write operation is persistently recorded in the log, the data storage system can send an acknowledgement to the client regarding successful completion of the write operation. At some point in time subsequent to logging the write operation the log, the write operation is flushed or destaged from the log to the BE PDs. In connection with flushing the recorded write operation from the log, the data written by the write operation is stored on nonvolatile physical storage of a BE PD. The space of the log used to record the write operation that has been flushed can now be reclaimed for reuse. The write operation can be recorded in the log in any suitable manner and can include, for example, recording a target logical address to which the write operation is directed and recording the data written to the target logical address by the write operation.

In the log, each logged operation can be recorded in the next logically sequential record of the log. For example, a logged write I/O and write data (e.g., write I/O payload) can be recorded in a next logically sequential record of the log. The log can be circular in nature in that once a write operation is recorded in the last record of the log, recording of the next write proceeds with recording in the first record of the log.

The typical I/O pattern for the log as a result of recording write I/Os and possibly other information in successive consecutive log records includes logically sequential and logically contiguous writes (e.g., logically with respect to the logical offset or ordering within the log). Data can also be read from the log as needed (e.g., depending on the particular use or application of the log) so typical I/O patterns can also include reads. The log can have a physical storage layout corresponding to the sequential and contiguous order in which the data is written to the log. Thus, the log data can be written to sequential and consecutive physical storage locations in a manner corresponding to the logical sequential and contiguous order of the data in the log. Additional detail regarding use and implementation of the log in at least one embodiment in accordance with the techniques of the present disclosure is provided below.

Referring to FIG. 2B, shown is an example 200 illustrating a sequential stream 220 of operations or requests received that are written to a log in an embodiment in