#### US012087397B1

## (12) United States Patent

#### Asnaashari

# (54) DYNAMIC HOST ALLOCATION OF PHYSICAL UNCLONABLE FEATURE OPERATION FOR RESISTIVE SWITCHING MEMORY

(71) Applicant: Crossbar, Inc., Santa Clara, CA (US)

(72) Inventor: Mehdi Asnaashari, Danville, CA (US)

(73) Assignee: Crossbar, Inc., Santa Clara, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 226 days.

(21) Appl. No.: 17/708,491

(22) Filed: Mar. 30, 2022

#### Related U.S. Application Data

- (63) Continuation-in-part of application No. 17/223,824, filed on Apr. 6, 2021, now Pat. No. 11,430,517. (Continued)

- (51) Int. Cl.

G11C 7/00 (2006.01)

G06F 3/06 (2006.01)

(Continued)

- (52) **U.S. Cl.**CPC ...... *G11C 7/24* (2013.01); *G06F 3/0604* (2013.01); *G06F 3/0655* (2013.01); (Continued)

- (58) Field of Classification Search

CPC ..... G11C 7/24; G11C 13/004; G11C 13/0059;

G11C 16/08; G11C 16/16; G11C 16/22;

(Continued)

### (10) Patent No.: US 12,087,397 B1

(45) **Date of Patent:** Sep. 10, 2024

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,270,590 A 12/1993 Pascucci 5,491,662 A 2/1996 Pezzini (Continued)

#### FOREIGN PATENT DOCUMENTS

| CN | 111952333 A    | 11/2020 |

|----|----------------|---------|

| WO | 0030118 A1     | 5/2000  |

| WO | 2013-126109 A1 | 8/2013  |

#### OTHER PUBLICATIONS

Notice of Allowance for U.S. Appl. No. 17/503,890 dated Mar. 27, 2023, 9 pages long.

(Continued)

Primary Examiner — Thong Q Le

(74) Attorney, Agent, or Firm — Wegman Hessler Valore

(57) ABSTRACT

An integrated circuit device can be configured to characterize portions of a resistive switching device array according to one or more operational characterizations. The memory device can store trim instructions defining signal processes implementing the operational characterizations. Examples of resistive switching device characterizations can include: a physical unclonable feature (PUF) memory characterization, a one-time programmable (OTP) memory characterization, a many-time programmable (MTP) memory characterization, and a random number generation (RNG) memory characterization, among others. The integrated circuit device can characterize portions of the resistive switching device array in response to an instruction from an external host device, exposing control over the selective characterization of the portions of the resistive switching device array to the external host device.

#### 20 Claims, 15 Drawing Sheets

#### 2013/0094294 A1 4/2013 Kwak et al. Related U.S. Application Data 2013/0301336 A1 11/2013 Sills 1/2014 Aoki et al. 2014/0027699 A1 Provisional application No. 63/005,879, filed on Apr. 2014/0036587 A1 2/2014 Tannhof et al. 6, 2020. 2014/0173184 A1 6/2014 Kim et al. 8/2014 Perniola 2014/0226391 A1 8/2014 Givant et al. Int. Cl. 2014/0233339 A1 (51)12/2014 Rogers et al. 2014/0372743 A1 G11C 7/24 (2006.01)12/2015 Goda et al. 2015/0378815 A1 G11C 13/00 (2006.01)2016/0086670 A1 3/2016 Gross et al. U.S. Cl. (52)2016/0099810 A1 4/2016 Li et al. CPC ...... *G06F 3/0673* (2013.01); *G11C 13/0023* 2016/0165642 A1 6/2016 Lunden et al. 2016/0225824 A1 8/2016 Jo et al. (2013.01); *G11C 13/0069* (2013.01); *G11C* 2017/0048849 A1 2/2017 Fiallos et al. *13/0097* (2013.01) 3/2017 Roy 2017/0062049 A1 (58)Field of Classification Search 2017/0200508 A1 7/2017 Grigoriev CPC ........ G11C 16/26; G11C 16/34; G11C 11/56; 7/2017 Kelly 2017/0212687 A1 9/2017 Tanamoto 2017/0272258 A1 G11C 13/0023; G11C 13/0026; G11C 2017/0278577 A1 9/2017 La Rosa et al. 13/0028; G11C 13/0069; G11C 2018/0137927 A1 5/2018 Zhang 2013/0054; G11C 13/0064; G11C 6/2018 Hung 2018/0176012 A1 2029/4402; G11C 2029/5002; G11C 8/20; 11/2018 Kvatinsky 2018/0316493 A1 2018/0349148 A1 12/2018 Ish G06F 12/0246; G06F 12/1009; G06F 4/2019 Asnaashari et al. 2019/0103162 A1 12/1475; G06F 3/0688; G06F 21/72; 5/2019 Lee et al. 2019/0130953 A1 G06F 13/1668; G06F 21/44; G06F 21/73; 2019/0130971 A1 5/2019 Rajamohanan G06F 21/34; G06F 21/52; G06F 21/75; 6/2019 Mirichigni et al. 2019/0198099 A1 G06F 21/78 7/2019 Quan 2019/0215739 A1 8/2019 Lai et al. 2019/0252029 A1 See application file for complete search history. 2019/0253266 A1 8/2019 Lee 8/2019 Asnaashari 2019/0259452 A1 **References Cited** (56)9/2019 Hu 2019/0272115 A1 2019/0272882 A1 9/2019 Guy et al. U.S. PATENT DOCUMENTS 2019/0278687 A1 9/2019 Kameo 9/2019 Lee 2019/0279709 A1 5/1997 Tang 5,629,892 A 10/2019 Kim 2019/0304527 A1 10/1998 Hollmer 5,828,601 A 2019/0304557 A1 10/2019 Her et al. 5/2000 Jenq 6,057,575 A 11/2019 Gopinath 2019/0348112 A1 10/2000 Eitan et al. 6,128,226 A 2020/0066984 A1 2/2020 Liu 7/2001 Cremonesi et al. 6,268,247 B1 6/2020 Kim 2020/0183614 A1 7,715,246 B1 5/2010 Kim 6/2020 Hung 2020/0186339 A1 12/2010 Thummalapally et al. 7,848,130 B1 2020/0192970 A1 6/2020 Ma 10/2012 Takagi et al. 8,279,657 B2 6/2020 Edge 2020/0196101 A1 3/2015 Mu et al. 8,995,200 B1 8/2020 Jo et al. 2020/0259081 A1 3/2016 Tendulkar 9,276,210 B1 2020/0295249 A1 9/2020 Ambrose 9,318,196 B1 4/2016 Kasai et al. 10/2020 Ciprut 2020/0312408 A1 9,466,376 B1 10/2016 Lee et al. 11/2020 Zhang 2020/0350030 A1 9,502,110 B1 11/2016 Tailliet 12/2020 Kozicki 2020/0381372 A1 9,767,901 B1 9/2017 Sharma et al. 3/2021 Lee 2021/0083886 A1 2/2020 Shieh 10,572,190 B2 2021/0135886 A1 5/2021 Lee 6/2020 Ryu 10,700,878 B1 2021/0203513 A1 7/2021 Chang 2/2021 Huang 10,910,051 B1 2021/0280781 A1 9/2021 Kim 10,990,542 B2 \* 4/2021 Ju ..... G06F 12/1475 2021/0312984 A1 10/2021 Jo et al. 11,537,754 B1 12/2022 Jameson 10/2021 Jo et al. 2021/0312985 A1 2003/0016572 A1 1/2003 Pascucci 2022/0005527 A1 1/2022 Nazarian 7/2004 Wuidart et al. 2004/0136238 A1 1/2022 Fourquin 2022/0029835 A1 2004/0141379 A1 7/2004 La Malfa et al. 5/2022 Otsuka et al. 2022/0146922 A1 2005/0105329 A1 5/2005 Nazarian 2022/0199187 A1 6/2022 Rayaprolu et al. 2005/0270833 A1 12/2005 Seevinck et al. 2022/0232360 A1 7/2022 Wei et al. 2006/0044049 A1 3/2006 Ouellette 2007/0242518 A1 10/2007 Seidel OTHER PUBLICATIONS 2007/0274120 A1 11/2007 Pinnow et al. 1/2008 Scheuerlein et al. 2008/0025068 A1 2008/0137436 A1 6/2008 Salter et al. Final Office Action for U.S. Appl. No. 17/899,356 dated Jul. 12, 7/2008 Suh et al. 2008/0176349 A1 2023, 13 pages long. 2008/0198640 A1 8/2008 Leistad Shrivastava, Ayush, RRAM-based PUF: Design and Applications in 2009/0212347 A1 8/2009 Goarin et al. Cryptography, Aug. 2015, Arizona State University, 68 pages. 11/2009 Majewski et al. 2009/0285007 A1 Notice of Allowance for U.S. Appl. No. 17/503,924 dated Jul. 14, 2010/0054045 A1 3/2010 Ho et al. 4/2010 Miyairi et al. 2010/0102313 A1 2023, 19 pages long. 2011/0051500 A1 3/2011 Takagi et al. Seyed Nima Mozaffari Mojaveri, "Design and Test of Digital 2011/0062433 A1 3/2011 Yamazaki Circuits and Systems Using CMOS and Emerging Resistive Devices", 3/2011 Yamazaki et al. 2011/0062435 A1 May 1, 2018, Southern Illinois University at Carbondale, All pages. 2011/0069554 A1 3/2011 Lo Giudice et al. Notice of Allowance for U.S. Appl. No. 17/223,817 dated Mar. 10, 2011/0122714 A1 5/2011 Chen et al. 2022, 12 pages long. 1/2012 Steiner et al. 2012/0005558 A1 Notice of Allowance for U.S. Appl. No. 17/223,827 dated Apr. 26, 2012/0069622 A1 3/2012 Parkinson et al. 2022, 15 pages long. 4/2012 Kawabata 2012/0081946 A1 Notice of Allowance for U.S. Appl. No. 17/223,832 dated May 2, 2012/0239976 A1 9/2012 Cometti et al.

2022, 13 pages long.

2012/0243346 A1

9/2012 Chen et al.

### (56) References Cited

#### OTHER PUBLICATIONS

Meng-Yi Wu, et al., "A PUF Scheme Using Competing Oxide Rupture with Bit Error Rate Approaching Zero", ISSCC 2018, Session 7, Neuromorphic, Clocking and Security Circuits 7.7, 2018 IEEE International Solid-State Circuits Conference, pp. 130-132. Non-Final Office Action for U.S. Appl. No. 17/899,356 dated Mar. 7, 2023, 21 pages long. Non-Final Office Action for U.S. Appl. No. 17/503,924 dated Mar. 27, 2023, 23 pages long. Notice of Allowance for U.S. Appl. No. 17/899,356 dated Oct. 19, 2023, 18 pages long.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

US 12,087,397 B1

FIG. 6

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

## DYNAMIC HOST ALLOCATION OF PHYSICAL UNCLONABLE FEATURE OPERATION FOR RESISTIVE SWITCHING MEMORY

## CROSS REFERENCE TO RELATED APPLICATION

The present application for patent is a continuation-in-part of U.S. patent application Ser. No. 17/223,824 filed Apr. 6, 2021 and titled DISTINCT CHIP IDENTIFIER SEQUENCE UTILIZING UNCLONABLE CHARACTER-ISTICS OF RESISTIVE MEMORY ON A CHIP, which claims the benefit of U.S. Provisional Application No. 63/005,879 filed Apr. 6, 2020, each of which are hereby incorporated by reference herein in their respective entireties and for all purposes.

#### INCORPORATION BY REFERENCE

Each of the following: U.S. patent application Ser. No. 17/223,817 filed Apr. 6, 2021, and U.S. patent application Ser. No. 17/223,816 filed Apr. 6, 2021, are hereby incorporated by reference herein in their respective entireties and for 25 all purposes.

#### TECHNICAL FIELD

The subject disclosure relates generally to two-terminal <sup>30</sup> resistive switching memory, and as one illustrative example, enabling a host device to characterize cells of a resistive switching memory for differing cell operations.

#### BACKGROUND

Resistive-switching memory represents a recent innovation within the field of integrated circuit technology. While much of resistive-switching memory technology is in the development stage, various technological concepts for resistive-switching memory have been demonstrated and are in one or more stages of verification to prove or disprove associated theories or techniques. Resistive-switching memory technology is expected to show compelling evidence of substantial advantages over competing technologies in the semiconductor electronics industry in the near future.

Proposals for practical utilization of resistive-switching technology to memory applications for electronic devices 50 have been put forth. For instance, resistive-switching elements are often theorized as viable alternatives, at least in part, to metal-oxide semiconductor (MOS) type memory transistors employed for electronic storage of digital information. Models of resistive-switching memory devices provide some potential technical advantages over non-volatile FLASH MOS type transistors, for instance.

Monolithic integration of resistive-switching memory within integrated circuit processes has been supported by other proposed models. Some models of resistive-switching 60 memory are designed for front-end-of-line processing on a substrate, whereas other models are designed for back-end-of-line processing above the substrate. As a result, resistive-switching memory is expected to be compatible with embedded memory applications to support various integrated 65 circuit devices as well as a stand-alone integrated circuit memory chip.

2

In light of the above, the Assignee of the present disclosure continues to develop and pursue practical utilizations of resistive-switching technology.

#### SUMMARY

The following presents a simplified summary of the specification in order to provide a basic understanding of some aspects of the specification. This summary is not an extensive overview of the specification. It is intended to neither identify key or critical elements of the specification nor delineate the scope of any particular embodiments of the specification, or any scope of the claims. Its purpose is to present some concepts of the specification in a simplified form as a prelude to the more detailed description that is presented in this disclosure.

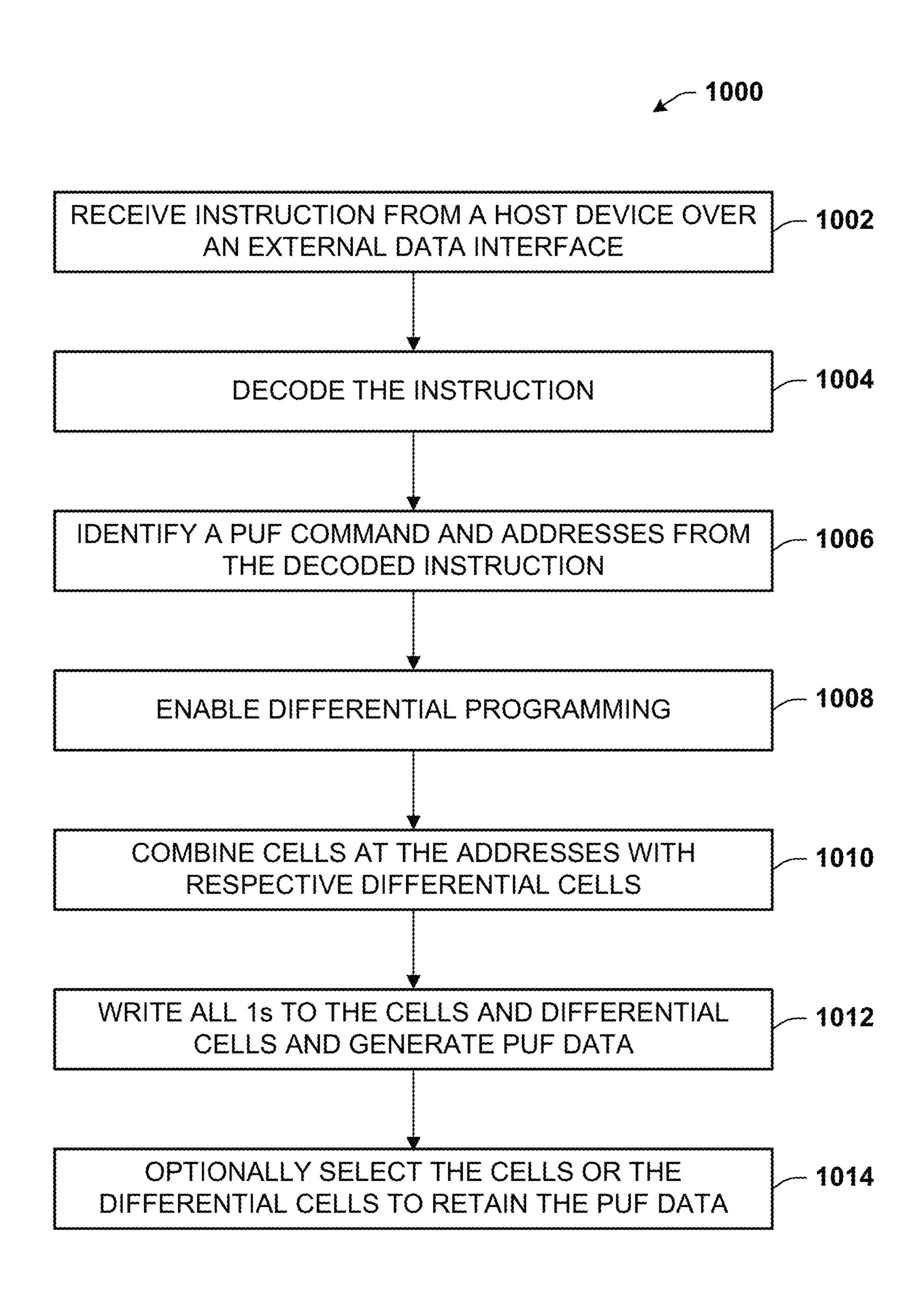

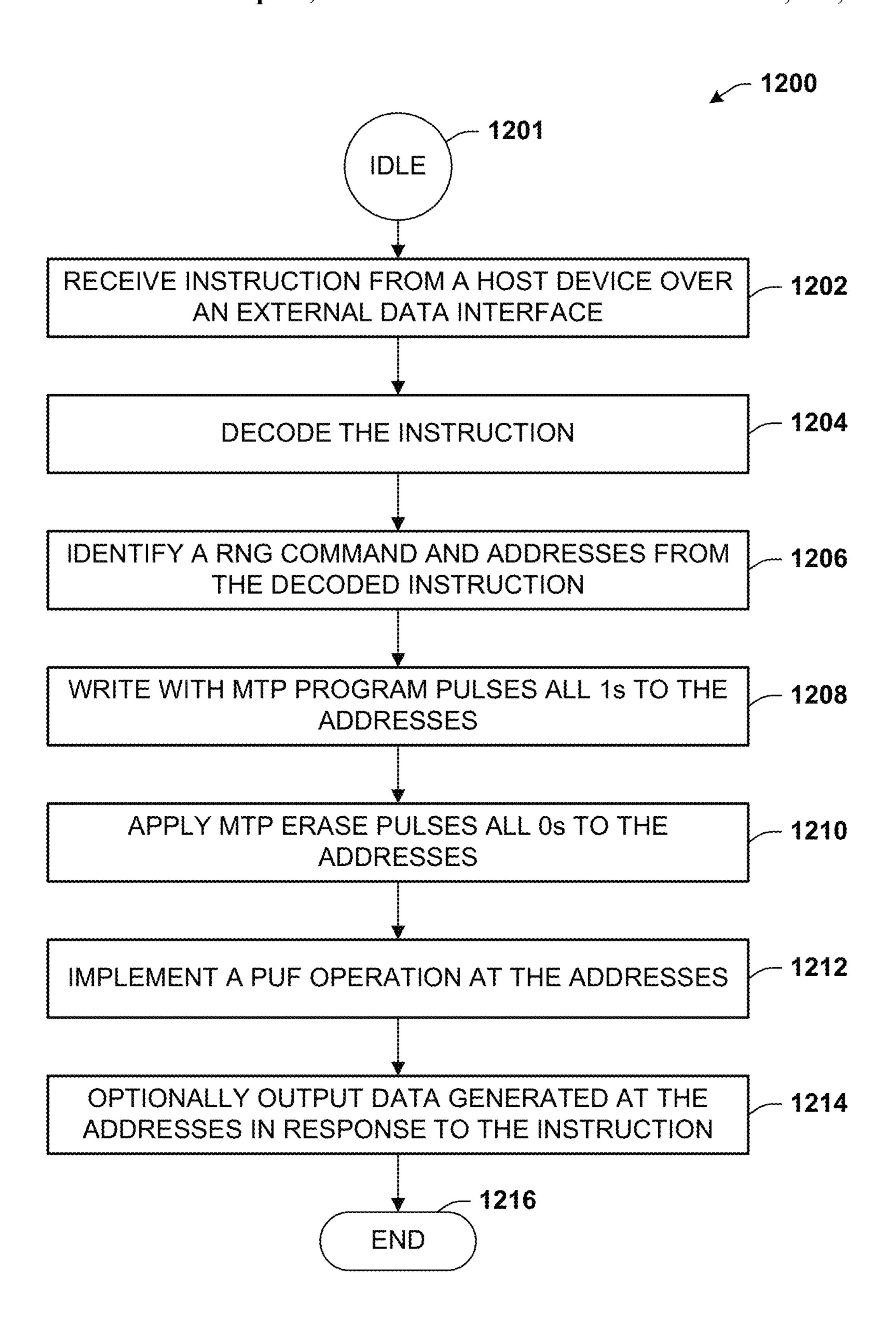

Embodiments of the present disclosure provide a memory device comprising an array of resistive switching memory cells. According to various embodiments, the memory 20 device is configured to characterize subsets of resistive switching memory cells of the array in response to a host command. The memory device can store trim instructions defining memory characterizations and suitable operations consistent with the memory cell characterizations. Examples of memory characterizations disclosed herein include: a physical unclonable feature (PUF) memory characterization, a one-time programmable (OTP) memory characterization, a many-time programmable (MTP) memory characterization, and a random number generation (RNG) memory characterization, among others. Upon decoding the host command, the memory device can determine an operation command and one or more addresses of memory cells specified by the host command. Stored trim instructions can be referenced to configure memory cells at addresses speci-35 fied by the host command consistent with a characterization associated with the operation command, and implement the operation command consistent with the characterization. In at least some embodiments, the host command can specify a type of operation to be implemented on specific memory addresses of a resistive switching memory array. The type of operation can include a PUF operation, an OTP operation, a MTP operation or a RNG operation, among others. In response to the host command, a disclosed memory device can prepare memory cells at the specified memory addresses for the type of operation based on stored trim instructions, and implement the operation at least in part on the specified memory addresses.

In one or more embodiments of the present disclosure, provided is an electronic device. The electronic device can comprise an interface configured to receive at the electronic device a communication from a host device that is external to the electronic device, wherein the communication includes first data indicative of an address of a group of memory cells of the plurality of resistive switching memory cells of the resistive switching memory array for implementing a memory command and second data specifying the memory command from a set of memory commands. Additionally, the electronic device can comprise a set of trims that store instructions for configuring the resistive switching memory array to implement memory commands of the set of memory commands and for executing the memory command, wherein the set of trims includes a first trim defining a configuration of the resistive switching memory array and of program signal characteristics for implementing a physical unclonable feature (PUF) write command for the group of memory cells. Further, the electronic device can comprise a memory controller configured to characterize the group of

memory cells associated with the address indicated by the first data with a characterization matching the memory command specified by the second data. The memory controller can also be configured to implement the memory command at least on the group of the plurality of resistive switching memory cells having the characterization consistent with the memory command. In addition, the memory controller can be configured to characterize the group of memory cells as PUF memory cells in response to the memory command being the PUF write command and implement the PUF write command on a set of native resistive switching memory cells of the plurality of resistive switching memory cells that includes at least the group of memory cells in response to the memory command being the PUF write command.

In further disclosed embodiments, there is described a method for operating a memory controller of a resistive switching memory array comprising a plurality of resistive switching memory cells. The method can comprise receiv- 20 ing a command from a host device external to the resistive switching memory array, and can comprise decoding the command to determine a selection of memory cells of the resistive switching memory array. In some embodiments, the selection of memory cells can be a portion of the plurality of 25 resistive switching memory cells. The method can also comprise determining a memory operation to be implemented on the selection of memory cells in response to the command, the memory operation is determined to be one memory operation selected from a group of memory opera- 30 tions consisting of: a one-time programmable (OTP) memory operation, a many-time programmable (MTP) memory operation, a random number generation (RNG) memory operation and a physical unclonable feature (PUF) memory operation. Additionally, in response to determining 35 the memory operation is the RNG memory operation or the PUF memory operation, the method can further comprise enabling differential programming for the selection of memory cells, and implementing the RNG memory operation or the PUF memory operation at least on the selection 40 of memory cells.

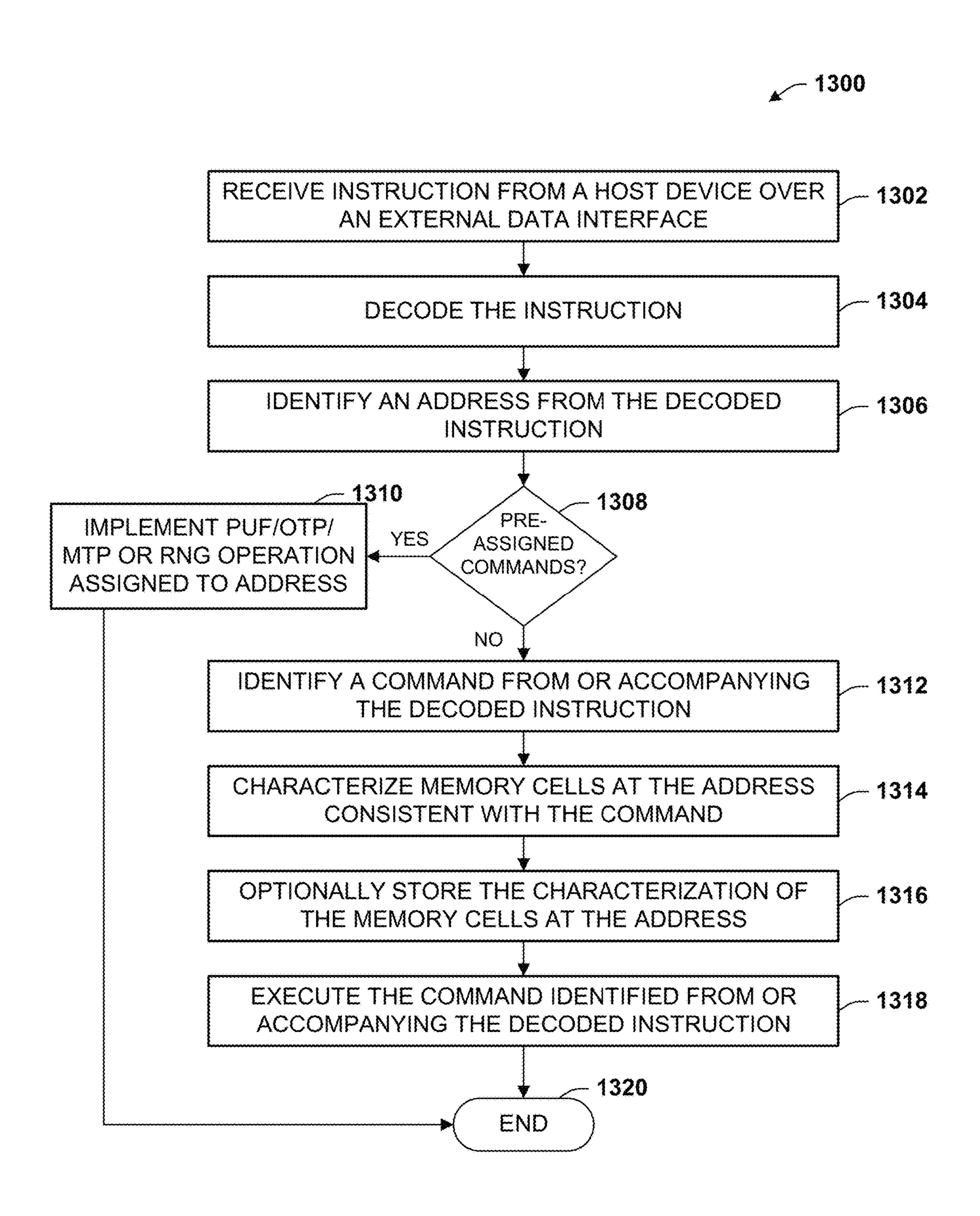

In still further embodiments, disclosed is a method. The method can comprise receiving at a resistive switching memory device over an external command interface an instruction from a host device external to the resistive 45 switching memory device, and decoding the instruction. The method can further comprise determining, from the decoded instruction, an address within an array of resistive switching memory associated with a group of resistive switching memory cells of the array. In response to the address within 50 the array of resistive switching memory having no preassigned characterization defining a memory command for the address, the method can additionally comprise determining a memory command from the decoded instruction or provided in conjunction with the instruction, characterizing 55 the group of resistive switching memory cells at the address according to the determined memory command and implementing the memory command at least on the group of resistive switching memory cells.

The following description and the drawings set forth 60 certain illustrative aspects of the specification. These aspects are indicative, however, of but a few of the various ways in which the principles of the specification may be employed. Other advantages and novel features of the specification will become apparent from the following detailed description of 65 the specification when considered in conjunction with the drawings.

4

#### BRIEF DESCRIPTION OF THE DRAWINGS

Various aspects or features of this disclosure are described with reference to the drawings, wherein like reference numerals are used to refer to like elements throughout. In this specification, numerous specific details are set forth in order to provide a thorough understanding of this disclosure. It should be understood, however, that certain aspects of the subject disclosure may be practiced without these specific details, or with other methods, components, materials, etc. In other instances, well-known structures and devices are shown in block diagram form to facilitate describing the subject disclosure.

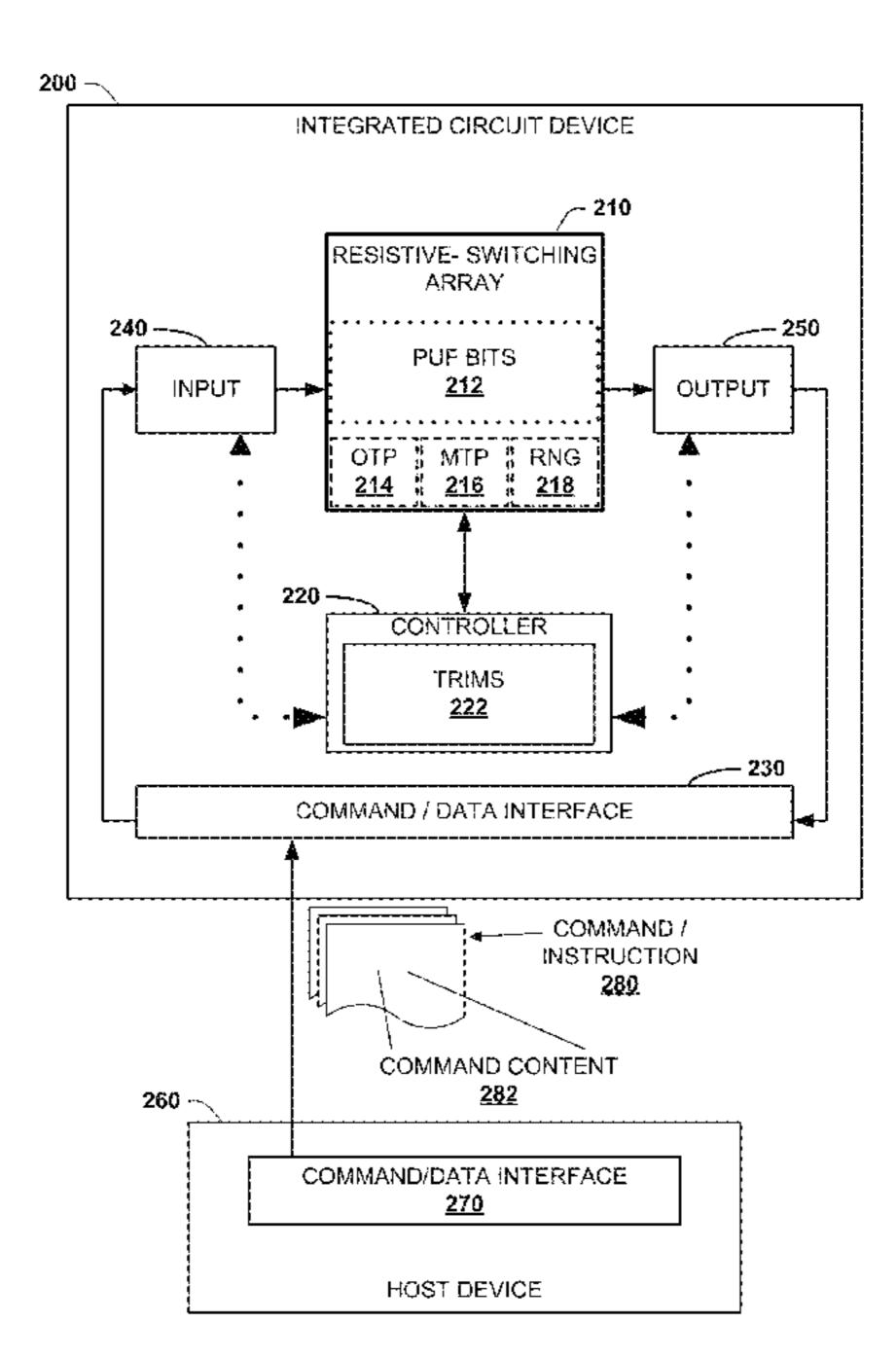

- FIG. 1 depicts a block diagram of a sample electronic device for operationally characterizing subsets of resistive switching (RS) devices in an array, in some embodiments;

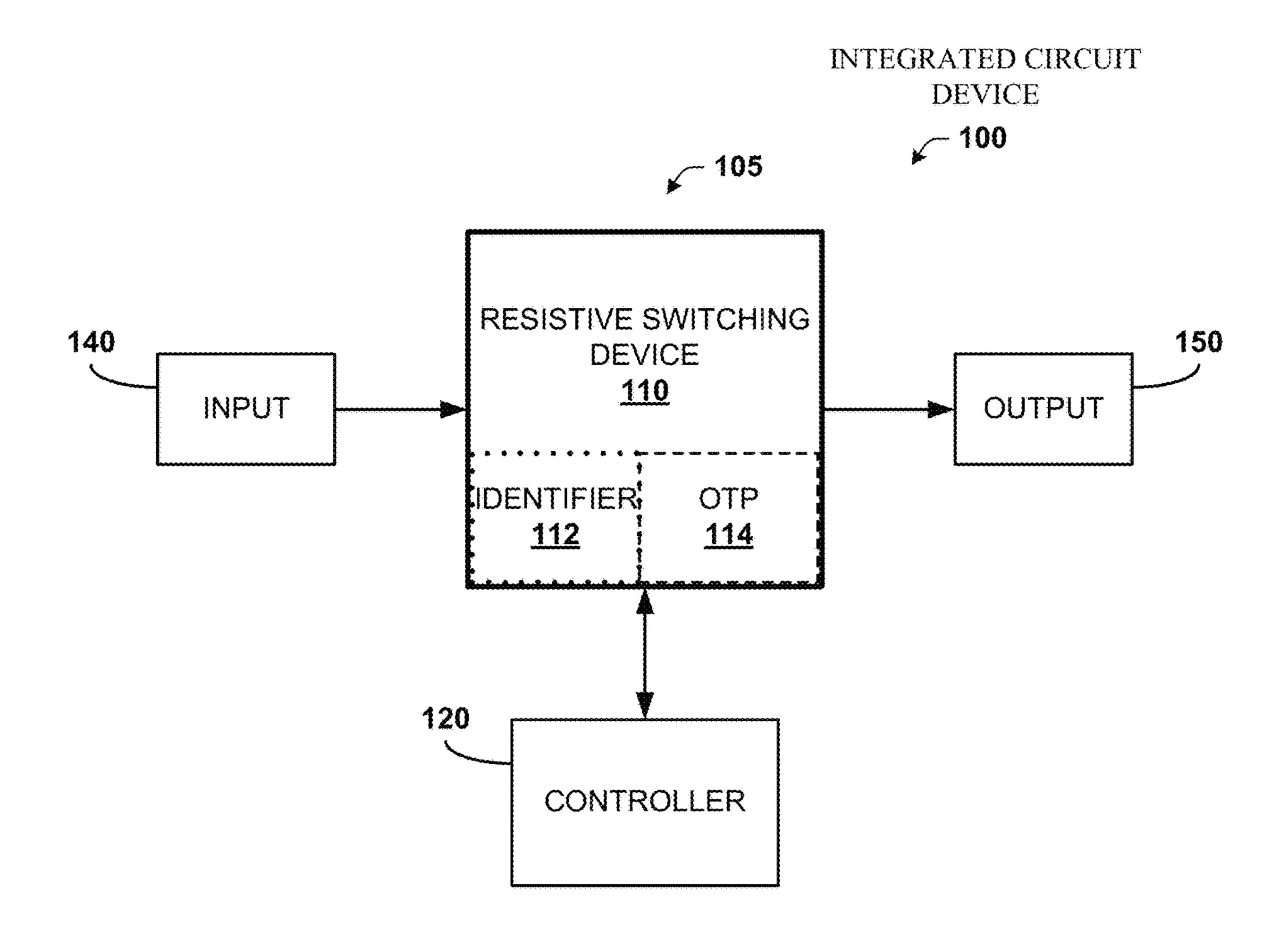

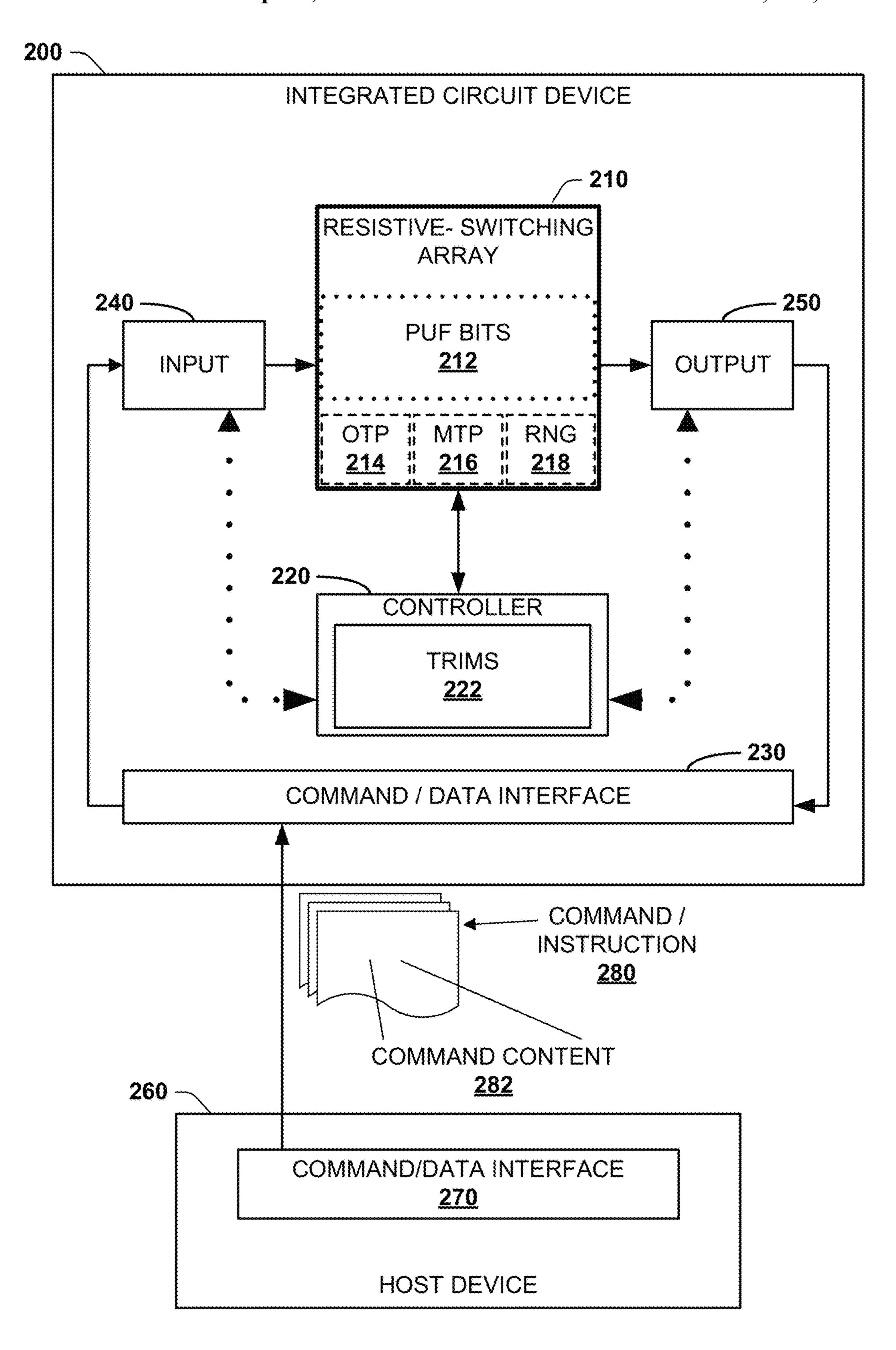

- FIG. 2 illustrates a block diagram of an example IC device that characterizes operation of subsets of RS devices in a RS array in response to an external host command;

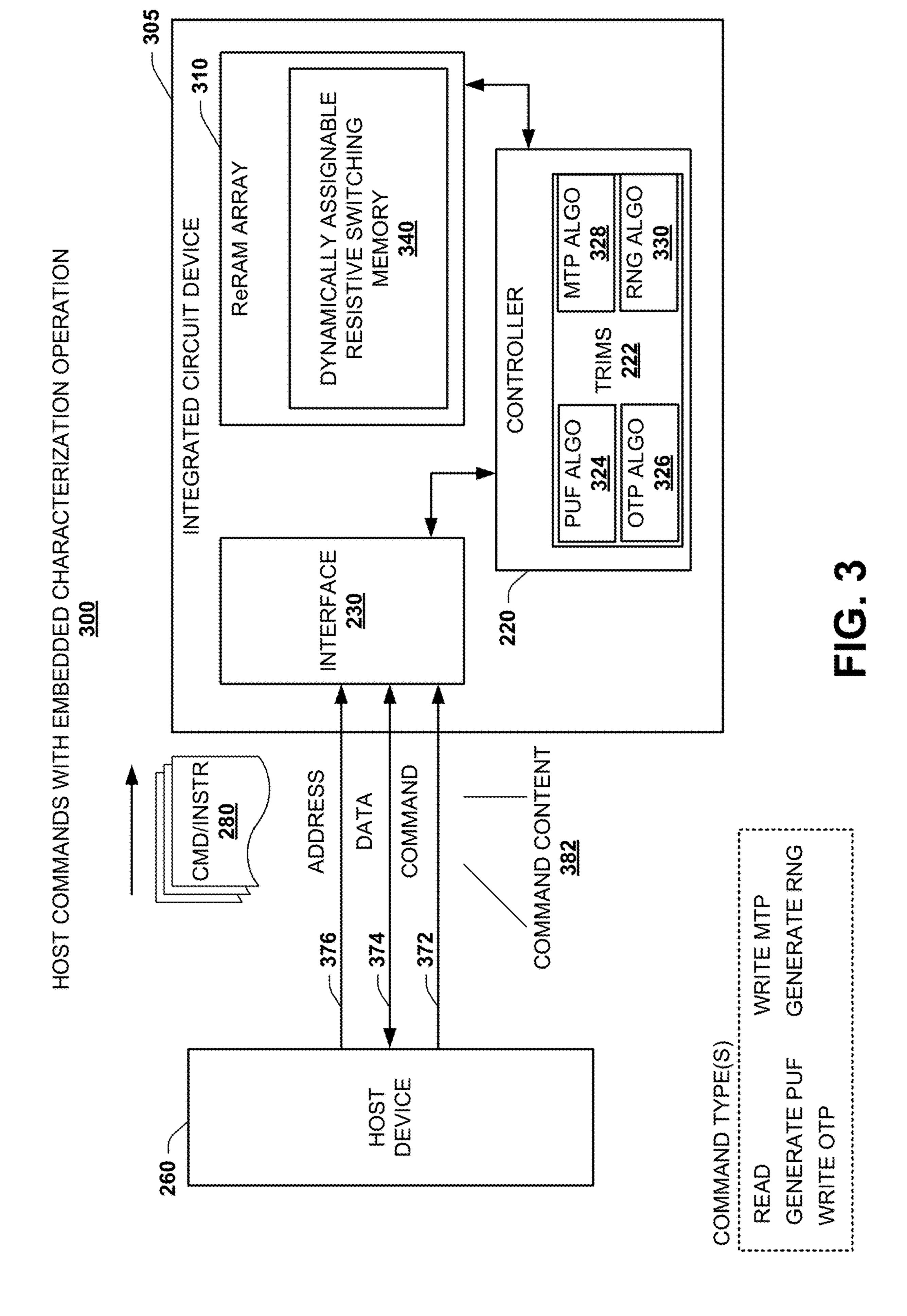

- FIG. 3 depicts a block diagram of a sample IC device enabling an external host device to operationally characters subsets of RS devices in a RS array; in further embodiments;

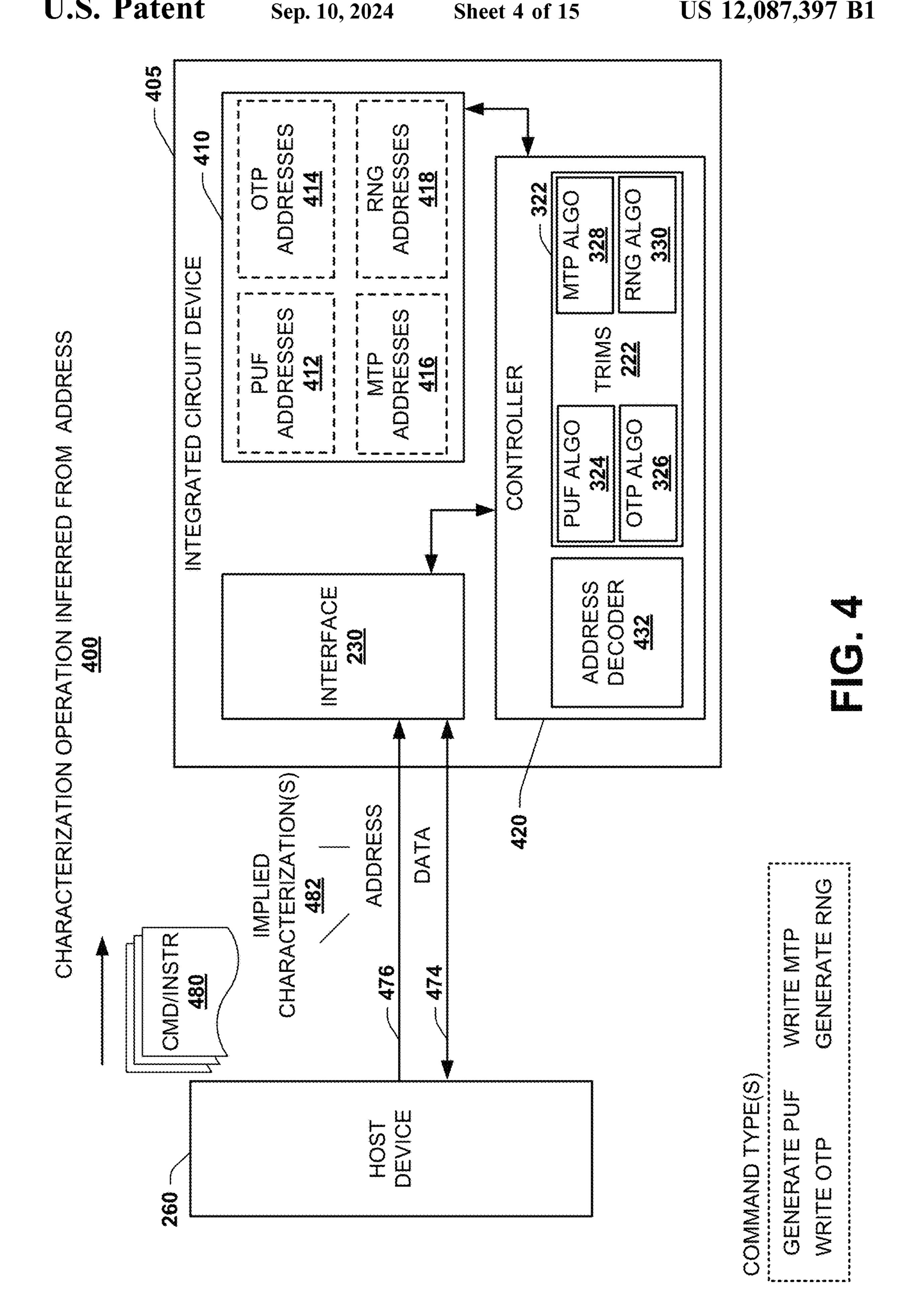

- FIG. 4 illustrates a block diagram of a sample IC device having pre-assigned operational characteristics assigned to groups of addresses in the RS array, in an embodiment(s);

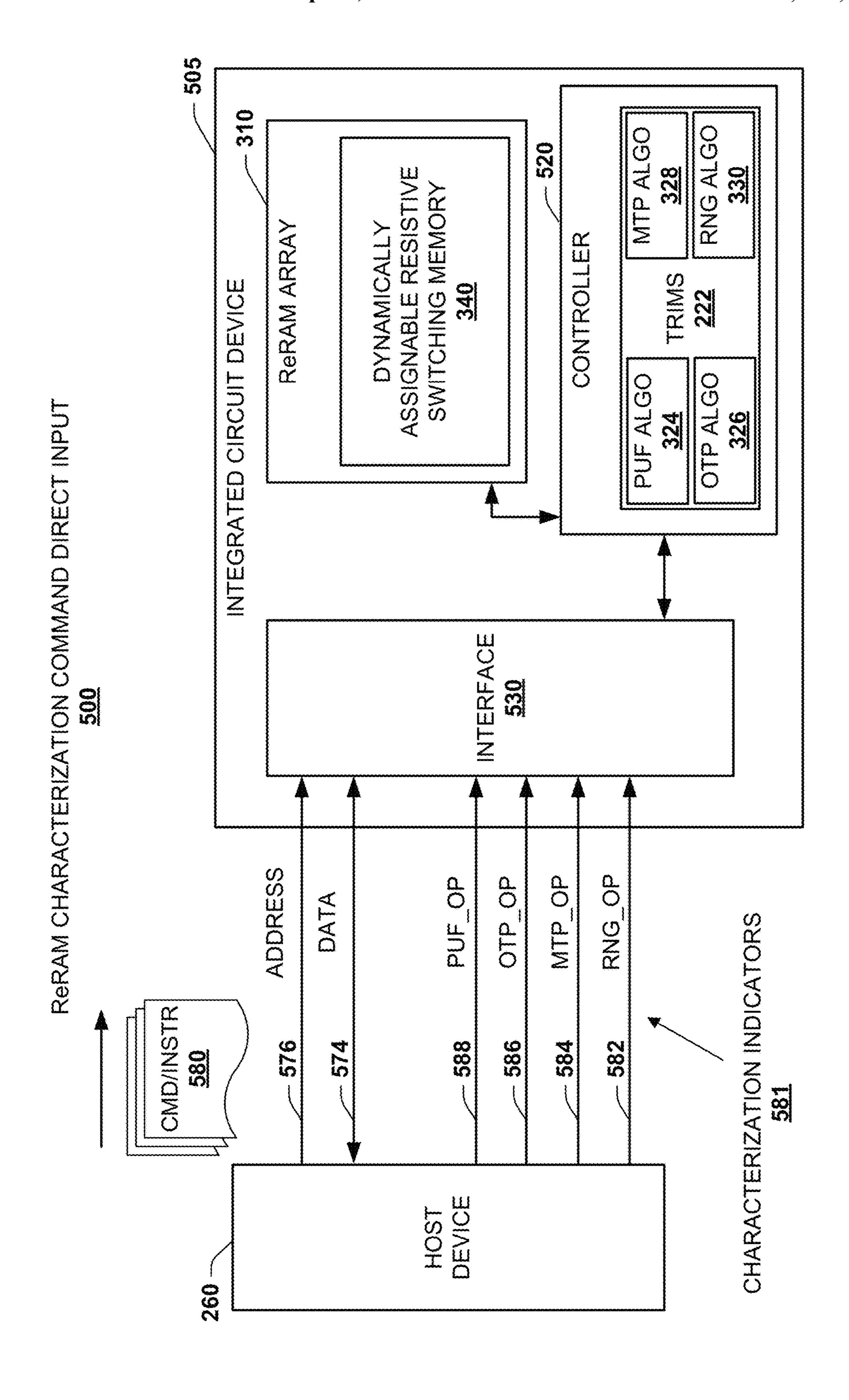

- FIG. 5 illustrates a block diagram of a sample RS memory device with operational characterization settable by an external host device, in further embodiments;

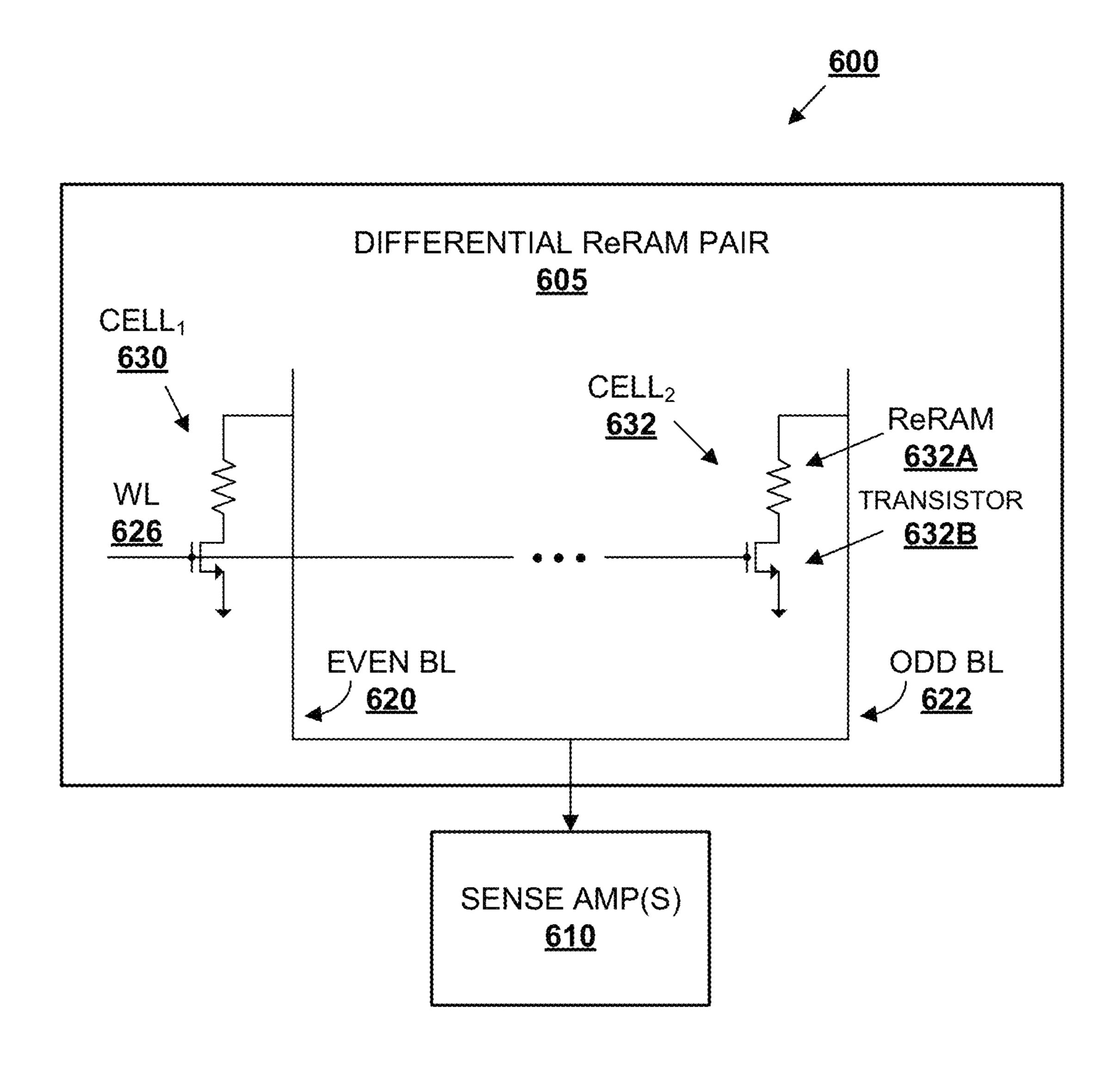

- FIG. 6 depicts a block diagram of an example differential resistive switching memory coupling for differential memory operations, in one or more embodiments;

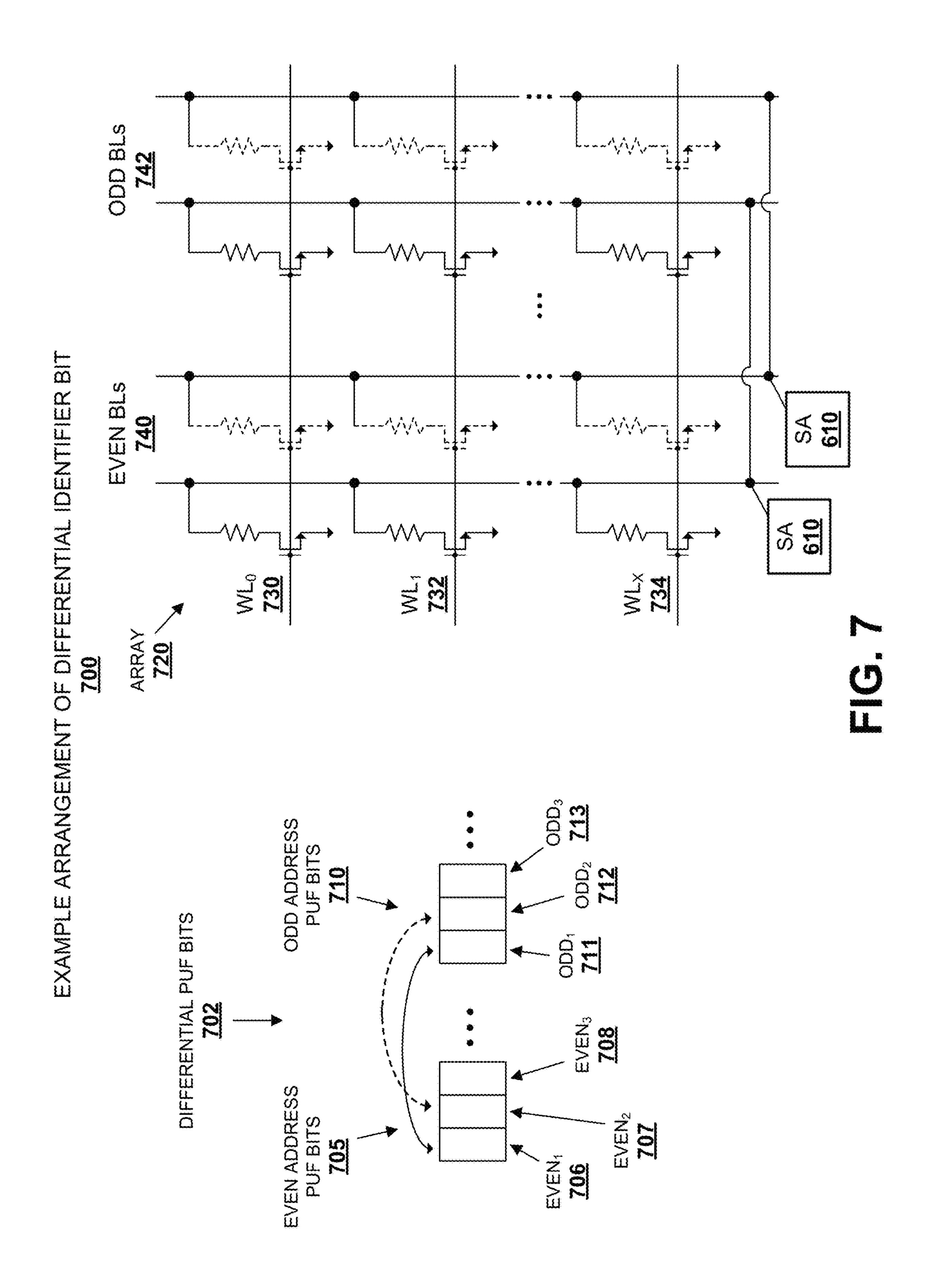

- FIG. 7 depicts a block diagram of an example multi-bit differential bit coupling for physical unclonable feature (PUF) differential sequence generation, in an embodiment (s);

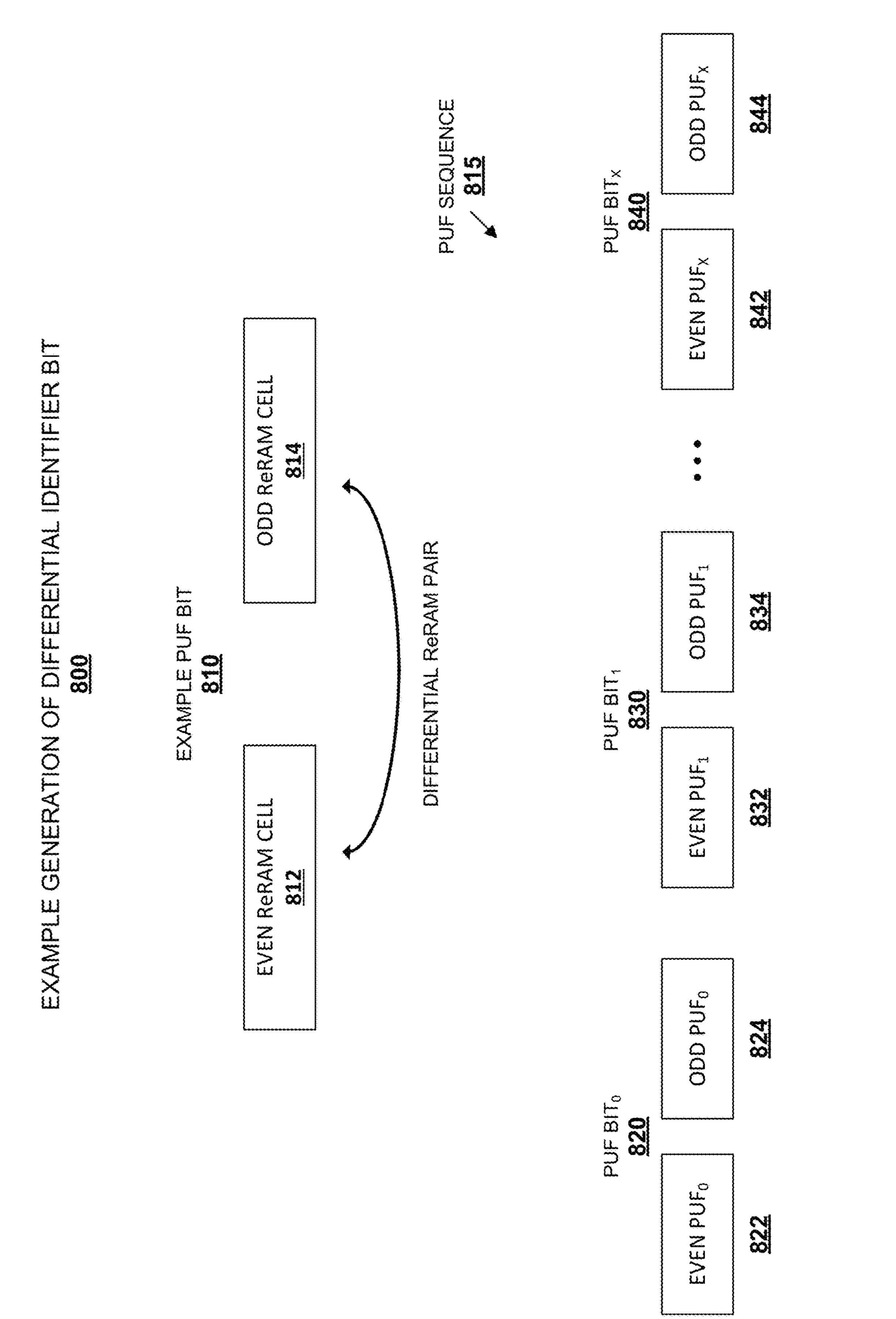

- FIG. 8 illustrates an example diagram of a sequence of differential PUF bits according to still further embodiments of the present disclosure;

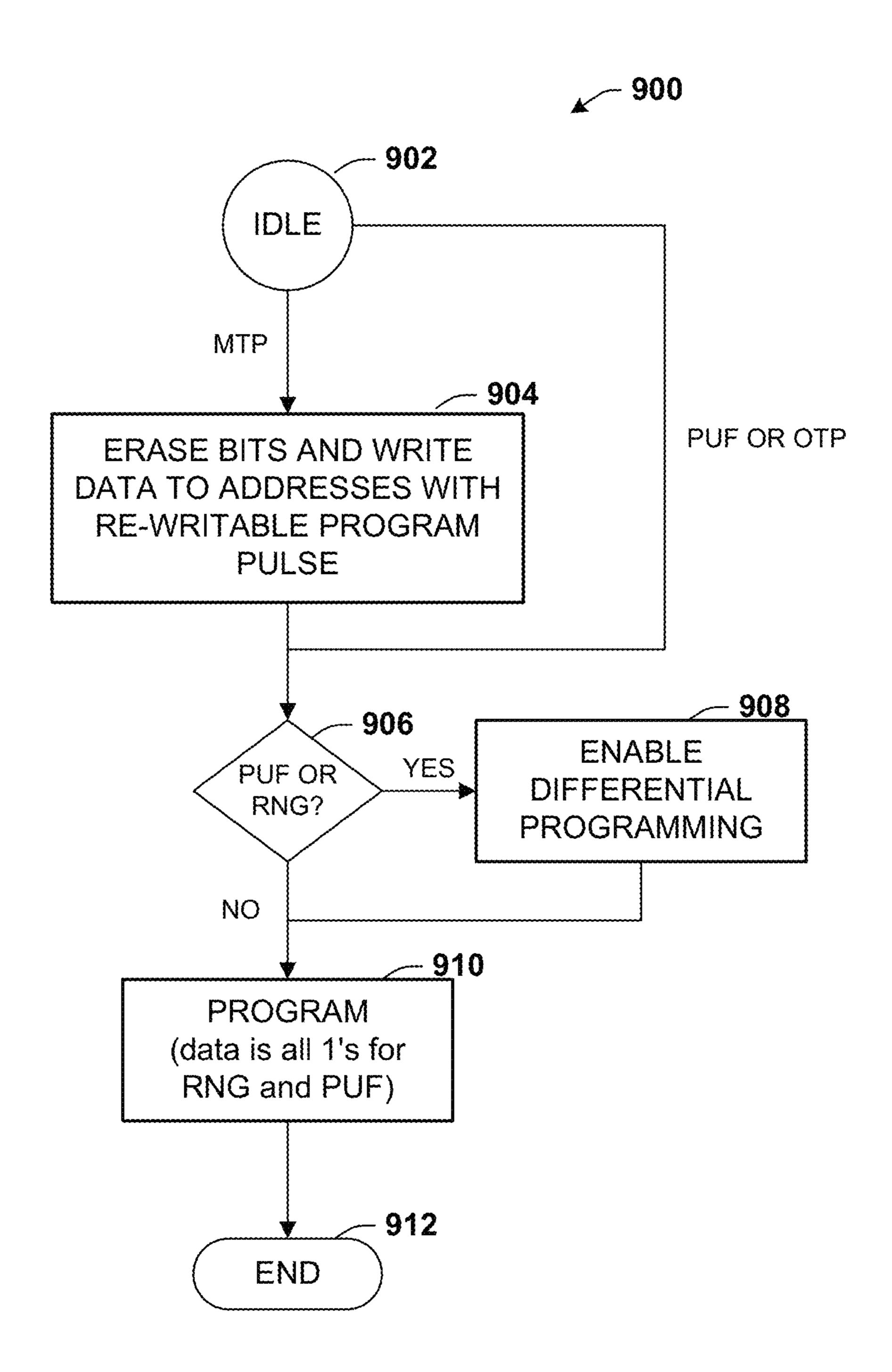

- FIG. 9 depicts a flowchart of a sample method for managing operational characteristics of a RS array in response to external host device commands, in an embodiment;

- FIG. 10 illustrates a flowchart of an example method for implementing a PUF operation on host-selected addresses within an RS array, in additional embodiments;

- FIG. 11 depicts a flowchart of a sample method of implementing differential PUF data generation in response to an external host command, in further embodiments;

- FIG. 12 illustrates a flowchart of an example method for implementing a random number generation (RNG) command on a RS array, in other embodiments;

- FIG. 13 depicts a flowchart of a sample method for managing operational characteristics of a RS array in response to external host commands, in additional embodiments;

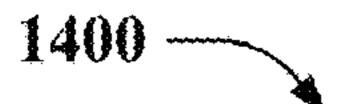

- FIG. 14 illustrates a block diagram of a sample electronic operating environment in accordance with certain embodiments presented herein;

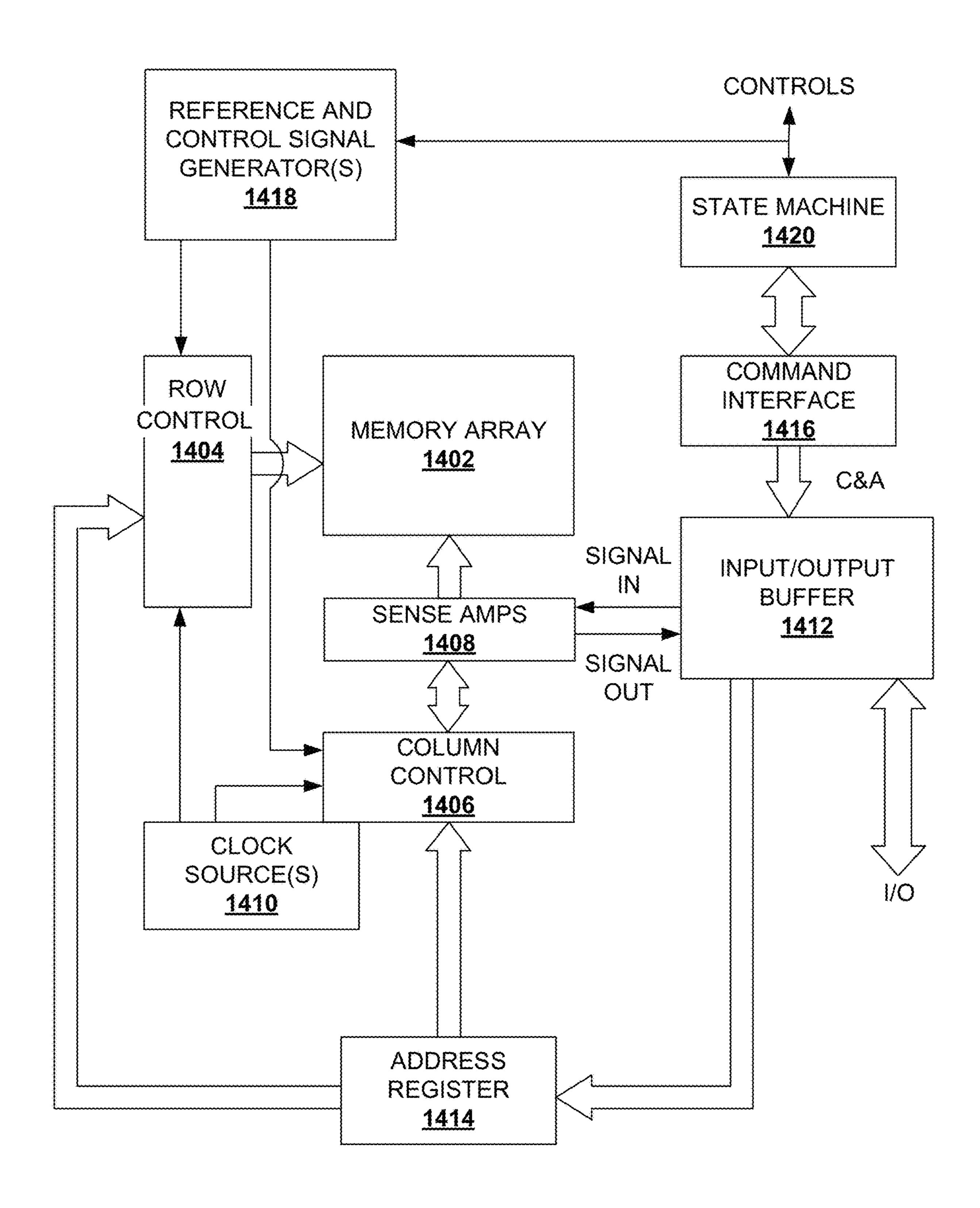

- FIG. 15 depicts a block diagram of an example computing environment for implementing one or more disclosed embodiments of the present disclosure.

#### DETAILED DESCRIPTION

#### Introduction

One or more embodiments of the present disclosure provide a two-terminal resistive switching memory array in

which subsets of memory cells of the array can be characterized or configured for disparate operations, including operations not traditionally associated with non-volatile memory. Examples of non-traditional operations can include random number generation (RNG) operations and physical 5 unclonable feature (PUF) operations by applying disclosed signal processes and digitizing results of those signal processes. In addition to the foregoing, disclosed resistive switching memory arrays can export operational characterization to an external host device in one or more disclosed 10 embodiments. In at least one embodiment, a host command can specify (or imply) a type of operation for memory cells at an identified address. A disclosed resistive switching memory device can decode the command, determine the type of operation, characterize memory cells at the identified 15 address for the type of operation in response to the host command, and implement the type of operation on the characterized memory cells.

Embodiments of the present disclosure provide mechanisms by which a host device can characterize subsets of an 20 array of resistive switching memory devices for particular types of operation. Trim settings stored at the array or at a memory device comprising the array can store configuration settings and operation requirements for a set of operation types. Examples of such operation types can include: many- 25 time programmable (MTP) operation—also referred to as rewritable operation, one-time programmable (OTP) operation, RNG operation and PUF operation, among other types of operations. By reference the trim settings, a disclosed memory controller can characterize or configure memory 30 devices for a particular type of operation, and determine requirements (e.g., applied signal characteristics, differential program constraints—e.g., see FIGS. 6-8, infra, or the like) to implement the operations on the resistive switching memory devices. In one embodiment, a host device com- 35 mand can explicitly specify a selected operation type from a set of operation types stored in trim settings of the memory device. In another embodiment, the host device can set 'high' a hi/low pin of a set of hi/low pins respectively assigned to the types of operation in conjunction with a host 40 device command. In yet another embodiment, groups of addresses of the array can be pre-assigned to respective operation types, and a host command can specify an address pre-assigned to one operation type to instruct the memory device to execute the pre-assigned operation type of memory 45 cells located (or associated with, in the case of a virtual addressing system) at the specified address.

A PUF operation (also referred to herein as an identifier operation—e.g., producing substantially unique data—or other suitable nomenclature) can leverage stochastic or 50 substantially stochastic physical characteristics of nanoscale resistive switching devices to generate data. Being generally random, stochastic features of resistive switching devices can be leveraged to produce data that has little to no correlation among individual resistive switching memory 55 devices of an array of such resistive switching memory devices. As a result, that data can be suited to applications requiring distinct or unique identification, such as identification and authorization applications pertaining to a device (e.g., a semiconductor die—also referred to herein as a 60 semiconductor chip—or a semiconductor wafer, group(s) of dies, group(s) of wafers, an electronic device incorporating a semiconductor die(s), and so forth). Thus, in some examples, identifier data according to various embodiments of the present disclosure can generate a chip ID utilizing a 65 resistive switching array fabricated on a given chip. Further, highly non-correlated data can also be utilized for security

6

applications, such as random number generation, cryptography key security applications, such as Elliptic Curve cryptography (ECC), Advanced Encryption System (AES) or hash-based message authentication code (HMAC), and the like.

In addition, stochastic characteristics of disclosed resistive switching device processes can be utilized to generate high-entropic data sequences that meet or exceed scientific standards for randomness, and are comparable with high-quality cryptographic random number sources. Moreover, the switching device processes utilized to generate data sequences can be selected from native resistive switching devices (e.g., devices that have not previously been programmed, and are original or virgin devices post-fabrication) that most closely leverage nano-scale unclonable physical characteristics of the resistive switching devices. This achieves high non-correlation among devices on a die (intra-die), among dies on a wafer (inter-die) and among wafers in a fabrication facility.

In one or more additional embodiments, some disclosed sequence generation processes can be rendered permanent through one-time programmable processes, allowing a sequence to be reliably re-read over a very large number of read cycles to reliably and accurately reproduce a previously generated data sequence, achieving extremely low bit error rates. In still further embodiments, disclosed processes for generating non-correlated data sequences can involve processes compatible with two-terminal resistive switching device operation, allowing a set of two-terminal resistive switching devices to be selected post-fabrication from any suitable subset of such devices within an array or selected from different resistive switching device arrays on a chip. Systems and methods are further provided to export control of resistive switching device selection, data sequence process selection and process configuration—associated with physically unclonable data sequence generation disclosed herein—to a host device external to the chip following fabrication of the chip. Various other embodiments will be readily apparent based on the disclosure herein and the associated drawings.

As the name implies, a two-terminal resistive switching device has two terminals or electrodes. Herein, the terms "electrode" and "terminal" are used interchangeably; moreover, a two-terminal resistive switching device includes a non-volatile two-terminal memory device as well as a volatile two-terminal switching device. Generally, a first electrode of a two-terminal resistive switching device is referred to as a "top electrode" (TE) and a second electrode of the two-terminal resistive switching device is referred to as a "bottom electrode" (BE), although it is understood that electrodes of two-terminal resistive switching devices can be according to any suitable arrangement, including a horizontal arrangement in which components of a memory cell are (substantially) side-by-side rather than overlying one another. Between the TE and BE of a two-terminal resistive switching device is typically an interface layer sometimes referred to as a switching layer, a resistive switching medium (RSM) or a resistive switching layer (RSL); such devices are not limited to these layers, however, as one or more barrier layer(s), adhesion layer(s), ion conduction layer(s), seed layer(s), particle source layer(s) or the like as disclosed herein, disclosed within a publication incorporated by reference herein, as generally understood and utilized in the art or reasonably conveyed to one of ordinary skill in the art by way of the context provided herein and its addition to the general understanding in the art or the incorporated publications—may be included between or

adjacent one or more of the TE, the BE or the interface layer consistent with suitable operation of such device.

Composition of memory cells, generally speaking, can vary per device with different components, materials or deposition processes selected to achieve desired character- 5 istics (e.g., stoichiometry/non-stoichiometry, volatility/nonvolatility, on/off current ratio, switching time, read time, memory durability, program/erase cycle, and so on). One example of a filamentary-based device can comprise: a conductive layer, e.g., metal, metal-alloy, metal-nitride, 10 (e.g., comprising TiN, TaN, TiW, or other suitable metal compounds), an optional interface layer (e.g., doped p-type (or n-type) silicon (Si) bearing layer (e.g., a p-type or n-type Si bearing layer, p-type or n-type polysilicon, p-type or n-type polycrystalline SiGe, etc.)), a resistive switching 15 layer (RSL) and an active metal-containing layer capable of being ionized. Under suitable conditions, the active metalcontaining layer can provide filament-forming ions to the RSL. In such embodiments, a conductive filament (e.g., formed by the ions) can facilitate electrical conductivity 20 through at least a subset of the RSL, and a resistance of the filament-based device can be determined, as one example, by a tunneling resistance between the filament and the conductive layer. A memory cell having such characteristics may be described as a filamentary-based device.

A RSL (which can also be referred to in the art as a resistive switching media (RSM)) can comprise, e.g., an undoped amorphous Si-containing layer, a semiconductor layer having intrinsic characteristics, a stoichiometric or non-stoichiometric silicon nitride (e.g., SiN, Si<sub>3</sub>N<sub>4</sub>, SiN<sub>x</sub>, 30 etc.), a Si sub-oxide (e.g.,  $SiO_x$  wherein x has a value between 0.1 and 2), a Si sub-nitride, a metal oxide, a metal nitride, a non-stoichiometric silicon compound, and so forth. Other examples of materials suitable for the RSL could include Si<sub>x</sub>Ge<sub>y</sub>O<sub>z</sub> (where x, y and z are respective suitable 35 positive numbers), a silicon oxide (e.g.,  $SiO_N$ , where N is a suitable positive number), a silicon oxynitride, an undoped amorphous Si (a-Si), amorphous SiGe (a-SiGe),  $TaO_B$ (where B is a suitable positive number), HfO<sub>C</sub> (where C is a suitable positive number), TiO<sub>D</sub> (where D is a suitable 40 number),  $Al_2O_E$  (where E is a suitable positive number) and so forth, a nitride (e.g., AlN, SiN), or a suitable combination thereof.

In some embodiments, a RSL employed as part of a non-volatile memory device (non-volatile RSL) can include 45 a relatively large number (e.g., compared to a volatile selector device) of material voids or defects to trap neutral metal particles (e.g., at low voltage) within the RSL. The large number of voids or defects can facilitate formation of a thick, stable structure of the neutral metal particles. In such 50 a structure, these trapped particles can maintain the nonvolatile memory device in a low resistance state in the absence of an external stimulus (e.g., electrical power), thereby achieving non-volatile operation. In other embodiments, a RSL employed for a volatile selector device (vola- 55 tile RSL) can have very few material voids or defects for trapping particles. Because of the few particle-trapping voids/defects, a conductive filament formed in such an RSL can be quite thin (e.g., one to a few particles wide depending on field strength, particle material or RSL material, or a 60 suitable combination of the foregoing), and unstable absent a suitably high external stimulus (e.g., a non-zero electric field, voltage, current, joule heating, or a suitable combination thereof). Moreover, the particles can be selected to have high surface energy, and good diffusivity within the RSL. 65 This leads to a conductive filament that can form rapidly in response to a suitable stimulus, but also deform quite readily,

8

e.g., in response to the external stimulus dropping below a deformation magnitude (which can be lower than a formation magnitude of the external stimulus associated with forming the volatile conductive filament, e.g., in response to a current flowing through the selector device; see U.S. Pat. No. 9,633,724 B2 hereby incorporated by reference herein in its entirety and for all purposes). Note that a volatile RSL and conductive filament for the selector device can have different electrical characteristics than a conductive filament and non-volatile RSL for the non-volatile memory device. For instance, the selector device RSL can have higher material electrical resistance, and can have higher on/off current ratio, among others.

An active metal-containing layer for a filamentary-based memory cell can include, among others: silver (Ag), gold (Au), titanium (Ti), titanium-nitride (TiN) or other suitable compounds of titanium, nickel (Ni), copper (Cu), aluminum (Al), chromium (Cr), tantalum (Ta), iron (Fe), manganese (Mn), tungsten (W), vanadium (V), cobalt (Co), platinum (Pt), hafnium (Hf), and palladium (Pd). Other suitable conductive materials, as well as stoichiometric or nonstoichiometric: compounds, nitrides, oxides, alloys, mixtures or combinations of the foregoing or similar materials can be employed for the active metal-containing layer in 25 some aspects of the subject disclosure. Further, a nonstoichiometric compound, such as a non-stoichiometric metal oxide/metal-oxygen or metal nitride/metal nitrogen (e.g., AlO<sub>x</sub>, AlN<sub>x</sub>, CuO<sub>x</sub>, CuN<sub>x</sub>, AgO<sub>x</sub>, AgN<sub>x</sub>, and so forth, where x is a suitable positive number or range of numbers, such as: 0 < x < 2, 0 < x < 3, 0 < x < 4 or other number/range of numbers depending on metal compound, which can have differing values for differing ones of the non-stoichiometric compounds) or other suitable metal compound can be employed for the active metal-containing layer, in at least one embodiment.

In one or more embodiments, a disclosed filamentary resistive switching device can include an active metal layer comprising a metal-nitrogen selected from the group consisting of: TiN<sub>x</sub>, TaN<sub>x</sub>, AlN<sub>x</sub>, CuN<sub>x</sub>, WN<sub>x</sub> and AgN<sub>x</sub>, where x is a positive number (or range of numbers) that can vary per metal-nitrogen material. In a further embodiment(s), the active metal layer can comprise a metal-oxygen selected from the group consisting of:  $TiO_x$ ,  $TaO_x$ ,  $AlO_x$ ,  $CuO_x$ ,  $WO_x$ and  $AgO_x$  where x is a positive number (or range of numbers) that can likewise vary per metal-oxygen material. In yet another embodiment(s), the active metal layer can comprise a metal oxygen-nitrogen selected from the group consisting of:  $TiO_aN_b$ ,  $AlO_aN_b$ ,  $CuO_aN_b$ ,  $WO_aN_b$  and  $AgO_a$  $N_b$ , where a and b are suitable positive numbers/ranges of numbers. The disclosed filamentary resistive switching device can further comprise a switching layer comprising a switching material selected from the group consisting of:  $SiO_{\nu}$ ,  $AlN_{\nu}$ ,  $TiO_{\nu}$ ,  $TaO_{\nu}$ ,  $AlO_{\nu}$ ,  $CuO_{\nu}$ ,  $TiN_{x}$ ,  $TiN_{\nu}$ ,  $TaN_{x}$ ,  $TaN_{v}$ ,  $SiO_{x}$ ,  $SiN_{v}$ ,  $AlN_{x}$ ,  $CuN_{x}$ ,  $CuN_{v}$ ,  $AgN_{x}$ ,  $AgN_{v}$ ,  $TiO_{x}$ ,  $TaO_x$ ,  $AlO_x$ ,  $CuO_x$ ,  $AgO_x$ , and  $AgO_v$ , where x and y are positive numbers (or ranges), and y is larger than x. Various combinations of the above are envisioned and contemplated within the scope of embodiments of the present invention.

In one example, a disclosed filamentary resistive switching device comprises a particle donor layer (e.g., the active metal-containing layer) comprising a stoichiometric or non-stoichiometric metal compound (or mixture) and a resistive switching layer. In one alternative embodiment of this example, the particle donor layer comprises a metal-nitrogen: MN<sub>x</sub>, e.g., AgN<sub>x</sub>, TiN<sub>x</sub>, AlN<sub>x</sub>, etc., and the resistive switching layer comprises a metal-nitrogen: MN<sub>y</sub>, e.g., AgO<sub>y</sub>, TiO<sub>y</sub>, AlO<sub>y</sub>, and so forth, where y and x are positive

numbers (or ranges), and in some cases y is larger than x. In an alternative embodiment of this example, the particle donor layer comprises a metal-oxygen:  $MO_x$ , e.g.,  $AgO_x$ ,  $TiO_x$ ,  $AlO_x$ , and so on, and the resistive switching layer comprises a metal-oxygen:  $MO_y$ , e.g.,  $AgO_y$ ,  $TiO_y$ ,  $AlO_y$ , or 5 the like, where y and x are positive numbers (or ranges), and in some cases y is larger than x. In yet another alternative, the metal compound of the particle donor layer is a  $MN_x$  (e.g.,  $AgN_x$ ,  $TiN_x$ ,  $AlN_x$ , etc.), and the resistive switching layer is selected from a group consisting of  $MO_y$  (e.g.,  $AgO_y$ , 10  $TiO_y$ ,  $AlO_y$ , etc.) and  $SiO_y$ , where x and y are typically non-stoichiometric values, or vice versa in a still further embodiment.

As utilized herein, variables x, y, a, b, and so forth representative of values or ratios of one element with respect 15 to another (or others) in a compound or mixture can have different values (or ranges) suitable for respective compounds/mixtures, and are not intended to denote a same or similar value or ratio among the compounds. Mixtures can refer to non-stoichiometric materials with free elements 20 therein—such as metal-rich nitride or oxide (metal-oxide/ nitride with free metal atoms), metal-poor nitride or oxide (metal-oxide/nitride with free oxygen/nitrogen atoms)—as well as other combinations of elements that do not form traditional stoichiometric compounds as understood in the 25 art. Some details pertaining to embodiments of the subject disclosure can be found in the following U.S. patent applications that are licensed to the assignee of the present application for patent: Application Ser. No. 11/875,541 filed Oct. 19, 2007 and application Ser. No. 12/575,921 filed Oct. 30 8, 2009; each of the foregoing patent applications are hereby incorporated by reference herein in their respective entireties and for all purposes in addition to those incorporated by reference elsewhere herein.

It should be appreciated that various embodiments herein 35 may utilize a variety of memory cell technologies, having different physical properties to generate PUF data, or random number generation (RNG) data. Physical properties suitable to non-correlated data can be associated with a fabrication process or processes, and can have stochastic or 40 substantially stochastic characteristics that mitigate or avoid replication or repetition among fabricated memory cells, even when made by the same process. As one example, one or more layers of a disclosed resistive switching device can have a root mean square (RMS) surface roughness of >0.2nm, up to a maximum of about 10.0 nm surface roughness, in an embodiment, or any suitable value or range there between in other embodiments (e.g., 0.4 nm-8 nm; 0.8 nm-6 nm; 1 nm-5 nm, and so forth). This results in random or near-random variation in layer thickness, including unpre- 50 dictable changes in physical characteristics of such devices. In some theoretical models the RMS surface roughness can affect the geometry of a resistive switching material layer inducing stochastic or substantially stochastic variations in resistive switching devices properties such as: native or 55 virgin (e.g., as fabricated) current conductance, program voltage, differential program voltage, program speed, differential program speed, among others disclosed throughout this specification. As further examples, different resistiveswitching memory cells and cell technologies can have 60 different discrete programmable resistances, different associated program/erase voltages, as well as other differentiating characteristics. In an embodiment, a resistive switching memory device resulting from a 28 nm photolithographic process with device size between about 50 nanometer (nm) 65 width and about 130 nm width (e.g., about 100 nm width, about 56 nm width, about 75 nm width, about 128 nm width,

**10**

and so forth) can be suitable to achieve stochastic physical characteristics disclosed herein. In other embodiments, a 22 nm photolithographic process producing a device size between 40 nm and 100 nm width (e.g., about 44 nm width, about 60 nm width, about 66 nm width, about 88 nm width, and so forth) can achieve stochastic physical characteristics.

Upon fabrication, disclosed resistive-switching devices can have native physical features generated from the fabrication process utilized to produce the resistive switching devices. These native physical features can have inherent stochastic or substantially stochastic properties that vary from resistive switching device to resistive switching device in a group of such devices, and can vary among devices in a die and among devices on a wafer or multiple wafers. As a result, minimal correlation in the native physical features among resistive switching devices within an array of such devices, among dies, among wafers and so forth, can yield minimal correlation between operational processes and data derived from such processes among devices, dies, wafers and so on. For instance, a native electrical resistance of a resistive switching layer (RSL) can depend at least in part on these non-correlated physical features and can vary from device to device even for adjacent devices in a single array on a single die (and, as previously stated, among multiple dies, wafers, and so on). Further, a current flow through the RSL in a native un-programmed state, a program voltage in the native un-programmed state, a program speed in the native un-programmed state, differential program voltage/ current/speed in the native un-programmed state, and so on, can vary among resistive switching devices. Processes disclosed herein for forming resistive switching devices and for leveraging stochastic or substantially stochastic physically unclonable features of resistive switching devices can provide excellent non-correlated data sequences.

As utilized herein, the term "native", "original", "virgin" or the like refers to post-fabrication but pre-commercial operation of resistive switching devices on a semiconductor die. Native (and like terminology) can, in various embodiments, include some or all post-fabrication operations such as quality testing or other verification routines performed by a manufacturer, and even some pre-commercial operation by a non-manufacturer such as testing to ensure manufacturer quality specifications are met by a chip, chip setup routines or configuration routines (e.g., defining one-time programmable memory or identifier memory within an array of resistive switching memory; see e.g., FIGS. 1 and 2, infra), among others. In general, a resistive switching device is in a native state, as utilized herein, if it has not yet received a stimulus (e.g., electrical, thermal, magnetic, or a like stimulus known in the art, suitable combinations thereof, and so forth) suitable to form a conductive filament within the resistive switching device and change the resistive switching device from an electrically resistive state to an electrically conductive state as described herein or known in the art.

Some embodiments of the subject disclosure can employ a bipolar switching device that exhibits a first switching response (e.g., programming to one of a set of program states) to an electrical signal of a first polarity and a second switching response (e.g., erasing to an erase state) to the electrical signal having a second polarity. The bipolar switching device is contrasted, for instance, with a unipolar device that exhibits both the first switching response (e.g., programming) and the second switching response (e.g., erasing) in response to electrical signals having the same polarity and different magnitudes.

In various embodiments, filamentary-based resistance switching devices can operate in a bipolar fashion, behaving

differently in response to different polarity (or direction, energy flow, energy source orientation, etc.) external stimuli. For the volatile filamentary-based selector device, as an illustrative example, in response to a first polarity stimulus exceeding a first threshold voltage (or set of voltages), the 5 filamentary selector device can change to a second resistance state from a first resistance state. Moreover, in response to a second polarity stimulus exceeding a second threshold voltage(s), the filamentary selector device can change to a third state from the first state. In some embodiments, the third state can be substantially the same as the first state, having the same or similar measurably distinct characteristic (e.g., electrical conductivity, and so forth), having the same or similar magnitude of threshold stimulus (though of opposite polarity or direction), or the like. In 15 other embodiments, the third state can be distinct from the second state, either in terms of the measurable characteristic (e.g., different electrical conductivity value in response to the reverse polarity as compared to the forward polarity) or in terms of threshold stimulus associated with transitioning 20 out of the first state (e.g., a different magnitude of positive voltage required to transition to the second state, compared to a magnitude of negative voltage required to transition to the third state).

For bipolar operation of a non-volatile filamentary-based 25 memory cell, a conductive path or a filament forms through a non-volatile RSL in response to a suitable program voltage applied across the memory cell. In particular, upon application of a programming voltage, metallic ions are generated from the active metal-containing layer and migrate into the 30 non-volatile RSL layer. The metallic ions can occupy voids or defect sites within the non-volatile RSL layer. In some embodiments, upon removal of the bias voltage, the metallic ions become neutral metal particles and remain trapped in voids or defects of the non-volatile RSL layer. When sufficient particles become trapped, a filament is formed and the memory cell switches from a relatively high resistive state, to a relatively low resistive state.

Once a conductive filament is formed, trapped conductive particles provide the conductive path or filament through the 40 non-volatile RSL layer, and the resistance is typically determined by a tunneling resistance between one or more such particles and an electrical conductive material adjacent to the non-volatile RSL layer. In some resistive-switching devices, an erase process can be implemented to deform the 45 conductive filament, at least in part, causing the memory cell to return to the high resistive state from the low resistive state. More specifically, upon application of an erase bias voltage, the metallic particles trapped in voids or defects of the non-volatile RSL become mobile ions and migrate back 50 towards the active metal layer, or disassociate within the RSL (or a combination of the foregoing) to break electrical conductivity of the conductive filament through the RSL layer. This change of state, in the context of memory, can be associated with respective states of a binary bit. For an array 55 of multiple memory cells, a word(s), byte(s), page(s), block(s), etc., of memory cells can be programmed or erased to represent zeroes or ones of binary information, and by retaining those states over time in effect storing the binary information. In various embodiments, multi-level informa- 60 tion (e.g., multiple bits) may be stored in such memory cells.

By mapping digital information to non-volatile resistance states of a two-terminal memory cell, digital information can be stored at such device. Still further, by mapping digital information to process results applied to groups of two- 65 terminal memory cells, PUF data or RNG data can be provided that leverage stochastic physical characteristics of

12

the two-terminal resistive switching memory cells. An electronic device containing many of these two-terminal memory cells can receive external host commands specifying (or implying) a type of operation in conjunction with an address and optionally data for the command. The electronic device can decode the host command, identify the address and the type of operation, characterize two-terminal resistive switching memory cells located at the address for the type of operation, and implement the type of operation on the two-terminal resistive switching memory cells in response to the host command.

As utilized herein, the term "substantially" and other relative terms or terms of degree (e.g., about, approximately, substantially, and so forth) are intended to have the meaning specified explicitly in conjunction with their use herein, or a meaning which can be reasonably inferred by one ordinary skill in the art, or a reasonable variation of a specified quality(ies) or quantity(ies) that would be understood by one of ordinary skill in the art by reference to this entire specification (including the knowledge of one of ordinary skill in the art as well as material incorporated by reference herein). As an example, a term of degree could refer to reasonable manufacturing tolerances about which a specified quality or quantity could be realized with fabrication equipment. Thus, as a specific illustration, though nonlimiting, for an element of a resistive switching device expressly identified as having a dimension of about 50 angstroms (Å), the relative term "about" can mean reasonable variances about 50 A that one of ordinary skill in the art would anticipate the specified dimension of the element could be realized with commercial fabrication equipment, industrial fabrication equipment, laboratory fabrication equipment, or the like, and is not limited to a mathematically precise quantity (or quality). In other examples, a term of degree could mean a variance of  $\pm -0.3\%$ ,  $\pm -0.5\%$ , or +/-0-10% of an expressly stated value, where suitable to one of ordinary skill in the art to achieve a stated function or feature of an element disclosed herein. In still other examples, a term of degree could mean any suitable variance in quality(ies) or quantity(ies) that would be suitable to accomplish one or more explicitly disclosed function(s) or feature(s) of a disclosed element. Accordingly, the subject specification is by no means limited only to specific qualities and quantities disclosed herein, but includes all variations of specified quality(ies) or quantity(ies) reasonably conveyed to one of ordinary skill in the art by way of the context disclosed herein.

#### Overview

FIG. 1 illustrates a block diagram of an example integrated circuit device 100 for an electronic device according to one or more embodiments of the present disclosure. Integrated circuit device 100 includes an array(s) of memory 105. Array(s) of memory 105 can include two-terminal resistive switching devices 110, characterized by integrated circuit device 100 to operate as identifier memory 112 and one-time programmable (OTP) memory 130, among other operation characterizations (e.g., MTP memory, RNG devices, etc.). Two-terminal resistive switching devices can also be referred to herein as resistive switching devices (e.g., volatile devices, non-volatile devices), resistive switching cells, resistive switching memory devices, two-terminal memory devices, and similar descriptions. In various embodiments, resistive switching devices 110 can include non-volatile two-terminal resistive-switching memory devices, volatile two-terminal resistive-switching devices, or a combination of non-volatile two-terminal resistiveswitching memory devices and volatile two-terminal resis-

tive-switching devices (where the latter e.g., serves as a selector device for a non-volatile memory, or operates independently as a volatile latch, switch, or the like). In some embodiments, array(s) of memory 105 can include other memory cell technologies, such as phase change memory, oxygen vacancy memory cells, magnetic memory, conductive bridge memory, and so forth.

Identifier memory 112 as utilized herein can refer to memory utilized to store or operate in a fashion to generate uncorrelated data, generally understood to be suitable for 10 distinguishing one set of identifier data from another set of identifier data, and respective devices associated with that data. Specific examples of identifier memory 112 can include resistive switching cells characterized to operate as PUF memory, RNG memory, or the like. Other disclosed 15 embodiments disclose an array(s) of resistive switching memory characterized with OTP memory, MTP memory, RNG memory in addition to identifier memory, sometimes specifically identified as a PUF memory (e.g., see FIGS. 2 and 7-8, infra, among others).

Identifier memory 112 and OTP memory 130 can be separate memory structures from array(s) of memory 105 (e.g., located externally to array(s) of memory 105 on a semiconductor chip) or can be at least in part included within array(s) of memory 105 (e.g., an array among a set of arrays 25 that embody array(s) of memory 105, a block of memory within such an array(s), a set of pages within one or more blocks or arrays, or other suitable arrangement). In one embodiment(s), identifier memory 112 and OTP memory 130 can have a fixed size or number of memory cells located 30 within a group of addresses of array(s) of memory 105 pre-assigned to one operational characteristic (e.g., MTP) operation, OTP operation, RNG operation, PUF operation, or the like; see, e.g., FIG. 4, infra). In such embodiments, a host command received by controller 120 identifying 35 addresses of target memory cells can be operated upon according to the pre-assigned operational characteristic associated with those addresses.

In other embodiments, some or all of array(s) of memory 105 can be dynamically characterized as one operational 40 type of a set of available operational types, post-fabrication. For instance, controller 120 can dynamically characterize a set of memory cells identified in a host command as MTP memory, OTP memory, RNG memory or PUF memory, in response to the host command. Trim instructions can be 45 referenced by controller 120 to implement protocols necessary to execute the operations associated with the characterization of the memory cells (e.g., see FIG. 2, infra). In some disclosed embodiments, the host command can include data distinguishing a selected operational character- 50 ization from a set of operational characterizations. In other disclosed embodiments, the host command can be accompanied by selection of a pin setting (e.g., a hi/low pin setting) associated by controller 120 with the selected operational characterization. The selected pin setting can be, for 55 instance, a member of a set of pin settings respectively associated with different operational characterizations of the set of operational characterizations, with the selected pin setting associated with the selected operational characterization (e.g., see FIG. 5). As introduced previously, in 60 alternative embodiments and with some additional detail: controller 120 can infer an operational characterization for the set of memory cells from addresses of the memory cells (e.g., identifying or implying their location within array(s) of memory 105) specified in the host command, and a stored 65 association of the addresses with the operational characterization.

14

Also illustrated in integrated circuit device 100 is an input(s) 140 and output(s) 150. In some embodiment, input(s) 140 can include (or provide a pathway for) data to be stored within resistive switching devices 110, identifier memory 112 or OTP memory 130. Output(s) 150 can output data stored within resistive switching devices 110, identifier memory 112 or OTP memory 130. In some embodiments, output(s) 150 can output data that results from computations utilizing data stored in identifier memory 112, or stored within resistive switching devices 110 or OTP memory 130 resulting from such computations, in further embodiments.

In addition to the foregoing, disclosed resistive switching devices have excellent properties for generating identifier data sequences. Such properties include high entropy, which is suitable for generating random or substantially random numbers, low BER, inherent difficulty in reverse engineering or illicit side-channel data access, and fast sensing times. For example, a bit sequence of 128 or 256 identifier (e.g., PUF) bits can be formed from 128 or 256 resistive switching devices (as described herein) or 128/256 groups of multiple such resistive switching devices (as described in differential identifier bit generation; see FIGS. 6-8, infra). High randomness in generating identifier bits minimizes non-random patterns between bits (resistive switching devices/groups of such devices) of a sequence, mitigating or avoiding false rejection rates. In addition, high randomness enhances security margin by minimizing hamming distance values for multiple read operations of an identifier sequence on a single die and providing an ideal gaussian distribution of hamming distance values among multiple dies of resistive switching devices. This can increase a total number of semiconductor chips that can achieve distinct identifier sequences for a given sequence bit count, even with high security margin (e.g., defined by a number of distinct bits differentiating different PUF sequences).

In one or more embodiments, controller 120 can be operable to perform memory operations on array(s) of memory 105. For instance, controller 120 can be operable to perform sensing operations pertaining to generating an identifier data bit from one (or a group of) resistive switching device(s) operably characterized as identifier memory cells 112, in an embodiment(s). Examples of sensing operations pertaining to generating an identifier bit can include: native current of a never-programmed resistive switching device in the context of PUF data (or leak current of an un-programmed device in the context of RNG data) in response to a sub-program voltage, native electrical resistance of a resistive switching device, detection of program events, detection of speed or timing of program events, a program voltage, a program current, an on-state (programmed) resistance, an erase voltage or current, a delay frequency, a parasitic resistance or capacitance, a program or erase minimum pulse width, and so forth, or suitable combinations of the foregoing, as described herein (or as described within U.S. application Ser. No. 17/223,817 incorporated by reference hereinabove). In general, however, these sensing operations can be digitized to generate PUF or RNG data by comparing a measured result of a sensing operation (native current in response to sub-program voltage, detection of program event in response to a program signal, speed or timing of program event, a voltage at which a device becomes programmed, and so forth) to a threshold value stored in trim settings (e.g., trims 222 of FIG. 2, infra) of controller 120. Generation of PUF data usually involves never-programmed resistive switching memory cells, whereas generation of RNG data can involve never-programmed cells, or un-programmed cells with relatively low

program counts (e.g., fewer than 10 program events; fewer than 50 program events; fewer than 100 program events; fewer than 1000 program events; or other suitable value, or any suitable value or range there between).

As further examples, controller 120 can be operable to 5 perform a program operation(s) pertaining to generating an identifier data bit utilizing an identifier memory cell(s) 112 of array(s) of memory 105. Examples of such program operations include: applying a program voltage magnitude to a never-programmed (or un-programmed for RNG data) 10 memory cell and determining whether the cell is programmed or not programmed in response to the selected program voltage magnitude (program voltage magnitude differentiation). The identifier data bit can be digitized by assigning a '1' if the cell is programmed, and '0' if not 15 programmed (or vice versa). Further examples include: applying a program signal of selected pulse duration to a never-programmed (or un-programmed) memory cell and determining whether the cell is programmed or not programmed after the selected pulse duration (program time 20 differentiation). Similar to the previous example, the identifier data bit can be digitized by assigning a '1' if the cell is programmed, and '0' if not programmed (or vice versa). Another example includes: applying a sub-program voltage to a never-programmed (or un-programmed) memory cell 25 and determining whether a native (or leak) non-programmed current is above or below a preselected current threshold (native/leak current differentiation). The identifier bit can be digitized by assigning a '1' if native current is above the threshold and assigning a '0' if native current is below the 30 threshold (or vice versa). Other examples or combinations of the foregoing known in the art or reasonably suggested to one of ordinary skill in the art by way of the context provided herein are considered within the scope of the present disclosure.

In still other embodiments, controller 120 can be configured to implement differential operations pertaining to generating an identifier bit from a plurality of resistive switching devices. Generally, differential operations compare response of one or more cells of a plurality of memory cells 40 to a memory operation and digitize an identifier bit associated with the plurality of memory cells based on relative responses of the one or more memory cells. Differential operations usable to generate an identifier bit according to aspects of the present disclosure can include: differential 45 program speed of a group of never (or un) programmed memory cells, differential native program voltage of the group of memory cells, differential native (leak) current of the group of memory cells, differential native electrical resistance of the group of memory cells, differential on-state 50 resistance of the group of memory cells, differential erase voltage or current of the group of memory cells, differential delay frequency of the group of memory cells, differential parasitic resistance or capacitance of the group of memory cells, a differential program or erase minimum pulse width 55 or duration of the group of memory cells, or the like, or a suitable combination of the foregoing. For differential operations, using the exemplary case of two cells per identifier bit (though the rule can be extended to three or more cells per identifier bit through proportional logic, optionally 60 for generating multi-bit identifier data with suitable numbers of differential cells), the identifier bit can be digitized by assigning a '0' value to identifier bits in which a first memory cell has higher (or lower) native current/on-state resistance/erase voltage/delay frequency/parasitic resistance 65 or capacitance/program or erase speed, etc., and assigning a '1' to identifier bits in which a second memory cell has the

**16**

higher (or lower) native current/on-state resistance/erase voltage/delay frequency/parasitic resistance or capacitance/program or erase speed, and so forth. Rules for digitizing identifier bits utilizing differential operations on multiple memory cells can be stored in trims 222, in an embodiment (see, e.g., FIG. 2, infra) or elsewhere in controller 120 or integrated circuit device 100.

In yet other embodiments, controller 120 can be operable to selectively implement one-time programmable operations on selected identifier memory cells 112 to render permanent an identifier bit sequence generated with a program event at a set of identifier memory cells 112 (or, e.g., stored at a set of memory cells in response to generation at other memory cells by a non-program event, such as native leak current or the like). Described differently, a PUF data sequence comprising program and un-programmed bits can be reinforced with a strong program pulse, e.g., a one-time programmable pulse, to make program bits of the PUF data sequence non-erasable and create large sensing margin between the program bits and the un-programmed bits of the PUF data sequence. This can serve to greatly enhance longevity and accurate read cycle counts of the identifier bit sequence.

In still additional embodiments, controller 120 can be operable to establish one or more threshold metric levels (e.g., current level(s), resistance level(s), program voltage level(s), program speed level(s), etc.) for defining identifier bit values (e.g., logic levels; a '0' bit and a '1' bit in the binary context) from sensing operations or program operations performed on identifier memory cells 112, as described herein. As an illustrative example, if an operational characteristic selected to generate identifier bit data is a native leak current, a current value threshold (or small range of values) (e.g., 500 nA, or any other suitable value or range) can be selected and resistive switching devices above the current value threshold can be allocated a '1' identifier bit value and devices below the current value threshold can be allocated a '0' identifier bit value. In other embodiments, a range of threshold values with a lower threshold and an upper threshold (e.g., a lower threshold of 400 nA and an upper threshold of 600 nA, or any other suitable threshold value or range of values) can be utilized. Devices with native current below 400 nA can be allocated a 'O' identifier bit value; devices with native current above 600 nA can be allocated a '1' identifier bit value, and devices between 400 nA and 600 nA can be discarded, in an embodiment. In an embodiment, further read operations can use a 500 nA threshold to regenerate the '0' bit values and '1' bit values. Using lower and higher initial threshold values can increase sensing margin and reduce bit error rates, according to embodiments of the present disclosure.

It should be appreciated that a suitable threshold or set of thresholds can be established for other resistive switching device operational characteristics selected for generating identifier bits information. As another (non-limited) illustrative example, a logic level 0 can be associated with a program voltage of 2 volts or higher and a logic level 1 associated with a program voltage of 1.8 volts or below. As stated previously, other suitable thresholds can be used to define logic level values for identifier bits as disclosed herein. In some embodiments, when a large number of resistive switching devices are sensed as part of generating identifier bits, a threshold voltage, current, pulse width etc., can be selected such that approximately half of the devices become associated with a logic level 0 and another half become associated with a logic level 1. In some embodiments, threshold settings can be performed manually by way of controller 120; in other embodiments default threshold

settings can be set (optionally stored in trims 222 of FIG. 2) upon initializing a semiconductor chip.

In further embodiments, a sensing operation or program event utilized to generate a PUF bit sequence can be selected such that disclosed resistive switching memory cells could 5 have the same or substantially the same measurement over time in response to the sensing operation/program event, over many read cycles and at a range of temperatures common to semiconductor chips. This leads to very low bit error rate for disclosed identifier bit sequences. As an 10 illustrative example, a native leak current (or other physical unclonable characteristic) for a resistive switching device measured for the first time on day 1 at room temperature can measure the same or substantially the same (e.g., relative to a constant native leak current threshold) years later, at 100 15 degrees C. after a million read operations. Values of the resistance switching device can be determined upon demand by controller 120. As another illustrative example, to determine an electrical resistance of a resistive switching device, a current source can be applied to the resistive switching 20 device, a voltage drop measured and resistance calculated. Other techniques for measuring or determining physical characteristics of resistive switching devices known in the art or reasonably conveyed to one of ordinary skill in the art are considered within the scope of the present disclosure.

In addition to the foregoing, controller 120 can be configured to define an arrangement or ordering of resistive switching devices (or groups of resistive switching devices) to create a multi-bit sequence of identifier bits. As one illustrative example, resistive switching devices 0:7 can be 30 read and assigned to bits 0:7 of a bit sequence. In other embodiments, the bit sequence need not be derived from resistive switching devices arrayed in a particular order. As an example, from an ordinal line of resistive switching devices, devices 15, 90, 7, 21, 50, 2, 37, 19 can be read and 35 respectively assigned to bits 0:7 of an output bit string. The bit string can be of any selected length. For instance, bit strings of 64 bits, 256 bits, 1024 bits, 64 kbits, or any other suitable subset of identifier memory cells 112 up to all of identifier memory cells 112 (which can include all of 40 array(s) of memory 105 in at least some embodiments) may be employed for a bit string. As another non-limiting illustration, for a 256-bit PUF data sequence utilized for a cryptographic key, controller 120 can characterize a set of memory cells as PUF bits and define an ordering of resistive 45 switching memory cells assigned to the PUF bits to correspond with a sequence of 256 bits. Bit values (e.g., logic levels, . . . ) generated from the assigned resistive switching memory cells can then be ordered by controller 120 consistent with the device(s) ordering to thereby create the 256-bit 50 identifier sequence. As a specific illustration: where a row of 256 resistive switching devices in an array is selected for generating an identifier sequence, identifier bit values of the 256 resistive switching devices can be arranged in the order the resistive switching devices are physically situated in the 55 row; however, this is an illustrative example only and any other suitable arrangement or ordering can be implemented by controller 120 as an alternative or in addition.

As is evident from the disclosure as a whole, any suitable number of bits of array(s) of memory 105 can be operation-60 ally characterized as PUF bits, RNG bits, OTP or MTP bits, and so forth. Further, controller 120 can operationally characterize such bits in response to a host command identifying addresses of target bits and specifying an associated operation to implement on the target bits. Where the operation is 65 a PUF write operation for defining a cryptographic key, controller 120 can be operable to characterize the target bits

**18**

as PUF bits, optionally assign differential memory cells from resistive switching device 110 to the target bits for differential PUF operation, implement the PUF write and define an order to aggregate 256 bits of data generated from the PUF write as the cryptographic key. In one or more embodiments, controller 120 can implement methods 900-1300 of FIGS. 9-13 on array(s) of memory 105.

In one or more additional embodiments, controller 120 can be operable to characterize resistive switching devices of array(s) of memory 105 as MTP memory cells (e.g., resistive switching devices 110) or OTP memory cells 114, and to store data in MTP memory cells 110 or OTP memory cells 114. Controller 120 can receive an input data word from input(s) 140 to be stored, as an example. In some embodiments, controller 120 can combine the input data word with an identifier data sequence stored at/generated at identifier/PUF memory cells 112 to generate an output data word. This output data word can be stored in MTP memory cells 110, in an embodiment. The input word can optionally be deleted. Subsequently, to recreate the input data, the output data word stored in MTP memory cells 110 can be combined with the identifier data sequence (optionally computed on-the-fly by controller 120), and the recreated input data word can be output via output(s) 150. In various embodiments, such an input data word can be a password, a document, a cryptographic key, or any other suitable data to be stored securely.

In should be understood that operations, configurations, characteristics and various illustrations and descriptions of controller 120 can be applicable to other controllers disclosed herein in various embodiments (e.g., controller 220 of FIGS. 2 and 3, controller 420 of FIG. 4, controller 520 of FIG. 5). Conversely, operations, configurations, characteristics and various illustrations and descriptions of other controllers disclosed herein can be applicable to controller 120 in one or more embodiments.

Referring now to FIG. 2, there is depicted an integrated circuit device 200 that provides a novel mechanism for exporting control over PUF data generated from resistive switching memory cells located on integrated circuit device 200 to a host device 260 external to the integrated circuit device 200. PUF data generated from resistive switching memory cells (e.g., included within resistive-switching array 210) is anticipated to have better randomness and enhanced longevity, among other features, than other mechanisms for generating PUF data. For example, use of static random access memory (SRAM) for generating identifier sequence data has met with fairly high bit error rate (BER), from 3% to 15% depending on implementation. To reduce BER associated with SRAM identifier sequence generation, complicated circuitry is coupled to the SRAM bits upon fabrication. This permanently fixes the SRAM bits that can be utilized for identifier sequence generation at manufacture, and further adds significant hardware overhead to a semiconductor die. Disclosed resistive switching devices can generate identifier sequence data with extremely low BER (e.g., see FIG. 7 of U.S. patent application Ser. No. 17/223, 816 filed Apr. 6, 2021, incorporated by reference hereinabove), avoiding special BER-reducing circuitry permanently affixed to specific memory cells as is utilized in the SRAM context. As a result, embodiments disclosed herein can utilize row and column selection circuitry (including multiplexers) and processes associated with implementing read, write, erase and other memory operations on resistive switching devices (e.g., see FIGS. 14 and 15, infra), and extend those circuitry and processes to generating or storing PUF data, RNG data, OTP data, MTP data, and so forth. In

such embodiments, resistive switching devices utilized for MTP memory operations, identifier data or OTP storage need not be fixed on manufacture, and instead can be dynamically exposed for selection and re-configuration post-fabrication (e.g., by way of controller 220). In at least 5 some embodiments, that selection and re-configuration can be exported to external host device 260, which is separate from integrated circuit device 200. In various example implementations, integrated circuit device 200 and host device 260 can be manufactured separately and interconnected by one or more network or device interfaces, such as command/data interface 230 and command/data interface 270, among others.

Integrated circuit device 200 can comprise a resistiveswitching array 210 comprising an array (or multiple arrays) 15 of resistive-switching devices. In an embodiment, resistiveswitching array 210 can include non-volatile resistive switching memory devices. In another embodiment, resistive-switching array 210 can include volatile resistive switching devices (e.g., selectors, switches, latches, and so 20 forth). In still other embodiments, resistive-switching array 210 can include a portion comprising non-volatile resistive switching memory devices and a second portion comprising volatile resistive switching devices. In at least one embodiment, resistive-switching array 210 can comprise memory cells that respectively include an electrical series combination of a non-volatile resistive switching device and a volatile resistive switching device. Resistive-switching array 210 can comprise portions having combinations of the foregoing, in one or more embodiments.

Resistive-switching array 210 illustrates portions of resistive switching devices of different operational characterizations: PUF bits 212, OTP bits 214, MTP bits 216 and RNG bits 218. It should be understood that no spatial orientation, relative or absolute, is implied by the position of the dotted 35 tive-switching array 220 utilized by host device 260 that are blocks within resistive-switching array 210 (or like illustrations in other Figures), and furthermore some or all of the resistive switching devices of resistive-switching array 210 can be operationally uncharacterized upon manufacture. Further, some or all resistive switching devices can be 40 changed from one operational characterization to a different operational characterization, or from an operational characterization to no operational characterization by controller 220 (effectively making some or all of the resistive switching devices a default characterization, e.g., MTP).