## US011973015B2

# (12) United States Patent Hoya

# (54) PLURALITY OF OVERLAPPING POWER TERMINALS IN A SEMICONDUCTOR MODULE

(71) Applicant: FUJI ELECTRIC CO., LTD.,

Kawasaki (JP)

(72) Inventor: Masashi Hoya, Kawasaki (JP)

(73) Assignee: FUJI ELECTRIC CO., LTD.,

Kawasaki (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 208 days.

(21) Appl. No.: 17/349,125

(22) Filed: **Jun. 16, 2021**

(65) Prior Publication Data

US 2021/0407899 A1 Dec. 30, 2021

## (30) Foreign Application Priority Data

(51) **Int. Cl.**

H01L 23/498

(2006.01)

H01L 23/495

(2006.01)

H01L 25/07

(2006.01)

H01L 25/075

(2006.01)

H01L 23/00

(2006.01)

(52) U.S. Cl.

CPC .. *H01L 23/49844* (2013.01); *H01L 23/49537* (2013.01); *H01L 23/49541* (2013.01);

(Continued)

(58) Field of Classification Search

CPC ...... H01L 23/49844; H01L 23/49811; H01L 23/498894; H01L 23/48838;

(Continued)

## (10) Patent No.: US 11,973,015 B2

(45) **Date of Patent:** Apr. 30, 2024

## (56) References Cited

#### U.S. PATENT DOCUMENTS

5,471,089 A 11/1995 Nagatomo et al. 5,751,058 A 5/1998 Matsuki (Continued)

#### FOREIGN PATENT DOCUMENTS

P H06-021323 A 1/1994 P H09-121019 A 5/1997 (Continued)

## OTHER PUBLICATIONS

Japan Patent Office, "Office Action for Japanese Patent Application No. 2020-109252," Mar. 5, 2024.

Primary Examiner — Alonzo Chambliss (74) Attorney, Agent, or Firm — Manabu Kanesaka

## (57) ABSTRACT

The present invention is directed to provide a semiconductor module capable of achieving miniaturization and reduced manufacturing cost while suppressing surge voltage generated when switching the semiconductor elements. A semiconductor module includes a negative terminal and a positive terminal. The negative terminal has a negative fastening portion for fastening a negative polarity-side external terminal, a negative connection portion connected to a laminated substrate, and a negative intermediate portion arranged between the negative fastening portion and the negative connection portion. The positive terminal has a positive fastening portion for fastening a positive polarityside external terminal, positive connection portions connected to the laminated substrate, and a positive intermediate portion facing the negative intermediate portion with a predetermined gap and arranged between the positive fastening portion and the positive connection portions.

## 20 Claims, 12 Drawing Sheets

## US 11,973,015 B2 Page 2

| (52)                                              | U.S. Cl.                                                 | ,                   | ,                        |        | Doo H02G 5/005                |  |

|---------------------------------------------------|----------------------------------------------------------|---------------------|--------------------------|--------|-------------------------------|--|

|                                                   | CPC <i>H01L 23/49548</i> (2013.01); <i>H01L 23/49575</i> | 2004/01             | 113268 A1*               | 6/2004 | Shirakawa H01L 25/18          |  |

|                                                   | (2013.01); <i>H01L 23/49811</i> (2013.01); <i>H01L</i>   | 2010/0              | 40000 414                | 6/2010 | 257/E23.173                   |  |

|                                                   | 23/49838 (2013.01); H01L 23/49861                        | 2010/01             | 148298 A1*               | 6/2010 | Takano                        |  |

|                                                   | (2013.01); <i>H01L 23/49894</i> (2013.01); <i>H01L</i>   | 2015/01             | 171578 A1*               | 6/2015 | 257/500<br>Taylor H01R 25/161 |  |

|                                                   | 25/072 (2013.01); H01L 25/0753 (2013.01);                | 2015/01             | 1/13/0 A1                | 0/2013 | 439/251                       |  |

|                                                   | H01L 24/46 (2013.01); H01L 24/49 (2013.01)               | 2017/00             | )42053 A1                | 2/2017 | Soyano et al.                 |  |

| (50)                                              |                                                          |                     | )13752 A1                |        | Nakamura                      |  |

| (58)                                              | Field of Classification Search                           |                     | 118613 A1                |        | Reiter et al.                 |  |

|                                                   | CPC H01L 23/49861; H01L 23/498; H01L                     | 2021/01             | 110015 711               | 1/2021 | TCHCH Ct til.                 |  |

|                                                   | 23/4952; H01L 23/49537; H01L                             | EODEIGNI DATE       |                          |        | NT DOCLIMENTS                 |  |

|                                                   | 23/49575; H01L 23/49548; H01L 24/49;                     |                     | FOREIGN PATENT DOCUMENTS |        |                               |  |

|                                                   | H01L 24/46; H01L 25/072; H01L                            | JP                  | H10-022                  | 451 A  | 1/1998                        |  |

|                                                   | 25/0753; H01L 23/49894                                   | JP                  | 2006-210                 |        | 8/2006                        |  |

| See application file for complete search history. |                                                          | JP                  | 2007-096                 | 004 A  | 4/2007                        |  |

|                                                   |                                                          | JP                  | 2010177                  | 573 A2 | * 8/2010                      |  |

| (50)                                              | References Cited                                         | JP                  | 2017-037                 | 892 A  | 2/2017                        |  |

| (56)                                              |                                                          | JP                  | 2020-009                 | 834 A  | 1/2020                        |  |

|                                                   |                                                          | JP                  | 2020-053                 | 622 A  | 4/2020                        |  |

|                                                   | U.S. PATENT DOCUMENTS                                    |                     | 2020-072                 | 106 A  | 5/2020                        |  |

|                                                   |                                                          | JP                  | 2020-080                 | 348 A  | 5/2020                        |  |

|                                                   | 6,525,950 B1* 2/2003 Shirakawa H02M 7/003                | WO                  | 2017/221                 |        | 12/2017                       |  |

|                                                   | 307/148                                                  |                     |                          |        |                               |  |

| 10,326,378 B2 * 6/2019 Doo                        |                                                          | * cited by examiner |                          |        |                               |  |

4----

303 Sup 22 CV Carl I 2202 2022 2023 الإسا أسأسا Tenas

FIG. 6A

Apr. 30, 2024

FIG. 6B

Apr. 30, 2024

F [G. 10]

(\frac{1}{2})

(2) (2)

## PLURALITY OF OVERLAPPING POWER TERMINALS IN A SEMICONDUCTOR MODULE

## RELATED APPLICATIONS

The present application is based on, and claims priority from, Japanese Application No. JP2020-109252 filed Jun. 25, 2020, the disclosure of which is hereby incorporated by reference herein in its entirety.

#### TECHNICAL FIELD

The present invention relates to a semiconductor module intended to be applied to a power conversion device or the like.

## BACKGROUND ART

A variety of types of modules are used as power semiconductor devices for inverter devices or the like that <sup>20</sup> convert DC power to AC power depending on applications and the like. A 2-in-1 type semiconductor module has a structure in which a half-bridge circuit formed by connecting in series unit arms each including a set of a semiconductor switching element and a rectifier element connected <sup>25</sup> in parallel and connecting positive (P) and negative (N) terminals connected to DC power, and an AC phase (U) terminal connected to AC power is built into a single package.

A 4-in-1 type semiconductor module has a single-phase <sup>30</sup> AC compatible structure in which a circuit made up of two parallel half-bridge circuits connected by positive (P) and negative (N) terminals is built into a single package. A 6-in-1 type semiconductor module has a three-phase AC compatible structure in which a circuit made up of three parallel <sup>35</sup> half-bridge circuits connected by positive (P) and negative (N) terminals is built into a single package.

PTL 1 discloses a 2-in-1 type semiconductor module. In the technology described by PTL 1, an AC-phase (U) wiring bar connected to emitters of upper arm-side semiconductor elements above the upper arm-side semiconductor elements and extending along an array of the plurality of upper arm-side semiconductor elements and a negative (N) wiring bar connected to emitters of lower arm-side semiconductor elements above the lower arm-side semiconductor elements 45 and extending along an array of the plurality of lower arm-side semiconductor elements are arranged to face, in parallel to, and in close proximity to each other. This reduces wiring inductance to suppress surge voltage generated when switching the semiconductor elements.

PTL 2 describes a power semiconductor device including bent main terminals each having projections on a lower surface of thereof.

## CITATION LIST

Patent Literature

PTL 1: JP 2017-037892 A PTL 2: WO 2017/221730

## SUMMARY OF INVENTION

## Technical Problem

In the structure in which the main circuit wiring bars are arranged to face, in parallel to, and in close proximity to

2

each other above the upper arm-side semiconductor elements and the lower arm-side semiconductor elements in order to reduce wiring inductance, restrictions are likely to occur in terms of a gate wiring layout for each semiconductor element and positions of the semiconductor elements mounted on an insulating substrate. This makes it difficult to miniaturize the semiconductor module.

Additionally, such a structure requires a high-level assembly technology, which may increase manufacturing cost in terms of equipment, man-hours, and yield.

It is an object of the present invention to provide a semiconductor module capable of achieving miniaturization and reduced manufacturing cost while suppressing surge voltage generated when switching semiconductor elements.

#### Solution to Problem

To achieve the above object, a semiconductor module according to one aspect of the present invention includes a first power supply terminal connected to a first polarity side of DC power, a second power supply terminal connected to a second polarity side of the DC power, a plurality of semiconductor elements connected in series between the first power supply terminal and the second power supply terminal, and a substrate including the plurality of semiconductor elements, in which the first power supply terminal has a first fastening portion for fastening an external terminal of the first polarity side, a first connection portion connected to the substrate, and a first intermediate portion arranged between the first fastening portion and the first connection portion, and in which the second power supply terminal has a second fastening portion arranged adjacent to the first fastening portion and being for fastening an external terminal of the second polarity side, a pair of second connection portions arranged across the first connection portion and connected to the substrate, and a second intermediate portion at least apart of which faces the first intermediate portion with a predetermined gap and which is arranged between the second fastening portion and the pair of second connection portions.

## Advantageous Effects of Invention

According to the one aspect of the present invention, miniaturization and reduced manufacturing cost can be achieved while suppressing surge voltage generated when switching the semiconductor elements.

## BRIEF DESCRIPTION OF DRAWINGS

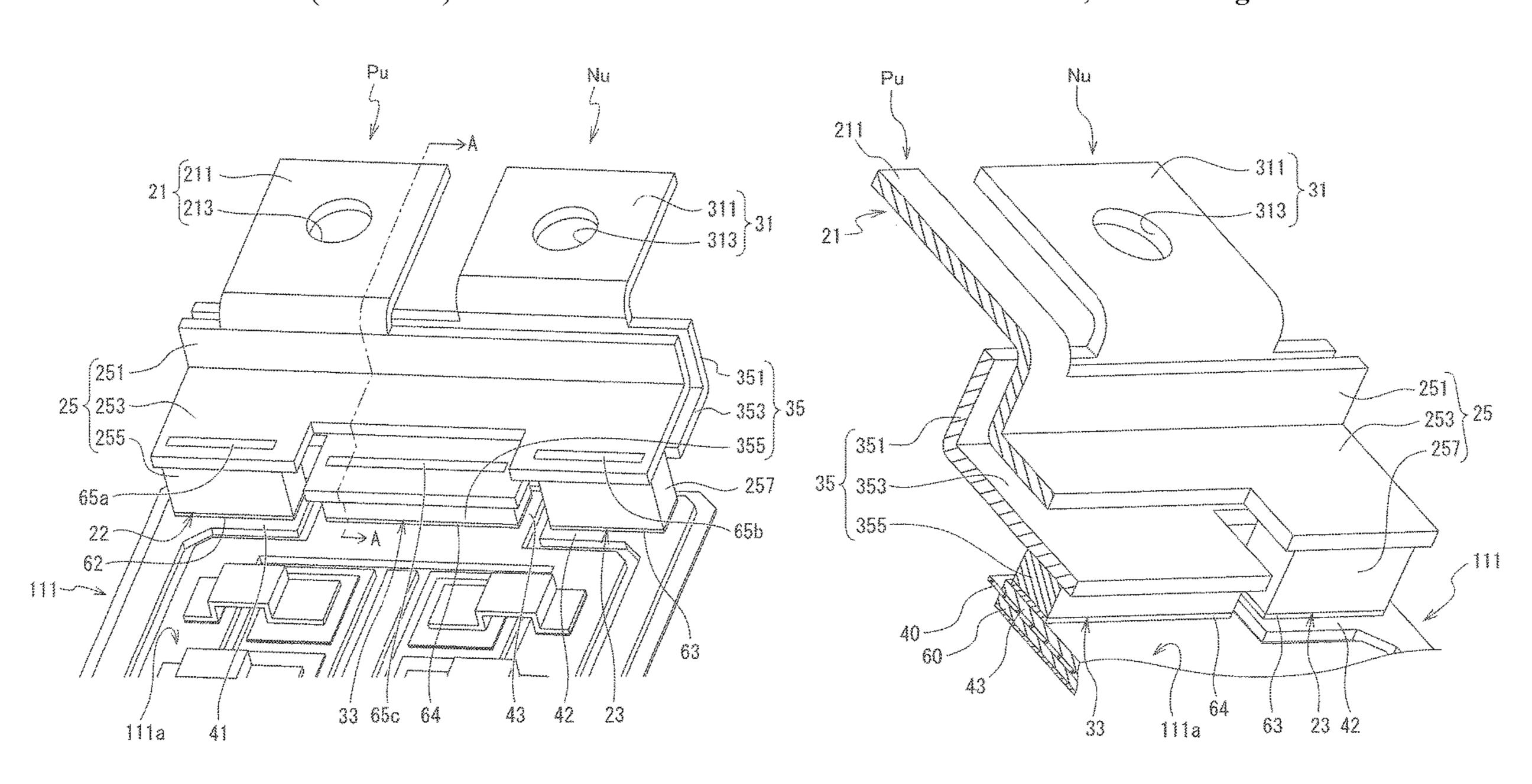

- FIG. 1 is a diagram illustrating a schematic configuration of a main part of a semiconductor module according to a first embodiment of the present invention;

- FIG. 2 is a circuit diagram of the semiconductor module according to the first embodiment of the present invention;

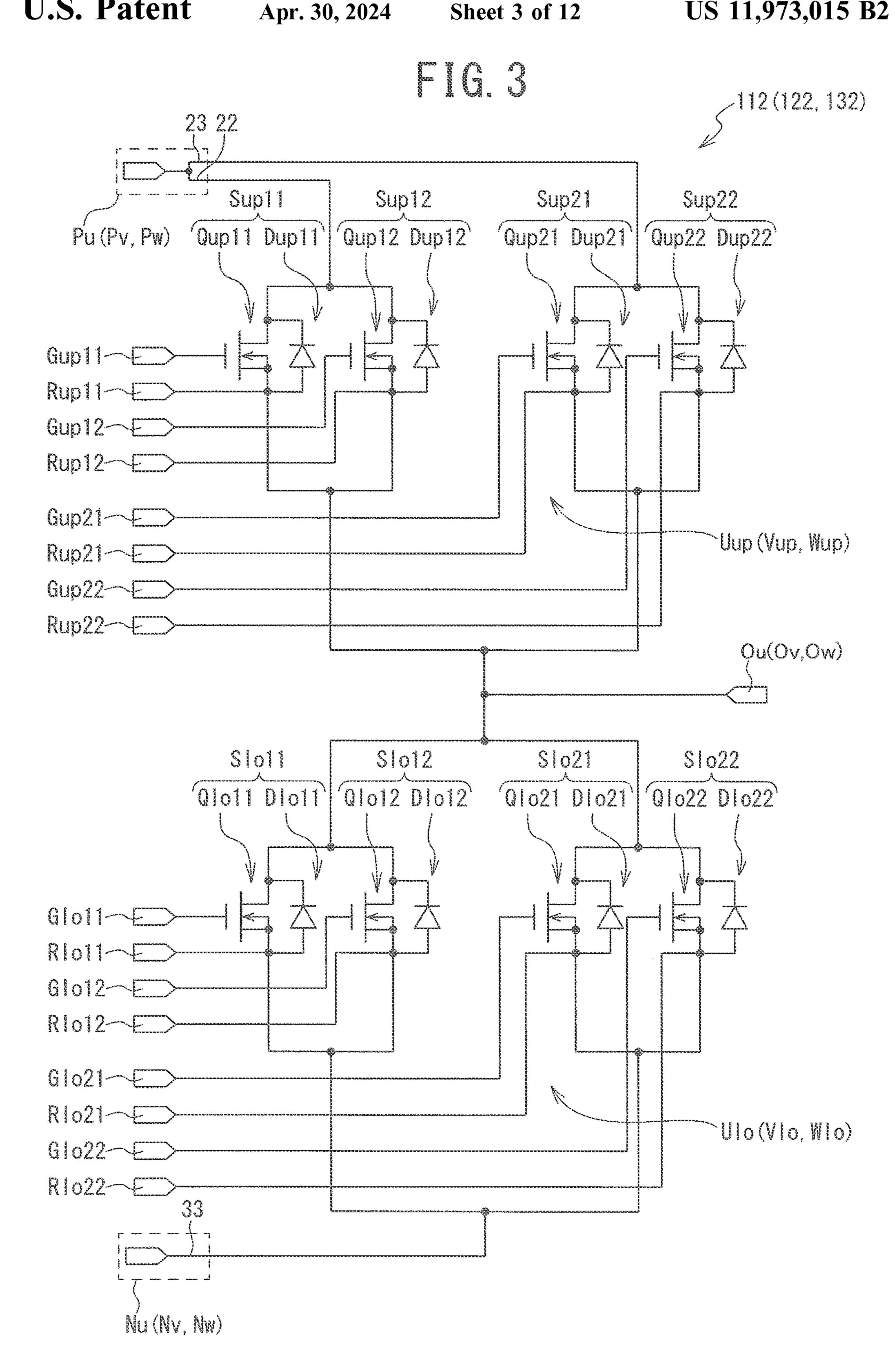

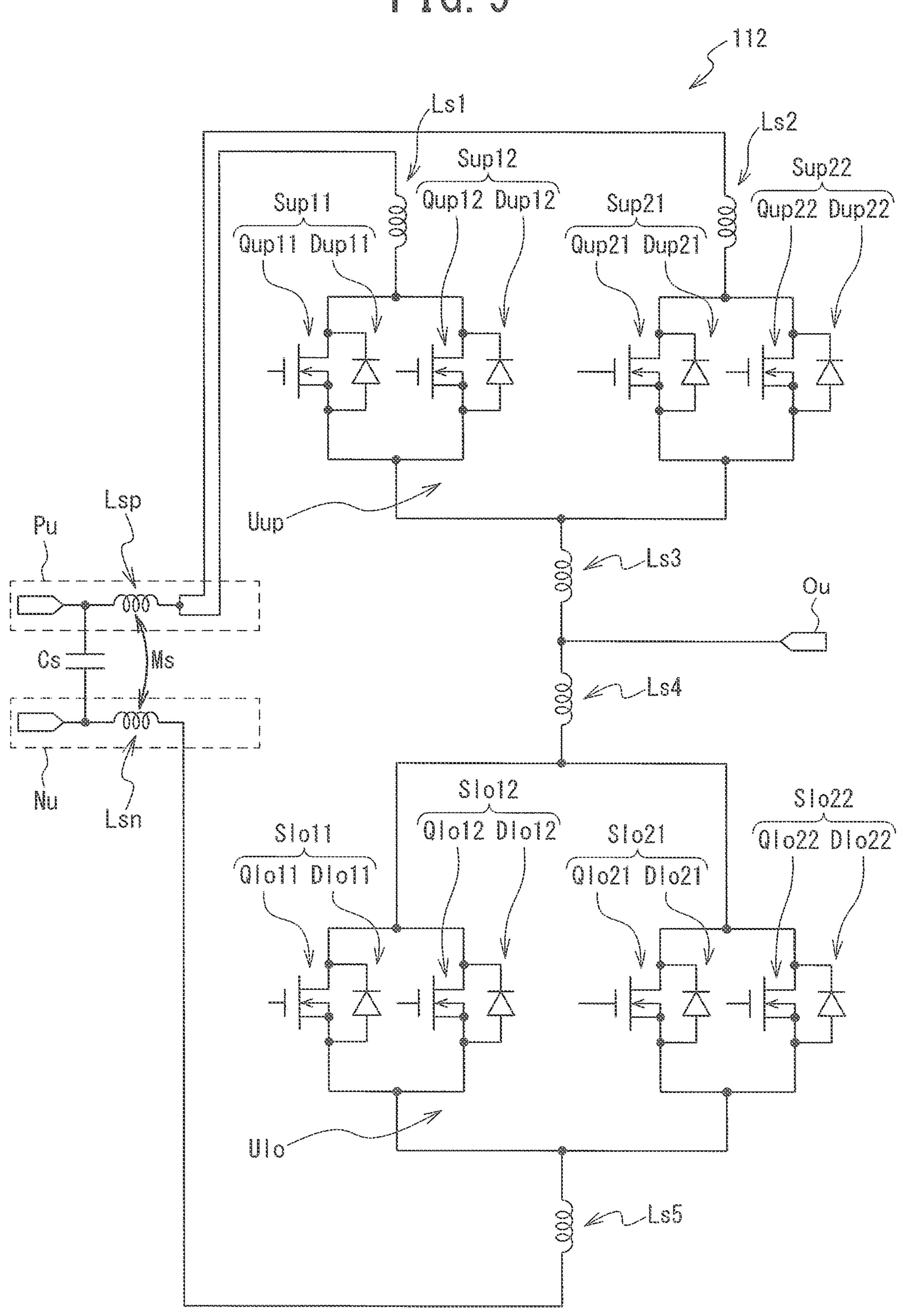

- FIG. 3 is a circuit diagram of an inverter circuit included in the semiconductor module according to the first embodiment of the present invention;

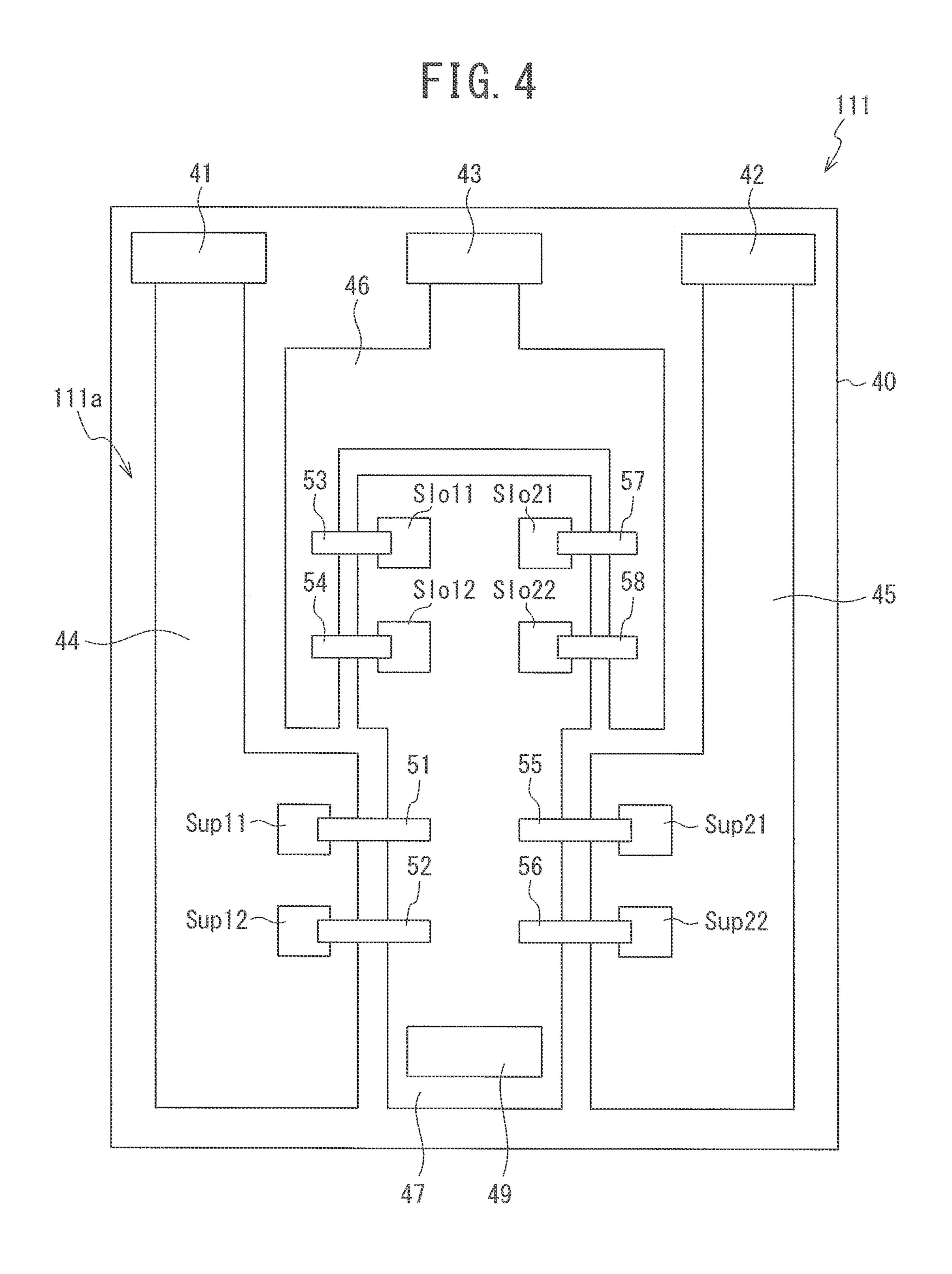

- FIG. 4 is a diagram illustrating an example of a wiring pattern formed on a laminated substrate included in the semiconductor module according to the first embodiment of the present invention;

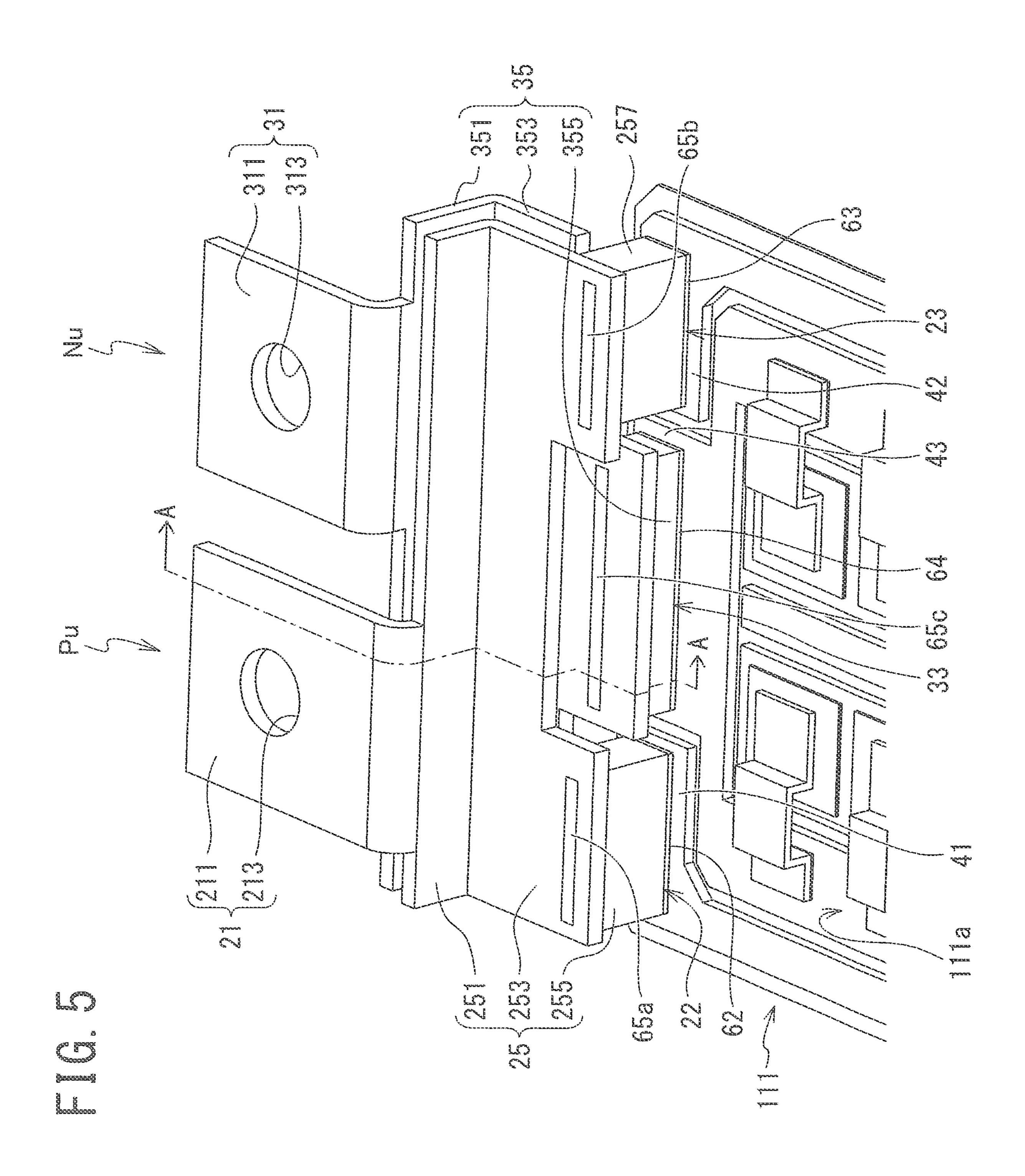

- FIG. **5** is a perspective diagram illustrating an example of power supply terminals included in the semiconductor module according to the first embodiment of the present invention;

FIGS. 6A and 6B are a schematic diagram for explaining positive connection portions and a negative connection portion of the power supply terminals included in the semiconductor module according to the first embodiment of the present invention;

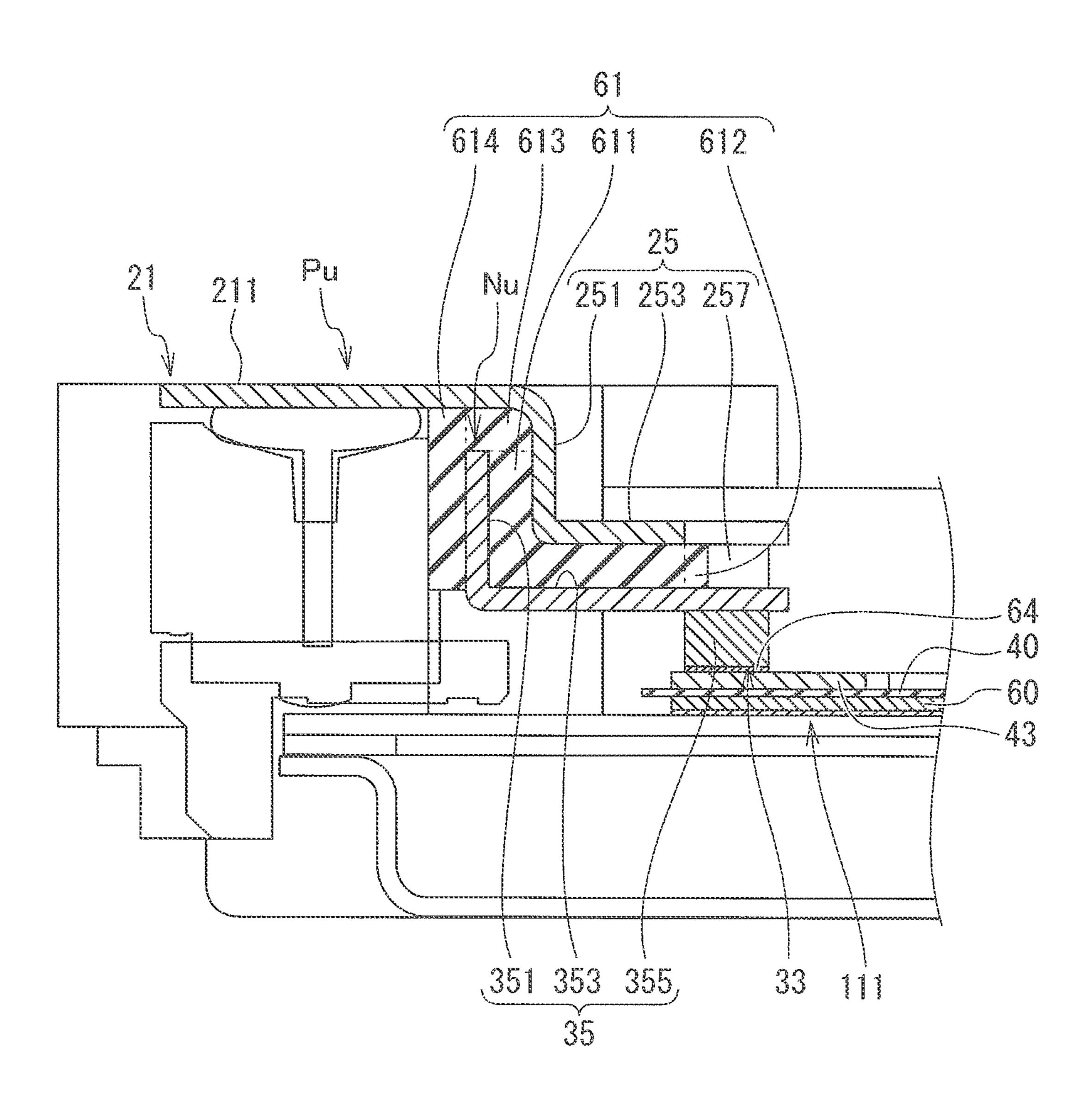

FIG. 7 is a cross-sectional perspective diagram illustrating an example of the power supply terminals included in the semiconductor module according to the first embodiment of the present invention;

FIG. 8 is a cross-sectional diagram illustrating an example of the power supply terminals included in the semiconductor module according to the first embodiment of the present invention;

FIG. 9 is a circuit diagram for explaining effects of the semiconductor module according to the first embodiment of 15 the present invention;

FIG. 10 is a cross-sectional diagram illustrating an example of power supply terminals included in a semiconductor module according to a modification of the first embodiment of the present invention;

FIG. 11 is a diagram illustrating a schematic configuration of a main part of a semiconductor module according to a second embodiment of the present invention; and

FIG. 12 is a perspective diagram illustrating an example of power supply terminals included in the semiconductor <sup>25</sup> module according to the second embodiment of the present invention.

#### DESCRIPTION OF EMBODIMENTS

Each embodiment of the present invention exemplifies devices and methods for embodying the technological idea of the present invention, and the technological idea of the present invention does not limit materials, shapes, structures, arrangement, and the like of the components to those described below. Various modifications can be added to the technological idea of the present invention without departing from the technological scope defined by the claims described in CLAIMS.

## First Embodiment

A semiconductor module according to a first embodiment of the present invention will be described using FIGS. 1 to 10. First, a schematic configuration of the semiconductor 45 module according to the present embodiment will be described using FIGS. 1 to 4. In the present embodiment, a power conversion module capable of converting DC to AC power will be described as an example of the semiconductor module.

As illustrated in FIG. 1, a semiconductor module 1 according to the present embodiment includes a case 10 having a rectangular shape in planar view. The case 10 has a storage section 11 for storing a U-phase inverter portion, a storage section 12 for storing a V-phase inverter portion, 55 and a storage section 13 for storing a W-phase inverter portion. The semiconductor module 1 has a U-phase laminated substrate 111 (an example of a substrate) stored in the storage section 11 and a U-phase inverter circuit 112 mounted on the laminated substrate 111. The semiconductor 60 module 1 has a V-phase laminated substrate 121 (an example of the substrate) stored in the storage section 12 and a V-phase inverter circuit 122 mounted on the laminated substrate 121. The semiconductor module 1 has a W-phase laminated substrate 131 (an example of the substrate) stored 65 in the storage section 13 and a W-phase inverter circuit 132 mounted on the laminated substrate 131.

4

The case 10 is arranged to surround a plurality of semiconductor elements (see details given later), the laminated substrates 111, 121, and 131, a plurality of wiring patterns (see details given later), and a plurality of connection members (see details given later) in the case 10. The case 10 is mounted on a heat dissipation base or cooler (neither illustrated), and is mechanically fixed to the heat dissipation base or cooler by a case bonding material (unillustrated). This allows the case 10 to dissipate heat generated from the semiconductor elements to an outside of the case 10.

The semiconductor module 1 includes a U-phase negative terminal Nu (an example of a first power supply terminal) connected to a negative polarity (an example of a first polarity) side of DC power and a positive terminal Pu (an example of a second power supply terminal) connected to a positive polarity (an example of a second polarity) side of the DC power. The negative terminal Nu and the positive terminal Pu are provided on one of both sides of the storage section 11, at one longitudinal end portion of the case 10. The semiconductor module 1 also includes an output terminal Ou for outputting U-phase AC power. The output terminal Ou is provided on the other one of both sides of the storage section 11, at the other longitudinal end portion of the case 10. The positive terminal Pu and the negative terminal Nu are arranged to face the output terminal Ou across the storage section 11.

The semiconductor module 1 includes a V-phase negative terminal Nv (an example of the first power supply terminal) connected to the negative polarity (an example of the first 30 polarity) side of DC power and a positive terminal Pv (an example of the second power supply terminal) connected to the positive polarity (an example of the second polarity) side of the DC power. The negative terminal Nv and the positive terminal Pv are provided on one of both sides of the storage section 12, at one longitudinal end portion of the case 10. The semiconductor module 1 also includes an output terminal Ov for outputting V-phase AC power. The output terminal Ov is provided on the other one of both sides of the storage section 12, at the other longitudinal end portion of 40 the case 10. The positive terminal Pv and the negative terminal Nv are arranged to face the output terminal Ov across the storage section 12.

The semiconductor module 1 includes a W-phase negative terminal Nw (an example of the first power supply terminal) connected to the negative polarity (an example of the first polarity) side of DC power and a positive terminal Pw (an example of the second power supply terminal) connected to the positive polarity (an example of the second polarity) side of the DC power. The negative terminal Nw and the positive 50 terminal Pw are provided on one of both sides of the storage section 13, at one longitudinal end portion of the case 10. The semiconductor module 1 also includes an output terminal Ow for outputting W-phase AC power. The output terminal Ow is provided on the other one of both sides of the storage section 13, at the other longitudinal end portion of the case 10. The positive terminal Pw and the negative terminal Nw are arranged to face the output terminal Ow across the storage section 13.

Next, circuit structures of the inverter circuits 112, 122, and 132 included in the semiconductor module 1 will be described using FIGS. 2 to 4.

As illustrated in FIG. 2, the inverter circuit 112 provided in the semiconductor module 1 includes a plurality of semiconductor elements Sup11, Sup12, Sup21, and Sup22 and a plurality of semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in series between the negative terminal Nu and the positive terminal Pu. In the inverter

circuit 112, the semiconductor elements Sup11, Sup12, Sup21, and Sup22 are connected in parallel, and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 are connected in parallel. The semiconductor elements Sup11, Sup12, Sup21, and Sup22 connected in parallel and the 5 semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in parallel are connected in series between the negative terminal Nu and the positive terminal Pu. In the inverter circuit 112, a connection portion between the semiconductor elements Sup11, Sup12, Sup21, and Sup22 connected in parallel and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in parallel is connected to the output terminal Ou for outputting U-phase AC power. In other words, in the inverter circuit 112, the semiconductor elements Sup11, Sup12, Sup21, and Sup22 form an upper arm Uup for U-phase AC power, and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 form a lower arm Ulo for U-phase AC power.

As illustrated in FIG. 2, the inverter circuit 122 provided 20 in the semiconductor module 1 includes a plurality of semiconductor elements Sup11, Sup12, Sup21, and Sup22 and a plurality of semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in series between the negative terminal Nv and the positive terminal Pv. In the inverter 25 circuit 122, the semiconductor elements Sup11, Sup12, Sup21, and Sup22 are connected in parallel, and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 are connected in parallel. The semiconductor elements Sup11, Sup12, Sup21, and Sup22 connected in parallel and the 30 semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in parallel are connected in series between the negative terminal Nv and the positive terminal Pv. In the inverter circuit 122, a connection portion between the semiconductor elements Sup11, Sup12, Sup21, and Sup22 con- 35 nected in parallel and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in parallel is connected to the output terminal Ov for outputting V-phase AC power. In other words, in the inverter circuit 122, the semiconductor elements Sup11, Sup12, Sup21, and Sup22 form an upper 40 arm Vup for V-phase AC power, and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 form a lower arm Vlo for V-phase AC power.

As illustrated in FIG. 2, the inverter circuit 132 provided in the semiconductor module 1 includes a plurality of 45 semiconductor elements Sup11, Sup12, Sup21, and Sup22 and a plurality of semiconductor elements Slo11, Slo12, Slo21, and Slo22 connected in series between the negative terminal Nw and the positive terminal Pw. In the inverter circuit 132, the semiconductor elements Sup11, Sup12, 50 Sup21, and Sup22 are connected in parallel, and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 are connected in parallel. The semiconductor elements Sup11, Sup12, Sup21, and Sup22 connected in parallel and the semiconductor elements Slo11, Slo12, Slo21, and Slo22 55 connected in parallel are connected in series between the negative terminal Nw and the positive terminal Pw. In the inverter circuit 132, a connection portion between the semiconductor elements Sup11, Sup12, Sup21, and Sup22 connected in parallel and the semiconductor elements Slo11, 60 Slo12, Slo21, and Slo22 connected in parallel is connected to the output terminal Ow for outputting W-phase AC power. In other words, in the inverter circuit 132, the semiconductor elements Sup11, Sup12, Sup21, and Sup22 form an upper arm Wup for W-phase AC power, and the semiconductor 65 elements Slo11, Slo12, Slo21, and Slo22 form a lower arm Wlo for W-phase AC power.

6

The output terminals Ou, Ov, and Ow are connected to, for example, a motor, which is an object to be driven by the semiconductor module 1. This allows the semiconductor module 1 to supply U-phase AC power to the motor via the output terminal Ou of the inverter circuit 112, supply V-phase AC power thereto via the output terminal Ov of the inverter circuit 122, and supply W-phase AC power thereto via the output terminal Ow of the inverter circuit 132.

The semiconductor elements Sup11, Sup12, Sup21, Sup22, Slo11, Slo12, Slo21, and Slo22 included in each of the inverter circuits 112, 122, and 132 have the same configuration as each other. Thus, hereinafter, using FIG. 3, the semiconductor elements Sup11, Sup12, Sup21, Sup22, Slo11, Slo12, Slo21, and Slo22 included in the inverter circuit 112 will be exemplified to describe the semiconductor elements Sup11, Sup12, Sup21, Sup22, Slo11, Slo12, Slo21, and Slo22 included in each of the inverter circuits 112, 122, and 132.

As illustrated in FIG. 3, the semiconductor element Sup11 has a transistor Qup11, which is, for example, an N-type MOSFET, and a freewheeling diode Dup11 connected antiparallel to the transistor Qup11. The transistor Qup11 and the freewheeling diode Dup11 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qup11 is formed by, for example, a wide-bandgap semiconductor element containing SiC, GaN, diamond, a gallium nitride-based material, a gallium oxide-based material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qup11 is connected to a cathode of the freewheeling diode Dup11, and a source of the transistor Qup11 is connected to an anode of the freewheeling diode Dup11.

The semiconductor element Sup12 has a transistor Qup12, which is, for example, an N-type MOSFET, and a freewheeling diode Dup12 connected anti-parallel to the transistor Qup12. The transistor Qup12 and the freewheeling diode Dup12 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qup12 is formed by, for example, a wide-bandgap semiconductor element containing SiC, GaN, diamond, a gallium nitride-based material, a gallium oxide-based material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qup12 is connected to a cathode of the freewheeling diode Dup12, and a source of the transistor Qup12 is connected to an anode of the freewheeling diode Dup12.

The drain of the transistor Qup11 and the cathode of the freewheeling diode Dup11 are connected to the drain of the transistor Qup12 and the cathode of the freewheeling diode Dup12. The drain of the transistor Qup11, the cathode of the freewheeling diode Dup11, the drain of the transistor Qup12, and the cathode of the freewheeling diode Dup12 are connected to a positive connection portion 22 (see details given later) provided in the positive terminal Pu.

The source of the transistor Qup11 and the anode of the freewheeling diode Dup11 are connected to the source of the transistor Qup12 and the anode of the freewheeling diode Dup12. The source of the transistor Qup11, the anode of the freewheeling diode Dup11, the source of the transistor Qup12, and the anode of the freewheeling diode Dup12 are connected to the output terminal Ou.

As illustrated in FIG. 3, the semiconductor element Sup21 has a transistor Qup21, which is, for example, an N-type MOSFET, and a freewheeling diode Dup21 connected antiparallel to the transistor Qup21. The transistor Qup21 and the freewheeling diode Dup21 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qup21 is formed by, for example, a wide-bandgap semiconductor element containing SiC, GaN,

diamond, a gallium nitride-based material, a gallium oxidebased material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qup21 is connected to a cathode of the freewheeling diode Dup21, and a source of the transistor Qup21 is connected to an anode of the freewheeling diode Dup21.

The semiconductor element Sup22 has a transistor Qup22, which is, for example, an N-type MOSFET, and a freewheeling diode Dup22 connected anti-parallel to the transistor Qup22. The transistor Qup22 and the freewheeling diode Dup22 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qup22 is formed by, for example, a wide-bandgap semiconductor element containing SiC, GaN, diamond, a gallium nitride-based material, a gallium oxide-based material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qup22 is 15 connected to a cathode of the freewheeling diode Dup22, and a source of the transistor Qup22 is connected to an anode of the freewheeling diode Dup22.

The drain of the transistor Qup21 and the cathode of the freewheeling diode Dup21 are connected to the drain of the 20 transistor Qup22 and the cathode of the freewheeling diode Dup22. The drain of the transistor Qup21, the cathode of the freewheeling diode Dup21, the drain of the transistor Qup22, and the cathode of the freewheeling diode Dup22 are connected to a positive connection portion 23 (see details 25) given later) provided in the positive terminal Pu.

The source of the transistor Qup21 and the anode of the freewheeling diode Dup21 are connected to the source of the transistor Qup22 and the anode of the freewheeling diode Dup22. The source of the transistor Qup21, the anode of the 30 freewheeling diode Dup21, the source of the transistor Qup22, and the anode of the freewheeling diode Dup22 are connected to the output terminal Ou.

As illustrated in FIG. 3, the semiconductor element Slo11 has a transistor Qlo11, which is, for example, an N-type 35 MOSFET, and a freewheeling diode Dlo11 connected antiparallel to the transistor Qlo11. The transistor Qlo11 and the freewheeling diode Dlo11 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qlo11 is formed by, for example, a wide- 40 bandgap semiconductor element containing SiC, GaN, diamond, a gallium nitride-based material, a gallium oxidebased material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qlo11 is connected to a cathode of the freewheeling diode Dlo11, and a source of the transistor Qlo11 is 45 connected to an anode of the freewheeling diode Dlo11.

The semiconductor element Slo12 has a transistor Qlo12, which is, for example, an N-type MOSFET, and a freewheeling diode Dlo12 connected anti-parallel to the transistor Qlo12. The transistor Qlo12 and the freewheeling diode 50 Dlo12 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qlo12 is formed by, for example, a wide-bandgap semiconductor element containing SiC, GaN, diamond, a gallium nitridebased material, a gallium oxide-based material, AlN, 55 nected to the output terminal Ou. AlGaN, ZnO, or the like. A drain of the transistor Qlo12 is connected to a cathode of the freewheeling diode Dlo12, and a source of the transistor Qlo12 is connected to an anode of the freewheeling diode Dlo12.

The source of the transistor Qlo11 and the anode of the 60 freewheeling diode Dlo11 are connected to the source of the transistor Qlo12 and the anode of the freewheeling diode Dlo12. The source of the transistor Qlo11, the anode of the freewheeling diode Dlo11, the source of the transistor Qlo12, and the anode of the freewheeling diode Dlo12 are 65 connected to a negative connection portion 33 (see details given later) provided in the negative terminal Nu.

The drain of the transistor Qlo11 and the cathode of the freewheeling diode Dlo11 are connected to the drain of the transistor Qlo12 and the cathode of the freewheeling diode Dlo12. The drain of the transistor Qlo11, the cathode of the freewheeling diode Dlo11, the drain of the transistor Qlo12, and the cathode of the freewheeling diode Dlo12 are connected to the output terminal Ou.

As illustrated in FIG. 3, the semiconductor element Slo21 has a transistor Qlo21, which is, for example, an N-type MOSFET, and a freewheeling diode Dlo21 connected antiparallel to the transistor Qlo21. The transistor Qlo21 and the freewheeling diode Dlo21 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qlo21 is formed by, for example, a widebandgap semiconductor element containing SiC, GaN, diamond, a gallium nitride-based material, a gallium oxidebased material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qlo21 is connected to a cathode of the freewheeling diode Dlo21, and a source of the transistor Qlo21 is connected to an anode of the freewheeling diode Dlo21.

The semiconductor element Slo22 has a transistor Qlo22, which is, for example, an N-type MOSFET, and a freewheeling diode Dlo22 connected anti-parallel to the transistor Qlo22. The transistor Qlo22 and the freewheeling diode Dlo22 are, for example, formed on a single semiconductor substrate and made into a single chip. The transistor Qlo22 is formed by, for example, a wide-bandgap semiconductor element containing SiC, GaN, diamond, a gallium nitridebased material, a gallium oxide-based material, AlN, AlGaN, ZnO, or the like. A drain of the transistor Qlo22 is connected to a cathode of the freewheeling diode Dlo22, and a source of the transistor Qlo22 is connected to an anode of the freewheeling diode Dlo22.

The source of the transistor Qlo21 and the anode of the freewheeling diode Dlo21 are connected to the source of the transistor Qlo22 and the anode of the freewheeling diode Dlo22. The source of the transistor Qlo21, the anode of the freewheeling diode Dlo21, the source of the transistor Qlo22, and the anode of the freewheeling diode Dlo22 are connected to the negative connection portion 33 (see details given later) provided in the negative terminal Nu. Furthermore, the source of the transistor Qlo21, the anode of the freewheeling diode Dlo21, the source of the transistor Qlo22, and the anode of the freewheeling diode Dlo22 are connected to the source of the transistor Qlo11, the anode of the freewheeling diode Dlo11, the source of the transistor Qlo12, and the anode of the freewheeling diode Dlo12.

The drain of the transistor Qlo21 and the cathode of the freewheeling diode Dlo21 are connected to the drain of the transistor Qlo22 and the cathode of the freewheeling diode Dlo22. The drain of the transistor Qlo21, the cathode of the freewheeling diode Dlo21, the drain of the transistor Qlo22, and the cathode of the freewheeling diode Dlo22 are con-

The source of the transistor Qup11, the anode of the freewheeling diode Dup11, the source of the transistor Qup12, and the anode of the freewheeling diode Dup12, the source of the transistor Qup21, the anode of the freewheeling diode Dup21, the source of the transistor Qup22, and the anode of the freewheeling diode Dup22, the drain of the transistor Qlo11, the cathode of the freewheeling diode Dlo11, the drain of the transistor Qlo12, and the cathode of the freewheeling diode Dlo12, and the drain of the transistor Qlo21, the cathode of the freewheeling Dlo21, the drain of the transistor Qlo22, and the cathode of the freewheeling diode Dlo22 are connected to each other.

A gate of the transistor Qup11 is connected to a gate signal input terminal Gup11. The source of the transistor Qup11 is connected to a reference signal input terminal Rup11. The gate signal input terminal Gup11 and the reference signal input terminal Rup11 are connected to a control circuit 5 (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Gup11 and the reference signal input terminal 10 Rup11, and is, as a gate-source voltage, applied between the gate and the source of the transistor Qup11. The transistor Qup11 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level.

A gate of the transistor Qup12 is connected to a gate signal input terminal Gup12. The source of the transistor Qup12 is connected to a reference signal input terminal Rup12. The gate signal input terminal Gup12 and the reference signal input terminal Rup12 are connected to the 20 control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Gup12 and the 25 reference signal input terminal Rup12, and is, as a gatesource voltage, applied between the gate and the source of the transistor Qup12. The transistor Qup12 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level. 30

A gate of the transistor Qup21 is connected to a gate signal input terminal Gup21. The source of the transistor Qup21 is connected to a reference signal input terminal Rup21. The gate signal input terminal Gup21 and the control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Gup21 and the 40 reference signal input terminal Rup21, and is, as a gatesource voltage, applied between the gate and the source of the transistor Qup21. The transistor Qup21 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level. 45

A gate of the transistor Qup22 is connected to a gate signal input terminal Gup22. The source of the transistor Qup22 is connected to a reference signal input terminal Rup22. The gate signal input terminal Gup22 and the reference signal input terminal Rup22 are connected to the 50 control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Gup22 and the 55 reference signal input terminal Rup22, and is, as a gatesource voltage, applied between the gate and the source of the transistor Qup22. The transistor Qup22 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level. 60

Although details will be given later, the semiconductor module 1 according to the present embodiment is configured such that the transistors Qup11, Qup12, Qup21, and Qup22 are simultaneously switched from off to on and simultaneously switched from on to off. Therefore, the gates of the 65 transistors Qup11, Qup12, Qup21, and Qup22 may be connected to a common gate signal input terminal, and the

**10**

sources of the transistors Qup11, Qup12, Qup21, and Qup22 may be connected to a common reference signal input terminal.

A gate of the transistor Qlo11 is connected to a gate signal input terminal Glo11. The source of the transistor Qlo11 is connected to a reference signal input terminal Rlo11. The gate signal input terminal Glo11 and the reference signal input terminal Rlo11 are connected to the control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Glo11 and the reference signal input terminal Rlo11, and is, as a gate-source voltage, applied between the 15 gate and the source of the transistor Qlo11. The transistor Qlo11 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level.

A gate of the transistor Qlo12 is connected to a gate signal input terminal Glo12. The source of the transistor Qlo12 is connected to a reference signal input terminal Rlo12. The gate signal input terminal Glo12 and the reference signal input terminal Rlo12 are connected to the control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Glo12 and the reference signal input terminal Rlo12, and is, as a gate-source voltage, applied between the gate and the source of the transistor Qlo12. The transistor Qlo12 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level.

A gate of the transistor Qlo21 is connected to a gate signal reference signal input terminal Rup21 are connected to the 35 input terminal Glo21. The source of the transistor Qlo21 is connected to a reference signal input terminal Rlo21. The gate signal input terminal Glo21 and the reference signal input terminal Rlo21 are connected to the control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Glo21 and the reference signal input terminal Rlo21, and is, as a gate-source voltage, applied between the gate and the source of the transistor Qlo21. The transistor Qlo21 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level.

> A gate of the transistor Qlo22 is connected to a gate signal input terminal Glo22. The source of the transistor Qlo22 is connected to a reference signal input terminal Rlo22. The gate signal input terminal Glo22 and the reference signal input terminal Rlo22 are connected to the control circuit (unillustrated) for controlling the inverter circuits 112, 122, and 132. The control circuit generates a gate pulse signal by modulating a command value and a reference waveform. The gate pulse signal is applied between the gate signal input terminal Glo22 and the reference signal input terminal Rlo22, and is, as a gate-source voltage, applied between the gate and the source of the transistor Qlo22. The transistor Qlo22 is turned on when the gate pulse signal has a high voltage level, and is turned off when the gate pulse signal has a low voltage level.

> When at least one the transistors Qup11, Qup12, Qup21 and Qup22 are turned on and the transistors Qlo11 and Qlo12 and the transistors Qlo21 and Qlo22 are turned off, the positive terminal Pu is connected to the output terminal

Ou. On the other hand, when the transistors Qup11 and Qup12 and the transistors Qup21 and Qup22 are turned off and at least one the transistors Qlo11, Qlo12, Qlo21 and Qlo22 are turned on, the negative terminal Nu is connected to the output terminal Ou. As described above, in the 5 semiconductor module 1 according to the present embodiment, the transistors Qup11, Qup12, Qup21, and Qup22 are controlled so as to be simultaneously switched from off to on and simultaneously switched from on to off. Therefore, the gates of the transistors Qup11, Qup12, Qup21, and Qup22 may be connected to a common gate signal input terminal, and the sources of the transistors Qup11, Qup12, Qup21, and Qup22 may be connected to a common reference signal module 1 according to the present embodiment, the transistors Qlo11, Qlo12, Qlo21, and Qlo22 are controlled so as to be simultaneously switched from off to on and simultaneously switched from on to off. Therefore, the gates of the transistors Qlo11, Qlo12, Qlo21, and Qlo22 may be con- 20 nected to a common gate signal input terminal, and the sources of the transistors Qlo11, Qlo12, Qlo21, and Qlo22 maybe connected to a common reference signal input terminal. Furthermore, in the semiconductor module 1 according to the present embodiment, switching operation is con- 25 trolled so that the transistors Qup11, Qup12, Qup21, and Qup22 and the transistors Qlo11, Qlo12, Qlo21, and Qlo22 are not turned on simultaneously (non-overlap control).

Turn-on/turn-off of the transistors Qup11, Qup12, Qup21, and Qup22 and turn-off/turn-on of the transistors Qlo11, 30 Qlo12, Qlo21, and Qlo22 are alternately repeated, whereby an AC voltage formed from a positive polarity voltage and a negative polarity voltage is output from the output terminal Ou. When a turn-on period of the transistors Qup11, Qup12, Qup21, and Qup22 is longer than a turn-off period of the 35 transistors Qlo11, Qlo12, Qlo21, and Qlo22 in the alternate repetition of the turn-on/turn-off of the transistors Qup11, Qup12, Qup21, and Qup22 and the turn-off/turn-on of the transistors Qlo11, Qlo12, Qlo21, and Qlo22, a voltage level output from the output terminal Ou rises, at a maximum, to 40 a voltage level of the positive polarity voltage supplied to the positive terminal Pu. On the other hand, when a turn-off period of the transistors Qup11, Qup12, Qup21, and Qup22 is longer than a turn-on period of the transistors Qlo11, Qlo12, Qlo21, and Qlo22 in the alternate repetition of the 45 turn-on/turn-off of the transistors Qup11, Qup12, Qup21, and Qup22 and the turn-off/turn-on of the transistors Qlo11, Qlo12, Qlo21, and Qlo22, a voltage level output from the output terminal Ou drops, at a minimum, to a voltage level of the negative polarity voltage supplied to the negative 50 terminal Nu.

By appropriately adjusting a pulse width of the gate pulse signal input to the gate of each of the transistors Qup11, Qup12, Qup21, and Qup22 and a pulse width of the gate pulse signal input to the gate of each of the transistors Qlo11, 55 Qlo12, Qlo21, and Qlo22, the inverter circuit 112 can supply AC power having a desired waveform (for example, sine wave AC power) to the motor from the output terminal Ou to drive the motor.

The inverter circuit **122** has the same configuration as that 60 of the inverter circuit 112 when the positive terminal Pu is replaced by the positive terminal Pv, the negative terminal Nu is replaced by the negative terminal Nv, and the output terminal Ou is replaced by the output terminal Ov. The inverter circuit 132 has the same configuration as that of the 65 inverter circuit 112 when the positive terminal Pu is replaced by the positive terminal Pw, the negative terminal Nu is

replaced by the negative terminal Nw, and the output terminal Ou is replaced by the output terminal Ow.

The gate pulse signal input to the gate of each of the transistors Qup11, Qup12, Qup21, and Qup22 provided in the inverter circuit 112, the gate pulse signal input to the gate of each of the transistors Qup11, Qup12, Qup21, and Qup22 provided in the inverter circuit 122, and the gate pulse signal input to the gate of each of the transistors Qup11, Qup12, Qup21, and Qup22 provided in the inverter circuit 132 are 10 different signals from each other.

Additionally, the gate pulse signal input to the gate of each of the transistors Qlo11, Qlo12, Qlo21, and Qlo22 provided in the inverter circuit 112, the gate pulse signal input to the gate of each of the transistors Qlo11, Qlo12, input terminal. In addition, similarly, in the semiconductor 15 Qlo21, and Qlo22 provided in the inverter circuit 122, and the gate pulse signal input to the gate of each of the transistors Qlo11, Qlo12, Qlo21, and Qlo22 provided in the inverter circuit 132 are different signals from each other.

> As a result, the semiconductor module 1 can supply U-phase AC power, V-phase AC power, and W-phase AC power having phases shifted from each other by a predetermined amount to the motor from the output terminals Ou, Ov, and Ow.

> Next, the laminated substrates 111, 121, and 131 will be described using FIG. 4 and with reference to FIGS. 1 and 3. The laminated substrates 111, 121, and 131 have the same configuration as each other. Therefore, hereinafter, the laminated substrate 111 will be exemplified to describe the laminated substrates 111, 121, and 131.

> As illustrated in FIG. 4, the laminated substrate 111 has a rectangular insulating substrate 40 and a heat dissipation pattern layer 60 having a predetermined shape (unillustrated in FIG. 4; see FIGS. 7 and 8) formed on a lower surface of the insulating substrate 40. The laminated substrate 111 has a first positive-side input terminal pattern 41, a second positive-side input terminal pattern 42, and a negative-side input terminal pattern 43 formed on one short side of both short sides of the insulating substrate 40. The negative-side input terminal pattern 43 is arranged between the first positive-side input terminal pattern 41 and the second positive-side input terminal pattern 42. The laminated substrate 111 has an output terminal pattern 49 formed on the other short side of the insulating substrate 40. The output terminal pattern 49 is arranged to face the negative-side input terminal pattern 43.

> The laminated substrate 111 has a first positive portion pattern 44 formed on the insulating substrate 40 on one long side of both long sides of the insulating substrate 40. The first positive portion pattern 44 is arranged to extend between both the short sides of the insulating substrate 40 along the one long side of the insulating substrate 40. In the first positive portion pattern 44, a pattern width of the other short side of the insulating substrate 40 is larger than a pattern width of the one short side of the insulating substrate 40 relative to a longitudinal center part. The first positiveside input terminal pattern 41 is formed on one end portion of the first positive portion pattern 44. As a result, the first positive portion pattern 44 and the first positive-side input terminal pattern 41 are electrically connected to each other.

> The laminated substrate 111 has a second positive portion pattern 45 formed on the insulating substrate 40 on the other long side of both the long sides of the insulating substrate 40. The second positive portion pattern 45 is arranged to extend between both the short sides of the insulating substrate 40 along the other long side of the insulating substrate 40. In the second positive portion pattern 45, a pattern width of the other short side of the insulating substrate 40 is larger than

a pattern width of the one short side of the insulating substrate 40 relative to a longitudinal center part. The second positive-side input terminal pattern 42 is formed on one end portion of the second positive portion pattern 45. As a result, the second positive portion pattern 45 and the second 5 positive-side input terminal pattern 42 are electrically connected to each other.

The laminated substrate 111 has a negative portion pattern 46 formed on the insulating substrate 40 between a portion of the first positive portion pattern 44 with a relatively 10 narrow pattern width and a portion of the second positive portion pattern 45 with a relatively narrow pattern width. The negative portion pattern 46 has a bifurcated shape that is stretched out from the one short side of the insulating substrate 40 by a predetermined length and that extends 15 from the stretched portion along each of the first positive portion pattern 44 and the second positive portion pattern 45. The negative-side input terminal pattern 43 is formed at an end portion of the negative portion pattern 46 on the one short side of the insulating substrate 40. As a result, the 20 negative portion pattern 46 and the negative-side input terminal pattern 43 are electrically connected to each other.

The laminated substrate 111 has an output portion pattern 47 formed on the insulating substrate 40 and extending from the other short side of the insulating substrate 40 toward a 25 center part thereof. The output portion pattern 47 is arranged to extend up to a space portion formed by bifurcating the negative portion pattern 46 in the center part of the laminated substrate 111. As a result, a part of the output portion pattern 47 is arranged to be sandwiched between the bifur- 30 cated portions of the negative portion pattern 46. The output terminal pattern 49 is formed at an end portion of the output portion pattern 47 on the other short side of the insulating substrate 40. As a result, the output portion pattern 47 and each other.

As illustrated in FIG. 4, on a portion of the first positive portion pattern 44 with a relatively large pattern width, the semiconductor element Sup11 is mounted in electrical connection with the first positive portion pattern 44. As a result, 40 the drain (see FIG. 3) of the transistor Qup11 and the cathode (see FIG. 3) of the freewheeling diode Dup11 included in the semiconductor element Sup11 are electrically connected with the first positive portion pattern 44. Additionally, a connection member 51 made of a conductive material is 45 arranged between the semiconductor element Sup11 and the output portion pattern 47. The connection member 51 is configured by, for example, a copper bar. The connection member 51 is adapted to electrically connect the source (see FIG. 3) of the transistor Qup11 and the anode (see FIG. 3) 50 of the freewheeling diode Dup11 included in the semiconductor element Sup11 with the output portion pattern 47.

On the portion of the first positive portion pattern 44 with the relatively large pattern width, the semiconductor element Sup12 is mounted side by side with the semiconductor 55 element Sup11 while being electrically connected with the first positive portion pattern 44. As a result, the drain (see FIG. 3) of the transistor Qup12 and the cathode (see FIG. 3) of the freewheeling diode Dup12 included in the semiconductor element Sup12 are electrically connected with the 60 first positive portion pattern 44. Additionally, a connection member 52 made of a conductive material is arranged between the semiconductor element Sup12 and the output portion pattern 47. The connection member 52 is configured by, for example, a copper bar. The connection member **52** is 65 adapted to electrically connect the source (see FIG. 3) of the transistor Qup12 and the anode (see FIG. 3) of the free14

wheeling diode Dup12 included in the semiconductor element Sup12 with the output portion pattern 47.

As illustrated in FIG. 4, on a portion of the second positive portion pattern 45 with a relatively large pattern width, the semiconductor element Sup21 is mounted in electrical connection with the second positive portion pattern 45. As a result, the drain (see FIG. 3) of the transistor Qup21 and the cathode (see FIG. 3) of the freewheeling diode Dup21 included in the semiconductor element Sup21 are electrically connected with the second positive portion pattern 45. Additionally, a connection member 55 made of a conductive material is arranged between the semiconductor element Sup21 and the output portion pattern 47. The connection member 55 is configured by, for example, a copper bar. The connection member 55 is adapted to electrically connect the source (see FIG. 3) of the transistor Qup21 and the anode (see FIG. 3) of the freewheeling diode Dup21 included in the semiconductor element Sup21 with the output portion pattern 47.

On the portion of the second positive portion pattern 45 with the relatively large pattern width, the semiconductor element Sup22 is mounted side by side with the semiconductor element Sup21 while being electrically connected with the second positive portion pattern 45. As a result, the drain (see FIG. 3) of the transistor Qup22 and the cathode (see FIG. 3) of the freewheeling diode Dup22 included in the semiconductor element Sup22 are electrically connected with the second positive portion pattern 45. Additionally, a connection member 56 made of a conductive material is arranged between the semiconductor element Sup 22 and the output portion pattern 47. The connection member 56 is configured by, for example, a copper bar. The connection member 56 is adapted to electrically connect the source (see FIG. 3) of the transistor Qup22 and the anode (see FIG. 3) the output terminal pattern 49 are electrically connected to 35 of the freewheeling diode Dup22 included in the semiconductor element Sup22 with the output portion pattern 47.

As illustrated in FIG. 4, on the part of the output portion pattern 47 arranged in the center part of the laminated substrate 111, the semiconductor element Slo11 is mounted in electrical connection with the output portion pattern 47. As a result, the drain (see FIG. 3) of the transistor Qlo11 and the cathode (see FIG. 3) of the freewheeling diode Dlo11 included in the semiconductor element Slo11 are electrically connected with the output portion pattern 47. Additionally, a connection member 53 made of a conductive material is arranged between the semiconductor element Slo11 and the negative portion pattern 46. The connection member 53 is configured by, for example, a copper bar. The connection member 53 is adapted to electrically connect the source (see FIG. 3) of the transistor Qlo11 and the anode (see FIG. 3) of the freewheeling diode Dlo11 included in the semiconductor element Slo11 with the negative portion pattern 46.

On the part of the output portion pattern 47 arranged in the center part of the laminated substrate 111, the semiconductor element Slo12 is mounted side by side with the semiconductor element Slo11 while being electrically connected with the output portion pattern 47. As a result, the drain (see FIG. 3) of the transistor Qlo12 and the cathode (see FIG. 3) of the freewheeling diode Dlo12 included in the semiconductor element Slo12 are electrically connected with the output portion pattern 47. Additionally, a connection member 54 made of a conductive material is arranged between the semiconductor element Slo12 and the negative portion pattern 46. The connection member 54 is configured by, for example, a copper bar. The connection member 54 is adapted to electrically connect the source (see FIG. 3) of the transistor Qlo12 and the anode (see FIG. 3) of the free-

wheeling diode Dlo12 included in the semiconductor element Slo12 with the negative portion pattern 46.

On the part of the output portion pattern 47 arranged in the center part of the laminated substrate 111, the semiconductor element Slo21 is mounted in electrical connection with the 5 output portion pattern 47. As a result, the drain (see FIG. 3) of the transistor Qlo21 and the cathode (see FIG. 3) of the freewheeling diode Dlo21 included in the semiconductor element Slo21 are electrically connected with the output portion pattern 47. Additionally, a connection member 57 10 made of a conductive material is arranged between the semiconductor element Slo21 and the negative portion pattern 46. The connection member 57 is configured by, for example, a copper bar. The connection member 57 is adapted to electrically connect the source (see FIG. 3) of the 15 transistor Qlo21 and the anode (see FIG. 3) of the freewheeling diode Dlo21 included in the semiconductor element Slo21 with the negative portion pattern 46.

On the part of the output portion pattern 47 arranged in the center part of the laminated substrate 111, the semiconductor 20 element Slo22 is mounted side by side with the semiconductor element Slo21 while being electrically connected with the output portion pattern 47. As a result, the drain (see FIG. 3) of the transistor Qlo22 and the cathode (see FIG. 3) of the freewheeling diode Dlo22 included in the semicon- 25 ductor element Slo22 are electrically connected with the output portion pattern 47. Additionally, a connection member 58 made of a conductive material is arranged between the semiconductor element Slo22 and the negative portion pattern 46. The connection member 58 is configured by, for 30 example, a copper bar. The connection member 58 is adapted to electrically connect the source (see FIG. 3) of the transistor Qlo22 and the anode (see FIG. 3) of the freewheeling diode Dlo22 included in the semiconductor element Slo22 with the negative portion pattern 46.

The positive connection portion 22 (see FIG. 5; details will be given later) of the positive terminal Pu is electrically connected to and mounted on the first positive-side input terminal pattern 41. The output terminal Ou (see FIG. 3) is electrically connected to and mounted on the output terminal 40 pattern 49. Accordingly, the semiconductor element Sup11 and the semiconductor element Sup12 are connected in parallel between the positive terminal Pu and the output terminal Ou via the first positive-side input terminal pattern 41 and the first positive portion pattern 44, and via the 45 connection members 51 and 52, the output portion pattern 47, and the output terminal pattern 49.

The positive connection portion 23 (see FIG. 5; details will be given later) of the positive terminal Pu is electrically connected to and mounted on the second positive-side input 50 terminal pattern 42. The output terminal Ou (see FIG. 3) is electrically connected to and mounted on the output terminal pattern 49. Accordingly, the semiconductor element Sup21 and the semiconductor element Sup22 are connected in parallel between the positive terminal Pu and the output 55 terminal Ou via the second positive-side input terminal pattern 42 and the second positive portion pattern 45, and via the connection members 55 and 56, the output portion pattern 47, and the output terminal pattern 49.

The negative connection portion 33 (see FIG. 5; details 60 will be given later) of the negative terminal Nu is electrically connected to and mounted on the negative-side input terminal pattern 43. The output terminal Ou (see FIG. 3) is electrically connected to and mounted on the output terminal pattern 49. Accordingly, the semiconductor element Slo11 65 and the semiconductor element Slo12 are connected in parallel between the output terminal Ou and the negative

**16**

terminal Nu via the output portion pattern 47 and the output terminal pattern 49, and via the connection members 53 and 54, the negative portion pattern 46, and the negative-side input terminal pattern 43.

The negative connection portion 33 of the negative terminal Nu is electrically connected to and mounted on the negative-side input terminal pattern 43. The output terminal Ou (see FIG. 3) is electrically connected to and mounted on the output terminal pattern 49. Accordingly, the semiconductor element Slo21 and the semiconductor element Slo22 are connected in parallel between the output terminal Ou and the negative terminal Nu via the output portion pattern 47 and the output terminal pattern 49, and via the connection members 57 and 58, the negative portion pattern 46, and the negative-side input terminal pattern 43. As a result, the inverter circuit 112 has a half-bridge circuit configuration.

Although illustration is omitted, the laminated substrates 121 and 131 also have the same configuration as that of the laminated substrate 111. Therefore, the inverter circuits 122 and 132 each have a half-bridge circuit configuration. Thus, the semiconductor module 1 is configured by a 6-in-1 module in which the U-phase inverter circuit 112 having the half-bridge circuit configuration, the V-phase inverter circuit 122 having the half-bridge circuit configuration, and the W-phase inverter circuit 132 having the half-bridge circuit configuration are combined into a single module.

The first positive portion pattern 44, the second positive portion pattern 45, the negative portion pattern 46, and the output portion pattern 47 are formed adjacent to each other with a predetermined insulation distance to prevent them from being short-circuited with each other. Additionally, all or some of the first positive portion pattern 44, the second positive portion pattern 45, the negative portion pattern 46, and the output portion pattern 47 are sealed and fixed with an insulating resin provided in the case 10 (see FIG. 1). This further improves insulation properties of the first positive portion pattern 44, the second positive portion pattern 45, the negative portion pattern 45, and the output portion pattern 47.

Apart of each of the positive terminal Pu, the negative terminal Nu, and the output terminal Ou is arranged at a periphery of the case 10 and exposed out of the insulating resin provided in the case 10. As a result, the positive terminal Pu can be electrically connected to an external terminal to which positive-side DC power is supplied. Additionally, the negative terminal Nu can be electrically connected to an external terminal to which negative-side DC power is supplied. Furthermore, the output terminal Ou can be electrically connected to a power supply terminal of the motor to be driven.

The laminated substrate 111 is mounted on the heat dissipation base or cooler, and is thermally and mechanically bonded to the heat dissipation base or cooler by means of a material for bonding under substrate (unillustrated). Additionally, as described above, the case 10 is mechanically fixed to the heat dissipation base or cooler. Accordingly, the semiconductor module 1 can discharge heat generated in the semiconductor elements Sup11, Sup12, Sup21, Sup22, Slo11, Slo12, Slo21, and Slo22 to the heat dissipation base or cooler via the laminated substrate 111 and the case 10. As a result, the semiconductor module 1 can prevent the semiconductor elements Sup11, Sup12, Sup21, Sup22, Slo11, Slo12, Slo21, and Slo22 from being damaged due to heat generation.

(Configurations of First Power Supply Terminal and Second Power Supply Terminal)

Next, configurations of the negative terminals Nu, Nv, and Nw (an example of the first power supply terminal) and the positive terminals Pu, Pv, and Pw (an example of the second 5 power supply terminal) included in the semiconductor module 1 according to the present embodiment will be described using FIGS. 5 to 9 and with reference to FIGS. 1 to 4. The negative terminals Nu, Nv, and Nw have the same configuration. Therefore, the negative terminal Nu will be exemplified to describe the configuration of the negative terminals Nu, Nv, and Nw. In addition, the positive terminals Pu, Pv, and Pw have the same configuration. Therefore, the positive terminal Pu will be exemplified to describe the configuration of the positive terminals Pu, Pv, and Pw.

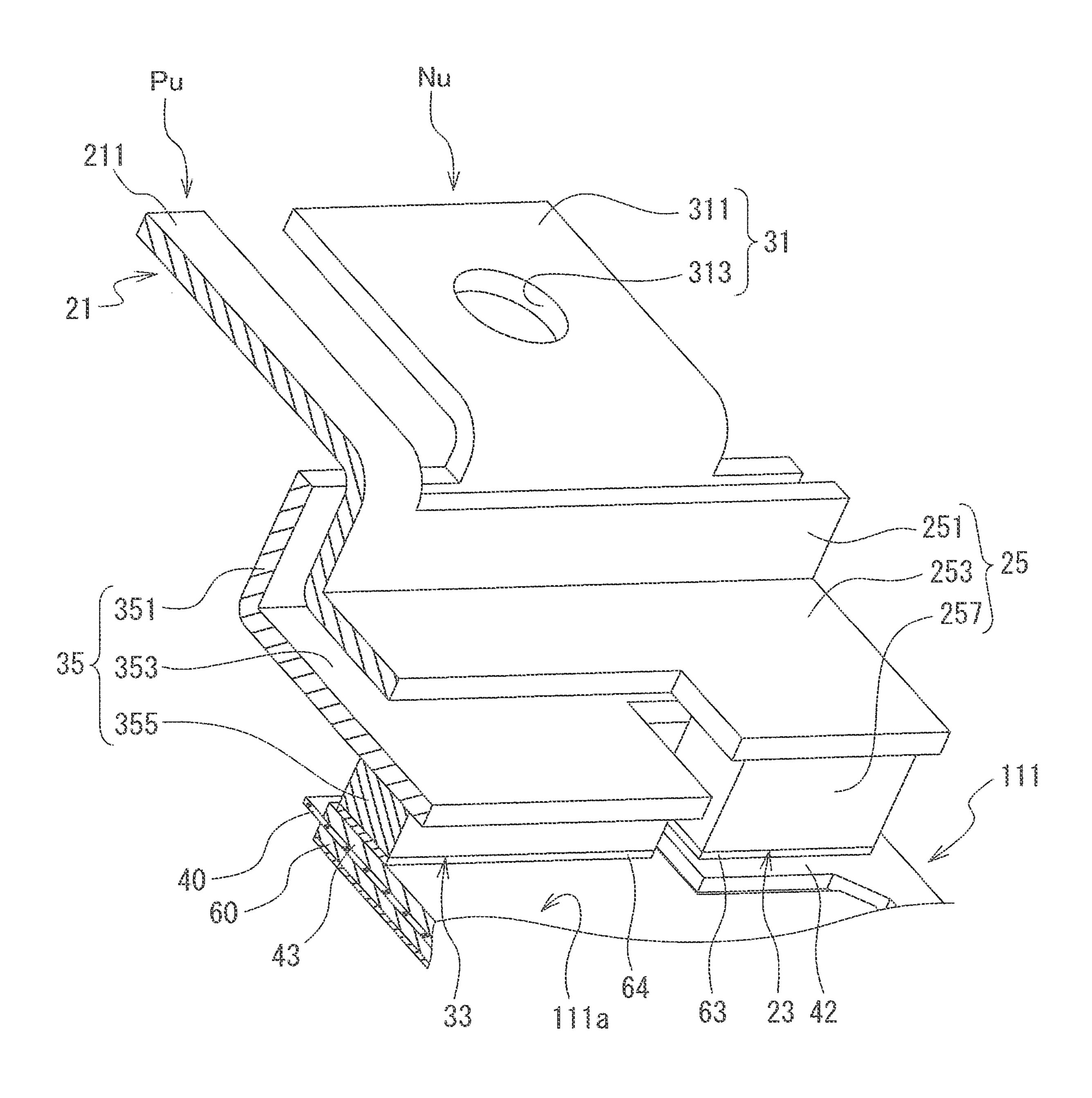

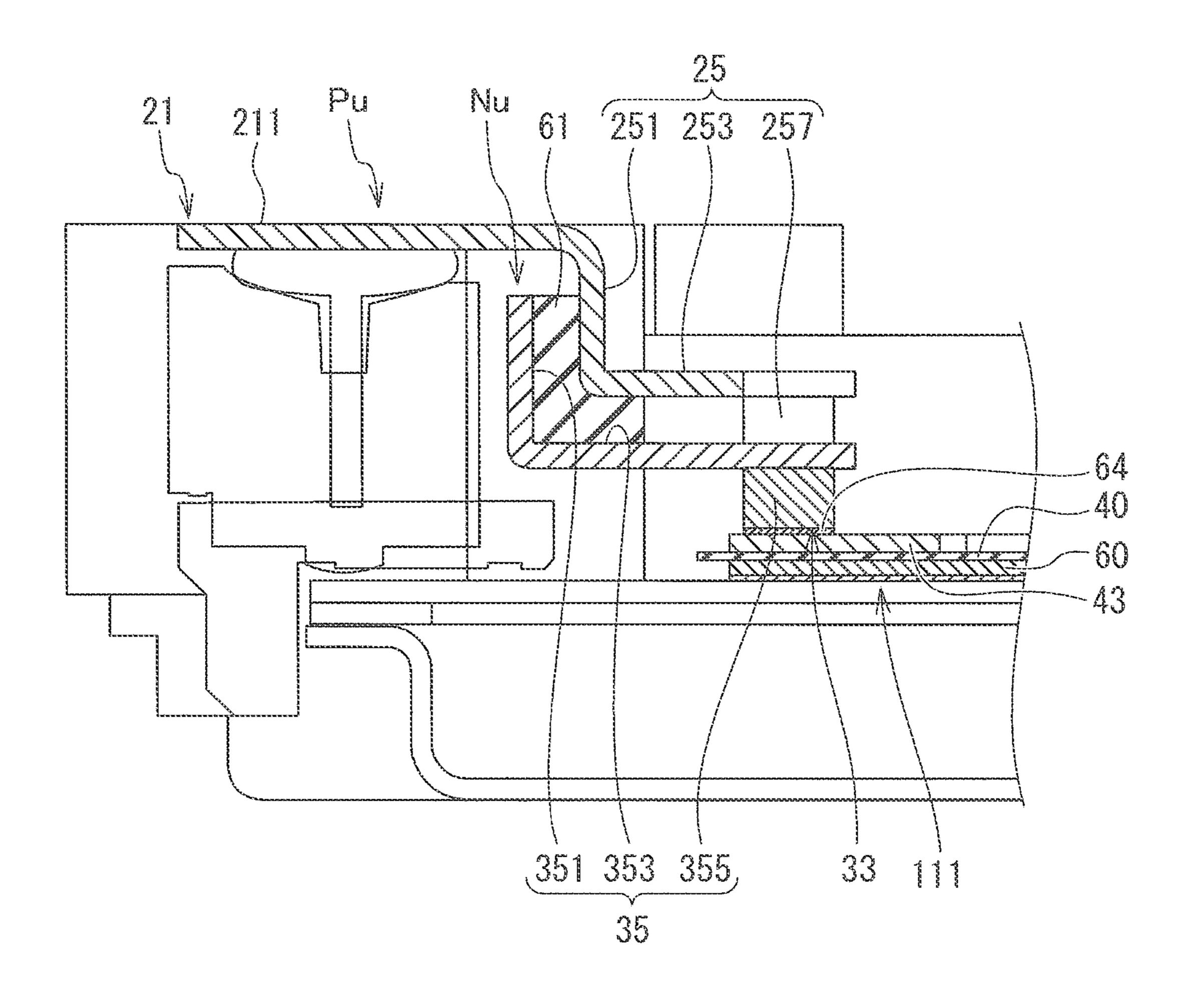

As illustrated in FIG. 5, the negative terminal Nu has a negative fastening portion (an example of a first fastening portion) 31 for fastening an external terminal (unillustrated) of a negative polarity side, the negative connection portion (an example of a first connection portion) 33 connected to 20 the laminated substrate 111, and a negative intermediate portion (an example of a first intermediate portion) 35 arranged between the negative fastening portion 31 and the negative connection portion 33. The positive terminal Pu has a positive fastening portion (an example of a second fasten- 25 ing portion) 21, which is arranged adjacent to the negative fastening portion 31 and which is for fastening an external terminal (unillustrated) of a positive polarity side, a pair of the positive connection portions (an example of a second connection portion) 22 and 23 arranged across the negative 30 connection portion 33 and connected to the laminated substrate 111, and a positive intermediate portion (an example of a second intermediate portion) 25 at least apart of which faces the negative intermediate portion 35 with a predetermined gap and which is arranged between the positive 35 fastening portion 21 and the pair of positive connection portions 22 and 23.

The negative fastening portion 31 has an arrangement portion 311 for arranging a negative-side external terminal in contact therewith and a through hole 313 formed by 40 penetrating through the arrangement portion 311. The arrangement portion 311 has a flat plate shape. The through hole 313 is formed at a substantially center of the arrangement portion 311. The through hole 313 is provided to mount a jig (for example, a screw or a vis) for fastening the 45 external terminal to the negative fastening portion 31.

The positive fastening portion 21 has an arrangement portion 211 for arranging a positive-side external terminal in contact therewith and a through hole 213 formed by penetrating through the arrangement portion 211. The arrangement portion 211 has a flat plate shape. The through hole 213 is formed at a substantially center of the arrangement portion 211. The through hole 213 is provided to mount a jig (for example, a screw or a vis) for fastening the external terminal to the positive fastening portion 21.

The negative fastening portion 31 and the positive fastening portion 21 overlap one side of the laminated substrate 111 or are positioned outside the one side thereof when a contact surface 111a is viewed in an orthogonal direction, and are arranged along the one side of the laminated 60 substrate 111. Note that viewing the contact surface 111a in the orthogonal direction may be referred to as "planar view of the contact surface 111a". In the present embodiment, the negative fastening portion 31 and the positive fastening portion 21, respectively, are arranged outside an end portion 65 of the laminated substrate 111. More specifically, the arrangement portion 311 of the negative fastening portion 31

**18**

and the arrangement portion 211 of the positive fastening portion 21 are arranged in a position outside a short side that is one side of the laminated substrate 111.

The negative fastening portion 31 and the positive fastening portion 21 are arranged side by side along the end portion of the laminated substrate 111. More specifically, additionally, the arrangement portion 311 and the arrangement portion 211 are arrayed adjacent to each other along the one side of the laminated substrate 111. The negative fastening portion 31 and the positive fastening portion 21 are arranged side by side so that a straight line connecting the center of the through hole 313 and the center of the through hole 213 is substantially in parallel to the short side of the laminated substrate 111.

The negative connection portion 33 is a portion of the negative terminal Nu that is in facing contact with the negative-side input terminal pattern 43 (see FIG. 4) formed on the insulating substrate 40 provided on the laminated substrate 111. The pair of positive connection portions 22 and 23 are portions of the positive terminal Pu that are in facing contact with the first positive-side input terminal pattern 41 and the second positive-side input terminal pattern 42 (see FIG. 4) formed on the insulating substrate 40. The negative connection portion 33 and the pair of positive connection portions 22 and 23 are arranged substantially in a straight line in the planar view of the contact surface 111a. The negative connection portion 33 and the pair of positive connection portions 22 and 23 are arranged so as to be substantially in parallel to the short side of the laminated substrate 111 that is parallel to a direction in which the negative fastening portion 31 and the positive fastening portion 21 are lined up in the planar view of the contact surface 111a. Accordingly, the negative connection portion 33 and the pair of positive connection portions 22 and 23 are arranged side by side substantially in parallel to the direction in which the negative fastening portion 31 and the positive fastening portion 21 are lined up in the planar view of the contact surface 111a.

The laminated substrate 111 has the contact surface 111a with which the negative connection portion 33 and the pair of positive connection portions 22 and 23 are contacted. As illustrated in FIGS. 5 to 8, the negative intermediate portion 35 has a negative facing portion (an example of a first facing portion) 353 arranged to face a plane including the contact surface 111a. The negative intermediate portion 35 also has a negative outer extension portion (an example of a first outer extension portion) 351 arranged between the negative facing portion 353 and the negative fastening portion 31 and extending in a direction intersecting with the contact surface 111a. The negative intermediate portion 35 further has a negative inner extension portion (an example of a first inner extension portion) 355 arranged between the negative facing portion 353 and the negative connection portion 33 and extending in the direction intersecting with the contact 55 surface **111***a*.

The positive intermediate portion 25 has a positive facing portion (an example of a second facing portion) 253 arranged to face the plane including the contact surface 111a. The positive intermediate portion 25 also has a positive outer extension portion (an example of a second outer extension portion) 251 arranged between the positive facing portion 253 and the positive fastening portion 21 and extending in the direction intersecting with the contact surface 111a. The positive intermediate portion 25 further has a pair of positive inner extension portions (an example of a second inner extension portion) 255 and 257 arranged between the positive facing portion 253 and the pair of

positive connection portions 22 and 23 and extending in the direction intersecting with the contact surface 111a.

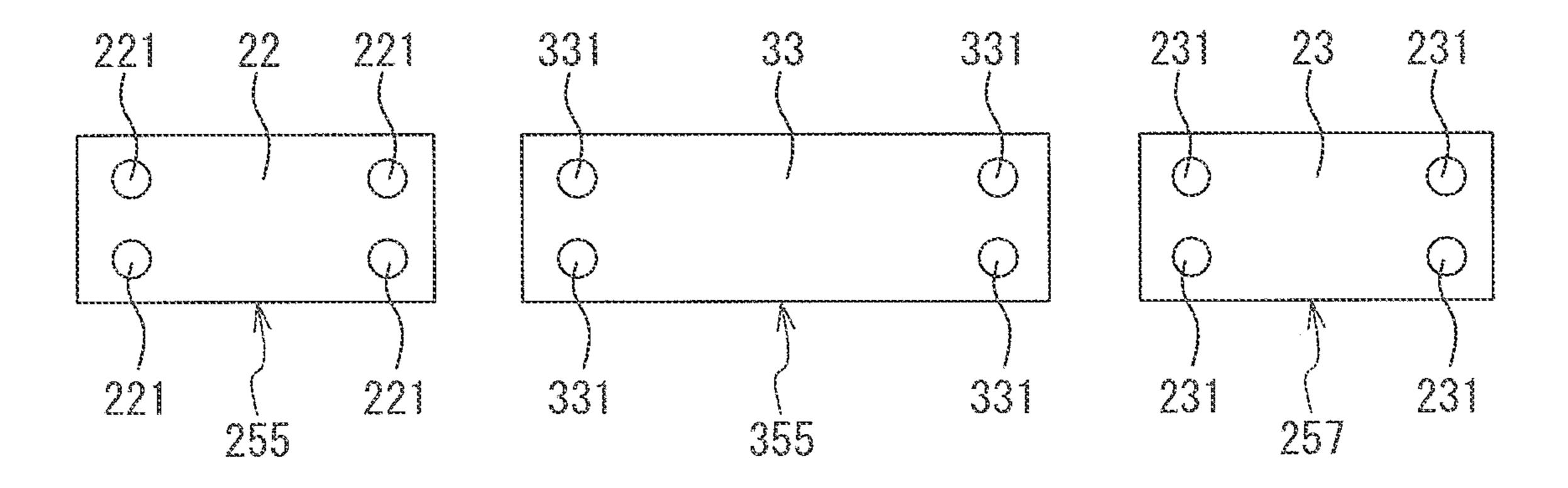

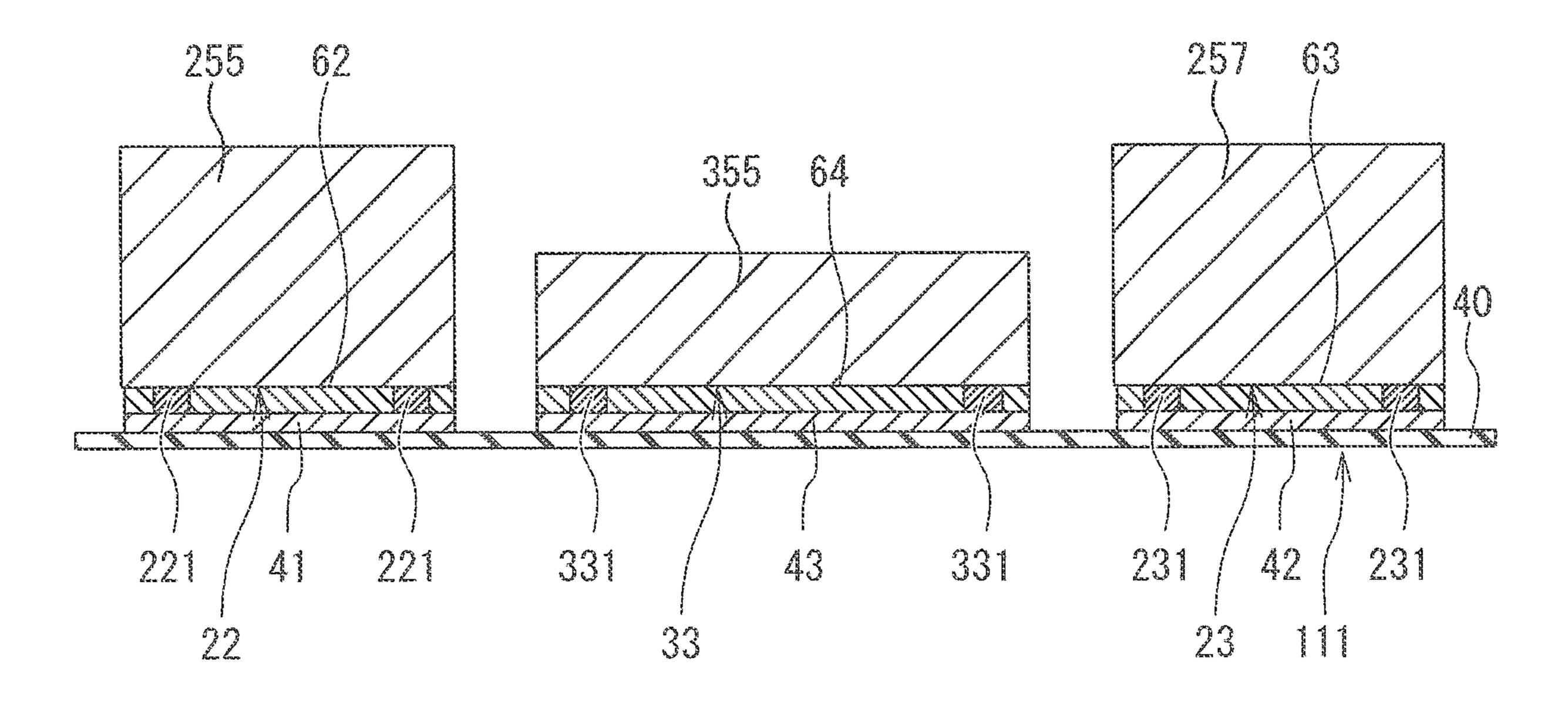

FIG. 6A is a diagram schematically illustrating the positive connection portions 22 and 23 and the negative connection portion 33 as viewed from a side facing the lami- 5 nated substrate 111. FIG. 6B is a diagram schematically illustrating a cross section obtained by cutting the positive inner extension portions 255 and 257 and the negative inner extension portion 355 mounted on the laminated substrate 111 at positions where a convex portion (see details given 10 later) provided on each of the positive connection portions 22 and 23 and the negative connection portion 33 is formed.

As illustrated in FIG. 6A, the negative connection portion 33 is provided on an end face of the laminated substrate 111 negative intermediate portion 35. The positive connection portion 22 is provided on an end face of the laminated substrate 111 side of the positive inner extension portion 255 of the positive intermediate portion 25. The positive connection portion 23 is provided on an end face of the 20 laminated substrate 111 side of the positive inner extension portion 257 of the positive intermediate portion 25.

The negative connection portion 33 has a convex portion 331 (an example of a first convex portion) protruding toward the laminated substrate 111. The negative connection portion 25 33 has the convex portion 331, for example, at each of four corners. The negative connection portion 33 and the four convex portions 331 are, for example, integrally formed. Thus, the four convex portions 331 are integrally formed with, for example, the negative inner extension portion **355**. 30

The positive connection portion 22 has a convex portion 221 (an example of a second convex portion) protruding toward the laminated substrate 111. The positive connection portion 22 has the convex portion 221, for example, at each of four corners. The positive connection portion 22 and the 35 four convex portions 221 are, for example, integrally formed. Thus, the four convex portions **221** are integrally formed with, for example, the positive inner extension portion 255.

The positive connection portion 23 has a convex portion 40 231 (an example of the second convex portion) protruding toward the laminated substrate 111. The positive connection portion 23 has the convex portion 231, for example, at each of four corners. The positive connection portion 23 and the four convex portions 231 are, for example, integrally 45 formed. Thus, the four convex portions **231** are integrally formed with, for example, the positive inner extension portion 257.

As illustrated in FIG. 6B, the positive connection portion 22 is fixed while being connected to the first positive-side 50 input terminal pattern 41 by, for example, a solder 62. The positive connection portion 23 is fixed while being connected to the second positive-side input terminal pattern 42 by, for example, a solder 63. The negative connection portion 33 is fixed while being connected to the negative- 55 side input terminal pattern 43 by, for example, a solder 64.

The four convex portions 221 provided on the positive connection portion 22 have a height that can ensure a thickness of the solder 62. Here, the height of each convex portion 221 is a length from the positive connection portion 60 22 to an end portion of the convex portion 221 of the laminated substrate 111 side. Similarly, the four convex portions 231 provided on the positive connection portion 23 have a height that can ensure a thickness of the solder 63. Here, the height of each convex portion **231** is a length from 65 the positive connection portion 23 to an end portion of the convex portion 231 of the laminated substrate 111 side.

**20**

Similarly, the four convex portions 331 provided on the negative connection portion 33 have a height that can ensure a thickness of the solder **64**. Here, the height of each convex portion 331 is a length from the negative connection portion 33 to an end portion of the convex portion 331 of the laminated substrate 111 side. In this way, by having the convex portions 221 in the positive connection portion 22, the convex portions 231 in the positive connection portion 23, and the convex portions 331 in the negative connection portion 33, the semiconductor module 1 can achieve improved stability of the positive terminal Pu and the negative terminal Nu mounted to the laminated substrate 111.