### US011888931B1

# (12) United States Patent

Matthews et al.

# (54) MASSIVELY PARALLEL IN-NETWORK COMPUTE

(71) Applicant: Innovium, Inc., San Jose, CA (US)

(72) Inventors: William Brad Matthews, San Jose, CA (US); Puneet Agarwal, Cupertino, CA (US); Bruce Hui Kwan, Sunnyvale,

CA (US)

(73) Assignee: Innovium, Inc., San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 17/742,354

(22) Filed: May 11, 2022

## Related U.S. Application Data

- (63) Continuation of application No. 17/200,463, filed on Mar. 12, 2021, now Pat. No. 11,425,195.

- (51) Int. Cl.

H04L 67/1074 (2022.01)

H04L 49/15 (2022.01)

G06N 20/00 (2019.01)

G06N 3/045 (2023.01)

H04L 45/02 (2022.01)

(52) **U.S. Cl.**CPC ...... *H04L 67/1076* (2013.01); *G06N 3/045* (2023.01); *G06N 20/00* (2019.01); *H04L 49/15* (2013.01); *H04L 45/08* (2013.01)

(58) Field of Classification Search

CPC ..... H04L 49/15; H04L 45/08; H04L 67/1076; G06N 20/00; G06N 3/045

See application file for complete search history.

# (10) Patent No.: US 11,888,931 B1

(45) Date of Patent: \*Jan. 30, 2024

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 10,167,800 B1<br>10,931,588 B1<br>10,931,602 B1 | 2/2021<br>2/2021 | Chung et al.<br>Matthews et al.<br>Matthews et al. |

|-------------------------------------------------|------------------|----------------------------------------------------|

| 11,048,661 B2                                   | 6/2021           | Sankaralingam et al.                               |

|                                                 | (Continued)      |                                                    |

#### OTHER PUBLICATIONS

Dean, Jeffrey, and Sanjay Ghemawat. "MapReduce: simplified data processing on large clusters." Communications of the ACM 51.1: 107-113. (Year: 2008).\*

(Continued)

Primary Examiner — John M Macilwinen (74) Attorney, Agent, or Firm — Shield Intellectual Property PC; Zhichong Gu

### (57) ABSTRACT

Efficient scaling of in-network compute operations to large numbers of compute nodes is disclosed. Each compute node is connected to a same plurality of network compute nodes, such as compute-enabled network switches. Compute processes at the compute nodes generate local gradients or other vectors by, for instance, performing a forward pass on a neural network. Each vector comprises values for a same set of vector elements. Each network compute node is assigned to, based on the local vectors, reduce vector data for a different a subset of the vector elements. Each network compute node returns a result chunk for the elements it processed back to each of the compute nodes, whereby each compute node receives the full result vector. This configuration may, in some embodiments, reduce buffering, processing, and/or other resource requirements for the network compute node or network at large.

## 18 Claims, 13 Drawing Sheets

# (56) References Cited

#### U.S. PATENT DOCUMENTS

11,425,195 B1 \* 8/2022 Matthews ...... G06F 15/17318 2011/0060891 A1 3/2011 Jia 2019/0188239 A1 6/2019 Serrano et al. 2019/0303387 A1 10/2019 Smarda et al.

#### OTHER PUBLICATIONS

Luo, Liang, et al. "Parameter hub: a rack-scale parameter server for distributed deep neural network training." Proceedings of the ACM Symposium on Cloud Computing. (Year: 2018).\*

Zhang, Kuo, Salem Alqahtani, and Murat Demirbas. "A comparison of distributed machine learning platforms." 2017 26th international conference on computer communication and networks (ICCCN). IEEE. (Year: 2017).\*

Liu, Yang, Lixiong Xu, and Maozhen Li. "The parallelization of back propagation neural network in mapreduce and spark." International Journal of Parallel Programming 45: 760-779. (Year: 2017).\*

Chahal, Karanbir Singh, et al. "A hitchhiker's guide on distributed training of deep neural networks." Journal of Parallel and Distributed Computing 137: 65-76. (Year: 2020).\*

Abadi, Martín, et al. "Tensorflow: Large-scale machine learning on heterogeneous distributed systems." arXiv preprint arXiv:1603. 04467. (Year: 2016).\*

Devendar, "Sharp: In-Network Scalable Streaming Hierarchical Aggregation And Reduction Protocol", Aug. 31, 2020 (Aug. 31, 2020), pp. 1-36, Retrieved From The Internet: URL: https://mug.mvapich.cse.ohio-state.edu/static/media/mug/presentation/20/bureddy-mug-20.pdf.

He et al., "High-Performance Support Vector Machines And Its Applications", ArXiv abs/1905.00331 (Year: 2019).

Sapio et al., "Scaling Distributed Machine Learning With In-Network Aggregation", ArXiV abs/1903.06701 (Year 2020).

Sapio et al., "Scaling Distributed Machine Learning With In-Network Aggregation", arxiv.org, Cornell University Library, 201 Olin Library Cornell University, Ithaca, NY 14853, Sep. 30, 2020 (Sep. 30, 2020).

United States Patent and Trademark Office, U.S. Appl. No. 17/200,463, Non-Final Office Action dated Jan. 3, 2022.

United States Patent and Trademark Office, U.S. Appl. No. 17/200,463, Notice of Allowance dated Apr. 7, 2022.

Wickramasinghe et al., "A Survey Of Methods For Collective Communication Optimization And Tuning", ArXiV abs/1611.06334 (Year: 2016).

World Intellectual Property Organization, Application No. PCT/US22/20087, International Search Report dated Jul. 19, 2022.

\* cited by examiner

FIG. 2

<u>200</u>

\* \* \* \* \* \* \* \* \* . . . . . . . . .

500

650d NCN3 670d NCP3 650d N 650c NCN2 650c 650b NCN1 670b NCP1 670b NCP1 650b NCN1 670b 670a NCPO 650a NCPO 670a NCPO 650a NCNO 670a NCL 670a NCPO 650a 670a Compute Plane 0 <u>610a</u> 610b 655b Compute 655a Plane

8

Jan. 30, 2024

FIG. 8

<u>800</u>

FIG. 9

<u>900</u>

FIG. 10

<u>1290b</u> 1200 <u>1245</u> Queues Processor(s) Packet 1250 <u>1542n</u> Memory Manager 1240 Traffic **1542c** <u>1542P</u> <u>1245a</u> Port

# MASSIVELY PARALLEL IN-NETWORK COMPUTE

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a Continuation of U.S. patent application Ser. No. 17/200,463 filed on Mar. 12, 2021, the contents of which are incorporated herein by reference in their entireties. The applicant(s) hereby rescind any disclaimer of claim scope in the parent application(s) or the prosecution history thereof and advise the USPTO that the claims in this application may be broader than any claim in the parent application(s).

This application is related to: U.S. patent application Ser. No. 16/409,695, filed on May 10, 2019, entitled "Network" Switch with Integrated Compute Subsystem for Distributed Artificial Intelligence and Other Applications," by Matthews, et al.; U.S. patent application Ser. No. 16/409,699, filed on May 10, 2019, entitled "Egress-Based Compute 20 Architecture for Network Switches in Distributed Artificial Intelligence and Other Applications," by Matthews, et al.; U.S. patent application Ser. No. 16/409,701, filed on May 10, 2019, entitled "Parallelized Ingress Compute Architecture for Network Switches in Distributed Artificial Intelligence and Other Applications," by Matthews, et al.; U.S. patent application Ser. No. 16/409,703, filed on May 10, 2019, entitled "Network Switch with Integrated Gradient Aggregation for Distributed Machine Learning," by Matthews, et al.; and U.S. patent application Ser. No. 16/552, 938, filed on Aug. 27, 2019, entitled "Distributed Artificial Intelligence Extension Modules For Network Switches," by Matthews, et al. The entire contents of each of these applications are hereby incorporated by reference for all purposes as if fully set forth herein.

## TECHNICAL FIELD

Embodiments relate generally to distributed computing systems, and, more specifically, to network switch-based 40 architectures for distributed machine learning systems and other applications.

## **BACKGROUND**

The approaches described in this section are approaches that could be pursued, but not necessarily approaches that have been previously conceived or pursued. Therefore, unless otherwise indicated, it should not be assumed that any of the approaches described in this section qualify as prior 50 art merely by virtue of their inclusion in this section.

Computationally-intense applications in computing systems can often be implemented by dividing the applications into distinct tasks that can be performed in parallel, and distributing those tasks amongst a number of computing 55 devices. These computing devices are typically interconnected by a communications network via which they share data related to the computations, and are said to form a distributed computing system. Distributed computing systems may be used in a large variety of complex computing 60 applications, such as, without limitation, simulations, language translation, image recognition, fraud detection, and so forth, as well as emerging applications.

For example, machine learning algorithms, and deep learning algorithms in particular, are commonly used to 65 create computational models that perform mission critical computing functions. Such models may involve oft-complex

2

series of calculations that input and process a set of values (often referred to as an input vector or feature vector) to generate an output value or values. The output value(s) generally classify the input vector in some manner. For instance, the output of a model used for image recognition might classify an input vector of pixels, image attributes, or other image data as being either a dog or cat, depending on the purpose of the neural network. A model may include a variety of parameters, such as weights, biases, coefficients, support vectors, and so forth, that affect how the input values are processed and how the output value(s) are calculated.

Example types of models may include, without limitation, neural networks or belief networks, which pass input values through one or more layers of interconnected nodes (referred to herein as "neurons"). Each neuron of a neural network accepts one or more inputs from the input vector and/or other neurons. These inputs form the connections of the neural network. Each neuron is associated with an output function that computes the value output from the neuron based on the inputs to the neuron. The connections may be assigned weights. The weight of a connection, generally speaking, controls how heavily the input associated with that connection factors into the output function. For instance, a neuron might have an input p0 with a weight of 0.4 and an input p1 with a weight of 0.2. The value of the input p0 may therefore more heavily impact the output of the neuron (e.g., in the case of a simple summation of the products of each input and their weights, twice as much).

In some embodiments, the neurons may be organized into two or more layers, including an input layer wherein each neuron outputs a value of the input vector, zero or more intermediate layers in which each neuron inputs one or more values output by an immediately previous layer and then outputs values to one or more neurons of an immediately subsequent layer, and a final output layer that inputs values output by an immediately previous layer and outputs the results of the neural network.

By carefully setting the weights and/or other parameters of a neural network or other model, the model may be configured to accurately or semi-accurately make classifications or other determinations based on input vectors. Suitable weights for a model configured to make a certain type of determination based on a certain type of data may be "learned" through various training algorithms. These training algorithms iteratively adjust the weights over time through a series of steps, including a forward pass, loss computation, and backward pass, until arriving at an "optimal" set of weights for the model, or until all training data has been processed.

The forward pass through the model processes an input vector selected from a suitable set of vectors (e.g., a set of "training data") using a test set of weights to produce an output often referred to herein as a prediction. The loss computation computes the error in that prediction using linear regression or any other suitable technique. From the error, a gradient descent algorithm calculates (e.g. using partial derivatives or other means) a gradient vector comprising a number of gradient elements. Each gradient element corresponds to a different weight of the model, and indicates an adjustment to (e.g. an absolute or relative amount by which to change) the corresponding weight. The gradient descent algorithm selects the adjustment in a manner intended to minimize the computed loss in subsequent iterations. Finally, the backward pass updates the test weights in the model based on the corresponding gradient element so as to arrive at a new set of weights to test. The training process is repeated until arriving at some terminal

condition, such as the performance of a certain number of iterations, or the loss computation determining that the latest parameters have achieved what is considered to be an acceptable or optimal loss, depending on the embodiment.

Distributed deep learning techniques have been devel- 5 oped in which training tasks are spread out across any number of physically networked computing devices, referred to as "compute nodes." Each compute node comprises one or more compute entities, such as central processing units ("CPUs"), graphics processing units 10 ("GPUs"), tensor processing units ("TPUs"), floating point units ("FPUs"), or other accelerators, configured to perform compute processes, such as training a model. For example, each compute node may be assigned a different set of input 15 vectors (e.g., from a set of training data) to process with the model. The compute nodes share local gradients from forward passes of their respective input vectors over a physical network, such as a local area network, via which they are connected. These gradients are reduced together in a "reduc- 20" tion" phase to form a result gradient. The compute nodes then use the result gradient in a backward pass to determine new weights to test for the model. Another approach is model parallelism, where portions of the model are assigned to each compute node and the interconnections (e.g., acti- 25 vations) between the various model layers are sent via the physical network as part of the forward pass.

Early distributed deep learning approaches made use of a centralized parameter server to reduce gradients and return results to compute nodes. In such approaches, the centralized parameter server is typically implemented using the same hardware as any other compute node, having significant computing power but limited connectivity. The centralized parameter server is therefore often a significant bottleneck, on account of network latency and/or limited network 35 bandwidth to and from the centralized parameter server.

Another common distributed approach is known as "All Reduce." Each compute node assumes responsibility for reducing a different gradient portion. Each node generates a gradient. Each node then sends to each other node the 40 portion of that gradient that the other node is responsible for reducing. Each node then reduces the portions it receives together and returns the resulting reduced portion back to each other node. This approach places significant demands on the network interconnecting the nodes.

Multiple algorithms exist for performing an All Reduce operation. A commonly used approach is "Ring All Reduce." In Ring All Reduce, a first compute node in such a system may be configured to pass on a gradient portion to a second node, which may be configured to reduce or otherwise 50 aggregate the result with the same portion of its gradient. The second node then passes the result on to a third node, and this process repeats in a ring, tree, or other suitable pattern until all of the nodes have combined their chunk of the gradient together. The final result is then passed back 55 through the topology. The amount of time needed to reduce the gradients and propagate the result throughout the system is a significant bottleneck to the learning process.

Another approach, described in the afore-mentioned U.S. application Ser. No. 16/552,938, involves placing compute 60 logic in, or closely coupled to, the same network hardware that is used to interconnect the compute nodes, such as an otherwise conventional layer 2 or layer 3 network switch. Such network hardware may be referred to as a network compute node. A network compute node may be configured 65 to perform any number of collective operations, including reduction, thereby avoiding the need to pass gradients on to

4

a centralized parameter server, while leveraging the high bandwidth and interconnectivity of the underlying networking hardware.

The introduction of compute functionality at the network compute node increases resource demands on the underlying hardware. For instance, the network compute node must devote processing resources to performing the collective operations and buffer resources to storing vector data until it is ready to perform the operations. The additional resource demands of the compute functionality are met by repurposing existing resources of the network hardware—thereby reducing the resources that would otherwise be available for network hardware—and/or by additional hardware that must be added to the network hardware. These resource demands may increase exponentially when processing larger data sets and/or when many compute nodes are involved. Moreover, a large set of compute nodes working together requires significant numbers of network compute nodes, typically interconnected in a hierarchical fashion, with each of the network compute nodes requiring a significant amount of resources to provide compute functionality.

More generally, the communication of data and other information between nodes of distributed computing systems has consistently proven to be a significant bottleneck in the performance of the distributed system.

### BRIEF DESCRIPTION OF THE DRAWINGS

The present inventive subject matter is illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings and in which like reference numerals refer to similar elements and in which:

FIG. 1 illustrates an example distributed computing system for machine learning;

FIG. 2 illustrates an example distributed computing system in which compute entities are organized into compute nodes;

FIG. 3 illustrates an example distributed machine learning system that supports intra-node reduction and/or vector partitioning to reduce network bandwidth consumption;

FIG. 4 illustrates a distributed machine learning system comprising four network compute nodes in a hierarchical arrangement;

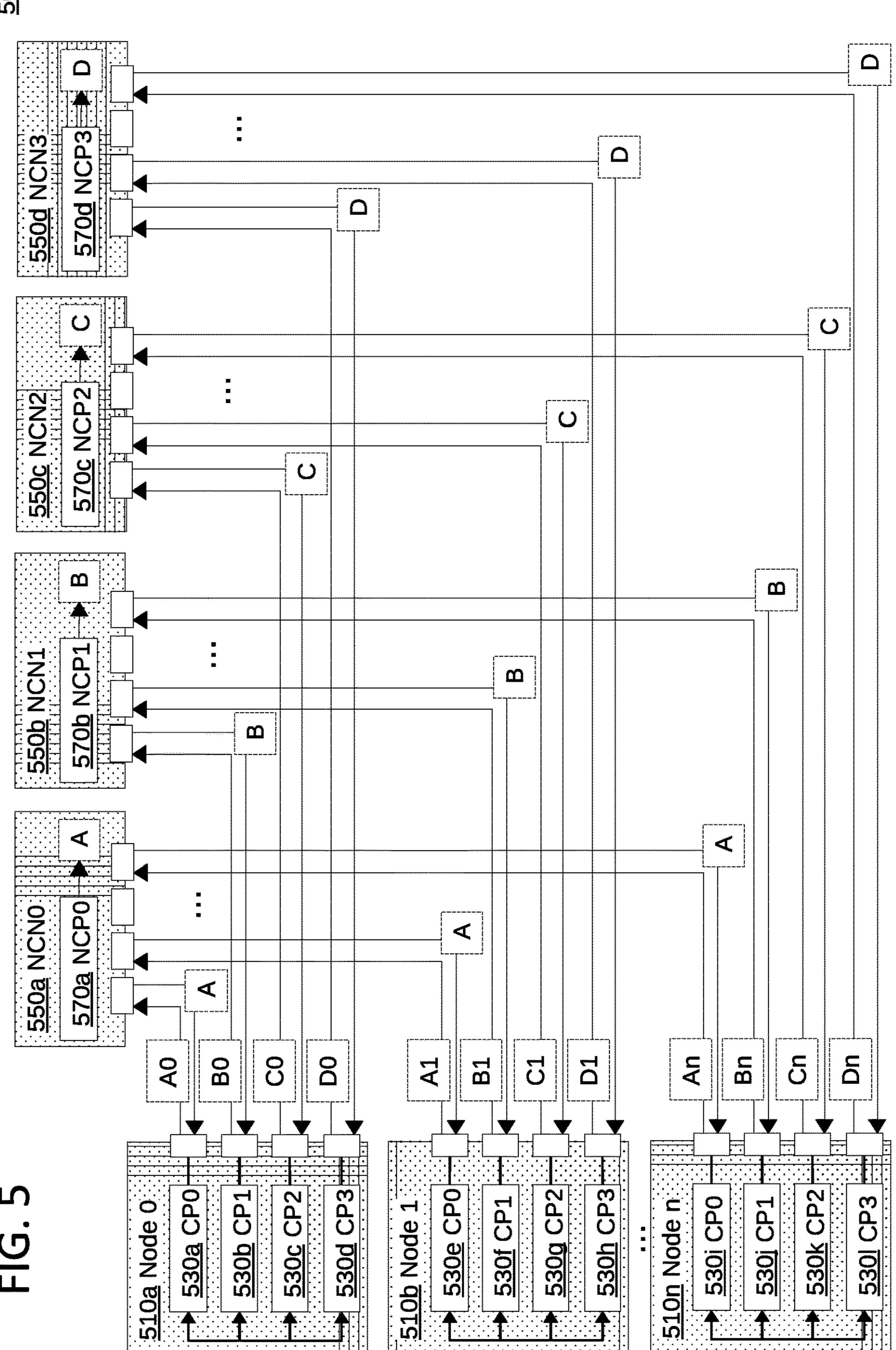

FIG. 5 illustrates a distributed learning system in which each compute node is connected to multiple compute-enabled switches;

FIG. 6 illustrates an example distributed learning system for a distributed application that utilizes compute planes;

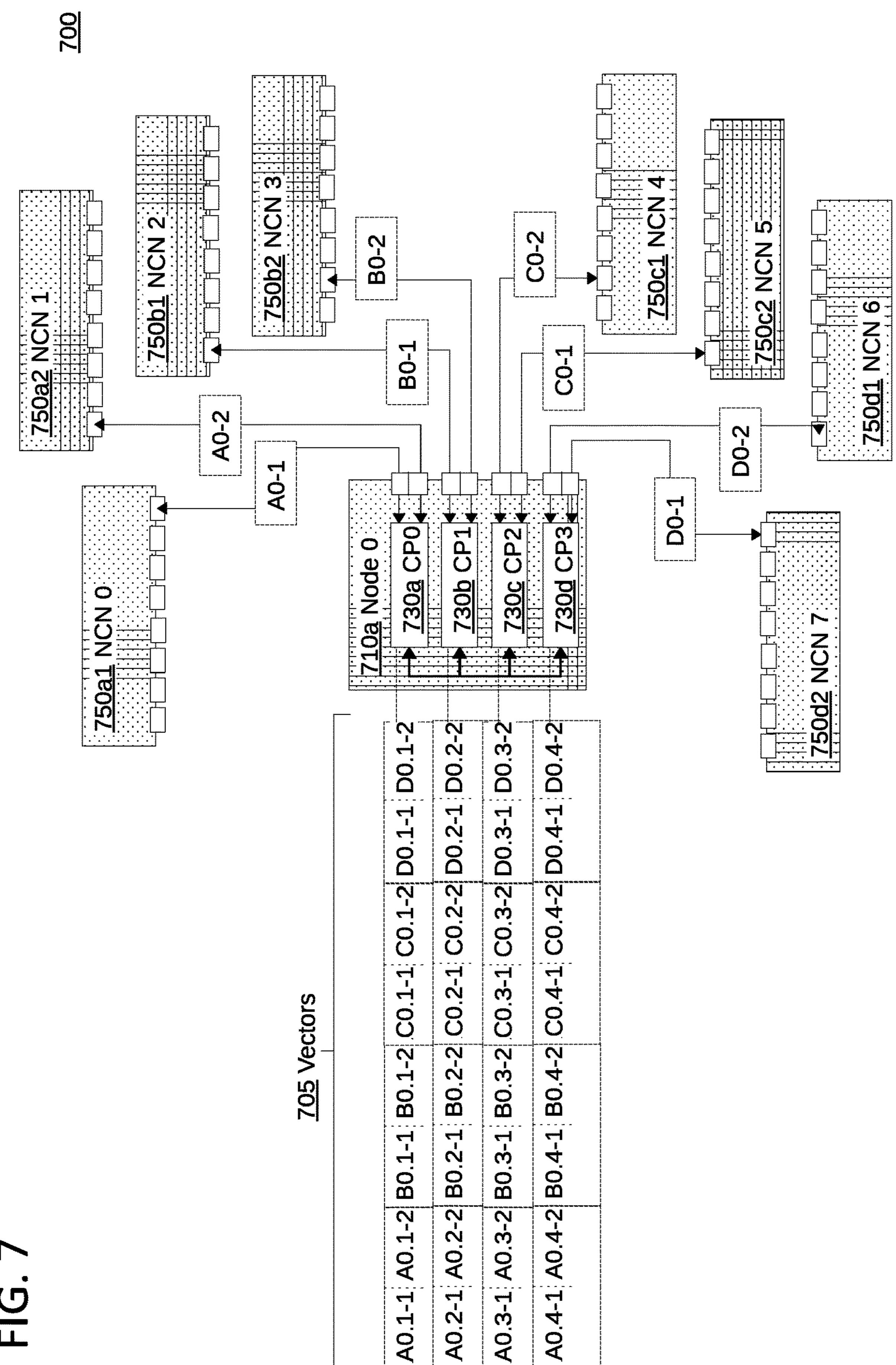

FIG. 7 illustrates a distributed learning system in which a compute process is configured to divide a chunk into multiple sub-chunks that can be sent to the network compute node separately via different ports;

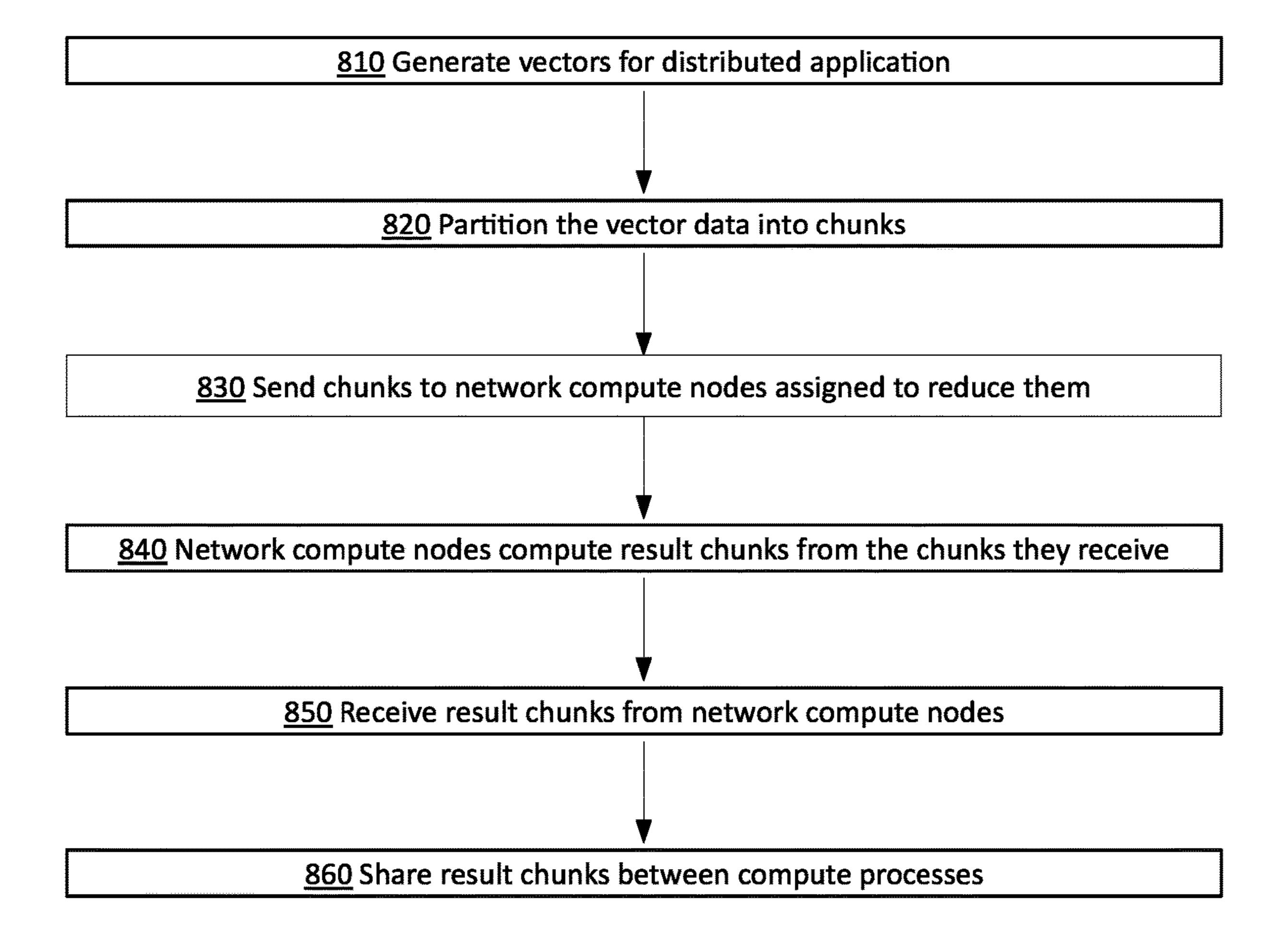

FIG. 8 illustrates a system-level flow for distributed compute operations in a network;

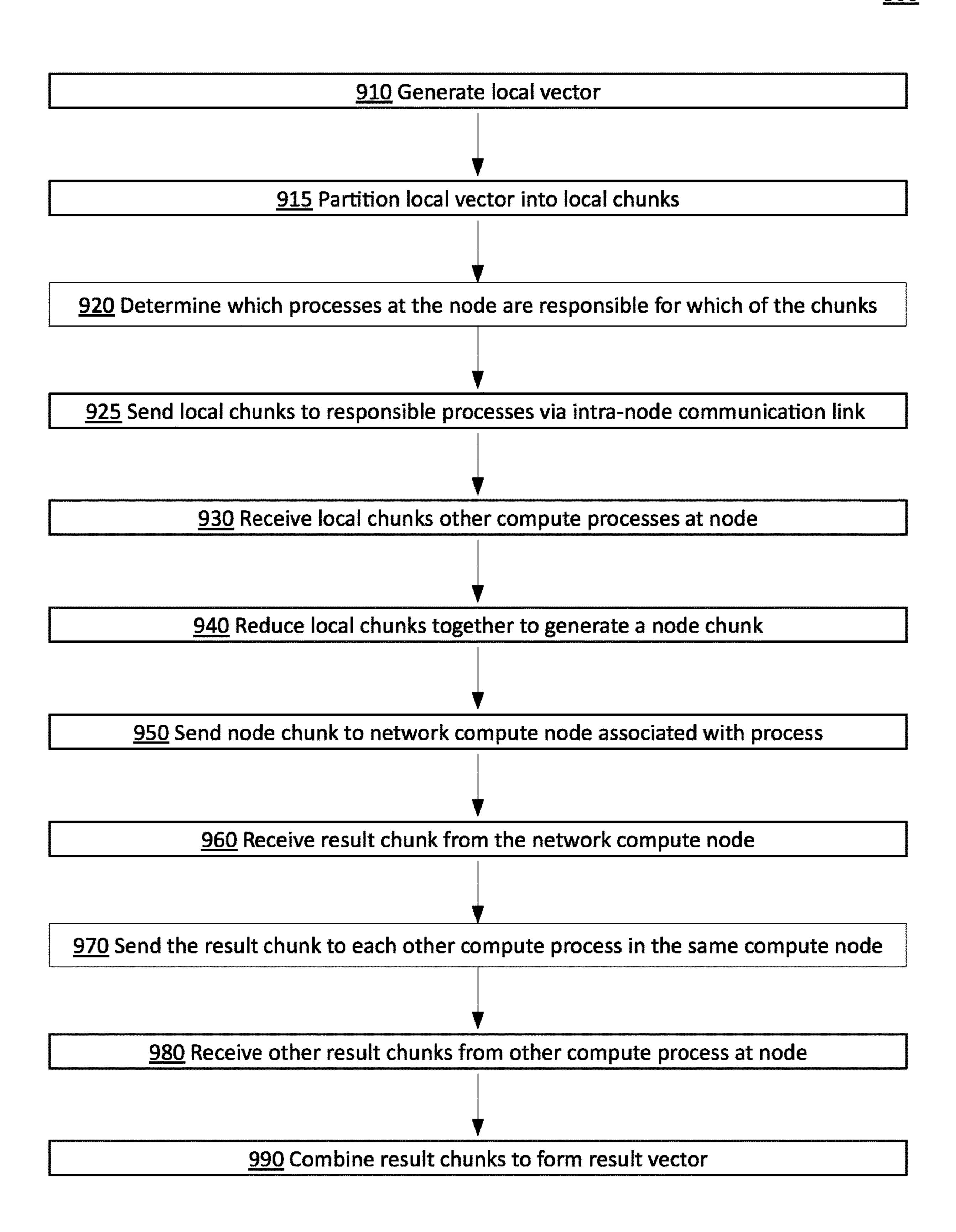

FIG. 9 illustrates a flow for distributing and receiving vector chunks at a particular compute process;

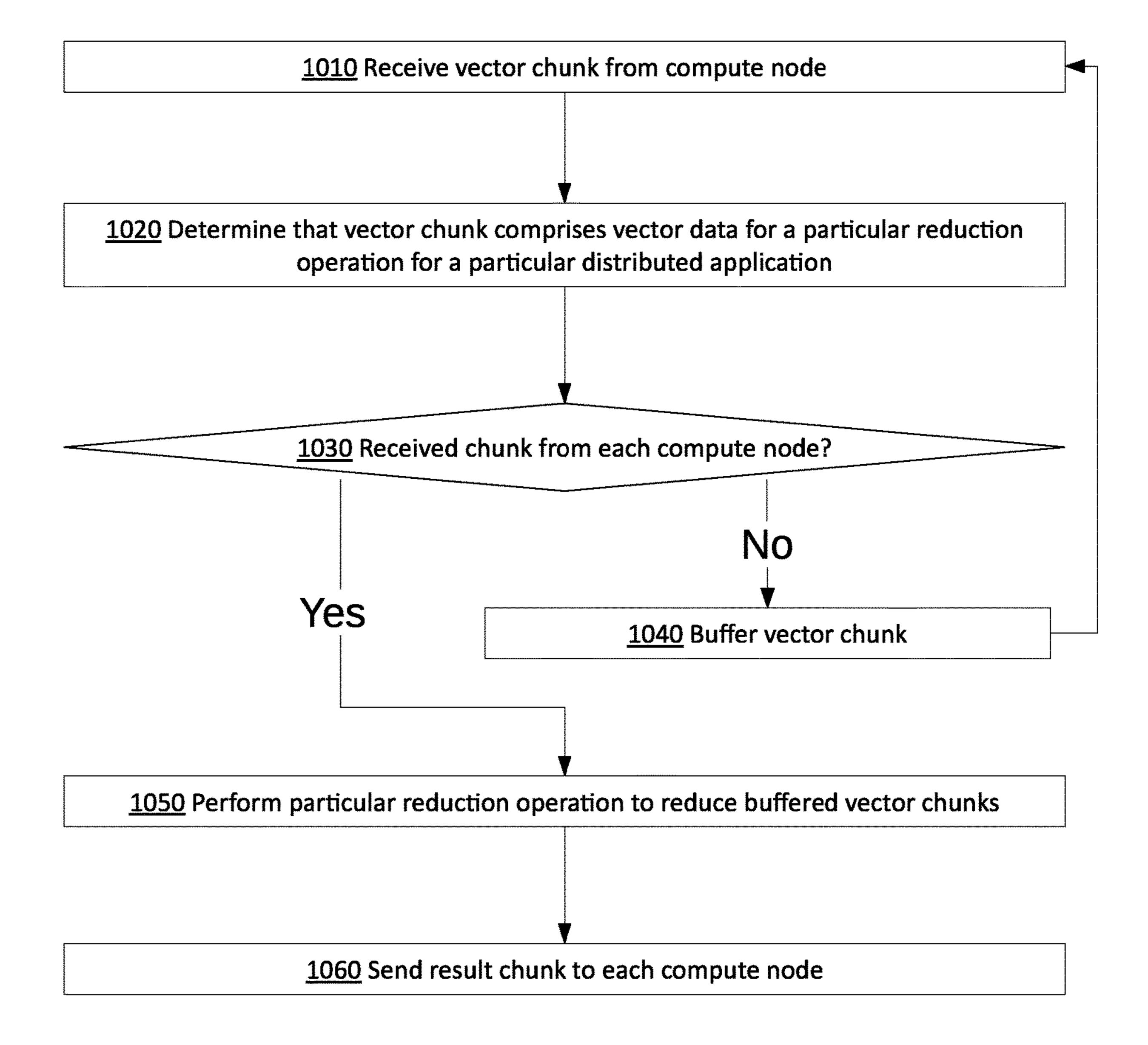

FIG. 10 illustrates a flow for generating result chunks at a network compute node;

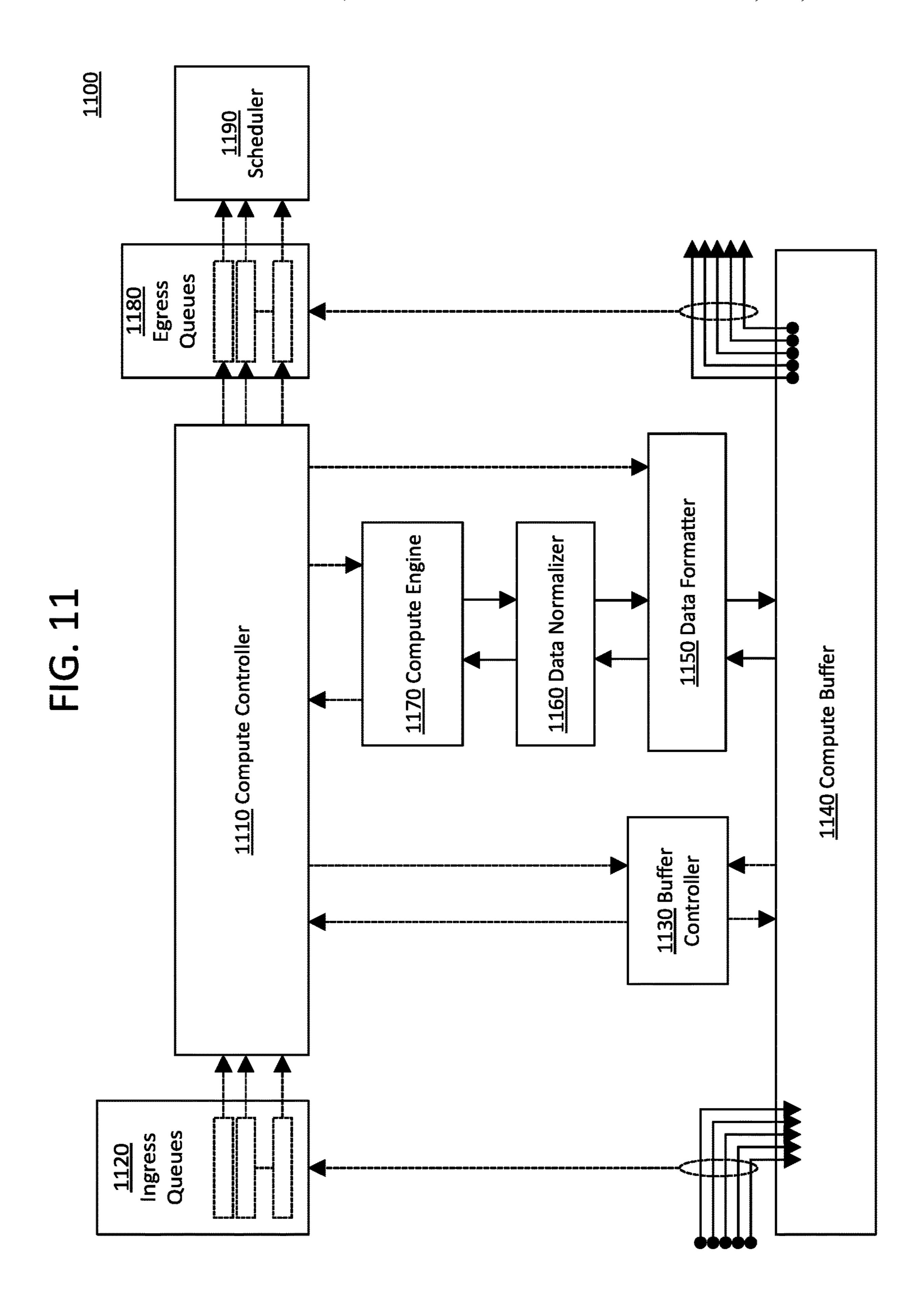

FIG. 11 illustrates an example compute subsystem;

FIG. 12 is an illustrative view of various aspects of packet-switching logic within an example network device;

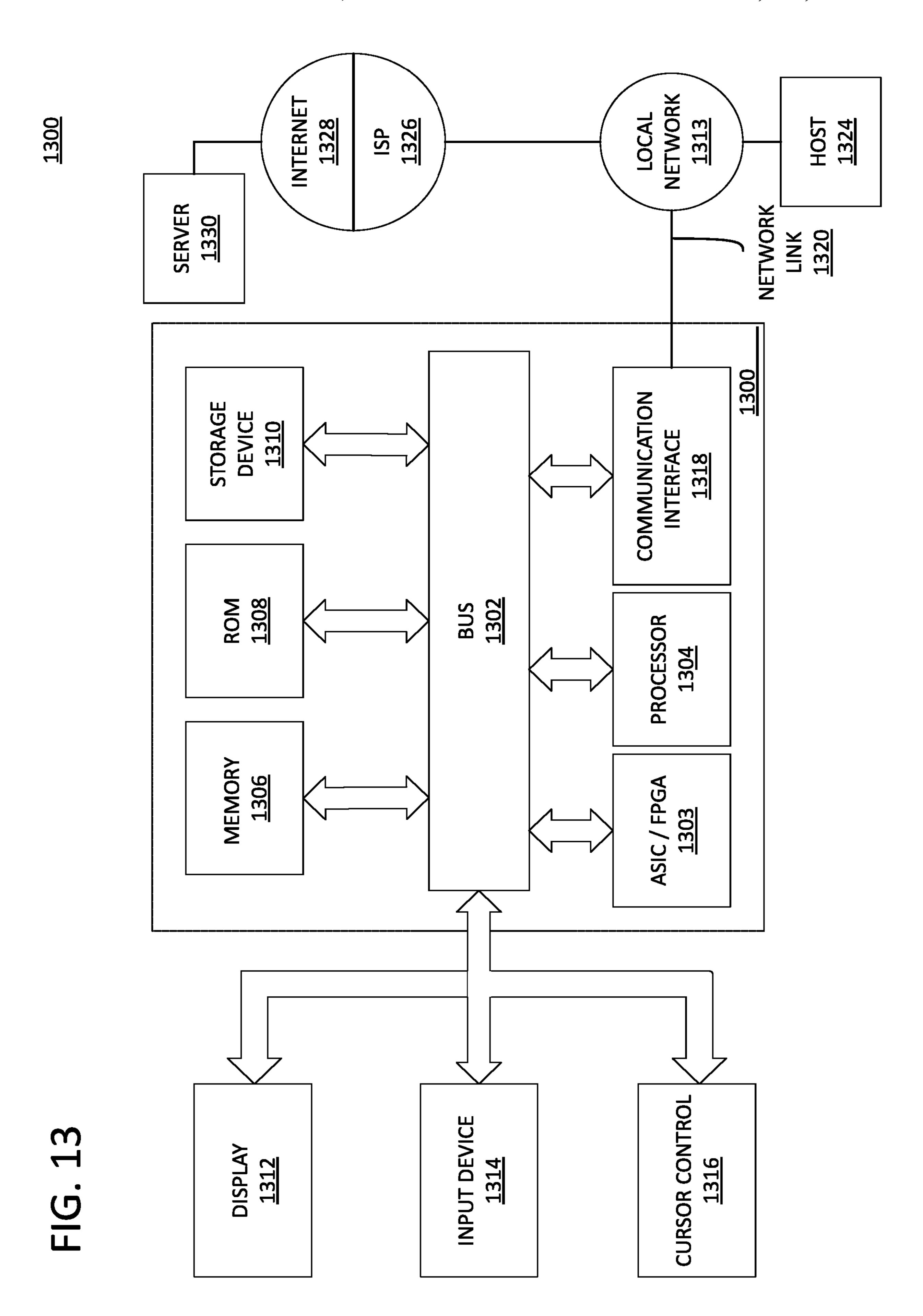

FIG. 13 is a block diagram that illustrates an example computer system that may be utilized in implementing the above-described techniques.

# DETAILED DESCRIPTION

In the following description, for the purposes of explanation, numerous specific details are set forth in order to

provide a thorough understanding of the present inventive subject matter. It will be apparent, however, that the present inventive subject matter may be practiced without these specific details. In other instances, well-known structures and devices are shown in block diagram form in order to avoid unnecessarily obscuring the present inventive subject matter.

## 1.0. General Overview

Approaches, techniques, and mechanisms are disclosed for efficiently scaling in-network compute operations to large numbers of compute nodes by connecting each compute node to a same plurality of network compute nodes, 15 such as compute-enabled network switches. Compute processes at the compute nodes generate local gradients or other vectors by, for instance, performing a forward pass on a neural network. Each vector comprises values for a same set of vector elements. These local vectors should be reduced 20 using one or more collective operations, such as aggregation, to produce a result vector, which the compute processes may require before proceeding with further calculations (e.g., to perform a backward pass of the neural network). Each network compute node is assigned to perform the 25 collective operation(s), based on the local vectors, for a different a subset of the vector elements. Each network compute node returns a result chunk for the elements it processed back to each of the compute nodes, whereby each compute node receives the full result vector.

Since a network compute node need not handle or even receive vector portions that do not contain those elements, this configuration may, in some embodiments, reduce buffering, processing, and/or other resource requirements for the network compute node. Moreover, since each of the communication links of a compute node need not be physically connected to the same network compute node, a network compute node may receive and process vectors from many more compute nodes than it might otherwise have been connected to, thereby reducing the need to resort to a 40 hierarchy of network compute nodes to interconnect the compute nodes, along with the complexities and resource demands consequential to such a configuration.

In an embodiment, each compute node comprises a plurality of interconnected compute entities. Each compute 45 entity within that compute node may execute a compute process that generates a local vector for a particular distributed application. For instance, each compute process may use a set of parameters (e.g. weights, biases, etc.) to process a training data set of inputs that has been assigned to the 50 compute process, based upon which the compute process generates a local gradient. Each compute node further comprises a plurality of different communication interfaces. Each interface may be connected, either directly or indirectly, to a different network compute node. Each compute 55 node sends, to each network compute node of these network compute nodes, vector data for a specific subset of vector elements—referred to as a chunk—that the network compute node is responsible for reducing. This vector data may be a corresponding chunk of each local vector, or the 60 compute node may be configured to reduce the chunks locally, and send an intermediate result chunk to the network compute node. Each network compute node reduces the vector elements it is responsible for and returns a final result chunk comprising the reduced values for these vector ele- 65 ments back to each compute node via the corresponding communication interface. When the compute node receives

6

a result chunk from the network compute node, it distributes the result chunk to each of the compute entities.

In an embodiment, each compute entity comprises or is assigned to a specific communication interface. For instance, in an embodiment, a compute entity may be a GPU that is directly coupled to a network interface, such as an Ethernet interface, or Ethernet functionality could be incorporated directly into a GPU. Each compute entity is further responsible for sending all vector data for the specific set of 10 elements that is assigned to the network compute node connected to that communication interface. Hence, each compute entity in a compute node may be interconnected via an intra-node communication mechanism by which it may receive the relevant vector chunks from other compute entities in the compute node. In an embodiment, a compute entity may further be responsible for reducing the vector chunks it receives and sending a resulting reduced chunk to the network compute node. Each compute entity is further responsible for receiving a result chunk from the network compute node connected to its communication interface. The compute entity may share this result chunk with each of the other compute entities in the compute node via the intra-node communication mechanism.

According to an embodiment, a group of compute nodes, and the group of network compute nodes to which that group is connected, may be organized into a compute plane. There may be any number of compute planes involved in a compute task, each operating on a different set of the training data. The network compute node that is operating on 30 a specific subset of vector elements in each compute plane is interconnected with the network compute nodes operating on that specific subset of vector elements in each other compute plane, either directly, or indirectly via a ring, mesh, torus, or other suitable topology. These network compute nodes each produce an intermediate result vector chunk based on the vector chunks they receive from the compute nodes in their respective planes. Then, via their inter-plane connections to other network compute nodes, the network compute nodes combine their intermediate result vector chunks to produce a final result vector chunk to return to the compute nodes in their respective planes.

In other embodiments, the techniques described herein may be applied more generally to any distributed compute task, including tasks unrelated to machine learning. For example, the vectors may comprise values for any set of elements, and not just for gradients or other machine learning constructs. Rather than generating such vectors in a forward pass of a model, the compute processes may have generated such vectors for any purpose using any suitable set of calculations. Moreover, rather than utilizing a result vector for a backward pass of a model, the compute processes may utilize the result vector for any suitable purpose.

# 2.0. System Overview

# 2.1. Distributed Learning System

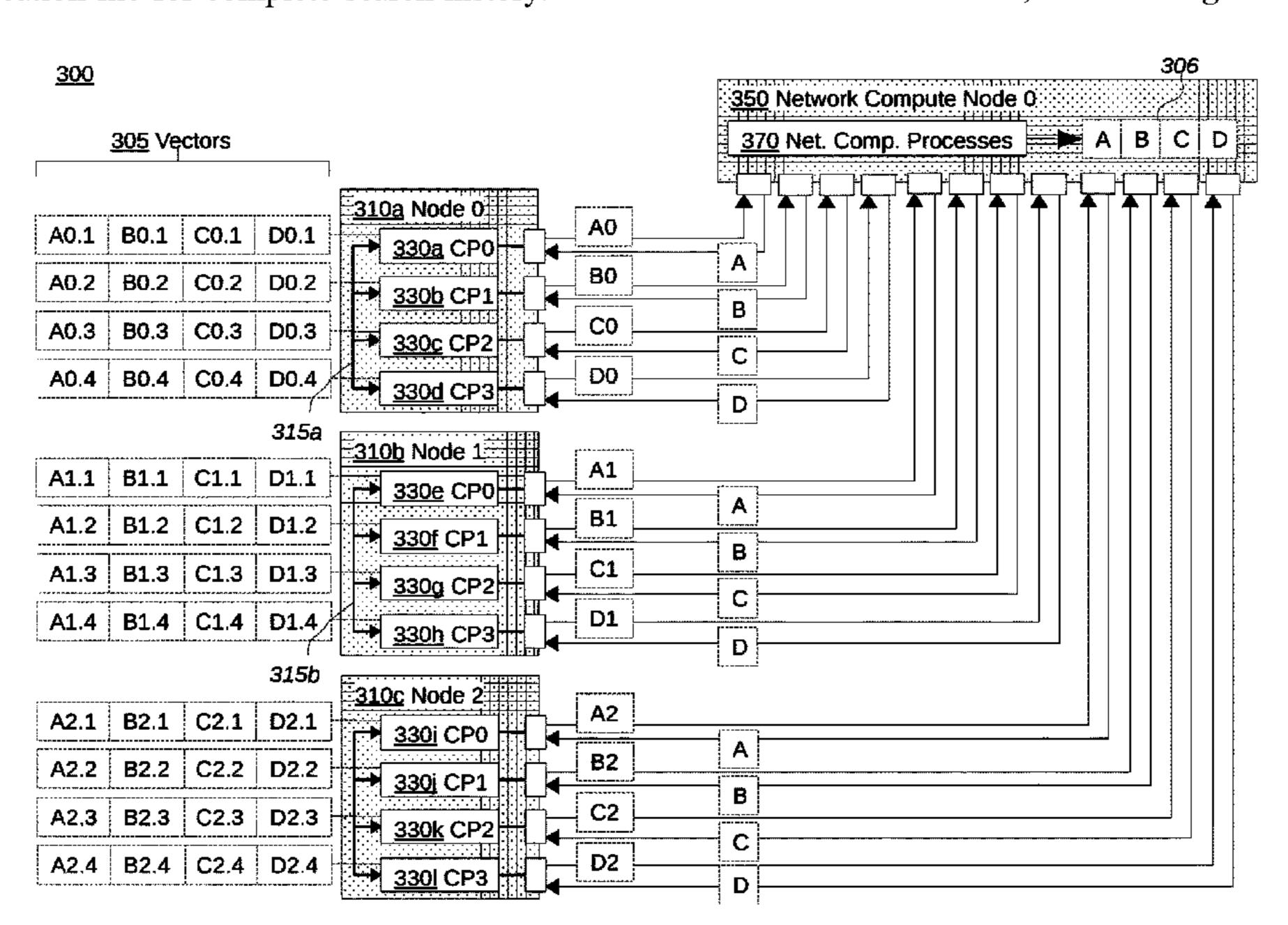

FIG. 1 illustrates an example distributed computing system 100 for machine learning, according to an embodiment. The distributed computing system 100 is a network of computing devices, including compute entities 120a-n (collectively "compute entities 120") and the compute-enabled switching device 150. The number of compute entities 120 and compute-enabled switching devices 150 may vary depending on the embodiment. Moreover, the network may include other devices that are not depicted, which may or may not participate in machine learning tasks.

A compute entity 120 may be any suitable type of computing device. For example, a compute entity 120 may be implemented on a server, workstation, or general-purpose computer system. In an embodiment, each compute entity 120 is, or comprises, one or more GPUs, CPUs, TPUs, 5 accelerators, or other hardware configured to perform, among other processes, machine learning tasks. More specifically, each compute entity implements training logic 130 for training a model 132 on a data set 136. The model 132 may be any type of model susceptible to training, including without limitation a neural network, or any other distributed computing operation.

The model 132 has a number of parameters 134 that the training logic 130 may adjust over time. These parameters may be, for instance, weights, biases, or any other parameter of the model 132, depending on the type of model 132 being trained. Over a number of iterations, referred to herein as epochs, the training logic 130 inputs the data from the training data set 136 into the model 132. In an embodiment, each compute entity 120 includes or is coupled a relatively large amount of storage to store the training data set 136, which may or may not be distinct for each entity 120. The entity's training logic 130 executes the model 132 on some or all of the data in its data set 136 using parameters 134 chosen for the current epoch (e.g. by doing a forward pass of a neural network).

The result of executing the model 132 may be a single value, set of values, classification, decision, or any other suitable output. The training logic 130 computes a loss and/or error for this output based on an expected output 30 indicated for the data set 136. Based on this loss and/or error, the training logic 130 computes a gradient 105 (e.g. using a gradient descent algorithm). For any given epoch, each compute entity may compute a different gradient 105 as a result of operating on a different data set 136 (or, in some 35 embodiments, a different set of parameters 134). The gradient 105 generated by an entity's training logic 130 is thus specific to that entity, and therefore referred to as a local gradient 105.

In a non-distributed system, if some terminal condition 40 had not been reached, training logic 130 would complete the epoch by adjusting the parameters 134 based on the local gradient 105, using each gradient element to adjust a corresponding weight or other parameter 134. The training logic 130 would then begin a new epoch. However, in the 45 distributed system, each of the local gradients 105 must be reduced together using some collective operation (e.g. summation, average, minimum, maximum, etc.) to produce a result gradient. The parameters 134 are then adjusted based on the result gradient.

To this end, each compute entity 120 further includes or is coupled to one or more communication interfaces by which the compute entity 120 is connected to the network. Each communication interface of a compute entity 120 enables the compute entity 120 to form direct communication links with other devices on the network, typically by means of cabling plugged into the communication interface of the compute entity 120 on one end and a communication interface of the other device on the other end. However, fixed wiring or wireless communication links may also or 60 instead be utilized. In an embodiment, the links may be indirect, passing through one or more intermediate switch devices.

A compute entity 120 will typically have a direct communication link to a switch, such as switching device 150, 65 which enables indirect communication links to other devices on the network via the switch. In many embodiments,

8

Ethernet-based communications are utilized. However, other communication standards may also or instead be utilized, such as InfiniBand, Fibre Channel, and so forth. In an embodiment, InfiniBand semantics—particularly those related to reliable connections and Remote Direct Memory Access ("RDMA")—may be utilized, even in non-InfiniBand networks. This switch 150 will typically, but need not necessarily, include packet-switching logic 152 for forwarding data units between entities 120 and/or other devices on the network.

A compute-enabled switching device 150, referred to as switch 150 for short, is a network device configured to interconnect a plurality of computing devices, including compute nodes 120. Switch 150 may be, for instance, a top-of-rack ("TOR"), end-of-row ("EOR"), access, aggregation, core, or any other suitable type of network switching device. Switch 150 may take any suitable physical form, including a standalone computing device or a rack-mountable line card within a chassis adapted for hosting any number of computing devices. In an embodiment, switch 150 comprises a plurality of physical ports by which switch 150 may be connected directly to other computing devices via data cables. Switch 150 may further be interconnected to computing devices indirectly, via direct connections to other switches that are directly or indirectly connected to those computing devices. In some embodiments, switch 150 may also or instead include one or more wireless communication interfaces by which switch 150 is directly connected to certain computing devices.

According to an embodiment, to accelerate distributed machine-learning tasks, a switch 150 may include, or be tightly coupled to, a compute subsystem 160. The compute subsystem 160 may be implemented on the same chip as the packet-switching logic 152 or on a separate chip inside the switch 150. In some embodiments, the compute subsystem 160 may be an external module that is plugged directly into one or more Ethernet ports or other interfaces of the switch, as described in the afore mentioned patent application, "Distributed Artificial Intelligence Extension Modules for Network Switches."

A switch with a compute subsystem 160 is referred to herein as a "compute-enabled switch" or a switch with "in-network compute" capabilities. Depending on the network, compute entities 120 may be directly connected to a compute-enabled switch 150, or may be connected to a compute-enabled switch 150 via one or more intermediary switches that are not compute-enabled.

When the switch 150 detects data units that contain local gradients 105 (or other vector data), the switch 150 may forward the data units to the compute subsystem 160. The compute subsystem 160 collects the local gradients 105 for a given distributed application, task, and/or epoch, and performs an associated collective operation to reduce those local gradients 105 into a result gradient. This process may also be described as "reduction," with the result gradient being an example of "reduced data." The compute subsystem 160 then returns a result 106 back to each compute entity 120, which may be the result gradient or, in some embodiments, adjusted parameters 134 that the compute entity 120 should use for the next epoch.

Optionally, system 100 may comprise one or more orchestrator nodes 195. An orchestrator node 195 may be implemented at any computing device within the network, including at the compute entities 120 or the compute-enabled switch 150. The orchestrator node 195 may be responsible for administrative tasks, such as initializing compute entities 120 to execute distributed applications, establishing worker

sets, providing data to the compute entities 120 to process, configuring and/or sending compute instructions to the compute-enabled switch 150 as to what data to expect and what operations to perform on that data, and so forth. In an embodiment, the orchestrator node **195** may also or instead 5 coordinate the launching of jobs, resolve communications patterns (e.g. ring allreduce, tree-allreduce, etc.), terminate certain distributed applications, and/or manage resource sharing. In an embodiment, an orchestrator node **195** may comprise interfaces via which a human operator may 10 instruct the orchestrator node 195 to do some or all of the foregoing.

FIG. 1 illustrates but one example distributed computing system in which the described techniques may be applied. Other such systems may include additional or fewer ele- 15 ments in varying arrangements. For instance, gradient 105 may more generally be replaced by any type of vector. Similarly, training logic 130 may be replaced by any suitable compute process that generates a vector and consumes a result vector reduced from that vector and other similar 20 generated by other compute processes. Moreover, other systems may include any number of compute entities 120 as well as additional switches or other network entities.

# 2.2. Compute Nodes

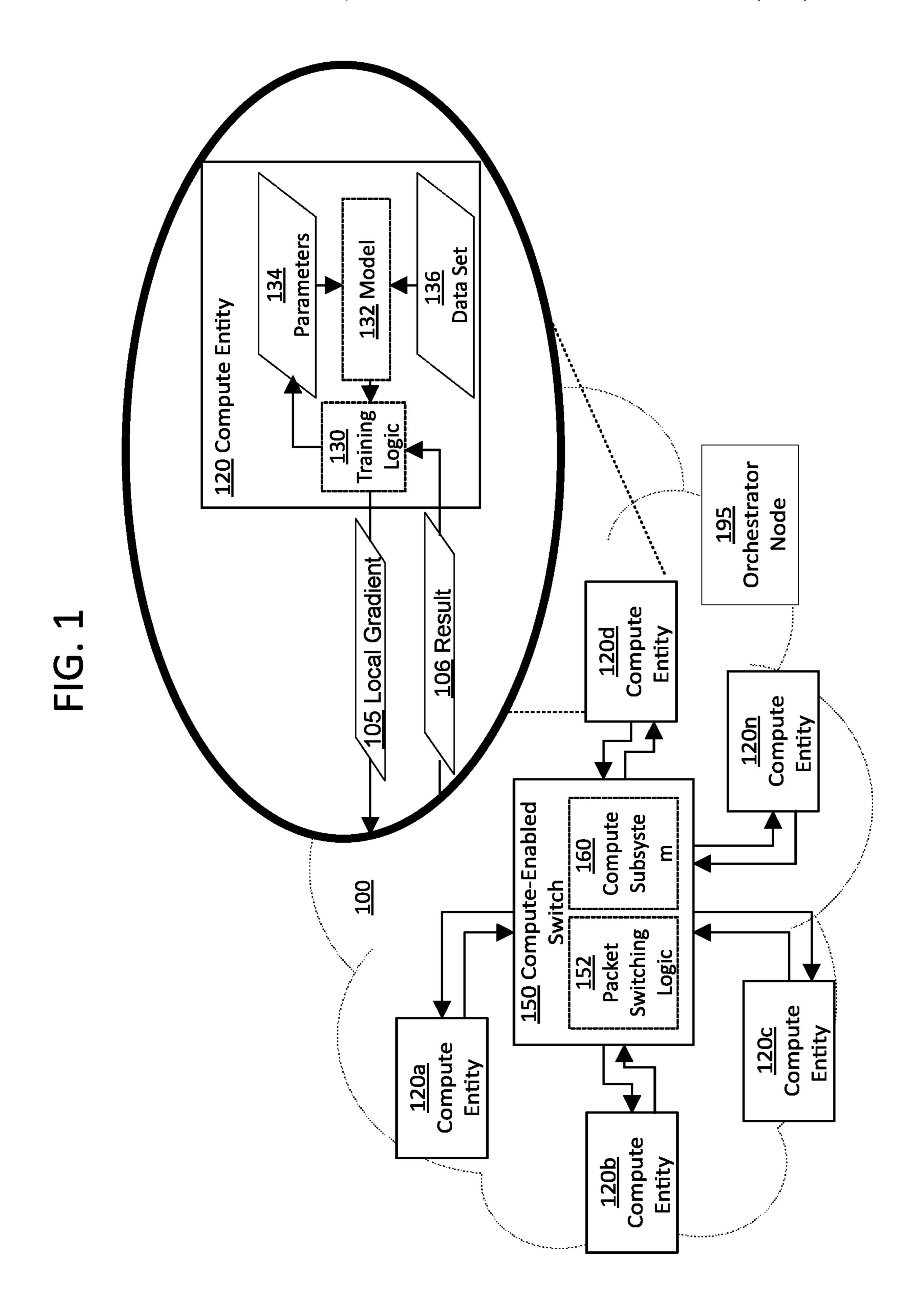

FIG. 2 illustrates an example distributed computing system 200 in which compute entities 220 are organized into compute nodes 210, according to an embodiment. Each compute node 210 is a separate physical grouping of compute entities 220, typically coupling its constituent compute entities 220 in some manner. For example, the compute entities 220 in a compute node may be physically attached to a same baseboard or plane card in a chassis. In an resources, such as a power supply, a CPU or set of CPUs that manage operations of the compute entities 220, or even memory or storage resources.

For instance, a compute node **210** might be an AI server system, such as without limitation a Nvidia DGX series 40 system. The system may comprising four, eight, sixteen, or even greater numbers of GPUs, with each GPU being a different compute entity 220. In another embodiment, a compute node 210 may be a server rack of GPUs or GPU systems. In another embodiment, a compute entity 220 may 45 be a virtualized device, such that a single GPU (or other processing hardware) may appear as multiple compute entities 220, each executing a distinct compute process 230.

Each compute entity 220 in a compute node 210 implements one or more compute processes 230. A compute 50 process 230 is an implementation of logic for performing certain tasks of one or more distributed applications, such as training (or re-training) different neural network models, running different simulations, and so forth. For instance, the compute process 230 may implement training logic 130 of 55 FIG. 1, though in other embodiments, other types of compute processes 230 may be performed. For simplification, the examples herein typically mention only a single compute process 230 being implemented by a compute entity 220 for a single distributed application. However, it will be recog- 60 nized that in some embodiments, a compute entity 220 may actually implement multiple compute processes 230 for multiple distributed applications concurrently.

Each compute entity 220 may perform a compute process 230 in parallel with compute processes 230 performed at 65 other compute entities 220 in the system 200. A group of compute processes 230 working together to execute a dis-

tributed application may be referred to as a compute worker set. The compute entities 220 performing these processes 230 may be characterized as "compute workers" that are in, or belong to, the compute worker set. In some embodiments, there is a one-to-one mapping between distributed applications and worker sets. In other embodiments, a distributed application may include multiple worker sets performing different sets of tasks. Not all compute entities 220 connected to a compute-enabled switch 250, or even in a single compute node 210, need participate in the same distributed application. For instance, different subsets of compute entities 220 in a compute node 210, or different compute nodes 210, may train different neural network models concurrently. While only two compute nodes 210 are depicted, system 200 may include any number of compute nodes 210, each comprising any number of compute entities 220.

Logic implemented by a compute entity 220 in the course of executing a compute process 230 may be referred to herein as "worker logic" (e.g. training logic 130). Depending on the system and/or implemented tasks, the worker logic may be programmable (e.g., a software-based program of instructions executed by central processor units, graphics processor units, etc.), or the worker logic may be hard-coded logic performed by special-purpose hardware. In some 25 embodiments, some or all of the worker logic within a distributed application are instances of the same logic, while in other embodiments, different compute entities 220 may implement different worker logic for the same application.

Each compute entity **220** is mapped to at least one specific port 240 within its corresponding compute node 210. Each port **240** is a communication interface, such as an Ethernet port, InfiniBand port, Fibre Channel port, etc. The compute entity 220 may be on the same chip as the underlying hardware for the communication interface, connected to the embodiment, the compute entities 220 may share common 35 port 240 via direct wiring, or in some cases indirectly coupled to the port 240 via a shared bus or other mechanism. In an embodiment, there is a one-to-one mapping or oneto-many mapping from compute entities 220 to ports 240, such that each port 240 can only be used by the compute entity 220 to which the port 240 is mapped. A compute process 230 may send and receive data units, including those containing gradients or other vector data, via the port or ports 240 mapped to the compute entity 220 that is executing the compute process 230.

> Each port 240 may be connected to a port 290 of the compute-enabled switch 250 via cabling or any other suitable mechanism. Although direct connections between ports 240 and 290 may be desirable in certain embodiments for reduced latency and/or other reasons, ports 240 may also be connected to ports 290 indirectly, via an intermediate, noncompute enabled switch or other network device.

> When performing a compute process 230, a compute entity 220 may generate output data that needs to be reduced or otherwise utilized in conjunction with output data generated by other compute entities 220 in the same worker set. The output data of a compute entity **220** may be referred to herein as a vector, of which local gradient data 105 is an example.

> A compute entity 220 may send this vector to the compute-enabled switch 250 via a port 240 that is mapped to the compute entity 220. Upon receiving the vector at the corresponding one of its ports 290, the switch 250 may forward the vector to a network compute process 270 executed by a network compute entity 260.

> The switch 250, or more specifically the compute subsystem of the switch 250, may comprise one or more network compute entities 260 configured to perform collec-

tive operations on vector data that the switch 250 receives. Like compute entities 120/220, each network compute entity 260 may be a CPU, GPU, TPU, accelerator, or any other hardware capable of performing collective operations. In an embodiment, a network compute entity 260 may be a specialized compute engine, such as described in the aforementioned "Network Switch with Integrated Compute Subsystem for Distributed Artificial Intelligence and Other Applications."

A network compute entity **260** may execute any number 10 of network compute processes 270. Each distributed application being executed by the network may have its own set of one or more network compute processes 270. For instance, if compute processes 230a-h are all part of a single machine learning task, there may be a specific set of one or 15 more network compute processes 270 configured to collect vector data from the compute processes 230a-h and perform collective operations on the collected vector data. The collective operation may include, for instance, a reduction operation such as summation, multiplication, average, maxi- 20 mum, minimum, and so forth, a scan operation, a broadcast operation, a scatter operation, a gather operation, a barrier operation, or any other suitable action. A network compute process 270 may send results of a collective operation—e.g. result gradients-back to each compute process 230 in the 25 distributed application via the corresponding ports 290/240.

Different applications and/or worker sets may require different collective operations. In some embodiments, compute entities **220** may send compute instructions to the compute-enabled switch **250**. Compute instructions may identify the specific reduction operations or other collective operations for the network compute processes **270** to perform on particular vector data sets. Instructions may further specify data type(s) for specific vector data elements or other information related to data structure. In other embodiments, the network compute process **270** may be configured to discern the compute operation(s) to perform directly from the vector data and/or metadata associated with the vector data.

The compute-enabled switch **250** may include one or 40 more buffer memories 280 for storing vector data until a network compute process is ready to process it. For example, a network compute process 270 may be unable to perform a collective operation in a certain epoch until it has received vector data from each compute process 230 45 involved in a certain distributed application. It may therefore store each vector data unit it receives in a buffer 280 until all compute processes 230 have sent vector data for that epoch. Or, the network compute process 270 may utilize a buffer 280 known as a processing buffer to store an intermediate 50 "running" result, such as a running sum, of the vector data it has already received for the epoch, while waiting for additional vector data for that epoch. In some cases, vector data may arrive more quickly than it can be processed, and hence stored in a staging buffer 280 until a corresponding 55 network compute process 270 can process it. Moreover, a processing buffer 280 may be utilized to store intermediate and/or final results of the collective operations until the switch 250 is ready to send those results. The buffer 280 may or may not be shared with packet-switching logic, depend- 60 ing on the embodiment.

# 2.3. Intra-Node Reduction and Vector Partitioning

In some embodiments, compute-node-based systems such as system 200 may realize certain benefits by performing an in-node reduction of local vectors prior to sending vector

12

data to the network compute node. The compute processes produce local vectors, as explained above, but take advantage of an intra-node communication mechanism to aggregate or otherwise reduce the local vectors together at the node level, thereby producing an intermediate result referred to herein as a node vector. The compute nodes then need only send their node vectors to the network compute node, reducing network utilization between the compute nodes and the network compute node. The node vectors from each compute node may then be aggregated or otherwise reduced at the network compute node to produce a result vector.

In some embodiments, compute-node-based systems such as system 200 may also or instead realize certain benefits through vector partitioning. Vectors may be partitioned into partitions referred to herein as chunks. The partitioning scheme for each vector in the distributed application is the same, meaning that the first chunk of each vector contains values for a same first set of elements, the second chunk of each vector contains values for a same second set of elements, and so forth. In an embodiment, a compute node may be configured to partition the local vectors, or the node vector, into chunks prior to transmission to the network compute node, and then send each chunk to the network compute node via a different communication interface. The network compute node may similarly return the result vector as chunks via the different communication interfaces, thereby reducing the amount of time necessary to transmit the vectors.

Chunks of the local vectors generated by each compute process are referred to as local chunks. Chunks of node vectors that are aggregated or otherwise reduced at the node-level are referred to as node chunks. The chunks of the result vector that is returned to each compute process (e.g. the result gradient used for the backward pass of machine learning logic) are referred to as result chunks. Logically, all chunks that contain values for the same set of vector elements may be said to belong to a chunk grouping referred to herein as a chunk column.

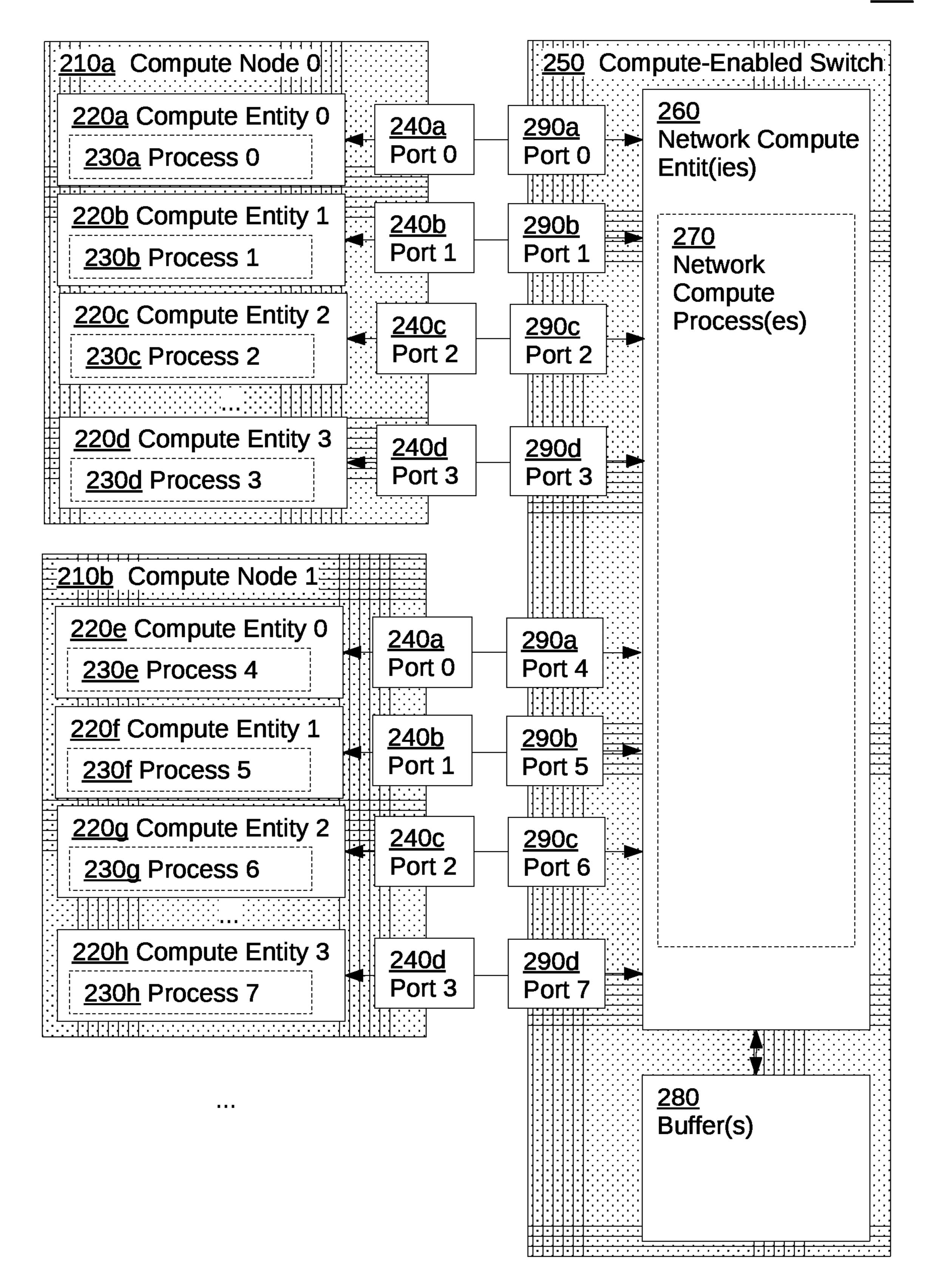

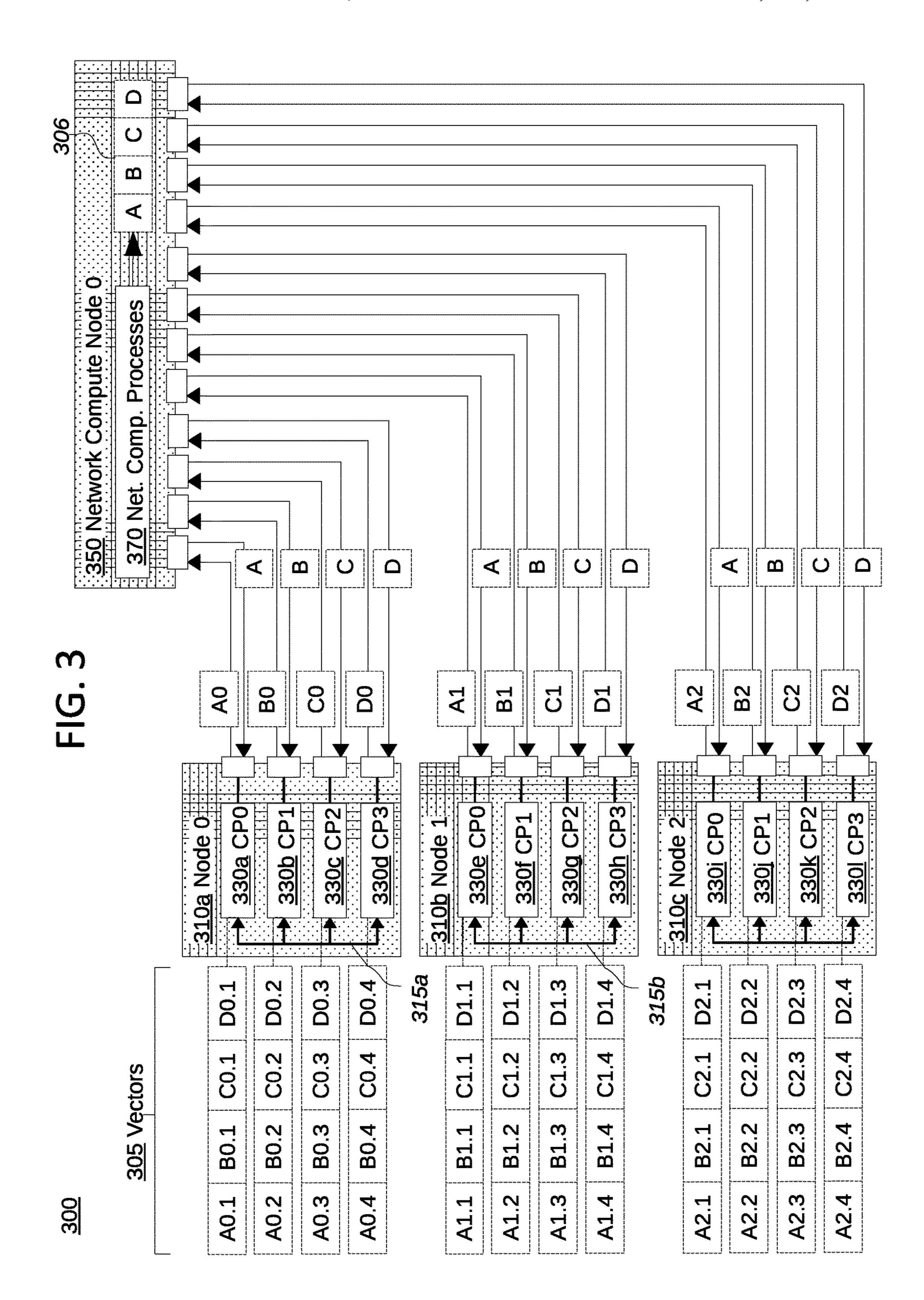

FIG. 3 illustrates an example distributed machine learning system 300 that supports intra-node reduction and/or vector partitioning to reduce network bandwidth consumption, according to an embodiment. System 300 is in many ways similar to systems 100 and 200. For example, system 300 includes compute nodes 310 similar to compute nodes 210. Each compute node 310 includes a number of compute entities similar to compute entities 220, though these compute entities are not illustrated for simplification. Each compute entity executes a compute process 330, similar to a compute process 230. Like compute processes 230, each compute process 330 is mapped to a port (not labeled) by which it is coupled to a port (again unlabeled) of network compute node 350. Network compute node 350, meanwhile, is an example of a compute-enabled switch 250. Network compute node 350 includes one or more undepicted compute entities which execute network compute processes 370, similar to network compute processes 270.

However, the compute entities of each node 310, and hence the compute processes 330 executed at that node 310, are each coupled to each other via an intra-node communication mechanism 315, and therefore capable of intra-node communication. The communication mechanism may be, for instance, a bus or other interconnect. Or, the compute entities may be connected in a ring or other topology (e.g. to two adjacent entities).

The compute processes 330 may be configured to leverage intra-node communication in several manners. First, the compute processes 330 may divide the local vectors 305

they generate into chunks. Each compute process 330 generates a local vector 305 in the normal manner. However, after the compute process generates a local vector 305, it divides the local vector into a series of chunks. For example, compute process 330a may divide its vector into chunks 5 A0.1, B0.1, C0.1, and D0.1, where each chunk comprises values for a different subset of vector elements in vector 305. Each compute process 330a should divide its vector up in the same manner, so as to produce the same number of chunks as each other compute process 330 in the same 10 distributed application.

Moreover, like-numbered chunks in the series should include values for the same subset of elements. For instance, suppose chunk A0.1 includes vector elements 1-99, chunk B0.1 includes vector elements 100-149, chunk C0.1 includes 15 vector elements 150-199, and chunk D0.1 includes vector elements 200-400. Compute process 330b would thus be expected to include its vector elements 1-99 in its chunk A0.2, vector elements 100-149 in chunk B0.2, vector elements 150-199 in chunk C0.2, and vector elements 200-400 20 in chunk D0.2. Conceptually, like-numbered chunks in each local vector (that is, chunks having the same set of vector elements) may be said to be in the same chunk column. Hence, in FIG. 3, each local vector 305 has a chunk for each of columns A, B, C, and D.

The compute processes 330 at a node 310 utilize the intra-node communication mechanism 315 to share the local vectors 305 they generate, or specific chunks thereof, with each other. The compute processes 330 may perform a local reduction or other collective operation(s) associated with the 30 relevant distributed application on the local vectors. In an embodiment, each compute process 330 assumes responsibility for performing local collective operation(s) on a different chunk column. The compute process 330 then sends the resulting chunk of the collective operation-referred 35 to as a "node chunk"-out over its associated port to the network compute node 350.

For example, compute process 330a may be assigned to reduce the first chunk in each local vector 305 to produce a node chunk A0. Similarly, compute process 330b may be 40 responsible for generating a node chunk B0 from the second chunk in each local vector 305, compute process 330c may generate a node chunk C0 from the third chunk in each local vector 305, and compute process 330c may generate a node chunk D0 from the last chunk in each local vector 305. A 45 compute process 330 need only receive the local vector chunks it is responsible for over the interconnect 315, but may optionally receive other chunks or even all of the local vectors 305 generated in the node 310.

Alternatively, the node **310** may include other compute 50 entities configured to perform local collective operations, or a single compute entity that performs the local collective operation for all local vectors, which may then return at least the relevant node chunks to compute processes **330** responsible for sending those chunks.

In either case, in each node 310, there will be one compute process assigned to each chunk column (that is, to each set of chunks that contains the same vector elements). As depicted in FIG. 3, each compute process 330 is given a label, and this label indicates the chunk column to which the 60 compute process 330 is assigned. For example, compute processes 330a, 330e, and 330i are each assigned within their respective nodes 310 to the chunk column "A", and hence share the label CP0.

Note that, as illustrated in FIG. 3, the number of chunks 65 into which each vector 305 is divided is the same as the number of compute processes 330 (and hence compute

**14**

entities) executed by each node 310. This need not always be the case, but the number of chunks in a vector 305 should be at least as great as the minimum number of compute processes 330 executed in each node 310 for the relevant distributed application, so that there may a compute process responsible 330 for each chunk column in each node 310. This may be two, four, eight, sixteen, or any other suitable number of chunks, depending on the embodiment and application configuration.

A network compute process 370 may perform a collective operation between node chunks in the same chunk column. For instance, the network compute process 370 may receive node chunk A0 from compute process 330a, node chunk A1 from compute process 330e of node 310b, and node chunk A2 from compute process 330i of node 310c. Based on metadata associated with these node chunks, and/or the ports over which these node chunks were received, the network compute process 370 may determine that each of these node chunks includes values for the same set of vector elements, and therefore perform a collective operation between the node chunks to generate a result chunk A. The network compute process may send the result of the collective operation back to each compute process 330 that sent a node chunk based upon which the result was calculated. For instance, the network compute process 370 may return the result chunk A back to each of compute processes 330a, **330***e*, and **330***i*.

In some embodiments, there may be a separate network compute process 370 for each chunk into which a vector 305 may be divided. For instance, one network compute process 370 may generate the result chunk A from node chunks A0-A2, another network compute process 370 may generate the result chunk B from node chunks B0-B2, and so forth. These network compute processes 370 may be, for instance, tied to specific ports of the network compute node 350 over which the corresponding node chunks would be received, and be assigned different buffers, network compute entities, and/or other resources. On the other hand, a single network compute process 370, network compute entity, and buffer may be utilized for all of the chunks in other embodiments.

In an embodiment, the set of all result chunks generated by the network compute node 350 forms a result vector 306 that may be utilized by the compute processes 330 to adjust parameters for a next epoch. However, the network compute node 350 need not necessarily (but may) send the entire vector 306 to each compute process 330, or even ever merge the result chunks to form vector 306. Rather, upon receiving a result chunk, a compute process 330 may use the intranode communication mechanism 315 to share the result chunk with each other compute process 330 at the same node 310, thereby allowing each compute process 330 to form the result vector 306.

In system 300, there is no longer any need to send all of the local vectors 305 to network compute node 350, but rather only a single node vector for each node 310, thereby significantly reducing the amount of network bandwidth utilized. Moreover, since each compute process 330 may share the burden of sending the node vector and receiving the result vector, the capacity of the network resources of each compute node 310 and the network compute node 350 may be more optimally utilized.

Note that the depicted number of nodes 310, ports, chunks, and compute processes 330 is merely illustrative. There may be greater numbers of nodes 310, ports, chunks, and so forth, depending on the embodiment.

# 2.4. Hierarchical In-Network Compute

For some distributed applications, it may be desirable to utilize more than one compute-enabled switch. For example,

if the number of compute processes exceed the number of available ports on a compute-enabled switch, it may be desirable to use additional compute-enabled switches so that each compute process may be directly connected to a compute-enabled switch. However, as the number of compute-enabled switches rise, a number of issues of scale may result.

For example, FIG. 4 illustrates a distributed machine learning system comprising four network compute nodes **450** in a hierarchical arrangement, according to an embodiment. Each of network compute nodes **450***a***-450***c* are coupled to three different compute nodes **410**. Each compute node **410** may execute any number of compute processes, and each network compute node **410** may include a separate port for each of these compute processes. For instance, each compute node may execute eight compute processes, and each network compute node **450** may therefore be at least a twenty-four-port switch. However, for simplification, separate compute processes and ports for each compute node **410** are not depicted.

In order to generate a final result vector for the compute processes at nodes 410, a network compute node 450a-cwould need access to all node (or local) vectors sent by the nodes 410 for the relevant epoch. This would require network compute nodes 450a-c to be linked to each other, either 25 directly or through another switch, so as to share this information with each other. Unfortunately, this increases the resource requirements at each network compute node **450**a-c, as each must devote additional buffer resources to buffering intermediate results for each chunk column for a 30 potentially longer period of time. Moreover, each network compute node must devote resources to performing compute operations on different chunk data sets, which may require frequent context switching, reprogramming of a compute entity for each chunk data set, and other relatively expensive 35 operations.

The redundancy and increased buffering requirements at network compute nodes **450***a-c* may, in some embodiments, be alleviated somewhat by employing a compute hierarchy, where each network compute node **450***a-c* sends its intermediate results to a network compute node **450***d*. Network compute node **450***d* may then generate the result vector, and return it to network compute nodes **450***a-c*. However, this solution comes at the expense of additional switches in the hierarchy, which can grow to multiple levels as the number 45 of compute processes increase to hundreds or even thousands.

## 2.5. Node Multi-Switch Connection Architecture

FIG. 5 illustrates a distributed learning system 500 in which each compute node 510 is connected to multiple compute-enabled switches 550, according to an embodiment. System 500 is in many ways similar to system 300. Nodes 510, for example, may be similar to nodes 310, in that 55 they both include multiple compute entities. The compute entities of node 510 execute compute processes 530, which are similar to compute processes 330. More specifically, compute processes 530 generate local vectors in the same manner that compute processes 330 generate local vectors 60 305. Those vectors are, like vectors 350, divided into chunks, and each compute process 530 is assigned responsibility for a different column of the chunks. Vector data is shared between the compute processes 530 in a node 510 via an intra-node communication mechanism, as in system 300. 65

However, unlike in system 300, system 500 includes multiple network compute nodes 550*a*-*d*. Rather than a node

**16**

510 being connected entirely or predominately to a single network compute node 550, each compute process 530 of each node 510 is coupled to a different network compute node 550. For example, compute process 530a may be wired directly (or otherwise connected) to a port on network compute node 550a, compute process 530b may be wired directly (or otherwise connected) to a port on network compute node 550b, compute process 530c may be wired directly (or otherwise connected) to a port on network compute node 550c, and compute process 530d may be wired directly (or otherwise connected) to a port on network compute node 550d. As a result, each network compute node 550 is connected to each compute node 510 that participates in the distributed learning system 500.

The connections between compute nodes **510** and network compute nodes **550** are arranged such that each network compute node **550** receives and processes vector data for a different chunk column. For example, network compute node **550***a* is coupled to compute processes **530***a*, 20 **530***e*, and **530***i*, which only send the network compute node **550***a* vector data for chunk column A. Meanwhile, network compute nodes **550***b*, **550***c*, and **550***d* only receive and process vector data for chunk columns B, C, and D, respectively. Note that the number of chunk columns in a vector is the same as the number of network compute nodes **550**.

As in system 300, each compute process 550a may perform a local collective operation to produce a node chunk to send to the corresponding network compute node 550a. For instance, compute process 530a may send node chunk A0 to network compute node 550a, compute process 530e may send node chunk A1 to network compute node 550a, and compute process 530n may send node chunk An to network compute node 550a. However, in some embodiments, a compute process 530 may simply send all local vector chunks for its chunk column directly to the network compute node 550a, rather than performing a local collective operation.

Each network compute node **550** comprises a network compute entity that implements a network compute process **570**. As would a network compute process **370**, network compute process **570** performs a collective operation between each chunk it receives for a given chunk column in a given epoch for a given application. Likewise, the network compute process **570** returns a result vector chunk to each compute process **530** that it is coupled to. For instance, network compute node **550***a* returns a result chunk A to compute processes **530** then share the result chunks they receive with each other compute process **530** in their respective nodes **510** via the intra-node communication mechanism.

None of the network compute nodes 550 need to receive or process a full vector, or even be aware that other vector chunk columns exist. Consequently, the network compute nodes 550 need not reserve buffer space or devote processing resources to reduce chunks from non-assigned chunk columns. For instance, whereas network compute node 350 would need a separate processing buffer to store an intermediate result for each column of a result vector, the network compute nodes 550 each need a processing buffer for only one column of the result vector. Moreover, the network compute processing logic demands on any given network compute node 550a may be fewer than those on a network compute node 350, since network compute processes 570 at a given network compute node 550a need only be configured to operate on a single chunk column for any given distributed application. This may reduce the need for context switching and reconfiguration between different

collective operations for different chunk columns, and/or reduce the demand for a staging buffer to store vector data that is awaiting processing. Moreover, a staging buffer may support a greater number of outstanding data elements for processing due to the fact that there is only a single column being processed in a particular network compute node. As a result, the resource requirements to provide in-network compute at any given network compute node **550** may be greatly reduced.

Moreover, all other aspects of systems 300 and 500 being 10 equal (e.g., number of ports per compute node and network compute node), system 500 may scale better than system 300. System 300 requires additional network compute nodes once the total number of compute processes 330 exceed the number of ports at network compute node 330, and these 15 additional network compute nodes come at the expense of network bandwidth and other resources to support communication of vector data between the network compute nodes, as illustrated in FIG. 4. Given that distributed learning tasks may involve hundreds, thousands, or even more compute 20 processes 530, the ports in even very large compute-enabled switches may quickly become exhausted. By contrast, even though additional network compute nodes may be required in system 500, the expense of communicating vector data between network compute nodes **550** is altogether avoided 25 until the number of compute nodes 510 exceeds the number of ports available at any given network compute node 550 (which may, in some embodiments, number in the hundreds or even more).

FIG. 5 illustrates but one example of a system with a 30 node-to-multi-switch architecture. Other such systems may include additional or fewer elements, in varying arrangements. For example, the number of compute nodes 510, compute processes 530 per compute node 510, network compute nodes 550, ports per network compute nodes 550, 35 and chunk columns per vector may vary, and depending on the embodiment.

Moreover, network compute nodes **510** may feature additional compute processes executed by other compute entities that are not involved in the same distributed application as 40 compute processes **530**. These compute processes may or may not be connected to some or all of network compute nodes **550**. Similarly, network compute nodes **550** may be connected to other devices than compute nodes **510**, and these devices need not be involved in the same distributed 45 application, or indeed any distributed application. The network compute nodes **550** may simply be configured to treat traffic from these other devices as standard network traffic, and provide packet-switching function for that traffic.

In other embodiments, additional devices connected to network compute nodes **550** and/or additional compute processes at nodes **510** connected to network compute nodes **550**, may be involved in other distributed applications. Some or all of network compute nodes **550** may implement network compute processes for these other distributed applications, potentially using some or all of the same buffer and/or processing resources. For instance, a network compute entity may be scheduled to switch between collective operations of different distributed applications based on the availability of vector data for those distributed applications, priority levels, and/or other considerations. The set of network compute nodes involved in one distributed application may partially or fully overlap with the set of network compute nodes involved in another distributed application.

In an embodiment, a network compute node may be 65 connected to more than one compute process at each compute node 510, and therefore perform collective operations

**18**

for more than one chunk. All compute processes 530 responsible for chunks in the same column would still connect to the same network compute node 550, which would be responsible for computing a result chunk for that column. For instance, instead of four network compute nodes 550, there may be two network compute nodes 550. Network compute node 550a might be connected, via different ports, to the compute processes 530 labeled CP0 and CP1, and return result chunks A and B to those compute processes 530, respectively. Meanwhile, network compute node 550b might be connected, via different ports, to the compute processes 530 labeled CP2 and CP3, and return result chunks C and D to those compute processes 530 respectively.

In an embodiment, a network compute node may be configurable to operate in a multiple chunk mode, as with network compute node 330, or a single chunk mode, as with network compute nodes 530, and/or in a hybrid mode, as explained in the previous paragraph. In some embodiments, the mode in which a network compute node operates may be a function of which vector chunks it receives and/or which nodes it is connected to (as discernable from metadata or instructions received in association with the vector data). In other embodiments, an orchestrator node configures a network compute node in the proper mode using suitable compute instructions.

# 2.6. Compute Planes

As suggested above, a system using the node-to-multiswitch architecture may eventually exhaust the number of ports available at each of the network compute nodes **550**. In these and other situations, an architectural construct referred to as a compute plane may be utilized to scale to even greater numbers of compute nodes.

FIG. 6 illustrates an example distributed learning system 600 for a distributed application that utilizes compute planes 655a-c, according to an embodiment. Each compute plane 655 includes its own set of compute nodes 610 and network compute nodes 650, which is arranged within the plane in similar manner to the compute nodes 510 and network compute nodes 550 of system 500. All of these compute nodes 610 and network compute nodes 650 are configured to generate and operate on vector data for the same distributed application.

The compute nodes 610 and network compute nodes 650 in a given plane operate within that plane 655 in the same manner as compute nodes 510 and network compute nodes 550 operate within system 500, with the exception that the network compute processes 670 from each plane 695 must communicate with counterpart network compute processes 670 in each of the other planes 655 via an inter-plane communication mechanism 695 to exchange intermediate result data prior to calculating the final result chunks. For each chunk column, there will be a separate network compute node 650 in each compute plane 655, and these network compute nodes may each be linked via an inter-plane communication mechanism 695 to enable reduction of a result chunk for that chunk column.

For instance, the network compute process 670a in plane 655a may generate an intermediate result chunk Aa, also referred to as a plane chunk Aa, from the vector data it receives from the compute nodes 610 in plane 655a. Similarly, the network compute process 670a in compute plane 655b might generate a plane chunk Ab, and the network compute process 670a in compute plane 655c might generate a plane chunk Ac. The network compute processes 670a

may then utilize inter-plane communication mechanism 695a to share plane chunks Aa, Ab, and Ac, so as to enable calculation of the result chunk A that is to be returned to each compute node 610 in their respective planes 655.

The network compute nodes 650b use inter-plane com- 5 munication mechanism 695c to generate the final result chunk B, the network compute nodes 650c use inter-plane communication mechanism 695c to generate the final result chunk C, and the network compute nodes 650d use interplane communication mechanism 695d to generate the final 10 result chunk D. Since the different final result vector chunks need not be combined to form the result vector until they arrive back at the compute nodes 610, the inter-plane communication mechanisms 695 connecting each set of network communication nodes 650a, 650b, 650c, and 650d 15 may be separate and distinct.

The inter-plane communication mechanisms 695 may each be any suitable communication mechanism. For example, the planes 655 may be linked by one or more central hubs, where an available port at each network 20 compute node 650 is connected to a hub. There may be a separate central hub that connects the network compute nodes 650 for each chunk column (e.g. a first hub connecting network compute nodes 650a, a second hub connecting network compute nodes 650b, and so forth). Or, a single hub 25 may connect all network nodes 650.

A central hub may broadcast each of the plane chunks it receives to the responsible network compute nodes 655 in each of the other planes 655. For instance, a central hub might share a plane chunk Aa computed by network com- 30 pute node 650a in compute plane 655a with each of the other network compute nodes 650a in compute planes 655b and 655c. The network compute nodes 650 may then each calculate the final result vector chunk themselves. Or, a figured to compute a final result chunk and return it to each of the planes 655. For instance, a central hub may compute a final result chunk A from the plane chunks it receives from all of the network compute nodes 650a, and return this back to each of the network compute nodes 650a.

As another example, the planes 655 may be linked using a ring topology, where each plane 655 is linked to two adjacent planes 655. That is, the planes 655 are organized such that each plane is adjacent to exactly two other planes in a ring formation. Each network compute node **650** may 45 have one port linked to a network compute node 650 in one adjacent plane, and another port linked to a network compute node 650 in another adjacent planes.

In an embodiment, with such a mechanism, an All-Reduce strategy may be used to share data. For instance, a first 50 network node 650 may pass its plane chunk on to the corresponding network node 650 in the next plane 655. That network compute node 650 may reduce the plane chunk it receives with its own plane chunk. That network compute node 650 may then pass this intermediate result on to the 55 next plane 655, which reduces it with its plane chunk, and so forth. A final result chunk will eventually be generated by the last network compute node 650 in the ring to process the vector data, and the final result chunk may then be propagated back through the ring. Of course, any other strategy for 60 sharing vector data between the compute planes 655 may be utilized.

FIG. 6 illustrates but one example arrangement of compute planes. Other systems may include additional or fewer elements in varying arrangements. For instance, there may 65 be additional compute planes, or additional compute nodes and/or network compute nodes per compute plane. Any

**20**

other suitable topology may be utilized for inter-node communication mechanisms 695, including more complex hierarchical topologies. Moreover, the topology within each compute plane 655 may vary—for instance, a ring topology might be used in one compute plane, while a full mesh topology might be used in another. Regardless of the topology within a plane, the planes would still be connected using an inter-plane communication mechanism, as in FIG. 6.

## 2.7. Sub-Partitioning

FIG. 7 illustrates a distributed learning system 700 in which a compute process 730 is configured to divide a chunk into multiple sub-chunks that can be sent to a network compute node separately via different ports, according to an embodiment. The compute processes 730 at a compute node generate vectors 705, which are partitioned into chunks, as in the previous examples. Each compute process 730 is also assigned responsibility for a different chunk column, as explained in the previous examples.

However, before a compute process 730 sends a chunk, whether it be a local chunk or a node chunk reduced from the local chunks that the compute process is responsible for, the compute process 730 divides the chunk into two or more sub-chunks. For example, compute process 730a may reduce a node chunk A0 from local chunks A0.1, A0.2, A0.3, and A0.4. Compute process 730a may divide the node chunk A0 into sub-chunks A0-1 and A0-2. Of course, compute process 730a could also have divided each local chunk prior to the local reduction operation and then reduced the subchunks separately.

The compute process 730 then sends each sub-chunk to a different network compute node 750. For example, compute process 730a sends sub-chunk A0-1 to network compute central hub may itself comprise a compute subsystem con- 35 node 750al and sub-chunk A0-2 to network compute node 750a2. In an embodiment, each compute process 730 may be coupled to or assigned two or more network communication interfaces, each of which may be connected to a different network compute node 750, and the sub-chunks 40 may thus be sent out different ones of these network communication interfaces.

> Each network compute node 750 may perform collective operations to reduce the sub-chunks it receives in the same manner as it reduces full-size chunks, as described elsewhere herein. In fact, in an embodiment, the network compute nodes 750 need not even be aware that they are performing a collective operation on a sub-chunk as opposed to a chunk (or even an entire vector). Note that, although only one compute node 710 is depicted, each network compute node 750 would in fact be connected to and receive sub-chunks from a potentially much greater number of compute nodes 710. Network compute nodes 750 return the result chunks they reduce back to the compute processes 730 to which they are connected via the corresponding network communication interfaces.

> While FIG. 7 illustrates only two sub-chunks per chunk, other embodiments may have three, four, or even greater numbers of sub-chunks per chunk. Note that both the number of network compute nodes 750 to which each compute node 710 is connected as well as the number of communication interfaces needed at each compute node 710 increase by a factor of the number of sub-partitions for each chunk.

> In an embodiment, each compute entity that implements a compute process 730 may be coupled to a SerDes or other communication hardware that a systems integrator may configure as a single high-bandwidth network interface, or