#### US011856871B2

# (12) United States Patent Lanting et al.

#### (54) QUANTUM PROCESSORS

(71) Applicant: **D-WAVE SYSTEMS INC.**, Burnaby (CA)

(72) Inventors: Trevor M. Lanting, Vancouver (CA);

Danica W. Marsden, West Vancouver

(CA); Byong Hyop Oh, San Jose, CA

(US); Eric G. Ladizinsky, Manhattan

Beach, CA (US); Shuiyuan Huang,

Eagan, MN (US); J. Jason Yao, San

Ramon, CA (US); Douglas P. Stadtler,

Morgan Hill, CA (US)

(73) Assignee: **D-WAVE SYSTEMS INC.**, Burnaby (CA)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 17/681,303

(22) Filed: Feb. 25, 2022

(65) Prior Publication Data

US 2022/0263007 A1 Aug. 18, 2022

#### Related U.S. Application Data

(63) Continuation of application No. 16/681,431, filed on Nov. 12, 2019, now abandoned.

(Continued)

(51) Int. Cl.

H01L 39/02 (2006.01)

H10N 60/80 (2023.01)

(Continued)

### (10) Patent No.: US 11,856,871 B2

(45) **Date of Patent:** Dec. 26, 2023

#### (58) Field of Classification Search

CPC ...... H10N 60/805; H10N 60/0156; H10N 60/0912; H10N 60/12; H10N 69/00; G06N 10/00

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,028,714 A 6/1977 Henkels 4,454,522 A 6/1984 De (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1471180 A 1/2004 CN 101088102 A 12/2007 (Continued)

#### OTHER PUBLICATIONS

Racah et al., "Properties of normal metal/dielectric/high-Tejunctions obtained by in-situ oxidation", Physica C 263, 1996. (Continued)

Primary Examiner — Jarrett J Stark (74) Attorney, Agent, or Firm — Cozen O'Connor

#### (57) ABSTRACT

Systems and methods for fabricating a superconducting integrated circuit that includes wiring layers comprising low-noise material are described. A superconducting integrated circuit can be implemented in a computing system that includes a quantum processor. Such a superconducting integrated circuit includes a first set of one or more wiring layers that form a noise-susceptible superconducting device that can decrease processor when exposed to noise. The superconducting integrated circuit can further include a second set of one or more wiring layers that form a superconducting device that is less susceptible to noise. Fabricating a superconducting device that contains low-noise material can include depositing and patterning a wiring layer comprising a first material that is superconductive in a respective range of temperatures and depositing and pattern-(Continued)

| ing a     | different wirin              | ıg laver co                    | mprising a second material that     | 6,627,915                    | В1           | 9/2003     | Ustinov et al.                      |

|-----------|------------------------------|--------------------------------|-------------------------------------|------------------------------|--------------|------------|-------------------------------------|

| _         |                              | sective range of temperatures. | 6,715,944                           | B2                           | 4/2004       | Oya et al. |                                     |

| -         | -                            | -                              | onsidered a low-noise material.     | 6,753,546<br>6,767,840       |              |            | Tzalenchuk et al.<br>Uehara et al.  |

|           |                              |                                |                                     | 6,803,599                    |              |            | Amin et al.                         |

|           | 18 Cl                        | laims, 14                      | Drawing Sheets                      | 6,882,293                    |              |            | Shoji et al.                        |

|           |                              |                                |                                     | 6,905,887                    |              |            | Amin et al.                         |

|           |                              |                                |                                     | 6,979,836<br>7,091,132       |              |            | Zagoskin et al.<br>Tan et al.       |

|           |                              |                                |                                     | 7,031,132                    |              |            | Amin et al.                         |

|           | Relat                        | ed U.S. A                      | Application Data                    | 7,418,283                    | B2           | 8/2008     |                                     |

| (60)      | Drozzicionol c               | nnliantia                      | No. 62/760 252, filed on New        | 7,533,068                    |              |            | Maassen et al.                      |

| (00)      | 13, 2018.                    | іррпсацы                       | n No. 62/760,253, filed on Nov.     | 7,619,437<br>7,624,088       |              |            | Thom et al.<br>Johnson et al.       |

|           | 15, 2016.                    |                                |                                     | 7,638,434                    |              |            | Helneder                            |

| (51)      | Int. Cl.                     |                                |                                     | 7,639,035                    |              | 12/2009    | •                                   |

| ( )       | G06N 10/00                   |                                | (2022.01)                           | 7,843,209<br>7,876,248       |              |            | Berkley<br>Berkley et al.           |

|           | H10N 60/12                   |                                | (2023.01)                           | 7,878,218                    |              |            | Harris et al.                       |

|           | H10N 60/01                   | •                              | (2023.01)                           | 8,008,942                    |              |            | Van et al.                          |

|           | H10N 69/00                   | )                              | (2023.01)                           | 8,018,244<br>8,035,540       |              |            | Berkley  Berkley et al              |

| (52)      | U.S. Cl.                     |                                |                                     | 8,033,340                    |              |            | Berkley et al.<br>Bunyk et al.      |

| , ,       | CPC                          | H10N 60                        | 0/0912 (2023.02); H10N 60/12        | 8,169,231                    |              |            | Berkley                             |

|           |                              | (20)                           | 23.02); <i>H10N 69/00</i> (2023.02) | 8,190,548                    |              | 5/2012     |                                     |

| . <b></b> |                              |                                |                                     | , ,                          |              |            | Rose et al.<br>Van Den Brink et al. |

| (56)      |                              | Referen                        | ices Cited                          | , ,                          |              |            | Tolpygo H10N 60/805                 |

|           | HS                           | PATENT                         | DOCUMENTS                           |                              |              |            | 505/190                             |

|           | 0.5.                         | 17111/11                       | DOCOMENTS                           | 8,421,053                    |              |            | Bunyk et al.                        |

|           | 4,490,733 A                  | 12/1984                        | Kroger                              | 8,437,818<br>8,536,566       |              |            | Tolpygo et al.<br>Johansson et al.  |

|           | ,                            |                                | Jillie et al.                       | 8,611,974                    |              |            | Maibaum et al.                      |

|           | 4,689,559 A<br>4,749,888 A   |                                | Hastings et al.<br>Sakai et al.     | 8,644,898                    |              |            | De Andrade et al.                   |

|           | 4,912,975 A                  |                                | Ohta et al.                         | 8,742,594                    |              |            | Daubenspeck et al.                  |

|           | 5,055,158 A                  |                                | Gallagher et al.                    | 8,854,074<br>8,933,695       |              |            | Berkley<br>Kornev et al.            |

|           | , ,                          |                                | Matsubara et al.                    | , ,                          |              |            | Ladizinsky et al.                   |

|           | 5,087,605 A<br>5,131,976 A   |                                | Hegde et al.<br>Hoko                |                              |              |            | Tolpygo H01L 23/48                  |

|           | 5,157,466 A                  |                                |                                     | 9,136,457<br>9,183,508       |              |            |                                     |

|           | 5,250,817 A                  | 10/1993                        |                                     |                              |              |            | Shea et al.                         |

|           | 5,274,249 A<br>5,290,761 A   | 12/1993                        | Xi et al.<br>Keating et al.         | 9,490,296                    | B2*          | 11/2016    | Ladizinsky B82Y 10/00               |

|           | 5,307,068 A                  |                                | Hartemann                           | , ,                          |              |            | Chudak et al.                       |

|           |                              | 6/1994                         | Katayama et al.                     | , ,                          |              |            | Mukhanov et al.<br>Chang et al.     |

|           | 5,323,520 A                  |                                | Peters et al.                       | 9,634,224                    |              |            | Ladizinsky et al.                   |

|           | 5,339,457 A<br>5,358,928 A   |                                | Kawasaki et al.<br>Ginley et al.    | 9,768,371                    |              |            | Ladizinsky et al.                   |

|           | 5,548,130 A                  |                                | Shimizu et al.                      | 9,971,970<br>9,978,809       |              |            | Rigetti et al.<br>Ladizinsky et al. |

|           | 5,627,139 A                  |                                | Chin et al.                         | , ,                          |              |            | Tuckerman                           |

|           | 5,672,212 A<br>5,767,043 A   |                                | Manos<br>Cantor et al.              | 10,454,015                   | B2           | 10/2019    | Lanting et al.                      |

|           | 5,776,863 A                  | 7/1998                         |                                     | 10,528,886                   |              |            | Boothby  Barlelary et al            |

|           | , ,                          | 9/1998                         |                                     | 10,938,346<br>11,038,095     |              |            | Berkley et al.<br>Huang et al.      |

|           | 5,846,846 A<br>5,858,106 A   |                                | Suh et al.                          | 11,105,866                   |              |            | Swenson et al.                      |

|           | 5,863,868 A                  |                                |                                     | 11,127,893                   |              |            | Johnson et al.                      |

|           | 5,869,846 A                  | 2/1999                         | Higashino et al.                    | 11,295,225<br>2001/0020701   |              |            | Hoskinson et al.<br>Zagoskin        |

|           | 5,880,069 A                  |                                | Nakao et al.                        | 2002/0017906                 |              |            | Ho et al.                           |

|           | 5,892,243 A<br>5,962,865 A   | 4/1999<br>10/1999              |                                     | 2002/0117738                 |              |            | Amin et al.                         |

|           | , ,                          |                                | DiIorio et al.                      | 2002/0180006<br>2002/0188578 |              |            | Franz et al.                        |

|           | 6,011,981 A                  |                                |                                     | 2002/01003/0                 |              |            |                                     |

|           | 6,165,801 A<br>6,188,919 B1  |                                | Burns et al.<br>Lagraff et al.      | 2002/0190381                 | A1           | 12/2002    | Herr et al.                         |

|           | 6,242,387 B1                 |                                | Cukauskas et al.                    | 2003/0027724                 |              |            | Rose et al.                         |

|           | 6,284,721 B1                 | 9/2001                         | Lee                                 | 2003/0068832<br>2003/0089987 |              | 5/2003     | Koval et al.<br>Parikh              |

|           | 6,362,638 B1                 |                                | Ashton et al.                       | 2003/0003307                 |              |            | Il et al.                           |

|           | 6,384,423 B1<br>6,384,424 B1 |                                | Kerber et al.<br>Kugai et al.       | 2003/0107033                 |              |            | Tzalenchuk et al.                   |

|           | 6,420,189 B1                 |                                | -                                   | 2004/0077504                 |              |            | Adachi et al.                       |

|           | 6,459,097 B1                 | 10/2002                        | Zagoskin                            | 2004/0155237<br>2004/0191697 |              |            | Kerber<br>Nakatsuka et al.          |

|           | 6,476,413 B1<br>6,495,854 B1 |                                | Jia et al.<br>Newns et al.          | 2004/0191097                 |              |            | Hinode et al.                       |

|           | 6,517,944 B1                 |                                |                                     | 2005/0029512                 |              |            | Hato et al.                         |

|           | 6,541,789 B1                 | 4/2003                         | Sato et al.                         | 2005/0062131                 |              |            | Murduck et al.                      |

|           | 6,563,311 B2                 |                                | Zagoskin                            | 2005/0107261                 |              |            |                                     |

|           | 6,569,252 B1<br>6,624,122 B1 |                                | Sachdev et al.<br>Holesinger et al. | 2006/0197193<br>2008/0001699 |              |            | Gu et al.<br>Gardner et al.         |

|           | 0,027,122 DI                 | J/ ZUUJ                        | more of al.                         | 2000/0001033                 | 4 <b>3 1</b> | 1/2000     | Saranoi et ai.                      |

| (56)      |         | Referen       | ces Cited             | JP        | 2004079382 A           | 3/2004      |

|-----------|---------|---------------|-----------------------|-----------|------------------------|-------------|

|           |         |               |                       | JP        | 2004519102 A           | 6/2004      |

|           | U.S.    | <b>PATENT</b> | DOCUMENTS             | JP        | 2005-39244 A           | 2/2005      |

|           |         |               |                       | JP        | 2005039244 A           | 2/2005      |

| 2008/0070 | 325 A1  | 3/2008        | Tolpygo               | JP        | 2007150257 A           | 6/2007      |

| 2009/0078 |         |               | Berkley               | JP        | 2009111306 A           | 5/2009      |

| 2009/0203 | 192 A1  |               | Kaltalioglu et al.    | JP        | 2012519379 A           | 8/2012      |

| 2011/0022 | 2820 A1 | 1/2011        |                       | JP        | 6059754 B2             | 12/2016     |

| 2011/0065 | 586 A1  |               | Maibaum et al.        | KR        | 20000026669 A          | 5/2000      |

| 2011/0089 | 405 A1* | 4/2011        | Ladizinsky B82Y 10/00 | KR        | 20010067425 A          | 7/2001      |

|           |         |               | 257/31                | KR        | 20190035900 A          | 4/2019      |

| 2012/0319 | 211 A1  | 12/2012       | Van Dal et al.        | WO        | 99/14800 A1            | 3/1999      |

| 2013/0116 |         | _             | Pollard et al.        | WO        | 9914800 A1             | 3/1999      |

| 2014/0111 |         |               | Xie et al.            | WO        | 0201327 A2             | 1/2002      |

| 2015/0032 |         |               | Chudak et al.         | WO        | 02069411 A2            | 9/2002      |

| 2015/0046 |         | 2/2015        |                       | WO        | 2005093649 A1          | 10/2005     |

| 2015/0119 |         |               | Ladizinsky et al.     | WO        | 2007085074 A1          | 8/2007      |

| 2015/0119 |         |               | Yohannes et al.       | WO        | 2008138150 A1          | 11/2008     |

| 2015/0219 | 730 A1  | 8/2015        | Tsukamoto et al.      | WO        | 2009120638 A2          | 10/2009     |

| 2015/0236 | 5235 A1 | 8/2015        | Ladizinsky et al.     | WO        | 2009149086 A2          | 12/2009     |

| 2016/0079 | 968 A1  |               | Strand et al.         | WO        | 2013180780 A2          | 12/2013     |

| 2016/0170 | 675 A1  | 6/2016        | Pickerell et al.      | WO        | 2016025598 A1          | 2/2016      |

| 2018/0053 | 689 A1  | 2/2018        | Kirby et al.          | WO        | 2016183213 A1          | 11/2016     |

| 2018/0145 | 631 A1  |               | Berkley et al.        | WO        | 2017192733 A2          | 11/2017     |

| 2018/0219 | 150 A1  |               | Lanting et al.        | WO        | 2018144601 A1          | 8/2018      |

| 2018/0308 | 8896 A1 | 10/2018       | Ladizinsky et al.     | WO        | 2019055002 A1          | 3/2019      |

| 2018/0337 | '138 A1 |               | Luu et al.            | WO        | 2019179732 A1          | 9/2019      |

| 2019/0019 | 099 A1  | 1/2019        | Hoskinson et al.      | WO        | 2020212437 A1          | 10/2020     |

| 2019/0044 | 044 A1  | 2/2019        | Lampert et al.        | WO        | 2021231224 A1          | 11/2021     |

| 2019/0164 |         |               | Thomas et al.         | WO        | 2021262741 A1          | 12/2021     |

| 2019/0288 |         |               | Yoscovits et al.      | WO        | 2022178130 A1          | 8/2022      |

| 2019/0332 |         |               | Barends               |           |                        |             |

| 2019/0369 |         |               | Swenson et al.        |           | OTHER PU               | BLICATIO    |

| 2020/0012 |         |               | Kelly et al.          |           |                        |             |

| 2020/0012 |         |               | Huang et al.          | Muller et | al., "Towards understa | anding two- |

| 2020/0144 |         | 5/2020        | Truang Ct al.         | 1         | 1'1 T '1' C            | maing two-  |

#### FOREIGN PATENT DOCUMENTS

5/2020 Lanting et al.

8/2020 Boothby et al.

6/2021 Swenson et al.

12/2021 Sterling et al.

1/2023 Harris et al.

4/2022 Swenson et al.

2020/0152851 A1

2020/0266234 A1

2021/0190885 A1

2021/0375516 A1

2022/0123048 A1

2023/0004851 A1

| CN | 102334206 A   | 1/2012  |

|----|---------------|---------|

| CN | 105914219 A   | 8/2016  |

| EP | 0329603 A2    | 8/1989  |

| EP | 0437971 A1    | 7/1991  |

| EP | 046661 1 A1   | 1/1992  |

| EP | 0476844 A1    | 3/1992  |

| EP | 0477495 A1    | 4/1992  |

| EP | 0732756 A2    | 9/1996  |

| EP | 0756335 A1    | 1/1997  |

| EP | 2401776 B1    | 8/2016  |

| JP | S60140885 A   | 7/1985  |

| JP | S6215869 A    | 1/1987  |

| JP | S6257263 A    | 3/1987  |

| JP | S62200777 A   | 9/1987  |

| JP | 63007675 A    | 1/1988  |

| JP | S637675 A     | 1/1988  |

| JP | S63226981 A   | 9/1988  |

| JP | S6411357 U    | 1/1989  |

| JP | S6476610 A    | 3/1989  |

| JP | H027583 A     | 1/1990  |

| JP | H03286578 A   | 12/1991 |

| JP | H04246871 A   | 9/1992  |

| JP | H04334074 A   | 11/1992 |

| JP | H05102547 A   | 4/1993  |

| JP | H05114756 A   | 5/1993  |

| JP | H06260692 A   | 9/1994  |

| JP | H07066462 A   | 3/1995  |

| JP | H07245404 A   | 9/1995  |

| JP | H08236823 A   | 9/1996  |

| JP | H104223 A     | 1/1998  |

| JP | 2001516970 A  | 10/2001 |

| JP | 2001516970T A | 10/2001 |

| JP | 2003092436 A  | 3/2003  |

| JP | 2004-079882   | 3/2004  |

|    |               |         |

#### ONS

o-level-systems in amorphous solids—Insights from quantum circuits", arXiv:1705. 01108v3, Oct. 10, 2019.

Makhlin et al., "Quantum-state engineering with Josephsonjunction devices," Reviews of Modern Physics 73 (2):357-400, Apr.

Malissa et al., "Superconducting coplanar waveguide resonators for low temperature pulsed electron spin resonance spectroscopy", Review of Scientific Instruments, Feb. 1, 2013.

Martens et al., "Sparameter measurements on singe superconducting thin-film three-terminal devices made of high-Tc and low-Tc materials", J. Appl. Phys. 65, 1989.

Mason, "Surface Impedance of Thin Superconducting Films", California Institute of Technology, 1962.

McRae et al., "Materials loss measurements using superconducting microwave resonators", arXiv:2006.04718 [physics, physics:quantph], Sep. 1, 2000.

Mooij et al., "Josephson Persistent-Current Qubit," Science 285:1036-1039, Aug. 13, 1999.

Morton & Bertet, "Storing quantum information in spins and high-sensitivity ESR", Journal of Magnetic Resonance, 287:128-139, Feb. 1, 2018.

N/A, "Antifuse", Wikipedia, Nov. 16, 2019.

N/A, "Low-k dielectric", Wikipedia, Apr. 14, 2020.

Niepce et al., "Geometric scaling of two-level-system loss in superconducting resonators", Superconducting Science and Technology, 33(2):025013, Jan. 1, 2020.

NSA, "Superconducting Technology Assessment", National Security Agency Office of Corporate Assessments, Aug. 1, 2005, 257 pages.

Office Action in Application No. 2019-562235, dated Mar. 11, 2022 (English translation, 5 pages).

Oliver et al., "MRS Bulletin" vol. 38, pp. 816-825 (2013).

Peltonen, J.T., et al., "Hybrid rf SQUID qubit based on high kinetic inductance," Scientific Reports, Jul. 3, 2018, 8 pages.

Place et al., "New material platform for superconducting transmon qubits with coherence times exceeding 0.3 milliseconds", arXiv, Feb. 28, 2020.

Place et al., "Supplementary Materials for New material platform for superconducting transmon qubits with coherence times exceeding 0.3 milliseconds", Feb. 1, 2021.

#### (56) References Cited

#### OTHER PUBLICATIONS

Ramzi et al., "Niobium and Aluminum Josephson Junctions Fabricated with a Damascene CMP Process", Physics Procedia, vol. 36, 2012, p. 211-216.

Schulz et al., "Design and realization of an all d-wave dc pisuperconducting quantum interference device", Appl. Phys. Lett. 76, 2000.

Schuster et al., "High cooperativity coupling of electron-spin ensembles to superconducting cavities", Physical Review Letters, 105(14):140501, Sep. 1, 2010.

Sears, "Extending Coherence in Superconducting Qubits: from microseconds to milliseconds", PhD thesis, Yale, Jan. 1, 2013.

Sigillito et al., "Fast, low-power manipulation of spin ensembles in superconducting microresonators", Applied Physics Letters, 104(22):222407, Jun. 1, 2014.

Sun et al., "Direction of tunneling in Pb/ I /YBa2Cu3O7-x tunnel junctions", Phys Rev B 54, 1996.

Swenson et al., "Operation of a titanium nitride superconducting microresonator detector in the nonlinear regime," arXiv:1305. 4281v1 [cond-mat.supr-con], May 18, 2013, 11 pages.

Tokunaga et al., "SiO2 passivation film effects on YBCO junctions", Science Direct, Sep. 10, 1998.

Tolpygo et al., "Advanced Fabrication Processes for Superconducting Very Large Scale Integrated Circuits," IEEE Transactions on Applied Superconductivity 26(3):1-10, Jan. 19, 2016.

Tolpygo et al., "Deep sub-micron stud-via technology of superconductor VLSI circuits," Supercond. Sci. Technol. 27:1-9, Jan. 14, 2014.

Valles et al., "Electron tunneling into single crystals of YBa2Cu3O7-δ", Phys. Rev. B 44, 1991.

Verjauw et al., "Investigation of microwave loss induced by oxide regrowth in high-Q Nb resonators", Physical Review Applied, p. 16, Jan. 1, 2020.

VLSI-expert.com, "Parasitic Interconnected Corner (RC corner) Basics—Part 1", hhtp:www.visi-expert.com/2012/02/parasitic-interconnected-corner-rc-corner.html, Feb. 12, 2012 (Year:2012), 7 pages.

Voesch et al., "On-Chip ESR Measurements of DPPH at mK Temperatures", Physics Procedia, 75:503-510, Jan. 1, 2015.

Voss et al., "Submicron Nb—Al-oxide-Nb junctions for frequency mixers", Superconductor Science and Technology 6, 1993.

Wallace & Silsbee, "Microstrip resonators for electron-spin resonance", Review of Scientific Instruments, 62 (7):1754-1766, Jul. 1, 1991.

Wang et al., "FTIR Characterization of Fluorine Doped Silicon Dioxide Thin Films Deposited by Plasma Enhanced Chemical Vapor Deposition", IOP Science, Apr. 21, 2000.

Weichselbaumer et al., "Quantitative modeling of superconducting planar resonators with improved field homogeneity for electron spin resonance", Physical Review Applied, 12(2):024021, Aug. 1, 2019. Winkel, "Implementation of a transmon qubit using superconducting granular aluminum", arXiv, Nov. 7, 2019.

Woods et al., "Determining interface dielectric losses in superconducting coplanar waveguide resonators", arXiv:1808.10347 [cond-mat,physics:quant-ph], Aug. 1, 2018.

Written Opinion for PCT/US2018/016237, dated Jul. 2, 2018, 30 pages.

Written Opinion for PCT/US2020/018137, dated Jun. 3, 2020, 10 pages.

Tolpygo, Sergey K., et al., "Superconductor Electronics Fabrication Process with MoNx Kinetic Inductors and Self-Shunted Josephson Junctions," IEEE Transactions on Applied Superconductivity 28(4), Jun. 2018, 12 pages.

Whittaker, J.D., et al., "A frequency and sensitivity tunable microresonator array for high-speed quantum," arXiv:1509. 05811v2 [quant-ph], Apr. 22, 2016, 8 pages., Apr. 22, 2016.

Anlage, et al., "A current controlled variable delay superconducting transmission line", IEEE, pp. 1388-1391.

Berkley, et al., "A scalable readout system for a superconducting adiabatic quantum optimization system", arXiv, May 6, 2009, 18 pages.

Dagan, et al., "Absence of Andreev reflections and Andreev bound states above the critical temperature", Phys. Rev. B 61, 2000, 5 pages.

Eom, et al., "A Wideband, Low-Noise Superconducting Amplifier with High Dynamic Range", arXiv, Jan. 11, 2012, 23 pages.

Kerber, et al., "An improved NbN integrated circuit process featuring thick NbN ground plane and lower parasitic circuit inductances", IEEE, Jun. 1997, 6 pages.

Lisitskii, et al., "Annular Josephson junctions for radiation detection: fabrication and investigation of the magnetic behavior", Nuclear Instruments & Methods in Physics Research, Apr. 2000, 11 pages. Macco, et al., "Atomic-layer deposited Nb2O5 as transparent passivating electron contact for c-Si solar cells", Science Direct, Sep. 2018, 7 pages.

Nicoletti, et al., "Bi-epitaxial YBCO grain boundary Josephson junctions on SrTiO3 and sapphire substrates", Physica C 269, 1996, 13 pages.

Tolpygo, et al., "Advanced Fabrication Processes for Superconducting Very Large-Scale Integrated Circuits", IEEE, Jan. 19, 2016.

Yoon, et al., "Atomic-scale chemical analyses of niobium oxide/niobium interfaces via atom-probe tomography", AIP Applied Physics Letters, Oct. 2, 2008, 3 pages.

Blanquart et al., "Evaluation and Comparison of Novel Precursors for Atomic Layer Deposition of Nb2O5 Thin Films", Chem. Mater., Feb. 8, 2012, 6 pages.

Born, et al., "Fabrication of Ultrasmall Tunnel Junctions by Electron Beam Direct-Writing", IEEE, 2001, 4 pages.

Buchholz, et al., "LTS junction technology for RSFQ and qubit circuit applications", Science Direct, Jul. 24, 2006, 8 pages.

Campbell, et al., "Dynamics of Oxidation of Aluminum Nanoclusters using Variable Charge Molecular-Dynamics Simulations on Parallel Computers", APS Physics, Jun. 14, 1999, 4 pages.

Chan, et al., "Interface between gold and superconducting YBa2Cu3O7-x", J. Mater. Res, 1995, 6 pages.

Cucolo, et al., "Linear normal conductance in copper oxide tunnel junctions", Phys. Rev. B 54, 1996, 3 pages.

Dagan, et al., "C-axis tunneling on YBCO films", Eur. Phys. J. B 19, 2001, 5 pages.

Dimos, et al., "Orientation Dependence of Grain-Boundary Critical Currents in YBa2Cu3O7 Biocrystals", Physical Review Letters, Jul. 11, 1988, 5 pages.

Dolata, et al., "Platinum thin film resistors with Cr under- and overlayers for Nb/Al2O3/Nb technology", Science Direct, Jul. 19, 2005, 4 pages.

Faucher, et al., "Niobium and niobium nitride SQUIDs based on anodized nanobridges made with an atomic force microscope", Science Direct, Mar. 1, 2002, 7 pages.

Geerlings, et al., "Improving the Quality Factor of Microwave Compact Resonators by Optimizing their Geometrical Parameters", Applied Physics Letters, 2012, 4 pages.

Grabert, et al., "Mesoscopic Josephson effect", Superlattices and Microstructures 25, 2019, 10 pages.

Grünhaupt, et al., "Granular aluminum: A superconducting material for high impedance quantum circuits", arXiv, Sep. 27, 2018, 9 pages.

Grünhaupt, et al., "Quasiparticle dynamics in granular aluminum close to the superconductor to insulator transition", arXiv, Feb. 7, 2018.

Hadfield, et al., "Novel Josephson junction geometries in NbCu bilayers fabricated by focused ion beam microscope", Physica C, North-Holland Publishing, Amsterdam, Feb. 15, 2002, 9 pages.

Harris, "Improved coherence leads to gains in quantum annealing performance", D-Wave, 2019, 4 pages.

Havemann, et al., "High-performance interconnects: an integration overview", IEEE, May 2001, 16 pages.

Herr, et al., "Reproducible Operating Margins on a 72,800-Device Digital Superconducting Chip", arXiv, Oct. 5, 2015, 6 pages.

Hilgenkamp, et al., "Implications of dx2-y2 symmetry and faceting for the transport properties of grain boundaries in high-TC superconductors", Physical Review B 53, 1996, 8 pages.

#### (56) References Cited

#### OTHER PUBLICATIONS

Hinode, et al., "Fabrication of reliable via conductors for niobium SFQ devices", Science Direct, Jul. 19, 2005, 8 pages.

Hypres, "Niobium Integrated Circuit Fabrication Process #S45/100/200 Design Rules", Hypres, Mar. 10, 2015, 9 pages.

Iguchi, et al., "Experimental evidence for a d-wave pairing state in YBa2Cu3O7-y from a study of YBa2Cu3O7-y/ insulator/Pb Josephson tunnel junctions", Phys. Rev. B 49, 1994, 4 pages.

Il'Ichev, et al., "Nonsinusoidal Current-Phase Relationship of Grain Boundary Josephson junctions in High-Tc Superconductors", Physical Review Letters 81, 1998, 4 pages.

Joyez, et al., "Observation of Parity-Induced Suppression of Josephson Tunneling in the Superconducting Single Electron Transistor", Phys. Rev., Lett. 72, Jul. 19, 2005, 5 pages.

Koelle, et al., "High-transition-temperature superconducting quantum interference devices", Reviews of Modern Physics 71, 199, 56 pages.

Kohl, "Low-Dielectric Constant Insulators for Future Integrated Circuits and Packages", Georgia Tech, Mar. 14, 2011, 25 pages. Kouznetsov, et al., "c-axis Josephson Tunneling between YBa2Cu3O7-δ and Pb: Direct Evidence for Mixed Order Parameter Symmetry in a High-Tc Superconductor", Phys. Rev. Lett. 79, 1997, 4 pages. Kubatkin, et al., "Coulomb blockade electrometer with a high-Tcisland", JETP Letters 63, 1996, 7 pages.

Levinsen, "Electromagnetic properties of the Dayem bridge", HAL Archives, Jan. 1, 1974, 11 pages.

Maleeva, et al., "Circuit Quantum Electrodynamics of Granular Aluminum Resonators", arXiv, Feb. 7, 2018, 17 pages.

Martinis, et al., "Critical Field for Complete Vortex Expulsion from Narrow Superconducting Strips", UCSB, Mar. 5, 2004, 4 pages. Matveev, et al., "Parity-Induced Suppression of the Coulomb Blockade of Josephson Tunneling", Phys. Rev. Lett. 70, 1993, 4

pages.

McKenney, et al., "Design considerations for a background limited 350 micron pixel array using lumped element superconducting microresonators", SPIE, Sep. 24, 2012, 10 pages.

Nagasawa, et al., "Development of advanced Nb process for SFQ circuits", Science Direct, Jun. 9, 2004, 8 pages.

Potts, et al., "CMOS compatible fabrication methods for submicron Josephson junction qubits" IEEE, Sep. 5, 2001, 4 pages.

Russo, et al., "Characterization of Superconducting Thin Films and nanoSQUIDs for Nanoparticle Investigation at High Magnetic Field", IEEE, Feb. 18, 2012, 4 pages.

Satoh, et al., "Fabrication process of planarized multi-layer Nb integrated circuits", IEEE, Jun. 13, 2005, 4 pages.

Satoh, et al., "Planarization of Josephson junctions for large-scale integrated Nb SFQ circuits by mechanical polishing", Science Direct, 1999, 4 pages.

Tafuri, et al., "Feasibility of Biepitaxial YbaCuO Josephson Junctions for Fundamental Studies and Potential Circuit Implementation", Los Alamos National Laboratory preprint server condmat, Dec. 18, 2002, 21 pages.

Tolpygo, et al., "Deep Sub-Micron Stud-via Technology for Superconductor VLSI Circuits", IOP Science, Jan. 14, 2014, 10 pages. Tsuei, et al., "Pairing symmetry in cuprate superconductors", Reviews of Modern Physics 72, 2000, 48 pages.

Valenti, et al., "Interplay between kinetic inductance, non-linearity and quasiparticle dynamics in granular aluminum MKIDs", arXiv, Nov. 10, 2018, 14 pages.

Van Harlingen, "Phase-sensitive tests of the symmetry of the pairing state in the high-temperature superconductors—Evidence for dx2-y2 symmetry", Rev. Mod. Phys. 67, 1995, 23 pages.

Vinante, et al., "Hot-electron effect in palladium thin films", APS Physics, Mar. 13, 2007, 5 pages.

Wen, et al., "Microstructure of ramp-edge Yba2Cu3O3/ PrBa2Cu3O2 Josephson junctions on different substrates", Physica C 255, 1995, 13 pages.

Wollman, et al., "Evidence for dx2-y2 Pairing from the Magnetic Field Modulation of YBa2Cu3O7-Pb Josephson Junctions". Phys. Rev. Lett 74, Jan. 30, 1995, 4 pages.

Yohannan, "Characterization of alpha and beta phases of tantalum coatings", New Jersey Institute of Technology, Aug. 31, 2001, 107 pages.

Zantye, Parshuram B, et al., "Chemical mechanical planarization for microelectronics application", Materials Science and Engineering R 45 (2004) 89-220. 2004 (Year: 2004), 132 pages.

Barends, et al., "Superconducting quantum circuits at the surface code threshold for fault tolerance", Nature vol. 508, pp. 500-503 (2014).

Blatter et al., "Design aspects of superconducting-phase quantum bits," Physical Review B 63: 174511-1-174511-9, 2001.

Bunyk et al., "Architectural Considerations in the Design of a Superconducting Quantum Annealing Processor," IEEE Trans. Appl. Supercond., 24, arXiv:1401.5504v1 [quant-ph] Jan. 21, 2014, 9 pages.

Calusine et al., "Analysis and mitigation of interface losses in trenched superconducting coplanar wave resonators", Applied Physics Letters, 112(6):062601, Feb. 1, 2018.

Cava, et al., "Electrical and magnetic properties of Nb2O5- crystallographic shear structures", Phys. Rev. B44, 6973—Published Oct. 1, 1991.

Clauss et al., "Broadband electron spin resonance from 500 MHz to 40 GHz using superconducting coplanar waveguides", Applied Physics Letters, Apr. 1, 2013.

Clauss et al., "Optimization of Coplanar Waveguide Resonators for ESR Studies on Metals", Journal of Physics: Conference Series, Mar. 1, 2015.

Daalmans, "HTS DC SQUIDs for practical applications", Science Direct, Jul. 1, 1995.

De Graaf et al., "Direct Identification of Dilute Surface Spins on Al2O3: Origin of Flux Noise in Quantum Circuits", Physical Review Letters, Jan. 1, 2017.

De Graaf et al., "Suppression of low-frequency charge noise in superconducting resonators by surface spin desorption", Nature Communications, 9(1):1143, Dec. 1, 2018.

Diniz et al., "Intrinsic photon loss at the interface of superconducting devices", arXiv, Mar. 10, 2020.

Doerner, S., et al., "Compact microwave kinetic inductance nanowire galvanometer for cryogenic detectors at 4.2 K," J. Phys. Commun., 2018, 8 pages.

Extended European Search Report for EP 18747998.5, dated Sep. 3, 2020, 8 pages.

Friedrich et al., "Onset of phase diffusion in high kinetic inductance granular aluminum micro-SQUIDs", arXiv, Aug. 29, 2019.

Gao et al., "Experimental evidence for a surface distribution of two-level systems in superconducting lithographed microwave resonators", Applied Physics Letters, 92(15):152505, Apr. 1, 2018.

Gao, Jiansong, "The Physics of Superconducting Microwave Resonators," Thesis, In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy, California Institute of Technology Pasadena, California, May 28, 2008, 197 pages.

Hinode et al., "Fabrication of reliable via conductors for niobium SFQ devices," Physica C 426-431:1533-1540, 2005.

Holzman et al., "On-chip integrable planar NbN nanoSQUID with broad temperature and magnetic-field operation range", AIP Advances, Oct. 23, 2019.

Hori et al., "Electron spin resonance study on pure single crystalline sapphire", P hys. Status Solidi C 10, No. 12, 1681-1683 (Nov. 5, 2013).

Hunt et al., "NbN/MgO/NbN edge-geometry tunnel junctions", Applied Physics Letters 55, 1982.

International Search Report for PCT/US2018/016237, dated Jul. 2, 2018, 6 pages.

International Search Report for PCT/US2020/018137, dated Jun. 3, 2020, 4 pages.

Japanese Office Action for Japanese Patent Application No. 2020-073654, dated Aug. 17, 2021 (with English Translation) 5 pages. Johnson et al., "Scalable Control System for a Superconducting Adiabatic Quantum Optimization Processor," Superconductor Science & Technology (2010).

Kwon et al., "Magnetic Field Dependent Microwave Losses in Superconducting Niobium Microstrip Resonators", Journal of Applied Physics, 124(3):033803, Jul. 1, 2018.

#### (56) References Cited

#### OTHER PUBLICATIONS

Lanting et al., "Evidence for temperature-dependent spin diffusion as a mechanism of intrinsic flux noise in SQUIDs", Physical Review B 89, 014503 (Jan. 7, 2014).

Lanting et al., "Geometrical dependence of the low-frequency noise in superconducting flux qubits", Physical Review B, 79, 060509, Jun. 5, 2009, 4 pages.

Levy-Bertrand et al., "Electrodynamics of granular aluminum from superconductor to insulator: observation of collective superconducting modes", arXiv, Mar. 13, 2019.

Lomatch et al., "Multilayer Josephson Flux Quantum Devices," IEEE Trans. Appl. Superconductivity, vol. 5, No. 2, Jun. 2, 1995. Lucero, "Computing prime factors using a Josephson phase-qubit architecture: 15=3x5", A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Physics, University of California Santa Barbara.

Il'ichev, et al. "Degenerate ground state in a mesoscopic YBa2Cu3O7-x grain boundary Josephson junction", Physical Review Letters, vol. 86, No. 23, Jun. 4, 2001, 4 pages.

Annunziata, et al., "Tunable superconducting nanoinductors", IOP Science, Oct. 15, 2010, 11 pages.

Balashov, et al., "Superconductor-insulator-normal- conductor-insulator-superconductor process development for integrated circuit applications", IOP Science, Dec. 1, 1998, 11 pages.

Bruder, et al., "Tunnel junctions of Unconventional Superconductors", Physical Review, 1995, 5 pages.

Larsson, et al., "Transport properties of submicron YBa2Cu3O7-d step-edge Josephson junctions", J. Appl. Phys. 90, 2001, 24 pages. Lombardi, et al., "Tunnel barriers for an all-high-Tc single electron tunneling transistor", Physica C 368, 2002, 6 pages.

Martinis, et al., "UCSB final report for the CSQ program: Review of decoherence and materials physics for superconducting qubits", arXiv, Oct. 21, 2014, 10 pages.

Mazin, et al., "Thin film dielectric microstrip kinetic inductance detectors", arXiv, Feb. 1, 2010, 10 pages.

Ortlepp, et al., "RSFQ Circuitry Using Intrisic π-Phase Shifts", IEEE, Jun. 2007, 5 pages.

Schrieffer, et al., "Superconductivity", Rev. Mod. Phys., 71, 1999, 5 pages.

Sigrist, et al., "Unusual paramagnetic phenomena in granula high-temperature superconductors—A consequence of d-wave pairing?", Rev. Mod. Phys. 67, 1995, 5 pages.

Smilde, et al., "Y—Ba—Cu—O / Au / Nb Ramp-type Josephson Junctions", IEEE, 2001, 5 pages.

Tanaka, et al., "Theory of Josephson effects in anisotropic superconductor", Physical Review B 56, 1997, 21 pages.

Tolpygo, "Superconductor Digital Electronics: Scalability and Energy Efficiency Issues", arXiv, Feb. 10, 2016, 20 pages.

Tosi, et al., "Silicon quantum processor with robust long-distance qubit couplings", Nature, Sep. 6, 2017, 11 pages.

D-Wave Whitepaper, Early Progress on Lower Noise, 2022.

Fritzsch et al., "SNS and SIS Josephson junctions with dimensions down to the sub-µm region prepared by an unified technology," Supercond. Sci. Tech. 12: 880-882, 1999.

Gao et al., A Semiempirical Model for Two Level System Noise In Superconducting Microresonators, Applied Physics, 2008.

International Search Report and Written Opinion, dated Oct. 13, 2021. for PCT/US2021/038519, 9 pages.

Kauppinen, et al., "Coulomb Blockade Thermometer: Tests and Instrumentation", Review of Scientific Instruments, vol. 69, #12, 1998.

Kosen, et al., "Building Blocks of a Flip Chip Integrated Superconducting Quantum Processor", arXiv 2112.02717v2, 2022.

Lee, "The Feasibility of Au Bonding on SN-Plated Cu", Journal of Electronic Materials, 2007.

Logothetidis, et al., "Room Temperature Oxidation Behavior of TiN Thin Films", 1999.

Luo, "Superconductivity In Noble-Metal-Rich Hexagonal Close-Packed Phases", 1970.

McCrory, et al., "Wafer-Level Electrically Detected Magnetic Resonance: Magnetic Resonance In a Probing Station", 2018.

Mcintyre, "The Effect of Annealing and Heating Deposition on Alpha and Beta Phase Formation for Tantalum Thin Films", 2018. Narkowicz, et al., "Planar Microresonators for EPR Experiments", Science Direct, 2005.

Ni, et al., "Demonstration of Tantalum as a Structural Material for MEMS Thermal Actuators", 2021.

Non-Final Office Action Issued in U.S. Appl. No. 16/870,537, dated Jul. 19, 2023, 9 pages.

Shoji et al., "New fabrication process for Josephson tunnel junctions with (niobium nitride, niobium) double-layered electrodes," Appl. Phys. Lett. 41(11): 1097-1099, Dec. 1, 1982.

Veinger, "Technique for Magnetic Susceptibility Determination in the High Doped Semiconductors by Electron Spin Resonance", 2013.

Vladoiu, "Growth and Characteristics of Tantalum Oxide Thin Films Deposited Using Thermionic Vacuum Arc Technology", 2010.

Wang, "Towards Practical Quantum Computers: Transmon Qubit With a Lifetime Approaching 0.5 Milliseconds", 2022.

Zednicek, "Niobium and Niobium Oxide Capacitors Overview", 2019.

Zhang, et al., "Characterization of Surface Oxidation Layers On Ultrathin NvTiN Films", 2018.

Chinese Office Action dated Mar. 30, 2023, for Chinese Application No. 201880021010X, 12 pages (English translation of action).

<sup>\*</sup> cited by examiner

FIGURE 1A

FIGURE 1D

FIGURE 1E

100g 116

114

110

108

104

102

FIGURE 1G

FIGURE 1H

Dec. 26, 2023

FIGURE 2

FIGURE 3

FIGURE 4

Dec. 26, 2023

FIGURE 5A

FIGURE 5B

FIGURE 5C

FIGURE 5D

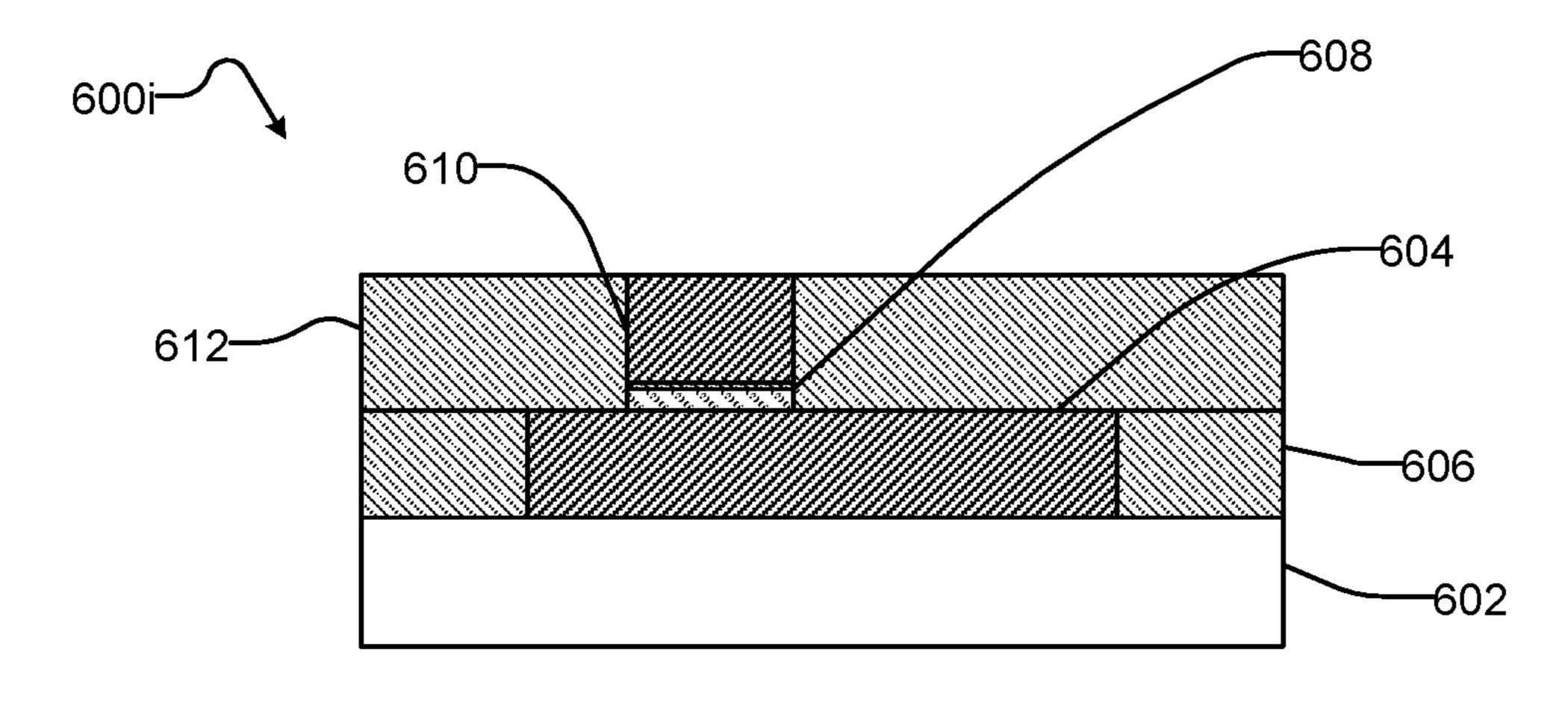

FIGURE 6C

FIGURE 6D

FIGURE 6E

FIGURE 6F

FIGURE 6G

FIGURE 6H

FIGURE 6I

FIGURE 7

FIGURE 8

## **QUANTUM PROCESSORS**

#### **FIELD**

This disclosure generally relates to quantum processors, and in particular, relates to quantum processors that include a set of wiring layers comprising more than one type of material to reduce noise in superconductive devices and a base electrode that has been planarized.

#### BACKGROUND

#### Superconductive Processor

A quantum processor may take the form of a superconducting processor. However, superconductive processors can include processors that are not intended for quantum computing. For instance, some embodiments of a superconductive processor may not focus on quantum effects such as quantum tunneling, superposition, and entanglement but may rather operate by emphasizing different principles, such as for example the principles that govern the operation of classical computer processors. However, there may still be certain advantages to the implementation of such superconducting "classical" processors. Due to their natural physical 25 properties, superconducting classical processors may be capable of higher switching speeds and shorter computation times than non-superconducting processors, and therefore it may be more practical to solve certain problems on superconducting classical processors. The present systems and 30 methods are particularly well-suited for use in fabricating both superconducting quantum processors and superconducting classical processors.

#### Superconducting Qubits

Superconducting qubits are a type of superconducting 35 propylene, temperature-controlled baths. quantum device that can be included in a superconducting integrated circuit. Superconducting qubits can be separated into several categories depending on the physical property used to encode information. For example, they may be separated into charge, flux and phase devices. Charge 40 devices store and manipulate information in the charge states of the device. Flux devices store and manipulate information in a variable related to the magnetic flux through some part of the device. Phase devices store and manipulate information in a variable related to the difference 45 in superconducting phase between two regions of the device. Recently, hybrid devices using two or more of charge, flux and phase degrees of freedom have been developed. Superconducting qubits commonly include at least one Josephson junction. A Josephson junction is a small interruption in an 50 otherwise continuous superconducting current path and is typically realized by a thin insulating barrier sandwiched between two superconducting electrodes. Thus, a Josephson junction is usually formed as a three-layer or "trilayer" structure. Superconducting qubits are further described in, 55 for example, U.S. Pat. Nos. 7,876,248, 8,035,540, and 8,098,179.

#### Integrated Circuit Fabrication

Traditionally, the fabrication of superconducting integrated circuits has not been performed at state-of-the-art 60 semiconductor fabrication facilities. This may be due to the fact that some of the materials used in superconducting integrated circuits can contaminate the semiconductor facilities. For instance, gold may be used as a resistor in superconducting circuits, but gold can contaminate a fabrication 65 tool used to produce complementary metal-oxide-semiconductor (CMOS) wafers in a semiconductor facility.

Superconductor fabrication has typically been performed in research environments where standard industry practices could be optimized for superconducting circuit production. Superconducting integrated circuits are often fabricated with tools that are traditionally used to fabricate semiconductor chips or integrated circuits. Due to issues unique to superconducting circuits, not all semiconductor processes and techniques are necessarily transferrable to superconductor chip manufacture. Transforming semiconductor processes and techniques for use in superconductor chip and circuit fabrication often requires changes and fine adjustments. Such changes and adjustments typically are not obvious and may require a great deal of experimentation. The semiconductor industry faces problems and issues not necessarily 15 related to the superconducting industry. Likewise, problems and issues that concern the superconducting industry are often of little or no concern in standard semiconductor fabrication.

Any impurities within superconducting chips may result in noise which can compromise or degrade the functionality of the individual devices, such as superconducting qubits, and of the superconducting chip as a whole. Since noise is a serious concern to the operation of quantum computers, measures should be taken to reduce noise wherever possible. Etching

Etching removes layers of, for example, substrates, dielectric layers, oxide layers, electrically insulating layers and/or metal layers according to desired patterns delineated by photoresists or other masking techniques. Two exemplary etching techniques are wet chemical etching and dry chemical etching.

Wet chemical etching or "wet etching" is typically accomplished by submerging a wafer in a corrosive bath such as an acid bath. In general, etching solutions are housed in poly-

Dry chemical etching or "dry etching" is commonly employed due to its ability to better control the etching process and reduce contamination levels. Dry etching effectively etches desired layers through the use of gases, either by chemical reaction such as using a chemically reactive gas or through physical bombardment, such as plasma etching, using, for example, argon atoms.

Plasma etching systems have been developed that can effectively etch, for example, silicon, silicon dioxide, silicon nitride, aluminum, tantalum, tantalum compounds, chromium, tungsten, gold, and many other materials. Two types of plasma etching reactor systems are in common use—the barrel reactor system and the parallel plate reactor system. Both reactor types operate on the same principles and vary primarily in configuration. The typical reactor consists of a vacuum reactor chamber made usually of aluminum, glass, or quartz. A radiofrequency or microwave energy source (referred to collectively as RF energy source) is used to activate etchants, for example, fluorine-based or chlorinebased gases. Wafers are loaded into the chamber, a pump evacuates the chamber, and the reagent gas is introduced. The RF energy ionizes the gas and forms the etching plasma, which reacts with the wafers to form volatile products which are pumped away.

Physical etching processes employ physical bombardment. For instance, argon gas atoms may be used to physically bombard a layer to be etched, and a vacuum pump system removes dislocated material. Sputter etching is one physical technique involving ion impact and energy transfer. The wafer to be etched is attached to a negative electrode, or "target," in a glow-discharge circuit. Positive argon ions bombard the wafer surface, resulting in the dislocation of the

surface atoms. Ion beam etching and milling are physical etching processes which use a beam of low-energy ions to dislodge material. The ion beam is extracted from an ionized gas (e.g., argon or argon/oxygen) or plasma, created by an electrical discharge.

Reactive-ion etching (RIE) is a combination of chemical and physical etching. During RIE, a wafer is placed in a chamber with an atmosphere of chemically reactive gas (e.g., CF<sub>4</sub>, CCl<sub>4</sub> and many other gases) at a low pressure. An electrical discharge creates an ion plasma with an energy of a few hundred electron volts. The ions strike the wafer surface vertically, where they react to form volatile species that are removed by the low pressure in-line vacuum system. Planarization

The use of chemical-mechanical planarization (CMP) 15 allows for a near flat surface to be produced. CMP is a standard process in the semiconductor industry. The CMP process uses an abrasive and corrosive chemical slurry in conjunction with a polishing pad and retaining ring that are pressed together by a dynamic polishing head. The dynamic 20 polishing head is rotated with different axes of rotation (i.e., not concentric). This removes material and tends to even out any irregular topography, making the wafer flat or planar. The chemicals in the slurry also react with and/or weaken the material to be removed such that certain materials can be 25 preferentially removed while leaving others relatively intact. The abrasive accelerates this weakening process and the polishing pad helps to wipe the reacted materials from the surface. Advanced slurries can be used to preferentially remove areas of the wafer which are relatively high or 30 protrude in relation to areas of the wafer which are relatively low in order to planarize the topography of the wafer. Hamiltonian Description of a Quantum Processor

In accordance with some embodiments of the present systems and devices, a quantum processor may be designed 35 to perform adiabatic quantum computation and/or quantum annealing. A common problem Hamiltonian includes first component proportional to diagonal single qubit terms and a second component proportional to diagonal multi-qubit terms. The problem Hamiltonian, for example, may be of the 40 form:

$$H_P \propto -\frac{\varepsilon}{2} \left[ \sum_{i=1}^{N} h_i \sigma_i^z + \sum_{j>i}^{N} J_{ij} \sigma_i^z \sigma_j^z \right]$$

(1)

where N represents the number of qubits,  $\sigma_i^z$  is the Pauli z-matrix for the i<sup>th</sup> qubit, h<sub>i</sub> and J<sub>i,j</sub> are dimensionless local fields for the qubits, and couplings between qubits, and  $\varepsilon$  is 50 some characteristic energy scale for H<sub>P</sub>. Here, the  $\sigma_i^z$  and  $\sigma_i^z \sigma_j^z$  terms are examples of "diagonal" terms. The former is a single qubit term and the latter a two qubit term. Hamiltonians may be physically realized in a variety of different ways, for example, by an implementation of superconduct- 55 ing qubits.

Noise in a Quantum Processor

Low-noise is a desirable characteristic of quantum devices. Noise can compromise or degrade the functionality of the individual devices, such as superconducting qubits, 60 and of the superconducting processor as a whole. Noise can negatively affect qubit coherence and reduce the efficacy of qubit tunneling. Since noise is a serious concern to the operation of quantum processors, measures should be taken to reduce noise wherever possible so that a transition from 65 coherent to incoherent tunneling is not induced by the environment.

4

Impurities may be deposited on the metal surface and/or may arise from an interaction with the etch/photoresist chemistry and the metal. Noise can be caused by impurities on the upper surface of the quantum processor. In some cases, superconducting devices that are susceptible to noise are fabricated in the top wiring layers of a superconducting integrated circuit and are thus sensitive to post-fabrication handling. There is a risk of introducing impurities that cause noise during post-fabrication handling. One approach to reducing noise is using a barrier passivation layer, for example, an insulating layer, to overlie the topmost wiring layer. The use of a barrier passivation layer to minimize noise from impurities on the upper surface of a quantum processor is described in U.S. Pat. No. 10,454,015.

Noise can also result from an external environment or surrounding circuitry in a superconducting processor. In a quantum processor, flux noise on qubits interferes with properly annealing the quantum processor because of the steep transition between qubit states as the flux bias is swept. Flux noise can be a result of current flowing through wiring of other devices included in the superconducting processor and can have a particularly negative effect on qubits at their respective degeneracy points. For example, flux noise can introduce errors in calculations carried out by the superconducting processor due to inaccuracies in setting flux bias and coupling strength values. Such values are important to using an integrated circuit as part of a quantum processor. Much of the static control error can be designed out of the processor with careful layout and high-precision flux sources, as well as by adding circuitry, such as an on-chip shield, to tune away any non-ideal flux qubit behavior. However, in many cases, limitations in integrated circuit fabrication capabilities can make it difficult to address noise by changing processor layout and adding circuitry. There is thus a general desire for systems and methods to for fabricating integrated circuits that have reduced flux noise without having to compromise the quantum processor layout by adding additional layers or circuitry.

The foregoing examples of the related art and limitations related thereto are intended to be illustrative and not exclusive. Other limitations of the related art will become apparent to those of skill in the art upon a reading of the specification and a study of the drawings.

#### **BRIEF SUMMARY**

There exists a need for scalable systems and methods for fabricating integrated circuits that have reduced flux noise. Past approaches necessitate additional layers, such as overlying passivation layers, or additional circuitry such as on chip shields. The present systems and methods describe fabrication of a superconducting integrated circuit including fabrication of a superconducting integrated circuit with low-noise layers.

A method for fabricating a superconducting integrated circuit may be summarized as including: depositing a first wiring layer comprising a first material that is superconductive in a first range of temperatures, the first range of temperatures including a respective critical temperature; patterning the first wiring layer to form a first set of one or more superconducting traces; depositing a first dielectric layer; polishing the first dielectric layer back to an upper surface of the first wiring layer; depositing a passivation layer to overlie at least a portion of the first wiring layer, the passivation layer comprising a second material that is superconductive in a second range of temperatures, the second range of temperatures including a respective critical tem-

perature; patterning the passivation layer; depositing a second dielectric layer to overlie at least a portion of the passivation metal layer; patterning the second dielectric layer to expose at least a portion of the passivation layer; depositing a second wiring to overlie at least a portion of the 5 passivation layer, the second wiring layer comprising the second material that is superconductive in the second range of temperatures; forming a first set of vias electrically coupling the second wiring layer to the passivation layer, the first set of vias comprising the second material that is 10 superconductive in the second range of temperatures; and patterning the second wiring layer to form a second set of one or more superconducting traces. a first wiring layer including a first set of one or more superconducting traces, the first wiring layer comprising a first material that is 15 superconductive in a first range of temperatures; a passivation layer overlying the first wiring layer, the passivation layer comprising a second material that is superconductive in a second range of temperatures; a second wiring layer including a second set of one or more superconducting 20 traces, the second wiring layer comprising the second material that is superconductive in the second range of temperatures; a first set of vias electrically coupling the passivation layer to the second wiring layer, the first set of vias comprising the second material that is superconductive in the 25 coupler. second range of temperatures; a third wiring layer including a third set of one or more superconducting traces, the third wiring layer comprising the second material that is superconductive in the second range of temperatures; and a second set of vias electrically coupling the second wiring 30 layer to the third wiring layer, the second set of vias comprising the second material that is superconductive in the second range of temperatures.

Depositing the first wiring layer may include depositing superconductive at a respective critical temperature that is different from a respective critical temperature of the second range of temperatures. a first wiring layer including a first set of one or more superconducting traces, the first wiring layer comprising a first material that is superconductive in a first 40 range of temperatures; a passivation layer overlying the first wiring layer, the passivation layer comprising a second material that is superconductive in a second range of temperatures; a second wiring layer including a second set of one or more superconducting traces, the second wiring layer 45 comprising the second material that is superconductive in the second range of temperatures; a first set of vias electrically coupling the passivation layer to the second wiring layer, the first set of vias comprising the second material that is superconductive in the second range of temperatures; a 50 third wiring layer including a third set of one or more superconducting traces, the third wiring layer comprising the second material that is superconductive in the second range of temperatures; and a second set of vias electrically coupling the second wiring layer to the third wiring layer, 55 the second set of vias comprising the second material that is superconductive in the second range of temperatures.

The method may further include polishing the second dielectric layer back to an upper surface of the passivation metal layer and re-depositing the second dielectric layer, 60 after depositing the second dielectric layer to overlie at least a portion of the passivation metal layer. The method may further include depositing a third dielectric layer to overlie at least a portion of the second wiring layer. The method may further polishing the third dielectric layer back to the upper 65 surface of the second wiring layer and re-depositing the third dielectric layer.

The method may further include patterning the third dielectric layer to expose at least a portion of the second wiring layer. The method may further include depositing a third wiring layer to overlie the third dielectric layer, the third wiring layer comprising the second material that is superconductive in the second range of temperatures. The method may further include patterning the third wiring layer to form a third set of one or more superconducting traces. The method may further include forming a second set of vias electrically coupling the third wiring layer to the second wiring layer, the second set of vias comprising the second material that is superconductive in the second range of temperatures.

Depositing a first wiring layer may include depositing the first wiring layer to overlie an additional wiring layer, the additional wiring layer comprising the first material that is superconductive in the first range of temperatures. Patterning the first wiring layer to form a first set of one or more superconducting traces may include patterning the first wiring layer to form at least one of: a magnetometer, a transformer, at least a portion of an on-chip shield. Patterning the second wiring layer to form a second set of one or more superconducting traces may include patterning the second wiring layer to form at least one of: a qubit and a

A superconducting integrated circuit may be summarized as including: a first wiring layer including a first set of one or more superconducting traces, the first wiring layer comprising a first material that is superconductive in a first range of temperatures; a passivation layer overlying the first wiring layer, the passivation layer comprising a second material that is superconductive in a second range of temperatures; a second wiring layer including a second set of one or more superconducting traces, the second wiring layer the first wiring layer comprising the first material that is 35 comprising the second material that is superconductive in the second range of temperatures; a first set of vias electrically coupling the passivation layer to the second wiring layer, the first set of vias comprising the second material that is superconductive in the second range of temperatures; a third wiring layer including a third set of one or more superconducting traces, the third wiring layer comprising the second material that is superconductive in the second range of temperatures; and a second set of vias electrically coupling the second wiring layer to the third wiring layer, the second set of vias comprising the second material that is superconductive in the second range of temperatures.

> The first range of temperatures and the second range of temperatures may each include a respective critical temperature, and the critical temperature of the first range of temperatures is higher than the critical temperature of the second range of temperatures. The first material may be or may include niobium. The second material may be or may include aluminum.

> The superconducting integrated circuit may include a substrate and a trilayer Josephson junction, the substrate carrying: the trilayer Josephson junction, the first wiring layer, the passivation layer, the second wiring layer, the first set of vias, the third wiring layer, and the second set of vias.

> The superconducting integrated circuit may further includes a fourth wiring layer and a third set of vias each overlying the trilayer Josephson junction, the third set of vias electrically coupling the trilayer Josephson junction to the fourth wiring layer. The superconducting integrated circuit may further include a fifth wiring layer and a fourth set of vias each overlying the fourth wiring layer, the fourth set of vias electrically coupling the fourth wiring layer to the fifth wiring layer.

The superconducting integrated circuit may further include a first dielectric layer interposed between the passivation layer and the second wiring layer, the first dielectric layer comprising silicon dioxide. The superconducting integrated circuit may even further include a second dielectric layer interposed between the second wiring layer and the third wiring layer, the second dielectric layer comprising silicon dioxide. The first wiring layer may be thicker than the passivation layer.

The first set of one or more superconducting traces may advantageously form at least a portion of an on-chip shield. The first set of one or more superconducting traces may form at least a portion of a magnetometer. The second set of one or more superconducting traces may form at least a portion of a noise-susceptible device. The second set of one or more superconducting traces may form at least one qubit. The second set of one or more superconducting traces may form at least one or more superconducting traces may form at least a portion of a noise-susceptible device. The third set of one or more superconducting traces may form at least one qubit. The third set of one or more superconducting traces may form at least one qubit. The third set of one or more superconducting traces may form at least one qubit.

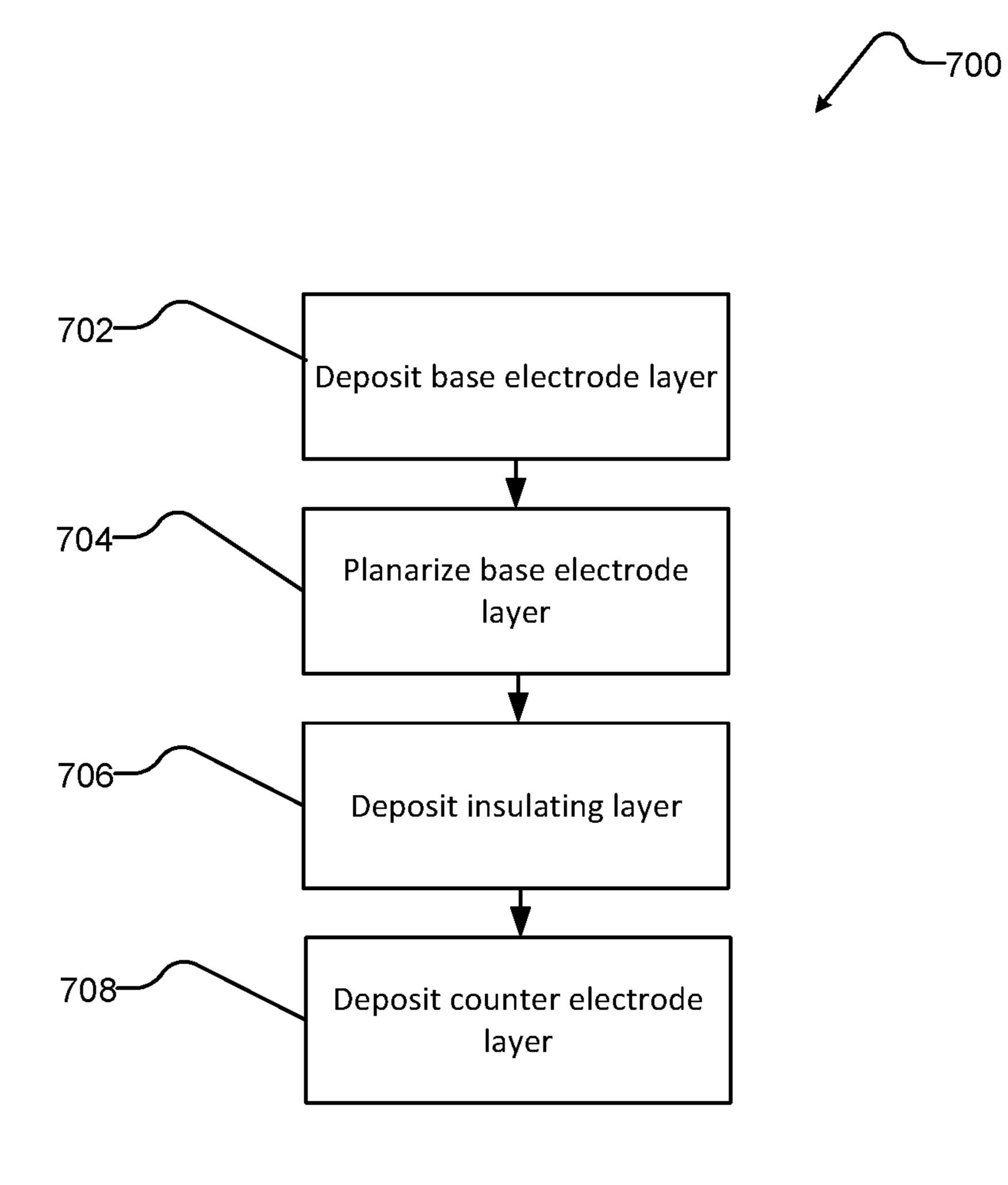

A method for fabricating a superconducting integrated circuit may be summarized as including: depositing a base 25 electrode layer, the base electrode layer comprising a deposited top surface having a first roughness; planarizing the base electrode layer, the base electrode layer subsequently comprising a planarized top surface having a second surface roughness, the second surface roughness being less than the first surface roughness; depositing an insulating layer to overly at least a portion of the planarized top surface of the base electrode layer; and depositing a counter electrode layer to overly at least a portion of the insulating layer.

Planarizing the base electrode layer may comprise a 35 chemical-mechanical planarization process, and planarizing the base electrode layer may comprise planarizing the base electrode layer such that the planarized top surface of the base electrode layer is atomically smooth.

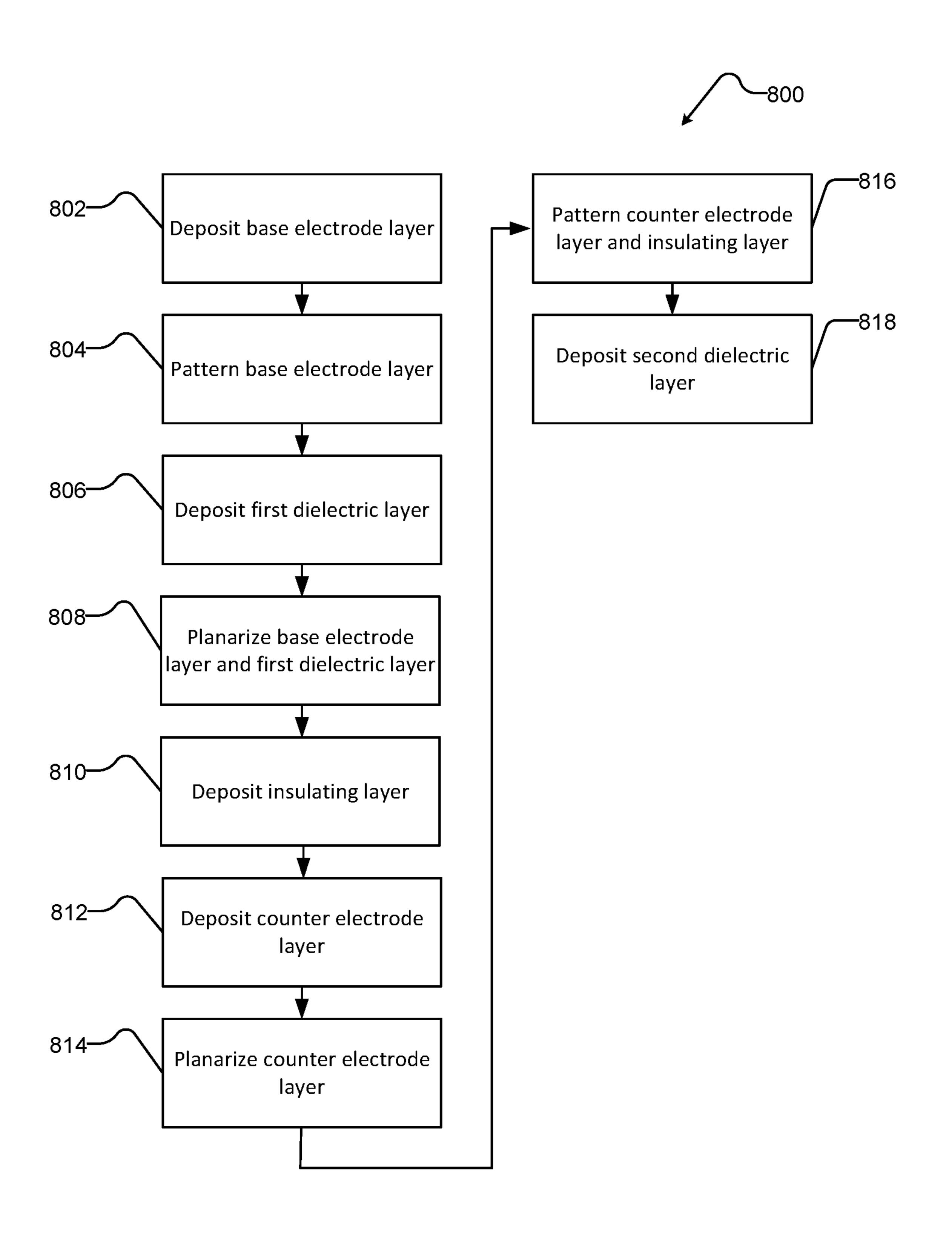

The method may further include patterning the base 40 electrode layer and depositing a first dielectric layer prior to planarizing the base electrode layer, and planarizing the base electrode layer may further comprise planarizing the dielectric layer. The method may further include planarizing the counter electrode layer.

Depositing a base electrode layer may comprise depositing niobium, depositing a counter electrode layer may comprise depositing niobium, and depositing an insulating layer may comprise depositing a layer of aluminum and oxidizing the layer of aluminum to form aluminum oxide.

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING(S)

In the drawings, identical reference numbers identify similar elements or acts. The sizes and relative positions of elements in the drawings are not necessarily drawn to scale. For example, the shapes of various elements and angles are not necessarily drawn to scale, and some of these elements may be arbitrarily enlarged and positioned to improve drawing legibility. Further, the particular shapes of the elements as drawn, are not necessarily intended to convey any information regarding the actual shape of the particular elements, and may have been solely selected for ease of recognition in the drawings.

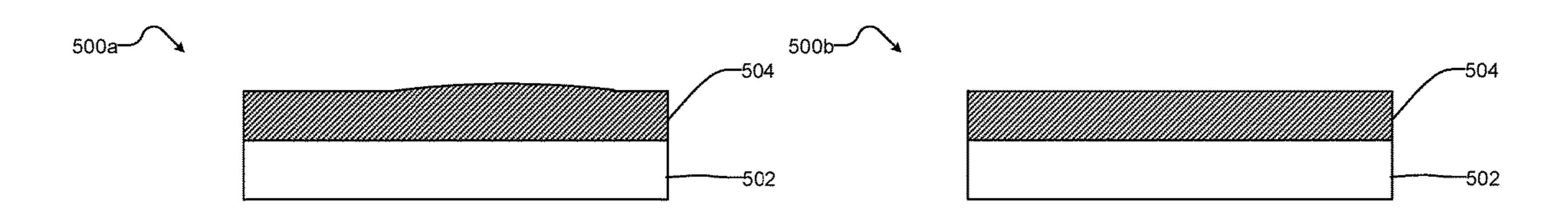

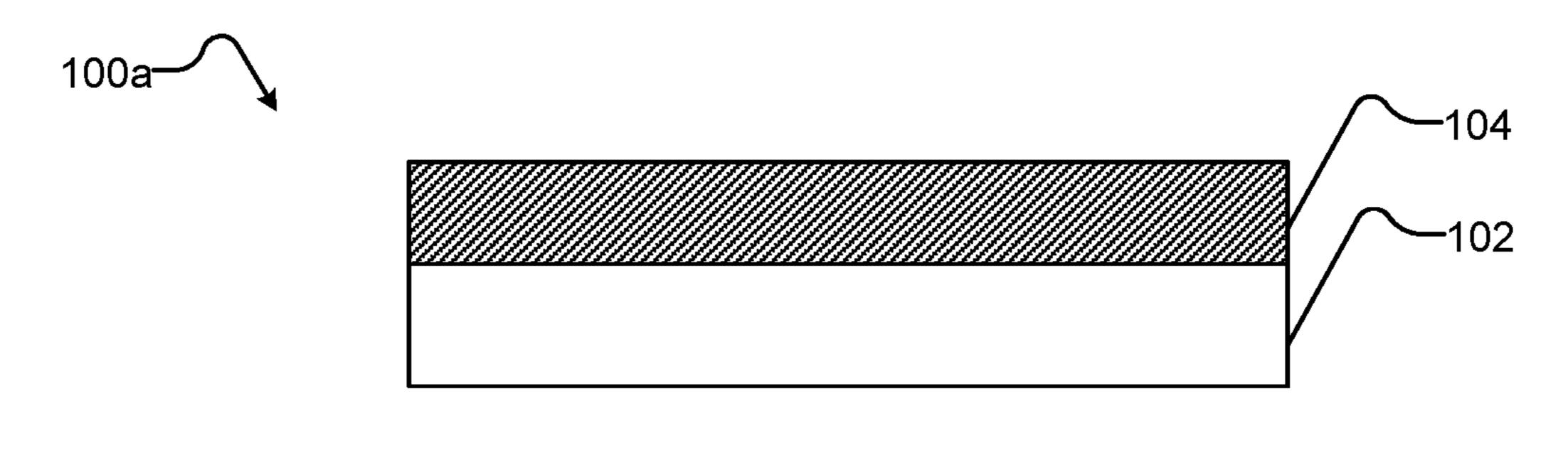

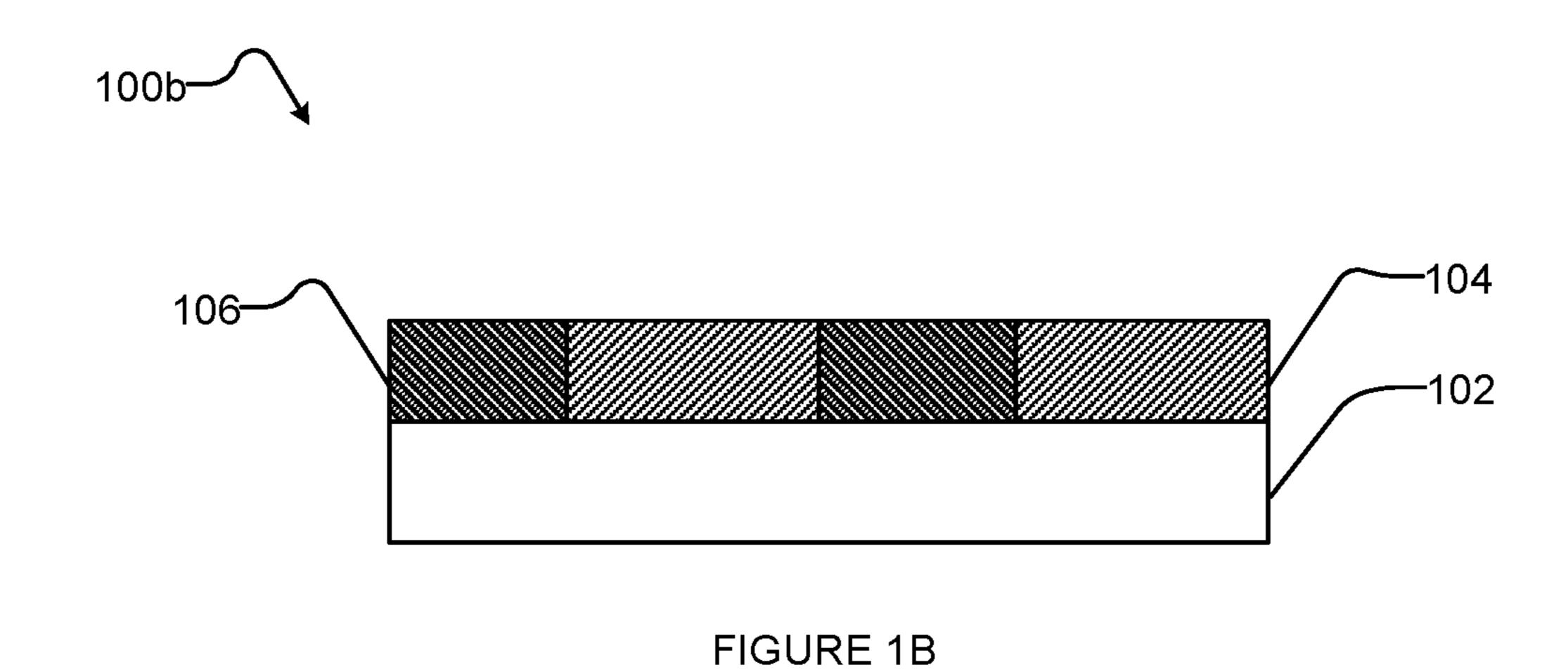

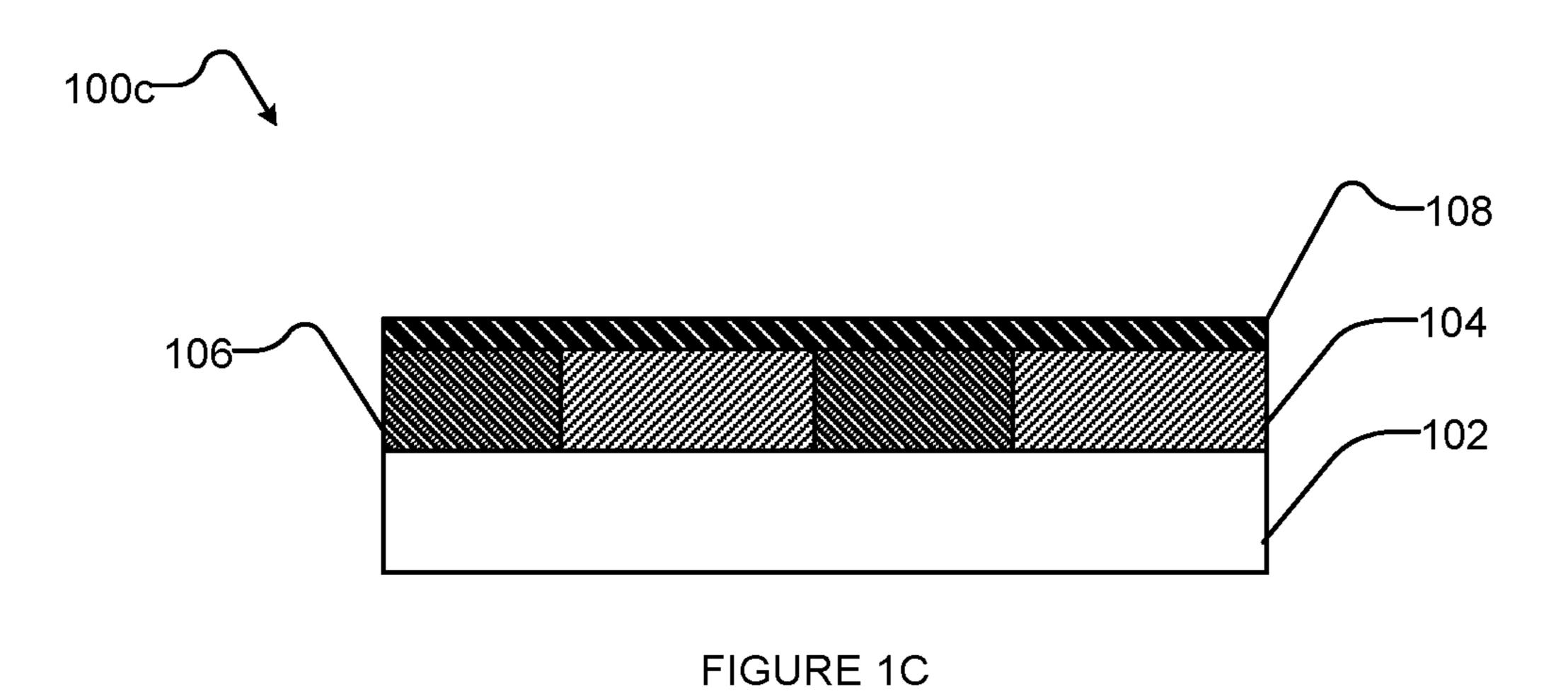

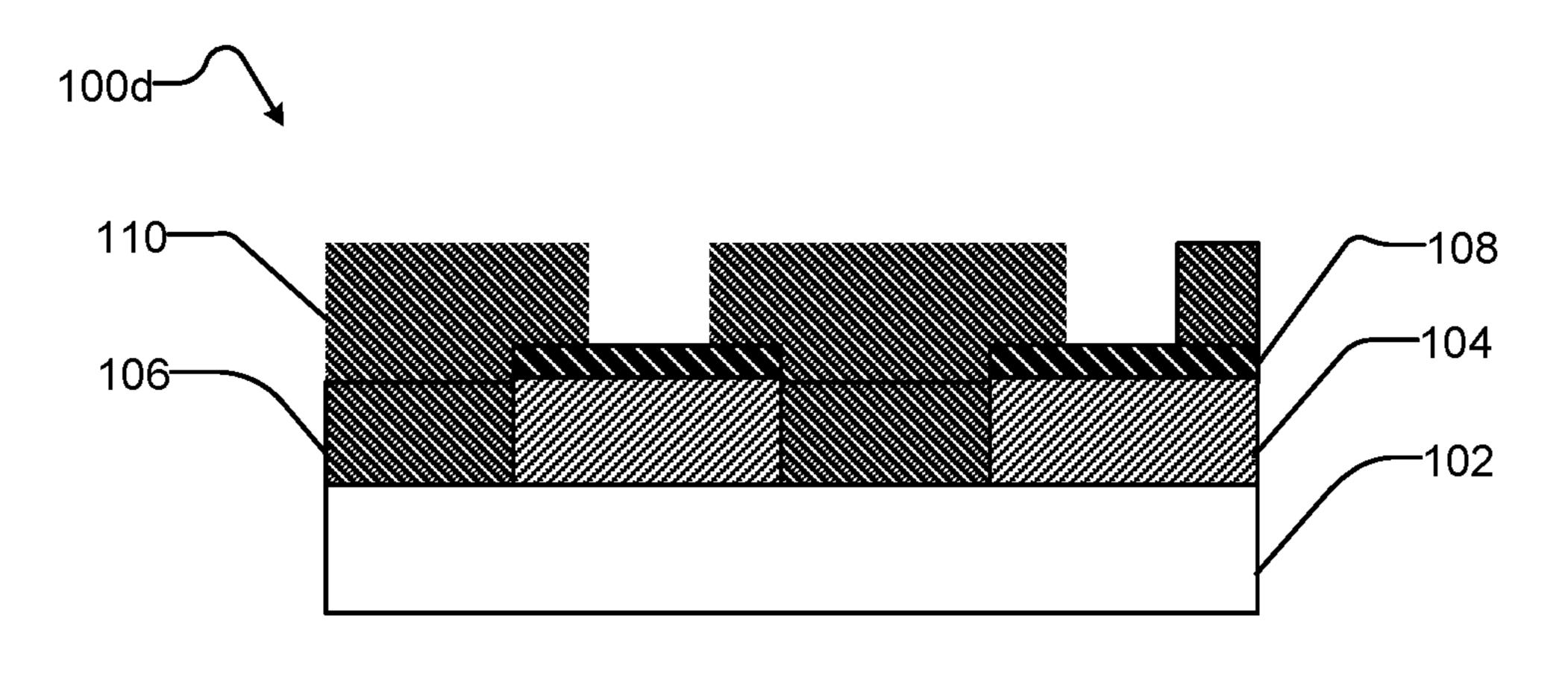

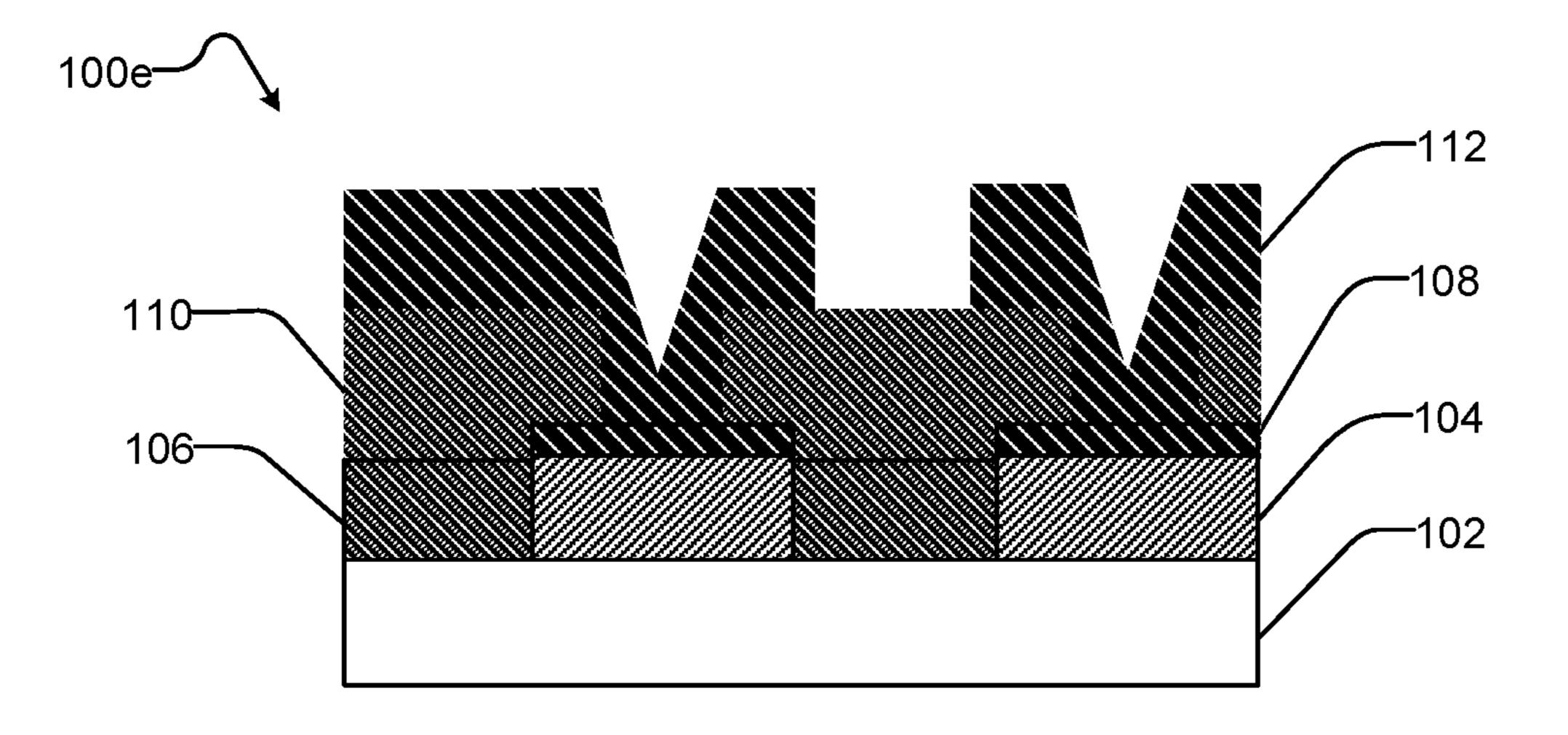

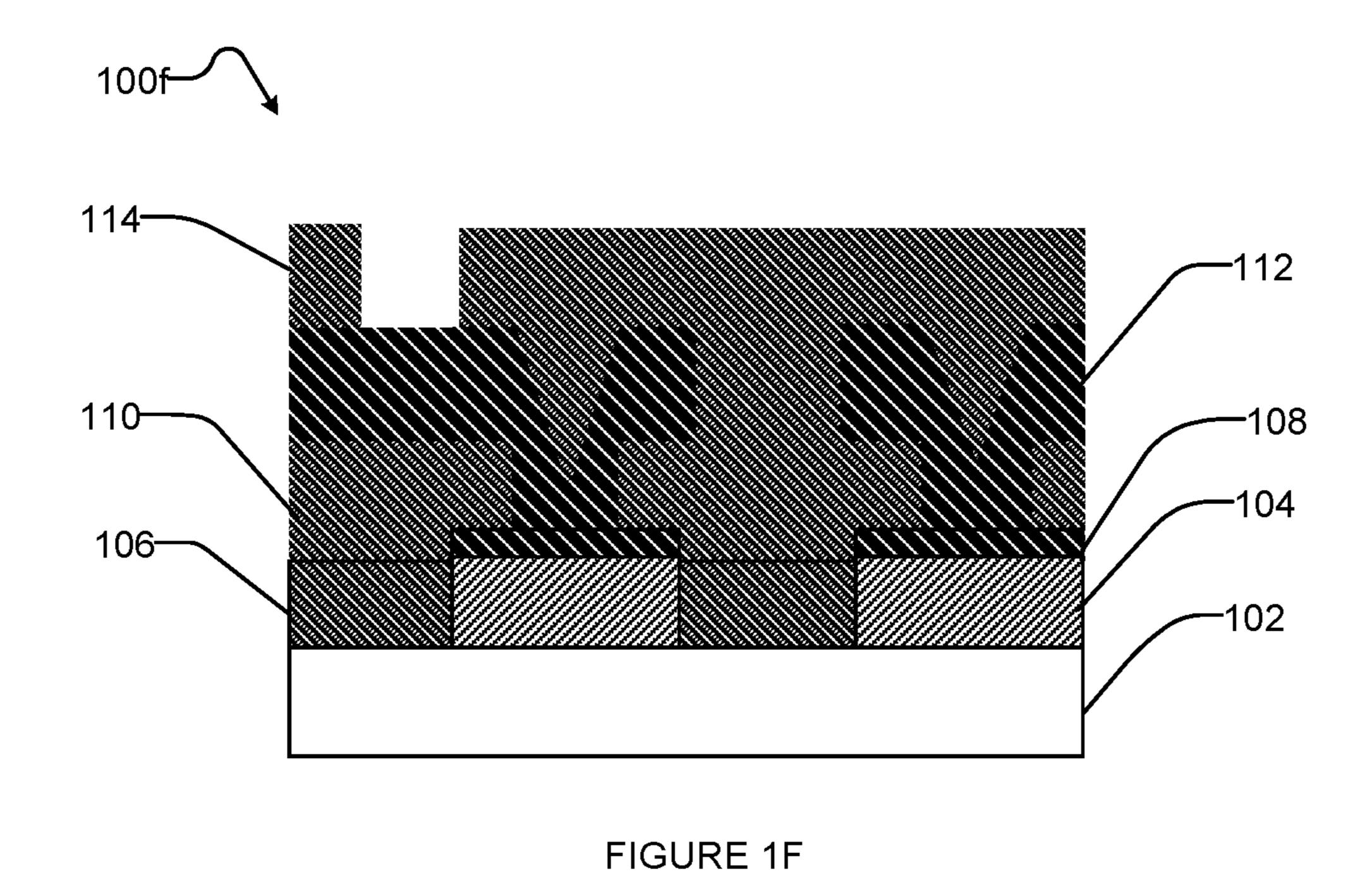

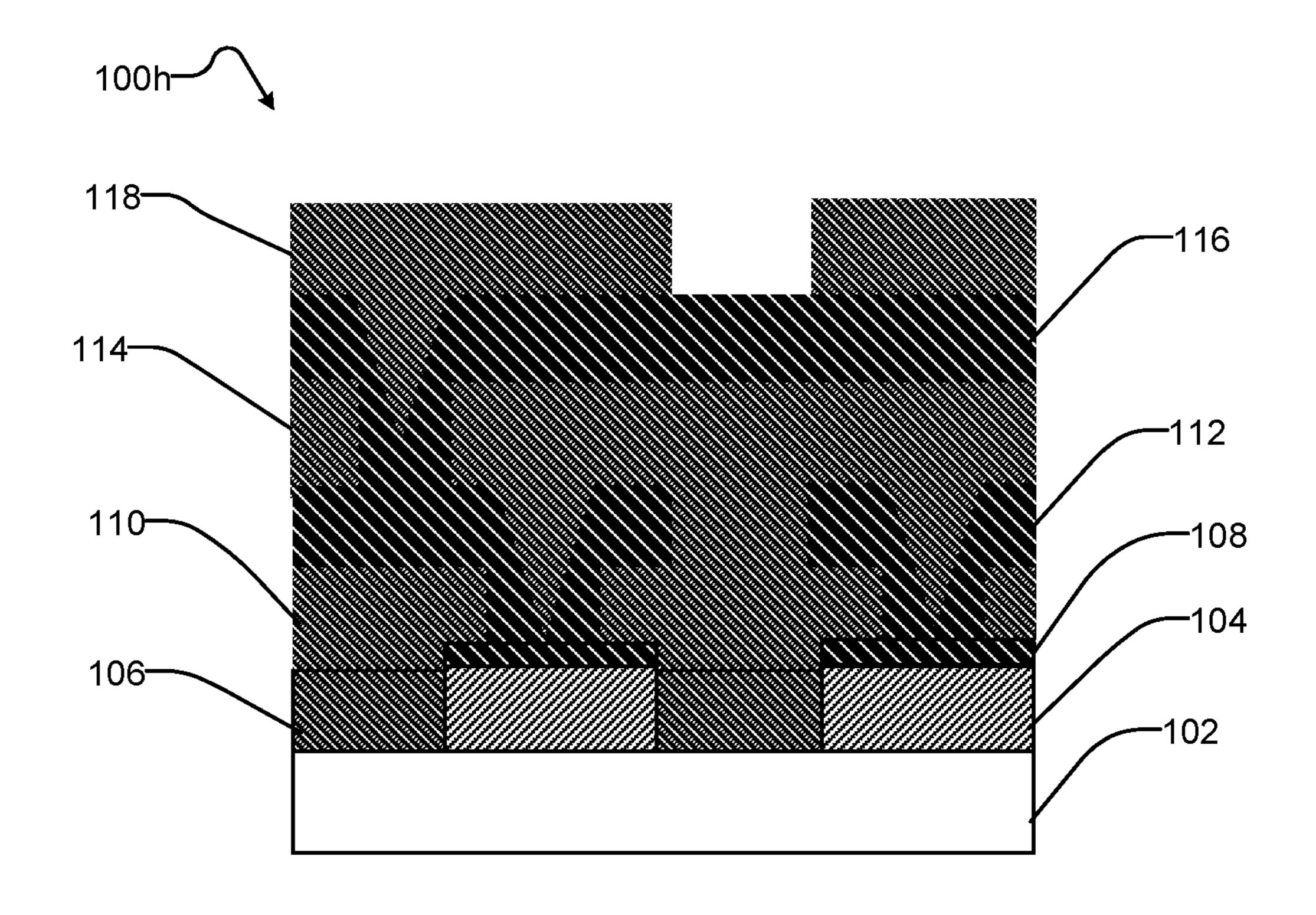

FIGS. 1A to 1H are each a respective sectional view of a portion of a superconducting integrated circuit fabricated at

8

successive stages of fabrication, in accordance with the present methods and systems.

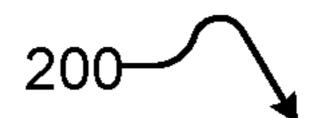

FIG. 2 is a sectional view of a portion of a superconducting integrated circuit comprising a trilayer Josephson junction and low-noise wiring layers, in accordance with the present systems and methods.

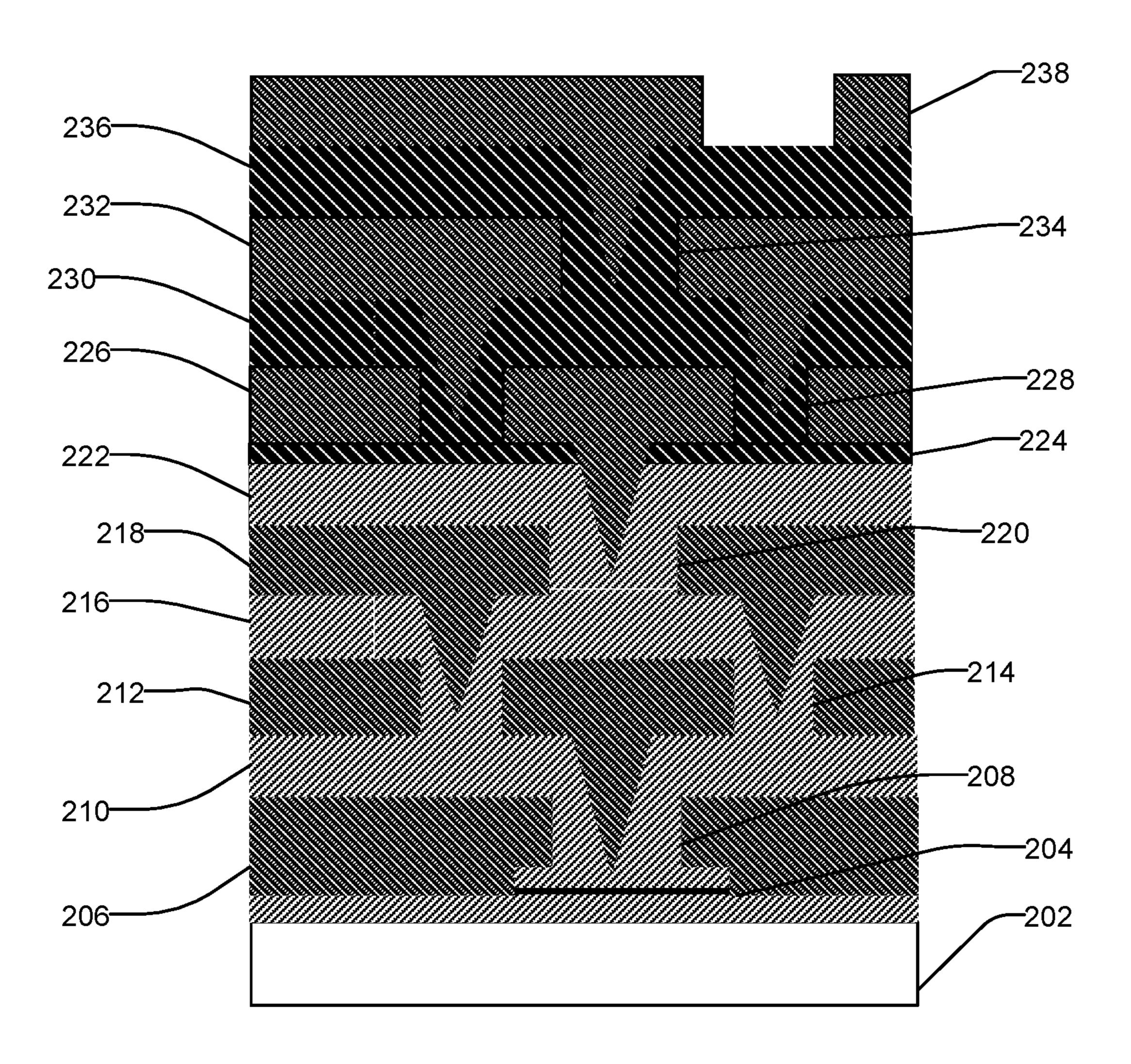

FIG. 3 is a flowchart illustrating a method for fabricating a portion of a superconducting integrated circuit comprising low-noise wiring layers, in accordance with the present systems and methods.

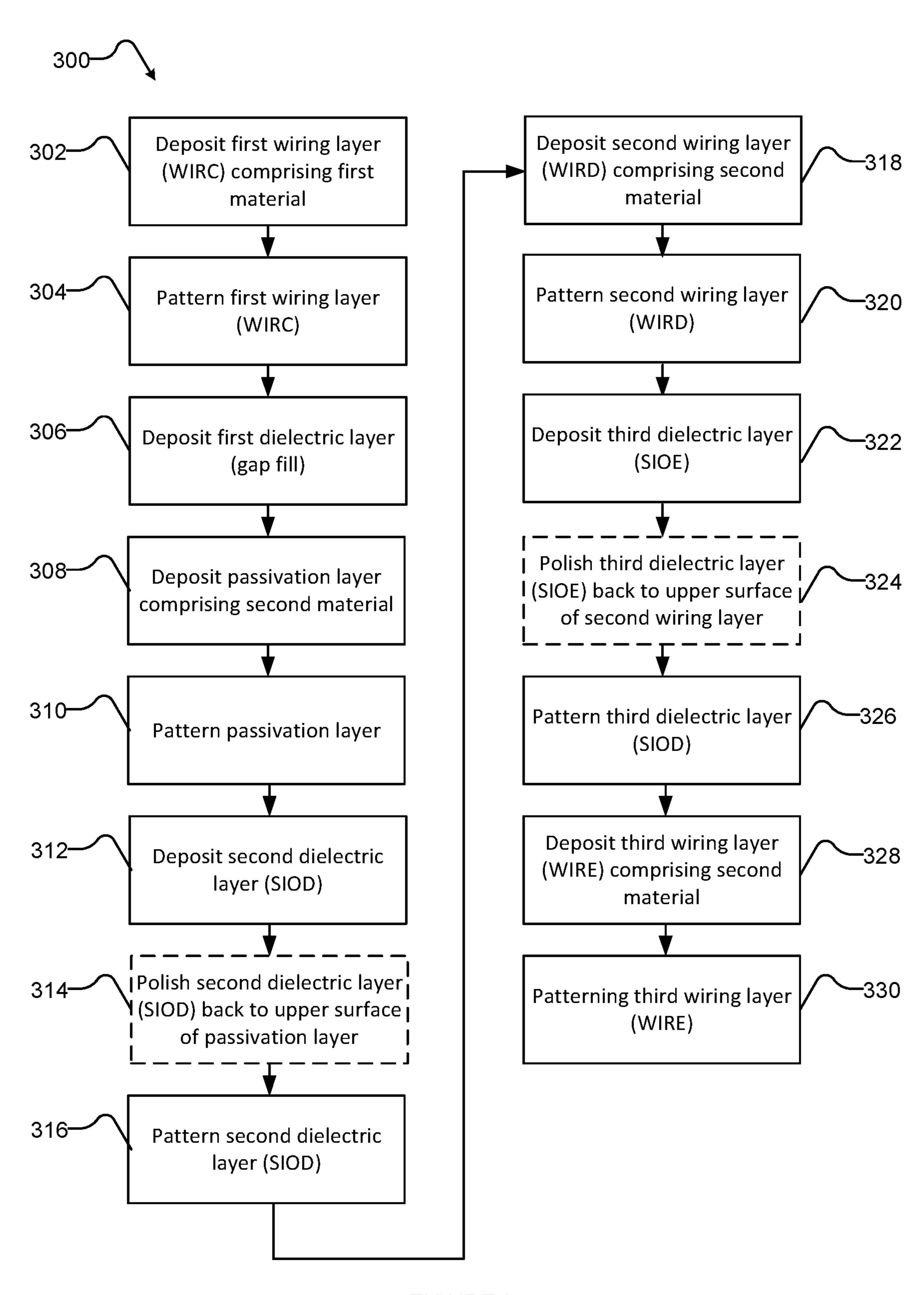

FIG. 4 is a schematic diagram illustrating a computing system comprising a digital computer and an analog computer that includes a superconducting integrated circuit, in accordance with the present systems and methods.

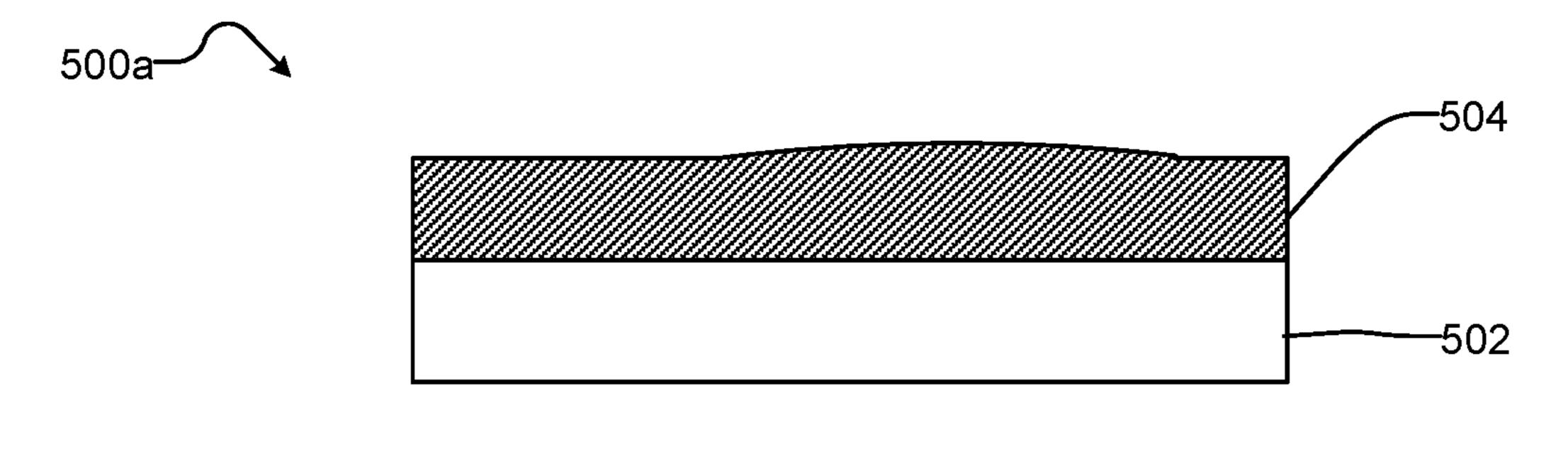

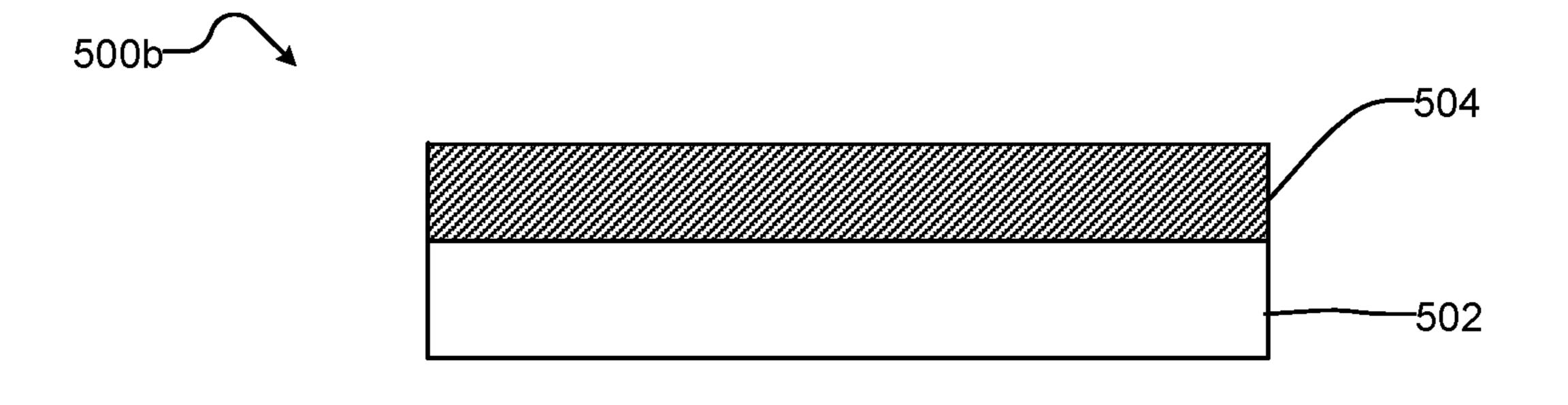

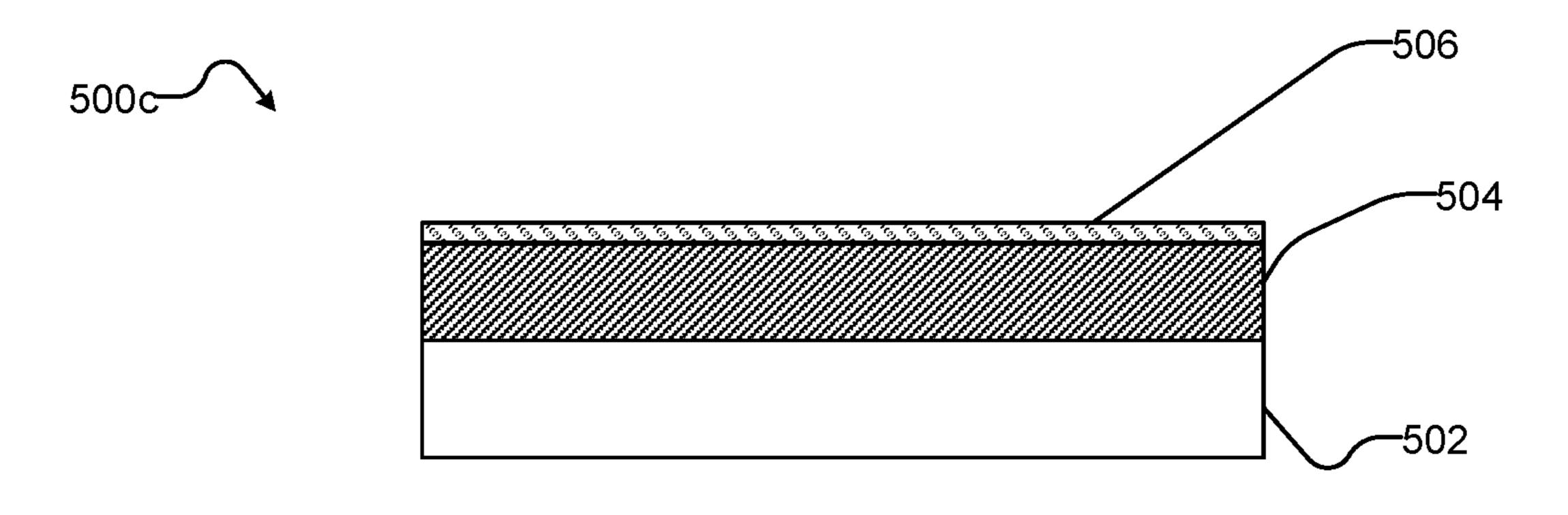

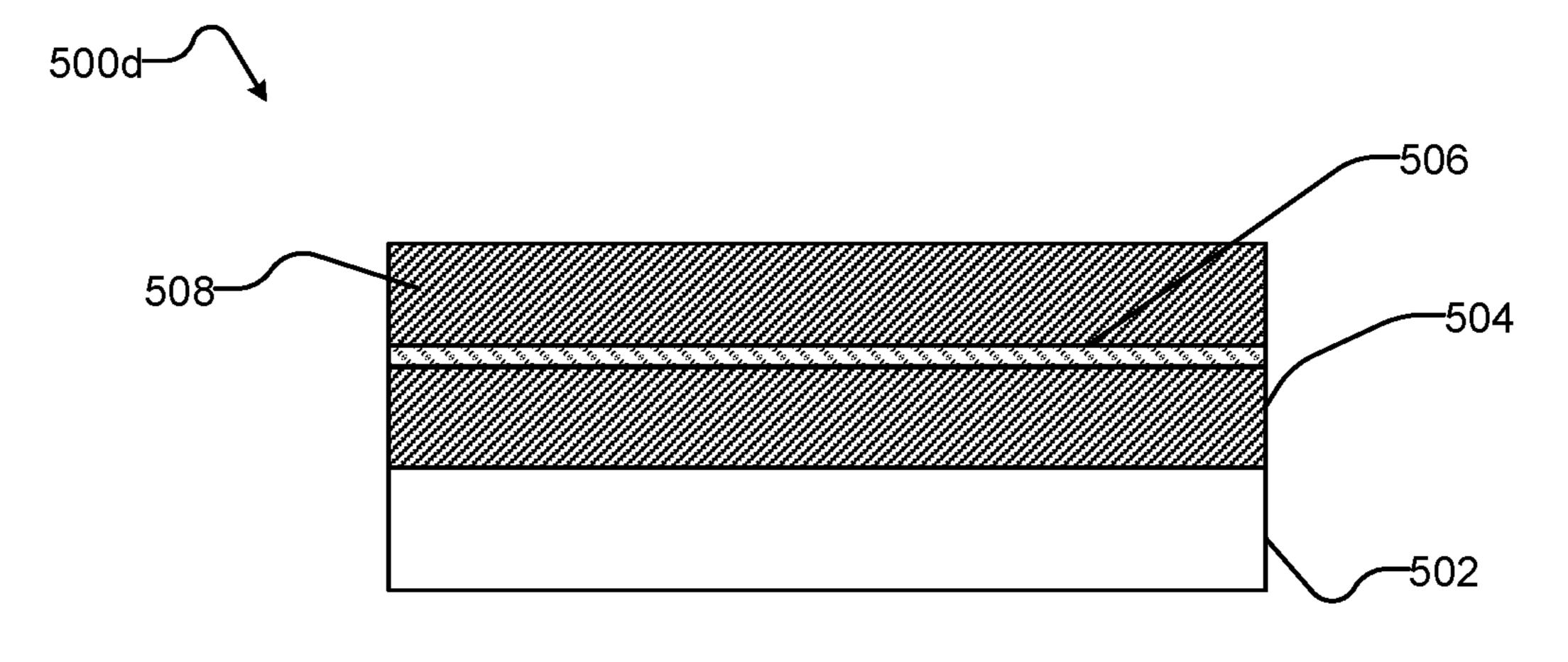

FIGS. **5**A to **5**D are each a respective sectional view of a portion of a superconducting integrated circuit fabricated at successive stages of fabrication, in accordance with the present methods and systems.

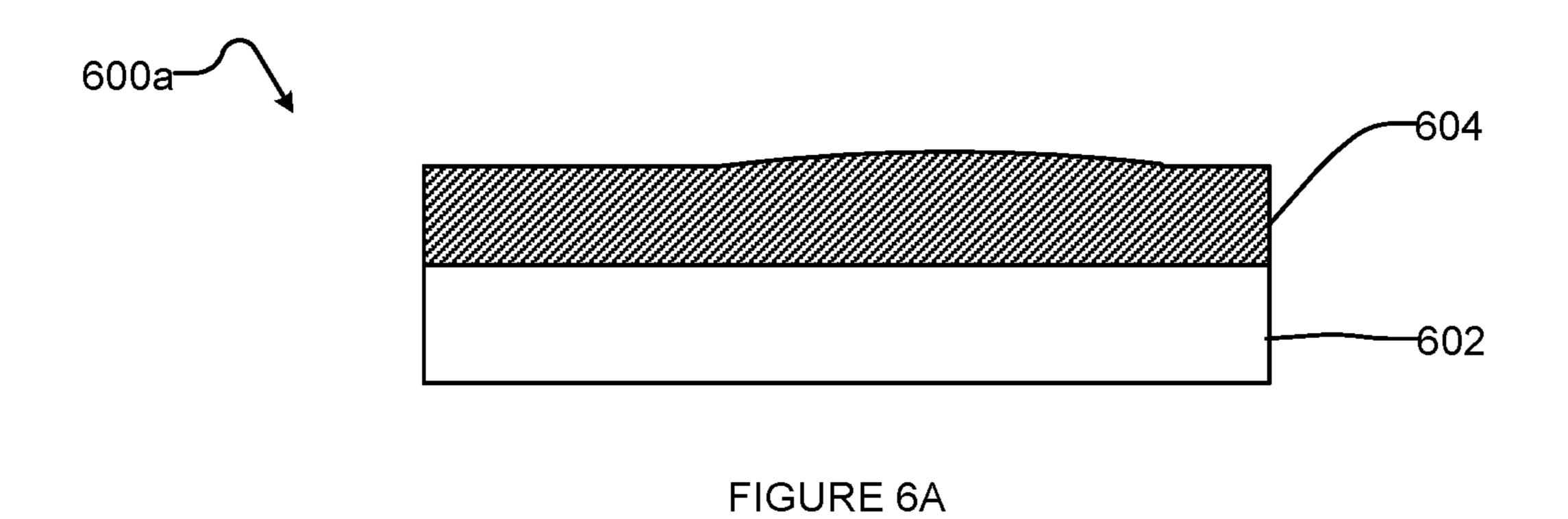

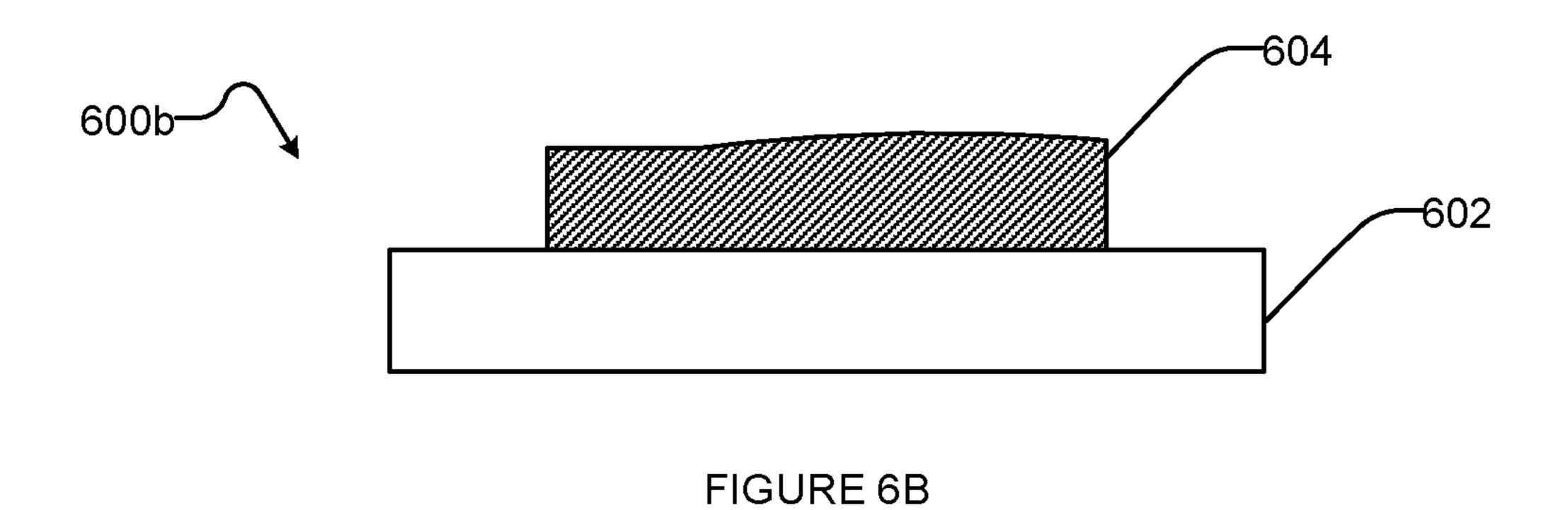

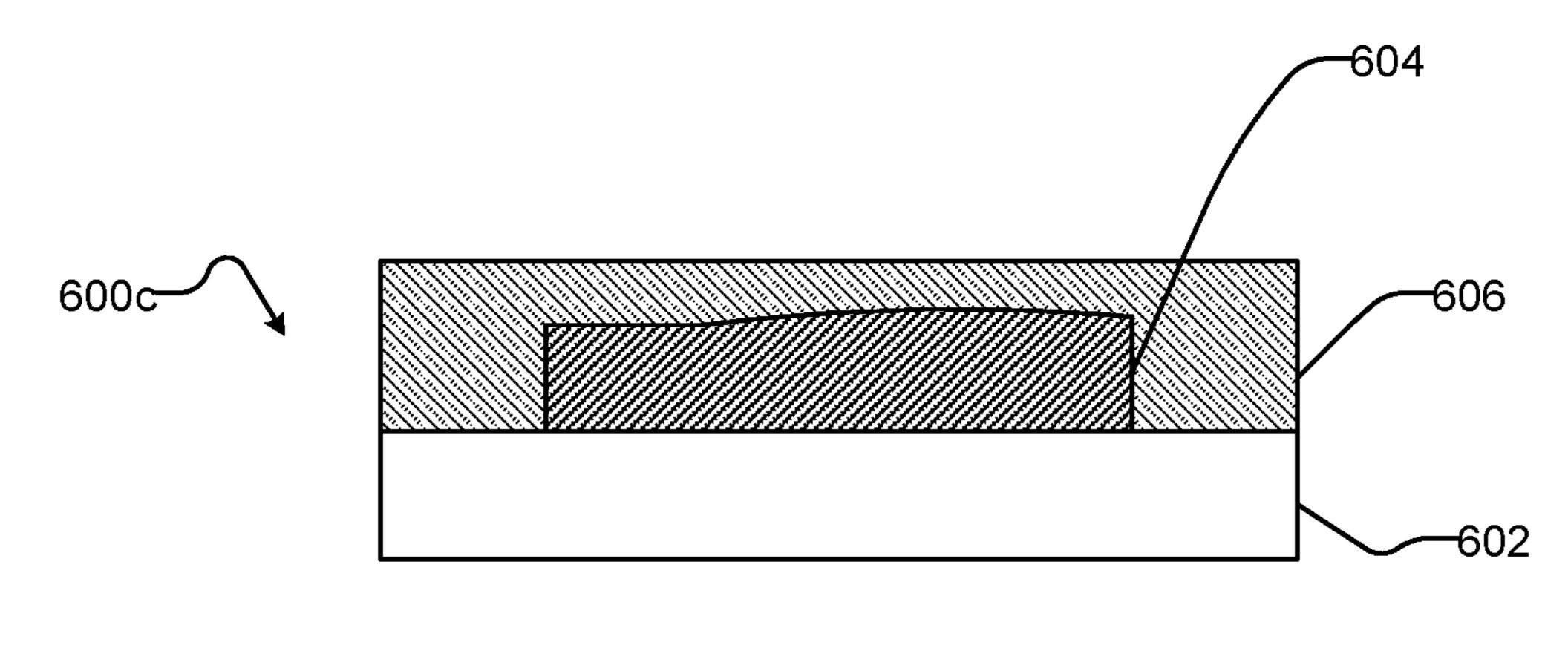

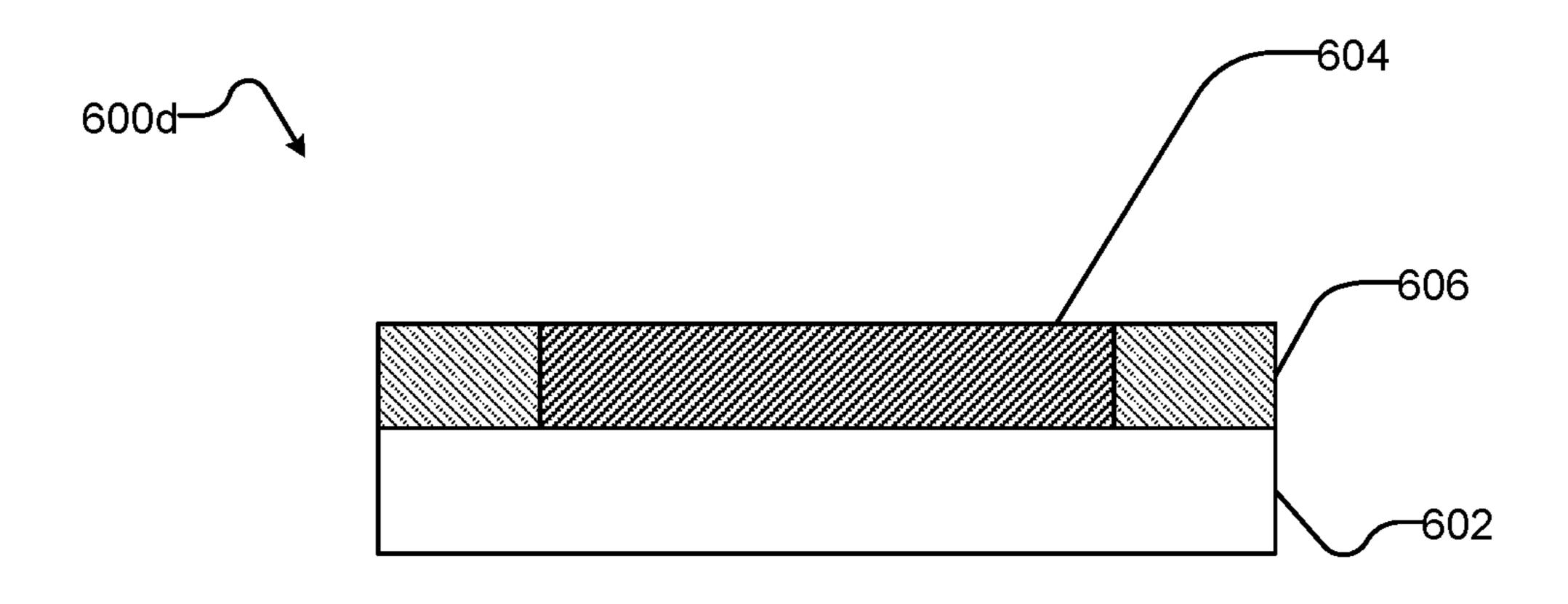

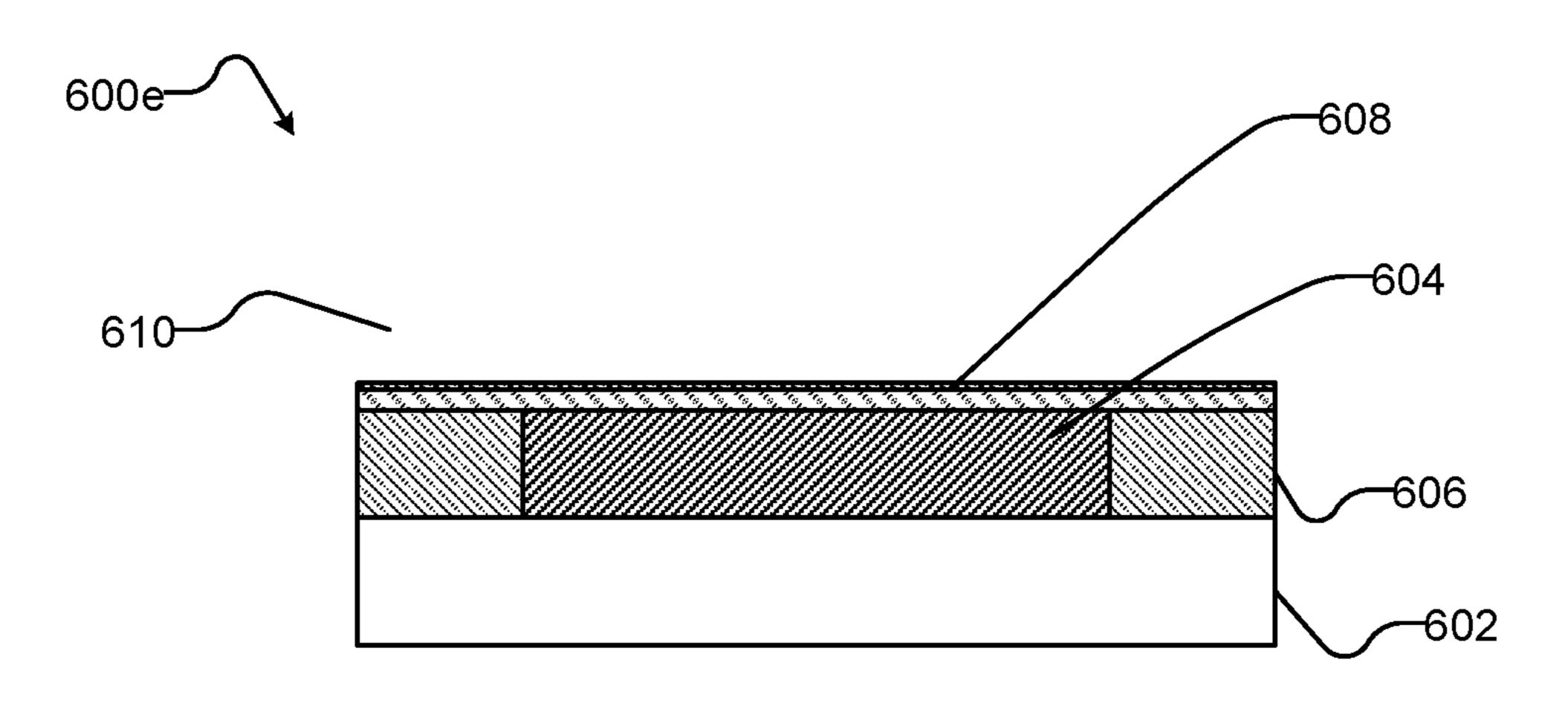

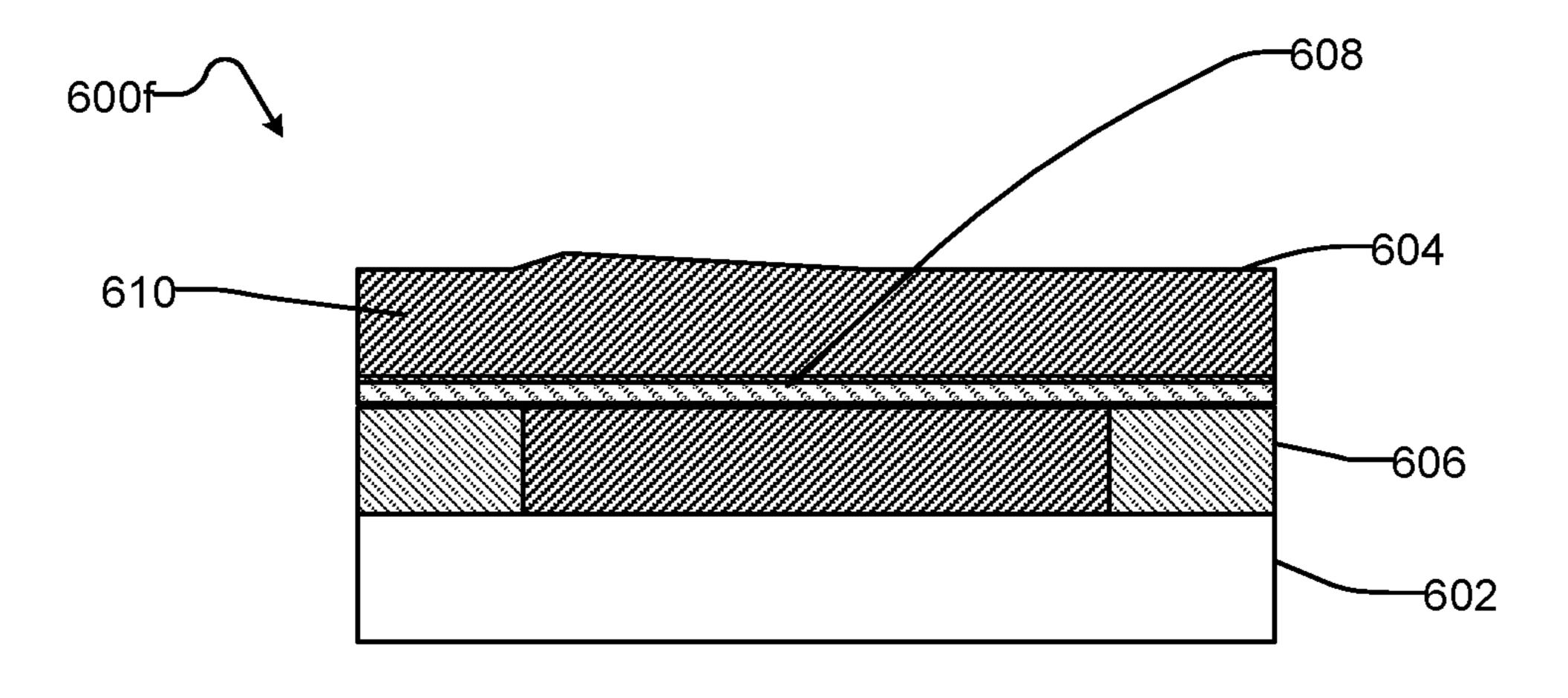

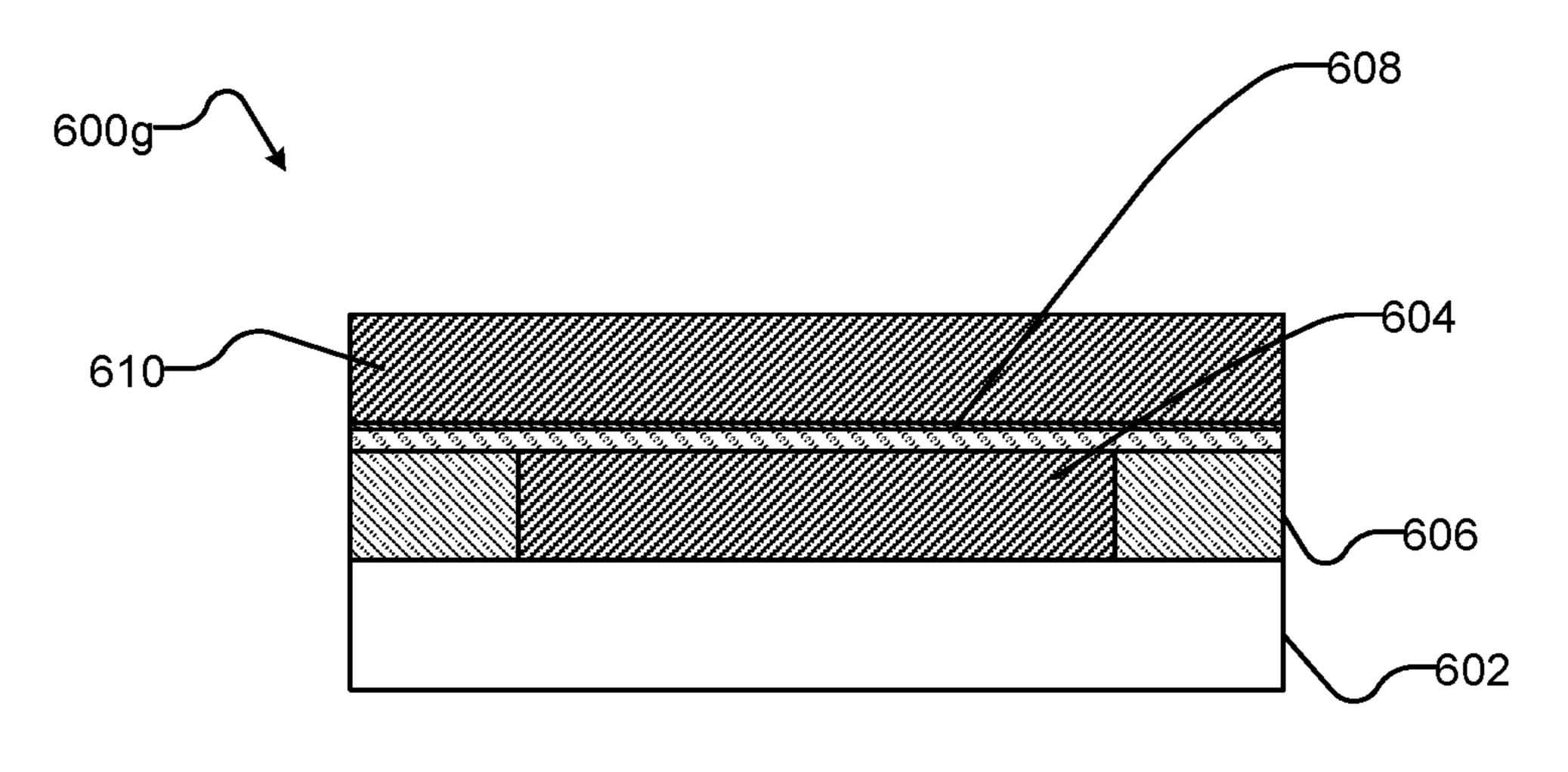

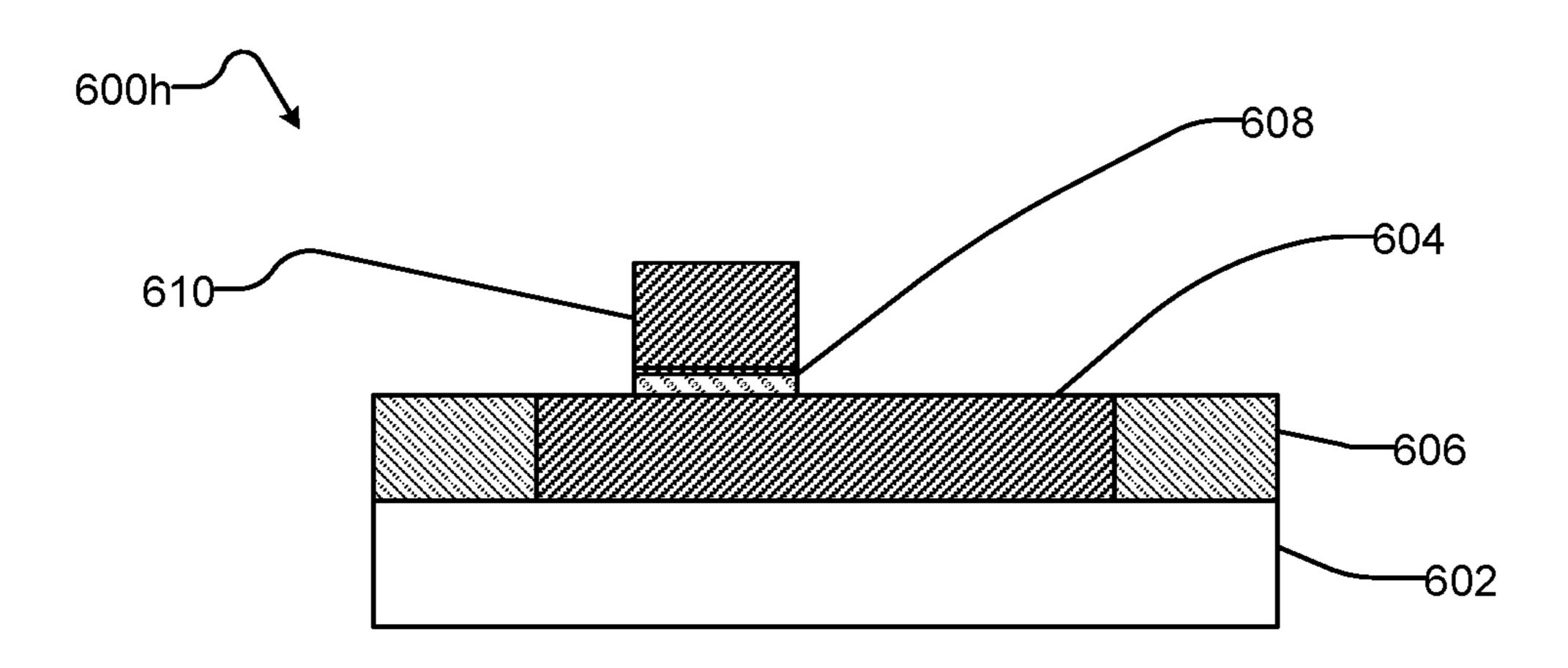

FIGS. 6A to 6I are each a respective sectional view of a portion of a superconducting integrated circuit fabricated at successive stages of fabrication, in accordance with the present methods and systems.

FIG. 7 is a flow chart illustrating a method for fabricating a portion of a superconducting integrated circuit comprising a planarized base electrode, in accordance with the present systems and methods.

FIG. 8 is a flow chart illustrating another implementation of a method for fabricating a portion of a superconducting integrated circuit comprising a planarized base electrode, in accordance with the present system and methods.

#### DETAILED DESCRIPTION

In the following description, certain specific details are set forth in order to provide a thorough understanding of various disclosed implementations. However, one skilled in the relevant art will recognize that implementations may be practiced without one or more of these specific details, or with other methods, components, materials, etc. In other instances, well-known structures associated with computer systems, server computers, and/or communications networks have not been shown or described in detail to avoid unnecessarily obscuring descriptions of the implementations.

Unless the context requires otherwise, throughout the specification and claims that follow, the word "comprising" is synonymous with "including," and is inclusive or openended (i.e., does not exclude additional, unrecited elements or method acts).

Reference throughout this specification to "one implementation" or "an implementation" means that a particular feature, structure or characteristic described in connection with the implementation is included in at least one implementation. Thus, the appearances of the phrases "in one implementation" or "in an implementation" in various places throughout this specification are not necessarily all referring to the same implementation. Furthermore, the particular features, structures, or characteristics may be combined in any suitable manner in one or more implementations.

As used in this specification and the appended claims, the singular forms "a," "an," and "the" include plural referents unless the context clearly dictates otherwise. It should also be noted that the term "or" is generally employed in its sense including "and/or" unless the context clearly dictates otherwise.

The headings and Abstract of the Disclosure provided herein are for convenience only and do not interpret the scope or meaning of the implementations.

A quantum processor may require a local bias to be applied on a qubit to implement a problem Hamiltonian. The local bias applied on the qubit can depend on persistent current  $I_P$  and external flux bias  $\phi_a$  as described below:

$$\delta h_i = 2|I_P|\delta \phi_a$$

Noise can affect the local bias  $\delta h_i$  in the same way as the external flux bias  $\phi_q$  and thus change the specification of the qubit terms in the problem Hamiltonian. By altering the problem Hamiltonian, noise can introduce errors into the computational result from quantum annealing.

Throughout the present specification, the phrase "noisesusceptible superconducting device" is used to describe a superconducting device for which proper performance is essential to properly annealing a quantum processor. Poor performance of a noise-susceptible device may result in the 20 quantum processor producing inaccurate or suboptimal solutions to a problem. For example, a qubit may be considered a noise-susceptible device or device that is susceptible to noise because noise on the qubits can interfere with properly annealing the quantum processor and/or can lead to a 25 different problem being solved. In comparison, a magnetometer in the quantum processor has a primary purpose of measuring external magnetic fields to support minimizing trapped flux. Noise on a magnetometer may not interfere with properly annealing the quantum processor, and thus, in 30 the present specification, a magnetometer is an example of a device may be described as less susceptible or not susceptible to noise. Note that the phrase "noise-susceptible" or "susceptible to noise" does not necessarily suggest that the device itself is physically more or less sensitive to noise 35 compared to other devices that are not described as noisesusceptible. Sensitivities to processor performance is higher in noise-susceptible devices relative to devices that are described as less susceptible to noise.

Noise in a quantum processor can cause qubits to decohere which reduces the efficacy of tunneling. As a result, processor performance can be diminished, and solutions generated from the processor can be suboptimal. Existing approaches for reducing noise involve modifying processor layouts or adding circuitry to shield qubits which, in some 45 cases, can be impractical. The present systems and methods describe a design in which noise can be reduced in a quantum processor without necessitating significant modifications to the processor layout.

Performance of a superconducting processor can be easily 50 affected by certain superconducting devices that are considered analog circuits, for example, qubits and couplers. Analog circuits can be very susceptible to noise. Since processor performance is particularly sensitive to proper or improper operation of these devices, it is desirable to reduce 55 noise in these devices as much as possible. For a superconducting processor, one of the dominant sources of environmental noise is flux noise. Flux noise can cause decoherence which induces a transition from coherent to incoherent tunneling before the transition is induced by intrinsic phase 60 transitions, which is undesirable as it limits the speed and/or accuracy with which the processor can evolve and produce solutions. Additionally, flux noise can increase spin bath susceptibility which is a "memory" effect that results in diminished sampling and optimization performance. Sys- 65 tems and methods to reduce spin bath polarization are described in U.S. patent application Ser. No. 16/029,026.

10