## US011856804B2

# (12) United States Patent

Ikeda et al.

# (10) Patent No.: US 11,856,804 B2 (45) Date of Patent: Dec. 26, 2023

# (54) IMAGING DISPLAY DEVICE AND ELECTRONIC DEVICE

# (71) Applicant: Semiconductor Energy Laboratory

Co., Ltd., Atsugi (JP)

(72) Inventors: Takayuki Ikeda, Kanagawa (JP);

Naoto Kusumoto, Kanagawa (JP)

# (73) Assignee: Semiconductor Energy Laboratory

Co., Ltd., Atsugi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 17/563,187

(22) Filed: **Dec. 28, 2021**

# (65) Prior Publication Data

US 2022/0123070 A1 Apr. 21, 2022

## Related U.S. Application Data

(63) Continuation of application No. 16/605,253, filed as application No. PCT/IB2018/052615 on Apr. 16, 2018, now Pat. No. 11,217,635.

# (30) Foreign Application Priority Data

(51) **Int. Cl.**

*H10K 59/60* (2023.01) *G06N 3/02* (2006.01)

(Continued)

(52) **U.S. Cl.**

## (58) Field of Classification Search

CPC ...... H01L 27/3227; H01L 27/1225; H01L 27/14612; H01L 51/50; G06N 3/02; (Continued)

# (56) References Cited

#### U.S. PATENT DOCUMENTS

6,747,638 B2 6/2004 Yamazaki et al. 7,525,523 B2 4/2009 Yamazaki et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 101751846 A 6/2010 EP 1122792 A 8/2001 (Continued)

## OTHER PUBLICATIONS

International Search Report (Application No. PCT/IB2018/052615) dated Jun. 19, 2018.

(Continued)

Primary Examiner — Thanh T Nguyen

(74) Attorney, Agent, or Firm — Fish & Richardson P.C.

# (57) ABSTRACT

An imaging display device which can quickly display a captured image is provided. The imaging display device includes an imaging portion on a first surface and a display portion on a second surface that is opposite to the first surface. The imaging portion includes a photoelectric conversion element configured to receive light delivered to the first surface. The display portion includes a light-emitting element configured to emit light in a direction opposite to the first surface. A pixel in the imaging portion is electrically connected to a pixel in the display portion. An image signal obtained at the imaging portion can be directly input to the display portion. Accordingly, the time delay due to data conversion can be eliminated, so that a captured image can be displayed in a moment.

# 16 Claims, 27 Drawing Sheets

# US 11,856,804 B2 Page 2

| (51) Int. Cl.                                     | FOREIGN PATENT DOCUMENTS                                       |

|---------------------------------------------------|----------------------------------------------------------------|

| H04N 7/14 (2006.01)                               | TD 0.50.5000 A 0.0010                                          |

| $H01L\ 27/12$ (2006.01)                           | EP 3525238 A 8/2019                                            |

| $H01L\ 27/146$ (2006.01)                          | JP 08-102924 A 4/1996                                          |

| (58) Field of Classification Search               | JP 09-252433 A 9/1997                                          |

|                                                   | JP 2001-292276 A 10/2001                                       |

| CPC H04N 7/144; H04N 5/3745; H04N 5/379;          | JP 2002-237923 A 8/2002<br>IP 2008-177738 * 7/2008 H04N 5/335  |

| H04N 5/22525                                      | 2000 177730 772000 110 111 37333                               |

| See application file for complete search history. | JP 2008-177738 A 7/2008                                        |

|                                                   | JP 2008-241827 * 10/2008 G09F 9/00<br>JP 2008-241827 A 10/2008 |

| (56) References Cited                             | JP 2008-241827 A 10/2008<br>JP 2010-139895 A 6/2010            |

| (50)                                              | JP 2010-139893 A 6/2010<br>JP 2011-119711 A 6/2011             |

| U.S. PATENT DOCUMENTS                             | JP 2017-055448 A 3/2017                                        |

| O.D. ITHERT DOCUMENTS                             | JP 2017-055446 A 3/2017<br>2018-060980 A 4/2018                |

| 8,378,391 B2 2/2013 Koyama et al.                 | KR 2010-0069591 A 6/2010                                       |

| 8,456,459 B2 6/2013 Yamazaki et al.               | TW 2010 303331 11 8/2010                                       |

| 8,654,231 B2 2/2014 Kurokawa et al.               | TW 201445717 12/2014                                           |

| 8,830,217 B2 9/2014 Yamazaki et al.               | WO WO-2002/065752 8/2002                                       |

| 8,836,626 B2 9/2014 Ikeda                         | WO WO-2011/111490 9/2011                                       |

| 8,916,869 B2 12/2014 Koyama et al.                | WO WO-2018/066225 4/2018                                       |

| 8,976,155 B2 3/2015 Kurokawa et al.               | 11 O 11 O 2010/000223                                          |

| 9,111,836 B2 8/2015 Kurokawa et al.               |                                                                |

| 9,331,112 B2 5/2016 Koyama et al.                 | OTHER PUBLICATIONS                                             |

| 9,575,381 B2 2/2017 Kurokawa et al.               |                                                                |

| 9,728,569 B2 8/2017 Sato                          | Written Opinion (Application No. PCT/IB2018/052615) dated Jun. |

| 9,773,814 B2 9/2017 Koyama et al.                 | 19, 2018.                                                      |

| 10,211,246 B2 2/2019 Sato                         | Taiwanese Office Action (Application No. 111115890) dated Jun. |

| 11,057,551 B2 7/2021 Nishide et al.               | , ,                                                            |

| 2010/0149079 A1 6/2010 Yamashita et al.           | 27, 2023.                                                      |

| 2019/0222733 A1 7/2019 Nishide et al.             |                                                                |

| 2021/0297565 A1 9/2021 Nishide et al.             | * cited by examiner                                            |

TIG. 2

mig. 3

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

Dec. 26, 2023

FIG. 8A

FIG. 8B

FIG. 8C

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

MIG. 11A

FIG. 11B

FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13B

FIG. 14A

Dec. 26, 2023

FIG. 14B

FIG. 15A

FIG. 15B

FIG. 15C

FIG. 16

FIG. 17A

FIG. 17B

FIG. 17C

FIG. 18

RATE A WDREF F Same processors and a second Commence of the Commence of th

Socoooo)

X000000X

FIG. 23A

FIG. 23B

113

112

115

331

332

333

163

381

381

370

361

393

395

FIG. 24A

FIG. 24B

FIG. 26A

430a

430b

430c

4400

410

400

FIG. 26B

FIG. 26C

FIG. 27A

Dec. 26, 2023

FIG. 27B

mig. 270

# IMAGING DISPLAY DEVICE AND ELECTRONIC DEVICE

# CROSS REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. application Ser. No. 16/605,253, filed Oct. 15, 2019, now allowed, which is a U.S. National Phase application under 35 U.S.C. § 371 of International Application PCT/IB2018/052615, filed on Apr. 16, 2018, and claims the benefit of a foreign priority application filed in Japan on Apr. 28, 2017, as Application No. 2017-090230, all of which are incorporated by reference.

## TECHNICAL FIELD

An embodiment of the present invention relates to an imaging display device.

Note that one embodiment of the present invention is not limited to the above technical field. The technical field of one embodiment of the invention disclosed in this specification and the like relates to an object, a method, or a manufacturing method. Furthermore, one embodiment of the present invention relates to a process, a machine, manufacture, or a composition of matter. Specifically, examples of the technical field of one embodiment of the present invention disclosed in this specification include a semiconductor device, a display device, a liquid crystal display device, a light-emitting device, a lighting device, a power storage device, a memory device, an imaging device, a method for driving any of them, and a method for manufacturing any of them.

In this specification and the like, a semiconductor device generally means a device that can function by utilizing semiconductor characteristics. A transistor and a semiconductor circuit are embodiments of semiconductor devices. In some cases, a memory device, a display device, an imaging device, or an electronic device includes a semiconductor device.

## BACKGROUND ART

A technique for forming transistors using oxide semiconductor thin films formed over a substrate has been attracting attention. For example, Patent Document 1 discloses an 45 imaging device in which a transistor including an oxide semiconductor with an extremely low off-state current is used in a pixel circuit.

Imaging devices are incorporated in a variety of electronic devices together with display devices, which enables users to see captured images on the spot. Furthermore, augmented reality (AR) technology which combines a captured realworld image and additional data obtained from a server or the like, such as text data or computer graphics (CG), on the display device has been used.

## REFERENCE

# Patent Document

[Patent Document 1] Japanese Published Patent Application No. 2011-119711

# DISCLOSURE OF INVENTION

Because image data obtained with an imaging device is analog data, the data is converted into digital data and

2

transmitted to a storage medium or a display device. In the display device, the digital data is converted into analog data and a display element is driven with the analog data. Therefore, even in the case where the captured image is displayed in real time, there arise a time lag between reality and the actually displayed image on the display device.

In AR-displaying additional data, it takes time to communicate with a server and process the data. In order to ensure consistency between reality and the displayed additional data, a reduction of a load on the server and the employment of a high-performance data processing device as well as higher-speed communication with the server are effective.

Another display method with the use of a see-through display has been proposed, in which the reality is a real image that has passed through the display and only additional data is displayed on the display. However, a relationship between the position of a viewer and the position of the display is not always the same and therefore the positional adjustment between the reality and the additional data is necessary. For example, even when the display is seen from the front and an object and additional data such as text are displayed overlapping with each other, the object and the additional data do not look overlapping appropriately when the display is seen obliquely.

In view of the foregoing circumstance, an object of one embodiment of the present invention is to provide an imaging display device which can transmit analog data that is obtained with an imaging portion to a display portion without converting the analog data into digital data. Another object of one embodiment of the present invention is to provide an imaging display device which can quickly obtain additional data for AR display. Another object of one embodiment of the present invention is to provide an imaging display device which eliminates the need for the positional adjustment between the displayed reality and additional data in performing AR display.

Another object of one embodiment of the present invention is to provide an imaging display device with low power 40 consumption. Another object of one embodiment of the present invention is to provide an imaging display device capable of capturing an image with little noise. Another object of one embodiment of the present invention is to provide an imaging display device that can capture an image with high sensitivity. Another object of one embodiment of the present invention is to provide an imaging display device with high reliability. Another object of one embodiment of the present invention is to provide a novel imaging display device or the like. Another object of one embodiment of the present invention is to provide a method for driving any of the above-described imaging display devices. Another object of one embodiment of the present invention is to provide a novel semiconductor device or the like.

Note that the descriptions of these objects do not disturb the existence of other objects. In one embodiment of the present invention, there is no need to achieve all the objects. Other objects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

One embodiment of the present invention relates to an imaging display device which includes an imaging portion on a first surface and a display portion on a second surface that is opposite to the first surface.

One embodiment of the present invention is an imaging display device which includes an imaging portion on a first surface and a display portion on a second surface that is opposite to the first surface. The imaging portion includes a

photoelectric conversion element configured to receive light delivered to the first surface. The display portion includes a light-emitting element configured to emit light in a direction opposite to the first surface. The photoelectric conversion element is electrically connected to a gate of a transistor. The light-emitting element is electrically connected to one of a source and a drain of the transistor.

The imaging display device can further include a data processing portion. The data processing portion includes a neural network configured to estimate the kind of an object. 10 Moreover, the data processing portion can be positioned between the photoelectric conversion element and the light-emitting element.

Another embodiment of the present invention is an imaging display device which includes a first layer, a second 15 layer, and a third layer. The second layer is positioned between the first layer and the third layer. The first layer includes a light-emitting element. The second layer includes a first transistor and a second transistor. The third layer includes a photoelectric conversion element. The light-20 emitting element is electrically connected to the first transistor. The photoelectric conversion element is electrically connected to the second transistor. The first transistor is electrically connected to the second transistor.

The imaging display device of the above-described 25 embodiment can further include a fourth layer. The fourth layer is positioned between the second layer and the third layer. The fourth layer includes a third transistor. The third transistor is electrically connected to the second transistor. The first transistor and the second transistor each include a 30 metal oxide in a channel formation region, and the third transistor includes silicon in a channel formation region.

The metal oxide preferably includes In, Zn, and M (M is Al, Ti, Ga, Sn, Y, Zr, La, Ce, Nd, or Hf).

The photoelectric conversion element preferably includes 35 selenium or a compound including selenium.

Another embodiment of the present invention is an imaging display device which includes a first transistor, a second transistor, a third transistor, a photoelectric conversion element, and a light-emitting element. One electrode of the 40 photoelectric conversion element is electrically connected to one of a source and a drain of the first transistor. The one electrode of the photoelectric conversion element is electrically connected to one of a source and a drain of the second transistor. A gate of the third transistor is electrically connected to the other of the source and the drain of the second transistor. One electrode of the light-emitting element is electrically connected to one of a source and a drain of the third transistor.

The imaging display device of the above-described 50 embodiment can further include a fourth transistor. One of a source and a drain of the fourth transistor is electrically connected to the other of the source and the drain of the second transistor. The other of the source and the drain of the fourth transistor is electrically connected to the gate of the 55 third transistor.

With one embodiment of the present invention, an imaging display device which can transmit analog data that is obtained with an imaging portion to a display portion without converting the analog data into digital data can be 60 provided. An imaging display device which can quickly obtain additional data for AR display can be provided. An imaging display device which eliminates the need for the positional adjustment between the displayed reality and additional data in performing AR display can be provided. 65

An imaging display device with low power consumption can be provided. An imaging display device capable of

4

capturing an image with little noise can be provided. An imaging display device that can capture an image with high sensitivity can be provided. An imaging display device with high reliability can be provided. A novel imaging display device or the like can be provided. A method for driving any of the above-described imaging display devices can be provided. A novel semiconductor device or the like can be provided.

#### BRIEF DESCRIPTION OF DRAWINGS

In the accompanying drawings:

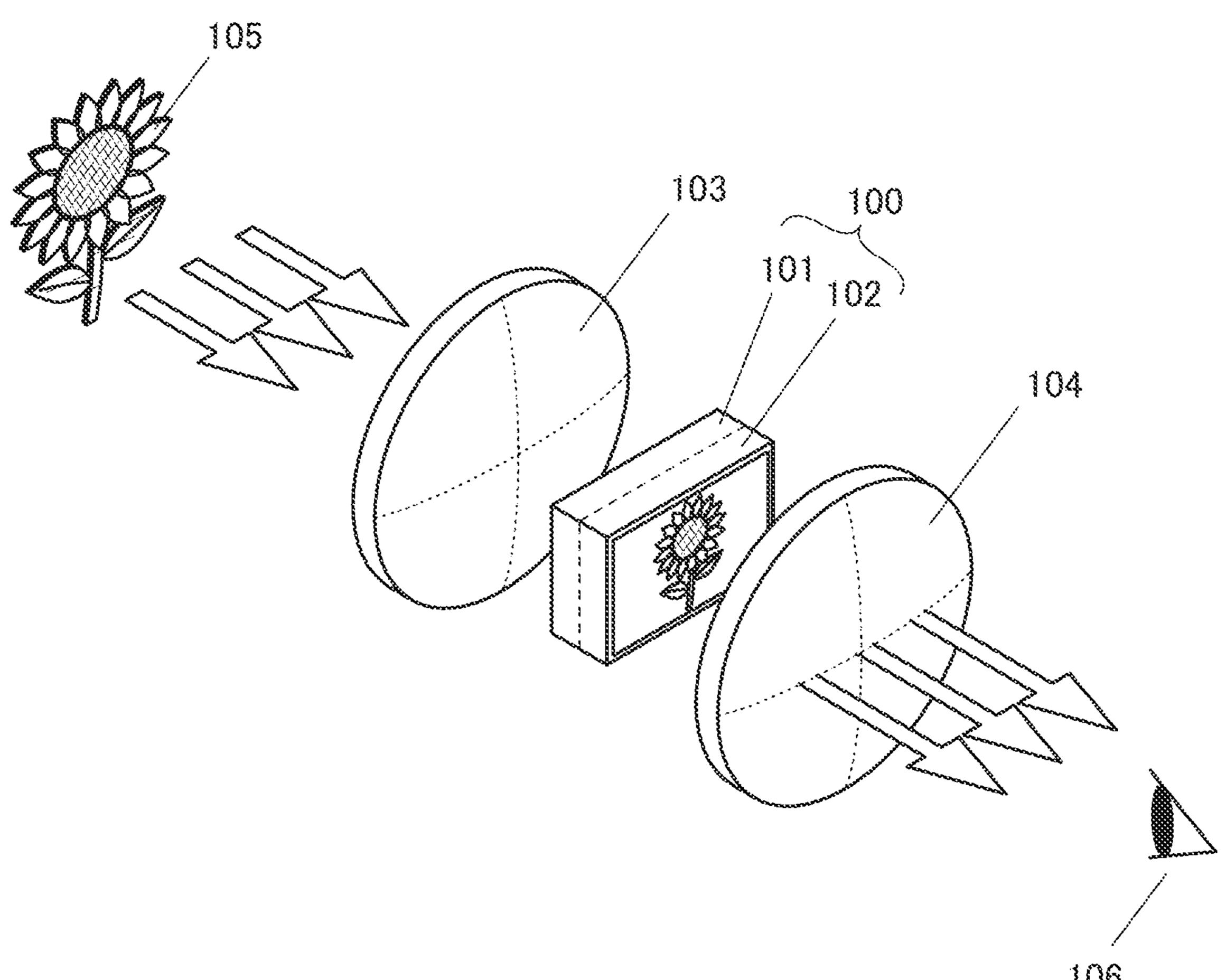

FIG. 1 illustrates an imaging display device;

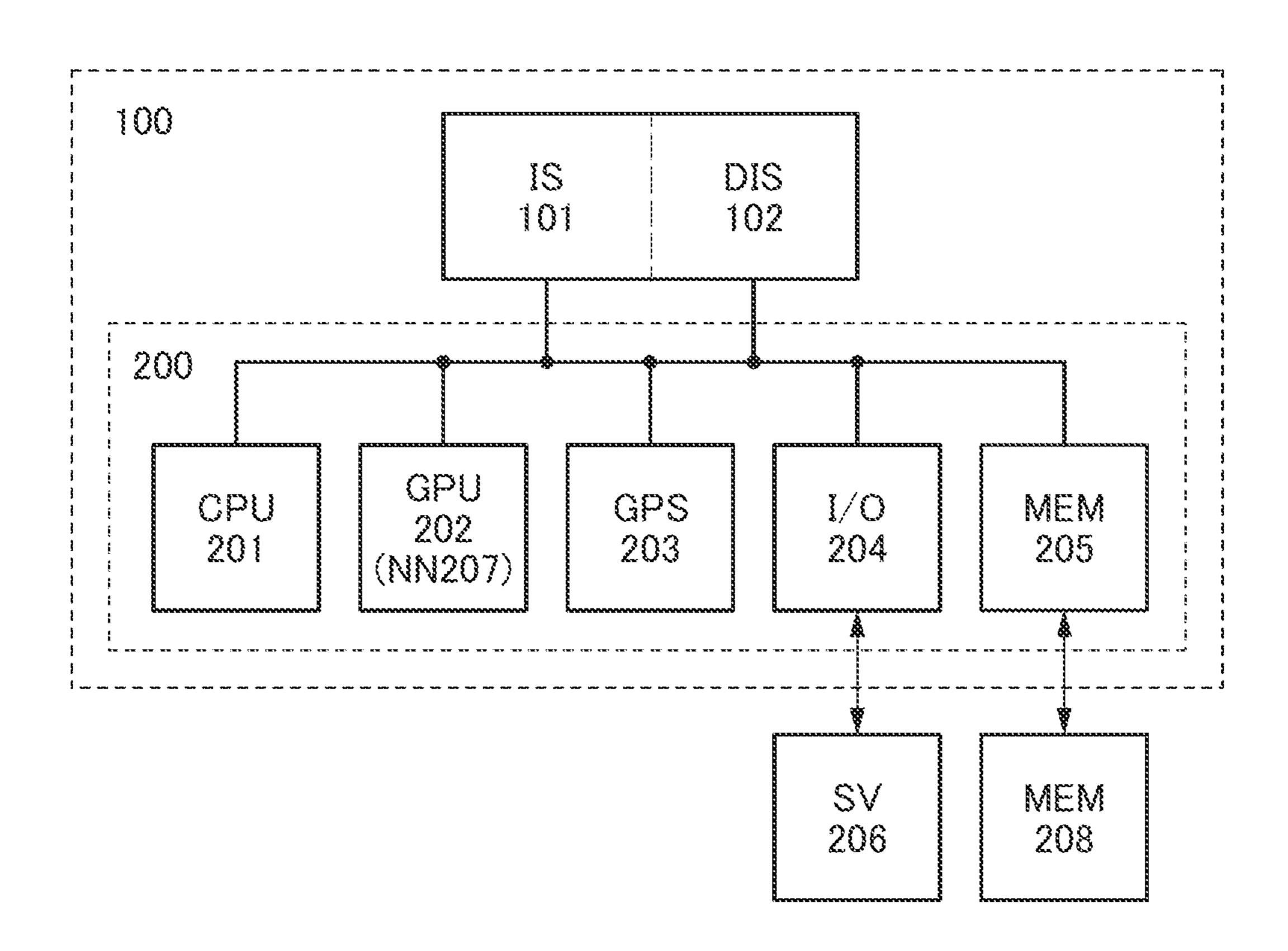

FIG. 2 is a block diagram of an imaging display device; FIG. 3 is a flow chart illustrating an operation for dis-

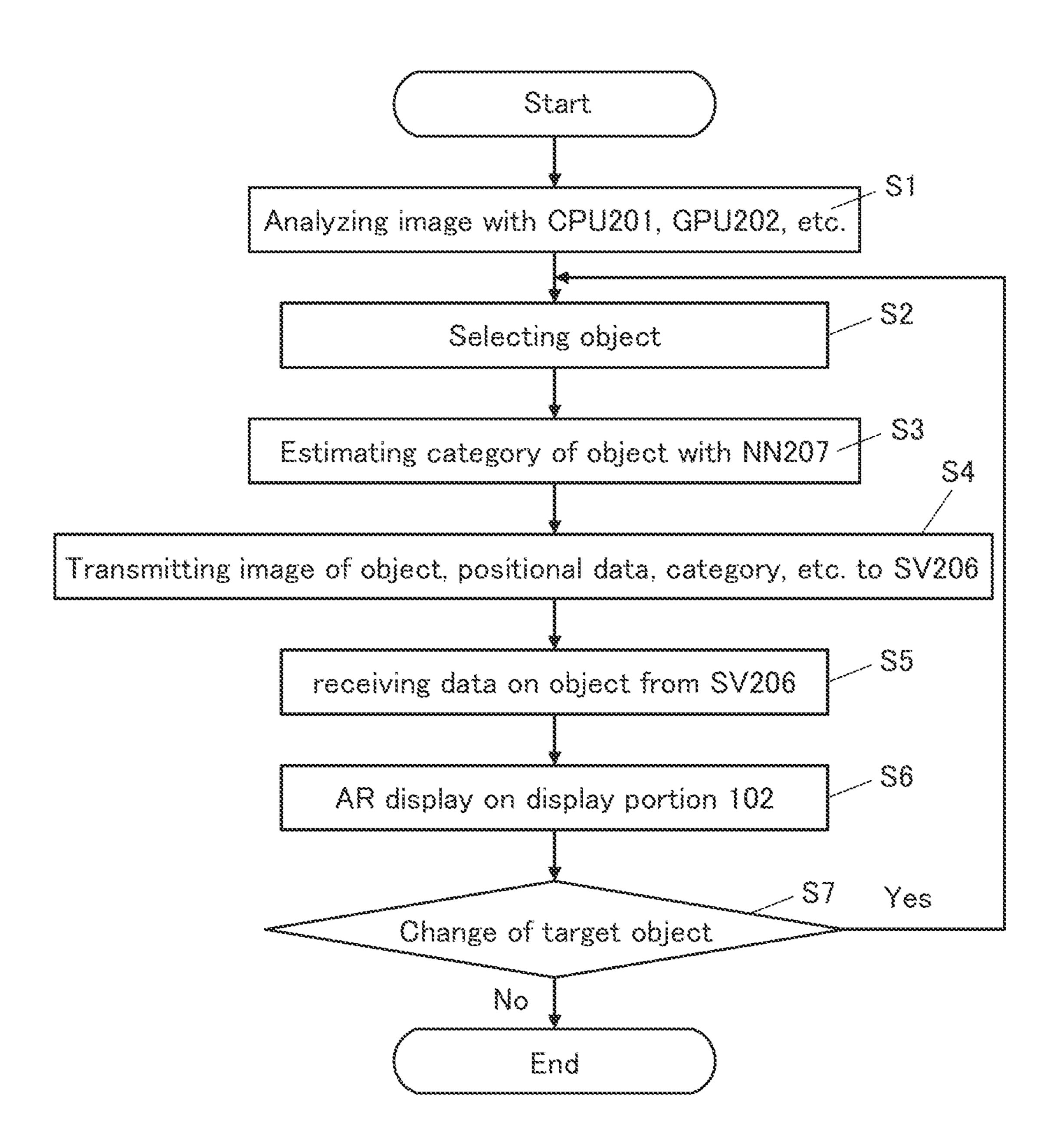

FIG. 3 is a flow chart illustrating an operation for displaying data on an object;

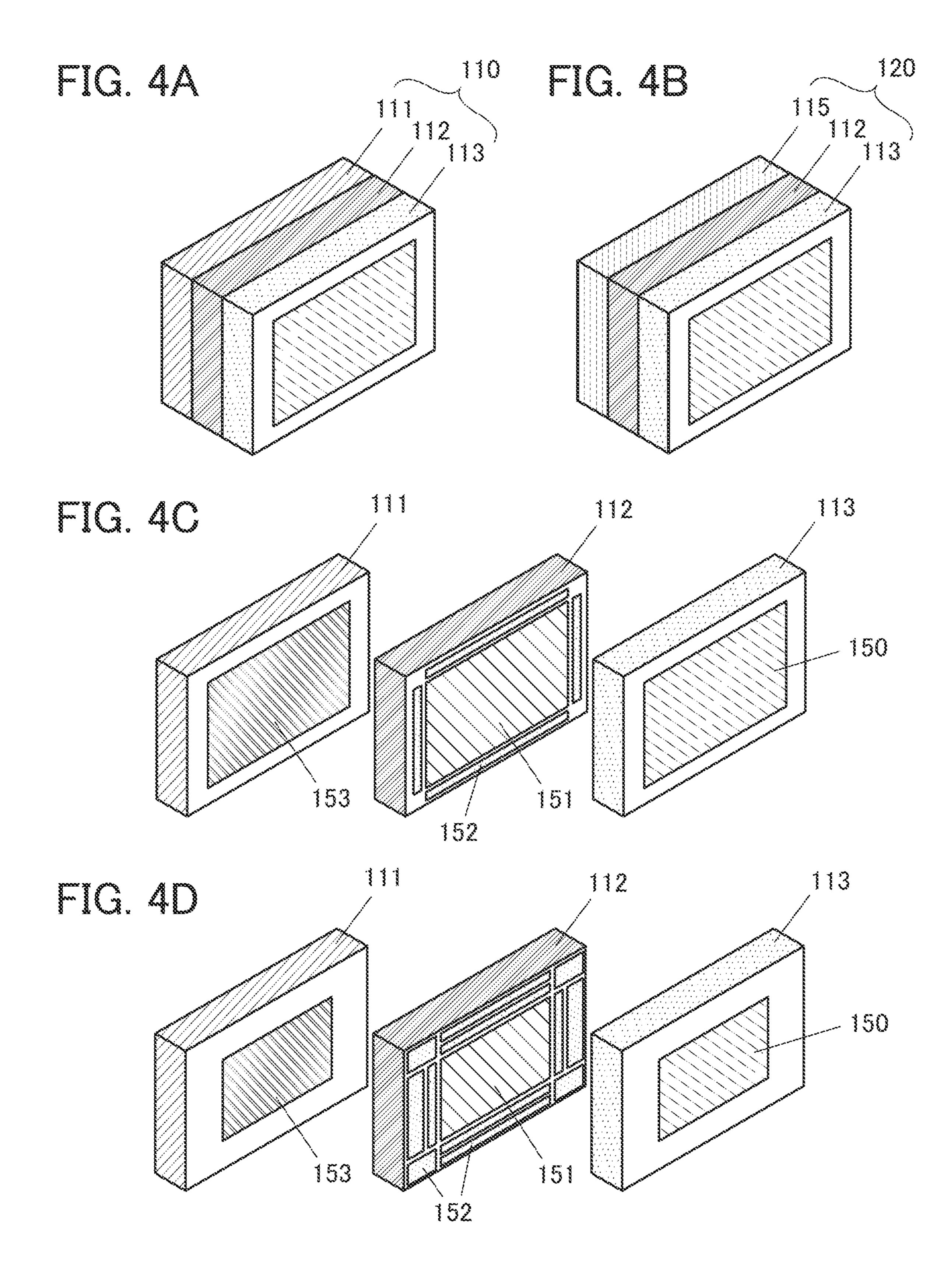

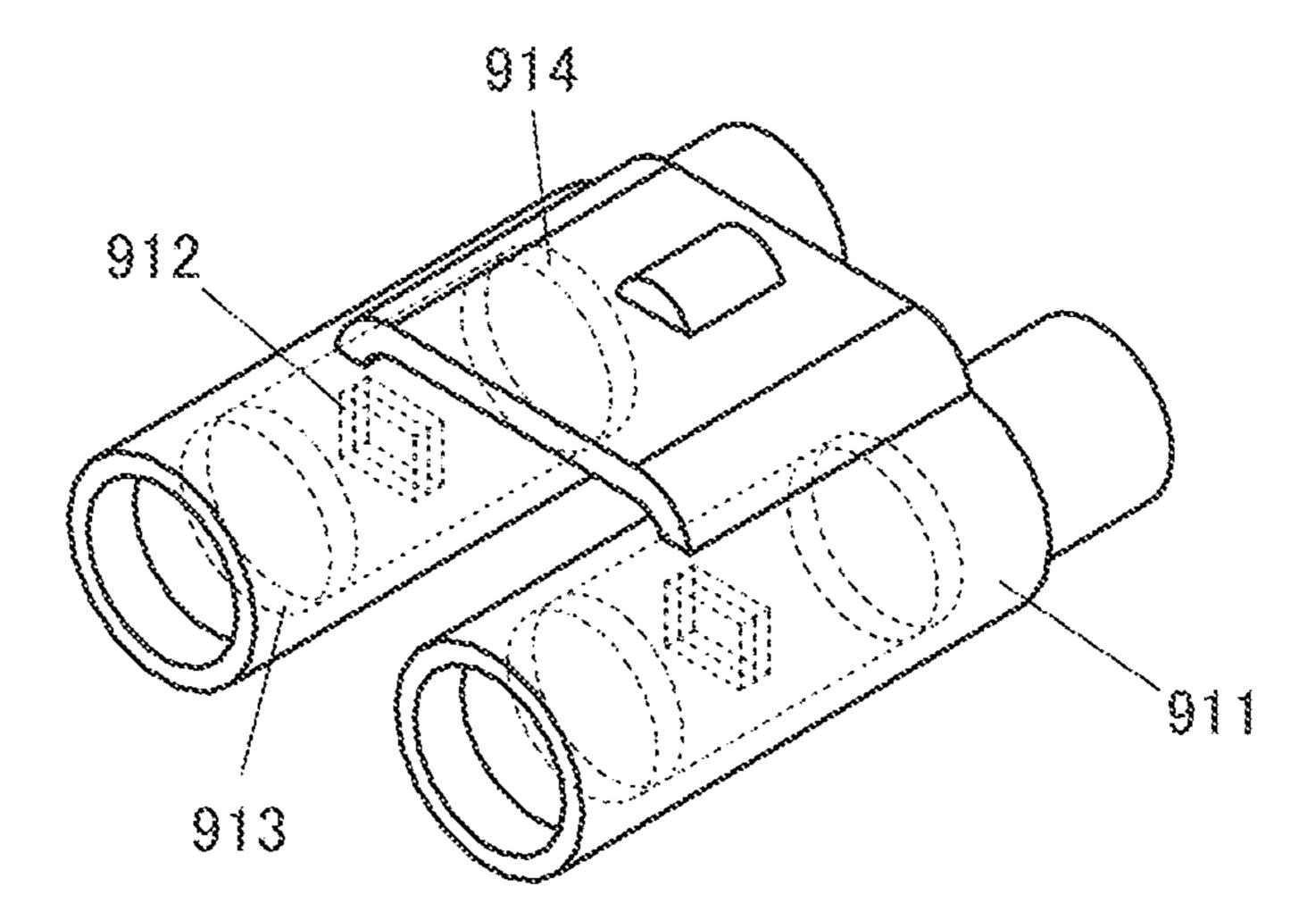

FIGS. 4A to 4D illustrate structure examples of an imaging display device;

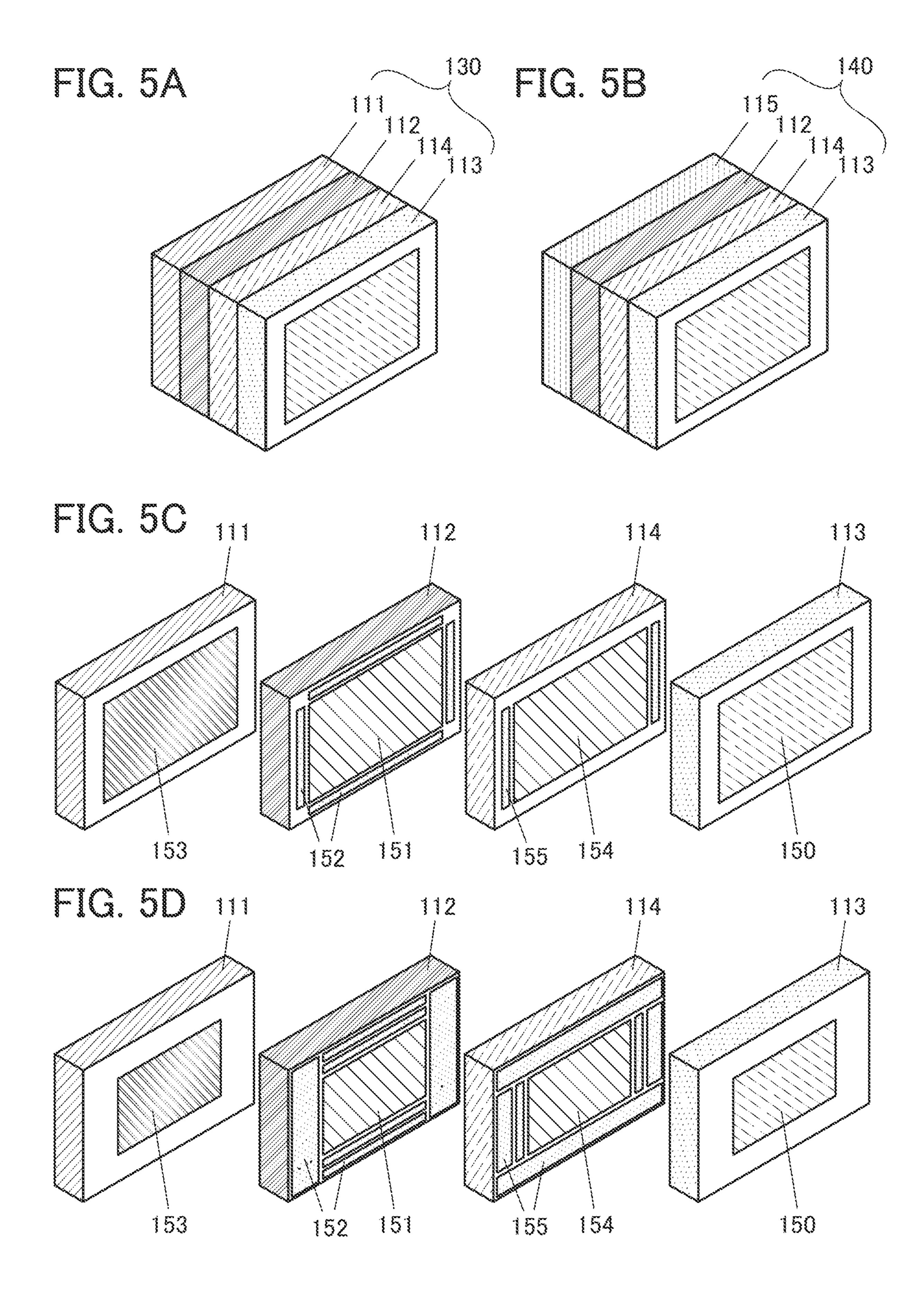

FIGS. **5**A to **5**D illustrate structure examples of an imaging display device;

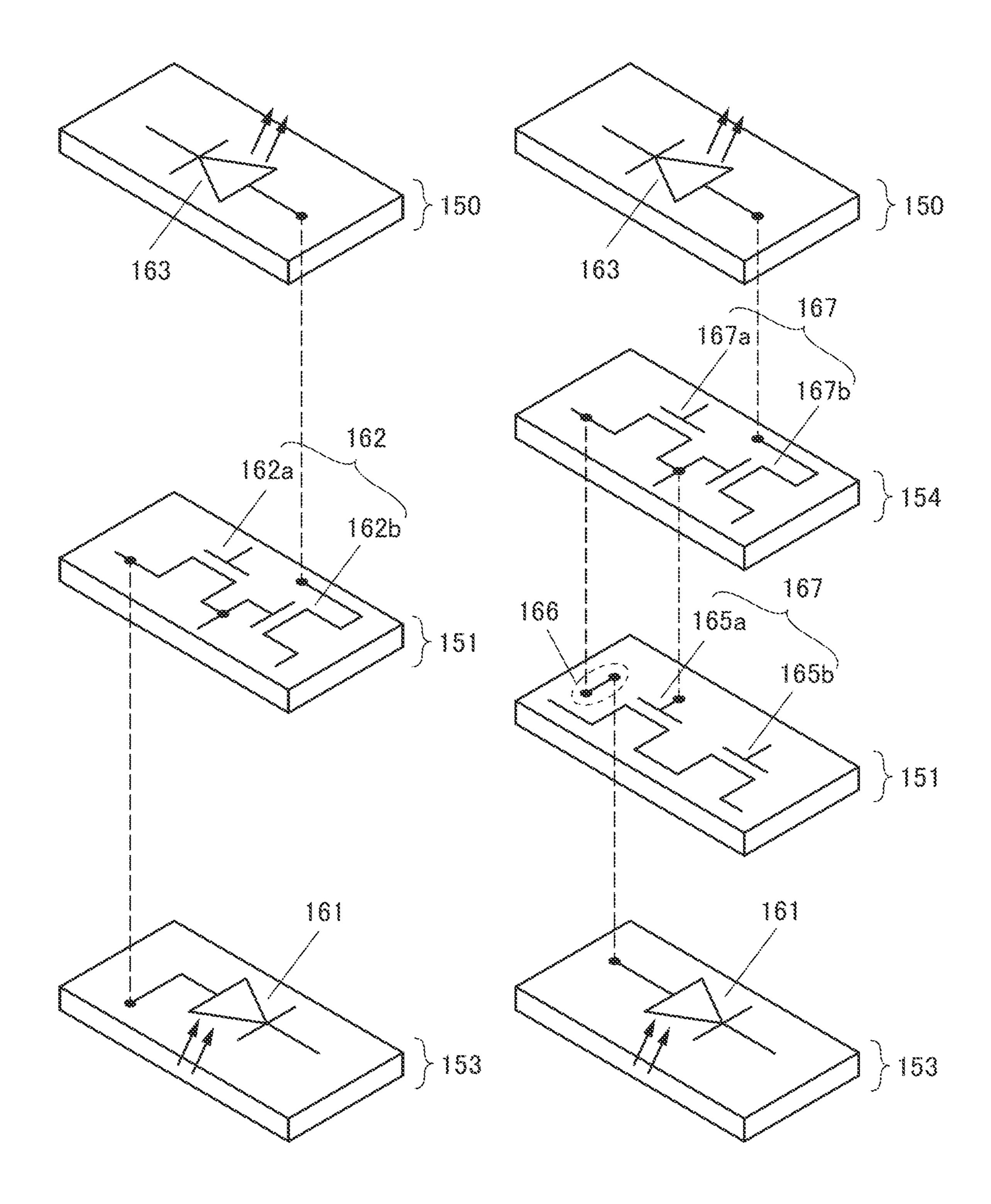

FIGS. 6A and 6B each illustrate an electric connection between components included in an imaging display device;

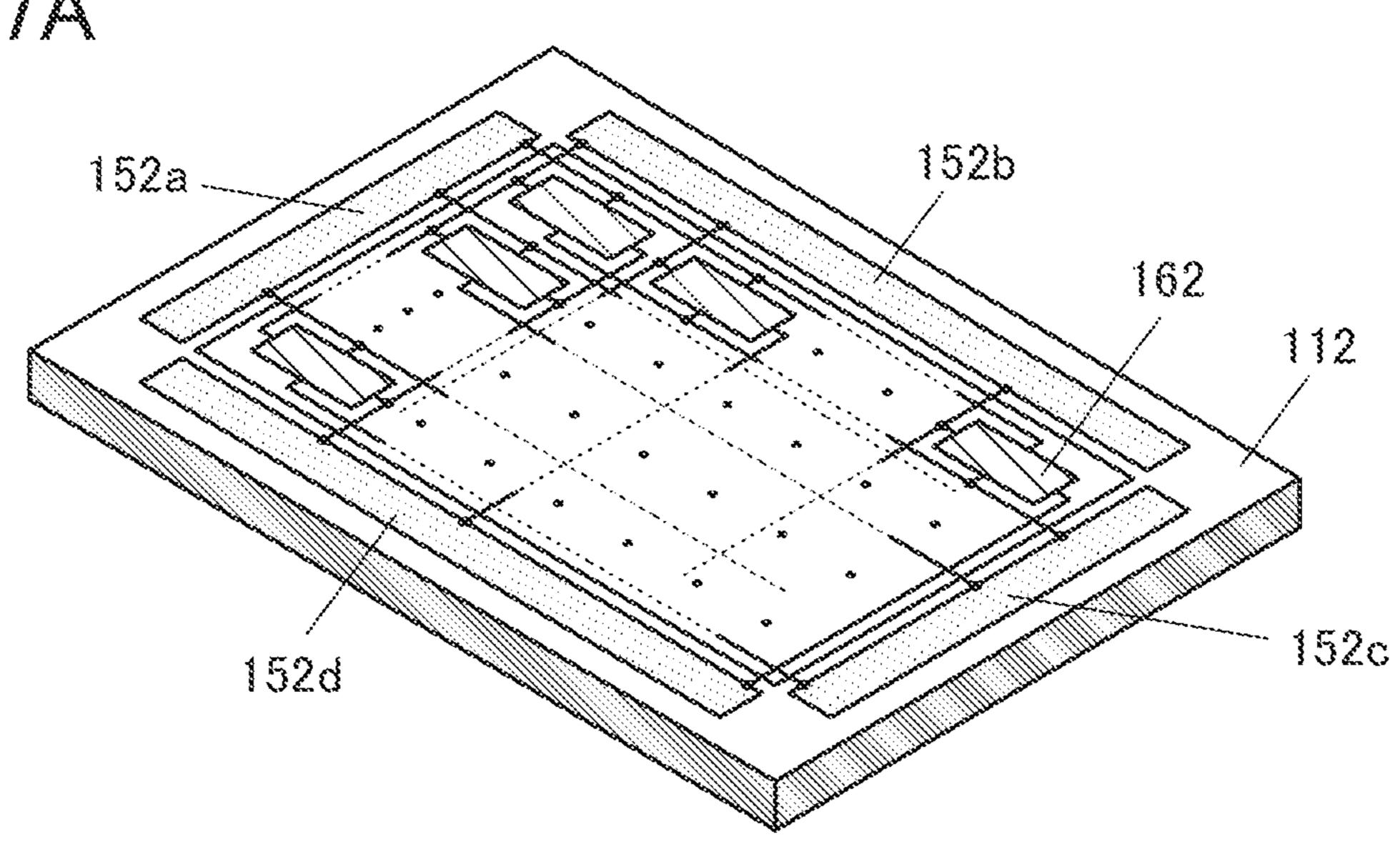

FIGS. 7A and 7B each illustrate an electric connection between a pixel circuit and other circuits;

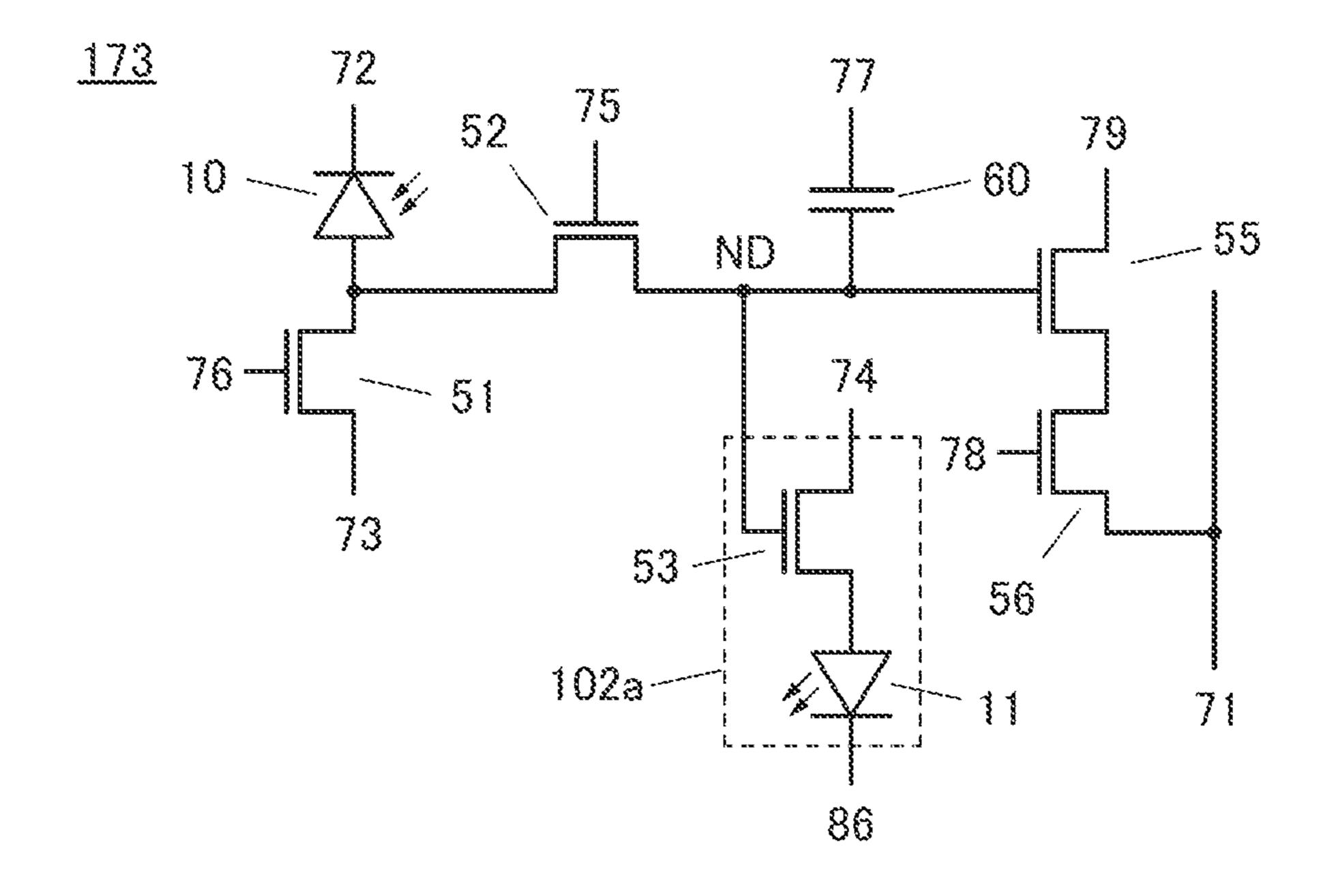

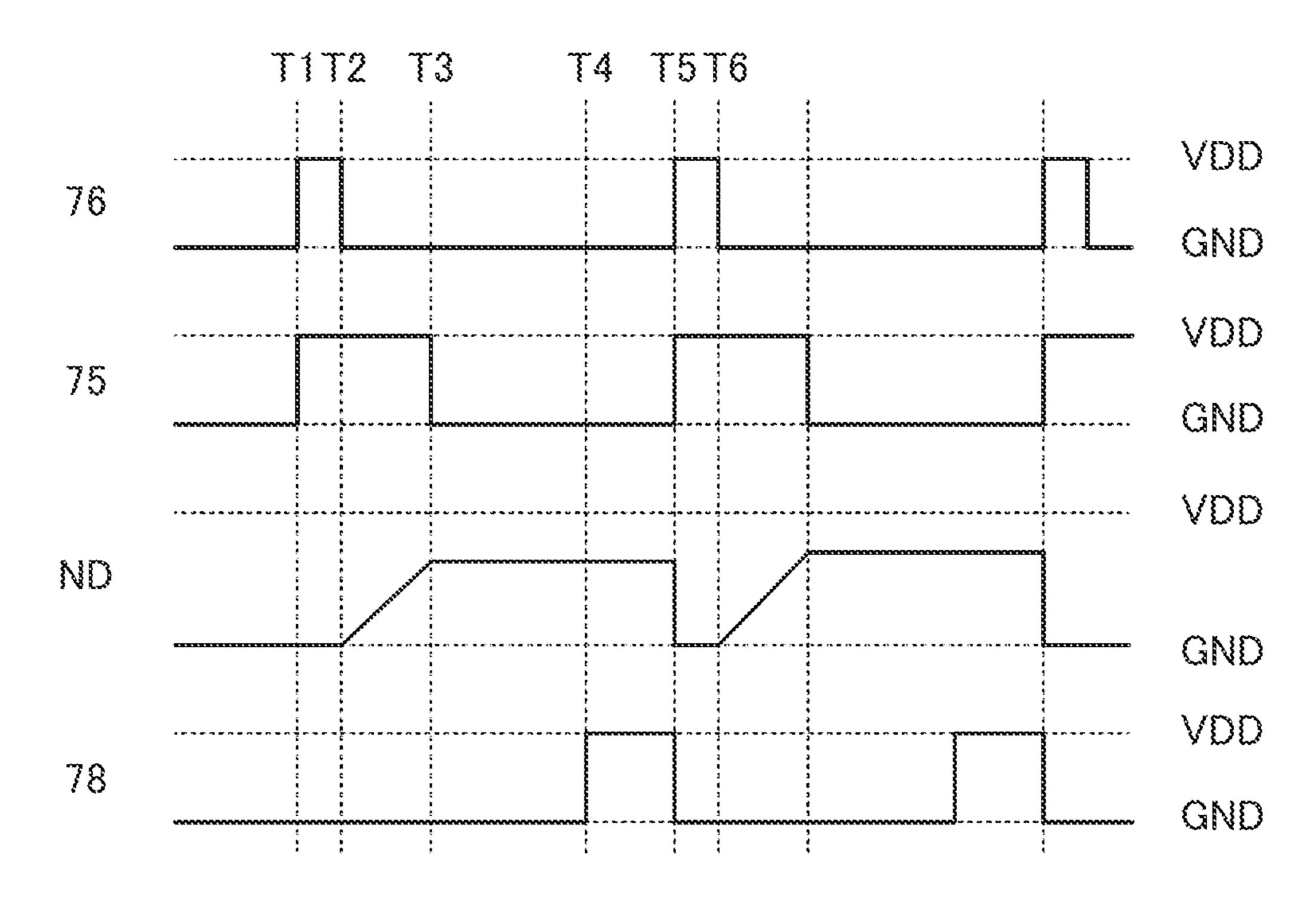

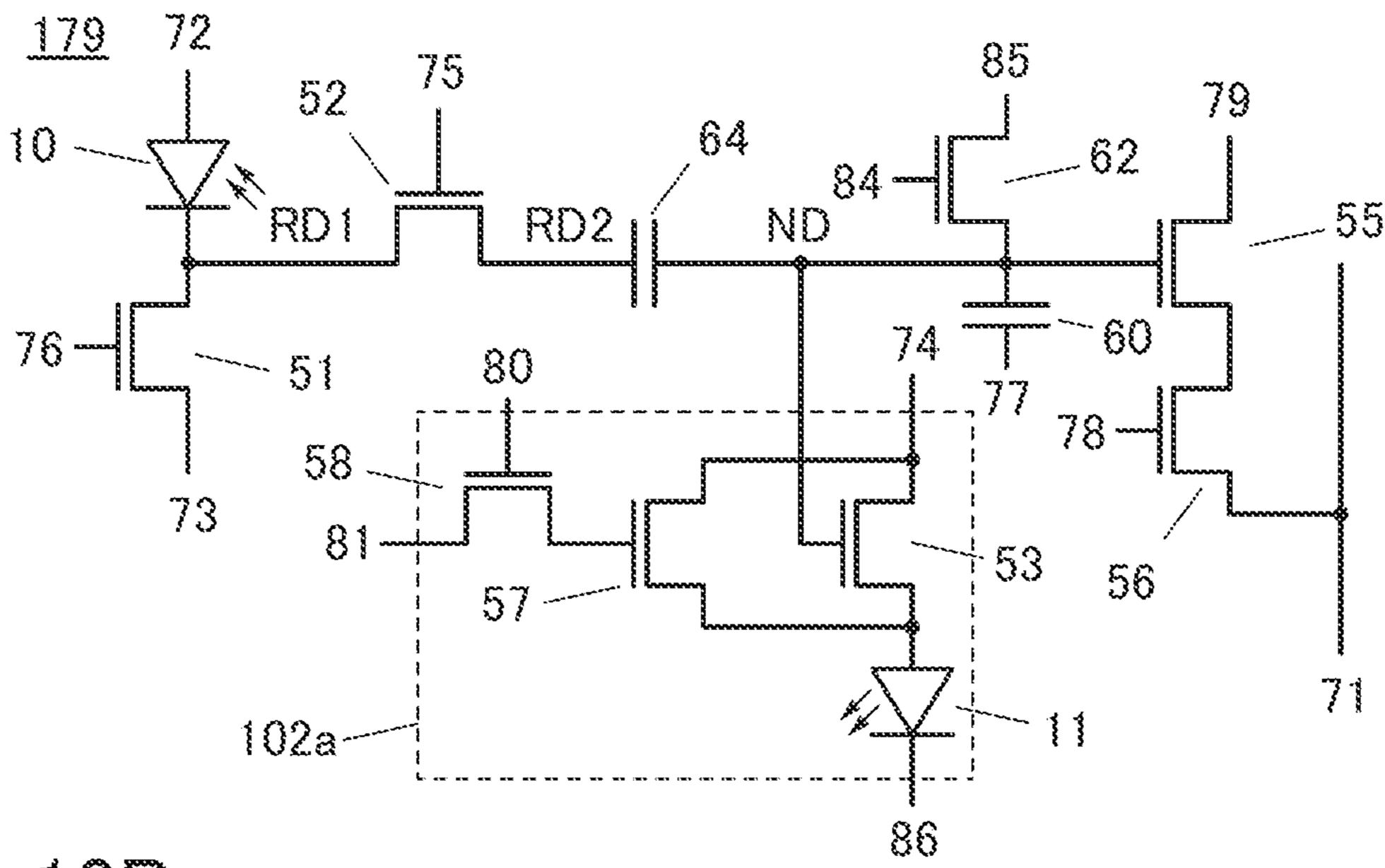

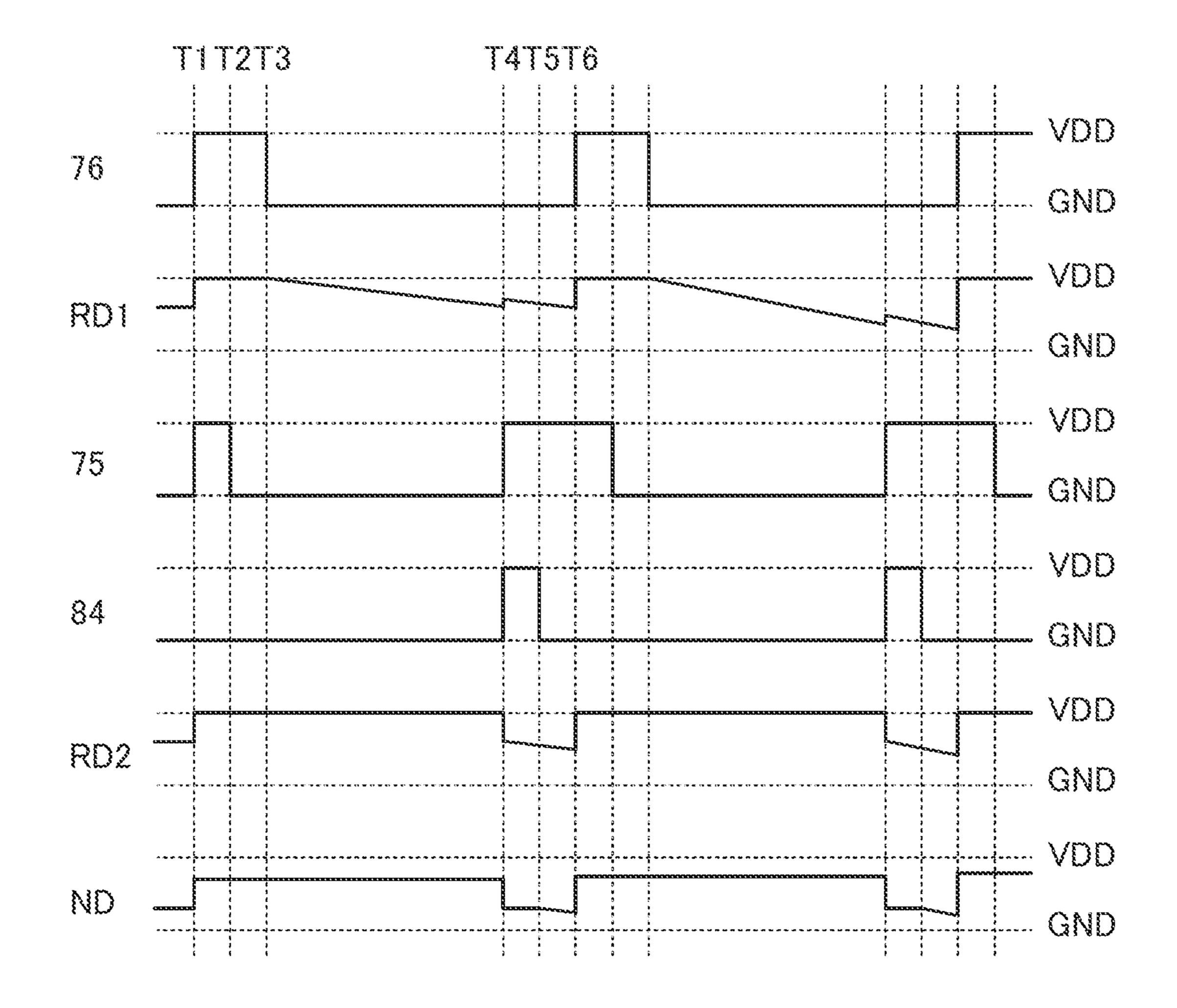

FIGS. 8A and 8B each illustrate a pixel circuit, and FIG. 8C is a timing chart;

FIG. 9A illustrates a pixel circuit, and FIG. 9B is a timing chart;

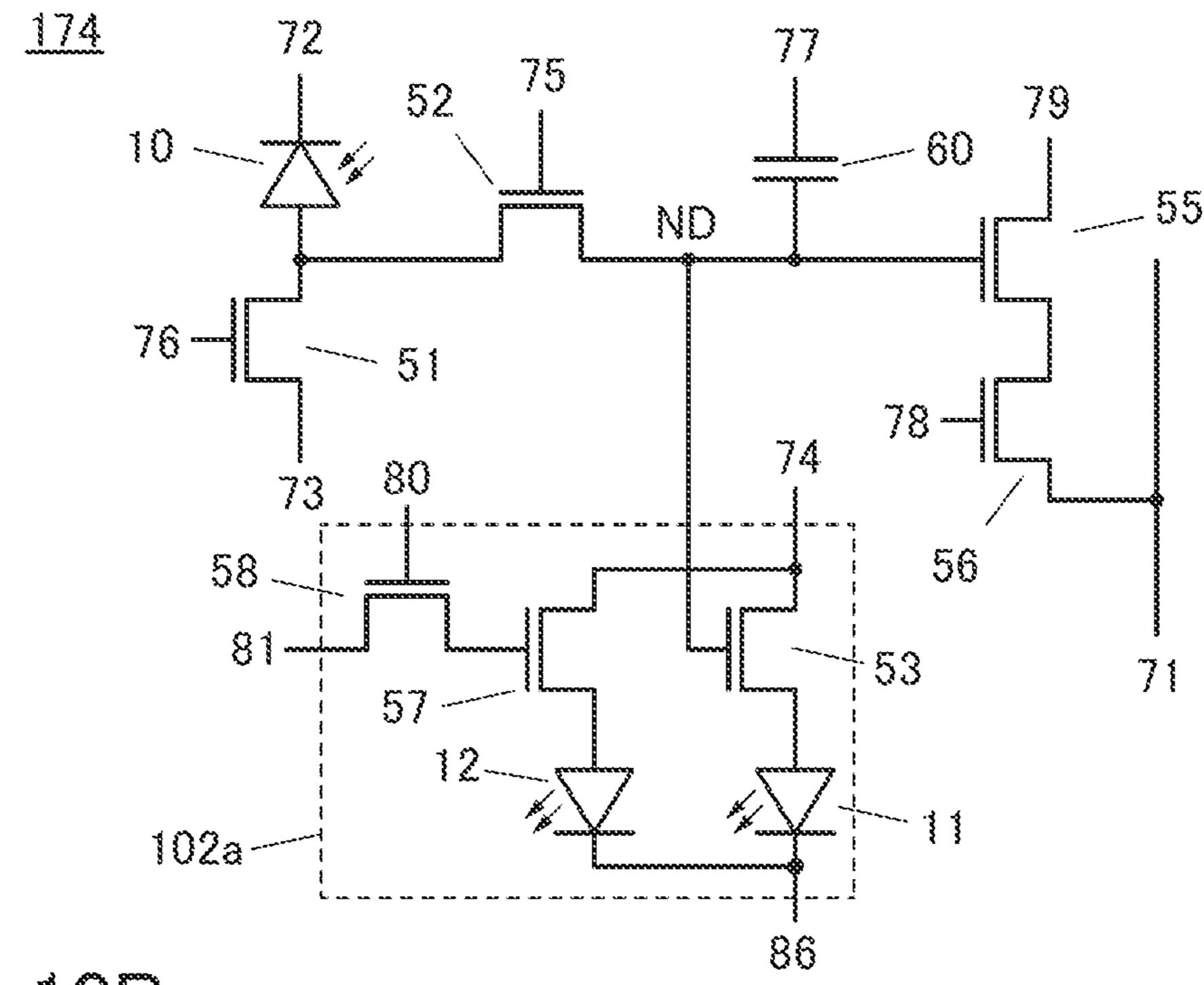

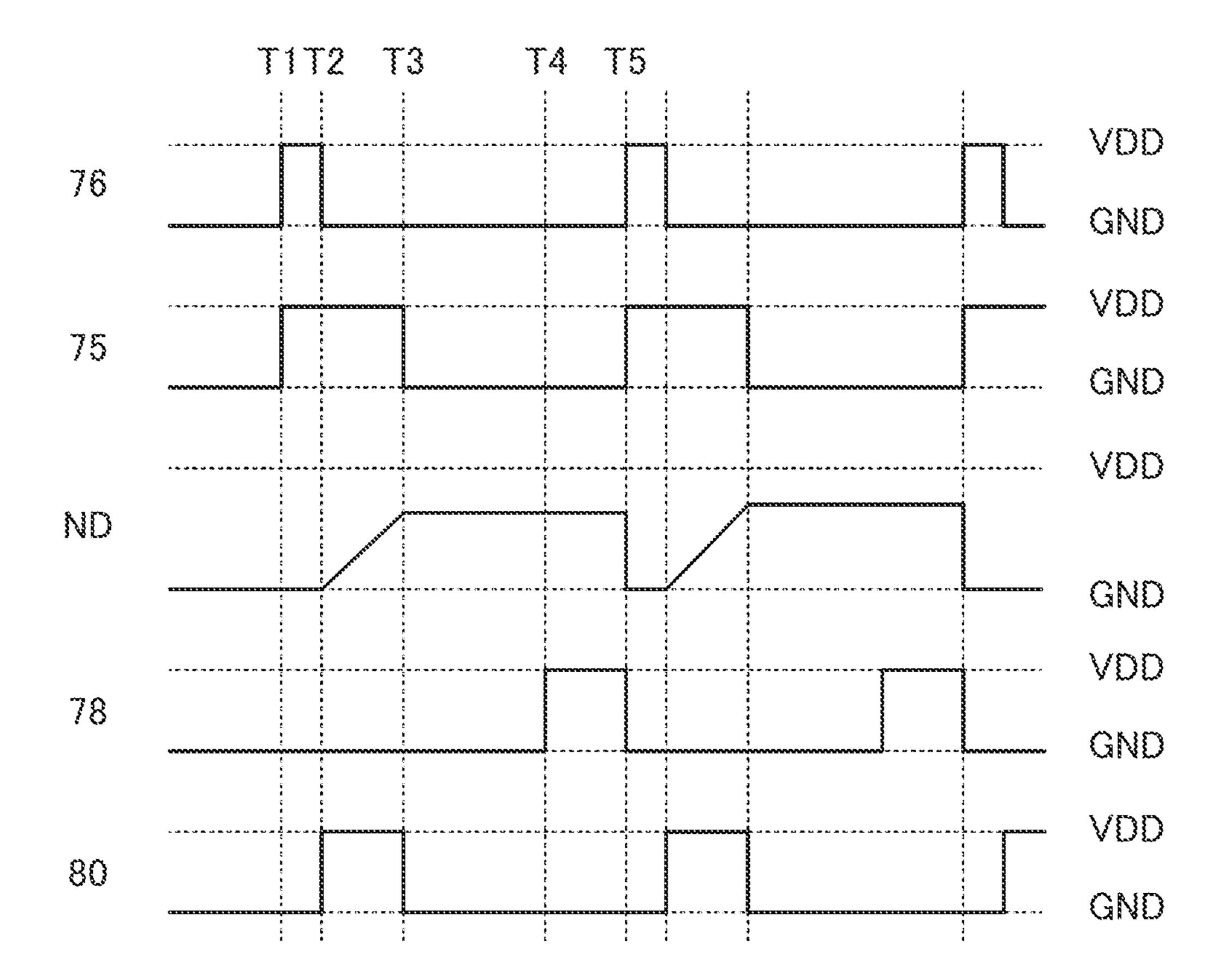

FIG. 10A illustrates a pixel circuit, and FIG. 10B is a timing chart;

FIGS. 11A and 11B each illustrate a pixel circuit;

FIGS. 12A and 12B each illustrate a pixel circuit;

FIG. 13A illustrates a pixel circuit, and FIG. 13B is a timing chart;

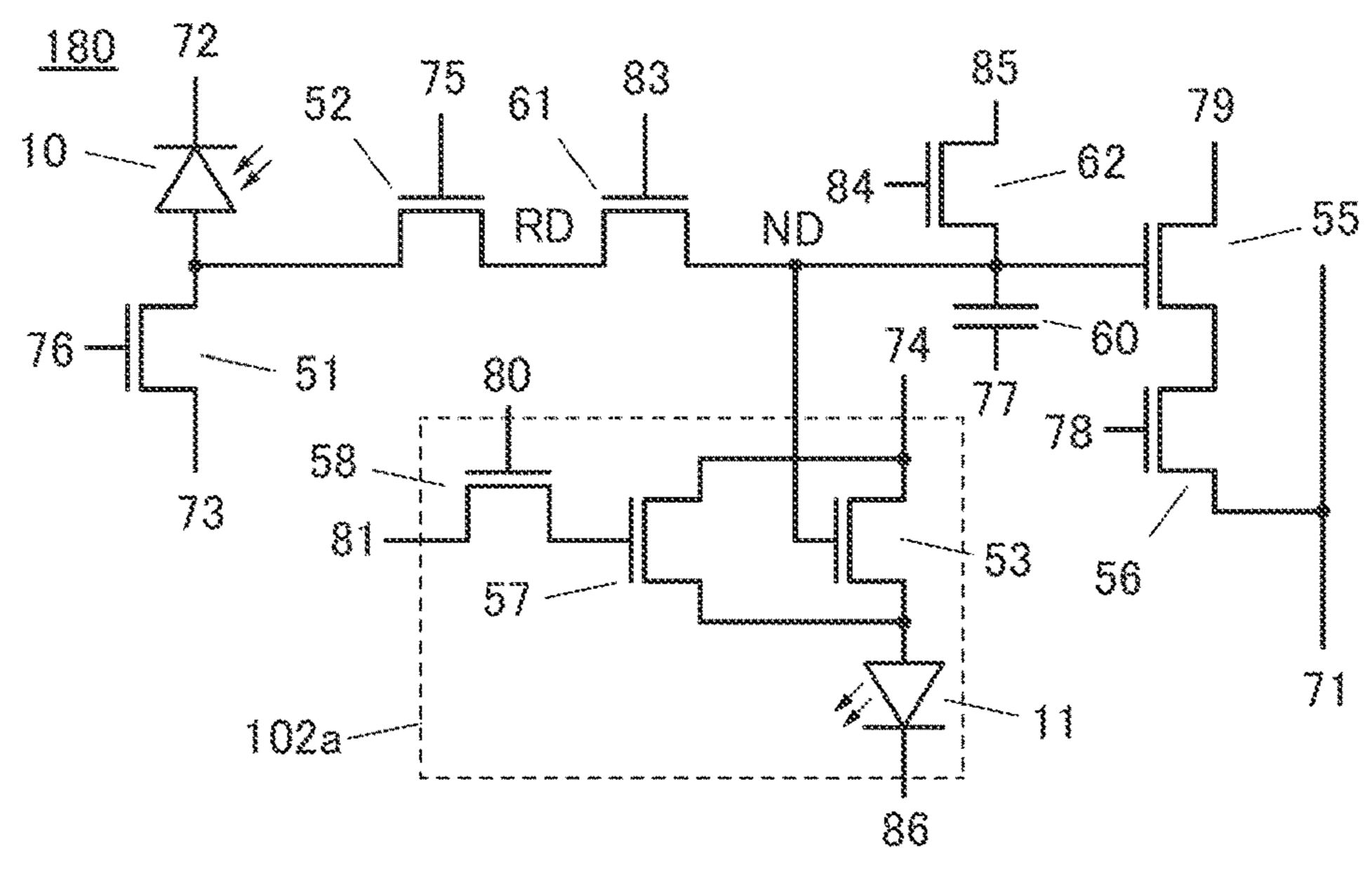

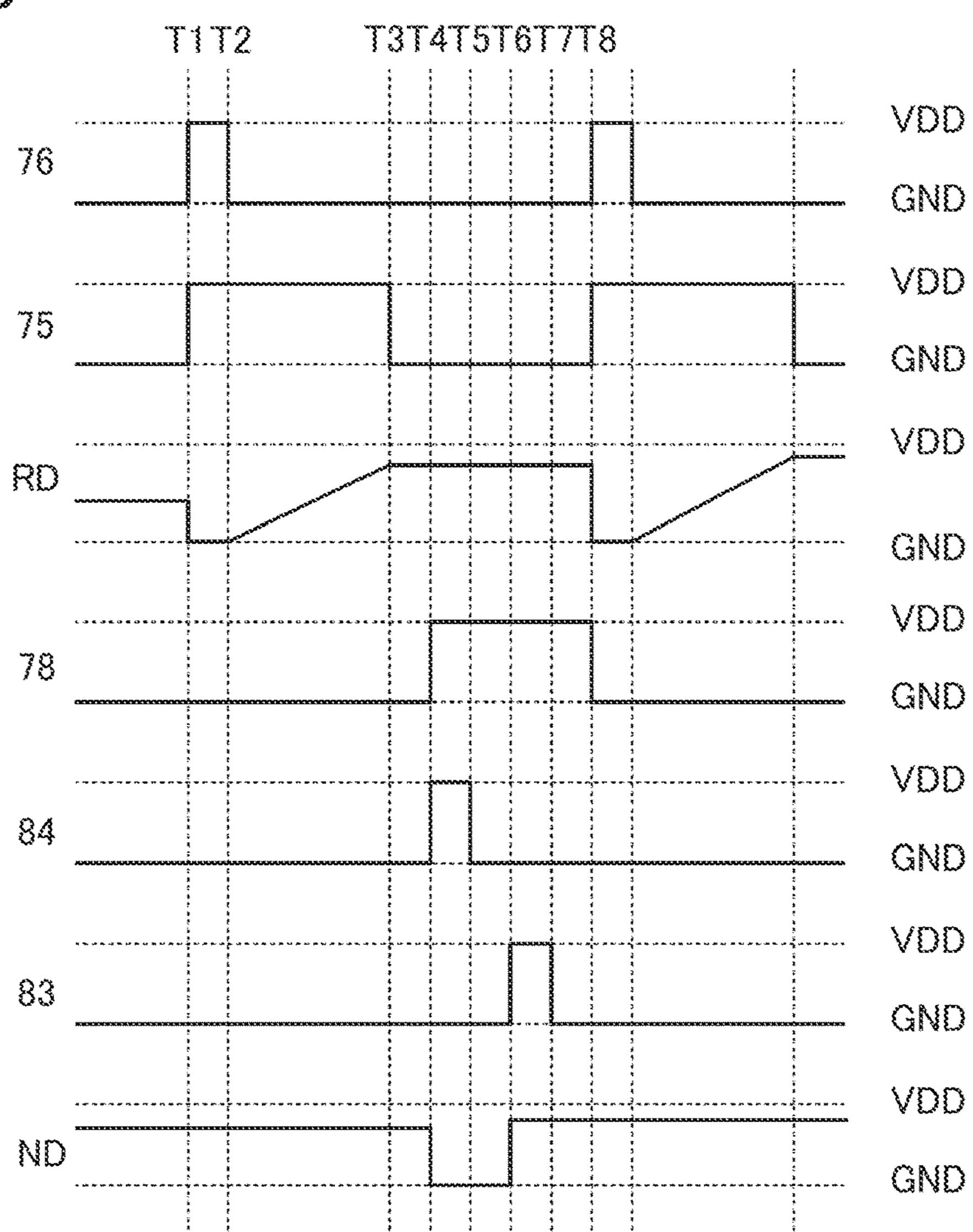

FIG. 14A illustrates a pixel circuit, and FIG. 14B is a timing chart;

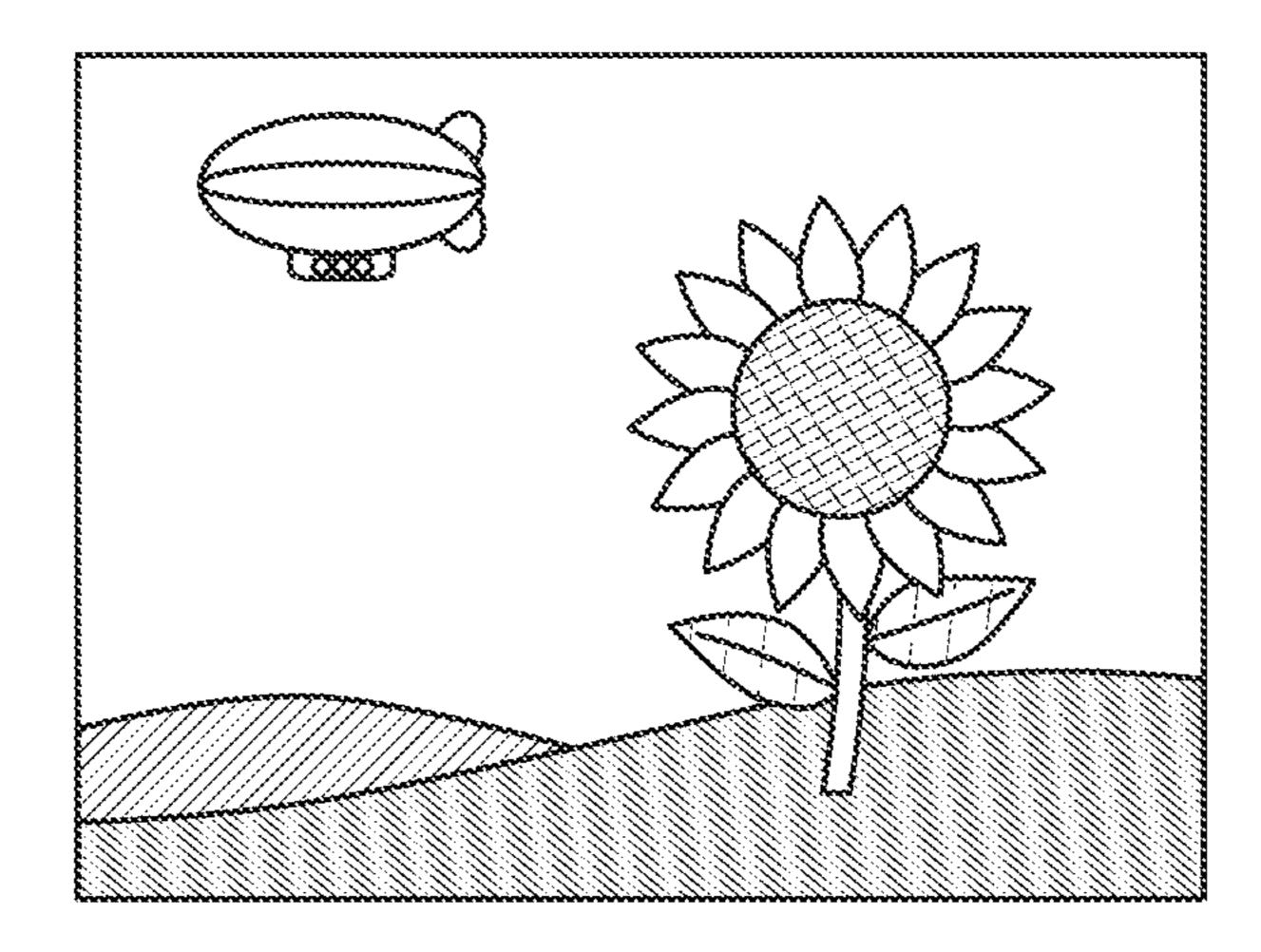

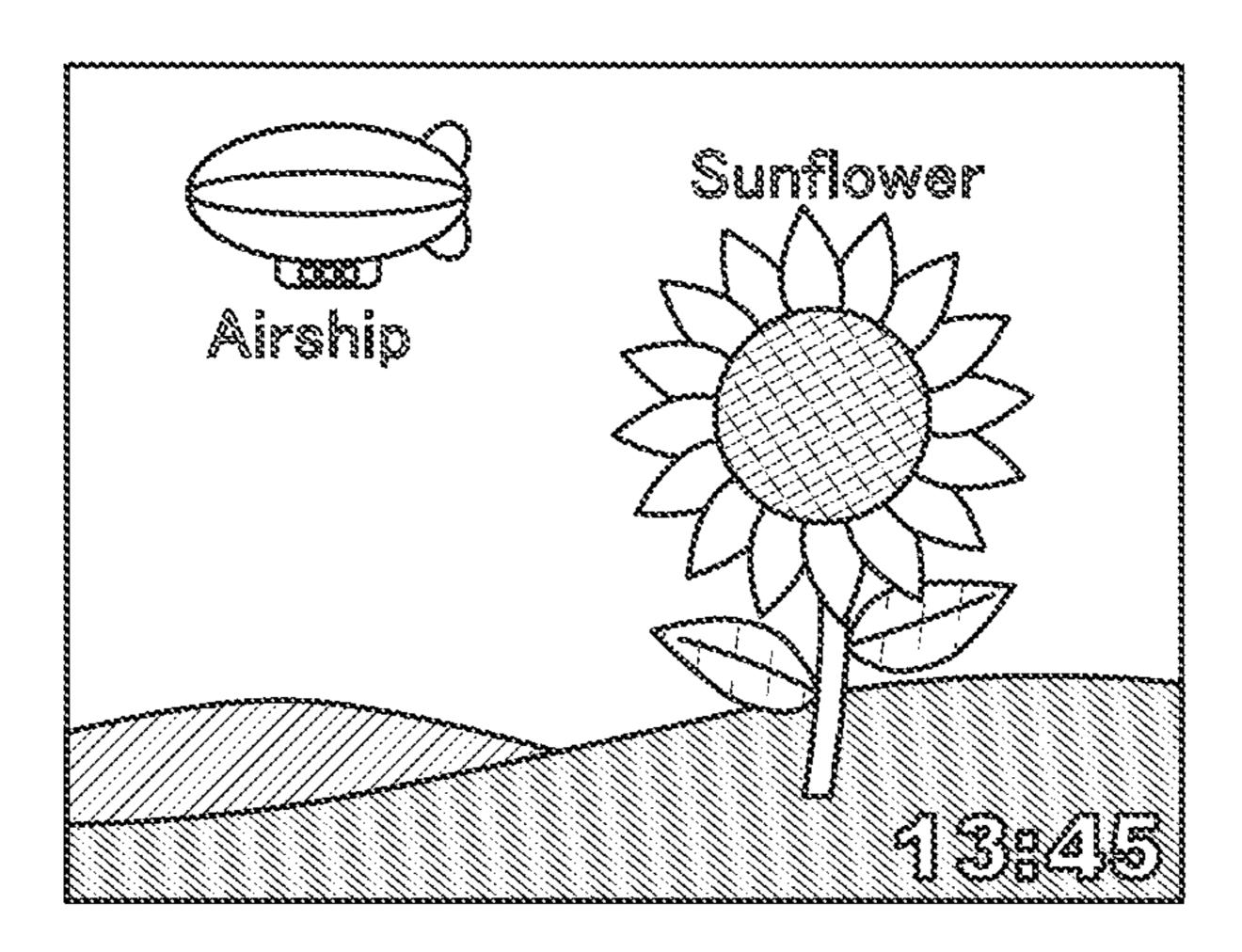

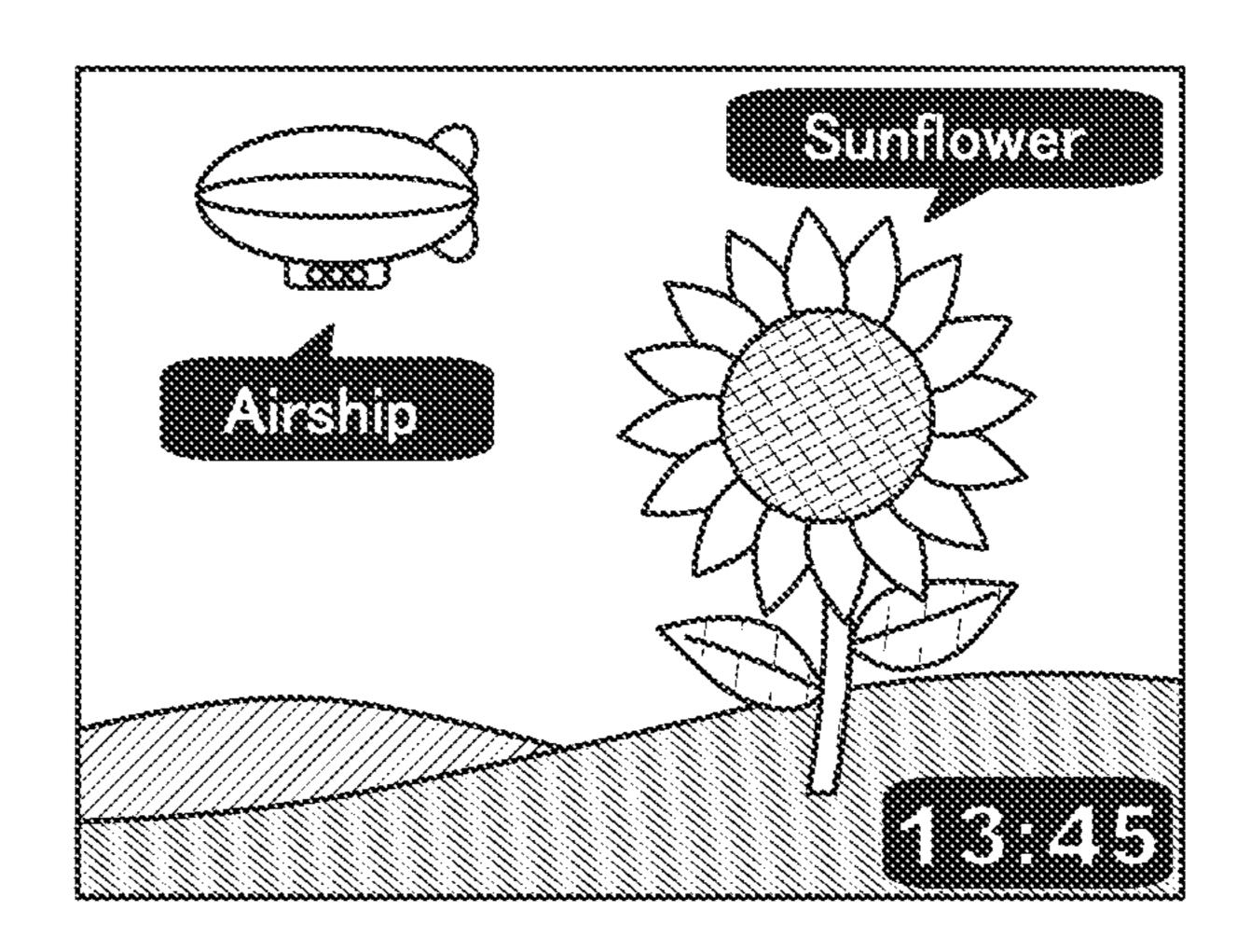

FIGS. 15A to 15C illustrate examples of an image displayed on a display portion;

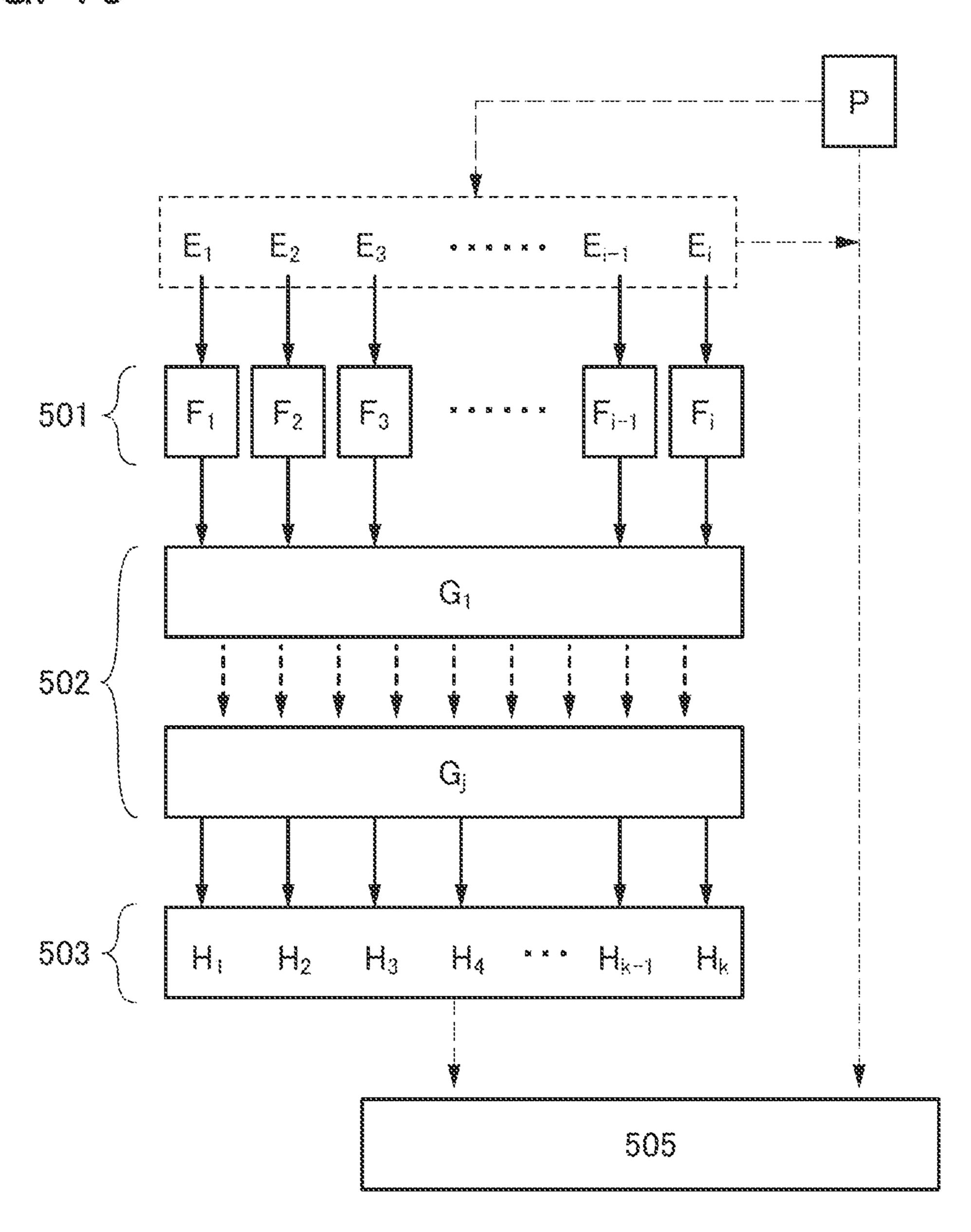

FIG. 16 illustrates an operation for estimating the category of an object with a neural network;

FIGS. 17A to 17C each illustrate a structure example of a neural network;

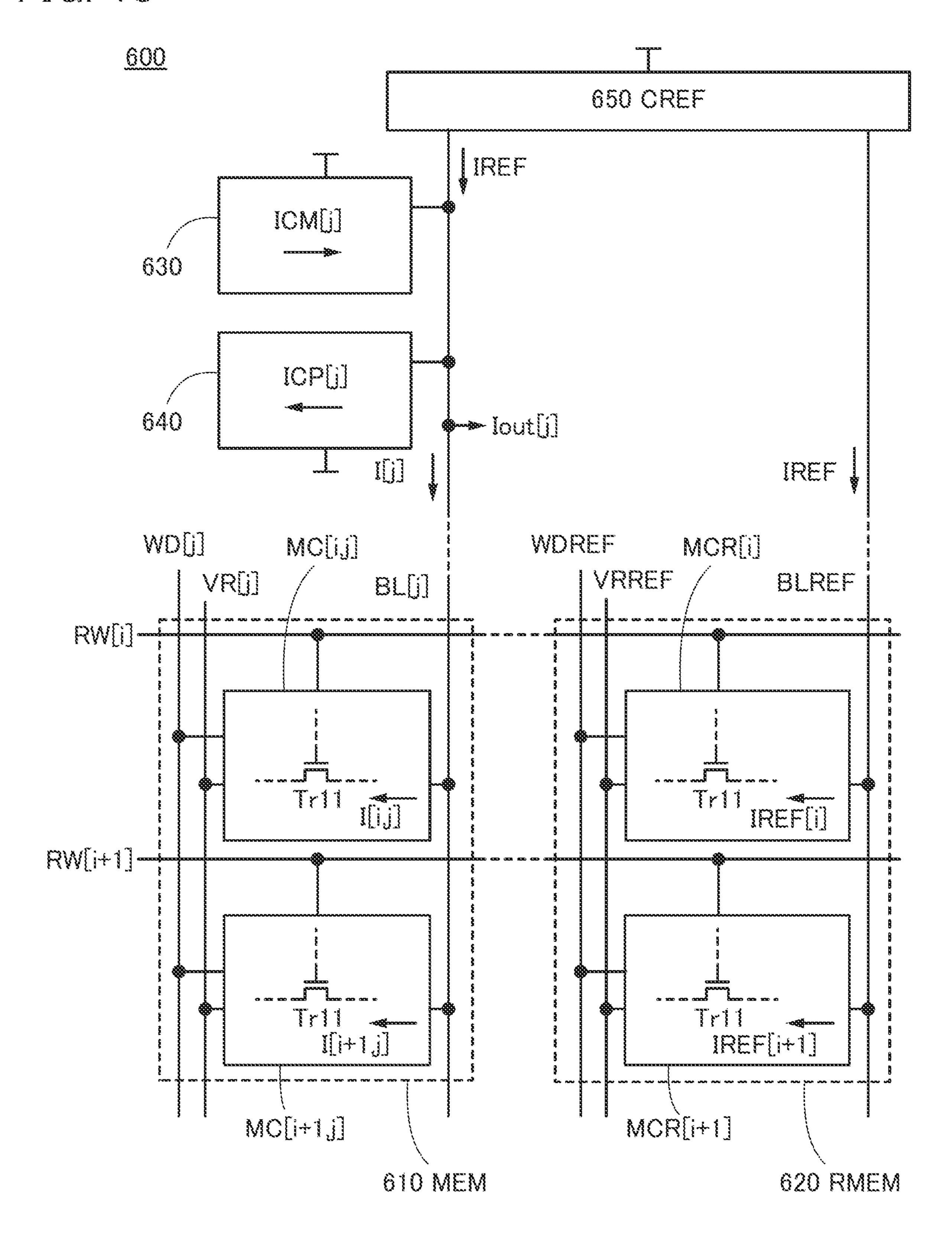

FIG. 18 illustrates a structure example of a semiconductor device;

FIG. 19 illustrates a structure example of a memory circuit;

FIG. 20 illustrates a structure example of memory cells;

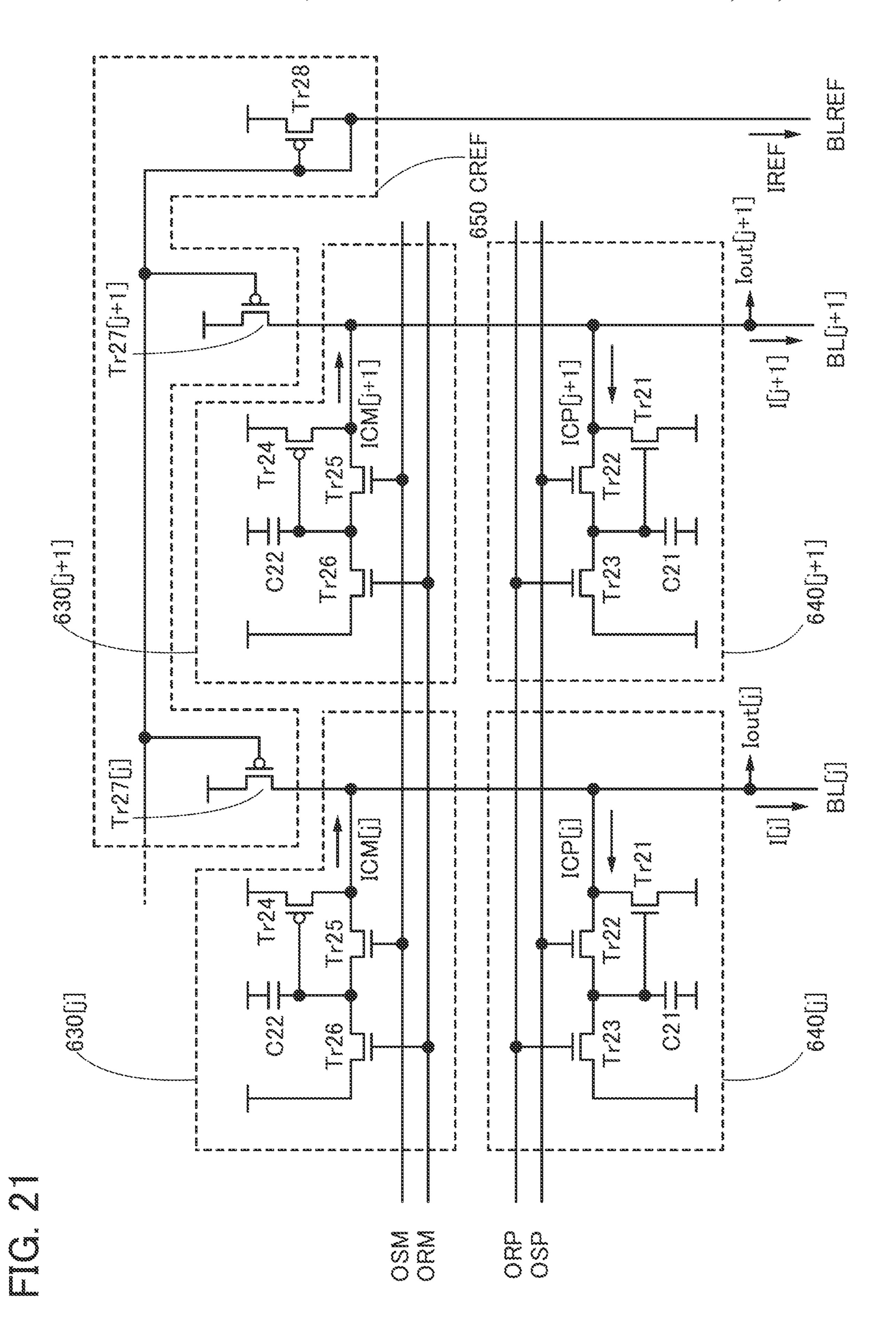

FIG. 21 illustrates structure examples of circuits;

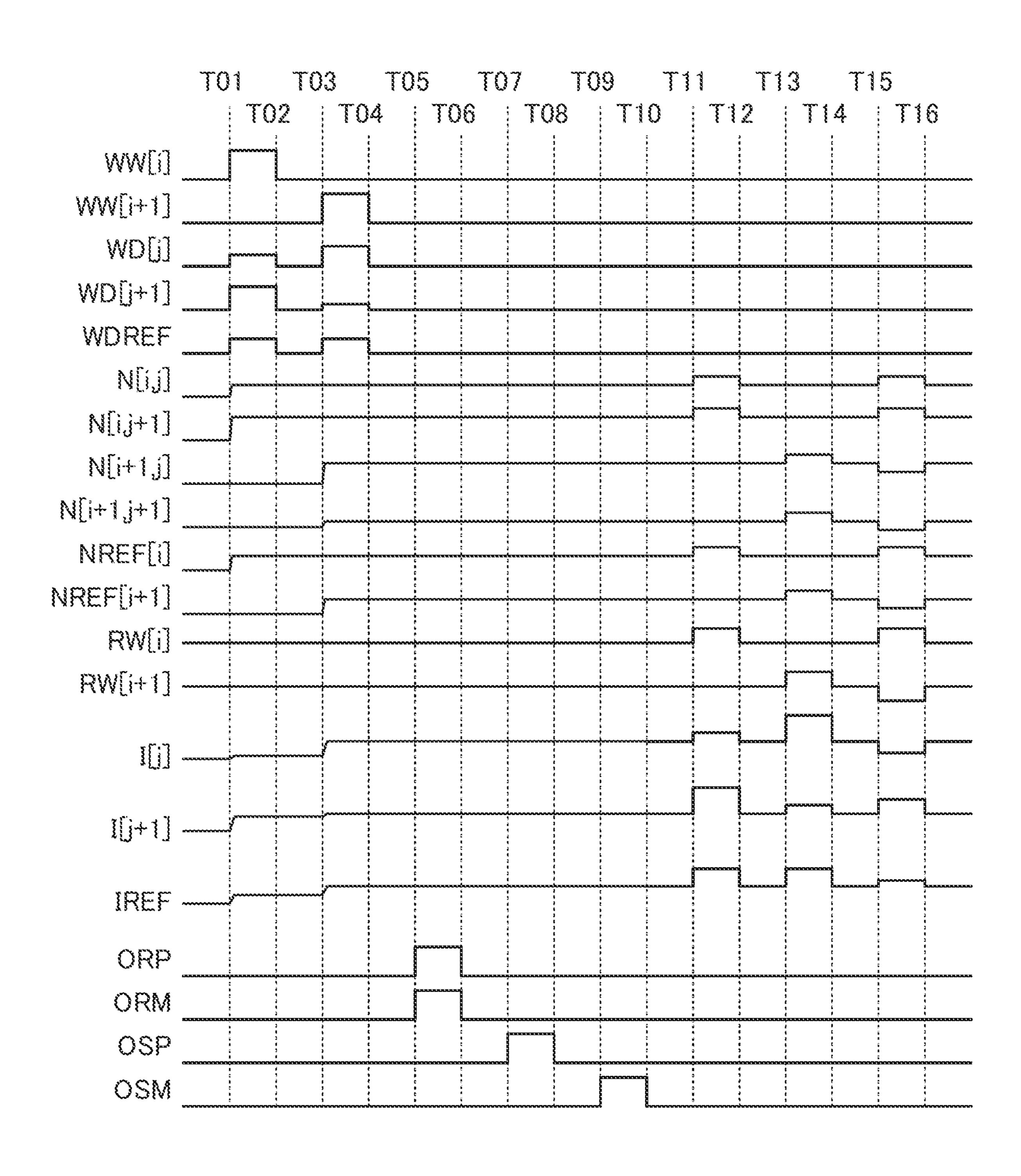

FIG. 22 is a timing chart illustrating an operation of a semiconductor device;

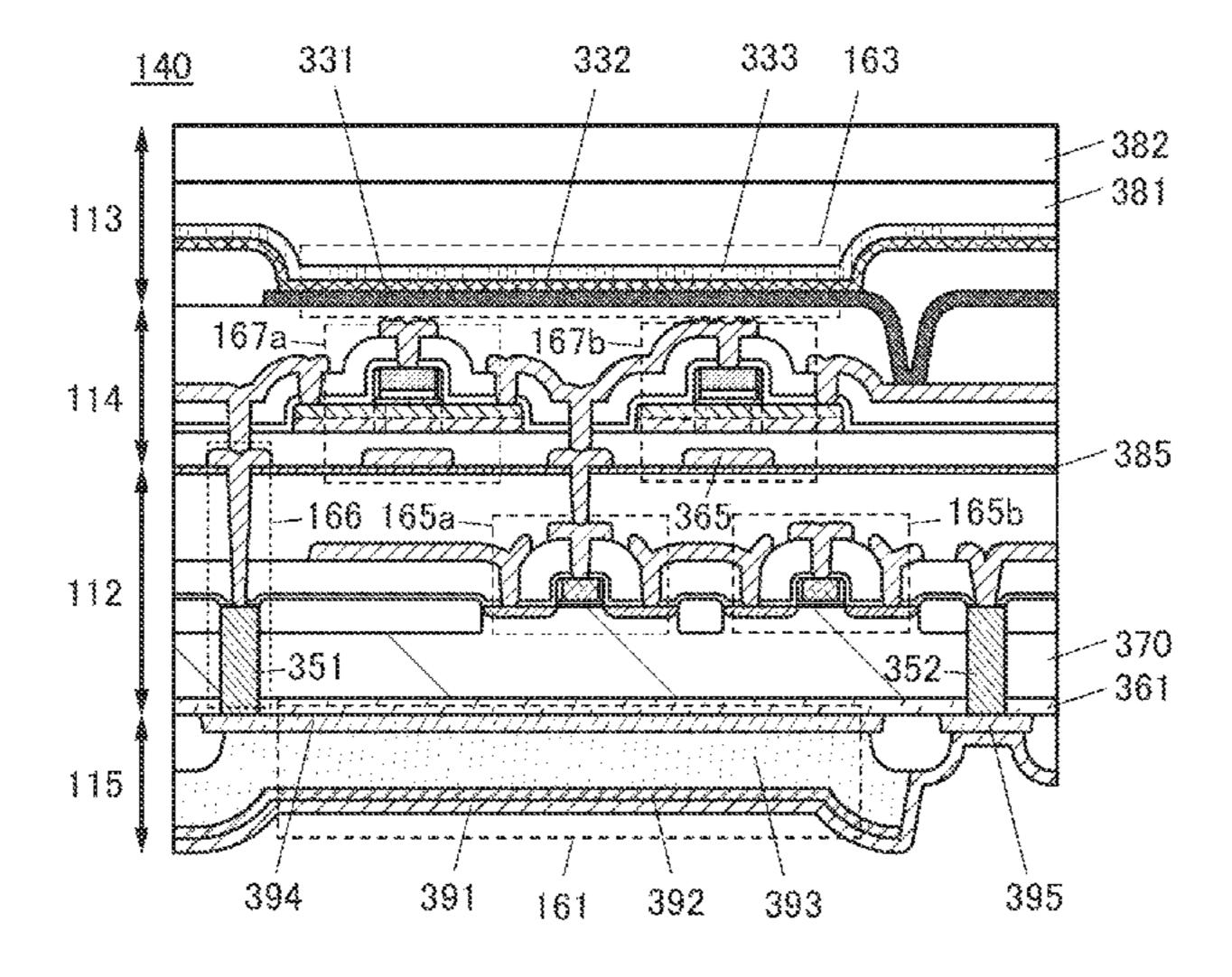

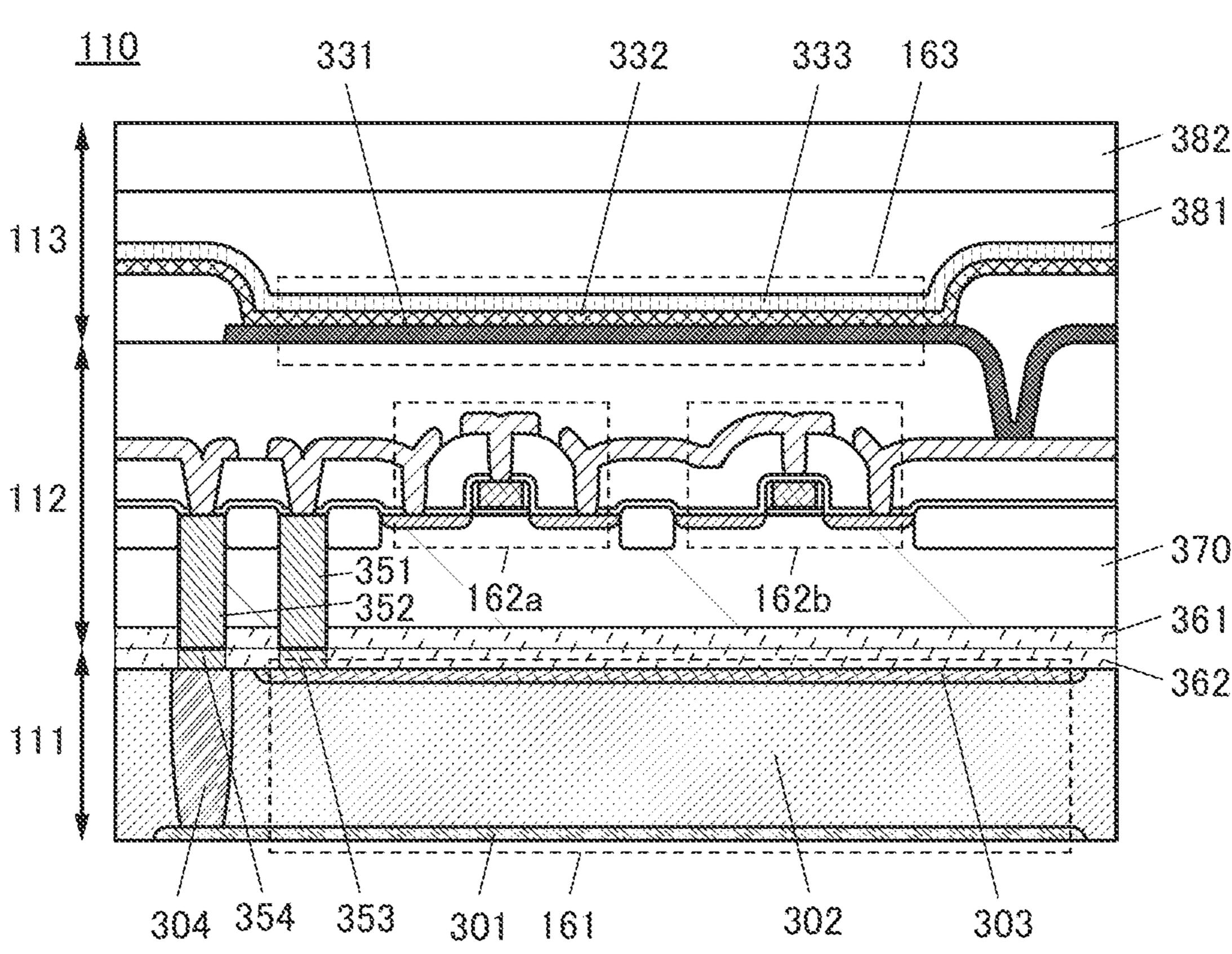

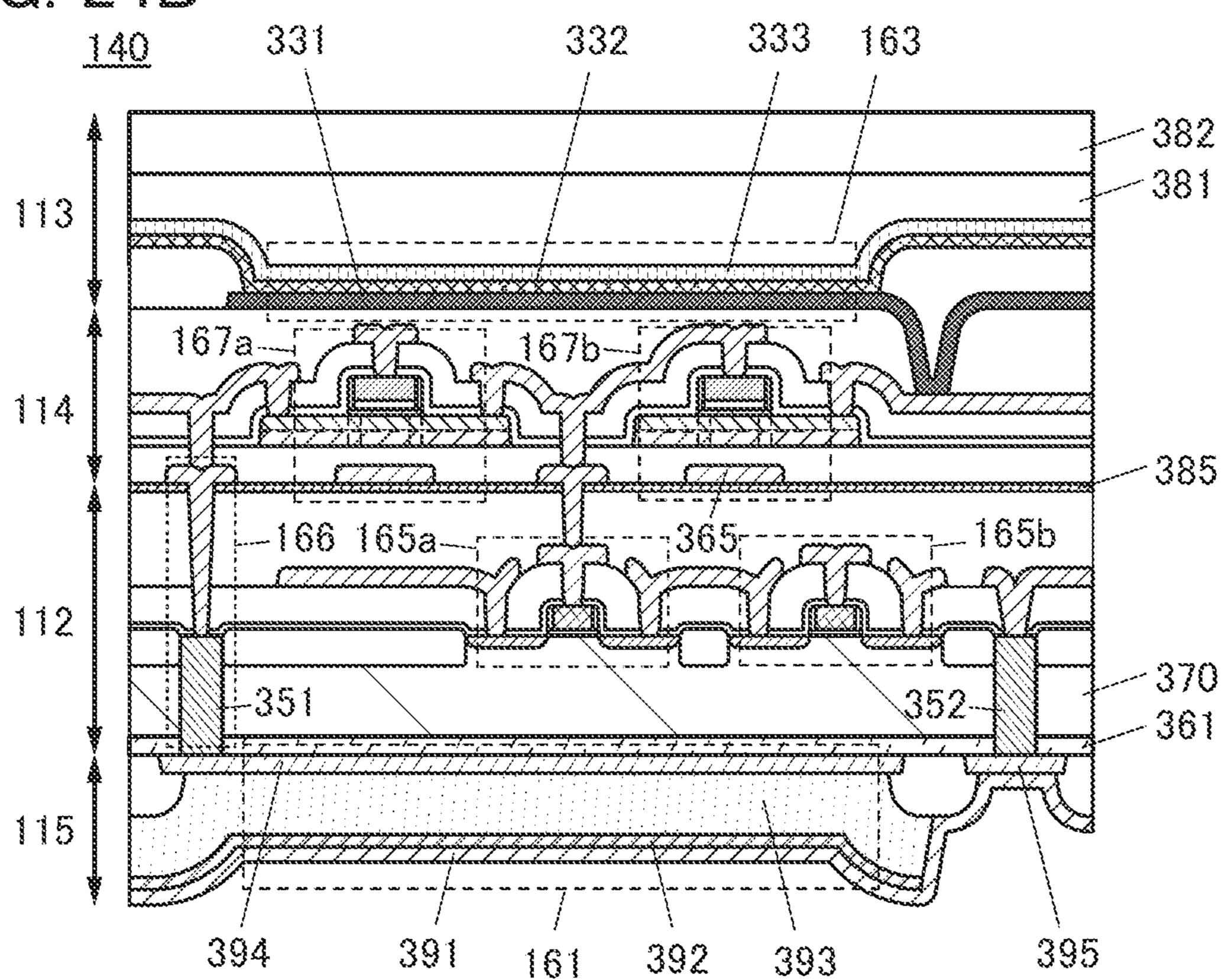

FIGS. 23A and 23B each illustrate a structure of a pixel in an imaging device;

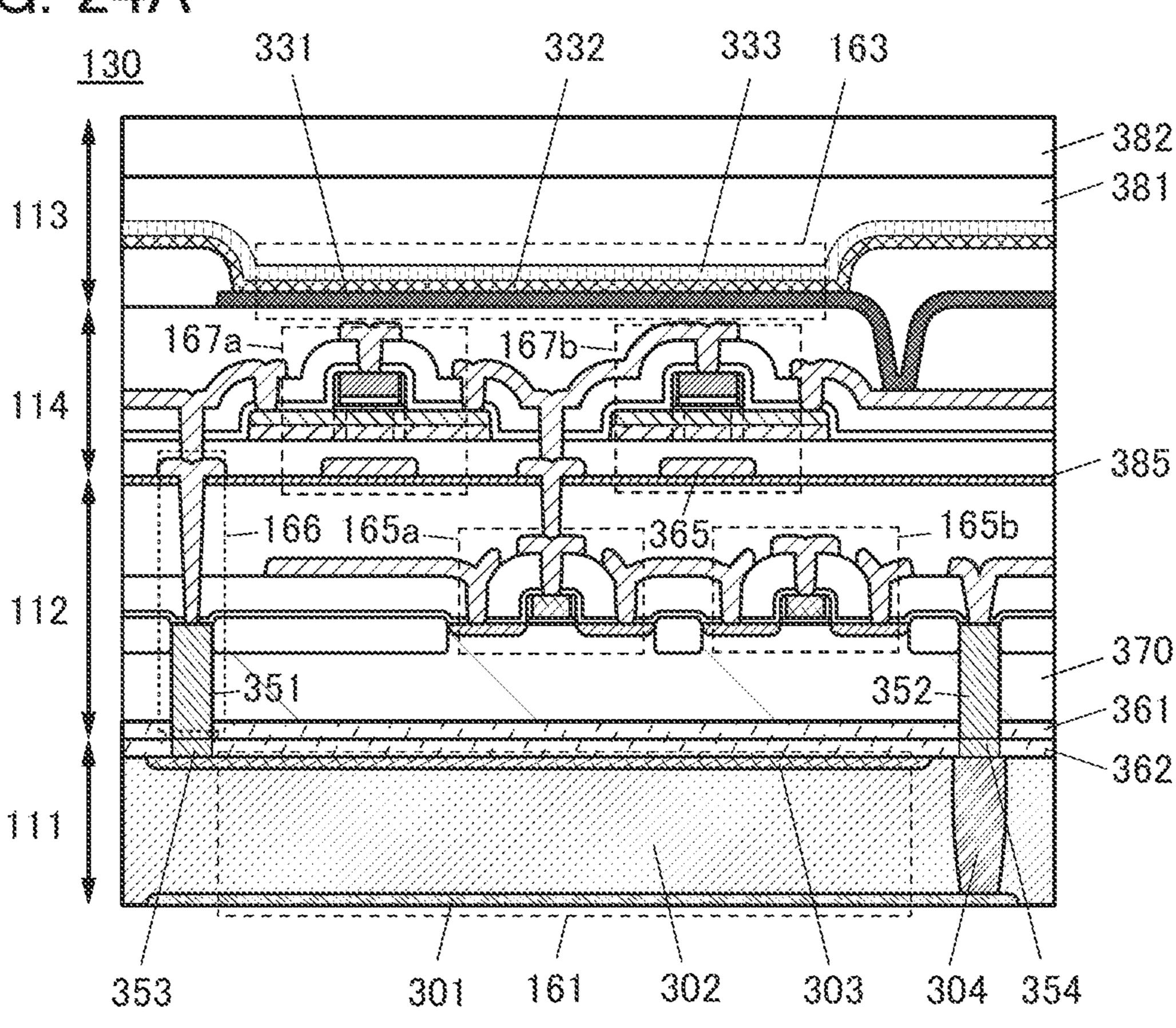

FIGS. 24A and 24B each illustrate a structure of a pixel in an imaging device;

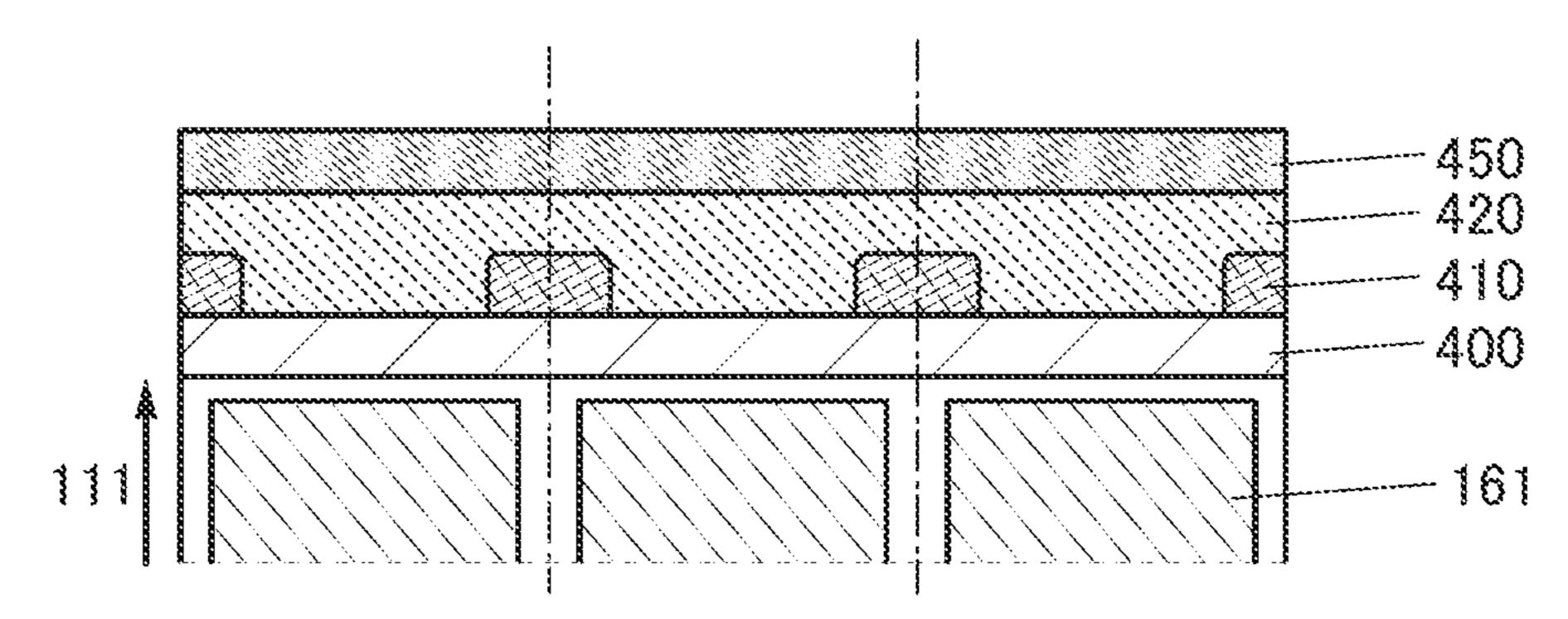

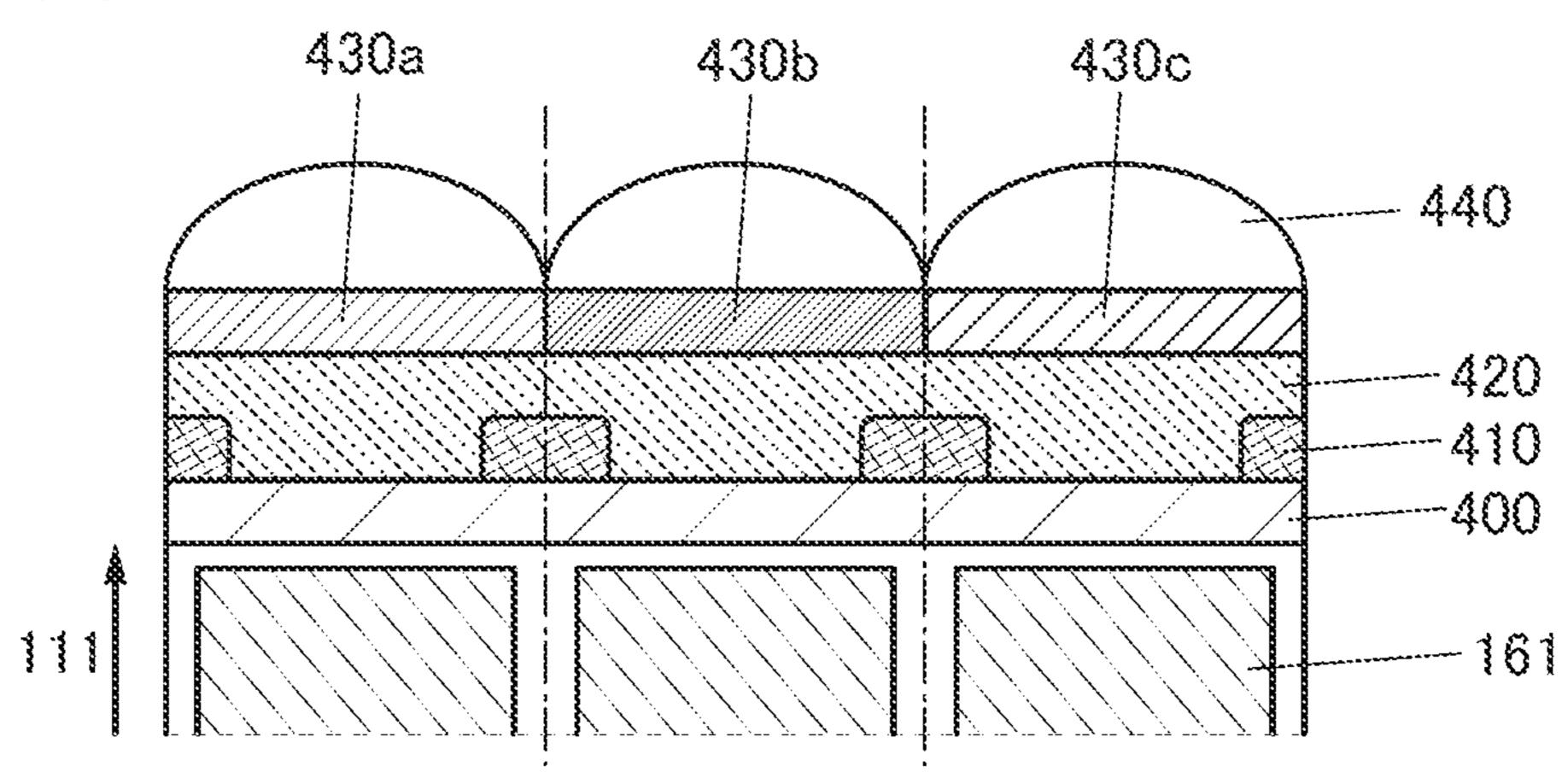

FIGS. 25A to 25E each illustrate a structure of a pixel in an imaging device;

FIGS. 26A to 26C each illustrate a structure of an imaging device; and

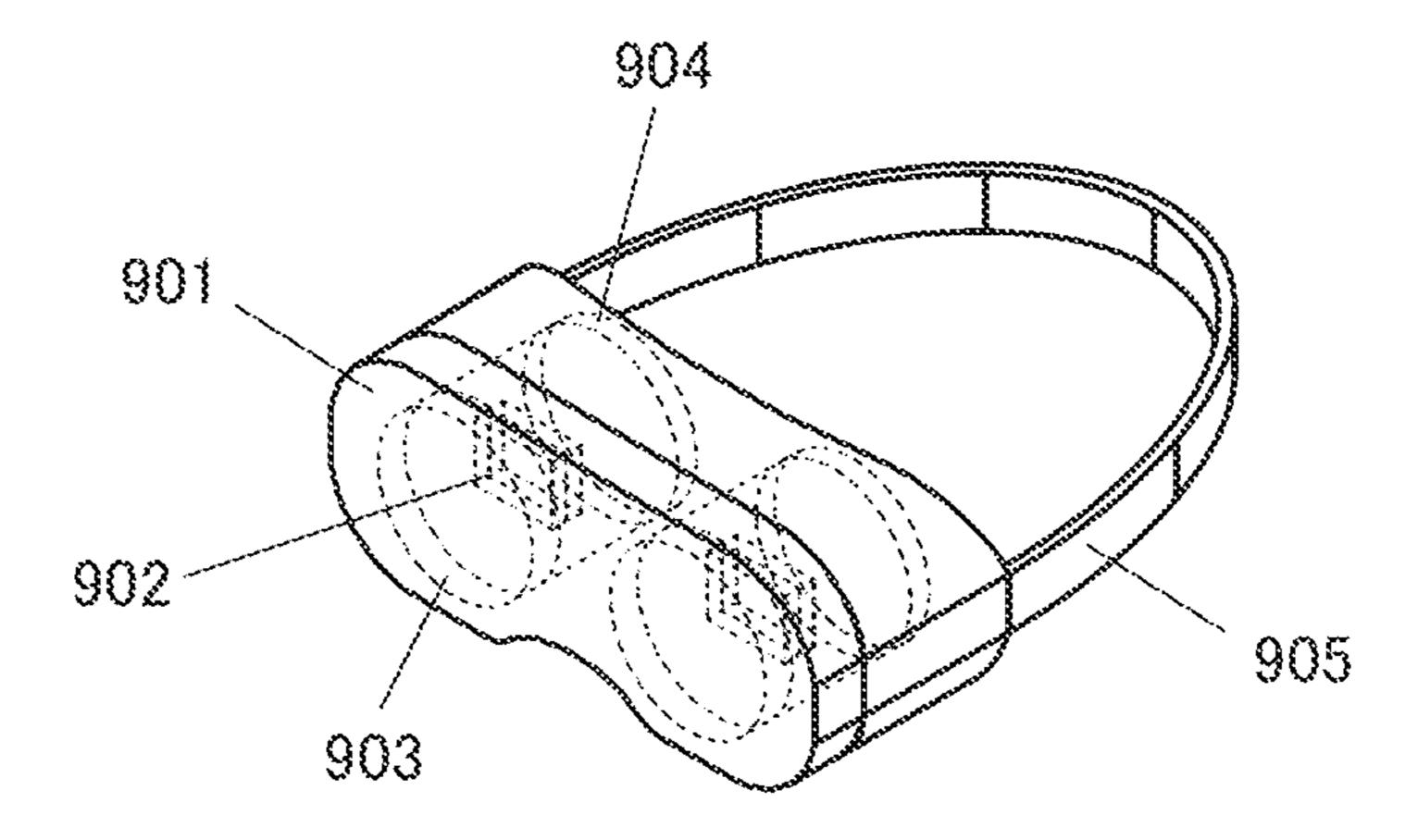

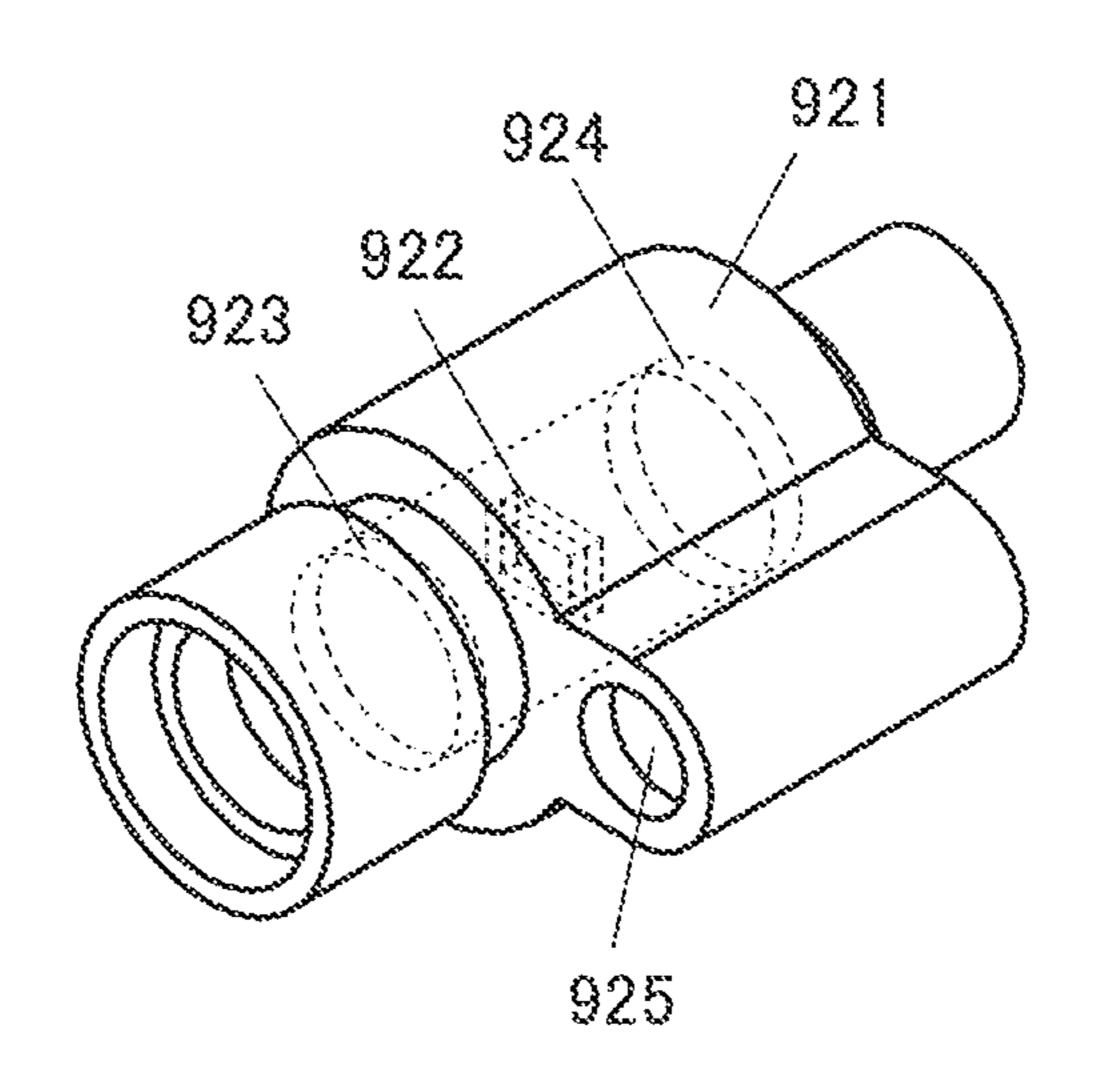

FIGS. 27A to 27C each illustrate an electronic device.

# BEST MODE FOR CARRYING OUT THE INVENTION

Embodiments will be described in detail with reference to the drawings. Note that the present invention is not limited to the following description and it will be readily appreciated by those skilled in the art that modes and details can be

modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the present invention should not be interpreted as being limited to the description of embodiments below. Note that in structures of the invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description thereof is not repeated in some cases. It is also to be noted that the same components are denoted by different hatching patterns in different drawings, or the hatching patterns are omitted in 10 some cases.

#### Embodiment 1

In this embodiment, an imaging display device of one 15 embodiment of the present invention will be described with reference to drawings.

One embodiment of the present invention is an imaging display device including an imaging portion and a display portion. The imaging display device includes the imaging 20 portion on a first surface and the display portion on a second surface that is opposite to the first surface. Since the light sensing surface and the light emission surface face the opposite directions, the structure of this imaging display device is suitable for smart glasses, a telescope, binoculars, 25 a monocle, a microscope, a night scope, and the like.

The imaging display device includes a pixel in each of the imaging portion and the display portion, and the pixel in the imaging portion is electrically connected to the pixel in the display portion. In other words, a portion functioning as the 30 imaging portion and a portion functioning as the display portion are included in one pixel. With such a structure, an image signal obtained at the imaging portion can be directly input to the display portion. Accordingly, the time delay due to data conversion can be eliminated, so that a captured 35 image can be displayed in a moment.

FIG. 1 illustrates an imaging display device of one embodiment of the present invention. An imaging display device 100 includes an imaging portion (IS) 101 and a display portion (DIS) 102. A lens 103 may be provided 40 between the imaging portion 101 and an object 105. Furthermore, a lens 104 may be provided between the display portion 102 and a viewer 106.

For example, the lens 103 has a function of demagnifying an image of the object 105 and throwing the image onto the 45 imaging portion 101. Furthermore, the lens 104 has a function of magnifying the image displayed on the display portion 102 for the viewer 106. Although the lenses 103 and 104 are each illustrated as consisting of one convex lens in FIG. 1, the structures and functions thereof are determined 50 as needed, and a combination lens or the like may be used as well. Moreover, a mirror which adjusts the optical path may be provided between the display portion 102 and the object 105.

Pixels in the imaging portion 101 are each electrically 55 connected to corresponding pixels in the display portion 102 with one-to-one correspondence. Accordingly, analog data obtained at the pixels in the imaging portion 101 as image signals is transmitted to the pixels in the display portion 102 without being converted into digital data, and display is 60 performed.

Therefore, the imaging display device of one embodiment of the present invention can significantly reduce the delay in displaying the reality.

FIG. 2 illustrates an example of a block diagram of the 65 imaging display device 100. The imaging display device 100 includes a data processing portion 200 in addition to the

6

imaging portion 101 and the display portion 102. The data processing portion 200 includes an arithmetic portion (CPU) 201, an image processing portion (GPU) 202, a position sensor (GPS) 203, an input output portion (I/O) 204, and a memory portion (MEM) 205, for example.

The imaging portion 101, the display portion 102, and the components of the data processing portion 200 are electrically connected to each other, and can transmit signals and data as necessary. Note that any of the components is not electrically connected to any of the other components, in some cases. Furthermore, any of the components has a function of any of the other components, in some cases. Moreover, a function of one component is distributed among a plurality of components, in some cases.

The imaging portion 101 has a function of capturing image data, and an imaging device such as a CMOS image sensor can be used, for example. The display portion 102 has a function of displaying image data, and a display device including a light-emitting element such as an organic EL element is preferably used, for example.

The arithmetic portion 201 has a function of performing an arithmetic operation associated with the operation of the whole imaging display device 100, and a central processing unit (CPU) or the like can be used, for example.

The image processing portion 202 has a function of processing data on images, and a graphics processing unit (GPU) or the like can be used, for example. Furthermore, the image processing portion 202 can include a neural network (NN) 207 for analyzing images.

The position sensor 203 has a function of specifying the position of the imaging display device 100, and a global positioning system (GPS) receiver can be used, for example. Moreover, a gyro sensor, an acceleration sensor, an optical sensor, a temperature sensor, or the like may be included.

The input output portion 204 has a function of obtaining data from the outside or a function of outputting data to the outside. For example, the input output portion 204 can be connected to a wired or wireless network, and data can be input to and output from a server (SV) 206 via the network. A medium which stores data to which the obtained image data is compared may be connected to the input output portion 204.

The memory portion 205 has a function of storing programs and items to set which are responsible for operating the imaging display device 100. Furthermore, the memory portion 205 has a function of storing image data captured with the imaging portion 101. A detachable storage medium (MEM) 208 which functions as part of the memory portion 205 may be used.

The neural network 207 performs an operation of estimating the category of an object whose image is captured with the imaging portion 101 (whether the object is a building, a plant, or a human, for example). In the case where AR display of data on an object is desired for example, data on an object that is not specified by the position is conventionally hard to obtain although it is possible to obtain data on a building, a road, or the like by using the position sensor 203.

In the case where only image data on an object is transmitted to the server 206 to obtain related data, the server 206 needs to analyze the category of the object and then identify the object, which is a big burden on the server 206 and requires much time for retrieval. Moreover, in some cases, analysis cannot be performed owing to the lack of data or additional data is necessary to accomplish the analysis.

The neural network 207 estimates the category and transmits the category estimation result as well as image data. This can significantly reduce the analysis burden on the server 206. In addition, data obtained with the position sensor 203 may be transmitted to the server 206 together. 5 Transmission of data to the server **206** after determining the category allows a retrieval result to be quickly obtained from the server 206.

Thus, in the imaging display device of one embodiment of the present invention where the category of an object is 10 estimated by using the neural network, an image that well matches the reality can be AR-displayed.

Here, an example of an operation of performing AR display at a given timing in a period when an imaging operation at the imaging portion 101 and a display operation 15 at the display portion 102 are repeated in the imaging display device 100 will be described with reference to a flow chart of FIG. 3. It is assumed that the positional data is obtained with the position sensor 203 at the same time as the imaging operation or the like is performed. Furthermore, it is 20 assumed that in the case where other sensors are provided, a variety of environmental data are obtained with the other sensors at the same time as the imaging operation or the like is performed.

First, an object is extracted from an image captured with 25 the arithmetic portion 201, the image processing portion **202**, and the like, and image analysis is performed. In this step, the number of objects in the image and the shape, color, and the like of the object are classified (S1).

Next, an object for which data display is performed is 30 selected (S2). Note that settings may be made previously so that all the objects in the image can be selected.

Next, the category of the selected object is estimated with the neural network 207 by using the already obtained from the image analysis in S1 (S3).

Next, the image of the object, data used for the category estimation in S3, and the category estimation result are transmitted to the server 206, and data on the object is retrieved in the server **206** (S4).

Then, data on the object is received from the server 206 (S5), and the data is AR-displayed on the display portion 102 (S6).

To change the object for which data display is performed, the process returns to S2 and the object selection is made 45 agaın.

Next, structure examples that can be used for the imaging display device 100 will be described with reference to FIGS. **4**A to **4**D, FIGS. **5**A to **5**D, FIGS. **6**A and **6**B, and FIGS. **7**A and 7B. Components common to FIGS. 4A to 4D, FIGS. 5A 50 to **5**D, FIGS. **6**A and **6**B, and FIGS. **7**A and **7**B are denoted by the same reference numerals.

An imaging display device 110 illustrated in FIG. 4A has a structure in which a layer 111, a layer 112, and a layer 113 are sequentially stacked. In the imaging display device 110, 55 components of the imaging portion 101 can be provided in the layer 111 and the layer 112. Furthermore, components of the display portion 102 can be provided in the layer 112 and the layer 113.

FIG. 4C illustrates the layers in the imaging display 60 device 110. The layer 111 includes a region 153 in which a photodiode is provided. As the photodiode, a PN photodiode or a PIN photodiode which includes a silicon substrate as a photoelectric conversion layer is preferably used.

The layer 112 includes a region 151 and regions 152 65 which are provided in a silicon substrate. The region **151** and the regions 152 each include a transistor whose channel

formation region is formed using silicon. The number of regions 152 is more than one, and each of the regions 152 can be provided with a circuit having a function different from each other.

The region 151 has a structure in which both a pixel circuit (excluding the photoelectric conversion element) of the imaging portion 101 and a pixel circuit (excluding a display element) of the display portion 102 are provided. The regions 152 can be provided with a driver circuit, a reading circuit, or the like for the pixel circuits of the imaging portion 101 and the display portion 102.

The layer 113 includes a region 150 provided with the display element. As the display element, a light-emitting element including an organic EL layer is preferably used.

Note that the region 153, the region 151, and the region 150 substantially have the same area.

FIG. 6A illustrates an electric connection between components constituting one pixel of the imaging display device 110. The region 153 includes a photoelectric conversion element 161. The region 151 includes a transistor 162a and a transistor 162b. The region 150 includes a display element **163**.

The transistors 162a and 162b are components of a pixel circuit 162 in the imaging portion 101 and the display portion 102. The photoelectric conversion element 161, the transistors 162a and 162b, and the display element 163 are arranged in a matrix in the region 153, the region 151, and the region 150, respectively.

The photoelectric conversion element **161** is placed so as to include a region overlapping with the transistors 162a and **162***b*. One electrode of the photoelectric conversion element **161** is electrically connected to one of a source and a drain of the transistor **162***a*.

The transistors 162a and 162b are placed so as to include positional data or the like on the object and data obtained 35 a region overlapping with the display element 163. One of a source and a drain of the transistor 162b is electrically connected to one electrode of the display element 163.

Note that the other of the source and the drain of the transistor 162a is electrically connected to a gate of the transistor 162b. A circuit corresponding to the pixel circuit 162 will be described in detail later.

FIG. 7A illustrates an electric connection between the pixel circuit 162 and circuits 152a, 152b, 152c, and 152dprovided in the regions 152 in the imaging display device 110. Note that the circuits 152a, 152b, 152c, and 152d can have a function of driving the pixel circuit 162, a function of reading out a signal from the pixel circuit 162, or the like.

The circuit 152a can have a function of a row driver for the imaging portion 101. The circuit 152a is electrically connected to a component of the pixel circuit 162 through a wiring. The circuit 152b can have a function of the column driver for the imaging portion 101. The circuit 152b may also have a function of a correlated double sampling (CDS) circuit for removing noise and a function of an A/D converter. The circuit 152b is electrically connected to the component of the pixel circuit 162 through a wiring.

The circuit 152c can have a function of a row driver for the display portion 102. The circuit 152c is electrically connected to the component of the pixel circuit 162 through a wiring. The circuit **152**d can have a function of a column driver for the display portion 102. The circuit 152d is electrically connected to the component of the pixel circuit **162** through a wiring.

As in FIG. 4D illustrating the layers, by reducing the relative area of the region 151 in the layer 112, the relative area of the regions 152 in the layer 112 can be increased. In this case, the regions 152 may be provided with not only the

above-described driver circuits but also any of components included in the data processing portion 200 or some circuits included in the components.

Furthermore, the imaging display device 100 may have a structure of an imaging display device 120 illustrated in FIG. 5

4B. The imaging display device 120 is different from the imaging display device 110 in the structure of the photoelectric conversion element and includes a layer 115.

The photoelectric conversion element provided in the layer 115 preferably includes selenium or a selenium compound. A photoelectric conversion element including a selenium-based material can increase the light sensitivity under low illumination by utilizing the avalanche effect. Moreover, a photoelectric conversion layer may be used.

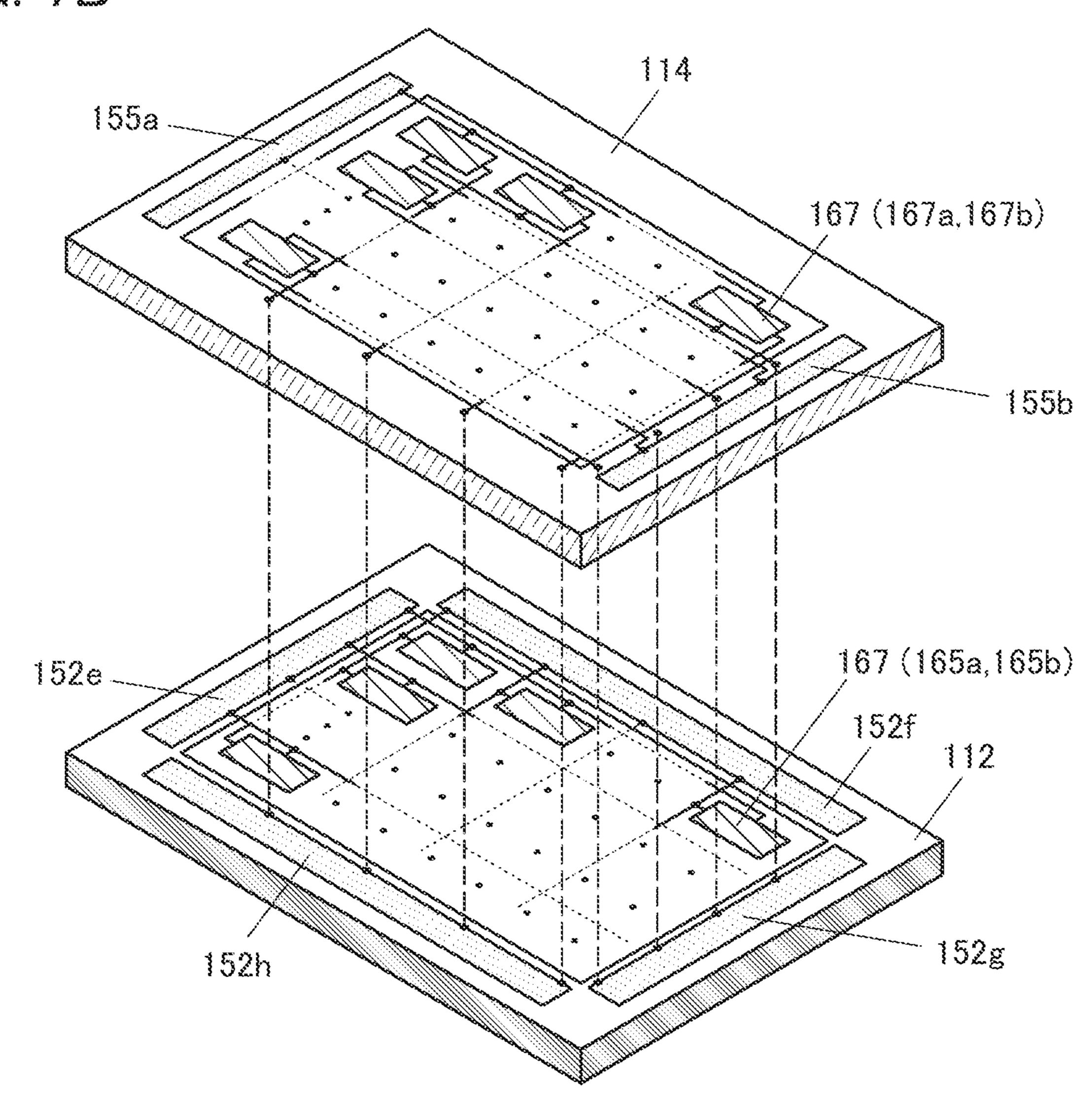

Moreover, the imaging display device 100 may have a structure of an imaging display device 130 illustrated in FIG. 5A. The imaging display device 130 has a structure in which the layer 111, the layer 112, a layer 114, and the layer 113 are sequentially stacked.

In the imaging display device 130, the components of the imaging portion 101 can be provided in the layer 111, the layer 112, and the layer 114. Furthermore, the components of the positive of the display portion 102 can be provided in the layer 112, 25 wiring. The layer 114, and the layer 113.

As in FIG. 5C illustrating the layers, the layer 114 includes a region 154 and regions 155. The region 154 and the regions 155 each include a transistor whose channel formation region is formed using a metal oxide. The number 30 of regions 155 is more than one, and each of the regions 155 can be provided with a circuit having a function different from each other.

The region 154 has a structure in which both components of a pixel circuit of the imaging portion 101 (excluding the 35 photoelectric conversion element) and components of a pixel circuit of the display portion 102 (excluding the display element) are provided. The regions 155 can be provided with a driver circuit or the like for the pixel circuits of the imaging portion 101 and the display portion 102.

FIG. 6B illustrates an example of an electric connection between components constituting a pixel of the imaging display device 130. The region 153 includes the photoelectric conversion element 161. The region 151 includes a transistor 165a, a transistor 165b, and a connection portion 45 166. The region 154 includes a transistor 167a and a transistor 167b. The region 150 includes the display element 163.

The transistors 165a, 165b, 167a, and 167b are components of a pixel circuit 167 in the imaging portion 101 and 50 the display portion 102. The connection portion 166 can be a through hole or the like formed in the silicon substrate.

The photoelectric conversion element 161, the transistors 165a and 165b, the transistors 167a and 167b, and the display element 163 are arranged in a matrix in the region 55 153, the region 151, the region 154, and the region 150, respectively.

The photoelectric conversion element **161** is placed so as to include a region overlapping with the transistors **165***a* and **165***b*. One electrode of the photoelectric conversion element 60 **161** is electrically connected to one of a source and a drain of the transistor **167***a* through the connection portion **166**.

One of the transistors 165a and 165b is placed so as to include a region overlapping with one of the transistors 167a and 167b. A gate of the transistor 165a is electrically 65 connected to the other of the source and the drain of the transistor 167a.

**10**

The transistors 167a and 167b are placed so as to include a region overlapping with the display element 163. One of a source and a drain of the transistor 167b is electrically connected to one electrode of the display element 163.

Note that the other of the source and the drain of the transistor 167a is electrically connected to a gate of the transistor 167b. A circuit corresponding to the pixel circuit 167 will be described in detail later.

FIG. 7B illustrates an electric connection among the pixel circuit 167, circuits 155a and 155b in the regions 155, and circuits 152e, 152f, 152g, and 152h, in the imaging display device 130. Note that the circuits 155a, 155b, 152e, 152f, 152g, and 152h can have a function of driving the pixel circuit 167, a function of reading out a signal from the pixel circuit 167, or the like.

The circuits 155a and 155b provided in the layer 114 can have a function of a row driver for the display portion 102. The circuits 155a and 155b can each be electrically connected to the component of the pixel circuit 167 provided in the layer 114 through a wiring.

The circuit 152h provided in the layer 112 can have a function of a column driver for the display portion 102. The circuit 152h can be electrically connected to the component of the pixel circuit 167 provided in the layer 114 through a wiring.

The circuits 152e and 152g provided in the layer 112 can have a function of a row driver for the imaging portion 101. The circuit 152e can be electrically connected to the component of the pixel circuit 167 provided in the layer 112 through a wiring. The circuit 152g can be electrically connected to the component of the pixel circuit 167 provided in the layer 114 through a wiring.

The circuit 152f provided in the layer 112 can have a function of a column driver for the imaging portion 101. The circuit 152f may have a function of a CDS circuit for removing noise and a function of an A/D converter. The circuit 152f is electrically connected to the component of the pixel circuit 167 provided in the layer 112 through a wiring.

As in FIG. 5D illustrating the layers, by reducing the relative area of the region 154 in the layer 114, the relative area of the regions 155 in the layer 114 can be increased. In this case, the regions 155 may be provided with not only the above-described driver circuits but also any of components included in the data processing portion 200 or some circuits included in the components.

Furthermore, the imaging display device 100 may have a structure of an imaging display device 140 illustrated in FIG. 5B. The imaging display device 140 is different from the imaging display device 130 in the structure of the photoelectric conversion element and includes the layer 115 in which a photoelectric conversion element including selenium or a selenium compound is provided.

Although the circuits electrically connected to the imaging portion 101 or the display portion 102 are provided in the regions 152 or the regions 155 in the above-described examples, such circuits may be provided in an external IC chip.

Structure examples of a pixel circuit that can be used as the above-described pixel circuit 162 or 167 will be described with reference to FIGS. 8A to 8C, FIGS. 9A and 9B, FIGS. 10A and 10B, FIGS. 11A and 11B, FIGS. 12A and 12B, FIGS. 13A and 13B, and FIGS. 14A and 14B. Note that components (e.g., transistors) having functions common to FIGS. 8A to 8C, FIGS. 9A and 9B, FIGS. 10A and 10B, FIGS. 11A and 11B, FIGS. 12A and 12B, FIGS. 13A and 13B, and FIGS. 14A and 14B are denoted by the same reference numerals. Although not strictly separable, a por-

tion which mainly operates as the pixels of the display portion 102 is referred to as a circuit portion 102a.

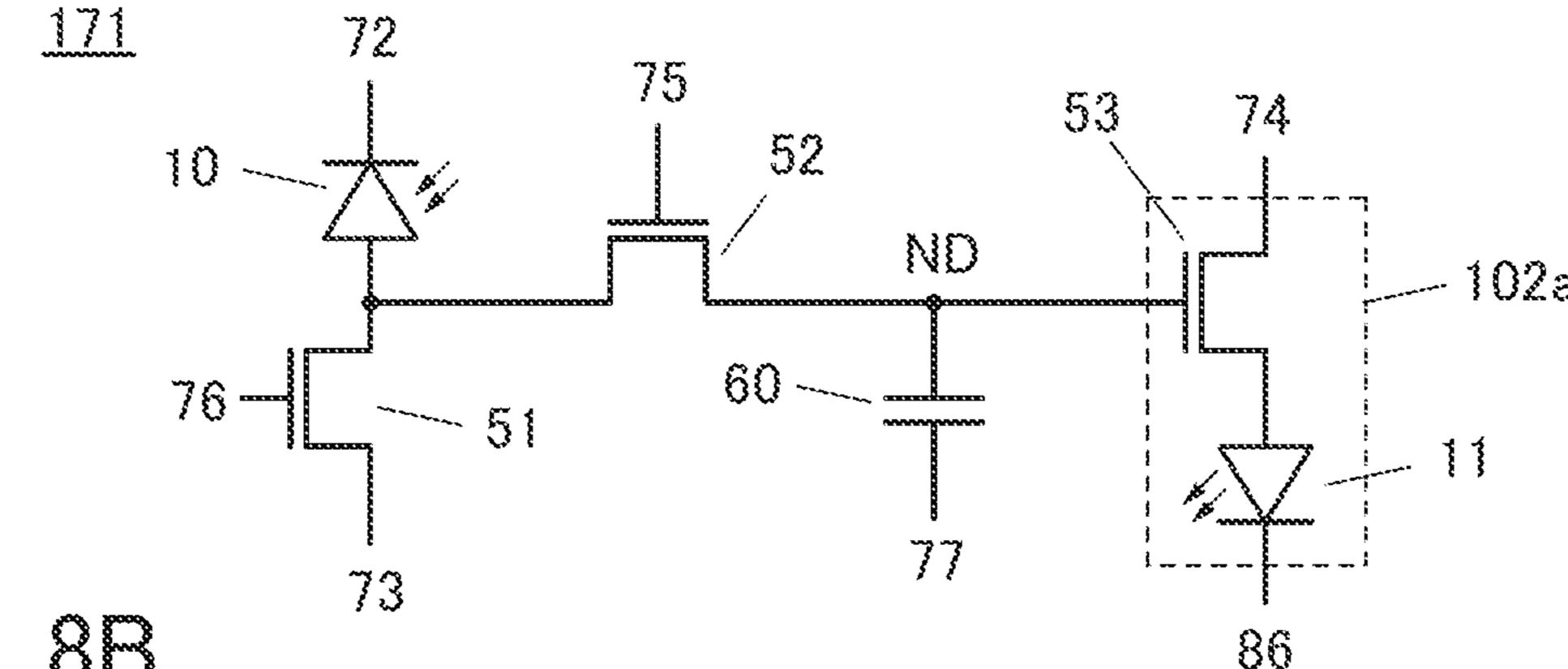

A pixel circuit 171 illustrated in FIG. 8A is a fundamental structure of one embodiment of the present invention. The pixel circuit 171 has a function of determining a potential of 5 a charge detection portion ND by a photoelectric conversion element and making a display element emit light in accordance with the potential of the charge detection portion ND. Accordingly, an operation from image capturing to image display can be performed at high speed, without a step for 10 data conversion or the like.

The pixel circuit 171 includes a photoelectric conversion element 10, a transistor 51, a transistor 52, a transistor 53, a display element 11, and a capacitor 60.

Note that the photoelectric conversion element 10 corresponds to the photoelectric conversion element 161 illustrated in FIG. 6A or 6B. The transistor 52 corresponds to the transistor 162a or 167a illustrated in FIG. 6A or 6B. The transistor 53 corresponds to the transistor 162b or 167b illustrated in FIG. 6A or 6B. The display element 11 corresponds to the display element 11 corresponds to the display element 163 illustrated in FIG. 6A or 6B.

One of a source and a drain of the transistor 51 is electrically connected to one electrode (anode) of the photoelectric conversion element 10. The one electrode of the 25 photoelectric conversion element 10 is electrically connected to one of a source and a drain of the transistor 52. The other of the source and the drain of the transistor 52 is electrically connected to a gate of the transistor 53. One of a source and a drain of the transistor 53 is electrically 30 connected to one electrode (anode) of the display element 11. The gate of the transistor 53 is electrically connected to one electrode of the capacitor 60. Note that a structure without the capacitor 60 may also be employed.

The other electrode (cathode) of the photoelectric conversion element 10 is electrically connected to a wiring 72. A gate of the transistor 51 is electrically connected to a wiring 76. A gate of the transistor 52 is electrically connected to a wiring 75. The other of the source and the drain of the transistor 51 is electrically connected to a wiring 73. 40 The other of the source and the drain of the transistor 53 is electrically connected to a wiring 74. The other electrode (cathode) of the display element 11 is electrically connected to a wiring 86. The other electrode of the capacitor 60 is electrically connected to a wiring 77.

The wirings 72, 73, 74, 77, and 86 can each have a function of a power supply line. For example, the wirings 73, 77, and 86 can function as low power supply lines, and the wiring 74 can function as a high power supply line. The wirings 75 and 76 can function as signal lines for controlling 50 on/off of the transistors.

As the photoelectric conversion element 10, a photoelectric conversion element which causes the avalanche effect may be used to increase the light sensitivity under low illumination. A relatively high potential HVDD (e.g., higher 55 than 10 V and higher than VDD) is necessary to cause the avalanche effect. Accordingly, it is preferable to electrically connect the wiring 72 to a power supply that can feed the potential HVDD. Note that the photoelectric conversion element 10 can also be used in the state of being supplied 60 with a potential which does not cause the avalanche effect. Furthermore, an element which does not cause the avalanche effect can also be used as the photoelectric conversion element 10.

The transistor **51** can have a function of initializing the potential of the charge detection portion ND. The transistor **52** can have a function of controlling the charge detection

12

portion ND. The transistor 53 can have a function of controlling a current that flows toward the display element 11 in accordance with the potential of the charge detection portion ND.

As in a pixel circuit 172 illustrated in FIG. 8B, one of a source and a drain of a transistor 54 may be electrically connected to the gate of the transistor 53, and the other of the source and the drain of transistor 54 may be electrically connected to the one electrode of the capacitor 60. In this case, a wiring 87 that can function as a signal line is electrically connected to a gate of the transistor 54.

With the structure of the pixel circuit 172, the capacitance of the charge detection portion ND can be varied. Thus, by turning off the transistor 54 under low illumination, an image can be captured with high sensitivity. Furthermore, by turning on the transistor 54 under high illumination, an image can be captured with low sensitivity.

In the pixel circuits 171 and 172, sensitivity-adjustable image capturing is possible also by setting the potential supplied to the wiring 74 to be variable. In particular, increasing the potential supplied to the wiring 74 is suitable for the uses such as a night scope because it can increase the luminance of the display element 11.

In the case where high voltage is applied to the photoelectric conversion element 10, a transistor connected to the photoelectric conversion element 10 needs to withstand the high voltage. As the transistor that can withstand high voltage, for example, a transistor including a metal oxide in a channel formation region (hereinafter referred to as an OS transistor) or the like can be used. Specifically, OS transistors are preferably used as the transistors 51 and 52.

A period during which charges can be held in the charge detection portion ND can be extremely long owing to the low off-state current characteristics of the transistors 51 and same time 76. A gate of the transistor 52 is electrically conceted to a wiring 75. The other of the source and the drain

Accordingly, in the case where high voltage is applied to the photoelectric conversion element 10, the structure of the imaging display device 130 or 140 is preferably used. Note that in the case where the pixel circuit 171 or 172 is used in the imaging display device 130 or 140, the transistors 165a and 165b are not necessary.

Moreover, in the case where the photoelectric conversion element 10 is used without application of high voltage, transistors including silicon in their active layers or active regions (hereinafter referred to as Si transistors) may be used as the transistors 51 and 52. Accordingly, the structure of the imaging display device 110 or 120 can also be used.

As the display element 11, a light-emitting element is preferably used. An organic EL element (OLED) including an organic light-emitting layer or the like can be used as the light-emitting element. An organic EL element shows diode characteristics and a current can flow therethrough by application of a forward bias. By adjusting the current with the transistor, the luminance can be changed.

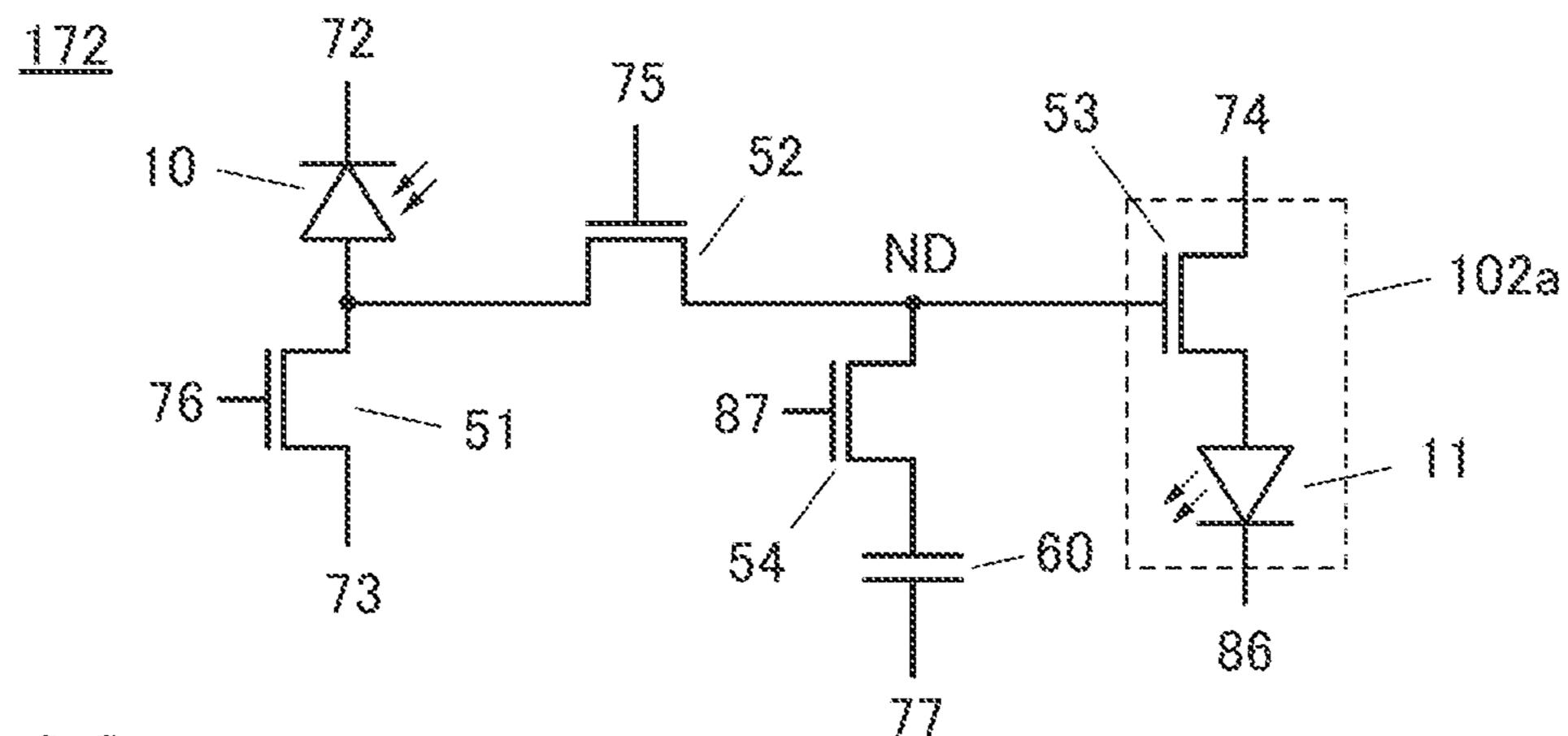

Next, a fundamental operation of the pixel circuits 171 and 172 will be described with reference to a timing chart of FIG. 8C. Note that in the following operation example, VDD and GND are supplied to the wirings 75 and 76 as "H" and "L", respectively; VDD is supplied to the wirings 72 and 74; and GND is supplied to the wirings 73, 77, and 86. Other potentials can also be supplied to the wirings.

At Time T1, the wiring 76 is set at "H" and the wiring 75 is set at "H", to make the charge detection portion ND have

a reset potential (GND) (reset operation). At this time, the transistor 53 is off and the display element 11 does not emit light.

At Time T2, the wiring 76 is set at "L" and the wiring 75 is set at "H", to make the potential of the charge detection portion ND start changing (accumulation operation). The potential of the charge detection portion ND is changed from GND to VDD at the maximum depending on the intensity of light that has entered the photoelectric conversion element 10.

At Time T3, the wiring 75 is set at "L" to settle the potential of the charge detection portion ND. At this time, if the potential of the charge detection portion ND is higher than the threshold of the transistor 53, the transistor 53 is turned on, and the display element 11 emits light in accordance with the current value (display operation).

The display state continues for a certain period of time, and then the reset operation is performed again at Time T4. The above-described operations are repeated; thus, image capture and display operations can be performed at high speed. Furthermore, black display is inserted by the reset operation at proper intervals, which can reduce the afterimage or the like of moving images.

In the case where the pixel circuits 171 and 172 are used, 25 image capture and display of images can be performed by the above-described simple control method. In such a case, a pixel selection circuit or the like such as a shift register is unnecessary, and the reset operation, the accumulation operation, or the display operation can be performed in all 30 the pixels at the same time.

Furthermore, one embodiment of the present invention may have a structure of a pixel circuit 173 illustrated in FIG. 9A. The pixel circuit 173 is different from the pixel circuit 171 in having a capability of outputting captured data to the 35 outside of the pixel.

The pixel circuit 173 includes the structure of the pixel circuit 171, a transistor 55, and a transistor 56. A gate of the transistor 55 is electrically connected to the other of the source and the drain of the transistor 52. One of a source and 40 a drain of the transistor 55 is electrically connected to one of a source and a drain of the transistor 56.

Note that the transistor 55 corresponds to the transistor 165a illustrated in FIG. 6B. The transistor 53 corresponds to the transistor 165b illustrated in FIG. 6B. The transistors 55 45 and 56 may also be provided in the region 151 of the imaging display devices 110 and 120.

The other of the source and the drain of the transistor 55 is electrically connected to a wiring 79. The other of the source and the drain of the transistor 56 is electrically 50 connected to a wiring 71. A gate of the transistor 56 is electrically connected to a wiring 78.

The wiring **79** can have a function of a power supply line. For example, the wiring **79** can function as a high potential power supply line. The wiring **71** can have a function of an 55 output line which outputs a signal from the pixel. The wiring **78** can function as a signal line which controls on/off of the transistor.

The transistor **55** can have a function of outputting a signal determined in accordance with the potential of the 60 charge detection portion ND. The transistor **56** can have a function of selecting a pixel from which a signal is read.

Because the transistor **55** is desired to have excellent amplifying characteristics, the transistor **55** preferably has a high on-state current. Accordingly, it is preferable to use Si 65 transistors as the transistors **55** and **56**. As a matter of course, OS transistors may be used as the transistors **55** and **56**.

**14**

Next, a fundamental operation of the pixel circuit 173 will be described with reference to a timing chart of FIG. 9B. Note that in the following operation example, VDD and GND are supplied to the wirings 75, 76, and 78 as "H" and "L", respectively; VDD is supplied to the wirings 72, 74, and 79; and GND is supplied to the wirings 73, 77, and 86. Other potentials can also be supplied to the wirings.

The description of FIG. 8B can be referred to for operations from Time T1 to Time T3.

At Time T4, the wiring 78 is set at "H" to turn on the transistor 56. Thus, an image signal corresponding to the potential of the charge detection portion ND is output to the wiring 71.

At Time T5, the reset operation is performed again. The above-described operations are repeated; thus, image capture and display operations can be performed at high speed and image data can be output to the outside.

In the case where the pixel circuit 173 is used, a row driver and a column driver for selecting a pixel for image capture are necessary. The row driver and the column driver can be provided in the regions 152 or the like.

Furthermore, one embodiment of the present invention may have a structure of a pixel circuit 174 illustrated in FIG. 10A. The pixel circuit 174 is different from the pixel circuit 173 in having a capability of displaying a given image superimposed on a captured image.

The pixel circuit 174 includes the structure of the pixel circuit 173, a transistor 57, a transistor 58, and a display element 12.

One of a source and a drain of the transistor 57 is electrically connected to one electrode of the display element 12. A gate of the transistor 57 is electrically connected to one of a source and a drain of the transistor 58. The other of the source and the drain of the transistor 57 is electrically connected to the wiring 74. The other electrode of the display element 12 is electrically connected to the wiring 86. The other of the source and the drain of the transistor 58 is electrically connected to a wiring 81. A gate of the transistor 58 is electrically connected to a wiring 80.

Note that the transistors 57 and 58 can be provided in the region 151 of the imaging display devices 110 and 120 or the region 154 of the imaging display devices 130 and 140. An element similar to the display element 11 can be used as the display element 12. The display element 12 can be provided in the region 150.

The wirings 80 and 81 can have a function of signal lines. For example, the wiring 80 can function as a signal line which controls on/off of the transistor 58. The wiring 81 can function as a signal line which supplies an image signal.

The transistor 57 can have a function of controlling a current that flows toward the display element 12 in accordance with the potential supplied from the wiring 81. The transistor 58 can have a function of selecting a pixel which displays a given image.

Since the imaging display device using the pixel circuit 174 can display a given image using the transistors 57 and 58 and the display element 12, AR display in which data is superimposed on the displayed reality can be performed.

Next, a fundamental operation of the pixel circuit 173 will be described with reference to a timing chart of FIG. 10B. Note that in the following operation example, VDD and GND are supplied to the wirings 75, 76, 78, and 80 as "H" and "L", respectively; VDD is supplied to the wirings 72, 74, and 79; GND is supplied to the wirings 73, 77, and 86; and an arbitrary potential (image signal) is supplied to the wirings 81. Other potentials can also be supplied to the wirings.

The description of FIG. 8B can be referred to for an operation at Time T1.

At Time T2, the wiring 76 is set at "L", the wiring 75 is set at "H", and the wiring 80 is set at "H", to make the potential of the charge detection portion ND start changing 5 (accumulation operation). The potential of the charge detection portion ND is changed from GND to VDD at the maximum depending on the intensity of light that has entered the photoelectric conversion element 10. In addition, an image signal supplied from the wiring 81 is written to the 10 gate of the transistor 57.

At Time T3, the wiring 75 is set at "L" and the wiring 80 is set at "L", to settle the potential of the charge detection portion ND. At this time, if the potential of the charge detection portion ND is higher than the threshold of the 15 transistor 53, the transistor 53 is turned on, and the display element 11 emits light in accordance with the current value. Furthermore, if the potential of the gate of the transistor 57 is higher than the threshold of the transistor 57, the transistor 57 is turned on, and the display element 12 emits light in 20 accordance with the current value (display operation).

The description of FIG. 9B can be referred to for an operation after Time T4.

In the case where the pixel circuit **174** is used, a row driver and a column driver for selecting a pixel for image 25 capturing and display are necessary. The row driver and the column driver can be provided in the regions **152** and **155** or the like.

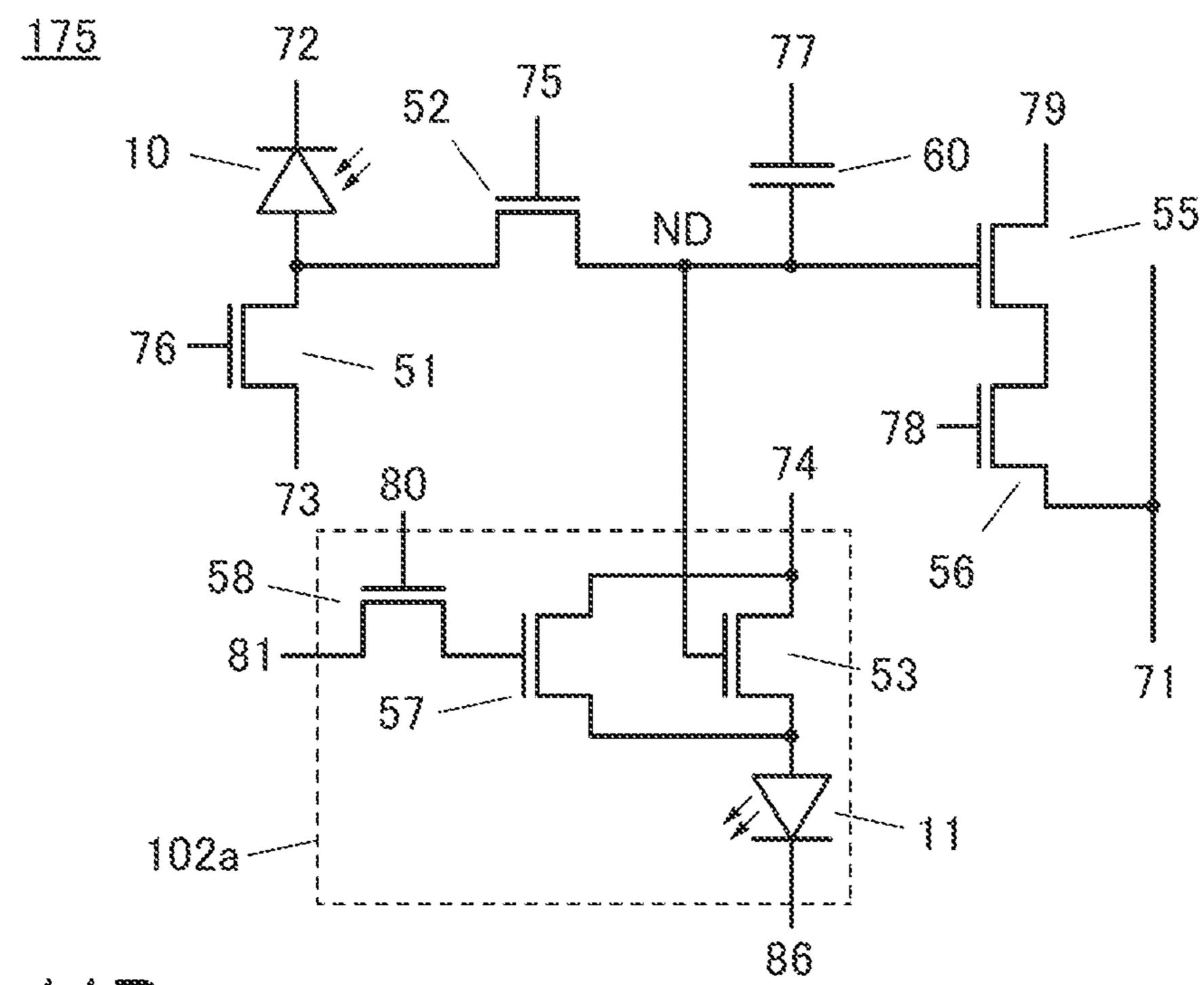

Moreover, one embodiment of the present invention may have a structure of a pixel circuit 175 illustrated in FIG. 11A. The pixel circuit 175 has a structure in which the display element 12 is eliminated from the pixel circuit 174, where the other of the source and the drain of the transistor 57 is electrically connected to the one electrode of the display element 11.

In the structure illustrated in FIG. 10A, either of the display elements 11 and 12 having a higher emission intensity is dominant in the displayed image. Thus, in order that an arbitrary image is displayed by the display element 12, the emission intensity of the display element 12 has to be increased so that the display element 12 can overwrite the image displayed by the display element 11. In the structure of FIG. 11A, the display element 12 can be eliminated because a signal can be input from the wiring 81 to overwrite the previous image displayed by the display element 11.

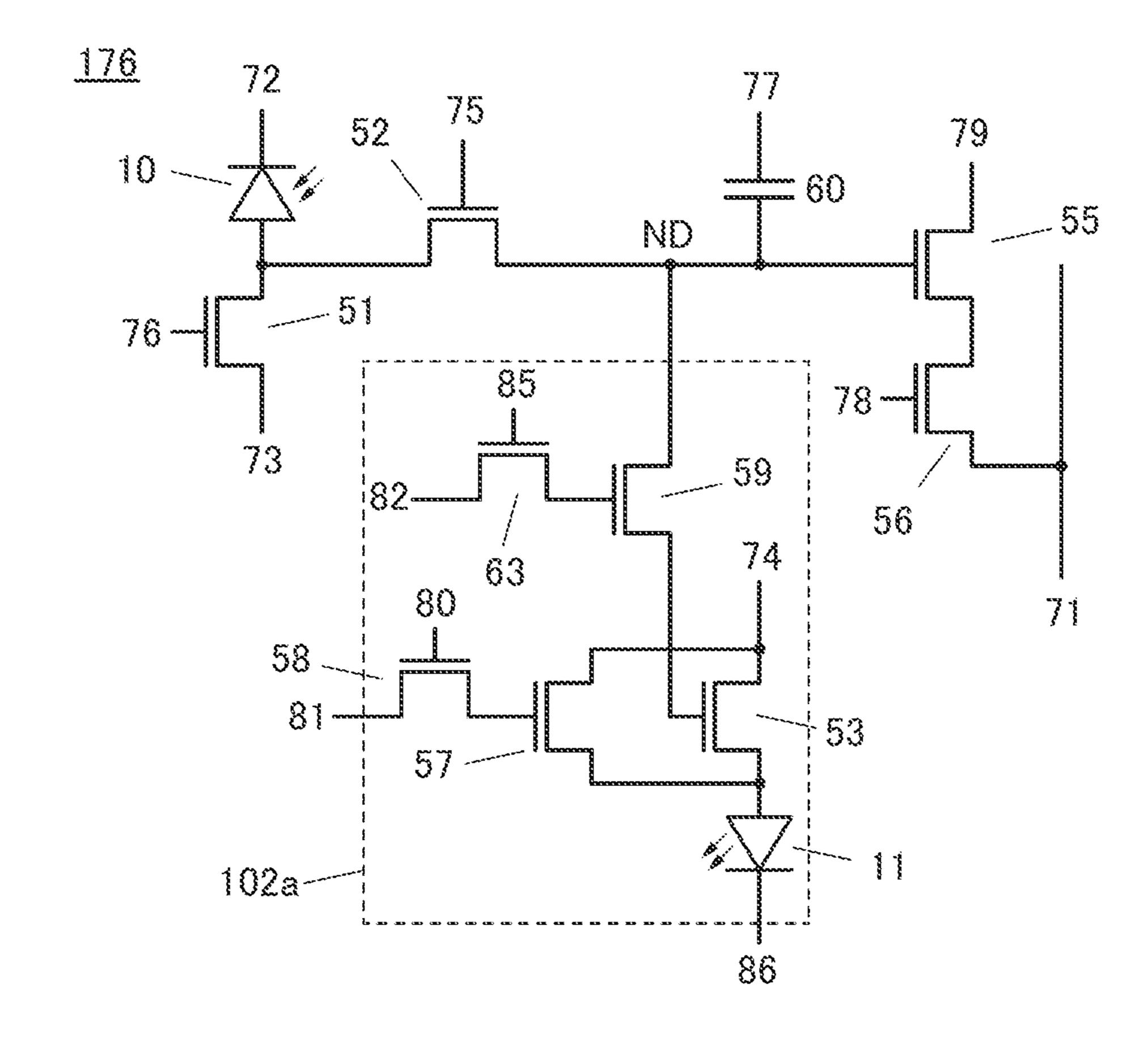

Moreover, one embodiment of the present invention may have a structure of a pixel circuit 176 illustrated in FIG. 11B. The pixel circuit 176 includes the structure illustrated in FIG. 11A, a transistor 59, and a transistor 63.

One of a source and a drain of the transistor **59** is 50 electrically connected to the other of the source and the drain of the transistor **52**. The other of the source and the drain of the transistor **59** is electrically connected to the gate of the transistor **53**. A gate of the transistor **59** is electrically connected to one of a source and a drain of the transistor **63**. 55 A gate of the transistor **63** is electrically connected to a wiring **85**. The other of the source and the drain of the transistor **63** is electrically connected to a wiring **85**.

The wiring **82** can function as a signal line which controls on/off of the transistor **59**. The wiring **85** can function as a 60 signal line which selects a pixel. Note that a structure without the transistor **63**, where the gate of the transistor **59** is electrically connected to the wiring **82**, can be employed as well.

When the transistor **59** is turned off, display of an image 65 simultaneous with image capture can be stopped. When the transistor **59** is turned off in all the pixels, arbitrary image

**16**

data supplied from the wiring **81** can be displayed in the entire display portion **102**. Data that has been taken out to the outside through the wiring **71** and processed may be supplied from the wiring **81** and displayed. In this case, for example, the captured image can be subjected to enlargement, processing, or the like.

When a pixel is selected and the transistor **59** is turned off, display of an image simultaneous with image capture can be stopped in the selected pixel. Furthermore, when the transistor **59** is turned off in a reset period, the transistor **53** is off and black display can be performed. By displaying arbitrary image data supplied form the wiring **81** on the background pixel where black display is performed, vivid AR display can be performed.

Note that if a low potential power supply line is electrically connected to the gate of the transistor 53 via a switch (e.g., a transistor), the transistor 53 can be turned off and black display can be performed at any given time as well as in the reset period.

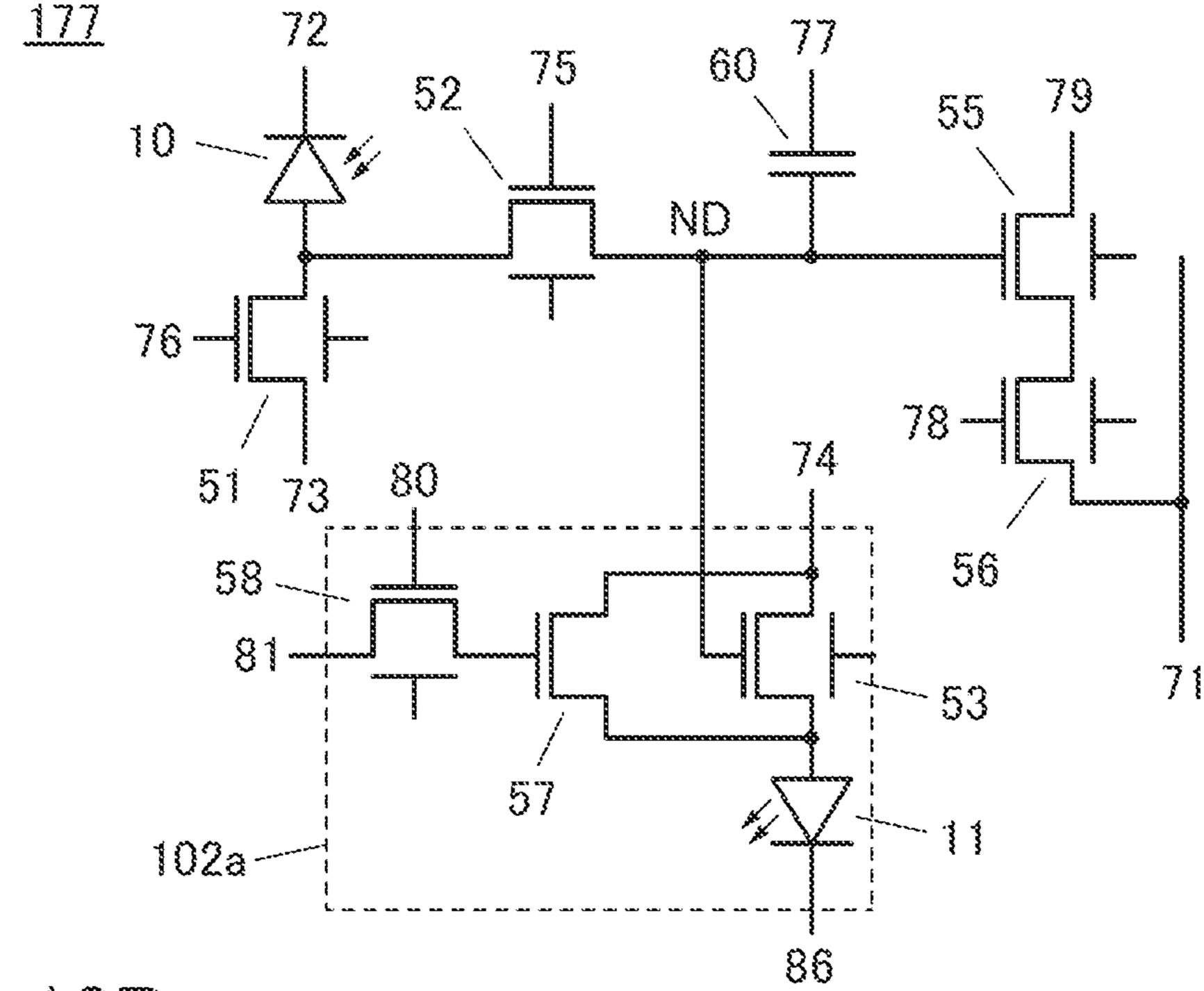

Furthermore, one embodiment of the present invention may have a structure of a pixel circuit 177 illustrated in FIG. 12A. In the pixel circuit 177, each transistor has a backgate. The application of a constant voltage to the backgate can adjust the threshold of the transistor. The same potential as the potential applied to the front gate may be applied to control the on-state current and the off-state current. Although all of the transistors have a backgate in FIG. 12A, a transistor not provided with a backgate may also be included

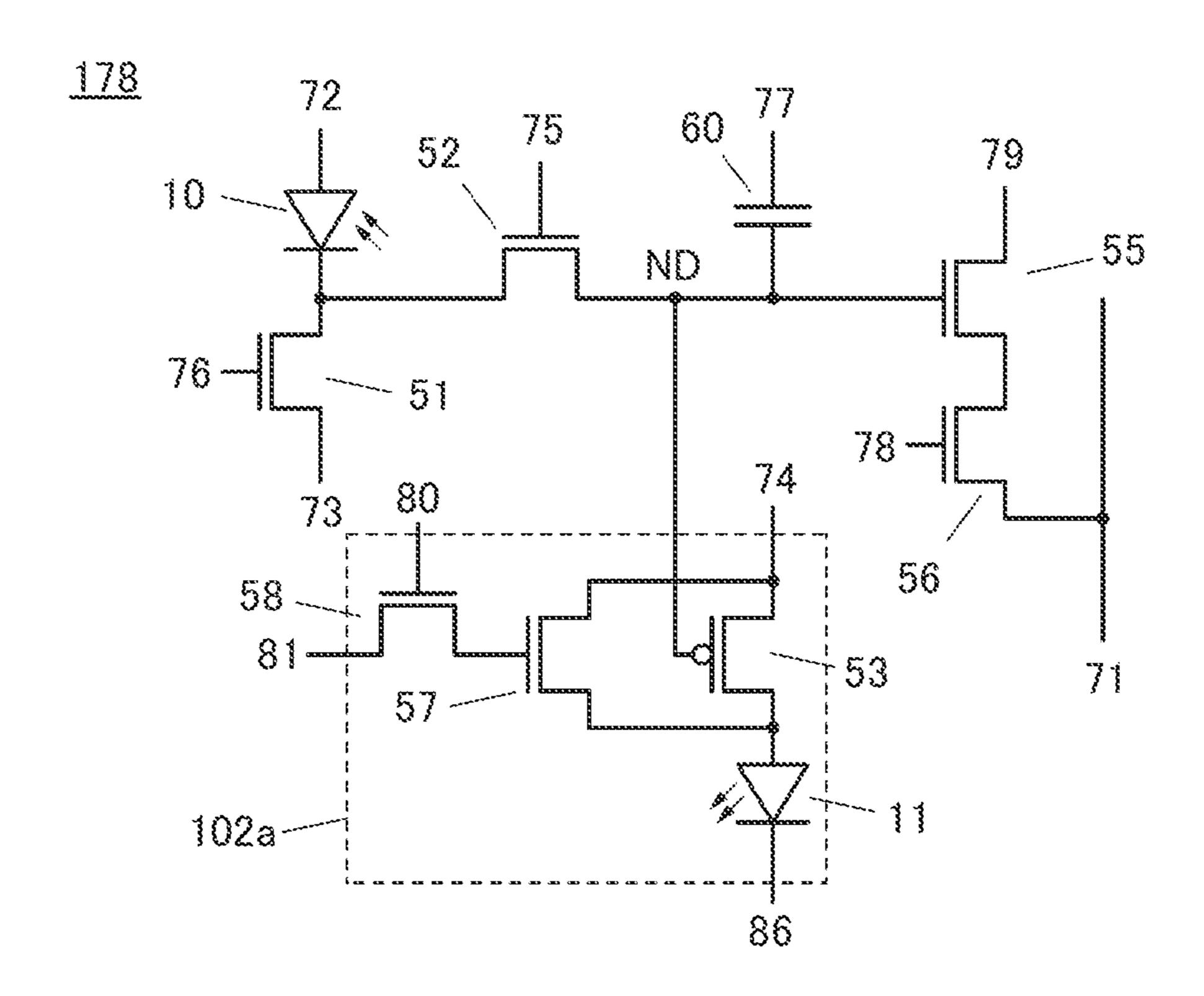

Furthermore, one embodiment of the present invention may have a structure of a pixel circuit 178 illustrated in FIG. 12B. The pixel circuit 178 is an example of a structure in which the charge detection portion ND can be reset to a high potential in the operation.

The pixel circuit 178 is different from the above-described pixel circuit in that the connection direction of the photo-electric conversion element 10 is opposite and the transistor 53 is of a p-channel type. In this example, the transistor 53 is preferably a Si transistor. In the operation of the pixel circuit 178, the wiring 72 is set at a low potential, and the wiring 73 is set at a high potential.

In the pixel circuit 178, the potential of the charge detection portion ND is relatively low when the light intensity is high, and is relatively high when the light intensity is low. Accordingly, a p-channel transistor is used as the transistor 53 so that bright light can be emitted from the display element 11 when the potential of the charge detection portion ND is low.

Furthermore, one embodiment of the present invention may have a structure of a pixel circuit 179 illustrated in FIG. 13A. The pixel circuit 179 can reset the charge detection portion ND to a high potential in the operation.

The pixel circuit 179 includes a transistor 62 and a capacitor 64 in addition to the structure of the pixel circuit 175. One of a source and a drain of the transistor 62 is electrically connected to the gate of the transistor 55. One electrode of the capacitor 64 is electrically connected to the other of the source and the drain of the transistor 52. The other electrode of the capacitor 64 is electrically connected to the gate of the transistor 55. Furthermore, the connection direction of the photoelectric conversion element 10 is opposite to that in the pixel circuit 175.

The other of the source and the drain of the transistor 62 is electrically connected to the wiring 85, and a gate of the transistor 62 is electrically connected to a wiring 84. The wiring 85 can have a function of a power supply line and can

supply a high potential. The wiring 84 can have a function of a signal line which controls on/off of the transistor 62.

Note that a wiring which connects the one electrode of the photoelectric conversion element 10 to the one of the source and the drain of the transistor 52 is referred to as a charge accumulation portion RD1. In addition, a wiring which connects the other of the source and the drain of the transistor 52 to the capacitor 64 is referred to as a charge accumulation portion RD2.

Next, a fundamental operation of the pixel circuit 179 will be described with reference to a timing chart of FIG. 13B. Note that in the following operation example, VDD and GND are supplied to the wirings 75, 76, 78, 80, and 84 as "H" and "L", respectively; GND is supplied to the wirings 72, 77, and 85; VDD is supplied to the wirings 73, 74, and 79; and an arbitrary potential (image signal) is supplied to the wirings 81. Other potentials can also be supplied to the wirings.

At Time T1, the wiring 76 is set at "H" and the wiring 75 20 is set at "H", to set the potentials of the charge accumulation portions RD1 and RD2 to a first reset potential (VDD). At this time, in some cases, the potential of the charge detection portion ND is increased owing to capacitive coupling by the capacitor 64, which turns on the transistor 53, leading to 25 light emission from the display element 11.

At Time T2, the wiring 75 is set at "L", and at Time T3, the wiring 76 is set at "L", to make the potential of the charge accumulation portion RD1 start changing. The potential of the charge accumulation portion RD1 is changed from 30 VDD to GND at the minimum depending on the intensity of light that has entered the photoelectric conversion element 10.

At Time T4, the wiring 75 is set at "H" and the wiring 84 is set at "H", so that the potential of the charge accumulation 35 portion RD2 becomes equal to the potential of the charge accumulation portion RD1. In addition, the potential of the charge detection portion ND is set at a second reset potential.

At Time T5, the wiring 84 is set at "L", so that the potential of the charge detection portion ND is decreased 40 owing to capacitive coupling by the capacitor 64.

At Time T6, the wiring 76 is set at "H", so that the potential of the charge accumulation portion RD1 becomes the first reset potential (VDD). In other words, the potentials of the charge accumulation portions RD1 and RD2 are 45 increased by the amount decreased in the exposure period (from Time T3 to Time T6). At this time, the potential of the charge detection portion ND is increased in response to the increase in the potentials of the charge accumulation portions RD1 and RD2 due to capacitive coupling by the 50 capacitor 64. That is, the charge detection portion ND becomes to have a potential reflecting the exposure period, and the display element 11 emits light in accordance with the potential.

In this operation, the higher the light intensity, the potentials of the charge accumulation portions RD1 and RD2 are lower in the exposure period, increasing the difference between the potentials of the charge accumulation portions RD1 and RD2 and the first reset potential. Thus, when the light intensity is high, the potential of the charge detection 60 portion ND is relatively high, and when the light intensity is low, the potential of the charge detection portion ND is relatively low.

Thus, even in the case where the transistor **53** is of an n-channel type, the pixel circuit **179** can be configured so 65 that the display element **11** emits bright light when the potential of the charge detection portion ND is high.

**18**

Note that T6 corresponds to T1, and the repetition of the above-described operation enables high-speed image capture and display operation.

Furthermore, one embodiment of the present invention may have a structure of a pixel circuit 180 illustrated in FIG. 14A. The pixel circuit 180 is an example of a pixel circuit for correlated double sampling which cancels out noise of a component included in a circuit, such as a transistor. Note that a CDS circuit which performs correlated double sampling is provided so as to be electrically connected to the wiring 71. In the correlated double sampling, a signal at the time of the reset operation is subtracted from an image signal taken out to the wiring 71.

The pixel circuit **180** is obtained by replacing the capacitor **64** of the pixel circuit **179** with a transistor **61**. In addition, the connection direction of the photoelectric conversion element is opposite to that in the pixel circuit **179**. One of a source and a drain of the transistor **61** is electrically connected to the other of the source and the drain of the transistor **52**. The other of the source and the drain of the transistor **61** is electrically connected to the gate of the transistor **55**.

A gate of the transistor **61** is electrically connected to a wiring **83**. The wiring **83** can have a function of a signal line which controls on/off of the transistor **61**.

Note that a wiring which connects the other of the source and the drain of the transistor 52 to the one of the source and the drain of the transistor 61 is referred to as a charge accumulation portion RD.

Next, a fundamental operation of the pixel circuit **180** will be described with reference to a timing chart of FIG. **14B**. Note that in the following operation example, VDD and GND are supplied to the wirings **75**, **76**, **78**, **80**, and **84** as "H" and "L", respectively; VDD is supplied to the wirings **72**, **74**, and **79**; GND is supplied to the wirings **73**, **77**, and **85**; and an arbitrary potential (image signal) is supplied to the wirings.

At Time T1, the wiring 76 is set at "H" and the wiring 75 is set at "H", to make the charge accumulation portion RD have a reset potential (GND) (reset operation).

At Time T2, the wiring 76 is set at "L" to make the potential of the charge accumulation portion RD start changing (accumulation operation). The potential of the charge accumulation portion RD is changed from GND to VDD at the maximum depending on the intensity of light that has entered the photoelectric conversion element 10.

At Time T3, the wiring 75 is set at "L" to settle the potential of the charge accumulation portion RD.

At Time T4, the wiring 78 is set at "H" and the wiring 84 is set at "H", so that the potential of the charge detection portion ND becomes the reset potential (GND) and the reset potential (GND) containing a noise signal due to a transistor or the like is read to the wiring 71. In this case, the reset potential (GND) is stored in the CDS circuit. Note that the display element 11 does not emit light at Time T4.

The wiring **84** is set at "L" at Time T5, and the wiring **83** is set at "H" at Time T6, so that the potential of the charge detection portion ND becomes equal to the potential of the charge accumulation portion RD and a potential of an image signal containing a noise signal due to a transistor or the like is read to the wiring **71**. At Time T5, the display element **11** emits light in accordance with the potential of the charge detection portion ND.

The CDS circuit performs an operation of subtracting the previously stored reset potential (GND) containing the noise signal due to the transistor or the like, from the potential of

the image signal containing the noise signal due to the transistor or the like, whereby a net image signal is obtained.

The wiring **83** is set at "L" at Time T**7**, and the wiring **78** is set at "L" at Time T**8**. Thus, extraction of the image data from which noise is removed is completed. Note that Time T**8** corresponds to Time T**1**, and the repetition of the above-described operation enables high-speed image capture and display operation and extraction of image data from which noise is removed.

Note that the structures of the pixel circuits 171 to 180 10 described above as one embodiment of the present invention can be freely combined with one another.

FIGS. 15A to 15C illustrate examples of an image displayed on the display portion 102. For example, an image of objects such as a flower blooming on the hill and an airship 15 floating in the air as illustrated in FIG. 15A is captured.

FIG. 15B is an example of adding time and AR-displayed data on the objects. As described above, in the case of displaying added data on the display portion, an operation of overwriting the background image is performed. In the case where the color of the background image is dark, visibility is enhanced by displaying the data in a bright color. In the case where the color of the background is bright, visibility is hard to increase even when the luminance of the displayed data is increased.

In such a case, it is preferable to display the data in a color complementary to the color of the background. For example, the words "Airship" and "Sunflower" are displayed preferably in orange or yellow, which is a color complementary to blue for the sky or a color close to the complementary color. 30 Furthermore, the numbers for the time are displayed preferably in red or magenta, which is a color complementary to green for the hill or a color close to the complementary color.

Moreover, by using the structure of the pixel circuit 176, display of an image simultaneous with image capture can be 35 stopped in the selected pixel. Accordingly, as illustrated in FIG. 15C, the background captured image in the region where data such as the words are displayed is made not to be displayed (made to be displayed in black), and the data is made to be displayed in a bright color. In this way, 40 visibility can be enhanced.

In the imaging display device of one embodiment of the present invention, unlike a see-through display, an AR-displayed image can be added to a captured image and thus the position of the AR-displayed image does not need to be 45 adjusted with respect to the position of a viewer.

In the case where data of an object as illustrated in FIG. **15**A is obtained from a server, if the object is an unknown object, the following process is required: an image of the object and data on the periphery are uploaded to the server, 50 and data such as the shape, color, place, and time is compared with massive data in a database to obtain a retrieval result. Accordingly, in the case where data is obtained from the server, as described above, categories of the object are preferably narrowed down before the retrieval 55 from the server.

The categories are preferably narrowed down by estimation using a neural network.

FIG. 16 illustrates an operation of estimating categories of an object using a neural network. Input data  $E_1$  to  $E_i$  (i is a 60 natural number) correspond to features extracted from an image P of the object, such as the shape, color, and size, and data which can be obtained by the imaging display device, such as the position and time.

The input data  $E_1$  to  $E_i$  are respectively input to nodes  $F_1$  65 to  $F_i$  in an input layer **501**, and the weighted data is input to a first layer  $G_1$  in a middle layer **502**. Here, the middle layer

20

**502** includes an arbitrary number of layers  $G_1$  to  $G_j$  (j is a natural number). In addition, each of the layers in the middle layer **502** includes an arbitrary number of nodes. Data output from the last layer  $G_j$  of the middle layer **502** is input to an output layer **503**. The output layer **503** outputs any one of  $H_1$  to  $H_k$  (k is a natural number), which are results of the category estimation of the object, or outputs some of the category estimation results with high possibility.

Note that  $H_1$  to  $H_k$ , which are the results of the category estimation, may be at any level, from rough categories of whether the object is a natural object, an artificial object, or a living thing to detailed categories that can identify the object.

Then, the image P of the object, the input data  $E_1$  to  $E_i$ , and the category estimation result are transmitted to a server **505**, and data on the object is searched. The detailed estimation result can narrow down the databases to search in the server **505** and thus shorten the search time.

However, the imaging display device has a limitation on the chip area and processing speed of the neural network. Therefore, the estimation of the category is preferably done to a minimum necessary extent and utilized in conjunction with the server 505. For example, on the precondition that data is contained in databases included in the server 505, in the case where the object is a building, if there are an estimation result that the object is categorized as "building", an image of the object, and positional data, sufficiently accurate data can be quickly obtained. Furthermore, in the case where the object is a human, if there are an estimation result that the object is categorized as "human" (containing data on the sex, height, age, and the like) and an image of the human (preferably containing an image of the face), an individual can be identified quickly.

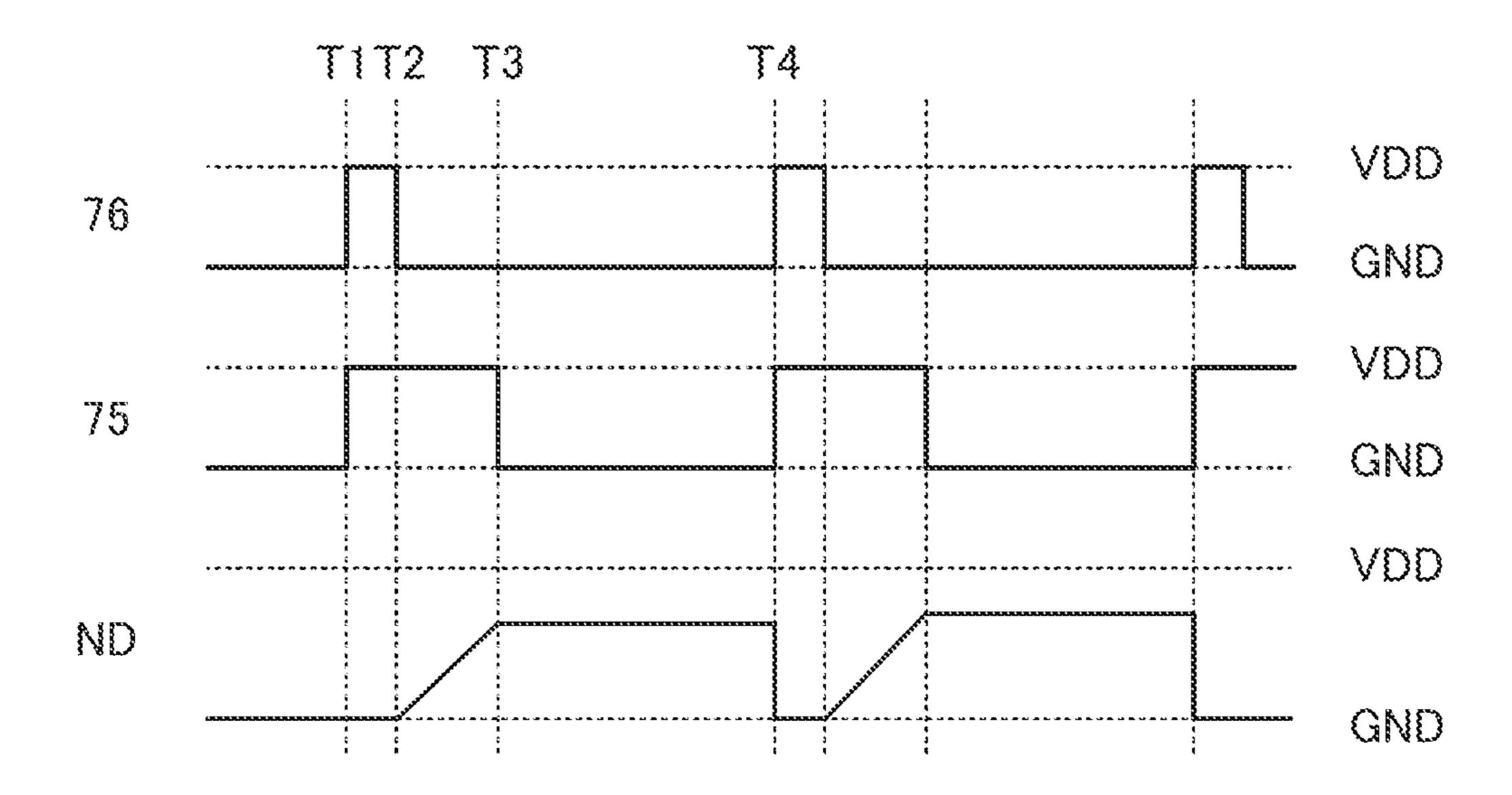

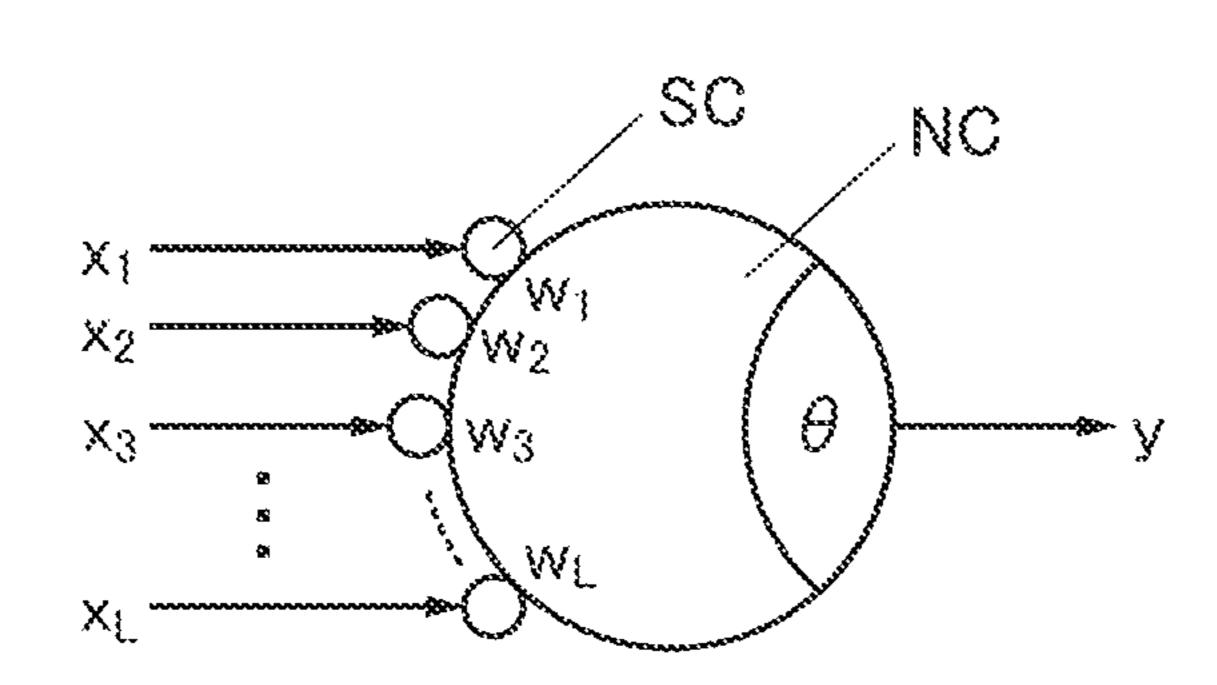

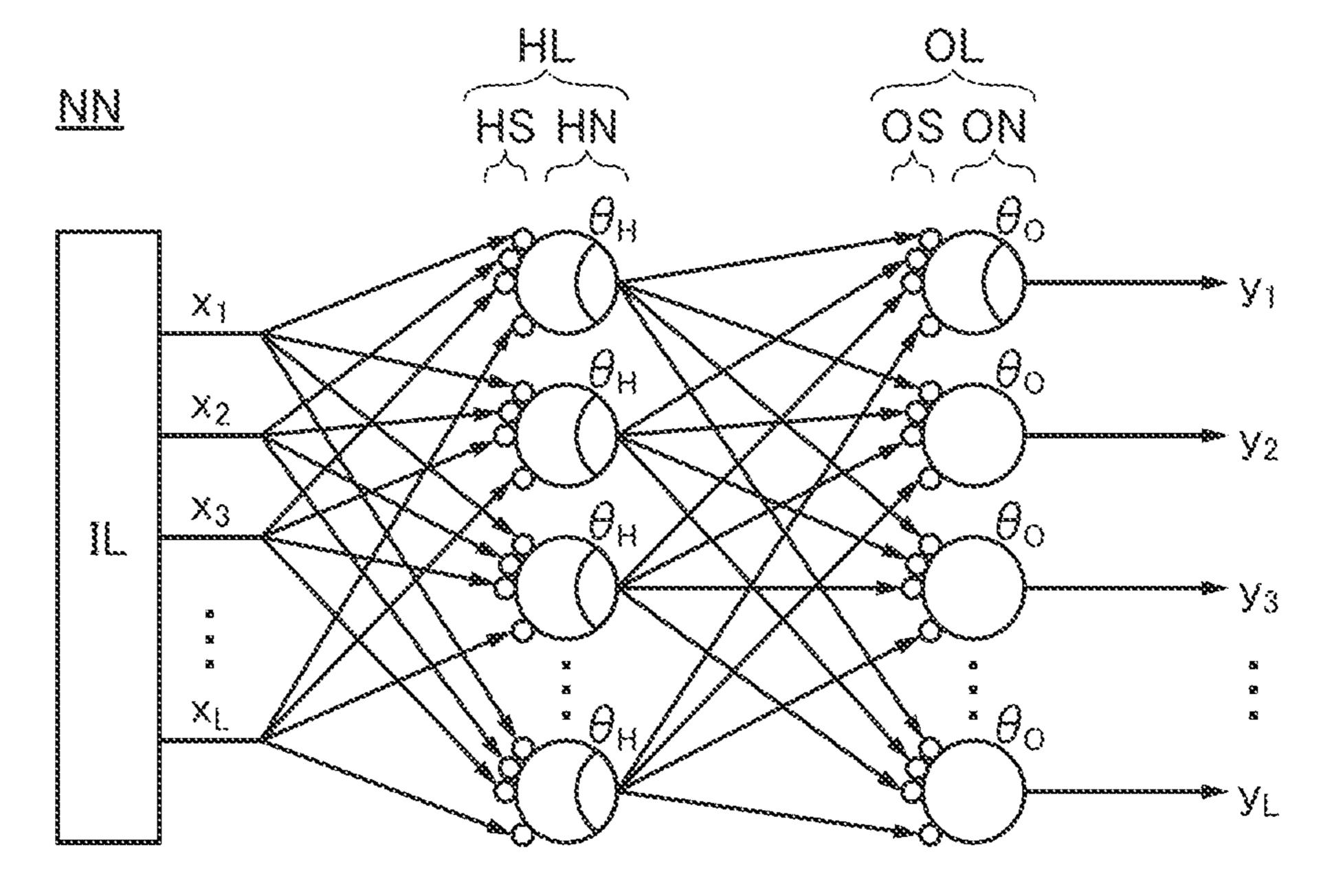

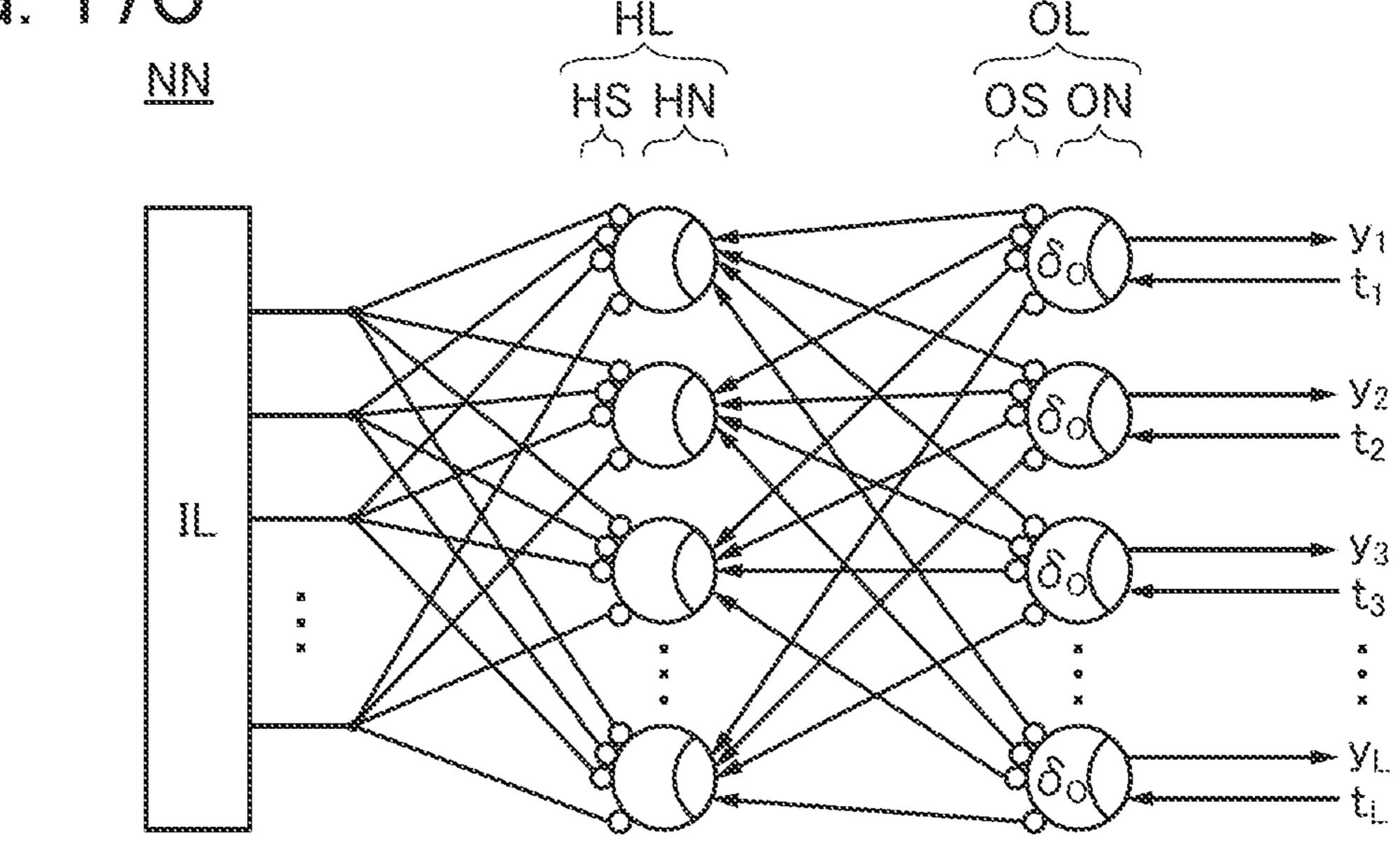

Next, structure examples of a neural network that can be used in one embodiment of the present invention will be described in detail with reference to FIGS. 17A to 17C. A neural network NN includes neuron circuits and synapse circuits provided between the neuron circuits.

FIG. 17A illustrates structure examples of a neuron circuit NC and synapse circuits SC that constitute the neural network NN. Input data  $x_1$  to  $x_L$  (L is a natural number) are input to the synapse circuits SC. In addition, the synapse circuits SC each have a function of storing a weight coefficient  $w_k$  (k is an integer of 1 to L inclusive). The weight coefficient  $w_k$  corresponds to the connection strength between the neuron circuits NC.