#### US011741285B2

## (12) United States Patent

Yang et al.

### (10) Patent No.: US 11,741,285 B2

(45) Date of Patent: Aug. 29, 2023

# (54) SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

### (71) Applicant: Samsung Electronics Co., Ltd.,

Suwon-si (KR)

(72) Inventors: Giyoung Yang, Seoul (KR); Ingyum

Kim, Bucheon-si (KR)

(73) Assignee: SAMSUNG ELECTRONICS CO.,

LTD., Suwon-si (KR)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 219 days.

(21) Appl. No.: 17/361,854

(22) Filed: Jun. 29, 2021

### (65) Prior Publication Data

US 2022/0058327 A1 Feb. 24, 2022

### (30) Foreign Application Priority Data

Aug. 18, 2020 (KR) ...... 10-2020-0103161

(51) **Int. Cl.**

G06F 30/392 (2020.01) G06F 30/396 (2020.01) H01L 27/088 (2006.01)

(52) **U.S. Cl.**

CPC ...... *G06F 30/392* (2020.01); *G06F 30/396* (2020.01); *H01L 27/0886* (2013.01)

(58) Field of Classification Search

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 8,698     | ,205 B2* | 4/2014  | Tzeng H01L 27/11807 |

|-----------|----------|---------|---------------------|

|           |          |         | 257/574             |

| 8,728     | ,892 B2* | 5/2014  | Ou H01L 21/823431   |

|           |          |         | 257/E29.026         |

|           | ,978 B2* |         | Baek H01L 23/5286   |

| 10,497.   | ,693 B1* | 12/2019 | Huang H01L 27/0924  |

| 2016/0055 |          |         | Baek                |

|           |          |         | 716/122             |

| 2019/0148 | 8407 A1* | 5/2019  | Guo H01L 27/11807   |

|           |          |         | 257/206             |

| 2020/0006 | 5335 A1  | 1/2020  | Zhuang et al.       |

| 2020/0006 | 5481 A1  | 1/2020  | Yang et al.         |

| 2022/0058 | 327 A1*  | 2/2022  | Yang G06F 30/392    |

| 2023/0004 | 857 A1*  |         | Shoham G06F 18/23   |

|           |          |         |                     |

<sup>\*</sup> cited by examiner

Primary Examiner — Mohammed Alam (74) Attorney, Agent, or Firm — Muir Patent Law, PLLC

### (57) ABSTRACT

A semiconductor device includes a substrate having an active region, first standard cells arranged in a first row on the active region, second standard cells arranged in a second row on the active region and having a first boundary with the first standard cells, a third standard cells arranged in a third row on the active region and having a second boundary with the first standard cells, and a plurality of power supply lines, respectively arranged along boundaries. Each of the first to third standard cells includes a plurality of fin patterns extending in the first direction, and the plurality of fin patterns are arranged in a second direction, so as not to be disposed on at least one boundary, among the first and second boundaries.

### 20 Claims, 33 Drawing Sheets

FIG. 1

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

FIG. 5A

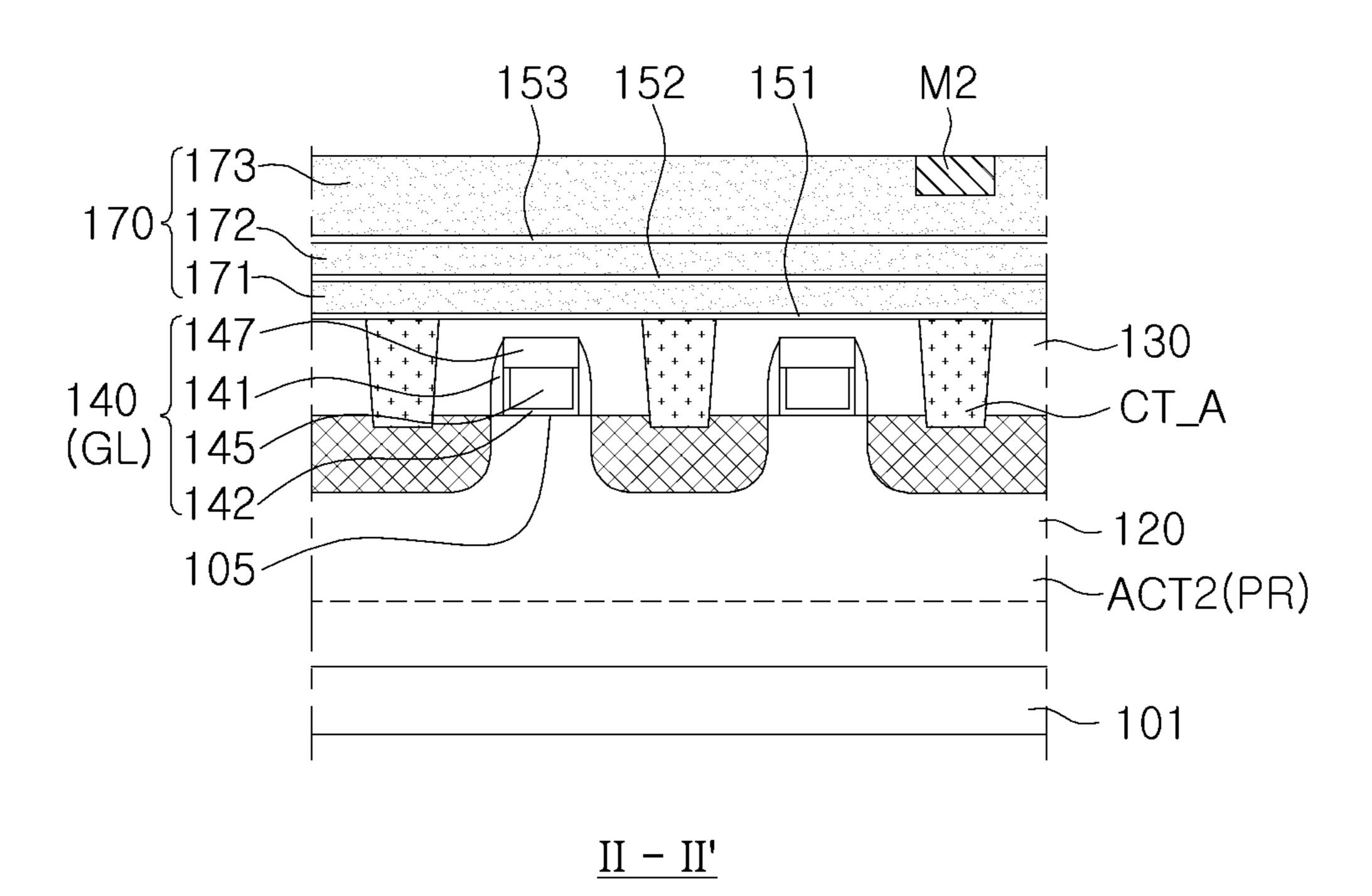

<u>100</u>

FIG. 5B

FIG. 5C

### <u>100A</u>

FIG. 6

FIG. 7A

FIG. 7B

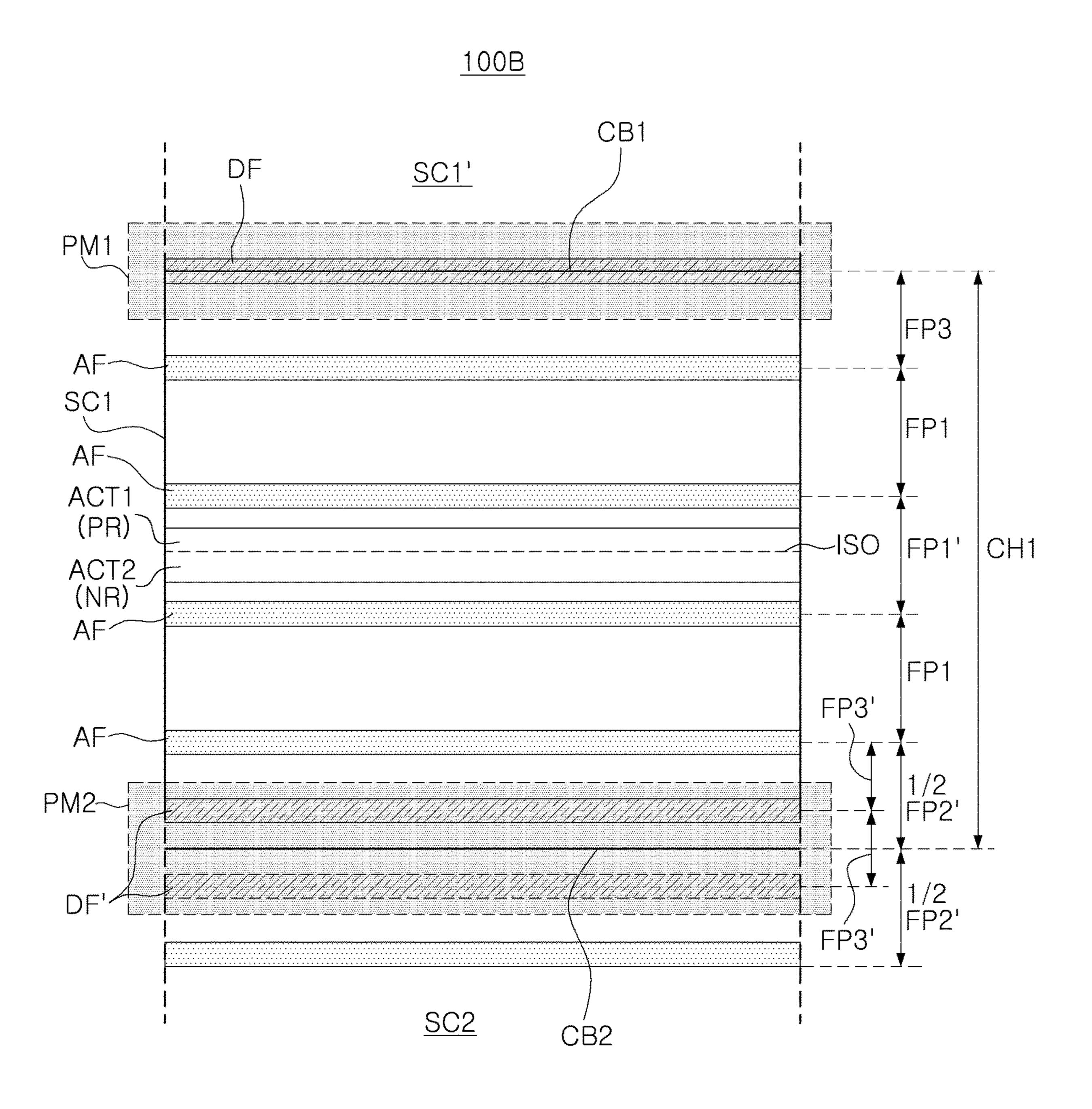

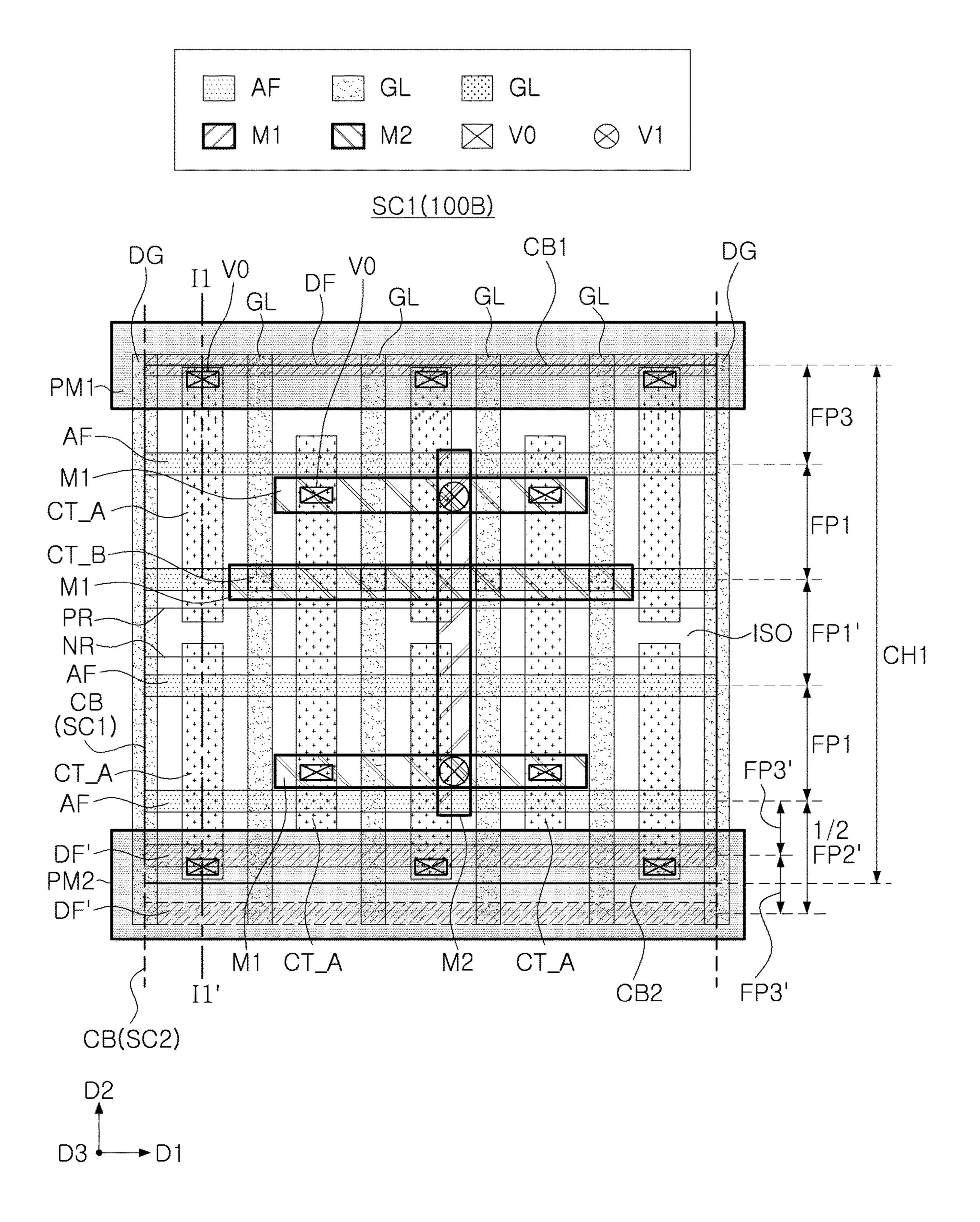

### 100B

FIG. 8

FIG. 9A

FIG. 9B

FIG. 9C

FIG. 10A

FIG. 10B

1<u>00</u>C

FIG. 11A

FIG. 11B

FIG. 11C

FIG. 12

<u> 200</u>

FIG. 13

### 200A

FIG. 14A

### 200B

FIG. 14B

FIG. 15

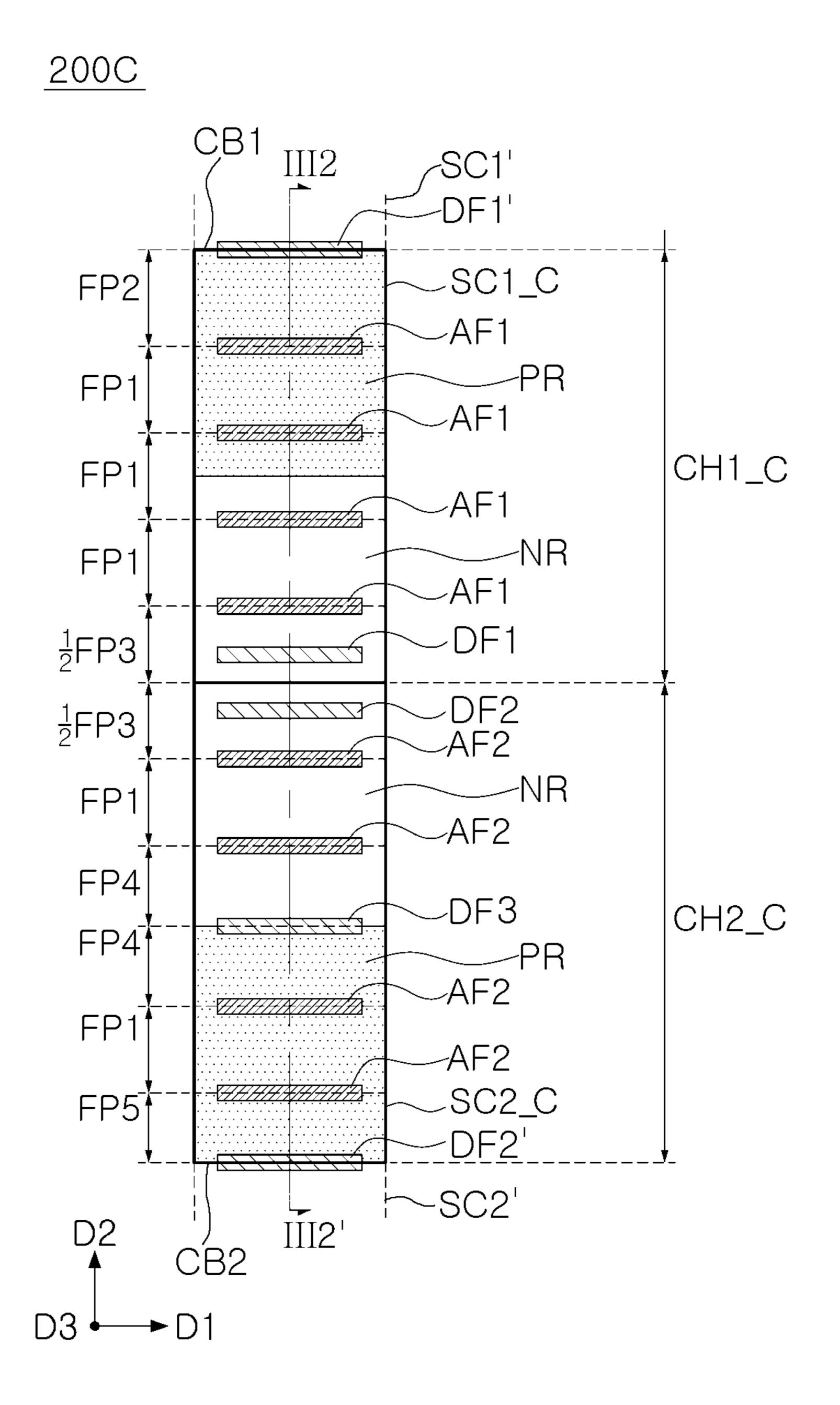

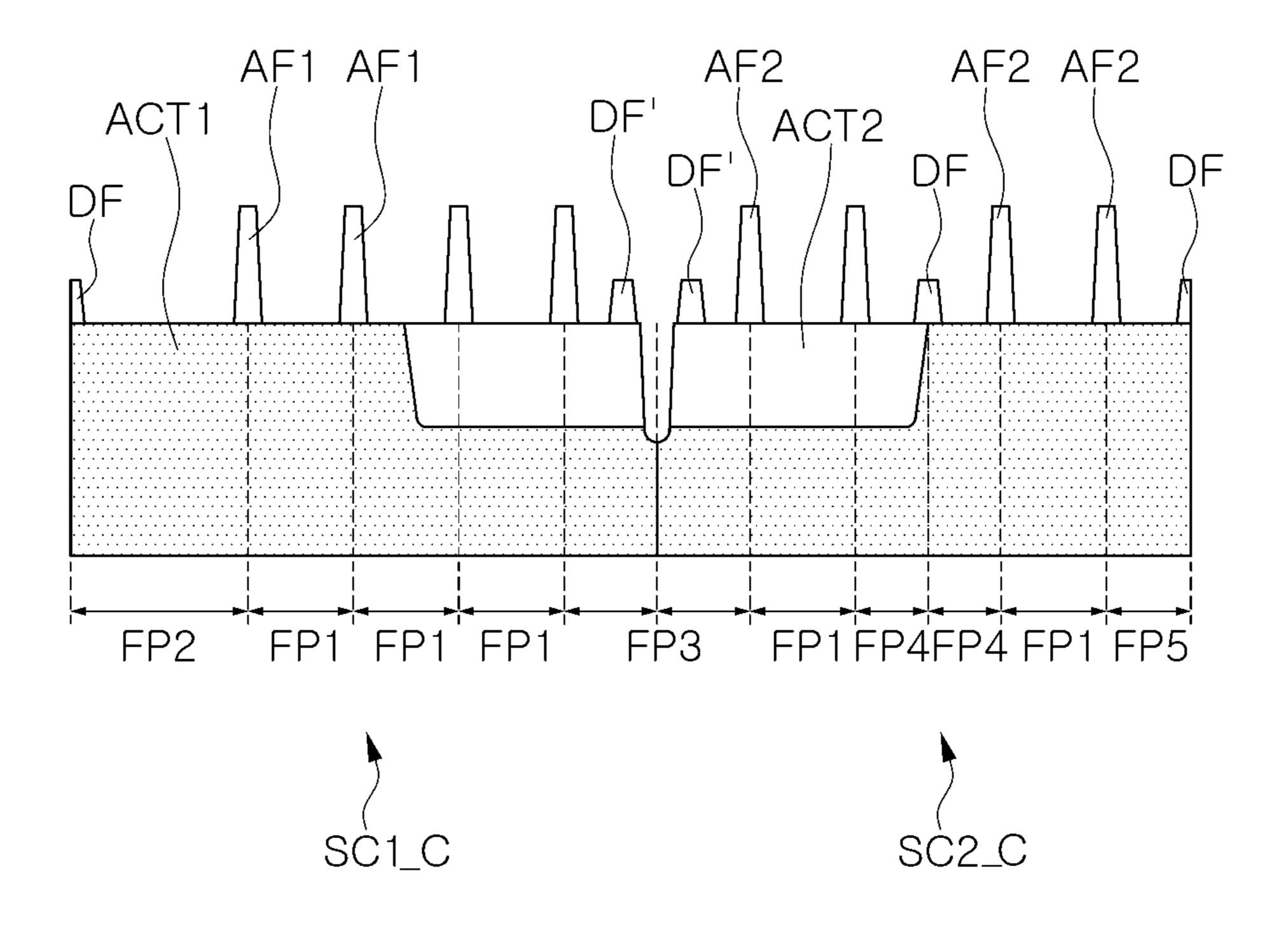

### 200C

<u>III2-III2'</u>

FIG. 16

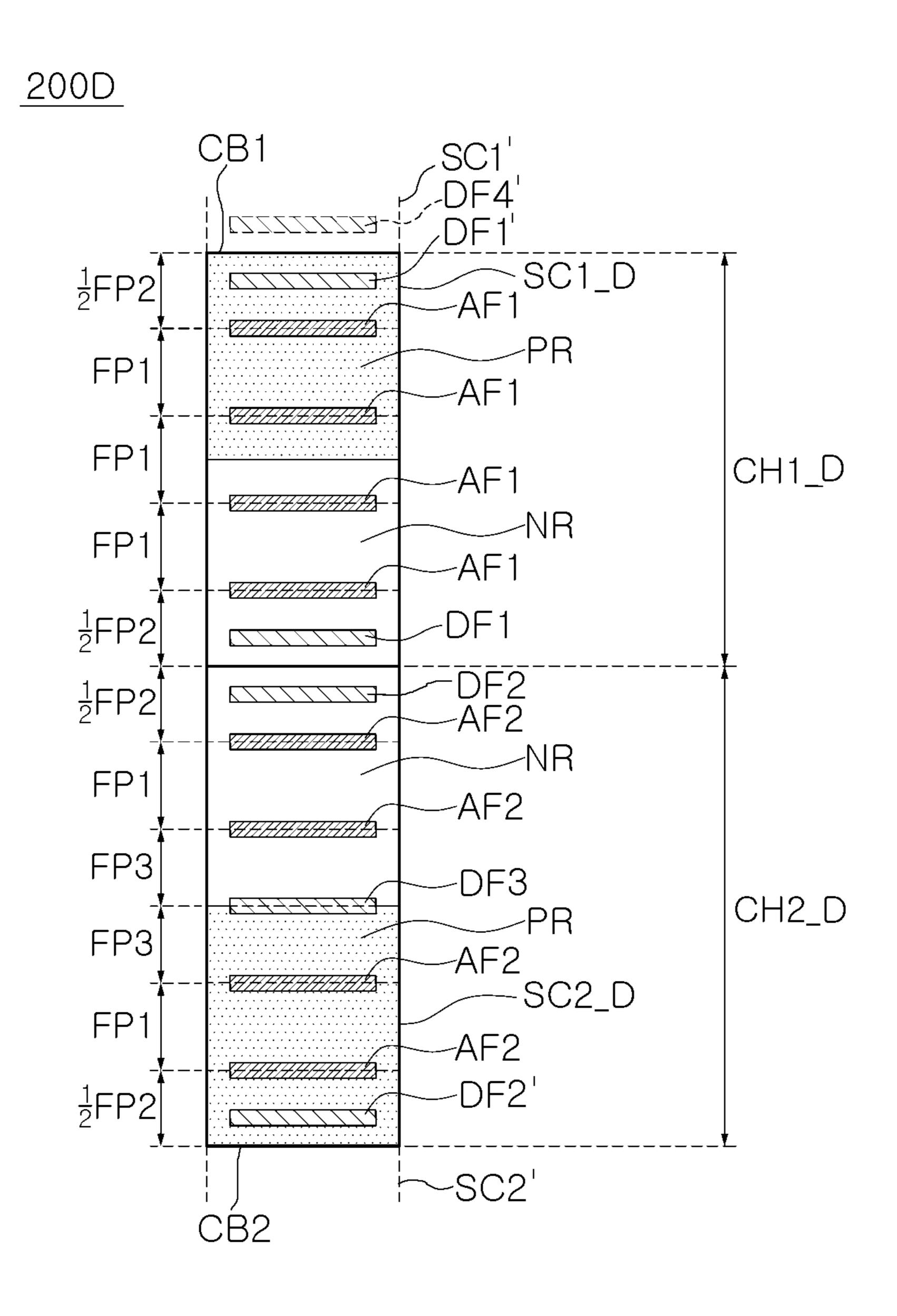

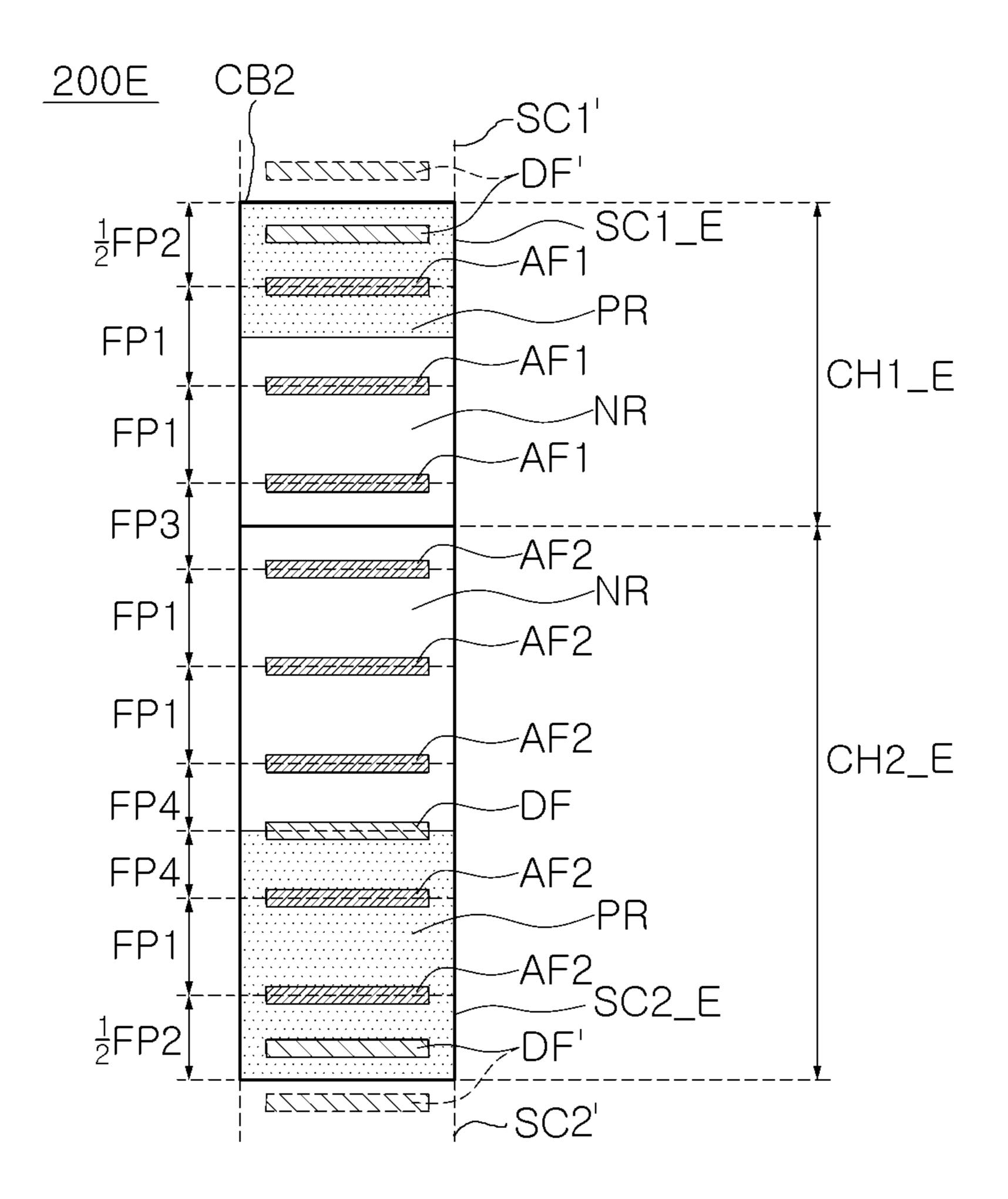

FIG. 17A

FIG. 17B

FIG. 18

FIG. 19A

FIG. 19B

FIG. 20A

FIG. 20B

### SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

### CROSS-REFERENCE TO RELATED APPLICATION(S)

This application claims benefit of priority to Korean Patent Application No. 10-2020-0103161 filed on Aug. 18, 2020 in the Korean Intellectual Property Office, the disclosure of which is herein incorporated by reference in its 10 entirety.

#### BACKGROUND

The present inventive concept relates to a semiconductor 15 device.

As the demand for high performance, high speed, and/or multifunctionality in semiconductor devices has increased, the integration density of semiconductor devices has increased. With the trend for high density of semiconductor 20 devices, various studies have been conducted to increase the degree of design freedom.

#### **SUMMARY**

Example embodiments provide a semiconductor device having improved integration density and reliability. Example embodiments also provide methods for manufacturing the semiconductor device.

According to an embodiment of the present inventive 30 concept, a semiconductor device includes a substrate having an active region, a first group of standard cells arranged in a first row region of the active region, the first row region of the active region extending lengthwise in a first direction, a region of the active region, the second row region extending lengthwise in the first direction along a first side of the first row region, and a first boundary extending in the first direction and being formed between the first row region and the second row region, a third group of standard cells 40 arranged in a third row region of the active region, the third row region extending lengthwise in the first direction along a second side of the first row region, a second boundary extending in the first direction and being formed between the first row region and the third row region, and the first side 45 of the first row region and the second side of the first row region being opposite with each other in a second direction different from the first direction, a first power supply line extending lengthwise in the first direction along the first boundary between the first row region and the second row 50 region, and overlapping partially each of the first row region and the second row region, and a second power supply line extending lengthwise in the first direction along the second boundary between the first row region and the third row region, and overlapping partially each of the first row region 55 and the third row region. Each of the first to third groups of standard cells comprises a plurality of transistors including a plurality of active fins which is provided with the active region. The plurality of active fins protrude from a main surface of the active region and extend in the first direction. 60 The plurality of active fins are spaced apart from each other in the second direction without overlapping the first and second boundaries.

According to an embodiment of the present inventive concept, a semiconductor device includes a substrate having 65 an active region, a plurality of standard cells arranged in a plurality of row regions of the active region, each of the

plurality of row regions extending lengthwise in a first direction, and the plurality of row regions being arranged in a second direction different from the first direction, each of the plurality of standard cells comprising a plurality of transistors including a plurality of active fins which are provided with the active region, the plurality of active fins protruding from a main surface of the active region and extending lengthwise in the first direction, each of the plurality of row regions including a first boundary with its upper row region and a second boundary with its lower row region, and each of the first boundary and the second boundary extending lengthwise in the first direction, a plurality of power supply lines extending lengthwise in the first direction along first and second boundaries of the plurality of row regions and being spaced apart, in the second direction, from each other, each of the plurality of power supply lines partially overlapping each of corresponding two adjacent row regions among the plurality of row regions, and a plurality of interconnection lines disposed above the plurality of standard cells and electrically connected to the plurality of standard cells. Each of the plurality of row regions of the active region comprises a first active region doped with an impurity of a first conductivity type and a second active region doped with an impurity of a 25 second conductivity type which is different from the first conductivity type. The first active region and the second active region of each of the plurality of row regions of the active region are arranged in the second direction. The plurality of active fins which are disposed in each of the plurality of row regions comprise a first active fin disposed in the first active region of each of the plurality of row regions, and a second active fin disposed in the second active region of each of the plurality of row regions. A first distance between a first boundary of a first row region among the second group of standard cells arranged in a second row 35 plurality of row regions and the first active fin among a plurality of active fins disposed in the first row region is different from a second distance between a second boundary of the first row region and the second active fin among the plurality of active fins disposed in the first row region.

According to an embodiment of the present inventive concept, a semiconductor device includes a substrate having an active region, a plurality of standard cells arranged in a plurality of row regions, each of the plurality of row regions extending lengthwise in a first direction, and the plurality of row regions being arranged in a second direction different from the first direction, each of the plurality of standard cells comprising a plurality of transistors including a plurality of active fins which are provided with the active region, a plurality of gate structures, a plurality of first source/drain regions, a plurality of second source/drain regions, and a plurality of contact structures, the plurality of active fins protruding from a main surface of the active region and extending lengthwise in the first direction, the plurality of gate structures extending lengthwise in the second direction and overlapping the plurality of active fins, the plurality of first source/drain regions and the plurality of second source/ drain regions being disposed in a plurality of first regions of the plurality of active fins and a plurality of second regions of the plurality of active fins, respectively, the plurality of first regions and the plurality of second regions being disposed on opposite sides of each of the plurality of gate structures, and the plurality of contact structures comprising a plurality of first contact structures connected to the plurality of first source/drain regions, and a plurality of second contact structures connected to the plurality of second source/drain regions, and a plurality of power supply lines extending lengthwise in the first direction along boundaries

of the plurality of row regions, and disposed one by one on in the second direction. Each of the plurality of power supply lines is shared by a plurality of standard cells disposed in each of corresponding two adjacent row regions among the plurality of row regions. A dummy fin is disposed 5 in a first row region among the plurality of row regions and extends lengthwise in the first direction. The shortest distance between the dummy fin and a boundary of the first row region is smaller than the shortest distance between the boundary of the first row region and a first active fin, closest 10 to the boundary, among a plurality of active fins in the first row region. The dummy fin is spaced apart, in the second direction, from a first power supply line among the plurality of power supply lines without overlapping the first power supply line. The first power supply line overlaps the bound- 15 ary of the first row region.

#### BRIEF DESCRIPTION OF DRAWINGS

The above and other aspects, features, and advantages of 20 the present disclosure will be more clearly understood from the following detailed description, taken in conjunction with the accompanying drawings.

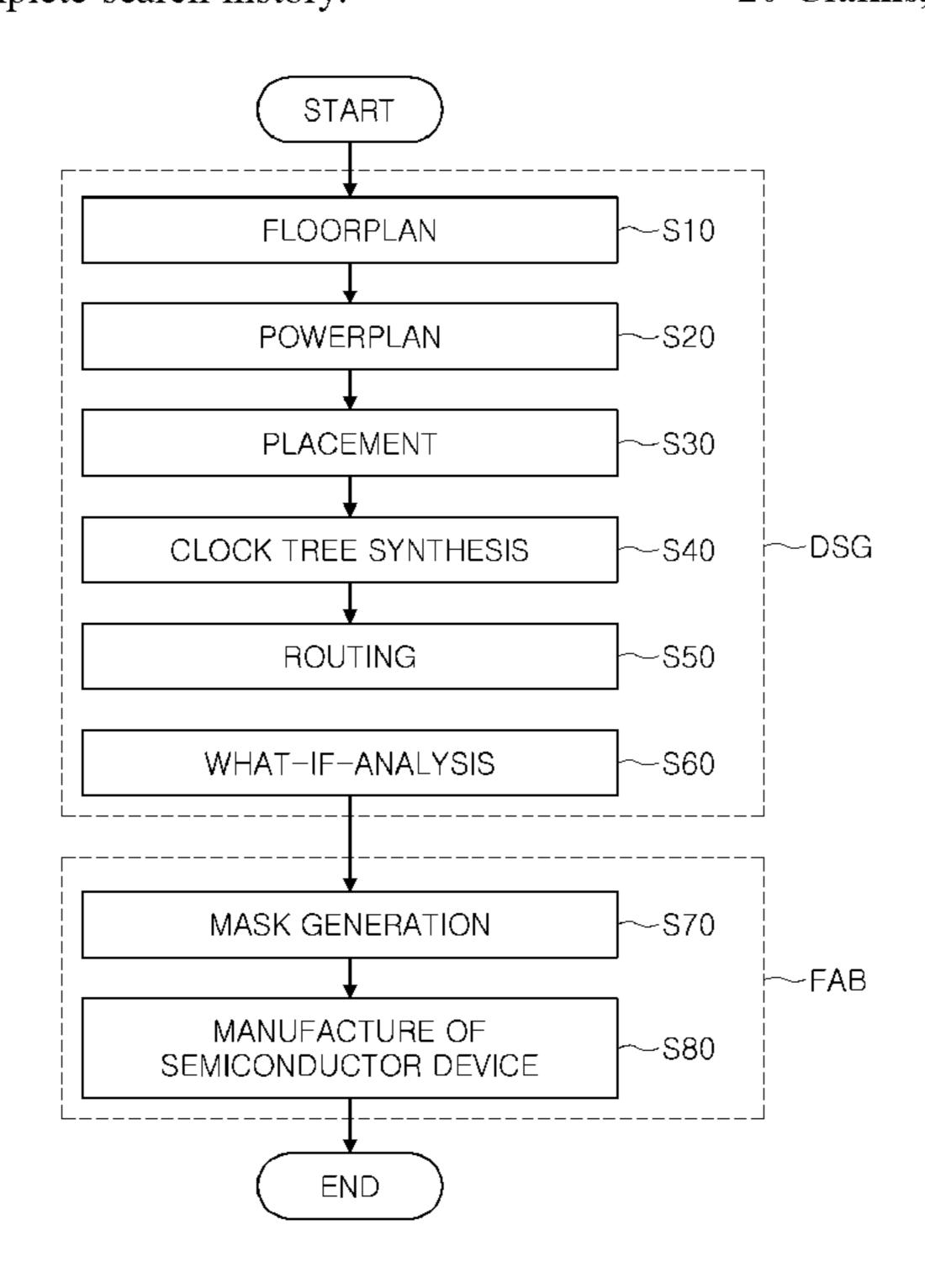

FIG. 1 is a flowchart illustrating a method of manufacturing a semiconductor device according to an example 25 embodiment.

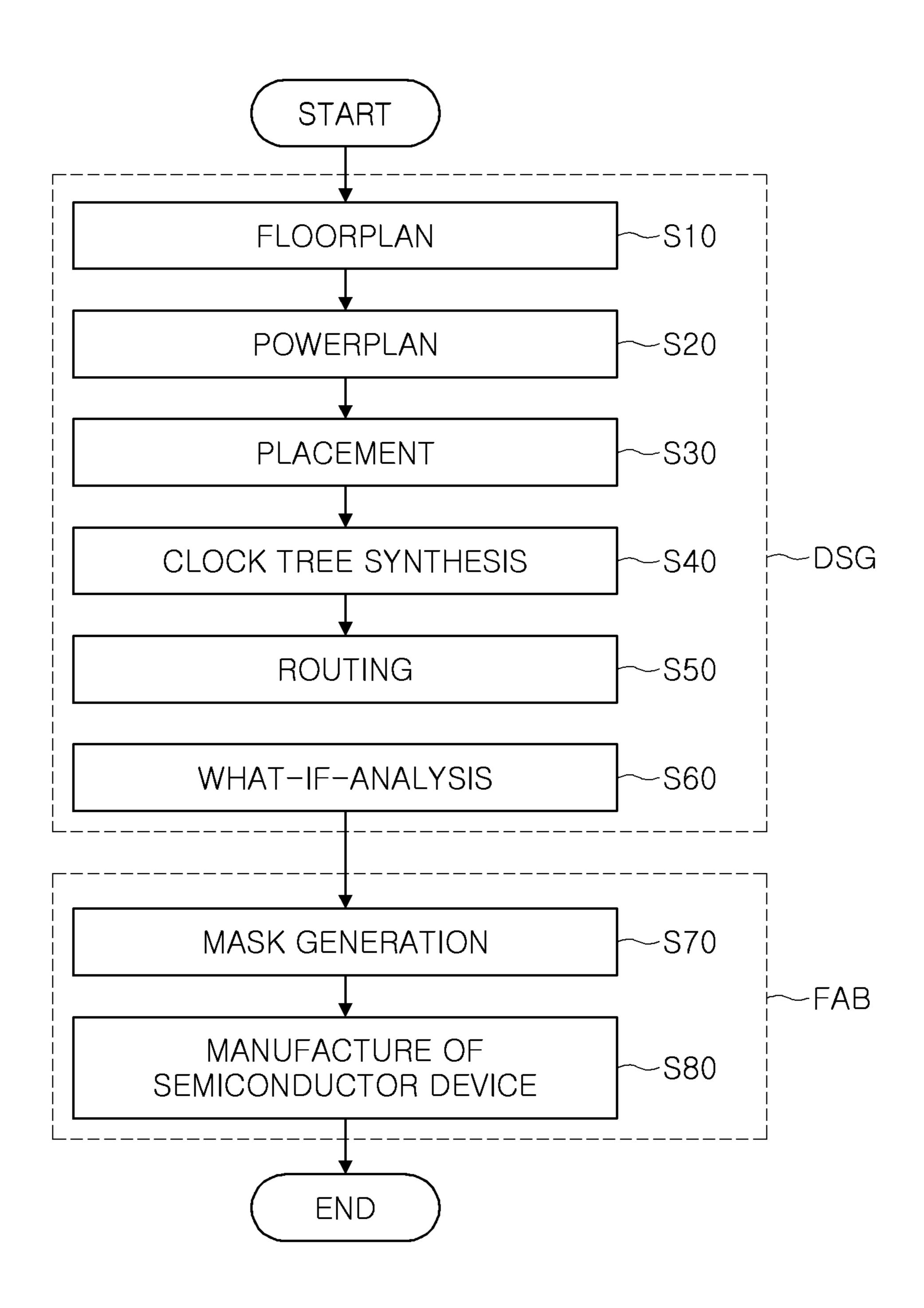

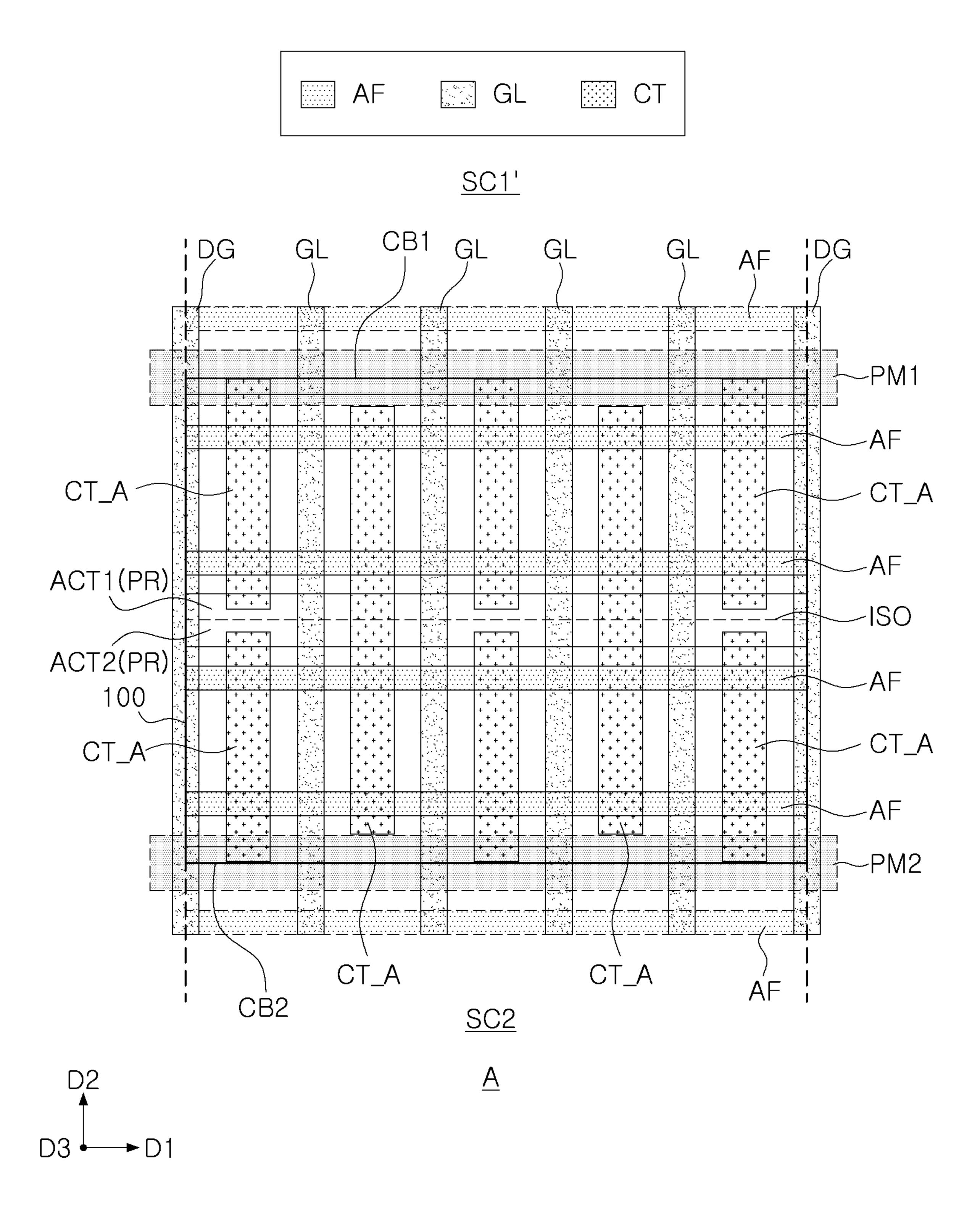

FIG. 2 is a layout diagram of a semiconductor device according to an example embodiment.

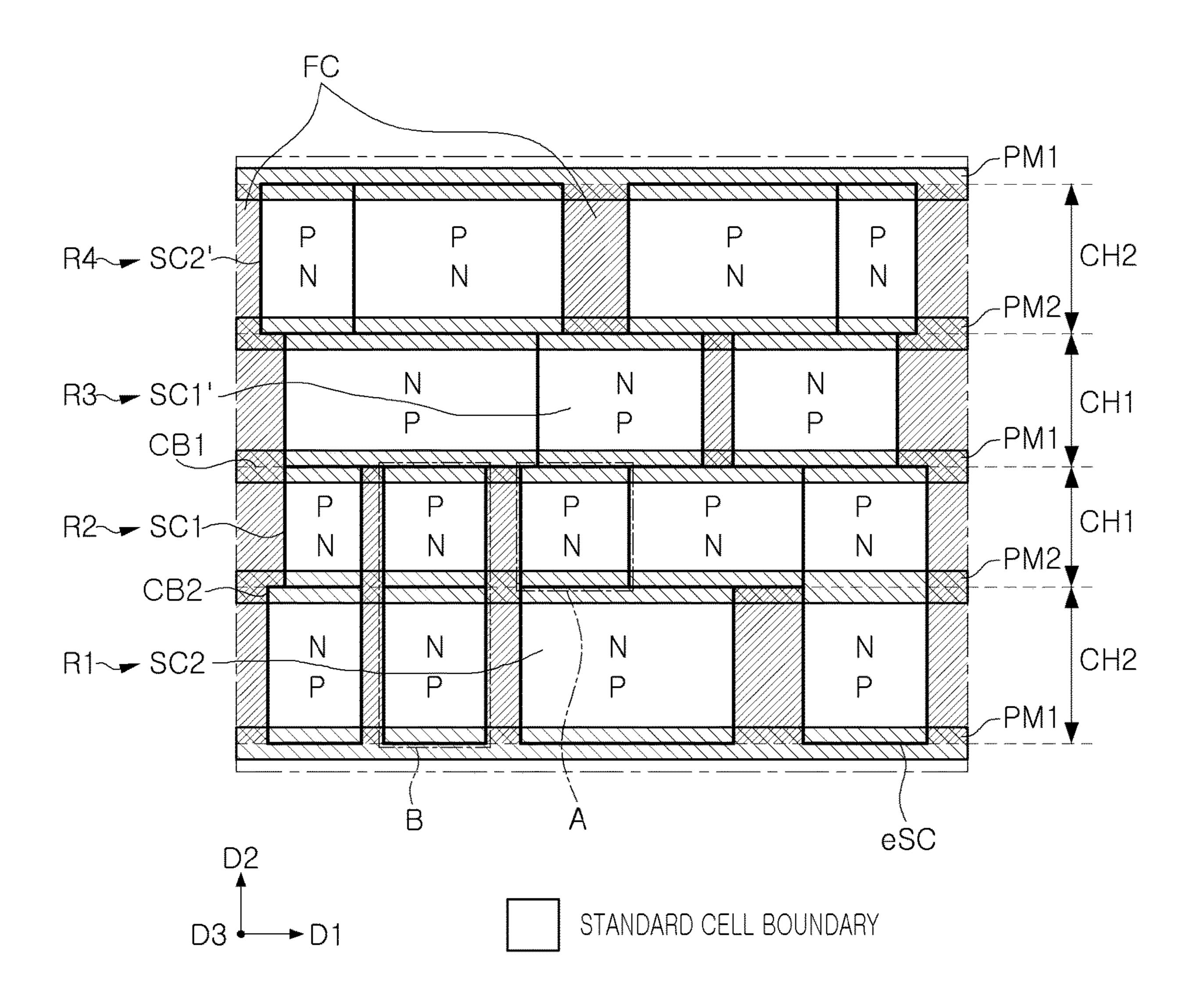

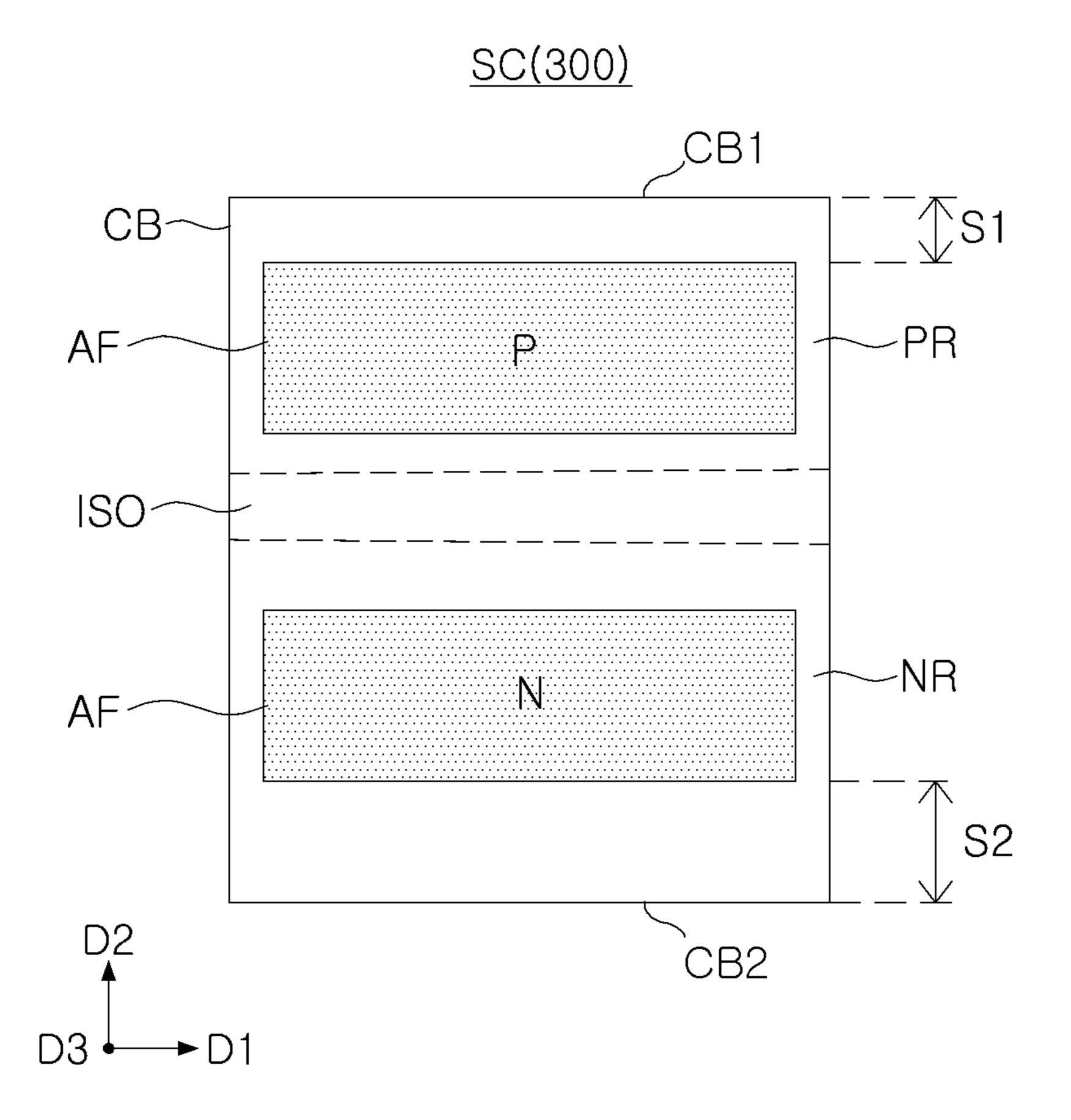

FIG. 3 is a layout diagram of a fin pattern of a standard cell according to an example embodiment.

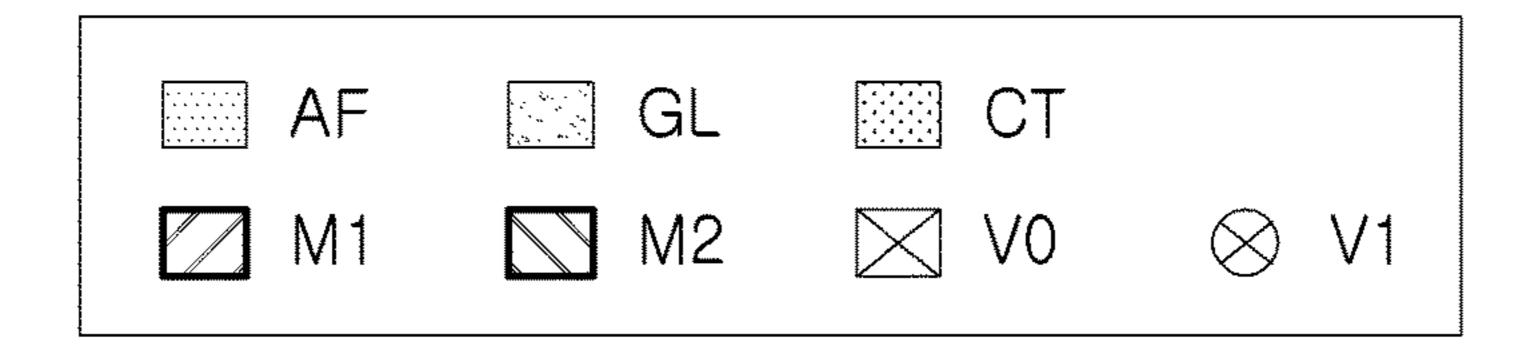

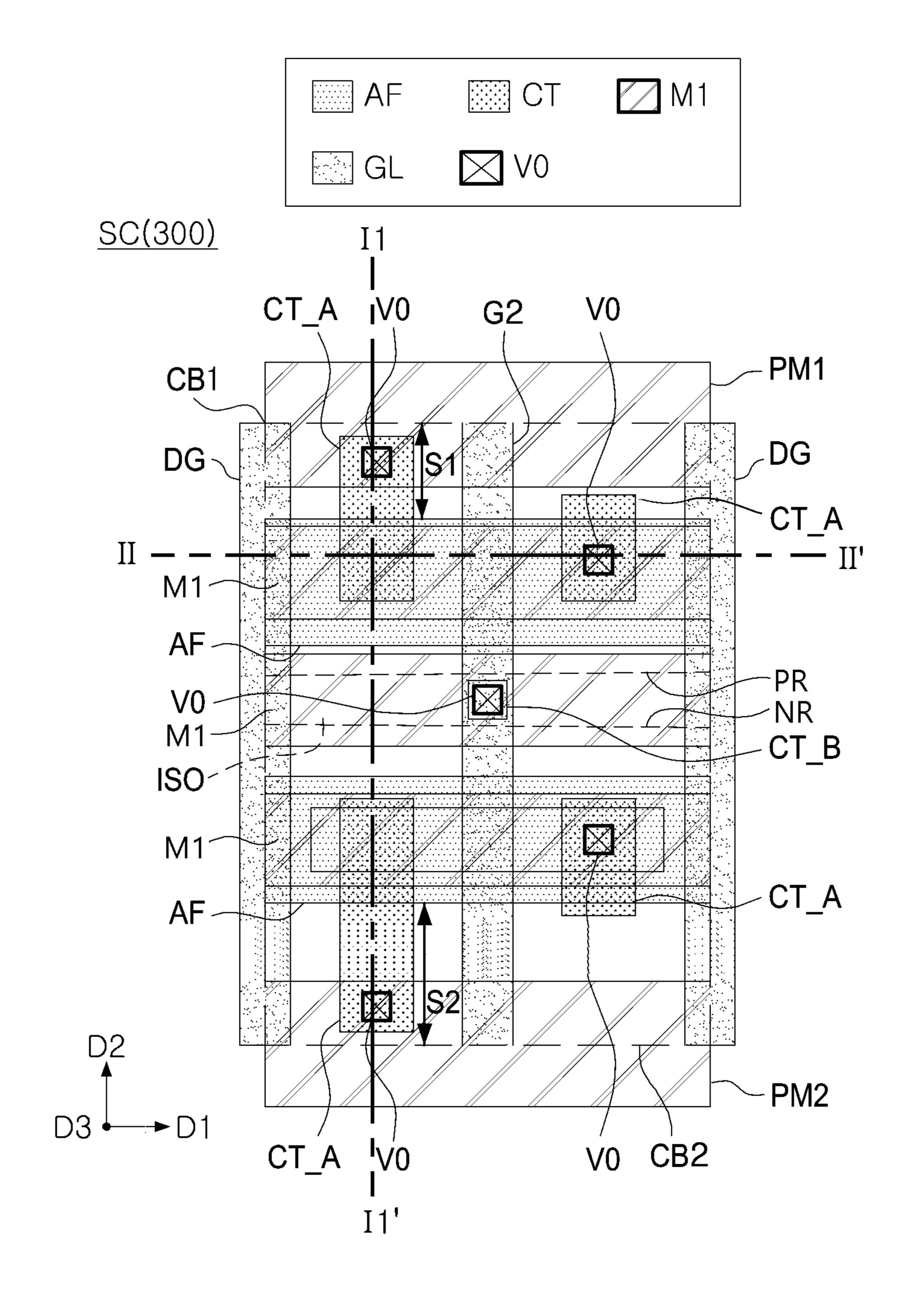

FIGS. 4A and 4B are layout diagrams of an intermediate stage (gate lines and contact structures) and a final stage (interconnection lines) of a standard cell according to an example embodiment, respectively.

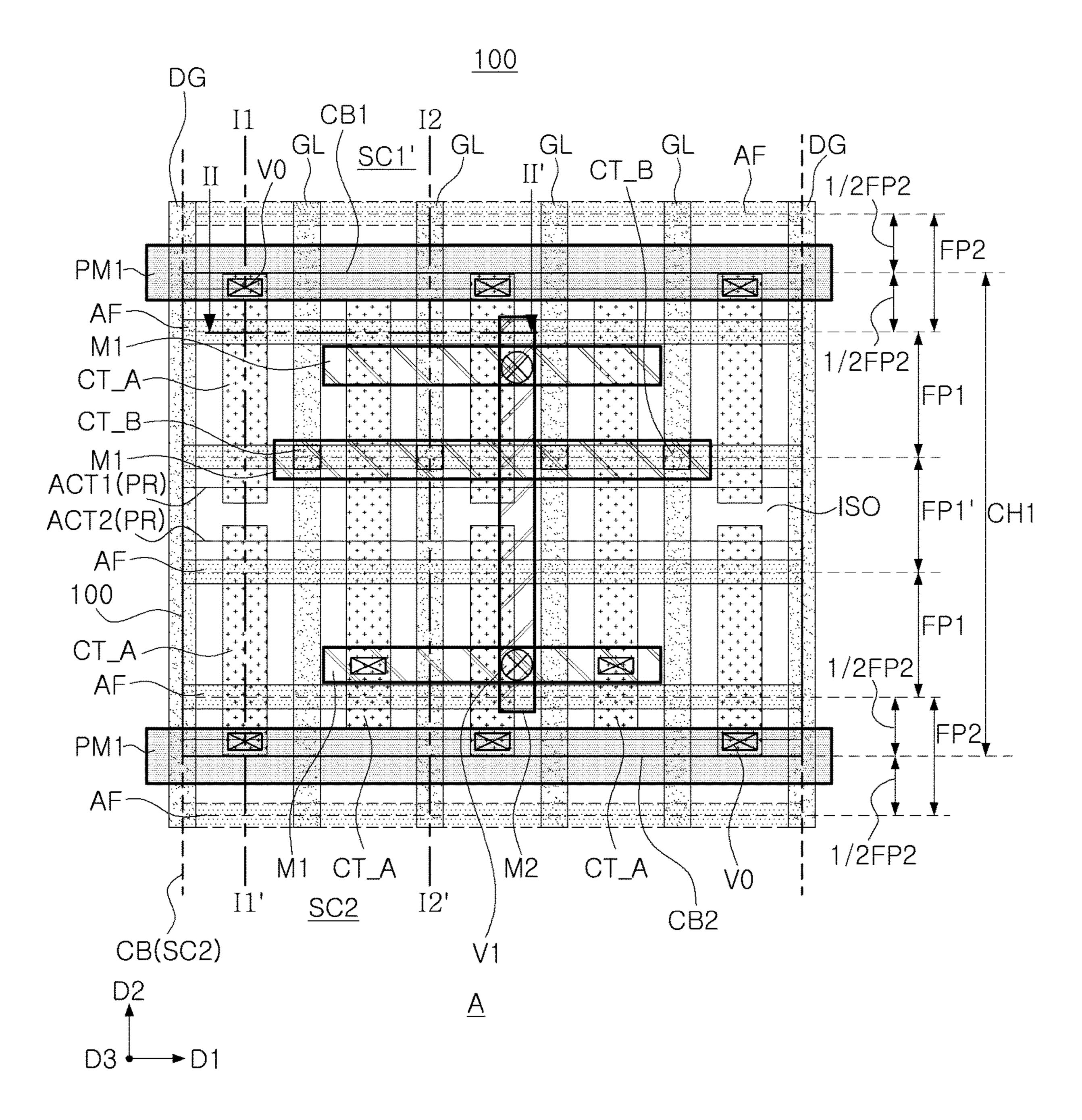

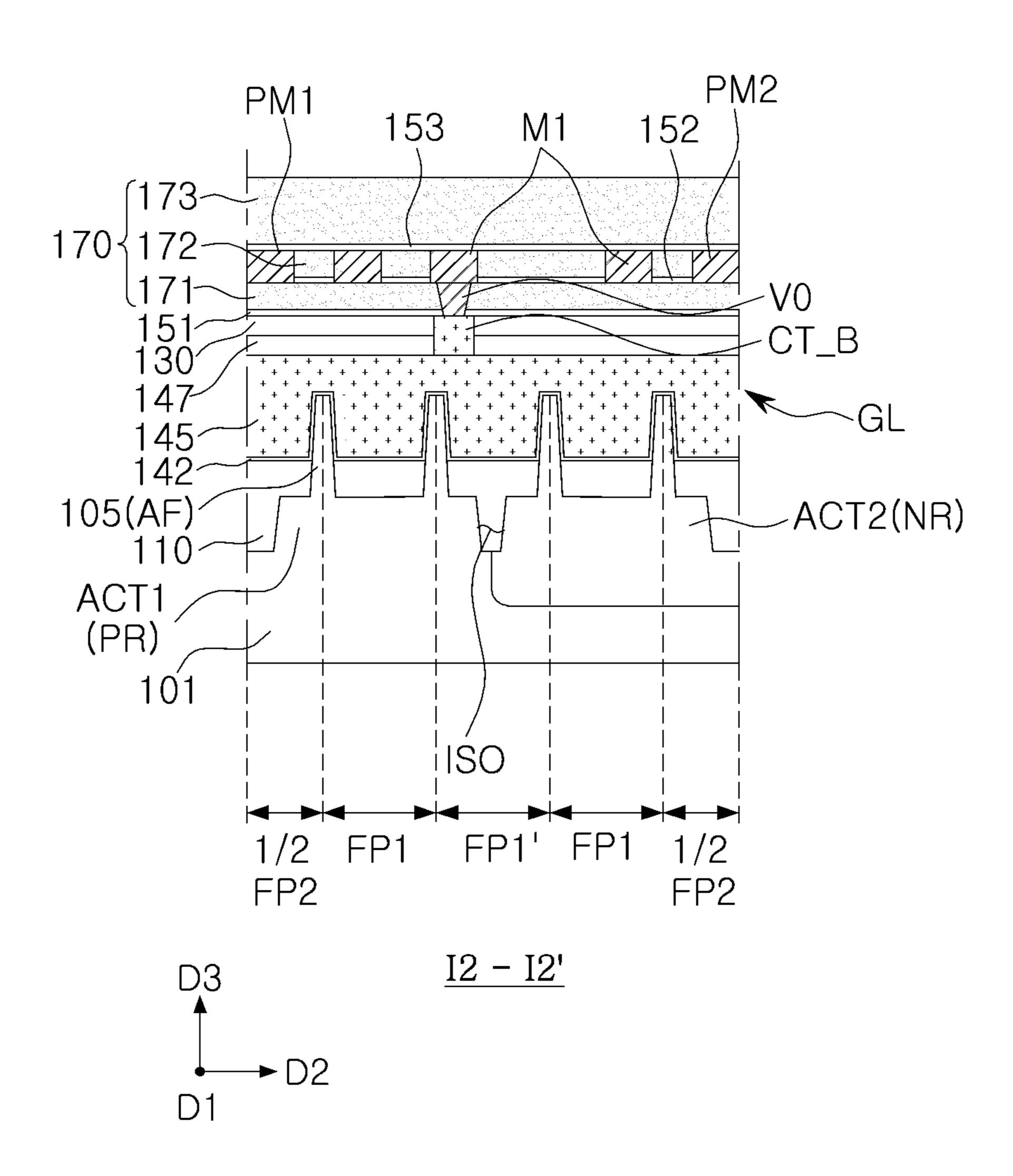

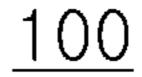

cell of FIG. 4, taken along lines I1-I1', I2-I2', and II-II' of FIG. 4, respectively.

FIG. 6 is a layout diagram of fin patterns of a standard cell according to an example embodiment.

FIGS. 7A and 7B are layout diagrams of fin patterns of a 40 standard cell and a final standard cell according to an example embodiment, respectively.

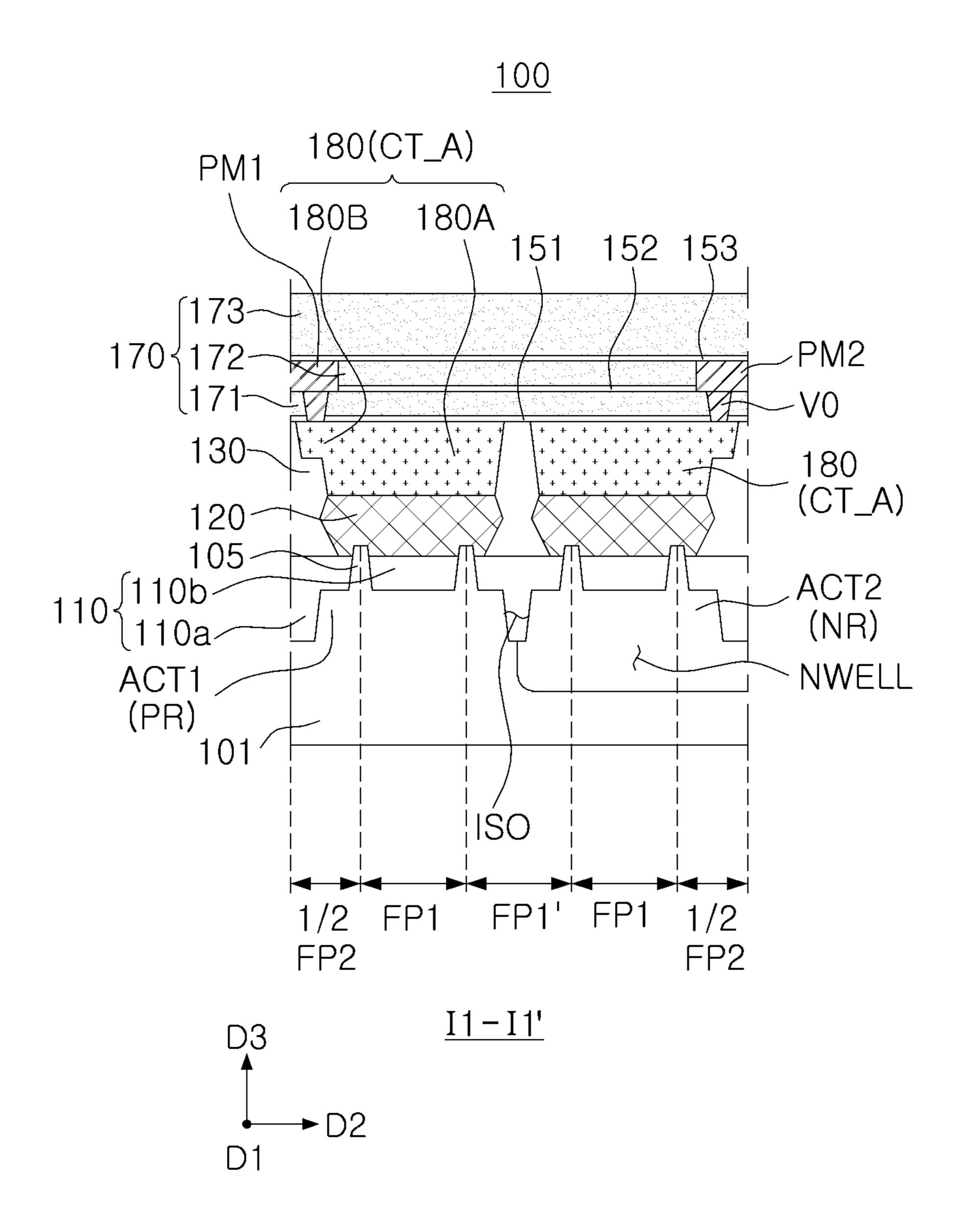

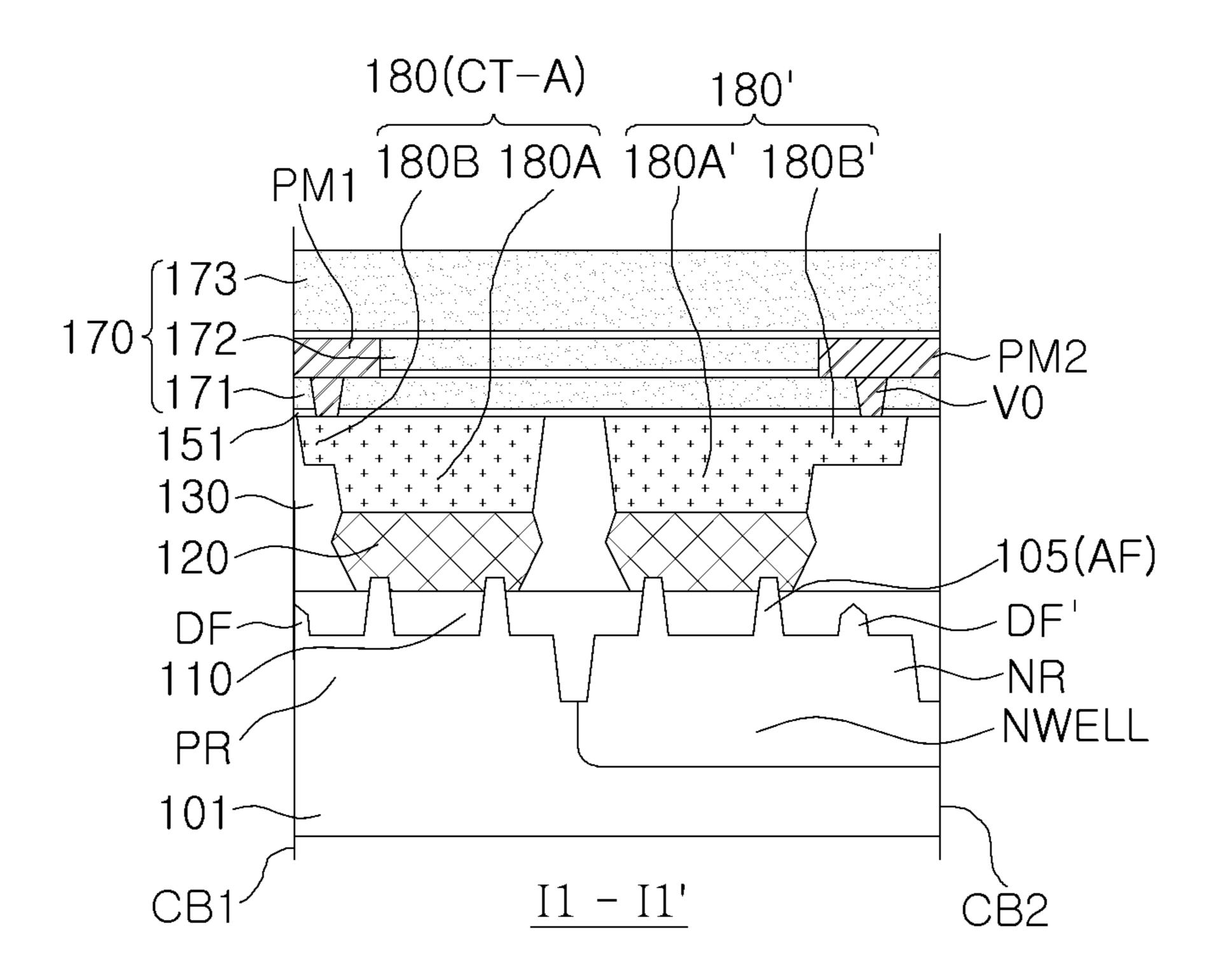

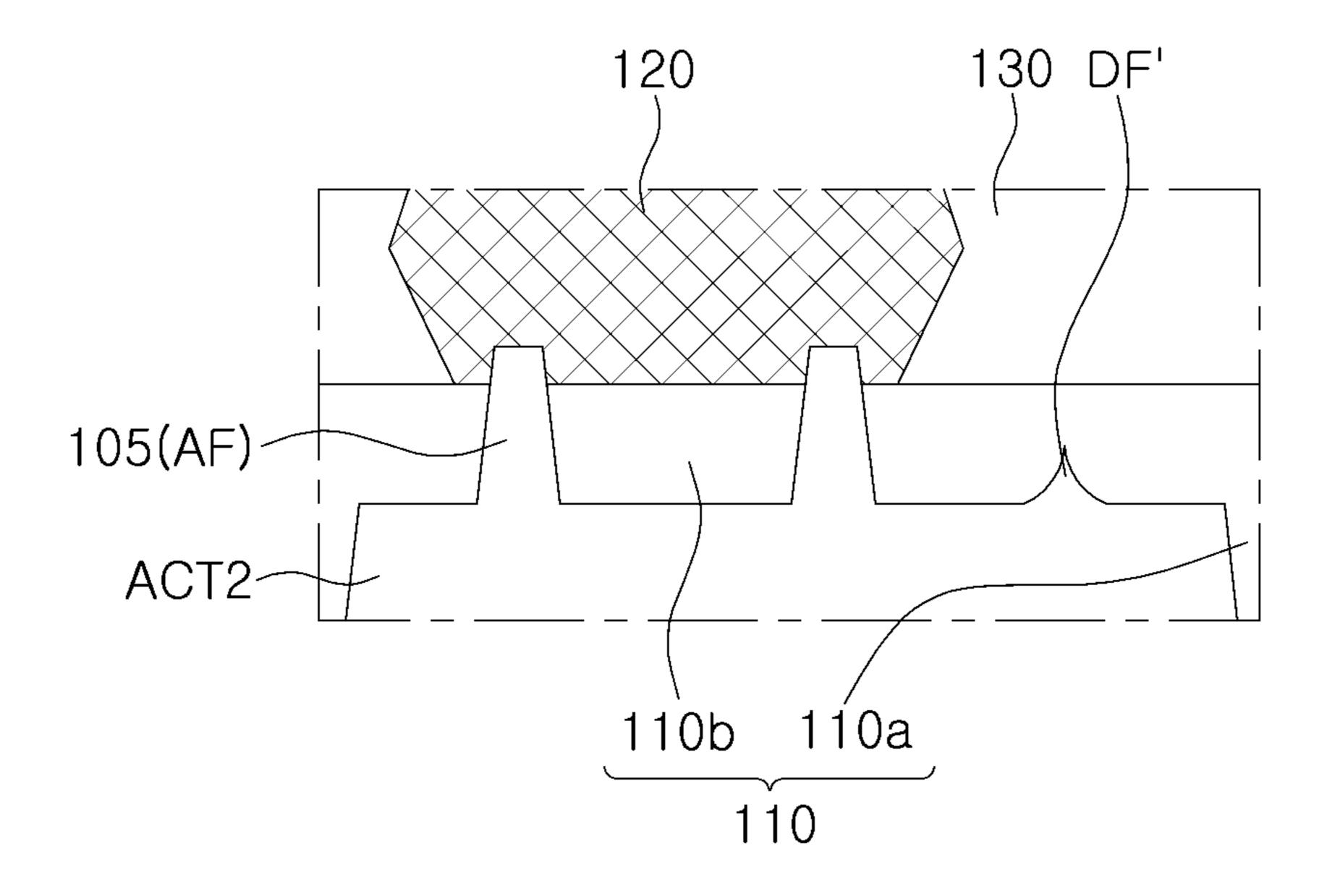

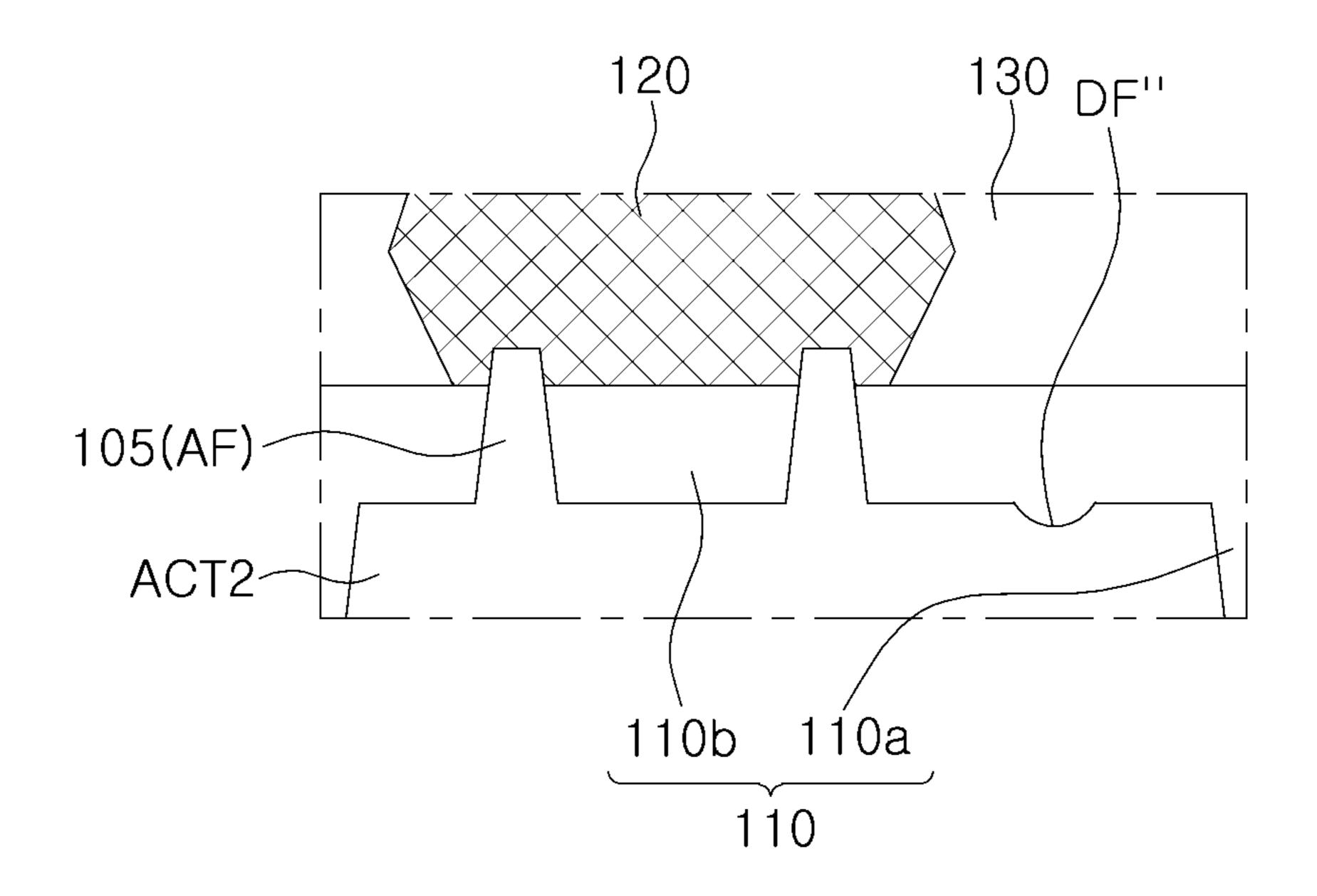

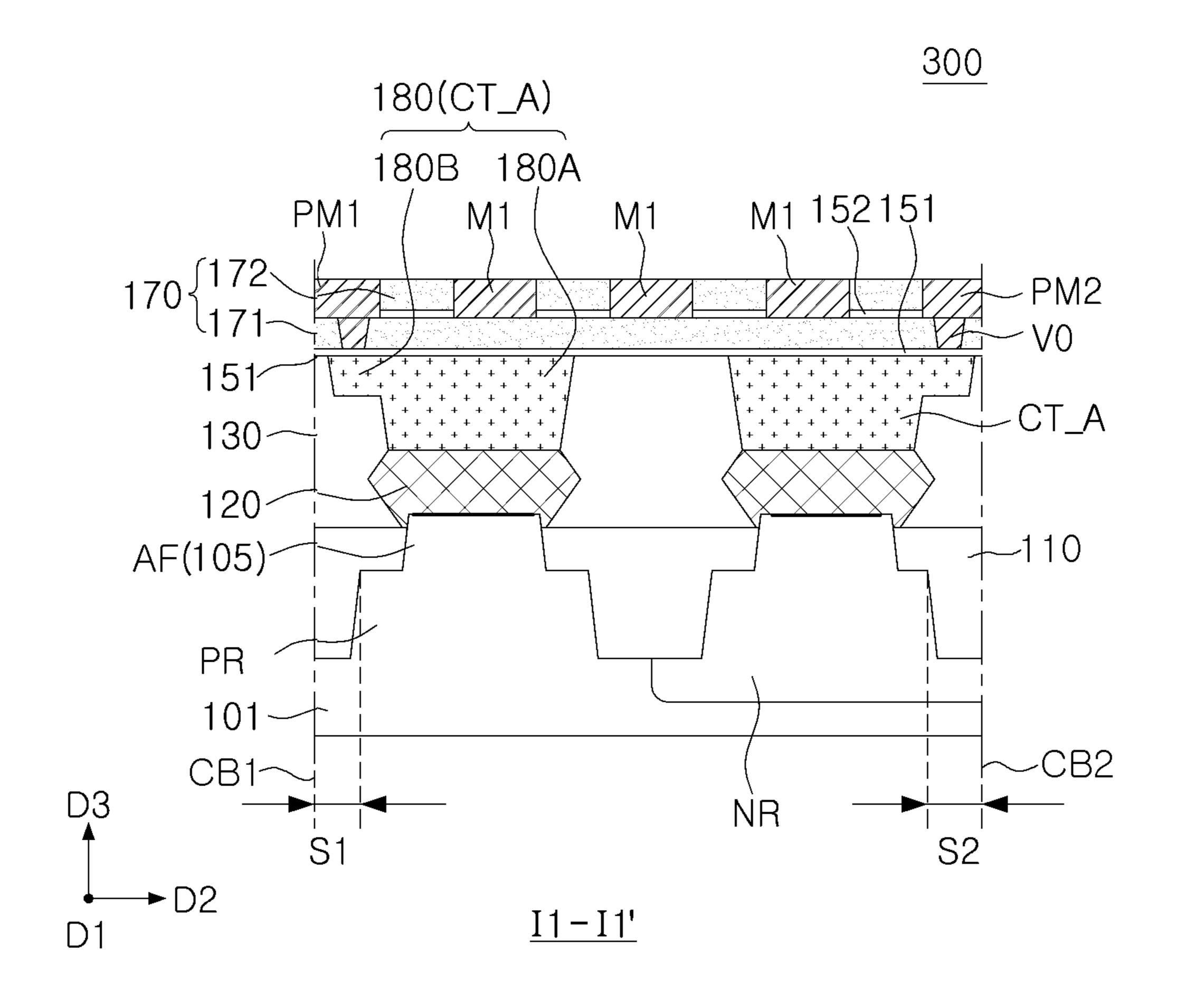

FIG. 8 is a cross-sectional view of the standard cell FIG. 7B, taken along line I1-I1' of FIG. 7B.

trating various examples related to a dummy fin.

FIGS. 10A and 10B are layout diagrams of fin patterns of a standard cell and a final standard cell according to an example embodiment, respectively.

FIGS. 11A and 11B are cross-sectional views of the 50 standard cell of FIG. 10B, taken along lines I1-I1' and II-II' of FIG. 10B, respectively, and FIG. 11C is a bottom view of the standard cell of FIG. 10B.

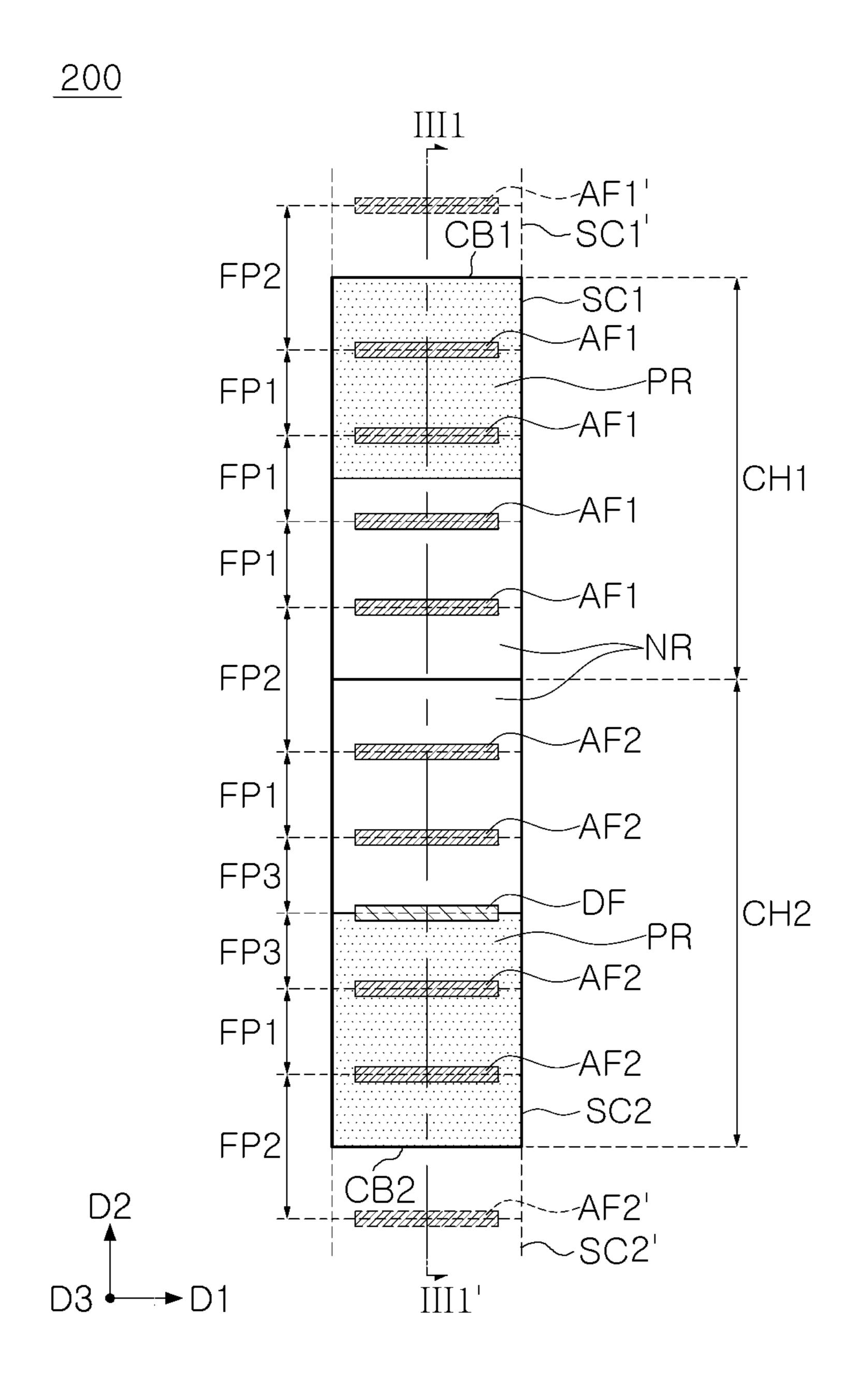

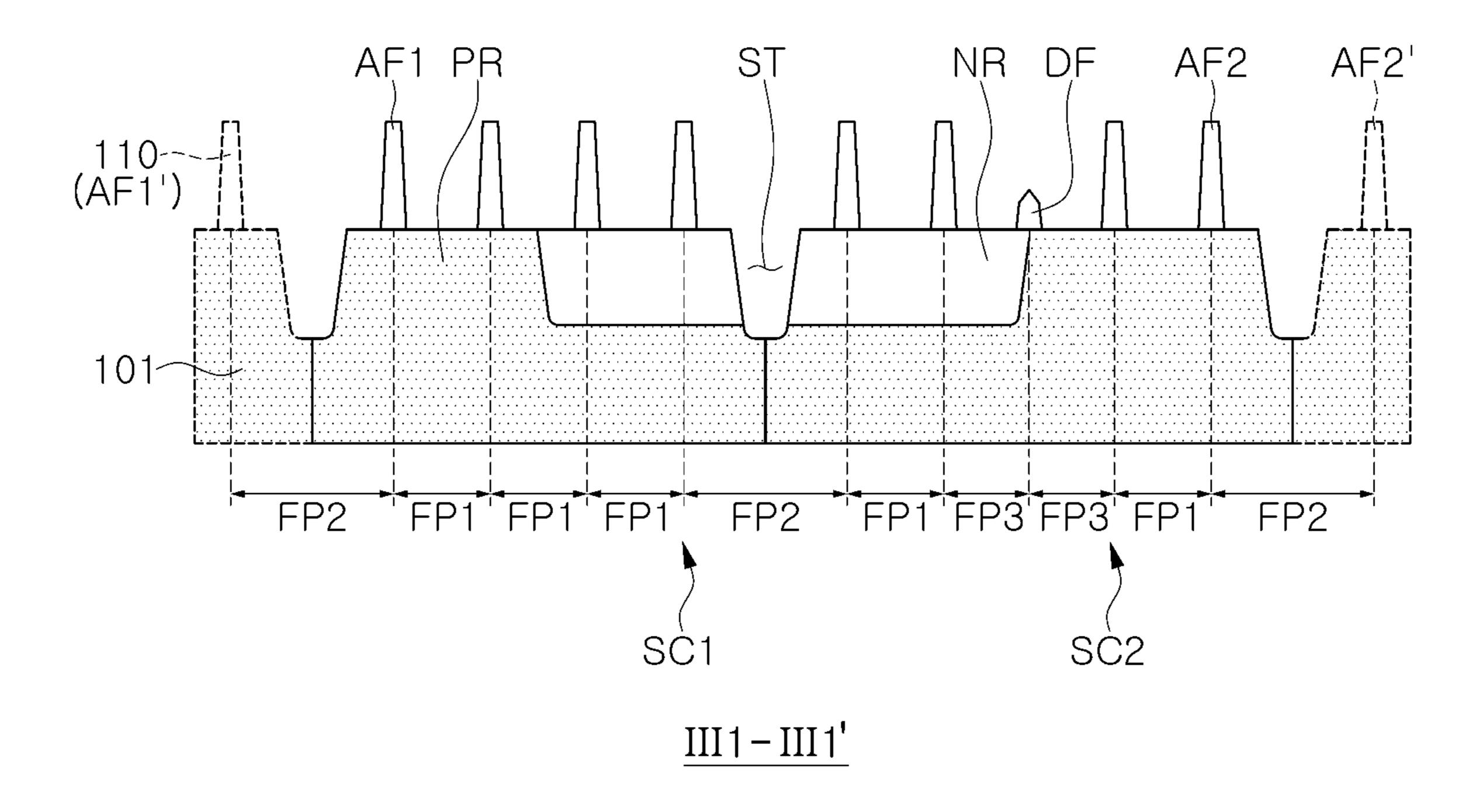

FIG. 12 is a layout diagram of fin patterns of a semiconductor device (standard cells) according to an example 55 embodiment.

FIG. 13 is a cross-sectional view of the semiconductor device of FIG. 12, taken along line III1-III1' of FIG. 12, and illustrates an arrangement of the fin patterns.

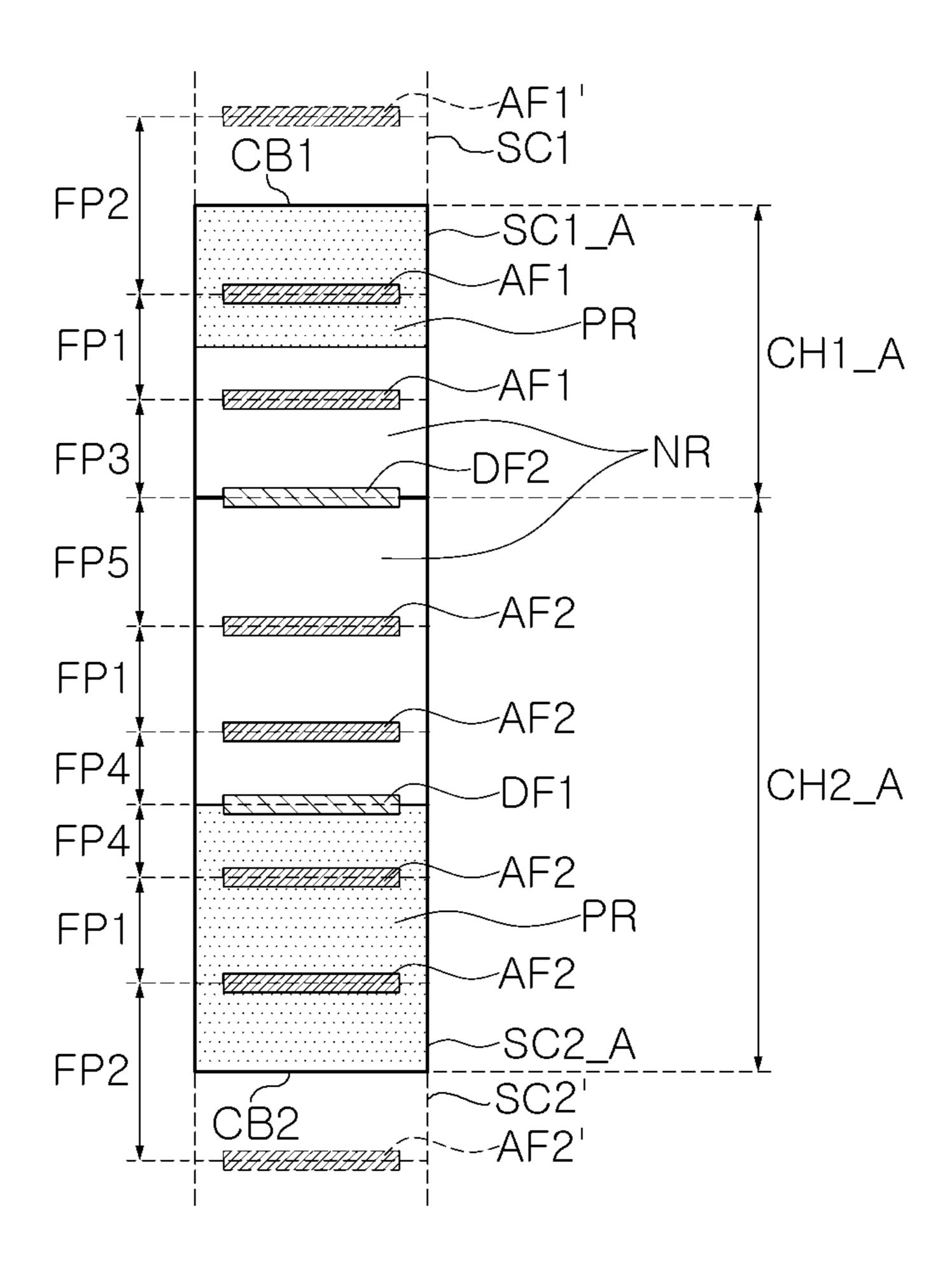

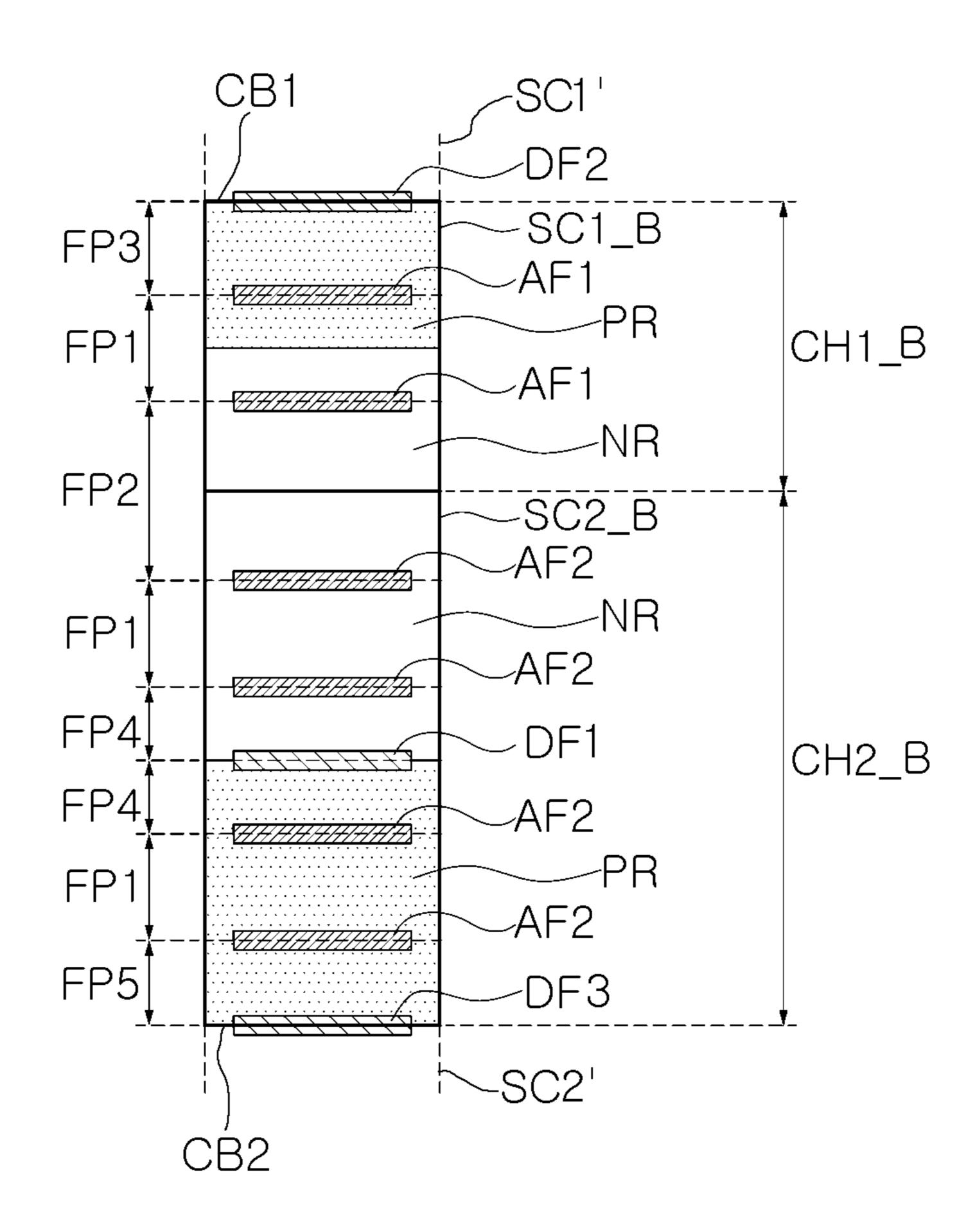

FIGS. 14A and 14B are layout diagrams of fin patterns of 60 a semiconductor device according to various embodiments.

FIG. 15 is a layout diagram of fin patterns of a semiconductor device (standard cells) according to an example embodiment.

FIG. 16 is a cross-sectional view of the semiconductor 65 device of FIG. 15, taken along line III2-III2' of FIG. 15, and illustrates an arrangement of the fin patterns.

FIGS. 17A and 17B are layout diagrams of fin patterns of a semiconductor device according to various embodiments.

FIG. 18 is a layout diagram of active fins of a standard cell according to an example embodiment.

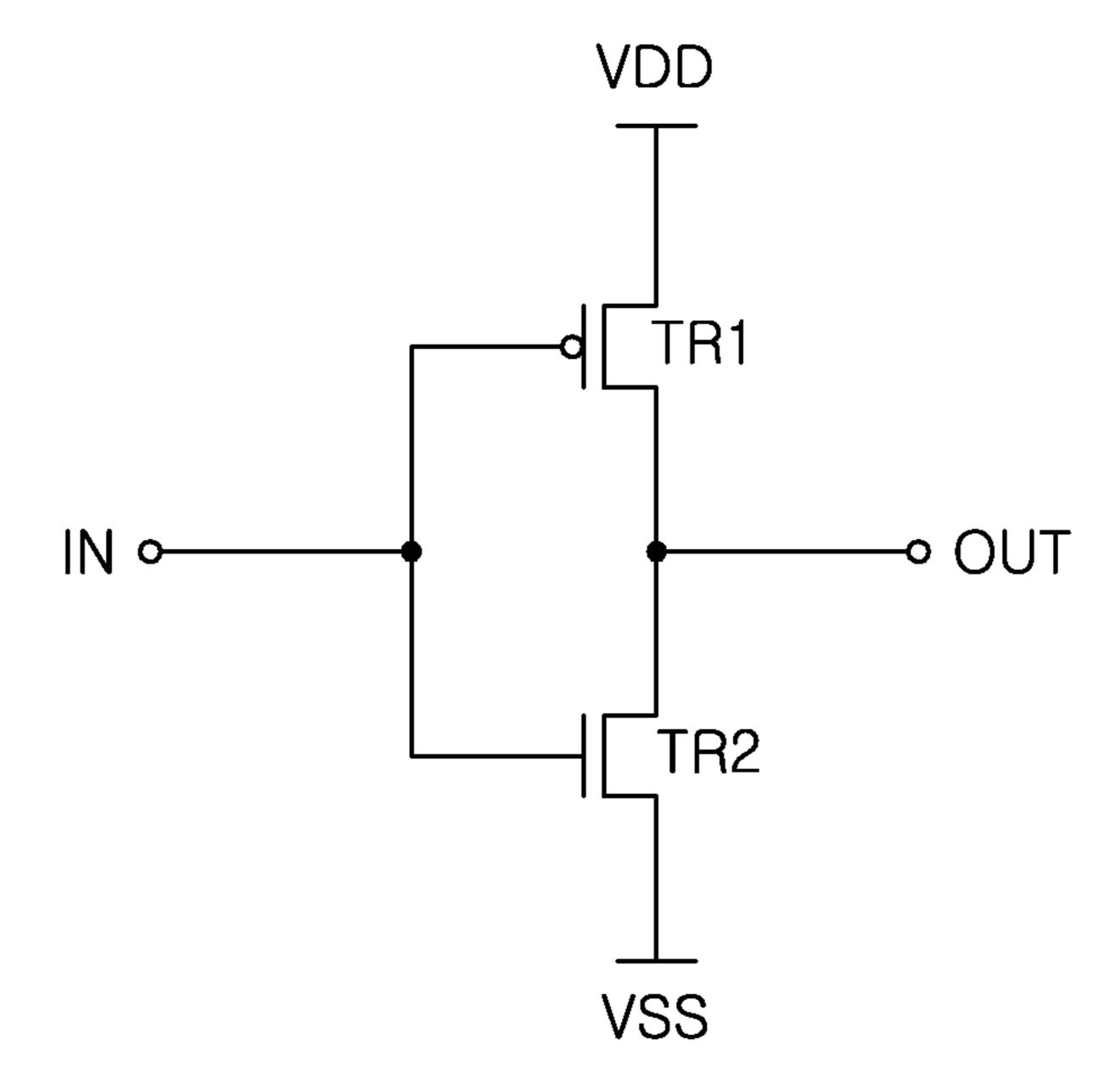

FIGS. 19A and 19B are an equivalent circuit diagram and a layout diagram of a standard cell according to an example embodiment, respectively.

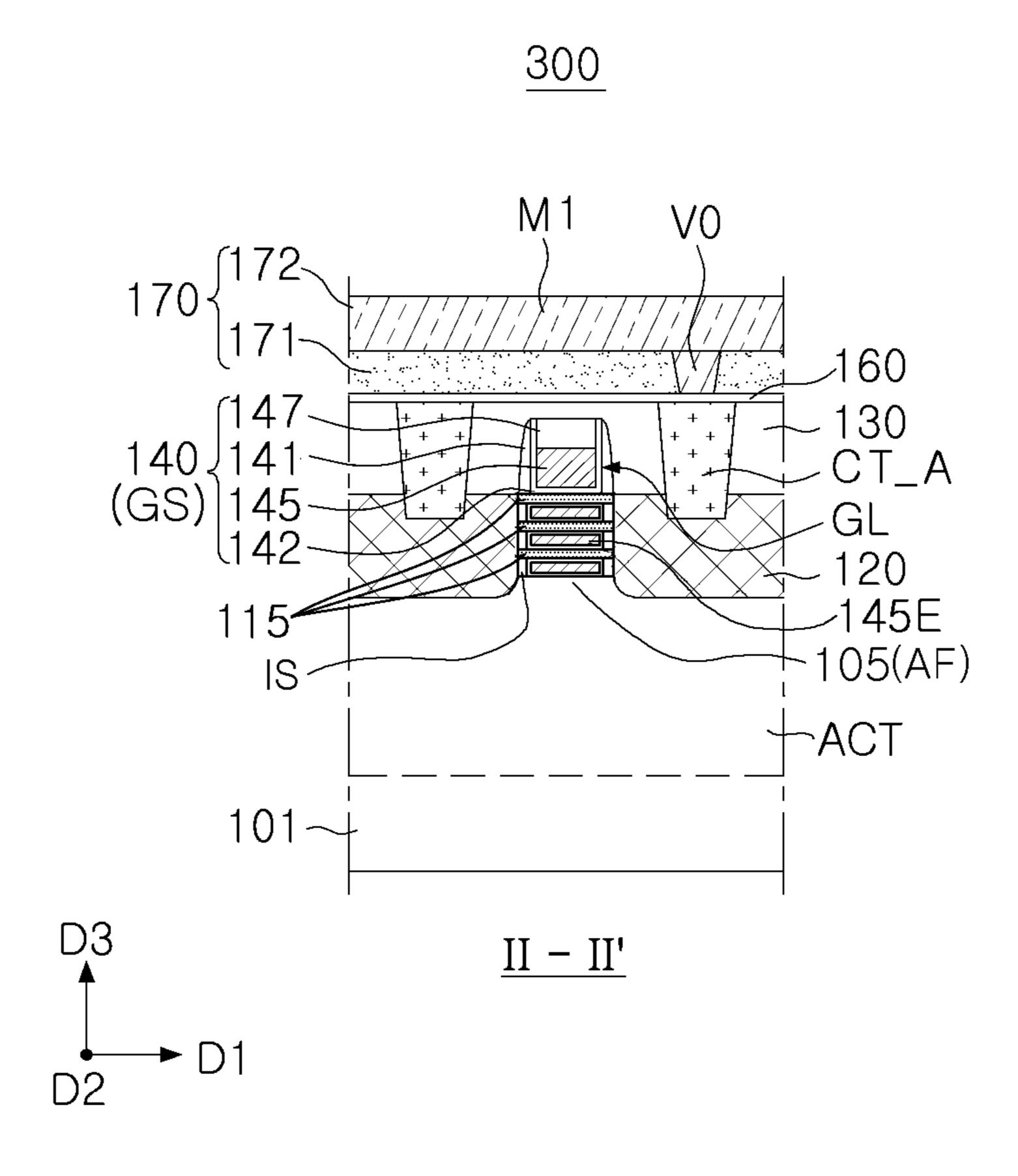

FIGS. 20A and 20B are cross-sectional views of the standard cell of FIG. 19B, taken along lines I1-I1' and II-II' of FIG. 19B, respectively.

#### DETAILED DESCRIPTION

Hereinafter, example embodiments will be described with reference to the accompanying drawings.

FIG. 1 is a flowchart illustrating a method of manufacturing a semiconductor device according to an example embodiment.

Referring to FIG. 1, a method of manufacturing a semiconductor device according to the present embodiment may include a design step DSG of the semiconductor device and a fabrication process step FAB of the semiconductor device.

The design step DSG may be a step of designing a layout for a circuit, and may be performed using a tool for circuit design. The tool may be a program including a plurality of instructions executed by a processor. Accordingly, the design step DSG may be a computer implemented step for circuit design. The fabrication process step FAB may be a 30 step of fabricating a semiconductor device based on a designed layout, and may be performed by a semiconductor process module.

The design step DSG may include a floorplan step S10, a powerplan step S20, a placement step S30, and a clock tree FIGS. 5A to 5C are cross-sectional views of the standard 35 synthesis (CTS) step S40, a routing step S50, and a whatif-analysis step S60.

The floorplan step S10 may be a step of cutting and transporting a logically designed schematic circuit to be physically designed. In the floorplan step S10, a memory or functional blocks may be disposed. In this step, for example, functional blocks which will be placed adjacent to each other may be identified, and the functional blocks may be assigned in consideration of an available space and required performance. For example, the floorplan step S10 may FIGS. 9A to 9C are enlarged cross-sectional views illus- 45 include a step of generating a site-row and a step of forming a metal routing track on the generated site-row. The site-row may be a frame for placing standard cells stored in a cell library, based on a specified design rule. Standard cells, each having the same height, may be placed in each site-row. Some site-rows may provide a site for placing the standard cells to have a height different from a height of standard cells of other site-rows. In the fabrication step FAB which will be later described, the site-rows will be transferred onto row regions of a substrate. For example, in each row region, the standard cells of a corresponding site-rows will be formed using transistors, for example.

The powerplan step S20 may be a step of placing patterns of interconnections connecting local power, for example, a driving voltage source or ground, in the disposed functional blocks. For example, patterns of interconnections connecting power or grounds may be formed in the form of a net (i.e., a mesh) such that the power is uniformly supplied to entire chip. In the specification, the patterns may also be referred to as a power rail or a power line. In the present step, the interconnections may be formed in the form of a net through various placement rules of the interconnection patterns.

The placement step S30 may be a step of placing patterns of elements constituting the functional block, and may include a step of placing standard cells. In some embodiments, each of the standard cells may include semiconductor elements (e.g., transistors) and first interconnection lines 5 connected to the semiconductor elements. The first interconnection lines may include a power transmission line connected to power or ground, and an interconnection line transmitting a control signal, an input signal, or an output signal. Empty regions in each row-site may be present 10 between standard cells placed in the placement step S30, and may be filled with filler cells. Unlike standard cells including an operable semiconductor element and a unit circuit implemented by semiconductor elements, the filler cells may be dummy regions. After completing the placement step S30, a 15 shape or a size of a pattern for transistors and interconnections to be formed on a semiconductor substrate may be defined. For example, layout patterns such as a PMOS, an NMOS, an N-WELL, a gate electrode, and interconnections to be disposed thereon may be appropriately placed to form 20 an inverter circuit, for example, on an actual semiconductor substrate.

The CTS step S40 may be a step of forming patterns of signal lines of a center clock related to a response time determining performance of a semiconductor device. The 25 routing step S50 may be a step of forming an upper interconnection structure or a routing structure including second interconnection lines connecting the placed standard cells. For example, in this step, a power distribution network (PDN) may be implemented. The second interconnection lines may be electrically connected to the first interconnection lines in the standard cells, and the standard cells may be electrically connected to each other or may be connected to power or ground. The second interconnection lines may be physically formed above the first interconnection lines.

The what-if-analysis step S60 may be a step of verifying and correcting the generated layout. Items to be verified may include design rule check (DRC) verifying whether a layout generated meets a design rule, electrical rule check (ERC) verifying whether circuits implemented with the layout 40 generated are properly connected with each other without electrical disconnection, and layout vs schematic (LVS) checking whether the layout matches a gate-level net list.

The fabrication process step FAB may include a mask generation step S70 and a semiconductor device manufac- 45 turing step S80.

The mask generation step S70 may include a step of performing optical proximity connection (OPC), or the like, on layout data generated in the design step DSG to generate mask data for forming various patterns on a plurality of 50 layers and a step of generating a mask based on the mask data. The OPC may modify mask patterns formed using the layout to increase the printability on the semiconductor substrate. The mask may be generated in a manner of drawing layout patterns using a chromium thin film applied 55 on a glass substrate or a quartz substrate.

In the semiconductor device manufacturing step S80, various types of exposure and etching processes may be performed repeatedly. Such processes may be performed repeatedly to sequentially form shapes of the patterns 60 according to a layout generated during the layout design, on a semiconductor substrate such as silicon. For example, various semiconductor processes may be performed on a semiconductor substrate such a wafer using a plurality of masks to form a semiconductor device in which integrated 65 circuits are implemented. The semiconductor process, employed in the present embodiment, may be performed by

6

a lithography process using light such as extreme ultraviolet (EUV). Masks may have patterns which are generated using a lithography process. The semiconductor process may include a deposition process, an etching process, an ion implantation process, a cleaning process, and the like. The semiconductor process may further include a packaging process in which a semiconductor device is mounted on a printed circuit board (PCB), and then encapsulated by an encapsulant, and a test process for screening a faulty device from the semiconductor device or a package thereof manufactured in the fabrication process step FAB.

FIG. 2 is a schematic plan view of a semiconductor device 300 according to an example embodiment.

Referring to FIG. 2, the semiconductor device 300 may include standard cells SC and filler cells FC. The filler cells FC may fill empty regions of the standard cells SC, and may be provided as dummy regions. Each of the standard cells SC may be disposed in a corresponding row region of the four regions R1 to R4. Each row region may extend lengthwise in a first direction D1, and the row regions R1 to R4 may be arranged in a second direction D2, perpendicular to the first direction D1. In an embodiment, each row region may include a plurality of standard cells SC. For the simplicity of drawings, each of the standard cells SC may be represented using a rectangular with a thick line without showing transistors implemented therein. For example, the first row region R1 has four standard cells including a standard cell SC2. At least one of the four standard cells of the first row region R1 may be a standard cell different from the others thereof. The second row region R2 has five standard cells including a standard cell SC1. At least one of the five standard cells of the second row region R2 may be a standard cell different from the others thereof. The third row region R3 has three standard cells including a standard 35 cell SC1', and at least one of the three standard cells may be a standard cell different from the others. The fourth row region R4 has four standard cells including a standard cell SC2', and at least one of the four standard cells may be a standard cell different from the others. As described with reference to FIG. 1, each row region may be defined by a corresponding row-site formed in the placement step S30 of the design step DSG. Hereinafter, a row may refer to a row region as described above, unless otherwise described. Ordinal numbers such as "first," "second," "third," etc. may be used simply as labels of certain elements, steps, etc., to distinguish such elements, steps, etc. from one another. Terms that are not described using "first," "second," etc., in the specification, may still be referred to as "first" or "second" in a claim. In addition, a term that is referenced with a particular ordinal number (e.g., "first" in a particular claim) may be described elsewhere with a different ordinal number (e.g., "second" in the specification or another claim).

A standard cell layout, illustrated in FIG. 2, is a layout designed by the method described with reference to FIG. 1, but may also be understood as a plane of an actual semiconductor device manufactured based on the layout.

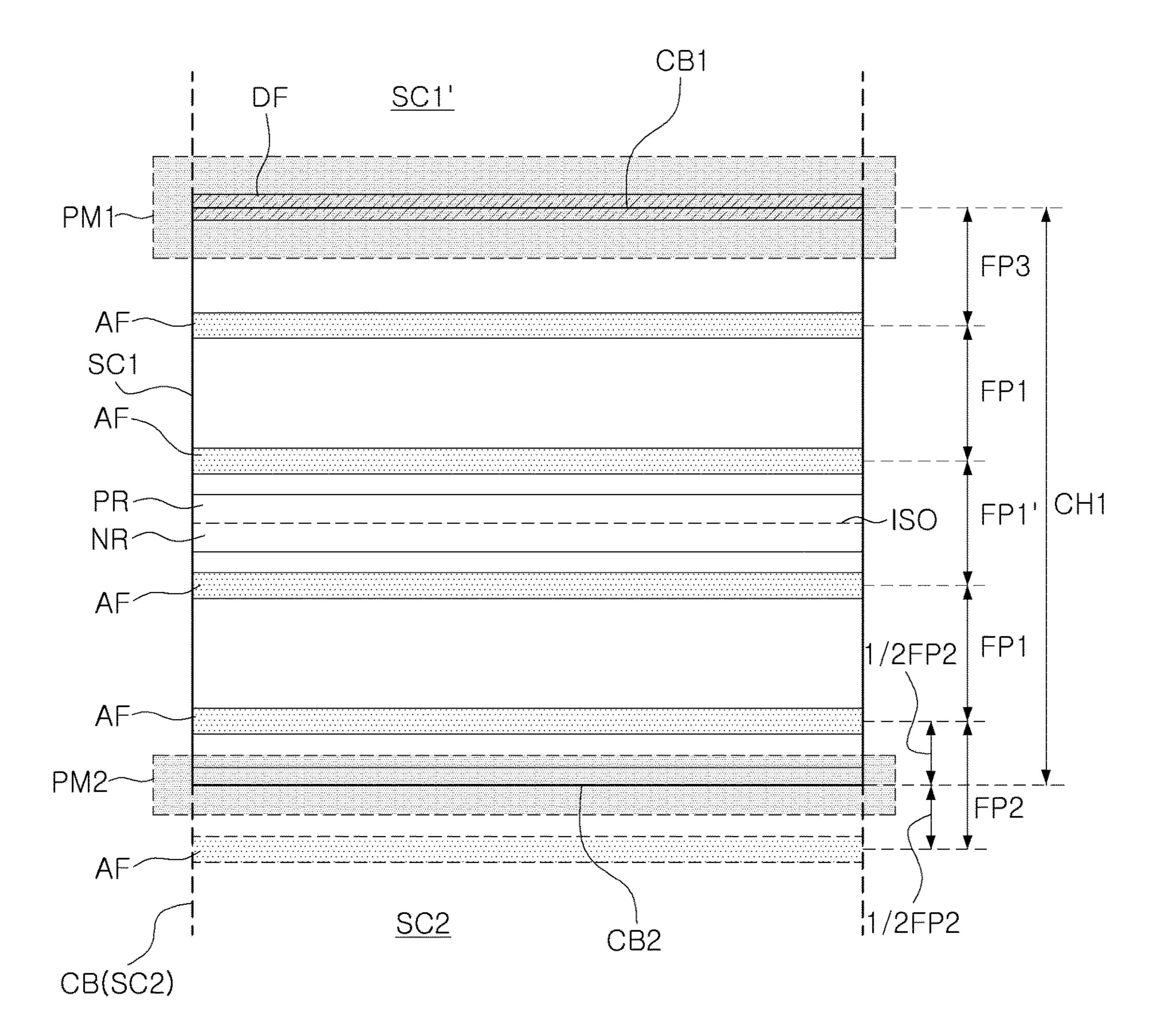

Standard cells SC2, SC1, SC1', and SC2' may be arranged in the first to fourth rows R1, R2, R3, and R4, respectively. The standard cells SC1 and SC1' in the second and third rows R2 and R3, respectively, may have a cell height CH1 in the second direction D2, which corresponds to a shorter side of each of the second and third rows R2 and R3. The standard cells SC2 and SC2' in the first and fourth rows R1 and R4, respectively, may have a cell height CH2 in the second direction D2, which corresponds to a shorter side of each of the first and fourth rows R1 and R4. The cell height

CH1 of the standard cells SC1 and SC1', disposed in some rows R2 and R3, may be different from the cell height CH2 of the standard cells SC2 and SC2' disposed in other rows R1 and R4.

In the present embodiment, the standard cells SC1 and 5 SC1', respectively arranged in the second and third rows R2 and R3, may have the same first cell height CH1, and the standard cells SC2 and SC2', respectively arranged in first and fourth rows R1 and R4, may have the same second cell height CH2 smaller than the first cell height CH1. At least 10 one of a plurality of standard cells disposed in each row may have a width, in the first direction D1, different from the others. For example, the fourth row R4 has four standard cells including the standard cell SC2' therein. The standard standard cells in the fourth row S4, and a width different from the other standard cells in the fourth row S4.

Most of the standard cells SC1, SC1', SC2, and SC2' are each arranged in a single row, but at least one of the standard cells may be an extension-type standard cell eSC arranged 20 across two or more adjacent rows R1 and R2. A cell height of such extension-type standard cells eSC may have the sum of heights of adjacent rows. For example, the extension-type standard cells eSC may be disposed in the first and second rows R1 and R2 and may have a cell height corresponding 25 to the sum (CH1+CH2) of the first cell height CH1 and the second cell height CH2.

In the present embodiment, boundaries of the second and third rows R2 and R3 having the first cell height CH1 may extend lengthwise in the first direction D1 and may be 30 spaced apart from each other in a column direction, for example, the second direction D2. Boundaries of the first and fourth rows R1 and R4 having the second cell height CH2 may extend in lengthwise in the first direction D1 and may be spaced apart from each other in the second direction 35 D2. In the present embodiment, the rows have been described as having two cell heights, but rows having three or more different cell heights may be provided and the arrangement thereof may vary. For example, the second and third rows R2 and R3 having the first cell height CH1 and 40 the first and fourth rows R1 and R4 having the second cell height CH2 may be alternately arranged in the second direction D2.

Each of the standard cells SC1, SC1', SC2, and SC2' may have an active region having a first conductivity type (for 45) example, a p-type active region) and an active region having a second conductivity type (for example, an n-type active region) arranged in the column direction, for example, the second direction D2. For the simplicity of drawings, the p-type active region is represented with a character "P", and 50 the n-type active region is represented with a character "N". The standard cells SC1, SC1', SC2, and SC2', disposed in two adjacent rows among the first to fourth rows R1, R2, R3, and R4, may be arranged such that active regions having the same conductivity type are adjacent to each other in the 55 second direction D2. For example, the standard cells SC1 and SC1' of the second and third rows R2 and R3 may be arranged such that p-type active regions are adjacent to each other, and the standard cells SC2 and SC1 of the first and second rows R1 and R2 and the standard cells SC1' and SC2' of the third and fourth rows R3 and R4 may be arranged such that n-type active regions are adjacent to each other in the second direction D2.

A plurality of first and second power supply lines PM1 and PM2, which supply power to the plurality of standard 65 cells SC1, SC2, SC1', and SC2', may each extend lengthwise in the first direction along boundaries of the plurality of

standard cells SC1, SC2, SC1', and SC2'. Each of the plurality of first and second power supply lines PM1 and PM2 may supply different voltages to the standard cells SC1, SC2, SC1', and SC2' disposed therebetween. Among the plurality of first and second power supply lines PM1 and PM2, a power supply line, disposed on a boundary between standard cells of two adjacent rows, may a power supply line shared by adjacent standard cells. For example, one of two power supply lines PM2 may extend in the first direction D1 along a boundary between two adjacent rows (e.g., the third row R3 and the fourth row R4), and may partially overlap each of the two adjacent rows, and the other of the two power supply lines PM2 may extend in the first direction D1 along a boundary between two adjacent rows (e.g., the first cell SC2' has the same cell height CH2 with the other 15 row R1 and the second row R2), and may partially overlap each of the two adjacent rows.

> As illustrated in FIG. 2, the plurality of first power supply lines PM1 may be disposed on a boundary between p-type active regions (for example, between the second row R2 and the third row R3) adjacent to external boundaries (for example, a lower boundary of the first row R1 and an upper boundary of the fourth row R4) adjacent to the p-type active region, and the plurality of second power supply lines PM2 may be arranged on a boundary adjacent to the n-type active region and boundaries between adjacent n-type device regions (for example, boundaries between the first row R1 and the second row R2 and between the third row R3 and the fourth row R4). The first power supply lines PM1 and the second power supply lines PM2 may be alternately arranged in the column direction, for example, the second direction D**2**.

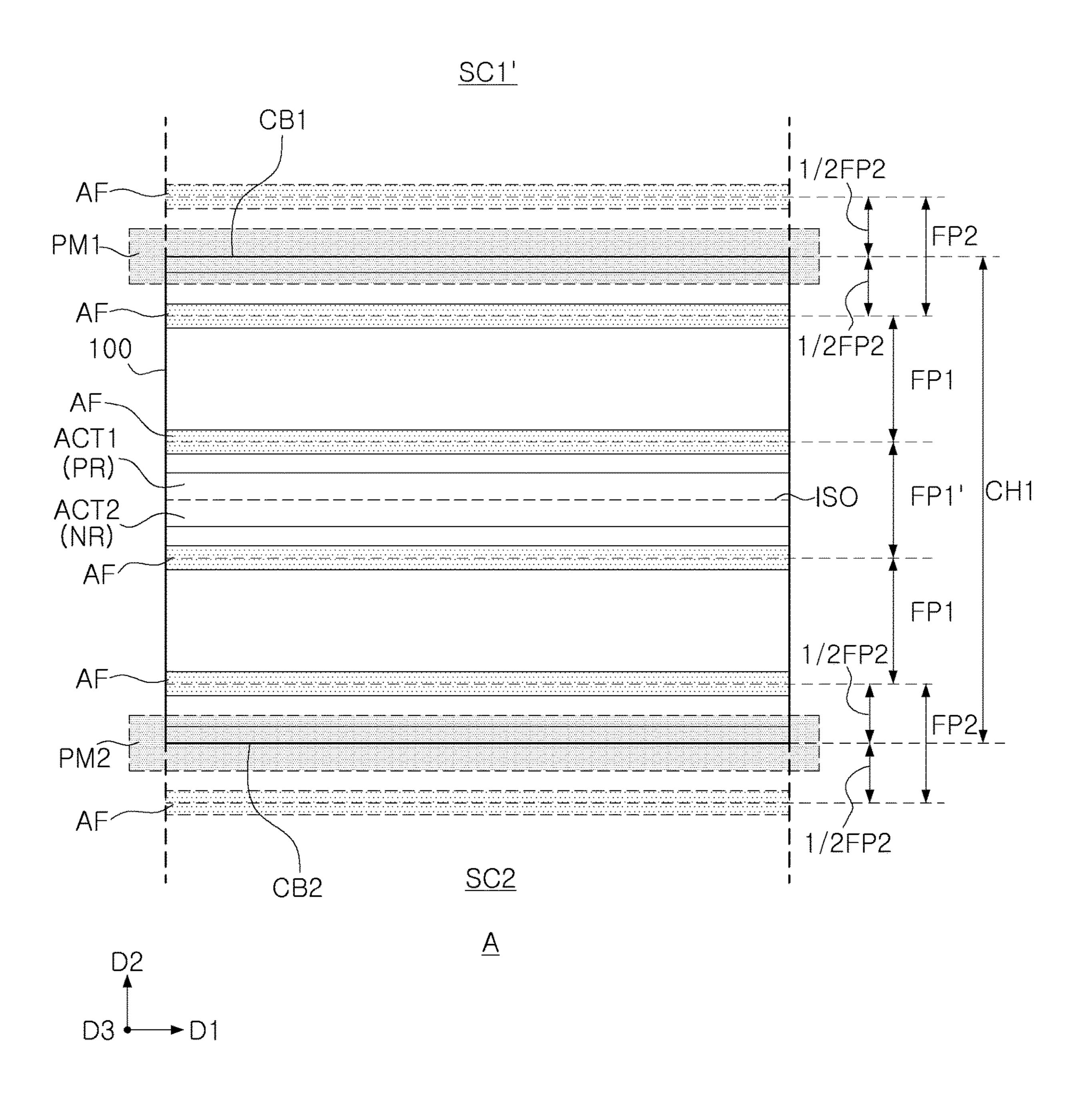

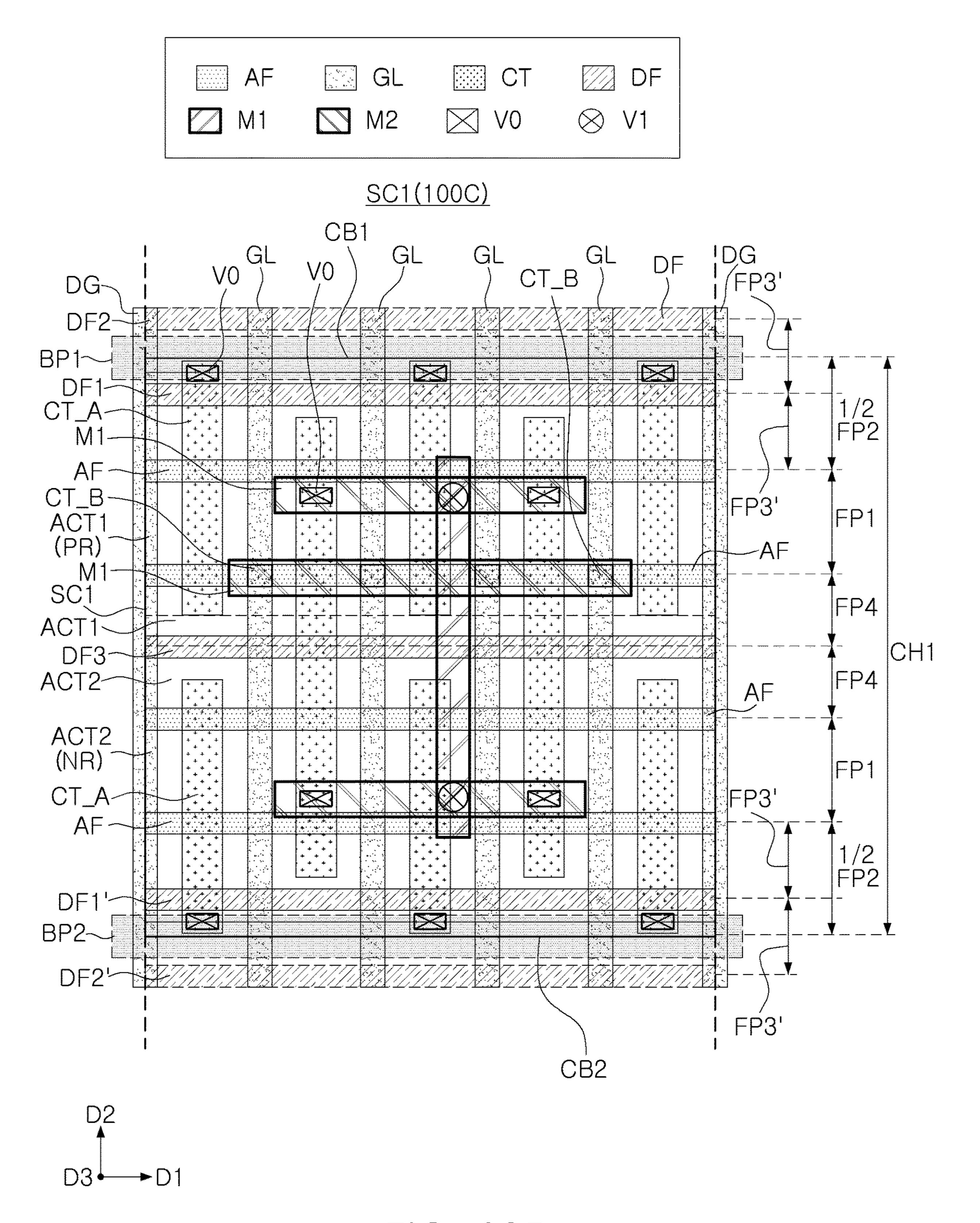

> FIG. 3 is a layout diagram of a fin pattern of a standard cell 100 according to an example embodiment. FIGS. 4A and 4B are layout diagrams of an intermediate stage and a final stage of a standard cell 100 according to an example embodiment, respectively.

> The standard cell 100 according to the present embodiment may be a unit standard cell indicated by "A" in the layout of FIG. 2, which may also be referred to as a standard cell 100. As illustrated in FIG. 4B, the standard cell 100 may be an inverter element including four p-type transistors and four n-type transistors between a first power supply line PM1, which supplies a first voltage, and a second power supply line PM2, which supplies a second voltage different from the first voltage.

> Referring to FIG. 3, the standard cell 100 according to the present embodiment may include first and second active regions ACT1 and ACT2, having different conductivity types, and a plurality of active fins AF protruding from the first and second active regions ACT1 and ACT2 in a third direction D3 and extending in the row direction, for example, the first direction D1.

> For example, the first active region ACT1 may be a p-type active region PR provided as a p-type semiconductor substrate or a p-type well, and may be provided as a region for an n-type transistor. The second active region ACT2 may be an n-type active region NR provided as an n-type well, and may be provided as a region for a p-type transistor.

> As illustrated in FIG. 3, the plurality of active fins AF may include four active fins, and two active fins AF may be disposed in each of the first and second active regions ACT1 and ACT2. The four active fins AF may be disposed to be spaced apart from each other in the second direction D2.

> Standard cells SC1' and SC2 of different rows (R3 and R1) of FIG. 2) may be disposed to be adjacent to each other on two boundaries CB1 and CB2 of the standard cell 100. The two boundaries CB1 and CB2 may extend lengthwise in the

first direction D1 and may be spaced apart from each other in the second direction D2. For example, the standard cell 100 according to the present embodiment may have a first boundary CB1 with the standard cell SC1' of the third row R3 and a second boundary CB2 with the standard cell SC2 5 of the first row R1.

The four active fins AF may be arranged to be spaced apart from each other in the second direction D2 so as not to be disposed on the first and second boundaries CB1 and CB2. The four active fins AF may be disposed between the 10 first and second boundaries CB1 and CB2, without overlapping the first and second boundaries CB1 and CB2. As illustrated in FIG. 3, two active fins AF disposed in the first and second active regions ACT1 and ACT2 may be arranged 15 AF disposed in the first and second active regions ACT1 and at a first pitch FP1, and active fins AF adjacent to an isolation region ISO may be arranged at a third pitch FP1' different from the first pitch FP1.

Active fins AF adjacent to the first and second boundaries CB1 and CB2 may be arranged at a second pitch FP2 with 20 adjacent active fins AF of other neighboring standard cell SC2 and SC1'. In the standard cell 100, the active fins AF adjacent to the first and second boundaries CB1 and CB2 may be spaced apart from the first and second boundaries CB1 and CB2, respectively. In the present embodiment, 25 among the active fins AF of other neighboring standard cells SC2 and SC1', a pair of active fins AF adjacent to the first boundary CB1 may be arranged at the same pitch (or distance) ½FP2 with the first boundary CB1. Similarly, a pair of active fins AF adjacent to the second boundary CB2 30 may also be arranged at the same pitch (or distance) ½FP2 with the second boundary CB2. The cell height CH1 of the standard cell 100, employed in the present embodiment, may be defined as FP1'+2FP1+FP2.

include only active fins AF of transistors, without including a dummy fin. A dummy fin may be omitted to implement a unit circuit for the same function in a standard cell having a relatively small cell height and to further diversify a cell library. The term "dummy fin" refers to a structure derived 40 from a fin structure protruding from an active region, similarly to the active fin, but not being a part of a transistor in a final semiconductor device. The final semiconductor device may not include any transistor formed with using the dummy fin (e.g., may not include any transistor having a 45 channel region formed from a portion of the dummy fin). Such dummy fins may have various shapes and structures (see FIGS. 10A and 10B).

In the present embodiment, the plurality of active fins AF may include four active fins, and the same number of active 50 fins AF (for example, two active fins AF) may be disposed in each of the first and second active regions ACT1 and ACT2. However, different numbers of active fins AF (one or three or more active fins AF) may be disposed in the first and second active regions ACT1 and ACT2. Accordingly, the 55 first and second active regions ACT1 and ACT2 may also have different areas (for example, heights defined in the second direction D2). In some embodiments, the pitch of the active fins AF may also be implemented under other conditions, as set forth in embodiments to be described later.

FIGS. 4A and 4B illustrate layouts of an intermediate stage and a final stage of the standard cell 100, for example, a standard cell 100 implemented based on the layout of the fin pattern illustrated in FIG. 3, respectively.

Referring to FIG. 4A, a standard cell 100 may include six 65 gate lines GL and DL extending in a column direction, for example, a second direction D2 to intersect four active fins

**10**

AF. The gate lines GL and DL may be arranged in a first direction D1 at a constant pitch.

In the present embodiment, two gate lines passing through first and second boundaries CB1 and CB2 facing each other in the first direction D1 of the standard cell 100 may be provided as a dummy gate structure DL. Four gate lines, disposed between the dummy gate structures DL, may be provided as gate structures GL constituting a transistor.

First contact structures CT\_A may be disposed on the active fins AF and may be disposed on opposite sides of each of four gate structures GL. In the present embodiment, the first contact structures CT\_A may extend lengthwise in the second direction D2 and may overlap at least two active fins ACT2. The first contact structures CT\_A may be provided as a source/drain contact. Some of the first contact structures CT\_A may extend to the first and second boundaries CB1 and CB2, facing each other in the second direction D2. Some of the first contact structures CT\_A may be connected to the first power supply line PM1, and some of the first contact structures CT\_A may be connected to the second power supply line PM2. (see FIG. 5A).

Referring to FIG. 4B, the standard cell 100 may include second contact structures CT\_B for a gate contact, first and second interconnection lines M1 and M2, and first and second power supply lines PM1 and PM2 which are added on the layout illustrated in FIG. 4A.

The first and second power supply lines PM1 and PM2 may be disposed on the boundaries CB1 and CB2 facing each other in the second direction D2 of the standard cell 100. In an embodiment, the first boundary CB1 may be disposed between the standard cell 100 and a standard cell SC1', and the first power supply line PM1 may partially In the present embodiment, the standard cell 100 may 35 overlap each of the standard cell 100 and the standard cell SC1'. In an embodiment, the second boundary CB1 may be disposed between the standard cell 100 and a standard cell SC2, and the second power supply line PM2 may partially overlap each of the standard cell 100 and the standard cell SC2. Three first interconnection lines M1, extending in the first direction D1, may be arranged between the first and second power supply lines PM1 and PM2. The first and second power supply lines PM1 and PM2 and the three first interconnection lines M1 may be arranged at a constant pitch in the second direction D2. However, some interconnection lines may be omitted. In this case, two interconnection lines adjacent to an omitted region may be arranged at a pitch two times the constant pitch. In the present embodiment, it will be understood that a single interconnection line is omitted between a lowermost first interconnection line and a next lowermost interconnection line, among the first interconnection lines M1.

> Each of the first and second power supply lines PM1 and PM2 may be connected to a portion of the first contact structures CT\_A by first vias V0 (see FIG. 5A), and each of the two first interconnection lines M1, respectively adjacent to the PM1 and PM2, may be connected to another portions of the first contact structures CT\_A by the first vias V0. The first interconnection line M1, disposed between the adjacent two first interconnection lines M1, may be connected to four gate structures GL by second contact structures CT\_B, respectively provided as gate contacts (see FIG. 5B).

> A second interconnection line M2 may be disposed on the first interconnection lines M1. In the present embodiment, the second interconnection line M2 may extend in the second direction D2. The second interconnection line M2 may be connected to two first interconnection lines M1,

respectively adjacent to the first and second power supply lines PM1 and PM2, by second vias V1.

As described above, the standard cell 100 according to the present embodiment may be provided as an inverter element including four p-type transistors and four n-type transistors 5 disposed between the first and second power supply lines PM1 and PM2.

FIGS. 5A to 5C are cross-sectional views of the standard cell of FIG. 4, taken along lines I1-I1', I2-I2', and II-II' of FIG. 4, respectively.

Referring to FIGS. 5A to 5C, a standard cell 100 according to the present embodiment may include a substrate 101, active regions 102 having active fins 105 or AF, an isolation layer 110, and source/drain regions 120, gate structures 140 each having a gate electrode **145**, a lower interlayer insu- 15 lating layer 130, a contact structure 180, for example, CT\_A or CT\_B, an upper interlayer insulating layer 170, and first and second interconnection lines M1 and M2. The standard cell 100 may include Fin-type field effect transistor (Fin-FET) devices in which channels are formed in an active fin. 20 The present invention is not limited thereto. In an embodiment, the standard cell 100 may include nanosheets (for example, MBCFET®) as channels.

As described above, in the present embodiment, active fins AF are not disposed on first and second boundaries CB1 25 and CB2 on which the first and second power supply lines PM1 and PM2 are disposed, and dummy fins, not constituting a transistor, are not present, as illustrated in FIGS. 5A and **5**B.

The substrate **101** may have an upper surface extending in 30 a first direction D1 and a second direction D2. The substrate 101 may include a semiconductor material, for example, a group IV semiconductor, a group III-V compound semiconductor, or a group II-VI compound semiconductor. For example, the group IV semiconductor may include silicon, 35 germanium, or silicon-germanium. The substrate 101 has a first active region ACT1, and a second active region ACT2 may be provided by a doped region such as an N-well NWELL.

The isolation layer 110 may define active regions 102 in 40 the substrate 101. The isolation layer 110 may be formed by, for example, a shallow trench isolation (STI) process. As illustrated in FIG. 5A, the isolation layer 110 may include a region 110a extending deeper downwardly of the substrate 101 between the first and second active regions ACT1 and 45 ACT2, and a region 110b surrounding lower portions of the active fins 105. In an embodiment, the region 110a of the isolation layer 110 may define the first and second active regions ACT1 and ACT2. The present inventive concept is not limited thereto. In some embodiments, the isolation layer 50 110 may have a curved upper surface having a level increased in a direction toward the active fins 105. The isolation layer 110 may be formed of an insulating material such as an oxide, a nitride, or a combination thereof.

layer 110 in the substrate 101, and may extend in the first direction D1. The active fins 105 may have a structure protruding from the substrate 101 in a third direction D3. Upper ends of the active fins 105 may be disposed to a predetermined height. The active fins **105** may be formed as a portion of the substrate 101. The present inventive concept is not limited thereto. In an embodiment, the active fins 105 may be an epitaxial layer grown from the substrate 101. A portion of the active fins 105 may be recessed on 65 opposite sides adjacent to the gate structures GL, and source/drain regions 120 may be disposed on the recessed

active fins 105. In some embodiments, the active regions ACT may have doped regions including impurities. For example, the active fins 105 may include impurities diffused from the source/drain regions 120 in a region in contact with the source/drain regions 120. It will be understood that when an element is referred to as being "connected" or "coupled" to or "on" another element, it can be directly connected or coupled to or on the other element or intervening elements may be present. In contrast, when an element is referred to 10 as being "directly connected" or "directly coupled" to another element, or as "contacting" or "in contact with" another element, there are no intervening elements present at the point of contact.

The source/drain regions 120 may be disposed on regions, in which the active fins 105 are recessed, on opposite sides adjacent to the gate structures GS. In the present embodiment, the source/drain regions 120 may have an upper surface on a higher level than an upper surface of the active fin 105. To form the source/drain regions 120, a recess may be formed in a certain region of the active fin 105, and then selective epitaxial growth (SEG) may be performed on the recess, thereby forming the source/drain regions 120. The source/drain regions 120 may be provided as a source region or a drain region of transistors. Upper surfaces of the source/drain regions 120 may be disposed on the same or similar height level as a lower surface of the gate structure GL, when viewed from the cross section illustrated in FIG. **5**C. In another embodiment, a relative height of the source/ drain regions 120 and the gate structure GL may vary.

The source/drain regions 120 may have a merged shape in which they are connected to each other between adjacent active fins 105 in a second direction D2, as illustrated in FIG. 5A, but the present disclosure is not limited thereto. The source/drain regions 120 may have angular side surfaces, when viewed from the cross section illustrated in FIG. **5**A. However, in example embodiments, the source/drain regions 120 may have various shapes, and may have one of, for example, polygonal, circular, elliptical, and rectangular shapes.

The source/drain regions 120 may be formed of an epitaxial layer and may include, for example, silicon (Si), silicon germanium (SiGe), or silicon carbide (SiC). The source/drain regions 120 may further include impurities such as arsenic (As) and/or phosphorus (P). In some embodiments, the source/drain regions 120 may include a plurality of regions including elements and/or doping elements having different concentrations.

The gate structure GL may intersect the active fins **105** to extend in the second direction D2. Channel regions of transistors may be formed in the active fins 105 intersecting the gate structure GS. The gate structure GL may include gate spacers 141, a gate insulating layer 142, a gate electrode 145, and a gate capping layer 147.

The gate insulating layer **142** may be disposed between The active regions 102 may be defined by the isolation 55 the active fin 105 and the gate electrode 145. In some embodiments, the gate insulating layer 142 may include a plurality of layers or may be disposed to extend upwardly along a side surface of the gate electrode 145. The gate insulating layer 142 may include an oxide, a nitride, or a protrude from an upper surface of the isolation layer 110 to 60 high-k dielectric material. The high-k dielectric material may be a dielectric material having a higher dielectric constant than a silicon oxide film (SiO<sub>2</sub>).

> The gate electrode 145 may include a conductive material, for example, a metal nitride such as titanium nitride (TiN), tantalum nitride (TaN), or tungsten nitride film (WN), and/or a metal material such as aluminum (Al), tungsten (W), molybdenum (Mo), or a semiconductor material such

as doped polysilicon. The gate electrode 145 may have a multilayer structure including two or more layers. The gate electrode 145 may be disposed to be separated from each other, in the second direction D2, between at least some adjacent transistors, depending on a circuit layout of the 5 standard cell **100**. For example, a gate-cut may be additionally formed in the gate electrode 145 to divide the gate electrode 145 into a plurality of gate electrodes.

The gate spacers 141 may be disposed on opposite side surfaces of the gate electrode 145. The gate spacers 141 may 10 insulate the source/drain regions 120 from the gate electrode **145**. In some embodiments, the gate spacer layers **146** may have a multilayer structure. The gate spacers 141 may include an oxide, or a low dielectric material such a nitride include at least one of SiO<sub>2</sub>, SiN, SiCN, SiOC, SiON, and SiOCN.

The gate capping layer 147 may be disposed on the gate electrode 145, and a lower surface and side surfaces of the gate capping layer 147 may be surrounded by the gate 20 electrode **145** and the gate spacers **141**, respectively. For example, the gate capping layer 147 may include an oxide, a nitride, and an oxynitride.

The lower interlayer insulating layer 130 may be disposed to cover the source/drain regions 120 and the gate structure 25 GL. The lower interlayer insulating layer 130 may include, for example, at least one of an oxide, a nitride, and an oxynitride, and may include a low dielectric material.

The contact structure 180 may include a first contact structure CT\_A, connected to the source/drain regions 120 30 through the lower interlayer insulating layer 130, and a second contact structure CT\_B connected to the gate electrode 145 through the gate capping layer 147 and the lower interlayer insulating layer 130. The first contact structure CT\_A may have a lower end buried in the source/drain 35 regions 120 to a predetermined depth as shown in FIG. 5C, but the present inventive concept is not limited thereto.

The contact structure 180 may include a conductive barrier 182 and a contact plug 185. For example, the contact plug 185 may include a metal material such as tungsten (W), 40 aluminum (Al), copper (Cu), or a semiconductor material such as doped polysilicon. In some embodiments, the contact structure 180 may further include a metal-semiconductor layer such as a silicide layer disposed on an interface between the contact structure 180 and the source/drain 45 regions 120, and between the contact structure 180 and the gate electrode 145.

The upper interlayer insulating layer 170 may cover the contact structures 180 and may include first to third dielectric layers 171, 172, and 172. First and second interconnec- 50 tion lines M1 and M2 may be disposed between the first to third dielectric layers 171, 172, and 172. A first via V0 may penetrate through the first dielectric layer 171 to connect the contact structure 180 and the first interconnection lines M1 to each other, and a second via V1 may penetrate through the 55 second dielectric layer 172 to connect the first interconnection lines M1 and the second interconnection line M2 to each other. For example, the first to third dielectric layers 171, 172, and 172 may include at least one of SiO, SiN, SiCN, SiOC, SiON, and SiOCN. The first and second interconnection lines M1 and M2 and the first and second vias V0 and V1 may each include at least one of aluminum (Al), copper (Cu), and tungsten (W).

The etch-stop layers 151, 152, and 153 may be disposed on lower surfaces of the first to third dielectric layers 171, 65 172, and 173, respectively. The etch-stop layers 151, 152, and 153 may be used as etch-stop elements in an etching

14

process for forming the first via V0, the first interconnection lines M1, the second via V1, and the second interconnection line M2. The etch-stop layers 151, 152, and 153 may include a high-k dielectric material, for example, a silicon nitride or an aluminum oxide.

Such fin patterns including active fins and/or dummy fins may be formed through a photolithography process, a double patterning technology (DPT) process, a quadruple patterning technology (QPT) process, an extreme ultraviolet (EUV) process, or the like.

The fin patterns, which may be employed in the present embodiment, may be modified in various forms. For example, a standard cell according to the present embodiment may include at least one dummy fin. In some embodiand an oxynitride. For example, the gate spacers 141 may 15 ments (for example, FIGS. 6 and 7A), at least one dummy fin may be disposed on one of the first and second boundaries. In some embodiments (for example, FIGS. 7A and **8**A), at least one dummy fin may include a pair of dummy fins arranged adjacent to each other with at least one of the first and second boundaries interposed therebetween.

> In some embodiments (for example, FIGS. 6 and 7A), fin patterns disposed in a first active region and a second active region of standard cells may be asymmetrically arranged. For example, even in a single standard cell, the number of active fins and/or dummy fins, a pitch of fin patterns, and a distance between a boundary and a fin pattern adjacent to the boundary may be different from each other.

> FIG. 6 is a layout diagram of fin patterns of a standard cell according to an example embodiment.

> Referring to FIG. 6, a standard cell 100A according to the present embodiment may be understood be similar to the standard cell 100, illustrated in FIGS. 2 to 5C, except that a dummy fin DF is disposed on one boundary of the standard cell 100A. Components of the present embodiment may be understood with reference to the descriptions of the same or similar components of the standard cell 100 illustrated in FIGS. 2 to 5C, unless otherwise specified.

> The standard cell **100A** according to the present embodiment may include first and second boundaries CB1 and CB2, respectively adjacent to standard cells SC1' and SC2 of other adjacent rows (R3 and R1 in FIG. 2). A dummy fin DF of the standard cell 100A may be arranged to be disposed on the first boundary CB1, but no dummy fin is disposed on the second boundary CB2. The first boundary CB1 may be disposed between the standard cell 100A, which is disposed in the second row R2 (see, FIG. 2), and a standard cell SC1', which is disposed in the third row R3 which is adjacent to the second row R2, and the dummy fin DF may partially overlap each of the standard cell 100A (or the second row R2) and the standard cell SC1' (or the third row R3). The second boundary CB2 may be disposed between the standard cell 100A, which is disposed in the second row R2, and a standard cell SC2, which is disposed in the first row R1. Similarly to the previous embodiment (see FIG. 3), no active fin AF and no dummy fin DF may be disposed on the second boundary CB2.

> As illustrated in FIG. 6, two active fins AF, respectively disposed in the first and second active regions PR and NR, may be arranged at a first pitch FP1, and active fins AF adjacent to an isolation region ISO may be arranged at a pitch FP1' different from the first pitch FP1.

> Active fins AF adjacent to the first and second boundaries CB1 and CB2 within the standard cell 100A may be asymmetrically spaced from the first and second boundaries CB1 and CB2, respectively. In the present embodiment, the active fins AF adjacent to the first boundary CB1 may be arranged at a third pitch FP3 with a dummy fin DF disposed on the

first boundary CB1. Similarly to the previous embodiment, an active fin AF of another standard cell SC2 neighboring the active fin AF adjacent to the second boundary CB2 may be arranged at the same pitch ½FP2 as the second boundary CB**2**.

As described above, a cell height of the standard cell 100A, employed in the present embodiment, may be defined as FP1'+2FP1+½FP2+FP3, and the fin patterns AF and DF disposed in the first active region PR and the second active region NR of the standard cells according to the present embodiment may be disposed asymmetrically arranged with respect to each other. For example, active fins AF adjacent to the first and second boundaries CB1 and CB2 within the standard cell 100A may be spaced apart from the first and second boundaries CB1 and CB2 at different pitches FP3 and ½FP2 (or different distances).

FIGS. 7A and 7B are layout diagrams of fin patterns of a standard cell and a final standard cell according to an example embodiment, respectively.

Referring to FIGS. 7A and 7B, a standard cell 100B according to the present embodiment will be understood to be similar to the standard cell 100, described with reference to FIGS. 2 to 5C, except that a dummy fin DF is disposed on one side boundary and a pair of fin patterns adjacent to the 25 other side boundary are dummy fins DF'. Components of the present embodiment may be understood with reference to the descriptions of the same or similar components of the standard cell 100 illustrated in FIGS. 2 to 5C, unless otherwise specified.

As illustrated in FIG. 7A, similarly to the standard cell **100**A illustrated in FIG. **6**, a standard cell **100**B according to the present embodiment may include fin patterns adjacent to a first boundary CB1 without overlapping a second boundpatterns adjacent to the second boundary CB2 may be a pair of dummy fins DF'. The pair of dummy fins DF' may be arranged at a constant pitch FP3', and may be arranged at a constant distance (for example, ½FP3') with the second boundary CB2 interposed therebetween. For example, the 40 second boundary CB2 is disposed between the pair of dummy fins DF'. A first dummy fin of the pair of dummy fins DF' is disposed in the standard cell 100, and the other is disposed in a standard cell SC2 adjacent to the standard cell 100. The first dummy fin is spaced apart, in the second 45 direction D2, from the second boundary CB2 at a distance of ½FP3'. The first dummy fin is spaced apart, in the second direction D2 at a pitch FP3', from an active fin AF which is closest to the second boundary CB2 among the four active fins AF disposed in the standard cell **100**B.

Similarly to the previous embodiment, two active fins AF, respectively disposed in first and second active regions PR and NR, may be arranged at a first pitch FP1, and active fins AF adjacent to an isolation region ISO may be arranged at a pitch FP1' different from the first pitch FP1.

Similarly to the standard cell 100A, active fins AF adjacent to the first and second boundaries CB1 and CB2 within the standard cell 100B may be asymmetrically spaced apart from the first and second boundaries CB1 and CB2, respectively. For example, an active fin AF which is closest to the 60 second boundary CB2 among the four active fins AF is spaced apart, in the second direction D2, from the second boundary CB2 at a distance of ½FP2', and an active fin AF which is closest to the first boundary CB1 among the four active fins AF is spaced apart, in the second direction D2, 65 from the first boundary CB1 at a distance of FP3 which is different from the pitch ½FP2'.

**16**

As described above, a cell height CH1 of the standard cell 100B may be defined as FP1'+2FP1+½FP2'+FP3, and the active fins AF adjacent to the first and second boundaries CB1 and CB2 within the standard cell 100B may be spaced apart from the first and second boundaries CB1 and CB2 at different distances FP3 and ½FP2', respectively.

The layout, illustrated in FIG. 7B, the standard cell 100B may include gate lines GL and DL, first and second contact structure CT\_A and CT\_B, first and second interconnection 10 lines M1 and M2, and first and second power supply lines PM1 and PM2 which are added on the pattern layout illustrated in FIG. 7A. A unit circuit, implemented in the standard cell 100B of FIG. 7B, may be an inverter element including four p-type transistors and four n-type transistors 15 disposed between the first and second power supply lines PM1 and PM2 to perform the same function as the layout of the standard cell illustrated in FIG. 4B. Each of the components of the present embodiment and connection relationships thereof will be understood with reference to what was 20 described in FIGS. 4A and 4B.

FIG. 8 is a cross-sectional view of the standard cell FIG. 7B, taken along line I1-I1' of FIG. 7B.

Referring to FIG. 8, similarly to the standard cell 100 illustrated in FIGS. 3A to 3C, the standard cell 100B according to the present embodiment may include a substrate 101, active region having active fins 105 or AF, an isolation layer 110, source/drain regions 120, gate structures 140 each having a gate electrode 145, a lower interlayer insulating layer 130, a contact structure 180, for example, 30 CT\_A or CT\_B, an upper interlayer insulating layer 170, and first and second interconnection lines M1 and M2.

The standard cell **100**B according to the present embodiment may include two dummy fins DF and DF', respectively disposed in first and second active regions ACT1 and ACT2. ary CB2. However, unlike the previous embodiment, fin 35 The dummy fin DF in the first active region ACT1 may be disposed on the first boundary CB1, and the dummy fin DF' in of the second active region ACT2 may be disposed adjacent to the second boundary CB2. Unlike the standard cell 100 illustrated in FIG. 3A, the fin patterns AF, DF, and DF' of the standard cell 100B may be asymmetrically arranged in the first and second active regions ACT1 and ACT**2**.

> As illustrated in FIG. 8, a distance between the second boundary CB2 and an active fin AF adjacent to the second boundary CB2 may be greater than a distance between the first boundary CB1 and an active fin AF adjacent to the first boundary CB1. Accordingly, an extension portion 180B' of a first contact structure 180', connected to the second power supply line PM2, may extend longer an extension portion 50 **180**B of a first contact structure **180** in a second direction D2. The extension portion 180B' may be a portion extended, in the second direction D2, from a contact portion 180A' which contacts a first source/drain region 120 (i.e., the right one of the two source/drain regions 120). The extension 55 portion 180B may be a portion extended, in the second direction D2, from a contact portion 180A which contact a second source/drain region 120 (i.e., the left one of the two source/drain regions 120).

In some embodiments, when a fin pattern such as an active fin is formed, a dummy fin has the same or similar structure formed by the same process as the active fin, but may be an element having at least a portion removed through an additional process such as a fin-cut process (for example, a selective etching process) so as so as not to serve as a portion of the semiconductor device. Similarly to an active fin, such a dummy fin may remain in standard cells in a row direction (for example, a first direction D1) in various forms.

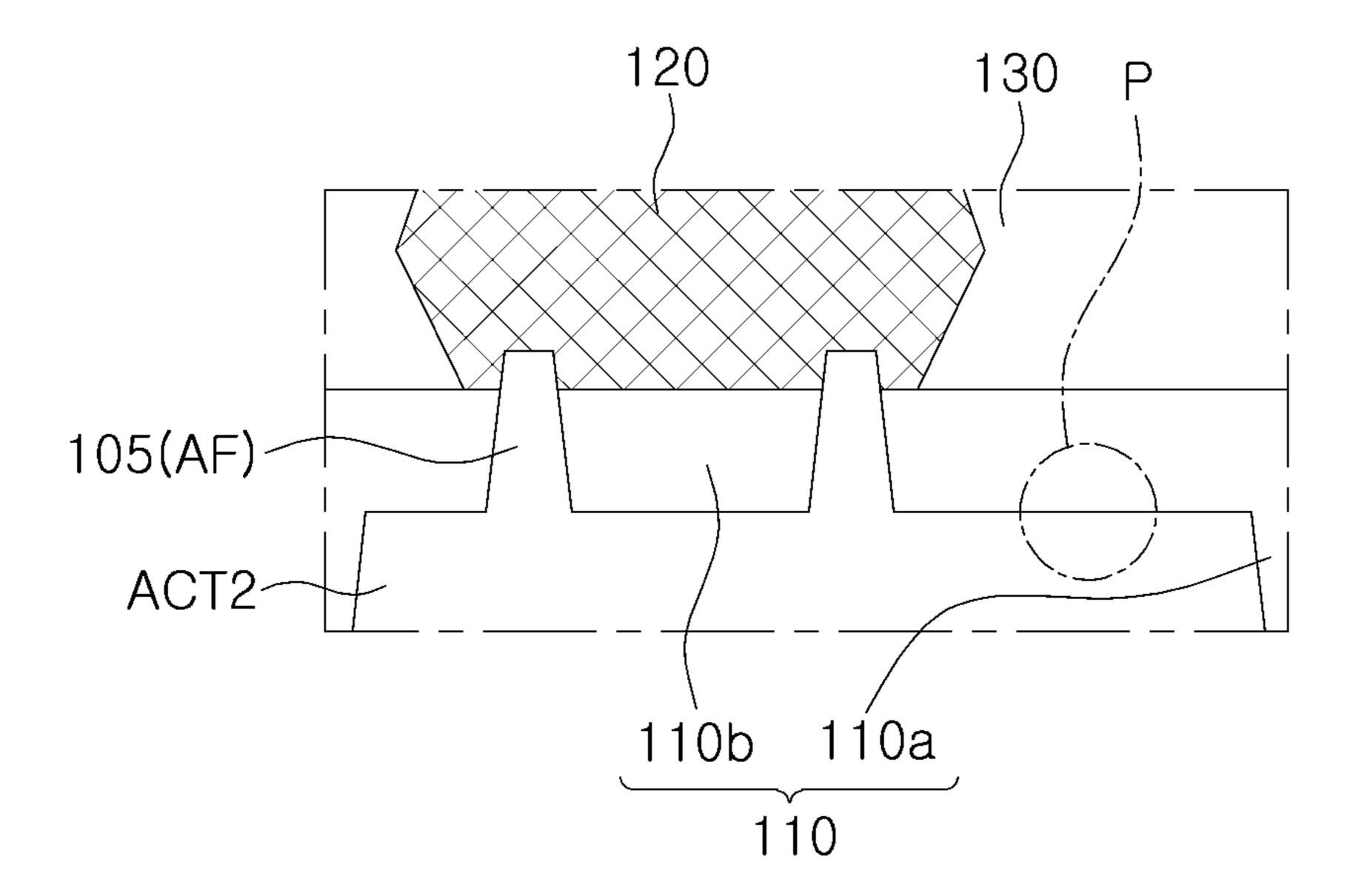

FIGS. 9A to 9C are enlarged cross-sectional views illustrating various examples related to a dummy fin.

A dummy fin DF', illustrated in FIG. 9A, may be almost removed by a fin-cut process such as an etching process. The fin-cut process may be performed in such a manner that, 5 similarly to the dummy fins DF and DF' illustrated in FIG. **8**, a portion of a fin pattern is removed to have a small height so that the fin pattern is not exposed from an upper surface of an isolation layer (110 in FIG. 8). In some embodiments, the dummy fin DF' may be sufficiently removed to remain in 10 a form sharply protruding from an upper surface of an active region. When the dummy fin DF' is additionally etched, a dummy fin region DF" may have a concave structure, as illustrated in FIG. 9B. For example, the dummy fin region DF" is a recessed region of the second active region ACT2 15 where a fin pattern existed and then disappeared due to the additional etching. The concave structure DF", extending in the first direction D1 as described above, may also be understood to be a region in which the fin pattern is removed by intentionally applying etching. In other embodiments, 20 only the active fins may be formed without the dummy fins by appropriately adjusting a pitch when a fin pattern is formed. In this case, as illustrated in FIG. 9C, a relatively planar bottom surface P, obtained during formation of an active fin (for example, an STI process), may be provided. 25 For example, the standard cell illustrated in FIG. 3 may be manufactured in such a manner that a dummy fin is not formed by appropriately adjusting a pitch.

As described above, a dummy fin may have various structures, other than a fin structure similar to a structure of 30 an active fin. For example, a dummy fin which extends in the first direction D1 may be a small portion, of an active region, protruding from an upper surface of an active region or a concaved region of an active region, according to a fin-cut process.

FIGS. 10A and 10B are layout diagrams of fin patterns of a standard cell and a final standard cell according to an example embodiment, respectively.

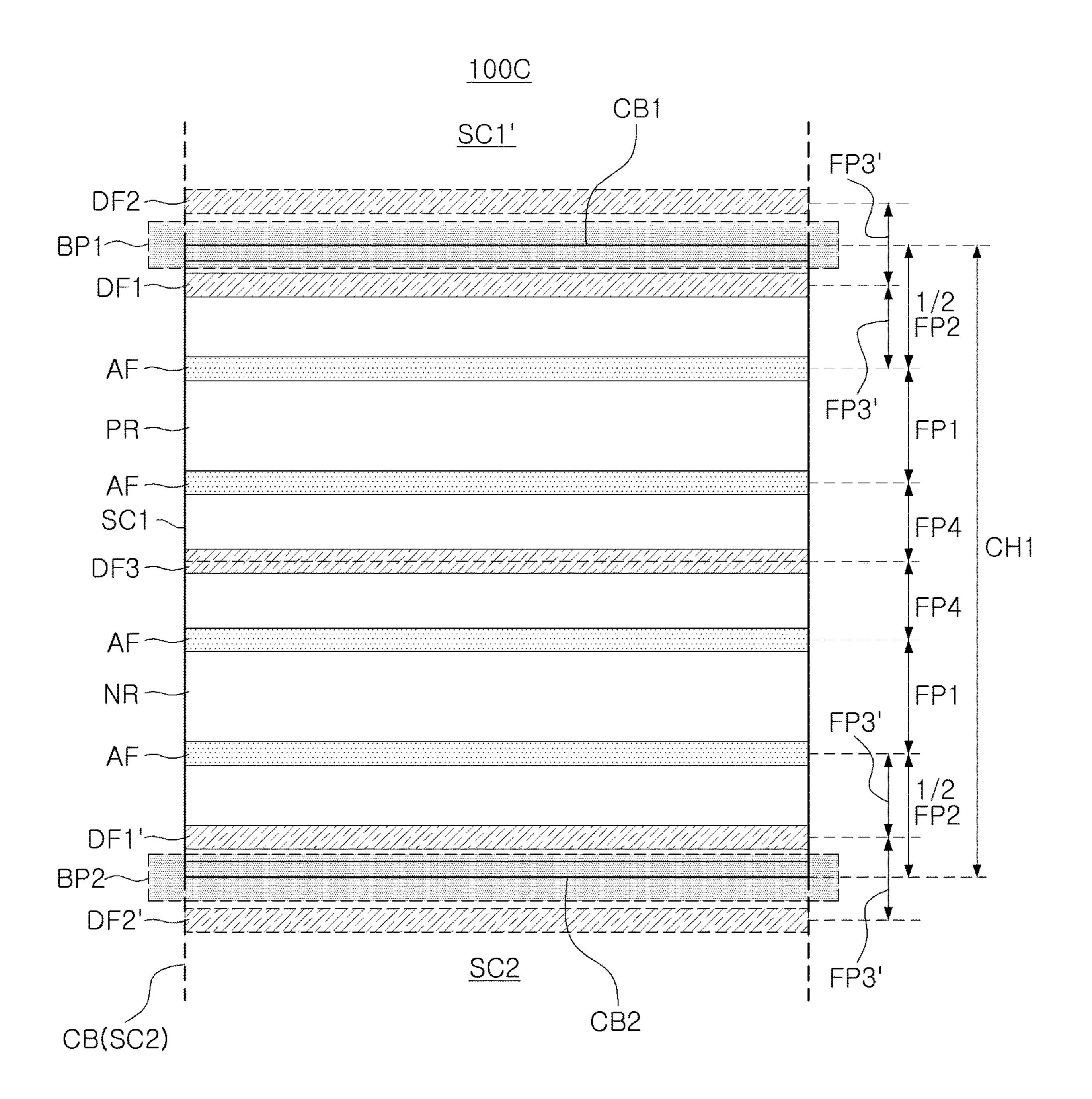

Referring to FIGS. 10A and 10B, a standard cell 100C according to the present embodiment may be understood to 40 be similar to the standard cell 100, illustrated in FIGS. 2 to 5C, except that first and second buried power supply lines BP1 and BP2 are employed as power supply lines and fin patterns DF' adjacent to boundaries do not overlap the first and second buried power supply lines BP1 and BP2 in a 45 third direction D3. Components of the present embodiment may be understood with reference to the descriptions of the same or similar components of the standard cell 100 illustrated in FIGS. 2 to 5C, unless otherwise specified.

Fin patterns of a standard cell 100C according to the 50 present embodiment may include a plurality of active fins AF and a plurality of dummy fins DF and DF' which are disposed between the first and second boundaries CB1 and CB2. The first buried power supply line BP1 may be disposed between a first dummy pattern DF1 of the standard 55 cell 100C and a second dummy pattern DF2 of another standard cell SC1' adjacent to the standard cell 100C. The first dummy pattern DF1 may be in a first active region PR and adjacent to the first boundary CB1 without overlapping the first buried power supply line BP1. The second dummy 60 in a vertical direction. pattern DF2 which is disposed in another standard cell SC1' may be adjacent to the first boundary CB1 without overlapping the first buried power supply line BP1. Each of the first dummy pattern DF1 and the second dummy pattern DF2 may be spaced apart from the first boundary CB1 at the same 65 distance (e.g., ½FP3'). The FP3' represents a pitch between the first dummy pattern DF1 and the second dummy pattern

**18**

DF2. The second buried power supply line BP2 may be disposed between a first dummy pattern DF1' of the standard cell 100C and a second dummy pattern DF2' of another standard cell SC2 adjacent to the standard cell 100C. The first dummy pattern DF1' may be in a second active region NR and adjacent to the second boundary CB2 without overlapping the second buried power supply line BP2. The second dummy pattern DF2' which is disposed in another standard cell SC2 may be adjacent to the second boundary CB2 without overlapping the second buried power supply line BP2. Each of the first dummy pattern DF1' and the second dummy pattern DF2' may be spaced apart from the second boundary CB2 at the same distance (e.g., ½FP3'). The pitch between the first dummy pattern DF1' and the second dummy pattern DF2' may be the same as the pitch between the first dummy pattern DF1 and the second dummy pattern DF2. When the standard cell 100C is viewed in a plan view, a third dummy fin DF3 may be disposed on a boundary, which is shown as a dashed line, between the first and second active regions PR and NR.

As illustrated in FIGS. 10A and 10B, two active fins AF, respectively disposed in the first and second active regions PR and NR, may be arranged at a first pitch FP1, and the third dummy fin DF3 may be spaced apart, at a pitch FP4, from an active fin AF which is closest to the third dummy fin DF3. The pitch FP4 may be different from a pitch (e.g., FP1) between the two active fins AF which are disposed in each of the first and second active region PR and NR. One of the two active fins AF which are disposed in the first active region PR may be spaced apart, at a distance of ½FP2, from the first boundary CB1. One of the two active fins AF which are disposed in the second active region NR may be spaced apart, at the distance of ½FP2, from the second boundary CB2.

As described above, a cell height of the standard cell 100C employed in the present embodiment may be 2FP4+2FP1+FP2, and the fin patterns AF, DF1, DF1' disposed in the first active region PR and the second active region NR may be symmetrically arranged with respect to the third dummy pattern DF3.

A power supply line, employed in the present embodiment, may include first and second buried power supply lines PB1 and BP2, respectively buried in the first and second boundaries CB1 and CB2 between the adjacent standard cells SC land SC' and between the adjacent standard cells SC and SC2. Each of the first and second buried power supply lines BP1 and BP2 may be buried in an isolation layer (110 of FIG. 11A), disposed on the first and second boundaries CB1 and CB2, and/or an active region (102 of FIG. 11A). In the present embodiment, both the first and second power supply lines are illustrated as being provided as buried power supply lines. However, in some embodiments, only some of the first and second power supply lines may be provided as a buried power supply lines.

Among the dummy fins DF1, DF2, and DF3, the dummy fins DF1 and DF2 may be disposed closer to the first and second buried power supply lines BP1 and BP2, respectively, than the third dummy fin DF3, without overlapping the first and second buried power supply lines BP1 and BP2 in a vertical direction.

As illustrated in FIG. 10B, the standard cell 100C may include gate lines GL and DL, first and second contact structures CT\_A and CT\_B, first and second interconnection lines M1 and M2, and first and second power supply lines PM1 and PM2 which are added on the fin pattern layout illustrated in FIG. 10A. A unit circuit, implemented in the standard cell 100B of FIG. 10B, may be an inverter element

including four p-type transistors and four n-type transistors disposed between the first and second power supply lines PM1 and PM2 to perform the same function as the layout of the standard cell illustrated in FIG. 10B. Each of the components of the present embodiment and connection 5 relationships thereof will be understood with reference to what was described in FIGS. 4A and 4B.

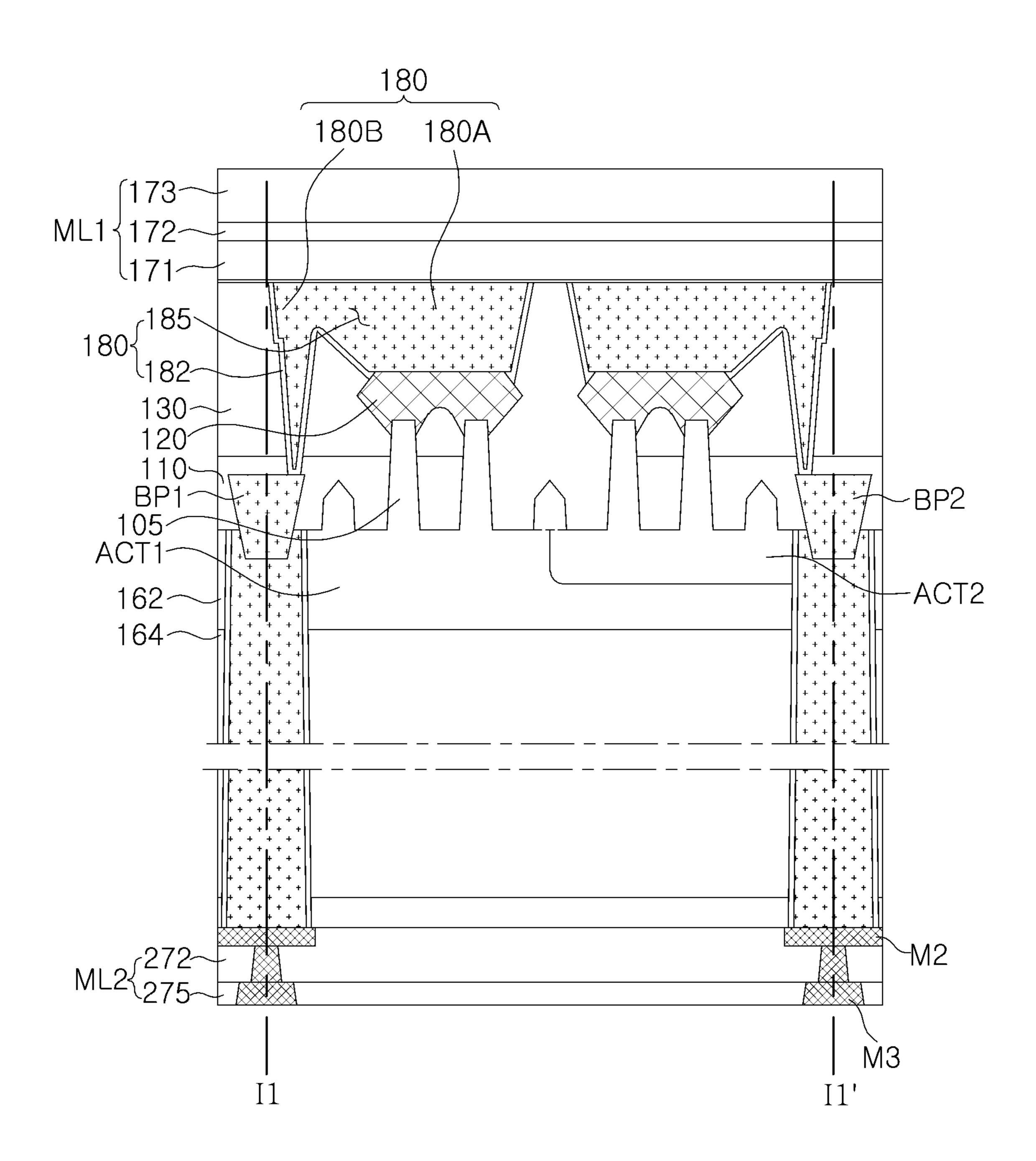

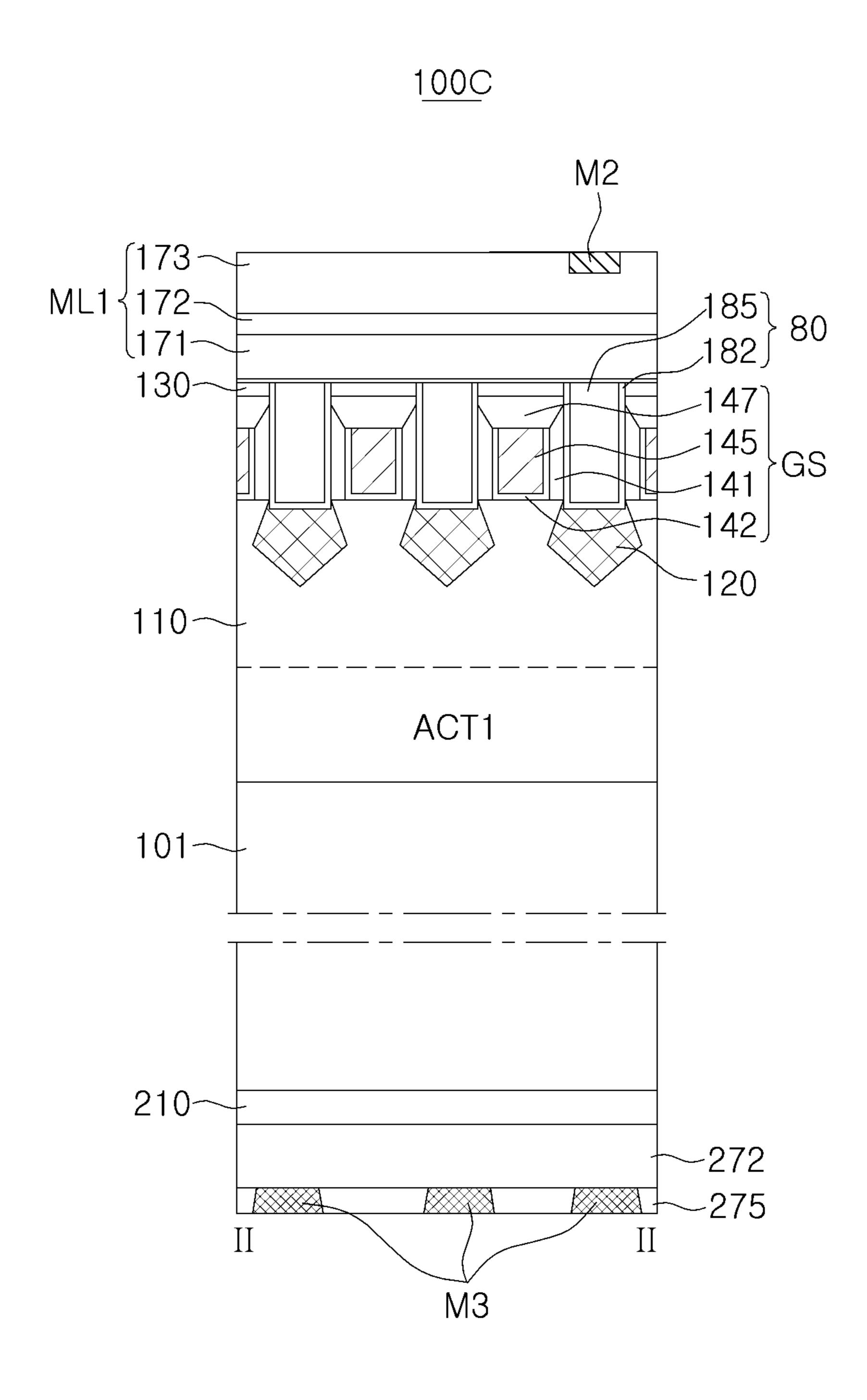

FIGS. 11A and 11B are cross-sectional views of the standard cell of FIG. 10B, taken along lines I1-I1' and II-II' of FIG. 10B, respectively, and FIG. 11C is a bottom view of 10 the standard cell of FIG. 10B.

Referring to FIGS. 11A and 11B, a standard cell 100C according to the present embodiment may include a substrate 101 having an active region 102. A plurality of active fins 105 may be disposed on the active region 102.

Similarly to the previous embodiment, each of the plurality of active fins 105 may have a structure protruding from an upper surface of the active region 102 in a third direction D3. The plurality of active fins 105 may be arranged parallel to each other on the upper surface of the active region 102 to extend in a first direction D1. The active fins 105 may be provided as an active region of each transistor. In the present embodiment, two active fins 105 are connected to a source/drain region 120, but the number of active fins which are connected to the source/drain region 120 is not limited 25 thereto. In other embodiments, one, or three or more active fins 105 may be provided. As the number of the active fins 105 connected to a source/drain region increases, a width of channel region of a transistor increases.

Source/drain regions 120 may be formed in some regions 30 of the active fins 105 disposed on opposite sides adjacent to the gate structure GL. In the present embodiment, the source/drain region 120 may have an upper surface having a higher level than an upper surface of the active fin 105 by forming a recess in a certain region of the active fin 105 and 35 performing selective epitaxial growth on the recess.

The standard cell 100C according to the present embodiment may include a gate structure GL. Referring to FIGS. 10B and 11B, the gate structure GL may have a line structure extending in the second direction D2. The gate structure GL 40 may overlap one region of the active fins 105.

The gate structure GL, employed in the present embodiment, may include gate spacers 141, a gate insulating layer 142 and a gate electrode 145 sequentially disposed between the gate spacers 141, and a gate capping layer 147 disposed 45 on the gate electrode 145.

The standard cell 100C may include an isolation layer 110. The isolation layer 110 may include a first isolation region 110a, defining an active region 102, and a second isolation region 110b adjacent to the first isolation region 50 110a and defining a plurality of active fins 105 (see FIG. 5A).

The standard cell 100C according to the present embodiment may include first and second buried power supply lines BP1 and BP2 buried in the second isolation region 110b to 55 the active region 102. For example, the first and second buried power supply lines BP1 and BP2 may be divided into a portion buried in the second isolation region 110b and a portion buried in the active region 102. The first and second buried power supply lines BP1 and BP2 may extend in the 60 first direction D1 along boundaries CB1 and CB2 of a standard cell.

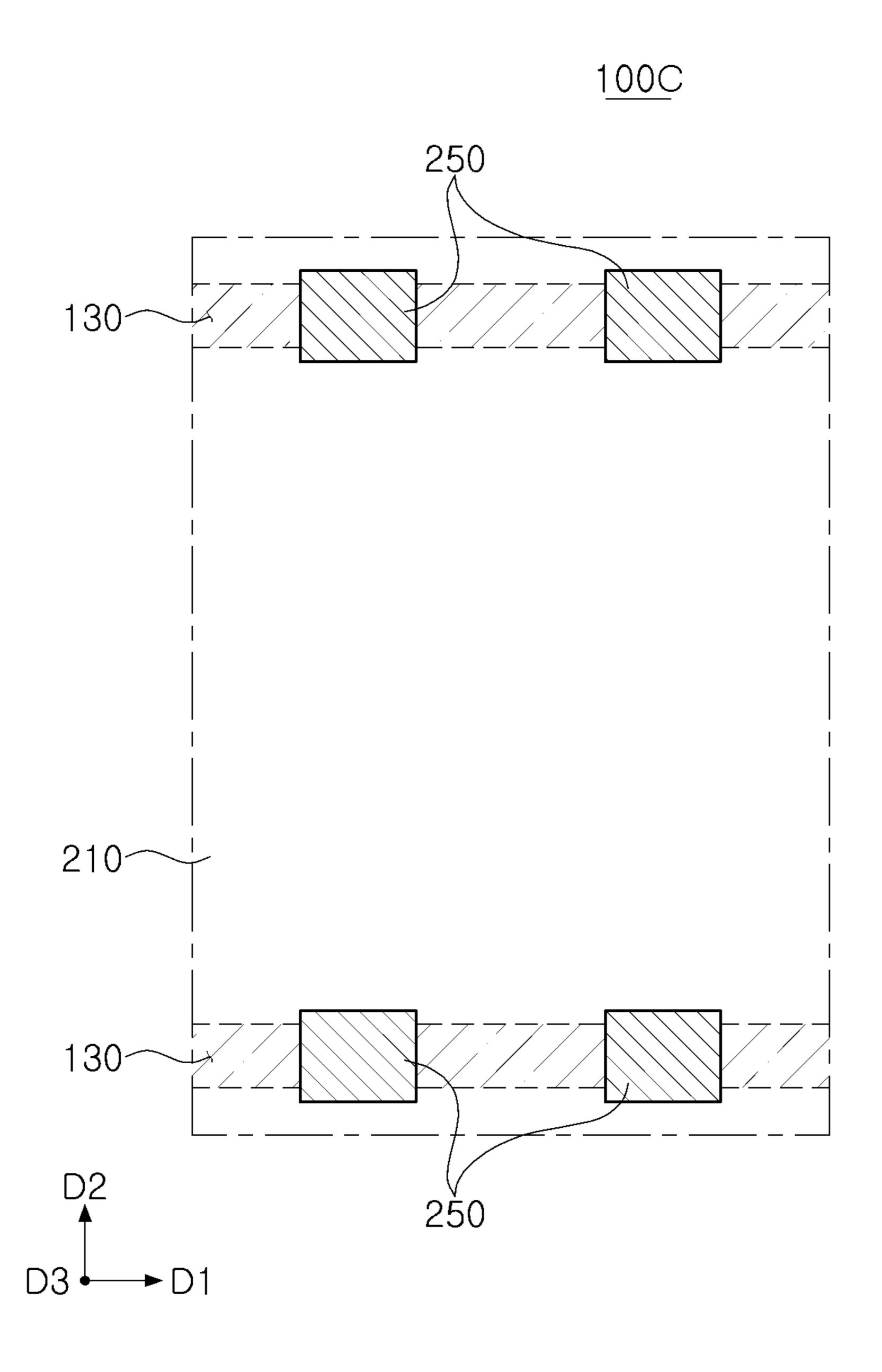

A conductive through-structure 250 may include a filled through-via 255, extending from a lower surface of the substrate 101 toward an upper surface of the substrate 101, 65 and an insulating liner 251 disposed between the through-via 255 and the substrate 101. For example, the conductive

**20**

through-structure 250 may be a through-silicon via (TSV). The conductive through-structure 250 may be formed from the rear surface of the substrate 101 to be connected to the first and second buried power supply lines BP1 and BP2.

A lower interlayer insulating layer 130 may be disposed on the isolation layer 110 to cover the source/drain regions 120 and the first and second buried power supply lines BP1 and BP2. The second isolation region 110b of the isolation layer 110 may include portions covering the first and second buried power supply lines BP1 and BP2.

Each of the first and second buried power supply lines BP1 and BP2 may have an upper surface lower than an upper end of the active fin 105. For example, the first and second buried power supply lines BP1 and BP2 may not be exposed outwardly during a process of forming the source/drain region 120. The upper surfaces of the first and second buried power supply lines BP1 and BP2 may be higher than upper surfaces of the first and second active regions ACT1 and ACT2.

The first and second buried power supply lines BP1 and BP2 may be electrically connected to the first contact structure 180 or CT\_A. In some embodiments, the first contact structure 180 may include a conductive barrier 182 and a contact plug 185.

The first contact structure 180, employed in the present embodiment, may be connected to each of the source/drain regions 120 and the first and second buried power supply lines BP1 and BP2. The first contact structure 180 may include a first contact portion 180A, connected to the source/drain region 120, and an extension portion 180B connected to the first contact portion 180A and connected to the first and second buried power supply lines BP1 and BP2. The extension portion 180B may extend deeper than the first contact portion 180A to be electrically connected to each of the first and second buried power supply lines BP1 and BP2.

The first contact structure **180** may be connected to a first interconnection portion ML1 constituting back end of lines (BEOL). The first interconnection portion ML1 may connect a plurality of devices (for example, transistors) implemented on the active region **102** of the substrate **101** with each other. Similarly to the previous embodiment, the first interconnection portion ML1 may include a plurality of dielectric layers **171**, **172**, and **173**, first to second interconnection lines M1 and M2, and vias V0 and V1. An etch-stop layer may be further included below the dielectric layers **171**, **172**, and **173**.

In the present embodiment, a plurality of elements (for example, the source/drain region 120, and the like) formed on the substrate 101 may be connected to a second interconnection portion ML2, disposed on the rear surface of the substrate 101, through the first and second buried power supply lines BP1 and BP2 and the conductive throughstructure 250. The second interconnection portion ML2 may be a power supply line and signal supply lines implemented on the rear surface of the substrate 101, and will be understood to be an interconnection structure replacing a portion of required BEOL. The second interconnection portion ML2 may provide a signal line and a power supply line for a plurality of elements (for example, transistors) implemented on the upper surface of the substrate 101 through the buried power supply line BP and the conductive through-structure **250**.

An insulating layer 210 may be formed on the rear surface of the substrate 101, and then the conductive throughstructure 250 may be formed thereon. The second interconnection portion ML2 may be provided on the insulating layer 210. The second interconnection portion ML2 may

include a plurality of low-k dielectric layers 272 and 275, interconnection lines M3 and M4, and a via V2.

FIG. 11C illustrates a layout of the conductive throughstructure 250 and the first and second buried power supply lines BP1 and BP2, when viewed from a lower surface of the substrate 101. A plurality of conductive through-structures 250 may be arranged to be connected to the first and second buried power supply lines BP1 and BP2 extending in a first direction D1. In FIG. 11C, a cross section of the conductive through-structure 250 is illustrated as having a substantially rectangular shape in which a length in the first direction D1 is greater than a length in a second direction D2, perpendicular to the first direction D1. However, in other embodiments, the conductive through-structure 250 may have another shape (for example, a circular shape or an elliptical shape), among various other shapes. In the present embodiment, the conductive through-structures 250 are illustrated as being arranged on the same line in the second direction D2. However, in other embodiments, the conductive 20 through-structures 250 may have another arrangement. For example, the conductive through-structures 250 may be arranged in a zig-zag manner in the second direction D2 or in the first direction D1.